**Titre:** Conception, réalisation et tests d'une interface intégrée pour l'acquisition et l'analyse des signaux nerveux

Title: l'acquisition et l'analyse des signaux nerveux

**Auteur:** Adnan Harb

Author:

**Date:** 2004

**Type:** Mémoire ou thèse / Dissertation or Thesis

**Référence:** Harb, A. (2004). Conception, réalisation et tests d'une interface intégrée pour l'acquisition et l'analyse des signaux nerveux [Thèse de doctorat, École Polytechnique de Montréal]. PolyPublie. <https://publications.polymtl.ca/7560/>

Citation:

## Document en libre accès dans PolyPublie

Open Access document in PolyPublie

**URL de PolyPublie:** <https://publications.polymtl.ca/7560/>

PolyPublie URL:

**Directeurs de recherche:** Mohamad Sawan

Advisors:

**Programme:** Non spécifié

Program:

**UNIVERSITÉ DE MONTRÉAL**

**Cette thèse intitulée :**

**CONCEPTION, RÉALISATION ET TESTS D'UNE INTERFACE

INTÉGRÉE POUR L'ACQUISITION ET L'ANALYSE

DES SIGNAUX NERVEUX**

**ADNAN HARB**

**DÉPARTEMENT DE GÉNIE ÉLECTRIQUE

ÉCOLE POLYTECHNIQUE DE MONTRÉAL**

**THÈSE PRÉSENTÉE EN VUE DE L'OBTENTION

DU DIPLÔME DE PHILISOPHIAE DOCTOR (Ph.D.)

(GÉNIE ÉLECTRIQUE)**

**AOÛT 2004**

Library and

Archives Canada

Published Heritage

Branch

395 Wellington Street

Ottawa ON K1A 0N4

Canada

Bibliothèque et

Archives Canada

Direction du

Patrimoine de l'édition

395, rue Wellington

Ottawa ON K1A 0N4

Canada

*Your file* *Votre référence*

ISBN: 978-0-494-16997-1

*Our file* *Notre référence*

ISBN: 978-0-494-16997-1

#### NOTICE:

The author has granted a non-exclusive license allowing Library and Archives Canada to reproduce, publish, archive, preserve, conserve, communicate to the public by telecommunication or on the Internet, loan, distribute and sell theses worldwide, for commercial or non-commercial purposes, in microform, paper, electronic and/or any other formats.

The author retains copyright ownership and moral rights in this thesis. Neither the thesis nor substantial extracts from it may be printed or otherwise reproduced without the author's permission.

In compliance with the Canadian Privacy Act some supporting forms may have been removed from this thesis.

While these forms may be included in the document page count, their removal does not represent any loss of content from the thesis.

#### AVIS:

L'auteur a accordé une licence non exclusive permettant à la Bibliothèque et Archives Canada de reproduire, publier, archiver, sauvegarder, conserver, transmettre au public par télécommunication ou par l'Internet, prêter, distribuer et vendre des thèses partout dans le monde, à des fins commerciales ou autres, sur support microforme, papier, électronique et/ou autres formats.

L'auteur conserve la propriété du droit d'auteur et des droits moraux qui protège cette thèse. Ni la thèse ni des extraits substantiels de celle-ci ne doivent être imprimés ou autrement reproduits sans son autorisation.

Conformément à la loi canadienne sur la protection de la vie privée, quelques formulaires secondaires ont été enlevés de cette thèse.

Bien que ces formulaires aient inclus dans la pagination, il n'y aura aucun contenu manquant.

\*\*

**Canada**

UNIVERSITÉ DE MONTRÉAL

ÉCOLE POLYTECHNIQUE DE MONTRÉAL

Cette thèse intitulée:

CONCEPTION, RÉALISATION ET TESTS D'UNE

INTERFACE INTÉGRÉE POUR L'ACQUISITION

ET L'ANALYSE DES SIGNAUX NERVEUX

présentée par: HARB Adnan

en vue de l'obtention du diplôme de Philosophiae Doctor

a été dûment acceptée par le jury d'examen constitué de:

M. SAVARIA Yvon, Ph.D., président

M. SAWAN Mohamad, Ph.D., membre et directeur de recherche

M. GUARDO Robert, Ph.D., membre

M. ALKHALILI Asim, Ph.D., membre externe

## DÉDICACE

*A ma mère*

*A mon père*

*A mon épouse*

*A mes deux enfants*

## REMERCIEMENTS

Je tiens à remercier M. Mohamad Sawan, professeur au Département de génie électrique, qui a accepté de diriger ce travail en m'accueillant au sein de son équipe PolySTIM, où il m'a été possible d'effectuer mes recherches dans des conditions tout à fait excellentes et très appréciées.

Je tiens également à adresser des remerciements aux professeurs Yvon Savaria, pour avoir bien voulu présider le jury de cette thèse, Asim Al-Khalili de l'Université Concordia et Robert Guardo, qui ont accepté de faire partie de ce jury et à tous mes collègues et personnel du GRM qui m'ont apporté leur savoir et leur amitié tout au long de ce travail. Plus particulièrement, je remercie Yamu Hu pour sa participation dans le premier article.

Je voudrais encore souligner la collaboration du Dr. Elhilali et son équipe d'urologie au centre McIntyre d'animalerie de l'Université McGill pour la réalisation des sessions d'expérimentation en phase aiguë. Je leur en suis très reconnaissant.

J'aimerais aussi remercier le Conseil de Recherches en Sciences Naturelles et en Génie du Canada (CRSNG) pour m'avoir accordé une bourse doctorale et pour le support financier du projet, la Société Canadienne en Microélectronique (SCM) pour la fabrication

de circuits intégrés, et STMicroelectronics pour l'utilisation du laboratoire pour les tests des circuits intégrés. Je tiens également à remercier Madame Selma Tischer, traductrice et rédactrice technique, pour la relecture attentive du texte.

Je dois aussi une grande reconnaissance à Madame Ghyslaine Ethier-Carrier pour son aide constante tout au long de cette thèse et de son dévouement et sa bonne humeur. Je n'oublie pas Réjean Lepage, administrateur du système, qui s'est toujours montré d'une grande disponibilité et d'une grande patience face à mes sollicitations.

Finalement, c'est avec beaucoup de reconnaissance que je remercie mes parents, mon épouse et mes deux enfants qui ont, avec beaucoup de patience, accepté de vivre dans des conditions difficiles pendant de longues années tout en me fournissant un support précieux; sans leurs sacrifices, ce travail n'aurait pu être accompli.

## RÉSUMÉ

La restitution des fonctions motrices des organes paralysés à la suite d'un accident ou d'une maladie est un ancien rêve. L'avancement de la technologie et des neurosciences au cours des dernières années a ouvert la voie à la concrétisation d'un tel rêve.

Après plusieurs années de recherche, la restauration des fonctions motrices d'un organe par stimulation électrique suite à une lésion de la moelle épinière est devenue possible. Cependant, en raison de la fatigue musculaire, l'application d'une stimulation électrique constante ne fournit pas nécessairement une force motrice constante. De plus, si la fonction sensorielle est aussi affectée, elle doit être remplacée par un capteur artificiel. Son rôle est de fermer la boucle de la stimulation composée du stimulus (entrée), de l'organe (système excité) et des signaux nerveux (sortie, reflétant l'état de l'organe). Il s'agit d'une interface électronique capable d'acquérir et de traiter les signaux nerveux émis par l'organe afin de transmettre les résultats au contrôleur de la stimulation.

Cette thèse présente un système intégré implantable en technologie CMOS pour l'acquisition et l'analyse des signaux nerveux. Un tel module électronique complète le système implantable de stimulation en surveillant et en communiquant l'état de l'organe au processeur central de l'implant en temps réel. Ceci permet au processeur de régler l'intensité de la stimulation en fonction de l'activité de l'organe, et d'informer le patient de son état le cas échéant.

Bien qu'une application particulière est décrite dans cette thèse, le système proposé pourrait servir dans beaucoup d'applications similaires. Cependant, des modifications mineures pourraient être nécessaires.

Le système réalisé est formé des circuits suivants:

- Un préamplificateur à faible bruit basé sur un amplificateur stabilisé par hachage car l'amplitude des signaux nerveux est faible et peut varier entre 1  $\mu$ V et quelques dizaines de  $\mu$ V;

- Un amplificateur d'instrumentation à gain programmable selon l'amplitude du signal acquis;

- Un échantillonneur-bloqueur dont la sortie est toujours valide;

- Un redresseur à double alternance suivi d'un intégrateur par période multi-étages pour accomplir le traitement de signal requis.

Comme la tension d'alimentation et la consommation d'énergie sont des éléments clefs dans les dispositifs électroniques implantables, le système présenté est conçu pour fonctionner avec une tension d'alimentation plus basse que celle recommandée pour la technologie CMOS 0.35  $\mu$ m utilisée. Aussi, une attention particulière a été accordée pour réaliser des circuits à faible consommation d'énergie. Il s'agit d'un critère nécessaire à respecter pour être en mesure d'alimenter l'ensemble de l'implant par l'énergie transmise à travers la peau et portée par des ondes électromagnétiques.

En résumé, les contributions de cette thèse sont les suivantes:

1. La confirmation par des mesures *in vivo* de la relation électroneurogramme-volume vésical. Réussir cette procédure, qui entre autre nécessitait la construction d'un système d'acquisition à composants discrets, était un pas nécessaire à franchir afin de pouvoir passer à la conception du circuit intégré;

2. La réalisation du premier module CMOS intégré pour l'acquisition et le traitement des signaux nerveux. Le module ainsi conçu est utilisable dans plusieurs applications de réadaptation;

3. La conception de plusieurs modules électroniques à haute performance tels un préamplificateur à faible bruit, un amplificateur d'instrumentation programmable, un échantillonneur/bloqueur, un redresseur à double alternance et un intégrateur par période.

Le travail effectué et présenté dans cette thèse ouvre la voie à un aspect très important et critique des systèmes de réadaptation. Nous espérons modestement qu'il pourra contribuer à l'amélioration de la qualité de vie des patients.

## ABSTRACT

To recover motor functions of organs paralyzed as a result of an accident or a disease is an ancient dream. Only in the last few years, however, have technology and neuroscience advanced to the point that practical systems can be envisaged to realize this dream partially.

After many years of research in electrical stimulation, restoration of significant motor function of an organ by electrical stimulation after spinal cord injury is now becoming possible. However, during neuromuscular stimulation, constant electrical stimulation does not yield constant muscular force because of fatigue. Additionally, in the case where sensory function is lost, it is required that artificial sensors to replace lost natural sensors. Their role is to close the feedback loop composed of the stimulus (input), the organ (excited system) and the nerve signal (output, reflecting the status of the organ). The main role of this artificial sensor is to record the nerve signal, analyze it, and transmit the results to the controller of the stimulation.

In this thesis a CMOS integrated implantable system dedicated to the acquisition and analysis of nerve signals is presented. This electronic module completes the implantable stimulation system by supervising and communicating the status of the organ to the central processor of the implant in real time. This allows the processor to monitor and

manage the stimulation intensity vs. organ activity, and to inform the patient of its status if necessary.

Although the proposed system is designed for a specific application, it could be used in many similar applications. However, minor modifications might be necessary.

The system that has been implemented is composed of the following circuits:

- A low-noise preamplifier based on the chopper stabilization technique because the nerve signal amplitude is very low and ranges from  $1 \mu\text{V}$  to few tens of  $\mu\text{V}$ ;

- A programmable gain instrumentation amplifier. The gain is set in function of the amplitude of the recorded signal;

- A sample and hold circuit with an always valid output;

- A full-wave rectifier followed by a multi-stage bin-integrator to perform the required signal processing.

Since supply voltage and power consumption are key issues in implantable devices, the data acquisition system is designed to work at a supply voltage lower than the nominal supply voltage of the technology used (CMOS 0.35  $\mu\text{m}$ ). Also, a special attention was paid to reduce the overall power consumption. This is an essential criteria to be able to power the whole implant with the energy carried by electromagnetic waves transmitted through the skin.

In summary, the contributions of this thesis are:

1. We succeeded in recording nerve signals *in vivo* to confirm the relationship between electroneurogram and bladder volume. To complete this procedure, a data acquisition system based on discrete components was built. *In vivo* measurements were a necessary step before starting the design of an integrated system;

2. We implemented the first CMOS integrated module dedicated to nerve signal acquisition and processing. This module can be used in many rehabilitation applications;

3. We designed several high performance units: low noise preamplifier, programmable instrumentation amplifier, sample-and-hold, full-wave rectifier, and 200 ms bin integrator.

The work performed for this thesis opens the door widely to a very important and critical part in rehabilitation systems. We hope modestly that it will constitute a contribution to improving patients quality of life.

## TABLE DES MATIÈRES

|                                                                |       |

|----------------------------------------------------------------|-------|

| DÉDICACE .....                                                 | IV    |

| REMERCIEMENTS .....                                            | V     |

| RÉSUMÉ .....                                                   | VII   |

| ABSTRACT .....                                                 | X     |

| TABLE DES MATIÈRES .....                                       | XIII  |

| LISTE DES FIGURES .....                                        | XVI   |

| LISTE DES TABLEAUX .....                                       | XXVI  |

| LEXIQUE .....                                                  | XXVII |

| INTRODUCTION .....                                             | 1     |

| CHAPITRE 1: REVUE DE LITTÉRATURE .....                         | 4     |

| 1.1. Le système nerveux .....                                  | 4     |

| 1.2. Historique .....                                          | 8     |

| 1.3. Enregistrement des signaux nerveux: état actuel.....      | 10    |

| 1.4. Utilisation des signaux nerveux dans la réadaptation..... | 12    |

|                                                                                                                                                                          |            |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

| 1.5. Systèmes électroniques d'acquisition de l'ENG.....                                                                                                                  | 22         |

| 1.6. Travail proposé dans cette thèse .....                                                                                                                              | 32         |

| 1.7. Méthodologie.....                                                                                                                                                   | 34         |

| <b>CHAPITRE 2: UNE INTERFACE CMOS À BASSE PUISSANCE POUR L'ENREGISTREMENT ET LE TRAITEMENT DE SIGNAUX DE TRÈS FAIBLE AMPLITUDE .....</b>                                 | <b>36</b>  |

| 2.1. Introduction .....                                                                                                                                                  | 36         |

| 2.2. Article: Low-power CMOS interface for recording and processing very low amplitude signals .....                                                                     | 40         |

| <b>CHAPITRE 3: UN CIRCUIT DE REDRESSEMENT ET D'INTÉGRATION PAR PÉRIODE À CAPACITÉS COMMUTÉES POUR LE TRAITEMENT DES SIGNAUX NERVEUX .....</b>                            | <b>80</b>  |

| 3.1. Introduction .....                                                                                                                                                  | 80         |

| 3.2. Article: Fully integrated electroneurogram acquisition and processing front-end dedicated to monitor the bladder activities: design and measurements... <td>83</td> | 83         |

| <b>CHAPITRE 4: COMPLÉMENTS DE RÉSULTATS.....</b>                                                                                                                         | <b>109</b> |

| 4.1. Simulation de l'échantillonneur-bloqueur .....                                                                                                                      | 109        |

| 4.2. Les phases d'horloge .....                                                                                                                                          | 110        |

|                                                                   |            |

|-------------------------------------------------------------------|------------|

| 4.3. Contenu fréquentiel de l'ENG .....                           | 117        |

| 4.4. Résultats détaillés des dix puces mesurées .....             | 119        |

| <b>DISCUSSION GÉNÉRALE ET CONCLUSION .....</b>                    | <b>120</b> |

| <b>BIBLIOGRAPHIE .....</b>                                        | <b>125</b> |

| <b>ANNEXE A: DESCRIPTION DES BROCHES DU CIRCUIT INTÉGRÉ .....</b> | <b>135</b> |

## LISTE DES FIGURES

|             |                                                                                                                                                                                                                                                                                                                                                                                                        |    |

|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Figure 1.1. | La vessie est composée de deux parties: le détrusor et le trigone.....                                                                                                                                                                                                                                                                                                                                 | 6  |

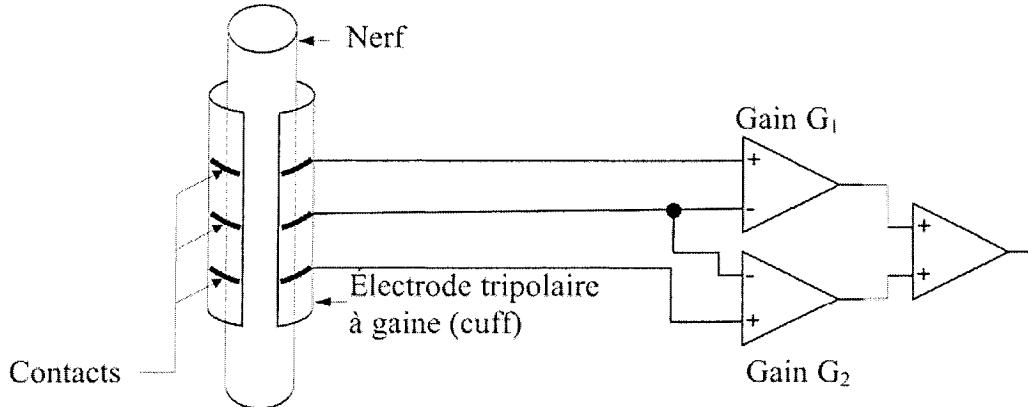

| Figure 1.2. | Enregistrement utilisant une gaine à trois contacts [54]. .....                                                                                                                                                                                                                                                                                                                                        | 12 |

| Figure 1.3. | Mesures chroniques de l'ENG: (A) forces perpendiculaires (ligne continue) et latérales (ligne pointillée) appliquées sur le côté latéral du pied, (B) l'ENG brut, (C) l'ENG redressé et intégré par période (ligne pointillée) et le modèle élaboré par les auteurs qui relie l'ENG-RBI à la force perpendiculaire appliquée (ligne continue) [25].....                                                | 15 |

| Figure 1.4. | Résultats typiques des mesures effectuées sur un patient marchant à pieds nus sans (panneau gauche) et avec stimulation (panneau droit) des dorsifléchisseurs de la cheville. (A) le signal nerveux sural redressé et intégré par période, (B) le signal en A après filtrage passe haut, et (C) le signal du capteur sur le talon et le signal du contrôle du stimulateur (surface hachurée) [52]..... | 18 |

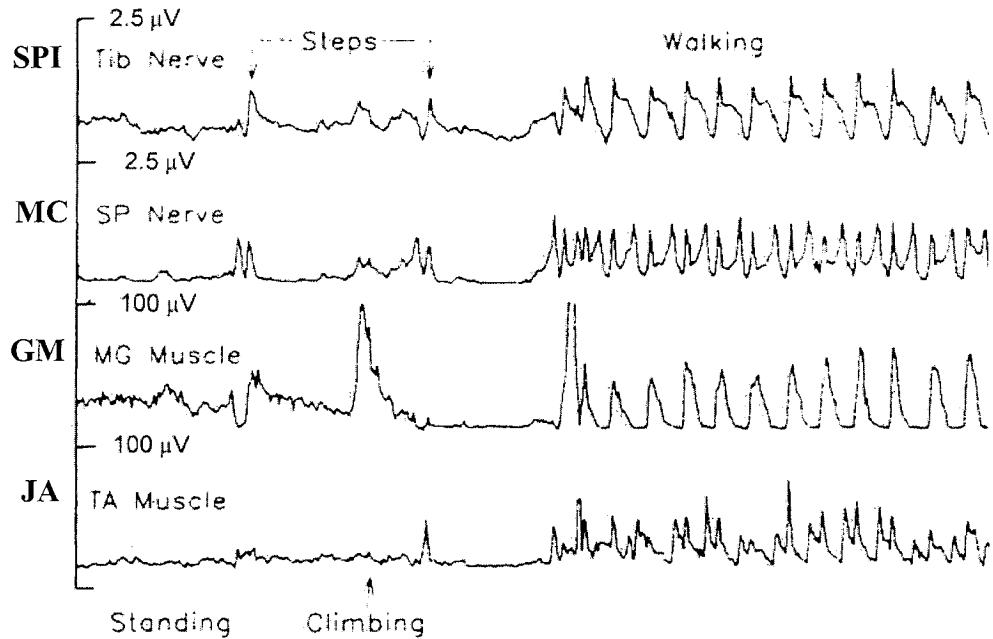

| Figure 1.5. | L'enregistrement des signaux du nerf musculo-cutané (MC) et du nerf sciatique poplité interne (SPI) ainsi que les signaux du muscle gastronémien médial (GM), et le muscle jambier antérieur (JA) en fonction du temps (axe des x en secondes). Cet enregistrement de 20 s est présenté pour montrer les                                                                                               |    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                               |    |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| différentes activités rythmiques dans les nerfs périphériques et les muscles de la cheville dans des comportements différents [45].....                                                                                                                                                                                                                                                                                                                       | 20 |

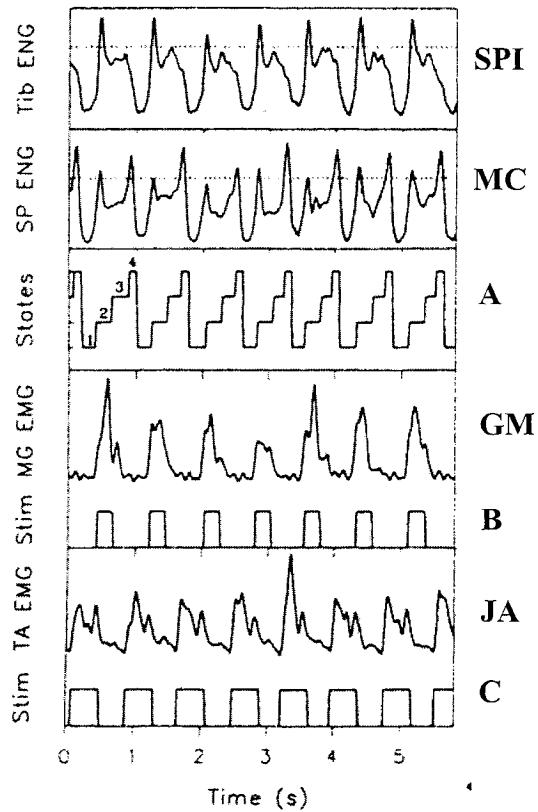

| Figure 1.6. On a attribué des niveaux de seuil (lignes en pointillé en SPI et MC) à l'amplitude des ENGs traités. À chaque fois que l'ENG de MC ou celui de SPI franchit le seuil, le système de stimulation passe à un nouvel état (1, 2, 3, ou 4 dans A). Durant l'état 2 (resp. 4), le circuit de stimulation du muscle GM (resp. JA) est activé pendant une période fixe (B, resp. C) égale à la durée moyenne des activités du GM (resp. JA) [45]. ..... | 21 |

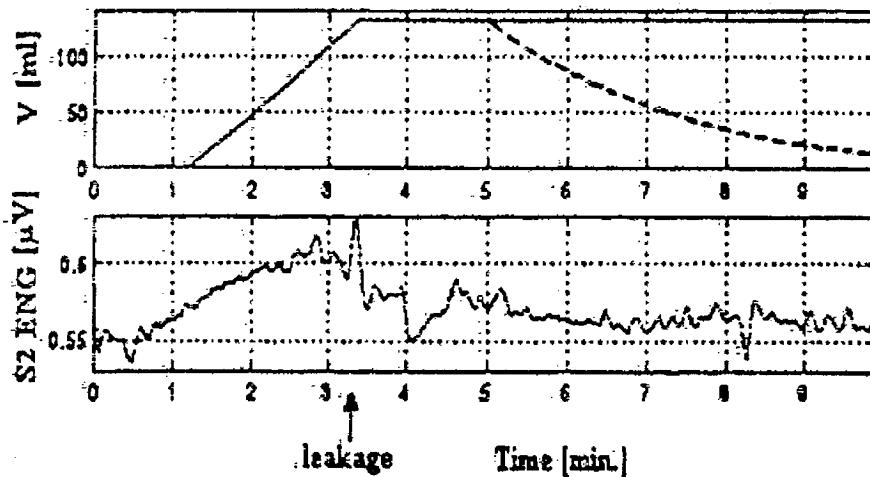

| Figure 1.7. Volume vésical et l'ENG traité du S2 pendant le remplissage et la vidange de la vessie [33]. .....                                                                                                                                                                                                                                                                                                                                                | 22 |

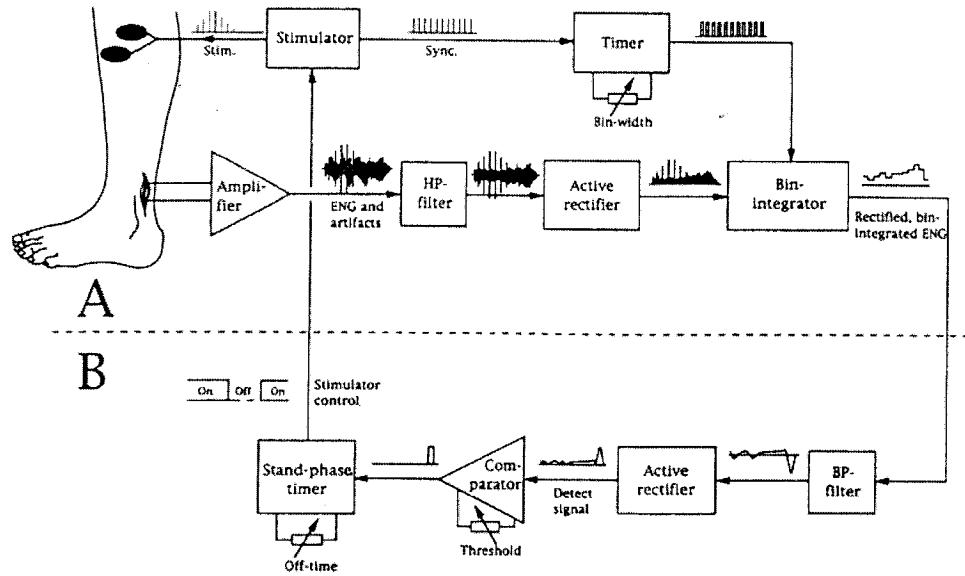

| Figure 1.8. Schéma d'ensemble de l'unité de correction du pied tombant. (A) Intégrateur par période et éliminateur d'artefacts, (B) Détecteur de pas et contrôleur de stimulation [26]. .....                                                                                                                                                                                                                                                                 | 24 |

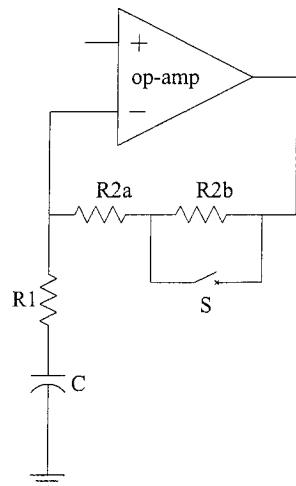

| Figure 1.9. Filtre passe-haut à gain variable. La capacité n'est pas intégrée sur la puce [42].....                                                                                                                                                                                                                                                                                                                                                           | 25 |

| Figure 1.10. Structure d'une vraie connexion tripolaire [43,48].....                                                                                                                                                                                                                                                                                                                                                                                          | 26 |

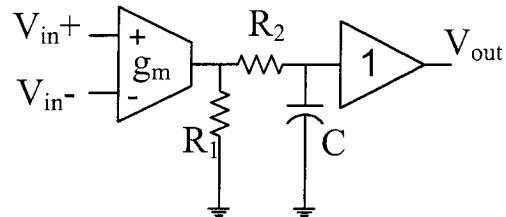

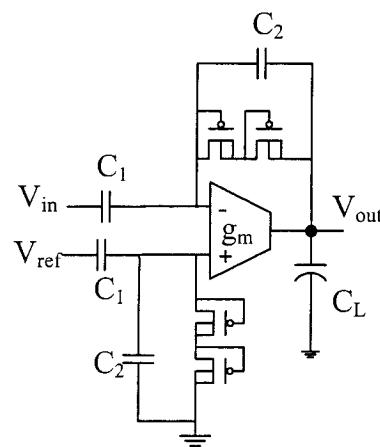

| Figure 1.11. Architecture de base du préamplificateur [48]. $R_1$ sert à établir le gain DC, $R_2$ et $C$ forment un filtre passe-bas et le suiveur est implémenté pour le test. Les performances de $g_m$ ont été vérifiées en CMOS et BiCMOS                                                                                                                                                                                                                |    |

|                                                                                                                                                                                                                                                                                                                                                                                         |    |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| (tableau 1.1). ....                                                                                                                                                                                                                                                                                                                                                                     | 27 |

| Figure 1.12. Schématique du bioamplificateur utilisant des pseudo-résistances proposé par Harrison et Charles. [24].....                                                                                                                                                                                                                                                                | 28 |

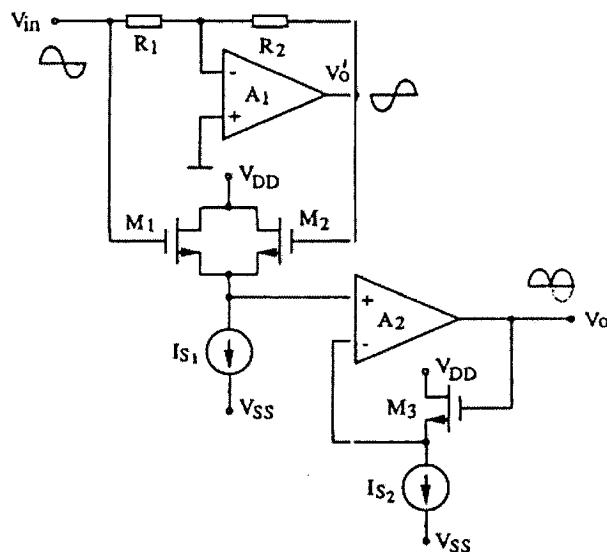

| Figure 1.13. La réalisation d'un redresseur avec la technique du suiveur de tension alternative. Dépendamment du signe de l'entrée Vin, l'un ou l'autre des transistors $M_1$ et $M_2$ conduit, amenant un signal toujours positif à l'entrée du suiveur. Le transistor $M_3$ et la source $I_{S2}$ servent à compenser la chute de tension grille-source de $M_1$ et $M_2$ [60]. ..... | 29 |

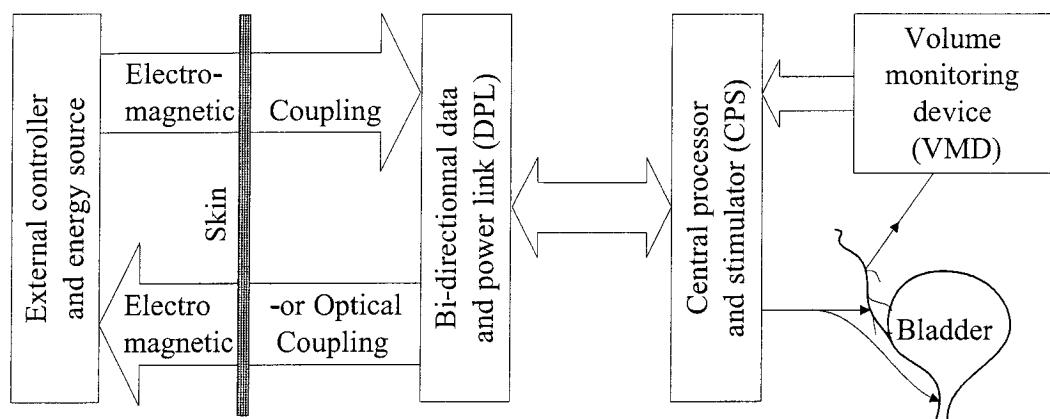

| Figure 2.1. A simplified block diagram of the global bladder controller.....                                                                                                                                                                                                                                                                                                            | 45 |

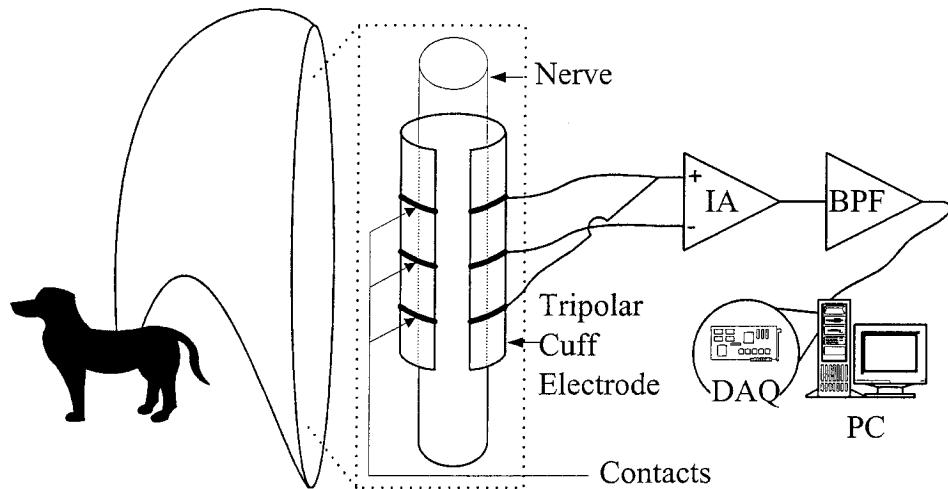

| Figure 2.2. The discrete nerve signal recording system: the tripolar electrode is cuffing the sacral nerve S2. The signal is amplified with IA and band-pass filtered before being stored on a PC to be processed off-line. .....                                                                                                                                                       | 47 |

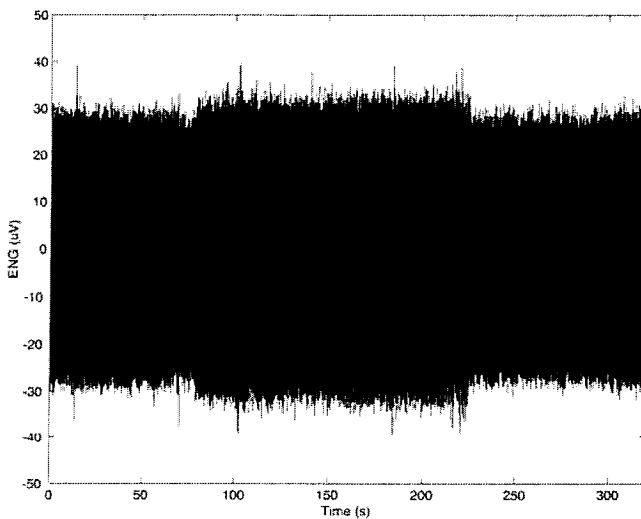

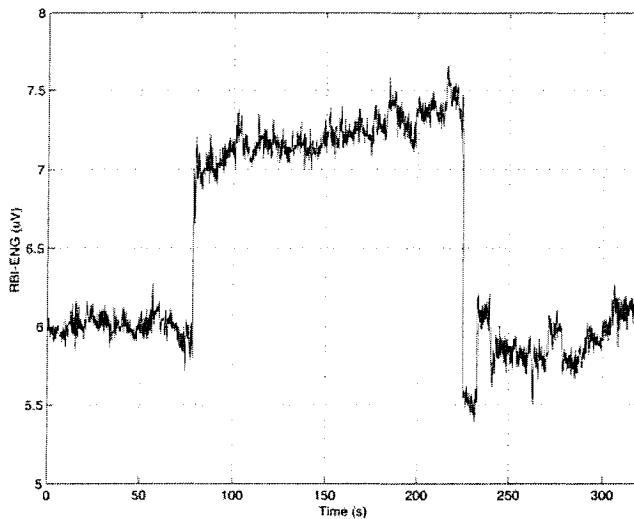

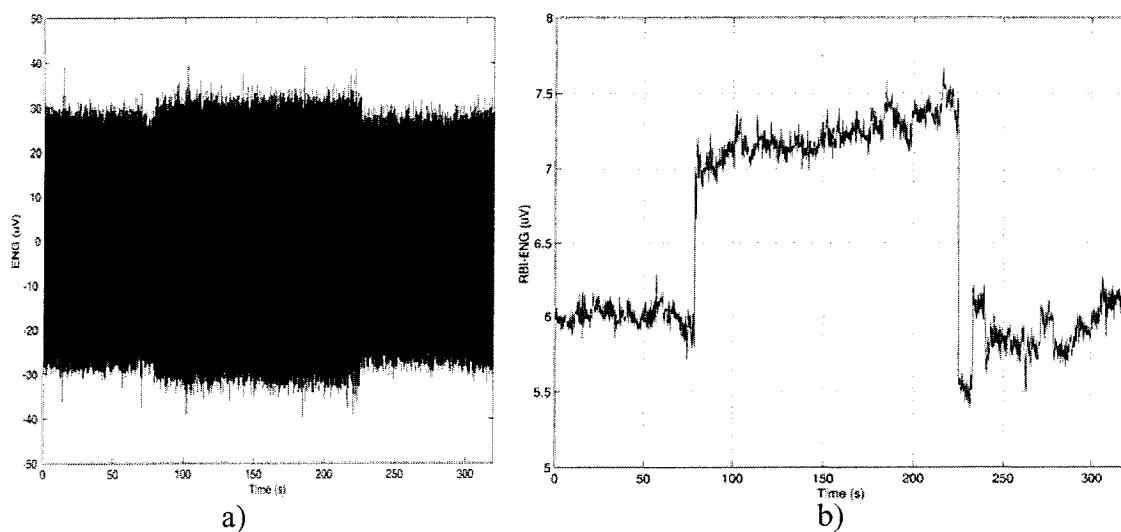

| Figure 2.3. Nerve signal activity increasing with time that is proportional to the volume of the bladder. ....                                                                                                                                                                                                                                                                          | 48 |

| Figure 2.4. Rectified and bin-integrated ENG vs. bladder filling with time.....                                                                                                                                                                                                                                                                                                         | 49 |

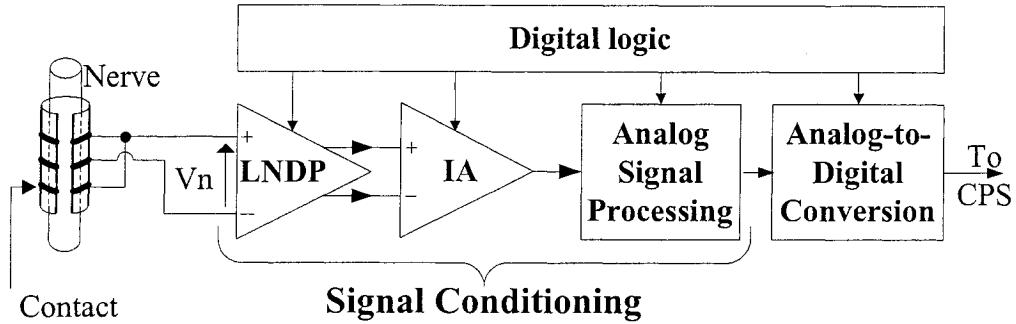

| Figure 2.5. Building blocks of the volume monitoring device.....                                                                                                                                                                                                                                                                                                                        | 50 |

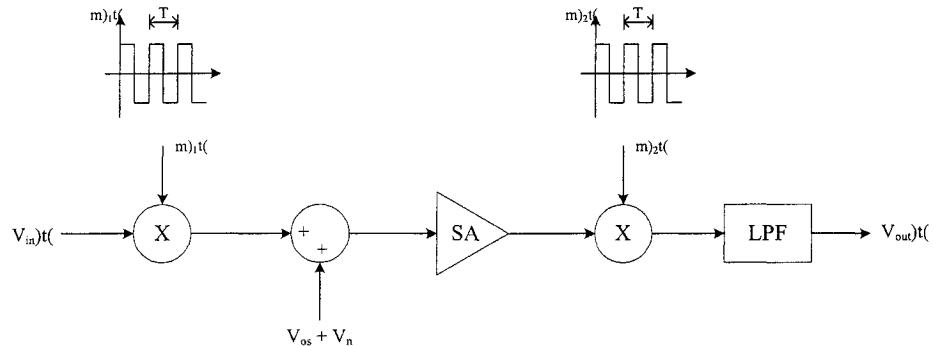

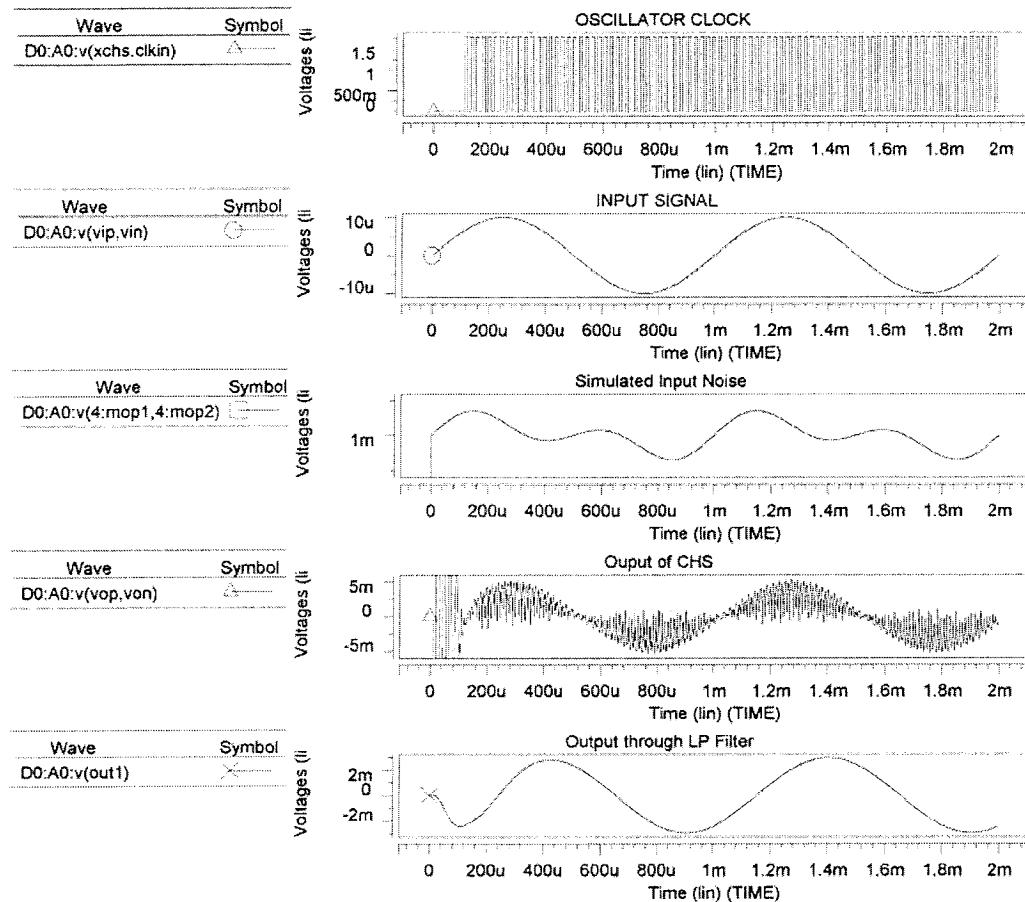

| Figure 2.6. The principle of Chopper Stabilization technique. ....                                                                                                                                                                                                                                                                                                                      | 52 |

|                                                                                                                                                                                                                                                                    |    |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

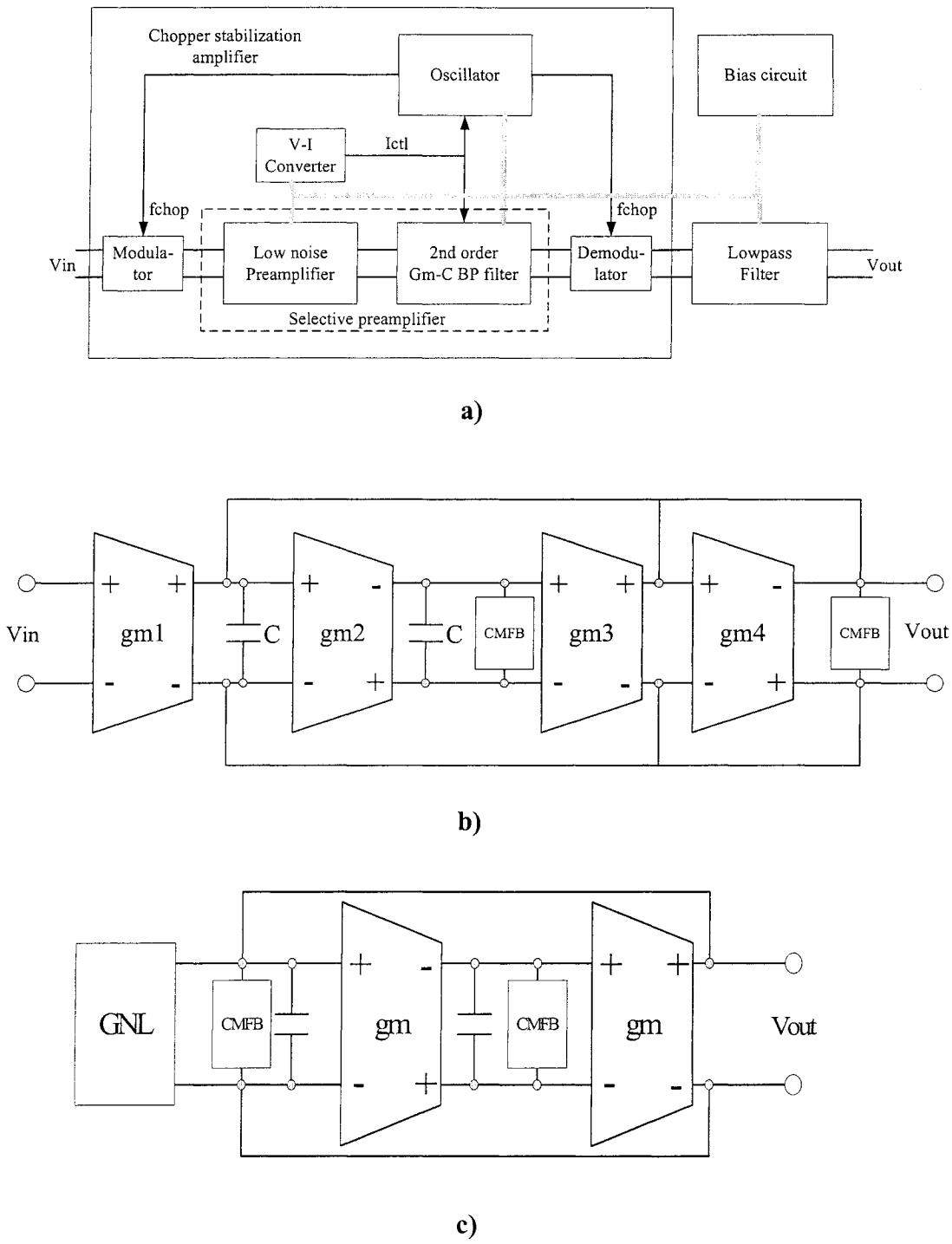

| Figure 2.7. The Low noise differential preamplifier: a) Simplified block diagram, b) and c) Preamplifier and band pass filter respectively that form the selective preamplifier.....                                                                               | 54 |

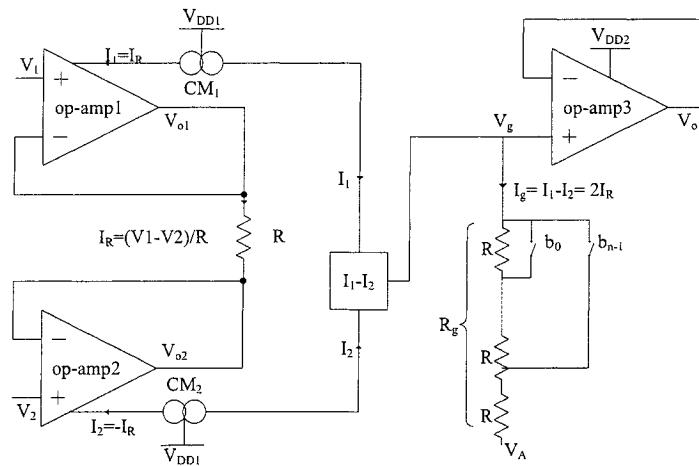

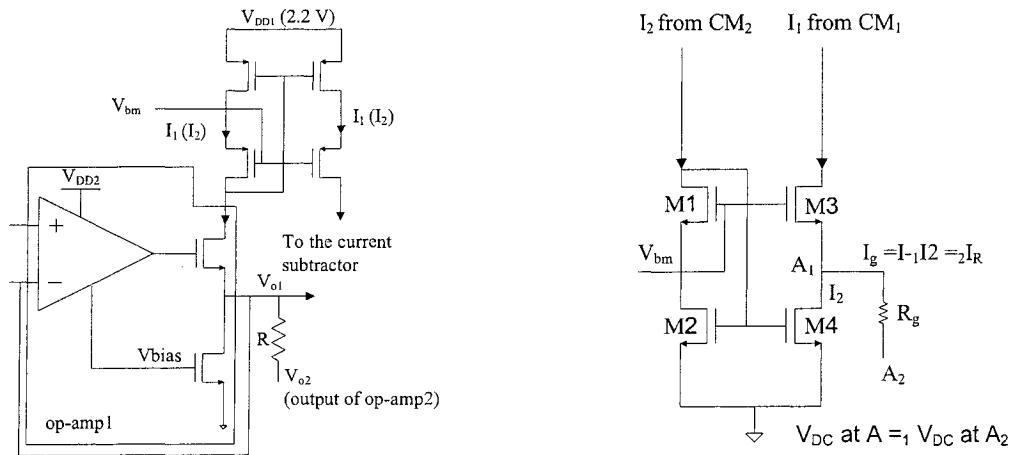

| Figure 2.8. The proposed instrumentation amplifier: a) Simplified block diagram, b) Simplified schematic of op-amp1 and op-amp2 with connection to the current mirror, c) Current subtractor.....                                                                  | 56 |

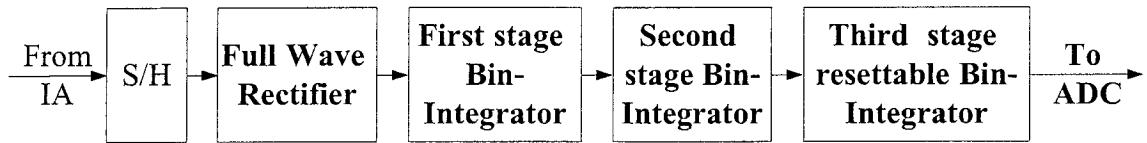

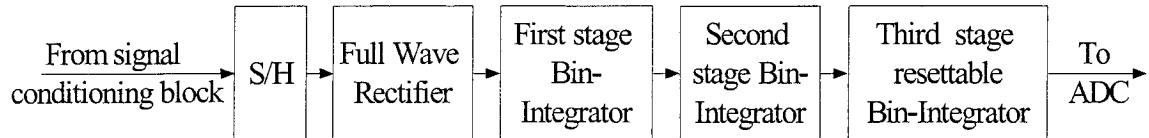

| Figure 2.9. Block-diagram of the analog signal processing unit.....                                                                                                                                                                                                | 58 |

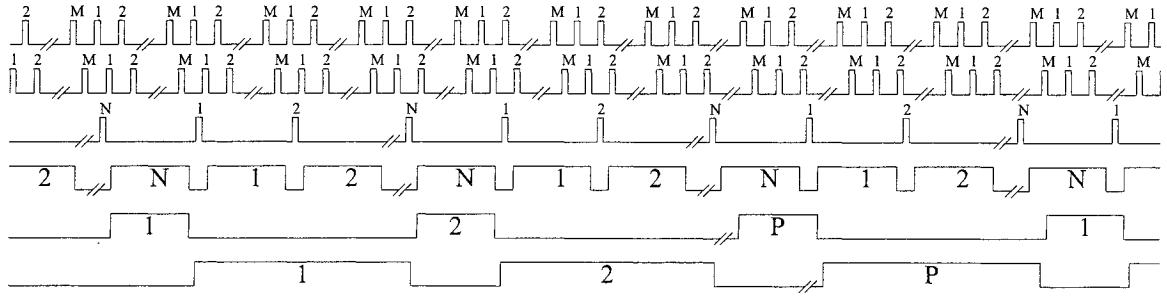

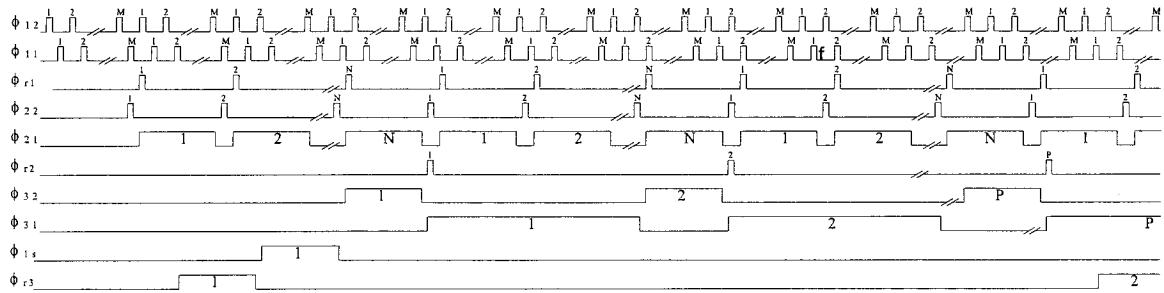

| Figure 2.10. Simplified clock phases that control the three integration stages. ( $\phi_{12}, \phi_{11}$ ), ( $\phi_{22}, \phi_{21}$ ), and ( $\phi_{32}, \phi_{31}$ ) are the non overlapping clocks for integration stages 1, 2 and 3 respectively.....          | 60 |

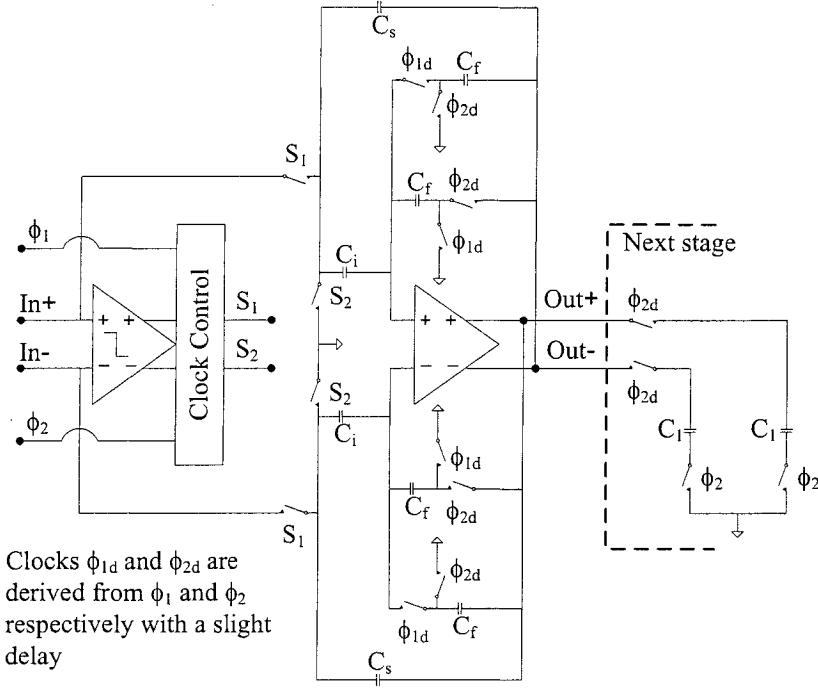

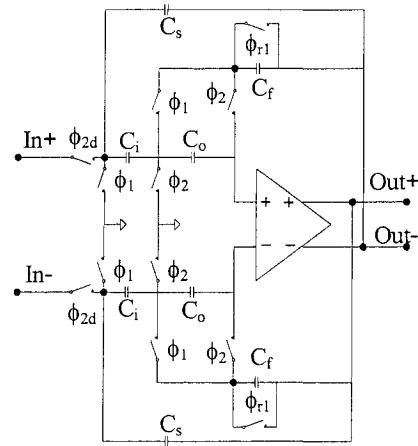

| Figure 2.11. Switched capacitor fully differential full wave rectifier. $\phi_1$ and $\phi_2$ are non-overlapping clock phases.....                                                                                                                                | 62 |

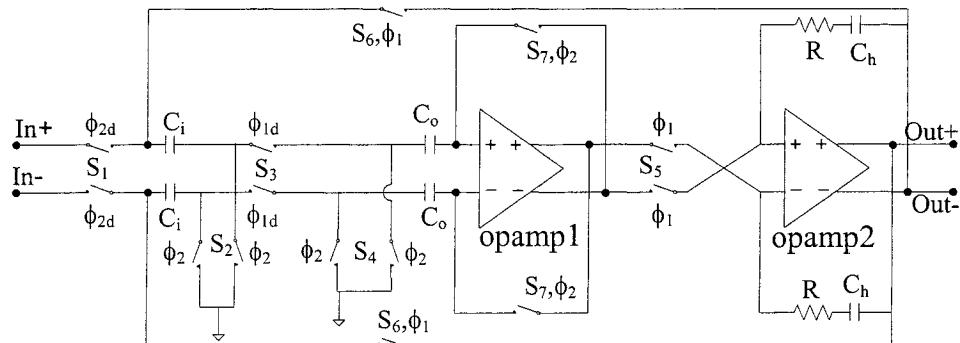

| Figure 2.12. Fully differential sample-and-hold circuit with always valid output.....                                                                                                                                                                              | 63 |

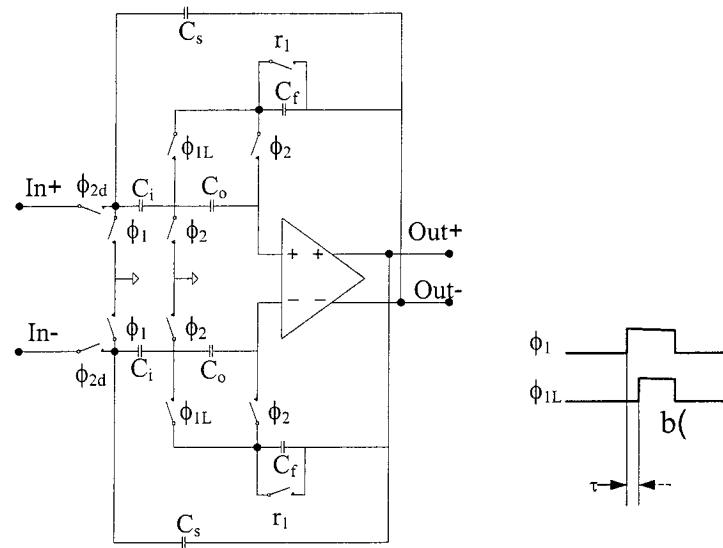

| Figure 2.13. Fully differential resettable integrator used in BIN integration stages 1 and 2. ....                                                                                                                                                                 | 65 |

| Figure 2.14. Third stage fully differential integrator with capability to be set at a fixed voltage $-2V_{ref}$ and its corresponding clock phases. The clock phases used in this circuit are derived from $\phi_{r3}, \phi_{1s}, \phi_{32}$ and $\phi_{31}$ ..... | 66 |

|                                                                                                                                                                                                                                       |    |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

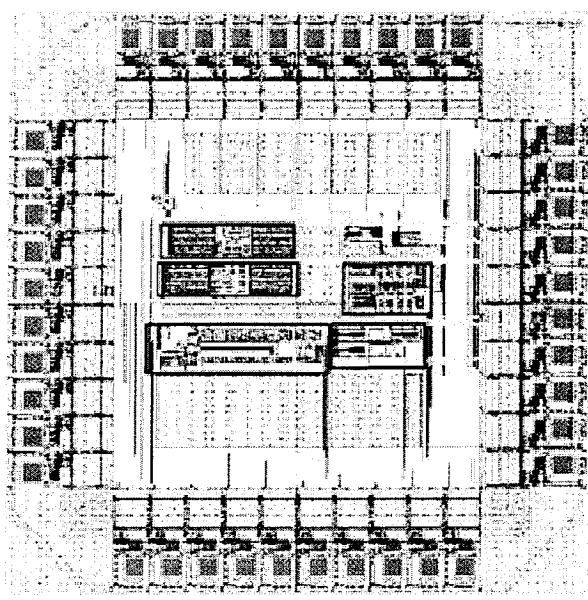

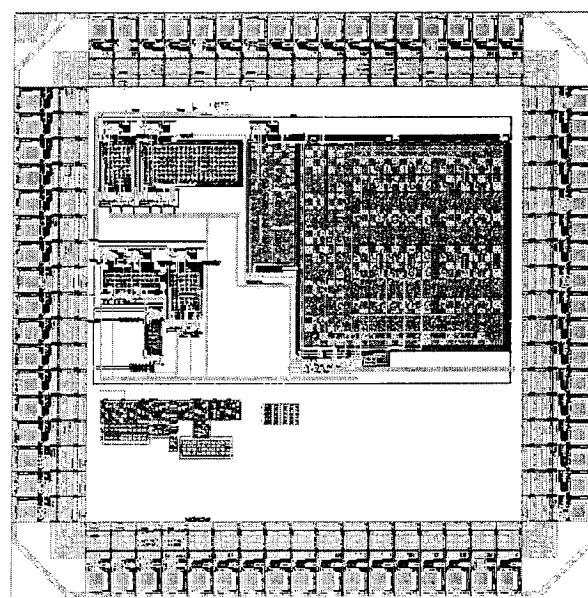

| Figure 2.15. Layout of the a) Low-noise differential preamplifier and the instrumentation amplifier and b) Analog signal processing block. ....                                                                                       | 67 |

| Figure 2.16. Noise performance of the preamplifier a) illustrated by the simulation, b) measurement of output noise. ....                                                                                                             | 69 |

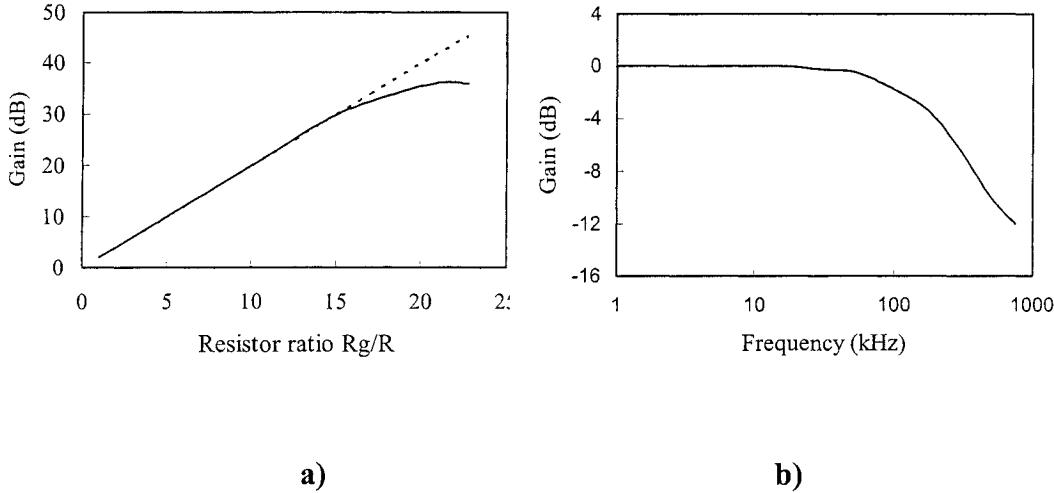

| Figure 2.17. The IA measurement results: a) Gain linearity versus resistor ratio (simulation: dotted line, measurement: solid line), b) Frequency response at gain=0 dB.....                                                          | 70 |

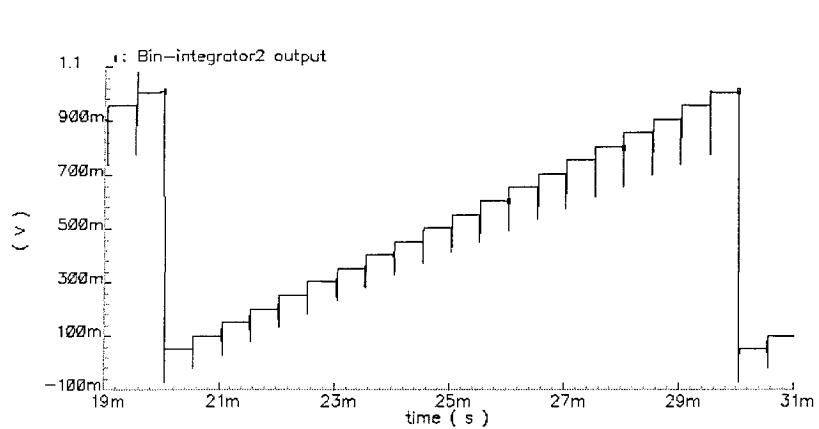

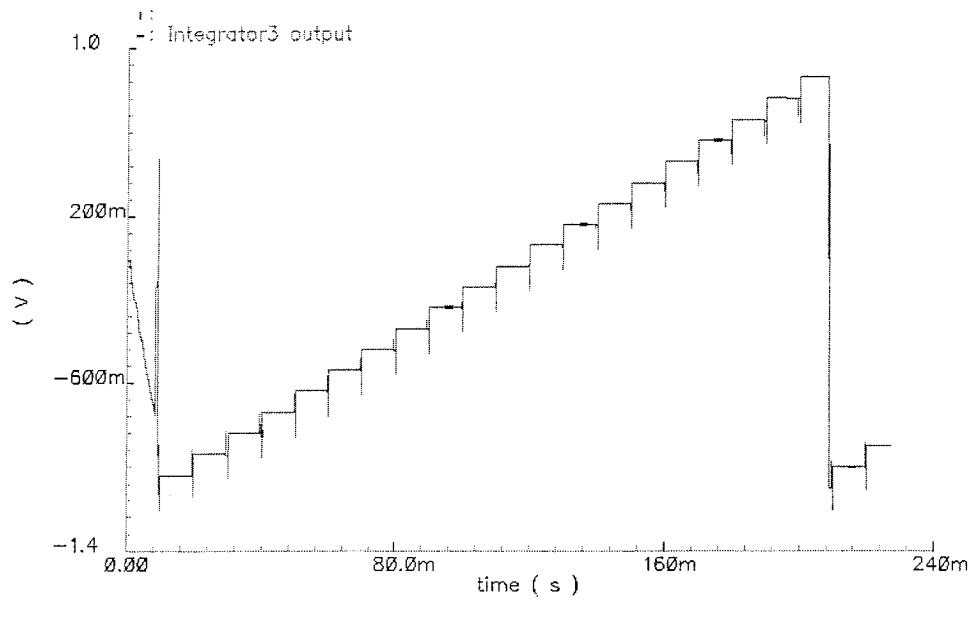

| Figure 2.18. Outputs of the a) first, b) second, and c) third integrator for M= N= P= 20, A=4, B= 8 and C= 10.....                                                                                                                    | 72 |

| Figure 3.1. Typical raw (a) and rectified and 200 ms bin-integrated (b) ENG from a dog sacral nerve (S2) as a function of its bladder volume. The bladder is filled linearly with time. ....                                          | 86 |

| Figure 3.2. The block-diagram of the rectifier and bin-integrator module. ....                                                                                                                                                        | 87 |

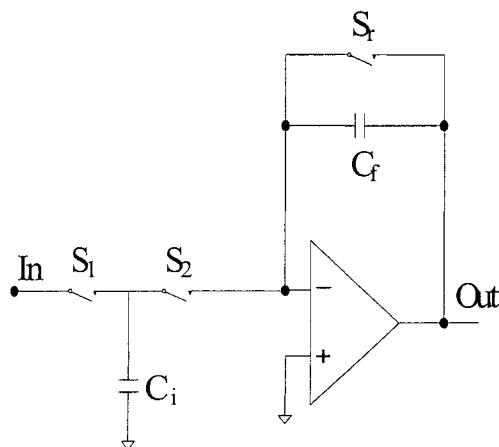

| Figure 3.3. Simplified schematic of a bin-integration stage. $S_r$ resets the output at a period equal to a bin. A gain of 1/8000 implies that $C_f/C_i = 8000$ which is difficult to implement. ....                                 | 88 |

| Figure 3.4. Simplified clock phases that control the three integration stages. $(\phi_{12}, \phi_{11}, \phi_{r1})$ , $(\phi_{22}, \phi_{21}, \phi_{r2})$ , and $(\phi_{32}, \phi_{31}, \phi_{r3})$ are the non overlapping clocks and |    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |    |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| reset signal for integration stage 1, 2 and 3 respectively. $\phi_{1s}$ together with $\phi_{r3}$ are used to reset stage 3 at $-2V_{ref}$ .....                                                                                                                                                                                                                                                                                                                                                                             | 90 |

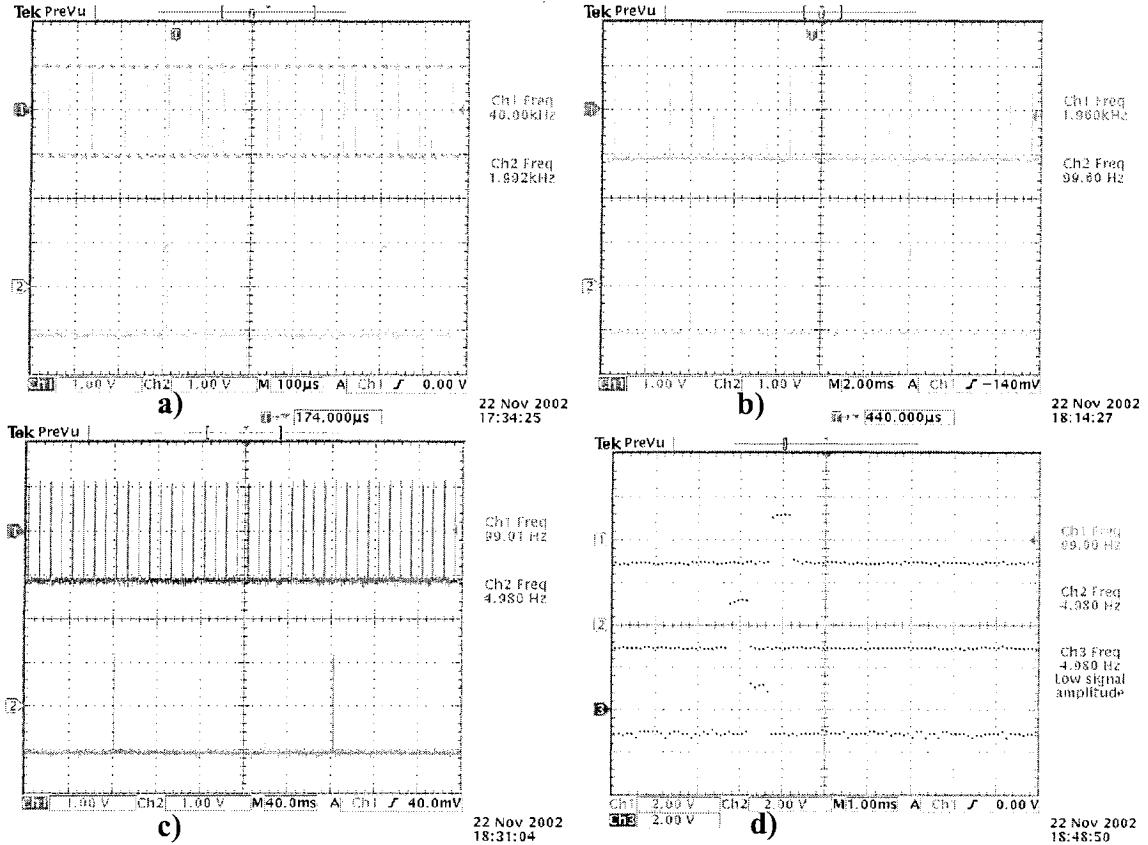

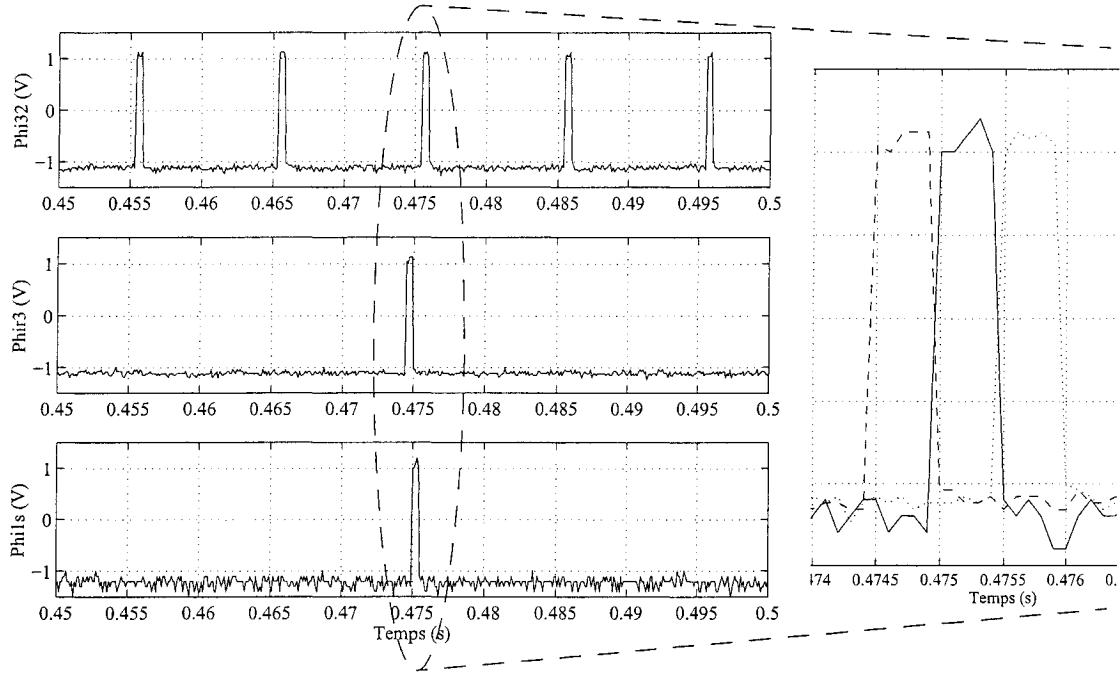

| Figure 3.5. Examples of the measured clock phases: a) The reset phase $\phi_{r1}$ (lower trace) of stage one synchronized with $\phi_{12}$ (upper trace), b) The reset phase $\phi_{r2}$ (lower trace) of stage two synchronized with $\phi_{22}$ (upper trace), c) The reset phase $\phi_{r3}$ (lower trace) of stage three synchronized with $\phi_{32}$ (upper trace), and d) The reset phase $\phi_{r3}$ pulse (middle trace) of stage three followed by $\phi_{1s}$ (lower trace) then $\phi_{32}$ (upper trace). ..... | 91 |

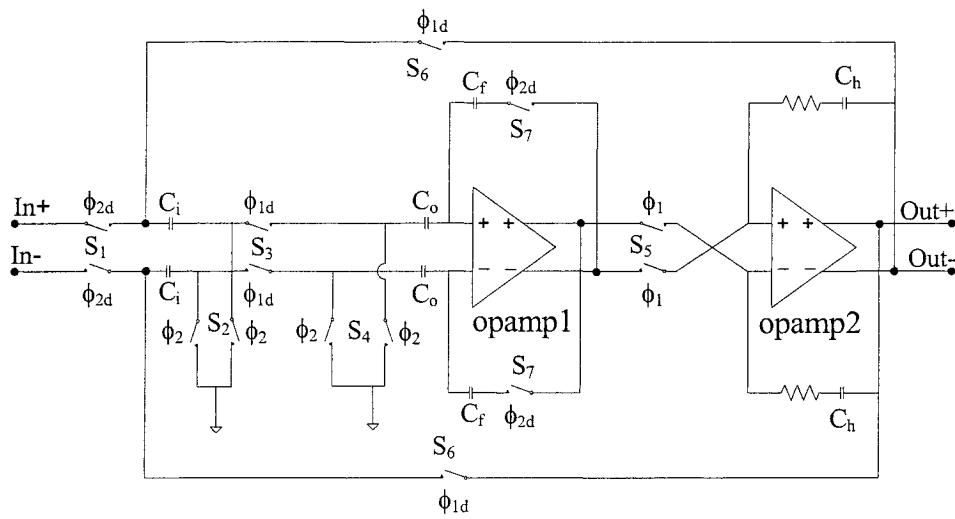

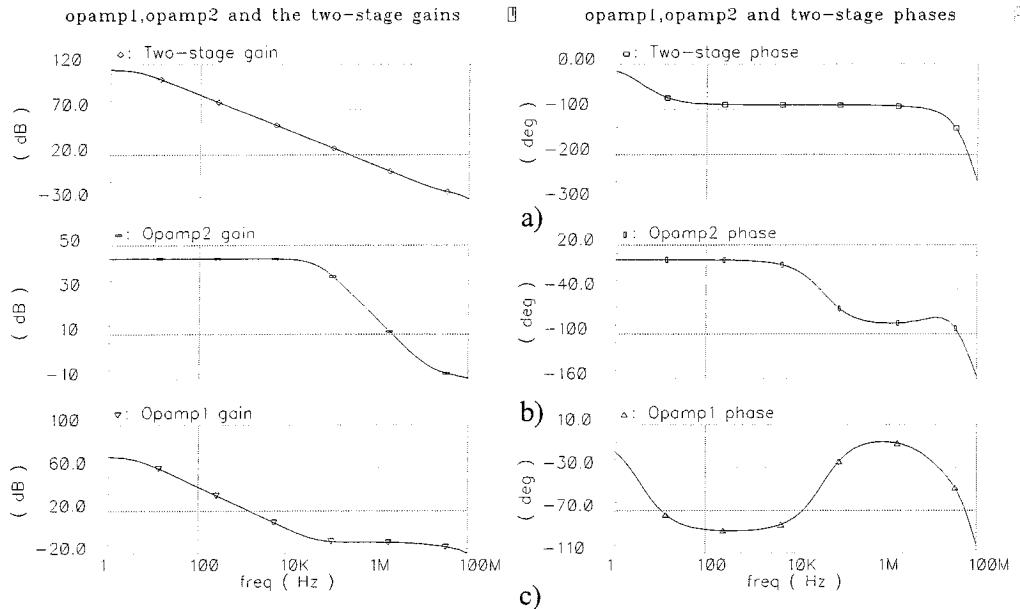

| Figure 3.6. Fully differential sample-and-hold circuit with always valid output. $C_i = C_o = 1 \text{ pF}$ , $C_h = 1.5 \text{ pF}$ and $R = 20 \text{ k}\Omega$ . .....                                                                                                                                                                                                                                                                                                                                                    | 93 |

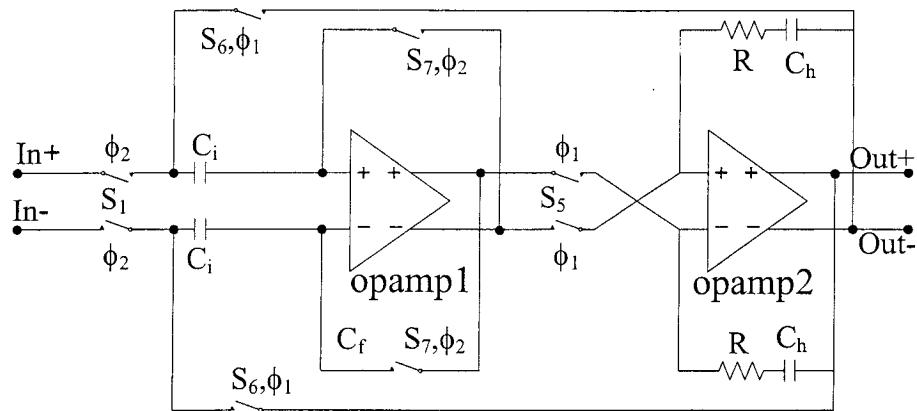

| Figure 3.7. Open loop gain (left) and phase (right) of the two-stage (a), opamp2 (b) and opamp1 (c) of the sample and hold block.....                                                                                                                                                                                                                                                                                                                                                                                        | 94 |

| Figure 3.8. The proposed fully differential sample-and-hold circuit with the usual technique for offset cancellation. .....                                                                                                                                                                                                                                                                                                                                                                                                  | 95 |

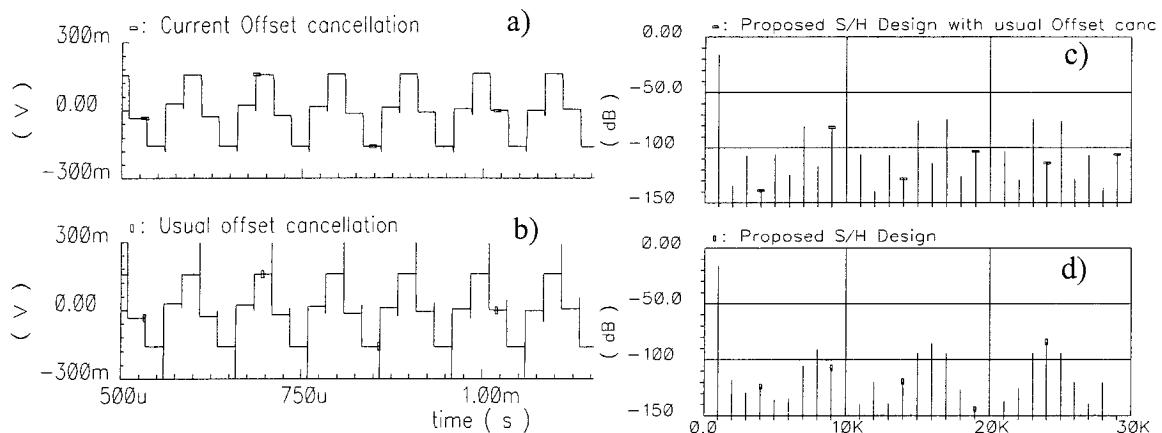

| Figure 3.9. Outputs of S/H: a) circuit of Figure 3.6 b) circuit of Figure 3.8. The proposed design is almost free of spikes. c) and d) are the DFT of a) and b) respectively. ....                                                                                                                                                                                                                                                                                                                                           | 95 |

| Figure 3.10. Fully differential resettable bin-integrator used in stages 1 and 2. Capacitors values in stage 1 (stage 2): $C_i = 1 \text{ pF}$ ( $4 \text{ pF}$ ), $C_o = 1 \text{ pF}$ ( $1 \text{ pF}$ ), $C_f = 4 \text{ pF}$                                                                                                                                                                                                                                                                                             |    |

|              |    |

|--------------|----|

| (32 pF)..... | 96 |

|--------------|----|

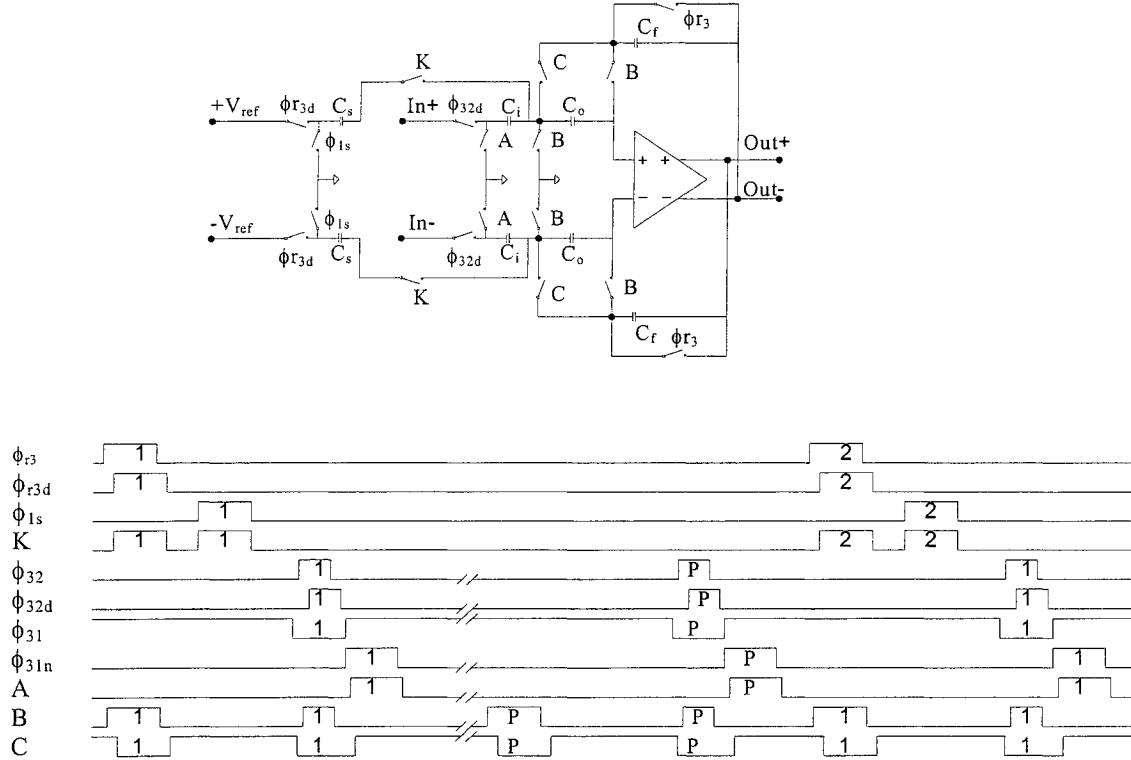

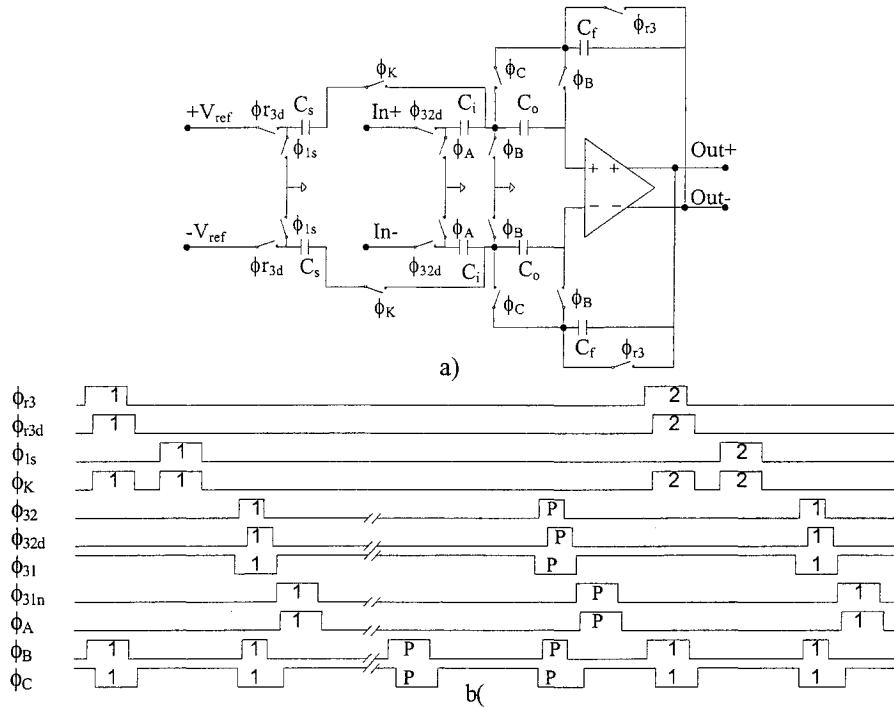

Figure 3.11. Third stage fully differential bin-integrator with capability to be set at a constant voltage  $-2 V_{ref}$  (a) and its corresponding clock phases (b). The clock phases used in this circuit derive from  $\phi_{r3}$ ,  $\phi_{1s}$ ,  $\phi_{32}$ , and  $\phi_{31}$ . Capacitors values:  $C_s = 150 \text{ pF}$ ,  $C_i = 30 \text{ pF}$ ,  $C_1 = 1 \text{ pF}$ ,  $C_f = 300 \text{ pF}$ .....97

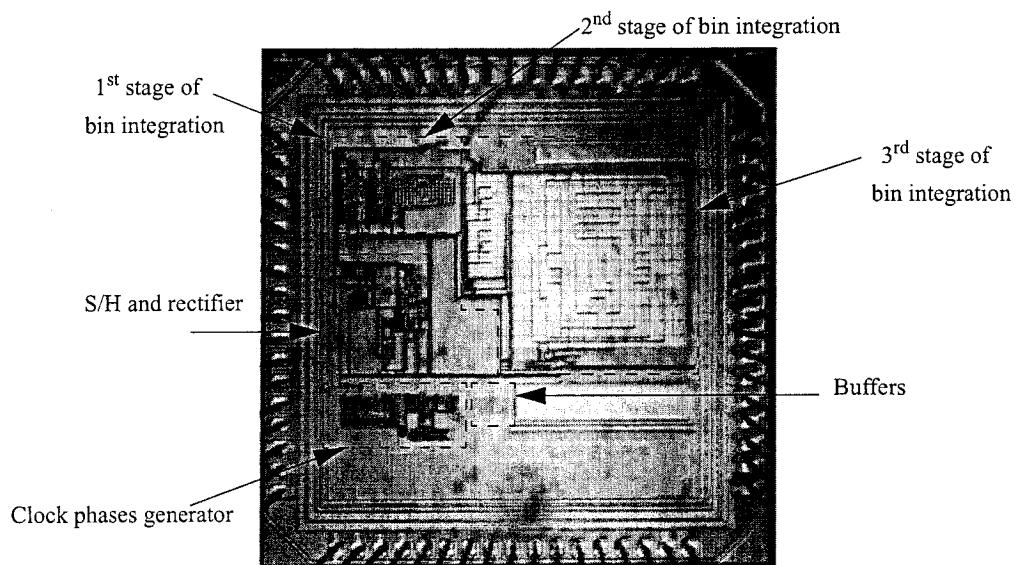

Figure 3.12. Microphotograph of the RBI module implemented with CMOS 0.35  $\mu\text{m}$ . Die area is  $2650 \times 2200 \mu\text{m}^2$ .....99

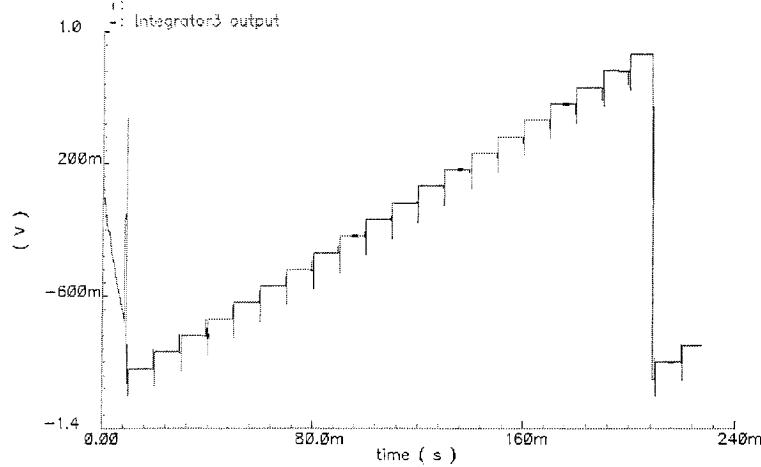

Figure 3.13. Output of the third stage of the bin-integrator. Simulation performed with  $M = N = P = 20$ ,  $A = 4$ ,  $B = 8$ ,  $C = 10$ , and DC input = 80 mV. The random output at the begining is due to the fact that the third stage doesn't receive any clock or input signal before 10 ms.....100

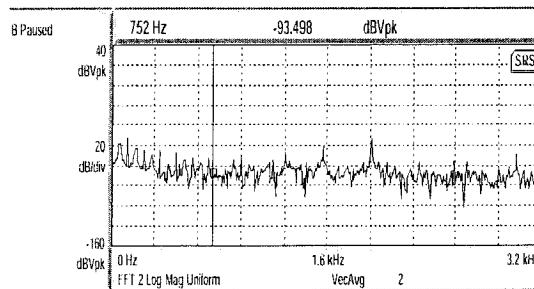

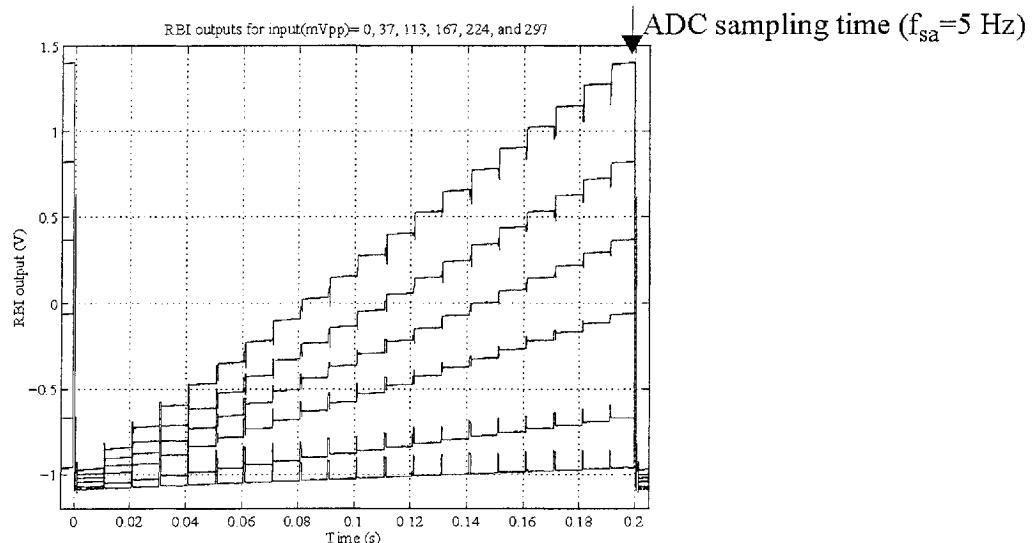

Figure 3.14. RBI result as measured at the output of the third bin-integration stage. From the lowest trace to the highest one, the sinewave input amplitude varies from  $0 \text{ V}_{pp}$  (offset) to  $297 \text{ mV}_{pp}$  respectively. Each increment represents the average of the subsequent MN input samples. The last step (the maximum value) that is the average of MNP samples ( $P=20$ ) is to be sampled and converted by the ADC. ....101

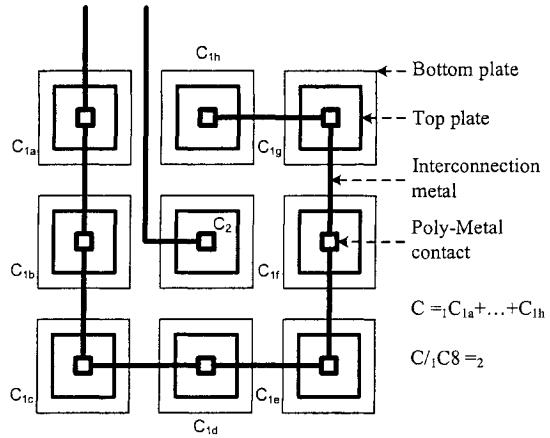

Figure 3.15. The parasitic capacitance between the interconnect metal and the bottom plate increases with the number of units of  $C1$ .....103

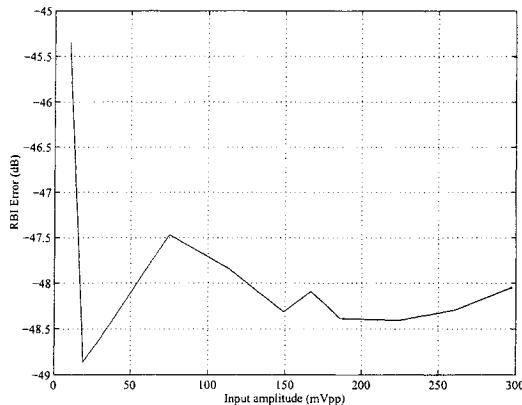

- Figure 3.16. RBI error vs. input: The error is computed as the difference between the measured RBI minus the offset and the ideal calculated value using Matlab.

An example of capacitance matching with ratio= 8. ....103

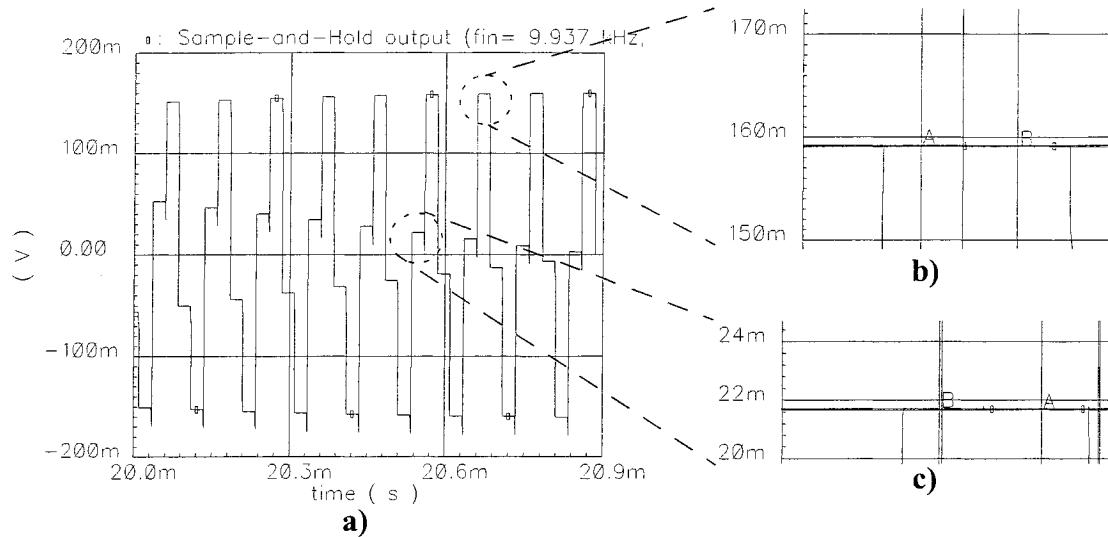

- Figure 4.1. (a) la sortie temporelle de l'échantillonneur-bloqueur pour une entrée sinusoïdale d'une fréquence de 9.937 kHz et d'amplitude de 180 mV<sub>pp</sub>. (b) et (c): Un zoom autour d'une valeur élevée (b) et faible (c) de l'entrée. Les marqueurs A et B sont placés à l'endroit des deux phases de fonctionnement du bloc: mise à jour de la sortie et échantillonnage de l'entrée. L'erreur pour les faibles amplitudes d'entrée est de 0.069%; celle pour les amplitudes élevées est de 0.009%. .....110

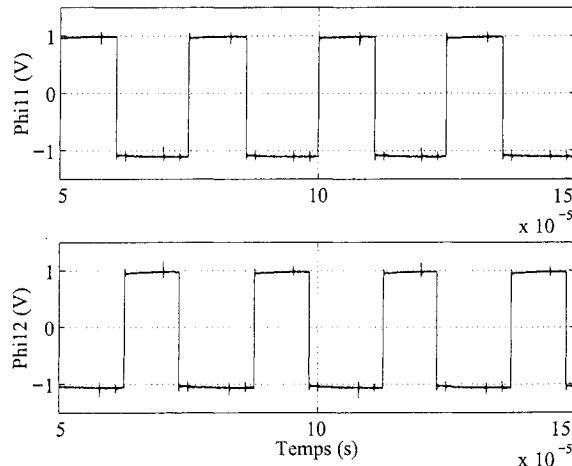

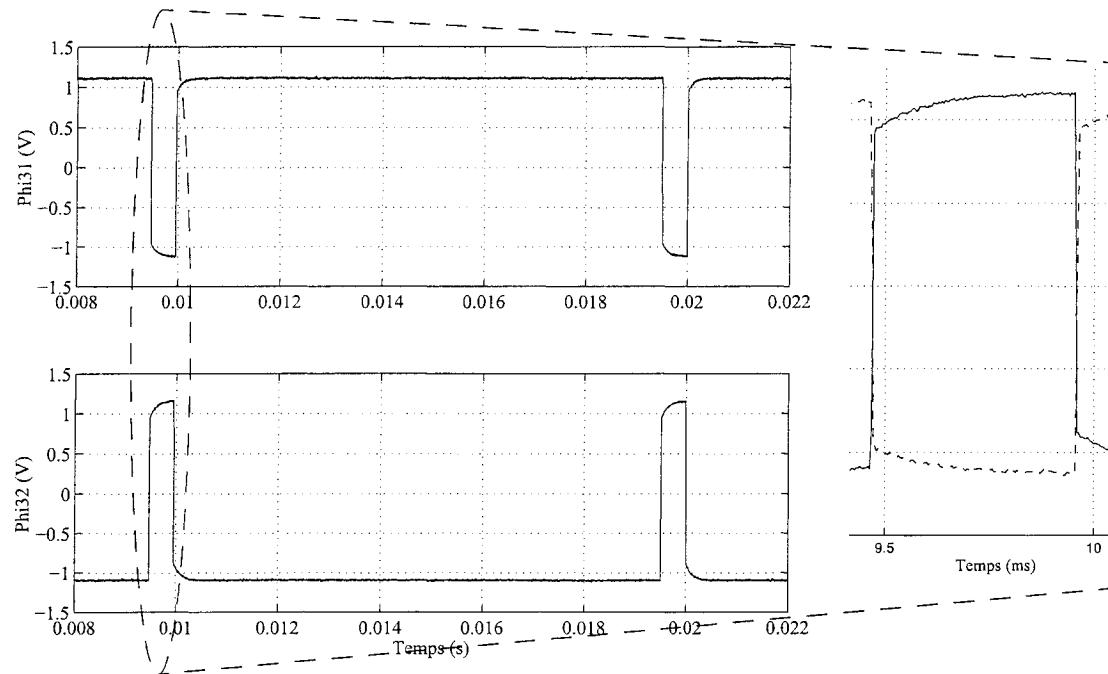

- Figure 4.2. Les deux phases non chevauchées du premier étage d'intégration par période  $\phi_{11}, \phi_{12}$ . La fréquence est de 40 kHz. ....111

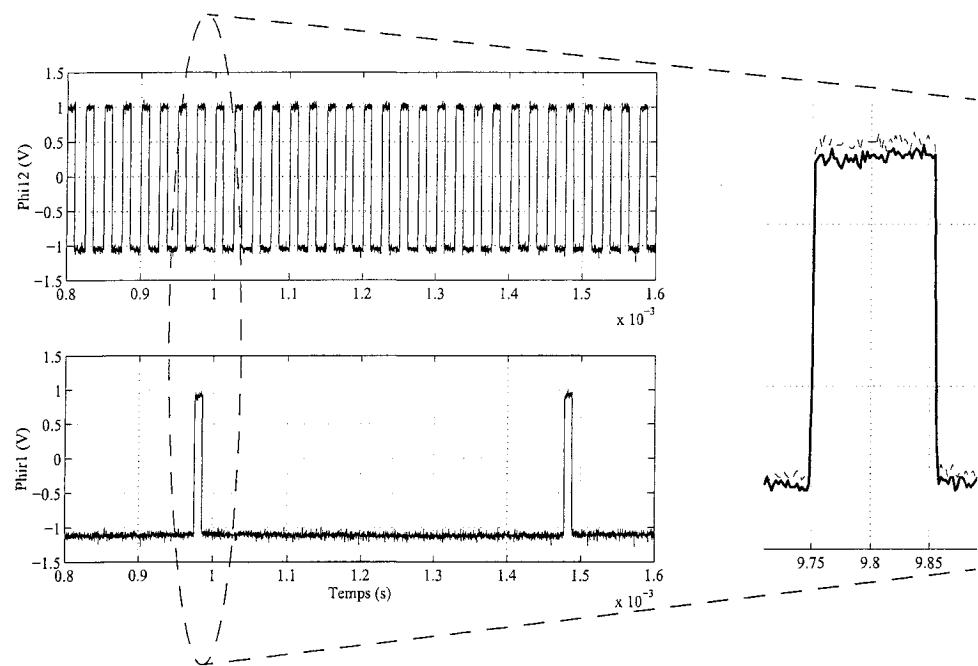

- Figure 4.3. L'horloge d'initialisation ( $\phi_{r1}$ ) du premier étage d'intégration par période. Elle est synchronisée avec  $\phi_{12}$  (le zoom à droite où la ligne pointillée=  $\phi_{12}$  et la ligne continue=  $\phi_{r1}$ ) pour assurer que l'initialisation de la sortie se fait après chaque 20 échantillons d'entrée (gauche) pendant le chargement des capacités d'entrée. La fréquence de  $\phi_{r1}$  est de 40 kHz/20= 2 kHz. ....112

- Figure 4.4. Les deux phases non chevauchées du deuxième étage d'intégration par période  $\phi_{21}, \phi_{22}$ . La fréquence est de 2 kHz (gauche). Le zoom à droite montre le non-chevauchement des deux phases (ligne pointillée=  $\phi_{22}$  et ligne

continue=  $\phi_{21}$ ). La phase  $\phi_{22}$  est la phase pendant laquelle le circuit échantillonne l'entrée et la phase  $\phi_{21}$  est la phase pendant laquelle le circuit transmet les charges échantillonnées aux capacités de sortie (capacités de rétroaction).....113

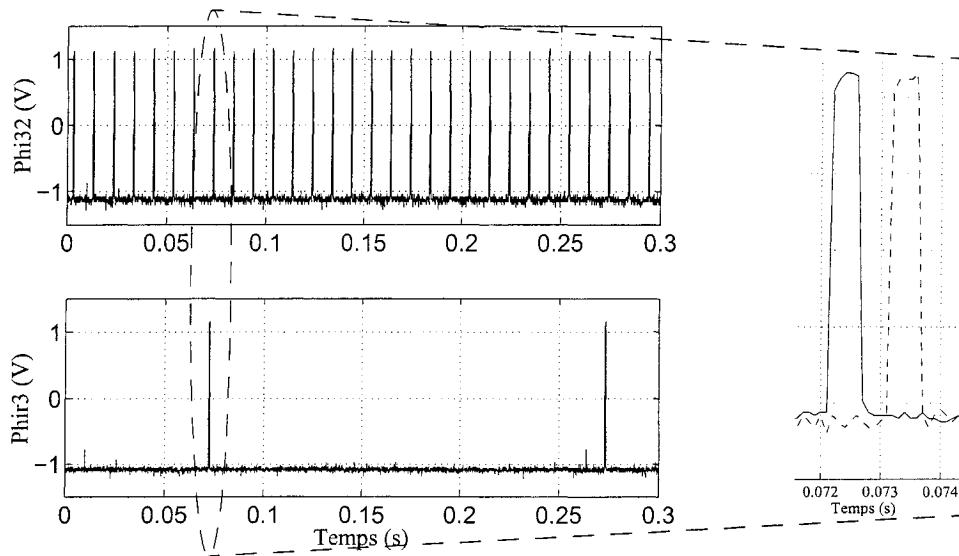

Figure 4.5. L'horloge d'initialisation ( $\phi_{r2}$ ) du deuxième étage d'intégration par période. Elle est synchronisée avec  $\phi_{22}$  (le zoom à droite où graphe du haut=  $\phi_{22}$  et graphe du bas=  $\phi_{r2}$ ) pour assurer que l'initialisation se fait après chaque 20 échantillons d'entrée de l'étage (gauche) pendant le chargement des capacités d'entrée. La fréquence de  $\phi_{r2}$  est de 100 Hz. ....114

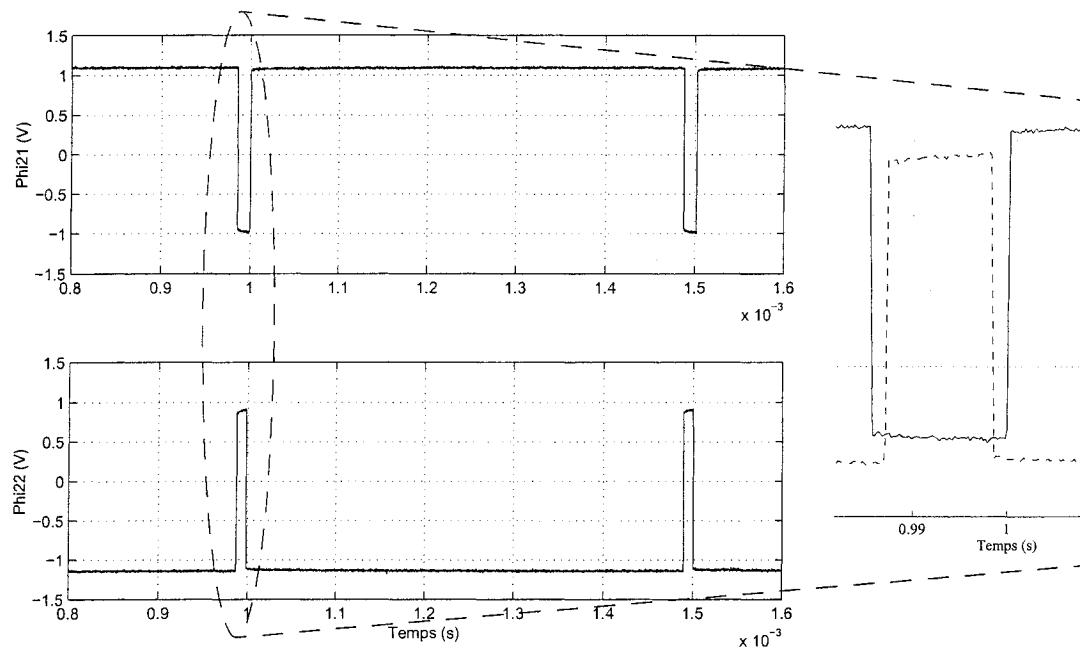

Figure 4.6. Les deux phases non chevauchées du troisième étage d'intégration par période  $\phi_{31}, \phi_{32}$ . La fréquence est de 100 Hz (gauche). Le zoom à droite montre le non-chevauchement des deux phases (ligne pointillée=  $\phi_{32}$  et ligne continue=  $\phi_{31}$ ). La phase  $\phi_{32}$  est la phase pendant laquelle le circuit échantillonne l'entrée et la phase  $\phi_{31}$  est la phase pendant laquelle le circuit transmet les charges échantillonnées aux capacités de sortie (capacités de rétroaction). ....115

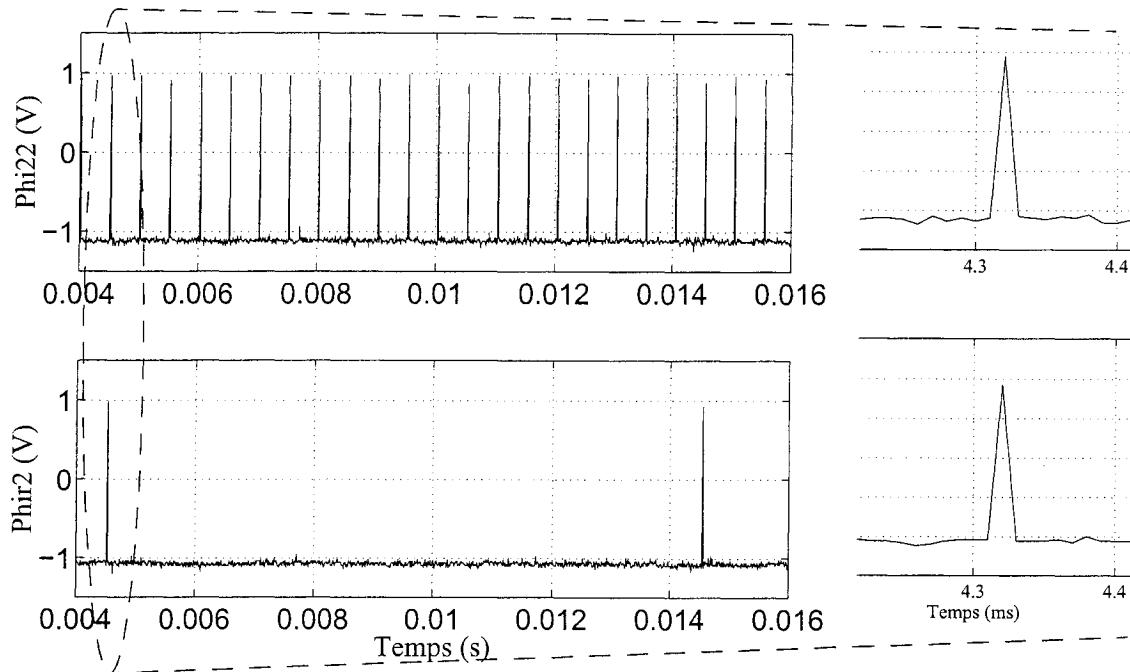

Figure 4.7. L'horloge d'initialisation ( $\phi_{r3}$ ) du troisième étage d'intégration par période. Elle est synchronisée avec  $\phi_{32}$  (le zoom à droite où ligne continue=  $\phi_{r3}$  et ligne pointillée=  $\phi_{32}$ ) pour assurer que l'initialisation se fait après chaque 20 échantillons d'entrée de l'étage (gauche) pendant le chargement des capac-

ités d'entrée. Les détails de fonctionnement se trouvent dans la figure suivante. La fréquence de  $\phi_{r3}$  est de 5 Hz. ....116

Figure 4.8. Les horloges d'initialisation ( $\phi_{r3}$  et  $\phi_{1s}$ ) du troisième étage d'intégration par période. Pendant  $\phi_{r3}$  les capacités d'entrée d'initialisation ( $C_s$  dans la figure 3.11) sont chargées à  $\pm V_{ref}$  et en même temps les capacités de sortie sont déchargées. Ensuite et pendant  $\phi_{1s}$ , ces dernières sont chargées à  $\pm V_{ref}$ . L'intégration par période commence avec la première pulse de  $\phi_{32}$  suivant  $\phi_{1s}$ . La séquence de ces trois impulsions est mise en évidence dans le zoom à droite. ....117

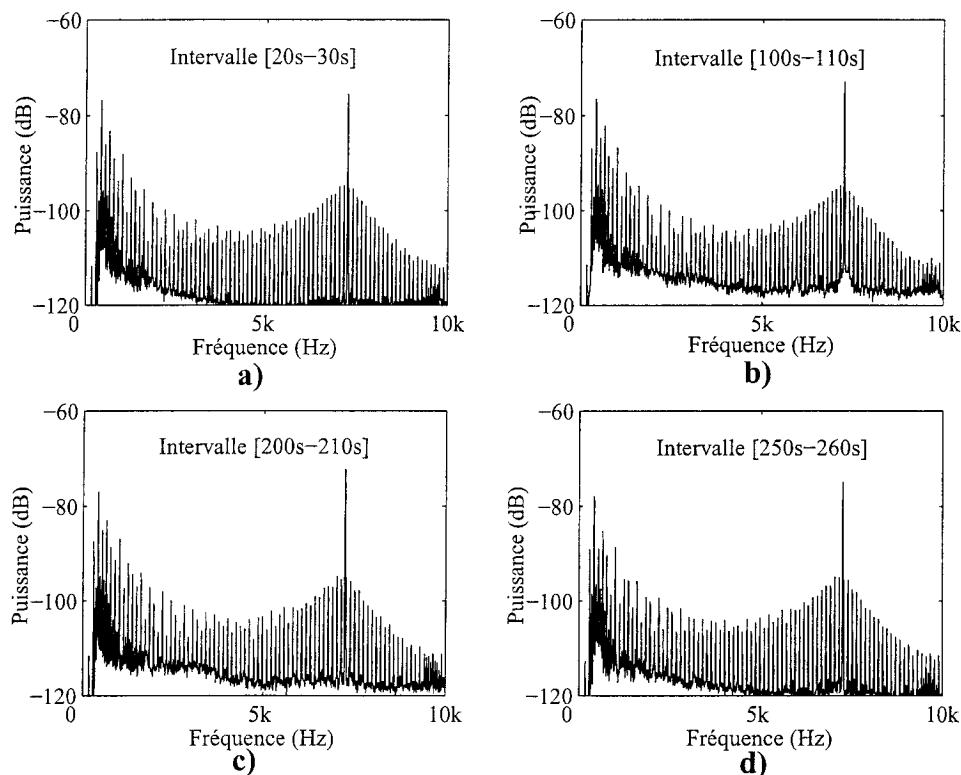

Figure 4.9. Contenu fréquentiel de l'ENG à différents moments ([20s- 30s]: (a), [100s- 110s]: (b), [200s- 210s]: (c), et [250s- 260s]: (d)) pendant le remplissage de la vessie qui a duré 320 s. Les composantes fréquentielles demeurent inchangées durant la variation du volume de la vessie ce qui montre que la fréquence de l'ENG ne peut pas être utilisée comme indicateur du volume. Paramètres de l'analyse spectrale: fréquence d'échantillonnage= 30 kHz, nombre de points= 10 s/(1/30 kHz)= 300000, fenêtre de Hanning. ....118

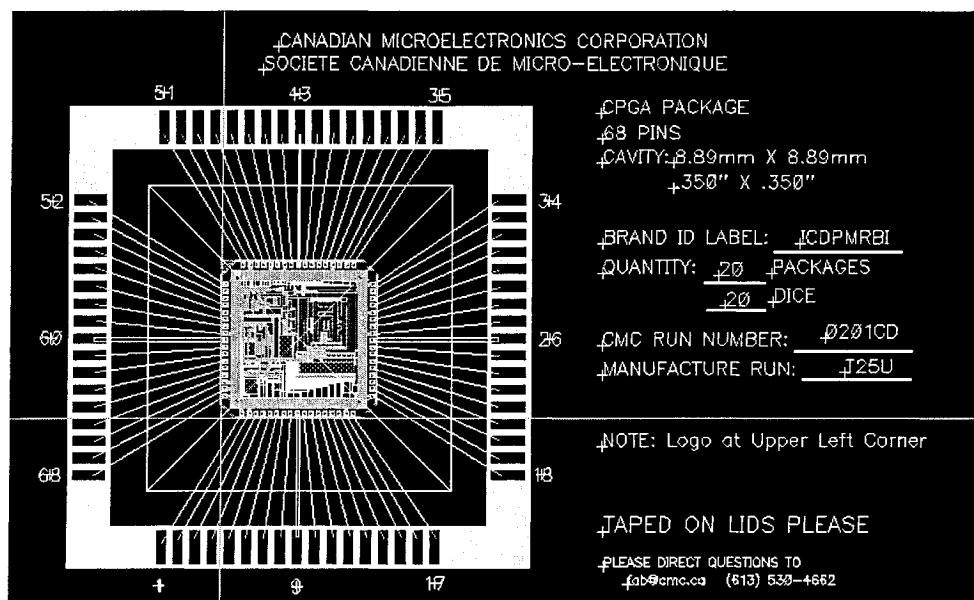

Figure A.1. Le diagramme de connexion du circuit aux broches du boîtier PGA68..135

## LISTE DES TABLEAUX

|                                                                                                                                                                |       |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| Tableau L.1. Liste des abréviations.....                                                                                                                       | xxvii |

| Tableau L.2. Terminologie médicale .....                                                                                                                       | xxvii |

| Tableau 1.1. Performances des trois variétés d'AOTs [48].....                                                                                                  | 27    |

| Tableau 2.1. LNDP, IA, and ASP performance .....                                                                                                               | 73    |

| Tableau 3.1. RBI circuit performance: simulated and measured results. The integrated circuit is designed and fabricated in 3.3 V CMOS 0.35 $\mu$ m technology. | 104   |

| Tableau 4.1. Paramètres mesurés des dix puces .....                                                                                                            | 119   |

| Tableau A.1. Description des signaux du circuit de test .....                                                                                                  | 136   |

## LEXIQUE

**Tableau L.1. Liste des abréviations**

| Français | Anglais | Description                                          |

|----------|---------|------------------------------------------------------|

| AI       | IA      | Amplificateur d'Instrumentation                      |

| AOT      | OTA     | Amplificateur Opérationnel à Transconductance        |

| CAN      | ADC     | Convertisseur Analogique-Numérique                   |

| ENG-RIP  | RBI-ENG | l'ÉlectroNeuroGramme Redressé et intégré par période |

| PDFB     | LNDP    | Préamplificateur Différentiel à Faible Bruit         |

| PSN      | DSP     | Processeur de Signal Numérique*                      |

| RIP      | RBI     | Redressé et Intégré par Période                      |

\* [www.ofl.gouv.qc.ca](http://www.ofl.gouv.qc.ca)

**Tableau L.2. Terminologie médicale**

| Français<br>(Anglais)                                  | Abr. | Description                                                                                                              |

|--------------------------------------------------------|------|--------------------------------------------------------------------------------------------------------------------------|

| Afférente (fibre nerveuse)<br>(Afferent nervous fibre) |      | Les fibres nerveuses afférentes reliées au récepteur stimulé, conduisent des messages vers le centre nerveux du réflexe. |

| Crochet<br>(Hook)                                      | -    | Un instrument ayant 2 ou 3 terminaux en forme de U et utilisé pour saisir et exposer le nerf.                            |

**Tableau L.2. Terminologie médicale**

| <b>Français<br/>(Anglais)</b>                               | <b>Abr.</b> | <b>Description</b>                                                                                                           |

|-------------------------------------------------------------|-------------|------------------------------------------------------------------------------------------------------------------------------|

| Cunéiforme<br>(Cuneiform)                                   | -           | Trois des os qui forment le tarse                                                                                            |

| Efférente (fibre nerveuse)<br>(Efferent nervous fibre)      |             | Les fibres efférentes conduisent les messages efférents par la racine ventrale du nerf rachidien aux effecteurs musculaires. |

| Électrocardiogramme<br>(Electrocardiogram)                  | ECG         | Représentation graphique des signaux électriques émis par le cœur en fonction du temps.                                      |

| Électromyogramme<br>(Electromyogram)                        | EMG         | Représentation graphique des signaux électriques qui accompagnent l'activité musculaire en fonction du temps.                |

| Électroneurogramme<br>(Electroneurogram)                    | ENG         | Représentation graphique des signaux électriques qui accompagnent l'activité neurale en fonction du temps.                   |

| Enregistrement continu<br>(Chronic recording)               | -           | Enregistrement d'une longue durée (plusieurs minutes) du signal nerveux ENG.                                                 |

| Extenseurs<br>(Extensor)                                    | -           | Muscle qui étend un membre du corps.                                                                                         |

| Fléchisseurs<br>(Flexor)                                    | -           | Muscle qui met en flexion un membre du corps.                                                                                |

| Muscle Gastrocnémien<br>Médial<br>(Medial Gastrocnemius MG) | GM          | Muscle extenseur de la cheville.                                                                                             |

**Tableau L.2. Terminologie médicale**

| Français<br>(Anglais)                                                       | Abr. | Description                                                                                                                                                                                                                                                                                                                          |

|-----------------------------------------------------------------------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Muscle Jambier Antérieur ou fléchisseur de la cheville (Tibial Anterior TA) | JA   | Muscle de la loge antérieure de la jambe, tendu du tibia au premier cunéiforme et au premier métatarsien. Il est releveur du pied.                                                                                                                                                                                                   |

| Nerf Musculo-Cutané (Superficial Peroneal nerve SP)                         | MC   | Il a deux fonctions:<br>- Motrice: par son innervation de la loge antérieure des muscles du bras, le nerf musculo cutané est le nerf de la flexion du bras sur l'avant bras mais aussi le nerf de la supination;<br>- Sensitive: face externe de l'avant bras.                                                                       |

| Nerf saphène (tibial) (Sural nerve)                                         | -    | Une continuation du nerf tibial qui a deux fonctions:<br>- Motrice: il assure l'innervation de la loge postérieure de la jambe et de la plante du pied;<br>- Sensitive: territoires sensitifs du membre inférieur.                                                                                                                   |

| Nerf Sciatique Poplité Interne (Tibial nerve TI)                            | SPI  | C'est une continuation du nerf sciatique qui a deux fonctions:<br>- Motrice: il innerve les muscles de la loge postérieure de la cuisse et assure donc la flexion de la jambe sur la cuisse. Par ses branches terminales, il assure l'innervation de la jambe et du pied;<br>- Sensitive: face post-latérale de la jambe et le pied. |

| Nerveux (Nervous)                                                           | -    | Qui se rapporte aux nerfs.                                                                                                                                                                                                                                                                                                           |

**Tableau L.2. Terminologie médicale**

| <b>Français<br/>(Anglais)</b>                                     | <b>Abr.</b> | <b>Description</b>                                                                                                                           |

|-------------------------------------------------------------------|-------------|----------------------------------------------------------------------------------------------------------------------------------------------|

| Neural<br>(Neural)                                                | -           | Qui se rapporte au système nerveux.                                                                                                          |

| Péphérie<br>(Periphery)                                           | -           | Surface ou circonference extérieure du corps.<br>Exemple: La paume.                                                                          |

| Péphérique<br>(Peripheral)                                        | -           | Qui se rapporte à la périphérie.                                                                                                             |

| Pied tombant<br>(Drop foot)                                       | -           | Caractéristique de la marche due à un manque de contrôle de la flexion plantaire par les fléchisseurs dorsaux au début de la phase d'appui.  |

| Redressé et intégré par période<br>(Rectified and bin-integrated) | RIP         | Consiste à redresser une fonction et générer un point à partir de la moyenne d'un ensemble de points sur une période déterminée appelée bin. |

| Tibia<br>(Tibia)                                                  | -           | Le plus gros des deux os de la jambe.                                                                                                        |

## INTRODUCTION

Selon sa gravité, une lésion de la colonne vertébrale pourrait avoir des effets désastreux, non seulement sur la qualité de vie de la personne atteinte, mais aussi sur celle de son entourage familial et social. En effet, une personne indépendante et active pourrait ne plus être capable d'accomplir les tâches quotidiennes liées aux fonctions physiologiques, ce qui exigerait la présence continue d'une personne de l'entourage afin de pallier cette déficience.

Les recherches médicales et chirurgicales intensives n'ont pas abouti jusqu'à présent à une solution qui pourrait guérir ou même diminuer l'effet d'une lésion de la colonne vertébrale. La réadaptation reste la seule méthode pour améliorer la qualité de vie des patients. Une des méthodes de réadaptation est de recréer les fonctions motrices (exemple: miction, mouvement d'une jambe paralysée) avec la stimulation électrique. Dans le but de bien contrôler la force motrice ainsi induite, il est désirable de la mesurer ou bien de mesurer son résultat afin de l'utiliser en rétroaction pour la stimulation. Parmi les exemples d'applications possibles, citons le contrôle de l'équilibre entre l'intensité de stimulation et le volume vésical et de l'équilibre entre l'intensité d'une stimulation et le mouvement d'un pied paralysé). Il serait donc d'une grande importance d'utiliser les nerfs transmettant des signaux en provenance de l'organe.

Le dispositif électronique implantable dédié à la réadaptation assure les fonctions suivantes:

- Il reçoit le signal nerveux des électrodes en contact avec les nerfs, le traite, et en extrait l'information;

- Il contrôle la stimulation et surveille le contact électrodes-nerf;

- Il communique avec le monde extérieur.

La plupart des prothèses neurales consistent en un implant central connecté aux électrodes d'enregistrement et de stimulation par un nombre restreint de fils. Une bonne synchronisation permet d'utiliser les mêmes électrodes pour la stimulation et l'enregistrement.

D'une façon plus particulière, on peut récupérer les fonctions urinaires (rétenzione et évacuation) d'un individu – un paraplégique par exemple – en stimulant à l'aide d'un faible courant électrique la racine sacrée S2: ce courant amène la vessie en contraction et par le fait même, force l'évacuation de l'urine. Entre les phases de stimulation, l'implant réalise l'acquisition du signal nerveux par le même nerf et en utilisant les mêmes électrodes.

Le signal nerveux est un signal de très faible amplitude, fortement contaminé par d'autres signaux physiologiques et divers types d'interférences. De plus, le niveau élevé du bruit 1/f (bruit de flicker) des transistors MOS, combiné au faible niveau du signal traité, demeure un défi pour le concepteur du circuit de traitement du signal. Alors que

tous les circuits utilisés pour l'acquisition et l'analyse de l'électroneurogramme sont à composants discrets, la contribution principale de cette thèse est la proposition d'une alternative intégré sur puce. Ce circuit est capable de:

- surmonter l'effet du bruit de flicker;

- réduire l'interférence des signaux indésirables (rejet du mode commun);

- amplifier l'amplitude du signal avec un gain programmable pour rendre son niveau compatible avec l'entrée du circuit de traitement du signal;

- réaliser le traitement du signal désiré. Dans la plupart des cas, ceci consiste en un redressement et une intégration par période.

Dans le premier chapitre, nous passons en revue l'état des travaux dédiés à la mesure des signaux nerveux et à son utilisation dans la réadaptation. L'article (en anglais) à paraître dans le journal "Analog Integrated Circuits and Signal Processing" tient lieu de chapitre 2. Il décrit nos travaux de mesure réalisés *in vivo* et permet une vue globale du système d'acquisition intégré CMOS, ainsi que les résultats de mesure en laboratoire de certaines de ses composantes. Le chapitre 3 consiste en un article qui a été soumis (mars 2004) au journal "IEE Medical & Biological Engineering and Computing". Cette partie expose les mesures expérimentales du circuit produisant le redressement et l'intégration par période du signal. Des compléments d'analyse de l'ENG et des résultats supplémentaires de mesures feront l'objet du Chapitre 4. Nous terminerons par une conclusion sur l'ensemble des travaux de cette thèse et par des propositions de développements futurs.

## CHAPITRE 1

# REVUE DE LITTÉRATURE

### 1.1. LE SYSTÈME NERVEUX

Tout organisme vivant est en interaction constante avec son environnement. Ces interactions lui permettent de se déplacer ou de réagir vis à vis des stimulations du monde extérieur et de son propre monde intérieur. Elles nécessitent la collecte permanente d'information et la circulation de messages entre les différentes cellules de l'organisme. Le système nerveux est, avec le système endocrinien, l'un des deux grands systèmes de communication intercellulaire. Certaines cellules du système nerveux se sont différenciées en récepteurs sensoriels, capables de coder les messages renseignant l'organisme sur les variations des paramètres physico-chimiques de l'environnement (toucher, lumière, etc.) et de son propre milieu intérieur (douleur, etc.). La somme des impressions provenant des organes sensoriels entraîne une sensation, qui, interprétée en fonction de notre expérience, constitue la perception.

Le stimulus, qu'il provienne du monde extérieur ou du milieu intérieur, doit d'abord être converti en un influx nerveux, puis être transmis le long des fibres nerveuses (appelée fibres nerveuses afférentes), et franchir plusieurs jonctions synaptiques avant de parvenir à la structure nerveuse qui assurera sa perception au niveau du cortex cérébral. La

jonction synaptique assure la transmission entre deux neurones grâce à un transmetteur chimique. À noter que les fibres efférentes conduisent les messages efférents par la racine ventrale du nerf rachidien aux effecteurs musculaires.

### **1.1.1. Le potentiel d'action et l'électroneurogramme**

La conversion de l'énergie du stimulus en énergie électrique, base visible de l'influx nerveux, a lieu au niveau du récepteur. Les récepteurs vont jouer le rôle de transducteur, c'est-à-dire transformer l'énergie physique ou chimique en un signal électrique dont l'expression, visible à l'oscilloscope à l'extrémité de la fibre nerveuse, sera constituée du potentiel de récepteur. Ce dernier déclenche le potentiel d'action s'il y a une dépolarisation d'amplitude suffisante.

Le potentiel d'action constitue l'onde porteuse de l'information. Cette variation de potentiel qui parcourt la fibre nerveuse à vitesse constante et sans décrément est la résultante de phénomènes bioélectriques complexes. L'électroneurogramme (ENG) est le signal électrique enregistré à la surface d'un nerf soumis ou non à une stimulation. Si l'enregistrement est effectué avec des électrodes entourant le nerf entier, l'ENG rassemble les manifestations électriques des potentiels d'actions de toutes les fibres du nerf et, par conséquent, les informations transmises.

### 1.1.2. L'innervation de la vessie

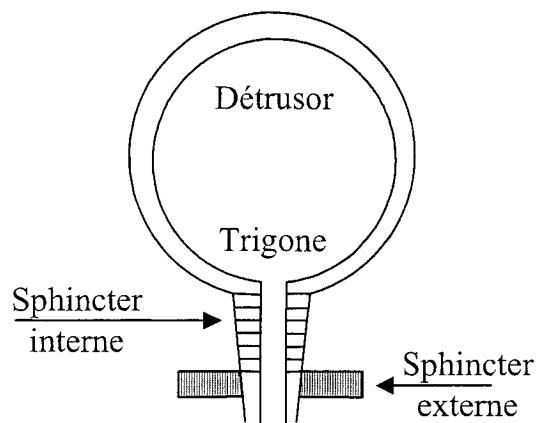

La vessie comprend deux parties principales (figure 1.1):

- Le dôme: c'est le muscle détrusor qui représente un réservoir pendant la phase de remplissage et un moteur pendant la phase d'évacuation;

- La base: c'est le trigone, la partie initiale de l'urètre et son sphincter qui assurent la continence.

Les nerfs moteurs allant au détrusor et au sphincter externe partent des nerfs S2 et S4. Ils sont les principaux responsables de la contraction du détrusor et le contrôle du sphincter.

**Figure 1.1. La vessie est composée de deux parties: le détrusor et le trigone.**

Les sensations perçues dans l'urètre et la vessie gagnent le système nerveux central par des fibres nerveuses qui suivent à la fois les nerfs moteurs parasympathiques et somatiques (S2 et S4) et les nerfs moteurs sympathiques issus de D9 à L2. Cette voie véhicule les signaux sensitifs de distension vésicale responsables du réflexe d'activation détrusoriale et quelques signaux sensitifs douloureux. Elle transporte aussi des signaux proprioceptifs sensitifs des muscles du plancher pelvien et sensitifs vrais de l'urètre.

Les fibres afférentes et efférentes du segment sacré de la moelle (S2-S4) forment un arc réflexe simple dont dépend la fonction vésicale.

Dans cette thèse, la vessie est utilisée comme exemple d'application et pas la seule application du travail proposé. La raison du choix des dysfonctions de la vessie est qu'un microstimulateur avancé de la vessie a déjà été conçu par l'équipe PolySTIM qui fournit un cadre de réalisation à nos travaux. Comme ça va être expliqué plus tard, le circuit conçu peut être utilisé dans d'autres applications d'analyse de signaux nerveux.

### **1.1.3. Les dysfonctions vésicales**

Les causes de ces problèmes sont nombreuses: sclérose en plaque, Parkinson, déformations congénitales, diabète, lésions spinales, cancer, suites d'accidents, etc. Les dysfonctions vésicales se divisent en deux grandes classes: l'incontinence et la rétention.

- L'incontinence urinaire: elle est définie par l'incapacité d'empêcher l'urine de s'écouler hors du corps;

- La rétention urinaire: Dans ce cas-ci le patient ne peut relâcher les muscles qui bloquent l'écoulement de l'urine.

Des millions de personnes dans le monde souffrent de dysfonctions vésicales. Un système urinaire non-fonctionnel peut causer des troubles graves d'intoxication si l'évacuation n'est pas faite comme elle le devrait. Dans ces conditions, la personne atteinte est confrontée à des défis débilitants dans sa vie quotidienne. Elle reste préoccupée par les fréquentes utilisations des toilettes et la crainte de fuite d'urine. Plusieurs patients ne peuvent supporter ces conditions et deviennent isolés et déprimés.

## 1.2. HISTORIQUE

L'étude du contrôle neural des différents organes du corps humain a débuté en 1910 avec les travaux de Sherringtonen qui a décrit les réflexes des fléchisseurs et des extenseurs croisés chez le chat [51]. Depuis, les rôles du système nerveux central dans la moelle épinière et des récepteurs sensoriels des périphéries font l'objet de nombreux travaux de recherche [3,15,17,30,36,37,38,53]. L'acquisition des signaux nerveux constitue une partie intégrante de ce domaine.

Les deux méthodes typiques d'acquisition des signaux utilisent les micro-électrodes et les crochets (hooks) [9,49,50,55]. Dans le premier cas, une électrode métallique

avec un bout très fin ou bien une micro-pipette en verre remplie d'électrolyte est insérée dans le corps pour atteindre les cellules nerveuses. Une différence de potentiel peut être enregistrée entre l'électrode et une électrode de référence insérée à une certaine distance dans le corps. L'utilisation de crochets nécessite la dissection, soit une ouverture de plusieurs millimètres pour exposer les nerfs périphériques recherchés. Ceux-ci sont ensuite placés sur deux crochets métalliques et immergés dans un milieu non-conducteur. Une différence de potentiel d'un signal est enregistrée entre les deux crochets ou bien entre un crochet et une électrode de référence placée dans le corps.

Des techniques d'enregistrement sur des animaux partiellement immobilisés ont été ensuite développées comme la technique de la "chambre implantable" fixée au crâne [10,32,47]. Une autre technique, utilisant des électrodes flottantes montées sur la surface du cerveau, a été proposée par Goldstein [14], car le tissu cervical n'est pas fixe par rapport au crâne.

Hagbarth et Vallbo [19] ont enregistré les signaux provenant des fibres afférentes des muscles pendant les contractions musculaires volontaires, en utilisant des micro-électrodes insérées manuellement. Cette méthode est limitée car la région de mesure doit rester relativement immobile. Ces enregistrements, considérés comme semi-continus (semi-chronic), étaient d'une grande importance pour ce domaine de recherche. Les travaux de Hoffer [27] constituent la première réussite pour enregistrer des signaux des nerfs périphériques intacts des mammifères durant leur mouvement normal et pour une longue durée.

Dans le but de coupler les électrodes aux fibres nerveuses d'une façon permanente, certains travaux ont utilisé une gaine de matériau non-conducteur enroulée autour d'une partie du nerf [2,12]. Hoffer, dans ses études [27], a fait appel à la micro dissection d'une partie du nerf. Cette partie a été placée, sans toutefois couper le nerf, dans une gaine en silastomère contenant des électrodes sur sa face interne pour établir le contact avec le nerf.

### **1.3. ENREGISTREMENT DES SIGNAUX NERVEUX: ÉTAT ACTUEL**

L'enregistrement continu des signaux nerveux offre la possibilité d'étudier les mêmes fibres sous différentes conditions et, surtout, ouvre la voie à des applications de réadaptation (membre artificiel, contrôle de la vessie, etc.). Cependant les défis sont d'éviter d'endommager les fibres nerveuses et d'extraire l'électroneurogramme (ENG) de très faible amplitude, tout en rejetant les autres sources d'interférences comme l'électromyogramme (EMG), les artefacts et l'interférence due au couplage avec les lignes d'alimentation du secteur à 60 Hz.

Les principes d'enregistrement continu (chronique) des signaux nerveux cités par Stein et al. [54] sont, sans doute, la base de tous les travaux ultérieurs. Après avoir cité l'importance de l'application de la technique des micro-électrodes sur le cerveau [10] et sur les nerfs périphériques [58,59] dans la compréhension du système nerveux moteur, il explique les deux facteurs qui limitent l'utilisation des micro-électrodes aux expériences aiguës, à savoir leur sensibilité au mouvement et le besoin d'un dispositif externe pour les

fixer soigneusement. L'enregistrement continu de l'ENG se base sur les facteurs et techniques suivants:

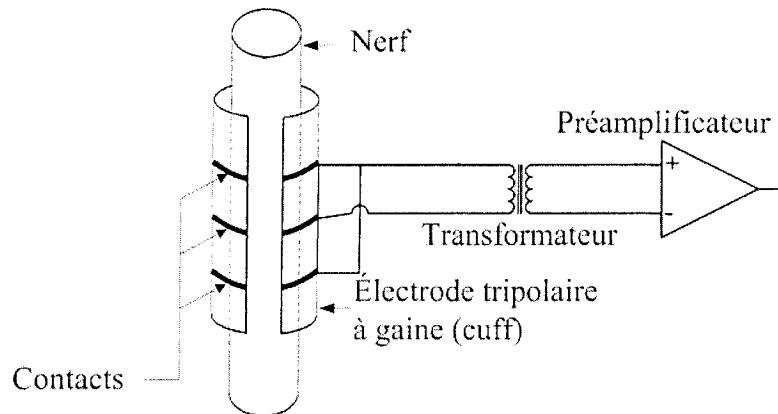

- **L'électrode tripolaire:** Le signal provenant de l'activité musculaire (EMG) a une amplitude beaucoup plus grande que celle provenant des nerfs, car les fibres musculaires sont plus grosses et plus nombreuses que celles des nerfs. Un bon rejet de l'EMG peut être obtenu en utilisant une électrode tripolaire comme le montre la Figure 1.2. L'enregistrement est effectué entre le contact central et les deux contacts aux extrémités interconnectés. En effet, les contacts aux extrémités court-circuitent les signaux provenant de l'extérieur du nerf comme l'EMG et l'ECG (ÉlectroCardioGramme). Par contre, les signaux provenant de l'intérieur du nerf comme les axones ne sont pas court-circuités et génèrent une différence de potentiel (ENG) entre le contact central et les contacts aux extrémités [29]. De plus, l'ECG et l'EMG sont filtrés en traversant le corps avant d'atteindre les nerfs. Au nerf, et sous l'effet du filtrage passe-bas naturel causé par le corps, seules les composantes de faible fréquence (au-dessous de quelques centaines de hertz) subsistent. Ceci oblige ces signaux à circuler à la surface du nerf et par conséquent d'être court-circuités par les contacts aux extrémités de l'électrode tripolaire [18];

- **La géométrie:** Les contacts aux extrémités doivent être placés symétriquement par rapport au contact central. Le placement asymétrique réduit l'amplitude du signal nerveux et augmente cette de l'EMG.

**Figure 1.2. Enregistrement utilisant une gaine à trois contacts [54].**

- **L'adaptation d'impédances:** Dans le cas où le préamplificateur n'est pas optimisé pour des sources à basse impédance, l'adaptation de son impédance d'entrée à celle des électrodes aide à augmenter l'amplitude du signal nerveux capté. Dans cet exemple, l'adaptation a été réalisée avec un transformateur. Sa caractéristique de filtrage passe-bas réduit davantage l'amplitude de l'EMG. Ainsi l'adaptation d'impédances atténue un signal pendant qu'elle permet de tirer le maximum de l'autre;

- **Le filtrage:** Le contenu fréquentiel de l'EMG s'étend dans les basses fréquences. Ainsi, un filtrage passe-bas de 300 Hz fait mieux ressortir le signal nerveux du signal mesuré [54].

#### 1.4. UTILISATION DES SIGNAUX NERVEUX DANS LA RÉADAPTATION

Les travaux de Haugland et Sinkjær [25,26,52] démontrent la possibilité d'utiliser

l'ENG du nerf entier, enregistré à l'aide d'électrodes à gaine (cuff), au lieu d'exploiter seulement les fibres constituant ce nerf comme signal de rétroaction dans un système de stimulation électrique fonctionnelle (Functional Electrical Stimulation- FES). Le but de l'enregistrement est de détecter l'application d'une force sur le côté latéral du pied. Les avantages d'un tel signal sont que:

- L'information fournie provient de plusieurs fibres qui rassemblent diverses formes de sensations générée par une plus grande surface cutanée (où la force est appliquée) que dans le cas de la microneurographie (dans le cas de la détection d'une force appliquée sur la peau);

- Ce signal est moins sensible à l'emplacement de l'électrode à gaine et aux faibles variations du patron d'entrée sur la peau car il présente une moyenne temporelle et spatiale;

- Le signal du nerf entier est reproductible et peut rester stable pendant plusieurs mois.

Les électrodes à gaine utilisées dans l'application ci-dessus ont été conçues selon la méthode de Hoffer [28] (Figure 1.2). La gaine, de longueur 30 mm et de diamètre 2 à 2.5 mm, contient trois contacts circulaires répartis entre son centre et ses deux extrémités. Les impédances des électrodes par rapport à une électrode de référence externe encerclant la cuisse du patient sont mesurées à 1 kHz. L'impédance de l'électrode centrale est de l'ordre de 1.5 k $\Omega$  et celles des autres sont de 1 k $\Omega$  chacune. Les deux électrodes des extrémités sont connectées comme illustré à la Figure 1.2. Les auteurs ont réalisé deux séries d'expériences: aiguës et chroniques. Dans le premier cas, l'ENG a été enregistré pendant

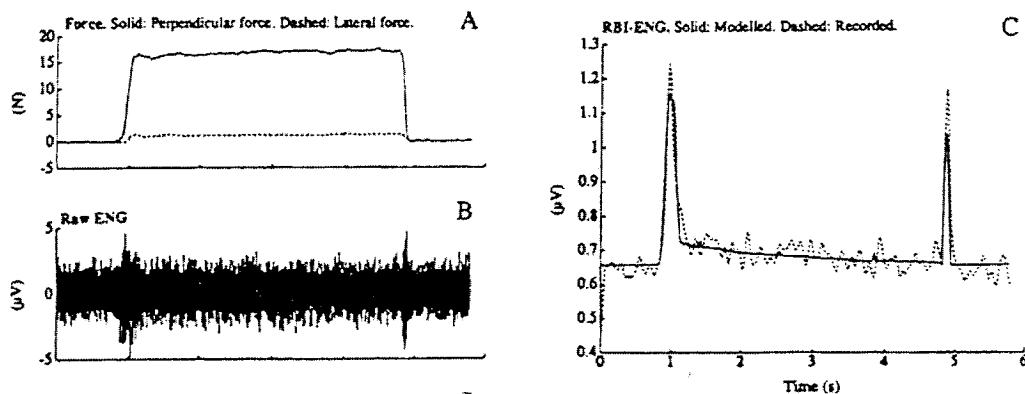

une demi-heure qui est la période de l'implantation des électrodes. Dans le deuxième cas, les électrodes ont été implantées, après une anesthésie locale, et les patients ont porté le système pendant plusieurs mois. Dans les deux séries, l'implantation a été faite sur le nerf saphène externe (sural nerve) à proximité de la malléole latérale de la cheville du pied. En phase aiguë, l'expérience consistait à appliquer une force (à différentes intensités horizontales et verticales) sur la peau de la partie latérale du pied. Le signal nerveux a été amplifié  $7 \times 10^4$  fois avec un amplificateur d'instrumentation et filtré passe-bande entre 80 Hz et 10 kHz. Le signal est ensuite échantillonné à 20 kHz et traité avec un processeur spécialisé (DSP) où il est redressé et intégré par période (Rectified and Bin-Integrated- RBI) avec des périodes d'intégration de 10 ms chacune. La Figure 1.3 présente un exemple des signaux obtenus lors de l'application d'une force perpendiculaire sur la partie latérale du pied (simulation du pas). Avant l'application de la force, le bruit est le seul signal mesuré. Il a une valeur DC (après RBI) d'environ 0.6  $\mu$ V. Quand la force est appliquée, le système mesure un niveau crête (pic) et retourne à un niveau légèrement supérieur à celui avant l'application de cette force. La suppression de la force donne lieu à un autre pic.

Le signal nerveux obtenu ressemble beaucoup, mais en moins bruyant, au signal obtenu du nerf tibial du chat lors de l'application d'une force sur la partie centrale du pied. Dans le modèle reliant la force au ENG-RBI, l'amplitude de ce dernier varie entre 0.6  $\mu$ V et 1.3  $\mu$ V, ce qui est légèrement plus faible que le signal du nerf tibial du chat. Ceci est attribué à deux effets:

- Le diamètre intérieur de l'électrode par rapport au diamètre du nerf est plus grand chez l'homme;

- La surface d'innervation de la peau stimulée mécaniquement est plus petite chez l'homme.

**Figure 1.3. Mesures chroniques de l'ENG:** (A) forces perpendiculaires (ligne continue) et latérales (ligne pointillée) appliquées sur le côté latéral du pied, (B) l'ENG brut, (C) l'ENG redressé et intégré par période (ligne pointillée) et le modèle élaboré par les auteurs qui relie l'ENG-RBI à la force perpendiculaire appliquée (ligne continue) [25].

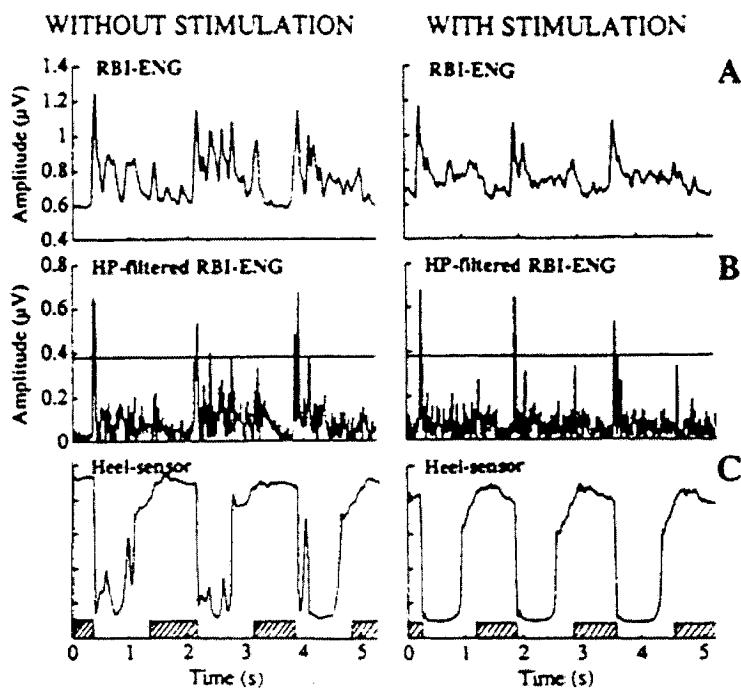

En phase chronique, le signal est utilisé pour contrôler la stimulation électrique fonctionnelle (FES) chez un patient hémiplégique avec un pied tombant (drop-foot). En se basant sur le signal nerveux traité, une impulsion de déclenchement (trigger-pulse) est délivrée par un stimulateur externe pour aider le patient à lever son pied et à le maintenir en l'air. La stimulation est faite au moyen d'une électrode de référence au-dessus du muscle tibial antérieur et d'une électrode active au-dessus du nerf périnéal commun.

L'amplificateur du signal nerveux est alimenté par une pile et est optiquement isolé du secteur pour augmenter le taux de rejet en mode commun (Common Mode Rejection Ratio- CMRR) et assurer une utilisation sécuritaire. Une électrode externe est placée entre les électrodes de stimulation et l'électrode à gaine pour réduire davantage le bruit. Le signal nerveux est ensuite filtré avec un filtre du quatrième ordre dont la bande passante se situe entre 0.7 kHz et 10 kHz. Ce filtrage a pour but de réduire la composante à 50 Hz (la fréquence du secteur au Danemark) et le signal EMG jusqu'à un niveau négligeable. À noter que la bande passante du signal nerveux enregistré se situe entre 0.2 kHz et 3 kHz. L'expérience consiste à enregistrer l'ENG pendant que le patient marche de quatre façons: à pieds nus et avec chaussures, sans et avec stimulation.

La Figure 1.4 présente le résultat des mesures pour trois pas sans et avec stimulation des dorsiflétrisseurs de la cheville. Le signal nerveux redressé et intégré par période est illustré par la Figure 1.4A alors que la Figure 1.4B montre le signal en A après filtrage passe-haut et la Figure 1.4C montre le signal du capteur posé sur le talon. Le contact au sol du pied est détecté par le capteur: le signal est bas lors du contact et haut ailleurs (Figure 1.4C); l'ENG-RBI présente alors un pic de tension au contact du talon avec le sol (Figure 1.4A). Quand le pied est levé (dans le premier pas, cette phase se situe entre 1.5 et 2 s: surface hachurée dans la Figure 1.4C), l'activité neurale diminue au niveau du bruit  $\sim 0.6 \mu\text{V}$  et le signal délivré par le capteur est haut. Pour bien distinguer et détecter le pic de l'activité neurale, l'ENG est redressé, intégré par période et filtré avec un filtre passe haut (Figure 1.4B). Quand le signal traité dépasse  $0.38 \mu\text{V}$ , donc quand le pied touche à