| <b>Titre:</b> Title:    | An iterated tabu search algorithm for the design of fir filters                                                                                                                                                                              |  |  |

|-------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Auteur: Author:         | Katayoon Moazzami                                                                                                                                                                                                                            |  |  |

| Date:                   | 2011                                                                                                                                                                                                                                         |  |  |

| Type:                   | Mémoire ou thèse / Dissertation or Thesis                                                                                                                                                                                                    |  |  |

| Référence:<br>Citation: | Moazzami, K. (2011). An iterated tabu search algorithm for the design of fir filters [Master's thesis, École Polytechnique de Montréal]. PolyPublie. <a href="https://publications.polymtl.ca/755/">https://publications.polymtl.ca/755/</a> |  |  |

# Document en libre accès dans PolyPublie Open Access document in PolyPublie

| URL de PolyPublie:<br>PolyPublie URL:    | https://publications.polymtl.ca/755/ |

|------------------------------------------|--------------------------------------|

| Directeurs de<br>recherche:<br>Advisors: | Michel Gendreau, & François Gagnon   |

| <b>Programme:</b> Program:               | Mathématiques appliquées             |

#### UNIVERSITÉ DE MONTRÉAL

#### AN ITERATED TABU SEARCH ALGORITHM FOR THE DESIGN OF FIR FILTERS

## KATAYOON MOAZZAMI DÉPARTEMENT DE MATHÉMATIQUES ET DE GÉNIE INDUSTRIEL ÉCOLE POLYTECHNIQUE DE MONTRÉAL

MÉMOIRE PRÉSENTÉ EN VUE DE L'OBTENTION DU DIPLÔME DE MAÎTRISE ÈS SCIENCES APPLIQUÉES (MATHÉMATIQUES APPLIQUÉES) DÉCEMBRE 2011

#### UNIVERSITÉ DE MONTRÉAL

## ÉCOLE POLYTECHNIQUE DE MONTRÉAL

Ce mémoire intitulé:

#### AN ITERATED TABU SEARCH ALGORITHM FOR THE DESIGN OF FIR FILTERS

présenté par : MOAZZAMI Katayoon.

en vue de l'obtention du diplôme de : Maîtrise ès sciences appliquées a été dûment accepté par le jury constitué de :

- M. HERTZ Alain, Doct. ès Sc., président

- M. GENDREAU Michel, Ph.D., membre et directeur de recherche

- M. GAGNON François, Ph.D., membre et codirecteur de recherche

- M. POTVIN Jean-Yves, Ph.D., membre

To my best friend, my greatest supporter and my eternal love my husband, Marc.

# **ACKNOWLEDGEMENTS**

First, I would like to thank my supervisors, Dr.Michel Gendreau and Dr.François Gagnon for their support and confidence throughout my studies and research.

Second, I would like to thank my family and friends for being present and helpful during difficulties I faced. Last and definitely not least, I would like to thank my husband Dr.Marc Joliveau for his infinite support and understanding.

# **RÉSUMÉ**

Les systèmes modernes de télécommunication sans fils occupent une place majeure dans la société actuelle. Dans les dernières années, la complexité des outils qui en découlent n'a cessé d'augmenter car, en plus de prendre en charge les tâches basiques de communication vocale, ceux-ci doivent également supporter une quantité croissante de modules et d'applications parallèles (connexion internet, capture vidéo, guidage par satellite, etc.). En conséquence, l'évolution rapide subie par ces outils qui, dans la majorité des cas, sont alimentés par batteries, a singulièrement accru l'importance du rôle joué par la consommation énergétique, et a ainsi fait de l'efficacité énergétique et de l'informatique éco-responsable des caractéristiques essentielles dans les développements récents de la micro-éléctronique. Afin d'offrir une solution à ces problèmes énergétiques, une partie des recherches s'est focalisée sur la conception de filtres numériques efficaces. Les filtres numériques sont la pierre angulaire de tous les systèmes de traitement de signal numérique. Chaque filtre est implanté par un circuit intégré, qui, lui-même, est composé d'une liste d'éléments de base incluant des additionneurs, des multiplicateurs, des inverseurs, etc. La piste principale suivie par les chercheurs dans le but de réduire la quantité d'énergie consommée par les filtres numériques propose de remplacer les multiplicateurs dans les circuits par des éléments moins énergivores, tels que des additionneurs, des décaleurs et des inverseurs. L'objectif des méthodes introduites dans ce sens consiste généralement à remplacer les multiplicateurs tout en utilisant le moins d'additionneurs possible. En effet, en l'absence de multiplicateurs dans les circuits, les additionneurs deviennent l'élément le plus demandant en ressource énergétique. Dans les faits, la quantité d'additionneurs contenue dans un circuit sans multiplicateurs, aussi connue comme son coût en additionneurs, est communément utilisée afin d'estimer sa consommation énergétique.

Nos travaux se concentrent sur la conception de filtres numériques sans multiplicateurs énergétiquement efficaces. Ils se décomposent en deux contributions majeures : un nouveau modèle de représentation efficace des circuits intégrés, et un algorithme innovateur destiné à la conception de filtres numériques efficaces. Dans un premier temps, notre modélisation des circuits sous la forme de graphes pondérés a l'avantage d'offrir une représentation concise des circuits intégrés, tout en annulant la symétrie présente dans les modèles de représentation actuels. Dans un second temps, notre métaheuristique, qui combine à la

fois une recherche tabou et une recherche tabou itérée, offre un contrôle direct du niveau d'énergie consommée par le circuit qu'elle construit, en fixant la quantité d'additionneurs qu'il contient avant le démarrage du processus de conception. En outre, contrairement aux méthodes existantes, notre approche ne se réfère à aucune architecture spécifique afin de concevoir un circuit. Ce degré de liberté permet à notre méthode d'atteindre une optimisation plus globale de la structure du circuit en comparaison des autres méthodes et, ainsi, de posséder un contrôle plus précis de sa consommation énergétique.

L'algorithme proposé est testé sur un jeu de données contenant plus de 700 filtres de complexité variée. Les résultats obtenus démontrent les performances élevées de notre approche car, en se basant sur le coût en additionneurs, dans plus de 99% des cas, notre méthode conçoit des filtres numériques avec un niveau de consommation énergétique total équivalent au niveau induit uniquement par l'architecture à laquelle les méthodes actuelles se réfèrent. En parallèle, notre méthode fournit également un meilleur contrôle de la longueur de mot interne dans les circuits, qui représente un autre aspect crucial de leur efficacité énergétique. La comparaison avec l'algorithme Heuristic cumulative benefit (Hcub) qui, à ce jour, est la méthode la plus performante montre que les filtres construits par notre algorithme utilisent 55% moins d'additionneurs que Hcub, tout en réduisant la taille de ces additionneurs de 33%. Ces améliorations sont obtenues au simple coût d'une augmentation de 17% du nombre de délais dans les circuits. Cependant, la consommation énergétique d'un délai étant de l'ordre de 20% de celle d'un additionneur, si l'on considère le nombre et la taille des additionneurs ainsi que la quantité de délais inclus dans nos circuits afin d'estimer leur consommation énergétique, on peut s'attendre à une économie globale de l'ordre de 65% en comparaison de la meilleure méthode actuelle.

## **ABSTRACT**

In today's modern society, we rely on wireless telecommunication devices that use applications and modules to perform many different tasks and are growing in their complexity day by day. Consequently, the fast evolution of these devices, which, most of the time, are battery-powered, drastically increased the importance of their energy consumption and made energy efficiency and green computing essential features of recent developments in microelectronics.

To deal with the related issues, many researchers have focused their attention to designing energy-efficient digital filters, which are essential building blocks of all digital signal processing systems. Any digital filter is implemented by an integrated circuit composed by a list of basic elements, including adders, multipliers, shifts, etc. One of the paths that researchers have followed in order to decrease the amount of energy used by the integrated circuits was to replace the multipliers in the circuit structure with less energy-consuming elements such as adders, shifts and inverters. The goal of these methods is usually to perform the replacement of multipliers while using the least amount of adders, as, for multiplier-less circuits, adders become the most energy-consuming elements. In fact, the quantity of adders contained in a multiplierless circuit, also known as its adder cost, is commonly used as an estimate of its power consumption.

In our research we focus on energy-efficient multiplierless filters. Our work has two main contributions: a new model to efficiently represent integrated circuits, and an innovative algorithm to design efficient digital filters. On one hand, the main advantage of our new graph-based model is that it is able to represent any integrated circuit in a concise form, while avoiding symmetry in the representation. On the other hand, our metaheuristic, that combines both a tabu search and an iterated tabu search, offers a direct control of the level of energy consumed by the circuits it constructs, by fixing the number of adders that they contain. Besides, unlike other existing methods used for designing multiplierless filters, our approach does not refer to any specific architecture in the corresponding circuit structure. This degree of freedom allows our method to have a more globalized view on the optimization of circuit structure compared to the other methods, and thus, a better control on its power consumption.

The proposed algorithm is tested on a benchmark containing more than 700 filters of dif-

ferent orders of complexity. The obtained results demonstrate the high accuracy of the proposed approach as, based on the adder cost estimation, in more than 99% of the cases our method designs integrated circuits with a level of energy consumption equivalent to those implied only by the most accurate circuit architectures from which existing algorithms build their circuits, and absolutely no deviation from the desired filtering specifications. In parallel, our method also provides a better control of the internal wordlength in the circuits, which is another crucial point to improve the energy-efficiency. The comparison to the current state-of-the-art algorithm Heuristic cumulative benefit (Hcub) when designing all the benchmark filters shows that filters constructed with our algorithm are using 55% less adders than Hcub, while decreasing their size by 33%. This improvement can be reached at the cost of an increase of 17% in the number of delays in the circuits. However, by considering the number and the size of adders used in the circuit as well as the quantity of delays it contains as an estimate of the power consumed by the circuit, assuming that the energy consumption of a delay is in the order of 20% of the consumption of an adder, we can approximately expect an overall energy saving of 65% in our circuits compared to the best current method.

# TABLE OF CONTENTS

| DEDIC  | ATION  |                                                               | . ii |

|--------|--------|---------------------------------------------------------------|------|

| ACKNO  | OWLED  | GEMENTS                                                       | . iv |

| RÉSUM  | 1É     |                                                               | . 1  |

| ABSTR  | ACT .  |                                                               | . vi |

| LIST O | F TABL | ES                                                            | . X  |

| LIST O | F FIGU | RES                                                           | . xi |

| СНАРТ  | ER 1   | INTRODUCTION                                                  | . 1  |

| 1.1    | Proble | em definition                                                 | . 1  |

| 1.2    | Resear | rch objectives                                                | . 2  |

| 1.3    | Thesis | s structure                                                   | . 3  |

| СНАРТ  | ER 2   | LITERATURE REVIEW                                             | . 4  |

| 2.1    | Digita | l filtering                                                   | . 4  |

|        | 2.1.1  | Canonical representation and order of a filter                | . 6  |

|        | 2.1.2  | Digital filter design                                         | . 6  |

|        | 2.1.3  | Multiplier-less filters                                       | . 8  |

| 2.2    | Tabu s | search                                                        | . 10 |

|        | 2.2.1  | Neighborhood search                                           | . 11 |

|        | 2.2.2  | Tabu search algorithm                                         | . 12 |

|        | 2.2.3  | Aspiration function                                           |      |

|        | 2.2.4  | Intensification and diversification                           | . 15 |

| СНАРТ  | ER 3   | MODEL & ALGORITHM                                             | . 19 |

| 3.1    | A new  | graph-based model to accurately represent integrated circuits | . 19 |

|        | 3.1.1  | Model definition                                              | . 21 |

|        | 3.1.2  | Ensuring the feasibility of the circuit structure             | . 21 |

|        | 3.1.3  | Prohibiting the symmetry in the representation     | 23 |

|--------|--------|----------------------------------------------------|----|

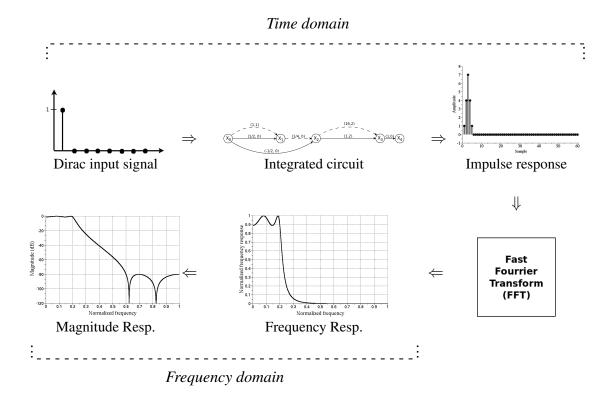

| 3.2    | Evalua | ation of integrated circuits for digital filtering | 25 |

|        | 3.2.1  | Time domain and frequency domain                   | 25 |

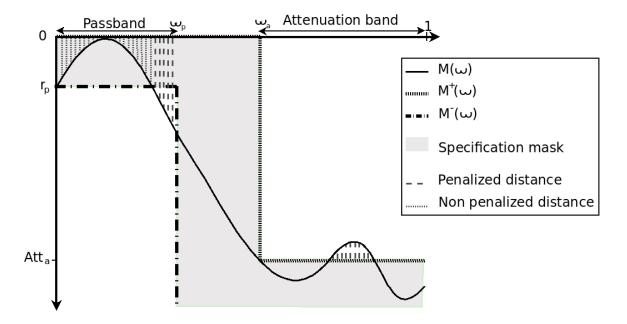

|        | 3.2.2  | Passband and attenuation band                      | 25 |

|        | 3.2.3  | Specification mask and fitness function            | 26 |

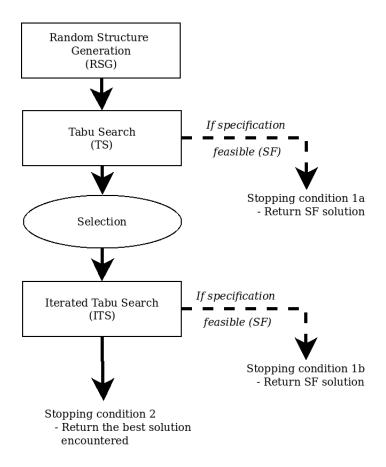

| 3.3    | An ite | rated tabu search for integrated circuit design    | 29 |

|        | 3.3.1  | Random Structure Generation (RSG)                  | 30 |

|        | 3.3.2  | Tabu Search (TS)                                   | 31 |

|        | 3.3.3  | Selection                                          | 32 |

|        | 3.3.4  | Iterated Tabu Search (ITS)                         | 32 |

| СНАРТ  | ER 4   | EXPERIMENTAL RESULTS                               | 35 |

| 4.1    |        | mark and algorithm parameters                      |    |

| 4.2    | Algori | thm analysis                                       | 37 |

|        | 4.2.1  | Neighbourhood study                                | 37 |

|        | 4.2.2  | Stopping conditions                                | 37 |

|        | 4.2.3  | Parallelization                                    | 39 |

| 4.3    | Perfor | mance analysis                                     | 41 |

|        | 4.3.1  | Design accuracy                                    | 43 |

|        | 4.3.2  | Evolution of the error rate                        | 43 |

| 4.4    | Power  | consumption                                        | 47 |

|        | 4.4.1  | Minimum adder cost                                 | 47 |

|        | 4.4.2  | Minimum adder size                                 | 48 |

|        | 4.4.3  | Quantity of delay                                  | 51 |

|        | 4.4.4  | Energy efficiency                                  | 51 |

|        | 4.4.5  | Free structure of the integrated circuits          | 52 |

| СНАРТ  | ER 5   | CONCLUSION                                         | 54 |

| 5.1    | Summ   | ary                                                | 54 |

| 5.2    | Limita | ations of the proposed solution                    | 55 |

| 5.3    | Future | e work                                             | 56 |

| DEEEDI | ENICES |                                                    | 57 |

# LIST OF TABLES

| Table 2.1 | List of the components used in multiplier-less integrated circuits         |    |

|-----------|----------------------------------------------------------------------------|----|

|           | for digital signal processing                                              | 8  |

| Table 3.1 | Illustration of the 3 rules to avoid symmetry in the model                 | 24 |

| Table 4.1 | Proportion of local optima identified by each sub-neighbourhood            |    |

|           | while performing TS and ITS                                                | 37 |

| Table 4.2 | Distribution of the stopping condition activated to terminate the          |    |

|           | algorithm (Cond. 1a: during TS, Cond. 1b: during ITS, Cond. 2:             |    |

|           | after ITS) when designing filters of order $n \in [10, 15]$ with circuits  |    |

|           | containing <i>n</i> adders                                                 | 38 |

| Table 4.3 | Comparison of the average computation time (s) needed by the al-           |    |

|           | gorithm to design filters of order $n \in [10, 15]$ with circuits contain- |    |

|           | ing $n$ adders executed using a single core and using 16 cores in          |    |

|           | parallel                                                                   | 38 |

| Table 4.4 | Average and standard deviation of the error rate (%) when design-          |    |

|           | ing filter of order $n \in [10, 15]$ with circuits containing $n$ adders   | 42 |

| Table 4.5 | Average and standard deviation of the net error (dB) when design-          |    |

|           | ing filter of order $n \in [10, 15]$ with circuits containing $n$ adders   | 42 |

| Table 4.6 | Comparison of the minimum adder-cost needed by our algorithm               |    |

|           | (TS-ITS) and Hcub to construct circuit with a design error smaller         |    |

|           | than 1% error                                                              | 47 |

| Table 4.7 | Comparison of the average minimum adder size in the circuits de-           |    |

|           | signed by our algorithm (TS-ITS) and Hcub (NOFS minimization)              |    |

|           | with a maximum design error is fixed to 1%                                 | 50 |

| Table 4.8 | Comparison of the number of delays in the circuits designed by our         |    |

|           | algorithm (TS-ITS) and Hcub with a design error smaller than 1%            | 51 |

# LIST OF FIGURES

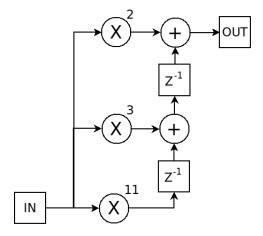

| Figure 2.1 | Illustration of a typical Finite Impulse Response (FIR) digital filter.     |    |

|------------|-----------------------------------------------------------------------------|----|

|            | The circuit, built according to the transpose form architecture, per-       |    |

|            | forms simple operations such as multiplications by a given constant         |    |

|            | $c (\otimes^c)$ , additions $(\oplus)$ , and delays $(z^{-1})$              | 5  |

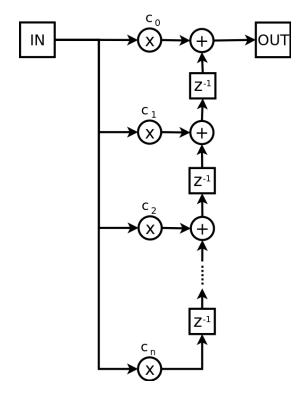

| Figure 2.2 | Generic form of a FIR filter under its canonical representation. Ac-        |    |

|            | cording to this structure, a filter of order $n$ is implemented by a        |    |

|            | circuit containing $n$ adders, $n$ delays and $n+1$ multipliers             | 5  |

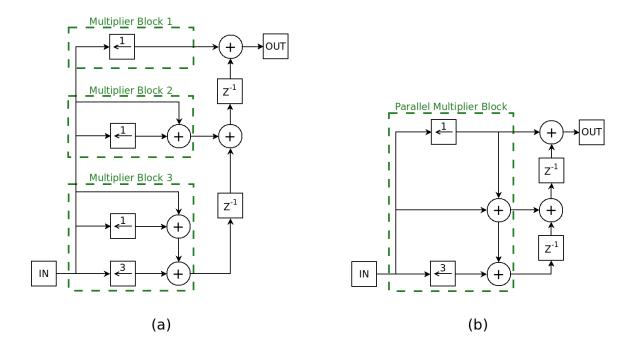

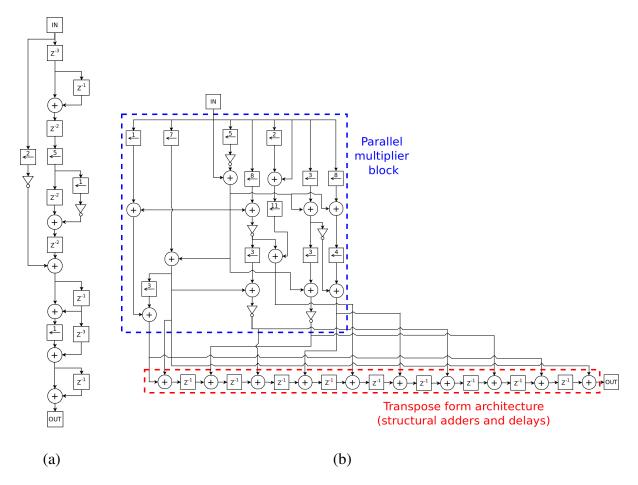

| Figure 2.3 | Design of the FIR filter of Figure 2.1 using MCM methods in order           |    |

|            | to (a) replace each multiplier by a multiplier block or (b) replace         |    |

|            | all three multipliers by a unique parallel multiplier block                 | 10 |

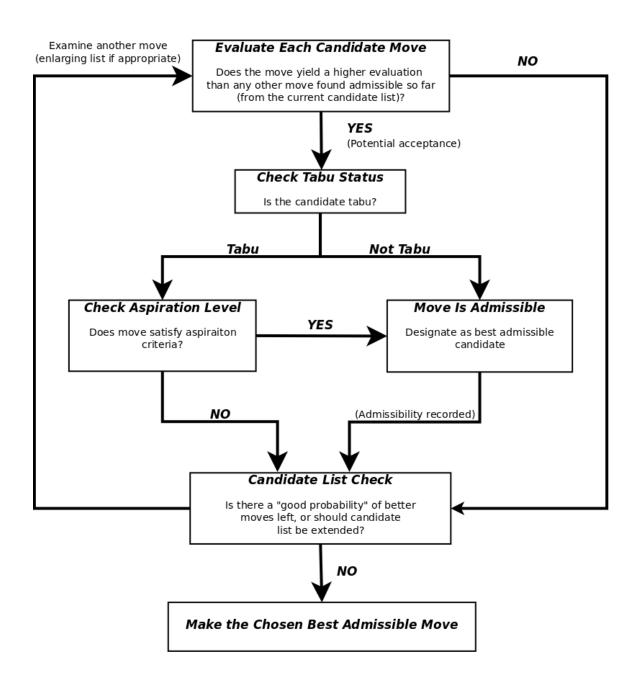

| Figure 2.4 | Evaluation of moves                                                         | 14 |

| Figure 2.5 | Tabu search                                                                 | 16 |

| Figure 2.6 | Generalized framework of an iterated tabu search                            | 18 |

| Figure 3.1 | An example of the symmetry in the traditional schematic represen-           |    |

|            | tation                                                                      | 20 |

| Figure 3.2 | Illustration of the same integrated circuit using the traditional schematic | c  |

|            | representation and the proposed graph-based representation                  | 22 |

| Figure 3.3 | Extraction of the filter specification from its circuit implementation.     | 26 |

| Figure 3.4 | Evaluation of an integrated circuit: Example of a low-pass filter           | 28 |

| Figure 3.5 | Schematics of the algorithm                                                 | 30 |

| Figure 3.6 | Illustration of the diversification process executed in our Iterated        |    |

|            | Tabu Search algorithm for circuit design                                    | 33 |

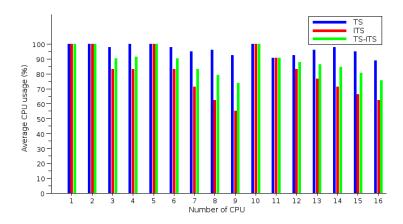

| Figure 4.1 | Average usage of a CPU (%) according to the number of processors            |    |

|            | used during the parallelization                                             | 39 |

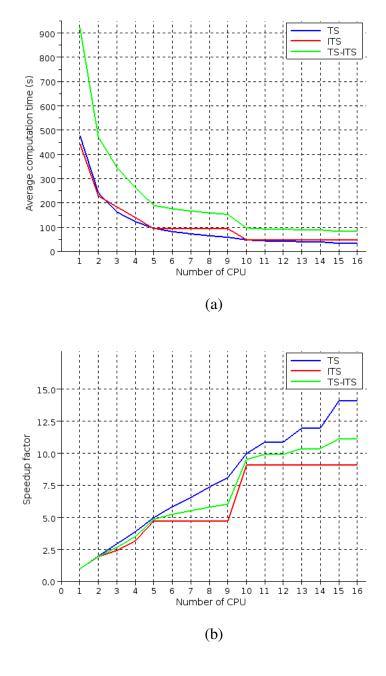

| Figure 4.2 | Evolution of (a) the average computation time (s) and (b) the speedup       |    |

|            | factor according to the number of CPU used when designing filters           |    |

|            | for every mask of the benchmark                                             | 40 |

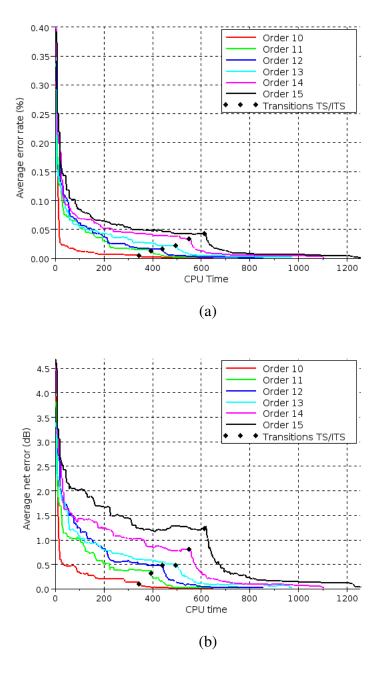

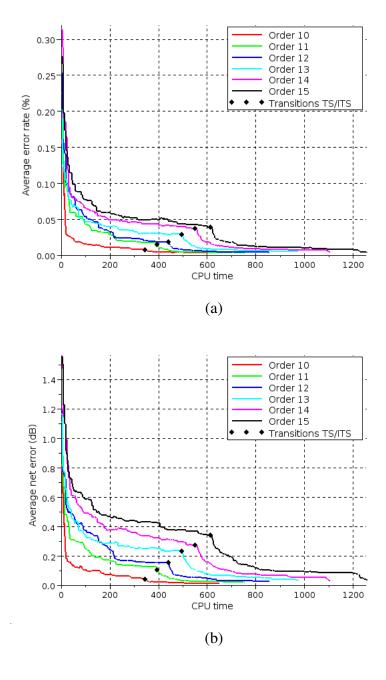

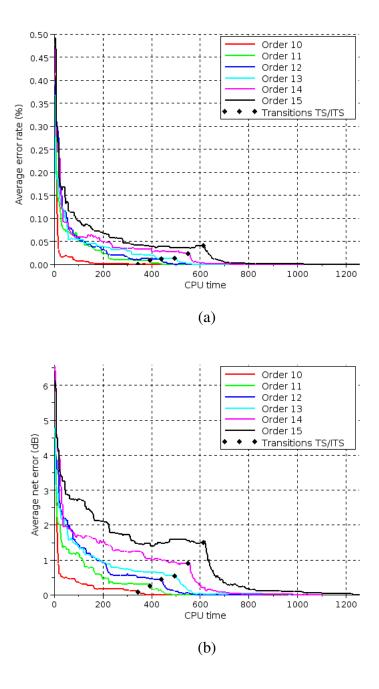

| Figure 4.3 | Evolution of (a) the total average error rate (%) and (b) the total         |    |

|            | average net error (dB) when constructing filters of order $n \in [10, 15]$  |    |

|            | with circuits containing $n$ adders                                         | 44 |

| Figure 4.4 | Evolution of (a) the passband average error rate (%) and (b) the                            |    |

|------------|---------------------------------------------------------------------------------------------|----|

|            | passband average net error (dB) when constructing filters of order                          |    |

|            | $n \in [10, 15]$ with circuits containing $n$ adders                                        | 15 |

| Figure 4.5 | Evolution of (a) the attenuation band average error rate (%) and                            |    |

|            | (b) the attenuation band average net error (dB) when constructing                           |    |

|            | filters of order $n \in [10, 15]$ with circuits containing $n$ adders 4                     | 16 |

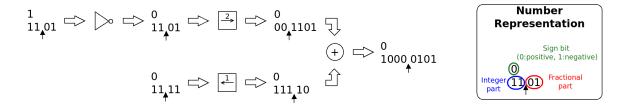

| Figure 4.6 | Binary evolution of two numbers through a small sub-circuit com-                            |    |

|            | posed of one inverter, one left shift of 1 bit, one right shift of 2 bits                   |    |

|            | and an adder                                                                                | 18 |

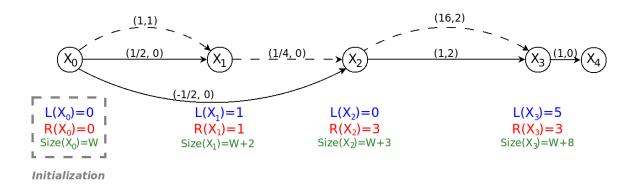

| Figure 4.7 | Computation of the size of adders in an integrated circuit 4                                | 19 |

| Figure 4.8 | Illustration of the integrated circuit designed to implement a low-                         |    |

|            | pass filter ( $\omega_p = 0.5$ , $\omega_a = 0.8566$ , $r_p = 1$ dB, $Att_a = 50$ dB) using |    |

|            | (a) our algorithm and (b) Hcub                                                              | 53 |

# **Chapter 1**

# INTRODUCTION

#### 1.1 Problem definition

The demand for increasing level of performance in third and fourth generation telecommunication systems calls for devices with more competitive properties, one of which is energy-efficiency. This has made low-power high-performance digital signal processing (DSP) a critical path to follow.

Digital filters, which are some of the basic instrument to process a signal, are considered as essential bluiding blocks of DSP systems. Any filter is implemented by an integrated circuit, which in turn, is composed of different basic elements such as shifts, registers, adders and multipliers. In this work, we introduce a new graph-based model for representing the integrated circuits efficiently and concisely.

Using operations research methods for designing efficient digital filters is not new. Many different optimization algorithms have been applied to filter design, as it will be shown in the next chapter. These algorithms are usually based on graph theory, linear programming or metaheuristic approaches such as genetic algorithms, simulated annealing, tabu search and so forth.

One way to improve the energy consumption of a circuit is to reduce the occurence of the elements that consume the most amount of energy in the circuits. Since multipliers are the most energy consuming components in the circuits, and as adders are the second ones, a great amount of research has been dedicated to the design of efficient multiplier-less filters that require the least number of adders in their circuit structure.

Therefore, many research efforts have been dedicated to the design of low-complexity multiplier-less filters, most of which are focused on an important family of filters, namely, Finite Impulse Response (FIR) filters. FIR filters do not allow any recursive loops in their circuit structure, in other words, the output of these filters depends on the present and previous values of the input signal and no output values. Our research is also adapted to the design of energy-efficient multiplier-less FIR filters, as we do not allow any loops in the

model we use for representing the integrated circuits that the filters are based on.

Most of the works that have focused on minimizing the complexity of filters in order to optimize their energy consumption are based on circuit structures derived from existing architectures. However, there are a few papers that do not follow this hypothesis and consider their circuit structures to be free (Châtelain et Gagnon (2007); Joliveau *et al.* (2011)). Our work is based on the same idea, which means that we do not refer to any defined architecture. Thus, our algorithm has a higher degree of liberty concerning the placements of the circuit elements. This results in the design of non-traditional-looking circuit structures that require much less circuit elements.

In order to analyze the performance of filters, their specifications in the frequency domain are tested: the magnitude response of each filter must fit into a given mask, which usually defines the locations of the passbands and the attenuation bands, as well as the level of error tolerated. In order to provide accurate filters, our algorithm tries to reduce the average distance between the magnitude response of the filter it is designing and the specification mask. Notions related to the filters, their properties and their fitness are discussed in length in the next chapters.

As mentioned before, one of the operations research methods that has been used in filter design and has yielded interesting results is tabu search (Glover (1986)). There is also another version of tabu search that is considered to be an extension to it, the iterated tabu search proposed by Misevicius *et al.* (2006)). Our algorithm is a combination of tabu search and iterated tabu search. The design of more than 700 digital filters with various degrees of complexity using this algorithm and the comparison to the state-of-the-art method *Heuristic cumilative benefit (Hcub)* demonstrate the very high accuracy of our approach. The details of algorithm stages and experimental results are extensively discussed in the following chapters.

## 1.2 Research objectives

In our research, we address the issues related to the design of low-complexity energy-efficient filters. To do so, we focused our attention towards the design of non-recursive multiplier-less filters that consume much less energy compared to those produced by state-of-the-art algorithms. We made this possible by developing an algorithm that benefits from a well-defined model for representing the integrated circuits, as well as by taking advantage of powerful metaheuristics like tabu search and iterated tabu search. It is also important to

note that the proposed methodology offers a very higher degree of liberty than traditional approaches, as it does not rely to any defined circuit architectures. Although it considerably increases the size of the solution space that the method must explore, it also opens to the potential identification of a new family of efficient integrated circuits with free structure and low power consumption, that would have been ignored until today, because of the limitations of classical methods.

#### 1.3 Thesis structure

In this chapter we have given an overview of the problem in hand and the approach we use to solve it. In the second chapter, we discuss the previous work in digital filter design and the related operations research methods used in this field. We will also introduce basic notions regarding digital filtering, tabu search and iterated tabu search metaheuristics. In the third chapter, we present our graph-based model for representation of integrated circuits and then move on to describing our algorithm and its basic ingredients. Chapter 4 is dedicated to the presentation and a discussion of computational results achieved. In chapter 5, some conclusions are drawn and directions for future work are proposed.

# **Chapter 2**

## LITERATURE REVIEW

As this research is a combination of the two very different domains of operations research and electronics, we will explain the concepts and related work in these two domains to familiarize the reader with the context of our research. This chapter consists of two main sections. In section 2.1 digital filtering and other signal processing notions related to our research are discussed. Section 2.2 focuses on operations research and mainly on the tabu search metaheuristic that is applied in our work.

## 2.1 Digital filtering

Digital signal processing (DSP) algorithms are used to transform and analyze signals that have been collected from various sources. Digital signal processing has various applications such as communication, control, meteorology and biomedical. Unlike analog systems, the performance of a digital system is not dependent on the tolerance of electrical components. Digital filters can be considered as the essential building blocks of digital signal processing, as any time invariant DSP algorithm can be described as a digital filter. Physically, filtering is performed by integrated circuits. These integrated circuits, or digital filters, are used to execute various basic functions, such as pulse shading, modulation, demodulation, as well as more complex applications like image compression, audio equalization, interference reduction or even separation of the POTS (Plain Old Telephone Service) and DSL (Digital Subscriber Line) signals (Smith (2007)).

The circuits contain simple elements that perform basic operations such as addition, multiplications by a constant, and delay. Figure 2.1 shows an example of an integrated circuit that implements a digital filter.

Figure 2.1 Illustration of a typical Finite Impulse Response (FIR) digital filter. The circuit, built according to the transpose form architecture, performs simple operations such as multiplications by a given constant c ( $\otimes^c$ ), additions ( $\oplus$ ), and delays ( $z^{-1}$ ).

Figure 2.2 Generic form of a FIR filter under its canonical representation. According to this structure, a filter of order n is implemented by a circuit containing n adders, n delays and n+1 multipliers.

#### 2.1.1 Canonical representation and order of a filter

The circuits implementing a filter are designed according to a defined architecture. Among these architectures, the canonical representation of a filter, also known as the transpose form architecture, is the circuit structure that uses the least amount of multipliers, adders and delays to implement a digital filter. This architecture is also used to determine the order of a filter. By definition, the order of a filter corresponds to the number of adders needed to implement a filter according to its canonical representation, which is also equal to the number of multipliers minus one. According to this definition, the order of a filter is usually considered as an indicator of its complexity. The concept of order can also be applied to circuits, assuming that the order of a circuit is equal to the order of the filter it implements. Figure 2.2 illustrates the generic form of a filter of order n implemented under its canonical representation.

## 2.1.2 Digital filter design

Traditionally, two principal families of filters exist: Finite Impulse Response (FIR) and Infinite Impulse Response (IIR) filters. The main difference between these families is that, IIR circuits contain recursive loops (i.e., cycles) whereas FIR circuits do not allow them. This basically means that the response of a FIR filter is dependent only on present and a finite number of previous values of the input signal while, IIR filters depend not only on input data, but also on some output values.

The use of operations research (OR) techniques in the design of digital filters is not new. Throughout the years, many different algorithms have been proposed for optimizing different aspects of filter design. Genetic algorithms are one of the most popular algorithms used (Suckley (1991); Cemes et Ait-Boudaoud (1993); Wade *et al.* (1994); Xu et Daley (1995); Lee *et al.* (1998); Oner (1998); Lian et Cen (2003); Ling et Yong (2004); Ahmad et Antoniou (2006); Dey *et al.* (2010); Shing-Tai (2010); Boudjelaba *et al.* (2011)), but other techniques such as local search (Kodek et Steiglitz (1981); Samueli (1989); Xu et Nowrouzian (1999)), ant colony optimization (Karaboga *et al.* (2004)), simulated annealing (Ling (2007); Boudjelaba *et al.* (2011)) and tabu search (Karaboga *et al.* (1997); Fanni *et al.* (1998); Traferro *et al.* (1999); Traferro et Uncini (2000); Kalinli et Karaboga (2005); Watcharasitthiwat *et al.* (2006); Ling (2007); Boudjelaba *et al.* (2011)) have been employed as well. The earlier algorithms, which mainly applied local search techniques or genetic algorithms, lacked a certain level of elegance as they were not completely adapted

to the problems they were applied to. Later on, better algorithms were developed. These algorithms were mainly based on tabu search (Karaboga *et al.* (1997); Fanni *et al.* (1998); Traferro *et al.* (1999); Traferro et Uncini (2000); Kalinli et Karaboga (2005); Watcharasitthiwat *et al.* (2006); Ling (2007); Boudjelaba *et al.* (2011)) or more complex genetic algorithms (Lian et Cen (2003); Ling et Yong (2004); Ahmad et Antoniou (2006); Ling (2007)) and they yielded better results than their predecessors.

Currently, much more sophisticated algorithms are used. These algorithms, which are mainly hybrid algorithms, try to design better filters by incorporating favorable aspects of other traditional algorithms such as GAs, tabu search and ant colony algorithms (Karaboga *et al.* (2004); Kalinli et Karaboga (2005); Ling (2007)). In order to improve the computation time, parallel versions of metaheuristic algorithms have also been considered (Xu et Daley (1995); Karaboga *et al.* (1997); Kalinli et Karaboga (2005); Watcharasitthiwat *et al.* (2006)).

Algorithms proposed for optimization of filter design have concentrated on optimization of different aspects, such as the value of objective function (usually based on frequency response of the filter) (Cemes et Ait-Boudaoud (1993); Wade et al. (1994); Xu et Daley (1995); Watcharasitthiwat et al. (2006); Ling (2007)), computational complexity (Suckley (1991); Fanni et al. (1998); Dey et al. (2010); Boudjelaba et al. (2011)), coefficient accuracy (Samueli (1989); Oner (1998); Xu et Nowrouzian (1999); Kalinli et Karaboga (2005); Shing-Tai (2010)), low filter complexity (Samueli (1989); Lian et Cen (2003); Kalinli et Karaboga (2005)), high speed (Lian et Cen (2003); Kalinli et Karaboga (2005)) or chip area (Wade et al. (1994)). These algorithms have been applied to both IIR filters (Xu et Nowrouzian (1999); Karaboga et al. (2004)) and FIR filters, but mainly to FIR filters (Cemes et Ait-Boudaoud (1993); Wade et al. (1994); Traferro et al. (1999); Xu et Nowrouzian (1999); Kalinli et Karaboga (2005); Ahmad et Antoniou (2006); Watcharasitthiwat et al. (2006); Ling (2007)), and most of all to multiplier-less FIR filters (i.e., FIR filters that do not contain multipliers) (Cemes et Ait-Boudaoud (1993); Wade et al. (1994); Fanni et al. (1998); Lee et al. (1998); Lian et Cen (2003); Ahmad et Antoniou (2006); Ling (2007)). A majority of the algorithms proposed for designing multiplier-less FIR filters are based on signed powers-of-two (SPoT) approaches that express the coefficients of the filter as sums of signed powers-of-two (Cemes et Ait-Boudaoud (1993); Traferro et al. (1999); Xu et Nowrouzian (1999); Lian et Cen (2003); Ahmad et Antoniou (2006); Shing-Tai (2010)).

This research looks into designing FIR filters that have a low filter complexity and, as a

result, consume less energy. Multipliers are the type of circuit elements that use the most amount of energy in the circuit, so we will focus on the design of multiplier-less FIR filters. But our research idea goes further than that. Unlike other existing algorithms that optimize the filter while keeping the underlying architectures, filters designed by our algorithm will not be limited by any circuit structures. Thus, the process that is proposed is more global as it considers the entire circuit, whereas existing methods only focus on the replacement of multipliers. This idea of free structure circuits was first proposed in Châtelain et Gagnon (2007) for IIR filters, where the authors designed a genetic algorithm that achieved lower filter complexity and higher data rate. The concept of energy efficient circuits with free structure was then improved in Joliveau *et al.* (2011), where the authors proposed an evolutionary variable neighbourhood search (E-VNS) algorithm for designing IIR multiplier-less filters. This work will focus on developing an iterated tabu algorithm that provides low-complexity multiplier-less FIR filters with a fixed level of energy consumption.

#### 2.1.3 Multiplier-less filters

Although FIR and IIR filters in their traditional sense are simple and fast, they use multipliers. Unfortunately, multipliers consume significant amount of power in comparison to other elements in the circuit. Thus, the main trend followed for obtaining energy-efficient filters, is the replacement of multipliers by other circuit elements. This process consists of replacing the constant multiplication (multipliers) by multiplier blocks, which are subcircuits essentially constituted of additions (adders), multiplication by -1 (inverters) and multiplication by power of 2 (left and right shifts)(table 2.1).

Table 2.1 List of the components used in multiplier-less integrated circuits for digital signal processing.

| Name        | Symbol            | Signal processing                       |

|-------------|-------------------|-----------------------------------------|

| Adder       | $\oplus$          | Adds the two input signals              |

| Delay       | $z^{-1}$          | Delays the signal of 1 time clock       |

| Left shift  | $\leftarrow$      | Multiplies the input signal by $2^n$    |

| Right shift | $\xrightarrow{n}$ | Multiplies the input signal by $2^{-n}$ |

| Inverter    | ⊳०                | Multiplies the input signal by $-1$     |

In the absence of multipliers in the circuit, adders become the new central element concerning circuit complexity and power consumption. Consequently, the goal of multiplierless circuit design methods is to use the least number of adders in the circuit. In fact, the number of adders that the circuit contains, also known as *adder cost*, is commonly used as a good estimate of its energy consumption.

Generation of multiplier blocks from a set of constants is known as the Multiple Constant multiplication or MCM problem and finding its optimal solution (i.e., the one with the fewest additions) is NP-Hard. Among the existing algorithms, three principal approaches can be distinguished:

- digit-based recoding (Avizienis (1961)), which generates the decomposition of the coefficients directly from their digit representation;

- common subexpression elimination (Pasko et al. (1999); Coleman (2001); Macleod et Dempster (2005); Thong et Nicolici (2009)), which are extensions of digit-based recoding methods, whose basic idea is to find common subpatterns in the representation of the coefficients after they are converted to a convenient number system;

- graph-based algorithms (Bernstein (1986); Bull et Horrocks (1991); Dempster et Macleod (1995); Gustafsson et al. (2006); Voronenko et Puschel (2007)), which iteratively construct the graph representing the multiplier blocks.

These techniques, which are usually based on evolutionary methods such as genetic algorithm, allow designing accurate low complexity digital filters with a small adder cost.

While the digit-based recoding methods, such as the *Canonical Signed Digit* (CSD) representation (Avizienis (1961)), try to express independently each multiplier by a multiplier block (Figure 2.3a), common subexpression elimination and graph-based algorithms, including the *Bull-Horrocks algorithm* (BHA) (Bull et Horrocks (1991)), the *n-dimensional Reduced Adder Graph* (RAG-n) algorithm (Dempster et Macleod (1995)), and the *heuristic cumulative benefit* (Hcub) (Voronenko et Puschel (2007)), reach lower adder costs by considering parallel multiple constant multiplication (Figure 2.3b).

Although these methods, and particularly the state-of-the-art algorithm Hcub, manage to construct multiplier-less circuits with few adders and low power consumption, their approach is limited, as they focus only on the replacement of multipliers. They thus rely on existing architectures, which imply the presence of extra adders, to define the remaining part of the circuit. In order to provide a more global approach, we propose a new multiplier-less circuit design algorithm that optimizes the entire circuit structure without referring to

Figure 2.3 Design of the FIR filter of Figure 2.1 using MCM methods in order to (a) replace each multiplier by a multiplier block or (b) replace all three multipliers by a unique parallel multiplier block.

any defined architecture. In the following section we will discuss the notions and previous work related to the operations research part of our work.

## 2.2 Tabu search

Tabu search is an adaptive procedure used for solving a wide range of combinatorial optimization problems. Tabu search, as it is known today, was proposed by Glover (1986) who viewed it as a metaheuristic (i.e., a master strategy that guides and uses heuristics to solve combinatorial problems) rather than a heuristic (i.e., intelligent procedures that seek optimal or near-optimal solutions but cannot guarantee reaching such solutions). It is worth mentioning that at the same time, a very similar heuristic called *steepest ascent*, *mildest descent* was independently proposed by Hansen (1986).

Origins of tabu search go back to procedures applied in solving non-linear integer programming problems (the method was used as a tool for implementing the oscillating assignment strategy) (Glover (1977)). Tabu search has proven to be very efficient in finding optimal

or near-optimal solutions for many different combinatorial optimization problems, including traveling salesman problems (Knox et Glover (1989); Malek *et al.* (1989b,a)), graph coloring (Hertz et de Werra (1987)), scheduling problems (Glover et McMillan (1986); Eck (1989)), maximum stable set problems (Friden *et al.* (1989)), stochastic programming (Lokketangen et Woodruff (1996)), mixed integer programming (Lokketangen et Glover (1996); Cranic *et al.* (2000)), real-time decision problems (Gendreau *et al.* (1999)) and so forth.

#### 2.2.1 Neighborhood search

Assuming that a combinatorial optimization problem *P* can be represented by:

(P) Minimize

$$c(x): x \in X \subset \mathbb{R}_n$$

,

where the objective function c(X) can be linear or nonlinear. Most heuristic methods that tries to solve a combinatorial optimization problem can thus be viewed as a sequence of *moves* from one solution of X to the other. Therefore, a move can be described as a mapping defined on X:

$$s: X \to X$$

.

The set of moves that can be applied to a solution x can be represented by the set S(x), and all the solutions that may be reached from a solution x form the neighbourhood N(x) of x.

Neighborhood searches generally consists of exploring the solution space by iteratively moving from a solution x to a solution in its neighborhood N(x). Hill climbing heuristics are the simplest of neighborhood searh heuristics. A summarized version of the hill climbing heuristic can be seen below (Glover (1989b)).

#### **Hill Climbing Heuristic for (P)**

- 1. Select an initial  $x \in X$ .

- 2. Select some  $s \in S(x)$  such that

$$c(s(x)) < c(x)$$

.

If not such s exists, x is a local optimum and the method stops. Otherwise,

3. Let x := s(x) and return to step 2.

The hill climbing method basically moves from one solution to another until it reaches a local optimum. The main problem of this heuristic is that when the local optimum is found, the algorithm stops and there is a good chance that this local optimum is not the global optimum.

#### 2.2.2 Tabu search algorithm

Tabu search can be seen as an extension of hill climbing heuristics. The main difference between the two methods is that, unlike hill climbing heuristics, tabu search does not stop in local optima but it keeps moving to the best solution inside the neighborhood of the current solution, while expecting that this non-improving move can lead to the identification of a better local optimum further in the process. In order to avoid cycling between a solution and a local optimum that has been previously visited by the algorithm, tabu search uses information structures called *tabu lists*. This list stores a given number of moves that would lead to a previous local optimum.

The size and contents of tabu lists depend on the problem but they are usually not very long (typically short-term memory is used for the lists) and mostly they contain the inverse of the last few modifications made to the current solution. Based on the characteristics of the problem in hand, some *tabu constraints* are defined and tabu lists are constructed according to these constraints. Tabu constraints are usually stated to make reversal or in some cases repetition of some moves impossible. This, in most cases, is done by forbidding certain attributes of these moves.

Thus, a tabu list can be defined as T where:

$$T(x) = \{s \in S : s(x) \text{ violates the tabu conditions}\}.$$

A simple tabu search (Gendreau et Potvin (2010)) is presented in the following template which applies the most commonly used version of tabu search called the *best improvement* tabu search (i.e., at each iteration the best available move is chosen):

#### SIMPLE TABU SEARCH

#### Notation

- S: the current solution,

- $-S^*$ : the best-known solution,

- $f^*$ : the value of  $S^*$ ,

- -N(S): the neighborhood of S,

- $-\tilde{N}(S)$ : the admissible subset of N(S) (i.e., non-tabu or allowed by aspiration),

- T: the tabu list.

#### Initialization

Choose (construct) an initial solution  $S_0$ .

Set

$$S \leftarrow S_0$$

,  $f^* \leftarrow f(S_0)$ ,  $S^* \leftarrow S_0$ ,  $T \leftarrow \emptyset$ .

#### Search

While termination criterion not satisfied do

```

select S'' in argmin_{S' \in \tilde{N}(S)}[f(S')];

set S \leftarrow S'';

if f(S) < f^*, then set f^* \leftarrow f(S), S^* \leftarrow S;

record tabu for the current move in T (delete oldest entry if necessary).

```

In the following subsections, we will discuss some features that can be added to tabu search in order to improve its adaptability to complex implementations.

## 2.2.3 Aspiration function

Although tabu lists are powerful tools for avoiding cycling, they may also prohibit attractive moves. Thus, there is another important aspect of tabu search to consider and that is a function called *aspiration criteria* which basically defines the criteria where we

Figure 2.4 Evaluation of moves.

can ignore the tabu constraints. In other words, tabu lists and the aspiration function play a dual role; you can choose a move by ignoring tabu conditions, while aspiration criteria are satisfied. This can be very well seen in Figure 2.4. The most commonly used aspiration function, allows a move to be chosen if its resulting objective function value is better than the current best solution.

For a more complete description of aspiration functions one can refer to Glover (1989b); Glover et Laguna (2002). There are also more complex examples of aspiration levels that can be found in de Werra et Hertz (1989); Hertz et de Werra (1991).

#### 2.2.4 Intensification and diversification

The basic idea of intensification is to explore regions of the search space that seem more promising more thoroughly. But intensification by itself is not sufficient for reaching the best results, therefore a complementary concept called diversification has been proposed which diversifies the search by guiding it to lesser or never explored regions of the search space.

While applying tabu search to search space one can use short-term, intermediate and long-term memory as a tool to achieve better results. Short-term memory is usually used for tabu lists and intermediate and long-term memories serve in two more complicated elements that can be incorporated into tabu search, namely, search intensification and diversification.

Intermediate memory is used as a means for learning about favourable features of good solutions during a particular period of time. Through this learning period, certain good characteristics or *attributes* of attractive solutions are distinguished. Then, this knowledge is applied for seeking new solutions that contain these attributes. For a better understanding of intensification, one can refer to Glover (1990).

In order to prohibit the tabu search from spending most of its efforts in a limited region of the search space (something the search has a tendency towards) and probably missing some good solutions in other regions, long-term memory is used. Long-term memory works as a tool for diversifying the search and as a result guides the search to regions that have not been explored or have been explored less. There are three main ways for achieving diversification: strategic oscillation, restart diversification and continuous diversification. For more information on these techniques one can refer to Glover (1989b, 1990); Soriano et Gendreau (1996).

Short-term memory is considered as the core of tabu search, as it is an aggressive way to

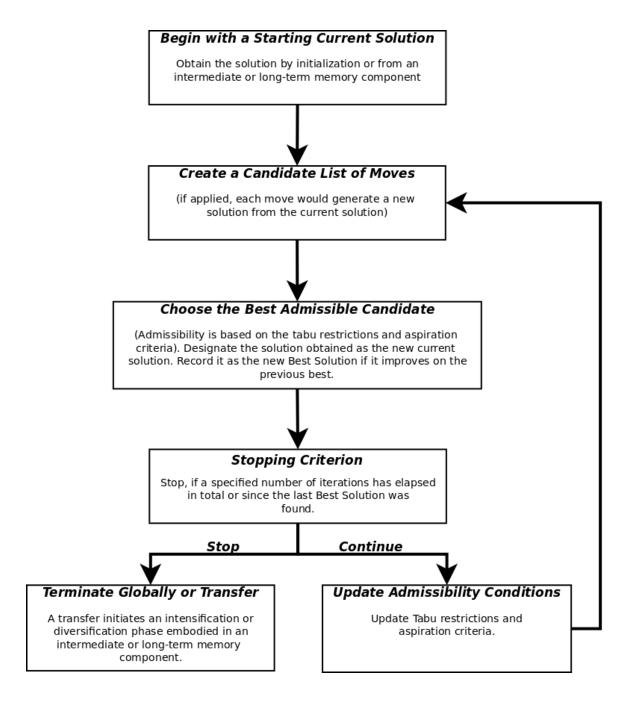

Figure 2.5 Tabu search

find the best possible moves. The choice of best move is usually related to the change in objective value it causes. But if the real objective function value is complex to determine, approximation is used. For better understanding of evaluation process one can refer to Glover (1989a); Glover et Laguna (2002). A general view of tabu search and its components discussed earlier is provided in Figure 2.5.

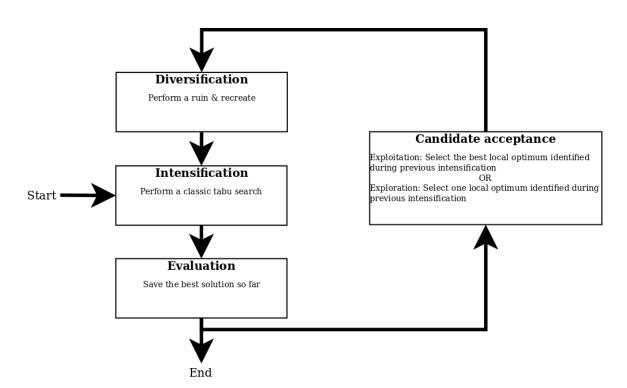

According to Misevicius *et al.* (2006), the repetitive transition between an intensification phase handled by a classic tabu search, and a diversification phase that follows a *reconstruct and improve* paradigm can be considered as an *iterated tabu search* (ITS). In this framework, the goal of the intensification phase is to search for better (locally optimal) solutions in a specific area of the solution space, whereas the diversification phase escapes local optimum by moving towards new regions in the solution space. In this sense, the diversification can follow a *ruin and recreate* principle, that consists of deleting a part of a solution (ruin) and then reconstructing a new solution from the part that has not been destructed (recreate). The principle advantage of this strategy is its effectiveness in dealing with solution spaces that contain deep valleys.

Except for the first iteration, intensification is always applied to the solution that has just been reconstructed (i.e., the output of diversification). However, there are two main alternatives for selecting the candidate for diversification: exploitation and exploration. Exploitation is achieved by choosing the best local optimum identified during the previous intensification phase as a candidate for destruction and reconstruction. In the case of exploration a variety of policies may be used. In fact, each locally optimized solution encountered during the intensification can be considered as a potential candidate for diversification. Figure 2.6 illustrates the general framework of an iterated tabu search.

Figure 2.6 Generalized framework of an iterated tabu search.

# **Chapter 3**

## **MODEL & ALGORITHM**

This chapter presents our approach to designing low complexity multiplier-less digital filters. Section 3.1 defines the graph-based model that we introduce to accurately represent integrated circuits. Section 3.2 describes the fitness function that we use to estimate the quality of a filter. And section 3.3 is dedicated to the different components of our optimization algorithm.

# 3.1 A new graph-based model to accurately represent integrated circuits

As previously illustrated in Figure 2.1, integrated circuits are traditionally characterized by a diagram that indicates how the elements that constitute a circuit are assembled. This schematic representation is based on a library of symbols that allocates a specific icon to each type of circuit element (Table 2.1). These symbols are linked by lines or arrows that indicate the connections between the circuit elements.

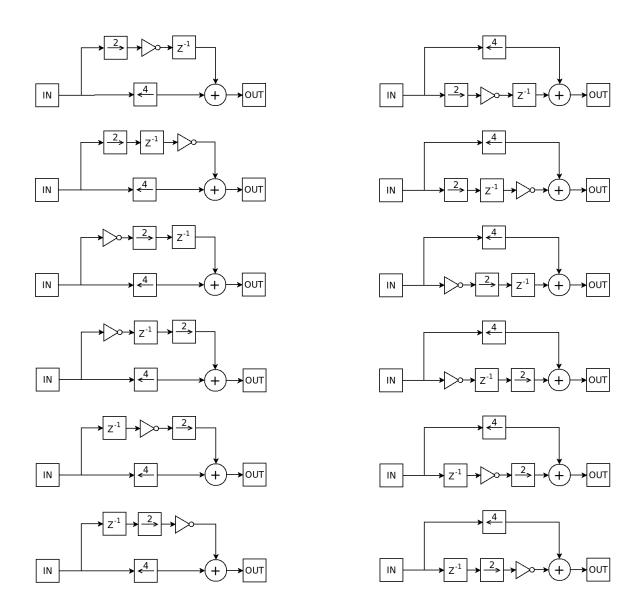

Although this traditional representation has the advantage of being easy to read and understand, the same circuit realization can be represented in different ways. Figure 3.1 shows a graphical example of how the same circuit realization can be represented in 12 different ways using the traditional schematic representation. This symmetry in the representation, which is mostly due to the commutativity of the operators inside the circuits (addition, multiplication), can cause serious problems for an optimization algorithm to accurately explore the solution space during the design process. That is the reason why we developed a new graph-based model that prohibits symmetry in the representation of integrated circuits.

Figure 3.1 An example of the symmetry in the traditional schematic representation.

#### 3.1.1 Model definition

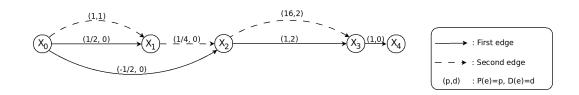

In order to face the issues of the traditional schematic representation related to symmetry, Joliveau *et al.* (2011) introduced a binary tree model to efficiently represent any multiplier-less integrated circuit realization (recursive and non-recursive) under a unique way. As our research only focuses on FIR digital filters, we derived the idea of a unique representation to non-recursive circuits from Joliveau *et al.* (2011) and defined a graph-based model adapted to our context. This model is centered around the location of adders in the circuits and their connections with other circuit elements (shift, inverter and delay). Following our model, a circuit containing N adders is thus symbolized by a directed acyclic graph G = (X, E) with a source  $X_0$  that stands for the circuit input, a sink  $X_{N+1}$  that stands for the circuit output, and N vertices  $X_i$ ,  $i \in [1, N]$  that represent the adders. Each edge of the graph symbolizes a *connection path* between two adders of the circuit, or between an adder and the circuit input/output. A connection path is defined as a path between two adders in the circuit that does not pass through another adder. Since adders have two inputs, there can be a maximum of two connection paths between two given adders i and j, which would lead to a graph with up to two distinct edges linking the vertices  $X_i$  and  $X_j$ .

Each edge of the graph  $e_k \in E$  is weighted according to two functions: the process function  $P(e_k)$  and the delay function  $D(e_k)$ . The process function considers all the shifts and the inverters on the connection path represented by the edge and indicates the corresponding constant by which the signal is multiplied. For example, if a connection path represented by the edge  $e_k$  contains one inverter (i.e., a multiplication by -1) and three left shifts (i.e., three consecutive multiplications by 2), the process value of  $e_k$  will be given by  $P(e_k) = -2^3$ . As for the delay function, it simply shows the number of delays on the connection path.

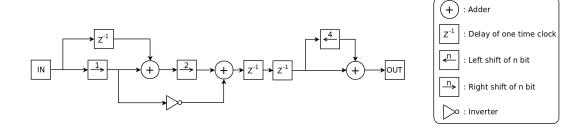

Figure 3.2 gives an example of how the same integrated circuit is illustrated according to the classical schematic model and the proposed graph-based model.

## 3.1.2 Ensuring the feasibility of the circuit structure

While presenting a novel approach to represent non recursive integrated circuits, one of the priorities is to provide a model that guarantees the feasibility of the circuit structure. This can be done by introducing a set of rules for the model which ensure that the quantity of inputs and outputs of each element is respected and that there are no recursive loops. In order to describe these rules, we must introduce the functions  $d_{\Gamma}^{-}(X)$ ,  $d_{\Gamma}^{+}(X)$  and  $N_{\Gamma}^{-}(X)$  that respectively indicate the in-degree (i.e., the number of predecessors), the out-degree

#### Traditional schematic representation

#### Proposed Graph-based representation

Figure 3.2 Illustration of the same integrated circuit using the traditional schematic representation and the proposed graph-based representation.

(i.e., the number of successors) and the in-neighborhood (i.e., the list of predecessors) of a given vertex X.

Rule 1: Respecting the number of input and output of circuit elements

Rule 1a: The circuit input has no predecessors and at least one successor

$$d_{\Gamma}^{-}(X_{0}) = 0$$

and  $d_{\Gamma}^{+}(X_{0}) >= 1$ .

Rule 1b: The circuit adders have exactly two predecessors and at least one successor

$$\forall i \in [1, N], \ d_{\Gamma}^{-}(X_i) = 2 \text{ and } d_{\Gamma}^{+}(X_i) > = 1.$$

Rule 1c: The circuit output has exactly one predecessor and no successor

$$\forall i \in [1,N], d_{\Gamma}^{-}(X_{N+1}) = 1 \text{ and } d_{\Gamma}^{+}(X_{N+1}) = 0.$$

Rule 2: non-recursivity of the circuit

$$\forall i \in [1, N+1], i \in N_{\Gamma}^{-}(X_i) \Rightarrow i < j.$$

## 3.1.3 Prohibiting the symmetry in the representation

As mentioned before, one of the goals of our model is to avoid symmetry in the representation. In order to achieve this goal, we add another set of rules to the model. By defining the weight function for the graph edges, our model already takes care of the symmetry related to shift, delays and inverters. Thus, only the symmetry stemming from the commutativity of the addition remains. This can be addressed by defining an order on the two edges  $e_{k1}$  and  $e_{k2}$  respectively connecting vertices  $X_{i_1}$  and  $X_{i_2}$  to vertex  $X_j$ . A function  $ArgTail(e_k)$  that indicates the index of the tail (i.e., the initial vertex) of an edge  $e_k \in E$ , is used for this matter.

**Rule 3**: Determining which of the two edges entering in a vertex  $X_j$ ,  $j \in [1, N]$  representing an adder is the first edge  $(Edge_1(j))$  and which is the second edge  $(Edge_2(j))$

**Rule 3a**: The index of the tail of the first edge is less than or equal to the index of the tail of the second edge:

$$ArgTail(Edge_1(X_j)) \le ArgTail(Edge_2(X_j)).$$

**Rule 3b**: If both edges  $e_{k1}$  and  $e_{k2}$  come from the same predecessor, the first edge contains less delays than the second edge:

$$if (X_{i_1} = X_{i_2}),$$

$$D(Edge_1(X_i)) \le D(Edge_2(X_i)).$$

**Rule 3c**: If both edges  $e_{k1}$  and  $e_{k2}$  come from the same predecessor and contain the same number of delays, the multiplication constant of the first edge is less than the multiplication constant of the second edge

$$if ((X_{i_1} = X_{i_2}) \wedge (D(Edge_1(X_j)) = D(Edge_2(X_j))),$$

$$P(Edge_1(X_j)) \leq P(Edge_2(X_j)).$$

A graphical example of each of these rules can be viewed in Table 3.1.

Table 3.1 Illustration of the 3 rules to avoid symmetry in the model.

| Rule    | Illustration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Rule 3a | Traditional schematic representation $ \begin{array}{ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|         | Proposed Graph-based representation $ \begin{array}{ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Rule 3b | Traditional schematic representation $ \begin{array}{ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|         | (8,2) $(2)$ $(4,1)$ $(3)$ $(4,1)$ $(4,1)$ $(4,1)$ $(4,1)$ $(4,1)$ $(4,1)$ $(4,1)$ $(4,1)$ $(4,1)$ $(4,1)$ $(4,1)$ $(4,1)$ $(4,1)$ $(4,1)$ $(4,1)$ $(4,1)$ $(4,1)$ $(4,1)$ $(4,1)$ $(4,1)$ $(4,1)$ $(4,1)$ $(4,1)$ $(4,1)$ $(4,1)$ $(4,1)$ $(4,1)$ $(4,1)$ $(4,1)$ $(4,1)$ $(4,1)$ $(4,1)$ $(4,1)$ $(4,1)$ $(4,1)$ $(4,1)$ $(4,1)$ $(4,1)$ $(4,1)$ $(4,1)$ $(4,1)$ $(4,1)$ $(4,1)$ $(4,1)$ $(4,1)$ $(4,1)$ $(4,1)$ $(4,1)$ $(4,1)$ $(4,1)$ $(4,1)$ $(4,1)$ $(4,1)$ $(4,1)$ $(4,1)$ $(4,1)$ $(4,1)$ $(4,1)$ $(4,1)$ $(4,1)$ $(4,1)$ $(4,1)$ $(4,1)$ $(4,1)$ $(4,1)$ $(4,1)$ $(4,1)$ $(4,1)$ $(4,1)$ $(4,1)$ $(4,1)$ $(4,1)$ $(4,1)$ $(4,1)$ $(4,1)$ $(4,1)$ $(4,1)$ $(4,1)$ $(4,1)$ $(4,1)$ $(4,1)$ $(4,1)$ $(4,1)$ $(4,1)$ $(4,1)$ $(4,1)$ $(4,1)$ $(4,1)$ $(4,1)$ $(4,1)$ $(4,1)$ $(4,1)$ $(4,1)$ $(4,1)$ $(4,1)$ $(4,1)$ $(4,1)$ $(4,1)$ $(4,1)$ $(4,1)$ $(4,1)$ $(4,1)$ $(4,1)$ $(4,1)$ $(4,1)$ $(4,1)$ $(4,1)$ $(4,1)$ $(4,1)$ $(4,1)$ $(4,1)$ $(4,1)$ $(4,1)$ $(4,1)$ $(4,1)$ $(4,1)$ $(4,1)$ $(4,1)$ $(4,1)$ $(4,1)$ $(4,1)$ $(4,1)$ $(4,1)$ $(4,1)$ $(4,1)$ $(4,1)$ $(4,1)$ $(4,1)$ $(4,1)$ $(4,1)$ $(4,1)$ $(4,1)$ $(4,1)$ $(4,1)$ $(4,1)$ $(4,1)$ $(4,1)$ $(4,1)$ $(4,1)$ $(4,1)$ $(4,1)$ $(4,1)$ $(4,1)$ $(4,1)$ $(4,1)$ $(4,1)$ $(4,1)$ $(4,1)$ $(4,1)$ $(4,1)$ $(4,1)$ $(4,1)$ $(4,1)$ $(4,1)$ $(4,1)$ $(4,1)$ $(4,1)$ $(4,1)$ $(4,1)$ $(4,1)$ $(4,1)$ $(4,1)$ $(4,1)$ $(4,1)$ $(4,1)$ $(4,1)$ $(4,1)$ $(4,1)$ $(4,1)$ $(4,1)$ $(4,1)$ $(4,1)$ $(4,1)$ $(4,1)$ $(4,1)$ $(4,1)$ $(4,1)$ $(4,1)$ $(4,1)$ $(4,1)$ $(4,1)$ $(4,1)$ $(4,1)$ $(4,1)$ $(4,1)$ $(4,1)$ $(4,1)$ $(4,1)$ $(4,1)$ $(4,1)$ $(4,1)$ $(4,1)$ $(4,1)$ $(4,1)$ $(4,1)$ $(4,1)$ $(4,1)$ $(4,1)$ $(4,1)$ $(4,1)$ $(4,1)$ $(4,1)$ $(4,1)$ $(4,1)$ $(4,1)$ $(4,1)$ $(4,1)$ $(4,1)$ $(4,1)$ $(4,1)$ $(4,1)$ $(4,1)$ $(4,1)$ $(4,1)$ $(4,1)$ $(4,1)$ $(4,1)$ $(4,1)$ $(4,1)$ $(4,1)$ $(4,1)$ $(4,1)$ $(4,1)$ $(4,1)$ $(4,1)$ $(4,1)$ $(4,1)$ $(4,1)$ $(4,1)$ $(4,1)$ $(4,1)$ $(4,1)$ $(4,1)$ $(4,1)$ $(4,1)$ $(4,1)$ $(4,1)$ $(4,1)$ $(4,1)$ $(4,1)$ $(4,1)$ $(4,1)$ $(4,1)$ $(4,1)$ $(4,1)$ $(4,1)$ $(4,1)$ $(4,1)$ $(4,1)$ $(4,1)$ $(4,1)$ $(4,1)$ |

|         | Traditional schematic representation $ \begin{array}{c}                                     $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

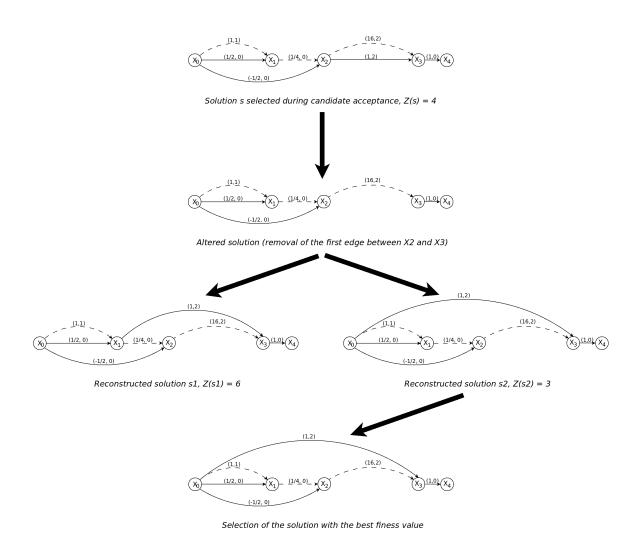

| Rule 3c | + $+$ $+$ $+$ $+$ $+$ $+$ $+$ $+$ $+$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |