**Titre:** Modélisation et conception d'une plate-forme de traitement et

Title: transmission de signaux vidéo numériques

**Auteur:** M. Dubois

Author:

**Date:** 2004

**Type:** Mémoire ou thèse / Dissertation or Thesis

**Référence:** Dubois, M. (2004). Modélisation et conception d'une plate-forme de traitement et

transmission de signaux vidéo numériques [Mémoire de maîtrise, École

Polytechnique de Montréal]. PolyPublie. <https://publications.polymtl.ca/7479/>

Citation:

## Document en libre accès dans PolyPublie

Open Access document in PolyPublie

**URL de PolyPublie:** <https://publications.polymtl.ca/7479/>

PolyPublie URL:

**Directeurs de recherche:** Yvon Savaria, & Guy Bois

Advisors:

**Programme:** Non spécifié

Program:

# **NOTE TO USERS**

This reproduction is the best copy available.

**UNIVERSITÉ DE MONTRÉAL**

**MODÉLISATION ET CONCEPTION D'UNE PLATE-FORME DE

TRAITEMENT ET TRANSMISSION DE SIGNAUX VIDÉO

NUMÉRIQUES**

**MATHIEU DUBOIS**

**DÉPARTEMENT DE GÉNIE ÉLECTRIQUE

ÉCOLE POLYTECHNIQUE DE MONTRÉAL**

**MÉMOIRE PRÉSENTÉ EN VUE DE L'OBTENTION

DU DIPLÔME DE MAÎTRISE EN SCIENCES APPLIQUÉES

EN GÉNIE ÉLECTRIQUE**

**JUILLET 2004**

Library and

Archives Canada

Bibliothèque et

Archives Canada

Published Heritage

Branch

Direction du

Patrimoine de l'édition

395 Wellington Street

Ottawa ON K1A 0N4

Canada

395, rue Wellington

Ottawa ON K1A 0N4

Canada

*Your file Votre référence*

*ISBN: 0-612-97942-3*

*Our file Notre référence*

*ISBN: 0-612-97942-3*

#### NOTICE:

The author has granted a non-exclusive license allowing Library and Archives Canada to reproduce, publish, archive, preserve, conserve, communicate to the public by telecommunication or on the Internet, loan, distribute and sell theses worldwide, for commercial or non-commercial purposes, in microform, paper, electronic and/or any other formats.

The author retains copyright ownership and moral rights in this thesis. Neither the thesis nor substantial extracts from it may be printed or otherwise reproduced without the author's permission.

#### AVIS:

L'auteur a accordé une licence non exclusive permettant à la Bibliothèque et Archives Canada de reproduire, publier, archiver, sauvegarder, conserver, transmettre au public par télécommunication ou par l'Internet, prêter, distribuer et vendre des thèses partout dans le monde, à des fins commerciales ou autres, sur support microforme, papier, électronique et/ou autres formats.

L'auteur conserve la propriété du droit d'auteur et des droits moraux qui protège cette thèse. Ni la thèse ni des extraits substantiels de celle-ci ne doivent être imprimés ou autrement reproduits sans son autorisation.

---

In compliance with the Canadian Privacy Act some supporting forms may have been removed from this thesis.

While these forms may be included in the document page count, their removal does not represent any loss of content from the thesis.

Conformément à la loi canadienne sur la protection de la vie privée, quelques formulaires secondaires ont été enlevés de cette thèse.

Bien que ces formulaires aient inclus dans la pagination, il n'y aura aucun contenu manquant.

**UNIVERSITÉ DE MONTRÉAL**

**ÉCOLE POLYTECHNIQUE**

Le titre du mémoire :

**MODÉLISATION ET CONCEPTION D'UNE PLATE-FORME DE

TRAITEMENT ET TRANSMISSION DE SIGNAUX VIDÉO

NUMÉRIQUES**

Présenté par : Mathieu Dubois

En vue de l'obtention du diplôme de : Maîtrise en sciences appliquées

A été dûment accepté par le jury de l'examen constitué de :

M. Yves Audet, Président

M. Yvon SAVARIA, Ph.D., membre et directeur de recherche

M. Guy BOIS, Ph.D., membre et codirecteur de recherche

M. Mohamad Sawan, membre

## REMERCIEMENTS

J'aimerais remercier tout d'abord mon directeur de recherche, Yvon Savaria et la compagnie Gennum pour leur soutien financier. De plus, je remercie messieurs Savaria et Guy Bois pour leur encadrement pendant l'élaboration de ce projet de recherche.

Je tiens à remercier tous les étudiants du GRM (Groupe de Recherche en Microélectronique) qui ont contribué à l'avancement du projet de conception sur les convertisseurs de protocoles réseaux et de la plate-forme de traitement vidéo. Plus particulièrement, j'aimerais remercier Serge Catudal pour le développement en C++ de l'architecture de Wiener. En plus, je remercie Maurice Kouam pour avoir fourni un module de réducteur de bruit en SystemC pour le développement de ma méthode. Ces personnes et Robert Groulx ont collaboré à la nouvelle plate-forme de traitement vidéo.

Enfin, je remercie mes parents et mon frère Martin Dubois pour leur soutien dans ce travail.

## RÉSUMÉ

L'application visée dans ce projet de maîtrise concerne une plate-forme SoC (System on Chip) pour le traitement et la transmission vidéo. La transmission sera réalisée par un processeur réseau d'abord conçu pour la conversion de protocoles. Le traitement vidéo sera exploré au travers une plate-forme vidéo conçue pour exécuter l'algorithme de Wiener. Dans les deux cas, nous emploierons un modèle de plate-forme générique.

Ce travail discutera d'une nouvelle méthode pour concevoir un SoC avec plusieurs langages et il discutera des modules d'intercommunication dans une plate-forme SoC. La réduction du temps, des coûts de développement et une mise en marché plus rapide découleront de cette recherche. Une exploration des capacités de quelques langages permettra d'élaborer une nouvelle méthode à double profilage utilisant le meilleur de chacun.

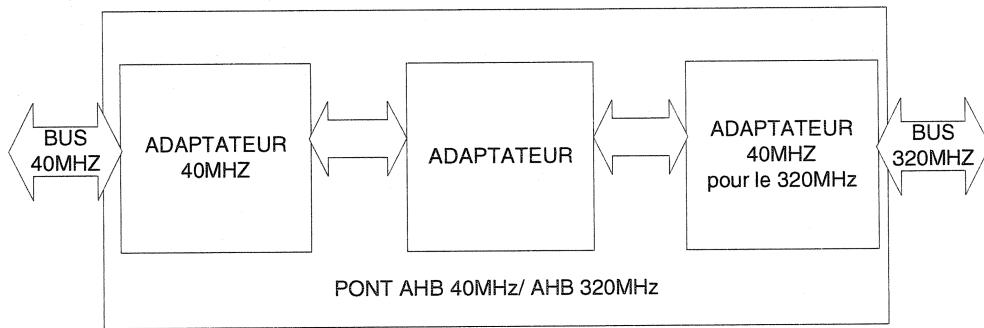

Relier l'ensemble des modules d'une plate-forme SoC exige la compatibilité des modules. Plusieurs solutions sont disponibles, mais elles sont caractérisées par une bande passante insuffisante ou un manque de flexibilité. Ce travail propose une architecture d'intercommunication pour un milieu de communication flexible de haute performance pouvant fournir une largeur de bande variable. Il est basé sur le bus AHB de AMBA. L'architecture proposée a été implémentée dans l'environnement HDL Designer Series<sup>TM</sup> de Synopsis, en utilisant la technologie CMOS 0.18 micron avec des outils de Cadence pour valider le concept proposé. Nos travaux montrent qu'il est possible d'obtenir un pont AHB/AHB multi-fréquentiel avec de nouvelles caractéristiques. Ce pont permet la synchronisation automatique entre les domaines d'horloges opérant autour de 500MHz.

## ABSTRACT

The thesis is concerned will the development of a System on Chip (SoC) platform for transmission and processing of video. The transmission will be done using a network processor first developed for protocol conversion applications while video processing will be explored through a video platform developed for the Wiener noise reduction algorithm. In both cases, we will use a generic platform model.

This work will discuss a new method to design a SoC using several languages, and it will explore means of interconnecting modules in a SoC platform. The research aims at reducing development time and costs. We explore several languages that can be leveraged in an effective SoC platform design methodology. We propose a method based on a double profiling to leverage advantages of the various languages.

Interconnecting modules in a SoC platform requires modules compatibility. Several solutions are available, but they either lack the necessary throughput or flexibility. This work proposes an interconnection architecture to implement a flexible on-chip high-performance communication medium that can provide variable bandwidth. It is based on the AHB AMBA bus. The proposed architecture has been implemented with the Synopsis HDL Designer environment and laid out using a 0.18 micron CMOS with Cadence tools to validate the proposed concept.

Our results demonstrate that it is possible to get a multi frequency AHB/AHB bridge with several interesting features that can be used to synchronize multiple clock domains with different frequencies operating up to 500MHz.

## TABLE DES MATIÈRES

|                                                                                                                      |      |

|----------------------------------------------------------------------------------------------------------------------|------|

| REMERCIEMENTS.....                                                                                                   | iv   |

| RÉSUMÉ .....                                                                                                         | v    |

| ABSTRACT.....                                                                                                        | vi   |

| LISTE DES FIGURES .....                                                                                              | xi   |

| LISTE DES TABLEAUX.....                                                                                              | xiv  |

| LISTE DES NOTATIONS ET SYMBOLES .....                                                                                | xv   |

| LISTE DES ANNEXES .....                                                                                              | xvi  |

| AVANT-PROPOS .....                                                                                                   | xvii |

| <br>CHAPITRE 1 INTRODUCTION .....                                                                                    |      |

| 1.1 Motivations .....                                                                                                | 1    |

| 1.2 Contributions.....                                                                                               | 2    |

| 1.3 Organisation du mémoire.....                                                                                     | 3    |

| <br>CHAPITRE 2 L'ÉTAT DE L'ART : OUTILS DE CONCEPTION, PLATE-FORME<br>SoC POUR LE VIDEO ET INTERCONNEXIONS SoC ..... |      |

| 2.1 Introduction à la conception des systèmes embarqués .....                                                        | 5    |

| 2.2 Aperçus des outils.....                                                                                          | 9    |

| 2.2.1 HDL Designer.....                                                                                              | 9    |

| 2.2.2 Matlab .....                                                                                                   | 9    |

| 2.2.3 SystemC .....                                                                                                  | 11   |

| 2.2.4 Seamless.....                                                                                                  | 13   |

| 2.2.5 Modelsim [32].....                                                                                             | 15   |

| 2.2.6 SystemVerilog.....                                                                                             | 16   |

| 2.2.7 UML.....                                                                                                       | 16   |

| 2.3 Convertisseur de protocoles.....                                                                                 | 16   |

| 2.4 Autres architectures des plate-formes SoC vidéo .....                                                            | 19   |

| 2.4.1 VC01 .....                                                                                                     | 19   |

|                                          |                                                      |    |

|------------------------------------------|------------------------------------------------------|----|

| 2.4.2                                    | Nexperia .....                                       | 20 |

| 2.5                                      | Interconnexion d'une plate-forme SoC .....           | 21 |

| 2.5.1                                    | Interconnexion d'une plate-forme Nexperia-DVP .....  | 22 |

| 2.5.2                                    | Star-IP Bus .....                                    | 23 |

| 2.5.3                                    | Le bus CoreConnect .....                             | 25 |

| 2.6                                      | Conclusion .....                                     | 26 |

| CHAPITRE 3 MODÉLISATION HÉTÉROGÈNE ..... |                                                      | 27 |

| 3.1                                      | Plate-forme SoC .....                                | 27 |

| 3.1.1                                    | Concept .....                                        | 27 |

| 3.1.2                                    | Intégration .....                                    | 28 |

| 3.2                                      | Modélisation hétérogène .....                        | 28 |

| 3.2.1                                    | Le concept .....                                     | 28 |

| 3.2.2                                    | Niveaux d'abstraction .....                          | 30 |

| 3.3                                      | Méthodes d'interconnexion des langages .....         | 31 |

| 3.3.1                                    | Structure d'intercommunication .....                 | 31 |

| 3.3.2                                    | Méthode standard .....                               | 32 |

| 3.3.3                                    | Méthode de connexion par mémoire partagée UNIX ..... | 33 |

| 3.3.4                                    | Méthode de connexion par lien TCP/IP .....           | 34 |

| 3.3.5                                    | Comparaison des Méthodes .....                       | 35 |

| 3.4                                      | Adaptateurs .....                                    | 35 |

| 3.4.1                                    | Matlab .....                                         | 35 |

| 3.4.2                                    | Liens entre SystemC et VHDL .....                    | 37 |

| 3.4.3                                    | PIM et FLI .....                                     | 39 |

| 3.5                                      | Conception d'une plate-forme SoC .....               | 40 |

| 3.5.1                                    | Proposition d'une architecture générale .....        | 40 |

| 3.5.2                                    | Flot de conception .....                             | 42 |

| 3.5.3                                    | Niveau algorithmique .....                           | 43 |

| 3.5.4                                    | Niveau logiciel embarqué .....                       | 45 |

| 3.5.5                                    | Niveau UFT (untimed functional) .....                | 48 |

|                                                        |                                                              |           |

|--------------------------------------------------------|--------------------------------------------------------------|-----------|

| 3.5.6                                                  | Niveau Architectural .....                                   | 50        |

| 3.5.7                                                  | Raffinement des modules.....                                 | 51        |

| 3.5.8                                                  | Raffinement des communications.....                          | 55        |

| 3.5.9                                                  | Co-vérification et bus de contrôle.....                      | 55        |

| 3.6                                                    | L'utilisation adéquate des langages .....                    | 58        |

| 3.7                                                    | Conclusion .....                                             | 60        |

| <b>CHAPITRE 4 BUS GÉNÉRIQUE DE HAUTE VITESSE .....</b> |                                                              | <b>62</b> |

| 4.1                                                    | Modèle d'interconnexion .....                                | 63        |

| 4.1.1                                                  | Méthode de conception .....                                  | 63        |

| 4.1.2                                                  | Structure du système d'interconnexion.....                   | 64        |

| 4.2                                                    | Bus AMBA AHB .....                                           | 65        |

| 4.2.1                                                  | Modules maître et esclave d'un bus AHB .....                 | 66        |

| 4.2.2                                                  | Décodeur et arbitre.....                                     | 66        |

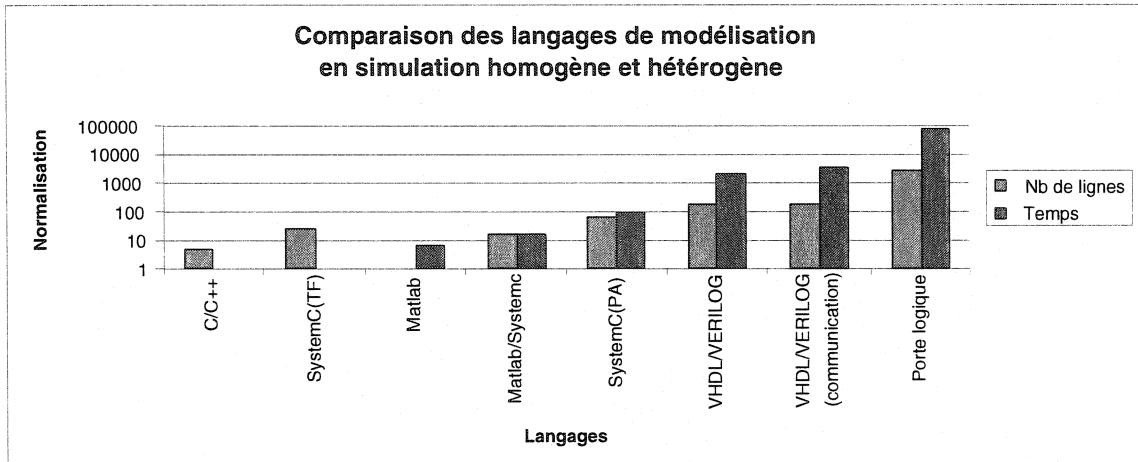

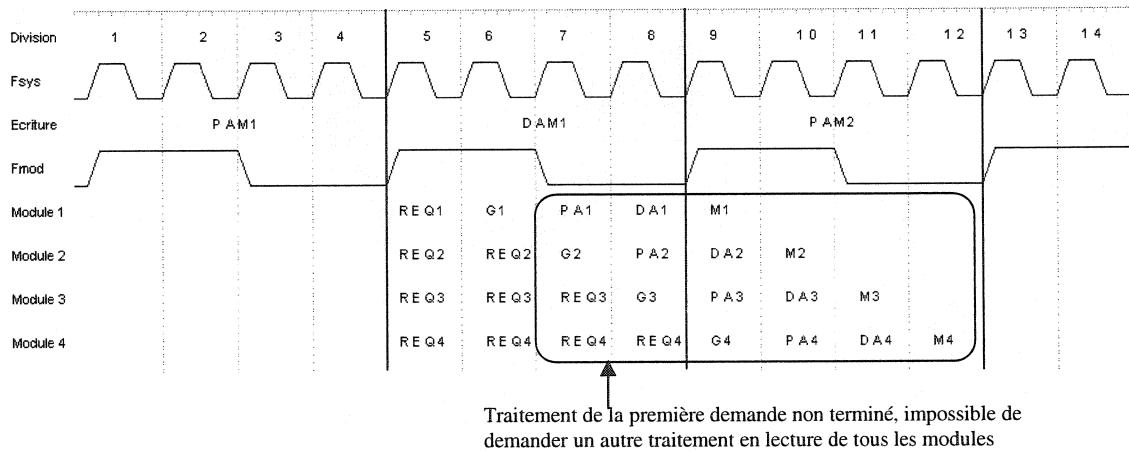

| 4.3                                                    | Analyse temporelle du signal.....                            | 67        |

| 4.3.1                                                  | Problématique d'interphase et d'optimisation des accès ..... | 67        |

| 4.3.2                                                  | Zone d'exclusion des modules.....                            | 69        |

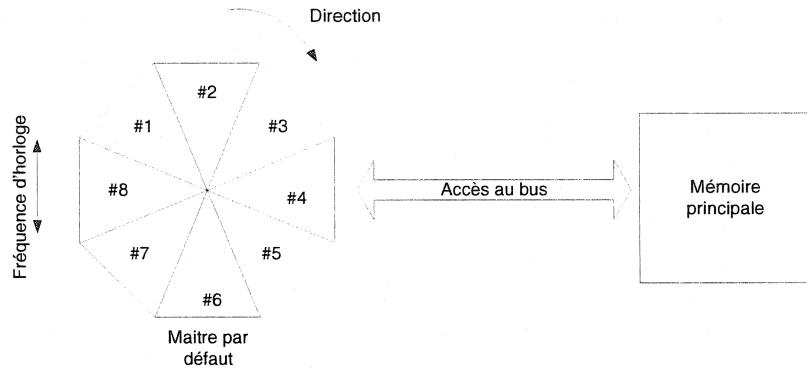

| 4.4                                                    | Bus par arbitrage circulaire .....                           | 70        |

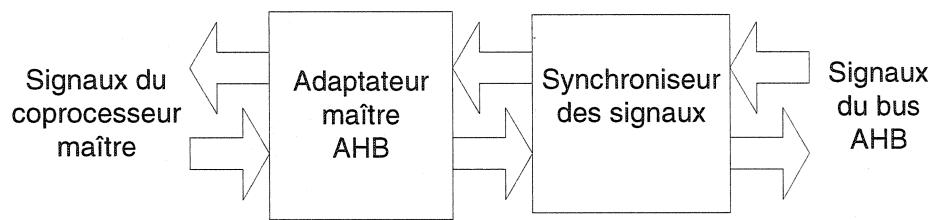

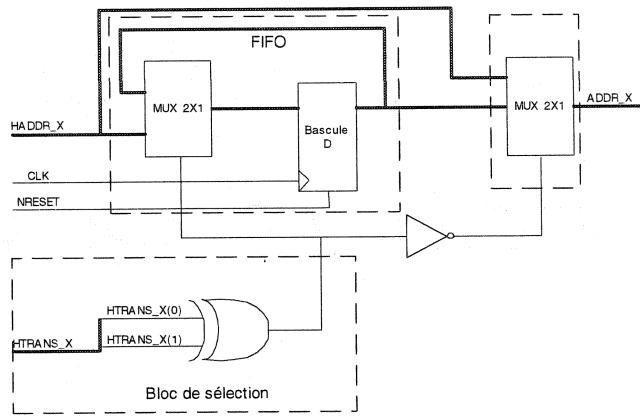

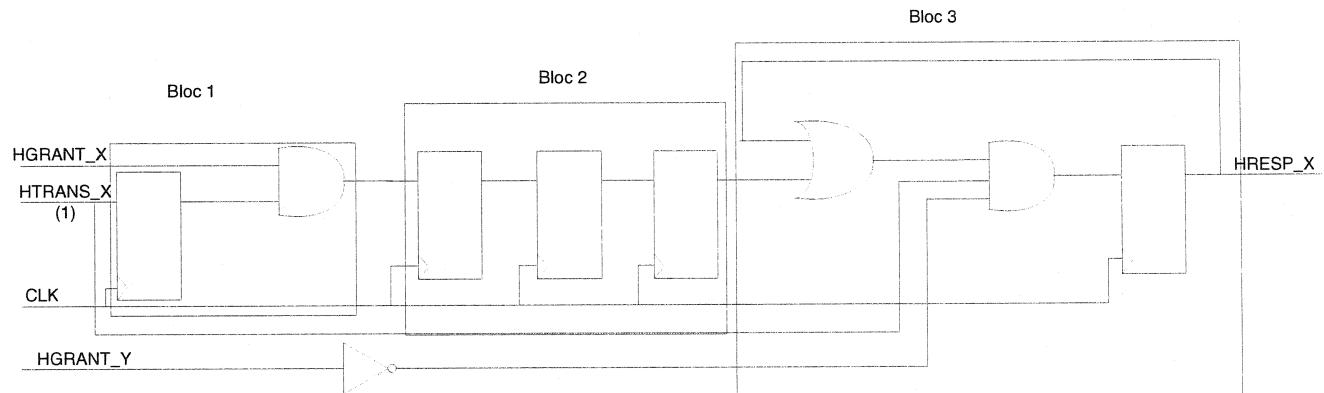

| 4.4.1                                                  | Les synchroniseurs.....                                      | 71        |

| 4.4.2                                                  | Arbitrage .....                                              | 73        |

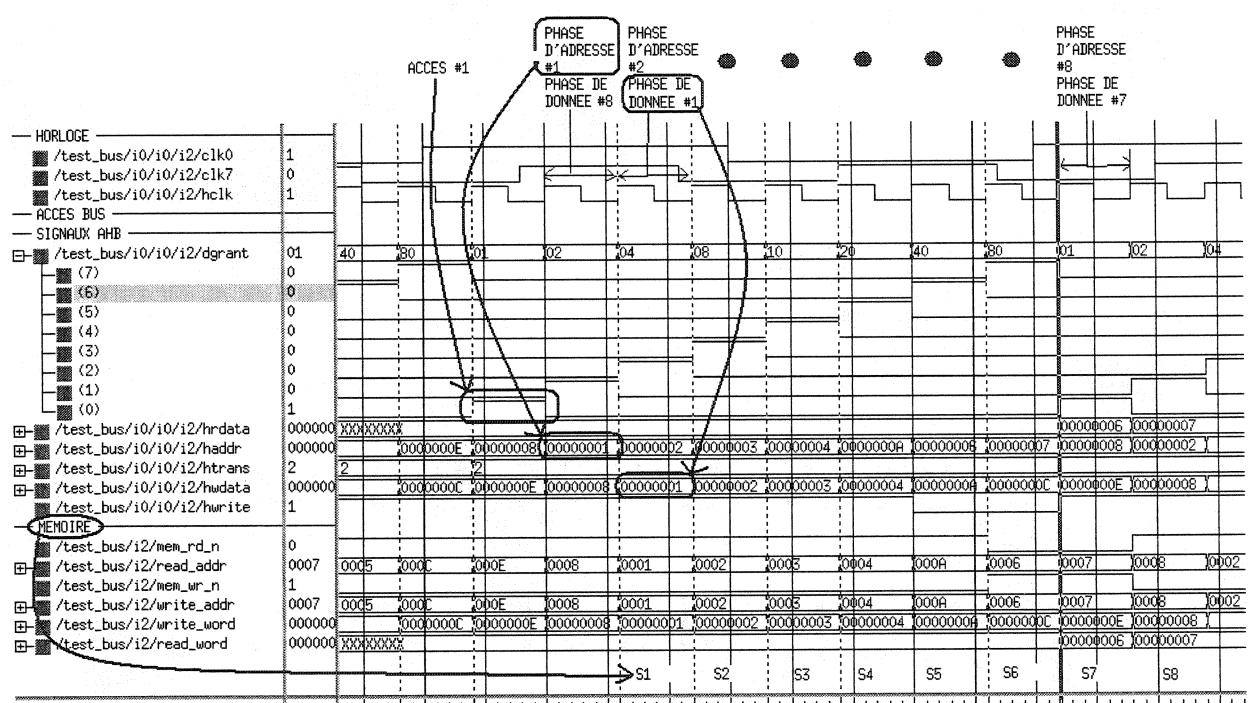

| 4.4.3                                                  | Résultat de simulation.....                                  | 75        |

| 4.4.4                                                  | Méthode de vérification .....                                | 75        |

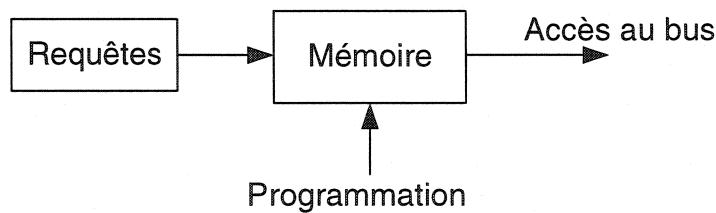

| 4.5                                                    | Bus par arbitrage de mémoire .....                           | 76        |

| 4.5.1                                                  | Les synchroniseurs.....                                      | 76        |

| 4.5.2                                                  | Arbitrage .....                                              | 77        |

| 4.5.3                                                  | Résultat de simulation.....                                  | 77        |

| 4.5.4                                                  | Méthode de vérification .....                                | 78        |

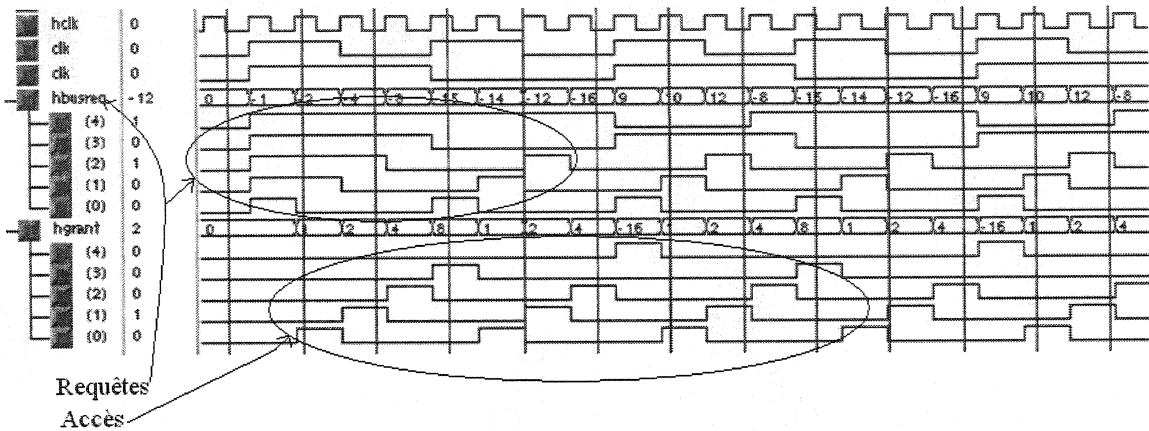

| 4.6                                                    | Bus dynamique par encodage de priorité.....                  | 78        |

| 4.6.1                                                  | Les synchroniseurs de l'adaptateur générique .....           | 78        |

| 4.6.2                                                  | Arbitrage .....                                              | 85        |

|                                               |                                       |    |

|-----------------------------------------------|---------------------------------------|----|

| 4.6.3                                         | Résultats de simulation .....         | 86 |

| 4.6.4                                         | Méthode de vérification .....         | 88 |

| 4.7                                           | Comparaison des trois méthodes .....  | 90 |

| 4.8                                           | Conclusion .....                      | 91 |

| CHAPITRE 5 CONCLUSION ET TRAVAUX FUTURS ..... |                                       | 93 |

| 5.1                                           | Conclusion sur les travaux .....      | 93 |

| 5.2                                           | Limitations et recherche future ..... | 95 |

## LISTE DES FIGURES

|                                                                                             |    |

|---------------------------------------------------------------------------------------------|----|

| Figure 2-1 Illustration du Co-design.....                                                   | 5  |

| Figure 2-2 Comparaison des niveaux de performance [23].....                                 | 6  |

| Figure 2-3 Flot typique de conception.....                                                  | 7  |

| Figure 2-4 Prix normalisés des outils.....                                                  | 8  |

| Figure 2-5 Flot de conception de Matlab pour DSP .....                                      | 10 |

| Figure 2-6 Illustration des interfaces .....                                                | 11 |

| Figure 2-7 Flot de conception avec SystemC .....                                            | 12 |

| Figure 2-8 Simulation avec C-Bridge .....                                                   | 13 |

| Figure 2-9 Seamless avec SystemC .....                                                      | 14 |

| Figure 2-10 Plate-forme du convertisseur de protocole.....                                  | 17 |

| Figure 2-11 Schéma bloc de la puce d'Alphamosaic .....                                      | 20 |

| Figure 2-12 DVP-based IC .....                                                              | 21 |

| Figure 2-13 Application des ports MTL dans un SoC de Nexperia .....                         | 22 |

| Figure 2-14 Illustration générale de l'interface pour les contrôles des périphériques ..... | 23 |

| Figure 2-15 Plate-forme PrimeXsys .....                                                     | 24 |

| Figure 2-16 Diagramme bloc du PowerNp [21] .....                                            | 25 |

| Figure 3-1 Modèle d'interconnexions des langages .....                                      | 29 |

| Figure 3-2 Mixage des niveaux d'abstraction .....                                           | 30 |

| Figure 3-3 Méthode d'échange des structures entre langages .....                            | 31 |

| Figure 3-4 Méthode standard de simulation .....                                             | 32 |

| Figure 3-5 Méthode de simulation par mémoire partagée .....                                 | 33 |

| Figure 3-6 Méthode de simulation par lien TCP/IP .....                                      | 34 |

| Figure 3-7 Comparaison entre le FLI et le PIM.....                                          | 39 |

| Figure 3-8 Modèle de plate-forme générique .....                                            | 41 |

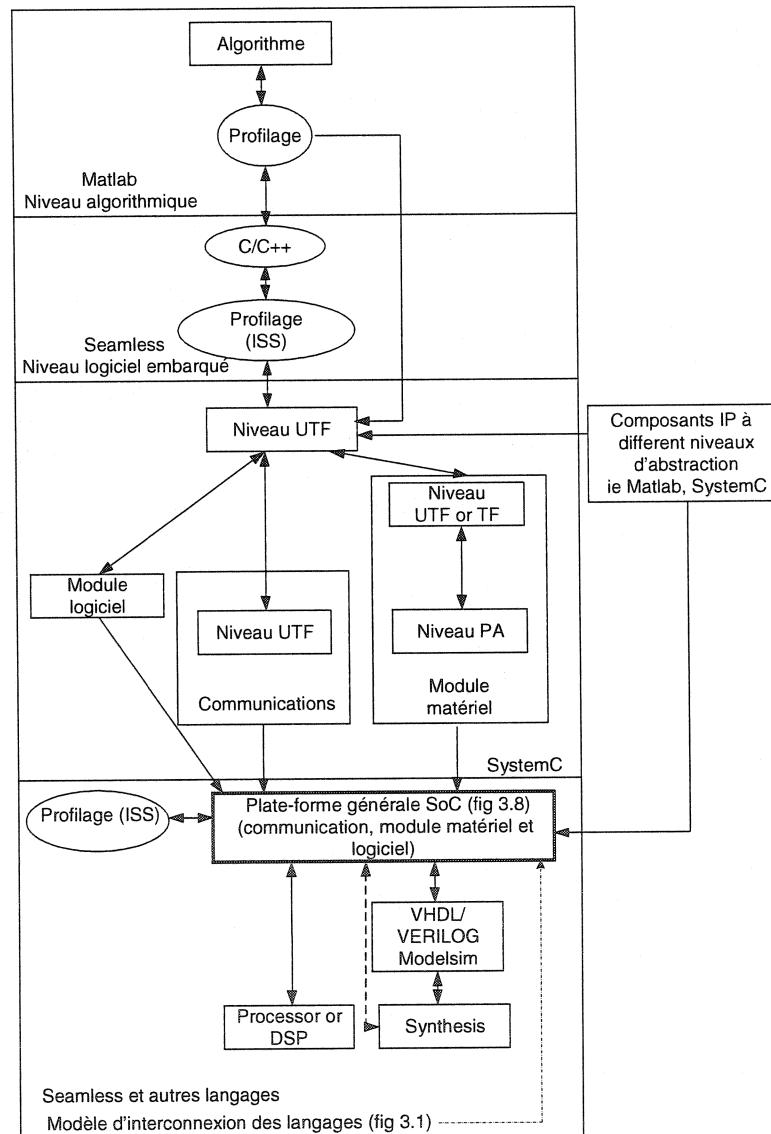

| Figure 3-9 Méthode de conception .....                                                      | 42 |

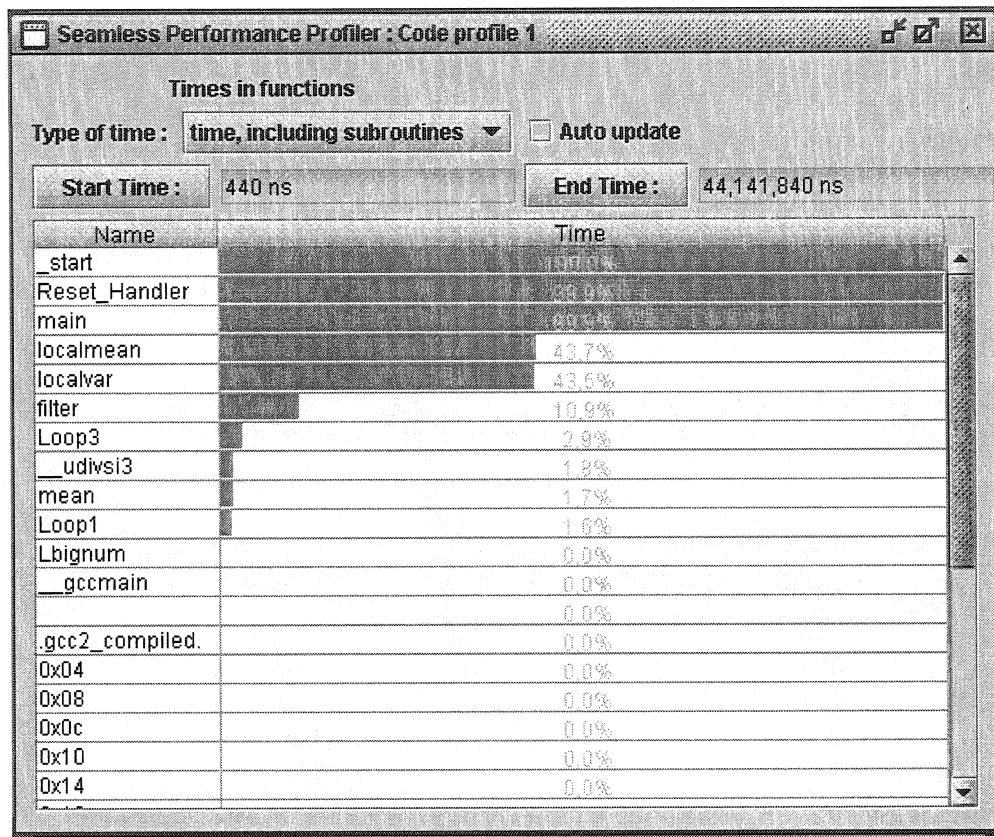

| Figure 3-10 Deuxième niveau de profilage (processeur).....                                  | 46 |

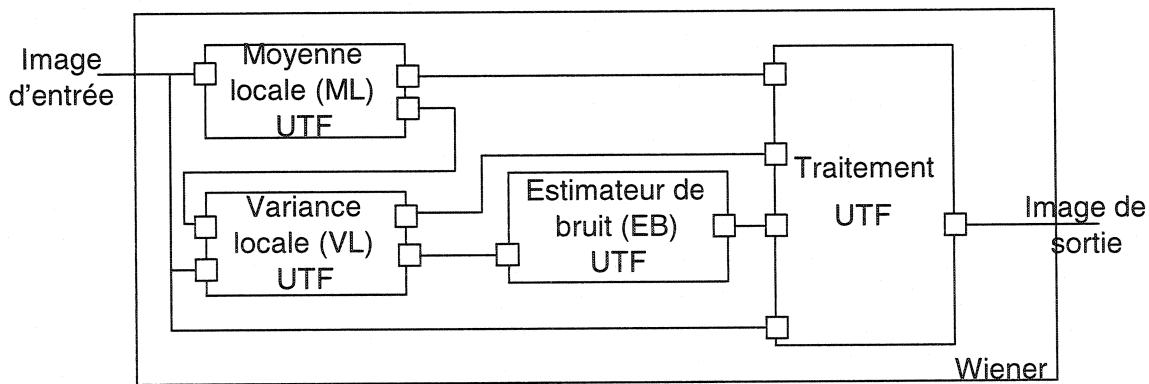

| Figure 3-11 Niveau UTF de l'algorithme de Wiener .....                                      | 48 |

|                                                                                                               |    |

|---------------------------------------------------------------------------------------------------------------|----|

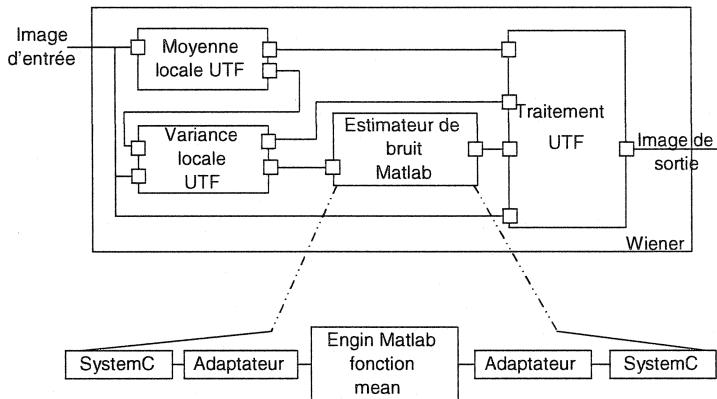

| Figure 3-12 Représentation de niveau UTF de l'algorithme de Wiener combinant des modèles Matlab/SystemC ..... | 50 |

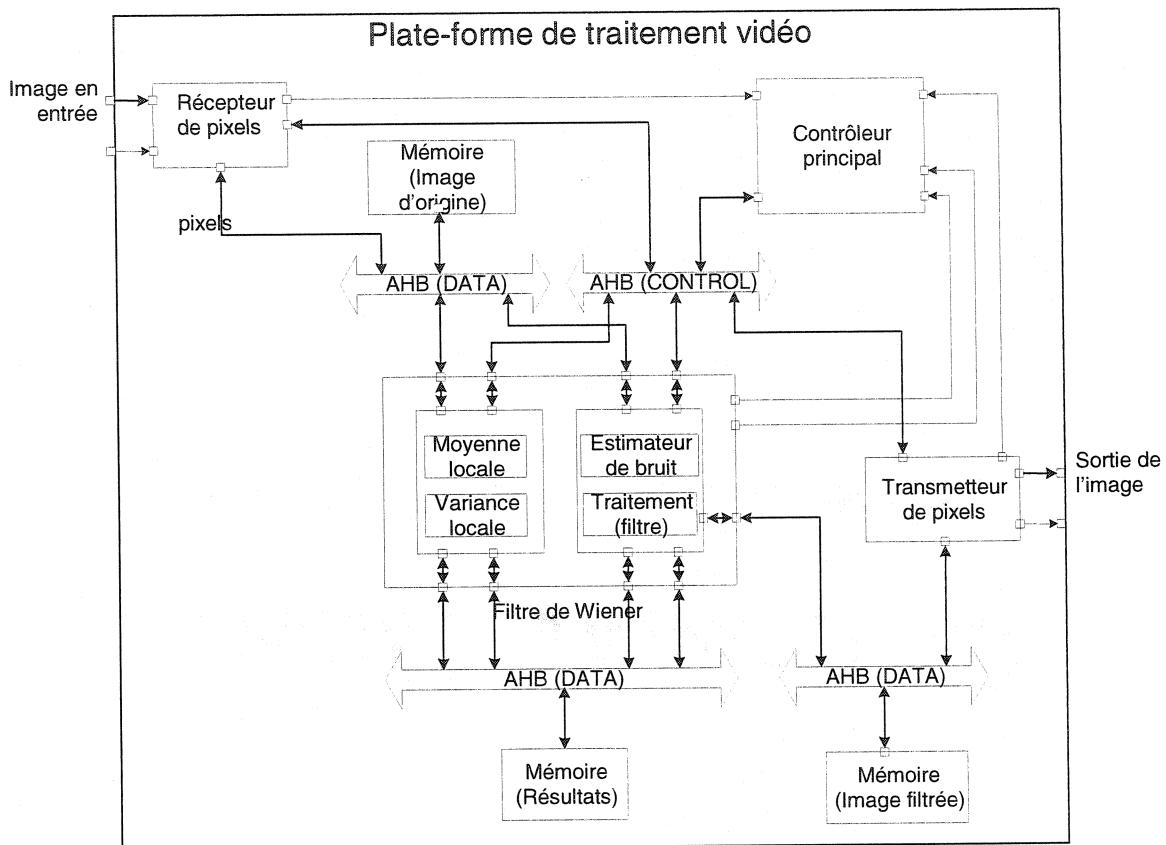

| Figure 3-13 Architecture d'une plate-forme vidéo .....                                                        | 51 |

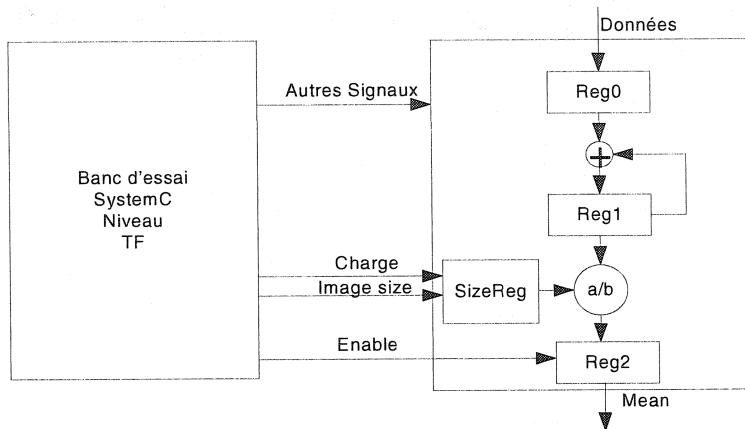

| Figure 3-14 Modèle de niveau PA de réducteur de bruit vidéo .....                                             | 52 |

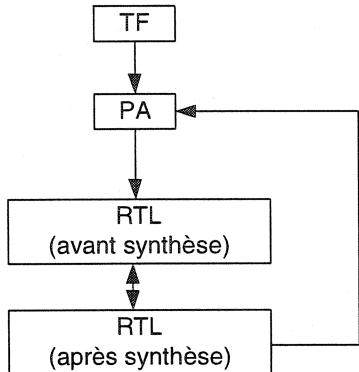

| Figure 3-15 Raffinement à un plus bas niveau d'abstraction .....                                              | 53 |

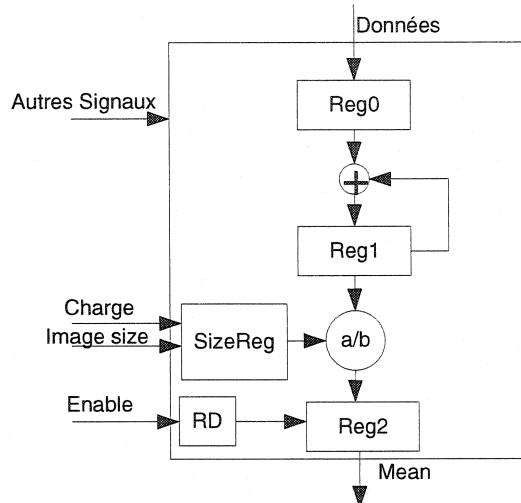

| Figure 3-16 Ajustement du module de l'estimateur à partir des composants disponibles                          | 53 |

| Figure 3-17 Simulation modelsim (VHDL/Verilog) .....                                                          | 54 |

| Figure 3-18 Simulation SystemC .....                                                                          | 54 |

| Figure 3-19 Illustration de l'ajout du délai dans une simulation SystemC/VHDL .....                           | 54 |

| Figure 3-20 Étape de raffinement d'un module .....                                                            | 55 |

| Figure 3-21 Pont AHB 40MHz/ AHB 320MHz .....                                                                  | 56 |

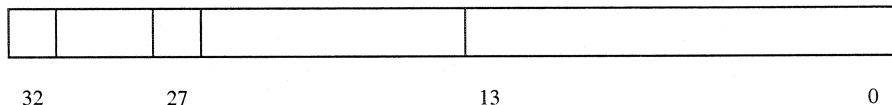

| Figure 3-22 Affichage de l'écran avec le bus de contrôle 40MHz .....                                          | 57 |

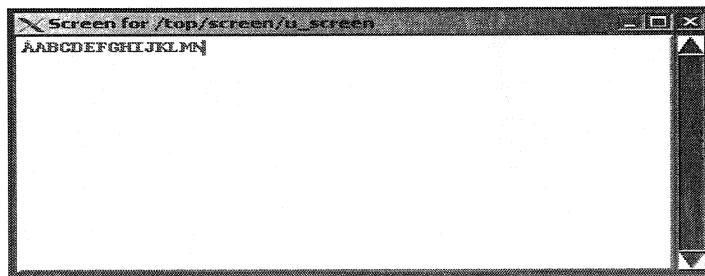

| Figure 3-23 Comparaison de l'hétérogénéité des langages .....                                                 | 58 |

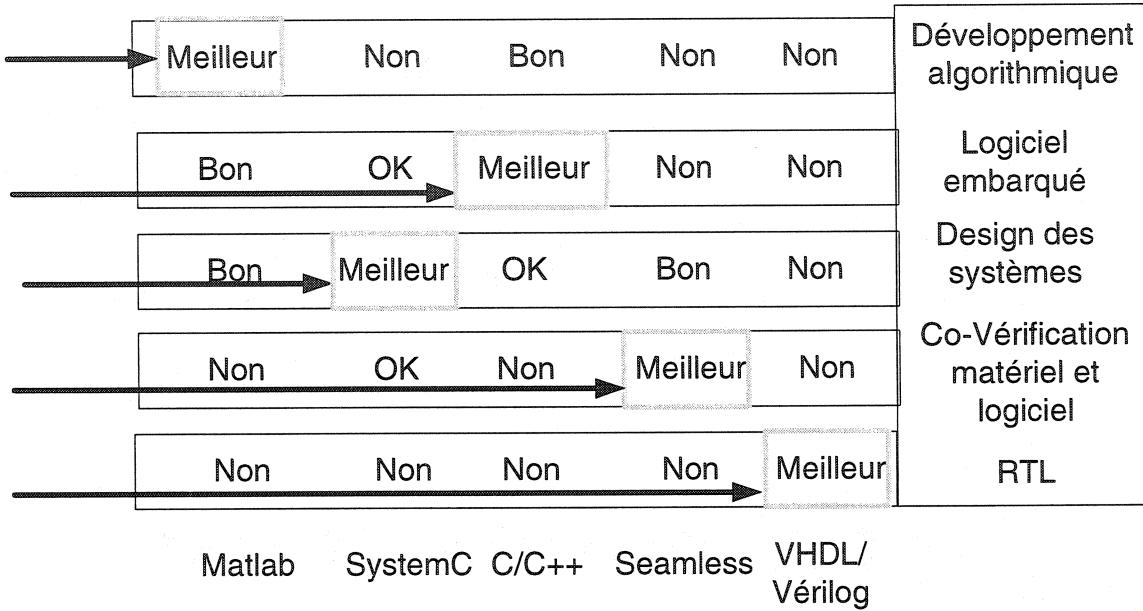

| Figure 3-24 Comparaison des langages avec leur capacités .....                                                | 60 |

| Figure 4.1 Aperçu de la structure proposée .....                                                              | 64 |

| Figure 4.2 Illustration du bus AMBA .....                                                                     | 66 |

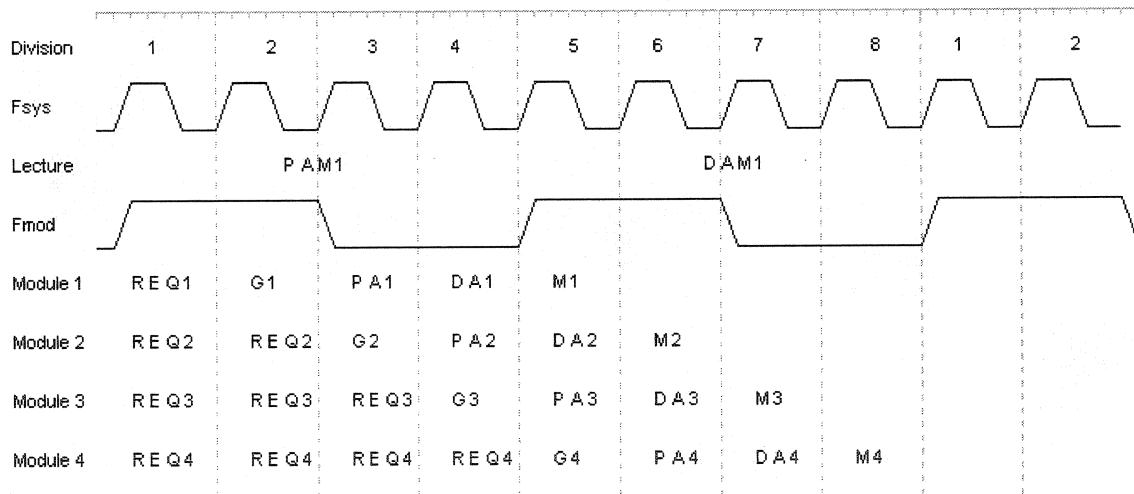

| Figure 4.3 Exemple de lecture sur le bus. Fsys est 4 fois plus rapide que Fmod. ....                          | 67 |

| Figure 4.4 Exemple d'écriture sur le bus .....                                                                | 68 |

| Figure 4.5 Diagramme d'une interface d'un bus AHB .....                                                       | 71 |

| Figure 4.6 Circuit permettant la synchronisation d'adresse .....                                              | 72 |

| Figure 4.7 Schéma logique du synchronisateur de réponse ( <i>HRESP</i> ) .....                                | 73 |

| Figure 4.8 Mécanisme d'arbitrage circulaire .....                                                             | 74 |

| Figure 4.9 Illustration du bus AHB 320 MHz opérant en pipeline .....                                          | 75 |

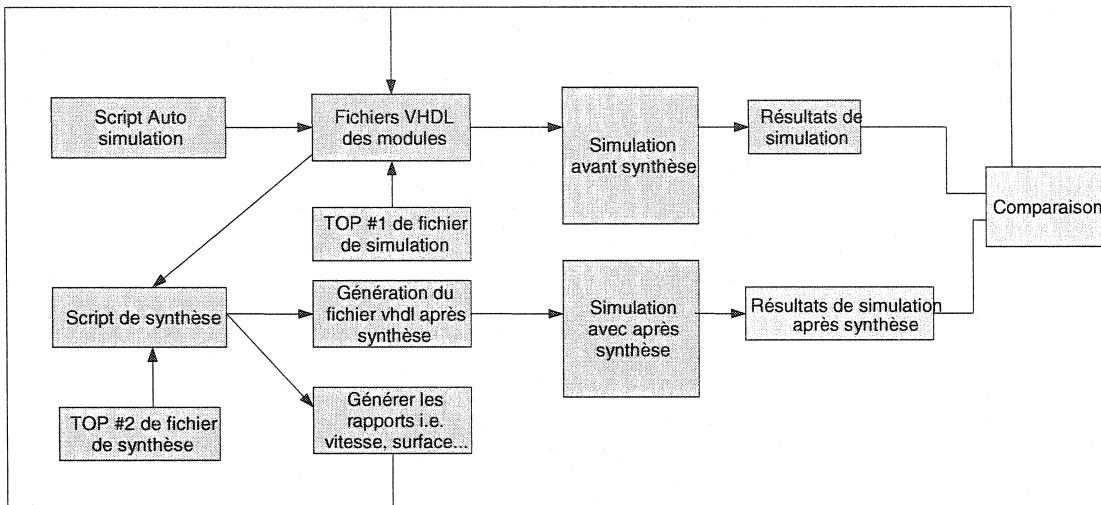

| Figure 4.10 Test automatique du bus 320MHz .....                                                              | 76 |

| Figure 4.11 Arbitrage par mémoire .....                                                                       | 77 |

| Figure 4.12 Illustration de l'arbitrage par mémoire .....                                                     | 78 |

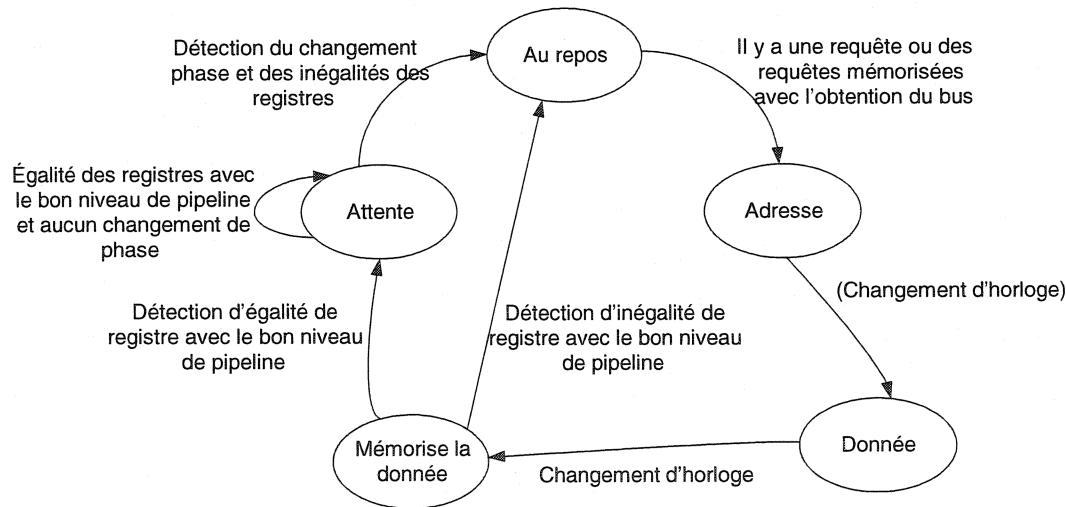

| Figure 4.13 Machine à états du bus dans l'adaptateur .....                                                    | 79 |

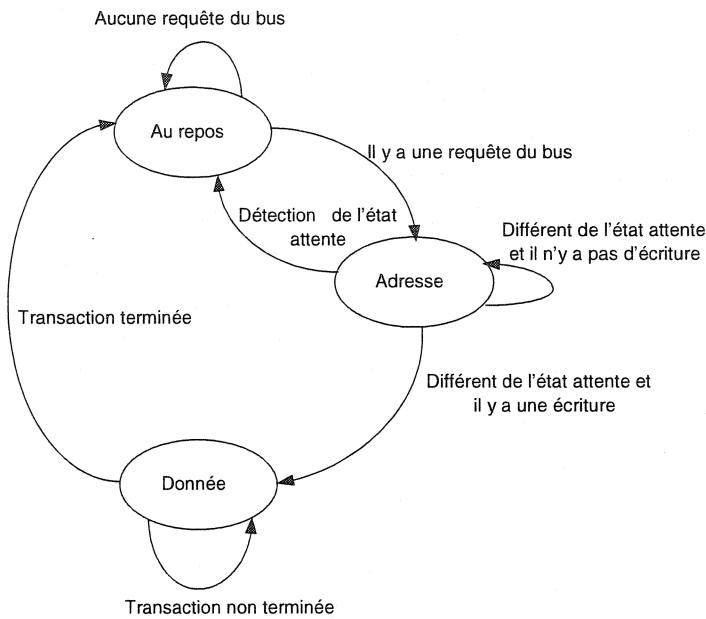

| Figure 4.14 Machine à état du module dans l'adaptateur .....                                                  | 80 |

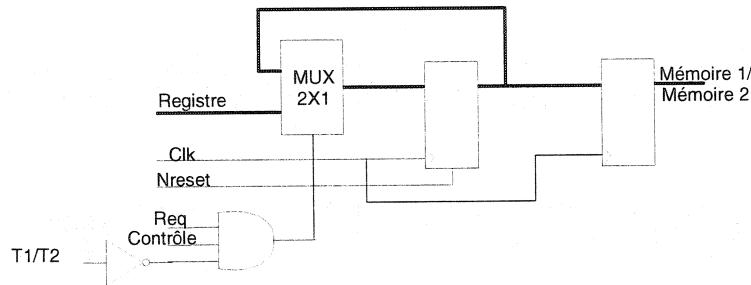

| Figure 4.15 Circuit de contrôle 2 de l'adaptateur .....                                                       | 81 |

|                                                                       |    |

|-----------------------------------------------------------------------|----|

| Figure 4.16 Circuit de contrôle de l'adaptateur .....                 | 81 |

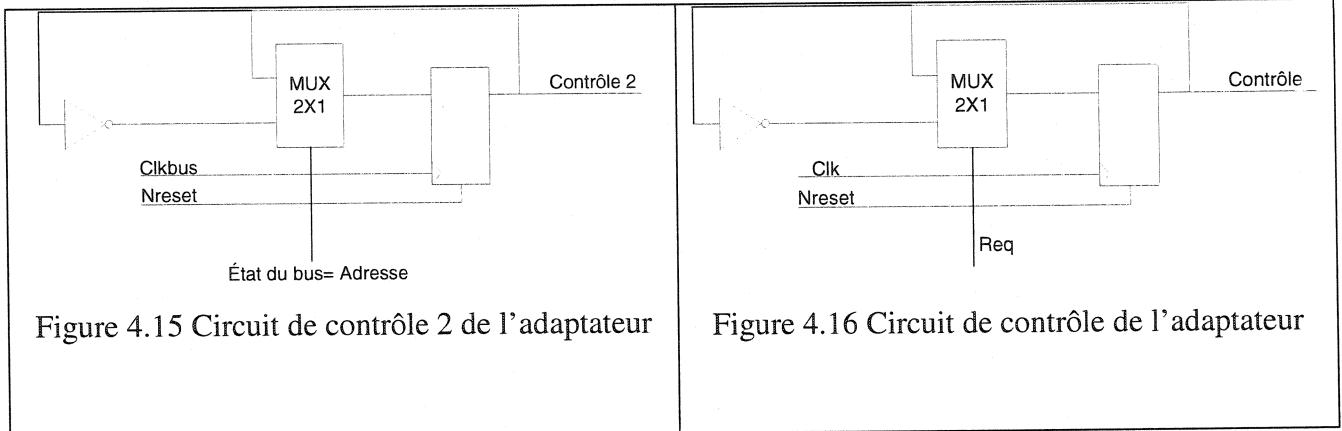

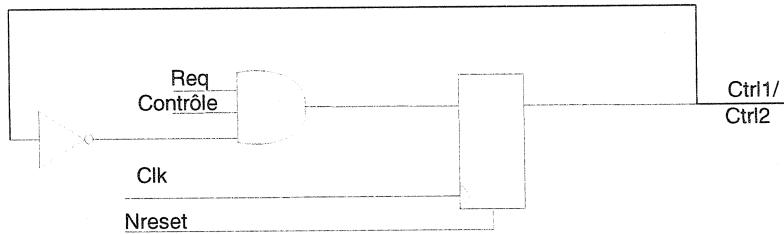

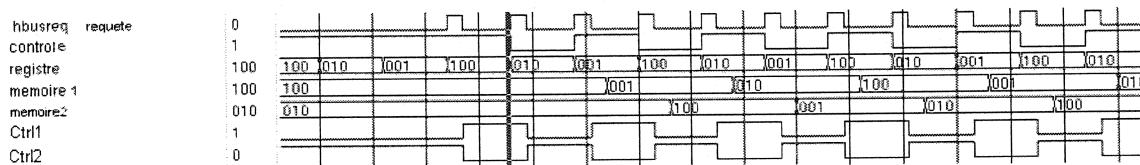

| Figure 4.17 Temporisation du registre.....                            | 81 |

| Figure 4.18 Génération des signaux <i>Ctrl1</i> et <i>Ctrl2</i> ..... | 82 |

| Figure 4.19 Illustration de la commutation du bus .....               | 82 |

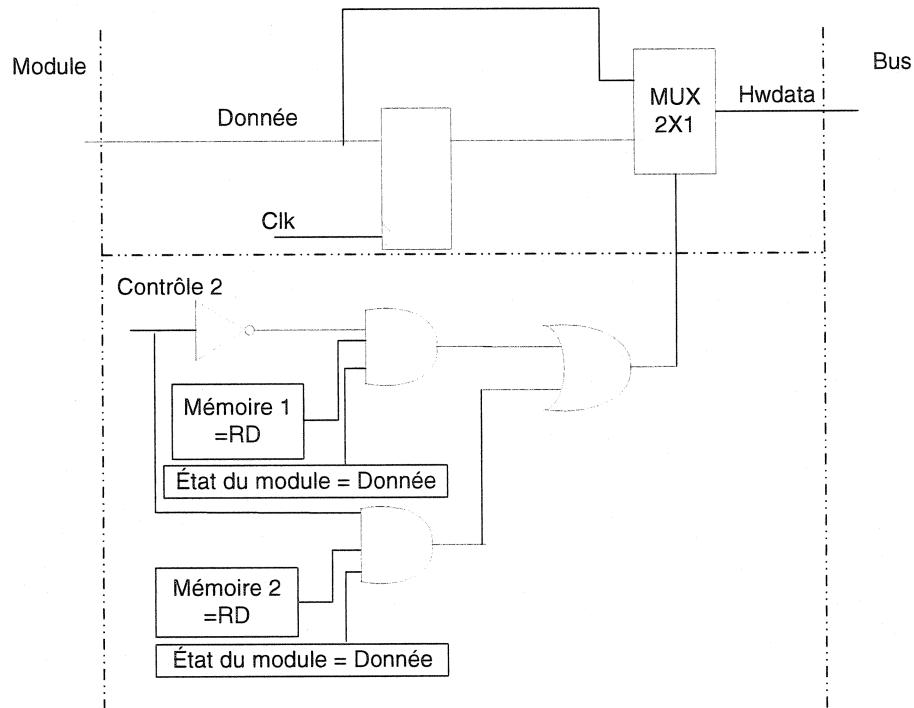

| Figure 4.20 Synchronisateur de l'écriture de <i>Hwdata</i> .....      | 83 |

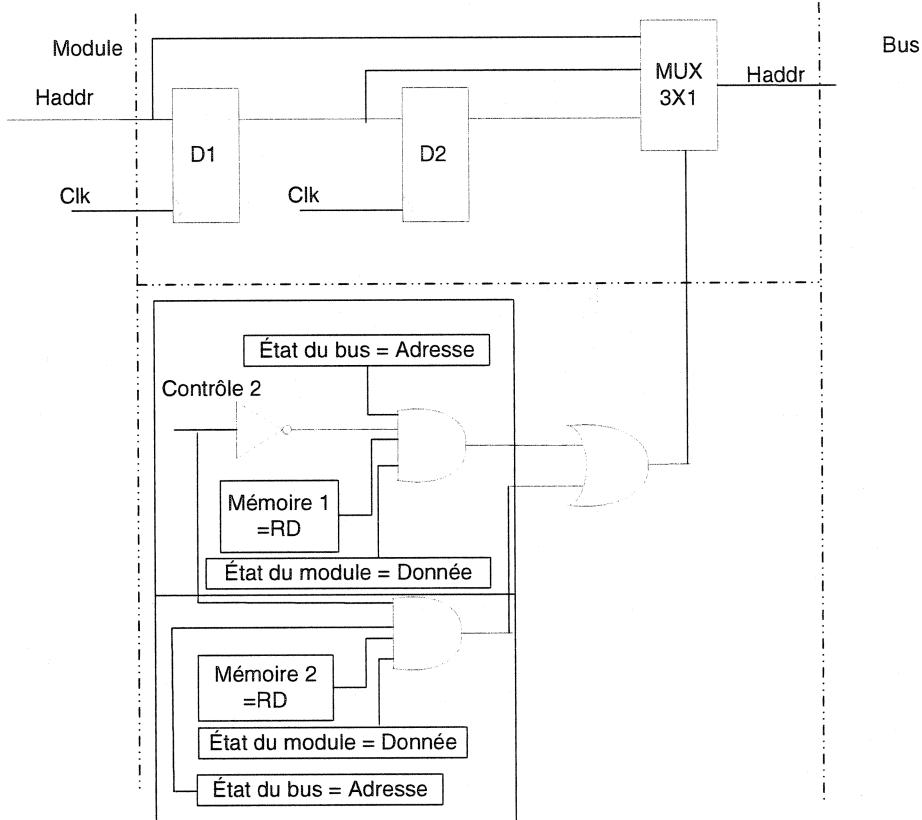

| Figure 4.21 Synchroniseur d'adresse .....                             | 84 |

| Figure 4.22 Synchroniseur de lecture .....                            | 85 |

| Figure 4.23 Arbitrage par encodeur de priorité .....                  | 86 |

| Figure 4.24 Fréquence du bus en fonction des modules.....             | 87 |

| Figure 4.25 Schéma du système.....                                    | 89 |

| Figure 4.26 Schéma de vérification du bus.....                        | 90 |

## LISTE DES TABLEAUX

|                                                                                                     |    |

|-----------------------------------------------------------------------------------------------------|----|

| Tableau 3-1 : Différentes possibilités offertes par les deux méthodes étudiées .....                | 36 |

| Tableau 3-2 : Premier niveau de profilage (algorithmique).....                                      | 44 |

| Tableau 3-3 : Deuxième niveau de profilage (processeur) .....                                       | 47 |

| Tableau 3-4 : Informations récapitulatif de langages .....                                          | 59 |

| Tableau 4-1 : Définition des variables qui composent le modèle des contraintes<br>temporelles ..... | 70 |

| Tableau 4-2 : Résumé des différents modules de sélection des synchroniseurs.....                    | 72 |

| Tableau 4-3 : Possibilités de combinaison de modules offertes par le bus implémenté...<br>86        | 86 |

| Tableau 4-4 : Comparaison des mécanismes d'interconnexion.....                                      | 91 |

## LISTE DES NOTATIONS ET SYMBOLES

|      |                                                                    |

|------|--------------------------------------------------------------------|

| AC   | : Address Converter                                                |

| AHB  | : Advanced High Performance Bus                                    |

| AMBA | : Advanced Microcontroller Bus Architecture                        |

| APB  | : Advanced Peripheral Bus                                          |

| ASB  | : Advanced Serial Bus                                              |

| ASIC | : Application Specific Integrated Circuit                          |

| CG   | : Checksum Generator                                               |

| CMOS | : Complementary Metal-Oxide Semiconductor                          |

| CV   | : Checksum Verifier                                                |

| DSP  | : Digital Signal Processor/Processing                              |

| FPGA | : Field Programmable Gate Array                                    |

| GF   | : General Formatter                                                |

| GRM  | : Groupe de recherche en microélectronique                         |

| IP   | : Intellectual Property                                            |

| OSI  | : Open System Inteconnect                                          |

| MB   | : Mailbox                                                          |

| MMAD | : Main Memomry Address Distributor                                 |

| PAx  | : Packet Assembler (instance #x)                                   |

| PRx  | : Packet Receiver (instance #x)                                    |

| RAM  | : Random Access Memory                                             |

| RISC | : Reduced Instruction Set Computer                                 |

| SoC  | : System-On-Chip                                                   |

| SRAM | : Synchronous Random Access Memory                                 |

| VHDL | : Very high speed integrated circuit Hardware Description Language |

**LISTE DES ANNEXES**

|                                       |     |

|---------------------------------------|-----|

| ANNEXE A Modélisation hétérogène..... | 100 |

| ANNEXE B Bus de communication .....   | 127 |

## AVANT-PROPOS

Cette recherche a été effectuée en étroite collaboration avec deux groupes de la Société Gennum, à Burlington, Ontario. Le premier groupe s'intéresse au développement d'un système de transmission de données vidéo à travers des réseaux de communications hétérogènes et le deuxième s'intéresse au développement d'une plate-forme de traitement vidéo.

Cette recherche a visé deux buts principaux, soit une modélisation hétérogène et la conception d'un bus de haute performance. La modélisation hétérogène permet l'utilisation efficace de plusieurs outils de conception communicant entre eux. Nous modéliserons une plate-forme SoC spécialisée en transmission et en traitement vidéo. Un autre aspect important se rapporte aux interconnexions entre les modules de la plate-forme. Les systèmes d'interconnexions des SoC manquent soit de bande passante ou de flexibilité. Dans le cadre de cette recherche, nous élaborerons des mécanismes permettant de réaliser des interconnexions flexibles et de haute performance.

## CHAPITRE 1

### INTRODUCTION

#### 1.1 Motivations

Les systèmes embarqués demandent de plus en plus de capacité de calcul. Par exemple, une application vidéo HTDV exige une plate-forme capable de traiter 1.49 Gbps [45]. Les systèmes doivent être configurable et de haute performance. Aussi, le temps de mise en marché d'un produit doit être le plus court possible. Il est nécessaire d'avoir une méthode de conception descendante qui va du haut niveau vers le bas niveau. Donc, le premier objectif de ce mémoire sera l'exploration d'un environnement hétérogène permettant l'utilisation appropriée des langages de modélisation selon leurs capacités. De plus, les systèmes possèdent des interconnexions entre les modules matériels ou logiciels pouvant mener à des latences significatives. Il y a une division des modules en sous système tel que les processeurs, la mémoire et les périphériques d'entrées et de sorties. Il existe des protocoles de communication tel qu' AMBA, CoreConnect, etc. Certains d'entre eux manquent de flexibilité ou offrent une bande passante insuffisante pour les besoins de l'application.

Le deuxième objectif est de concevoir une plate-forme SoC générique pour la transmission et le traitement vidéo. Cette plate-forme pour la transmission est réalisée dans le cadre du projet de recherche Netpro du GRM (Groupe de recherche en microélectronique) de l'École Polytechnique. Il vise à l'élaboration d'un convertisseur de protocoles. Quant à elle, la plate forme pour le traitement vidéo est issue du projet VPM (Video Processing Module), une extension du projet Netpro. Les mécanismes d'interconnexion de la plate-forme de conversion de protocoles basés sur la norme AMBA ne supportent pas des communications complètement génériques. En conséquence, il faut adapter le matériel lorsqu'on change le nombre de modules du système. Donc, ce deuxième objectif impliquera la création d'une nouvelle méthode d'interconnexion générique pour relier des modules basés sur la norme AMBA et

pouvant opérer jusqu'à 500MHz dépendant du nombre de modules connectés sur le bus. La combinaison des deux objectifs permet la création d'une nouvelle méthode de conception utilisant le meilleur de chaque langage parmi un ensemble de langages disponibles. Dans ce cas, l'interconnexion des modules du système se fera sans exiger de changement sur ces mêmes modules. Le raffinement des communications des modules dans la méthode de conception sera déjà réalisé par un bus de haute performance. Il ne restera qu'à faire un raffinement au niveau des modules. Le canal de communication suivra la norme AHB d'AMBA. La plate-forme développée servira de référence pour le développement d'autres applications utilisant un environnement de conception hétérogène.

## 1.2 Contributions

L'objectif de ce travail est la création d'une plate-forme générique de haute performance avec une méthode à double profilage permettant de réaliser des systèmes pour différentes classes d'applications.

Les contributions majeures sont les suivantes :

- La création d'une méthode de conception hétérogène à double profilage. Cette méthode inclut une étude sur les langages de conception en fonction de leurs capacités et des niveaux d'abstraction. Dans le cadre de cette méthode, nous avons conçu différents adaptateurs permettant la connexion entre les langages.

- La création de trois méthodes d'interconnexions basée sur le protocole AMBA soit la méthode de connexion circulaire, par mémoire et par encodage de priorité. La dernière méthode permet une interconnexion multi fréquentielle des différents modules avec une mémoire principale opérant autour de 500MHz. Elle constitue un bus avec un adaptateur générique auto synchronisant qui ne requiert aucune programmation.

- La conception et l'analyse de l'architecture du convertisseur de protocole. À partir de analyse, il y a été possible d'élaborer une nouvelle structure d'interconnexion.

- À partir de la première plate-forme, nous avons conçu une nouvelle plate-forme pour le traitement et la transmission vidéo utilisant la méthode d'interconnexion des modules par encodage de priorité.

### 1.3 Organisation du mémoire

La première partie du chapitre 2 sera une introduction aux systèmes embarqués et présentera les langages de modélisation avec un cheminement typique de conception. À partir de ces informations, nous élaborerons une méthode de conception utilisant le meilleur de chaque langage. Par la suite, nous ferons une exploration des différentes plates-formes existantes dédiées au traitement vidéo. Aussi, nous discuterons de la plate-forme de conversion de protocoles avec son fonctionnement. De plus, les différents standards (protocoles) de communication feront l'objet d'une description sommaire. Nous discuterons notamment les normes AMBA, OpenCore et les mécanismes de connexion de la plate-forme Nexperia.

Le chapitre 3 présente le concept de plate-forme SoC et les éléments essentiels pour la connexion des langages entre eux. D'après l'analyse, nous pourrons connaître leurs caractéristiques communes et nous présenterons trois méthodes d'interconnexion entre les langages. Par la suite, nous élaborons des adaptateurs spécifiques aux langages permettant une simulation hétérogène. À partir des informations recueillies au chapitre 2 et 3, nous créerons une méthode de conception à double profilage à travers tous les langages présentés, c'est-à-dire le profilage d'un code sur deux niveaux d'abstraction différents mais complémentaires. De même, les méthodes d'analyse des plates-formes seront discutées. La méthode sera expliquée par l'algorithme de Wiener et découlera des résultats de simulations, de profilages et de comparaisons entre les langages.

Le chapitre 4 traitera de la réalisation d'un bus de haute performance. Nous présenterons le modèle d'interconnexion avec le bus AHB. Nous expliquerons les problèmes de synchronisation des horloges avec leurs phases. Suite à cette analyse, nous approfondirons trois méthodes d'interconnexion soit les connexions circulaires, par

mémoire et par encodage de priorité. De même, la création d'un adaptateur générique AHB sera présentée. Nous éliminerons les goulets d'étranglement de la plate-forme sur des flots de traitements avec le bus AHB. La fréquence d'opération supportée pourra atteindre 500MHz selon le nombre de modules lui accédant. L'adaptateur a été conçu à l'aide des bibliothèques de modules d'une technologie CMOS 0.18 micron. Enfin, le chapitre 5 présentera nos conclusions. Nous résumerons l'ensemble des travaux réalisés et présenterons les travaux futurs dans le cadre de cette recherche.

## CHAPITRE 2

### L'ÉTAT DE L'ART : OUTILS DE CONCEPTION, PLATE-FORME SoC POUR LE VIDEO ET INTERCONNEXIONS SoC

#### 2.1 Introduction à la conception des systèmes embarqués

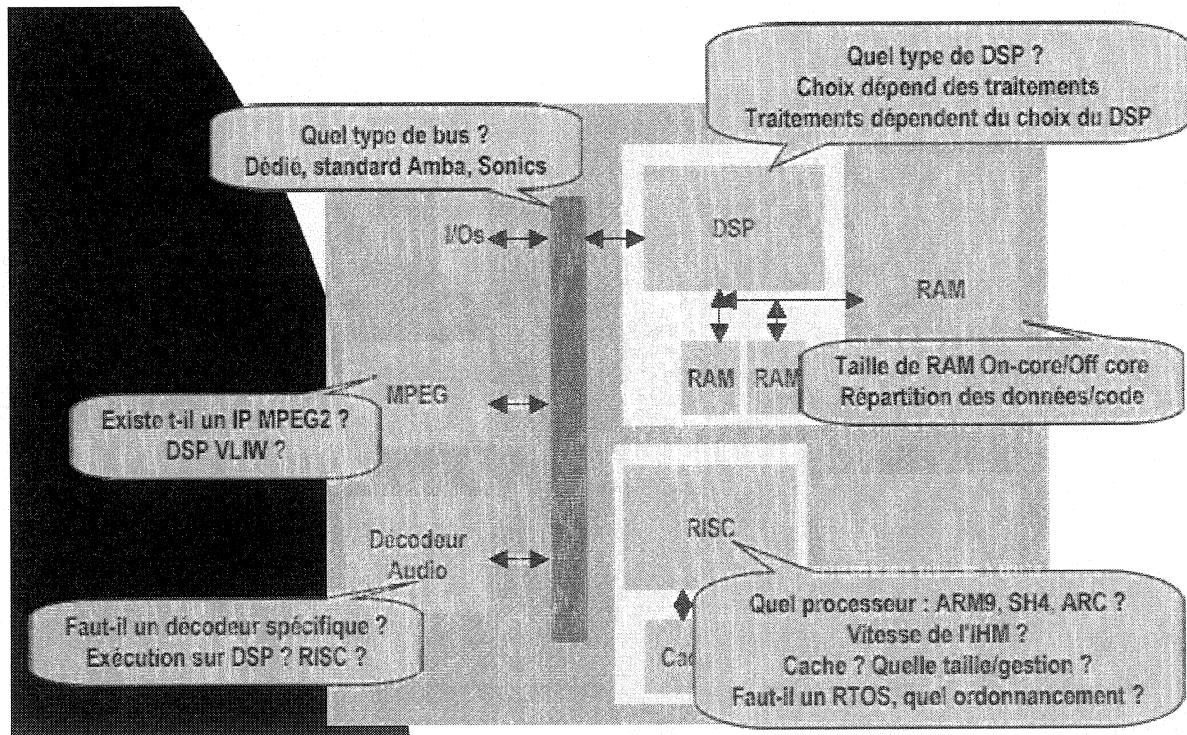

Les systèmes embarqués sont composés de différents modules matériels et logiciels. Il faut avoir les éléments adéquats permettant de réaliser une application souhaitée. La figure suivante présente la problématique de conception [16].

Figure 2-1 Illustration du Co-design

Une exploration rapide de plusieurs architectures (RISC, FPGA, ASIC, IP, DSP, ASSP, Analogique ...) est requise et peut être possible grâce aux outils de codesign. L'évaluation des outils de conception et des méthodes qui y sont associées sera nécessaire pour connaître leurs capacités dans la réalisation d'un système sur puce. Il y a beaucoup d'outils sur le marché. Ils sont offerts à divers prix et tous ne sont pas bons à

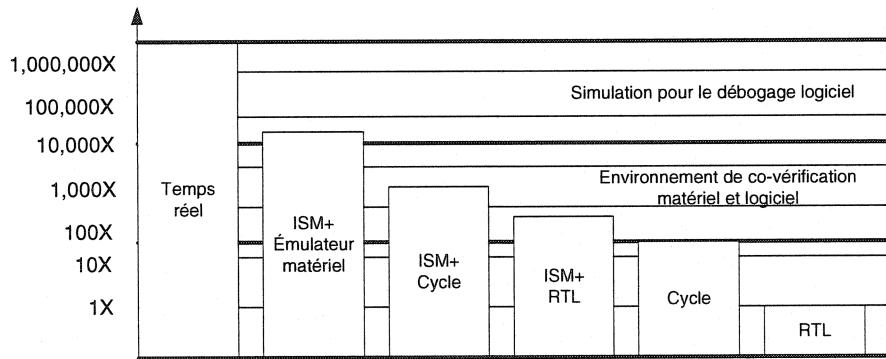

tous les niveaux d'abstraction [29]. De plus, la diminution du temps de conception peut être réalisée en combinant judicieusement les langages entre eux. Idéalement, il faut des outils nécessitant un court temps de simulation de la spécification à l'implémentation physique. La figure suivante compare le temps de simulation pour différents niveaux d'abstraction. On remarque que le temps de simulation est plus court en logiciel qu'en matériel (RTL). Il faut simuler le matériel et le logiciel en même temps. Nous utilisons le VHDL pour une simulation du matériel et un modèle de jeux d'instruction (ISM pour Instruction Set Model) pour une simulation du logiciel dans un système embarqué. Dans un modèle ISM, le processeur est décrit en terme des instructions qu'il supporte.

Figure 2-2 Comparaison des niveaux de performance [23]

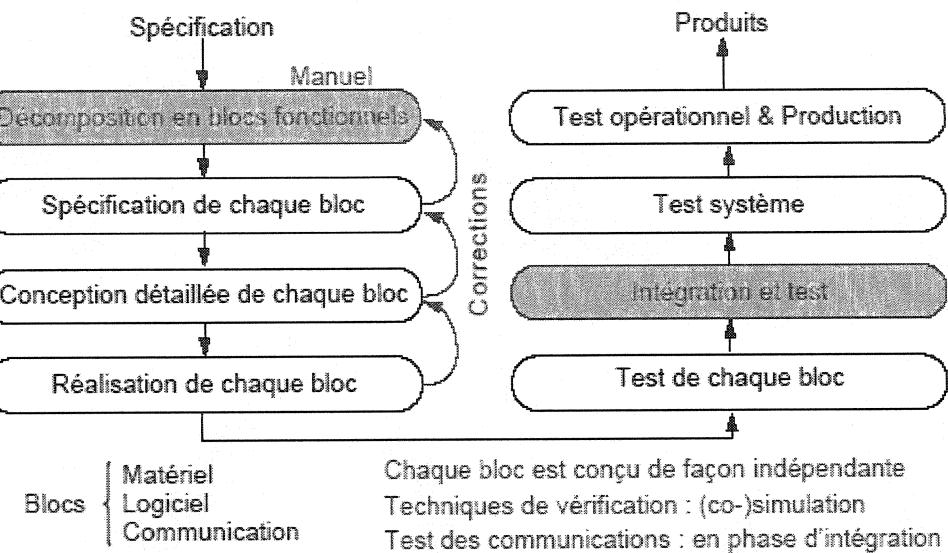

Le développement des algorithmes, ainsi que leurs spécifications et leur implémentation nécessitent plusieurs outils. Dans ce qui suit, nous mettrons l'emphase sur les outils suivants: Matlab, SystemC, Modelsim, Seamless. Mais avant tout, il est important de connaître un flot de conception typique tel qu'illustré à la figure suivante tirée de [7]. La plupart des outils sont basés sur le C/C++ et ils peuvent supporter des étapes différentes du processus de la conception. Ici, il est important de souligner l'importance des méthodes fondées sur le langage C/C++ tel que SystemC dans la conception d'un SoC. Pour cette analyse, il y a quatre phases [37]: l'architecture, l'implémentation, la vérification et autres éléments. Tout d'abord, l'architecture permet de définir un système selon les spécifications du client et tous les éléments nécessaires avant la conception. Il y a aussi le choix des interconnexions et des modules IP.

Figure 2-3 Flot typique de conception

Ces derniers peuvent être un CPU, un DSP, un noyau Ethernet etc. Entre l'architecture et l'implémentation il y a la spécification exécutable. Par exemple, SystemC permet la création d'un prototype en C/C++ exécutable, qui fournit une représentation flexible exprimée au niveau système. De plus, il peut y avoir des modules matériels. Aussi SystemC permet la séparation entre l'infrastructure des communications et les modules de traitement. Cette séparation permet une plus grande flexibilité. Ensuite, il y a l'implémentation englobant tous les niveaux d'activité des blocs et des supers blocs incluant le niveau bloc du design et le test de l'intégration du système. Dans cette phase, la plupart des bancs d'essais n'ont pas avantage à utiliser du C/C++ parce qu'il n'y a pas un grand contenu algorithmique.

La seconde phase est la vérification. Lors de la conception de SoC de grande complexité, la productivité du processus de vérification est un grand obstacle pour rencontrer la demande de mise en marché. Ici, tout comme pour l'architecture, le C/C++ est utilisé pour augmenter la productivité et les aspects de performance [37]. Les nouveaux outils séparent les fonctions de communication permettant de modéliser un système facilement et offrent un gain de productivité global. Le dernier aspect est constitué des autres

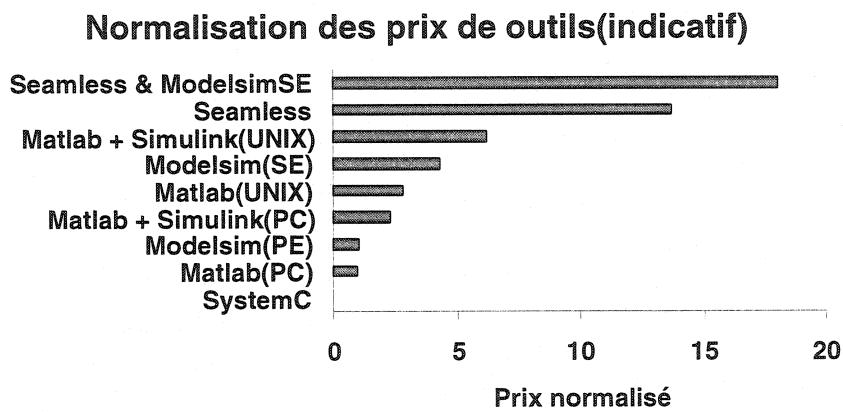

éléments qui peuvent survenir après une vérification fonctionnelle [37]. D'autres facteurs importants dans le choix d'un outil sont sa capacité et son coût récurrent ou non. La figure suivante présente sous une forme normalisée les prix des outils. Cette comparaison normalisée est basée sur des estimations des prix du marché en 2003 receuillis de diverses source sur le réseau et dans la littérature techico-commerciale.

Figure 2-4 Prix normalisés des outils

Nous constatons que les prix des outils sur PC sont deux fois et demie moins cher que sous Unix. Tous les outils mentionnés sont disponibles sous UNIX ou PC, sauf Seamless qui n'est pas disponible sur les systèmes d'exploitation windows. Il est important de mentionner que les licences sont attribuées par utilisateur ou par machine et qu'elles font l'objet de frais récurrents. Lors d'une simulation, il est généralement important d'exploiter au maximum les ressources matérielles et le minimum des licences logicielles (jetons). L'utilisation maximale d'une licence d'une machine peut être réalisée avec des connexions TCP/IP permettant une simulation à distance partagée où la licence est exploitée par plusieurs utilisateurs.

Nous avons donc intérêt à utiliser SystemC dans notre méthode, car il est gratuit. La section suivante présente principalement les outils HDL Designer, Matlab, SystemC et Modelsim.

## 2.2 Aperçus des outils

### 2.2.1 HDL Designer

La conception des SoC requiert de la programmation au niveau logiciel et/ou matériel. Il est important d'avoir un outil permettant l'intégration des modules sous différentes formes de textes ou de graphiques et permettant l'incorporation de divers langages comme VHDL, C et C++. Un mode graphique permet de visualiser plus facilement le fonctionnement d'un module en représentant la fonctionnalité voulue sous forme graphique, par exemple, une machine à états finis. L'outil HDL Designer [31] servira de contrôleur de version, de gestionnaire de bibliothèques et il fournit un ensemble d'autres fonctionnalités connexes à la gestion d'un projet de conception d'un système embarqué. De plus, son interface permet de démarrer une simulation avec d'autres langages. Une représentation graphique et modulaire d'un système est plus facilement compréhensible lors de la conception. Nous l'utiliserons dans le cadre de notre projet.

### 2.2.2 Matlab

La modélisation d'un système peut être faite avec Matlab [26]. Cet outil permet la modélisation à plusieurs niveaux d'abstraction. Il a son propre flot de conception. Il permet un prototypage rapide avec les FPGA. Il a six champs d'applications:

- Calcul Technique

- Analyse, visualisation et développement d'algorithmes

- La conception du contrôle

- L'outil fournit des modèles de design de base pour le contrôle;

- Il permet de décrire l'algorithme par la création d'un modèle et il permet la simulation de ce modèle;

- Il permet ensuite le prototypage rapide;

- Il permet enfin la génération du code pour les systèmes embarqués.

- Traitement de signal (DSP) et conception des système de communication

- Il permet d'effectuer la conception au niveau système pour le DSP et les systèmes de communication;

- Il permet de décrire chaque algorithme par la création d'un modèle et il permet la simulation de ce modèle;

- Il permet ensuite le prototypage rapide;

- Il permet enfin la génération du code pour les systèmes embarqués.

- Tests et mesures

- L'outil supporte la collecte des données à partir de plate-forme matérielle.

- Traitement d'images

- L'outil supporte l'acquisition et l'importation d'images et leur analyse;

- Il permet de perfectionner et de développer des applications.

- Analyse et modèle financier

- Il supporte l'analyse, la modélisation, la simulation et l'optimisation des données financières.

Matlab permet un raffinement progressif partant d'un haut niveau d'abstraction en allant vers le bas. Il permet deux types de génération de code automatique. Premièrement, l'outil Real-Time Workshop peut générer automatiquement du code C ANSI à partir d'un modèle Simulink pour le téléchargement vers un processeur DSP ou un processeur embarqué. De plus, des mises en œuvre matérielles peuvent être générées par le générateur de système de Xilinx. Matlab présente des avantages pour le développement automatisé ciblé FPGA et des applications DSP. La figure suivante présente sa méthode de conception.

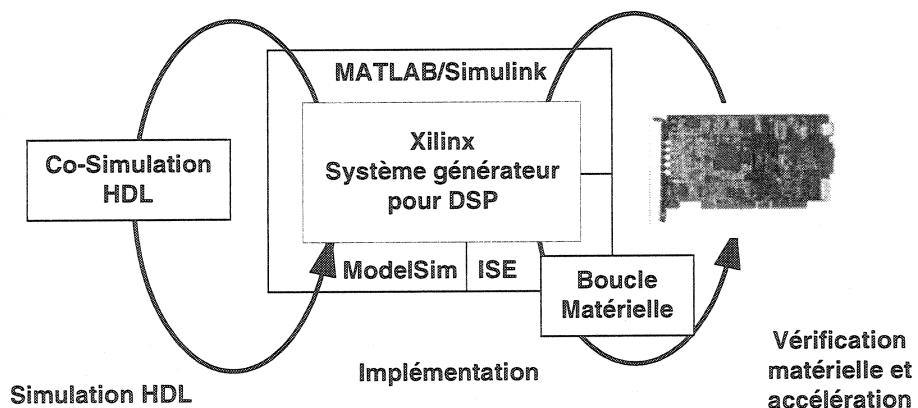

Figure 2-5 Flot de conception de Matlab pour DSP

Cette méthode permet le développement sur FPGA. D'autre part, la traduction du code Matlab en C/C++ peut être réalisée par l'outil MCC et le code produit peut être récupérédans une simulation hétérogène. De plus, Matlab fournit des fonctions API permettant au C de communiquer et de démarrer Matlab.

### 2.2.3 SystemC

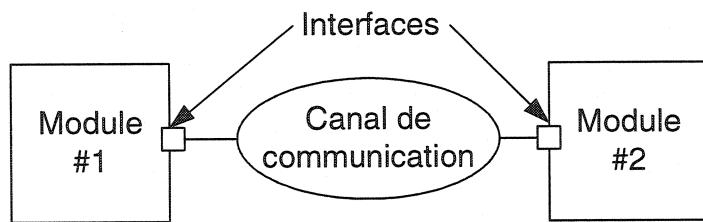

Un autre langage important lors de la conception est SystemC. C'est une bibliothèque en C++ orienté objet pour la modélisation logicielle et matérielle. Cette section discute des possibilités d'utilisation de ce langage dans la conception d'un SoC. Il possède des modules, des ports et des canaux de communication. L'intérêt de ce langage est de pouvoir raffiner les modules et les méthodes de communication individuellement. La figure suivante présente l'interconnexion possible entre deux modules.

Figure 2-6 Illustration des interfaces

Il possède des processus, des ports, des types de données et des signaux d'horloges. Les processus offert en SystemC sont sc\_method, sc\_thread, sc\_cthread. Le premier permet d'exprimer des processus combinatoires. Le deuxième et le troisième permettent la description d'une exécution séquentielle. Le dernier a les mêmes caractéristiques que le deuxième processus, mais il a uniquement une horloge comme liste de sensibilité. Nous trouvons dans ce langage les notions de traitement combinatoire et séquentiel comme dans le langage VHDL. Il permet de spécifier les ports d'entrées, les ports de sorties et les ports bidirectionnels. Ces derniers permettent une communication entre les modules. Le type de données matérielles est disponible grâce à l'objet sc\_signal<T>. Des signaux pour la manipulation de bits, le traitement de vecteurs et des entiers sont aussi possibles. Un autre signal important dans la conception d'un système est l'horloge. Ce dernier exprime l'information temporelle et permet la synchronisation des processus entre eux.

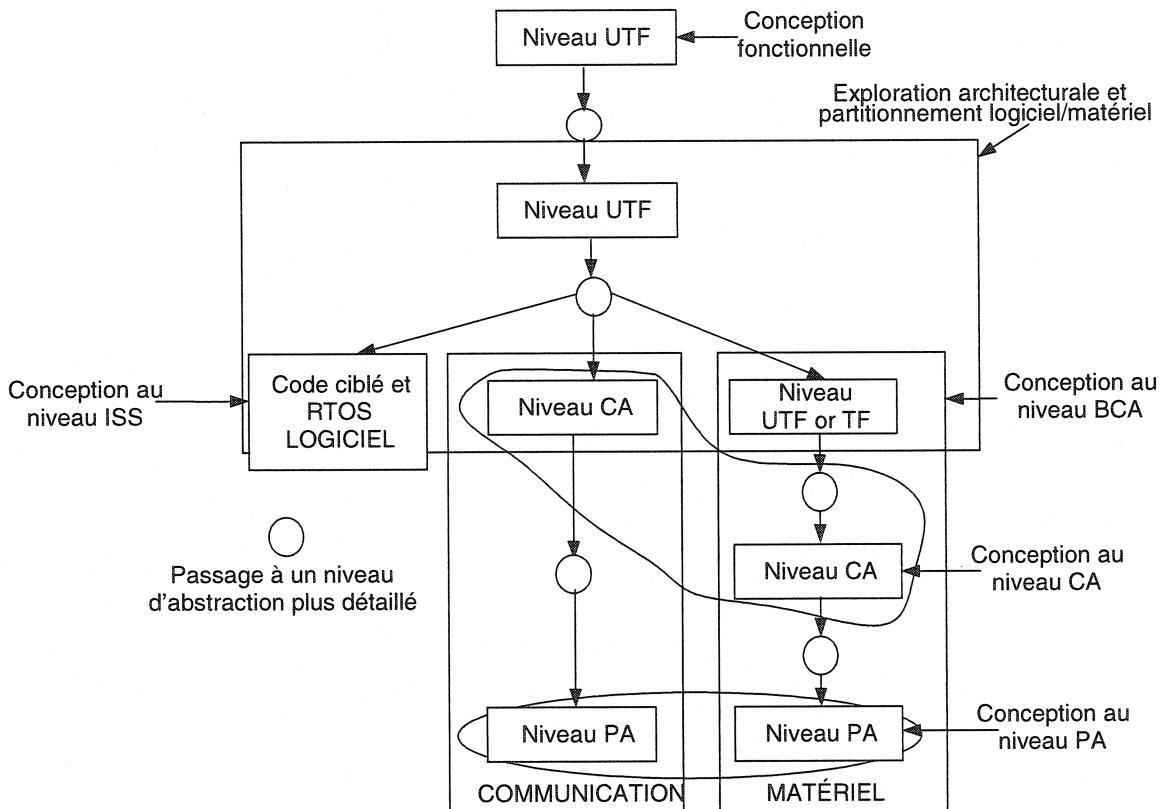

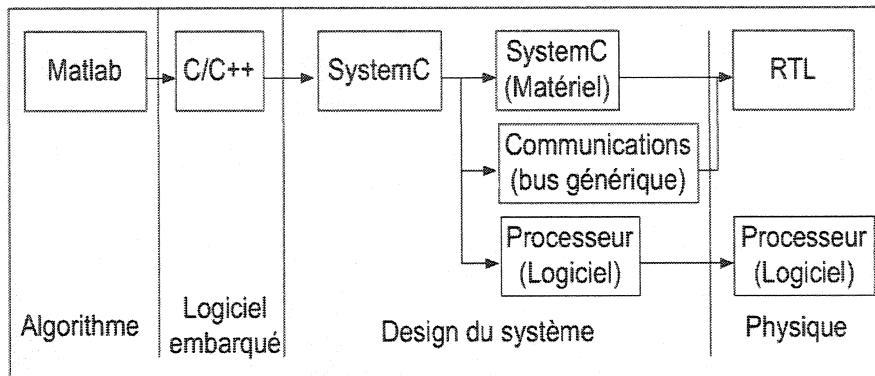

SystemC permet six niveaux d'abstraction : UTF (UnTimed Functional), TF (Timed Functional), ISS (Instruction Set Simulator), CA (Cycle Accurate), BCA (Bus Cycle Accurate), PA (PIN accurate). La figure suivante présente un flot possible pour le raffinement d'une spécification [13].

Figure 2-7 Flot de conception avec SystemC

Le plus haut niveau UTF permet une conception fonctionnelle d'un système. De plus, une exploration rapide de plusieurs architectures, impliquant le partitionnement logiciel et matériel, peut être réalisée à partir des niveaux d'abstraction UTF, TF et ISS. Le niveau ISS permet le raffinement de la partition logicielle à partir du niveau TF. Le raffinement matériel se fait à trois niveaux. Tout d'abord, il faut faire une synthèse des communications à l'aide du niveau BCA. Ce dernier permet de décrire un médium de communication au cycle près tout en conservant la simplicité du niveau UTF. Ensuite, en synthétisant celui-ci, nous obtenons une description au niveau CA. À ce niveau, les

communications ne sont pas encore détaillées entre les modules et les communications. Celui-ci permet de diminuer le temps de simulation tout en ayant une simulation précise au cycle près. En terminant, lorsqu'on a raffiné les communications abstraites, il faut passer au niveau PA qui exprime tous les signaux au niveau broche. Un autre aspect important lors de la conception est d'obtenir des informations permettant l'analyse de notre système. Le prochain outil permet cette analyse.

#### 2.2.4 Seamless

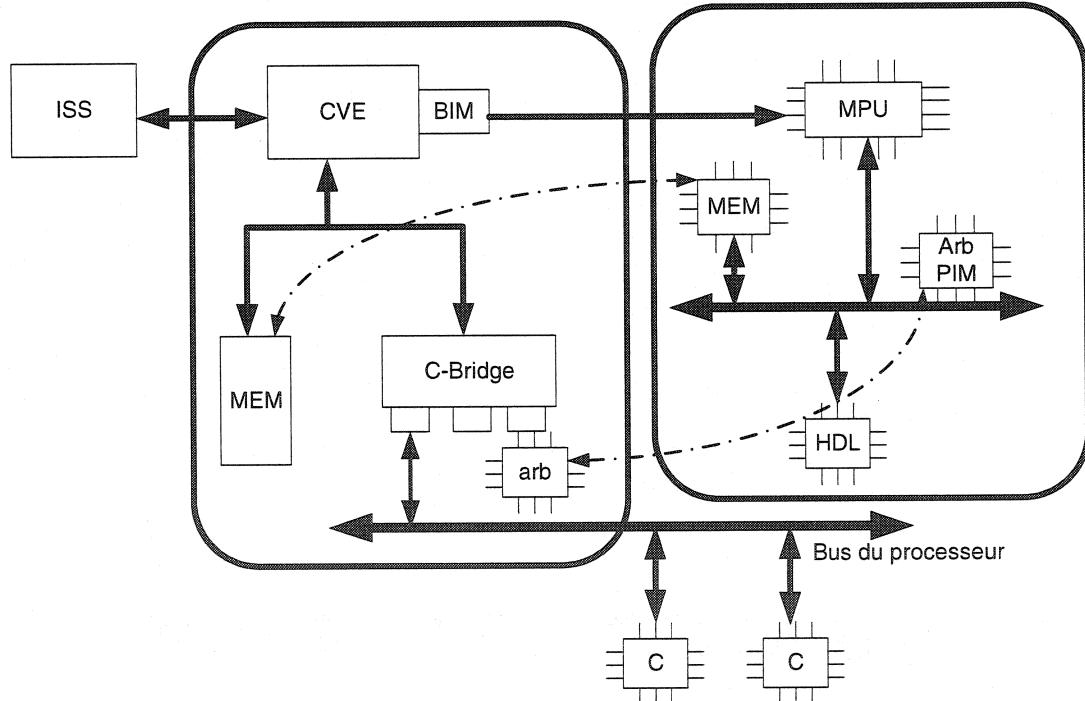

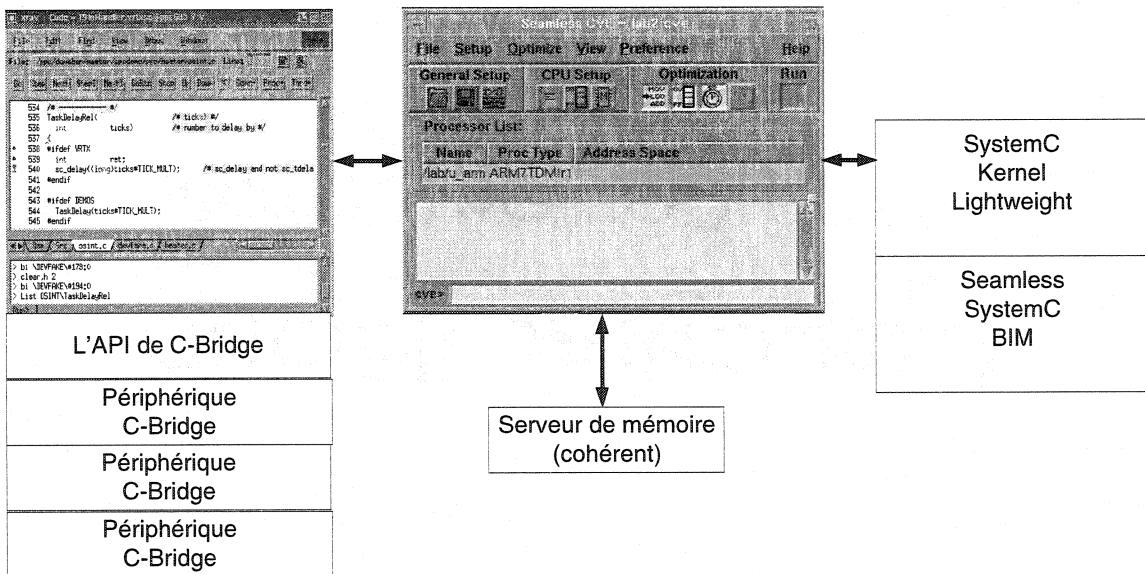

Une simulation hétérogène de plusieurs outils peut être effectuée par Seamless [30]. Il offre la conception de système à plusieurs niveaux d'abstraction. Une simulation mixte VHDL et C/C++ est possible par l'API C-Bridge comme l'illustre la figure suivante [22].

Figure 2-8 Simulation avec C-Bridge

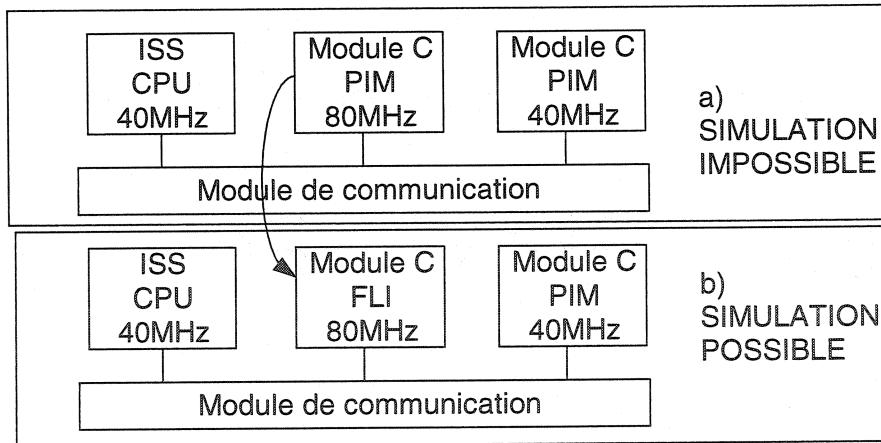

Par exemple, une mémoire (MEM) peut être modélisée en C et ensuite transférée dans le modèle RTL. Seamless permet deux niveaux d'abstraction soit le BIM (Bus Interface Model) et le PIM (Pin Interface Model). Le BIM permet d'être à un plus haut niveau d'abstraction que le PIM. Il permet de réaliser des simulations sans notion de temps. Les

méthodes de communication sont des requêtes et des accusés de réception permettant d'avoir un bus transactionnel. Le deuxième type (PIM) permet la connexion d'une interface VHDL au C/C++. Lors du raffinement, il est important de pouvoir garder le plus longtemps possible un niveau d'abstraction de haut niveau pour avoir un temps de simulation plus rapide. Nous pouvons transformer notre modèle de C/C++ en VHDL tout en conservant le reste de l'architecture. Une autre approche de conception est aussi possible avec la dernière version de Seamless (version 5) [11]. En effet, il est possible de simuler sans simulateur VHDL, c'est-à-dire uniquement à partir d'un simulateur ISS et de SystemC. La figure suivante illustre ce propos.

Figure 2-9 Seamless avec SystemC

L'idée est de réaliser les blocs matériels en C/C++ plutôt qu'en VHDL. Il y a plusieurs avantages à cette méthode. Tout d'abord le temps de simulation est réduit. La création d'une modélisation est plus simple en C qu'en VHDL. Il y a aussi une possibilité de passer d'un haut niveau d'abstraction en C/C++ à un modèle implanté en RTL. L'API C-Bridge permet la simulation d'un module créé en C/C++ représentant un comportement matériel. Par exemple, le matériel modélisé en C/C++ peut correspondre à un niveau d'abstraction TF. La compagnie Mentor Graphics fabriquant Seamless intègre Modelsim, SystemC, et les modèles ISS ensemble. De plus, cette méthode permet d'avoir une

spécification exécutable. Tous les éléments du système sont écrits en C/C++. Lors d'un raffinement, le code en C/C++ pour le logiciel peut être mis dans un processeur. Le matériel peut être transformé de SystemC à VHDL. Un autre avantage de la nouvelle version est la possibilité de faire de l'analyse de performance (essentiel au codesign). En effet, il y a quatre nouvelles analyses disponibles [30]. Premièrement, un profileur de code permet d'examiner le temps d'exécution d'un logiciel. Deuxièmement, il est possible de caractériser l'utilisation de la bande passante d'un bus. Troisièmement, il est possible de caractériser le délai d'arbitrage d'un bus, c'est-à-dire combien de temps un maître doit attendre pour avoir le bus. Quatrièmement, il est possible d'évaluer l'information concernant les données sur les transactions en mémoire, soient les accès manqués en cache ou les accès réussis.

### 2.2.5 Modelsim [32]

Le prochain outil nommé Modelsim permet une simulation à un plus bas niveau d'abstraction. ModelSim est un simulateur VHDL largement répandu et un simulateur mixte combinant le VHDL et le Verilog. Les produits ModelSim® ont une architecture unique basée sur des technologies comme *Optimized Direct Compile* pour des compilations et des simulations rapides par le *Single Kernel Simulation* (SKS). De plus, il incorpore le langage TCL/TK pour une grande flexibilité et une vérification rapide. Une personnalisation facile est permise par le TCL/TK. Ce dernier permet de développer des interfaces graphiques. Il possède également des connexions FLI (Foreign Language Interface) / PLI (Programming Language Interface) permettant une intégration du C/C++. Les nouvelles versions possèdent un débogueur intégré pour faciliter la vérification d'un système. Modelsim inclut un comparateur de chronogramme, des analyseurs de performance et la capacité de donner la couverture de code. Le comparateur de chronogramme permet d'augmenter la vitesse de vérification entre deux simulations pour identifier les erreurs. Il permet aussi d'analyser la vitesse de simulation en identifiant les congestions. Celui-ci peut découvrir les codes qui ne sont pas efficaces, les cellules d'une bibliothèque non accélérées, des signaux inutiles dans la liste de sensibilité, etc. La couverture de code permet de connaître combien de fois l'exécution

d'un segment de code a été effectué. Le Signal Spy permet de voir à travers la hiérarchie. Il est possible de mettre un moniteur sur un signal et de le voir directement dans le banc d'essai.

### 2.2.6 SystemVerilog

Un autre outil nommé SystemVerilog [40][15] est une extension majeure de la norme IEEE 1364-2001 qui spécifie le langage Verilog. Il a été développé par Accellera pour améliorer la productivité dans la conception des circuits intégrés à grande échelle basés sur des IP et des systèmes de bus. Il supporte la modélisation à haut niveau et la vérification avec des assertions. Il permet un appel direct de fonctions en C/C++/SystemC en utilisant son *Direct Programming Interface* (DPI). SystemVerilog possède les types de données comme le C et la possibilité de créer des classes en ayant aussi les signaux au niveau matériel. De plus, il est possible de créer ses propres structures. Des notions d'interfaces existent, ainsi que des primitives de niveau système et des mécanismes de communication tel que les boîtes aux lettres et les sémaphores, etc.

### 2.2.7 UML

Un autre outil permettant la modélisation à un niveau d'abstraction plus élevé est le *Unified Modeling Language* (UML) qui a été créé par OMG (Object Management Group) pour le développement des systèmes logiciels. La compagnie Fujitsu a développé une nouvelle méthode de conception utilisant UML et le langage C pour la création d'un SoC [17]. UML est un outil de modélisation visuel avec un haut niveau d'abstraction permettant une spécification exécutable d'un système. Pour plus de détails sur son fonctionnement, [28] permet de connaître davantage ses capacités et ses lacunes pour les spécifications d'un système embarqué ainsi que sa conception.

## 2.3 Convertisseur de protocoles

La communication entre les systèmes embarqués d'aujourd'hui est basée sur des protocoles de communication distincts. Chacun d'eux permettent la communication entre différents périphériques matériels tels que les ordinateurs, les caméras, les systèmes de

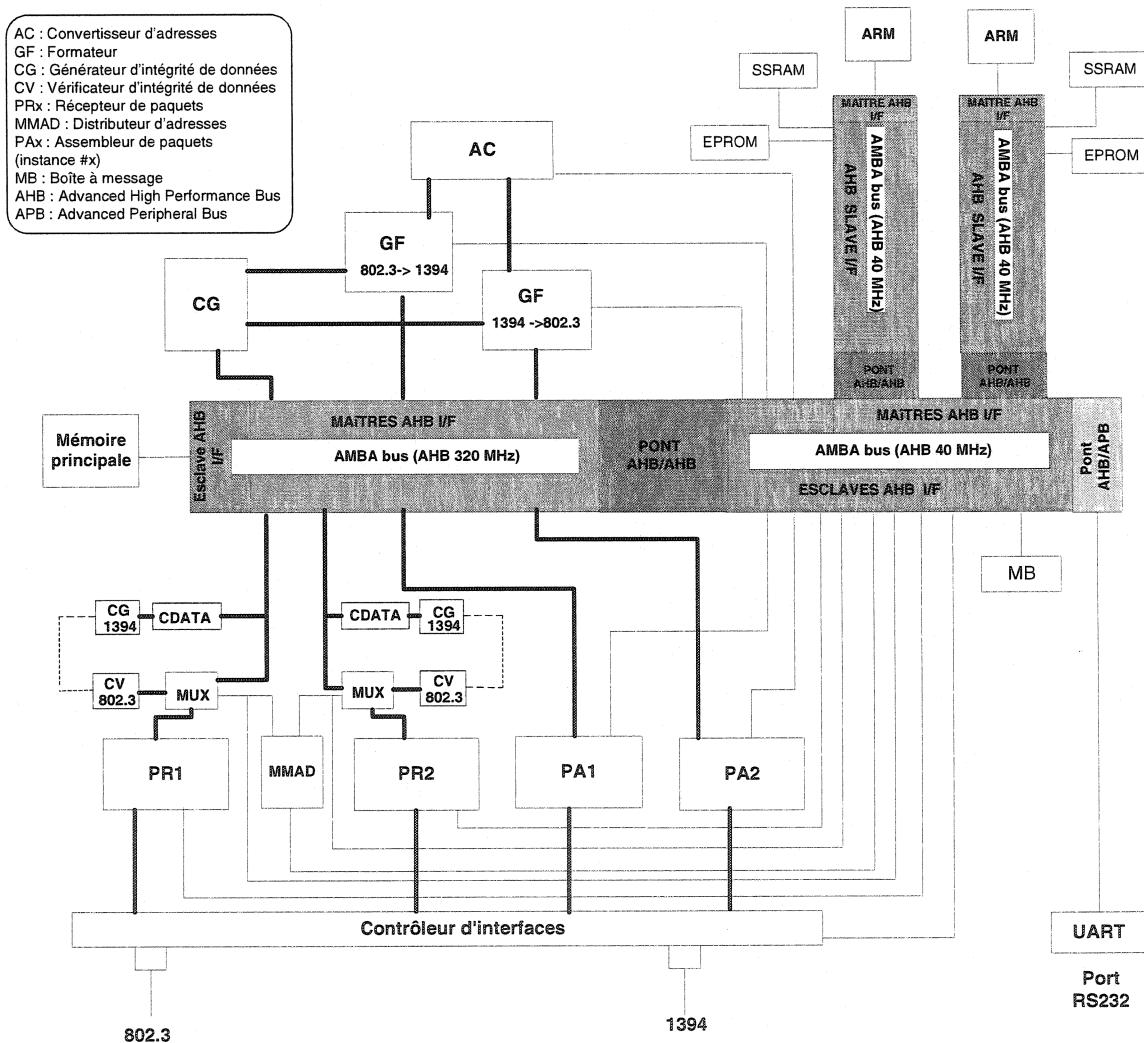

télésurveillance, etc. Notre objectif dans ce cas-ci est une communication entre le protocole IEEE 802.11 (Ethernet) à IEEE 1394 (Firewire), et vice versa. Le convertisseur fait correspondance à une couche précise du modèle OSI les différents protocoles de communication. L'illustration suivante présente la plate-forme d'un convertisseur de protocoles.

Figure 2-10 Plate-forme du convertisseur de protocole

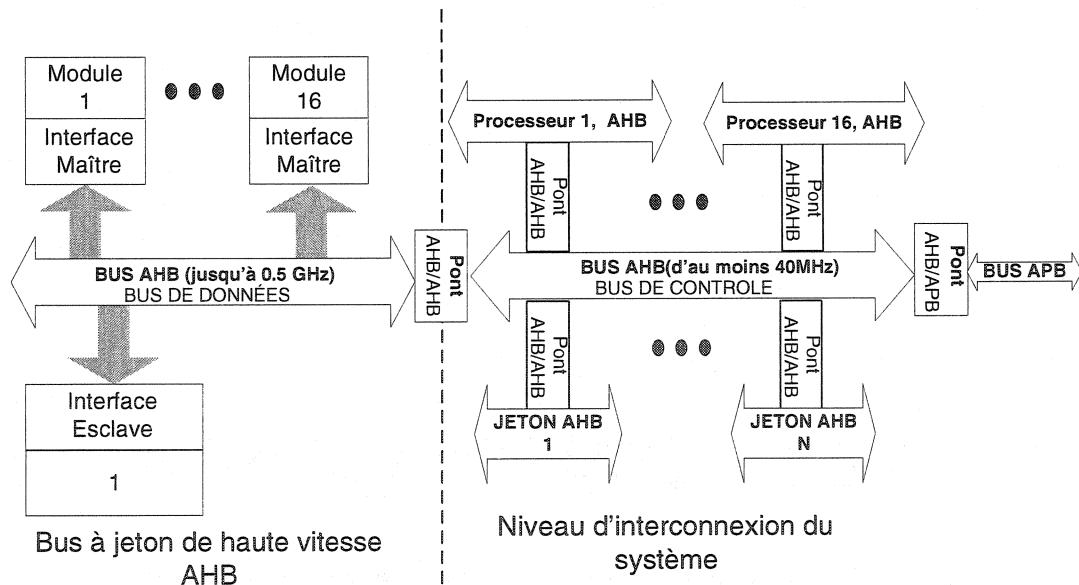

Nous avons deux modules de réception de paquets, soit PR1 et PR2, ainsi que deux modules de transmission de paquets, PA1 et PA2. Il y a quatre processeurs, soit 2 ARMs avec 2 GFs et huit principaux modules matériels. Nous employons une mémoire centrale

avec un port d'accès. La configuration de cette plate-forme est possible par le UART ou par un lien Ethernet. Nous avons une plate-forme *multi-threaded*. C'est un système de conversion bidirectionnel. Le logiciel est exécuté sur un ARM7TDMI connecté par un bus de commande AMBA AHB. Selon les besoins de l'application, un deuxième ARM peut faire un traitement sur un paquet tel que la reconnaissance de protocoles. Les processeurs ARMs ont été isolés avec leur propre bus AMBA pour réduire au minimum le trafic sur le bus de contrôle. Les deux ARMs ne peuvent pas accéder en même temps au bus de commande.

Tout d'abord, un paquet arrive d'un lien physique par le PR. Ce dernier vérifie s'il peut identifier le protocole, sinon il envoie une requête au ARM pour un décodage logiciel. Le PR mettra le paquet en mémoire. Par la suite, le formateur (GF, pour *general formatter*) le prendra pour le convertir avec son entête à un autre protocole à partir de ses différentes couches. Les résultats seront mis dans la mémoire principale. L'assembleur de paquet rassemblera les entêtes et les données du paquet pour les transmettre dans un autre protocole. Le ARM de contrôle permettra de suivre l'état du paquet en cours de traitement. De plus, il contrôlera chaque module du système pour leur indiquer leur tâche à suivre. Le MMAD (Main Memory Address Distributor) permet l'attribution des plages mémoires occupées par les paquets. Il y a aussi une boîte aux lettres permettant la communication entre les deux processeurs ARM. Le bus de donnée à haute vitesse permet le lien entre les modules et la mémoire de façon concurrente. Les paquets peuvent être acheminés de la mémoire aux modules et vice versa sans avoir un problème de contention. Chacun d'eux peut réaliser une opération sur le paquet et le remettre en mémoire. De plus, c'est une mémoire à un seul port qui permet la réduction de la surface comparativement à une mémoire multiport. Un autre module nécessaire est le CG (*Checksum Generator*) qui permet de savoir s'il y a eu des erreurs sur les paquets. L'interface contrôleur permet à la plate-forme et de s'interfacer aux protocoles traités. Dans la mise en œuvre envisagée, le bus de contrôle opère à 40MHz et le bus de données à 320MHz. Le GF et le CA opèrent à 80MHz, tandis que les autres modules opèrent à

40MHz. Les modules sur le bus de données sont des maîtres pouvant initialiser des requêtes. Les modules du bus de contrôle sont des esclaves recevant des ordres provenant des ARM. Les ARM peuvent accéder à la mémoire à travers deux pont AHB/AHB. Le pont AHB/APB permet l'interconnexion au système des périphériques lents. Plus particulièrement, le convertisseur traitera une transmission de paquets de type vidéo.

## 2.4 Autres architectures des plate-formes SoC vidéo

Un des objectifs de ce travail est de définir une plate-forme générique permettant une application de traitement et de transmission vidéo. À titre de revue de littérature, nous allons présenter deux plate-formes vidéo, soit la VC01 de Alphamosaic et la Nexpria-DVP de Philips.

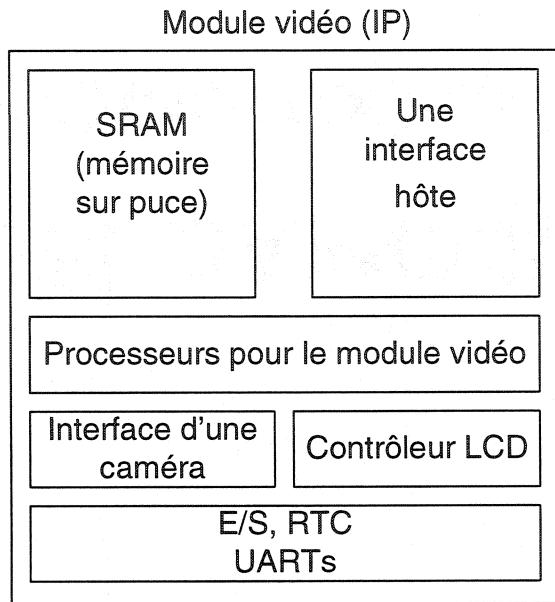

### 2.4.1 VC01

Alphamosaic offre un circuit intégré VCO1 [2] permettant le traitement vidéo à faible consommation de puissance. Il est programmable et une bibliothèque logicielle est disponible pour réaliser des fonctions tel que l'évaluation du mouvement, DCT, l'analyse en ondelettes, l'application d'opérateurs de morphologie mathématique, etc. Les applications visées peuvent être le téléphone vidéo, la vidéo sans fils, les assistant digitaux etc. Il est basé sur l'utilisation de processeurs DSP avec unités VLIW vectorielles de traitement comprenant 16 chemins de données en parallèle (16 processeurs) opérant jusqu'à 125MHz. De plus, il est associé à un processeur scalaire RISC de 32 bits. Il a un registre 2D agissant comme une fenêtre sur l'image, permettant au maximum un groupe de pixels de 64x64. Il peut faire 6 milliards d'opérations scalaires équivalents (BOPS). Cette architecture possède une mémoire interne de 8 MBits. La figure suivante présente une vue de la structure interne de ce circuit intégré [3].

Figure 2-11 Schéma bloc de la puce d'Alphamosaic

Il supporte le système d'exploitation en temps réel tel Nucleus [1]. VC01 exploite la dernière technologie CMOS 0.13 micron.

#### 2.4.2 Nexperia

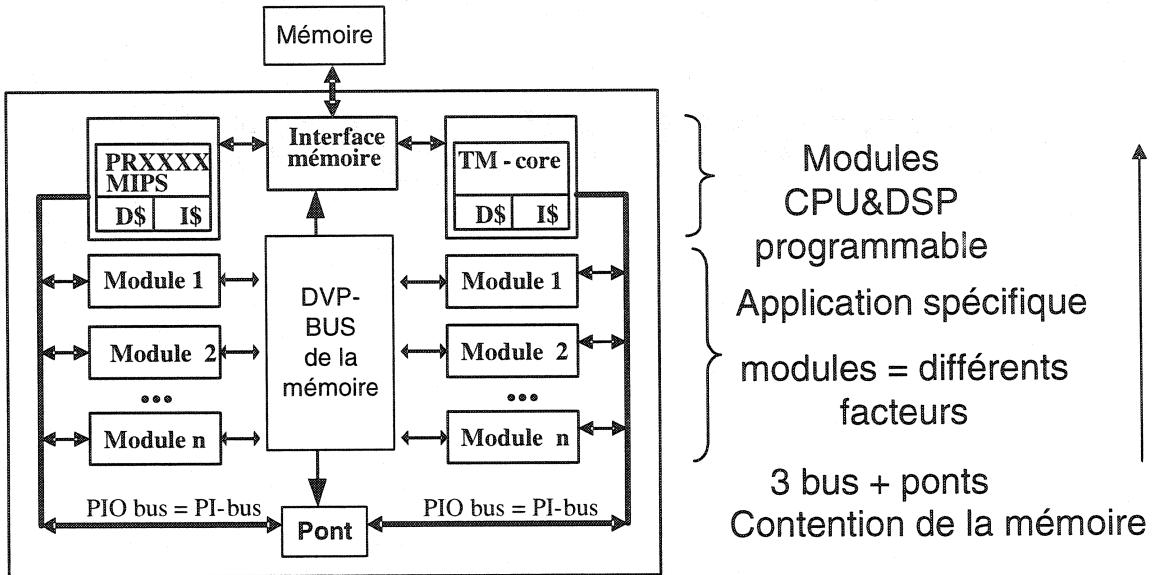

Les plates-formes Nexperia de la compagnie Philips Semiconductors représentent une famille de solutions SoC flexibles permettant des applications multimédia. L'approche de Phillips fut de développer un système flexible à travers la programmation et l'utilisation de blocs IP ainsi que d'une architecture de base. Le PNX-8525 et la PNX-8550 sont des exemples de circuits intégrés qu'on retrouve sur la Nexperia-DVP. L'architecture de base de la DVP est représentée par la figure 2-12 [5].

Les principaux éléments sont les processeurs, les blocs IP, le réseau de connexion et l'interface à la mémoire principale. Il y a deux processeurs, le premier est un processeur MIPS servant pour le contrôle de la plate-forme et le deuxième est un processeur multimédia pour le traitement vidéo.

L'architecture comprend trois niveaux abstractions soit les règles logicielles et matérielles, le niveau de transaction des modules (DTL) et la connexion réseau.

Figure 2-12 DVP-based IC

Le premier sert à définir le logiciel vu comme du matériel. Le deuxième permet le transfert entre les modules et le dernier est le niveau bus de communication. La prochaine section discute plus en détails des interconnexions entre les modules d'un système sur puce. Tout comme le VC01, la plate-forme possède un système exploitation. Il y a toujours un processeur de contrôle et un autre pour le traitement des données. Dans la figure 2.12, on observe qu'il y a un bus dédié à chaque type de processeur et ils sont reliés par un pont.

## 2.5 Interconnexion d'une plate-forme SoC

L'interconnexion des modules d'une plate-forme SoC requiert une capacité d'échanger des données qui satisfait la bande passante requise par l'application visée. Nous traiterons trois manières permettant la réalisation des interconnexions d'une plate-forme SoC, dont deux se basent sur des normes de communication existantes: celles de la plate-forme Nexpria , du Star-IP bus utilisant AMBA et finalement OCP d'IBM.

### 2.5.1 Interconnexion d'une plate-forme Nexperia-DVP

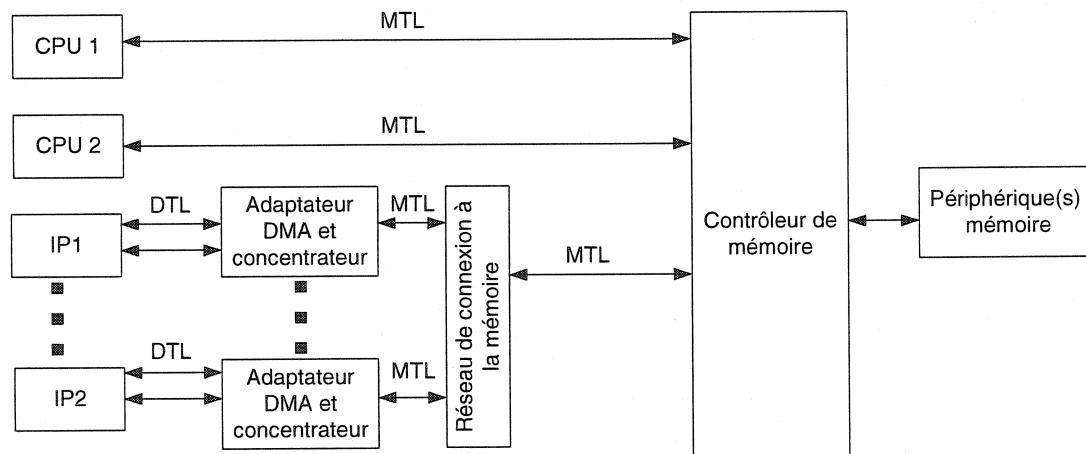

La connexion d'un module avec la mémoire se fait en utilisant deux types de port de communication. Nous avons le MTL (*Memory Transaction Level*) et le DTL (*Device Transfer Level*). La figure 2.13 permet l'illustration des ports MTL dans un SoC de Nexperia.

Figure 2-13 Application des ports MTL dans un SoC de Nexperia

Le MTL est un protocole de communication optimisé pour un contrôleur de mémoire DRAM. La connexion à la mémoire utilise un PMAN (*Pipeline Memory Access Network*). Le protocole DTL précède et ressemble à l'interface VCI de VSIA [43]. La différence est qu'il y a une abstraction de certains aspects du système comme la bande passante de la mémoire, la longueur optimale des transactions, etc. Plus précisément, il n'y a pas de détails relatifs au protocole de communication dans le développement des IP.

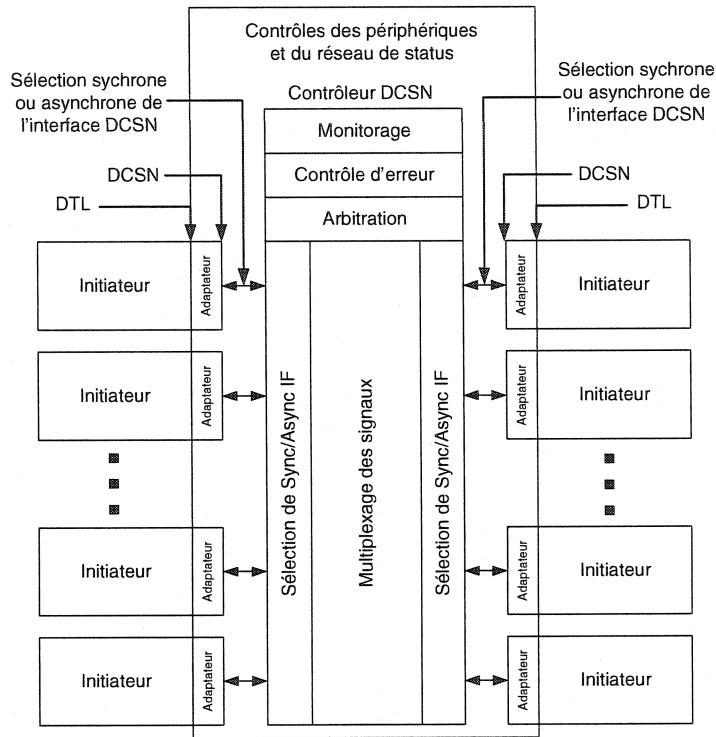

Un autre aspect important est la connexion réseau au niveau du bus. La figure 2.14 présente le système d'états et le contrôle des périphériques de la Nexperia [5]. Il comprend un contrôleur d'état de réseau pour les modules et un réseau d'interconnexion pour la mémoire. Le réseau DCS permet l'implémentation d'îlots synchrones. Il est nécessaire d'avoir un adaptateur DTL-DCS. Chaque module peut opérer à une fréquence de 70 à 150MHz avec une horloge de DCS de 200MHz.

Figure 2-14 Illustration générale de l'interface pour les contrôles des périphériques

Il est configuré à chaque initiateur ou cible avec des mécanismes synchrone ou asynchrone. La bande passante du système peut être fixe ou dynamique selon l'application souhaitée.

### 2.5.2 Star-IP Bus

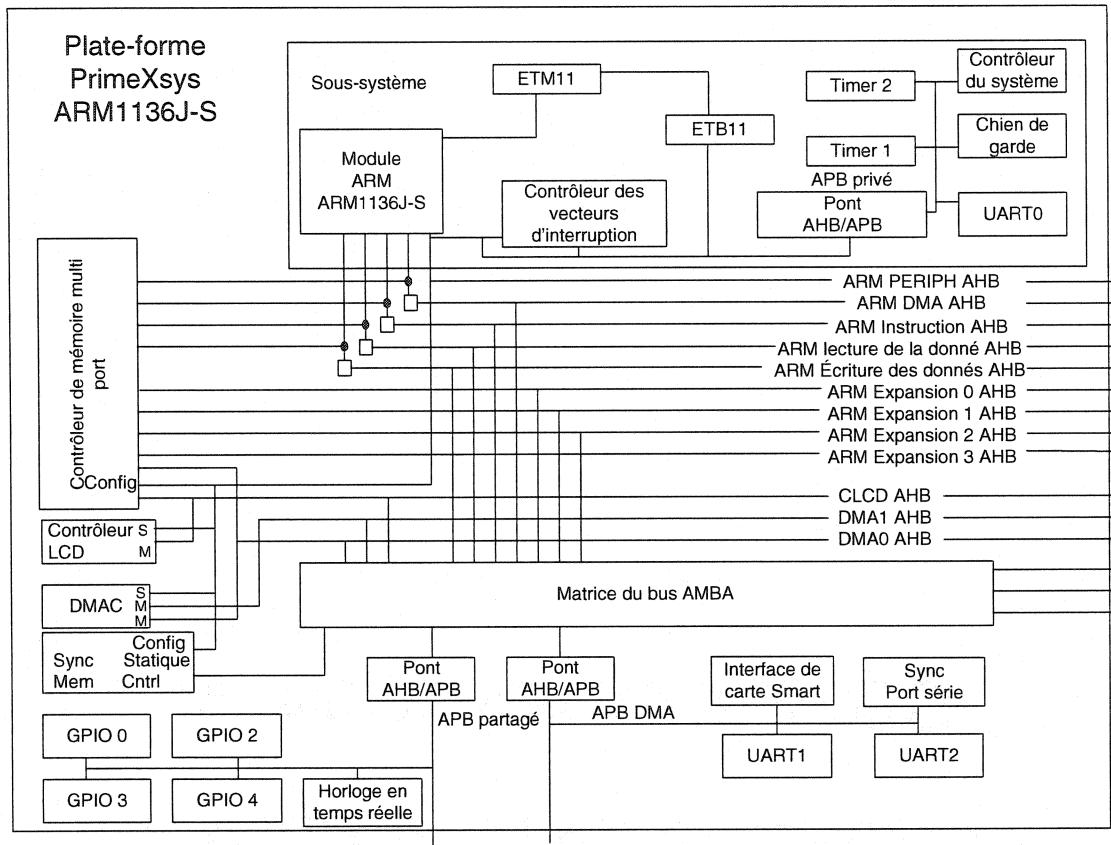

Une autre approche de conception des interconnexions est le noyau Star-Ip [4]. C'est une architecture de plate-forme basée sur des sous systèmes. Nous allons voir son application sur la plate-forme ARM(R) PrimeXsys™ [9]. L'architecture est composée de sous systèmes embarqués constituant un module ARM, un protocole de communication AMBA et un système d'exploitation. AMBA est utilisé dans plusieurs champs d'application. La figure suivante présente ses éléments.

Nous avons plusieurs bus AHB avec plusieurs ponts et un processeur ARM. Nous pouvons connecter des périphériques rapides ou lents sur les bus AHB et APB

respectivement. AHB est un protocole à haute vitesse, tandis que le APB fonctionne à plus faible fréquence et du même coup à une plus faible consommation de puissance.

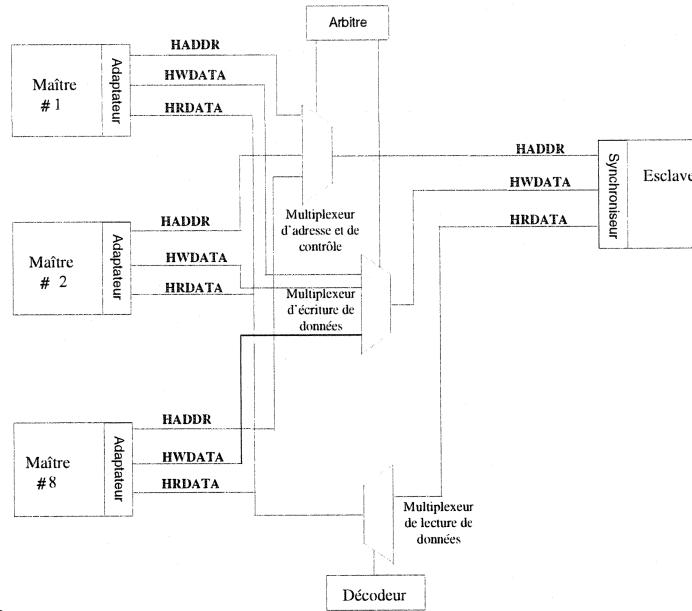

Figure 2-15 Plate-forme PrimeXsys

La norme AHB permet la connexion de 16 maîtres au maximum et d'autant d'esclaves que l'on désire. Le logiciel est exécuté sur le processeur. Dans cette architecture d'interconnexion, les modules compatibles AHB peuvent se connecter sur le bus. Il fonctionne avec un arbitre, des maîtres et des esclaves. Les maîtres initient les requêtes et les esclaves leur répondent. Il y a deux phases. La première est la phase d'adresse permettant de connaître ce que le maître veut et la deuxième est la phase de donnée pour écrire ou lire une valeur au module esclave. Dans cette plate-forme, une matrice de bus AMBA permet la communication simultanée de plusieurs maîtres sur le bus à des différents esclaves. La réduction du temps de conception est possible grâce à l'intégration de différentes plates-formes sur une puce utilisant AMBA.

### 2.5.3 Le bus CoreConnect

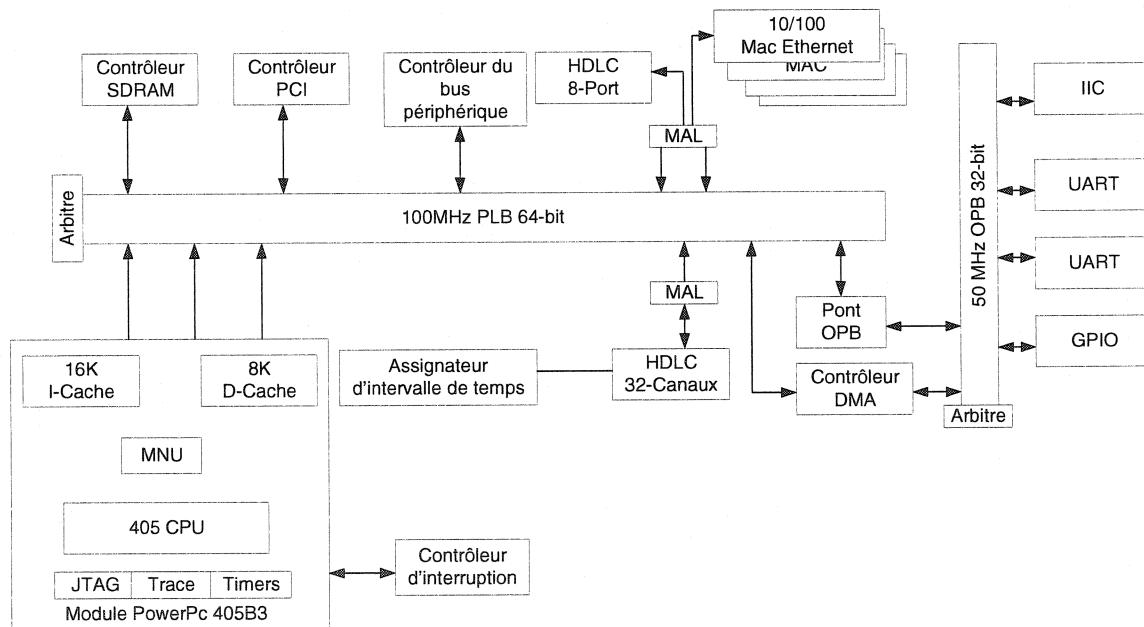

La réalisation des interconnexions entre les modules peut se faire par une méthode différente, soit celle développée par la compagnie IBM avec son bus CoreConnect [20]. Il a été initialement développé pour l'utilisation d'un processeur embarqué PowerPC 405 avec une technologie  $0.5\mu\text{m}$ . Il possède trois niveaux hiérarchiques soit le *Processor Local Bus* (PLB), le *On-chip Peripheral Bus* (OPB) et le *Device Control Register* (DCR). Le premier sert de communication pour les processeurs avec une bande passante élevée. Le deuxième permet la connexion de périphériques opérant à basse vitesse. Le dernier sert à la configuration nécessaire pour certaines instructions du PowerPC. Son système d'interconnexion est illustré par le diagramme suivant.

Figure 2-16 Diagramme bloc du PowerNp [21]

Il vise à créer un environnement de conception facilitant l'intégration de modules provenant de différents concepteurs. Tout comme les autres plates-formes, il utilise une plate-forme de référence pour le développement d'un nouveau système.

## 2.6 Conclusion

La réduction du temps de conception des systèmes complexes est réalisée par une méthode d'intégration des modules dans une plate-forme de référence. Il y a différentes manières de connecter les modules entre eux. Dans la revue de littérature, il y a presque toujours deux bus dans un SoC. Un bus permettant une connexion à haute vitesse pour les processeurs et un autre permettant la communication avec des périphériques opérant à basse vitesse. L'utilisation d'un pont permet la connexion des deux bus. Dans les plates-formes multimédia, nous retrouvons un bus de contrôle et un bus de traitement. Le premier permet la gestion de la plate-forme et le deuxième sert pour le traitement d'une application souhaitée. Pour atteindre une mise en marché rapide, les concepteurs utilisent des normes de communications entre les modules. Nous avons discuté particulièrement de la norme AMBA et CoreConnect.

De plus, la conception d'un système nécessite plusieurs langages ayant chacun leur caractéristiques. Ces derniers ne sont pas efficaces à tous les niveaux d'abstraction. Il est nécessaire d'avoir une méthode de conception exploitant le maximum de capacités de chaque langage. Ainsi, l'utilisation de plus d'un langage avec une méthode d'interconnexion de modules permet de réduire le temps de conception. La simulation des composants créée par des tiers sous différents langages avec un système d'interconnexion, par exemple AMBA, est possible grâce à un environnement hétérogène.

## CHAPITRE 3

### MODÉLISATION HÉTÉROGÈNE

Un objectif de ce travail de recherche est de créer un environnement hétérogène exploitant plusieurs langages de conception en utilisant le meilleur de chacun. La création de cet environnement permettra une utilisation de bibliothèques matérielles et logicielles dans un flot de conception non homogène. Cette méthode permettra la création d'une plate-forme de conception virtuelle de transmission et de traitement vidéo. Ce chapitre discutera de l'interconnexion des langages de modélisation permettant une simulation hétérogène. À partir des possibilités d'une simulation des composantes hétérogènes, nous développerons une méthode de raffinement progressif à double profilage appliquée à l'algorithme de Wiener [24]. Ce dernier est un filtre adaptatif 2-D pour la réduction du bruit sur une image. Le filtre Wiener permet d'avoir une image filtrée où le bruit présent dans l'image est atténué. L'atténuation du bruit est obtenue par l'équation suivante qui produit les pixels dans l'image de sortie en ajoutant à la moyenne locale une partie de la différence entre les pixels d'entrée et cette même moyenne locale calculée sur un voisinage d'une taille spécifiée par l'utilisateur.

$$F(k,l) = \mu + \frac{\sigma^2 - v^2}{\sigma^2} (G(k,l) - \mu)$$

#### **3.1 Plate-forme SoC**

##### **3.1.1 Concept**

Le concept de plate-forme SoC n'est pas entièrement nouveau. Il a été utilisé avec succès à travers les années. Cependant, il existe plusieurs interprétations du terme plate-forme [38]. Dans ce mémoire, une plate-forme SoC est généralement composée de modules matériels dédiés et de processeurs capables d'exécuter des modules fonctionnels exprimés sous la forme logiciels. Ces divers modules sont normalement reliés par un ou plusieurs médiums de communication. Cette architecture, programmable ou fixe est

souvent optimisée pour une classe d'applications. Aujourd'hui, le concept de la réutilisation des composants conçus est la clef fondamentale du succès pour la conception d'une plate-forme SoC. Dans le cadre de cette recherche, nous utiliserons le terme plate-forme pour désigner une architecture comportant des processeurs et des modules matériels avec des bus de communication. La réduction du temps de design est possible grâce à ce concept pour un système sur puce comprenant plusieurs millions de portes logiques.

### 3.1.2 Intégration

L'intégration est importante pour les plate-formes. Elle consiste à intégrer une collection de modules fonctionnels développés individuellement [38]. L'industrie développe des normes de communication permettant l'uniformisation des interfaces de communication entre les composants. Par exemple, la compagnie Infinite Technologie Corporation propose une intégration «multi-core» pour les systèmes SoC utilisant la norme AMBA [42]. Une méthode de conception est nécessaire pour réaliser l'intégration et la validation du système avec des langages de modélisation. La prochaine section discutera de cette dernière.

## 3.2 Modélisation hétérogène

La modélisation d'un SoC pour le traitement vidéo demande des outils de conception capables de représenter les limitations et les contraintes de la technologie souhaitée. Dans les systèmes vidéos, les calculs matriciels sont requis pour le traitement en temps réel des images. Le passage de la théorie à l'implémentation demande plusieurs étapes de conception.

### 3.2.1 Le concept

Lors de la conception d'un système embarqué, il y a deux aspects différents à considérer. Le premier aspect est le développement des modules nécessaires au traitement des données et le deuxième est la méthode de communication entre ces modules. Ce dernier sera traité plus en détail au chapitre suivant. Avant de proposer une méthode de

raffinement progressif entre les langages, il est important de connaître les canaux de communication entre les modules au niveau SoC disponibles à divers niveaux d'abstraction. Ces canaux permettront la communication entre des modules spécifiés par des langages différents.

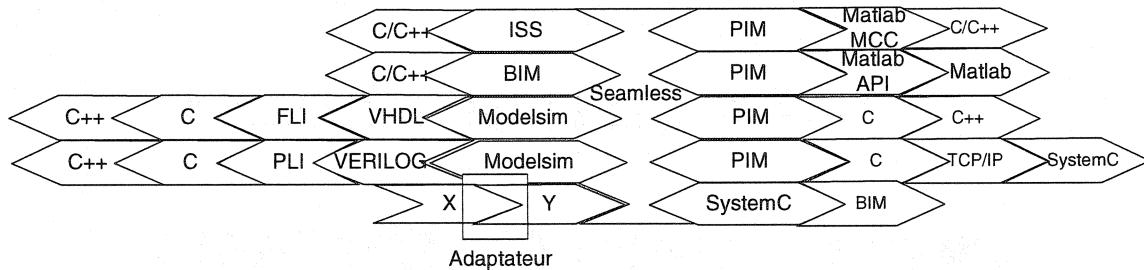

L'hétérogénéité des SoC requiert une validation par simulation des modules décrits à différents niveaux d'abstraction. L'interconnexion des langages sera possible grâce aux adaptateurs. Ces derniers peuvent transformer des structures pour des besoins spécifiques. La figure 3-1 permet d'expliquer plus facilement ce concept.

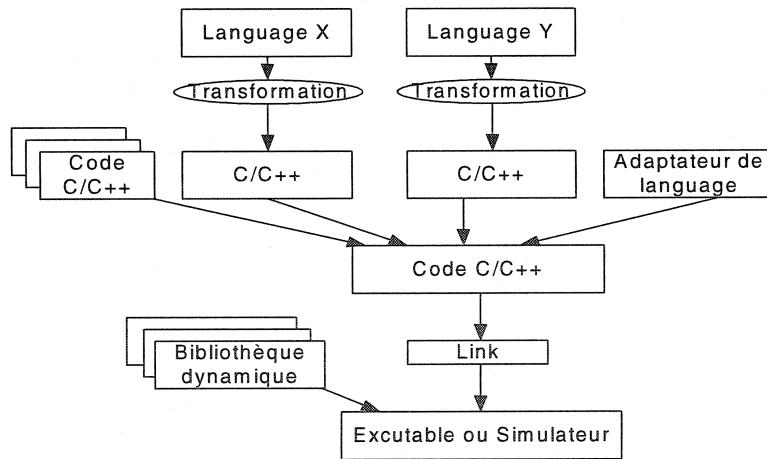

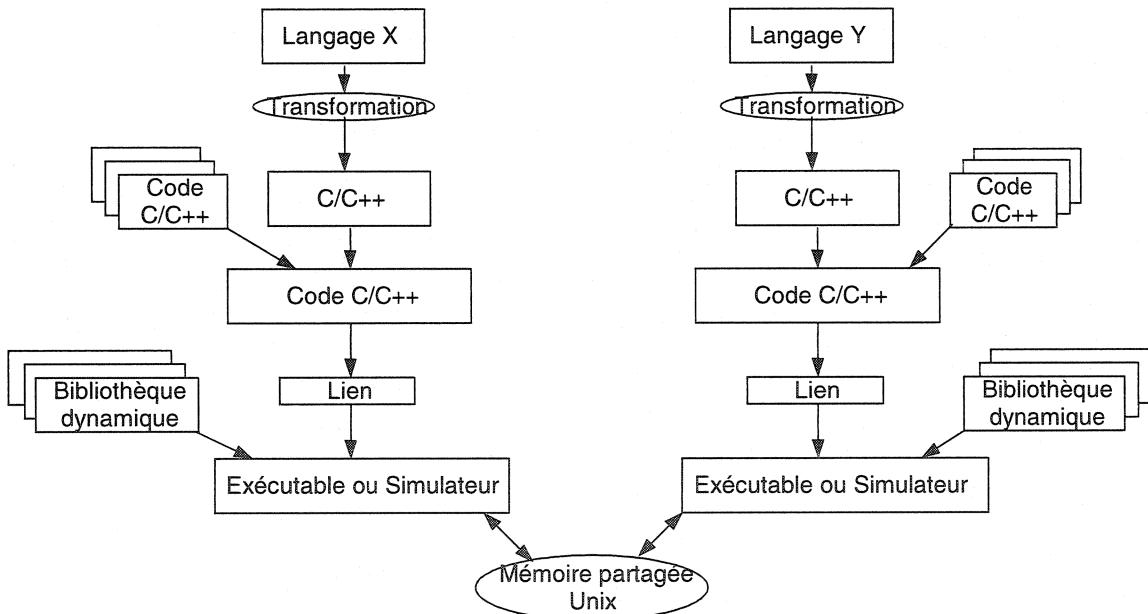

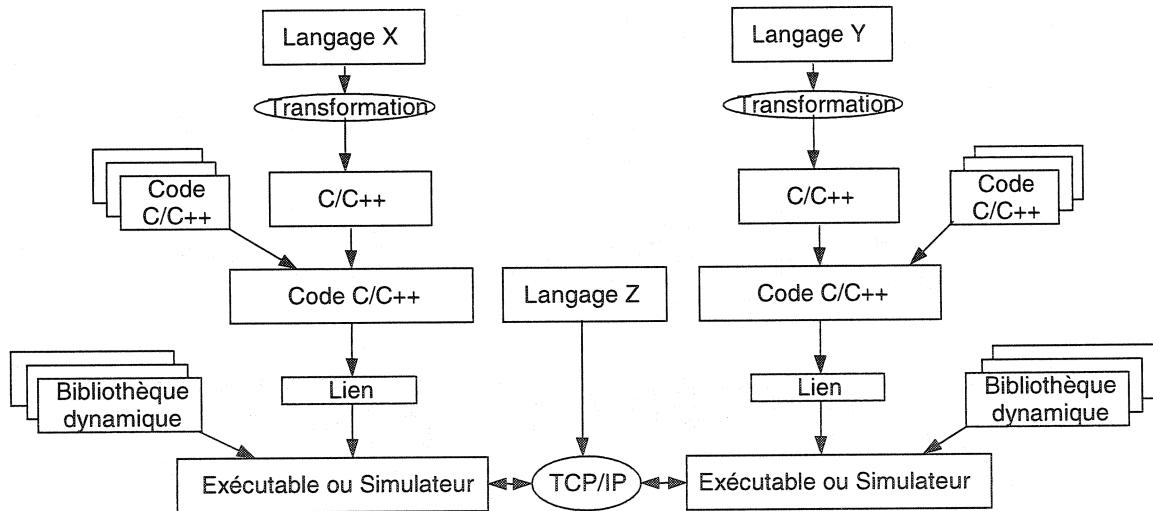

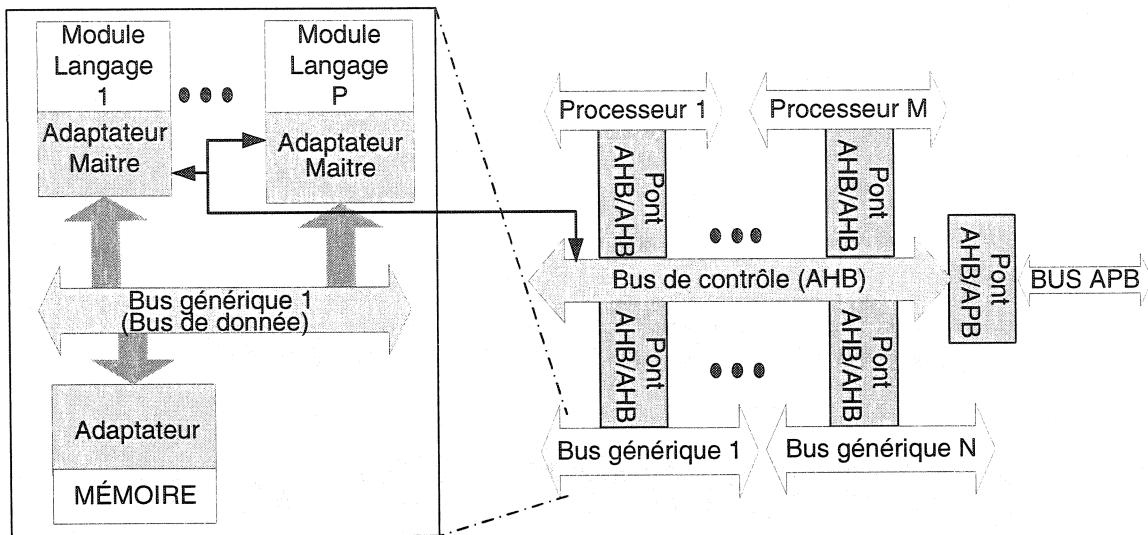

Nous pouvons voir les possibilités d'intégration des outils. De façon générale, on veut connecter plusieurs langages ensemble par l'intermédiaire d'adaptateur. Nous définirons trois méthodes pour la réalisation des adaptateurs, soit la méthode directe (par une compilation commune), la méthode par mémoire partagée et la méthode par l'emploi de liens TCP/IP.

Figure 3-1 Modèle d'interconnexions des langages

Les sections suivantes présentent des adaptateurs spécifiques avec leurs avantages et leurs inconvénients.

L'utilisation d'un environnement hétérogène permet une réduction du temps de développement des systèmes embarqués. En effet, le temps de conception peut être réduit en exploitant divers composants réutilisables exprimés grâce à différents langages et niveaux d'abstraction.

### 3.2.2 Niveaux d'abstraction

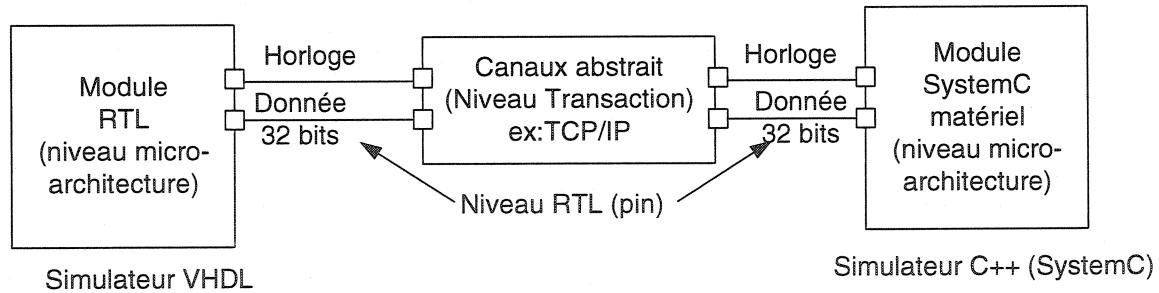

Avant la création d'un modèle hétérogène, il est important de définir quatre niveaux d'abstraction. Chaque module communique à travers des canaux pour échanger des informations avec d'autres composantes du système. En [25], les niveaux d'abstraction sont représentés en fonction du concept. Il y a quatre niveaux de communication lors du raffinement d'un système SoC, soit les niveaux service, transaction, macro-architecture et micro-architecture (RTL). La modélisation hétérogène doit pouvoir supporter tous ces niveaux d'abstraction dans une simulation [25]. Dans ce chapitre, nous utiliserons trois des quatre niveaux d'abstraction, soit les niveaux : transaction, macro-architecture et microarchitecte. L'objectif est de créer une méthode d'interconnexion des langages. Il sera possible d'utiliser les divers niveaux d'abstraction de façon transparente aux modules. C'est-à-dire une communication RTL combinée à une communication transactionnelle de deux simulateurs. La figure 3-2 présente un exemple d'une combinaison de deux niveaux d'abstraction.

Cette première méthode d'interconnexion sera étudiée plus en détail dans les sections suivantes. Dans ce cas, deux simulateurs communiquent par un canal transactionnel.

Figure 3-2 Mixage des niveaux d'abstraction

Les informations au niveau broche sont encapsulées pour être transmises et recomposées pour être interprétées par l'autre simulateur. Il est important aussi de connaître les limites des outils et leurs capacités. Les langages principaux avec les niveaux de communication communément utilisés sont décrits en [25]. Les outils disponibles ne supportent généralement pas tous les niveaux d'abstraction pour le raffinement d'un système SoC

[29]. L'accélération du temps de simulation est possible en combinant judicieusement les outils. La capacité de ces derniers a été brièvement décrite dans le chapitre précédent. La section suivante présente trois méthodes générales d'interconnexion applicables à la conception des systèmes embarqués.

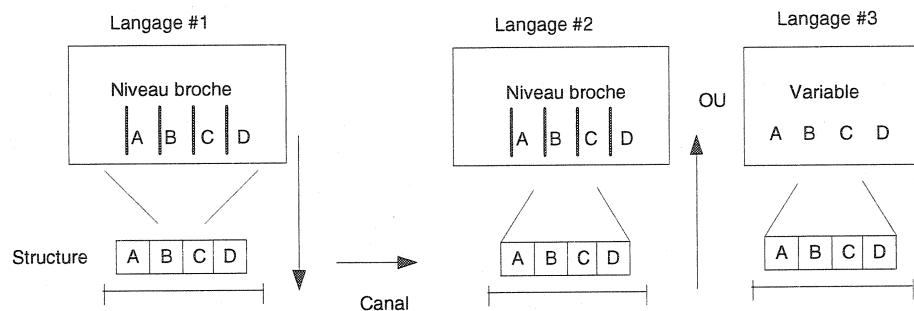

### 3.3 Méthodes d'interconnexion des langages

L'hétérogénéité des composants d'un modèle SoC pour une application requiert plusieurs outils possédant des caractéristiques propres. Dans le cadre de notre recherche sur les outils et leur interaction, nous pouvons définir des méthodes d'intercommunication entre les langages de modélisation. Un langage peut se connecter à un autre langage lorsqu'il possède des caractéristiques communes. La majorité des langages de conception sont capables d'avoir des notions compatibles en C. De plus, certains langages peuvent générer du C ou C++, permettant ainsi une plus grande inter-connectivité dans le cas de langages comme Matlab, UML etc. Donc, le langage doit être capable de se connecter via un API ou de générer du C/C++. Le point commun entre les outils peut être soit le C/C++, une communication réseau ou une plage mémoire partagée (unix).

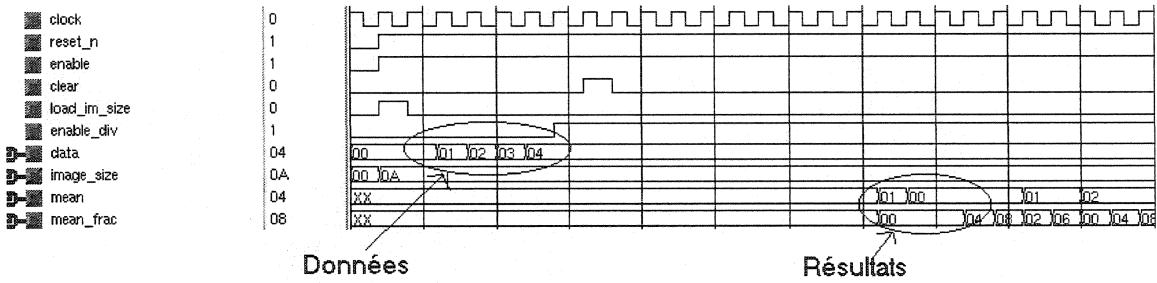

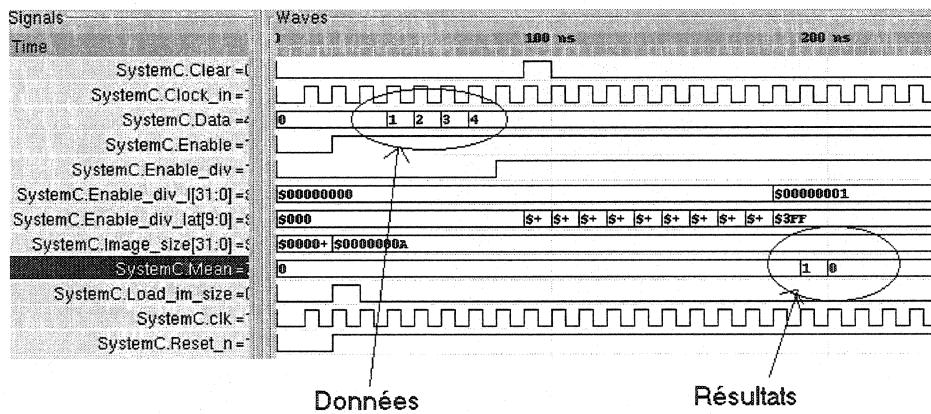

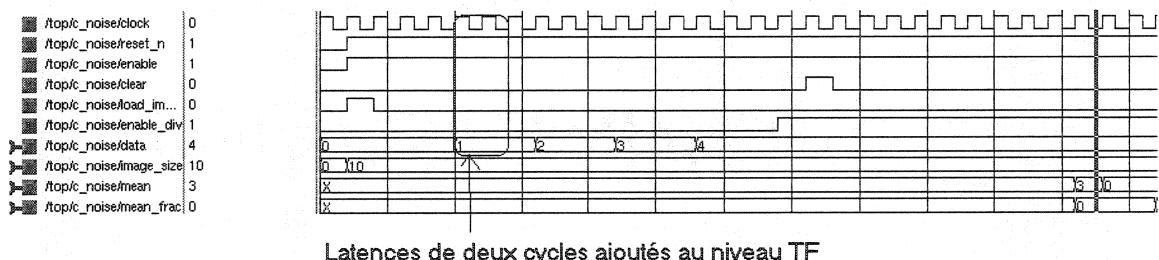

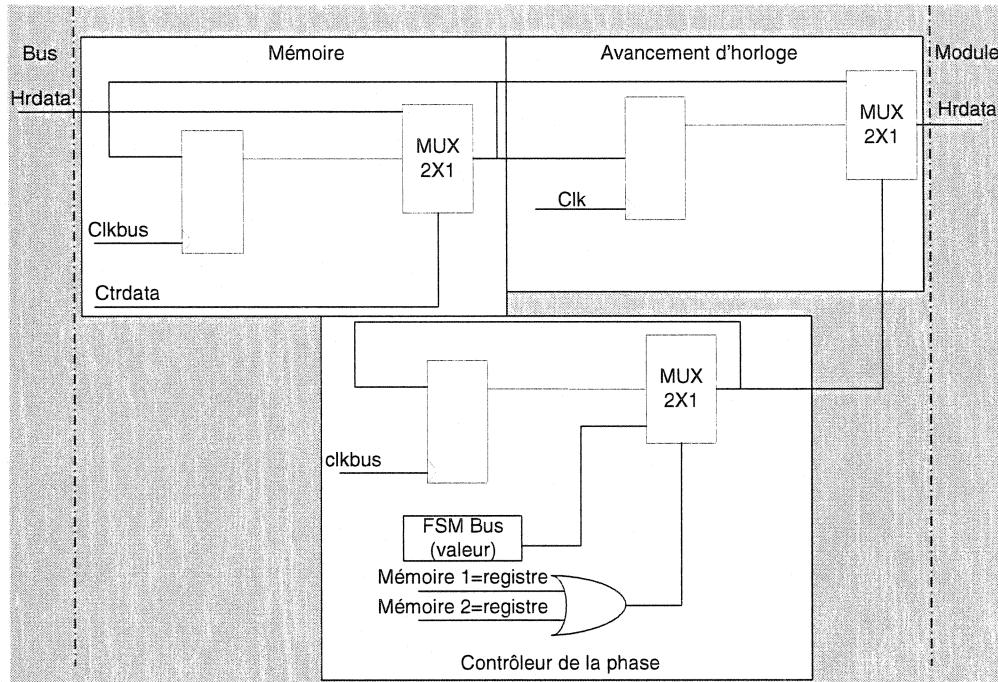

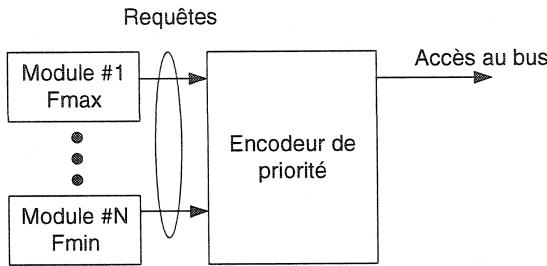

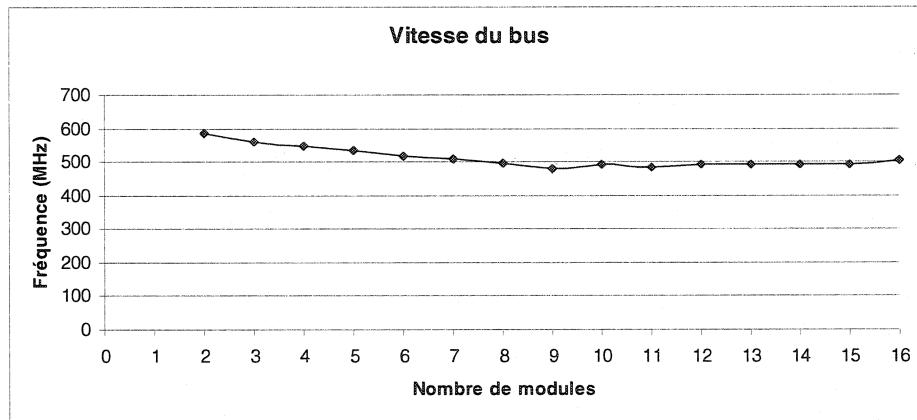

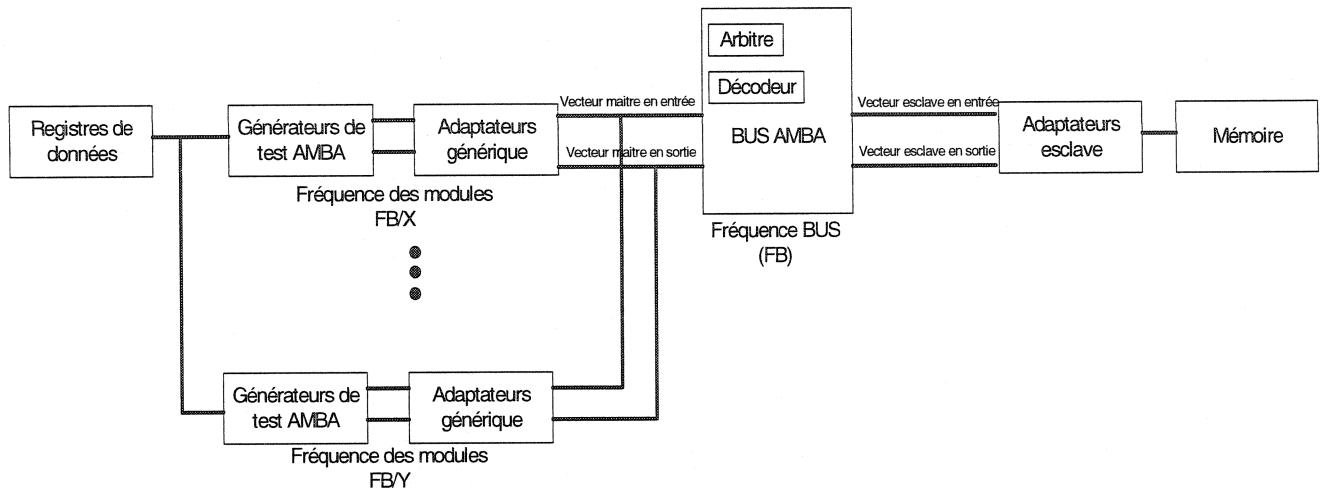

#### 3.3.1 Structure d'intercommunication