**Titre:** Compensation de la tension de décalage du CFOA et applications aux filtres passe-bandes à fréquence programmable

Title: Compensation of the CFOA's phase shift voltage and its applications to programmable bandpass filters

**Auteur:** Moncef Djebbi

Author:

**Date:** 2004

**Type:** Mémoire ou thèse / Dissertation or Thesis

**Référence:** Djebbi, M. (2004). Compensation de la tension de décalage du CFOA et applications aux filtres passe-bandes à fréquence programmable [Mémoire de maîtrise, École Polytechnique de Montréal]. PolyPublie.

Citation: <https://publications.polymtl.ca/7475/>

**Document en libre accès dans PolyPublie**

Open Access document in PolyPublie

**URL de PolyPublie:** <https://publications.polymtl.ca/7475/>

PolyPublie URL:

**Directeurs de recherche:** Mohamad Sawan

Advisors:

**Programme:** Non spécifié

Program:

UNIVERSITÉ DE MONTRÉAL

**COMPENSATION DE LA TENSION DE DÉCALAGE DU CFOA

ET APPLICATIONS AUX FILTRES PASSE - BANDES

À FRÉQUENCE PROGRAMMABLE**

MONCEF DJEBBI

DÉPARTEMENT DE GÉNIE ÉLECTRIQUE

ÉCOLE POLYTECHNIQUE DE MONTRÉAL

MÉMOIRE PRÉSENTÉ EN VUE DE L'OBTENTION DU DIPLÔME DE

MAÎTRISE ÈS SCIENCES APPLIQUÉES

(GÉNIE ÉLECTRIQUE)

AOÛT 2004

Library and

Archives Canada

Published Heritage

Branch

395 Wellington Street

Ottawa ON K1A 0N4

Canada

Bibliothèque et

Archives Canada

Direction du

Patrimoine de l'édition

395, rue Wellington

Ottawa ON K1A 0N4

Canada

*Your file* *Votre référence*

*ISBN: 0-612-97940-7*

*Our file* *Notre référence*

*ISBN: 0-612-97940-7*

#### NOTICE:

The author has granted a non-exclusive license allowing Library and Archives Canada to reproduce, publish, archive, preserve, conserve, communicate to the public by telecommunication or on the Internet, loan, distribute and sell theses worldwide, for commercial or non-commercial purposes, in microform, paper, electronic and/or any other formats.

The author retains copyright ownership and moral rights in this thesis. Neither the thesis nor substantial extracts from it may be printed or otherwise reproduced without the author's permission.

In compliance with the Canadian Privacy Act some supporting forms may have been removed from this thesis.

While these forms may be included in the document page count, their removal does not represent any loss of content from the thesis.

#### AVIS:

L'auteur a accordé une licence non exclusive permettant à la Bibliothèque et Archives Canada de reproduire, publier, archiver, sauvegarder, conserver, transmettre au public par télécommunication ou par l'Internet, prêter, distribuer et vendre des thèses partout dans le monde, à des fins commerciales ou autres, sur support microforme, papier, électronique et/ou autres formats.

L'auteur conserve la propriété du droit d'auteur et des droits moraux qui protège cette thèse. Ni la thèse ni des extraits substantiels de celle-ci ne doivent être imprimés ou autrement reproduits sans son autorisation.

Conformément à la loi canadienne sur la protection de la vie privée, quelques formulaires secondaires ont été enlevés de cette thèse.

Bien que ces formulaires aient inclus dans la pagination, il n'y aura aucun contenu manquant.

UNIVERSITÉ DE MONTRÉAL

ÉCOLE POLYTECHNIQUE DE MONTRÉAL

Ce mémoire intitulé:

**COMPENSATION DE LA TENSION DE DÉCALAGE DU CFOA

ET APPLICATIONS AUX FILTRES PASSE - BANDES

À FRÉQUENCE PROGRAMMABLE**

Présenté par: **DJEBBI MONCEF**

en vue de l'obtention du diplôme de: **Maîtrise ès sciences appliquées**

a été dûment accepter par le jury d'examen constitué de:

M. Jean - Jules Brault, Ph.D., président

M. Mohamad Sawan, Ph.D., membre et directeur de recherche

M. Christian Fayomi, Ph.D., membre

À ma famille

## REMERCIEMENTS

Mes remerciements à tous ceux qui ont grandement contribué à la réalisation de ce mémoire par leurs supports et leurs encouragements constants. Un chaleureux remerciement spécial pour chaque membre de ma famille qui m'a donné autant de pouvoir afin de réussir ce projet de recherche.

Bien évidemment, je dois remercier le professeur Mohamad Sawan pour m'avoir offert la chance de réaliser ce projet. De plus, je tiens à remercier mes collègues de l'équipe POLYSTIM et du GRM, pour leur présence et leur support technique.

Finalement, je désire exprimer ma reconnaissance envers le Conseil de Recherche en Sciences Naturelles et en Génie Électrique "CRSNG" ainsi que la Société Canadienne de Microélectronique "CMC" pour le soutien matériel et logiciel.

## RÉSUMÉ

La tendance à développer des circuits miniatures et à faible consommation d'énergie est en pleine croissance. Cela est dû au besoin d'améliorer les performances de dispositifs électroniques dédiés aux nombreuses applications telles que : la télécommunication, le biomédical, le traitement de signal, etc.

Ce projet de maîtrise concerne:

Premièrement, le développement et la conception en technologie *CMOS* d'un amplificateur opérationnel (ampop) à rétroaction en mode courant (*Current Feedback Operational Amplifier - CFOA*) avec un circuit de correction de la tension de décalage. Le circuit de compensation est autonome et engendre des effets négligeables sur les caractéristiques du *CFOA* tels que : la pente maximale de la tension de sortie, la bande passante, la distorsion harmonique, le gain *DC* et la consommation d'énergie. Le *CFOA* et le circuit de compensation sont intégrés sur le même substrat.

Deuxièmement, le circuit conçu dans la première partie de ce travail sera utilisé pour concevoir et intégrer dans un seul circuit une nouvelle architecture de filtre en technologie *CMOS*. Le filtre proposé est de type passe-bande à fréquence programmable et répond aux performances: pas et gain constant, faible niveau de bruit dans la bande passante ciblée. La variation de la fréquence s'effectue à l'aide d'un circuit numérique

qui est peu sensible aux erreurs du procédé de fabrication et présente des effets négligeables sur la performance du filtre.

Le *CFOA* avec compensation de la tension de décalage a été fabriqué en technologie *CMOS 0.18µm*. Les résultats obtenus par simulation et par tests expérimentaux sont excellents et prouvent l'originalité des solutions proposées pour réduire la tension de décalage et varier la fréquence centrale du filtre passe-bande.

## ABSTRACT

The tendency to develop miniature circuits and with low consumption of energy is in full growth. That is due to the needs to improve the electronic performances of devices dedicated to the many applications such as telecommunication, the biomedical and the signal processing, etc.

This project of master concerns:

First, the development and design in technology *CMOS* of an operational amplifier (*ampop*) with feedback in current (*Current Operational Feedback To amplify - CFOA*) with a circuit of correction of the tension of offset. The compensation circuit is autonomous and generates negligible effects on the characteristics of *the CFOA* such as: the maximum slope of the output voltage, the bandwidth, the harmonic distortion, gain *DC* and the consumption of energy. The *CFOA* and the compensation circuit are integrated on the same substrate.

Finally, the circuit designed in the first part of this work will be to use to conceive and integrate in only one circuit a new architecture of filter in technology *CMOS*. The band pass filter proposed is characterized by a programmable frequency and the performances: constant step and gain, low level of noise in the targeted bandwidth.

The frequency programming using a digital circuit that is not very sensitive to the errors generated by manufacturing process and characterized by negligible effects on the performance of the filter.

The *CFOA* with compensation of the tension of offset was manufactured in technology CMOS 0.18 $\mu$ m. The results of simulation and experimental obtained are excellent and prove the originality of the suggested solutions to reduce the tension of offset and to vary the frequency of the band pass filter.

## TABLE DES MATIÈRES

|                                                                                                  |       |

|--------------------------------------------------------------------------------------------------|-------|

| DÉDICACE .....                                                                                   | iv    |

| REMERCIEMENTS .....                                                                              | v     |

| RÉSUMÉ .....                                                                                     | vi    |

| ABSTRACT.....                                                                                    | viii  |

| TABLE DES MATIÈRES .....                                                                         | x     |

| LISTE DES FIGURES .....                                                                          | xv    |

| LISTE DES TABLEAUX.....                                                                          | xviii |

| LISTE DES SYMBOLES ET DES ABRÉVATIONS .....                                                      | xix   |

| <br>                                                                                             |       |

| CHAPITRE 1 : INTRODUCTION.....                                                                   | 1     |

| <br>                                                                                             |       |

| 1.1    Technologie et intégration .....                                                          | 1     |

| 1.2    Filtres intégrés programmables.....                                                       | 2     |

| 1.3    Amplificateurs opérationnels en mode courant .....                                        | 3     |

| 1.4    Techniques de programmation des paramètres de filtre intégré .....                        | 4     |

| 1.5    Objectifs de recherche.....                                                               | 5     |

| 1.6    Contenu du mémoire.....                                                                   | 6     |

| <br>                                                                                             |       |

| CHAPITRE 2 : AMPLIFICATEUR OPÉRATIONNEL À RÉTROACTION EN<br>COURANT ET RÉCENT DÉVELOPPEMENT..... | 9     |

|       |                                                    |    |

|-------|----------------------------------------------------|----|

| 2.1   | Introduction.....                                  | 9  |

| 2.2   | Caractéristiques de l'ampop.....                   | 10 |

| 2.3   | Ampop à rétroaction en courant.....                | 10 |

| 2.3.1 | Architecture du CFOA.....                          | 11 |

| 2.3.2 | Pente maximale de la tension de sortie .....       | 13 |

| 2.3.3 | Tension de décalage.....                           | 15 |

| 2.3.4 | Distorsion harmonique.....                         | 17 |

| 2.4   | Caractéristiques du CFOA et limites .....          | 19 |

| 2.4.1 | Réponse en fréquence .....                         | 19 |

| 2.4.2 | Effets de la résistance de l'entrée négative ..... | 22 |

| 2.4.3 | Linéarité de phase et stabilité.....               | 24 |

|                                                                                                   |                                                     |    |

|---------------------------------------------------------------------------------------------------|-----------------------------------------------------|----|

| <b>CHAPITRE 3 : AMPLIFICATEUR À RÉTROACTION EN COURANT À TENSION<br/>DE DÉCALAGE RÉDUITE.....</b> | <b>38</b>                                           |    |

| 3.1                                                                                               | Introduction.....                                   | 38 |

| 3.2                                                                                               | CFOA en technologie CMOS .....                      | 39 |

| 3.2.1                                                                                             | Analyse de la tension de décalage du CFOA.....      | 39 |

| 3.2.2                                                                                             | Effets de la tension de décalage .....              | 42 |

| 3.3                                                                                               | Compensation de la tension de décalage du CFOA..... | 44 |

| 3.3.1                                                                                             | Schéma du principe de la compensation.....          | 44 |

| 3.3.2                                                                                             | Circuit de compensation proposée .....              | 46 |

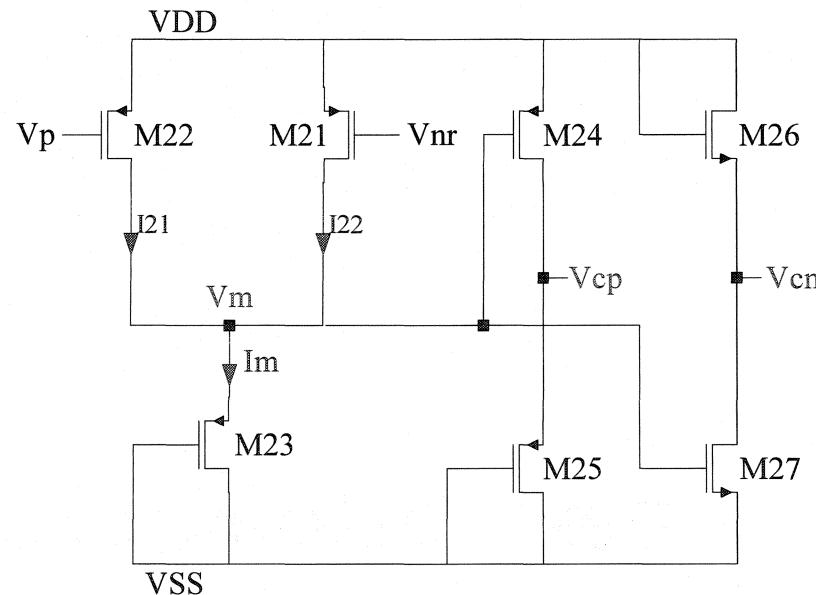

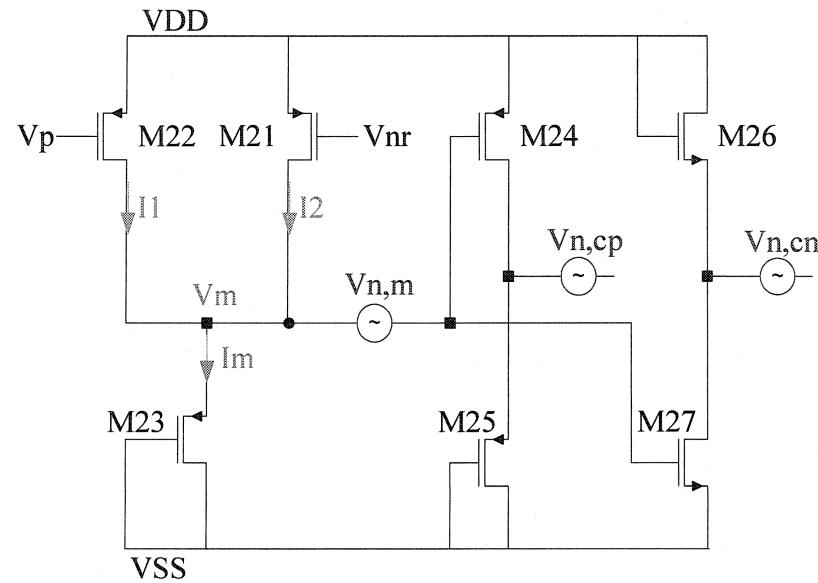

| 3.3.2.1                                                                                           | Circuit de moyenne .....                            | 47 |

|                                                                                   |    |

|-----------------------------------------------------------------------------------|----|

| 3.3.2.2 Circuits soustracteurs analogiques .....                                  | 47 |

| 3.3.3 Considérations pratiques de conception.....                                 | 48 |

| 3.3.3.1 Dessins des masques .....                                                 | 49 |

| 3.3.3.2 Effets de bruits et réponse en fréquence du circuit de compensation ..... | 50 |

| 3.4 Description du CFOA en technologie CMOS .....                                 | 53 |

| 3.4.1 Polarisation de l'étage d'entrée.....                                       | 53 |

| 3.4.2 Polarisation de l'étage d'amplification .....                               | 54 |

| 3.4.3 Sources de bruits et leurs effets .....                                     | 55 |

| 3.5 Conception d'intégrateurs basés sur le CFOA.....                              | 57 |

| 3.6 Conclusion .....                                                              | 59 |

## CHAPITRE 4 : FILTRE PASSE – BANDE À FRÉQUENCE PROGRAMMABLE .... 60

|                                                                                                                 |    |

|-----------------------------------------------------------------------------------------------------------------|----|

| 4.1 Introduction.....                                                                                           | 60 |

| 4.2 DESIGN OF MONOLITHIC TUNABLE CMOS BAND - PASS FILTER<br>USING CURRENT FEEDBACK OPERATIONAL AMPLIFIERS ..... | 61 |

| 4.2.1 Introduction.....                                                                                         | 63 |

| 4.2.2 Offset compensated CFOA .....                                                                             | 64 |

| 4.2.2.1 The CFOA circuit analysis.....                                                                          | 64 |

| 4.2.2.2 Simulation and experimental results of the CFOA .....                                                   | 67 |

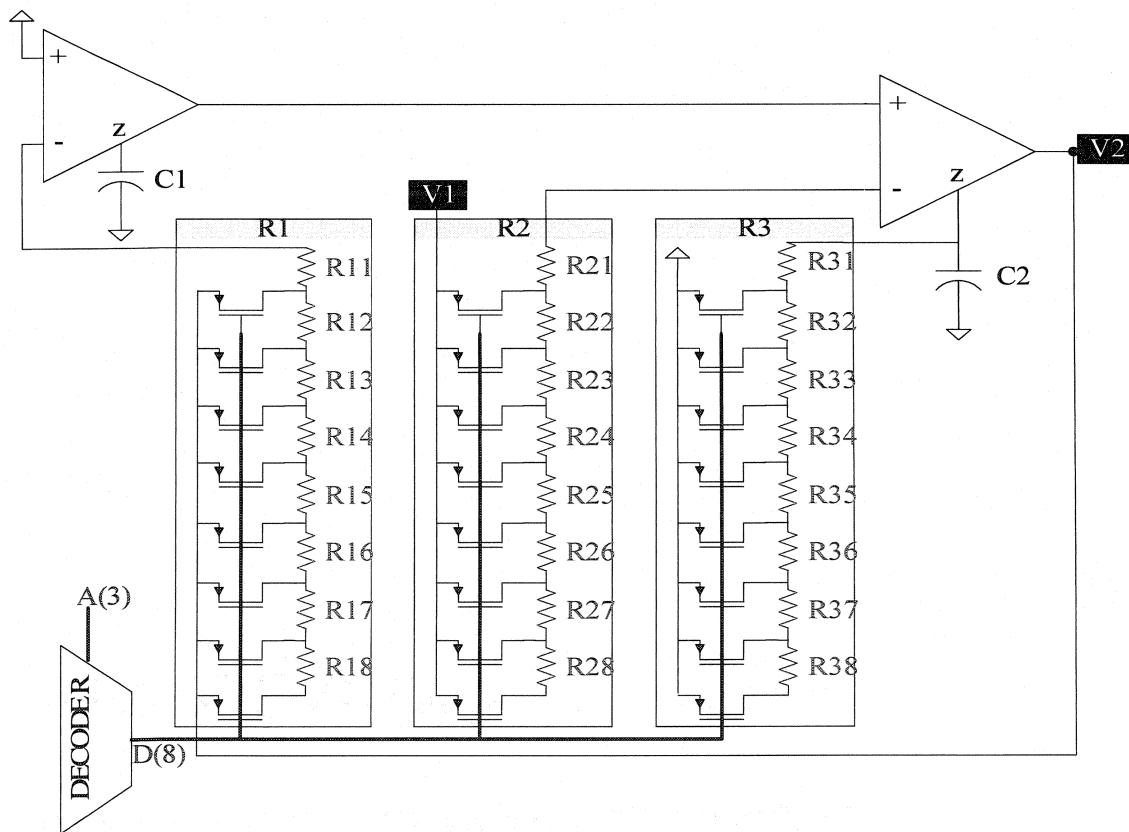

| 4.2.3 CFOA-based tunable band-pass filter .....                                                                 | 68 |

| 4.2.3.1 Filter configuration .....                                                                              | 68 |

|                                             |    |

|---------------------------------------------|----|

| 4.2.3.2 On-chip digital tuning circuit..... | 71 |

| 4.2.4 The filter simulation results .....   | 74 |

| 4.2.5 Conclusion .....                      | 74 |

| REFERENCES .....                            | 76 |

| LIST OF FIGURES .....                       | 78 |

| LIST OF TABLES.....                         | 86 |

| 4.3 Conclusion .....                        | 89 |

## CHAPITRE 5 : ANALYSES DES RÉSULTATS COMPLÉMENTAIRES DU CFOA ET DU FILTRE .....

90

|                                                       |     |

|-------------------------------------------------------|-----|

| 5.1 Introduction.....                                 | 90  |

| 5.2 Caractéristiques du CFOA avec compensation.....   | 90  |

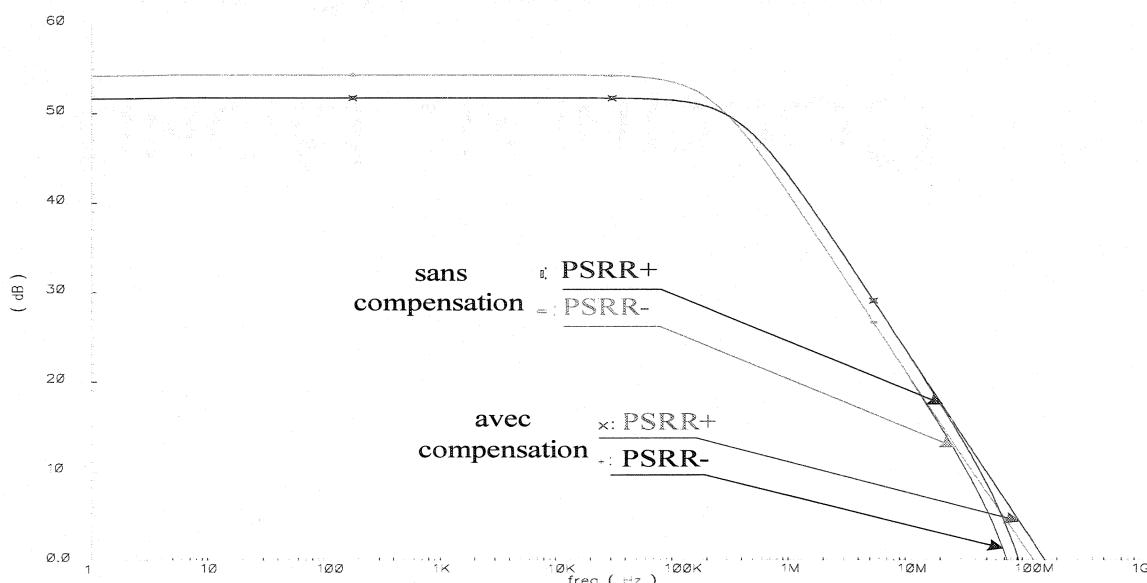

| 5.2.1 Taux de rejet de la tension d'alimentation..... | 91  |

| 5.2.2 Taux de rejet du mode commun.....               | 92  |

| 5.2.3 Pente de la tension de sortie.....              | 92  |

| 5.2.4 Plage de la tension de sortie.....              | 93  |

| 5.2.5 Bruit reflété à l'entrée .....                  | 95  |

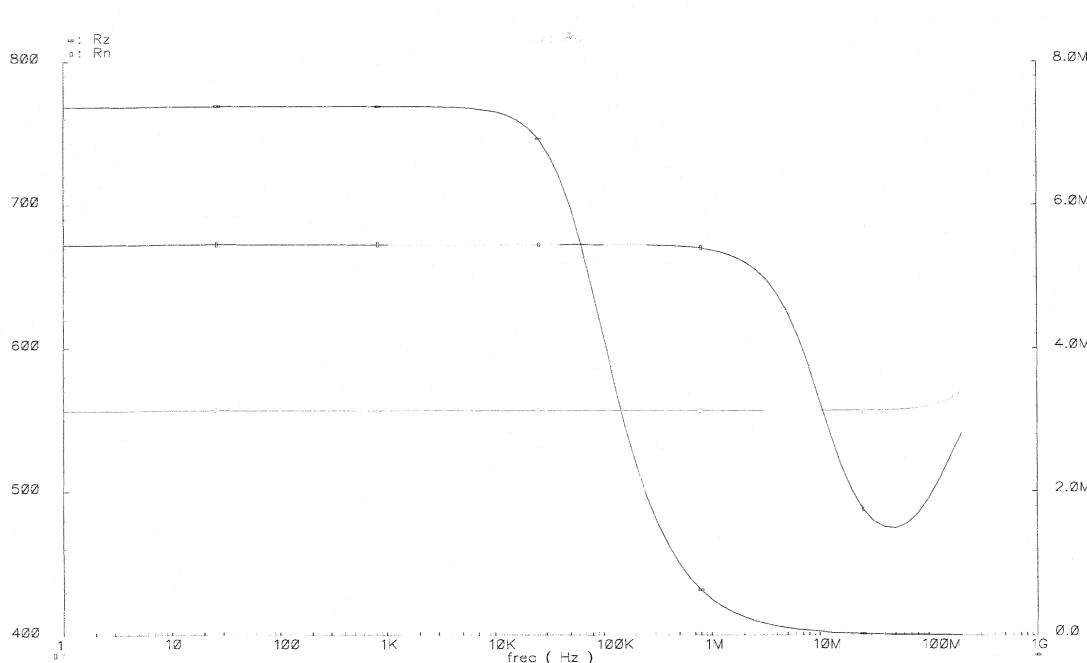

| 5.2.6 Résistances et effets .....                     | 95  |

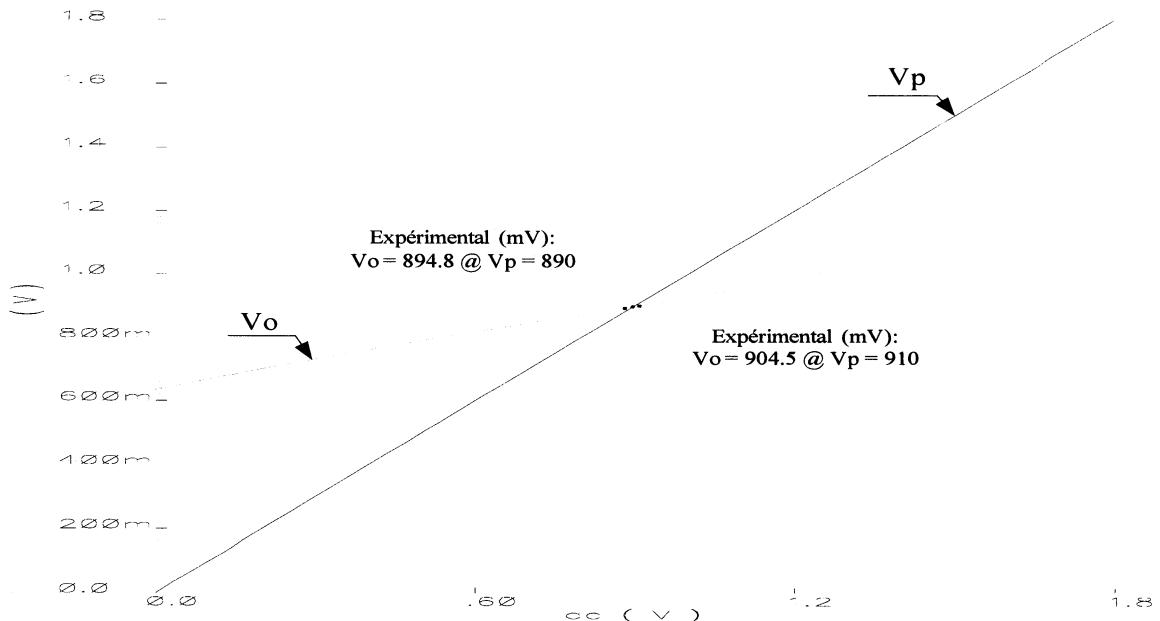

| 5.2.7 Tension de décalage.....                        | 96  |

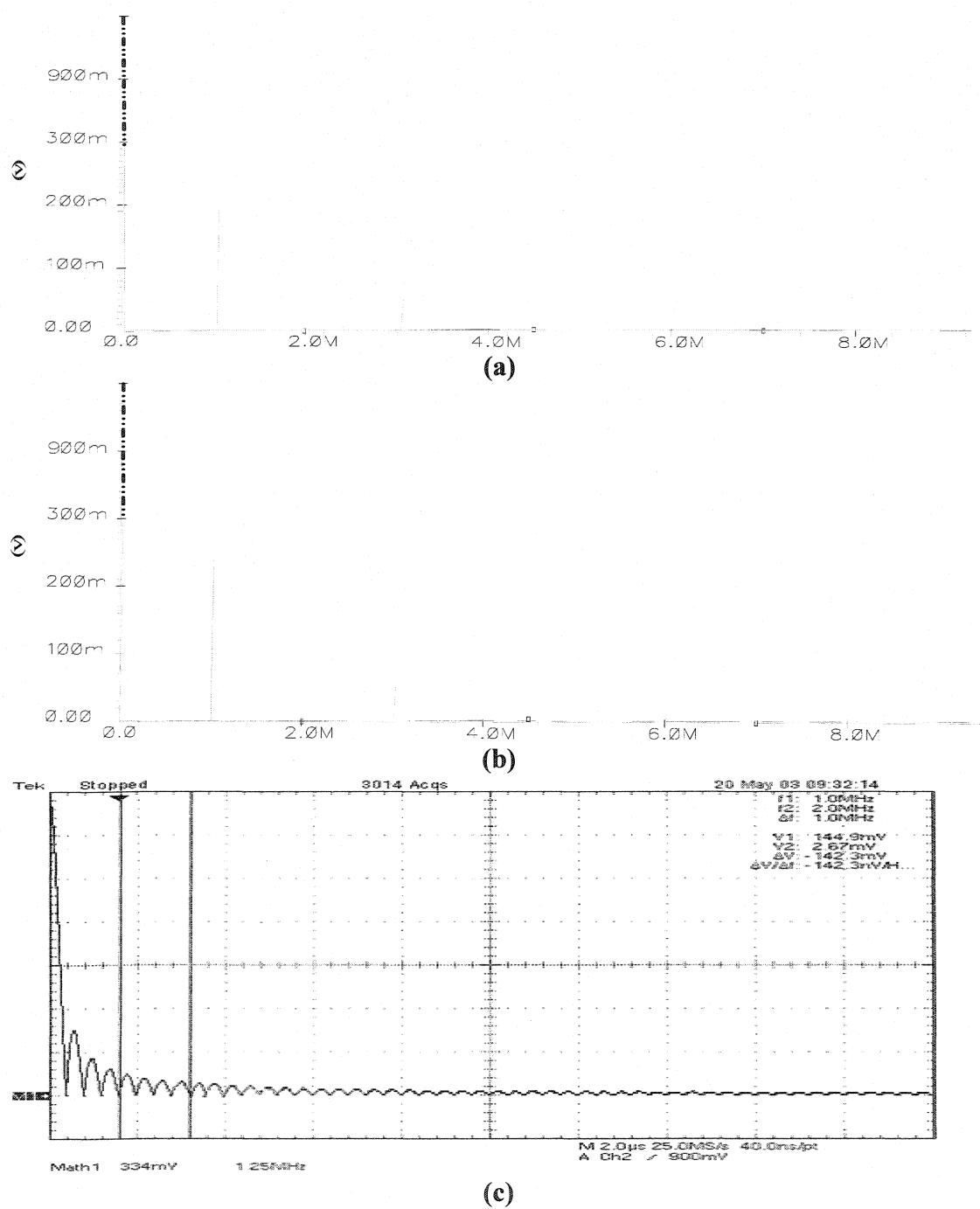

| 5.2.8 Résultats de la distorsion d'amplitude .....    | 97  |

| 5.2.9 Caractéristiques en boucle fermée .....         | 100 |

|                                                          |                                                  |     |

|----------------------------------------------------------|--------------------------------------------------|-----|

| 5.3                                                      | Caractéristiques du circuit de compensation..... | 100 |

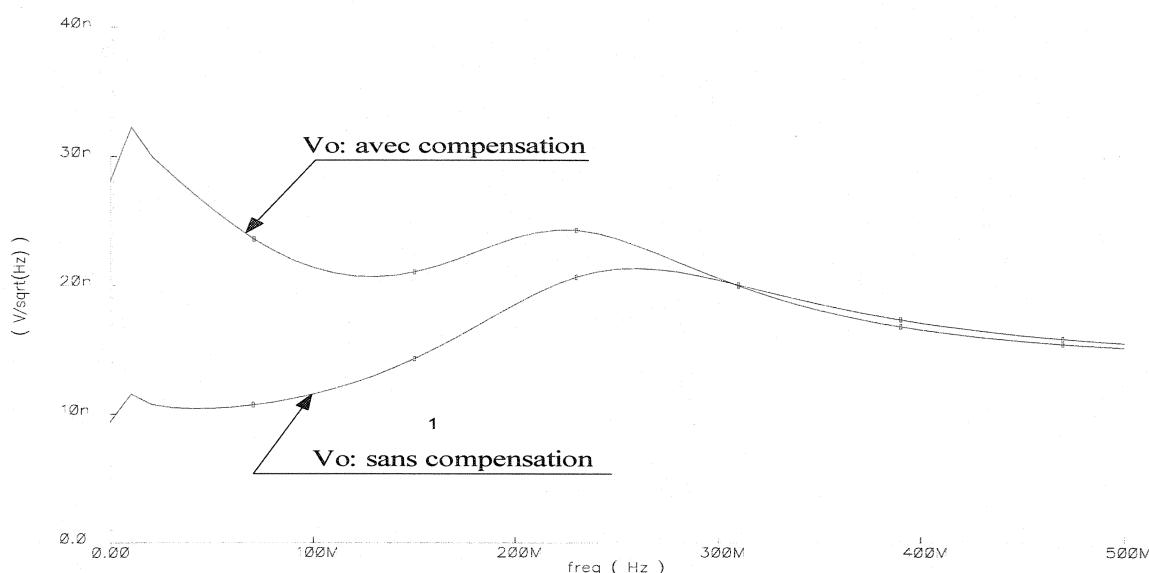

| 5.3.1                                                    | Densité du bruit et effets.....                  | 101 |

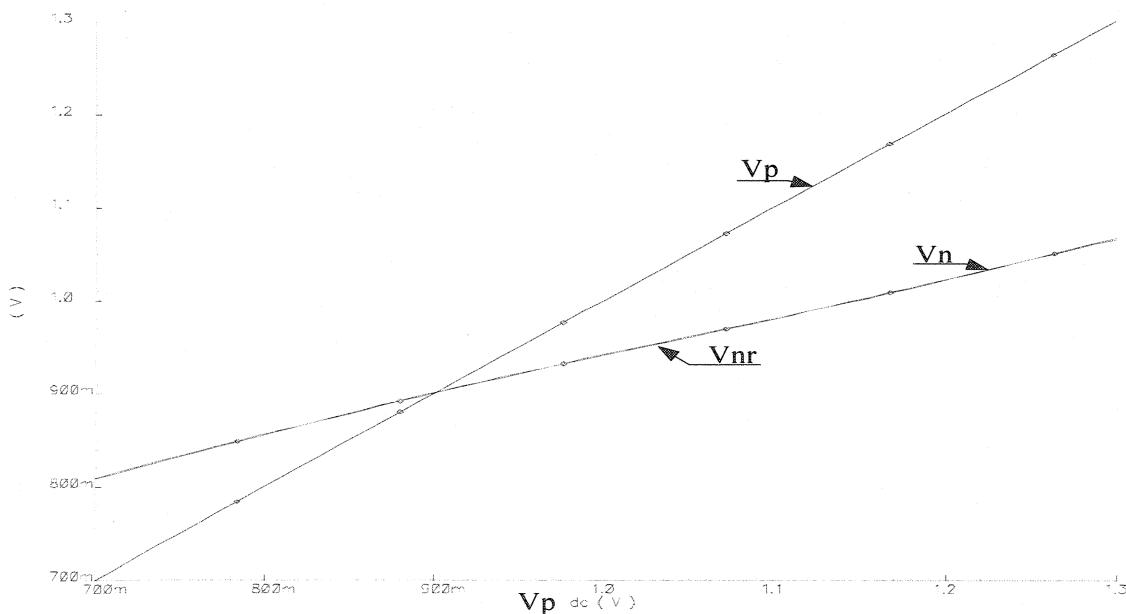

| 5.3.2                                                    | Caractéristiques statiques.....                  | 103 |

| 5.3.3                                                    | Techniques de dessins des masques.....           | 105 |

| 5.4                                                      | Filtre passe – bande programmable .....          | 106 |

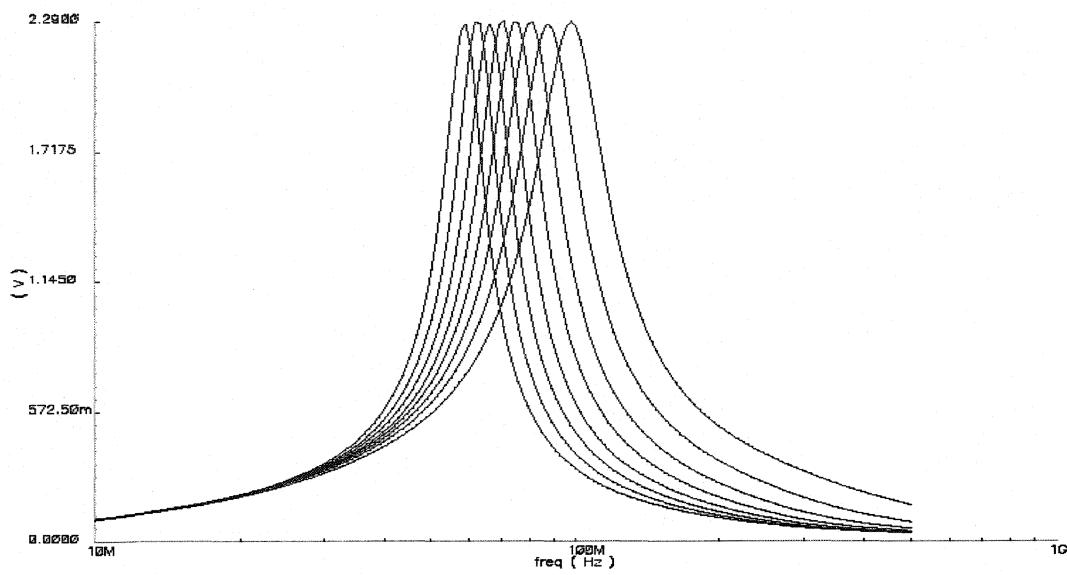

| 5.4.1                                                    | Réponse en fréquence .....                       | 106 |

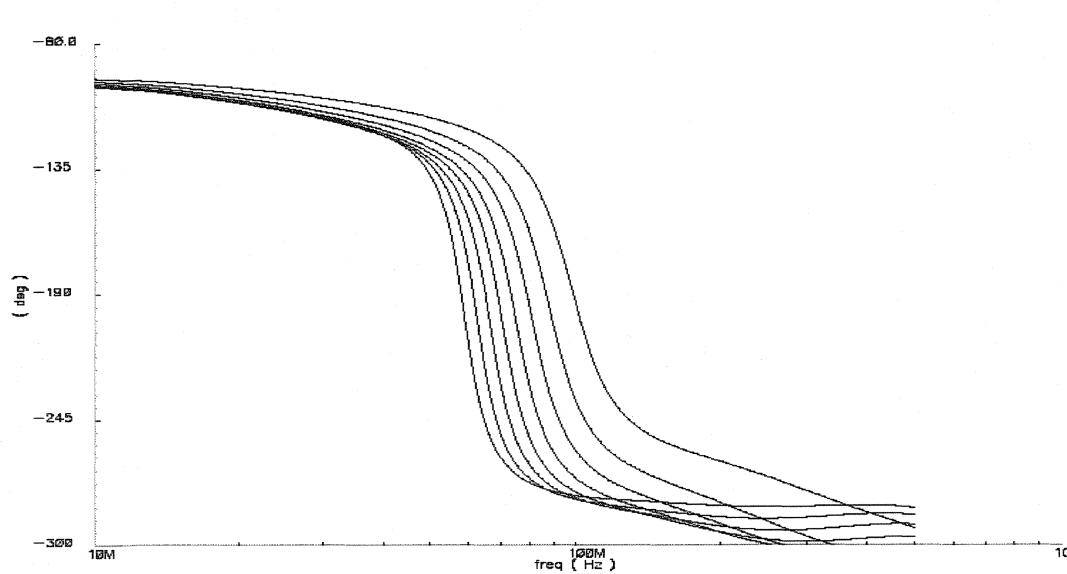

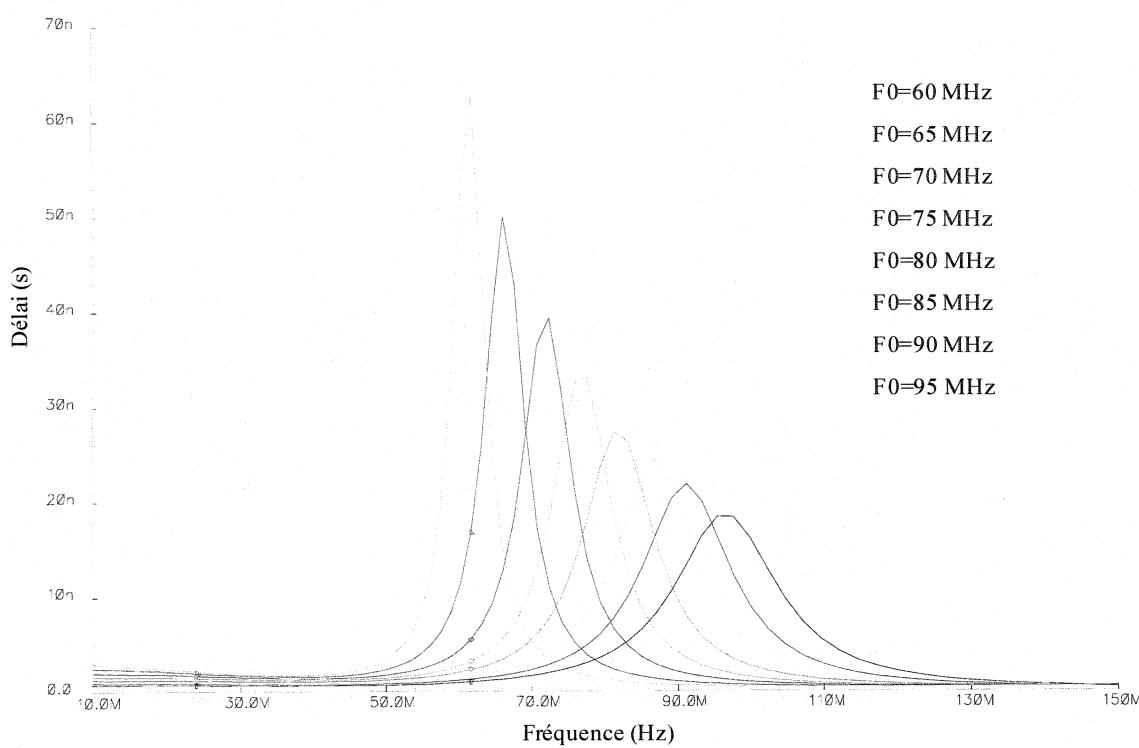

| 5.4.2                                                    | Retard de groupe .....                           | 107 |

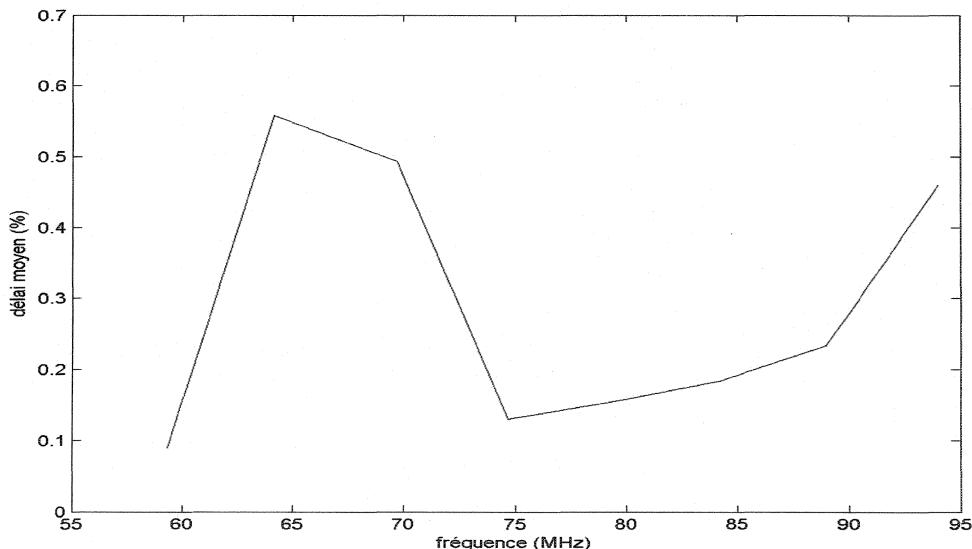

| 5.4.3                                                    | Distorsion harmonique du filtre .....            | 111 |

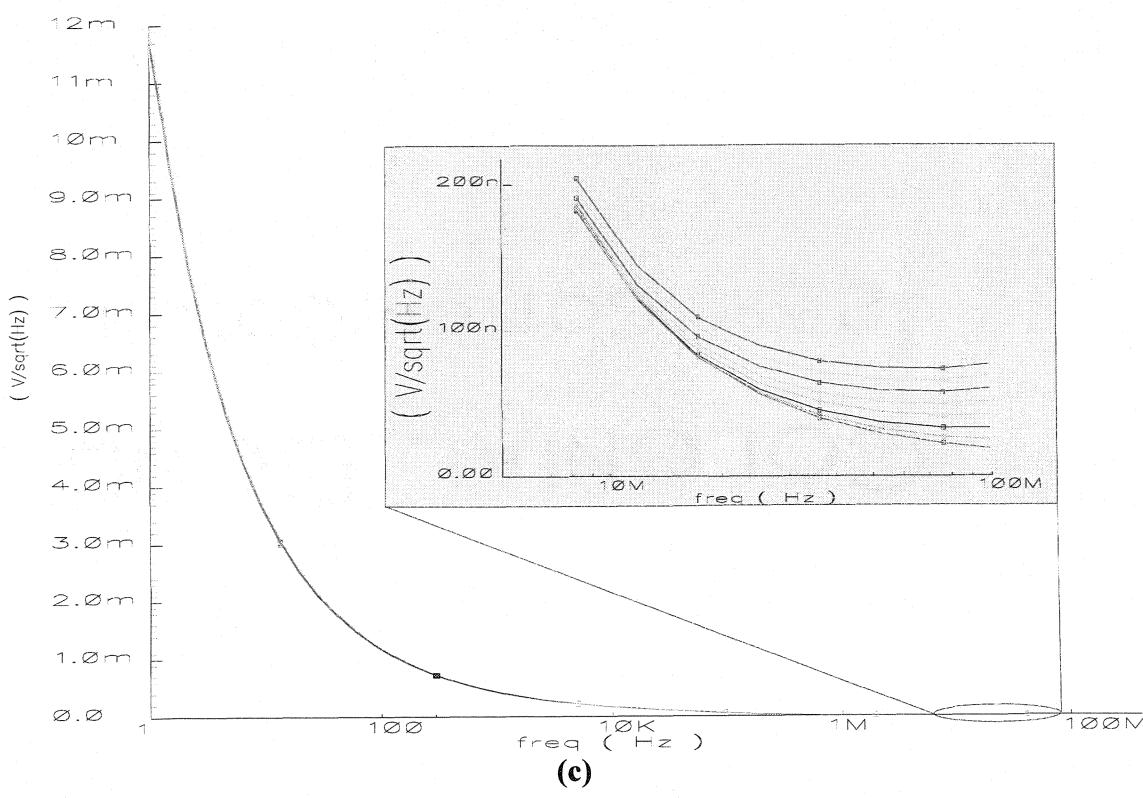

| 5.4.4                                                    | Analyse de la densité du bruit.....              | 112 |

| 5.5                                                      | Conclusion .....                                 | 114 |

| CHAPITRE 6 : DISCUSSION GÉNÉRALE ET TRAVAUX FUTURS ..... |                                                  | 115 |

| 6.1                                                      | Discussion générale .....                        | 115 |

| 6.2                                                      | Travaux futurs.....                              | 116 |

| RÉFÉRENCES .....                                         |                                                  | 118 |

## LISTE DES FIGURES

|                                                                                                                        |    |

|------------------------------------------------------------------------------------------------------------------------|----|

| Figure 2.1. CFOA en technologie bipolaire.....                                                                         | 12 |

| Figure 2.2. Réponse temporelle d'Ampop.....                                                                            | 14 |

| Figure 2.3. Modèle simplifié du CFOA.....                                                                              | 19 |

| Figure 2.4. Réponse idéale en fréquence : a) CFOA, b) VFOA.....                                                        | 22 |

| Figure 2.5. Réponse fréquentielle du CFOA en fonction de.....                                                          | 24 |

| Figure 2. 6. Étage d'entrée d'un CFOA: a) source suiveur complémentaire, b) source suiveur complémentaire cascade..... | 27 |

| Figure 2. 7. CFOA avec correction du courant de polarisation .....                                                     | 28 |

| Figure 2. 8. CFOA avec réduction de la tension de décalage .....                                                       | 29 |

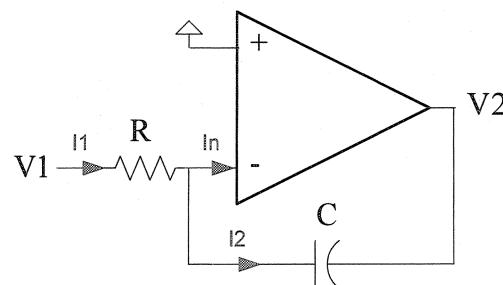

| Figure 2.9. Intégrateur RC .....                                                                                       | 32 |

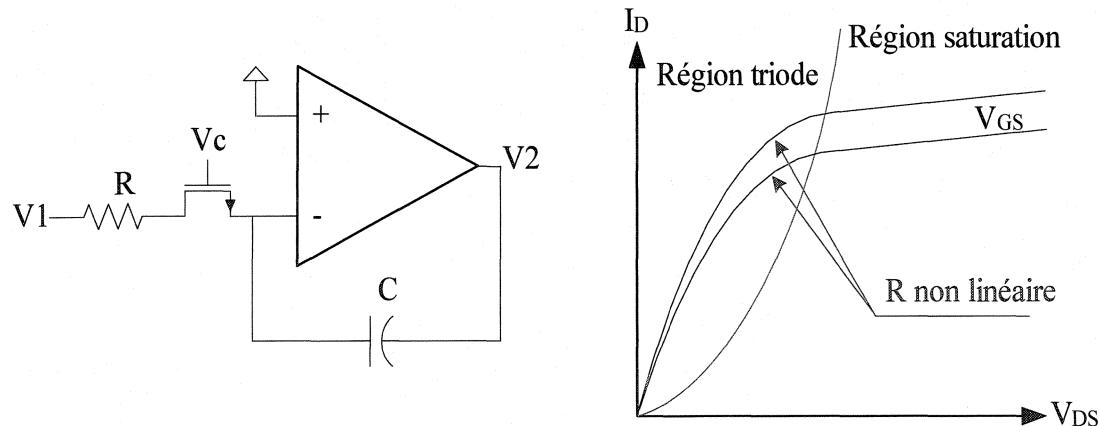

| Figure 2.10. Intégrateur ajustable : a) Circuit à MOSFET RC, b) Caractéristiques du MOSFET .....                       | 34 |

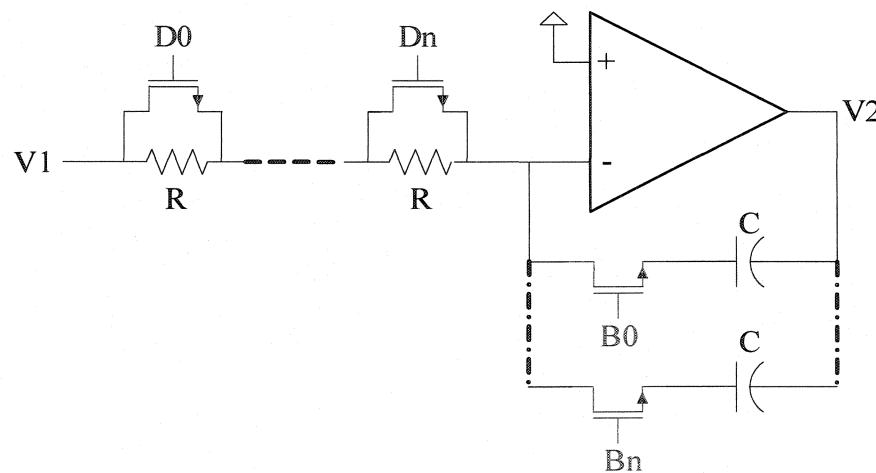

| Figure 2.11. Ampop MOSFET RC programmable.....                                                                         | 35 |

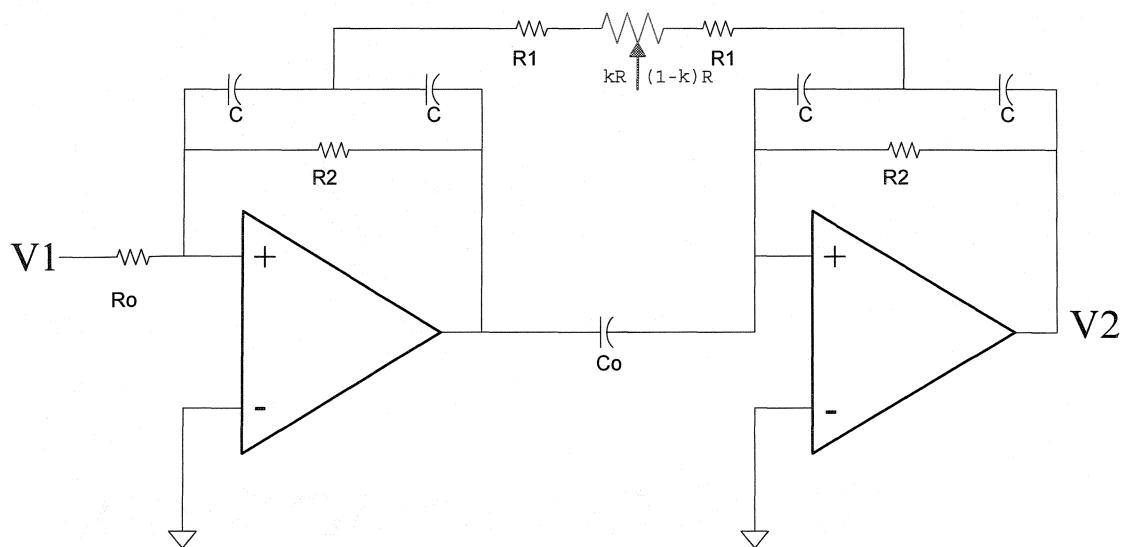

| Figure 2.12. Filtre passe-bande de 4 <sup>eme</sup> ordre .....                                                        | 36 |

| Figure 3.1. Schéma simplifié du CFOA.....                                                                              | 41 |

| Figure 3.2. Principe de compensation du CFOA .....                                                                     | 45 |

| Figure 3.3. Circuit de compensation du CFOA .....                                                                      | 48 |

| Figure 3.4. Sources de bruits dans le circuit de compensation .....                                                    | 52 |

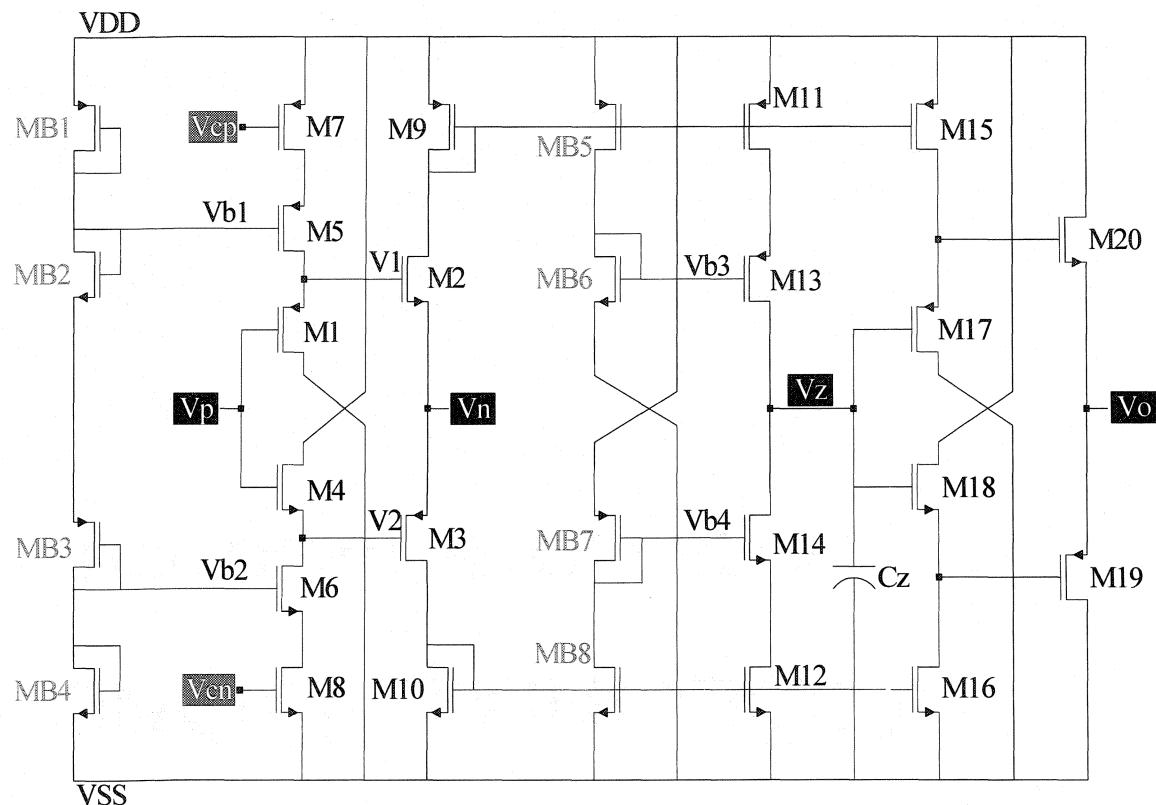

| Figure 3.5. Schéma du CFOA en CMOS.....                                                                                | 55 |

|                                                                                |    |

|--------------------------------------------------------------------------------|----|

| Figure 3.6. Intégrateur à entrée simple: a) inverseur, b) non - inverseur..... | 58 |

| Figure 3.7. Intégrateur à entrée différentielle .....                          | 58 |

|                                                                                |    |

| Figure 4.1 The offset compensated CFOA circuit .....                           | 79 |

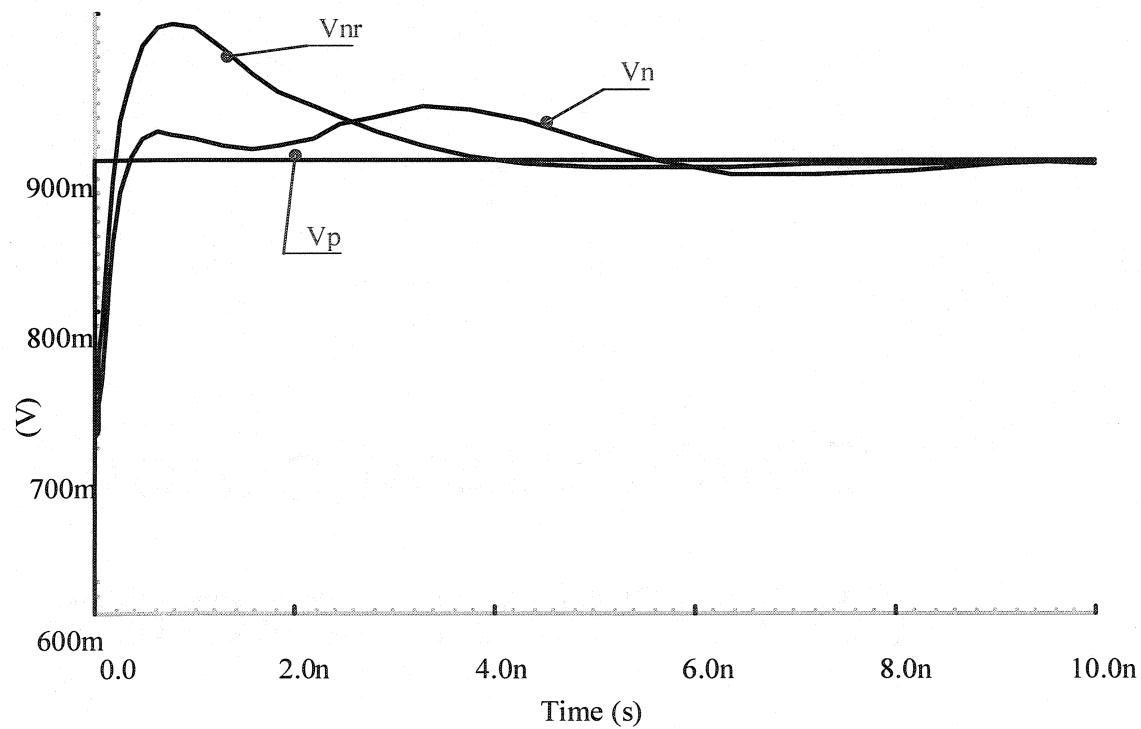

| Figure 4.2 Stabilization of the compensated CFOA .....                         | 79 |

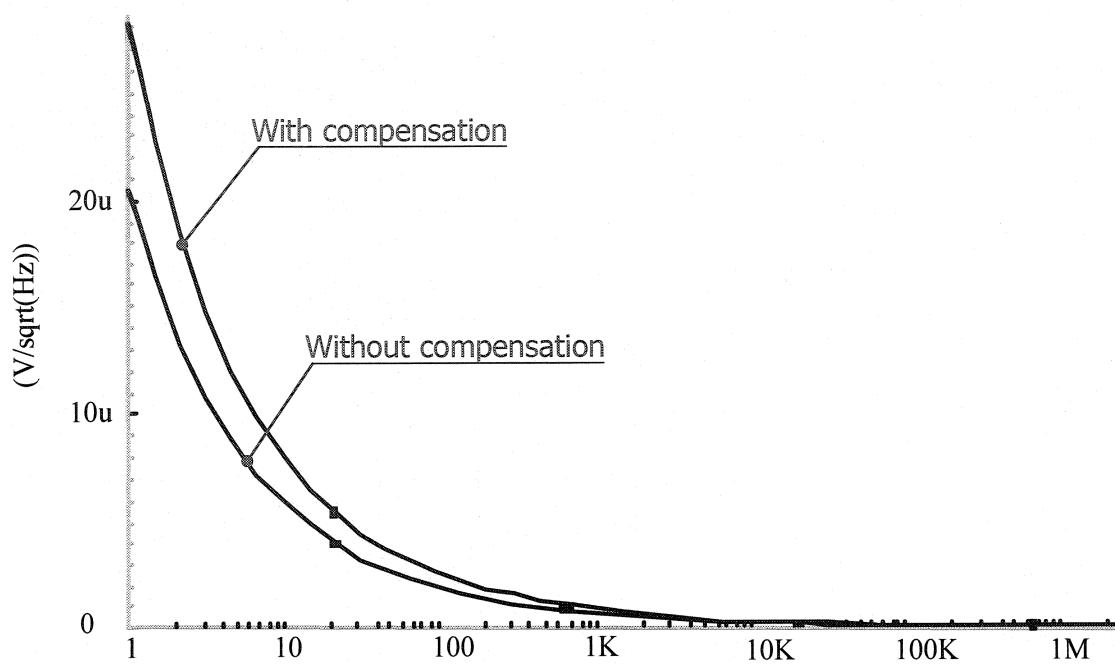

| Figure 4.3 Voltage noise versus frequency of the CFOA.....                     | 80 |

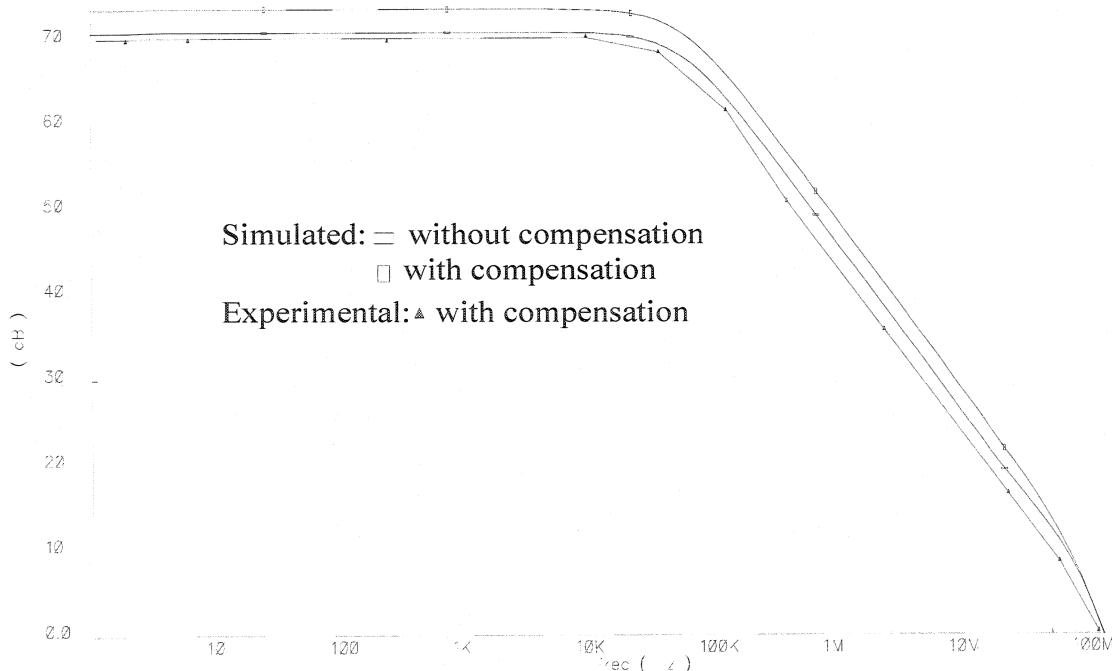

| Figure 4.4 Frequency response of the CFOA .....                                | 80 |

| Figure 4.5 The CFOA offset voltage .....                                       | 81 |

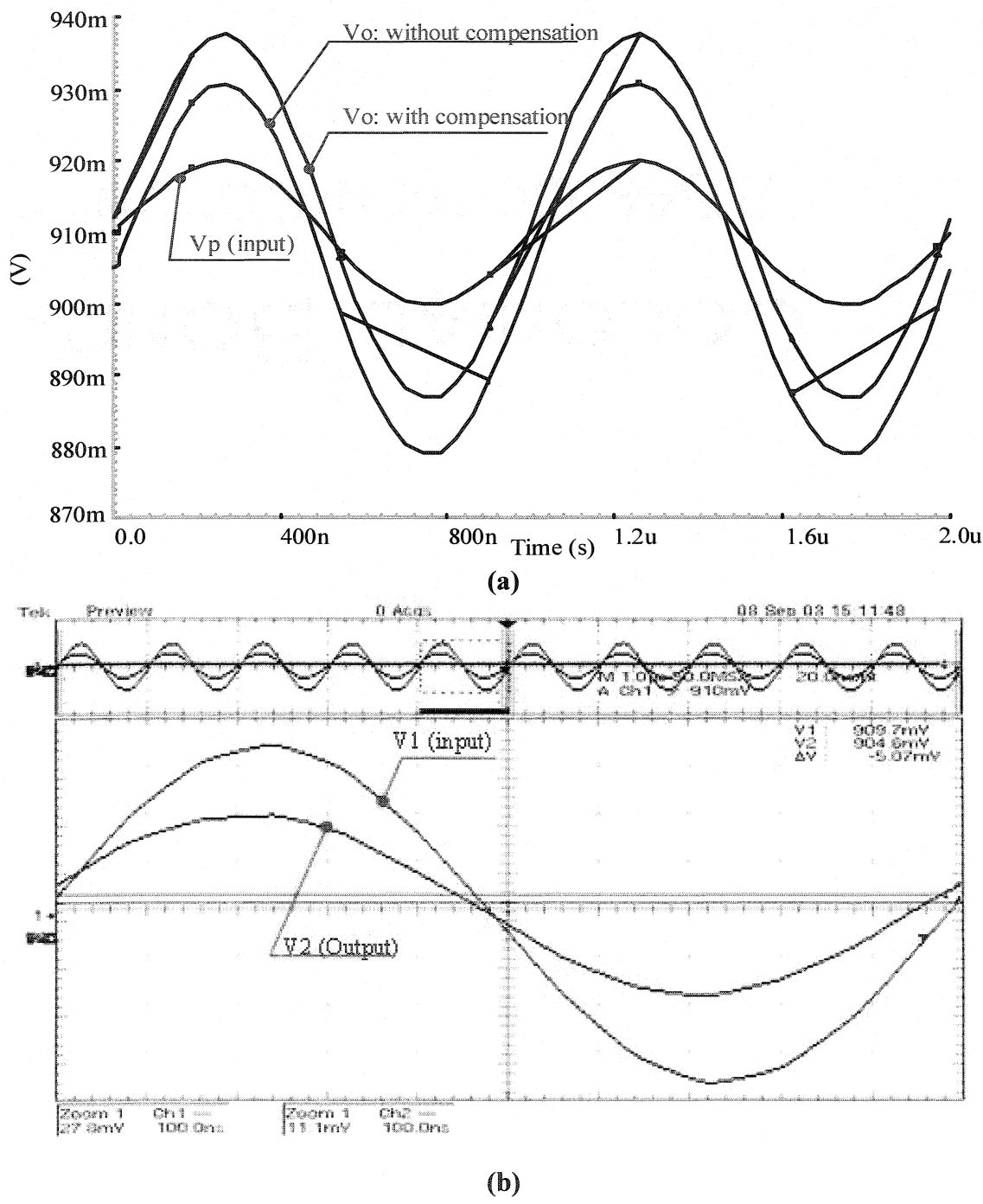

| a) Simulation results;                                                         |    |

| b) Experimental results.                                                       |    |

|                                                                                |    |

| Figure 4.6 The CFOA microphotograph.....                                       | 82 |

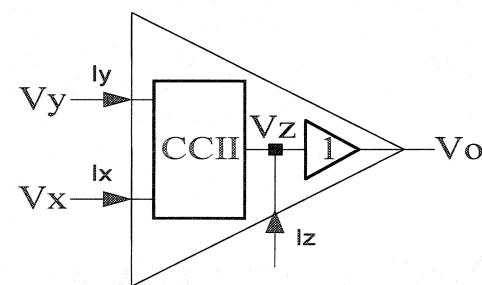

| Figure 4.7 Circuit symbol of the CFOA .....                                    | 82 |

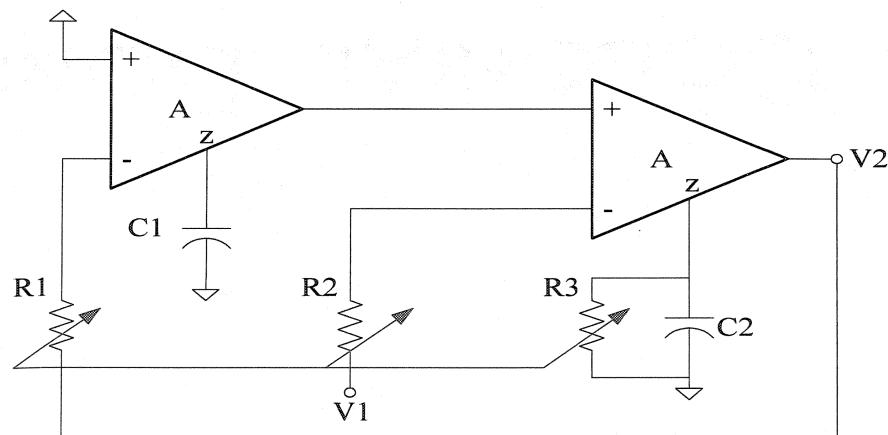

| Figure 4.8 The proposed tunable band-pass filter.....                          | 82 |

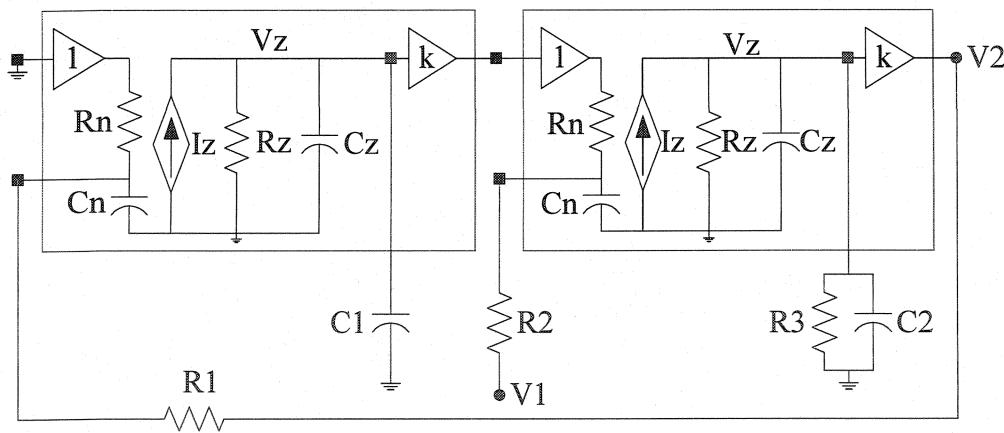

| Figure 4.9 AC equivalent model of the proposed filter circuit .....            | 83 |

| Figure 4.10 The digital tuning circuit .....                                   | 83 |

| Figure 4.11 Center frequency tuning of the band-pass filter .....              | 85 |

| a) Magnitude.                                                                  |    |

| b) Phase.                                                                      |    |

| c) Voltage noise versus frequency.                                             |    |

|                                                                                |    |

| Figure 5.1. Simulation du PSRR du CFOA .....                                   | 93 |

| Figure 5.2. Simulation des résistances $R_n$ , $R_o$ et $R_z$ du CFOA.....     | 95 |

|                                                                                                                                   |     |

|-----------------------------------------------------------------------------------------------------------------------------------|-----|

| Figure 5.3. Résultats de la tension de décalage du CFOA.....                                                                      | 96  |

| Figure 5.4. Distorsion harmonique: a) simulée sans compensation, b) simulée avec compensation, c) mesurée avec compensation. .... | 99  |

| Figure 5.5. Caractéristique en boucle fermée du CFOA.....                                                                         | 101 |

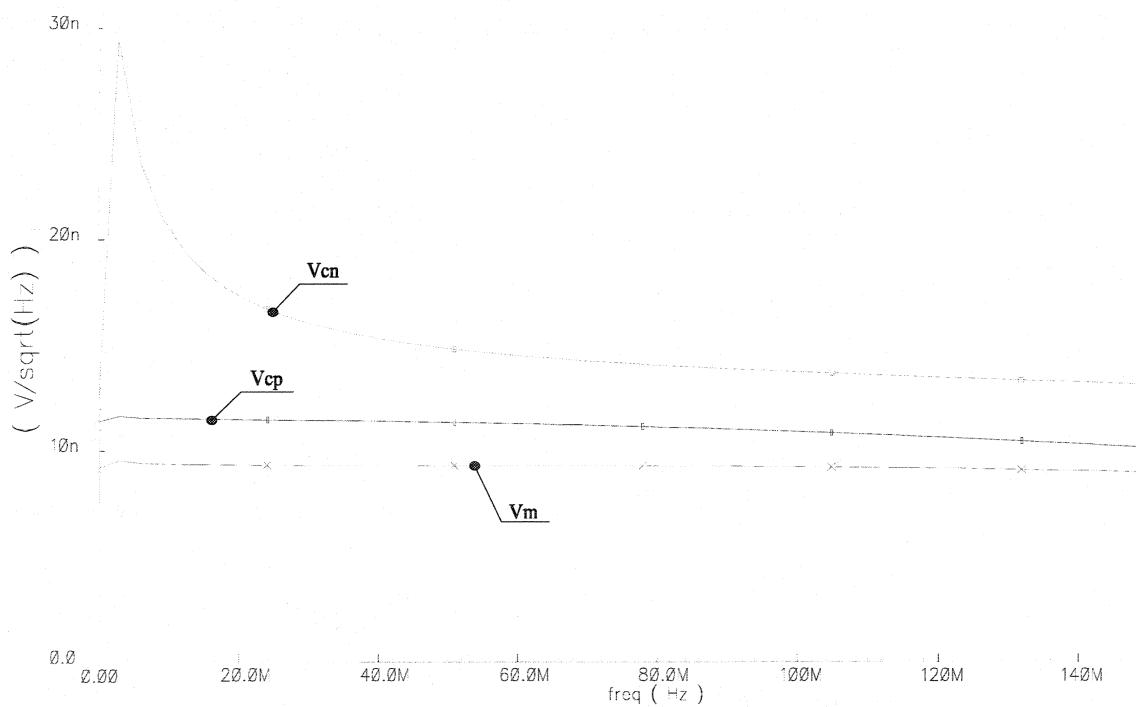

| Figure 5.6. Densité spectrale du bruit du circuit de compensation.....                                                            | 102 |

| Figure 5.7. Densité spectrale du bruit du CFOA .....                                                                              | 103 |

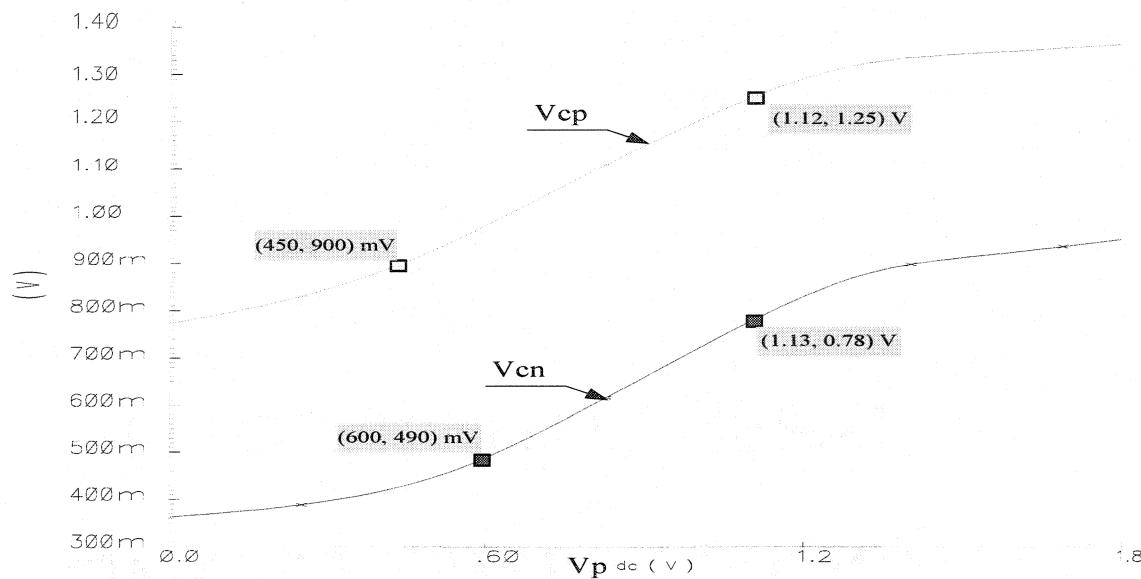

| Figure 5.8. Réponse <i>DC</i> du circuit <i>Vnr</i> .....                                                                         | 104 |

| Figure 5.9. Réponse <i>DC</i> du circuit de compensation.....                                                                     | 105 |

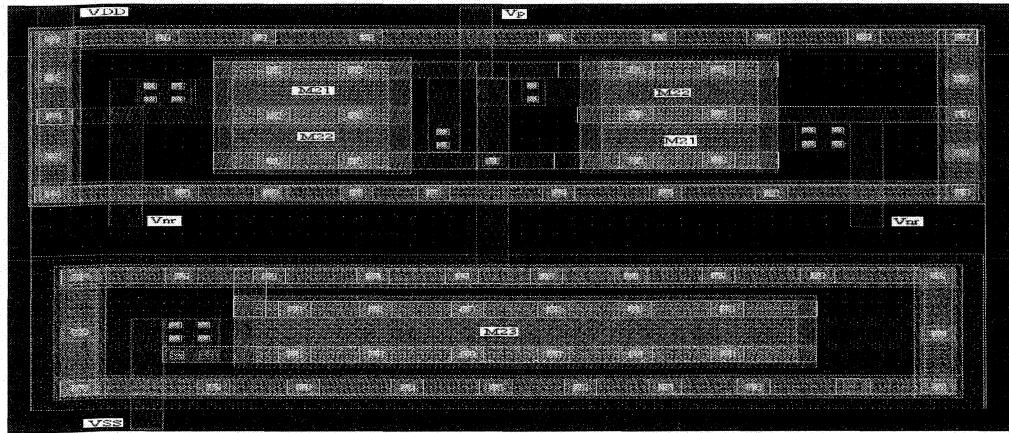

| Figure 5.10. Dessin des masques du circuit de moyenne .....                                                                       | 106 |

| Figure 5.11. Groupe de délai en fonction de la fréquence .....                                                                    | 109 |

| Figure 5.12. Distorsion de phase dans la bande passante du filtre .....                                                           | 110 |

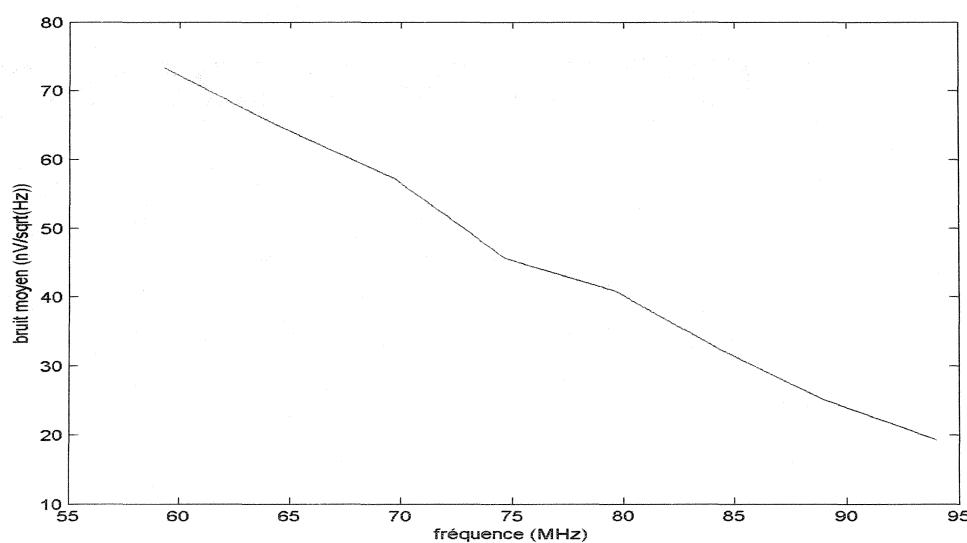

| Figure 5.13. Bruit moyen dans la bande passante du filtre.....                                                                    | 113 |

**LISTE DES TABLEAUX**

|                                                                             |     |

|-----------------------------------------------------------------------------|-----|

| Tableau 2.1. Types d'amplificateurs opérationnels .....                     | 11  |

| Table 4.1 Harmonic distortion of the CFOA .....                             | 86  |

| Table 4.2 The simulated and measured results of the CFOA .....              | 87  |

| Table 4.3 Voltage noise of the filter Harmonic distortion of the CFOA ..... | 88  |

| Table 4.4 Programming the band-pass filter.....                             | 88  |

| Tableau 5.1. Caractéristiques du <i>CFOA</i> proposé .....                  | 94  |

| Tableau 5.2. Distorsion harmonique du CFOA .....                            | 98  |

| Tableau 5.3. Caractéristiques du CFOA en boucle fermée.....                 | 100 |

| Tableau 5.4. Retard de groupe dans la bande passante.....                   | 109 |

| Tableau 5.5. Distorsion d'amplitude du filtre .....                         | 111 |

| Tableau 5.6. Densité du bruit en fonction de la fréquence .....             | 113 |

## LISTES DES SYMBOLES ET DES ABRÉVIATIONS

### SYMBOLES

|          |                                              |

|----------|----------------------------------------------|

| $A_{cl}$ | Gain en boucle fermée du CFOA (dB)           |

| $A_{cp}$ | Gain du soustracteur N (dB)                  |

| $A_{cn}$ | Gain du soustracteur P (dB)                  |

| $A_m$    | Gain du circuit de moyenne (dB)              |

| $A_{ol}$ | Gain en boucle ouverte du CFOA (dB)          |

| $A_{vb}$ | Gain en tension du tampon (dB)               |

| $A_1$    | Gain de l'amplificateur classe A (P) en (dB) |

| $A_2$    | Gain de l'amplificateur classe A (N) en (dB) |

| $B$      | Gain de rétroaction d'un système (dB)        |

| $BW$     | Bande passante (Hz)                          |

| $C_c$    | Capacité de compensation ( $\mu\text{F}$ )   |

| $CMRR$   | Taux de rejet du mode commun (dB)            |

| $C_{ox}$ | Capacité grille ( $\text{F}/\text{m}^2$ )    |

| $C_z$    | Capacité parasite ( $\mu\text{F}$ )          |

| $dB$     | Décibel                                      |

| $F_c$    | Fréquence de coupure (Hz) à $-3$ dB          |

| $F_m$    | Fréquence centrale (Hz)                      |

|             |                                                                                    |

|-------------|------------------------------------------------------------------------------------|

| $F_{\max}$  | Fréquence maximale (Hz)                                                            |

| $F_u$       | Fréquence à gain unitaire (Hz)                                                     |

| $F_l$       | Fréquence de coupure inférieure (Hz)                                               |

| $g_{ds}$    | Résistance drain source ( $\Omega$ )                                               |

| $g_m$       | Transconductance ( $\mu\text{A}/\text{V}$ )                                        |

| $HD_2$      | Distorsion harmonique                                                              |

| $H(s)$      | Fonction de transfert                                                              |

| $H_I$       | Fonction de transfert d'intégrateur                                                |

| $H_{ID}$    | Fonction de transfert d'intégrateur différentiateur                                |

| $\text{Hz}$ | Unité de mesure de la fréquence                                                    |

| $H_1, H_2$  | Premier et deuxième harmonique d'un signal (mV)                                    |

| $I_{cn}$    | Courant DC ( $\mu\text{A}$ ) générer par un transistor NMOS ( $\mu\text{A}$ )      |

| $I_{cp}$    | Courant DC ( $\mu\text{A}$ ) générer par un transistor PMOS ( $\mu\text{A}$ )      |

| $I_{er}$    | Courant d'erreur ( $\mu\text{A}$ ) de l'entrée inveseuse du CFOA ( $\mu\text{A}$ ) |

| $I_p$       | Courant DC ( $\mu\text{A}$ ) générer par un transistor PMOS ( $\mu\text{A}$ )      |

| $I_n$       | Courant DC ( $\mu\text{A}$ ) générer par un transistor NMOS ( $\mu\text{A}$ )      |

| $I_m$       | Courant moyenne ( $\mu\text{A}$ )                                                  |

| $I_{ss}$    | Courant de polarisation ( $\mu\text{A}$ )                                          |

| $I_x$       | Courant de l'entrée $V_x$ du convoyeur de courant ( $\mu\text{A}$ )                |

| $I_y$       | Courant de l'entrée inveseuse du convoyeur de courant ( $\mu\text{A}$ )            |

|                |                                                                         |

|----------------|-------------------------------------------------------------------------|

| $I_z$          | Courant de l'étage de transimpédance ( $\mu\text{A}$ )                  |

| $I_1$          | Courant générer par la tension non inverseuse du CFOA ( $\mu\text{A}$ ) |

| $I_2$          | Courant générer par la tension Vnr du CFOA ( $\mu\text{A}$ )            |

| $k$            | Gain en tension (dB)                                                    |

| $k_B$          | Constante de Boltzmann                                                  |

| $k_p$          | Constante du procédé de fabrication                                     |

| $Q$            | Facteur de qualité                                                      |

| $R$            | Résistance ( $\Omega$ )                                                 |

| $R_{cp}$       | Résistance de sortie du soustracteur (S1) ( $\Omega$ )                  |

| $R_{cn}$       | Résistance de sortie du coutracteur (S2) ( $\Omega$ )                   |

| $R_m$          | Résistance de sortie du circuit de moyenne ( $\Omega$ )                 |

| $R_s$          | Résistance équivalente d'un interrupteur en MOS ( $\Omega$ )            |

| $R_n$          | Résistance de l'entrée inverseuse du CFOA ( $\Omega$ )                  |

| $R_z$          | Résistance de sortie au nœud Z ( $\Omega$ )                             |

| $R_{o1}$       | Résistance de sortie du nœud $V_1$ ( $\Omega$ )                         |

| $R_{o2}$       | Résistance de sortie au nœud $V_2$ ( $\Omega$ )                         |

| $s$            | Opérateur de Laplace                                                    |

| $SR$           | Taux maximal de la tension de sortie (V/ $\mu\text{S}$ )                |

| $PSRR$         | Taux de rejet de l'alimentation (dB)                                    |

| $T(j\omega_0)$ | Gain à fréquence centrale (dB)                                          |

|            |                                                                    |

|------------|--------------------------------------------------------------------|

| $V_m$      | Tension moyenne (V)                                                |

| $V_{thn}$  | Tension de seuil pour NMOS (mV)                                    |

| $V_{thp}$  | Tension de seuil pour PMOS (mV)                                    |

| $V_{th}$   | Tension de seuil du transistor PMOS ou NMOS (mV)                   |

| $V_{cp}$   | Tension DC de polarisation (V)                                     |

| $V_{cn}$   | Tension DC de polarisation (V)                                     |

| $V_{pp}$   | Tension Peak to Peak (V)                                           |

| $V_{nr}$   | Copie de la tension inverseuse du CFOA (V)                         |

| $V_1, V_2$ | Tension de polarisation DC de l'étage d'entrée du CFOA (V)         |

| $V_3, V_4$ | Tension de polarisation DC du miroir CMP et CMN (V)                |

| $V_g$      | Tension appliquer sur la grille d'un transistor MOS (V)            |

| $V_{os}$   | Tension de décalage (mV)                                           |

| $V_{gsp}$  | Tension grille source pour PMOS (V)                                |

| $V_{gsn}$  | Tension grille source pour NMOS (V)                                |

| $V_n$      | Tension inverseuse (V)                                             |

| $V_p$      | Tension non – inverseuse (V)                                       |

| $V_x$      | Tension non – inverseuse du convoyeur de courant (V)               |

| $V_y$      | Tension inverseuse du convoyeur de courant en (V)                  |

| $\omega_0$ | Fréquence centrale (Hz)                                            |

| $W, L$     | Largeur et longueur du canal d'un transistor MOS ( $\mu\text{m}$ ) |

|                         |                                                                            |

|-------------------------|----------------------------------------------------------------------------|

| $\overline{V_{n,m}^2}$  | Tension du bruit du circuit de moyenne (V <sup>2</sup> /Hz)                |

| $\overline{V_{n,cp}^2}$ | Tension du bruit du soustarcteur P (V <sup>2</sup> /Hz)                    |

| $\overline{V_{n,cn}^2}$ | Tension du bruit du soustracteur N (V <sup>2</sup> /Hz)                    |

| $\overline{V_{n,1}^2}$  | Tension du bruit au nœud V <sub>1</sub> du CFOA (V <sup>2</sup> /Hz)       |

| $\overline{V_{n,2}^2}$  | Tension du bruit au nœud V <sub>2</sub> du CFOA (V <sup>2</sup> /Hz)       |

| $\mu_n, \mu_p$          | Mobilité des porteurs de type n et p respectivement (m <sup>2</sup> /V.s)  |

| $\beta$                 | Conductane du transistor MOS ( $\mu\text{A}/\text{V}^2$ )                  |

| $1/f$                   | Flicker noise ( $\mu\text{A}/\text{V}^2$ )                                 |

| $\phi$                  | Phase en degré                                                             |

| $\tau$                  | Groupe de délai en seconde                                                 |

| $\Delta V_{th}$         | Variation de la tension de seuil du transistor MOS (mV)                    |

| $\Delta\beta$           | Variation de la conductance du transistor MOS ( $\mu\text{A}/\text{V}^2$ ) |

## ABRÉVIATIONS

|                    |                            |

|--------------------|----------------------------|

| <i>AMP</i> OP      | Amplificateur Opérationnel |

| <i>C_M</i> oy      | Circuit de moyenne         |

| <i>CLASSE - A</i>  | Amplificateur de type A    |

| <i>CLASSE - AB</i> | Amplificateur de type AB   |

|                         |                                          |

|-------------------------|------------------------------------------|

| <i>CMP</i> , <i>CMN</i> | Miroir de courant de type P et de type N |

| <i>CFOA</i>             | Current Feedback Operational Amplifier   |

| <i>CMRR</i>             | Taux de rejet du mode commun             |

| <i>DFT</i>              | Discrete Fourier Transform               |

| <i>FFT</i>              | Fast Fourier Transform                   |

| <i>GBW</i>              | Produit gain bande passante              |

| <i>GM – C</i>           | Intégrateur transconductance - capacité  |

| <i>HD</i> <sub>2</sub>  | Harmonic distorsion                      |

| <i>MOS</i>              | Metal Oxyde Semiconductor                |

| <i>MIC</i>              | Monolithic integrated circuit            |

| <i>NMOS</i>             | Transistor de type N                     |

| <i>SR</i>               | Slew rate                                |

| <i>S1</i>               | Soustracteur analogique (P)              |

| <i>S2</i>               | Soustracteur analogique (N)              |

| <i>PSRR</i>             | Taux de rejet de l'alimentation          |

| <i>PMOS</i>             | Transistor de type N                     |

| <i>OLG</i>              | Gain en boucle ouverte                   |

| <i>UGBW</i>             | Fréquence de coupure à Gain unitaire     |

| <i>VFOA</i>             | Voltage Feedback Operational Amplifier   |

## CHAPITRE 1

### INTRODUCTION

#### 1.1 Technologie et intégration

La conception des circuits analogiques a toujours été conditionnée, voire même gênée, par les limitations du procédé de fabrication. Dans un monde guidé par le développement technologique rapide, la tendance actuelle est à la miniaturisation des circuits électroniques existants et/ou d'apporter les modifications nécessaires afin d'améliorer leur rendement statique et dynamique. En effet, en réduisant la tension d'alimentation on obtient des circuits qui peuvent atteindre des fréquences très élevées dans le domaine numérique et analogique, mais avec quelques inconvénients pour les circuits analogiques par exemple, réduction de la plage de tension de sortie d'un *ampop*. Ceci impose donc une phase de conception rigoureuse du circuit souhaité. Cette phase doit en plus permettre la prédiction des performances du circuit électronique réalisé afin de vérifier qu'elles répondent aux spécifications désirées (faible bruit, distorsion d'amplitude, etc.). Il en est de même pour les applications nécessitant l'utilisation de filtres analogiques intégrés programmables. Certes, la conception des filtres opérant à haute fréquence dans les circuits intégrés monolithiques (*MIC*) est limitée par différents facteurs qui dépendent

de l'architecture employée, du type des amplificateurs opérationnels (*CFAO, VFOA OTA* etc.) et des imperfections du procédé de fabrication.

## 1.2 Filtres intégrés programmables

Au fil des ans, plusieurs techniques de conception de filtres intégrés monolithiques à fréquence programmable par exemple, ont été développées pour répondre aux besoins grandissants de certaines applications. La réalisation de circuit monolithique offre un meilleur rendement en fréquence versus la puissance consommée et la surface du silicium.

En effet, une première catégorie de filtres, composés par des circuits à condensateurs commutés ou encore à courants commutés, est limitée à des fréquences peu élevées. Elle offre une meilleure précision, mais nécessite un circuit de variation de fréquence complexe et sensible au bruit de l'échantillonnage [32]. Une deuxième catégorie de filtres composée par des intégrateurs de type «*GM-C* ». Ce type de filtres à précision modérée, offre la possibilité de varier la fréquence, mais souffre des limites imposées par les éléments parasites qui ne peuvent être éliminés par aucune technique connue [23]. Une dernière catégorie de filtres, composée d'intégrateurs à amplificateur opérationnel, se distingue par rapport aux deux précédentes catégories par une meilleure précision de la variation de fréquence et une faible consommation d'énergie. L'*ampop* nécessaire doit répondre aux critères suivants : tension de décalage nul, faible bruit et taux de distorsion

harmonique, et large bande passante [12]. De plus, l'architecture de l'*ampop* doit être moins sensible aux erreurs du procédé de fabrication et doit répondre aux critères du filtre tels que : gain et bande passante constants, etc.

### 1.3 Amplificateurs opérationnels en mode courant

Récemment, la conception de filtres analogiques utilisant des intégrateurs en mode courant a acquis une grande popularité due aux bonnes performances offertes par les amplificateurs en mode courant (*Current Feedback Operational Amplifier - CFOA*) [13].

Les *CFOAs* opèrent à des fréquences élevées avec un faible niveau de bruit, taux de distorsion harmonique, pente de tension de sortie très élevée, puissance consommée et une meilleure linéarité de phase que ces concurrents opérant en mode tension (*Voltage Feedback Operational Amplifier - VFOA*). Cependant, il souffre d'une tension de décalage due à la difficulté de concevoir des transistors identiques (appariement) dans l'étage d'entrée de l'*ampop* [3]. En effet, nous retrouvons dans la littérature plusieurs travaux proposés pour réduire la tension de décalage de ce circuit [1], [18]. Ces travaux ne répondent pas aux critères requis pour concevoir de filtres à large bande programmable en technologie à faible alimentation (1.8 V par exemple) et destinés à des applications de plus en plus exigeantes en ce qui a trait au niveau de bruit, taux de distorsion harmonique et occupe peu de surface de silicium. Ces contraintes, imposent aux concepteurs de circuit analogique de faire l'évaluation des solutions possibles pouvant réduire la tension de décalage du *CFOA* tout en respectant les critères du filtre.

Dans le cadre de ce mémoire, nous proposons une nouvelle technique de réduction de la tension de décalage du *CFOA*. Elle est indépendante de la technologie (*CMOS* ou bipolaire) qui se caractérise par un fonctionnement autonome et un effet négligeable sur les performances du *CFOA*. Le *CFOA* obtenu est ensuite utilisé pour concevoir un filtre passe-bande à fréquence programmable [9]. La variation de la fréquence se fait à l'aide d'un circuit numérique par pas constant. L'architecture du filtre que nous proposons et la méthode de contrôle sont peu sensibles aux erreurs du procédé de fabrication.

#### **1.4 Techniques de programmation des paramètres de filtre intégré**

La majorité des techniques de réduction de consommation ont porté sur la diminution de la consommation dynamique, soit les charges et décharges des capacités parasites, la réduction de la tension de seuil et de l'alimentation. Ils ont pour effet, une consommation statique, résultant des courants de fuite des transistors, était négligeable par rapport aux consommations dynamiques. En effet avec l'arrivée des technologies submicroniques par exemple,  $0.18\mu\text{m}$ , la consommation statique a pris de l'importance, au point de devenir aujourd'hui un problème majeur pour certaines applications [29] telles que : biomédical, télécommunication à haut débit, etc.

Les techniques utilisées pour varier un ou plusieurs paramètres d'un filtre sont soumises à plusieurs critères de sélection. Ils dépendent de la topologie du filtre, type de signal

(audio, vidéo, etc.), mode de contrôle numérique ou analogique, et enfin de l'enivrement de l'application.

La majorité des techniques existantes privilégient une approche de contrôle de transconductance par tension ou par courant. Cette méthode souffre d'une consommation d'énergie et de surface de silicium importante, qui constraint le champ d'application de ce type de filtre.

Dans le cadre de ce mémoire, nous proposons une approche différente que celle utilisée pour des filtres réalisés à l'aide des amplificateurs en mode tension ou en mode transconductance. Notre approche consiste à activer un seul commutateur pour chaque résistance, ceci se traduira par un gain en puissance statique et dynamique.

### **1.5 Objectifs de recherche**

L'objectif principal de ce mémoire est le développement d'un filtre actif à fréquence programmable répondant aux critères de performance très pointus : rapidité, précision, faible niveau de bruit, faible taux de distorsion d'amplitude, faible consommation d'énergie et de surface de silicium. Pour répondre aux critères requis, à la conception et à l'intégration des filtres à larges bandes, le *CFOA* est l'amplificateur qui répond le mieux à ces critères. Le filtre devrait fonctionner dans une plage de fréquences allant de 60 MHz à 95 MHz. Nous accordons une attention particulière au choix de l'architecture du filtre

qui permet de programmer la fréquence centrale par un pas constant sans toutefois affecter sa bande passante et son gain.

Le filtre recherché devrait être moins sensible aux erreurs du procédé de fabrication CMOS 0.18  $\mu\text{m}$ , pour atteindre cet objectif, nous employons la technique permettant la réalisation des composantes géométriquement identiques (*matching*).

Le circuit de compensation que nous proposons dans le cadre de ce mémoire de recherche se distingue par un effet négligeable sur les performances dynamiques et statiques du CFOA, faible complexité et large plage de correction de la tension de décalage. Alors que, le circuit de programmation de la fréquence du filtre est caractérisé par une complexité modérée, faible consommation en puissance statique et dynamique et se prête bien à l'une des techniques de conception des composants identiques.

## 1.6 Contenu du mémoire

Ce mémoire est constitué principalement de cinq chapitres.

Le premier chapitre est une introduction, dans laquelle nous avons discuté des avantages et limites de la technologie submicronique dans le domaine analogique, des filtres actifs programmables, des mérites de l'amplificateur en mode courant et de la problématique de

sa tension de décalage. Finalement, nous présentons les objectifs de ce mémoire de recherche.

Le deuxième chapitre consiste en une revue des amplificateurs à rétroaction en mode courant, des techniques utilisées pour réduire leur tension de décalage. De plus, les architectures disponibles de filtres actifs intégrés utilisant l'amplificateur à rétroaction en mode courant, ainsi que les techniques de programmation de leur fréquence centrale seront élaborées. Au terme de ce chapitre, nous serons en mesure de distinguer les avantages des circuits en mode courant.

Dans le troisième chapitre, nous analyserons l'origine et les effets de la tension de décalage sur la performance statique et dynamique d'un amplificateur opérationnel tout en mettant l'accent sur le *CFOA*. Nous présenterons ensuite une nouvelle architecture de compensation de la tension de décalage sans que celle-ci ne dégrade les caractéristiques du *CFOA* : Gain *DC*, produit gain bande passante, faible bruit et distorsion harmonique. Ensuite, nous proposerons deux intégrateurs en mode courant *CFOA\_MOSFET\_RC* conçus autour d'un *CFOA* avec variation de sa fréquence.

Le quatrième chapitre fera l'objet d'un article accepté pour publication dans le journal Kluwer « *Analog Integrated Circuit And Signal Processing* ». Dans ce chapitre, nous proposons un filtre passe-bande à fréquence centrale programmable. Cette nouvelle architecture est composée d'intégrateurs *CFOA\_MOSFET\_RC*, la variation de la

fréquence est obtenue par des résistances ajustables numériquement. La technique proposée est choisie de façon à minimiser les erreurs dues au procédé de fabrication. Des résultats de simulation et expérimentaux du *CFOA* avec compensation de la tension de décalage et du filtre seront présentés.

Dans le cinquième chapitre, des résultats supplémentaires sur l'amplificateur en mode courant et le filtre seront présentés pour documenter davantage l'originalité de ce travail. Le circuit de compensation de la tension de décalage du *CFOA* et le circuit de contrôle de la fréquence du filtre sont analysés en fonction des résultats obtenus.

Enfin, dans le dernier chapitre, nous présentons une discussion générale sur l'ensemble du travail réalisé dans ce projet de recherche. Pour conclure ce mémoire, on propose des idées d'améliorations des caractéristiques du CFOA et du filtre.

## CHAPITRE 2

# AMPLIFICATEUR OPÉRATIONNEL À RÉTROACTION EN COURANT ET RÉCENT DÉVELOPPEMENT

### 2.1 Introduction

L'amplificateur opérationnel (*ampop*) est une composante fondamentale pour la réalisation de fonctions analogiques ou mixtes. Depuis l'apparition du premier *ampop* intégré, l'amélioration de ces performances ne cesse de croître par l'amélioration de l'architecture et de la technologie.

Le premier *ampop* réalisé est un amplificateur à rétroaction en tension (*Voltage Feedback Operational Amplifier - VFOA*), qui ne répond pas à certaines spécifications. Par exemple, linéarité de phase, faible taux de distorsion harmonique, pente maximale de tension et une bande passante constante et indépendante du gain. Ces spécifications sont nécessaires pour réaliser des circuits dédiés aux applications de traitement de signal et de télécommunications. En effet, l'amplificateur à rétroaction en courant (*Current Feedback Operational Amplifier – CFOA*) a été proposé pour satisfaire ces critères et spécifications.

Nous exposons dans les prochaines sections les caractéristiques statiques, dynamiques de deux types d'*ampop* et nous donnons une revue de littérature sur les travaux de recherches récents dans ce domaine. Nous proposons aussi, une revue de quelques architectures d'intégrateurs ajustables.

## 2.2 Caractéristiques de l'ampop

L'*ampop* idéal est caractérisé par une impédance d'entrée infinie, celle de sortie nulle, un gain *DC* infini, une bande passante infinie, une tension de décalage nulle et un niveau de bruit nul. Le modèle de ce dernier est intéressant pour étudier la plupart des montages à basse fréquence. Cependant, le modèle idéal ne suffit plus pour analyser des circuits analogiques fonctionnant à haute fréquence.

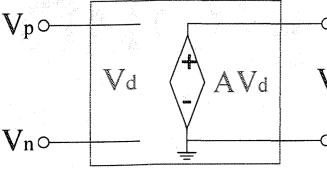

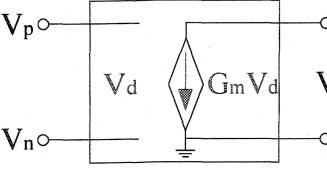

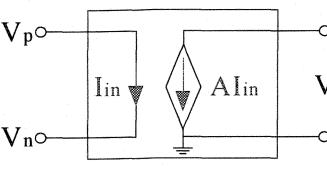

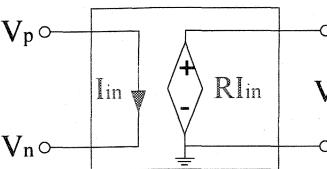

Un *ampop* idéal est modélisé par une source de courant/tension commandée par une source de courant/tension. Le tableau 2.1 résume les quatre types d'*ampop* et leurs modes de fonctionnement.

## 2.3 Ampop à rétroaction en courant

Le *CFOA*, ou amplificateur de transimpédance, a été largement analysé par plusieurs chercheurs [15] [13]. Dans la section suivante nous rappelons l'architecture générale de l'*ampop*, les paramètres qui le distinguent de son concurrent le *VFOA*.

**Tableau 2.1.** Types d'amplificateurs opérationnels

| MODÈLE IDEAL                                                                        | TYPE             | ENTRÉE | SORTIE | GAIN  |

|-------------------------------------------------------------------------------------|------------------|--------|--------|-------|

|    | Tension          | V      | V      | $A_v$ |

|    | Transconductance | V      | I      | $G_m$ |

|   | Courant          | I      | I      | $A_i$ |

|  | Transimpédance   | I      | V      | $R_m$ |

### 2.3.1 Architecture du CFOA

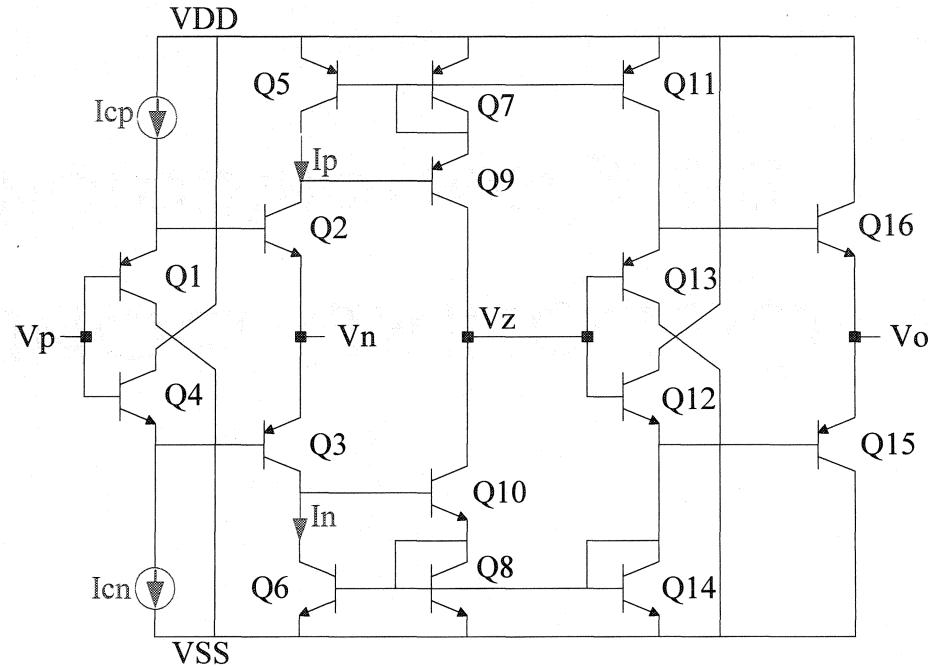

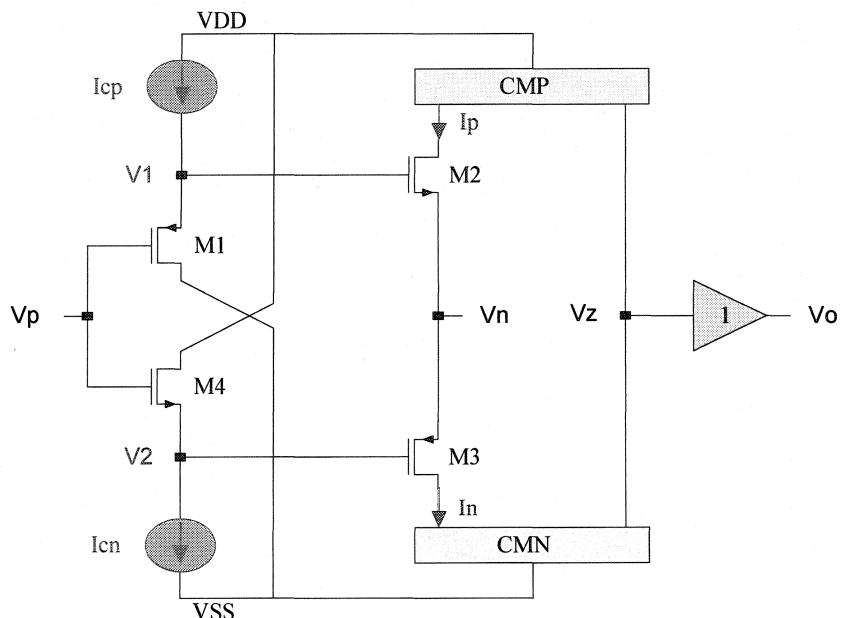

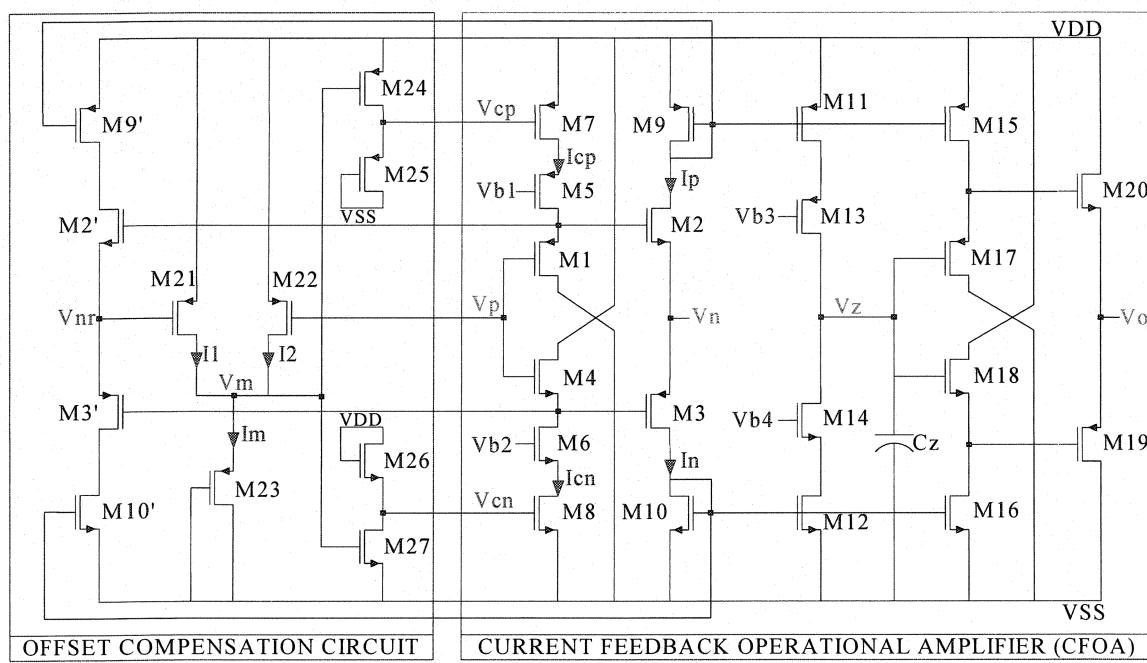

La figure 2.1 présente le schéma d'un *CFOA* en technologie bipolaire. Il est composé par trois étages:

**Étage d'entrée.** Il est composé par un amplificateur classe *AB* qui réunit les propriétés suivantes : faible impédance d'entrée  $V_n$  (idéalement nulle), impédance d'entrée  $V_p$  très élevée (idéalement infinie), gain en tension unitaire. Il se caractérise aussi par, un faible

taux de distorsion harmonique, qui est dû à la symétrie de la topologie; pour chaque transistor npn il y a un transistor pnp [4] [21]. Il a pour rôle de transférer la tension qui se trouve à son entrée  $V_p$  à l'entrée  $V_n$ .

**Figure 2.1.** CFOA en technologie bipolaire

**Étage de gain.** C'est un étage à transimpédance et constitué par deux miroirs de courant. Le courant de déséquilibre ( $I_p - I_n = I_{er}$ ) est convoyé par les deux miroirs de courant ( $I_z = I_{er}$ ) au nœud  $V_z$  pour être converti ensuite en une tension. Pour atteindre une meilleure performance dynamique et statique de l'étage de gain, il faut considérer des miroirs de courant de type Wilson ou ceux de type cascode. Ils offrent une large bande passante, gain élevé et un faible taux de distorsion harmonique qui présente un facteur important pour certaines applications [6].

**Étage de sortie.** Il est composé par un amplificateur classe *AB*, pour transporter l'amplitude du nœud *Z* à la sa sortie avec un gain en tension unitaire ( $V_o = A_{vb}V_z$ ). Il a les mêmes caractéristiques dynamiques et statiques que l'étage d'entrée.

### 2.3.2 Pente maximale de la tension de sortie

La pente maximale de la tension (*Slew rate - SR*) est améliorée par la topologie du *CFOA*. Elle est proportionnelle au taux aux quels les deux transistors (Q9, Q10) peuvent charger le condensateur de compensation  $C_c$  (nœud  $V_z$ ). Le courant généré par ces transistors est dynamique, il n'est limité à aucune valeur fixe comme c'est le cas dans les architectures de *VFOA*. Au premier ordre, il n'y a aucune limite de taux de groupe dans cette topologie. Une large bande et une pente de tension de sortie très élevée permettent à des dispositifs de *CFOA* d'avoir une distorsion harmonique respectable tout en dissipant une puissance inférieure à ces concurrents.

Cependant, les limites surviennent seulement par les capacités parasites des transistors qui composent l'étage d'entrée et beaucoup de travaux en technologie bipolaire ont été faits pour réduire leurs effets.

Le *SR* d'un *CFOA* est donné par :

$$SR = \frac{dv(t)}{dt} = \frac{I_z}{C_z} \quad 1.1$$

$C_z$  représente la capacité parasite vue au nœud  $V_Z$ .

Pour un signal sinusoïdal ayant une pente inférieure ou égale à la pente maximale de la tension maximale, il n'y a pas d'effet et le signal de sortie ne subit pas une distorsion d'amplitude. Cependant, lorsque la pente du signal sinusoïdal est supérieure à la pente maximale de la tension, alors il y a une distorsion d'amplitude du signal.

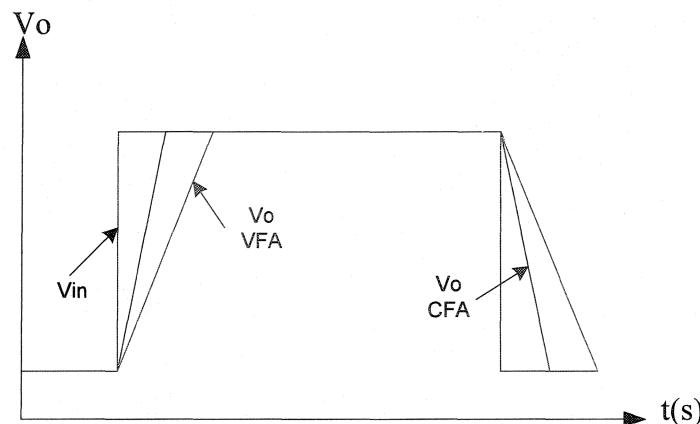

Figure 2.2. Réponse temporelle d'Ampop

La fréquence d'un signal sinusoïdal en fonction de la pente maximale est déterminée par l'équation (2.2):

$$F_{\max} = \frac{SR}{2\pi V_{pp}} \quad 2.2$$

Pour que le signal de sortie ne subisse une distorsion d'amplitude (Équ.2.2), il y a deux solutions envisageables. La première, consiste en une diminution de la fréquence ou de

l'amplitude du signal d'entrée et la deuxième une augmentation de la pente maximale de la tension  $SR$  en augmentant le courant  $I_Z$  (Équ.2.1).

On note selon la figure 2.2 que la réponse à un échelon du *CFOA* est plus rapide que celle du *VFOA*. Car le  $SR$  de ce dernier dépend du courant de polarisation et de la valeur de la capacité de compensation.

### 2.3.3 Tension de décalage

L'étage d'entrée du *CFOA*, classe *AB*, offre plusieurs avantages, mais cette topologie présente une difficulté aux concepteurs d'implémenter les couples de transistors Q1/Q2 et Q3/Q4 géométriquement identiques. Ces contraintes jumelées aux imperfections du procédé de fabrication et la distribution de la température engendrent une différence de tension entre  $V_p$  et  $V_n$ . Cette différence représente la tension de décalage et elle est déterminée par l'équation (2.3) :

$$V_p - V_n = V_{BE}(P) - V_{BE}(N) \quad 2.3$$

Les imperfections du procédé de fabrication sont en général dues à la limite de résolution de la photolithographie qui ne garantie pas l'exactitude des dimensions (W/L) des transistors similaires, vieillissement des composantes, dégradation de l'épaisseur de l'oxyde, variation de la concentration de la densité des impuretés, irrégularités des

profondeurs de dopage, et l'asymétrie de la distribution de température. Toutes ces contraintes résultent en une variation des paramètres électriques des transistors tels que : la conductance, la tension de seuil et la longueur de modulation, etc.

La tension de décalage est une composante d'erreur *DC*, elle a plusieurs effets sur les performances statiques et dynamiques de l'*ampop*:

Le premier est la réduction de la plage dynamique de sortie et le déplacement de la symétrie *DC* à la sortie. Cette diminution provoque une distorsion d'amplitude du signal (compression et décompression), qui est un facteur déterminant dans plusieurs applications destinées au traitement des signaux analogiques audio et vidéo.

Le deuxième est la difficulté d'utiliser l'amplificateur avec un signal à faible fréquence, car le signal dans ce cas est considéré comme un signal continu *DC*.

Les derniers effets sont la variation du gain et de la fréquence de coupure pour lesquelles l'amplificateur a été configuré. Cette variation est due à une diminution ou une augmentation du courant de l'étage de gain. Il peut être un étage de gain en tension ou de gain en courant. La variation de la fréquence de coupure engendre deux états imprévus de fonctionnement du circuit:

- Déplacement de la fréquence de coupure vers une valeur supérieure, alors on se trouve avec une bande passante supérieure à celle prévue. Dans cette situation, les signaux ayant des fréquences non désirées seront traités comme des signaux porteurs de l'information utile.

- Si la fréquence de coupure est inférieure à la fréquence maximale du signal appliqué à l'entrée de l'*ampop*, ce dernier sera atténué. Une conséquence directe de cette situation est la perte de l'information que transporte le signal en question.

Il faut noter que ce problème se présente de la même manière pour un *CFOA* en technologie *CMOS*.

### 2.3.4 Distorsion harmonique

La distorsion harmonique d'un amplificateur opérationnel dépend de la rapidité du *SR* en boucle fermée, la symétrie de la topologie des étages qui le composent et la tension de décalage  $V_{os}$ . La distorsion harmonique se classe principalement en deux catégories : distorsion d'amplitude et distorsion de fréquence. Tous ces phénomènes contribuent à la création de nouvelles harmoniques qui n'existaient pas dans le signal d'entrée. Alors on parle d'un fonctionnement non linéaire et la tension de sortie n'est plus une réplique amplifiée de la tension d'entrée. Une analyse fréquentielle nous montre l'effet de la composante *DC* sur le signal de sortie. Ce signal contient une composante continue, une

composante fondamentale et des harmoniques supérieures qui indiquent la nocivité de la distorsion.

La distorsion de fréquence est distincte de la distorsion non linéaire, elle peut survenir en fonctionnement en petits signaux; c'est-à-dire une variation du gain en fonction de la fréquence. La distorsion de fréquence n'est donc qu'une variation de spectre du signal causée par le déplacement de la fréquence de coupure.

Un signal sinusoïdal appliqué à l'entrée d'un circuit analogique de la forme :

$$V_{in} = V_a \cos(\omega t) \quad 2.4$$

Par décomposition en série de Fourier, le signal de sortie s'écrit sous la forme :

$$V_o = V_{in} + V_1 \cos(\omega t) + V_2 \cos(2\omega t) + \dots + V_n \cos(n\omega t) \quad 2.5$$

Cette décomposition nous donne l'information sur la distorsion d'amplitude du signal.

$$DH_2 = \frac{V_2}{V_1}, \quad DH_3 = \frac{V_3}{V_1} \quad 2.6$$

Comme nous l'avons décrit dans les paragraphes précédents, un *CFOA* se caractérise par une architecture quasi symétrique et une pente de tension de sortie très élevée. Ces caractéristiques lui confèrent un meilleur taux de distorsion harmonique qu'un *VFOA*.

## 2.4 Caractéristiques du CFOA et limites

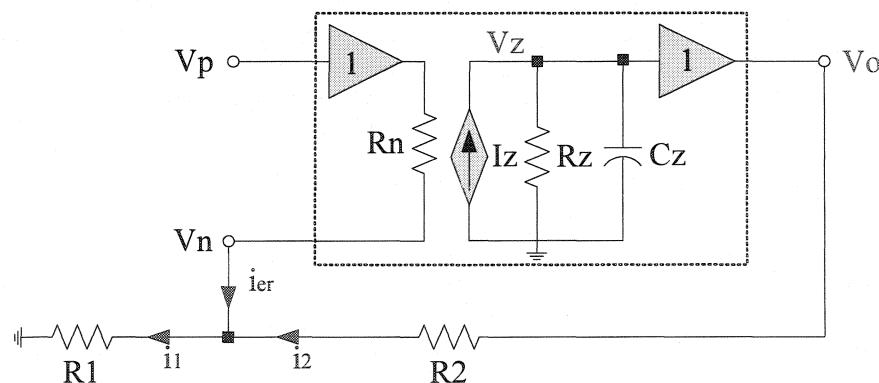

Le modèle petit signal du *CFOA* est présenté à la figure 2.4. Le circuit possède deux entrées asymétriques : une entrée  $V_p$  de haute impédance et une entrée  $V_n$  d'impédance nulle. L'entrée  $V_p$  est reliée à  $V_n$  par un tampon de gain en tension unitaire. Le courant  $I_n$  sortant de l'entrée  $V_n$  est recopié en interne  $I_z$  et traverse une résistance de forte valeur  $R_2$  en parallèle avec une capacité  $C_z$  pour être convertie en une tension avant d'être transportée à la sortie par un étage à gain unitaire.

### 2.4.1 Réponse en fréquence

Figure 2.3. Modèle simplifié du CFOA

En utilisant le théorème de Kirchhoff relative au courant, on peut écrire l'équation de courant sortant de l'entrée  $V_n$  (Fig.2.3).

$$I_{er} = I_1 - I_2 \quad 2.7$$

Si on suppose que le courant  $I_z$  est copie idéale du courant  $I_{er}$ , en traversant une résistance  $R_z$  en parallèle avec la capacité  $C_z$  il créera une tension égale à:

$$V_z = I_z (R_z // C_z) \quad 2.8$$

En résolvant par rapport à  $V_z$ , on obtient la fonction de transfert du circuit présenté par la figure 2.3:

$$\frac{V_o}{V_p} = \frac{A_{cl}}{\left(1 + \frac{A_{cl}R_n + R_2}{R_z}\right) + \left(2\pi F_c \frac{A_{cl}R_n + R_2}{1 + (A_{cl}R_n + R_2)/R_z}\right)} \quad 2.9$$

Si ( $R_n \approx 0$ ) et ( $R_z \gg R_2$ ), alors le terme  $((A_{cl}R_n + R_2)/R_z \approx 0)$  s'annule et l'équation 2.9 devient alors:

$$\frac{V_o}{V_p} = \frac{A_{cl}}{1 + j\omega C_z R_2} \quad 2.10$$

$A_{cl}$  est le gain idéal en boucle fermée :

$$A_{cl} = 1 + R_2/R_1 \quad 2.11$$

La fréquence de coupure s'écrit alors:

$$F_c = \frac{1}{2\pi R_2 C_z} \quad 2.12$$

Selon l'équation (2.12), on remarque que la fréquence de coupure ne dépend plus de  $R_z$ .

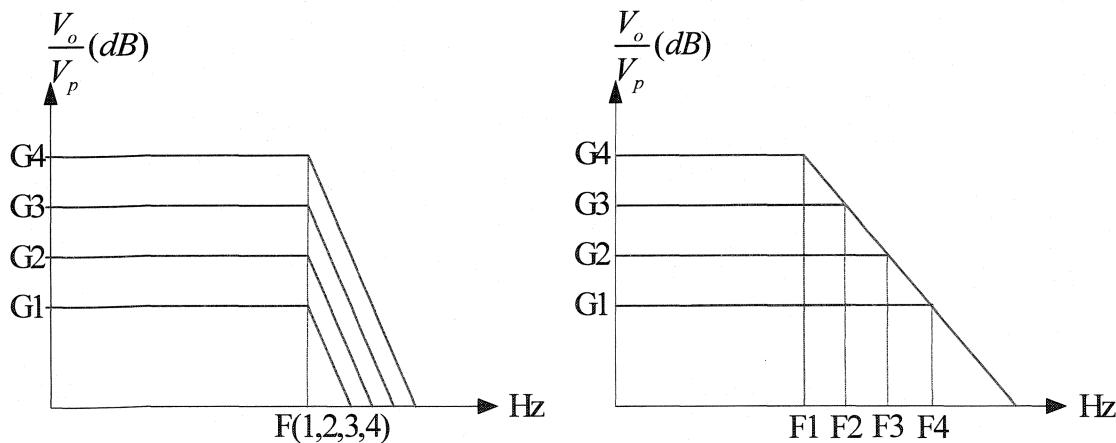

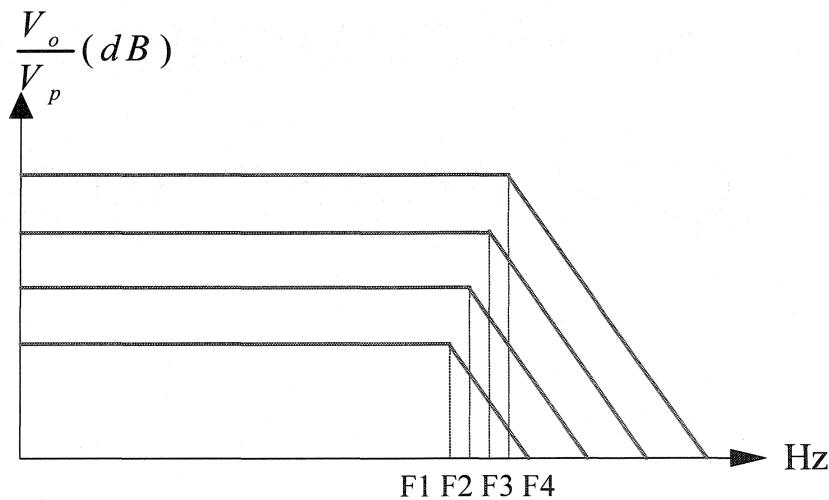

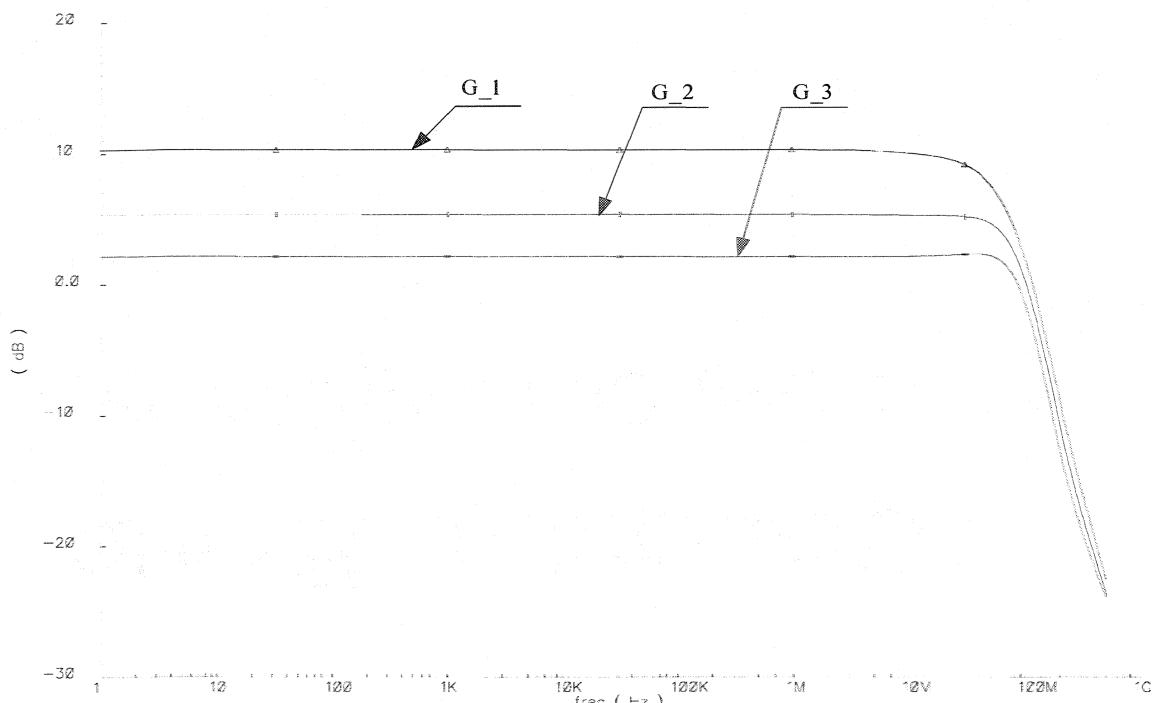

Pour ajuster la fréquence et le gain, il suffit de varier  $R_2$  et  $R_1$  respectivement. Cette indépendance entre le gain et la fréquence de coupure est très demandée dans plusieurs applications, par exemple augmenter le gain d'un filtre sans affecter la fréquence et la bande passante. Le diagramme du gain en fonction de la fréquence d'un CFOA en boucle fermée est présenté à la figure 2.4 (a). On remarque que la variation du gain se fait sans effet sur la fréquence de coupure, mais ceci est vrai si la résistance inverseuse  $R_n$  est égale à zéro (idéalement).

L'amplificateur à rétroaction en tension (Fig.2.4 (b)) n'offre pas les mêmes performances statiques et dynamiques que celles à rétroaction en courant. La pente de variation de la tension est fixée internement et dépend de la valeur du courant (Équ.2.1) de l'étage

d'entrée. L'étage d'entrée est différentiel, mais n'est pas symétrique, et a un gain  $DC$  de quelques dizaines de  $dB$ , ce qui augmente le délai total de l'amplificateur.

Dans certaines topologies de *VFOA*, la valeur de la capacité parasite vue à l'entrée est multipliée par la valeur de transconductance de l'étage différentiel d'entrée. Cette capacité provoque une baisse considérable de la fréquence et une diminution de la pente maximale de la tension de sortie. D'où une plus grande distorsion harmonique du signal par rapport à celle obtenue par un *CFOA*.

**Figure 2.4.** Réponse idéale en fréquence : a) CFOA, b) VFOA

#### 2.4.2 Effets de la résistance de l'entrée négative

La réponse en fréquence montrée à la figure 2.5 nous permet d'observer une réduction de la bande passante qui est moins drastique que celle observée pour un *VFOA*. Cette réduction est due à la valeur non nulle de la résistance  $R_n$  qui est idéalement zéro pour

avoir une bande passante constante. Cependant, cette résistance est différente de zéro et on se trouve avec un produit gain bande passante variable. Pour tenir compte et minimiser son effet sur la réponse en fréquence (Fig.2.5), il faut l'inclure dans les équations caractéristiques (2.11) et (2.12).

En appliquant le théorème de Kirchhoff au schéma présenté dans la figure 2.3, on obtient l'expression donnant le courant qui traverse la résistance  $R_n$ .

$$I_{er} = \frac{V_p - V_n}{R_n} \quad 2.13$$

Si on considère que le courant  $I_z$  est équivalent au courant  $I_{er}$ , la tension  $V_z$  est égale à:

$$V_o = \frac{I_z R_n}{1 + 2\pi F_c R_z C_z} \quad 2.14$$

Si  $R_n \neq 0$  et  $R_z \gg R_2$ , alors l'équation de transfert du CFOA (Equ.2.9) en fonction de  $Rn$  est égale à:

$$\frac{V_o}{V_p} = \frac{A_{cl}}{2\pi C_z [R_2 + A_{cl}] R_n} \quad 2.15$$

Et la fréquence de coupure est donnée par :

$$F_c = \frac{1}{2\pi C_z [R_2 + A_{cl}] R_n} \quad 2.16$$

En fixant le gain (Équ.2.15) et à l'aide de l'équation (2.16), on peut écrire la nouvelle expression  $R_2$  en fonction de  $R_n$  et du gain:

$$R_2 = \frac{1}{2\pi F_c C_z} - A_{cl} R_n \quad 2.17$$

**Figure 2.5.** Réponse fréquentielle du CFOA en fonction de  $R_n$

#### 2.4.3 Linéarité de phase et stabilité

La linéarité de phase d'un *ampop* dépend de la symétrie des étages qui le composent et du circuit de stabilisation [22] [30]. Le *CFOA* a une architecture quasi symétrique, il est composé de deux étages classe *AB* un comme tampon d'entrée et l'autre comme tampon

de sortie et d'un étage intermédiaire de gain. L'étage de gain en transimpédance est composé de deux miroirs de courants *CMP* et *CMN* comme le montre la figure 2.1.

Dans un montage amplificateur dont l'entrée et la sortie sont connectées entre eux par une admittance et qui présente un gain en tension  $B$  et un gain en tension en boucle ouverte  $A_{ol}$ . La stabilité du circuit est obtenue si la phase soit inférieure à  $135^0$  pour un module  $A_{ol}B = 1$

$$A_{ol} = \frac{V_o}{V_p} = \frac{R_z}{(sC_z R_z + 1)R_n} \quad 2.18$$

Le module et la phase sont donnés respectivement par:

$$A_{ol} = \frac{V_o}{V_p} = \frac{R_z}{(sC_z R_z + 1)R_n} \quad 2.19$$

$$\varphi = \operatorname{tg}^{-1} \frac{A_{ol}}{R_2 \left(1 + \frac{R_n}{R_2} // R_1\right)} \quad 2.20$$

Deux paramètres qui peuvent affecter la stabilité de l'amplificateur : le gain de transimpédance et la résistance  $R_2$ , mais qui peuvent être conçus de façon à respecter la stabilité. En insérant une capacité de compensation au nœud  $V_z$ , les paramètres externes qui peuvent stabiliser l'amplificateur : Les résistances de la rétroaction  $I_n$  et  $R_2$  dans

certains cas on ajoute l'accès au nœud  $V_Z$ . Donc la stabilité du *CFOA* dépend des valeurs et de la méthode de compensation que le concepteur utilise pour garantir la stabilité en boucle fermée.

Selon l'équation (2.19), la phase qui assure la stabilité de l'amplificateur dépend de  $R_2$ . En effet, une restriction sur la valeur de  $R_2$  est imposée pour assurer la stabilité ou d'ajouter une capacité de compensation au nœud  $V_Z$ . Cette restriction ne permet pas l'utilisation d'une capacité à la place de  $R_2$  pour réaliser un intégrateur selon les topologies connues avec le *VFOA*.

Finalement, un avantage caché du *CFOA* est qu'il exige habituellement moins d'étages internes que le *VFOA*. Un *CFOA* est composé par trois étages. Donc avoir moins d'étages signifie un faible délai en boucle ouverte; ceci se traduit par une large bande passante. Alors que l'amplificateur en tension exige plusieurs étages pour avoir un gain élevé, ce qui augmente le délai qui se traduira par une diminution de la bande passante.

## 2.5 Développement de CFOA en technologie CMOS

Le *CFOA* tire ces avantages principalement de la symétrie de ces étages (cf. 2.2): Étage d'entrée à gain unitaire, étage de transimpédance et étage de sortie. Dans la section suivante, on discutera des deux architectures classe *AB* utilisées pour réaliser un étage d'entrée en ce qui a trait à leurs performances dynamiques et leurs limites statiques.

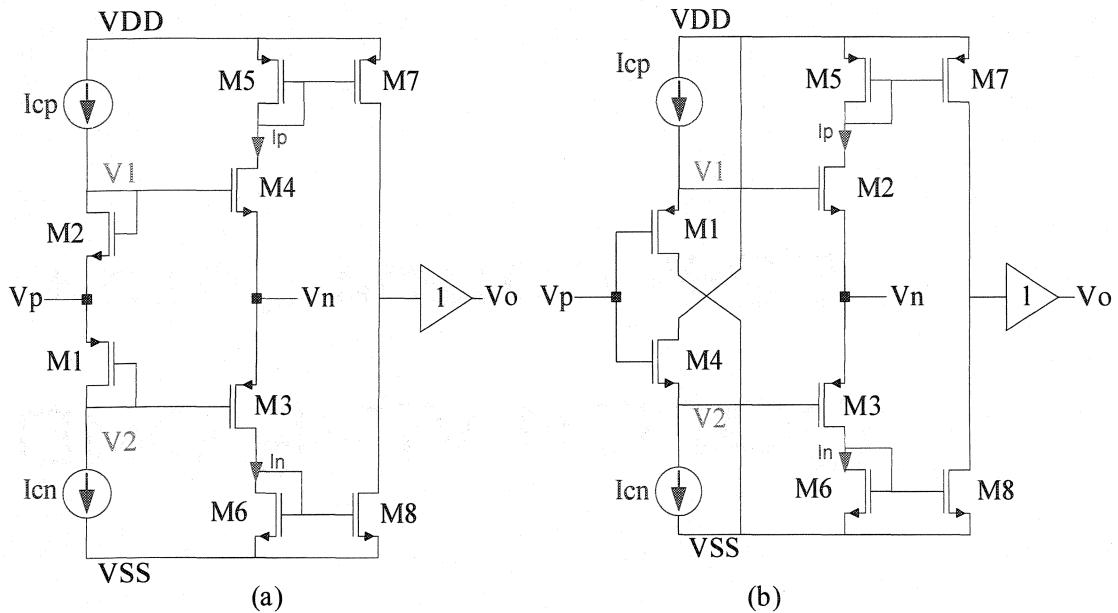

**Figure 2.6.** Étage d'entrée d'un CFOA: a) source suiveur complémentaire, b) source suiveur complémentaire cascade

Enfin, une revue de techniques pour améliorer le rendement statique d'un *CFOA* en technologie bipolaire ou en technologie CMOS.

### 2.5.1 CFOA suiveur complémentaire

La figure 2.6 (a) illustre un *CFOA* dont son étage d'entrée est un amplificateur classe *AB* de type suiveur complémentaire qui se caractérise par un gain unitaire et une impédance finie à l'entrée non inverseuse, d'où un courant  $I_p$  non nul. Si les transistors (M1, M2) et (M3, M4) ne sont pas géométriquement identiques, on est en présence d'un déséquilibre

entre les courants  $I_p$  et  $I_n$ . Ceci se traduit par une erreur de courant qui est problématique à compenser.

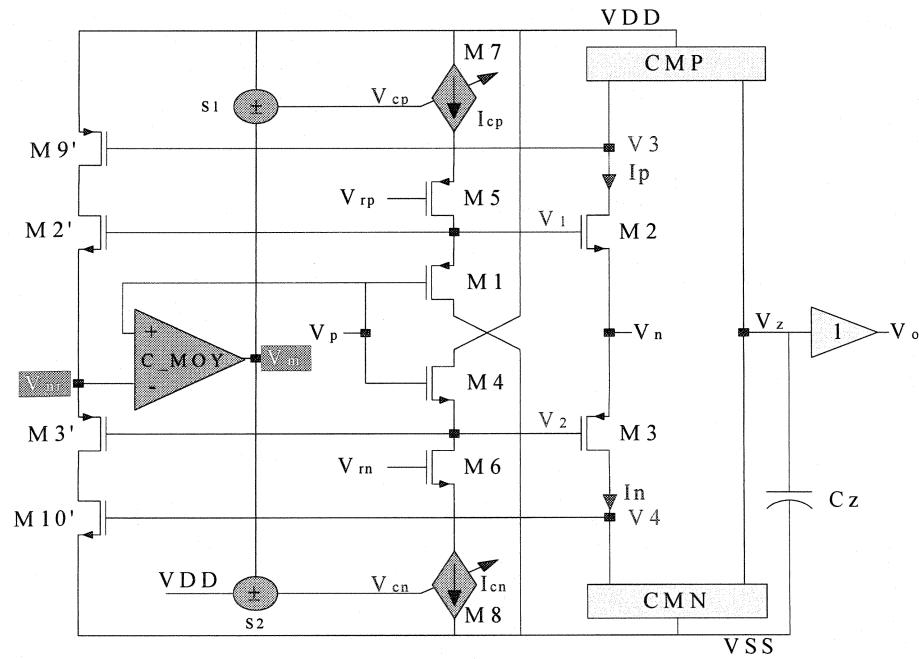

Pour réduire la tension de décalage du circuit suiveur complémentaire, Bruun [4] a proposé un circuit de correction des courants  $I_p$  et  $I_n$  en technologie CMOS (Fig.2.7). L'analyse des résultats obtenus démontre que la stabilité du courant dépend de la stabilité de la tension de seuil  $V_{th}$  en fonction du procédé de fabrication. Le circuit composé par les deux sources de courant présente deux limites importantes : une diminution de la résistance d'entrée non inverseuse, et une variation du gain en transimpédance du CFOA.

Figure 2. 7. CFOA avec correction du courant de polarisation

Une deuxième solution consiste à insérer deux résistances de faible valeur en série avec  $V_n$  et les transistors M2 et M3. L'ajout de deux résistances a pour but de faire chuter

tension  $V_n$  en fonction du courant de déséquilibre et le circuit se trouve avec une compensation de la tension de décalage. Cependant, le bruit thermique d'une résistance constraint l'utilisation du *CFOA* pour réaliser des circuits analogiques à faible amplitude.

### 2.5.2 CFOA suiveur complémentaire cascade

La figure 2.6 (b) présente un circuit suiveur complémentaire cascade qui se caractérise par un gain unitaire et une impédance très élevée à l'entrée non inverseuse, d'où un courant  $I_p$  presque nul. Vu la difficulté de concevoir des paires de transistors (M1, M2) et (M3, M4) géométriquement identiques, une erreur entre les courants générés par les transistors M2 et M3 de l'entrée inverseuse. Ceci se traduit par une tension de décalage et une variation de résistance  $R_n$ .

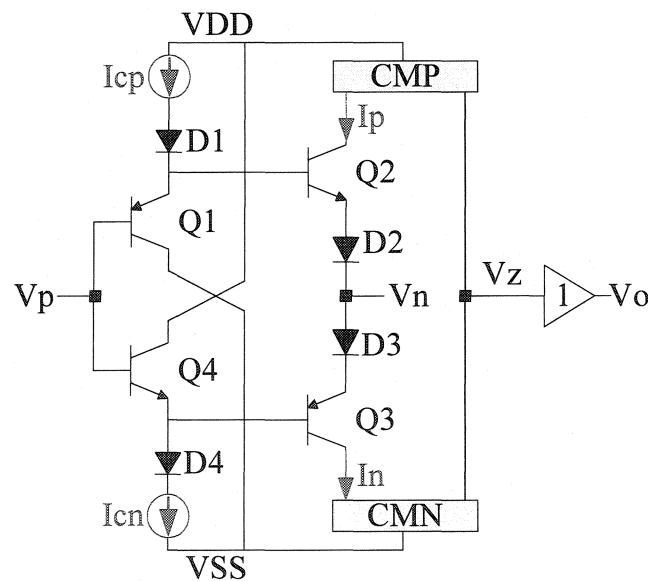

Figure 2.8. CFOA avec réduction de la tension de décalage

En technologie bipolaire, l'auteur propose l'insertion de quatre diodes dans l'étage d'entrée comme le montre la figure 2.8 [31]. En effet, cette solution réduit la tension de décalage, mais elle augmente la résistance inverseuse et diminue la plage dynamique de l'entrée non-inverseuse. Ces deux inconvénients limitent l'amplitude du signal traité et réduisent la bande passante de l'amplificateur. De plus, la valeur de la résistance des diodes, montées en mode blocage, est très élevée, ce qui signifie que le bruit thermique est important.

Alors qu'en technologie CMOS, les auteurs ont proposé un circuit de compensation qui est constitué par un comparateur de tension et deux intégrateurs de courant [1]. Cette technique de compensation a permis d'obtenir de bons résultats, mais elle se caractérise par plusieurs limites importantes:

- Difficulté de transférer la topologie proposée vers une technologie à faible alimentation, par exemple 1.8 V;

- La nouvelle résistance  $R_n$  devient l'équivalent de  $R_n$  du CFOA en parallèle avec la résistance vue à l'entrée du comparateur de tension;

- La capacité parasite vue à l'entrée  $Vn$  est la somme de  $Cn$  et de la capacité parasite vue à l'entrée du comparateur. Ces deux nouvelles valeurs de  $Rn$  et  $Cn$ ,

imposent une diminution de la bande passante et une augmentation du niveau de bruit de l'*ampop*.

- L'intégrateur de courant et le comparateur de tension du circuit de compensation ont un gain supérieur à l'unité. Cette propriété a pour conséquence d'augmenter le taux de distorsion harmonique et de diminuer la pente de la tension de sortie du *CFOA*.

Dans le troisième chapitre, on propose une nouvelle technique de compensation de l'erreur *DC* du *CFOA* avec peu d'effets sur ces caractéristiques dynamiques et statiques.

## 2.6 Filtre actif intégré

Récemment les filtres analogiques réalisés par des *CFOAs* ont attiré l'attention des concepteurs des circuits analogiques [20]. Ceci est dû à la simplicité de conception et aux performances dynamiques de type *CFOA*. Plusieurs auteurs ont publié de nouvelles architectures de filtre actif utilisant des intégrateurs en mode tension/courant. Dans la section suivante, on examinera des techniques de réalisation d'intégrateurs et des techniques employées pour ajuster un ou plusieurs paramètres d'un filtre.

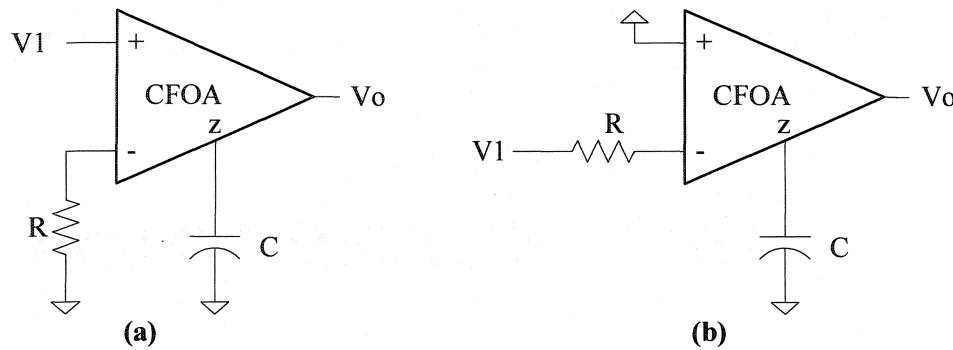

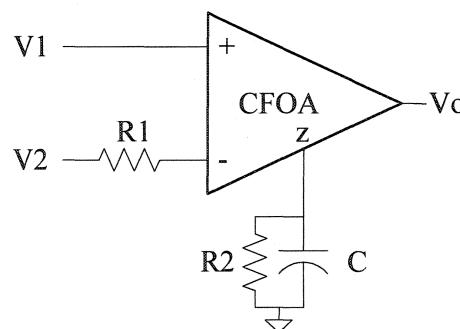

### 2.6.1 Architectures d'intégrateurs

L'analyse du circuit montré à la figure 2.9 nous permet de trouver la fonction de transfert d'un intégrateur idéal (équ.2.21). En examinant le schéma, on note que cette topologie ne peut se réaliser qu'avec des *ampop* ayant une stabilité définie lors de la conception.

$$\frac{V_2}{V_1} = -\frac{1}{sCR} \quad 2.21$$

En présence de tension de décalage qui se superpose à la tension d'entrée  $V_1$ , la sortie de l'intégrateur tend vers la saturation. Théoriquement cette situation est définie par la relation suivante:

$$\frac{V_2}{V_1} = -\frac{1}{sCR} - \frac{I_n}{sC} \quad 2.22$$

Figure 2.9. Intégrateur RC

Pour réduire l'effet de décalage de tension à l'entrée, on diminue le gain en tension aux basses fréquences en ajoutant une résistance en parallèle avec le condensateur; où on

utilise un *ampop* avec tension de décalage nulle ou compensée par l'une des techniques connues.

Dans la section suivante, nous passons en revue quelques techniques de conception d'intégrateurs qui constituent l'élément de base des filtres actifs intégrés avec la possibilité d'ajuster leurs paramètres tels que : fréquence de coupure, gain, facteur de qualité, etc.

### 2.6.2 Technique de variation de la fréquence d'un filtre

Pour réaliser un intégrateur ajustable, il suffit d'ajouter à la résistance de l'intégrateur de la figure 2.9 un transistor *MOSFET*. Le circuit résultant est présenté dans la figure 2.10 et a pour fonction de transfert :

$$\frac{V_2}{V_1} = -\frac{1}{sCR_{eq}} \quad 2.23$$

Avec

$$R_{eq} = R + \frac{L}{W(V_c - V_{th})\mu Cox} \quad 2.24$$

$R_{eq}$  est la résistance équivalente du transistor *MOSFET* fonctionnant en région triode.

Cette résistance n'est pas linéaire dans toute la région triode et souffre de la tension de seuil du transistor qui présente une des limites de cette technique. Une proposition pour remédier à ce problème est présentée dans les références [7] [32].

Le circuit de la figure 2.10 nécessite un *ampop* stable et sans erreur de tension à la sortie. Alors ce type d'intégrateurs ne peut être utilisé avec un *CFOA* qui demande un minimum de résistance pour assurer sa stabilité (cf.2.4.3). Dans le quatrième chapitre, nous proposons une nouvelle topologie d'intégrateur ajustable utilisant un *CFOA*.

**Figure 2.10.** Intégrateur ajustable : a) Circuit à MOSFET RC, b) Caractéristiques du MOSFET

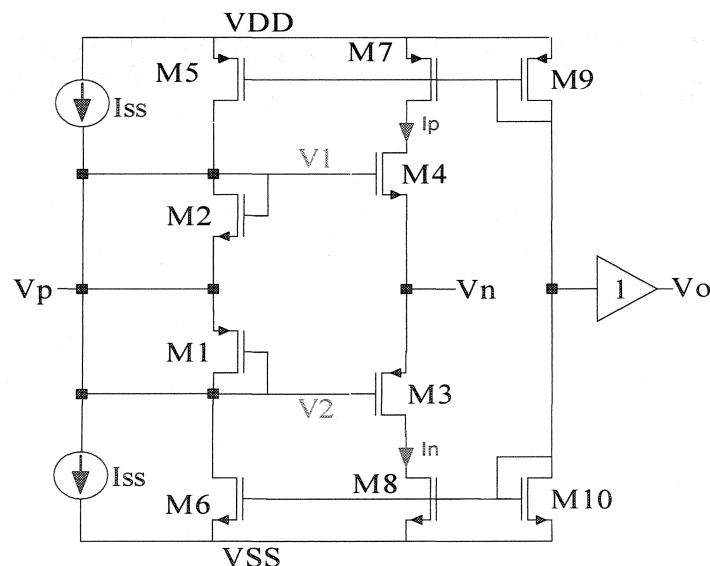

Une des techniques utilisées pour réaliser un intégrateur ajustable est illustrée par la figure (2.11). La variation de la fréquence se fait à l'aide des interrupteurs qui sont réalisés par des transistors MOS. La résistance et la capacité en fonction du code binaire commandant les interrupteurs ( $D_0 \dots D_n$ ) et ( $B_0 \dots B_n$ ) sont données respectivement par :

$$R_{eq} = (R // R_{ds})(2^0 D_0 + 2^1 D_1 \cdots + 2^{n-1} D_{n-1}) \quad 2.25$$

$$C_{eq} = C(2^0 B_0 + 2^1 B_1 \cdots + 2^{n-1} B_{n-1}) \quad 2.26$$

Où : ( $B_i$  et  $D_i$ )= coefficient binaire (0 ou 1).

On observe que ce type de filtres souffre d'une limite de la plage de fréquence que l'on peut réaliser avec cette architecture. Les transistors *MOSFET* formant les interrupteurs de programmation ont des capacités et des résistances parasites. Par conséquent, la réponse en fréquence de cette topologie est affectée et il faut tenir compte de leurs effets pour réaliser ce genre de filtre.

Figure 2.11. Ampop MOSFET RC programmable

Une des propositions pour réaliser un filtre passe-bande à fréquence variable est présentée sur la figure 2.12 [8]. La variation de la fréquence se fait par la variation de la

résistance  $R$ . La performance de cette topologie souffre de la linéarité du potentiomètre. Les résultats obtenus par ce circuit montrent une déviation de la bande passante (10-20kHz) et une variation du gain linéaire de 0.2 à 1. Ces variations sont obtenues pour une fréquence centrale comprise entre 300 kHz et 320 kHz.

**Figure 2.12.** Filtre passe-bande de 4<sup>eme</sup> ordre

## 2.7 Conclusion

Au cours du présent chapitre, nous avons présenté une revue des principaux avantages et inconvénients des amplificateurs à rétroaction de type *CFOA* et *VFOA*. Nous avons ensuite discuté des limites de quelques techniques utilisées pour réduire la tension de décalage d'*ampop* à basse alimentation *DC*. Finalement, nous avons présenté quelques topologies de réalisation de filtre analogique à fréquence ajustable dans le domaine intégré et le domaine discret. Dans le deuxième chapitre, une nouvelle solution de

réduction de la tension de décalage est proposée. Il s'agit d'un circuit qui exploite les techniques analogiques de moyenne et de soustraction et qui répond aux thèmes : faible bruit, faible distorsion harmonique, et simple à intégrer avec le *CFOA* en technologie *CMOS 0.18μm*.

## CHAPITRE 3

# AMPLIFICATEUR À RÉTROACTION EN COURANT À TENSION DE DÉCALAGE RÉDUITE

### 3.1 Introduction

Depuis son apparition vers les années quatre vingt, le *CFOA* est devenu un élément clé pour la réalisation des fonctions analogiques avec un rendement supérieur à celles réalisées par le *VFOA*.