**Titre:** Élaboration d'un module de traitement d'image pour un stimulateur visuel cortical

Title: visuel cortical

**Auteur:** Louis-Xavier Buffoni

Author:

**Date:** 2004

**Type:** Mémoire ou thèse / Dissertation or Thesis

**Référence:** Buffoni, L.-X. (2004). Élaboration d'un module de traitement d'image pour un stimulateur visuel cortical [Mémoire de maîtrise, École Polytechnique de Montréal]. PolyPublie. <https://publications.polymtl.ca/7466/>

Citation:

## Document en libre accès dans PolyPublie

Open Access document in PolyPublie

**URL de PolyPublie:** <https://publications.polymtl.ca/7466/>

PolyPublie URL:

**Directeurs de recherche:** Mohamad Sawan

Advisors:

**Programme:** Non spécifié

Program:

# **NOTE TO USERS**

This reproduction is the best copy available.

UNIVERSITÉ DE MONTRÉAL

ÉLABORATION D'UN MODULE DE TRAITEMENT

D'IMAGE POUR UN STIMULATEUR VISUEL CORTICAL

LOUIS-XAVIER BUFFONI

DÉPARTEMENT DE GÉNIE ÉLECTRIQUE

ÉCOLE POLYTECHNIQUE DE MONTRÉAL

MÉMOIRE PRÉSENTÉ EN VUE DE L'OBTENTION

DU DIPLÔME DE MAÎTRISE ÈS SCIENCES APPLIQUÉES

(GÉNIE ÉLECTRIQUE)

JUILLET 2004

Library and

Archives Canada

Published Heritage

Branch

395 Wellington Street

Ottawa ON K1A 0N4

Canada

Bibliothèque et

Archives Canada

Direction du

Patrimoine de l'édition

395, rue Wellington

Ottawa ON K1A 0N4

Canada

*Your file* *Votre référence*

*ISBN:* 0-612-97931-8

*Our file* *Notre référence*

*ISBN:* 0-612-97931-8

#### NOTICE:

The author has granted a non-exclusive license allowing Library and Archives Canada to reproduce, publish, archive, preserve, conserve, communicate to the public by telecommunication or on the Internet, loan, distribute and sell theses worldwide, for commercial or non-commercial purposes, in microform, paper, electronic and/or any other formats.

The author retains copyright ownership and moral rights in this thesis. Neither the thesis nor substantial extracts from it may be printed or otherwise reproduced without the author's permission.

In compliance with the Canadian Privacy Act some supporting forms may have been removed from this thesis.

While these forms may be included in the document page count, their removal does not represent any loss of content from the thesis.

#### AVIS:

L'auteur a accordé une licence non exclusive permettant à la Bibliothèque et Archives Canada de reproduire, publier, archiver, sauvegarder, conserver, transmettre au public par télécommunication ou par l'Internet, prêter, distribuer et vendre des thèses partout dans le monde, à des fins commerciales ou autres, sur support microforme, papier, électronique et/ou autres formats.

L'auteur conserve la propriété du droit d'auteur et des droits moraux qui protège cette thèse. Ni la thèse ni des extraits substantiels de celle-ci ne doivent être imprimés ou autrement reproduits sans son autorisation.

Conformément à la loi canadienne sur la protection de la vie privée, quelques formulaires secondaires ont été enlevés de cette thèse.

Bien que ces formulaires aient inclus dans la pagination, il n'y aura aucun contenu manquant.

UNIVERSITÉ DE MONTRÉAL

ÉCOLE POLYTECHNIQUE DE MONTRÉAL

Ce mémoire intitulé :

ÉLABORATION D'UN MODULE DE TRAITEMENT D'IMAGE POUR

UN STIMULATEUR VISUEL CORTICAL

présenté par : BUFFONI Louis-Xavier

en vue de l'obtention du diplôme de : Maîtrise ès Sciences Appliquées

présenté au jury d'examen constitué de :

M. KHOUAS Abdelhakim, Doct., Président

M. SAWAN Mohamad, Ph.D., Directeur

M. ABOULHAMID El Mostapha, Ph.D., Membre

## REMERCIEMENTS

Je tiens à remercier mon directeur de recherche, Mohamad Sawan, pour m'avoir accordé la chance de faire partie de cet ambitieux projet qu'est le stimulateur visuel cortical, pour m'avoir guidé et conseillé tout en m'affichant une totale confiance.

Merci à tous mes collègues de l'équipe PolySTIM pour leur bonne compagnie, et particulièrement à Jonathan Coulombe qui m'a pris sous son aile avant le début, et qui a continué à me conseiller tout au long de cette maîtrise. Merci également aux secrétaires pour leur bienveillance qui m'a sauvé en plusieurs occasions ... elles se reconnaîtront.

Je remercie toute ma famille, élargie, et particulièrement mes parents, Diane Comtois et Jean-François Buffoni, pour leur aide infaillible et leur intérêt.

Enfin, je tiens à remercier tous mes amis pour, entre autres, m'avoir rappelé qu'il y a un soleil, dehors. Un merci particulier à mes deux colocataires successifs, pour m'avoir enduré et inspiré grâce à leur autodiscipline exemplaire.

## RÉSUMÉ

L'avancement de la technologie nous permet d'envisager qu'un jour, certaines pertes de fonctions physiologiques complexes comme la vision soient récupérées, du moins partiellement, grâce à la stimulation physiologique. Plusieurs avenues de recherches vont dans ce sens, mais une des plus prometteuses est la stimulation visuelle corticale, qui consiste à envoyer des impulsions de courant électrique dans le cortex visuel, ayant pour effet de produire des sensations lumineuses ponctuelles appelées phosphènes. La plupart des travaux ayant été effectués à ce jour concernent l'électronique du stimulateur, les microélectrodes, l'interface tissus-électrode, ou les travaux d'ordre purement neurologique. Le présent projet s'inscrit dans cet effort de recherche. Plus précisément, il s'agit d'élaborer un système permettant de transformer les images provenant d'une caméra transportée par l'aveugle en commandes de stimulation vers un stimulateur implanté dans le cortex. Cet objectif nécessite de déterminer une ou des façons plausibles de générer des percepts ordonnés dans le champ visuel, à partir des images, qui permettent à un usager de comprendre son environnement le plus efficacement possible. Nous verrons que la réponse est loin d'être triviale.

La première étape du projet a été de faire une recherche la plus exhaustive possible des connaissances actuelles dans le domaine biomédical concernant les phosphènes, leur aspect, leur organisation et surtout, lorsqu'ils sont évoqués en même temps, leur capacité à être identifiés comme représentant des formes. Les connaissances actuelles sur ce sujet étant encore rudimentaires, le système conçu permettra l'application de diverses stratégies pour transformer des images en patrons de phosphènes compréhensibles, avec un niveau de réalisme variable.

Ces stratégies sont constituées d'algorithmes de traitement d'image qui ont d'abord été implémentés de manière logicielle afin de les évaluer. Un système logiciel complet, faisant le lien entre la caméra et une future interface avec le contrôleur de l'impant, a été réalisé. Ce système est assorti d'un logiciel d'interface-usager permettant à un expérimentateur de le contrôler.

Parmi les traitements d'image choisis, un effort particulier a été mis dans la conception d'un algorithme de segmentation étant donné son utilité cruciale dans cette application. En effet, il sert simultanément à réduire la résolution de l'image de manière efficace et à la découper en zones de mêmes caractéristiques. Cet algorithme est décrit en détail. Avec des données de distance des objets fournies par un éventuel détecteur de distance, seules les zones stratégiques seront affichées sous forme de taches de lumière. Cela constitue une des approches les plus réalistes, car les phosphènes sont évoqués en mode « tout-ou-rien », et fournira certainement l'usager avec des indices utiles qui lui permettront de comprendre son environnement.

Le système de traitement d'image sous forme logicielle a été implémenté principalement pour évaluer la qualité des algorithmes, et également pour vérifier la compatibilité avec le logiciel d'interface-usager. Un système embarqué a également été développé pour être utilisé pour des tests *in vivo*, car l'évaluation des stratégies de traitement d'image nécessite que le système frontal du stimulateur visuel cortical soit portable. Dans son état actuel, il est remis sous la forme d'un groupe de modules logiciels et matériels codés en VHDL.

La version embarquée du système a également été complétée parce que les algorithmes implémentés en logiciel ne permettent pas le calcul d'un résultat en un temps suffisant pour être utilisé avec un stimulateur visuel. Une part de calcul a dû être laissée à un coprocesseur dédié. Il a été implémenté en VHDL et le design complet, intégré dans une architecture AMBA avec un processeur ARM, a été validé dans un environnement de simulation de co-design (logiciel et matériel simultanément). Les résultats montrent que les algorithmes sont fonctionnels et atteignent les performances voulues.

## ABSTRACT

Continuous technological advances may soon allow some lost complex physiological functions like vision be recovered, at least partially, with physiological stimulation. Many research avenues are striving to meet this goal, but one of the most promising is the visual cortical stimulation, which consists in injecting current pulses in the visual cortex, producing punctual visual sensations called phosphenes. Most of research teams have been focusing on designing microstimulators, microelectrodes, bio-electrode interfaces, or purely neurological researches. This project is part of this research effort. More precisely, it consists of elaborating a system to allow images captured by a video camera carried by the blind be transformed into stimulation command signals for an implant. In order to achieve this goal, we need to determine adequate ways of transforming images into percepts that would be disposed in the visual field, allowing a user to understand his surroundings. The answer to that issue is not trivial.

The first step of the project has been to seek, as exhaustively as possible, actual knowledge in the biomedical field about phosphenes, their aspect, their organization, and above all, their ability in being accurately identified as shapes when many of them are evoked at the same time. Knowledge in this field still being in its early beginnings, the system described in this master thesis implements multiple strategies in transforming images into intelligible phosphene patterns, with variable realism.

These strategies are constituted of image processing algorithms that have first been implemented in software for evaluation purposes. A complete software has been developed, making the link between the input device and an interface with the implant controller. It is also assort with a user-interface software allowing its control.

Among the selected image processing techniques, particular attention has been paid to a segmentation algorithm because of its crucial use in this application. As a matter of fact, it is simultaneously used to efficiently reduce image resolution as well as to separate the image

into areas of same characteristics. This algorithm implementation is described in great details. With distance data obtained by an range finder, only the strategical areas will be displayed in the form of light patches. It constitutes one of the most realistic strategies, because phosphenes are evoked in an on/off fashion, and this will hopefully offer valuable clues about the user's surroundings.

The software image processing system has been principally implemented in order to evaluate the quality of the algorithms, and also to validate compatibility with the user-interface software. An embedded system has also been developed to be used for in vivo tests, because these tests require that the front-end subsystem of the visual cortical stimulator be portable. It is actually in the form of a set of software and *soft* hardware modules, that is coded in VHDL.

The embedded counterpart of the system has also been completed because the algorithms implemented in software could not meet speed performance needed to be used with a visual stimulator. A fraction of processing must have been left to a dedicated coprocessor. It has been implemented in VHDL and the complete design, integrated in an AMBA bus architecture with an ARM processor, has been validated in a codesign simulation environment (simultaneous software and hardware simulation). The algorithms functionality have been validated and their requested performance are met.

## TABLE DES MATIÈRES

|                                                                        |              |

|------------------------------------------------------------------------|--------------|

| <i>Remerciements</i>                                                   | <i>iv</i>    |

| <i>Résumé</i>                                                          | <i>v</i>     |

| <i>Abstract</i>                                                        | <i>vii</i>   |

| <i>Table des matières</i>                                              | <i>ix</i>    |

| <i>Liste des figures</i>                                               | <i>xii</i>   |

| <i>Liste des tableaux</i>                                              | <i>xv</i>    |

| <i>Liste des sigles et abréviations</i>                                | <i>xvi</i>   |

| <i>Liste des annexes</i>                                               | <i>xviii</i> |

| <i>Introduction</i>                                                    | <i>1</i>     |

| <i>Chapitre 1</i>                                                      | <i>4</i>     |

| <i>Contexte biomédical</i>                                             | <i>4</i>     |

| <b>1.1 Introduction</b>                                                | <b>4</b>     |

| <b>1.2 Dispositifs visuels</b>                                         | <b>4</b>     |

| 1.2.1 Stimulation neuronale                                            | 4            |

| 1.2.2 Système visuel humain et maladies de la vision                   | 7            |

| 1.2.3 Avenues de recherche pour la récupération partielle de la vision | 9            |

| <b>1.3 Microstimulation intracorticale</b>                             | <b>11</b>    |

| 1.3.1 Phosphènes et organisation visuotopique                          | 11           |

| 1.3.2 Systèmes de stimulation visuelle corticale                       | 13           |

| 1.3.3 Reconnaissance de patrons de phosphènes                          | 14           |

| 1.3.4 Distribution spatiale des phosphènes                             | 15           |

| <b>1.4 Conclusion</b>                                                  | <b>16</b>    |

|                                                                                                        |           |

|--------------------------------------------------------------------------------------------------------|-----------|

| <i>Chapitre 2</i>                                                                                      | <b>17</b> |

| <i>Stratégies de traitement d'image</i>                                                                | <b>17</b> |

| <b>2.1 Introduction</b>                                                                                | <b>17</b> |

| <b>2.2 « Multiple Image Processing Strategies Dedicated to Visual Cortical Stimulators: A Survey »</b> | <b>18</b> |

| Abstract                                                                                               | 18        |

| I. Introduction                                                                                        | 19        |

| II. Phosphene appearance and organization                                                              | 20        |

| III. Image processing for visual stimulators                                                           | 23        |

| IV. Image Processing Strategies                                                                        | 26        |

| V. Results                                                                                             | 31        |

| VI. Conclusion                                                                                         | 32        |

| Acknowledgements                                                                                       | 33        |

| References                                                                                             | 33        |

| List of figures and tables                                                                             | 36        |

| Figures                                                                                                | 37        |

| <b>2.3 Conclusion</b>                                                                                  | <b>40</b> |

| <i>Chapitre 3</i>                                                                                      | <b>42</b> |

| <i>Version logicielle du système de traitement d'image</i>                                             | <b>42</b> |

| <b>3.1 Introduction</b>                                                                                | <b>42</b> |

| <b>3.2 Bases théoriques des traitements d'image</b>                                                    | <b>43</b> |

| 3.2.1 Méthodologie                                                                                     | 43        |

| 3.2.2 Traitements d'image de bas niveau                                                                | 44        |

| 3.2.3 Traitements de niveau moyen                                                                      | 47        |

| 3.2.4 Traitements de haut-niveau                                                                       | 49        |

| <b>3.3 Algorithmes de segmentation</b>                                                                 | <b>49</b> |

| 3.3.1 Avenues envisagées                                                                               | 49        |

|                                                                                                    |           |

|----------------------------------------------------------------------------------------------------|-----------|

| 3.3.2 Comparaison des différentes implémentations                                                  | 50        |

| <b>3.4 Modèle du système de traitement d'image sur PC</b>                                          | <b>53</b> |

| 3.4.1 Architecture                                                                                 | 53        |

| 3.4.2 Programme d'interface usager                                                                 | 55        |

| 3.4.3 Communication                                                                                | 55        |

| <b>3.5 Conclusion</b>                                                                              | <b>56</b> |

| <i>Chapitre 4</i>                                                                                  | 57        |

| <i>Version embarquée du système de traitement d'image</i>                                          | 57        |

| <b>4.1 Introduction</b>                                                                            | <b>57</b> |

| <b>4.2 « Design and Test of a Novel Image Processor Dedicated to Visual Cortical Stimulation »</b> | <b>58</b> |

| Abstract                                                                                           | 58        |

| I. Introduction                                                                                    | 59        |

| II. Segmentation Algorithm by Boundary Melting                                                     | 61        |

| III. Implementation in an Embedded Architecture                                                    | 67        |

| IV. Dedicated coprocessor                                                                          | 69        |

| V. Results and discussion                                                                          | 71        |

| VI. Conclusion                                                                                     | 73        |

| Acknowledgements                                                                                   | 74        |

| References                                                                                         | 74        |

| List of figures and tables                                                                         | 76        |

| Figures and tables                                                                                 | 78        |

| <b>4.3 Conclusion</b>                                                                              | <b>85</b> |

| <i>Conclusion</i>                                                                                  | 87        |

| <i>Bibliographie</i>                                                                               | 90        |

| <i>Annexes</i>                                                                                     | 98        |

## LISTE DES FIGURES

|            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |    |

|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

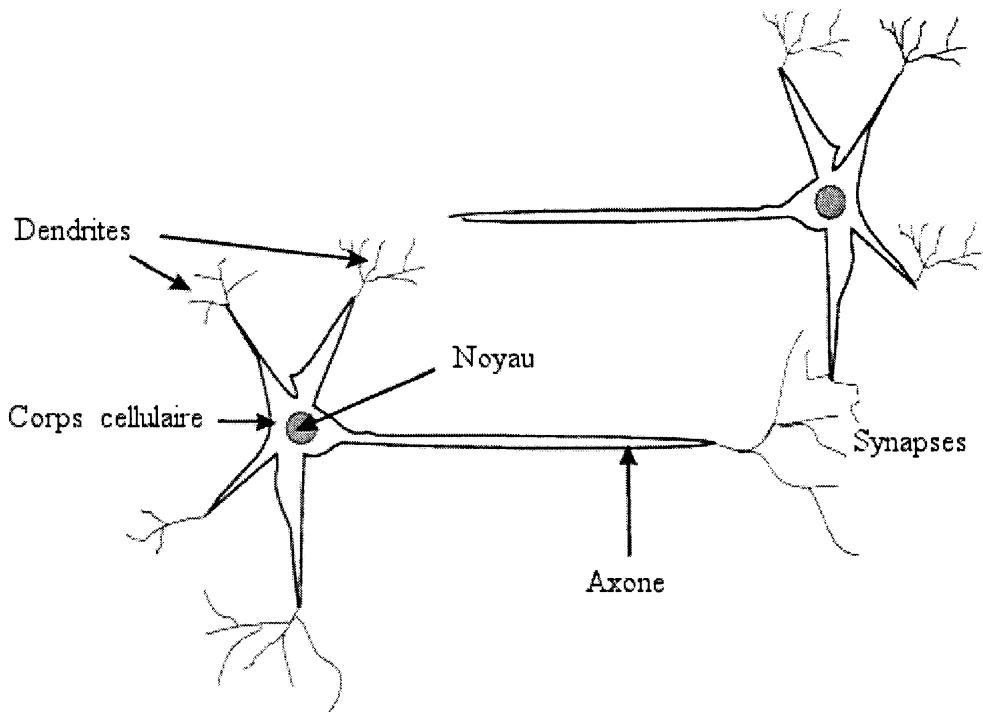

| Figure 1.1 | Schéma simplifié d'une cellule nerveuse (tiré de [72]).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 6  |

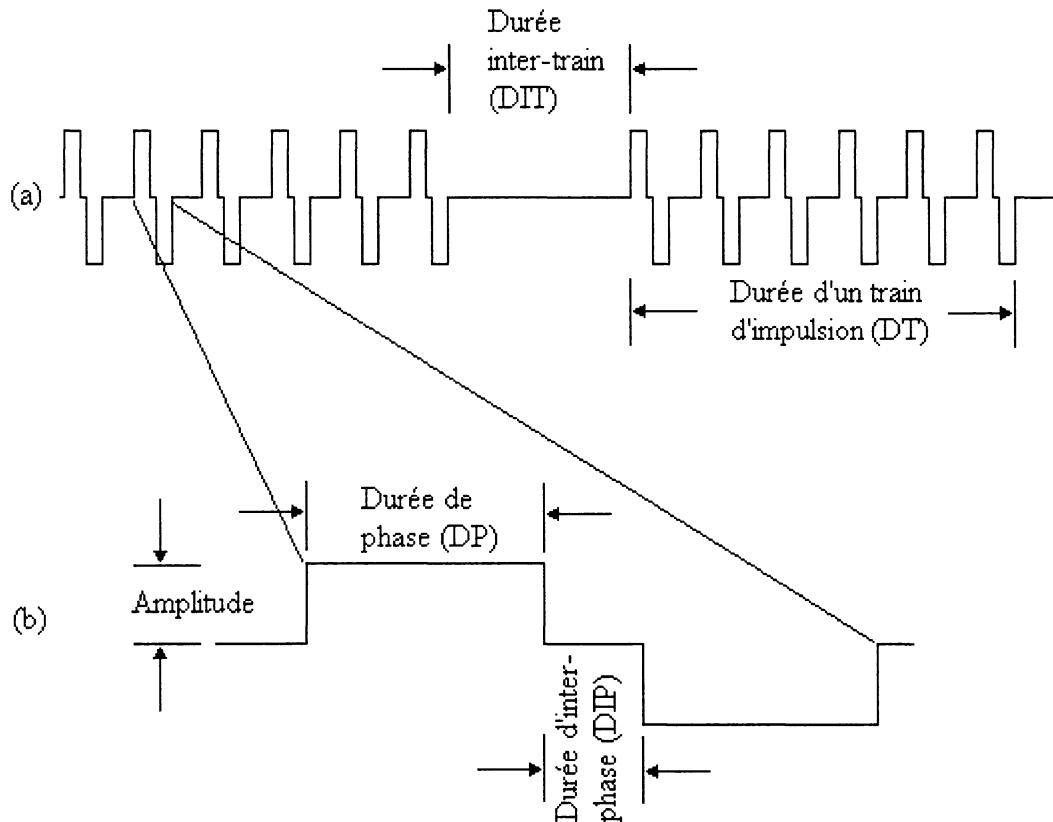

| Figure 1.2 | Formes d'ondes utilisées pour la stimulation intracorticale.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 7  |

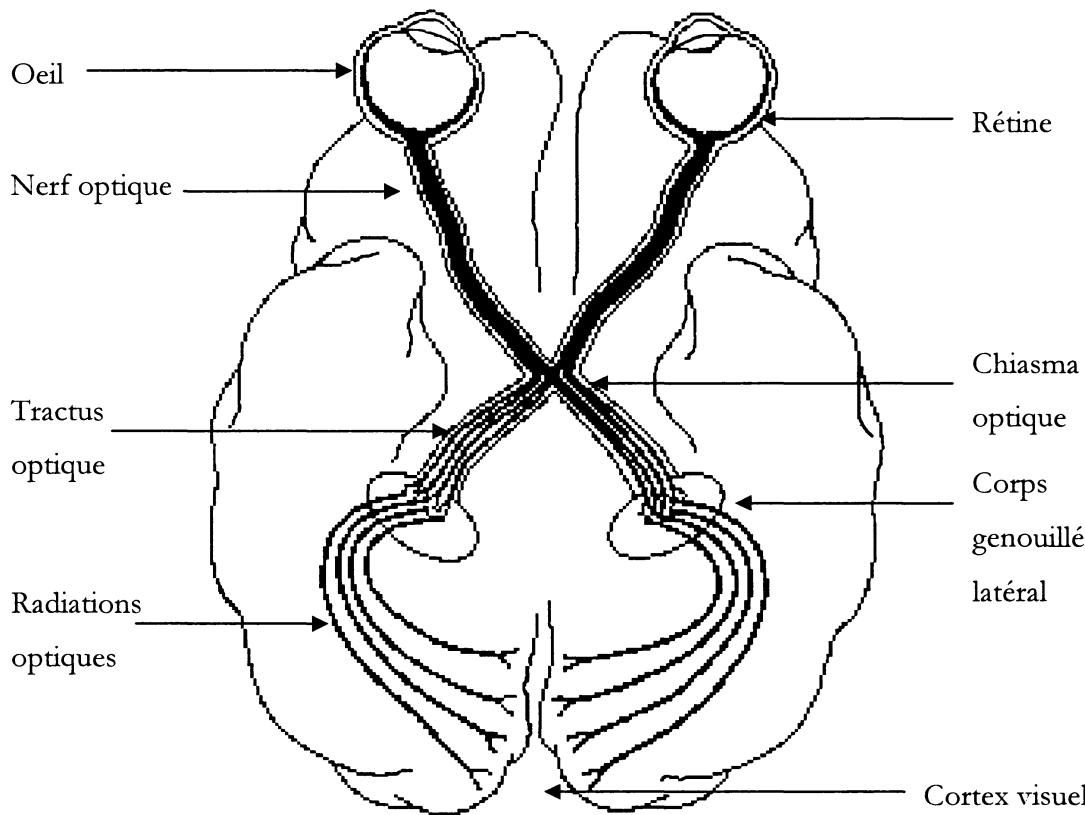

| Figure 1.3 | Système visuel humain.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 8  |

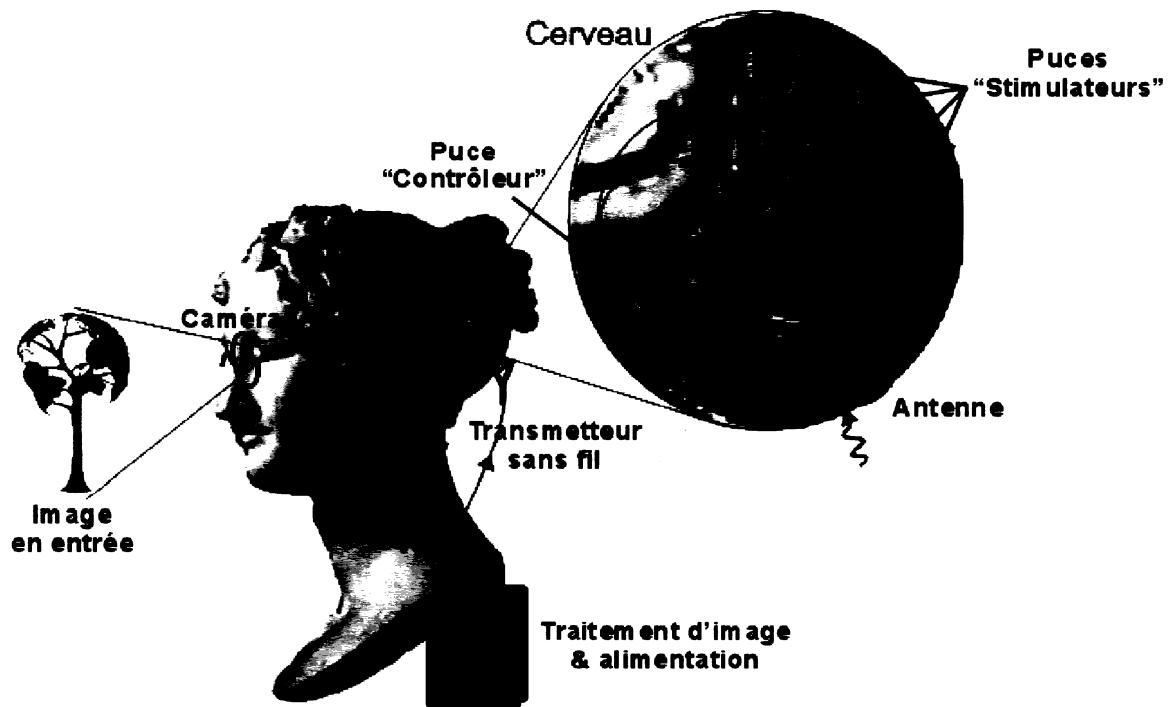

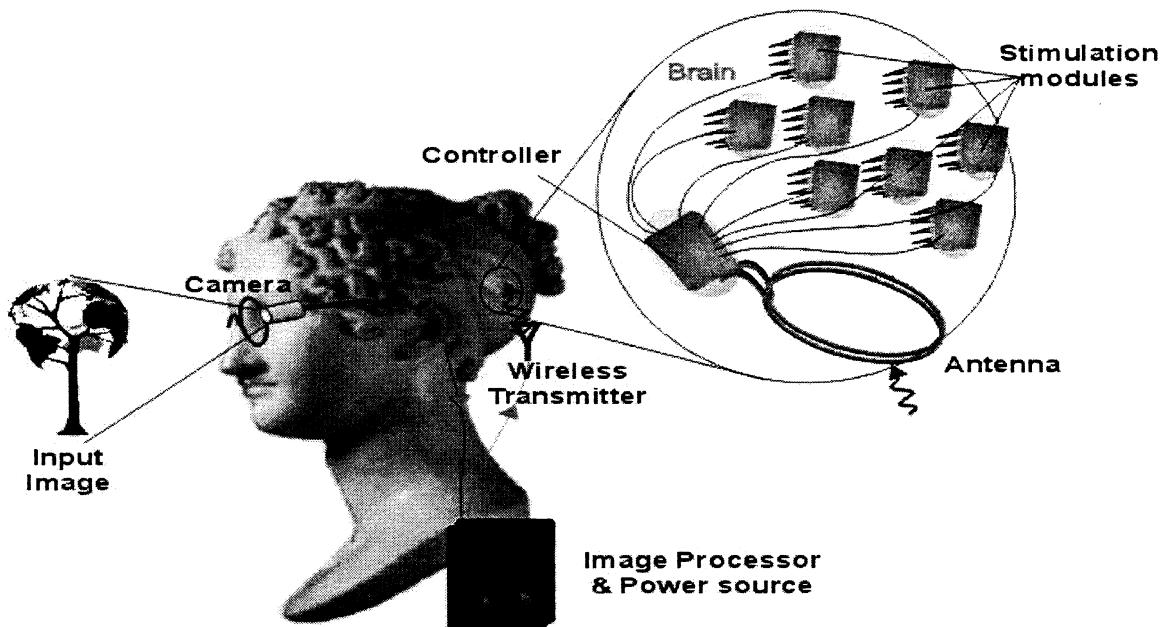

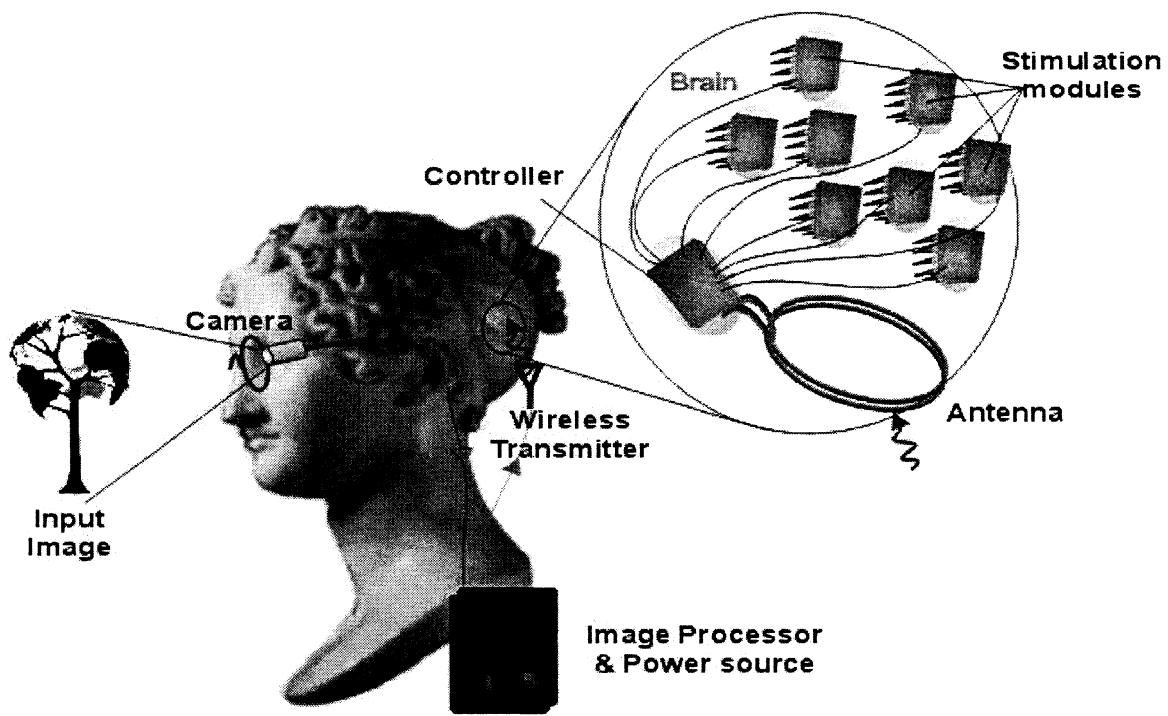

| Figure 1.4 | Schéma de principe du système de stimulation visuelle corticale proposé par l'équipe PolySTIM.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 14 |

| Figure 2.1 | Complete visual cortical stimulation system. The image processing system is integrated in the external controller.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 37 |

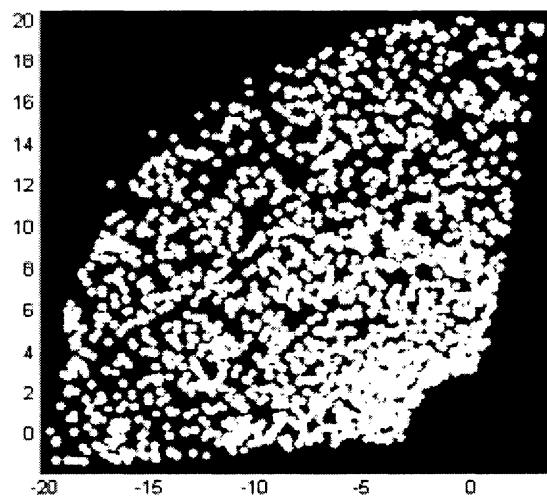

| Figure 2.2 | Artificial phosphene map: 1500 phosphenes, disposed between 10° and 185° of lateral angle, and from 3° to 20° of eccentricity. Phosphene diameter = 0.6°.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 37 |

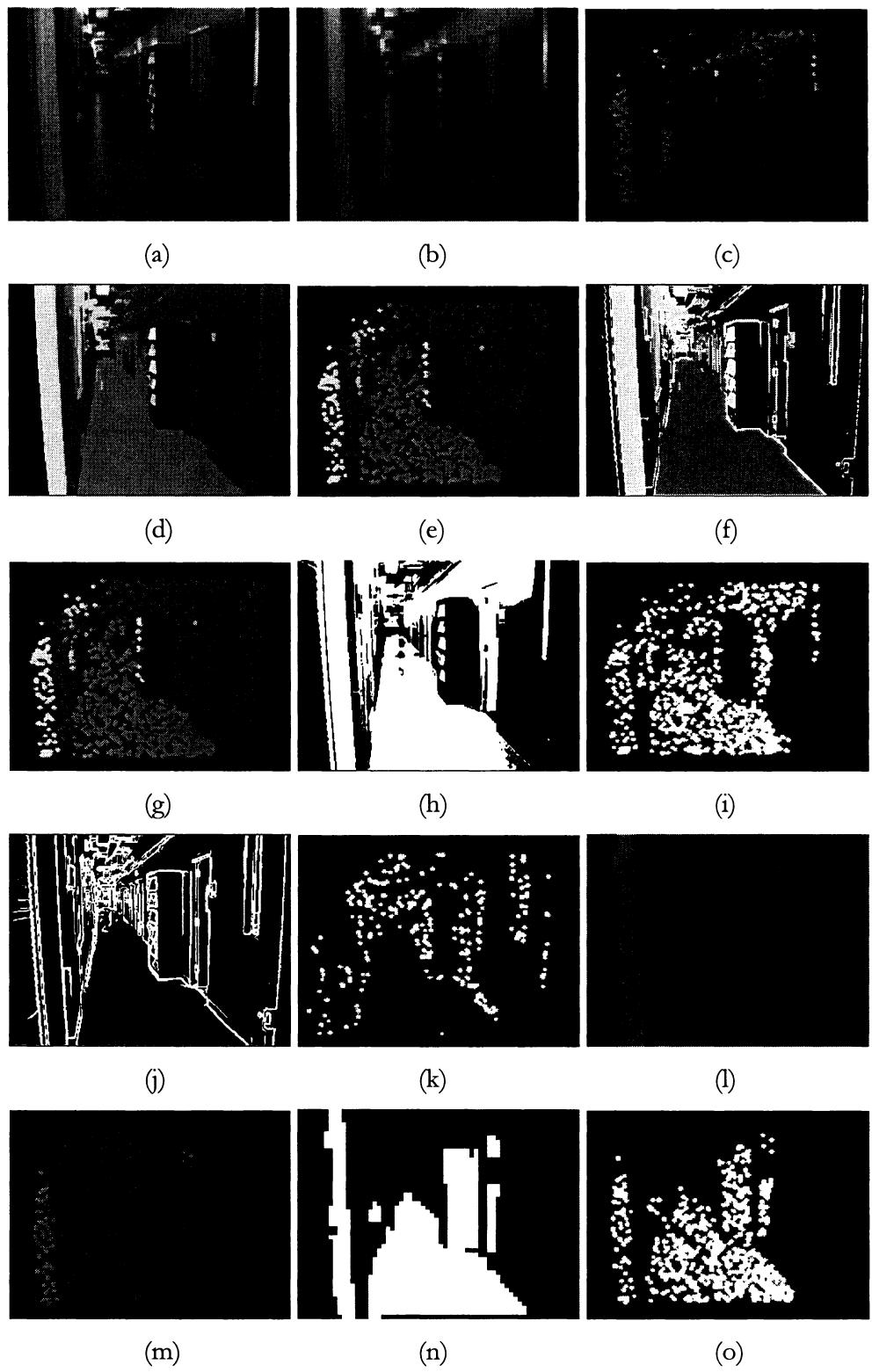

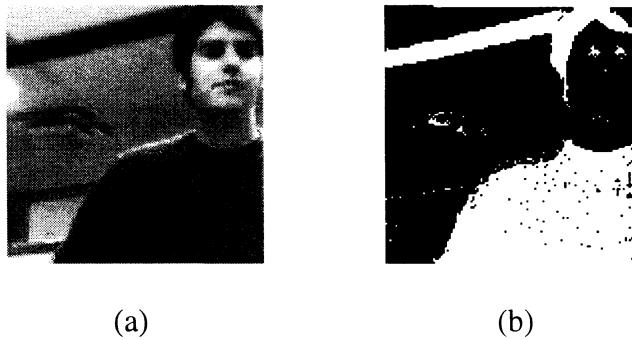

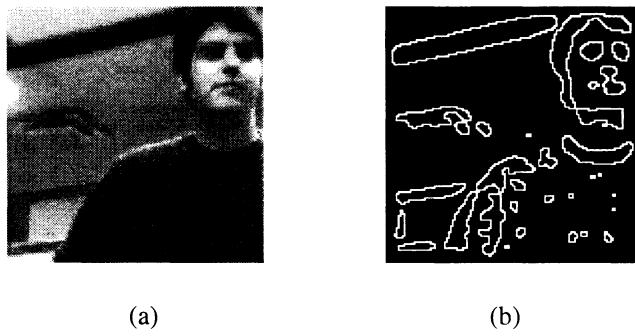

| Figure 2.3 | Various image processing and representation strategies: a) original image, b) resolution reduction by mean of neighboring pixels, c) phosphene representation of (b), d) resolution reduction by growth of zones, e) phosphene representation of (d), f) resolution reduction with edges enhanced, g) phosphene representation of (f), h) image threshold, i) phosphene representation of (h), j) edge image from a Sobel filter and hysteresis filtering, k) phosphene representation of (j), l) segmented image, m) phosphene representation of (l), n) segmented region selection based on distance, o) phosphene representation of (n). | 38 |

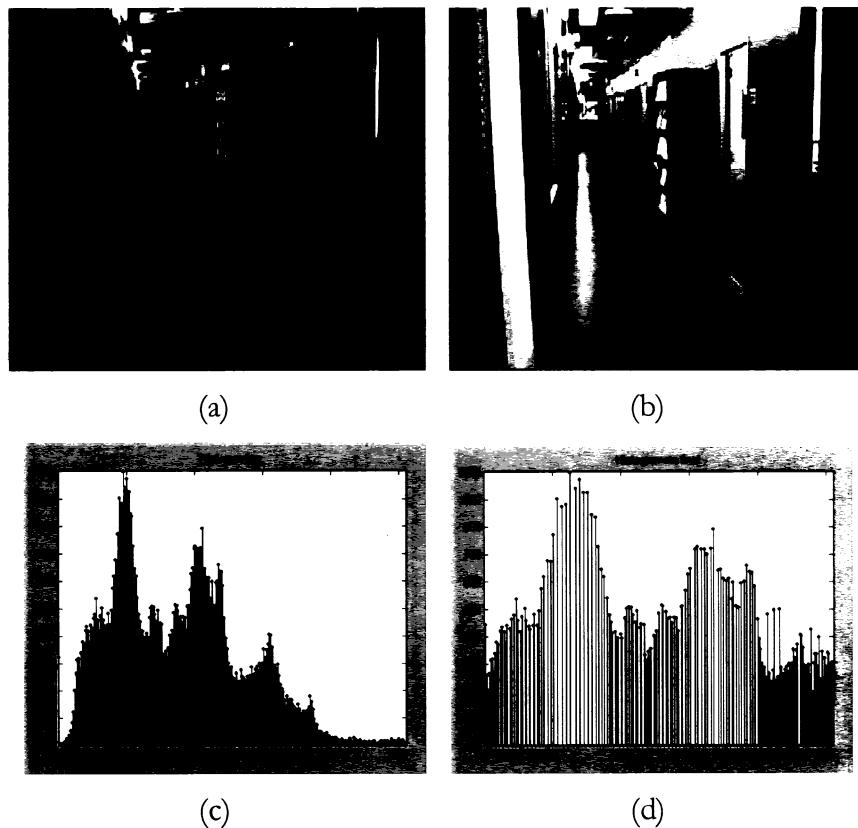

| Figure 3.1 | Égalisation d'histogramme global : a) image originale, b) image traitée, c) histogramme original, d) histogramme obtenu après traitement. L'axe des ordonnées est le nombre de pixels à une intensité donnée. L'axe des abscisses est l'intensité, de 0 à 255 (8 bits).                                                                                                                                                                                                                                                                                                                                                                     | 45 |

| Figure 3.2 | Filtrage médian : a) image originale, corrompue avec du bruit d'impulsion, b) image filtrée.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 46 |

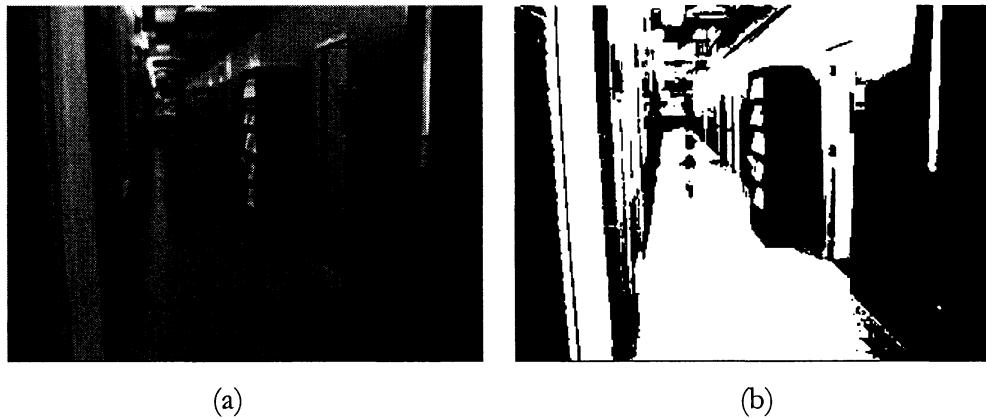

| Figure 3.3 | Détermination optimale du seuil global de binarisation : a) image originale, b) image binarisée en 5 itérations, avec un seuil automatique final de 89 (sur 255).                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 48 |

|            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |    |

|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

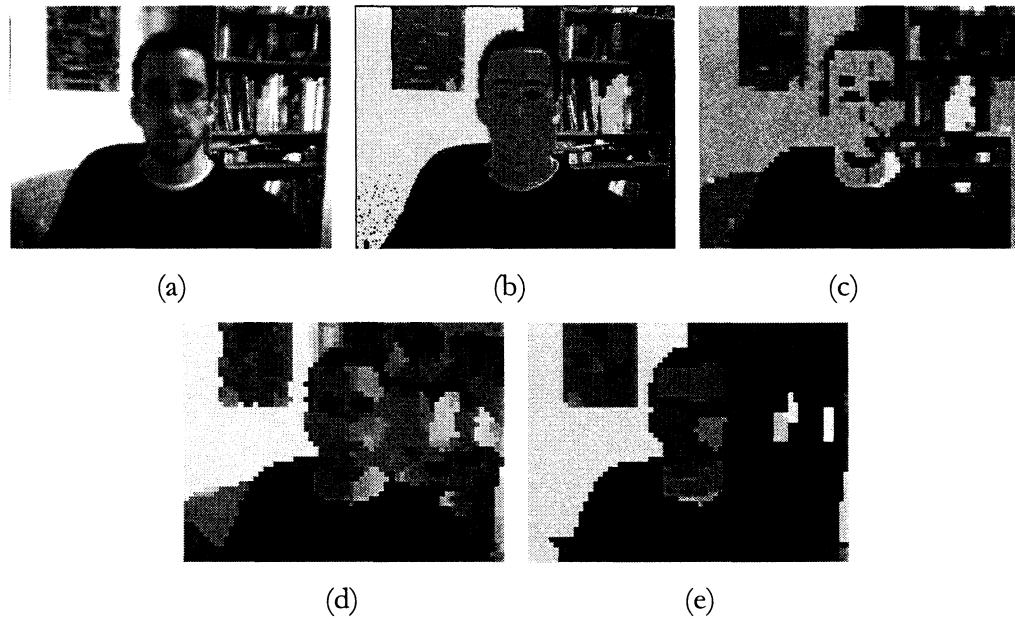

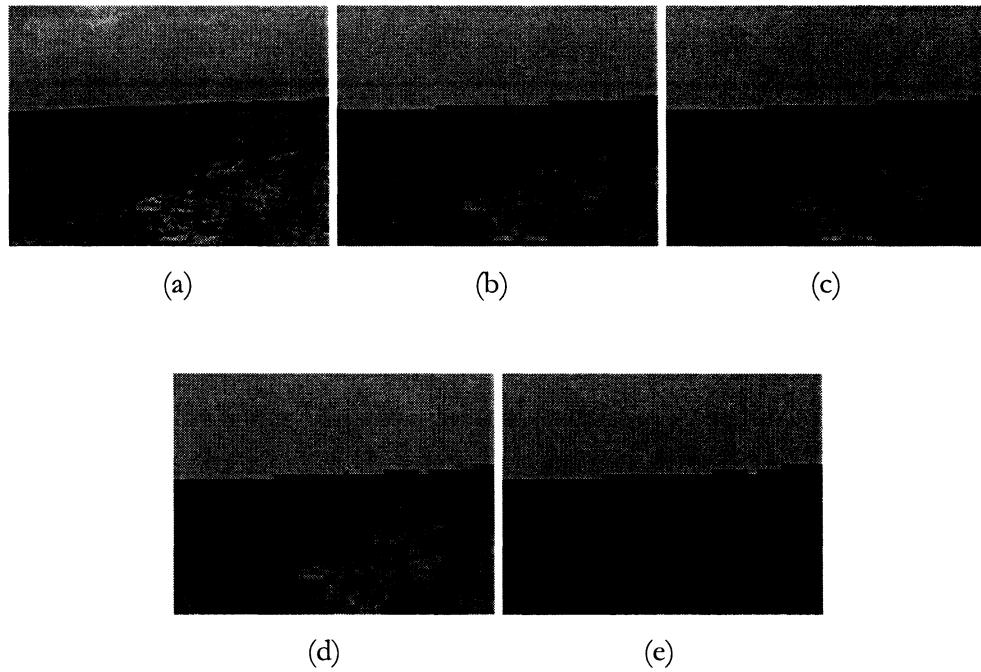

| Figure 3.4 | Résultats de segmentation des différents algorithmes. L'image originale (a) est suivie respectivement par le résultat du <i>growth of zones</i> (b), <i>region merging</i> (c), <i>region-and-edges</i> (d) et <i>boundary melting</i> (e). _____                                                                                                                                                                                                                                                 | 53 |

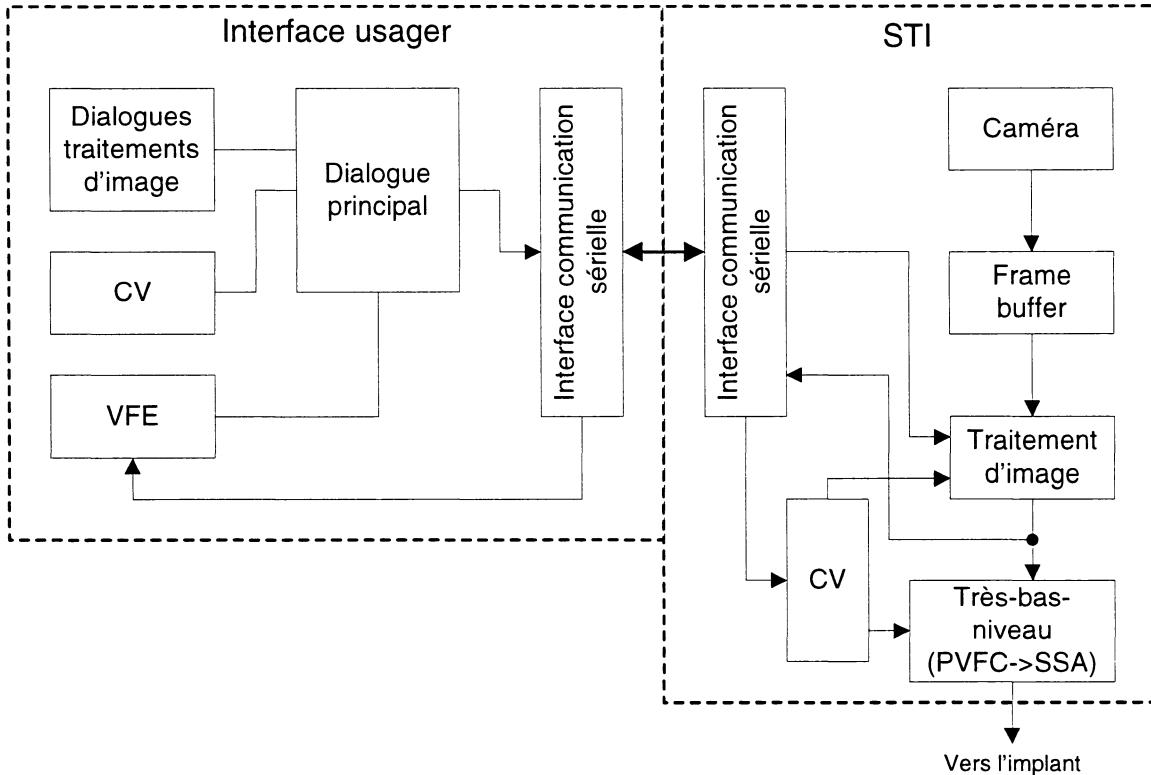

| Figure 3.5 | Schéma-bloc de la version logicielle du STI (avec interface usager). L'étiquette CV désigne la carte visuotopique, et VFE le module de visualisation des patrons de phosphènes dans le champ visuel. _____                                                                                                                                                                                                                                                                                        | 54 |

| Figure 4.1 | Complete visual cortical stimulation system. The image processing system is contained in the external controller. _____                                                                                                                                                                                                                                                                                                                                                                           | 78 |

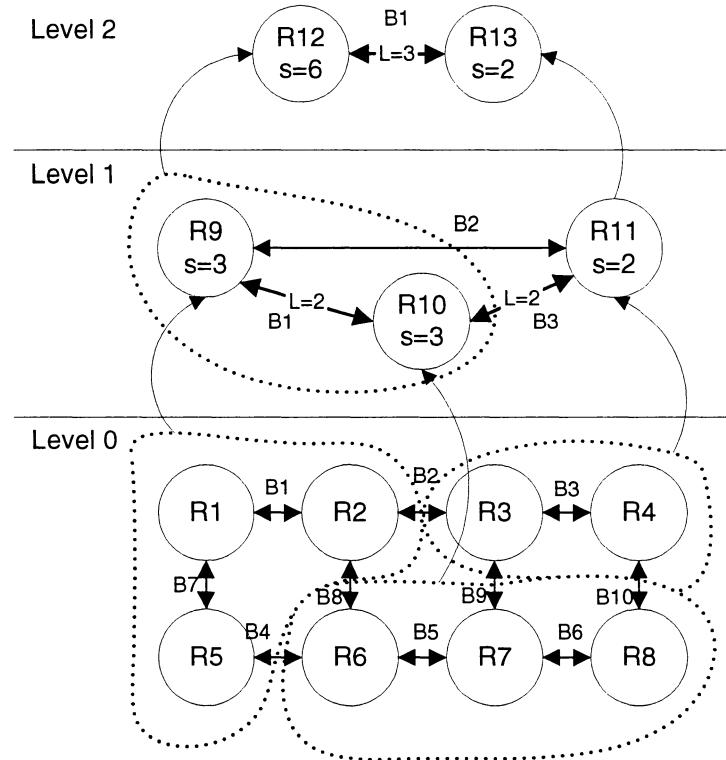

| Figure 4.2 | Planar graph representation of segmentation objects: regions (circles R) with their size S, and boundaries (arcs B) with their length L, at 3 levels of processing. S and L in level 0 equal 1, so they are not displayed. At the end of level 0, regions are grouped (dashed lines), corresponding parent regions are created in level 1, and new boundary objects are computed. Bold arcs represent boundaries whose length is greater than 1. Curved arrows are pointers to the parents. _____ | 79 |

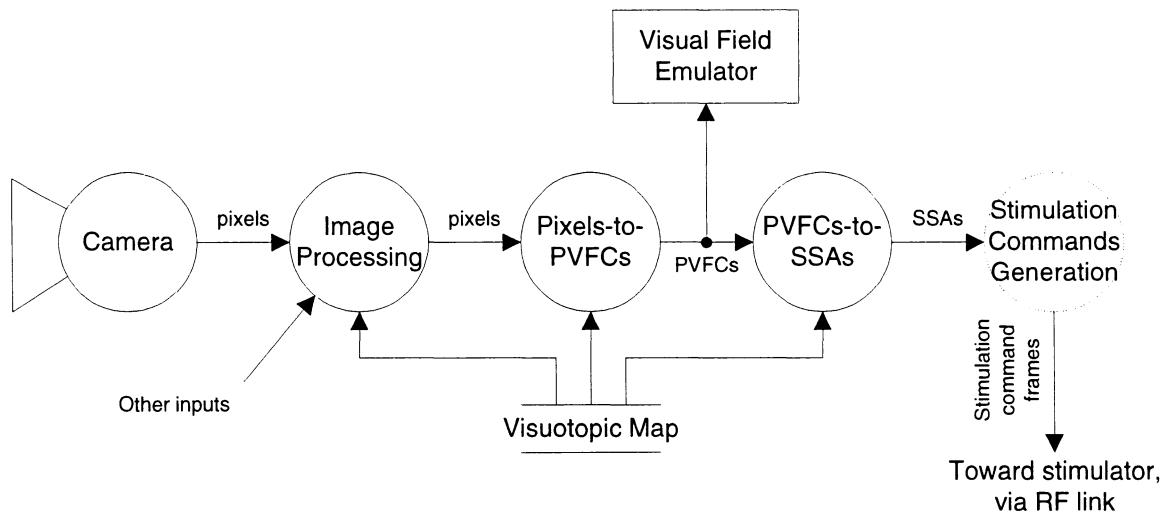

| Figure 4.3 | Dataflow diagram of the image processing system. Other types of input may later be added to the image processing unit. _____                                                                                                                                                                                                                                                                                                                                                                      | 80 |

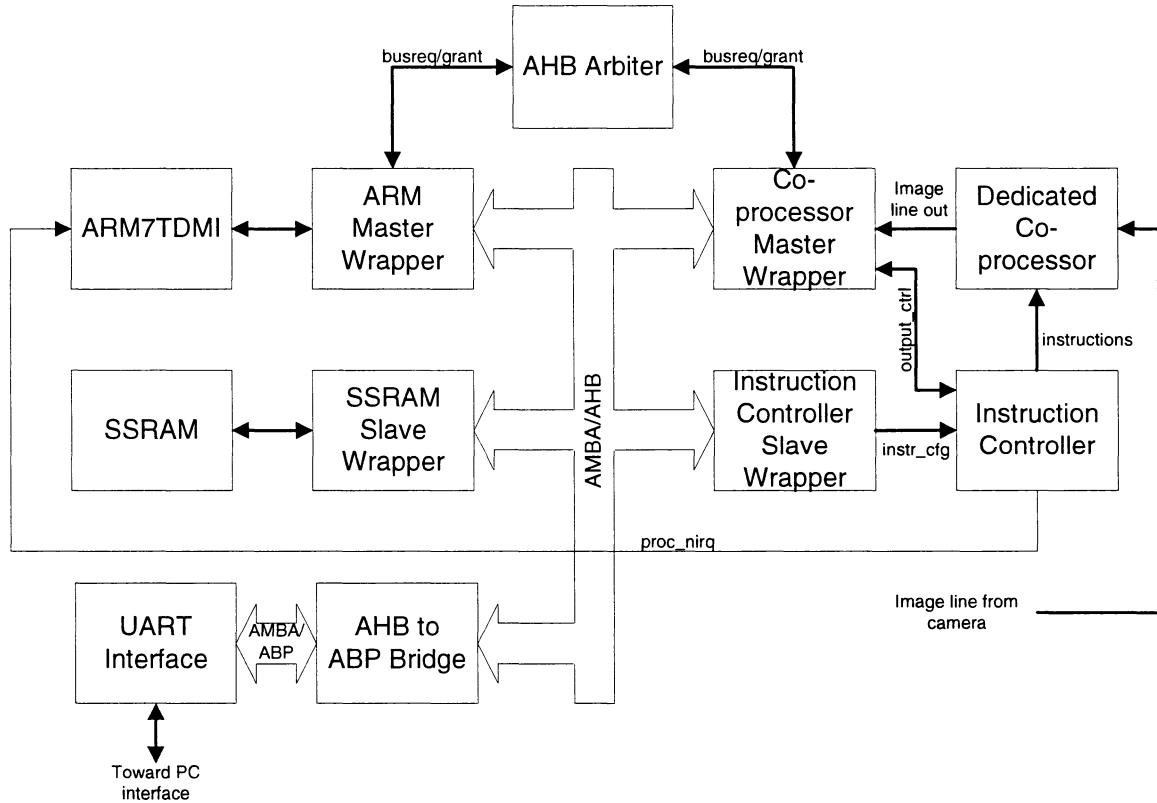

| Figure 4.4 | Block diagram of the image processing system in an AMBA/AHB bus architecture. An image line from camera is inputted in the dedicated coprocessor (on the right), and is outputted to its AMBA bus master-type wrapper, controlled by the instruction controller. The latter module receives coprocessor instructions at configuration ( <i>instr_gf</i> ) and route them to the coprocessor at run-time. When the image is done, an interrupt is raised through <i>proc_nirq</i> . _____          | 81 |

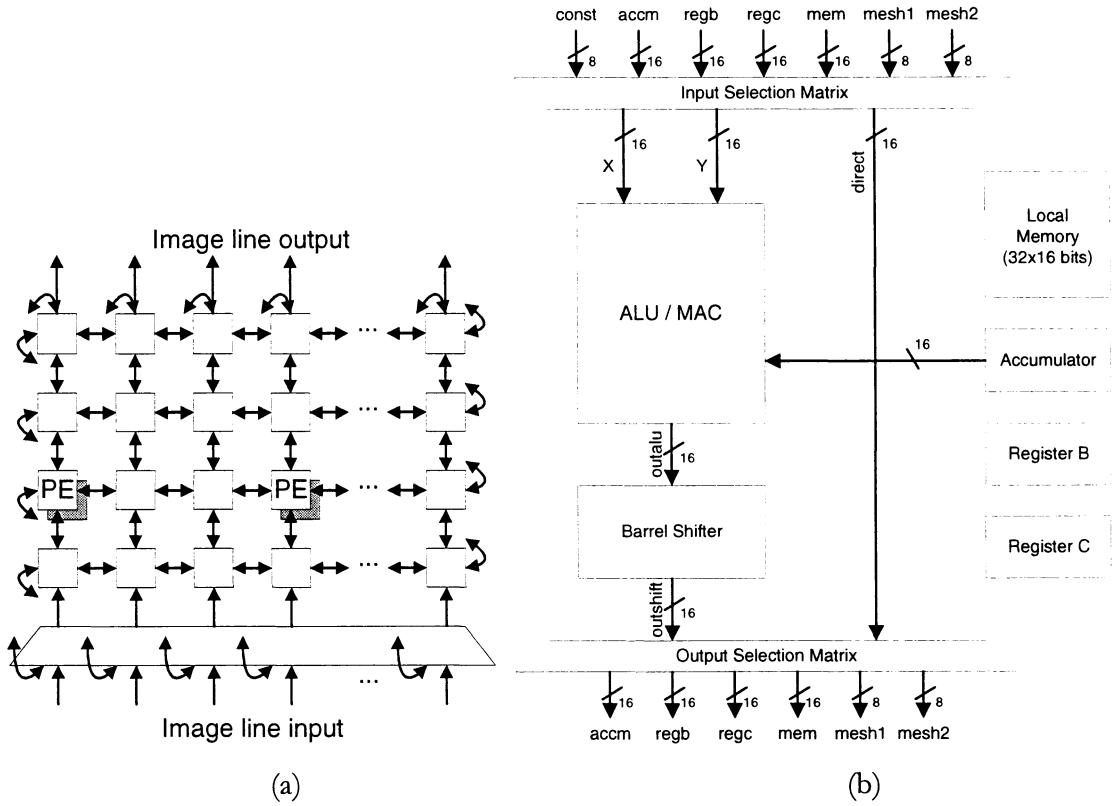

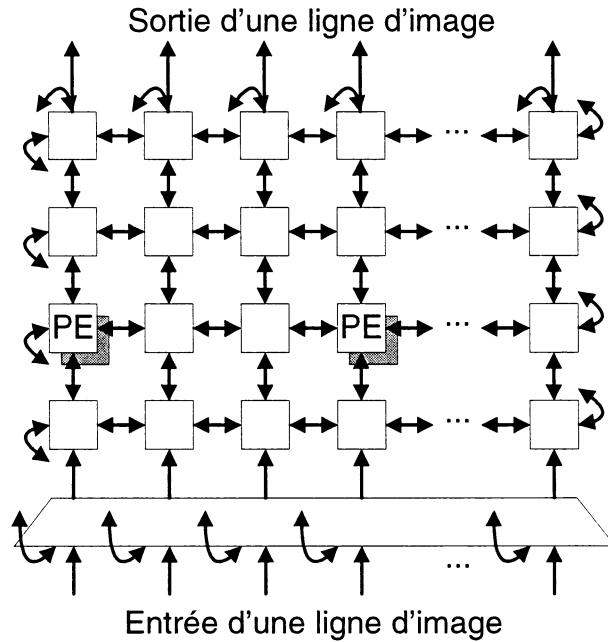

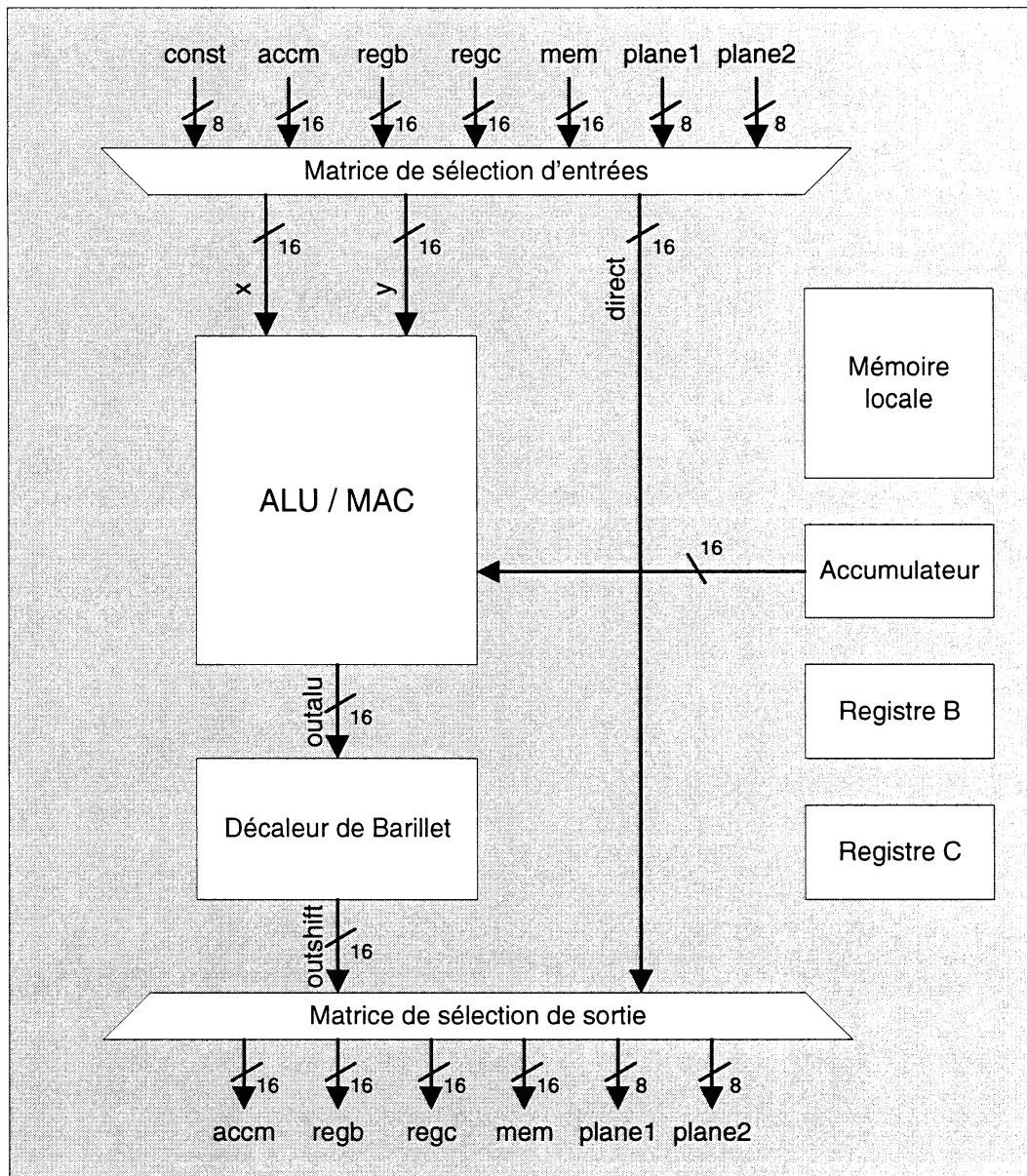

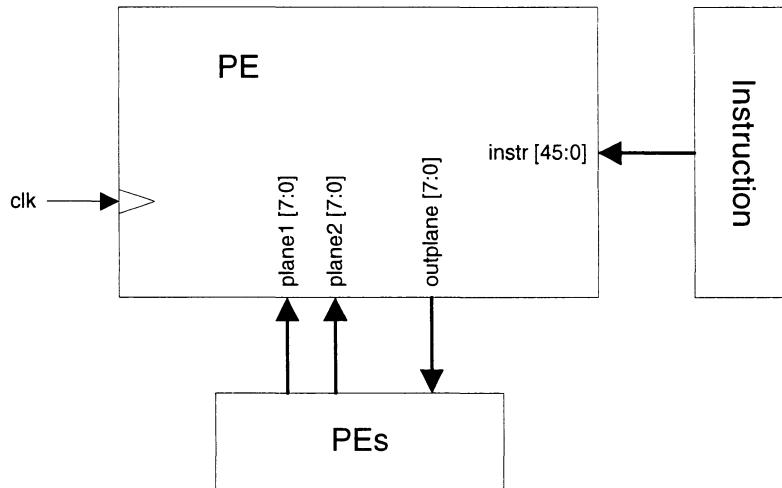

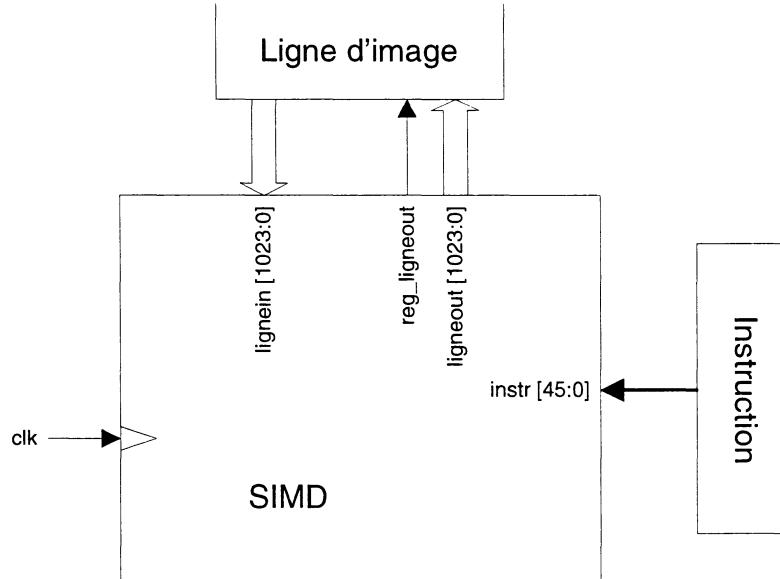

| Figure 4.5 | a) Block diagram of the SIMD coprocessor: squares are the mesh registers, curved arrows indicate wrapping of data around the mesh, and “PE” boxes represent special registers that are overlaid by a PE. b) Internal architecture of a PE. Inputs and outputs are its memory ressources: accumulator ( <i>accm</i> ), register B and C ( <i>regb</i> , <i>regc</i> ), local memory ( <i>mem</i> ) and the underlying mesh registers ( <i>mesh1</i> , <i>mesh2</i> ). _____                        | 82 |

|             |                                                                                                                                                                                                                                                                                                                                                                      |     |

|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

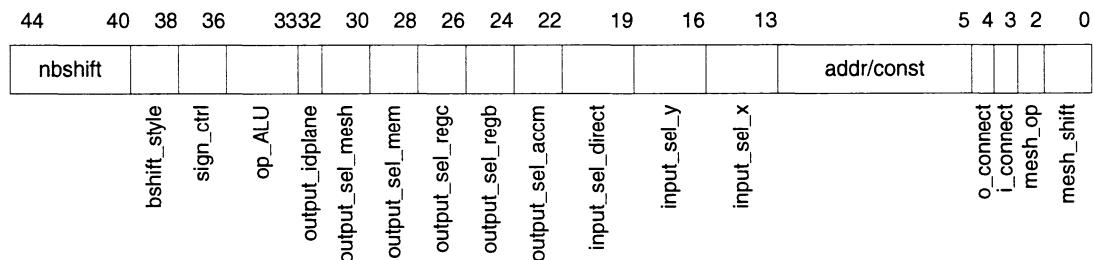

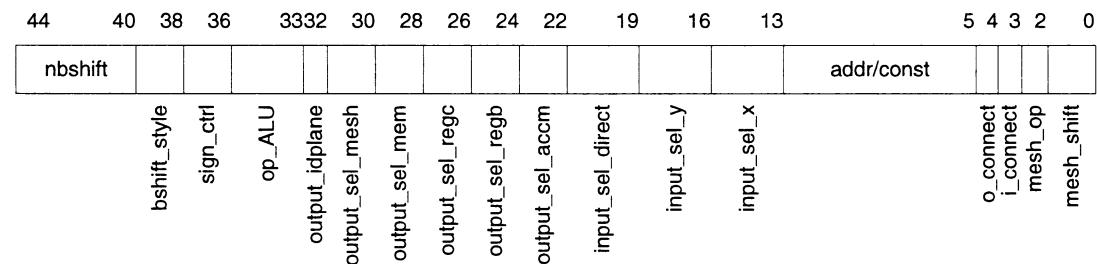

| Figure 4.6  | SIMD coprocessor instruction word.                                                                                                                                                                                                                                                                                                                                   | 82  |

| Figure 4.7  | Segmentation result: a) original image, b) result after step1 ( $T_1 = 0.8$ ), c) result after step 2 ( $T_2 = 0.8$ ), d) result after step 3 ( $T_3 = 0.7$ ), and e) result after post-processing ( $T_4 = 10$ blobs).                                                                                                                                              | 83  |

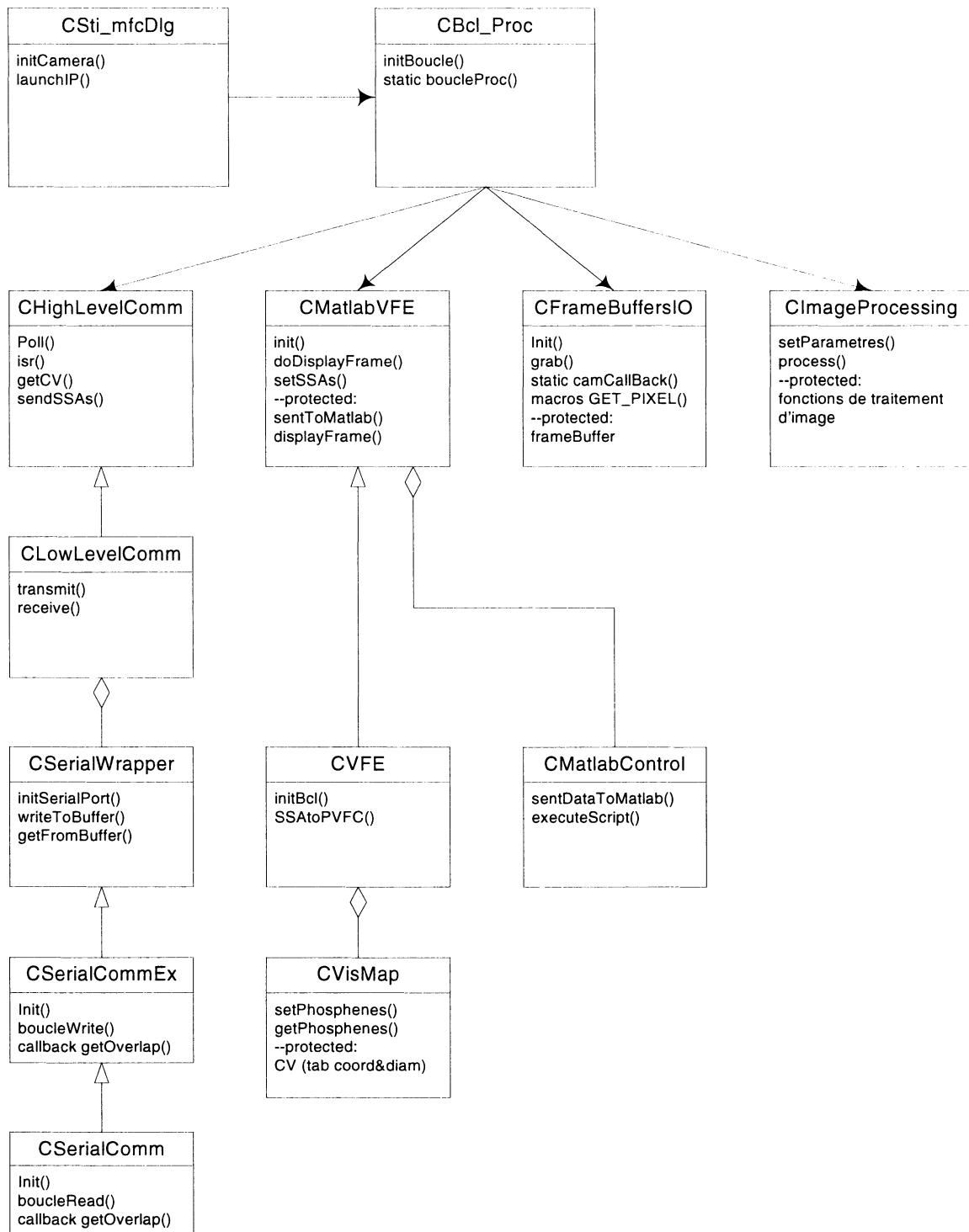

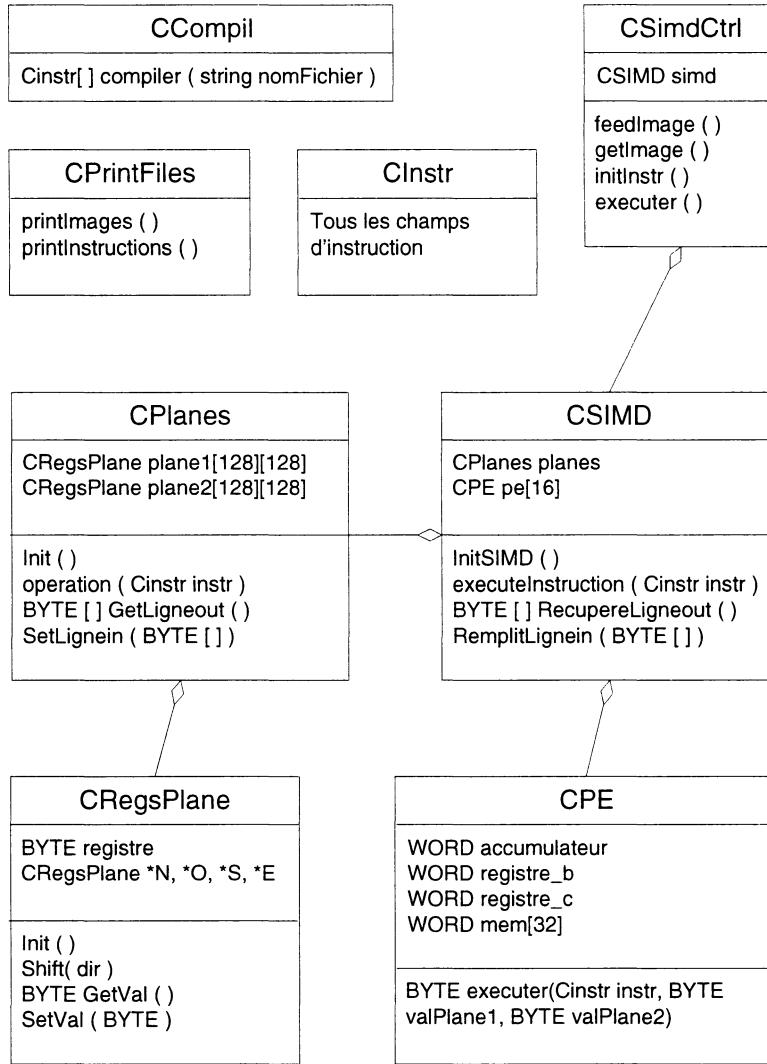

| Figure A.1  | Diagramme de classe de la version logicielle du système de traitement d'image.                                                                                                                                                                                                                                                                                       | 100 |

| Figure B.1  | Seuillage : a) image originale, b) image binarisée.                                                                                                                                                                                                                                                                                                                  | 111 |

| Figure B.2  | Laplacien d'une Gaussienne : a) image originale, b) image traitée.                                                                                                                                                                                                                                                                                                   | 112 |

| Figure B.3  | Détection des passages par zéro d'une DoG : a) image originale, b) contours.                                                                                                                                                                                                                                                                                         | 113 |

| Figure B.4  | Architecture générale de l'accélérateur de calcul.                                                                                                                                                                                                                                                                                                                   | 114 |

| Figure B.5  | Architecture d'un élément de traitement.                                                                                                                                                                                                                                                                                                                             | 117 |

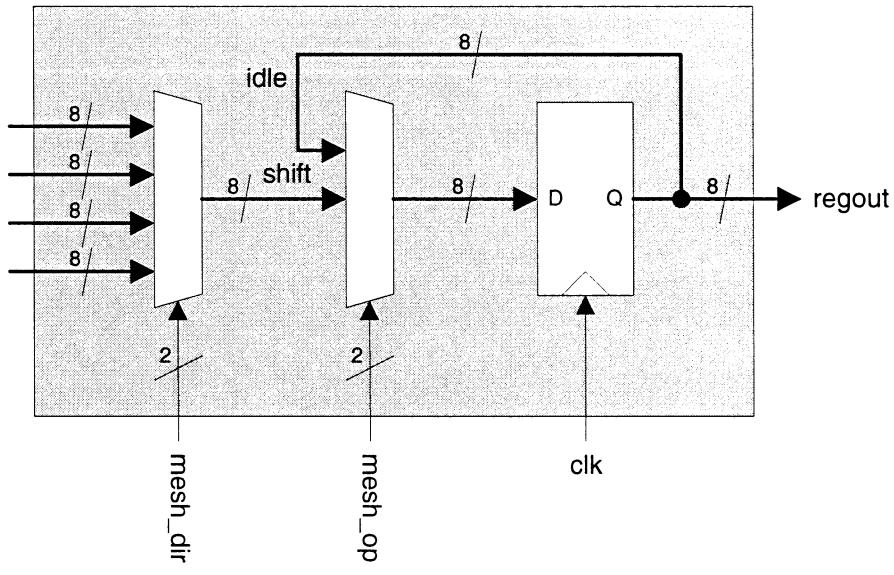

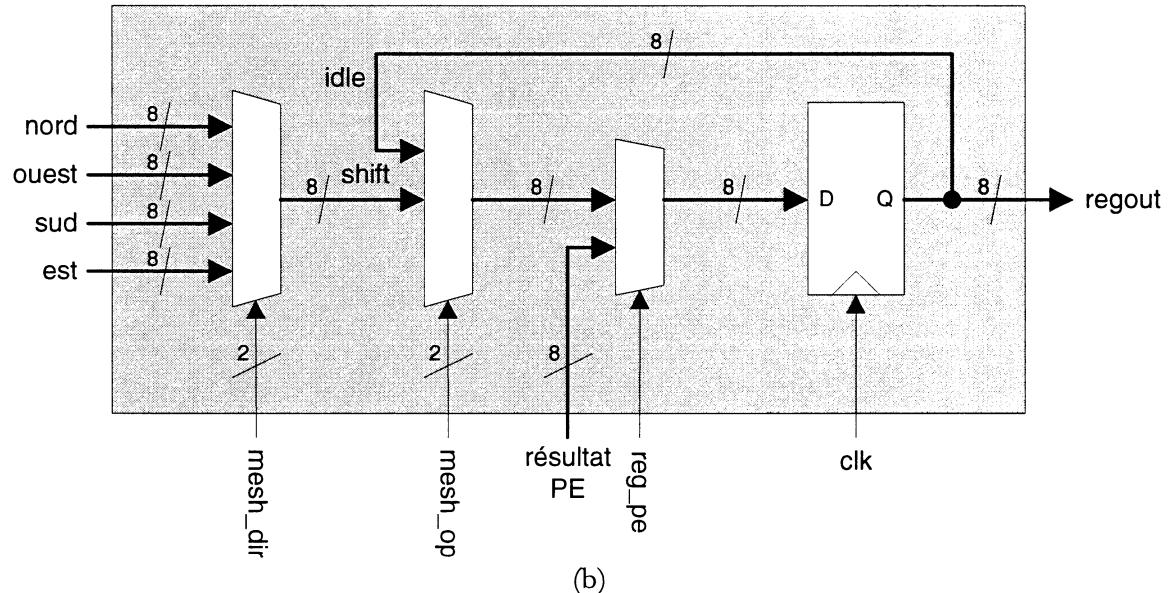

| Figure B.6  | Élément de mémoire du grille : a) normal, b) spécial.                                                                                                                                                                                                                                                                                                                | 120 |

| Figure B.7  | Mot d'instruction.                                                                                                                                                                                                                                                                                                                                                   | 121 |

| Figure B.8  | Diagramme de classes du modèle objet de haut-niveau.                                                                                                                                                                                                                                                                                                                 | 125 |

| Figure B.9  | Ordre de visite des pixels pour le seuillage, pour un PE donné.                                                                                                                                                                                                                                                                                                      | 130 |

| Figure B.10 | Ordre de visite des pixels d'une convolution 3x3, pour un pixel donné.                                                                                                                                                                                                                                                                                               | 131 |

| Figure B.11 | Ordre de visite des pixels pour une convolution 5x5.                                                                                                                                                                                                                                                                                                                 | 133 |

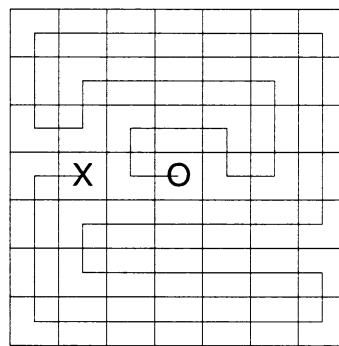

| Figure B.12 | Ordre de visite des pixels pour une convolution 7x7 (le « X » est la position de départ, le « O » la position d'arrivée où le résultat est enregistré).                                                                                                                                                                                                              | 133 |

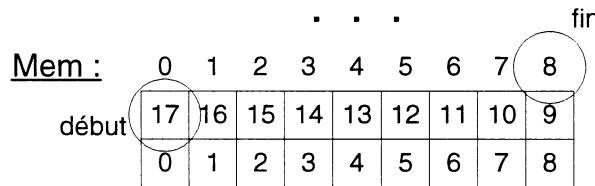

| Figure B.13 | Ordre de parcours des pixels pour la détermination du signe. Les chiffres représentent l'adresse de la mémoire dans laquelle sont stockés les signes. Le cercle « début » indique le début du parcours pour le marquage des contours. À la fin, le pixel marqué du cercle « fin » se trouve sous le PE, prêt à calculer les passages par zéro de la prochaine ligne. | 135 |

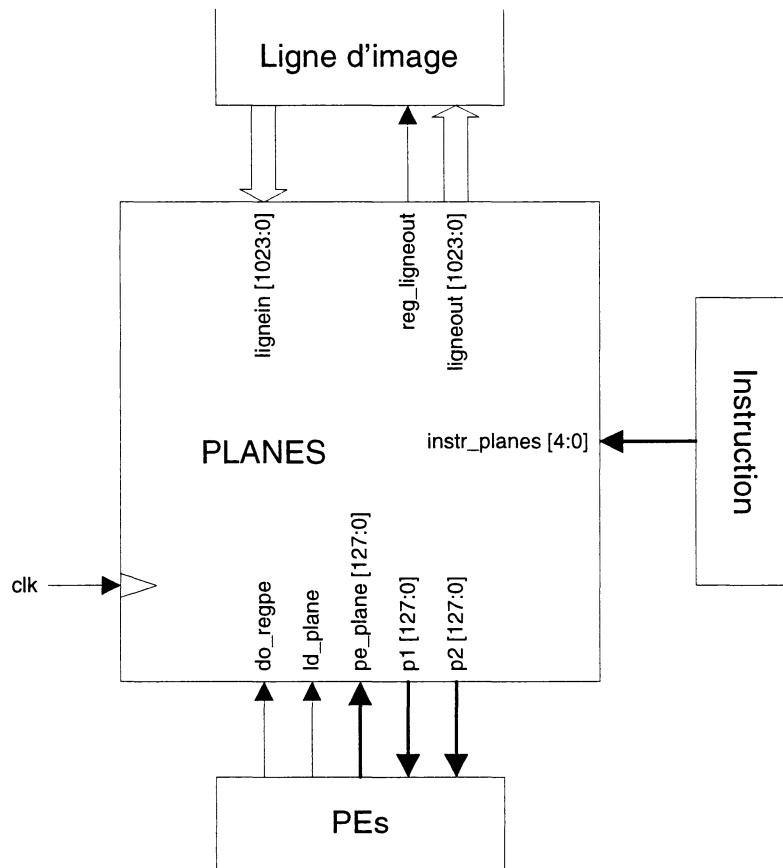

| Figure B.14 | Interfaces logiques des grilles.                                                                                                                                                                                                                                                                                                                                     | 141 |

| Figure B.15 | Interfaces logiques du PE.                                                                                                                                                                                                                                                                                                                                           | 144 |

| Figure B.16 | Interfaces logiques du SIMD.                                                                                                                                                                                                                                                                                                                                         | 146 |

## LISTE DES TABLEAUX

|             |                                                                                                                                                                                                                                                                                                                                                                                                                     |     |

|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Tableau 1.1 | Avantages et inconvénients des différentes approches de recouvrement de la vision.                                                                                                                                                                                                                                                                                                                                  | 11  |

| Tableau 2.1 | Execution time results for elementary operations used by the image processing strategies. Classification is done according to their complexity.                                                                                                                                                                                                                                                                     | 39  |

| Tableau 2.2 | Total execution time for the image processing strategies in embedded system. Constituting elementary operations are indicated with codes defined in table 1. Image size is 320x240 pixels.                                                                                                                                                                                                                          | 40  |

| Tableau 3.1 | Comparaison des implémentations de segmentation par fusionnement de régions.                                                                                                                                                                                                                                                                                                                                        | 52  |

| Tableau 4.1 | SIMD coprocessor instruction word fields.                                                                                                                                                                                                                                                                                                                                                                           | 84  |

| Tableau 4.2 | Execution time results of various image processing algorithms for 320x240 images. Column 4 shows the speed-up values for the algorithm that can be executed by the coprocessor, that is, all of them, except segmentation and geometric transform. Segmentation results exclude Sobel calculation. Execution times are those of the hardware (at 33 MHz) when applicable, or else those of the software at 100 MHz. | 85  |

| Tableau A.1 | Liste des traitements implémentés dans la classe CImageProcessing.                                                                                                                                                                                                                                                                                                                                                  | 103 |

| Tableau B.1 | Champs du mot d'instruction.                                                                                                                                                                                                                                                                                                                                                                                        | 122 |

| Tableau B.2 | Symboles valides du langage d'assemblée pour l'accélérateur de calcul.                                                                                                                                                                                                                                                                                                                                              | 128 |

| Tableau B.3 | Interfaces logiques de l'ALU.                                                                                                                                                                                                                                                                                                                                                                                       | 137 |

| Tableau B.4 | Interfaces logiques de l'unité MAC.                                                                                                                                                                                                                                                                                                                                                                                 | 138 |

| Tableau B.5 | Interfaces logiques du décaleur de Bamillet.                                                                                                                                                                                                                                                                                                                                                                        | 139 |

| Tableau B.6 | Interfaces logiques des grilles.                                                                                                                                                                                                                                                                                                                                                                                    | 142 |

| Tableau B.7 | Interfaces logiques du PE.                                                                                                                                                                                                                                                                                                                                                                                          | 144 |

| Tableau B.8 | Interfaces logiques du SIMD.                                                                                                                                                                                                                                                                                                                                                                                        | 146 |

## LISTE DES SIGLES ET ABRÉVIATIONS

|        |                                                                  |

|--------|------------------------------------------------------------------|

| A      | Amplitude de l'onde de stimulation                               |

| AHB    | Advanced High-Speed Bus                                          |

| ALU    | Arithmetic-Logic Unit                                            |

| AHB    | Advanced High-performance Bus                                    |

| APB    | Advanced Peripheral Bus                                          |

| AMBA   | Advanced Microcontroller Bus Architecture                        |

| ASIC   | Application Specific Integrated Circuit                          |

| CMC    | Canadian Microelectronics Corporation                            |

| CMOS   | Complementary Metal-Oxyde-Semiconductor                          |

| CNA    | Convertisseur Analogique-Numérique                               |

| CV     | Carte Visuotopique                                               |

| DI     | Durée d'interphase de l'onde de stimulation                      |

| DIT    | Durée inter-train de l'onde de stimulation                       |

| DoG    | Difference of Gaussians                                          |

| DP     | Durée de phase de l'onde de stimulation                          |

| DP-RAM | Dual-Port Random-Access-Memory                                   |

| DSP    | Digital Signal Processor                                         |

| DT     | Durée de train de l'onde de stimulation                          |

| DUT    | Device Under Test                                                |

| ENG    | Electroneurogramme                                               |

| F      | Fréquence de l'onde de stimulation / Stimulation pulse frequency |

| FIFO   | First-In First-Out                                               |

| FPGA   | Field Programmable Gate Array                                    |

| GRM    | Groupe de recherche en microélectronique                         |

| HLRG   | Hybrid-Linkage Region Growing                                    |

| I      | Stimulation Current Amplitude                                    |

| IPI    | Inter-Pulse Interval                                             |

| IPS    | Image Processing System                                          |

|      |                                                                  |

|------|------------------------------------------------------------------|

| ITI  | Inter-Train Interval                                             |

| LoG  | Laplacian of Gaussian                                            |

| LUT  | Look-Up Table                                                    |

| MAC  | Multiplying Accumulator                                          |

| MEMS | Micro-Electrical Mechanical System                               |

| PC   | Personal Computer                                                |

| PD   | Pulse duration                                                   |

| PE   | Processing Element                                               |

| PVFC | Phosphene Visual Field Coordinates                               |

| RAM  | Random Access Memory                                             |

| RISC | Reduced Instruction Set Computing                                |

| ROI  | Region of Interest                                               |

| RTL  | Register-Transfer Level                                          |

| SEQ  | Set Equal                                                        |

| SIMD | Single-Instruction Multiple-Data                                 |

| SLRG | Single-Linkage Region Growing                                    |

| SLT  | Set Lower Than                                                   |

| SoC  | System on Chip                                                   |

| SSA  | Stimulation Site Addresses                                       |

| STI  | Système de Traitement d'Image                                    |

| SVC  | Stimulateur Visuel Cortical                                      |

| TI   | Texas Instruments                                                |

| TL   | Train length                                                     |

| UAL  | Unité arithmétique et logique                                    |

| USB  | Universal Serial Bus                                             |

| VCS  | Visual Cortical Stimulator                                       |

| VFE  | Visual Field Emulator                                            |

| VHDL | Very high speed integrated circuit Hardware Description Language |

| VM   | Visuotopic Map                                                   |

## **LISTE DES ANNEXES**

|          |                                                                                     |     |

|----------|-------------------------------------------------------------------------------------|-----|

| Annexe A | Complément d'information sur la version logicielle du système de traitement d'image | 98  |

| Annexe B | Complément d'information sur le coprocesseur dédié                                  | 107 |

| Annexe C | Sources                                                                             | 149 |

## INTRODUCTION

Près de 35 millions de personnes dans le monde sont affectées par une grave maladie de la vue. Leurs conséquences sont très problématiques pour le fonctionnement de ces personnes en société. En particulier pour ce qui a trait au déplacement. Plusieurs solutions ont été envisagées au cours du temps pour réduire ce handicap, comme par exemple l'alphabet Braille pour rendre la lecture par voie tactile plus efficace. Récemment, de nouvelles techniques médicales ont vu le jour, comme la stimulation physiologique. La récupération de fonctions par cette méthode repose sur notre capacité à produire des réactions suite à la stimulation de cellules nerveuses. Cette technique pourrait être appliquée à la vision en stimulant électriquement certaines cellules nerveuses sur le chemin visuel. En particulier, il a été démontré que la stimulation du cortex visuel, centre principal de traitement de la vue dans le cerveau, générait des percepts lumineux appelés « phosphènes ». C'est sur ce principe que repose le fonctionnement d'un stimulateur visuel cortical (SVC) dont le but est de rendre une vision partielle à un patient dont le système visuel aurait été rendu non fonctionnel.

L'idée d'un tel stimulateur est simple à prime abord. Une caméra, fixée sur un monture de lunette portée par l'aveugle et regardant devant lui, prendrait des images du monde extérieur qui seraient ensuite traitées et transformées en commandes destinées à un implant situé dans la boîte crânienne. Celui-ci aurait la tâche de stimuler adéquatement le cortex visuel de manière à créer des percepts qui donneraient une idée à l'aveugle de ce que la caméra capte. De nos jours, les travaux qui portent sur un tel dispositif se concentrent sur le développement du stimulateur en tant que tel. Par contre, la partie frontale du système, c'est-à-dire la transformation des images en commandes de stimulation, n'est pas triviale car elle doit tenir en considération les contraintes physiologiques liées à la stimulation corticale, dont la compréhension est encore très limitée. Le projet de maîtrise présenté dans ce mémoire concerne le développement de cette partie frontale. Plus précisément, il s'agit d'envisager la façon dont les images seront transformées de manière à donner de l'information utile à un aveugle par le biais de son stimulateur visuel cortical, et ce, à la lumière des contraintes physiologiques connues.

Nous verrons que le grand nombre d'incertitudes liées à ces contraintes nécessite d'envisager un système permettant plusieurs stratégies de transformation des images. Le but est de concevoir un module flexible, faisant le pont entre la caméra et le stimulateur, qui permettra de procéder à des tests *in vivo* afin d'examiner réellement les stratégies employées et de plus tard les raffiner. Évidemment, la réussite de ces tests repose sur l'accès à un stimulateur robuste, lui-même testé en laboratoire, ce qui les repousse à une date se situant bien au-delà du cadre de la présente maîtrise. Le système qui a été développé constitue un premier pas vers la partie frontale d'un tel système. De plus, il se concentre sur l'aide à la mobilité. Enfin, une caméra vidéo est considérée comme dispositif d'entrée. D'autres avenues pourront être explorées dans le futur.

Le premier chapitre s'applique à exposer les résultats des études biomédicales précédentes portant sur le fonctionnement de la vision dans la perspective de la stimulation physiologique. Certains enjeux et défis ayant une influence directe sur le développement de la partie frontale d'un SVC seront mis en évidence.

Le chapitre 2 est un article soumis à la revue « Artificial Organs » qui présente d'abord une revue des efforts qui ont été faits par les diverses équipes de recherche en vue de développer la partie frontale d'un SVC. À la lumière du contexte physiologique, nous réaliserons qu'à cause des nombreuses incertitudes, il faudra envisager plusieurs stratégies de traitement des images. Ces stratégies sont présentées, et ensemble, elles constituent le cœur d'un système de traitement d'image dédié à un SVC.

Afin de valider les algorithmes constituant le module de traitement d'image, ces stratégies ont été implémentées de manière purement logicielle. Ce logiciel est présenté au chapitre 3, qui débute par une présentation générale des techniques usuelles de traitement d'image.

De tous les algorithmes implémentés au sein du système, le plus crucial est la segmentation d'image. Cet algorithme est décrit en détail dans un deuxième article, soumis à la revue « IEE

Medical and Biological Engineering and Computing », qui constitue le chapitre 4. Le design de cet algorithme a orienté l'implémentation de l'architecture d'un système embarqué, qui s'avèrera nécessaire pour la vérification *in vivo* du système de stimulation complet. Cette architecture est également présentée dans ce chapitre.

Finalement, en annexe se trouvent des détails supplémentaires sur l'implémentation logicielle et matérielle du module de traitement d'image pour le SVC. Les fichiers des sources s'y trouvent également.

# CHAPITRE 1

## CONTEXTE BIOMÉDICAL

### 1.1 Introduction

Nous abordons ce chapitre par la définition de la stimulation électrique et celle du système visuel humain. Les diverses approches pour la récupération de la vision sont ensuite examinées, avant de se pencher plus particulièrement sur celle qui nous intéresse, soit la stimulation corticale. Un bref historique expose le concept de phosphène, son apparence, son organisation spatiale, la manière dont il est évoqué par stimulation électrique, et les travaux de pointe dans le domaine de la reconnaissance de patrons de phosphènes. Suivent ensuite une description des stimulateurs visuels corticaux, ainsi qu'un survol des études portant sur le traitement d'image destiné à ces stimulateurs. La dernière section est consacrée plus précisément à l'organisation visuotopique et sur ce qui a été fait dans le cadre de ce projet pour représenter l'effet hypothétiquement perçu des patrons de phosphènes qui seront générés à la suite du traitement de l'image.

### 1.2 Dispositifs visuels

#### 1.2.1 Stimulation neuronale

La stimulation neuromusculaire est couramment utilisée pour rétablir certaines fonctions du corps humain qui ont été rendues invalides par une maladie ou un accident. Les méthodes utilisées peuvent être classées en trois grandes catégories :

- l'injection de substances chimiques à un groupe de cellules nerveuses, modifiant ainsi les propriétés d'inhibition et d'exhibition de leurs activités synaptiques [23],

- la stimulation magnétique et qui crée un potentiel d'action par induction électromagnétique

- la stimulation électrique qui créent un potentiel d'action par le passage d'un courant ionique [29,75,78].

De nos jours, la stimulation par substance chimique n'est qu'au stade de développement, et peu d'applications de réhabilitation utilisent cette méthode [78]. Quant à la stimulation magnétique, bien qu'elle soit avantageuse en termes de non-invasibilité, elle est davantage utilisée pour le diagnostic de maladies neuromusculaires [35]. Aucun dispositif n'utilisant cette méthode n'est en mesure d'être assez précis. La stimulation électrique est la seule qui est présentement utilisée pour la réhabilitation de fonctions d'organes. On la retrouve entre autres dans les implants urinaires et cochléaires [58,74]. Elle nécessite l'emploi d'électrodes, et donc certaines considérations de biocompatibilité doivent être prises en compte étant donnée la présence d'un contact métal-tissu. Pour mieux comprendre les phénomènes liés à la stimulation neuromusculaire, il importe de préciser le fonctionnement d'une cellule nerveuse.

La figure 1.1 est un schéma simplifié d'une cellule nerveuse, ou neurone. Elle est composée de dendrites qui reçoivent les impulsions des neurones en amont, et de l'axone qui propage ces informations vers les neurones en aval. Les propriétés électrochimiques du neurone font en sorte qu'il conserve une différence de potentiel fixe entre l'extérieur et l'intérieur. Le bris momentané de cet équilibre crée ce qui est communément appelé un potentiel d'action, qui se propage rapidement à travers l'axone, jusqu'aux dendrites des cellules en aval à travers le milieu intercellulaire, riche en ions. Cette interface s'appelle la synapse [45].

**Figure 1.1 – Schéma simplifié d'une cellule nerveuse (tiré de [72]).**

Le neurone agit comme un interrupteur : il décide de propager ou non un potentiel d'action en fonction de ses entrées, c'est-à-dire des potentiels d'action provenant des cellules qui sont reliées à ses dendrites. Tel est le but de la réhabilitation de fonctions nerveuses par la stimulation : créer un ensemble de potentiels d'actions formant un électroneurogramme (ENG) afin de remplacer celui échangé avec l'organe original. Il est alors propagé par les neurones subséquents.

Dans le cas de la stimulation électrique, c'est l'injection de courant, et donc le déplacement de charges, dans le milieu ionique qui déclenche le potentiel d'action. L'injection de charges peut être dommageable pour les tissus, c'est pourquoi le stimulus électrique est typiquement une onde biphasique, c'est-à-dire que le courant circulera dans les deux sens, afin d'introduire une quantité de charge nette nulle. La figure 1.2 illustre la forme d'onde utilisée

dans la plupart des applications biomédicales [69,87], et particulièrement la stimulation corticale.

**Figure 1.2 – Formes d'ondes utilisées pour la stimulation intracorticale.**

### 1.2.2 Système visuel humain et maladies de la vision

La figure 1.3 illustre la structure du système visuel humain. L'œil a pour principale fonction de focaliser la lumière provenant de l'extérieur sur sa rétine, composée de capteurs. Deux sortes de cellules jouent ce rôle : les cônes, sensibles à la couleur et situés en majorité près de la fovea où la densité de capteurs est la plus grande, et les bâtonnets, insensibles à la couleur et situés sur toute la surface de la rétine. L'information visuelle provenant de ces cellules est traitée immédiatement par deux étages de cellules, les cellules ganglionnaires et les cellules bipolaires. Les signaux sont ensuite transportés par le nerf optique, composé d'environ 1 million de fibres, vers le chiasma optique, point de croisement entre les nerfs optiques des deux yeux.

deux yeux. L'information passe alors par les tractus optiques vers les corps genouillés latéraux où elle est traitée davantage. Elle arrive enfin au cortex visuel situé à l'arrière du cerveau, où plusieurs étages de traitement font le lien entre l'information visuelle et les autres parties du cerveau liées à son interprétation. L'information voyage dans les deux directions, ce qui implique un phénomène de rétroaction entre le cortex visuel et les couches de neurones en amont.

**Figure 1.3 – Système visuel humain.**

Dès la rétine, les signaux sont inhibés ou exhibés, de manière à faire ressortir les contrastes et les contours [54]. Au niveau cortical, l'information visuelle brute a déjà subi beaucoup d'autres traitements. L'information est encodée de manière très complexe : non seulement l'intensité, mais la couleur, l'orientation, le mouvement relatif, la différence stéréoscopique et

la dominance oculaire sont transportés [67]. Par contre, ces informations restent relativement locales, ce qui fait en sorte qu'il existe encore à cet étage une relation entre la position visuelle d'un stimulus et l'endroit sur la surface du cortex qui le traitera.

Les maladies de la vision les plus répandues en Amérique du Nord sont, dans l'ordre, la dégénérescence maculaire, le glaucome, la rétinopathie diabétique, rétinite pigmentaire et finalement la cataracte [11,59]. La dégénérescence maculaire est un trouble où la macula (centre de la rétine) cesse de répondre à la lumière. Le glaucome est une complication liée à l'humeur aqueuse dans l'œil qui ne s'écoule pas normalement. La rétinopathie diabétique est due au fait que des vaisseaux sanguins formés anormalement éclatent, endommageant la rétine. La cataracte est un problème au niveau du cristallin de l'œil qui s'épaissit, se durcit et devient opaque bloquant le passage de la lumière. Finalement, la rétinite pigmentaire est causée par la dégénérescence de la rétine. La déficience visuelle est quelque fois causée par des lésions au niveau du nerf optique, ce qui entraîne alors des pertes unilatérales de champ visuel ou par des lésions au niveau du chiasma optique ou plus loin, ce qui entraîne généralement des pertes bilatérales [72].

### **1.2.3 Avenues de recherche pour la récupération partielle de la vision**

Dans le domaine de la restauration de la fonction visuelle par stimulation électrique, trois principales avenues ont été envisagées à ce jour en ce qui concerne l'endroit dans le chemin visuel (*visual path*) où la fonction est rétablie : la stimulation de la rétine, du nerf optique et du cortex visuel. Plus la fonction est rétablie tôt dans la chaîne, plus les percepts produits ont des chances de ressembler à la vision normale, étant donné qu'on bénéficie des étages de traitement naturels.

Les techniques de stimulation de la rétine se séparent en plusieurs sous-groupes : implants sous-rétinaux (sous la rétine), epi-rétinaux (sur la rétine), neurotransmetteurs (par injection chimique de glutamate stimulé par fibre optique) et hybrides (culture de neurones dans un MEMS). Cette avenue très populaire est étudiée par plusieurs groupes de recherche, dont les

équipes de Zrenner [38], Schubert et Chow pour les implants sous-rétinaux, Humayun et Liu [49], Rizzo et Wyatt [87] pour les implants epi-rétinaux, Iezzi pour l'implant neurotransmetteur, et Yagi pour l'implant hybride [50].

L'équipe de Veraart [85] étudie la stimulation du nerf optique, beaucoup moins populaire.

La stimulation corticale est quant à elle étudiée par les équipes de Normann de l'Université du Utah [60], Schmidt du NIH [54], Troyk du Illinois Institute of Technology [55,57], de Dobelle [32], de McAllister du Wayne State University et de Sawan de l'École Polytechnique de Montréal [43].

Le tableau 1.1 résume les principaux avantages et inconvénients des trois principales avenues susmentionnées. Il est pertinent de définir ici l'organisation visuotopique, qui aura une grande importance dans la discussion qui suivra. Il s'agit d'un terme utilisé avec plus ou moins de rigueur dans la littérature, particulièrement en ce qui concerne les implants visuels. C'est un terme large qui concerne l'organisation des champs d'activité sur la surface du cortex, par exemple la symétrie par rapport à l'hémisphère, les frontières, les discontinuités et le degré de rétinotopie [21]. Nous y reviendrons plus tard. Pour l'instant, il faut noter qu'on considère que l'organisation visuotopique est bonne lorsqu'il y a un fort degré de corrélation entre la position des cellules de la rétine avec la position de la surface stimulée (degré de rétinotopie). Les implants rétiniens ont généralement une bonne organisation visuotopique étant donnée la proximité des photorécepteurs avec la surface de stimulation. Le nerf optique possède une mauvaise organisation à cause de la surface stimulée : la proximité des millions de fibres qui le compose rendent la stimulation sélective difficile. Le cortex visuel possède également une faible organisation visuotopique, dans ce cas à cause des multiples étages de traitement qui le séparent des photorécepteurs.

Le projet dans lequel s'inscrit ce mémoire concerne la mise en œuvre d'un système de stimulation du cortex visuel afin de rendre une vue partielle aux aveugles. La prochaine section est consacrée davantage à la stimulation corticale.

**Tableau 1.1 – Avantages et inconvénients des différentes approches de recouvrement de la vision.**

| Approche      | Avantages                                                                                                                                                                   | Inconvénients                                                                                                                                         |

|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|

| Rétine        | Bénéficie du traitement rétinien, thalamique et cortical<br>Bonne organisation visuotopique                                                                                 | Nécessite un chemin visuel fonctionnel<br>Accès chirurgical difficile<br>Bloque la rétine de l'irrigation de certains nutriments                      |

| Nerf optique  | Peu de complications chirurgicales                                                                                                                                          | Accès chirurgical très difficile<br>Nécessite un nerf optique fonctionnel<br>Mauvaise organisation visuotopique<br>Matrice d'électrodes très complexe |

| Cortex visuel | Approprié pour toutes les maladies de la vision<br>Site de l'implant robuste et protégé par le crâne<br>Accès chirurgical facile<br>Grande densité d'électrodes atteignable | Loin des photorécepteurs<br>Mauvaise organisation visuotopique<br>Encodage complexe des caractéristiques d'image                                      |

### 1.3 Microstimulation intracorticale

#### 1.3.1 Phosphènes et organisation visuotopique

En 1918, Löwenstein et Borchardt rapportèrent que pendant une intervention chirurgicale au cerveau, le lobe occipital gauche du patient fut accidentellement stimulé électriquement, et il perçut un scintillement dans le champ visuel droit. Foerster [36] et Krause [52] reportèrent des phénomènes similaires en 1929. Cette importante découverte mit en évidence le fait que la stimulation électrique du lobe occipital induit des percepts visuels d'une part, et surtout que la position de ces percepts dans le champ visuel du patient dépend de l'endroit sur le cortex qui est stimulé. Le concept de phosphène était né : une sensation visuelle localisée

produite par la stimulation électrique ponctuelle d'un endroit du cortex visuel. Penfield et Jasper [65] stimulèrent électriquement le cortex visuel d'humains qui décrivirent les phosphènes perçus comme « des étoiles, des roues, des disques, des points, des raies, ou des lignes ». En 1972, Brindley [12-15] implanta 80 électrodes sur la surface du lobe occipital d'une patiente de 52 ans. Pendant les 3 années suivantes, il s'employa à cartographier la position des phosphènes dans le champ visuel. Par la suite, Dobelle implanta plusieurs patients avec des électrodes de surface, et les soumit à des tests d'habileté qui se révélèrent fonctionnels mais peu performants [30,31].

Les études précédentes utilisaient des électrodes de surface, avec des courants relativement grands (de l'ordre du milliampère). Au début des années 1980, Barlett et Doty [8] effectuèrent les premiers essais de stimulation intracorticale sur des primates. La stimulation intracorticale consiste à enfoncer des microélectrodes très fines, à la pointe exposée, de quelques millimètres à l'intérieur du cortex. Il en résulte des courants de stimulation de plusieurs ordres de grandeur inférieurs au courant des électrodes de surface pour évoquer des phosphènes (de l'ordre des microampères), et des phosphènes distincts pour une distance d'électrodes au moins 5 fois plus petite.

Les travaux les plus avancés dans la stimulation intracorticale sont ceux de Schmidt et al entre 1990 et 1996 [4,41,42,76]. Ils ont implanté 38 électrodes dans le cortex visuel d'une dame de 42 ans, aveugle depuis 22 ans à la suite d'un glaucome. Cela a permis de prouver que le cortex visuel peut réagir à la stimulation malgré plusieurs années d'inactivité, et que la stimulation sur une grande période de temps est viable car les percepts produits sont restés stables tout au long des 4 mois qu'a duré l'expérience. Ils ont aussi aidé à caractériser l'effet des paramètres d'ondes de stimulation (figure 1.2) sur l'apparence des phosphènes, que la patiente a décrit comme des points blanchâtres ou grisâtres, de la taille d'une pointe d'aiguille à celle d'un 5 cents tenu à bout de bras. D'autres données intéressantes sont rapportées. Des électrodes espacées de 500  $\mu\text{m}$  produisent généralement deux phosphènes distincts alors qu'ils sont confondus lorsqu'elles sont séparées de 250  $\mu\text{m}$ . Ils ont souvent une couleur orangée ou violette lorsque l'amplitude du courant est près du seuil d'apparition. Ils se

déplacent lorsque les yeux bougent. Quelques niveaux distincts de brillance peuvent être observés (entre 5 et 12). D'autres phénomènes ayant une incidence directe sur la conception d'un stimulateur comme l'accommodation à la stimulation et l'interaction entre phosphènes stimulés simultanément sont rapportés dans l'étude, et la première section du chapitre suivant y reviendra.

Un des buts de cette étude était de déterminer si la génération simultanée de plusieurs sites s'intégrait afin de produire des patrons intelligibles. Une caractéristique importante qui a été relevée est que la stimulation simultanée de 3 phosphènes ou plus les fait apparaître coplanaires et d'apparence semblable. Lorsque 6 phosphènes choisis de manière à être alignés de manière verticale ont été générés, la patiente rapporte qu'elle pourrait l'identifier à un I ou à la patte d'une lettre comme un M. Tel est l'état de l'art en matière de reconnaissance de patrons de phosphènes par microstimulation intracorticale.

Il est impensable dans un avenir proche de stimuler précisément un seul neurone à la fois, en imitant parfaitement l'information visuelle provenant des étages précédents. Un phosphène est le résultat de la stimulation simultanée d'un paquet de neurones conçus pour véhiculer des informations très différentes. Il faut envisager la vision par stimulation corticale comme la génération de patrons de phosphènes servant à donner des indices à l'aveugle pour qu'il puisse fonctionner. Les connaissances actuelles dans le domaine de la neurologie et de la microfabrication ne laissent pas croire qu'il sera un jour possible de faire vivre aux aveugles une expérience visuelle similaire à celle que nous vivons.

### 1.3.2 Systèmes de stimulation visuelle corticale

L'illustration de la figure 1.4 est un élégant schéma de principe d'un stimulateur visuel cortical. Toutes les équipes de recherche travaillant sur l'implant cortical, celle de Normann, Troyk, Schmidt, Dobelle et Sawan [4,31,60,64] suivent ce principe. Une caméra capte les images en face de l'aveugle. Ces images sont traitées et transformées en commandes de stimulation qui sont envoyées à l'implant via un lien inductif, qui envoie également l'énergie

pour alimenter l'implant. Ce dernier, totalement isolé à l'intérieur du crâne, décode les commandes et contrôle ses convertisseurs numérique-analogique (CNA) afin d'envoyer du courant à travers des électrodes micromachinées insérées dans le cortex, conformément aux paramètres d'onde requis. Des détails sur l'implant actuel du laboratoire PolySTIM, de même que sur son protocole de communication, peuvent être trouvées dans [72,17,27].

Figure 1.4 – Schéma de principe du système de stimulation visuelle corticale proposé par l'équipe PolySTIM.

### 1.3.3 Reconnaissance de patrons de phosphènes

Quelques équipes qui développent des systèmes de stimulation corticale se sont déjà penchés sur la faisabilité de tels systèmes au point de vue de la reconnaissance de patrons de faible résolution. Ces études peuvent se regrouper en diverses catégories. La première s'applique à déterminer les conditions minimales concernant les images de faible résolution avec des expériences psychophysiques sur des voyants, en simulant la vision sous forme de phosphènes. Citons les études de Hayes et al [44], et de Cha et al [22]. Cette dernière a fixé à