|                         | Methods for the modeling and analysis of MIS interconnects in VLSI circuits                                                                                                                                                                             |

|-------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Auteur: Author:         | Zhongfang Jin                                                                                                                                                                                                                                           |

| Date:                   | 2002                                                                                                                                                                                                                                                    |

| Type:                   | Mémoire ou thèse / Dissertation or Thesis                                                                                                                                                                                                               |

| Référence:<br>Citation: | Jin, Z. (2002). Methods for the modeling and analysis of MIS interconnects in VLSI circuits [Thèse de doctorat, École Polytechnique de Montréal]. PolyPublie. <a href="https://publications.polymtl.ca/7448/">https://publications.polymtl.ca/7448/</a> |

### Document en libre accès dans PolyPublie Open Access document in PolyPublie

| <b>URL de PolyPublie:</b> PolyPublie URL: | https://publications.polymtl.ca/7448/ |

|-------------------------------------------|---------------------------------------|

| Directeurs de<br>recherche:<br>Advisors:  | Jean-Jacques Laurin, & Yvon Savaria   |

| <b>Programme:</b> Program:                | Non spécifié                          |

### UNIVERSITÉ DE MONTRÉAL

## METHODS FOR THE MODELING AND ANALYSIS OF MIS INTERCONNECTS IN VLSI CIRCUITS

## ZHONGFANG JIN DÉPARTEMENT DE GÉNIE ÉLECTRIQUE ÉCOLE POLYTECHNIQUE DE MONTRÉAL

THÈSE PRÉSENTÉE EN VUE DE L'OBTENTION DU DIPLÔME DE PHILOSOPHIAE DOCTOR (Ph.D.) (GÉNIE ÉLECTRIQUE)

DÉCEMBRE 2002

Library and Archives Canada

Published Heritage Branch

395 Wellington Street Ottawa ON K1A 0N4 Canada Bibliothèque et Archives Canada

Direction du Patrimoine de l'édition

395, rue Wellington Ottawa ON K1A 0N4 Canada

> Your file Votre référence ISBN: 0-612-98179-7 Our file Notre référence ISBN: 0-612-98179-7

### NOTICE:

The author has granted a non-exclusive license allowing Library and Archives Canada to reproduce, publish, archive, preserve, conserve, communicate to the public by telecommunication or on the Internet, loan, distribute and sell theses worldwide, for commercial or non-commercial purposes, in microform, paper, electronic and/or any other formats.

The author retains copyright ownership and moral rights in this thesis. Neither the thesis nor substantial extracts from it may be printed or otherwise reproduced without the author's permission.

### AVIS:

L'auteur a accordé une licence non exclusive permettant à la Bibliothèque et Archives Canada de reproduire, publier, archiver, sauvegarder, conserver, transmettre au public par télécommunication ou par l'Internet, prêter, distribuer et vendre des thèses partout dans le monde, à des fins commerciales ou autres, sur support microforme, papier, électronique et/ou autres formats.

L'auteur conserve la propriété du droit d'auteur et des droits moraux qui protège cette thèse. Ni la thèse ni des extraits substantiels de celle-ci ne doivent être imprimés ou autrement reproduits sans son autorisation.

In compliance with the Canadian Privacy Act some supporting forms may have been removed from this thesis.

While these forms may be included in the document page count, their removal does not represent any loss of content from the thesis.

Conformément à la loi canadienne sur la protection de la vie privée, quelques formulaires secondaires ont été enlevés de cette thèse.

Bien que ces formulaires aient inclus dans la pagination, il n'y aura aucun contenu manquant.

### UNIVERSITÉ DE MONTRÉAL

### ÉCOLE POLYTECHNIQUE DE MONTRÉAL

### Cette thèse intitulée:

## METHODS FOR THE MODELING AND ANALYSIS OF MIS INTERCONNECTS IN VLSI CIRCUITS

Présentée par: <u>JIN Zhongfang</u>

en vue de l'obtention du diplôme de <u>Philosophiae Doctor</u>

a été dûment acceptée par le jury d'examen constitué de :

- M. MARTINU Ludvik, Ph.D., président

- M. KOUKI Ammar, Ph.D., membre

- M. LAURIN Jean-Jacques, Ph.D., membre et directeur de recherche

- M. SAVARIA Yvon, Ph.D., membre et codirecteur de recherche

- M. WU Ke, Ph.D., membre

To my family

### **ACKNOWLEDGMENTS**

I would like to sincerely thank my research supervisors Prof. Jean-Jacques Laurin and Yvon Savaria, for their guidance, patience, expertise and financial support during my research. Their supports are immeasurable for my accomplishing this work.

Acknowledgment is extended to Prof. Martin Ludvik and Ammar Kouki for their kind acceptance as members of my defense jury and their comprehensive review of this thesis, to Prof. Renato G. Bosisio for his excellent course, and to Prof. Ke Wu for his knowledge and advice during my graduate study.

I would like to express my gratitude to Dr. Zhonghua Wang for his beneficial help during my study.

Thanks also go to Mme Nathalie Lévesque, Ginette Desparois and Ghyslaine Ethier-Carrier for their kind helps during my graduate study, Mr. René Archambault and Réjean Lepage for their computer administrations, Mr. Jules Gauthier for his technical support, and all professors and colleagues in Poly-Grames and Microelectronic Research Groups for their kindness and helpful discussions.

Finally, I extend my deepest appreciation to my wife Mme Mingying Yang, for her understanding and support, and to my daughter Yifan and son Kelvin, for their encouraging me to speak French.

### RÉSUMÉ

Les objectifs de cette thèse sont: 1. la modélisation de longues interconnexions en configuration Métal-Isolant-Semi-conducteur (MIS), 2. le développement d'une méthode visant à simplifier la modélisation de ces interconnexions et 3. une analyse de l'intégrité du signal dans des réseaux renfermant de longues interconnexions.

Dans cette thèse, une méthode innovatrice est proposée pour estimer l'erreur de simulation induite pour un modèle développé dans le domaine du temps, en utilisant les paramètres du circuit dans le domaine fréquentiel. Une telle méthode se base sur le spectre fréquentiel d'une source de tension et sur la différence des fonctions de transfert de tension entre un modèle et sa référence. Concrètement, les fonctions de transfert de tension peuvent être obtenues à partir de la matrice de répartition normalisée (paramètres S). Pour illustrer la méthode, un simple modèle de ligne RC avec résistance de source  $R_s$  et charge capacitive  $C_L$  est utilisé. Il est démontré que l'estimation que fournit ladite méthode pour l'erreur induite par un modèle fournit une borne supérieure de l'erreur dans le cadre d'une simulation de circuit dans le domaine du temps.

Une approche pratique est proposée pour modéliser une interconnexion MIS simple dans un circuit intégré à très grande échelle (ITGE). Trois étapes composent cette méthode. En premier lieu, mettant à profit la littérature concernant le sujet, on construit un modèle RLCG-B original avec cinq paramètres de circuit. Deux largeurs physiques équivalentes sont proposées pour la trace de métal, représentant respectivement les distributions de champ pour les couches d'isolant et de semi-conducteur. Le modèle RLCG-B original étend la validité de certaines expressions d'un espace unidimensionnel (1D) à un espace 2D en plus d'être validé par des simulations numériques pour des fréquences allant jusqu'à 10 GHz et pour des substrats avec des résistivités supérieures à 1 Ω·cm.

En second lieu, le modèle RLCG-B original est modifié dans le but d'incorporer des modèles simples de circuits équivalents dans des logiciels de simulation tel SPICE. Le nouveau modèle est appelé modèle RLCG-B modifié. Deux paramètres de circuit variant avec la fréquence et reliés aux impédances série dans le modèle RLCG-B original sont remplacés dans le modèle modifié par un sous-circuit RL renfermant quatre paramètres de circuit indépendants de la fréquence. Des expressions analytiques sont proposées pour obtenir les quatre nouveaux paramètres de circuit. Des simulations numériques démontrent que la différence entre les modèles RLCG-B original et modifié en ce qui concerne les impédances séries par unité de longueur est minime et peut être négligée pour les plages de fréquence et de résistivité d'intérêt (fréquence≤10 GHz et résistivité≥1 Ω·cm).

Le modèle modifié se révèle précis, cependant qu'il met à forte contribution les ressources de temps et de mémoire. Conséquemment, quelques simplifications sont finalement apportées au modèle modifié RLCG-B, de façon à obtenir un modèle efficace. Partant du modèle RLCG-B modifié comme référence, cinq modèles simplifiés sont analysés soit en négligeant l'effet pelliculaire dans la trace de métal, en négligeant les pertes diélectriques dans la couche semi-conductrice ou encore en considérant la couche semi-conductrice comme un conducteur électrique parfait. En mettant à profit la méthode présentée dans cette thèse, l'erreur de simulation induite respectivement par les cinq modèles simplifiés est estimée en considérant les conditions à la source et à la charge. En combinant le spectre fréquentiel d'une source de tension avec la différence entre les fonctions de transfert des modèles simplifiés et de la référence, la différence absolue entre les tensions de charge des modèles simplifiés versus le modèle de référence sont obtenues. Pour un cas donné, il est démontré que l'erreur induite par le modèle dans le domaine du temps est minime si l'on néglige l'effet pelliculaire dans la trace métallique, cependant que l'erreur est grande si les pertes diélectriques sont négligées. Il est intéressant de constater que l'erreur de modélisation reste raisonnable lorsqu'on considère la couche semi-conductrice comme un conducteur électrique parfait.

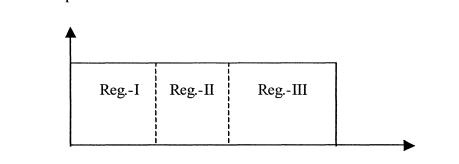

Dans le but d'analyser la précision de modélisation en terme d'erreur de simulation, l'intervalle de fréquence d'intérêt dicté par le spectre fréquentiel de la tension de charge est divisé en trois sous-régions fréquentielles. La largeur de bande de la tension de charge dépend de deux facteurs: la largeur de bande de la source de tension ainsi que celle de la fonction de transfert de l'interconnexion. Pour le même cas donné plus haut, les résultats numériques montrent que la précision de modélisation a beaucoup d'impact sur l'erreur de simulation pour la partie du spectre fréquentiel de tension se situant entre le courant continu et le point à -3 dB, région où se concentre la majeure partie de l'énergie. Hors de cette région fréquentielle, la contribution à l'erreur totale de simulation est faible.

Pour faciliter la modélisation d'une interconnexion simple en configuration MIS, un plan  $\gamma_n$  normalisé est défini dans le but de visualiser les différences existant entre les caractéristiques de propagation du modèle simplifié et d'une référence. Dans ce plan, tout le spectre de fréquences d'intérêt peut être représenté par une courbe. Ainsi, en comparant la courbe d'un modèle simplifié avec celle d'une référence dans la plan  $\gamma_n$  normalisé, on constante les différences d'atténuation d'amplitude et de délai de phase entre le modèle et la référence lorsque que des signaux parcourent l'interconnexion. Ceci implique que les impédances de source et de charge soient toutes deux égales à l'impédance caractéristique de la ligne.

Pour fins de comparaison, la modélisation d'une interconnexion simple sera mise en parallèle avec la modélisation d'une configuration à deux interconnexions MIS couplées et dont l'une des deux est utilisée pour le retour de courant (mode impair). Cette configuration fait également l'objet de cette thèse. Deux étapes sont nécessaires pour créer un modèle efficace pour le mode impair de deux interconnexions couplées. Basé sur le modèle RLCG-B original pour une interconnexion simple et d'autres modèles de la littérature, un modèle RLCG-B hybride est d'abord élaboré pour le mode impair de deux interconnexions couplées. Ce modèle hybride est alors modifié pour devenir un

simple modèle RLC en considérant le semi-conducteur comme un diélectrique parfait et en négligeant l'impact du plan métallique de mise à la masse sur les deux interconnexions. En comparant la constante de propagation complexe du modèle simple RLC avec les résultats fournis par des modèles basés sur la méthode des moments, nous pouvons affirmer que le modèle simple RLC reproduit fidèlement le comportement électrique du mode impair de deux interconnexions si l'espace entre les deux conducteurs  $s_m$  est comparable à la largeur du conducteur  $w_m$ . Il existe une valeur seuil de  $s_m/w_m$ . En deçà de ce seuil, un fort couplage existe entre les deux interconnexions et des prédictions fiables peuvent être obtenues avec un modèle RLC simple. Au-dessus du seuil, le couplage devient faible. Ainsi, l'impact du plan arrière en métal sur les deux interconnexions ne peut plus être négligé, et le modèle RLC simple devient non approprié pour modeler le mode impair des deux interconnexions. Dans certains cas avec la technologie à l'échelle du micron, en considérant une tranche de silicium de 300  $\mu$ m d'épaisseur, la valeur seuil  $s_m/w_m$  observée est autour 8, ce qui correspond à un espacement de moins de 25  $\mu$ m entre les deux interconnexions.

Cependant, dans ces conditions de couplage faible, la différence entre les caractéristiques de propagation des interconnexions couplées et d'une interconnexion simple est minime. Ainsi, deux interconnexions couplées avec un faible couplage peuvent être considérées comme deux interconnexions simples sans couplage. Ce qui revient à dire qu'un modèle tel que le RLCG-G modifié, développé pour une interconnexion MIS simple peut également prédire le comportement électrique de deux interconnexions MIS couplées. De la même façon que pour le modèle simple RLC, une valeur seuil de  $s_m/w_m$  est utilisée pour déterminer si le modèle à une ligne décrit bien le mode impair de deux interconnexions. Au-dessus de ce seuil, le couplage est faible et des prédictions de qualité peuvent être obtenues du modèle à une ligne. Basé sur des résultats numériques, la gamme valide de  $s_m/w_m$  pour le modèle à une ligne semble être

recouverte par celui pour le modèle simple RLC. Anisi, une valeur-seuil de  $s_m/w_m$  peut être placée pour les deux modèles.

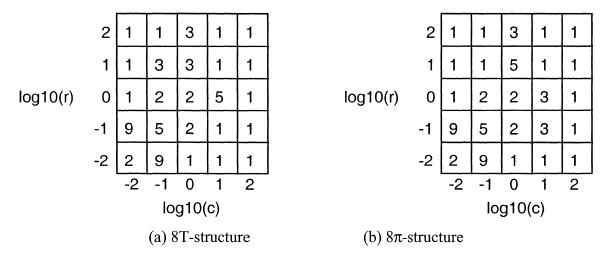

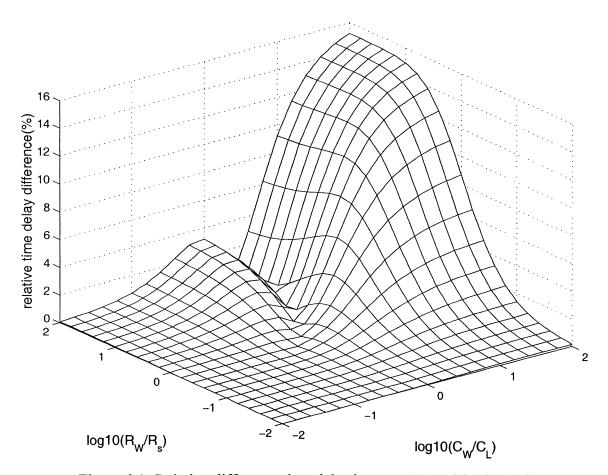

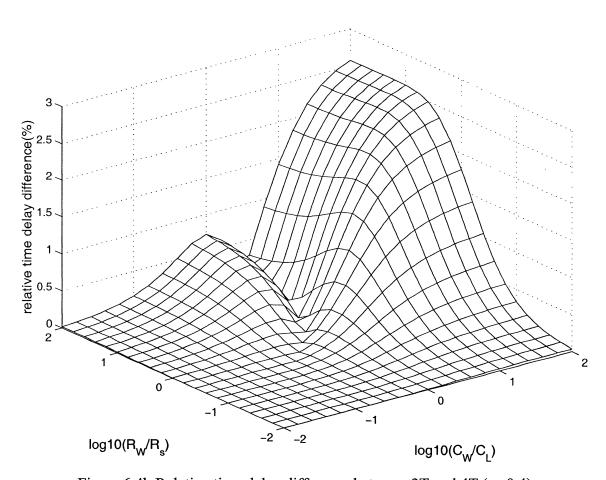

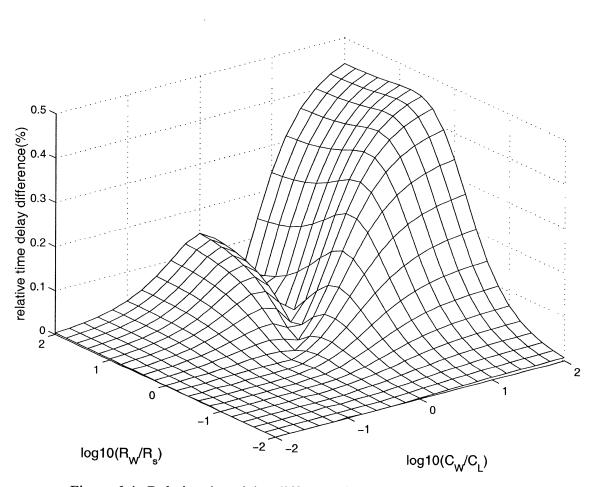

Ces efforts de modélisation mènent à une analyse d'intégrité pour un signal parcourant des interconnexions MIS. Dans cette thèse, deux démarches sont investiguées. La première consiste à évaluer le délai temporel de propagation pour des lignes RC avec impédance de source  $R_S$  et charge capacitive  $C_L$  dans des circuits ITGE. On recherche les conditions de validité qui permettraient de modéliser une ligne avec des sections RC d'eléments discrets. Puisque l'évaluation de forme d'onde asymptotique est une procédure ayant fait ses preuves pour ce qui est de prédire la réponse temporelle de circuits linéaires, cette méthode est ici utilisée pour analyser le délai de propagation sur des lignes RC. Un nombre limité de pôles est utilisé dans l'analyse pour éviter l'instabilité numérique, même si cela peut introduire de l'imprécision dans le cas de circuits compliqués. La précision des modèles discrets avec un certain nombre de sections est représentée dans un plan r-c normalisé, lequel plan est valide pour diverses technologies. En utilisant l'information détaillée dans cette thèse, un utilisateur peut sélectionner un modèle de complexité minimale qui remplit les exigences de précision d'une approximation donnée. Dans certains cas, la structure de base d'une section (T ou  $\pi$ ) exerce une influence significative sur la précision d'une certaine complexité de modèle. Cette thèse guide l'utilisateur vers le choix du modèle le plus efficace.

Le nombre essentiel de sections T ou  $\pi$  pour des modèles de lignes RC est également mis en relation avec la largeur de bande de la tension de charge. Pour une source de tension échelon, le spectre fréquentiel de la tension de charge sera déterminé uniquement par la bande passante du système, qui peut être estimée par le délai temporel de propagation. Ainsi, pour une ligne RC spécifique, la largeur de bande de la tension aux bornes d'une petite charge associée à une forte source est supérieure à la largeur de bande de la tension aux bornes d'une grosse charge associée à une faible source. Considérant ceci, la précision de modélisation d'une ligne RC distribuée a davantage

d'impact sur l'erreur de simulation induite par la modélisation dans le premier cas mentionné et donc, plus de sections T ou  $\pi$  sont nécessaires dans le modèle.

L'autre volet de l'analyse d'intégrité de signal étudié porte sur la divergence des temps de propagation dont l'analyse est faite. Dans cette thèse, une nouvelle méthode hybride est proposée pour réduire la divergence des temps de propagation. Cette méthode comporte trois outils. Des directions de propagation alternatives sont utilisées pour des signaux parallèles afin de réduire l'interférence électromagnétique entre lignes voisines. Un agencement de phase en zigzag est instauré pour les signaux voyageant dans la même direction afin de réduire davantage l'interférence entre les lignes. Des suiveurs et des inverseurs sont alternativement insérés en guise de répéteur dans chaque interconnexion pour compenser l'effet de l'interférence due aux cas de double polarité sur l'incertitude des délais de propagation. Pour des applications pratiques, nous recommandons premièrement l'utilisation d'inverseurs seulement afin de réduire la divergence des temps de propagation. Si celle-ci surpasse toujours les tolérances permises, l'usage alternatif de suiveurs comme répéteurs pour réduire l'effet de couplage sur la divergence des temps de propagation. Les dimensions des suiveurs et inverseurs devraient être ajustées avec soin pour éviter d'obtenir des valeurs variables de divergence de temps de propagation, ce qui peut arriver avec des répéteurs présentant des caractéristiques différentes.

### **ABSTRACT**

The objectives of this thesis are: 1.modeling of long interconnects in the metal-insulator-semiconductor (MIS) configuration, 2.developing a method to simplify modeling of long interconnects and 3.analyzing signal integrity of networks including long interconnects.

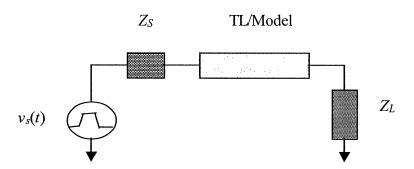

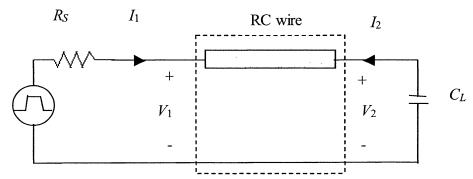

In this thesis, a novel method is presented to estimate the time-domain model-induced simulation error using frequency domain circuit parameters. Such method is based on the spectrum of voltage source and on the difference of the voltage transfer functions between a model and a reference. Practically, the voltage transfer functions can also be obtained from the renormalized S-parameters. A simple RC transmission line net with source resistance  $R_S$  and load capacitance  $C_L$  is used to illustrate this method. It is demonstrated that the model-induced error produced by the proposed method provides an upper limit for the time-domain simulation error obtained from circuit simulator.

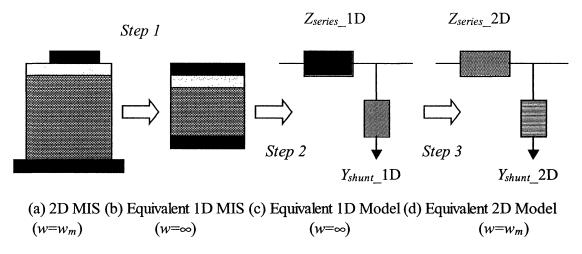

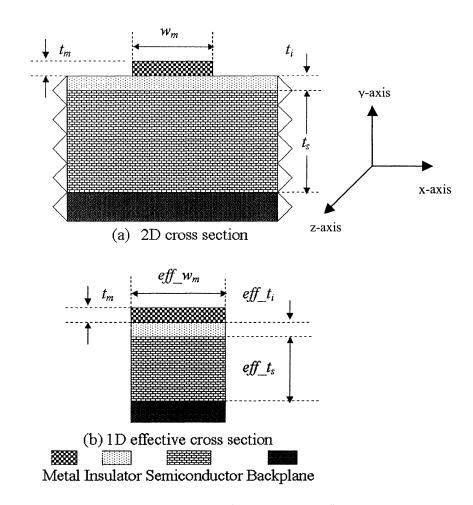

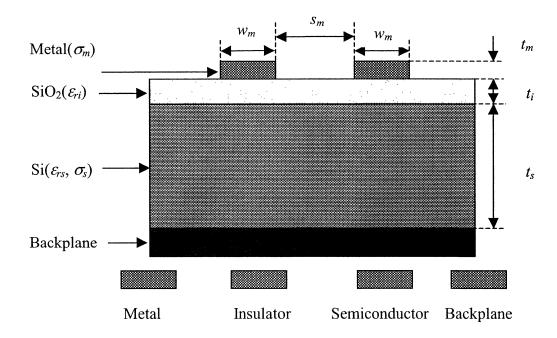

A practical approach is presented to model a single MIS interconnect in VLSI circuits. Three steps are taken in this approach. At first, based on the literature, an "original RLCG-B" model with five equivalent circuit parameters is constructed for a single MIS interconnect. Two equivalent widths are proposed for the physical metal strip, reflecting the field spread for the insulator and semiconductor layers, respectively. The original RLCG-B model extends the validity range of some closed-form expressions from 1D to 2D, and is validated by numerical simulations for frequencies up to 10 GHz and for substrate resistivities greater than 1  $\Omega$ ·cm.

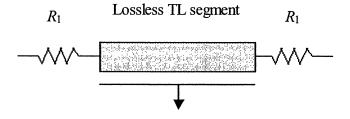

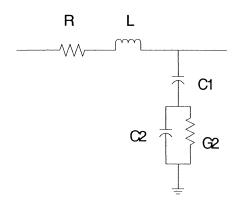

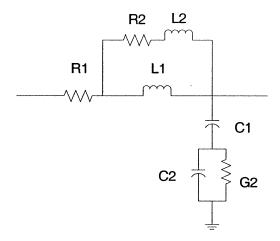

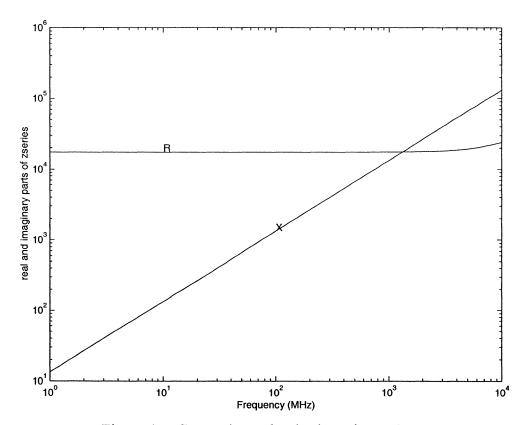

Secondly, the original RLCG-B model is revised for the purpose of embedding simple equivalent circuit models into simulation software such as SPICE. The new model is called a "modified RLCG-B" model. Two frequency-dependent circuit parameters related to the series impedance in the original RLCG-B model are replaced by a RL sub-

network of four frequency-invariant circuit parameters in the modified RLCG-B model. Analytical expressions are proposed to obtain the values of the four new circuit parameters. Numerical simulations demonstrate that the difference of series impedance per unit length between the modified and the original RLCG-B models is small and can be neglected for frequency and resistivity ranges of interest (frequency $\leq$ 10 GHz and rersistivity $\geq$ 1  $\Omega$ ·cm).

The modified model is accurate, however, it is time-and-memory consuming. Thus, some simplifications are finally performed for the modified RLCG-B model in order to obtain an efficient model. Regarding the modified RLCG-B model as a reference, five simplified models are analyzed either by neglecting the skin effect in metal strip, or by neglecting the dielectric losses in the semiconductor layer, or by treating the semiconductor layer as a perfect electric conductor. Using the method proposed in this thesis, the model-induced simulation error for those five simplified models is estimated by including the conditions on the source and load. Combining the spectrum of a voltage source with the differences of voltage transfer functions between the simplified models and the reference, the absolute difference of load voltages between the simplified models and the reference is obtained. For a special case, it is demonstrated that the time-domain model-induced error is small if the skin effect in the metal strip is neglected but the error is large if the dielectric losses are neglected. It is interesting see that the model-induced error is not large if the semiconductor layer is treated as a perfect electric conductor.

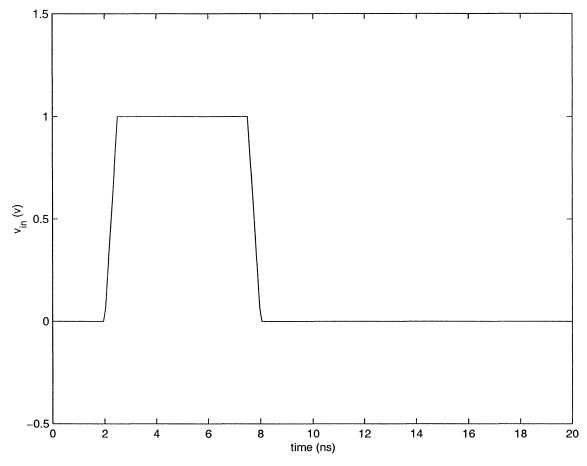

In order to analyze the modeling accuracy over different frequency sub-regions on the simulation error, the whole frequency range of interest is divided into three frequency sub-regions according to the bandwidth of the load voltage. Here, the bandwidth of the load voltage depends on both the bandwidth of voltage source and the one of the interconnect. For the specific case above, numerical results show that the modeling accuracy has great impact on the simulation error inside the voltage spectra from DC to

the -3 dB point, where most of the energy is concentrated, and that the contribution to the total simulation error outside is small.

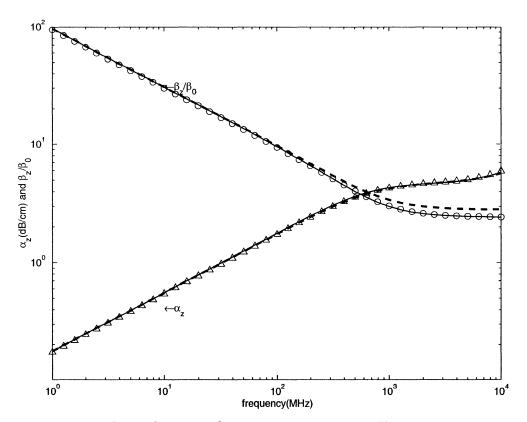

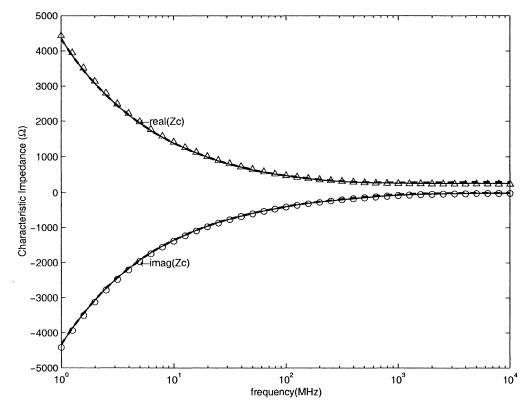

In the practical approach to model a single interconnect in the MIS configuration, a newly normalized  $\gamma_n$ -plane is defined in order to display the difference of propagation characteristics between simplified model and a reference, where the whole frequency range from DC to the highest frequency of interest can be mapped-out by a curve. Therefore, by comparing the curve of a simplified model with the one of a reference in the normalized  $\gamma_n$ -plane, we can assess the differences of magnitude attenuation and phase delay between the model and the reference as signals travel through the interconnect. Here, it is assumed that the source and load impedances are both equal to the characteristic impedance of the wire.

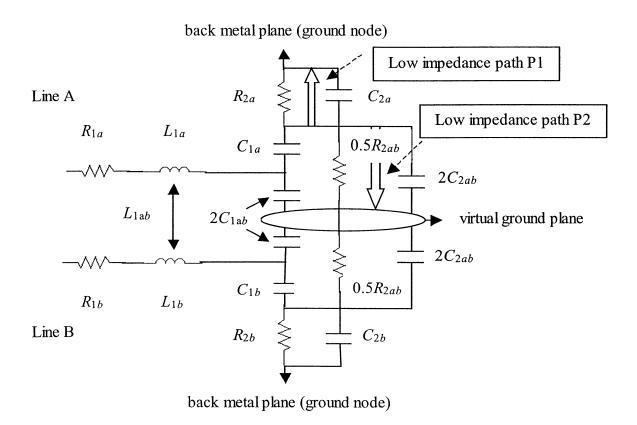

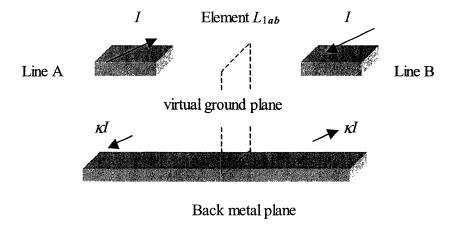

Besides modeling of a single MIS interconnect, for comparison, a topology of two coupled interconnects in the MIS configuration is also investigated in this thesis, where one of the two coupled interconnects is used as current returning path. There are two steps to create an efficient model for the odd mode of two coupled interconnects. Based on the original RLCG-B model for a single interconnect and other models in the literature, a "hybrid RLCG-B" model is first constructed for the odd-mode of two coupled interconnects. This hybrid RLCG-B model is then evolved into a simple RLC model by assuming the semiconductor as a perfect electric conductor and by neglecting the impact of the back metal plane on the two interconnects. By comparing the complex propagation constant of the simple RLC model with the results predicted by moment method models, we find that the simple RLC model captures the electrical behavior of the odd-mode of coupled interconnects well if the wire spacing  $s_m$  is comparable to the line width  $w_m$ . It seems that there is a threshold value of  $s_m/w_m$ . Under the threshold, a strong coupling exists between the two interconnects and a good prediction can be obtained with the simple RLC model. Above the threshold, the coupling between the two interconnects becomes weak. So, the impact of the back metal plane on the two

interconnects can no longer be neglected, and the simple RLC model becomes not suitable to model the odd-mode of two interconnects. For a group of special cases with micron technology, it is found that for a typical 300  $\mu$ m thick Si wafer, the threshold value of  $s_m/w_m$  is around 8, which corresponds to the spacing between two interconnects less than 25  $\mu$ m.

On the contrary, the difference of propagation characteristics between single and coupled interconnects is small under the conditions of weak coupling. Therefore, two coupled interconnects with weak coupling can be approximately treated as two single interconnects without coupling. That is to say, a one-wire model such as the modified RLCG-B model originally for a single MIS interconnect, can also approximate the electrical behavior of two coupled MIS interconnects. Similarly to the simple RLC model, a threshold value of  $s_m/w_m$  is used to determine if the one-wire model is suitable for the odd mode of two interconnects. Above the threshold, a coupling is weak and a good prediction can be obtained from the one-wire model. Based on numerical results, the valid range of  $s_m/w_m$  for the one-wire model seems to be partially overlapped by the one for the simple RLC model. Thus, a threshold value of  $s_m/w_m$  can be set for both models.

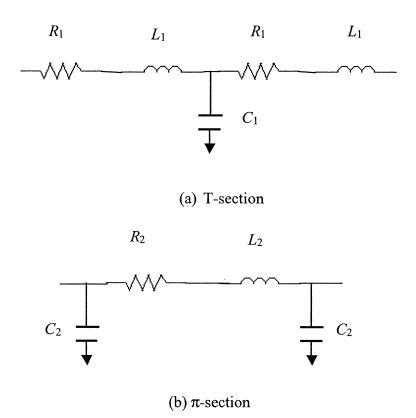

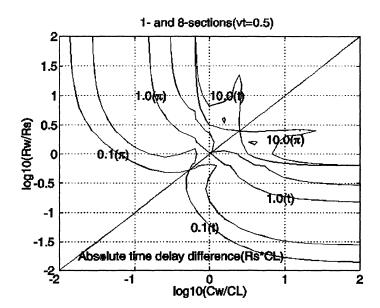

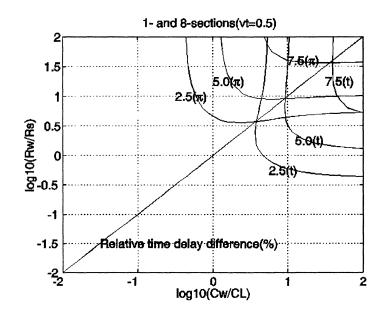

The purpose of modeling is for signal integrity analysis. In this thesis, two issues are studied. One issue is the propagation time delay for RC wires with source impedance  $R_S$  and capacitive load  $C_L$  in VLSI circuits. The validity conditions are investigated for modeling a wire with lumped RC sections. Since asymptotic waveform evaluation (AWE) is a well-known procedure to predict the time response of linear circuits, it is implemented to analyze time delay on RC wires. A limited number of AWE poles are used to avoid the numerical instability, though it may lead to inaccuracy for complicated circuits. The accuracy of lumped models with the number of sections is mapped in a normalized r-c plane, which is valid for different technologies. Using the information provided in this thesis, a user can select a model of minimal complexity that meets the

accuracy requirements of a given approximation. In some cases, the basic cell structure (T- or  $\pi$ -) has a significant impact on accuracy for a given model complexity, and this thesis allows selecting the most efficient model.

The essential number of T- or  $\pi$ - sections for RC wire models is also illustrated with respect to the bandwidth of the load voltage. For a step voltage source, the bandwidth of the load voltage will only be determined by the bandwidth of the system, which can be estimated by the propagation time delay. Thus, for a specific RC wire, the bandwidth of load voltage with a strong driver and a light load is wider than that of load voltage with a weak driver and a heavy load. Thus, the modeling accuracy of a distributed RC wire has more impact on the time-domain model-induced simulation error for the front case, and more T- or  $\pi$ - sections are needed for RC wire models.

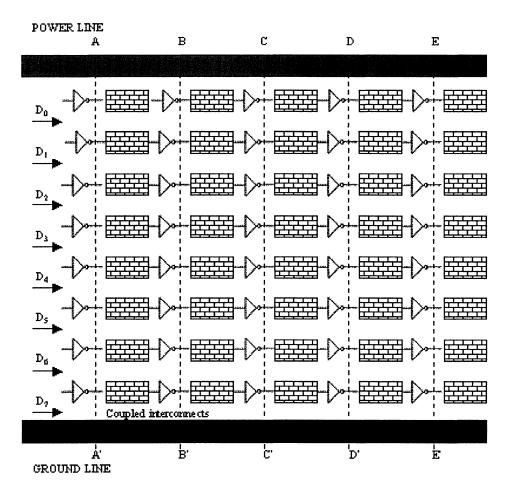

The other issue on signal integrity analysis is the propagation time skew analysis. In this thesis, a new combined method is proposed to reduce propagation time skew. There are three features in our method. Alternative propagation directions are used for parallel signals to reduce the electromagnetic interference (EMI) intervals among neighbour wires. A zigzag phase pattern implementation for the same direction signals is implemented to further reduce the crosstalk among neighbour wires. Alternatively buffers and inverters as repeaters are inserted in each interconnect to compensate the impact of dual-polarity crosstalk on the propagation time delay uncertainty. For practical applications, we first recommend using the method of inverters only to reduce the propagation time skew. If the time skew is still larger than tolerated, then we select alternative usage of both buffers and inverters as repeaters to reduce the impact of the coupling effect on the propagation time delay uncertainty. The sizes of buffers and inverters should be carefully adjusted to minimize the variation of propagation time skew due to the different characteristics of buffers and inverters.

### CONDENSÉ EN FRANÇAIS

# MÉTHODES POUR LA MODÉLISATION ET L'ANALYSE DES INTERCONNEXIONS DANS DES CIRCUITS INTÉGRÉS À TRÈS GRANDE ÉCHELLE

Les objectifs de cette thèse sont: la modélisation de longues interconnexions en configuration Métal-Isolant-Semi-conducteur (MIS), le développement d'une méthode visant à simplifier la modélisation de ces interconnexions et une analyse de l'intégrité du signal dans des réseaux renfermant de longues interconnexions.

### 0.1 Introduction

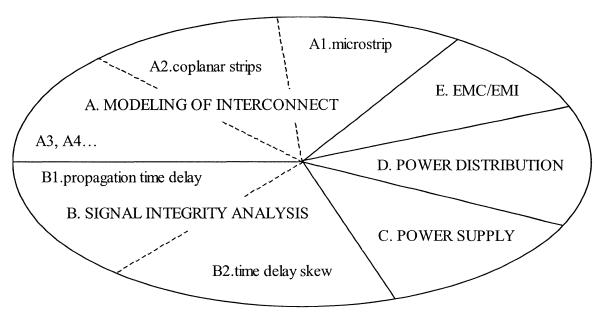

La croissance rapide et effrénée de la technologie d'intégration à très grande échelle (ITGE) a été rendue possible par les progrès constants réalisés dans la miniaturisation des dispositifs ITGE. Une évolution aussi soutenue est lourde d'impacts sur la conception des interconnexions. Les performances électriques des interconnexions sont devenues un facteur important lorsque vient le temps d'évaluer le rendement d'un système. Puisque l'analyse du comportement électrique des interconnexions dans un circuit ITGE est un sujet très large, nous avons concentré nos efforts sur la modélisation électrique d'interconnexions et sur l'analyse d'intégrité de signal, qui sont de près reliées à deux projets industriels nous impliquant. D'autres volets tels l'optimisation de la dissipation de puissance dans les interconnexions sont mis sur la glace pour le futur.

### 0.2 Revue bibliographique

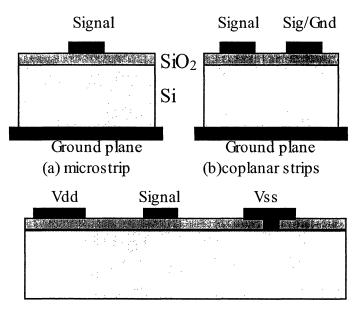

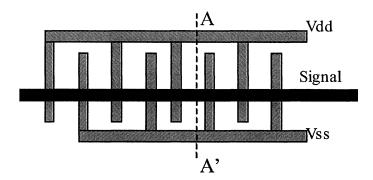

À cause de la contribution significative des interconnexions aux temps de propagation, une modélisation équivalente et efficace d'interconnexions sur puces utilisant la technologie ITGE est devenue extrêmement nécessaire. Il y a plusieurs arrangements dignes d'intérêt pour des interconnexions en configuration MIS tel que montré à la figure 2.1. La figure 2.1a montre une ligne microruban en configuration MIS, pour laquelle le plan de masse est utilisé en guise de retour de courant. Les premières études concernant les lignes microruban remontent aux années'60 [33,34]. Un arrangement un peu plus complexe consiste en deux interconnexions MIS couplées, pour lesquelles une des deux peut agir comme retour de courant. D'autres arrangements plus complexes encore existent, telle est la situation montrée dans la figure 2.1c, qui est en fait une vue de coupe sur le plan défini par la ligne AA' dans le circuit de la figure 2.1d, laquelle représente une longue trace porteuse de signal qui traverse une géométrie interdigitée de traces d'alimentation et de masse. De telles conceptions complexes existent pour conjuguer deux réalités particulières présentes dans les circuits ITGE modernes. Dans cette thèse, nous concentrons nos efforts sur la modélisation d'une interconnexion MIS simple, en considérant que l'étude d'un cas aussi simple peut aider à la compréhension des mécanismes fondamentaux de propagation configuration MIS. en Comparativement, nous étudions également un modèle de circuit équivalent pour le mode impair de deux interconnexions MIS couplées, pour lesquelles une des deux peut agir comme retour de courant. Malgré la disponibilité de plusieurs modèles [10-12][14,15][84,85], ceux-ci ne répondent pas aux critères de performance recherchés en simulation, puisqu'ils consomment temps et mémoire en trop grandes quantités. Conséquemment, des modèles simples deviennent nécessaires dans le but de les incorporer dans des simulateurs tels SPICE, fonctionnant dans le domaine du temps.

Dès que les paramètres du circuit distribué équivalent sont connus, il devient possible de construire des modèles de circuit en utilisant plusieurs techniques [21] telles que

l'obtention de circuits discrets itératifs (« ILC : iterated lumped circuits») et la méthode des caractéristiques (MC). À ce stade, une méthode générique est nécessaire pour estimer l'erreur de simulation commise entre un modèle approximatif et une référence. En se basant sur cette méthode, on peut déterminer si un modèle simple représente fidèlement une interconnexion simple ou deux interconnexions couplées. Plus que tout, en étudiant l'impact de la précision de la modélisation sur l'erreur de simulation dans le domaine du temps, on peut déterminer si de plus ou moins grandes variations de la constante complexe de propagation et de l'impédance caractéristique complexe peuvent être tolérées, ces quantités étant calculées dans le domaine fréquentiel.

Le but de la modélisation d'interconnexions dans le contexte de circuits intégrées à très grande échelle réside dans la nécessité de procéder à des analyses d'intégrité de signal [29], lesquelles se basent sur des paramètres tels les temps de propagation, le sousdépassement, le sur-dépassement et d'autres encore. En guise d'exemple, une ligne RC distribuée est utilisée pour étudier le temps de propagation dans les circuits ITGE. Les lignes RC ont déjà fait l'objet d'études poussées [55,56], or les paramètres physiques de celles-ci varient selon les différentes technologies. Donc, une approche générique est nécessaire pour sélectionner les paramètres appropriées au modèle d'une ligne RC donnée. Un autre paramètre de l'analyse d'intégrité de signal est la divergence des temps de propagation qui se révèle d'une grande importance dans le cadre de l'utilisation d'une technologie ITGE sur grandes surfaces («WSI»). Des applications haute vitesse développées avec des circuits «WSI» imposent des spécifications excessivement sévères pour les interconnexions de grande longueur. Les méthodes existantes [59-68] capables de réduire la divergence des temps de propagation relèvent du logiciel, du matériel ou d'une combinaison des deux. Des méthodes simples et pratiques sont requises pour réduire la divergence des temps de propagation dans un bus d'interconnexions parallèles.

## 0.3 Méthode d'estimation de l'erreur temporelle de simulation dans le domaine fréquentiel

La plupart des publications concernant la modélisation des interconnexions utilisent des validations dans le domaine fréquentiel, lesquelles sont réalisées en comparant pour le modèle et la référence des paramètres tels la constante complexe de propagation, l'impédance caractéristique complexe, les matrices d'impédance et d'admittance et d'autres types des caractéristiques. Ces comparaisons dans le domaine fréquentiel sont valables, mais davantage appropriées à une utilisation dans les applications radio fréquences (RF). En technologie ITGE, le domaine du temps offre un point de vue de prédilection pour évaluer les distorsions de signal, les délais de propagation, etc. De plus, la validation des modèles dans le domaine fréquentiel peut se révéler exigeante en ressources lorsqu'on travaille à de hautes fréquences, auxquelles une grande précision peut ne pas être nécessaire pour obtenir des prédictions satisfaisantes dans le domaine du temps.

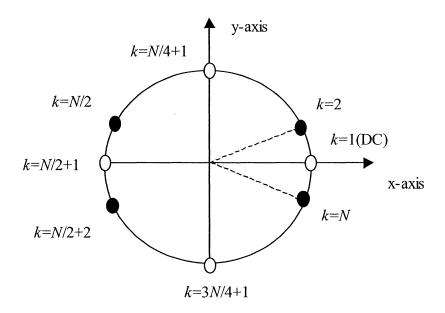

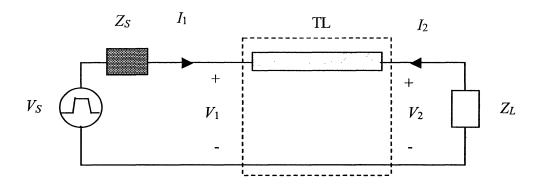

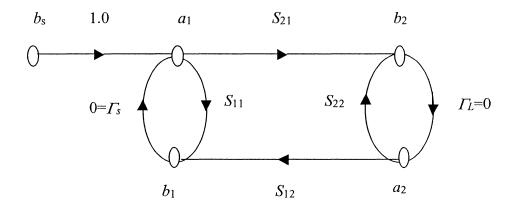

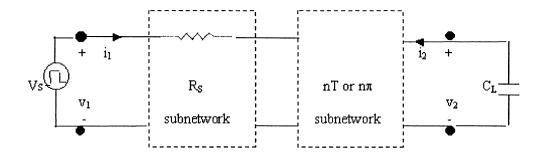

Dans la section 3.2, nous proposons une méthode générique pour estimer l'erreur temporelle dans le pire des cas en utilisant les caractéristiques des interconnexions dans le domaine fréquentiel. Cette méthode se base sur le spectre fréquentiel d'une source de tension et sur la différence des fonctions de transfert de tension entre un modèle et sa référence. Dans la section 3.2.2, la bande fréquence d'intérêt est divisée en plusieurs régions afin d'illustrer la contribution des composantes d'un groupe de fréquences à la forme du signal temporel. Ceci est fait en se basant sur la largeur de bande d'une source transitoire de tension, avec ou sans considération pour la bande passante du système. La limite supérieure d'erreur de simulation temporelle impliquant des interconnexions ITGE est démontrée à la section 3.3 avec un exemple simple tel que montré à la figure 3.1. Puis, une relation entre la fonction de transfert de tension et les paramètres S est obtenue à la section 3.4. L'avantage d'utiliser les paramètre S fait également l'objet de discussions dans ce chapitre.

### 0.4 Modélisation d'une interconnexion simple en configuration MIS

Ce chapitre traite de l'obtention de modèles d'interconnexions précis. La méthode proposée dans le troisième chapitre est utilisée pour étudier l'impact de l'imprécision engendrée par la modélisation sur l'erreur de simulation temporelle. Dans la section 4.2, un modèle RLCG-B original est élaboré avec cinq paramètres de circuit équivalent. Dans ce cas, deux largeurs physiques équivalentes sont proposées pour la trace de métal, représentant respectivement les distributions de champ pour les couches d'isolant et de semi-conducteur. Le modèle RLCG-B a été validé par des simulations numériques pour des fréquences allant jusqu'à 10 GHz et pour des substrats avec des résistivités supérieures à 1 Ω·cm.

De façon à obtenir un modèle avec des paramètres insensibles à la fréquence, le modèle RLCG-B original est alors modifié avec un sous-circuit RL à la section 4.3. Les valeurs des nouveaux paramètres de circuit sont calculées de façon analytique. Des simulations numériques furent utilisées pour vérifier la précision des impédances série linéiques obtenues avec le modèle RLCG-B modifié. La différence obtenue étant minime, elle peut être négligée sans conséquences. Le modèle modifié sera donc utilisé comme référence pour la suite.

Dans la section 4.4, nous analysons l'impact de l'effet pelliculaire et des pertes diélectriques sur les modèles de circuit. Une façon de ne pas considérer l'effet pelliculaire dans la trace métallique est d'utiliser les valeurs de la résistance et de l'inductance séries dans les équations 4-10a et 4-10b. De la même façon pour les pertes diélectriques, deux moyens existent pour négliger leur impact. La première consiste à considérer le semi-conducteur comme un isolant idéal. Aucune contribution à la résistance série ne provient de la couche semi-conductrice. La seconde façon consiste à traiter le semi-conducteur comme un conducteur électrique parfait.

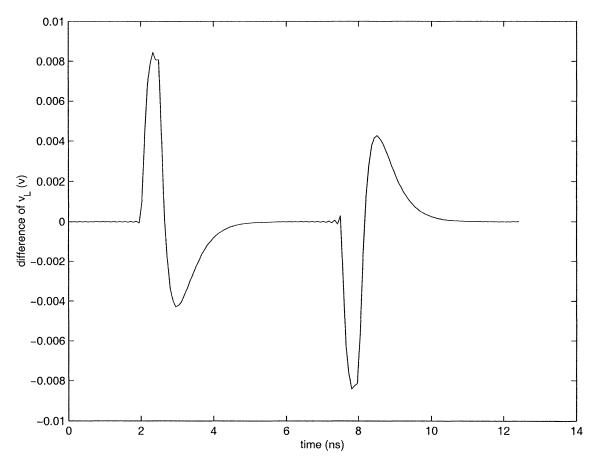

En combinant l'effet pelliculaire et l'impact des pertes diélectriques sur les paramètres de circuit, nous proposons cinq modèles simplifiés énoncés dans le tableau 4.1. Dans la section 4.5, les différences absolues entre les tensions de charge obtenues des modèles simplifiés et de la référence sont estimés dans le cas d'un exemple simple : une ligne avec résistance de source  $R_s$  et charge capacitive  $C_L$ . Les résultats numériques regroupés dans le tableau 4.5 montrent que les valeurs estimées fournissent une limite supérieure évidente pour la différence maximale entre les tensions de charge des modèles et de leur référence. En nous basant sur ces résultats estimés et pour une tolérance d'erreur donnée, nous pouvons juger de la pertinence des modèles simplifiés sans procéder à des simulations dans le domaine du temps.

### 0.5 Modélisation d'interconnexions couplées en configuration MIS

Le chapitre précédent portait sur la modélisation d'une interconnexion simple, une seule ligne MIS avec l'arrière-plan métallique utilisé comme retour de courant. Pour fins de comparaisons, ce chapitre porte sur l'étude d'une autre configuration, une interconnexion double couplée avec retour de courant sur une deux deux lignes (mode impair). Pour la simplicité, nous analysons seulement le mode impair de deux interconnexions en considérant la source et la charge balancées.

À la section 5.2, partant du modèle original RLCG-B pour une interconnexion simple proposé à la section 4.2 et d'autres modèles documentés, un modèle RLCG-B hybride est élaboré pour le mode impair de deux interconnexions couplées. Ce modèle hybride est ensuite modifié pour devenir un simple modèle RLC en considérant la couche semi-conductrice comme un conducteur électrique parfait et en négligeant l'impact de l'arrière-plan métallique sur le couplage des interconnexions. Dans la section 5.3, en comparant la constante de propagation complexe obtenue de l'équation 5.4 basée sur le modèle simple RLC avec le résultat prédit par une simulation sur ADS Momentum

(Agilent Technologies), on peut vérifier les conditions de validité du modèle RLC simple.

Pour les cas spécifiquement abordés dans ce chapitre, il est démontré que le modèle RLC simple (modèle à deux lignes simple) reproduit fidèlement le comportement électrique du monde impair de deux interconnexions couplées si l'espacement entre les deux lignes  $s_m$  est comparable à la largeur de la ligne  $w_m$ . Il semble que il y a une valeur seuil de  $s_m/w_m$ . En deçà de ce seuil, un fort couplage existe entre les deux interconnexions et des prédictions fiables peuvent être obtenues avec un modèle à deux lignes simple. Cependant, au-dessus du seuil, le couplage entre les deux interconnexions se révèle être faible et l'influence du plan de masse ne peut plus être négligée : le comportement du modèle à deux lignes simple s'éloigne alors du mode impair pour deux interconnexions. Dans certains cas avec la technologie à l'échelle du micron, en considérant une gaufre de silicium de 300  $\mu$ m d'épaisseur, la valeur seuil de  $s_m/w_m$  est autour 8, ce qui correspond à un espacement de moins de 25  $\mu$ m entre les deux interconnexions.

Parallèlement, nous trouvons que deux interconnexions couplées avec un faible couplage peuvent être considérées comme deux interconnexions simples sans couplage. Ce qui revient à dire qu'un modèle tel que le RLCG-G modifié, développé pour une interconnexion MIS simple peut également prédire le comportement électrique de deux interconnexions MIS couplées. De la même façon que pour le modèle à deux lignes, une valeur seuil de  $s_m/w_m$  est utilisée. Au-dessus de ce seuil, le couplage est faible et des prédictions de qualité peuvent être obtenues du modèle à une ligne. Basé sur des résultats numériques, la gamme valide de  $s_m/w_m$  pour le modèle à une ligne semble être partiellement recouverte par celui pour le modèle à deux lignes. Anisi, une valeur-seuil de  $s_m/w_m$  peut être placée pour les deux modèles. Donc, un modèle simple, soit à une

ou deux lignes, peut reproduire fidèlement les caractéristiques de propagation du mode impair de deux interconnexions couplées avec la valeur seuil de  $s_m/w_m$ .

## 0.6 Analyse du délai de propagation d'une ligne RC distribuée avec résistance de source $R_S$ et charge capacitive $C_L$

Les derniers chapitres présentaient les considérations de modélisation des interconnexions en ITGE et analysaient la précision de ces modèles avec un regard à l'erreur temporelle de simulation. Le reste de la thèse porte sur l'analyse d'intégrité de signal. Dans ce chapitre, nous utilisons une simple ligne RC distribuée comme exemple pour étudier le délai temporel de propagation dans un circuit ITGE. Le chapitre suivant est en fait une étude de la divergence des temps de propagation pour des interconnexions couplées en configuration MIS.

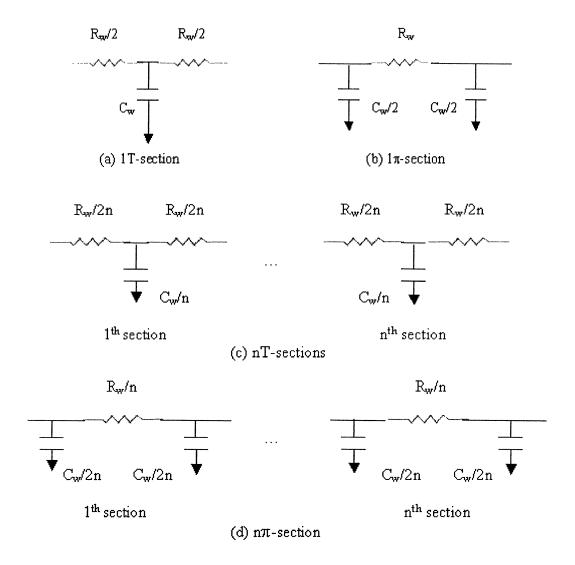

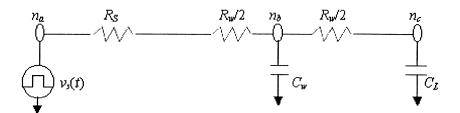

La structure de notre modèle de circuit équivalent pour une ligne RC est montrée à la figure 6.1. Dans ce cas, des modèles discrets construits par itération (sections T ou  $\pi$ ) ont été choisies pour modéliser des lignes RC. Dans la figure 6.1, la résistance de ligne  $R_w$  peut être obtenue en multipliant la résistance linéique de la ligne  $R_w^l$  ( $\Omega/m$ ) par la longueur de celle-ci d (m). De la même façon, la capacitance de la ligne  $C_w$  peut être obtenue en multipliant la capacité linéique  $C_w^l$  (F/m) par la longueur de la ligne d (m). Les figures 6.1a et 6.1b montrent une section T et une section  $\pi$ . Les figures 6.1c et 6.1d montrent des structures de n sections en T et de n section en  $\pi$ .

En utilisant les modèles de circuit équivalent appropriés, la réponse à une entrée échelon des lignes RC avec résistance de source  $R_S$  et charge capacitive  $C_L$  est analysée. Une évaluation asymptotique de forme d'onde à deux ou trois pôles est utilisée pour analyser le délai de propagation sur les lignes RC. Tel qu'anticipé, la précision des modèles discrets augmente avec le nombre de sections utilisées. En utilisant

l'information détaillée dans cette thèse, un utilisateur peut sélectionner un modèle de complexité minimale qui remplit les exigences de précision d'une approximation donnée. Dans certains cas, la structure de base d'une section (T ou  $\pi$ ) exerce une influence significative sur la précision d'une certaine complexité de modèle. Cette thèse guide l'utilisateur vers le choix du modèle le plus efficace.

## 0.7 Analyse de la divergence de temps de propagation dans une configuration de circuit WSI

Tel que mentionné ci-haut, la divergence des temps de propagation est un autre sujet d'intérêt abordé dans cette thèse. Des applications haute vitesse développées avec des circuits utilisant la technologie ITGE à l'échelle de la gaufre («wafer scale integrated WSI») imposent des spécifications excessivement sévères pour les interconnexions de grande longueur La divergence des temps de propagation devient très importante pour la conception de ces circuits «WSI». Dans ce chapitre, une nouvelle méthode combinée est proposée pour réduire la divergence des temps de propagation. Elle s'énonce en trois volets :

- Des directions de propagation alternatives sont utilisées pour des signaux parallèles afin de réduire l'interférence électromagnétique entre lignes voisines.

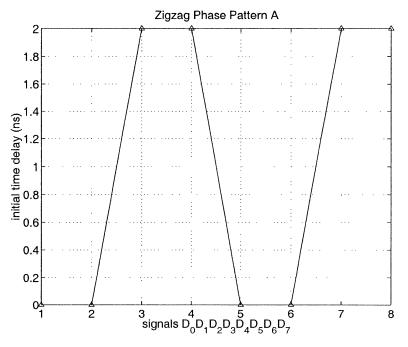

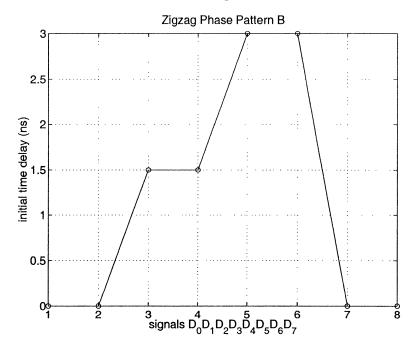

- Un agencement de phase en zigzag est instauré pour les signaux voyageant dans la même direction afin de réduire davantage l'interférence entre les lignes.

- Des suiveurs et des inverseurs sont alternativement insérés en guise de répéteur dans chaque interconnexion pour compenser l'effet de l'interférence due aux cas de double polarité sur l'incertitude des délais de propagation

Pour des applications pratiques, nous recommandons premièrement l'utilisation d'inverseurs seulement afin de réduire la divergence des temps de propagation. Si celleci surpasse toujours les tolérances permises, l'usage alternatif de suiveurs comme répéteurs pour réduire l'effet de couplage sur la divergence des temps de propagation.

Les dimensions des suiveurs et inverseurs devraient être ajustées avec soin pour éviter d'obtenir des valeurs variables de divergence de temps de propagation, ce qui peut arriver avec des répéteurs présentant des caractéristiques différentes.

### 0.8 Conclusion

Cette thèse contribue à plusieurs aspects concernant les interconnexions. De façon à simplifier la modélisation de longues interconnexions, une nouvelle méthode est proposée pour estimer l'erreur temporelle induite par le modèle dans une simulation en utilisant les paramètres du circuit dans le domaine fréquentiel. Les résultats numériques démontrent qu'avec cette méthode, l'erreur engendrée par la modélisation est bornée supérieurement pour les simulations temporelles.

Pour la modélisation de longues interconnexions dans un circuit ITGE, une approche pratique a été proposée pour modéliser une interconnexion simple MIS. Pour une telle interconnexion avec une source et une charge typiques, nous avons démontré que l'erreur induite par la modélisation dans le domaine du temps est minime si l'effet pelliculaire dans la trace métallique est négligé, cependant que cette erreur est non-négligeable si on ne considère pas les pertes diélectriques. Il fut intéressant de constater que l'erreur de modélisation demeure petite si la couche semi-conductrice est traitée comme un conducteur électrique parfait. Ceci nous confirme que la couche semi-conductrice peut être traitée comme un plan de masse virtuel sans perte d'intégrité du signal pour les plages de fréquence et de résistivité qui nous intéressent. Dans cette thèse, les contributions de différentes sous-régions fréquentielles à l'erreur de modélisation totale dans le domaine du temps furent également étudiées. La plage de fréquence d'intérêt a été divisée en trois sous-régions en se basant sur la largeur de bande de la tension de charge.

En plus de présenter la modélisation d'une interconnexion simple et pour fins de comparaisons, l'étude d'une autre configuration, une interconnexion double couplée avec retour de courant sur une des deux lignes (mode impair) a également été réalisée. Quelques cas furent analysés et les résultats de simulation ont montré que la constante complexe de propagation varie grandement entre une ligne MIS simple et deux lignes MIS fortement couplées. Nous avons démontré qu'il était possible de construire un modèle équivalent efficace pour les deux interconnexions couplées. Ce modèle peut être à une ou deux lignes. Un seuil est utilisé pour déterminer si l'un ou l'autre des deux modèles reproduit adéquatement le comportement électrique des deux interconnexions couplées.

Dans cette thèse, deux volets traitent de l'intégrité de signal. Le premier concerne le délai de propagation dans des lignes RC avec impédance de source  $R_S$  et charge capacitive  $C_L$  dans un circuit ITGE. Nous avons étudié les conditions de validité d'une modélisation de ligne à base de sections RC discretes. Une méthode d'évaluation asymptotique de forme d'onde (« AWE ») a été élaborée pour analyser le délai de propagation sur des lignes RC. Un nombre restreint de pôles "AWE" furent utilisées pour éviter l'instabilité numérique, même si cela peut engendrer de l'imprécision dans le cas de circuits compliqués. La précision de modèles discrets avec un certain nombre de sections a été représentée dans un plan r-c normalisé, qui est valide pour différentes technologies. En utilisant l'information détaillée dans cette thèse, un utilisateur peut sélectionner un modèle de complexité minimale qui remplit les exigences de précision d'une approximation donnée. Dans certains cas, la structure de base d'une section (T ou  $\pi$ ) exerce une influence significative sur la précision d'une certaine complexité de modèle. Cette thèse guide l'utilisateur vers le choix du modèle le plus efficace.

L'autre volet traitant de l'intégrité de signal porte sur la divergence des temps de propagation. Dans cette thèse, nous avons proposé une méthode combinée pour réduire ce paramètre. Des recommandations pratiques sont également mises de l'avant.

### TABLE OF CONTENTS

| DEDICATION                            | iv  |

|---------------------------------------|-----|

| ACKNOWLEDGMENTS                       | v   |

| RÉSUMÉ                                | vi  |

| ABSTRACT                              | kii |

| CONDENSÉ EN FRANÇAIS                  | vii |

| TABLE OF CONTENTS                     | ii  |

| LIST OF TABLES                        | ii  |

| LIST OF FIGURES                       | v   |

| LIST OF SYMBOLS                       | ii  |

| LIST OF ABBREVIATIONS xli             | ii  |

| CHAPTER 1: INTRODUCTION               | 1   |

| 1.1 Introduction                      | 1   |

| 1.2 Objectives of this thesis         | 2   |

| 1.3 Organization of this thesis       | 5   |

| 1.4 Main contributions of this thesis | 6   |

| CHAPTER 2: REVIEW OF LITERATURE       | 7   |

| 2.1 Modeling of interconnects                                                  | 7  |

|--------------------------------------------------------------------------------|----|

| 2.1.1 Microstrip                                                               | 9  |

| 2.1.2 Coplanar strips and coplanar striplines                                  | 9  |

| 2.1.3 Other interconnect topologies                                            | 10 |

| 2.1.4 Modeling of microstrip and coplanar strips in the MIS configuration      | 13 |

| 2.2 Simulation error vs. modeling accuracy                                     | 17 |

| 2.3 Signal integrity analysis – propagation time delay                         | 18 |

| 2.4 Signal integrity analysis – propagation time skew                          | 19 |

| 2.5 Summary                                                                    | 21 |

| CHAPTER 3: METHOD OF ESTIMATING TIME-DOMAIN SIMULATION                         |    |

| ERRORS FROM ERRORS IN THE FREQUENCY DOMAIN                                     |    |

| RESPONSE                                                                       | 23 |

| 3.1 Introduction                                                               | 23 |

| 3.2 Derivation of a general formula for the worst-case time-domain error       | 24 |

| 3.2.1 Definition of time-domain error                                          | 25 |

| 3.2.2 Division of frequency regions                                            | 26 |

| 3.2.3 Estimation of the time domain simulation errors from errors              |    |

| in the frequency domain response                                               | 28 |

| 3.3 Validation with practical interconnect models                              | 33 |

| 3.3.1 Description of two circuit techniques                                    | 34 |

| 3.3.2 Derivation of the transfer function for an interconnect model            | 35 |

| 3.3.2.1 ABCD matrix of a two-port network                                      |    |

| with an RC transmission line                                                   | 36 |

| 3.3.2.2 ABCD matrix of a two-port network                                      |    |

| with an ILC model of T-sections                                                | 37 |

| 3.3.2.3 Voltage transfer function of a two-port network with $R_S$ and $C_L$ . | 39 |

| 3.3.3 Example of comparisons between estimated errors and those from           |    |

| the simulator                                                                  | 42 |

| 3.4 Relation between the voltage transfer function and S-parameters             | 47 |

|---------------------------------------------------------------------------------|----|

| 3.4.1 Renormalized S-parameter $S_{21}$                                         | 49 |

| 3.4.2 Voltage transfer function $H(s)$                                          | 51 |

| 3.5 Discussion                                                                  | 53 |

| CHAPTER 4: MODELING OF A SINGLE INTERCONNECT IN THE MIS                         |    |

| CONFIGURATION                                                                   | 54 |

| 4.1 Introduction                                                                | 54 |

| 4.2 Original RLCG-B model                                                       | 57 |

| 4.2.1 Calculation of effective parameters for 1D MIS configuration              | 58 |

| 4.2.2 Extraction of 1D equivalent circuit parameters                            | 61 |

| 4.2.3 Extraction of 2D equivalent circuit parameters                            | 63 |

| 4.3 Modified RLCG-B model                                                       | 65 |

| 4.4 Impact of skin effect and dielectric losses                                 | 67 |

| 4.4.1 Impact of skin effect and dielectric losses on circuit models             | 67 |

| 4.4.2 Criterion for selecting simplified models                                 | 69 |

| 4.4.2.1 Impacts of $\gamma_z$ and $Z_C$ on the voltage transfer function $H(s)$ | 69 |

| 4.4.2.2 Estimation of simulation errors                                         | 73 |

| 4.5 Numerical simulations                                                       | 75 |

| 4.5.1 Validation of the RLCG-B model                                            | 76 |

| 4.5.2 Demonstration of error criterion                                          | 81 |

| 4.5.2.1 Propagation constant $\gamma_z$ and characteristic impedance $Z_C$      | 82 |

| 4.5.2.2 Voltage transfer function $H(s)$                                        | 84 |

| 4.6 Summary                                                                     | 89 |

| CHAPTER 5: MODELING OF TWO COUPLED INTERCONNECTS                                |    |

| IN THE MIS CONFIGURATION                                                        | 91 |

| 5.1 Introduction                                                                | 91 |

| 5.2 Odd-mode model of two coupled interconnects                                 | 92 |

| 5.2.1 Coupled interconnects in the MIS configuration                | 92  |

|---------------------------------------------------------------------|-----|

| 5.2.2 Hybrid RLCG-B model                                           | 94  |

| 5.2.3 Simple RLC model                                              | 95  |

| $5.2.3.1$ Effective inductance $L_{eff}$                            | 99  |

| $5.2.3.2$ Effective capacitance $C_{eff}$                           | 101 |

| 5.2.3.3 Effective resistance $R_{eff}$                              | 104 |

| 5.3 Validation of the simple RLC model                              | 105 |

| 5.4 Summary                                                         | 112 |

| CHAPTER 6: PROPAGATION TIME DELAY ANALYSIS OF                       |     |

| A DISTRIBUTED RC WIRE WITH $R_S$ AND $C_L$                          | 115 |

| 6.1 Introduction                                                    | 115 |

| 6.2 AWE method                                                      | 117 |

| 6.3 Iterative lumped circuits (ILC) model                           | 118 |

| 6.4 Estimation of voltage waveforms                                 | 119 |

| 6.5 Analysis of propagation time delay                              | 120 |

| 6.6 Numerical results                                               | 128 |

| 6.7 Summary                                                         | 141 |

| CHAPTER 7: PROPAGATION TIME SKEW ANALYSIS                           |     |

| IN WSI CIRCUIT DESIGN                                               | 142 |

| 7.1 Introduction                                                    | 142 |

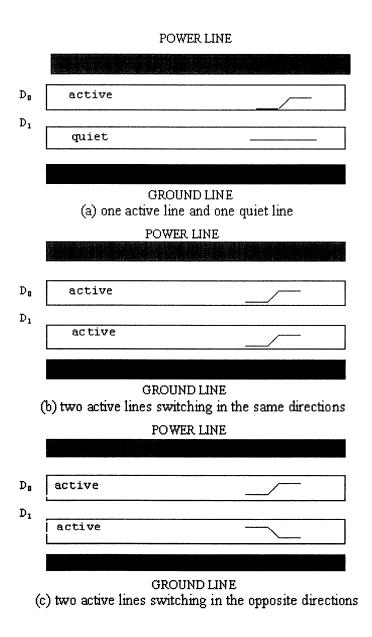

| 7.2 Considered structure and problem formulation                    | 142 |

| 7.2.1 Analysis of the "2+2" topology                                | 144 |

| 7.2.2 Analysis of the "8+2" topology                                | 146 |

| 7.3 Proposed approach for wafer scale integrated system             | 151 |

| 7.3.1 Approach one — Bus with interspersed directions of data flow  | 151 |

| 7.3.2 Approach two — Spatially modulated signal phase               | 153 |

| 7.3.3 Approach three — Skew compensation by dual-polarity crosstalk | 155 |

| 7.4 Simulation results                                              | 157 |

|---------------------------------------------------------------------|-----|

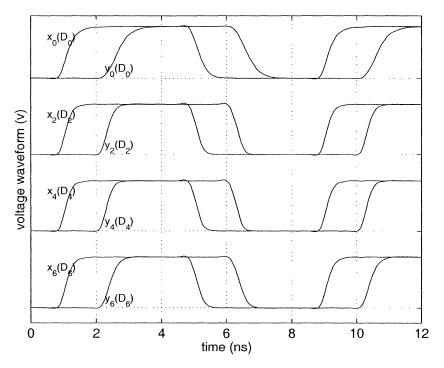

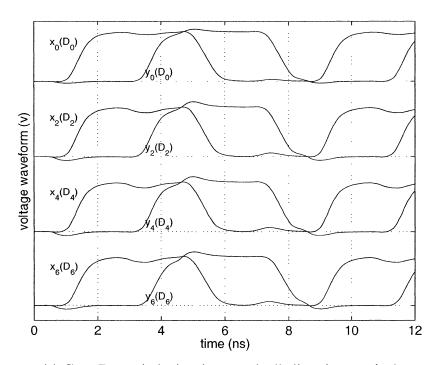

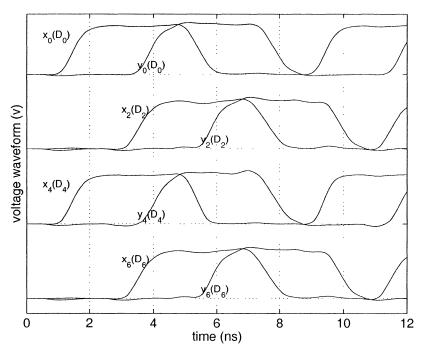

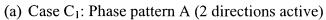

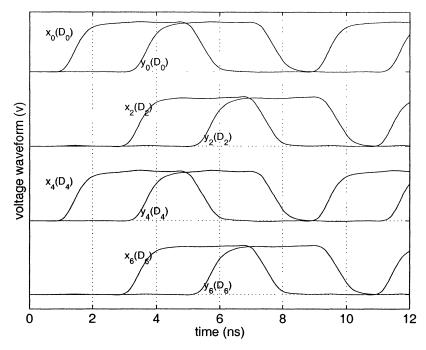

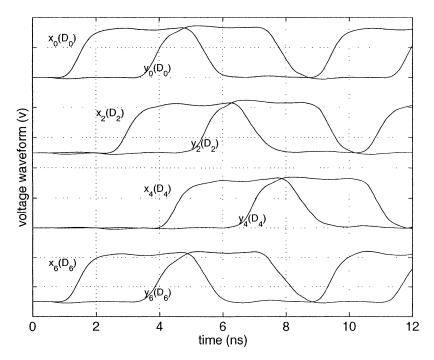

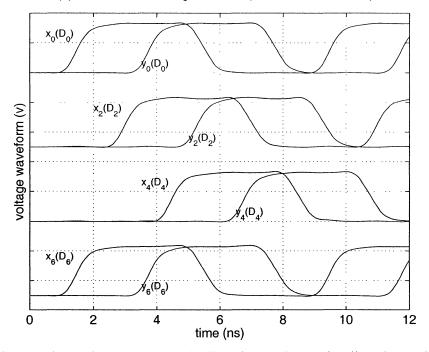

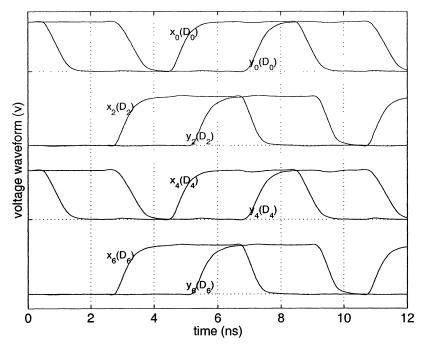

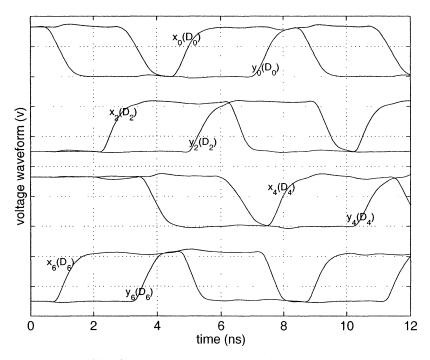

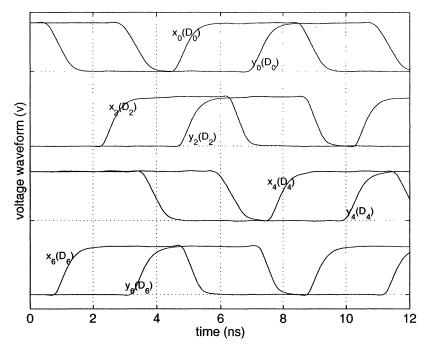

| 7.4.1 Cases $A_1$ and $A_2$                                         | 158 |

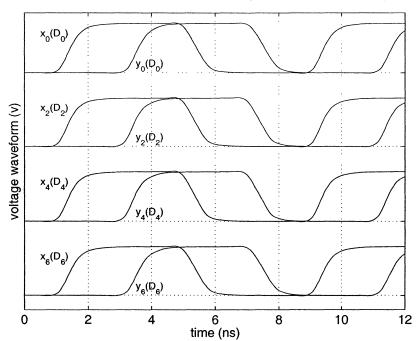

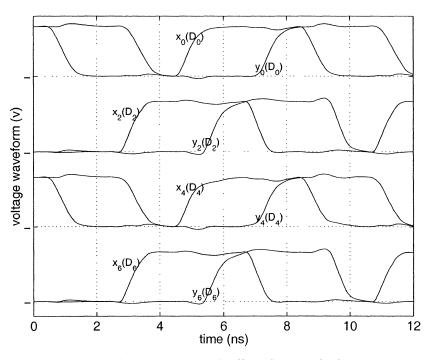

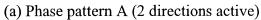

| 7.4.2 Cases $B_1$ and $B_{10}$ , and $B_2$ and $B_{20}$             | 159 |

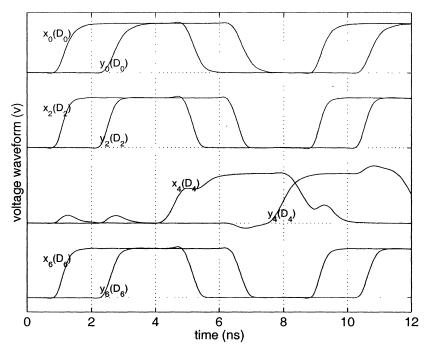

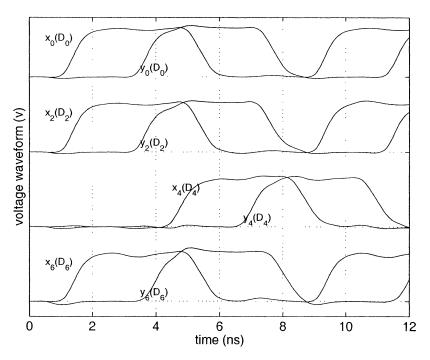

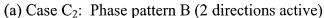

| 7.4.3 Cases $C_1$ and $C_{10}$ , and $C_2$ and $C_{20}$             | 163 |

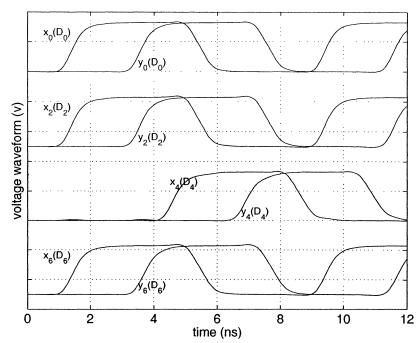

| 7.4.4 Cases $D_1$ and $D_{10}$ , and $D_2$ and $D_{20}$             | 166 |

| 7.5 Conclusions                                                     | 169 |

| CHAPTER 8: CONCLUSIONS                                              | 171 |

| 8.1 Method of estimating time-domain model-induced simulation error | 171 |

| 8.2 Practical approach of modeling a single MIS interconnect        | 171 |

| 8.3 Comparison between single and coupled MIS interconnects         | 174 |

| 8.4 Propagation time delay analysis                                 | 175 |

| 8.5 Propagation time skew analysis                                  | 176 |

| 8.6 Suggestions for future work                                     | 177 |

| BIBLIOGRAPHY                                                        | 178 |

| APPENDIX A: ELMORE DELAY MODEL                                      | 187 |

| APPENDIX B: ASYMPTOTIC WAVEFORM EVALUATION (AWE)                    |     |

| METHOD                                                              | 189 |

### LIST OF TABLES

| Table 4.1 : | Model selection                                                          | 68  |

|-------------|--------------------------------------------------------------------------|-----|

| Table 4.2 : | Main parameters in the MIS configuration                                 | 77  |

| Table 4.3a: | Differences of $\gamma_z$ and $Z_C$ between full-wave field analysis and |     |

|             | original RLCG-B circuit model ( $\rho_s$ =100 Ω·cm)                      | 77  |

| Table 4.3b: | Differences of $\gamma_z$ and $Z_C$ between full-wave field analysis     |     |

|             | and original RLCG-B circuit model ( $\rho_s$ =1 $\Omega$ ·cm)            | 77  |

| Table 4.4 : | Differences of $Z_{series}$ between modified and original RLCG-B         |     |

|             | circuit models                                                           | 81  |

| Table 4.5 : | Upper limits of voltage differences for a 1 volt pulse (unit: mV).       | 88  |

| Table 5.1 : | Main parameters of coupled interconnects in the MIS configuration.       | 93  |

| Table 5.2 : | Capacitance $C_{eff}$                                                    | 104 |

| Table 6.1 : | Maximam relative time delay differences between AWE and SPICE            |     |

|             | (T- and $\pi$ -structures)                                               | 130 |

| Table 6.2 : | Relative time delay differences (T- and $\pi$ -structures)               | 137 |

| Table 7.1 : | Main parameters of multilayer substrate and interconnects                | 148 |

| Table 7.2 : | Sizes of inverters and buffers                                           | 148 |

| Table 7.3 : | Propagation time skew analysis                                           | 157 |

| Table 7.4 : | Propagation time delays for difference cases                             | 159 |

### LIST OF FIGURES

| Figure 1.1:   | Topics related to VLSI/WSI circuit design                                        | 3  |

|---------------|----------------------------------------------------------------------------------|----|

| Figure 2.1:   | Topologies of interconnects in VLSI circuits                                     | 8  |

| Figure 3.1:   | A two-port network with a voltage source $v_s(t)$ , source impedance $Z_S$       |    |

|               | and load impedance $Z_L$                                                         | 25 |

| Figure 3.2:   | Division of frequency regions                                                    | 27 |

| Figure 3.3:   | N sampling points on a unit circle                                               | 31 |

| Figure 3.4:   | A two-port network with an RC wire, source resistance $R_S$ and load             |    |

|               | capacitance $C_L$                                                                | 34 |

| Figure 3.5:   | T- and $\pi$ - sections used in ILC models                                       | 35 |

| Figure 3.6:   | An MC cell                                                                       | 35 |

| Figure 3.7:   | Two sub-networks for one T-section                                               | 38 |

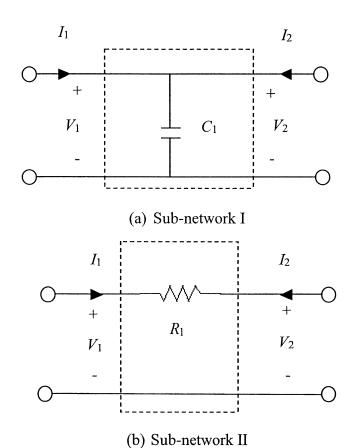

| Figure 3.8:   | Pulse voltage source                                                             | 43 |

| Figure 3.9a:  | Magnitude of voltage transfer functions for ILC and TL models                    | 44 |

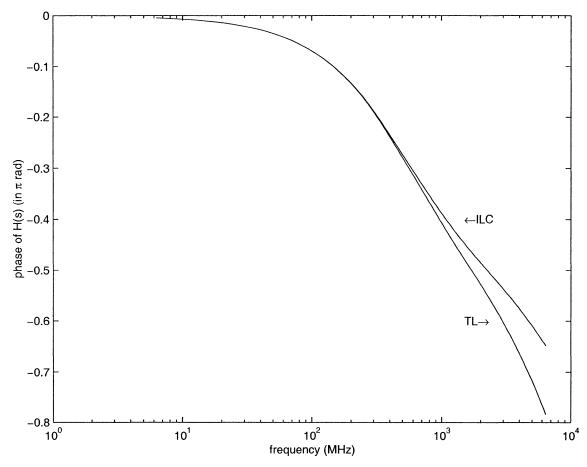

| Figure 3.9b:  | Phase of voltage transfer functions for ILC and TL models                        | 45 |

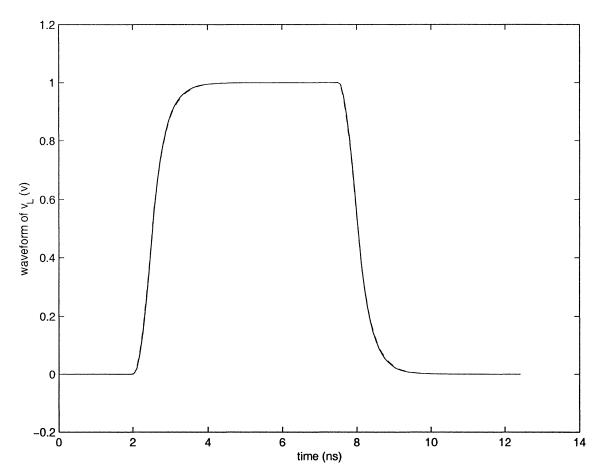

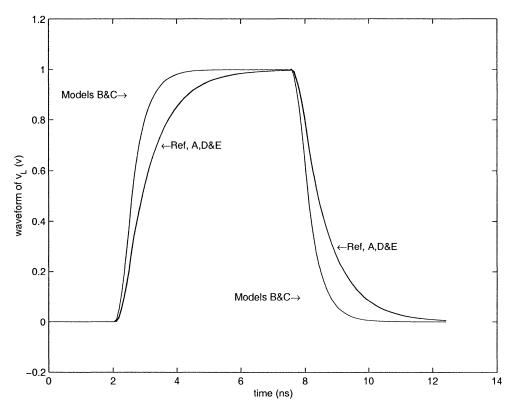

| Figure 3.10a: | Waveform of load voltages for ILC and TL models                                  | 46 |

| Figure 3.10b: | Voltage difference between the circuits with ILC and TL models                   | 47 |

| Figure 3.11:  | A two-port network with source impedance $Z_S$ and load $Z_L$                    | 48 |

| Figure 3.12:  | Signal flow graph of a two-port network with $Z_S$ and $Z_L$                     |    |

|               | $(Z_{01}=Z_S \text{ and } Z_{02}=Z_L) \ldots \ldots \ldots \ldots \ldots \ldots$ | 50 |

| Figure 4.1:   | Steps for constructing the original RLCG-B model                                 | 58 |

| Figure 4.2:   | Cross section of a microstrip in the MIS configuration                           | 59 |

| Figure 4.3:   | Original RLCG-B model                                                            | 64 |

| Figure 4.4:   | Modified RLCG-B model                                                            | 65 |

| Figure 4.5:   | Comparison of propagation constant $\gamma_z$ among Agilent-ADS,                 |    |

|               | Tuncer et al's model and ours, for the parameters given in Table 4.2             |    |

|               | with $w_m=1$ um and $\rho_0=1$ $\Omega$ cm                                       | 78 |

| Figure 4.6:   | Comparison of characteristic impedance $Z_C$ among Agilent-ADS,                 |     |

|---------------|---------------------------------------------------------------------------------|-----|

|               | Tuncer et al's model and ours, for the parameters given in Table 4.2            |     |

|               | with $w_m=1 \mu m$ and $\rho_s=1 \Omega \cdot cm \dots \dots \dots \dots \dots$ | 79  |

| Figure 4.7:   | Comparison of series impedance $Z_{series}$                                     |     |

|               | between modified and original RLCG-B models                                     | 80  |

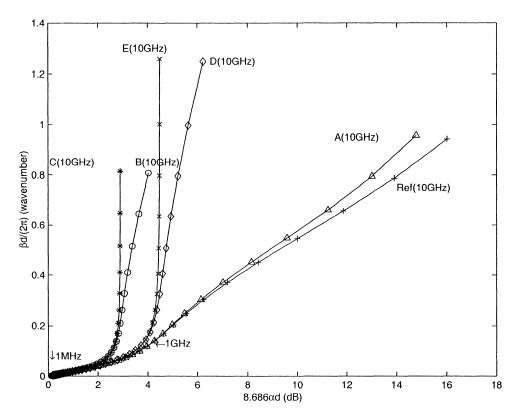

| Figure 4.8:   | Comparison of magnitude and phase of $e^{\gamma_n}$                             |     |

|               | between simplified models and reference                                         | 83  |

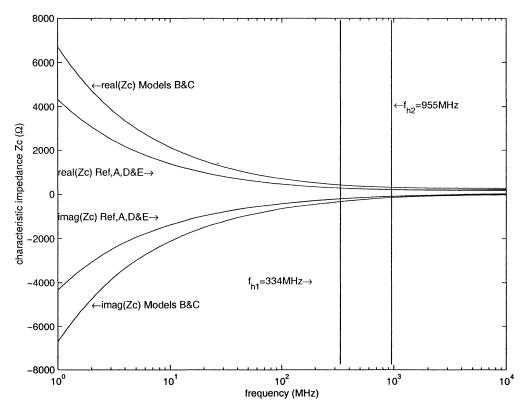

| Figure 4.9:   | Comparison of characteristic impedance $Z_C$                                    |     |

|               | between simplified models and reference                                         | 84  |

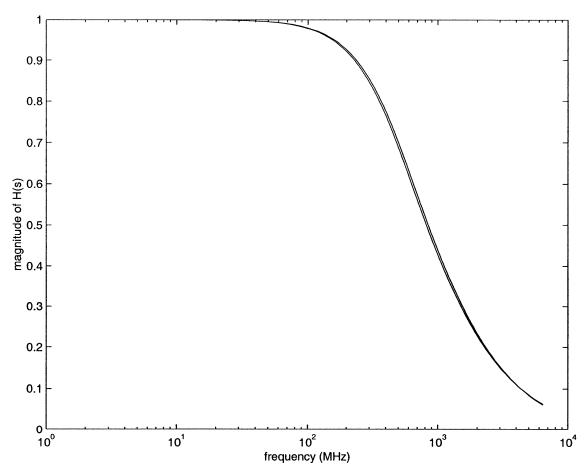

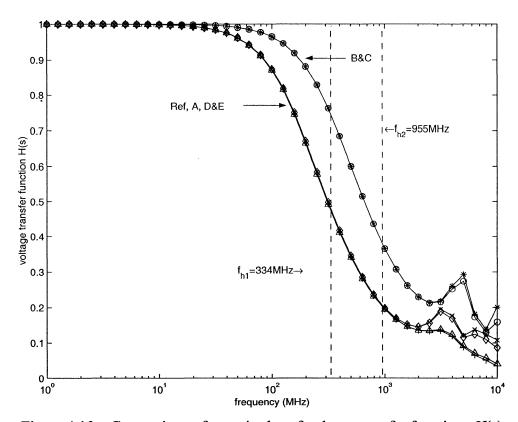

| Figure 4.10a: | Comparison of magnitudes of voltage transfer functions $H(s)$                   |     |

|               | between simplified models and reference                                         | 85  |

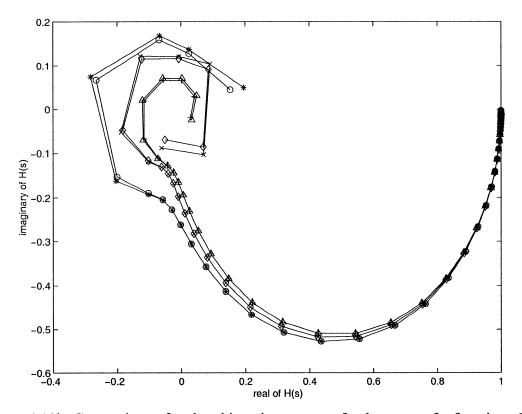

| Figure 4.10b: | Comparison of real and imaginary parts of voltage transfer functions $H(s)$     | )   |

|               | between simplified models and reference                                         | 86  |

| Figure 4.11:  | Comparison of load voltages $v_L(t)$                                            |     |

|               | between simplified models and reference                                         | 87  |

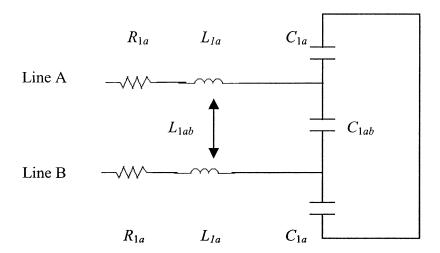

| Figure 5.1:   | Coupled interconnects in the MIS configuration                                  | 93  |

| Figure 5.2:   | A hybrid RLCG-B model                                                           |     |

|               | for the odd-mode of two coupled interconnects                                   | 95  |

| Figure 5.3:   | Currents flowing on three conductors forming the interconnect                   | 96  |

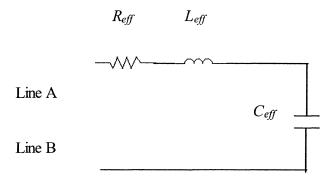

| Figure 5.4a:  | RLC model for the odd mode of two coupled interconnects                         |     |

|               | (five-element RLC model)                                                        | 97  |

| Figure 5.4b:  | RLC model for the odd mode of two coupled interconnects                         |     |

|               | (three-element RLC model)                                                       | 98  |

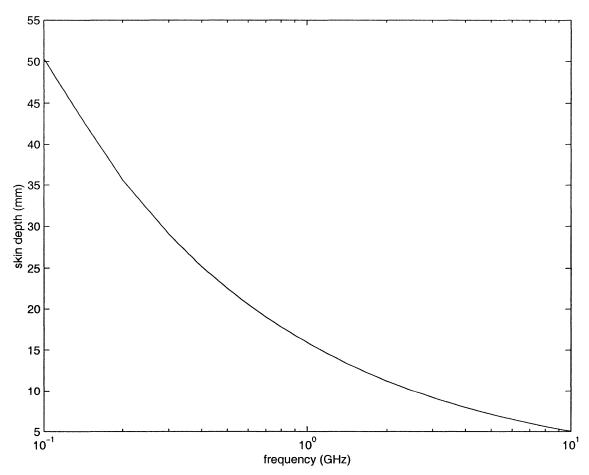

| Figure 5.5:   | Skin depth of the semiconductor with the resistivity of 100 $\Omega$ ·cm        | 99  |

| Figure 5.6:   | Geometrical transform                                                           | 00  |

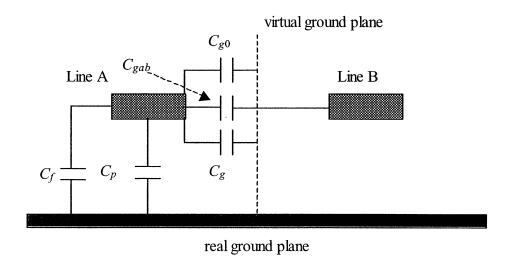

| Figure 5.7:   | Odd-mode capacitances                                                           | 02  |

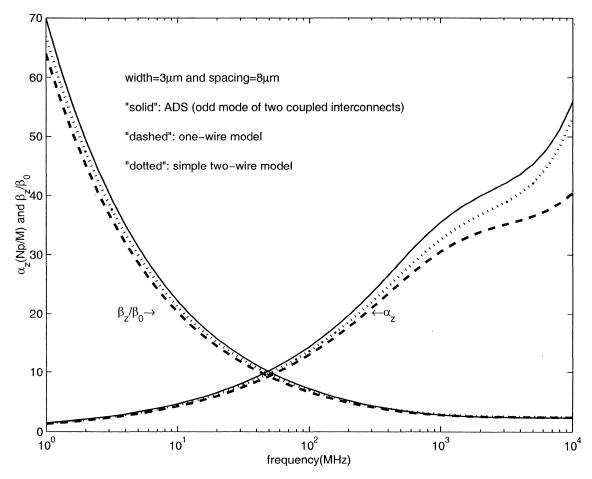

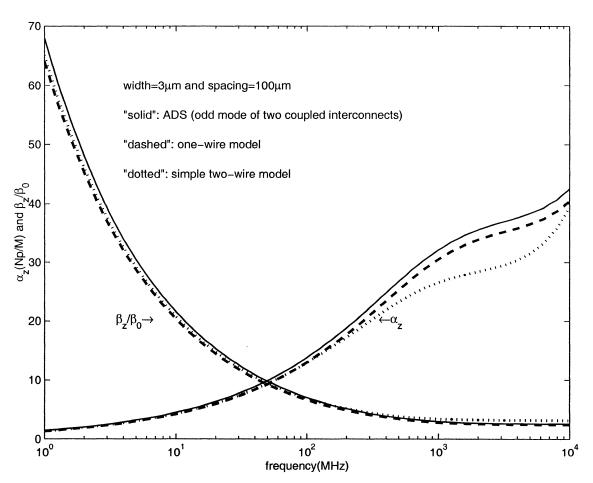

| Figure 5.8a:  | Comparisons of complex propagation constant among one-wire model,               |     |

|               | simple two-wire model and ADS for two coupled interconnects with a              |     |

|               | wire spacing of 8 µm                                                            | .06 |

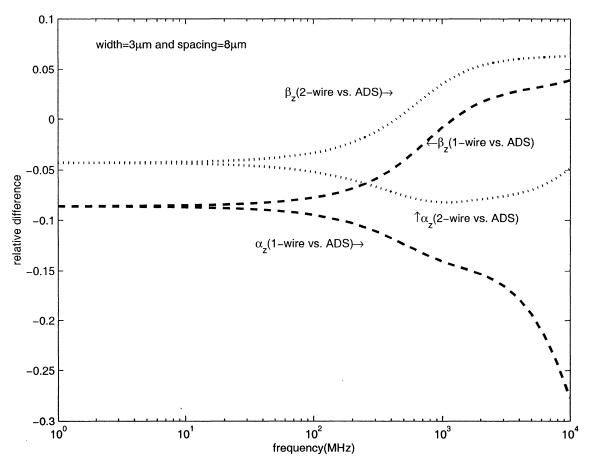

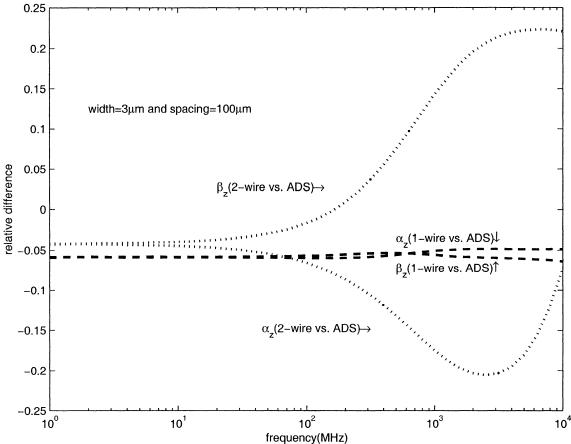

| Figure 5.8b:  | Relative differences of complex propagation constant between one-wire        | 2   |  |

|---------------|------------------------------------------------------------------------------|-----|--|

|               | model and ADS, and between simple two-wire model and ADS for two             | )   |  |

|               | coupled interconnects with a wire spacing of 8 $\mu m$                       | 107 |  |

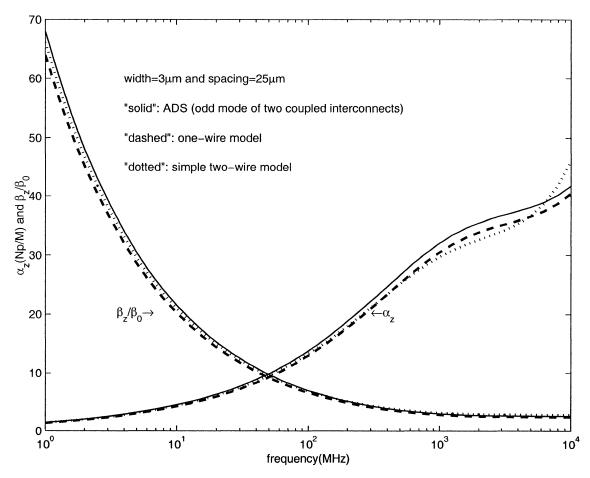

| Figure 5.9a:  | Comparisons of complex propagation constant among one-wire model,            |     |  |

|               | simple two-wire model and ADS for two coupled interconnects with a           |     |  |

|               | wire spacing of 25 $\mu m$                                                   | 108 |  |

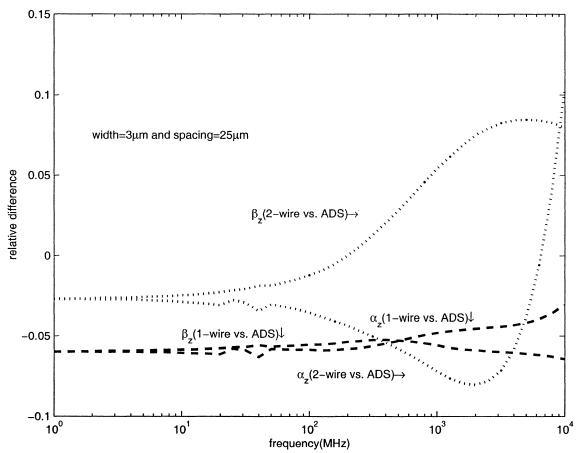

| Figure 5.9b:  | Relative differences of complex propagation constant between one-wire        | •   |  |

|               | model and ADS, and between simple two-wire model and ADS for two             |     |  |

|               | coupled interconnects with a wire spacing of 25 µm                           | 109 |  |

| Figure 5.10a: | Comparisons of complex propagation constant among one-wire model,            |     |  |

|               | simple two-wire model and ADS for two coupled interconnects with a           |     |  |

|               | wire spacing of 100 µm                                                       | 110 |  |

| Figure 5.10b: | Relative differences of complex propagation constant between one-wir         | е   |  |

|               | model and ADS, and between two-wire model and ADS for two coupled            |     |  |

|               | interconnects with a wire spacing of 100 μm                                  | 112 |  |

| Figure 6.1:   | Equivalent circuits for a distributed RC wire                                | 119 |  |

| Figure 6.2:   | A two-port network with source resistance $R_S$ and load capacitance $C_L$   | 120 |  |

| Figure 6.3:   | Relative time delay difference (1/10000) between AWE and SPICE.              | 129 |  |

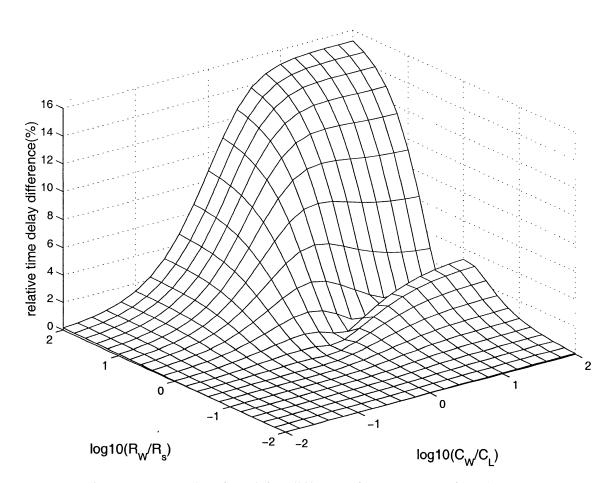

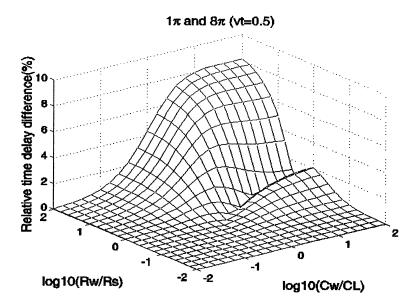

| Figure 6.4a:  | Relative time delay difference between 1T and 8T ( $v_t$ =0.4)               | 131 |  |

| Figure 6.4b:  | Relative time delay difference between 2T and 8T ( $v_t$ =0.4)               | 132 |  |

| Figure 6.4c:  | Relative time delay difference between 4T and 8T ( $\nu_t$ =0.4)             | 133 |  |

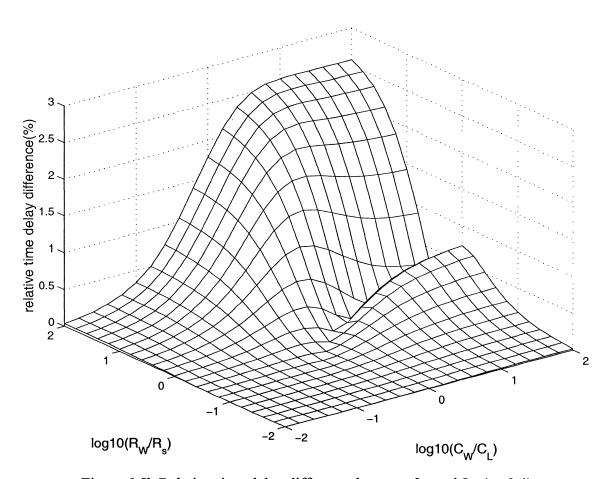

| Figure 6.5a:  | Relative time delay difference between $1\pi$ and $8\pi$ ( $\nu_r$ =0.4)     | 134 |  |

| Figure 6.5b:  | Relative time delay difference between $2\pi$ and $8\pi$ ( $v_i$ =0.4)       | 135 |  |

| Figure 6.5c:  | Relative time delay difference between $4\pi$ and $8\pi$ ( $v_i$ =0.4)       | 136 |  |

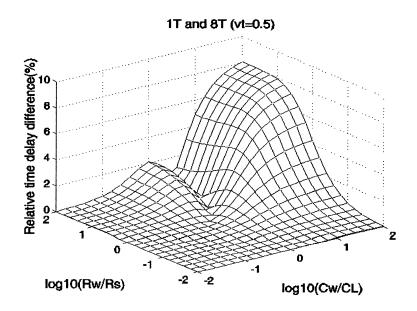

| Figure 6.6a:  | Relative time delay difference between 1T- and 8T-sections models            |     |  |

|               | $(v_t=0.5)$                                                                  | 138 |  |

| Figure 6.6b:  | Relative time delay difference between $1\pi$ - and $8\pi$ - sections models |     |  |

|               | $(v_t=0.5)$                                                                  | 138 |  |

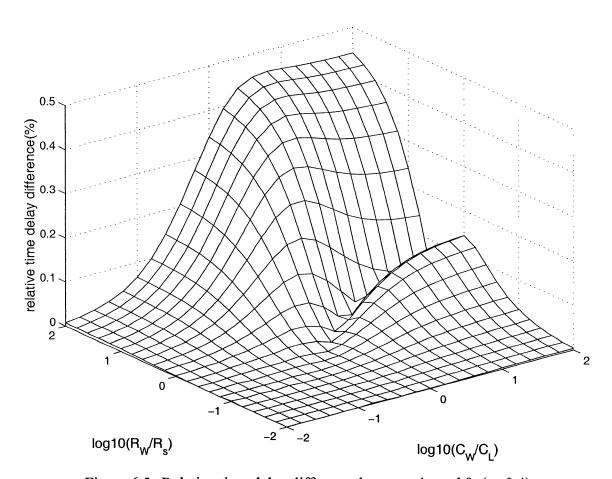

| Figure 6.7a:  | Absolute time delay difference between 1- and 8- sections ( $v_t$ =0.5).     | 139 |  |

| Figure 6.7b: | Relative time delay difference between 1- and 8- sections ( $v_t$ =0.5) . | 140 |  |

|--------------|---------------------------------------------------------------------------|-----|--|

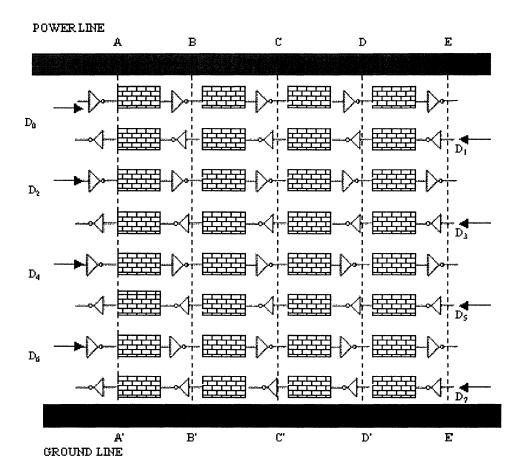

| Figure 7.1:  | Topology of "8+2" interconnects with inverters only                       |     |  |

|              | (signals propagate in the same direction)                                 | 143 |  |

| Figure 7.2:  | Topology of "2+2" interconnects                                           | 144 |  |

| Figure 7.3:  | Equivalent circuit of two coupled interconnects                           |     |  |

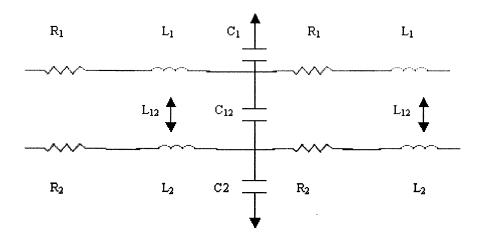

|              | with power and ground lines                                               | 145 |  |

| Figure 7.4:  | Propagation time skew analysis for "8+2" structure with inverters only    |     |  |

|              | (8 signals propagating in one direction)                                  | 150 |  |

| Figure 7.5:  | Topology of "8+2" interconnects with inverters only                       |     |  |

|              | (signals propagate in opposite directions)                                | 152 |  |

| Figure 7.6:  | Zigzag phase patterns                                                     | 154 |  |

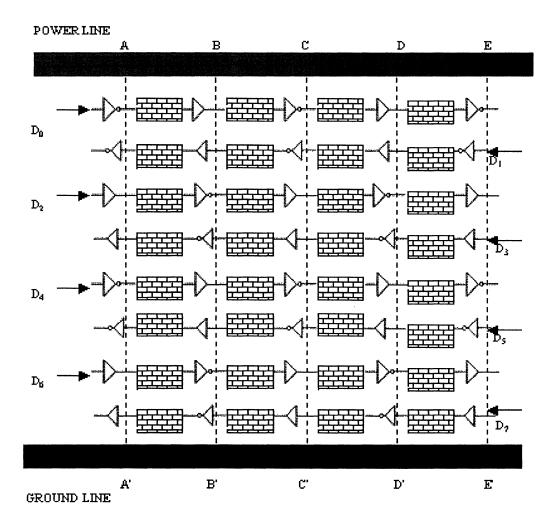

| Figure 7.7:  | Topology of "8+2" interconnects with both buffers and inverters           |     |  |

|              | (signals propagate in two directions)                                     | 156 |  |

| Figure 7.8:  | Propagation time skew analysis for "8+2" structure with inverters only    | 7   |  |

|              | (fast cases, 8 signals propagate in two directions)                       | 161 |  |

| Figure 7.9:  | Propagation time skew analysis for "8+2" structure with inverters only    | 7   |  |

|              | (slow cases, 8 signals propagate in two directions)                       | 162 |  |

| Figure 7.10: | Propagation time skew analysis for "8+2" structure with inverters only    | 7   |  |

|              | (8 signals propagate in two directions and switch in phase pattern A).    | 164 |  |

| Figure 7.11: | Propagation time skew analysis for "8+2" structure with inverters only    |     |  |

|              | (8 signals propagate in two directions and switch in phase pattern B).    | 165 |  |

| Figure 7.12: | Propagation time skew analysis for "8+2" structure with both buffers a    | and |  |

|              | inverters (8 signals propagate in two directions and switch in phase      |     |  |

|              | pattern A)                                                                | 167 |  |

| Figure 7.13: | Propagation time skew analysis for "8+2" structure with both buffers a    | nd  |  |

|              | inverters (8 signals propagate in two directions and switch in phase      |     |  |

|              | pattern B)                                                                | 168 |  |

| Figure A.1:  | An RC tree                                                                | 187 |  |

## LIST OF SYMBOLS

| $a_1, a_2$                         | incident waves $[V/\sqrt{\Omega}]$                            |

|------------------------------------|---------------------------------------------------------------|

| $a_1, a_2, a_k$                    | coefficient functions in ABCD-matrix [no unit]                |

| $b_1, b_2$                         | reflection waves $\left[\sqrt[V]{\sqrt{\Omega}}\right]$       |

| $b_1$ , $b_2$ , $b_k$              | coefficient functions in ABCD-matrix [no unit]                |

| $b_s$                              | source wave $\left[\sqrt[V]{\sqrt{\Omega}}\right]$            |

| c                                  | velocity of light [m/s]                                       |

| c                                  | normalized capacitance [no unit]                              |

| $C_i$ , $C_s$                      | shunt capacitance [F/m <sup>2</sup> ] (1D model)              |

| $C_L$                              | load capacitance [F]                                          |

| $C_w$                              | wire capacitance [F]                                          |

| $C_w^l$                            | wire capacitance per unit length [F/m]                        |

| $C$ , $C_1$                        | capacitance element [F]                                       |

| $C, C_1, C_2, C_{12}$              | capacitance per unit length [F/m]                             |

| $C_{1a}$ , $C_{2a}$                | capacitance per unit length [F/m]                             |

| $C_{1b}, C_{2b}, C_{2ab}, C_{eff}$ | capacitance per unit length [F/m]                             |

| $C_f, C_p$                         | capacitance per unit length [F/m]                             |

| $C_{g0}, C_{gab}, C_g$             | capacitance per unit length [F/m]                             |

| d                                  | length of wire [m]                                            |

| $f_{h1}, f_{h2}$                   | frequency [Hz]                                                |

| $f_s$                              | sampling frequency [Hz]                                       |

| $G_s$                              | shunt conductance [Simens] (1D model)                         |

| G, $G$ 2                           | shunt conductance [Simens/m] (2D model)                       |

| $G_{\mathrm{n}}$                   | normalized conductance [no unit]                              |

| $H, H_{eq}$                        | height [m]                                                    |

| $H(s), H_{mod}(s), H_{tl}(s)$      | voltage transfer functions in s $(=j\omega)$ domain [no unit] |

$\widetilde{H}_{mod}(k)$ ,  $\widetilde{H}_{tl}(k)$  samples of  $H_{mod}(s)$ ,  $H_{tl}(s)$  [no unit]