|                         | Low power and high speed arithmetic circuits for software assisted wireless systems                                                                                                                                                                            |

|-------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Auteur: Author:         | Wei Ling                                                                                                                                                                                                                                                       |

| Date:                   | 2004                                                                                                                                                                                                                                                           |

| Type:                   | Mémoire ou thèse / Dissertation or Thesis                                                                                                                                                                                                                      |

| Référence:<br>Citation: | Ling, W. (2004). Low power and high speed arithmetic circuits for software assisted wireless systems [Master's thesis, École Polytechnique de Montréal]. PolyPublie. <a href="https://publications.polymtl.ca/7434/">https://publications.polymtl.ca/7434/</a> |

# Document en libre accès dans PolyPublie Open Access document in PolyPublie

| URL de PolyPublie:<br>PolyPublie URL:    | https://publications.polymtl.ca/7434/ |

|------------------------------------------|---------------------------------------|

| Directeurs de<br>recherche:<br>Advisors: | Yvon Savaria                          |

| Programme:<br>Program:                   | Unspecified                           |

# UNIVERSITÉ DE MONTRÉAL ÉCOLE POLYTECHNIQUE DE MONTRÉAL

# LOW POWER AND HIGH SPEED ARITHMETIC CIRCUITS FOR SOFTWARE ASSISTED WIRELESS SYSTEMS

### **WEI LING**

DÉPARTEMENT DE GÉNIE ÉLECTRIQUE ÉCOLE POLYTECHNIQUE DE MONTRÉAL

MÉMOIRE PRÉSENTÉ EN VUE DE L'OBTENTION

DU DIPLÔME DE MAÎTRISE EN SCIENCES APPLIQUÉES

(GÉNIE ÉLECTRIQUE)

Décembre 2004

Library and Archives Canada

Published Heritage Branch

395 Wellington Street Ottawa ON K1A 0N4 Canada Bibliothèque et Archives Canada

Direction du Patrimoine de l'édition

395, rue Wellington Ottawa ON K1A 0N4 Canada

> Your file Votre référence ISBN: 0-494-01360-5 Our file Notre référence ISBN: 0-494-01360-5

### NOTICE:

The author has granted a non-exclusive license allowing Library and Archives Canada to reproduce, publish, archive, preserve, conserve, communicate to the public by telecommunication or on the Internet, loan, distribute and sell theses worldwide, for commercial or non-commercial purposes, in microform, paper, electronic and/or any other formats.

The author retains copyright ownership and moral rights in this thesis. Neither the thesis nor substantial extracts from it may be printed or otherwise reproduced without the author's permission.

### AVIS:

L'auteur a accordé une licence non exclusive permettant à la Bibliothèque et Archives Canada de reproduire, publier, archiver, sauvegarder, conserver, transmettre au public par télécommunication ou par l'Internet, prêter, distribuer et vendre des thèses partout dans le monde, à des fins commerciales ou autres, sur support microforme, papier, électronique et/ou autres formats.

L'auteur conserve la propriété du droit d'auteur et des droits moraux qui protège cette thèse. Ni la thèse ni des extraits substantiels de celle-ci ne doivent être imprimés ou autrement reproduits sans son autorisation.

In compliance with the Canadian Privacy Act some supporting forms may have been removed from this thesis.

While these forms may be included in the document page count, their removal does not represent any loss of content from the thesis.

Conformément à la loi canadienne sur la protection de la vie privée, quelques formulaires secondaires ont été enlevés de cette thèse.

Bien que ces formulaires aient inclus dans la pagination, il n'y aura aucun contenu manquant.

# UNIVERSITÉ DE MONTRÉAL ÉCOLE POLYTECHNIQUE DE MONTRÉAL

### Ce mémoire intitulé:

# LOW POWER AND HIGH SPEED ARITHMETIC CIRCUITS FOR SOFTWARE ASSISTED WIRELESS SYSTEMS

Présenté par : Wei Ling

en vue de l'obtention du diplôme de : <u>Maîtrise ès sciences</u> <u>appliquées</u> a été dûment accepté par le jury d'examen constitué de :

- M. KHOUAS Abdelhakim, Ph.D., président

- M. SAVARIA Yvon, Ph.D., directeur de recherche

- M. THIBEAULT Claude, Ph.D., membre

## **DEDICATE**

I would like to dedicate this thesis to my wife and parents,

### **ACKNOWLEDGEMENTS**

First of all I would like to express my sincerest gratitude to my directeur de recherche Prof. Yvon Savaria, who guided me from the beginning with excellent supervision and invaluable suggestions. I would like also thanks Prof. Claude Thibeault and Prof. Hakim Khouas for providing detailed corrections. I would like to acknowledge the help from research group Multi-Equalizer and Software Defined Radio. Special thanks also go to my wife Minjie, for her continuous support as well as the love she has brought to me.

### **RÉSUMÉ**

Il devient de plus en plus commun que les systèmes de communication ajustent leur performance, leur débit et leur puissance selon la tâche, la qualité du canal et les services à fournir. Une approche récente, appelé Software Assisted (Defined) Radio (SDR) attire énormément d'attention. Cette approche répond aux demandes d'adaptabilité et de faible consommation de puissance dans les prochaines générations de système de communication sans fil.

Dans ce mémoire, nous passerons d'abord en revue quelques architectures existantes de SDR, les techniques de modulation adaptative et les techniques de conception de système électronique à basse puissance. Ensuite, nous présentons un multiplieur de précision variable pour l'égaliseur de SDR. Ce multiplieur réduit la puissance dissipée en ajustant la largeur des mots traités selon le type de modulation. Il existe un bon choix de la longueur de mot pour l'égaliseur LMS associé à divers types de modulation. Il est avantageux de réaliser l'égaliseur LMS en utilisant une longueur de mot variable. L'économie de puissance en employant l'égaliseur LMS avec une longueur de mot variable peut atteindre 85% pour chaque multiplication.

Puis, nous présentons un multiplieur pipeliné conçu selon la structure logique Domino pour le processeur DSP. La question des variations paramétriques et leur impact sur la puissance dissipée au sein d'un multiplieur pipeliné profond conçu selon la structure Domino est également discutés. Nous trouvons que le circuit vague-Domino bloquant avec pied est plus approprié à des applications où les pipelines sont profonds. De plus, on

propose aussi une solution de porte dynamique inverseuse afin d'empêcher le problème classique de précharge des circuits Domino. Le multiplieur 9 bits vague-Domino a été conçu en technologie TSMC 0.18µm CMOS. Une économie de puissance de 40% est enregistrée en employant la porte dynamique inverseuse proposée. Le multiplieur 9 bits vague-Domino a été comparé avec du multiplieur réalisé par le circuit statique non-pipeliné. En effet, le circuit vague-Domino pipeliné élimine les courses internes qui peuvent produire des commutations multiples. Nos résultats montrent que sa consommation de puissance est inférieure à celle du multiplieur réalisé avec le circuit statique non-pipeliné.

### **ABSTRACT**

It becomes more and more common that communication systems adjust their performance, throughput and power consumption according to workload, channel quality and service requirements. The emerging concept, ---- Software Assisted (Defined) Radio (SDR), is proposed to meet the requirements of adaptive and low power for next generation wireless communication systems.

In this thesis, we first give some reviews of SDR architectures and implementations, the adaptive features of next generation wireless communication standards, and existing popular VLSI low power design techniques. Then we will focus on a DSP building block ----- an array multiplier, which is heavily used in SDR systems.

We will study the word length implementation of a VLSI array multiplier under an adaptive modulation scheme. We will show that there exists a good choice of I word length implementation for a LMS equalizer for each modulation scheme. Increasing the word length beyond this good choice does little to improve performance. Based on this word length, a variable word length array multiplier is developed using dynamic voltage scaling and gating techniques. The simulation results demonstrate that a LMS equalizer based on a variable-precision multiplier can produce an 85% power reduction without performance and throughput penalties.

A long pipelined array multiplier using high-speed wave Domino circuit, which is suitable for implementing SDR cores, is also studied. Since the long pipelined circuit is more vulnerable to parametric variations, statistical timing relations are developed for characterizing performance impacts of the parametric variations in different wavepipelined Domino circuits and clocking styles. We demonstrate that the clock delayed,

footed Domino circuit style is the most suitable for deeply pipelined array multipliers. In

addition, an improved inverting dynamic gate solution is proposed to reduce the usage of

dual-rail Domino logics in this array multiplier. A 40% power saving is achieved for a 15stage wave pipelined array multiplier in using these improved inverting dynamic gates.

Finally, the comparisons of two array multiplier implementations, one using static circuit

and another using wave pipelined Domino circuit, are performed. The results show that

the wave pipelined array multiplier consumes less power per operation compared to a

static circuit implementation that is not pipelined.

### CONDENSÉ EN FRANÇAIS

Il devient de plus en plus commun que les systèmes de communication ajustent leur performance, leur débit et leur puissance selon la tâche, la qualité du canal et les services à fournir. Une approche récente, appelé Software Assisted (Defined) Radio (SDR) attire énormément d'attention. Cette approche répond aux demandes d'adaptabilité et de faible consommation de puissance dans les prochaines générations de système de communication sans fil.

Dans ce mémoire, nous passerons d'abord en revue quelques architectures existantes de SDR, les techniques de modulation adaptative et les techniques de conception de système électronique à basse puissance. Ensuite, nous présentons un multiplieur de précision variable pour l'égaliseur de SDR. Ce multiplieur réduit la puissance dissipée en ajustant la largeur des mots traités selon le type de modulation. Puis, nous présentons un multiplieur pipeliné conçu selon la structure logique Domino pour le processeur DSP. La question des variations paramétriques et leur impact sur la puissance dissipée au sein d'un multiplieur pipeliné profond conçu selon la structure Domino est également discutés. Enfin, des comparaisons de la consommation de puissance entre l'implémentation d'un circuit en logique statique et en logique Domino multiphasée d'un multiplieur ont été effectuées.

#### Revue de littérature

Les architectures récemment proposées pour la mise en œuvre des systèmes SDR peuvent être divisées en 3 catégories : 1) Les systèmes SDR implémentés dans un ou plusieurs processeurs DSP; 2) Les systèmes SDR établis sur un ou plusieurs FPGA; 3) Les systèmes SDR basés simultanément sur la combinaison de processeurs DSP et de FPGA. Dans ce dernier cas, les opérations intensives en calcul et critiques dans le temps sont exécutées dans des FPGA, et le reste des opérations sont effectuées par les processeurs DSP. [34][45][84][87]

La modulation adaptative est actuellement supportée par les systèmes sans fil OFDM et TDMA et elle sera aussi disponible dans les futurs systèmes CDMA. Deux approches largement répandues pour la modulation adaptative sont l'adaptation basée sur la qualité de canal, et celle basée sur le service. [12]

Les techniques pour la conception de systèmes à faible puissance et à faible courant de fuite utilisées dans ce mémoire incluent l'emploi de tensions d'alimentation multiples, de seuils multiples et la technique d'activation sélective (gating).

### **Multiples Tensions d'Alimentation**

Dans cette approche, différentes tensions d'alimentation sont choisies selon la tâche. Ces techniques sont notamment connues sous les vocables a) Cluster Voltage Scaling (CVS) et Dynamic Voltage Scaling (DVS). La technique de CVS divise le circuit en plusieurs zones, et applique les tensions d'alimentation les plus basses possibles sur chacune d'elles en évitant de violer les contraintes de temps. Le manque d'outils de conception supportant cette approche est un gros inconvénient. La technique de DVS permet d'ajuster dynamiquement la tension d'alimentation et la fréquence d'horloge d'un circuit

selon sa tâche. L'économie de puissance réalisée selon cette approche est énorme. Cependant, en raison de la surcharge en puissance causée par l'ajout du circuit de régulation de tension et de fréquence, l'utilisation de cette approche est limitée.[32][97][20][62][114][53][17][86][71][77][74]

### **Technique d'activation sélective (***Gating***)**

La technique d'activation sélective permet d'identifier des périodes d'inactivité dans les sections d'un circuit, et de désactiver l'horloge ou les commutations dans ces sections aux moments appropriés.[9][10][65][80][105][90]

### **Technique des Seuils Multiples**

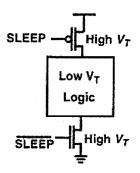

Une approche populaire consiste à définir des sections du circuit où le seuil des transistors est bas, à l'aide de commutateurs à seuil élevé reliés en série. Ces zones peuvent être définies dynamiquement pendant des périodes inactives. Pendant les périodes actives, les commutateurs à seuil élevé sont mis en marche, et les circuits reprennent les opérations à grande vitesse et à seuil bas. Comme la tension de seuil est plus basse, la vitesse du circuit peut rester inchangée quand la tension d'alimentation est réduite. Une difficulté importante avec cette technique est de trouver un algorithme de détermination de la taille des commutateurs.[75][15][7][47][90]

### Multiplieur de Basse Puissance pour l'Égaliseur

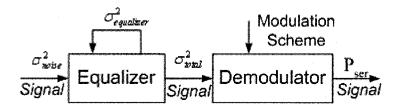

La partie d'un système de communication considérée dans cette section est un récepteur qui se compose d'un quantificateur, d'un égaliseur LMS (Least-Mean-Square) et d'un démodulateur adaptatif. Les données sont modulées soit en QPSK, soit en

16/64/256QAM et elles sont envoyées par un canal Gaussien entaché de Bruit Blanc additif (AWGN) sujet à des interférences inter-symbole (ISI de type A [78]). Le récepteur quantifie les données, passe ces données à l'égaliseur, puis envoie les résultats au démodulateur pour détecter les données originales.

Afin de trouver l'influence de la longueur de mot sur la performance, c.-à-d. la probabilité d'erreur de symbole (P<sub>set</sub>) du démodulateur, nous devons caractériser la sensibilité de la probabilité d'erreur de symbole en fonction de la variance du bruit, qui peut être définie comme suit:

Sensitivity =

$$\frac{\partial \sigma_{noise}^2}{\partial P_{ser}} \Delta P_{ser} \cong \frac{\Delta \sigma_{noise}^2}{\Delta 10 \log P_{ser}} \times 1$$

(3.4)

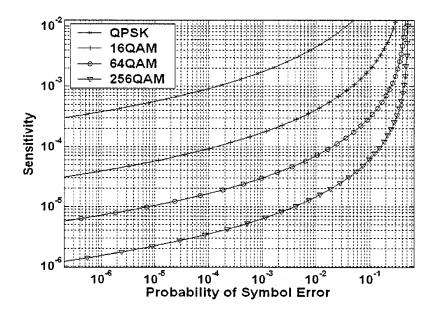

$\Delta\sigma_{noise}^2$  est le changement du bruit reçu du démodulateur,  $\Delta 10\log P_{ser}$  est le changement de la probabilité d'erreur de symbole en échelle logarithmique, et  $\Delta P_{ser}=1$  pour le cas où la probabilité d'erreur change de 1dB. Les courbes de sensibilité au bruit des différents types de modulation pour tous les points de  $P_{ser}$  sont tracées à la fig. 13. L'avantage d'utiliser la sensibilité au lieu d'une valeur absolue du bruit est que, nous pouvons évaluer l'effet de la longueur de mot fini sur la performance de la détection de symbole, sans considérer aucun détail de l'algorithme de modulation adaptative et les imperfections de l'égaliseur. Le bruit à l'entrée du démodulateur est le bruit à la sortie de l'égaliseur LMS, qui peut être

$$\sigma_{lotal}^{2} = J_{min} + \frac{N\sigma_{c}^{2}}{2\mu} + (\left|w^{*}\right|^{2} + 1)\sigma_{d}^{2}$$

(3.5)

exprimé selon [21] comme suit:

Le première terme est l'erreur de la moyenne carrée de l'algorithme LMS de précision infinie. Le deuxième terme existe à cause de l'erreur dans le vecteur de poids quantifiés. N

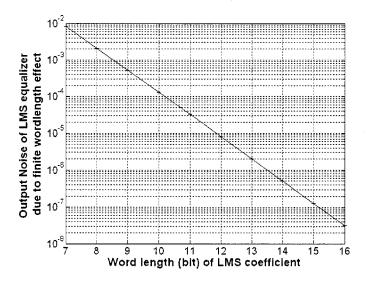

est le nombre de poids quantifiés. Le troisième terme est produit par l'erreur de quantification des données en entrée. La variance introduite par la taille finie des poids est:  $\sigma_c^2 = 2^{-2Bc}/12$ . La longueur de mot des poids est  $B_c$ . La variance introduite par les données d'entrée est  $\sigma_d^2 = 2^{-2Bd}/12$ . La longueur de mot des données d'entrée est  $B_d$ . D'autre part,  $|w^*|$  est le vecteur optimal de Weiner. Afin d'étudier les effets de la longueur du mot fini, nous nous sommes seulement intéressés au deuxième et troisième termes dans l'équation (3.5). La somme de ces deux termes est représentée à la fig. 14. Une méthode qui permet de choisir une longueur de mot d'un égaliseur est de s'assurer que le bruit produit par l'effet de la longueur de mot finie de l'égaliseur cause seulement un changement négligeable de  $P_{ser}$ . Nous définissons le changement négligeable de  $P_{ser}$  comme suit  $\Delta \log P_{ser} = 1/10$ , ce qui est tracé à l'échelle à la fig. 13. Combinant la fig. 13 et la fig. 14, nous obtenons des bons choix de la longueur de mot pour différents types de modulation (tableau 4).

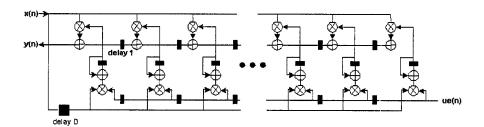

La structure d'un égaliseur LMS légèrement modifié (forme directe retardée avec retiming) [8] est montrée sur la fig. 15. Les éléments de base de l'égaliseur sont des registres, des additionneurs et des multiplieurs. L'avantage d'employer cette architecture d'égaliseur est que le DVS peut être appliqué à l'égaliseur entier, ce qui réduit au minimum les coûts additionnels.

Ce mémoire propose un multiplieur signé en complément à 2 de précision variable. Le multiplieur est basé sur un multiplieur de 15-bit Baugh-Wooley (voir fig. 16). Quand ce multiplieur ne fonctionne pas en pleine précision, seulement la partie gauche inférieure

est utilisée. Les additionneurs du niveau supérieur sont ignorés et forcés à zéro. Le chemin critique de ce multiplieur est proportionnel à la longueur de mot. Par conséquent, la tension d'alimentation peut changer selon la longueur de mot, sans réduction de performance.

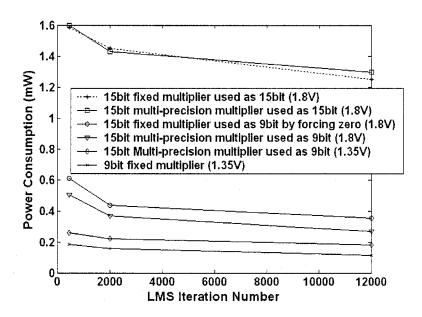

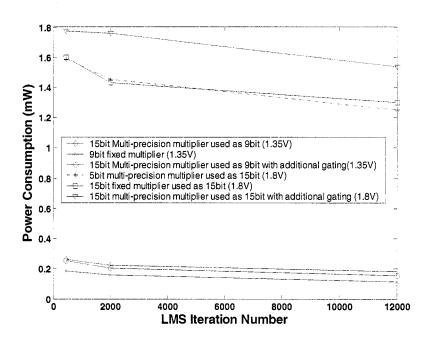

La consommation de puissance de notre multiplieur multiprécision (mis en application avec une technologie CMOS de 180nm) est simulée avec Spectre dans Cadence et est tracée à la fig. 17. La consommation de puissance d'un multiplieur 15 bits multi précision, quand ce dernier est utilisé comme multiplieur 15 bits, est presque identique à la consommation de puissance d'un multiplieur à précision fixe de 15 bits. La consommation de puissance de notre multiplieur 15-bit multi précision utilisé comme multiplieur de 9 bits est 18-28% plus élevée que celle d'un multiplieur à précision fixe de 9 bits. Ceci est le prix à payer pour un multiplieur multi précision. Cette consommation pourra être réduite dans des travaux futurs.

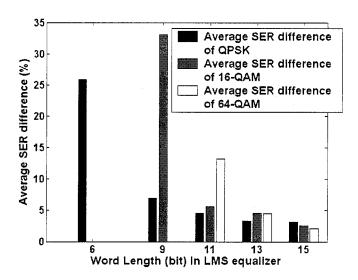

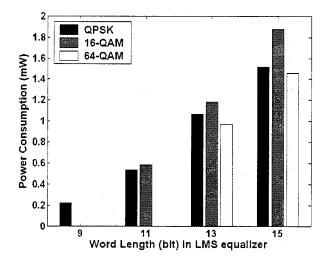

Les performances du récepteur utilisant la modulation adaptative sont représentées à la fig. 19 avec une longueur de mot différente. La puissance consommée moyenne d'un multiplieur multi précision est tracée à la fig. 20. À partir des fig. 19 et 20, nous constatons que, pour la modulation QPSK, à partir de 9 bits, la différence de P<sub>ser</sub> entre l'implémentation avec une longueur de mot limitée et celle à virgule flottante de 32 bits est inférieure à 6%. L'implémentation à 15 bits ramène cette différence à seulement 3%. Cependant, la puissance consommée par l'implémentation de 11 bits est 3 fois supérieure à celle de l'implémentation de 9 bits. Par conséquent, 9 bits apparaît être le bon choix de la longueur de mot dans ce cas quand on cherche un compromis efficace entre la

puissance dissipée et la probabilité d'erreur. De même, pour la modulation 16-QAM, à partir de 11 bits, la différence de P<sub>ser</sub> entre l'implémentation à précision limitée et celle à virgule flottante est inférieure à 5.6%. La consommation de puissance de l'implémentation à 13 bits est 1.6 fois plus grande que celle à 11 bits. Par conséquent, l'implémentation à 11 bits semble fournir le meilleur rapport performance/puissance consommée. Une analyse similaire pour le 64-QAM nous amène à conclure que 13 bits est un bon choix de la longueur de mot.

# Multiplicateur de Type Vague-Domino (*Wave-Domino*) pour le Traitement DSP

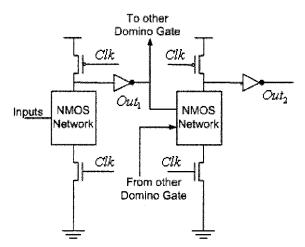

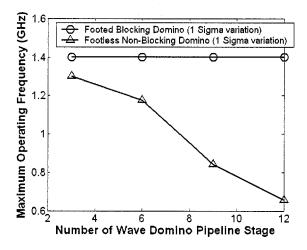

Les circuits de type vague-Domino pipelinés (Wave-Domino pipelined), aussi appelés vague-Domino, ont été largement utilisés dans les microprocesseurs à grande vitesse. Différents types d'horloges, comme les horloges bloquantes et non-bloquantes, et différents types de circuits Domino, par exemple ceux qui comportent un pied (footed) et ceux sans pied (footless), sont proposés dans la littérature [94], [24] [85] [6] [113]. La logique sans pied (footless) est plus rapide, puisqu'elle élimine le transistor de pied. Le style de d'horloge bloquante doit assurer que l'horloge d'évaluation monte après que la dernière entrée soit stable. Dans le style d'horloge non-bloquante, l'horloge d'évaluation arrive avant les transitions de données sur le chemin critique. L'inconvénient d'une horloge non bloquante est que les entrées à chaque porte dynamique doivent monter de façon monotone.

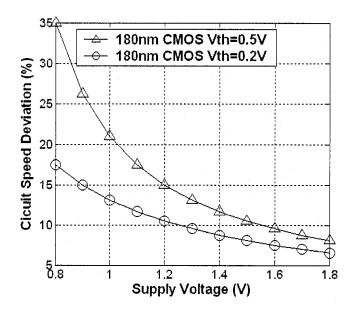

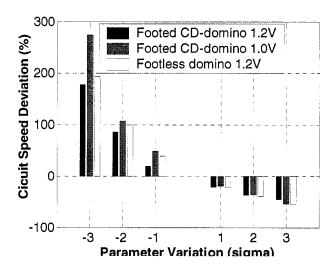

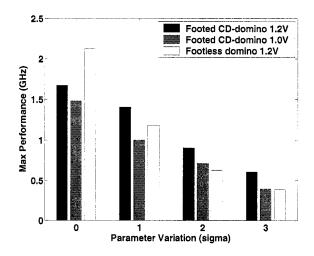

En raison des contraintes serrées de synchronisation, ce genre de circuit dynamique est plus vulnérable aux variations paramétriques. Les variations paramétriques sont un souci croissant dans la conception de circuits de performance élevée. Les facteurs environnementaux, tels que les variations de la température et de la tension d'alimentation, et les facteurs physiques pendant la fabrication, telle que la tension de seuil et la variation géométrique, sont des sources de variations paramétriques. Dans cette section, nous établissons des modèles statistiques pour comparer l'impact des variations paramétriques de circuits vague-Domino.

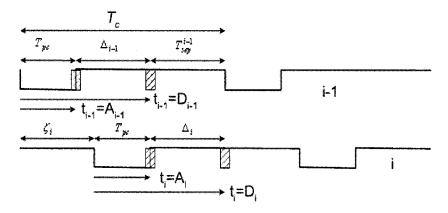

Le circuit vague-Domino peut être modélisé comme à la fig. 22. Nous supposons que tous les étages dans le pipeline partagent un signal d'horloge de période  $T_c$ . La durée de la phase de précharge est  $T_{pc}$  La période de déphasage de l'étape i-1 à i est  $\zeta_i$ . De plus, nous supposons que  $T_c$ ,  $T_{pc}$  et  $\zeta_i$  sont constant. Afin d'étudier l'impact des variations paramétriques, la période d'arrivée  $A_i$  des entrées, le temps  $D_i$  de départ du signal et le temps d'évaluation  $\Delta_i$  de l'étape i sont considérés comme des variables aléatoires dont les espérances mathématiques sont  $E(A_i)$ ,  $E(D_i)$ ,  $E(\Delta_i)$ . Leurs déviations respectives dans le pire cas sont  $\delta(A_i)$ ,  $\delta(D_i)$  et  $\delta(\Delta_i)$ . Afin de propager un signal qui traverse les circuits Domino pipelinés avec une horloge à N phases, les contraintes suivantes doivent être respectées:

- Contrainte de séparation de précharge et de déphasage [59]:

$$T_{sep}^{i-1} \ge D_i + \zeta_i - D_{i-1}$$

(4.2)

$T_{sp}^{il}$  est le temps entre le départ du signal et le commencement de la prochain précharge (voir fig. 22).

- Contrainte de séparation de l'onde (wave)[59]:

$$\zeta_i \leq D_{i-1}^{min}$$

(4.5)

Pour le circuit vague-Domino non-bloquant sans pied (footless), la période d'arrivée du signal de l'étage i dépend de la période de départ du signal de l'étage précédent. Nous avons  $A_i = \max\{D_{i-1} - \zeta_i, T_{pc}\}$  et  $A_i + \Delta_i = D_i$ . Afin de réduire au minimum le retard, tous les signaux en entrée sont supposés arrivés en même temps, et le front montant de l'horloge locale devrait être conçu tel que  $\zeta_i + T_{pc} = E(D_{i-1})$ . Selon les contraintes ci-dessus, la période d'horloge de ce circuit doit être choisie en tenant compte du pire cas comme :

$$T_c \ge T_{pc} + E(\Delta_i) + E(\Delta_{i+1}) + \sum_{j=1}^{i+1} \delta(\Delta_j)$$

(4.22)

Il est clair que la période d'horloge augmente avec l'augmentation de la profondeur du pipeline. Par conséquent, la fréquence de fonctionnement est dégradée. Le même résultat peut être appliqué au circuit vague-Domino non-bloquant avec pied.

Pour le circuit vague-Domino bloquant avec pied, le front montant de l'horloge locale arrive toujours plus tard que le départ du signal du pire cas de l'étape précédente. Donc, nous avons

$$\zeta_i + T_{pc} \ge D_{i-1}^{\text{max}} \tag{4.28}$$

D'autre part, le temps de départ du signal est entièrement contrôlé par le front montant de l'horloge locale. Il devient  $D_i = \Delta_i + T_{pc}$ . Selon la relation précédente, en considérant le pire cas, la période d'horloge du circuit vague-Domino doit être choisie comme:  $T_c \ge T_{pc} + E(\Delta_i) + E(\Delta_{i+1}) + \delta(\Delta_i) + \delta(\Delta_{i+1})$  (4.36)

Il est clair qu'aucune accumulation des variations paramétrique ne se produit ici. Par conséquent ce type de circuit est plus approprié à des applications où les pipelines sont profonds.

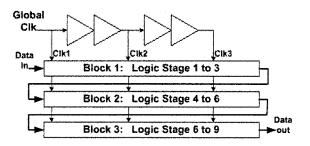

On propose aussi une ligne de distribution d'horloge (fig. 23). Cette ligne de distribution d'horloge élimine l'accumulation des variations paramétriques dans la distribution de l'horloge. En utilisant cette ligne de distribution d'horloge, la somme des intervalles des pires cas de déphasage dans chaque bloc doit être égale à une période d'horloge et dans ce cas:

$$\sum_{i=1}^{m} \zeta_i^{\max} = T_c \tag{4.37}$$

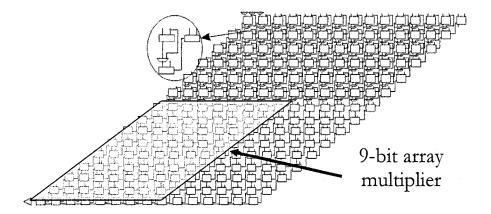

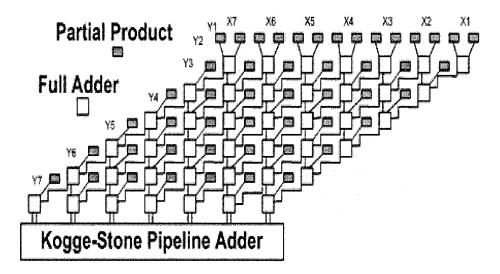

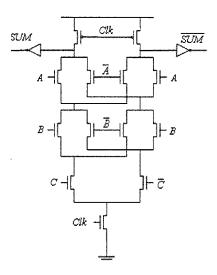

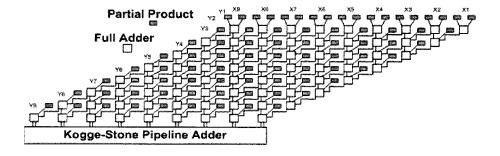

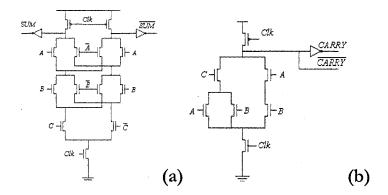

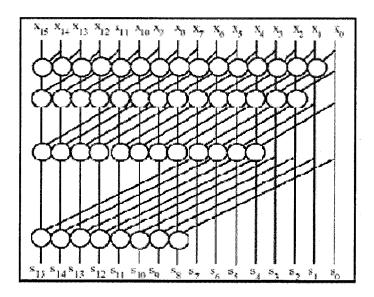

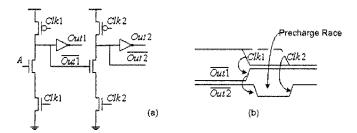

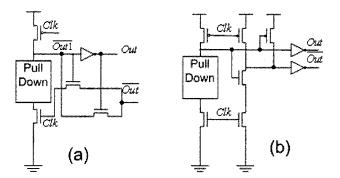

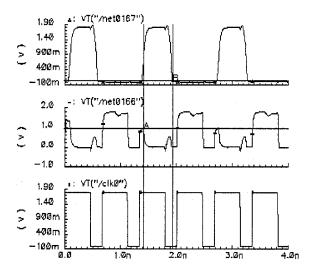

Un multiplieur de 9 bits (fig 30) pour le SDR utilisant les circuits vague-Domino bloquants avec pied est mis en application. La logique Domino à Simple-rail est employée pour économiser la puissance. On propose aussi une solution de porte dynamique inverseuse afin d'empêcher le problème classique de précharge (figue 33) des circuits Domino. Le circuit proposé est montré aux figures 34a et 35. Une économie de puissance de 39% est enregistrée en employant la porte dynamique inverseuse proposée dans le multiplicateur de rangée du vague-Domino de 9 bits (Table 7).

### Conclusion

Il existe un bon choix de la longueur de mot pour l'égaliseur LMS associé à divers types de modulation. Il est avantageux de réaliser l'égaliseur LMS en utilisant une longueur de mot variable. L'économie de puissance en employant l'égaliseur LMS avec une longueur de mot variable peut atteindre 85% pour chaque multiplication.

Le multiplieur multiprécision proposé (15 bits) supporte les précisions qui changent de 9 à 15 bits. Le multiplieur multiprécision occupe 12% plus de surface et a une dissipation 2-28% plus élevée. Considérant l'économie de surface, comparé au cas ou on utiliserait des multiplieurs dédiés pour chaque longueur de mot, le multiplieur multiprécision est une solution très attrayante.

Le multiplieur 9 bits vague-Domino a été conçu en technologie TSMC 0.18µm CMOS. Nos résultats montrent que sa consommation de puissance est 40% inférieure à celle du multiplieur réalisé avec le circuit statique non-pipeliné. En effet, le circuit vague-Domino pipeliné élimine les courses internes qui peuvent produire des commutations multiples. Il est plus avantageux, du point de vue puissance et flexibilité, de partager le multiplieur vague-Domino dans un microprocesseur, que de le mettre en application individuellement dans du matériel dédié.

## TABLE OF CONTENTS

| DEDICATE                                                    | IV     |

|-------------------------------------------------------------|--------|

| ACKNOWLEDGEMENTS                                            | V      |

| RÉSUMÉ                                                      | VI     |

| ABSTRACT                                                    | VIII   |

| CONDENSÉ EN FRANÇAIS                                        | X      |

| TABLE OF CONTENTS                                           | XXI    |

| TABLE OF FIGURES                                            | XXVI   |

| TABLE OF TABLES                                             | XXVIII |

| ABREVIATIONS                                                | XXIX   |

| CHAPTER 1 INTRODUCTION                                      | 1      |

| 1.1 Motivation                                              | 1      |

| 1.2 Contributions of this thesis                            | 2      |

| 1.2.1 Variable-Precision Multiplier for Adaptive Modulation | 2      |

| 1.2.2   | Wave-Pipelined Domino Logic and Clocking Styles in Long Pipe | lined |

|---------|--------------------------------------------------------------|-------|

| Applica | ations                                                       | 3     |

| CHAPTE  | ER 2 LITERATURE SURVEY                                       | 4     |

| 2.1 So  | oftware Defined Radio                                        | 4     |

| 2.1.1   | A Typical Radio Applications                                 | 6     |

| 2.1.2   | DSP Processor Based SDR System                               | 10    |

| 2.1.3   | FPGA based SDR system                                        | 10    |

| 2.1.4   | DSP Processor and FPGA Mixed SDR system                      | 12    |

| 2.1.5   | Discussions                                                  | 13    |

| 2.1.6   | Customizable Processor                                       | 14    |

| 2.2 Ac  | daptive Modulation Scheme and Algorithm                      | 15    |

| 2.2.1   | OFDM (802.11) System                                         | 15    |

| 2.2.2   | TDMA System                                                  | 17    |

| 2.2.3   | CDMA System                                                  | 19    |

| 2.3 Lo  | ow Power Techniques                                          | 19    |

| 2.3.1   | Overview                                                     | 19    |

| 2.3.2   | Power Dissipation Model                                      | 20    |

| 2.3.3   | Multiple Supply Voltage Approach                             | 21    |

| 2.3.4   | Voltage Regulator and Scheduler                              | 25    |

| 235     | Gating Techniques                                            | 20    |

| 2.3 | 3.6  | Power Awareness Design Style                                   | 30 |

|-----|------|----------------------------------------------------------------|----|

| 2.3 | 3.7  | GALS Design Style                                              | 31 |

| 2.3 | 3.8  | Parametric Variance in Low Power Applications                  | 32 |

| 2.4 | Lea  | nkage Reduction                                                | 32 |

| 2.4 | 4.1  | Multi-threshold approaches                                     | 33 |

| 2.4 | 1.2  | Threshold voltage biasing                                      | 34 |

| 2.4 | 4.3  | Input Vector Approach                                          | 35 |

| 2.5 | Sur  | nmary                                                          | 35 |

| СНА | PTEF | R 3 LOW POWER MULTIPLIER FOR EQUALIZER                         | 36 |

| 3.1 | Int  | roduction                                                      | 36 |

| 3.2 | Ada  | aptive Demodulation and System Word Length                     | 37 |

| 3.3 | LM   | IS Equalizer Architecture                                      | 44 |

| 3.4 | Vai  | riable-Precision Multiplier                                    | 46 |

| 3.4 | 1.1  | Variable precision multiplier architecture                     | 46 |

| 3.4 | 1.2  | Power Consumption of variable precision multiplier             | 48 |

| 3.4 | 1.3  | Advantage of a variable precision multiplier in LMS equalizers | 51 |

| 3.4 | 1.4  | Discussion                                                     | 53 |

| CHAPTER 4 WAVE DOMINO MULTIPLIER FOR DSP CORE SUBJECT TO |                         |                                              |    |

|----------------------------------------------------------|-------------------------|----------------------------------------------|----|

| PA                                                       | PARAMETRIC VARIATIONS55 |                                              |    |

| 4.1                                                      | Ir                      | ntroduction                                  | 55 |

| 4.2                                                      | D                       | omino Logic and Clocking Style Analysis      | 57 |

| 4                                                        | 1.2.1                   | Dynamic Logic                                | 57 |

| 4                                                        | 1.2.2                   | Domino logics and clocking styles            | 58 |

| 4                                                        | 1.2.3                   | Clock model                                  | 58 |

| 4                                                        | 1.2.4                   | Clock delay line                             | 66 |

| 4                                                        | 1.2.5                   | Threshold voltage mismatch and circuit delay | 68 |

| 4                                                        | 1.2.6                   | Simulation result and comparison             | 72 |

| 4.3                                                      | A                       | rray Multiplier                              | 76 |

| 4                                                        | 1.3.1                   | Multiplier structure                         | 76 |

| 4                                                        | 1.3.2                   | Precharge race prevention                    | 79 |

| 4                                                        | 1.3.3                   | Design process of wave-Domino multiplier     | 81 |

| 4                                                        | 1.3.4                   | Simulation result and discussion             | 83 |

| СН                                                       | CHAPTER 5 CONCLUSIONS85 |                                              |    |

| 5.1                                                      | V                       | ariable Precision Multiplier                 | 85 |

| 5.2                                                      | Pi                      | pelined Wave-Domino Multiplier               | 86 |

| 5.3 | Software Defined Radio Platform | 87 |

|-----|---------------------------------|----|

|     |                                 |    |

|     |                                 |    |

|     |                                 |    |

| REF | ERENCE                          | 89 |

### TABLE OF FIGURES

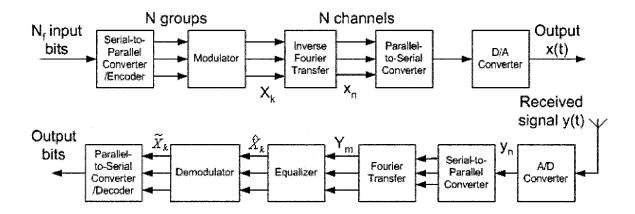

| Figure 1  | OFDM wireless communication system (baseband part)                               |

|-----------|----------------------------------------------------------------------------------|

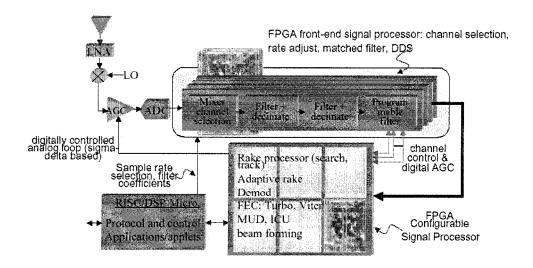

| Figure 2  | FPGA reconfigurable receiver [C.H.Dick, 34]10                                    |

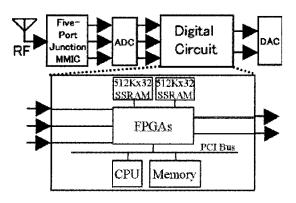

| Figure 3  | SOPRANO platform [S. Haruyama, 45]11                                             |

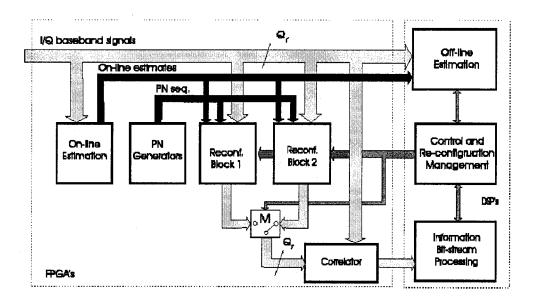

| Figure 4  | Block-diagram of a software radio implementation [I.P.Seskar, 84]12              |

| Figure 5  | Block diagram of SDR prototype [H. Shiba, 87]                                    |

| Figure 6  | Typical Dual-Supply-Voltage Layout [S. Dhar, 32]22                               |

| Figure 7  | Charge Pump for 8 delay-line taps [Dhar, 33]                                     |

| Figure 8  | Buck converter [Wei, 107]26                                                      |

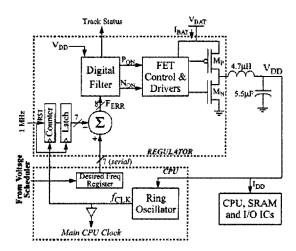

| Figure 9  | Frequency and Voltage feedback loop [T.D. Burd, 17]28                            |

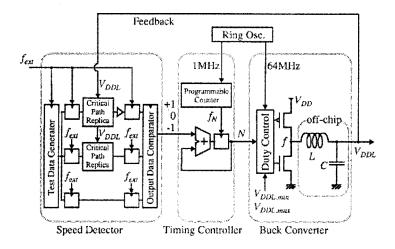

| Figure 10 | Variable supply-voltage scheduler [T.Kuroda, 51]29                               |

| Figure 11 | Leakage gating [A. Chandrakasan, 75]34                                           |

| Figure 12 | Wireless receiver                                                                |

| Figure 13 | Sensitivity of demodulation performance as a function of symbol error            |

| pı        | cobability of different modulation scheme. (Sensitivity is defined as the excess |

| no        | oise that leads an increase of error symbol probability by 1 dB)40               |

| Figure 14 | Finite Word Length effects on LMS Equalizer output noise                         |

| Figure 15 | LMS Equalizer (Delayed direct Form with retiming)                                |

| Figure 16 | 15-bit Signed variable precision array multiplier47                              |

| Figure 17 | Multiplier comparison (33MHz)49                                                  |

| Figure 18 | Power consumption comparison between the fully gated variable precision          |

| mı        | altiplier and the variable precision multiplier of Figure 16)50                        |

|-----------|----------------------------------------------------------------------------------------|

| Figure 19 | SER difference between finite and infinite word length implementations51               |

| Figure 20 | Power Consumption comparisons of different word length implementations                 |

| (33       | 53 (SMHz)                                                                              |

| Figure 21 | Domino logic (NMOS structure) [24]57                                                   |

| Figure 22 | Wave Domino Clocking                                                                   |

| Figure 23 | 9- Stage pipeline sharing clock delay elements67                                       |

| Figure 24 | Delay deviation as a function of supply voltage (3 $\sigma$ $\Delta V_{th}$ = 0.07V)70 |

| Figure 25 | 7-bit array multiplier                                                                 |

| Figure 26 | Dual rail Domino Sum Cell                                                              |

| Figure 27 | Circuit speed deviation (0.13µm) as a function of parameter variation74                |

| Figure 28 | Max performance of wave Domino pipeline76                                              |

| Figure 29 | Operating frequency and pipeline depth76                                               |

| Figure 30 | A 9-bit array multiplier77                                                             |

| Figure 31 | Sum and Carry Cells78                                                                  |

| Figure 32 | 16-bit Kogge-Stone adder [E.Abramson, 2]78                                             |

| Figure 33 | Precharge Race Problem79                                                               |

| Figure 34 | Inverting dynamic gate solutions80                                                     |

| Figure 35 | Pass transistor inverting dynamic gate simulated signals (top plot, signal Out;        |

| mie       | ddle plot, signal $\overline{Out}$ ; bottom, local clock.)81                           |

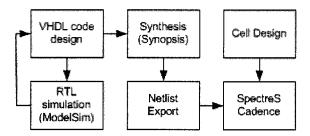

| Figure 36 | Design process                                                                         |

### TABLE OF TABLES

| Table 1 | Major parameters of the OFDM Physical Layer                           | 16 |

|---------|-----------------------------------------------------------------------|----|

| Table 2 | Modulation type and data bits                                         | 17 |

| Table 3 | A summary of adaptive modulation for packet data services in TDMA     | 18 |

| Table 4 | Modulation Type and Choice of Processing Word Length                  | 43 |

| Table 5 | Critical Path and Supply Voltage of the Variable Precision Multiplier | 48 |

| Table 6 | Parameters for 0.18µm CMOS process                                    | 71 |

| Table 7 | Simulation results                                                    | 83 |

### **ABREVIATIONS**

ADC Analog to digital converter

AGC Analog gain controller

ALU Arithmetic logic unit

ASIC Application specific integrated circuits

AWGN Additive White Gaussian Noise

BER Bit error rate

BPSK Binary phase shift keying

CAD Computer aid design

CDFG Control data flow

CDMA Code division multiple access

CLB Configurable Logic Block

CQF Channel quality feedback

CVS Clustered voltage scaling

DAC Digital to analog converter

DFT Discrete Fourier transfer

DLMS Delayed least-mean-square algorithm

DSP Digital signal processing

DVS Dynamic voltage scaling

EGPRS Enhanced General Packet Radio Service

FPGA Field programmable gate arrays

FFT Fast Fourier Transform

GALS Globally Asynchronous Locally Synchronous

GPRS General Packet Radio Service

GSM Groupe Spécial Mobile

ISI Inter Symbol Interference

ISR Ideal software radio

IDFT Inverse discrete Fourier transform

LMS Least-mean-square

MAC Multiplier-adder unit

MMAC Mobile Multimedia access Communication

NextG Next-generation wireless communications

OFDM Orthogonal frequency-division multiplexing

QAM Quadrature amplitude modulation

QoS Quality of Service

QPSK Quadrature phase shift keying

PLL Phase lock loop

PN Pseudo-random Noise

PWM Pulse width modulator

RF Radio frequency

RISC Reduced instruction set computer

RTL Register transistor level

SDR Software defined radio

SER Symbol error rate

SINR Signal to interference plus noise ratio

SNR Signal to noise ratio

SoC System on chips

SSRAM Static Random Access Memory

TDMA Time division multiple access

USR Ultimate software radio

VLIW Very long instruction word

VLSI Very large scale integration

VPCS Variable period clock synthesis

WiFi Wireless Fidelity, commonly using the 802.11 protocol

WLAN Wireless local area networking

### CHAPTER 1

### INTRODUCTION

### 1.1 Motivation

Next-generation wireless (NextG) communications will be a major move toward ubiquitous wireless communications systems and seamless high-quality wireless services [12]. This NextG will use concepts and technologies for innovations in adaptive and highly efficient modulation/coding, spectrum allocation/utilization, in radio communications, networks, services and applications. The NextG will also bring new challenges to VLSI system design. Dynamic and adaptive systems that provide a new paradigm for smart resource management, ultra connectivity, high data rates with effective QoS, scalable power control, and multi-standard adaptation capabilities are attracting the most attention under this aspect.

In designing for this kind of extreme levels of adaptability and re-configurability, as a greater degree of programmability is being made available recently on devices that are nearly as inexpensive as fixed function devices, more and more designers are looking at Software Defined (or Assisted) Radio (SDR) concept for solving the NextG challenges. However, SDR is still a pretty new and vague concept. The progress of digital signal processing, and general-purpose logic, field programmable gate arrays (FPGAs), application specific integrated circuits (ASICs), digital signal processors, and other programmable devices continue to provide new options in the evolution of SDR. Under this perspective, one of the objectives of this thesis work is to investigate the high

adaptive and low power implementation options for SDR using some currently available VLSI technologies. Furthermore, some improvements, in VLSI system and circuit design, are also studied in order to support the new capabilities described by the NextG.

### 1.2 Contributions of this thesis

In this thesis work, more specifically, both power scalable ASIC implementation and high-speed wave pipelined Domino implementation of a SDR building block, an array multiplier, are studied. System and circuit level optimizations and improvements are made. The main contributions are in the following two areas.

### 1.2.1 Variable-Precision Multiplier for Adaptive Modulation

The impact of word length in a Least-Mean-Square (LMS) equalized adaptive demodulator is studied. Analytic and simulation results in this thesis work show that there exists a good choice of word length implementation for LMS equalizer for each modulation scheme. Increasing the word length beyond this one does little to improve performance. In order to achieve an optima power/performance ratio, a variable word length datapath solution is needed for different modulation types. A basic building block of this kind of datapath, a variable-precision multiplier using Dynamic Voltage Scaling (DVS) and Gating techniques are proposed and implemented. Simulation results show that a LMS equalizer based on a variable-precision multiplier can produce an 85% power reduction without performance and throughput penalties.

### 1.2.2 Wave-Pipelined Domino Logic and Clocking Styles in Long

### **Pipelined Applications**

In recent years, wave-pipelined Domino logic has received much attention as means to implement high-speed circuits. However, they are vulnerable to parametric variations and the situation will degrade as technology scales down. In this part of the thesis, statistical timing relations are developed for characterizing performance impacts of parametric variations in different wave-pipelined Domino circuits and clocking styles. Power consumption of an array multiplier implemented with wave pipelined Domino logic is also studied. An improved inverting dynamic gate solution is proposed to reduce the usage of dual-rail Domino logics. A 40% power saving is achieved for a 15-stage wave pipelined array multiplier compared to using existing inverting dynamic gates.

### CHAPTER 2

### LITERATURE SURVEY

In this chapter, some recent developments of 1) SDR concepts, 2) SDR system and architecture, 3) wireless standards and adaptive modulation scheme, are discussed. They are the applications and requirements that we would like to consider. The currently available and widely used low power and low leakage VLSI design techniques, as well as the impact of parameter variations in high performance VLSI system design, are also reviewed. This thesis applies low power and high performance VLSI design techniques to SDR systems.

### 2.1 Software Defined Radio

Traditional communication systems have typically been implemented using custom hardware solutions. Chip rate, symbol rate, and bit rate coprocessors are often coordinated by programmable digital signal processors, but the digital signal processor does not typically participate in computationally intensive tasks. On the other hand, even with a single communication system, the hardware development cycle is onerous, often requiring multiple chip redesigns late into the certification process. When multiple communication systems requirements are considered, both silicon area and design validation are major inhibitors to commercial success. A software-based platform capable of dynamically reconfiguring communication systems enables elegant reuse of silicon area and dramatically reduces time to market through software modifications (usually taking

days) instead of time-consuming hardware redesigns (normally taking months due to manufacturing delays). Digital signal processors are now capable of executing many billions of operations per second at power efficiency levels appropriate for handset deployment. This has brought software-defined radio (SDR) to prominence.

The advantages of reconfigurable SDR solutions vs. hardware solutions are significant [38]. First, reconfigurable solutions are more flexible, allowing multiple communication protocols to dynamically execute on the same transistors, thereby reducing hardware costs. Specific functions such as filters, modulation schemes, and encoders/decoders can be reconfigured adaptively at runtime. Second, several communication protocols can be efficiently stored in memory and coexist or execute concurrently. This significantly reduces the cost of the system for both the end user and the service provider. Third, remotely reconfigurable protocols provide simple and inexpensive software version control and feature upgrades. This allows service providers to differentiate products after the product is deployed. Fourth, the development time of new and existing communication protocols is significantly reduced, providing an accelerated time to market. Development cycles are no more limited by long and laborious hardware design cycles. With SDR, new protocols are quickly added as soon as the software is available for deployment. Fifth, SDR provides an attractive method of dealing with new standard releases while ensuring backward compatibility with existing standards.

The SDR Forum [83] defines five tiers of solutions. Tier 0 is a traditional radio implementation in hardware. Tier 1, software-controlled radio, implements control features for multiple hardware elements in software. Tier 2, software-assisted-radio, implements modulation and baseband processing in software, but allows for multiple

frequency fixed function RF hardware. Tier 3, ideal software radio (ISR), extends programmability through the radio frequency (RF) with analog conversion at the antenna. Tier 4, ultimate software radio (USR), provides for fast (millisecond) transitions between communication protocols in addition to digital processing capability.

In the following sections, a typical SDR application and several recent proposed SDR systems (tier 1 and tier 2) are presented.

## 2.1.1 A Typical Radio Applications

Tier 1 and Tier 2 SDR are realistic approaches considering currently available VLSI technologies. In these approaches, only the baseband digital signal processing will be implemented using SDR concepts.

In this section, a baseband wireless communication system based on OFDM within a multi-path fading environment is considered. OFDM is a relatively new and complex wireless communication system. It includes not only standard radio modules, but also some new components, such as DFT/IDFT processing modules. By studying the OFDM system, we can cover most technologies used for wireless transmitters and receivers, which will helps us understand the requirements for software defined radio. Figure 1 illustrates a block diagram of a typical OFDM wireless communication system.

Figure 1 OFDM wireless communication system (baseband part)

The original  $N_f$  bits information sequence is segmented into N groups by a serial-to-parallel converter, where the ith group is assigned  $\widetilde{n}_i$  bits, and  $\sum_{i=1}^N \widetilde{n}_i = N_f$ . Each group may be encoded separately, so that the number of output bits from the encoder from the ith group can be  $n_i \geq \widetilde{n}_i$ . These groups can then be modulated and put into N independent channels using Inverse Discrete Fourier Transform (IDFT) technique. The N-point IDFT is applied to the N groups to yield a sequence in time domain [78]:

$$x_n = \frac{1}{\sqrt{N}} \sum_{k=0}^{N-1} X_k e^{j2\pi nk/N}, \quad n = 0, 1, \dots N-1$$

(2.1)

where  $x_n$  can be considered as a discrete time sequence sampled at  $t = \frac{nT}{N}$ . Each channel operates at the same symbol rate 1/T, with a distinct constellation  $X_k$ , k=0,1,...N-1. The sub-channel carrier frequency is chosen as  $f_k = \frac{k}{T}$ , k=1...N. After passing the D/A converter, the transmitted signal becomes [78]:

$$x(t) = \frac{1}{\sqrt{N}} \sum_{k=0}^{N-1} X_k e^{j2\pi kt/T}$$

(2.2)

The transmitted signals pass a multi-path fading channel. The received signal can be written as:

$$y(t) = x(t) * h(t) + u(t).$$

(2.3)

where \* means convolution operation, h(t) is the channel impulse response and u(t) is white Gaussian noise (AWGN). The received signal after the A/D converter becomes:

$$y_n = \sum_{l=0}^{L-1} h_{n,l} x_{n-l} + w_n \tag{2.4}$$

where  $h_{n,l}$  and  $w_n$  represent the complex random variable for the l-th path of the channel impulse response and additive white Gaussian noise at time n. Here we assume that the multi-path fading channel consists of L discrete paths.

As defined in the standard, a cyclic extension of length  $T_g$  is used to avoid intersymbol interference (ISI) and to preserve the orthogonality of subchannels. It is also assumed that the entire channel impulse response lies inside the guard interval. The modulated signal in the frequency domain is recovered by taking the N-point Fast Fourier Transform (FFT) of  $y_n$  as:

$$Y_m = \sum_{n=0}^{N-1} y_n e^{-2\pi j mn/N} + W_m \tag{2.5}$$

Finally, we can get [46]:

$$Y_{m} = \sum_{k=0}^{N-1} \sum_{l=0}^{L-1} X_{k} \left[ \sum_{n=0}^{N-1} h_{n,l} e^{-2\pi i (m-k)n/N} \right] e^{-2\pi i lk/N} + W_{m}$$

(2.6)

$$Y_{m} = \sum_{k=0}^{N-1} \sum_{l=0}^{L-1} X_{k} H_{m-k}^{l} e^{-2\pi j lk/N} + W_{m}$$

(2.7)

where  $H_{m-k}^{l}$  represents the FFT of l-th path m-th channel impulse response. Equation (2.7) can also be rewritten as:

$$Y_{m} = \sum_{l=0,k=m}^{L-1} X_{k} H_{0}^{l} e^{-2\pi j l k/N} + \sum_{k=0,k\neq m}^{N-1} \sum_{l=0}^{L-1} X_{k} H_{m-k}^{l} e^{-2\pi j l k/N} + W_{m}$$

(2.8)

The first item on the right hand side of equation (2.8) represents multi-path distortion at desired sub-channel. The second item represents Inter Channel Interference (ICI). The third item shows AWGN added during transmission.

In order to recover the original signal  $\tilde{X}_k$ , equalization and diversity techniques are needed to cancel channel distortion. A demodulator is also needed to detect the original constellation. The channel impulse response H is estimated based on received signals or training signals, and the received signals are passed through an adaptive filter whose taps are correlated according to the estimated H. The Fast Fourier Transfer module (IDFT and FFT) is used to increase bandwidth efficiency. It is mainly performed in a Butterfly structure that consists of 50-100 MAC (Multiplication Accumulation) units.

It is clear that the baseband wireless application, such as the system shown in figure 1, is a computationally intensive application. The basic operations are encoding/decoding, multiplications/additions, plus data flow controlling. How to partition these operations into hardware and software in an efficient way is the key to designing SDR systems. In the following 3 sections, we will go through some existing examples.

## 2.1.2 DSP Processor Based SDR System

[37] developed a pure software based simplified OFDM system using 16-bit C code on a DSP core. The OFDM system he considered includes 168 data channels, 22 pilot channels and 66 null channels with QPSK as modulation scheme. The channel model is an AWGN channel without any fading and multi-path. Computationally intensive signal processing operations, such as channel estimation, are not considered.

[58] [26] designed a new DSP processor with additional instructions for complex wireless communication algorithms calculation (i.e. channel estimation, FFT, Viterbi algorithm). The new instructions introduce some additional data flow to accelerate signal processing. These ASIC based DSP processors are application specific processors. Their flexibility and performance are limited by the fixed hardware implementation.

## 2.1.3 FPGA based SDR system

[34] revealed a FPGA based SDR architecture. The proposed system is shown in figure 2.

Figure 2 FPGA reconfigurable receiver [C.H.Dick, 34]

In this proposed SDR system, all digital signal processing is realized with FPGA in order to increase the throughput. The digital signal processing includes an adaptive matched filter. 20 simplified DLMS (Delayed Least-Mean-Square algorithm) engines (total of 180 multipliers) are used to adjust 40 tap coefficients of the filter. According to the author, the standard DSP processor, even with advanced architectural extensions (VLIW, very long instruction word) does not satisfy the arithmetic or I/O requirements of a modern communication signal processing engine.

[45] revealed a software radio platform called SOPRANO. This platform comprises a Sixport direct RF conversion and a software assisted PLL with multi-modulation format tracking capability. The block diagram of the platform is shown in figure 3. It can be seen that a FPGA data path controlled by a CPU processor is implemented in the system. The main digital processing task, such as demodulation, timing recovering and filtering etc., are performed through the FPGA. The software functionality is limited in controlling data flow.

Figure 3 SOPRANO platform [S. Haruyama, 45]

## 2.1.4 DSP Processor and FPGA Mixed SDR system

[84] developed a reconfigurable software radio architecture for linear multiuser detection in CDMA system (Figure 4). The reconfigurable receivers (equalizer) allow for the integration of multimedia services over wireless channels with variable QoS requirements. To achieve this reconfigurability, the proposed system is partitioned functionally into two core technologies, FPGA and DSP chips. An online channel estimation (which only performs timing estimation), PN generation, and reconfigurable equalizer are implemented with FPGA. Some additional algorithmically complex operations, such as multi-user channel estimation, bit-stream processing, control and reconfiguration management, are partitioned into the DSP chips.

Figure 4 Block-diagram of a software radio implementation [I.P.Seskar, 84]

[87] proposed a SDR system that supports both the wide-area wireless standard (PHS) and local-area wireless standard (IEEE 802.11). The system architecture is shown in figure 5.

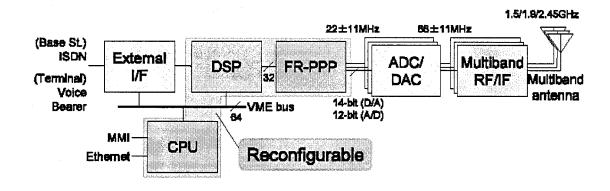

Figure 5 Block diagram of SDR prototype [H. Shiba, 87]

The DSP module in the system consists of 4 DSP chips and a shared memory. This module is used for differential modulation/demodulation. The CPU unit comprise 1 CPU and some RAM. This unit handles the access control and call control. The FR-PPP module is responsible for Direct-sequence de-spreading, timing recovery and channel filtering. This module is implemented with FPGA in order to process high-speed signals. Even though calculation intensive channel equalization is not implemented in the DSP module and the load of the DSP module is not very heavy, it was still reported that the VME bus between the CPU and the DSP causes significant processing delays.

#### 2.1.5 Discussions

Based on the above review, we can find that:

- 1) DSP based SDR system may have some performance issues if the processing intensive real time operations are introduced into the system, such as channel estimation, channel selection, direct-sequence dispreading, etc.

- 2) The data path and the controlling path need to be separated in order to increase the system throughput.

- 3) The DSP and FPGA mixed system have more advantages in point view of performance, flexibility and signal processing qualities.

#### 2.1.6 Customizable Processor

Performance of general purpose DSP processors usually limits them to baseband computations, and full FPGA implementations are costly and inefficient from the silicon area and power consumption standpoint. A good compromise is offered by some FPGA vendors, such as Altera. In their approach, a customizable processor (Nios®) is available on some FPGA devices, i.e. Stratix® and Cyclone®. Instructions of the customizable processor can be extended if DSP blocks in FPGA device are configured to connect to the processor's pins. The DSP block contains high performance full custom multipliers and adders, which can perform multiplication/addition and related operations within 1-2 clock cycle. As a typical Stratix II® FPGA device consists of up to 96 DSP block and 384 18-bit multipliers, many complex digital signal processing tasks are possible and can be configured to be executed through extended software instructions within few clock cycles, which greatly enhances the software capability. As the DSP blocks do not contain application specific operators. They are reusable and can be redeployed as needed. The

Configurable Logic Block (CLB) in the FPGA device is used to route the data flow, link DSP blocks and perform some specific operations.

This customizable processor solution is very attractive in SDR applications. Because it not only has high performance and efficiency due to the use of ASIC implementation of DSP blocks, but is also flexible as the software embedded in the FPGA device plays a major role in the whole data processing. As the DSP blocks are implemented in ASIC, it has another advantage of accessing currently available low power techniques to reduce power.

# 2.2 Adaptive Modulation Scheme and Algorithm

It becomes more and more common that communication systems adjust their performance and throughput according to channel quality and service requirements. An adaptive modulation scheme can be very suitable for this kind of situation. In the following sections, we are reviewing adaptive modulation schemes and algorithms used in recent and next generation wireless systems.

# 2.2.1 OFDM (802.11) System

Orthogonal frequency-division multiplexing (OFDM), has already been accepted for the new wireless local area network (WLAN) standards (IEEE802.11), the European Telecommunications Standards Institute's (ETSI) High Performance Local Area Network Type 2 (HIPERLAN/2) and Japan's Mobile Multimedia access Communication (MMAC) system. In the wide-area cellular network, the OFDM system is also becoming a promising technology for providing high-speed multimedia services.

The high-rate and spectrum efficient OFDM systems, employing multilevel modulation schemes with non-constant amplitude, generally require estimation and tracking of the fading channel parameters to perform coherent demodulation. In the IEEE 802.11 OFDM standard, a wireless LAN solution with data payload communication capabilities of 6, 9, 12, 18, 24, 36, 48, and 54 Mbit/s is provided. The system uses 52 sub-carriers that are modulated using binary or quadrature phase shift keying (BPSK/QPSK), 16-quadrature amplitude modulation (QAM), or 64-QAM etc. Forward error correction coding (convolutional coding) is used with coding rates of 1/2, 2/3, or 3/4. In this system, the symbol rate is kept constant.

The following tables summarizes the major parameters of the 802.11a system:

| 6, 9, 12, 18, 24, 36, 48 and 54      |  |  |

|--------------------------------------|--|--|

| Mbit/s                               |  |  |

| (6, 12 and 24 Mbit/s are             |  |  |

| mandatory)                           |  |  |

| BPSK OFDM                            |  |  |

| QPSK OFDM                            |  |  |

| 16-QAM OFDM                          |  |  |

| 64-QAM OFDM                          |  |  |

| K = 7 (64 states) convolutional code |  |  |

| 1/2, 2/3, 3/4                        |  |  |

| 52                                   |  |  |

| 4.0 μs (i.e. max. 0.25Msymbol/sec)   |  |  |

| 0.8 μs                               |  |  |

| 16.6 MHz                             |  |  |

|                                      |  |  |

Table 1 Major parameters of the OFDM Physical Layer

| Modulation | Data I+jQ   |

|------------|-------------|

| BPSK       | 1 bit+0 bit |

| QPSK       | 1 bit+1 bit |

| 16-QAM     | 2 bit+2 bit |

| 64-QAM  | 3 bit+3 bit |

|---------|-------------|

| 128-QAM | 4 bit+4 bit |

| 256-QAM | 5 bit+5 bit |

Table 2 Modulation type and data bits

The 802.11 standard specifies the multiple data transfer rate capabilities that allow implementations to perform dynamic rate switching (adaptive modulation) with the objective of improving performance. The standard does not define the algorithm for adaptive modulation. However, in most applications, the optimum modulation scheme is assigned for each sub-channel according to its instantaneous distortion and fading characteristics. In other words, the system employs higher order modulation schemes for the sub-carriers with good channel conditions so as to carry more bits, and it employs lower order modulation schemes for those sub-carriers affected by deep fading.

## 2.2.2 TDMA System

In TDMA systems, slot-by-slot data rate adaptation is achieved through adaptive coding and modulation, while the symbol rate and block size are left unchanged. Time slot aggregation is also carried out in General Packet Radio Service (GPRS)-136 (1-3 time slots/20ms) and GPRS/Enhanced GPRS (EGPRS) (1-8 time slots/GSM frame) to achieve higher data rates. Channel quality is estimated at the receiver and the information is provided to the transmitter through appropriately defined messages. Metrics that have been proposed for estimating channel quality are as follows:

- Frame error rate.

- Mean and standard deviation of symbol error rate (SER) or bit error rate (BER).

Average SINR (signal to interference plus noise ratio), which may be computed

using the minimum Euclidean distance metric derived from a Viterbi decoder or

alternatively computed using subspace projection techniques.

In both GPRS and EGPRS systems, measurement reports are included in supervisory ARQ status messages. The GPRS measurement reports consist of an estimated BER and a variance of the BER estimated over a short moving window. In GPRS-136, the receiver provides channel quality feedback as an indication of the modulation schemes that are permitted based on the estimated SINR.

Table 3 summarizes the adaptive modulation techniques in the second and third generation packet data standards for TDMA [12].

| System or    | Method of rate  | Channel quality    | Peak      |

|--------------|-----------------|--------------------|-----------|

| Standard     | adaptation      | feedback           | data rate |

| GPRS         | Time slot       | Measurement report | 160 kb/s  |

| (General     | aggregation     | in ARQ status      |           |

| Packet Radio | Adaptive coding | message:           |           |

| Service)     |                 | Signal and         |           |

|              |                 | interference       |           |

|              |                 | Bit error rate     |           |

|              |                 | Signal variance    |           |

| TDMA 136     | Time slot       | Channel quality    | 44.4      |

|              | aggregation     | feedback (CQF):    | kb/s      |

|              | Adaptive        | In uplink ARQ      |           |

|              | modulation      | status message     |           |

|              | Incremental     | In downlink packet |           |

|              | redundancy      | channel feedback   |           |

| EGPRS        | Time slot       | Measurement        | 473.6     |

| (Enhanced    | aggregation     | reports in ARQ     | kb/s      |

| General      | Adaptive coding | status message:    |           |

| Packet Radio | Adaptive        | Signal and         |           |

| Service      | modulation      | interference       |           |

|              | Incremental     | Bit error rate     |           |

|              | redundancy      |                    |           |

Table 3 A summary of adaptive modulation for packet data services in TDMA

Some other adaptive modulation algorithm, such as QoS driven adaptive modulation algorithm (Variable Target SER) is also proposed [4], In this algorithm, low SER is used for voice or video communication, and high order modulation scheme and high SER is used for data communication.

## 2.2.3 CDMA System

In second and third generation CDMA system, rate adaptation is achieved through a combination of variable spread coding and code aggregation. The adaptive modulation scheme is not standardized, but is under intensive research [12].

# 2.3 Low Power Techniques

The latest market growth of battery-powered wireless devices has set new goals in the design of systems-on-a-chip (SoCs). These goals include the need for energy-efficient, and power scalable SoC designs that would provide high-performance electronic devices with prolonged battery life. In the following sections, we will go through some widely used circuit level and system level low power techniques, which are suitable for SDR applications.

#### 2.3.1 Overview

According to [10] and [61], available system and circuit level low power techniques can be summarized as follow:

Multiple Supply-Voltage strategy, which includes: Dynamic voltage scaling (DVS)

and Clustered voltage scaling (CVS).

- Clock Gating and Operand Gating.

- Approximate signal processing. This approach allows some inaccuracies in the computation in order to reduce power dissipation.

- Control-data-flow (CDFG) transformations. This technique is to transform

CDFG to reduce switching activities.

- Dynamic power management, in this approach, sleep state and idle state of each component are introduced and managed dynamically.

- Interface power minimization, this approach is to reduce power in on-chip or offchip busses through signal encoding or physical/logical memory mapping optimization.

- Memory optimization techniques, which include: a) Caching/memory access partitioning; b) Control data transfer and placement.

- Hardware software partitioning optimization for low power.

- Instruction level power optimization.

Besides, some other techniques are also reported, they are:

- Globally Asynchronous Locally Synchronous (GALS) design style. This technique aims at reducing power consumption in clock distribution networks.

- Power awareness design style [104].

# 2.3.2 Power Dissipation Model

The power dissipation of a VLSI system is mainly due to 1) circuit switching power, 2) short circuit power and 3) current leakage power. It can be modeled as:

$$P = P_{\text{switching}} + I_{\text{short-circuit}} V_{\text{dd}} + I_{\text{leakage}} V_{\text{dd}}$$

(2.9)

where  $V_{dd}$  is the operating supply voltage.  $I_{short-circuit}$  and  $I_{leakage}$  are short circuit current and leakage current respectively. The switching (or dynamic) power is:

$$P_{switching} = (\sum N_i C_i V_{dd}^2) f_{clock}$$

(2.10)

here  $C_i$  is the average capacitance switched per operation of type i (corresponding to addition, multiplication, etc.),  $N_i$  is the number of operations of type i performed per clock cycle (switching activity).  $N_i$  is proportional to bit width of data.  $f_{clock}$  are the clock frequency of the system.

## 2.3.3 Multiple Supply Voltage Approach

As we can see from equations (2.9) and (2.10), the power savings obtained by reducing the supply voltage is significant due to the quadratic relationship between voltage and power. However a lowered supply voltage reduces circuit speed in most VLSI circuit. Thus, supply voltage is constrained by the worst-case critical path delay. In order to optimize the selection of supply voltage, a multiple supply voltage approach can be used on chip either dynamically (i.e. Dynamic voltage scaling (DVS)) or statically (i.e. Clustered voltage scaling (CVS)) according to workload.

#### 2.3.3.1 Clustered Voltage Scaling (CVS)

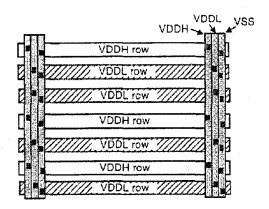

The basic idea of Clustered Voltage Scaling is to partition the circuit into several clusters and apply the lowest possible supply voltages on different clusters without violating the time constrains. It is reported that 2 or 3 different fixed supply voltages are usually sufficient to get most of the benefits of that approach [32]. A typical compact layout is shown in figure 6.

One overhead of this approach is the need of voltage level converters while signal passes from low  $V_{dd}$  clusters to high  $V_{dd}$  clusters. However, if a latch is used between clusters, the overhead can be minimized. In fact, with some slight modifications, a latch can have the level converter functionality [97].

Figure 6 Typical Dual-Supply-Voltage Layout [S. Dhar, 32]

Lack of design tools for doing CVS floorplanning and layout is a major disadvantage of this technique. CAD tools for selecting supply voltages, routing the supply voltage line and identifying clusters are active research directions. [20] presented a dynamic programming approach for assigning voltage levels to the modules in non-pipelining and functionally pipelined data-paths. [114] developed a tool to automatically identify the critical path and select the optimal supply voltage for a cluster. [62] developed an algorithm based on efficient distribution of different supply voltage among the nodes in the data-flow graph. The Lagrange multiplier method is used in an iterative fashion in his algorithm.

#### 2.3.3.2 Voltage Island

Due to the difficulty of floorplanning of small size clusters, the voltage island concept was introduced recently. The basic idea of the voltage island is almost the same as CVS, however, by separating large functional block into different voltage island, modular design is achieved and the system becomes more manageable especially in large SOC design.

[22] developed a 3.2-Gbps multi-protocol serial-link receiver logic core using the voltage island concept. According to them, the power consumption is significantly reduced by powering a large portion of the digital logic at a low supply voltage, while the analog portion runs at a higher supply level. The main advantages of voltage island concept are:

- Standard ASIC methodology and CAD tools can be used during each island design.

- The inter-connections between different voltage islands are limited.

- The power supply of different voltage islands can be different and can be switched off individually. [53]

- The transistor threshold voltage can be different in different voltage island in order to reduce the stand by power consumption [53]

A disadvantage of the voltage island technique is that its power saving is smaller than that of CVS.

#### 2.3.3.3 Dynamic Voltage Scaling (DVS)

The basic idea of this technique is to dynamically adjust the supply voltage and clock frequency of a circuit according to its workload. Due to the area and power overhead of voltage/frequency regulator and complexity of control algorithm (performed by software), this technique is mostly used for a microprocessor.

[51] published the first experimental results on a general-purpose processor. The architecture of a R3900 RISC core was enhanced with a critical path replica to measure the minimal required supply voltage. The RISC core operates on 1.9 V at 40 MHz and on 1.3 V at 10 MHz. All intermediate frequencies are also supported. This first general purpose implementation did not have a full chip-set and lacked an operating system. [40] presented experimental results on a complete general-purpose platform, called Itsy, running the Linux operating system. Itsy uses a standard commercial StrongARM SA1100 processor that supports voltage scaling. The savings by the Itsy are very modest because only two voltage levels have been implemented, 1.5 V (≥162 MHz) and 1.23 V (<162 MHz). The resulting difference in processor power consumption between the two levels is only 15%. Better results are obtained with the SmartBadge platform [86], which is similar to the Itsy. Extensive power measurements on real-time MP3 audio decoding and MPEG video decoding show that an energy reduction of 40% is possible. [17] designed and implemented a voltage-scaling capable processor based on an ARM8 core. Their processor is fabricated in 600-nm technology and uses aggressive power saving features. In high-performance mode, it runs at a speed of 80 MHz and consumes 476 mW at 3.8 V. When running at 5 MHz and 1.2 V, the processor only consumes 3.24 mW. Thus, power consumption is reduced with a factor of 147, while performance drops by a factor 16. [71] designed a 32-bit PowerPC Soc platform with DVS and Frequency Scaling. The PowerPC system-on-a-chip processor makes use of dynamic voltage scaling and on-thefly frequency scaling. It adapts to dynamically changing performance demands and power

consumption constraints. It achieves frequencies as high as 380 MHz at a supply of 1.8 V, but the power consumption reduces to 53 mW at a supply of 1.0 V. The voltage and frequency scaling is under software control. [77] developed an energy priority scheduling algorithm that uses workload descriptions to compute energy-efficient schedules, to support power-aware applications on an Intel StrongARM microprocessor. The scheduling algorithm is part of their Linux OS. Their platform supports 128-different supply-voltage levels. A supply voltage of 0.79 V is used when running the processor at 59 MHz. A frequency of 251 MHz requires 1.65 V.

There are very little applications that use DVS technique to reduce power dissipation for a datapath or clusters. [74] developed on-chip controller which dynamically assigns the lowest possible supply voltage to a datapath. The controller selects the suitable supply voltage based on a built-in scan self-test.

# 2.3.4 Voltage Regulator and Scheduler

Supply voltage reduction can save a great deal of power. However, the voltage and frequency regulator circuit is complex and also consumes power. Understanding the overhead of the regulator circuit is essential while implementing the DVS techniques. In this section, an overview of existing voltage and frequency regulator circuits is presented.

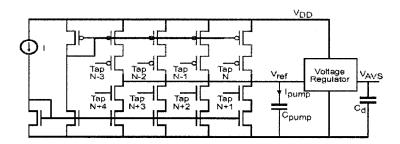

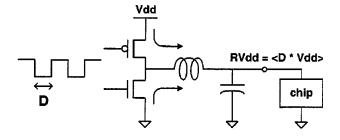

#### 2.3.4.1 Voltage regulator