|                         | Built-in self-test and self-repair architecture for defect-tolerant word-<br>oriented large capacity memories                                                                                                                                                                           |

|-------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Auteur: Author:         | Nader Ghattas                                                                                                                                                                                                                                                                           |

| Date:                   | 2004                                                                                                                                                                                                                                                                                    |

| Type:                   | Mémoire ou thèse / Dissertation or Thesis                                                                                                                                                                                                                                               |

| Référence:<br>Citation: | Ghattas, N. (2004). Built-in self-test and self-repair architecture for defect-tolerant word-oriented large capacity memories [Master's thesis, École Polytechnique de Montréal]. PolyPublie. <a href="https://publications.polymtl.ca/7386/">https://publications.polymtl.ca/7386/</a> |

# Document en libre accès dans PolyPublie Open Access document in PolyPublie

| <b>URL de PolyPublie:</b> PolyPublie URL: | https://publications.polymtl.ca/7386/ |

|-------------------------------------------|---------------------------------------|

| Directeurs de<br>recherche:<br>Advisors:  | Yvon Savaria                          |

| <b>Programme:</b> Program:                | Unspecified                           |

# UNIVERSITÉ DE MONTRÉAL

# BUILT-IN SELF-TEST AND SELF-REPAIR ARCHITECTURE FOR DEFECT-TOLERANT WORD-ORIENTED LARGE CAPACITY MEMORIES

# NADER GHATTAS DÉPARTEMENT DE GÉNIE ÉLECTRIQUE ÉCOLE POLYTECHNIQUE DE MONTRÉAL

MÉMOIRE PRÉSENTÉ EN VUE DE L'OBTENTION

DU DIPLÔME DE MAÎTRISE ÈS SCIENCES APPLIQUÉES

(GÉNIE ÉLECTRIQUE)

DÉCEMBRE 2004

Library and Archives Canada

Published Heritage Branch

395 Wellington Street Ottawa ON K1A 0N4 Canada Bibliothèque et Archives Canada

Direction du Patrimoine de l'édition

395, rue Wellington Ottawa ON K1A 0N4 Canada

> Your file Votre référence ISBN: 0-494-01331-1 Our file Notre référence ISBN: 0-494-01331-1

#### NOTICE:

The author has granted a non-exclusive license allowing Library and Archives Canada to reproduce, publish, archive, preserve, conserve, communicate to the public by telecommunication or on the Internet, loan, distribute and sell theses worldwide, for commercial or non-commercial purposes, in microform, paper, electronic and/or any other formats.

The author retains copyright ownership and moral rights in this thesis. Neither the thesis nor substantial extracts from it may be printed or otherwise reproduced without the author's permission.

#### AVIS:

L'auteur a accordé une licence non exclusive permettant à la Bibliothèque et Archives Canada de reproduire, publier, archiver, sauvegarder, conserver, transmettre au public par télécommunication ou par l'Internet, prêter, distribuer et vendre des thèses partout dans le monde, à des fins commerciales ou autres, sur support microforme, papier, électronique et/ou autres formats.

L'auteur conserve la propriété du droit d'auteur et des droits moraux qui protège cette thèse. Ni la thèse ni des extraits substantiels de celle-ci ne doivent être imprimés ou autrement reproduits sans son autorisation.

In compliance with the Canadian Privacy Act some supporting forms may have been removed from this thesis.

While these forms may be included in the document page count, their removal does not represent any loss of content from the thesis.

Conformément à la loi canadienne sur la protection de la vie privée, quelques formulaires secondaires ont été enlevés de cette thèse.

Bien que ces formulaires aient inclus dans la pagination, il n'y aura aucun contenu manquant.

# UNIVERSITÉ DE MONTRÉAL

## ÉCOLE POLYTECHNIQUE DE MONTRÉAL

#### Ce mémoire intitulé:

# BUILT-IN SELF-TEST AND SELF-REPAIRARCHITECTURE FOR DEFECT-TOLERANT WORD-ORIENTED ULTRA-LARGE CAPACITY MEMORIES USING HIERARCHICAL REDUNDANCY

présenté par: <u>GHATTAS Nader</u>

en vue de l'obtention du diplôme de: <u>Maîtrise ès sciences appliquées</u>

a été dûment acceptée par le jury d'examen constitué de:

- M. KHOUAS Abdelhakim, Ph.D., président

- M. SAVARIA Yvon, Ph.D., membre et directeur de recherche

- M. BOIS Guy, Ph.D., membre

# Acknowledgments

I would like to convey my sincere gratitude to all the people who helped me in the realization of this project. In particular, I would like to express my deepest appreciation to my supervisor professor Yvon Savaria. He provided me with guidance and support throughout my work on this thesis. His advices were always invaluable.

I would also like to thank the Canadian Microelectronics Corporation (CMC) for its continuous support and for permitting us the fabrication of the prototype chip through access to Taiwan Semiconductor's CMOS processes. It supplied us with all the required CAD tools, licenses and test equipment.

I am also grateful to Hyperchip Inc. for funding my research. It gave me the opportunity to interact with a number of technically brilliant research colleagues and I would like to heartily thank: Jacques Taillefer, Meng Lu, Bing Qiu and Daniel Picard.

Special thanks are due to all the members of "Groupe de Recherche en Microélectronique" (GRM) laboratory, particularly, to my brother, Hany Ghattas, for his continuous help and encouragement.

My parents deserve heartfelt thanks for their emotional support that kept me going. They were an inexhaustible source of encouragement throughout the period of my studies.

I extend an acknowledgment to our microelectronics technician, Martin Paré, for his help in the test procedure.

Last but not the least, I am grateful to our system administrator, Réjean Lepage, and computer technician, Alexandre Vesey, for their great effort in keeping the computer system constantly operational.

### **Abstract**

Nowadays, SRAM chips use sub-micron technology to achieve high capacity memories. An increase in the memory capacity beyond the technology limits will normally result in very poor yields. The defect tolerance becomes then of a great importance for the realization of ultra-large capacity memory chips.

This project presents a self-testing and self-repairing strategy for ultra-high capacity memories. The self-testing and self-repairing structure applies tests that allow to locate faults and repair them without any external assistance from either test engineer or test equipment. This method will drastically improve the yield and reduce the production cost of embedded memories. The efficiency of self-testing and self-repairing strategy is supported by a hierarchical memory organization.

The redundant memory cells are introduced at different levels of hierarchy. At the lowest level of hierarchy, redundant words are introduced. If the local self-repairing logic can repair all the faults at the local level, the entire memory system can be restored to its fullest intended capacity. However, if a memory block has an excessive number of faults such that the local self-repairing logic is not able to restore its intended capacity at the local level, this memory block must be excluded from being accessed during normal

operations. Any attempt to access this faulty memory block will be diverted to a functional memory block.

A prototype memory chip of 4096 words by 4 bits with fault-tolerance has been designed and manufactured in CMOS 0.18 µm technology. Although the chip has a relatively modest storage capacity, it incorporates all the required self-testing and self-repairing structures. The memory array is divided into 4 blocks of 1024 words by 4 bits. Each block contains 2 redundant words. A redundant memory block is added at the top level.

A thorough study has been undertaken to identify the factors which can influence the area overhead, the yield and the access time of ultra-large capacity memories.

## Résumé

De nos jours, les puces SRAM utilisent la technologie MOS sub-micronique pour réaliser des mémoires de haute capacité. Une augmentation de la capacité de la mémoire au-delà des limites de la technologie se traduira normalement par des rendements très faibles. La tolérance aux défectuosités devient alors d'une grande utilité pour la réalisation de puces de mémoire de grande capacité.

Ce projet présente une stratégie pour effectuer la réparation automatique des mémoires de très grande capacité. Cette structure automatique applique des tests qui permettent de localiser les défectuosités et de les réparer sans assistance externe d'un ingénieur ou d'un équipement de test. La méthode permet d'améliorer le rendement des mémoires et d'en réduire les coûts de production. L'efficacité de la structure automatique de test et de réparation des mémoires est supportée par une organisation hiérarchique.

Des cellules de mémoire redondantes sont introduites à plusieurs niveaux de la hiérarchie. Au plus bas niveau, des mots redondants sont introduits. Si la logique locale de réparation automatique peut réparer toutes les pannes au niveau local, le système de mémoire fonctionnera à pleine capacité. Cependant, si le bloc mémoire contient un nombre excessif de défectuosités qui ne peuvent être réparées automatiquement au niveau local, ce bloc ne doit pas être accessible durant le fonctionnement normal. Une tentative d'accéder à ce bloc doit être dirigée vers un bloc redondant fonctionnel.

Une puce de mémoire prototype de 4096 mots de 4 bits avec une tolérance aux pannes a été conçue et fabriquée en technologie CMOS 0.18 µm. Bien que la puce ait une capacité de mémoire relativement modeste, elle incorpore toutes les structures d'auto-test et de réparation automatique requises. La matrice de mémoire est divisée en 4 blocs de 1024 mots de 4 bits. Chaque bloc contient deux mots redondants. Un bloc redondant de mémoire est ajouté au niveau supérieur.

Une étude approfondie a été menée pour déceler les facteurs qui peuvent influencer le matériel additionnel, le rendement et le temps d'accès dans les mémoires de très grande capacité.

# CONDENSÉ EN FRANÇAIS

#### INTRODUCTION

Il existe une limite à la complexité maximale des circuits réalisables avec les technologies d'intégration modernes. Au-delà de cette complexité, les rendements des procédés de fabrication chutent rapidement. L'emploi de redondance dans des structures tolérantes aux pannes permet d'atteindre une production plus économique des circuits de grande complexité.

Les circuits intégrés à grande échelle, tels que les processeurs vidéo, tendent à consacrer plus de transistors à la réalisation des mémoires embarquées qu'a leurs parties logiques. Il est prévu que la proportion de la complexité que représentent les mémoires embarquées augmentera encore plus dans le futur lorsque les puces réalisées deviendront des systèmes complets.

L'utilisation de RAM embarquées tolérantes aux pannes constitue une manière prometteuse pour préserver et augmenter le rendement global de production. La tolérance aux pannes des RAM peut être accomplie en utilisant des techniques de redondance combinées avec un auto-test intégré (BIST).

Une méthode efficace pour rendre des RAM statiques embarquées 'orientées-mot' tolérantes aux défectuosités fait l'objet de ce travail. La tolérance aux pannes de la RAM est basée sur une technique de redondance hiérarchique utilisant un auto-test déterministe ainsi qu'une logique d'auto-reconfiguration. Cette méthodologie est applicable à toute mémoire standard générée par un compilateur de mémoires. Il n'est donc pas nécessaire de connaître ou modifier la conception physique de la RAM.

Le prototype, présenté dans le cadre de ce mémoire, est basé sur une redondance à deux niveaux. Par conséquent, la mémoire est divisée en b blocs de RAM de même taille, auxquels s'ajoute un bloc redondant. Un circuit d'auto-test détecte toutes les pannes présentes dans chacun des blocs en les testant en parallèle. Chacun de ces b+1 blocs est équipé de deux mots redondants et il contient une logique simple d'auto-réparation pour masquer les pannes localement en remplaçant les mots défectueux. À haut niveau, les b blocs reconfigurés (sans défaut) forment la RAM.

Cette technique de redondance mène à une augmentation significative du rendement avec une surface additionnelle comparativement basse. En outre, seulement un délai modéré est ajouté sur le chemin emprunté par le signal, de telle sorte qu'il n'y ait presque aucune diminution dans la performance de la mémoire.

Ce condensé est structuré comme suit : la section 2 donne une vue d'ensemble sur le test des RAMs embarquées et une description de l'algorithme de test choisi ainsi que son

implantation. Dans la section 3, la logique de reconfiguration pour la redondance à deux niveaux sera présentée. Dans la section 4, une puce prototype qui a été conçue sera présentée et différentes analyses de rendement se rapportant à cette puce seront fournies. La section 5 offrira une brève conclusion et des recommandations pour des travaux futurs.

## STRATÉGIES D'AUTO-TEST POUR MÉMOIRES EMBARQUÉES

L'utilisation de mémoires embarquées mène à des problèmes de test avec les méthodes de test externes conventionnelles, comme la mémoire n'est pas nécessairement connectée aux broches d'entrée et de sortie de la puce. En conséquence, diverses techniques d'autotest intégré doivent être appliquées aux blocs de mémoire embarquée.

Le test des mémoires a fait l'objet de recherches depuis plusieurs années et divers algorithmes qui détectent une variété de classes de pannes ont été développés. Il existe deux méthodes générales pour tester les mémoires : la première est le test déterministe avec des algorithmes qui sont basés sur un modèle de pannes fixé précédemment et la seconde utilise des séquences de test pseudo-aléatoires. Cette dernière méthode ne se base sur aucun modèle de pannes spécifique et ne garantit pas de détecter une certaine classe de pannes avec une probabilité de 100%. Le test déterministe le plus répandu dans l'industrie est le "March-test". Ce dernier détecte toutes les pannes collées-à, collées-ouvert, de transition et de couplage.

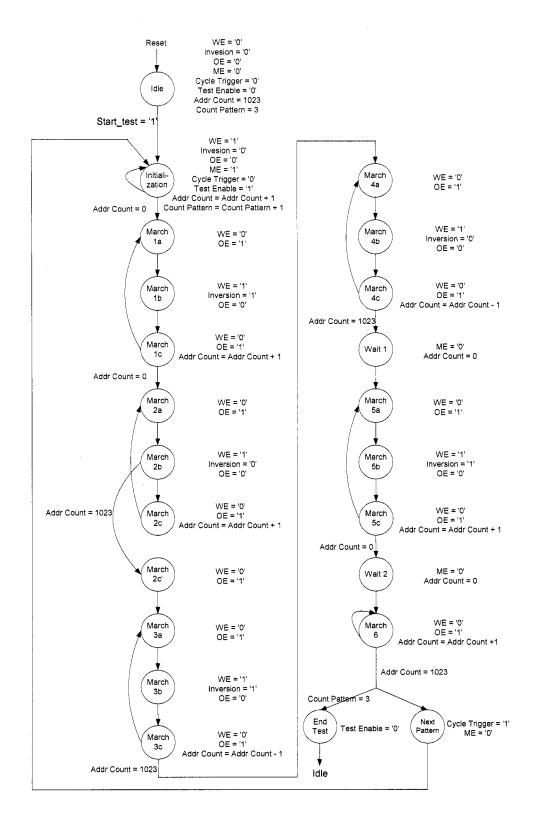

L'auto-test intégré (BIST) a été retenu, puisqu'il permet de tester rapidement et de fournir des conditions de test réalistes et des durées de test plus courtes. Les étapes pour obtenir un algorithme de test efficace, utilisé dans la conception du BIST, sont les suivantes. En premier lieu, nous avons développé un modèle de pannes réaliste qui est basé sur les défectuosités réelles qui peuvent se produire dans la RAM pendant la fabrication. Ensuite, un algorithme de test a été identifié. Il s'agit du *13N March test*. Cet algorithme présenté au chapitre 2 donne un taux de couverture de 100% des pannes considérées. De plus, il conduit à une surface additionnelle et une dégradation de performance acceptables. Ces dernières sont dues au matériel supplémentaire d'auto-test requis.

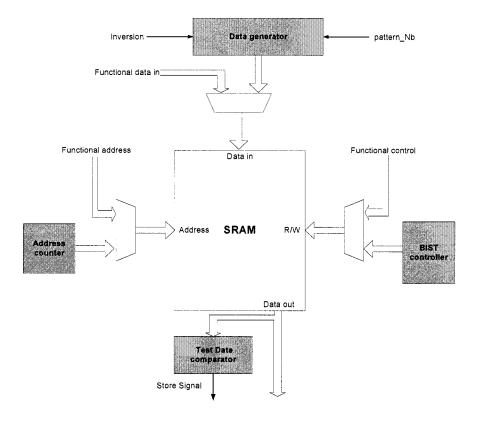

Plusieurs blocs logiques sont nécessaires pour l'exécution de l'algorithme de test. Parmi les modules requis on retrouve:

- Un compteur d'adresses qui génère la séquence d'adresses de 0 à N-1.

- Un générateur de données qui génère la valeur du fond de données et son complément.

- Un comparateur des données de test qui se compose d'un comparateur au niveau du bit qui compare les données reçues du SRAM pendant une lecture aux données prévues.

- Un *contrôleur du BIST* qui exécute l'algorithme de test à l'aide d'un circuit séquentiel pour produire les signaux de commande nécessaires pour contrôler la RAM et les autres blocs du BIST.

## TECHNIQUE DE REDONDANCE À DEUX NIVEAUX

Deux types de défectuosités peuvent se produire dans les blocs de mémoire, en l'occurrence, les petites défectuosités "spot defects" et les défectuosités de plus grande taille qui peuvent affecter plusieurs rangées de bits (ex. défectuosités de masque ou défectuosités groupés). Par conséquent, une technique de redondance à deux niveaux a été utilisée. Il est à noter qu'il est possible de réparer des défectuosités de grande taille avec une redondance à un seul niveau. Dans ce cas, la redondance se manifeste généralement sous la forme de multiple rangées redondantes dans la mémoire. Cependant, ceci conduit à une pénalité importante en terme de surface additionnelle. Ça peut aussi augmenter la complexité de la logique de reconfiguration et augmenter les délais de façon importante.

Notons que si la logique de reconfiguration est défectueuse, la mémoire entière sera probablement non-fonctionnelle. Cependant, ceci est peu probable, étant donné que la surface occupée par le circuit de réparation est minime en comparaison à celle de la mémoire.

Le partitionnement de la mémoire en plusieurs blocs, comme proposé dans ce travail, permet un test parallèle des blocs de mémoire. Si la taille nominale de la RAM est de  $2^n$  x p bits, elle est divisée en  $b = 2^{n-k}$  blocs, avec  $(2^k + r)$  x p bits chacun, pour un décodage d'adresse commode, où r est le nombre de rangées redondantes par bloc de mémoire.

La reconfiguration à bas niveau implique plusieurs étapes. D'abord, il faut tester la mémoire, pour ensuite localiser toutes les pannes de façon à pouvoir finalement reconfigurer la mémoire en remplaçant les modules défectueux par des modules de remplacement. Ainsi, n'importe quelle rangée de la mémoire peut être remplacée par une des rangées redondantes.

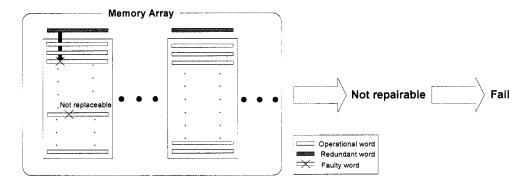

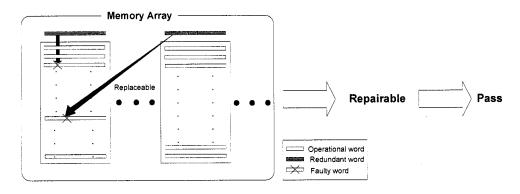

Supposant que la mémoire contient un bloc redondant pour la reconfiguration à haut niveau, chacun des b+1 blocs fournit un signal à la logique de contrôle de haut niveau indiquant son état de fonctionnalité. Si tous les b blocs réguliers sont sans défaut ou ont été reconfigurés avec succès, le bloc redondant n'est pas utilisé. Si un des blocs n'a pas pu être reconfiguré à bas niveau, un bloc redondant sera utilisé à sa place. Typiquement, ceci se produit si le nombre de modules de remplacement est trop petit ou s'il y a une défectuosité dans un élément critique qui n'est pas redondant. Avec plus qu'un bloc qui échoue, la mémoire ne peut pas être réparée. Elle fournit alors un signal au contrôleur indiquant qu'elle est défectueuse (résultat de test négatif).

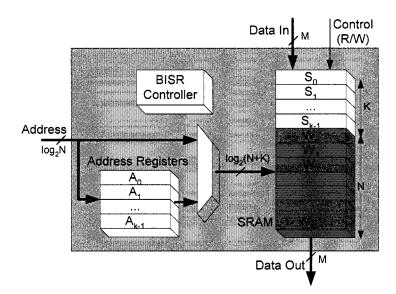

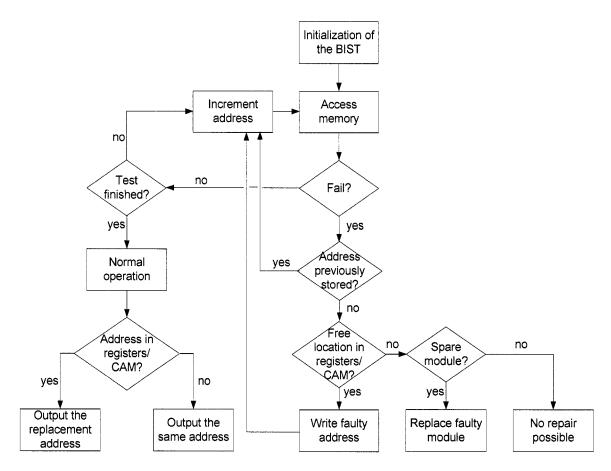

Le contrôleur d'auto-réparation intégrée (BISR) implante l'algorithme de réparation pour remplacer les cellules défectueuses. D'abord, le BIST et la mémoire sont initialisés. Puis, l'algorithme de test est appliqué à la SRAM. Si une panne est détectée, le contrôleur de BISR vérifie que l'adresse actuelle n'avait pas été stockée précédemment. Dans un tel cas, elle assigne un espace libre dans les registres et enregistre la nouvelle adresse défectueuse. Au cas où le nombre d'échecs excéderait le nombre de mots redondants

dans le module de mémoire, le contrôleur remplacera ce module par un bloc redondant, s'il y en a un. Autrement, aucune réparation n'est possible.

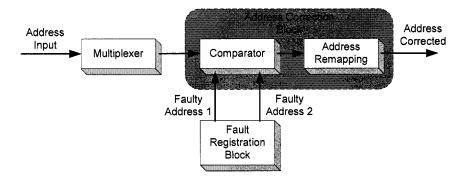

Quand le test se termine, le système entre dans le mode d'opération normale. Dans ce mode, quand une adresse est consultée, elle est d'abord recherchée dans les registres d'adresse. Si elle correspond à une adresse trouvée défectueuse, l'adresse de remplacement du mot redondant est transmise. Autrement, l'adresse initiale est transférée directement au module de mémoire.

Le module de mémoire tolérante aux pannes se compose de plusieurs blocs :

- Bloc de correction d'adresse : ce bloc est responsable de réorienter une adresse entrante, destinée à un contenu défectueux dans la mémoire, vers une nouvelle adresse d'un mot redondant.

- Bloc d'enregistrement des pannes : ce bloc sauvegarde l'adresse de mémoire où la panne s'est produite.

- Bloc de mémoire : il s'agit de la matrice de mémoire SRAM synchrone et à double port, générée par le compilateur de Virage Logic.

Nous avons supposé que les petites défectuosités sont distribués uniformément et qu'il existe deux rangées redondantes par bloc de mémoire et un bloc redondant au plus haut niveau. Ainsi, cet arrangement peut tolérer jusqu'à 2b petites défectuosités affectant une simple rangée et une défectuosité de grande taille pouvant couvrir la surface d'un bloc

entier de mémoire. Donc, avec une qualité suffisante du procédé de fabrication, le rendement de production peut atteindre presque 100%. Le processus de reconfiguration peut être répété à chaque mise sous tension, afin de détecter et de masquer les pannes, incluant celles qui apparaissent après le déploiement du circuit. Il n'y a donc aucun besoin d'appareil de contrôle externe pour exécuter l'auto-réparation.

### IMPLANTATION ET RÉSULTATS

Une puce de mémoire prototype de 4096 mots par 4 bits comprenant toutes les fonctions discutées précédemment a été conçue et fabriquée en technologie CMOS 0.18 µm. Bien que la puce ait une capacité de mémoire relativement modeste, elle incorpore toutes les structures d'auto-test et de réparation automatique requises. La matrice de mémoire est divisée en 4 blocs de 1024 mots par 4 bits. Chaque bloc contient deux mots redondants. Un bloc redondant de mémoire est ajouté au niveau supérieur.

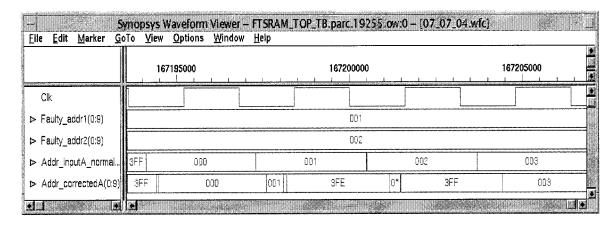

La conception entière a été réalisée en code VHDL. Les noyaux de mémoire ont été générés par le compilateur de mémoire de *Virage Logic* et ont été utilisés comme instances dans le code. Les simulations ont été exécutées sur Synopsys [2001]. Le dé occupe une surface de 4 mm² et est logé dans un boîtier PGA de 84 broches.

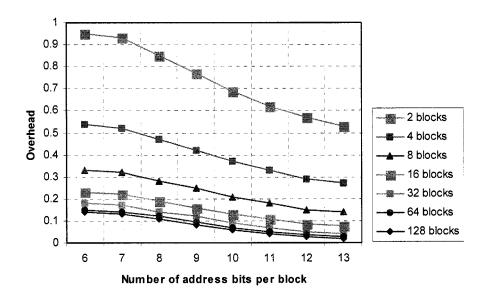

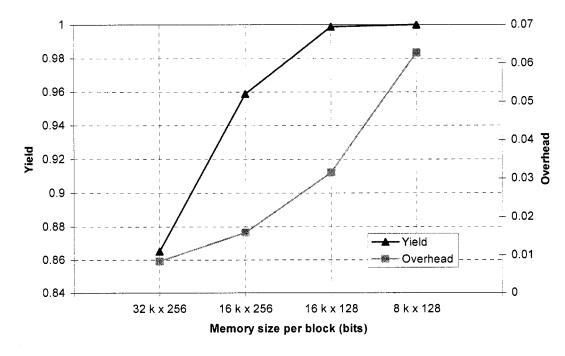

Des estimations du matériel additionnel requis pour l'auto-test et le circuit d'autoréparation ont été effectuées. Ces estimations sont basées sur le dessin de masques réel de la puce et la surface des cellules standards utilisées. En utilisant cette configuration de redondance, la surface supplémentaire diminue considérablement en divisant la RAM en plus de blocs. En outre, il peut être observé que la pénalité au niveau de la surface est assez grande pour les RAM de petites tailles. En conséquence, il n'est pas avantageux d'employer les stratégies d'auto-test et de réparation automatique avec les petites RAM. Il est préférable de les remplacer complètement.

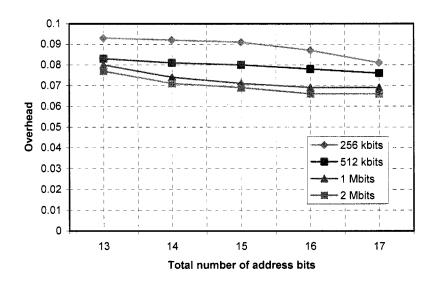

En mettant en oeuvre ces stratégies d'auto-test et de réparation automatique, il n'est pas suffisant de considérer la taille de la RAM seulement. Sa configuration réelle (c.-à-d. le nombre de bits d'adresse et de données) doit être aussi prise en considération.

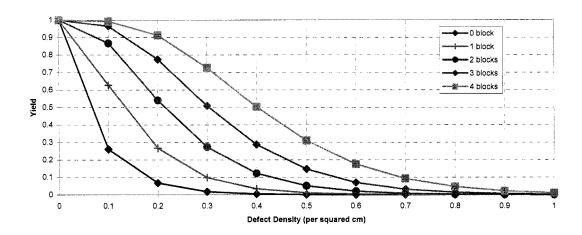

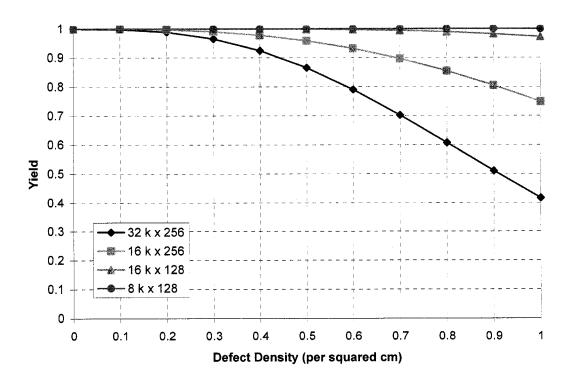

Une estimation du rendement est essentielle parce que trop de redondance signifie une perte dans la surface de silicium et trop peu mène à un faible rendement. Afin d'estimer l'amélioration du rendement grâce à la conception proposée et ainsi évaluer l'effet des différents paramètres du système, plusieurs calculs numériques ont été exécutés. Le rendement a été calculé en fonction de la densité de défectuosités en utilisant les équations basées sur les modèles de Poisson ainsi que le modèle binomial négatif.

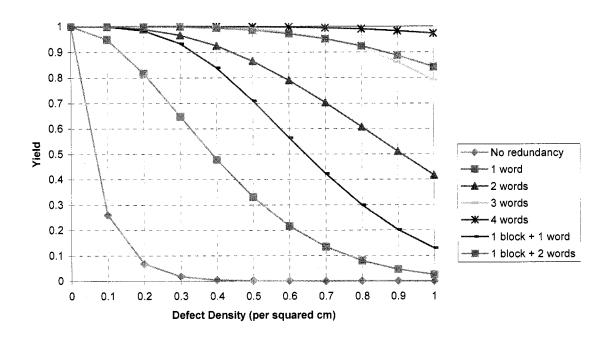

L'amélioration du rendement, résultant de l'ajout de blocs redondants au niveau supérieur de mémoire, est généralement constatée à des basses densités de défectuosités. À des densités de défectuosités élevées, on observe que cette amélioration du rendement devient insignifiante. On remarque aussi que le rendement total augmente avec le nombre de

mots redondants inclus dans chaque bloc. Cependant, après une certaine valeur, il devient plus avantageux d'ajouter des blocs redondants au niveau supérieur que d'insérer plus de mots redondants localement.

Le rehaussement du rendement, dû à la division de la mémoire en de nombreux blocs plus petits, est plus significatif à des densités de défectuosités élevées. Cependant, avoir plus de blocs causera une augmentation de la surface de silicium, due à la complexité supplémentaire de l'adressage à haut niveau et au câblage additionnel requis. Ceci amène aussi une augmentation du temps d'accès de la mémoire.

#### CONCLUSION

Un nouveau concept de mémoire avec des capacités d'auto-test et d'auto-réparation intégrées, basé sur le remplacement des mots au lieu des rangées ou des colonnes redondantes, a été présenté. Il permet de réparer des RAM générées par un compilateur de mémoire sans modifier leur architecture de base. Cette méthodologie de test et de réparation de mémoire ajoute deux blocs principaux aux modules de mémoire. Une logique de BIST de mémoire met en oeuvre l'algorithme de test et examine la RAM lors de sa mise sous tension. De plus, un bloc de BISR stocke les adresses qui échouent pendant le test et remplace les mots défectueux. Le concept d'auto-test combiné avec la réparation automatique sera essentiel pour réduire les coûts et améliorer le rendement des futures puces de mémoire de très grande capacité.

# TABLE OF CONTENTS

| ACKNOWLEDGMENTS                                 | IV     |

|-------------------------------------------------|--------|

| ABSTRACT                                        | VI     |

| RÉSUMÉ                                          | VIII   |

| CONDENSÉ EN FRANÇAIS                            | X      |

| INTRODUCTION                                    | X      |

| STRATÉGIES D'AUTO-TEST POUR MÉMOIRES EMBARQUÉES | XII    |

| TECHNIQUE DE REDONDANCE À DEUX NIVEAUX          | XIV    |

| IMPLANTATION ET RÉSULTATS                       | XVII   |

| CONCLUSION                                      | XIX    |

| TABLE OF CONTENTS                               | XX     |

| LIST OF FIGURES                                 | XXV    |

| LIST OF TABLES                                  | XXVIII |

| LIST OF ACRONYMS                                | XXIX   |

| LIST OF APPENDICES                              | XXXI   |

| 1 INTRODUCTION AND MOTIVATION                   | 1      |

| 1.1 INTRODUCTION                                | 1      |

|   | 1.2      | SCOPE AND ORGANIZATION OF THE THESIS5                                       |

|---|----------|-----------------------------------------------------------------------------|

| 2 | TEST ALC | GORITHMS AND DETERMINING FACTORS IN CHOOSING A                              |

|   | REPAIR A | ARCHITECTURE11                                                              |

|   | 2.1      | INTRODUCTION                                                                |

|   | 2.2      | COMPARISON OF REPAIR METHODS11                                              |

|   | 2.2.1    | Conventional test and repair method                                         |

|   | 2.2.2    | Advanced self-repairing method                                              |

|   | 2.3      | TEST ALGORITHMS                                                             |

|   | 2.3.1    | Mscan test [15]                                                             |

|   | 2.3.2    | Checkerboard test [15]                                                      |

|   | 2.3.3    | Five-cell-neighborhood static-pattern-sensitive fault test [15] and [16] 17 |

|   | 2.3.4    | Row/column weight-sensitive fault test [15] and [18]                        |

|   | 2.3.5    | Marching test [15, 44]                                                      |

|   | 2.4      | YIELD AND RELIABILITY FACTORS                                               |

|   | 2.4.1    | Type and amount of redundant elements                                       |

|   | 2.4.2    | Fault detection and localization                                            |

|   | 2.4.3    | Redundancy allocation                                                       |

|   | 2.4.4    | Repair strategy                                                             |

|   | 2.4.5    | Reconfiguration mechanism                                                   |

|   | 2.5      | YIELD MODEL AND ESTIMATION                                                  |

|   | 2.5.1    | Yield with no redundancy                                                    |

|   | 2.5.2    | Yield using redundant rows or columns only                                  |

|   | 2.5.3    | Yield using redundant rows or columns and redundant blocks | 32 |

|---|----------|------------------------------------------------------------|----|

| , | 2.6      | CONCLUSION                                                 | 33 |

| 3 | GLOBAL . | ARCHITECTURE AND THE SELF-TESTING FUNCTION                 | 34 |

|   | 3.1      | INTRODUCTION                                               | 34 |

|   | 3.2      | GLOBAL ARCHITECTURE                                        | 34 |

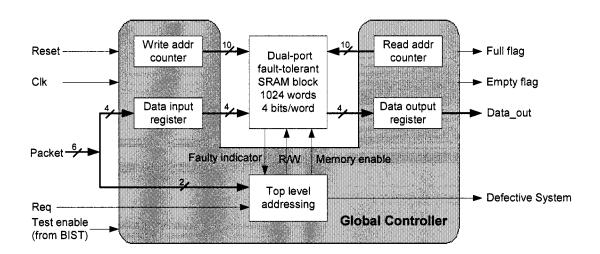

|   | 3.2.1    | Global Controller                                          | 37 |

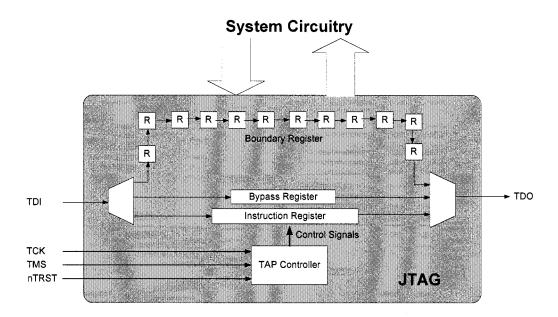

|   | 3.2.2    | Boundary Scan (JTAG)                                       | 38 |

|   | 3.3      | THE SELF-TESTING FUNCTION                                  | 40 |

|   | 3.3.1    | SRAM fault model                                           | 41 |

|   | 3.3.2    | Test algorithm                                             | 44 |

|   | 3.3.3    | Memory Fault Coverage                                      | 47 |

|   | 3.3.4    | Architecture of the BIST                                   | 49 |

|   | 3.4      | CONCLUSION                                                 | 54 |

| 4 | THE SELI | F-REPAIRING FUNCTION AND THE SRAM BLOCK                    | 55 |

|   | 4.1      | INTRODUCTION                                               | 55 |

|   | 4.2      | THE SELF-REPAIR CONFIGURATION                              | 55 |

|   | 4.3      | METHODOLOGY                                                | 57 |

|   | 4.4      | REPAIR ALGORITHM FLOW                                      | 59 |

|   | 4.5      | FAULT-TOLERANT SRAM BLOCK ARCHITECTURE                     | 60 |

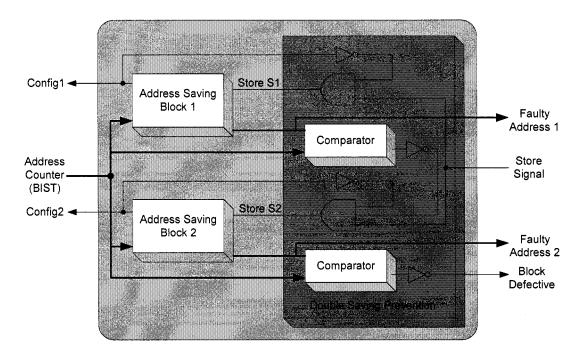

|   | 4.5.1    | Fault Registration Block                                   | 61 |

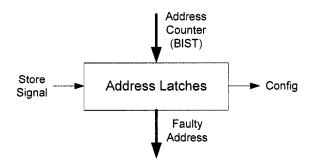

|   | 4.5.2    | Address Correction Block                                   | 64 |

|   | 4.5.3    | SRAM block                                                      | 66   |

|---|----------|-----------------------------------------------------------------|------|

|   | 4.6      | FAULT REPAIRING PROCEDURE                                       | 69   |

|   | 4.6.1    | Test mode                                                       | . 69 |

|   | 4.6.2    | Normal operation mode                                           | . 72 |

|   | 4.7      | CONCLUSION                                                      | . 73 |

| 5 | IMPLEMI  | ENTATION AND RESULTS                                            | . 74 |

|   | 5.1      | INTRODUCTION                                                    | . 74 |

|   | 5.2      | IMPLEMENTATION                                                  | . 74 |

|   | 5.3      | AREA OVERHEAD ESTIMATIONS                                       | . 76 |

|   | 5.3.1    | Area Overhead Dependence with the RAM Block Size and the Number | of   |

|   |          | RAM Blocks                                                      | . 78 |

|   | 5.3.2    | Area Overhead in Dependence of the RAM Block Configuration      | . 79 |

|   | 5.3.3    | Area Overhead Projection for Ultra-Large Capacity Memory Chips  | . 80 |

|   | 5.4      | YIELD ANALYSIS                                                  | . 82 |

|   | 5.4.1    | Redundant Blocks Effect                                         | . 82 |

|   | 5.4.2    | Redundant Words Effect                                          | . 83 |

|   | 5.4.3    | Block Size Effect                                               | . 85 |

|   | 5.5      | TIMING PENALTY                                                  | . 87 |

|   | 5.6      | CONCLUSION                                                      | . 89 |

| C | ONCLUSIO | ON AND FUTURE WORK                                              | . 90 |

|   | FUTURE   | $V \cap \mathbf{R} K$                                           | 92   |

| REFERENCES | 95  |

|------------|-----|

| APPENDIX A | 103 |

| APPENDIX B | 104 |

# LIST OF FIGURES

| Figure 1.1 According to Semiconductor Industry Association (SIA) and International             |

|------------------------------------------------------------------------------------------------|

| Technology Roadmap for Semiconductors (ITRS) 2001 [54], embedded memory                        |

| will continue to dominate SoC content in the next several years, approaching 94% of            |

| the die area by 2014.                                                                          |

| Figure 1.2 Memory yield improvement [54]                                                       |

| Figure 1.3 Simplified representation of the proposed concept                                   |

| Figure 1.4 Conceptual architecture of the proposed self-repairing SRAM 8                       |

| Figure 1.5 The hierarchical redundancy structure.                                              |

| Figure 2.1 External test and repair method                                                     |

| Figure 2.2 Advanced self-repairing method                                                      |

| Figure 2.3 Tiling a memory array for the checkerboard test : (a) pattern one: (b) pattern      |

| two                                                                                            |

| Figure 2.4 Tiling a memory array for the static-pattern-sensitive fault test: (a) phase 1; (b) |

| phase 2                                                                                        |

| Figure 2.5 Partitioning a memory array into four in the row/column weight-sensitive fault      |

| test: (a) memory array with the border cells tested; (b) memory array partitioned into         |

| four                                                                                           |

| Figure 2.6 Embedded memory repair strategies: (a) hard, (b) soft, (c) combinational, and       |

| (d) cumulative27                                                                               |

| Figure 2.7 Memory with redundancy model                                                 | ) |

|-----------------------------------------------------------------------------------------|---|

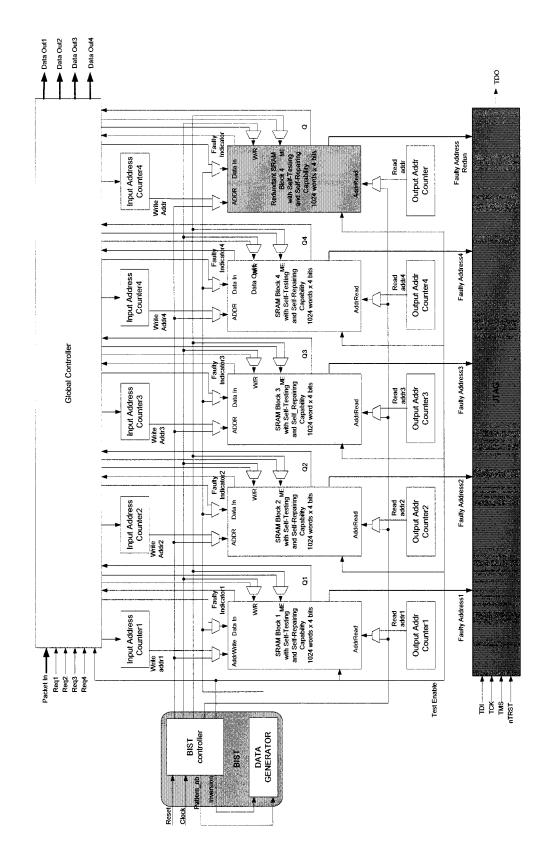

| Figure 3.1 Global architecture of the implemented chip                                  | 5 |

| Figure 3.2 Functional model of the global controller                                    | 7 |

| Figure 3.3 Basic architecture of the JTAG Boundary Scan                                 | 9 |

| Figure 3.4 BIST implementation procedure                                                | 1 |

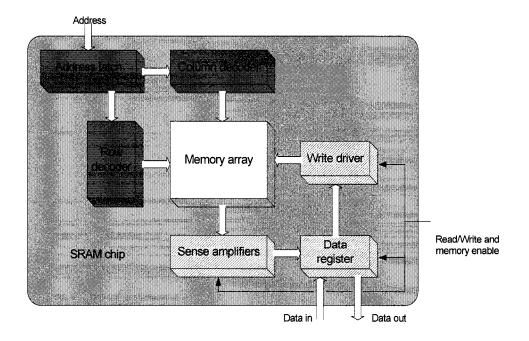

| Figure 3.5 Functional model of an SRAM chip                                             | 2 |

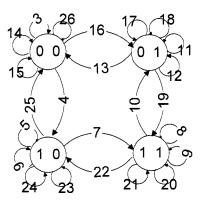

| Figure 3.6 State diagram for two random cells in the memory array                       | 9 |

| Figure 3.7 Global architecture of the self-testable SRAM                                | 0 |

| Figure 3.8 State diagram of the BIST controller                                         | 3 |

| Figure 4.1 BISR basic architecture                                                      | 8 |

| Figure 4.2 The BISR algorithm                                                           | 0 |

| Figure 4.3 Fault-Tolerant SRAM Block. 63                                                | 1 |

| Figure 4.4 The Fault Registration Block                                                 | 2 |

| Figure 4.5 Address Saving Block                                                         | 2 |

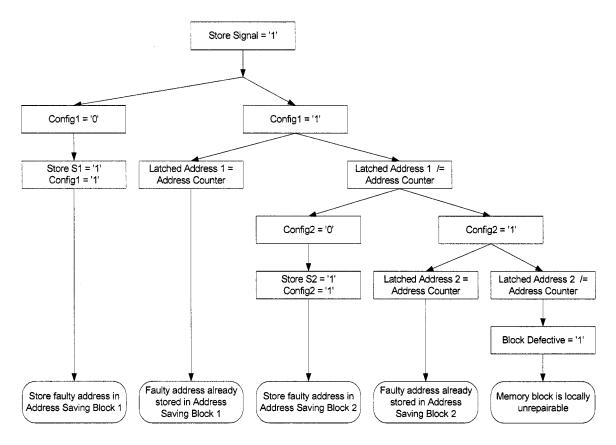

| Figure 4.6 Flow for storing a faulty address                                            | 4 |

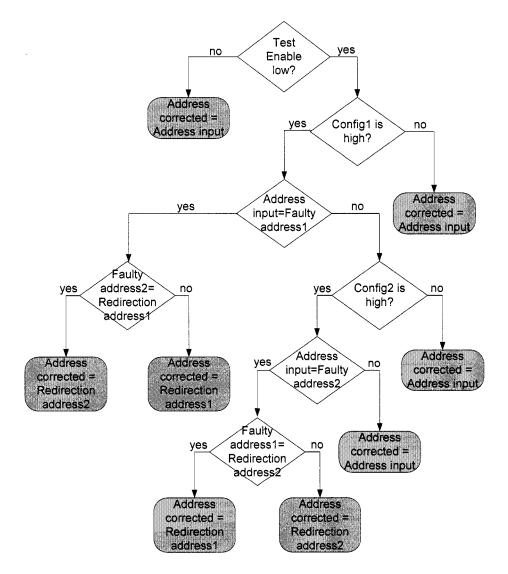

| Figure 4.7 Flow of address correction.                                                  | 5 |

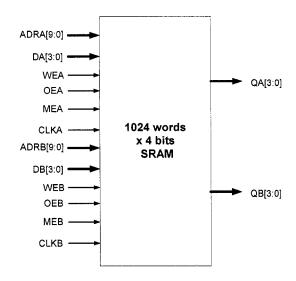

| Figure 4.8 Symbol of the used memory                                                    | 9 |

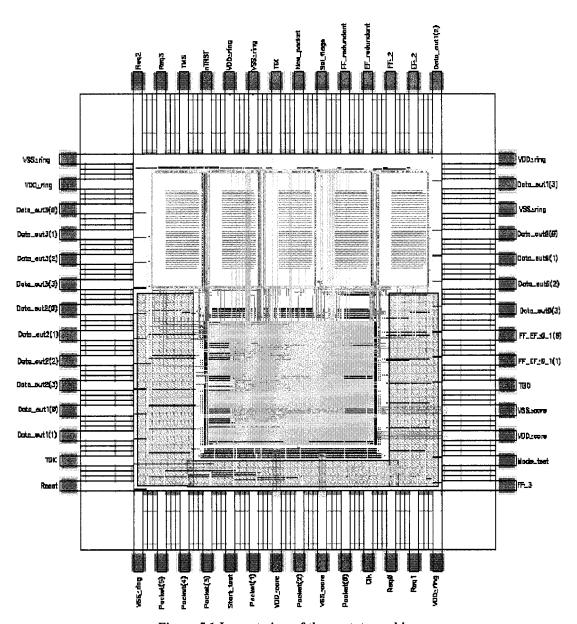

| Figure 5.1 Layout view of the prototype chip                                            | 5 |

| Figure 5.2 Area overhead for implementing the self-test and self-repair structure in    |   |

| dependence of the RAM block size for different numbers of blocks                        | 9 |

| Figure 5.3 Overhead in dependence of the total number of address bits and data bits for |   |

| different RAM sizes divided into sixteen blocks plus one redundant block                | ሰ |

| Figure 5.4 Yield as a function of the defect density for different numbers of redundant |    |

|-----------------------------------------------------------------------------------------|----|

| blocks.                                                                                 | 83 |

| Figure 5.5 Yield as a function of the defect density for different numbers of redundant |    |

| words per block and redundant blocks                                                    | 84 |

| Figure 5.6 Yield as a function of the defect density for different blocks sizes         | 85 |

| Figure 5.7 Yield improvement due to dividing the memory into smaller blocks and its     |    |

| corresponding area overhead.                                                            | 86 |

| Figure 5.8 Self-repairing circuit on the memory critical path.                          | 87 |

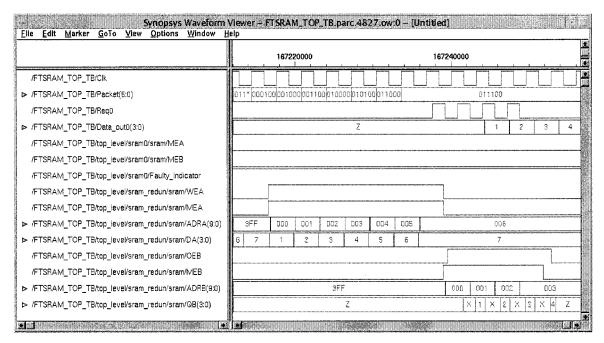

| Figure 5.9 Waveform simulation showing the signal delay through the address correction  | on |

| block                                                                                   | 88 |

| Figure 5.10 Waveform simulation showing the signal delay caused by the top level        |    |

| addressing block                                                                        | 89 |

| Figure 6.1 Word redundancy scheme with no flexibility.                                  | 92 |

| Figure 6.2 Suggested word redundancy scheme with flexibility.                           | 93 |

| Figure 6.3 Sketch of the conceptual architecture using a CAM                            | 94 |

# LIST OF TABLES

| Table 3.1 | The 13N marching test algorithm for SRAMs plus data retention test 4           | •5 |

|-----------|--------------------------------------------------------------------------------|----|

| Table 4.1 | Description of the input and output pins of the SRAM block                     | '0 |

| Table 5.1 | Sizes of several functional blocks of the fault-tolerant memory prototype chip |    |

| •••••     |                                                                                | '6 |

| Table 5.2 | Estimation of the area overhead for different memory capacities                | 31 |

| Table 5.3 | Different arrangements for a 128-Mb RAM                                        | 36 |

## LIST OF ACRONYMS

**ASAP** Area, Speed, and Power

**BIRA** Built-In Redundancy Allocation

BISR Built-In Self-Repair

**BIST** Built-In Self-Test

BISD Built-In Self-Diagnosis

**CAD** Computer Aided Design

**CAM** Content Access Memory

**CMC** Canadian Microelectronics Corporation

**CMOS** Complementary Metal Oxide Semiconductor

**DRC** Design Rule Check

**EDA** Electronic Design Automation

**FIFO** First In First Out

FSM Finite State Machine

**GRM** Groupe de Recherche en Microélectronique

**HD** High Density

**HS** High Speed

IC Integrated Circuit

ITRS International Technology Roadmap for Semiconductors

JTAG Joint Test Action Group

LVS Layout Versus Schematic

MCM Multichip Module

**PCB** Printed Circuit Board

PDA Personal Digital Assistant

**PGA** Pin Grid Array

**RAM** Random Access Memory

**RTL** Register Transfer Level

SIA Semiconductor Industry Association

**SoC** System on Chip

**SRAM** Synchronous Random Access Memory

**TAP** Test Access Port

TCK Test Clock

**TDI** Test Data In

**TDO** Test Data Out

TMS Test Mode Select

**TRST** Test Reset

**TSMC** Taiwan Semiconductor Manufacturing Company

**ULP** Ultra-Low Power

VHDL VHSIC (Very High Speed Integrated Circuits) Hardware Description

Language

Y Yield

# LIST OF APPENDICES

| APPENDIX A COMPILER PARAMETER RANGES    | 103   |

|-----------------------------------------|-------|

| APPENDIX B MEMORY BLOCK CHARACTERISTICS | . 104 |

# Chapter 1

## INTRODUCTION AND MOTIVATION

In this chapter, the studied problem and the main objectives are introduced. Then, the strategy employed to obtain the proposed fault-tolerant SRAM and the thesis outline are presented.

#### 1.1 INTRODUCTION

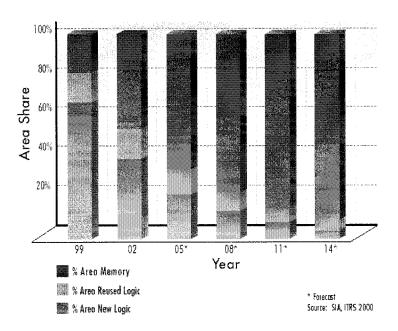

Today's ICs are memory dominated. Demand for more and more memory is driven by the need to support various high-bandwidth, high-capacity applications. This includes communications and networking products that must handle large amount of data in real time, applications for low-power portable devices such as PDAs and wireless phones, and high-speed processing applications requiring large and fast memories for program and data storage. In recent years, the amount of memory as a percentage of the total die area has increased dramatically attaining 70% or more. As illustrated in Figure 1.1, according to Semiconductor Industry Association (SIA) and International Technology Roadmap for Semiconductors (ITRS) 2001, embedded memories will continue to dominate SoCs (systems on chip) content in the next several years, approaching 94% of the die area by 2014.

Many designers have turned to embedded memories to improve system speed, lower power consumption and reduce costs. Thus, memories keep growing in size, which obviously affects the overall die size, requiring more silicon and increasing the production costs. Perhaps less obvious, but equally costly, is the increased risk of defects.

Figure 1.1 According to Semiconductor Industry Association (SIA) and International Technology Roadmap for Semiconductors (ITRS) 2001 [54], embedded memory will continue to dominate SoC content in the next several years, approaching 94% of the die area by 2014.

Having more embedded memory on a die makes it more vulnerable to failure due to manufacturing defects. Moreover, memory blocks are more susceptible to defects than logic. Memories are the densest circuits fabricated today. Because their transistors and

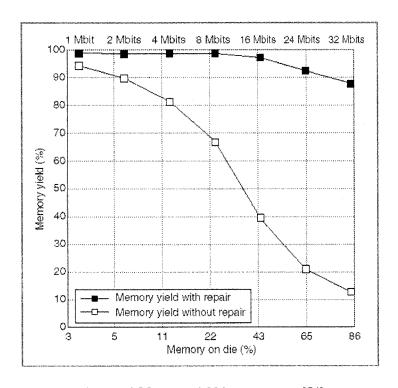

wires are packed so closely together, memory blocks suffer from a very high average number of physical defects per unit of area compared with other types of circuits. So, the greater the area of the die occupied by memory, the greater the risk of producing an IC that does not work and will cause the entire system to fail. Therefore, the total chip yield drops dramatically. One way to solve this problem is to enhance memories by adding redundant memory locations and test and repair algorithms [8] and [31]. Figure 1.2, presented by Zorian [54], compares the estimated yield of an embedded memory making use of these enhancements to the yield of the same memory, evaluated before adding test and repair capabilities, as a function of aggregate memory bit count in a SoC. It also shows the relationship between the memory yield and the die area occupied by memory. For instance, the yield of 24 Mbits of embedded memory, occupying 65% of the die area, can be increased from close to 20% to higher than 90% using an adequate repair strategy. This example assumes a 12-mm x 12-mm chip, in 0.13-micron technology, with a 0.12-per-square-centimeter memory defect density.

Recently, redundancy and repair have been extensively practiced for enhancing defect and fault tolerance. Unlike in legacy PCB (printed circuit board) or MCM (multichip module) based systems, embedded core components cannot be physically replaced once they are fabricated in a SoC. To realize enhanced manufacturing yield, a BISR (built-inself-repair) must be used to allocate redundancy for embedded memory system cores. Building in redundancy allows the memories to be repaired. This has a significant impact on yield [22]. By being able to repair defects in the memory, the yield can be raised at an

acceptable level. For embedded memories totaling more than 1 MB, redundancy is essential to maintaining high yield.

Figure 1.2 Memory yield improvement [54]

Therefore, fault-tolerance is an important issue in designing memory chips with ultralarge capacity. The common approaches to fault-tolerance include introducing spare rows and columns into the memory array [30]. The introduction of redundant rows and columns are often carried out by laser or by on-chip fuse/antifuse devices. These repairing techniques are referred to as "surgical repairing". They are simple techniques operated in a production environment; and they usually have minimum impact on memory performance. These techniques allow one-time programming and are considered as hard repair. Any field related error correction and fault-tolerance cannot be achieved. Therefore, there is a growing interest to develop techniques for repairing these faults on the fly in any operating environment with the need of no external equipment.

#### 1.2 SCOPE AND ORGANIZATION OF THE THESIS

This project goal was to develop a built-in self-testing (BIST) and self-repairing (BISR) SRAM offering the following characteristics:

- Self-testing function capable of detecting faulty cells that need to be repaired.

- Self-repairing function performed on-line and transparently, without the user intervention.

- Self-repairing independent from the memory physical implementation. Most of the self-repairing approaches proposed so far are based on row/column repair strategy requiring the knowledge of the memory layout. To achieve user level memory repairing, a method based on cell replacement is presented.

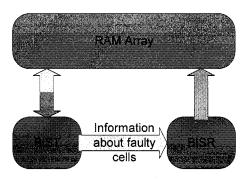

Figure 1.3 shows a simplified representation of the proposed concept. A BIST tests the memory and provides information about faulty cells, while a BISR uses this information to repair the memory [10].

Figure 1.3 Simplified representation of the proposed concept.

The proposed word oriented static RAM Built-In-Self-Repair methodology allows to use standard RAMs generated from memory compilers without spare rows or spare columns and add to them some redundant logic. This permits to build a self-repairing memory without modifying the memory module. The redundancy and BIST logic is fully parametric, synthesizable and reusable. It is highly flexible and can be used with various memory types that do not have any redundancy capabilities. The implemented self-repair strategy using redundant words can be summarized as follows:

- Partition a large SRAM array into several identical sub-blocks. This is generally

a common practice for high performance embedded RAMs [2], [3] and [11].

Each sub-block is supported by dedicated logic to allow replacing defective cells

[12].

- 2. Repair each sub-block independently of the others. In other words, each sub-block has its own spare words that are not shared across sub-blocks.

- 3. Provide 2 spare words for each sub-block. When a repair is needed, the entire word is used to replace an equivalent defective word in the SRAM.

- 4. Provide one spare sub-block at the top level to replace a sub-block that has more than 2 different defective words and is therefore locally unrepairable.

- 5. Develop and implement an on-line repair algorithm [4], [7], [23] and [34] that detects and diagnoses the failure information on the fly during self-test and maintains an up-to-date fault map which consists of a list of the locations where a failure occurred and the corresponding spares used to replace them.

As the memory, the decoder and the read-write logic form an integrated full custom module generated by a RAM generator, the self-test as well as the self-configuration strategy must not intervene between the memory field, the decoder and the read-write logic.

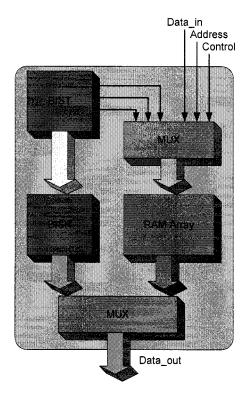

The concept of enhancing the SRAM with self-repairing capability is illustrated in Figure 1.4. First, a suitable test algorithm is chosen and implemented as a built-in self-test (BIST) with low area overhead. A multiplexer placed in front of the SRAM is widely used to provide the memory with the test pattern generated by the BIST. Then, a circuit that stores the faulty addresses and redirects them into functional ones is developed. When a fault is detected, the self-repair logic automatically reconfigures the memory

using redundant cells in the form of words and blocks replacing the defective ones [33]. When a faulty cell is addressed, the circuit reacts by changing the address value to the address of the redundant cell.

Figure 1.4 Conceptual architecture of the proposed self-repairing SRAM.

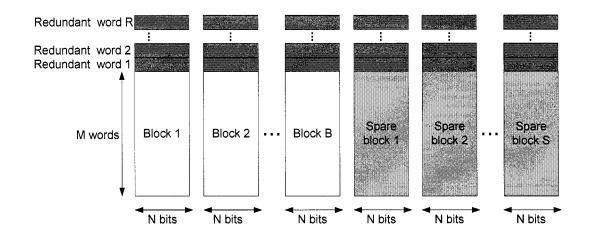

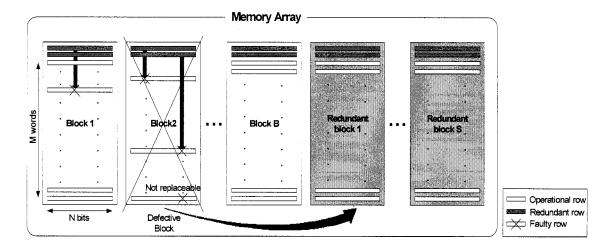

In this approach, a two-level redundancy has been implemented [32], as illustrated in Figure 1.5. Therefore, the RAM is split up into B blocks of M words by N bits. On the lower level, each block is equipped with additional memory cells in the form of R spare words. On the higher level, S additional redundant blocks are provided to mask larger defects. This hierarchical redundancy structure achieves a significantly higher yield with a rather low area overhead [20].

Figure 1.5 The hierarchical redundancy structure.

The thesis is organized as follows. In chapter 2, all the determining factors that have to be considered when selecting a self-repairing technique will be treated. These factors influence the repair efficiency and thus the yield of the embedded memory. A model will be proposed to estimate the overall yield considering different redundancy configurations. In chapter 3, the global architecture of the proposed self-testing and self-repairing SRAM design will be introduced. This architecture is divided into two major segments: the self-testing function which makes the object of chapter 3 and the self-repairing component which will be treated in chapter 4. In chapter 5, the implementation procedure of the entire system will be given as well as the most relevant results and analysis. Finally, a brief conclusion and some suggestions for future work will be presented in chapter 6.

In this chapter, the yield deterioration problem resulting from including more embedded memory on the die has been exposed. Existing solutions to deal with this problem have been considered and the major objectives have been specified. Finally, the methodology used to realize a self-testing and self-repairing embedded memory has been proposed.

## Chapter 2

# TEST ALGORITHMS AND DETERMINING FACTORS IN CHOOSING A REPAIR ARCHITECTURE

#### 2.1 INTRODUCTION

In this chapter, the traditional test and repair method is compared to an advanced self-repairing technique. Several test algorithms found in the literature are enumerated with a brief description. The major factors that influence the yield and reliability of the embedded memory are enumerated. A yield model that can be applied to predict the yield of a memory array using different redundancy configurations is also developed in this chapter.

#### 2.2 COMPARISON OF REPAIR METHODS

The conventional method of using external test and repair equipments presents several drawbacks. To overcome them, a more advanced method to repair embedded memories is proposed.

#### 2.2.1 Conventional test and repair method

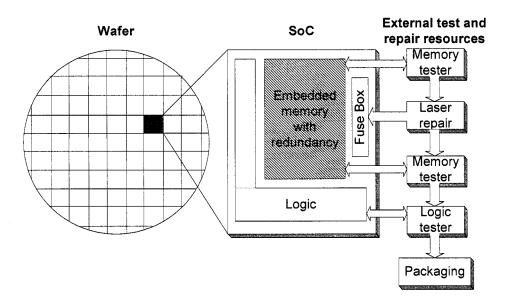

The most common approach to perform memory repair is using external test and repair. As illustrated in Figure 2.1, this method can be divided into four main steps, all taking place at wafer level:

An external memory tester applies a wafer-level memory test on the embedded memory with redundancy and stores the failed bit map in a large capture memory.

Then this failed bit map is used by a redundancy allocation software to determine the best way to allocate redundant resources to replace defective locations and generate the reconfiguration data.

Figure 2.1 External test and repair method

2. These reconfiguration data are then transferred to the laser repair equipment, which programs them by blowing fuses in laser fuse boxes corresponding to the defective memories.

- 3. When the repair is accomplished, a retest is applied by a second memory tester to make sure that the repair was successfully performed.

- 4. Before packaging, an external logic tester applies a test on the remaining logic part of the SoC.

Due to the massive use of external and expensive equipment, this test and repair method largely increases the total manufacturing cost of a chip [38]. In addition, this method requires a high bandwidth access to the embedded memory during memory test performed by the functional tester. The fact that this method uses a general-purpose redundancy allocation algorithm restricts its repair efficiency. Furthermore, this technique does not allow any field repair.

#### 2.2.2 Advanced self-repairing method

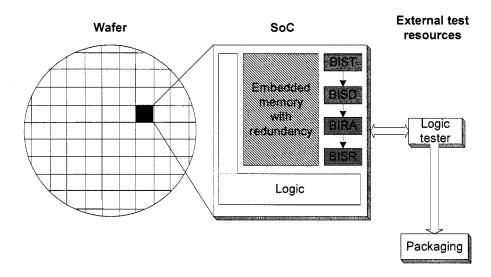

To overcome the drawbacks of the conventional external test and repair method, presented in the preceding section, an effective self-repairing technique using an on-chip logic structure, which can be activated in any operating environment, is highly desirable [6]. This will allow a periodic field level repair and power-up soft repair for the embedded memories. The process of self-repairing, shown in Figure 2.2, can be divided into several steps, all built-in the RAM architecture:

1. Built-In Self-Test (BIST): In the first place, a test algorithm is executed on the memory array to detect faults.

2. Built-In Self-Diagnosis (BISD): If a fault is detected, it is necessary to locate it (diagnosis).

Figure 2.2 Advanced self-repairing method

- 3. Built-In Redundancy Allocation (BIRA): Here, it allocates the redundant memory space available.

- 4. Built-In Self-Repair (BISR): Finally, it replaces the faulty cells.

This method reduces considerably the manufacturing cost, since external test and repair equipment is not needed as discussed in [8] and [39]. The logic tester by itself is sufficient to perform the memory test and repair process followed by testing of the random logic blocks. Moreover, it improves the repair efficiency due to the fact that the memory can be reconfigured several times in the field.

#### 2.3 TEST ALGORITHMS

Over the years, several algorithms of different complexities ranging from O(N) to  $O(N^2)$ , where N is the total number of memory cells, have been developed to test RAMs. The early algorithms were developed in an ad hoc manner; whereas the later algorithms were specifically designed to detect faults associated with various fault models. Many of those algorithms have been applied to BIST. Three classes of test algorithms can be distinguished: deterministic, pseudo random and pseudo exhaustive tests [55]. A review of these test algorithms can be found in [16], [17], [43] and [47].

All test algorithms consist of a sequence of writes and reads applied to the cells in the memory array. In the subsequent subsections,  $W_i \leftarrow v$  means writing value v into cell i and  $R_i (= v)$  stands for reading cell i, with v as the expected value.

#### 2.3.1 Mscan test [15]

Memory scan is a trivial test procedure developed in an ad hoc manner. It consists of writing a 0 to each cell then reading it, followed by writing a 1 and reading it. The formal algorithm can be summarized as shown below:

For

$$i = 0, 1, ..., N - 1$$

$$W_i \leftarrow 0$$

$$R_i (= 0)$$

$$W_i \leftarrow 1$$

$$R_i (= 1)$$

The deterministic fault coverage of this test method is rather low. All that is known at the end is that there is at least one cell in the RAM that can be set to 0 and 1. This is because a fault in the decoder may cause the same cell to be referenced each time. Its length is 4N since it performs four operations on each cell.

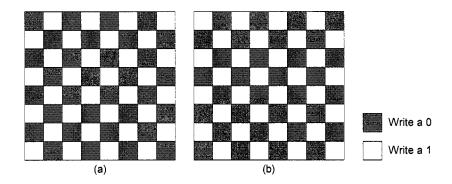

#### 2.3.2 Checkerboard test [15]

This simple algorithm, developed in an ad hoc manner, is designed for two-dimensional memory architectures. The algorithm fills the memory array with a checkerboard pattern by writing 0's and 1's in alternate cells. The two patterns shown in Figure 2.3 are written. The cells are read after the application of each checkerboard pattern.

Figure 2.3 Tiling a memory array for the checkerboard test: (a) pattern one: (b) pattern two.

The formal algorithm is given below:

Step 1.

$$W_{(i,j)} \leftarrow 0$$

for  $i + j = even$

$$W_{(i, j)} \leftarrow 1 \text{ for } i + j = \text{odd}$$

Step 2.

$$R_{(i, j)}$$

(= 0) for  $i + j$  = even  $R_{(i, j)}$  (= 1) for  $i + j$  = odd

Step 3. Repeat steps 1 and 2, interchanging 0's and 1's.

The deterministic fault coverage of this test procedure is rather low. As with the Mscan test, a decoder fault may cause only four cells at most to be referenced. Therefore, all that is known at the end of this test is that at least four cells in the RAM can be set to 0 and 1.

# 2.3.3 Five-cell-neighborhood static-pattern-sensitive fault test [15] and [16]

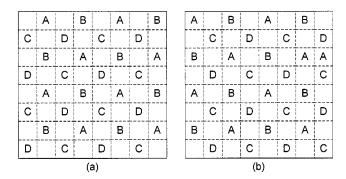

Many algorithms have been proposed to detect five-cell-neighborhood pattern-sensitive faults. All these algorithms are based on tiling the memory array. Kinoshita and Saluja [25] suggested an algorithm based on the tiling arrangements shown in Figure 2.4. The unmarked cells are the base cells. Each base cell is surrounded by four characters (A, B, C and D).

The first phase of the test uses the tiling arrangement illustrated in Figure 2.4a. During this phase, the base cells are kept fixed at logic 0. The five-cell-neighborhood patterns are applied to the base cells using all four-tuples (16 patterns), consisting of Boolean

variables A, B, C, and D. The base cells are read after the application of each pattern. The second phase uses the tiling arrangement of Figure 2.4b, and the above process is repeated. Then both phases are repeated with the base cells at logic 1. This algorithm is based on the abstract logical neighborhood, as opposed to the actual physical neighborhood, assuming that the two neighborhoods are identical. If the assumption is invalid, such tiling methods can go haywire. Franklin and Saluja proposed in [18] a test algorithm to detect five-cell physical neighborhood pattern sensitive faults, even if the logical and physical addresses are different and the physical-to-logical address mapping is not available. This algorithm has a test length of O(N[log<sub>3</sub>N]<sup>4</sup>).

Figure 2.4 Tiling a memory array for the static-pattern-sensitive fault test: (a) phase 1; (b) phase 2

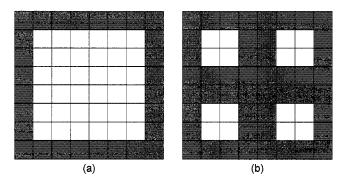

#### 2.3.4 Row/column weight-sensitive fault test [15] and [18]

Different test algorithms of varying test length have been proposed for testing RAMs for row/column weight-sensitive faults [19]. All the tests are of length  $O(N^{3/2})$  and use divide and conquer by recursive partitioning as the basic strategy. First, the border cells of an array are tested. Then, the two middle rows and columns are tested, thereby

effectively partitioning the array into four, as illustrated in Figure 2.5. Partitioning continues recursively until all the cells of the array are tested. The test procedure can be conceptually divided into the following steps:

- Step 1 Test the four corner cells of the RAM simultaneously, for states with cell values 0 and 1.

- Step 2 Test the border cells consisting of the top row, bottom row, leftmost column and rightmost column cells for states with cell value 0.

- Step 3 Test the partitioning cells consisting of the two middle rows and middle columns, for states with cell value 0. This step partitions the array into four parts, with the border of each partition completely tested for states with cell value 0.

Figure 2.5 Partitioning a memory array into four in the row/column weight-sensitive fault test: (a) memory array with the border cells tested; (b) memory array partitioned into four.

Step 4 Partition the memory array recursively by executing step 3 till all the cells within a partition are tested completely. At the end of this step, all cells in the array will be completely tested for cell value 0.

Step 5 Repeat steps 2 to 4 for testing the non-corner cells of the array for states with cell value 1.

Testing the border cells involves scanning the memory array as in the marching test, and this helps to detect decoder faults, stuck-at, stuck-open, transition and coupling faults. However, the row/column weight-sensitive fault test has a higher length.

#### 2.3.5 Marching test [15, 44]

The most widely used deterministic test algorithm in the industry is the marching test. The reason for its popularity is its simplicity coupled with a moderate fault coverage. This algorithm detects all faults affecting the decoder, all stuck-at faults in the read/write logic and all single and multiple stuck-at, stuck-open, transition and non-inverting coupling faults.

The March algorithm consists of a finite sequence of March elements applied to each cell in the memory in a given order [44]. First, it initializes the memory array to all 0's, and then scans the memory cells in ascending and descending orders. For each cell, scanning involves reading the cell for the expected value, writing the complement value, and reading it again. The formal algorithm can be expressed as follows:

Step 1. For

$$i = 0, 1, ..., N-1$$

$$W_i \leftarrow 0$$

Step 2. For

$$i = 0, 1, ..., N-1$$

$$Ri (= 0)$$

$$W_{i} \leftarrow 1$$

$$Ri (= 1)$$

Step 3. For  $i = N-1, N-2, ..., 0$

$$Ri (= 1)$$

$$W_{i} \leftarrow 0$$

$$Ri (= 0)$$

Step 4. Repeat steps 1 through 3, interchanging 0's and 1's.

The idea behind this algorithm is that, while scanning the memory in ascending order, any direct coupling between the current cell and a higher address cell is detected when reading the latter. Moreover, any error in the higher address cell due to decoder faults will also be detected. Similarly, scanning the memory in the descending order detects all the effects on lower address cells.

Different variations of the marching test, all of complexity O(N), have been seen in the literature [15], [46] and [49]. In [14], Dekker suggested a 9N and a 13N algorithms for testing SRAM's. According to him, these test algorithms count among the best of all available test algorithms as far as fault coverage and testing time are concerned. The 13N

test algorithm has been chosen to implement the BIST in our design and will be described in more details in chapter 3.

#### 2.4 YIELD AND RELIABILITY FACTORS

According to Zorian [53], several factors can contribute to the yield and reliability optimization of an embedded memory, namely: the type and amount of redundant elements, the fault detection and localization algorithm, the redundancy allocation algorithm, the repair strategy, and the reconfiguration mechanism. The way each factor is selected plays a significant role in the repair efficiency and thereby in the yield of the embedded memory. Each one of these factors will be treated in this section.

#### 2.4.1 Type and amount of redundant elements

The type and amount of redundant elements incorporated in the memory constitutes a determining factor in the yield optimization and the repair efficiency. A prediction of the post-repaired yield allows determining the amount of redundancy required to attain some target yield. Deciding on the amount of redundancy to include in the embedded memory is very critical because implementing too much redundancy will cause a waste in the silicon area, and implementing too little will result in a poor yield. Typically, memories smaller than 1 Mbit do not necessitate redundancy.

#### 2.4.1.1 Types of redundancy

Different types of redundancy exist [5] and [37]. This section gives an overview of each type.

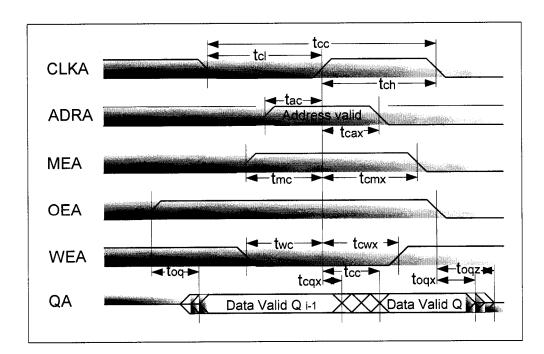

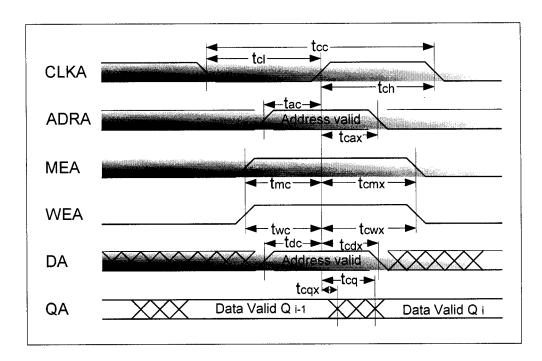

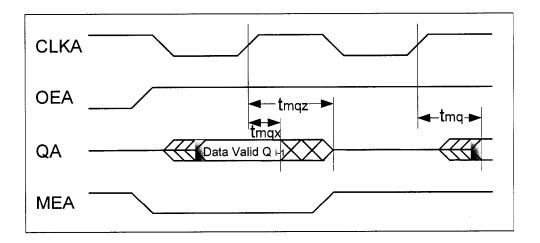

#### ➤ Wordline (row) redundancy

Wordline redundancy allows replacing one or more rows with spare ones. A special dedicated logic is added around the memory array to assure this replacement. The only timing penalty of this configuration is a slight degradation of the address setup time, caused by the presence of an address comparator used to detect the access to the redundant location. More details concerning this timing penalty will be provided in section 5.5. Moreover, the area overhead to implement this type of redundancy is quite low.

#### > Bitline (column) redundancy

Bitline redundancy is similar to the wordline redundancy, except that spare columns are added to the embedded memory instead of rows. Designing an efficient architecture to implement bit line redundancy allowing the redundant columns to be shared throughout the memory array is usually difficult due to the presence of bit lines multiplexers which choose one bit line among several ones before the output sense amplifier.

#### ➤ Word (cell) redundancy

Word redundancy consists in adding a few redundant words, each corresponding to a logical RAM address. This organization allows a more flexible configuration compared to physical wordlines [40].

#### 2.4.1.2 Redundant space configuration

Embedded memories can use a single type of redundant elements or a combination of multiple types. Based on the three redundancy approaches described in section 1.4.1.1, redundant space can be inserted in three different ways in the memory array:

#### 1. Row/Column Only

The memory is provided with spare rows or columns. In this case, all spares are of the same type, row or colums but not both. When a fault is detected, the row/column where the fault occurred is replaced by one of the spare rows/columns. However, this configuration does not use the redundant space in an optimal way, given that a whole row/column has to be allocated to repair a single fault.

#### 2. Row-column

The memory is provided with both spare rows and spare columns. Any fault can be repaired by using either a spare row or a spare column. When multiple faults occur, the best combination of spare rows/columns is chosen to optimize the redundant space while repairing the faults efficiently.

#### 3. Word (cell) only

The memory is enhanced with spare words. Each word corresponds to an addressable location in the RAM. When a fault occurs, the faulty address is redirected to a spare word, instead of replacing a complete row or column. Therefore, this configuration allows an optimal use of the redundant space and it has been adopted in the proposed design.

#### 2.4.2 Fault detection and localization

In order to improve the memory yield and reliability, faults need not only to be detected; but also to be located for further repair. Fault localization is required to identify the faulty cells that need to be replaced. Therefore, the test algorithm should employ efficient procedures for effective detection and location of the faulty cells to reach a higher yield.

### 2.4.3 Redundancy allocation

Redundancy allocation consists in determining the best way to assign redundant resources to replace faulty locations [28]. In the case where only one type of redundant elements is used, row-only redundancy for instance, the redundancy allocation is

straightforward. On the other hand, if a combination of various redundant elements types is used, an optimal reconfiguration has to be found and redundancy allocation becomes more complex. An algorithm needs to be developed and implemented to determine the most efficient solution to repair the memory [9]. This redundancy allocation algorithm has to run on the fly, meaning in real-time, while the fault detection and localization are performed.

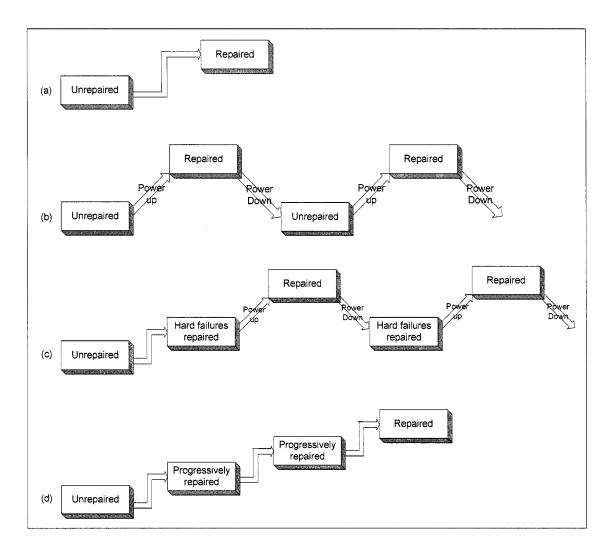

#### 2.4.4 Repair strategy

The repair strategy consists in the methodology employed to perform the actual repairing. The selection of a repair strategy can influence dramatically the repair efficiency and thereby the yield. Four different strategies, illustrated in Figure 2.6, can be distinguished. A brief description of each one of them is given below:

#### 2.4.4.1 Hard repair

Hard repair necessitates the use of a permanent storage to retain the repair information after power is turned off. This repair is performed only once using some fuse box and does not need retesting or reconfiguration at every power-up.

#### 2.4.4.2 Soft Repair

Soft repair is performed at every power-up for an unlimited number of times. It does not require a fuse box given that the repair information does not need to be held upon power-

down. This method is able to detect different faults at different times allowing field repair and thus improving reliability.

Figure 2.6 Embedded memory repair strategies : (a) hard, (b) soft, (c) combinational, and (d) cumulative.

#### 2.4.4.3 Combinational repair

Combinational repair starts with a hard repair in the factory followed by a soft repair in the factory or in the field. This method offers the best of both hard and soft repair. It is better than each one operating alone. However, the information acquired from each soft repair is not stored and cannot be reused upon the next power-up.

#### 2.4.4.4 Cumulative repair

At the beginning of each test and repair cycle, the memory uses the previously acquired repair data and adds new data obtained during the current cycle by storing them in a reprogrammable nonvolatile fuse box [35]. In that way, it constructs progressively its repair information. This method can reach higher yields by identifying more faults over time. Programming the fuse box multiple times allows detecting defects under different environmental conditions, an unfeasible characteristic using the one-time repair. Therefore, the cumulative methodology achieves the highest repair efficiency.

#### 2.4.5 Reconfiguration mechanism

The memory reconfiguration can be accomplished through true repair or a bypass technique. The bypass technique consists in replacing the faulty locations by redundant ones using multiplexers. On the other hand, true repair disconnects the faulty bit line from the power source while replacing it, thus preventing any possible memory performance degradation that can be caused by a leakage current. However, true repair requires full access to the memory layout since the redundancy multiplexers need to be integrated in it, compared to the bypass technique where the multiplexers are implemented at the RTL outside the RAM. This may have a slight impact on the memory performance and the area overhead.

#### 2.5 YIELD MODEL AND ESTIMATION

It is not easy to predict with exactitude the yield of a memory array using redundancy. Nevertheless, assuming the defect distribution is exactly represented by the Poisson and the binomial distributions, the suggested model offers a close approximation of the actual yield. This expected value can be evaluated for many possible internal structures when designing a memory with redundancy. In the proposed fault tolerant array structure, shown in Figure 2.7, the SRAM memory chip is partitioned into B identical blocks of (M+R) rows by N bits. Each block contains R redundant rows for local repair within the same memory block. Moreover, the model includes S redundant blocks to replace the defective ones (i.e. blocks with more than R faulty rows).

Figure 2.7 Memory with redundancy model

The yield analysis is carried out by applying two extensively used analytical models: the Poisson distribution and the binomial distribution [26], [27] and [36]. First, the Poisson distribution is employed to calculate the yield of a single bit-cell. Then, the negative

binomial distribution is used through several steps to finally obtain the yield of the memory core [41].

The yield of a single cell is the probability of one cell to operate properly and can be given by equation (2.1).

$$Y_{\text{cell}} = e^{-\lambda \text{cell}} = e^{-(D_o \cdot A_{\text{cell}})}$$

(2.1)

where  $\lambda_{cell}$  designates the average number of faults per cell,  $D_o$  is the defect density of the process and  $A_{cell}$  is the bit-cell area.

#### 2.5.1 Yield with no redundancy

If no redundancy is used, the memory is unable to tolerate any faults. Any presence of faults cannot be repaired and results in a defective memory. The yield of such a memory is defined as the probability of not containing any faults. The yield of one memory block without redundancy, i.e. the probability that the block will operate with no faults, can be described by equation (2.2).

$$Y_{bnr} = e^{-(D_o.A_{cell}.M.N)}$$

(2.2)

where M is the number of words, N is the number of bits per word in one block and  $Y_{bnr}$  stands for the yield of one block with no redundancy. Given that there are B blocks in the memory core and that they all have equal probability of being defective, the yield of the entire core can be expressed by equation (2.3).

$$Y_{nr} = (Y_{bnr})^{B} \tag{2.3}$$

where  $Y_{nr}$  stands for the core yield with no redundancy.

#### 2.5.2 Yield using redundant rows or columns only

If only one type of redundant elements is used: rows or columns, the yield can be defined as the probability of having a number of faulty rows or columns that does not exceed the number of redundant elements incorporated in the memory block [24]. The case where the memory only has redundant rows has been taken as an example. Making use of the Poisson distribution, the yield of one row, which can be viewed as the probability that this row contains no faults, is given by equation (2.4).

$$Y_{row} = e^{-(D_o \cdot A_{cell} \cdot N)} \tag{2.4}$$

Using the binomial distribution, the probability of having r faulty rows out of the M rows present in a block is expressed in equation (2.5).

$$P mtext{ (r faulty rows)} = {M \choose r} (1 - Y_{row})^r Y_{row}^{(M-r)} mtext{ (2.5)}$$

Assuming  $R_{row}$  is the number of redundant rows included locally in each block, this memory can tolerate a maximum of  $R_{row}$  faulty rows per block. Thus, the yield of one block, i.e. the probability of finding no more than  $R_{row}$  rows with defects, can be described by equation (2.6).

$$Y_{block} = \sum_{r=0}^{R_{row}} {M \choose r} (1 - Y_{row})^r Y_{row}^{(M-r)}$$

(2.6)

These are the probabilities for the rows that need to be fixed, and for which there are redundant rows available within the block. The yield of the entire core partitioned into B blocks can be given by equation (2.7).

$$Y_{rro} = (Y_{block})^{B}$$

(2.7)

where Y<sub>rro</sub> stands for the yield of a memory core provided with redundant rows only.

#### 2.5.3 Yield using redundant rows or columns and redundant blocks

Moreover, if the memory is enhanced with spare blocks to replace the defective ones, the yield of the whole core becomes as given in equation (2.8).

$$Y_{core} = \sum_{i=0}^{S} {B \choose i} (1 - Y_{block})^{i} Y_{block}^{B-i}$$

(2.8)

where S is the number of spare blocks in the core. This corresponds to the probability of having no more than S locally unrepairable blocks, i.e. blocks that contain more than  $R_{row}$  faulty rows.

Results obtained using the equations in sections 2.5.2 and 2.5.3 will be presented in section 5.4.

#### 2.6 CONCLUSION

In this chapter, an advanced self-repairing strategy has been weighed against the traditional test and repair method. It reduces significantly the manufacturing cost by eliminating the need for external test and repair equipments. Also, it increases the repair efficiency by allowing field repair. Many test algorithms were discussed and compared. The 13N algorithm was chosen for implementation for its simplicity and its high fault coverage. The main factors affecting the yield of embedded memories have been discussed. Moreover, a model to compute the yield of a memory array using redundancy has been presented.

# Chapter 3

# GLOBAL ARCHITECTURE AND THE SELF-TESTING FUNCTION

#### 3.1 INTRODUCTION

In this chapter, a global architecture of the proposed self-testing and self-repairing SRAM is presented. The procedure to obtain an efficient Built-In-Self-Test (BIST) is suggested. A fault model is adopted and a test algorithm is developed and implemented. The BIST architecture with all its sub-blocks is also treated here.

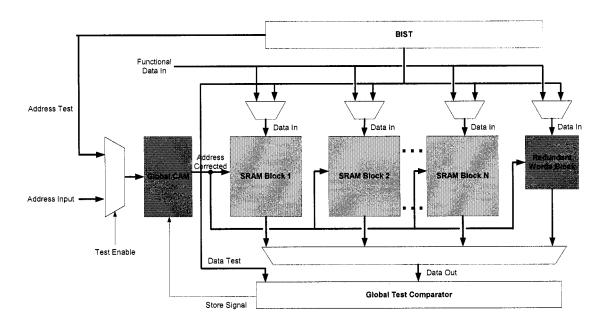

#### 3.2 GLOBAL ARCHITECTURE

In telecommunication, First-In-First-Out (FIFO) memories are becoming widely used as buffers between subsystems operating at different data rates [45]. In the suggested architecture, we have one host that needs to communicate with 4 terminals. However, this host is sending data at a higher rate than the clients can receive. Therefore, a buffer storage between the host and the client is needed. This buffer is implemented using a dual-port SRAM-type FIFO with 2 independent counters to specify the read and write

addresses to the memory via separate ports [48]. Moreover, these SRAM's are enhanced with a self-testing and self-repairing capability.

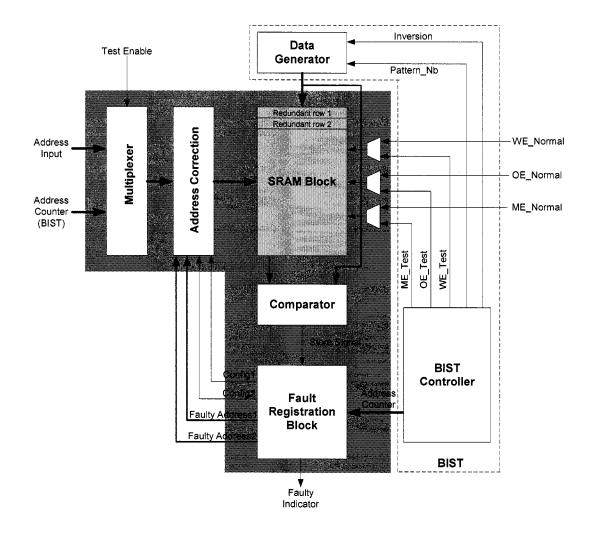

As shown in Figure 3.1, at power on, the five SRAM blocks, including the redundant one, are tested simultaneously by the shared BIST. Given that the four memory blocks are identical, a unique BIST has been used for diagnosis in order to minimize the area overhead. However, a self-repairing scheme, including the test data comparator, was incorporated in each block to support memory reconfiguration in case of failure.