**Titre:** Analyse et conception de registres à décalage pour la réalisation de décodeurs à seuil itératifs configurables

Title: [Analyse et conception de registres à décalage pour la réalisation de décodeurs à seuil itératifs configurables](#)

**Auteur:** Martin Dubois

Author: [Martin Dubois](#)

**Date:** 2004

**Type:** Mémoire ou thèse / Dissertation or Thesis

**Référence:** Dubois, M. (2004). Analyse et conception de registres à décalage pour la réalisation de décodeurs à seuil itératifs configurables [Master's thesis, École Polytechnique de Montréal]. PolyPublie. <https://publications.polymtl.ca/7369/>

Citation: [Dubois, M. \(2004\). Analyse et conception de registres à décalage pour la réalisation de décodeurs à seuil itératifs configurables \[Master's thesis, École Polytechnique de Montréal\]. PolyPublie. https://publications.polymtl.ca/7369/](#)

## Document en libre accès dans PolyPublie

Open Access document in PolyPublie

**URL de PolyPublie:** <https://publications.polymtl.ca/7369/>

PolyPublie URL: [https://publications.polymtl.ca/7369/](#)

**Directeurs de recherche:** Yvon Savaria, & David Haccoun

Advisors: [Yvon Savaria](#), [David Haccoun](#)

**Programme:** Unspecified

Program: [Unspecified](#)

**UNIVERSITÉ DE MONTRÉAL**

**ANALYSE ET CONCEPTION DE REGISTRES À DÉCALAGE POUR

LA RÉALISATION DE DÉCODEURS À SEUIL ITÉRATIFS

CONFIGURABLES**

**MARTIN DUBOIS**

**DÉPARTEMENT DE GÉNIE ÉLECTRIQUE

ÉCOLE POLYTECHNIQUE DE MONTRÉAL**

**MÉMOIRE PRÉSENTÉ EN VUE DE L'OBTENTION

DU DIPLÔME DE MAÎTRISE EN SCIENCES APPLIQUÉES

(GÉNIE ÉLECTRIQUE)**

**AOÛT 2004**

Library and

Archives Canada

Bibliothèque et

Archives Canada

Published Heritage

Branch

Direction du

Patrimoine de l'édition

395 Wellington Street

Ottawa ON K1A 0N4

Canada

395, rue Wellington

Ottawa ON K1A 0N4

Canada

*Your file Votre référence*

*ISBN: 0-494-01312-5*

*Our file Notre référence*

*ISBN: 0-494-01312-5*

#### NOTICE:

The author has granted a non-exclusive license allowing Library and Archives Canada to reproduce, publish, archive, preserve, conserve, communicate to the public by telecommunication or on the Internet, loan, distribute and sell theses worldwide, for commercial or non-commercial purposes, in microform, paper, electronic and/or any other formats.

The author retains copyright ownership and moral rights in this thesis. Neither the thesis nor substantial extracts from it may be printed or otherwise reproduced without the author's permission.

#### AVIS:

L'auteur a accordé une licence non exclusive permettant à la Bibliothèque et Archives Canada de reproduire, publier, archiver, sauvegarder, conserver, transmettre au public par télécommunication ou par l'Internet, prêter, distribuer et vendre des thèses partout dans le monde, à des fins commerciales ou autres, sur support microforme, papier, électronique et/ou autres formats.

L'auteur conserve la propriété du droit d'auteur et des droits moraux qui protège cette thèse. Ni la thèse ni des extraits substantiels de celle-ci ne doivent être imprimés ou autrement reproduits sans son autorisation.

---

In compliance with the Canadian Privacy Act some supporting forms may have been removed from this thesis.

While these forms may be included in the document page count, their removal does not represent any loss of content from the thesis.

Conformément à la loi canadienne sur la protection de la vie privée, quelques formulaires secondaires ont été enlevés de cette thèse.

Bien que ces formulaires aient inclus dans la pagination, il n'y aura aucun contenu manquant.

**UNIVERSITÉ DE MONTRÉAL**

**ÉCOLE POLYTECHNIQUE**

Le titre du mémoire :

ANALYSE ET CONCEPTION DE REGISTRES À DÉCALAGE POUR

LA RÉALISATION DE DÉCODEURS À SEUIL ITÉRATIFS

CONFIGURABLES

Présenté par : Martin Dubois

En vue de l'obtention du diplôme de : Maîtrise en sciences appliquées

A été dûment accepté par le jury de l'examen constitué de :

M. Christian Cardinal, Ph.D., Président

M. Yvon Savaria, Ph.D., membre et directeur de recherche

M. David Haccoun, Ph.D., membre et codirecteur de recherche

M. Mohamad Sawan, Ph.D., membre

## REMERCIEMENTS

Je remercie mon directeur de recherche, Yvon Savaria, pour son encadrement et ses suggestions lors de la réalisation de ce projet, ainsi que mon codirecteur de recherche David Haccoun pour son encadrement, ses conseils et son soutien financier. De plus, je remercie Christian Cardinal pour ses conseils et ses suggestions pendant l'élaboration de ce projet de recherche et de sa réalisation.

Je tiens à remercier tous les autres membres de l'équipe tel que Marc-André Cantin, Professeur Mohamad Sawan, Ghislain Provost et Alexandre Raymond pour leurs collaboration et contributions au projet. Plus particulièrement, j'aimerais remercier Normand Bélanger pour son aide et ses précieux conseils pour la rédaction des articles. Mes remerciements vont aussi au personnel administratif tel que Ghyslaine E-Carrier et Claudine Ouellet.

Enfin, je remercie mes parents et mon frère Mathieu Dubois pour leur soutien dans ce projet de recherche.

## RÉSUMÉ

Le décodage à seuil itératif est une approche simple permettant de contourner les problèmes de latence et de complexité du décodage Turbo. Ce projet de maîtrise consiste à concevoir un décodeur à seuil itératif configurable. Un décodeur configurable permet d'avoir plusieurs décodeurs dans un design en ajustant le nombre de connexions. Cet ajustement permet de changer de performance dans un contexte donné sans avoir à synthétiser un nouveau design. Évidemment, l'adaptation de ce décodeur configurable est d'un grand attrait parce qu'il permet d'obtenir des meilleures performances en terme de probabilité d'erreur. Ce dernier facteur est influencé par le rapport signal sur bruit du canal qui est parfois variable pour certaines applications.

Comme le décodeur est composé d'une architecture pipeline, le travail a été séparé en deux grandes parties. Ceci a permis d'écrire deux articles qui correspondent respectivement au chapitre 3 et au chapitre 4. La première partie discutera de nouvelles méthodes et structures pour la conception et la réalisation de registres à décalage de petite, moyenne et grande taille. Cette partie se concentrera sur l'aspect de la réduction de puissance des registres à décalages et la possibilité d'avoir des structures consommant le moins d'énergie possible tout en étant configurables. Avec ces nouvelles méthodes et structures, la réalisation d'un décodeur configurable deviendra possible. La deuxième partie discutera de la façon de concevoir un décodeur configurable. Les méthodes actuelles ne sont pas adéquates pour cette conception. Cette partie se concentrera sur les méthodes et sur la modélisation de plusieurs décodeurs afin de les fusionner. De plus, il

existe plus d'un code pour chaque décodeur, le concept d'exploration de la fusion afin de trouver le meilleur ensemble de codes pour une performance donnée sera montré.

## ABSTRACT

Iterative threshold decoding is an easy approach to circumvent the latency problems and complexity of Turbo decoding. This thesis explores the design of a class of configurable iterative threshold decoders. A configurable decoder allows having multiple decoders in a system at a cost smaller than the sum of the individual decoders it can implement. It allows changing the code and the error performance without having to synthesize a new design. Obviously, the configurable decoder is very attractive because it can be adjusted to give the needed performance in term of error probability, while minimizing power consumption when less powerful codes are sufficient. Selection of the optimal decoder is influenced by the channel signal to noise ratio. The decoder is a heavily pipelined architecture. This work is split in two main parts that led to two articles presented in chapter 3 and chapter 4. The first part discusses new methods and structures to design and implement small, medium size and long shift registers. This part will focus on power reduction. It will also propose means to get configurable size structures. With these new methods and structures, configurable decoders can be easily implemented. The second part will propose systematic methods to generate configurable decoders by merging together several decoders. The existing design methods are not adequate for this task. As several codes exist for the same decoder size, this allows exploring the performance of various codes more effectively.

## TABLE DES MATIÈRES

|                                          |      |

|------------------------------------------|------|

| REMERCIEMENTS .....                      | iv   |

| RÉSUMÉ .....                             | v    |

| ABSTRACT .....                           | vii  |

| TABLE DES MATIÈRES .....                 | viii |

| LISTE DES FIGURES .....                  | xii  |

| LISTE DES TABLEAUX.....                  | xii  |

| LISTE DES NOTATIONS ET SYMBOLES .....    | xiii |

| AVANT-PROPOS .....                       | xiv  |

| CHAPITRE 1 INTRODUCTION .....            | 1    |

| 1.1 Motivations .....                    | 1    |

| 1.2 Contributions.....                   | 2    |

| 1.3 Organisation du mémoire.....         | 2    |

| CHAPITRE 2 REVUE DE LA LITTÉRATURE ..... | 4    |

| 2.1 Principes de codage et décodage..... | 4    |

| 2.1.1 Codage .....                       | 4    |

| 2.1.2 Décodage.....                      | 6    |

| 2.2 Registres à Décalage .....           | 11   |

| 2.3 Méthodologie de conception.....      | 12   |

| 2.3.1 Conception niveau RTL.....         | 13   |

| 2.3.2 Synthèse de haut niveau.....       | 16   |

| 2.4 Architectures reconfigurables .....  | 19   |

|                                                                                                                                                                             |    |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| CHAPITRE 3 REGISTRE À DÉCAGE GÉNÉRIQUE ET CONFIGURABLE DE FAIBLE CONSOMMATION DE PUISSANCE POUR LA RÉALISATION MATÉRIELLE D'ENCODEURS ET DE DÉCODEURS CONVOLUTIONNELS ..... | 23 |

| 3.1    Sommaire .....                                                                                                                                                       | 23 |

| 3.2    On low power configurable and generic shift register hardware realizations for convolutional encoders and decoders .....                                             | 25 |

| 3.2.1    Abstract .....                                                                                                                                                     | 25 |

| 3.2.2    Introduction .....                                                                                                                                                 | 25 |

| 3.2.3    Problem Formulation .....                                                                                                                                          | 28 |

| 3.2.4    New Low-Power Shift Register Structures .....                                                                                                                      | 30 |

| 3.2.5    Architecture Analysis and Method to Minimize Power Dissipation .....                                                                                               | 41 |

| 3.2.6    Conclusion .....                                                                                                                                                   | 47 |

| CHAPITRE 4 MÉTHODOLOGIES DE CONCEPTION POUR SÉLECTIONNER ET IMPLÉMENTER DES DECODEURS CONFIGURABLES .....                                                                   | 48 |

| 4.1    Sommaire .....                                                                                                                                                       | 48 |

| 4.2    Design methodologies to select and implement configurable decoders .....                                                                                             | 50 |

| 4.2.1    Abstract .....                                                                                                                                                     | 50 |

| 4.2.2    Introduction .....                                                                                                                                                 | 50 |

| 4.2.3    Problem Formulation .....                                                                                                                                          | 53 |

| 4.2.4    Methods to Represent Decoders .....                                                                                                                                | 54 |

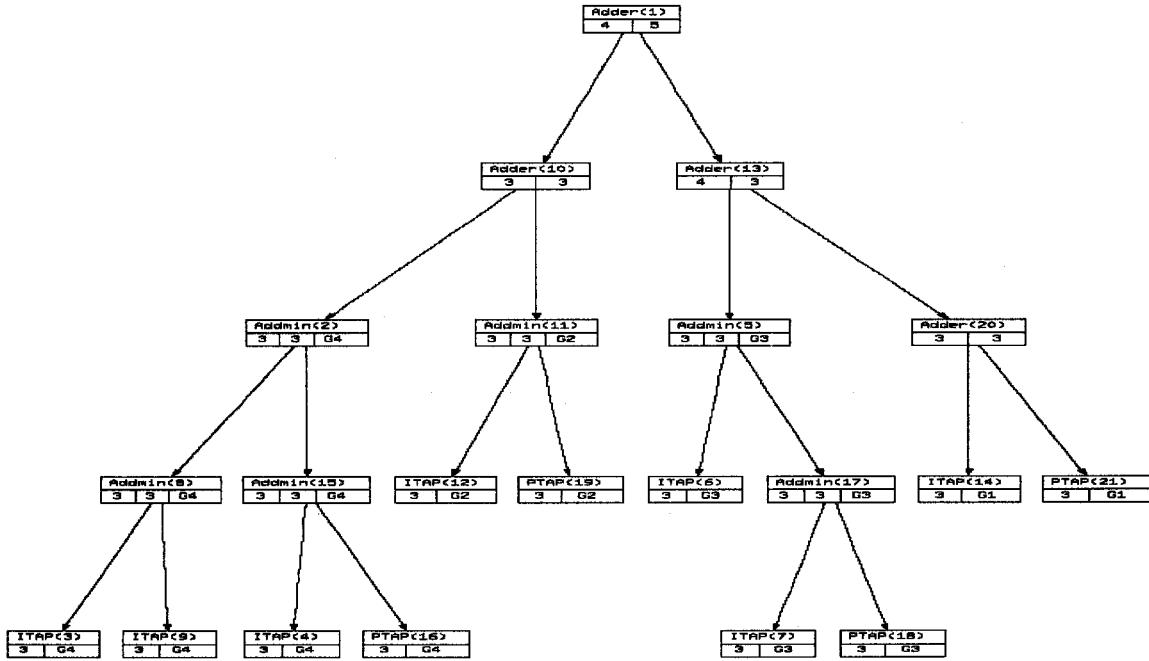

| 4.2.5    Decoder Merging .....                                                                                                                                              | 61 |

| 4.2.6    Configurable Decoder Exploration .....                                                                                                                             | 67 |

|                          |                                             |    |

|--------------------------|---------------------------------------------|----|

| 4.2.7                    | Conclusion .....                            | 71 |

| CHAPITRE 5               | CONCLUSION ET TRAVAUX FUTURS .....          | 72 |

| 5.1                      | Conclusion sur le projet de recherche ..... | 72 |

| 5.2                      | Limitations et recherches futures .....     | 73 |

| DISCUSSION GÉNÉRALE..... |                                             | 74 |

| RÉFÉRENCES .....         |                                             | 76 |

## LISTE DES FIGURES

|                                                                                                                                   |    |

|-----------------------------------------------------------------------------------------------------------------------------------|----|

| Figure 2.1 Modèle simplifié d'un système de communication numérique.....                                                          | 4  |

| Figure 2.2 Exemple de codeur CSO2C J=4 .....                                                                                      | 5  |

| Figure 2.3 Décodeur à seuil avec J=4 .....                                                                                        | 7  |

| Figure 2.4 Flot de conception RTL.....                                                                                            | 14 |

| Figure 2.5 Exemple RTL .....                                                                                                      | 15 |

| Figure 3.1 Selective activation method.....                                                                                       | 31 |

| Figure 3.2 Configurable selective activation method .....                                                                         | 34 |

| Figure 3.3 Distribution of possibilities vs. length for $M' = Lm' = 5$ .....                                                      | 35 |

| Figure 3.4 Multi-phase configurable selective activation method.....                                                              | 36 |

| Figure 3.5 Example of memory with converter structure.....                                                                        | 38 |

| Figure 3.6 Example of a memory based SR with input and output converters .....                                                    | 39 |

| Figure 3.7 Power dissipated by the memory-based SR structure with converters<br>implementing a 6-bit wide SR of length 1698 ..... | 39 |

| Figure 3.8 Configurable memory-based shift registers.....                                                                         | 40 |

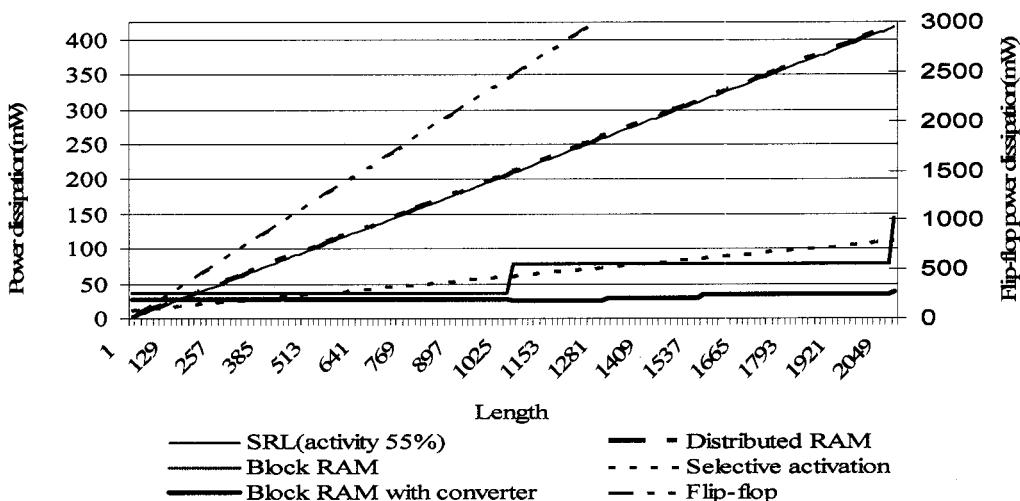

| Figure 3.9 Power dissipation for various 6-bit wide SRs .....                                                                     | 42 |

| Figure 4.1 First iteration of the decoder.....                                                                                    | 55 |

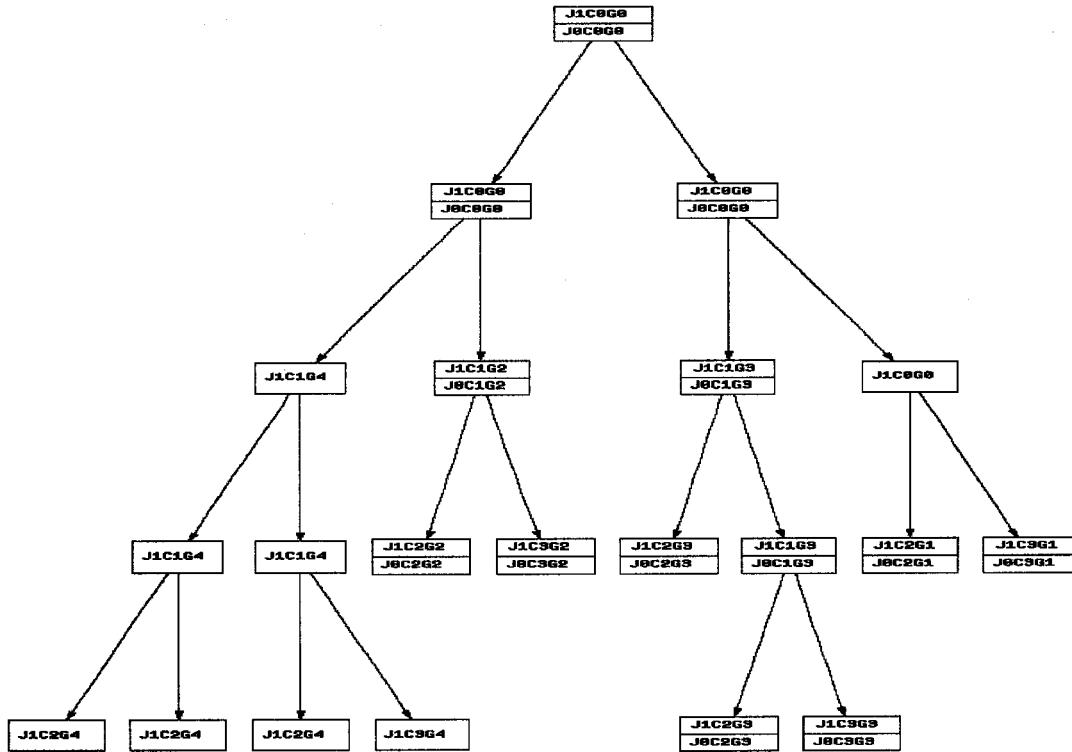

| Figure 4.2 The first iteration of a J=4 decoder described as a tree .....                                                         | 60 |

| Figure 4.3 Logical structure merge (J=3 and J=4).....                                                                             | 64 |

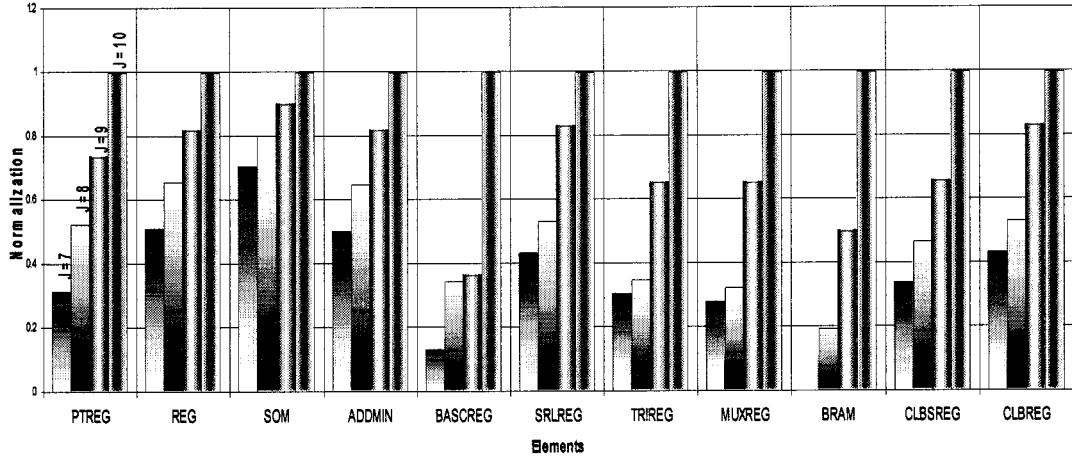

| Figure 4.4 Comparison of several decoders parameters for $7 \leq J \leq 10$ .....                                                 | 69 |

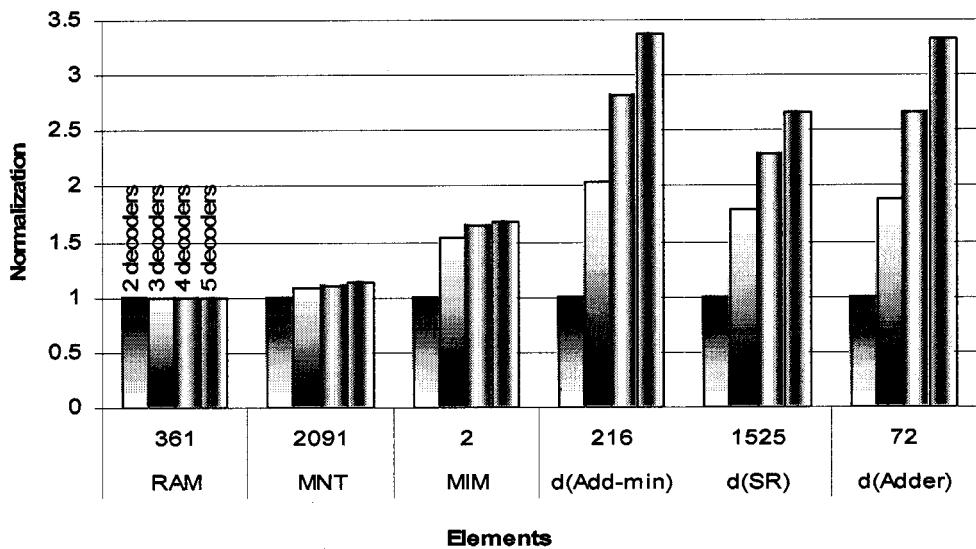

| Figure 4.5 2 to 5 decoders merged with 8 iterations.....                                                                          | 70 |

## LISTE DES TABLEAUX

|                                                                                                                                     |    |

|-------------------------------------------------------------------------------------------------------------------------------------|----|

| Tableau 2.1 Codes convolutionnels doublement orthogonaux tirés de [6], [7] et [16] .....                                            | 9  |

| Tableau 2.2 Construction d'un registre d'information.....                                                                           | 10 |

| Tableau 2.3 Architecture reconfigurable à gros grain [17].....                                                                      | 20 |

| Table 3.1 SRs in Two Typical Decoders with 8 Iterations .....                                                                       | 29 |

| Table 3.2 Resource and Power Dissipation for a 6-bit Wide, 1698 Bit Long Shift Register<br>implemented in a VIRTEX 2000-E FPGA..... | 42 |

| Table 3.3 Summary of Best SR Structures that Minimize Power Dissipation in VIRTEX-<br>E Technology at 100 MHz.....                  | 44 |

| Table 3.4 Resource, Speed and Complexity for 4 SR Structures .....                                                                  | 45 |

| Table 3.5 Total Shift Registers Power Dissipation for Two Typical Designs.....                                                      | 46 |

| Table 4.1 SRs in Two Typical Decoders with 8 Iterations .....                                                                       | 53 |

| Table 4.2 Information .....                                                                                                         | 57 |

| Table 4.3 Parity .....                                                                                                              | 57 |

| Table 4.4 Fustemp matrix ID .....                                                                                                   | 62 |

| Table 4.5 Fusmap matrix ID .....                                                                                                    | 63 |

## **LISTE DES NOTATIONS ET SYMBOLES**

|       |                                                                    |

|-------|--------------------------------------------------------------------|

| ASAP  | : As soon as possible                                              |

| ALAP  | : As late as possible                                              |

| ALU   | : Arithmetic logic unit                                            |

| AR    | : Architecture reconfigurable                                      |

| ASIC  | : Application-Specific Integrated Circuit                          |

| CSO2C | : Convolutional self-doubly orthogonal codes                       |

| DSP   | : Digital signal processing                                        |

| LFSR  | : Linear feedback shift register                                   |

| FDS   | : Force-directed scheduling                                        |

| RAM   | : Random Access Memory                                             |

| RTL   | : Register transfer level                                          |

| SRL16 | : Left shift register 16 bit                                       |

| VHDL  | : Very high speed integrated circuit Hardware Description Language |

| VLSI  | : Very large scale integration                                     |

## AVANT-PROPOS

Cette recherche a été effectuée en étroite collaboration entre deux groupes de recherche de l'École Polytechnique de Montréal. Le premier groupe s'intéresse à la recherche du décodeur et du codeur permettant d'avoir des meilleures performances sur un canal de transmission. Le deuxième s'intéresse aux méthodes et aux implémentations d'un ou plusieurs décodeurs.

Cette recherche vise deux principaux objectifs soit la création de registres à décalages configurables tout en minimisant la consommation de puissance et des méthodes pour concevoir un décodeur configurable. Ces méthodes permettent de modéliser plusieurs décodeurs tout en permettant d'implémenter un décodeur configurable.

## CHAPITRE 1

### INTRODUCTION

#### 1.1 Motivations

Le domaine des télécommunications demande de plus en plus des systèmes performants pour la correction d'erreurs. Ils ont besoin de latence faible et de taux de transfert élevé. Il y a aussi une tendance à adapter les systèmes aux canaux de communication. Par conséquent, une technique efficace et pratique de correction d'erreurs utilisant les codes convolutionnels, basée sur des codes doublement orthogonaux, traités avec le décodage à seuil itératif a été proposée par Cardinal, Haccoun et Gagnon [6], [7]. Cette approche simple permet de contourner les problèmes de latence et de complexité du décodage Turbo conventionnel [6]. Donc, le premier objectif est de connaître la meilleure approche pour réaliser ce type de décodeur. Comme ce décodeur comporte principalement des registres à décalage, compte tenu de la grande activité que ces registres peuvent générer, il est nécessaire d'avoir des structures qui consomment le moins possible de puissance. Par la suite, il faut les rendre configurables pour leur intégration dans un décodeur configurable, ce qui représente notre second objectif. Le décodeur peut être utilisé dans deux principales applications. La première application est pour la recherche. À titre d'exemple, un décodeur configurable peut valider cinq codes au lieu de nécessiter la mise en œuvre de cinq décodeurs. Cette opération permet de ne pas passer par cinq processus de conception et de synthèse. La

deuxième application est de prendre un ensemble de codes pour en faire un décodeur configurable qui peut s'adapter à son environnement ou à son canal de communication.

## 1.2 Contributions

Les principales contributions de ce projet sont :

- La création de méthodes et de structures pour la réalisation de registres à décalage qui consomment moins de puissance tout en étant configurables.

- La création de méthodes pour la conception de décodeurs configurables et d'un outil qui implémente ces méthodes.

## 1.3 Organisation du mémoire

Le chapitre 1 présente une revue de la littérature sur les registres à décalage statiques et configurables. De plus, le décodeur, les méthodes de conception traditionnelles et les architectures configurables seront revus brièvement. Le chapitre 2 couvre l'aspect de la réduction de la consommation de puissance des registres et propose des méthodes pour les rendre configurables. Deux nouvelles structures sont présentées. Ces structures configurables permettent une réduction de puissance importante. Par conséquent, nous proposons une méthode pour choisir la meilleure structure pour une configuration donnée de registres à décalage. Ceci sera fait par un article que nous présentons. Le chapitre 3 consiste à l'introduction des méthodes pour l'exploration et la conception d'un décodeur configurable sous forme d'article. La première phase étant de modéliser un décodeur, la deuxième phase montre des méthodes pour fusionner plusieurs décodeurs ensemble. La dernière étape est de choisir le meilleur ensemble de codes pour

une performance donnée, ce qui nous amène à l'exploration des décodeurs fusionnés ou non.

Enfin, le chapitre 5 présente nos conclusions. Nous résumons l'ensemble des travaux réalisés et nous suggérons des pistes de travaux futurs pour cette recherche.

## CHAPITRE 2

### REVUE DE LA LITTÉRATURE

#### 2.1 Principes de codage et décodage

Dans cette section, nous décrivons les concepts de codage et de décodage. Notre intention étant de donner un aperçu sommaire afin de comprendre les bases et non pas de faire une étude approfondie sur les façons de faire. En première partie, nous introduisons la notion de codage de canal dans un système de communication numérique. Ensuite, nous décrivons la façon de décoder pour finalement se concentrer sur la version du décodeur qui nous a servi de référence.

##### 2.1.1 Codage

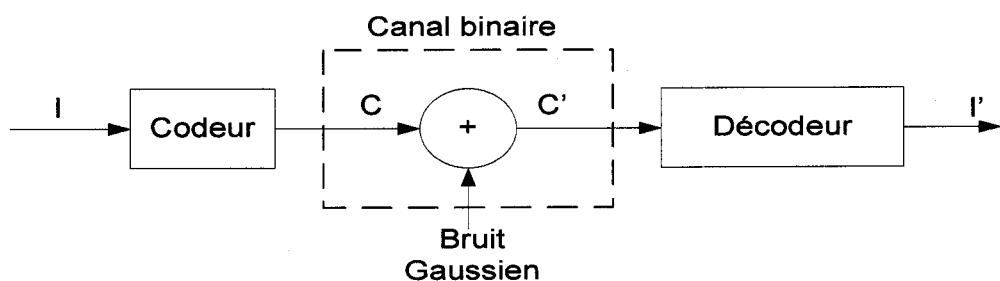

Dans cette section, nous faisons un survol d'un modèle de communication numérique et de la façon avec laquelle on code l'information afin de la récupérer à la sortie du système de communication. Tout d'abord, la Figure 2.1 illustre un modèle simplifié d'un système de communication numérique. I, C, C' et I' représentent respectivement l'information à transmettre, l'information encodée, l'information reçue du canal et l'information récupérée.

Figure 2.1 Modèle simplifié d'un système de communication numérique

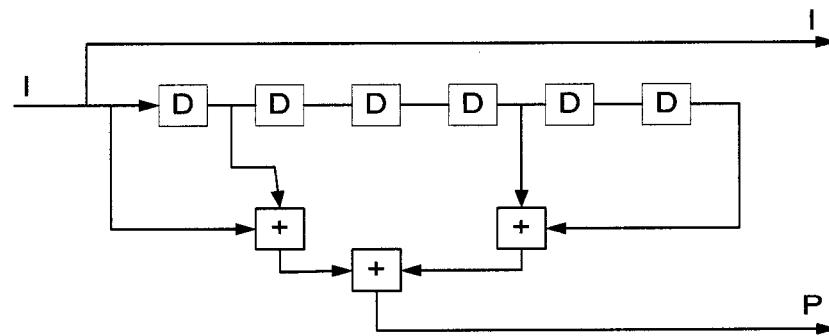

Dans tout système de communication, il y a du bruit. Ce bruit affecte l'information transmise dans le canal. Selon le type de canal, nous choisissons le type de codage et de décodage. L'objectif ultime étant d'avoir  $I=I'$ . Par conséquent, l'objectif du codage et du décodage est de réussir à contrôler les erreurs qui sont introduites par le bruit sur le canal. Bien sûr, ce n'est pas le seul facteur pour créer des erreurs sur l'information transmise. Pour nos besoins, nous conservons cette simplicité. Par conséquent, un système de communication avec codage peut être évalué par sa capacité de corriger les erreurs, son taux de transmission et sa complexité. Le processus de codage est relativement simple par rapport au processus de décodage. Le codage est le processus qui produit à chaque instant des symboles qui sont transmis dans le canal de communication. Par exemple, nous transmettons sur le canal l'information et la parité tel qu'illustré sur la Figure 2.2. Ceci est pour un codage avec un code particulier appelé convolutionnel doublement orthogonal et dénoté CSO2C. Doublement orthogonal signifie que les différences entre toutes les différences sont distinctes.

Figure 2.2 Exemple de codeur CSO2C J=4

I, P, + et D sur la Figure 2.2 représentent respectivement le symbole d'information, le symbole de parité, un opérateur modulo-2 et une bascule. J représente le nombre d'équations de parité. Pour chaque J, il existe plusieurs CSO2C possible, mais en général, on choisit celui de longueur minimale. Dans notre exemple, J=4 et un ensemble constitué de 0, 1, 4, 6 définit les interconnexions au codeur aussi bien qu'au décodeur.

L'algorithme de codage est relativement simple, il suffit de faire un modulo-2 entre certains signaux extraits du registre à décalage pour produire le symbole P. Ainsi, avec l'information et la parité, un décodeur peut grâce à un algorithme de décodage corriger les erreurs et récupérer I, l'information originale.

### 2.1.2 Décodage

L'algorithme de décodage permet de corriger les erreurs et de récupérer l'information originale. Cependant, cette partie est la plus complexe. Les méthodes actuelles telles le décodage de Viterbi et le décodage Turbo sont complexes et ont une latence importante, en particulier le décodage Turbo. La latence est définie par le temps qu'il faut au système pour sortir l'information par rapport à son entrée. Pour certaines applications en temps réel, cela peut être critique. Par exemple, lorsqu'on parle au téléphone, on ne veut pas avoir trois à quatre secondes d'intervalle entre chaque interlocuteur. D'autre part, pour des systèmes qui reçoivent des images de l'espace la latence est moins importante. On peut alors se permettre des systèmes très complexes pour récupérer les informations bruitées. Par conséquent, une technique efficace et pratique de correction d'erreurs utilisant les codes convolutionnels doublement orthogonaux, avec décodage à seuil

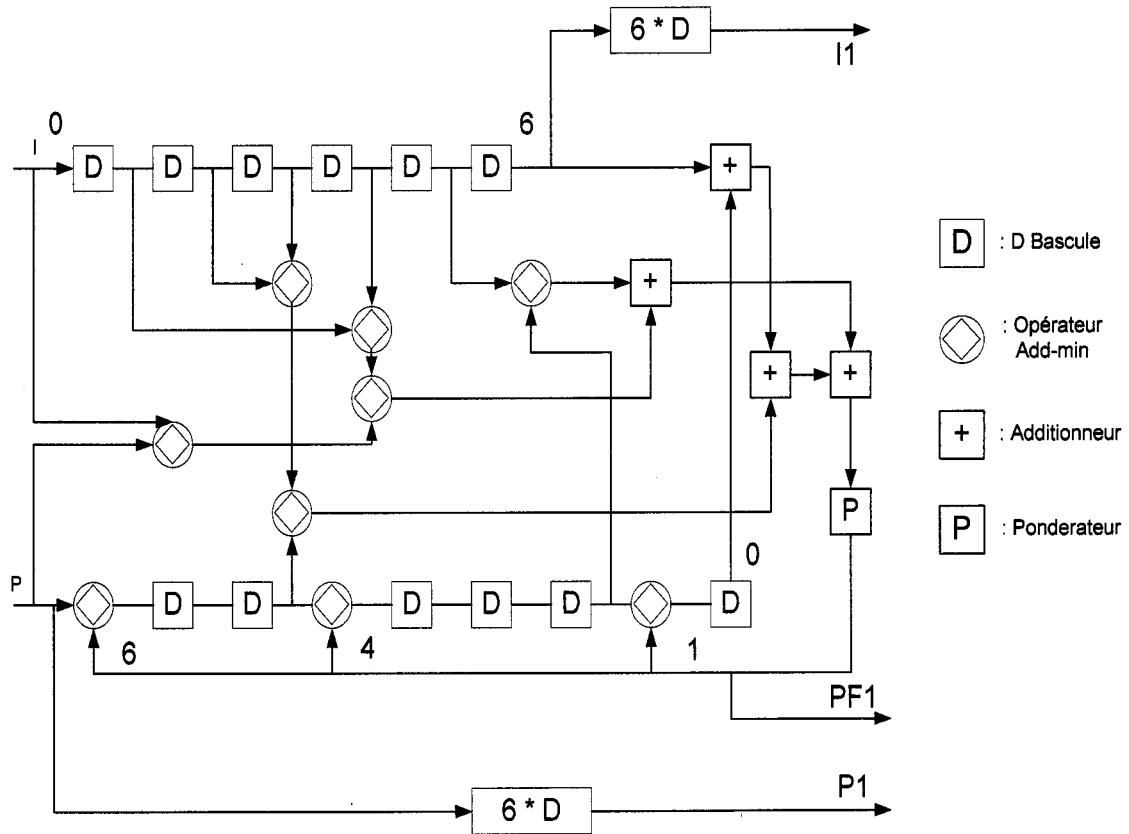

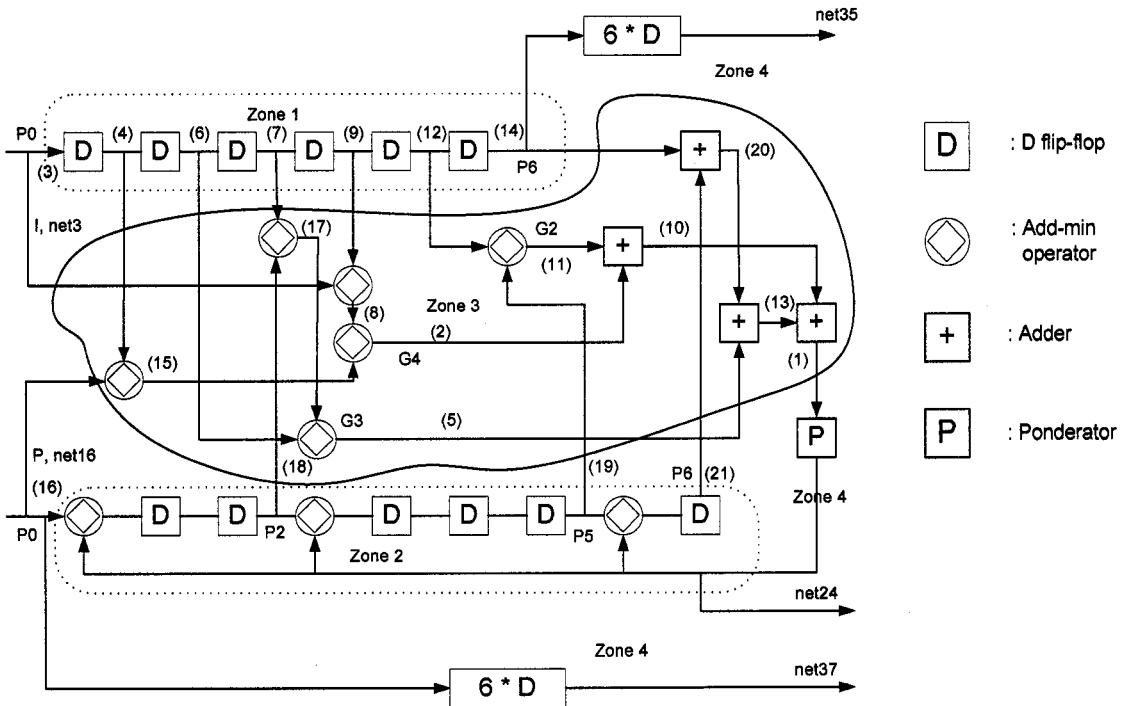

itératif a été proposée par Cardinal, Haccoun et Gagnon [6], [7]. Cette approche simple permet de contourner les problèmes de latence et de complexité du décodage Turbo conventionnel. C'est un décodage symbole par symbole. Cette méthode se distingue des autres parce qu'elle ne nécessite aucun entrelacement ni au codage et ni au décodage. De plus, cette méthode itérative est plus simple et elle permet une réduction de la latence. Le décodeur peut avoir un ou plusieurs étages. Ces étages sont connectés en cascade et selon nos besoins, nous choisissons le nombre d'étages requis. Le premier étage est différent des autres en termes d'équations. La Figure 2.3 montre le premier étage d'un décodeur à 8 étages pour  $J=4$ .

Figure 2.3 Décodeur à seuil avec  $J=4$

Dans la Figure 2.3, I, P, D, +, et le losange dans un cercle représentent respectivement l'information, la parité, une bascule, un additionneur et un opérateur add-min. L'opérateur add-min représenté avec un losange est défini comme étant :

$$A \diamond B = -\text{sign}(A)\text{sign}(B)\text{Min}(|A|, |B|) \quad (2.1)$$

Comme nous pouvons le remarquer, le décodeur comporte aussi un codeur. C'est-à-dire qu'une copie du codeur est en sorte imbriquée dans le décodeur. Le décodeur est construit selon un code particulier et un J donné. Le Tableau 2.1 liste des codes que nous utilisons dans le cadre de notre recherche [6], [7] et [16].

Tableau 2.1 Codes convolutionnels doublement orthogonaux tirés de [6], [7] et [16]

| <b>J</b> | <b>Codes</b>                                                                                      | <b>J</b> | <b>Codes</b>                                                                                                                                                                                                                                                                                                                                                                                           |

|----------|---------------------------------------------------------------------------------------------------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2        | 0,1                                                                                               | 7        | 0,1,53,128,207,216,222<br>0,1,9,71,177,215,222<br>0,13,51,157,219,227,228<br>0,1,13,83,196,201,229<br>0,28,33,146,216,228,229<br>0,1,14,74,178,227,231<br>0,4,53,157,217,230,231<br>0,1,5,141,193,216,232<br>0,16,39,91,227,231,232<br>0,12,54,71,200,223,232<br>0,9,32,161,178,220,232                                                                                                                |

| 3        | 0,2,5                                                                                             | 8        | 0,43,139,322,422,430,441,459<br>0,18,29,37,137,320,416,459<br>0,13,102,146,393,454,459,461<br>0,2,7,68,315,359,448,461<br>0,22,73,87,209,427,473,474<br>0,1,47,265,387,401,452,474<br>0,9,44,82,110,342,451,475<br>0,24,133,365,393,431,466,475                                                                                                                                                        |

| 4        | 0,1,4,6<br>0,4,14,15                                                                              | 9        | 0,9,21,395,584,767,871,899,912<br>0,13,41,145,328,517,891,903,912<br>0,2,140,267,304,822,858,916,943<br>0,27,85,121,639,676,803,941,943<br>0,34,48,60,386,743,836,935,979<br>0,4,155,191,216,330,857,969,999<br>0,30,144,669,783,808,844,995,999<br>0,101,118,269,459,944,1021,1025,1044<br>0,19,23,100,585,775,926,943,1044<br>0,7,23,241,419,740,980,1034,1046<br>0,12,66,306,627,805,1023,1039,1046 |

| 5        | 0,1,24,37,41<br>0,4,17,40,41                                                                      | 10       | 0,29,40,43,1020,1328,1495,1606,1696,1698<br>0,27,93,503,600,1247,1646,1714,1825,1835<br>0,52,144,186,564,667,1120,1748,1814,1835<br>0,49,115,743,1196,1299,1677,1719,1811,1863<br>0,92,104,176,339,1311,1325,1738,1845,1876<br>0,31,138,551,565,1537,1700,1772,1784,1876<br>0,176,200,338,557,1375,1401,1844,1871,1876<br>0,5,32,475,501,1299,1538,1676,1700,1876                                      |

| 6        | 0,51,64,76,78,98<br>0,1,17,70,95,100<br>0,5,30,83,99,100<br>0,2,13,72,97,102<br>0,5,30,89,100,102 | 11       | 0,220,521,695,908,926,1059,2457,<br>3367,3458,3490                                                                                                                                                                                                                                                                                                                                                     |

| 12       | 0,48,212,1014,1381,2217,4198,4373,4766,4885,4914,5173                                             |          |                                                                                                                                                                                                                                                                                                                                                                                                        |

Notre objectif n'est pas de construire de nouveaux codes, mais plutôt de les implémenter en pratique. Par exemple, si nous voulons implémenter le code  $J=4$ , nous prenons  $J=4$  avec le code 0, 1, 4, 6 tel qu'illustré sur la Figure 2.3 pour le premier étage. Pour ce qui est des interconnexions du registre de parité. Nous partons de la droite vers la gauche, et chaque position donne un add-min incorporé dans le registre à décalage et selon le cas, nous construisons les interconnexions pour les connecter aux add-min. Pour ce qui est du registre d'information nous obtenons la structure dont les caractéristiques sont résumées au Tableau 2.2.

Tableau 2.2 Construction d'un registre d'information

| Différence | Position,<br># ports sur add-min | Différence | Position,<br># ports sur add-min |

|------------|----------------------------------|------------|----------------------------------|

| 6 - 4      | 2, 4                             | 4 - 1      | 3, 3                             |

| 6 - 1      | 5, 4                             | 4 - 0      | 4, 3                             |

| 6 - 0      | 6, 4                             | 1 - 0      | 1, 2                             |

Il existe plusieurs codes pour un  $J$  donné. La performance du décodeur va varier selon  $J$  et le nombre d'itérations et non selon le code. Par exemple, les codes 0, 1, 4, 6 et 0, 4, 14, 15 pour  $J=4$  donnent la même performance en terme de correction d'erreurs pour un nombre d'itérations données, mais le second code a une latence plus grande. Cette latence augmente avec chaque itération. Maintenant que nous avons fait un survol très rapide de la partie télécommunication, les prochaines sections couvrent les aspects d'intégration: Nous discutons notamment les méthodes de conception et les architectures reconfigurables pour donner une bonne idée de l'approche que nous avons préconisée dû aux lacunes des méthodes de conception actuelles.

## 2.2 Registres à Décalage

Les registres à décalage sont des circuits séquentiels qui permettent de décaler les données dans un sens ou dans l'autre tout en étant une source de stockage d'information numérique. Il existe divers types de registres à décalage. Certains sont unidirectionnels d'autres sont bidirectionnels. Les registres à décalage peuvent être implémentés différemment selon leurs applications. Les trois aspects importants à considérer sont la puissance consommée, les ressources matérielles utilisées et la configurabilité.

Sur le premier aspect, George et Alfke [13] ont décrit une implémentation d'un registre à décalage avec rétroaction linéaire (LFSR) de 15 bits qui utilise seulement une tranche d'un bloc de logique configurable avec une macro SRL16. Cette macro permet de réaliser un registre à décalage configurable de 1 bit de large par 16 bits de profond dans un module de base d'un FPGA. Alfke [1] propose une implémentation qui utilise de la mémoire à accès aléatoire (RAM) et un compteur LFSR pour simplifier la conception.

Pour le deuxième aspect, deux approches sont considérées. La première approche présentée par Lowy [18] est une structure parallèle. Cette technique permet de réduire la consommation de puissance par un facteur allant jusqu'à 3 pour une fréquence d'opération donnée.

La deuxième approche présentée par Chandrakasan [8] montre comment la technique multi-phase peut réduire la puissance par un facteur égal au nombre de phases. Par exemple, une architecture avec deux phases réduit la puissance par un facteur de deux.

Pour le dernier aspect, la flexibilité est requise pour configurer les registres à décalage sans avoir à passer par une nouvelle synthèse. La littérature est relativement pauvre en articles pour des registres à décalage configurables. Pour de petites longueurs de registre à décalage, l'utilisation de multiplexeurs est largement préconisée, telle que les SRL16 du FPGA [14]. De plus, Gigliotti [14] propose une façon efficace de créer des registres à décalage qui utilisent plusieurs interconnexions configurées dynamiquement.

Ces structures sont utilisées pour les petits et moyens registres à décalage. D'autre part, ces techniques demandent beaucoup de ressources pour implémenter les petits, moyens et longs registres à décalage lorsque ceux-ci doivent réaliser toutes les longueurs d'un registre à décalage.

### **2.3 Méthodologie de conception**

Dans cette section, nous ne prétendons pas établir une revue de littérature élaborée des méthodologies de conception compte tenu de la richesse du domaine. Nous désirons plutôt présenter brièvement les concepts connexes à ceux que nous explicitons dans ce mémoire afin de situer notre travail par rapport aux méthodes actuelles. Dans une méthodologie de conception, on a plusieurs niveaux d'abstraction. Chacun des niveaux d'abstraction inclut des langages qui procurent des avantages et des inconvénients pour la réalisation comportementale ou matérielle d'un système. Par exemple, la conception haut niveau en utilisant Matlab, C, ou C++ donne la flexibilité permettant de faire une description fonctionnelle d'un système sans pour autant avoir les contraintes d'une implémentation physique. Dans ce sens, un design doit être fait avec un niveau

d'abstraction le plus élevé possible pour être en mesure d'exploiter les différentes implémentations possibles avec un des degrés de liberté disponibles. D'autre part, le design à haut niveau d'abstraction ne permet pas d'avoir une implémentation la plus optimale pour une spécification donnée. À l'opposé, un langage de bas niveau d'abstraction comme le RTL permet d'optimiser l'implémentation et de la rendre optimale pour une technologie donnée et un algorithme ciblé. La façon de concevoir un système dépend du niveau d'abstraction et du langage utilisé. Par exemple, prenons une spécification d'un décodeur qu'on veut implémenter. La première étape consiste à prendre un langage tel que C++ pour faire une validation comportementale. Cette phase est requise pour valider un concept. Par la suite, nous voulons l'implémenter dans une technologie donnée. Plusieurs approches peuvent être considérées, nous en considérons deux pour faire le survol des méthodologies de conception reliée à nos travaux de recherche. Nous présentons à la section suivante deux approches traditionnelles. La première approche est la conception au niveau RTL en utilisant par exemple le langage VHDL. La deuxième approche consiste à la synthèse de haut niveau. Celle-ci contient la première approche, mais de façon indirecte, car c'est fait automatiquement par un outil logiciel.

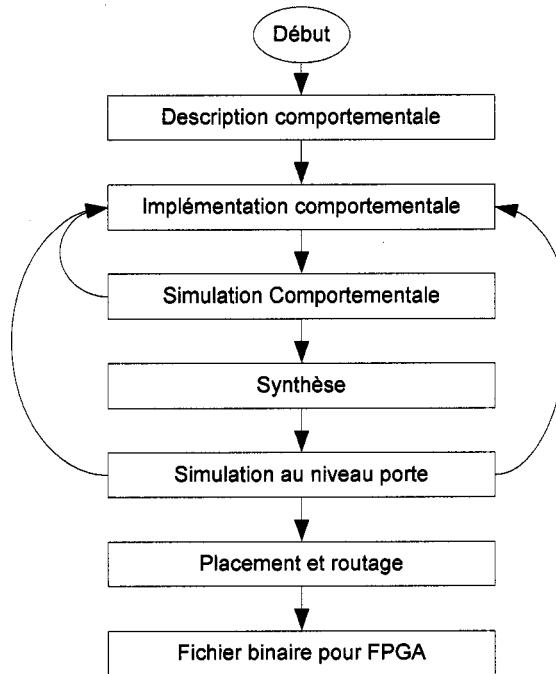

### 2.3.1 Conception niveau RTL

Cette méthode de conception permet de faire des implémentations matérielles. À partir de ce niveau, un outil de synthèse fait pour une technologie donnée, transforme la

spécification RTL en circuits réels. La Figure 2.4 montre le flot de conception pour réaliser ce dernier.

Figure 2.4 Flot de conception RTL

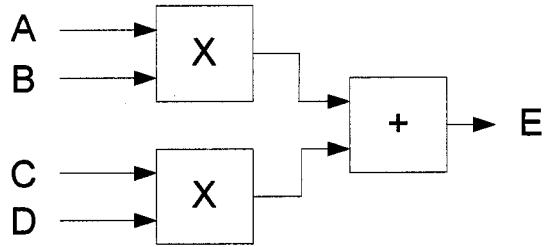

La première étape consiste à faire une description comportementale du système. Dans cette étape, on définit comment le système doit réagir : ceci peut être exprimé comme une équation ou une opération mathématique. Par exemple, si on veut faire  $E=A*B+C*D$ , ceci correspond à une description fonctionnelle. La deuxième étape consiste à implémenter un modèle de ce comportement en utilisant un langage RTL comme le VHDL. Ce langage permet de faire des modules et de les interconnecter ensemble en tenant compte de l'implémentation future du système. Dans notre exemple, on peut faire trois modules tel qu'ilustré à la Figure 2.5.

Figure 2.5 Exemple RTL

Cette figure montre comment on passe d'une spécification descriptive à une implémentation comportementale. L'équation est séparée en modules qui sont écrits avec le langage VHDL. Avec ce langage, on peut faire en sorte que les modules fonctionnent avec une horloge commune pour traiter les données à chaque coup d'horloge. La prochaine étape est la simulation comportementale. Cette étape est critique, car elle permet de simuler et de valider le modèle VHDL avec un simulateur tel que *MODELSIM*. Une fois la validation du code VHDL faite et que l'opération voulue est simulée correctement, on passe à l'étape de synthèse. Cette phase permet de prendre le code VHDL pour en générer des portes logiques. Ceci correspond au passage d'un niveau d'abstraction à un autre. Par la suite, on peut simuler à nouveau pour valider encore le concept au niveau porte. Une fois que cette étape est remplie, on passe à la phase du placement routage. Celle-ci permet de faire le placement des portes sur une implémentation réelle et de router les interconnexions. À ce niveau, on change encore de niveau d'abstraction puisqu'on passe du niveau des portes logiques à une implémentation au niveau transistor, ce qui mène à produire un fichier binaire pour configurer le FPGA. On va utiliser le VHDL, langage de bas niveau, pour faire l'optimisation de puissance et

de ressource des modules. Cette approche a été longtemps utilisée, cependant elle commence à n'être plus efficace puisque les systèmes actuels sont de plus en plus complexes. Les concepteurs demandent de plus en plus d'elever le niveau d'abstraction auquel s'effectue le travail de conception. Ceci pousse au développement d'outils.

### **2.3.2 Synthèse de haut niveau**

Cette approche consiste à prendre des outils de synthèse haut niveau pour faire une implémentation de bas niveau comme mentionné à la section précédente. Ces outils permettent de passer d'un haut niveau d'abstraction à un bas niveau comme le niveau RTL. L'avantage de cette façon de faire est qu'un concepteur de système n'ayant pas de connaissance au niveau RTL peut produire une implémentation matérielle. Quelques avantages qui découlent de l'utilisation de la synthèse de haut niveau sont la réduction du temps de conception, la réduction des erreurs et la capacité de faire de l'exploration architecturale tel que présenté en [21]. Ce processus permet de produire plus d'un design en un temps réduit pour permettre aux développeurs d'explorer, par exemple, les compromis entre le coût, la vitesse et la dissipation de puissance. De plus, la synthèse haut niveau permet d'avoir un flot de conception auto documenté, c'est-à-dire que l'outil permet de garder les choix de design et leurs impacts. Ces méthodes améliorent l'accessibilité des technologies VLSI en réduisant les détails technologiques que les concepteurs doivent connaître. Les grandes étapes de la synthèse haut niveau sont présentées en [21] et [22]. Nous retiendrons quatre grandes étapes importantes : la compilation, l'ordonnancement, l'allocation et la liaison. La première étape consiste à

prendre la description comportementale pour la traduire en une représentation interne. Cette étape est réalisée par la transformation et l'analyse de la description comportementale pour en extraire une description graphique du comportement du système. Ceci permet d'avoir l'essentiel des opérations tout en tenant compte de la dépendance des données.

L'étape suivante consiste à faire l'ordonnancement. Cette étape permet de faire des compromis entre les performances et les coûts. Peng [22] définit trois types d'ordonnancement : constructif, global et de transformation. Nous allons voir quelques exemples pour chaque types. Les méthodes ASAP et ALAP sont des algorithmes constructifs. Le premier algorithme permet de faire les opérations le plus tôt possible, tandis que le deuxième organise les opérations pour qu'elles s'exécutent le plus tard possible. FDS est un algorithme global qui permet de balancer les opérations parallèles. Il permet de faire un graphique de distribution à partir des deux premiers algorithmes. L'objectif de ces algorithmes est d'ordonnancer les opérations pour qu'elles s'exécutent le plus rapidement possible tout en minimisant les ressources. Le dernier type d'ordonnancement est la transformation ; celle-ci s'obtient à partir d'un ordonnancement initial connu qui est graduellement transformé pour obtenir un ordonnancement final. Il existe des ordonnancements avancés qui tiennent compte, par exemple, des boucles et des opérations multi-cycle.

L'allocation est la prochaine étape. Celle-ci permet de déterminer le nombre d'unités fonctionnelles à partir du nombre d'éléments de mémoire de stockage et du nombre de

bus. Dans cette étape, nous considérons un ensemble d'éléments pour l'implémentation du circuit.

La liaison est la dernière étape, celle-ci fait le lien entre les étapes d'ordonnancement et les allocations. Cette étape a pour but de minimiser le coût matériel des registres, des unités opératoires, des bus et des multiplexeurs tout en réduisant les délais.

Les deux dernières étapes sont inter-reliées. Nous allons résumer quelques algorithmes existants présentées dans [22]. La discussion suivante présentera une méthode constructive, une formulation théorique sous forme de graphe et l'allocation par transformation. L'algorithme vorace, souvent appelé *Greedy*, commence avec un chemin de données vide et ajoute graduellement des ressources fonctionnelles pour le stockage et les interconnexions selon les besoins. Des algorithmes de formulation théorique sous forme de graphe comme le partitionnement par clique [22] permet de faire de l'allocation en faisant une représentation indirecte. Celle-ci utilise des heuristiques pour travailler sur la représentation indirecte pour faire des allocations et des liaisons.

Il existe selon [22] des concepts avancés de synthèse haut niveau selon lesquels on tient compte, par exemple, des pipelines, de la dissipation de puissance, de la testabilité et de la réutilisation des designs. Ces méthodes sont actuellement largement utilisées mais ne correspondent pas actuellement au besoin des architectures configurables. Cependant, la méthode proposée plus loin s'inspire des principales étapes telles que la compilation, l'ordonnancement, l'allocation et la liaison et pour tenir compte des pipelines, de la réutilisation des designs et de la dissipation de puissance. La prochaine section montre différentes aspects de la recherche pour cette sorte d'architecture.

## 2.4 Architectures reconfigurables

Dans cette section, nous faisons une brève revue de ce domaine pour mettre en relief nos travaux de recherche. Les architectures reconfigurables (AR) ont pour objectif de répondre aux besoins d'applications pour lesquelles les ASIC ne sont pas assez flexibles et les microprocesseurs ne sont pas assez performants [17]. De plus, ces architectures sont un nouveau concept pour répondre aux demandes de performance et de flexibilité pour des applications données [4]. La possibilité d'avoir un système basé sur une architecture reconfigurable, pour le personnaliser dans un contexte donné afin d'avoir le bon flot de données avec le bon flot d'opérations augmente significativement les bénéfices [4]. Les nouveaux concepts utilisant les architectures reconfigurables promettent des solutions intermédiaires dans l'espace de conception en ce qui a trait au compromis entre la flexibilité et les performances. En utilisant des AR, les performances doivent être maintenues tout en accroissant la flexibilité. Dans cette section, nous résumons quelques aspects de ce domaine de recherche en nous basant sur le traitement de K. Bondalapati et V. K. Prasanna, [4]. Ces auteurs présentent cinq de ces aspects qui vont des architectures, aux modèles théoriques, aux applications, en passant par les algorithmes et les méthodes de synthèse et les outils qui les implémentent.

Les architectures présentées dans [17] et [4] sont des classes et systèmes d'architecture qui proposent des façons différentes d'organiser et d'interfacer la logique configurable. Ces architectures sont conçues avec une granularité fixe ou variable. La granularité représente le niveau auquel on configure les composantes. Par exemple, une granularité

fine permet la configuration au niveau des portes logiques, tandis qu'une grande granularité traite le problème au niveau des opérateurs tels que les additionneurs, les soustracteurs et les pondérateurs.

La granularité va affecter les réseaux d'interconnexions et la façon dont les unités sont disposées. En général, une granularité trop fine n'est pas efficace parce qu'elle demande beaucoup de ressources de routage et ne permet pas beaucoup de flexibilité pour router. Dans la majorité des cas, une grande granularité sera explicitée dans ces architectures [17] qui sont classées selon le nombre de bits par opérateur (ALU). Par exemple, une granularité de 16 bits indique que la configurabilité se fait au niveau de variables de 16 bits. Par exemple, nous pouvons avoir 4 ALU de 4 bits pour faire le 16 bits. Les architectures actuelles sont conçues pour être utilisées pour des applications spécifiques.

Le Tableau 2.3 montre 5 exemples d'architectures tirés de [17].

Tableau 2.3 Architecture reconfigurable à gros grain [17]

| Projet | 1 <sup>ère</sup> publ. | Source | Granularité                  | Application ciblé                 |

|--------|------------------------|--------|------------------------------|-----------------------------------|

| PADDI  | 1990                   | [9]    | 16 bits                      | DSP                               |

| RaPID  | 1996                   | [12]   | 16 bits                      | Pipeline                          |

| RAW    | 1997                   | [23]   | 8 bits, granularité variable | Expérimentale                     |

| CHESS  | 1999                   | [19]   | 4 bit, granularité variable  | Multimédia                        |

| DreAM  | 2000                   | [3]    | 8 & 16 bits                  | Sans-fil,<br>prochaine génération |

Ces architectures ont été développées dans un but précis avec des applications ciblées. À l'heure actuelle, aucune de ces architectures ne procure une solution à nos objectifs. Cependant, nous allons couvrir les autres aspects des AR. Pour utiliser ces architectures de façon optimale, on a besoin d'un modèle théorique.

Les modèles théoriques servent à prendre un algorithme et à en faire l'analyse pour configurer une architecture de façon efficace. De plus, les architectures reconfigurables sont créées et optimisées pour certaines applications tel qu'il a été montré au Tableau 2.3. En plus des modèles théoriques, pour être en mesure d'exploiter au maximum une architecture configurable, il faut aussi avoir des algorithmes de synthèse.

Les algorithmes de synthèse dans les architectures reconfigurables doivent organiser le flot de données et faire face au problème de mapping. Les méthodes actuelles sont conçues de façon générale pour des boucles dans des programmes généraux. Ceux-ci procurent des opérations répétitives et mettent l'accent sur le pipeline et les opérations parallèles tout en ciblant le matériel reconfigurable.

Présentement, les outils de mapping ne sont pas faits pour les architectures reconfigurables. Cependant, quelques outils sont en développement pour avoir des langages de hauts niveaux comme le C et faire la simulation de systèmes reconfigurables. Cela mènera à la plate-forme configurable dynamiquement.

Nous avons vu que les méthodes de conception évoluent avec la technologie et les besoins. Nous avons commencé avec une méthode de bas niveau tel que le VHDL. Ensuite, on a utilisé des outils de synthèse de haut niveau pour générer des systèmes plus complexes et ce, le plus rapidement possible. Maintenant, la forte demande pour des architectures reconfigurables afin d'avoir à la fois les performances des ASIC et la flexibilité de microprocesseur ne cesse de croître. La flexibilité et l'utilisation d'une architecture configurable seront traitées pour notre cas. Pour faire le lien avec nos travaux de recherche, nous empruntons des éléments de plusieurs méthodes de

conception pour faire un décodeur reconfigurable. Le chapitre suivant propose diverses structures de registres à décalage configurables ou non, avec le VHDL, pour en réduire la puissance tout en utilisant les ressources matérielles de façon judicieuse. L'utilisation du VHDL est requis dans ce cas, car nous travaillons au niveau de la technologie. Ensuite le chapitre suivant montre certains concepts pour arriver à produire un décodeur configurable. L'utilisation des principales étapes et des concepts avancés de la synthèse haut niveau seront utilisés. De plus, les concepts d'architectures reconfigurables seront utilisés, tel que la granularité variable et les modèles de l'architecture.

# **CHAPITRE 3**

## **REGISTRE À DÉCAGE GÉNÉRIQUE ET CONFIGURABLE DE FAIBLE CONSOMMATION DE PUISSANCE POUR LA RÉALISATION MATÉRIELLE D'ENCODEURS ET DE DÉCODEURS CONVOLUTIONNELS**

Ce chapitre présente un article, écrit en collaboration avec Y. Savaria, D. Haccoun et N. Bélanger, qui a été soumis en 2004 dans IEE Proceedings on Circuits Devices and Systems. La première section fait un sommaire en français de cet article.

### **3.1 Sommaire**

L'article que nous présentons dans ce chapitre décrit de nouvelles méthodes pour implémenter les registres à décalage génériques configurables avec une faible dissipation de puissance. En introduction, les problématiques matérielles de l'algorithme du décodeur sont décrites telles que les pipelines qui sont prédominants et de leur accroissement selon le code de l'algorithme choisi. Par la suite, une revue de la littérature est faite. Ensuite, nous faisons ressortir l'importance de l'impact d'avoir des registres à décalage avec une consommation de puissance très faible et d'avoir des registres à décalage configurables.

De nouvelles méthodes sont montrées telle que la structure d'activation. Cette façon de faire tire profit de deux méthodes actuelles : multi phase et parallèle. Nous suggérons une nouvelle méthode pour avoir les mêmes avantages sans toutefois avoir la complexité du multi phase. Une fois que cette méthode est décrite, nous analysons son impact sur la dissipation de puissance. Par la suite, nous produisons avec cette nouvelle méthode une

structure configurable. Nous indiquons que la structure d'activation, configurable ou non, peut-être utilisée avec le multi phase toutefois avec sa complexité. Cette structure est bonne pour des registres à décalage de tailles moyennes et larges.

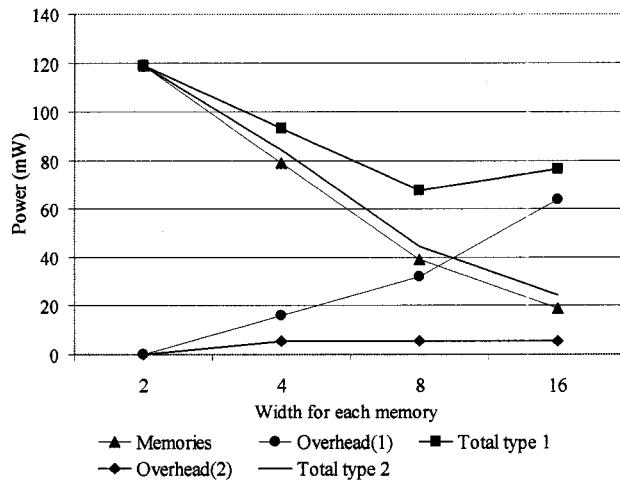

Pour faire des longs registres à décalage, nous avons recours aux mémoires. La méthode actuelle est un registre à décalage basé sur la mémoire. Nous proposons d'ajouter un convertisseur d'entrée et de sortie à cette structure. Celle-ci donne naissance à la structure basée sur la mémoire avec convertisseur, le but étant toujours de réduire la dissipation de puissance. En utilisant, la structure d'activation précédemment décrite comme convertisseur, nous arrivons à réduire considérablement la dissipation de puissance. La structure basée sur la mémoire avec convertisseur est ensuite convertie en structure configurable. Nous gardons toujours la réduction de puissance des nouvelles structures tout en les rendant configurables.

L'analyse de chaque type de registre à décalage qu'il soit connu ou nouveau est analysée au niveau des ressources et de la dissipation de puissance. Ainsi, nos deux nouvelles méthodes de base sont comparées avec les méthodes conventionnelles. Par la suite, nous montrons une méthode sélective pour choisir quelle structure est la plus appropriée dans un contexte donné. Nous illustrons les résultats produits par cette recherche exhaustive.

Finalement, nous comparons avec des estimateurs de puissance deux décodeurs pour plusieurs combinaisons de méthodes d'implémentation des registres à décalage. À ce niveau on utilise le langage VHDL pour faire la comparaison qui sera faite à très bas niveau.

## 3.2 On low power configurable and generic shift register hardware realizations for convolutional encoders and decoders

### 3.2.1 Abstract

Novel methods to implement low power hardware and configurable architectures comprising several different kinds of shift registers in FPGAs are presented. New approaches are also described to reduce power dissipation of shift register structures without compromising their configurability. The proposed structures are particularly effective to reduce the power dissipation of shift registers of medium and large lengths. A systematic method to select the best shift register structure is also provided. The proposed structures and the selection method are generic, and they can be configured statically or dynamically. It is shown that they are well suited for implementing powerful convolutional encoders and suitable decoders associated with forward error correction techniques, such as iterative threshold decoding.

### 3.2.2 Introduction

A powerful and practical forward error correction technique using specific convolutional codes called convolutional self-doubly orthogonal codes, in conjunction with a simple iterative threshold decoding technique was recently proposed by Cardinal, Haccoun and Gagnon [6], [7]. This paper explores the implementation of that error control technique using field programmable gate arrays (FPGAs). The decoding algorithm proposed in [7] can easily be mapped into hardware. This mapping produces a heavily pipelined

architecture with a large portion of its hardware composed of long shift registers (SRs), tapped at specific intervals that specify the particular code of a family of so-called systematic self-doubly orthogonal convolutional codes. The sizes of the SRs correspond to the length or memory of the code and are strongly dependent on a parameter of the encoder called  $J$ , which is the number of parity equations used. That number  $J$  determines the error correcting capability of the code. The length of the shift register of the encoder (also called span) grows approximately according to a fourth order polynomial in  $J$  [7]. In order to improve its error correcting capability, the proposed decoding algorithm operates iteratively, but the improvements tend to saturate after only a few iterations, typically 5 to 8. This is significant since the decoding cost is directly proportional to the number of iterations. The number of taps in the SRs of the decoder grows as  $(J*(J-1))/2$  [6], [7], while their size, which corresponds to the memory of the encoder, grows as the same fourth order polynomial in  $J$  as in the encoder. For example, with  $J=9$ , the length of the largest required SR is 912, while for  $J=10$ , the required length reaches 1698 stages.

The target hardware implementation of the decoder requires various types of SRs. Some have taps while others have none. In general, a tapped register can be assembled by connecting untapped registers of lengths determined by the distance between the required taps. Untapped registers can be implemented in several ways. Moreover, when the target implementation has more than one decoder, it should include dynamically configurable SRs in order to share hardware as much as possible.

This paper explores the tradeoffs involved in assembling the best SRs to match the application's requirements. Optimality is measured in terms of the implementation

complexity, configurability and power dissipation.

In FPGAs, SRs can be implemented in different ways depending on their target use. Typically, a first concern is the minimization of the resources consumed for implementing them. George and Alfke [13] described an implementation of a 15-bit linear feedback shift register (LFSR) that uses only one slice of a configurable logic block (CLB) with the SRL16 macro. This macro is a 1-bit wide shift register configurable from 1 to 16-stages and implemented in Xilinx FPGAs. Alfke [1] further proposes an efficient implementation of a long SR using random access memory (RAM) and a LFSR counter, which simplifies the design even more, and makes the design even simpler.

A second concern of growing interest is the reduction of the power dissipated by SRs. It has been addressed by Lowy [18] where he proposed a parallel structure for implementing LFSRs. His technique reduces the power dissipation by a factor of up to 3 for a given speed of operation. On the same problem, Chandrakasan [8] shows how a multiphase architecture can reduce the power dissipation by a factor that is close to the number of phases.

Flexibility is a third concern, as there is a growing demand for hardware structures that can be configured statically or dynamically. This feature enables reuse and can significantly improve the efficiency of the design. However, until now, little has been reported about length-configurable SRs. For small length shift registers, it is common to use multiplexers to set the length of the register, like in SRL16 [14] constructed using FPGAs. In [14], an efficient multi-tap shift register is proposed. This structure is used with a medium size shift register. Unfortunately, implementing those techniques is rather

costly when a wide range of SR lengths must be supported.

The paper is organized as follows. Section 3.2.3 elaborates on the problem formulation. In Section 3.2.4, parallel and multiphase structures are proposed to reduce the power dissipation in long and medium length SRs. These structures directly target FPGA implementations, although they could also be adapted to ASIC frameworks. In Section 3.2.5, a method for choosing the best structure among a set of considered alternatives is presented and applied to six types of SRs. Moreover, the various available SR implementation styles are compared with respect to cost and configurability. Finally, Section 3.2.6 presents some concluding remarks.

### **3.2.3 Problem Formulation**

Shift Registers are key components of our target decoder architecture. In the two reference designs discussed in this paper, using a  $J=10$  code and a  $J=9$  code respectively, the desired error performance is obtained with eight iterations. Each iteration of the algorithm is implemented by a dedicated pipeline stage of the decoder, where the first stage of the decoder is different from all the others [7]. Table 3.1 summarizes the SRs that are required to implement these two decoders. This table gives the number of shift registers (#SRs) that have a given number of taps (#TAPs), and their respective length and width for the two reference designs. As an example, the third line states that seven 903-stage 6-bit wide shift registers with 35 taps each are required.

Table 3.1 SRs in Two Typical Decoders with 8 Iterations

|                         | #SRs | #TAPs | Length | Width |

|-------------------------|------|-------|--------|-------|

| <b>J=9,<br/>M=912</b>   | 14   | 0     | 912    | 3     |

|                         | 1    | 36    | 912    | 3     |

|                         | 7    | 35    | 903    | 6     |

|                         | 8    | 8     | 912    | 3     |

| <b>J=10,<br/>M=1698</b> | 14   | 0     | 1698   | 3     |

|                         | 1    | 45    | 1698   | 3     |

|                         | 7    | 44    | 1696   | 6     |

|                         | 8    | 9     | 1698   | 3     |

Reading from Table 3.1, the total number of bits to shift is roughly equal to  $111*M$ , where  $M$  is the length of the code. Each SR with taps is assembled by connecting untapped registers of lengths determined by the distance between the required taps. The number of shift registers grows as  $8*((J*(J-1))/2) + J - 1$ . Hence for  $J=9$ , 100854 SR bits in 359 untapped SRs are needed, whereas for  $J=10$ , that number grows to 188394 bits spread over 439 SRs. Clearly, high density and low power SRs are highly desirable for implementing the considered decoder. Moreover, some applications, such as conducting research on convolutional coding and iterative threshold decoding require that we merge codes together to enable a quick switching from one to the other. For those applications, configurable shift registers are clearly very advantageous. The remainder of the paper presents an effective implementation methodology for shift registers of different sizes and widths that are critical for our reference designs.

### 3.2.4 New Low-Power Shift Register Structures

In this section, two structures are proposed to reduce the power dissipation in SRs. The first is based on a parallel, multiphase memory-based structure. The second structure is designed to reduce power dissipation when longer SRs are needed. The flexibility of those structures, designed to be dynamically configurable, will be demonstrated.

#### 3.2.4.1 Shift Register Power Reduction Methods

This section reviews the parallel multiphase technique and proposes the selective activation method to reduce SRs power dissipation. The second part of this section will demonstrate the flexibility of the selective activation method with regards to configuration.

##### 3.2.4.1.1 Parallel Multiphase Technique

A parallel multiphase implementation uses multiple clocks to selectively activate SR sections [18]. The goal is to reduce the switching activity. It can be applied to small, medium and long SRs. For example, an N-stage SR can be controlled by four phases, each driving one of four registers of length  $N/4$ . Thus, to implement a SR that appears to work at 100 MHz, a 25 MHz multiphase parallel structure would be used. The two structures are functionally equivalent, but the activity (and power consumption) of the multiphase implementation is reduced by a factor that is close to four. Note that the reduction in power consumption partly comes from a reduced load on the clock distribution network (i.e. only one fourth of the load is driven at each clock cycle). In

FPGAs, this technique is constrained by the number of clock networks and the power reduction is obtained at the cost of an increased complexity.

### ***3.2.4.1.2 Proposed structure***

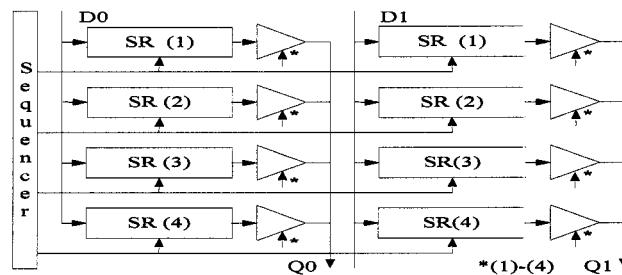

A structure that leverages the advantages of multiphase operation without its complexity is now proposed. An example is shown in Figure 3.1 for an N-stage SR. In this example, a two-bit wide structure is driven by four enabling strobes. Each column handles one of the bits of the data items to be shifted, and each row corresponds to a time strobe. Here, the basic SR modules have a length of  $N/4$ . These modules can be based on SRL16, flip-flops or memories. In the first time interval, the first row buffers are enabled, in the second time interval, the second row buffers are enabled, and so on. This scheme can be generalized to M rows and M strobes, where M is any positive integer.

Figure 3.1 Selective activation method

An M stage one-hot sequencer produces the desired strobes. In order to support register lengths that are not a multiple of four, the output has to be skewed with regards to the input. This means that the strobe used to select the output bit is the input strobe delayed by the required number of clock cycles.

### ***3.2.4.1.3 Impact on Power Dissipation***

The proposed structure adds little to the complexity of the SR, while reducing very significantly the activity. Activity is reduced by a factor close to M (number of strobes). Thus, the power dissipation is reduced by a similar factor albeit slightly smaller because the activity on the clock distribution network is not reduced. Alternately, as described in Section 3.2.4.1.1, selective activation can be used in a multiphase implementation in order to further reduce the power dissipation, but at a higher implementation cost.

The tri-state bus connections in Figure 3.1 could be replaced by conventional multiplexers. This structure works best for medium length, wide SRs. The next subsections describe a configurable version of this structure while section 3.2.4.2 proposes an approach more suited for long SRs. Also, it is shown in section 3.2.5 which structure has the lowest power dissipation for a given SR length.

### ***3.2.4.1.4 Configurable Selective Activation Method***

There is a growing interest for configurable architectures where a single design can serve multiple applications. Dynamic configurability also allows changing functionality to respond to changing needs. This section shows how to make the selective activation architecture configurable while keeping its power reduction properties. It does so by reusing components as much as possible, as opposed to replicating them. Figure 3.2 shows how to implement the generic configuration. As will be shown, the proposed structure is very flexible since it provides more than one way to implement the same target SR length. This feature allows making complexity and power efficiency tradeoffs

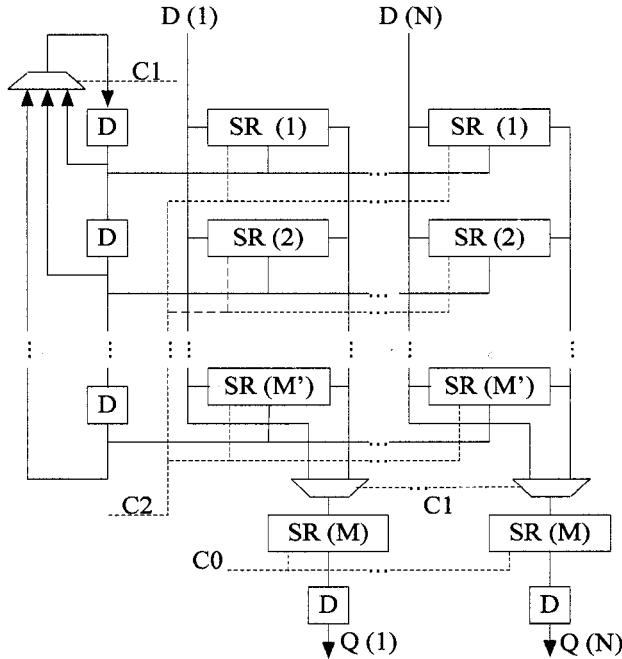

as explained later. Note that each SR is terminated by a flip-flop to make it fully synchronous, which helps reaching high performance. Also note that configuration using this technique can only be done off-line. This structure is configured using 3 registers providing respective control words C0, C1 and C2, as shown on the figure.

This architecture is used as follows. A series of sub-SRs (SR(1) to SR( $M'$ )) form the greater part of the SR, and their outputs drive the input of another sub-SR: SR( $M$ ). As with the selective activation method, each sub-SR is shifted (and its output used) according to the state of a one-hot sequencer (located on the left of Figure 3.2) that is implemented with the C1 register, composed of flip-flops (identified by the boxes labeled D on the left of the figure) and of a multiplexer controlled by the C1 control word. If the total length of the SR is not a multiple of the number of sub-SR (i.e.  $M'$  in the figure) then the last sub-SR (SR( $M$ )) is used to complete the SR.

The three configuration registers, C0, C1, and C2 respectively control the length of SR( $M$ ), the number of sub-SR used, and the length of those sub-SR. Let us define  $M$  as the total number of SR rows, and  $M'$  as the number of rows controlled by the sequencer ( $M' = M - 1$ ). The configured number of rows controlled by the sequencer is defined as  $Mv'$ . In Figure 3.2, N is the word length of the data items to be shifted and thus, it can be seen that each sub-SR column handles one bit of the data items.

Figure 3.2 Configurable selective activation method

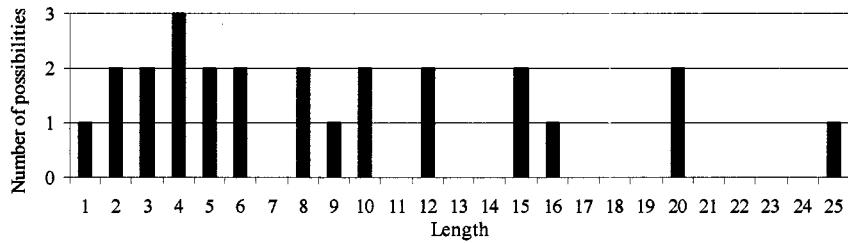

The physical length of each sub-SR is defined as  $Lm'$  and the configured length used in a given context is  $Lv'$ . Note that, in order to reduce the implementation cost and to avoid unnecessary redundancy, all the sub-SRs controlled by the sequencer have the same configured length. Moreover, the last sub-SRs row (i.e. not controlled by the one-hot sequencer) has a maximal size  $Lm$  and a configured length  $Lv$ . The minimum length of this configuration is 2 (because the data has to go through the SR(M) sub-SRs and the final flip-flops at the bottom of the Figure 3.2). In consequence, the maximum length is  $M'*Lm'+Lm+1$ . The length of the SR, when configured, is defined as  $A$  and is computed as  $Mv'*Lv'+Lv+1$ . Configuration registers  $C0$ ,  $C1$  and  $C2$  affect respectively  $Lv$ ,  $Mv'$  and  $Lv'$ . This architecture is generic. It is also redundant as some lengths can be configured in different ways as shown in Figure 3.3, which shows the histogram of the

number of ways to configure the different possible SR lengths when changing only the values of C1 and C2. The total redundancy is even higher than shown in Figure 3.3 when C0 is considered, but as is apparent from Figure 3.3, some SR lengths cannot be obtained if it is configured only through C1 and C2. However, controlling only C0-C1 or only C0-C2 allows producing all possible lengths.

Figure 3.3 Distribution of possibilities vs. length for  $M' = Lm' = 5$

Indeed, when C0 and C2 are used, if  $Lm$  is equal to  $M'$  (the stride caused by an incremental change in C2) all possible lengths can be obtained. Similarly, when C0 and C1 are used,  $Lm$  should be equal to  $M'$  to enable producing all possible lengths without redundancy. Thus, this architecture is generic and it can be easily configured to any length through C0 and C1 or through C0 and C2.

When more than one set of parameters gives the desired SR length, the choice of the best control parameters set should be done according to user defined objectives, such as decreasing power dissipation or reducing hardware complexity. Depending on the technology used for the implementation, the sub-SR power dissipation can be constant or it can change following the configured length of the sub-SRs. For example, an implementation based on flip-flops has a power consumption that changes with the length of the SRs, while an implementation based on memories has constant sub-SR power

consumption. Thus, when the power dissipation of the sub-SRs is variable, C0 and C2 should be used in order to minimize the power consumption of the sub-SRs. On the other hand, when their power dissipation is constant, any pair can be used, because the total power consumption is constant since only one sub-SR is activated at a time per column. But if hardware complexity is an important criterion, C0 and C1 should be used because, in this situation, the sub-SRs do not need to be configurable, thus reducing hardware complexity and avoiding routing of C2.

#### ***3.2.4.1.5 Multi-phase Configurable Selective Activation Method***

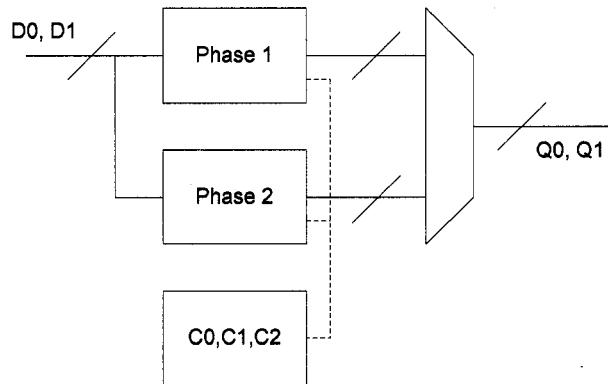

As mentioned in section 3.2.4.1.1, the proposed configurable selective activation structure can be combined with a multiphase clock. For example, a system with two phases may divide the shift register in two sections as shown in Figure 3.4.

Figure 3.4 Multi-phase configurable selective activation method

If A is the total target length of the SR, we can design two SRs of length  $\lfloor (A+1)/2 \rfloor$  using the method of section 3.2.4.1.4 to adjust the size of each SR by configuring parameters C0, C1, and C2. If A is odd, output data must be read from the phase 1 SR when input

data is being written into the phase 2 SR, and vice versa. If  $p > 2$  phases are available, the proposed architecture can be generalized with  $p$  SRs of length  $\lfloor (A+p-1)/p \rfloor$ , complemented by a controller that will skew as required the reading and writing operations. This method reduces power dissipation by a factor close to the number of phases (as explained in Section 3.2.4.1.1). The cost of this structure is slightly higher than the cost of the structure in Figure 3.2. It may be worthwhile to note that this structure can be transformed into a multi tap SR but it introduces several design constraints and their analysis is beyond the scope of this paper.

### **3.2.4.2 Memory-based Shift Registers**

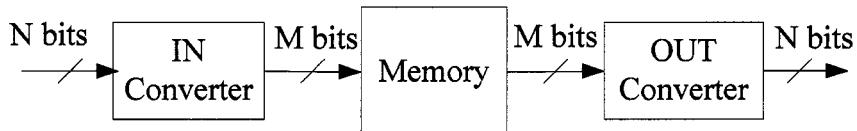

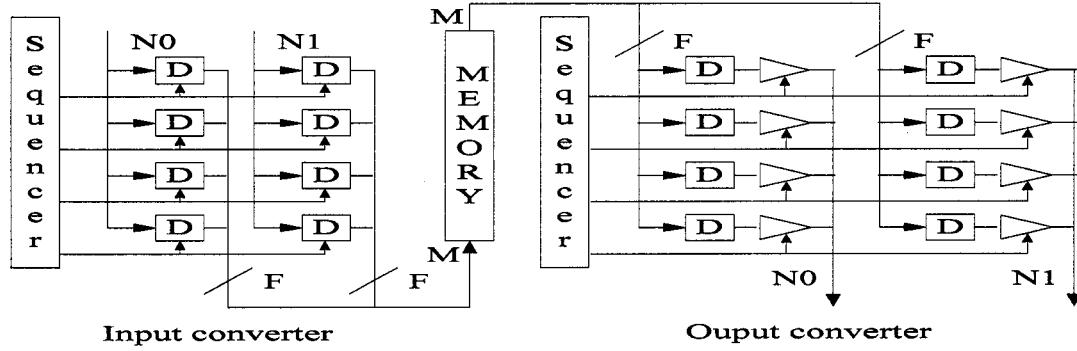

This section investigates effective methods to implement SRs based on memory. A method to reduce their power dissipation is also proposed. The objective is to better support long SRs. This is significant as it will be shown in Section 3.2.5 that memory-based SRs have the lowest power dissipation.

It is well known that long SRs are advantageously implemented using memories addressed by pointers. At each clock cycle, one data element is read out, while a new data element is written in its place. Power dissipation can be reduced because in a long SR, most of the data in the memory not involved with the words written or read do not move. However, power is dissipated by the required peripheral logic and counters used to implement the required pointers. Again, power dissipation can be reduced by lowering the activity. Later in this section, we show how power dissipation can be further reduced using data format converters that reduce activity. This concept applies to ASIC and

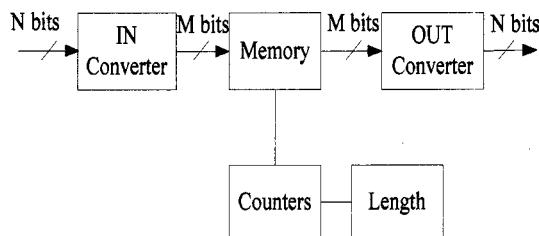

FPGA implementations, but it is particularly useful in FPGAs where fixed size embedded RAMs supporting selected word widths (1, 2, 4, 8 and 16) are available. For example, a straightforward implementation of a 1698 stage 6-bit wide SR could use 3 2-bit wide memories of 2048 words. Alternately, 3 8-bit wide memories of 512 words would behave identically when combined with suitable format converters on input and output as shown in Figure 3.5.

Figure 3.5 Example of memory with converter structure