**Titre:** Une plateforme de mesure de caractéristiques électroniques pour les nanostructures

Title: [Une plateforme de mesure de caractéristiques électroniques pour les nanostructures](#)

**Auteur:** Olivier Duval

Author: [Olivier Duval](#)

**Date:** 2005

**Type:** Mémoire ou thèse / Dissertation or Thesis

**Référence:** Duval, O. (2005). Une plateforme de mesure de caractéristiques électroniques pour les nanostructures [Mémoire de maîtrise, École Polytechnique de Montréal].

Citation: [PolyPublie. <https://publications.polymtl.ca/7364/>](https://publications.polymtl.ca/7364/)

## Document en libre accès dans PolyPublie

Open Access document in PolyPublie

**URL de PolyPublie:** <https://publications.polymtl.ca/7364/>

PolyPublie URL: <https://publications.polymtl.ca/7364/>

**Directeurs de recherche:** Yvon Savaria

Advisors: [Yvon Savaria](#)

**Programme:** Non spécifié

Program: [Non spécifié](#)

# **NOTE TO USERS**

This reproduction is the best copy available.

**UMI**<sup>®</sup>

UNIVERSITÉ DE MONTRÉAL

UNE PLATEFORME DE MESURE DE CARACTÉRISTIQUES

ÉLECTRONIQUES POUR LES NANOSTRUCTURES

OLIVIER DUVAL

DÉPARTEMENT DE GÉNIE ÉLECTRIQUE

ÉCOLE POLYTECHNIQUE DE MONTRÉAL

MÉMOIRE PRÉSENTÉ EN VUE DE L'OBTENTION

DU DIPLÔME DE MAÎTRISE ÈS SCIENCES APPLIQUÉES

(MICROÉLECTRONIQUE)

MAI 2005

Library and

Archives Canada

Published Heritage

Branch

395 Wellington Street

Ottawa ON K1A 0N4

Canada

Bibliothèque et

Archives Canada

Direction du

Patrimoine de l'édition

395, rue Wellington

Ottawa ON K1A 0N4

Canada

*Your file* *Votre référence*

ISBN: 0-494-01310-9

*Our file* *Notre référence*

ISBN: 0-494-01310-9

#### NOTICE:

The author has granted a non-exclusive license allowing Library and Archives Canada to reproduce, publish, archive, preserve, conserve, communicate to the public by telecommunication or on the Internet, loan, distribute and sell theses worldwide, for commercial or non-commercial purposes, in microform, paper, electronic and/or any other formats.

The author retains copyright ownership and moral rights in this thesis. Neither the thesis nor substantial extracts from it may be printed or otherwise reproduced without the author's permission.

#### AVIS:

L'auteur a accordé une licence non exclusive permettant à la Bibliothèque et Archives Canada de reproduire, publier, archiver, sauvegarder, conserver, transmettre au public par télécommunication ou par l'Internet, prêter, distribuer et vendre des thèses partout dans le monde, à des fins commerciales ou autres, sur support microforme, papier, électronique et/ou autres formats.

L'auteur conserve la propriété du droit d'auteur et des droits moraux qui protège cette thèse. Ni la thèse ni des extraits substantiels de celle-ci ne doivent être imprimés ou autrement reproduits sans son autorisation.

---

In compliance with the Canadian Privacy Act some supporting forms may have been removed from this thesis.

While these forms may be included in the document page count, their removal does not represent any loss of content from the thesis.

Conformément à la loi canadienne sur la protection de la vie privée, quelques formulaires secondaires ont été enlevés de cette thèse.

Bien que ces formulaires aient inclus dans la pagination, il n'y aura aucun contenu manquant.

UNIVERSITÉ DE MONTRÉAL

ÉCOLE POLYTECHNIQUE DE MONTRÉAL

Ce mémoire intitulé:

UNE PLATEFORME DE MESURE DE CARACTÉRISTIQUES

ÉLECTRONIQUES POUR LES NANOSTRUCTURES

présenté par: DUVAL Olivier

en vue de l'obtention du diplôme de: Maîtrise ès sciences appliquées

a été dûment accepté par le jury d'examen constitué de:

M LAURIN Jean-Jacques, PhD, président

M SAVARIA Yvon, PhD, membre et directeur de recherche

M KHOUAS Abdelhakim, PhD, membre

À Gordon Moore, prophète malgré lui.

## REMERCIEMENTS

Merci à Marc-André Cantin, Louis-Pierre Lafrance, Jean-François Coulombe, Abdelaziz Trabelsi et Yamu Hu pour leur aide inestimable et soutenue tout au long de ma maîtrise.

Merci à Patrick Desjardins, Richard Martel et Alain Rochefort de m'avoir partagé une part de leurs connaissances immenses.

Merci à mon directeur Yvon Savaria pour avoir allumé en moi la flamme de la recherche scientifique. En gardant son enthousiasme malgré des difficultés et des échecs déchirants, il m'a grandement aidé à garder le cap tout au long de ce projet.

Merci à mes parents François et Francine, qui ne m'ont jamais empêché d'embarquer dans les projets les plus ambitieux.

Merci à mes amis Pierre-Alexandre et Guillaume, vous m'avez sauvé du pétrin en maintes occasions.

Merci à Christine, ton soutien m'a permis d'oublier mes angoisses et de garder le sourire.

## RÉSUMÉ

Ce projet vise à réduire le pont séparant l'univers de la microélectronique de celui des nanotechnologies. La fabrication d'une plateforme microélectronique de mesure de caractéristiques électriques de nanostructures s'inscrit doublement dans cet objectif.

D'abord, la façon de lier la nanostructure sous test à la plateforme est un problème important. En effet, les méthodes de fabrication de plusieurs nanostructures sont actuellement incompatibles avec la fabrication de circuits électroniques conventionnels. Nous avons donc conçu la plateforme de test de façon à recevoir les nanostructures sur des électrodes fabriquées à même la couche métallique supérieure du circuit.

Une fois fabriquée, la plateforme permet la mesure de caractéristiques électriques de nanostructures dans le but d'établir des modèles de ces nanostructures.

Dans le cadre de ce projet, nous avons conçu et fabriqué une plateforme de test en utilisant la technologie TSMC CMOS 180nm. Cette plateforme de test n'a pas fonctionné comme les simulations le prévoient à cause de problèmes de design. Pour la création de modèles de nanostructures, nous avons toutefois établi un modèle de transistor à base de nanotube de carbone.

Les résultats de la recherche que ce mémoire rapporte s'inscrivent dans un projet qui s'échelonnera sur plusieurs années et qui utilisera ces résultats pour, espérons-le, fabriquer un jour un nanodispositif fonctionnel, une tâche très ardue à l'heure actuelle.

## ABSTRACT

This project aims at the reduction of the gap separating the microelectronic to nanotechnology worlds. The fabrication of a microelectronic platform for the measurement of electronic characteristics in nanostructures answers to this objective in two distinct ways.

First, linking nanostructures under test to a platform is not a simple task. Most nanoelectronic fabrication methods currently used are not compatible with the creation of microelectronic devices. We have designed and built this test platform to permit the inclusion of nanostructures on electrodes built on the top layer of the circuit. Secondly, by measuring electronic characteristics for a given nanostructure, we used these measurements to complete electronic models describing their behaviour.

For this project, we have designed and built a test platform using the TSMC CMOS 180nm technology. This platform did not work as predicted because of problems in the design of its high-level architecture. Nonetheless, we used prior experimental nanostructure measurements in order to create a model for a carbon nanotube based transistor.

The research results for this thesis are part of a project that spans over a long period of time. We can only hope that our successors will use the results of this research to create a useful nanodevice, which is very difficult for now.

**TABLE DES MATIÈRES**

|                                                        |      |

|--------------------------------------------------------|------|

| DÉDICACE . . . . .                                     | iv   |

| REMERCIEMENTS . . . . .                                | v    |

| RÉSUMÉ . . . . .                                       | vi   |

| ABSTRACT . . . . .                                     | vii  |

| TABLE DES MATIÈRES . . . . .                           | viii |

| LISTE DES FIGURES . . . . .                            | xii  |

| LISTE DES TABLEAUX . . . . .                           | xv   |

| LISTE DES NOTATIONS ET DES SYMBOLES . . . . .          | xvi  |

| LISTE DES ANNEXES . . . . .                            | xvii |

| INTRODUCTION . . . . .                                 | 1    |

| CHAPITRE 1 REVUE DE LITTÉRATURE . . . . .              | 3    |

| 1.1 Nanostructures . . . . .                           | 3    |

| 1.1.1 CMOS à double grille . . . . .                   | 3    |

| 1.1.2 Dispositifs quantiques . . . . .                 | 5    |

| 1.1.2.1 Diodes à effet tunnel . . . . .                | 5    |

| 1.1.2.2 Spintronics . . . . .                          | 9    |

| 1.1.3 Nanotubes de carbone . . . . .                   | 14   |

| 1.1.3.1 Fullerènes . . . . .                           | 14   |

| 1.1.3.2 Premiers nanotubes de carbone . . . . .        | 15   |

| 1.1.3.3 Structures moléculaires de nanotubes . . . . . | 16   |

|          |                                                                      |    |

|----------|----------------------------------------------------------------------|----|

| 1.1.3.4  | Propriétés électriques des SWCNTs . . . . .                          | 17 |

| 1.1.3.5  | Propriétés électriques des MWNTs . . . . .                           | 18 |

| 1.1.3.6  | Méthodes de fabrication de CNTs . . . . .                            | 19 |

| 1.1.3.7  | Fabrication de CNTFETs . . . . .                                     | 21 |

| 1.1.3.8  | Placement des CNTs sur une paire d'électrodes .                      | 22 |

| 1.1.3.9  | Tri des Nanotubes de Carbone . . . . .                               | 23 |

| 1.1.3.10 | Exemple d'application: une porte logique en CNT                      | 26 |

| 1.1.3.11 | Applications des nanotubes . . . . .                                 | 27 |

| 1.2      | Mesures de précision . . . . .                                       | 29 |

| 1.2.1    | Mesure de délais . . . . .                                           | 30 |

| 1.2.1.1  | Télécommunications . . . . .                                         | 30 |

| 1.2.1.2  | VLSI . . . . .                                                       | 32 |

| 1.2.1.3  | Autres sources sur des mesures intégrées à haute précision . . . . . | 36 |

|          | CHAPITRE 2 PLATEFORME DE TEST . . . . .                              | 39 |

| 2.1      | Mesures à effectuer . . . . .                                        | 40 |

| 2.1.1    | Mesure I-V . . . . .                                                 | 40 |

| 2.1.1.1  | Précision et modèle recherchés . . . . .                             | 41 |

| 2.1.2    | Mesure de délais . . . . .                                           | 42 |

| 2.1.2.1  | Précision recherchée . . . . .                                       | 42 |

| 2.2      | Système électronique de mesure et contrôle . . . . .                 | 43 |

| 2.2.1    | Module de mesure DC . . . . .                                        | 44 |

| 2.2.1.1  | Porte de transmission utilisée dans le module de mesure DC . . . . . | 46 |

| 2.2.2    | Module de validation d'intégrité technologique . . . . .             | 47 |

| 2.2.3    | Module de JTAG . . . . .                                             | 48 |

| 2.2.4    | Module de mesure de délai . . . . .                                  | 49 |

|                                                       |                                                                              |    |

|-------------------------------------------------------|------------------------------------------------------------------------------|----|

| 2.2.4.1                                               | Module de mesure de délai proposé . . . . .                                  | 49 |

| 2.2.4.2                                               | Formules utilisées pour calculer le délai mesuré . .                         | 52 |

| 2.2.4.3                                               | Discussion sur la précision du module de mesure de délai . . . . .           | 53 |

| 2.3                                                   | Intégration de nanostructures . . . . .                                      | 54 |

| 2.3.1                                                 | Architectures utilisables . . . . .                                          | 55 |

| 2.3.1.1                                               | Plaque de silicium “nue” . . . . .                                           | 55 |

| 2.3.1.2                                               | Circuits intégrés configurables . . . . .                                    | 56 |

| 2.3.1.3                                               | Circuits intégrés à application spécifique . . . . .                         | 56 |

| 2.3.2                                                 | Intégration de CNTs à la plateforme de test . . . . .                        | 57 |

| 2.3.2.1                                               | Choix de la méthode de fabrication . . . . .                                 | 57 |

| 2.3.2.2                                               | Choix de la méthode de placement . . . . .                                   | 58 |

| 2.3.3                                                 | Conception de la surface d'électrodes de contact . . . . .                   | 59 |

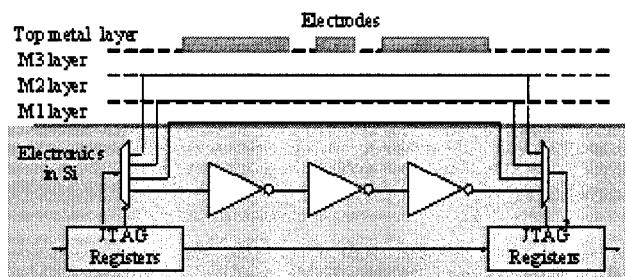

| 2.3.3.1                                               | Emplacement des électrodes de contact . . . . .                              | 60 |

| 2.3.3.2                                               | Liaison des électrodes aux modules de mesure internes                        | 61 |

| 2.4                                                   | Conclusions du chapitre . . . . .                                            | 61 |

| CHAPITRE 3 MODÉLISATION D'UN NANO-COMPOSANT . . . . . |                                                                              | 62 |

| 3.1                                                   | Modèles de transistors . . . . .                                             | 62 |

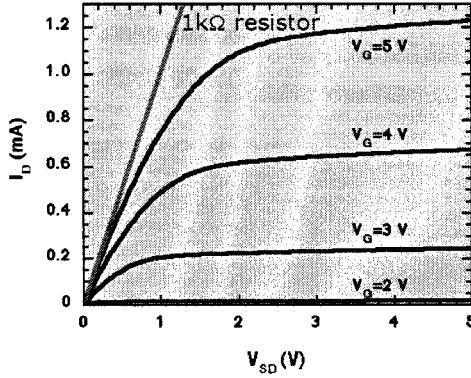

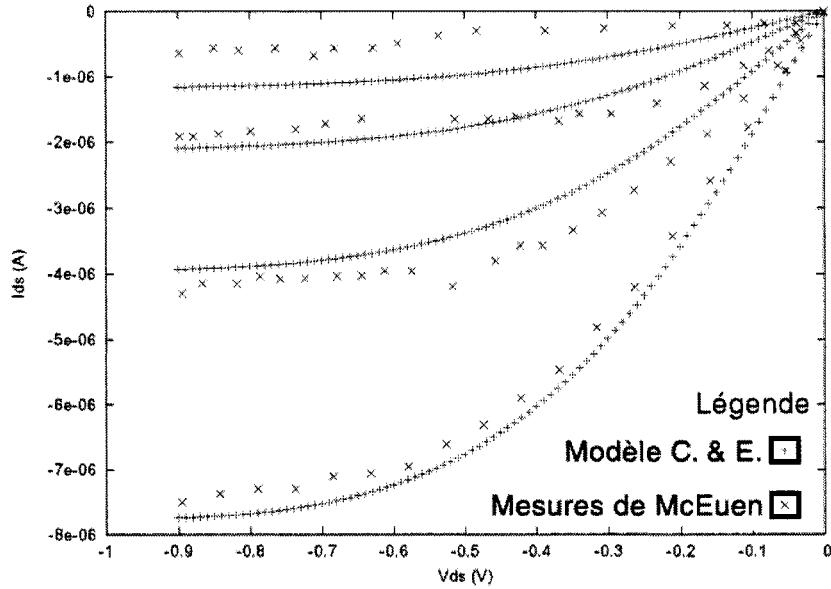

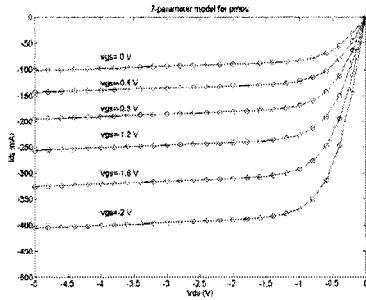

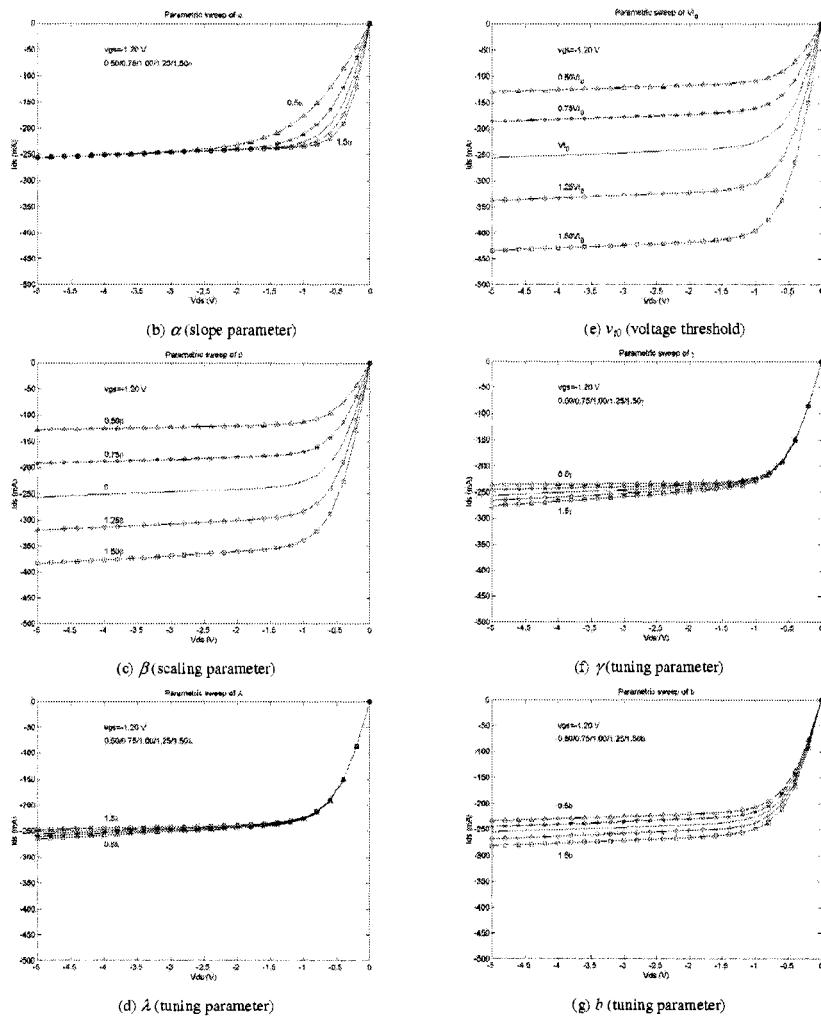

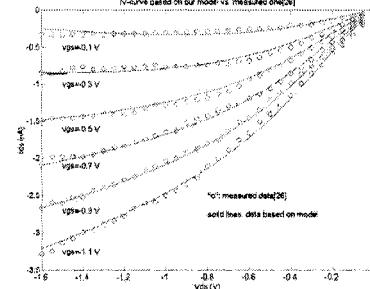

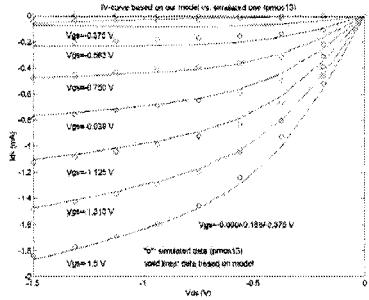

| 3.2                                                   | Modèle et données expérimentales traités avec le programme . . . . .         | 63 |

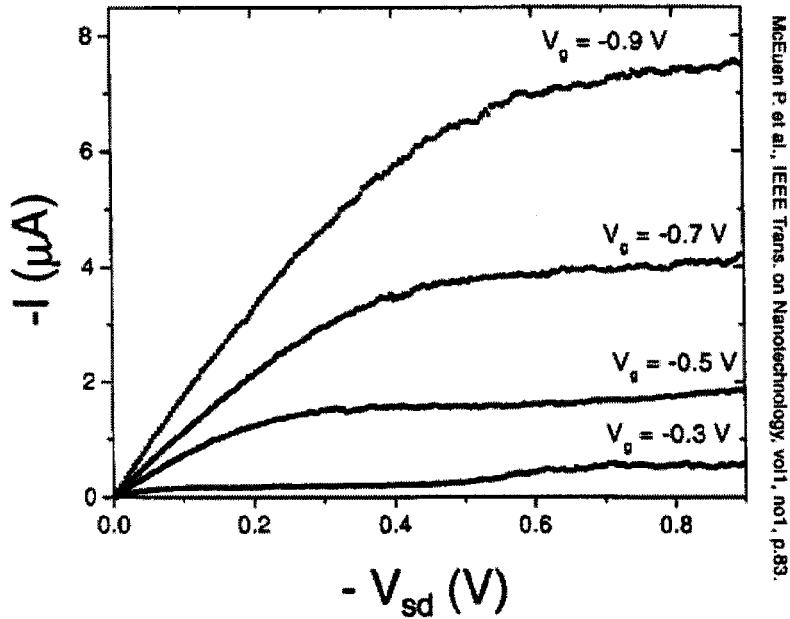

| 3.2.1                                                 | CNTFET de McEuen et al. . . . .                                              | 64 |

| 3.2.2                                                 | Modèle de FET de Curtice et Ettenberg modifié . . . . .                      | 65 |

| 3.2.3                                                 | Description des paramètres fixes du modèle de Curtice et Ettenberg . . . . . | 66 |

| 3.3                                                   | Programme de génération de paramètres pour le modèle C. & E. .               | 67 |

| 3.3.1                                                 | Pseudocode de l'algorithme génétique utilisé dans ce programme . . . . .     | 67 |

| 3.3.2                                                 | Description du code du programme . . . . .                                   | 68 |

|                                                                    |    |

|--------------------------------------------------------------------|----|

| 3.4 Résultats . . . . .                                            | 71 |

| 3.5 Conclusion du chapitre . . . . .                               | 73 |

| <br>                                                               |    |

| CHAPITRE 4 CARACTÉRISATION PAR SIMULATION DES STRUC-               |    |

| TURES DE TEST . . . . .                                            | 74 |

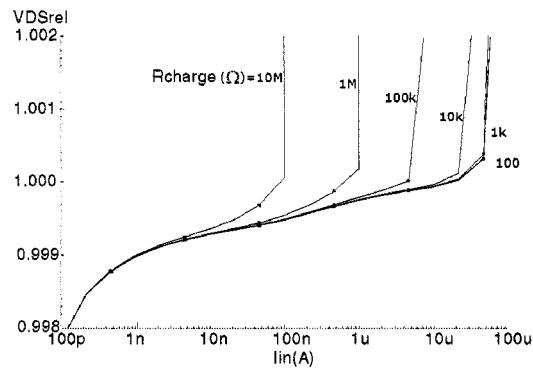

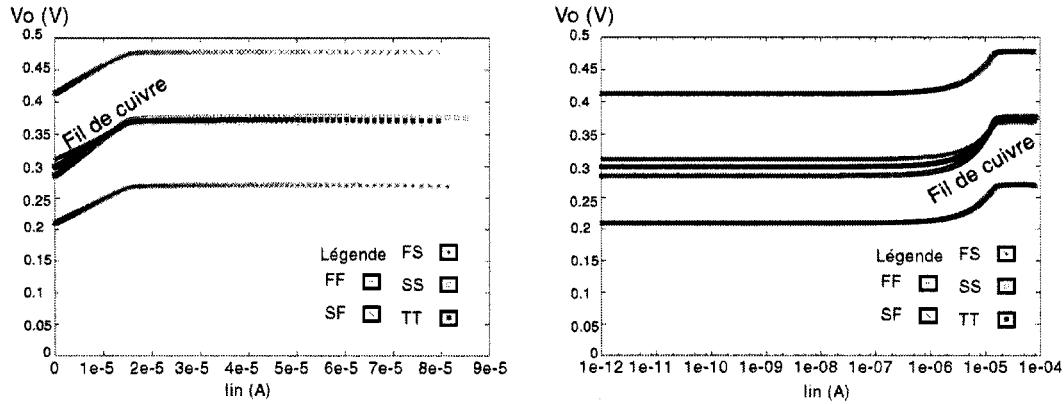

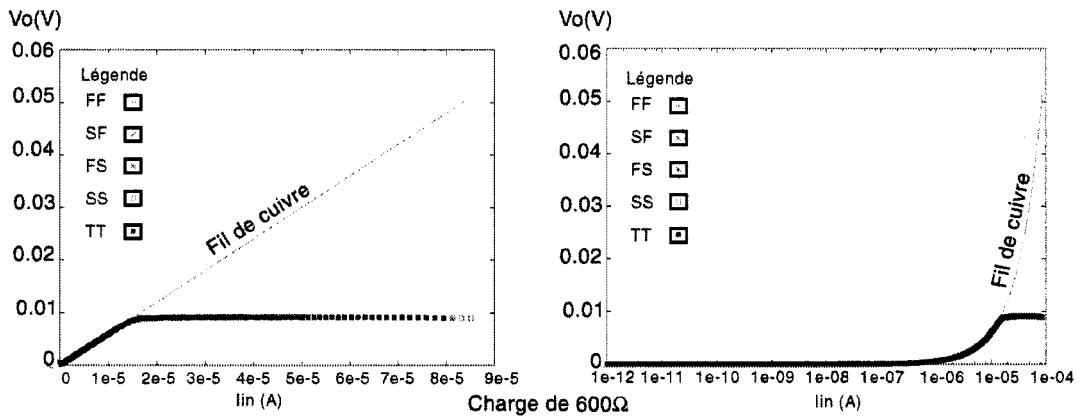

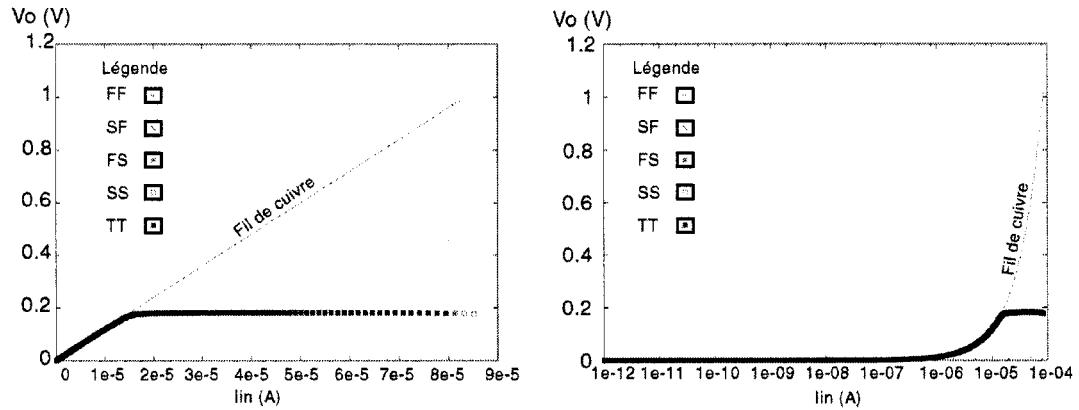

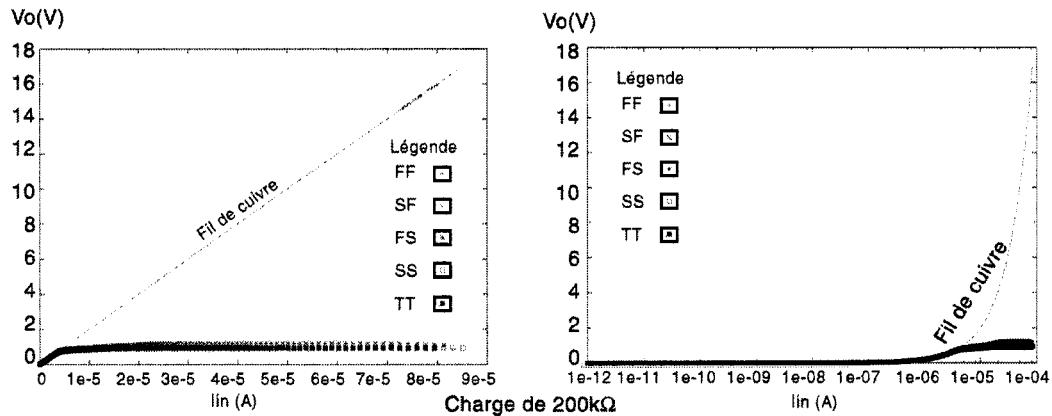

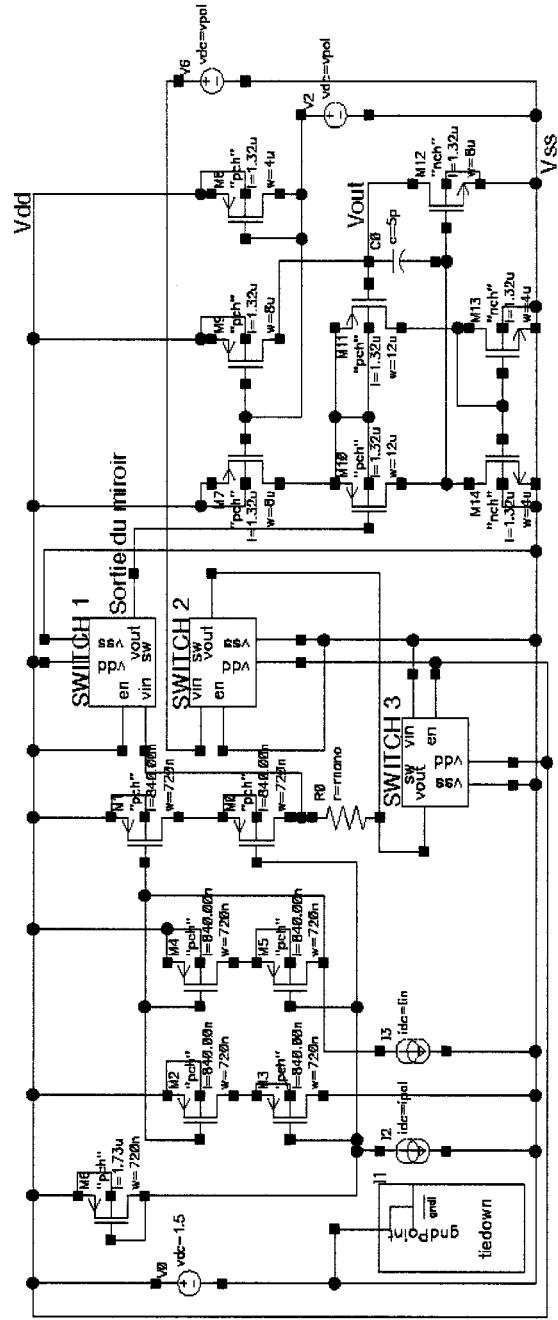

| 4.1 Résultats de simulation du module DC . . . . .                 | 74 |

| 4.1.1 Incertitude structurelle du module DC . . . . .              | 74 |

| 4.1.2 Incertitude du module DC causée par les aléas de fabrication | 75 |

| 4.1.2.1 Définition des tests de coin . . . . .                     | 76 |

| 4.1.2.2 Description des tests de coin . . . . .                    | 77 |

| 4.1.3 Discussion des résultats de simulation DC . . . . .          | 78 |

| 4.2 Simulation du module de mesure de délai . . . . .              | 80 |

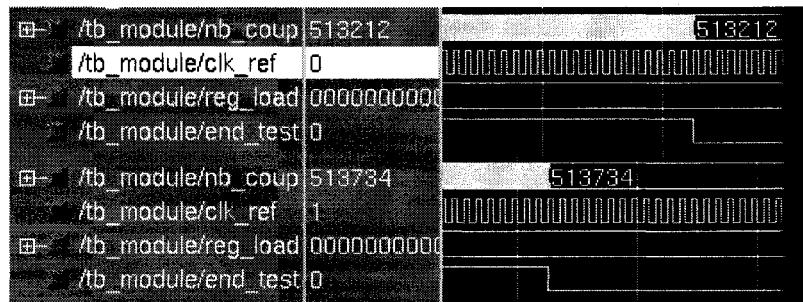

| 4.2.1 Simulation numérique du module de mesure de délai . . . . .  | 80 |

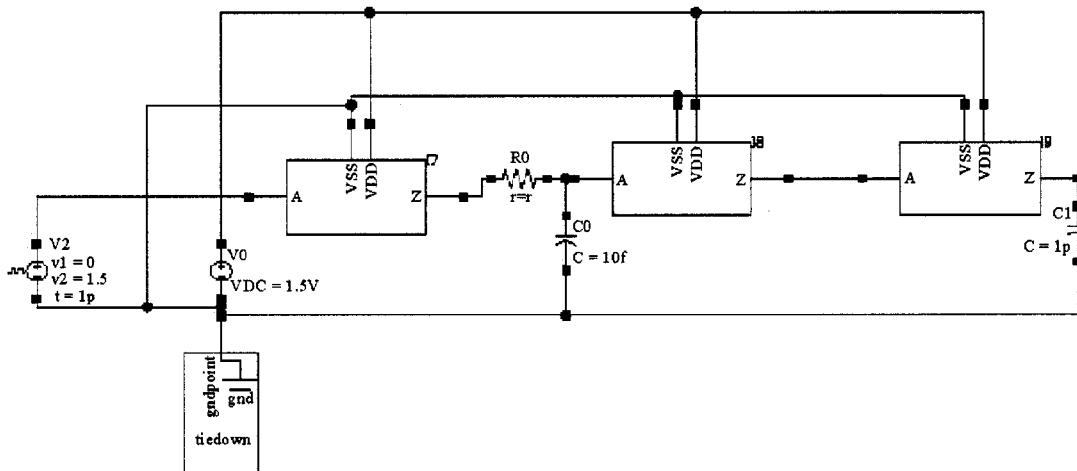

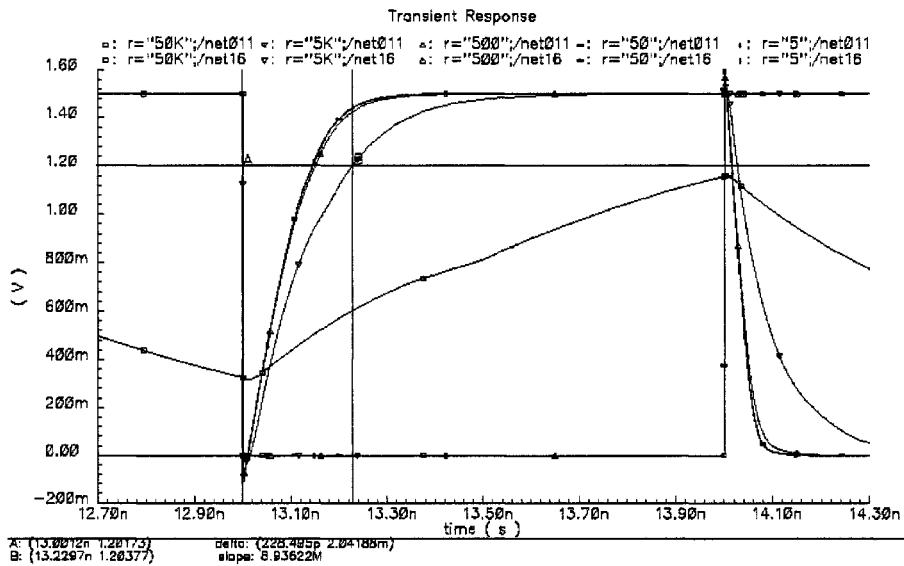

| 4.2.2 Simulation analogique du module de mesure de délai . . . . . | 82 |

| 4.3 Conclusion des simulations . . . . .                           | 83 |

| <br>                                                               |    |

| CHAPITRE 5 RÉSULTATS . . . . .                                     | 86 |

| 5.1 Évaluation du procédé de fabrication . . . . .                 | 86 |

| 5.1.1 Électrodes de test . . . . .                                 | 87 |

| 5.1.2 Structure de caractérisation hors règles de design . . . . . | 87 |

| 5.2 Mesures effectuées avec la plateforme . . . . .                | 88 |

| 5.2.1 Montage du circuit de mesure sur carte . . . . .             | 89 |

| 5.2.2 Mesures effectuées sur l'analyseur logique . . . . .         | 89 |

| 5.3 Conclusion des mesures . . . . .                               | 90 |

| <br>                                                               |    |

| CONCLUSION . . . . .                                               | 91 |

| <br>                                                               |    |

| RÉFÉRENCES . . . . .                                               | 93 |

| <br>                                                               |    |

| ANNEXES . . . . .                                                  | 99 |

## LISTE DES FIGURES

|             |                                                                                                                                                                |    |

|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

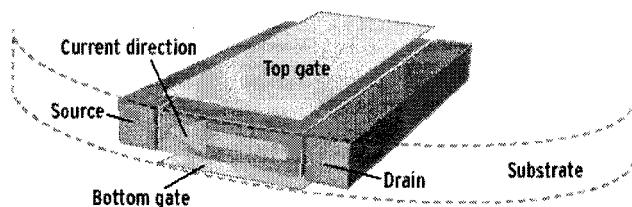

| Figure 1.1  | MOSFET à double grille planaire . . . . .                                                                                                                      | 4  |

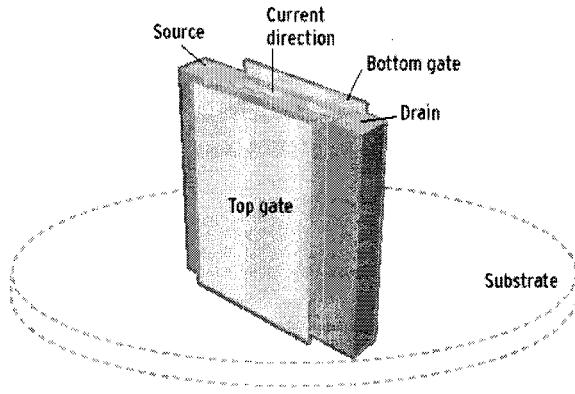

| Figure 1.2  | MOSFET à double grille non-planaire . . . . .                                                                                                                  | 5  |

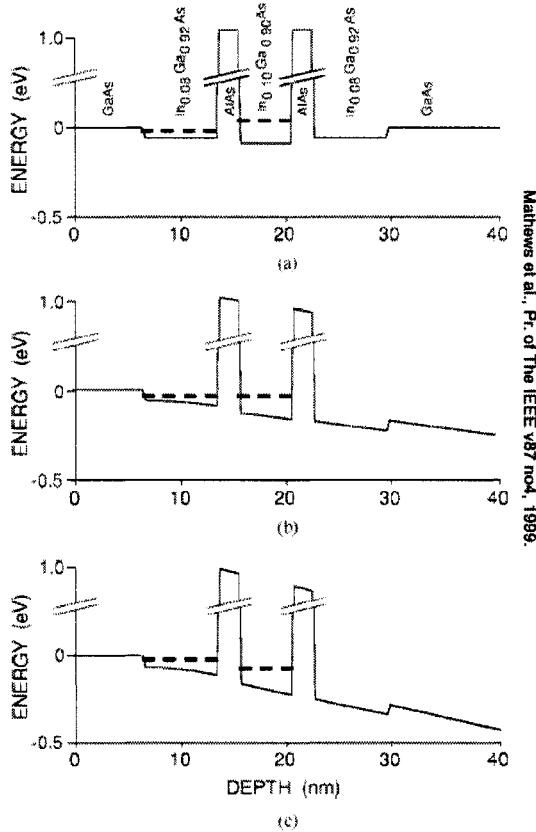

| Figure 1.3  | Alignement des états quasi-liés dans une RTD: a. Maximum d'énergie pour l'effet tunnel b. État de résonance c. Minimum d'énergie pour l'effet tunnel . . . . . | 7  |

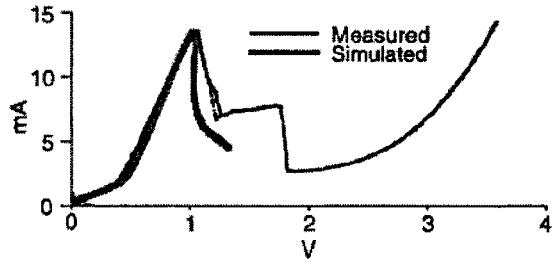

| Figure 1.4  | Courbe I-V d'une RTD . . . . .                                                                                                                                 | 8  |

| Figure 1.5  | Une mémoire bistable à base de RTD . . . . .                                                                                                                   | 8  |

| Figure 1.6  | Topologie de mémoire FIFO-RTD en 3D . . . . .                                                                                                                  | 9  |

| Figure 1.7  | Dessin de masques d'une mémoire 128kB en MRAM . . . . .                                                                                                        | 11 |

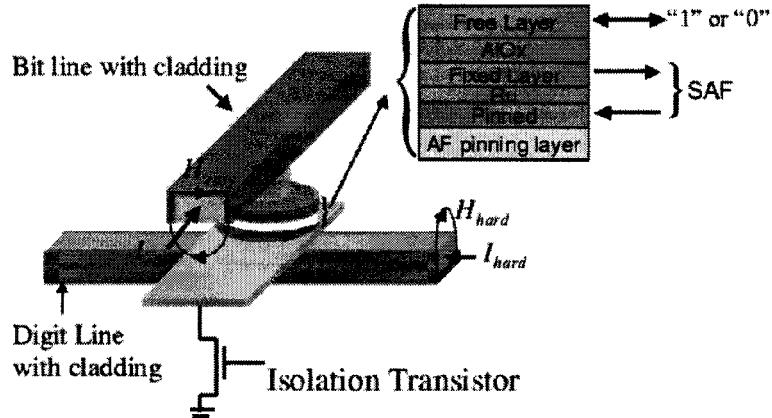

| Figure 1.8  | Schéma simplifié d'une cellule 1T1MTJ de IBM . . . . .                                                                                                         | 11 |

| Figure 1.9  | Schéma simplifié d'une cellule 1T1MTJ de Motorola . . . . .                                                                                                    | 12 |

| Figure 1.10 | Fonctionnement interne d'une cellule MTJ . . . . .                                                                                                             | 12 |

| Figure 1.11 | Une molécule de fullerène . . . . .                                                                                                                            | 14 |

| Figure 1.12 | Senseur piézoélectrique en fullerène . . . . .                                                                                                                 | 15 |

| Figure 1.13 | Coupes de plans de graphite . . . . .                                                                                                                          | 16 |

| Figure 1.14 | Nanotubes à simple et multi-couche . . . . .                                                                                                                   | 17 |

| Figure 1.15 | Procédés de fabrication de nanotubes . . . . .                                                                                                                 | 20 |

| Figure 1.16 | Un des premiers modèles de CNTFETs . . . . .                                                                                                                   | 21 |

| Figure 1.17 | Modèle récent de CNTFET . . . . .                                                                                                                              | 22 |

| Figure 1.18 | Système de nanofabrication . . . . .                                                                                                                           | 24 |

| Figure 1.19 | Méthode d'effeuillage de MWNTs . . . . .                                                                                                                       | 25 |

| Figure 1.20 | Mesures effectuées en cours de filtration . . . . .                                                                                                            | 26 |

| Figure 1.21 | Écrasement de MWCNT entre une pointe d'AFM et un substrat . . . . .                                                                                            | 27 |

| Figure 1.22 | Un inverseur logique à base de CNTFETs . . . . .                                                                                                               | 28 |

| Figure 1.23 | Mesures de permittivité relative et de $\alpha$ conductivité . . . . .                                                                                         | 29 |

|             |                                                                                |    |

|-------------|--------------------------------------------------------------------------------|----|

| Figure 1.24 | Une pointe d'AFM avec terminaison en CNT . . . . .                             | 30 |

| Figure 1.25 | Ligne de délai pour la synchronisation . . . . .                               | 31 |

| Figure 1.26 | Système de mesure de délais de Petre et al. . . . .                            | 32 |

| Figure 1.27 | Montage de mesure de délai . . . . .                                           | 33 |

| Figure 1.28 | Configuration de mesure de délai d'interconnexions . . . . .                   | 34 |

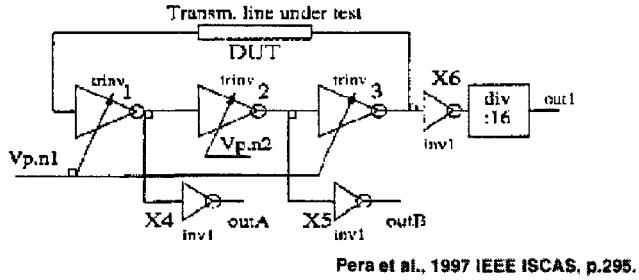

| Figure 1.29 | Oscillateur bouclé de Pera et al. . . . .                                      | 35 |

| Figure 1.30 | Détecteur de phase de Pera et al. . . . .                                      | 36 |

| Figure 1.31 | Mesure de délai de Sato et al. . . . .                                         | 38 |

| Figure 2.1  | courbes I-V d'un transistor CMOS et d'un fil de cuivre . .                     | 41 |

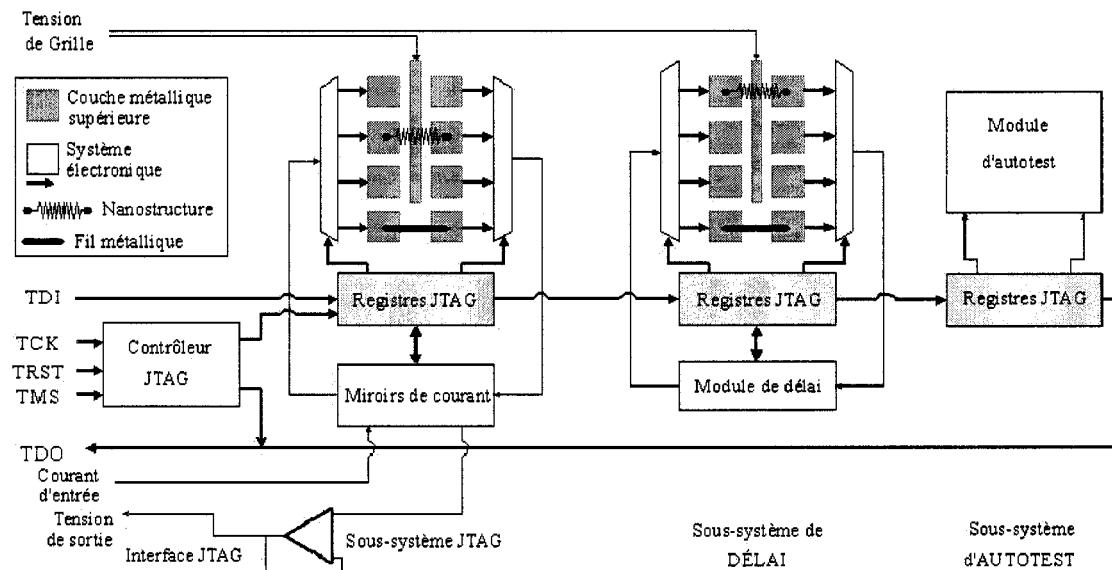

| Figure 2.2  | Système électronique global . . . . .                                          | 43 |

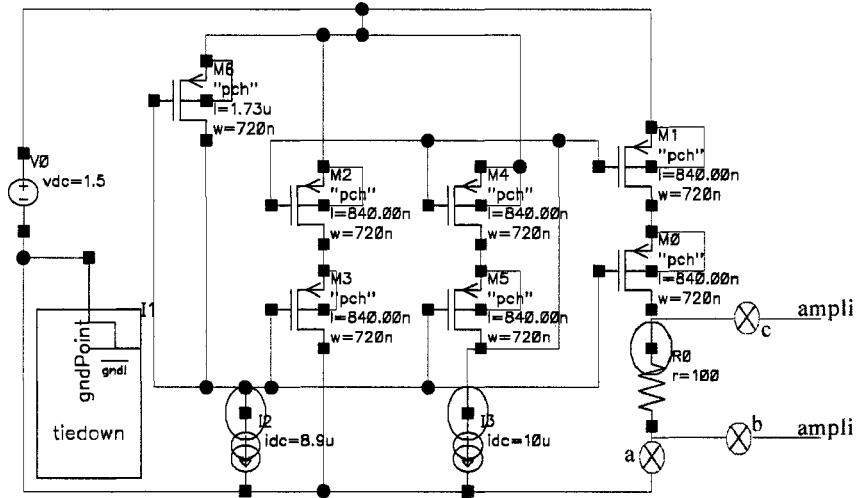

| Figure 2.3  | Miroir de courant du module de mesure DC . . . . .                             | 45 |

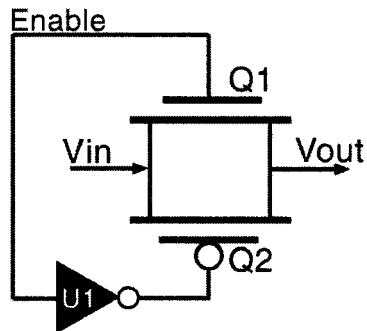

| Figure 2.4  | Porte de transmission utilisée dans le module . . . . .                        | 46 |

| Figure 2.5  | Le module d'autotest . . . . .                                                 | 47 |

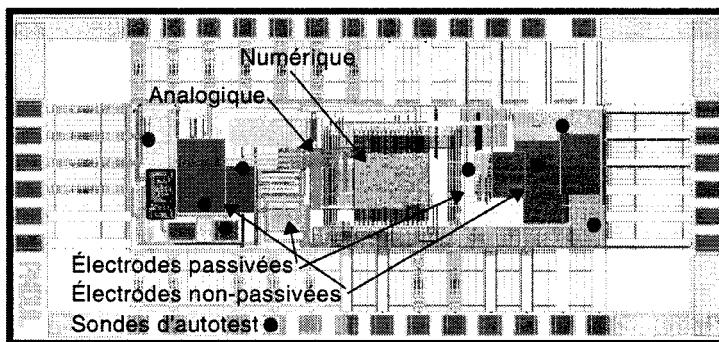

| Figure 2.6  | Emplacement des sondes d'autotest . . . . .                                    | 48 |

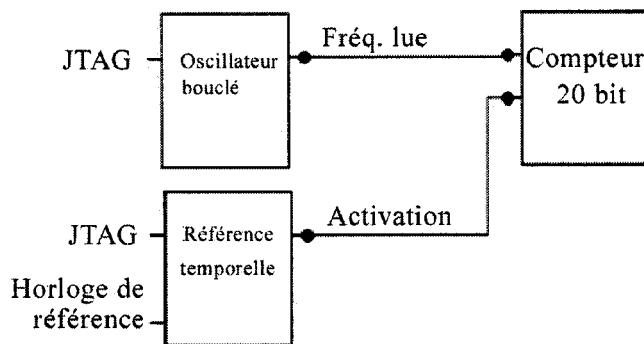

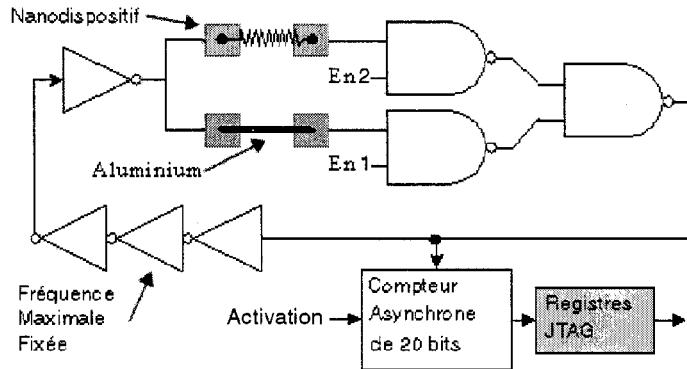

| Figure 2.7  | Schéma-bloc du module de mesure de délai . . . . .                             | 50 |

| Figure 2.8  | Oscillateur bouclé configurable . . . . .                                      | 51 |

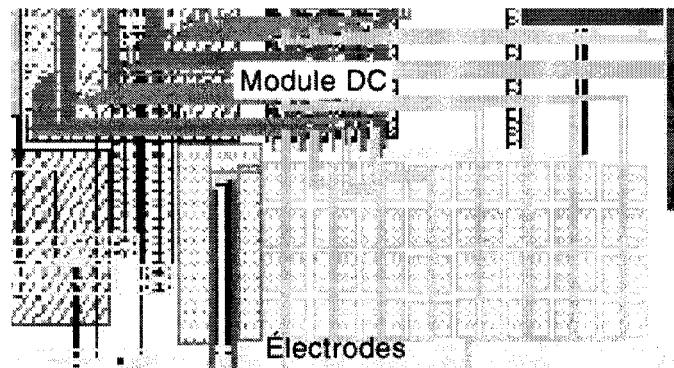

| Figure 2.9  | Dessin de masques des électrodes de contact . . . . .                          | 60 |

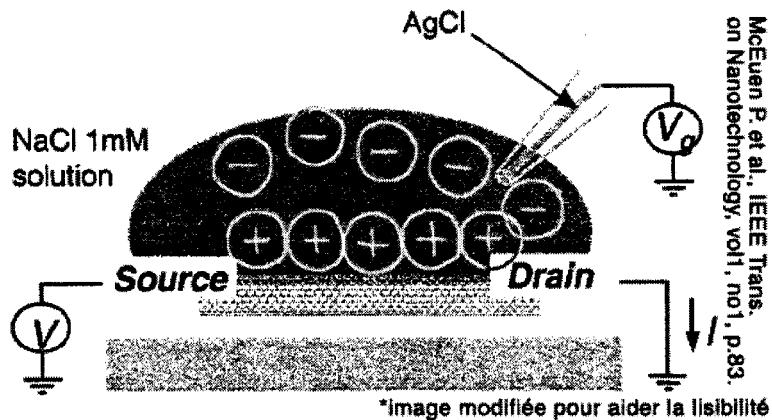

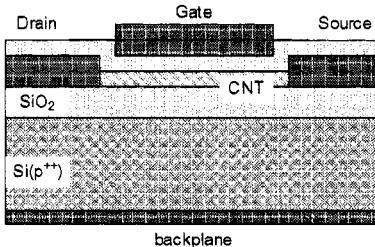

| Figure 3.1  | Transistor électrolytique de McEuen et al. . . . .                             | 64 |

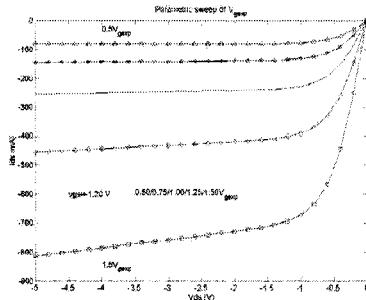

| Figure 3.2  | Courbe I-V du transistor de McEuen et al. . . . .                              | 65 |

| Figure 3.3  | Courbe I-V expérimentale de McEuen vs modèle de Curtice et Ettenberg . . . . . | 72 |

| Figure 4.1  | Précision de la mesure du module DC . . . . .                                  | 75 |

| Figure 4.2  | Test de coin de référence ( $R=1\Omega$ ) . . . . .                            | 78 |

| Figure 4.3  | Test de coin avec $R=600\Omega$ . . . . .                                      | 78 |

| Figure 4.4  | Test de coin avec $R=12k\Omega$ . . . . .                                      | 79 |

| Figure 4.5  | Test de coin avec $R=200k\Omega$ . . . . .                                     | 79 |

| Figure 4.6  | Simulation numérique du module de mesure de délai . . . .                      | 81 |

|            |                                                                            |    |

|------------|----------------------------------------------------------------------------|----|

| Figure 4.7 | Circuit utilisé pour la simulation analogique du module de délai . . . . . | 82 |

| Figure 4.8 | Simulation analogique du module de mesure de délai . . . . .               | 83 |

| Figure 4.9 | Circuit utilisé pour les tests de coin . . . . .                           | 85 |

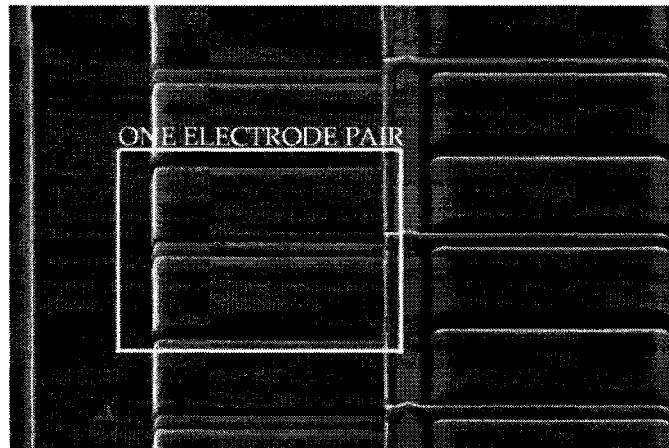

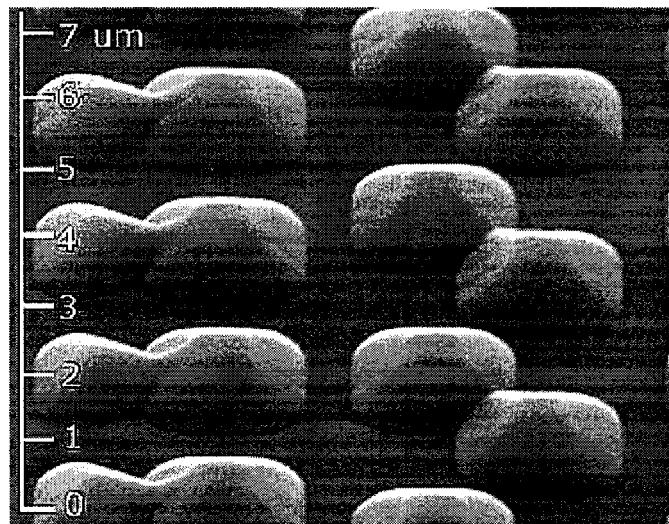

| Figure 5.1 | Micrographie des électrodes fabriquées . . . . .                           | 87 |

| Figure 5.2 | Micrographie des électrodes fabriquées . . . . .                           | 88 |

**LISTE DES TABLEAUX**

|             |                                                               |    |

|-------------|---------------------------------------------------------------|----|

| Tableau 3.1 | Définition des paramètres du modèle C. & E. modifié . . . . . | 66 |

| Tableau 3.2 | Paramètres du modèle du transistor de McEuen . . . . .        | 73 |

## LISTE DES NOTATIONS ET DES SYMBOLES

## LISTE DES ACRONYMES

|           |                                                         |

|-----------|---------------------------------------------------------|

| AFM       | Atomic Force Microscope                                 |

| CMOS      | Complementary Metal Oxide Semiconductor                 |

| CNT       | Carbon NanoTube                                         |

| CFP       | Ceramic Flat Pack                                       |

| CVD       | Chemical Vapor Deposition                               |

| dg-MOSFET | double-gated MOSFET                                     |

| FED       | Field Emission Display                                  |

| FIFO-RTD  | Élément de mémoire First In First Out en RTD            |

| GHz       | GigaHertz                                               |

| IBM       | International Business Machines Corporation             |

| JTAG      | Joint Test Action Group                                 |

| LASER     | Light Amplification by Stimulated Emission of Radiation |

| MBE       | Molecular Beam Epitaxy                                  |

| MOS       | Metal-Oxide Semiconductor                               |

| MOSFET    | Metal-Oxide Semiconductor Field-Effect Transistor       |

| MRAM      | Magnetic Random Access Memory                           |

| MWCNT     | Multi-Wall CNT                                          |

| NDR       | Negative Differential Resistance                        |

| NEC       | Nippon Electric Company, Ltd.                           |

| NVRAM     | Non-Volatile Random Access Memory                       |

| RAM       | Random Access Memory                                    |

| RF        | Radio Frequency                                         |

| RTD       | Resonant-Tunneling Diode                                |

| SWCNT     | Single-Wall CNT                                         |

| TSMC      | Taiwan Semiconductor Manufacturing Corporation          |

| VDD       | Voltage Drain Drain                                     |

**LISTE DES ANNEXES**

|            |                                                                |     |

|------------|----------------------------------------------------------------|-----|

| ANNEXE I   | CODE VHDL DE LA PLATEFORME DE TEST . . . . .                   | 99  |

| ANNEXE II  | CODE SCHEME DU MODÈLE DE CURTICE ET ETTENBERG . . . . .        | 173 |

| ANNEXE III | ARTICLE DE JIN SUR LE MODULE DE CURTICE ET ETTENBERG . . . . . | 191 |

## INTRODUCTION

La très grande majorité des circuits électroniques sont fabriqués avec une technologie CMOS. La robustesse, la rapidité de commutation, l'accessibilité de fabrication à grande échelle et la faible consommation énergétique des circuits CMOS ont poussé l'industrie des semiconducteurs à améliorer les performances de cette technologie des années 1970 jusqu'à nos jours. Notre société pourrait difficilement se passer d'ordinateurs, de téléphones cellulaires, d'équipements médicaux, qui demandent des améliorations constantes de cette technologie.

Cette forte demande a poussé la recherche, notamment dans le domaine de la microfabrication, à fournir des efforts gigantesques depuis plus de 40 ans. La réduction d'échelle continue alimente la prophétie annoncée en 1965 par Gordon Moore, cofondateur de Intel corp., voulant que la densité en transistors sur les circuits intégrés double à tous les 18 mois. Plusieurs obstacles de taille ont été surmontés contre toute attente durant ces décennies. Le prochain obstacle qui se dresse devant l'entreprise de réduction d'échelle du CMOS risque fort de ne jamais être surmonté: les dimensions des transistors s'approchent de la taille de l'atome de silicium.

C'est face à ce mur que la recherche de dispositifs nanoélectroniques a littéralement explosé depuis environ une décennie. Les premiers dispositifs commerciaux exploitant des nanostructures sont apparus sur le marché, mais un véritable dispositif nanoélectronique actif fabriqué en série tarde à venir.

La première approche pour la création de tels dispositifs consiste d'abord à créer un hybride entre les nouveaux nano-dispositifs et la technologie CMOS, dont les méthodes de fabrication sont éprouvées depuis longtemps. Une première approche consiste donc à fabriquer une plateforme de test sur laquelle on intégrera des nanostructures. Cette plateforme répond donc à un double objectif:

- Offrir une première hybridation entre le procédé CMOS et des nanotechnologies.

- Mesurer des caractéristiques électriques inconnues de ces nanostructures dans le but de créer et d'améliorer des modèles de nano-dispositifs.

Ce document débute avec une revue de la littérature touchant la fabrication de nanostructures et des techniques de mesure électroniques intégrées avancées. Au deuxième chapitre, nous verrons l'architecture envisagée pour la fabrication de la plateforme de mesure de caractéristiques électroniques de nanostructures. Au chapitre 3, nous verrons un modèle de transistor à base de nanotube de carbone que nous avons perfectionné. Le chapitre 4 montre les simulations que nous avons effectuées lors de la conception de la plateforme de test et nos résultats expérimentaux sont présentés au 5<sup>ième</sup> chapitre.

## CHAPITRE 1

### REVUE DE LITTÉRATURE

#### 1.1 Nanostructures

Ce projet vise l'intégration de nanostructures à un circuit électronique standard. Une revue de littérature importante est nécessaire afin de choisir un nombre limité de nanostructures jugées à la fois prometteuses au niveau des performances électroniques et dont l'intégration à un circuit CMOS standard est plausible. Cette section met en relief des nanostructures qui répondent à ces critères à différents niveaux en mettant un accent sur les nanotubes de carbone qui offrent, aux yeux de l'auteur, le meilleur tandem performance-intégrabilité.

##### 1.1.1 CMOS à double grille

Un large éventail de variations à des procédés CMOS standard est actuellement disponible chez les fabricants de semiconducteurs. Par exemple, une architecture basée sur des hétérojonctions bipolaires en AlGaAs/GaAs permet de créer des systèmes plus performants à haute fréquence. Il est donc possible d'utiliser la technologie sur silicium existante comme base pour créer des dispositifs alternatifs au transistor CMOS standard, chacune de ces alternatives ayant ses applications spécialisées.

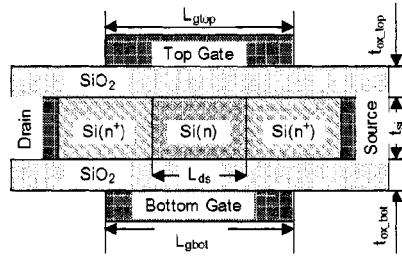

Nous nous intéressons ici à l'ajout d'une seconde grille à un transistor MOS conventionnel pour former des *dual-gated MOSFETs*. Des estimations qui datent de 1992 montrent que des dg-MOSFETs repoussent la limite de réduction d'échelle du

CMOS à 30 nm (Frank, 1992). Des simulations démontrent qu'un dg-MOSFET de type n réduit les effets de canaux courts, permettant ainsi une réduction d'échelle substantielle.

Il est aussi possible d'utiliser cette architecture à une échelle plus grande. En effet, Zhang (Zhang, 2003) a fabriqué un dispositif dont le canal mesure  $0,35 \mu\text{m}$ . Ce dispositif est destiné à des applications pour lesquelles la tension de seuil change dynamiquement. La fabrication de ce dispositif montre sa faisabilité, mais la fabrication de plus petits dispositifs demeure un défi important.

Deux architectures de dg-MOSFETS sont proposées. L'architecture planaire (fig1.1) est similaire à un transistor CMOS standard, mais auquel on a ajouté une grille sous le canal. Bien qu'elle prenne avantage des procédés de fabrication existants, cette méthode amène des défis de fabrication importants. La fabrication de la grille du dessous et du diélectrique qui la jouxte est plutôt difficile. De plus, se connecter à la grille du dessous est difficile et réduit la densité d'intégration.

L'architecture non-planaire (fig 1.2) permet de contourner les problèmes relatifs aux dg-MOSFETS mentionnés ci-haut. Par contre, cette approche compromet l'uniformité dans l'épaisseur du canal, ce qui nuit aux performances du transistor. Cette approche complique aussi la fabrication des autres parties du transistor, car elle s'éloigne beaucoup des procédés de fabrication couramment utilisés.

Geppert, L., IEEE Spectrum, October 2002, p.33.

Figure 1.1 MOSFET à double grille planaire

Geppert, L., IEEE Spectrum, October 2002, p.33.

Figure 1.2 MOSFET à double grille non-planaire

Les transistors CMOS à double grille offrent donc des performances intéressantes et leur fabrication est relativement simple par rapport à d'autres nanostructures. Par contre, leur miniaturisation demandera des méthodes de fabrication qui résolveront les problèmes d'alignement des grilles inhérents à cette architecture.

### 1.1.2 Dispositifs quantiques

Dans cette section, nous décrivons la fabrication et le comportement de dispositifs nanoélectroniques prometteurs. Néanmoins, la fabrication de ces dispositifs est complexe au point où leur utilisation dans un circuit commercialisable apparaît peu probable à moyen terme.

#### 1.1.2.1 Diodes à effet tunnel

La physique classique ne peut expliquer l'effet tunnel, il faut se tourner vers la physique quantique pour comprendre ce phénomène. Selon la physique classique, si une particule frappe une barrière de potentiel dont l'énergie  $V$  est plus élevée que sa propre énergie  $E$ , elle est repoussée. Sinon, elle peut passer l'obstacle qui

induit cette barrière. Selon la physique quantique, la particule a une probabilité non-nulle de passer l'obstacle même si  $E < V$ , mais cette probabilité est faible tant que  $E$  n'est pas près de  $V$ . Si la particule passe l'obstacle alors que  $E < V$ , on assiste à l'effet tunnel et la particule émerge de l'autre côté de l'obstacle avec la même énergie  $E$ .

La diode à effet tunnel résonant (RTD) est un dispositif qui exploite l'effet tunnel. Dans une façon populaire de les fabriquer, elles sont composées de minces couches de matériaux à large bande interdite, tel le *AlGaAs*. Divers composants moléculaires peuvent aussi se comporter comme des RTD. Les couches externes du dispositif servent de barrière d'énergie potentielle pour former des états quasi-liés dans la couche centrale. Pour permettre la fabrication des couches minces d'éléments à concentration contrôlée, on fait appel à des techniques de déposition épitaxiale telle que l'épitaxie par jets moléculaires (MBE) (Mathews, 1999).

La figure 1.3 illustre la structure et le fonctionnement de ce dispositif. En partant de la gauche, un électron tente de traverser les barrières énergétiques que constituent la diode pour continuer son chemin vers la droite du graphique. Les lignes pointillées dans ces graphiques illustrent les états quasi-liés selon trois niveaux de tension de polarisation dans le dispositif.

La figure 1.3b illustre la RTD en résonance<sup>1</sup> alors que les figures 1.3a et 1.3c montrent les limites supérieure et inférieure de tension de polarisation en deçà desquelles l'effet tunnel a peu de chances de se manifester. La figure 1.4 illustre les courbes I-V simulées et mesurées par Mathews et al. Lorsque la tension de polarisation est située entre 1 et 2 V, le RTD entre en résonance et offre une résistance différentielle négative (NDR).

---

<sup>1</sup>La tension de polarisation appliquée sur la RTD aligne l'état quasi-lié entre les barrières avec l'énergie des états fortement occupés adjacents

Figure 1.3 Alignement des états quasi-liés dans une RTD: a. Maximum d'énergie pour l'effet tunnel b. État de résonance c. Minimum d'énergie pour l'effet tunnel

Cette caractéristique des RTDs, combinée à leur faible capacité parasite et à leur forte densité de courant, fait de cette nanostructure un élément de circuit non-linéaire très rapide. Plusieurs applications électroniques ont été proposées et expérimentées pour exploiter les RTDs:

1. L'intégration de RTDs dans un circuit CMOS standard (Bergman, 1999) en améliore la performance en termes de vitesse, de consommation de puissance et de densité de dispositifs actifs. Des RTDs ont été utilisées dans plusieurs circuits à haute performance tels des oscillateurs, mélangeurs, multiplicateurs de fréquence, détecteurs RF et comme étage d'entrée de circuits analogiques

Mathews, R.H. et al., Proc. of the IEEE, vol87, no4, 1999, p.597.

Figure 1.4 Courbe I-V d'une RTD

à haute vitesse.

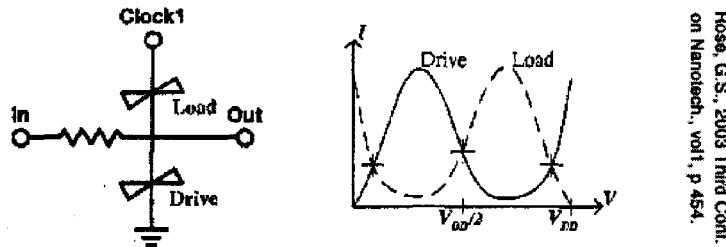

2. On exploite la caractéristique de NDR pour former un dispositif constitué d'une paire de RTDs placées en série (fig.1.5) qui se comporte comme un bistable<sup>2</sup> appelée *RTDlatch* ou *gotopair*. Cette topologie ne requiert aucune

Figure 1.5 Une mémoire bistable à base de RTD

rétroaction comme pour un circuit CMOS et est plus compacte. Rose (Rose, 2003) propose une architecture de circuit mémoire en format FIFO exploitant des RTD moléculaires et n'ayant besoin d'aucun dispositif pour sélectionner les bits individuels dans la mémoire. Seul le dispositif moléculaire et des connexions sont nécessaires dans le noyau de cette architecture. Cette topologie

<sup>2</sup>Le terme bistable est employé ici comme un élément de mémoire logique, i.e. un latch.

facilite la régularisation géométrique et l'alignement des éléments mémoire par rapport au CMOS standard. On peut aussi envisager des topologies de mémoire en 3-D (fig.1.6), augmentant la densité et la performance des éléments mémoire.

Figure 1.6 Topologie de mémoire FIFO-RTD en 3D

### 1.1.2.2 Spintronics

L'archivage et le traitement de données suit une tendance de miniaturisation depuis la première pierre gravée jusqu'aux éléments mémoire dynamiques, où un simple condensateur est utilisé pour conserver pendant un court laps de temps de l'information sous la forme de tension électrique. En suivant cette tendance, les nanostructures actuellement disponibles qui poussent le plus loin cette tendance sont les dispositifs spintroniques. C'est pour cette raison que nous nous sommes intéressés à ce champ de recherche qui recoupe plusieurs disciplines incluant la physique des matières condensées, l'étude des matériaux, l'optique et le génie électrique. Ce champ de recherche est divisé en deux approches:

1. Intégration d'éléments magnétiques dans un dispositif électronique pour créer

de nouvelles fonctionnalités exploitant des propriétés uniques de matériaux ferromagnétiques. Cette approche se base sur le fait que le transport d'électrons de conduction dépend de leur spin pour intégrer un bit d'état magnétique à des dispositifs électroniques basés sur la charge. Parmi les applications de cette approche, on retrouve les têtes de lecture utilisant des senseurs de champs magnétique ou des éléments mémoire RAM magnétique.

2. Utilisation de populations d'électrons au spin polarisé, i.e. au moment magnétique individuel, pour créer de nouvelles méthodes de traitement de l'information telle l'informatique quantique. De cette façon il serait possible d'accélérer exponentiellement la vitesse de traitement de certains calculs parallélisables.

Si les applications exploitant la première approche sont fonctionnelles et apportent des avantages concrets par rapport au CMOS, notamment au plan de la conception de mémoires, celles touchant la deuxième approche demeure inatteignable à court terme. La recherche dans ce domaine est actuellement stimulée par les résultats commercialisables à court terme de la première approche. Les mémoires magnétiques à accès aléatoires - MRAMs - offrent des avantages importants par rapport aux mémoires CMOS ou aux RAMs non-volatiles, les NVRAMs.

En effet, en utilisant le magnétisme plutôt que la charge électrique pour le stockage d'information, on peut créer des éléments mémoire non-volatiles. L'apport d'éléments spintroniques à ce domaine est qu'ils augmentent grandement la densité des éléments mémoire par rapport à des éléments mémoire actuellement utilisés comme les mémoires Flash.

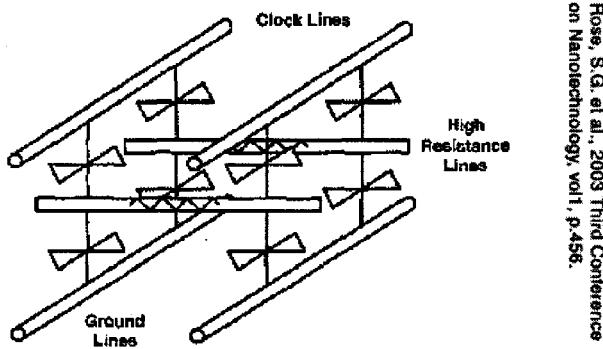

Un premier prototype de MRAM à 128 kB a été présenté au “2003 Symposium on VLSI Circuits” (Bette, 2003) par une équipe de recherche regroupant *IBM* et *Infini-

eon Technologies*. La figure 1.7 montre le dessin de masques de ce circuit CMOS 180 nm au centre duquel sont regroupés les éléments de mémoire. Ces éléments

Figure 1.7 Dessin de masques d'une mémoire 128kB en MRAM

mémoire, les 1T1MTJ<sup>3</sup>, occupent chacun une superficie de  $1.4\mu m^2$  (fig. 1.8).

[http://www.research.ibm.com/resources/news/20001207\\_mramimages.shtml](http://www.research.ibm.com/resources/news/20001207_mramimages.shtml)

Figure 1.8 Schéma simplifié d'une cellule 1T1MTJ de IBM

Une équipe de recherche chez Motorola (Tehrani, 2003) a fabriqué une MRAM de 1-Mbit presqu'en même temps qu'IBM. Dans cette publication, Tehrani et al. décrivent le fonctionnement de leurs MRAMs à base de MTJs<sup>4</sup> comme étant des dispositifs qui changent de résistance selon leur état magnétique. La miniaturisation de ces dispositifs est rendue possible grâce à l'utilisation de matériaux

<sup>3</sup>1-Transistor/1-Magnetic Tunnel Junction

<sup>4</sup>Magnetic Tunnel Junction

Tehrani et al., Proc. of the IEEE, vol91, no5, may 2003, p.704.

Figure 1.9 Schéma simplifié d'une cellule 1T1MTJ de Motorola

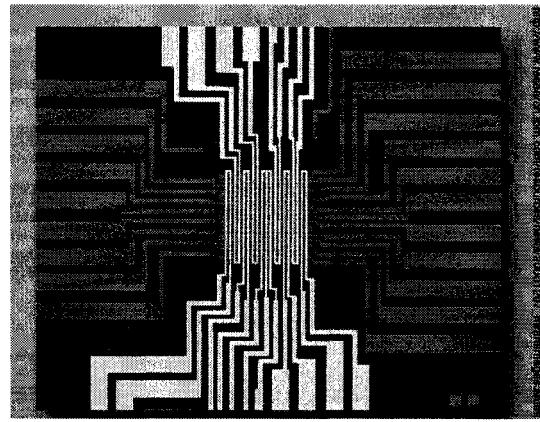

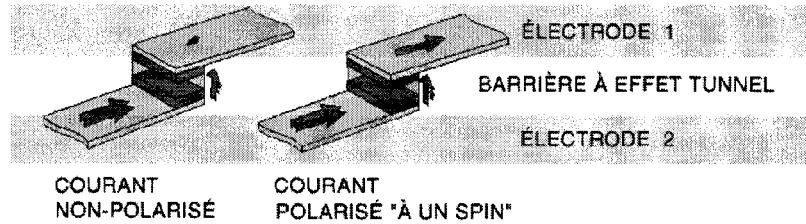

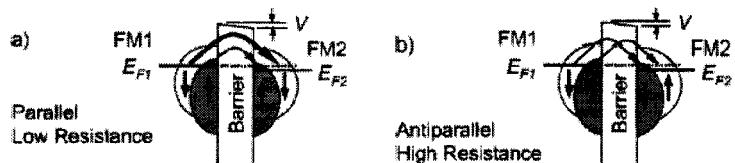

magnétorésistifs disposés en couches minces. La figure 1.10 illustre un modèle simplifié de densités d'états d'une MTJ. La MTJ est composée de deux couches magnétiques, FM1 et FM2, séparées par une barrière diélectrique.

Ce dispositif offre une résistance faible lorsque la magnétisation des couches

Tehrani et al., Proc. of the IEEE, vol91, no5, may 2003, p.705.

Figure 1.10 Fonctionnement interne d'une cellule MTJ

magnétiques est parallèle (fig 1.10a). Il offre au contraire une résistance élevée lorsque la magnétisation des couches externes est antiparallèle (fig 1.10b). Sur la figure, chacune des couches magnétiques est composée d'une bande minoritaire, représentée en gris et d'une bande majoritaire, représentée en blanc. Les flèches incluses dans ces couches montrent le sens de magnétisation. La flèche en gras

dans la figure 1.10a montre le fort courant d'électrons qui passent d'une bande magnétique à l'autre par effet tunnel quand la magnétisation des deux bandes externes est parallèle. L'intensité du courant provient des polarisations de spin dans les bandes magnétiques qui contribuent à rendre disponibles un plus grand nombre d'états de tunnel quantiques.

Les dispositifs les plus intéressants offrent un rapport courant ouvert/courant fermé élevé. Dans cette optique, on s'intéresse aux matériaux qui ont le plus grand "débancement" entre les densités d'états des bandes minoritaire et majoritaire au niveau de Fermi. On peut définir ce débancement en termes de polarisation de spin  $P$ :

$$P = (N \uparrow - N \downarrow) / (N \uparrow + N \downarrow)$$

où  $N \uparrow$  et  $N \downarrow$  représentent le nombre d'états spin-up et spin-down disponibles qui contribuent au courant de tunnel quantique. Rose et al. ont donc choisi du nickel, du fer et du cobalt, des matériaux ferromagnétiques à fort "débancement" pour fabriquer leur MTJ.

En plus d'offrir une densité très intéressante, les cellules des MRAMs commutent en un temps inférieur à 5 ns. Des dispositifs à quelques MB sont attendus pour l'année 2005 sur le marché. Ces dispositifs pourraient provoquer une révolution entre autres dans le domaine de l'architecture des ordinateurs, rendant instantané le processus de "boot up". Les MRAMs ont un fort potentiel d'être la première nanotechnologie à avoir un impact concret sur le domaine de l'électronique.

### 1.1.3 Nanotubes de carbone

Le nanotube de carbone est une molécule dont le potentiel pour des applications nanoélectroniques est très tangible. Le grand nombre d'articles récents traitant du sujet en témoigne. La plateforme de test qui fait l'objet de ce mémoire vise d'abord la mesure de caractéristiques électriques de nanotubes de carbones. Nous examinerons cette molécule sous plusieurs angles sans en analyser les détails techniques. Nous suggérons au lecteur curieux d'en connaître plus de consulter l'imposante bibliographie de cette section.

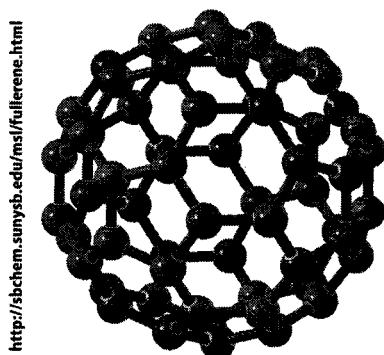

#### 1.1.3.1 Fullerènes

La découverte des nanotubes de carbone part de la recherche sur les fullerènes ou *buckyballs*. En 1985, Richard Smalley, de l'université Rice, découvre une molécule de carbone ressemblant à un dôme géodésique (fig.1.11). Cette molécule a suscité de

Figure 1.11 Une molécule de fullerène

grands espoirs d'applications pour former entre autres des agents d'administration de médicaments, des traceurs environnementaux et des supraconducteurs (Madou, 2002). L'équipe de Wudl (Wudl, 2002), à l'Université de Californie à Santa Bar-

bara, a réussi à stocker des molécules à l'intérieur de ces fullerènes pour en faire de véritables nano-contenants très stables.

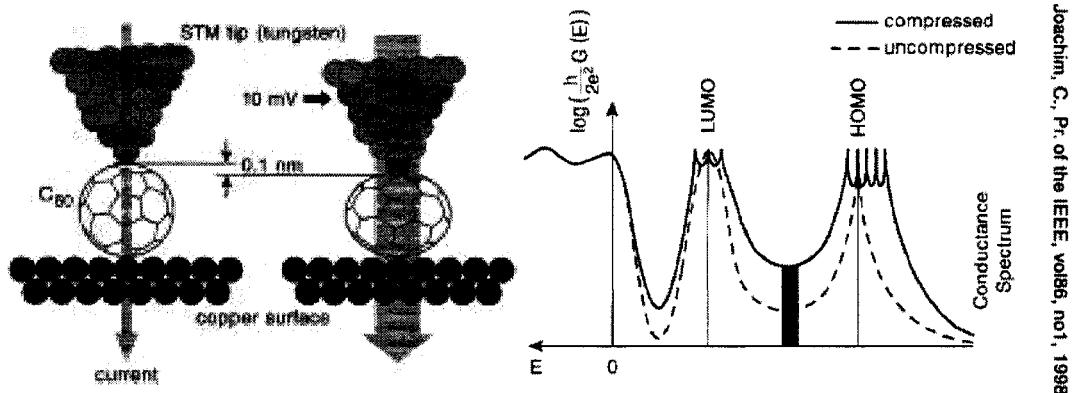

Les applications des fullerènes en électronique sont rares, les nanotubes de carbone prenant une place beaucoup plus importante dans les recherches publiées. Une application intéressante qu'offrent les fullerènes exploite une propriété électromécanique surprenante de cette nanostructure (Joachim, 1998). Les auteurs ont placé le fullerène au bout d'une pointe d'AFM<sup>5</sup>, (fig.1.12a). Ils ont relié ce montage à un système de lecture qui permet d'amplifier un signal généré par un effet piézoélectrique dans le fullerène. De cette façon, ils sont parvenus à mesurer des compressions mécaniques aussi faibles que 0.1 nm. Une compression aussi faible augmente l'intensité du courant mesuré de deux ordres de grandeur dans la molécule (fig.1.12b).

Figure 1.12 Senseur piézoélectrique en fullerène

### 1.1.3.2 Premiers nanotubes de carbone

En 1991, c'est en étudiant le processus de synthèse des fullerènes que Sumio Iijima (Iijima, 1991), chercheur chez NEC, Japon, observe le premier des nanotubes de

<sup>5</sup>Atomic Force Microscope

carbone. Leur structure hexagonale, symétrique comme les fullerènes, mais mince et très longue a ouvert la porte à une étude scientifique intense.

### 1.1.3.3 Structures moléculaires de nanotubes

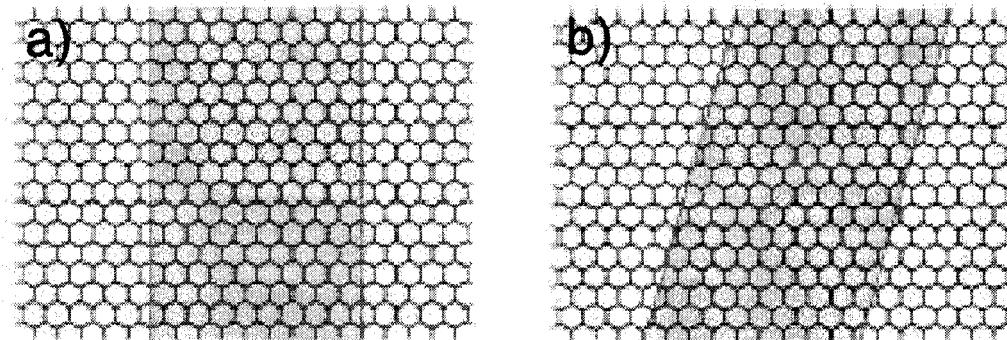

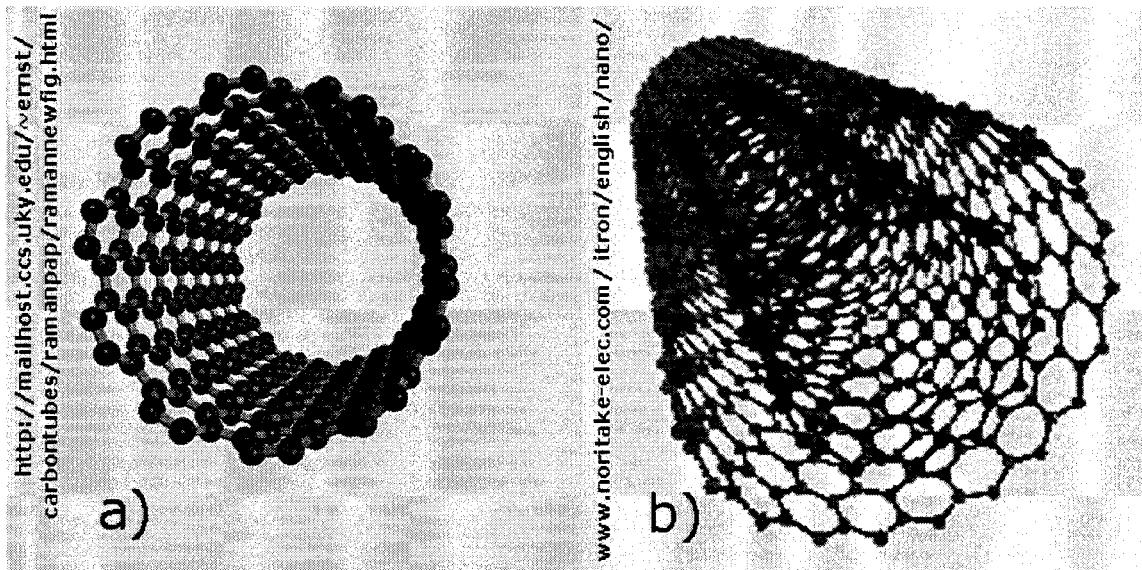

La structure du nanotube de carbone peut être vue comme un enroulement d'une couche de graphite coupée par deux axes parallèles (fig.1.13) puis recollée pour former un long cylindre. La chiralité<sup>6</sup> du nanotube influence beaucoup ses propriétés électriques (Collins, 2000). En effet, certains nanotubes sont conducteurs et d'autres semiconducteurs. Les premiers nanotubes de carbone observés par Iijima étaient composés de plusieurs couches concentriques de graphite. On appelle ces structures des "multi-walled carbon nanotubes" ou MWCNTs (fig.1.14b). Les "single-walled" nanotubes - SWCNTs (fig.1.14a)- furent observés pour la première fois en 1993 par (Iijima, 1993) et (Bethune, 1993).

Collins, P.G., *Scientific American*,

December 2000, p 84.

Figure 1.13 Coupes de plans de graphite

---

<sup>6</sup>L'angle auquel la coupe dans la feuille de graphite est effectuée

Figure 1.14 Nanotubes à simple et multi-couche

#### 1.1.3.4 Propriétés électriques des SWCNTs

Les propriétés des nanotubes de carbone sont simplement phénoménales, même en les comparant à une technologie mature comme le CMOS. Collins (Collins, 2000) a regroupé cinq propriétés intéressantes pour des applications électroniques:

1. À cause des liaisons électroniques entre les atomes de carbone inhérentes à leur structure moléculaire, le transport électrique s'effectue en une seule dimension. Cela permet d'envisager que le transport dans les CNTs est balistique<sup>7</sup>. Une conséquence de cette propriété est une réduction de la consommation de puissance par rapport à des conducteurs ohmiques comme le cuivre. Le comportement électrostatique des CNTs est différent de ce qu'on observe dans les dispositifs en silicium. Des champs électriques élevés sont atteignables avec de faibles tensions.

<sup>7</sup>Comme l'électron voyage dans un environnement à une seule dimension, la probabilité d'entrainer une collision entre 2 particules est faible. Dans les nanotubes de longueur inférieure à 1  $\mu\text{m}$ , on estime qu'il n'y a aucune collision dans un CNT (Berger, 2001)

2. Tous les liens chimiques entre les atomes de carbone sont remplis. Cela annule le besoin pour une passivation de liens flottants comme dans les technologies à base de silicium. Une technologie à base de CNT pourrait n'avoir nul besoin de  $SiO_2$  ou d'un autre diélectrique comme isolant. On pourrait le remplacer par une structure cristalline à forte constante diélectrique, ce qui permet, entre autres, de fabriquer des structures tridimensionnelles.

3. Les liens covalents très forts des CNTs leur donnent une forte stabilité mécanique et thermique ainsi qu'une protection contre l'électromigration<sup>8</sup>. Les CNTs peuvent soutenir des densités de courant atteignant  $10^9 A/cm^2$  (Frank, 1998).

4. La dimension critique des CNTs, leur diamètre, est contrôlée par des procédés chimiques et non par des méthodes conventionnelles de fabrication.

5. En principe, il est possible de fabriquer des dispositifs actifs (transistors) et des interconnexions avec, respectivement, des CNTs semiconducteurs et métalliques.

#### 1.1.3.5 Propriétés électriques des MWNTs

Les MWCNTs offrent des propriétés électriques moins impressionnantes que les SWCNTs. Leur structure complexe peut être vue comme un assemblage concentrique de plusieurs SWCNTs ayant chacun des caractéristiques électriques et une chiralité différente. Par contre, il a été démontré qu'avec des conditions particulières (Bachtold, 1999), la conduction dans les MWCNTs est dominée par le

---

<sup>8</sup>(Savaria, 1988) Électromigration, phénomène d'usure associé aux métallisations. L'électromigration est une conséquence du fait que le passage du courant d'un grain à l'autre tend à déplacer des atomes d'aluminium (ou autres conducteurs). L'électromigration est un obstacle à la miniaturisation de circuits, car la densité de courant augmente d'un facteur égal à la réduction d'échelle d'une technologie.

tube le plus en périphérie. Par contre, la largeur de la bande interdite étant inversement proportionnelle au diamètre du tube, seuls les plus petits MWCNTs pourraient fournir un rapport de commutation<sup>9</sup> satisfaisant à température de la pièce. Comme les SWCNTs sont plus petits que les plus petits MWCNTs, ils leur sont préférables pour fabriquer des dispositifs commutants comme des transistors.

#### 1.1.3.6 Méthodes de fabrication de CNTs

Trois méthodes sont présentement connues pour produire des nanotubes de carbone avec un rendement satisfaisant:

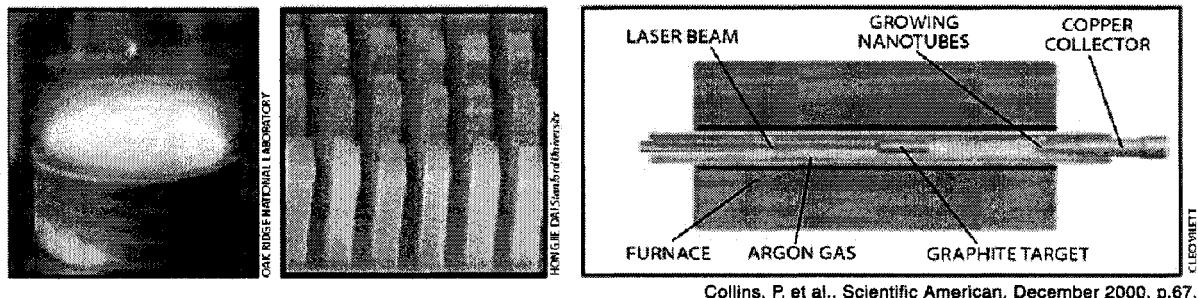

##### 1. Par choc électrique

En 1992, Ebbesen et al. (Ebbesen, 1992) publient la première méthode pour fabriquer une grande quantité de nanotubes. On place deux tiges de graphite à une source électrique, on les place à quelques millimètres l'une de l'autre et on fait grimper le courant à 100 A. L'arc électrique créé vaporise le carbone dont une partie se recondense et forme des nanotubes (fig.1.15: gauche).

- Rendement massique: 30%

- Avantages: En ajoutant des catalyseurs métalliques, on obtient des MWNTs et des SWCNTs avec peu ou pas de défauts structurels.

- Désavantages: Les tubes sont relativement courts ( $< 50 \mu\text{m}$ ) et se déposent à des positions et selon des orientations aléatoires.

##### 2. Par déposition de vapeurs chimiques (CVD)

En 1995, Endo et al. (Endo, 1995) placent un substrat dans un four à  $600^\circ\text{C}$  et ajoutent lentement du

---

<sup>9</sup>rapport des courants quand le dispositif est ouvert et fermé

Figure 1.15 Procédés de fabrication de nanotubes

gaz porteur de carbone comme du méthane. Le gaz se décompose, libère des atomes de carbone, qui se recombinent et forment des nanotubes. Dai et al. (Dai, 1998) ont déposé un motif de catalyseurs sur le substrat (fig.1.15: centre) et travaillent actuellement à combiner cette croissance contrôlée avec des procédés CMOS standards. La très haute température du procédé de CVD rend par contre cet objectif très difficile à atteindre.

- Rendement massique: de 20 à 100%

- Avantages: La méthode CVD est la plus simple des trois méthodes pour fabriquer des dispositifs à plusieurs centaines de milliers de transistors comme le CMOS. Elle permet aussi de fabriquer des tubes très longs, condition nécessaire pour fabriquer des fibres utilisées dans des composites.

- Désavantages: La majorité des nanotubes fabriqués par CVD sont des MWNTs et peu sont exempts de défauts. Par conséquent, ces tubes ont une résistance mécanique en tension 10 fois plus faible que les tubes fabriqués à l'arc électrique.

3. Par impact LASER Smalley et al. (Scott, 2001), à l'Université Rice attaquent des tubes de graphite dans un four à  $1200^{\circ}\text{C}$  avec un LASER pulsé et forment ainsi les gaz porteurs de carbone à partir desquels les nanotubes se forment

(fig.1.15: droite). En variant les types de catalyseurs, ce groupe est parvenu à produire des quantités prodigieuses de SWCNTs.

- Rendement massique: inférieur à 70%

- Avantage: Production de SWCNTs au diamètre contrôlable par la température de réaction.

- Désavantages: Les lasers utilisés pour cette technique font exploser ses coûts de production.

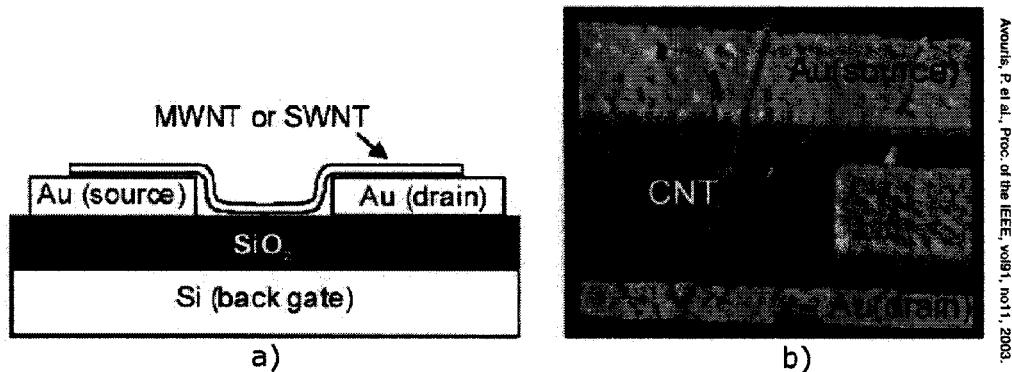

#### 1.1.3.7 Fabrication de CNTFETs

Les propriétés semiconductrices des CNTs poussent naturellement la recherche vers la fabrication de transistors à effet de champs à base de nanotubes de carbone ou CNTFETs. Les premiers CNTFETs furent fabriqués en 1998 (Martel, 1998; Tans, 1998). Le nanotube joue ici le rôle de canal de conduction entre deux électrodes métalliques: le drain et la source (fig.1.16). La grille, placée sous une couche de

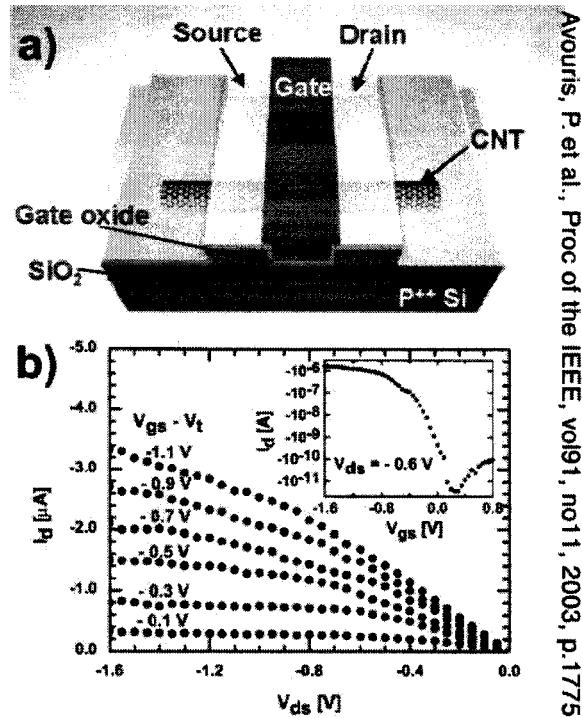

Avouris, P. et al., Proc. of the IEEE, vol91, no11, 2003.

Figure 1.16 Un des premiers modèles de CNTFETs

$SiO_2$ , est fabriquée en silicium hautement dopé. Les performances de ce premier transistor furent décevantes, notamment à cause des contacts entre le tube et les

électrodes. En effet, seules les forces de Van der Waal<sup>10</sup> retenaient le tube aux plaquettes d'or. En utilisant des électrodes en titane placées au dessus des nanotubes et soumises à un recuit thermique (fig.1.17), Martel et al.(Martel, 2001) ont amélioré les caractéristiques du transistor, notamment la transconductance.

Avouris, P. et al., Proc of the IEEE, vol91, no11, 2003, p.1775.

Figure 1.17 Modèle récent de CNTFET

### 1.1.3.8 Placement des CNTs sur une paire d'électrodes

Pour placer les CNTs sur les électrodes de contact, l'équipe du IBM research center effectue la gravure d'une matrice d'électrodes sur la surface de silicium. Ensuite, des nanotubes de carbone sont insérés en solution dans du dichloroéthane selon une densité contrôlée. Cette solution est versée sur la surface de test, puis on souffle

<sup>10</sup>On peut également dire une force d'attraction intermoléculaire entre le nanotube et la plaquette d'or. Cette force est suffisante pour garder le tube en place, mais ce lien n'offre pas un contact électrique adéquat.

le liquide avec un soufflet à gaz comprimé. Les forces de Van der Waal retiennent des nanotubes sur la surface. Ensuite, un AFM est utilisé pour déterminer la disposition des nanotubes. On se fie à la chance pour qu'un et un seul CNT aille se placer entre deux électrodes. Si tel est le cas, cette paire d'électrodes est reliée à des macroplaques qui serviront à lier les électrodes à des sondes extérieures. Les mesures sont effectuées par des machines de test externes.

Une alternative à cette méthode que l'on peut juger incertaine est d'utiliser des pointes d'AFM pour placer un nanotube à l'endroit désiré. Le problème avec cette approche est la difficulté de manipuler les CNTs. En effet, les tubes offrent une grande force d'attraction de Van der Waal, ce qui le rend "collant". Dans le cas qui nous concerne, il s'agit bien sûr de placer le CNT entre deux électrodes de contact, une cible très grande à l'échelle des nanotubes. C'est pourquoi certaines équipes de recherche arrivent à fabriquer des nanostructures avec cette méthode.

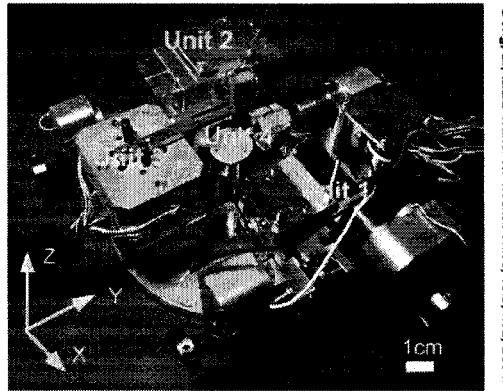

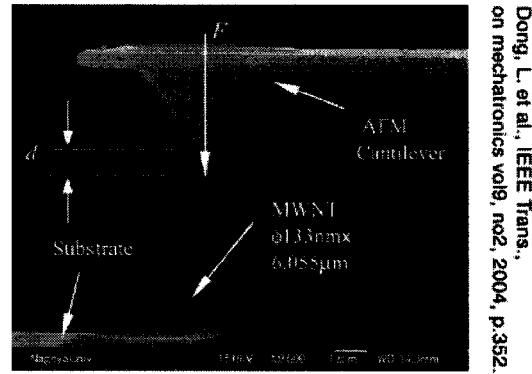

En effet, l'équipe de Fukuda, Université de Nagoya, Japon (Dong, 2004), manipule des CNTs en trois dimensions pour caractériser leurs propriétés mécaniques. Avec une précision de 30 nm, cette méthode pourrait être utilisée pour placer des CNTs à l'endroit désiré avec une précision suffisante pour créer des CNTFETs. Jusqu'à ce jour, les publications de ce groupe ne font pas état de manipulation de SWNTs, seulement des MWNTs. De plus, le système de fabrication (fig.1.18) composé d'équipements nanorobotiques utilisé par cette équipe semble très coûteux et difficile à reproduire à court terme.

#### 1.1.3.9 Tri des Nanotubes de Carbone

Les méthodes énoncées à la section 1.1.3.6 ont en commun le problème qu'elles créent un amas de nanotubes possédant toute une gamme de longueurs, de types et des défauts structurels. Les CNTs fabriqués par choc électrique sont recueillis dans une poudre de carbone contenant des impuretés qui doivent être ensuite

Figure 1.18 Système de nanofabrication

purifiées. La purification de ces nanotubes de carbone repose sur de nombreuses méthodes de filtration, centrifugation et des techniques de chromatographie pour séparer les nanotubes d'impuretés inhérentes à cette technique (Niyogi, 2000).

De plus, lorsqu'ils sont créés, les SWCNTs sont souvent regroupés en cordons, qui doivent être défaits pour que les SWCNT puissent être utilisés en tant que dispositif nanoélectronique. Les MWCNTs (sect 1.1.3.5) ont des propriétés électroniques moins intéressantes que les SWNTs, mais en enlevant des couches aux MWNTs, il est possible de se rapprocher de dispositifs viables électroniquement.

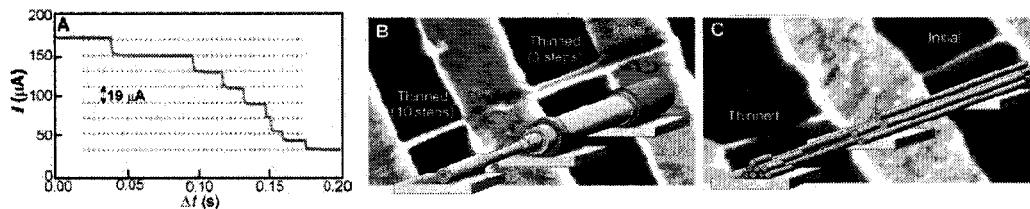

Aucune méthode ne permet de contrôler la propriété de conduction des nanotubes lors de leur fabrication. Une approche intéressante consiste à utiliser un amalgame de CNTs de diverses formes comme matière première pour obtenir des CNTs de forme désirée. L'équipe du IBM Research Division a mis au point une méthode de séparation par claquage sélectif de MWNTs ou de cordons de SWCNTs (Collins, 2001) placés sur une paire d'électrodes. Comme la couche extérieure du MWCNT est la seule qui touche aux électrodes de stimulation, la majorité du courant injecté dans la nanostructure demeure dans cette couche. La figure 1.19a montre les échelons de courant injecté pour successivement brûler des couches de MWCNTs. Les figures 1.19b et 1.19c montrent les effeuillages partiels de MWCNTs résultants des stimulations de courant. Si l'on place un cordon de SWCNT sur

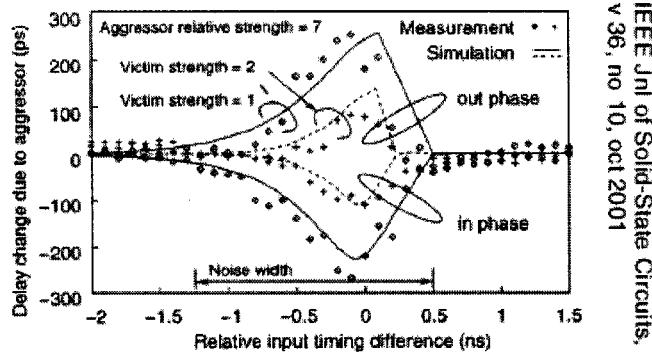

Figure 1.19 Méthode d'effeuillage de MWNTs

les électrodes plutôt qu'un MWCNT, on utilise une grille pour appauvrir le transport dans les CNTs semiconducteurs permettant ainsi d'injecter un fort courant dans les seuls SWCNT conducteurs. La figure 1.20A montre la conductance initiale du cordon de SWCNTs et la conductance finale sans SWCNTs métalliques. La figure 1.20B montre un cordon un peu plus gros et la figure 1.20C un cordon très large. Dans des cordes larges, certains SWCNTs semiconducteurs doivent être sacrifiés pour atteindre les conducteurs au centre du cordon. Les figures 1.20D et 1.20E montrent la structure à trois terminaux utilisée pour faire contact avec les dispositifs. Même si un cordon n'offre initialement aucun comportement semiconducteur 1.20F, les dispositifs purifiés ont de bonnes caractéristiques de CNTFET. L'équipe de l'Université Nagoya (sect 1.1.3.8) a démontré des méthodes de fabrication de CNTs à dimensions contrôlées en utilisant des méthodes mécaniques (Dong, 2004). Elle consiste à écraser le CNT entre une pointe d'AFM et un substrat (fig.1.21). Cette méthode permet plusieurs modifications de MWCNTs dont notamment l'effeuillage de couches du tube, qui n'est pas sans rappeler la méthode énoncée par (Collins, 2001). La précision atteinte par ce dernier est par contre nettement supérieure à la méthode mécanique de Dong et al. Des résultats futurs plus intéressants pourraient conduire à l'adoption des méthodes élaborées par ces chercheurs pour la fabrication de CNTFETs.

Collins, P.G., Science, vol292, 2001, p.708.

Figure 1.20 Mesures effectuées en cours de filtration

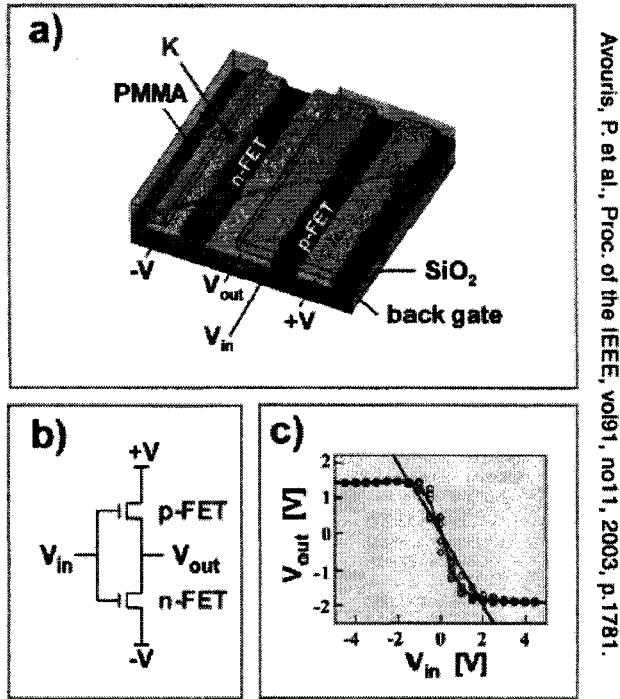

### 1.1.3.10 Exemple d'application: une porte logique en CNT

Lors de la fabrication de CNTFETs, les figures 1.16 et 1.17 illustrent qu'une seule grille était juxtaposée au nanotube. Ce dernier forme le canal de conduction du transistor. Il est toutefois possible d'utiliser plus d'une grille sur un seul nanotube pour former deux transistors - un n-FET et un p-FET - (fig.1.22 a et b) pour former un inverseur logique. En comparaison, les portes logiques en CMOS standard sont fabriquées avec des transistors ayant des canaux de conduction distincts. Cela cause un débancement que des circuits logiques à base de CNTFETs pourraient réduire. Ce dispositif, fabriqué par l'équipe du IBM Research Division (Avouris, 2003), offre un gain en tension de près de 2 V/V (fig.1.22c). Ce dispositif n'ayant pas été l'objet d'une construction optimisant sa performance, on peut envisager l'apparition de circuits logiques à base de CNTFETs plus complexes et offrant une performance améliorée.

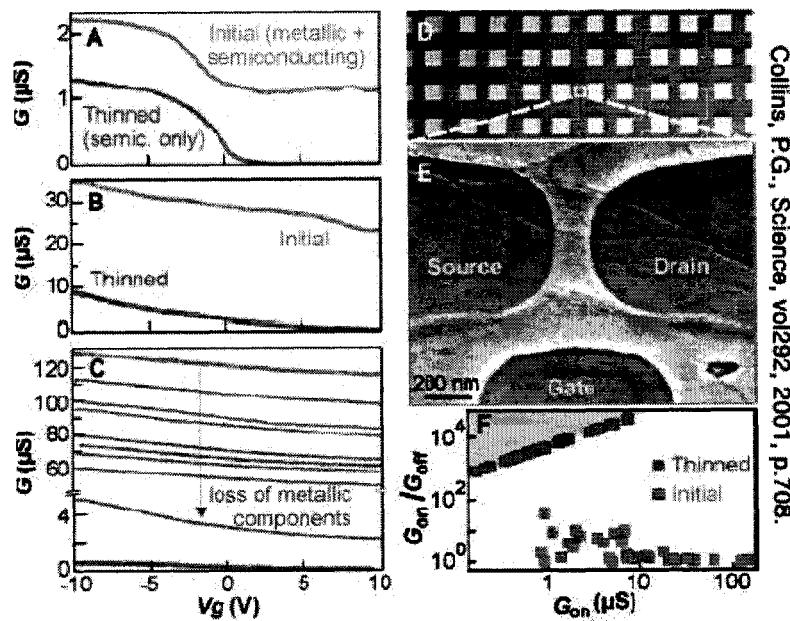

Figure 1.21 Écrasement de MWCNT entre une pointe d'AFM et un substrat

### 1.1.3.11 Applications des nanotubes

Les technologies exploitant les nanotubes de carbone sont très jeunes, si on les compare au CMOS. Néanmoins, plusieurs idées sont présentement étudiées et certaines applications exploitent déjà des propriétés intéressantes des nanotubes de carbone.

- Les forts champs électriques générés par les nanotubes de carbone permettent de produire des écrans à émission de champs à basse consommation énergétique. Les méthodes de microfabrication sont ici plus simples que celles énoncées en 1.1.3.7 et 1.1.3.10, parce que les nanotubes sont utilisés dans un amalgame plus ou moins ordonné. Ren (Ren, 2003) a mis au point une pâte de nanotubes de carbone destinée à la conception de dispositifs à émission de champs (FED). Les compagnies Motorola, DuPont et Samsung intensifient la recherche pour des FEDs à base de CNTs et fabriquent actuellement leurs premiers prototypes d'écrans (Stuart, 2003). La consommation de puissance étant un obstacle majeur dans la fabrication d'écrans plasma, des disposit-

Avouris, P. et al., Proc. of the IEEE, vol 91, no 11, 2003, p.1781.

Figure 1.22 Un inverseur logique à base de CNTFETs

tifs moins énergivores ouvrent la porte d'un marché de quelques milliards de dollars.

- La conduction ballistique dans les nanotubes de carbone permet aux électrons de préserver leur spin quand ils se déplacent dans le tube (Collins, 2000). Des chercheurs tentent d'utiliser cette propriété dans des systèmes spintroniques qui commutent de 0 à 1 selon le spin de l'électron plutôt qu'en fonction de sa charge.

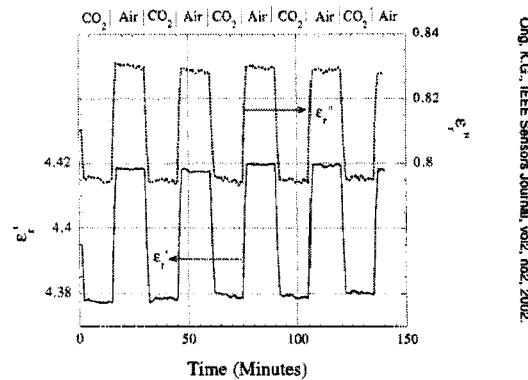

- Les CNTs, lorsqu'exposés à certains gaz comme le  $NH_3$ , changent de caractéristiques électriques. En effet, en variant la concentration de  $NH_3$  autour de senseurs à base de CNTs, à température ambiante, (Moon, 2003) a mesuré des changements notables dans le courant électrique. Ong, (Ong, 2002) a mesuré des temps de réaction entre 45 s et 4 min face à des changements de concentration de  $O_2$ ,  $NH_3$  et  $CO_2$  dans des senseurs de gaz à base

de CNTs. Ce sont la permittivité relative et la conductivité du CNT qui varient avec la concentration de gaz. Ces paramètres sont traduits en une inductance et une capacité qui sont mesurables avec des appareils de mesure précis. La figure 1.23 montre les mesures de permittivité relative  $\epsilon'_r$  et de conductivité  $\propto \epsilon''_r$ <sup>11</sup> en fonction du temps pour des expositions successives au  $CO_2$  et à l'air.

Figure 1.23 Mesures de permittivité relative et de conductivité

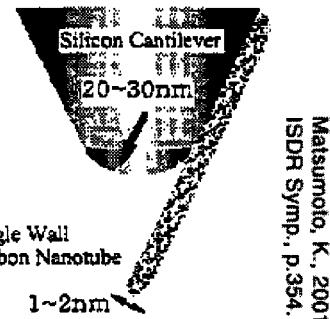

- Les nanotubes de carbone sont aussi utilisés comme pointe pour des microscopes à force atomique. Les CNTs sont de 10 à 20 fois plus petits que les pointes de silicium les plus fines utilisées. Matsumoto (Matsumoto, 2001) est parvenu à faire croître des nanotubes directement sur la pointe en silicium de l'AFM (fig.1.24) par procédé CVD.

## 1.2 Mesures de précision

La seconde partie de cette revue de littérature consiste à brosser un tableau de développements récents se rapportant aux dispositifs de mesures à haute précision.

<sup>11</sup> Mesure directement proportionnelle à la conductivité

Figure 1.24 Une pointe d'AFM avec terminaison en CNT

Cette étude montre les bases théoriques justifiant les choix architecturaux pour la plateforme de test que nous présenterons au chapitre 2.

### 1.2.1 Mesure de délais

Le délai est défini comme étant le temps requis par un signal pour traverser un échantillon de test.

La mesure de délai est un sujet très vaste qui s'étend aux domaines des communications optiques et électriques, aux mesures de délais d'interconnexion "on-chip" et à des mesures expérimentales. Dans le cas qui nous intéresse, nous cherchons à mesurer le délai dans un nanotube de carbone ou dans un dispositif nanoélectronique à base de nanotube de carbone.

#### 1.2.1.1 Télécommunications

La synchronisation de différents circuits électroniques est un problème intimement relié à la conception d'un réseau de communication. Les débits de données augmentant, le niveau de précision de la mesure des délais de propagation des signaux

doit être de plus en plus élevé.

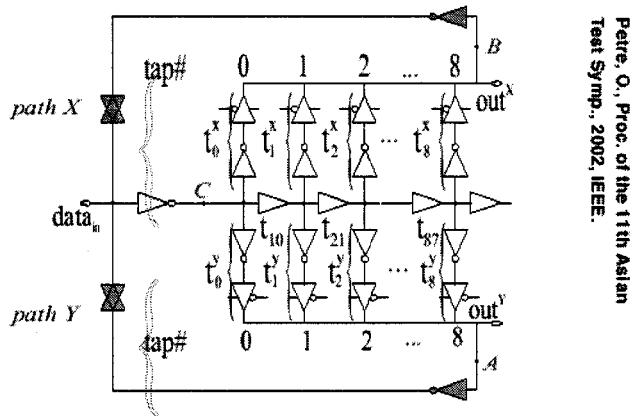

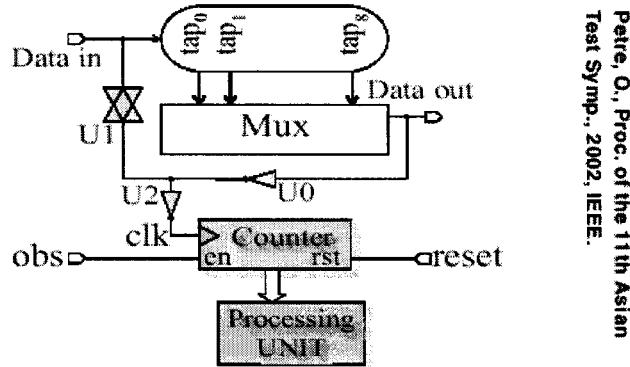

Petre (Petre, 2002) fait état d'une méthode de mesure de délai qui permet de mesurer le temps requis pour transférer une donnée entre deux circuits intégrés. Pour ce problème, il est nécessaire de mesurer précisément, rapidement et avec un minimum de ressources, le délai dans quelques lignes à délai. Ces lignes à délai sont des circuits numériques configurables (fig. 1.25) qui offrent deux chemins à délais distincts. Chacun de ces chemins ne peut activer qu'un tampon de sortie à la fois. Ces lignes à délai sont utilisées pour générer des signaux de test desquels on mesurera ensuite le délai. La mesure de délai proprement dite est effectuée avec un système basé sur un oscillateur bouclé et un compteur (fig. 1.26). La technique de mesure consiste à mettre le compteur à zéro, puis à l'activer avec le signal "obs" qui signifie qu'on observe la fréquence d'horloge. Quand on remet le signal "obs" à zéro, le nombre d'oscillations dans la boucle est comptabilisé.

Figure 1.25 Ligne de délai pour la synchronisation

Cette approche est très intéressante pour le cas qui nous intéresse. En effet, la grande précision offerte par la répétition de la mesure permet d'accroître la performance des circuits électroniques numériques standard à une précision que même des circuits analogiques faits sur mesure et très performants ne peuvent atteindre. Par contre, en utilisant un multiplexeur standard, on inclut une différence

Petre, O., Proc. of the 11th Asian Test Symp., 2002, IEEE.

Figure 1.26 Système de mesure de délais de Petre et al.

de délai entre les chemins de propagation. Cette différence de délai, relativement imprévisible, demeure une source élevée d'incertitude sur la mesure finale. De plus, le fait que l'on mesure ici un temps absolu et non relatif à une référence fiable introduit de nombreuses sources d'incertitude. En effet l'auteur mentionne des sources d'erreur telles que la température et des variations de tension d'alimentation. Ces sources d'erreur variables diminuent la précision des mesures et forcent l'auteur à considérer plusieurs de ses variables en tant que variables aléatoires. On pourrait ajouter aux sources d'erreurs soulevées par Petre et al. les variations de tailles de transistors inhérentes aux imperfections que même les techniques de fabrication de circuits intégrés les plus précises conservent. Nous utiliserons une partie des résultats des travaux de Petre et al. en améliorant la précision des mesures à la section 2.2.4.1.

### 1.2.1.2 VLSI

Lors de la conception de circuits intégrés dédiés, il est impensable d'obtenir une haute performance sans connaître précisément les délais de propagation propres aux composants utilisés. Les délais dans les circuits logiques MOS sont dus aux effets combinés des résistances et des capacités parasites (Savaria, 1988). On peut séparer

les sources de ces délais en deux groupes: les transistors et les interconnexions.

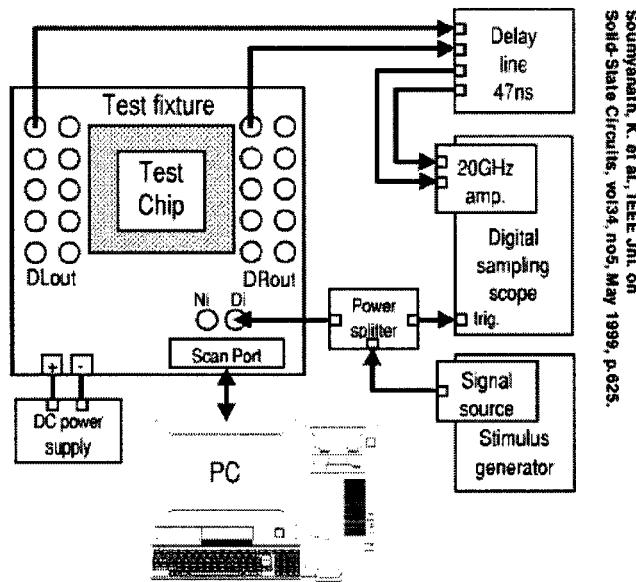

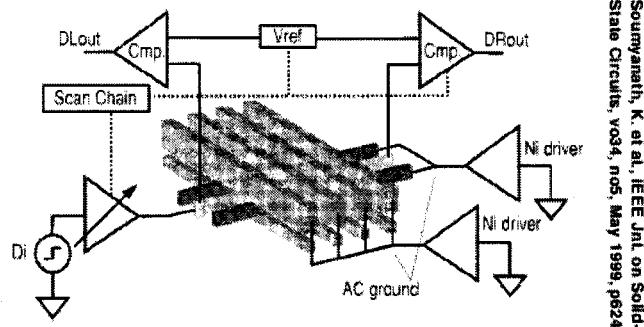

Soumyanath (Soumyanath, 1999) mesure le délai dans le domaine du temps entre des interconnexions dans un circuit intégré selon une technique basée dans le domaine du temps. Le circuit intégré contient plusieurs matrices de test de paires d'interconnexions (fig. 1.28) dont on veut mesurer le comportement. Un signal de test est propagé dans ces structures, puis échantillonné à l'extérieur du circuit. Un montage très soigné est requis pour réduire les sources d'erreur: des plots à faible inductance, un amplificateur à 20 GHz et d'autres composants précis.

Figure 1.27 Montage de mesure de délai

L'intérêt de cette technique par rapport à celle de Petre est que la mesure est ici analogique, ce qui permet d'obtenir plus d'information sur le signal que le délai entre deux interconnexions. En effet, on peut mesurer le bruit induit par le passage d'un signal près de l'interconnexion que l'on mesure. Le fait d'utiliser une mesure extérieure au circuit réduit néanmoins la performance de la mesure de délai par

Figure 1.28 Configuration de mesure de délai d'interconnexions

la faiblesse relative de la largeur de bande des plots d'entrée/sortie de tout circuit intégré. Ceci est vrai même si le circuit a des plots à faible inductance.

Les auteurs sont parvenus à mesurer des délais de l'ordre de 15 ps avec cette technique. Le montage de mesure qu'ils ont utilisé (fig. 1.28) pour ce faire est hautement spécialisé aux mesures d'interconnexions dans le circuit de test. La méthode de mesure de délai est intrinsèquement liée à la forme des matrices de mesure d'interconnexions (fig. 1.28) et non à des mesures de dispositifs sous test à deux ou à trois broches. De plus, comme les mesures de bruit ne sont pas dans le spectre d'intérêt de ce projet, la technique proposée par Soumyanath et al. ne sera pas utilisée.

Pera (Pera, 1997) montre deux techniques de mesure de délai dont l'une est semblable à celle de Petre (Petre, 2002) pour mesurer le délai entre des interconnexions avec une précision atteignant 100 ps. Cette publication, parue il y a 7 ans, avec une technologie de  $1.5\mu\text{m}$ , moins performante en termes de temps de commutation que celle possible avec des technologies actuelles comme le CMOS 130nm. Il est donc permis de croire qu'une réactualisation des circuits de Pera à une technologie plus récente pourrait améliorer cette performance. L'auteur utilise un oscillateur bouclé (fig. 1.29) dont la boucle contient un échantillon sous test. La fréquence d'oscillation de la boucle est échantillonée et ralentie par des diviseurs de fréquence

et ensuite expédiée à l'extérieur du circuit intégré.

Figure 1.29 Oscillateur bouclé de Pera et al.

Ralentir ainsi la fréquence d'oscillation de la boucle est un bon moyen de contourner les capacités parasites des plots de sortie, mais cela réduit la précision offerte par la mesure. Ce choix de design permet aussi de procéder à des mesures de délais sans consommer l'espace requis par un module intégré de mesure de délai.

En ce qui concerne notre plateforme de mesure, il est plus intéressant d'effectuer les mesures sur le circuit qu'à l'extérieur. En effet, seule la précision des mesures nous importe.

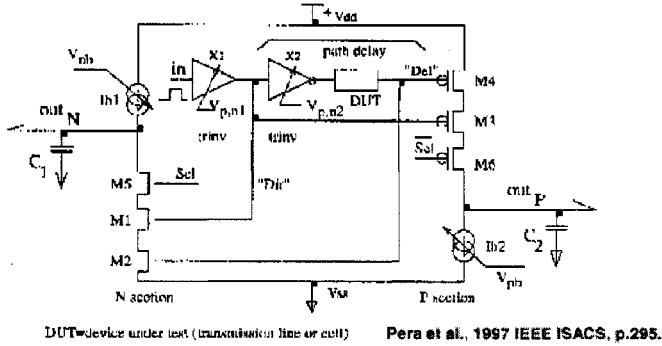

La seconde méthode utilisée par Pera pour mesurer des délais est un détecteur de phase appliquée à la mesure de délai (fig. 1.30). Ce module sert pour mesurer les délais de propagation propres aux montées ou descentes de tension. À la figure 1.30, on peut observer les sorties  $out_P$  et  $out_N$  qui représentent respectivement les temps de montée et de descente du signal.

De tels détails de mesures sont certes très intéressants. Par contre, les caractéristiques électroniques des nanostructures sous test étant très peu connues à l'heure actuelle, il est préférable de ne pas effectuer des mesures que l'on peut juger un peu trop pointues pour le moment. La mesure des temps de montée ou de descente du signal pourrait constituer un ajout intéressant à une version prochaine la plateforme de test.

Figure 1.30 Détecteur de phase de Pera et al.

### 1.2.1.3 Autres sources sur des mesures intégrées à haute précision

Plusieurs autres articles ont été étudiés lors de la conception des circuits constituant la plateforme de test. Les articles présentés plus tôt dans cette section en ont beaucoup influencé la conception. Nous présentons ici d'autres publications qui, après une lecture approfondie, n'ont pas été retenues comme des avenues intéressantes pour le problème qui nous intéresse. Il est toutefois important de nous positionner par rapport à ces résultats de recherche touchant des domaines connexes au nôtre.

Brock (Brock, 1995) présente un système de mesure de délais de portes logiques offrant une précision sous la picoseconde. Cette performance est très impressionnante pour un circuit datant d'une dizaine d'années. Malheureusement, les portes logiques dont ce système mesure le délai aussi finement sont fabriquées en technologie RFSQ<sup>12</sup>. Cette technologie, basée sur des jonctions de Josephson, tire avantage des délais réduits que l'on observe lorsqu'un canal est utilisé en supraconducteur. Évidemment, les moyens techniques énormes nécessités par ce genre de montage ne nous sont pas accessibles. Il nous sera donc impossible de recréer les conditions préalables à la mesure de délais aussi fins que ceux présents dans cet article.

Par contre, on remarque que pour atteindre une précision de mesure élevée, les au-

## <sup>12</sup>Rapid Flux Single Quantum

teurs ont procédé à une calibration très poussée du système de mesure. Les efforts que les auteurs ont mis à parfaire cette technique sont justifiables par le fait que la précision de la mesure dépend presqu'exclusivement de cette calibration. La lecture de cet article confirme nos présomptions que la calibration est une considération de conception très importante d'un instrument de mesure de haute précision.

Laquai (Laquai, 1995) montre une structure de test pour la mesure de signaux internes dans des circuits VLSI CMOS. Cet instrument est composé de sondes qui échantillonnent des signaux analogiques à l'intérieur de circuits intégrés. La mesure, effectuée par exemple sur un noeud d'intérêt dans un circuit intégré, échantillonne le comportement à ce noeud à plusieurs pendant plusieurs oscillations et retourne un courant DC. La valeur de ce courant DC est proportionnelle à la valeur maximale de courant des échantillons mesurés. Si le signal mesuré respecte plusieurs conditions dont la périodicité et une phase constante, ce courant permet d'extraire beaucoup d'information du signal d'entrée.

Cette méthode est certes intéressante et a permis de mesurer des délais de propagation de l'ordre de 200ps en utilisant une technologie CMOS 0.5  $\mu\text{m}$ . Nous recherchons par contre des résultats plus précis. De plus, cette méthode préconise l'utilisation d'une source contrôlée comme référence pour la mesure de délai. Bien entendu, cela est nécessaire pour montrer la performance du circuit à un moment donné, mais, comme cette mesure est directe plutôt que relative, elle ne permet pas de réduire plusieurs sources d'imprécision variables comme par exemple la température.