**Titre:** Conception et réalisation d'un échantillonneur bloqueur à 14 bit et

Title: 50 MÉ/S dédié à un CAN pipeliné

**Auteur:** Younes Chouia

Author:

**Date:** 2004

**Type:** Mémoire ou thèse / Dissertation or Thesis

**Référence:** Chouia, Y. (2004). Conception et réalisation d'un échantillonneur bloqueur à 14 bit et 50 MÉ/S dédié à un CAN pipeliné [Mémoire de maîtrise, École Polytechnique de Montréal]. PolyPublie. <https://publications.polymtl.ca/7353/>

## Document en libre accès dans PolyPublie

Open Access document in PolyPublie

**URL de PolyPublie:** <https://publications.polymtl.ca/7353/>

PolyPublie URL:

**Directeurs de recherche:** Mohamad Sawan, & Fadhel M. Ghannouchi

Advisors:

**Programme:** Non spécifié

Program:

UNIVERSITÉ DE MONTRÉAL

CONCEPTION ET RÉALISATION D'UN ÉCHANTILLONNEUR BLOQUEUR À

14 BIT ET 50MÉ/S DÉDIÉ À UN CAN PIPELINÉ

YOUNES CHOUIA

DÉPARTEMENT DE GÉNIE ÉLECTRIQUE

ÉCOLE POLYTECHNIQUE DE MONTRÉAL

MÉMOIRE PRÉSENTÉ EN VUE DE L'OBTENTION

DU DIPLÔME DE MAÎTRISE ÉS SCIENCES APPLIQUÉES

(GÉNIE ÉLECTRIQUE)

DÉCEMBRE 2004

Library and

Archives Canada

Published Heritage

Branch

395 Wellington Street

Ottawa ON K1A 0N4

Canada

Bibliothèque et

Archives Canada

Direction du

Patrimoine de l'édition

395, rue Wellington

Ottawa ON K1A 0N4

Canada

*Your file Votre référence*

*ISBN: 0-494-01298-6*

*Our file Notre référence*

*ISBN: 0-494-01298-6*

#### NOTICE:

The author has granted a non-exclusive license allowing Library and Archives Canada to reproduce, publish, archive, preserve, conserve, communicate to the public by telecommunication or on the Internet, loan, distribute and sell theses worldwide, for commercial or non-commercial purposes, in microform, paper, electronic and/or any other formats.

The author retains copyright ownership and moral rights in this thesis. Neither the thesis nor substantial extracts from it may be printed or otherwise reproduced without the author's permission.

#### AVIS:

L'auteur a accordé une licence non exclusive permettant à la Bibliothèque et Archives Canada de reproduire, publier, archiver, sauvegarder, conserver, transmettre au public par télécommunication ou par l'Internet, prêter, distribuer et vendre des thèses partout dans le monde, à des fins commerciales ou autres, sur support microforme, papier, électronique et/ou autres formats.

L'auteur conserve la propriété du droit d'auteur et des droits moraux qui protège cette thèse. Ni la thèse ni des extraits substantiels de celle-ci ne doivent être imprimés ou autrement reproduits sans son autorisation.

---

In compliance with the Canadian Privacy Act some supporting forms may have been removed from this thesis.

While these forms may be included in the document page count, their removal does not represent any loss of content from the thesis.

Conformément à la loi canadienne sur la protection de la vie privée, quelques formulaires secondaires ont été enlevés de cette thèse.

Bien que ces formulaires aient inclus dans la pagination, il n'y aura aucun contenu manquant.

UNIVERSITÉ DE MONTREAL

ÉCOLE POLYTECHNIQUE DE MONTRÉAL

Ce Mémoire intitulé :

CONCEPTION ET RÉALISATION D'UN ÉCHANTILLONNEUR BLOQUEUR À 14

BIT ET 50MÉ/S DÉDIÉ À UN CAN PIPELINÉ

Présenté par: Younes Chouia

En vue de l'obtention du diplôme de Maîtrise és Sciences Appliquées

Jury d'examen constitué de :

M. SAVARIA Yvon, Ph.D., Président

M. SAWAN Mohamad, Ph.D., membre et directeur de recherche

M. GHANNOUCHI Fadhel, Ph.D., membre et codirecteur

M. AUDET Yves, D.Sc.A., membre

*À mes Parents,

à Nina et à toute ma Famille*

# REMERCIEMENTS

Je tiens à remercier chaleureusement mon directeur de recherche Mohamad Sawan et mon codirecteur Fadhel Ghannouchi pour m'avoir proposé cette étude aussi enrichissante que diversifiée. Leurs précieux conseils ainsi que leurs aides technique, morale et financière, m'ont permis de mener à bien ma maîtrise.

Je souhaite également remercier le groupe des étudiants qui m'ont soutenu sans discontinuer.

Enfin, je souhaite remercier la Société Canadienne de Microélectronique (SCM) pour les outils de conception et simulation et pour la fabrication de circuit intégré, ainsi que le Conseil de recherche en sciences naturel et en génie du Canada (CRSNG) pour le support financier de ce projet.

# RÉSUMÉ

L'échantillonneur bloqueur (EB) frontal du CAN est un circuit fondamental du point de vue réduction des erreurs dynamiques, spécialement quand il s'agit des signaux d'entrée à haute fréquence. Une topologie de «condensateurs commutés» (Switched Capacitor-SC) a été utilisée pour la réalisation du circuit EB, malgré que cette technique n'est pas souhaitable dans les applications à basse consommation puisque la tension qui contrôle les commutateurs est insuffisante, c'est pour cette raison que la technique d'«amorçage» (bootstrapping) a été proposée afin de résoudre ce problème.

Basée sur la modélisation comportementale de chaque élément du circuit, et en utilisant le langage Verilog-A, une telle approche nous permet d'obtenir une meilleure optimisation du circuit, avec peu du temps de simulation.

Les résultats basés sur des simulations avec Cadence en utilisant les modèles de transistors de la technologie CMOS  $0.18\mu\text{m}$ , et en introduisant les transistors natifs, montrent une résolution de 14 bits avec 7mW en consommation de puissance pour une

largeur de bande qui atteint 20MHz à un taux d'échantillonnage de 50MHz. Après l'implémentation du dessin des masques du circuit conçu, la simulation de ce dernier a montré une dégradation de seulement 2 bits pour avoir une résolution de 12 bits, ce qui reste dans les limites du bon fonctionnement du circuit.

# ABSTRACT

The front end sample and hold (SH) circuit used in ADCs is a fundamental component that reduce the in dynamic errors, especially with high frequency input signals.

A "switched capacitors" (SC) circuit topology was used in the realization of the SH circuit, although this technique is not desirable in low power applications, since the voltage that control the switches is insufficient. In order to avoid associated performance degradation the "bootstrapping" technique was proposed.

Based on the behavioral modeling of each element of the circuit, and by using the Verilog-A language, it was possible to better optimize the circuit with very fast simulations.

Results based on simulations with Cadence using transistors' models of the  $0.18\mu\text{m}$  CMOS technology, and native transistors, gave a 14 bits resolution with a power consumption of 7mW and a bandwidth of 20MHz at a sampling rate of 50MHz.

Based on a layout implementation of the designed circuit, simulations of an extracted model showed a degradation of only 2 bit to end up with a 12 bits resolution, which remains within the limits of the needed operation of the circuit.

# TABLE DES MATIÈRES

|                                                           |       |

|-----------------------------------------------------------|-------|

| DÉDICACE .....                                            | iv    |

| REMERCIEMENT .....                                        | v     |

| RÉSUMÉ .....                                              | vi    |

| ABSTRACT .....                                            | viii  |

| TABLE DES MATIÈRES .....                                  | x     |

| LISTE DES FIGURES .....                                   | xiv   |

| LISTE DES TABLEAUX .....                                  | xviii |

| LISTE DES ABRÉVIATIONS .....                              | xix   |

| LISTE DES ANNEXES .....                                   | xxi   |

| INTRODUCTION .....                                        | 01    |

| I.1 Motivation .....                                      | 01    |

| I.2 Organisation du mémoire .....                         | 03    |

| CHAPITRE 1 – LES CIRCUITS ÉCHANTILLONNEUR-BLOQUEURS ..... | 05    |

| 1.1 Principe de fonctionnement .....                      | 05    |

|                                                                      |    |

|----------------------------------------------------------------------|----|

| 1.2 Analyse spectrale de l'échantillonnage .....                     | 08 |

| 1.3 Le bruit dans les circuits EB .....                              | 10 |

| 1.3.1 Le bruit thermique .....                                       | 10 |

| 1.3.2 Gigue de l'horloge d'échantillonnage .....                     | 12 |

| 1.3.3 Autres sources de bruit .....                                  | 12 |

| 1.4 Architectures des circuits EB.....                               | 13 |

| 1.4.1 Architectures à boucle ouverte .....                           | 13 |

| 1.4.2 Architectures à boucle fermée .....                            | 14 |

| 1.5 Exemples des circuits EB .....                                   | 16 |

| 1.5.1 Circuits EB à capacité de Miller .....                         | 16 |

| 1.5.2 Circuits EB à gain défini par le rapport des résistances ..... | 18 |

| 1.5.3 Circuits EB à gain défini par le rapport des capacités .....   | 19 |

| 1.5.4 Circuits EB sans la phase de remise à zéro .....               | 20 |

| CHAPITRE 2 – L'AMPLIFICATEUR OPÉRATIONNEL .....                      | 24 |

| 2.1 Amplificateur à compensation de Miller .....                     | 25 |

| 2.2 Amplificateur cascode plié (folded) .....                        | 26 |

| 2.3 Amplificateur cascode télescopique .....                         | 27 |

| 2.3.1 Le bruit thermique .....                                       | 29 |

| 2.3.2 Le bruit de clignotement .....                                 | 30 |

| 2.3.3 Le gain DC .....                                               | 31 |

| 2.3.4 L'établissement linéaire .....                                 | 31 |

| 2.3.5 Le temps de réaction .....                                     | 34 |

|                                                              |    |

|--------------------------------------------------------------|----|

| 2.3.6 Rétroaction du mode commun .....                       | 34 |

| 2.3.7 La polarisation .....                                  | 35 |

| 2.4 La modélisation comportementale .....                    | 37 |

| CHAPITRE 3 – LES AUTRES BLOCS DU CIRCUIT EB .....            | 38 |

| 3.1 L'injection de charge .....                              | 39 |

| 3.2 La technique d'embase (bottom plate) .....               | 42 |

| 3.3 La non-linéarité des commutateurs .....                  | 44 |

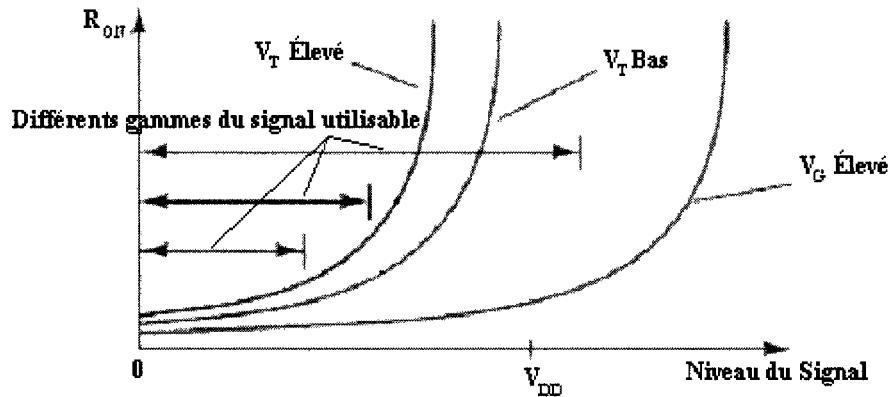

| 3.3.1 La linéarisation des commutateurs de base .....        | 45 |

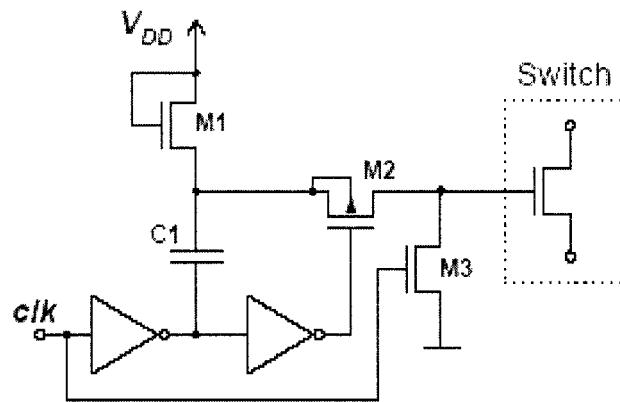

| 3.3.2 L'amorçage (boosting) de la grille .....               | 47 |

| 3.3.3 L'amorçage (bootstrapping) simple du commutateur ..... | 49 |

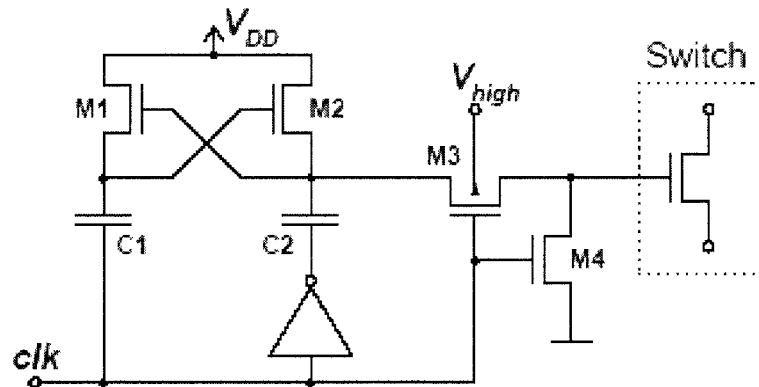

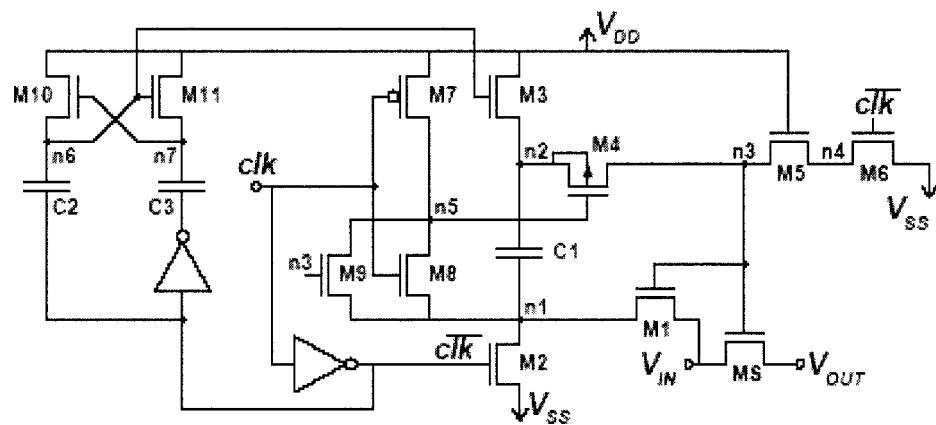

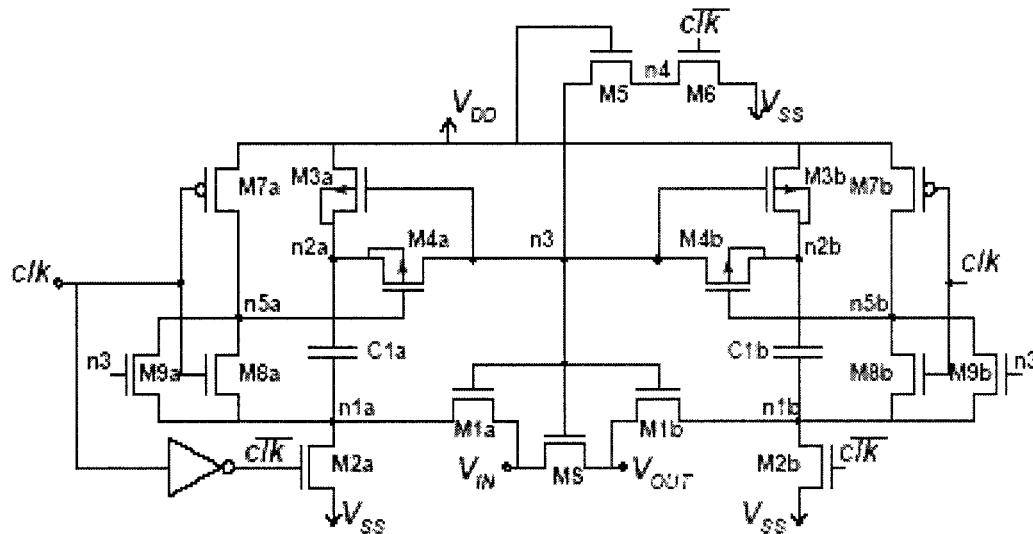

| 3.3.4 Le commutateur à double amorçage .....                 | 50 |

| 3.4 La modélisation comportementale .....                    | 52 |

| 3.5 Génération du signal d'horloge .....                     | 53 |

| 3.5.1 La gigue .....                                         | 54 |

| 3.5.2 Le circuit d'horloge .....                             | 55 |

| 3.5.3 Les tampons de sortie .....                            | 56 |

| CHAPITRE 4 – METHODOLOGIE DE CONCEPTION .....                | 58 |

| 4.1 L'amplificateur opérationnel .....                       | 59 |

| 4.1.1 Le gain DC .....                                       | 60 |

| 4.1.2 La fréquence du gain unitaire .....                    | 61 |

| 4.1.3 Le temps de réaction .....                             | 61 |

| 4.1.4 L'optimisation de l'amplificateur.....                 | 62 |

|                                               |     |

|-----------------------------------------------|-----|

| 4.2 Les commutateurs .....                    | 67  |

| 4.3 L'horloge .....                           | 69  |

| 4.4 Dessin des masques .....                  | 73  |

| CHAPITRE 5 – IMPLÉMENTATION & RÉSULTATS ..... | 77  |

| 5.1 L'amplificateur opérationnel .....        | 78  |

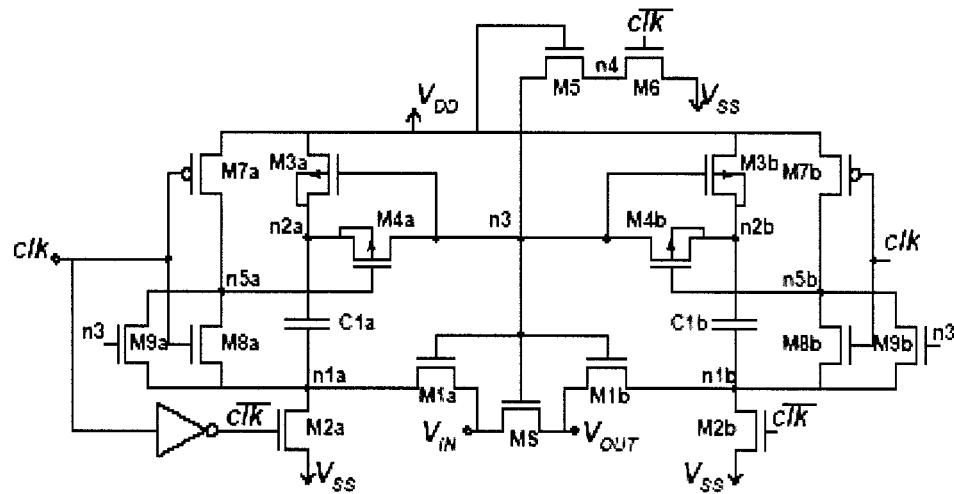

| 5.2 Le commutateur à double amorçage .....    | 80  |

| 5.3 Le circuit EB .....                       | 83  |

| 5.4 Statut de la puce .....                   | 89  |

| CONCLUSION .....                              | 92  |

| BIBLIOGRAPHIE .....                           | 94  |

| ANNEXES .....                                 | 101 |

# LISTE DES FIGURES

|             |                                                                                             |    |

|-------------|---------------------------------------------------------------------------------------------|----|

| Figure I-1  | Conversion AN directe du signal RF .....                                                    | 02 |

| Figure 1-1  | Les sorties des différents circuits EB .....                                                | 06 |

| Figure 1-2  | Spécifications dans le domaine du temps .....                                               | 07 |

| Figure 1-3  | Échantillonnage dans le domaine du temps .....                                              | 08 |

| Figure 1-4  | Exemple d'échantillonnage d'un signal .....                                                 | 09 |

| Figure 1-5  | Exemple du sous-échantillonnage d'un signal .....                                           | 09 |

| Figure 1-6  | Modèle du bruit thermique introduit par le commutateur de l'EB .....                        | 10 |

| Figure 1-7  | (a) Symbole d'un circuit EB, (b) Son utilisation pratique.....                              | 14 |

| Figure 1-8  | Circuit EB simple avec rétroaction.....                                                     | 15 |

| Figure 1-9  | Circuit EB à condensateurs commutés .....                                                   | 15 |

| Figure 1-10 | Circuit EB à capacité de Miller .....                                                       | 17 |

| Figure 1-11 | Circuit EB à gain défini par le rapport des résistances.....                                | 18 |

| Figure 1-12 | Circuit EB à gain défini par le rapport des capacités .....                                 | 19 |

| Figure 1-13 | La moitié d'un circuit EB complètement différentiel sans la phase de remise<br>à zéro ..... | 21 |

|                                                                                                                                         |    |

|-----------------------------------------------------------------------------------------------------------------------------------------|----|

| Figure 1-14 L'architecture adoptée pour le circuit EB.....                                                                              | 23 |

| Figure 2-1 Amplificateur à deux étages avec la compensation de Miller .....                                                             | 26 |

| Figure 2-2 Amplificateur cascode plié (folded) .....                                                                                    | 27 |

| Figure 2-3 Amplificateur opérationnel cascode télescopique .....                                                                        | 28 |

| Figure 2-4 Le modèle petit signal du bruit thermique d'un transistor simple à source<br>commune.....                                    | 29 |

| Figure 2-5 Le modèle petit signal d'un l'amplificateur cascode télescopique à deux<br>étages .....                                      | 32 |

| Figure 2-6 Le circuit de rétroaction du mode commun pour le premier étage de<br>l'amplificateur.....                                    | 35 |

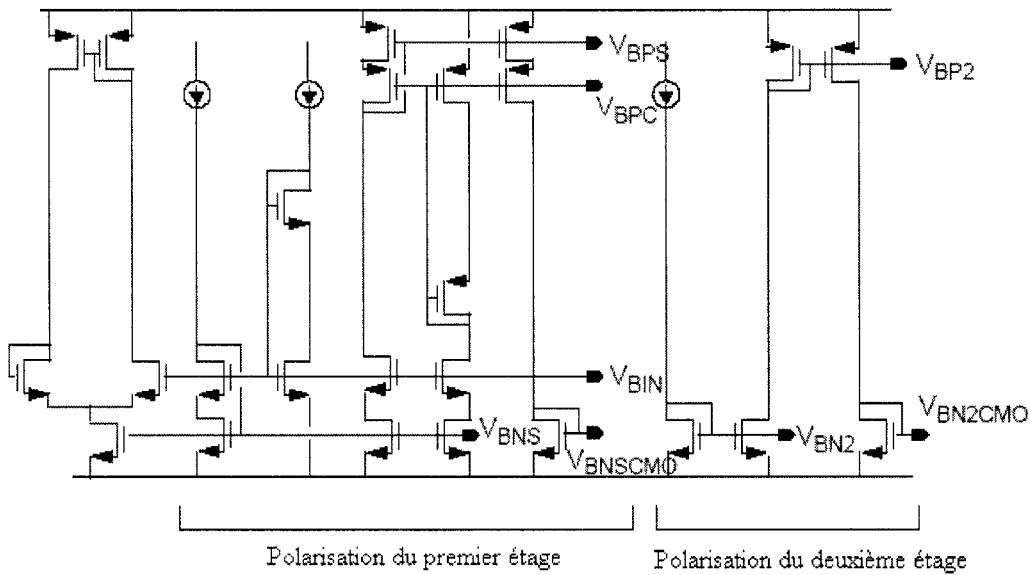

| Figure 2-7 Le circuit de polarisation de l'OTA .....                                                                                    | 36 |

| Figure 2-8 Le circuit cascode de polarisation interne de l'OTA .....                                                                    | 36 |

| Figure 2-9 Modèle petit signal (small signal) d'un amplificateur .....                                                                  | 37 |

| Figure 3-1 EB en MOS: (a) circuit simple (b) circuit RC équivalent.....                                                                 | 39 |

| Figure 3-2 Circuit EB simple .....                                                                                                      | 40 |

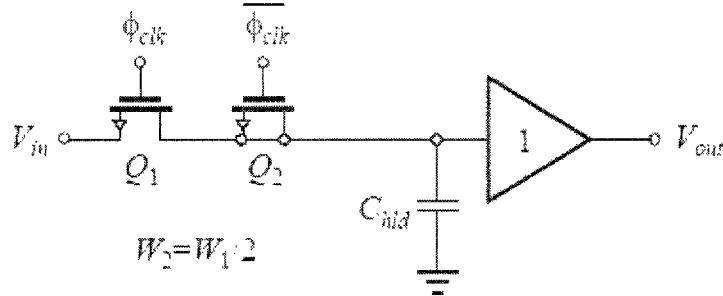

| Figure 3-3 Circuit EB avec un «dummy» .....                                                                                             | 42 |

| Figure 3-4 Un exemple d'une architecture en boucle fermée où le commutateur<br>d'échantillonnage fonctionne avec une tension fixe ..... | 43 |

| Figure 3-5 Échantillonnage avec «embase» (bottom-plate) .....                                                                           | 43 |

| Figure 3-6 La résistante-ON d'un commutateurs NMOS en fonction du niveau du<br>signal.....                                              | 47 |

| Figure 3-7 Commutateur MOS avec le circuit local d'«amorçage» (boosting) de la                                                          |    |

|                                                                                                                                           |    |

|-------------------------------------------------------------------------------------------------------------------------------------------|----|

| tension de grille .....                                                                                                                   | 48 |

| Figure 3-8 Un autre circuit local d'«amorçage» (boosting) de grille pour un commutateur MOS .....                                         | 48 |

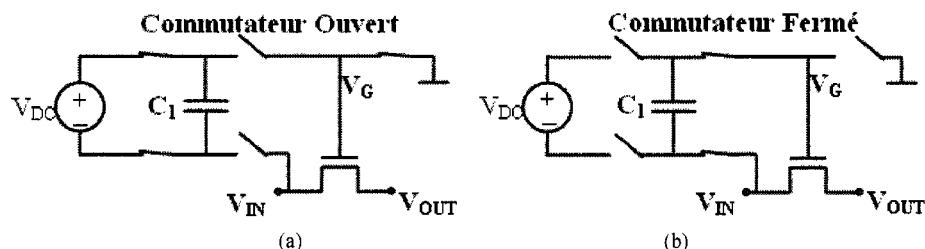

| Figure 3-9 Un commutateur «amorcé» (bootstrapped) (a) ouvert (b) fermé .....                                                              | 49 |

| Figure 3-10 Un commutateur amorcé fiable à long terme .....                                                                               | 50 |

| Figure 3-11 Un commutateur à double amorçage .....                                                                                        | 51 |

| Figure 3-12 Le modèle du commutateur utilisé .....                                                                                        | 52 |

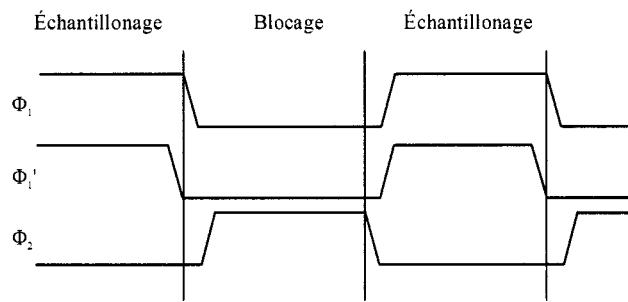

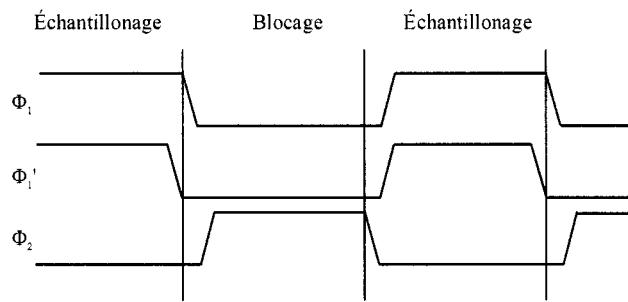

| Figure 3-13 Les signaux d'horloge utilisés dans le circuit EB .....                                                                       | 55 |

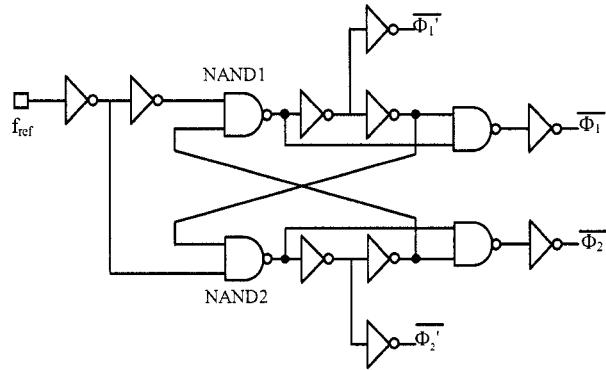

| Figure 3-14 Le circuit d'horloge utilisé dans l'EB .....                                                                                  | 56 |

| Figure 4-1 L'architecture du circuit EB.....                                                                                              | 59 |

| Figure 4-2 L'amplificateur utilisé pour concevoir l'EB .....                                                                              | 60 |

| Figure 4-3 Circuit de polarisation de l'amplificateur.....                                                                                | 64 |

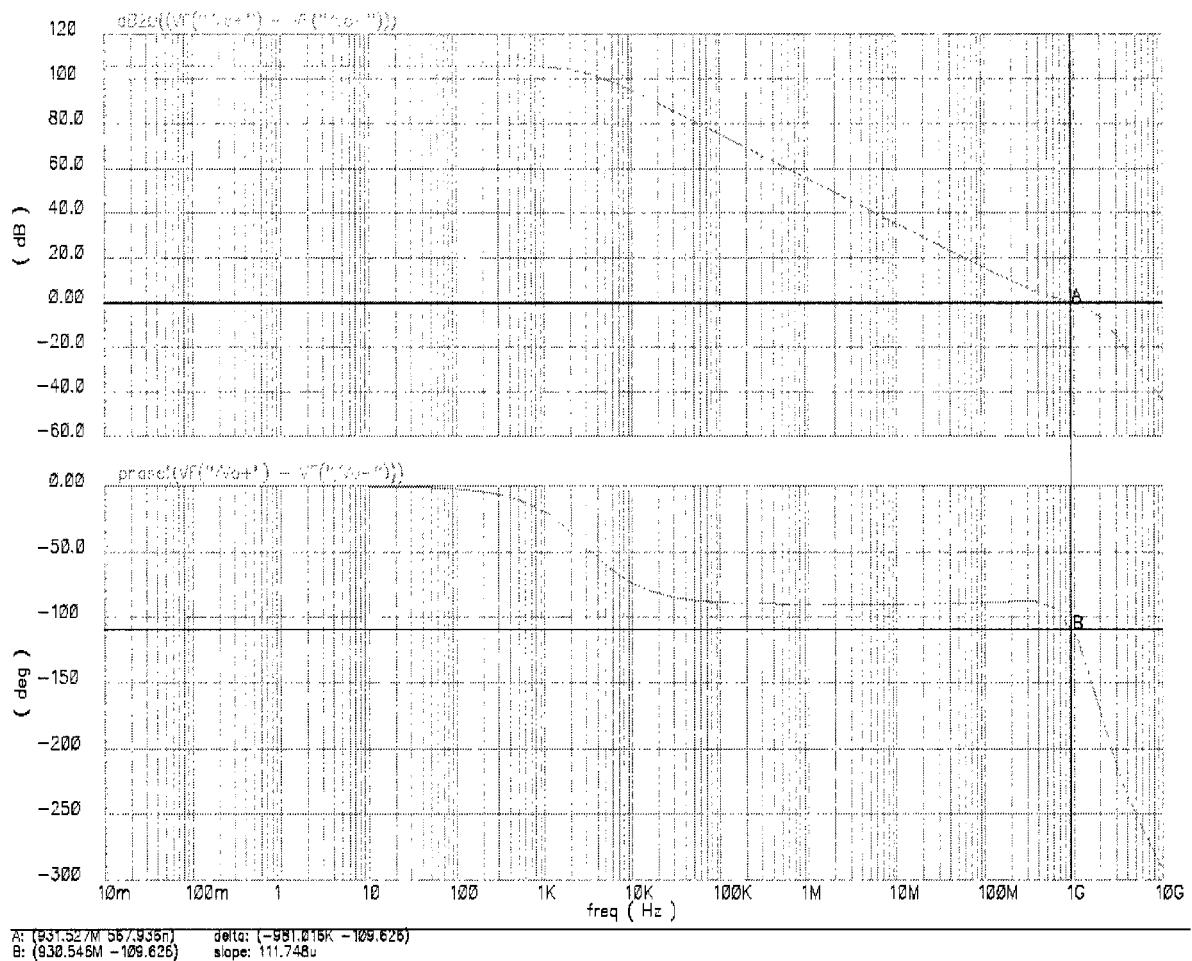

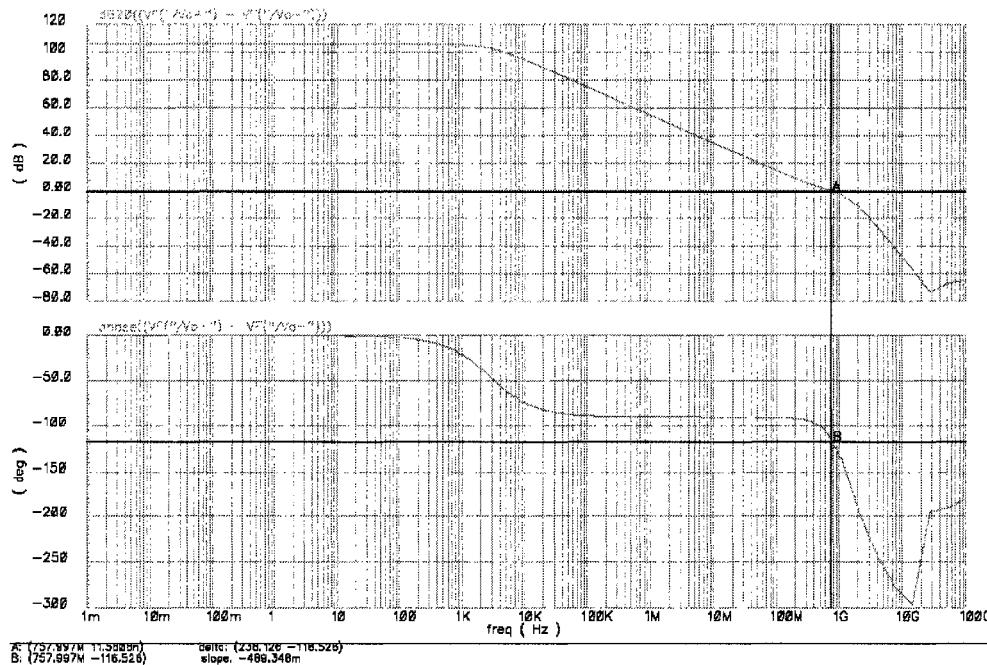

| Figure 4-4 Caractéristiques fréquentielles de l'amplificateur.....                                                                        | 65 |

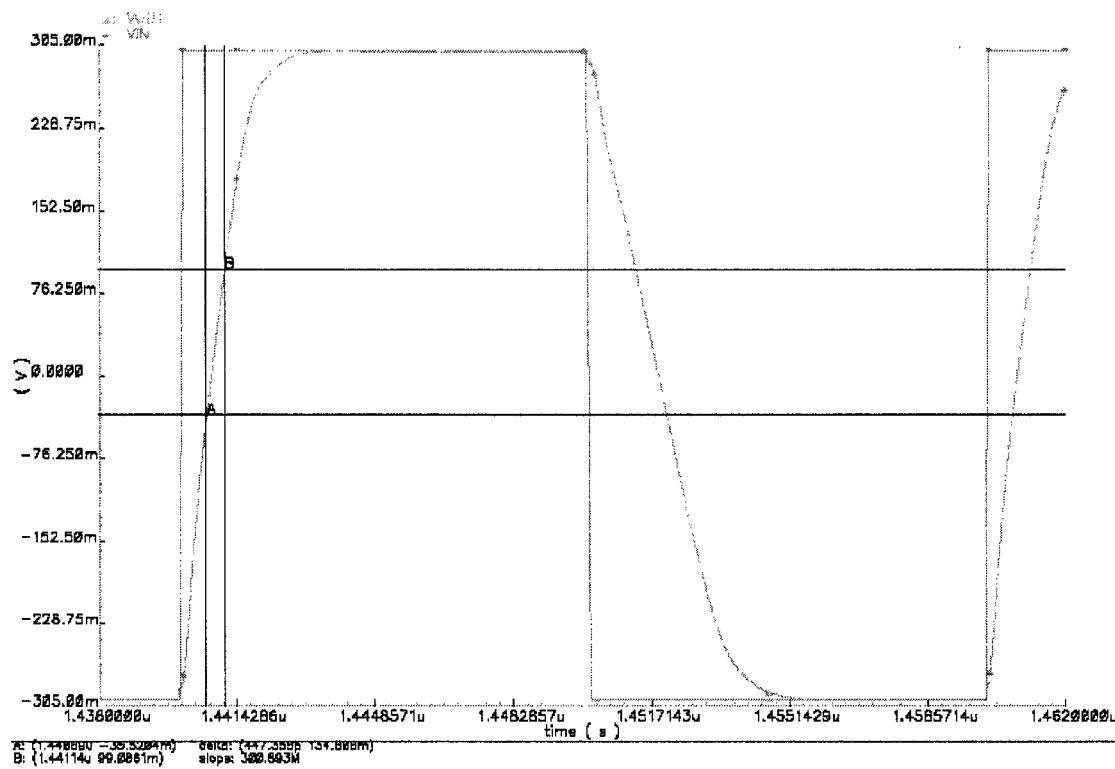

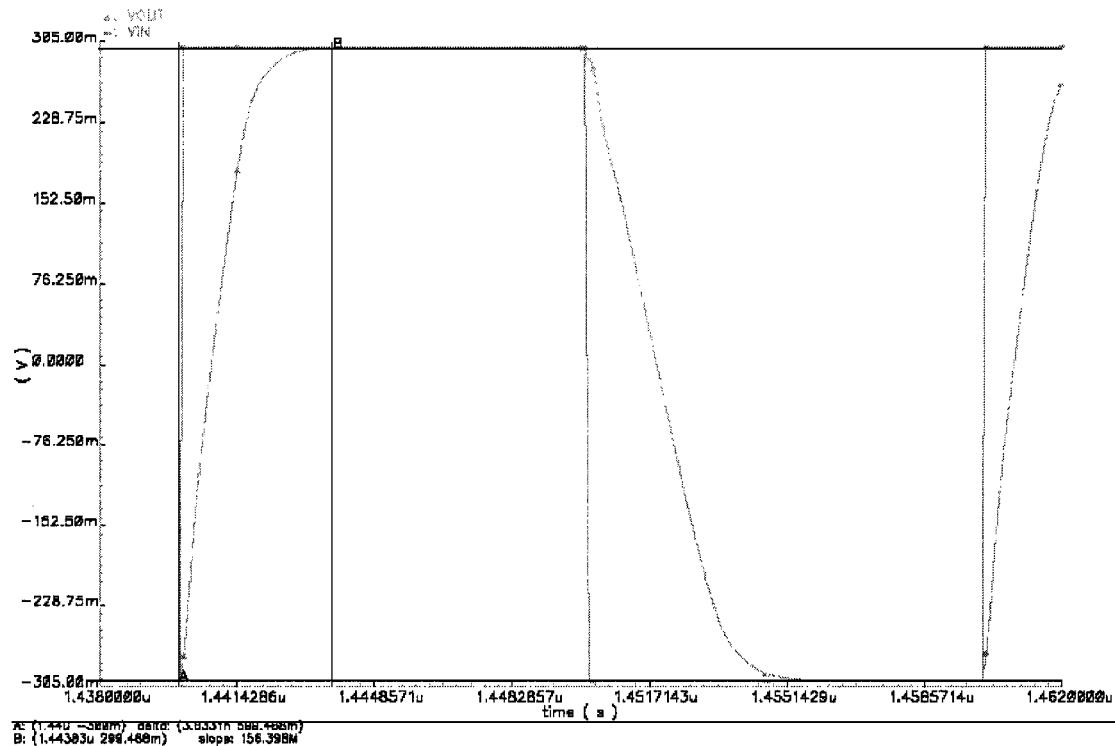

| Figure 4-5 Taux de réaction de l'amplificateur .....                                                                                      | 66 |

| Figure 4-6 Temps de stabilisation de l'amplificateur.....                                                                                 | 66 |

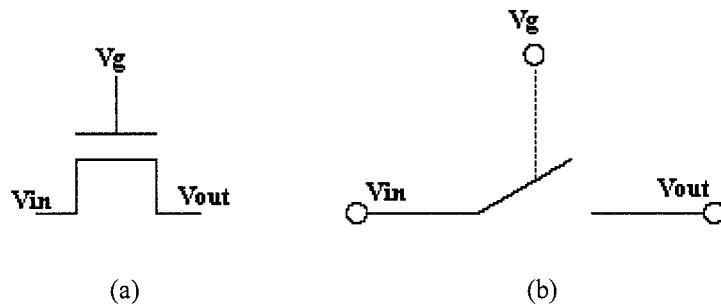

| Figure 4-7 Commutateur utilisé: (a) transistor NMOS, (b) modèle Verilog-A .....                                                           | 68 |

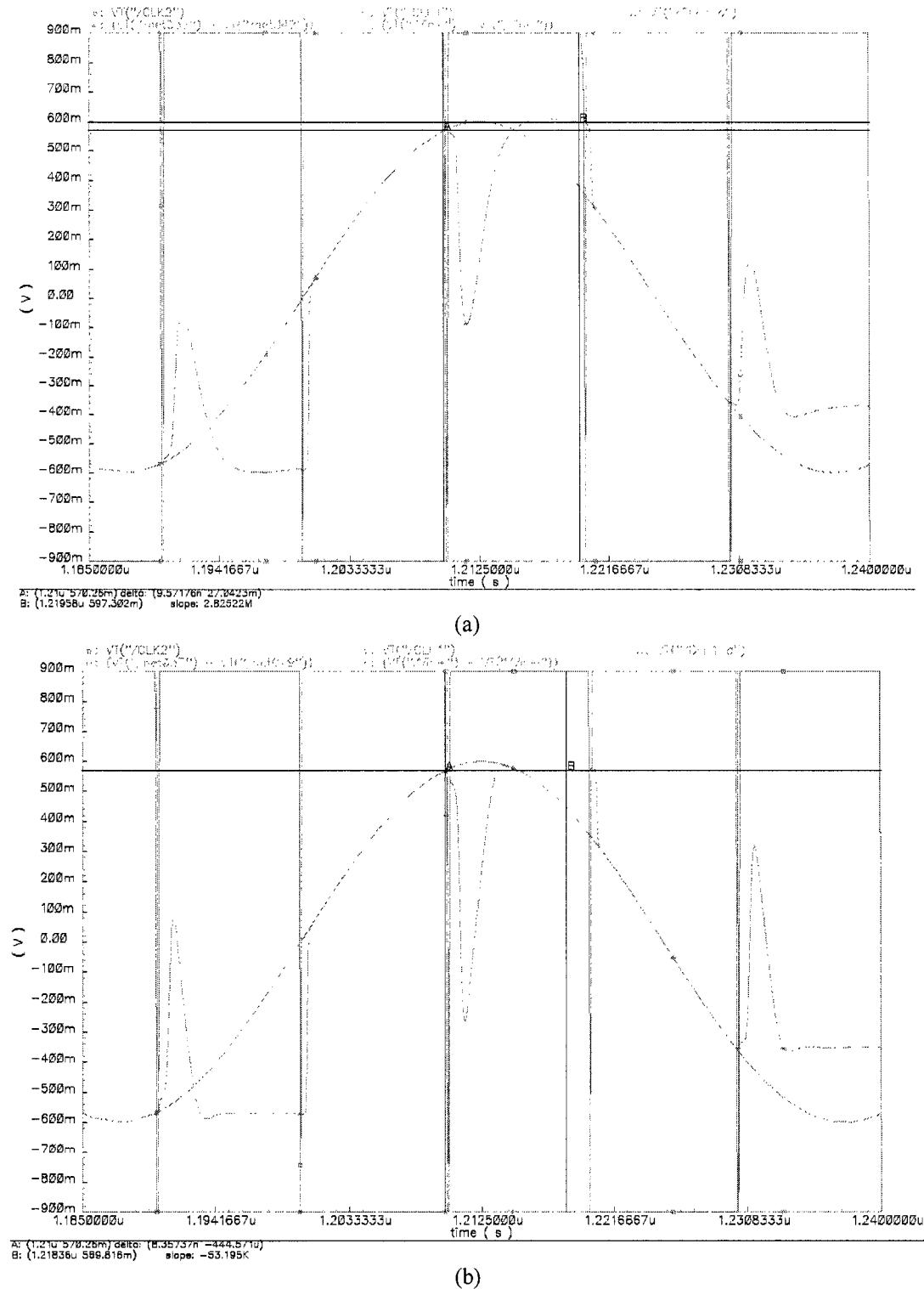

| Figure 4-8 Signal de sortie de l'EB en remplaçant le commutateur S( $\Phi_2$ ) par (a) un transistor normal (b) un transistor natif ..... | 70 |

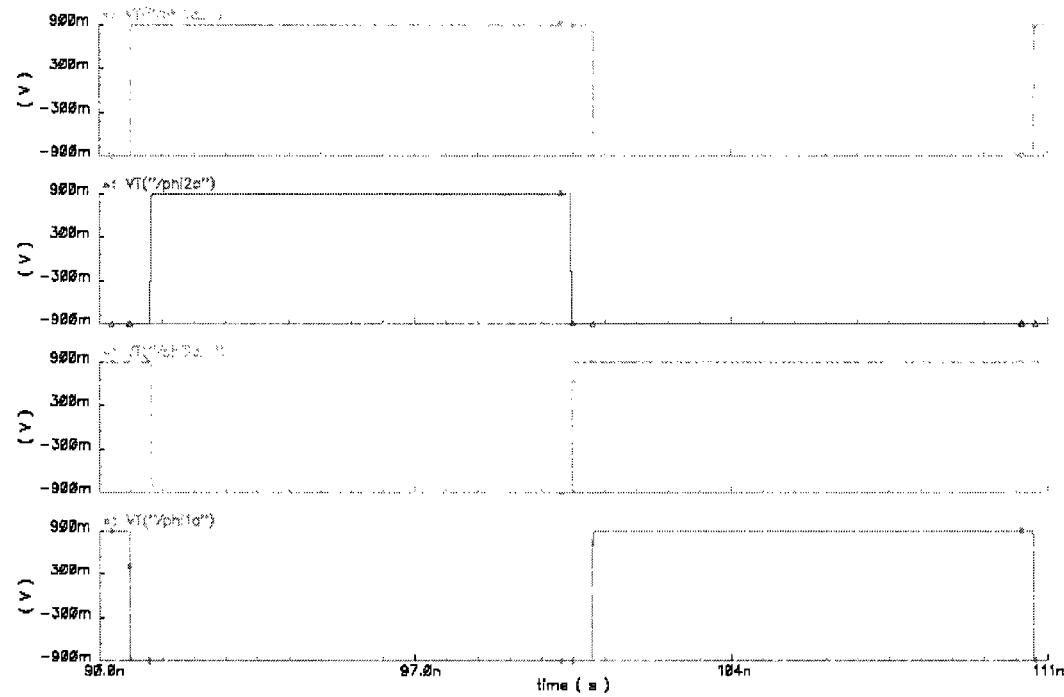

| Figure 4-9 Les signaux d'horloge utilisés dans le circuit EB .....                                                                        | 71 |

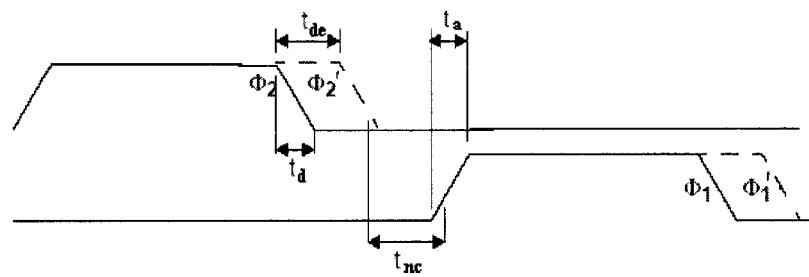

| Figure 4-10 Paramètres temporels des signaux d'horloge.....                                                                               | 71 |

| Figure 4-11 Simulation de signaux d'horloge.....                                                                                          | 72 |

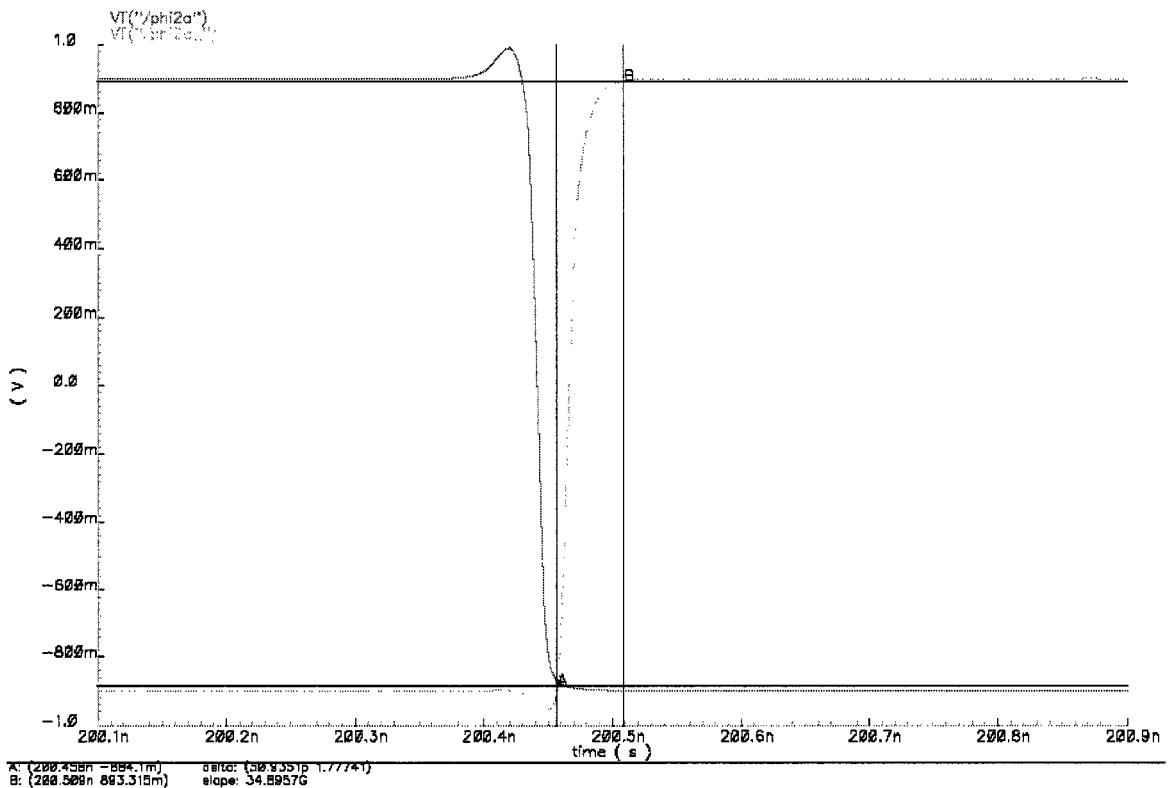

| Figure 4-12 Transition simulée de signaux d'horloge .....                                                                                 | 72 |

|             |                                                                                                                                                            |    |

|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

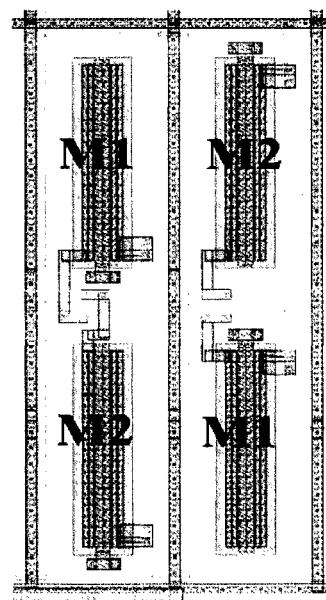

| Figure 4-13 | Anneaux d'armature des transistors .....                                                                                                                   | 74 |

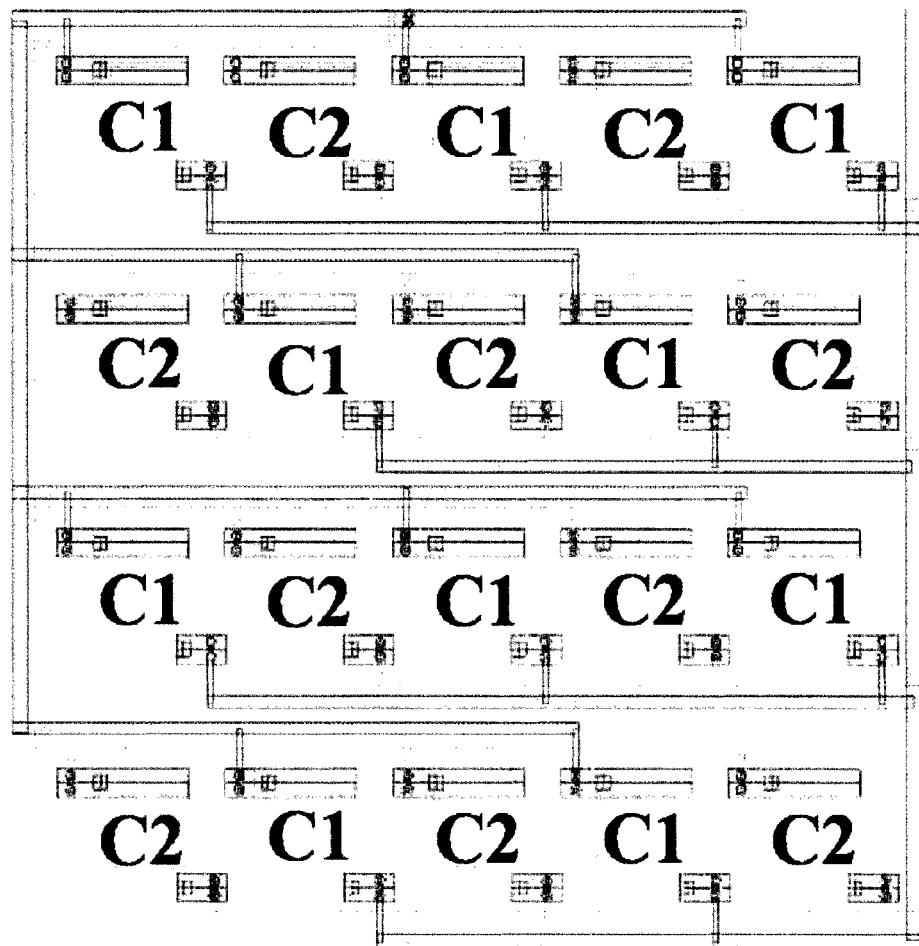

| Figure 4-14 | Assortiment (matching) des transistors .....                                                                                                               | 74 |

| Figure 4-15 | Assortiment des condensateurs .....                                                                                                                        | 75 |

| Figure 5-1  | Simulation de la réponse en fréquence du dessin de masques de l'amplificateur.....                                                                         | 79 |

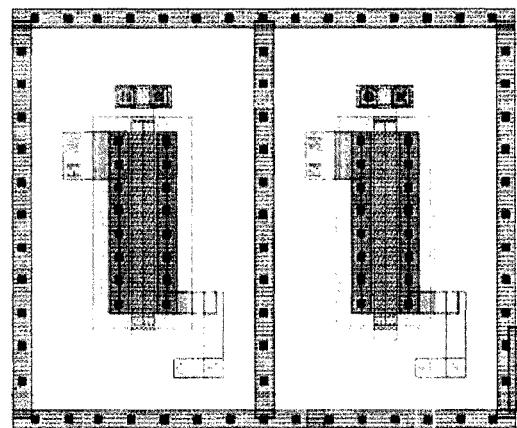

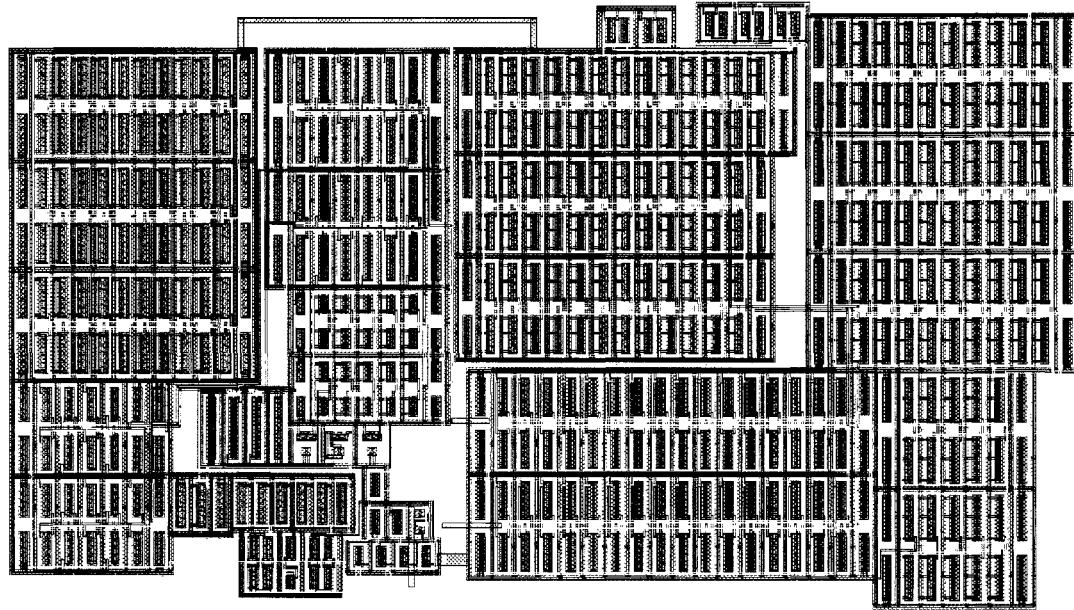

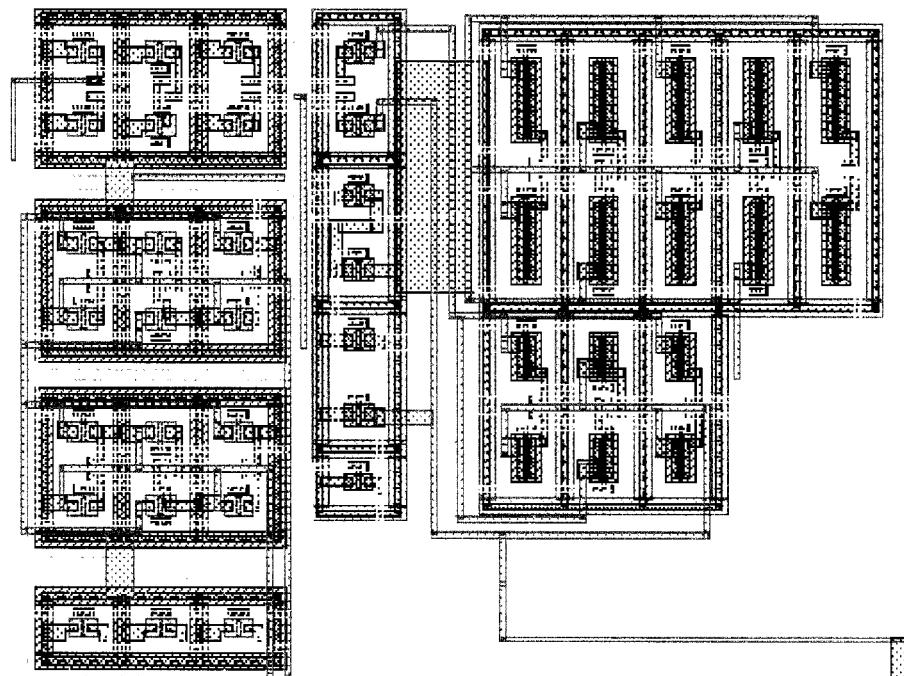

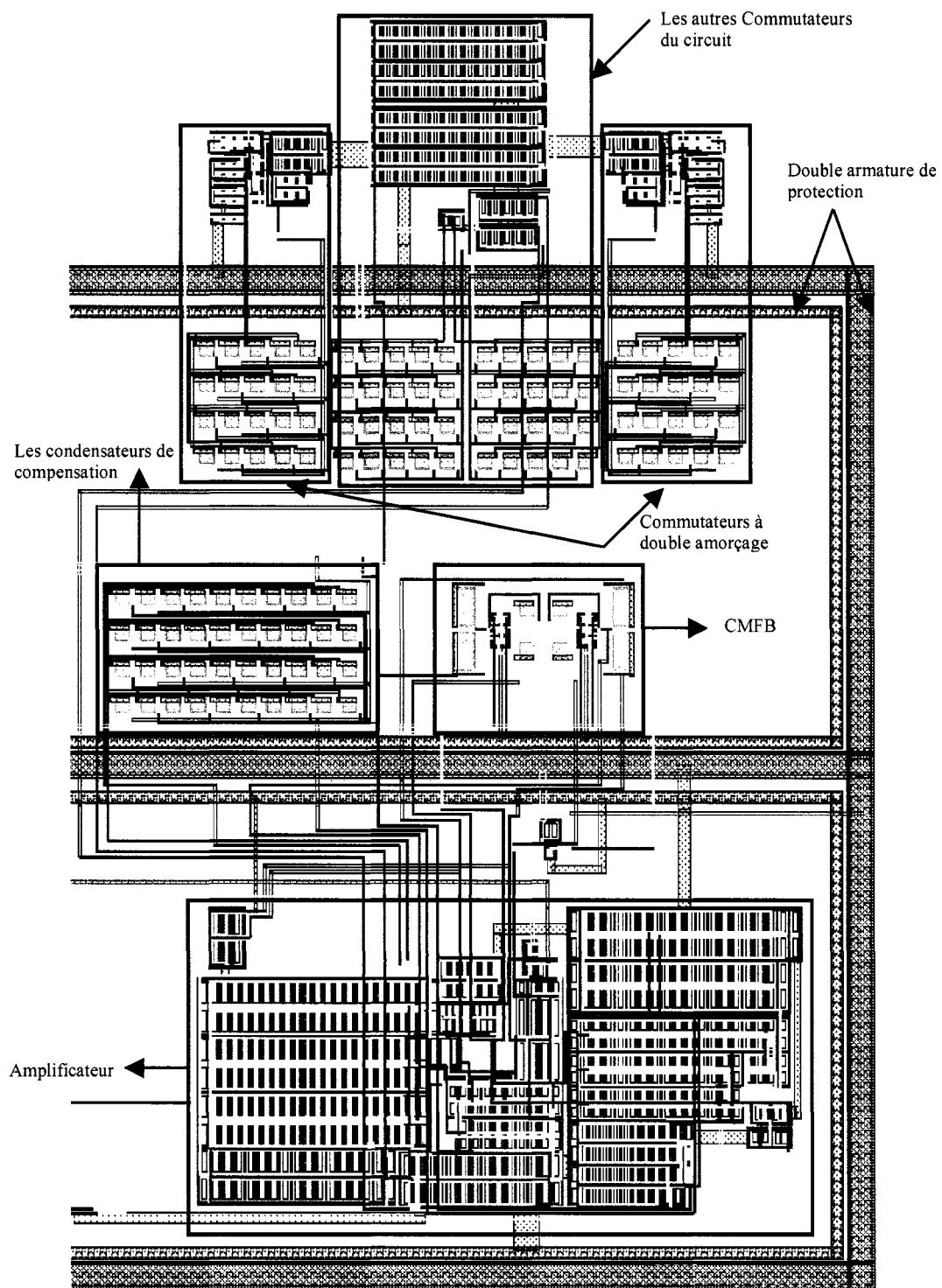

| Figure 5-2  | Dessin des masques de l'amplificateur utilisé .....                                                                                                        | 80 |

| Figure 5-3  | Commutateur à double amorçage .....                                                                                                                        | 81 |

| Figure 5-4  | Dessin de masques du commutateur à double amorçage.....                                                                                                    | 81 |

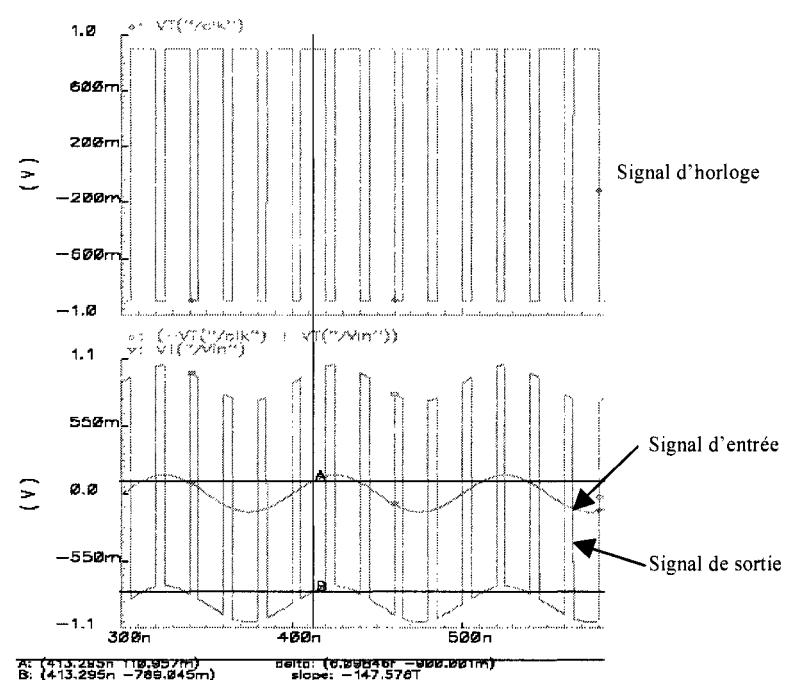

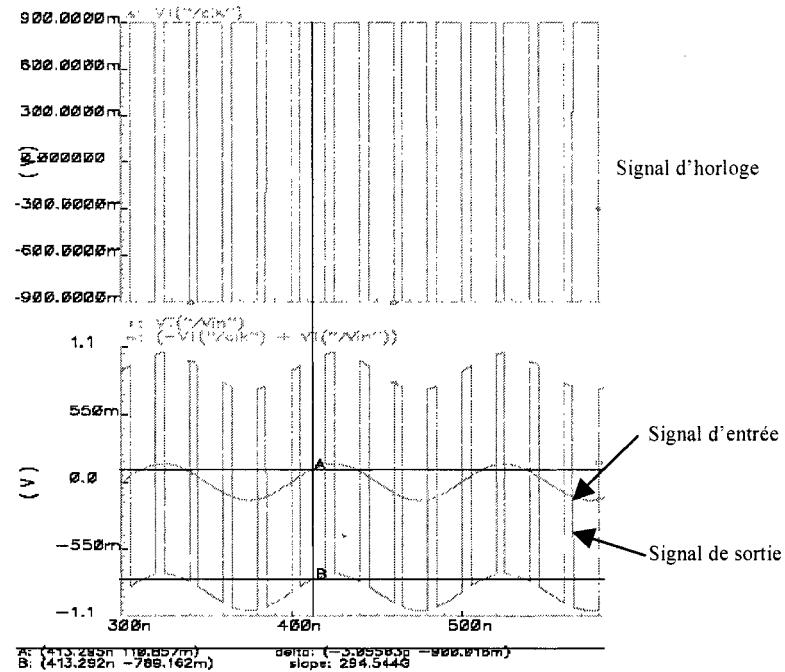

| Figure 5-5  | Simulation du commutateur (entrée et sortie)à double amorçage (a) schématique, (b) dessin des masques .....                                                | 82 |

| Figure 5-6  | Dessin de masques de l'EB proposé.....                                                                                                                     | 84 |

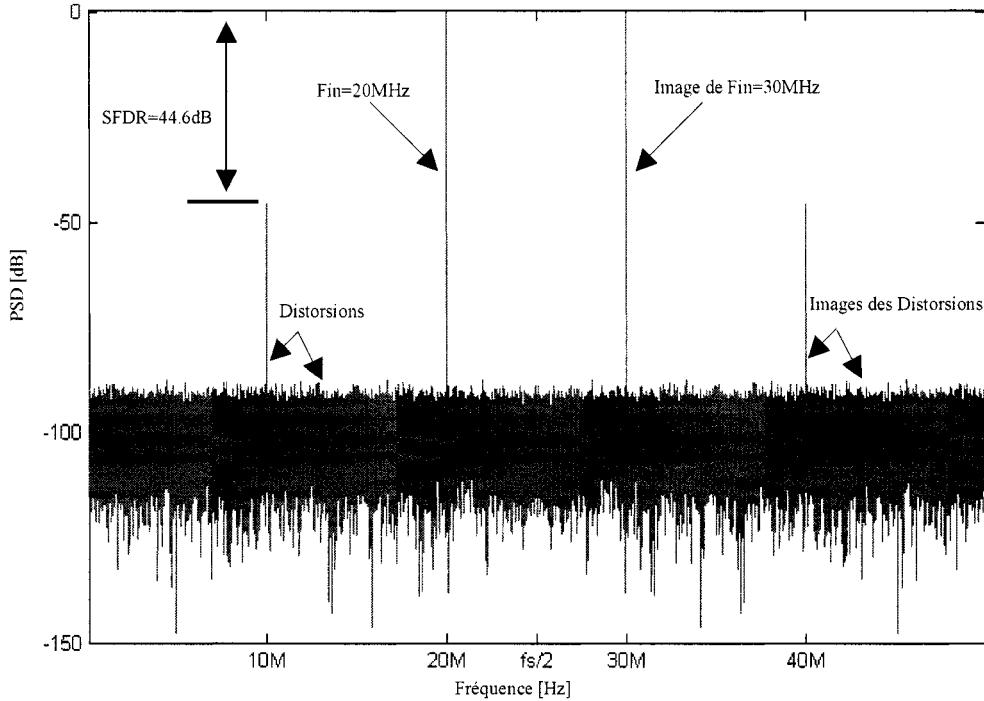

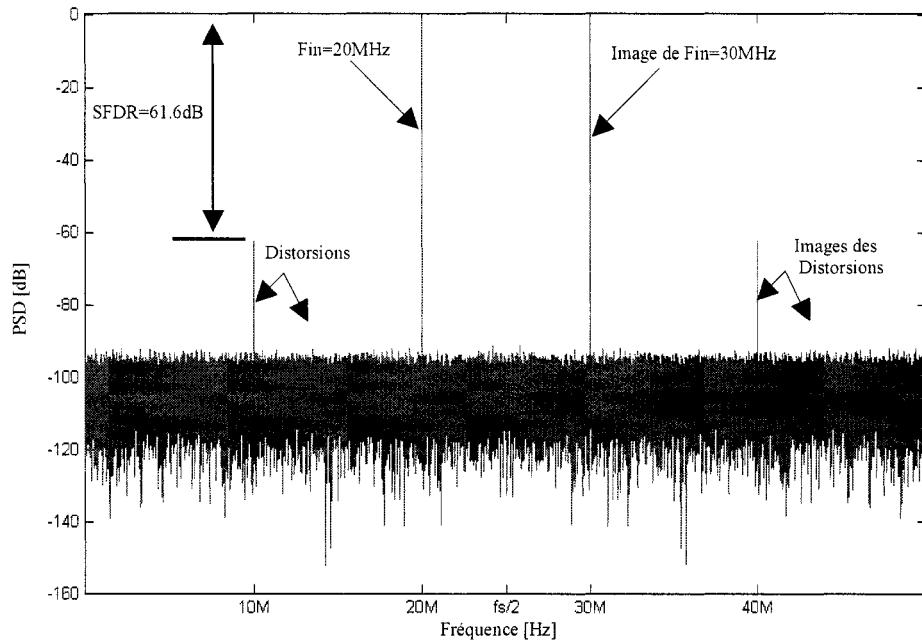

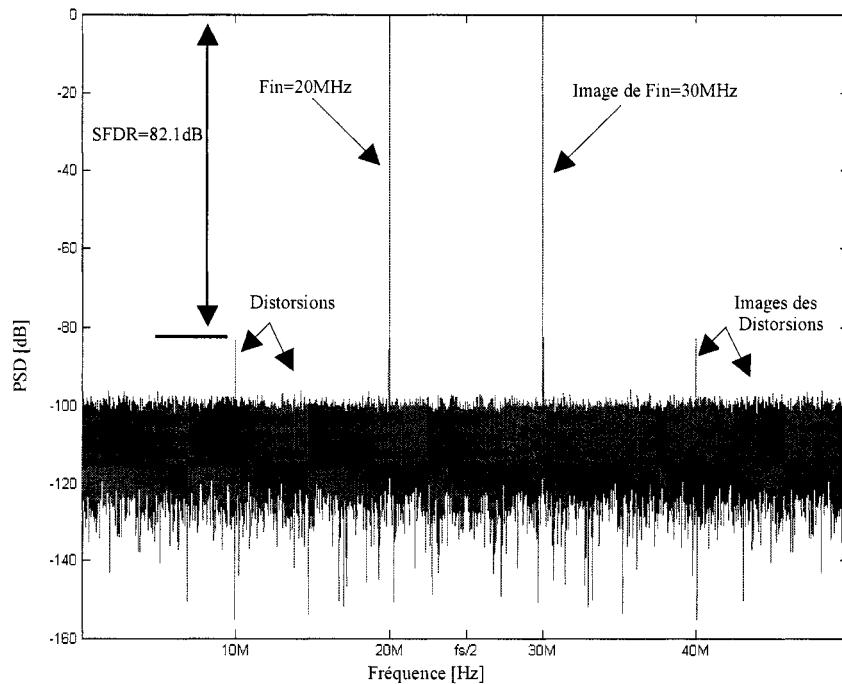

| Figure 5-7  | FFT du signal de sortie de l'EB avec un commutateur NMOS à l'entrée .....                                                                                  | 85 |

| Figure 5-8  | FFT du signal de sortie de l'EB avec une porte de transmission à l'entrée .....                                                                            | 86 |

| Figure 5-9  | FFT du signal de sortie de l'EB avec un commutateur à amorçage simple .....                                                                                | 86 |

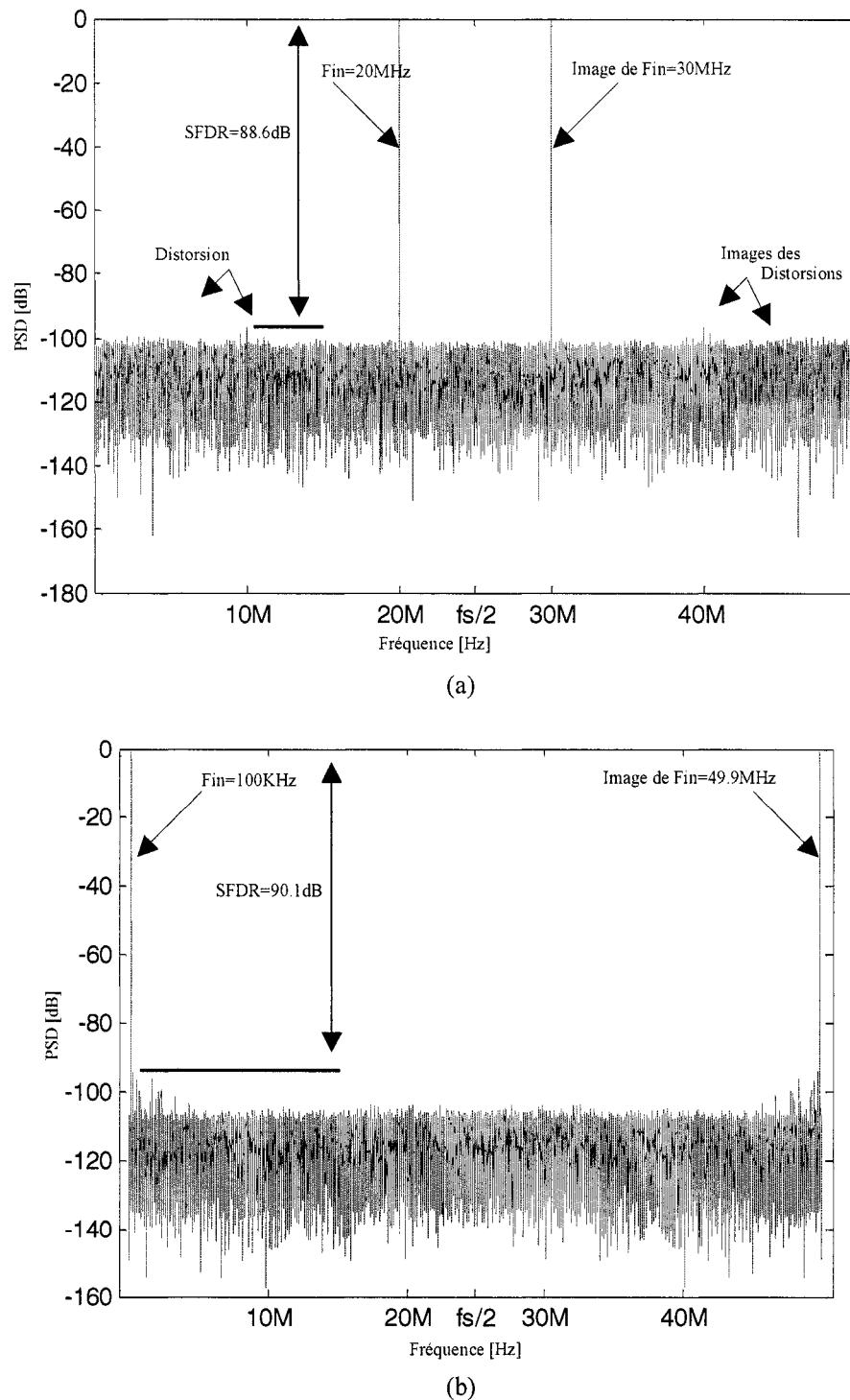

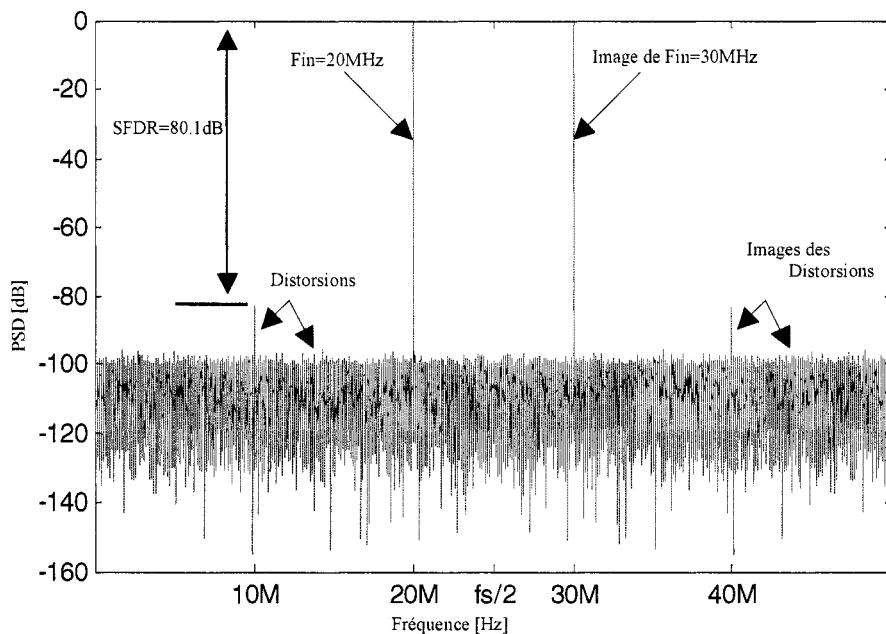

| Figure 5-10 | FFT du signal de sortie de l'EB avec un commutateur à double amorçage pour. (a) une fréquence d'entrée de 20MHz, (b) une fréquence d'entrée de 100KHz..... | 88 |

| Figure 5-11 | FFT du signal de sortie de l'EB implémenté .....                                                                                                           | 89 |

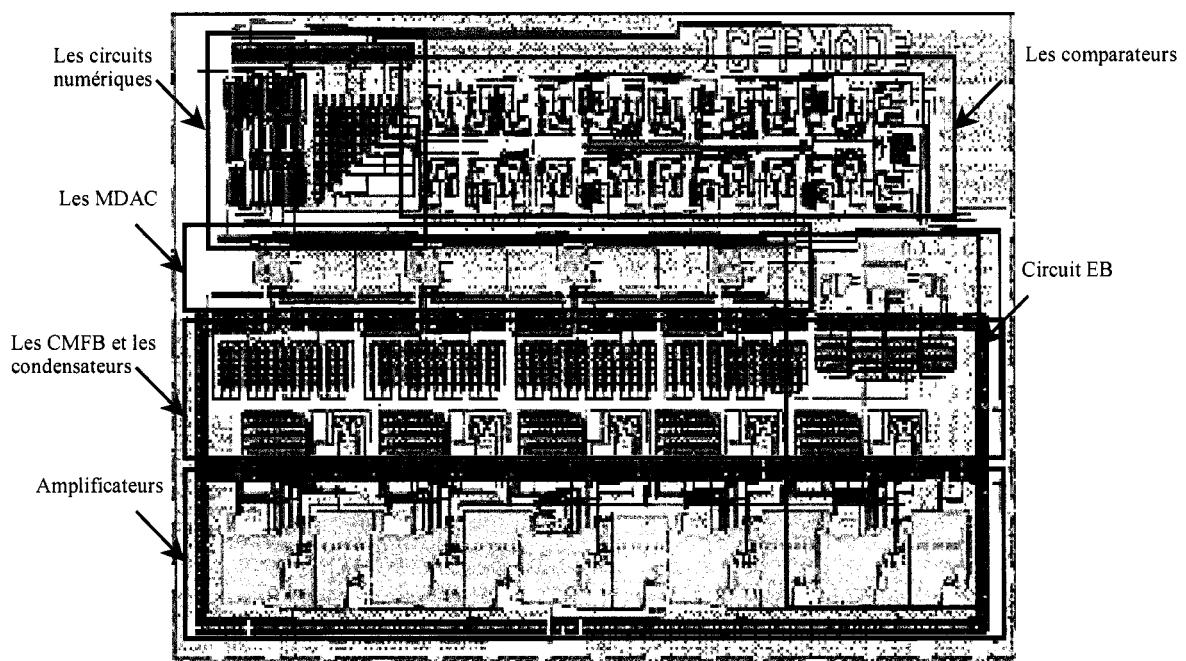

| Figure 5-12 | la puce du CAN envoyée pour fabrication.....                                                                                                               | 90 |

# LISTE DES TABLEAUX

|             |                                                                                                |    |

|-------------|------------------------------------------------------------------------------------------------|----|

| Tableau 4-1 | Directives d'optimisation .....                                                                | 62 |

| Tableau 4-2 | Valeurs des tensions VDS des transistors de l'amplificateur.....                               | 62 |

| Tableau 4-3 | Les dimensions des différents dispositifs de l'amplificateur .....                             | 63 |

| Tableau 4-4 | Tensions de polarisations de l'amplificateur.....                                              | 64 |

| Tableau 4-5 | Optimisation des commutateurs (modèles Verilog-A).....                                         | 68 |

| Tableau 4-6 | Adaptation du circuit avec des transistors (CMOS 0.18 $\mu$ m) .....                           | 69 |

| Tableau 5-1 | Résultats des performances de l'EB avec les différents types de<br>commutateurs utilisés ..... | 87 |

# LISTE DES ABRÉVIATIONS

|      |                                                     |

|------|-----------------------------------------------------|

| ADC  | Analog to Digital Converter                         |

| AN   | Analogique Numérique                                |

| BW   | BandWidth                                           |

| CAN  | Convertisseur Analogique Numérique                  |

| CMFB | Common Mode FeedBack                                |

| CMOS | Complementary Metal-Oxyde Semiconductor             |

|      | Taux de rejet du mode commun (Common Mode Rejection |

| CMRR | Ratio)                                              |

| EB   | Échantillonneur Bloqueur                            |

| ENOB | Effective Number Of Bits                            |

| FFT  | Fast Fourier Transform                              |

| GBW  | Gain BandWidth                                      |

| L    | Length                                              |

| LSB  | Least Significant Bit                               |

|      |                                                                |

|------|----------------------------------------------------------------|

| MS   | Main Switch                                                    |

| NMOS | Negatively doped Metal-Oxide Semiconductor                     |

| OTA  | Operational Transconductance Amplifier                         |

| PMOS | Positively doped Metal-Oxide Semiconductor                     |

| PSSR | Taux de rejet des alimentations (Power Supply Rejection Ratio) |

| RF   | Radio Frequency                                                |

| RMS  | Root Mean Square                                               |

| SC   | Switched Capacitor                                             |

| SCM  | Société Canadienne de Microélectronique                        |

| SFDR | Spurious Free Dynamic Range                                    |

| SH   | Sample and Hold                                                |

| SNDR | Signal to Noise and Distortion Ratio                           |

| SNR  | Signal to Noise Ratio                                          |

| SOC  | System On Chip                                                 |

| SR   | Slew Rate                                                      |

| W    | Width                                                          |

## **LISTE DES ANNEXES**

|          |                                            |     |

|----------|--------------------------------------------|-----|

| ANNEXE A | DÉFINITIONS DES PERFORMANCES DE L'EB ..... | 101 |

| ANNEXE B | PROGRAMMES EN VERILOG-A .....              | 103 |

# INTRODUCTION

## I.1 Motivation

La communication sans-fil a été un domaine très actif pendant la dernière décennie, là où la tendance d'avoir plus de performances est basée sur l'utilisation d'une largeur de bande et d'un rapport signal/bruit (signal-to-noise ratio-SNR) plus élevés.

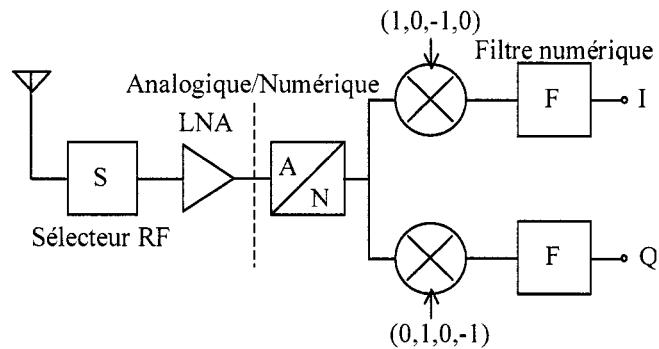

En même temps, les architectures des radios, dans beaucoup d'applications, évoluent vers la radio à base de logiciel, dont l'une des caractéristiques principales est le décalage de la frontière analogique/numérique plus près de l'antenne comme le montre la figure 1-1. En raison de ces tendances, il y a un besoin urgent de convertisseurs de données avec des taux de conversion et de résolution élevés. Une partie de cette mise à niveau nécessaire des performances vient avec l'évolution de la technologie. Le niveau croissant d'intégration mène à des systèmes avec moins de puces, le but final étant simplement une seule puce, le système sur puce (system-on-chip-SoC). Ceci signifie que les circuits analogiques et numériques doivent être intégrés sur la même matrice de silicium, ce qui apporte des défis additionnels dans la conception de circuits analogiques et numériques.

Ces tendances influencent les caractéristiques des convertisseurs analogique/numérique (CAN) dans les récepteurs radios, le but final étant un récepteur avec un CAN connecté directement au signal RF, cependant, ceci exigerait un CAN avec un taux d'échantillonnage dans l'ordre des fréquences RF d'entrée, qui peuvent monter à plusieurs giga Hertz, et d'une gamme dynamique capable de traiter des signaux avec des amplitudes de l'ordre de nano volt en présence de fortes interférences.

**Figure I-1.** Conversion AN directe du signal RF.

L'échantilleur bloqueur (EB) frontal est un bloc fondamental dans les CAN. Son utilisation permet aux erreurs dynamiques des CAN d'être réduites, particulièrement celles qui apparaissent avec les signaux d'entrée à haute fréquence. D'autre part, puisque la gamme dynamique du convertisseur entier ne peut jamais excéder celle de l'EB frontal, les performances de ce dernier sont cruciales.

Le but de ce projet est de concevoir un EB frontal, pour être utilisé dans un CAN pipliné à 10 bit de résolution et possédant une fréquence d'échantillonnage de 50MHz. Il est conçu dans un procédé 0.18 $\mu$ m CMOS, qui tolère seulement une tension d'alimentation de 1.8Volts.

Les considérations principales de conception sont de réduire au minimum la consommation de puissance, pour augmenter au maximum le rapport signal/bruit (signal-to-noise-ratio-SNR). Ce dernier peut être augmenté en réduisant les non linéarités des commutateurs utilisés, qui représentent la partie la plus importante dans le circuit du point de vue bruit, puisque le circuit peut être utilisé dans un émetteur récepteur mobile. L'outil de programmation analogique Verilog-A est utilisé pour permettre une meilleure optimisation du circuit afin d'atteindre les performances spécifiées sans pour cela utiliser une grande surface.

## I.2 Organisation du mémoire

Ce mémoire est divisé en trois parties. La première, constituée du chapitre 1, qui introduit la théorie de l'échantillonneur bloqueur (EB), les différents paramètres intervenants, leurs sources d'imperfections et les architectures commune pour réaliser ces circuits. De plus, nous ferons un survol de la revue de littérature par le biais des principales publications récentes qui traitant le sujet.

La seconde partie, constituée des chapitres 2 et 3, traite les différents blocs de l'EB qui vont être utilisés dans le circuit à concevoir, l'amplificateur, les commutateurs et le générateur d'horloges. Le chapitre 2 est relatif aux choix de l'amplificateur opérationnel à utiliser dans l'EB et nous analysons sa théorie de fonctionnement afin d'avoir un compromis entre la puissance, le gain et la fréquence unitaire, à la fin on explique le modèle comportemental de ce bloc en Verilog-A. Nous discutons au chapitre 3 les commutateurs, leurs imperfections, et les différentes techniques pour les maîtriser. Nous

présentons aussi le modèle comportemental de ce bloc en Verilog-A. Nous traitons enfin la génération des horloges, et d'un facteur important qui est associé à savoir le non chevauchement de ses phases, qui doit être délicatement respecté.

La dernière partie, constituée des chapitres 4 et 5, traite de l'environnement de conception de l'EB, qui a fait l'objet de ces travaux. Dans le chapitre 4 les différentes étapes de conception sont présentées et expliquées. Le chapitre 5 présente les résultats finaux et les commentaires. Finalement, quelques conclusions faites pendant la conception sont présentées, aussi bien que quelques suggestions pour de futures améliorations.

Le mémoire se termine par les annexes où se trouvent la définition des différentes performances de l'EB, ainsi que les codes des blocs qui ont été conçus en Verilog-A.

## CHAPITRE 1

# LES CIRCUITS ÉCHANTILLONNEUR-BLOQUEURS

### 1.1 Principe de fonctionnement

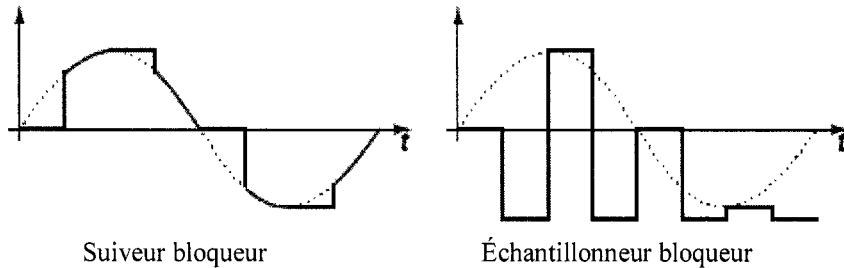

La fonction principale de l'échantillonneur bloqueur (EB) est de prendre des échantillons du signal d'entrée et de les faire tenir sur la sortie pour une certaine période de temps. En général, les échantillons sont pris à intervalles uniformes de temps; ainsi, le taux d'échantillonnage du circuit peut être déterminé. Le fonctionnement d'un circuit EB peut être divisé en mode d'échantillonnage (parfois réfééré comme mode d'acquisition) et mode de blocage, dont les durées n'ont pas besoin d'être égales. En mode de blocage, la sortie du circuit est égale à la valeur précédemment prélevée de l'entrée. En mode d'échantillonnage, la sortie peut suivre l'entrée, dans ce cas le circuit s'appelle suiveur bloqueur, ou elle peut être remise à une certaine valeur fixe. Dans quelques circuits, la sortie est tenue au cours de toute la période de l'horloge d'échantillonnage comme le

montre la figure 1-1. Ceci est réalisé en ayant des circuits séparés pour effectuer les opérations d'échantillonnage et de blocage.

**Figure 1-1.** Les sorties des différents circuits EB.

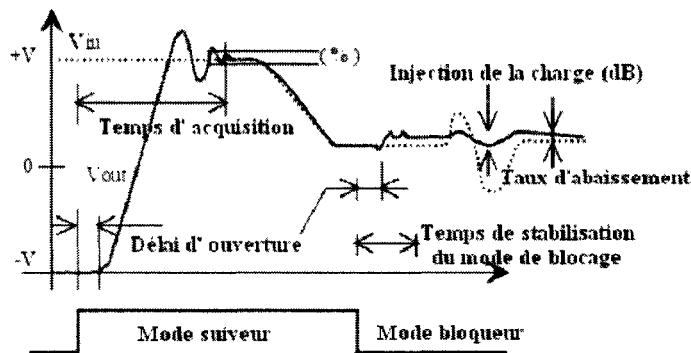

Les spécifications les plus communes utilisées pour les circuits EB sont brièvement présentées dans le reste de cette section. L'importance de chaque paramètre par rapport à un autre dépend considérablement de l'application du circuit EB. Pour entièrement caractériser un circuit EB, des paramètres dans le domaine du temps et dans le domaine des fréquences doivent être définis.

- *Temps d'acquisition:* c'est le temps entre la commande de commutation du mode de blocage au mode d'échantillonnage jusqu'au moment où le circuit est prêt à prendre un nouvel échantillon (Fig. 1-2). Le temps d'acquisition est l'un des paramètres qui définit le taux maximum d'échantillonnage réalisable.

- *Temps d'ouverture* (ou le *délai d'ouverture*): c'est le temps fixe entre la commande d'échantillonnage jusqu'au moment où la prise de l'échantillon est considérée réellement. La variation aléatoire du moment d'échantillonnage est connue comme l'*incertitude d'ouverture* ou la *gigue (jitter) d'ouverture*.

- *Temps de stabilisation du mode de blocage:* ce paramètre détermine le temps à partir du moment d'échantillonnage jusqu'au moment où la valeur du signal de sortie du

circuit s'établit à sa valeur d'état d'équilibre. Si le circuit EB est utilisé devant un CAN, ce dernier peut numériser la valeur du signal de sortie du circuit EB produite à ce moment. Le temps de stabilisation du mode de blocage a un impact important sur le taux maximum d'échantillonnage de l'EB.

Figure 1-2. Spécifications dans le domaine du temps.

- *Taux d'abaissement*: une fuite sur le signal de sortie peut se produire en mode de blocage. Le changement de la sortie qui résulte de ce fait est spécifié par le *taux d'abaissement*.

- *pas de blocage* (ou *l'erreur piédestal*): il est habituellement défini pour les circuits suiveur-bloqueurs. C'est la différence entre les valeurs de la sortie à la fin du mode suiveur et celle pendant le mode de blocage. Le piédestal peut être dépendant du signal et produire ainsi une déformation harmonique.

- *Erreur de gain*: habituellement, les circuits EB ont un gain unitaire (c.-à-d. l'amplitude du signal de sortie est égale à l'amplitude du signal d'entrée), mais d'autres valeurs de gain peuvent être aussi bien employées. L'*erreur de gain* détermine la déviation du gain à partir de la valeur nominale.

- *Gamme dynamique*: c'est la différence en décibels entre la tension d'entrée maximale permise et la tension d'entrée minimale qui peut être prélevée avec un niveau d'exactitude indiqué.

En plus de ces spécifications dans le domaine du temps, nous avons introduit en annexe-A celles du domaine des fréquences.

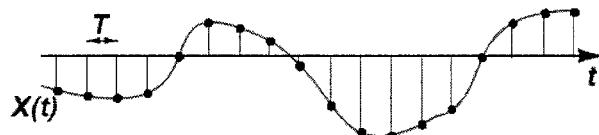

## 1.2 Analyse spectrale de l'échantillonnage

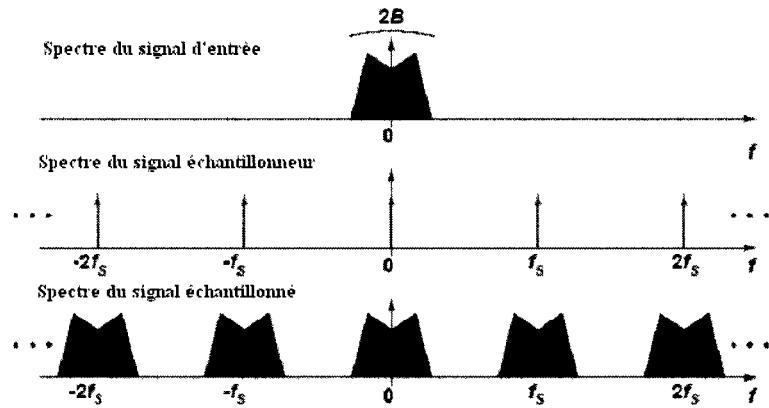

Un circuit EB idéal prend des échantillons d'un signal d'entrée à intervalles uniformes  $T$ . Dans le domaine du temps, ceci correspond à multiplier le signal avec un train d'impulsions (équation 1-1).

$$y(t) = x(t) \cdot \sum_{n=-\infty}^{\infty} \delta(t - nT) \quad (1-1)$$

Où le  $\delta(t)$  représente la fonction delta de Dirac. Le résultat est un train d'impulsions dont les valeurs correspondent aux valeurs instantanées du signal d'entrée (Fig. 1-3). Le spectre du signal prélevé (équation 1-2) est une convolution du spectre d'entrée et du spectre du train d'impulsions, qui est également un train d'impulsions.

**Figure 1-3.** Échantillonnage dans le domaine du temps.

$$Y(f) = X(f) \cdot \sum_{n=-\infty}^{\infty} \frac{1}{T} \delta\left(f - \frac{n}{T}\right) \quad (1-2)$$

Ceci est illustré sur la figure 1-4, où  $f_s$  est la fréquence d'échantillonnage et  $B$  est la largeur de bande du signal à échantillonner. Le spectre résultant est le spectre original

plus un nombre infini d'images du même spectre centré aux multiples de la fréquence d'échantillonnage. La figure montre également que, tant que la largeur de bande du signal d'entrée est moins que la moitié de la fréquence d'échantillonnage, les images ne recouvrent pas et le signal original peut être reconstitué ainsi par le filtrage.

**Figure 1-4.** Exemple d'échantillonnage d'un signal.

Si cette condition (connue par le critère de Nyquist) n'est pas assurée, une partie du spectre d'image sera chevauché avec la bande désirée du signal, causant une déformation irréversible. Pour cette raison, le signal d'entrée doit habituellement être à bande limitée avant l'échantillonnage, afin d'éviter le chevauchement des autres signaux en dehors du signal désiré. En cas de sous-échantillonnage, le chevauchement est utilisé pour échantillonner les signaux à bande étroite et à haute fréquence (Fig. 1-5).

**Figure 1-5.** Exemple du sous-échantillonnage d'un signal.

## 1.3 Le bruit dans les circuits EB

### 1.3.1 Le bruit thermique

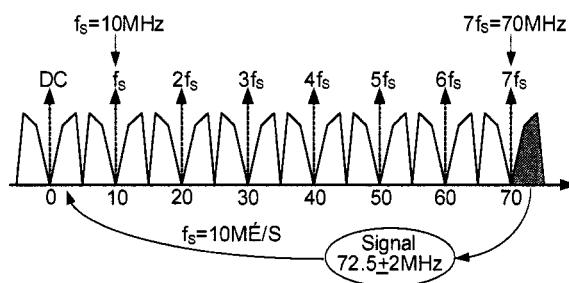

Les circuits d'échantillonnage regroupent généralement au moins un commutateur et un condensateur comme illustré à la figure 1-6. Le commutateur (dans l'état fermé) a toujours une résistance finie qui produit du bruit thermique.

Figure 1-6. Modèle du bruit thermique introduit par le commutateur de l'EB (tiré de [10]).

La densité spectrale de puissance de ce bruit est donnée par:

$$\delta = 4kTRV^2 \text{ (Hz)} \quad (1-3)$$

où k est la constante de Boltzmann, T est la température absolue, et R est la résistance du commutateur dans l'état fermé. Le bruit dans l'échantillon de tension ( $\sigma^2$ ) est le bruit dans une résistance filtré par le circuit du filtre passe-bas constitué par le condensateur d'échantillonnage et la résistance du commutateur.

Ce processus de filtrage conduit à une puissance de bruit exprimée par:

$$\begin{aligned}

\sigma^2 &= 4kTR \int_0^\infty \frac{1}{1+(f2\pi RC)^2} df \\

&= \frac{4kTR}{(2\pi RC)^2} \Big|_0^\infty 2\pi RC \arctan(f2\pi RC) \\

&= \frac{kT}{C}

\end{aligned} \tag{1-4}$$

Ces résultats démontrent que la puissance du bruit thermique est proportionnelle au facteur  $kT/C$ . Un point intéressant est que la tension de bruit ne dépend pas de la valeur de la résistance du commutateur, et le seul paramètre qui peut être ajusté pour lutter contre le bruit est ainsi la valeur du condensateur d'échantillonnage. Bien que la largeur de bande désirée du signal est en général au moins un ordre de grandeur plus petite que la largeur de bande du bruit du circuit d'échantillonnage, le bruit échantillonné est encore déterminé par l'équation (1-4). Dans les CAN, une condition commune est que la puissance de bruit thermique soit plus petite que la puissance du bruit de quantification (qui est égale à  $V_{LSB}^2/12$ ) [16]. Ceci fixe la plus basse limite pour la valeur C du condensateur tel que montré à l'équation (1-5).

$$C > \frac{kT \cdot 12}{V_{LSB}^2} = \frac{kT \cdot 12}{V_{EM}^2 / 2^{2N}} \tag{1-5}$$

Où N est le nombre de bits et  $V_{EM}$  la tension correspondant à l'échelle maximum du CAN. Parfois la condition est plus rigoureuse, permettant seulement 1 dB de dégradation du SNR. Selon l'équation (1-5), dans le cas où la tension a une valeur maximale de 1-volt, les valeurs du condensateur exigées pour une résolution de 10 et 16 bits sont de 0.052 pF

et 210 pF respectivement. Notons que la valeur de condensateur minimale requise pour la résolution de 16 bits est trop grande pour l'intégration sur une puce. Pour surmonter ceci, le sur-échantillonnage est une solution efficace pour les applications à haute résolution. Dans ce cas, la taille du condensateur peut être réduite linéairement avec le rapport de sur-échantillonnage.

### **1.3.2 Gigue de l'horloge d'échantillonnage**

La variation aléatoire de l'instant de l'échantillonnage est connue sous le nom de gigue (jitter). Elle provient notamment du bruit de phase du générateur de l'horloge et du bruit du circuit d'échantillonnage. Comment la gigue est transformée en une erreur d'amplitude dans les tensions échantillonnées, elle peut être expliquée comme suit : l'erreur dans la tension échantillonnée est égale au changement de la tension d'entrée entre l'instant d'échantillonnage idéal et l'instant d'échantillonnage réel. Le changement de tension est proportionnel à la gigue et au taux de changement du signal d'entrée (dérivée). Pour une entrée sinusoïdale, la dérivée est la fonction de cosinus multipliée par la fréquence, qui signifie que l'erreur de tension est proportionnelle à la fréquence et à l'amplitude du signal d'entrée.

$$\delta V = \frac{dV}{dt} \Delta t = 2\pi f V \quad (1-6)$$

### **1.3.3 Autres sources de bruit**

La plupart des circuits EB ont besoin d'un tampon ou d'un amplificateur. Il est nécessaire en mode de blocage. Les sources de bruit internes des amplificateurs utilisés s'ajoutent en

puissance au bruit thermique du commutateur dans son état fermé. Dans l'échantillonnage passif, le bruit est à bande limitée par la constante de temps RC du circuit d'échantillonnage. Quand un amplificateur contribue à la fonction de transfert du circuit, ce qui est habituellement le cas en mode de blocage et, aussi en mode d'échantillonnage, sa largeur de bande finie est susceptible d'être le facteur dominant qui vient limiter la bande passante de l'échantillonneur. En plus du bruit blanc, les circuits d'EB souffrent également du bruit «flicker» ou 1/f. Cependant, dans les applications à haute vitesse (une fréquence d'horloge de plusieurs mégahertz), le bruit blanc domine typiquement.

## 1.4 Architectures des circuits EB

Les architectures des circuits EB peuvent être divisées en ceux à boucle ouverte et d'autres à boucle fermée. La différence principale entre les deux catégories c'est que dans les architectures à boucles fermées, le condensateur, sur lequel la tension est échantillonnée, est enfermée dans une boucle de rétroaction, au moins en mode de blocage.

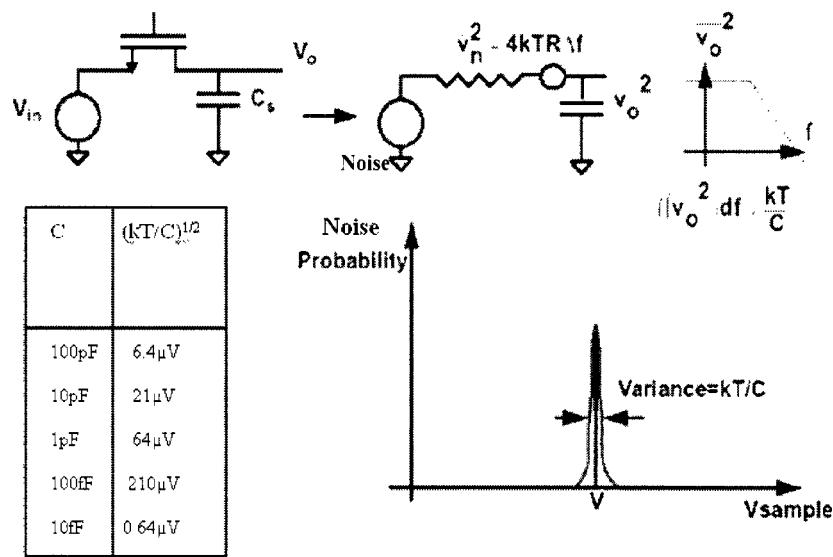

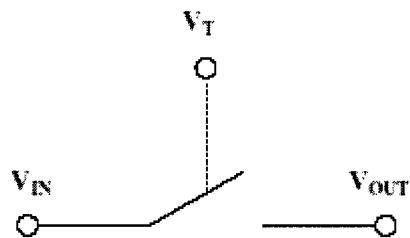

### 1.4.1 Architectures à boucle ouverte

Le circuit EB le plus simple se compose d'un commutateur et d'un condensateur comme il est illustré sur la figure 1-7a. En mode d'échantillonnage, le commutateur est fermé et la tension sur le condensateur suit le signal d'entrée. Pendant le mode de blocage le commutateur est ouvert et la valeur de tension d'entrée au moment d'ouverture du commutateur reste dans le condensateur. Ce circuit, cependant, n'est en mesure

d'alimenter aucune charge. Par conséquent, un tampon doit être utilisé pour alimenter la charge. Un tampon d'entrée peut également être nécessaire pour ajuster le niveau du signal à un niveau approprié au commutateur et pour réduire l'injection de charge du mode de blocage (Fig. 1-7b).

**Figure 1-7.** (a) Symbole d'un circuit EB (b) Son utilisation pratique.

L'avantage principal de cette architecture d'EB en boucle ouverte est sa grande vitesse. L'exactitude, cependant, est limitée par la déformation harmonique résultant du gain non linéaire des amplificateurs opérationnels et l'injection de charge du commutateur est dépendante du signal d'entrée.

#### 1.4.2 Architectures à boucle fermée

Une technique bien connue pour améliorer la linéarité est l'utilisation de la rétroaction négative. La rétroaction peut être employée dans les amplificateurs disposés en boucle ouverte, tel que montré à la figure 1-7b. Cependant, ceci n'aide pas à compenser la déformation induite par le commutateur. La figure 1-8 montre un circuit EB en boucle fermée explicitant cette idée [33, 26].

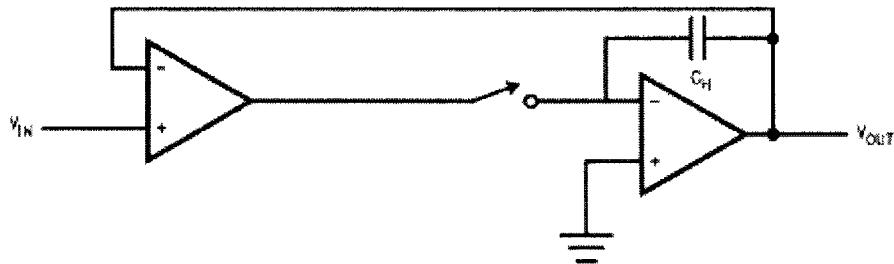

Figure 1-8. Circuit EB simple avec rétroaction.

Puisque la boucle de rétroaction enferme deux amplificateurs en mode suiveur, le circuit doit être fortement compensé afin d'éviter l'instabilité. Ceci réduit naturellement la vitesse du circuit. Un autre inconvénient potentiel est l'injection de charges du mode de blocage par l'intermédiaire des capacités parasites d'entrée de l'amplificateur.

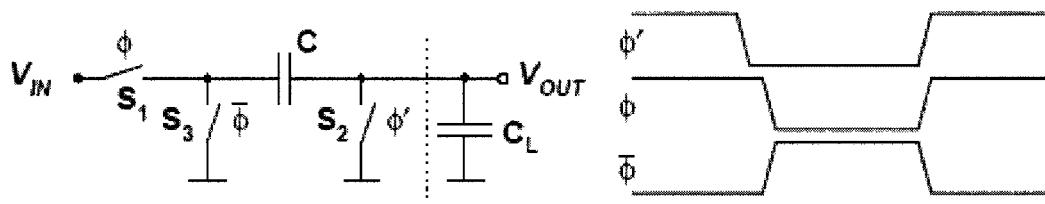

Une architecture d'EB en boucle fermée, généralement utilisée dans des circuits à condensateurs commutés (switched-capacitor-SC), appelée EB «flip-around», est illustrée sur la figure 1-9. Elle effectue l'échantillonnage passivement, c.-à-d. qu'il est fait sans amplificateur opérationnel, ce qui rend l'acquisition du signal rapide. En mode de blocage, le condensateur d'échantillonnage est déconnecté de l'entrée et mis dans une boucle de rétroaction autour de l'amplificateur, comme dans le circuit représenté sur la figure 1-6.

Figure 1-9. Circuit EB à condensateurs commutés.

L'injection de charges des commutateurs qui dépend du signal d'entrée est évitée par une technique appelée «Bottom Plate», qui est fondé sur la synchronisation spéciale des signaux de commande du commutateur. Cette technique est discutée en détail dans le chapitre 3.

## 1.5 Exemples des circuits EB

Le compromis entre la vitesse et la linéarité entraîne l'adoption de l'une ou l'autre de deux approches lors de la conception des circuits EB CMOS à haute résolution et grande vitesse. La première approche qui est à boucle ouverte permet de maximiser la linéarité, et l'autre qui est à boucle fermée facilite l'obtention d'une haute vitesse. Cette section donne une courte description des architectures d'EB trouvées dans des publications récentes.

### 1.5.1 Circuit EB à capacité de Miller

Dans [21] une approche intéressante est employée pour réduire l'injection de charge dépendante du signal d'entrée. L'idée est d'employer l'effet de Miller (équation 1-7) qui consiste à augmenter la capacité efficace ( $C_{hld-eff}$ ) en mode de blocage afin de rendre négligeable le niveau de tension résultant de l'injection de charge.

$$C_{hld-eff} = (1 + A) \left( \frac{C_1 C_2}{C_1 + C_2} \right) \quad (1-7)$$

où A est le gain de boucle ouverte de l'amplificateur montré à la figure 1-10.

L'échantillonnage est rapide et les tailles des commutateurs peuvent être gardées petites, grâce à la petite taille du condensateur d'échantillonnage, qui n'est pas multipliée par l'effet de Miller en mode d'échantillonnage. Le circuit proposé est montré sur la figure 1-10. Son fonctionnement est comme suit. En mode d'échantillonnage les commutateurs (transistors) M1 et M2 conduisent et l'amplificateur est relié ainsi à la rétroaction de gain unitaire.

Figure 1-10. Circuit EB à capacité de Miller [21].

La capacité d'échantillonnage est constituée de la combinaison parallèle des condensateurs C1 et C2, tous les deux reliés à la sortie à basse impédance de l'amplificateur. En mode de blocage, M1 et M2 sont ouverts. Le transistor M2 fonctionne à un potentiel constant et ainsi la charge qu'il injecte dans C1 ne produit pas la déformation. Cependant, Le transistor M1 injecte une charge dépendante de l'entrée dans le noeud x. Puisque le chemin de rétroaction autour de l'amplificateur est ouvert, la valeur efficace de C2 est multipliée par  $(A+1)$ , où A est le gain de boucle ouverte de l'amplificateur (équation 1-7). En raison de la capacité accrue, la charge injectée produit un changement de tension négligeable sur le noeud x.

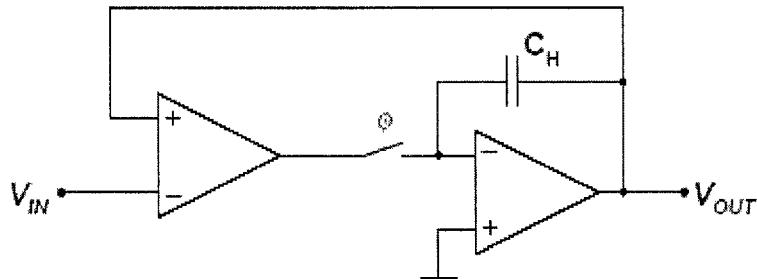

### 1.5.2 Circuit EB à gain défini par le rapport des résistances

Un circuit EB en boucle fermée proposé dans [14] est illustré sur la figure 1-11. En mode suiveur (le commutateur étant fermé) l'amplificateur est relié dans une configuration d'amplificateur inverseur de rétroaction et la tension de sortie du circuit est  $-(R_2/R_1)*V_{IN}$ . Quand le commutateur est ouvert cette tension est échantillonnée dans le condensateur de blocage  $C_H$ . Puisque le commutateur est mis à la masse virtuelle à travers la l'entrée négative de l'amplificateur, il n'introduit pas une erreur de charge dépendante du signal d'entrée. La largeur de bande du mode suiveur du circuit est étendue en ajoutant le condensateur  $C_C$  parallèlement à la résistance  $R_1$  pour créer un zéro, qui est employé pour éliminer le pôle dû au  $C_H$ .

**Figure 1-11.** Circuit EB à gain défini par le rapport des résistances.

Puisque le gain du circuit est facilement ajustable, il peut être employé comme EB inter étages dans les CAN pipeliné. Le circuit peut atteindre des taux d'échantillonnage très élevés (50 MS/s [14]). L'injection de charge en mode de blocage peut également devenir un problème, puisqu'il y a un chemin de couplage connectant l'entrée à la sortie par les résistances. En outre, l'assortiment des résistances est connu pour être plus problématique que celui des condensateurs. Ainsi, il est préférable d'utiliser un circuit dont le gain est

déterminé par un rapport de condensateurs dans les applications où un gain précis est nécessaire.

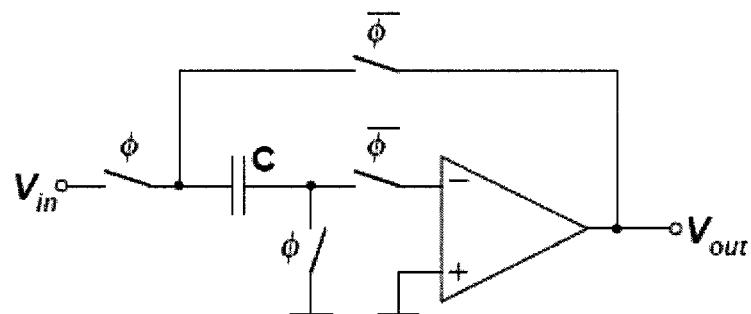

### 1.5.3 Circuit EB à gain défini par le rapport des capacités

Quand un circuit EB avec un gain précis (près de un) est nécessaire, un circuit à condensateurs commutés avec un gain défini par le rapport des condensateurs est la meilleure solution. La figure 1-12 illustre le circuit EB utilisé dans une architecture de CAN pipeliné [20]. La tension d'entrée est échantillonnée passivement dans les condensateurs  $C_1$  et en mode de blocage, la charge échantillonnée est transférée aux condensateurs  $C_2$ . Le rapport de la tension de sortie maintenue sur la tension d'entrée échantillonnée est défini par  $C_1/C_2$ . En mode d'échantillonnage les charges dans  $C_2$ , aussi bien que la sortie de l'amplificateur, sont remis à zéro. Le facteur de rétroaction du circuit dépend du rapport des condensateurs et ainsi du gain.

**Figure 1-12.** Circuit EB à gain défini par le rapport des capacités.

Une modification du circuit représenté sur la figure 1-12 permet un établissement (settling) plus rapide par le moyen d'une configuration d'échantillonnage modifiée. Au lieu de remettre à zéro le condensateur C2 en mode d'échantillonnage, on le dispose parallèlement à C1. En conséquence, la valeur de C1 doit être réduite par celle de C2 pour obtenir le même gain qu'avec le circuit original. La réduction de la valeur C1 augmente le facteur de rétroaction en mode de blocage, ce qui accélère l'établissement. L'amélioration est significative seulement avec des petites valeurs de gain. Une modification proposée dans [22] ajoute un commutateur d'échantillonnage entre les entrées de l'amplificateur. Maintenant, les principaux commutateurs d'échantillonnage, qui sont ouverts légèrement avant le nouveau commutateur, auront besoin de passer seulement un signal en mode commun, qui permet de les rendre petits. En conséquence l'injection déséquilibrée de charge est réduite. L'injection de charge dépendante du signal d'entrée est réduite aussi, puisque dans la nouvelle configuration, la chute de tension entre les entrées de l'amplificateur est seulement la moitié en comparaison de celle résultant de la technique utiliser dans [20] quand la même taille de commutateur est utilisée.

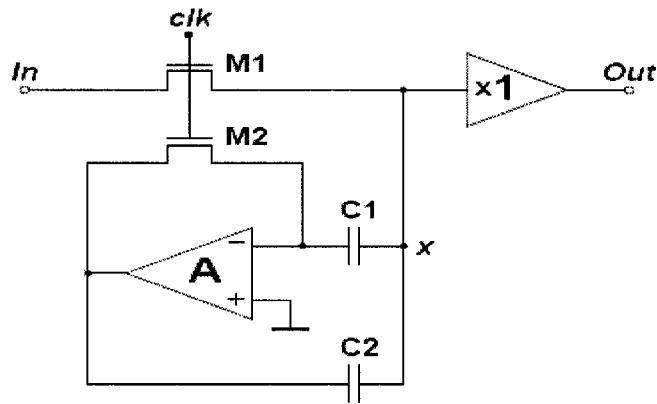

#### **1.5.4 Circuit EB sans la phase de remise à zéro**

L'exigence sur le temps de réaction (slew rate) d'un circuit EB est définie par la différence entre les niveaux successifs de sortie. Un circuit EB à sortie simple qui impose, en mode d'échantillonnage, une nouvelle valeur qui reste à proximité de son dernier niveau de blocage précédent est présenté dans [37]. Dans [28] l'idée est développée en prolongeant la durée la phase de blocage à toute la période d'horloge. Un

circuit entièrement différentiel a été utilisé plus tard dans [18] et sa conception est également rapportée dans [17].

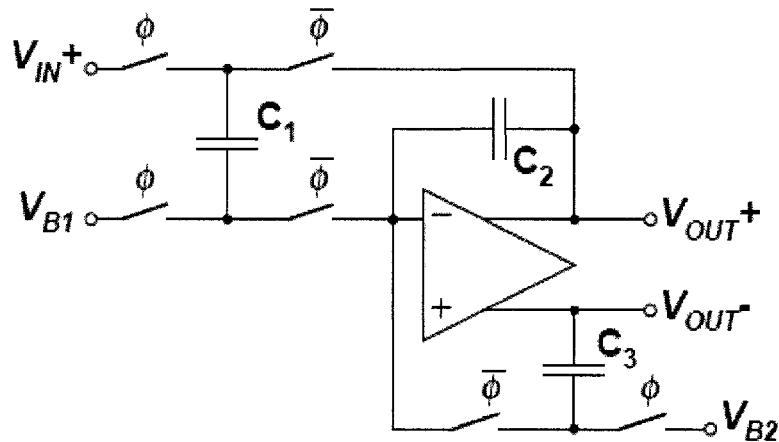

Le circuit de la référence [28] est illustré sur la figure 1-12. Pour plus de clarté, les condensateurs et les commutateurs de seulement la moitié du circuit sont dessinés. L'échantillonnage est effectué passivement avec le condensateur  $C_1$  comme il a été fait pour le circuit de la figure 1-9. Pendant l'échantillonnage, le condensateur  $C_3$  est relié entre  $V_{OUT}$  et à la tension de polarisation  $V_{B2}$ , qui est également le niveau du signal d'entrée en mode commun de l'amplificateur. Dans la transition vers le mode de blocage, le condensateur d'échantillonnage  $C_1$  est relié parallèlement à  $C_2$  et la borne inférieure de  $C_3$  est commutée à l'entrée négative de l'amplificateur. Puisque les tensions sur les condensateurs  $C_2$  et  $C_3$  sont complémentaires, elles s'annulent quand les condensateurs sont reliés en configuration série au début du mode de blocage. Ceci exige naturellement que les condensateurs soient de même valeur.

**Figure 1-13.** La moitié d'un circuit EB complètement différentiel sans la phase de remise à zéro.

L'annulation effectue la remise à zéro du condensateur de blocage  $C_2$  et aucune phase additionnelle de remise à zéro n'est ainsi nécessaire. À la fin du mode de blocage, le condensateur  $C_1$  est déconnecté de la boucle de rétroaction, mais la tension de sortie reste tenue par le condensateur  $C_2$ . Ainsi la phase de blocage est efficacement prolongée pour chevaucher avec la période d'échantillonnage suivante. Ceci, cependant, n'allège pas la condition d'établissement (settling) du circuit, puisque la sortie doit être entièrement établie avant que  $C_1$  soit déconnecté. En raison du manque d'une phase de remise à zéro et du grand facteur de rétroaction, le circuit réalise des taux d'échantillonnage élevés. Un taux d'échantillonnage de 100 MS/s avec approximativement une résolution de 9-bit est réalisé dans [18].

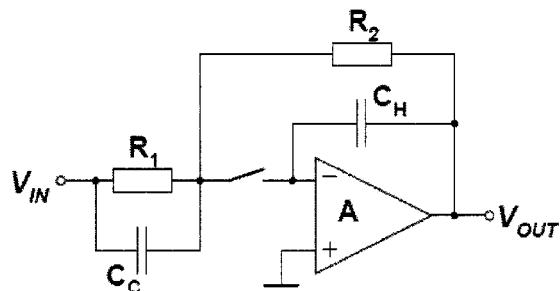

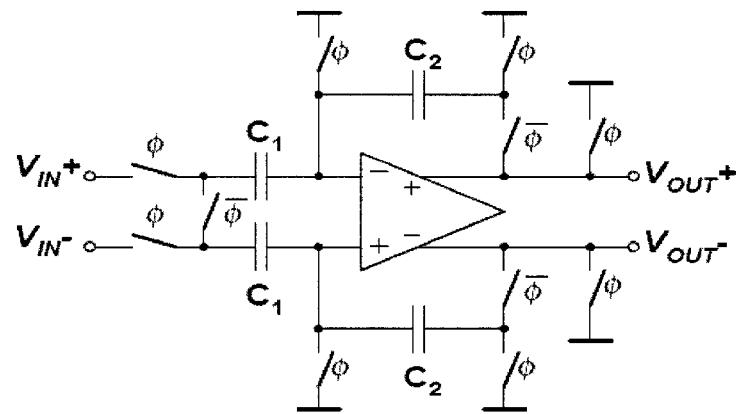

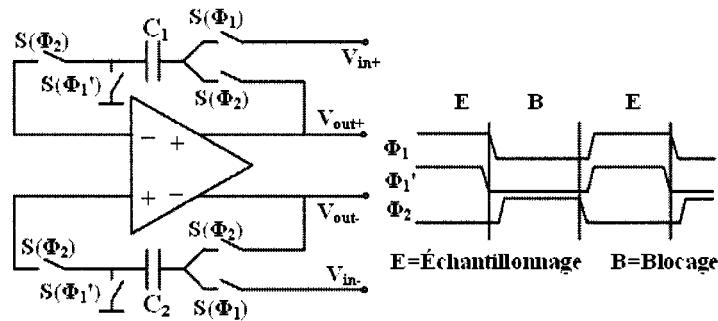

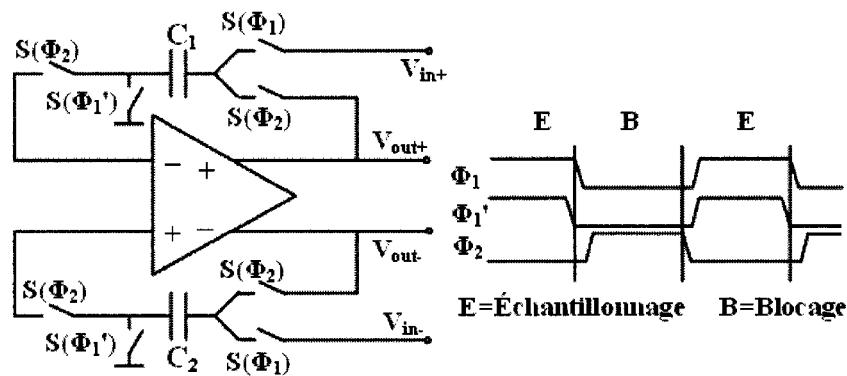

Comme le circuit EB a concevoir est dédié pour un ADC pipeliné de 10bits et 50MS/s, on a pas utilisé l'architecture à capacité de Miller puisqu'elle n'est convenable que pour les applications à basse fréquences [15]. De plus, l'architecture à gain défini par un rapport des résistances a besoin d'un amplificateur à haute vitesse capable d'alimenter une charge résistive, ce qui est difficile à réaliser en CMOS [15]. Concernant le reste des architectures à condensateurs commutés (utilisant un rapport de capacités) présentées dans cette section, qui sont très souhaitables pour les applications à haute vitesse, l'inconvénient c'est la précision exigée dans les tailles des condensateurs. Ceci est difficile du point de vue implémentation. L'architecture à condensateurs commutés adoptée est illustrée sur la figure 1-14 [29, 36], qui est convenable pour une application à haute vitesse, sans avoir d'exigence sur la précision des tailles des condensateurs. Dans la figure 1-14, les condensateurs  $C_1$  et  $C_2$  sont les mêmes pour les deux phases

d'échantillonnage (les commutateurs  $S(\Phi_1)$  et  $S(\Phi'_1)$  sont fermés), et de blocage (les commutateurs  $S(\Phi_2)$  sont fermés).

**Figure 1-14.** L'architecture adoptée pour le circuit EB.

En étudiant chaque élément dans le circuit afin de réduire au maximum la distorsion, un circuit EB bien optimisé peut être conçu avec moins d'exigences et plus de performances, le chapitre qui suit donnera une étude détaillée sur l'amplificateur opérationnel choisi.

## CHAPITRE 2

# L'AMPLIFICATEUR OPÉRATIONNEL

L'amplificateur opérationnel, formant le noyau d'un EB à base de condensateurs commutés est le bloc le plus important pour construire des circuits performants. La résolution et la vitesse de l'EB sont habituellement déterminées par l'amplificateur. En général, le gain DC des amplificateurs en boucle ouverte limite le temps d'établissement de leur signal de sortie, alors que la largeur de bande et le temps de réaction déterminent la fréquence maximale de l'horloge de l'EB. Pour maximiser le rapport signal/bruit de l'amplificateur, la gamme dynamique (plage de variation) du signal de sortie doit être maximisée. Il est donc à noter que l'amplificateur requis pour concevoir un circuit EB à grande vitesse et à haute résolution doit être à gain DC très élevé, une largeur de bande grande et un temps de réaction haut. La manière la plus simple de répondre à ces exigences est d'utiliser les amplificateurs à deux étages (cascode, plié (folded) ou télescopique). L'inconvénient de ces topologies, particulièrement avec l'alimentation à

basse tension, est la plage dynamique du signal de sortie. Les topologies d'amplificateurs et leurs conception sont les matières principales des divers livres et publications [19, 11, 13].

## 2.1 Amplificateur à compensation de Miller

À partir de plusieurs amplificateurs à deux étages, la figure 2-1 montre un amplificateur à compensation de Miller [13]. Avec tous les transistors dans l'étage de sortie de cet amplificateur placés dans la région de saturation, le signal de sortie a une oscillation différentielle de  $2V_{DD}-4V_{DS\text{-sat}}$ , où  $V_{DD}$  est la tension d'alimentation et  $V_{DS\text{-sat}}$  est la tension de saturation d'un transistor. Pour un  $V_{DS\text{-sat}}$  typique de 200mV, l'oscillation différentielle résultante est  $2V_{DD}-0.8V$ , qui est meilleur que celui de la plupart des autres topologies. Le pôle non-dominant, résultant du noeud de sortie, est situé à:

$$P_1 = \frac{g_{m5} \cdot C_c}{C_L \cdot C_c + C_L \cdot C_{L1} + C_c \cdot C_{L1}} = \frac{g_{m5}}{C_L \left( 1 + \frac{C_{L1}}{C_c} \right) + C_{L1}} \quad (2-1)$$

Où  $g_{m5}$  est la transconductance de  $M_5$  (ou  $M_6$ ),  $C_{L1}$  est la capacité parasite entre la grille de  $M_5$  (ou  $M_6$ ) et la masse,  $C_c$  est le condensateur de compensation et  $C_L$  est la capacité de charge. Puisque ce pôle est déterminé principalement par une capacité de charge explicite, l'effet de la compensation Miller s'avère efficace du point de vue augmentation de la fréquence du gain unitaire en augmentant le condensateur de compensation  $C_c$ , ce qui représente l'avantage principal de cette architecture. La largeur de bande au gain unitaire (GBW) d'un amplificateur à compensation de Miller est donné approximativement par:

$$GBW = \frac{g_{m1}}{C_c} \quad (2-2)$$

Où  $g_{m1}$  est la transconductance de  $M_1$  (ou  $M_2$ ). En général, le gain DC de la boucle ouverte de la configuration de base n'est pas assez grand pour les applications à haute résolution. Un autre inconvénient de cette architecture est un faible rejet de bruit d'alimentation aux hautes fréquences en raison du raccordement de  $V_{DD}$  à travers les condensateurs grille/source ( $C_{gs}$ ) de  $M_5$ ,  $M_6$  et  $C_c$ .

**Figure 2-1.** Amplificateur à deux étages avec la compensation de Miller.

## 2.2 Amplificateur cascode plié (folded)

La topologie d'amplificateur cascode plié est montrée à la figure 2-2. La plage de variation de la sortie de cette structure est contrôlée par son étage du type cascode. Tenant compte des marges de sécurité, et de  $V_{DS\text{-sat}}$  exigé à travers cette topologie, l'oscillation du signal de sortie différentiel est  $2V_{DD}-8V_{DS\text{-sat}}-4V_{marge}$ , où  $V_{marge}$  est une petite marge de sécurité supplémentaire à  $V_{DS\text{-sat}}$ . Avec une marge de tension de 100mV, ceci donne  $2V_{DD}-2.0V$ , qui est beaucoup moins que celui d'un amplificateur à

compensation Miller. Le deuxième pôle de cet amplificateur est situé à  $g_{m7}/C_{par}$ , où  $g_{m7}$  est la transconductance de  $M_7$  (ou  $M_8$ ) et  $C_{par}$  est la somme des capacités parasites des transistors  $M_1$ ,  $M_7$  et  $M_9$  à la source du transistor  $M_7$ . La dissipation de puissance de l'amplificateur cascode plié est comparable à celle d'un amplificateur à deux étages. Son GBW est donné par l'équation 2-3.

$$GBW = \frac{g_{m1}}{C_L} \quad (2-3)$$

Où  $g_{m1}$  est la transconductance des transistors  $M_1$  (ou  $M_2$ ),  $C_L$  est la capacité de charge. Ainsi, le GBW est limité par la capacité de charge.

Figure 2-2. Amplificateur cascode plié (folded).

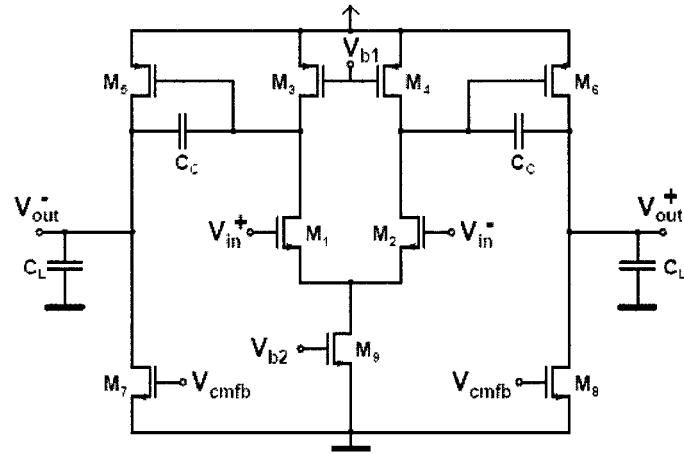

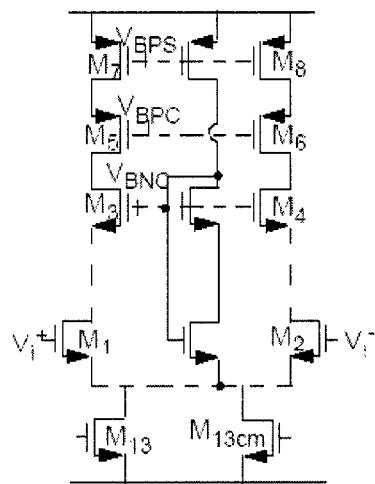

## 2.3 Amplificateur cascode télescopique

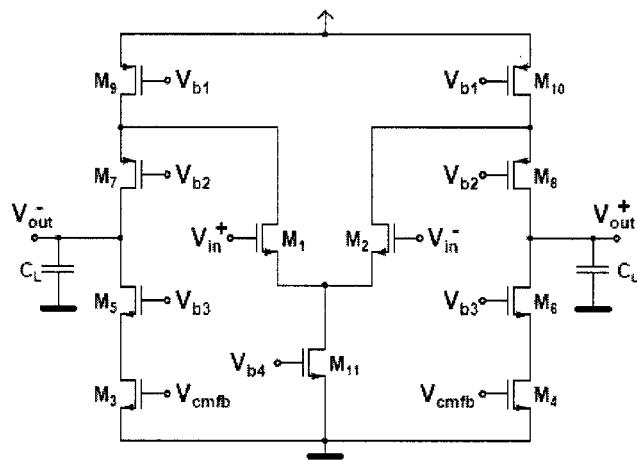

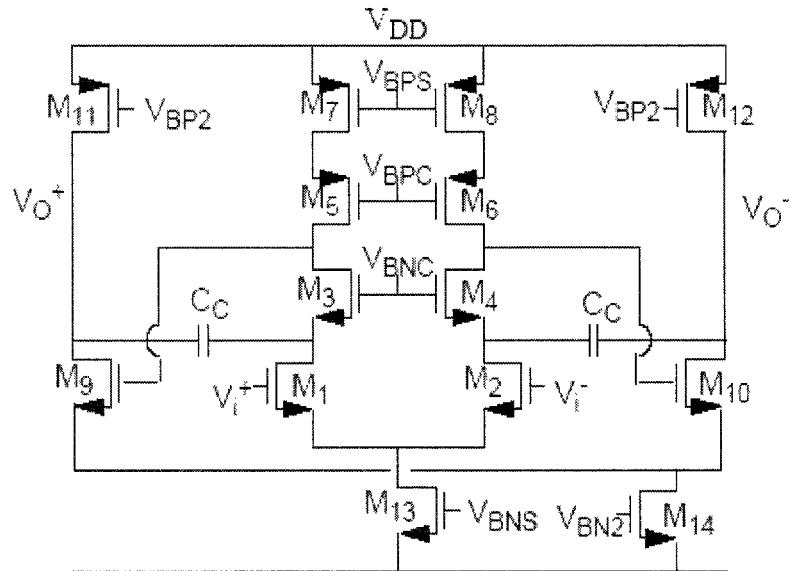

Les conditions du gain DC et de l'oscillation de sortie nécessitent l'utilisation d'un amplificateur à deux étages. La figure 2-3 montre un amplificateur à transconductance (Operational Transconductance Amplifier-OTA) complètement différentiel utilisé dans ce projet. Le premier étage est un amplificateur télescopique, suivi d'une paire

différentielle dans le deuxième étage. Avec cette architecture, un gain DC élevé peut être réalisé. Cette architecture facilite la conception d'un amplificateur à une basse consommation de puissance. Cependant son inconvénient est sa faible plage dynamique du signal différentiel de sortie, qui s'avère  $2V_{DD} - 10V_{DS\text{-sat}} - 6V_{marge}$ . Avec une marge de tension de 100mV, ceci donne  $2V_{DD} - 2.6V$ , qui est beaucoup plus petite que ceux des deux amplificateurs à compensation Miller et le cascode plié. La réponse fréquentielle à large bande résulte du fait que le deuxième pôle, correspondant aux sources de transistors N, qui est déterminé par leurs transconductances, résulte seulement de deux transistors. Ainsi, le GBW est limité par la capacité de charge (équation 2-3). En raison de la simplicité de topologie et du calcul des dimensions de composants, l'amplificateur cascode télescopique est préféré si la plage dynamique du signal de sortie est assez grande pour une application spécifique.

**Figure 2-3.** Amplificateur opérationnel cascode télescopique.

Le signal de sortie de cette architecture peut être élargi en opérant les transistors  $M_7$ ,  $M_8$  et  $M_{13}$  dans la région linéaire tel que proposé à [11]. Afin de préserver des bons rapports

de rejet de mode commun (CMRR) et de source d'alimentation (PSRR) pour cette topologie, des circuits additionnels de rétroaction pour la compensation ont été ajoutés.

Nous examinerons dans les prochaines sections les différents paramètres qui caractérisent l'OTA soient le bruit, la vitesse et la dissipation de puissance.

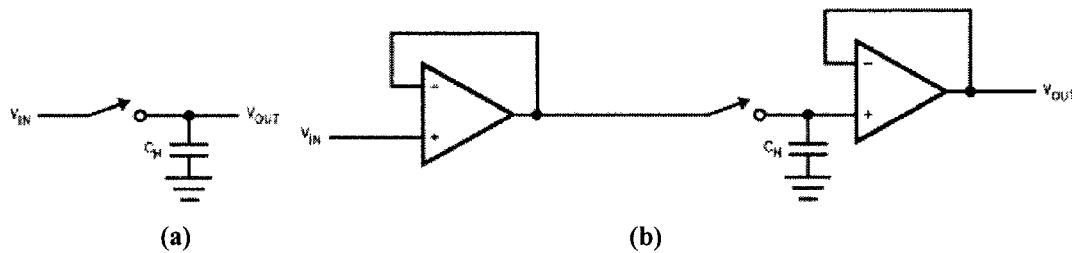

### 2.3.1 Le bruit thermique

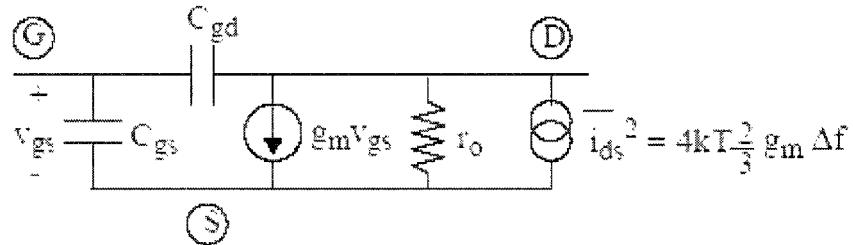

Le bruit thermique à l'entrée d'un transistor simple à source commune, montré dans la figure 2-4, peut être donné approximativement par l'équation 2-4.

$$\overline{v_{n,m}^2} \approx \overline{i_{ds}^2} / g_m^2 = 4kT \cdot \frac{2}{3} \cdot \frac{1}{g_m} \cdot n_{sc} \Delta f \quad (2-4)$$

Le facteur  $n_{sc}$  tient compte du bruit additionnel dans les dispositifs à canal court ( $L \leq 1\mu m$ ), et il est dépendant de la polarisation.

**Figure 2-4.** Le modèle petit signal du bruit thermique d'un transistor simple à source commune.

Le résultat de l'équation 2-4 peut être utilisé pour déterminer le bruit thermique à l'entrée de l'OTA. Le bruit des dispositifs du deuxième étage, en se référant à l'entrée de l'OTA, est atténué par le carré du gain du premier étage. En tant que tels, le bruit thermique à

l'entrée est dominé par les transistors d'entrée ( $M_1, M_2$ ) et les transistors de charge ( $M_7, M_8$ ), comme il est montré à la figure 2-3 et dans l'équation 2-5.

$$\begin{aligned} P_{n,OTA} &= 2 \cdot \left\{ v_{n1,m}^2 + \left( \frac{G_{m3}}{g_{m1}} \right)^2 v_{n3,m}^2 + \left( \frac{G_{m5}}{g_{m1}} \right)^2 v_{n5,m}^2 + \left( \frac{g_{m7}}{g_{m1}} \right)^2 v_{n7,m}^2 + \left( \frac{1}{A_{de1}} \right)^2 \left[ v_{n9,m}^2 + \left( \frac{g_{m11}}{g_{m9}} \right)^2 v_{n11,m}^2 \right] \right\} \\ &\approx 2 \cdot \left\{ 4kT \cdot \frac{2}{3} \cdot \frac{1}{g_{m1}} \left[ 1 + \left( \frac{g_{m7}}{g_{m1}} \right) \right] \right\} \Delta f \end{aligned} \quad (2-5)$$

L'équation 2-5 nous permet de constater que la diminution du rapport ( $g_{m7}/g_{m1}$ ) réduit le bruit thermique de l'OTA. Puisque la transconductance  $g_m$  est donnée par l'équation 2-6, il est souhaitable de réduire au minimum le rapport  $V_{DS1-sat}/V_{DS7}$ .

$$g_m \approx \frac{2I_{DS}}{V_{DS-sat}} \quad (2-6)$$

### 2.3.2 Le bruit de clignotement

Le bruit de clignotement (flicker) est dû au fait que des porteurs minoritaires entrent et sortent aléatoirement dans le canal d'un dispositif MOS. Puisque les fluctuations dans la densité des porteurs de charges dans le canal ont une constante de temps relativement grande, la densité de puissance du bruit est inversement proportionnelle à la fréquence. C'est pourquoi le bruit de clignotement est connu aussi comme le bruit 1/f. Ce bruit à l'entrée d'un transistor simple à source commune est donné par l'équation 2-7.

$$v_{fl,m} = \frac{K_F}{W \cdot L \cdot C_{OX} f} \cdot \Delta f \quad (2-7)$$

La constante  $K_F$  est un paramètre qui diffère d'un processus à un autre. De plus, le NMOS démontre un niveau de bruit plus élevé comparé au PMOS. Une stratégie directe pour

réduire le bruit de clignotement consiste à augmenter la surface de la grille, c.-à-d. largeur et longueur, du dispositif.

Pour la simplicité de la conception, la contribution de bruit de clignotement de l'OTA est réduite en augmentant les tailles des dispositifs d'entrée ( $M_1, M_2$ ) et ceux de la charge ( $M_7, M_8$ ). En augmentant la largeur et la longueur par le même facteur, la surface de la grille est augmentée sans faire changer le rapport de W/L. Pour un courant fixe, ceci garde la transconductance ( $g_m$ ) et la tension de saturation  $V_{DS}$  constantes.

### 2.3.3 Le gain DC

Le gain DC de l'amplificateur (figure 2-3) est le produit du gain des deux premiers étages.

$$A_{DC} = \{g_{m1} \cdot (g_{m3}r_{o3}r_{o1} \| g_{m5}r_{o5}r_{o7})\} \{g_{m9} \cdot (r_{o9} \| r_{o11})\} \quad (2-8)$$

La résistance de sortie du transistor,  $r_o$ , est proportionnelle à la longueur du canal du dispositif.  $M_7, M_8, M_{11}$  et  $M_{12}$  peuvent être faits à long canal pour maximiser  $r_{o7}$  et  $r_{o11}$  dans le gain DC.

### 2.3.4 L'établissement linéaire

L'OTA doit avoir une largeur de bande suffisante pour que l'établissement du signal soit linéaire dans la moitié de la période d'horloge, comme il est montré dans l'équation 2-9.

$$\omega_{uT} = \frac{1}{\tau} \geq 2f_s \cdot n_\tau \quad (2-9)$$

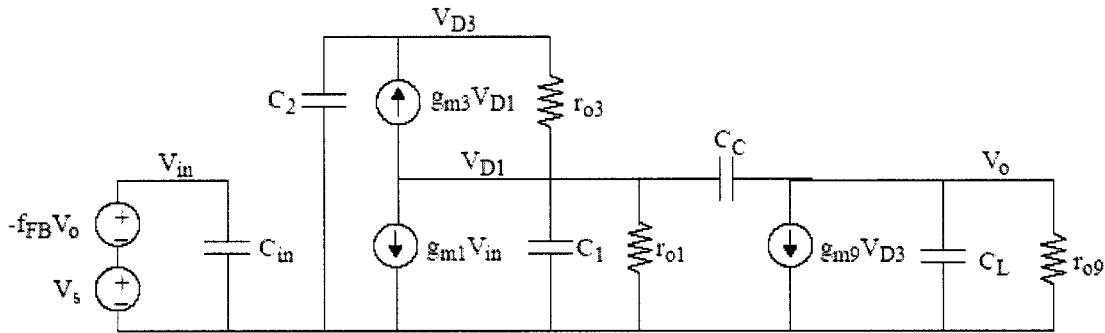

Où  $f_s$  est la fréquence d'échantillonnage, et  $n_T$  est le nombre des constantes de temps. La réponse en fréquence de l'amplificateur sera maintenant analysée pour identifier la façon dont les paramètres du circuit affectent la largeur de bande à gain unitaire. La figure 2-5 illustre le modèle petit signal de l'amplificateur télescopique.

**Figure 2-5.** Le modèle petit signal de l'amplificateur cascode télescopique à deux étages.

Les condensateurs dans la figure sont définis ci-dessous.

$$C_m = C_{gs1} \quad (2-10a)$$

$$C_1 = C_{gd1} + C_{gs3} \quad (2-10b)$$

$$C_2 = C_{gd3} + C_{gd5} + C_{gs9} \quad (2-10c)$$

$$C_L = C_{gd9} + C_{gd11} + C_{C-bottom} \quad (2-10d)$$

$C_{C-bottom}$  représente les capacités parasites d'embase des condensateurs de compensation. Assumons une résistance de sortie infinie,  $r_o$ , la fonction de transfert de l'OTA est donnée par l'équation 2-10 [7].

$$H(s) = \frac{\frac{g_{m1}}{C_2 C_T^2} (g_{m3} g_{m9} - C_2 C_C s^2)}{s^3 + \left[ \frac{g_{m3} (C_L + C_C) - f g_{m1} C_C}{C_T^2} \right] s^2 + \frac{g_{m3} g_{m9} C_C}{C_2 C_T^2} s + \frac{f g_{m1} g_{m3} g_{m9}}{C_2 C_T^2}} \quad (2-10)$$

Où  $C_T^2 = C_1C_L + C_1C_c + C_LC_c$

Bien que l'équation 2-10 fournisse une solution quantitative complète, elle est compliquée pour des calculs à main. Quelques simplifications peuvent être faites afin de permettre au concepteur de trouver une approximation des endroits des pôles. En effet, la bande à gain unitaire en boucle fermée dans l'équation 2-9 peut être réécrite en termes des paramètres du circuit (équation 2-11).

$$\omega_{uT} \approx \frac{g_{m1}}{C_c} \cdot F_{FB} \quad (2-11)$$

Puisque le facteur de rétroaction  $F_{FB}$  est constant pour un gain fixe, et parce que le condensateur de compensation  $C_c$  est déterminé par les considérations du bruit thermiques, la transconductance minimale des dispositifs d'entrée  $g_{m1}$  peut être calculée à partir des équations 2-9 et 2-11. Aussi, les deux pôles non dominants de boucle ouverte peuvent être approximés par les équations 2-12 et 2-13.

$$|p_2| \approx \frac{g_{m9}}{C_{gd11} + C_L} \quad (2-12)$$

$$|p_3| \approx \frac{g_{m3}}{C_c + C_{gs3} + C_{sb3} + C_{gd1}} \quad (2-13)$$

Pour que l'amplificateur reste stable, les pôles non-dominants devraient être rendus beaucoup plus grand que la largeur de bande à gain unitaire. À partir des équations 2-11 et 2-12 on déduit l'équation 2-14.

$$g_{m9} \gg g_{m1} \cdot F_{FB} \cdot \frac{1}{C_c} \quad (2-14)$$

À partir des équations 2-11 et 2-13, les transconductances des dispositifs NMOS ( $M_3$ ,  $M_4$ ) devraient être rendues plus grandes que les transconductances des dispositifs d'entrée ( $M_1$ ,  $M_2$ ), ce qui donne l'équation 2-15.

$$g_{m3} \gg g_{m1} \cdot F_{FB} \quad (2-15)$$

### 2.3.5 Le temps de réaction

Quand une large impulsion est appliquée à l'entrée de l'amplificateur, sa sortie ne peut pas suivre le grand taux de changement de cette entrée. C'est dû à la limite dans le courant différentiel que l'amplificateur de classe A peut fournir. Cette réponse non linéaire est connue par le taux de réaction de l'amplificateur. L'amplificateur peut approcher une limite de réaction dans le premier ou le deuxième étage. La limite de réaction du premier étage est déterminée par la nécessité de charger le condensateur de compensation à la source de  $M_3$  et de  $M_4$ , alors que la limite de réaction du deuxième étage est fixée par la nécessité de charger les condensateurs de charge et de compensation. Ceci requiert qu'avec des spécifications d'établissement fixes, le taux de réaction puisse être amélioré en augmentant le  $V_{GS}-V_{TH}$  des transistors d'entrée ( $M_1$ ,  $M_2$ ,  $M_9$  et  $M_{10}$ ). Ceci exige l'augmentation du courant de polarisation, tel que montré par l'équation 2-16.

$$SR = \min\left(\frac{2I_1}{C_C}, \frac{2I_9}{C_C + C_L}\right) \quad (2-16)$$

### 2.3.6 Rétroaction du mode commun

La rétroaction du mode commun est exigée dans les amplificateurs complètement différentiels pour définir les tensions aux noeuds de sortie à haute impédance.

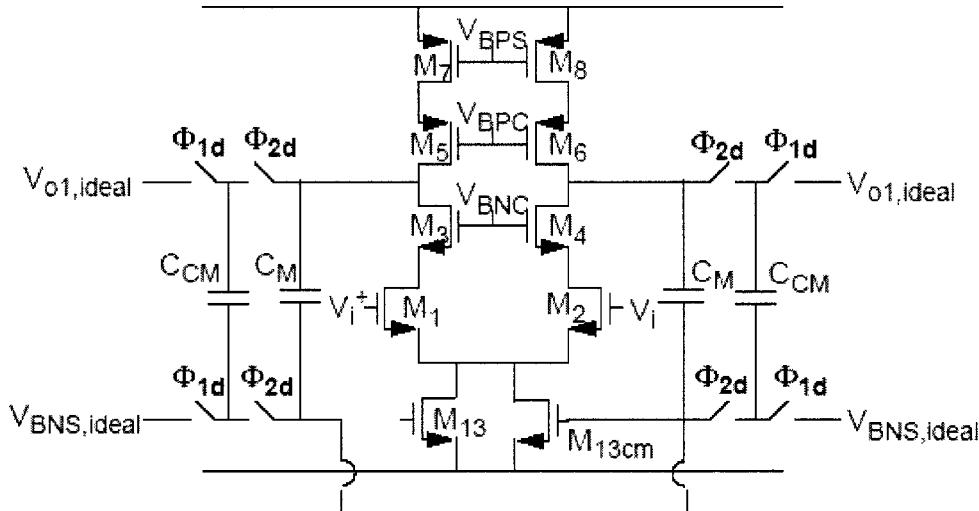

L'amplificateur utilise une rétroaction en mode commun dynamique ou à condensateur commuté. Le deuxième étage complètement différentiel élimine le besoin d'étage d'inversion dans la boucle de rétroaction du mode commun. La figure 2-6 illustre la boucle de rétroaction du mode commun pour le premier étage de l'amplificateur. Les condensateurs  $C_M$  sont utilisés pour saisir la tension du mode commun de la sortie. Pendant  $\Phi_{2d}$ , les condensateurs commutés  $C_{CM}$  définissent la tension DC appropriée sur les condensateurs de sensation. La boucle fonctionne par l'absorption du courant à partir de la source de courant  $M_{13cm}$ . La source totale du courant de queue a été divisée entre  $M_{13}$  et  $M_{13cm}$  pour une meilleure stabilité. Une boucle semblable est conçue pour le deuxième étage de l'amplificateur.

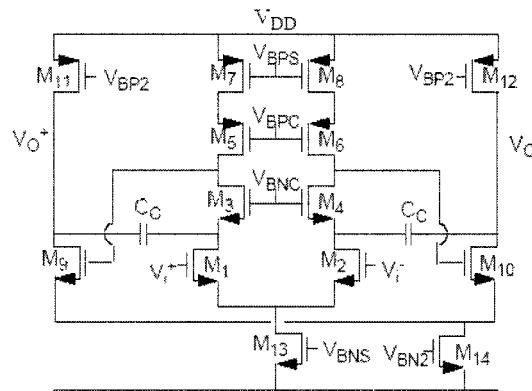

**Figure 2-6.** Le circuit de rétroaction du mode commun pour le premier étage de l'amplificateur.

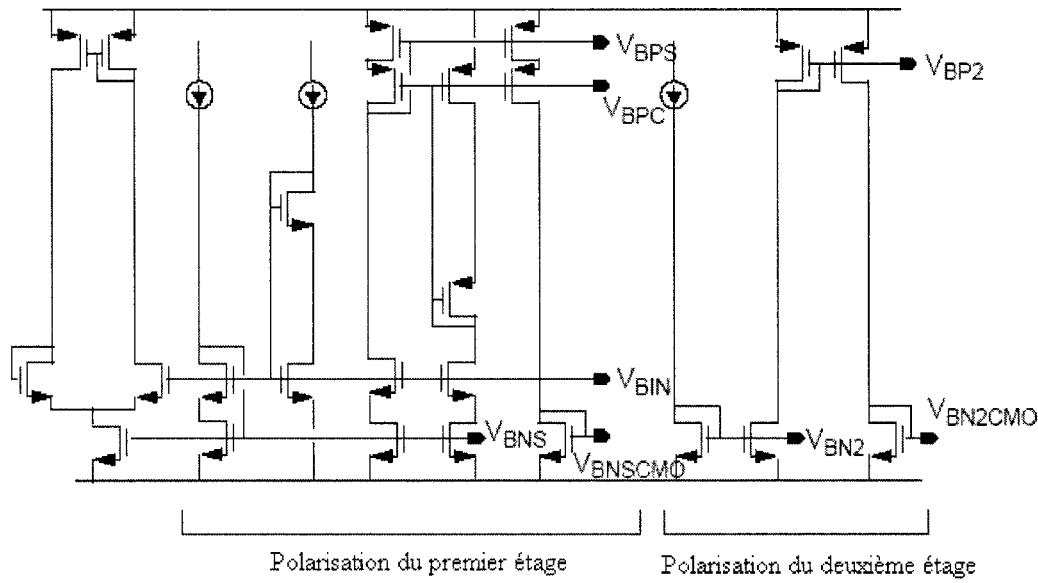

### 2.3.7 La polarisation

La figure 2-7 montre le circuit de polarisation de l'amplificateur. Une polarisation cascode à large oscillation (wide swing) est utilisée. Aussi, une polarisation interne est

utilisée pour les dispositifs NMOS cascode ( $V_{BNC}$ ) dans le première étage, comme représenté sur la figure 2-8. Pour fournir un bon isolement entre les deux étages de l'amplificateur, le premier OTA (où les performances sont les plus critiques) a son propre circuit de polarisation tandis que le deuxième étage a un autre circuit.

Figure 2-7. Le circuit de polarisation de l'OTA.

Figure 2-8. Le circuit cascode de polarisation interne de l'OTA.

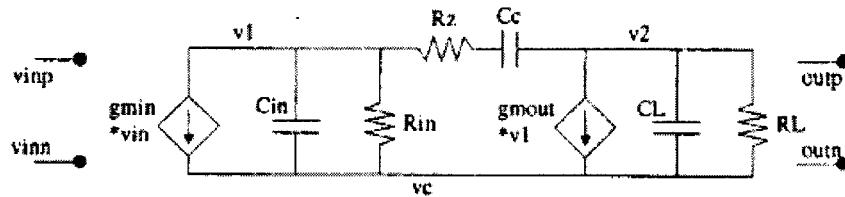

## 2.4 La modélisation comportementale

Pour obtenir un comportement AC précis d'un modèle d'amplificateur en Verilog-A il est souhaitable de remplacer en premier lieu l'amplificateur par son modèle petit signal (small signal model), comme le montre la figure 2-9. Les paramètres du haut niveau du programme sont: la fréquence du gain unitaire, le gain DC, la tension d'offset, la résistance d'entrée, la résistance de sortie et le temps de réaction, concernant le dernier paramètre il est calculé en limitant le courant d'entrée.

**Figure 2-9.** Modèle petit signal (small signal) d'un amplificateur.

En changeant ces paramètres le bloc réalisé peut remplacer un amplificateur réel avec les mêmes paramètres mais en réduisant le temps de simulation, ce qui permet d'optimiser l'échantillonneur bloqueur en moins de temps. L'intérêt dans cette nouvelle méthodologie est d'avoir un amplificateur avec un gain DC et une fréquence de gain unitaire qui sont simplement des paramètres qui peuvent être changer à partir de la fenêtre des propriétés du bloc, ce qui permet d'avoir les meilleurs paramètres de l'amplificateur à concevoir afin que l'EB puisse fournir les meilleures performances requises. Le programme en Verilog-A de l'amplificateur utilisé est fourni en annexe B.

## CHAPITRE 3

# LES AUTRES BLOCS DU CIRCUIT EB

Habituellement, une fois utilisé comme commutateur, un transistor de type MOS opère dans la région de triode (ou la région linéaire). Alors le circuit équivalent pour le transistor est une résistance dont la valeur est commandée par la tension de la grille du transistor. Quand le commutateur est fermé, la valeur de la résistance varie de quelques ohms à quelques kilo-ohms et elle est souvent appelée résistance-ON. En revanche, la résistance d'un commutateur ouvert est si haute que dans la pratique le commutateur est un circuit ouvert, elle est souvent appelée résistance-OFF.

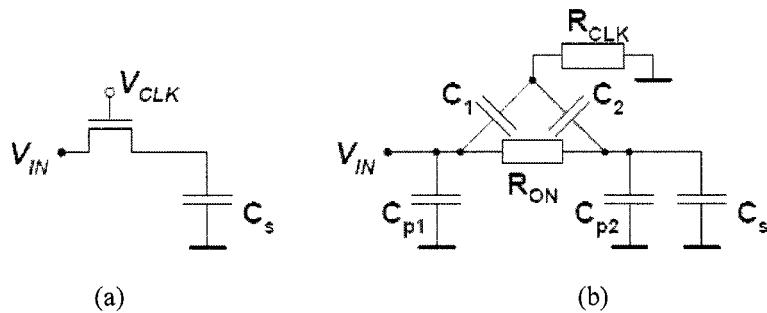

En plus de la résistance-ON finie, il y a également des capacités parasites liées au commutateur. Ce circuit d'échantillonnage simple en MOS est montré sur la figure 3-1a et son circuit RC équivalent, y compris les capacités parasites qui se trouvent sur la figure 3-1b.  $C_{p1}$  et  $C_{p2}$  sont dues aux capacités de la jonction drain/source, et à la capacité de la

jonction canal/substrat. Les capacités parasites des jonctions grille/source et grille/drain et celles de la jonction grille/canal sont représentées par les condensateurs  $C_1$  et  $C_2$ . La résistance  $R_{CLK}$  reflète un modèle de l'impédance de sortie de l'horloge.

**Figure 3-1.** EB en MOS: (a) circuit simple (b) circuit RC équivalent.

La valeur de  $R_{CLK}$  joue un rôle important dans l'injection de charge du mode de blocage dans les applications à haute fréquence, puisqu'elle forme avec  $C_1$  et  $C_2$  un filtre passe haut après que le commutateur soit ouvert.

### 3.1 L'injection de charge

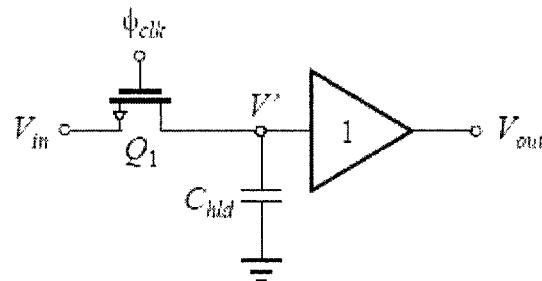

La limitation principale sur la résolution de l'EB est due à ce qui est désigné sous le nom de l'injection de charge (clock feedthrough).

Cette erreur est due aux charges non désirés étant injectés dans le circuit quand les commutateurs s'ouvrent. Pour l'EB dans la figure 3-2, les commutateurs sont normalement réalisés par des transistors de type N seuls, ou avec des portes de transmission CMOS (qui se composent de transistors de type N en parallèle avec des transistors de type P, dont tous les deux doivent s'ouvrir). Quand les commutateurs MOS s'ouvrent, les erreurs de charge se produisent par deux mécanismes. Le premier est dû

aux charges du canal, qui doivent couler en dehors de cette région vers les jonctions du drain et de la source. Les charges du canal d'un transistor qui a un  $V_{DS}$  égal à zéro est donnée par l'équation (3-1).

$$Q_{CH} = WLC_{OX}V_{eff} = WLC_{OX}(V_{GS} - V_t) \quad (3-1)$$

La deuxième catégorie de charges (en général faible, à moins que  $V_{eff}$  soit très petit) est due à la capacité de chevauchement entre la grille et les jonctions. Considérons d'abord quand le commutateur sur la figure 3-2 s'ouvre.

**Figure 3-2.** Circuit EB simple.

Si l'horloge est très rapide, la charge du canal due au commutateur passera à quantité égale vers les deux jonctions [31]. La charge  $Q_{CH}/2$  injectée dans  $C_{hld}$  fera changer  $V'$ , ce qui présente une erreur. Cette charge est donc donnée par

$$\Delta Q_{C_{hld}} = \frac{Q_{CH}}{2} = \frac{WLC_{OX}V_{eff}}{2} \quad (3-2)$$

D'où  $V_{eff}$  est donnée par

$$V_{eff} = V_{GS} - V_t = V_{DD} - V_t - V_m \quad (3-3)$$

Ici,  $V_{in}$  est la tension d'entrée au moment que le commutateur s'ouvre. Il faut noter qu'il est supposé que le signal d'horloge,  $\Phi_{CLK}$ , change entre  $V_{DD}$  et la tension la plus négative dans le circuit.

Le changement de la tension à travers le condensateur  $C_{hld}$  est trouvé de la manière suivante:

$$\Delta V = -\frac{\Delta Q_{C_{hld}}}{C_{hld}} = -\frac{WLC_{OX}V_{eff}}{C_{hld}} = -\frac{WLC_{OX}(V_{DD} - V_t - V_m)}{C_{hld}} \quad (3-4)$$