**Titre:** Capteur d'images CMOS à pixels numériques et à gamme dynamique élevée

Title: [Capteur d'images CMOS à pixels numériques et à gamme dynamique élevée](#)

**Auteur:** Jean-Luc Trépanier

Author: [Jean-Luc Trépanier](#)

**Date:** 2003

**Type:** Mémoire ou thèse / Dissertation or Thesis

**Référence:** Trépanier, J.-L. (2003). Capteur d'images CMOS à pixels numériques et à gamme dynamique élevée [Master's thesis, École Polytechnique de Montréal]. PolyPublie.

Citation: <https://publications.polymtl.ca/7306/>

## Document en libre accès dans PolyPublie

Open Access document in PolyPublie

**URL de PolyPublie:** <https://publications.polymtl.ca/7306/>

PolyPublie URL: <https://publications.polymtl.ca/7306/>

**Directeurs de recherche:** Mohamad Sawan, & Yves Audet

Advisors: [Mohamad Sawan](#), [Yves Audet](#)

**Programme:** Unspecified

Program: [Unspecified](#)

# **NOTE TO USERS**

This reproduction is the best copy available.

**UNIVERSITÉ DE MONTRÉAL**

**CAPTEUR D'IMAGES CMOS À PIXELS NUMÉRIQUES

ET À GAMME DYNAMIQUE ÉLEVÉE**

**JEAN-LUC TRÉPANIER**

**DÉPARTEMENT DE GÉNIE ÉLECTRIQUE

ÉCOLE POLYTECHNIQUE DE MONTRÉAL**

**MÉMOIRE PRÉSENTÉ EN VUE DE L'OBTENTION DU

DIPLÔME DE MAÎTRISE ÈS SCIENCES APPLIQUÉES**

**GÉNIE ÉLECTRIQUE**

**AOÛT 2003**

National Library

of Canada

Acquisitions and

Bibliographic Services

395 Wellington Street

Ottawa ON K1A 0N4

Canada

Bibliothèque nationale

du Canada

Acquisitions et

services bibliographiques

395, rue Wellington

Ottawa ON K1A 0N4

Canada

*Your file* Votre référence

ISBN: 0-612-90862-3

*Our file* Notre référence

ISBN: 0-612-90862-3

The author has granted a non-exclusive licence allowing the National Library of Canada to reproduce, loan, distribute or sell copies of this thesis in microform, paper or electronic formats.

L'auteur a accordé une licence non exclusive permettant à la Bibliothèque nationale du Canada de reproduire, prêter, distribuer ou vendre des copies de cette thèse sous la forme de microfiche/film, de reproduction sur papier ou sur format électronique.

The author retains ownership of the copyright in this thesis. Neither the thesis nor substantial extracts from it may be printed or otherwise reproduced without the author's permission.

L'auteur conserve la propriété du droit d'auteur qui protège cette thèse. Ni la thèse ni des extraits substantiels de celle-ci ne doivent être imprimés ou autrement reproduits sans son autorisation.

---

In compliance with the Canadian Privacy Act some supporting forms may have been removed from this dissertation.

While these forms may be included in the document page count, their removal does not represent any loss of content from the dissertation.

Conformément à la loi canadienne sur la protection de la vie privée, quelques formulaires secondaires ont été enlevés de ce manuscrit.

Bien que ces formulaires aient inclus dans la pagination, il n'y aura aucun contenu manquant.

# Canada

**UNIVERSITÉ DE MONTRÉAL**

**ÉCOLE POLYTECHNIQUE DE MONTRÉAL**

Ce mémoire intitulé:

**CAPTEUR D'IMAGES CMOS À PIXELS NUMÉRIQUES**

**ET À GAMME DYNAMIQUE ÉLEVÉE**

présenté par: TRÉPANIER Jean-Luc

en vue de l'obtention du diplôme de: Maîtrise ès sciences appliquées

a été dûment accepté par le jury d'examen constitué de:

M. KHOUAS Abdelhakim, Ph.D., président

M. SAWAN Mohamad, Ph.D., directeur de recherche

M. AUDET Yves, D.Sc.A., codirecteur de recherche

M. MEINGAN Remi, Ph.D., membre

## Remerciements

Je souhaiterais remercier mon directeur de recherche, Monsieur Mohamad Sawan et mon codirecteur, Monsieur Yves Audet, professeurs à l'École Polytechnique de Montréal, qui m'ont accueilli dans leur équipe de recherche et m'ont permis d'effectuer mes recherches dans d'excellentes conditions.

J'adresse également mes remerciements à Monsieur Abdelhakim Khouas, professeur à l'École Polytechnique de Montréal, et à Monsieur Remi Meingan, ingénieur chez DALSA Semiconducteurs, pour avoir accepté de participer au jury d'examen de ce mémoire.

Je tiens à saluer mes collègues de l'équipe de recherche PolyStim pour leur bonne compagnie et pour leur aide. En particulier, j'aimerais remercier Christian Fayomi pour m'avoir donné de bons points de départ pour la réalisation de ce projet ainsi que Jonathan Coulombe pour son aide et ses judicieux conseils.

Je ne saurais oublier ma grande copine, Isabelle Rousseau, ainsi que ma famille et amis proches pour leur soutien moral inconditionnel, et pour leurs encouragements tout au long de mes études.

Enfin, mes remerciements vont à la CMC, FCAR et le CRSNG pour leur soutien financier et technique.

## Résumé

La technologie à charges couplées (CCD) a été depuis longtemps la technologie de choix pour l'imagerie numérique haute qualité. Cependant, les désavantages liés à la forte consommation de puissance et l'impossibilité d'ajouter d'autres modules de traitement sur la même puce sont des caractéristiques des CCD. Avec l'échelle de technologie réduite du CMOS, il devient possible d'ajouter des modules de contrôle et traitement sur la même puce afin d'obtenir une caméra complètement intégrée sur une seule puce.

L'objectif de ce mémoire est de développer et valider une nouvelle architecture de capteur d'images numérique. Cette architecture doit permettre une flexibilité de façon à utiliser le bloc de base, le pixel numérique, afin de construire des capteurs de différentes résolutions selon l'application visée. De plus, on doit pouvoir contrôler numériquement la matrice photosensible de manière à optimiser la vitesse de capture ou la précision de la représentation numérique. L'architecture doit aussi permettre d'aller chercher le maximum de la gamme dynamique disponible afin de représenter le mieux possible celle de l'œil humain. De cette façon, le capteur doit fonctionner aussi bien dans la lumière intense du soleil que dans l'ombre de la nuit sans aucun ajustement manuel ou intervention externe.

Une nouvelle architecture répondant aux attentes du projet a été conçue et implémentée dans une puce de silicium à l'aide de la technologie CMOS  $0.18\mu\text{m}$ . Des pixels numériques sont à la base de cette nouvelle architecture. Ces pixels peuvent être utilisés afin de construire des matrices de tailles arbitraires sans engendrer de modifications majeures des modules de lecture. Une plaquette de test, un circuit discret ainsi qu'un contrôleur numérique ont été conçus afin de valider le fonctionnement des modules présents dans cette nouvelle architecture.

Les observations du fonctionnement de la puce et du système ont mené à des propositions d'améliorations pour les itérations subséquentes de ce capteur d'images numériques.

## Abstract

Charge coupled devices (CCD) technology has been for a long time the technology of choice in high quality image sensing. Drawbacks are high power consumption and no possible on-chip processing capabilities. With CMOS reduced feature size technology, it becomes possible to add on-chip control and processing units in order to obtain a fully integrated camera on a single chip.

The main objective of this thesis is to develop and validate a new digital image sensor architecture. This architecture must provide a flexible design in order to use the basic building block, the digital pixel, to implement different resolution sensors depending on the target application. It also must be possible to digitally control the sensor to optimize either the speed of the capture or the precision of the digital representation. The resulting architecture must be able to measure the maximum of the available dynamic range in order to represent the capabilities of the human eye. This implies that the sensor must be able to render good images in bright sunlight as well as in dark shadows without any manual adjustments or external interventions.

A new architecture meeting the project goals has been designed and implemented in a CMOS  $0.18\mu\text{m}$  silicon chip. Digital pixels are the basic blocs of this new architecture. These pixels can be used to implement any arbitrary size sensor matrix without involving any major modification in the readout module. A test bench, a discrete component circuit and a digital controller have been implemented to validate the functionality of all the modules of this new sensor architecture.

Observations from the experiments conducted on the chip as led to proposals of enhancement for further versions of this digital image sensor.

---

## Table des matières

---

|                                                               |              |

|---------------------------------------------------------------|--------------|

| <b>REMERCIEMENTS .....</b>                                    | <b>IV</b>    |

| <b>RÉSUMÉ .....</b>                                           | <b>V</b>     |

| <b>ABSTRACT .....</b>                                         | <b>VII</b>   |

| <b>TABLE DES MATIÈRES.....</b>                                | <b>VIII</b>  |

| <b>LISTE DES FIGURES.....</b>                                 | <b>XII</b>   |

| <b>LISTE DES TABLEAUX .....</b>                               | <b>XV</b>    |

| <b>DÉFINITIONS ET ACRONYMES .....</b>                         | <b>XVI</b>   |

| <b>LISTE DES ANNEXES.....</b>                                 | <b>XVIII</b> |

| <b>INTRODUCTION .....</b>                                     | <b>1</b>     |

| <b>CHAPITRE 1 ÉTUDE DES CAPTEURS D'IMAGES.....</b>            | <b>4</b>     |

| 1.1 INTRODUCTION .....                                        | 4            |

| 1.2 CAPTEURS D'IMAGES À BASE DE SEMI-CONDUCTEURS .....        | 5            |

| 1.2.1 Caractéristiques des éléments photosensibles .....      | 7            |

| 1.2.2 Performance des capteurs CMOS et CCD.....               | 9            |

| 1.3 ÉLÉMENTS PHOTOSENSIBLES .....                             | 10           |

| 1.3.1 Photodiode standard .....                               | 11           |

| 1.3.2 Photodiode à couche de semi-conducteur intrinsèque..... | 12           |

| 1.3.3 Phototransistor .....                                   | 13           |

| 1.3.4 Photo-grille .....                                      | 14           |

| 1.3.5 Photodiode à silicium amorphe .....                     | 15           |

| 1.3.6 Avenir des capteurs d'images CMOS .....                 | 15           |

|                                                                |                                                              |           |

|----------------------------------------------------------------|--------------------------------------------------------------|-----------|

| 1.4                                                            | CONSTITUTION DU CIRCUIT D'UN PIXEL.....                      | 16        |

| 1.4.1                                                          | Types de pixels CMOS.....                                    | 17        |

| 1.4.2                                                          | Pixels à circuiterie numérique .....                         | 18        |

| 1.5                                                            | MATRICE DE PIXELS.....                                       | 20        |

| 1.5.1                                                          | Sources d'erreur dans une matrice de pixels.....             | 21        |

| 1.5.2                                                          | Matrice pour la capture d'images couleur.....                | 22        |

| 1.5.3                                                          | Perception des images par l'œil humain .....                 | 24        |

| 1.6                                                            | CONVERSION ANALOGIQUE À NUMÉRIQUE.....                       | 25        |

| 1.6.1                                                          | Consommation de puissance des convertisseurs A/N .....       | 27        |

| 1.7                                                            | GAMME DYNAMIQUE DES CAPTEURS D'IMAGES .....                  | 27        |

| 1.7.1                                                          | Intrascène versus interscène .....                           | 28        |

| 1.7.2                                                          | Méthodes possibles pour élargir la gamme dynamique.....      | 29        |

| 1.8                                                            | COMPARAISON DE CAPTEURS D'IMAGES .....                       | 30        |

| 1.8.1                                                          | Capture rapide et pixel numérique de la référence [27] ..... | 32        |

| 1.8.2                                                          | Conversion analogique à numérique de la référence [46] ..... | 32        |

| 1.9                                                            | CONCLUSION .....                                             | 34        |

| <b>CHAPITRE 2 ARCHITECTURE DU CAPTEUR D'IMAGES .....</b>       |                                                              | <b>35</b> |

| 2.1                                                            | INTRODUCTION .....                                           | 35        |

| 2.2                                                            | ARCHITECTURE DU CAPTEUR.....                                 | 36        |

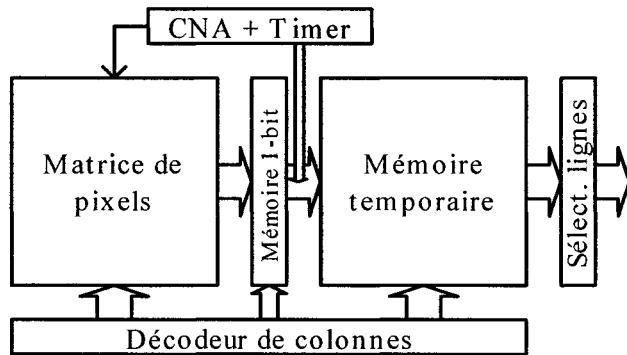

| 2.2.1                                                          | Conversions A/N et lecture des pixels de la matrice .....    | 36        |

| 2.2.2                                                          | Expositions multiples .....                                  | 38        |

| 2.2.3                                                          | Lecture rapide .....                                         | 46        |

| 2.3                                                            | ARCHITECTURE DU PIXEL NUMÉRIQUE.....                         | 49        |

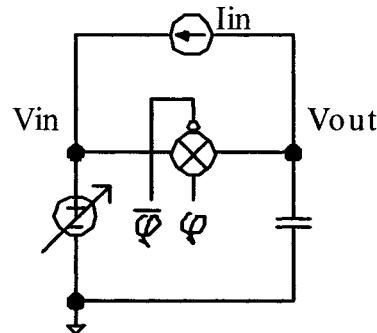

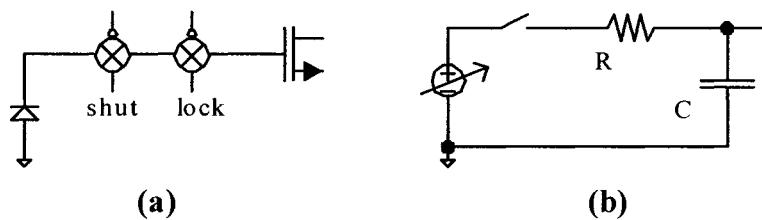

| 2.3.1                                                          | Obturateur et suiveur de la photodiode.....                  | 50        |

| 2.3.2                                                          | Loquet pour l'obturateur .....                               | 51        |

| 2.3.3                                                          | Comparateur intérieur au pixel .....                         | 52        |

| 2.4                                                            | CONCLUSION .....                                             | 53        |

| <b>CHAPITRE 3 DESIGN ET CONTRÔLE DU CAPTEUR D'IMAGES .....</b> |                                                              | <b>55</b> |

|                                             |                                                                      |           |

|---------------------------------------------|----------------------------------------------------------------------|-----------|

| 3.1                                         | INTRODUCTION .....                                                   | 55        |

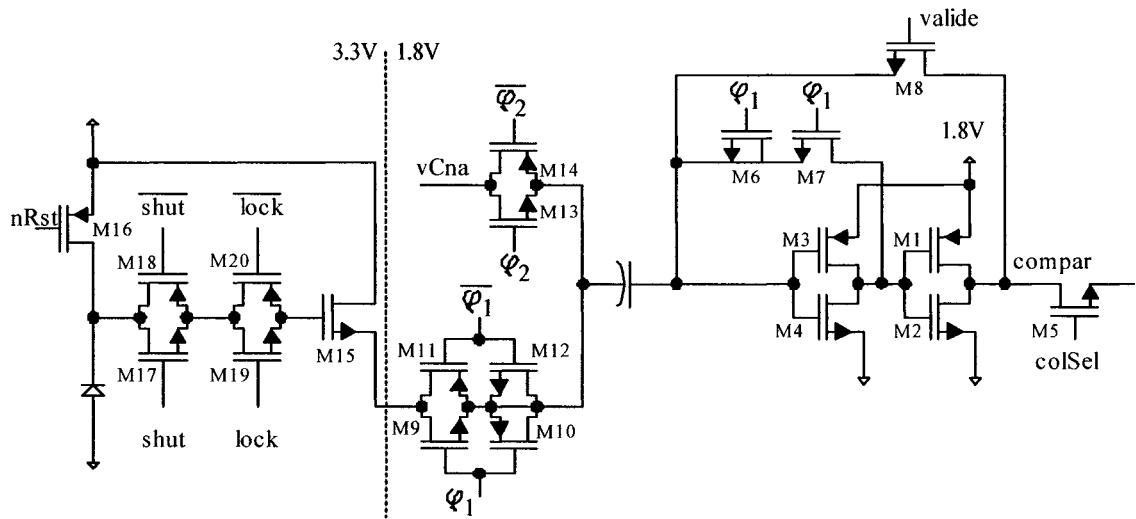

| 3.2                                         | DESIGN DU PIXEL NUMÉRIQUE .....                                      | 56        |

| 3.2.1                                       | Conversion de l'énergie photonique en énergie électrique .....       | 56        |

| 3.2.2                                       | Comparateur dynamique.....                                           | 57        |

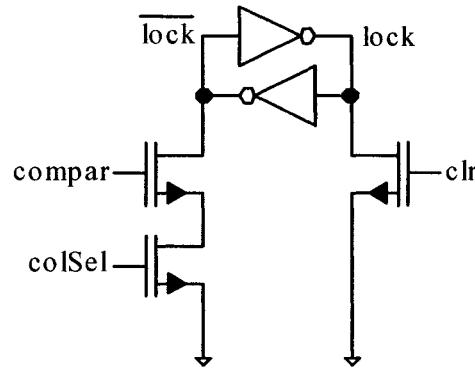

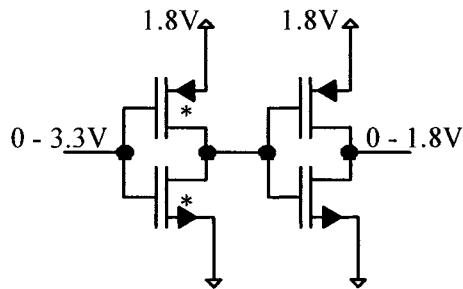

| 3.2.3                                       | Design des obturateurs et loquet.....                                | 60        |

| 3.2.4                                       | Loquet pour l'obturateur électronique .....                          | 62        |

| 3.2.5                                       | Dessin des masques du pixel .....                                    | 64        |

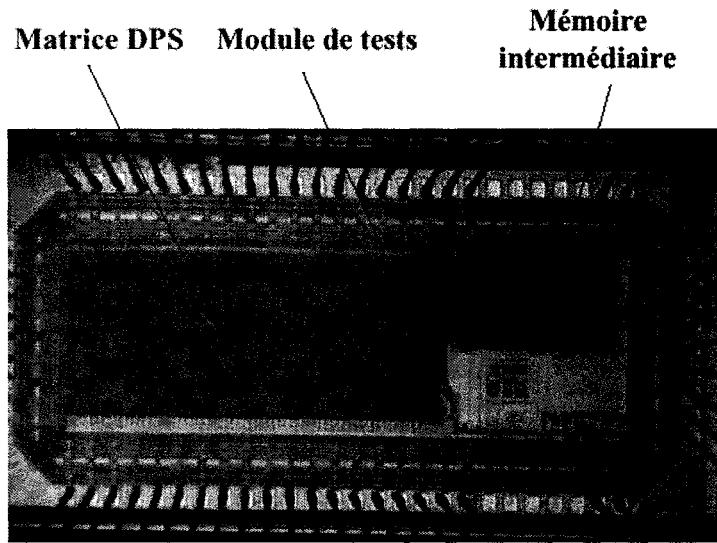

| 3.3                                         | CONCEPTION DE LA PUCE.....                                           | 66        |

| 3.3.1                                       | Matrice de pixels .....                                              | 67        |

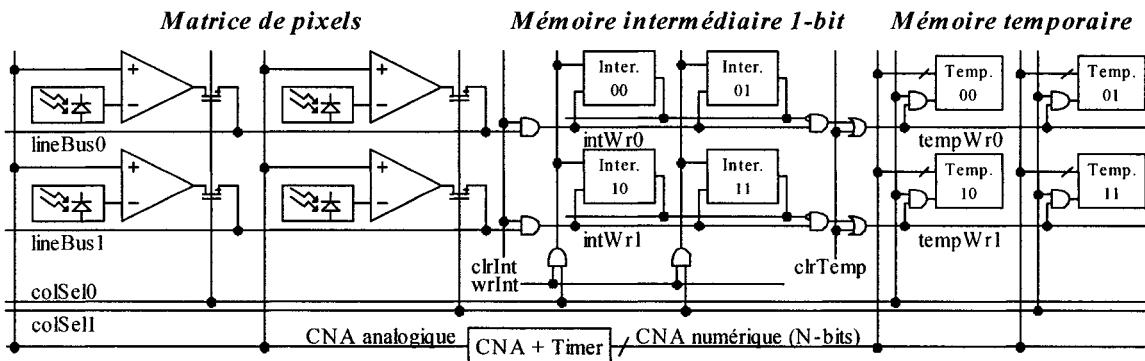

| 3.3.2                                       | Design des mémoires.....                                             | 68        |

| 3.3.3                                       | Module de test .....                                                 | 70        |

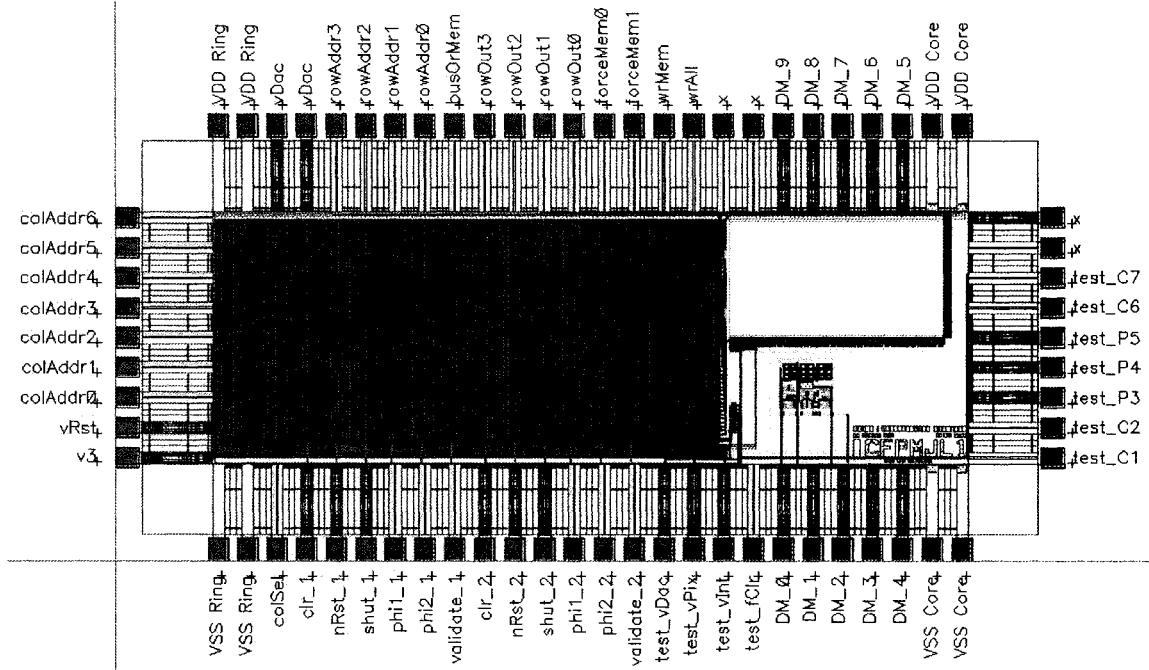

| 3.3.4                                       | Interconnections des blocs et puce complète.....                     | 71        |

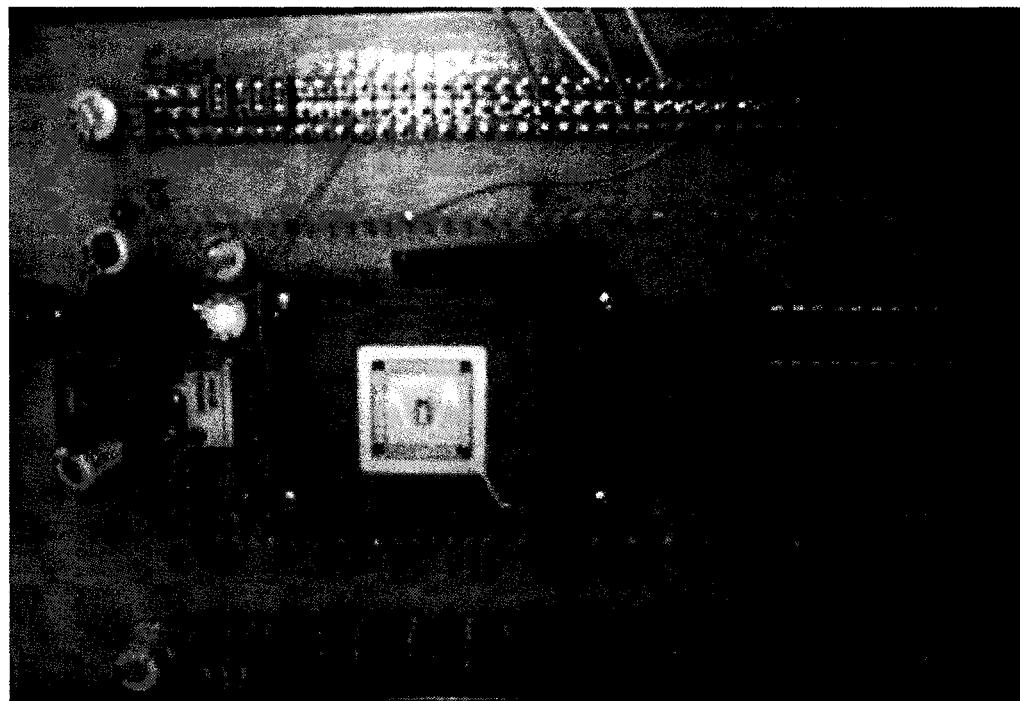

| 3.4                                         | SYSTÈME DE TEST .....                                                | 73        |

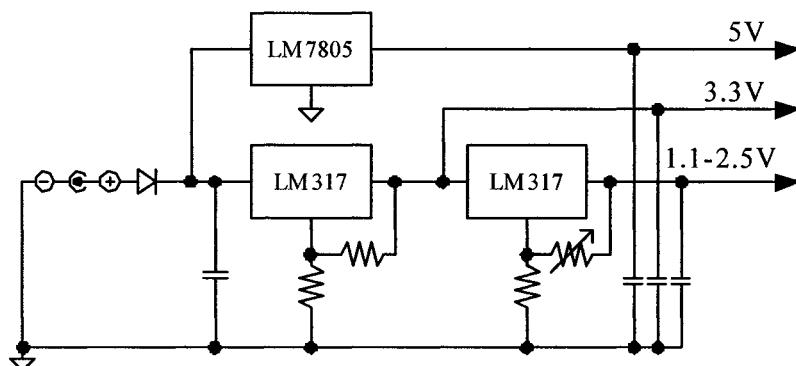

| 3.4.1                                       | Circuits de support.....                                             | 74        |

| 3.4.2                                       | Contrôle numérique .....                                             | 80        |

| 3.5                                         | CONCLUSION .....                                                     | 82        |

| <b>CHAPITRE 4 MESURES ET RÉSULTATS.....</b> |                                                                      | <b>84</b> |

| 4.1                                         | INTRODUCTION .....                                                   | 84        |

| 4.2                                         | PERFORMANCES DU CAPTEUR .....                                        | 84        |

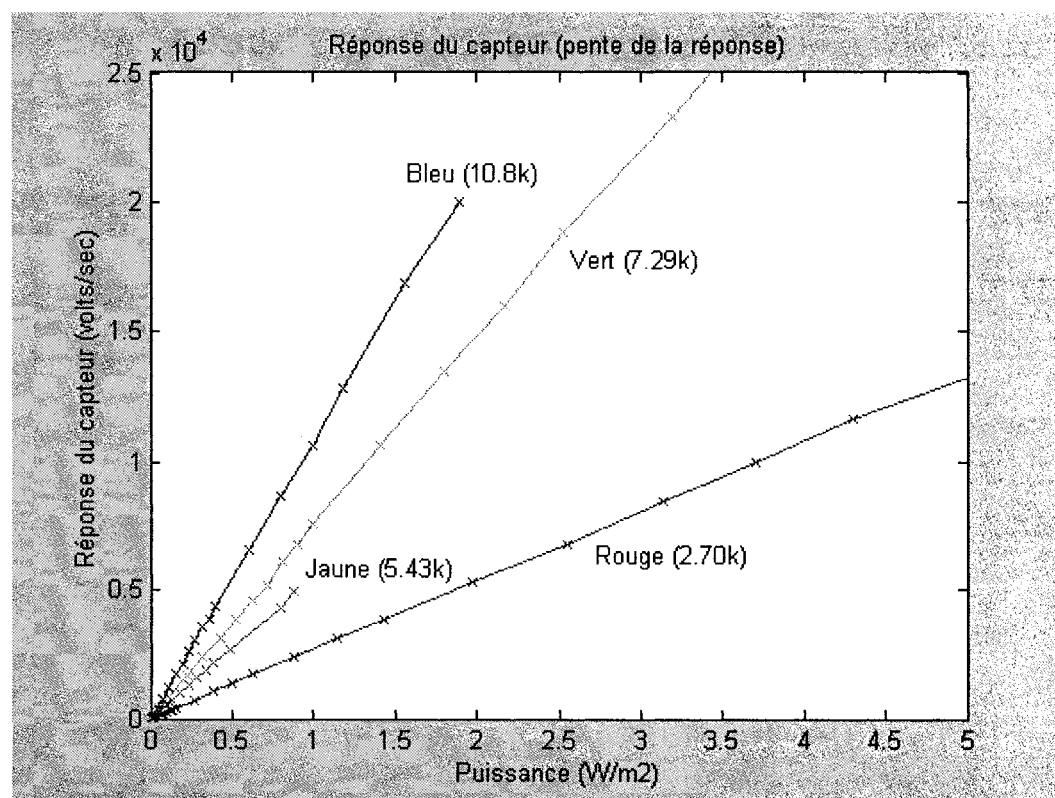

| 4.2.1                                       | Paramètres photoélectriques du capteur .....                         | 86        |

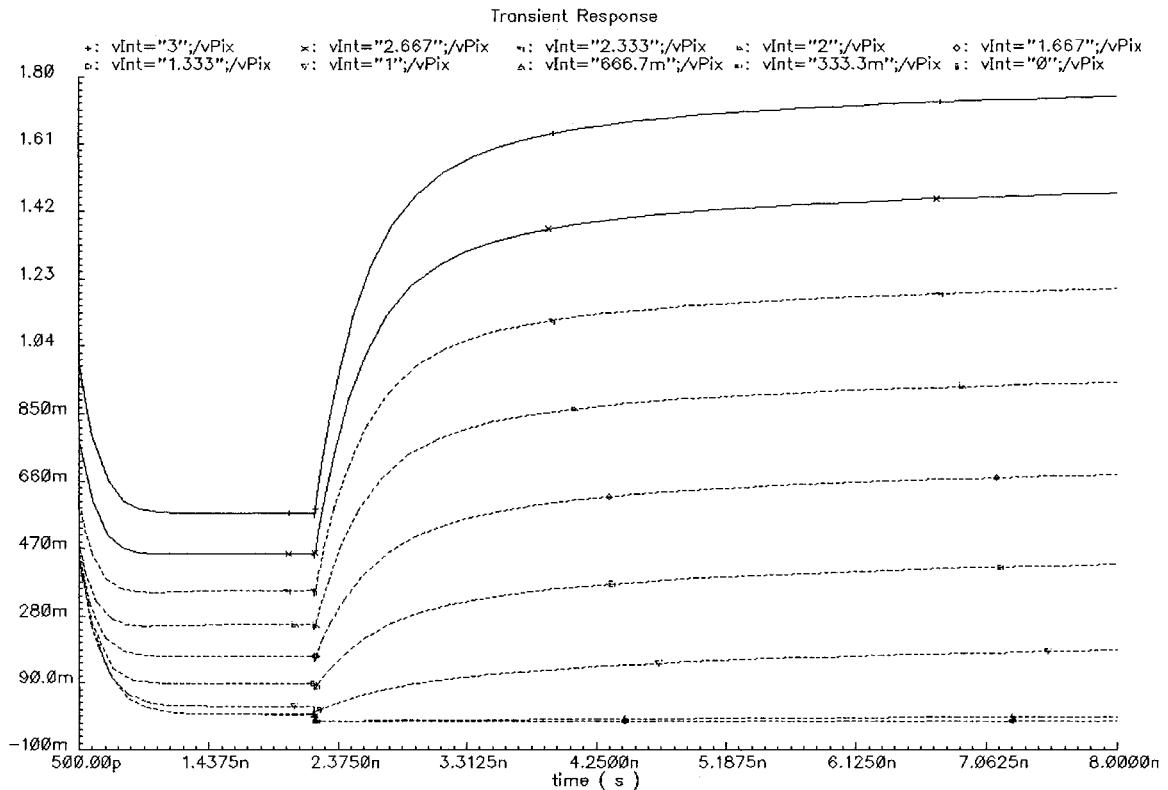

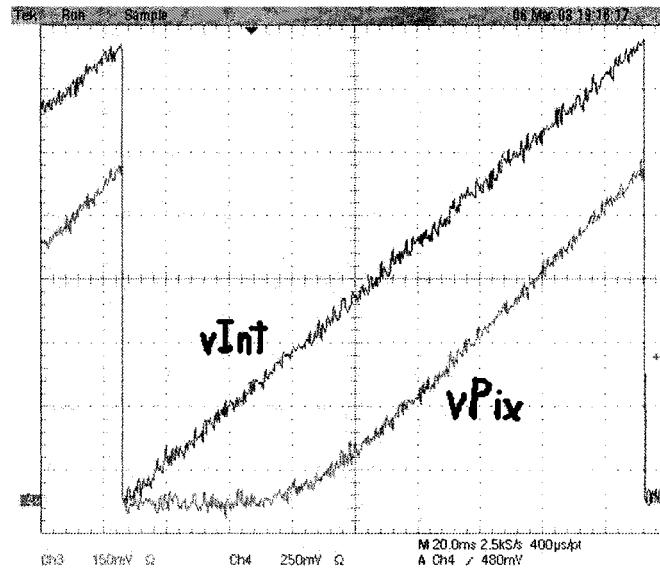

| 4.2.2                                       | Performances du suiveur dynamique.....                               | 88        |

| 4.2.3                                       | Précision du comparateur .....                                       | 91        |

| 4.2.4                                       | Gamme dynamique du capteur .....                                     | 97        |

| 4.2.5                                       | Transfert des données .....                                          | 105       |

| 4.2.6                                       | Performances de l'architecture proposée.....                         | 108       |

| 4.3                                         | DEVELOPPEMENTS FUTURS.....                                           | 109       |

| 4.3.1                                       | Amélioration potentielle de la qualité des images en CMOS.....       | 110       |

| 4.3.2                                       | Pixel numérique amélioré.....                                        | 114       |

| 4.3.3                                       | Intégration du capteur dans le cadre du projet d'implant visuel..... | 117       |

|                                                 |            |

|-------------------------------------------------|------------|

| 4.3.4 Méthodologie pour la suite du projet..... | 118        |

| 4.4 CONCLUSION .....                            | 120        |

| <b>CONCLUSION .....</b>                         | <b>122</b> |

| <b>BIBLIOGRAPHIE .....</b>                      | <b>125</b> |

## Liste des figures

---

---

|                                                                                  |    |

|----------------------------------------------------------------------------------|----|

| FIGURE 1.1: CAPTEUR CMOS STANDARD (TIRÉ DE [48]). .....                          | 5  |

| FIGURE 1.2: QUALITÉ DE SOUS-ÉCHANTILLONNAGE (TIRÉ DE [12]).....                  | 8  |

| FIGURE 1.3: PIXEL DE CAPTEUR STANDARD (TIRÉ DE [48]).....                        | 11 |

| FIGURE 1.4: PHOTODIODE PPD, STRUCTURE PIN. ....                                  | 12 |

| FIGURE 1.5: DESIGN DE DIFFÉRENTS PHOTOTRANSISTORS .....                          | 14 |

| FIGURE 1.6: NOMBRE DE TRANSISTORS INTÉGRÉS DANS UN PIXEL DPS (TIRÉE DE [15]).... | 20 |

| FIGURE 1.7: IMAGE SÉPARÉE PAR UN PRISME (TIRÉ DE [48])......                     | 23 |

| FIGURE 1.8: MOSAÏQUE À PATRON DE BAYER (TIRÉ DE [48]).....                       | 23 |

| FIGURE 1.9: TRANSMISSION DES FILTRES DE COULEUR (TIRÉ DE [48])......             | 25 |

| FIGURE 1.10: IMAGE DU CAPTEUR (TIRÉ DE [27]). .....                              | 32 |

| FIGURE 1.11: COMPOSANTES DU PIXEL (TIRÉ DE [46]).....                            | 33 |

| FIGURE 2.1: SCHÉMA DE L'ARCHITECTURE DU CAPTEUR. ....                            | 36 |

| FIGURE 2.2: MÉMORISATION DE LA SORTIE NUMÉRIQUE DES PIXELS. ....                 | 37 |

| FIGURE 2.3: SÉQUENCE LECTURE/ÉCRITURE POUR UNE IMAGE. ....                       | 38 |

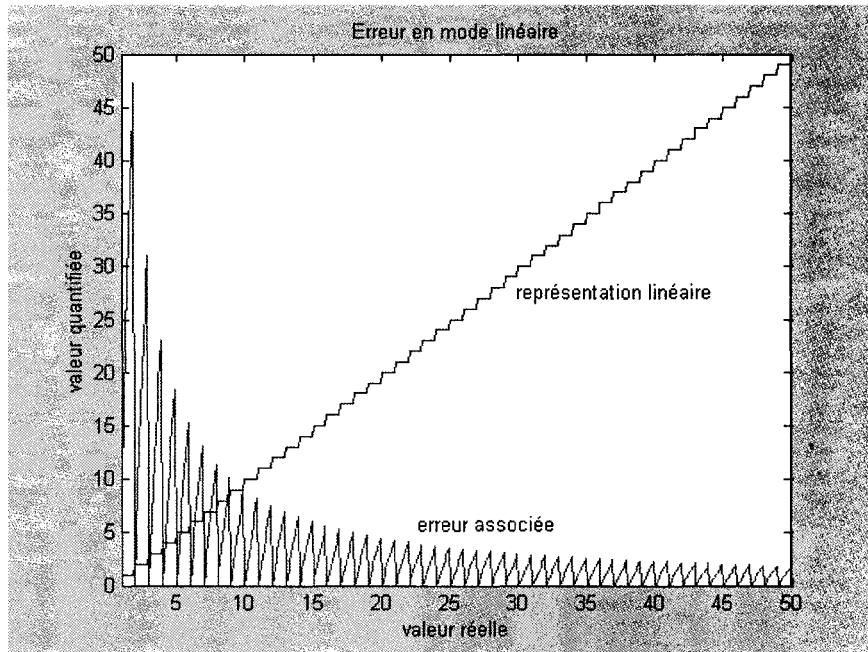

| FIGURE 2.4: ERREUR EN MODE LINÉAIRE. ....                                        | 40 |

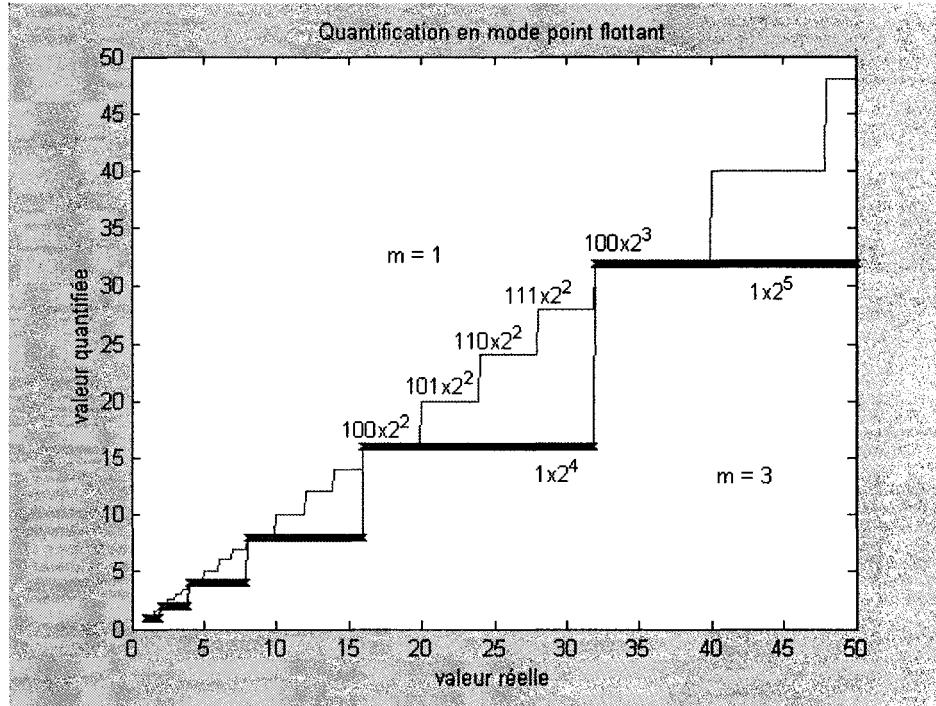

| FIGURE 2.5: REPRÉSENTATION EN MODE POINT FLOTTANT. ....                          | 41 |

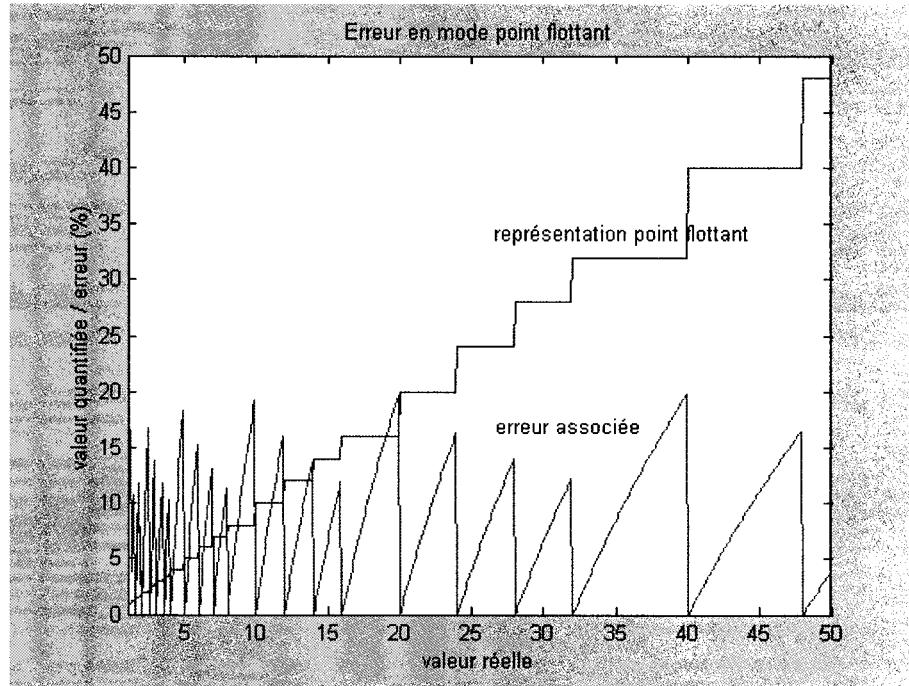

| FIGURE 2.6: ERREUR EN MODE POINT FLOTTANT. ....                                  | 42 |

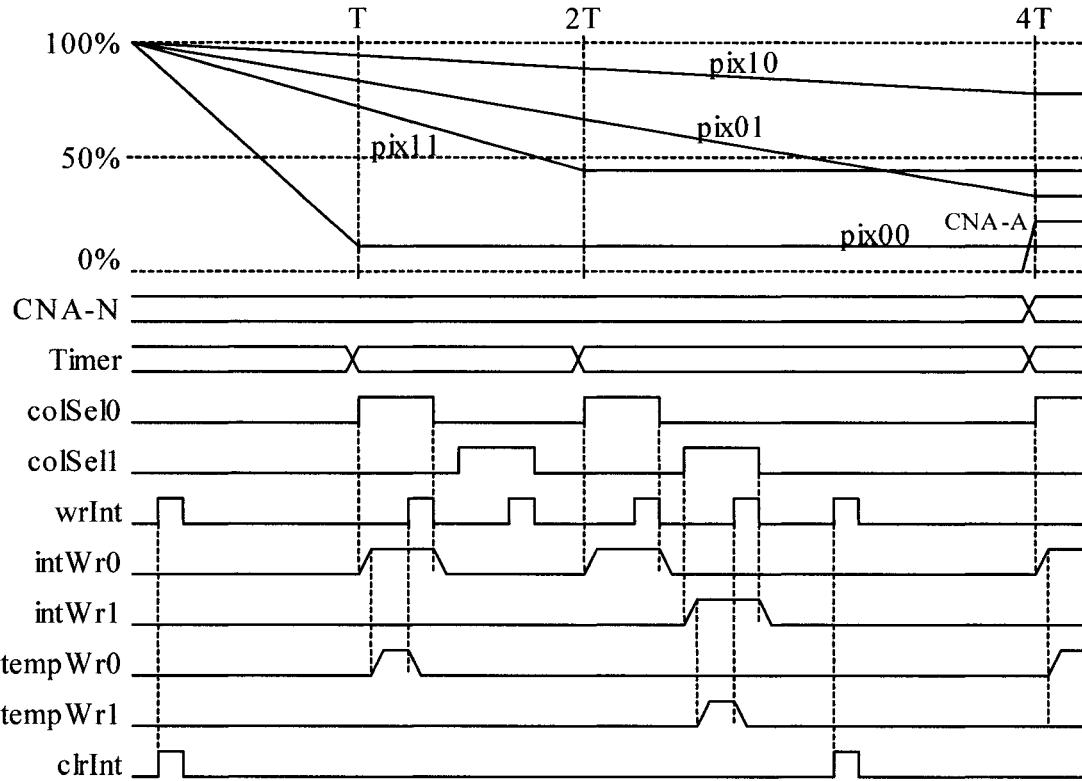

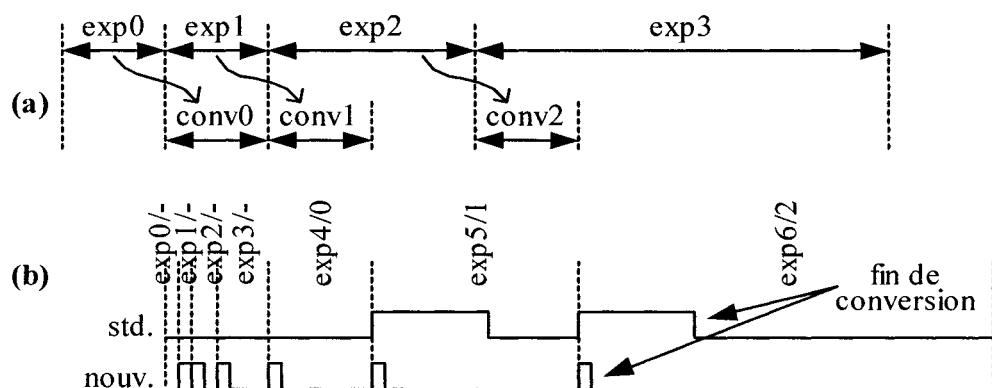

| FIGURE 2.7: SÉQUENCE LECTURE/ÉCRITURE EN MODE EXPOSITIONS MULTIPLES. ....        | 44 |

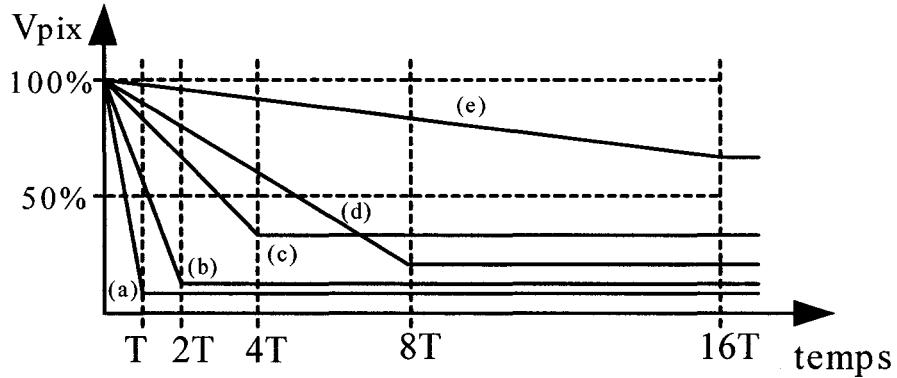

| FIGURE 2.8: EXPOSITIONS MULTIPLES POUR CINQ PIXELS DIFFÉRENTS.....               | 45 |

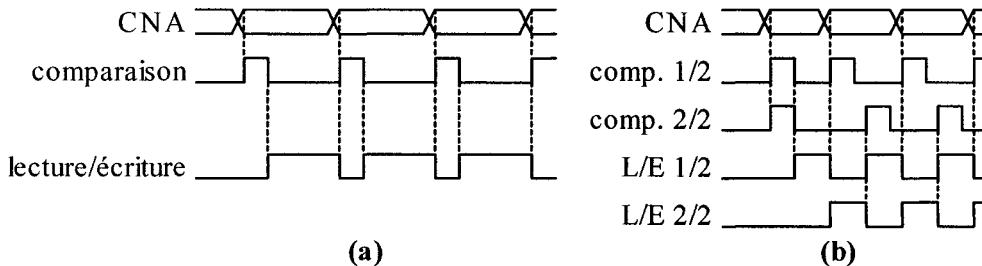

| FIGURE 2.9: PIPELINAGE DES PHASES DE LECTURE/ÉCRITURE .....                      | 46 |

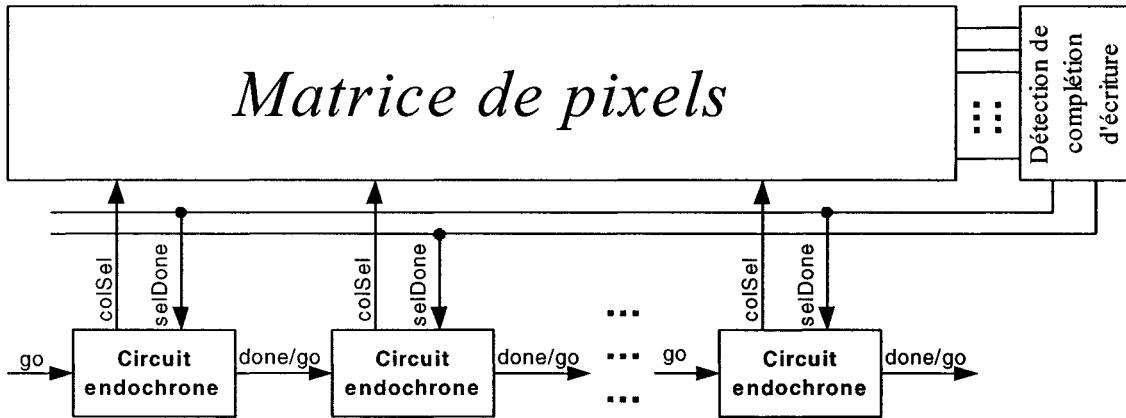

| FIGURE 2.10: ACTIVATION DES COLONNES À L'AIDE D'UN CIRCUIT ENDOCHRONE. ....      | 47 |

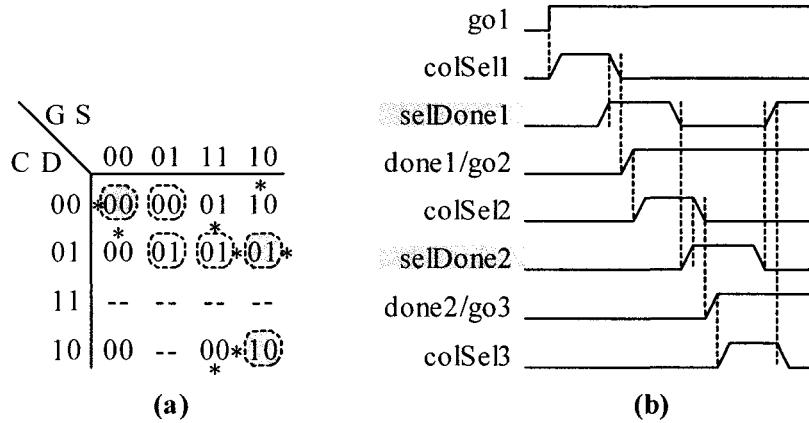

| FIGURE 2.11: DESIGN DU CIRCUIT ENDOCHRONE .....                                  | 48 |

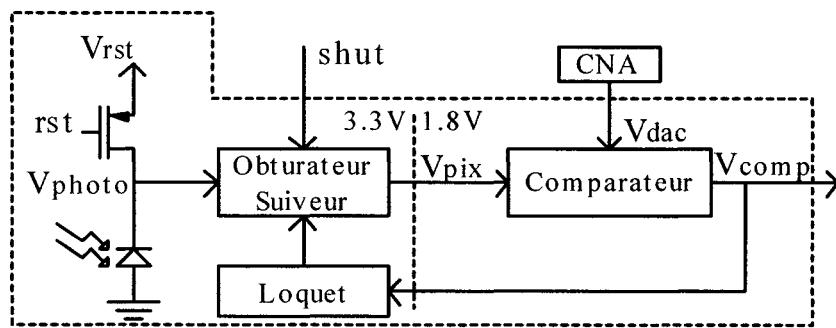

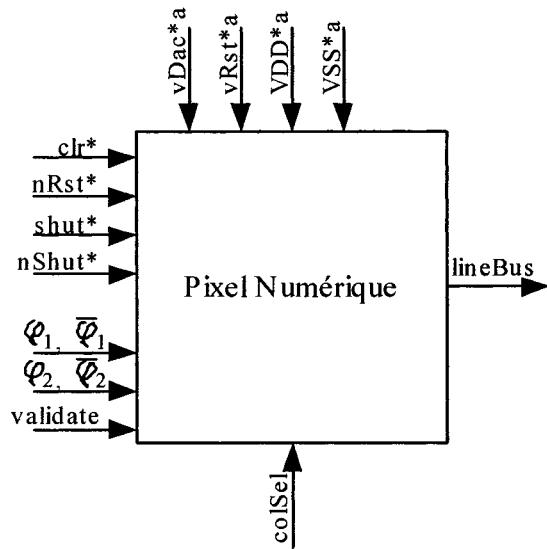

| FIGURE 2.12: SCHÉMA BLOC DU PIXEL NUMÉRIQUE.....                                 | 49 |

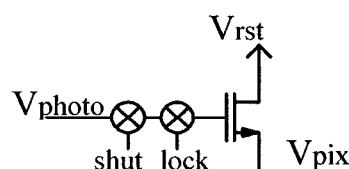

| FIGURE 2.13: CIRCUIT DE L'OBTURATEUR ET DU SUIVEUR. ....                         | 50 |

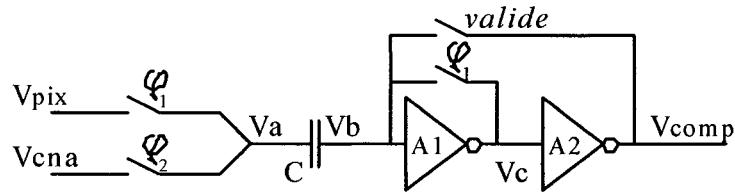

| FIGURE 2.14: CIRCUIT DU COMPARATEUR. ....                                        | 52 |

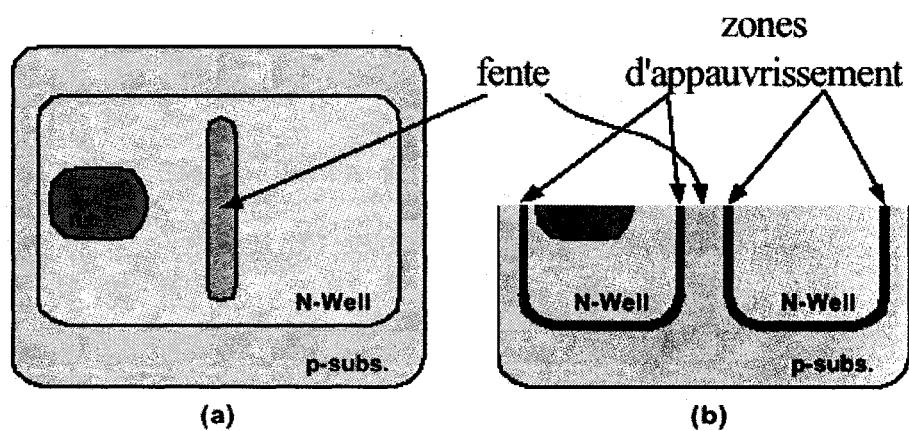

| FIGURE 3.1: TOPOLOGIES DE PHOTODIODES (PD).....                                  | 57 |

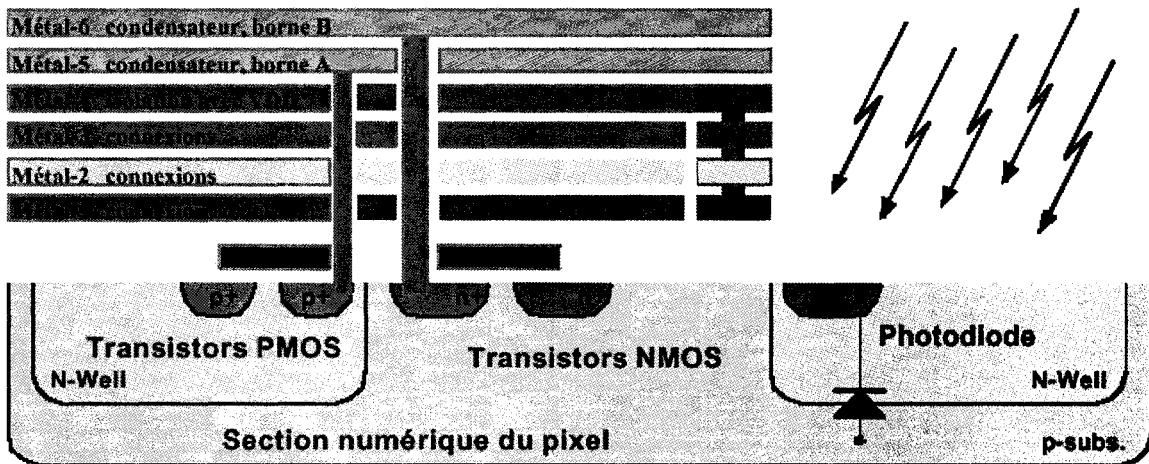

| FIGURE 3.2: VUE EN COUPE DU PIXEL NUMÉRIQUE. ....                                | 58 |

|                                                                                |    |

|--------------------------------------------------------------------------------|----|

| FIGURE 3.3: INJECTION DE CHARGES ET EXCURSION DE L'HORLOGE.....                | 59 |

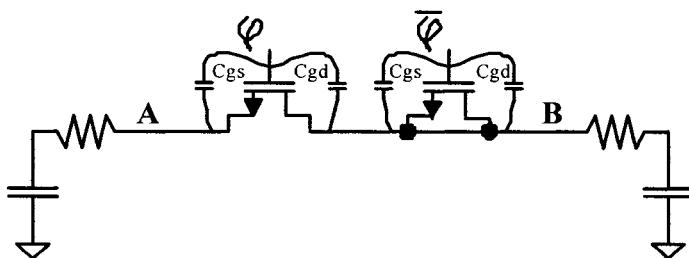

| FIGURE 3.4: TRANSISTORS D'UNE PORTE DE TRANSMISSION.....                       | 61 |

| FIGURE 3.5: OPTIMISATION D'UNE PORTE DE TRANSMISSION.....                      | 61 |

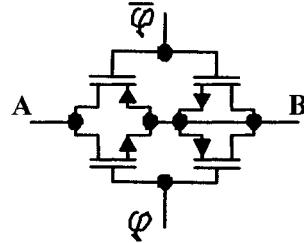

| FIGURE 3.6: MÉMOIRE STATIQUE POUR LE LOQUET. ....                              | 63 |

| FIGURE 3.7: CONVERSION 3.3V à 1.8V. ....                                       | 64 |

| FIGURE 3.8: DESSIN DU PIXEL AU NIVEAU TRANSISTORS. ....                        | 65 |

| FIGURE 3.9: DESSIN DES MASQUES DU PIXEL. ....                                  | 65 |

| FIGURE 3.10: SIGNAUX NÉCESSAIRES À CHAQUE PIXEL. ....                          | 68 |

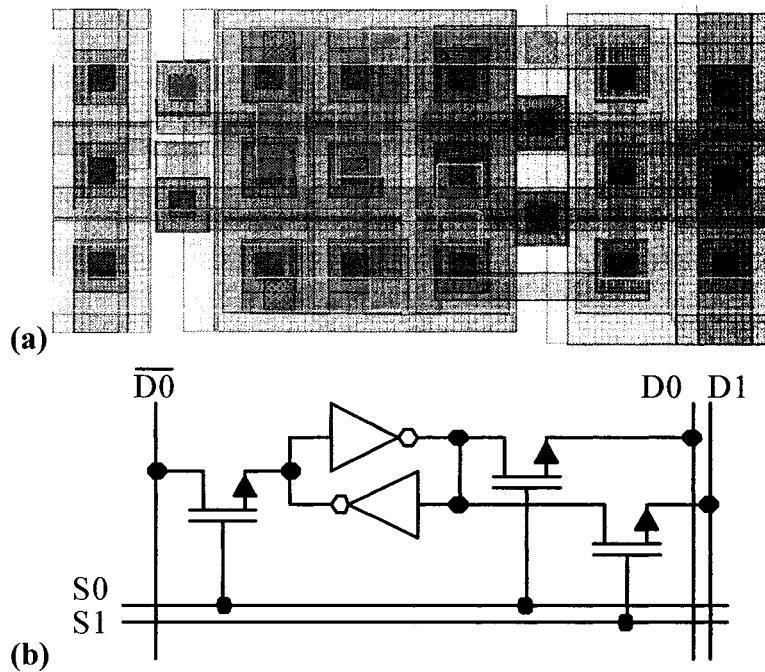

| FIGURE 3.11: CELLULE DE MÉMOIRE STATIQUE À DEUX PORTS.....                     | 69 |

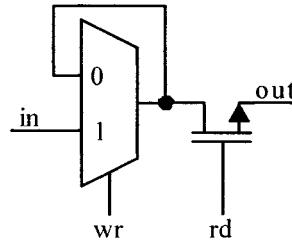

| FIGURE 3.12: CELLULE MÉMOIRE AVEC MULTIPLEXEUR.....                            | 70 |

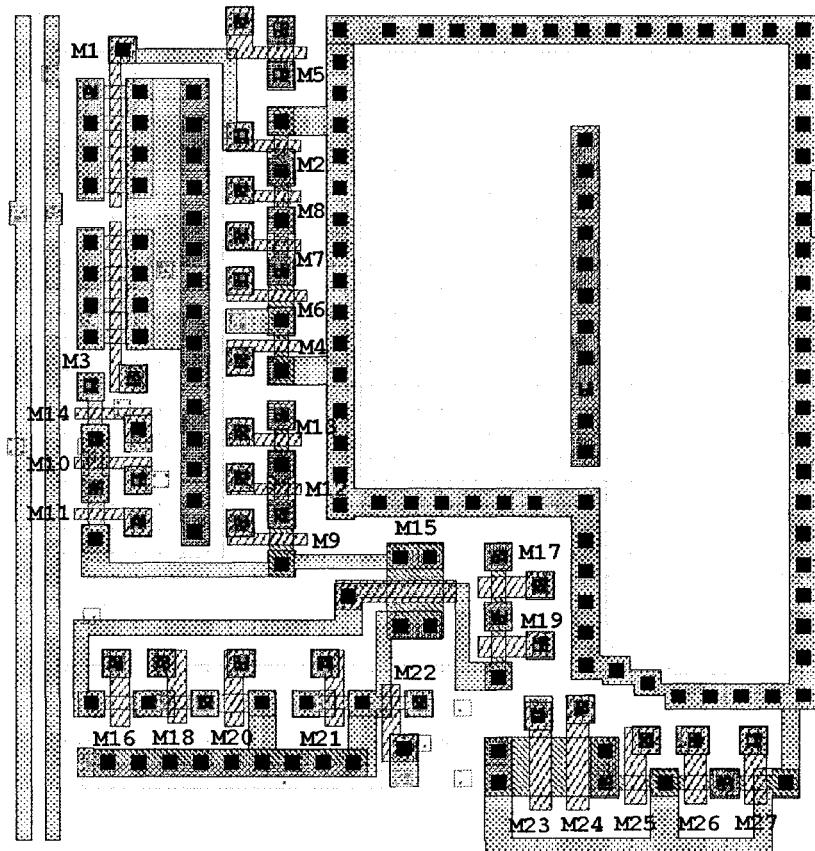

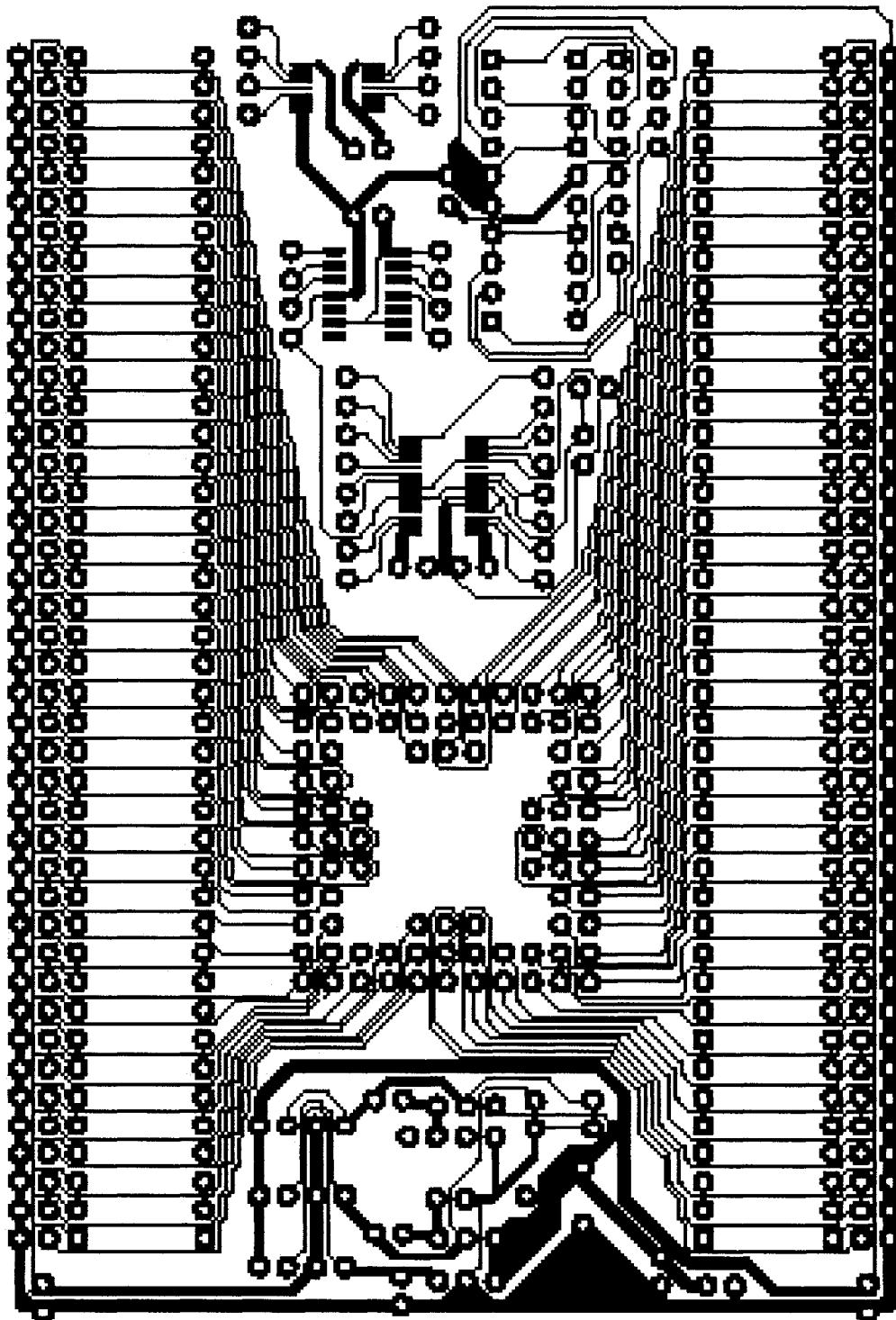

| FIGURE 3.13: DESSIN DES MASQUES DE LA PUCE ICFPMJL1, DEUXIÈME VERSION.....     | 72 |

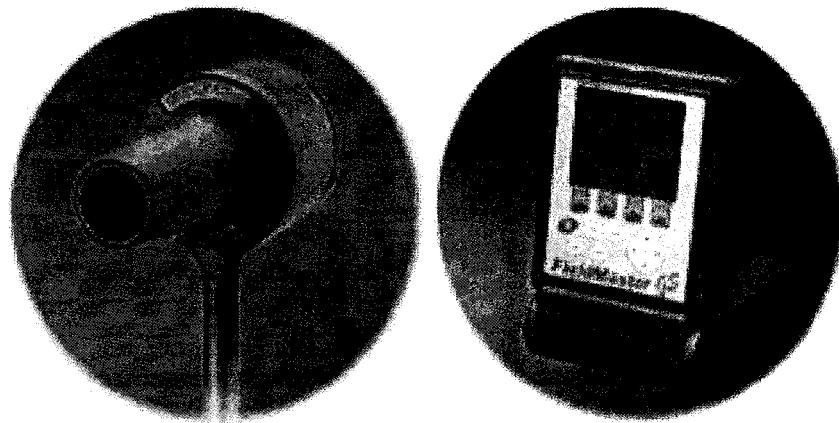

| FIGURE 3.14: APPAREIL DE MESURE D'INTENSITÉ LUMINEUSE.....                     | 74 |

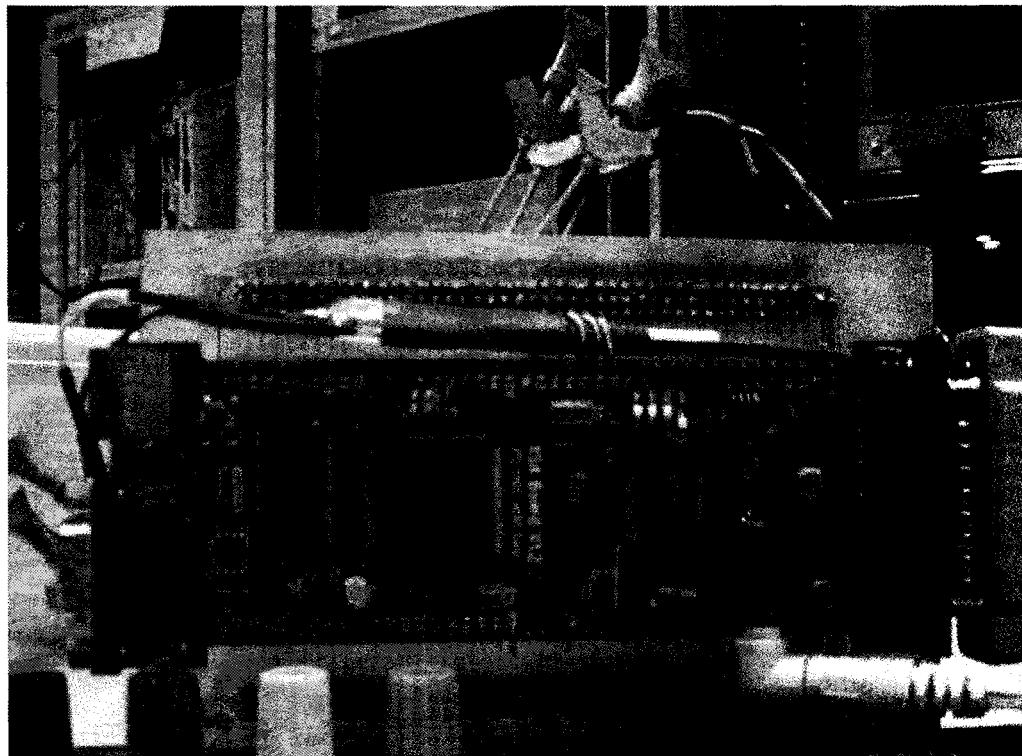

| FIGURE 3.15: BANC DE TEST.....                                                 | 75 |

| FIGURE 3.16: CIRCUIT D'ALIMENTATION.....                                       | 76 |

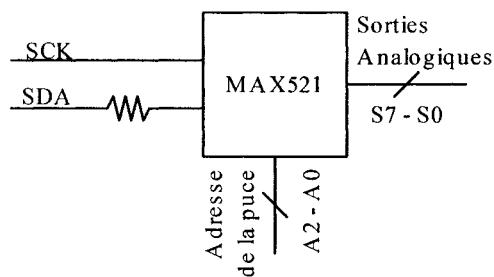

| FIGURE 3.17: SCHÉMA DU CNA MULTICANAUX.....                                    | 78 |

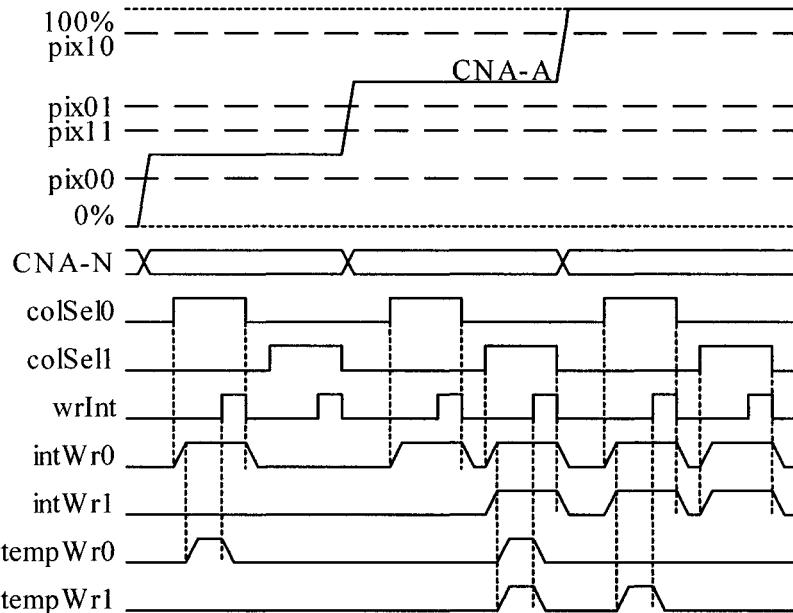

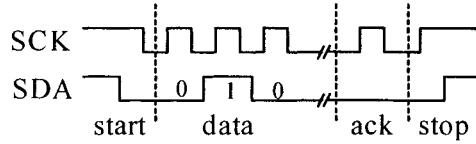

| FIGURE 3.18: SIGNAUX DE CONTRÔLE POUR LE CNA MULTICANAUX.....                  | 79 |

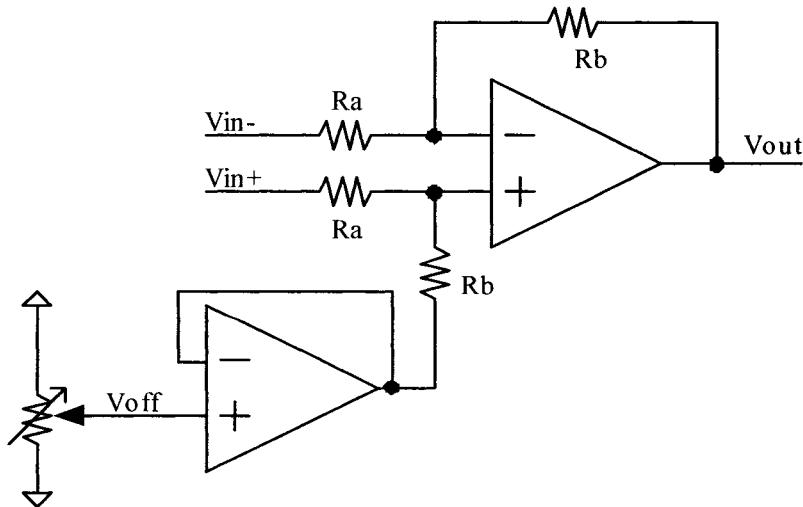

| FIGURE 3.19: AJUSTEMENT DE TENSION AVEC DEUX AMPLIFICATEURS OPÉRATIONNELS....  | 79 |

| FIGURE 3.20: CONTRÔLE NUMÉRIQUE AVEC FPGA.....                                 | 81 |

| FIGURE 4.1: PHOTOGRAPHIES DE LA PUCE ICFPMJL1.v2.....                          | 85 |

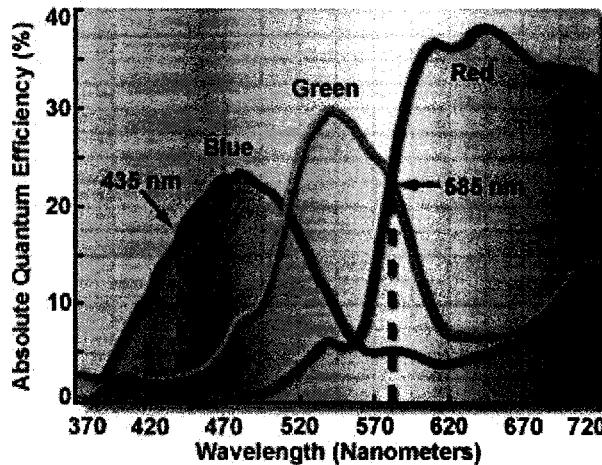

| FIGURE 4.2: RÉPONSE DU CAPTEUR EN FONCTION DE LA LONGUEUR D'ONDES .....        | 87 |

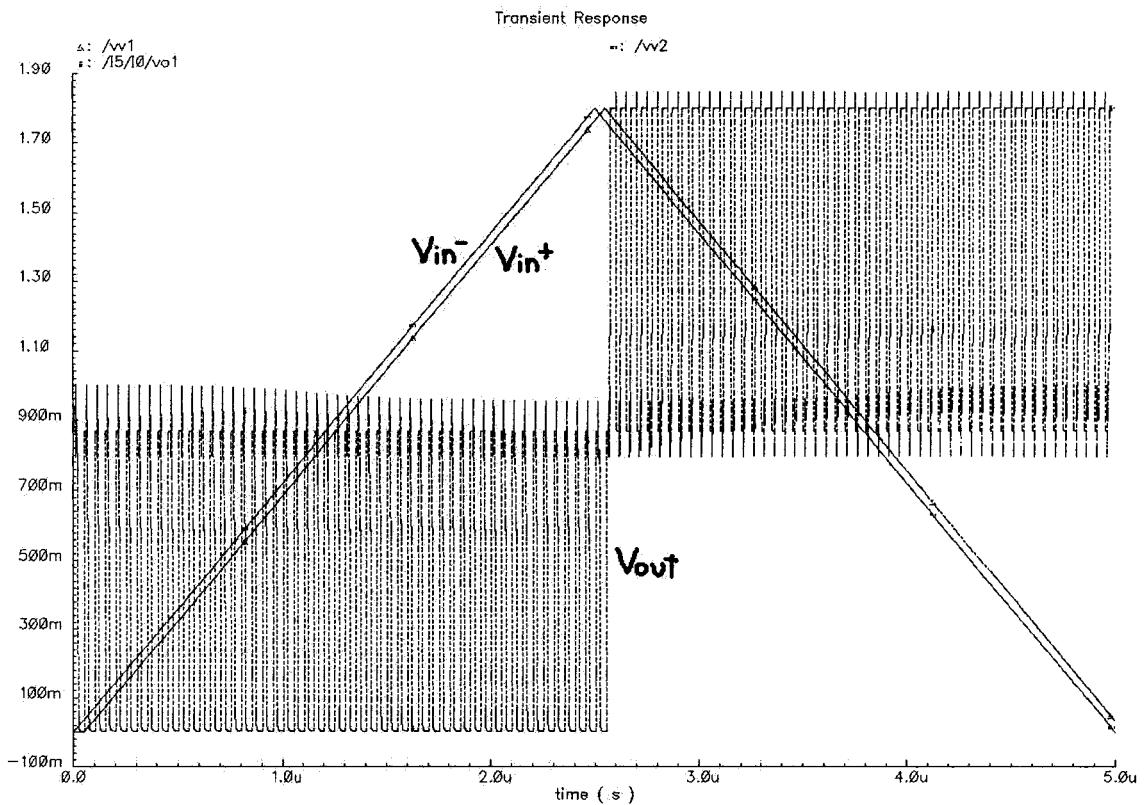

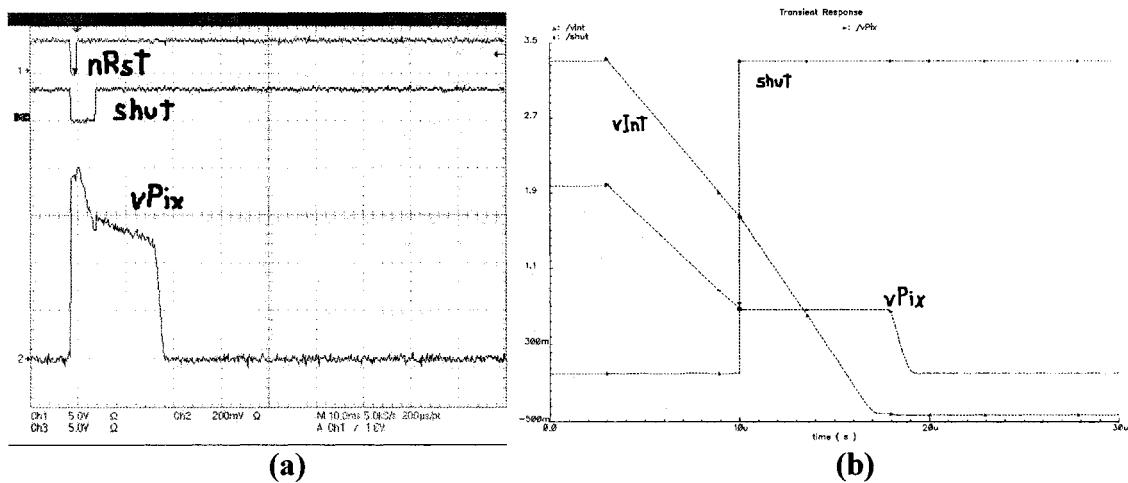

| FIGURE 4.3: RÉPONSE DYNAMIQUE DU SUIVEUR.....                                  | 89 |

| FIGURE 4.4: ANALYSE TRANSITOIRE DU SUIVEUR.....                                | 90 |

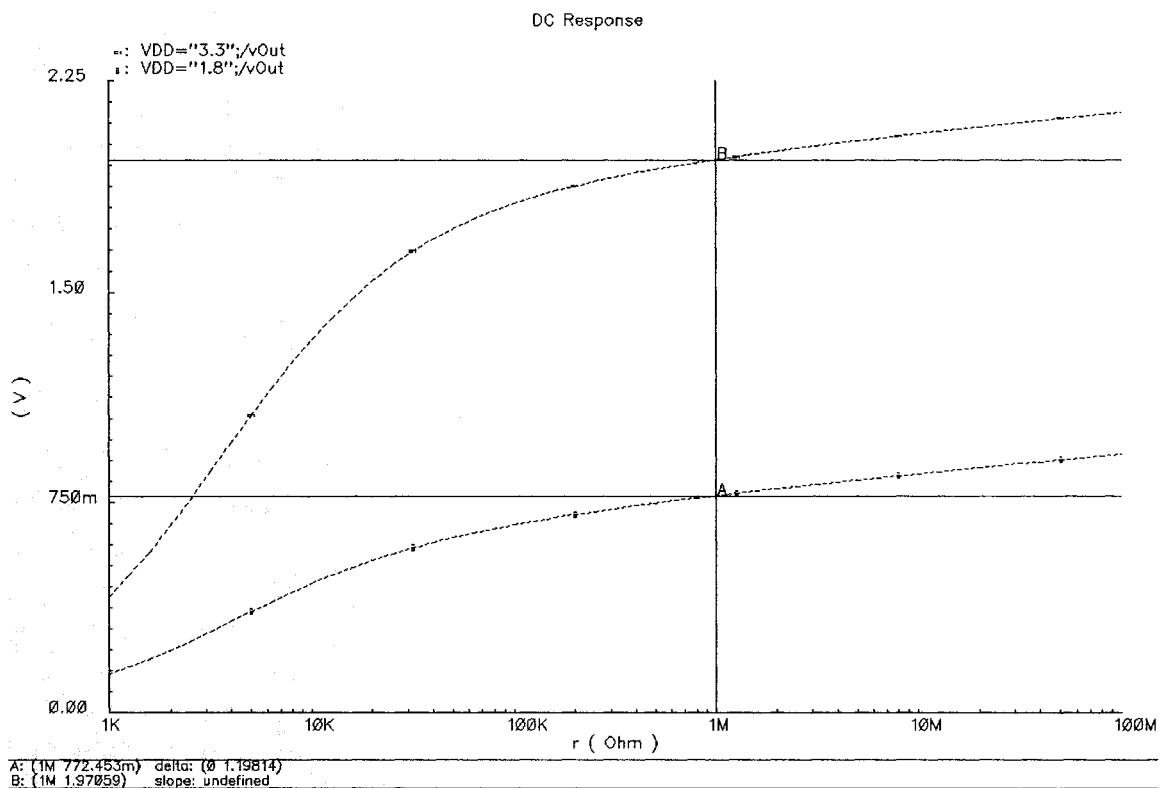

| FIGURE 4.5: SORTIE MAXIMALE DU SUIVEUR EN FONCTION DE LA RÉSISTANCE DE CHARGE. | 91 |

| .....                                                                          | 91 |

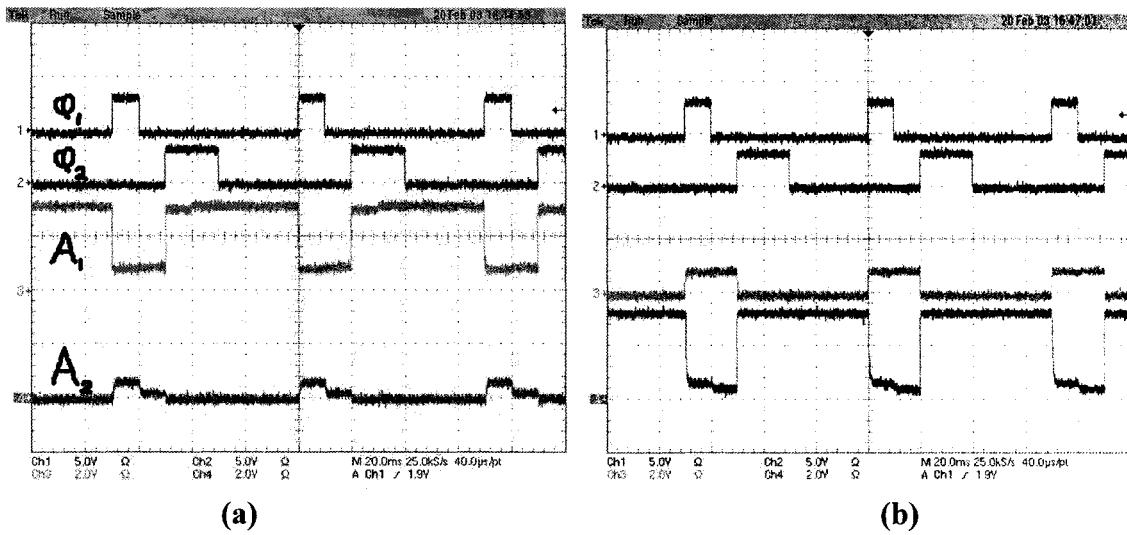

| FIGURE 4.6: SIGNAUX DE CONTRÔLE DU COMPARATEUR .....                           | 92 |

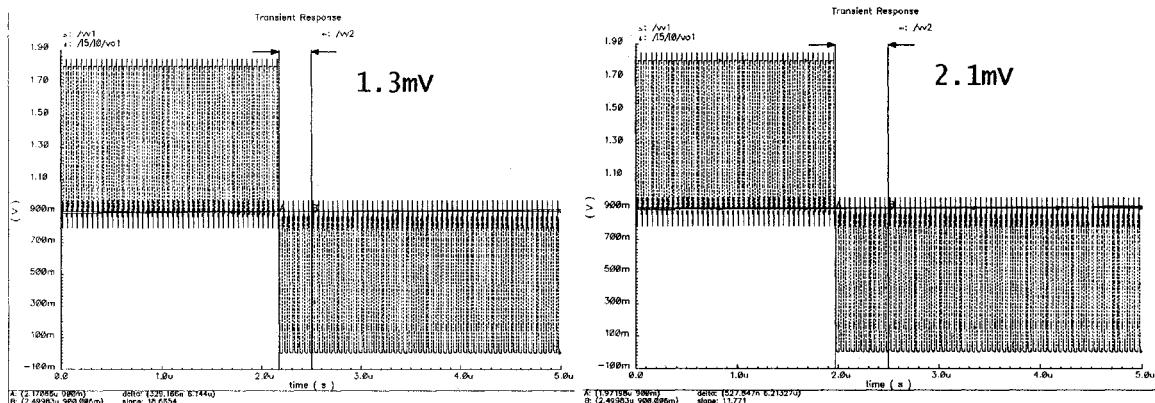

| FIGURE 4.7: EFFET DU SIGNAL <i>VALIDE</i> SUR LA SORTIE .....                  | 93 |

| FIGURE 4.8: AJOUT DE PRÉCISION AVEC LA PHASE <i>VALIDE</i> .....               | 94 |

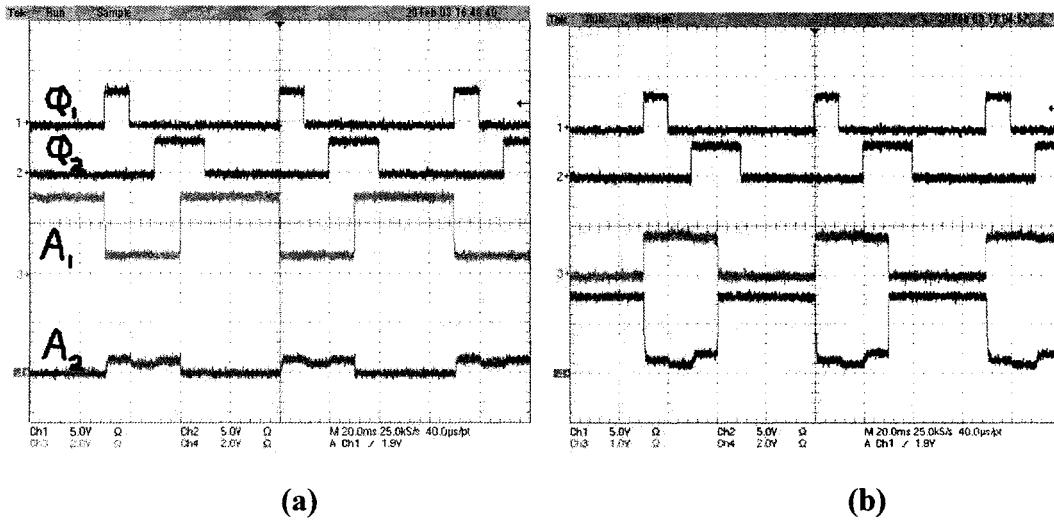

| FIGURE 4.9: COMPARATEUR FONCTIONNANT SUR LA TOTALITÉ DE LA GAMME DYNAMIQUE.    | 95 |

|                                                                                            |     |

|--------------------------------------------------------------------------------------------|-----|

| FIGURE 4.10: PRÉCISION DU COMPARATEUR.....                                                 | 96  |

| FIGURE 4.11: INTENSITÉ DU PHOTO-COURANT DE LA PHOTODIODE.....                              | 97  |

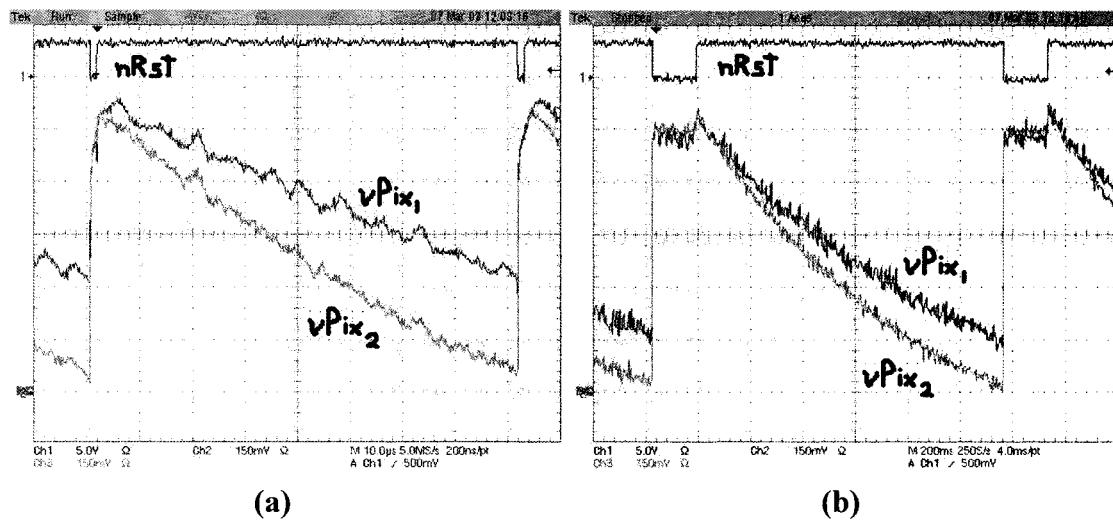

| FIGURE 4.12: COURANT DE FUITE DE LA PHOTODIODE.....                                        | 101 |

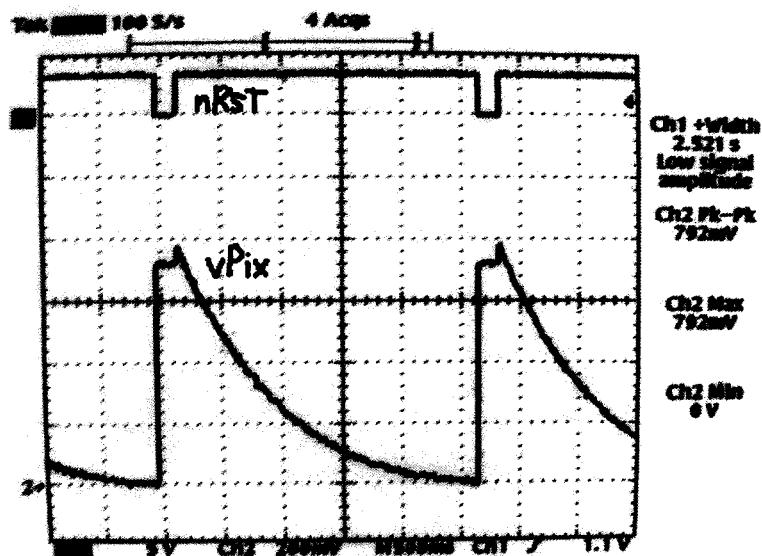

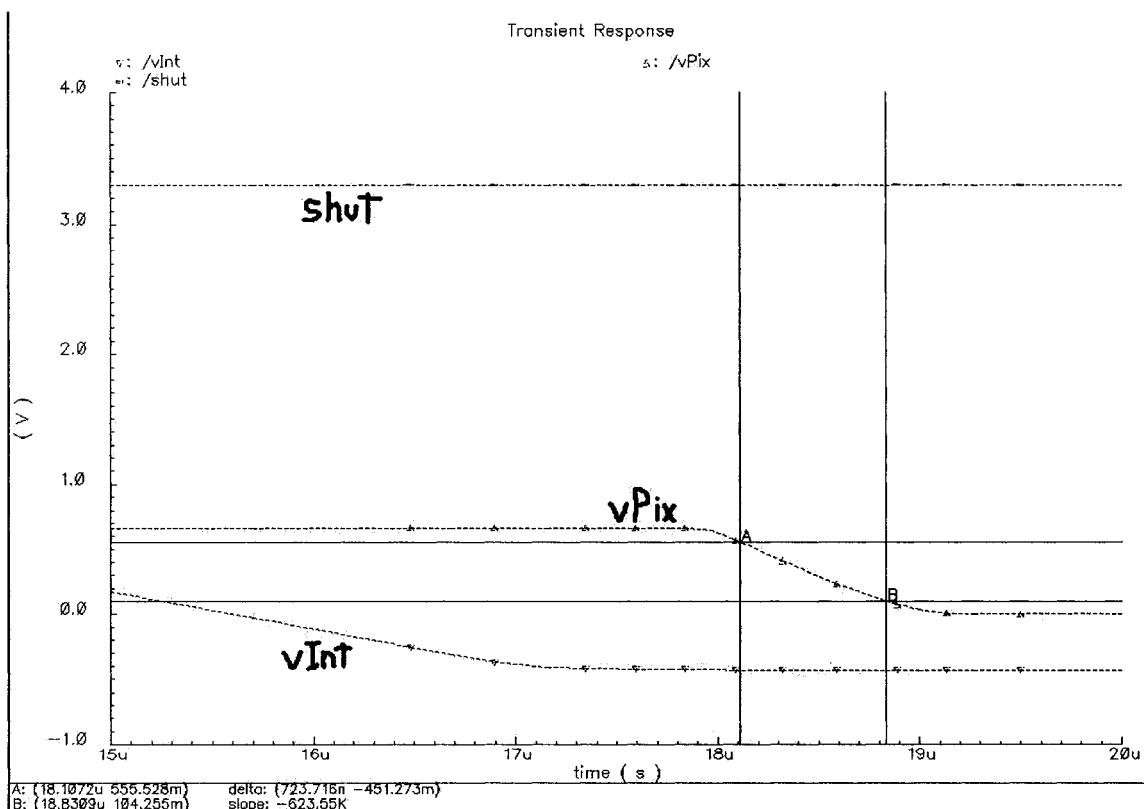

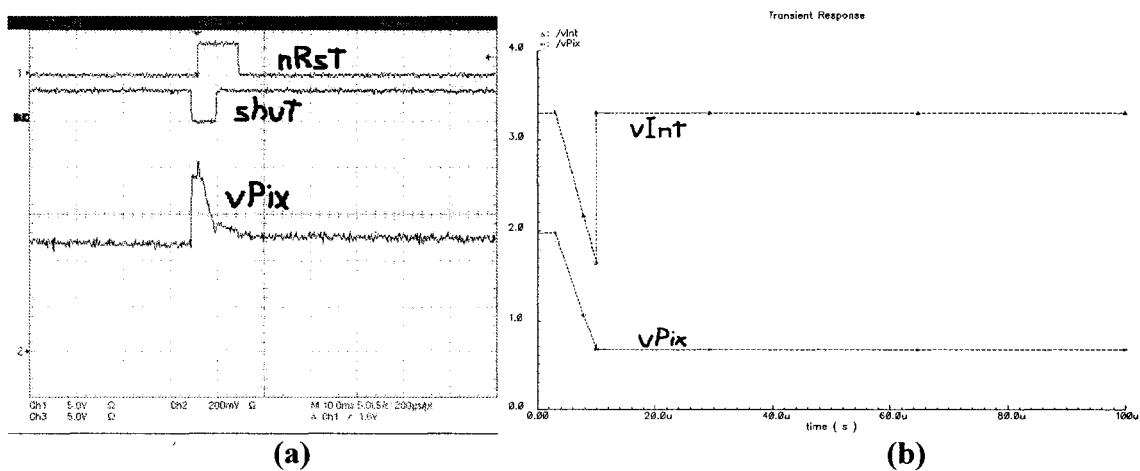

| FIGURE 4.13: FUITE DE L'OBTURATEUR.....                                                    | 103 |

| FIGURE 4.14: QUANTIFICATION DE LA FUITE PRONONCÉE DE L'OBTURATEUR .....                    | 103 |

| FIGURE 4.15: CORRECTION DE LA FUITE DE L'OBTURATEUR.....                                   | 104 |

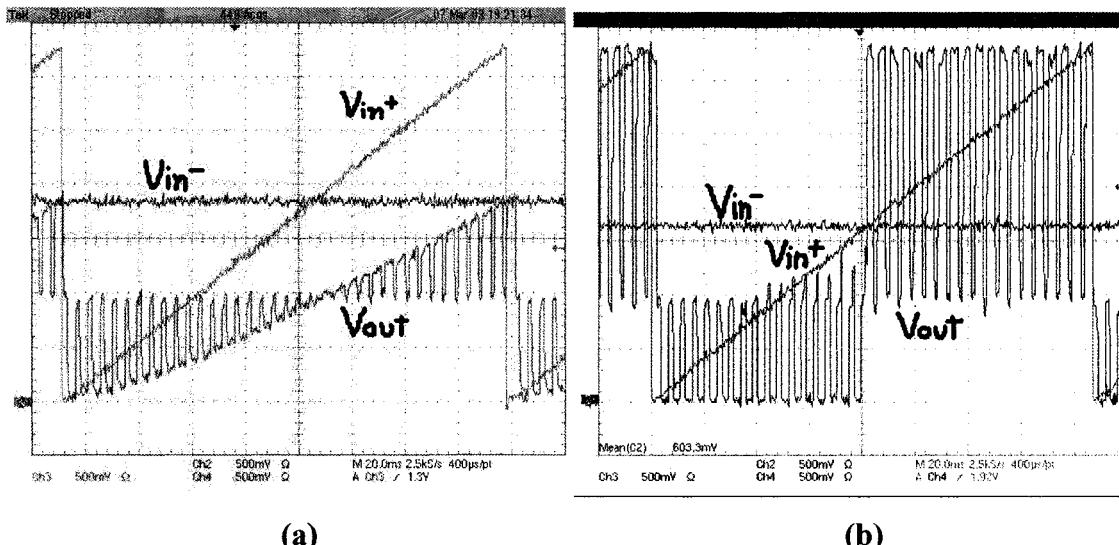

| FIGURE 4.16: EXPOSITIONS À LA LUMIÈRE ET TRAITEMENT DES DONNÉES.....                       | 107 |

| FIGURE 4.17: PHOTODIODE AVEC FENTES .....                                                  | 111 |

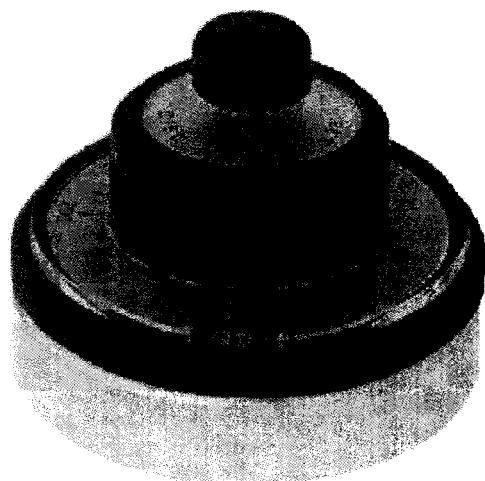

| FIGURE 4.18: TEST DU « FLIP-CHIP ».....                                                    | 113 |

| FIGURE 4.19: APPAREIL DE POLISSAGE POUR L'AMINCISSLEMENT DE L'ARRIERE DE LA PUCE.<br>..... | 113 |

| FIGURE 4.20: RAPIDITE DE DECHARGE DES CAPACITES PARASITES .....                            | 115 |

| FIGURE 4.21: VARIATION DE LA RESISTANCE D'UNE PORTE DE TRANSMISSION. ....                  | 116 |

| FIGURE 4.22: IMPLANT VISUEL .....                                                          | 118 |

## Liste des tableaux

---

|                                                                       |     |

|-----------------------------------------------------------------------|-----|

| TABLEAU 1.1: CARACTÉRISTIQUES DES CAPTEURS D'IMAGES .....             | 31  |

| TABLEAU 2.1: VALEURS DES PIXELS DE LA FIGURE 2.8 .....                | 45  |

| TABLEAU 4.1: CARACTÉRISTIQUES DE LA PUCE ICFPMJL1.v2.....             | 109 |

| TABLEAU 4.2: PROFONDEUR D'ABSORPTION DES PHOTONS PAR LE SILICIUM..... | 111 |

## Définitions et acronymes

|       |                                                                      |

|-------|----------------------------------------------------------------------|

| ADC   | Analog to Digital Converter                                          |

| BJT   | Bipolar Junction Transistor                                          |

| CAN   | Convertisseur Analogique à Numérique                                 |

| CNA   | Convertisseur numérique-analogique                                   |

| CCD   | Charge Coupled Device                                                |

| CDS   | Correlated Double Sampling                                           |

| CMC   | Canadian Microelectronics Corporation                                |

| CMOS  | Complementary Metal Oxide Semiconductor                              |

|       | convertisseur A/N convertisseur Analogique à Numérique               |

|       | convertisseur N/A convertisseur Numérique à Analogique               |

| CRSNG | Conseil de recherche en sciences naturelles et en génie du<br>canada |

| DAC   | Digital to Analog Converter                                          |

| DEL   | Diode électroluminescente                                            |

| DSP   | Digital Signal Processing                                            |

| FCAR  | Fonds par la formation des chercheurs et l'aide à la recherche       |

| FET   | Field Effect Transistor                                              |

| FPGA  | Field Programmable Logic Array                                       |

| FPN   | Fixed Pattern Noise                                                  |

| FSM   | Finite State Machine                                                 |

| IR    | Infrarouge                                                           |

| LED   | Light Emitting Diode                                                 |

| LSB   | Least Significant Bit                                                |

| MCBS  | Multi Channel Bit Serial                                             |

| MOS   | Metal Oxide Semiconductor                                            |

|        |                                         |

|--------|-----------------------------------------|

| MOSFET | Metal Oxide Field Effect Transistor     |

| MSA    | Machine séquentielle algorithmique      |

| MSB    | Most Significant Bit                    |

| NMOS   | N-channel Metal Oxide Semiconductor     |

| PMOS   | P-channel Metal Oxide Semiconductor     |

| PPD    | Pinned Photodiode                       |

| RAM    | Random Access Memory                    |

| RF     | Radio fréquence                         |

| SCM    | Société canadienne de microélectronique |

| SNR    | Signal to Noise Ratio                   |

| SoC    | System On Chip                          |

| SOI    | System On Insulator                     |

| TFA    | Thin Film on ASIC                       |

| UV     | Ultraviolet                             |

| VHDL   | VHSIC Hardware Description Language     |

| VHSIC  | Very High Speed Integrated Circuit      |

| VLSI   | Very Large Scale Integration            |

## **Liste des Annexes**

---

---

|                                                          |     |

|----------------------------------------------------------|-----|

| ANNEXE A: DESSIN DES MASQUES DE LA PUCE ICFPMJL1.V1..... | 128 |

| ANNEXE B: DESSIN DES MASQUES DU PIXEL NUMÉRIQUE.....     | 129 |

| ANNEXE C: CIRCUIT IMPRIMÉ DU MODULE DE TEST.....         | 130 |

| ANNEXE D: DESCRIPTION VHDL DU CONTRÔLEUR.....            | 131 |

## Introduction

La capture d'images a beaucoup évolué au cours du dernier siècle. Tout d'abord réalisée à l'aide de films (pellicules photosensibles), il est désormais possible de faire l'acquisition d'images à l'aide de semi-conducteurs. L'avantage de ceux-ci par rapport aux films est qu'ils peuvent être directement reliés à d'autres systèmes électroniques de façon à leur ajouter la possibilité de « voir » ce qui se passe. Les domaines d'applications possibles sont très vastes et vont du contrôle industriel aux systèmes de sécurité en passant par des applications de divertissements. De plus, les progrès réalisés dans le domaine de la microélectronique n'ont cessé de croître au fil des années, offrant de plus en plus de latitude avec une qualité toujours supérieure dans la conception de capteurs à base de semi-conducteurs. Puisque le présent mémoire porte sur les techniques électroniques intégrés de capteurs, seules les caractéristiques liées à ces capteurs seront traitées.

Avec l'augmentation de la densité et de la vitesse d'opération des circuits intégrés, de plus en plus de traitement est effectué de façon numérique, ajoutant ainsi de la flexibilité et éliminant le besoin d'ajustements au niveau analogique. La première génération de capteurs d'images CMOS était basée sur des pixels passifs (PPS) avec lecture analogique de la matrice. Ces capteurs, à base d'éléments passifs, souffraient d'une mauvaise qualité de signal due à la transmission directe de la tension du pixel (charges accumulées) sur le long bus de colonnes. À l'époque, les capteurs CCD étaient encore la technologie privilégiée pour l'imagerie numérique de qualité.

Pour la seconde génération de capteurs d'images CMOS, la qualité fut améliorée avec l'utilisation de pixels actifs (APS), où un transistor d'isolation (suiveur) a été ajouté afin d'empêcher la lecture destructive de la génération PPS. L'augmentation de la vitesse des circuits liée à la diminution d'échelle de la technologie et à la diminution des tensions d'alimentation, impose des contraintes de conception pour la section analogique du pixel

qui deviennent de plus en plus difficile à rencontrer. Grâce aux technologies CMOS sous-microniques, un bon nombre de transistors peuvent être ajouté par pixel, au point où la majeure partie de celui-ci est entièrement numérique. En fait, les tendances liées à la capture d'images se dirigent vers les capteurs à pixels numériques (DPS) qui offrent de nombreux avantages, notamment la résolution spatiale variable, la présence de modules de traitement à même la puce, faible consommation de puissance, large gamme dynamique ainsi qu'un coût de production plus faible. Le traitement numérique à l'intérieur d'un capteur CMOS peut être utilisé afin d'améliorer la qualité d'une image prise avec une large gamme dynamique. L'augmentation de la demande pour des appareils portatifs utilisant des capteurs d'images justifie ainsi la nécessité de concevoir de petits systèmes consommant peu de puissance.

Le présent projet a été réalisé au sein du laboratoire de recherche PolyStim de l'École Polytechnique de Montréal. Une des applications potentielle de ce capteur d'image à base de semi-conducteur est de l'intégrer à un système de stimulation intra-cortical visant à redonner un minimum de vision aux gens atteints de cécité profonde. La caractéristique fondamentale d'un système destiné à remplir cet objectif est de posséder une gamme dynamique élevée afin de représenter le mieux possible celle de l'œil humain. De plus, un tel système doit pouvoir fournir de bonnes performances sans modules de support (flash, lampe, etc.). De cette façon, il doit fonctionner aussi bien dans la lumière intense du soleil que dans l'ombre de la nuit sans aucun ajustement ou intervention externe. Afin de remplir chacun des objectifs mentionnés précédemment tout en ayant la flexibilité d'être intégré à d'autres systèmes développés par l'équipe PolyStim, la puce à base de semi-conducteurs doit être conçue à partir du procédé le plus récent disponible qui est le CMOS à une échelle de  $0.18\mu\text{m}$ .

À court terme, le projet vise à réaliser un capteur d'images générique dont les blocs de base, les pixels, pourront être utilisés dans un vaste éventail d'applications. Afin de pousser la recherche du côté du développement du pixel et de l'architecture des modules

qui l'entourent, la technologie CMOS offre une quantité incomparable de possibilités de conception par rapport à la technologie CCD qui ne permet pas d'ajouter des modules autres que le pixel analogique. Bien que le CMOS ait donné des images de qualité moindre que celle obtenues avec les capteurs CCD, tel que ceux utilisés dans la majeure partie des appareils photos et vidéo commerciaux, beaucoup de terrain a été rattrapé au cours des dix dernières années.

Dans le cadre de ce projet, nous avons élaboré une nouvelle architecture de capteurs d'images à base de pixel numérique. Cet aspect en fait un fonctionnement global différent des générations précédentes (PPS et APS) puisque chaque pixel intègre une partie des composantes normalement retrouvées à l'extérieur de la matrice photosensible. L'aspect modulaire de cette architecture le rend assez versatile pour être utilisé aussi bien dans un système nécessitant un haut taux de capture d'images que dans un système nécessitant une grande sensibilité à l'intérieur d'une large gamme dynamique.

L'organisation de ce mémoire se divise en quatre chapitres. Tout d'abord, un premier chapitre fait l'objet d'une introduction au fonctionnement des différents modules nécessaires aux capteurs d'images à base de semi-conducteurs tout en comparant ces caractéristiques avec les informations retrouvées dans la littérature. Un second chapitre présente l'architecture nouvelle élaborée dans ce présent projet ainsi que les caractéristiques de fonctionnement qui s'y rattachent. Un troisième chapitre décrit les détails de la conception des différents modules présentés au chapitre qui le précède. En dernier lieu, le chapitre quatre présente les résultats obtenus à partir de la puce de test du capteur conçu et fabriqué pour ce projet, suivit de quelques propositions pour le développement futur visant à améliorer les performances du capteur présenté.

# CHAPITRE 1

## Étude des capteurs d'images

### 1.1 Introduction

Les éléments d'intérêt dans la capture d'images électroniques sont très vastes et vont de la conversion de photons à électrons jusqu'au système de contrôle de la matrice photosensible, en passant par la constitution du pixel lui-même. Cette section présente donc les différents éléments de la chaîne de capture d'images à l'aide de semi-conducteurs ainsi que leurs avantages et inconvénients.

Le travail de recherche présenté ici propose une nouvelle architecture de capteur d'images au niveau du pixel et de l'interaction de ces pixels avec le système de contrôle. Le but de l'expérimentation est de maximiser la gamme dynamique de l'image acquise, et ce, sous tous les niveaux d'illumination possibles, soit sous un intense soleil autant que dans l'ombre de la nuit.

Nous commencerons donc par une brève description des différentes technologies qui rendent possible la capture d'images. Dans un deuxième temps, les différents éléments électroniques qui permettent la conversion de l'énergie photonique à de l'énergie électrique seront présentés. Une explication de différentes topologies possibles pour l'élément de base qu'est le pixel est donnée. Puis, on présente les différentes architectures de disposition et d'accès aux pixels ainsi que les méthodes utilisées pour les commander. Ensuite, on explique les méthodes pour les conversions analogiques à numériques des signaux capturés par les éléments photosensibles jusqu'à une représentation sous forme numérique de l'image. Par la suite, on présente les différentes méthodes qui permettent d'aller chercher l'information dans la totalité de la gamme dynamique dont l'image est

composée. Finalement, un tableau comparatif est dressé afin de comparer les principaux capteurs d'images à semi-conducteurs ayant été trouvés dans la littérature.

## 1.2 Capteurs d'images à base de semi-conducteurs

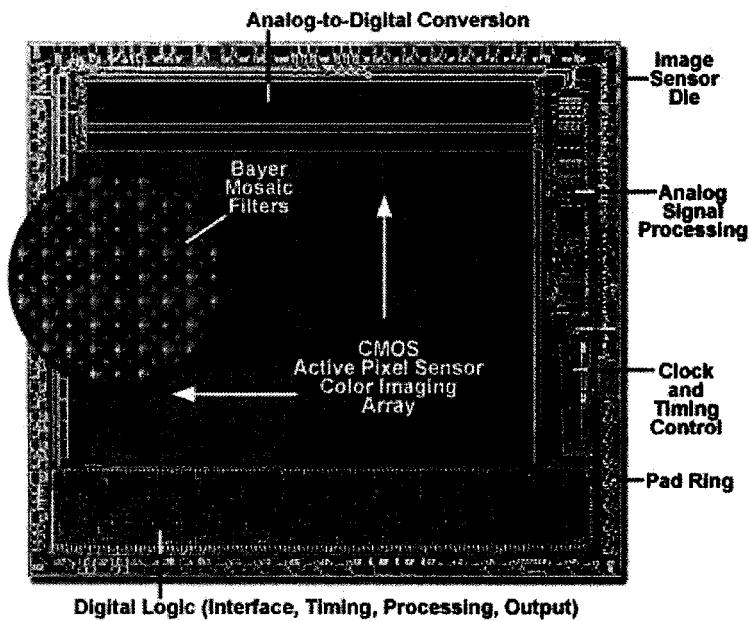

Deux matériaux différents nous permettent de capturer une image: les films et les semi-conducteurs. Les méthodes de réalisation de capteurs d'images électroniques se résument à deux différents procédés de fabrication de circuits intégrés. La technologie CCD (*Charge Coupled Devices*) communément utilisée dans les capteurs commerciaux que l'on retrouve de nos jours, apparue à la fin des années 1960 et fut optimisée pour l'imagerie dans les années 1980. La technologie MOS (*Metal Oxyde Semiconductor*) quant à elle, introduite au début des années 1960 et fut suivie de la technologie CMOS (*Complementary Metal Oxyde Semiconductor*) qui apparut dans les années 1970. Un capteur CMOS typique comporte une matrice photosensible et d'autres unités fonctionnelles tel qu'illustré à la Figure 1.1, tandis qu'un capteur CCD typique n'a qu'une matrice photosensible et une chaîne de lecture séquentielle (*raster scan*).

Figure 1.1: Capteur CMOS standard (tiré de [48]).

Du côté de la capture d'images, les premières diodes furent réalisées avec la technologie MOS en 1967 [12] et c'est en 1980 que furent conçus les premiers APS (*Active Pixel Sensor*, section 1.4.1). Il est important de noter que la technologie CMOS, contrairement à la technologie CCD, n'a pas été optimisée pour l'imagerie, mais plutôt pour des circuits numériques rapides. Ces circuits intégrés à applications spécifiques sont appelés ASIC (*Application Specific Integrated Circuits*). Il est cependant possible d'utiliser le procédé CMOS pour fabriquer des capteurs d'images tels que présentés dans ce mémoire.

Le procédé CCD a été inventé vers la fin des années 1960 par les chercheurs du *Bell Laboratories* qui visaient à concevoir un nouveau type de mémoire pour les ordinateurs. Bien que cet objectif ne se soit pas concrétisé, de subséquentes études sur le transfert de charges et les effets photoélectriques des CCD ont conduit ce procédé vers l'imagerie. Celui-ci a commencé à être optimisé en 1980 dans le seul but d'en améliorer les propriétés optiques et d'en augmenter la qualité de l'image captée par le senseur éventuel. Par contre, le procédé CMOS a un meilleur rendement de fabrication que celui du CCD car sont plus haut volume lui permet d'être à la fine pointe de la technologie en utilisant des équipements plus modernes [14]. De son côté, le CMOS standard a toujours été optimisé en fonction d'améliorer les performances des ASIC et non afin de rendre ses propriétés optiques meilleures.

Bien que les capteurs CMOS n'aient été utilisés qu'à des fins de recherche jusqu'en 1990, ils gagnent maintenant de plus en plus de popularité par rapport aux CCD et sont devenus intéressants pour plusieurs applications. L'avantage du procédé CMOS sur ce point est le coût de production significativement moindre grâce à l'utilisation de fonderies standard à haut volume. Puisque les capteurs CMOS utilisent le procédé le plus répandu et à plus haut volume, ils profitent de son évolution rapide et bénéficient ainsi de la possibilité grandissante d'intégrer un plus grand nombre de composants sur une même surface de silicium. De plus, ils peuvent capturer beaucoup plus d'images par seconde que les CCD car ils ne sont pas restreints à une lecture sérielle par balayage complet de la

matrice. La production à faible coût des capteurs CMOS a élargie leurs domaines d'application à des appareils tels que fax, scanners, caméras de surveillance, jouets, caméras web, téléphones cellulaires, lecteurs de code barre, souris optique et plusieurs autres. Leur rapidité de capture leur a permis d'entrer dans le domaine de l'inspection industrielle, de la dynamique des fluides, et des diagnostiques médicaux pour n'en nommer que quelques-uns.

Bien que le senseur traité dans le présent document soit un capteur générique, une de ses premières applications sera sans doute dans le cadre du projet d'implant visuel de l'équipe de recherche PolyStim [9]. Ceci s'explique par les deux caractéristiques principales, soit la possibilité d'y intégrer des fonctionnalités supplémentaires et la consommation de puissance réduite.

### **1.2.1 Caractéristiques des éléments photosensibles**

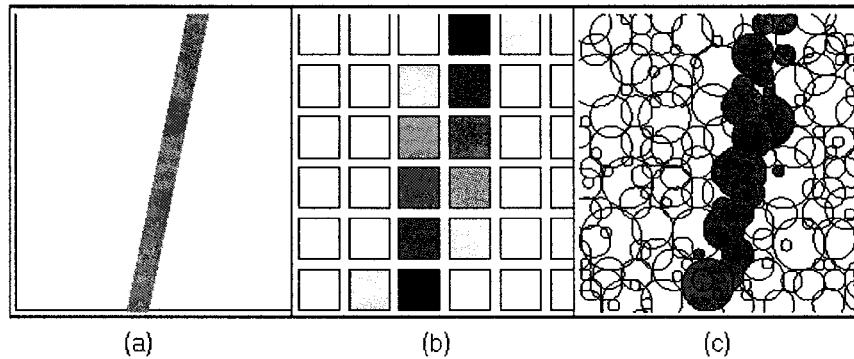

Sur une puce de silicium, les éléments de base, c'est-à-dire les pixels, sont disposés sous forme de matrice régulière. Les colonnes et rangées sont donc bien alignées, contrairement aux grains de la pellicule de film. Ces grains sont de différentes tailles ( $0.5\mu\text{m}$  à  $10\mu\text{m}$ ), placés aléatoirement et pouvant se chevaucher. Ceci confère un avantage à la pellicule du film qui n'a pas de problème de sous-échantillonnage, contrairement aux pixels de la puce de silicium. Ce problème survient lorsque l'image capturée comporte des changements de couleur et/ou d'intensité plus faiblement espacés que les pixels eux-mêmes, provoquant ainsi des portions de pixels différemment stimulés. La Figure 1.2 illustre cette propriété.

**Figure 1.2: Qualité de sous-échantillonnage (tiré de [12])**

**(a) image réelle; (b) représentation électronique; (c) représentation sur film.**

Les grains du film peuvent être noirs, s'ils ont absorbé une quantité suffisante de photons, ou bien rester blanc dans le cas contraire. C'est un processus qui détériore grandement la qualité de l'image aux forts effets non-linéaires survenant sous de faibles intensités lumineuses. De son côté, le pixel fonctionne par effet photoélectrique où les photons interagissent avec le silicium cristallisé afin de transporter les électrons de la bande de valence vers la bande de conduction [9]. Le courant ainsi généré est proportionnel à l'intensité de la lumière incidente et sa valeur peut être quantifiée sur plusieurs niveaux et ainsi éviter les effets non-linéaires notés ci-dessus.

Une autre différence entre les images capturées sur film et celles capturées à l'aide de semi-conducteurs est leur sensibilité à la portion bleue du spectre de la lumière visible. Les pellicules de films sont hypersensibles à cette lumière, tandis que les semi-conducteurs ont une réponse plus faible dans cette portion que dans le reste du spectre. Ceci est d'autant plus vrai pour les pixels à base de photo-grille, présentés à la section 1.3.4.

### 1.2.2 Performance des capteurs CMOS et CCD

Au point de vue de l'alimentation électrique du capteur, le CMOS n'en nécessite qu'une seule et de faible niveau, inférieure à 3.3 volts, tandis que le CCD doit en avoir plusieurs et de niveaux beaucoup plus élevés. Ceci est dû aux capacités plus grandes du circuit du pixel en technologie CCD. Ceci implique aussi la nécessité d'avoir des signaux de contrôle et des tensions de polarisation assez élevés. Les grandes variations entre les deux niveaux logiques des signaux, les nombreuses horloges à différentes vitesses, et la nécessité de convertisseurs DC-DC pour les alimentations multiples nécessaires (5 ou plus, [48]), font que les capteurs à base de CCD consomment beaucoup plus de puissance que les CMOS [37]. Par exemple, une caméra vidéo CCD peut facilement consommer un énorme 10W, soit 100 fois plus qu'un capteur CMOS du même type.

Ajoutons qu'il est impossible d'intégrer sur une même puce CCD d'autres fonctions que la matrice de pixels photosensibles et le circuit de lecture. Les systèmes d'imagerie à base de CCD doivent donc utiliser d'autres puces (CMOS) afin de pouvoir traiter l'image. L'information contenant l'image ne peut être transmise à l'extérieur de la puce CCD que sous sa forme analogique avec balayage sériel. Ceci implique que la conversion analogique à numérique doit être faite sur une seconde puce. Le fait d'utiliser plus d'une puce et un certain nombre de composantes discrets (pour les alimentations et les horloges multiples) explique que les systèmes à base de CCD sont plus énergivores. Ceci est un aspect limitant important pour les appareils portatifs. Par contre, les capteurs à base de CMOS sont des systèmes plus petits et moins énergivores pouvant être intégrés sur une seule puce.

Malgré tout, les CCD dominent toujours les marchés où la résolution et la sensibilité sont de mise. Cette sensibilité est due à la surface de l'élément photosensible par rapport à celle du pixel qui peut atteindre presque 100% pour certains CCD. D'un autre côté, les capteurs CMOS ont maintenant leur part du marché où la possibilité de miniaturisation est plus avantageuse, au détriment d'une image de qualité légèrement moindre (plus

bruitée). Par contre, avec l'optimisation du circuit du pixel, faisant l'objet de ce mémoire et traité au chapitres 2 et 3, le procédé CMOS permet la capture d'images avec un très faible niveau de bruit et ainsi une excellente qualité. Avec une gamme dynamique de 60dB, les capteurs CMOS commencent à rivaliser sérieusement avec les CCD.

De plus, le procédé CMOS standard tend à avoir une couche épitaxiale (EPI) [26] très mince afin d'éviter les « *latch-up* » dans les circuits numériques, ce qui a pour effet de diminuer la sensibilité dans la portion rouge (650nm - 700nm) du spectre électromagnétique. Aussi, afin de permettre une forte densité de transistors à grille courte nécessaire pour les circuits numériques rapides, les jonctions sont fortement *dopées*. Ceci implique une plus faible réponse dans la partie verte (500nm - 550nm) du spectre.

Selon Wong [43], le procédé CMOS va tendre vers le SOI (*Silicon On Insulator*) et il sera désormais impossible de fabriquer des capteurs photoniques à partir du procédé standard. La solution à ce problème est sans aucun doute la couche mince sur ASIC, nommée TFA (*Thin Film on Asic*), où les variations du procédé n'affecteront à peu près plus la conversion photons à électrons. Ce sujet sera traité à la section 1.3.5.

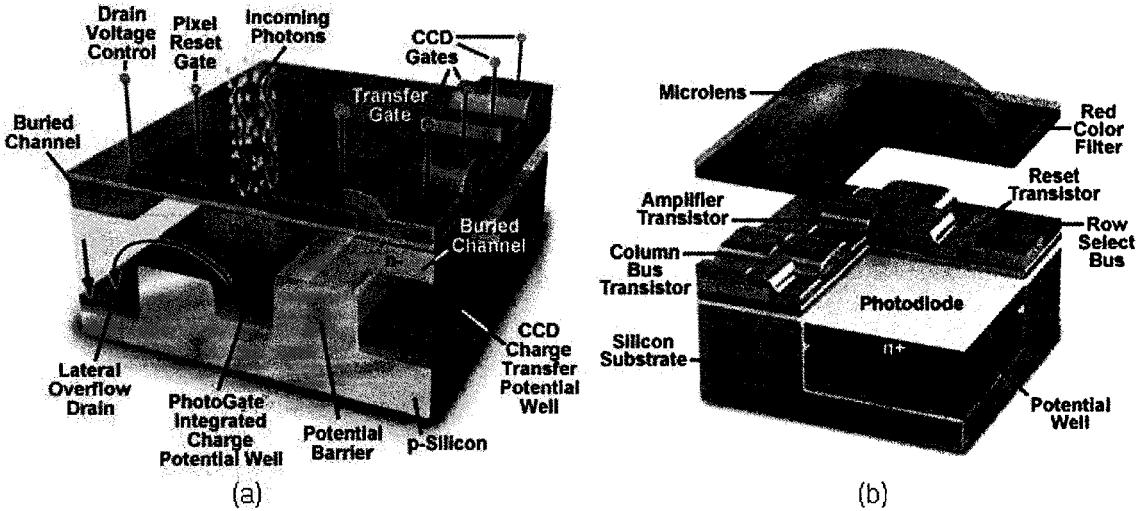

### 1.3 Éléments photosensibles

Les capteurs intégrés à base de silicium sont sensibles à la lumière pour les longueurs d'ondes allant des ultraviolets (UV), soit autour de 100nm, jusqu'aux infrarouges (IR), soit dans les environs de 1200nm [12]. Les capteurs qui nous intéressent, destinés aux implants visuels, doivent être sensibles dans le spectre de la lumière visible qui se situe entre 400nm et 700nm. Pour un même procédé de fabrication, il existe plusieurs méthodes et circuits différents pour convertir la lumière en signal électrique. Les éléments de base permettant cette conversion sont présentés dans les sous-sections qui suivent. La Figure 1.3 illustre les principales différences entre les pixels standards des capteurs CCD (a) et ceux des capteurs CMOS (b).

**Figure 1.3: Pixel de capteur standard (tiré de [48])**

(a) Pixel CCD; (b) Pixel CMOS.

### 1.3.1 Photodiode standard

La photodiode est probablement l'élément photosensible le plus simple côté topologie, contrôle et fonctionnement. Il s'agit de l'élément qui a d'abord été utilisé dans les premiers capteurs d'images CMOS. Son mode d'opération consiste à polariser la diode en inverse avant la capture d'image. Ensuite, les photons incidents produisent un courant de fuite proportionnel à l'intensité lumineuse pendant le temps d'exposition voulu. Finalement, la lecture de la tension restante aux bornes de la diode donne l'indication de l'intensité lumineuse. La variation idéale de la tension de la diode en fonction de la puissance incidente est donnée par l'équation (1.1) [34].

$$\frac{dV}{dt} = \frac{1.2\lambda P\eta}{c} \quad (1.1)$$

Dans cette formule,  $\lambda$  est la longueur d'onde de la source lumineuse et  $P$  représente sa puissance,  $\eta$  représente l'efficacité quantique et  $c$  est la vitesse de la lumière. Cette

formule ne tient pas compte de la taille de la diode, qui n'a pas d'effets dans le cas idéal. Par contre, en pratique, la capacité du contour de la photodiode et des transistors connectés à celle-ci s'ajoute à la capacité de la photodiode, laquelle peut affecter de façon non-linéaire la variation de la tension à ses bornes. Cette non-linéarité correspond à un gamma plus grand que un ( $V_{out} = V_{idéal}^{\gamma}$ ). Une grande capacité à l'endroit où s'accumulent les charges suite à l'effet de la lumière peut avoir un impact négatif sur la sensibilité du capteur. Il peut donc être avantageux de réduire la surface de la photodiode sans réduire son périmètre et ainsi ajouter, avec l'espace gagné, des transistors au pixel afin d'améliorer sa sensibilité. Ceci réduit la capacité de la photodiode tout en permettant la collecte de photons par les régions d'appauvrissement latérales. Une méthode plus certaine pour l'amélioration de la sensibilité peut se faire par l'ajout d'une micro-lentille à ménisque positif déposée par photolithographie sur les pixels afin de concentrer les rayons lumineux sur l'élément photosensible, tel qu'illustré à la Figure 1.3b.

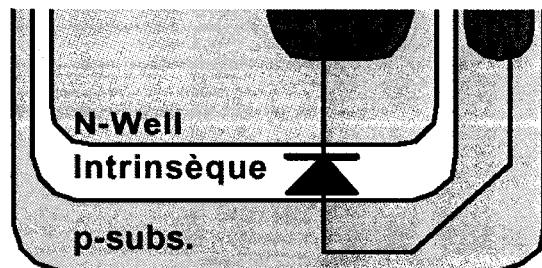

### 1.3.2 Photodiode à couche de semi-conducteur intrinsèque

La photodiode composée d'une structure PIN (silicium dopé P / silicium intrinsèque / silicium dopé N) est connue sous le nom PPD (*Pinned Photodiode*) (Figure 1.4). Lors de son exposition à la lumière, la PPD est initialement sans porteurs [22] et les porteurs majoritaires générés par la lumière sont accumulés dans la région d'appauvrissement, diminuant ainsi la tension à ses bornes [30].

**Figure 1.4: Photodiode PPD, structure PIN.**

Le courant de fuite généré par la PPD est en général moins élevé que celui de la photodiode. Aussi, l'efficacité quantique de la PPD surpassé celle de la photodiode et de la photo-grille. Ceci est possible à condition de bien contrôler plusieurs paramètres lors de la fabrication, entre autres la profondeur et le niveau de dopage des puits. Deux masques de production supplémentaire sont nécessaires afin d'obtenir des PPD [1]. Ces éléments ajoutent énormément de complexité et augmentent le coût du procédé CMOS, déviant ainsi de la méthode standard. Malgré ces considérations, il serait tout de même possible d'utiliser ce procédé de façon rentable pour la fabrication de capteurs d'images, à condition que la demande du marché soit présente.

### 1.3.3 Phototransistor

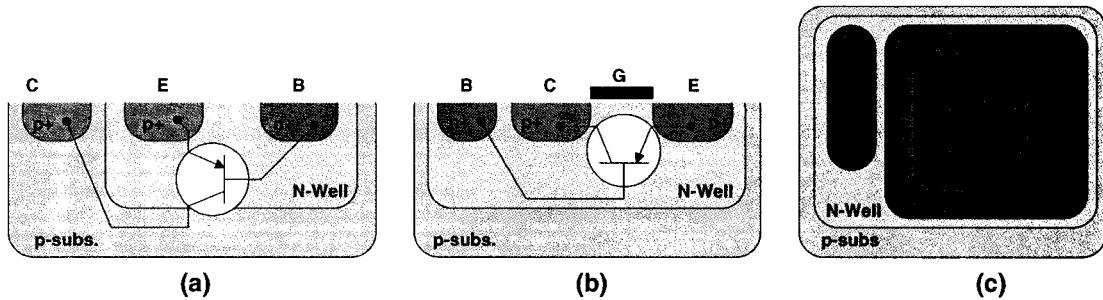

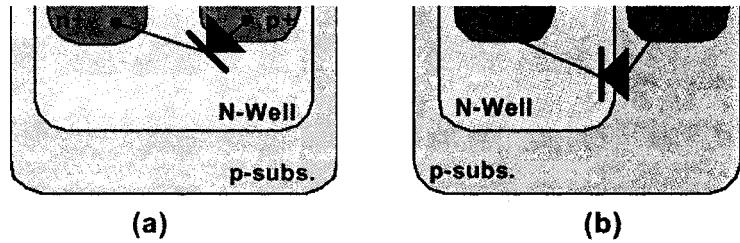

Le phototransistor peut être conçu de différentes façons pour la capture de la lumière. Bien que nous parlons ici de phototransistors conçus avec le procédé CMOS, ce ne sont pas les transistors à effet de champ (*Field Effect Transistor, FET*) standard de ce procédé, mais plutôt des transistors bipolaires (*Bipolar Junction Transistor, BJT*). Ils peuvent être verticaux (Figure 1.5a) avec le  $p^+$  pour l'émetteur,  $N\text{-Well}$  pour la base et le  $p\text{-substrat}$  pour le collecteur [21]. La Figure 1.5 (a), (b) et (c) illustre respectivement différentes méthodes de conception, soit vertical (vue en coupe), latéral (vue en coupe), et circulaire (vue de dessus). Les phototransistors circulaires sont tout simplement des phototransistors latéraux que l'on a fait tourner autour de l'émetteur [2]. En général pour les phototransistors latéraux et circulaires, la grille est laissée flottante, mais on peut lui appliquer une tension afin d'en changer leur gain. La caractéristique qu'ils ont de plus que la photodiode, leur gain ( $\beta$ ), amplifie le photo-courant afin de donner possiblement une meilleure lecture. Par contre, cet aspect n'est pas nécessairement avantageux car il donne lieu à de grandes variations d'un transistor à un autre en plus d'être très difficile à contrôler lors de la production. Ceci introduit un bruit à patron fixe (*Fixed Pattern Noise, FPN*) beaucoup trop élevé pour être acceptable. Il est à noter que le FPN peut être réduit en utilisant une photodiode à la place d'un phototransistor [45].

**Figure 1.5: Design de différents phototransistors**

**(a) vertical; (b) latéral; (c) circulaire.**

#### 1.3.4 Photo-grille

La photo-grille (PG) est une solution au problème de capacité élevée de la photodiode. Que la PG soit réalisée avec le procédé CCD ou le procédé CMOS, le principe de l'intégration, du transport et de la lecture des charges est sensiblement le même. Une illustration de la PG pour un capteur CCD est donnée à la Figure 1.3a. Lors de l'intégration, les charges s'accumulent sous la grille de polysilicium, dans le puit formé par la tension de polarisation appliquée à cette dernière. Par la suite, les charges sont transférées via une grille de transmission (TG) vers une diffusion flottante où sont transformées en tension pour finalement être lues. Afin d'obtenir un bon transfert, les deux grilles, PG et TG, doivent être très rapprochées pour ainsi mettre en contact leur puit de potentiel. Les procédés CMOS standard ne permettent en général qu'une seule grille. Ainsi pour réaliser PG et TG, il doit y avoir un minimum d'espacement entre les deux et les diffusions ne peuvent donc pas se chevaucher. Le procédé CCD, quant à lui, permet un chevauchement des grilles et donc un meilleur transfert des charges.

Étant donné que les charges s'accumulent sous la grille, le courant de fuite est pratiquement nul. Par contre, la lumière doit d'abord traverser cette grille avant de pénétrer le substrat et permettre à des charges de s'y accumuler, ce que seulement 22% des photons (à 500nm) réussissent à faire dû au matériel peut transparent dont est fait la

grille. À proximité du spectre de la lumière bleue (400nm), la transparence de la grille est encore plus faible [43]. Ceci a pour effet de diminuer l'efficacité quantique du capteur en plus de ne pas représenter adéquatement et justement les couleurs présentes dans la scène observée, en particulier le bleu.

### 1.3.5 Photodiode à silicium amorphe

Les photodiodes à silicium amorphe sont fabriquées à l'aide du procédé TFA (*Thin Film on ASIC*). Ce procédé est constitué d'une couche mince, formée de plusieurs étages de silicium amorphe, déposée sur un ASIC. L'avantage du silicium amorphe est son coefficient d'absorption de la lumière qui est 20 fois plus élevé que celui du silicium cristallin [7]. Ce dernier étant utilisé pour faire la puce elle-même ainsi que tous les autres éléments photosensibles présentés précédemment. Le résultat est donc une photodiode placée au-dessus de chaque pixel de la matrice. Les micro-lentilles ne sont pas nécessaires ici car le facteur de remplissage est tout près du 100%. Un procédé TFA bien développé permet une excellente isolation entre les pixels [4]. Un autre aspect intéressant est que le TFA est compatible avec tout procédé CMOS en plus d'être réalisable à faible coût. De plus, son utilisation permet de bénéficier de toutes les possibilités du procédé CMOS, telle une plus grande intégration de transistors par pixel et une faible consommation de puissance.

### 1.3.6 Avenir des capteurs d'images CMOS

Selon Lulé et al. [30], seulement la PPD et le TFA fournissent la sensibilité nécessaire pour permettre une réduction d'échelle sous les  $0.18\mu\text{m}$ . L'option d'utiliser la PPD a été écartée car elle nécessitait un procédé CMOS non-standard. Bien que le TFA nécessite lui aussi un traitement spécial (ajout de la couche mince), la fabrication du circuit lui-même se fait avec un procédé CMOS standard disponible pour ce projet. Dans le cas du présent mémoire, une photodiode sera utilisée pour capter la lumière puisque c'est l'élément qui

offre les meilleurs résultats avec un procédé CMOS standard [27]. Avec un circuit de pixel optimisé et une simple photodiode, il serait simple de remplacer cette dernière par le TFA pour obtenir un système à haute performance.

## 1.4 Constitution du circuit d'un pixel

Le pixel renferme l'élément photosensible et la circuiterie pour l'amplification et le traitement du signal selon des différentes phases. Ces phases d'opération débutent par une phase d'initialisation de l'élément photosensible. Il s'en suit une phase d'intégration, où la lumière incidente modifie la quantité de charges accumulées. Ensuite une phase de lecture retire hors de la matrice la valeur de la charge accumulée de chaque pixel. Certains capteurs utilisent une conversion directe du photo-courant à la tension de sortie, sans intégration [29].

Le rapport de la surface utilisée par l'élément photosensible sur la surface totale du pixel représente le facteur de remplissage. Celui-ci peut se situer autour de 20% pour certains APS, et se rapproche du 100% pour le TFA et pour certains CCD. Afin d'améliorer la performance de certains pixels ayant un faible taux de remplissage, des micro-lentilles, comme celle illustrée à la Figure 1.3b, peuvent être déposées sur la matrice de pixel de façon à focaliser la lumière sur l'élément photosensible.

La taille du pixel peut varier largement selon la technologie utilisée, la dimension minimale des transistors, le nombre de transistors par pixel et les caractéristiques de l'élément photosensible. Par contre, la taille minimale de l'élément photosensible sera limitée par des considérations optiques, et ce même si l'échelle de la technologie utilisée permet l'utilisation de plus petits pixels. Cette taille minimale se situe entre  $4\mu\text{m}$  et  $5\mu\text{m}$  [15] [12], qui est la limite pour éviter la diffraction lumineuse des micro-lentilles [19] ainsi que pour leur fabrication à un coût raisonnable. Selon Ihara et al. [24], les éléments photosensibles pourraient être plus petits que la limite fixée par les micro-lentilles à

condition de placer quatre éléments photosensibles (2x2 avec patron Bayer, Figure 1.1) sous une même micro-lentille. Ceci pourrait se réaliser en disposant les quatre éléments photosensibles de quatre pixels différents à proximité, par symétrie.

La circuiterie d'un pixel doit être protégée de la lumière incidente afin d'éviter l'influence des photo-courants parasites sur le fonctionnement du pixel. La protection se réalise en ajoutant une couche de métal au-dessous de la circuiterie du pixel. De plus, cette couche réduit la probabilité que les photons incidents causent un «*latch-up*».

#### 1.4.1 Types de pixels CMOS

Les premiers pixels CMOS étaient de type PPS (*Passive Pixel Sensor*) [28]. Ce type de pixels ne contenait qu'un transistor pour la remise à zéro et un autre pour la lecture, mais aucun pour l'isolation des charges intégrées car l'échelle du procédé de fabrication ne permettait pas un niveau d'intégration suffisant pour ajouter d'autres transistors et obtenir une résolution acceptable. Le problème majeur avec ce type de pixel est que la valeur qu'il contient, c'est-à-dire une quantité de charges accumulée, est réduite lors de la lecture suite à l'étalement des charges sur le bus de lecture.

Bien qu'inventés au courant des années 1980, c'est vers les années 1990 que les APS [11] sont devenus la nouvelle façon de faire. Avec l'aide de micro-lentilles, ils sont devenus de sérieux compétiteurs aux CCD. Les APS permettent actuellement quelques variantes quant à leur topologie et à leur sortie qui peut être une tension ou un courant. En mode courant, selon Coulombe et al. [10], la vitesse de lecture est plus élevée car les variations du niveau du signal de sortie sont plus faibles, réduisant les temps de charge et de décharge sur les bus de lecture. Par contre, la transmission d'un signal analogique sur un long bus de lecture est sujette au bruit. Ceci limite le rapport signal sur bruit (SNR, *Signal to Noise Ratio*) qui est directement relié à la gamme dynamique.

### 1.4.2 Pixels à circuiterie numérique

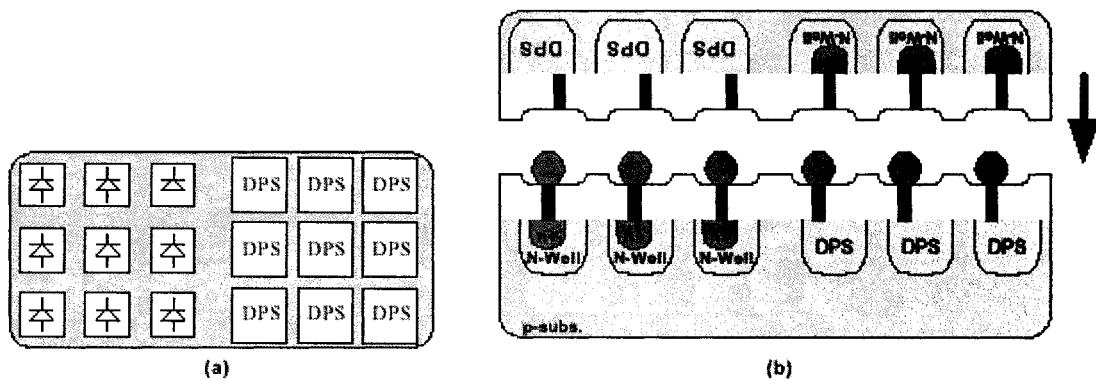

L'utilisation d'un grand nombre de transistors pour le conditionnement du signal et la conversion analogique à numérique (A/N) à l'intérieur du pixel est maintenant rendue possible et on la qualifie de pixel numérique (DPS, *Digital Pixel Sensor*). Dans le passé, une limitation due à l'échelle de la technologie a longtemps empêché l'utilisation de cette méthode. Aujourd'hui, l'avancement de la technologie a mené à la réduction de la taille du pixel. Ceci permet maintenant de réaliser une caméra sur une seule puce. Bien que cela puisse être l'objectif dans certains cas, cette idée ne vise pas à améliorer la qualité de la capture d'image. De plus, la réalisation de cette caméra sur une seule puce n'est possible qu'avec les nouvelles échelles de technologies sous-microniques car un grand nombre de transistors doivent être intégrés à chaque pixel de relativement faible dimensions. De plus, sous les  $4\mu\text{m}^2$  par élément photosensible, il sera impossible de gagner sur la surface du pixel, celui-ci étant limité par des considérations optiques dues aux micro-lentilles, tel que mentionné précédemment. Puisque la taille minimale du pixel reste constante et la taille des transistors diminue avec la progression de l'échelle de la technologie, il devient alors possible d'ajouter des transistors au pixel sans diminuer ses performances optiques. Ceci est encore plus vrai dans le cas du TFA où la totalité de la surface du pixel peut-être remplie de transistors puisque l'élément photosensible est déposé sur celui-ci.

Le DPS apporte de nombreux avantages par rapport aux PPS et APS qui regroupent des modules analogiques à l'extérieur du pixel pour traiter les signaux provenant de ces pixels. Lors de la lecture du DPS, il n'y a pas de détérioration de la qualité du signal analogique par le bruit de lecture sur le bus de colonne puisque cette information est numérique. Avec les PPS et APS, plus le nombre de pixels est élevé, plus le traitement analogique doit se faire rapidement (plus de pixels par colonne) pour traiter le même taux d'image à la seconde, forçant ainsi de nombreuses contraintes sur la circuiterie analogique. En utilisant un DPS, tout le traitement analogique s'effectue à l'intérieur de chaque pixel. La vitesse de la circuiterie analogique est donc indépendante du nombre de

pixels contenus dans la matrice et permet ainsi le traitement de matrices de taille plus élevée.

Les circuits analogiques ne tirent pas beaucoup d'avantages de la réduction d'échelle car les courants de fuite des transistors augmentent et la diminution de la tension d'alimentation réduit la plage de tension disponible pour le traitement analogique. Du côté numérique, le facteur de réduction d'échelle est inversement proportionnel au carré de la surface occupée, les performances en termes de vitesse en sont augmentées et la consommation de puissance en est diminuée. Le fait que le traitement analogique consomme moins de puissance et d'espace comparativement au traitement numérique devient de moins en moins vrai au fur et à mesure que l'échelle de la technologie diminue [15].

En ayant un contrôle numérique sur chacun des pixels, les paramètres d'exposition et de traitement peuvent être ajustés plus adéquatement. Certains types de DPS permettent de tester individuellement chaque pixels sans avoir recours à une source lumineuse, mais plutôt en appliquant des signaux de contrôle, analogiques et numériques [46].

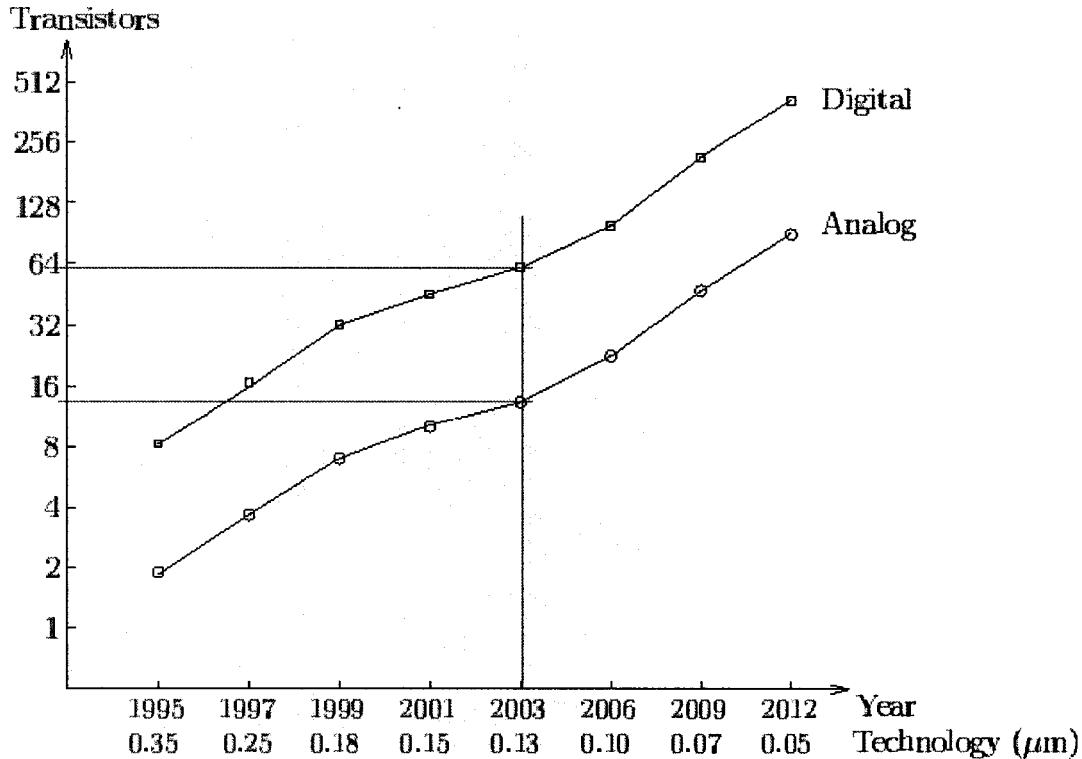

La Figure 1.6 présente une estimation du nombre de transistors en fonction de la taille minimale de la technologie avec un pixel de  $5 \times 5 \mu\text{m}^2$  et un facteur de remplissage de 30%. Les deux courbes, analogique (*analog*) et numérique (*digital*), représentent le type de transistors de grande taille et de taille minimale respectivement. On peut voir qu'il est aujourd'hui possible d'intégrer environ douze transistors analogiques et pas loin de 64 petits transistors. Ce nombre ne cesse de grandir avec la poussée technologique, confirmant les avantages du traitement numérique à même le pixel.

**Figure 1.6: Nombre de transistors intégrés dans un pixel DPS (tirée de [15]).**

## 1.5 Matrice de pixels

Contrairement aux capteurs CCD qui sont limités au balayage séquentiel des pixels pour la lecture de la matrice (*raster-scan*), les capteurs CMOS peuvent adresser les pixels de la matrice individuellement, de la même manière que la lecture d'une mémoire RAM. Ceci procure l'avantage de pouvoir réaliser facilement des fonctions, comme le sous-échantillonnage de la matrice ou un zoom numérique, sans avoir à lire la matrice entière. Lorsque le capteur est utilisé pour des applications en temps réel, il peut être intéressant d'obtenir plus rapidement certaines sections d'images afin de les traiter plus vite. Ce cas peut se produire lorsque la luminosité est relativement différente d'une section à l'autre de l'image. Les pixels les plus fortement illuminés complèteront leur intégration plus rapidement que ceux atteints d'une plus faible luminosité où plus de temps sera nécessaire afin d'accumuler une quantité de charges suffisante pour la lecture. Le capteur

réalisé par Brajovic et al. [6] trie les pixels en fonction de leur intensité lumineuse, les rendant disponibles à l'unité de traitement aussitôt que leur quantité de charges accumulées est suffisante.

Une des techniques utilisées permettant de réduire les contraintes de vitesse d'opération sur certaines parties du capteur consiste à répartir les séquences d'opération de lecture de façon séquentielle. Ceci est similaire à la technique de « *pipelinage* » utilisée dans les microprocesseurs. Pour un capteur d'images, ceci implique que la lecture et l'intégration ne se font pas en même temps pour toute la matrice. On active et désactive donc l'obturateur continuellement dans différentes sections de la matrice, habituellement une ligne à la fois. Cette technique est appelée « *rolling-shutter* ». Tel que discuté à la section 1.4.2, l'augmentation du nombre de pixels de la matrice ralentit ce type de lecture, laquelle est déjà sensible aux objets en mouvement et à la variation de luminosité. Ce problème est mieux connu sous le nom de « *motion blur* ».

### 1.5.1 Sources d'erreur dans une matrice de pixels

Lors de la fabrication de la matrice du capteur d'images, de légères variations du procédé peuvent mener à des transistors légèrement différents. Ceci introduit une erreur propre à chaque pixel qui est identique d'une capture d'images à une autre. On qualifie cette erreur de bruit à patron fixe (*fixed pattern noise, FPN*). Afin de corriger cette erreur, certains capteurs permettent de stimuler les pixels par un courant de référence au lieu d'un photocourant afin de calibrer ces derniers. Il est alors possible de quantifier cette erreur fixe. Une autre façon de corriger cette erreur, puisqu'elle est fixe, est de lire la valeur du pixel après sa remise à zéro, puis de lire la valeur qu'il contient après intégration pour finalement faire la différence entre ces deux valeurs. Cette technique porte le nom de double échantillonnage corrélé (*correlated double sampling, CDS*). Peu importe la méthode utilisée pour réaliser le CDS, une mémoire est nécessaire pour retenir la valeur du FPN du pixel. Cette mémoire peut être analogique et incorporée à l'intérieur même du

pixel, mais généralement, cette mémoire n'est pas sur la même puce que le capteur. Cependant, si l'espace le permet, il est possible de l'intégrer sur la même puce (à l'extérieur de la matrice du capteur) et d'obtenir un gain en vitesse.

La fabrication peut aussi causer des variations de propriétés pour les pixels du contour de la matrice, mais ce problème peut être évité en ajoutant des pixels non-utilisés (*dummy*) au pourtour de la matrice [29].

### **1.5.2 Matrice pour la capture d'images couleur**

Tous les types d'éléments photosensibles à base de semi-conducteurs peuvent aussi bien être utilisés pour des capteurs monochromes que pour des capteurs couleurs. Afin d'obtenir des images en couleur, il existe principalement quatre méthodes:

- a) La première consiste à illuminer la scène séquentiellement par trois sources de lumières de différentes couleurs et de prendre une photo de chacune de ces scènes. Cette méthode ne peut être utilisée que pour une scène statique et dans un environnement contrôlé. Ceci constraint largement l'utilisation de cette méthode.

- b) Une seconde méthode, elle aussi très peu utilisée, consiste à utiliser trois photodiodes réalisant la discrimination spectrale de façon verticale en utilisant différent niveaux de dopage du silicium selon la profondeur d'absorption. Ceci nécessite un procédé CMOS non-standard où il est encore difficile de réaliser la séparation spectrale de façon efficace [12].

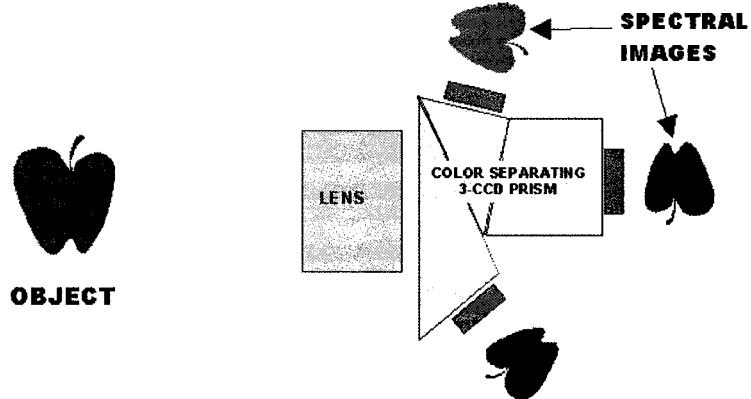

- c) La troisième méthode implique l'utilisation de trois matrices de senseurs qui obtiennent leur lumière d'un prisme qui a préalablement séparé les couleurs. De cette façon, il n'y a pas de problèmes de recouvrement spectral. La fabrication de ces systèmes est très

délicate et demande beaucoup de précision, mais donne d'excellents résultats et est utilisée dans les caméras de très haute gamme (Figure 1.7).

**Figure 1.7: Image séparée par un prisme (tiré de [48]).**

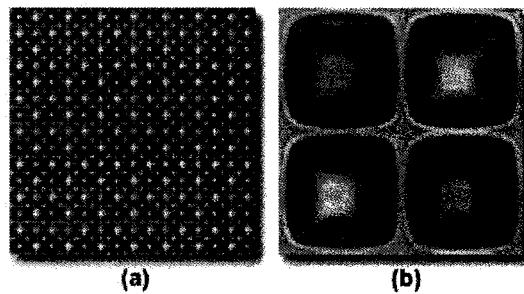

d) La dernière méthode, et la plus utilisée, consiste à appliquer un filtre de couleur identique pour chaque bloc de 2x2 pixels [48]. Le type de mosaïque utilisée est celle de Bayer, où deux filtres verts, un rouge et un bleu sont utilisés (Figure 1.8). Un inconvénient à cette méthode est le problème de sous-échantillonnage (section 1.2.1) qui peut survenir lorsque la scène comporte un brusque changement de couleurs.

**Figure 1.8: Mosaïque à patron de Bayer (tiré de [48])**

**(a) Matrice de pixels; (b) Un seul pixel comportant quatre éléments photosensibles.**

La mosaïque de la Figure 1.8 a été nommée d'après l'ingénieur Bryce E. Bayer de la compagnie Kodak. Elle est formée à partir de polymères des trois couleurs primaires:

rouge, vert et bleu (RVB). Le fait qu'il y ait deux fois plus de filtres verts que bleus ou rouges est dû à la plus grande sensibilité de notre œil dans cette région du spectre de la lumière visible. Notons qu'il est aussi possible d'utiliser un filtre CMY (*Cyan*, bleu pâle; *Magenta*, rose-mauve; *Yellow*, jaune). L'avantage de ce filtre est l'augmentation de la sensibilité du capteur car il laisse passer plus de lumière que le filtre RVB. Son côté négatif est l'augmentation de la complexité des calculs pour la reconstruction de l'image et l'ajout d'une erreur impliquée par cette conversion [48].

### 1.5.3 Perception des images par l'œil humain

L'application visée du capteur que nous proposons nous motive à comparer les capteurs électroniques et l'œil humain puisqu'elle vise à remplacer un système visuel humain non-fonctionnel.

Bien que quatre éléments photosensibles soient nécessaires afin d'obtenir un seul pixel de couleur, la résolution de la matrice n'en est pas pour autant diminuée. En fait, la résolution spatiale de l'œil humain est principalement déterminé par la luminance (intensité) et non par la chrominance (couleur). Ceci s'explique par le fait que le cerveau humain forme l'image précise à partir de la résolution en intensité, puis il y ajoute la couleur seulement de façon grossière. À l'intérieur d'un capteur électronique, seulement l'intensité de chaque élément photosensible est utilisée. Une interpolation est ensuite faite sur les différentes couleurs du pixel en tenant compte du recouvrement spectral des filtres de Bayer (Figure 1.9). Finalement, la couleur de chaque élément photosensible est déterminée par des algorithmes basés sur les valeurs des pixels voisins.

**Figure 1.9: Transmission des filtres de couleur (tiré de [48]).**

## 1.6 Conversion analogique à numérique

Lorsque l'on parle de capteurs PPS ou APS, les méthodes de conversion A/N possibles sont nombreuses puisque la conversion se fait à l'extérieur de la matrice où il n'y a pas de contraintes sur la surface utilisée par la circuiterie. On peut alors utiliser des circuits beaucoup plus volumineux renfermant un grand nombre de transistors. Par contre, avec une matrice DPS, l'espace disponible est très limité et on doit faire des compromis entre performance et surface utilisée. Le capteur de McIlrath [32] utilise un convertisseur A/N à un bit sigma-delta ( $\Sigma\Delta$ ) de premier ordre, ce qui est un compromis raisonnable entre surface et fonctionnalité. De plus, il est robuste aux variations du procédé de fabrication. Le problème avec ce type de convertisseur est le haut débit des données de sortie causé par le suréchantillonnage [21].

Les deux méthodes de base pour la conversion analogique à numérique à l'intérieur d'un DPS, le sigma-delta et celle des comparaisons successives, possèdent toutes deux leurs avantages et inconvénients. Par exemple, un convertisseur sigma-delta possède un plus grand FPN, tandis que celui à comparaisons successives a une meilleure robustesse au bruit des transistors [20]. Dans le cas des capteurs infrarouges, le FPN de la matrice n'est

pas critique car il y a déjà un taux élevé de FPN dans le signal incident. Le convertisseur sigma-delta est donc plus approprié dans ce cas. Les capteurs d'images (dans le domaine du visible) nécessitent un faible FPN ainsi qu'un faible débit de données provenant des pixels, étant donné la résolution plus élevée de ceux-ci. Les convertisseurs à comparaisons successives sont donc plus appropriés dans ce cas.

Yang et al. évitent le problème du haut débit des données de sortie du  $\Sigma\Delta$  en opérant à vitesse moindre, au taux de Nyquist, et en limitant les données de sorties aux bits nécessaires pour la quantification [46]. Ils proposent le MCBS (*multi-channel bit serial*) qui est composé d'un comparateur et d'une mémoire à un seul bit. La tension de sortie du pixel est comparée à une tension qui est générée par un convertisseur numérique à analogique (CNA) externe à la matrice. Les pixels de la matrice fonctionnent simultanément à l'aide d'un comparateur intérieur à chacun d'eux. Chacun des bits de la matrice est ensuite lu pour laisser place à une autre série de comparaisons successives. Il est à noter que d'autres méthodes de conversion sont possibles pour les DPS utilisant des comparaisons avec des tensions externes à la matrice.

Une méthode un peu plus particulière utilisée par Ripp et al. [38] est inspirée de la vision biologique. Basée sur le fait que les signaux incidents les plus forts provoquent une réponse avant les signaux de plus faible intensité, cette méthode est une sorte de conversion intensité-temps. L'avantage de cette méthode est une faible latence pour les régions de forts signaux incidents. Les sorties ne saturent jamais (au niveau théorique) puisque les pixels sont simplement triés de la plus forte intensité incidente à la plus faible intensité incidente. Cette méthode a été implémentée par Brajovic et al., sur un capteur à N niveaux de sortie où N est le nombre de pixels [6].

### 1.6.1 Consommation de puissance des convertisseurs A/N

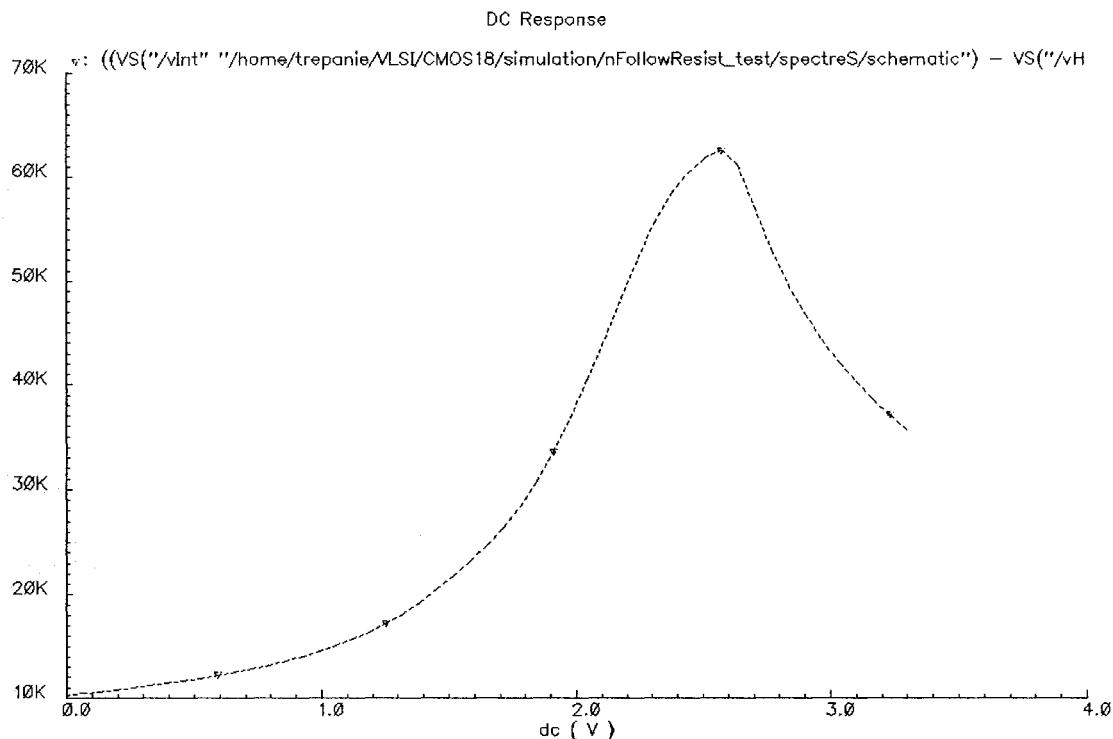

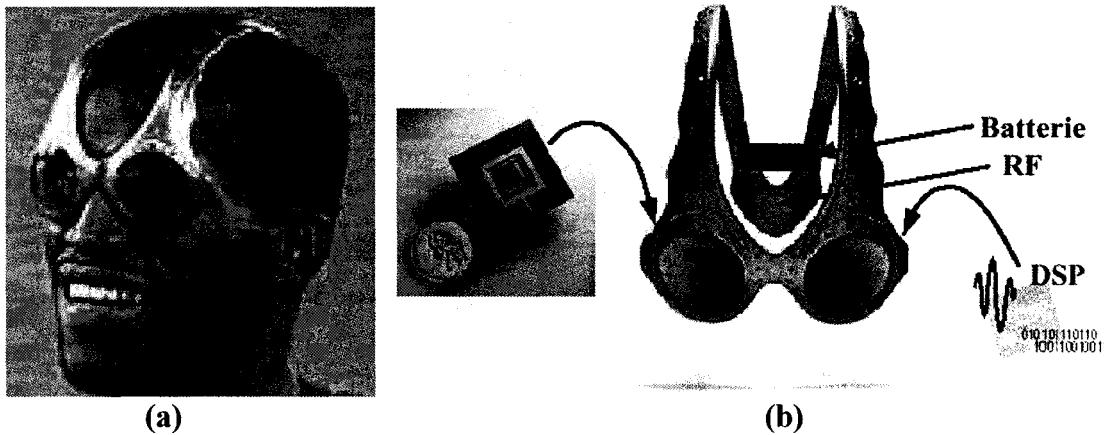

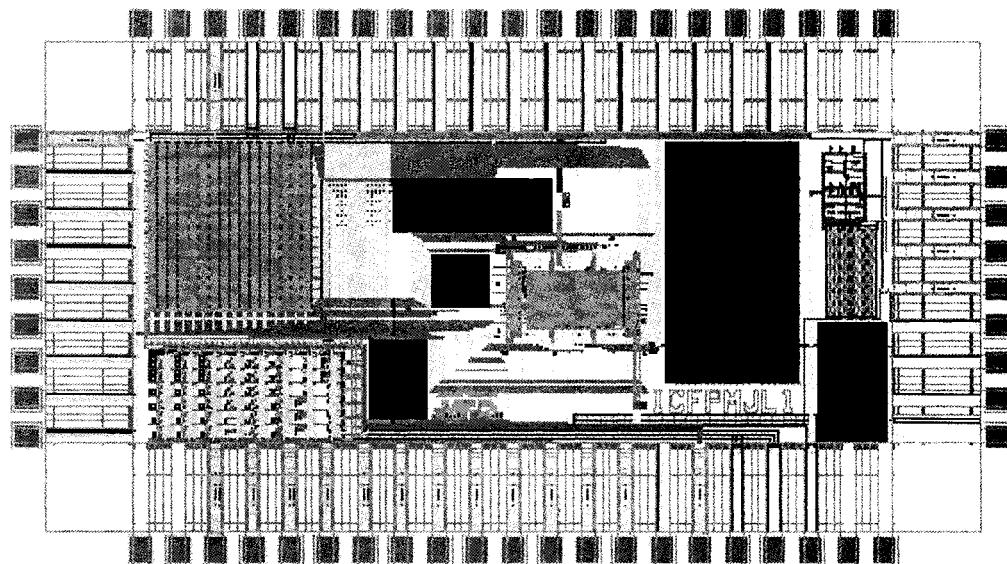

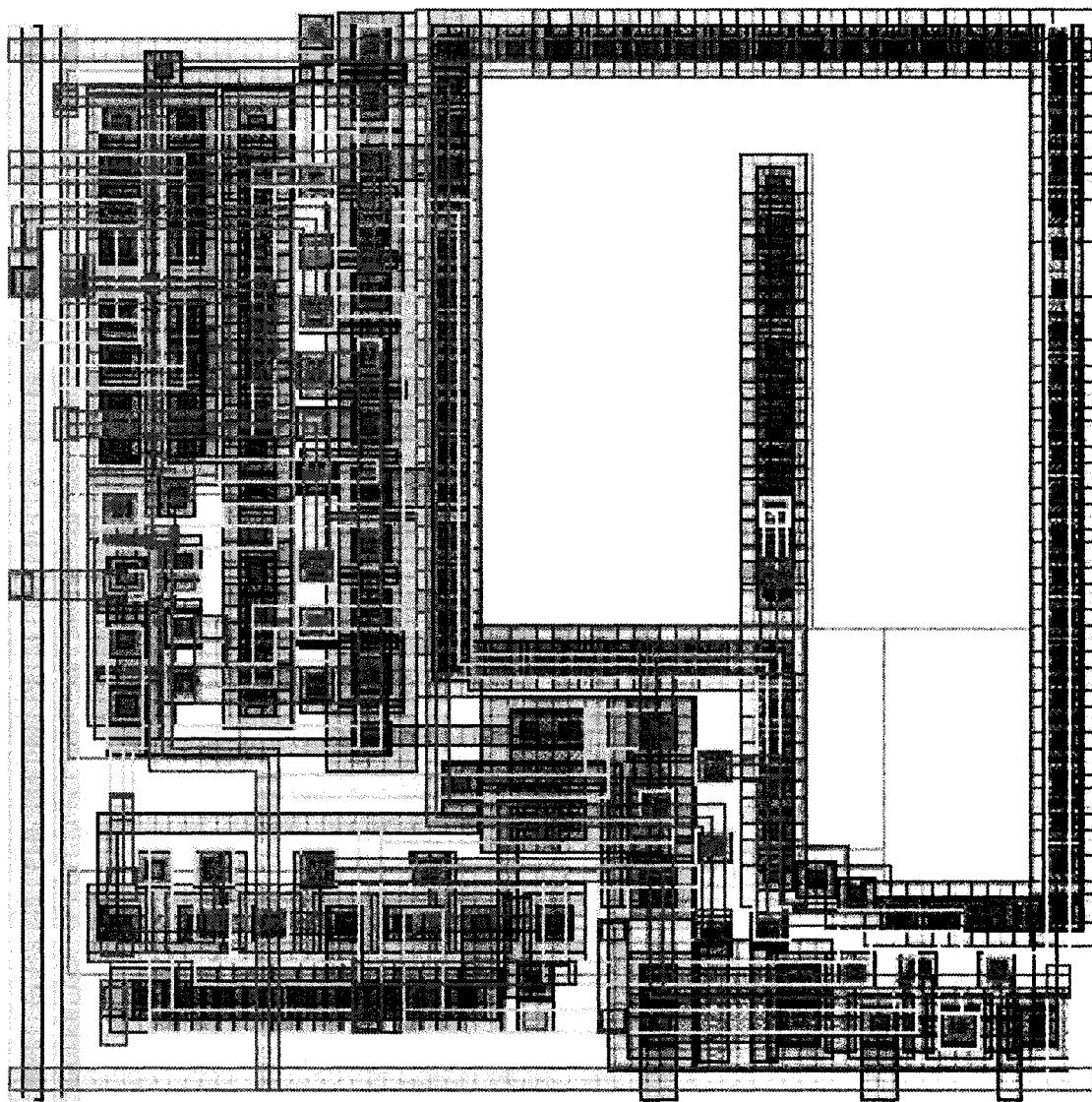

La consommation de puissance est une caractéristique importante à considérer lorsqu'on conçoit un système portable comme un capteur d'images. L'avantage que le CMOS possède sur le CCD est la capacité d'intégrer sur la même puce les convertisseurs A/N, ce qui réduit significativement la consommation de puissance. De la même façon, sur la même puce, il est encore possible de limiter le transport de tensions analogiques en convertissant la valeur du pixel avant de la transporter à l'extérieur de la matrice. Ceci évite d'utiliser des amplificateurs analogiques consommant beaucoup de puissance [37]. Puisque la dissipation de puissance en fonction de la fréquence augmente plus rapidement que linéairement dans les circuits analogiques et linéairement dans les circuits numériques, faire fonctionner N convertisseurs A/N requiert moins de puissance que un seul convertisseur fonctionnant N fois plus vite [36]. Les conversions A/N au niveau du pixel résultent donc en une plus faible consommation de puissance puisqu'ils opèrent en parallèle et à très basse vitesse.