**Titre:** Méthode de réutilisation et de couverture pour la vérification fonctionnelle des circuits numériques

Title: functionnal verification of digital circuits

**Auteur:** Sébastien Regimbal

Author:

**Date:** 2003

**Type:** Mémoire ou thèse / Dissertation or Thesis

**Référence:** Regimbal, S. (2003). Méthode de réutilisation et de couverture pour la vérification fonctionnelle des circuits numériques [Master's thesis, École Polytechnique de Montréal]. PolyPublie. <https://publications.polymtl.ca/7300/>

Citation:

## Document en libre accès dans PolyPublie

Open Access document in PolyPublie

**URL de PolyPublie:** <https://publications.polymtl.ca/7300/>

PolyPublie URL:

**Directeurs de recherche:** Yvon Savaria, & Guy Bois

Advisors:

**Programme:** Unspecified

Program:

UNIVERSITÉ DE MONTRÉAL

MÉTHODE DE RÉUTILISATION ET DE COUVERTURE

POUR LA VÉRIFICATION FONCTIONNELLE DES CIRCUITS NUMÉRIQUES.

SÉBASTIEN REGIMBAL

DÉPARTEMENT DE GÉNIE ÉLECTRIQUE

ÉCOLE POLYTECHNIQUE DE MONTRÉAL

MÉMOIRE PRÉSENTÉ EN VUE DE L'OBTENTION

DU DIPLÔME DE MAÎTRISE ÈS SCIENCES APPLIQUÉES

(GÉNIE ÉLECTRIQUE)

DÉCEMBRE 2003

National Library

of Canada

Bibliothèque nationale

du Canada

Acquisitions and

Bibliographic Services

Acquisitions et

services bibliographiques

395 Wellington Street

Ottawa ON K1A 0N4

Canada

395, rue Wellington

Ottawa ON K1A 0N4

Canada

*Your file* *Votre référence*

ISBN: 0-612-90856-9

*Our file* *Notre référence*

ISBN: 0-612-90856-9

The author has granted a non-exclusive licence allowing the National Library of Canada to reproduce, loan, distribute or sell copies of this thesis in microform, paper or electronic formats.

L'auteur a accordé une licence non exclusive permettant à la Bibliothèque nationale du Canada de reproduire, prêter, distribuer ou vendre des copies de cette thèse sous la forme de microfiche/film, de reproduction sur papier ou sur format électronique.

The author retains ownership of the copyright in this thesis. Neither the thesis nor substantial extracts from it may be printed or otherwise reproduced without the author's permission.

L'auteur conserve la propriété du droit d'auteur qui protège cette thèse. Ni la thèse ni des extraits substantiels de celle-ci ne doivent être imprimés ou autrement reproduits sans son autorisation.

---

In compliance with the Canadian Privacy Act some supporting forms may have been removed from this dissertation.

Conformément à la loi canadienne sur la protection de la vie privée, quelques formulaires secondaires ont été enlevés de ce manuscrit.

While these forms may be included in the document page count, their removal does not represent any loss of content from the dissertation.

Bien que ces formulaires aient inclus dans la pagination, il n'y aura aucun contenu manquant.

# Canadä

UNIVERSITÉ DE MONTRÉAL

ÉCOLE POLYTECHNIQUE DE MONTRÉAL

Ce mémoire intitulé :

MÉTHODE DE RÉUTILISATION ET DE COUVERTURE

POUR LA VÉRIFICATION FONCTIONNELLE DES CIRCUITS NUMÉRIQUES

présenté par: REGIMBAL Sébastien

en vue de l'obtention du diplôme de : Maîtrise ès sciences appliquées

a été dûment accepté par le jury d'examen constitué de :

M. BOYER François, Ph.D., président

M. SAVARIA Yvon, Ph.D., membre et directeur de recherche

M. BOIS Guy, Ph.D., membre et codirecteur de recherche

M. KHOUAS Abdelhakim, Doct., membre

## REMERCIEMENTS

En premier lieu, je tiens à remercier mon directeur de recherche Yvon Savaria pour m'avoir proposé ce projet motivant qui m'a permis de repousser les limites de mes connaissances. Avec son soutien et ses conseils avisés, j'ai été en mesure de compléter aisément ce projet. J'aimerais également remercier mon codirecteur Guy Bois, qui m'a aussi supporté dans ce projet. De plus, je remercie les organismes, la société PMC Sierra, Micronet et le CRSNG, qui ont subventionné mon travail de recherche.

Je remercie Jean-François Lemire, mon partenaire dans l'exploration de ce domaine de recherche, qui a été directement impliqué dans la réalisation de ce projet. Nos discussions en toutes circonstances m'ont permis de progresser. Je suis aussi reconnaissant envers les membres du GRM et le personnel du GRM qui m'ont permis de travailler dans un environnement stimulant. J'aimerais aussi remercier André Baron pour sa collaboration à ce projet.

Finalement, une attention particulière va pour ma copine Chantal Galipeau qui me soutient dans tout ce que je fais.

## RÉSUMÉ

Les méthodes et outils de conception de circuits numériques permettent le développement de systèmes complexes. Conséquemment la vérification fonctionnelle de tels systèmes devient de plus en plus difficile. D'autre part, puisque le coût de la fabrication des circuits a augmenté parallèlement à l'augmentation de la complexité des circuits, une erreur fonctionnelle détectée suite à sa fabrication engendre des coûts qui peuvent affecter la rentabilité commerciale d'un circuit. Il vaut donc mieux vérifier les fonctionnalités des circuits tout en respectant les échéanciers imposés par leur mise en marché. Ainsi, l'élaboration de nouvelles méthodologies, visant à accélérer les tâches de vérification et à augmenter la qualité de la vérification est essentielle afin de s'adapter aux contraintes actuelles régissant le développement des circuits numériques.

Ce mémoire apporte une contribution au niveau des méthodes de vérification fonctionnelle en introduisant deux méthodologies de vérification. La première méthode proposée est une méthode de conception de bancs d'essais favorisant la réutilisation. La méthode est basée sur l'utilisation d'un langage de vérification matérielle, le langage *e*, qui permet l'utilisation des méthodologies de conception orientées objets et aspects. Ainsi, un partitionnement orienté objets et aspects, dédié à la création de bancs d'essais, est proposé afin d'augmenter le potentiel de réutilisation d'un banc d'essais. Cette méthode permet d'accélérer le processus de conception des bancs d'essais. La deuxième méthode de vérification proposée est une technique systématique permettant de développer un module d'analyse de la couverture fonctionnelle d'un circuit numérique. La problématique reliée au développement de cette méthode est qu'il faut avoir des métriques fonctionnelles standardisées appliquées sur une description normalisée des fonctionnalités du circuit. Les fonctionnalités d'un circuit étant habituellement décrites sous forme textuelle dans un document de spécification, il est difficile de travailler de façon systématique avec ce genre de description. Ainsi, on propose d'effectuer une description standardisée de la spécification d'un circuit en utilisant un langage exécutable de haut niveau. En formulant une métrique fonctionnelle en fonction de la description

standardisée de la spécification, il est possible de créer un module d'analyse de la couverture de façon systématique. Le langage de spécification utilisé est le *Specification Description Language* (SDL). Ce langage est exécutable, ce qui permet de valider la spécification développée. La métrique fonctionnelle présentée dans ce mémoire est basée sur la technique de vérification des flots transactionnels. L'implémentation d'un module d'analyse de la couverture, en utilisant la méthode proposée, est faite en utilisant le langage *e*. Le module d'analyse de la couverture produit avec la méthode peut être incorporé dans n'importe quel banc d'essais dédié à la vérification d'un circuit au niveau *Register Transfer Level* (RTL). L'utilité de ce module est en fait de permettre la création d'une suite de tests qui permettra de couvrir la métrique définie et aussi de réduire l'application de tests redondants. Cela implique qu'avec ce module d'analyse de la couverture, il est possible de créer une suite de tests moins longue ayant aussi une plus grande puissance de détection d'erreurs

Ces méthodes ont été appliquées sur différents modèles. La méthode de conception a été utilisée par la création de bancs d'essais dédiés à la vérification d'une version d'un convertisseur de protocoles. Le projet de conversions de protocoles est développé par un groupe d'étudiants de cycles supérieurs du *Groupe de Recherche en Microélectronique* (GRM). Ensuite, la méthode de conception a aussi été utilisée pour la création d'un banc d'essais dédiés à un exemple simple d'un commutateur *Asynchronous Transfer Mode* (ATM). Le commutateur ATM a aussi servi d'exemple pour l'application de la méthode de couverture fonctionnelle. Ainsi, une spécification décrite avec le langage SDL a été développée pour le commutateur ATM. Ensuite, en utilisant la méthode de couverture développée, un module d'analyse de la couverture a été produit. En utilisant le module produit, il a été possible de développer une suite de tests efficaces qui couvre la métrique utilisée. Finalement, un module d'analyse de la couverture a aussi été produit pour un modèle fourni par la société PMC-Sierra. Les résultats de l'application sur cet exemple seront toutefois limités puisque les fonctionnalités et la structure de ce modèle sont confidentielles.

## ABSTRACT

Advances in microelectronic technologies allow development of complex digital systems. Consequently the functional verification of such systems becomes increasingly difficult. Moreover, since manufacturing costs of such circuits increase at the same time as the complexity of a circuit, functional errors detected following its manufacture generate costs that can seriously affect its commercial profitability. It is thus necessary to perform a more accurate verification while respecting the schedule imposed by time-to-market constraints. Hence, the development of new verification methodologies is essential to deal with the current constraints governing the development of digital circuits. These new verification methodologies must be aimed at accelerating verification tasks and at enhancing the quality of the overall verification process.

This thesis brings a contribution to the functional verification process by introducing two verification methodologies. The first method proposed in this thesis is a test-bench design methodology that promotes reuse. This method is based on the use of a *Hardware Verification Language* (HVL), the *e* language, that allows using object-oriented and aspect-oriented programming techniques. Hence, an object-oriented and an aspect-oriented partitioning dedicated to test-benches design are proposed in order to increase their reuse potential. This method attempts to accelerate test-bench design and implementation.

The second verification method proposed is a systematic method to develop a coverage analysis module for a digital circuit. The difficulties related to the development of this method are that we need a standardized functional metric applied on a standardized description of the functionalities of the circuit. The functionalities of a circuit are usually described by a functional specification in a textual format. However, it is difficult to work in a systematic way with this kind of description. Thus, we propose to define a standardized description of the specification using a high-level executable language. By formulating a functional metric according to the standardized description of the specification, it is possible to create systematically a coverage analysis module. The

specification language used is the *Specification Description Language* (SDL). This language is executable, which makes it possible to validate the developed specification. The functional metric presented in this thesis is based on the transaction-flow verification technique. A coverage analysis module is implemented using the *e* language and it can be connected in any test-bench dedicated to verify the *Design Under Verification* (DUV). Using our methodology, we are able to provide a quantitative evaluation of test suites aimed at exercising the functionalities defined in the executable specification. The application of these test suites on the *Register Transfer Level* (RTL) design increases error detection possibilities by a better exploration of the design and raises the degree of confidence in the design.

These methods have been applied on different designs. For instance, they were used to facilitate the development of test-benches for a version of a protocol converter. A team of graduate students in the *Groupe de Recherche en Microélectronique* (GRM) works on that protocol converter. Then, we used the design method to create a test-bench for an *Asynchronous Transfer Mode* (ATM) switch. We also used the ATM switch as a case study for the coverage model development methodology. Hence, a SDL specification has been developed for the ATM switch. Then using our methodology, we produced a coverage analysis module to facilitate development of an efficient test suite. The second application on which was applied the coverage model development methodology is a real industrial design developed by PMC-Sierra. For this example, we only provide qualitative results, since this design is confidential.

## TABLE DES MATIÈRES

|                                             |            |

|---------------------------------------------|------------|

| <b>Remerciements</b>                        | <hr/> IV   |

| <b>Résumé</b>                               | <hr/> V    |

| <b>Abstract</b>                             | <hr/> VII  |

| <b>Table des matières</b>                   | <hr/> IX   |

| <b>Liste des figures</b>                    | <hr/> XIII |

| <b>Liste des tableaux</b>                   | <hr/> XV   |

| <b>Liste des sigles et des abréviations</b> | <hr/> XVI  |

| <b>Liste des Annexes</b>                    | <hr/> XVII |

| <b>Chapitre 1 Introduction</b>              | <hr/> 1    |

| <b>Chapitre 2 Revue de littérature</b>      | <hr/> 6    |

| <b>2.1 La vérification</b>                  | <hr/> 6    |

| 2.1.1 Vérification versus Validation        | <hr/> 7    |

| 2.1.2 Principes du test                     | <hr/> 9    |

| 2.1.3 Testabilité du modèle                 | <hr/> 10   |

| 2.1.4 Type de vérification                  | <hr/> 12   |

| 2.1.4.1 Test structurel et test fonctionnel | <hr/> 12   |

|                   |                                                                               |           |

|-------------------|-------------------------------------------------------------------------------|-----------|

| 2.1.4.2           | Méthode de preuve formelle                                                    | 13        |

| 2.1.5             | Critère d'arrêt                                                               | 14        |

| <b>2.2</b>        | <b>Techniques et mesures de la vérification</b>                               | <b>15</b> |

| 2.2.1             | Visibilité                                                                    | 16        |

| 2.2.2             | Niveau d'abstraction                                                          | 17        |

| 2.2.3             | Techniques et métriques                                                       | 18        |

| 2.2.3.1           | Revue de code                                                                 | 18        |

| 2.2.3.2           | Techniques basées sur le code                                                 | 19        |

| 2.2.3.3           | Test par mutation                                                             | 20        |

| 2.2.3.4           | Analyse partitionnelle et test limites                                        | 21        |

| 2.2.3.5           | Techniques de vérification basées sur un graphe                               | 22        |

| 2.2.4             | Production de tests et couverture                                             | 23        |

| 2.2.4.1           | Test déterministe                                                             | 23        |

| 2.2.4.2           | Test pseudo-aléatoire                                                         | 23        |

| 2.2.4.3           | Tests automatiques                                                            | 24        |

| 2.2.5             | Vérification des réponses                                                     | 24        |

| 2.2.5.1           | Méthodes en post-simulation                                                   | 25        |

| 2.2.5.2           | Méthodes en cours de simulation                                               | 25        |

| <b>2.3</b>        | <b>Conception de bancs d'essais</b>                                           | <b>26</b> |

| 2.3.1             | Langage de vérification                                                       | 26        |

| 2.3.2             | Implantation d'un banc d'essais                                               | 28        |

| 2.3.3             | Réutilisation                                                                 | 29        |

| 2.3.3.1           | Composants réutilisables et patron de conception                              | 29        |

| <b>Chapitre 3</b> | <b>Méthodologie de conception de bancs d'essais axée sur la réutilisation</b> | <b>31</b> |

| <b>3.1</b>        | <b>Conception logiciel</b>                                                    | <b>33</b> |

|                                                       |                                                     |           |

|-------------------------------------------------------|-----------------------------------------------------|-----------|

| 3.1.1                                                 | Conception Orientée Objets                          | 33        |

| 3.1.2                                                 | Conception Orientée Aspects                         | 34        |

| <b>3.2</b>                                            | <b>Méthodologie proposée</b>                        | <b>37</b> |

| 3.2.1                                                 | Partitionnement par objets                          | 37        |

| 3.2.2                                                 | Partitionnement par aspects                         | 39        |

| <b>3.3</b>                                            | <b>Application de la méthodologie</b>               | <b>41</b> |

| 3.3.1                                                 | Le modèle sous vérification                         | 41        |

| 3.3.2                                                 | Conception d'un banc d'essais                       | 42        |

| 3.3.3                                                 | Réutilisation                                       | 45        |

| <b>3.4</b>                                            | <b>Discussion</b>                                   | <b>46</b> |

| 3.4.1                                                 | Remarques sur la méthode                            | 47        |

| 3.4.2                                                 | Extension de la méthodologie                        | 48        |

| <b>Chapitre 4 Méthode de Couverture fonctionnelle</b> |                                                     | <b>49</b> |

| <b>4.1</b>                                            | <b>Méthodologie de Couverture</b>                   | <b>51</b> |

| <b>4.2</b>                                            | <b>Système de couverture</b>                        | <b>54</b> |

| 4.2.1                                                 | Technique de vérification utilisée                  | 54        |

| 4.2.2                                                 | Définition de la spécification exécutable           | 58        |

| 4.2.3                                                 | Formulation de la métrique                          | 63        |

| 4.2.4                                                 | Abstraction de la métrique                          | 67        |

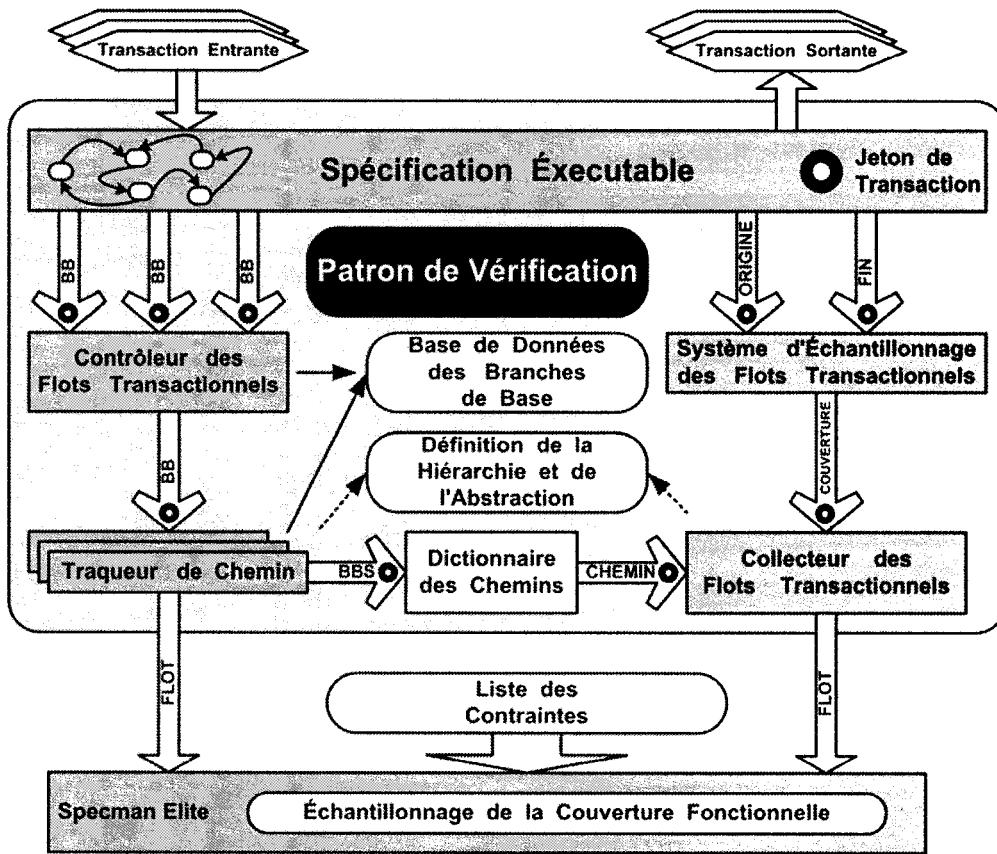

| <b>4.3</b>                                            | <b>Patron de vérification</b>                       | <b>70</b> |

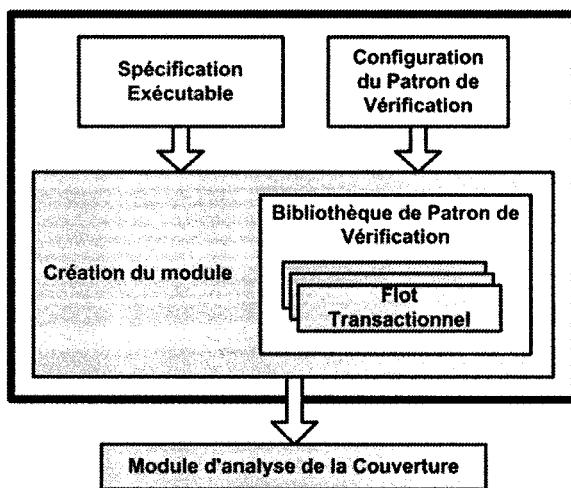

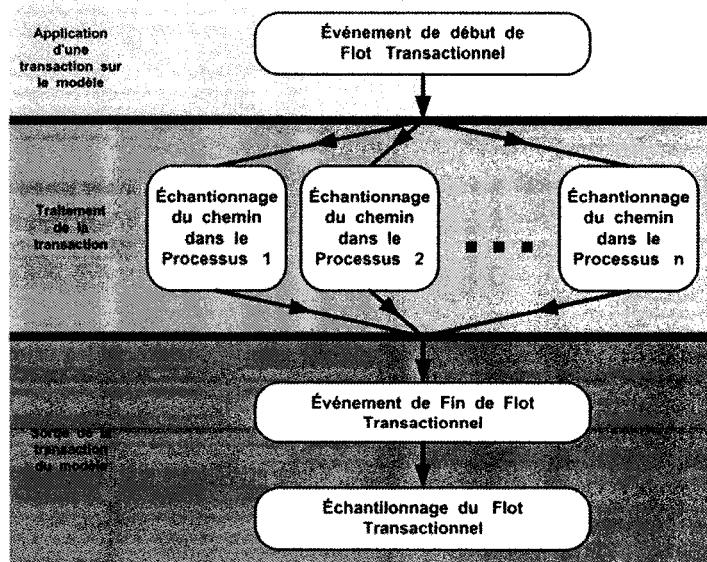

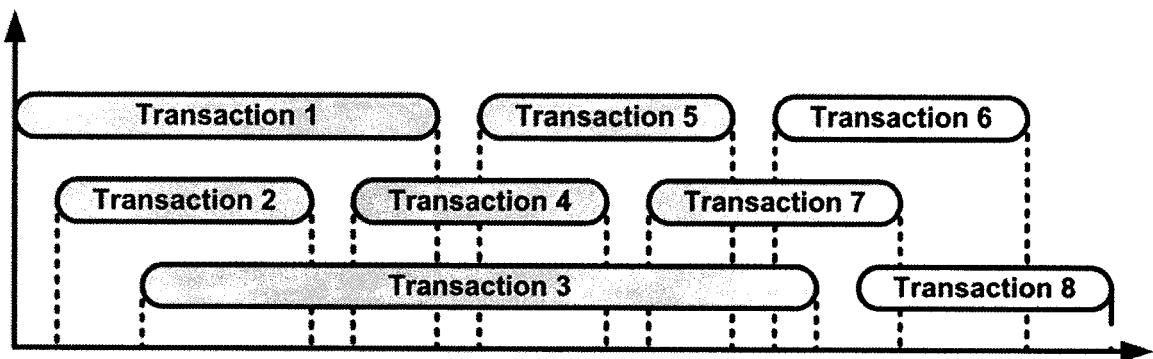

| 4.3.1                                                 | Fonctionnement du module                            | 71        |

| 4.3.2                                                 | Reconfiguration Automatique                         | 84        |

| 4.3.2.1                                               | Les macros du langage <i>e</i>                      | 84        |

| 4.3.2.2                                               | Algorithmes de génération des groupes de couverture | 85        |

|                                            |                                                          |            |

|--------------------------------------------|----------------------------------------------------------|------------|

| <b>4.4</b>                                 | <b>Discussion</b>                                        | <b>86</b>  |

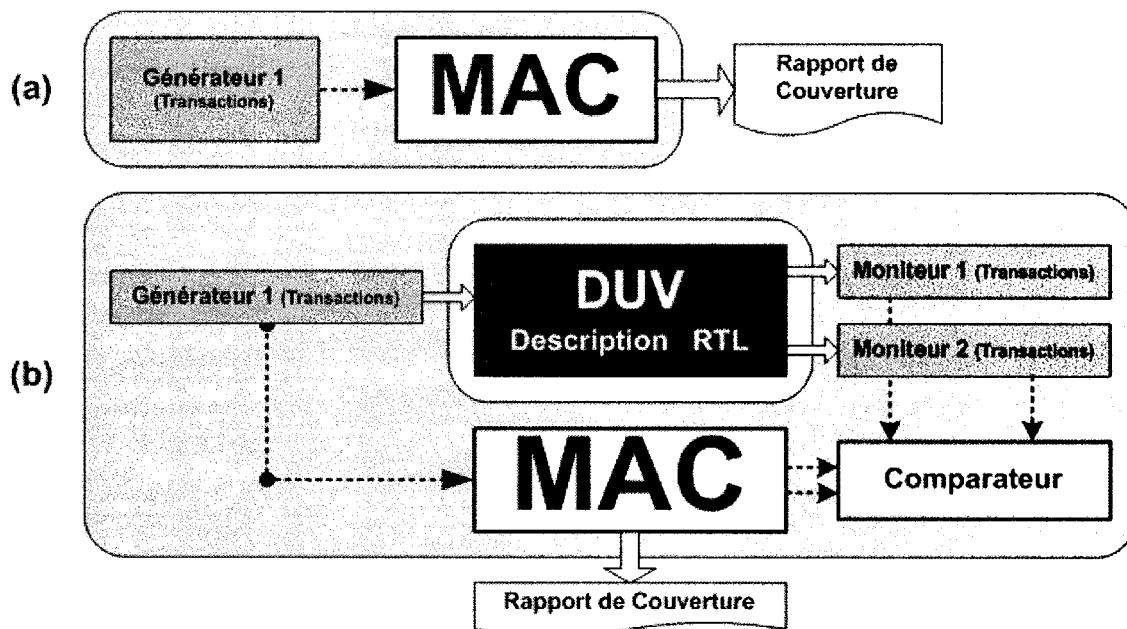

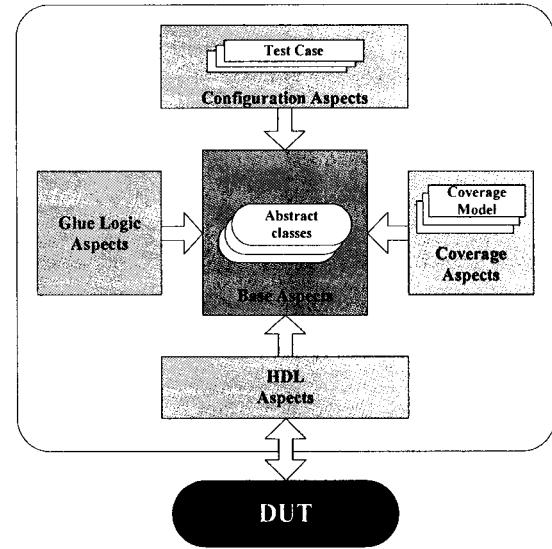

| 4.4.1                                      | Intégration du module avec la méthodologie de conception | 87         |

| 4.4.2                                      | Automatisation                                           | 88         |

| 4.4.3                                      | Extension de la méthode de couverture                    | 90         |

| 4.4.4                                      | L'efficacité de la vérification avec cette méthode       | 91         |

| <b>Chapitre 5 Application Des Méthodes</b> |                                                          | <b>92</b>  |

| <b>5.1</b>                                 | <b>Convertisseur de protocoles</b>                       | <b>92</b>  |

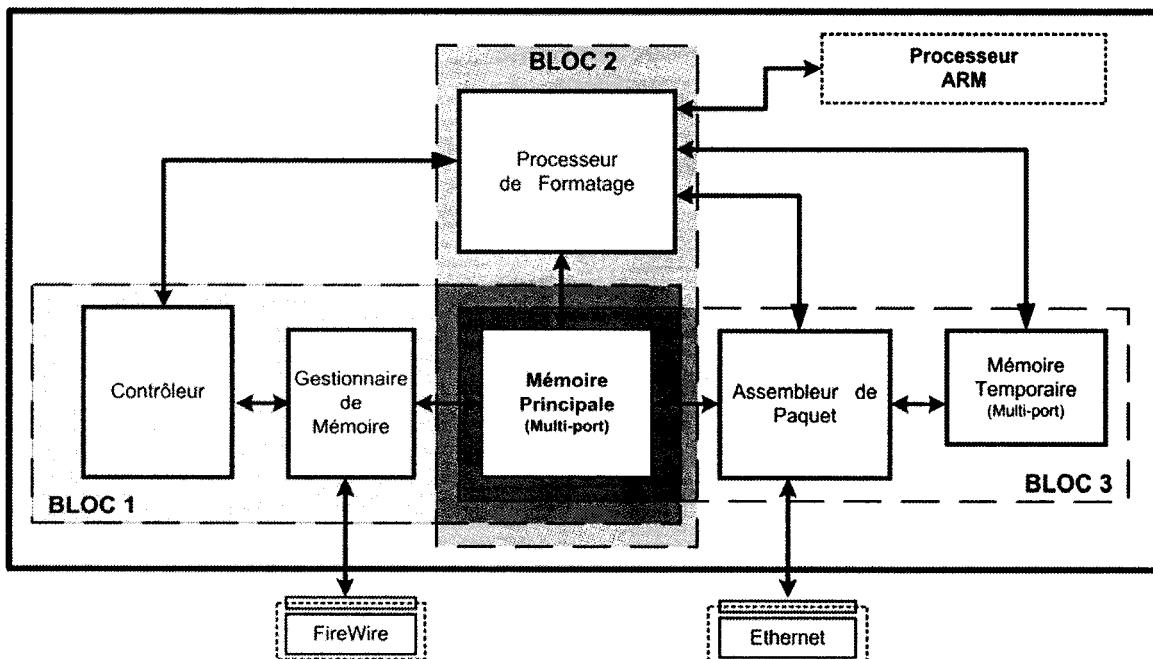

| 5.1.1                                      | Présentation du modèle                                   | 93         |

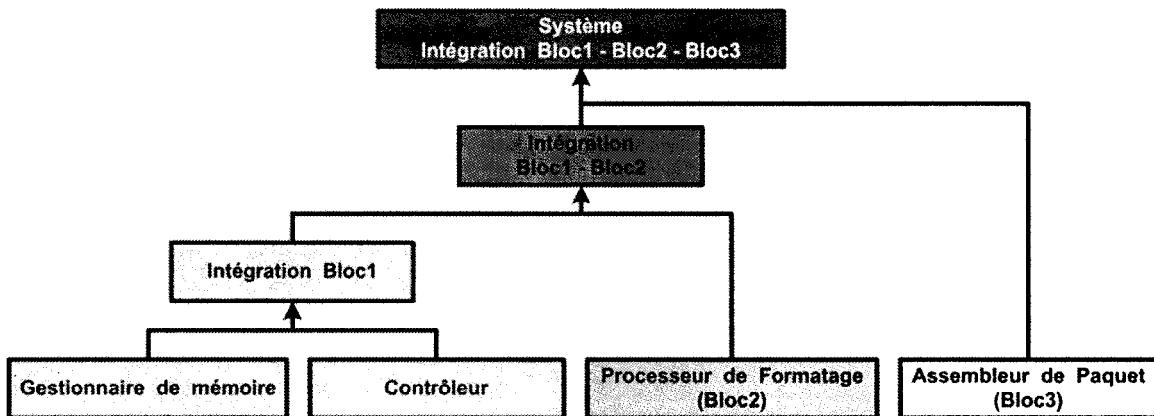

| 5.1.2                                      | Vérification du convertisseur de protocoles              | 95         |

| <b>5.2</b>                                 | <b>Commutateur ATM</b>                                   | <b>97</b>  |

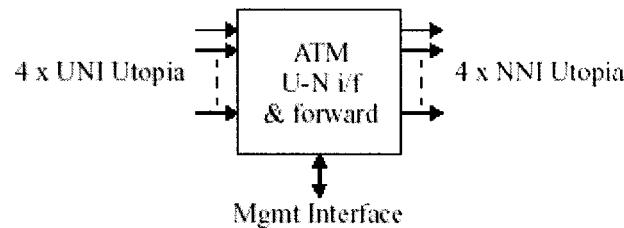

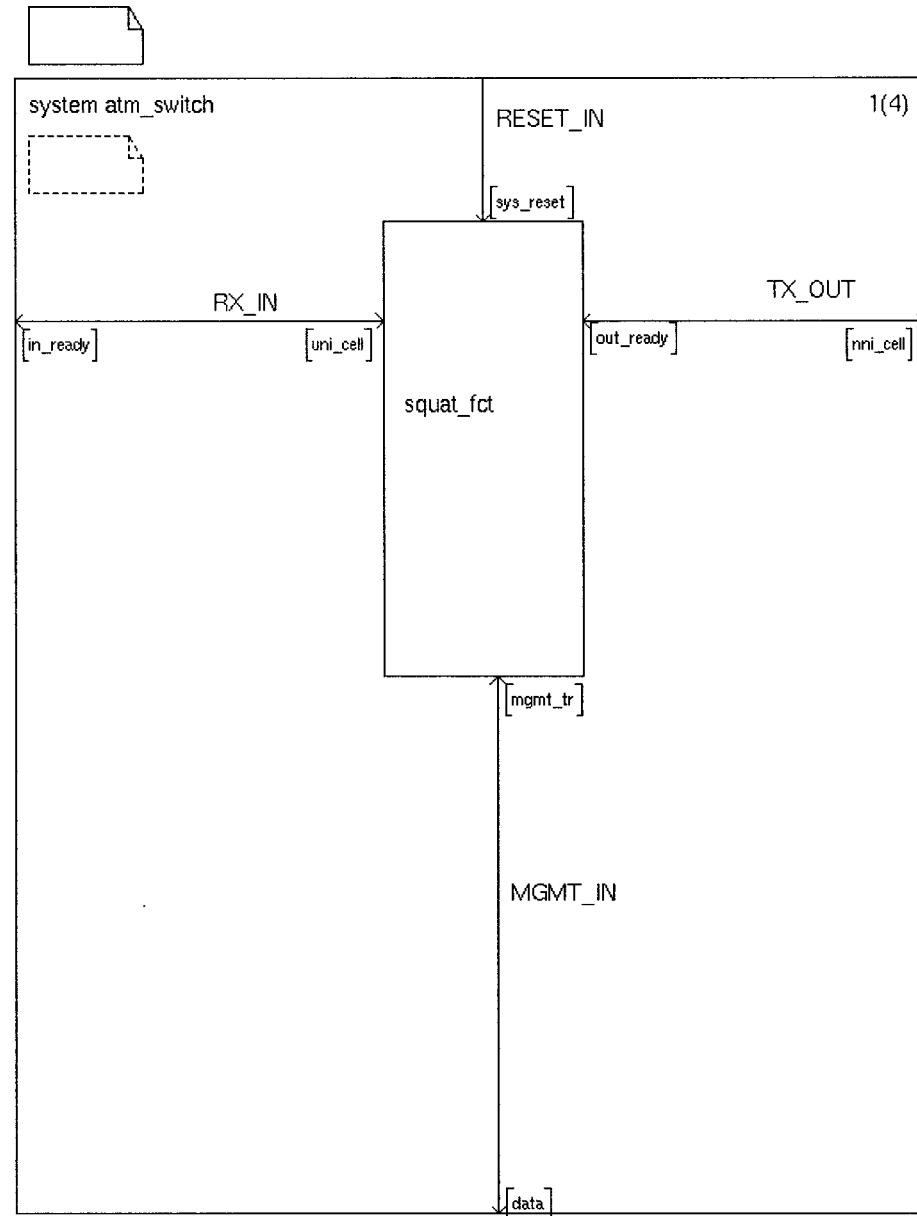

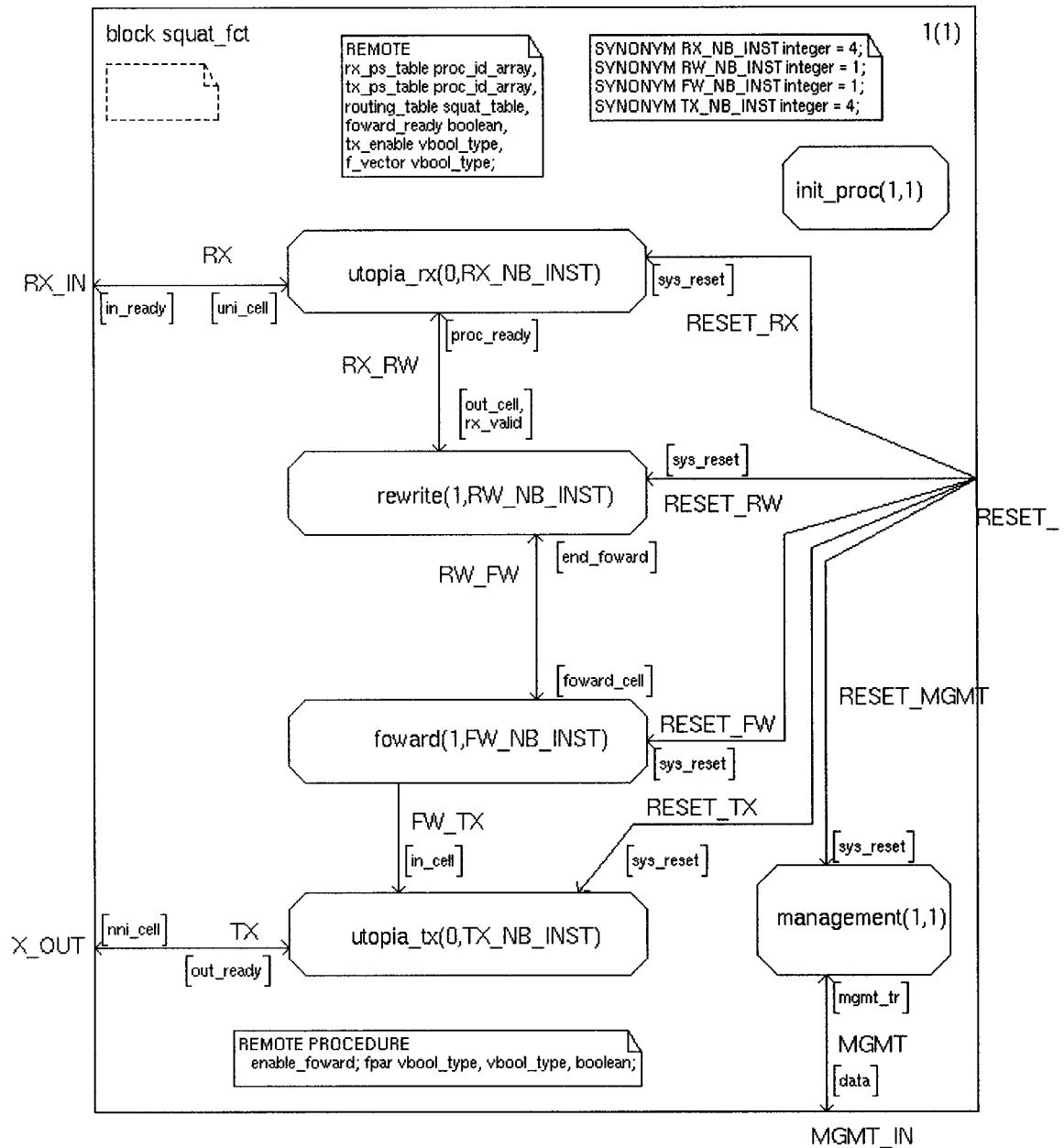

| 5.2.1                                      | Le fonctionnement du commutateur ATM                     | 97         |

| 5.2.2                                      | Le banc d'essais                                         | 99         |

| 5.2.3                                      | Application de la méthode de couverture                  | 101        |

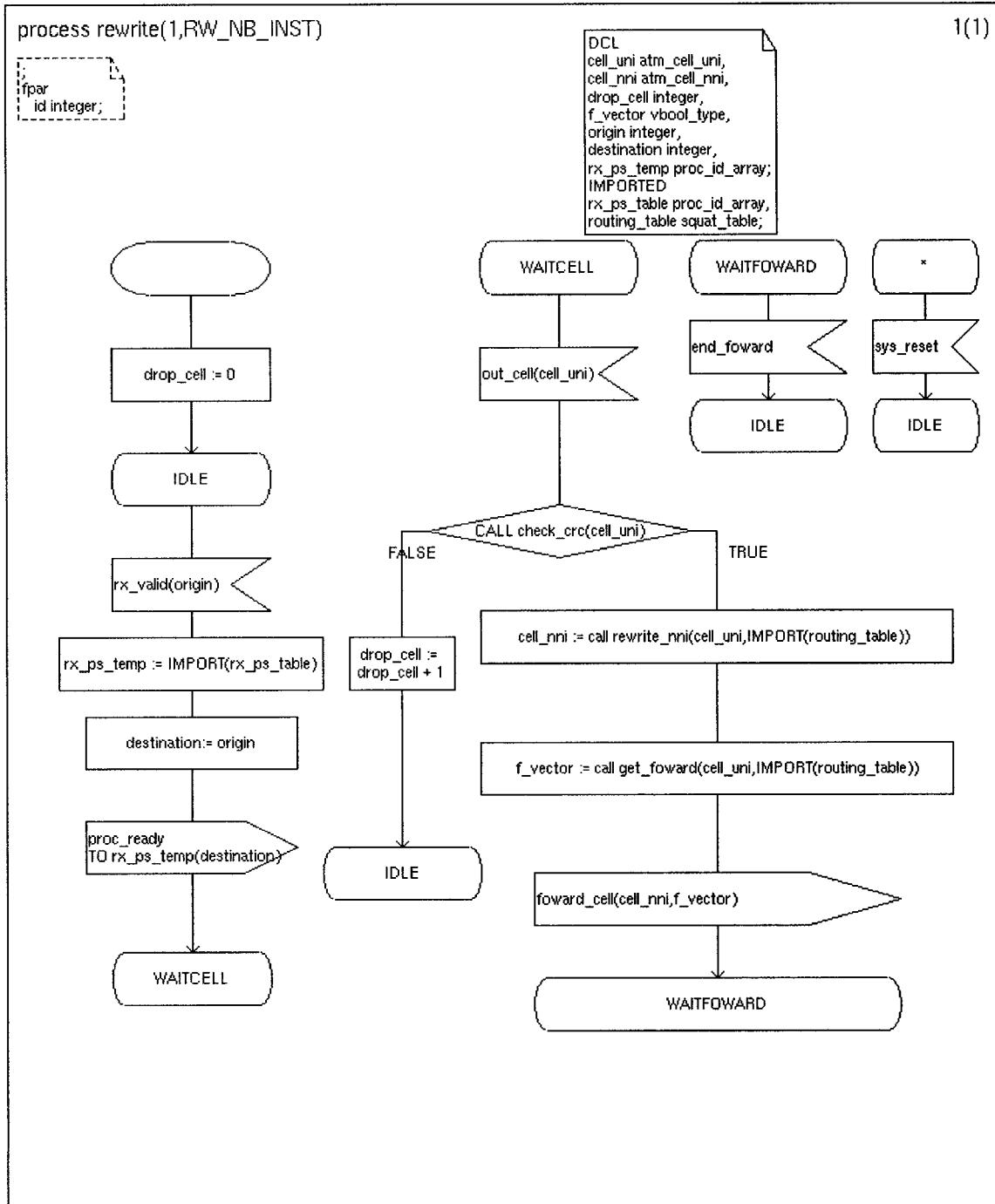

| 5.2.3.1                                    | Développement de la spécification exécutable             | 101        |

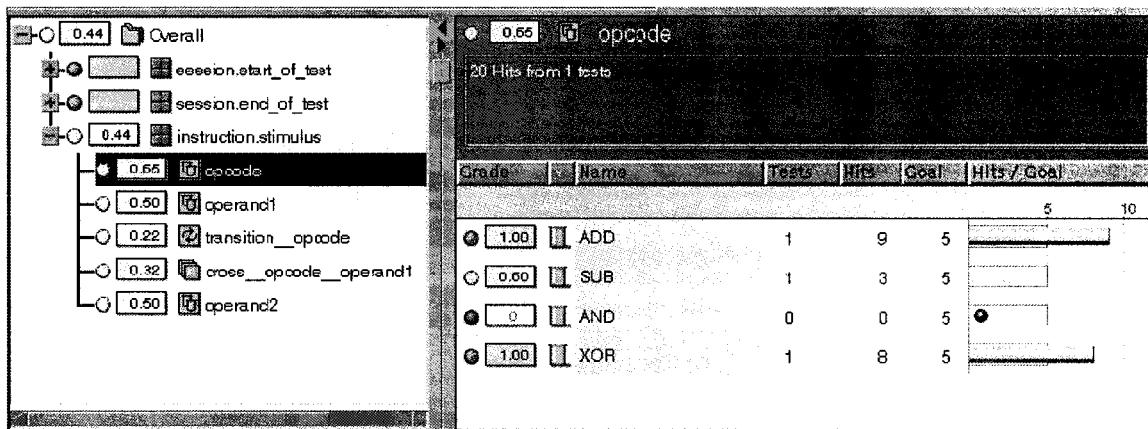

| 5.2.3.2                                    | Création du MAC                                          | 104        |

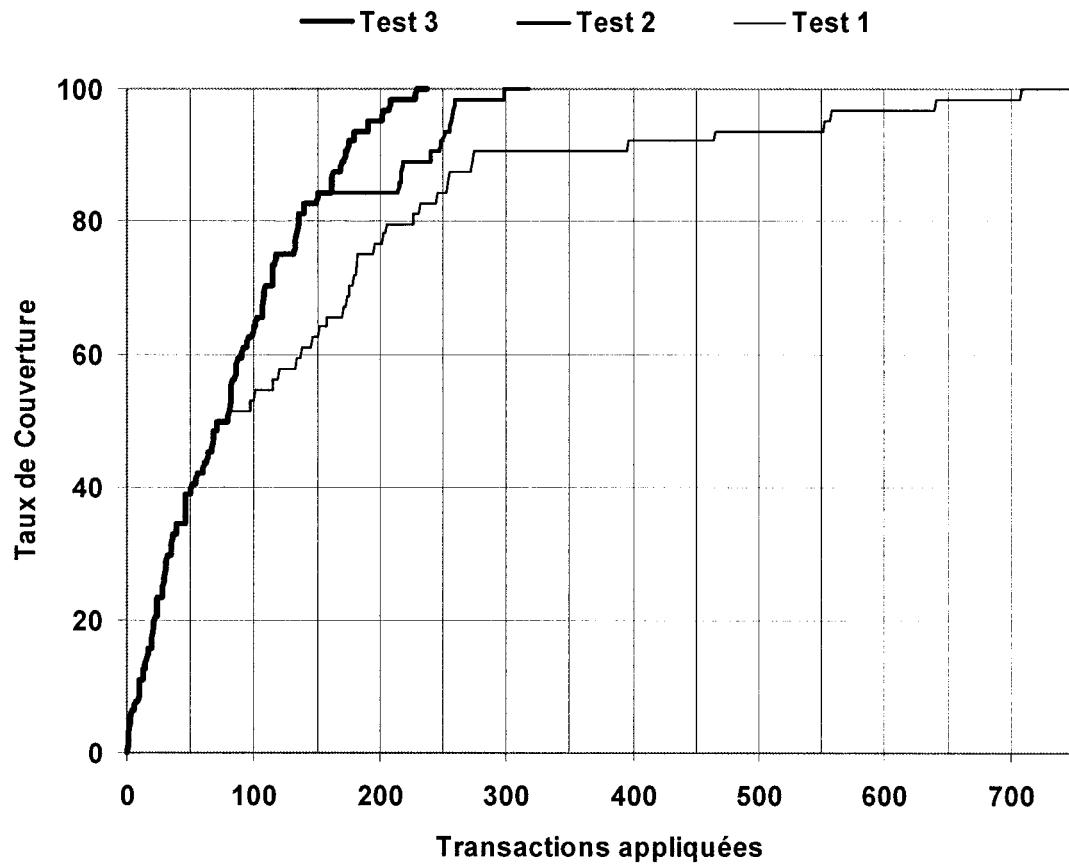

| 5.2.3.3                                    | Création d'une suite de tests                            | 105        |

| <b>5.3</b>                                 | <b>Module PMC-Sierra</b>                                 | <b>108</b> |

| <b>Chapitre 6 Conclusion</b>               |                                                          | <b>110</b> |

| <b>Références</b>                          |                                                          | <b>114</b> |

## LISTE DES FIGURES

|                                                                                              |    |

|----------------------------------------------------------------------------------------------|----|

| Figure 2-1: Type d'erreurs                                                                   | 8  |

| Figure 2-2: Indépendance de la vérification                                                  | 9  |

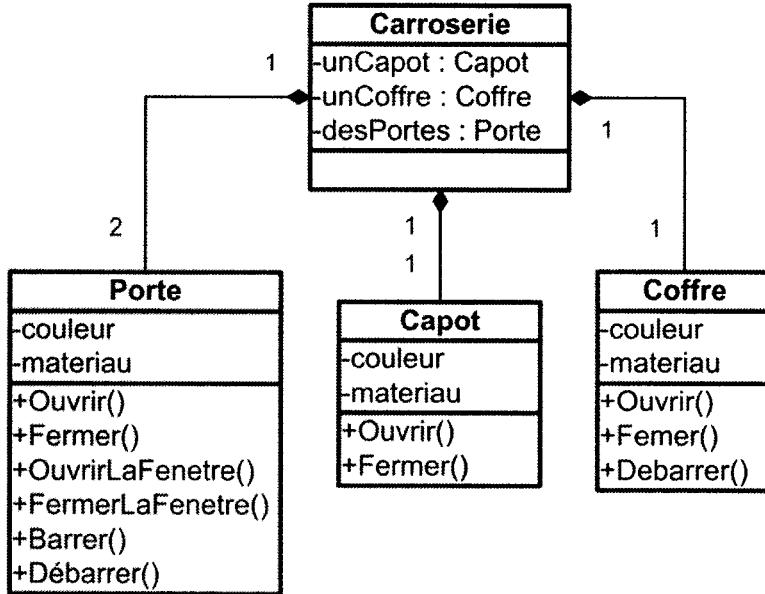

| Figure 3-1: Diagramme UML orienté objets                                                     | 35 |

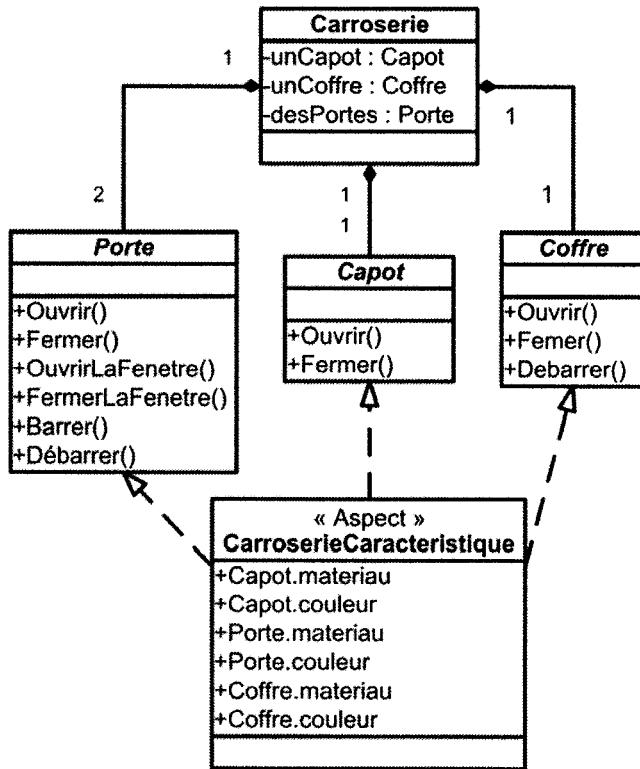

| Figure 3-2: Diagramme UML orienté aspects                                                    | 36 |

| Figure 3-3: Exemple du partitionnement par objets                                            | 38 |

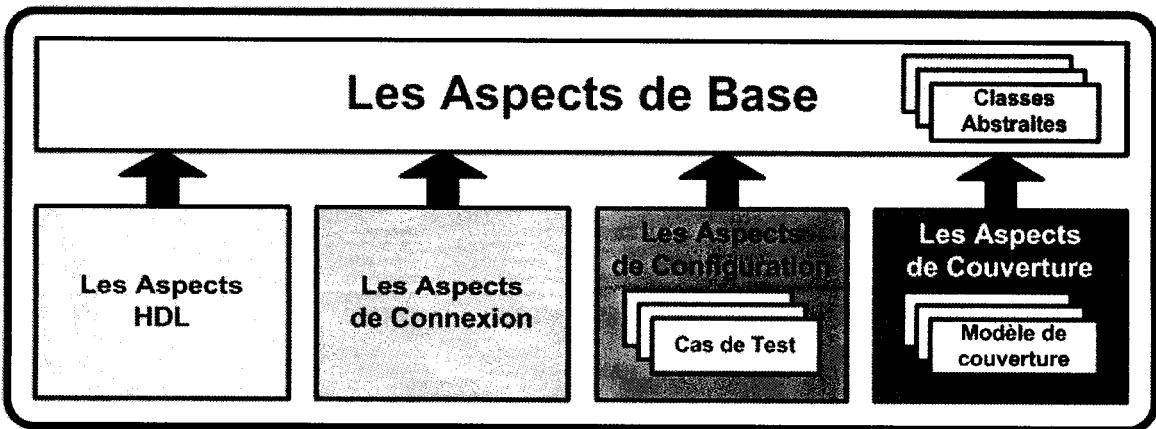

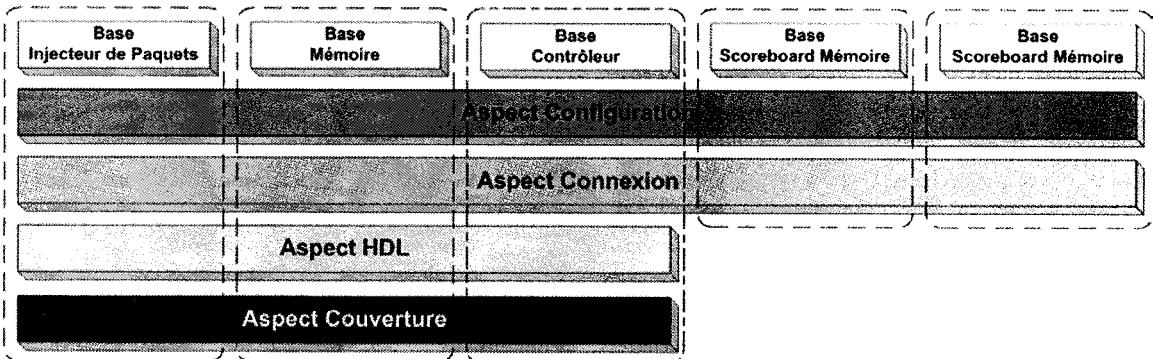

| Figure 3-4: Partitionnement par aspects                                                      | 39 |

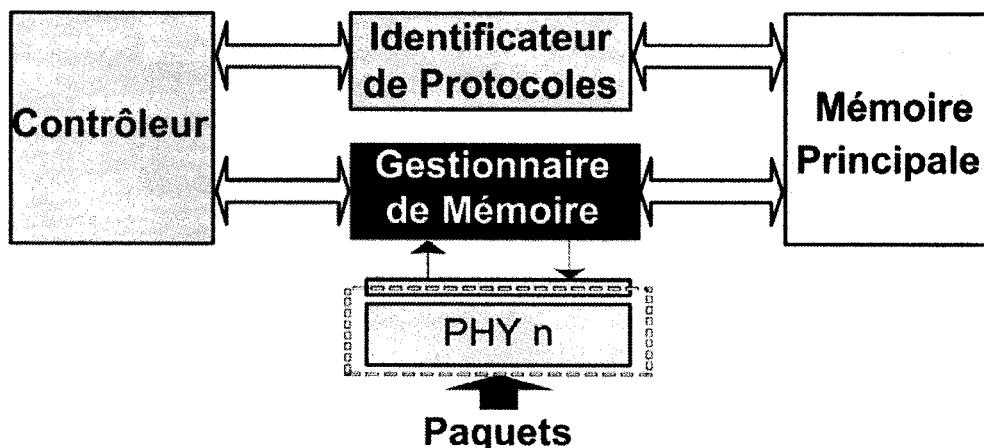

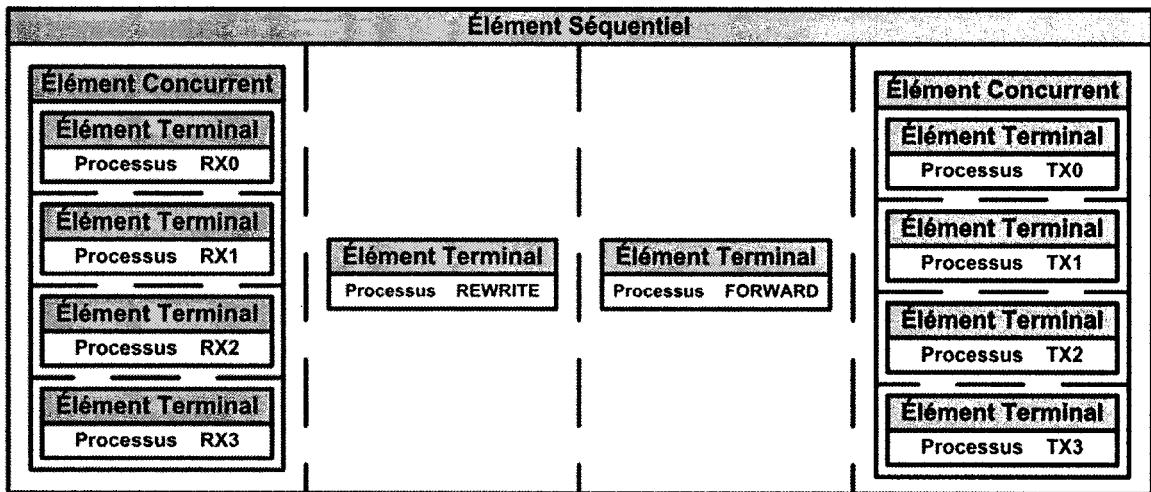

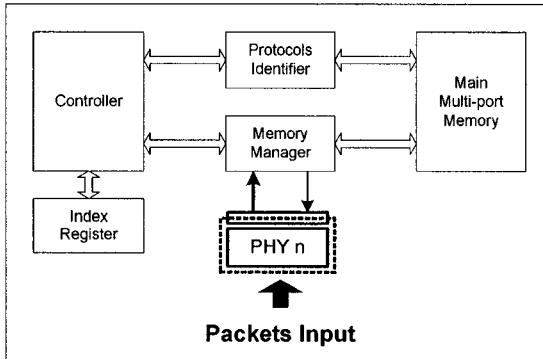

| Figure 3-5: Bloc 1 du convertisseur de protocoles                                            | 41 |

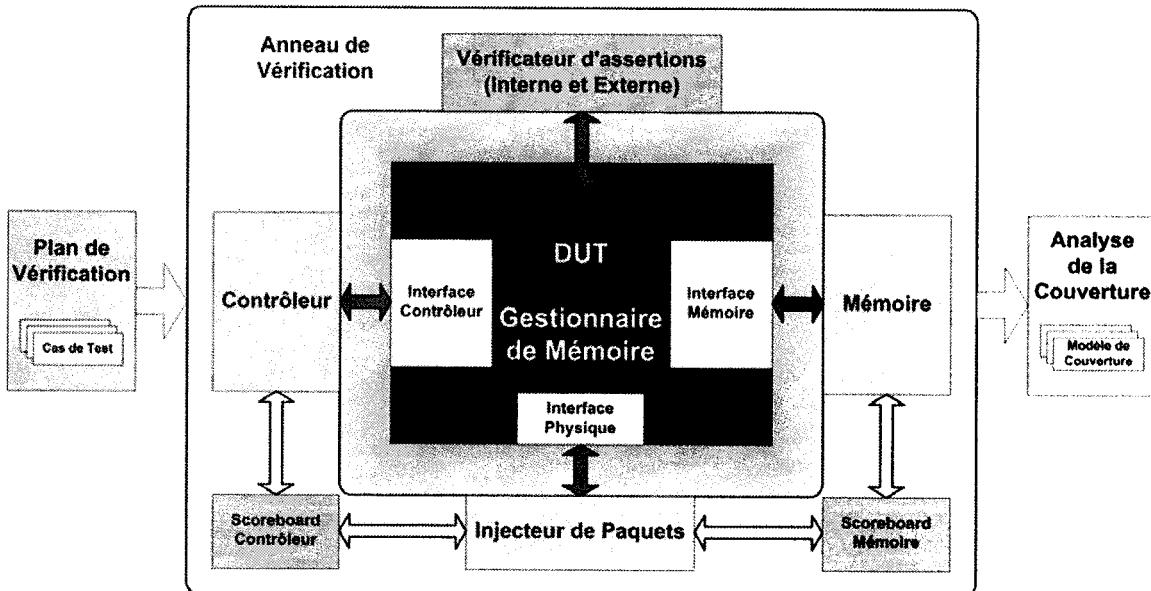

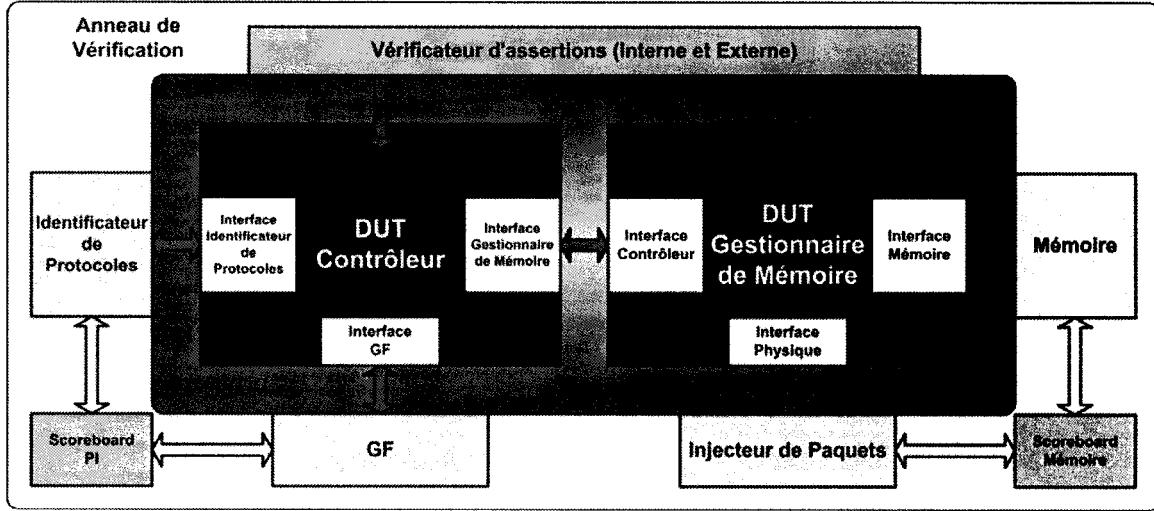

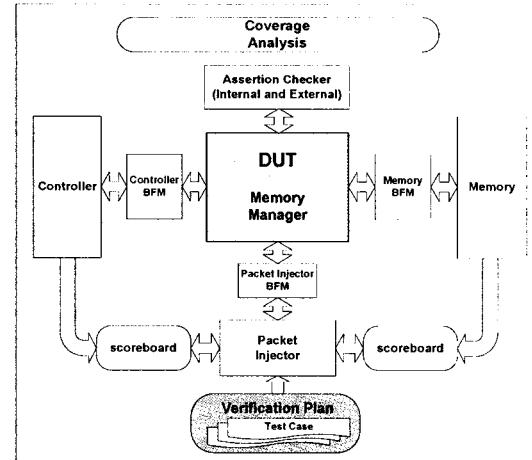

| Figure 3-6: Vue fonctionnelle du banc d'essais                                               | 42 |

| Figure 3-7: Vue fonctionnelle avec aspects                                                   | 44 |

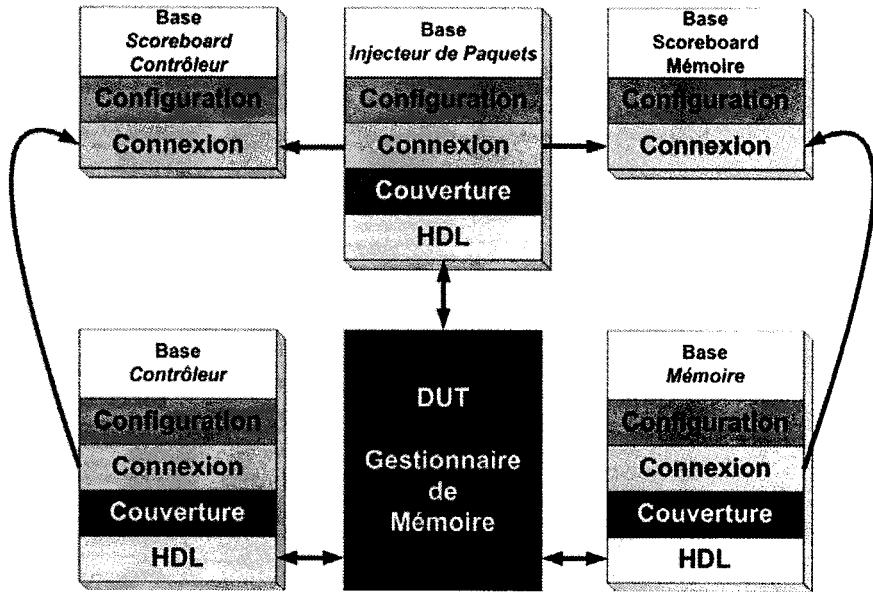

| Figure 3-8: Vue structurelle du banc d'essais avec aspects                                   | 44 |

| Figure 3-9: Adaptation du banc d'essais                                                      | 46 |

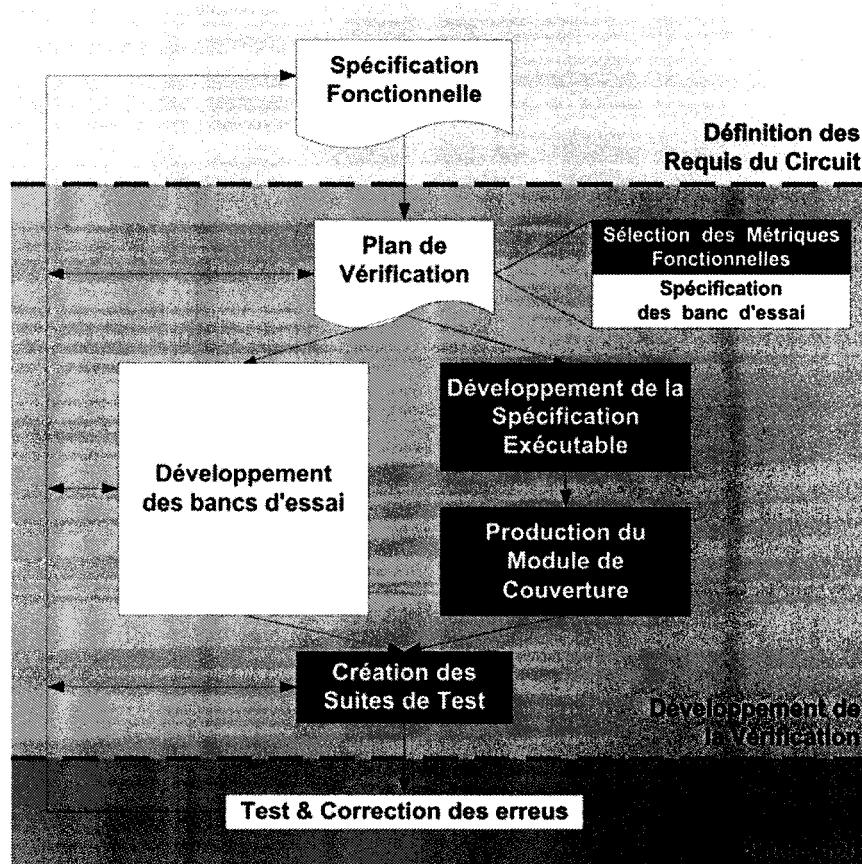

| Figure 4-1: Méthode de développement d'un MAC                                                | 52 |

| Figure 4-2: Processus de Vérification                                                        | 53 |

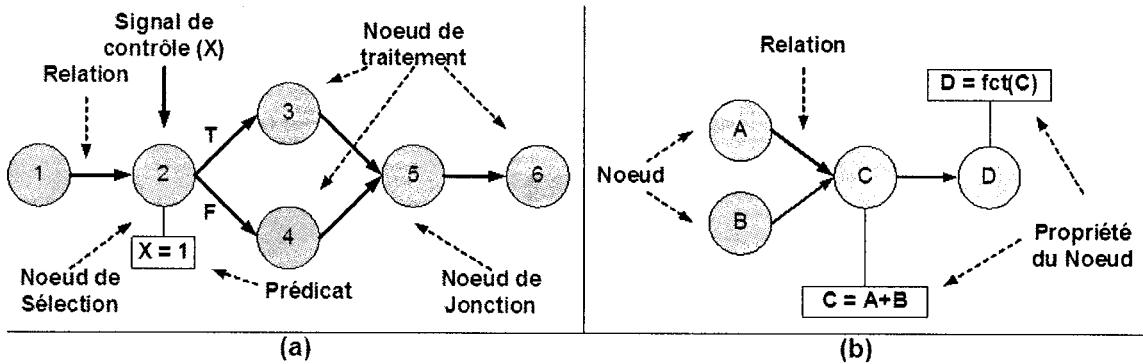

| Figure 4-3: Graphe de flot de contrôle et de flot de donnée                                  | 56 |

| Figure 4-4: Exemple d'un système de traitement de transactions                               | 57 |

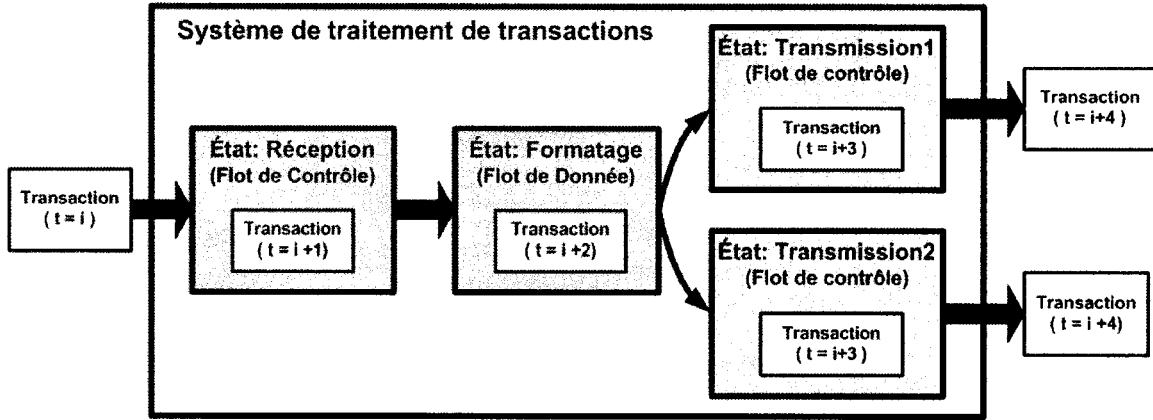

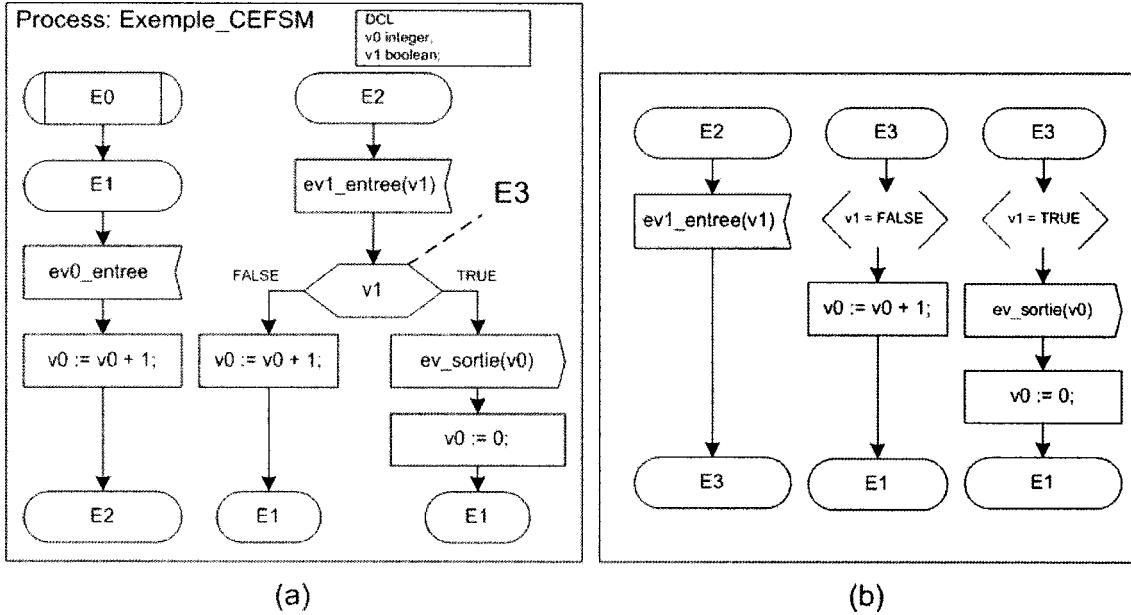

| Figure 4-5: Structure d'une modélisation SDL                                                 | 59 |

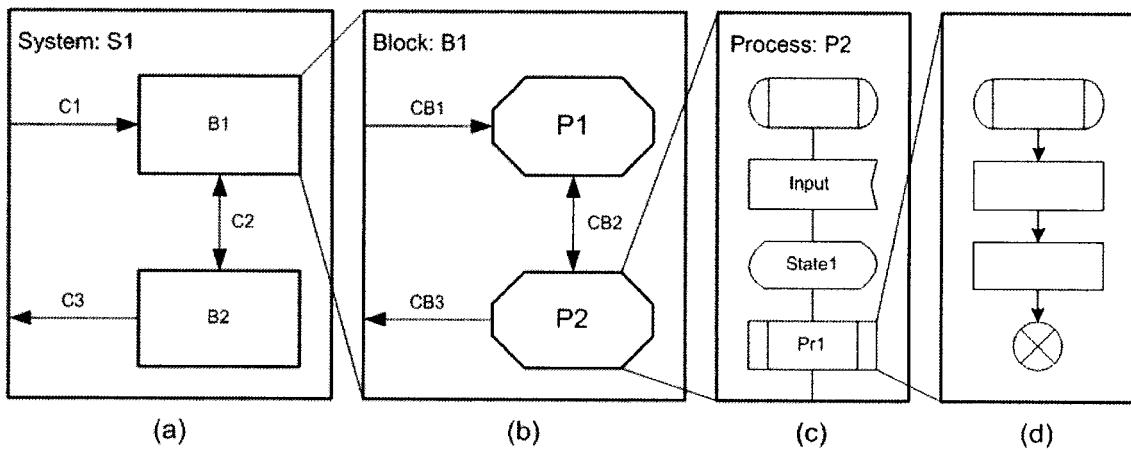

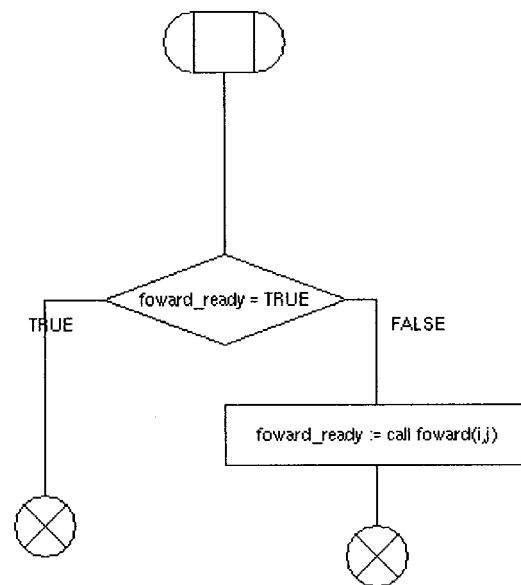

| Figure 4-6: Un exemple de CEFSM en version SDL                                               | 62 |

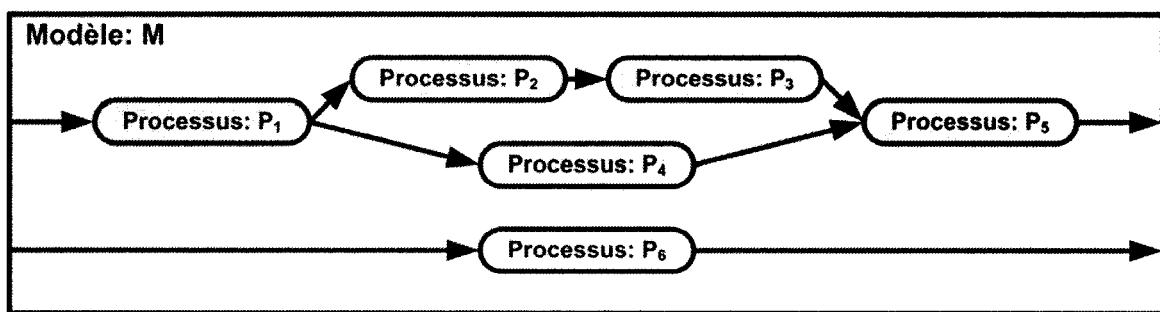

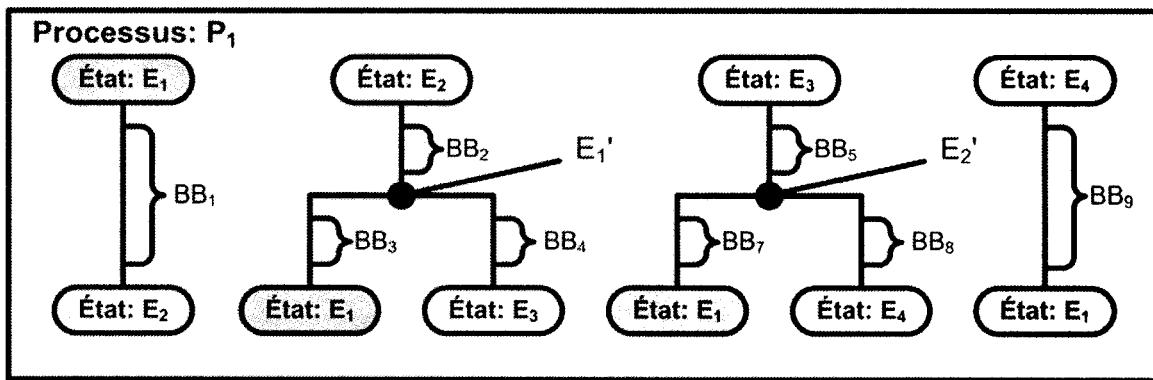

| Figure 4-7: Modèle théorique                                                                 | 63 |

| Figure 4-8: Processus théorique                                                              | 64 |

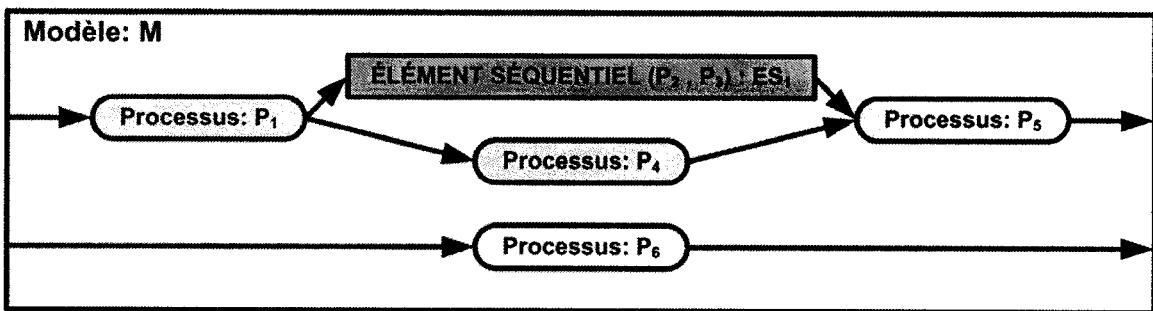

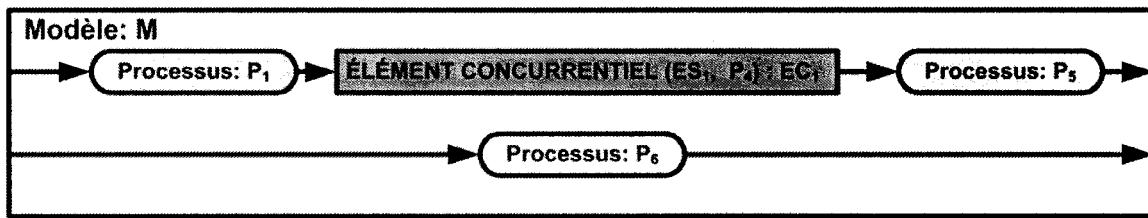

| Figure 4-9: Éléments hiérarchiques séquentiels                                               | 68 |

| Figure 4-10: Éléments hiérarchiques concurrentiels                                           | 69 |

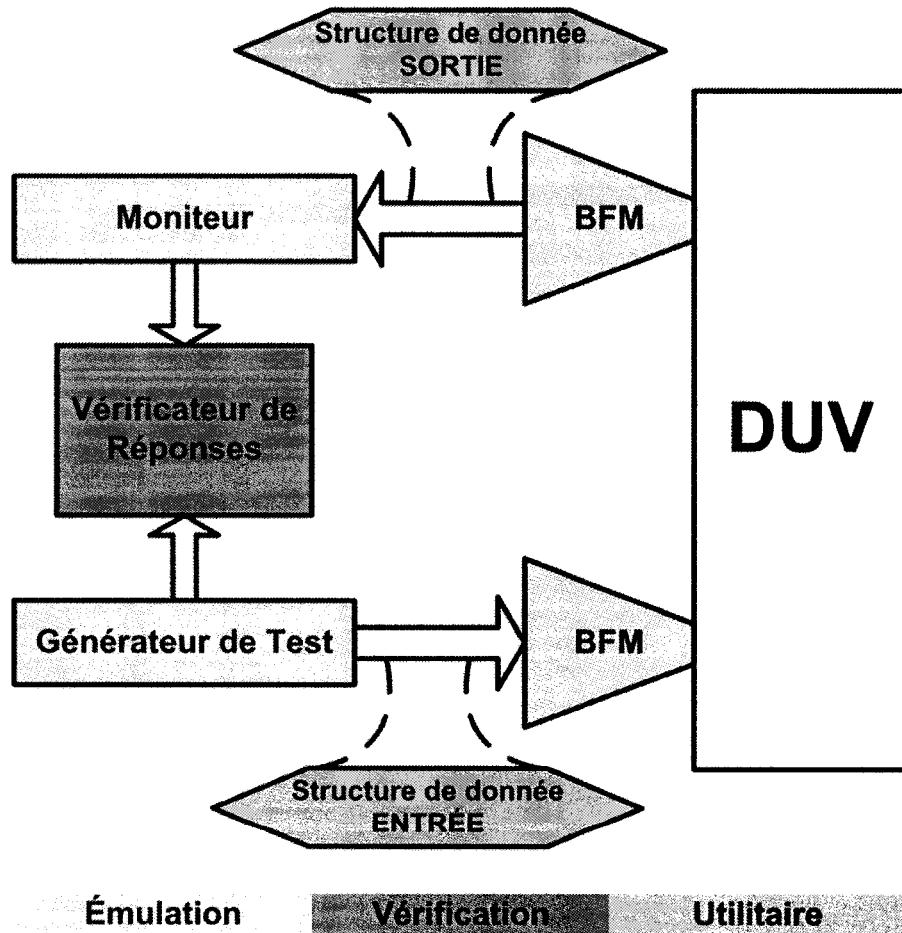

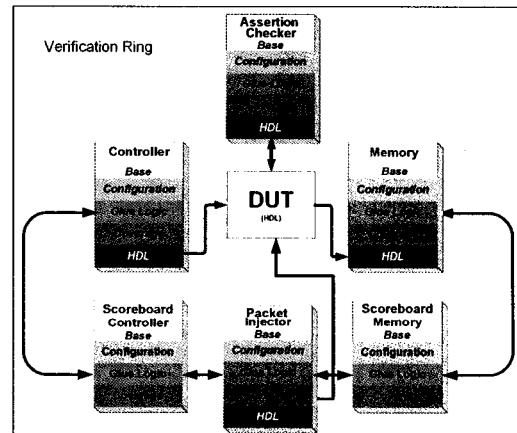

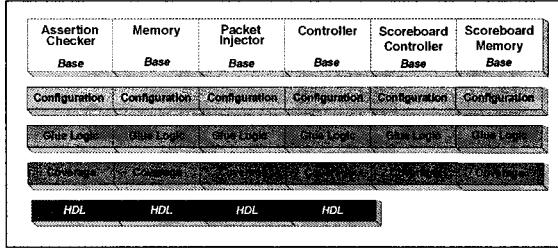

| Figure 4-11: Patron de Vérification                                                          | 72 |

| Figure 4-12: Exemple d'un groupe de couverture pour la couverture de chemin                  | 79 |

| Figure 4-13: Exemple d'un groupe de couverture pour la couverture des flots                  | 80 |

| Figure 4-14: Exemple d'un groupe de couverture pour la couverture des flots avec abstraction | 81 |

| Figure 4-15: Séquence de traitement d'une transaction par le système de couverture           | 82 |

|                                                                            |     |

|----------------------------------------------------------------------------|-----|

| Figure 4-16: Traitement de plusieurs transactions                          | 83  |

| Figure 4-17: Configuration d'un MAC dans un banc d'essais                  | 87  |

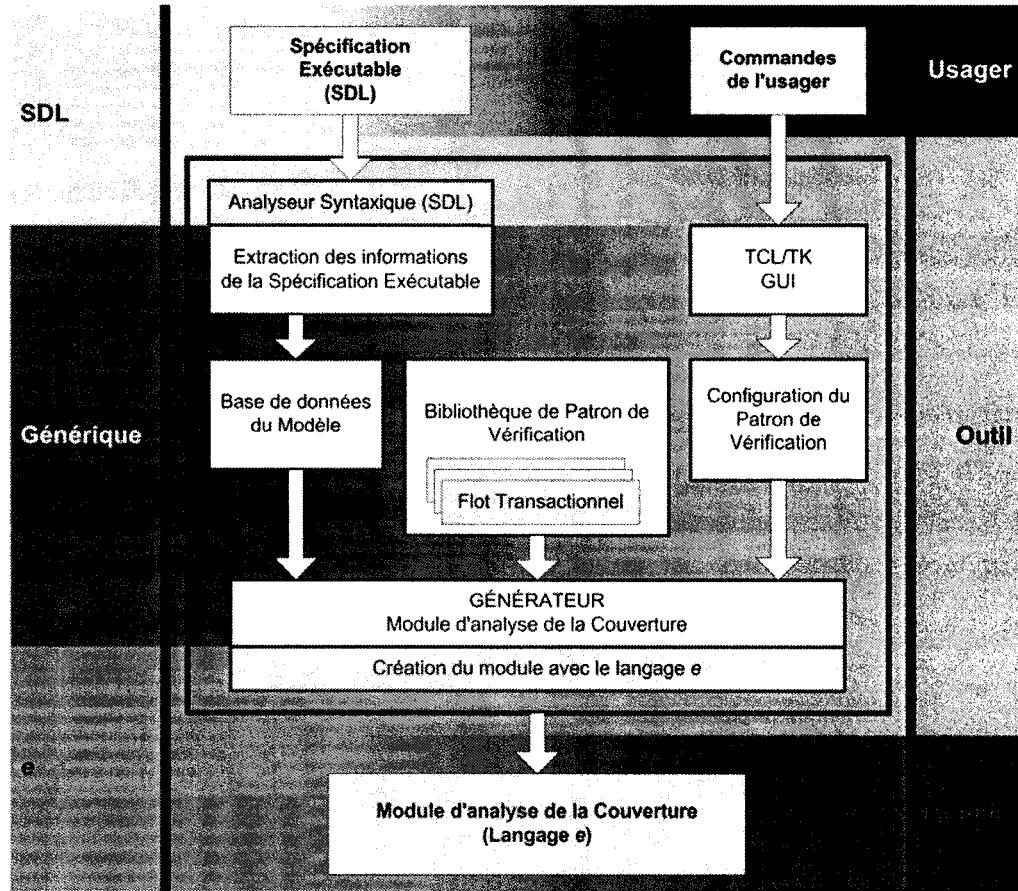

| Figure 4-18: Automatisation de la création d'un MAC                        | 89  |

| Figure 5-1: Architecture simplifiée du convertisseur de protocoles         | 93  |

| Figure 5-2: Approche de vérification ascendante                            | 96  |

| Figure 5-3: Interfaces du design ATM                                       | 98  |

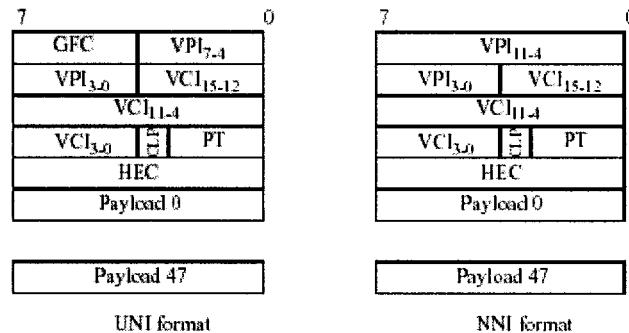

| Figure 5-4: Format des cellules ATM                                        | 98  |

| Figure 5-5: Vecteur de réécriture et de routage                            | 99  |

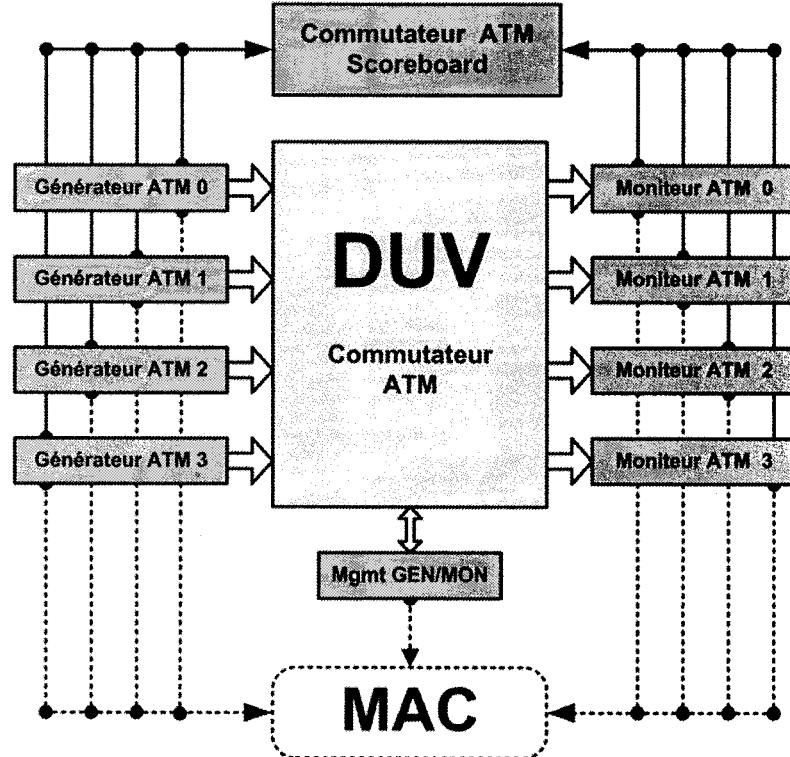

| Figure 5-6: Architecture du banc d'essais du design ATM                    | 100 |

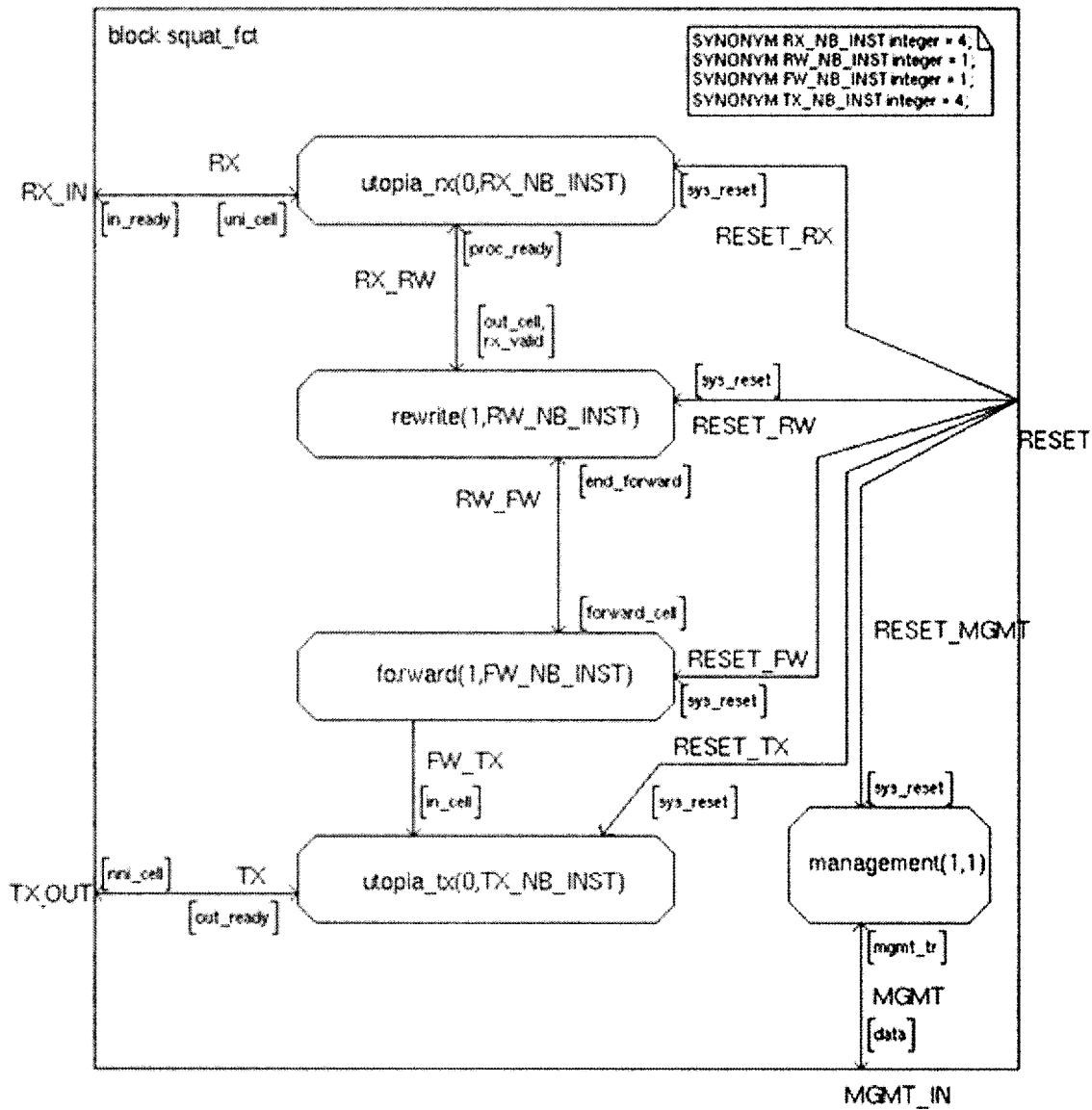

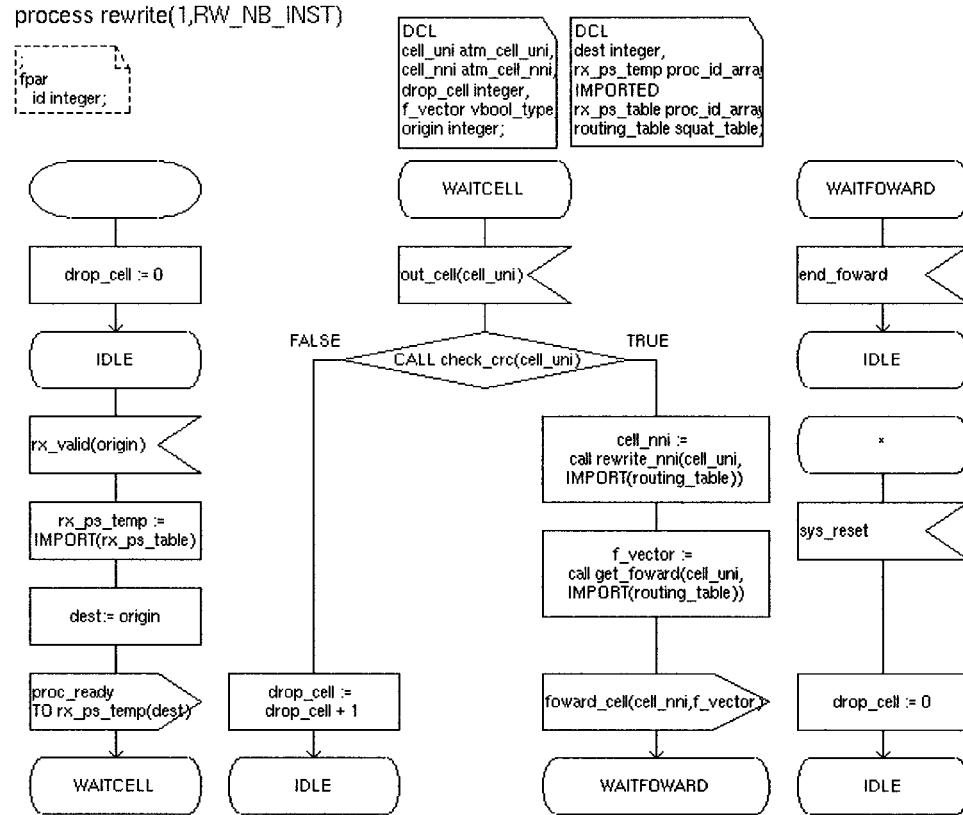

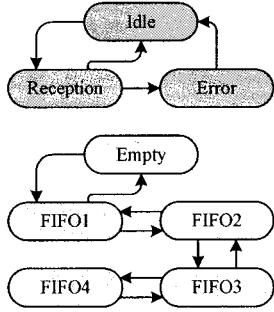

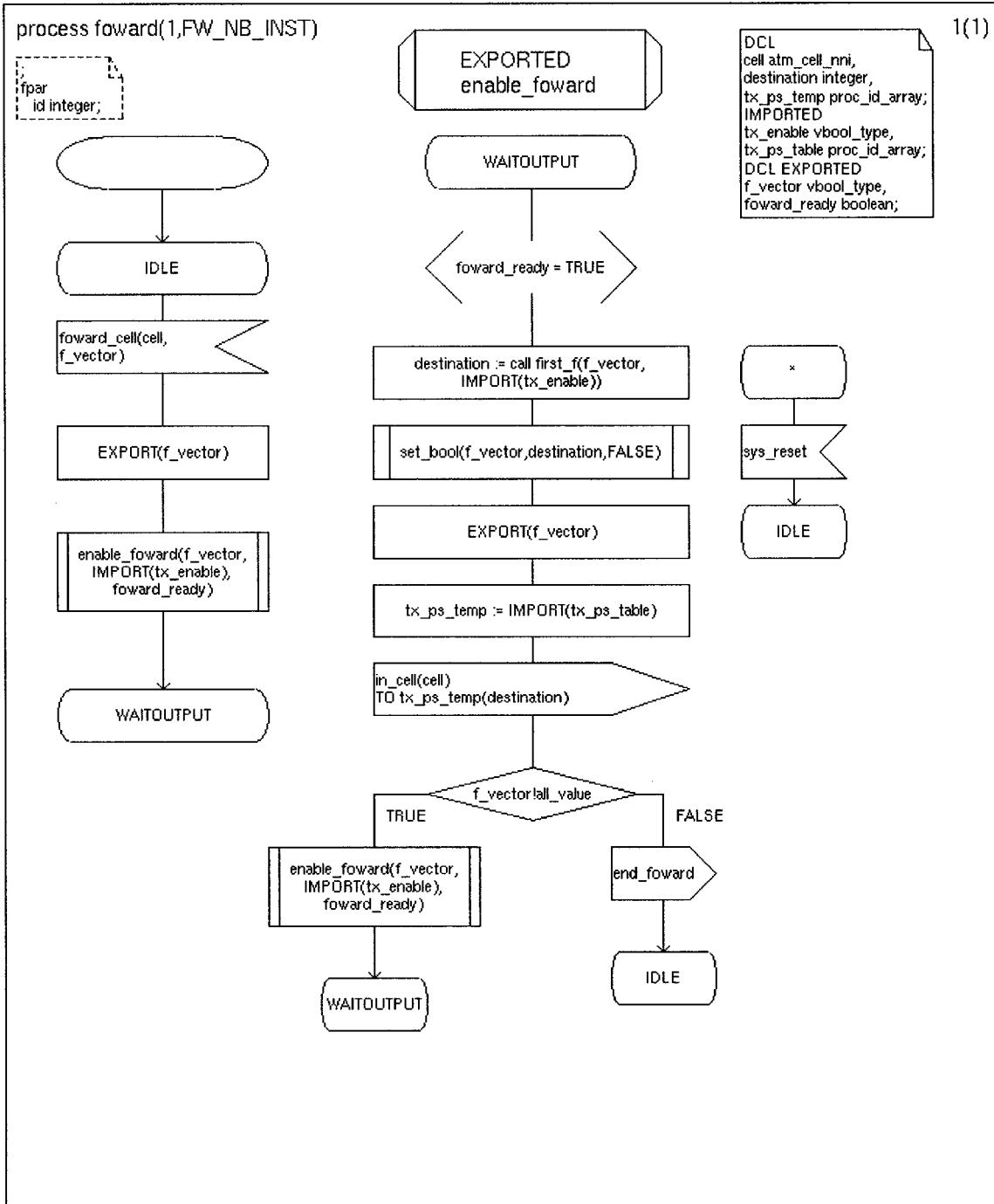

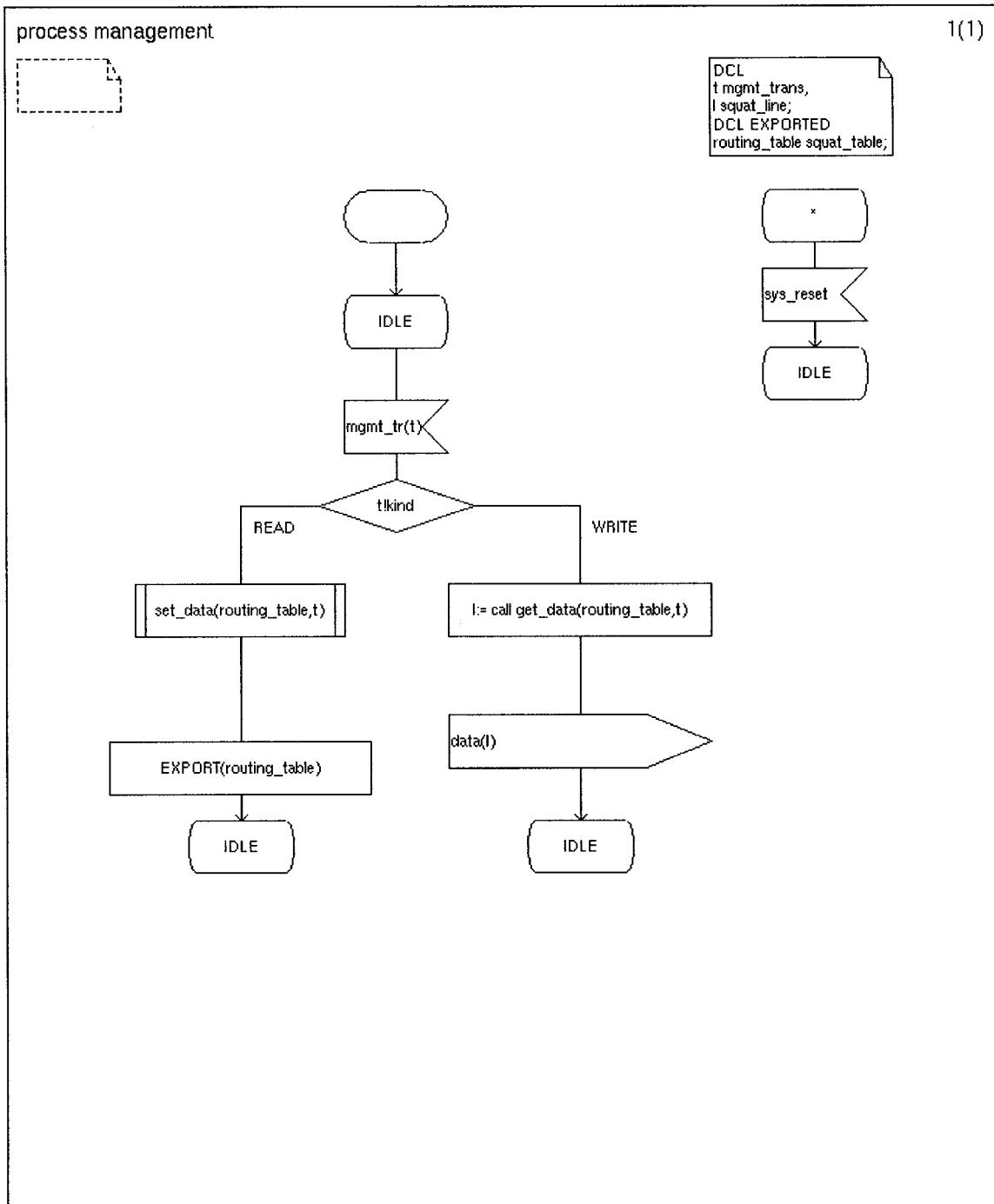

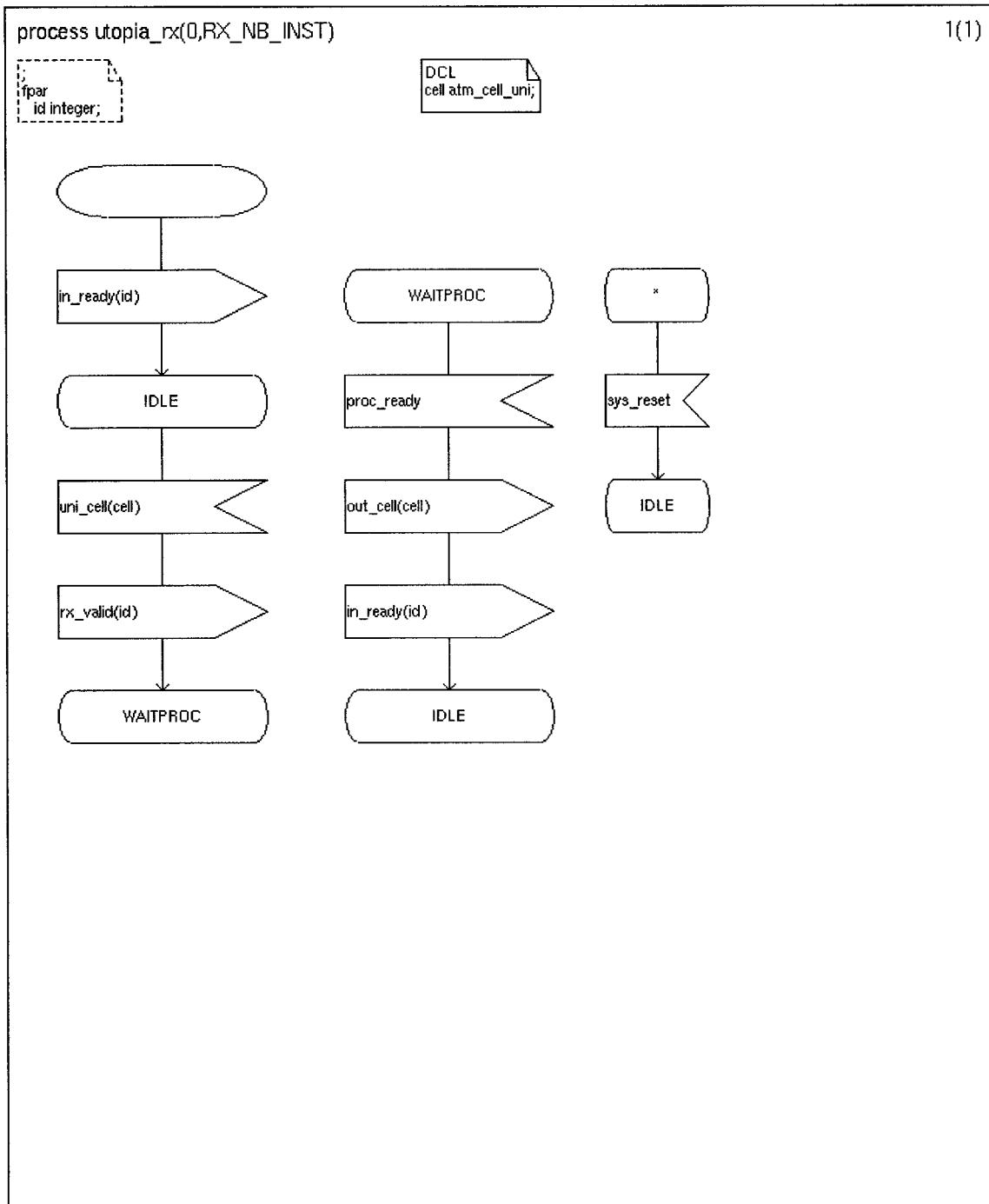

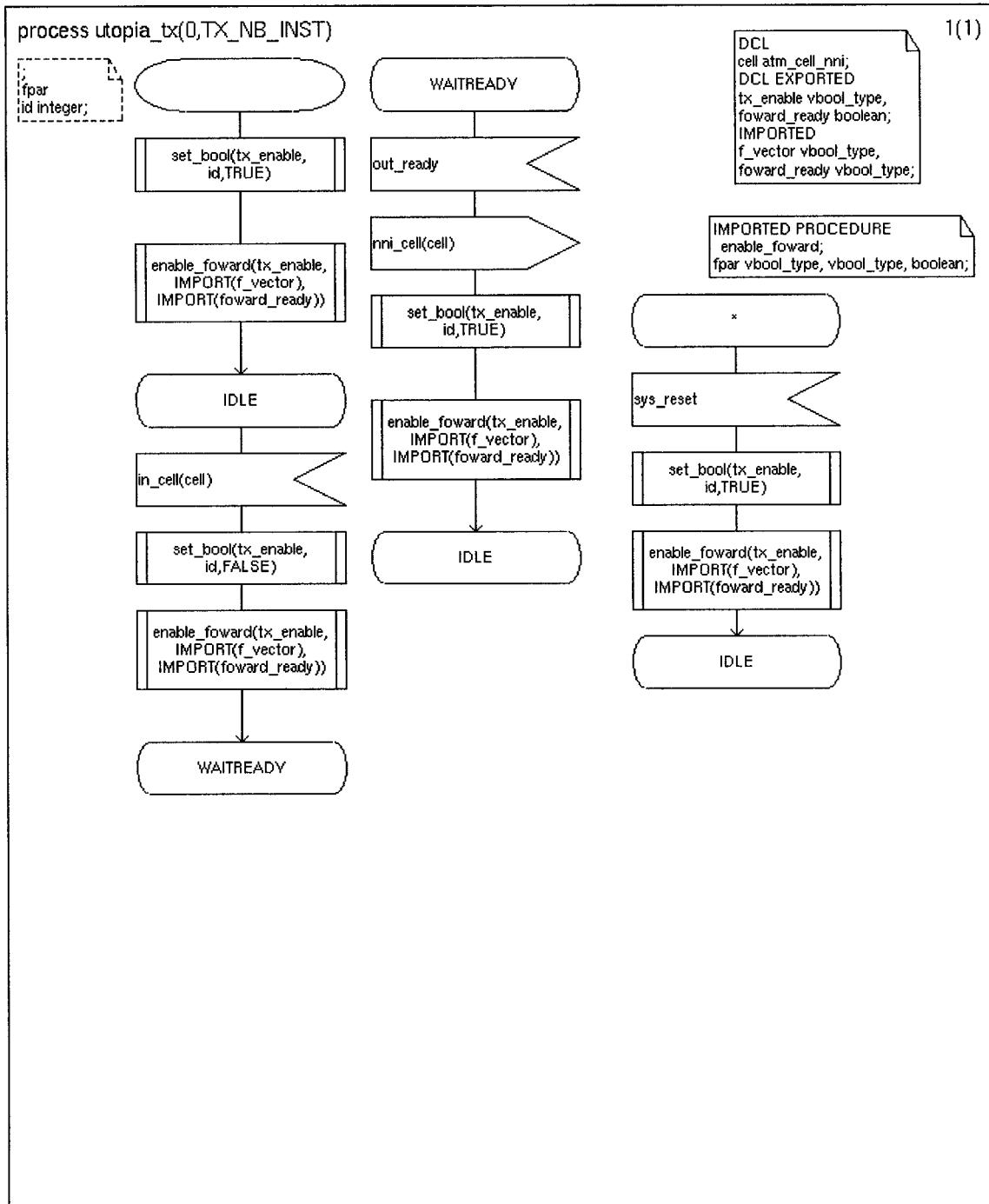

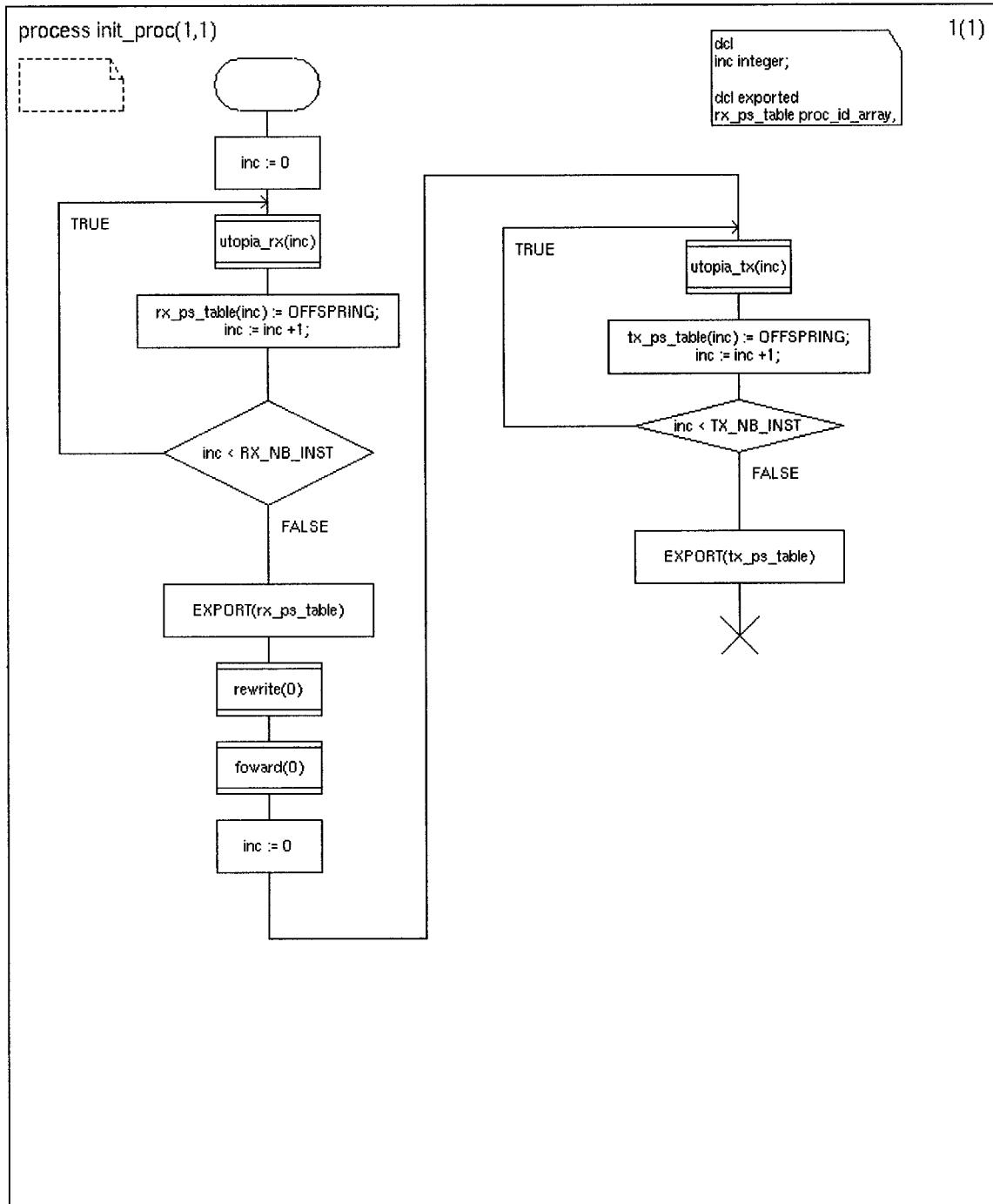

| Figure 5-7: Description SDL Structurelle                                   | 102 |

| Figure 5-8: Description SDL comportementale                                | 103 |

| Figure 5-9: Hiérarchie d'abstraction du commutateur ATM                    | 105 |

| Figure 5-10: Résultats de couverture                                       | 106 |

| Figure 5-11: Résultats de couverture (flux transactionnel)                 | 107 |

| Figure 5-12: Résultats de couverture (chemin d'un processus)               | 108 |

| Figure 5-13: Résultat de couverture (flux transactionnel avec abstraction) | 108 |

| Figure A-1: Problème de récursivité                                        | 126 |

| Figure A-2 : Exemple 1 d'un groupe de couverture                           | 127 |

| Figure A-3 : Résultats d'un test                                           | 130 |

| Figure A-4 : Exemple 2 d'un groupe de couverture                           | 131 |

| Figure A-5 : Algorithme de la méthode <i>scan_cover()</i>                  | 133 |

## LISTE DES TABLEAUX

|                                                                                   |     |

|-----------------------------------------------------------------------------------|-----|

| Tableau 2-1: Définition des termes pour la vérification versus la validation      | 7   |

| Tableau 2-2: Métriques Structurelles                                              | 20  |

| Tableau 2-3: Exemple de test par mutation                                         | 21  |

| Tableau 2-4: Type de techniques basées sur le graphe                              | 22  |

| Tableau 2-5: Méthodes de vérification des réponses en cours de simulation         | 25  |

| Tableau 2-6: Mécanismes de vérification fournis par les HVL                       | 27  |

| Tableau 4-1: Un exemple d'une CEFSM                                               | 61  |

| Tableau 4-2: Ensemble des chemins du processus $PC_1$                             | 65  |

| Tableau 4-3: Exemples de flots transactionnels                                    | 66  |

| Tableau 4-4: Exemples de contraintes définies pour la métrique                    | 67  |

| Tableau 4-5: Flots transactionnels avec abstraction                               | 69  |

| Tableau 5-1: Nombre de flots transactionnels en fonction de l'abstraction         | 109 |

| Tableau A-1 : Éléments contenus dans une <i>struct</i> en e                       | 119 |

| Tableau A-2 : Déclarations de champ de donnée                                     | 121 |

| Tableau A-3: Opération pouvant être effectuée dans une contrainte                 | 121 |

| Tableau A-4 : Exemples de contraintes appliquées sur l'ensemble des possibilités  | 122 |

| Tableau A-5 : Mécanismes permettant de définir d'autres contraintes de génération | 123 |

| Tableau A-6 : Niveaux d'ordonnancement des contraintes                            | 125 |

| Tableau A-7 : Les 3 types d'items d'un groupe de couverture                       | 129 |

| Tableau A-8: Formules pour le calcul de la pondération                            | 131 |

| Tableau A-9 : Description de l'API de couverture fournit par Specman Elite™       | 132 |

| Tableau D-1: Description des fichiers du module d'analyse de la couverture        | 155 |

## LISTE DES SIGLES ET DES ABRÉVIATIONS

|              |                                                     |

|--------------|-----------------------------------------------------|

| <b>AOP</b>   | : Aspect-Oriented Programming                       |

| <b>API</b>   | : Application Programmation Interface               |

| <b>ATM</b>   | : Asynchronous Transfer Mode                        |

| <b>BB</b>    | : Branche de Base                                   |

| <b>BFM</b>   | : Bus Functional Model                              |

| <b>CEFSM</b> | : Communicating Extended Finite State Machine       |

| <b>CRC</b>   | : Cycle Redundancy Check                            |

| <b>DUV</b>   | : Design Under Verification                         |

| <b>FIFO</b>  | : First-In First-Out                                |

| <b>HDL</b>   | : Hardware Description Language                     |

| <b>HEC</b>   | : Header Error Code                                 |

| <b>HVL</b>   | : Hardware Verification Language                    |

| <b>IEEE</b>  | : Institute of Electrical and Electronics Engineers |

| <b>MAC</b>   | : Module d'Analyse de la Couverture                 |

| <b>MISR</b>  | : Multiple Input Shift Register                     |

| <b>NNI</b>   | : Network Network Interface                         |

| <b>OOP</b>   | : Object-Oriented Programming                       |

| <b>RISC</b>  | : Reduced Instruction Set Computer                  |

| <b>RTL</b>   | : Register Transfert Level                          |

| <b>SDL</b>   | : Specification Description Language                |

| <b>UML</b>   | : Unified Modeling Language                         |

| <b>UNI</b>   | : User Network Interface                            |

| <b>VLSI</b>  | : Very Large Scale Integrated Circuit               |

| <b>VSIA</b>  | : Virtual Socket Interface Alliance                 |

## LISTE DES ANNEXES

|                                                                       |            |

|-----------------------------------------------------------------------|------------|

| <b>Annexe A Éléments spéciaux du langage <i>e</i></b>                 | <b>119</b> |

| <b>Annexe B Méthodologie de conception avec le langage <i>e</i></b>   | <b>134</b> |

| <b>Annexe C Modèle SDL du commutateur ATM</b>                         | <b>143</b> |

| <b>Annexe D L'implémentation du module d'analyse de la couverture</b> | <b>155</b> |

# Chapitre 1

## INTRODUCTION

La conception d'un circuit numérique se définit comme les tâches permettant de créer un circuit. La vérification fonctionnelle d'un circuit numérique se définit comme les tâches qui tentent de prouver que le circuit conçu est dépourvu d'erreurs fonctionnelles. L'importance de la vérification est incontestable puisque le dysfonctionnement d'un circuit a plusieurs conséquences. En fait, l'avenir commercial d'un circuit peut être compromis dû à une erreur fonctionnelle. D'autre part, les coûts de correction d'une erreur suite à l'entrée en marché d'un produit sont énormes. On peut mentionner, par exemple, l'erreur dans l'unité arithmétique virgule flottante du processeur Pentium de la société Intel qui a atteint de façon permanente la crédibilité de cette société [18] et qui leur a coûté des millions de dollars. De plus, dans le cas où un circuit serait utilisé dans un contexte critique, tel que dans le domaine médical ou aérospatial, le dysfonctionnement d'un circuit peut avoir des conséquences fatales.

La complexité des tâches de conception et la vérification d'un circuit numérique ont longtemps été équilibrées. Cependant, l'avancement des technologies reliées au milieu de la microélectronique permettent actuellement la réalisation de circuits de plus en plus complexes. Citons par exemple la possibilité de synthétiser automatiquement les circuits numériques à partir d'un langage de description matériel (HDL ou *Hardware Description Language*). Cela implique que les circuits entrant en production sont maintenant en mesure de réaliser un plus grand nombre d'opérations et qu'elles sont souvent plus complexes. Les techniques de vérification fonctionnelle des circuits n'ont pas évolué au même rythme que les techniques de conception. En sachant, que la complexité de la vérification fonctionnelle tend à augmenter environ comme le carré de la complexité des circuits numériques [40], il est évident qu'un écart croissant s'est créé entre la conception et la vérification d'un circuit. De ce fait, on avance qu'environ 70% de l'effort de développement d'un circuit est maintenant dédié aux tâches de vérification [6]. La

vérification est donc maintenant sur le chemin critique du processus de développement des circuits numériques. Ainsi, l'industrie et le milieu de la recherche travaillent actuellement au développement de méthodes et d'outils qui permettront de réduire le retard accumulé des méthodes de vérification par rapport aux techniques de conception des circuits numériques.

Le processus de vérification fonctionnelle sert à détecter des erreurs afin d'augmenter le degré de confiance dans le modèle sous vérification (DUV ou *Design Under Verification*). On peut améliorer ce processus en travaillant sur l'accélération de la conception et de la mise en œuvre des suites de test de vérification et sur l'augmentation de la qualité de la vérification. L'accélération de la conception et de la mise en œuvre des suites de test de vérification produit des bancs d'essais en utilisant des techniques plus efficaces. Ainsi, de nouveaux langages ont été développés afin de répondre aux besoins précis de la conception de bancs d'essais. Parmi ces langages de vérification matérielle (HVL ou *Hardware Verification Language*), on retrouve OpenVera™ [33] de Synopsys™, le langage *e* [36] de Verisity™ et TestBuilder™ [11] de Cadence™. Ces langages sont un mélange entre les langages de description de matériel et les langages de haut niveau tel que le C++. De plus, ils sont munis d'éléments spéciaux facilitant la vérification fonctionnelle. Ainsi, en utilisant un langage de haut niveau, il est maintenant possible de développer des méthodologies de conception de bancs d'essais basées sur les techniques développées dans le domaine du génie logiciel. Une approche de réutilisation au niveau des bancs d'essais permet d'accélérer leurs conception et mise en œuvre.

En plus de la réutilisation, l'efficacité de la vérification peut être rehaussée de plusieurs façons. L'utilisation de technologies de vérification formelle permet d'obtenir une vérification de qualité [5]. Néanmoins, la complexité de la vérification formelle limite son usage sur des modèles de grande complexité. Il est cependant possible de s'inspirer des techniques de vérification formelle pour améliorer la vérification basée sur la simulation. On appelle ce type de vérification la vérification semi-formelle. Au niveau des bancs d'essais, une meilleure détection des erreurs est essentielle. Ainsi, l'analyse des réponses du modèle en cours de simulation permet de détecter les erreurs au premier

moment où elles sont détectables. Pour ce faire, l'utilisation d'assertions, des propriétés comportementales que le modèle doit respecter en tout temps, permet une détection d'erreurs en cours de simulation. La création d'assertions complexes dans un banc d'essais est supportée par les HVL et s'inspire de la technique du *Model Checking* qui est une technique de vérification formelle. De plus, en ayant à notre disposition un langage de haut niveau pour la conception des bancs d'essais, il est possible de créer facilement des modules implantant une vérification automatique des réponses du DUV.

D'autre part, une détection plus rapide des erreurs est aussi un élément essentiel à la qualité de la vérification. Une détection rapide des erreurs est en fait le corollaire d'une meilleure exploration des fonctionnalités du DUV. Pour obtenir une meilleure exploration des fonctionnalités d'un modèle, il faut utiliser des métriques fonctionnelles afin de mesurer la couverture obtenue par l'application d'une suite de tests. La création d'une suite de tests en fonction du taux de couverture actuel de la métrique utilisée permet d'éviter l'application de tests redondants. Ainsi, l'analyse de la couverture fonctionnelle est un élément essentiel pour évaluer l'avancement de la vérification. L'analyse de la couverture sert aussi de base à la création de suite de tests efficaces. La création de suite de tests efficaces peut résulter, par exemple, de l'utilisation d'algorithmes de génération automatique des tests ou de l'adoption d'une approche de génération de test pseudo-aléatoire biaisée en fonction du taux de couverture actuel.

L'objectif du travail présenté dans ce mémoire est d'apporter une contribution aux niveaux des méthodes utilisées pour la vérification fonctionnelle des circuits numériques. Ainsi, deux méthodes pour la vérification sont présentées.

La première méthode sert à concevoir des bancs d'essais en favorisant la réutilisation. La méthode est basée sur l'utilisation d'un langage HVL, le langage *e*, qui permet l'utilisation des méthodologies de conception orientée objets et aspects. Ainsi, un partitionnement orienté objets et aspects, dédié à la création de bancs d'essais, est proposé afin d'augmenter le potentiel de réutilisation des bancs d'essais. Cette méthode qui permet d'accélérer le processus de conception des bancs d'essais a fait l'objet de deux communications de conférences [29] [30].

La deuxième méthode de vérification proposée est une technique systématique permettant de développer un module d'analyse de la couverture fonctionnelle d'un circuit numérique. La problématique reliée au développement de cette méthode est qu'il faut avoir des métriques fonctionnelles standardisées appliquées sur une description normalisée des fonctionnalités d'un circuit. Ces fonctionnalités sont habituellement décrites sous forme textuelle dans un document de spécification, il est difficile de travailler de façon systématique avec ce genre de description. Ainsi, on propose d'utiliser une description standardisée de la spécification d'un circuit en utilisant un langage exécutable de haut niveau. En formulant une métrique fonctionnelle en fonction de la description standardisée de la spécification, il est possible de créer un module d'analyse de la couverture de façon systématique. Le langage de spécification utilisé est le *Specification Description Language* (SDL) [21]. Ce langage, qui est décrit avec une notation graphique et textuelle, est utilisé pour la description de systèmes concurrents et interactifs. De plus, il est exécutable, ce qui permet de valider la spécification développée. La métrique fonctionnelle présentée dans ce mémoire est basée sur la technique de vérification des flots transactionnels [4]. L'implémentation d'un module d'analyse de la couverture, en utilisant la méthode proposée est faite en utilisant le langage *e*. Le module d'analyse de la couverture produit avec cette méthode peut être incorporé dans n'importe quel banc d'essais dédié à la vérification d'un circuit au niveau *Register Transfer Level* RTL. L'utilité de ce module est en fait de permettre la création d'une suite de tests qui permettra de couvrir la métrique définie et aussi de réduire l'application de tests redondants. Cela implique qu'avec ce module d'analyse de la couverture, il est possible de créer une suite de tests moins longue et ayant aussi une plus grande puissance de détection d'erreurs.

Ces méthodes ont été appliquées sur différents modèles. La méthode de conception a été utilisée pour la création de bancs d'essais dédiés à la vérification d'une version d'un convertisseur de protocoles. Le projet de conversion de protocoles est développé par un groupe d'étudiants de cycle supérieurs du *Groupe de Recherche en Microélectronique* (GRM). Ensuite, la méthode de conception a aussi été utilisée pour la création d'un banc

d'essais dédié à un exemple simple d'un commutateur *Asynchronous Transfer Mode* (ATM). Le commutateur ATM a aussi servi d'exemple pour l'application de la méthode de couverture fonctionnelle. Ainsi, une spécification décrite avec le langage SDL a été développée pour le commutateur ATM. Ensuite, en utilisant la méthode de couverture développée, un module d'analyse de la couverture a été produit. En utilisant, le module produit, il a été possible de développer une suite de tests efficaces qui couvre la métrique utilisée. Finalement, un module d'analyse de la couverture a aussi été produit pour un modèle fourni par la société PMC-Sierra. La présentation des résultats obtenus suite à l'application de notre méthode sur cet exemple sera toutefois limitée, puisque les fonctionnalités et la structure de ce modèle sont confidentielles.

Ce mémoire est divisé en six chapitres. Le chapitre 1 est la présente introduction de ce document. Le chapitre 2 présente une revue de littérature sur le thème de la vérification. Le chapitre 3 introduit la méthode de conception de bancs d'essais axée sur la réutilisation. La méthode est présentée avec des remarques critiques et aussi avec certaines extensions possibles. Le chapitre 4 expose la méthode de couverture fonctionnelle. Ainsi, le flot de développement d'un module d'analyse de la couverture est détaillé. De plus, le développement d'une spécification exécutable avec SDL est passé en revue et une formulation de la métrique utilisée, en fonction du format de la spécification exécutable, est donnée. Nous verrons ensuite de quelle façon est développée un module d'analyse de la couverture. Enfin, une critique du module produit à l'aide de la méthode et les extensions possibles seront exposées. Le chapitre 5 présente les applications des méthodes sur les différents exemples. Finalement, le chapitre 6 conclut ce mémoire.

## Chapitre 2

### REVUE DE LITTÉRATURE

Ce chapitre présente une revue de littérature sur le sujet de la vérification fonctionnelle des circuits numériques. En premier lieu, une définition de la vérification est donnée et les principes nécessaires à sa réalisation sont recensés. Ensuite, un survol des techniques de vérification est effectué en mettant l'accent sur les techniques applicables sur les circuits numériques au niveau fonctionnel. Finalement, les principes de base de la conception de banc d'essais sont exposés.

#### 2.1 La vérification

La vérification est le processus qui tente de prouver qu'un modèle est correct et donc dépourvu d'erreur. Dans le monde de la conception des circuits VLSI (*Very Large Scale Integrated Circuit*), on s'accorde pour affirmer que la vérification est devenue un aspect important puisqu'elle consomme environ 70% du temps de développement d'un circuit [6]. Ainsi, en considérant que la complexité des circuits croît de façon exponentielle, il ne faut pas oublier que cela affecte aussi la vérification. La différence est que la complexité de la vérification augmente encore plus rapidement que la complexité de la conception des circuits. Wilson [40] avance que la complexité de la vérification augmente au carré de la complexité de la conception d'un circuit. Parallèlement à l'augmentation de la complexité de la vérification, on demande que le temps de développement soit plus court et que la vérification soit plus efficace. Il faut donc recourir à des méthodologies éprouvées qui permettent de procéder à la vérification dans des temps raisonnables et avec une efficacité maximale.

Le même problème a déjà été identifié dans le monde de la conception logicielle. Le besoin de maintenance des logiciels existants a été à la source du problème. L'augmentation de la complexité des logiciels combinée avec le manque de méthodes utilisées par les concepteurs ont vraiment fait émerger la science de la vérification logicielle. Au niveau où est rendue la vérification fonctionnelle, la conception d'un banc

d'essais dédié à un circuit numérique doit être considérée comme un projet logiciel. Ainsi, on doit s'inspirer des techniques du génie logiciel établies. La littérature au niveau des fondements de la vérification fonctionnelle des circuits numériques n'est pas exhaustive. On retrouve donc dans la littérature portant sur la vérification fonctionnelle au niveau logiciel, des descriptions beaucoup plus riches sur les techniques de vérification de base.

### 2.1.1 Vérification versus Validation

Il existe une confusion pour ce qui est de la signification des termes *vérification* et *validation*. Beizer [3] propose une définition de ces termes. On peut définir que les requis sont ce que le modèle devrait faire et que la spécification d'un modèle est le document qui tente de représenter fidèlement les requis. Si on accepte les définitions des requis et de la spécification, la vérification est définie comme les activités qui tentent de comparer le modèle avec la spécification et la validation est définie comme les activités qui tentent de comparer les requis avec le modèle. Cependant, les requis sont une perception de ce que le modèle devrait faire et cette perception peut être différente pour les divers intervenants dans la conception du modèle. Étant donné que la spécification d'un modèle est la formulation plus ou moins formelle des requis, il est possible que des erreurs soient introduites dans la spécification. Ce type d'erreur n'est pas du ressort de la vérification, mais plutôt de la validation. Le Tableau 2-1 résume les définitions précédemment énoncées.

**Tableau 2-1: Définition des termes pour la vérification versus la validation**

| Terme                   | Définition                                                                                              |

|-------------------------|---------------------------------------------------------------------------------------------------------|

| Requis                  | Ce que le modèle devrait faire                                                                          |

| Spécification           | Le document formulant les requis                                                                        |

| Modèle                  | Le modèle dérivé de la spécification (Circuit, logiciel, SOC)                                           |

| Système de vérification | Un autre modèle ou un banc d'essais dérivé de la spécification implémentant une méthode de vérification |

Dans le domaine de la vérification, les requis n'existent pas de façon tangible. La base de la vérification étant la spécification, un système de vérification n'est pas en mesure de détecter une erreur provenant des spécifications. On peut donc avancer que la

validation est en quelques sortes la vérification des spécifications d'un modèle. Bergeron [6] complète ces définitions en résumant la vérification fonctionnelle par une hypothèse statistique. L'hypothèse sous-test est : *Est-ce que le modèle est fonctionnellement correct ?* La réponse est produite par le système de vérification. La Figure 2-1 présente l'analyse des types d'erreur qui découlent de la réponse obtenue de l'hypothèse sous test.

|                  |                          | Réponse à l'hypothèse     |              |

|------------------|--------------------------|---------------------------|--------------|

|                  |                          | Erreur                    | Pas d'erreur |

| Modèle incorrect |                          | Type II<br>(Faux Positif) |              |

|                  | Type I<br>(Faux Négatif) |                           |              |

Figure 2-1: Type d'erreurs

Les cas corrects se présentent lorsque le système de vérification détecte une erreur et que le modèle est effectivement incorrect, ainsi que lorsque le système de vérification ne détecte pas d'erreur et que le modèle est correct. Cependant, lorsque le système de vérification détecte une erreur et que le modèle est correct, nous sommes en présence d'une erreur de type I, ce qui signifie qu'il y a une erreur dans le système de vérification. En fait, la vérification sert à la fois à vérifier le modèle et le système de vérification. Il faut donc être critique lors de la détection d'une erreur en se demandant si elle provient du modèle ou du système de vérification. Cependant, il faut éviter les erreurs de type II qui signifient que le système de vérification ne détecte pas d'erreur lorsque le modèle est incorrect. Une erreur de type II est induite par une mauvaise interprétation des spécifications par les créateurs du modèle et du système de vérification. Il est aussi possible qu'une erreur de type II soit une erreur dans la spécification, ce qui signifie que c'est du ressort de la validation. Toutefois, si on veut réduire la fréquence des erreurs de type II au niveau de la vérification, il est important de respecter le schéma présenté à la Figure 2-2 tiré de [6].

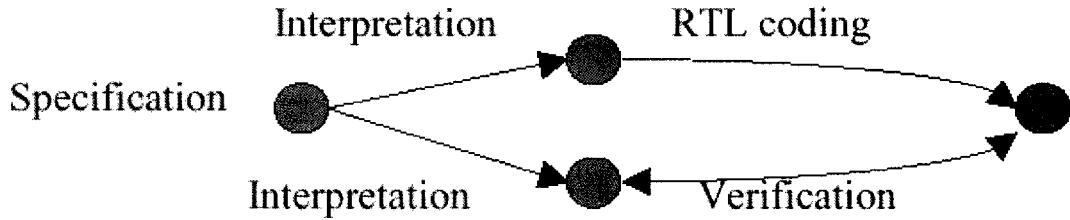

**Figure 2-2: Indépendance de la vérification**

En ayant deux interprétations différentes de la spécification, on réduit la probabilité d'obtenir des erreurs de type II. Cette approche est en fait un principe de base de la vérification.

### 2.1.2 Principes du test

Les tests sont l'unité de base du processus de vérification. Un test devrait pouvoir fournir une information ou plusieurs informations sur la validité du modèle. Myers [26] a défini certains principes qui devraient être suivis si on veut obtenir une stratégie de tests efficace.

- *Les tests doivent être basés sur les spécifications du système*

Les spécifications sont ce que les clients attendent du produit. Ainsi, il faut se concentrer sur cela pour leurs fournir ce qu'ils veulent.

- *La planification des tests doit être faite avant le début des tests*

Cela permet d'accélérer le processus de conception (parallélisme avec la conception du système) et de donner des mises en garde à l'équipe de conception du système. Plus une erreur est détectée tôt dans le processus de conception, moins les coûts de correction sont élevés.

- *Le principe de Pareto s'applique aux tests (80% des erreurs dans 20% des modules) ou la probabilité de trouver une erreur dans un module est proportionnelle au nombre d'erreur trouver dans ce même module*

Il faut tenter de découvrir les modules suspects. La leçon qu'il faut en tirer est que lorsqu'on trouve plusieurs erreurs dans un module, il faut l'étiqueter comme suspect et le vérifier plus intensément.

- *Les tests doivent être écrits autant pour les cas invalides et inespérés que pour les cas valides et espérés*

Un testeur écrit naturellement des cas de test pour vérifier les spécifications, mais l'inverse des spécifications fait autant partie des spécifications. Un test doit tenter de trouver des succès lorsqu'il introduit des entrées incorrectes aussi bien qu'il doit tenter de trouver des erreurs lorsqu'il introduit des entrées correctes.

- *Examiner ce que le design devrait faire est seulement la moitié du travail. L'autre moitié est d'examiner ce que le design ne devrait pas faire.*

C'est en quelque sorte la suite du principe précédent. Un système bancaire qui produit les paies pour tous ses employés est correct. Cependant, si le système produit aussi des paies pour des employés inexistants, il y a une erreur.

- *Pour être le plus efficace possible, les tests devraient être conçus par une équipe indépendante de l'équipe de conception*

Premièrement, les tests sont un processus destructif, où cependant le but ultime est constructif. Ainsi la personne qui a conçu quelque chose n'est pas la mieux placée pour tenter de la détruire. Ensuite, une erreur peut survenir du fait que le concepteur n'a pas bien compris ce qu'il avait à faire. Ainsi les tests qu'il élaborera contiendront la même erreur que le design.

D'autre part, un bon test doit posséder les caractéristiques suivantes :

- *Il doit avoir une haute probabilité de trouver une erreur;*

- *Il n'est pas redondant;*

- *Il doit être reproductible;*

- *Il ne doit pas être ni trop simple ni trop complexe.*

### 2.1.3 Testabilité du modèle

Tout modèle doit passer par une étape de vérification. Il est donc préférable d'en tenir compte lors de sa conception. Pressman [27] énumère les caractéristiques requises afin d'améliorer la testabilité et de faciliter la vérification des modèles.

- *Opérable : Mieux le système fonctionne, plus il est facile à tester*

Il ne doit pas y avoir d'erreurs qui bloquent l'exécution du modèle. De plus, le développement doit évoluer par fonctionnalité, afin de permettre de tester et de développer simultanément.

- *Observabilité : Ce que tu vois est ce que tu testes*

Les sources du code sont préférablement accessibles. L'interne du système est visible afin d'effectuer des tests de boîte blanche. Les erreurs internes sont automatiquement détectées et reportées.

- *Contrôlabilité : Plus on contrôle le modèle, plus on peut automatiser et optimiser la vérification*

Toutes les sorties peuvent être générées à partir de certaines combinaisons des entrées. Toutes les parties du modèle doivent être accessibles. Les états et les variables du modèle doivent pouvoir être contrôlés par l'ingénieur de test. Par exemple, un modèle qui possède un compteur de 64 bits devrait fournir une fonction de pré-chargement. Les formats des entrées et des sorties doivent être structurés et consistants.

- *Modularité : En contrôlant l'étendue des tests, on peut plus facilement isoler les problèmes et faire des tests plus intelligents*

Les modules qui composent le modèle doivent pouvoir être testés indépendamment.

- *Simplicité : Moins on en vérifie, plus la vérification se fait rapidement*

Des fonctionnalités simples définies par une structure simple et aussi un codage simple permettent des tests plus efficaces.

- *Stabilité : Moins on a de changements, moins la vérification sera perturbée*

Les changements sur le modèle ne doivent pas être fréquents, ils doivent être contrôlés et ne doivent pas invalider les tests existants. Le modèle doit bien récupérer suite à une erreur.

- *Compréhension : Plus on a d'information, plus la vérification sera intelligente*

Il faut bien comprendre le modèle. Les dépendances entre les composants internes et externes doivent être bien comprises. Les changements sur le modèle doivent être communiqués à l'ensemble des intervenants concernés. La documentation doit être instantanément accessible, bien organisée, spécifique, détaillée et précise.

#### 2.1.4 Type de vérification

La vérification d'un modèle peut être effectuée en utilisant trois approches. Dans cette section, il sera question de ces trois approches qui sont les tests structurels, les tests fonctionnels et les méthodes de preuves formelles.

##### 2.1.4.1 Test structurel et test fonctionnel

Les tests structurels et fonctionnels utilisent généralement la simulation afin d'exécuter les tests. Les tests structurels et les tests fonctionnels sont complémentaires et visent à obtenir un meilleur degré de confiance dans un modèle, mais d'une manière différente. Pour les tests structurels, on travaille avec des métriques qui sont directement dérivées de la structure du modèle. On peut considérer la structure d'un circuit au niveau porte logique ou encore au niveau de la description RTL. Ainsi, lorsqu'on vise à couvrir les branches, les énoncés, les états ou les transitions dans une machine à états, on parle de tests structurels. Les tests structurels sont finis mais, selon la métrique utilisée, une couverture totale devient plus ou moins accessible. Par exemple, la couverture complète des énoncés d'un modèle est facile à atteindre, car si on ne peut pas l'atteindre, c'est qu'il y a des énoncés inutiles ou insérés pour des fins d'optimisations. Les métriques structurelles peuvent se compliquer et le nombre de cas à couvrir augmente alors exponentiellement. Un exemple serait la couverture complète des chemins d'un modèle qui devient difficile lorsqu'il y a plusieurs éléments de décision et des boucles qui entrent en jeu. Ces métriques pourraient être tout de même qualifiées de métriques simples, car il existe une façon d'obtenir une couverture complète.

La couverture structurelle se complique vraiment lorsque le modèle est concurrent, car les métriques structurelles qu'on peut alors définir sont par exemple, la couverture de

couples ou de triplets d'états lorsqu'il y a plusieurs machines à états ou encore, la couverture de points de synchronisation entre plusieurs chemins. Ainsi, dans le cadre d'un modèle intensif, la couverture de ces métriques devient extrêmement complexe et impossible à obtenir dans un temps raisonnable. C'est ce qu'on pourrait appeler des métriques structurelles complexes.

Par contre, le fait qu'il soit ardu de couvrir convenablement ces métriques complexes n'empêche pas qu'il soit essentiel de couvrir certains cas pour obtenir un degré de confiance convenable dans le modèle. Les tests fonctionnels servent à définir des tests qui effectuent une couverture partielle de métriques structurelles dites complexes. Ainsi, en utilisant des techniques de tests fonctionnels, on tente de cibler les cas dans un large ensemble de cas qui seraient susceptibles de provoquer une erreur dont la conséquence serait significative. La manière utilisée pour caractériser les cas fonctionnels à vérifier est de créer un modèle fonctionnel. Un tel modèle est en fait une abstraction du modèle sous vérification. Les métriques de couverture fonctionnelle sont un mélange de comportement temporel et de données. Pour donner des exemples de test fonctionnel, il y a l'analyse transactionnelle et l'analyse de machines à états comportementales. L'analyse transactionnelle définit les chemins comportementaux que peut emprunter une transaction dans un modèle. Une transaction est une séquence d'actions appliquées sur le modèle. La technique de vérification de machines à états comportementales permet la couverture des états, des transitions, des séquences de transition ou encore du temps d'une transition. Les techniques de test fonctionnel seront exposées plus en détail à la section 2.2.

#### 2.1.4.2 Méthode de preuve formelle

Les méthodes de preuve formelle tentent de vérifier un modèle en se basant sur une représentation mathématique. Si on est en accord avec l'affirmation que les tests peuvent seulement détecter la présence d'erreurs et qu'ils ne peuvent pas prouver leur absence [14], cela implique que les tests devraient être abandonnés et seulement des méthodes de preuves formelles devraient être utilisées. Cependant, les méthodes de preuve ont des limitations et les tests ont des avantages importants par rapport à ces méthodes [20]. Premièrement, il n'y a pas de méthode de preuve absolue qui prouve qu'un modèle est

correct, il faut plutôt parler de preuve d'équivalence. Lorsqu'on sait que la preuve d'équivalence se fera sur la base d'une spécification, il faut se demander ce que vaut la spécification. Howden [20] explique que tous les modèles possèdent des fonctions explicites qu'on retrouve dans la spécification, mais aussi des fonctions implicites qu'on ne retrouve généralement pas dans la spécification. Ainsi, une spécification complète doit définir les fonctions implicites et explicites du modèle. Ensuite, lorsqu'on a une spécification complète, une preuve formelle tente de prouver que l'interprétation du concepteur est correcte et non de prouver l'intention de la spécification. De plus, les méthodes de preuve sont seulement applicables à des modèles de complexité modérée.

Rashinkar & al. [28] résument les méthodes de preuve formelle utilisées et développées dans un contexte de recherche. Premièrement, il y a la méthode formelle de preuve de modèle. Cette technique utilise des propriétés comportementales directement dérivées de la spécification du modèle et exprimées avec une logique temporelle. Un outil de preuve formelle de modèle tentera de prouver statiquement que les propriétés définies sont respectées dans le modèle. Ensuite, il y a la technique de preuve de théorème qui est encore au stade de la recherche. Cette technique est utilisée afin de prouver formellement des théorèmes qui représentent le comportement du modèle. Finalement, la technique de preuve d'équivalence est utilisée pour prouver de façon statique que deux modèles sont logiquement équivalents.

### 2.1.5 Critère d'arrêt

Théoriquement le critère d'arrêt de la vérification survient lorsque le modèle sous vérification est complètement exempt d'erreur. Il existe trois façons de parvenir au critère d'arrêt, quel qu'il soit: les tests structurels, les tests fonctionnels et les preuves formelles. La combinaison de ces trois méthodes de vérification mène à une vérification complète si on tient compte des limites théoriques de la vérification que Manna et Waldinger [24] ont énoncées :

- *On ne peut jamais être sûr que les spécifications sont correctes;*

- *On ne peut jamais être certain qu'un système de vérification est correct;*

- *Aucun système de vérification ne peut vérifier un modèle correct. En fait cela découle des deux énoncés précédents.*

Ainsi, le but du critère d'arrêt n'est pas de déterminer le point où on est certain qu'il n'y a plus d'erreur dans le modèle, mais le point où la probabilité qu'une erreur survienne est acceptable. Cette probabilité acceptable est définie selon différents facteurs tel que l'environnement où sera utilisé le circuit. Si nous prenons un circuit devant être utilisé dans un stimulateur cardiaque, le critère d'arrêt doit faire en sorte que la probabilité qu'une erreur survienne soit très faible, puisque dans le cas d'un dysfonctionnement, une erreur peut avoir des conséquences fatales.

Cependant, dans le but de fixer un critère d'arrêt concret dans le processus de vérification, la technique utilisée est la création d'un plan de vérification. L'élaboration d'un plan de vérification est une méthode systématiquement conseillée pour spécifier l'effort de vérification d'un projet [6][12][19][22][22][27][28][41]. Le plan de vérification est considéré comme la spécification de la vérification. On y définit, entre autre, les techniques de vérification utilisées, les bancs d'essais nécessaires à la vérification, les cas de test, les métriques utilisées, les méthodes de preuves utilisées pour certaines parties du modèle, les ressources allouées à la vérification et les échéanciers qui devront être respectés. C'est en se basant sur les objectifs définis dans le plan de vérification qu'on détermine concrètement l'atteinte du critère d'arrêt de la vérification. En fait, la couverture du plan de vérification est la métrique globale utilisée pour mesurer la complétude de l'effort de vérification.

## 2.2 Techniques et mesures de la vérification

La vérification basée sur une technique de simulation peut se résumer par l'application de tests sur le modèle sous vérification et par la vérification des réponses produites par le modèle. Les tests sont aussi appelés les cas de tests. Ces derniers sont définis dans le plan de vérification et doivent être définis de façon structurée. La définition des cas de test est effectuée en utilisant des techniques de vérification. Les techniques de vérification définissent en quelque sorte un modèle qui servira à la création des tests. La vérification est mesurée en utilisant des métriques. Il émane de chaque

technique de vérification une métrique qui sert à mesurer le taux de couverture résultant de l'application des tests. De plus, pour chaque technique de vérification il faut être en mesure de vérifier les réponses produites par l'application des tests sur le modèle.

Dans cette section, certains aspects reliés aux techniques de vérification seront exposés. En premier lieu, il sera question de la visibilité et des différents niveaux d'abstraction relatifs aux techniques de vérification. Ensuite, certaines techniques de vérification seront exposées. Finalement, il sera question de la production des tests et des techniques de vérification des réponses.

### 2.2.1 Visibilité

L'utilisation d'une technique de vérification requiert une certaine connaissance du modèle auquel on applique l'effort de vérification. En fonction de la visibilité qu'on a sur le modèle, trois approches sont définies. Il s'agit des approches dites :

- *Boîte blanche*;

- *Boîte noire*;

- *Boîte grise*.

Une technique de vérification dite de type boîte blanche implique une visibilité complète du modèle, c'est-à-dire qu'on connaît ses interfaces externes et sa structure interne. Une approche de type boîte blanche permet d'avoir une contrôlabilité et une observabilité totale sur le modèle. Les tests structurels utilisent une approche boîte blanche, car ce type de test dépend directement de la structure du modèle.

L'approche boîte noire implique une connaissance des interfaces externes du modèle et des fonctionnalités du modèle, mais sans connaître sa structure interne. Ainsi, une approche de type boîte noire permet de vérifier le modèle sous l'angle de ses fonctionnalités sans tenir compte de l'implantation. Les tests fonctionnels sont habituellement effectués en adoptant une approche boîte noire. Cependant, une approche boîte noire pose trois problèmes : le contrôle, l'observation, et les limites. Ayant seulement un contrôle sur les interfaces externes du modèle, il peut être difficile de déterminer certaines séquences complexes qui permettront de conduire à une erreur. D'autre part, l'observation des réponses du modèle se faisant toujours par les interfaces

externes du modèle, il est possible qu'une erreur interne soit stimulée, mais sans qu'on puisse l'observer dû à un masquage interne de l'erreur. Ce dernier problème, relié à l'approche boîte noire, est dû aux limites imposées par la structure interne du modèle, car plusieurs erreurs sont provoquées aux limites fonctionnelles et structurelles du modèle.

Le compromis qui permet de tirer avantage à la fois de l'approche boîte noire et boîte blanche est d'utiliser une approche boîte grise. Cette dernière permet de définir les tests de la même façon qu'une approche boîte noire, mais en ayant une certaine connaissance de la structure interne du modèle. Ainsi, la contrôlabilité et l'observabilité sont augmentées et on peut déterminer des tests qui permettront d'explorer les limites fonctionnelles et structurelles du modèle.

### 2.2.2 Niveau d'abstraction

Le concept de niveau d'abstraction est très important lors de l'étape de vérification d'un circuit. La complexité actuelle des circuits numériques requiert qu'on se serve d'une certaine forme d'abstraction afin de statuer sur la complétiion de la vérification. Par exemple, au niveau porte logique différents modèles de fautes sont utilisés afin de modéliser des défectuosités au niveau physique. Cependant, il existe plusieurs niveaux d'abstraction pour les modèles de pannes. Il y a le modèle de collage simple qui sert à vérifier si une broche d'une porte logique est collée à 0 ou à 1 suite à la fabrication du circuit. Ce modèle de panne devient inadéquat lorsque la complexité du circuit augmente. Il faut donc travailler avec un modèle de panne à plus haut niveau d'abstraction. Par exemple, il existe un modèle de panne spécialisé pour les processeurs qui considère les registres et les fonctions entre les registres au lieu de la valeur binaire des signaux. Ce dernier exemple est considéré comme étant du test fonctionnel, car on utilise un modèle fonctionnel pour abstraire des portes logiques.

De façon similaire à la vérification d'un circuit, la vérification d'un modèle HDL se fera à différent niveau d'abstraction. Il existe plusieurs techniques de vérification qui peuvent être considérées selon le niveau d'abstraction auquel on considère le modèle. En général, il s'agit du test fonctionnel ou du test structurel. Par exemple, la vérification d'une machine à états est une technique de vérification. Cette technique de vérification

sera du test structurel si on vérifie une machine à états implantée en RTL. Cependant, si on considère une machine à états comportementale représentant les fonctionnalités du modèle, on fait alors de la vérification fonctionnelle. Il est parfois ambigu de différencier si on est au niveau du test fonctionnel ou du test structurel. En fait, le niveau d'abstraction utilisé pour le développement des tests est le déterminant qui juge si on est au niveau fonctionnel ou structurel.

### 2.2.3 Techniques et métriques

Dans cette section, un survol des techniques de vérification est effectué. Cette section considère les techniques applicables sur un modèle HDL, on ne détaille pas les techniques de vérification applicables au niveau circuit. Une technique de vérification définit un modèle qui sera utilisé pour produire les tests. De plus, une technique fournit une métrique qui sert à mesurer l'avancement de la vérification en fonction de la technique utilisée. Les techniques décrites dans cette section sont la revue de code, les techniques basées sur le code, le test par mutation, l'analyse partitionnelle et aux limites et les techniques basées sur les graphes.

#### 2.2.3.1 Revue de code

La technique de revue de code est une technique de type boîte blanche qui ne requiert pas l'exécution du modèle. Cette technique de vérification a été proposée par Weinberg [38]. Le principe de la revue de code est d'exécuter mentalement le code source d'un modèle dans le but de trouver des erreurs. Premièrement, cette technique peut être appliquée par la majorité des programmeurs. De plus, un programmeur peut appliquer cette méthode formellement avec une liste de critères de revue de code, mais la méthode la plus efficace est celle des revues de code par groupe. Habituellement, une procédure est établie pour les revues de code de groupe. On forme un groupe de trois ou quatre personnes. Le premier est ordinairement un ingénieur d'assurance qualité qui agira comme modérateur. Ensuite, il y a le programmeur, qui passera sous révision, et les deux autres peuvent être des ingénieurs concepteurs ou testeurs. La procédure est la suivante :

1. *Le programmeur proclame à voix haute chaque énoncé du code.*

2. *À tout moment, les membres du groupe peuvent interrompre le narrateur lorsqu'on suspecte une erreur.*

3. *Le point est alors débattu pour confirmer ou infirmer s'il s'agit d'une erreur.*

4. *À la fin de la séance, la liste des erreurs trouvées est remise au programmeur pour qu'il corrige les erreurs après la séance de revue de code.*

L'expérience a démontré que la personne la plus efficace dans ces rencontres est le programmeur qui trouve ses propres erreurs. Un suivi des erreurs détectées doit être fait au début de la prochaine rencontre dans le but de confirmer la correction des erreurs. Il est aussi important dans ces revues de code de ne pas commencer à analyser le programmeur à la place du code, sinon on s'éloigne du but premier qui est de trouver des erreurs dans le code. Cette technique donne de très bon résultat. Plusieurs publications et études contrôlées [26] le confirment en avançant qu'on peut détecter environ 30% à 70% des erreurs. Il faut comprendre que ce pourcentage est pris sur le total des erreurs détectées et non sur le total des erreurs, car il est impossible de déterminer le nombre total absolu d'erreur dans un modèle. Un autre avantage de cette méthode est qu'elle permet la détection des erreurs tôt dans le projet et plus une erreur est détectée tôt dans le processus de conception, moins ça coûte cher [27]. Aussi, il est prouvé que le programmeur corrige mieux les erreurs lorsqu'elles sont trouvées au début du processus de conception comparativement aux corrections apportées vers la fin d'un projet où la pression est maximale. La métrique utilisée avec cette technique de vérification est la quantité de code passée sous revue.

Cette technique peut aussi être appliquée à tous les niveaux du développement d'un circuit. Par exemple, il est possible d'effectuer des revues pour les spécifications, le plan de vérification, l'architecture du circuit et pour la conception des bancs d'essais.

### 2.2.3.2 Techniques basées sur le code

Les techniques basées sur le code font partie des tests structurels et utilisent une approche boîte blanche. Chaque technique définit une métrique structurelle qui sert à vérifier le code. Le Tableau 2-2 résume les métriques structurelles énumérées dans le

document de taxonomie de la vérification fonctionnelle produit par *Virtual Socket Interface Alliance* (VSIA) [37].

**Tableau 2-2: Métriques Structurelles**

| Métrique                | Description                                                                                                                                                   |

|-------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Énoncé                  | Mesure les énoncés exécutés dans le code.                                                                                                                     |

| Bit                     | Mesure que chaque bit de tous les signaux du modèle ont été basculés.                                                                                         |

| Transition              | Mesure les transitions exercées dans une machine à états                                                                                                      |

| État visité             | Mesure les états visités dans une machine à états                                                                                                             |

| Liste de sensibilité    | Mesure que chaque processus a été déclenché par chaque signal défini dans sa liste de sensibilité.                                                            |

| Couverture de branche   | Mesure que les branches découlant des éléments décisionnels tel que les <i>case</i> et les <i>if-else</i> ont été exercées.                                   |

| Couverture d'expression | Mesure que toutes les combinaisons possibles des expressions logiques dans les conditions des éléments décisionnelles tel que les <i>if</i> ont été exercées. |

| Couverture de chemin    | Mesure que les chemins définis par les séquences de branches empruntées ont été exercés.                                                                      |

| Couverture de signal    | Mesure que les signaux d'états ou les adresses d'une mémoire ont été exercées.                                                                                |

Les techniques de couverture structurelle sont bien développées dû à l'indépendance qu'elles possèdent face au modèle. Cette indépendance permet la création d'outils automatiques qui permettent de mesurer la couverture de ces métriques structurelles. Il existe plusieurs outils commerciaux qui sont dédiés à l'analyse de la couverture de certaines de ces métriques pour des descriptions VHDL ou Verilog.

### 2.2.3.3 Test par mutation