**Titre:** Stimulations combinées dédiées au rétablissement de l'évacuation

Title: chez les patients souffrant de dysfonctions urinaires

**Auteur:** Aguibou Ba

Author:

**Date:** 2004

**Type:** Mémoire ou thèse / Dissertation or Thesis

**Référence:** Ba, A. (2004). Stimulations combinées dédiées au rétablissement de l'évacuation

chez les patients souffrant de dysfonctions urinaires [Master's thesis, École

Polytechnique de Montréal]. PolyPublie. <https://publications.polymtl.ca/7271/>

## Document en libre accès dans PolyPublie

Open Access document in PolyPublie

**URL de PolyPublie:** <https://publications.polymtl.ca/7271/>

PolyPublie URL:

**Directeurs de recherche:** Mohamad Sawan

Advisors:

**Programme:** Unspecified

Program:

UNIVERSITÉ DE MONTRÉAL

STIMULATIONS COMBINÉES DÉDIÉES AU RÉTABLISSEMENT DE

L'ÉVACUATION CHEZ LES PATIENTS SOUFFRANT DE DYSFONCTIONS

URINAIRES

AGUIBOU BA

DÉPARTEMENT DE GÉNIE ÉLECTRIQUE

ÉCOLE POLYTECHNIQUE DE MONTRÉAL

MÉMOIRE PRÉSENTÉ EN VUE DE L'OBTENTION

DU DIPLÔME DE MAÎTRISE ÈS SCIENCES APPLIQUÉES

(GÉNIE ÉLECTRIQUE)

JANVIER 2004

National Library

of Canada

Acquisitions and

Bibliographic Services

395 Wellington Street

Ottawa ON K1A 0N4

Canada

Bibliothèque nationale

du Canada

Acquisitions et

services bibliographiques

395, rue Wellington

Ottawa ON K1A 0N4

Canada

*Your file* *Votre référence*

ISBN: 0-612-91932-3

*Our file* *Notre référence*

ISBN: 0-612-91932-3

The author has granted a non-exclusive licence allowing the National Library of Canada to reproduce, loan, distribute or sell copies of this thesis in microform, paper or electronic formats.

L'auteur a accordé une licence non exclusive permettant à la Bibliothèque nationale du Canada de reproduire, prêter, distribuer ou vendre des copies de cette thèse sous la forme de microfiche/film, de reproduction sur papier ou sur format électronique.

The author retains ownership of the copyright in this thesis. Neither the thesis nor substantial extracts from it may be printed or otherwise reproduced without the author's permission.

L'auteur conserve la propriété du droit d'auteur qui protège cette thèse. Ni la thèse ni des extraits substantiels de celle-ci ne doivent être imprimés ou autrement reproduits sans son autorisation.

---

In compliance with the Canadian Privacy Act some supporting forms may have been removed from this dissertation.

Conformément à la loi canadienne sur la protection de la vie privée, quelques formulaires secondaires ont été enlevés de ce manuscrit.

While these forms may be included in the document page count, their removal does not represent any loss of content from the dissertation.

Bien que ces formulaires aient inclus dans la pagination, il n'y aura aucun contenu manquant.

# Canadä

UNIVERSITÉ DE MONTRÉAL

ÉCOLE POLYTECHNIQUE DE MONTRÉAL

Ce mémoire intitulé :

STIMULATIONS COMBINÉES DÉDIÉES AU RÉTABLISSEMENT DE

L'ÉVACUATION CHEZ LES PATIENTS SOUFFRANT DE DYSFONCTIONS

URINAIRES

Présenté par : BA Aguibou

en vue de l'obtention du diplôme de : Maîtrise ès sciences appliquées

a été dûment accepté par le jury d'examen constitué de :

M. BRAULT Jean-Jules, Ph.D ,président

M. SAWAN Mohamad, Ph.D., membre et directeur de recherche

Mme CHERIET Farida, Ph.D, membre

## DÉDICACE

*À mes parents, Aminata Sall et Ibrahima Ba,

Mon frère et ma sœur, Karimou et Hadja

Je vous aime.*

## REMERCIEMENTS

Je tiens avant tout à remercier mon directeur de recherche, Mohamad Sawan, qui a bien voulu m'accepter au sein de son équipe de recherche, pour ses conseils, ses suggestions ainsi que son support tout au long de ma maîtrise.

Un remerciement particulier à Grace pour sa présence ainsi que son soutien moral lors de ces deux dernières années.

Tous mes remerciements,

À Gaétan Décarie, technicien du DGE de l'ÉPM, pour son grand support technique ainsi que sa constante disponibilité, à Jonathan Coulombe et à Tommy Desilets pour leur support, respectivement lors de la réalisation de la puce, et lors de la validation de l'implant et la rédaction de ce mémoire.

À Madame Farida Cheriet et Monsieur Jean-Jules Brault, professeurs à l'École Polytechnique de Montréal, pour bien avoir voulu participer au jury d'examen de ce mémoire.

À mes amis ici ou à l'extérieur du continent ainsi que ma famille à Dakar et Nouakchott.

À tous les techniciens et techniciennes du département de génie électrique de l'École Polytechnique et mes collègues de l'équipe PolySTIM.

Enfin, je remercie la Société Canadienne de Microélectronique pour les outils et le support lors de la conception et la fabrication du circuit intégré.

## RÉSUMÉ

Les travaux présentés dans ce mémoire trouvent leur application dans le domaine de la récupération des fonctions du système urinaire. Nous présentons des dispositifs implantables utilisés pour le rétablissement des fonctions de la vessie chez les patients paraplégiques, ceux atteints de maladies congénitales ou ceux ayant perdu le contrôle volontaire de leur vessie suite à une lésion de la moelle épinière.

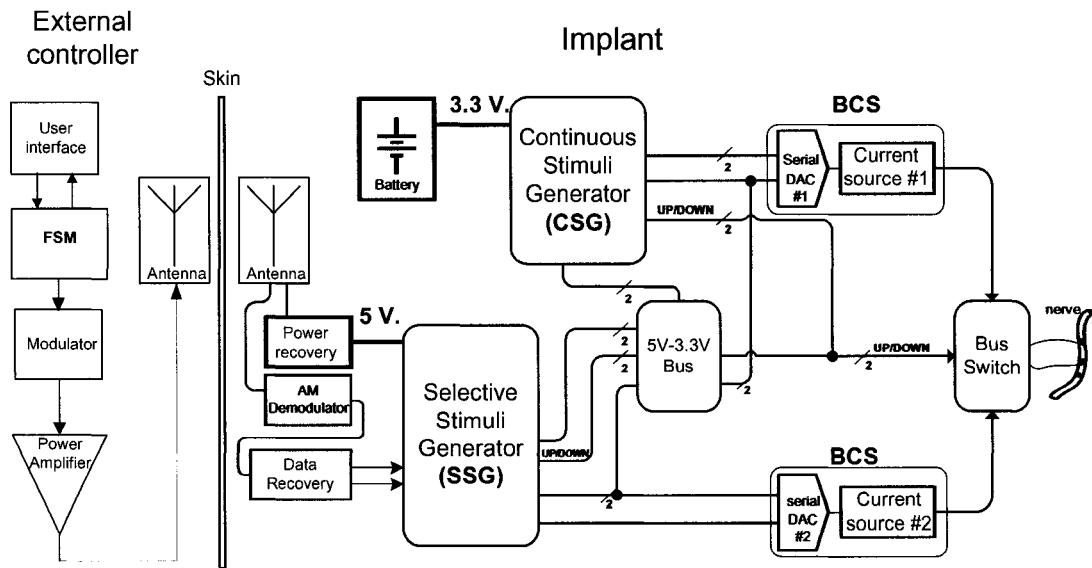

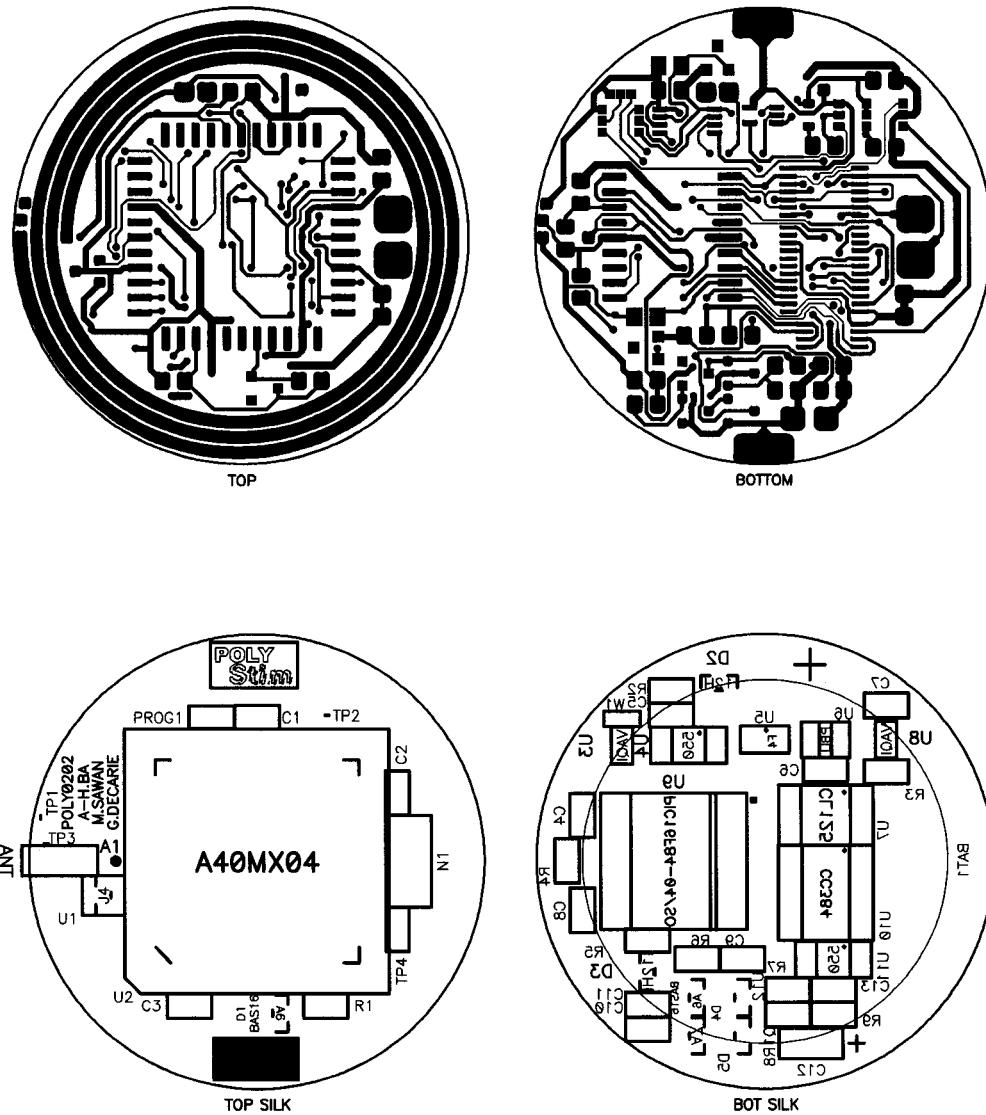

Nous présentons tout d'abord une nouvelle version d'un implant dédié réalisé sur un circuit imprimé de moins de 3 cm de diamètre avec des composants discrets disponibles commercialement. Cet implant est la version améliorée d'un système déjà fonctionnel. Placé sous la peau d'un patient, il est en mesure de réaliser deux types de stimulations pour la récupération des fonctions urinaires. Une stimulation sélective est appliquée pour rétablir la miction volontaire tandis qu'une fonction de stimulation permanente permet de réduire les problèmes d'hyperréflexie (contractions indésirées de la vessie). Le mode permanent est une stimulation à très basse fréquence et très basse amplitude alors que la stimulation sélective est ponctuelle, précise, à plus forte amplitude. Un contrôleur externe envoie à l'implant de façon transcutanée l'énergie ainsi que les paramètres de stimulation à l'aide d'un lien inductif opérant à haute fréquence. Ce stimulateur fonctionne avec deux tensions d'alimentation distinctes; l'une à 5V pour la stimulation sélective qui nécessite une tension élevée, et une pile de 3.3V dédiée à la stimulation permanente.

Des études expérimentales *in vivo*, afin de caractériser la fiabilité et la fonctionnalité du stimulateur, ont été menées sur des chiens à l'animalerie de l'Université McGill. Les résultats obtenus à partir des tests en laboratoire et des expérimentations chez l'animal avec les versions précédentes du système avaient déjà démontré le fonctionnement des méthodes de stimulation sélective et de stimulation permanente. Elles avaient aussi montré la pertinence de ces techniques, applicables sur le plan médical aussi bien au domaine de la réhabilitation vésicale qu'à d'autres types de réadaptation. Au moment de la rédaction de ce mémoire, d'autres expérimentations sont en cours afin de parfaire les techniques de stimulation et de valider les améliorations apportées au système.

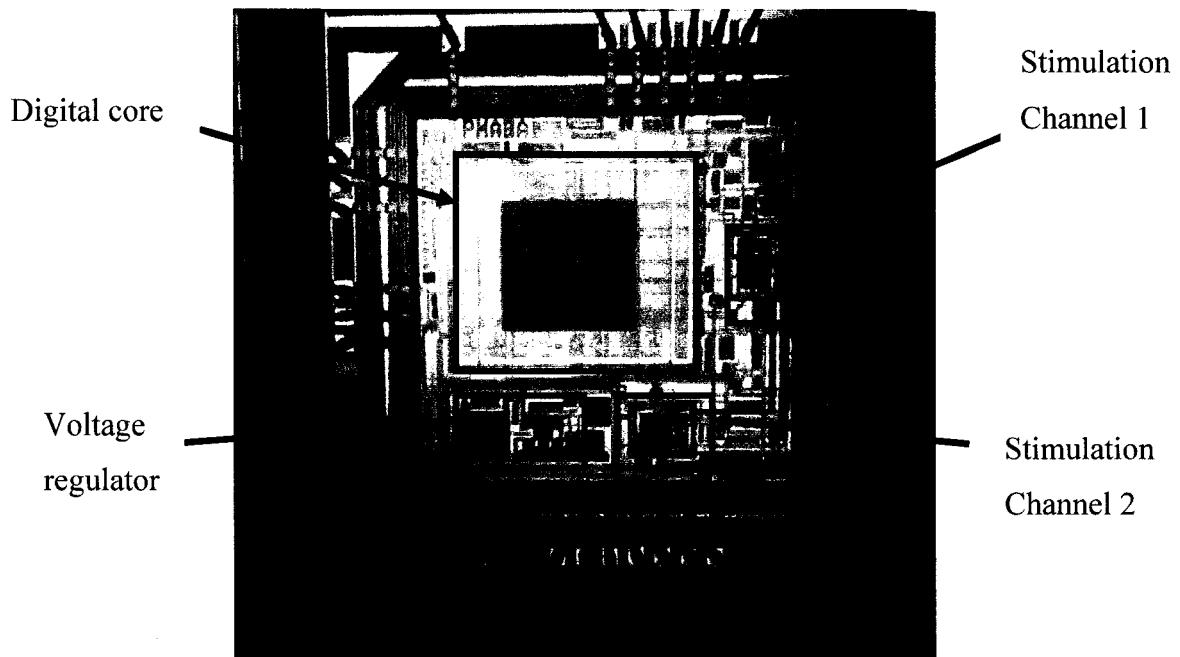

Un circuit intégré dédié a été réalisé et testé dans la technologie CMOS 0.18um. En plus de posséder toutes les fonctionnalités des stimulateurs précédemment réalisés en technologie discrète, il combine un nouveau type de stimulation sélective dite flexible permettant à l'usager de générer les formes d'ondes de stimuli de son choix. Le circuit contient aussi un module de mesure d'impédance permettant de caractériser l'interface électrode-nerf. Le design combine des fonctions numérique et analogique et occupe 1300x1300um<sup>2</sup> sans les plots de la puce. Le système a été conçu de façon à être aisément reprogrammable et ses deux canaux de sortie lui confère une flexibilité accrue.

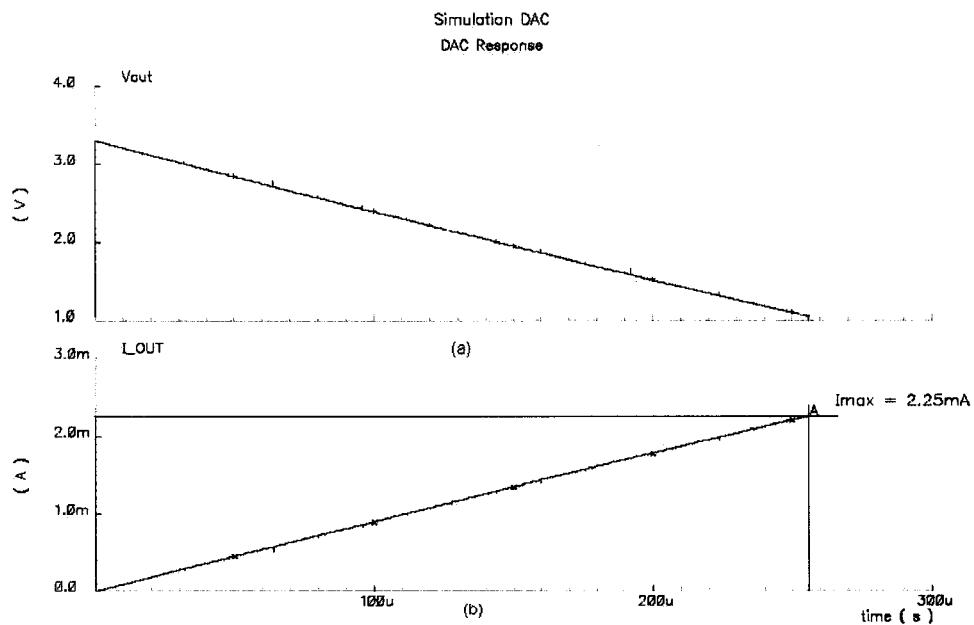

Les tests ont démontré que les hautes fréquences générées pouvaient atteindre 75 KHz tandis que les basses variaient de 4.6 Hz à 1.2 KHz. Le système de stimulation peut générer des durées d'impulsions avec une précision de 3 us. 32 valeurs d'amplitude de 8

bits chacune peuvent être placés dans la RAM, offrant ainsi une grande variété de formes d'ondes de stimulation.

Une erreur est survenue lors de l'interconnexion des blocs analogique et numérique, causant ainsi une impossibilité de varier l'amplitude des stimuli de sortie, cependant la fonctionnalité globale du système a été vérifiée. De plus, une version améliorée de cette puce est en cours de fabrication par la Société Canadienne de Microélectronique.

## ABSTRACT

The work presented in this master thesis is dedicated to the rehabilitation of the urinary system. The reported implantable devices allow to recuperate the bladder functions of paraplegic patients, those having lost the voluntary control of their bladder following a lesion of the spinal cord or those reached of diseases.

First, we present a new version of a dedicated implant mounted on a less than 3 cm diameter printed circuit board (PCB) with discrete components all commercially available. This implant, placed under the patient's skin, produces two types of stimulation techniques for the recovery of the urinary functions. A selective stimulation is applied to restore the voluntary micturition while a permanent stimulation technique makes possible the reduction of the hyperreflexia symptoms (unsolicited contractions of the bladder). The permanent mode is a very low frequency and very low amplitude stimulation, while the selective stimulation is more specific, and consists of a series of bi-frequency stimuli with higher amplitude. An external controller sends transcutaneously the needed power as well as the stimulation parameters through a high frequency inductive link. The stimulation system operates with two distinctive voltages; one at 5 V for the selective stimulation which requires high voltage, and an embedded battery of 3.3V is dedicated to permanent stimulation.

In vivo experimental studies, in order to characterize the reliability and the functionalities of the stimulator, were undertaken on dogs at the McGill University. The

results obtained from the circuits test and the experiments on dogs, with the previous versions of the system, had already shown the effectiveness of both selective and permanent stimulation methods. They had also shown the importance of these techniques, on a medical point of view, in fields not limited only to the bladder rehabilitation but also to others types of rehabilitation techniques. Also, others experiments are being conducted in order to improve the stimulation techniques and to validate the new version of the implant.

On the other hand, a dedicated integrated circuit was designed, fabricated and tested in CMOS 0.18um technology. In addition to having all the functionalities of our previous stimulation system realized in discrete technology, the new stimulator combines a novel type of selective stimulation called flexible stimulation. This mode allows the generation of a multitude of waveforms stimuli. The circuit contains also an impedance measurement building block making possible the characterization of the electrode-nerve interface. The design combines digital and analog blocks and occupies 1300x1300um<sup>2</sup> excluding the pads. The system was designed in order to be easily reprogrammable and its two output channels confers it an increased flexibility.

The tests showed that the generated high frequencies could reach 75 KHz while the low ones varied from 4.6 Hz to 1.2 KHz. The stimulation system can generate pulse widths with a precision of 3 us. 32 8-bits magnitude values can be placed in a register, thus offering a large variety of stimulation waveforms.

An error occurred while connecting the analog and the digital blocks, causing an impossibility to vary the amplitude of the delivered stimuli. However, the global functionalities of the system were demonstrated. Furthermore, a new integrated circuit is under fabrication to improve the design and correct the described dysfunction.

## TABLE DES MATIÈRES

|                                                                             |             |

|-----------------------------------------------------------------------------|-------------|

| <b>DÉDICACE .....</b>                                                       | <b>IV</b>   |

| <b>REMERCIEMENTS .....</b>                                                  | <b>V</b>    |

| <b>RÉSUMÉ .....</b>                                                         | <b>VI</b>   |

| <b>ABSTRACT .....</b>                                                       | <b>IX</b>   |

| <b>TABLE DES MATIÈRES.....</b>                                              | <b>XII</b>  |

| <b>LISTE DES FIGURES .....</b>                                              | <b>XVI</b>  |

| <b>LISTE DES TABLEAUX.....</b>                                              | <b>XX</b>   |

| <b>LISTE DES ANNEXES.....</b>                                               | <b>XXI</b>  |

| <b>LISTE DES SIGLES ET ABRÉVIATIONS .....</b>                               | <b>XXII</b> |

| <b>INTRODUCTION.....</b>                                                    | <b>1</b>    |

| <b>CHAPITRE 1 STIMULATION ÉLECTRIQUE NEURALE ET SYSTÈMES EXISTANTS.....</b> | <b>5</b>    |

| 1.1     LE SYSTÈME URINAIRE .....                                           | 5           |

| 1.1.1 <i>Vue d'ensemble du système urinaire.....</i>                        | 5           |

| 1.1.2 <i>Fonctionnement et dysfonctions urinaires.....</i>                  | 7           |

| 1.2     LA STIMULATION ÉLECTRIQUE FONCTIONNELLE .....                       | 9           |

| 1.2.1 <i>Alternatives de stimulation .....</i>                              | 9           |

| 1.2.2 <i>Incontinence.....</i>                                              | 14          |

|                                                                                                               |                                                                                                                                                       |           |

|---------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|

| 1.3                                                                                                           | DISPOSITIFS ET SYSTÈMES EXISTANTS.....                                                                                                                | 16        |

| 1.3.1                                                                                                         | <i>Systèmes commerciaux.....</i>                                                                                                                      | 16        |

| 1.3.2                                                                                                         | <i>Systèmes intégrés .....</i>                                                                                                                        | 17        |

| 1.3.3                                                                                                         | <i>Stimulation sélective .....</i>                                                                                                                    | 19        |

| 1.4                                                                                                           | CONCLUSION.....                                                                                                                                       | 24        |

| <b>CHAPITRE 2 SYSTÈME DE STIMULATIONS SÉLECTIVE ET PERMANENTE</b>                                             |                                                                                                                                                       | <b>25</b> |

| 2.1                                                                                                           | INTRODUCTION .....                                                                                                                                    | 25        |

| 2.2                                                                                                           | SPÉCIFICATIONS DU SYSTÈME INITIAL.....                                                                                                                | 26        |

| 2.2.1                                                                                                         | <i>Stimulation sélective .....</i>                                                                                                                    | 27        |

| 2.2.2                                                                                                         | <i>Stimulation permanente .....</i>                                                                                                                   | 27        |

| 2.3                                                                                                           | MODIFICATIONS DU DESIGN .....                                                                                                                         | 29        |

| 2.3.1                                                                                                         | <i>Passage de 3.3V à 5V.....</i>                                                                                                                      | 29        |

| 2.3.2                                                                                                         | <i>Étage de sortie amélioré .....</i>                                                                                                                 | 31        |

| 2.3.3                                                                                                         | <i>Communication PIC-FPGA.....</i>                                                                                                                    | 32        |

| 2.4                                                                                                           | ENCAPSULATION DES IMPLANTS .....                                                                                                                      | 36        |

| 2.5                                                                                                           | CONTROLEURS EXTERNES D'IMPLANTS.....                                                                                                                  | 38        |

| 2.6                                                                                                           | CONCLUSION.....                                                                                                                                       | 43        |

| <b>CHAPITRE 3 TECHNIQUES DE STIMULATIONS SELECTIVE ET<br/>PERMANENTE ET NOUVEAU STIMULATEUR INTÉGRÉ .....</b> |                                                                                                                                                       | <b>44</b> |

| 3.1                                                                                                           | INTRODUCTION .....                                                                                                                                    | 44        |

| 3.2                                                                                                           | DUAL STIMULATION TECHNIQUES TO RECUPERATE THE URINARY BLADDER<br>FUNCTIONS: CHRONIC EXPERIMENTS IN DOGS AND NEW IMPLANTABLE NEURAL<br>STIMULATOR..... | 46        |

| I.                                                                                                            | <i>INTRODUCTION.....</i>                                                                                                                              | 47        |

| II.                                                                                                           | <i>SELECTIVE AND CONTINUOUS NEUROSTIMULATOR.....</i>                                                                                                  | 52        |

| III.                                                                                                          | <i>CHRONIC EXPERIMENTS IN DOGS.....</i>                                                                                                               | 55        |

|                                                                                                    |            |

|----------------------------------------------------------------------------------------------------|------------|

| <i>IV. NEW FULLY INTEGRATED STIMULATOR .....</i>                                                   | 59         |

| <i>V. CONCLUSION.....</i>                                                                          | 64         |

| <i>ACKNOWLEDGEMENTS.....</i>                                                                       | 65         |

| <i>REFERENCES.....</i>                                                                             | 66         |

| 3.3 CONCLUSION.....                                                                                | 77         |

| <b>CHAPITRE 4 NEUROSTIMULATEUR PROGRAMMABLE INTÉGRÉ .....</b>                                      | <b>78</b>  |

| 4.1 SPÉCIFICATIONS .....                                                                           | 78         |

| 4.2 DESIGN DU CIRCUIT INTÉGRÉ .....                                                                | 80         |

| 4.2.1 <i>Modes de fonctionnement .....</i>                                                         | 80         |

| 4.2.2 <i>Protocole de communication .....</i>                                                      | 82         |

| 4.2.3 <i>Architecture du système .....</i>                                                         | 83         |

| 4.3 RÉALISATION DU CIRCUIT INTÉGRÉ .....                                                           | 100        |

| 4.3.1 <i>Bloc numérique .....</i>                                                                  | 100        |

| 4.3.2 <i>Étage analogique de sortie .....</i>                                                      | 101        |

| 4.3.3 <i>Interconnexion en partie numérique et analogique.....</i>                                 | 105        |

| 4.3.4 <i>Plots de sortie et testabilité.....</i>                                                   | 106        |

| 4.4 CONCLUSION.....                                                                                | 108        |

| <b>CHAPITRE 5 VALIDATION DES SYSTÈMES DE STIMULATION ET EXPÉRIMENTATIONS EN LABORATOIRES. ....</b> | <b>109</b> |

| 5.1 SYSTÈME DE STIMULATIONS SÉLECTIVE ET PERMANENTE .....                                          | 109        |

| 5.1.1 <i>Protocole expérimental.....</i>                                                           | 111        |

| 5.1.2 <i>Résultats.....</i>                                                                        | 114        |

| 5.2 NEUROSTIMULATEUR PROGRAMMABLE INTEGRE .....                                                    | 116        |

| 5.2.1 <i>Résultats de simulation .....</i>                                                         | 116        |

| 5.2.2 <i>Résultats expérimentaux .....</i>                                                         | 118        |

| <b>CHAPITRE 6 DISCUSSION GÉNÉRALE .....</b>                                                        | <b>122</b> |

|                           |            |

|---------------------------|------------|

| <b>CONCLUSION .....</b>   | <b>124</b> |

| <b>BIBLIOGRAPHIE.....</b> | <b>126</b> |

## LISTE DES FIGURES

|            |                                                                                                                                                       |    |

|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Figure 1-1 | : Vue d'ensemble du système urinaire.....                                                                                                             | 6  |

| Figure 1-2 | : Sites possibles de stimulation électrique .....                                                                                                     | 10 |

| Figure 1-3 | : Principe du blocage anodique pour l'activation sélective des petites fibres.....                                                                    | 14 |

| Figure 1-4 | : Forme d'onde d'un signal de stimulation sélective .....                                                                                             | 20 |

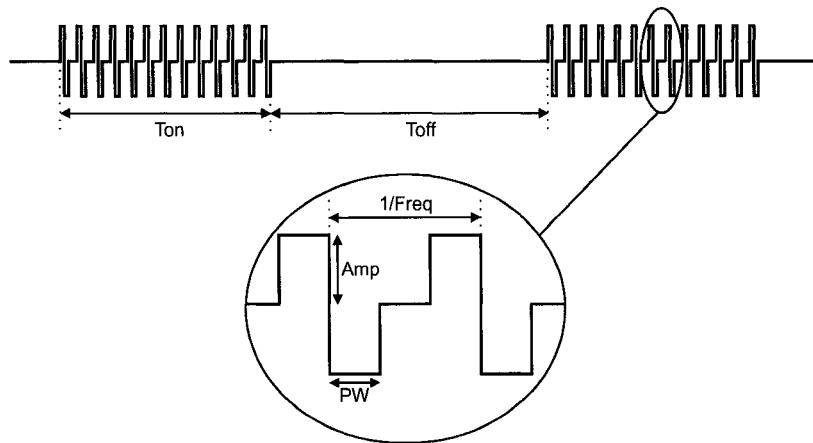

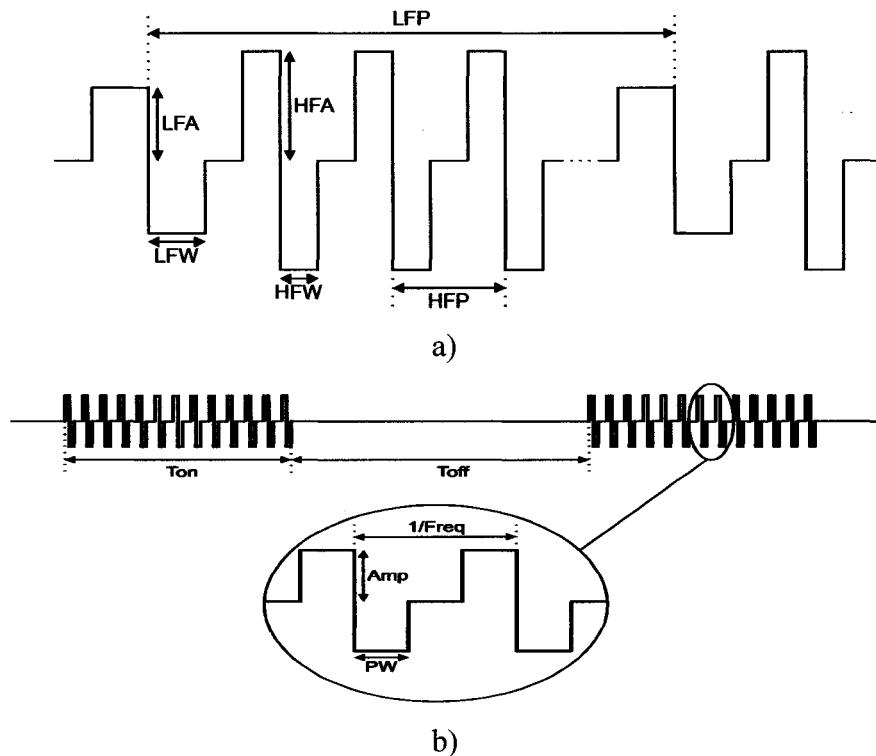

| Figure 2-1 | : Forme d'ondes d'un signal de stimulation permanente .....                                                                                           | 28 |

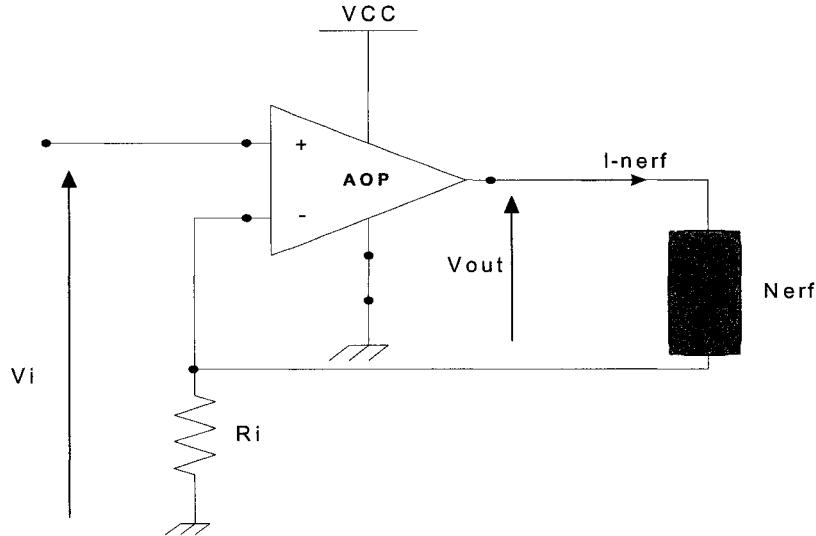

| Figure 2-2 | : Schéma équivalent de la source de courant du système .....                                                                                          | 30 |

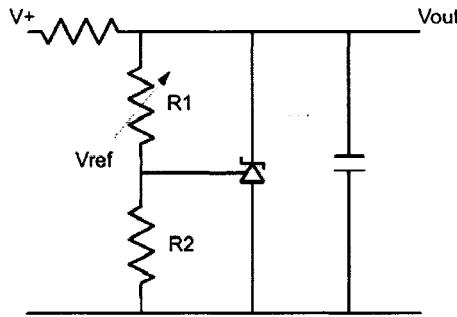

| Figure 2-3 | : schéma de fonctionnement du ZR431 .....                                                                                                             | 31 |

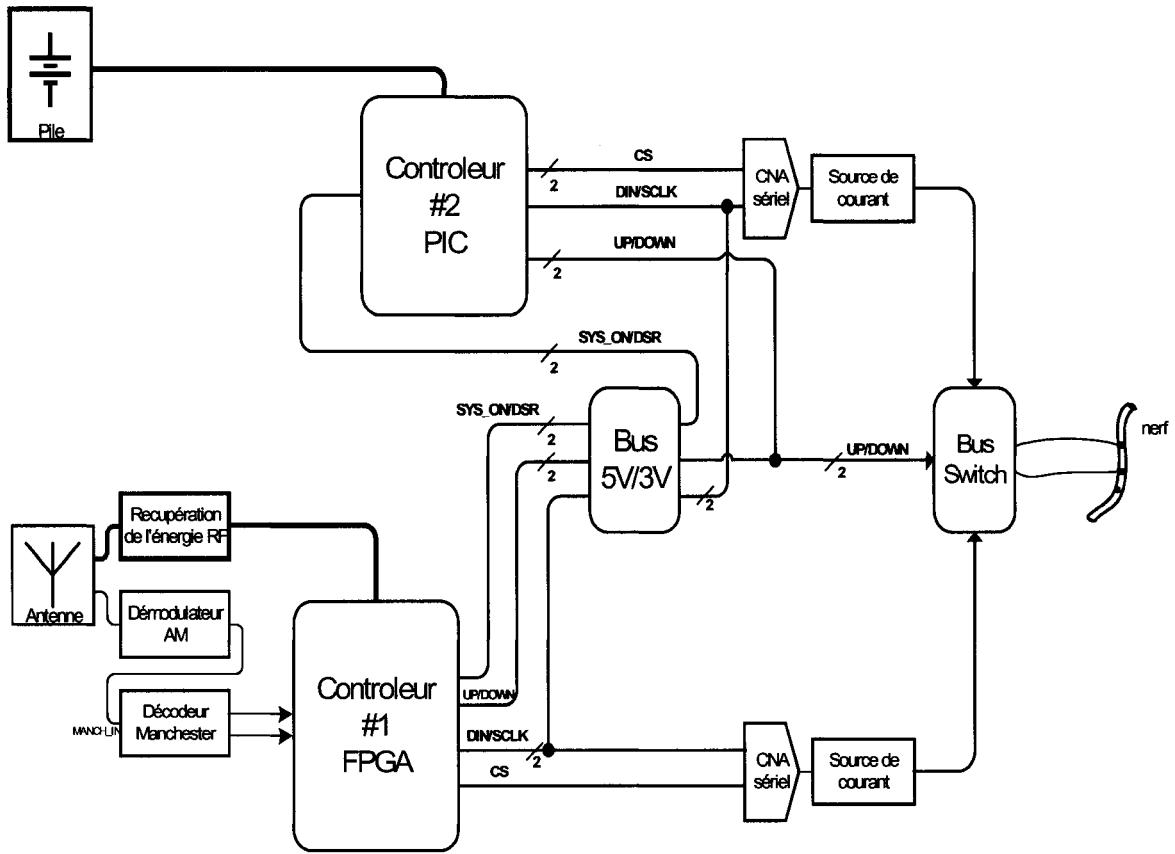

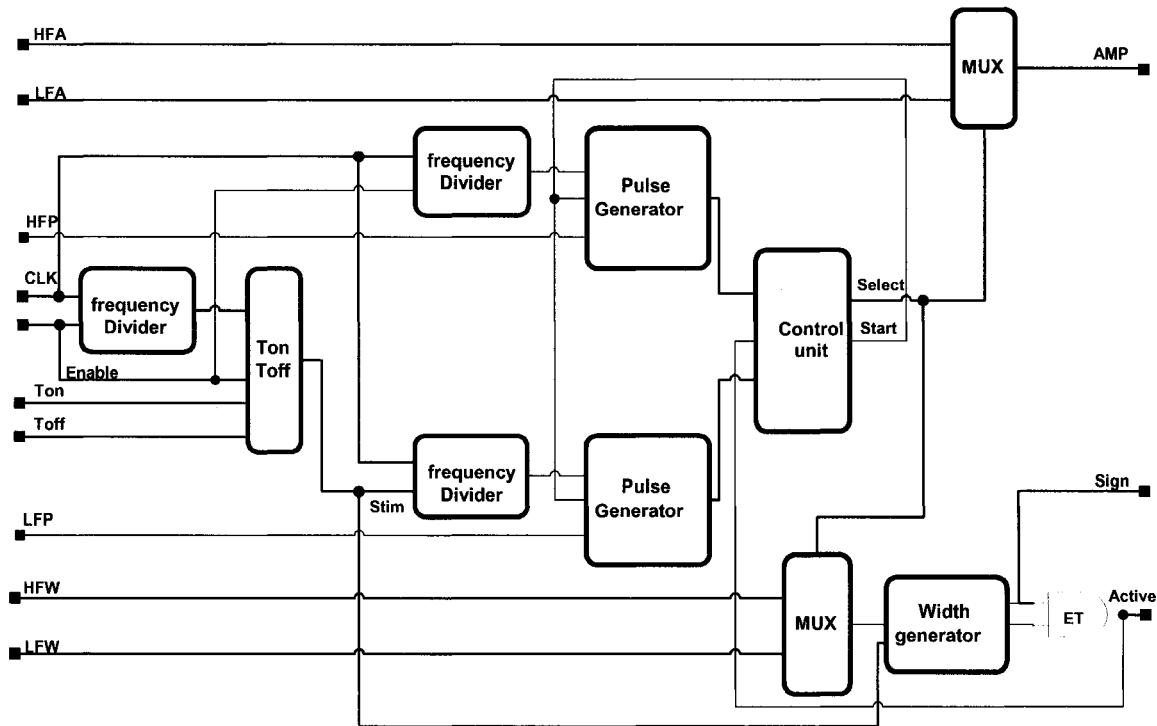

| Figure 2-4 | : Diagramme bloc du nouveau stimulateur implantable.....                                                                                              | 33 |

| Figure 2-5 | : Photographie du contrôleur externe.....                                                                                                             | 40 |

| Figure 2-6 | : Schéma de désactivation des amplificateurs par le PIC .....                                                                                         | 41 |

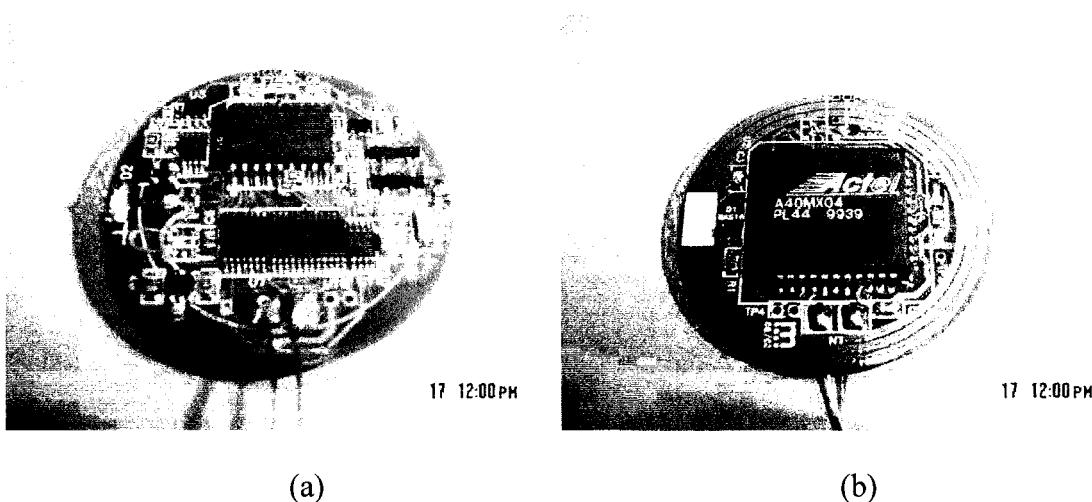

| Figure 2-7 | : Photographie du nouveau microstimulateur (échelle 1/1): (a) face supérieure, (b) face inférieure. ....                                              | 43 |

| Figure 3-1 | : Block diagram of the stimulation system. ....                                                                                                       | 70 |

| Figure 3-2 | : Stimulation waveforms: a) Selective stimulation ; b) Continuous stimulation. Parameters are described in Table 3.1 and Table 3.2 respectively. .... | 70 |

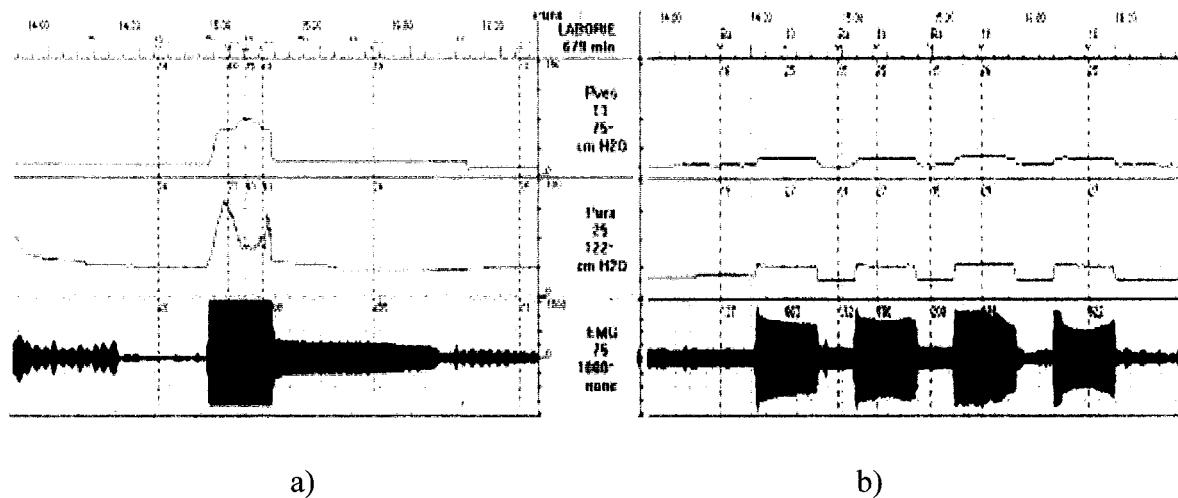

| Figure 3-3 | : Typical CMG during: a) selective stimulation; b) permanent stimulation.....                                                                         | 71 |

|             |                                                                                                                                                                                                                  |    |

|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

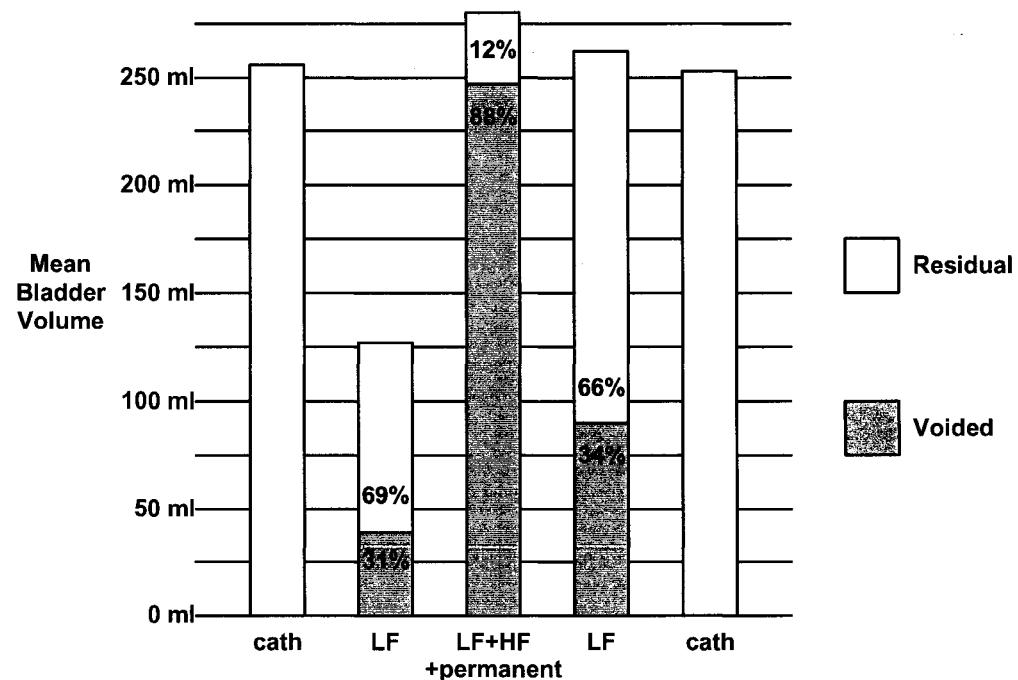

| Figure 3-4  | : Average bladder volume and voided urine for three stimulation steps.....                                                                                                                                       | 71 |

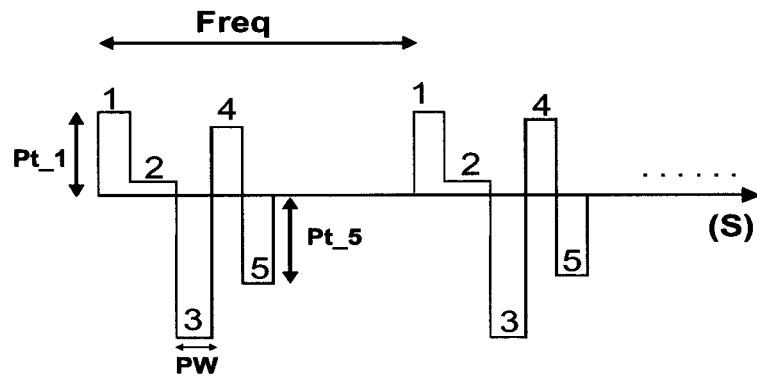

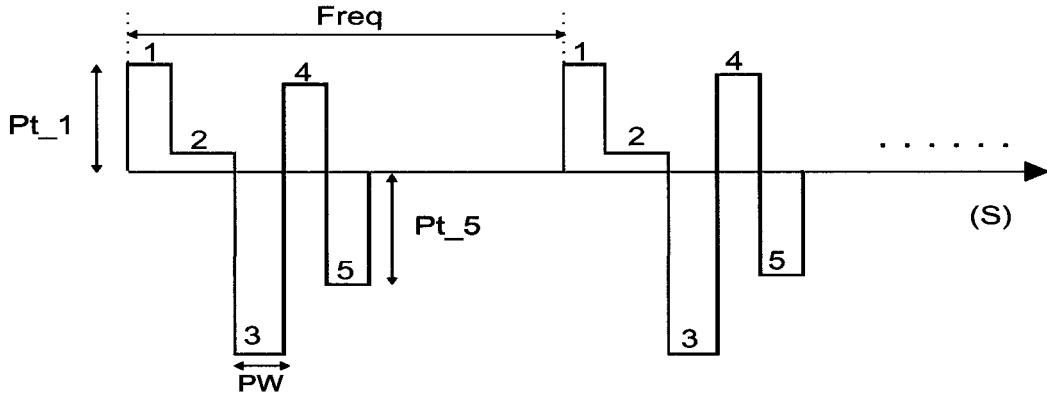

| Figure 3-5  | : Flexible selective stimulation waveform. Parameters are described in Table 3.4.....                                                                                                                            | 72 |

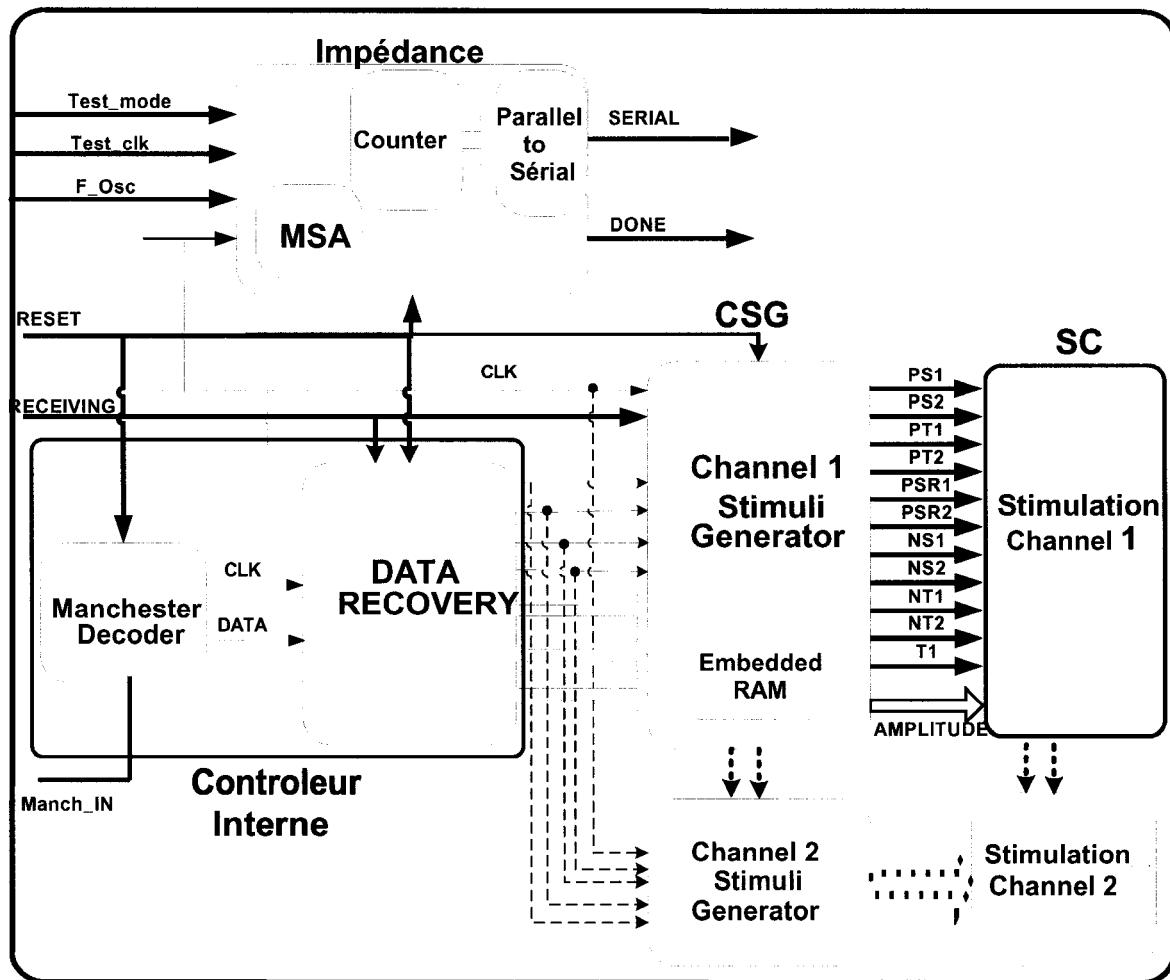

| Figure 3-6  | : Block diagram of the integrated microstimulator.....                                                                                                                                                           | 72 |

| Figure 3-7  | : Chip microphotography. Important blocks are identified.....                                                                                                                                                    | 73 |

| Figure 3-8  | : Simulation results of the impedance measurement's VCO.....                                                                                                                                                     | 73 |

| Figure 3-9  | : Simulation results of the DAC: a) Output Voltage; b) Output current after amplification.....                                                                                                                   | 74 |

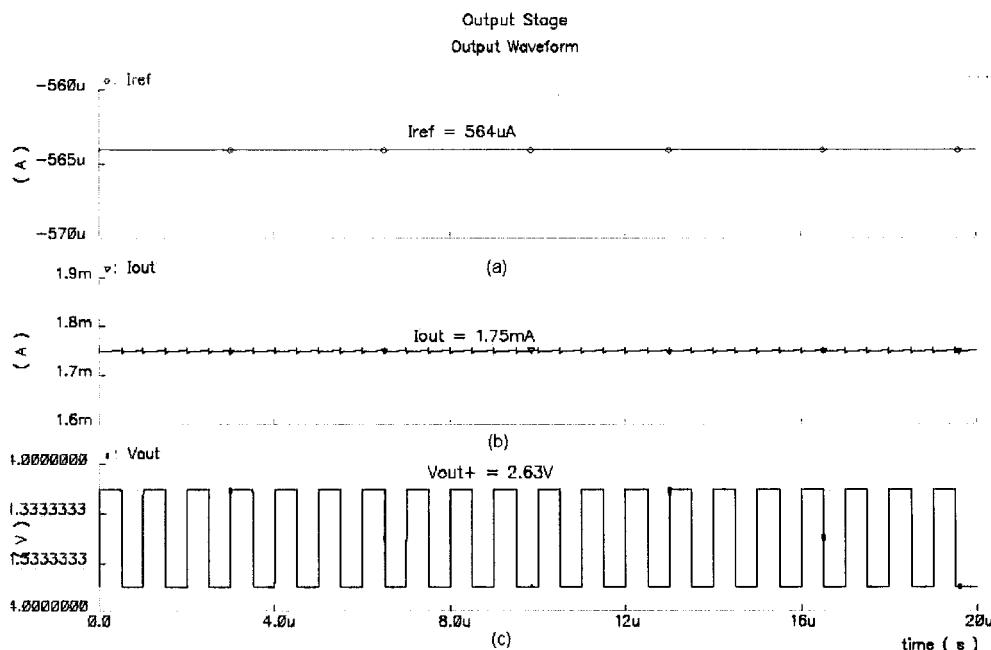

| Figure 3-10 | : Simulation results of the output stage: a) Reference current from DAC; b) Output current after amplification; c) Waveform of the applied stimulation voltage.....                                              | 74 |

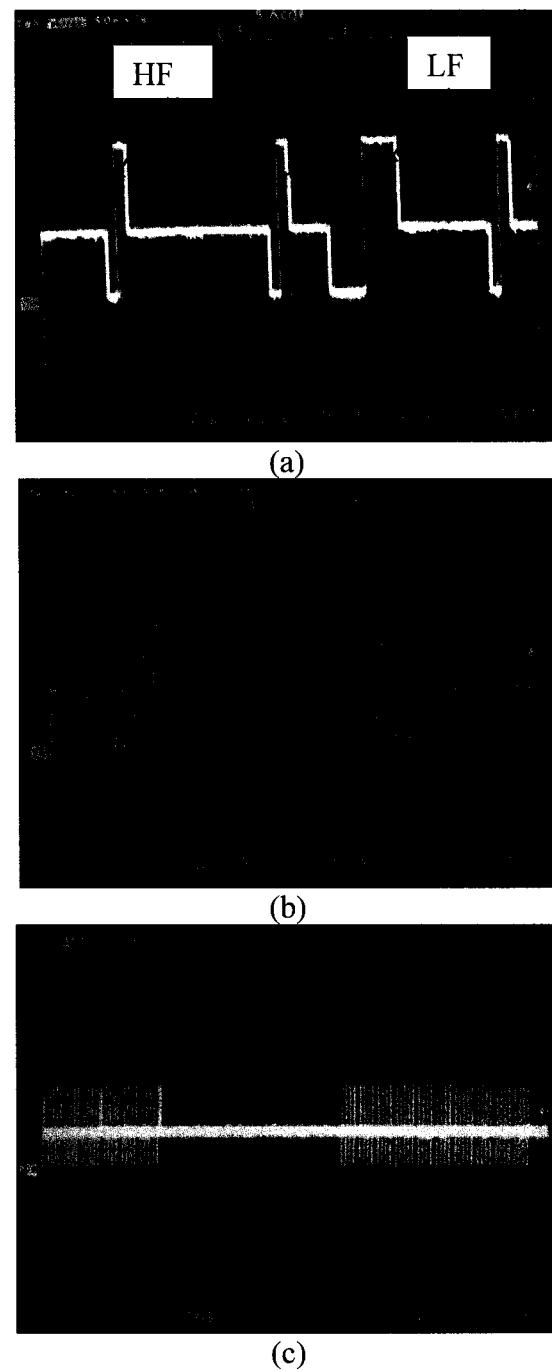

| Figure 3-11 | : Measurement results from the integrated microstimulator: a) Selective high (HF) and low (LF) frequency stimulation, b) Stimulation with arbitrary pattern, c) Continuous stimulation with train of pulses..... | 75 |

| Figure 4-1  | : Forme d'onde flexible générée à l'aide de la nouvelle architecture du stimulateur.....                                                                                                                         | 79 |

| Figure 4-2  | : Trames de stimulation pour le nouveau stimulateur intégré (Tableau 4.2 fournit les valeurs des paramètres) .....                                                                                               | 83 |

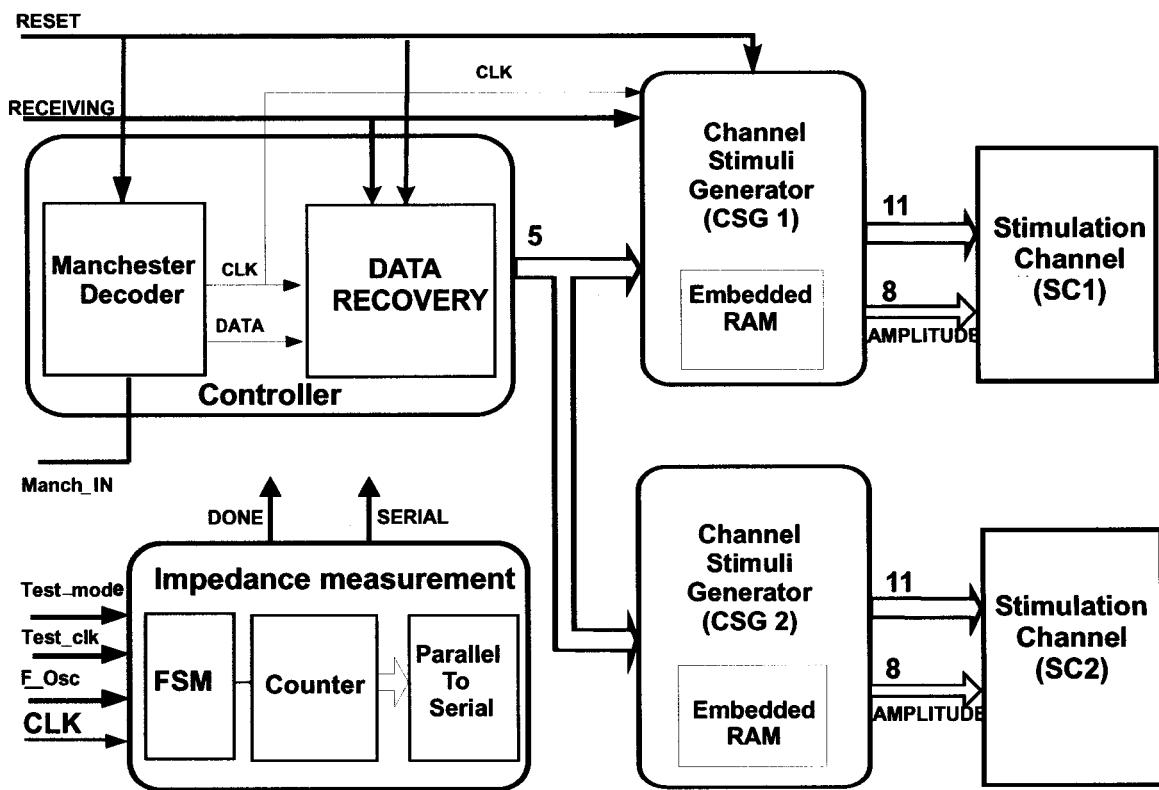

| Figure 4-3  | : Diagramme bloc du système global.....                                                                                                                                                                          | 84 |

|             |                                                                                                                    |     |

|-------------|--------------------------------------------------------------------------------------------------------------------|-----|

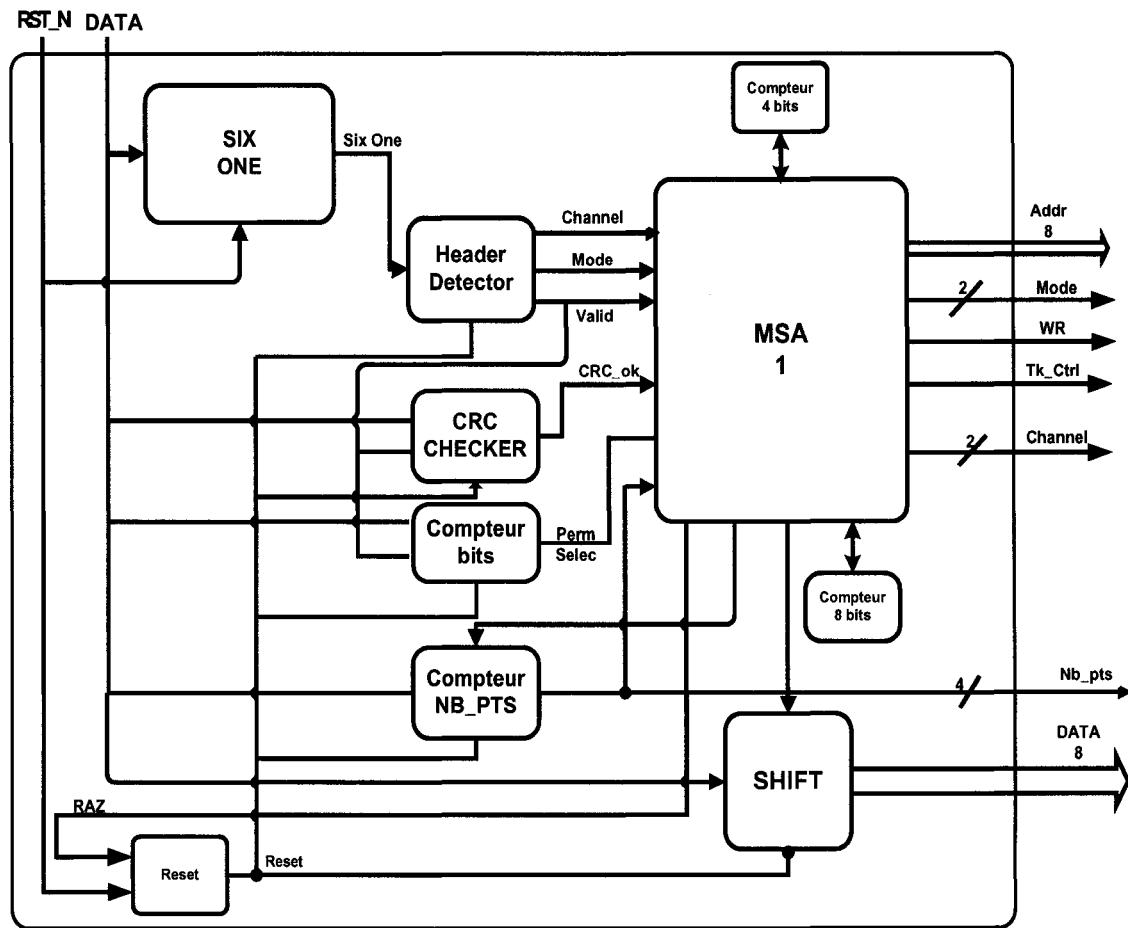

| Figure 4-4  | : Diagramme bloc du module de récupération de données.....                                                         | 85  |

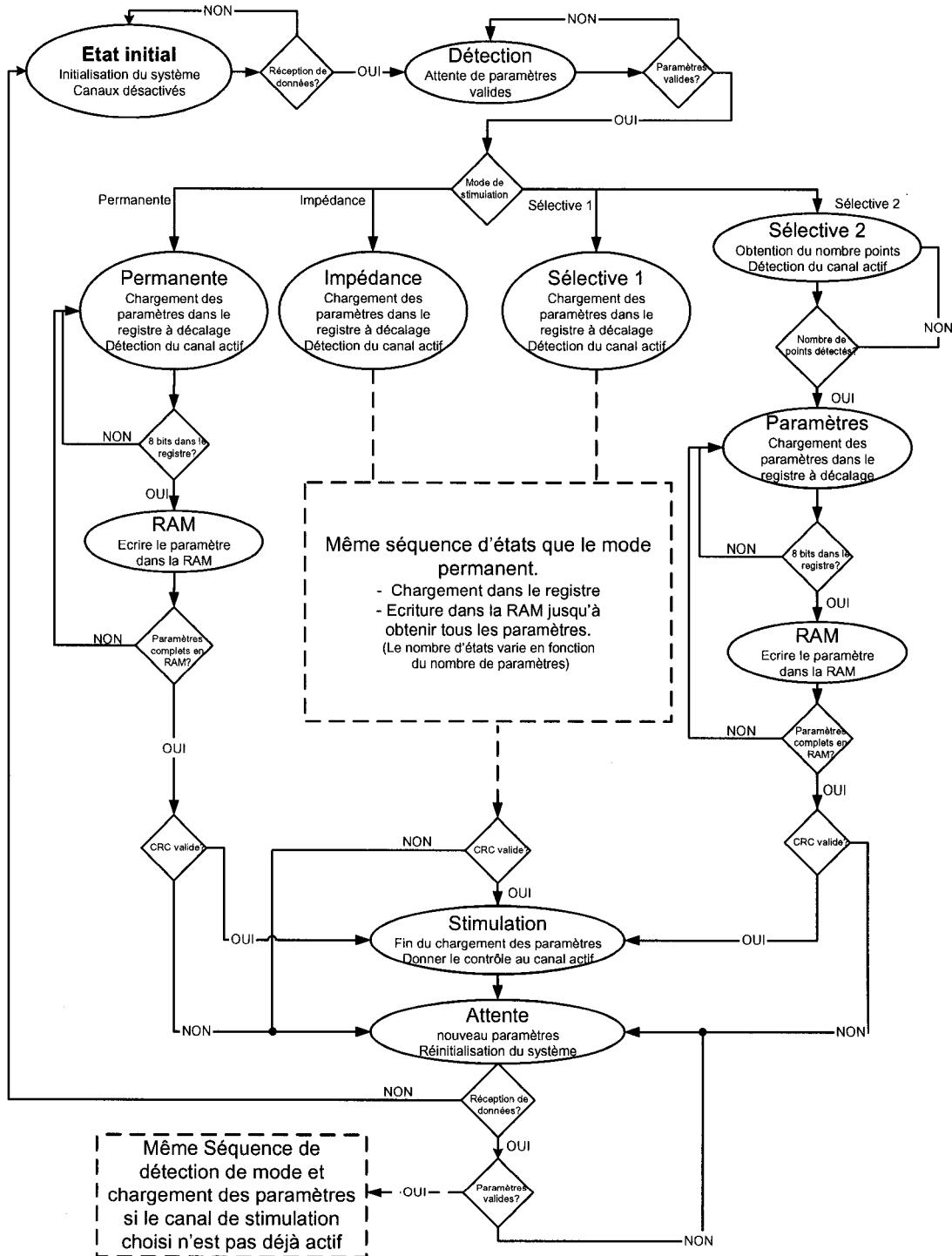

| Figure 4-5  | : Diagramme d'états de la machine à états contrôlant la récupération de données.....                               | 88  |

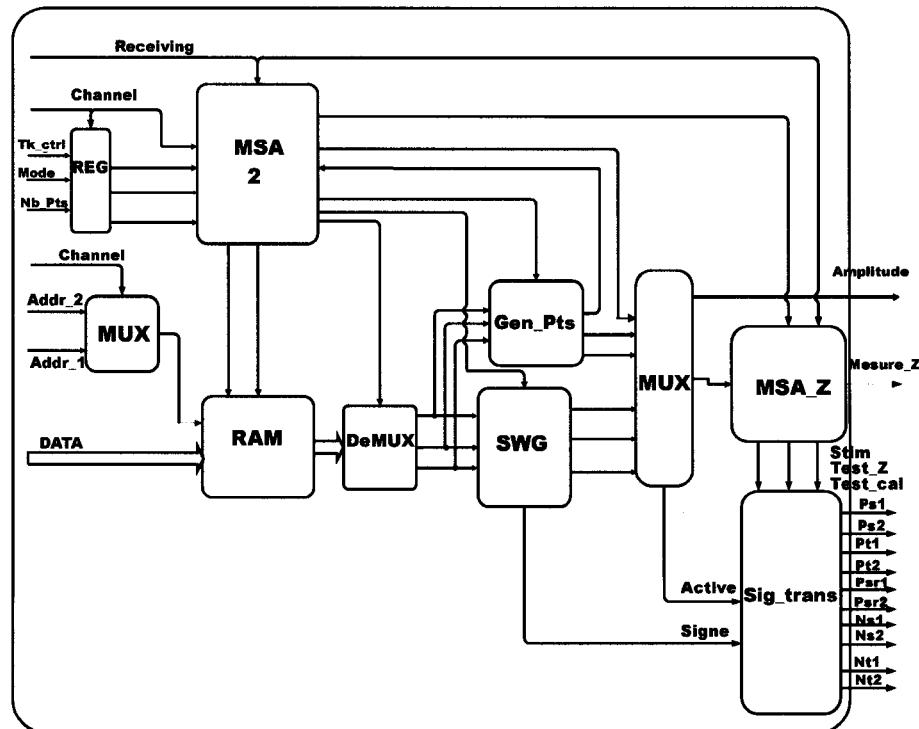

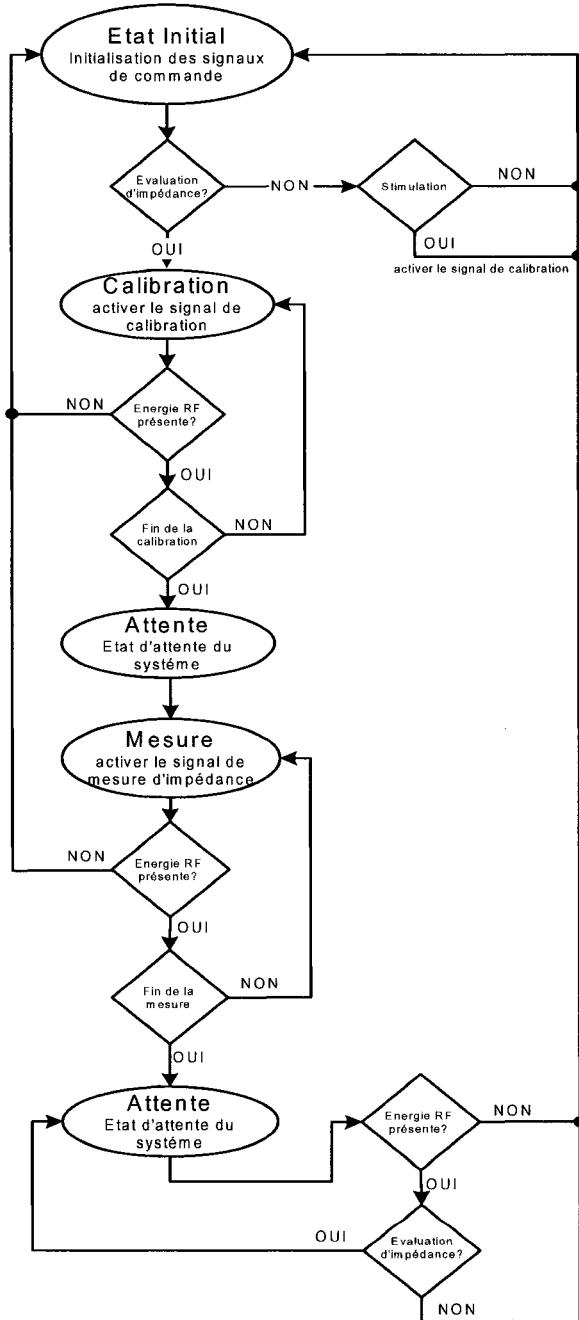

| Figure 4-6  | : Diagramme bloc du générateur de stimuli d'un canal .....                                                         | 89  |

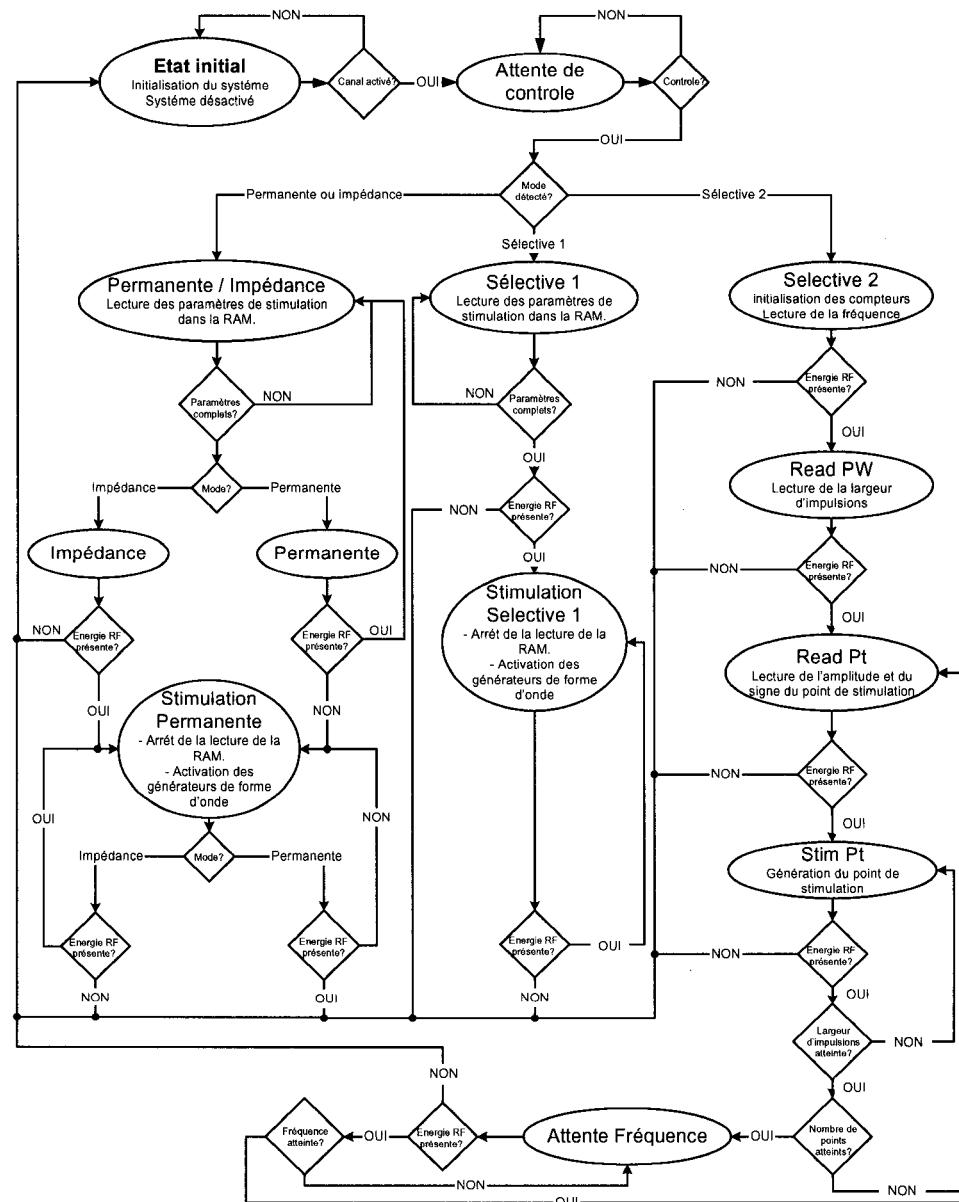

| Figure 4-7  | : Diagramme d'états du contrôleur MSA2 du générateur de stimuli.....                                               | 91  |

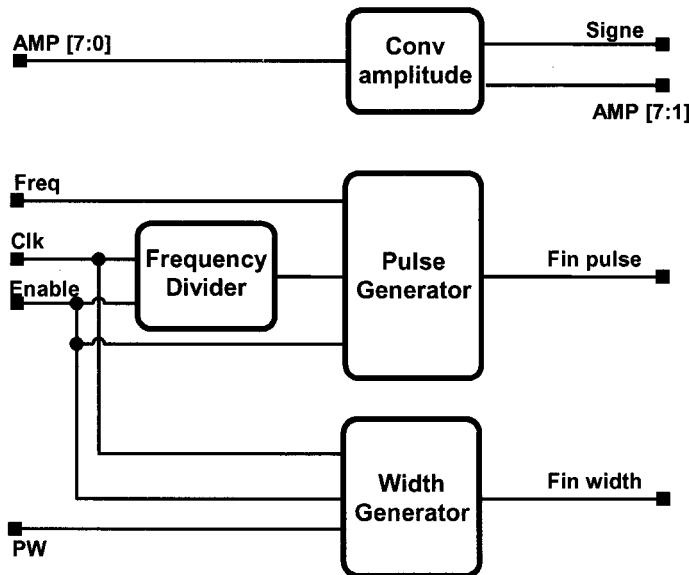

| Figure 4-8  | : Diagramme bloc du module de génération de stimuli .....                                                          | 93  |

| Figure 4-9  | : Diagramme bloc du module de génération de points .....                                                           | 94  |

| Figure 4-10 | : Diagramme d'états de la machine de conversion de signaux.....                                                    | 96  |

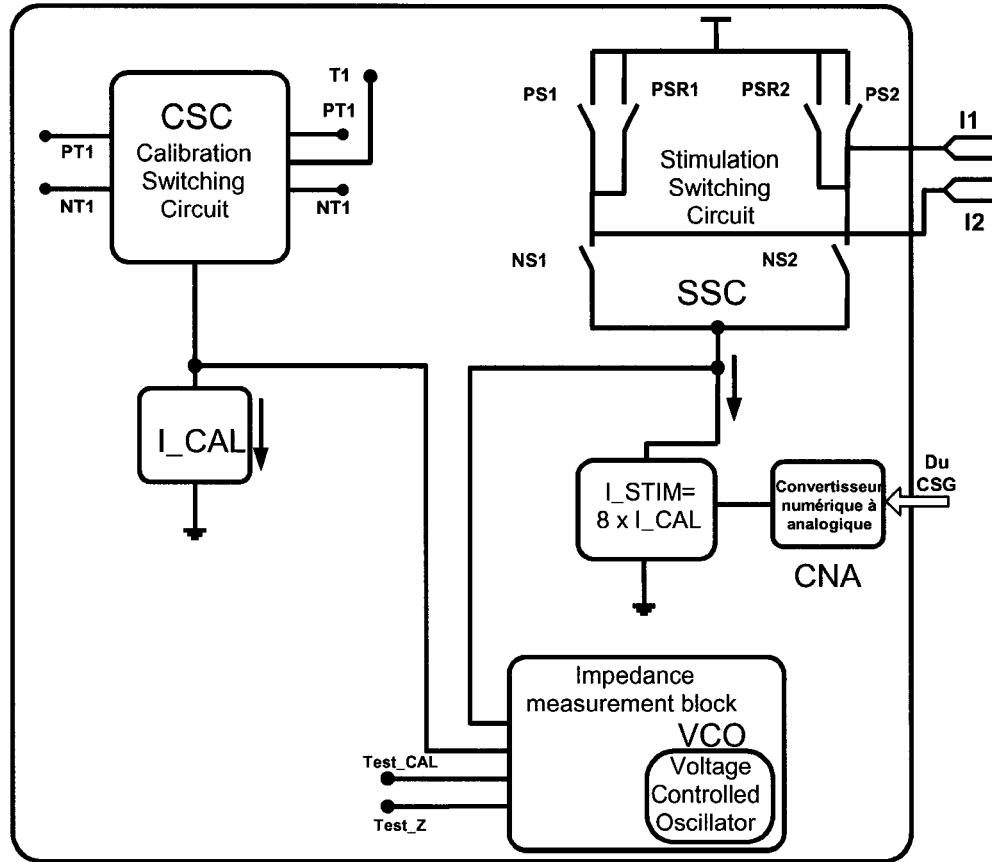

| Figure 4-11 | : Diagramme bloc du canal de stimulation (adapté de [44]).....                                                     | 98  |

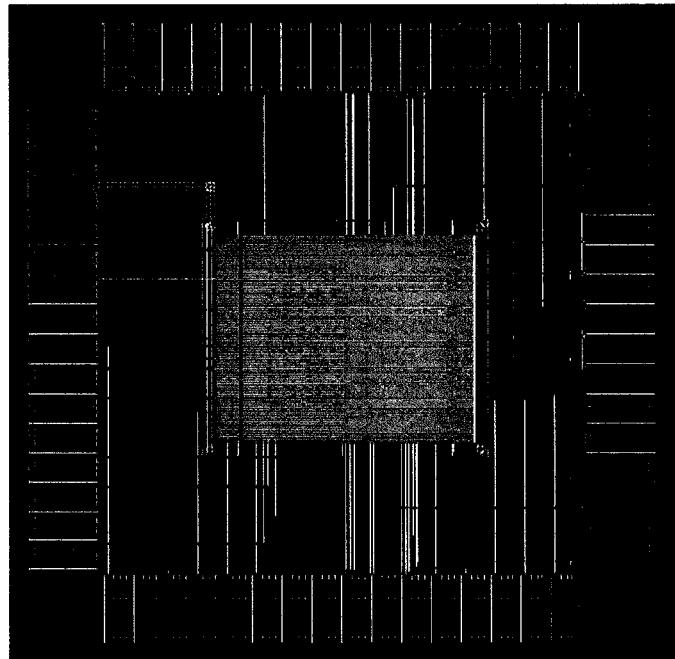

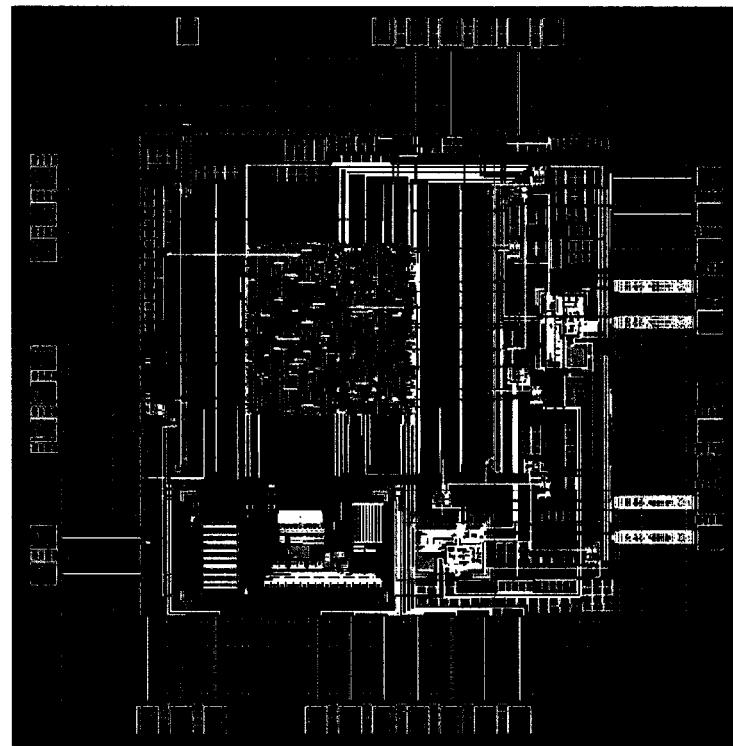

| Figure 4-12 | : Dessin de masques du bloc numérique ( $900 \times 710 \text{ } \mu\text{m}^2$ ).....                             | 101 |

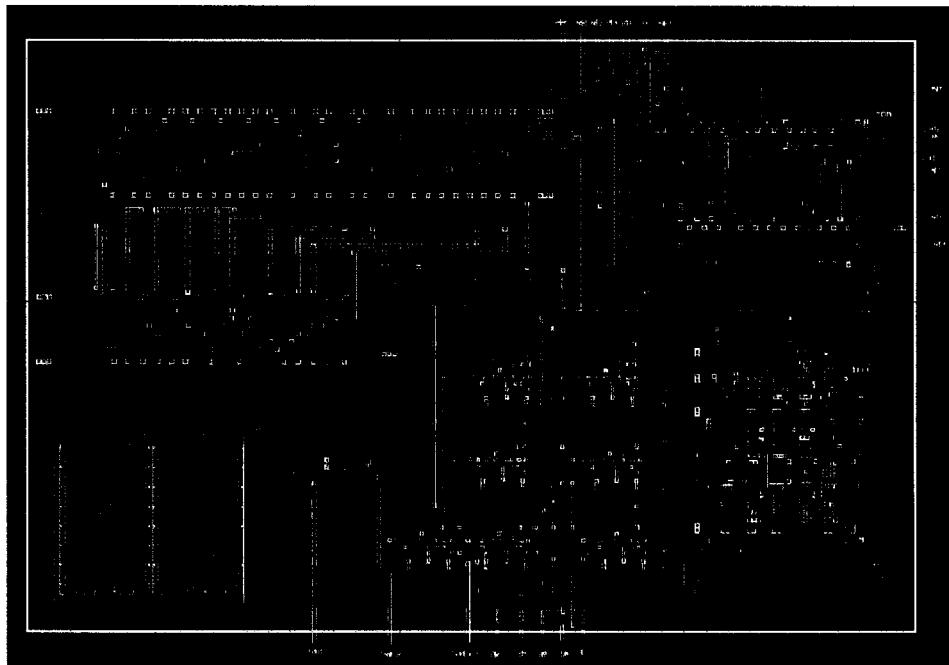

| Figure 4-13 | : Layout de l'étage analogique de sortie ( $200 \times 150 \text{ } \mu\text{m}^2$ ) .....                         | 103 |

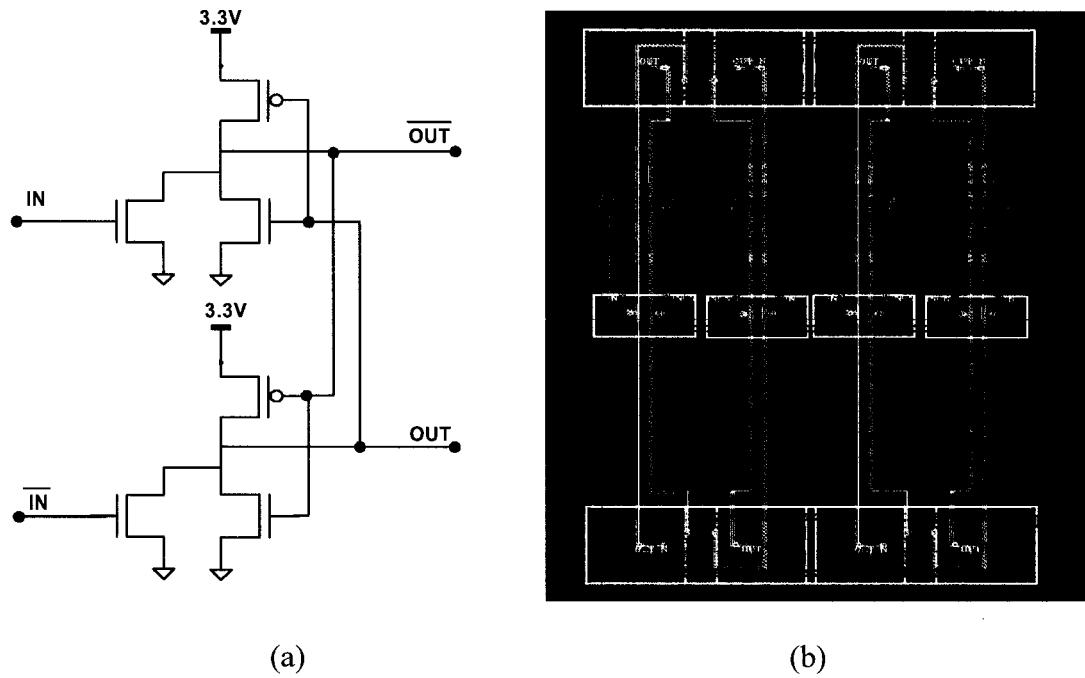

| Figure 4-14 | : Bloc de changement de niveau 1.8V-3.3V : a) Schéma ; b)<br>Layout ( $40 \times 50 \text{ } \mu\text{m}^2$ )..... | 106 |

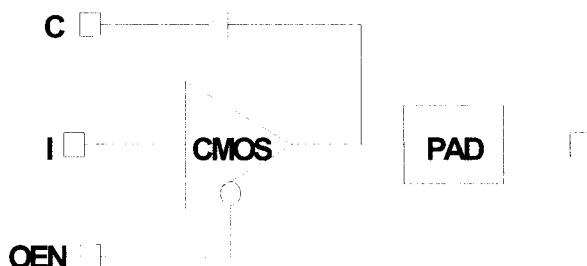

| Figure 4-15 | : (a) Table de vérité ; (b) Schéma illustratif des plots PDB04DGZ<br>(tirés de la CMC) .....                       | 107 |

| Figure 4-16 | : "Layout" de la puce dédiée ( $2000 \times 2000 \text{ } \mu\text{m}^2$ ).....                                    | 108 |

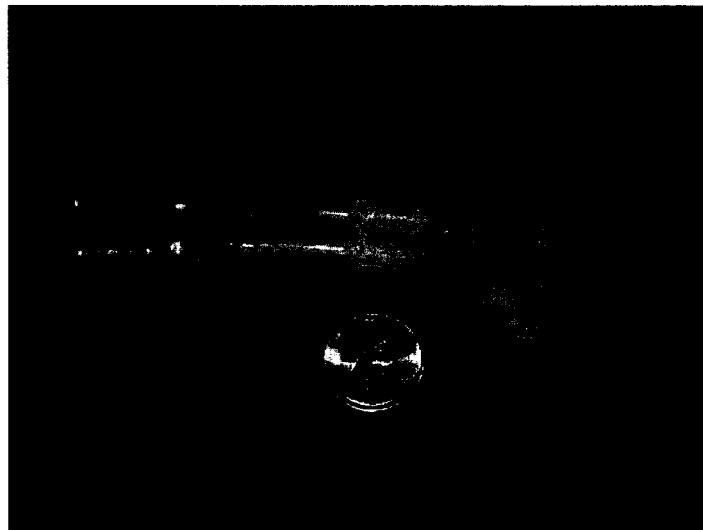

| Figure 5-1  | : Photographie du microstimulateur prêt à être implanté.....                                                       | 110 |

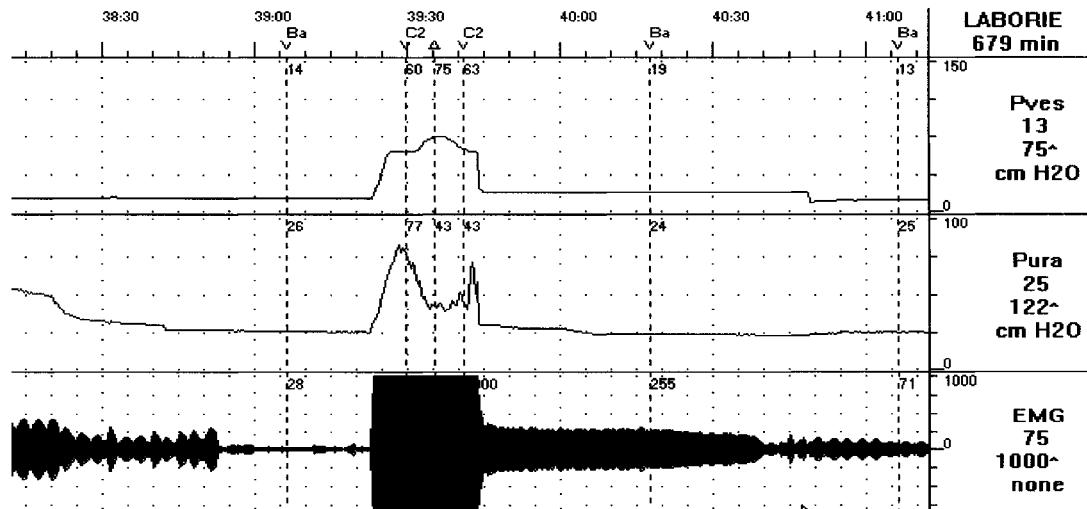

| Figure 5-2  | : Pression dans la vessie (Pves) et dans l'urètre (Pura) lors d'une stimulation sélective.....                     | 113 |

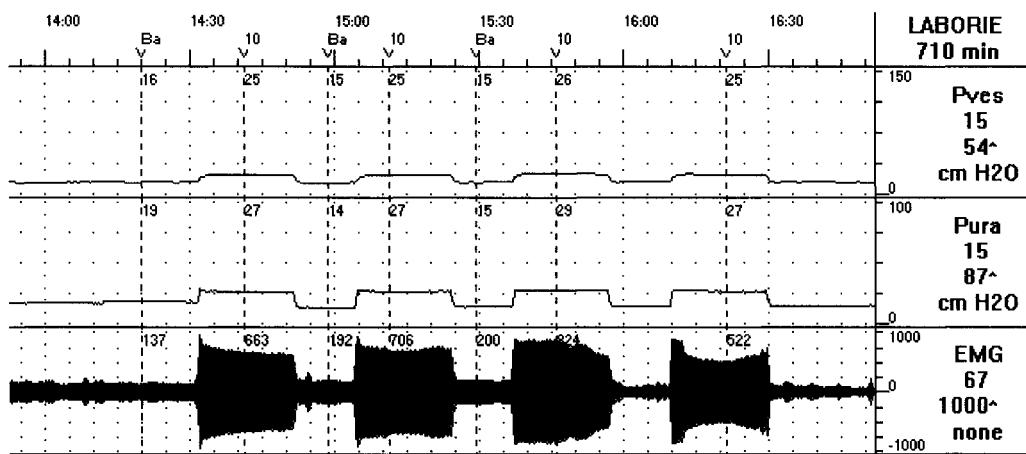

| Figure 5-3  | : Pression dans la vessie (Pves) et dans l'urètre (Pura) lors d'une stimulation permanente .....                   | 114 |

|            |   |                                                                                                                                                                                                                            |     |

|------------|---|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

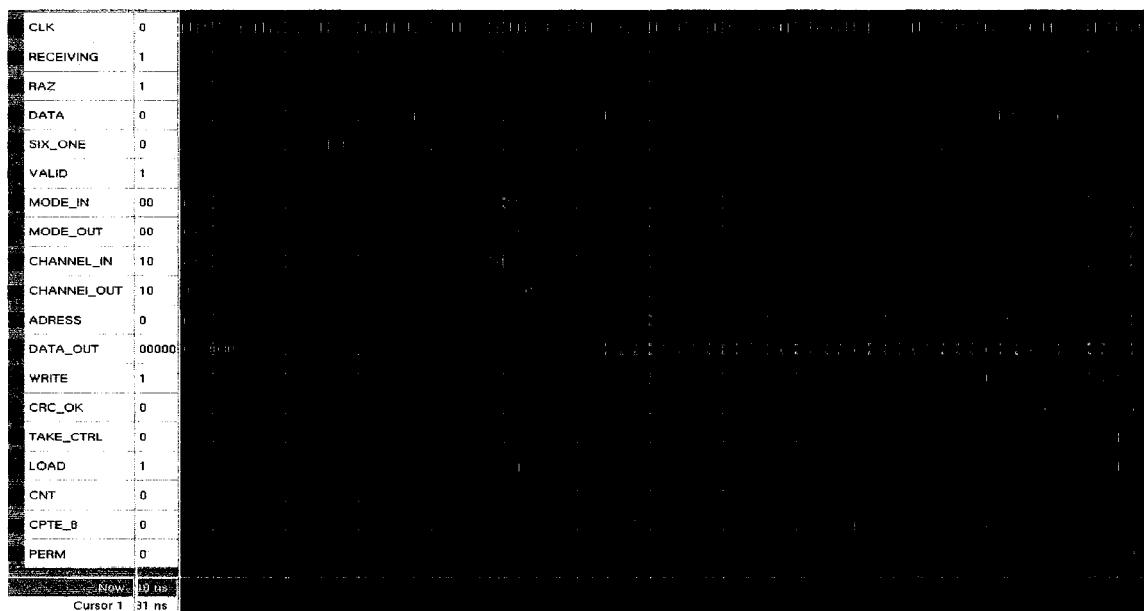

| Figure 5-4 | : | Résultats de simulation du bloc DATA RECOVER Y : détection d'une trame de stimulation valide, transfert des paramètres et activation du bloc générateur de stimuli.....                                                    | 117 |

| Figure 5-5 | : | Résultats de simulation du bloc numérique avec identification des signaux de commande de l'étage de sortie.....                                                                                                            | 118 |

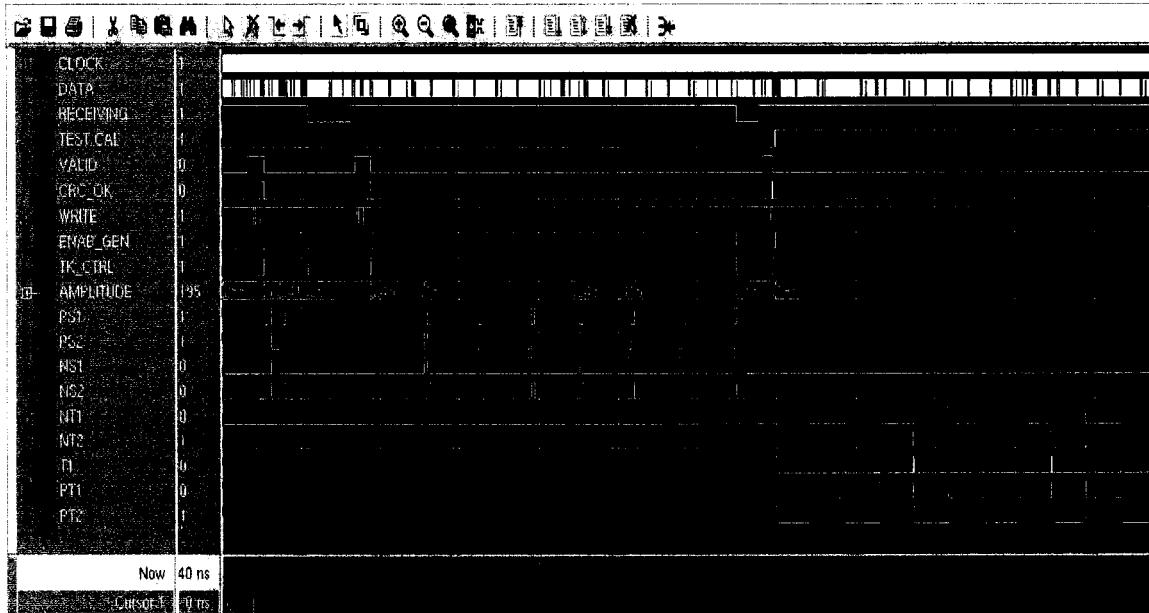

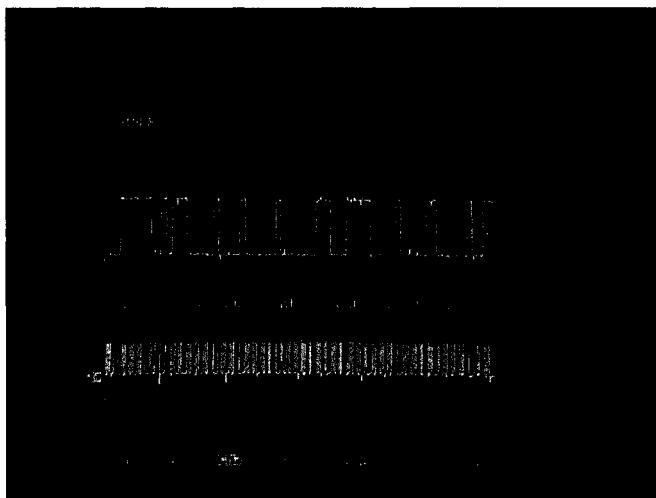

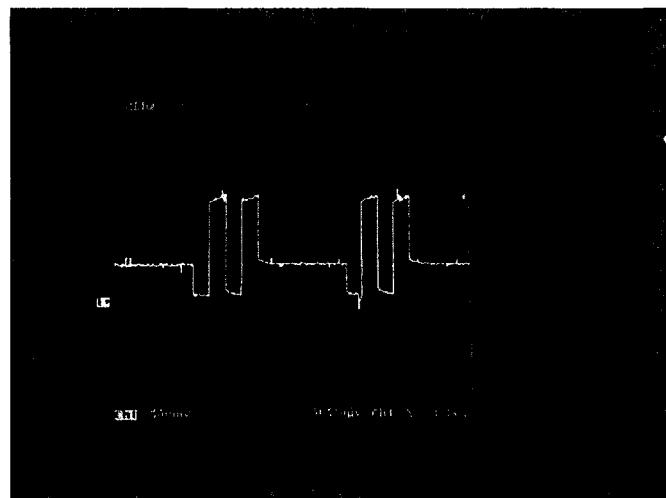

| Figure 5-6 | : | Résultats expérimentaux : décodage après réception de la trame des données de stimulation: le signal du haut est la trame de stimulation tandis que celui du bas montre le signal encodé Manchester.....                   | 119 |

| Figure 5-7 | : | Résultats expérimentaux: écriture des paramètres de stimulation dans la RAM : le signal du haut présente la trame de stimulation, tandis que celui du bas montre le signal d'activation de l'écriture en RAM (Wr_N). ..... | 119 |

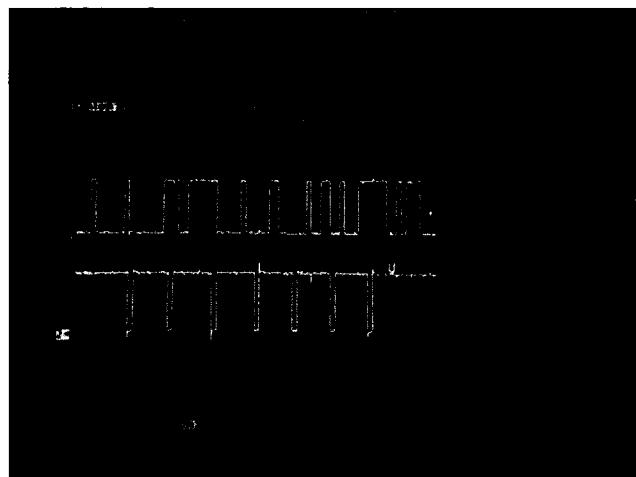

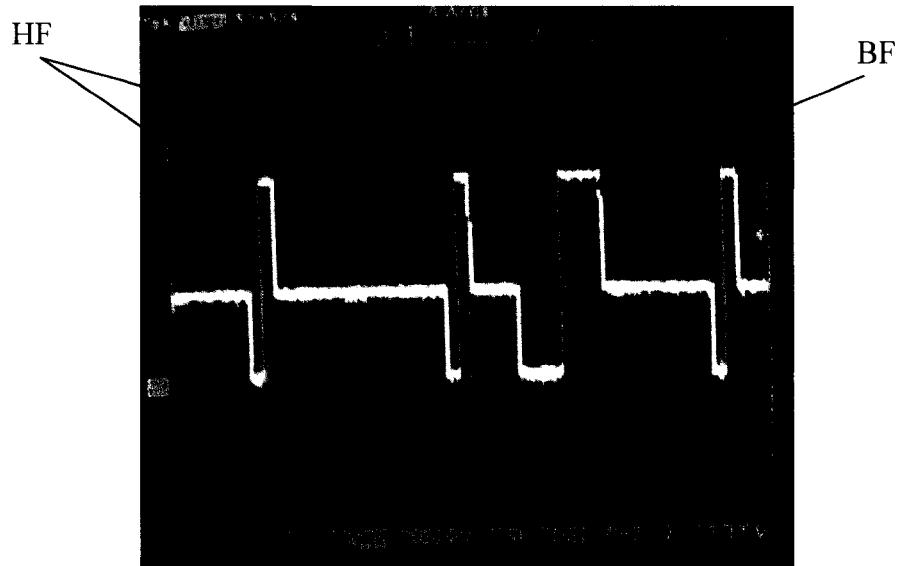

| Figure 5-8 | : | Résultats expérimentaux : présentation d'un signal de stimulation sélective avec identification de la haute (HF) et la basse fréquence (BF).....                                                                           | 121 |

| Figure 5-9 | : | Résultats expérimentaux : présentation d'un signal de stimulation flexible.....                                                                                                                                            | 121 |

| Figure A-1 | : | Schéma électrique du stimulateur sélectif et permanent.....                                                                                                                                                                | 135 |

| Figure A-2 | : | Dessin des masques à l'échelle 15/10 du stimulateur sélectif et permanent.....                                                                                                                                             | 136 |

## **LISTE DES TABLEAUX**

|             |                                                                                                              |     |

|-------------|--------------------------------------------------------------------------------------------------------------|-----|

| Tableau 1.1 | : Description des paramètres de la stimulation sélective .....                                               | 19  |

| Tableau 1.2 | : Description des paramètres de la stimulation selective .....                                               | 22  |

| Tableau 2.1 | : Paramètres de la stimulation sélective .....                                                               | 28  |

| Tableau 2.2 | : Paramètres pour la stimulation permanente.....                                                             | 28  |

| Tableau 3.1 | : Selective stimulation parameters of implanted devices.....                                                 | 76  |

| Tableau 3.2 | : Continuous stimulation parameters of implanted devices.....                                                | 76  |

| Tableau 3.3 | : Average voided urine for three stimulation steps: chronic<br>experiments in dogs .....                     | 76  |

| Tableau 3.4 | : Stimulation parameters of the integrated microstimulator .....                                             | 76  |

| Tableau 4.1 | : Paramètres du nouveau type de stimulus.....                                                                | 79  |

| Tableau 4.2 | : Description des paramètres de stimulation .....                                                            | 83  |

| Tableau 5.1 | : Résumé des résultats expérimentaux obtenus chez 4 chiens à l'<br>l'animalerie de l'université McGill. .... | 115 |

## **LISTE DES ANNEXES**

|                                                                                             |     |

|---------------------------------------------------------------------------------------------|-----|

| ANNEXE A : Schémas et Code du microstimulateur à stimulations sélective et permanente ..... | 134 |

| ANNEXE B : Codes VHDL du bloc Numerique .....                                               | 149 |

## **LISTE DES SIGLES ET ABRÉVIATIONS**

|        |                                                 |

|--------|-------------------------------------------------|

| AM     | Amplitude modulation                            |

| Amp    | Amplitude                                       |

| ASIC   | Application specific integrated circuit         |

| BICMOS | Bipolar complementary metal-oxide semiconductor |

| BCS    | Bipolar current source                          |

| CAN    | Convertisseur analogique à numérique            |

| CMC    | Canadian microelectronics corporation           |

| CMG    | Cystometrogram                                  |

| CMOS   | Complementary metal-oxide semiconductor         |

| CNA    | Convertisseur numérique à analogique            |

| CPF    | Contrôleur portatif flexible                    |

| CPS    | Contrôleur portatif simplifié                   |

| CRC    | Cyclic redundancy check                         |

| CTF    | Contrôleur de test flexible                     |

| DAC    | Digital to analog converter                     |

| DH     | Detrusor hyperreflexia                          |

| EMG    | Electromyogram                                  |

| EPROM  | Erasable programmable read only memory          |

| FPGA   | Field programmable gate array                   |

| Freq   | Frequency                                       |

| FSM    | Finite state machine                            |

| HFA    | High frequency amplitude                        |

| HFP    | High frequency period                           |

| HFW    | High frequency width                            |

|      |                                        |

|------|----------------------------------------|

| IVU  | Intravenous urography                  |

| LCD  | Liquid crystal display                 |

| LFA  | Low frequency amplitude                |

| LFP  | Low frequency period                   |

| LFW  | Low frequency width                    |

| LSK  | Load shift keying                      |

| MNS  | Microstimulateur neural sélectif       |

| NLB  | Neurostimulateur à lien bidirectionnel |

| NMOS | N-channel metal-oxide semiconductor    |

| NSP  | Neurostimulateur sélectif et permanent |

| PC   | Personal computer                      |

| PCB  | Printed circuit board                  |

| PIC  | Programmable integrated controller     |

| PMOS | P-channel metal-oxide semiconductor    |

| PW   | Pulse width                            |

| RAM  | Random access memory                   |

| RF   | Radio frequency                        |

| SG   | Stimuli generator                      |

| SMA  | Shape memory alloy                     |

| SWG  | Stimuli waveform generator             |

| VCO  | Voltage controlled oscillator          |

| VCUG | Voiding cystourethrogram               |

## INTRODUCTION

Au cours des dernières décennies, l'électronique et la microélectronique ont vu un grand nombre de leurs applications dirigées vers le domaine biomédical. Celles-ci sont couramment utilisées pour le traitement des dysfonctions neurologiques ainsi que le remplacement ou l'assistance des organes assurant les fonctions vitales. Ces recherches ont engendré plusieurs types de dispositifs électroniques implantables. Les stimulateurs cardiaques (pacemakers) sont certainement les plus populaires, mais on peut aussi retrouver les stimulateurs musculaires pour les membres paralysés, les stimulateurs pour le rétablissement de l'audition (implants cochléaires), les implants urinaires ainsi que les implants dédiés à la stimulation du cortex visuel (stimulateurs corticaux).

Nous nous intéressons dans ce travail au stimulateur urinaire. Plusieurs tentatives ont été faites pour récupérer les fonctionnalités du système urinaire chez les patients paraplégiques, ceux atteints de maladies variées ou encore ceux ayant subies une lésion de la moelle épinière. Ces fonctionnalités sont souvent perdues due à une rupture de la communication entre les organes de l'appareil urinaire et les différents centres nerveux de la miction (moelle épinière et cortex cérébral); cette rupture étant causée par des lésions des voies sensorielles et motrices.

Les patients souffrant d'une lésion de la moelle épinière subissent une perte de contrôle volontaire de la vessie et peuvent avoir des contractions simultanées de la vessie et du sphincter (Dyssynergie) qui empêchent ou limitent l'évacuation complète de la vessie (Rétention). De plus, l'hyperactivité du muscle de la vessie (Detrusor) conduit à un

phénomène, appelé hyperreflexie de la vessie, qui est caractérisé par des contractions involontaires de celle-ci et des pertes urinaires.

Plusieurs techniques de traitement de ces dysfonctions urinaires, telles que la cathéterisation et les différentes chirurgies, ont été couramment utilisées et ont permis d'obtenir divers résultats. Cependant les risques d'infections dues aux cathéterisations répétitives et les désagréments irréversibles causés par les chirurgies ont accéléré le développement des techniques de stimulation électrique pour la récupération de ces fonctions vésicales.

Notre équipe de recherche PolySTIM a introduit au fil des années plusieurs versions de stimulateurs appliquant diverses techniques de stimulation. Les validations de ces différentes versions de stimulateur ont conduit au développement d'une nouvelle technique de stimulation dite sélective permettant la récupération du contrôle volontaire de la miction. De plus, l'utilisation d'une stimulation électrique de basse fréquence et de faible amplitude, appliquée aux racines sacrées contrôlant les organes du système urinaire, a permis de réduire l'hyperréflexie.

La dernière version de stimulateurs de PolySTIM a été la base des travaux présentés dans ce mémoire. Le système de stimulation existant a permis d'obtenir des résultats prometteurs; cependant, quelques déficiences lors de son utilisation, notamment au niveau du procédé d'isolation électrique de l'implant face au milieu biologique corrosif dans lequel il est utilisé, la robustesse des contrôleurs externes, la fiabilité des circuits critiques du stimulateur ainsi que sa dépendance à la tension d'alimentation

utilisée nous ont conduit à la réalisation d'une nouvelle version de stimulateur basée sur la même architecture mais corigeant et améliorant les fonctionnalités déjà présentes.

Les pertes d'efficacité des stimulateurs lors des expériences de validation en phase chronique ont cependant rendu nécessaire la surveillance de l'évolution des implants ainsi que des paramètres caractérisant les interfaces électrodes-tissus pendant toute la durée d'une étude en phase chronique. Ces fonctions de mesure d'impédance de l'interface nerf-électrodes in-vivo permettent de prévenir et diagnostiquer les anomalies liées aux électrodes et aussi de préserver la sécurité des patients en cas d'apparition d'une anomalie quelconque (courant de stimulation élevé par exemple). Cette approche pourra permettre le développement de systèmes implantables beaucoup plus fiables car le retour de l'information a toujours été un des points faibles des stimulateurs et des systèmes implantables. Ils fonctionnent très souvent en boucle ouverte laissant l'usager dans l'ignorance complète de ce qui se passe réellement. De plus, les lacunes de la majorité des stimulateurs (manque de flexibilité des paramètres, limitation du nombre de canaux et des types de stimulation, manque de convivialité des interfaces ou encore manque de reprogrammabilité) ont motivé la conception et la réalisation d'une nouvelle version de stimulateur. Ce nouveau système intégré a été réalisé dans la technologie CMOS 0.18um pour parallèlement répondre à un besoin croissant de miniaturisation et de minimisation de la consommation d'énergie. Il combine ainsi toutes les fonctionnalités des systèmes de stimulation développés précédemment par notre équipe de recherche (Stimulation sélective et permanente, mesure d'impédance). De plus, un nouveau type de stimulation

dite flexible est intégré, et un deuxième canal indépendant de stimulation est ajouté. Ce dernier répond aux besoins de flexibilité et de reprogrammabilité précédemment énoncés.

Dans le chapitre 1 de ce mémoire, nous faisons une revue de littérature en présentant le système urinaire, les principes de la stimulation électrique neuronale ainsi que les systèmes de stimulation déjà existants. Le chapitre 2 présente un aperçu de l'architecture interne d'une nouvelle version de microstimulateur et décrit les modifications apportées à la version précédente du stimulateur. Dans le chapitre 3, nous présentons ce nouveau stimulateur intégré ainsi que son évaluation chez l'animal sous la forme d'un article soumis au journal « NEUROMODULATION », tandis que nous décrivons de façon détaillée la puce réalisée dans le chapitre 4. Finalement, nous dressons un bilan de travaux réalisés et présentons les résultats des systèmes testés dans le chapitre 5, et nous terminons par une série de recommandations sur la conception des futurs systèmes de stimulation et sur la méthodologie à suivre pour des futures expérimentations sur les dysfonctions du système urinaire.

# CHAPITRE 1

## STIMULATION ÉLECTRIQUE NEURALE ET SYSTÈMES EXISTANTS

### 1.1 *Le système urinaire*

#### 1.1.1 Vue d'ensemble du système urinaire

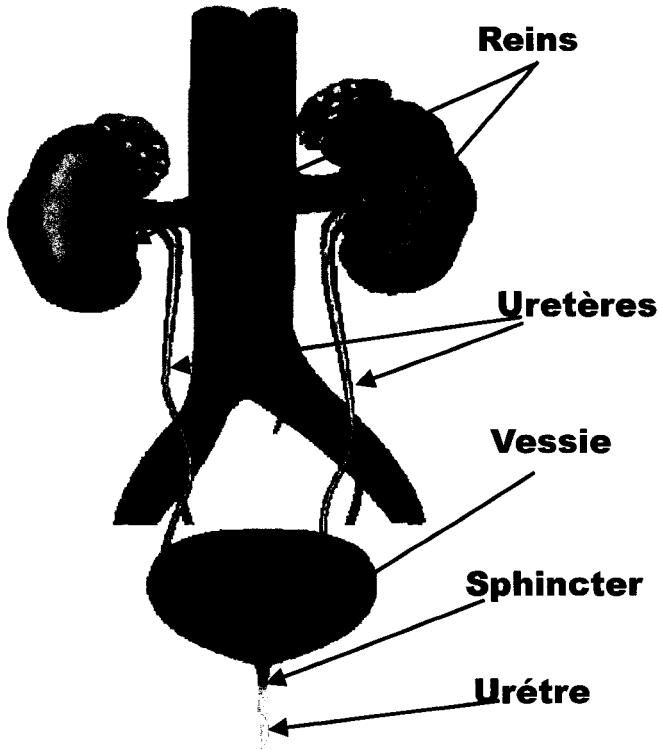

Le système urinaire est composé de deux ensembles complémentaires: les appareils urinaires supérieur et inférieur.

Le premier est composé des calices rénaux, de bassinets, des uretères et a pour fonction de recueillir l'urine des reins et de la transporter jusqu'à la vessie. L'appareil urinaire inférieur (Figure 1-1) est formé de la vessie, de l'urètre, du sphincter et gère le stockage et la vidange volontaire de l'urine [2],[32].

La vessie est un réservoir d'urine dont les parois sont formées par un muscle appelé detrusor. Celui-ci a une structure lisse. L'urètre véhicule l'urine de la vessie au milieu extérieur. A la frontière vessie-urètre, on trouve un épaississement de la couche musculaire moyenne de la vessie mêlé à des fibres de l'urètre qui constitue le sphincter lisse. Le sphincter strié constitue le dernier élément de l'appareil urinaire inférieur et est composé de fibres musculaires striées qui entourent l'urètre.

Les expériences de Stewart et al tendent à démontrer qu'il existe une région spécifique de la moelle épinière appelée centre sacré de la miction, qui reçoit, intègre et

**Figure 1-1: Vue d'ensemble du système urinaire.**

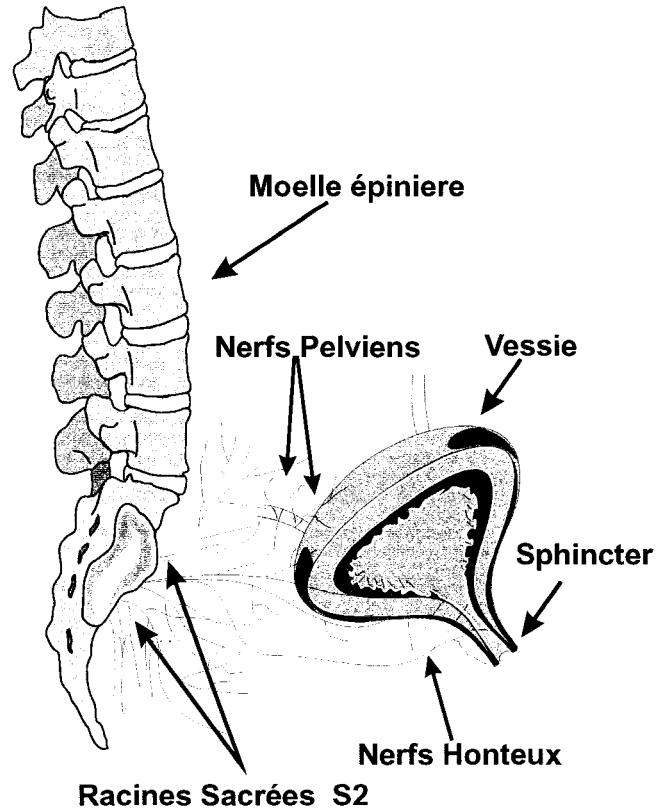

transmet les influx nerveux moteurs et sensoriels ainsi que les activités inhibitrices qui influencent les réflexes de la miction. Le centre sacré de la miction est relié aux différents nerfs innervant l'appareil urinaire inférieur: les nerfs pelviens (detrusor), les nerfs sacrés S2 à S4 (detrusor et sphincter), ainsi que le nerf honteux (sphincter externe) [20]. Le detrusor et le sphincter externe partagent les nerfs sacrés comme source commune d'innervation. Ceux-ci contiennent un mélange de fibres somatiques et autonomes qui font circuler des influx nerveux dans les deux sens (afférent et efférent). Les fibres nerveuses afférentes sont sensorielles tandis que celles efférentes sont motrices. Les voies nerveuses autonomes afférentes (parasympathiques et sympathiques) stimulent le réflexe sacré de la miction tandis que les voies somatiques efférentes, contrôlées consciemment

par le cerveau (cortex cérébral) et le cervelet, sont responsables de la plupart des réflexes inhibiteurs tels que la contraction du sphincter externe[13]. L'harmonie du centre de la miction, du cortex cérébral et des différentes terminaisons nerveuses assure le bon fonctionnement des mécanismes du système urinaire; cela se traduit par une synchronisation entre les contractions et les relaxations respectives de la vessie et des sphincters.

### **1.1.2 Fonctionnement et dysfonctions urinaires**

Le cycle normal de la miction est constitué d'une phase de remplissage de la vessie qui sera suivie par une phase de vidange de l'urine. Lors du stockage de l'urine, les fibres nerveuses sympathiques relâchent les fibres musculaires lisses de la vessie et maintiennent le sphincter lisse urétral fermé, permettant ainsi, grâce à une basse pression dans la vessie, le remplissage et l'accumulation d'un volume d'urine pouvant dépasser 500 ml. Lors de la phase mictionnelle, les fibres parasympathiques contractent la musculature lisse de la vessie et relâchent le sphincter urétral alors que le sphincter strié se contracte. Une augmentation de la pression dans la vessie opposée à une chute de la pression urétrale permet l'évacuation qui doit être complète [70].

Chez les patients paraplégiques, atteints de maladies variées (Parkinson, diabète ou cancer) ou à la suite d'une lésion de la moelle épinière, apparaissent des dysfonctions du système urinaire. Ces dysfonctions sont liées à des lésions à un niveau plus ou moins élevé des voies efférentes ou afférentes causant ainsi une rupture de la communication entre les organes de l'appareil urinaire et les différents centres de la miction.

Suite à une lésion de la moelle épinière, une perte de contrôle volontaire de la vessie peut se produire et des contractions peuvent empêcher son évacuation complète. L'activité de la vessie est aussi associée à une augmentation de la résistance urétrale et de la pression vésicale qui limite l'évacuation chez la majorité des patients avec une lésion de la moelle épinière [71]. Les conséquences sont un grand volume résiduel d'urine ainsi que des reflux vésico-uréteraux, des développements bactériens, des infections, des défaillances rénales ou encore l'apparition d'incontinence [28].

L'incontinence quant à elle se caractérise par une impossibilité de la vessie de retenir adéquatement l'urine. Cela est due à une hyperactivité du detrusor qui conduit à des contractions involontaires de la vessie et à des pertes urinaires. Ce phénomène est couramment appelé hyperreflexie de la vessie [13].

Les techniques courantes de traitement de la rétention incluent différentes formes de cathéterisation (intermittente, continue,...). Souvent des narcotiques ou des chirurgies sont utilisés pour réduire la résistance urétrale. Les cathéterisations permettent des évacuations à basse pression de la vessie. Cependant les problèmes vésicaux persistent et seront accompagnés par des contractions dyssynergiques. De plus, certains patients peuvent développer des infections dues à ces cathéterisations répétitives [28].

Un autre axe de recherche exploré depuis de nombreuses années qui a fourni des résultats prometteurs et qui fait l'objet du présent mémoire est la stimulation électrique pour la récupération des fonctions vésicales.

## 1.2 *La stimulation électrique fonctionnelle*

La stimulation électrique fonctionnelle est décrite comme étant la stimulation d'un muscle privé de contrôle nerveux, dans le but de produire un mouvement utile fonctionnellement.

La stimulation électrique par l'intermédiaire des nerfs peut inhiber l'action des muscles. Aussi, elle peut fournir un moyen d'interagir avec les réflexes neuraux et influencer le comportement des organes innervés par les nerfs sacrés ( vessie, sphincter, plancher pelvien) [13]. Le but de la stimulation électrique est de remédier aux dysfonctions de l'appareil urinaire sans cependant induire des dommages aux organes stimulés.

Les caractéristiques des muscles lisses et des muscles striés diffèrent aux niveaux des seuils de contractions, de la vitesse de conduction ou encore du seuil d'activation entre les axones somatiques et les fibres parasympathiques. Ces différences fournissent une alternative pour des manipulations electro-physiologiques du système urinaire neurologiquement déficient [66].

Il a été démontré que les stimulations à charges biphasiques balancées sont plus sécuritaires que celles à charges monophasiques et sont recommandées pour l'utilisation chronique [66].

### 1.2.1 Alternatives de stimulation

Quatre sites de stimulation peuvent être utilisés pour le contrôle de la vessie : le muscle de la vessie, les nerfs pelviens, les racines sacrées et la moelle épinière (Figure

1-2). Toutes ces méthodes de stimulation ont été évaluées dans des études expérimentales sur les animaux. Nous présentons ainsi un récapitulatif des avantages et des inconvénients de ces différentes techniques de stimulation [28],[31],[7],[25],[53].

**Figure 1-2 : Sites possibles de stimulation électrique pour évacuer l'urine de la vessie**

#### a) Muscle de la vessie

Cette technique consiste à stimuler directement le muscle de la vessie (detrusor) par l'intermédiaire d'électrodes insérées dans ou sur la surface du muscle. Ce type de stimulation n'avait pas permis l'évacuation de la vessie car les contractions résultantes du detrusor n'étaient ni homogènes ni suffisantes. Aussi, la douleur associée à la stimulation

de la vessie chez certains patients, la co-activation des membres inférieurs et la diffusion du courant de stimulation dans des tissus avoisinants ont entraîné l'abandon de cette technique. Des progrès ont été réalisés dans la réduction de la diffusion du courant en raffinant le design des électrodes et le protocole de stimulation [69],[6], mais pas suffisamment cependant pour faire de la stimulation directe de la vessie une technique clinique viable [66]. Une étude de Merril en 1976 a indiqué que 52% des 64 cas de patients avec des lésions neuronales profondes ont empiré car l'implant n'arrivait pas à remédier à la dyssynergie du sphincter et du detrusor [8].

#### ***b) Moelle épinière***

La stimulation du centre de la miction dans le cône médullaire a été examinée par Friedman et Nashold [43],[19], cependant cette technique n'a pas fait l'unanimité en raison de la faible sélectivité des électrodes de stimulation. Un placement précis des électrodes était nécessaire pour garantir un minimum de réussite. Cependant ici encore, la stimulation électrique utilisant des électrodes pénétrantes cause la double activation du muscle lisse de la vessie et du muscle strié du sphincter ainsi que des mouvements involontaires des membres inférieurs, de la transpiration, de l'hypertension ainsi que d'autres manifestations de la diffusion du courant [66].

#### ***c) Nerfs pelviens***

La stimulation vésicale par le biais des nerfs pelviens affecte les nerfs honteux en induisant une excitation simultanée du sphincter et de la vessie (dyssynergie). Une

solution médicale a été proposée, soit la neurotomie des nerfs honteux. Ensuite, la stimulation du nerf S2 à proximité du site de la section a conduit à une évacuation à faible pression, avec une résistance négligeable du sphincter. Cependant l'approche de section de nerfs fait de cette technique une méthode peu engageante [28]. De plus, les expériences antérieures ont montré que la neurotomie des nerfs honteux est associée couramment à des difficultés d'érections chez les hommes paraplégiques [38].

#### *d) Nerfs sacrés*

La stimulation des racines sacrées antérieures est l'approche la plus utilisée en clinique. La stimulation intermittente des racines sacrées pour l'évacuation de la vessie chez les patients paraplégiques a été rapportée par Brindley [28],[10]. Lorsque les racines sacrées sont stimulées de façon appropriée, le sphincter et le detrusor se contractent en même temps, mais seule la musculature striée du sphincter aura le temps de se relâcher dans l'intervalle entre les trains de stimulation, permettant ainsi l'évacuation de l'urine [66],[69]. Cependant, cette méthode de stimulation intermittente est caractérisée par des pressions intra-vésicales élevées nocives pour les reins et par une évacuation par jets [46].

Une autre technique de stimulation se servant des nerfs sacrés est dédiée à la fatigue sphinctérienne par le biais des nerfs honteux. Ensuite, les nerfs sacrés sont stimulés pour évacuer l'urine. Ici, la stimulation électrique prend avantage des différences de durées des phases de contraction et de relâchement entre la vessie et le sphincter externe. Le concept de la fatigue a été appliqué pour éviter la section de nerfs (rhizotomies ou neurotomies). La différence au niveau des propriétés physiologiques

dans les muscles en réponse à la neurostimulation a justifié la technique de la fatigue sphinctérienne [38]. Cependant cette technique ne produit pas un réel relâchement du sphincter car les fibres striées à faible contraction constituant l'urètre sont très résistantes à la fatigue.

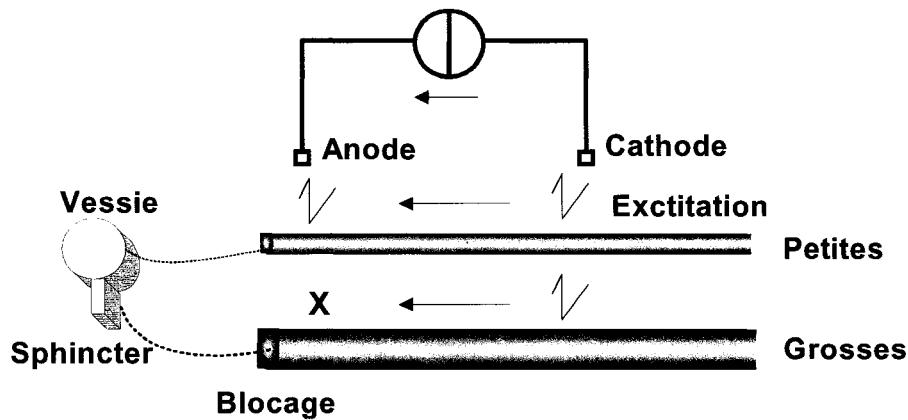

D'autres techniques réversibles, décrites comme blocages sélectifs, sont basées sur la différence dans les seuils d'excitation ou de blocage des fibres A-delta et A-alpha. Les différents types de blocages sont la collision des nerfs honteux [65], le blocage anodique par la stimulation des nerfs sacrés [9],[37] ou le blocage haute fréquence des nerfs honteux [33],[60].

Mortimer et al ont présenté une méthode d'activation sélective des petites fibres nerveuses dans les racines sacrées par la combinaison d'une excitation cathodique de toutes les fibres et un blocage anodique sélectif des grosses fibres [9], [1],[18]. Si à proximité d'une anode, les fibres nerveuses sont suffisamment hyperpolarisées par le courant anodique, les potentiels d'action ne peuvent plus se propager. Étant donné que les fibres à grand diamètre ont un seuil de courant inférieur pour leur blocage que celles à petit diamètre [1], l'activation sélective des petites fibres est possible en bloquant loin du site d'excitation (cathode) la propagation des potentiels d'action induits dans les grosses fibres (Figure 1-3). L'efficacité de cette méthode a été prouvée dans les nerfs périphériques [18]. Appliquée aux racines sacrées, l'activation sélective du muscle du detrusor est possible si les grosses fibres qui déclenchent le mécanisme de fermeture urétrale sont bloquées entraînant ainsi une nette amélioration de l'évacuation [46].

**Figure 1-3: Principe du blocage anodique pour l'activation sélective des petites fibres.**

En se basant sur le fait qu'une racine sacrée ventrale regroupe essentiellement deux classes de fibres, le blocage des grosses fibres somatiques peut être effectué par un stimulus de haute fréquence tandis que le detrusor peut (par le biais des petites fibres) être activé sélectivement par un signal de basse fréquence [75],[63]. Le blocage consiste à maintenir les nerfs et les extrémités motrices dans un état réfractaire empêchant ainsi les muscles de se contracter. Il a été montré [62] que la fréquence de blocage la plus efficace est de l'ordre de 600 Hz. Elle permet d'utiliser des durées d'impulsions moindres et de rester en dessous de la limite tolérable de charges par impulsion [60],[62],[77].

### 1.2.2 Incontinence

Les deux formes les plus communes de l'incontinence sont l'incontinence impérieuse (urgence mictionnelle) et l'incontinence de stress ou à l'effort. Le premier type d'incontinence se caractérise par une forte envie d'uriner qui résulte en une perte d'urine si le besoin n'est pas satisfait ou réprimé. Cette urgence est souvent reliée à l'instabilité du detrusor caractérisée par des contractions non inhibées de la vessie.

L'incontinence de stress est caractérisée par la perte involontaire d'urine lors d'activités physiques, lorsque l'on rie ou pendant un éternuement. Dans les cas plus sévères, la simple marche ou un changement de position peuvent déclencher l'évacuation d'urine. La cause principale est la dysfonction de l'urètre ou du col de la vessie qui conduit une insuffisance urétrale [13].

Walter et al ont introduit une méthode de traitement de l'incontinence par la neuromodulation pour induire une stabilité du muscle de la vessie. Celle ci consiste à stimuler les fibres somatiques afférentes dans les nerfs sacrés par un signal de basse fréquence assez effectif pour inhiber les activités de la vessie [71].

La plupart des systèmes implantables de stimulation fonctionnelle sont reliés aux nerfs par des électrodes dont le type et les formes varient selon les applications. Notre équipe de recherche a développé un nouveau type d'électrodes adapté à nos expérimentations [14]. La gaine de cette électrode se présente sous la forme de deux anneaux de platine fixés à l'intérieur d'un cylindre de silicium. Cette gaine s'enroule autour du nerf et les anneaux de platine assurent le contact électrique entre le nerf et le stimulateur. Le lien entre les deux contacts de la gaine et le microstimulateur est assuré par deux fils multibrins en acier inoxydable isolés par une couche de téflon. Pour maintenir l'électrode en place, nous utilisons des alliages à mémoire de forme que l'on intègre dans la structure de la gaine de silicium pour remplacer les fils de suture utilisés précédemment. Cette technique simplifie le travail du chirurgien, en lui évitant de faire des points de suture dans une cavité peu accessible lors de l'opération. De plus, cela ne risquera pas de comprimer le nerf à cause d'un point de suture trop serré. Pour permettre

la connexion directe des électrodes avec le microstimulateur, des connecteurs plaqués or et enrobés de silicium sont fixés aux extrémités des fils d'aciers inoxydables provenant des contacts de platine. Ainsi, seul le silicium sera en contact direct avec les tissus biologiques [54]. Ces précautions sont nécessaires car les dommages aux tissus sont liés aux propriétés mécaniques et chimiques des électrodes. Dans la région active des électrodes, à l'endroit où le métal est en contact direct avec les tissus, des dommages peuvent survenir en raison des réactions électrochimiques à la surface de l'électrode durant la stimulation [11],[12],[17],[42].

### ***1.3 Dispositifs et systèmes existants***

Nous avons survolé les bases de la stimulation électrique pour la réhabilitation du système urinaire ainsi que les différents principes et techniques de stimulation. Au niveau des systèmes implantables, plusieurs dispositifs ont été conçus et rendus commercialement disponibles et aident à améliorer le confort des patients dans leur vie sociale. Nous présentons une brève rétrospective de ces systèmes ainsi que leurs principales caractéristiques.

#### **1.3.1 Systèmes commerciaux**

Tout d'abord les laboratoires Avery® ont présenté en 1974 un stimulateur pour le traitement de la rétention. La première version effectuait une stimulation en tension monophasique; une version biphasique a été ensuite rendue disponible. En 1977 l'adaptation d'un pacemaker par Gorgis® conduit à un système ajustable à un canal pour

la rétention. La particularité de ce système est l'utilisation d'un aimant pour la gestion de l'alimentation. Finetech® a présenté en 1985 un triple stimulateur transcutané générant des stimuli monophasiques. En 1987, Phisico-Med® a introduit sa version du stimulateur mono-canal pour la rétention. Finalement la compagnie Medtronic [41] a présenté en 1997 un stimulateur transcutané qui traite l'incontinence. Plusieurs versions ont suivi et de nos jours, leur thérapie InterStim® permet de traiter l'incontinence et la rétention par le biais d'une stimulation électrique sur les nerfs sacrés.

Parallèlement à cela, plusieurs équipes de recherche ont proposé différentes prothèses vésicales. Celles ci ont connu plus ou moins de succès; Le manque d'engouement étant le plus souvent du à certaines lacunes de ses stimulateurs, notamment au niveau du manque de flexibilité des paramètres, des limitations au niveau du nombre de canaux et des types de stimulation (mono versus biphasique), de l'absence le plus souvent d'une interface usager conviviale ou encore de la faible efficacité de transmission de données et d'énergie. En fait, peu des stimulateurs disponibles combinaient la totalité de ces paramètres. C'est ainsi que la recherche a été de plus en plus axée vers la conception de systèmes implantables transcutanés complètement reprogrammables. Nous allons nous limiter à un survol des différents systèmes qui ont conduit à l'élaboration du système présenté dans ce mémoire.

### 1.3.2 Systèmes intégrés

Sawan et al présentent tout d'abord en 1992 un système multicanal implantable [50]. Ce système intégré et réalisé dans la technologie CMOS 3um est en mesure de

générer des stimuli par l'intermédiaire de 8 canaux monopolaires (4 canaux bipolaires). Aussi, deux types de contrôleurs ont été présentés pour faire fonctionner ce système. Le premier est basé sur un micro-ordinateur avec un logiciel dédié, tandis que le deuxième regroupe un circuit intégré dédié dans un module portable. Les deux contrôleurs envoient les paramètres de stimulation ainsi que l'énergie nécessaire par l'intermédiaire d'un lien inductif avec une porteuse à 20 MHz.

Arabi et Sawan ont ensuite introduit un micro-stimulateur intégré implantable [3], [4]. Avec huit canaux monopolaires transformables en 4 canaux bipolaires, il présente un grand degré de reprogrammabilité ainsi qu'une flexibilité permettant de l'adapter facilement. Capable de générer une grande variété de formes d'ondes, il peut combiner jusqu'à quatre différentes fréquences programmables sur chaque onde. Pour la fiabilité de la transmission, un protocole de détection et de correction d'erreur est utilisé. Une approche basée sur les techniques de chaînes de balayage est aussi utilisée pour améliorer la testabilité structurelle. Un circuit intégré dédié (ASIC) a été réalisé dans la technologie 1.2um CMOS4S. Ce système était dédié à la récupération des deux fonctions urinaires (réception et évacuation). Un canal dédié alimenté en permanence par une batterie contrôle le sphincter pour éviter l'incontinence en appliquant une stimulation basse fréquence en continu sur le nerf. Enfin l'une des dernières particularités réside dans le fait que les paramètres de stimulation sont stockés dans des cellules de RAM. Celles-ci contiennent des échantillons des dernières périodes de chaque forme d'onde primaire. La lecture séquentielle de ces cellules permet de générer les formes d'ondes programmées.

### 1.3.3 Stimulation sélective

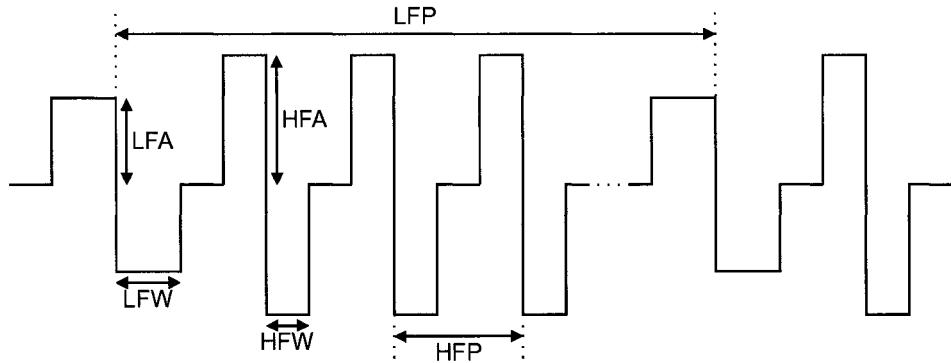

Une nouvelle technique de stimulation, dite stimulation sélective, basée sur le blocage haute fréquence des activités sphinctériennes par le biais des nerfs sacrés S2 est ensuite introduite par Robin et al [48],[47]. Ces derniers présentent un nouveau système implantable pour la stimulation sélective. Celui-ci contrôle un seul canal de sortie analogique servant à générer des stimuli de courant bipolaires à deux fréquences indépendantes et peut être commandé à l'aide de deux types de contrôleurs : un premier basé sur une interface PC pour les médecins avec un logiciel dédié permettant une flexibilité accrue pour l'ajustement des paramètres et un contrôleur portable dont l'architecture repose sur la combinaison d'un FPGA et d'une EPROM pour sauvegarder plusieurs combinaisons de paramètres (maximum huit). Le Tableau 1.1 présente les six paramètres contrôlables.

**Tableau 1.1: Description des paramètres de la stimulation sélective**

| Abréviations | Description du paramètres*                   |

|--------------|----------------------------------------------|

| <b>LFP</b>   | Période séparant 2 stimuli à basse fréquence |

| <b>HFP</b>   | Période séparant 2 stimuli à haute fréquence |

| <b>LFW</b>   | Largeur des stimuli basse fréquence          |

| <b>HFW</b>   | Largeur des stimuli haute fréquence          |

| <b>LFA</b>   | Amplitude des stimuli basse fréquence        |

| <b>HFA</b>   | Amplitude des stimuli haute fréquence        |

\*Les plages de variations sont présentées au chapitre 2

La Figure 1-4 représente la forme d'onde typique du signal de stimulation sélective généré par le microstimulateur, d'où son nom de microstimulateur neural sélectif (MNS).

**Figure 1-4: Forme d'onde d'un signal de stimulation sélective**

L'implant lui même est monté sur un circuit imprimé circulaire de 4 centimètres de diamètre et est structuré autour d'un FPGA qui contient toute la logique de contrôle de génération de stimuli. On retrouve sur l'implant un démodulateur AM ainsi qu'un bloc de récupération de données. Celui-ci permet de retrouver les données ainsi que l'horloge initialement codés ensemble en format Manchester. Un convertisseur numérique à analogique (CNA) génère une tension proportionnelle à l'amplitude de stimulation souhaitée. Celle-ci est ensuite convertie en courant par un amplificateur opérationnel configuré en source de courant. Le courant est finalement injecté dans le nerf via une structure de commutateurs en H, pour assurer la bipolarité des stimuli. Le FPGA par l'intermédiaire de deux générateurs de formes d'ondes produit les commandes pour les stimuli. Ceux-ci sont composés de deux trains d'impulsions bipolaires caractérisées par leur amplitude, leur fréquence ainsi que leur largeur. Les formes d'ondes sont ensuite

superposées pour produire des stimuli équilibrés et balancés pour éviter la polarisation du nerf par l'injection et l'accumulation de charges au niveau de l'interface électrode-tissu. Le système complet a été testé *in vivo* dans des expérimentations aussi bien en phase aiguë que chronique. Les résultats obtenus après plus de cinq mois d'évaluation ont présenté une augmentation supérieure à 50% dans le volume moyen d'urine évacué ainsi qu'une réduction du volume résiduel jusqu'à 9%.

Ces résultats ont encouragé l'intégration du système qui a été effectuée en utilisant la technologie BICMOS 0.8um.

Les tests en phase chronique ont cependant montré une perte d'efficacité de stimulation ou encore une interruption soudaine du fonctionnement de l'implant. Ces défaillances ont amené l'équipe PolySTIM à développer un système qui permettait de surveiller le fonctionnement de l'implant ainsi que l'évolution de certains paramètres [54] caractérisant les interfaces électrodes-tissus pendant toute la durée d'une étude en phase chronique.

Schneider et al ont conçu un nouveau système implantable capable de mesurer l'impédance de l'interface nerf-électrodes *in-vivo* et de retourner la valeur mesurée vers un afficheur externe [54]. Ce neurostimulateur à lien bidirectionnel (NLB) intègre aussi la fonction de stimulation dite sélective, décrite plus haut, permettant la miction volontaire. Des tests en laboratoire ont démontré la fonctionnalité souhaitée du système.

Le désir de trouver une solution à l'hyperreflexie et d'intégrer cette solution aux systèmes précédents a motivé ensuite le développement d'une troisième génération de neurostimulateurs qui inclut une nouvelle technique de stimulation, appelée stimulation

permanente, assurant une réhabilitation complète du système urinaire (miction complète et réduction ou annulation de l'hyperreflexie). Ce neurostimulateur sélectif et permanent (NSP) effectue deux sortes de stimulation; sélective et permanente [54]. La stimulation permanente est une stimulation à très basse fréquence et très basse amplitude qui nécessite une alimentation par pile. Les paramètres de ce type de stimulation sont présentés dans le Tableau 1.2 .

**Tableau 1.2: Description des paramètres de la stimulation selective**

| Abréviations | Descriptions du paramètre              |

|--------------|----------------------------------------|

| <b>Amp</b>   | Amplitude des stimuli                  |

| <b>Freq</b>  | Fréquence des impulsions               |

| <b>PW</b>    | Durée des pulses                       |

| <b>Ton</b>   | Temps d'activation de la stimulation   |

| <b>Toff</b>  | Temps d'inactivation de la stimulation |

\*Les plages de variations sont présentées au chapitre 2

Ce stimulateur possède ainsi deux sources d'alimentation qui sont adéquatement gérées pour maximiser la durée de vie de la pile. La présence d'une mémoire non volatile ainsi que la fonction d'économie d'énergie du microcontrôleur utilisé, associées aux bons résultats obtenus en stimulation sélective avec les FPGA dans les versions précédentes ont conduit à une architecture mixte utilisant deux types de contrôleurs : un FPGA alimenté par l'énergie inductive pour réaliser la fonction de stimulation sélective et un microcontrôleur (PIC) alimenté par une pile dédiée à la stimulation permanente. Les 2 contrôleurs partagent le même étage de sortie.

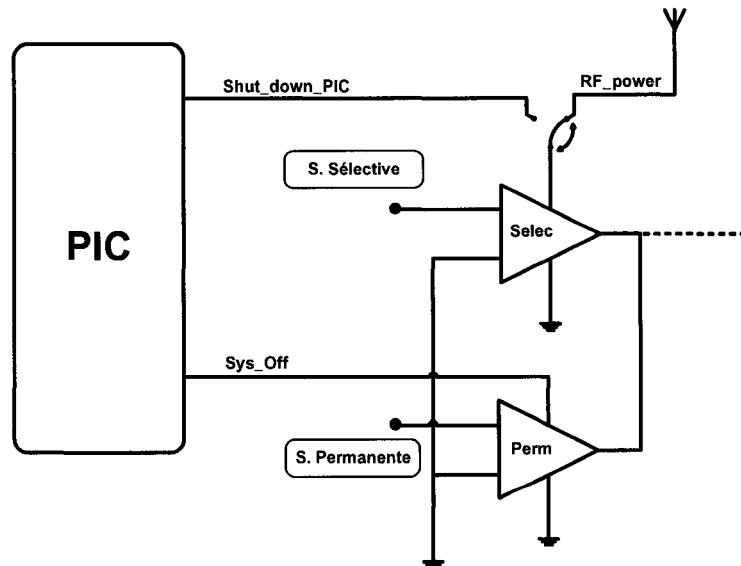

Le FPGA est alimenté à partir du lien inductif RF par une antenne et effectue la récupération ainsi que le décodage de l'ensemble des données (paramètres nécessaires à la génération des stimuli) transmises par le contrôleur externe à l'implant. Le FPGA est aussi responsable du transfert de données au PIC qui est uniquement alimenté par la pile. Dans le cas d'une stimulation sélective, le FPGA prend le contrôle de l'étage de sortie qui est alors alimenté par l'énergie RF. Lors d'une stimulation permanente, l'implant est alimenté par la batterie et le PIC utilise des paramètres de stimulation préprogrammés.

Le contrôleur externe envoie à l'implant un signal RF de 20MHz modulé en amplitude à un taux de 300Kbps. Un circuit analogique de régulation et de démodulation permet l'alimentation en énergie de la majeure partie de l'implant ainsi que la récupération d'un signal codé Manchester. De ce signal, le FPGA reconstitue l'horloge (300KHz) et extrait les paramètres de stimulation.

L'étage analogique de réception responsable de la régulation de tension et du décodage des données est identique aux circuits utilisés dans les versions antérieures du stimulateur (MNS et NLB). Le signal RF est redressé à double alternance puis filtré pour ensuite être régulé par une diode Zener à seuil ajustable. La démodulation est effectuée par un détecteur d'enveloppe.

Un prototype du neurostimulateur a été réalisé sur un circuit imprimé avec des circuits intégrés commerciaux programmables et des composants discrets. Huit exemplaires ont fait l'objet d'une étude expérimentale à long terme sur des animaux de laboratoire, afin de caractériser la fiabilité et la fonctionnalité de l'implant [54]. Les résultats de cette étude ont montré que le système de stimulation proposé ainsi que la

technique chirurgicale exercée répondait aux attentes quant à la résolution du problème d'évacuation et permettaient la réduction des manifestations de l'hyperréflexie chez les animaux paraplégiques.

#### ***1.4 Conclusion***

Nous avons présenté dans ce chapitre une vue d'ensemble du système urinaire et énoncé brièvement les différentes dysfonctions qui peuvent survenir lors de son fonctionnement. Les différentes techniques de stimulation électrique pour la correction de ces dysfonctions ont été aussi exposées. Nous avons poursuivi par la présentation de différents systèmes commerciaux et expérimentaux appliqués à la réhabilitation du système urinaire. Nous avons pu nous rendre compte que la stimulation sélective des nerfs sacrés basée sur la technique de blocage haute fréquence semblait être prometteuse pour la récupération de la miction volontaire et que l'application d'une stimulation permanente à basse fréquence permet la réduction de l'hyperreflexie chez les paraplégiques. Nous allons présenter dans le prochain chapitre les détails du design d'une nouvelle version du stimulateur exploitant les avantages présentées par les techniques de stimulation présentées ci haut.

## **CHAPITRE 2**

# **SYSTÈME DE STIMULATIONS SÉLECTIVE ET PERMANENTE**

### **2.1 *Introduction***

Notre équipe de recherche a développé lors des dernières années un système de stimulation électrique fonctionnelle effectuant deux types de stimulation : une dite sélective pour permettre de récupérer la fonction de miction volontaire chez les patients souffrant de lésions de la moelle épinière et une autre, dite permanente qui a pour but de réduire, et à long terme supprimer les symptômes de l'hyperreflexie [54]. Ce neurostimulateur sélectif et permanent a fait l'objet d'expérimentations chroniques chez des chiens à l'animalerie de l'Université McGill. Ces expérimentations, étalées généralement sur des durées moyennes de huit mois, ont permis de démontrer globalement le fonctionnement du système. Notamment plus de 75% du volume d'urine a été évacué lors des stimulations sélectives et une très nette réduction de la phase d'hyperréflexie a pu être observée sur tous les sujets traités par une stimulation permanente. Ce stimulateur a cependant présenté certaines défaillances lors de son fonctionnement. Celles-ci ont pu être parfois attribuées à des bris aux niveaux de contrôleurs externes, des électrodes de stimulation et quelques défauts ont aussi été notés au niveau de l'implant:

- L'isolation électrique insuffisante de la pile entraînait cette dernière à se décharger rapidement ce qui réduit la durée de fonctionnement du microstimulateur implanté;

- Un arrêt définitif de la stimulation sélective survient lorsque la pile est déchargée. Cela est entraîné par la mise en commun des circuits de stimulations sélective et permanente au niveau de l'étage de sortie;