|                         | Circuit techniques for low-voltage deep submicron CMOS analog-to-<br>digital converters                                                                                                                                                                             |

|-------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Auteur:<br>Author:      | Christian Jésus Bayodé Fayomi                                                                                                                                                                                                                                       |

| Date:                   | 2003                                                                                                                                                                                                                                                                |

| Type:                   | Mémoire ou thèse / Dissertation or Thesis                                                                                                                                                                                                                           |

| Référence:<br>Citation: | Fayomi, C. J. B. (2003). Circuit techniques for low-voltage deep submicron CMOS analog-to-digital converters [Ph.D. thesis, École Polytechnique de Montréal]. PolyPublie. <a href="https://publications.polymtl.ca/7169/">https://publications.polymtl.ca/7169/</a> |

## Document en libre accès dans PolyPublie Open Access document in PolyPublie

| URL de PolyPublie:<br>PolyPublie URL:    | https://publications.polymtl.ca/7169/ |

|------------------------------------------|---------------------------------------|

| Directeurs de<br>recherche:<br>Advisors: | Mohamad Sawan, & Gordon W. Roberts    |

| Programme:<br>Program:                   | Unspecified                           |

In compliance with the Canadian Privacy Legislation some supporting forms may have been removed from this dissertation.

While these forms may be included in the document page count, their removal does not represent any loss of content from the dissertation.

### UNIVERSITÉ DE MONTRÉAL

# CIRCUIT TECHNIQUES FOR LOW-VOLTAGE DEEP SUBMICRON CMOS ANALOG-TO-DIGITAL CONVERTERS

Christian Jésus Bayodé FAYOMI

DÉPARTEMENT DE GÉNIE ÉLECTRIQUE

ÉCOLE POLYTECHNIQUE DE MONTRÉAL

THÈSE PRÉSENTÉE EN VUE DE L'OBTENTION

DU DIPLÔME DE PHILOSOPHIAE DOCTOR (Ph.D.)

(GÉNIE ÉLECTRIQUE)

Août 2003

© Christian Jésus Bayodé FAYOMI, 2003.

National Library of Canada

Acquisitions and Bibliographic Services

395 Wellington Street Ottawa ON K1A 0N4 Canada Bibliothèque nationale du Canada

Acquisisitons et services bibliographiques

395, rue Wellington Ottawa ON K1A 0N4 Canada

> Your file Votre référence ISBN: 0-612-86443-X Our file Notre référence ISBN: 0-612-86443-X

The author has granted a nonexclusive licence allowing the National Library of Canada to reproduce, loan, distribute or sell copies of this thesis in microform, paper or electronic formats.

The author retains ownership of the copyright in this thesis. Neither the thesis nor substantial extracts from it may be printed or otherwise reproduced without the author's permission.

L'auteur a accordé une licence non exclusive permettant à la Bibliothèque nationale du Canada de reproduire, prêter, distribuer ou vendre des copies de cette thèse sous la forme de microfiche/film, de reproduction sur papier ou sur format électronique.

L'auteur conserve la propriété du droit d'auteur qui protège cette thèse. Ni la thèse ni des extraits substantiels de celle-ci ne doivent être imprimés ou aturement reproduits sans son autorisation.

## UNIVERSITÉ DE MONTRÉAL

## ÉCOLE POLYTECHNIQUE DE MONTRÉAL

#### Cette thèse intitulée

## CIRCUIT TECHNIQUES FOR LOW-VOLTAGE DEEP SUBMICRON CMOS ANALOG-TO-DIGITAL CONVERTERS

présentée par: <u>FAYOMI Christian Jésus Bayodé</u> en vue de l'obtention du diplôme de <u>Philosophiae Doctor</u> a été dûment acceptée par le jury d'examen constitué de:

- M. SAVARIA Yvon, Ph.D., président

- M. SAWAN Mohamad, Ph.D., membre et directeur de recherche

- M. ROBERTS Gordon W., Ph.D., membre et codirecteur de recherche

- M. BRAULT Jean-Jules, Ph.D., membre

- M. ISMAIL Elnaggar Mohammed, Ph.D., membre externe

To my future Wife,

To my father and mother,

To my brothers and sisters,

To my dearest friends

### **ACKNOWLEDGEMENTS**

It has been a real privilege being a graduate student in the Electrical Engineering department at "École Polytechnique de Montréal" working in close relationship with the MACS lab of McGill University. This experience gave me great opportunities to learn from engineering faculties of two universities having wide and deep expertise in engineering. I would like to directly thank people of these two universities who were particularly instrumental in contributing to my experience.

I would like to first thank my advisor, Professor Mohamad SAWAN, for his invaluable guidance throughout my long journey as a graduate student. His many years of circuit design experience have allowed me to focus on the critical and interesting issues of all the problems encountered. It has been a unique privilege to be in his group.

I would also like to express my gratitude to my co-advisor, Professor Gordon W. ROBERTS, not only for his guidance, energy and enthusiasm but also for his patience (he is the only person who knows the real meaning of this word), and for the freedom he has granted me throughout my years of study. The results of this research would not have been of the same quality without him pushing the design goals and test strategies always higher and higher.

I would like to thank the members of my thesis committee for their valuable feedback and contributions. I would like to thank Professor Yvon SAVARIA for his

Professor Jean-Jules BRAULT was a valuable member of my qualifying examination committee. I would like to thank him for giving me the opportunity to study the extension of this work application to neural network implementation in digital technology. Thanks to Professor Mohammed ISMAIL of Ohio State University for accepting to be the external reviewer of my thesis. My warmest thanks also go to Professor Ed van Tuijl of Twente University/Philips Research Laboratories Eindhoven (Netherlands) for reading my thesis and for his comments and suggestions. I would also like to thank Professor Daniel MASSICOTTE of "Université du Québec à Trois-Rivières", member of my qualifying examination committee, for his insightful comments on signal processing for communications systems and measurements.

I would like to thank my family for being very supportive and patiently listening to me trying to explain my research topic on the phone. I would like to thank my brothers and sisters Abel, Jean, Elizabeth, Cécile, and Lydia for believing in me. I could not forget my sister-in-law Ilona for always being there and feeding me when I was too tired to cook.

My sometimes flickering faith in God and in myself have remained constantly high enough to carry this work to the end. My wakefulness has become my dream and my dreams my reality. Now love is my altar, humility my strength.

I am specially thankful to Monique CHARRON LECLAIR and Gervais LECLAIR for believing me every time I said I was graduating "next year". Thanks for

their unconditional support and also for always being there and providing me with vacations that were so important and fun breaks from my work. I am very honored to be part of their family. Thanks to Lise CHARRON for reading the whole manuscript and also for her much appreciated comments and suggestions. Thanks also to Monique CARMEL for the french translation of the abstract.

I am also grateful to Gordon W. HARLING, founder of Goal Semiconductor Inc, and Marcel LAPOINTE who gave me the opportunity to design my first successive approximation analog-to-digital converter IC as first assignment as IC design engineer and thus opening a new era in my life.

Specials thanks to Micheline D. SAMSON, Vivian DUBREUIL, Marie-Josée MALETTE, Nathalie CHAGNON, Clarence K. MESSIE, Nathalie LE ROC'H, Carine LEMASSON, Isabelle LAPORTE, Maurice DUVAL and his family, Philomène R. FAYE, Nourr-Eddine RADI, Jacques SAMSON, Cécile ARSENAULT, Blandine LECLAIR, Normand LECLAIR, Damien LECLAIR, Claude CHARRON, Oury BA, Wassala NIMAGA, Ghyslain N., Pierre MARKON and his family, Jules GAUTHIER and his family, Édouard KOUASSI and his family, François ABIOLA and his family, Yves ALAVO and his family, Pascal NSAME and his family, Saba HANNA and his family, Steve STRATZ from ASIC North in Burlington (Vermont), Pierre HOUDAGBA and his family, Michel HOUENAGNON, Dorothée M., Alexandra PASSARO, Gratien L., Dominique T., Magdalina DIMITROVA, Patrick B., Mike P., Martin R., Geoffrey A, Normand G., for the support they freely provided during my long path as a student.

Thanks to John OLESZKIEWICZ from IBM Microelectronics Division at Essex Junction (VT) for the opportunity to design various kinds of analog-to-digital converters. Thanks also to my co-workers on high-speed pipelined ADC project, Christopher R., Chris S., and John B with Kai D. F. on SPMC project. I will not forget my friend, Joanne HELOUVRY, at Enoch Pratt Free Library of Baltimore (MD) for providing free hardcopy of technical papers and thus giving me the time to focus on other issues.

I would also like to thank my salsa dance partners and companions Marie-Josée M., Élise D., Nicolas St-O., Julie D., Solange B., Claude L., Dominique C., Giovanna Di G., Daniel B., Alexandre L., Christine L., Luce B., Carine T., Géneviève M., and France I. to just name a few who contributed in removing some stress from my student life.

Thanks to my outdoor activity friends Josephine, Jenica, Dorothée, Nadine, Bobby, Louis-André, Marie-Josée L., Nicolas, Capucine, Patrick, Isabelle, Christine R, Verena Jr. to just name a few for giving me the chance to explore additional dimensions of my life. Special thanks to Marie-Josée MALETTE, my hike partner on the "knife-edge trail", the first person to discover my fear of huge mountains besides all the appearance and who gave me the confidence to continue.

Graduate students really spend more hours than they would like in the lab. However, the people who were there with me helped making it a more interesting experience. It has been very helpful to have fellow students who were immediately accessible and who freely gave me their support when I had technical questions. I probably learned in the lab as much as I did in the classroom. I would like to thank many students of

MACS lab such as Mohamed H., Mona S.-H., Nazmy D. A., Mourad O., Sébastien L., Geoffrey D. and many others that eluded me. Thanks to PolyStim and GRM fellow students, technicians and support specialists Jieyan Z., Abdel D., Yamu H., Moncef D., Jean-Luc T., Annie T., Saeid H., Jonathan C., Jean-François G., Claudine O., Alexander V., Réjean L. and Ghyslaine É.-C. for their support. Each of them have contributed to different areas of this expertise by sharing their work and knowledge as well as providing me valuable feedback based on the application of parts of my research to some of their own work.

Lastly, but not the least, I would like to thank the Canadian Microelectronic Corporation for fabricating the test chips, Micronet, NSERC and NATEQ for their financial support.

To All of You, thank you so much for all the support you have given me during this research. You can't believe how much I appreciate it. Find through the above lines the expression of my heart and gratitude for all you have done for me.

## **RÉSUMÉ**

"Pour compléter la science, il faut que la pensée parcoure, d'un mouvement non interrompu et suivi, tous les objets qui appartiennent au but qu'il veut atteindre, et

qu'ensuite elle le résume dans une énumération méthodique et suffisante."

- Réné DESCARTES, Régles pour la direction de l'esprit

À mesure que la taille minimale du transistor des technologies CMOS diminue, la tension dans les oxydes de grille augmente au point de dépasser les limites permises dans le matériau. Les oxydes de grille nécessitent des tensions d'alimentation faibles afin d'éviter le claquage ou le quasi-claquage et du coup permettent de réduire la dissipation d'énergie dans le système.

L'obligation de réduire la tension complique de nos jours le processus de conception parce que les composants actifs se trouvent à fonctionner en dessous de leur seuil, ce qui a pour effet d'accroître les courants de fuite. Une solution consiste à utiliser une approche de polarisation dynamique du substrat qui, par la même occasion, devient un élément actif. Le concepteur doit toutefois doter le substrat d'un mécanisme de polarisation dépendant du niveau de signal à traiter. La seconde solution, qui consiste à réduire la tension d'alimentation des circuits, requiert une innovation tant au niveau de l'architecture qu'au niveau de la topologie afin d'assurer une certaine gamme dynamique quelle qu'elle soit.

Les convertisseurs analogique-numériques sont des composants essentiels assurant la communication entre les signaux analogiques externes et la puce électronique numérique. Ils ne doivent pas nuire à la précision même si le matériel dans lequel ils sont intégrés se compose de dispositifs très imparfaits. Voilà pourquoi les convertisseurs justifient toutes les connaissances acquises au cours des vingt dernières années en matière de conception, destinées à contourner les contraintes et les défaillances inhérentes aux circuits intégrés.

La présente thèse vise à étudier la faisabilité des techniques de conception de circuits microélectroniques fiables destinés aux convertisseurs opérant à bas voltage dans les procédés CMOS submicroniques standards et à développer celles-ci. Nous avons étudié les contraintes de tension inhérentes aux technologies CMOS submicroniques puis examiné la manière d'optimiser l'utilisation des transistors MOS afin de concevoir des circuits analogiques fiables. L'accent a été mis sur des solutions matérielles qui n'exigent aucune modification du procédé. Les contributions scientifiques suivantes découlent de notre travail:

- Une nouvelle méthode de conception du comparateur analogique différentiel à verrou (*latch*)en CMOS destiné aux applications à basse tension. Cette méthode repose sur l'étage d'entrée de type rail à rail à transconductance constante.

- Une nouvelle méthode de conception des échantillonneurs-bloqueurs. Cette conception repose sur une nouvelle approche d'intégration de l'interrupteur (switch) CMOS analogique à tension doublée. Une nouvelle façon de doubler la

tension d'horloge a aussi été proposée. L'interrupteur redondant a été utilisé afin de réduire l'injection de charge induite par l'interrupteur CMOS, ce qui a pour effet d'améliorer la précision de l'échantillonnage.

• Une stratégie de conception d'amplificateur opérationnel de type rail à rail afin de maximiser la gamme dynamique d'entrée/sortie. Le circuit utilise une nouvelle technique de décalage de niveau du signal d'entrée et un étage d'entrée de classe AB. L'étage de sortie utilise la technique de polarisation dynamique basée sur des circuits à condensateurs commutés.

Ces blocs analogiques ont permis de concevoir deux architectures de convertisseurs analogique-numériques à approximations successives dans la technologie submicronique CMOS standard de 0.18 µm. La résolution de ces convertisseurs opérant à une tension d'alimentation de 1 V est de 10 bits avec une fréquence de conversion de 200 K-échantillons par seconde.

Les contributions originales de cette thèse par articles ont fait l'objet d'un premier article de journal accepté pour publication dans la revue Kluwer Academic Publishers Analog Integrated Circuits and Signal Processing. Le second article est présentement à l'étude afin d'être publié dans la revue <u>IEEE Transactions on Circuits and Systems II</u>.

#### **ABSTRACT**

"The greater becomes the volume of our sphere of knowledge, the greater also becomes its surface of contact with the unknown."

- Jules SAGRET

As the devices scale to smaller dimensions, the voltage fields in the oxides grow to exceed the safe operating limits of the materials. The thinner oxides require reduction in the operating voltages to minimize field-induced oxide breakdown, while creating the "free" benefit of reducing the operating power.

This lower voltage complicates the design process. An issue with lower voltages is that the active devices may be operating at a subthreshold level, increasing leakage currents. One solution is to move to an active substrate biasing scheme, which means that substrates also become an active circuit element. The designer must add some function to the bulk biasing as a function of the absence or presence of the signals. Lower operating voltages require new architectures and circuit topologies to enable any dynamic range.

Data converters are essential parts that enable communication between the external analog world and the digital silicon chip. They should not compromise precision even though the hardware in which they are implemented relies on semiconductor devices known for their poor accuracy. Therefore, converters capitalize on design expertise accumulated during the last 20 years to circumvent the limitations and impairments inherent to integrated circuits.

The objective of this thesis is to investigate the feasibility of reliable data converters design techniques in standard CMOS processes for low-voltage operation. We examine the voltage limitations of CMOS technology and how analog circuits can maximize the utility of MOS devices without degrading reliability. Emphasis is placed on circuit solutions that do not require process enhancements. The specific research contributions of this work consist of:

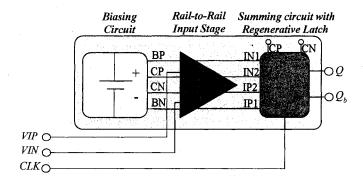

- A new approach to the design of a CMOS differential latched comparator suitable for low voltage applications. The novel approach makes use of the well-known constant-gm rail-to-rail input stage used in amplifiers.

- A sample-and-hold circuit based on a novel implementation of the bootstrapped low-voltage analog CMOS switch. The heart of this circuit is a new low-voltage and low-stress CMOS clock voltage signal booster. Through the use of a dummy switch, the charge injection induced by the bootstrapped switch is greatly reduced resulting in improved sample-and-hold accuracy.

- A design strategy for a rail-to-rail input / output operational amplifier. The circuit makes use of a novel level shifting technique of the input signal and a dynamically biased class AB output stage based on a switched-capacitor configuration.

Those building blocks have been used to implement two architectures for a 1-V, 10-bit 200-kS/s successive approximation analog-to-digital converter in a  $0.18~\mu m$  digital CMOS process.

The original contributions and main conclusions of this manuscript-paper based thesis are the subjects of a first journal manuscript accepted for publication in *Kluwer Academic Publishers Analog Integrated Circuits and Signal Processing* and of a second submitted for publication in *IEEE Transactions on Circuit and Systems II*.

## CONDENSÉ EN FRANÇAIS

"Pour découvrir la vérité, l'homme doit s'affrranchir de toute autorité; en lui brille la lumière qui éclaire tout homme venant en ce monde, dont les clartés peuvent seules lui faire découvrir ce qui est."

- Réné DESCARTES, Discours de la méthode

La réduction d'échelle des technologies est en train d'emmener les dispositifs CMOS au point de blocage. Il n'est pas question d'arrêter les développements des technologies CMOS, mais encore une fois, on se trouve devant une nécessité incontournable d'innovation. Ce blocage apparaît aussi bien au niveau du dispositif qu'au niveau des méthodes de conception des cellules microélectroniques.

La génération 0.1 µm semble être la dernière dans la longue chaîne des technologies qui, moyennant le changement d'échelle des dimensions, de la tension d'alimentation et du niveau de dopage, assuraient les performances et les densités d'intégrations accrues. Cette chaîne ne s'arrête pas brutalement mais sans introduction de nouveaux éléments et le développement de nouvelles approches de conception des circuits microélectroniques, les performances des dispositifs au lieu de croître pourront décroître.

Cette thèse propose une solution alternative, qui permet l'utilisation de la technologie CMOS standard, c'est-à-dire facilement accessible et pas très coûteuse, pour la conception des circuits microélectroniques intégrés dédiés aux convertisseurs analogique-numériques à basse tension d'alimentation.

Dans le texte suivant, le travail effectué est expliqué brièvement en soulignant l'apport original fourni par cette thèse par articles de revue avec comité de lecture. Les références aux figures, aux équations et aux indications bibliographiques sont référées au texte en anglais.

#### I. Introduction

L'augmentation de la densité d'intégration et la rapidité sans cesse croissante des circuits a conduit au développement des dispositifs microélectroniques. Chaque année, les chercheurs s'emploient à réduire la taille de ces dispositifs. L'épaisseur minimum d'oxyde de grille actuellement atteinte est de 20 Å, soit 7 couches atomiques.

L'organisation de ce document est le suivant. Dans la section II, nous aborderons les défis techniques liés à la conception de nouveaux dispositifs microélectroniques. Les approches de conception proposées seront discutées dans la section III. La section IV est exclusivement réservée aux résultats des tests expérimentaux et nous conclurons par la section V sur les applications et extensions futures du projet.

#### II. LES DÉFIS TECHNIQUES DE LA MICROÉLECTRONIQUE À BAS VOLTAGE

La réalisation des capacités est souvent indépendante de l'alimentation. Cependant, une superficie ou surface plus grande serait requise avec la réduction de la dimension minimale des procédés submicroniques. Des nouvelles approches doivent donc être développées.

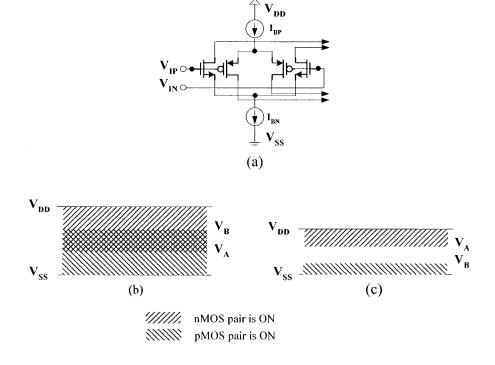

Le plus grand impact se fait sentir au niveau de la conception des amplificateurs opérationnels. Une des conséquences de la basse tension d'alimentation est la réduction

de la plage dynamique d'entrée comme le montre la figure 2.1. On assiste aussi à une réduction de la bande passante. Les nouvelles méthodes de conception doivent donc contribuer à maximiser la gamme dynamique du signal d'entrée tout en maximisant la bande passante [ABO99a]. Un survol détaillé des solutions adoptées a été présenté au chapitre 3. Elles consistent à utiliser le transistor MOS dans des régions d'opérations non conventionnelles difficilement modélisables au niveau des simulateurs actuels.

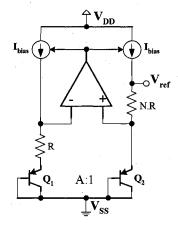

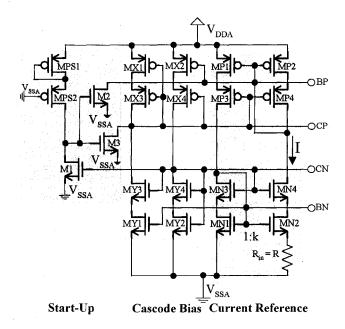

La conception des références de tension est aussi affectée par la réduction de l'alimentation dans les procédés submicroniques. La sortie typique d'une référence de tension est de l'ordre de 1.26 V. Elle est indépendante de la tension d'alimentation du circuit ainsi que de la température. Pour un fonctionnement optimal, ce circuit (figure 2.2) requiert une tension d'alimentation de l'ordre de 1.5 V. La conception d'une référence de tension dans un procédé submicronique alimenté à 1.0 V [SIA02] s'avère donc être un défi de taille. Une solution (au niveau circuit) doit être apportée. Certaines de ces approches ont été abordées au chapitre 3. Les approches de conception des références de tension à bas voltage d'alimentation ne font pas partie intégrante de cette thèse. Cependant les nouvelles techniques de conception des amplificateurs opérationnels proposées dans cette thèse peuvent être utilisées pour solutionner les problèmes liés aux références de tension.

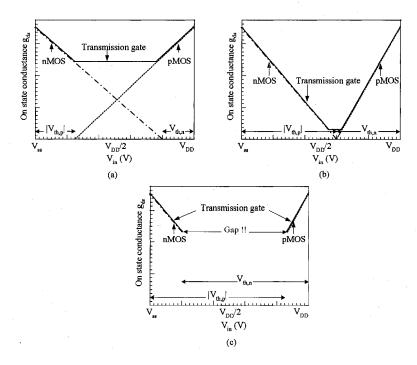

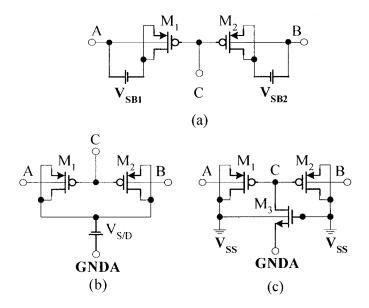

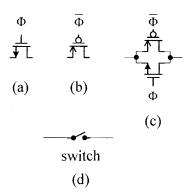

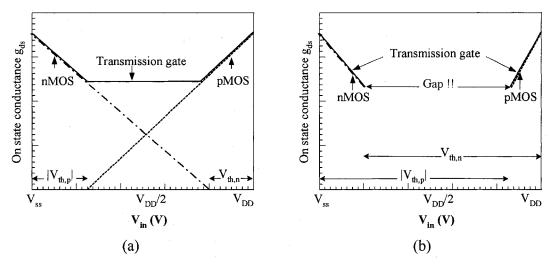

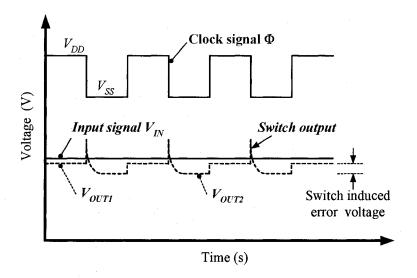

La conception des portes de transmission est aussi affectée par la réduction de l'alimentation comme en témoigne la figure 2.3. Pour des tensions d'alimentation très basse (de l'ordre de 0.65 V), une plage interdite apparaît. Dans cette plage, le signal d'entrée ne passe plus à travers la porte de transmission (figure 2.3c). Les approches de

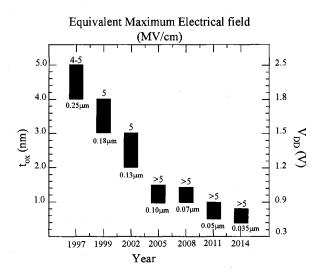

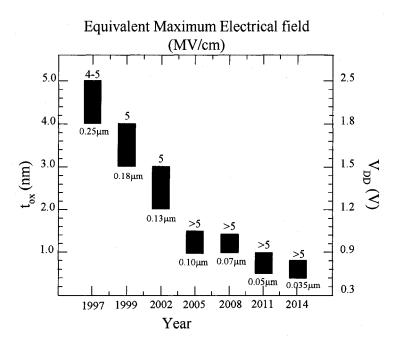

conception apportées afin de palier à cette situation consistent à doubler le signal de contrôle de la porte de transmission analogique et du coup peuvent induire d'autres problèmes tels que le claquage de l'oxyde de grille à cause de l'amincissement de cette dernière comme le montre la figure 2.4. Dans cette thèse, une solution a été apportée à ce problème.

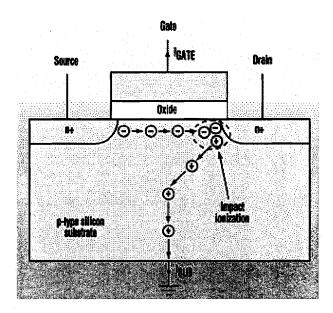

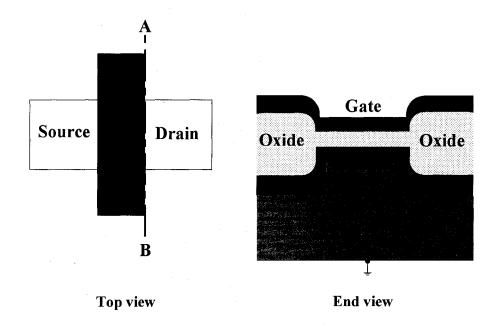

La structure MOS constitue l'élément de base des circuits intégrés. Elle est composée d'un sandwich grille-oxyde-silicium formant une capacité dont l'électrode de grille est accessible par les contacts source et drain. L'épaisseur de l'oxyde de grille, des technologies CMOS actuelles, atteint des valeurs de quelques nanomètres et sera bientôt inférieure à 2 nm pour les générations sous 0.1 μm. L'épaisseur de l'oxyde est estimée à 1/40 de la longueur minimale du transistor permise dans le procédé [MEA94]. Cette réduction de l'épaisseur du diélectrique de grille favorise l'apparition de phénomènes physiques comme la poly-déplétion de grille ou les effets quantiques qui limitent les performances des dispositifs MOS en terme de capacité et de courant de fuite. L'effet de poly-déplétion est dû à la chute de potentiel dans l'électrode de grille non métallique et réalisée en polysilicium pour les technologies CMOS. Cette perte de potentiel dans la grille entraîne une diminution de l'efficacité du couplage capacitif grille-canal et donc du courant disponible dans le transistor. Les effets de confinement quantique des porteurs à l'interface silicium-oxyde conduisent également à une réduction de la capacité maximum en inversion de la structure MOS atténuant du coup ses performances. Les phénomènes quantiques sont également responsables de l'accroissement des courants de fuite de grille par l'effet tunnel. De plus, les structures MOS à oxydes de grille ultra

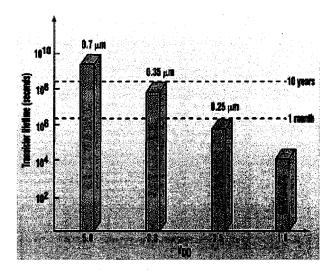

minces sont sensibles à de nouveaux mécanismes de dégradation, tels que les courants de fuite induits par le stress, le quasi-claquage et le claquage qui pourraient réduire leur durée de vie. Ces mécanismes de dégradation des oxydes sont d'autant plus critiques que leurs taux de génération sont exponentiellement accélérés par le champ électrique supporté par la structure comme le montre l'équation (2.12). Divers autres phénomènes tels que le «drain induced barrier», « lowering, punch-through», existent dans les procédés submicroniques pour ne citer que ceux-là. Les équations (2.14) à (2.16) les décrivent de façon quantitative.

Les approches de conception de circuits électroniques en technologie submicronique doivent donc tenir compte de ces phénomènes. La section ci-dessous décrit les méthodes de conception proposées. L'emphase a été mise sur la fiabilité à long-terme.

#### III. CIRCUITS INTÉGRÉS DÉDIÉS À DES APPLICATIONS À BAS VOLTAGE

Dans le souci constant de répondre aux défis liés à la conception de circuits intégrés, introduits par les nouvelles technologies CMOS submicroniques, des approches de conception fiables ont été proposées dans cette thèse. L'accent a été mis sur les modules couramment utilisés dans la conception des convertisseurs analogiquenumériques. Il s'agit entre autres de comparateurs analogiques, d'amplificateurs opérationnels, d'échantillonneur-bloqueurs puis de convertisseurs numériqueanalogiques.

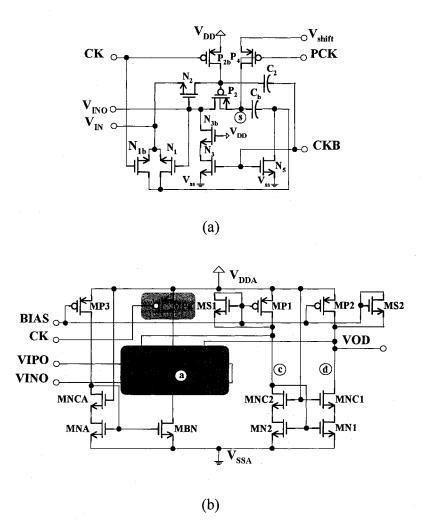

Le premier circuit proposé est un comparateur analogique à large gamme dynamique d'entrée, destiné à opérer à une tension d'alimentation de 1.65 V. Le fruit de

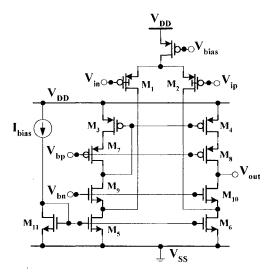

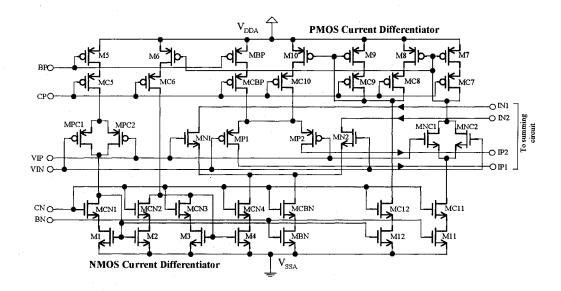

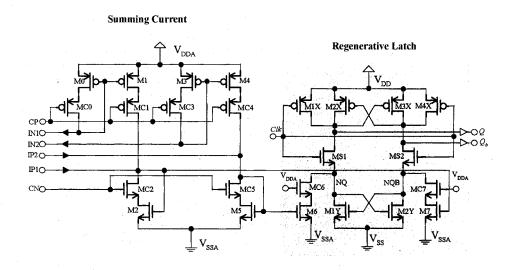

ce travail a été publié dans le compte rendu d'une conférence avec comité de lectures [FAY00a]. Le diagramme bloc du circuit est montré à la figure 5.6 et est constitué du circuit de polarisation, d'un étage d'entrée de type rail à rail et d'un bistable (*latch*). Les détails techniques de ces différents éléments constitutifs sont montrés aux figures 5.7 à 5.9. Les facteurs limitant la performance de ce circuit sont les tensions de décalage (*offset*) liées à l'étage rail à rail et au bistable. L'effet de décalage dû au latch est atténué par le gain de l'étage différentiel d'entrée. L'optimisation de cet étage permet de maximiser la performance sur cet aspect.

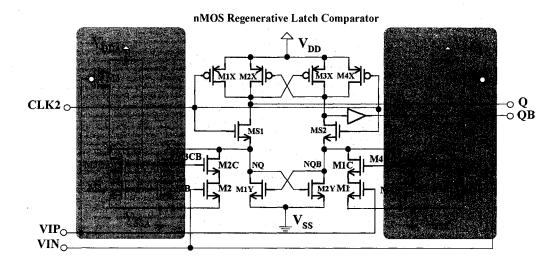

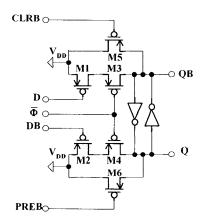

Une autre architecture de comparateur analogique à large gamme dynamique et pouvant opérer jusqu'à 0.65 V a été proposée telle qu'elle est montrée à la figure 5.10. Ce comparateur fut utilisé dans la conception d'un convertisseur analogique-numérique [FAY01b].

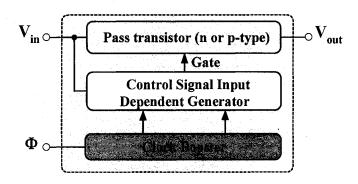

Un autre élément essentiel à la conception des convertisseurs analogique-numériques est l'interrupteur MOS (*switch*) souvent utilisé comme échantillonneur-bloqueur. Pour que cet interrupteur soit capable de transmettre tous les signaux entre la tension d'alimentation et la masse, il faut qu'il soit composé de deux transistors (un canal n et un canal p) montés en parallèle comme le montre la figure 4.1c. Un des problèmes liés au *scaling* de la technologie CMOS est que la valeur absolue des tensions de seuil des transistors n'est pas réduite dans le même rapport que la tension d'alimentation. Cette réduction est approximativement proportionnelle à la racine-carrée de l'alimentation [MEA94]. Si la tension d'alimentation baisse en dessous d'une certaine valeur critique V<sub>DD,crit</sub>, l'interrupteur n'est plus capable de transmettre les signaux analogiques dans une

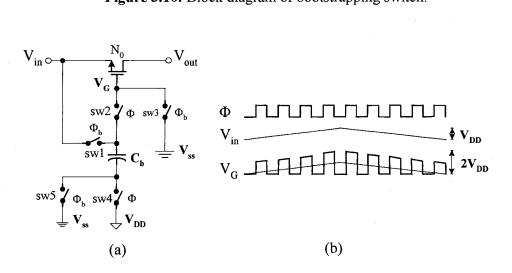

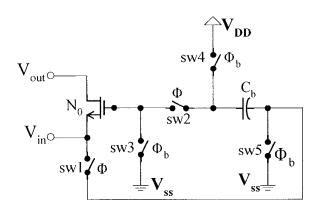

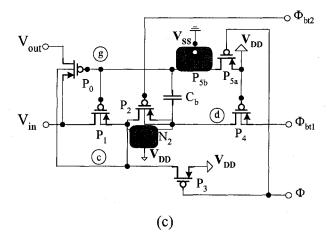

certaine gamme entre 0 V et V<sub>DD</sub> (figure 2.3c). Pour solutionner ce problème nous avons proposé une nouvelle approche de conception simple de ce circuit. Le diagramme bloc du circuit proposé est montré à la figure 4.4 tandis que les détails techniques sont fournis aux figures 4.5 à 4.11. Un des attributs de ce circuit est la constance de sa résistance en fonction du signal d'entrée, attribut essentiel à la réduction de la distorsion. Un autre critère dont nous avons tenu compte dans la conception est l'injection de charges qui peut aussi atténuer de façon significative les performances du circuit. Le circuit proposé dans cette thèse (figure 4.6) solutionne ces problèmes. Ce circuit a été utilisé dans la conception d'un échantillonneur-bloqueur pouvant fonctionner à des tensions d'alimentation aussi basses que 0.65 V. Les résultats de ce travail ont été publiés dans un compte rendu de conférence [FAY00b]. Une autre partie de ce travail est l'objet d'un article de journal avec comité de lecture <u>IEEE Transactions on Circuits and Systems II</u> et est présentement sous évaluation.

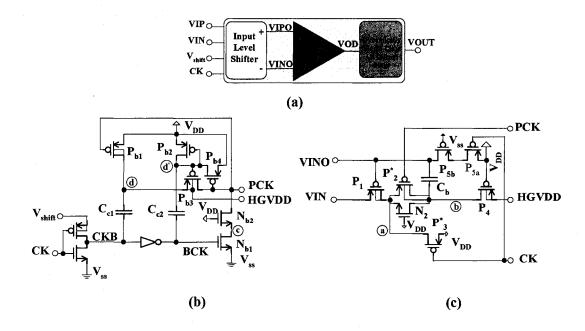

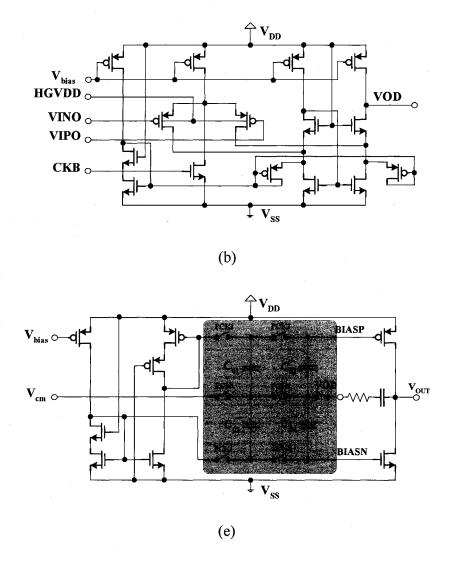

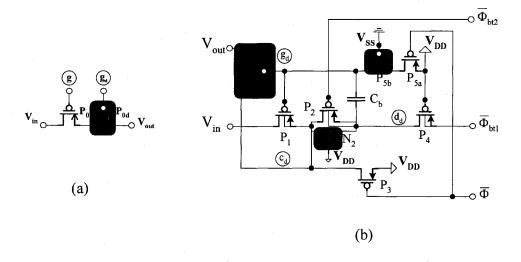

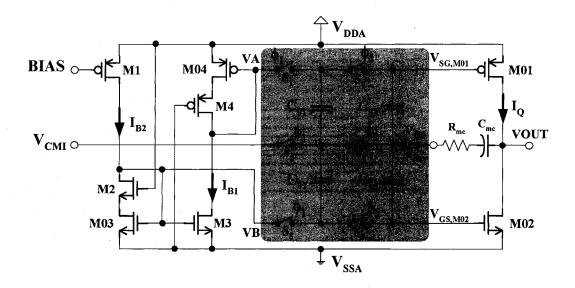

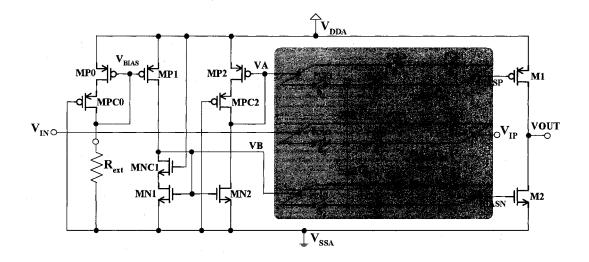

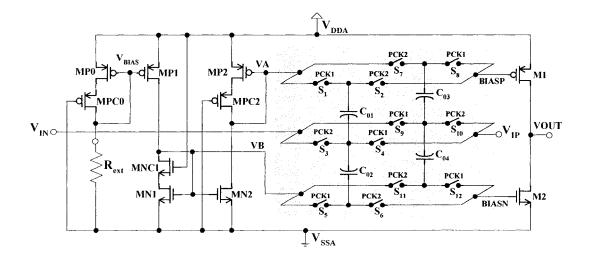

Le troisième circuit proposé est un amplificateur opérationnel de type rail à rail destiné à opérer à des tensions d'alimentation de l'ordre de 1-V et moins [FAY01a]. Le diagramme bloc de ce circuit est montré à la figure 5.1. Il est constitué d'un circuit de décalage de niveau, d'une paire différentielle et d'un étage de sortie de classe AB. Le circuit de décalage de niveau (figure 5.2) permet de convertir un signal analogique compris entre 0 V et V<sub>DD</sub> en un signal situé entre –V<sub>DD</sub> et 0 V. Ce signal est suffisant pour activer les transistors pMOS de la paire différentielle d'entrée (figure 5.3). De plus il permet de faire fonctionner tous les transistors en inversion forte (*strong inversion*). L'étage de sortie de type AB (figure 5.4) permet d'avoir une large gamme dynamique de

sortie. D'autres solutions alternatives de conception du circuit de décalage de niveau et de la paire différentielle d'entrée sont proposées à la figure 5.5. La caractéristique intéressante de ce circuit est la large gamme dynamique d'entrée/sortie.

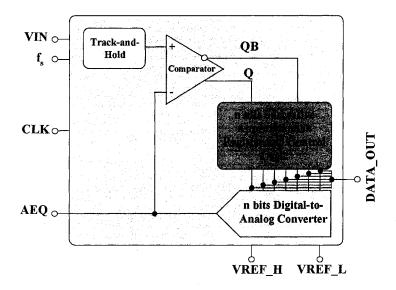

Un quatrième circuit plus complexe a été aussi proposé dans cette thèse. Il s'agit d'un convertisseur analogique-numérique de type rail à rail [FAY01b]. Ce circuit fait usage de certains des éléments décrits ci-dessus et son diagramme bloc est montré à la figure 5.13. Une analyse détaillée du choix des composants a été aussi abordée. Diverses solutions alternatives de conception ont été discutées.

La prochaine section porte sur les tests expérimentaux effectués pour vérifier la faisabilité des concepts abordées ci-dessus.

#### IV TESTS EXPÉRIMENTAUX ET SIMULATION

Après avoir démontré la faisabilité de circuits microélectroniques dans les technologies submicroniques à bas voltage, nous avons validé les concepts au niveau expérimental. Tous les circuits ont été implémentés dans la technologie 0.18 μm de TSMC. Il s'agit d'un procédé dédié aux circuits numériques. Il dispose d'un procédé à substrat de type p d'un puits (*well*) de type n disposant d'une seule couche de polysilicium. Les seuils typiques des transistors de type N et P sont de 0.5 V et –0.6 V respectivement. Les simulations ont été effectuées en utilisant le logiciel Hspice.

Au niveau test, les générateurs de signaux utilisés sont de type Hewlett Packard modèles HP81130A et HP33120A. Les signaux de sortie ont été visualisés avec les oscilloscopes de type Tektronix TDS320 et TDS7154.

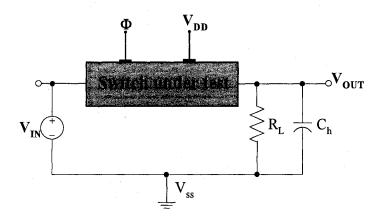

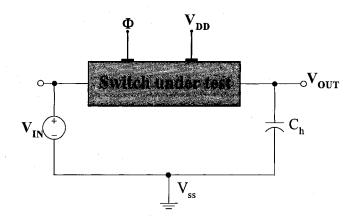

Le circuit de l'échantillonneur-bloqueur (figure 4.6) a été testé afin de vérifier la constance de la résistance, la linéarité de l'erreur dynamique induite et le niveau de distorsion.

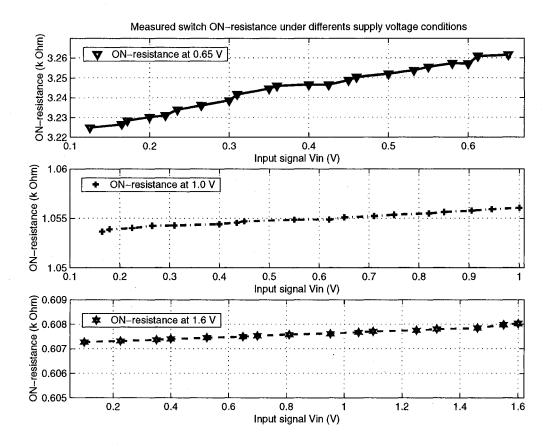

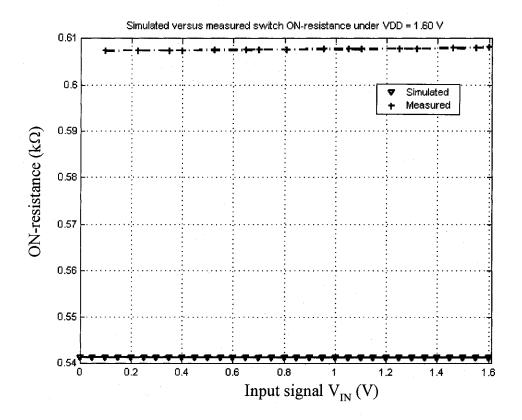

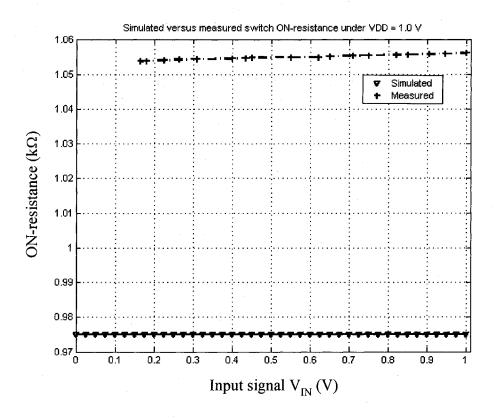

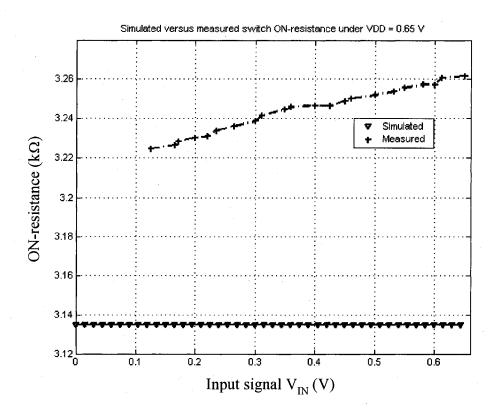

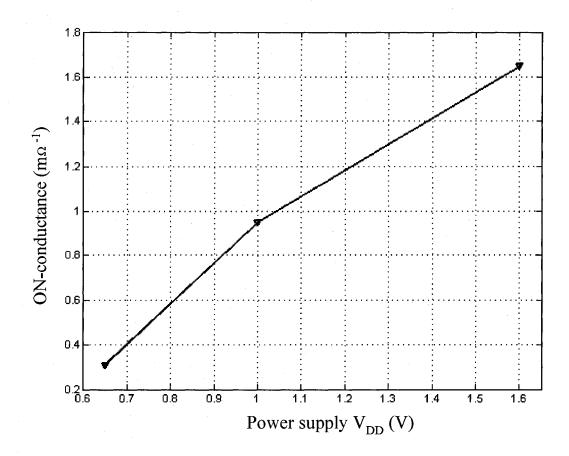

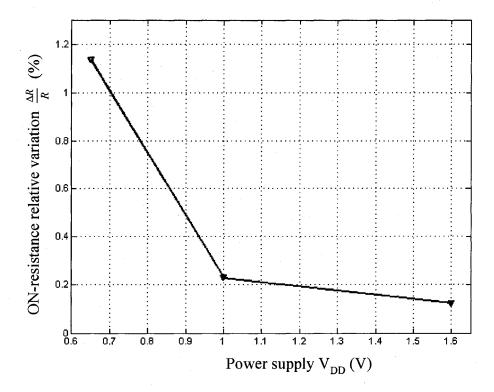

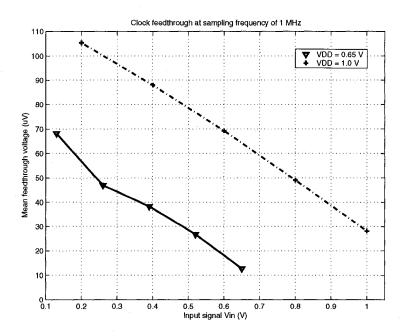

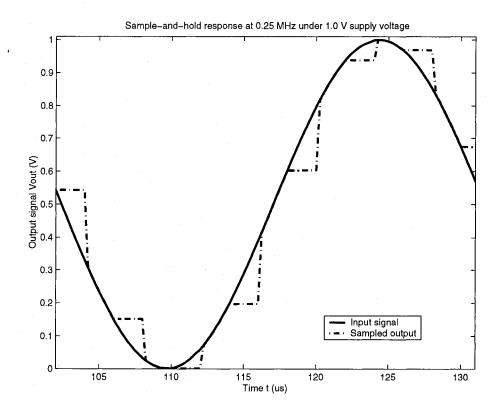

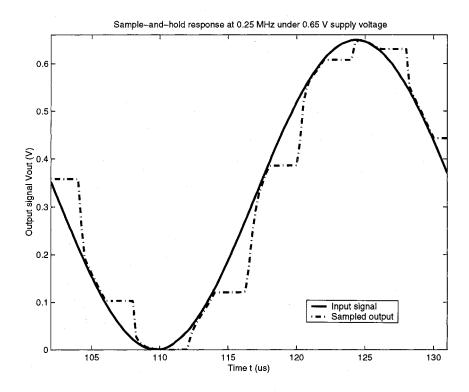

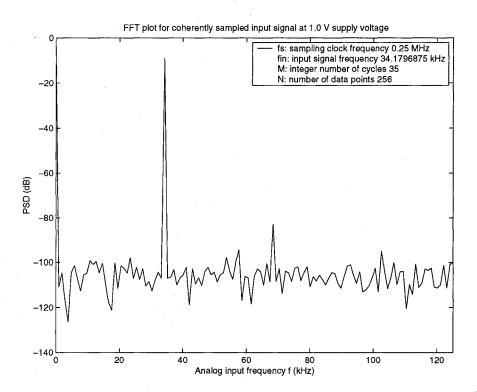

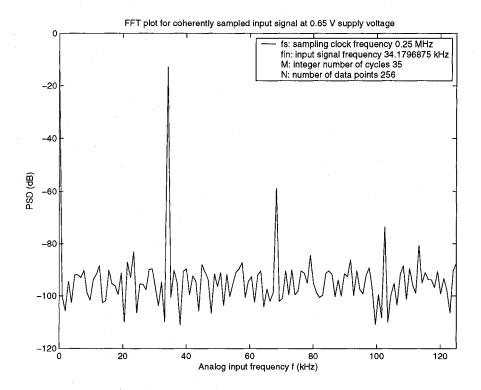

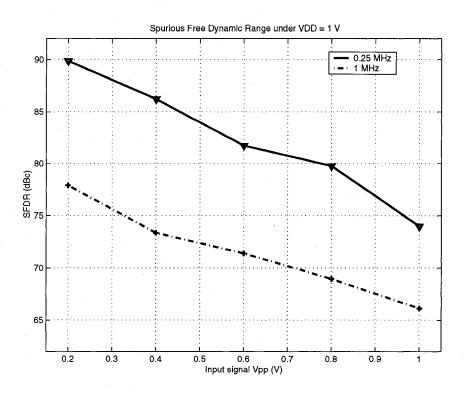

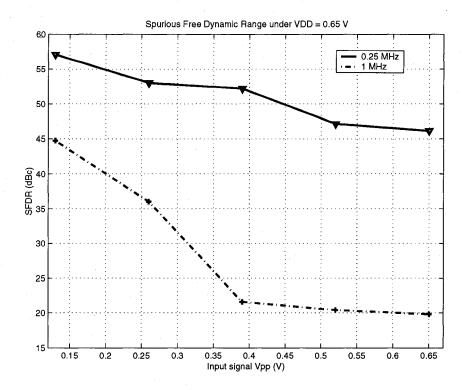

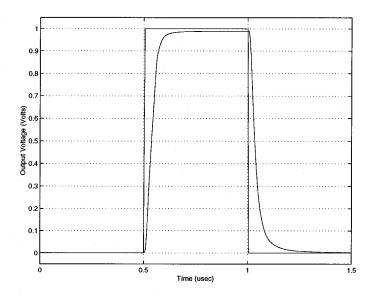

Nous avons mesuré la résistance de l'interrupteur (figure 4.6) en utilisant la configuration montrée à la figure 6.3. Les résultats obtenus (figures 6.4 à 6.6) confirment la constance de la résistance en fonction du signal d'entrée. La figure 6.7 montre la linéarité de la conductance moyenne de l'interrupteur en fonction de la tension d'alimentation. Ces résultats sont en conformité avec les modèles théoriques développés (relation 4.5) aux erreurs expérimentales près. Un test purement fonctionnel a été effectué afin de valider le concept échantillonnage-blocage. Le schéma de principe de la figure 6.9 a été utilisé à cette fin. Le test fonctionnel fût effectué pour les tensions d'alimentation de 0.65 et 1 V et les résultats obtenus sont montrés aux figures 6.12 à 6.13 respectivement pour une fréquence d'horloge (échantillonnage) de 250 KHz. L'erreur dynamique (injection de charge et clock feedthrough) induite dans l'échantillonneur-bloqueur varie linéairement en fonction du signal d'entrée comme le montre la figure 6.11. Le niveau de distorsion a été testé en utilisant le concept de l'échantillonnage cohérent [ROB95], [BUR01], [GRO97]. Une fenêtre constituée de 256 échantillons a été utilisée à cette fin. Les tests ont été effectués pour deux fréquences d'horloges (0.25 et 1 MHz) et pour des tensions d'alimentation de 0.65 et 1 V. Le signal de sortie a été prélevé et une analyse spectrale fût effectuée en utilisant Matlab. Les résultats de ces analyses sont montrés aux figures 6.14 à 6.17. Le rapport signal sur bruit est de l'ordre de 71.05 dB et 45.78 dB pour des tensions d'alimentation respectives de 1 V et 0.65 V sous une fréquence d'horloge de

0.25 MHz. Ces valeurs correspondent à une précision de 11.5 bits et 7.3 bits respectivement. Ces résultats sont excellents comparés aux circuits complexes utilisés à une tension d'alimentation de 3.3 V afin d'assurer le même niveau de performance [KOB01], [SUZ02], [WAL99].

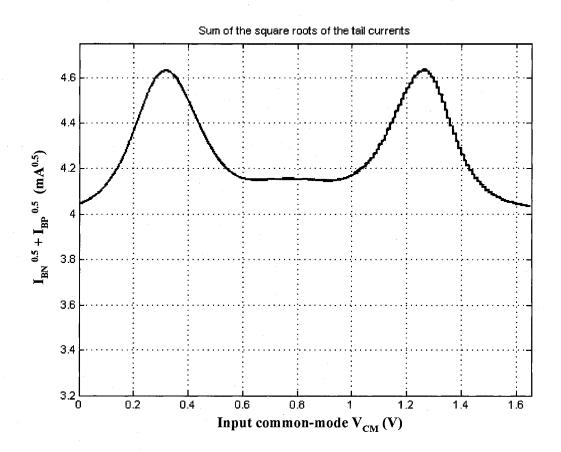

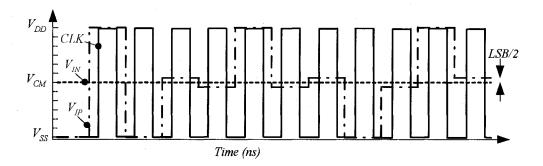

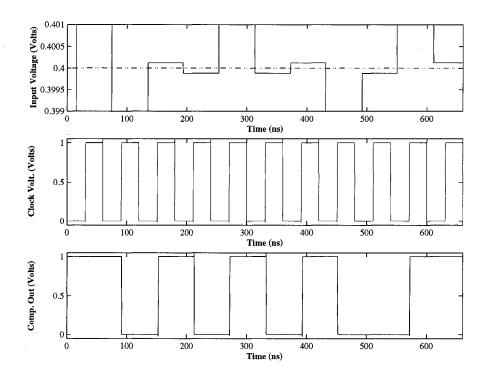

Des simulations ont été effectuées sur les autres circuits proposés. La constance de la transconductance de l'étage d'entrée différentielle du comparateur analogique (figure 4.25) a été démontrée. Les performances fonctionnelles dynamiques ont été également validées. Les résultats sont montrés aux figures 6.18, 6.19 et au tableau 6.1. Les temps de montée, de descente et les délais de propagation sont quasi-constants et presque indépendants du mode commun.

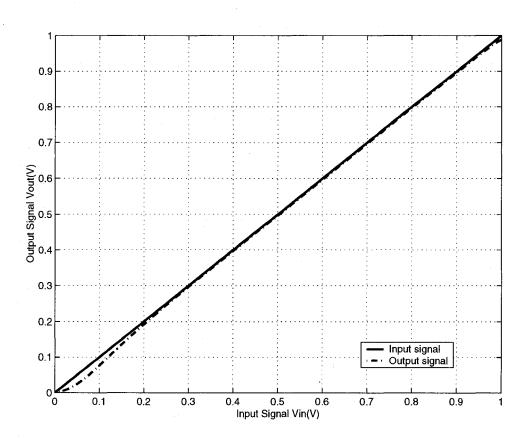

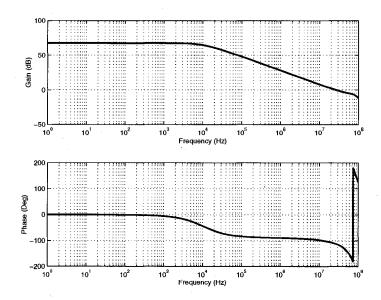

La gamme dynamique d'entrée/sortie de l'amplificateur opérationnel (figure 4.20) a été simulée au niveau logiciel ainsi que sa réponse en fréquence et au signal impulsionnel. Les résultats sont montrés aux figures 6.20 à 6.23. Le circuit possède une large bande dynamique d'entrée/sortie de presque 1 V. La bande passante du signal est de l'ordre de 26.6 MHz avec une marge de phase de 67 degrés sous une charge résistive et capacitive de 5pF et 20 k $\Omega$ . L'amplificateur opérationnel dissipe une puissance de 400  $\mu$ W.

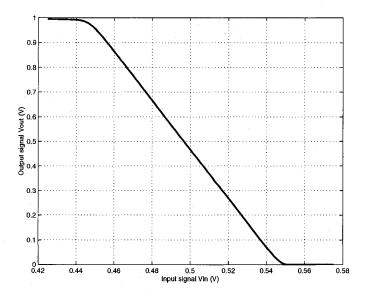

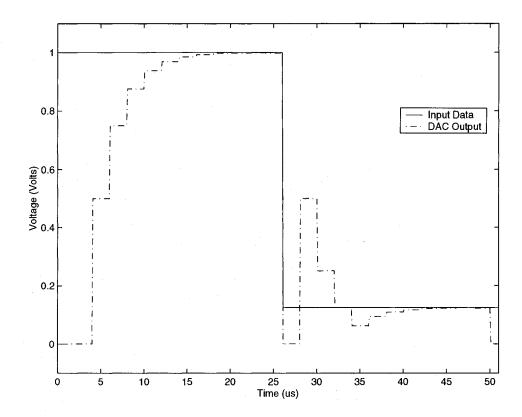

La simulation fonctionnelle du convertisseur analogique-numérique (figure 5.4) prouve que le circuit peut opérer à 1 V sous une fréquence d'échantillonnage de 200 K échantillons/secondes. La gamme du signal d'entrée peut aller de 0 à 1 V. Il est à noter que la fréquence d'échantillonnage choisie est intimement liée à la précision de l'échantillonneur-bloqueur. Ce dernier présente une résolution de l'ordre de 11.5 bits

sous une fréquence de 0.25 MHz comme le témoigne la figure 6.14. Une résolution de plus de 10 bits est difficilement réalisable avec ce type de configuration de convertisseurs. Cette limitation est due à la structure résistive du circuit de convertisseur numérique-analogique.

Pour résumer, les circuits proposés correspondent bien aux attentes des modèles théoriques développées. Les prochains paragraphes résument la performance et les futures orientations du projet.

#### V. CONCLUSION ET RECOMMANDATIONS

L'idée à la base de cette thèse est le développement des approches de conception de circuits microélectroniques dédiés aux convertisseurs analogique-numériques à bas voltage d'alimentation dans les technologies submicroniques. Pour cette raison nous avons étudié les problèmes liés aux technologies submicroniques standard. Cette étude nous a amené à développer des approches qui permettent de concevoir des circuits intégrés fiables et fonctionnels dans ces technologies. Les performances des circuits proposés ont été validées tant au niveau matériel qu'au niveau logiciel.

Une bonne continuation de ce projet serait de faire des tests de fiabilité à long terme sur les modules matériels développés. Le simulateur de fiabilité *Berkeley Reliability Tool* [HU92] peut être utilisé.

Les structures microélectroniques complètement différentielles présentent une bonne immunité au bruit. Une autre continuation de projet sera la modification des topologies proposées afin d'en faire des structures complètement différentielles. Finalement des tests expérimentaux au niveau matériel doivent être effectués afin de valider les modifications.

Une validation au niveau matériel de la technique de conversion analogiquenumérique à approximation successive proposée au chapitre 5 constitue également une bonne continuité du projet. Des tests intensifs des linéarités différentielle et intégrale ainsi que les mesures du gain et de la distorsion doivent être effectués. L'utilisation des circuits proposés dans la conception de convertisseurs analogique-numériques de type pipeline et à sur-échantillonnage, pour ne citer que ceux-là, serait souhaitable.

## TABLE OF CONTENTS

| P | ล | ø | e |

|---|---|---|---|

|   |   |   |   |

| DEDICATION                                                | iv      |

|-----------------------------------------------------------|---------|

| ACKNOWLEDGEMENTS                                          | vi      |

| RÉSUMÉ                                                    | Х       |

| ABSTRACT                                                  | xiii    |

| CONDENSÉ EN FRANÇAIS                                      | xvi     |

| TABLE OF CONTENTS                                         | xxviii  |

| LIST OF TABLES                                            | . xxxii |

| LIST OF FIGURES                                           | xxxiii  |

| LIST OF ABBREVIATIONS                                     | xlii    |

| LIST OF SYMBOLS                                           | xlv     |

| CHAPTER 1 INTRODUCTION                                    | 1       |

| 1.1 Motivation                                            | 1       |

| 1.2 Research objectives and methodologies                 | 4       |

| 1.3 Research contributions and organization of the thesis | 5       |

| CHAPTER 2 CHALLENGES IN DEEP SUBMICRON LOW-VOLTAGE        |         |

| CIRCUITS                                                  | 9       |

| 2.1 Low-voltage CMOS analog circuit design issues         | 9       |

|     |      | 2.1.1  | Capacitors                                                   | 9   |

|-----|------|--------|--------------------------------------------------------------|-----|

|     |      | 2.1.2  | Operational amplifiers                                       | 10  |

|     |      | 2.1.3  | Bandgap reference voltage                                    | 13  |

|     |      | 2.1.4  | MOS switches                                                 | 15  |

|     | 2.2  | Low-v  | voltage CMOS analog circuits and reliability                 | 18  |

|     |      | 2.2.1  | Physical limits on devices                                   | 22  |

|     |      | 2.2.2  | Power and temperature limits on circuits                     | 25  |

|     |      |        |                                                              |     |

| CH. | APTE | ER 3   | LOW-VOLTAGE ANALOG CIRCUITS IN DEEP SUBMICE                  | RON |

|     | CM   | OS: A  | REVIEW                                                       | 29  |

|     | 3.1  | CMO    | S bandgap reference circuits                                 | 30  |

|     | 3.2  | Other  | low-voltage techniques and analog building blocks            | 32  |

|     | 3.3  | Reliat | ole Circuit Techniques for Low-Voltage Analog Design in Deep |     |

|     |      | Subm   | icron Standard CMOS: A Tutorial (Journal paper no. 1)        | 33  |

|     |      |        |                                                              |     |

| CH  | APTI | ER 4   | RELIABLE IMPLEMENTATION OF A MOS SWITCH-BAS                  | SED |

|     | SAN  | MPLE-  | AND-HOLD CIRCUIT                                             | 80  |

|     | 4.1  | Analo  | og CMOS switches                                             | 80  |

|     | 4.2  | Low-   | Voltage Analog Switch in Deep Submicron CMOS: Design         |     |

|     |      | Techr  | nique and Subsequent Measurement (Journal paper no 2)        | 82  |

| ,   |      |        |                                                              |     |

| CH  |      |        | LOW-VOLTAGE TECHNIQUES AND OTHER ANALOG                      |     |

|     | BU   | ILDIN  | G BLOCKS IN DEEP SUBMICRON CMOS                              | 117 |

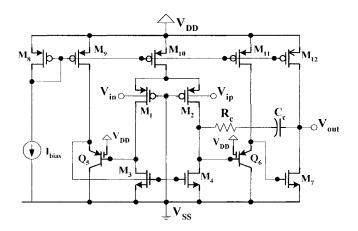

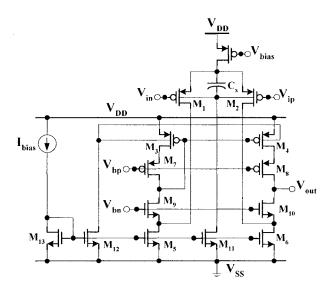

| 5.1 Low-  | -volt | tage rail-to-rail input/output opamp design                       | 18 |

|-----------|-------|-------------------------------------------------------------------|----|

| 5.1.      | .1    | Input level shifter circuit                                       | 19 |

| 5.1.      | .2. 1 | Differential input pair1                                          | 21 |

| 5.1.      | .3    | Class AB output stage                                             | 23 |

| 5.1.      | .4    | Input level shifter circuit alternative implementation            | 25 |

| 5.2 Low-  | -volt | tage rail-to-rail input analog comparator design                  | 26 |

| 5.2.      | .1    | Complementary nMOS/pMOS differential input based                  |    |

|           | (     | comparators                                                       | 27 |

| 5.2.      | .2    | Regenerative latch-based rail-to-rail comparators1                | 37 |

| 5.2.      | .3    | Other low-voltage rail-to-rail analog CMOS comparator 1           | 41 |

| 5.3 Low   | -volt | tage rail-to-rail successive approximation ADC 14                 | 42 |

| 5.3       | .1    | Track-and-hold circuit                                            | 43 |

| 5.3       | .2    | Rail-to-rail comparator1                                          | 44 |

| 5.3       | .3    | Successive approximation register and control logic 14            | 44 |

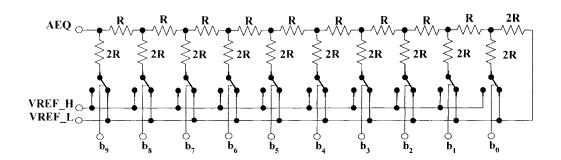

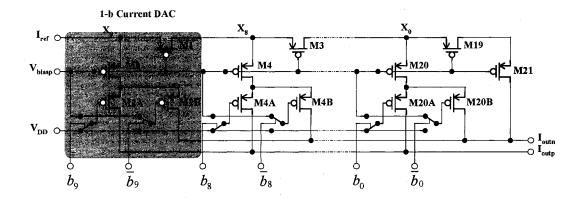

| 5.3       | .4    | Digital-to-analog converter circuit 14                            | 46 |

| 5.3       | 3.4.1 | Voltage mode R-2R DAC                                             | 46 |

| 5.3       | 3.4.2 | pMOS-only current mode R-2R DAC                                   | 52 |

|           |       |                                                                   |    |

| CHAPTER 6 | R     | ESULTS AND DISCUSSION 1                                           | 55 |

| 6.1 Tech  | hnol  | ogy and test setup1                                               | 55 |

| 6.2 Exp   | erim  | ental results of the bootstrapped switch based sample-and-hold 1: | 56 |

| 6.2       | 2.1   | Layout1                                                           | 56 |

|       | 6.2.2       | Switch ON-resistance                                  | 158 |

|-------|-------------|-------------------------------------------------------|-----|

|       | 6.2.3       | Clock feedthrough error voltage test                  | 164 |

|       | 6.2.4       | Linearity and switch-induced distortion test          | 167 |

| 6.    | 3 Simulat   | tion results                                          | 173 |

|       | 6.3.1       | Complementary nMOS/pMOS differential input based      |     |

|       |             | comparators                                           | 173 |

|       | 6.3.2       | Low-voltage rail-to-rail input/output opamp           | 176 |

|       | 6.3.3       | Low-voltage rail-to-rail successive approximation ADC | 179 |

|       |             |                                                       |     |

| CHAP  | TER 7       | CONCLUSION AND RECOMMENDATIONS                        | 182 |

| 7.    | .1 Origina  | al contributions of this thesis                       | 183 |

| 7.    | .2 Recom    | mendations for future work                            | 184 |

|       | 7.2.1       | Circuit reliability test                              | 184 |

| i     | 7.2.2       | Fully differential implementation                     | 184 |

|       | 7.2.3       | Extension to other low-voltage A/D conversion         | 185 |

|       |             |                                                       |     |

| BIBLI | OGRAPE<br>· | IY                                                    | 186 |

| APPE  | NDIX A:     | CURRENT DIVISION PRINCIPLE                            | 200 |

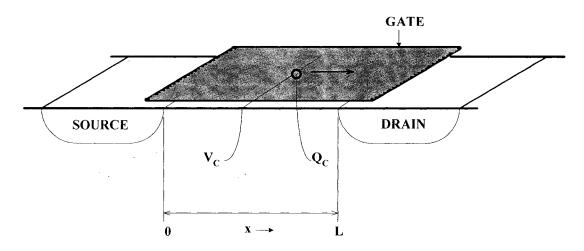

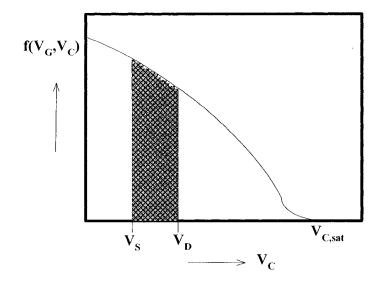

| A     | .1 Genera   | l MOS transistors model                               | 200 |

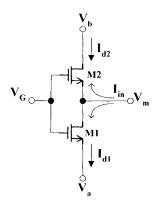

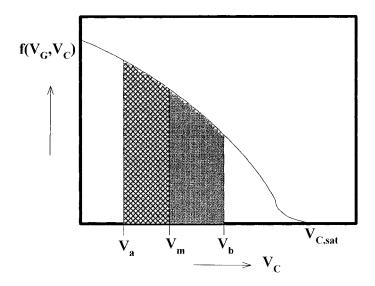

| A     | .2 Basic    | principle of the current division technique           | 204 |

## LIST OF TABLES

| Table 2.1 | Failures mechanism activation energies [LAK99]26                   |

|-----------|--------------------------------------------------------------------|

| Table 3.1 | Low-Voltage Bandgap References                                     |

| Table 3.2 | Trends in Low-Voltage CMOS opamp36                                 |

| Table 3.3 | Comparison of capacitors implementation in standard                |

|           | CMOS processes                                                     |

| Table 5.1 | The matching constants for threshold voltage $A_{Vth}$ and current |

|           | factor $A_{\beta}$ for different CMOS technologies                 |

| Table 5.2 | Properties of resistors in a submicron CMOS process [BAK02]151     |

| Table 6.1 | Summary of comparator simulation results                           |

## LIST OF FIGURES

| Figure 2.1  | Rail-to-rail opamp circuit:                                            |

|-------------|------------------------------------------------------------------------|

|             | (a) typical input stage, (b) operation zones for low supply voltage,   |

|             | (b) operation zones for extremely low supply voltage.                  |

| Figure 2.2  | Typical CMOS bandgap reference circuit14                               |

| Figure 2.3  | On-state conductance of MOSFET switch versus the potential of the      |

|             | switched input using various supply voltage:17                         |

|             | (a) regular, (b) near critical supply, (c) below critical supply.      |

| Figure 2.4: | MOS gate oxide thickness and maximum electrical field as a function of |

|             | time [SIA02]18                                                         |

| Figure 2.5  | Hot carrier induced phenomenon [CHE00]21                               |

| Figure 2.6  | Transistor lifetime as a function of supply voltage [CHE00]22          |

| Figure 3.1  | Low-voltage CMOS opamp using switched-capacitor level-shifter38        |

|             | (a) block diagram, (b) Clock booster(c) pMOS level shifter, (d) pMOS   |

|             | input stage, (e) dynamically biased class-AB output stage.             |

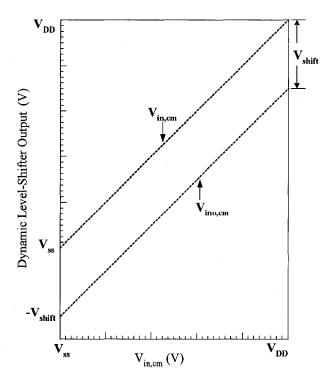

| Figure 3.2  | Level Shifter transfer function40                                      |

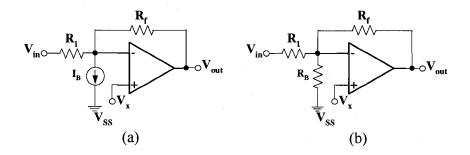

| Figure 3.3  | Biasing schemes for low-voltage CMOS opamp in a single-ended      |    |

|-------------|-------------------------------------------------------------------|----|

|             | configuration using                                               | 41 |

|             | (a) a current source and (b) a resistor.                          |    |

| Figure 3.4  | Opamp design using linear transconductor with resistor input      | 44 |

| Figure 3.5  | Low-voltage opamp using floating-gate transistors                 | 46 |

|             | (a) basic scheme,                                                 |    |

|             | (b) two-stage single ended scheme,                                |    |

|             | (c) two possible implementations of the floating battery.         |    |

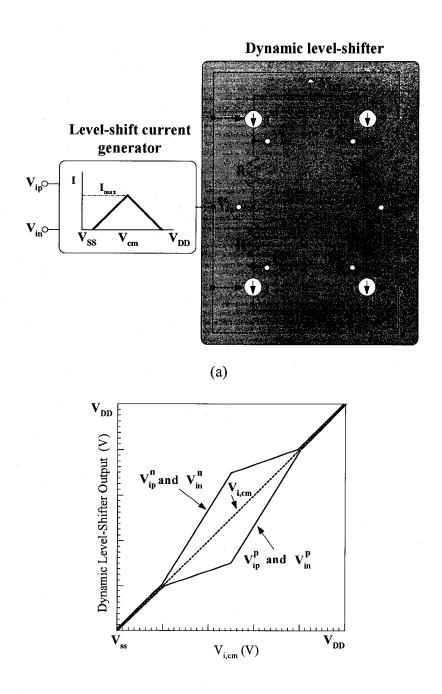

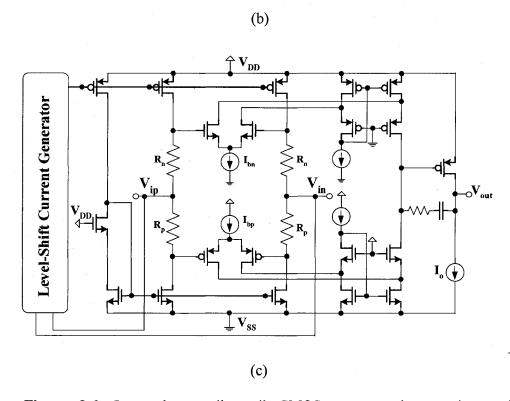

| Figure 3.6  | Low-voltage rail-to-rail CMOS opamp using continuous-time dynamic |    |

|             | level shifter                                                     | 50 |

|             | (a) conceptual schematic,                                         |    |

|             | (b) common-mode components versus input CM V <sub>i,cm</sub> ,    |    |

|             | (c) I-V rail-to-rail complementary input stage.                   |    |

| Figure 3.7  | 1-V rail-to-rail bulk driven CMOS opamp                           | 52 |

| Figure 3.8  | 1-V CDB folded cascode OTA                                        | 53 |

| Figure 3.9  | Low-voltage opamp based on DTMOS                                  | 54 |

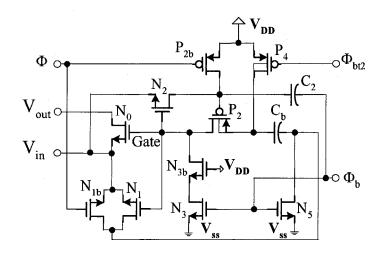

| Figure 3.10 | Block diagram of bootstrapping switch                             | 57 |

| Figure 3.11 | Bootstrapped-clock boosted input switch                           | 57 |

|             | (a) principle of operation, (b) interval node voltage variation.  |    |

| Figure 3.12 | Modified bootstrap switch principle58                              |

|-------------|--------------------------------------------------------------------|

| Figure 3.13 | Bootstrapped nMOS switch                                           |

| Figure 3.14 | Low-Voltage body-effect compensated pMOS switch59                  |

|             | (a) principle of operation, (b) MOS circuit implementation.        |

| Figure 3.15 | (a) Simple low-voltage pMOS bootstrapped switch60                  |

|             | (b) pMOS clock booster circuit.                                    |

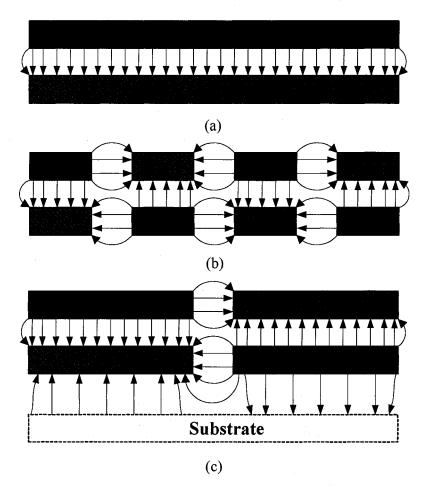

| Figure 3.16 | MOS gate capacitors61                                              |

| Figure 3.17 | Effect of scaling on lateral flux capacitors                       |

|             | (a) before scaling and (b) after scaling.                          |

| Figure 3.18 | Vertical versus lateral flux64                                     |

|             | (a) a standard parallel-plate structure,                           |

|             | (b) cross-connected metal layers and,                              |

|             | (c) reduction of the bottom-plate parasitic capacitance.           |

| Figure 3.19 | An interdigitated capacitor66                                      |

| Figure 3.20 | A floating MOS capacitor implementation67                          |

|             | (a) nMOS, (b) pMOS and its circuit realization (c) nMOS, (d) pMOS. |

| Figure 3.21 | Series compensation MOS capacitors using well-biased MOSFETs in    |

|             | depletion mode69                                                   |

|             | (a) principle of operation,                                        |

|            | (b) circuit realization without floating dc voltage source,                 |

|------------|-----------------------------------------------------------------------------|

|            | (c) circuit realization with fixed well bias and a high resistance element. |

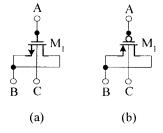

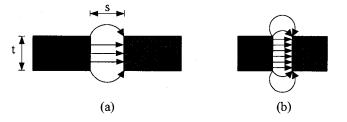

| Figure 4.1 | MOSFETs used as switches                                                    |

|            | (a) nMOS, (b) pMOS, (c) Transmission gate, (d) symbolic representation.     |

| Figure 4.2 | SIA forecast of MOS Gate oxide as a function of time85                      |

| Figure 4.3 | On state conductance of MOSFET switch versus the potential of the input     |

|            | signal87                                                                    |

|            | (a) low supply voltage (b) for extremely low supply voltage                 |

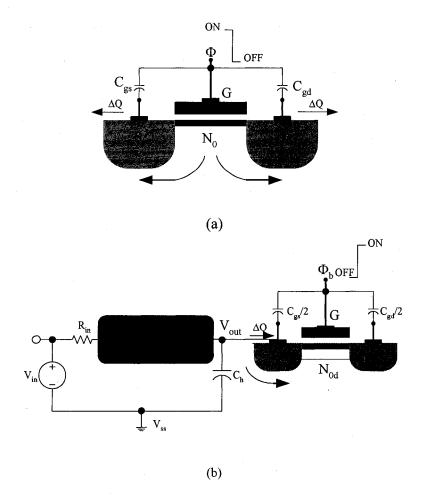

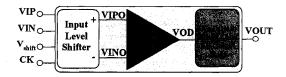

| Figure 4.4 | Block diagram of the bootstrapped Switch                                    |

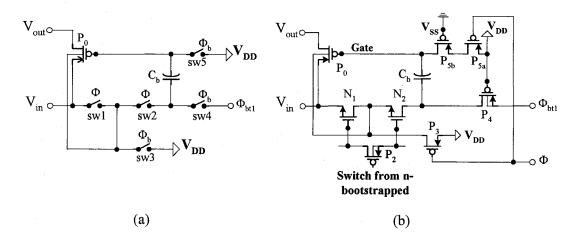

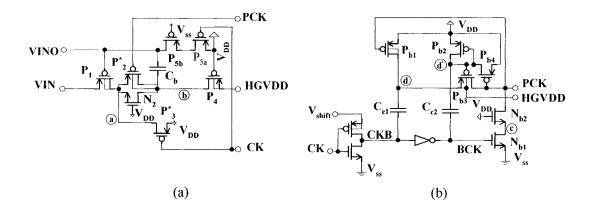

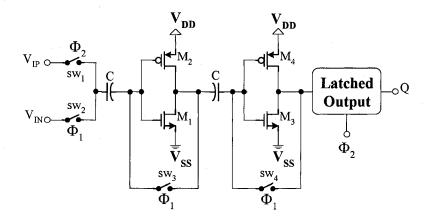

| Figure 4.5 | Clock voltage booster                                                       |

|            | (a) Principle of operation; (b) CMOS Circuit implementation                 |

| Figure 4.6 | Bootstrapped switch91                                                       |

|            | (a) principle of operation, (b) interval voltage variation                  |

|            | (c) pMOS-type pass transistor implementation.                               |

| Figure 4.7 | (a) Charge injection and clock feedthrough mechanism94                      |

|            | (b) Charge error cancellation mechanism.                                    |

| Figure 4.8 | (a) Bootstrapped switch compensation scheme95                               |

|            | (b) Dummy bootstrapped switch together with its control circuitry.          |

| Figure 4.9 | Weakest region of drain reverse breakdown                                   |

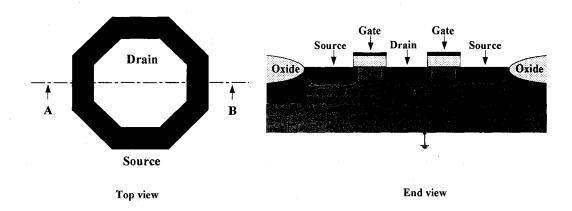

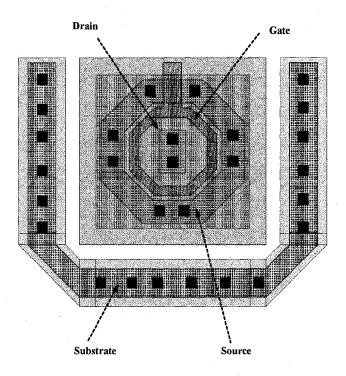

| Figure 4.10  | Circular or "doughnut" drain layout98                                                      |

|--------------|--------------------------------------------------------------------------------------------|

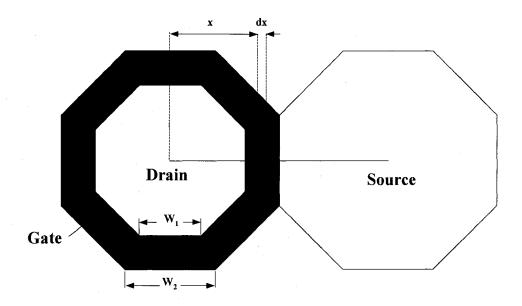

| Figure 4.11  | Calculation of the effective width for "doughnut" transistor99                             |

| Figure 4.12  | Simulated switch ON-resistance variation with supply voltage (0.18 μm                      |

|              | CMOS digital process)103                                                                   |

| Figure 4.13  | Simulated switch ON-resistance variation for ultra-low                                     |

|              | supply voltage ( $V_{DD} \le 0.7 \text{ V}$ )                                              |

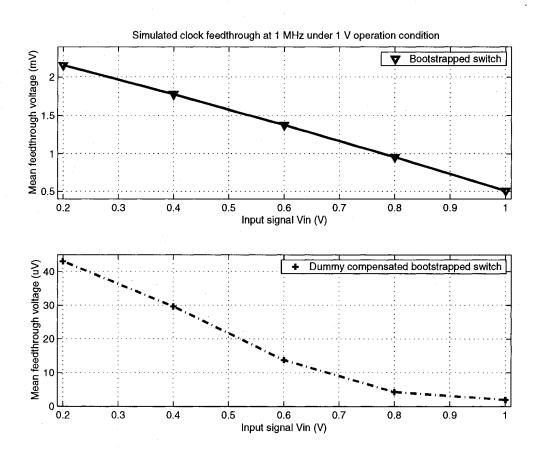

| Figure 4.14: | Simulated dependence of the feedthrough voltage on the analog input105                     |

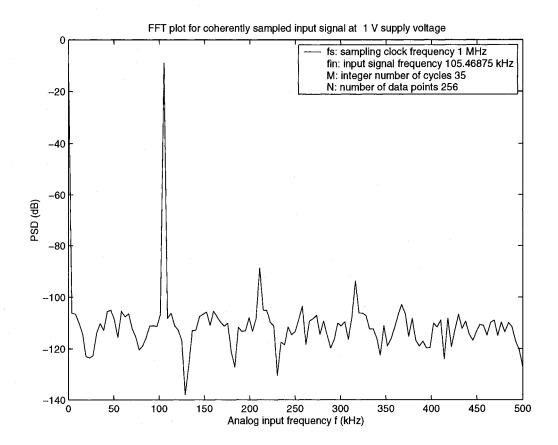

| Figure 4.15: | Simulated spectrum of the compensated bootstrapped switch under a                          |

|              | sampling frequency of 1 MHz, an input frequency of 105.46875 kHz                           |

|              | and a signal amplitude of 1 $V_{PP}$ under a supply voltage $V_{DD}$ = 1 $V$ 106           |

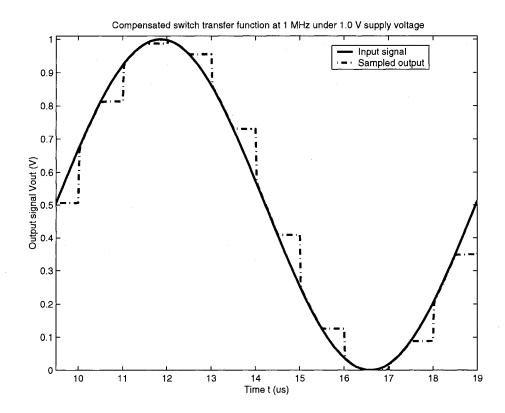

| Figure 4.16: | Simulated input/output of the bootstrapped switch under a sampling                         |

|              | frequency of 1 MHz, an input frequency of 105.46 kHz and a signal                          |

|              | amplitude of 1 $V_{PP}$ under $V_{DD} = 1 V$                                               |

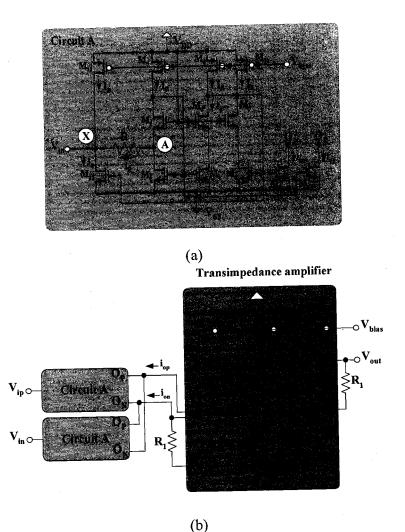

| Figure 4.17  | Photography of the test chip108                                                            |

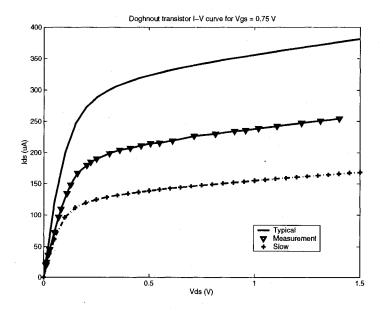

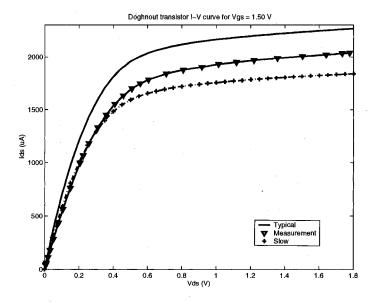

| Figure 4.18  | "Doughnut" transistor characteristics $I_{DS}$ = f ( $V_{DS}$ ) for $V_{GS}$ = 0.75 V108   |

| Figure 4.19  | "Doughnut" transistor characteristics $I_{DS} = f(V_{DS})$ for $V_{GS} = 1 V109$           |

| Figure 4.20  | "Doughnut" transistor characteristics $I_{DS} = f(V_{DS})$ for $V_{GS} = 1.5 \text{ V}109$ |

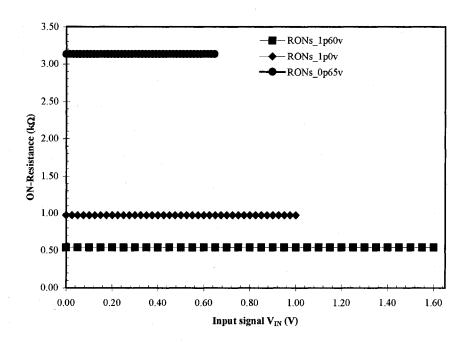

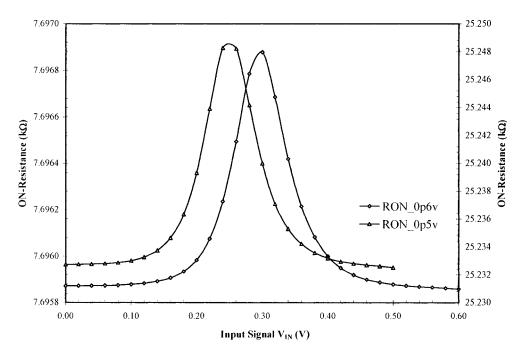

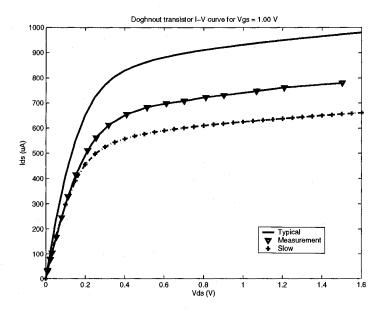

| Figure 4.21: | Measured ON-resistance under 0.65, 1.0 and 1.60 V supply voltages110                       |

| Figure 4.22 | Measured input-output waveform of the bootstrapped switch circuit test      |

|-------------|-----------------------------------------------------------------------------|

|             | chip with a sampling speed of 0.5 MHz, an input frequency of 100 kHz and    |

|             | a signal amplitude of 1 V under a supply voltage $V_{DD} = 1 \text{ V}$ 111 |

| Figure 4.23 | Measured input-output waveform of the bootstrapped switch circuit test      |

|             | chip with a sampling speed of 0.5 MHz, an input frequency of 100 kHz and    |

|             | a signal amplitude of 0.6 V under a supply voltage $V_{DD}$ =0.6 V112       |

|             |                                                                             |

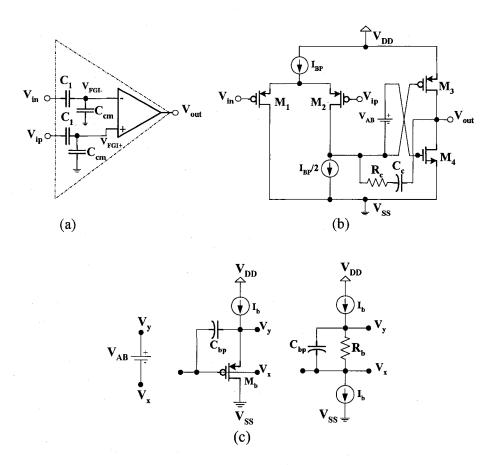

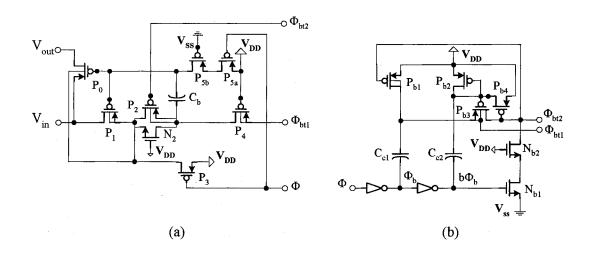

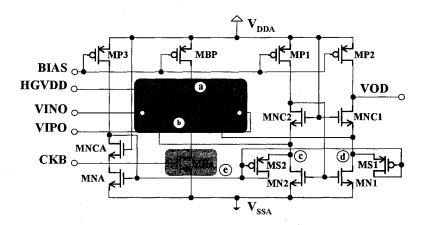

| Figure 5.1  | Low-voltage CMOS rail-to-rail input /output opamp block diagram 118         |

| Figure 5.2  | (a) pMOS input level shifter; (b) Clock booster circuit                     |

| Figure 5.3  | Low-voltage pMOS input stage                                                |

| Figure 5.4  | Low-voltage output stage                                                    |

| Figure 5.5  | Alternative implementation of low-voltage CMOS opamp126                     |

|             | (a) nMOS level shifter, (b) Low-voltage nMOS input stage                    |

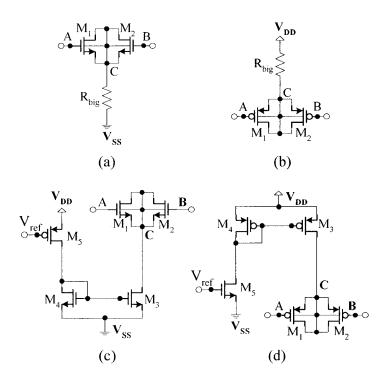

| Figure 5.6  | Comparator circuit block diagram                                            |

| Figure 5.7  | Comparator biasing circuit                                                  |

| Figure 5.8  | Constant-gm rail-to-rail comparator input stage132                          |

| Figure 5.9  | Summing circuit with regenerative latch                                     |

| Figure 5.10 | Low-voltage rail-to-rail latch comparator137                                |

| Figure 5.11 | Track-and-Latch stage                                                       |

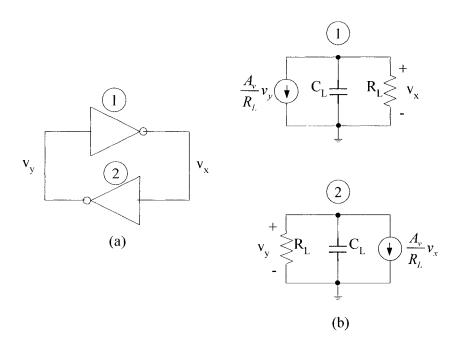

|             | (a) simplified model, (b) linearized model in the latch phase             |

|-------------|---------------------------------------------------------------------------|

| Figure 5.12 | Low-Voltage high-speed autozeroed comparator142                           |

| Figure 5.13 | Block diagram of a successive approximation ADC143                        |

| Figure 5.14 | Low-voltage latch circuit used in SAR                                     |

| Figure 5.15 | A 10-bit voltage-mode R-2R DAC147                                         |

| Figure 5.16 | MOSFET-only current DAC                                                   |

| Figure 5.17 | Low-voltage opamp used for current-to-voltage conversion154               |

|             |                                                                           |

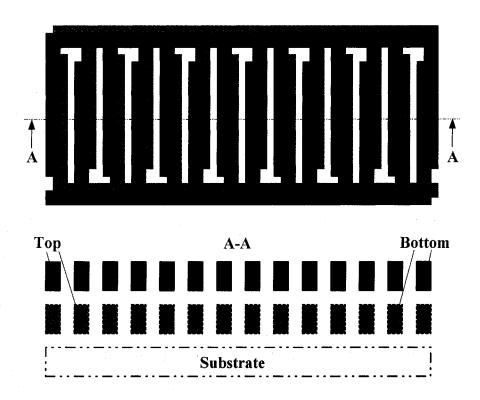

| Figure 6.1  | Physical layout of n-MOS doughnut transistor N <sub>b2</sub>              |

| Figure 6.2  | Physical layout of a 2pF fringing effects based metal-metal capacitors158 |

| Figure 6.3  | Switch ON-resistance test setup                                           |

| Figure 6.4  | Comparison between simulated and measured switch ON-resistance            |

|             | variation at 1.60 V supply voltage                                        |

|             | 11 7                                                                      |

| Figure 6.5  | Comparison between simulated and measured switch ON-resistance            |

|             | variation at 1.0 V supply voltage161                                      |

| Figure 6.6  | Comparison between simulated and measured switch ON-resistance            |

|             | variation at 0.65 V supply voltage162                                     |

| Figure 6.7  | Measured switch ON-conductance variation with respect                     |

|             | to supply voltage163                                                      |

| Figure 6.8  | Measured relative switch ON-resistance variation with respect to supply            |

|-------------|------------------------------------------------------------------------------------|

|             | voltage                                                                            |

| Figure 6.9  | Basic circuit used in measuring clock induced error voltage165                     |

| Figure 6.10 | Basic switched induced error voltage measurement procedure165                      |

| Figure 6.11 | Dependence of the feedthrough voltage on the analog input166                       |

| Figure 6.12 | Measured input/output of the bootstrapped switch circuit test chip with a          |

|             | sampling speed of 0.25 MHz, an input frequency of 34.179 KHz and a                 |

|             | signal amplitude of 1 V <sub>PP</sub> under V <sub>DD</sub> = 1 V                  |

| Figure 6.13 | Measured input/output of the bootstrapped switch circuit test chip with a          |

|             | sampling speed of 0.25 MHz, an input frequency of 34.179 KHz and a                 |

|             | signal amplitude of 0.65 $V_{PP}$ under $V_{DD} = 0.65 V$                          |

| Figure 6.14 | Measured spectrum of the bootstrapped switch based sample-and-held circuit test    |

|             | chip with a sampling speed of 0.25 MHz, an input frequency of $34.179kHz$ and a    |

|             | signal amplitude of 1 $V_{PP}$ under a supply voltage $V_{DD} = 1 V$               |

| Figure 6.15 | Measure spectrum of the bootstrapped switch based sample-and-held circuit test     |

|             | chip with a sampling speed of 0.25 MHz, an input frequency of 34.179 kHz and a     |

|             | signal amplitude of 0.65 $V_{PP}$ under a supply voltage $V_{DD} = 0.65 \text{ V}$ |

| Figure 6.16 | Measured SFDR versus input level under a supply                                    |

|             | voltage $V_{DD} = 1.0 \text{ V}$                                                   |

Figure 6.17 Measured SFDR versus input level under a supply

|             | voltage $V_{DD} = 0.65 \text{ V}$                                               | 173 |

|-------------|---------------------------------------------------------------------------------|-----|

| Figure 6.18 | Simulated variation of the sum of the square roots of the tail currents         |     |

|             | proportional to g <sub>m</sub>                                                  | 175 |

| Figure 6.19 | Waveform used for the dynamic testing on the comparator                         | 176 |

| Figure 6.20 | Simulated opamp input CMR                                                       | 177 |

| Figure 6.21 | Simulated opamp output swing                                                    | 178 |

| Figure 6.22 | Simulated opamp Frequency response                                              | 178 |

| Figure 6.23 | Simulated opamp step input response                                             | 179 |

| Figure 6.24 | Simulated rail-to-rail input regenerative latch based comparator                | 180 |

| Figure 6.25 | Simulation of two conversions cycle                                             | 181 |

| Figure A.1  | Cross view of a MOS transistor                                                  | 201 |

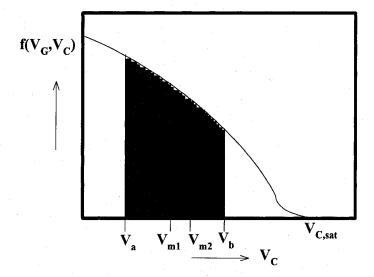

| Figure A.2  | Function $f(V_G, V_C)$ as a function of the channel voltage $V_C$               | 203 |

| Figure A.3  | Basic principle of the current division                                         | 204 |

| Figure A.4  | Drain current of the two MOST of figure A.3                                     | 205 |

| Figure A.5  | Drain current of the two MOS transistors before and after a current $I_{in}$ is | S   |

|             | injected in the input                                                           | 206 |

# LIST OF ABBREVIATIONS

A/D Analog-to-Digital

ADC Analog-to-Digital Converter

BGR BandGap Reference Voltage

BiCMOS Bipolar CMOS

BJT Bipolar Junction Transistor

CM Common Mode

CMFB Common Mode Feedback

CMOS Complementary Metal Oxyde Semiconductor

CMR Common Mode Range

D/A Digital-to-Analog

DAC Digital-to-Analog Converter

dB Decibel

DC Direct Current

DFT Discrete Fourier Transform

DIBL Drain Induced Barrier Lowering

DLL Delay Locked Loop

DNL Differential Non-Linearity

DR Dynamic Range;

DSP Digital Signal Processing

ENOB Effective Number Of Bits

FFT Fast Fourier Transform

GBW Gain-Bandwidth product

GIDL Gate Induced Drain Leakage

HCI Hot Carrier Induced

IC Integrated Circuit

INL Integral Non-Linearity

ITRS International Technology Roadmap for Semiconductors

LDD Lightly Doped Drain

LSB Least Significant Bit

MDAC Multiplying Digital-to-Analog Converter

MOS Metal Oxide Semiconductor

MOSFET Metal Oxide Semiconductor Field Effect Transistor

MOST MOS Transistor

MSB Most Significant Bit

nMOS n-channel Metal Oxide Semiconductor

NPN n-type Bipolar Transistor

OTA Operational Transconductance Amplifier

Opamp Operational Amplifier

PLL Phase Locked Loop

PNP P-type Bipolar Transistor

pMOS p-channel Metal Oxide Semiconductor

PSD Power Spectral Density

PSRR Power Supply Rejection Ratio

PTAT Proportional To Absolute Temperature

RMS Root Mean Square

SIA Semiconductor Industry Association

S/H Sample-and-Hold

SC Switched Capacitor

SNDR Signal-to-Noise-and-Distortion Ratio

SFDR Spurious Free Dynamic Range

SNR Signal-to-Noise Ratio

SO Switched Opamp

SoC System on a Chip

TDDB Time Dependent Dielectric Breakdown

T/H Track-and-Hold

THD Total Harmonic Distortion

VCO Voltage Controlled Oscillator

VHDL Very High Speed Integrated Circuits Hardware Description Language

VLSI Very Large Scale Integration

VSDM Very Deep Submicron

# LIST OF SYMBOLS

μ Carrier mobility

γ Body effect constant of MOSFET

λ Output impedance constant of MOSFET

$\sigma^2$  Variance

A Open-loop DC gain

A<sub>Vth</sub> Threshold voltage matching parameter

C<sub>G</sub> Gate capacitance

C<sub>L</sub> Load capacitance

Cox Capacitance per unit area

f Frequency

f<sub>S</sub> Sampling frequency

g<sub>m</sub> Gate small-signal transconductance

g<sub>ds</sub> Source drain small-signal conductance

I<sub>D</sub> Drain current

I<sub>DS</sub> Drain-to-source current (channel current)

k Boltzmann's constant

L Channel length

L<sub>min</sub> Minimum channel length

n Number of bits

N Number of bits

q Electron charge

R<sub>L</sub> Load resistance

R<sub>ON</sub> Switch ON-resistance

T Absolute Temperature, sampling period

t Time

t<sub>ox</sub> Oxide thickness

V<sub>A</sub> Characteristic voltage in first order channel length modulation

V<sub>B</sub> Body or bulk voltage

V<sub>D</sub> Drain voltage

V<sub>DD</sub> Positive supply voltage for digital circuit

V<sub>DDA</sub> Positive supply voltage for analog circuit

V<sub>DS</sub> Drain-source voltage

V<sub>DS, sat</sub> Drain-source saturation voltage

V<sub>eff</sub> Effective voltage of MOSFET

V<sub>FS</sub> Full scale voltage

V<sub>G</sub> Gate voltage

V<sub>g</sub> Gate voltage

V<sub>GS</sub> Gate-source voltage

V<sub>off</sub> DC offset voltage

V<sub>ref</sub> Reference voltage

V<sub>S</sub> Source voltage

V<sub>SB</sub> Source body (bulk) voltage

V<sub>SS</sub> Negative supply voltage for digital circuit

V<sub>SSA</sub> Negative supply voltage for analog circuit

V<sub>th</sub> Threshold voltage

V<sub>T</sub> Thermal Voltage

W Channel width

X Distance along the channel

# Chapter 1

# INTRODUCTION

"Every great advance in science has issue from a new audacity ... of the imagination."

- John Dewey

### 1.1 Motivation

Down-scaling of CMOS device dimensions has been the major stimulation for the continuing growth of the microelectronics industry over the past three decades. This trend of steady down-scaling was first formulated by Gordon E. Moore and is better known as Moore's law [MOO65]. In 1965 G. Moore, R&D director at Fairchild Semiconductor, today chairman emeritus of Intel Corporation, published a semi-log plot of the number of components on a silicon chip versus the date of first availability. The result was a straight line representing almost a doubling per year. In the later years, the rate relaxed somewhat to a doubling every 18 months. This is still the rate today and is expected to prevail for some time.

Metal-Oxide-Semiconductor Field Effect Transistors (MOSFETs) have been around quite some time now. The success of these silicon-based devices is due, apart from the possibility to reduce their dimensions down to almost nanometer scale dimensions, to the stable high quality silicon-silicon dioxide interface and to the ability

to interconnect millions to billions of devices on a single chip to form an integrated circuit. The basic concept of the MOSFET and its operation was formulated almost seventy years ago [LIL30], even before the experimental discovery of the bipolar junction transistor by J. Bardeen, W. H. Brattain and Shockley [BAR48], [SHO49]. However, it was not until 1960 that the first silicon MOSFET was built by Kahng and Attalla [KAH60]. Ironically enough, the main reason for the rather late realization of a functioning MOSFET was the difficulty to realize a high quality interface between a dielectric layer and a semiconductor, a requirement for proper MOSFET action. Today, after many generations of down-scaling of CMOS devices, the gate oxide thickness is approaching atomic dimensions and we are close to fundamental limits imposed by quantum mechanisms. Also, the reliability of the gate-oxide is becoming a major concern. If the scaling trend continues as predicted by the International Technology Roadmap for Semiconductors [SIA02], SiO<sub>2</sub> may not be able to meet the future reliability requirements under normal operating conditions [STA98].

In recent years, much attention has been paid to the reduction of the supply voltage and the power consumption of mixed-signal CMOS integrated circuits and systems. In addition to down scaling, this is primarily due to the increasing importance of battery-powered electronic. In fact, three main reasons can be given for the advent of low-voltage circuits:

As the channel length is scaled down into submicron and the gate oxide thickness becomes only several nanometers, the supply voltage has to be reduced in order to ensure device reliability (down to 1.5 V and below in the near future) [SIA02].

- The second reason emanates from the increasing number of components on a single chip. A silicon chip can only dissipate a limited amount of power per unit area. Since the increasing density of components allows more electronic functions per unit area, the power per electronic function has to be lowered in order to prevent overheating of the chip.

- The third reason is dictated by portable, battery-powered equipment. In

order to have an acceptable operation period from a battery, both the power

and the supply voltage have to be reduced considering the slow progress in

developing high capacity batteries.

A particular consequence of the lowered power supply is the need for rail-to-rail input stages in most current building blocks in order to compensate for the reduced input common-mode and dynamic range. The power dissipated by analog circuitry, however, does not necessarily decrease when the supply voltage lowers, as the traditional stacking of transistors has to be replaced by cascaded folding techniques, which inevitably increase the current drawn from the supply. Hence, to decrease the power dissipated in low-voltage analog circuits, the design has to be kept smaller and as simple as possible.

The new smaller size process technologies also offers opportunities to operate at high frequencies while consuming less power. This fact applies partially to analog circuits since additional current is often needed to keep the same performance when the power supply voltage is decreased.

Another important design aspect is the transistor region of operation. For instance, with transistors operating in strong inversion, more power (than the minimum required) is often used to meet the specifications. Optimal design involves minimum power consumption and/or silicon area while meeting performance requirements. Designers should also explore design using transistors operating in non-conventional ways. The extreme cases of weak and strong inversions do not provide, in most case, a good tradeoff between frequency response, power consumption and silicon area. Thus, we should consider a one-equation transistor model for all regions [SAN99], [CUN98], which would allow designers to optimize the circuit performance at minimum cost. Bulk-driven and floating-gate techniques which can help to produce efficient low-voltage circuits with reduced power supply restrictions, have been extensively discussed in [YAN00]. In this chapter, research objectives and methodologies are addressed in Section 1.2, while Section 1.3 presents a summary of the key contributions and of the thesis organization.

### 1.2 Research objectives and methodologies

The main objective of this thesis is to investigate the feasibility of reliable data converters design techniques in standard CMOS processes for low-voltage operation. We will propose circuit techniques and design methods for low-voltage analog building blocks such as sample-and-hold, opamp, comparator, etc. Those building blocks will be used to implement a complete successive approximation ADC.

The following systematic work methodology will be used to attain the main objective.

- Overview of past and current research status to cover the existing design techniques for low-voltage circuits;

- Investigation of the limitations imposed by the restriction of low supply voltage;

- Study of the reliability issues involved in deep submicron CMOS circuit design;

- Development of circuit techniques for low-voltage deep submicron building blocks used in the design of data converters (sample-and-hold, opamp, comparator, D flip-flop, digital-to-analog converters);

- Application of completed building blocks to design a 1-V successive approximation ADC in a 0.18 μm standard digital CMOS process;

- Results, synthesis and discussions with further development.

### 1.3 Research contributions and organization of the thesis

The contributions presented in this thesis have been partially reported in several conference and journal and summarized below.

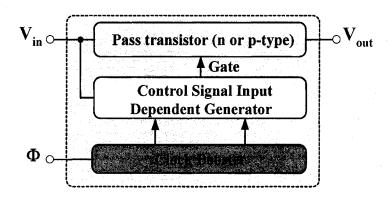

• We present in [FAY03a] an overview of circuit techniques used to design reliable low-voltage (1-V and below) analog building blocks in deep submicron standard CMOS processes. The challenges of designing such low-voltage and reliable analog circuits are addressed both at electronic circuit and physical layout levels. State-of-the-art circuit topologies and techniques (input level shifting, bulk and current driven, DTMOS), used to build main analog modules (operational

- amplifier, analog CMOS switches) are covered with the implementation of MOS capacitors.

- In [FAY00a], we proposed a new approach to the design of a CMOS differential latched comparator suitable for low voltage applications. The novel approach makes use of the well-known constant-gm rail-to-rail input stage used in amplifiers. The circuit consists of a constant-gm rail-to-rail common-mode OTA (compared to previous work [CHU99], [HES91], [KUM86] and [SHI91]) followed by a regenerative latch. The circuit dissipates less than 86 μA with a supply voltage of 1.65 V in a standard CMOS 0.18 μm digital process. At the heart of the design is a track-and-latch circuit. This circuit reduces the number of gain stages normally required in an asynchronous or multi-stage comparator [JOH97], thereby reducing the power and silicon area requirements, as well as decreasing the comparator settling time. The net result is a more power efficient comparator.

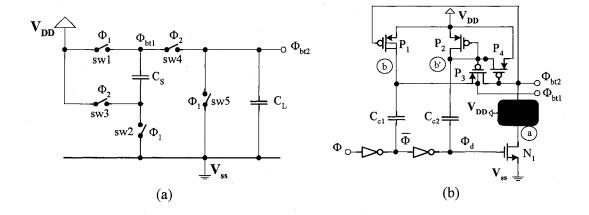

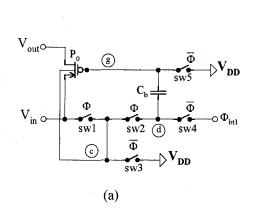

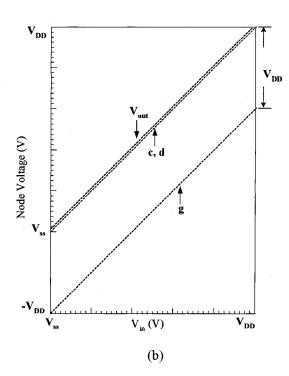

- We proposed in [FAY00b] a sample-and-hold circuit based on a novel implementation of the bootstrapped low-voltage analog CMOS switch. Also, corresponding experimental results were reported in [FAY03b]. The heart of this circuit is a new low-voltage and low-stress CMOS clock voltage signal booster. Through the use of a dummy switch, the charge injection induced by the bootstrapped switch is greatly reduced resulting in improved sample-and-hold accuracy. The circuit has been implemented in a standard CMOS 0.18 μm digital process. The experimental results show that operation is possible for supply voltages close to transistor threshold (0.6 V).