|                         | MPEG-2 data encryption for transport over ATM/SONET and its clock generator                                                                                                                                                                               |

|-------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Auteur: Author:         | Beisong Liu                                                                                                                                                                                                                                               |

| Date:                   | 2003                                                                                                                                                                                                                                                      |

| Type:                   | Mémoire ou thèse / Dissertation or Thesis                                                                                                                                                                                                                 |

| Référence:<br>Citation: | Liu, B. (2003). MPEG-2 data encryption for transport over ATM/SONET and its clock generator [Mémoire de maîtrise, École Polytechnique de Montréal]. PolyPublie. <a href="https://publications.polymtl.ca/7133/">https://publications.polymtl.ca/7133/</a> |

# Document en libre accès dans PolyPublie Open Access document in PolyPublie

URL de PolyPublie:

PolyPublie URL:

Directeurs de recherche:

Advisors:

Programme:

Program:

Non spécifié

In compliance with the Canadian Privacy Legislation some supporting forms may have been removed from this dissertation.

While these forms may be included in the document page count, their removal does not represent any loss of content from the dissertation.

#### UNIVERSITÉ DE MONTRÉAL

# MPEG-2 DATA ENCRYPTION FOR TRANSPORT OVER ATM/SONET AND ITS CLOCK GENERATOR

# BEISONG LIU DÉPARTEMENT DE GÉNIE ÉLECTRIQUE ÉCOLE POLYTECHNIQUE DE MONTRÉAL

MÉMOIRE PRÉSENTÉ EN VUE DE L'OBTENTION

DU GRADE DE MAÎTRISE ÈS SCIENCES APPLIQUÉES (M.Sc.A.)

(GÉNIE ÉLECTRIQUE)

Juillet 2003

National Library of Canada

Acquisitions and Bibliographic Services

395 Wellington Street Ottawa ON K1A 0N4 Canada Bibliothèque nationale du Canada

Acquisisitons et services bibliographiques

395, rue Wellington Ottawa ON K1A 0N4 Canada

> Your file Votre référence ISBN: 0-612-86411-1 Our file Notre référence ISBN: 0-612-86411-1

The author has granted a nonexclusive licence allowing the National Library of Canada to reproduce, loan, distribute or sell copies of this thesis in microform, paper or electronic formats.

The author retains ownership of the copyright in this thesis. Neither the thesis nor substantial extracts from it may be printed or otherwise reproduced without the author's permission.

L'auteur a accordé une licence non exclusive permettant à la Bibliothèque nationale du Canada de reproduire, prêter, distribuer ou vendre des copies de cette thèse sous la forme de microfiche/film, de reproduction sur papier ou sur format électronique.

L'auteur conserve la propriété du droit d'auteur qui protège cette thèse. Ni la thèse ni des extraits substantiels de celle-ci ne doivent être imprimés ou aturement reproduits sans son autorisation.

# UNIVERSITÉ DE MONTRÉAL ÉCOLE POLYTECHNIQUE DE MONTRÉAL

#### Ce mémoire intitulé:

# MPEG-2 DATA ENCRYPTION FOR TRANSPORT OVER ATM/SONET AND ITS CLOCK GENERATOR

présenté par: Beisong LIU

en vue de l'obtention du diplôme de: MAÎTRISE ÈS SCIENCES APPLIQUÉES a été dûment accepté par le jury d'examen constitué de:

M. YVON SAVARIA, Ph.D., Président

M. MOHAMAD SAWAN, Ph.D., Directeur

M. GUY BOIS, Ph.D., Membre

# **DEDICATION**

To my husband, Peijian

my son, Max,

and my parents

#### ACKNOWLEDGEMENTS

I am grateful to my supervisor, Professor Mohamad Sawan, for his constant confidence, support, encouragement, and guidance throughout this thesis. I am also thankful for the help and friendship of the members of the Polystim research team, who were always ready to engage in useful discussions.

I would like to express my appreciation to Yamu Hu, Mathieu Gagnon, Xiaohong Zhao, Abdelouahab Djemouai, Jean-Charles Voghell and Adel Belhaouane for helping me with various design tools.

I would also like to thank Brent Veitch and Hugh W. Pollitt-Smith, who are support engineers at Canadian Microelectronics Corporation. They answered my questions about this project from RTL description to completed custom design and FPGA designs using Synopsys and Xilinx tools.

I am especially grateful to Craig Piercey and Roger Langlois at Tundra Semiconductor Corporation for his English/ French writing and editorial assistance.

Many thanks to my friends for helping to establish a friendly environment in which to work and for providing moral support during the difficult stages of this work.

Finally, I would like to thank my husband, Peijian Yuan, to whom I owe much for his unending patience, encouragement, and understanding without which I could not have completed this work. Special thanks also to my lovely son Max Yuan, for his understanding and for not providing him with full attention during his growing years.

#### **ABSTRACT**

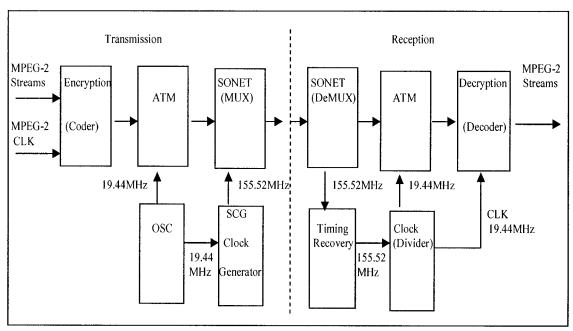

With the ever-increasing growth of data communication, the need for security and confidentiality has become a basic necessity. At the same time, it is expected that when Asynchronous Transfer Mode (ATM) / Synchronous Optical Network (SONET) higher transport frequencies become commonly available, the capacity of telecommunication networks will increase enormously, making media like video-conferencing and videophone a reality, rather than fiction. We propose in this Master thesis a system architecture to support encrypted Moving Pictures Expert Group (MPEG-2) stream transport over ATM/SONET. Some of the key technical issues are discussed and solved. The goals of our work include:

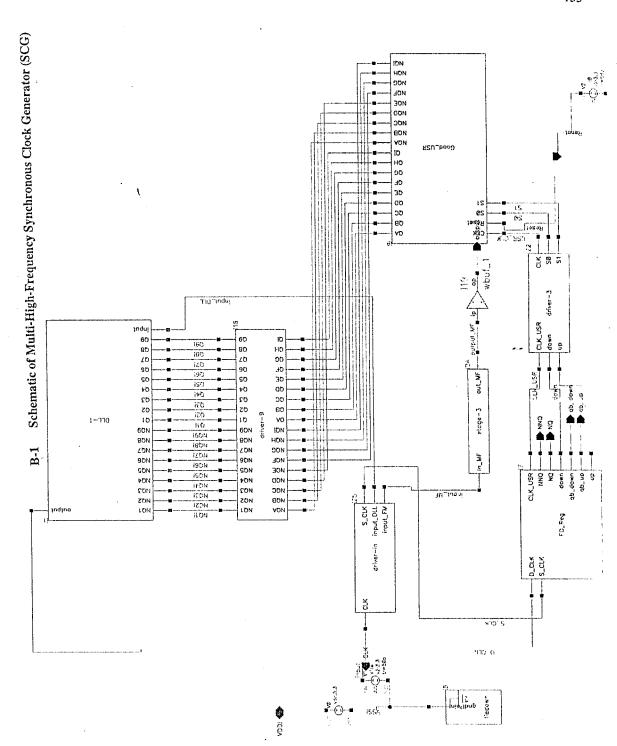

- Develop a new ALL-Digital Delay Locked Loop (ADDLL) function and a Mirror Delay Approach (MDA) to replace the Phase Locked Loop (PLL) technique in order to implement a Multiple-High-Frequency Synchronous Clock Generator (SCG) to support an encrypted MPEG-2 stream transport over an ATM/SONET system.

- Construct an encrypted MPEG-2 stream transport over ATM/SONET system. This

system can support three standards (MPEG-2/ATM/SONET). The emerging

information and data stream may be encrypted and decrypted at both transmission and

reception sides.

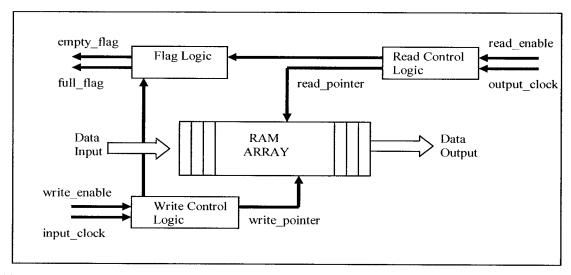

- Design of a synchronous dual-port FIFO memory dedicated to the transport of MPEG-2 data toward ATM cells. The implementation of its control unit is achieved using Verilog.

• Implement a Data Encryption Standard (DES) algorithm on an FPGA to validate its operation.

To achieve these goals, the research topics discussed in the following sections represent a summary of our efforts.

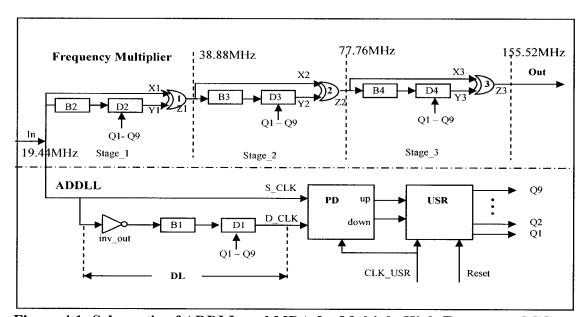

First, an All-digital delay locked loop (ADDLL) function is used as a new method to synchronize the input signal and output clocks (19.44 MHz and 155.52 MHz) of the transmission section, as well as timing recovery in the receiver section. Using ADDLL replaces a PLL function which has analog components with a fully digital design. It does not contain any passive components, such as resistors and capacitors. Therefore, the ADDLL overcomes inherent problems associated with analog circuits. The Mirror Delay Approach (MDA) uses the principle of symmetry and proportion to control mirror delay in a multiple-stage frequency generator. This means that the input delay in the phase detector and the input delay in the Frequency Generator are mirrors of each other and symmetric. The variable delay at each stage of the frequency multiplier and the variable delay of the control unit (ADDLL functional block) are proportional. A Multiple-High-Frequency (SCG) using both methods (ADDLL and MDA) is designed. Its frequency output is fixed at 38.88 MHz, 77.76 MHz, and 155.52 MHz from 19.44 MHz. The corresponding chip is fabricated with the CMOS 0.35-µm process from TSMC (Taiwan Semiconductor Manufacturing Company). The test results of the fabricated chip satisfied our expectations. This master thesis allows to prove that the ADDLL function for supporting the synchronization of transmission / reception stages is a valuable precise and

easy to implement method. Also, using an ADDLL and an MDA simplifies the design of a multi-high-frequency SCG.

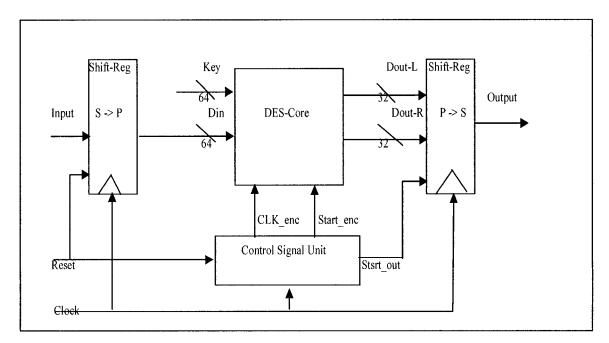

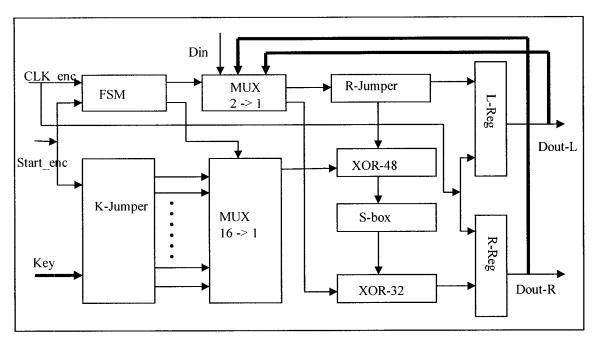

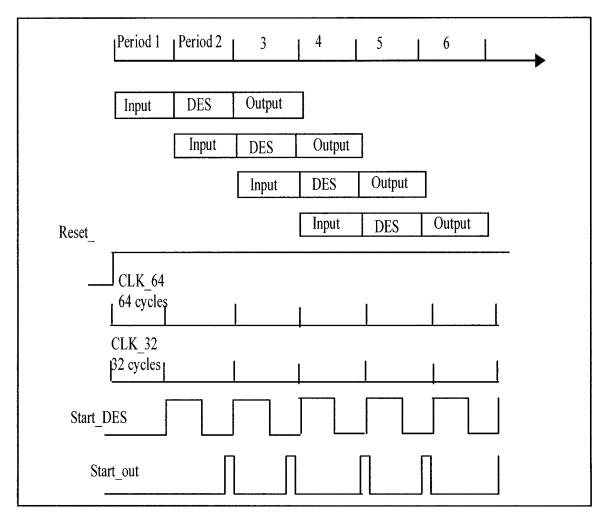

The second part of this master thesis concerns the encrypted data streams to be sent over ATM cells. In fact, the architecture of an interface that encrypts MPEG-2 streams to ATM cells is based on a synchronous, dual-ported RAM-based FIFO, which is used to access data. Using a dual-ported cell for the FIFO memory makes the control of the FIFO simpler because the read and write controls are non-correlated. Therefore, read and write data to or from the FIFO can occur at the same time without introducing wait states. This technique simplifies the operation of the dedicated finite state machine for this interface. The third part of our work is the implementation of the data encryption standard (DES) algorithm on FPGA. A key consideration in the implementation of the DES algorithm is that the data stream passes through the encryption block without impacting the transport speed. This DES algorithm's circuit architecture consists of processing the data 16 times through the same stage. The whole process for input, computing, and output data uses a pipeline architecture. The results obtained through VHDL simulations of the encryption DES algorithm are satisfactory. The mapping of the DES algorithm code to a Xilinx FPGA device (XC4028) is achieved. The design's simplicity and fast computation of the DES algorithm offer a dynamic structure for data encryption in data communication systems.

The results obtained during this research work prove that the ADDLL function can be used to easily and quickly construct a delay locked-loop function for timing synchronization on a circuit or system. The ADDLL function implemented is 100 percent

digital. The ADDLL function and MDA together can be used in the transmission section of a data communication system for designing a multiple-stage transmission clock generator. In addition, the ADDLL function may be used for timing recovery in the reception section. Further work is needed to determine more applications that can benefit from this approach.

Further work is also necessary to apply the ADDLL function for timing recovery in a reception, and to implement the whole transmission section on an integrated chip. Also, a more extensive analysis is required for a real system-level simulation, which would include the integration of the clock generator and the remaining part of the system.

#### **RÉSUMÉ**

Avec la croissance des communications numériques, les besoins de securité et de confidentialité sont devenus essentiels. De plus, il est possible de prévoir que lorsque les réseaux ATM/SONET deviendront disponibles à grande échelle, la capacité des réseaux de communication suivra une progression très rapide et du même coup, améliorera les moyens de communication tels que les conférences vidéo et les vidéophones. Ce mémoire de maîtrise décrit le diagramme fonctionnel d'un système permettant le transport d'images MPEG-2 encryptées à travers un lien ATM/SONET. Certains autres éléments clés sont également traités dans ce mémoire.

Les objectifs de ce mémoire sont:

- Concevoir un générateur d'horloge capable de produire plusieurs signaux d'horloge synchrones à haute-fréquence d'une façon purement digitale en utilisant le procédé CMOS 0.35 microns de la compagnie TSMC (Taiwan Semiconductor Manufacturing Company).

- Implémenter un algorithme d'encryptage de donneés (Data Encryption Standard DES) dans un FPGA (Field Programmable Gate Array). L'algorithme est programmé

en language VHDL et implémenté sur FPGA Xilinx en se servant de l'outil Synopsys.

- Décrire le code d'une pile FIFO (First In, First Out) synchrone dédiée au transport des données de MPEG-2 à une cellule ATM. Le language utilisé à cette fin est le Verilog.

Les paragraphes suivants sont un sommaire des travaux effectués dans ce mémoire.

Premièrement, un module de génération d'horloge synchrone (GHS) purement numérique est proposé. Il produit un signal dont les plages de fréquence vont de 19.44 MHz jusqu'à

38.88 MHz et de 77.76 MHz jusqu'à 155.52 MHz. Le système fait appel à la technique de boucle de délais de phase entièrement numérique (ALL-Digital Delay Locked Loop - ADDLL) et de l'approche à miroir de délais (Mirror Delay Approach - MDA). La technique ADDLL rend le circuit moins sensible aux variations de température, de tension d'alimentation, et du procédé de fabrication. De ce fait, elle réduit la sensibilité aux variations de fréquence et aux différences de délais provenant du système de distribution du signal d'horloge. Elle est également utilisée pour la synchronisation des données et le recouvrement des délais dans les systèmes de communication sériels. Le MDA est basée sur le principe de proportion et de symétries, afin de contrôler le miroir de délais. Le système utilisant les deux techniques, ADDLL et MDA, permet de produire un signal d'horloge synchrone à fréquences multiples. Le circuit intégré fut fabriqué en CMOS 0.35-um de la compagnie TSMC (Taiwan Semiconductor Manufacturing Company).

En second lieu, nous procédons au design d'un module dédié au transfert de trames encryptées MPEG-2 vers une interface ATM. L'utilisation d'une pile FIFO implementée à l'aide d'une mémoire RAM à deux ports est adoptée, l'avantage vient du fait que les accès aux deux ports de la mémoire sont asynchrones entre eux et donc indépendants. L'écriture peut donc être faite par un port donné, pendant que la lecture de la pile se fait par l'autre port, éliminant ainsi les cycles d'attente. Cette méthode simplifie les opérations de la machine à états synchrone qui contrôlent cette interface.

La troisième partie du mémoire concerne l'implementation d'un algorithme d'encryptage sur FPGA. En ce qui à trait à l'encryptage par l'algorithme DES (data encryption

standard) sur FPGA, le système est basé sur l'idée d'un traitement des données, sans impact sur la vitesse de tout réseau de transport, par une architecture à un étage, dans laquelle les données sont traitées 16 fois. Le procédé d'entrée, de traitement et de sortie des données utilise une architecture pipelinée. L'utilisation du Xilinx Design Manager (XC4028EX) donne une performance acceptable pour l'implémentation de l'algorithme d'encryption. La simplicité du système et la rapidité de traitement de l'algorithme DES offre une structure dynamique pour l'encryptage dans les systèmes de communication numérique.

Les résultats obtenus dans ce mémoire prouvent que l'utilisation d'un ADDLL et d'une MDA permettent de construire un système à boucle de délais pour la synchronisation des signaux. Nous avons produit un système à boucle de délais de phase entièrement numérique. Un générateur de signaux d'horloge synchrone à multiples haute-fréquences peut être utilisé dans la section de transmission des systèmes de communication, pour la génération du signal d'horloge de transmission. De plus, le ADDLL peut être utilisé pour la synchronisation des données dans la section de réception.

De plus amples travaux seront nécessaires pour appliquer la technique de ADDLLL pour le recouvrement d'une horloge en réception et pour l'implémentation d'une interface entre ce système et une interface PCI ou USB. De plus, une analyse plus approfondie est nécessaire pour l'implémentation du système complet sur une même puce.

#### **ABBREVIATIONS**

ADDLL ALL-Digital Delay Locked Loop

AAL ATM Adaptation Layer

ASIC Application Specific Integrated Circuits

ATM Asynchronous Transfer Mode

B-ISDN Broadband ISDN

CCITT International Consultative Committee for Telephones and Telegraphs

CDR Clock and Data Recovery

CLB Configurable Logic Blocks

CLP Cell Loss Priority

CMC Canadian Microelectronics Corporation

CS Convergence Sub-layer

DCO Digital Control Oscillator

DES Data Encryption Standard

DFED Differentiator with First Edge Detection

DL Delay Line

DPLL Digital Phase Locked Loop

FM Frequency Multiplier

FPGA Field Programmable Gate Array

FSM Finite State Machine

GFC Generic Flow Control

GHS Génération d'horloge synchrone

HDTV High-definition television

HEC Header Error Control

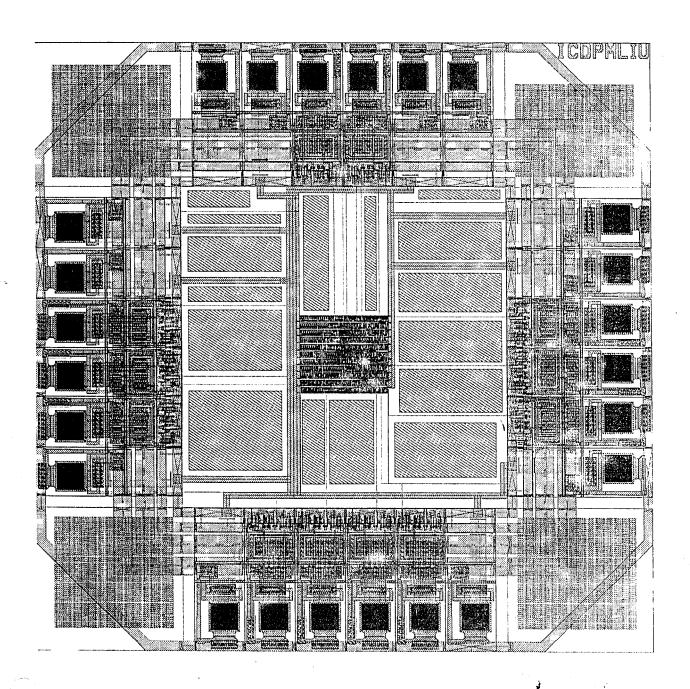

ICDPMLIU Synchronous clock generator chip ID

IOB Input/Output Block

ISDN Integrated Services Digital Network

ITU International Telecommunications Union

LAN Local Area Network

MDA Mirror Delay Approach

Mbps Mega bits per second

MPEG Moving Pictures Expert Group

NRZ Non-Return-to-Zero

NTSC National Television System Committee

OC Optical Carrier

OSC Oscillator

PCI Peripheral Component Interface

PD Phase Detector

PES Packetized Elementary Streams

PLCP Physical layer Convergence Protocol

PS Program Stream

PSTN Public Switched Telephone Network

RTL Release to Layout

SAR Segmentation and Reassembly

SDH Synchronous Digital Hierarchy

SCG Synchronous Clock Generator

SONET Synchronous Optical Network

STS Synchronous Transport Signal level

TDM Time-division Multiplexing

TOH Transport Overhead

TS Transport Stream

TSMC Taiwan Semiconductor Manufacturing Company

USB Universal Serial Bus

USR Universal Shift Register

VCI Virtual Channel Identifier

VHDL Very Hardware Description Language

VPI Virtual Path Identifier

WAN Wide Area Network

# **TABLE OF CONTENTS**

| DEDICATIONi                                                                    |

|--------------------------------------------------------------------------------|

| ACKNOWLEDGEMENTSi                                                              |

| ABSTRACT                                                                       |

| RÉSUMÉi                                                                        |

| ABBREVIATIONS xi                                                               |

| TABLE OF CONTENTSxx                                                            |

| LIST OF FIGURESxvii                                                            |

| LIST OF TABLESxvii                                                             |

| LIST OF APPENDICESxx                                                           |

|                                                                                |

|                                                                                |

| Chapter 1 INTRODUCTION                                                         |

| 1.1 Motivation                                                                 |

| 1.2 Standards                                                                  |

| 1.2.1 Moving Picture Experts Group – Phase (MPEG-2)                            |

| 1.2.2 Asynchronous Transfer Mode (ATM)                                         |

| 1.2.3 Synchronous Optical NETwork                                              |

| 1.2.4 Data Encryption Standard Algorithm                                       |

| 1.3 Contributions of this Master Thesis                                        |

| 1.3.1 Transmission clock generator and timing recovery in the reception side18 |

| 1.3.2 Interface for Encrypted MPEG-2 Streams to ATM Cell                       |

| 1.3.3 Data Encryption Standard (DES)                        | 20   |

|-------------------------------------------------------------|------|

| 1.4 Organization of the Master Thesis                       | 20   |

| Chapter 2 LITERATURE REVIEW AND PROSPECTS                   | 22   |

| 2.1 Surveying of Analog and Digital Phase-Locked Loops      | 22   |

| 2.2 Review of ADPLL technology                              | 23   |

| 2.2.1 Portable Design of ADPLL-Based Clock Recovery Circuit | 24   |

| 2.2.2 ADPLL with Simplified DCO Hardware                    | 27   |

| 2.3 Review of ATM/SONET Interface                           | 31   |

| 2.3.1 The CYS25G0101DX SONET OC-48 Transceiver              | 31   |

| 2.3.2 The S3019 SONET/SDH/ATM OC-3/12 Transceiver           | 33   |

| 2.4 Prospects                                               | 37   |

| Chapter 3 ENCRYPTED DATA TRANSMISSION OVER ATM/SONET        | 39   |

| 3.1 Description of the Data Transport Interface             | 39   |

| 3.2 Overview of the Physical Interface                      | 41   |

| 3.3 FIFO for Data Transport from MPEG-2 TS to ATM Cell      | 48   |

| 3.3.1 The Implementation of a FIFO                          | 48   |

| Chapter 4 MULTI-HIGH-FREQUENCY SYNCHRONOUS CLOCK GENERAT    | OR53 |

| 4.1 All Digital Delay Locked Loop and Mirror Delay Approach | 53   |

| 4.2 Basic Idea of the Multiple-High-Frequency SCG           | 55   |

| 4.3 SCG Architecture                                        | 59   |

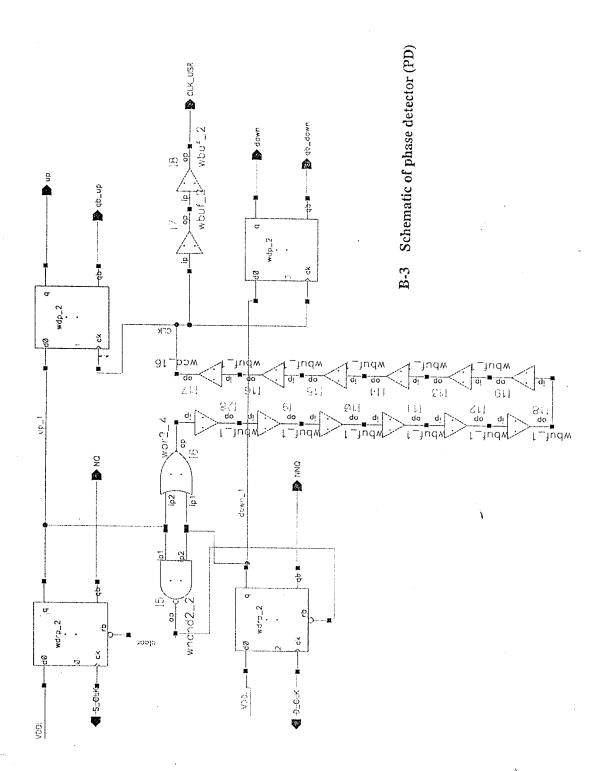

| 4.3.1 The Phase Detector                                    | 59   |

| 4.3.2 The Universal Shift Register                          | 60   |

| 4.3.3 The Delay Line                                        | 61  |

|-------------------------------------------------------------|-----|

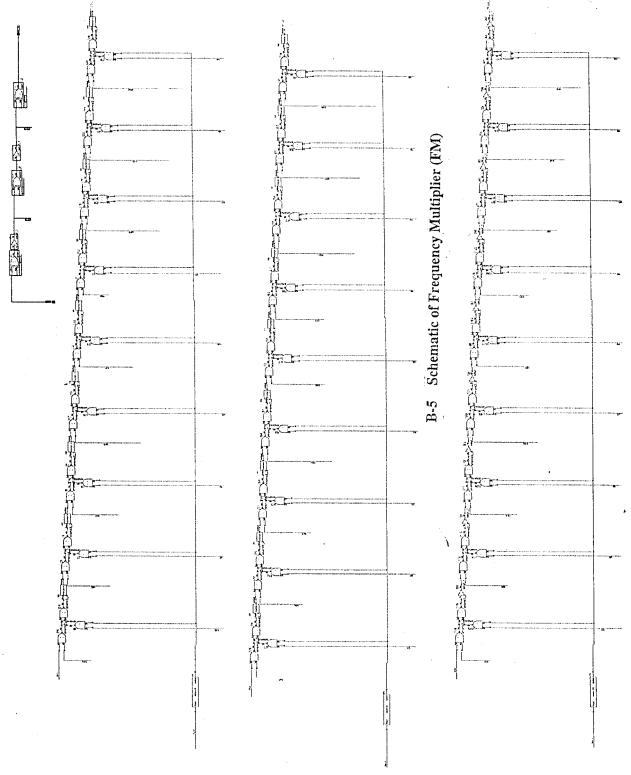

| 4.3.4 The Frequency Multiplier                              | 63  |

| 4.4 Implementation of the Synchronous Clock Generator       | 64  |

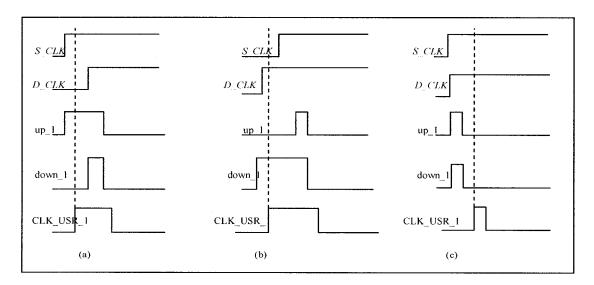

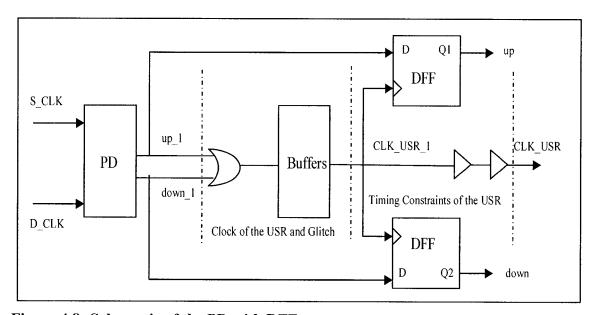

| 4.4.1 Clock of the USR and Glitching Noise                  | 64  |

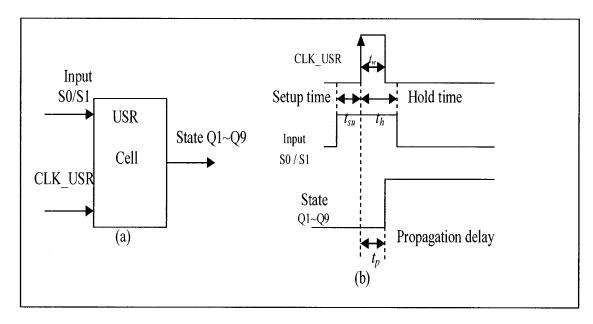

| 4.4.2 Timing Constraints of the USR                         | 65  |

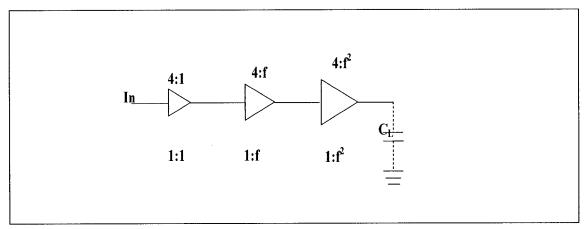

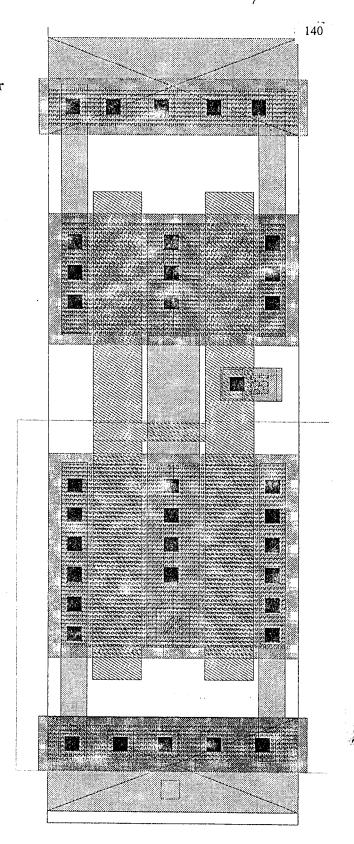

| 4.4.3 Driving Large Capacitive Loads                        | 67  |

| 4.4.4 Design Inverter Layout Cell for the Fixed Delay Line  | 68  |

| 4.5 Chip Characteristics and Design Flow                    | 69  |

| 4.6 ADDLL Function for Timing Recovery                      | 72  |

| Chapter 5 THE IMPLEMENTATION OF ENCRYPTION DES ALGORITHM    | 75  |

| 5.1 Review                                                  | 75  |

| 5.2 Architecture of the Coding DES Algorithm                | 75  |

| 5.3 Software-Based Logic Verification                       | 80  |

| 5.4 Prototyping for DES Algorithm using an FPGA             | 81  |

| 5.4.1 FPGA Design Flow and Report                           | 82  |

| Chapter 6 RESULTS                                           | 84  |

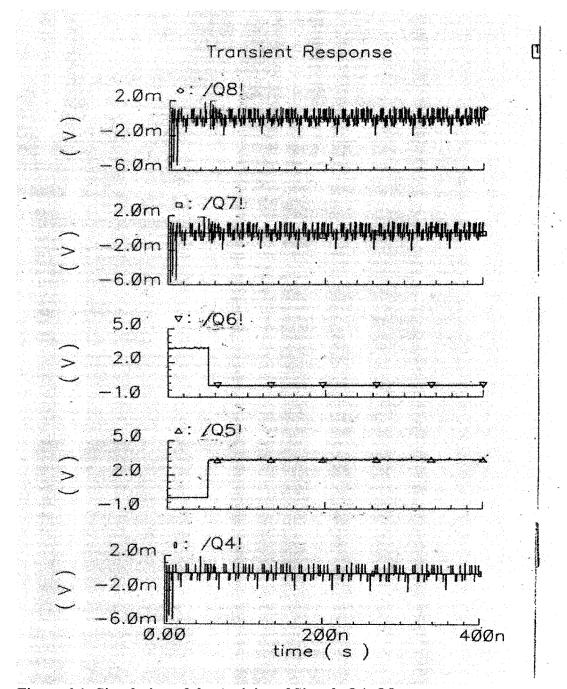

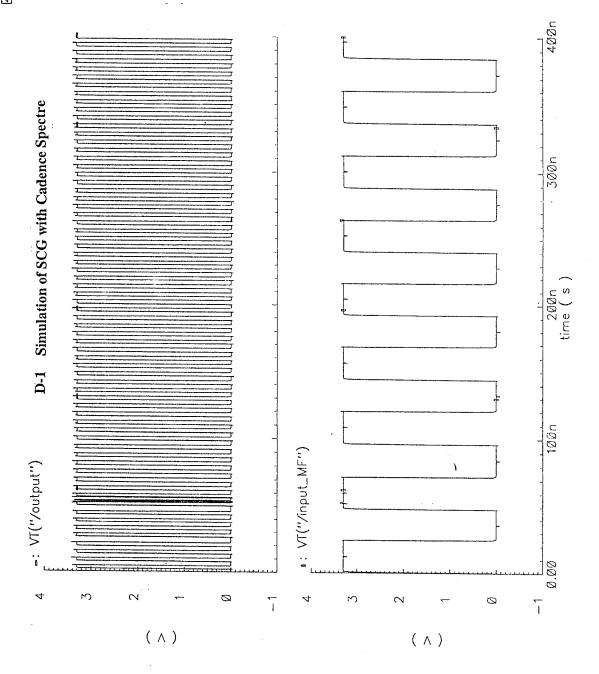

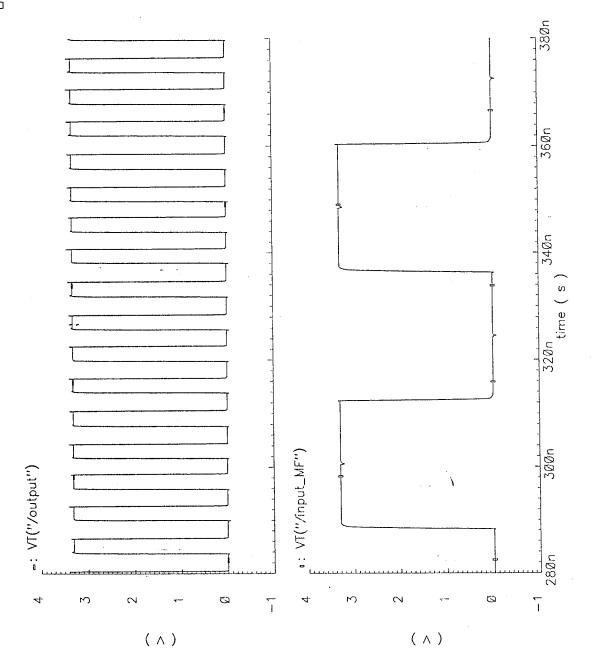

| 6.1 Simulation Result of the Multiple-High-Frequency SCG    | 84  |

| 6.2 Testing of the Fabricated ICDPMLIU Chip                 | 87  |

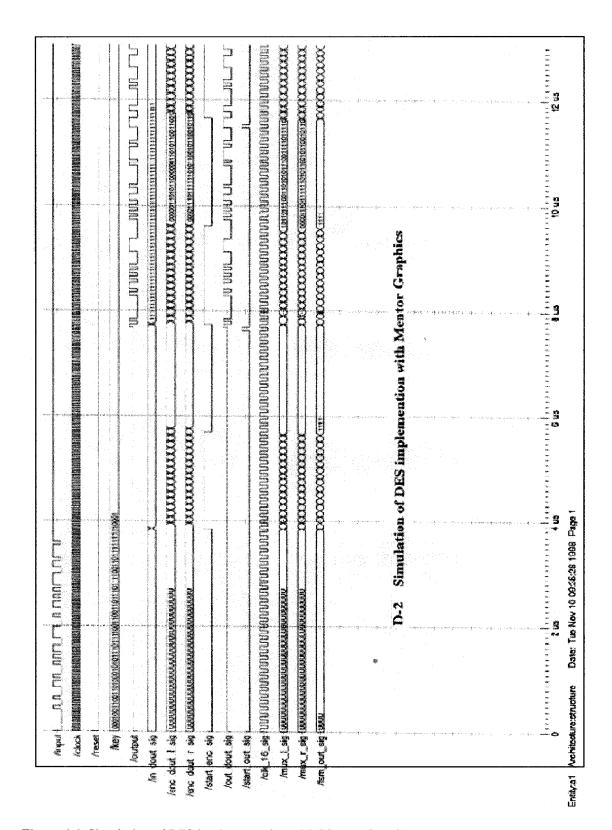

| 6.3 Verification of the Implementation of the DES Algorithm | 90  |

| Chapter 7 CONCLUSION AND FUTURE WORKS                       | 93  |

| BIBLIOGRAPHY                                                | 96  |

| A DDENIDICES                                                | 101 |

# LIST OF FIGURES

| Figure 1.1: Block Diagram of Broadband Audio/Visual Terminal            | 4  |

|-------------------------------------------------------------------------|----|

| Figure 1.2: Basic ATM Cell Structure                                    | 5  |

| Figure 1.3: Basic ATM Cell Header                                       | 5  |

| Figure 1.4: SONET/ATM Multiplexing Hierarchy                            | 7  |

| Figure 1.5: ATM Service Classes and AALs                                | 8  |

| Figure 1.6: ATM Adaptation Layer (AAL)                                  | 8  |

| Figure 1.7: STS-1 Frame Structure                                       | 11 |

| Figure 1.8: STM-1 Basic Frame Format                                    | 12 |

| Figure 1.9: Data Encryption and Decryption System                       | 13 |

| Figure 1.10: Complete Representation of the DES Operation               | 15 |

| Figure 1.11: One Stage of the DEC Algorithm                             | 16 |

| Figure 1.12: S-Boxes operation on eight 6-bit blocks                    | 17 |

| Figure 1.13: The Block Diagram for Representation of Our Research Areas | 17 |

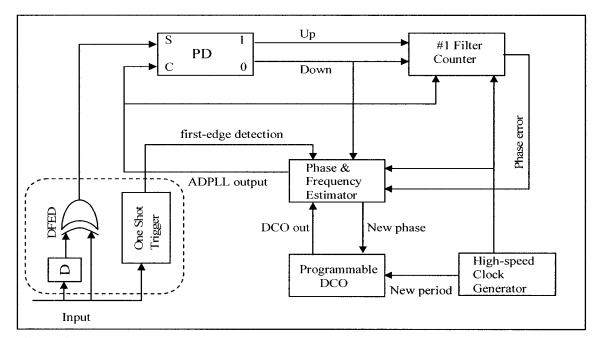

| Figure 2.1: Block Diagram of the Cell-based ADPLL Architecture          | 24 |

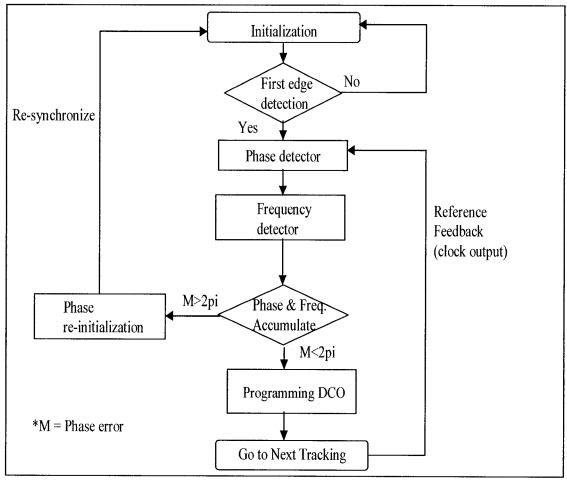

| Figure 2.2: Flowchart of the Proposed ADPLL Operation                   | 25 |

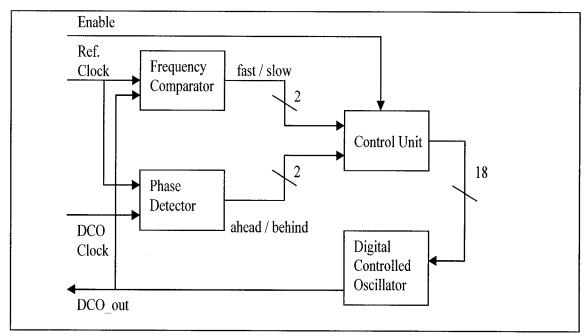

| Figure 2.3: ADPLL Block Diagram                                         | 28 |

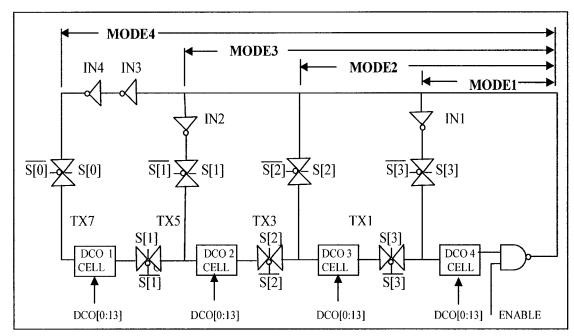

| Figure 2.4: Simplified Schematic of DCO Architecture                    | 29 |

| Figure 2.5: Simplified Circuit of a DCO Cell                            | 30 |

| Figure 2.6: Block Diagram of the CYS25G0101DX Transceiver [19]          | 32 |

| Figure 2.7: Block Diagram of S3019 Transceiver [20]                     | 34 |

| Figure 3.1: Functional Blocks of System                                 | 40 |

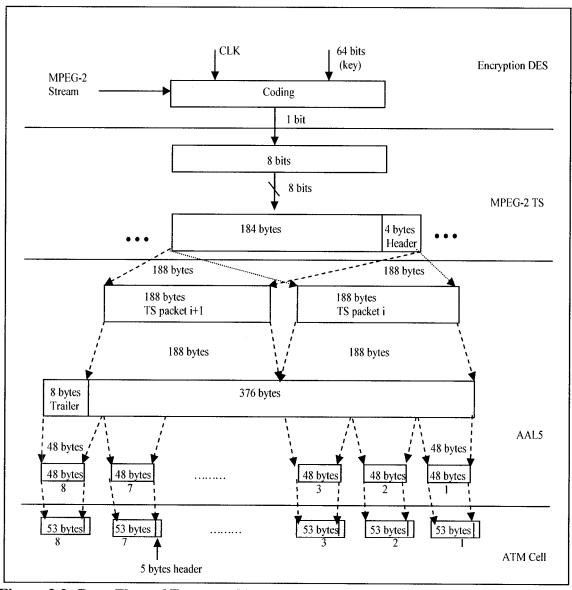

| Figure 3.2: Data Flow of Encrypted MPEG-2 TS / AAL-5/ATM Cell                | 32     |

|------------------------------------------------------------------------------|--------|

| Figure 3.3: Interface Architecture of Encrypted MPEG-2 Stream to ATM Cell Ma | apping |

|                                                                              | 43     |

| Figure 3.4: The Flowchart for Read Data Controls of the FSM                  | 41     |

| Figure 3.5: RAM-based FIFO                                                   | 48     |

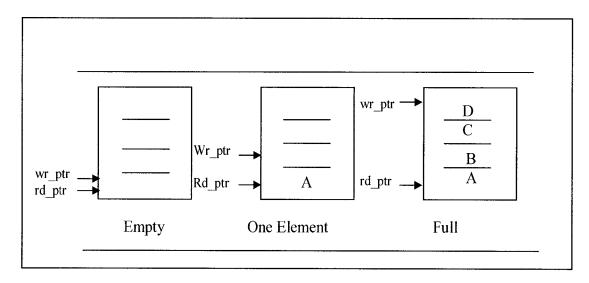

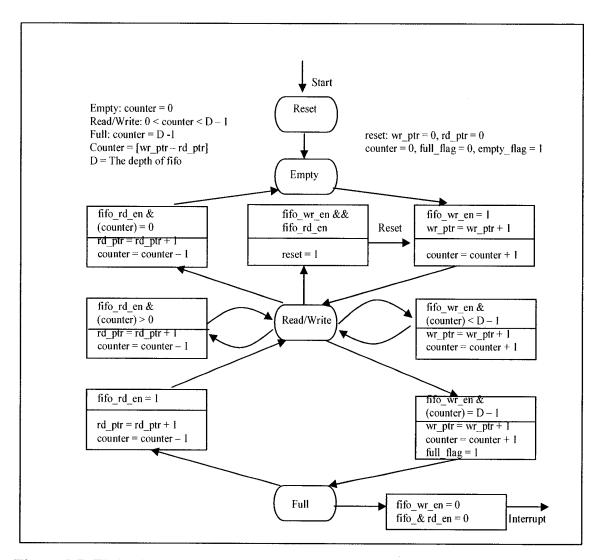

| Figure 3.6: The Operation of Read and Write Pointer in Memory                | 50     |

| Figure 3.7: Finite State Machine of FIFO (FSM)                               | 51     |

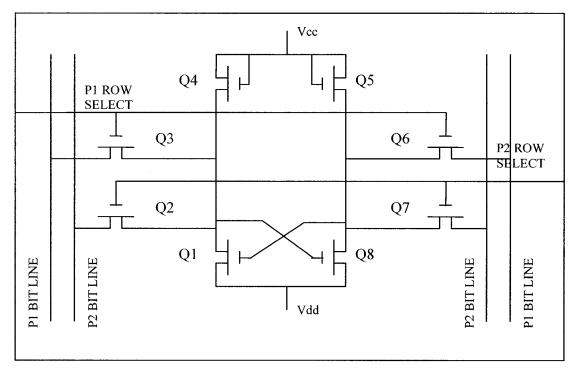

| Figure 3.8: Dual-Port Cell for the FIFO Memory                               | 52     |

| Figure 4.1: Schematic of ADDLL and MDA for Multi-High-Frequency SCG          | 55     |

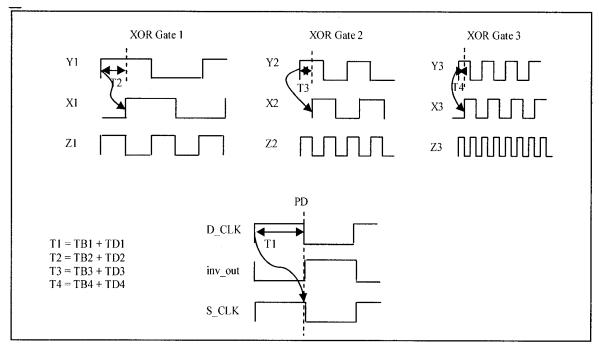

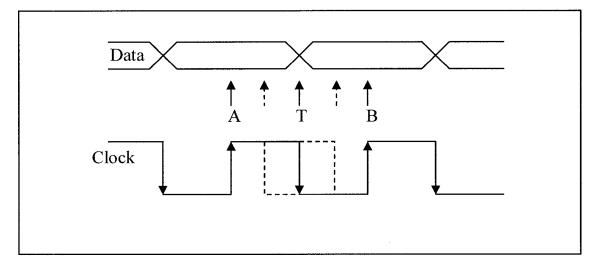

| Figure 4.2: Input and Output Waveforms of Each Gate and PD in ADDLL          | 57     |

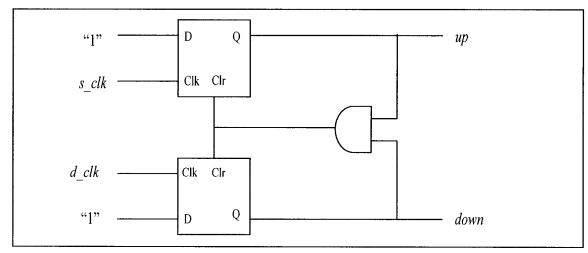

| Figure 4.3: Block Diagram of the Phase Detector                              | 59     |

| Figure 4.4: Input and Output Waveform of the Phase Detector                  | 60     |

| Figure 4.5: Schematic of Variable Delay Line                                 | 62     |

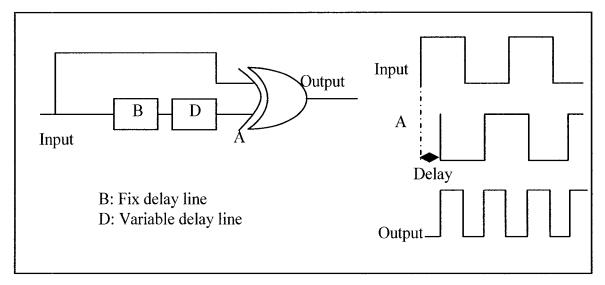

| Figure 4.6: Waveform of One Stage Frequency Multiplier                       | 63     |

| Figure 4.7: Waveforms without flip-flops in USR                              | 64     |

| Figure 4.8: Schematic of PD with DFF                                         | 65     |

| Figure 4.9:Timing Behaviour of the USR Cell                                  | 67     |

| Figure 4.10: Driving Large Capacitive                                        | 68     |

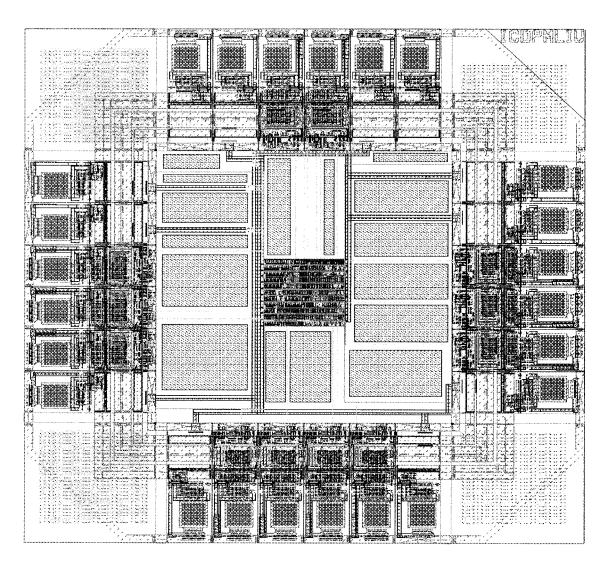

| Figure 4.11: Layout of SCG                                                   | 70     |

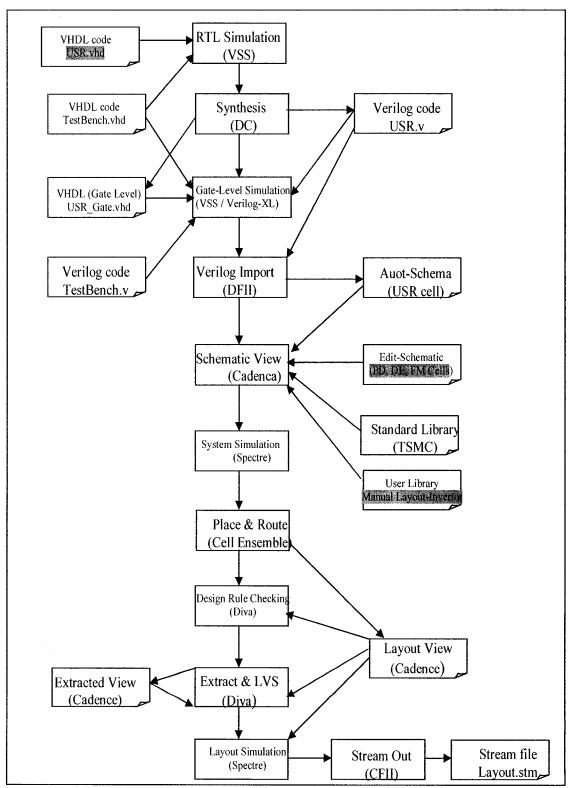

| Figure 4.12: Design Flow for Multiple-High Frequency SCG                     | 71     |

| Figure 4.13: Application of ADDLL Function for Timing Recovery               | 72     |

| Figure 4.14: Data Sampling                                                   | 73     |

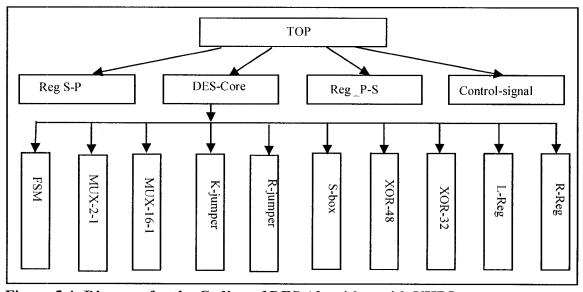

| Figure 5.1: Functional Block Diagram of Implemented DES Algorithm   | 76 |

|---------------------------------------------------------------------|----|

| Figure 5.2: Architecture of DES Core                                | 78 |

| Figure 5.3: Clock and Control Signal for Pipelining Data Processing | 79 |

| Figure 5.4: Diagram for the Coding of DES Algorithm with VHDL       | 80 |

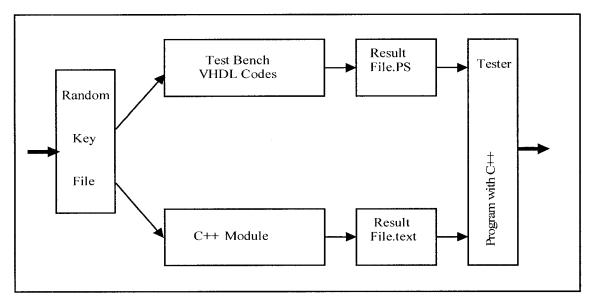

| Figure 5.5: Software-Based Method for Automatic Verification        | 81 |

| Figure 5.6: FPGA Design Flow                                        | 83 |

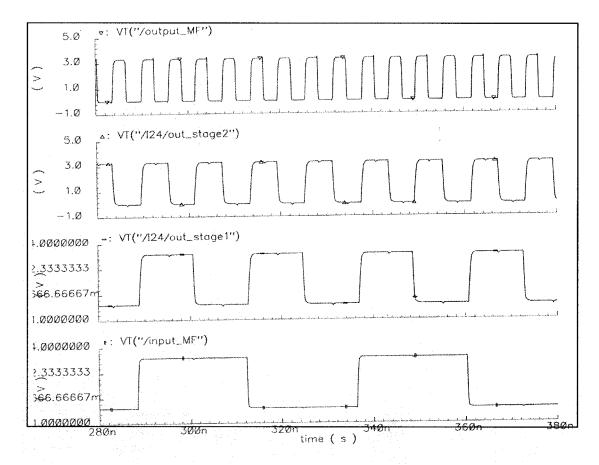

| Figure 6.1: Simulation of the Activity of Signala Q4~Q8             | 85 |

| Figure 6.2: The Simulation Results of ICDPMLIU Chip                 | 87 |

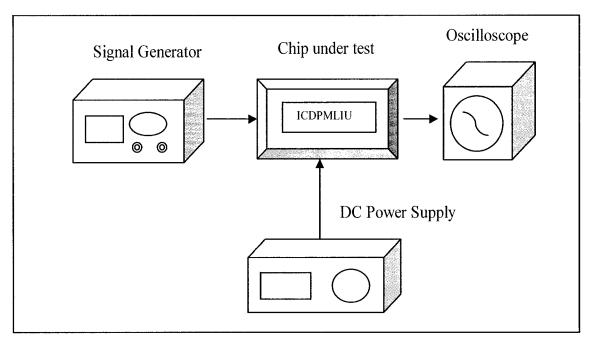

| Figure 6.3: The chip Testing Environment                            | 88 |

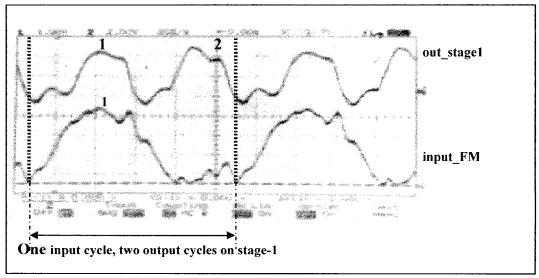

| Figure 6.4: Input and Output Signals on Stage-1                     | 88 |

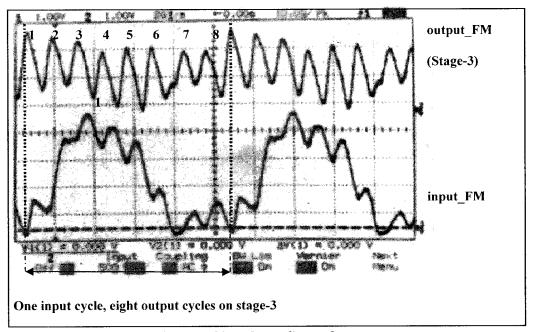

| Figure 6.5: Input and Output Signals on Stage-3                     | 89 |

| Figure 6.6: Simulation of DES Implementation with Mentor Graphic    | 91 |

# LIST OF TABLES

| Table 1.1: The specific functions of the ATM cell header                                  | 6  |

|-------------------------------------------------------------------------------------------|----|

| Table 1.2 : SONET and SDH Equivalent Designators                                          | 10 |

| Table 1.3: The Summary of Our Contributions                                               | 18 |

| Table 4.1: 2 <sup>n</sup> Relationship for Each Delay time TBx and TDx (x= 1, 2, 3 and 4) | 58 |

| Table 4.2: 9-bit Universal Shift Register                                                 | 61 |

| Table 4.3: Summary of the Chip's Features (ICDPMLIU)                                      | 70 |

| Table 6.1: Summary of Design Level and Simulation Tools for chip ICDPMLIU                 | 86 |

# LIST OF APPENDICES

| A   | VHDL/ Verilog Codes and Script file                              |

|-----|------------------------------------------------------------------|

| A-1 | Verilog codes for FIFO of data to ATM cells                      |

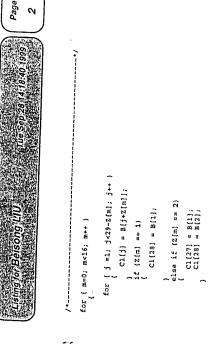

| A-2 | VHDL codes for universal shirt register (USR)104                 |

| A-3 | VHDL codes for test bench of universal shirt register (USR)106   |

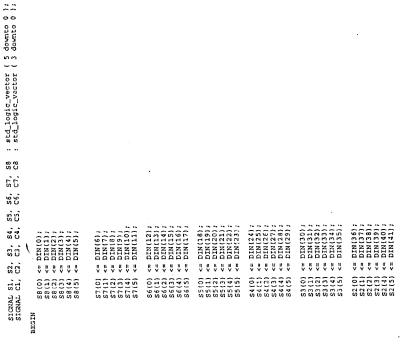

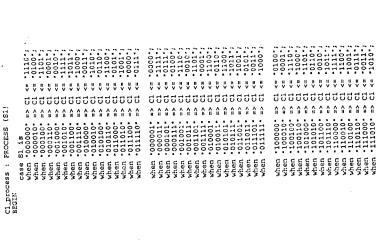

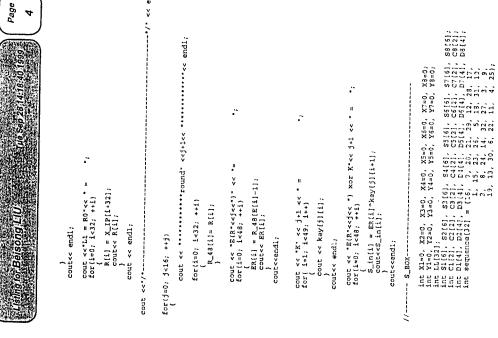

| A-4 | VHDL codes for encryption with DES algorithm108                  |

| A-5 | Script file for DES algorithm synthesis design on FPGA-based130  |

| В   | Circuit Schematic                                                |

| B-1 | Schematic of Multiple-High-Frequency Synchronous Clock Generator |

|     | (SCG)133                                                         |

| B-2 | Schematic of delay line (DL)                                     |

| B-3 | Schematic of Phase Detector (PD)                                 |

| B-4 | Schematic of Universal Shift Register (USR)                      |

| B-5 | Schematic of Frequency Multiplier (FM)                           |

| C   | AutoLayout / Manual Layout /Package                              |

| C-1 | Whole chip layout for Multiple-High-Frequency Synchronous Clock  |

|     | Generator (SCG)                                                  |

| C-2 | Layout for SCG core                                              |

| C-3 | Manual layout for bigger size inverter                           |

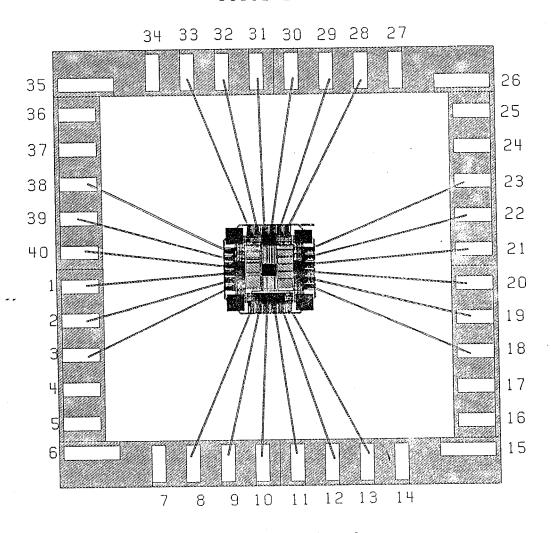

| C-4 | Ronding diagram for SCG chip package 141                         |

| Ð   | Simulation and Testing Results                              |

|-----|-------------------------------------------------------------|

| D-1 | Simulation of SCG with Cadence Spectre142                   |

| D-2 | Simulation of DES implementation with Mentor Graphics144    |

| D-3 | Timing report of DES implementation with the Xilinx 4028-EX |

|     | device145                                                   |

| D-4 | Mapping report of DES implementation with the Xilinx 4028   |

|     | EXdevice146                                                 |

|     |                                                             |

| E   | C++ Codes                                                   |

| E-1 | C++ codes for DES algorithm147                              |

#### CHAPTER 1 INTRODUCTION

#### 1.1 Motivation

In today's world, Internet, videoconferencing, videophone, high-definition television (HDTV), multimedia system, and computer telecommunication networks exist everywhere. Storage or transmission of digital images requires huge amounts of memory and a high bandwidth. Therefore, image compression technology is a very promising application field. At the same time, with the ever-increasing growth of these applications, the need for security and confidentiality has become a basic necessity. This is a reason why MEPG-2 encrypted data streams are used as the source data in such image processing systems.

In the past decade, the applications of ATM/SONET technology have exhibited huge progress. The capacity of telecommunication networks will increase enormously making media such as video-conferencing and videophone a reality. In this case, applications of ATM/SONET technology will remain hot topics in telecommunication due to the expected higher transmission rates. In this master thesis, the hardware architectures to implement interfaces to encrypt MPEG-2 streams in a ATM/SONET framework are discussed.

A telecommunication system normally includes transmission and reception sections. Many questions and issues need to be addressed. How to generate a standard high-frequency synchronous clock in the transmission section? How to implement timing recovery in the reception section? These topics are among the most challenging issues in

telecommunication system design. The most popular solution to the synchronization problem is to use a Phase Locked Loop (PLL) function. A PLL is a mixed-signal (analog-digital) circuit, which contains some passive components. These passive components make its design and implementation, in purely digital dedicated fabrication technology, difficult. We propose a synchronization method using a completely digital circuit to replace the PLL circuit, and using an ADDLL function. The Mirror Delay Approach (MDA) uses the principle of symmetry and proportion to control mirror delay in a multistage frequency generator. General ADDLL function without MDA only requires synchronous control phase locking for one stage output. The benefit of using both methods is that synchronous control phase locking for multi-stage output is achieved in a Frequency Multiplier.

#### 1.2 Standards

In order to better understand the MPEG-2 encrypted data transport over ATM/SONET system, the respective standards will be explained in the following sections.

#### 1.2.1 Moving Picture Experts Group – Phase II (MPEG-2)

MPEG is a video compression technology formulated by the Moving Pictures Experts Group, a joint committee of the International Organization for Standardization (ISO). The first MPEG standard, known as MPEG-1, was formalized by the MPEG committee in January 1992.

MPEG-1 compression incorporates both audio and video. For National Television Standards Committee (NTSC) video, MPEG-1 uses the Standard Image Format (SIF) of 352x240 at 30 frames per second. Audio is provided as16-bit data streams, stereo sampled at 44KHz. MPEG data rates are variable, although MPEG-1 was designed to provide VHS video quality, and CD-ROM audio quality at a combined data rate of 1.2 mega bits per second.

By resolution and data rate, MPEG-1 targets primarily the computer and games markets. By contrast, MPEG-2, adopted in the spring of 1994, can handle data rates ranging from 2 to 10 mega-bit per second. MPEG-2 is the core compression technology for DVD, the high-density CD-ROM standard that experts predict will replace VHS tapes as the standard for consumer video. MPEG-3 was dropped as a standard. MPEG-4 is a very low-bit-rate codec targeting videoconferencing, Internet, and other low-bandwidth applications.

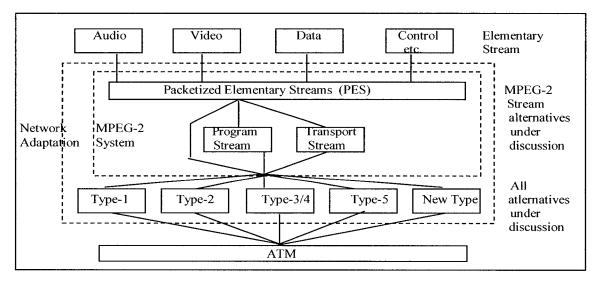

The MPEG -2 system specification [29] defines the syntax for a valid MPEG-2 bit-stream. This syntax allows the support of functions that include combining multiple coded streams of video, audio, data and other control into a single data stream. In MPEG-2, the coded video, audio, data and control bits, which are called Elementary Streams, are grouped into Packetized Elementary Streams (PES). Each PES packet can contain a varying number of coded bytes from one or several Elementary Streams. Multiple PES streams can be multiplexed into a single MPEG-2 system stream for storage or transmission. Two kinds of MPEG-2 system streams are defined: Program Stream (PS) and Transport Stream (TS).

The Program Stream is intended for a relatively error-free environment (or where errors are corrected, such as CD-ROM applications). The PS packets can vary in size and be relatively long in length (each packet may be a few thousands bytes). The Transport Stream is suitable for a relatively error-prone environment. The TS packets have a fixed length of 188 bytes (4-byte packet header and 184-byte payload). This length was chosen based on the following considerations:

- Encryption: 184 bytes is a multiple of 8 bytes, which is the block-size of popular encryption algorithms

- ATM adaptation: 8 + (2 x 188) = 8 x 48, which can fit into eight ATM cells (explained later in this master thesis).

Note that the PS and the TS are designed for different applications. It is possible to convert from one to the other; however, one is not a subset or superset of the other. Based on the match of encryption algorithms as description above, the focus of discussion is on the TS (Transport Stream) in this master thesis. A block diagram of broadband audio/visual terminal is shown in Figure 1.1.

Figure 1.1: Block Diagram of Broadband Audio/Visual Terminal [29]

It depicts an adaptation relationship of data packet from MPEG-2 format to ATM format. The format of Type-1, Type-2, Type-3/4, and Type5 will be explained in the next section.

#### 1.2.2 Asynchronous Transfer Mode (ATM)

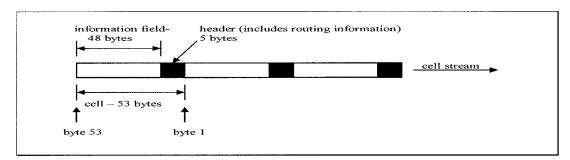

ATM is a cell-based technology supported by international standards [4]. ATM is designed to operate over a number of physical layers at data rates ranging from mega bits per second to giga-bit per second. ATM connections allow this operation to offer service from a few bits per second to nearly the giga-bit capacity of the underlying physical layers. An ATM cell consists of 53 bytes; five bytes are the header and the remaining 48 bytes are the payload. The basic structure of an ATM cell is shown in Figure 1.2.

Figure 1.2: Basic ATM Cell Structure [4]

The header appended by the ATM layer is made up of several fields in Figure 1.3

| bit | 8 7 6 5 | 4 3 2 | 1   |           |

|-----|---------|-------|-----|-----------|

|     | GFC     | VPI   |     | byte<br>l |

|     | VPI     | VCI   |     | 2         |

|     | VO      | CI    |     | 3         |

|     | VCI     | PTI C | CLP | 4         |

|     | Н       | EC    |     | 5         |

Figure 1.3: ATM Cell Header [4]

The specific functions of the ATM cell fields are elaborated in Table 1.1.

Table 1.1: The specific functions of the ATM cell header [4]

| ic functions of the ATM cell header [4]                                                 |

|-----------------------------------------------------------------------------------------|

| Generic flow control (4 bits) is not defined for a user-network interface (UNI).        |

| The value of this field is 0000. For a network interface (NNI), this field is used as   |

| a part of the VPI field, providing additional addressing capacity.                      |

| Virtual path identifier (8 bits) allows up to $2^8 = 256$ virtual paths. Each VP        |

| contains virtual channels. A virtual path is a bundle of virtual channels with the      |

| same VPI but different VCls.                                                            |

| Virtual channel identifier (16 bits) allows up to $2^{16} = 65,536$ virtual channels in |

| one VP.                                                                                 |

| Payload type (3 bits) allows ATM to carry up to $2^3 = 8$ types of payload. These       |

| payload types are identified by the payload type identifier (PTI).                      |

| Cell loss priority (1 bit) is used to determine the eligibility of a cell for discard   |

| when the network is congested. If CLP = 1, the cell can be discarded; otherwise, it     |

| cannot be discarded.                                                                    |

| Header error control (8 bits) is used for error correction on the other bits in the     |

| header. The HEC enables an ATM switch to detect multiple errors and correct             |

| single errors.                                                                          |

|                                                                                         |

ATM is a connection-based protocol. Before information transfer, a virtual connection set-up phase is required to reserve the necessary network resources. If sufficient resources are not available, the connection is refused. Each connection is associated with a VCI (Virtual Channel Identifier) and a VPI (Virtual Path Identifier) that are assigned during the call set-up. The VCI and VPI are used in an ATM switch to determine where to relay traffic to the next node. The VPI identifies a group of virtual channel links that

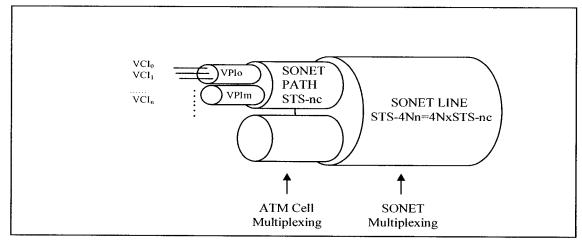

follow the same virtual path. The VCI and VPI have only local significance on the link between ATM nodes and can be changed in the networks. When the connection is released, the VCI and VPI values on the involved links are released, and can be reused by other connections. Figure 1.4 shows the SONET/ATM multiplexing hierarchy. The parameter "In" represents the identifier number of the virtual channels. "Im" represents the identifier number of virtual path. The parameter "nc" represents the number of SONET STS-1 frames (and therefore the line speed). For example, a designation of STS-3 means that the line has 3 times the speed of an STS-1 or 155.52 Mbps. When three STS-1 lines are concatenated such that the frames are phase-aligned and there is a single large payload envelope, it is called an STS-3c line. The parameter "N" represents the number of SONET path.

Figure 1.4: SONET/ATM Multiplexing Hierarchy [36]

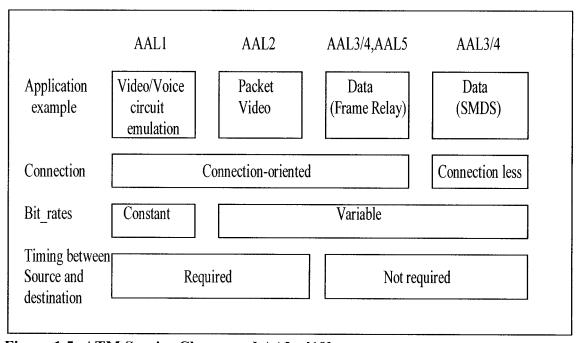

Although ATM is connection-based, it supports both connection-oriented and connection-less service which allows the transfer of information between service users without the need for end-to-end call establishment procedures. To accommodate various services, four types of ATM Adaptation Layer (AAL) [36], [32] are defined to provide

service specific functions as depicted in Figure 1.5. The selection of AALn/Type-n (n = 1, 2, 3/4 and 5) depends on four factors: data application requirements, connection mode, bit-rates and timing between source and destination. The AAL layer is responsible for acting as the interface between user applications and the ATM cell. The ATM Adaptation Layer (AAL) structure [19] is shown in Figure 1.6.

Figure 1.5: ATM Service Classes and AALs [19]

The standard proposes various AALs for different services:

- AAL1 (Type-1): Provides Constant Bit Rate

- AAL2 (Type-2): Provides Variable Bit Rate

- AAL3/4 (Type-3/4): Provides connection-oriented data protocols

- AAL5 (Type-5): Improves AAL3/4. This layer is most common for use in data and compressed video applications.

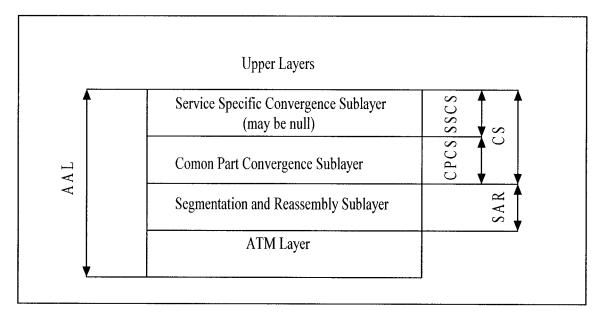

The AAL is subdivided into two sublayers: the Segmentation and Reassembly sublayer (SAR) and the Convergence Sublayer (CS). The CS depends on the specific service and many support different functions such as clock recovery and data structure recovery. It is divided into two parts. The first is the Service Specific Convergence Sublayer (SSCR). The section part is the Common Part Convergence Sublayer (CPCS). The SAR is responsible for segmentation and reassembly functions. The CS encapsulates the data arriving from upper levels: appends small headers, a CRC (Cyclic Redundancy Check) value, and trailers; and then prepares the data to be segmented in cells.

Figure 1.6: ATM Adaptation Layer (AAL)

The SAR is responsible for fragmenting the packets passed from the CS into the ATM layer. Different combinations of SAR and CS sublayers provide different service access points to the layer above the AAL. In some applications, the SAR and/or CS sublayers may be empty.

### 1.2.3 Synchronous Optical NETwork

Synchronous Optical NETwork (SONET) is a standard for optical telecommunications transport formulated by the Exchange Carriers Standards Association (ECSA) for the American National Standards Institute (ANSI), which sets standards in the U.S. for telecommunications [7]. The comprehensive SONET standard is expected to provide the transport infrastructure for worldwide telecommunications for at least the next two or three decades. The basic SONET frequency is 51.84 Mbps which is referred to as Synchronous Transport Signal level 1 (STS-1). The International Telecommunications Union (ITU) developed the Synchronous Digital Hierarchy (SDH) standard in 1988; SDH is based on SONET. The lowest transmission rate in the SDH standard is 155.52 Mbps; this is referred to as STM-1 (Synchronous Transport Module 1), its transmission rate is three times of STS-1. SONET/SDH standards have equivalent designators among various transmission rates, as shown in Table 1.2.

Table 1.2: SONET and SDH Equivalent Designators [7]

| SONET       | SDH         | Transmission Rate (Mbps) |

|-------------|-------------|--------------------------|

| Designation | Designation | •                        |

| STS-1       |             | 51.84                    |

| STS-3       | STM-1       | 155.52                   |

| STS-9       | STM-3       | 466.46                   |

| STS-12      | STM-4       | 622.08                   |

| STS-18      | STM-6       | 933.12                   |

| STS-24      | STM-8       | 1244.16                  |

| STS-36      | STM-12      | 1866.24                  |

The basic structure in SONET is a frame of 810 bytes, which is sent every 125 msec. This allows a single byte within a frame to be part of a 64-Kbps digital voice channel.

Since the minimum frame size is 810 bytes, then the minimum speed at which SONET will operate is 51.84 mega-bit per second as calculated in the equation (1.1):

810 bytes x 8000 frames/sec x 8 (bits) =

$$51.84$$

Mbps (1.1)

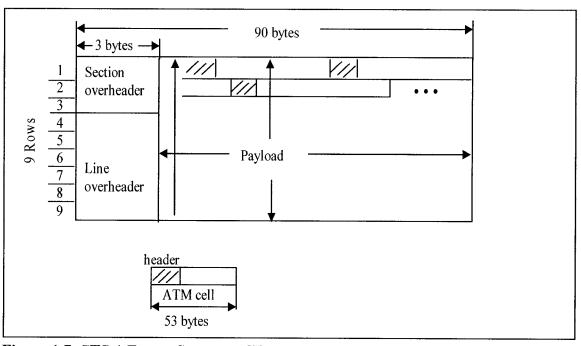

The basic frame is called Synchronous Transport Signal level 1 (STS-1). It is conceptualized as containing 9 rows of 90 columns each as shown in Figure 1.7:

Figure 1.7: STS-1 Frame Structure [7]

- The first three columns of every row are used for administration and control of the multiplexing system. They are called "overhead" in the standard but are very necessary for correct operation of the system.

- "Section overhead" defines the SONET frame and electrical-to-photonic signal conversion. "Line overhead" defines the synchronizing and multiplexing of data into SONET frames.

• The frame is transmitted row by row, from the top left of the frame to the bottom right.

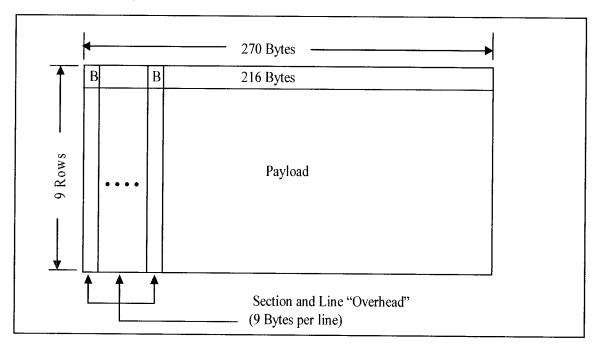

The ITU has defined a worldwide standard called the Synchronous Digital Hierarchy (SDH), which accommodates both SONET and the European line speeds. In this standard a basic frame is defined that is exactly equivalent to (SONET) STS-3c. This frame format has a new name, Synchronous Transport Module level one or STM-1, and has a basic rate (minimum speed) of 155.52 Mbps[1, 25]. This frame format is shown in Figure 1.8.

Figure 1.8: STM-1 Basic Frame Format [25]

# 1.2.4 Data Encryption Standard Algorithm

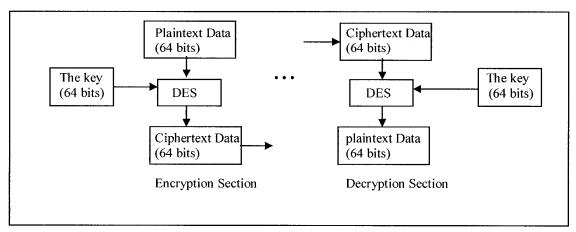

A complete description of the Data Encryption Standard (DES) [2] is given in the Federal Information Processing Standards Publication 46, published in 1977. This document describes the encryption of two words bit string x of length 64, using a key K of 64 bits

which includes the effective key size of 56 bits; obtaining an encryption (ciphertext) bit string which is again a bit string of length 64. For decryption, the inverse DES algorithm with the same key can be used. Figure 1.9 shows a simplified diagram of the data encryption and decryption system.

Figure 1.9: Data Encryption and Decryption System [2]

The DES algorithm proceeds in three stages:

• Give two words (64-bit) x, a bit string  $x_0$  is constructed by permuting the bits of x according to an *initial permutation IP* (fixed). We write

$$x_0 = IP(x) = L_0 R_0 \tag{1.2}$$

where  $L_0$  comprises the first 32 bits of  $x_0$ , and  $R_0$  the last 32 bits.

• Iteration of a certain function 16 times is then computed. We compute  $L_i R_i$ ,  $1 \le i \le 16$ , according to the following rule:

$$L_i = R_{i-1} \tag{1.3}$$

$$R_i - L_{i-1} \oplus f(R_{i-1}, K_i)$$

(1.4)

where:  $- \oplus$  denotes the exclusive-or of two bit strings.

- f defines some functions, including Compression Permutation (CP), Expansion Permutation (EP), S-box Substitution (S-box) and P-box Permutation (P-box).

- $K_1$ ,  $K_2$ ,...,  $K_i$  are strings of 48 bits each and are computed as a function of the key K.

- Apply the inverse permutation  $IP^{-1}$  to the bit string  $R_{16}L_{16}$ , obtaining the ciphertext y. That is,

$$y = IP^{-1}(R_{16}L_{16}) (1.5)$$

Note the inverted order of  $L_{16}$  and  $R_{16}$ .

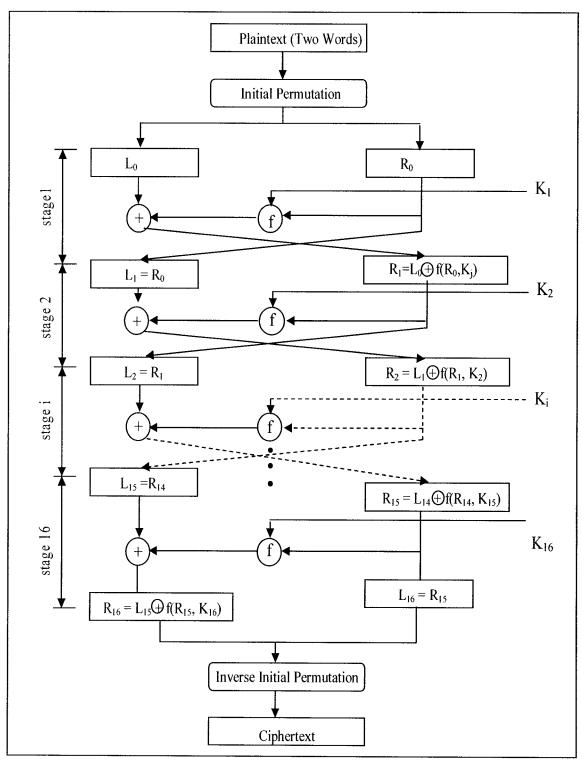

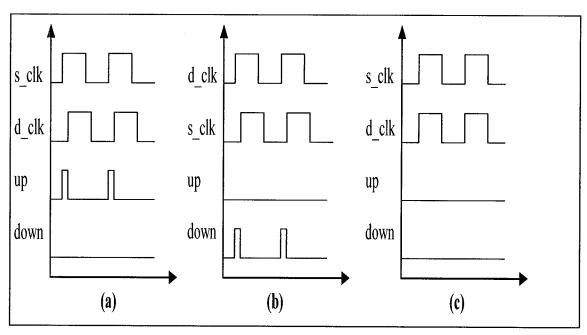

This algorithm may be divided into 16 identical stages as illustrated in Figure 1.10. DES operates on a 64-bit block of two words. First, an initial permutation is performed, where the block is broken into a right half and a left half: each half is 32-bit long. Then, there are 16 stages of identical operations, called Function f, in which the data are combined with the key. After the sixteenth stage computation is completed, the right and left halves are joined, and a final permutation (the inverse of the initial permutation) finishes off the algorithm.

Figure 1.10: Complete representation of the DES operation [2]

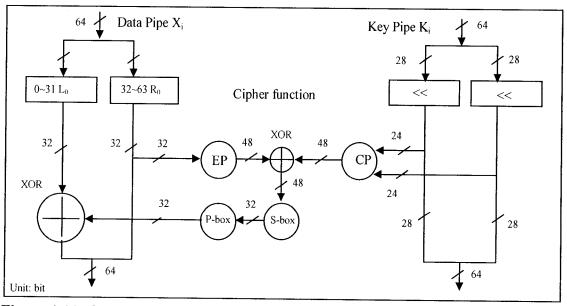

In each stage (Figure 1.11), the key bits are shifted (<<), and then 48 bits are selected from the 56 bits of the key (CP). The right half of the data is expanded to 48 bits via an Expansion Permutation (EP), combined with 48 bits of a shifted and permuted key via an XOR. The result is sent through 8 S-boxes producing 32 new bits (S-box), and permuted again (P-box). These four operations (CP, EP, S-box and P-box) make up Function f. The output of Function f is then combined with the left half via another XOR. The result of these operations becomes the new right half; the old right half becomes the new left half. These operations are repeated 16 times, comprising 16 stages of computations.

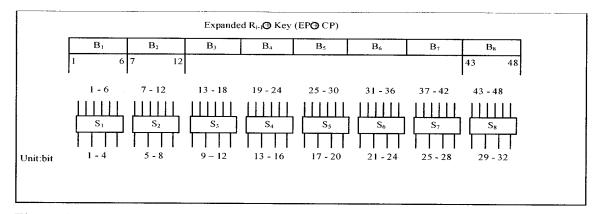

An S-box is a substitution operation in which six bits of data is replaced by four bits, see American National Standards Institute (ANSI) Inc., "American National Standard - Data Encryption Algorithm [2]. The 48-bit input is divided into eight 6-bit blocks, identified as  $B_1 B_2 ... B_8$ ; block  $B_j$  is operated on by S-box  $S_j$ , as shown in Figure 1.12. The data result of S-box substitution operation is 32 bits.

Figure 1.11: One Stage of the DEC Algorithm [2]

Figure 1.12: S-Boxes Operation on Eight 6-bit Blocks [2]

#### 1.3 Contributions of this Master Thesis

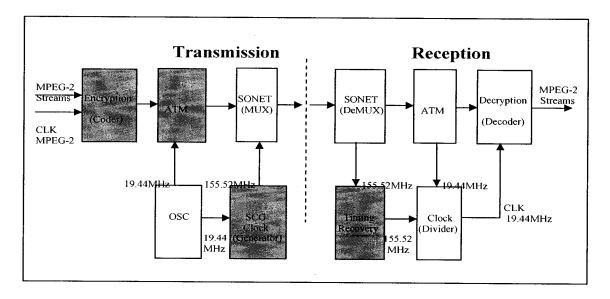

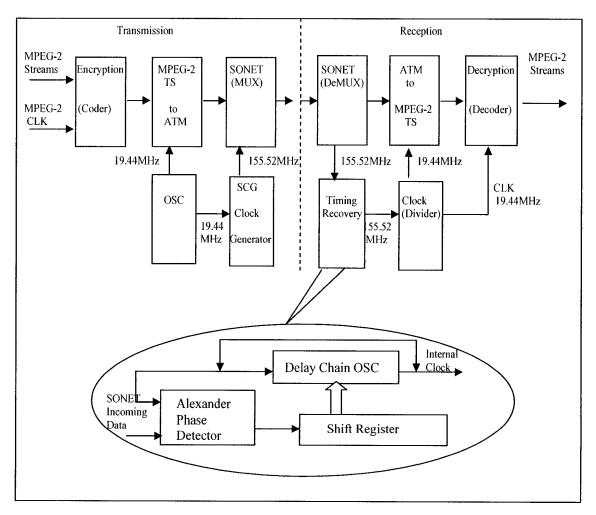

This thesis examines several technical issues to ensure the performance of transport encrypted MPEG-2 video/audio data over an ATM/SONET system. A representation of our research areas is shown in Figure 1.13 by the shaded blocks. The other blocks are not included in our present study. Table 1.3 summarizes our contributions in this master thesis.

Figure 1.13: The Block Diagram Representation of Our Research Areas

**Table 1.3:The Summary of Our Contributions**

| Blocks Name         | Methods                           | Completed Work                                                                                       |

|---------------------|-----------------------------------|------------------------------------------------------------------------------------------------------|

| SCG                 | ADDLL and MDA                     | Prototype Chip                                                                                       |

| Timing Recovery     | ADDLL                             | Design and Analysis                                                                                  |

| MPEG-2 to ATM/SONET | Standards<br>(MPEG-2, ATM, SONET) | 1.Architecture design for interface 2. Architecture design FIFO and RTL Coding for FIFO control unit |

| Encryption Coder    | DES                               | Mapping on FPGA                                                                                      |

# 1.3.1 Transmission Clock Generator and Timing Recovery in the

## **Reception Side**

One of the important functions of data transmission over ATM/SONET is to supply the clock information for transmission data. On the reception side, timing recovery is a key function. Currently, the most popular solution of the synchronization problem is to use a Phase Locked Loop (PLL) in the design. In this master thesis, an ALL-Digital Delay Locked Loop (ADDLL) technique is proposed as a new ALL-Digital method to generate the clocks of the transmission section, as well as to implement the timing recovery of the reception section. The benefits of using ADDLL technique are fast phase locking, easy design and implementation, and good stability with ADDLL block. Also, the real system-level integration will be improved due to full digitization synchronous control. A prototype chip of the Multiple-High-frequency Synchronous Clock Generator (SCG) with ADDLL technique and with a Mirror Delay Approach (MDA) is designed and fabricated with a CMOS 0.35-µm process from TSMC (Taiwan Semiconductor Manufacturing

Company). Using MDA allows a system to be implemented which is multi-stage synchronous; that is the system uses multiple synchronous clocks on a chip.

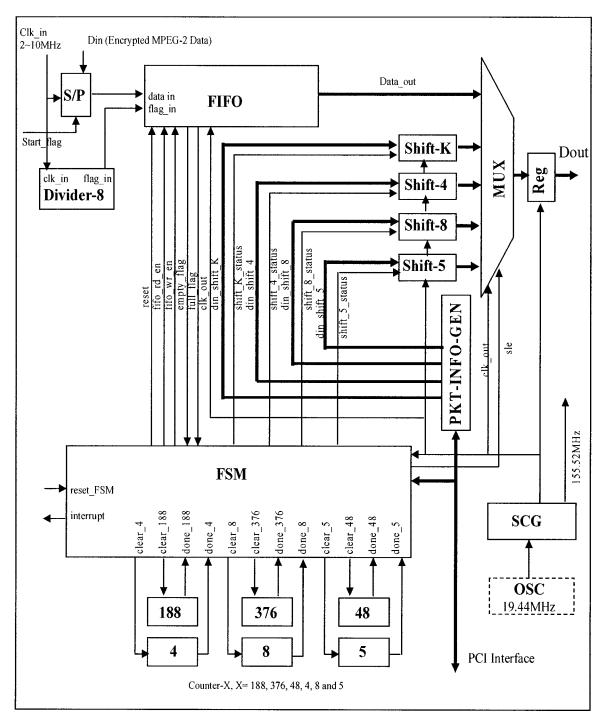

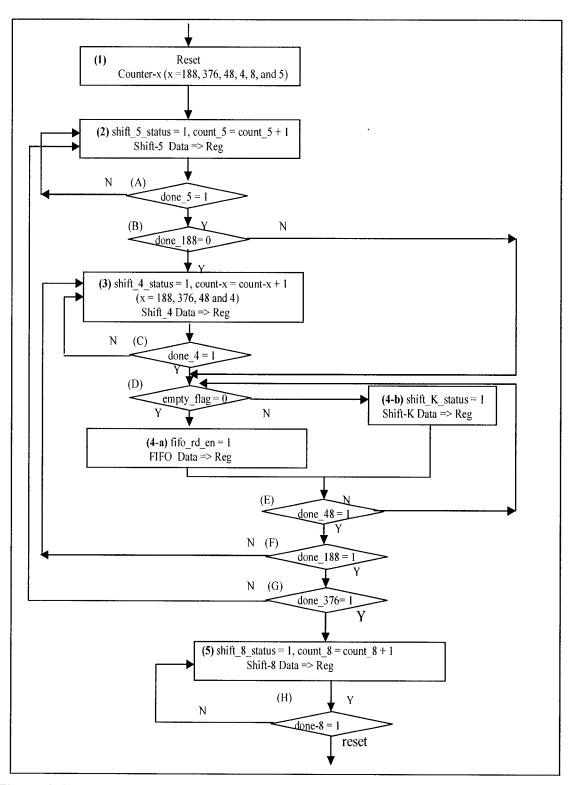

#### 1.3.2 Interface for Encrypted MPEG-2 Streams to ATM Cell

The architecture level design of the interface for the conversion of encrypted MPEG-2 streams to an ATM Cell is also described. The content of this interface include the following key building blocks:

- A FIFO Memory

- Control logic unit based on a Finite State Machine (FSM)

- Packet Information Generator

- Shift registers, counters and other registers.

This interface simplifies the implementation of functions dedicated to mapping the encrypted MPEG-2 streams to the ATM cells. A Multiple-High-frequency SCG is used to improve the performance of this interface. A synchronous, dual-ported RAM-based FIFO is designed. That allows simultaneous writes and reads of data. The FIFO allows data to be read and written separately, which allows the control logic to be simplified. A dual-ported cell simplifies the FIFO control logic because the reading and writing controls do not have to be correlated. Write and read operations to or from the FIFO can occur without inserting wait states. Also, the depth of the designed FIFO is 376 bytes, which is enough storage space for two complete MPEG-2 Transport Stream (TS) packets. For this FIFO, a diagram of the design, as well as the RTL code for the design of the control unit

of the FIFO in Verilog are provided. The Verilog language is used so the design can be consistent with the support environment.

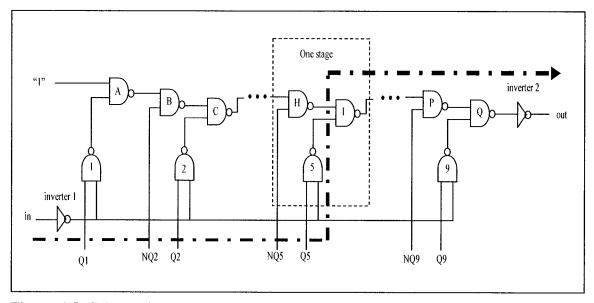

#### 1.3.3 Data Encryption Standard (DES)

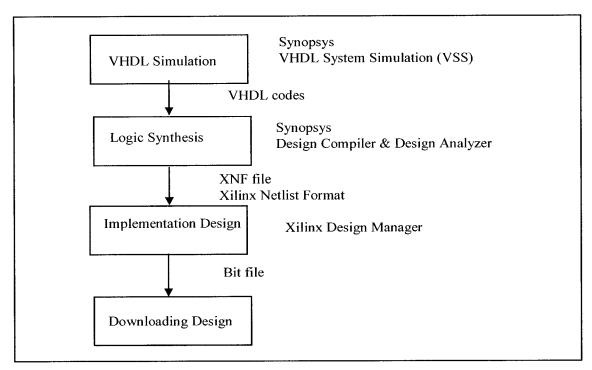

An efficient realization of the Data Encryption Standard (DES) algorithm using FPGA technology is proposed. This design approach is based on the idea of streamlining the data without impacting the speed of operation of any network transport. The system architecture consists of iterating the data through one stage block 16 times. The advantage of the proposed design is its hardware-efficiency and faster computation of the DES algorithm, which thereby offers a dynamic structure to access encrypted data by employing a Dual-ported Synchronous FIFO. The following steps have been completed.

- VHDL simulation using Synopsys and Mentor Graphic tools

- Logic synthesis using Synopsys tools

- Mapping to an FPGA device using Xilinx Design Manager tool

The implementation of these steps was done according to the Canadian Microelectronics Corporation's (CMC) tutorial, "Digital Logic Synthesis Using Synopsys and Xilinx".

# 1.4 Organization of the Master Thesis

This master thesis is composed of seven chapters. The current chapter present an introduction to the topic of the project. Definitions of main issues are given. The Moving Picture Experts Group - Phase 2 (MPEG-2), Asynchronous Transfer Mode (ATM), Synchronous Optical NETwork (SONET) and Data Encryption Standard Algorithm

(DES) are described. The motivation is then discussed and the work contributions are described.

In chapter 2, a literature review for main topics related to this project is provided.

In chapter 3, the implementation of the physical interface for the transmission of the encrypted MPEG-2 streams by ATM cells is discussed. A synchronous, dual-ported RAM-based FIFO is the focus of discussion.

In chapter 4, All-Digital Delay Locked Loop (ADDLL) functional features, as well as its application for clock generator and timing recover are described. A prototype chip design Multiple-High-Frequency Synchronous Clock Generator (SCG) with an ADDLL function with an MDA is presented and discussed. The results prove that using the ADDLL function with an MDA to support the synchronization of a multiple-stage FM are promising new techniques for implementing a data transmission system.

In chapter 5, the realization of the Data Encryption Standard (DES) algorithm using FPGA technology is discussed.

In chapter 6, the simulation results for the RTL code, the FPGA design and final chip testing are reported and analysed.

Conclusions and future directions of this research are presented in chapter 7.

# CHAPTER 2 LITERATURE REVIEW AND PROSPECTS

In this chapter, research related to our project during the last ten years is introduced. The chapter is divided into four sections. Two sections are historic a survey for research and development of All-Digital Phase-Locked Loops (ADPLL) technology. A third section is a literature review of ATM/SONET interface. Also, a related hot research topic about All-Digital Delay-Locked Loops (ADDLL) technology is explained in the final section.

### 2.1 Survey of Analog and Digital Phase-Locked Loops

Phase-locked loops (PLLs) have been in use for a long time. The key concept is to use a local oscillator to lock or track input signals in both phase and frequency [38]. In communication applications, a PLL can make a local clock synchronous with another reference signal. Because digital designs are popular, and they fit well with a baseband design, digital PLLs (DPLLs) are widely used in many modern applications, such as ethernet, asynchronous transfer mode, wireless local area network, microprocessors, digital signal processors, etc.

In the last ten years, many PLL/DPLL based designs have been developed. In [15], a non-return-to-zero (NRZ) timing recovery with a digital phase detector (PD), analog low-pass filter (LF), and voltage-controlled oscillator (VCO) are introduced for band-limited applications. In [28], a fully integrated CMOS frequency synthesizer is presented with an analog LF and current-controlled ring oscillator. [41] presents several design techniques

to improve the performance of a PLL with an analog LF and current steering amplifier ring oscillator. These techniques are usually based on conventional design techniques. In [8], the idea of implementing a variable-bandwidth DPLL by finite state machine (FSM) is described and simulated. This design can be completed by using full digital implementation, however a fully custom layout was still to be performed. In [23], ADPLL technology with Digital Control Oscillator (DCO) is proposed. Its characteristics are fast frequency locking, easy design, implementation and good stability.

Recently, a new algorithm for ADPLL with fast acquisition and fast pull-in range is presented in [24]. It is different from a conventional DPLL implementation in the tracking and locking mechanism. In the meantime, the development of ADDLL technology as an extension of ADPLL technology was a hot research topic.

# 2.2 Review of ADPLL technology

This review is limited to two representative designs [24,11] in order to focus on our research project:

- Portable Design of an ADPLL-Based Clock Recovery Circuit: its main feature is that

it can be developed using a hardware description language (HDL) to reduce the

design time as well as to improve the system-level integration simulation.

- ADPLL with DCO Hardware Circuit: its main feature is that it uses a switch-tuning

DCO to replace the classical VCO but has only half of the hardware cost.

# 2.2.1 Portable Design of ADPLL-Based Clock Recovery Circuit

The authors of [24] describe an ADPLL based clock recovery circuit. It has already met the system requirements of large pulling range, short lock-in time, high data rate, high operating frequency, and portability. In Figure 2.1, the major functional blocks of the clock recovery circuit are shown.

Figure 2.1: Block Diagram of the Cell-based ADPLL Architecture [24]

This ADPLL circuit contains six modules:

- Differentiator with first edge detection (DFED), whose function is to generate

differential pulses to increase resolution and detect the first edge from the input

signals to meet synchronous conditions;

- 2. Phase detector (PD), which is used to indicate phase differences between differential pulses and the digital-controlled oscillator (DCO) output;

- 3. Up/Down filter counter, which is used to determine the phase errors of two signals by referring to a high-speed clock;

- 4. Phase and frequency estimator, which is used to measure new phases and frequencies based on original information and new phase errors;

- 5. Programmable DCO, that is used to generate a target signal;

- 6. High-speed clock generator, which is used as an on-chip reference timing for controlling and synchronizing all modules to avoid timing errors.

The operation of this architecture is explained as follow (Figure 2.2):

Figure 2.2: Flowchart of the Proposed ADPLL Operation [24]

After the initial settings are loaded, the first valid edge of the input must be detected by the DFED for synchronous operation. By using the first valid edge to trigger all modules for extracting input information, the phase errors (M) are estimated by the filter counter to calculate the difference between the second valid edge of the input and the DCO output. This phase error (M) is used to determine a target period and phase for the DCO. If the phase error is greater than 2 pi, the DCO must be stopped, until the next input edge. This delay corrects the phase error. Finally both correct phase and period (frequency) are determined and fed into the DCO to generate synchronous signals for the next cycle.

These procedures are performed once per valid input transition to ensure that the ADPLL operates with minimum phase and period errors. In a noisy environment, both phase and period of the input signals change randomly, and all noisy phenomena can be classified into two cases. One occurs when the input phase is lagging the DCO output and the other occurs when the input phase is leading the DCO output. In both cases, the ADPLL estimates a new phase and period to minimize errors during input signal tracking. Although the ADPLL becomes stable with any initial setting or any condition, the lock-in time is always proportional to the initial setting.

The operating speed of this architecture is limited by the critical path from the filter counter to the phase and frequency estimator. Note that both the phase and period estimations need one high-speed clock. In addition, input tracking circuit needs at least one high-speed clock. Hence the maximum tracking frequency is equal to  $f_{clock}/3$  (without using a differentiator).

The clock recovery mechanism along with a function of frequency synthesizer and an on-chip clock generator [24] are fabricated using a 0.6-µm CMOS process. First, the whole design (including all function modules) is coded in Verilog-HDL using timing information from an in-house target standard-cell library. Then, the Verilog source code is synthesized to generate gate-level netlists and schematics for further simulation and verification.

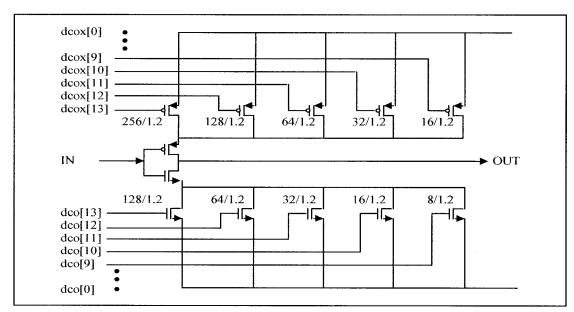

## 2.2.2 ADPLL with Simplified DCO Hardware

Generally, there are three types of DCOs. The first one is the "Path delay oscillator", which is designed by cascading many logic gates to form a circular oscillator. The frequency of the path delay oscillator is very limited and can not meet the high frequency requirement. The second DCO category is the "Schmitt-trigger based current-driven oscillator" [15]. It is based on a Schmitt-trigger inverter integrated together with a large capacitor (hundreds of pico farad capacitance) and several control MOS transistors to implement the oscillator. The third category is the "Current-starved ring oscillator". This type of DCO has good linearity and is used in many microprocessor systems. This DCO controls the different MOS switches to get different frequencies. However, the size of this DCO is large and requires a lot of hardware.

In [11], the DCO is a current-starved ring oscillator, but the hardware is smaller. It uses half the layout area of the conventional DCO. This ADPLL is composed of a frequency comparator, a phase detector, a control unit, and the DCO. Figure 2.3 shows the block diagram of the ADPLL.

Figure 2.3: ADPLL Block Diagram [11]

The frequency comparator receives the reference clock and the DCO output. The frequency comparator then generates two mutually exclusive "fast" and "slow" signals for the DCO.

The phase detector sets the alignment of the DCO clock edge to the reference clock edge. The phase detector logic block determines "ahead" or "behind" signals. The control unit receives the "fast" and "slow" results of the frequency comparator and the "ahead" and "behind" results of the phase detector as inputs. Mode signals "S[i] (i = 0, 1, 2, and 3)" and control word signals "DCO [0:13]" are output to the DCO. The corresponding simplified circuits are shown in Figure 2.4 and Figure 2.5.

Figure 2.4: Simplified Schematic of a DCO Architecture [11]

The heart of the ADPLL is the DCO. Like most voltage controlled oscillators (VCO), the DCO consists of a frequency-control mechanism with an oscillator block. There are two parameters to modulate the frequency of the ring oscillator. One is the propagation delay time of the inverters, and the other is the total number of the inverters. The conventional DCO tunes the first parameter, but ignores the second one.

The switch-tuning architecture of the DCO described in [11] is shown in Figure 2.4. This DCO is composed of four cells, several transmission gates, balance inverters, and one controlling NAND gate to enable the DCO. In each DCO cell, each inverter is cascaded with 14-bit control MOS devices. The size ratios of the control devices are two times higher than a conventional DCO as shown in Figure 2.5.

Figure 2.5: Simplified Circuit of a DCO Cell [11]

The most significant control bit (bit 13) corresponds to the largest control device (PMOS transistor), whose dimension (W x L) is 256 $\mu$ m x 1 $\mu$ m. In the DCO, as shown in Figure 2.4, each CMOS transmission gate is inserted to the series with a cell. Therefore, the total number of stages of the ring oscillator can be changed by setting one transmission gate ON and the others OFF. The size of the layout area is reduced significantly compared to the conventional current-starved DCO. This type of DCO [11] has four operating modes. The oscillating periods  $T_{osci}$  (i = 1, 2, 3 and 4) of the four modes depend on the following delays times:  $T_{not}$  (Inverter delay time),  $T_{ran}$  (Transmission gate delay time),  $T_{dco}$  (DCO cell delay time) and  $T_{nan}$  (NAND gate delay time).

Where,

$$T_{ocsl} = T_{not} + T_{tran} + T_{dco} + T_{nand} (2.1)$$

$$T_{ocs2} = 2T_{tran} + 2T_{dco} + T_{nand} (2.2)$$

$$T_{ocs3} = T_{not} + 3T_{tran} + 3T_{dco} + T_{nand}$$

(2.3)

$$T_{ocs4} = 2T_{not} + 4T_{tran} + 4T_{dco} + T_{nand}$$

(2.4)

Each operating mode uses a 14-bit control word to set the DCO oscillator frequency. Each mode has a specific frequency range, 60~150, 130~270, 240~357 and 340~430 MHz. The least significant bit resolution of the DCO is 177 ps. The prototype of this 3.3V ADPLL chip is designed and prototyped using TSMC's 0.6 μm CMOS process [11].

#### 2.3 Review of ATM/SONET Interface

Two block diagrams of commercially available ATM/SONET interface are described in this section. In order to focus on designs related to our project, we selected the two most appropriate devices:

- The CYS25G0101DX SONET OC-48 Transceiver (Cypress Semiconductor)

- The S3019 SONET/SDH/ATM OC-3/12 Transceiver (Applied Micro Circuits Corporation)

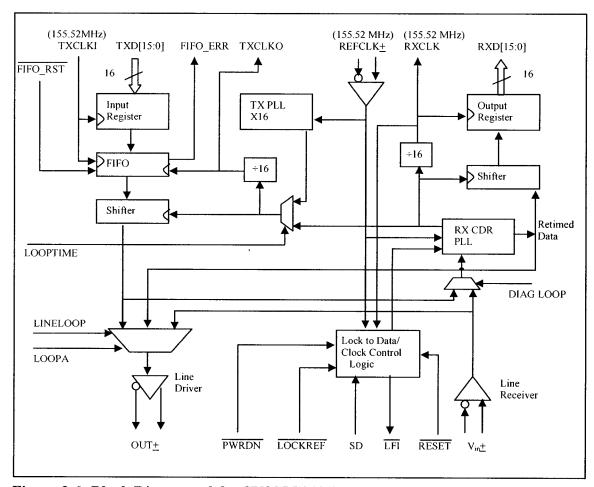

#### 2.3.1 The CYS25G0101DX SONET OC-48 Transceiver

This transceiver is a building block for a high-speed SONET data communication system. It provides complete parallel-to-serial and serial-to-parallel conversion, clock generation, and clock and data recovery operations in a single chip, optimized for full SONET compliance.

New data is accepted at the 16-bit parallel transmission (TXD [15:0]) interface at a rate of 155.52 MHz. This data is passed to a small integrated FIFO to allow flexible transfer of data between the Input Register and Shifter (Figure 2.6). As each 16-bit word is read

from the FIFO, it is serialized and sent through the high-speed differential Line Driver at a rate of 2.488 Gbits/second.

Figure 2.6: Block Diagram of the CYS25G0101DX Transceiver [12]

As serial data is received at the differential Line Receiver ( $V_{in} \pm$ ), it is passed to a clock and data recovery PLL (RX CDR PLL block), which extracts a high precision low-jitter clock from the transitions in the data stream. This bit-rate clock is then used to sample the data stream and receive the data. Every 16 bit-times, a new word is presented at the parallel receiver (RXD [15:0]) interface along with a clock.

The source clock for the transmission data path is selectable from either the recovered clock or an external Building Integrated Timing Source (BITS) reference clock. Multiple loop back and loop-through modes are available for both diagnosis and normal operation. For systems containing redundant SONET rings that are maintained in stand-by mode, the CYS25G0101DX may also be dynamically powered down to conserve system power.

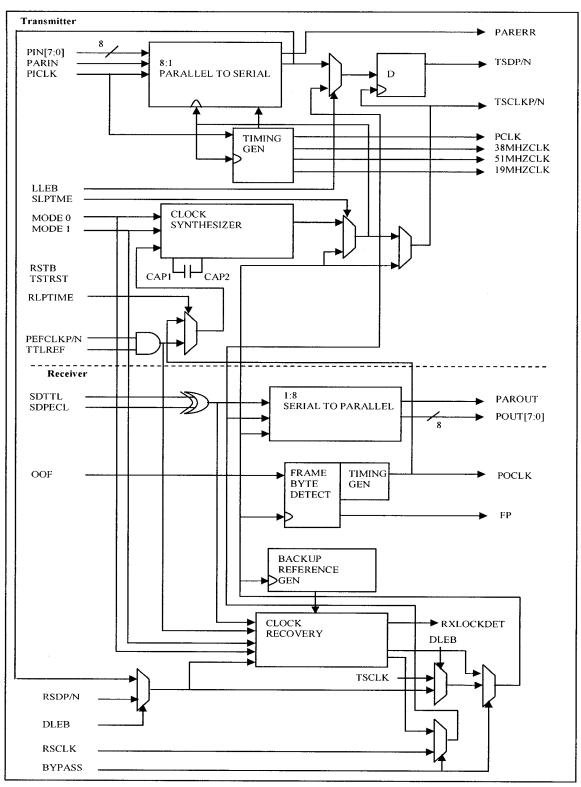

#### 2.3.2 The S3019 SONET/SDH/ATM OC-3/12 Transceiver

This transceiver implements several SONET/SDH serialization/deserialization, transmission, and frame detection/recovery functions on chip. Its block diagram is shown in Figure 2.7. It can be used to implement the front end of SONET equipments, which consists primarily of the serial transmit interface and the serial receive interface. The chip handles all the functions of these two elements, including parallel-to-serial and serial-to-parallel conversion, clock generation and recovery, and system timing. The system timing circuitry consists of management of the data stream, framing, and clock distribution throughout the front end.

At the transmission level, the serializing stage of the S3019 performs the processing of a transmission for a SONET STS-3 or STS-12-bit serial data stream. It converts the 8-bit parallel 19.44 or 77.76 Mbps data stream into bit serial format at 155.52 or 622.08 Mbps. A high-frequency serial data stream can be generated from a 19.44 or 77.76 MHz frequency reference by using an integrated frequency synthesizer consisting of a PLL circuit with a divider in the loop.

Figure 2.7: Block Diagram of the S3019 Transceiver [3]

This clock synthesizer is a monolithic PLL that generates the serial output clock phase synchronized with the input reference clock. The timing generation function provides a byte rate version of the transmission clock. This circuitry also provides an internally generated load signal, which transfers the data of the PIN [7:0] bus (Figure 2.7) from the parallel input register to the serial shift register.

The parallel-to-serial converter is composed of two byte-wide registers. The first register latches the data from the PIN [7:0] bus on the rising edge of PICLK (Figure 2.7). The second register (labelled on figure 2.7) is a parallel-load shift register which takes its parallel input from the output of the first register.

The S3019 transceiver receives the data and performs the frond-end stage of the digital processing algorithm. It converts the bit-serial 155.52 or 622.08 Mbps data stream into a 19.44 or 77.76 Mbps 8-bit parallel data format. Clock recovery is performed on the incoming scrambled NRZ data stream. A 19.44 or 77.76 MHz reference clock is required to start up the PLL to ensure proper operation under loss of signal conditions. An integral prescaler and PLL circuit is used to increase this reference clock to the nominal bit rate.

The clock recovery block generates a clock that is at the same frequency as the incoming data bit rate at the RSDP/N (Figure 2.7, RSDP/N pin) input, or in loop back the transmitter data output. The clock is phase aligned by a PLL so that it samples the data in the centre of the data eye pattern.

The backup reference generator provides backup reference clock signals to the clock recovery block when the clock recovery block detects a loss of signal condition. It

contains a counter that divides the clock output from the clock recovery block down to the same frequency as the reference clock REFCLKP/N (Figure 2.7, REFCLKP/N pin). The frame and byte boundary detection circuitry searches the incoming data for SONET frame and byte boundary. Framing pattern detection is enabled and disabled by the Out-Of-Frame (OOF) input. Detection is enabled by a rising edge on OOF, and remains enabled for the duration that OOF is set high. It is disabled when a framing pattern is detected and OOF is reset. When the framing pattern detection circuit is enabled, the framing pattern is used to locate byte and frame boundaries in the incoming data stream (RSD or looped transmitter data). The timing generator block takes the located byte boundary and uses it to block the incoming data stream into bytes for output on the parallel output data bus (Figure 2.7, POUTP/N [7:0] pin). The frame boundary is reported on the Frame Pulse (FP) output when any 48-bit pattern matching the framing pattern is detected on the incoming data stream. When the framing pattern detection circuit is disabled, the byte boundary is frozen to the location found when framing pattern detection circuit was previously enabled. Only framing patterns aligned to the fixed byte boundary are indicated on the FP output.

The Serial to Parallel Converter consists of three 8-bit registers. The first is a serial-in, parallel-out shift register, which performs serial-to-parallel conversion clocked by the clock recovery block. The second is an 8-bit internal holding register, which transfers data from the serial-to-parallel register on byte boundaries as determined by the frame and byte boundary detection block. On the falling edge of the free running POCLK

(Figure 2.7, POCLK pin), the data in the holding register is transferred to an output holding register which drives POUT [7:0] (Figure 2.7, POUT [7:0] pin).

Among the other operating modes, a diagnostic function which is Diagnostic Loopback is used. When the Diagnostic Loop back Enable (DLEB) input is low, a loop back path from the transmitter to the receiver at the serial data rate can be set up for diagnostic purposes. The differential serial output data from the transmitter is routed to the serial-to-parallel block in place of the normal data stream (RSDP/N). SDPECL (Figure 2.7) must be high for diagnostic loop back mode.

#### 2.4 Prospects

For digital very-large-scale-integration circuits, ADDLL function improves over existing techniques to meet the requirements of advanced computer and communication applications. By implementing the design in a hardware description language (HDL), it can be targeted to different CMOS processes through the use of synthesis tools. This process enhances design portability and reduces the design cycle, important issues in digital VLSI designs.

Traditional analog PLL technology is facing new challenges, integrating an analog circuit on a die with digital circuits generates a large amount of digital noise. Using ADDLL function in the design is becoming a popular way to overcome this noise problem. ADDLL offers fast frequency locking time, full digitization and good stability when implemented into a digital system on a chip design. ADDLL technology is maturing rapidly and more solutions using ADDLL may be adopted by industry soon.

Incorporating ADDLL into a design may also improve the system-level integration simulation.

In the past decade, the applications of ATM/SONET technology have exhibited huge progress. The capacity of telecommunication networks will continue to increase enormously, making media like video-conferencing and videophone more popular. In fact, these applications will become more critical due to higher integration levels at high transmission rates. Theses technologies are advantageously combined for image compression and security encryption.

To fit the above requirements for these applications, the architecture for an interface to transport MEPG-2/Encrypted data over ATM/SONET and its clock generator are presented in this master thesis as described below:

- Description of the proposed ADDLL circuit dedicated to implement a multiple-stage clock generator which will support the interface to transport MEPG-2/Encrypted data over ATM/SONET.

- Design of a clock generator using both VHDL and gate-level design techniques. This

design is targeted for implementation in standard-cell and custom-definited-cell

technologies through the use of standard layout tools.

# CHAPTER 3 ENCRYPTED DATA TRANSMISSION OVER ATM/SONET

In this chapter, MPEG-2 encrypted data and its transport over ATM/SONET are discussed.