**Titre:** Synthèse assistée de moniteurs d'assertions à partir d'une méthodologie d'encapsulation d'assertions dans une spécification exécutable

Title: Synthèse assistée de moniteurs d'assertions à partir d'une méthodologie d'encapsulation d'assertions dans une spécification exécutable

**Auteur:** Jean-François Lemire

Author: Jean-François Lemire

**Date:** 2003

**Type:** Mémoire ou thèse / Dissertation or Thesis

**Référence:** Lemire, J.-F. (2003). Synthèse assistée de moniteurs d'assertions à partir d'une méthodologie d'encapsulation d'assertions dans une spécification exécutable [Mémoire de maîtrise, École Polytechnique de Montréal]. PolyPublie.

Citation: Lemire, J.-F. (2003). Synthèse assistée de moniteurs d'assertions à partir d'une méthodologie d'encapsulation d'assertions dans une spécification exécutable [Mémoire de maîtrise, École Polytechnique de Montréal]. PolyPublie.

<https://publications.polymtl.ca/7131/>

## Document en libre accès dans PolyPublie

Open Access document in PolyPublie

**URL de PolyPublie:** <https://publications.polymtl.ca/7131/>

PolyPublie URL:

**Directeurs de recherche:** Guy Bois, & El Mostapha Aboulhamid

Advisors:

**Programme:** Non spécifié

Program:

In compliance with the

Canadian Privacy Legislation

some supporting forms

may have been removed from

this dissertation.

While these forms may be included

in the document page count,

their removal does not represent

any loss of content from the dissertation.

UNIVERSITÉ DE MONTRÉAL

SYNTHÈSE ASSISTÉE DE MONITEURS D'ASSERTIONS

À PARTIR D'UNE MÉTHODOLOGIE D'ENCAPSULATION D'ASSERTIONS

DANS UNE SPÉCIFICATION EXÉCUTABLE

JEAN-FRANÇOIS LEMIRE

DÉPARTEMENT DE GÉNIE INFORMATIQUE

ÉCOLE POLYTECHNIQUE DE MONTRÉAL

MÉMOIRE PRÉSENTÉ EN VUE DE L'OBTENTION

DU DIPLÔME DE MAÎTRISE ÈS SCIENCES APPLIQUÉES

(GÉNIE ÉLECTRIQUE)

JUIN 2003

National Library

of Canada

Acquisitions and

Bibliographic Services

395 Wellington Street

Ottawa ON K1A 0N4

Canada

Bibliothèque nationale

du Canada

Acquisitions et

services bibliographiques

395, rue Wellington

Ottawa ON K1A 0N4

Canada

*Your file* Votre référence

ISBN: 0-612-86409-X

*Our file* Notre référence

ISBN: 0-612-86409-X

The author has granted a non-exclusive licence allowing the National Library of Canada to reproduce, loan, distribute or sell copies of this thesis in microform, paper or electronic formats.

L'auteur a accordé une licence non exclusive permettant à la Bibliothèque nationale du Canada de reproduire, prêter, distribuer ou vendre des copies de cette thèse sous la forme de microfiche/film, de reproduction sur papier ou sur format électronique.

The author retains ownership of the copyright in this thesis. Neither the thesis nor substantial extracts from it may be printed or otherwise reproduced without the author's permission.

L'auteur conserve la propriété du droit d'auteur qui protège cette thèse. Ni la thèse ni des extraits substantiels de celle-ci ne doivent être imprimés ou autrement reproduits sans son autorisation.

# Canadä

UNIVERSITÉ DE MONTRÉAL

ÉCOLE POLYTECHNIQUE DE MONTRÉAL

Ce mémoire intitulé:

SYNTHÈSE ASSISTÉE DE MONITEURS D'ASSERTIONS

À PARTIR D'UNE MÉTHODOLOGIE D'ENCAPSULATION D'ASSERTIONS

DANS UNE SPÉCIFICATION EXÉCUTABLE

présenté par: LEMIRE Jean-François

en vue de l'obtention du diplôme de: Maîtrise ès sciences appliquées

a été dûment accepté par le jury d'examen constitué de:

M. MULLINS John, Ph.D., président

M. BOIS Guy, Ph.D., membre et directeur de recherche

M. ABOULHAMID El Mostapha, Ph.D., membre et codirecteur de recherche

Mme. BOUCHENEH Hanifa, Ph.D., membre

## REMERCIEMENTS

Je tiens à remercier ceux et celles qui ont, de près ou de loin, contribué à ce projet de recherche. Plus particulièrement, je tiens d'abord à remercier mon directeur de recherche M. Guy Bois pour le temps qu'il a consacré à l'avancement du projet ainsi que pour la confiance qu'il m'a accordée tout au long de mon cheminement. Ses judicieux conseils, sa très grande disponibilité ainsi que sa jovialité ont été des facteurs déterminants qui ont soutenu ma motivation tout au long du projet. Un énorme merci à M. Yvon Savaria pour son précieux encadrement, ses judicieux conseils ainsi que pour le temps qu'il a consacré au projet. J'aimerais remercier également mon codirecteur M. El Mostapha Aboulhamid pour ses judicieux conseils. J'ai grandement apprécié mon expérience aux études supérieures et je suis reconnaissant envers mon directeur et envers tous les professeurs qui ont investi leur temps pour me permettre de réaliser mes objectifs. Encore une fois, merci.

J'aimerais également remercier mon collègue Sébastien Regimbal pour son aide à la réalisation de ce projet ainsi qu'à la rédaction d'articles. Je tiens aussi à remercier l'entreprise PMC-Sierra, et plus particulièrement M. André Baron pour le support qu'il a généreusement accordé au projet ainsi que pour ses judicieux conseils pratiques.

Je tiens aussi à remercier le ReSMiQ pour la bourse qu'il m'a octroyée. J'aimerais en plus remercier PMC-Sierra, Micronet, et le Conseil de recherches en sciences naturelles et en génie du Canada (CRSNG) pour avoir supporté financièrement le projet.

J'aimerais réservé un merci particulier à mes parents et à ma sœur qui n'ont cessé de m'encourager à atteindre mes objectifs. Votre support n'a été autre qu'essentiel. Enfin, je réserve ce dernier merci tout spécial à mon épouse Mai Ly pour ses mots d'encouragement ainsi que son aide plus que précieuse.

## RÉSUMÉ

La vérification fonctionnelle est devenue un sérieux goulot d'étranglement dans tout processus de développement microélectronique. De nouvelles méthodologies sont requises afin d'améliorer le processus de conception de bancs d'essai ainsi que la qualité de la vérification. Ce qui était, il n'y a pas si longtemps, un domaine où des méthodes *ad hoc* étaient couramment utilisées est maintenant devenu un domaine clé pour introduire de nouvelles pratiques et de nouveaux standards. Une méthodologie de vérification axée sur l'utilisation d'assertions aide à formaliser le processus de vérification et permet de rehausser la qualité de la vérification.

L'objectif de ce projet est de proposer une méthode pour accélérer et optimiser la conception d'assertions lors de l'implantation de bancs d'essai en langage de vérification de modèles matériels (*HVL*). L'implantation de moniteurs d'assertions dans un banc d'essai est un processus long et sujet aux erreurs. Ainsi, un outil permettant la création automatique d'assertions en langage *e* est proposé. L'outil est au centre d'une méthodologie d'implantation d'assertions qui débute par la définition de celles-ci au niveau d'une spécification exécutable. Ainsi, un ensemble de types d'assertions permettant de spécifier de façon simple des comportements complexes, c'est-à-dire sans utiliser de primitives propres aux langages de vérification, est proposé. De façon plus précise, l'ensemble de types d'assertions proposé permet de spécifier des propriétés à différents niveaux d'abstraction d'une spécification *SDL* et regroupe les quatre types d'assertions suivants : assertions d'exclusion d'états, assertions de temps de préparation, assertions de temps de maintien et assertions de temps de validité d'un signal. L'utilisation de l'outil proposé permet de migrer automatiquement les assertions définies dans la spécification vers des moniteurs d'assertions utilisés dans un banc d'essai conçu en langage *e*. L'outil utilise des patrons d'implantation, définis au cours de ce travail de recherche, pour générer les quatre types d'assertions proposées. Ces patrons permettent

de générer des moniteurs d'assertions optimisés pour la réutilisation grâce à une méthodologie de partitionnement des aspects, aussi définie dans le cadre de ce travail de recherche, propres à l'implantation de tels moniteurs.

Dans le but d'expliquer la problématique actuelle de la vérification fonctionnelle et de bien positionner le projet dans ce domaine, un sondage sur les pratiques de la vérification fonctionnelle de modèles matériels en entreprise a été effectué et les résultats sont présentés. Les pratiques des répondants sont comparées aux diverses méthodologies proposées dans la littérature. On y voit entre autres qu'il n'existe aucun consensus sur le moment, à l'intérieur du processus de développement, où les répondants débutent l'implantation des bancs d'essais. Aussi, une méthodologie de vérification axée sur la simulation est encore beaucoup plus utilisée qu'une méthodologie de vérification tirant profit à la fois des méthodes formelles ainsi que de la simulation.

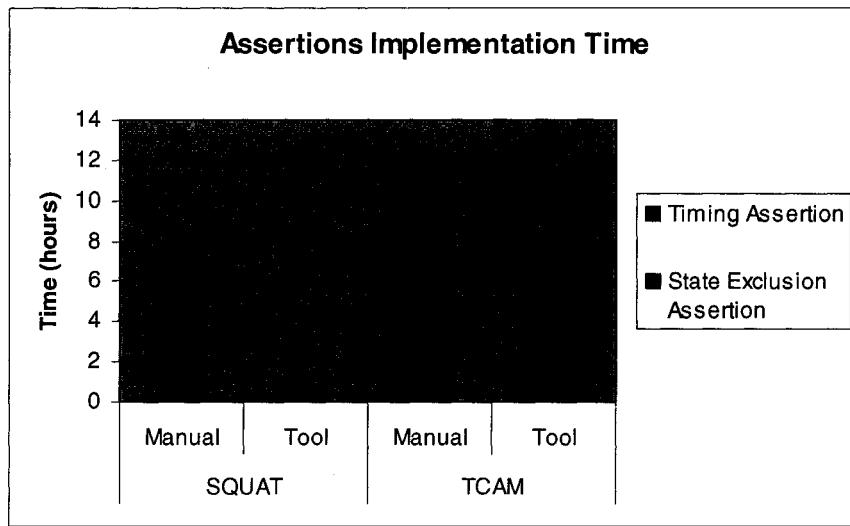

Les résultats de cette recherche démontrent, grâce à une preuve conceptuelle, qu'il est possible de créer des patrons d'implantation d'assertions en langage de vérification de modèles matériels. Aussi, cette recherche révèle la possibilité d'automatiser la création de moniteurs d'assertions à partir de patrons d'implantation prédéfinis. Ceci permet de réduire le temps nécessaire à l'implantation d'assertions et, de ce fait, permet de réduire le temps nécessaire à la conception de bancs d'essai. En effet, une comparaison des temps requis pour une implantation manuelle et une implantation automatique, à l'aide de l'outil proposé, d'un même ensemble d'assertions, pour la vérification de deux modèles matériels, démontre une diminution du temps d'implantation par un facteur d'au moins 20. En plus, cette recherche démontre l'intérêt d'encapsuler des assertions dans une spécification exécutable car ceci permet de spécifier des comportements particuliers dans une représentation d'un modèle qui sera utilisée par plusieurs partis impliqués dans le processus de développement. Finalement, cette recherche expose une méthode efficace pour maximiser le potentiel de réutilisation des moniteurs d'assertions contenus dans un banc d'essais.

## ABSTRACT

Functional verification has become an important bottleneck in every microelectronics development process. One of today's greatest verification challenges is to provide new methodologies and more automation to reduce the time required to create functional verification environments and to perform the verification task. What was not so long ago an *ad hoc* process is nowadays one of the most interesting fields to integrate new standards and structured practices. An assertion-based verification methodology helps formalize the verification process and enhances the quality of the verification task.

The main objective of this project is to propose a methodology to accelerate and optimize assertions design during the testbench implementation process using Hardware Verification Languages (HVLs). Assertion monitors implementation in a testbench is a long and error-prone process. Thus, a tool, which enables the automatic creation of *e* language assertions, is proposed. This tool is at the center of an assertions implementation methodology, which begins by the definition of these assertions at an executable specification level. Hence, an assertion set which enables the simple definition of complex behaviors at different abstraction levels of an SDL specification is proposed. It is then possible to specify assertions without using HVL primitives. Precisely, the proposed assertion set regroup four assertion types: state exclusion assertions, setup time assertions, hold time assertions and pulse width assertions. The proposed tool allows the migration of the specification's assertions towards *e* assertion checkers in order to perform the verification task. The tool uses implementation patterns, which were defined during the course of this research project, to generate the assertion checkers. These patterns enable the implementation of checkers that are optimized for reuse by using an aspect partitioning methodology, which has also been defined during the course of this project.

To explain the actual functional verification issue and to position the project in this domain, a survey of the actual industry functional verification practice has been performed and the results are presented. The survey's results are compared with the actual methodologies proposed in the literature. We can observe that, according to our respondents, there exist no standard moment within the development flow to begin testbench design. Also, a simulation-based verification methodology is more used than a mixed formal-simulation verification methodology.

The project's results show, as a proof of concept, that it is possible to create HVL assertion implementation patterns and that the automation of HVL assertion checkers based on these implementation patterns is also possible. Hence, this provides a way to efficiently accelerate the assertions implementation process which is beneficial for the entire functional verification flow. Indeed, a comparison of the time required to manually and automatically implement a set of assertions, for the verification of two hardware designs, reveals an acceleration by a factor of at least 20. Furthermore, this project shows that it is interesting to encapsulate assertions in an executable specification because this process enables the specification of particular design behaviors at a level of abstraction that will be used by many different design development stakeholders. Finally, this research proposes a method to maximise the assertions reuse potential in a HVL testbench.

## TABLE DES MATIÈRES

|                                                                                                                               |       |

|-------------------------------------------------------------------------------------------------------------------------------|-------|

| Remerciements .....                                                                                                           | iv    |

| Résumé .....                                                                                                                  | v     |

| Abstract.....                                                                                                                 | vii   |

| Table des matières .....                                                                                                      | ix    |

| Liste des figures.....                                                                                                        | xiii  |

| Liste des tableaux .....                                                                                                      | xv    |

| Liste des acronymes.....                                                                                                      | xvi   |

| Lexique .....                                                                                                                 | xvii  |

| Liste des annexes .....                                                                                                       | xxiii |

| INTRODUCTION .....                                                                                                            | 1     |

| <br>CHAPITRE 1: LA VÉRIFICATION FONCTIONNELLE (REVUE DE LITTÉRATURE<br>ET SYNTHÈSE DE L'ARTICLE PRÉSENTÉ AU CHAPITRE 2).....7 |       |

| 1.1 Formulation du problème de la vérification .....                                                                          | 7     |

| 1.2 Preuve d'exactitude d'un modèle .....                                                                                     | 9     |

| 1.3 La vérification fonctionnelle.....                                                                                        | 9     |

| 1.4 Limites de la vérification fonctionnelle.....                                                                             | 10    |

| 1.5 Détails de soumission de l'article du chapitre 2 .....                                                                    | 10    |

| 1.6 Méthodologie de travail.....                                                                                              | 10    |

| 1.7 Survol de l'article .....                                                                                                 | 11    |

| 1.8 Principales conclusions et résultats .....                                                                                | 12    |

| <br>CHAPITRE 2: A SURVEY ON CURRENT FUNCTIONAL VERIFICATION<br>PRACTICE .....                                                 |       |

| 2.1 Abstract.....                                                                                                             | 13    |

| 2.2 Introduction.....                                                                                                         | 14    |

| 2.3 Verification flow according to current literature.....                                                                    | 15    |

|                                                                                                                                             |    |

|---------------------------------------------------------------------------------------------------------------------------------------------|----|

| 2.3.1 Development Flow .....                                                                                                                | 15 |

| 2.3.2 Formal Techniques .....                                                                                                               | 16 |

| 2.3.3 Formal/Simulation-Based Functional Verification .....                                                                                 | 17 |

| 2.3.4 Traditional Simulation vs Formal Techniques .....                                                                                     | 18 |

| 2.3.5 Black-box, White-box and Grey-box Strategies.....                                                                                     | 20 |

| 2.3.6 Hardware Verification Languages.....                                                                                                  | 20 |

| 2.3.7 Levels of Abstraction.....                                                                                                            | 21 |

| 2.4 Survey Sample Structure .....                                                                                                           | 22 |

| 2.5 Results Analysis .....                                                                                                                  | 23 |

| 2.5.1 Respondents Profile.....                                                                                                              | 23 |

| 2.5.2 The Verification Process .....                                                                                                        | 24 |

| 2.5.3 Verification Strategies .....                                                                                                         | 25 |

| 2.5.4 Coverage.....                                                                                                                         | 27 |

| 2.5.5 Reuse .....                                                                                                                           | 29 |

| 2.5.6 Formal Verification/Assertion-Based Verification .....                                                                                | 29 |

| 2.6 Survey Results Implications and Discussion.....                                                                                         | 31 |

| 2.6.1 Verification Planning.....                                                                                                            | 32 |

| 2.6.2 Testbench Design .....                                                                                                                | 32 |

| 2.6.3 Verification Reuse .....                                                                                                              | 35 |

| 2.6.4 Formal Verification vs Simulation .....                                                                                               | 35 |

| 2.7 Conclusion .....                                                                                                                        | 36 |

| 2.8 Acknowledgements.....                                                                                                                   | 37 |

| <br>CHAPITRE 3: LA VÉRIFICATION BASÉE SUR LES ASSERTIONS (REVUE DE<br>LITTÉRATURE ET SYNTHÈSE DE L'ARTICLE PRÉSENTÉ AU<br>CHAPITRE 4) ..... | 38 |

| 3.1 La vérification basée sur les assertions.....                                                                                           | 38 |

| 3.1.1 Evénements.....                                                                                                                       | 41 |

| 3.1.2 Expression temporelles.....                                                                                                           | 42 |

| 3.1.3 Moniteurs d'assertions.....                                                                                                           | 42 |

|                                                                            |    |

|----------------------------------------------------------------------------|----|

| 3.1.4 Avantages des assertions utilisées lors de simulations .....         | 43 |

| 3.2 Classes d'assertions .....                                             | 43 |

| 3.2.1 Assertions procédurales et déclaratives .....                        | 43 |

| 3.2.2 Assertions de propriétés de sûreté (invariants) et de vivacité ..... | 45 |

| 3.3 Méthodes d'implantation d'assertions .....                             | 45 |

| 3.3.1 Assertions RTL déclaratives .....                                    | 46 |

| 3.3.2 Assertions RTL procédurales .....                                    | 47 |

| 3.3.3 Assertions décrites en langage formel ou HVL .....                   | 47 |

| 3.3.4 Assertions incluses dans des pseudo-commentaires .....               | 47 |

| 3.3.5 Analyse de l'historique de simulation .....                          | 47 |

| 3.4 SDL .....                                                              | 48 |

| 3.5 Le langage <i>e</i> .....                                              | 48 |

| 3.5.1 Définition d'événements en langage <i>e</i> .....                    | 50 |

| 3.5.2 Expressions temporelles du langage <i>e</i> .....                    | 50 |

| 3.5.3 Assertions en langage <i>e</i> .....                                 | 54 |

| 3.6 Méthodologie de recherche .....                                        | 55 |

| 3.7 Syntaxe des assertions SDL proposées .....                             | 56 |

| 3.7.1 Assertion d'exclusion d'états .....                                  | 57 |

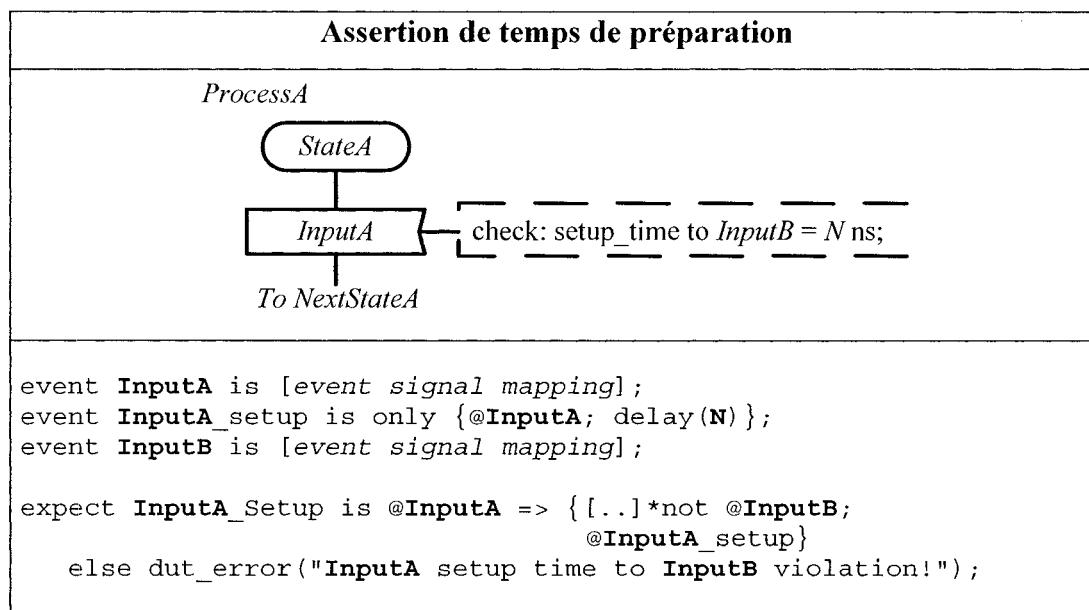

| 3.7.2 Assertion de temps de préparation .....                              | 57 |

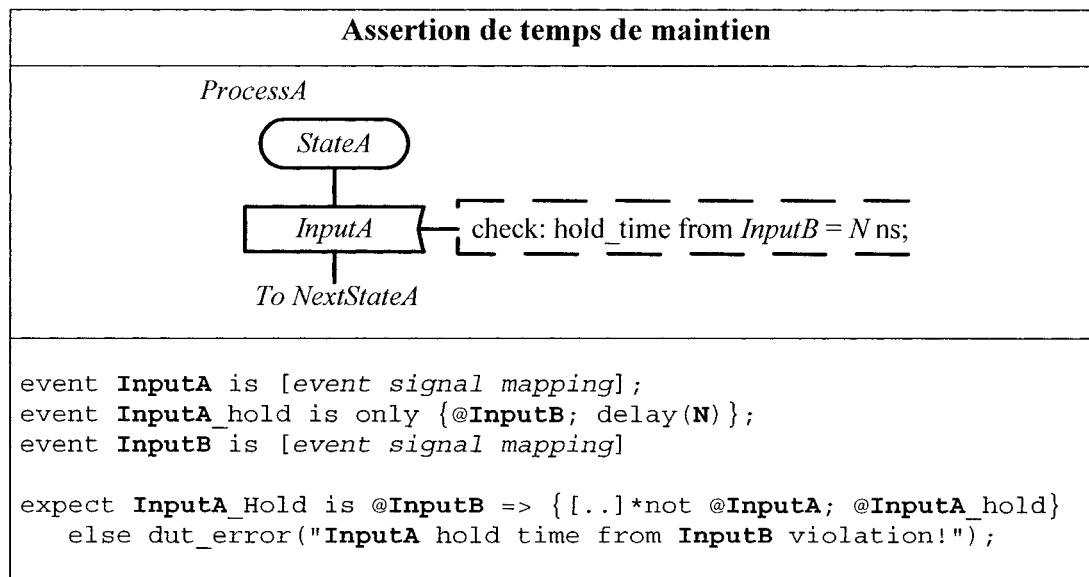

| 3.7.3 Assertion de temps de maintien .....                                 | 58 |

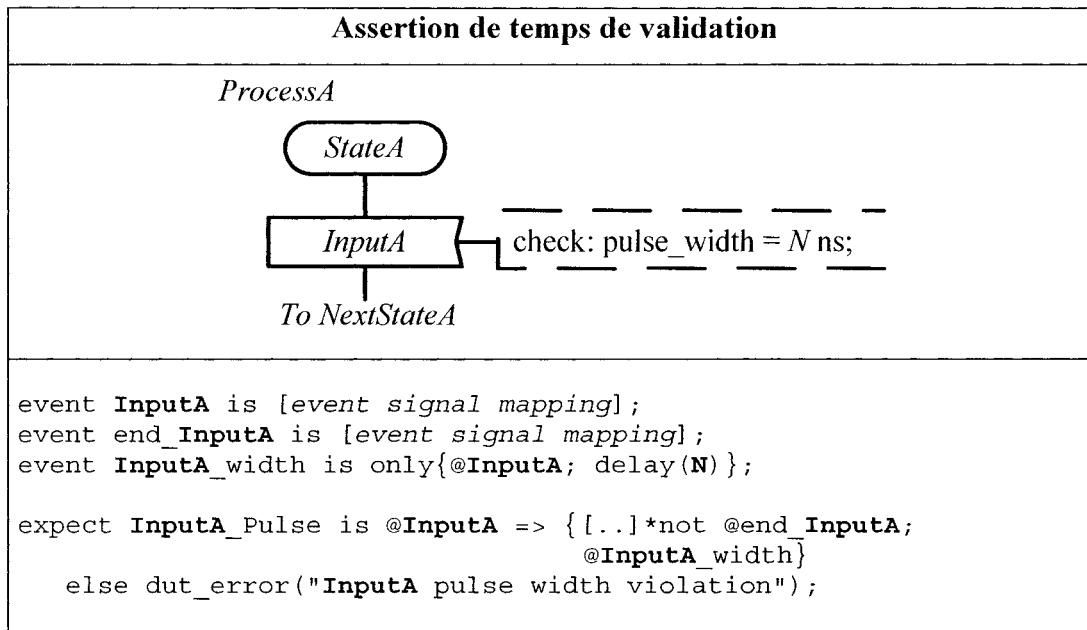

| 3.7.4 Assertion de temps de validité .....                                 | 58 |

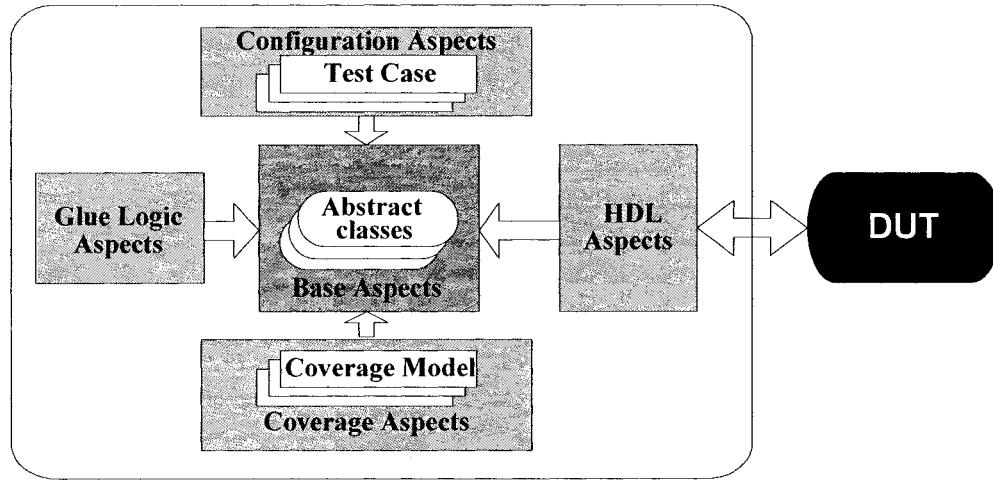

| 3.8 Méthodologie de partitionnement d'environnements de vérification ..... | 58 |

| 3.9 Détails de soumission de l'article du chapitre 4 .....                 | 61 |

| 3.10 Survol de l'article .....                                             | 61 |

| 3.11 Principales conclusions et résultats .....                            | 63 |

| CHAPITRE 4: METHODOLOGY FOR ASSERTION CHECKERS SYNTHESIS                   |    |

| FROM AN EXECUTABLE SPECIFICATION .....                                     | 65 |

| 4.1 Abstract .....                                                         | 65 |

| 4.2 Introduction .....                                                     | 66 |

|                                            |    |

|--------------------------------------------|----|

| 4.3 Assertion-Based Verification.....      | 69 |

| 4.4 Implementing Assertions for Reuse..... | 72 |

| 4.5 The Proposed Methodology.....          | 74 |

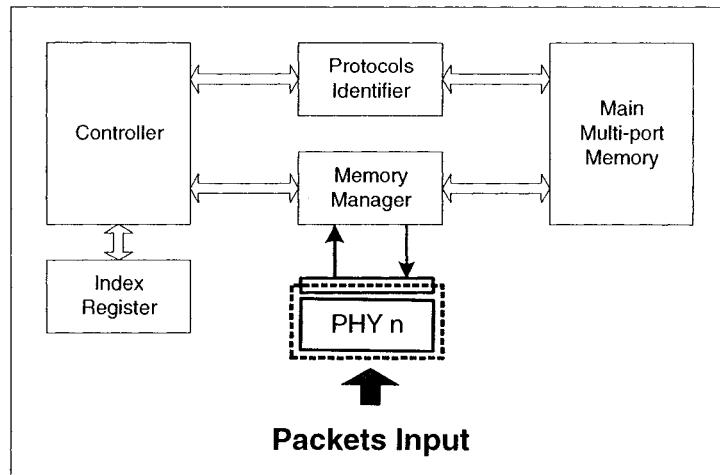

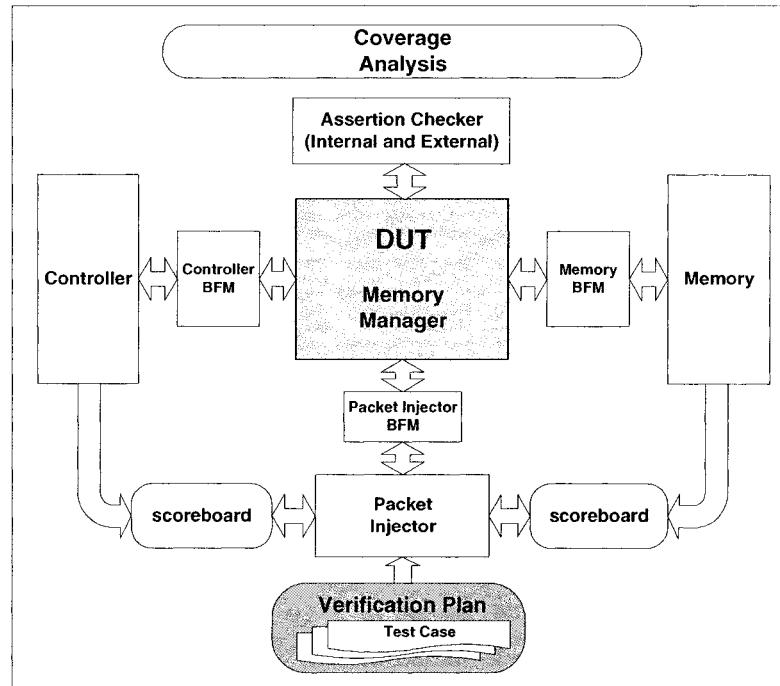

| 4.6 Application Example .....              | 77 |

| 4.7 Evaluation of the Methodology .....    | 85 |

| 4.8 Discussion.....                        | 87 |

| 4.9 Conclusion .....                       | 89 |

| 4.10 Acknowledgements.....                 | 89 |

| DISCUSSION GÉNÉRALE ET CONCLUSION .....    | 90 |

| Bibliographie .....                        | 94 |

## LISTE DES FIGURES

|                                                                                                                                         |    |

|-----------------------------------------------------------------------------------------------------------------------------------------|----|

| Figure 1.1 - Banc d'essai .....                                                                                                         | 8  |

| Figure 1.2 - La vérification fonctionnelle.....                                                                                         | 9  |

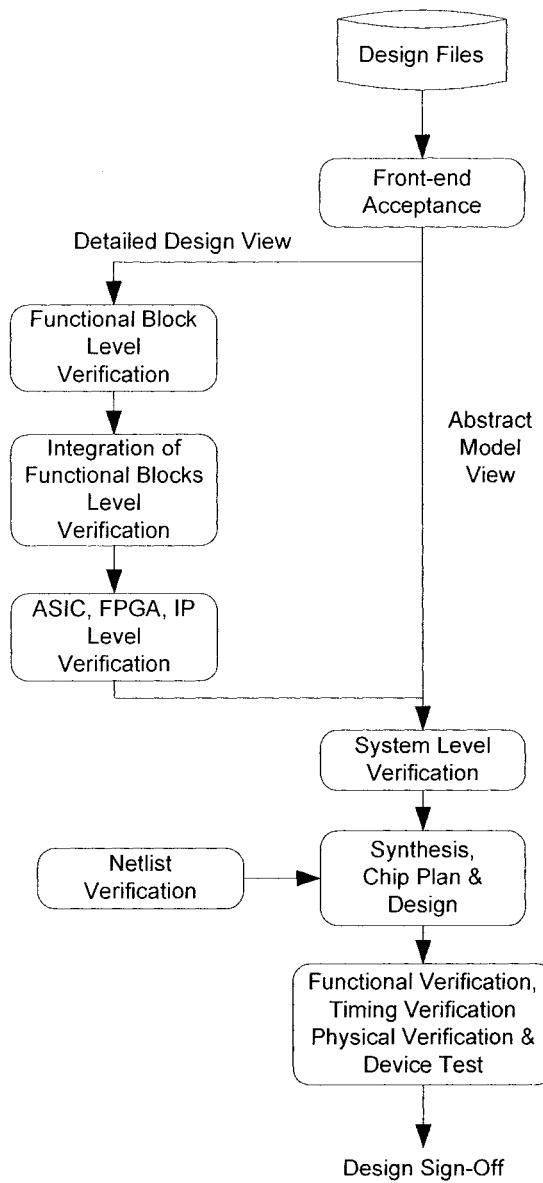

| Figure 2.1 - Proposed Development Flow.....                                                                                             | 16 |

| Figure 2.2 - Hardware Formal/Simulation-based verification.....                                                                         | 18 |

| Figure 2.3 - Bottom-up Verification Approach .....                                                                                      | 22 |

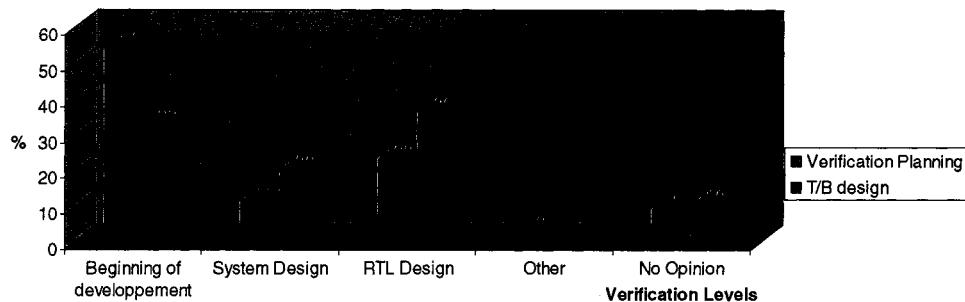

| Figure 2.4 - Start of Verification Planning and Testbench Design by Pourcentage of Respondents .....                                    | 25 |

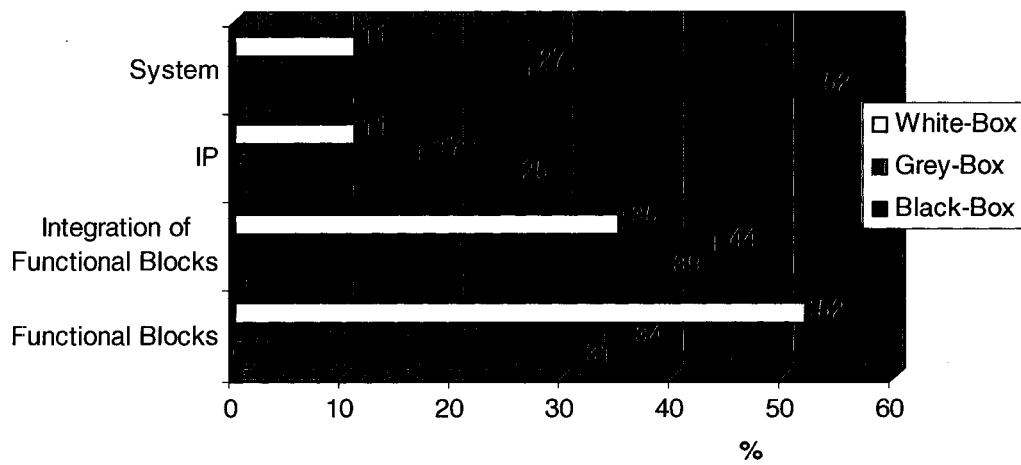

| Figure 2.5 - Verification Strategies by Percentage of Respondents.....                                                                  | 26 |

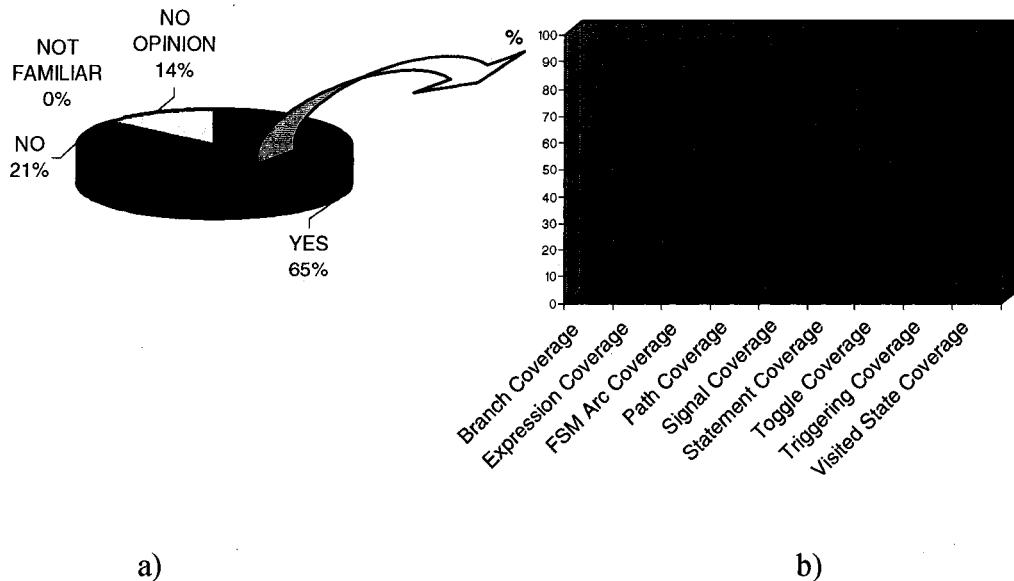

| Figure 2.6 - a) Code Coverage Usage and b) Type of Code Coverage by Percentage of Respondents .....                                     | 28 |

| Figure 2.7 - Functional Coverage Usage by Percentage of Respondents.....                                                                | 28 |

| Figure 2.8 - Model Checking Practice and Associated Verification Levels by Percentage of Respondents .....                              | 30 |

| Figure 2.9 - Equivalence Checking Practice and Associated Verification Levels by Percentage of Respondents .....                        | 30 |

| Figure 2.10 - Assertion-Based Verification Practice in Simulation and Associated Verification Levels by Percentage of Respondents ..... | 31 |

| Figure 2.11 - Testbench Coding Flow According to Survey Results.....                                                                    | 33 |

| Figure 3.1 - Assertion typique en C++ .....                                                                                             | 39 |

| Figure 3.2 - Exemple d'assertion en VHDL.....                                                                                           | 40 |

| Figure 3.3 - Syntaxe d'un événement <i>e</i> .....                                                                                      | 50 |

| Figure 3.4 – Syntaxe d'une assertion en langage <i>e</i> .....                                                                          | 54 |

| Figure 3.5 - Syntaxe de l'assertion SDL d'exclusion d'états .....                                                                       | 57 |

| Figure 3.6 - Syntaxe de l'assertion SDL de temps de préparation .....                                                                   | 57 |

| Figure 3.7 - Syntaxe de l'assertion SDL de temps de maintien .....                                                                      | 58 |

| Figure 3.8 - Syntaxe de l'assertion SDL de temps de validité .....                                                                      | 58 |

|                                                                          |    |

|--------------------------------------------------------------------------|----|

| Figure 4.1 - Assertion Checker Functional View .....                     | 72 |

| Figure 4.2 - <i>e</i> Assertion Checker Example.....                     | 72 |

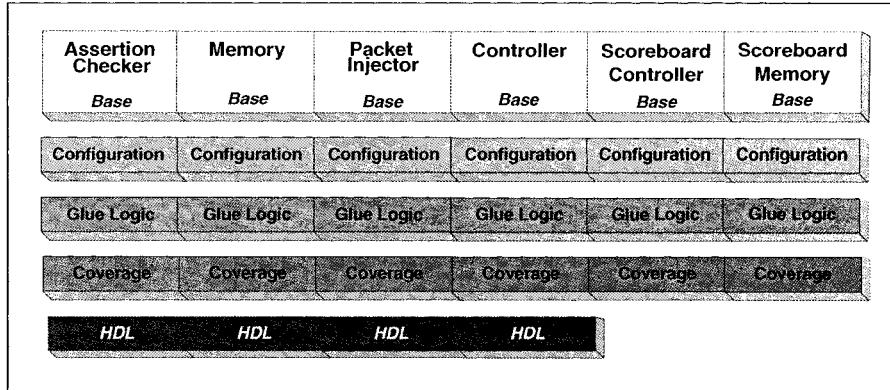

| Figure 4.3 - Assertion Checker Testbench Partitioning .....              | 73 |

| Figure 4.4 - Assertion Tool Overview.....                                | 75 |

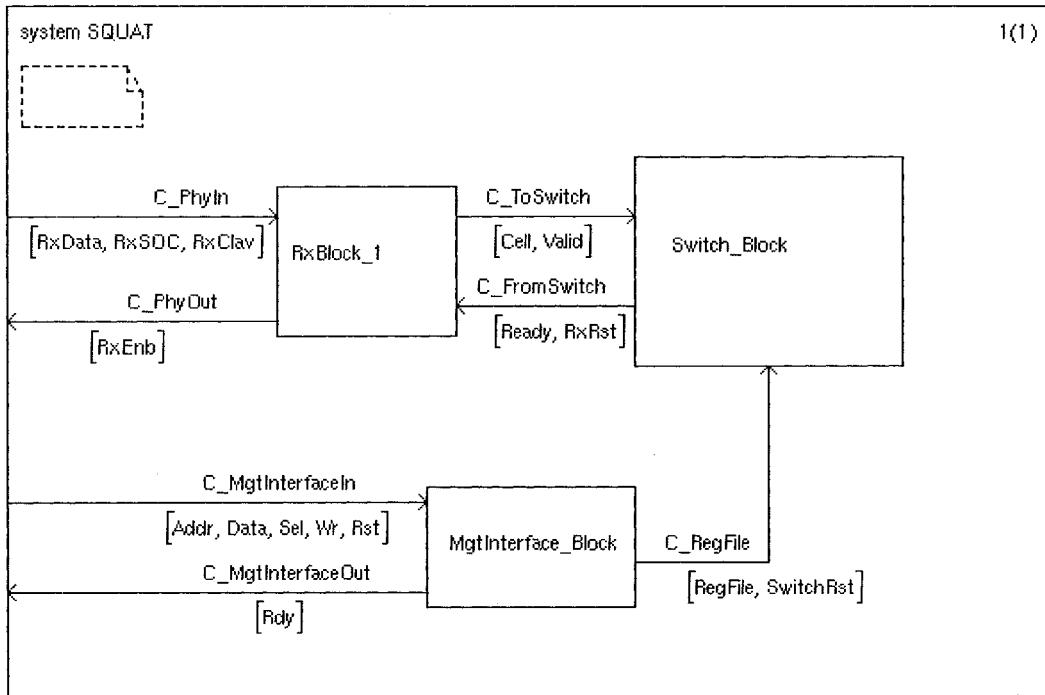

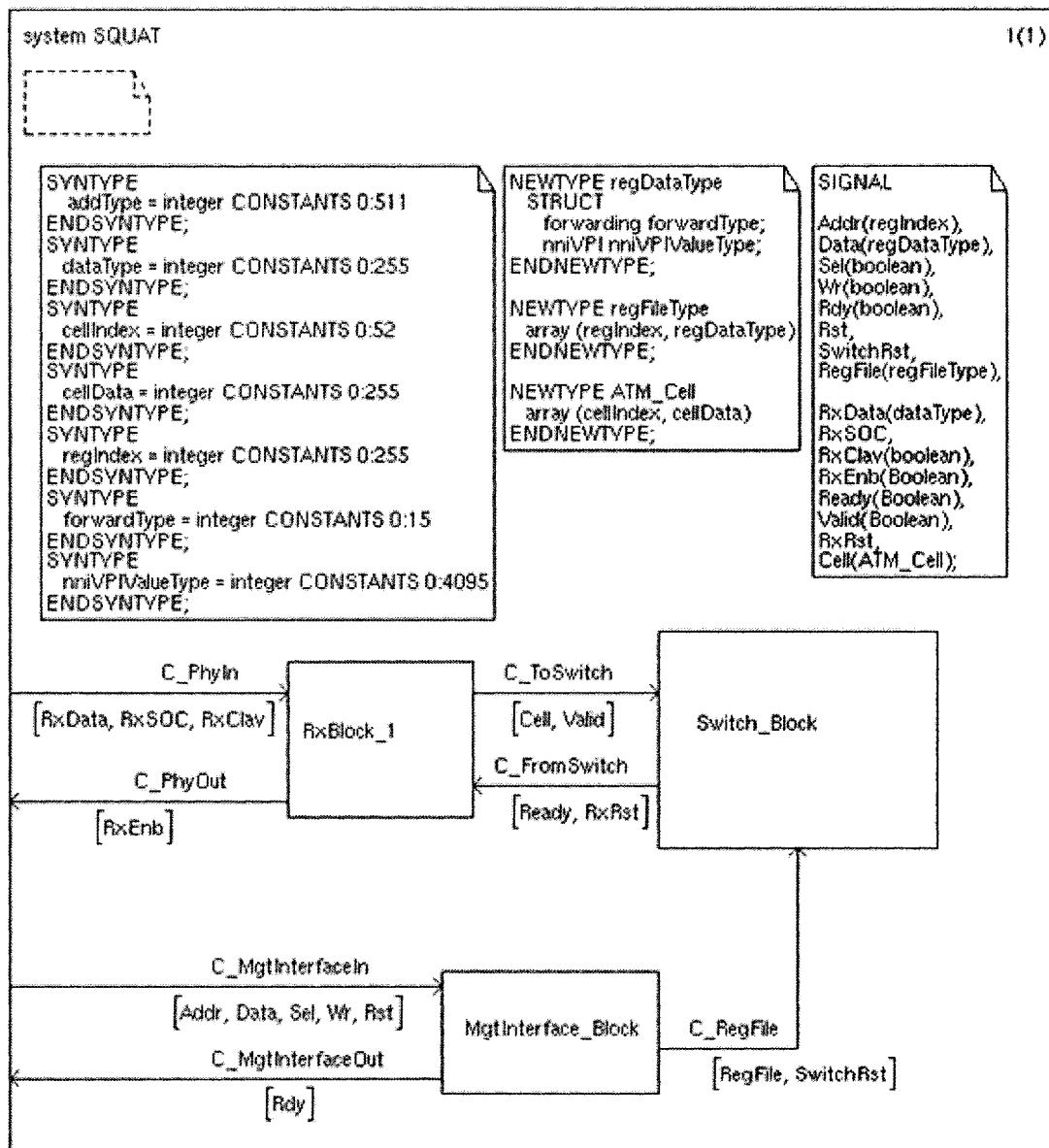

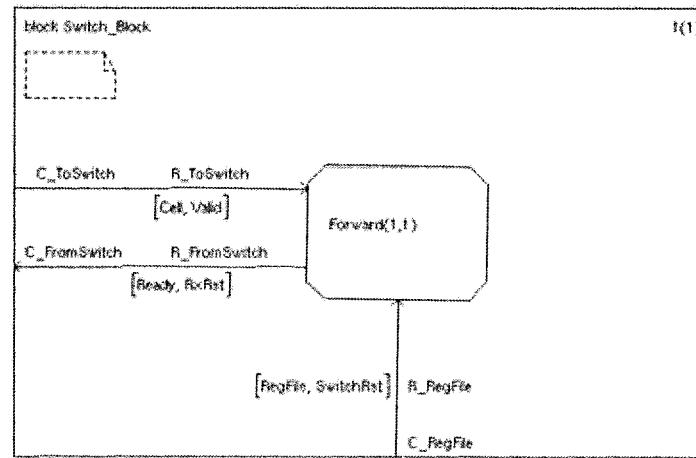

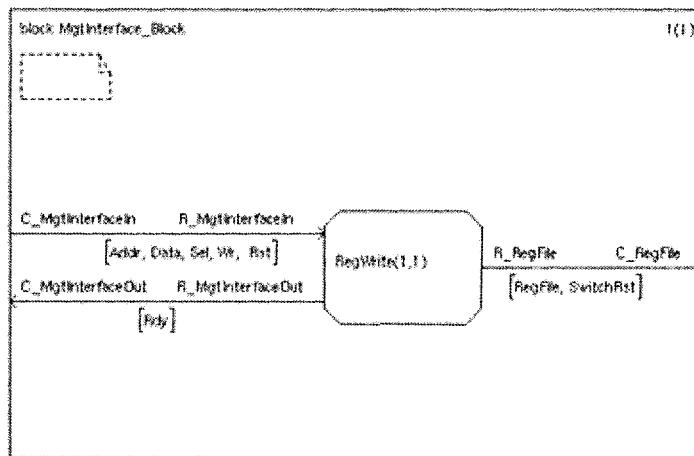

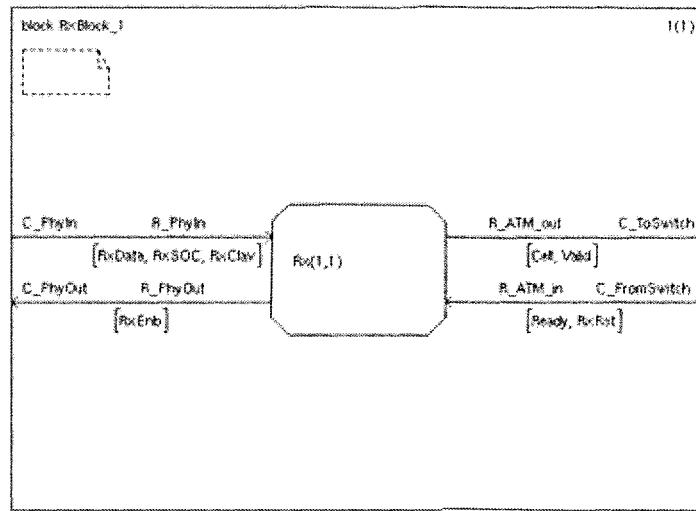

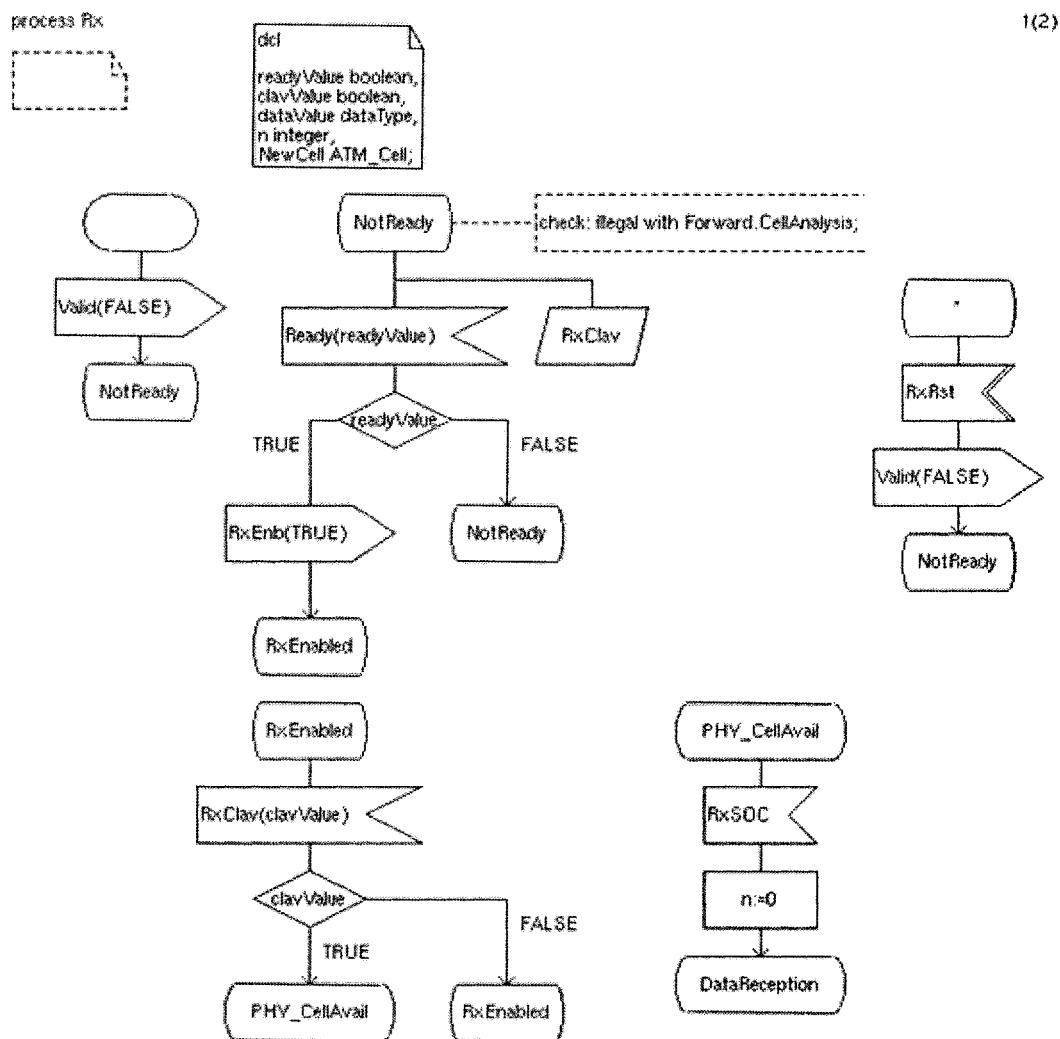

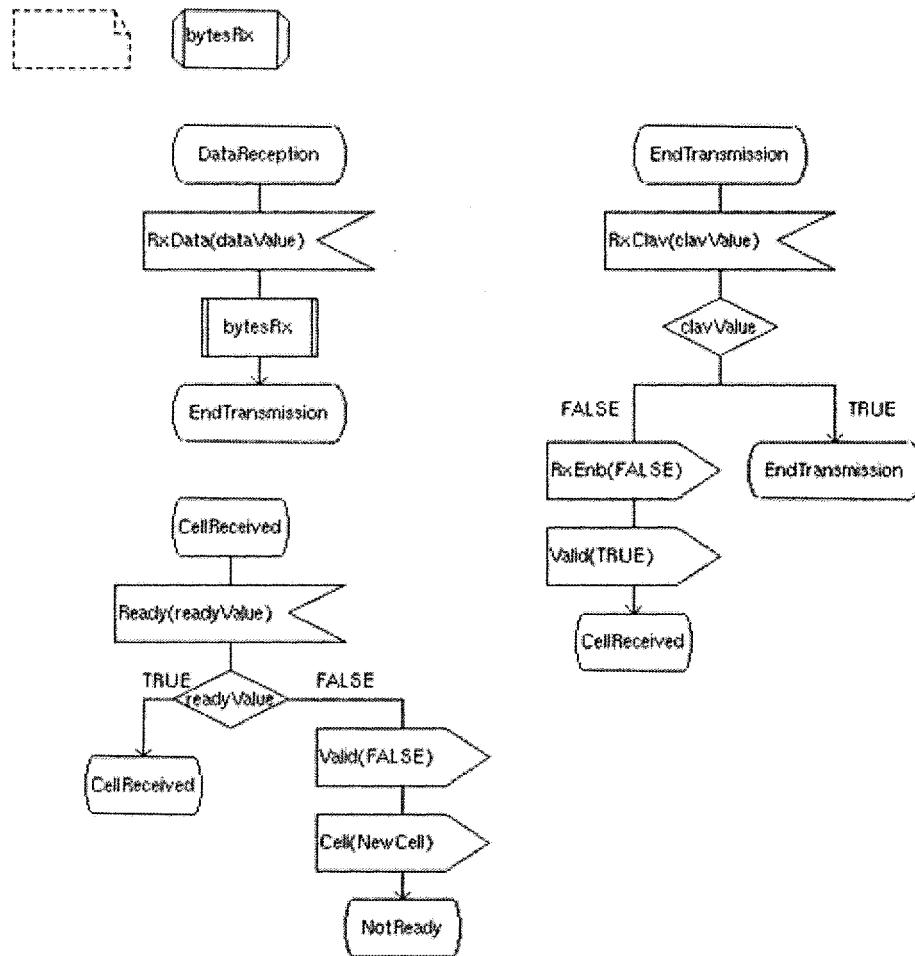

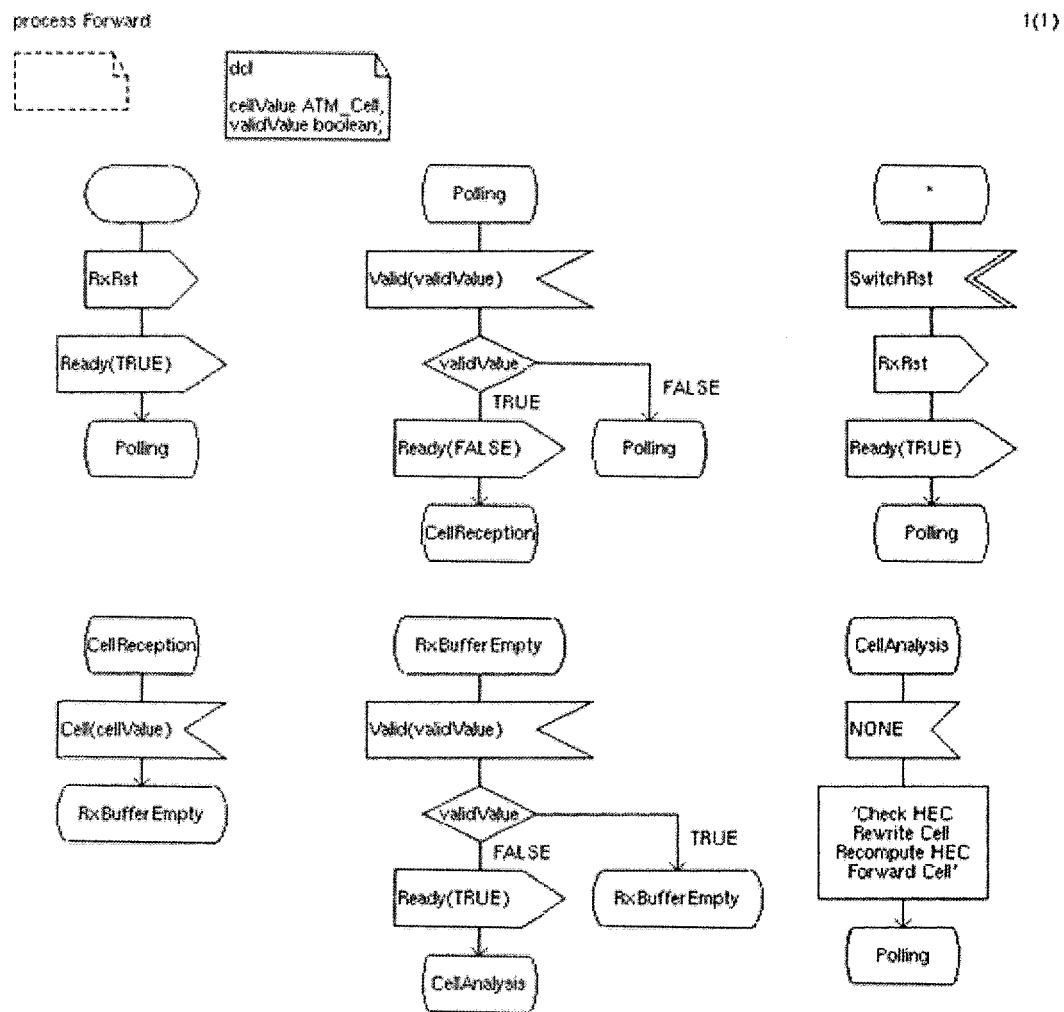

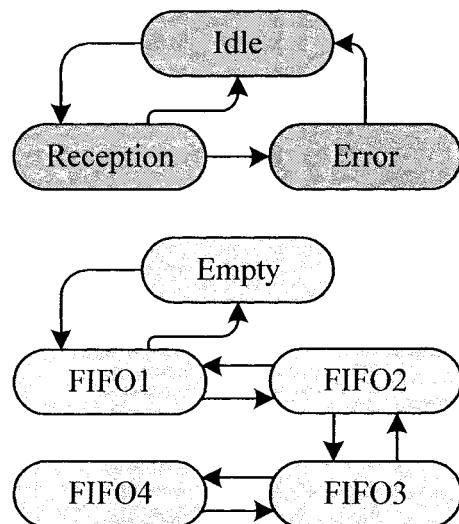

| Figure 4.5 - ATM Switch SDL System Example.....                          | 78 |

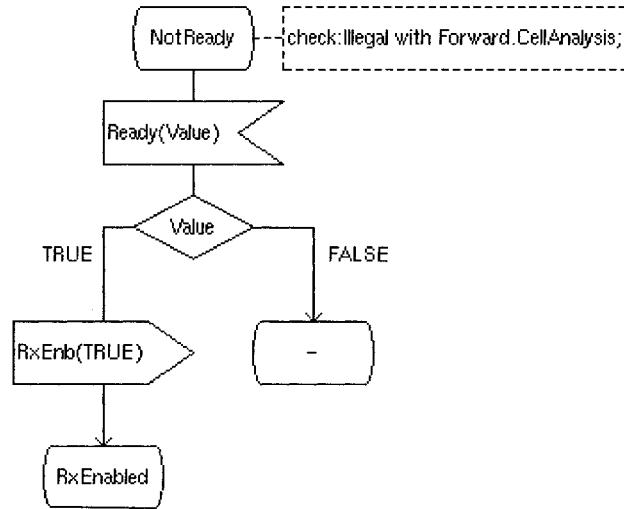

| Figure 4.6 - State Assertion Example.....                                | 79 |

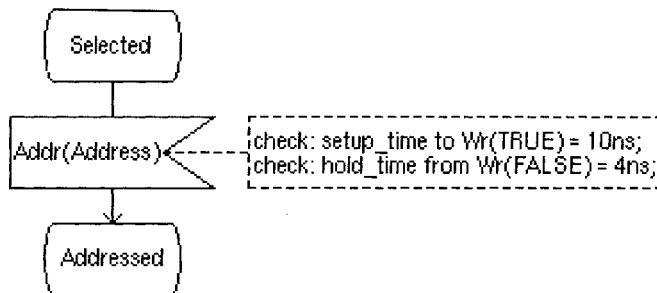

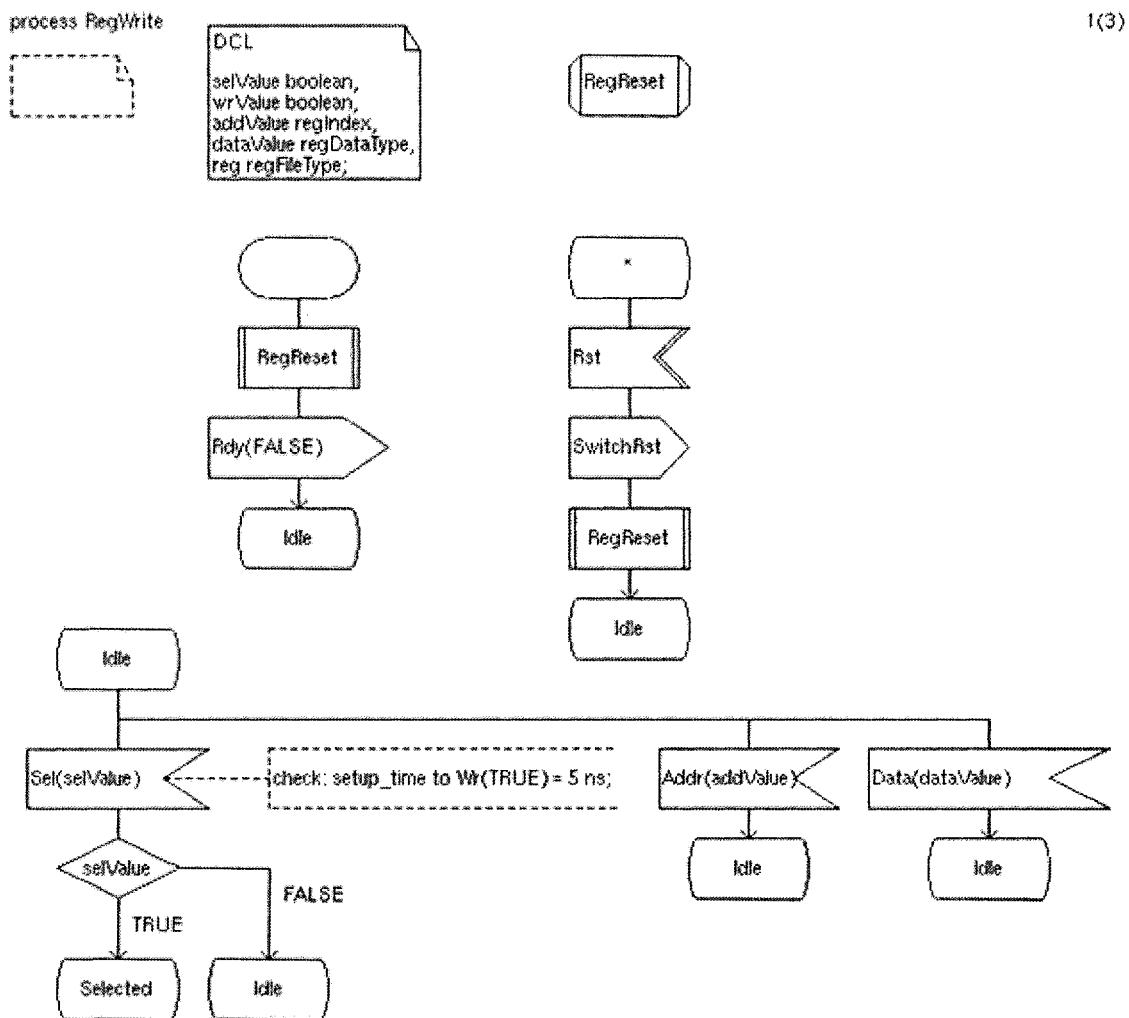

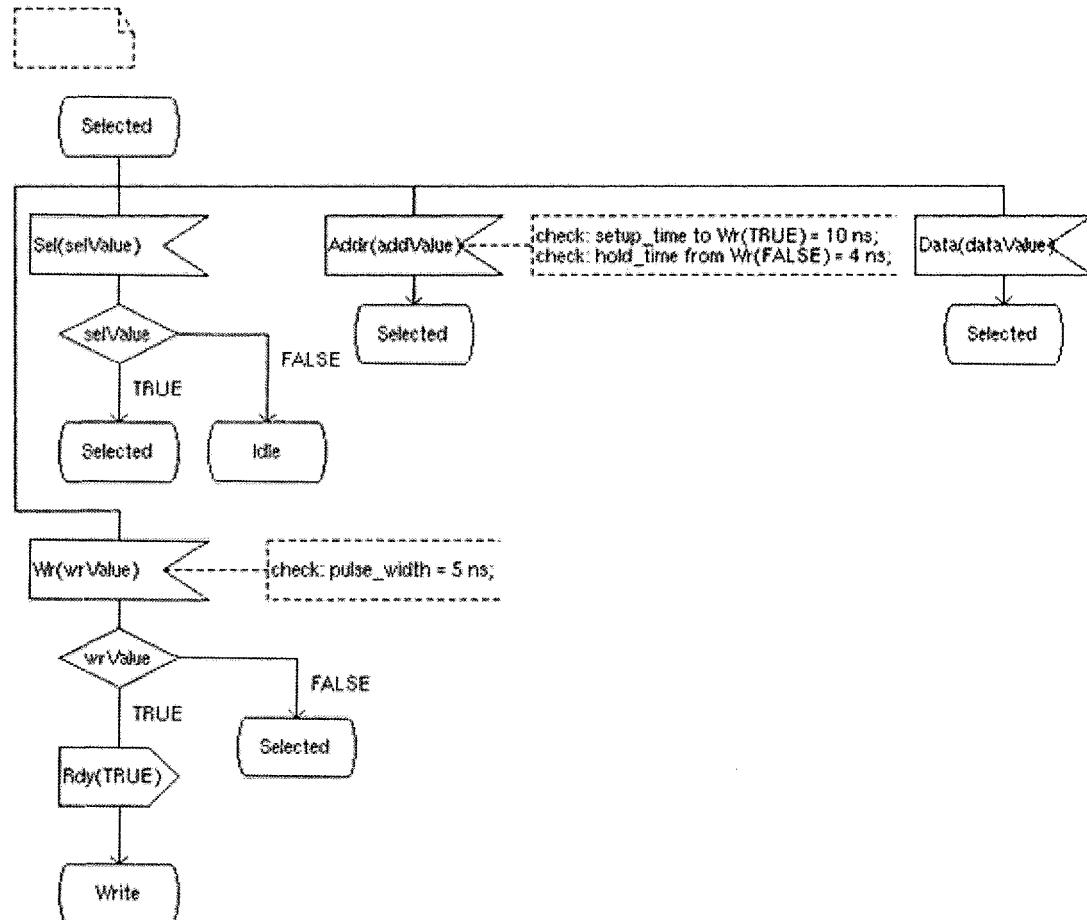

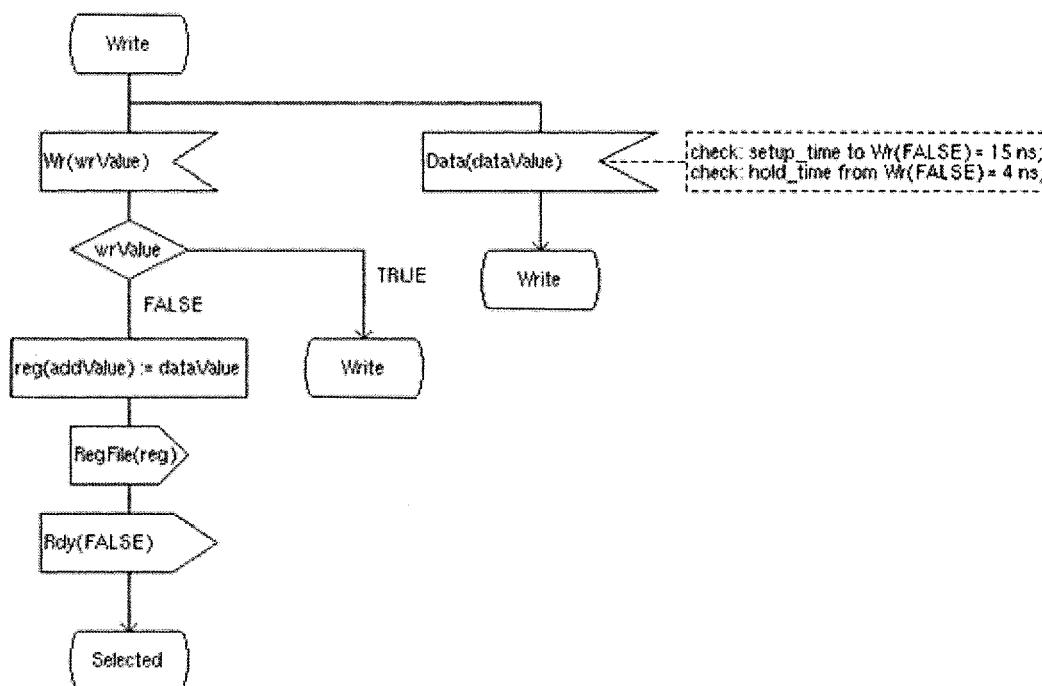

| Figure 4.7 - Timing Assertions Example.....                              | 80 |

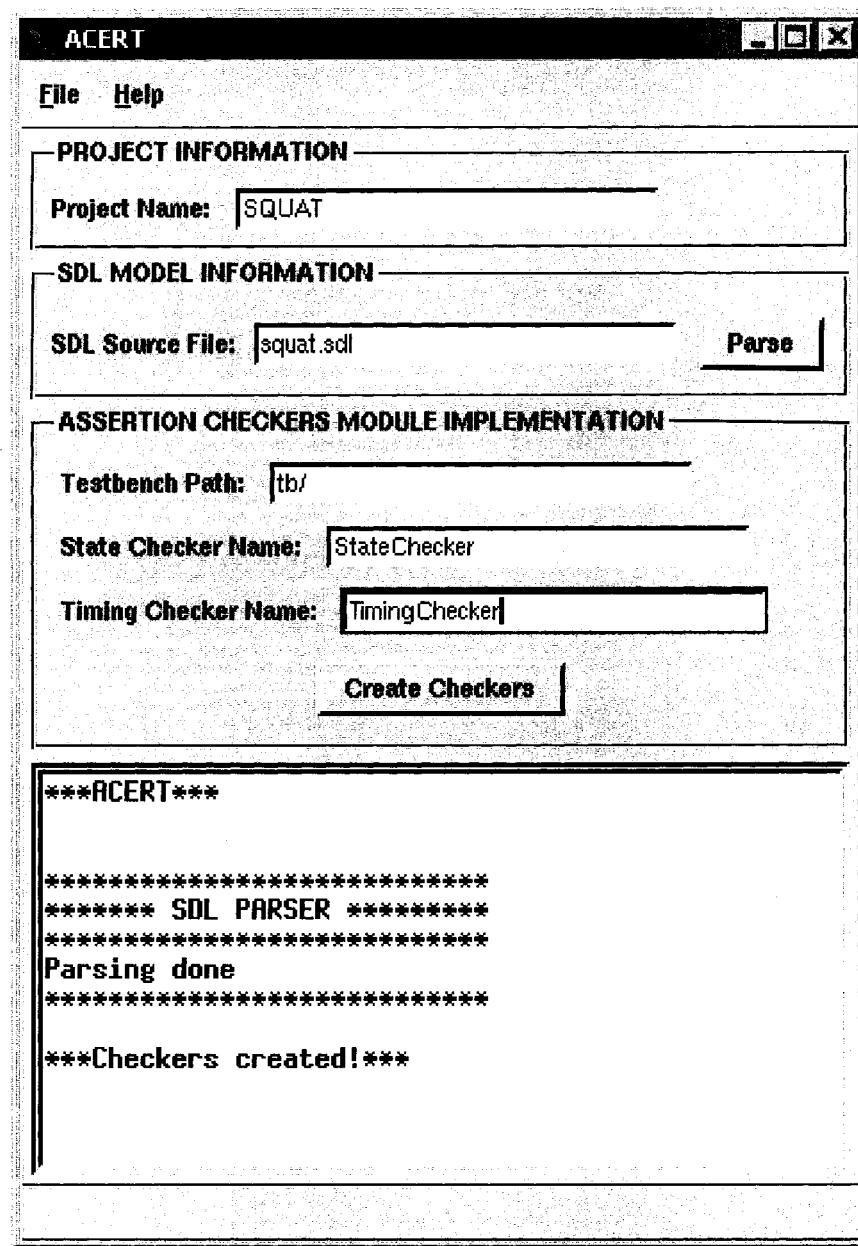

| Figure 4.8 - Assertion Tool GUI .....                                    | 81 |

| Figure 4.9 - State Exclusion Assertion Base Implementation .....         | 82 |

| Figure 4.10 - Timing Assertions Base Implementation.....                 | 83 |

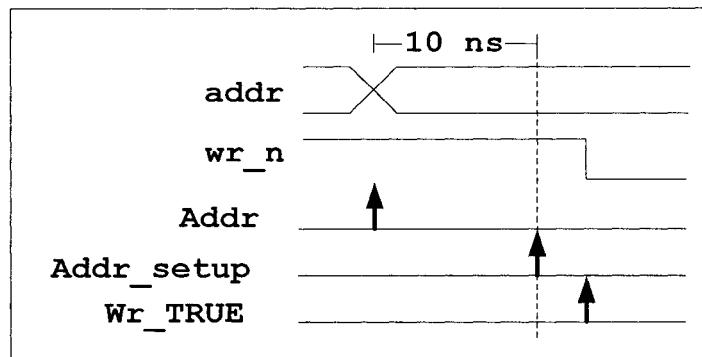

| Figure 4.11 - Address Setup-Time Assertion Timing Diagram .....          | 84 |

| Figure 4.12 - State Exclusion Assertion Checker Design Connections ..... | 85 |

| Figure 4.13 - Assertions Implementation Time.....                        | 87 |

## LISTE DES TABLEAUX

|                                                               |    |

|---------------------------------------------------------------|----|

| Tableau 3.1 - Opérateurs temporels du langage <i>e</i> .....  | 51 |

| Tableau 3.2 - Catégories d'aspects pour un banc d'essai ..... | 60 |

| Tableau 4.1 - SDL Assertion Set .....                         | 76 |

## LISTE DES ACRONYMES

|              |                                                  |

|--------------|--------------------------------------------------|

| <b>AOP</b>   | Aspect-Oriented Programming                      |

| <b>ASIC</b>  | Application Specific Integrated Circuit          |

| <b>ATM</b>   | Asynchronous Transfert Mode                      |

| <b>BFM</b>   | Bus-Functional Model                             |

| <b>EDA</b>   | Electronic Design Automation                     |

| <b>FIFO</b>  | First In First Out                               |

| <b>FPGA</b>  | Field-Programmable Gate Array                    |

| <b>FSM</b>   | Finite State Machine                             |

| <b>HDL</b>   | Hardware Description Language                    |

| <b>HVL</b>   | Hardware Verification Language                   |

| <b>IEEE</b>  | Institute of Electrical and Electronic Engineers |

| <b>IP</b>    | Intellectual Property                            |

| <b>OO</b>    | Object-Oriented                                  |

| <b>OOP</b>   | Object-Oriented Programming                      |

| <b>OVL</b>   | Open Verification Library                        |

| <b>PSL</b>   | Property Specification Language                  |

| <b>RTL</b>   | Register Transfert Level                         |

| <b>SDL</b>   | Specification and Description Language           |

| <b>SOC</b>   | System On a Chip                                 |

| <b>TB</b>    | Testbench                                        |

| <b>TCM</b>   | Time-Consuming Method ( <i>e</i> )               |

| <b>VHDL</b>  | VHSIC Hardware Description Language              |

| <b>VHSIC</b> | Very High-Speed Integrated Circuit               |

## LEXIQUE

|                           |                                                                                                                                                                                                                                                                                                     |

|---------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>Assertion</b>          | Expression d'un comportement attendu d'un modèle qui doit être vérifié (i.e. expression d'une propriété d'un modèle). L'objectif poursuivi par l'utilisation d'une assertion est d'assurer la cohérence entre l'intention d'un concepteur et ce qui est créé.                                       |

| <b>Banc d'essai</b>       | Simulation de l'environnement de travail réel d'un système dans le but de tester son bon fonctionnement.                                                                                                                                                                                            |

| <b>Constructeur</b>       | Fonction membre d'une classe logicielle qui est automatiquement invoquée à chaque fois qu'un objet de cette classe est créé (instancié).                                                                                                                                                            |

| <b>Couverture croisée</b> | Enregistrement de combinaison de valeurs scalaires en un point précis dans le temps à des fins d'analyse de la couverture fonctionnelle.                                                                                                                                                            |

| <b>Couverture d'items</b> | Enregistrement de valeurs scalaires individuelles en un point précis dans le temps à des fins d'analyse de la couverture fonctionnelle. L'objectif de la couverture d'items est de s'assurer que toutes les valeurs intéressantes et importantes d'un item ont été observées lors d'une simulation. |

|                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|----------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>Couverture de transitions</b>       | Enregistrement de valeurs scalaires en un point précis dans le temps dans le but de mesurer la présence ou la génération de séquences de valeurs. De façon conceptuelle, la couverture de transitions est semblable à la couverture de chemins dans une machine à états.                                                                                                                                                                                           |

| <b>Environnement de vérification</b>   | Ensemble des modules logiciels utilisés pour la vérification.                                                                                                                                                                                                                                                                                                                                                                                                      |

| <b>Événement</b>                       | Signal qui permet, par ses différents états, d'indiquer la situation ou l'évolution d'une partie d'un système.                                                                                                                                                                                                                                                                                                                                                     |

| <b>Expression temporelle</b>           | Définition déclarative d'un comportement temporel. De façon plus précise, il s'agit de la description de comportements à l'aide de combinaisons d'événements et d'opérateurs temporels.                                                                                                                                                                                                                                                                            |

| <b>Fil d'exécution (<i>thread</i>)</b> | Composante d'un processus, correspondant à une opération élémentaire effectuée dans un programme, et qui appartient à un seul processus.                                                                                                                                                                                                                                                                                                                           |

| <b>Machine à états finis étendus</b>   | Structure dans laquelle le calcul est modélisé sous la forme d'une transition d'un état vers un autre parmi un nombre fini d'états. Dans le cas du langage SDL, une machine à états est étendue par l'ajout de variables. Ceci permet d'effectuer des décisions de transition d'états basées sur la valeur associée à une variable de façon ce que l'état suivant ne soit pas seulement déterminé par l'état présent et les valeurs d'entrée de la machine à état. |

|                                 |                                                                                                                                                                                                                                                                                                                  |

|---------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>Machine à états finis</b>    | Structure dans laquelle le calcul est modélisé sous la forme d'une transition d'un état vers un autre parmi un nombre fini d'états.                                                                                                                                                                              |

| <b>Modèle sous vérification</b> | Modèle à vérifier.                                                                                                                                                                                                                                                                                               |

| <b>Moniteur d'assertion</b>     | Module d'un banc d'essai constitué d'assertions qui vérifient automatiquement le comportement d'un modèle sous vérification.                                                                                                                                                                                     |

| <b>Pointeur</b>                 | Élément de données (qui est lui-même une unité minimale d'information faisant partie d'un segment de données) indiquant la position d'un autre élément de données.                                                                                                                                               |

| <b>Processus</b>                | Instance d'une suite d'instructions nécessaires à l'exécution d'une tâche.                                                                                                                                                                                                                                       |

| <b>Propriété</b>                | Attribut comportemental utilisé pour caractériser un modèle. De façon plus formelle, une propriété est une collection de relations logiques et temporelles entre des expressions booléennes subordonnées, des expressions de séquences, et d'autres propriétés qui dans l'ensemble représentent un comportement. |

| <b>Propriété intellectuelle</b> | Bloc de conception dont la réutilisation pour fabriquer de nouveaux circuits est protégée par les règles de la propriété intellectuelle.                                                                                                                                                                         |

|                                             |                                                                                                                                                                                                                                                                                                                                                                          |

|---------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>Propriété de sûreté</b>                  | Propriété qui spécifie un invariant pour tous les états d'un modèle. L'invariant n'est pas nécessairement limité à un cycle mais il est limité dans le temps. De façon plus formelle, une propriété de sûreté est une propriété pour laquelle tout chemin violant la propriété possède un préfixe fini de façon à ce que chaque extension du préfixe viole la propriété. |

| <b>Propriété de vivacité</b>                | Propriété qui spécifie une fatalité qui est illimité dans le temps. De façon générale, une propriété de vivacité décrit que quelque chose de bien se produira fatalement. De façon plus formelle, une propriété de vivacité est une propriété pour laquelle tout chemin fini peut être étendu à un chemin qui satisfait la propriété.                                    |

| <b>Register Transfert Level (RTL)</b>       | Niveau d'abstraction associé à la description de modèles matériels où une correspondance exacte cycles par cycles ou états par états existe avec une implantation du modèle au niveau des portes logiques.                                                                                                                                                               |

| <b>Scénario de test (<i>test case</i>)</b>  | Instructions détaillées qui décrivent les données de base, les procédures et les résultats prévus d'un test en particulier.                                                                                                                                                                                                                                              |

| <b>Sortie standard</b>                      | En général, la sortie d'un programme est affichée à la sortie standard qui correspond à l'écran. La plupart des systèmes d'exploitation permettent de rediriger la sortie vers un fichier.                                                                                                                                                                               |

| <b>Temps de maintien (<i>hold time</i>)</b> | Temps de stabilité requis pour un signal suite à l'activation d'un autre signal.                                                                                                                                                                                                                                                                                         |

|                                                                 |                                                                                                                                                                                                                          |

|-----------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>Temps de préparation<br/>(setup time)</b>                    | Temps de stabilité requis pour un signal avant l'activation d'un autre signal.                                                                                                                                           |

| <b>Temps de validité<br/>(pulse width)</b>                      | Temps de stabilité requis pour un signal.                                                                                                                                                                                |

| <b>Test</b>                                                     | Opération destinée à contrôler la bonne exécution d'un programme dans son ensemble.                                                                                                                                      |

| <b><i>Time Consuming Method (TCM)</i></b>                       | Fonction utilisée pour synchroniser des processus d'un programme <i>e</i> avec des processus ou des événements d'un modèle HDL.                                                                                          |

| <b>Vérification boîte- blanche</b>                              | Stratégie de vérification qui est utilisée dans le but de vérifier la structure interne d'un système afin d'assurer la bonne marche de son fonctionnement externe.                                                       |

| <b>Vérification boîte-grise</b>                                 | Stratégie de vérification qui est utilisée dans le but de vérifier des propriétés spécifiques à l'implantation d'un système en contrôlant et en observant celui-ci via ses entrées et ses sorties.                       |

| <b>Vérification boîte-noire</b>                                 | Stratégie de vérification qui est utilisée dans le but de vérifier les entrées et les sorties d'un système sans se préoccuper de son fonctionnement interne.                                                             |

| <b>Vérification de bas en haut<br/>(bottom-up verification)</b> | Stratégie de vérification consistant à vérifier les composants d'un modèle de façon individuelle et à vérifier les fonctionnalités du système en intégrants les composants un à un dans l'environnement de vérification. |

**Vérification fonctionnelle**

Processus permettant de vérifier qu'un modèle possède les fonctionnalités décrites dans la spécification.

## **LISTE DES ANNEXES**

|                                                                                                |     |

|------------------------------------------------------------------------------------------------|-----|

| ANNEXE A - Questionnaire du sondage sur la vérification fonctionnelle.....                     | 105 |

| ANNEXE B - Patrons d'implantation d'assertions en langage e à partir d'assertions SDL<br>..... | 120 |

| ANNEXE C - Spécification SDL du commutateur ATM .....                                          | 123 |

| ANNEXE D - Code e généré par l'outil pour l'exemple du commutateur ATM .....                   | 131 |

| ANNEXE E - Aspect Partitioning for Hardware Verification Reuse .....                           | 141 |

| ANNEXE F - Applying Aspect-Oriented Programming to Hardware Verification with e<br>.....       | 154 |

# INTRODUCTION

Assurer l'exactitude fonctionnelle d'un modèle de conception matérielle est une étape laborieuse dans tout projet de conception microélectronique. Une implantation d'un modèle ne peut être exacte, sans erreur, par elle-même mais elle peut être exacte relativement à une spécification, une description de ce que l'implantation doit accomplir. Un des grands défis de la vérification matérielle basée sur la simulation est la génération d'un très grand nombre de stimuli de qualité, en déployant un effort minimal, dans le but de découvrir des erreurs qui se seraient glissées dans le modèle à vérifier. Un autre défi relié à la vérification fonctionnelle consiste en l'émulation précise de l'environnement d'un système sous vérification à l'aide d'un banc d'essai. Considérant que la vérification peut consommer jusqu'à 70% de l'effort dédié au développement d'un projet microélectronique, des méthodes efficaces pour accélérer l'implantation d'environnements de vérification ainsi que pour améliorer la qualité du processus de vérification sont requises.

Maximiser l'étendu de la réutilisation des parties d'un banc d'essai à l'intérieur ou même à l'extérieur d'un projet constitue un objectif fondamental pour réduire le temps accordé au processus de vérification. Lorsque des nouveaux composants d'un banc d'essai sont conçus, une approche de conception pour la réutilisation doit être considérée. Concevoir pour la réutilisation requiert l'application de solides concepts et de principes de conception logicielle. Ainsi, la vérification fonctionnelle est devenue une tâche logicielle très complexe.

L'implantation de bancs d'essai requiert l'utilisation de langages de programmation spécialisés. Les langages de description matérielle (*HDL*) comme le VHDL ou Verilog ont amélioré le processus de conception microélectronique en permettant de représenter la fonctionnalité d'un modèle d'implantation à un haut niveau

d'abstraction. Par contre, puisque la vérification fonctionnelle requiert des mécanismes logiciels complexes, les langages *HDL* ne sont pas idéals pour effectuer cette tâche. Certains langages reconnus tel C++ et Java, supportent des structures de données et des structures algorithmiques complexes nécessaires à la vérification fonctionnelle. Par contre, ces langages ne s'interfacent que très difficilement avec des modèles *HDL*. Certaines alternatives sont disponibles au concepteur de bancs d'essai pour contourner ces problèmes. D'une part, il est possible d'utiliser TestBuilder qui consiste en une bibliothèque de classes C++ qui permet le développement de bancs d'essai complexes. D'autre part, l'utilisation de langages de vérification matérielle (*HVL*) tels le langage *e* de Verisity ou OpenVera de Synopsys constituent d'autres alternatives. Ces langages offrent le support logiciel nécessaire à l'implantation de bancs d'essais complexes. Par exemple, l'utilisation du langage *e* permet de générer rapidement des vecteurs de tests grâce au moteur de génération pseudo-aléatoire de l'outil de simulation Specman Elite qui exécute le code *e*. En plus, ce langage possède les mécanismes nécessaires à l'établissement de modèles de couverture fonctionnelle. Pour sa part, Specman Elite possède des mécanismes d'analyse de la couverture fonctionnelle. Aussi, puisque cet outil s'exécute de façon concurrentielle avec un simulateur HDL, la valeur de chaque signal d'un modèle HDL sous vérification peut être échantillonnée et forcée à une valeur précise ce qui rehausse l'observabilité et la contrôlabilité de ce modèle.

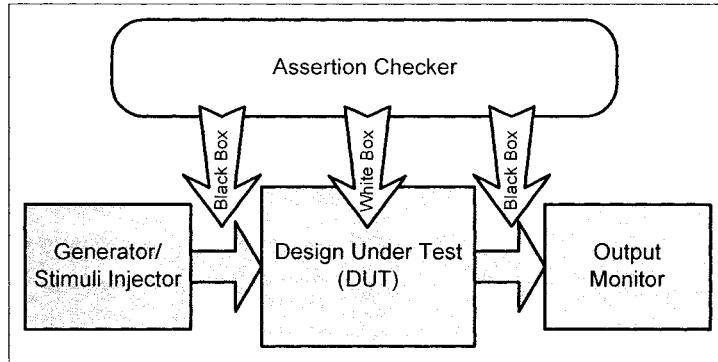

Par ailleurs, les langages de vérification permettent aux concepteurs d'implanter des moniteurs d'assertions à l'intérieur des bancs d'essais. Les moniteurs d'assertions permettent de rehausser la qualité du processus de vérification en analysant les comportements du modèle HDL et en rapportant toute violation. Aussi, les moniteurs d'assertions réduisent le temps requis pour mettre au point un modèle puisqu'ils peuvent être utilisés soit comme une technique de vérification boîte-noire, soit comme une technique boîte-blanche pour ainsi accroître la visibilité du modèle sous vérification. Cependant, même si la vérification basée sur des assertions est une méthode efficace pour vérifier des comportements complexes, notre expérience à coder des assertions montre qu'il est très difficile de coder des assertions efficaces. En plus, le processus

d'implantation d'assertions se révèle très sensible aux erreurs. En d'autres termes, il est facile de coder des assertions qui ne détecteront pas d'erreurs alors qu'elles sont supposées en détecter (erreurs fausses-positives), ou encore de coder des assertions qui détecteront de fausses erreurs (erreurs fausses-négatives). Pour ces raisons, le temps nécessaire pour déterminer des assertions est très significatif. Actuellement, aucun langage ne peut assurer la qualité d'un environnement de vérification. Conséquemment, de nouvelles méthodologies de conception de bancs d'essai supportées par ces langages sont tout de même requises.

Parallèlement, un élément clé d'un processus de développement consiste à l'intégration de la conception et de la vérification de manière concurrente. Lorsque la spécification est approuvée, la conception des bancs d'essais doit débuter en même temps que l'étape de développement. De façon idéale, lorsqu'un modèle RTL est prêt à être vérifié, des bancs d'essais sans erreurs devraient aussi être disponibles. La vérification du modèle RTL progresse ainsi beaucoup plus rapidement car le travail n'est pas retardé par la mise au point des bancs d'essai. Une spécification exécutable est un jalon dans l'établissement d'un processus parallèle de conception et de vérification car elle ne permet, en général, aucune ambiguïté dans son interprétation; ce qui n'est pas le cas avec des spécifications écrites en langage naturel car elles sont typiquement incomplètes et ambiguës. Une spécification exécutable peut représenter le comportement d'un système à différents niveaux d'abstraction et est vérifiable par simulation. Plusieurs langages standards sont disponibles pour spécifier le comportement d'un système à un haut niveau d'abstraction. C/C++ et SDL sont des exemples de langage de spécifications exécutables standards. En plus, SystemC, une bibliothèque de conception et de validation basée sur C++, supporte les étapes de conceptualisation ainsi que l'implantation autant matérielle que logicielle. SDL est un langage standard de spécification graphique et textuel. Ce langage est de plus en plus utilisé avec UML spécialement pour spécifier des actions d'un système opérant en temps réel. Ainsi, SDL est un langage approprié pour décrire des applications embarquées.

L'objectif premier de ce travail est de prouver qu'il est possible de simplifier et d'accélérer la création d'assertions réutilisables en langage *e* pour la vérification fonctionnelle par le biais d'un processus automatique de synthèse assistée d'assertions. Ce processus supporte une méthodologie d'implantation de bancs d'essai permettant :

- De définir les assertions à vérifier au niveau d'une spécification SDL exécutable.

- De simplifier l'implantation, dans un banc d'essai, des assertions définies dans la spécification en utilisant un outil permettant leur migration automatique vers des moniteurs d'assertions en langage *e*.

- De maximiser la réutilisation des assertions implantées en langage *e*.

Ce travail a été réalisé en deux étapes importantes. Tout d'abord, un sondage sur les pratiques de vérification de modèles matériels en entreprise a été effectué dans le but d'expliquer la problématique actuelle de la vérification fonctionnelle et de bien positionner le projet dans ce domaine. L'objectif principal du sondage était de répondre à ces deux questions:

1. Comment aborde-t-on et exécute-t-on la vérification fonctionnelle de modèles matériels en entreprise?

2. Existe-t-il une méthode intuitive ou efficace pour vérifier?

Les résultats de ce sondage sont présentés pour fournir une revue des méthodes de vérification utilisées dans l'industrie et les résultats sont comparés aux diverses méthodologies proposées dans la littérature.

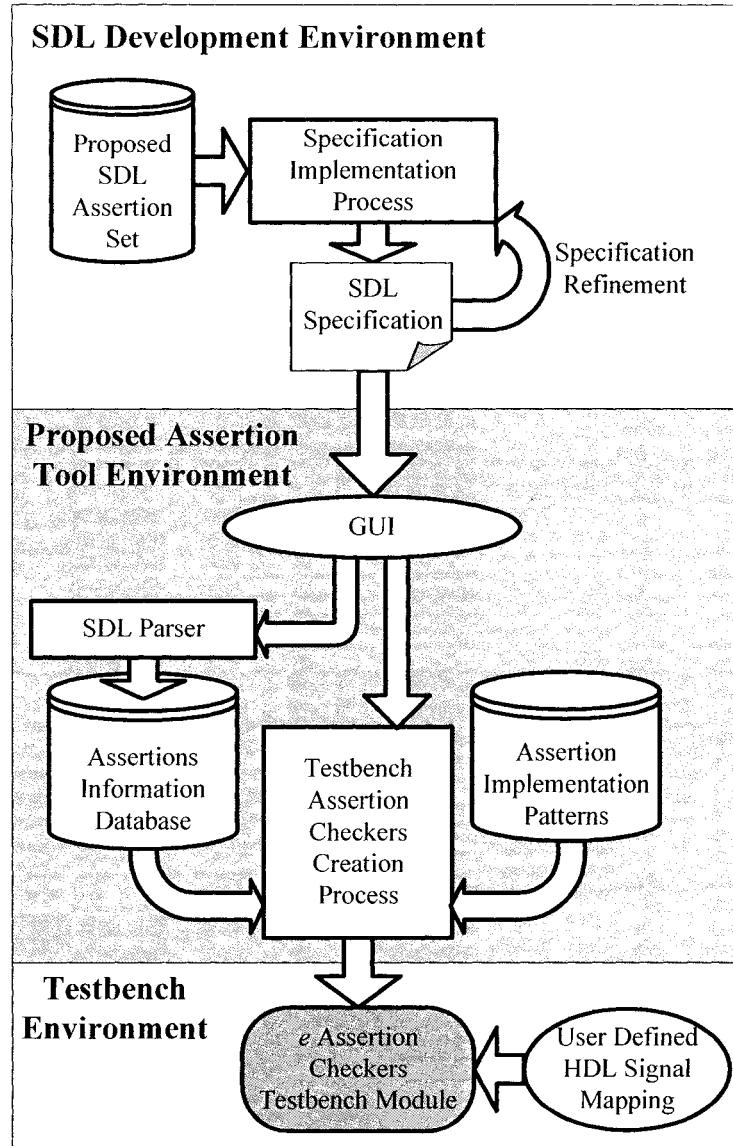

Ensuite, une méthodologie d'encapsulation d'assertions dans une spécification SDL est présentée. Les assertions implantées en SDL permettent de définir des comportements complexes au niveau de la spécification sans pour autant coder les assertions à partir de primitives propres aux langages de vérification. Définir une méthodologie d'encapsulation d'assertions dans une spécification standard au niveau système permet de spécifier plus précisément des propriétés d'un système dans une

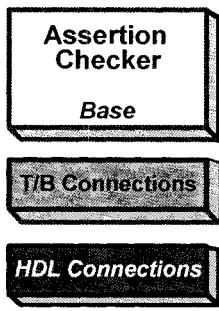

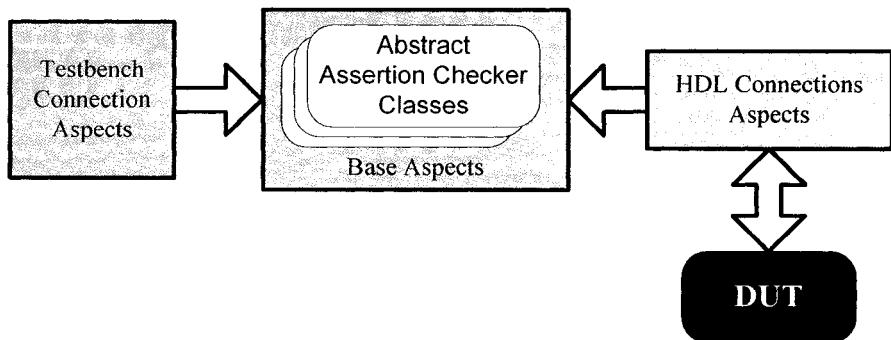

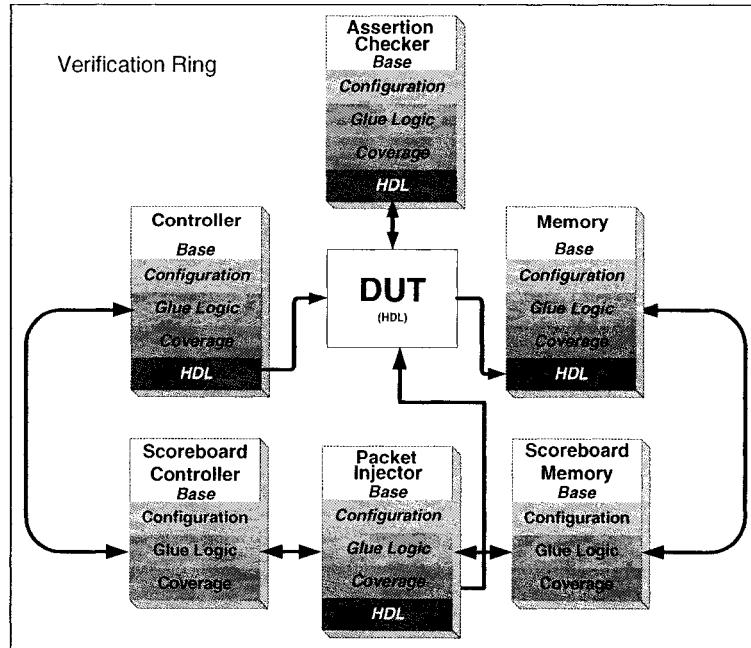

représentation qui sera utilisée par plusieurs personnes intéressées au développement. Un premier ensemble d'assertions, pour spécifier des comportements du système à haut-niveau, est inséré durant la capture de la spécification. Ensuite, lors du processus de raffinement de la spécification, de nouvelles assertions, pour spécifier des comportements à un niveau plus bas, peuvent être ajoutées. Quatre types d'assertions ont été sélectionnés pour être encapsulées dans la spécification. Plus précisément, la méthodologie présentée supporte des assertions d'exclusion d'états, des assertions de temps de préparation, des assertions de temps de maintien ainsi que des assertions de temps de validité d'un signal. Un outil est ensuite présenté dans le but d'assister le concepteur à la migration automatique des assertions définies dans la spécification vers des moniteurs d'assertions en langage *e*. Ce processus facilite l'implantation des bancs d'essai en utilisant directement l'information contenue dans une spécification pour créer des modules d'un banc d'essai. Des patrons d'implantation d'assertions en langage *e* sont utilisés pour créer les moniteurs d'assertion du banc d'essai. Ainsi, le potentiel de réutilisation des moniteurs d'assertions est optimisé d'abord en implantant des moniteurs génériques puis en les adaptant par la suite aux détails d'implantation spécifiques du système à vérifier. Cette méthodologie permet une séparation claire des aspects d'implantation des assertions, ce qui rehausse la réutilisation.

À l'aide d'un exemple concret, il est démontré qu'avec la méthodologie supportée par l'outil proposé, les concepteurs de système peuvent définir des assertions pour spécifier des comportements tant à haut-niveau qu'à bas niveau, dans une spécification exécutable, sans coder celles-ci à partir de primitives temporelles propres aux langages de vérification. Aussi, les bénéfices de la méthodologie proposée pour résoudre le problème de la conception des moniteurs d'assertions efficaces et réutilisables dans un environnement de vérification en *e* sont démontrés.

En résumé, les contributions originales de ce travail de recherche sont :

- L'établissement d'une base de connaissances sur la pratique de la vérification dans l'industrie par l'analyse des résultats d'un sondage conçu et publié par le groupe de recherche en microélectronique de l'École Polytechnique de Montréal.

- L'établissement d'une preuve de concept portant sur la génération assistée de moniteurs d'assertions à partir d'une spécification exécutable. Ceci implique :

- L'établissement d'une méthodologie d'encapsulation d'assertions dans une spécification SDL dans le but de rehausser le niveau de détail de la spécification.

- L'implantation d'un outil de génération assistée de moniteurs d'assertions pour des bancs d'essai.

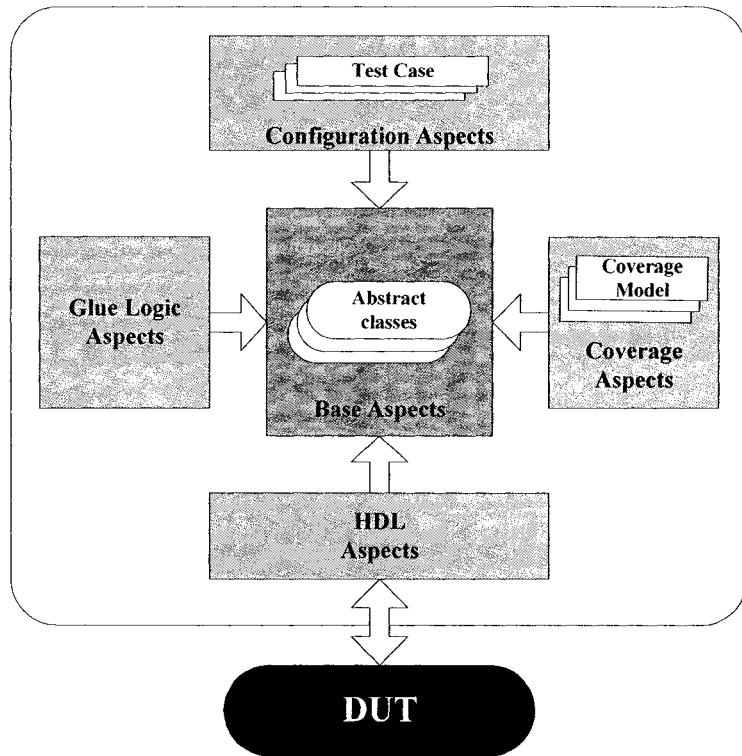

- L'établissement d'une méthodologie de partitionnement des aspects d'un environnement de vérification dans le but de rehausser le niveau de réutilisation du code du banc d'essai.

Ce projet a mené à la publication de trois articles. D'abord, (Regimbal, Lemire, Savaria, Bois, Aboulhamid et Baron 2002a) et (Regimbal, Lemire, Savaria, Bois, Aboulhamid et Baron 2002b), présentés aux annexes E et F, exposent une méthodologie de partitionnement par aspects pour rehausser la réutilisation lors de la conception d'environnements de vérification. Enfin, (Lemire, Regimbal, Bois, Savaria, Aboulhamid, Baron 2003) présente la méthodologie de synthèse d'assertions assistée à partir d'une spécification SDL.

Le corps de ce mémoire par article contient quatre chapitres. Il est principalement constitué des textes de deux articles. Le premier article, présenté au chapitre 2, dévoile les résultats et l'analyse d'un sondage sur les méthodes de vérification fonctionnelle en entreprise. Le deuxième article, présenté au chapitre 4, explique la méthodologie de synthèse d'assertions assistée à partir d'une spécification SDL exécutable. Les chapitres 1 et 3 présentent une synthèse de ces deux articles, discutent de leur pertinence dans le contexte de ce projet de recherche et présentent une analyse détaillée des résultats.

# CHAPITRE 1

## LA VÉRIFICATION FONCTIONNELLE (REVUE DE LITTÉRATURE ET SYNTHÈSE DE L'ARTICLE PRÉSENTÉ AU CHAPITRE 2)

Ce chapitre présente principalement l'article qui fera l'objet du deuxième chapitre de ce mémoire ainsi qu'une discussion générale des résultats qui ont mené à l'élaboration de celui-ci. Il présente aussi les notions et principes de la vérification fonctionnelle qui représente le sujet principal de l'article.

### 1.1 Formulation du problème de la vérification

L'exactitude d'un code HDL n'est pas une propriété absolue mais une propriété relative. Une description HDL ne peut être exacte, c'est-à-dire sans erreur, d'un point de vue absolu mais elle peut être exacte d'un point de vue relatif à une description de ce que l'usager voudrait qu'elle accomplisse (Bergeron 2003b, Bergeron 2000b, Bening, Foster 2001).

En général, on produit une spécification qui représente une compréhension informelle de ce que l'usager voudrait que l'implantation accomplisse. Lorsqu'un modèle est vérifié relativement à une spécification, deux modèles sont fondamentalement comparés. Donc, la vérification peut être définie comme étant l'action de comparer deux modèles. Soit  $m^*$  qui représente une spécification. Habituellement,  $m^*$  est implanté dans un langage connu de tous (ex : français, anglais etc.). Aussi, la spécification  $m^*$  peut être représentée sous forme d'un programme écrit dans un langage quelconque. À partir de la spécification, on génère un autre modèle,  $m$ , qui lui représente la source de l'implantation

du design. Dans le domaine de la conception matérielle, ce modèle  $m$  est une description HDL basée sur la spécification  $m^*$ .

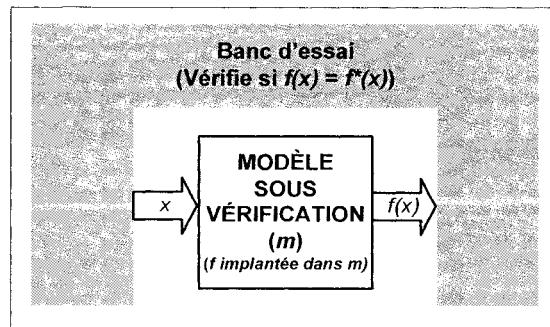

Soit maintenant  $f$  une fonction calculée par un modèle  $m$ . Il est alors possible d'imaginer l'existence d'une «version exacte»  $f^*$  de  $f$  qui correspond à ce que  $m$  devrait faire relativement à la spécification  $m^*$ . Pour démontrer que  $m$  est exact, il est nécessaire de prouver que  $f$  est équivalente à  $f^*$ . La connaissance de  $f^*$  provient en général de  $m^*$ , la spécification. Dans le domaine de la vérification fonctionnelle, on crée un banc d'essai à partir de  $m^*$  qui pour chaque valeur d'entrée  $x$  de  $m$ , est en mesure de déterminer si  $m$  calcule une valeur exacte pour  $f(x)$ , c'est-à-dire si  $f(x) = f^*(x)$  (Howden 1987). La figure 1.1 inspirée de (Bergeron 2003b, Bergeron 2000b) montre comment un banc d'essai interagit avec un modèle sous vérification. Le banc d'essai est un programme qui dans le domaine de la vérification matérielle est communément implanté en VHDL (Cohen 1999), Verilog (Bening, Foster 2001), e (Verisity 2002, Verisity 2003b) ou OpenVera (Synopsys 2003a, Haque, Khan, Michelson 2001), mais il peut aussi inclure des fichiers de données externes ou des sous-programmes en langage C. Ce programme est utilisé pour créer une séquence d'entrées  $x$  prédéterminées appliquées au modèle sous vérification  $m$ . La réponse du modèle aux entrées appliquées est aussi observée. On voit qu'il s'agit d'un système complètement fermé. C'est-à-dire que le système contenant le banc d'essai et le modèle sous vérification ne possède aucune entrée et aucune sortie. Le banc d'essai modélise l'environnement d'opération du modèle sous vérification.

**Figure 1.1 - Banc d'essai**

## 1.2 Preuve d'exactitude d'un modèle

Il serait possible de prouver l'exactitude de tout modèle en le vérifiant à l'aide de toutes les valeurs appartenant à son domaine d'entrées. En général, les domaines sont infinis. C'est pour cette raison qu'en pratique, un processus de preuve d'exactitude ne pourra utiliser la finitude des domaines d'entrées. La vérification fonctionnelle permet de contourner ce problème en divisant le problème de la comparaison de modèles en une série de petits problèmes dont il est possible de développer une théorie efficace.

## 1.3 La vérification fonctionnelle

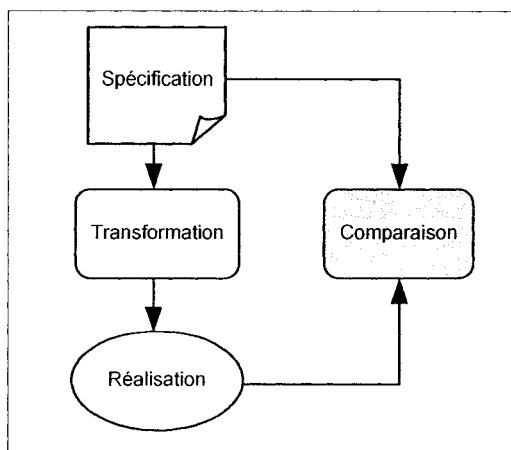

L'objectif principal de la vérification fonctionnelle est de s'assurer qu'un modèle implante bien les fonctionnalités attendues. Comme il est montré à la figure 1.2, la vérification fonctionnelle compare un modèle, qui constitue une réalisation de la spécification, avec sa spécification (Bergeron 2003b, Bergeron 2000b). Sans vérification fonctionnelle, il faudrait croire, par exemple, que la transformation d'une spécification en un modèle RTL a été effectuée correctement, sans interprétation erronnée de la spécification.

**Figure 1.2 - La vérification fonctionnelle**

## 1.4 Limites de la vérification fonctionnelle

Une des difficultés en vérification est de créer un modèle de référence qui capture complètement et correctement ce qu'on veut produire. Aussi, la vérification fonctionnelle pourrait ne pas détecter d'erreur dans un modèle pour les cas suivants (Howden 1987):

- Mauvaise identification des fonctions et des structures. Ceci survient lorsque l'analyse du modèle n'identifie pas toutes les fonctions et les structures utilisées par celui-ci.

- Banc de test incomplet.

- Mauvaise analyse des types de défaillances possibles.

## 1.5 Détails de soumission de l'article du chapitre 2

L'article présenté au chapitre 2 a pour titre « *A Survey on Current Functional Verification Practice* ». Il a été soumis au magazine *IEEE Design and Test of Computers* le 11 octobre 2002 et porte le numéro de manuscrit 117737. L'article est présentement en processus de recommandation finale par l'éditeur associé du magazine en vue d'une future publication.

## 1.6 Méthodologie de travail

La période de sondage a officiellement débutée le 4 juin 2002 et s'est terminée le 31 juillet 2002. Une implantation Web fut sélectionnée pour faciliter une publication à grande échelle ainsi que pour favoriser l'analyse automatique des résultats. Une version du sondage en format texte est présentée en annexe A. Le questionnaire était constitué de 45 questions. Les répondants ont été sondés sur les méthodes de vérification utilisées dans leur entreprise, leur opinion sur ce qui constitue un bon processus de vérification, ainsi que leur expérience technique.

Une invitation à répondre au sondage a été distribuée le 4 juin 2002 via le forum de discussion de la Guilde de Vérification (*Verification Guild*) vol. 3, no. 9 (Bergeron 2003a). L'invitation comportait un lien vers le site Web du sondage. À la fin de la période de sondage, 71 répondants avaient complété le questionnaire. Le sondage pouvait être complété de façon anonyme mais plusieurs répondants ont volontairement donné le nom de l'entreprise pour laquelle ils travaillaient. Ainsi, 31 différentes compagnies ont pu être identifiées comme ayant participé au sondage.

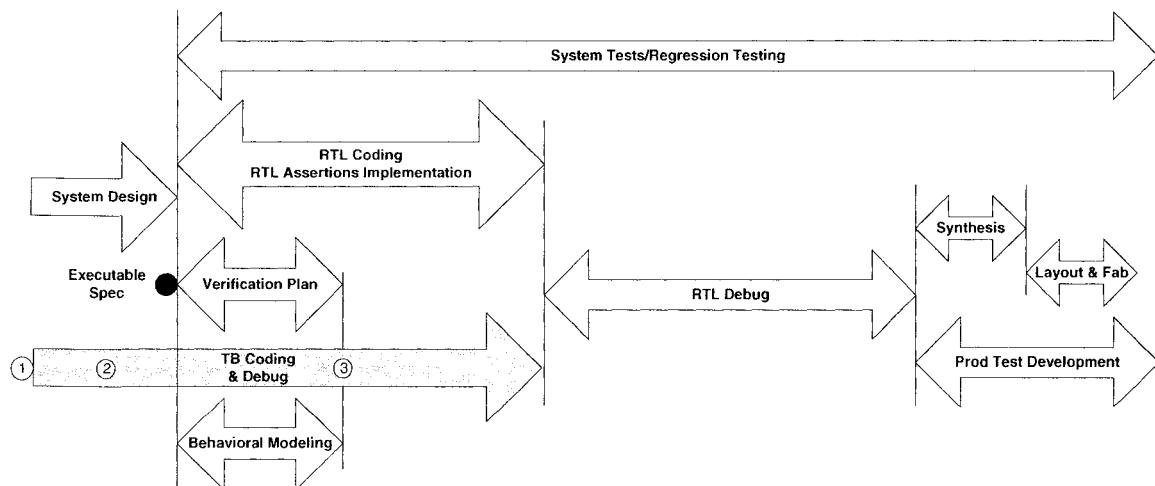

## 1.7 Survol de l'article

Pour établir le cadre d'application ainsi que définir la terminologie de ce projet de recherche, l'article débute par une revue des méthodes actuelles de vérification telles que proposées par la littérature. L'importance du parallélisme entre le déroulement des processus de conception et de vérification est exposée. À partir du moment où une spécification exécutable du modèle à planter est disponible, la conception du plan de vérification et des bancs d'essai peut s'exécuter en même temps que l'implantation du code RTL du modèle. De façon idéale, lorsqu'une description RTL du modèle est disponible, des bancs d'essais sans défaut sont aussi disponibles. Ceci permet de diminuer grandement le temps de développement du projet.

Une stratégie de vérification optimale basée sur les techniques et technologies actuelles est présentée. Cette stratégie consiste principalement en une intégration de la vérification formelle et de la simulation. Ensuite, les différents niveaux de vérification sont présentés soient la vérification au niveau des blocs fonctionnels, la vérification au niveau de l'intégration des blocs fonctionnels, la vérification au niveau des ASIC, des FPGA et des blocs IP, et la vérification au niveau système.

Ensuite, une analyse exhaustive des résultats du sondage est présentée. Cette analyse offre une perspective générale des pratiques actuelles de vérification des répondants. L'analyse est partitionnée selon les différents sujets abordés dans le sondage soient le profil des répondants, le processus de vérification, les stratégies de vérification,

les méthodes d'auto-vérification, la couverture, la réutilisation ainsi que la vérification formelle. Enfin, une discussion sur l'implication des résultats du sondage est présentée. On y retrouve une comparaison entre les méthodes de vérification fonctionnelle proposées dans la littérature et les méthodes actuelles des répondants.

## 1.8 Principales conclusions et résultats

Cette recherche a permis d'obtenir des résultats significatifs au niveau de plusieurs sujets reliés à la vérification fonctionnelle. Il est intéressant de remarquer que certaines méthodes de vérification bien documentées dans la littérature ne sont pas ou peu utilisées par les répondants. Aussi, il est possible de remarquer que certaines autres pratiques sont bien établies car elles sont utilisées par la majorité des répondants.

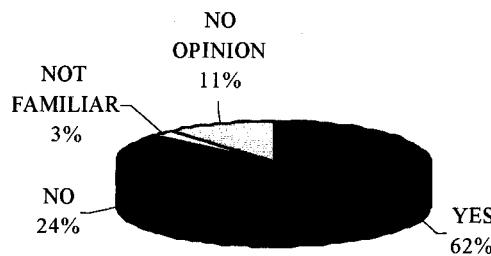

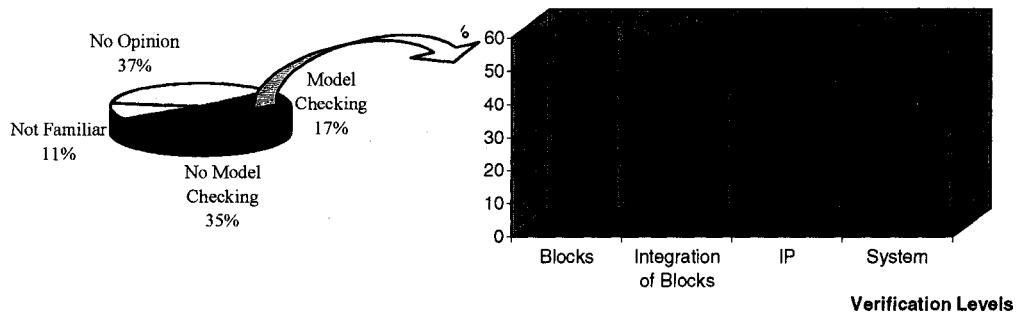

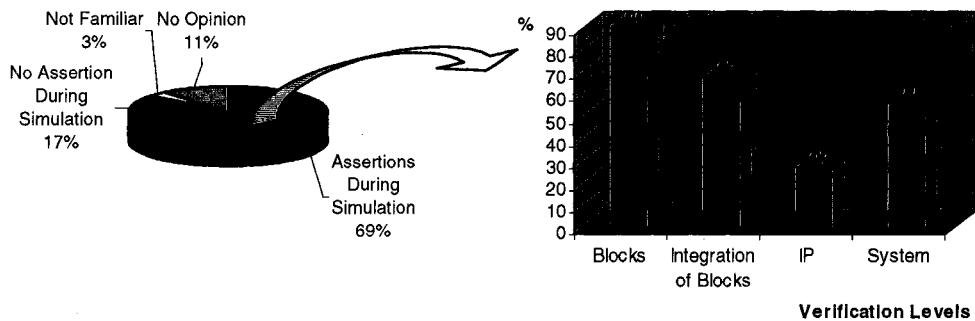

On y voit particulièrement que la vérification fonctionnelle est au centre des préoccupations de l'ensemble des répondants. Aussi, une méthodologie de vérification axée sur la simulation est encore beaucoup plus utilisée qu'une méthodologie de vérification tirant profit à la fois des méthodes formelles et de la simulation. On y voit aussi que la majorité des répondants génèrent les stimuli de leurs bancs d'essai au niveau transactionnel plutôt qu'à un bas niveau d'abstraction. Les langages HDL sont encore très utilisés dans la conception de bancs d'essai. La majorité des répondants utilise une méthodologie de vérification basée sur l'implantation d'assertions (voir chapitre 3 pour plus de détails sur la vérification basée sur des assertions). L'utilisation de la couverture de code ainsi que la couverture fonctionnelle est fréquente. La métrique de couverture de code la plus utilisée est la couverture d'instructions. Au niveau de la vérification formelle, une majorité de répondants utilise la vérification formelle d'équivalence de modèles (*formal equivalence checking*) au profit des autres méthodes formelles. Aussi, un grand nombre de répondants n'utilise ni des méthodes avancées de conception logicielle, ni des méthodes avancées de réutilisation dans l'élaboration de leurs bancs d'essai, et ce malgré le fait que la majorité d'entre eux croit que la conception de bancs d'essai relève principalement du domaine du logiciel.

# CHAPITRE 2

## A SURVEY ON CURRENT FUNCTIONAL VERIFICATION PRACTICE

Jean-François Lemire<sup>1</sup>,

Sébastien Regimbal<sup>1</sup>, Guy Bois<sup>1</sup>, Yvon Savaria<sup>1</sup> and El Mostapha Aboulhamid<sup>2</sup>

<sup>1</sup> Electrical Engineering Department, École Polytechnique de Montréal,

P.O. Box 6079, Succ. Centre-Ville, Montréal, Québec, Canada, H3C 3A7.

{lemire, regimbal, bois, savaria }@grm.polymtl.ca

<sup>2</sup> Department of Computer Science and Operational Research, Université de Montréal,

C.P. 6128, Succ. Centre-ville, Montréal, Québec, Canada, QC H3C 3J7.

aboulham@iro.umontreal.ca

### **2.1 Abstract**

Functional Verification of hardware designs is more than ever treated as a vital part of their development process. The effort required to verify complex designs is increasing at an alarming rate. In the beginning of June 2002, the Groupe de Recherche en Microélectronique of École Polytechnique de Montréal published an academic survey on functional verification methodologies to get a glimpse at today's functional verification practices in the microelectronics industry. The purpose of this paper is to provide a detailed analysis of the survey's results and thus getting a snapshot of the sampled respondents' verification practices. The paper provides an analysis of the state-of-the-art verification methodologies as proposed in the literature. In addition, the survey results are compared to the proposed methodologies and the missing links to a more effective verification practice are identified. Our study led to interesting findings related to various functional verification topics, such as the verification process, formal and

assertion-based verification, coverage, reuse and verification strategies. We noticed that some verification practices are well established, and are used by the majority of our respondents. Also, we discovered that certain verification methods, well documented in the literature, are seldom used by a significant percentage of respondents.

## 2.2 Introduction

Considering that hardware verification has become the most critical bottleneck in the digital design flow, new approaches and methods are more than ever required. To deal with this issue, several verification methods and tools are currently developed to help verification engineers cope with this difficult task. What was not so long ago an *ad hoc* process is nowadays one of the most interesting fields to integrate new standards and structured practices. To help position our research with respect to current state-of-the-art, we created and published a survey on functional verification (Lemire 2002). Our main objectives were to answer two questions:

- 1) How is functional verification addressed and performed in industry?

- 2) Is there an intuitive and/or effective way to perform functional verification?

To establish the framework and terminology of this study, the paper begins with a description of a state-of-the-art verification methodology, as proposed in the literature. It then presents the detailed analysis of the results collected through the survey. This analysis provides a good overall perspective of our respondents' verification practices, which can be compared with current theory to highlight any discrepancy. The survey period began officially on June 4th 2002 and ended on July 31st 2002. We chose a web survey implementation method because of its inherent publication ease and its automatic results analysis possibilities.

The remainder of this paper is organized as follows: We will first discuss, in section 2.3, the theoretical verification flow proposed in the literature. Then, in section 2.4, we will briefly present the sample structure of the survey and, in section 2.5, we will provide a detailed analysis of our findings. In section 2.6, we will discuss the implications of these results in relation to the proposed theoretical flow and our previously defined objectives. Finally, we will summarize our main conclusions.

## **2.3 Verification flow according to current literature**

Nowadays, design and verification methodologies are very important issues. Moreover, cost and time to market are predominant development success factors. This section presents a description of state-of-the-art verification methodologies, as proposed in the literature, to establish the framework and terminology of the survey. The survey results will be compared in section 2.6 with these methodologies.

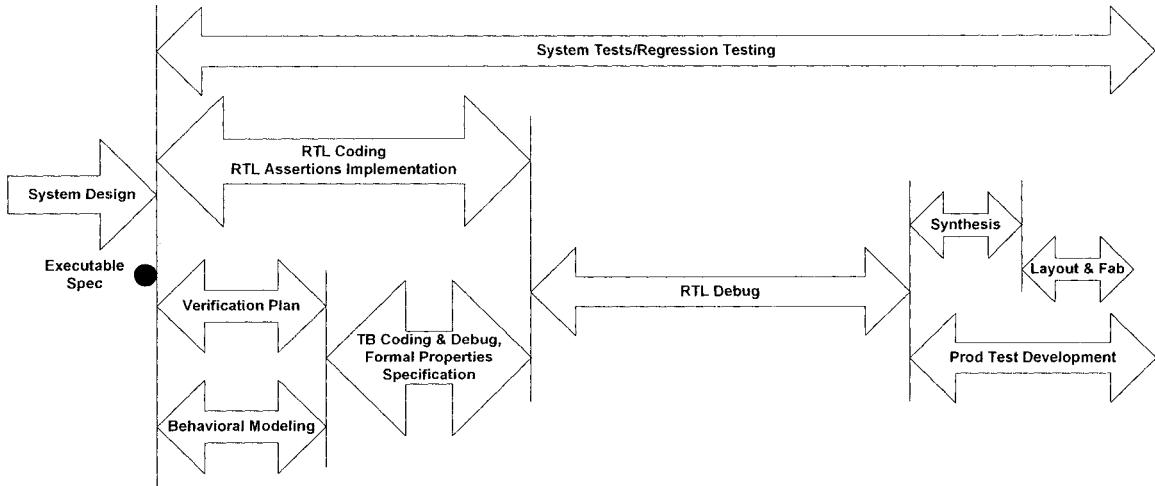

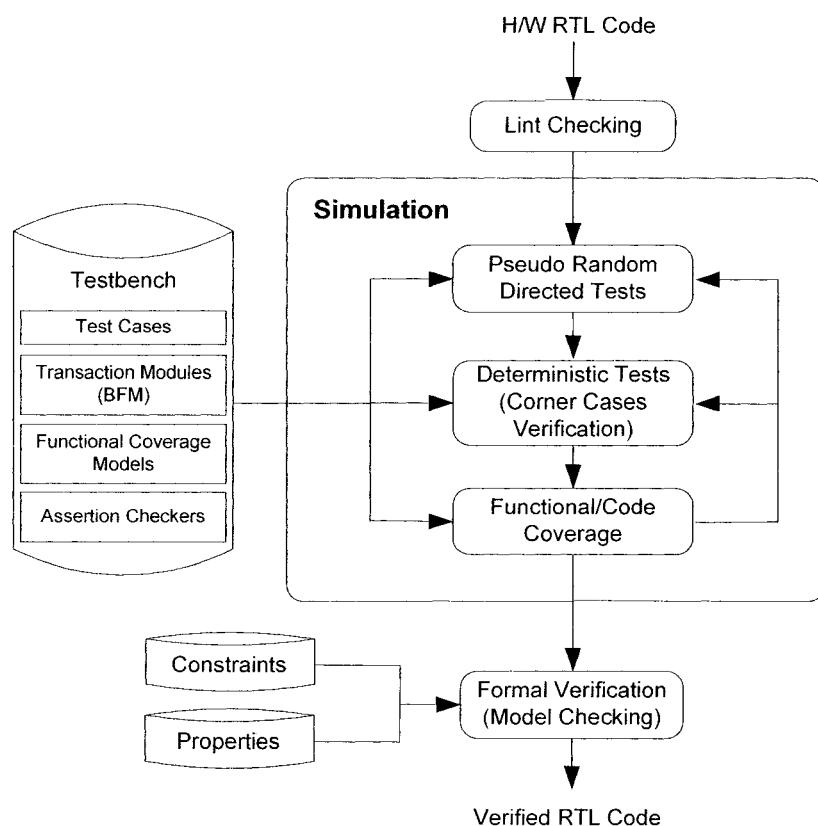

### **2.3.1 Development Flow**

A key point in a good development process is the integration of concurrent design/verification efforts and methodologies. Figure 2.1, inspired from (Sternberg 2000, Bergeron 2003b, James 1999), highlights the benefits of a concurrent approach. We see that once the specifications are approved, a verification effort begins in parallel with the design effort. The importance of a specification is summarized in (Bening, Foster 2001). The authors explain that the fundamental verification principle is to have a complete specification before RTL implementation to avoid unnecessarily complex and unverifiable designs. Furthermore, an executable specification allows no ambiguity in its interpretation, which is not the case with a natural language specification. This type of specification is directly verifiable through simulation, and hence is a milestone in the top down design of a system. Moreover, an executable specification can be used as a reference to generate the verification plan. Behavioral models are also created so that the simulation testbench can be debugged before the RTL is ready. These behavioral models are also available for verification in a bottom up fashion, where the testbench emulates

design blocks interfaces. They increase the thoroughness of the verification effort, and the speed at which developers can iterate through the process, due to faster simulation turn-around. Finally, once the specifications are approved, system engineers begin to work on the system-level testing and regression test suite.

**Figure 2.1 - Proposed Development Flow**

Ideally, when a RTL description is available for verification, testbenches are already available for simulation. RTL verification progresses faster because the effort is not delayed by the debugging of testbenches. As mentioned earlier, in a bottom-up verification process, only the portion of the design being verified can be represented in RTL. The simulation time is of course reduced if behavioral models represent the remainder of the system.

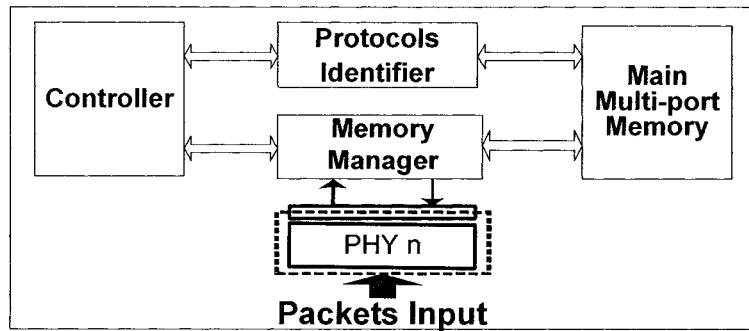

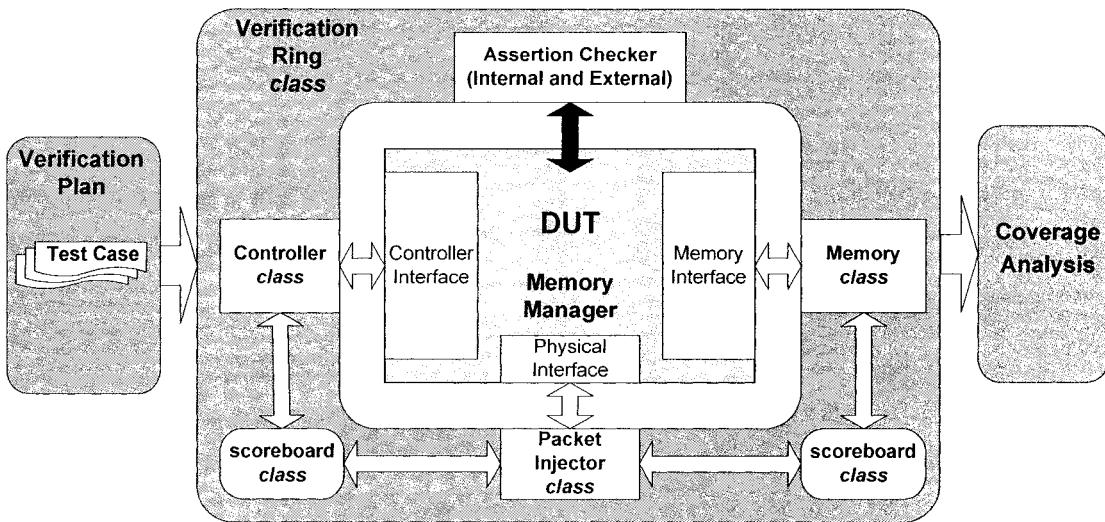

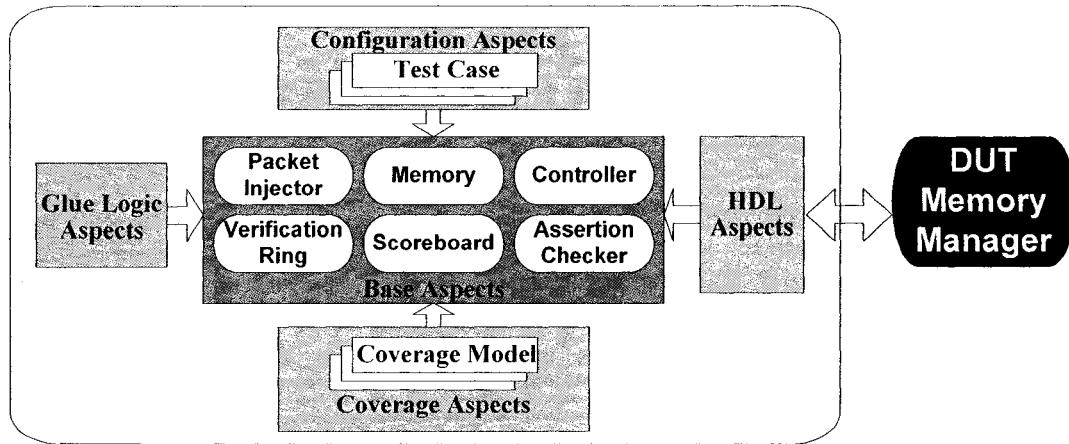

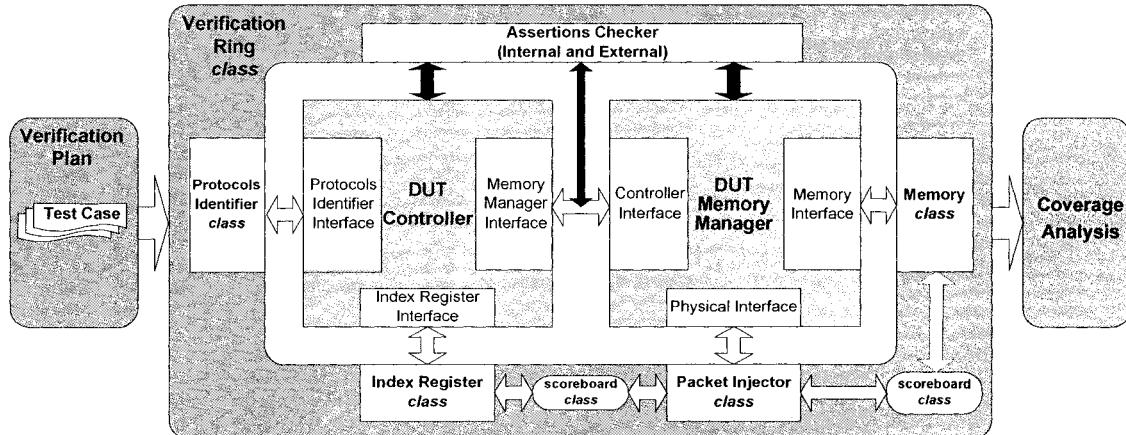

### 2.3.2 Formal Techniques