**Titre:** Conception d'un processeur embarqué de faible complexité dédié à une plate-forme SoC pour concevoir des processeurs réseaux

Title: [Conception d'un processeur embarqué de faible complexité dédié à une plate-forme SoC pour concevoir des processeurs réseaux](#)

**Auteur:** Hany Ghattas

Author: [Hany Ghattas](#)

**Date:** 2003

**Type:** Mémoire ou thèse / Dissertation or Thesis

**Référence:** Ghattas, H. (2003). Conception d'un processeur embarqué de faible complexité dédié à une plate-forme SoC pour concevoir des processeurs réseaux [Master's thesis, École Polytechnique de Montréal]. PolyPublie.

Citation: <https://publications.polymtl.ca/7123/>

## Document en libre accès dans PolyPublie Open Access document in PolyPublie

**URL de PolyPublie:** <https://publications.polymtl.ca/7123/>

PolyPublie URL: <https://publications.polymtl.ca/7123/>

**Directeurs de recherche:** Yvon Savaria

Advisors: [Yvon Savaria](#)

**Programme:** Unspecified

Program: [Unspecified](#)

**In compliance with the

Canadian Privacy Legislation

some supporting forms

may have been removed from

this dissertation.**

**While these forms may be included

in the document page count,

their removal does not represent

any loss of content from the dissertation.**

UNIVERSITÉ DE MONTRÉAL

CONCEPTION D'UN PROCESSEUR EMBARQUÉ DE FAIBLE COMPLEXITÉ

DÉDIÉ À UNE PLATE-FORME SoC POUR CONCEVOIR DES PROCESSEURS

RÉSEAUX

HANY GHATTAS

DÉPARTEMENT DE GÉNIE ÉLECTRIQUE

ÉCOLE POLYTECHNIQUE DE MONTRÉAL

MÉMOIRE PRÉSENTÉ EN VUE DE L'OBTENTION

DU DIPLÔME DE MAÎTRISE ÈS SCIENCES APPLIQUÉES

(GÉNIE ÉLECTRIQUE)

JUILLET 2003

National Library

of Canada

Acquisitions and

Bibliographic Services

395 Wellington Street

Ottawa ON K1A 0N4

Canada

Bibliothèque nationale

du Canada

Acquisitions et

services bibliographiques

395, rue Wellington

Ottawa ON K1A 0N4

Canada

*Your file* Votre référence

ISBN: 0-612-86400-6

*Our file* Notre référence

ISBN: 0-612-86400-6

The author has granted a non-exclusive licence allowing the National Library of Canada to reproduce, loan, distribute or sell copies of this thesis in microform, paper or electronic formats.

L'auteur a accordé une licence non exclusive permettant à la Bibliothèque nationale du Canada de reproduire, prêter, distribuer ou vendre des copies de cette thèse sous la forme de microfiche/film, de reproduction sur papier ou sur format électronique.

The author retains ownership of the copyright in this thesis. Neither the thesis nor substantial extracts from it may be printed or otherwise reproduced without the author's permission.

L'auteur conserve la propriété du droit d'auteur qui protège cette thèse. Ni la thèse ni des extraits substantiels de celle-ci ne doivent être imprimés ou autrement reproduits sans son autorisation.

# Canadä

UNIVERSITÉ DE MONTRÉAL

ÉCOLE POLYTECHNIQUE DE MONTRÉAL

Ce mémoire intitulé :

CONCEPTION D'UN PROCESSEUR EMBARQUÉ DE FAIBLE COMPLEXITÉ

DÉDIÉ À UNE PLATE-FORME SoC POUR CONCEVOIR DES PROCESSEURS

RÉSEAUX

présenté par : GHATTAS Hany

en vue de l'obtention du diplôme de : Maîtrise ès sciences appliquées

a été dûment accepté par le jury d'examen constitué de :

M. AUDET Yves, Ph.D., président

M. SAVARIA Yvon, Ph.D., membre et directeur de recherche

M. BOIS Guy, Ph.D., membre

## REMERCIEMENTS

J'aimerais tout d'abord remercier les organismes subventionnaires qui m'ont soutenu financièrement au cours de mes études de maîtrise et de la réalisation du projet décrit dans le présent mémoire. Ceux-ci sont : la compagnie Gennum Corporation ainsi que le réseau de centres d'excellence sur les dispositifs, circuits et systèmes microélectroniques, financé par le gouvernement fédéral et l'industrie au Canada et Micronet.

J'aimerais remercier les gens qui m'ont guidé tout au long de ce projet de recherche, soient mon directeur de recherche, le professeur Yvon Savaria de l'École Polytechnique de Montréal, ainsi que Messieurs Jean-Marc Tremblay et Arnold Veenstra, ingénieurs chez Gennum Corporation. Également, mes collègues de travail qui m'ont éclairé sous différents sujets, soient Mme Maria Mbaye, M. Sébastien Regimbal, M. Jean Pepga-Bissou étudiants en maîtrise à l'École Polytechnique de Montréal.

J'aimerais aussi remercier les gens avec qui j'ai travaillé ou que j'ai côtoyés tout au long de mes travaux. Ceux-ci sont : M. Tien Bui, M. Alexandre Chureau et M. Kevin Peterson.

Je voudrais enfin remercier ma mère Marie ainsi que mon père Victor, qui m'ont supporté pendant toute la durée de mes études.

## RÉSUMÉ

Les composants pour réaliser des systèmes de traitement de flot réseau («Network Processor ») sont des dispositifs programmables effectuant le traitement, dans des dispositifs de communication de données, des unités de données de protocole, à très haute vitesse. Ils ont émergé suite à la demande croissante des services améliorés pour une prochaine génération. Cette recherche fait partie d'un effort pour mettre en application une plate-forme « SoC » qui pourrait supporter des paquets vidéo numériques de très haute vitesse avec une basse latence. Cette plate-forme flexible est basée sur un processeur embarqué fait sur mesure. Nous avons également développé un assembleur qui sera utile pour différentes applications. Des algorithmes simples de conversion de protocole ont été codés pour ce processeur. Cette plate-forme « SoC » permet au concepteur de système de remplacer les puces intégrées à fonctionnalités fixes ainsi que les processeurs RISC, par des dispositifs intelligents et programmables qui maintiennent une très haute vitesse.

Ce mémoire présente une brève étude de plusieurs processeurs réseaux existant sur le marché. Il propose une architecture de plate-forme « SoC » capable de faire la conversion de protocoles, ainsi que plusieurs applications de télécommunication telle que la classification de paquets. Nous avons mis en œuvre un processeur embarqué fait sur mesure qui sera intégré dans cette plate-forme, utile pour la manipulation de paquets. Ce mémoire compare plusieurs versions de notre processeur embarqué avec le processeur ARM7, un processeur populaire dont le noyau est disponible sur le marché. Il démontre quelques avantages d'un processeur embarqué au cœur d'une plate-forme « SoC », consacrée à la transmission de paquets de vidéo numérique. Ce processeur, fait sur mesure, offre un rendement plus élevé, et pourrait être facilement adapté à nos besoins; cependant, nous n'avons pas réussi à atteindre la densité du processeur ARM7 à cause de la bibliothèque de cellules disponibles et de la méthodologie de conception physique choisie.

## ABSTRACT

Network processing system components are programmable devices performing wire-speed processing of ***Protocol Data Units*** in data communication devices. They emerged as a direct result of the growing demand for enhanced, flexible next generation communication services. This research is part of an effort to implement a SOC platform that could support high throughput and low latency real time video streaming. This flexible platform is based on a custom embedded processor for which we also developed an application specific assembler. Simple protocol conversion algorithms were coded for this processor. This SoC platform allows system designer to replace fixed-functionality ASICs and RISC CPUs in the critical path with intelligent, programmable devices that maintain wire speed.

This Master's thesis presents a brief study of several Network processors that are already in the market. It proposes a SoC platform architecture capable of doing protocols conversion among other telecommunication applications such as classification. We have implemented a custom embedded processor that will be integrated in this SoC platform for packets manipulation. This thesis compares several versions of our embedded processor with the ***ARM7***, a popular core processor available in the market. It demonstrates some benefits of an embedded processor in a SOC platform dedicated to video streaming packets. The custom processor offers a higher performance, and could be easily adapted to our needs; however, we could not approach the density of the ***ARM7*** with the available cell library and physical design flow.

## TABLE DES MATIÈRES

|                                                                               |             |

|-------------------------------------------------------------------------------|-------------|

| <b>REMERCIEMENTS .....</b>                                                    | <b>iv</b>   |

| <b>RÉSUMÉ .....</b>                                                           | <b>v</b>    |

| <b>ABSTRACT.....</b>                                                          | <b>vi</b>   |

| <b>LISTE DES FIGURES .....</b>                                                | <b>xi</b>   |

| <b>LISTE DES TABLEAUX.....</b>                                                | <b>xiii</b> |

| <b>LISTE DES ACRONYMES.....</b>                                               | <b>xiv</b>  |

| <b>INTRODUCTION.....</b>                                                      | <b>1</b>    |

| <b>CHAPITRE I.....</b>                                                        | <b>6</b>    |

| <b>    Revue critique de la littérature .....</b>                             | <b>6</b>    |

| 1.1     Évolution des processeurs réseau.....                                 | 6           |

| 1.1.1     Processeurs réseau Ethernet.....                                    | 6           |

| 1.1.2     Processeurs réseau Gigabit Ethernet, OC-12 et OC-48 .....           | 8           |

| 1.1.2.1     Commutateurs de réseau basés sur des processeurs RISC.....        | 8           |

| 1.1.2.2     Commutateurs réseau basés sur des circuits intégrés ASIC .....    | 9           |

| 1.1.2.3     Commutateurs réseau basés sur des processeurs RISC améliorés..... | 10          |

| 1.1.2.4     Commutateurs réseau basés sur des approches hybrides .....        | 12          |

| 1.1.2.5     Architecture de processeurs intermédiaires .....                  | 12          |

| 1.2     Processeur réseau .....                                               | 13          |

| 1.2.1     Définition d'un processeur réseau .....                             | 13          |

| 1.2.2     Caractéristiques d'un processeur réseau .....                       | 14          |

| 1.2.3     Le routage .....                                                    | 15          |

| 1.3     Le marché des processeurs réseau OC-192 .....                         | 16          |

| 1.3.1     Alchemy (Au1000) .....                                              | 17          |

| 1.3.1.1     Architecture interne .....                                        | 17          |

|                                                   |                                                                       |           |

|---------------------------------------------------|-----------------------------------------------------------------------|-----------|

| 1.3.1.2                                           | Programmabilité.....                                                  | 17        |

| 1.3.1.3                                           | Implantation .....                                                    | 18        |

| 1.3.2                                             | IBM (PowerNP) .....                                                   | 18        |

| 1.3.2.1                                           | Architecture interne .....                                            | 19        |

| 1.3.2.2                                           | Programmabilité.....                                                  | 19        |

| 1.3.2.3                                           | Implantation .....                                                    | 19        |

| 1.3.3                                             | Intel (IXP1200) .....                                                 | 20        |

| 1.3.3.1                                           | Architecture interne .....                                            | 21        |

| 1.3.3.2                                           | Programmabilité.....                                                  | 22        |

| 1.3.3.3                                           | Implantation .....                                                    | 22        |

| 1.3.4                                             | Motorola (C-5 DCP) .....                                              | 23        |

| 1.3.4.1                                           | Architecture interne .....                                            | 23        |

| 1.3.4.2                                           | Programmabilité.....                                                  | 23        |

| 1.3.4.3                                           | Implantation .....                                                    | 24        |

| 1.3.5                                             | Autres processeurs réseau .....                                       | 24        |

| 1.3.6                                             | Synthèse de trois principaux processeurs réseau .....                 | 25        |

| <b>CHAPITRE II</b>                                | .....                                                                 | <b>27</b> |

| <b>Architecture globale de la plate-forme SoC</b> | .....                                                                 | <b>27</b> |

| 2.1                                               | Architecture interne .....                                            | 27        |

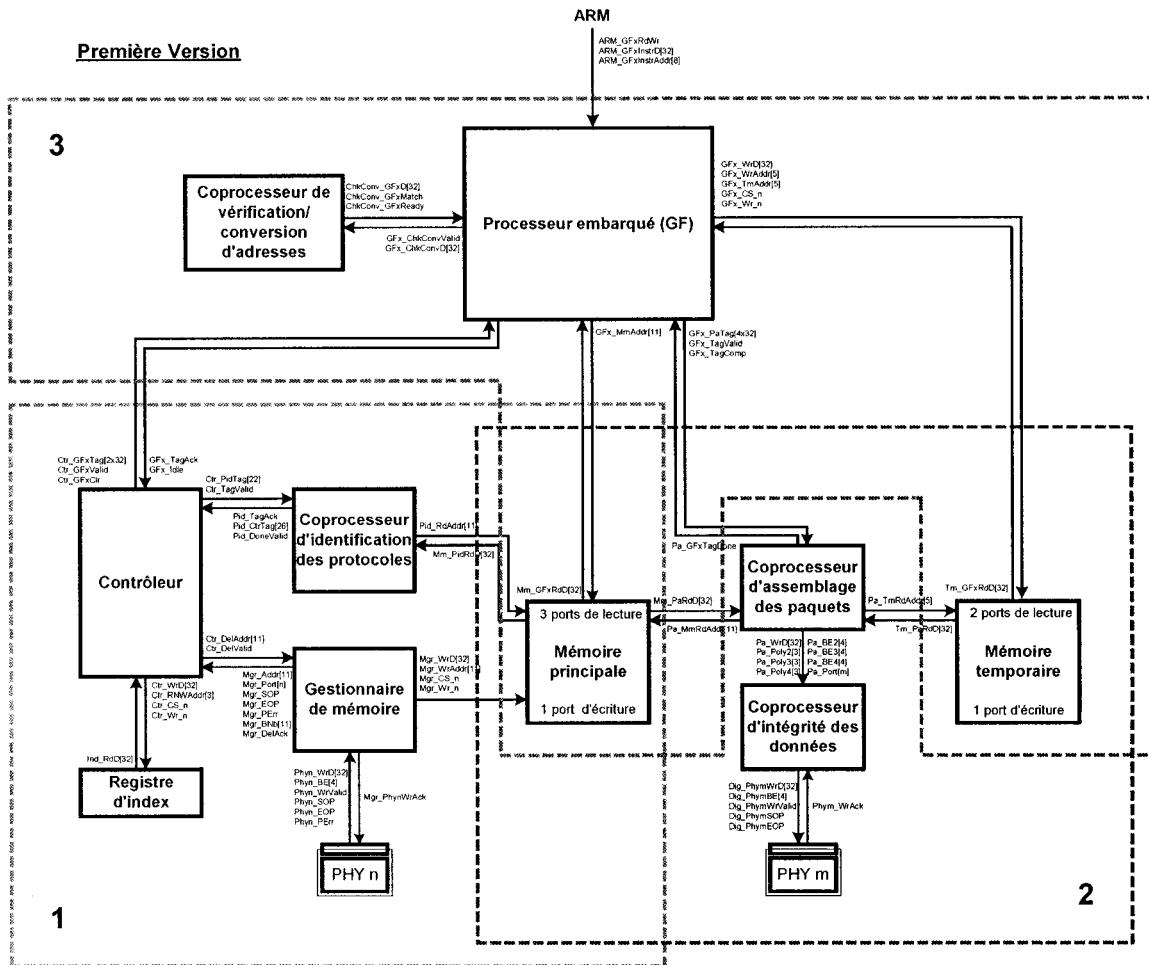

| 2.1.1                                             | Première version du modèle exécutable et processus de conversion..... | 27        |

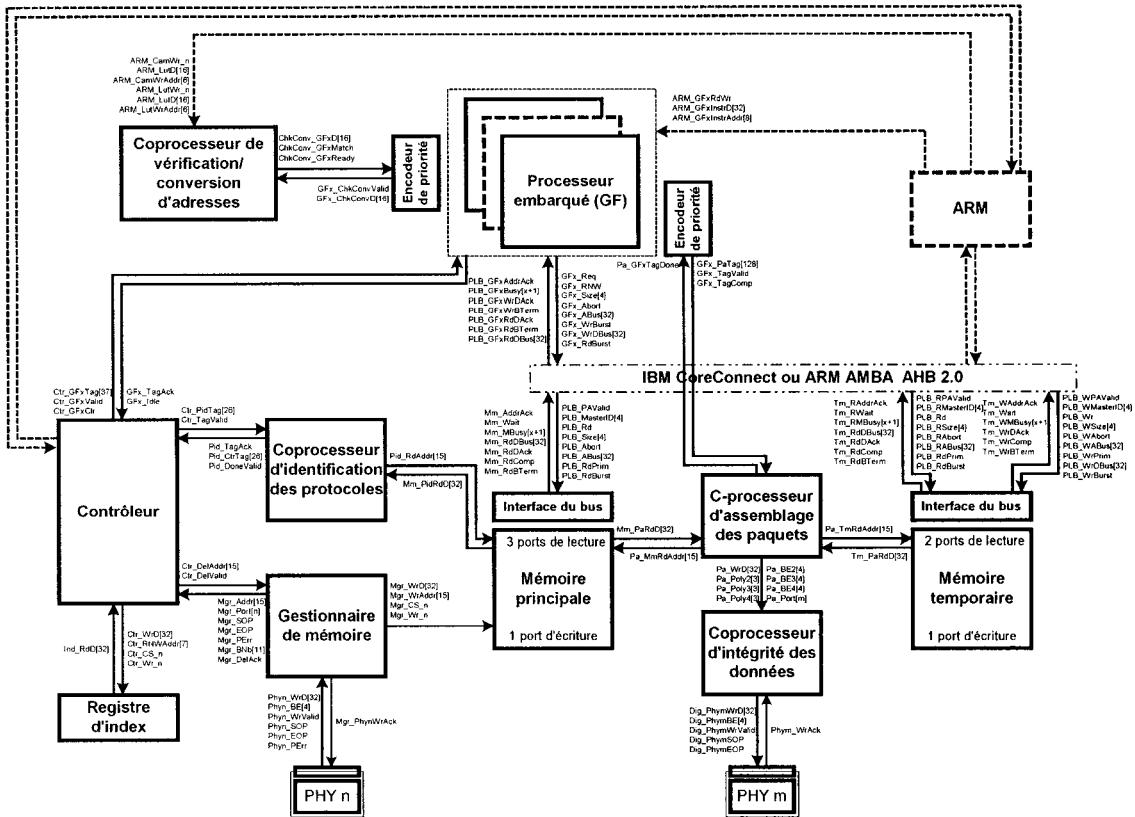

| 2.1.2                                             | Évolution de l'architecture.....                                      | 31        |

| 2.1.3                                             | Description des rôles des différents modules.....                     | 31        |

| 2.1.3.1                                           | Les interfaces .....                                                  | 31        |

| 2.1.3.2                                           | Le gestionnaire de mémoire.....                                       | 33        |

| 2.1.3.3                                           | Les mémoires .....                                                    | 33        |

| 2.1.3.4                                           | Le contrôleur.....                                                    | 33        |

| 2.1.3.5                                           | Le coprocesseur d'identification des protocoles.....                  | 34        |

| 2.1.3.6                                           | Le coprocesseur de vérification / conversion d'adresses.....          | 34        |

| 2.1.3.7                                           | Le coprocesseur d'assemblage des paquets .....                        | 34        |

|          |                                                                                                      |           |

|----------|------------------------------------------------------------------------------------------------------|-----------|

| 2.1.3.8  | Le coprocesseur d'intégrité des données .....                                                        | 35        |

| 2.1.3.9  | Le « Core Connect Bus » d'IBM .....                                                                  | 35        |

| 2.1.3.10 | Le processeur ARM .....                                                                              | 36        |

| 2.2      | Caractéristiques générales de la première version .....                                              | 37        |

| 2.2.1    | Évaluation des communications .....                                                                  | 37        |

| 2.2.1.1  | Évaluation de la largeur de bande utile disponible d'un réseau : analyse et comparaisons.....        | 38        |

| 2.2.1.2  | Évaluation de la largeur de bande nécessaire pour transmettre de la vidéo numérique de 360 Mbps..... | 40        |

| 2.2.1.3  | Évaluation du nombre d'opérations disponibles par paquet.....                                        | 41        |

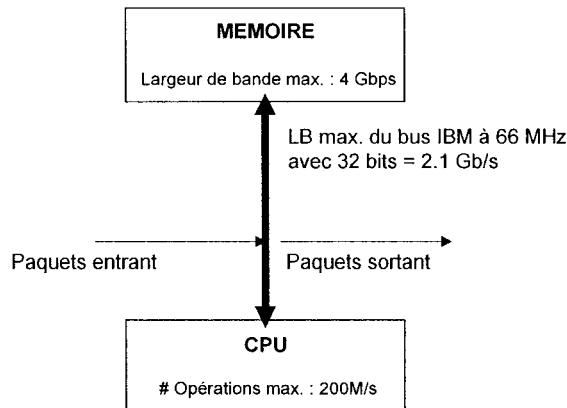

| 2.2.1.4  | Évaluation de la largeur de bande des bus de communication internes du processeur réseau .....       | 42        |

| 2.2.2    | Protocoles supportés .....                                                                           | 44        |

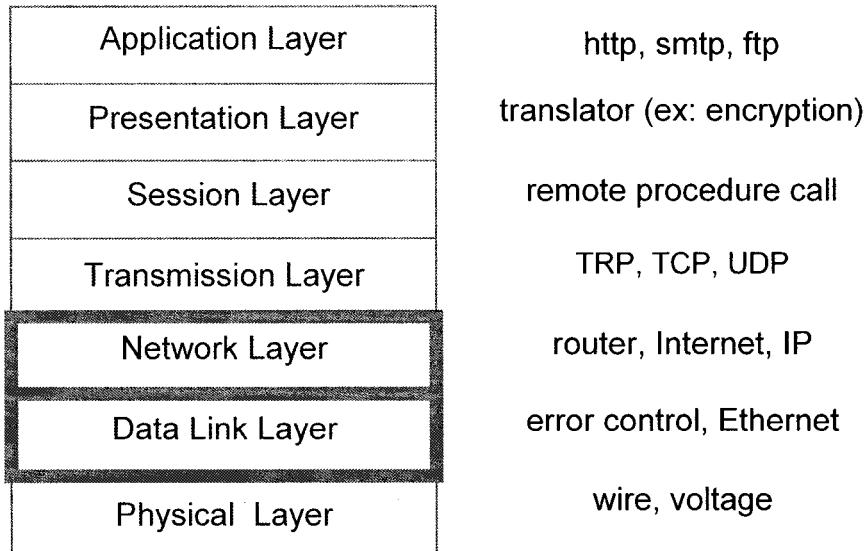

| 2.2.2.1  | Le modèle OSI .....                                                                                  | 44        |

| 2.2.2.2  | IEEE 802.3 (Gigabit Ethernet).....                                                                   | 46        |

| 2.2.2.3  | IEEE 1394 (Firewire).....                                                                            | 46        |

|          | <b>CHAPITRE III.....</b>                                                                             | <b>48</b> |

|          | <b>Conception d'un processeur embarqué dédié .....</b>                                               | <b>48</b> |

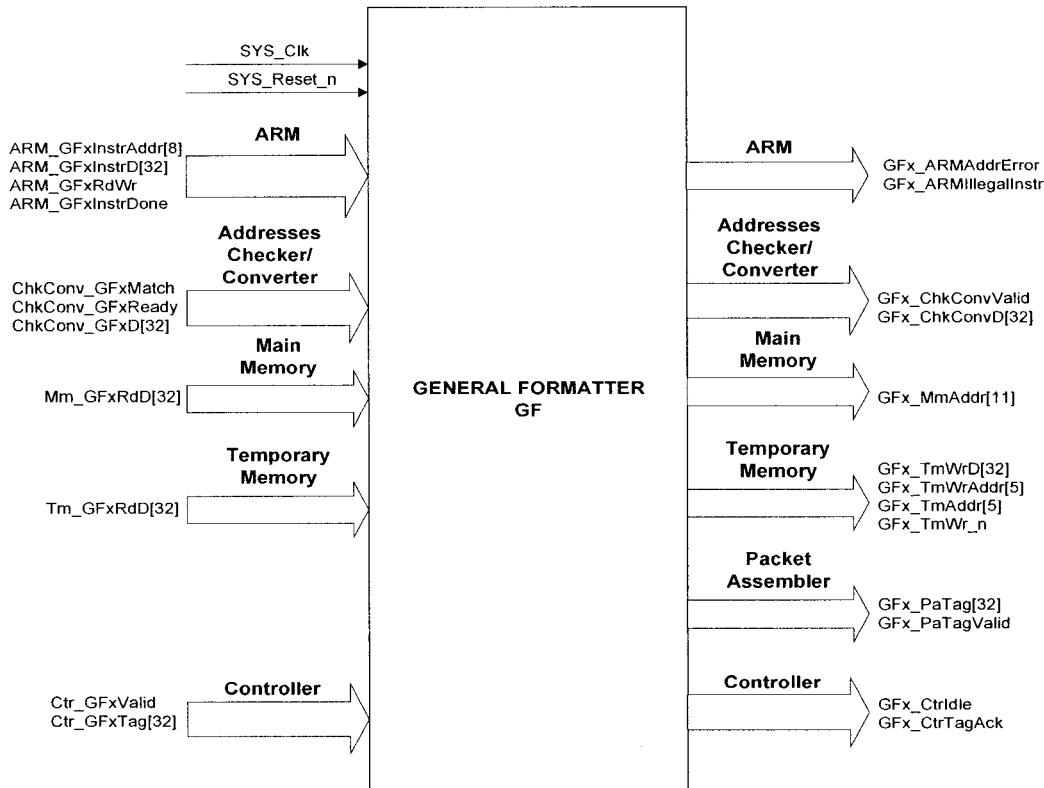

| 3.1      | Les entrées/sorties du processeur embarqué .....                                                     | 50        |

| 3.2      | Description des signaux d'Entrées/Sorties.....                                                       | 50        |

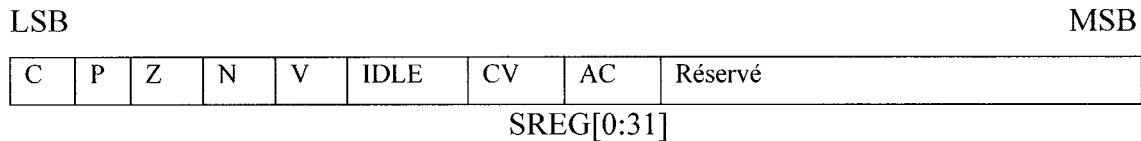

| 3.3      | Description des registres .....                                                                      | 53        |

| 3.4      | Détails des opérations de lecture et d'écriture .....                                                | 54        |

| 3.4.1    | Interface entre le GF et le processeur ARM7 .....                                                    | 54        |

| 3.4.2    | Interface entre le GF et le coprocesseur de conversion d'adresses AC ....                            | 55        |

| 3.4.3    | Interface entre le GF et la mémoire principale .....                                                 | 56        |

| 3.4.4    | Interface entre le GF et la mémoire temporaire .....                                                 | 57        |

| 3.4.5    | Interface entre le GF et le coprocesseur d'assemblage de paquets PA.....                             | 58        |

| 3.4.6    | Interface entre le GF et le contrôleur .....                                                         | 59        |

| 3.5      | Détails du Reset .....                                                                               | 60        |

|                                                     |                                                                                 |            |

|-----------------------------------------------------|---------------------------------------------------------------------------------|------------|

| 3.6                                                 | Détails des opérations arithmétiques, logiques, transfert et de branchement ... | 60         |

| 3.6.1                                               | Opérations arithmétiques et logiques.....                                       | 60         |

| 3.6.2                                               | Opérations de décalage .....                                                    | 61         |

| 3.6.3                                               | Opérations de transfert.....                                                    | 61         |

| 3.6.4                                               | Opérations de saut.....                                                         | 62         |

| 3.6.5                                               | Instructions spéciales .....                                                    | 62         |

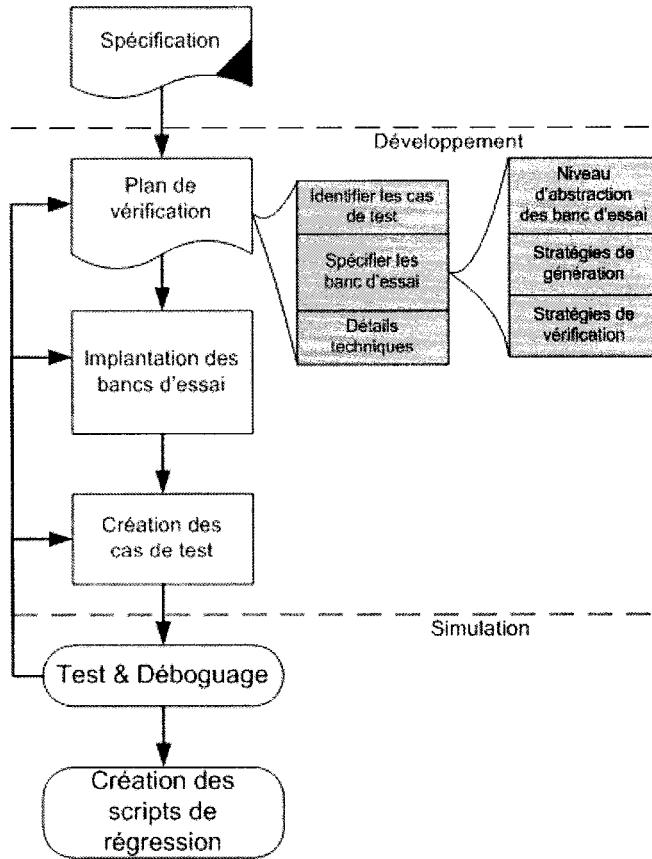

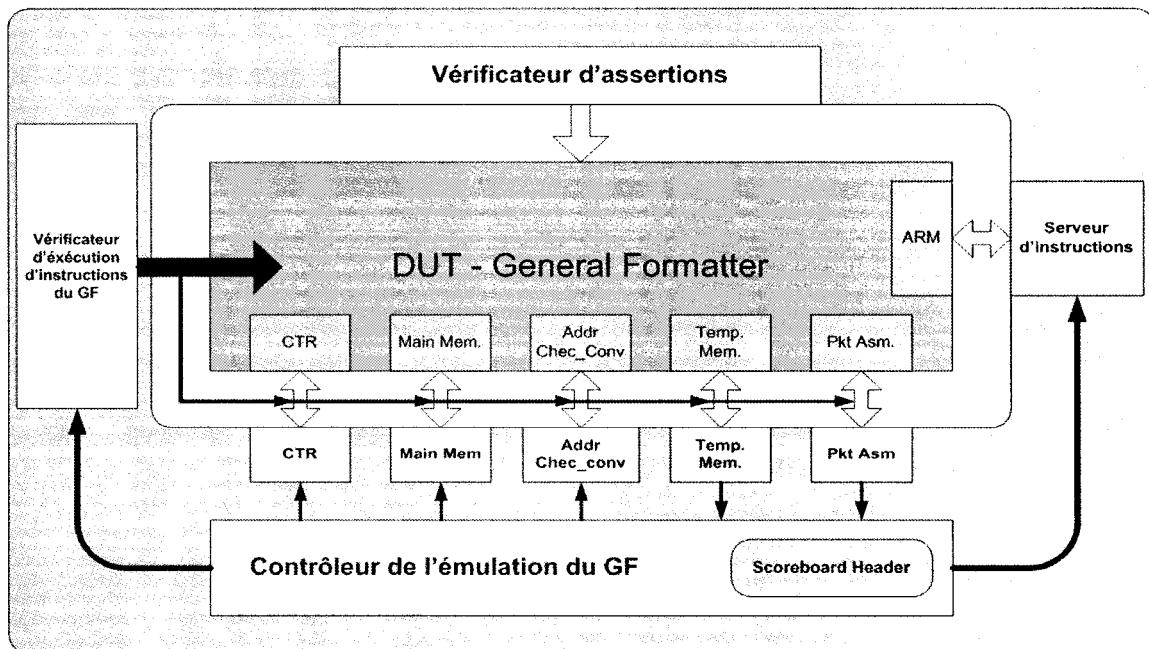

| 3.7                                                 | Méthodologie de vérification.....                                               | 63         |

| 3.7.1                                               | Cas de test .....                                                               | 67         |

| 3.7.2                                               | Cas de test du processeur embarqué .....                                        | 68         |

| 3.7.3                                               | Un condensé des fonctionnalités du GF.....                                      | 72         |

| <b>CHAPITRE IV</b>                                  | .....                                                                           | <b>79</b>  |

| <b>Implantations et résultats</b>                   | .....                                                                           | <b>79</b>  |

| 4.1                                                 | Assembleur .....                                                                | 79         |

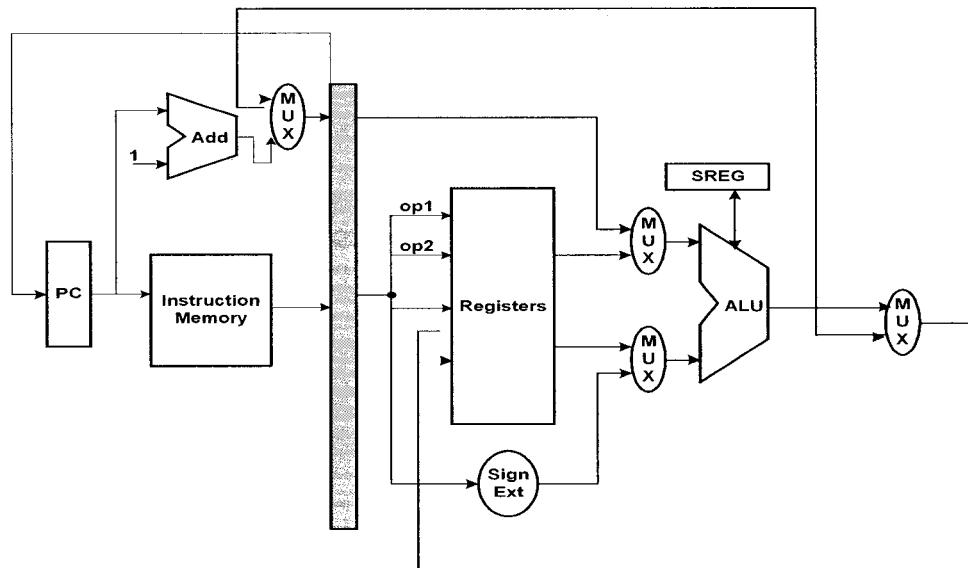

| 4.2                                                 | Architecture interne du processeur embarqué.....                                | 81         |

| 4.3                                                 | Résultats de synthèse sur un FPGA .....                                         | 83         |

| 4.4                                                 | Résultats de synthèse sur un circuit intégré ASIC .....                         | 84         |

| 4.5                                                 | Performance de notre processeur embarqué .....                                  | 84         |

| 4.6                                                 | Discussions .....                                                               | 89         |

| 4.6.1                                               | Les processeurs configurables .....                                             | 89         |

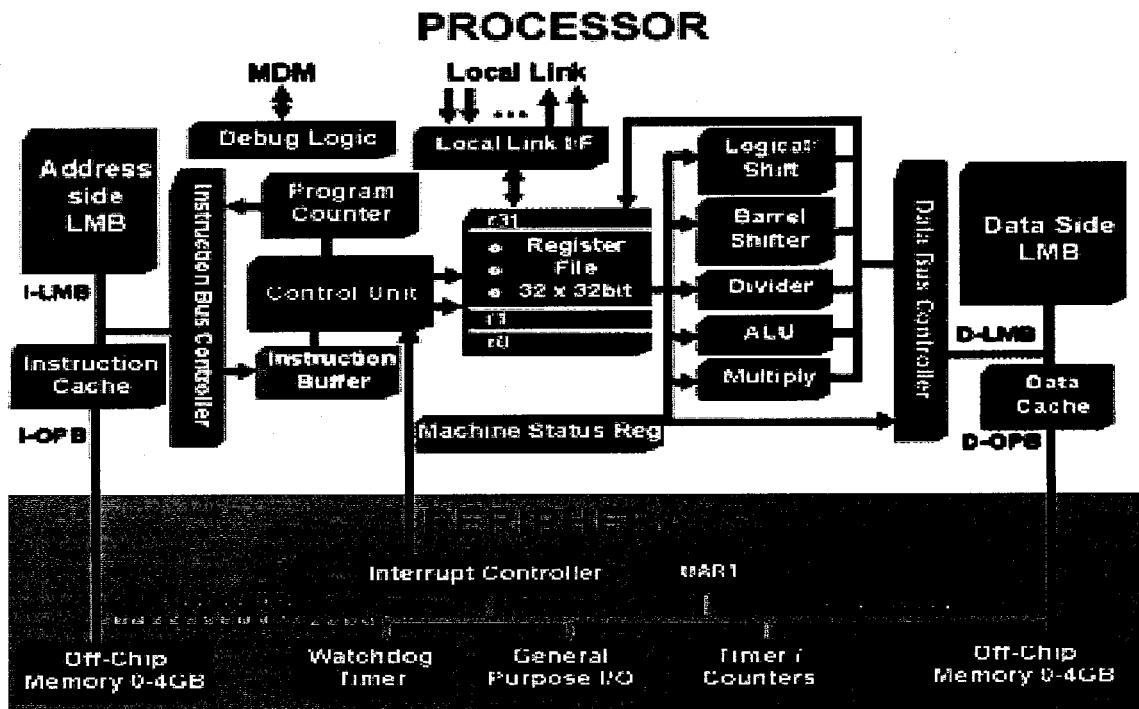

| 4.6.2                                               | Le processeur logiciel MicroBlaze offert par la compagnie Xilinx.....           | 90         |

| <b>CONCLUSION</b>                                   | .....                                                                           | <b>92</b>  |

| <b>RÉFÉRENCES</b>                                   | .....                                                                           | <b>96</b>  |

| <b>ANNEXE A.1</b>                                   | .....                                                                           | <b>100</b> |

| <b>Détails des opérations du jeu d'instructions</b> | .....                                                                           | <b>100</b> |

## LISTE DES FIGURES

|                                                                                                                                                  |    |

|--------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Figure 1.1 Architecture traditionnelle basée sur un processeur central .....                                                                     | 7  |

| Figure 1.2 Vitesse des réseaux et demande de bande passante comparées à la progression<br>des performances de la technologie d'intégration ..... | 9  |

| Figure 1.3 L'architecture interne du Au1000 [3].....                                                                                             | 18 |

| Figure 1.4 Schéma bloc de l'architecture interne d'un processeur réseau IBM-PowerNP<br>[20].....                                                 | 20 |

| Figure 1.5 Schéma bloc de l'architecture interne du Intel-IXP1200 [24].....                                                                      | 22 |

| Figure 2.1 Architecture de la première version .....                                                                                             | 30 |

| Figure 2.2 Architecture globale .....                                                                                                            | 31 |

| Figure 2.3 Largeur de bande (LB) max. du bus de communication .....                                                                              | 42 |

| Figure 2.4 Couches du modèle OSI .....                                                                                                           | 45 |

| Figure 3.1 Diagramme Bloc de haut-niveau du GF .....                                                                                             | 50 |

| Figure 3.2 Registre d'états (SREG) .....                                                                                                         | 53 |

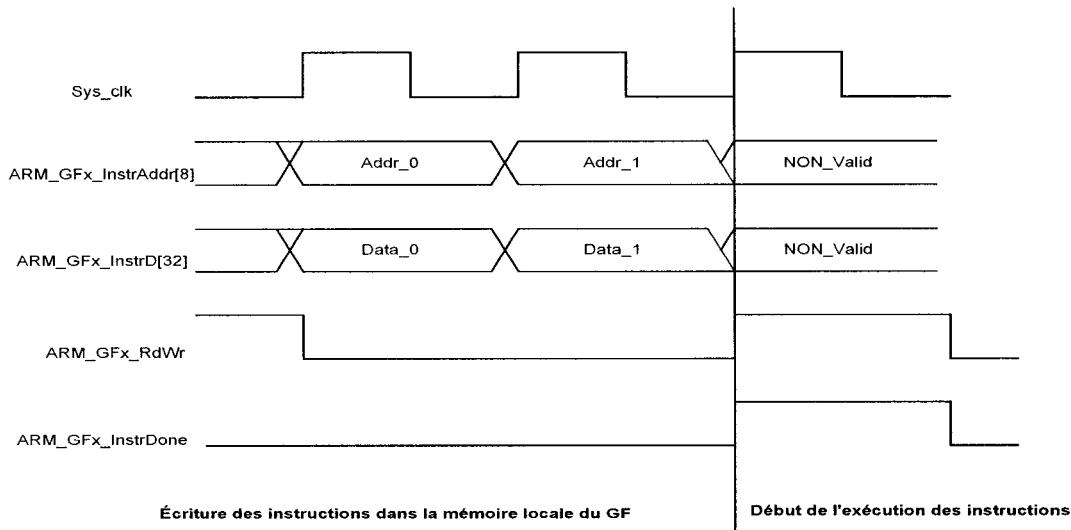

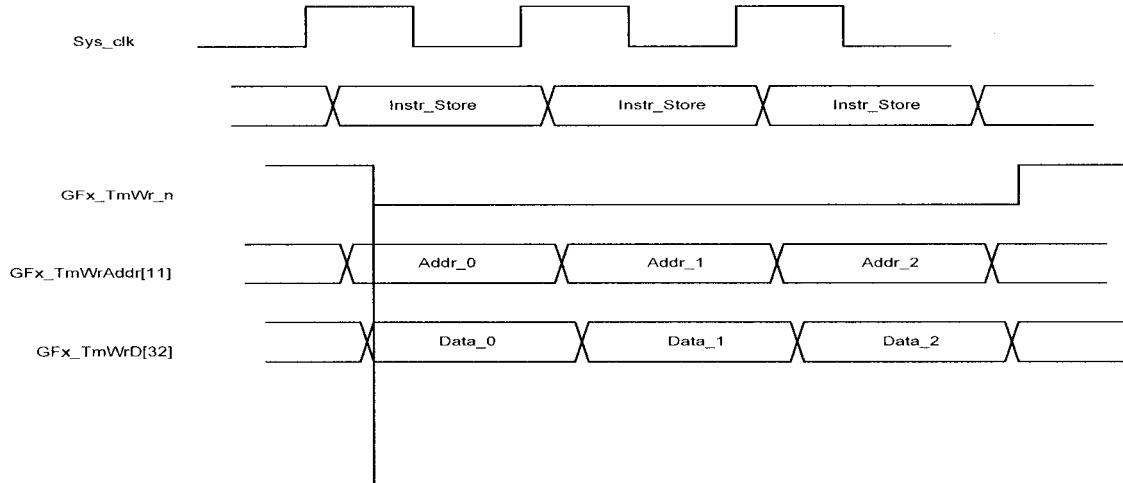

| Figure 3.3 Diagramme temporel de l'interface GF-ARM .....                                                                                        | 55 |

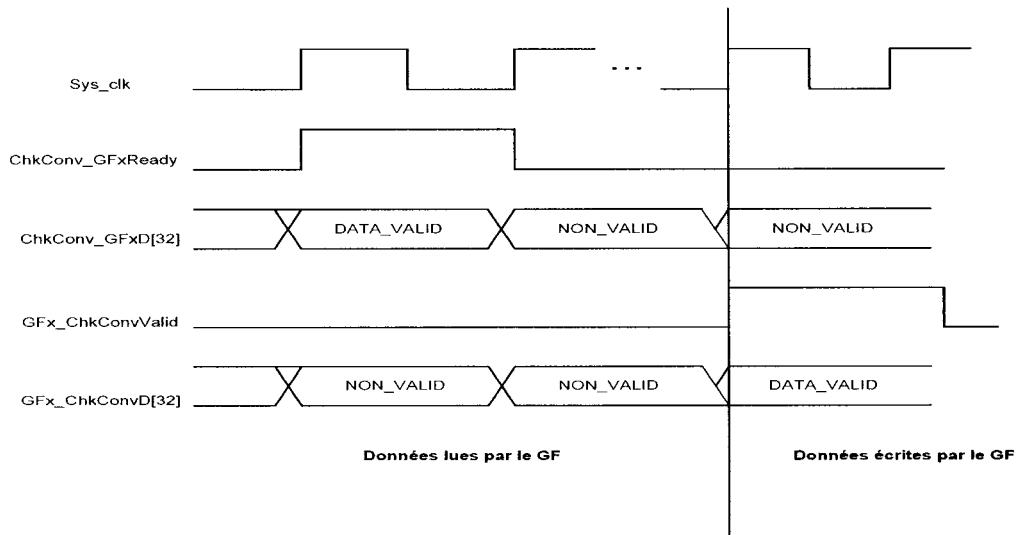

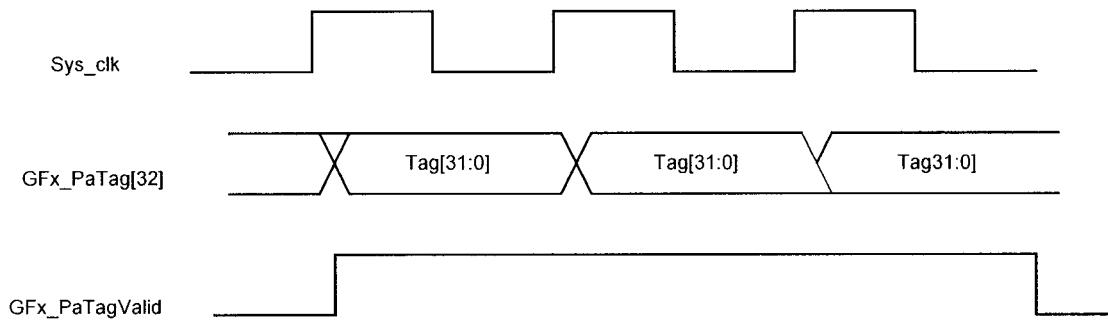

| Figure 3.4 Diagramme temporel de l'interface GF-AC.....                                                                                          | 56 |

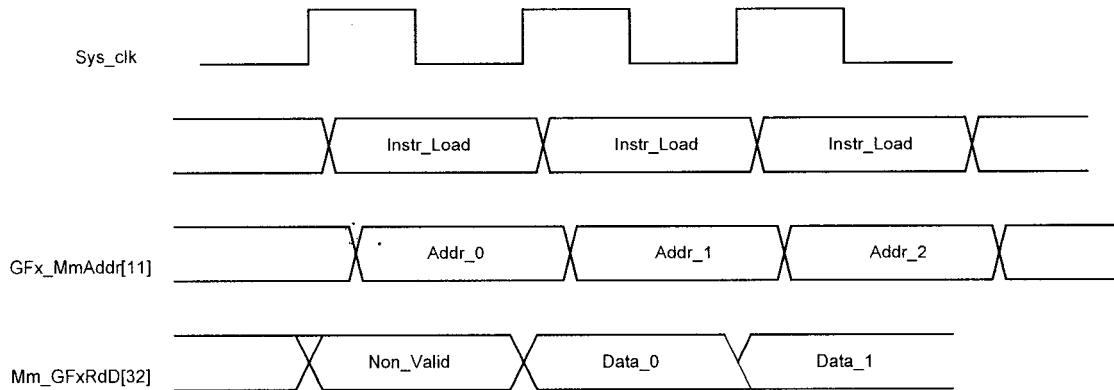

| Figure 3.5 Diagramme temporel de l'interface GF-Mémoire principale.....                                                                          | 57 |

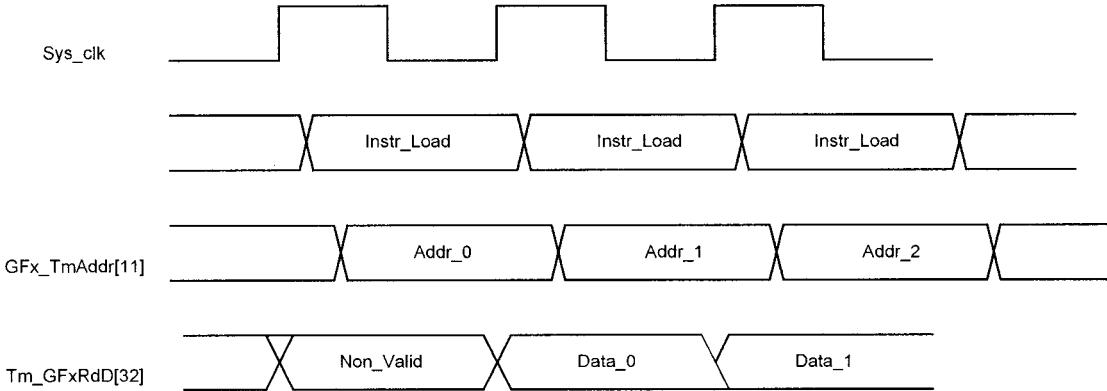

| Figure 3.6 Diagramme temporel de l'interface GF-Mémoire temporaire en mode lecture<br>.....                                                      | 58 |

| Figure 3.7 Diagramme temporel de l'interface GF-Mémoire temporaire en mode écriture<br>.....                                                     | 58 |

| Figure 3.8 Diagramme temporel de l'interface GF-PA .....                                                                                         | 59 |

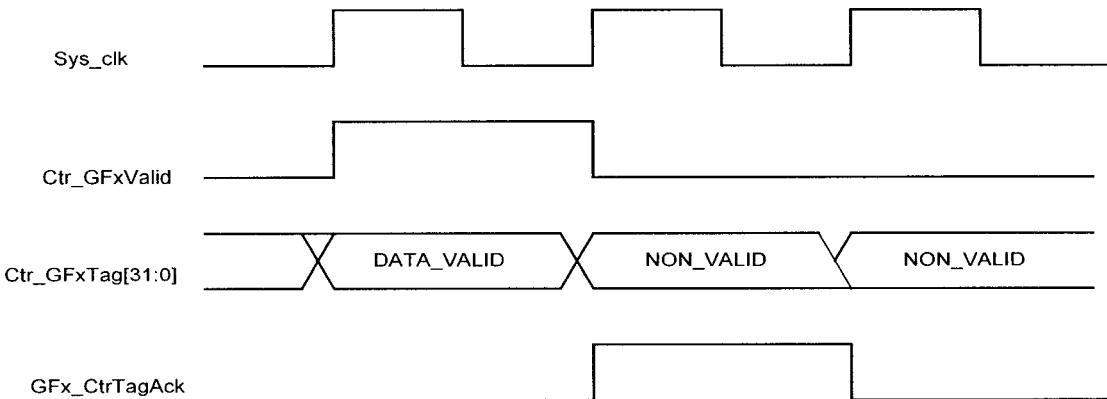

| Figure 3.9 Diagramme temporel de l'interface GF-CTR.....                                                                                         | 60 |

| Figure 3.10 : Méthodologie de vérification .....                                                                                                 | 64 |

| Figure 3.11 Schéma du banc d'essai du GF .....                                                                                                   | 73 |

| Figure 4.1 Un exemple de code d'assembleur .....                                                                                                 | 81 |

| Figure 4.2 Un exemple de code binaire .....                                                                                                      | 81 |

| Figure 4.3 Schéma bloc de haut niveau de l'architecture du processeur embarqué .....                                                             | 83 |

Figure 4.3 Architecture interne du processor logiciel *MicroBlaze* de Xilinx [50] ..... 91

## LISTE DES TABLEAUX

|                                                                                                                                                 |    |

|-------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Tableau 1.1 Synthèse et comparaison des trois principaux processeurs réseau .....                                                               | 26 |

| Tableau 2.1 Comparaison entre le bus ARM AMBA 2.0 et le bus IBM CoreConnect....                                                                 | 36 |

| Tableau 2.2 Largeurs de bande utilisées pour des paquets de tailles maximales .....                                                             | 39 |

| Tableau 2.3 Largeurs de bande utilisées pour des paquets de tailles minimales permettant<br>la transmission de vidéo numérique de 360 Mbps..... | 41 |

| Tableau 2.4 Largeurs de bande requises par les différents éléments de l'architecture....                                                        | 44 |

| Tableau 2.5 Description du paquet <i>Ethernet</i> .....                                                                                         | 46 |

| Tableau 2.6 Description du paquet <i>Firewire</i> .....                                                                                         | 47 |

| Tableau 3.1 Description du registre du statut .....                                                                                             | 53 |

| Tableau 3.2 Tableau illustrant la sélection d'un module par le GF .....                                                                         | 54 |

| Tableau 3.3 Le jeu d'instructions utilisé par l'engin de formatage .....                                                                        | 63 |

| Tableau 3.4 Détails du plan de vérification .....                                                                                               | 65 |

| Tableau 3.5 Description du partitionnement par aspect.....                                                                                      | 66 |

| Tableau 3.6 GF - Tests par fonctionnalité .....                                                                                                 | 69 |

| Tableau 3.7 GF - Test par interface .....                                                                                                       | 71 |

| Tableau 3.8 Résumé des fonctionnalités du GF.....                                                                                               | 73 |

| Tableau 4.1 Jeu d'instructions du GF contre celui d'un processeur RISC .....                                                                    | 85 |

| Tableau 4.2 Performances des trois versions du processeur embarqué .....                                                                        | 87 |

| Tableau 4.3 Performances de la version définitive du processeur embarqué contre<br><i>ARM7TDMI</i> .....                                        | 87 |

## LISTE DES ACRONYMES

|               |                                                            |

|---------------|------------------------------------------------------------|

| <b>ACL</b>    | <i>Access Control List</i>                                 |

| <b>ASIC</b>   | <i>Application Specific Integrated Circuit</i>             |

| <b>ASSP</b>   | <i>Application Specific Standard Product</i>               |

| <b>ATM</b>    | <i>Asynchronous Transfer Mode</i>                          |

| <b>CPU</b>    | <i>Central Processing Unit</i>                             |

| <b>CMC</b>    | <i>Canadian Microelectronics Corporation</i>               |

| <b>CRC</b>    | <i>Cyclic Redundancy Check</i>                             |

| <b>DA</b>     | <i>Destination Address</i>                                 |

| <b>DLL</b>    | <i>Data Link Layer</i>                                     |

| <b>DSP</b>    | <i>Digital Signal Processor</i>                            |

| <b>DUT</b>    | <i>Design Under Test</i>                                   |

| <b>EEPROM</b> | <i>Electrically Erasable Programmable Read-Only Memory</i> |

| <b>FCS</b>    | <i>Frame Check Sequence</i>                                |

| <b>FIFO</b>   | <i>First In First Out</i>                                  |

| <b>FPGA</b>   | <i>Field Programmable Gate Array</i>                       |

| <b>Gbps</b>   | <i>Giga bit per second</i>                                 |

| <b>GF</b>     | <i>General Formatter</i>                                   |

| <b>GRM</b>    | <i>Groupe de Recherche en Microélectronique</i>            |

| <b>HDLC</b>   | <i>High-level Data Link Control</i>                        |

| <b>IP</b>     | <i>Internet Protocol</i>                                   |

| <b>LAN</b>    | <i>Local Area Network</i>                                  |

| <b>LUT</b>    | <i>Look-Up Table</i>                                       |

| <b>Mbps</b>   | <i>Mega bit per second</i>                                 |

| <b>MIPS</b>   | <i>Millions of Instruction Per Second</i>                  |

| <b>NL</b>     | <i>Network Layer</i>                                       |

|              |                                                        |

|--------------|--------------------------------------------------------|

| <b>OSI</b>   | <i>Open System Interconnection</i>                     |

| <b>PCI</b>   | <i>Peripheral Connection Interface</i>                 |

| <b>RISC</b>  | <i>Reduced Instruction Set of Complexity</i>           |

| <b>RTL</b>   | <i>Register Transfer Language</i>                      |

| <b>RTP</b>   | <i>Real-Time Transport Protocol</i>                    |

| <b>SoC</b>   | <i>System on a Chip</i>                                |

| <b>SONET</b> | <i>Synchronous Optical Network</i>                     |

| <b>TCAM</b>  | <i>Ternary Content Addressable Memory</i>              |

| <b>TCP</b>   | <i>Transmission Control Protocol</i>                   |

| <b>TL</b>    | <i>Transport Layer</i>                                 |

| <b>UART</b>  | <i>Universal Asynchronous Receiver and Transmitter</i> |

| <b>UDP</b>   | <i>User Datagram Protocol</i>                          |

| <b>VLSI</b>  | <i>Very Large Scale Integrated Circuit</i>             |

| <b>WAN</b>   | <i>Wide Area Network</i>                               |

## INTRODUCTION

Le monde des télécommunications, entraîné par l'évolution rapide de la microélectronique, a connu de nombreuses mutations ces dernières décennies. Le marché se caractérise par une compétition intense et une course effrénée vers de plus grandes bandes passantes. La demande en bande passante est particulièrement pressante pour les réseaux, qui ont vu naître de nombreux protocoles. Ainsi, depuis le début des années 90, de nombreuses recherches ont été réalisées dans le but de développer de nouveaux protocoles de communication capables de supporter des débits de plus en plus grands. Ces protocoles, permettant un transfert de données pouvant s'élever à plus de 10 Gbps (*Giga bit per second*), sont en continue évolution, ce qui rend leur communication sur un même réseau extrêmement difficile. De plus, cette constante innovation dans le domaine de la communication, entraîne une diminution de la durée de vie des produits qui se trouvent dépassés dès qu'ils ne sont pas capables d'assurer une certaine vitesse de transmission. Par conséquent, sous peine de devoir renouveler des équipements entiers, il est devenu indispensable de faire communiquer des équipements supportant des protocoles hétérogènes entre eux. Pour ce faire, l'industrie des télécommunications a fait appel à des interfaces réseaux spécialisées : les convertisseurs de protocoles.

Cette large variété de protocoles hétérogènes crée des défis difficiles à relever pour les intégrateurs de réseaux. Cela implique la nécessité de permettre la communication entre équipements vieux et nouveaux. Ceci est accompli par les convertisseurs de protocoles. Ces derniers sont, soient implantés dans des circuits intégrés ASIC (*Application Specific Integrated Circuit*), soient basés sur des processeurs réseaux [1]. Dans le premier cas, les désavantages sont non seulement les coûts non-récurrents élevés et le délai d'arrivée sur le marché, mais également le manque de flexibilité. Quant aux processeurs embarqués standards, s'ils sont plus flexibles, ils sont néanmoins dérivés de processeurs RISC (*Reduced Instruction Set of Complexity*), et utilisent des jeux d'instructions qui ne sont

pas dédiés aux opérations de manipulation de paquets, notamment la conversion de protocoles. Ainsi, leur utilisation pourrait être non-optimisée.

Le projet de Convertisseur de Protocoles est un travail de recherche financé par l'entreprise GENNUM Corporation. C'est une entreprise canadienne implantée à Burlington en Ontario, qui conçoit, réalise et commercialise des composants électroniques, essentiellement des circuits intégrés à base de silicium et également des circuits hybrides pour des applications spécialisées. GENNUM subventionne ce projet afin d'acquérir en retour une base de données sur les choix technologiques et architecturaux, les problématiques rencontrées et les solutions envisagées. Ces informations serviront de base de travail pour la commercialisation future de convertisseurs de protocoles. Un premier mémoire de Maîtrise [25], dans le cadre de ce projet, a été déjà déposé par monsieur Lepage. Il a proposé une méthode d'identification par apprentissage applicable à la classification des paquets de haut niveau.

Le but de ce projet est de réaliser une entité qui assurera la conversion d'un protocole A en un protocole B. Ainsi, un flux de données (dans notre cas des données vidéo), ayant été transmis à l'aide d'un ensemble de protocoles, pourra être traité par une structure utilisant un ensemble de protocoles différents. Ce convertisseur doit être expressivement générique, pour pouvoir traiter le plus grand nombre de protocoles possibles, flexible [2], afin que le processus de conversion ne soit pas unique mais qu'il s'adapte au protocole traité, et enfin, réutilisable, pour pouvoir le faire évoluer en fonction de l'évolution de la technologie propre aux réseaux, notamment les nouveaux protocoles.

Ce convertisseur de protocoles trouverait son utilité dans un studio de montage vidéo; en effet, ce type de studio possède des outils de traitement de l'image très coûteux dont la conception ancienne n'autorise qu'un flot de données entrant supporté par un ensemble de protocoles défini. Par conséquent, il faut convertir les protocoles des données vidéo

reçues de façon à les rendre compatibles avec les protocoles attendus par les différents outils du studio, tout en conservant une qualité d'image optimale.

Dans un premier temps, le but est d'obtenir un modèle exécutable qui puisse démontrer le bon fonctionnement des différents modules du convertisseur en réalisant la conversion d'un protocole A (Ethernet ou Firewire) en un protocole B (Firewire ou Ethernet), deux protocoles de la couche liaison de données que nous décrirons brièvement ultérieurement. Par la suite, l'ensemble du convertisseur sera modifié de façon à devenir synthétisable et à supporter trois couches du modèle OSI (*Open System Interconnection*), qui sont la couche liaison de données, la couche réseau et la couche transport. Nous pourrons procéder à l'implantation de notre convertisseur sur une plate-forme ARM-FPGA.

La plate-forme du convertisseur de protocoles est basée sur un ou plusieurs processeurs embarqués, considérés comme des engins de formatage. Ces derniers réalisent l'essentiel de la conversion. Ils peuvent être configurés et programmés pour exécuter le programme de conversion. Ils confèrent un haut niveau de flexibilité. Chaque engin de formatage est en charge d'un paquet et travaille en parallèle avec les autres engins de formatage. Leur jeu d'instructions est dédié aux opérations de conversion.

Cette phase de recherche devrait nous conduire à réaliser des convertisseurs de protocoles supportant plus de protocoles, avec un nombre optimisé d'engins de formatage. Un processeur embarqué conventionnel, le *ARM7*, est chargé de la gestion d'exceptions. Quant à la conception physique, la première implémentation vise une plate-forme FPGA (*Field Programmable Gate Array*), un circuit intégré ASIC devrait suivre, lorsque l'architecture sera arrivée à maturité.

Notre proposition consiste en une nouvelle solution matérielle pour réaliser certaines applications de télécommunications, en l'occurrence, la conversion de protocoles. L'architecture proposée permettra également le traitement d'exceptions ou d'opérations

complexes à l'aide d'un processeur embarqué conçu sur mesure pour la manipulation des données de type vidéo numérique. Ce mémoire traitera principalement de la nécessité d'un processeur embarqué et du jeu d'instructions dédié aux traitements de paquets.

Dans un monde où l'évolution des développements technologiques se poursuit à un rythme accéléré, les concepteurs de circuits intégrés VLSI (*Very Large Scale Integrated Circuit*) doivent affronter un défi constant de performance. Ainsi, avec la forte croissance de la demande pour des équipements réseau à très grande largeur de bande, le processeur ou noyau principal des plates-formes réseau est bien loin de la performance désirée, malgré le succès exceptionnel de l'architecture des processeurs RISC. Les divers problèmes de flexibilité, de programmabilité et de temps de mise en marché ont poussé jusqu'à présent les spécialistes vers la recherche de solutions, visant à offrir de nouvelles architectures de processeurs réseau qui répondent aux besoins du marché.

Ce mémoire expose les travaux qui ont été effectués dans le cadre du développement d'une plate-forme SoC (*System on a Chip*) dédiée à la réalisation de processeurs réseau. Elle est basée sur un processeur embarqué dont le jeu d'instructions est spécifique pour le traitement de paquets à très haut débit.

Ainsi, le premier chapitre de ce mémoire est essentiellement une revue des réalisations commerciales et de la littérature en ce qui a trait au domaine des processeurs réseau. Il existe plusieurs modèles de processeurs réseau disponibles commercialement. En fait, ce chapitre présente un survol historique sur l'évolution des processeurs réseau des années 90 jusqu'à présent. Puis, une étude sur quatre processeurs réseau, fabriqués par des entreprises bien connues, sera présentée. Finalement, une foire aux processeurs réseau avec leurs pointeurs sera donnée au cas où le lecteur voudrait examiner plus de processeurs réseau.

Le deuxième chapitre présentera l'ensemble des critères qui nous ont permis d'élaborer le cahier de charges de notre plate-forme qui servira comme véhicule pour le convertisseur de protocoles. Ce sont ces attentes spécifiques qui, ajoutées aux spécifications propres aux protocoles et aux impératifs de la communication de signaux vidéo, nous ont permis d'aboutir à l'architecture interne de notre plate-forme que nous présenterons dans ce même chapitre. Cette architecture se veut un modèle exécutable capable d'effectuer la conversion d'un protocole A en un protocole B de la couche liaison de données.

Le troisième chapitre présentera le modèle du processeur embarqué qui a été développé pour devenir le cœur de notre plate-forme SoC. Ainsi, nous expliquerons d'abord le jeu d'instructions nécessaire pour accomplir une application de conversion de protocoles. Puis, les parties importantes du processeur, notamment les différentes interfaces nécessaires à la communication avec les divers coprocesseurs de la plate-forme, seront décrites. Finalement, nous discuterons de notre plan de vérification, pour assurer un minimum de niveau de confiance nécessaire lors de la réalisation de ce modèle de processeur.

Le quatrième et dernier chapitre présentera le travail qui a été réalisé pour implanter notre processeur embarqué. Nous commencerons par présenter l'assembleur qui a été développé par un chercheur stagiaire, monsieur Armin Schneider. Puis, nous illustrerons l'architecture interne de notre processeur qui sera suivie des résultats de synthèse sur un FPGA et sur un circuit intégré ASIC en technologie 0,35 µm. Finalement, une comparaison entre notre processeur embarqué et le processeur **ARM7**, déjà disponible sur le marché, sera détaillée.

# CHAPITRE I

## Revue critique de la littérature

Dans ce chapitre, nous ferons un bref historique des différentes architectures utilisées de nos jours, les limites rencontrées par ces machines, ainsi que les besoins urgents d'une nouvelle génération de processeurs réseau.

Ensuite, nous aborderons les détails de diverses architectures actuelles, que les compagnies conçoivent dans l'espoir de surpasser les limites rencontrées par les modèles précédents. Enfin, nous présenterons les différents processeurs réseau actuellement sur le marché, la vision des spécialistes et les perspectives des fabricants pour les prochaines années à venir.

### 1.1 Évolution des processeurs réseau

Les équipements réseau étaient généralement conçus à partir d'une combinaison de CPU (*Central Processing Unit*), de circuiterie logique, de produits standards d'application spécifique ASSP (*Application Specific Standard Product*), de contrôleur d'interface et de trans-récepteur. Tous ces composants exigeaient un logiciel assez dense, qui devenait de plus en plus complexe, quand il fallait ajouter ou modifier certaines fonctionnalités du réseau.

#### 1.1.1 Processeurs réseau Ethernet

Jusqu'à la fin des années 90, la majorité des commutateurs fonctionnant à des vitesses comparables à Ethernet (10 Mbps (*Mega bit per second*)) étaient basés sur une

architecture similaire à un ordinateur personnel. Un CPU performait toutes les fonctions de routage de paquets selon divers protocoles de communication.

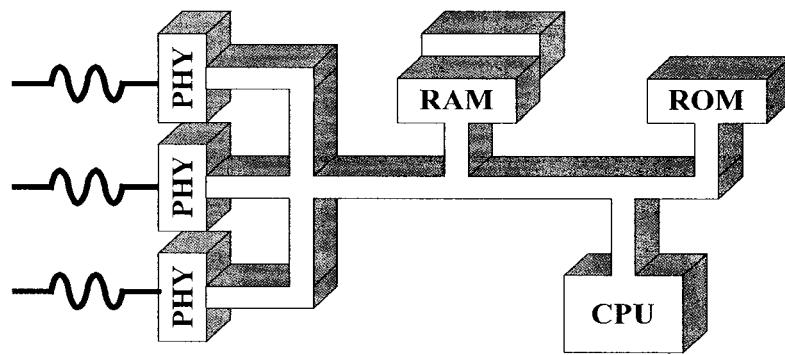

Le CPU recevait du système d'exploitation des instructions qui s'exécutaient dans la mémoire vive à partir des instructions de base qui étaient implantées dans la mémoire cache. L'avantage de ce type d'architecture résidait dans le fait, que toutes les instructions étaient contenues dans le programme, l'ajout de nouvelles fonctionnalités était facile via une modification dans le programme du système, sans toucher à l'architecture du processeur de base. Avec la demande élevée de largeur de bande et de nouvelles fonctions, cette architecture est devenue trop dispendieuse à maintenir. À mesure que la vitesse approche du 1 Gbps, les microprocesseurs traditionnels sont devenus surchargés et occasionnaient ainsi des délais considérables dans le réseau. De plus, les modèles que nous rencontrons sur le marché sont capables de supporter les signaux OC-3 à une vitesse pouvant atteindre 155 Mbps et dans les pires cas, ils pourraient être utilisés pour les signaux OC-12 à une vitesse atteignant 622 Mbps. Un exemple parfait de cette approche est le produit **CISCO 2500** [10] disponible dans diverses configurations selon l'application désirée. Nous pouvons disposer d'un simple port ou de multiples ports série de type « AUI » ou « Token Ring ». Chacune de ces architectures, utilisant un CPU, est connectée aux interfaces physiques et aux mémoires à travers un bus système. Ainsi, le dispositif est capable de traiter n'importe quelle fonction pour le flot de données entrant, à mesure que nous mettons à jour le logiciel. La figure 1.1 illustre l'architecture traditionnelle basée sur un processeur central.

**Figure 1.1 Architecture traditionnelle basée sur un processeur central**

## 1.1.2 Processeurs réseau Gigabit Ethernet, OC-12 et OC-48

Récemment, les commutateurs qui fonctionnent à des vitesses comparables aux Gigabit Ethernet (1000 Mbps), OC-12 (622 Mbps) et OC-48 (2488 Mbps), ont pu voir le jour grâce à l'adoption d'une architecture basée sur des processeurs RISC, des circuits intégrés à très grande échelle, des RISC améliorés et des modèles hybrides.

### 1.1.2.1 Commutateurs de réseau basés sur des processeurs RISC

Pour un processeur RISC, il faut plusieurs instructions pour exécuter une tâche simple. Le nombre d'instructions augmente avec la complexité de la tâche, ce qui augmente le temps d'exécution puisque chaque instruction prend un coup d'horloge.

En raison du nombre élevé d'instructions et du temps d'exécution des tâches, le processeur réseau basé sur un modèle RISC convient plus pour des commutateurs se limitant aux vitesses de OC-48. Si le nombre d'instructions est moins élevé, le processeur RISC fournit une bonne performance, une flexibilité et un haut degré de programmabilité. Néanmoins, un tel commutateur demeure lent en raison des décisions qui sont prises à l'intérieur du logiciel.

Les processeurs RISC sont souvent utilisés dans une configuration parallèle pour augmenter la vitesse de fonctionnement du commutateur. Cette architecture a désormais ses limites puisque le nombre de processeurs RISC pouvant être incorporé sur une même puce augmente sa complexité et ses dimensions. De plus, une telle architecture permet aux commutateurs de supporter une grande variété de protocoles et de spécifications, bien qu'ils ne s'adaptent pas facilement aux ajouts de fonctionnalités qui exigent des bandes passantes spécifiques. Par exemple, le rajout d'une fonction de contrôle d'accès ACL (*Access Control List*) sur une architecture à processeur RISC pourrait occasionner un niveau d'utilisation maximal et engendrer ainsi des perturbations au niveau du trafic.

Les processeurs RISC ont beaucoup de flexibilité puisqu'il suffirait de changer le programme à l'intérieur du processeur pour modifier ou ajouter des nouvelles fonctionnalités. Mais, ils n'ont pas la même capacité de traitement que les circuits intégrés dédiés, puisque leur architecture est de type général, c'est-à-dire qu'ils sont d'usage général et ne sont pas spécifiquement dédiés au domaine des réseaux.

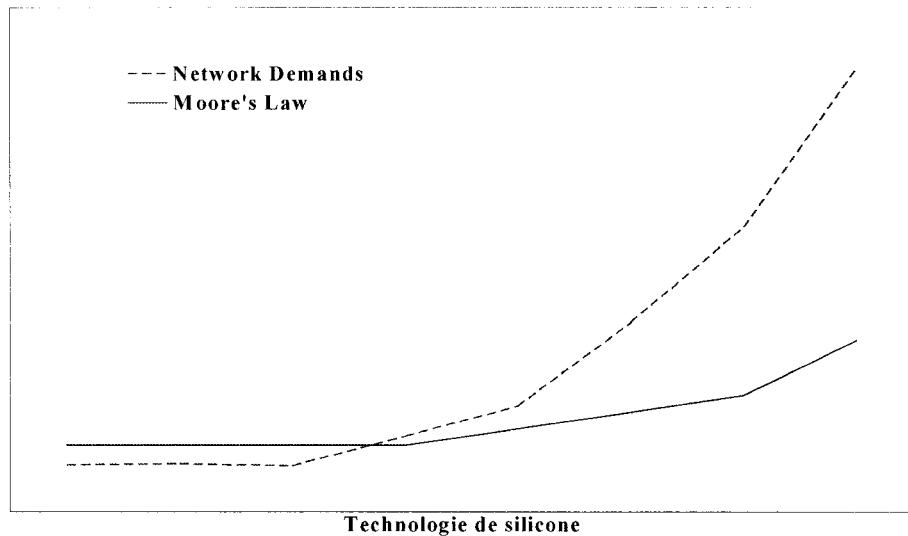

La performance des processeurs RISC s'est améliorée depuis des années, en accord avec la loi de Moore qui conduit à une augmentation de la densité des transistors à tous les 18 mois. Le diagramme de Moore, montré à la figure 1.2, prévoit des limites de réduction d'échelle par rapport aux exigences des réseaux.

**Figure 1.2 Vitesse des réseaux et demande de bande passante comparées à la progression des performances de la technologie d'intégration**

### 1.1.2.2 Commutateurs réseau basés sur des circuits intégrés ASIC

Nous pouvons augmenter la vitesse d'un commutateur basé sur des processeurs RISC en ajoutant des accélérateurs matériels. Ces derniers peuvent copier des paquets à des vitesses pouvant dépasser 10 Gbps mais ils ne sont pas flexibles ni programmables.

Généralement, un circuit intégré ASIC est conçu pour exécuter des tâches très spécifiques, qui améliorent le niveau de performance du commutateur, avec une flexibilité pour diverses fonctions. Ces puces sont dédiées au support du trafic à très haute vitesse mais elles ne sont pas capables de traiter des tâches additionnelles de gestion de trafic, telles que la classification, les contrôles d'accès, ... Ce genre de tâches est désormais réservé au processeur central. Les fabricants utilisent ainsi des circuits intégrés pour différentes tâches avec un processeur RISC comme processeur central.

Bien que ces puces aient la capacité de fonctionner à des vitesses de l'ordre du Gigabit par seconde et du Petabit par seconde, elles sont très dispendieuses et leur temps de développement peut prendre entre 12 et 18 mois, ce qui allonge le temps de mise en marché du produit. De plus, une fois que les instructions et la logique sont figées dans le silicium, il est difficile d'ajouter de nouvelles fonctionnalités pour améliorer la performance. Ainsi, pour ajouter de nouvelles fonctions, le fabricant doit remplacer le circuit intégré, ce qui retarde de 6 à 9 mois la mise en marché du produit modifié.

#### **1.1.2.3      Commutateurs réseau basés sur des processeurs RISC améliorés**

Afin de résoudre les différentes lacunes qu'ont connu les commutateurs basés sur des processeurs RISC, les fabricants ont développé plusieurs techniques :

- ***Le partitionnement*** : Il s'agit de séparer diverses fonctions dans les équipements du réseau et de les dédier aux processeurs appropriés. Les fonctions de type transfert « forwarding », routage/signalisation « routing/signaling » ainsi que les applications de segmentation et de ré-assemblage de paquets dans les cellules IP/ATM (*Internet Protocol/Asynchronous Transfer Mode*) peuvent être séparées du processeur central.

- ***Le parallélisme*** : Il s'agit d'utiliser plusieurs processeurs pour améliorer la performance globale du système. Par exemple, dans les routeurs IP, nous séparons de plus en plus la fonction de transfert (forwarding) du routage en assignant chaque fonction à un processeur. Cette forme de parallélisme améliore nettement le réseau jusqu'au point où le taux de données d'une simple interface excède les capacités des entrées/sorties associées au processeur. Il est à noter que tout changement de fonctionnalité affecte le système, car, il faudrait rajouter des processeurs parallèles et les redistribuer.

- ***L'optimisation de la mémoire cache*** : Le défi avec les processeurs cache-centriques qui traitent des opérations intensives d'entrées/sorties repose sur l'optimisation. Cette dernière permet de réduire le nombre d'instructions en mémoire principale ainsi que celui dans la mémoire cache des processeurs. Ceci a pour effet de minimiser les erreurs qui résultent de temps de traitement excessif quand les données ou segments de programmes importants ne sont pas dans la cache.

- ***L'optimisation du bus*** : Il s'agit de la réduction de la quantité de données requises par le processeur sur le réseau. Ceci aura pour effet d'améliorer suffisamment la capacité des entrées/sorties associées au processeur.

- ***L'accélération par le biais d'un coprocesseur*** : Il s'agit de dédier les fonctions assez complexes à des coprocesseurs matériels. De nos jours, la segmentation et le rassemblement de paquets ATM sont traités par des accélérateurs matériels. Également, les fonctions de liaison de couches comme le HDLC (*High-level Data Link Control*) sont déléguées à des circuits intégrés dédiés.

#### 1.1.2.4      **Commutateurs réseau basés sur des approches hybrides**

Les processeurs réseau pourraient être la solution à la demande grandissante de largeur de bande des applications réseau. Ils combinent la programmabilité, la flexibilité des processeurs RISC et la performance des circuits intégrés à l'intérieur d'un même produit. Ainsi, les tâches spécifiques sont attribuées aux circuits ASIC, tandis que le processeur RISC joue le rôle du processeur central. Un exemple de cette approche est le modèle **CISCO EXPRESS FORWARDING** [9] dont le processeur central détermine le chemin d'accès. Ensuite, il charge une copie complète de cette information dans la carte d'interface de ligne (ASIC) qui s'occupe de la commutation du trafic à très haute vitesse.

#### 1.1.2.5      **Architecture de processeurs intermédiaires**

Cette architecture est basée sur le pipeline et sur la technique de séparation des bus pour les opérations d'entrées/sorties. Avec l'arrivée des processeurs de traitement numérique du signal DSP (*Digital Signal Processor*), nous constatons que le traitement des signaux s'améliore à mesure que le nombre d'entrées/sorties augmente. Par exemple, l'architecture Harvard [45] sépare le chemin d'instructions et de données de celui des bus d'entrées/sorties. Ceci a permis d'utiliser un bus séparé pour les opérations d'entrées/sorties qui pouvait être réduit en fonction de la bande passante des signaux. Il en découle l'élimination du comportement « non-déterministic » dans le cas où ce bus serait partagé avec le chemin d'instructions et de données. Par contre, les DSPs sont extrêmement difficiles à programmer avec des langages de haut niveau. Autrement dit, l'utilisateur doit avoir une bonne connaissance de l'architecture de son composant s'il veut tirer pleinement avantage de sa puissance.

Ainsi, le parallélisme et le pipelinage sont des techniques importantes dans la conception des architectures de processeurs réseau qui permettent d'améliorer la performance des modèles de la nouvelle génération.

## 1.2 Processeur réseau

Le processeur réseau se distingue de tout autre processeur par sa fonctionnalité versatile. Les fonctions d'un processeur optimisé pour les applications du réseau traitent des opérations qui favorisent une réutilisation de son système. Autrement dit, il est capable de s'adapter à des nouvelles fonctionnalités.

### 1.2.1 Définition d'un processeur réseau

Dans le temps des commutateurs et des ponts basés sur un logiciel informatique, le besoin d'un processeur réseau spécialisé ne se faisait pas sentir. Le processeur d'interface physique décodait les paquets d'entrées du réseau auquel il était connecté et il passait les données à traiter au processeur central. Les décisions de commutation du trafic étaient basées sur des instructions fournies par un logiciel assez complexe comme illustré dans la figure 1.1.

Afin de supporter des réseaux à très haut débit tels que, Fast Ethernet (100 Mbps) et Gigabit Ethernet (1 Gbps), des processeurs réseau spécialisés sont désormais requis pour obtenir une performance acceptable. Ces processeurs sont constitués de plusieurs circuits intégrés spécialisés dont la fonctionnalité repose en partie sur l'analyse, le traitement des paquets et la classification des protocoles réseaux à très haute vitesse.

Typiquement, les processeurs réseau se situent sur le chemin de données entre l'interface physique et la carte mère (« backplane »). Les principales fonctions exécutées par un processeur réseau sont les suivantes :

- **Segmentation et rassemblement** : les paquets sont désassemblés, analysés et ensuite, rassemblés pour être envoyés.

- ***Identification de protocoles et classification*** : en se basant sur les informations que les paquets contiennent, telles que le type de protocole, le numéro de port et l'adresse de destination, ils sont alors identifiés.

- ***Contrôle d'accès*** : après avoir été identifiés, les paquets sont placés dans des queues pour être manipulés, notamment, l'ajout de priorité ainsi que la gestion de trafic. Les paquets sont aussi vérifiés pour la sécurité informatique.

- ***Gestion du trafic*** : certains protocoles ou applications exigent une gestion du trafic pour assurer un délai ou une variation des délais convenables.

- ***Qualité du service*** : en plus de la gestion du trafic pour assurer une bonne qualité du service, les paquets devront être étiquetés pour un traitement plus rapide dans les dispositifs subséquents.

### 1.2.2 Caractéristiques d'un processeur réseau

Selon le point de vue des fabricants d'équipements réseaux, le processeur réseau est une composante clé qu'ils peuvent utiliser pour différencier leurs produits de leurs compétiteurs [2]. En livrant des produits intégrants des processeurs réseau avec des capacités avancées, les fabricants peuvent offrir des fonctions et une performance accrue qui peuvent valoriser leurs produits par rapport à leurs compétiteurs. Par conséquent, les vendeurs matériels sont à la recherche de processeurs réseau qui peuvent leur donner cet avantage. Ainsi, un processeur réseau requiert les caractéristiques suivantes :

- ***Programmabilité*** : le processeur réseau doit être facilement programmable pour tenir compte des nouvelles caractéristiques et de l'intégration rapide des technologies existantes et nouvelles. Il devrait rendre facile la conception de produits qui utilisent différents trafics.

- **Performance** : le processeur réseau doit s'adapter rapidement aux demandes de bande passante. Il doit être capable de supporter des milliers de connexions presque simultanées.

- **Management** : il s'agit de la gestion des tâches, telles que l'identification, la classification et le contrôle du trafic.

- **Routage** : les décisions de routage sont basées sur de l'information pré-programmée.

### 1.2.3 Le routage

Une étude de processeurs réseau ne peut être complète sans une analyse des détails pertinents du routage.

Le routage est une tâche parallèle, puisque chaque paquet qui traverse un réseau est indépendant avec son propre en-tête de destination et sa charge de données. Un routeur de petite capacité sur un *LAN* (*Local Area Network*) contrôle un nombre relativement petit de destinations, telles que des terminaux et des imprimantes locales. Par contre, un routeur de grande capacité sur un *WAN* (*Wide Area Network*) est responsable de la circulation de millions de paquets indépendants qui ont des milliers de possibilités de destinations, telles que les serveurs Internet et les serveurs de courriels. La commutation de paquets permet de traiter indépendamment plusieurs paquets en parallèle, sans tenir compte de l'ordre d'arrivée. L'appareil qui reçoit ces paquets, est responsable de les remonter dans leur ordre original. Pour acheminer un paquet vers sa destination, un routeur doit lire l'en-tête pour trouver l'adresse de destination, ainsi que d'autres informations. Ensuite, il le dirigera le plus rapidement vers la bonne destination. Il est à noter qu'un paquet peut comporter multiples en-têtes, notamment, un en-tête *TCP*

(*Transmission Control Protocol*), un en-tête **IP** et un en-tête **Ethernet** dont la longueur variable.

De nos jours, les opérateurs de réseaux souhaitent une amélioration des routeurs en ce qui a trait à leur capacité de traitement des en-têtes, afin de prendre des décisions plus intelligentes dans le transfert des paquets, ce qui renforce la nécessité des processeurs réseau de haute performance.

### **1.3 Le marché des processeurs réseau OC-192**

Le marché des commutateurs réseau est estimé à plus de 10 milliards de dollars US cette année, 50 % de plus que l'année passée. Les fabricants de processeurs réseau se préparent pour faire face à ce marché grandissant. Ils trouvent la nécessité d'introduire des produits complexes et bien différents des microprocesseurs standards comme moteurs pour les commutateurs de grande capacité.

Le marché des processeurs réseau a connu une forte percée technologique chez plusieurs compagnies bien établies comme IBM Corp., Agere Inc. (acquise par Lucent Technologies) et C-Port Corp. (acquise par Motorola Inc.). Une nouvelle vague de petites entreprises (start-up) visent aussi ce marché, telles que Bay Microsystems Inc., Lara Networks, Ezchip Technologies et Zettacom Inc.

L'explosion de l'Internet et du commerce électronique requiert le déploiement d'équipements d'une grande bande passante et d'une meilleure flexibilité afin de supporter les différentes technologies de l'Internet. Les capacités du processeur réseau peuvent aider à intégrer ces nouvelles technologies. Les fabricants de puces électroniques visent le marché du trafic OC-192 pour lequel les débits de données peuvent atteindre 10 Gbps. Les premiers processeurs réseau sont en production depuis la fin de l'année 2000. Nous présenterons dans les prochaines sections quelques-uns des processeurs réseau qui sont présentement sur le marché.

### 1.3.1 Alchemy (Au1000)

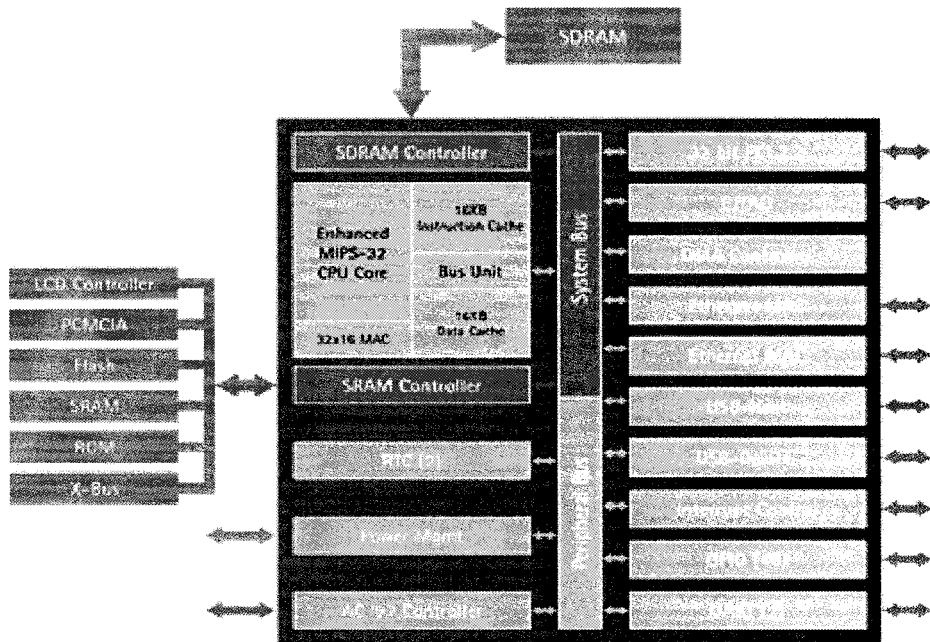

La puce de la compagnie Alchemy Semiconductor Inc. est surtout dédiée aux équipements d'accès [3]. Par contre, la compagnie prétend que son produit convient aussi pour les routeurs et les cartes d'interfaces. En fait, c'est une puce à faible puissance (300 mW) basée sur un processeur MIPS (*Millions of Instruction Per Second*) dont le jeu d'instructions est augmenté de quelques nouvelles instructions. Également, plusieurs variétés d'interfaces sont intégrées.

#### 1.3.1.1 Architecture interne

Le « Au1000 » est basé sur une machine MIPS de 32-bit. Ce processeur a une architecture pipeline de cinq étages, optimisée pour minimiser les pénalités de branchement. L'architecture contient aussi un multiplicateur-accumulateur de 32-bit qui fonctionne en parallèle avec le CPU pipeliné. De plus, cette puce supporte des instructions spéciales pour le déplacement conditionnel entre les registres et la pré-recherche de l'instruction dans la mémoire.

L'architecture contient aussi deux contrôleurs Ethernet, un port infrarouge, un port USB et quatre unités asynchrones de transmission et de réception UART (*Universal Asynchronous Receiver and Transmitter*). Il existe aussi une mémoire cache d'instructions et de données de 16Ko. L'architecture interne du Au1000 est montrée à la figure 1.3.

#### 1.3.1.2 Programmabilité

Étant donné que cette puce est basée sur une machine MIPS, nous pouvons la programmer en langage C. Un outil de développement logiciel est aussi fourni pour

programmer les applications. Les différents systèmes d'exploitation sont supportés tels que MS Windows CE, Linux et VxWorks.

**Figure 1.3 L'architecture interne du Au1000 [3]**

### 1.3.1.3 Implantation

Le Au1000 est disponible comme un « soft-core » supportant plusieurs fréquences d'opération, notamment 266 MHz, 400 MHz et 500 MHz. La puissance totale dissipée est alors inférieure à 300 mW, 500 mW et 900 mW respectivement.

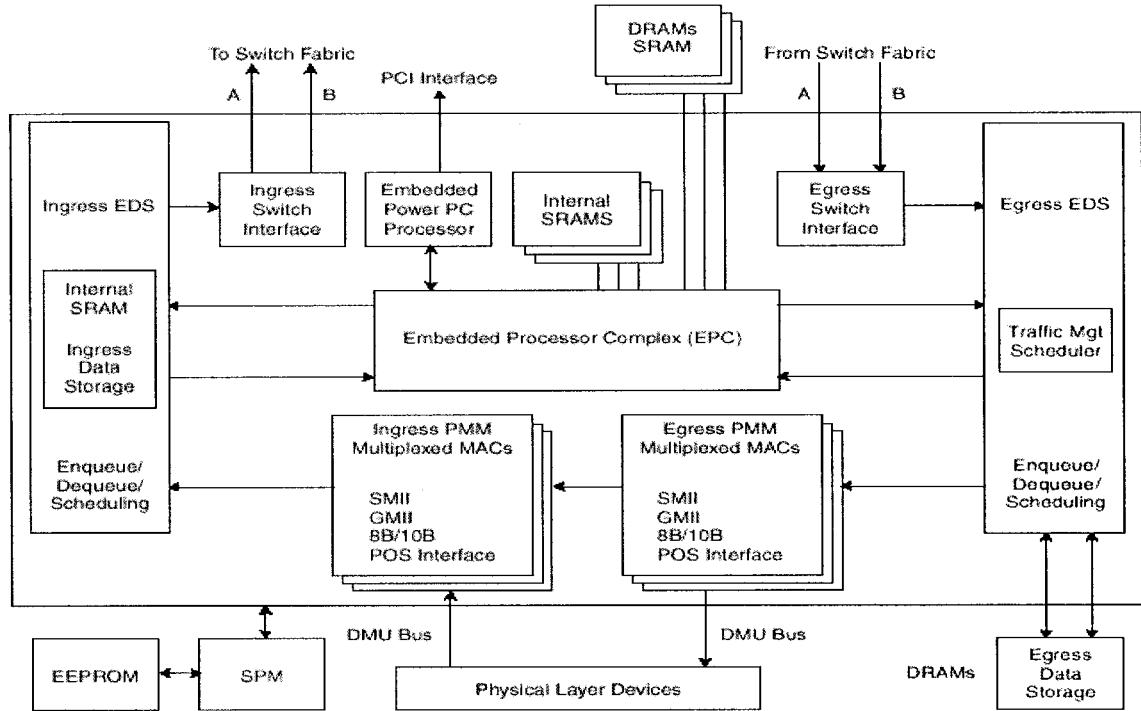

### 1.3.2 IBM (PowerNP)

La puce électronique fournie par IBM est une solution caractérisée par un processeur central PowerPC, 16 processeurs de protocoles qui sont inclus à l'intérieur d'un processeur embarqué complexe et 7 coprocesseurs matériels [20]. Elle supporte la technologie « Packet over SONET (*Synchronous Optical Network*)» et GigaBit Ethernet

avec une vitesse pouvant atteindre 2.5 Gbps. De plus, cette puce est ciblée pour le traitement des paquets entre les couches 2 à 5 du modèle OSI.

### **1.3.2.1      Architecture interne**

L'architecture interne de ce processeur réseau est constituée d'un processeur embarqué complexe, d'une partie matérielle spéciale et de plusieurs interfaces. Le cœur du processeur réseau est un processeur PowerPC405 [21] avec 16 processeurs de protocoles programmables. Chaque paire de processeurs de protocoles partage un coprocesseur matériel pour la recherche d'arbre et la modification des trames. Un processeur de protocoles possède un pipeline à trois étages. Il existe aussi sept coprocesseurs spécialisés dédiés à chacun des 16 processeurs de protocoles, dont les fonctions sont les suivantes : le rangement de données, le calcul du « checksum », le contrôle de flot, la mise à jour des processeurs de protocoles, les interfaces et la manipulation des données. Chaque processeur de protocoles possède une mémoire cache d'instructions de 8 Ko. La figure 1.4 illustre l'architecture interne d'un IBM-PowerNP.

### **1.3.2.2      Programmabilité**

L'outil de développement logiciel inclut un assembleur, un dévermineur et un simulateur.

### **1.3.2.3      Implantation**

La puce est implantée en utilisant la technologie CMOS 0.18µm. Elle dissipe une puissance de 20W et opère à une fréquence de 133 MHz [15].

Figure 1.4 Schéma bloc de l'architecture interne d'un processeur réseau IBM-PowerNP [20]

### 1.3.3 Intel (IXP1200)

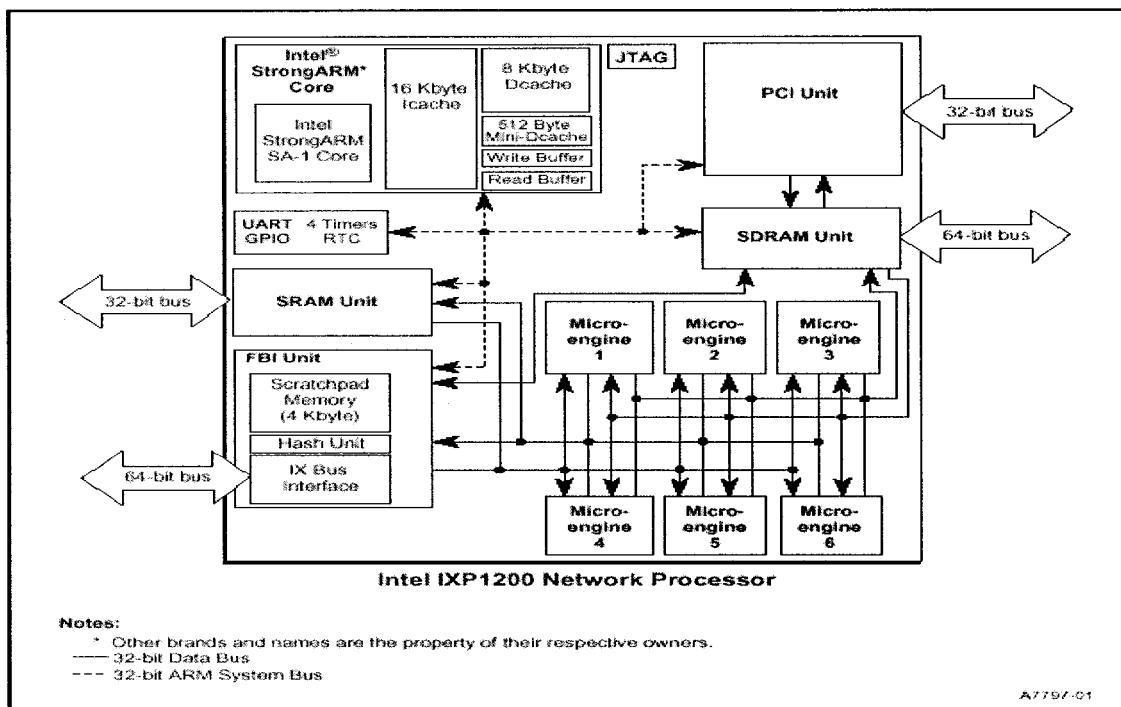

La société Intel est un des pionniers dans le domaine des processeurs réseau. Le IXP1200 cible la manipulation des paquets des couches 2 à 4 du système OSI. Il supporte un débit de 2.5 Mpaquets/s. Les couches supérieures peuvent être supportées en connectant des processeurs externes par l'intermédiaire de l'interface PCI (*Peripheral Connection Interface*). Le IXP1200 consiste en six « micro-engins » et un processeur central StrongARM qui agit comme contrôleur. Les « micro-engins » ont un support matériel pour servir jusqu'à quatre « threads ». De plus, il contient des coprocesseurs matériels pour calculer des fonctions spéciales telles que le décalage en un cycle, le « queuing » et le « hash ».

### 1.3.3.1      Architecture interne

L'architecture est composée de six processeurs embarqués programmables et d'un processeur central StrongARM qui fonctionne à 200 MHz et qui joue le rôle d'administrateur de système [24]. Un bus de 64-bit fournit une large bande passante nécessaire pour assurer une bonne connectivité entre les six processeurs embarqués, le processeur central, la mémoire et tous dispositifs externes tels que les interfaces physiques. D'autre part, le bus PCI permet une intégration avec un processeur externe de contrôle.

Les six processeurs embarqués exécutent toutes les tâches de manipulation sur les paquets. En fait, ils ont un support matériel pour effectuer quatre tâches chacun. Ceci nous offre un grand total de 24 tâches exécutables simultanées. Bien que les quatre tâches qui roulent sur un même processeur embarqué partagent le même fichier de registres temporaires, le logiciel divise ce dernier en quatre sections pour chaque tâche. Ceci est possible grâce à la capacité des micro-engins d'exécuter un changement de contexte en un seul cycle.

Le IXP1200 contient aussi des coprocesseurs matériels pour accélérer certaines fonctions. Il faut noter l'existence d'une machine programmable pour effectuer la fonction de « hash » ainsi que des queues qui sont partagées par les six processeurs embarqués et le processeur central. De plus, nous y trouvons des mémoires de type FIFO (*First In First Out*) qui agissent comme interfaces aux dispositifs d'interfaces physiques dans les cas de lecture et d'écriture. Finalement, nous dénotons l'existence d'une mémoire cache de 8 Ko pour les données et une autre mémoire cache de 16 Ko pour les instructions. La figure 1.5 illustre le schéma bloc de cette architecture.

### 1.3.3.2 Programmabilité

La programmation du IXP1200 se fait en langages assembleur et C [12]. Étant donné que les six processeurs embarqués travaillent en même temps, la tâche de programmation est très ardue. Il est aussi utile de mentionner que, malgré la difficulté rencontrée lors de la programmation, l'outil de développement fournit une aide extraordinaire pour faciliter à l'utilisateur la tâche de programmation. L'environnement de simulation configurable et la visualisation claire, montrant toutes les activités sur la puce, facilitent le déverminage.

Figure 1.5 Schéma bloc de l'architecture interne du Intel-IXP1200 [24]

### 1.3.3.3 Implantation

Le IXP1200 a été implanté en utilisant la technologie 0.18 µm. Il opère à une fréquence de 200 MHz tout en dissipant une puissance de 5 W [15].

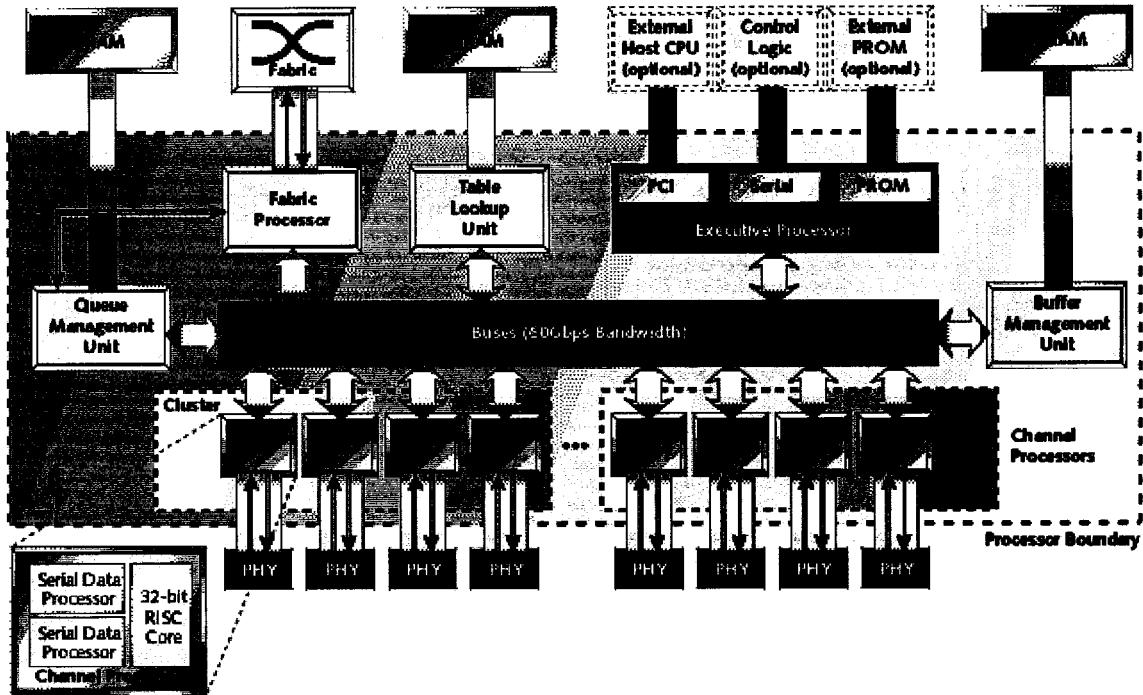

### **1.3.4 Motorola (C-5 DCP)**

Le processeur réseau C-5 de la compagnie Motorola est constitué de 16 processeurs avec cinq coprocesseurs et d'un processeur central qui agit comme coordonnateur de système [19] et [29]. Chaque processeur est un RISC avec deux processeurs de données série. Ce processeur réseau cible la manipulation de paquets des couches 2 à 7 du modèle OSI avec un taux de 2.5 Gbps.

#### **1.3.4.1 Architecture interne**

Les processeurs embarqués sont dédiés à la caractérisation et la classification des paquets ainsi que la gestion du trafic. Par contre, les deux processeurs de données série sont dédiés à la vérification des en-têtes, à l'extraction, à l'insertion, au calcul et à la vérification du CRC (*Cyclic Redundancy Check*). Les cinq coprocesseurs ont chacun des fonctions différentes, notamment, la mise à jour des tables de correspondance, la gestion des queues des paquets, la gestion de la mémoire, la coordination avec d'autres processeurs externes et l'utilisation de plusieurs processeurs réseau.

De plus, il existe trois bus internes qui ont une bande passante de 60 Gbps. L'architecture interne est montrée à la figure 1.6.

#### **1.3.4.2 Programmabilité**

Le C-5 DCP est programmable en utilisant le langage C/C++. L'outil de développement contient un ensemble vaste de plusieurs applications communes [30].

### 1.3.4.3 Implantation

Ce processeur réseau est implanté avec la technologie 0.18 µm et dissipe une puissance typique de 15 W.

Figure 1.6 Schéma bloc de l'architecture interne du processeur réseau de Motorola [19]

### 1.3.5 Autres processeurs réseau

Nous avons aussi fait l'étude de plusieurs autres processeurs réseau dont voici une liste avec les pointeurs respectifs :

- Agere (PayloadPlus) [27];

- AMCC (nP7xxx) [31];

- Bay Microsystems [46];

- BRECIS Communications (MSP5000) [8];

- **Broadcom (Mercurian SB-1250)** [37] et [38];

- **ClearSpeed** [11];

- **ClearWater Networks (CNP810SP)** [36]

- **Cognigine** [35];

- **Conexant (MXT4400)** [28];

- **Ezchip (NP-1)** [13] et [14];

- **Lexra (NetVortex, NVP)** [4] et [16];

- **PMC-Sierra** [33];

- **Vitesse (PRISM IQ2000)** [39];

- **Xelerated Packet Devices (T40, X40)** [47] et [48].

### 1.3.6 Synthèse de trois principaux processeurs réseau

Les processeurs réseau possèdent des éléments de conception communs :

- Accélération matérielle des tâches effectuées sur la majorité des informations traitées (ex. : CRC, queue management);

- Extensibilité (*Scalability*) : rend possible l'augmentation de la puissance de traitement par la collaboration de plusieurs exemplaires d'un élément;

- La majorité des processeurs contiennent un processeur générique pour le traitement des tâches de haut-niveau.

- System-on-a-chip (SOC) : combinaison de processeurs, mémoire et interface d'entrée/sortie sur une même pièce de silicium. Parmi des avantages associés à cette technologie : délai de propagation réduit entre les composantes et horloge plus rapide.

Le tableau suivant résume les caractéristiques de trois processeurs réseau principaux.

**Tableau 1.1 Synthèse et comparaison des trois principaux processeurs réseau**

|                                     | <b>Intel IXP1200</b>                                                                                                                                    | <b>IBM NP4GS3</b>                                                                                                                                                         | <b>Alchemy AU1000</b>                                                                       |

|-------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|

| Processeur générique                | Intel StrongARM                                                                                                                                         | Power PC 405                                                                                                                                                              | MIPS 32                                                                                     |

| Coprocresseurs spécialisés          | Hash Unit<br>Queue Management                                                                                                                           | Tree searching<br>Checksum<br>Enqueue<br>Interface<br>String Copy<br>Counter<br>Policy                                                                                    | Aucun<br><br><i>Dédié à chaque picoprocesseur</i>                                           |

| Unités fonctionnelles programmables | Microengines (6x)                                                                                                                                       | Pico-processeurs de protocoles (16x)                                                                                                                                      | Aucune                                                                                      |

| Vitesse de traitement               | 6.6 Gbps peak                                                                                                                                           | 4.5 Mpps                                                                                                                                                                  | N/D                                                                                         |

| Bus interne                         | ARM AMBA                                                                                                                                                | N/D                                                                                                                                                                       | N/D                                                                                         |

| Interfaces                          | POS<br>MAC<br>PCI<br>UART<br>GPIO                                                                                                                       | POS<br>MAC<br>PCI<br>DASL                                                                                                                                                 | MAC<br>IrDA<br>SSI<br>UART<br>GPIO<br>USB                                                   |

| Applications                        | Multi-layer LAN switches<br>Multi-protocol telecommunications products<br>Broadband cable products<br>Remote access devices<br>Intelligent PCI adapters | Layer 2 and Layer 3 switching<br>Packet classification<br>Multiple table lookups per frame<br>Packet Modification<br>Queue/Policy management<br>General packet processing | High performance at low power<br>PDA's<br>Wireless / remote access<br>Routers<br>Line cards |

| Protocoles supportés                | 10/100 Mbps Ethernet<br>Gigabit Ethernet<br>UTOPIA/POS                                                                                                  | 10/100 Mbps Ethernet<br>Gigabit Ethernet<br>OC-12 POS<br>OC-3 POS<br>802.3ad (Link Aggregation)<br>802.1q (VLAN)                                                          | 10/100 Mbps Ethernet<br>USB                                                                 |

Dans ce chapitre, nous avons fait un survol des différentes architectures de commutateurs. Afin d'assurer une flexibilité et une bonne programmabilité d'un processeur général tout en maintenant la performance à une vitesse atteignant 1 Gbps, il faudrait regarder au-delà des architectures basées sur des processeurs RISC . De nouvelles machines telles que les processeurs réseau programmables offrent une meilleure solution. Ces machines doivent combiner, d'une façon innovatrice, le pipeline, l'exécution parallèle et le déploiement matériel des nouveaux algorithmes. Une architecture réussie de processeur réseau doit tenir compte de la performance exigée de nos jours et de la flexibilité de rajouter des fonctionnalités futures.

## CHAPITRE II

### **Architecture globale de la plate-forme SoC**