**Titre:** Design et tests in vivo d'un microstimulateur urinaire sélectif implantable

Title: implantable

**Auteur:** Stéphane Boyer

Author:

**Date:** 2003

**Type:** Mémoire ou thèse / Dissertation or Thesis

**Référence:** Boyer, S. (2003). Design et tests in vivo d'un microstimulateur urinaire sélectif implantable [Master's thesis, École Polytechnique de Montréal]. PolyPublie.

Citation: <https://publications.polymtl.ca/7114/>

## Document en libre accès dans PolyPublie

Open Access document in PolyPublie

**URL de PolyPublie:** <https://publications.polymtl.ca/7114/>

PolyPublie URL:

**Directeurs de recherche:** Mohamad Sawan

Advisors:

**Programme:** Unspecified

Program:

In compliance with the

Canadian Privacy Legislation

some supporting forms

may have been removed from

this dissertation.

While these forms may be included

in the document page count,

their removal does not represent

any loss of content from the dissertation.

UNIVERSITÉ DE MONTRÉAL

DESIGN ET TESTS IN VIVO D'UN MICROSTIMULATEUR URINAIRE

SÉLECTIF IMPLANTABLE.

STÉPHANE BOYER

DÉPARTEMENT DE GÉNIE ÉLECTRIQUE

ÉCOLE POLYTECHNIQUE DE MONTRÉAL

MÉMOIRE PRÉSENTÉ EN VUE DE L'OBTENTION

DU DIPLÔME DE MAÎTRISE ÈS SCIENCES APPLIQUÉES (M.Sc.A.)

(GÉNIE ÉLECTRIQUE)

JUILLET 2003

National Library

of Canada

Acquisitions and

Bibliographic Services

395 Wellington Street

Ottawa ON K1A 0N4

Canada

Bibliothèque nationale

du Canada

Acquisitions et

services bibliographiques

395, rue Wellington

Ottawa ON K1A 0N4

Canada

*Your file* Votre référence

ISBN: 0-612-86386-7

*Our file* Notre référence

ISBN: 0-612-86386-7

The author has granted a non-exclusive licence allowing the National Library of Canada to reproduce, loan, distribute or sell copies of this thesis in microform, paper or electronic formats.

L'auteur a accordé une licence non exclusive permettant à la Bibliothèque nationale du Canada de reproduire, prêter, distribuer ou vendre des copies de cette thèse sous la forme de microfiche/film, de reproduction sur papier ou sur format électronique.

The author retains ownership of the copyright in this thesis. Neither the thesis nor substantial extracts from it may be printed or otherwise reproduced without the author's permission.

L'auteur conserve la propriété du droit d'auteur qui protège cette thèse. Ni la thèse ni des extraits substantiels de celle-ci ne doivent être imprimés ou autrement reproduits sans son autorisation.

# Canadä

UNIVERSITÉ DE MONTRÉAL

ÉCOLE POLYTECHNIQUE DE MONTRÉAL

Ce mémoire intitulé:

DESIGN ET TESTS IN VIVO D'UN MICROSTIMULATEUR URINAIRE

SÉLECTIF IMPLANTABLE.

présenté par: BOYER Stéphane

en vue de l'obtention du diplôme de: Maîtrise ès sciences appliquées

a été dûment accepté par le jury d'examen constitué de:

M. BOIS Guy, Ph.D., président

M. SAWAN Mohamad, Ph.D., membre et directeur de recherche

M. KHOUAS Abdelhakim, Ph.D., membre

À Fernande et Hervé.

## REMERCIEMENTS

Je tiens d'abord à remercier Mohamad Sawan, professeur à l'École Polytechnique et directeur du laboratoire PolySTIM, pour m'avoir permis de contribuer à un projet aussi gratifiant, pour son support moral et ses encouragements.

Je remercie également les membres de l'équipe PolySTIM, et plus particulièrement Luc Romain, Jean-François Harvey et Simon Robin, pour les nombreuses fois où ils ont su me faire voir un problème sous un angle différent et surtout pour avoir pavé la voie de l'inconnu devant moi.

Je salue aussi le personnel du centre de ressource animale (ARC) de l'Université McGill, sous la supervision du Docteur Mostafa M. Elhilali, pour leur patience et leur professionnalisme lors des expérimentations.

Pour terminer, je remercie la Fondation canadienne du rein et le Conseil de recherche en sciences naturelles et génie du Canada pour le soutien financier au projet.

## RÉSUMÉ

Parmi les traitements disponibles pour récupérer les fonctions urinaires chez les paraplégiques, la stimulation électrique des racines sacrées est l'une des avenues les plus prometteuses. Toutefois, la stimulation de ce site provoque la contraction simultanée de muscle entourant la vessie (détrusor) et du sphincter urétral externe, inhibant la miction et causant une pression anormalement élevée dans la vessie. La stimulation sélective à l'aide de deux trains d'impulsion de fréquence différente est l'une des techniques utilisées pour réduire la dyssynergie et favoriser la miction.

L'équipe de recherche PolySTIM met au point depuis plus d'une décennie différents stimulateurs implantables dédiés à la récupération des fonctions urinaires. Un nouveau microstimulateur intégré a été réalisé dans le cadre de cette maîtrise à l'aide d'un procédé de fabrication de  $0,35 \mu\text{m}$ . Le circuit mixte, intégrant un module numérique de génération de signaux et une source de courant bidirectionnel de 5 bits, permet de produire la forme d'onde nécessaire à la stimulation sélective.

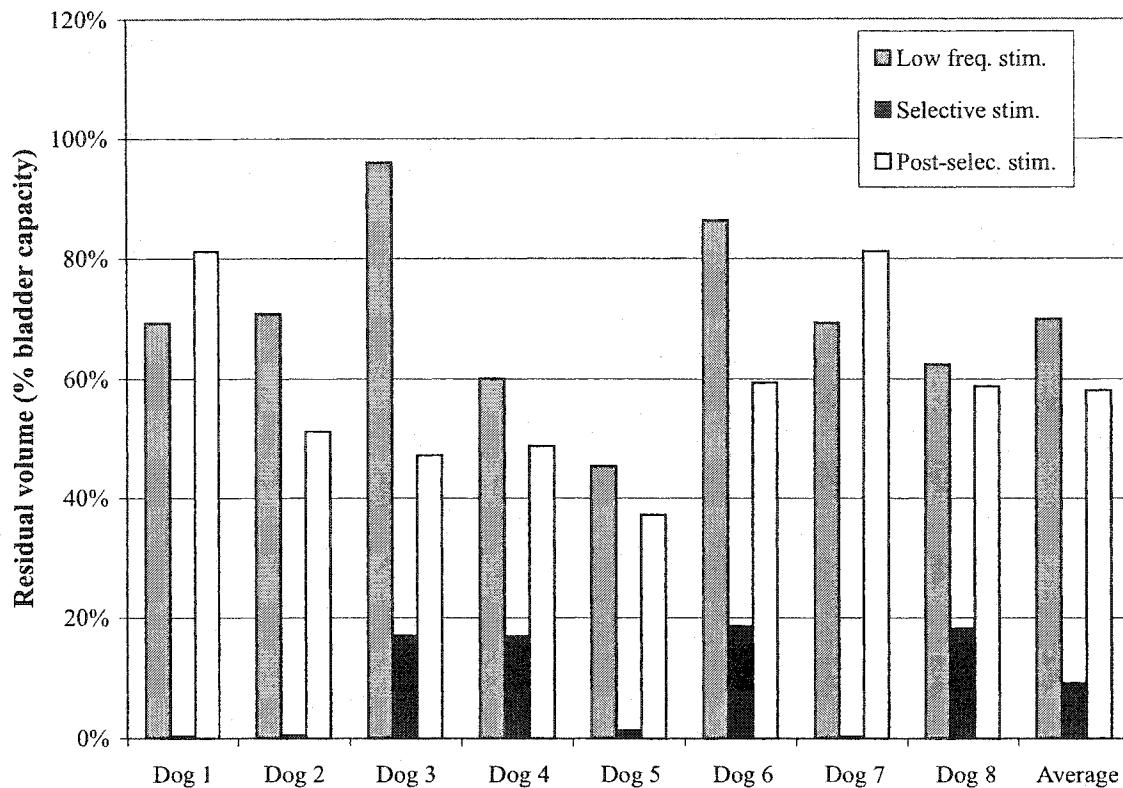

L'article «Implantable Selective Stimulator to Improve Bladder Voiding: Design and Chronic Experiments in Dogs», publié dans «IEEE Transactions On Rehabilitation Engineering», présente le système de stimulation, le protocole et les résultats d'essais en phase chronique réalisés sur 8 chiens. Les résultats montrent que la stimulation sélective des racines sacrées favorise la miction en inhibant la contraction du sphincter externe tout en permettant l'excitation du détrusor. Elle augmente

de plus de 50% l'évacuation d'urine de la vessie par rapport à une technique de stimulation basse fréquence uniquement.

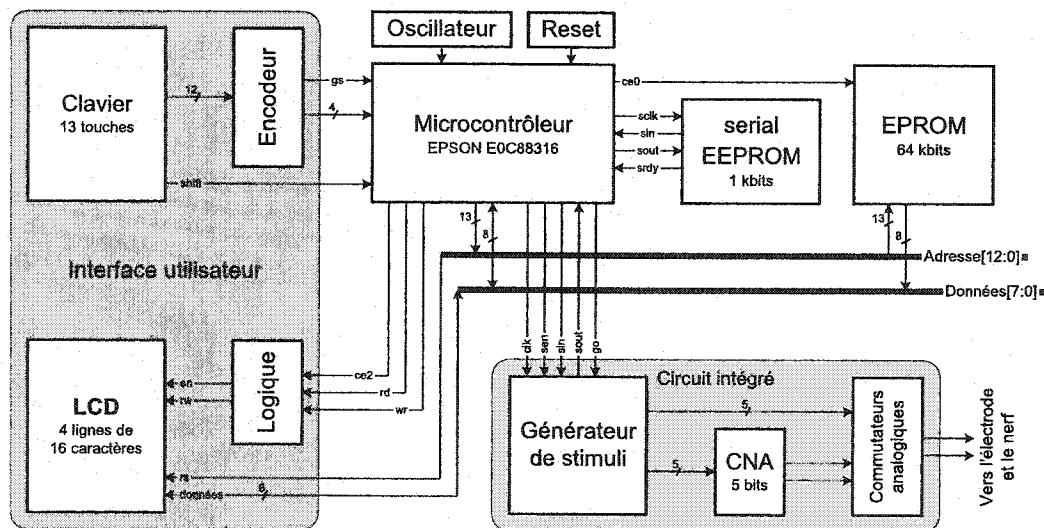

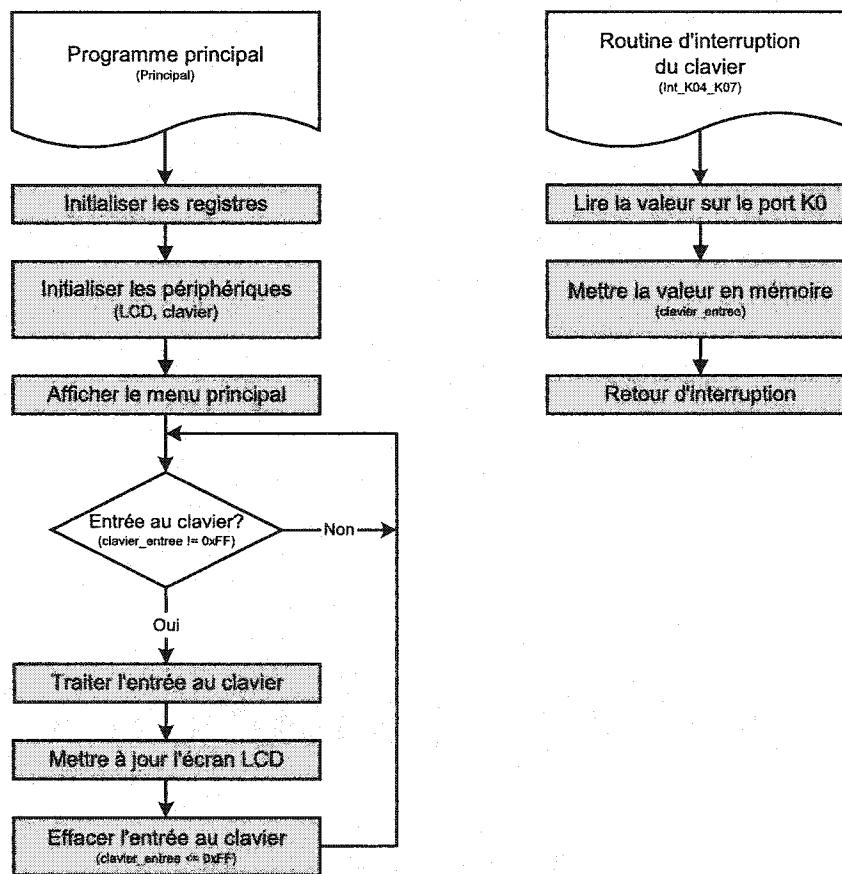

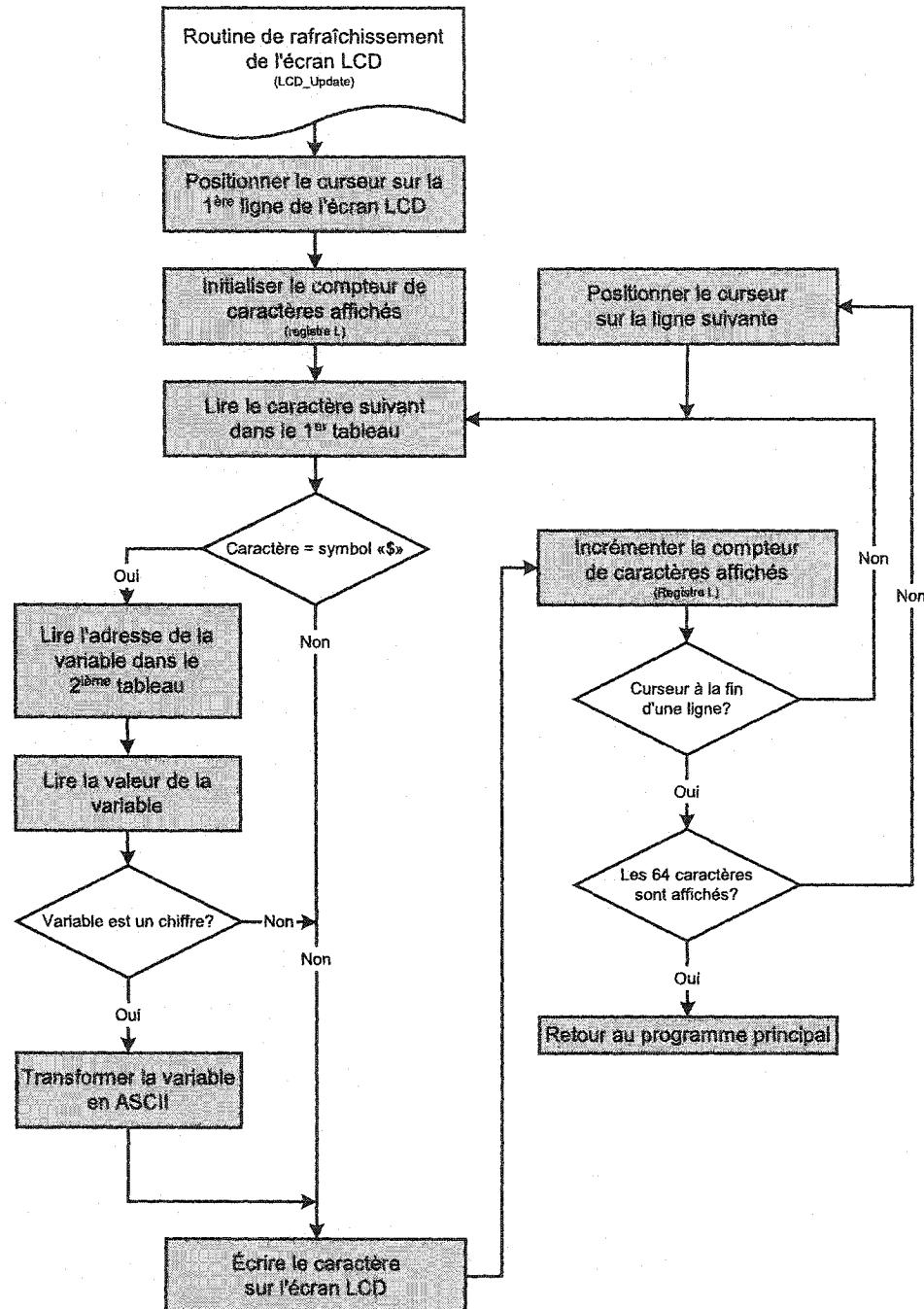

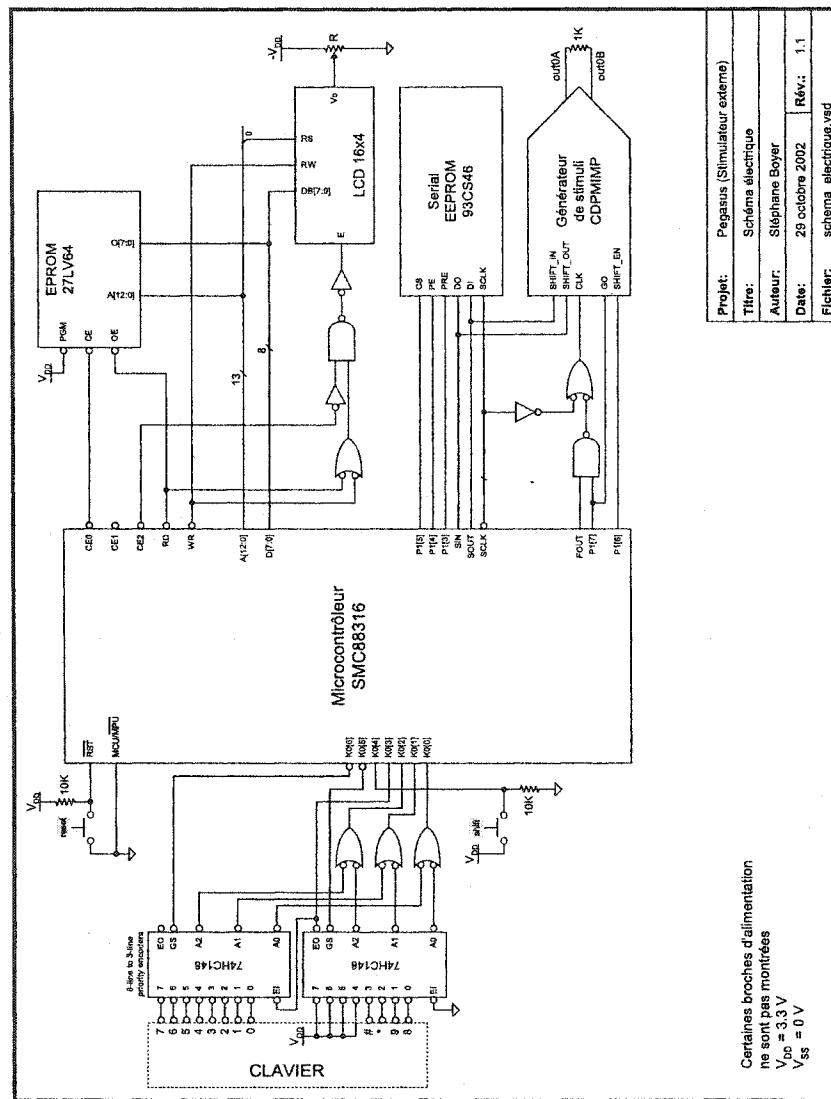

Enfin, un stimulateur externe et portable a également été réalisé à l'aide du microcontrôleur EPSON E0C88316. Ce système, utilisant un écran LCD et un clavier, offre une interface utilisateur évoluée permettant de modifier chacun des paramètres de stimulation, de conserver plusieurs ensembles de paramètres précédemment définis et de les récupérer au besoin. L'étage de sortie utilisé pour ce design est le même que celui présenté avec le nouveau stimulateur intégré et permet le contrôle du courant de stimulation. L'uniformisation des appareils utilisés tout au long du protocole devrait permettre de tirer des conclusions plus justes.

## ABSTRACT

Among the available treatment to retrieve bladder functions for paraplegics, electrical stimulation of the sacral roots seems to be one of the most promising solutions. However, neurostimulation of this site provokes a simultaneous contraction of the bladder muscle and the external urethral sphincter, preventing micturition and causing abnormally high bladder pressure. Selective stimulation using two series of impulsions at different frequencies is one of the techniques used to reduce the detrusor-sphincter dyssynergia and assist micturition.

The PolySTIM research team designs, since more than a decade, different types of implantable electrical stimulators used to retrieve bladder functions. In this master thesis, a new integrated microstimulator was carried out using a  $0.35\ \mu\text{m}$  fabrication process. The mixte circuit, integrating digital logic for waveform generation and an bidirectional 5-bit current source can produce the necessary waveform for selective stimulation.

The paper "Implantable Selective Stimulator to Improve Bladder Voiding: Design and Chronic Experiments in Dogs", published in "IEEE Transactions On Rehabilitation Engineering", presents the medical protocol and results of chronic studies on 8 mongrel dogs. Results show that selective stimulation of sacral roots promotes micturition by preventing external sphincter contraction and having little effect on detrusor contraction. This technique increases micturition volume

by more than 50% when compared with standard low-frequency only stimulation technique.

Finally, an external and portable stimulator has also been realized with the EPSON E0C88316 microcontroler. This system, fitted with an liquid crystal display (LCD) and a keyboard, offers a friendly user interface with which every stimulation parameter can be viewed and modified and, parameters' set can be saved and retrieved when necessary. The output stage of this design is the same as the implantable stimulator described earlier and enables to control the stimulation current. The uniformisation of devices' output stage used along each step of the protocol should allow to draw more accurate conclusions.

**TABLE DES MATIÈRES**

|                                                             |       |

|-------------------------------------------------------------|-------|

| DÉDICACE . . . . .                                          | iv    |

| REMERCIEMENTS . . . . .                                     | v     |

| RÉSUMÉ . . . . .                                            | vi    |

| ABSTRACT . . . . .                                          | viii  |

| TABLE DES MATIÈRES . . . . .                                | x     |

| LITSTE DES TABLEAUX . . . . .                               | xiv   |

| LITSTE DES FIGURES . . . . .                                | xv    |

| LITSTE DES NOTATIONS ET DES SYMBOLES . . . . .              | xviii |

| LITSTE DES ANNEXES . . . . .                                | xxi   |

| INTRODUCTION . . . . .                                      | 1     |

| CHAPITRE 1: LE SYSTÈME URINAIRE ET LA STIMULATION           |       |

| ÉLECTRIQUE . . . . .                                        | 4     |

| 1.1 Introduction . . . . .                                  | 4     |

| 1.2 L'appareil urinaire . . . . .                           | 4     |

| 1.2.1 La partie inférieure de l'appareil urinaire . . . . . | 5     |

|       |                                                             |    |

|-------|-------------------------------------------------------------|----|

| 1.2.2 | Les tissus musculaires de la vessie . . . . .               | 6  |

| 1.3   | Les voies neurales . . . . .                                | 6  |

| 1.3.1 | Les voies sensitives . . . . .                              | 7  |

| 1.3.2 | Les voies motrices de l'appareil urinaire . . . . .         | 8  |

| 1.3.3 | Les centres nerveux réflexes . . . . .                      | 8  |

| 1.3.4 | Les centres nerveux corticaux . . . . .                     | 9  |

| 1.4   | La miction normale . . . . .                                | 9  |

| 1.5   | Les effets d'un traumatisme . . . . .                       | 11 |

| 1.6   | La stimulation neuromusculaire . . . . .                    | 13 |

| 1.6.1 | Les sites de stimulation . . . . .                          | 13 |

| 1.6.2 | Les techniques de stimulation des racines sacrées . . . . . | 15 |

| 1.7   | Conclusion . . . . .                                        | 18 |

## **CHAPITRE 2: LE SYSTÈME DE STIMULATION NEUROMUS-**

|                          |                                                                       |    |

|--------------------------|-----------------------------------------------------------------------|----|

| <b>CULAIRE . . . . .</b> | <b>19</b>                                                             |    |

| 2.1                      | Introduction . . . . .                                                | 19 |

| 2.2                      | Les systèmes commerciaux . . . . .                                    | 19 |

| 2.3                      | Aperçu sur l'évolution de stimulateurs offerts par PolySTIM . . . . . | 20 |

| 2.4                      | Les contrôleurs externes . . . . .                                    | 24 |

| 2.5                      | Les électrodes . . . . .                                              | 26 |

| 2.6                      | Conclusion . . . . .                                                  | 27 |

**CHAPITRE 3: SIMULATEUR IMPLANTABLE ET VALIDATION

DE LA TECHNIQUE DE STIMULATION SÉLEC-**

**TIVE EN PHASE CHRONIQUE . . . . . 29**

|       |                                                                                                                         |    |

|-------|-------------------------------------------------------------------------------------------------------------------------|----|

| 3.1   | Introduction à l'article publié dans «IEEE Transactions on Rehabilitation Engineering» . . . . .                        | 29 |

| 3.2   | Article «Implantable Selective Stimulator to Improve Bladder Voiding: Design and Chronic Experiments in Dogs» . . . . . | 30 |

| 3.2.1 | Abstract . . . . .                                                                                                      | 30 |

| 3.2.2 | Introduction . . . . .                                                                                                  | 31 |

| 3.2.3 | Description of the Stimulation System . . . . .                                                                         | 37 |

| 3.2.4 | Experimental Protocol . . . . .                                                                                         | 42 |

| 3.2.5 | Results . . . . .                                                                                                       | 45 |

| 3.2.6 | Discussion . . . . .                                                                                                    | 51 |

| 3.3   | Conclusion . . . . .                                                                                                    | 53 |

**CHAPITRE 4: RÉALISATION ET TEST D'UN STIMULATEUR**

**IMPLANTABLE INTÉGRÉ . . . . . 55**

|       |                                                        |    |

|-------|--------------------------------------------------------|----|

| 4.1   | Introduction . . . . .                                 | 55 |

| 4.2   | Design . . . . .                                       | 57 |

| 4.2.1 | Architecture . . . . .                                 | 57 |

| 4.2.2 | Alimentation de l'implant et réception RF . . . . .    | 58 |

| 4.2.3 | Module numérique de réception et de contrôle . . . . . | 58 |

|                                                             |                                                                |           |

|-------------------------------------------------------------|----------------------------------------------------------------|-----------|

| 4.2.4                                                       | Étage analogique de sortie . . . . .                           | 59        |

| 4.3                                                         | Vérification, synthèse et dessin des masques . . . . .         | 62        |

| 4.4                                                         | Test du circuit intégré . . . . .                              | 66        |

| 4.5                                                         | Conclusion . . . . .                                           | 71        |

| <br><b>CHAPITRE 5: RÉALISATION D'UN STIMULATEUR EXTERNE</b> |                                                                |           |

| <b>PORTABLE . . . . .</b>                                   |                                                                | <b>73</b> |

| 5.1                                                         | Introduction . . . . .                                         | 73        |

| 5.2                                                         | Architecture générale . . . . .                                | 73        |

| 5.3                                                         | Interface utilisateur . . . . .                                | 76        |

| 5.3.1                                                       | Modification des paramètres . . . . .                          | 77        |

| 5.3.2                                                       | Gestion des espaces mémoires . . . . .                         | 78        |

| 5.3.3                                                       | Stimulation neuromusculaire . . . . .                          | 78        |

| 5.3.4                                                       | Sous-routine de rafraîchissement de l'affichage . . . . .      | 79        |

| 5.4                                                         | Génération des stimuli et étage analogique de sortie . . . . . | 81        |

| 5.5                                                         | Vérification et tests . . . . .                                | 82        |

| 5.6                                                         | Conclusion . . . . .                                           | 82        |

| <br><b>DISCUSSION GÉNÉRALE ET CONCLUSION . . . . .</b>      |                                                                | <b>84</b> |

| <br><b>BIBLIOGRAPHIE . . . . .</b>                          |                                                                | <b>89</b> |

**LISTE DES TABLEAUX**

|     |                                                                                                                                    |    |

|-----|------------------------------------------------------------------------------------------------------------------------------------|----|

| 1.1 | Résumé des techniques de stimulation des racines sacrées dédiées à la vidange de la vessie. . . . .                                | 18 |

| 2.1 | Résumé des caractéristiques des neurostimulateurs implantables. . .                                                                | 24 |

| 2.2 | Résumé des caractéristiques des contrôleurs externes. . . . .                                                                      | 26 |

| 3.1 | Frequently employed parameters: low-frequency only and selective stimulations. . . . .                                             | 44 |

| 3.2 | Voided and residual urine quantities in eight chronic dogs. . . . .                                                                | 48 |

| 4.1 | Plage disponible pour les paramètres de stimulation de l'implant. .                                                                | 56 |

| 4.2 | Comparaison des caractéristiques des sources développées par St-Amand (1995), Bourret (1999) et de la nouvelle version proposée. . | 70 |

**LISTE DES FIGURES**

|     |                                                                                                                                                                                                     |    |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 1.1 | Représentation simplifiée de l'appareil urinaire. . . . .                                                                                                                                           | 5  |

| 1.2 | Les voies neurales du système urinaire. . . . .                                                                                                                                                     | 7  |

| 2.1 | Diagramme simplifié du neurostimulateur introduit par Sawan. . . . .                                                                                                                                | 21 |

| 2.2 | Diagramme simplifié du neurostimulateur introduit par Arabi. . . . .                                                                                                                                | 22 |

| 2.3 | Schéma bloc du neurostimulateur introduit par Robin. . . . .                                                                                                                                        | 23 |

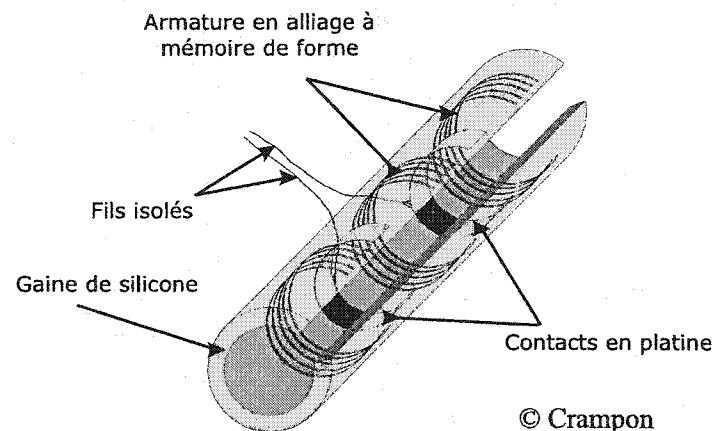

| 2.4 | Électrode à gaine cylindrique avec armature en alliage à mémoire de forme réalisée par Crampon. . . . .                                                                                             | 27 |

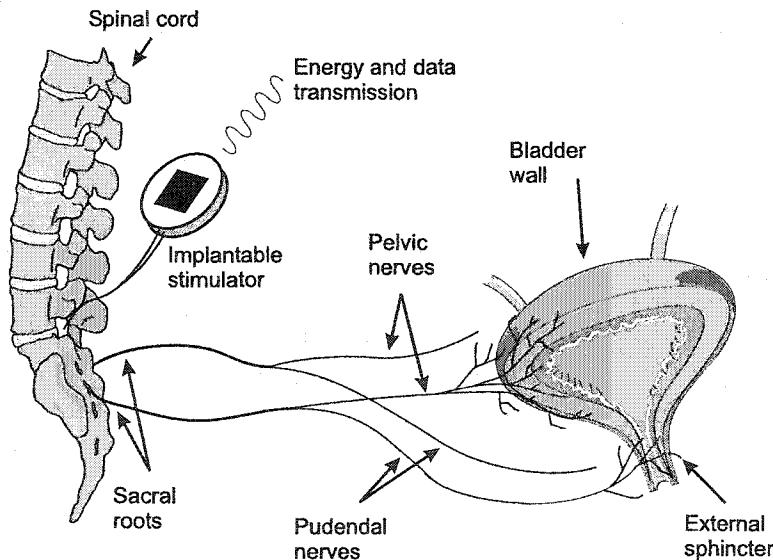

| 3.1 | Possible stimulation sites and implantable stimulator position for high-frequency inhibition. . . . .                                                                                               | 31 |

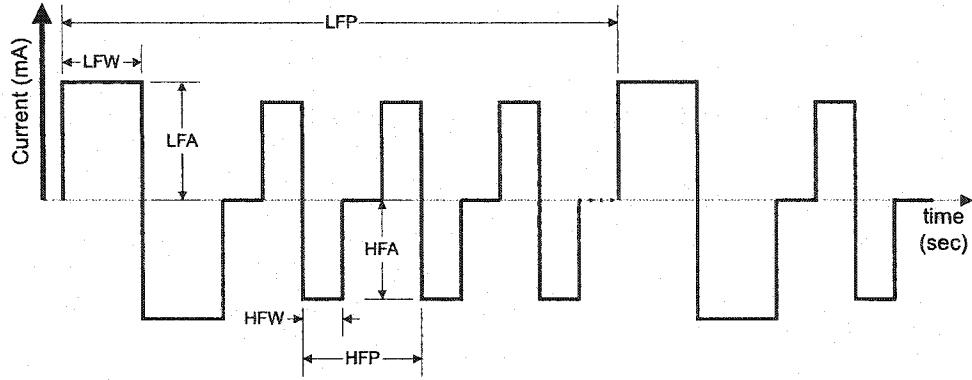

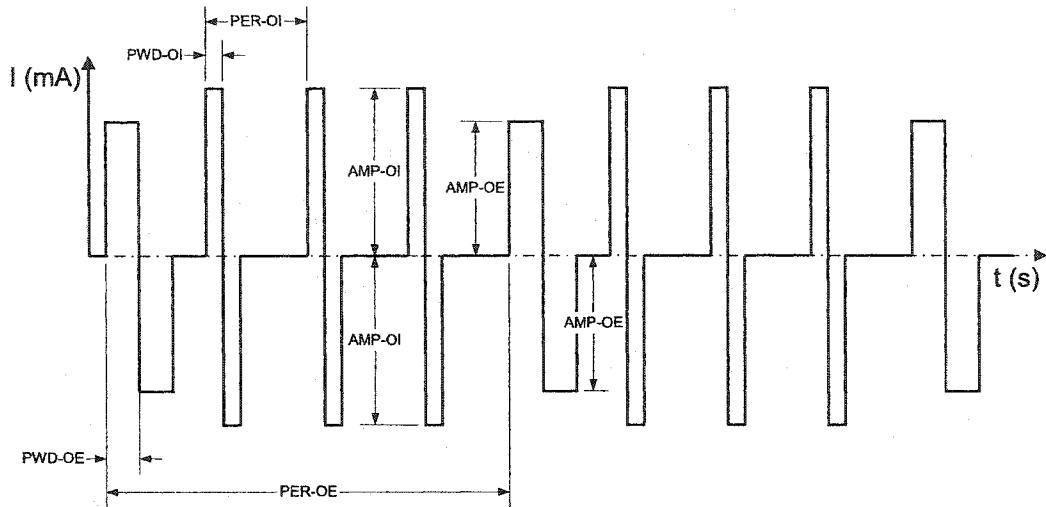

| 3.2 | Typical selective stimulation waveform intended to block the sphincter activation during bladder contraction (waveforms are not to scale; meaning of abbreviations are given in Table 3.1). . . . . | 38 |

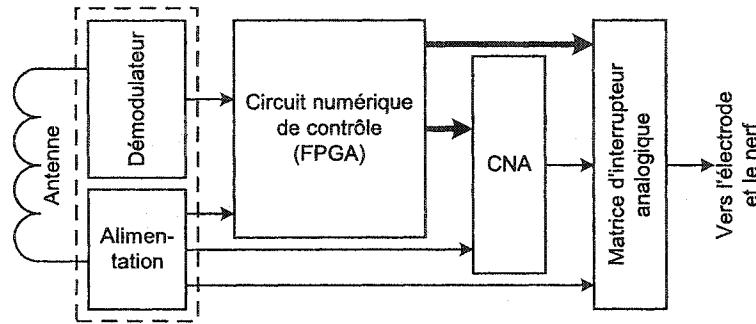

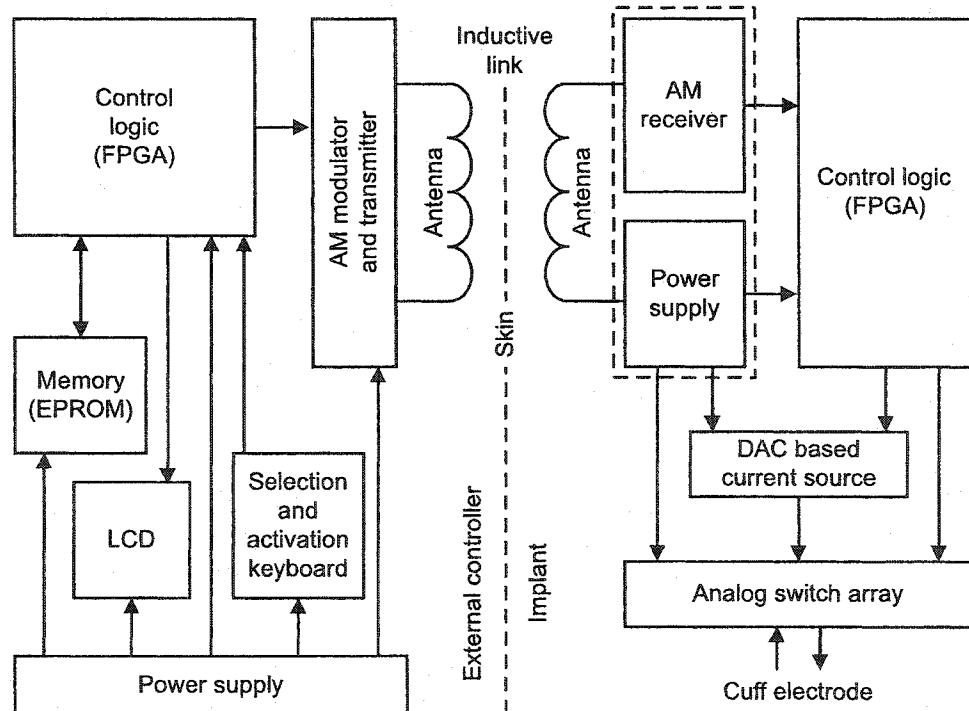

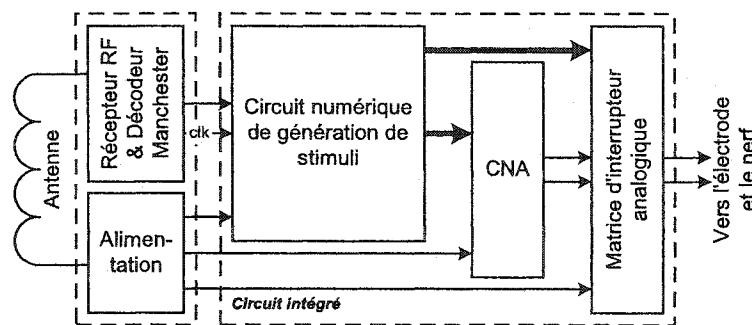

| 3.3 | Block-diagram of the whole proposed selective stimulator including the external controller, the implant and the electromagnetic link between both parts. . . . .                                    | 39 |

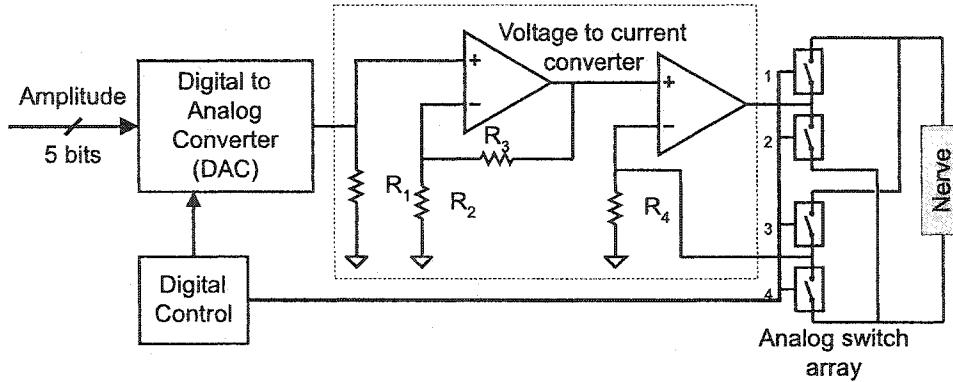

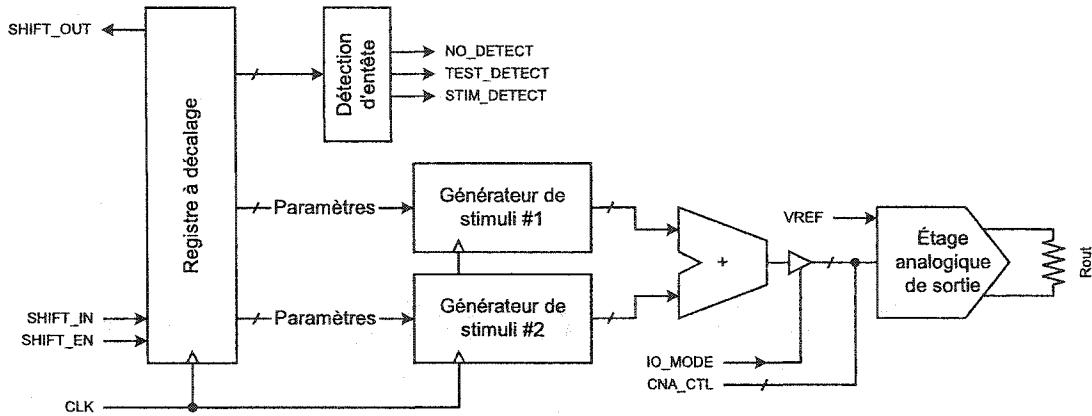

| 3.4 | Simplified block diagram of the output stage of the implant including an analog switch array to deliver fully balanced bipolar stimuli. . . . .                                                     | 41 |

|                                                                                                                                                                                                      |    |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

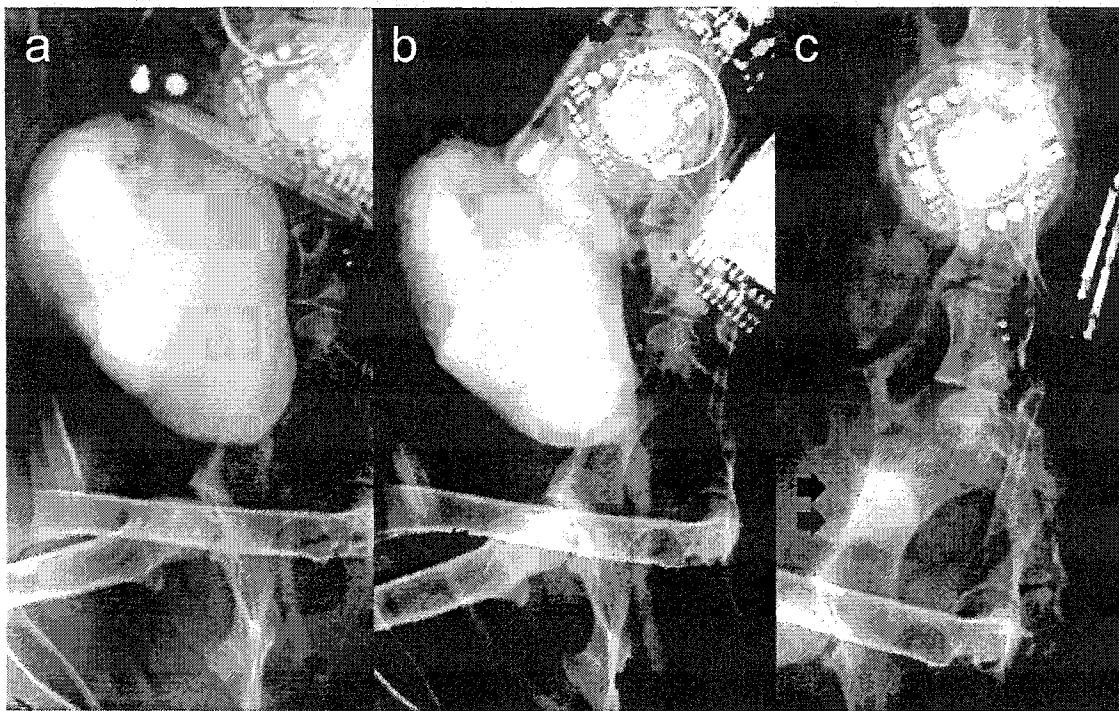

| 3.5 X-ray views of the bladder: a) external urethral sphincter (EUS)<br>contracted, b) EUS relaxes with selective stimulation and, c) residual<br>urine volume (shown by arrows). . . . .            | 47 |

| 3.6 Residual volume for three stimulation steps: low-frequency only, se-<br>lective and post-selective (for complementary information, see Ta-<br>ble 3.2). . . . .                                  | 49 |

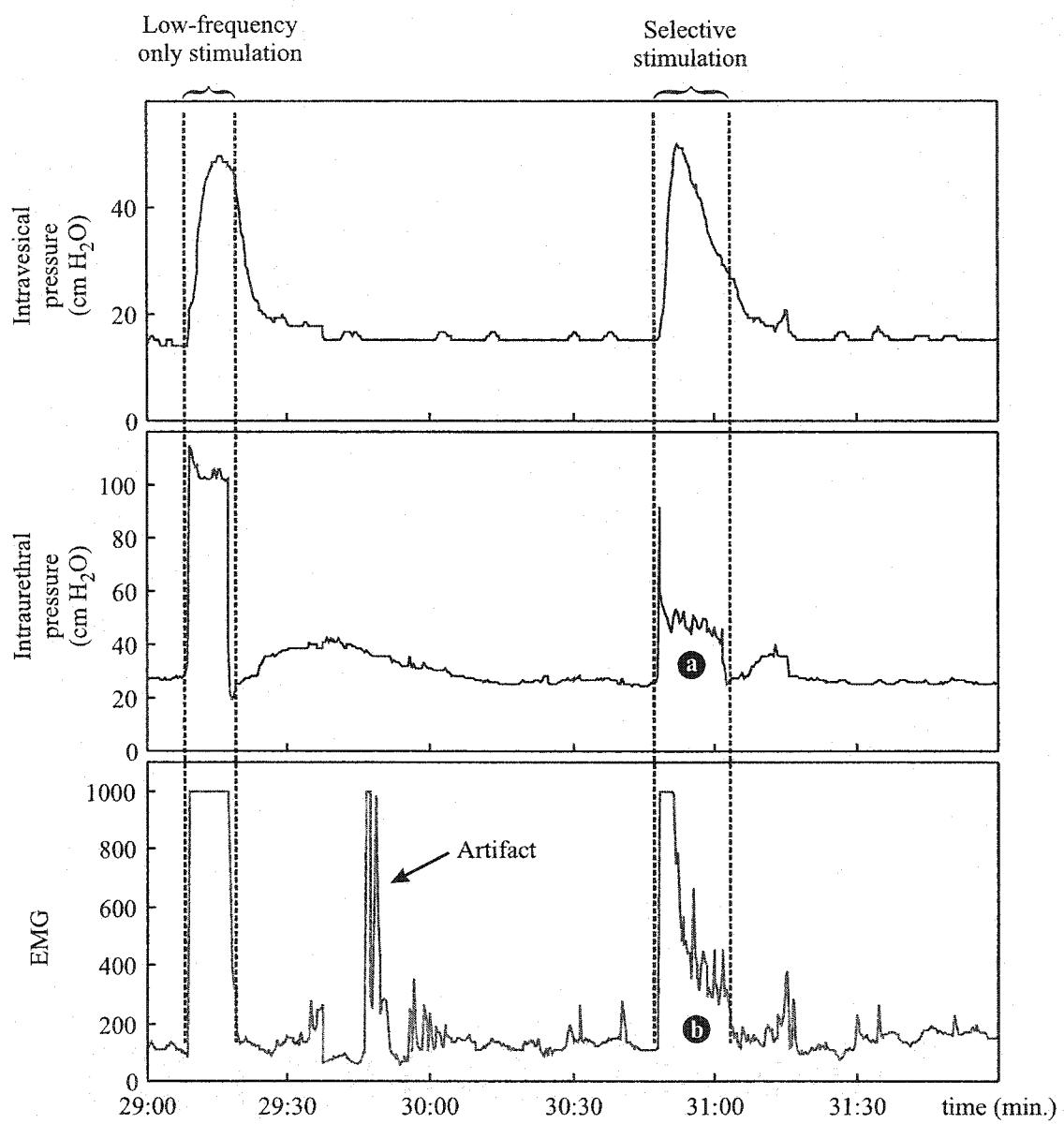

| 3.7 Intravesical and intraurethral pressures and EMG of the sphincter:<br>a) lower intraurethral pressure allows micturition; b) reduced EMG<br>coincides with lower intraurethral pressure. . . . . | 50 |

| 4.1 Forme du signal généré par le stimulateur implantable. . . . .                                                                                                                                   | 56 |

| 4.2 Schéma simplifié du stimulateur neuromusculaire implantable. . . .                                                                                                                               | 57 |

| 4.3 Schéma simplifié du circuit intégré dédié. . . . .                                                                                                                                               | 59 |

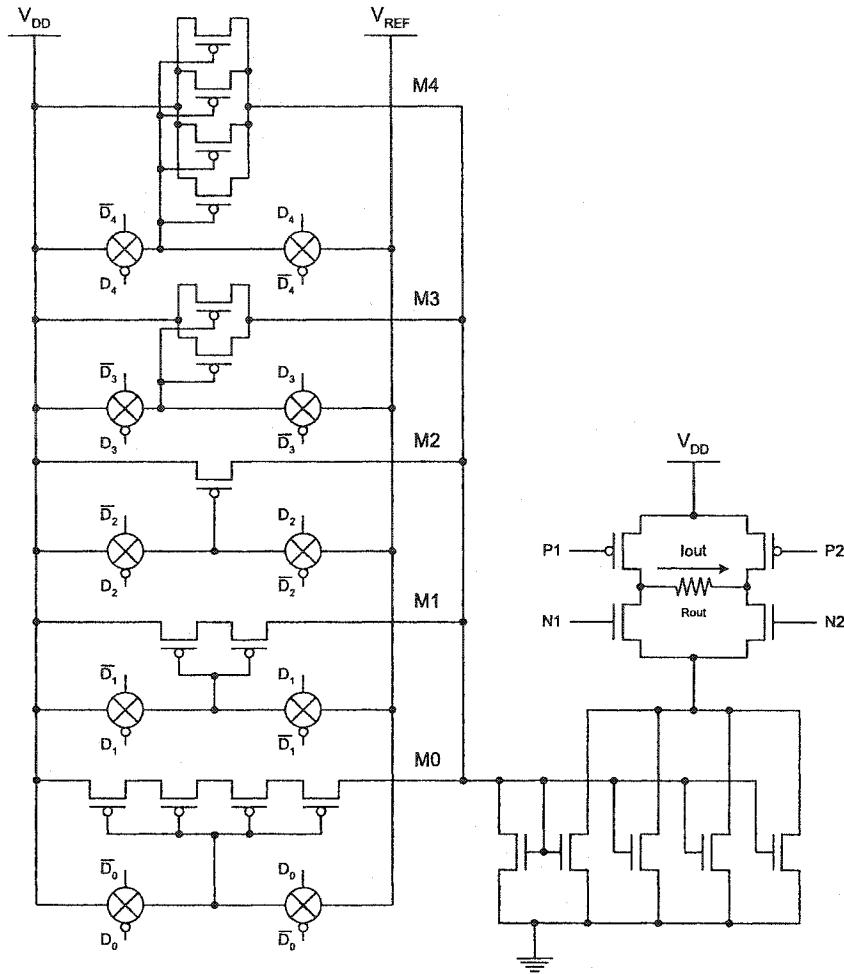

| 4.4 Schéma électrique de l'étage analogique de sortie (CNA et étage de<br>sortie bipolaire). . . . .                                                                                                 | 60 |

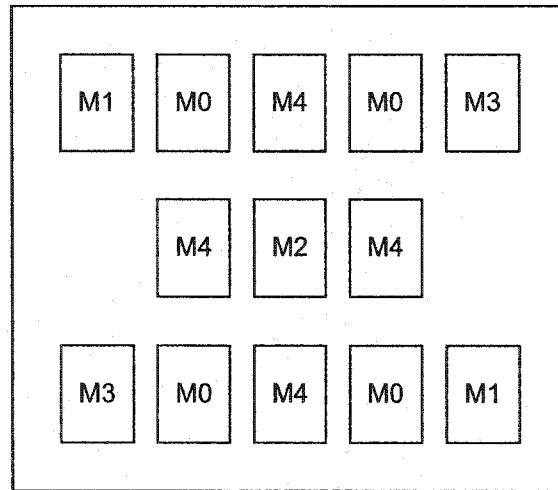

| 4.5 Géométrie de type centre de masse commun utilisée pour le CNA. .                                                                                                                                 | 62 |

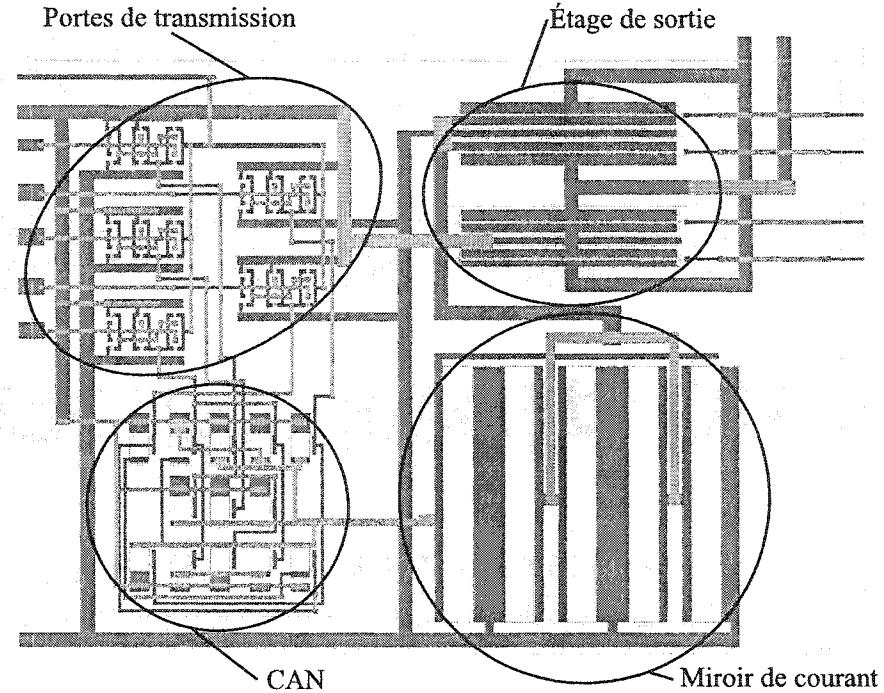

| 4.6 Dessin des masques de la source de courant. . . . .                                                                                                                                              | 63 |

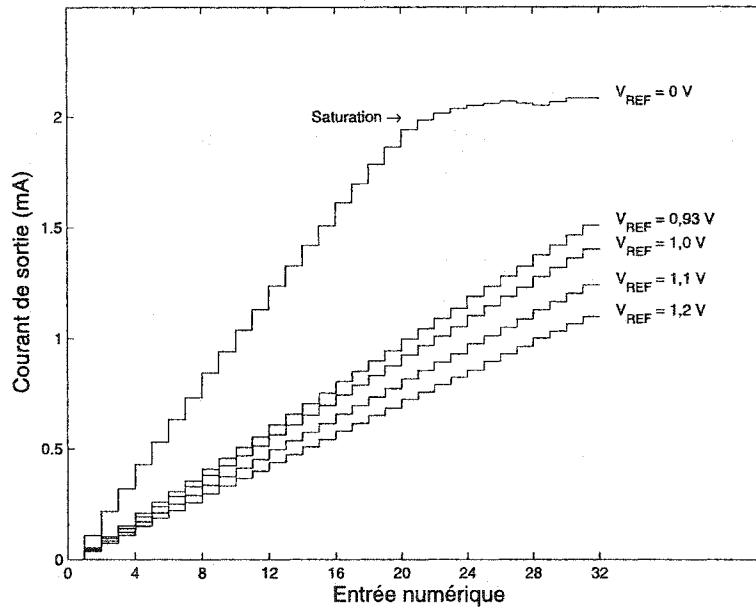

| 4.7 Courants de sortie mesurés en fonction de différentes tensions de<br>référence. . . . .                                                                                                          | 68 |

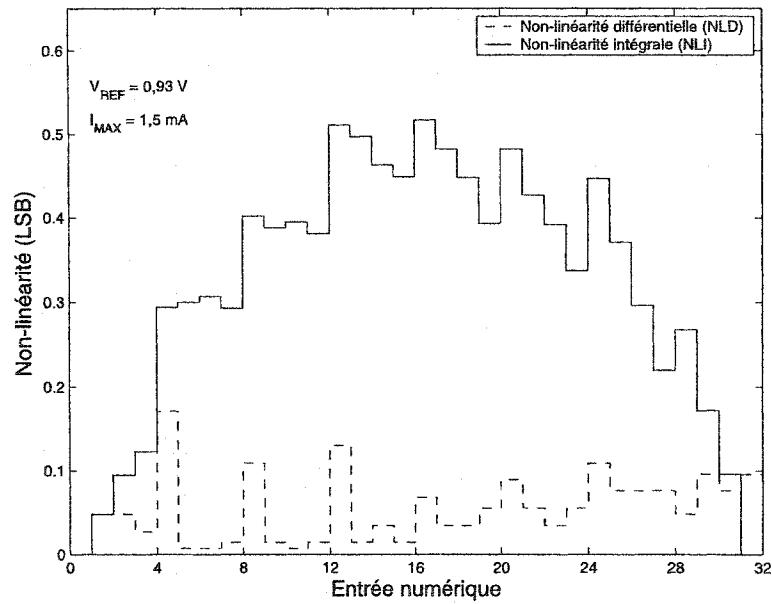

| 4.8 Non-linéarités différentielle et intégrale du convertisseur pour une<br>tension de référence de 0,93 volt. . . . .                                                                               | 69 |

|                                                                                                                         |     |

|-------------------------------------------------------------------------------------------------------------------------|-----|

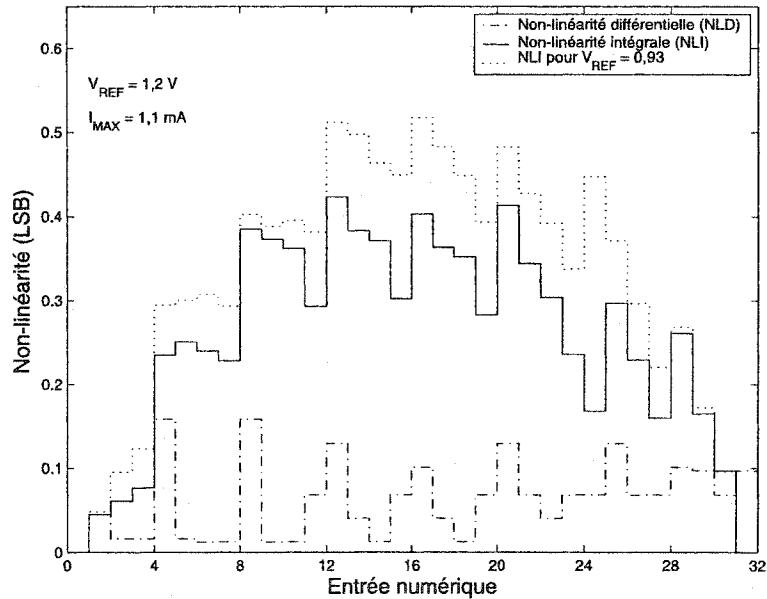

| 4.9 Non-linéarités différentielle et intégrale du convertisseur pour une tension de référence de 1,2 volt. . . . .      | 69  |

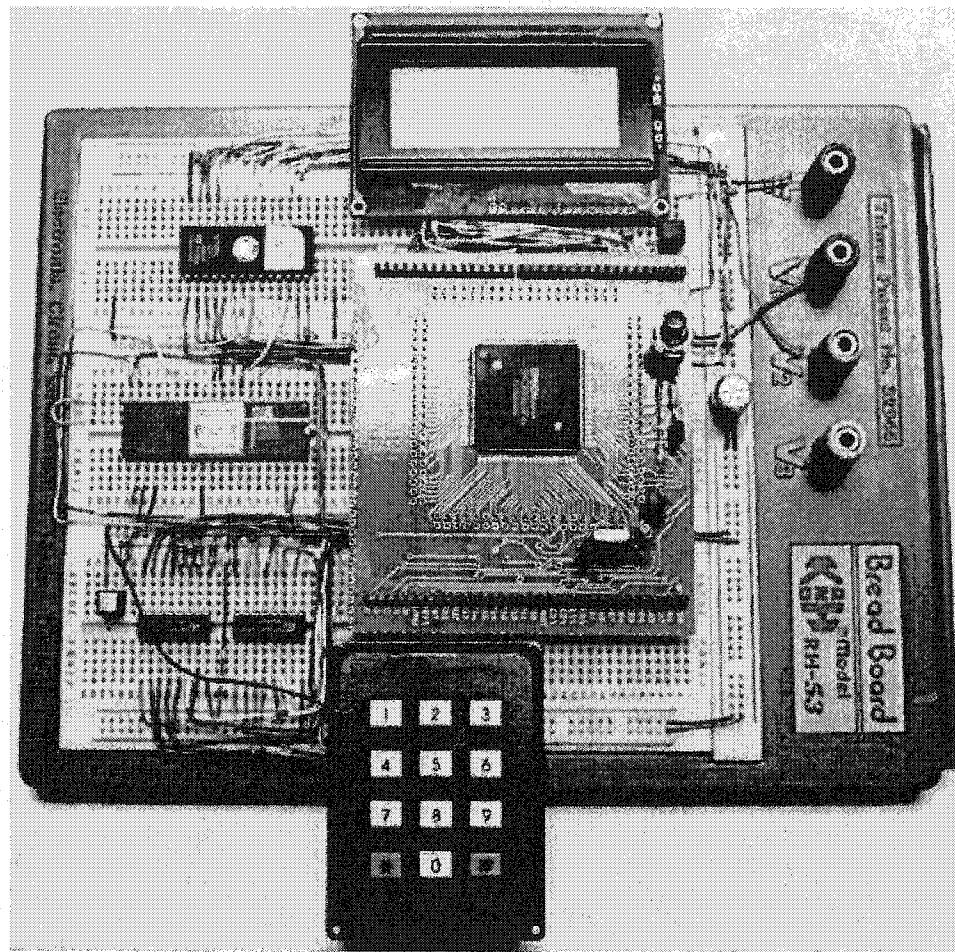

| 5.1 Photo du prototype du stimulateur externe portable. . . . .                                                         | 74  |

| 5.2 Architecture générale du stimulateur externe. . . . .                                                               | 75  |

| 5.3 Algorithmes du programme principal du stimulateur externe et de la routine d'exception d'entrée au clavier. . . . . | 76  |

| 5.4 Lorsque l'espace d'affichage est insuffisant, la navigation se fait à l'aide des flèches. . . . .                   | 77  |

| 5.5 Algorithme de la sous-routine de rafraîchissement de l'affichage de l'écran LCD. . . . .                            | 80  |

| II.1 Schéma électrique du stimulateur neuromusculaire externe et portable.                                              | 121 |

**LISTE DES NOTATIONS ET DES SYMBOLES**

|         |                                                                    |

|---------|--------------------------------------------------------------------|

| ASD:    | Analyse statique de délais                                         |

| ASK:    | Amplitude Shift Keying                                             |

| BiCMOS: | Bipolar and CMOS                                                   |

| CI:     | Circuit intégré                                                    |

| CMOS:   | Complementary Metal-Oxide Semiconductor                            |

| CNA:    | Convertisseur numérique à analogique                               |

| CRSNG:  | Conseil de recherches en sciences naturelles et en génie du Canada |

| DAC:    | Digital to Analog Converter                                        |

| DIP:    | Dual In-line Package                                               |

| DSD:    | Detrusor-Sphincter Dyssynergia                                     |

| EPROM:  | Electrically Erasable Programmable Read-Only Memory                |

| EMG:    | Electromyograph                                                    |

| EUS:    | External Urethral Sphincter                                        |

| FES:    | Functional Electrical Stimulation                                  |

| FPGA:   | Field Programmable Gate Array                                      |

| FSM:    | Finite State Machine                                               |

| IC:     | Integrated circuit                                                 |

| IEEE:   | Institute of Electrical and Electronics Engineers                  |

| IVU:    | Intravenous Urography                                              |

|        |                                                             |

|--------|-------------------------------------------------------------|

| KFC:   | Fondation canadienne du rein (Kidney Foundation of Canada)  |

| LCD:   | Liquid Crystal Display                                      |

| LED:   | Light Emitting Diode                                        |

| LSB:   | Least Significant Bit                                       |

| MSB:   | Most Significant Bit                                        |

| MSN:   | Microstimulateur neural sélectif                            |

| NLB:   | Neurostimulateur à lien bidirectionnel                      |

| NLD:   | Non-linéarité différentielle                                |

| NLI:   | Non-linéarité intégrale                                     |

| NSERC: | Natural Sciences and Engineering Research Council of Canada |

| NSP:   | Neurostimulateur sélectif et permanent                      |

| OE:    | Onde excitante                                              |

| OI:    | Onde inhibitrice                                            |

| PC:    | Ordinateur personnel (Personal Computer)                    |

| PCB:   | Printed Circuit Board                                       |

| PEPU:  | Processeur externe pour une prothèse urinaire               |

| RF:    | Radio-fréquence (Radio-frequency)                           |

| SCM:   | Société canadienne de micro-électronique                    |

| TSMC:  | Taiwan Semiconductor Manufacturing Company                  |

| VCUG:  | Voiding Cystourethrogram                                    |

| VHDL:  | VHSIC Hardware Description Langage                          |

VHSIC: Very High Speed Integrated Circuit

**LISTE DES ANNEXES**

|                   |                                                                                               |            |

|-------------------|-----------------------------------------------------------------------------------------------|------------|

| <b>Annexe I:</b>  | <b>Code VHDL du stimulateur implantable et de son environnement de vérification . . . . .</b> | <b>97</b>  |

| I.1               | Code VHDL du «test bench» . . . . .                                                           | 97         |

| I.2               | Code VHDL du stimulateur implantable . . . . .                                                | 100        |

| <b>Annexe II:</b> | <b>Schéma électrique et code assembleur du stimulateur externe portable . . . . .</b>         | <b>121</b> |

| II.1              | Schéma électrique . . . . .                                                                   | 121        |

| II.2              | Code assembleur du stimulateur externe . . . . .                                              | 122        |

## INTRODUCTION

Les forces électriques sont essentielles à la vie, que ce soit au niveau du métabolisme de la cellule que de la conscience humaine engendrée par l'activité du cerveau. En introduisant un courant produit de façon artificielle, il est possible de modifier ou d'activer ces forces électriques. Ce type d'interaction entre l'énergie électrique et le corps humain est connu depuis plus de 2000 ans [30]. L'utilisation des décharges électriques de la torpille (poisson) a été rapportée aussi tôt qu'en l'an 46 pour le traitement de la douleur, mais c'est en 1791 qu'une étude quantitative fut publiée par Luigi Galvani sur le phénomène de la stimulation électrique [12]. Galvani a observé la contraction des muscles d'une grenouille en touchant les nerfs avec une paire de ciseaux pendant un orage électrique et il s'est par la suite assuré que ce phénomène était relié à l'électricité. Au cours des quatre dernières décennies, les progrès des procédés de fabrication en électronique ont permis le développement de différents appareils dédiés à la récupération de fonctions motrices, viscérales et sensorielles. La science médicale utilise désormais les stimulateurs cardiaques pour régulariser le rythme du cœur, les implants cochléaires pour récupérer l'ouïe et d'autres stimulateurs électriques pour réduire la douleur, aider à la respiration et contrôler la fermeture de la main. Cependant, plusieurs dysfonctions, comme la perte des fonctions urinaires (évacuation et rétention), ne sont traitées que par médication ou par voies chirurgicales. La perte du contrôle volontaire de la vessie

peut survenir, entre autres, à la suite d'une blessure à la colonne vertébrale au niveau D12 ou supérieur. Pour récupérer les fonctions urinaires, différents sites de stimulation électrique sont possibles mais ce sont les racines sacrées S2 à S4 qui montrent les résultats les plus prometteurs [32]. Les racines sacrées contiennent des fibres nerveuses qui contrôlent (innervent) à la fois le muscle vésical (detrusor) et le sphincter urétral externe. Ainsi, une excitation de ces nerfs provoquent une contraction simultanée du detrusor qui augmentent la pression intravésicale, et du sphincter qui réduit ou inhibe l'évacuation d'urine (miction). Plusieurs solutions sont possibles pour contourner ce problème avec de nombreux avantages et inconvénients. La solution proposée par notre équipe consiste à stimuler les racines sacrées avec un signal composé de deux trains d'impulsions de courant bipolaires, un train basse fréquence - haute amplitude pour contracter la vessie, et un train haute fréquence - basse amplitude pour inhiber la fermeture du sphincter.

Du point de vue matériel, les stimulateurs électriques disponibles commercialement ne sont pas en mesure de produire les signaux nécessaires à la technique de stimulation sélective. Ils sont limités en fréquence, possèdent un nombre de canaux restreints et la forme du stimulus qu'il génère est prédéterminée. Un prototype de stimulateur implantable qui génère les stimuli nécessaires a été réalisé par Robin [34]. Ce stimulateur, réalisé sur circuit imprimé, a permis de valider la méthode de stimulation lors d'essais *in vivo*, de déterminer les gammes de paramètres utiles et de vérifier la fiabilité du système.

Suite aux succès du prototype et devant le besoin d'outils plus performants et versatiles, deux nouveaux stimulateurs ont été réalisés. Tout d'abord, une version miniaturisée de l'implant a permis de réduire la consommation de puissance et, éventuellement, de continuer la validation de la méthode de stimulation sur des petits animaux (rats, lapins). Ensuite, un stimulateur externe et portable offre de modifier ponctuellement les paramètres de stimulation à travers une interface usager simple à utiliser.

Le présent mémoire traite, dans le chapitre 1, du système urinaire et des effets d'un traumatisme ainsi que de la stimulation électrique dans le but de provoquer la miction. Le chapitre 2 offre une revue des systèmes de stimulation neuromusculaire commerciaux ainsi que ceux réalisés par l'équipe de recherche PolySTIM. Ce mémoire comprend également l'article «Implantable Selective Stimulator to Improve Bladder Voiding: Design and Chronic Experiments in Dogs» publié dans la revue «IEEE Transactions On Rehabilitation Engineering». L'article est intégré au chapitre 3 et traite, entre autres, des tests fonctionnels et des résultats expérimentaux d'essais en phase chronique. La réalisation, la vérification et le test du stimulateur implantable intégré sont introduits au chapitre 3 mais détaillés dans le chapitre 4. La réalisation d'un stimulateur externe portable, quand à elle, est discutée au chapitre 5 et est suivie des conclusions et recommandations.

## CHAPITRE 1

### LE SYSTÈME URINAIRE ET LA STIMULATION ÉLECTRIQUE

#### 1.1 Introduction

La connaissance du système urinaire est essentielle pour mener à terme un projet visant la récupération des fonctions vésicales. Pour concevoir un système de stimulation neuromusculaire dédié à évacuer l'urine de la vessie, il est nécessaire d'approfondir les notions de base sur l'anatomie et la physiologie de l'appareil urinaire ainsi que sur l'organisation du système nerveux. En plus de faire une revue rapide de ces notions, ce chapitre traite également des sites et techniques de stimulation électrique provoquant la miction.

#### 1.2 L'appareil urinaire

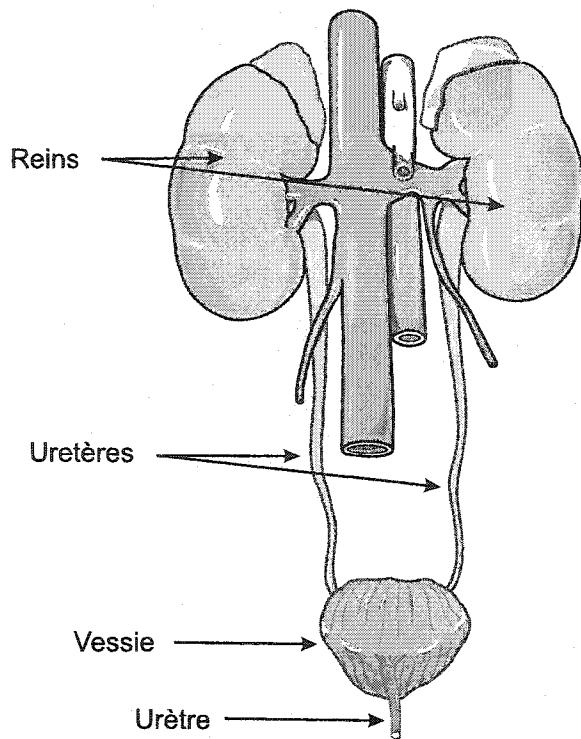

Le système urinaire regroupe les organes qui aident à maintenir le corps en état d'équilibre principalement par la filtration du sang, la fabrication, l'accumulation et l'évacuation de l'urine. Tel que montré à la figure 1.1, dans la partie supérieure, les reins éliminent les déchets et toxines accumulés dans le sang et les acheminent avec le surplus d'eau vers la vessie par les canaux collecteurs d'urines (bassinets) qui se prolongent en deux fins canaux (uretères) jusqu'à la vessie.

Figure 1.1: Représentation simplifiée de l'appareil urinaire.

### 1.2.1 La partie inférieure de l'appareil urinaire

Les uretères rejoignent la vessie à sa base en traversant obliquement la paroi musculaire (hiatus uréteral). L'urine est évacuée par l'urètre, le troisième orifice pouvant être vu de l'intérieur de la paroi vésicale; il est le lien entre la vessie et le méat urinaire (orifice externe de l'urètre). La résistance urétrale, lors de la miction, est naturellement plus importante chez l'homme dont l'urètre, plus long que celui de la femme, passe à travers la prostate et le pénis. Les points d'encrage des uretères dans la vessie ainsi que l'urètre forme l'entité topographique appelée «trigone». Cette partie de la vessie change de morphologie pendant l'évacuation de l'urine et il en sera question plus loin dans la description de la miction.

### **1.2.2 Les tissus musculaires de la vessie**

La rétention et l'évacuation de l'urine nécessitent principalement la coordination de trois muscles: le détrusor et les sphincters lisse et strié. Le détrusor représente les différentes couches musculaire de la vessie. Il est composé de fibres musculaires lisses organisées en trois couches réalisant une structure bien adaptée à la fonction contractile de la vessie. Le sphincter lisse est un prolongement du détrusor autour du col de la vessie et de l'urètre. Il est également composé de fibres lisses plus résistantes à la fatigue. Le sphincter strié entoure le sphincter lisse et prédomine 2 à 3 centimètres au-dessous du col. Ce dernier assure le contrôle de la continence active (i.e. consciente) lorsque la vessie approche sa pleine capacité et que le besoin d'uriner se fait ressentir. D'autres muscles peuvent jouer un rôle mineur dans le processus de la miction mais leur intérêt est réduit chez les paraplégiques qui, en général, n'ont pas le contrôle volontaire de ces muscles.

### **1.3 Les voies neurales**

Le contrôle des tissus musculaires est assuré par les centres nerveux via les voies sensitives et motrices. Pour produire un stimulus électrique capable de provoquer la miction, il est essentiel d'élaborer sur ces systèmes.

### 1.3.1 Les voies sensitives

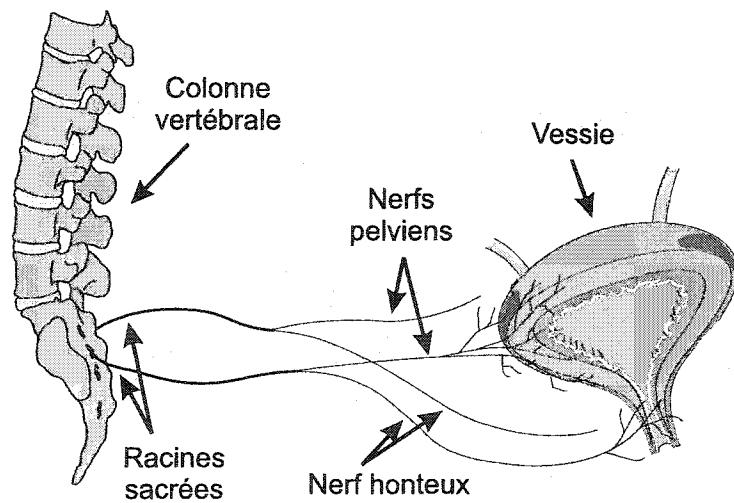

Les récepteurs sensitifs situés dans les viscères transmettent leurs influx aux centres nerveux par le biais des voies afférentes (sensitives). Les sensations sont divisées en deux catégories, la sensibilité extéroceptive regroupe les sensations de douleur, de température et de toucher, tandis que la sensibilité proprioceptive regroupe les sensations d'étirement et de tension des tissus musculaires. La majorité des neurones sensitifs atteignent la partie sacrée de la moelle épinière par l'intermédiaire des nerfs érecteurs et des nerfs honteux internes (figure 1.2). Une partie des neurones gagnent la moelle épinière au niveau thoraco-lombaire par l'intermédiaire des nerfs hypogastriques. Ces neurones afférents concernent surtout la sensibilité extéroceptive du trigone et ne seront pas abordés puisque nous nous concentrerons sur les fonctions urinaires de base.

Figure 1.2: Les voies neurales du système urinaire.

### **1.3.2 Les voies motrices de l'appareil urinaire**

Les influx nerveux contrôlant les muscles de l'appareil urinaire sont produits par le système nerveux centrale et acheminés aux tissus musculaires par le biais des voies efférentes (motrices) en empruntant l'innervation somatique ou l'innervation végétative (autonome). L'innervation végétative règle le fonctionnement des viscères et est composée de deux systèmes régulateurs, le sympathique et le parasympathique. Quand à l'innervation somatique, elle règle le fonctionnement moteur du corps. Le détrusor est approvisionné par les fibres parasympathiques via les nerfs pelviens tandis que le sphincter strié est innervé par les fibres somatiques via les nerfs honteux à partir de S2, S3 et S4. Ces conclusions ne font pas l'unanimité au sein de la communauté médicale et plusieurs travaux arrivent à des conclusions différentes [14] mais, du point de vue de la stimulation électrique, elles n'influencent pas l'analyse des résultats présentée plus loin.

### **1.3.3 Les centres nerveux réflexes**

Les centres réflexes se situent au point de rencontre d'un neurone sensitif et d'un neurone moteur. Ils organisent une activité réflexe et échappent au contrôle de la volonté. Ils restent cependant sous l'influence de l'ensemble du système nerveux et la libération de cette influence modifie définitivement leur fonctionnement. Le centre réflexe qui contrôle la contraction du sphincter en fonction du volume vésical est le principal responsable de la continence passive (i.e. la fermeture inconsciente

du sphincter lisse). Le centre réflexe reçoit les influx des neurones de sensibilité proprioceptive (tension et étirement) situés dans la paroi vésicale et commande la fermeture du sphincter lisse pour assurer la continence lorsque la vessie se remplit.

#### **1.3.4 Les centres nerveux corticaux**

Le contrôle de la vessie implique plusieurs centres nerveux situés dans le cerveau et au niveau de la colonne vertébrale. Les centres corticaux régissent les actions volontaires ou instinctives en percevant les informations venues de la périphérie et en émettant des ordres exécutés par les centres subalternes. Ils sont la base de l'élaboration de la pensée et la décision d'accomplir une action dépend à la fois de la perception des stimuli mais également de la personnalité, des habitudes ou de l'état d'esprit du sujet.

Des notions supplémentaires sur la propagation des potentiels d'action et la transmission des influx nerveux ont été rapportés par Arabi [3].

#### **1.4 La miction normale**

Maintenant que les organes, nerfs et tissus responsables de la miction ont été identifiés, nous pouvons décrire le processus normal d'évacuation de l'urine. Cet exercice permet de bien saisir la complexité de la miction et montre l'étendue de la tâche à accomplir.

Comme mentionné précédemment, les reins sont responsables du remplissage

graduel de la vessie. Au début du remplissage, la pression vésicale reste basse et la pression urétrale, nettement supérieure, s'élève graduellement par la contraction du sphincter lisse qui assure la continence. Cet automatisme vésico-sphinctérien constitue la continence passive et ne fait pas appel à la conscience [14]. Le point de départ de ce réflexe sympathique est la stimulation des récepteurs sensitifs situés dans la paroi vésicale. Les neurones afférents gagnent la moelle épinière par les nerfs érecteurs (pelviens) tandis que la réponse gagne la vessie et l'urètre par les nerfs hypogastriques (honteux). Ce réflexe n'intervient significativement qu'en fin de remplissage [31].

Le besoin d'uriner se fait sentir lorsque le volume d'urine atteint entre 250 et 350 ml et que la vessie est suffisamment distendue. Le sphincter lisse abandonne à ce moment la forme d'un disque horizontal pour prendre la forme d'un entonnoir dont l'effet est de redistribuer les forces et de favoriser la miction. Le sphincter strié doit alors être consciemment resserré pour éviter l'écoulement d'urine. La contraction du sphincter strié dépend du centre somatique sacré sous le contrôle des centres corticaux. L'innervation afférente autant que l'efférente emprunte les nerfs honteux internes pour rejoindre les neurones sensitifs et les muscles.

Au moment opportun, les sphincters lisse et strié sont relâchés par une décharge parasympathique. La pression urétrale diminue tandis que la pression vésicale augmente par la contraction du détrusor, faisant place à la miction. Le détrusor se contracte par la réduction d'influx inhibiteurs laissant ainsi agir les influx facilitants.

tateurs dont la source principale est la stimulation des récepteurs de tension du détrusor. Lorsque la contraction est amorcée, le phénomène s'amplifie de façon automatique et augmente le débit urinaire.

### 1.5 Les effets d'un traumatisme

Une lésion à la colonne vertébrale au niveau cervical ou dorsal peut provoquer plusieurs modifications irréversibles de l'appareil urinaire. La propagation des influx nerveux entre les centres sacrés et corticaux étant réduite, un déséquilibre entre les influx inhibiteurs et facilitateurs apparaît. La vessie autonome ne dépend plus des centres corticaux mais uniquement des centres réflexes qui régulent ses activités.

Un premier effet d'une lésion à la colonne vertébrale est la perte de sensation de plénitude de la vessie. Une personne paraplégique ne reçoit plus les informations concernant la quantité d'urine présente dans sa vessie. Ainsi, lorsque la vessie approche sa capacité maximale, l'individu ne peut entreprendre les actions nécessaires à l'évacuation de l'urine.

Un tel traumatisme provoque également la perte du contrôle volontaire de la vessie. L'influence des centres corticaux sur les centres réflexes, auparavant acheminé par des influx nerveux traversant la colonne vertébrale, est réduite ou inexiste. Les influx facilitateurs provenant des neurones sensitifs dans la paroi vésicale et qui provoquent la contraction du détrusor, ne peuvent être contre balancés par

des influx inhibiteurs supra-médullaires (corticaux). Le réflexe provoquant la contraction du détrusor se produit pour des volumes plus faibles ( vessie hyperactive), augmentant la pression vésicale pendant le remplissage et réduisant significativement la capacité vésicale à long terme [49]. Également, le sphincter strié n'est plus sous contrôle volontaire ce qui élimine la continence active du processus de la miction.

Des effets indirects d'un traumatisme peuvent aussi être observés. La pression vésicale plus élevée pendant de plus longues durées, causée par l'absence des influx inhibiteurs, provoque un reflux d'urine de la vessie vers les reins par les uretères. Ce reflux urétéal et la rétention chronique entraînent des troubles rénaux et éventuellement la défaillance rénale si aucune action n'est prise. L'incontinence est également une des complications remarquées chez les patients avec une lésion à la colonne vertébrale. Aussi, le cathétérisme intermittent, solution couramment employée pour la vidange de la vessie chez les individus privés du contrôle vésical consistant à insérer un cathéter par l'urètre jusque dans la vessie, conjugué à la stase urinaire favorisent les infections urinaires à répétition. L'ensemble des effets d'un traumatisme conduit souvent à la défaillance des fonctions rénales, une cause important de mortalité chez les paraplégiques [44]. Elle résulte principalement de la rétention chronique et de l'infection urinaire.

## 1.6 La stimulation neuromusculaire

Plusieurs options sont possibles pour vidanger la vessie et réduire les effets d'un traumatisme. La technique la plus utilisée, le cathétérisme intermittent, consiste à insérer un cathéter par l'urètre jusqu'à ce que l'extrémité pénètre dans la vessie pour faciliter l'écoulement d'urine. L'utilisation quotidienne de cette technique nécessite le plein contrôle des membres supérieurs, ce qui n'est pas le cas des quadriplégiques, et favorise les infections urinaires.

La stimulation neuromusculaire est assurément l'avenue la plus prometteuse pour la récupération des fonctions urinaires. Elle consiste à exciter les tissus musculaires toujours fonctionnels entourant la vessie par l'intermédiaire des nerfs moteurs du système vésical à l'aide de courants électriques pour provoquer la contraction du détrusor et induire la miction. Il y a présentement quatre sites connus pour provoquer la miction à l'aide de la stimulation électrique: le muscle de la vessie (détrusor), les nerfs pelviens, les racines sacrées et la colonne vertébrale. Chacun de ces sites a fait l'objet de recherches approfondies et présente plusieurs avantages et inconvénients.

### 1.6.1 Les sites de stimulation

Le détrusor fut le premier site de stimulation étudié [7]. Lorsqu'un stimulus électrique est appliqué par le biais d'électrodes cousues dans la paroi vésicale, le détrusor se contracte et provoque la miction. Cette méthode de stimulation très effi-

cace montre une faible résistance urétrale [47]. Cependant, les courants d'excitation nécessaires pour obtenir une contraction uniforme du muscle vésical doivent être élevés, ce qui, à long terme cause une désensibilisation des tissus autour des électrodes. Également, les mouvements du muscle vésical pendant le remplissage et la stimulation provoquent le bris prématûré des électrodes [32] [46].

La stimulation des nerfs pelviens gauche et droit entraîne aussi la miction. Toutefois, on peut observer une plus grande résistance urétrale que lors d'une stimulation du détrusor. Cette augmentation de résistance est due à la stimulation des neurones sensitifs afférents qui provoque une contraction du sphincter par le biais du centre réflexe sacré [26]. La vidange complète de la vessie est seulement obtenue après la section des nerfs honteux. Aussi, la chirurgie pour exposer les nerfs pelviens est plus difficile que les chirurgies pour les autres sites de stimulation.

La moelle épinière est le troisième site de stimulation pouvant provoquer l'évacuation de l'urine de la vessie. Des électrodes au bout non-isolé sont introduites sous la surface de la colonne vertébrale pour obtenir la stimulation de la vessie et le relâchement du sphincter produisant ainsi une miction à basse pression [16] [21] [22] [27]. Les résultats sont toutefois sensibles à la position des électrodes, ce qui réduit l'efficacité de ce site de stimulation. L'insertion d'électrodes dans la moelle épinière augmente également le risque d'infection chez les patients [32] [46].

Le site de stimulation le plus prometteur pour la récupération des fonctions vésicales reste sans doute les racines sacrées [39]. La stimulation électrique des nerfs

sacrés engendre la contraction de la vessie mais, comme dans le cas de l'excitation des nerfs pelviens, elle provoque également la contraction du sphincter. Les fibres somatiques qui innervent le sphincter urétral sont plus sensibles à la stimulation électrique que les fibres autonomes qui rejoignent la vessie. Ainsi, un courant assez élevé pour provoquer la contraction du détrusor activera inévitablement le sphincter réduisant ou annulant la miction<sup>[5]</sup>. Ce site de stimulation montre toutefois les résultats les plus encourageants.

### **1.6.2 Les techniques de stimulation des racines sacrées**

Il y a présentement quatre techniques de stimulation des racines sacrées (Tableau 1.1) destinées à surmonter la dyssynergie entre le détrusor et le sphincter et provoquer la miction: la vidange poststimulus, le blocage anodique, la fatigue du sphincter et la stimulation sélective par blocage haute-fréquence<sup>[39]</sup>.

#### **1.6.2.1 La vidange poststimulus**

La vidange poststimulus est une technique basée sur les temps de relaxation du détrusor et du sphincter<sup>[11] [48]</sup>. La musculature striée du sphincter externe se relâchant plus rapidement que la musculature lisse du détrusor, une stimulation des racines sacrées en utilisant un patron typique consistant en 3-6 secondes de stimulation en alternance avec 6-9 secondes de pause, provoque une vidange saccadée de la vessie.

Cette technique de stimulation est présentement la plus utilisée. Un stimulateur neuromusculaire conçu par Brindley, abordé au prochain chapitre, a été implanté dans plus de 1000 patients et donne de bons résultats cliniques.

#### **1.6.2.2 Le blocage anodique**

Le blocage anodique est une autre technique utilisée pour pallier la contraction simultanée du détrusor et du sphincter. Cette technique vise l'activation sélective des fibres parasympathiques en combinant la stimulation de toutes les fibres à un blocage anodique sélectif [32]. Comme le courant nécessaire au blocage des fibres somatiques est inférieur à celui nécessaire pour arrêter les potentiels d'action parcourant les fibres parasympathiques, l'hyperpolarisation partielle de la membrane nerveuse à l'anode de l'électrode tripolaire bloque la propagation des potentiels d'action vers le sphincter strié mais laisse passer ceux destinés au détrusor. Cette technique de stimulation prévient la dyssynergie vésico-sphinctérienne et permet la miction. La validation en phase aiguë sur des animaux montre que le blocage anodique peut réduire de plus de 80% la pression induite au niveau de l'urètre. Rijkhoff soutient également que cette technique peut être appliquée chez l'humain.

#### **1.6.2.3 La fatigue du sphincter**

La résistance urétrale lors de la miction peut être réduite par une stimulation haute-fréquence des nerfs honteux pour induire la fatigue du sphincter externe [28]

tout en maintenant une stimulation basse-fréquence au niveau des racines sacrées. Les fibres musculaires striées constituant le sphincter externe sont moins résistantes à la fatigue que la musculature lisse du détrusor. Après quelques secondes de stimulation, la pression urétrale exercée par le sphincter se relâche, permettant ainsi la miction. Des études en phase aiguë et chronique sur des chiens ont montré l'efficacité de cette méthode en donnant des résultats comparables à un groupe ayant subi une neurectomie des nerfs honteux. La chirurgie pour atteindre les nerfs honteux est toutefois extensive.

#### 1.6.2.4 La stimulation sélective

La dernière technique de stimulation, faisant l'objet des travaux rapportés dans ce mémoire, consiste à exciter les racines sacrées, innervant à la fois le détrusor et le sphincter, à l'aide d'un signal composé de deux trains d'impulsions bipolaires superposés [41] [9]. Un premier train d'impulsions basse-fréquence et d'amplitude élevée provoque la contraction du détrusor tandis que le second train d'impulsions haute-fréquence et d'amplitude réduite inhibe la contraction du sphincter. Les fibres nerveuses somatiques, contrôlant le sphincter, ont un seuil d'activation plus bas que les fibres parasympathiques innervant le détrusor. En choisissant une amplitude inférieure au seuil des fibres parasympathiques mais excitant les fibres somatiques, il est possible de provoquer, d'une part le relâchement du sphincter externe, et d'autre part, la contraction du détrusor afin d'entraîner la miction.

Tableau 1.1: Résumé des techniques de stimulation des racines sacrées dédiées à la vidange de la vessie.

| Technique             | Avantages & Inconvénients                                                                | État                                         |

|-----------------------|------------------------------------------------------------------------------------------|----------------------------------------------|

| Vidange poststimulus  | (+) 1 site d'implantation;<br>(-) Pression intravésicale élevée;<br>(-) Miction saccadée | Utilisation clinique                         |

| Blocage anodique      | (+) 1 site d'implantation                                                                | Essais en phase aiguë                        |

| Fatigue du sphincter  | (+) Faible dyssynergie;<br>(-) 2 sites d'implantation                                    | Essais en phase aiguë;<br>Technique obsolète |

| Stimulation sélective | (+) Faible dyssynergie;<br>(+) 1 site d'implantation                                     | Essais en phase chronique                    |

### 1.7 Conclusion

Ce premier chapitre couvre les notions essentielles au design d'un microstimulateur implantable pour la récupération des fonctions vésicales. En apportant une connaissance approfondie des différents mécanismes oeuvrant lors de la miction normale et des problèmes amenés par une lésion à la colonne vertébrale, elle permet de mieux comprendre et d'analyser les résultats expérimentaux chez l'animal.

## CHAPITRE 2

### LE SYSTÈME DE STIMULATION NEUROMUSCULAIRE

#### 2.1 Introduction

Parallèlement à l'évolution des techniques de stimulation présentées au chapitre précédent, les systèmes de stimulation neuromusculaire dédiés à la récupération des fonctions vésicales ont connu un développement continu. Le présent chapitre est consacré à la revue de systèmes disponibles commercialement ainsi que des neurostimulateurs et contrôleurs proposés par l'équipe PolySTIM<sup>[18]</sup>. Un bref aperçu des différentes électrodes est aussi donné.

#### 2.2 Les systèmes commerciaux

Le «Finetech-Brindley Bladder System» est un des produits disponibles pour la récupération des fonctions urinaires<sup>[10]</sup>. Ce système comprend un stimulateur implantable, composé de trois récepteurs identiques, et un contrôleur externe. Il génère une excitation basse fréquence en alternance avec des périodes de repos pour provoquer une vidange poststimulus. L'énergie nécessaire à la stimulation est transmise par le contrôleur externe par lien RF lors de l'activation de l'implant.

La thérapie InterStim® proposée par Medtronic, Inc. utilise également un neurostimulateur pour provoquer la vidange de la vessie. Cet implant, alimenté par

piles, offre une gamme de fréquences de 2,1 à 130 Hz avec une largeur d'impulsions allant de 60 à 450  $\mu$ s et une amplitude variant entre 0 et 10,5 volts. Il permet aussi d'utiliser une électrode bipolaire ou quadripolaire. La programmation et le test du neurostimulateur implantable sont réalisés à l'aide d'un programmeur destiné aux médecins tandis que l'activation quotidienne se fait à l'aide d'un aimant et est utilisé par le patient. Cet implant est aussi doté d'un système de télémesure pour confirmer la réception des paramètres [1].

Enfin, un système appelé «Urogenital Stimulator» est offert par Avery Laboratories, Inc. (Le groupe Dobelle). Il comprend lui aussi un contrôleur externe et un stimulateur implantable [23] mais peu de détails sont toutefois disponibles sur ce système.

### 2.3 Aperçu sur l'évolution de stimulateurs offerts par PolySTIM

L'équipe PolySTIM a mis en oeuvre plusieurs stimulateurs au cours de la dernière décennie. Un bref aperçu des différentes parties implantables des systèmes de stimulation neuromusculaire est donné dans cette section. Ces systèmes sont présentés dans un ordre chronologique.

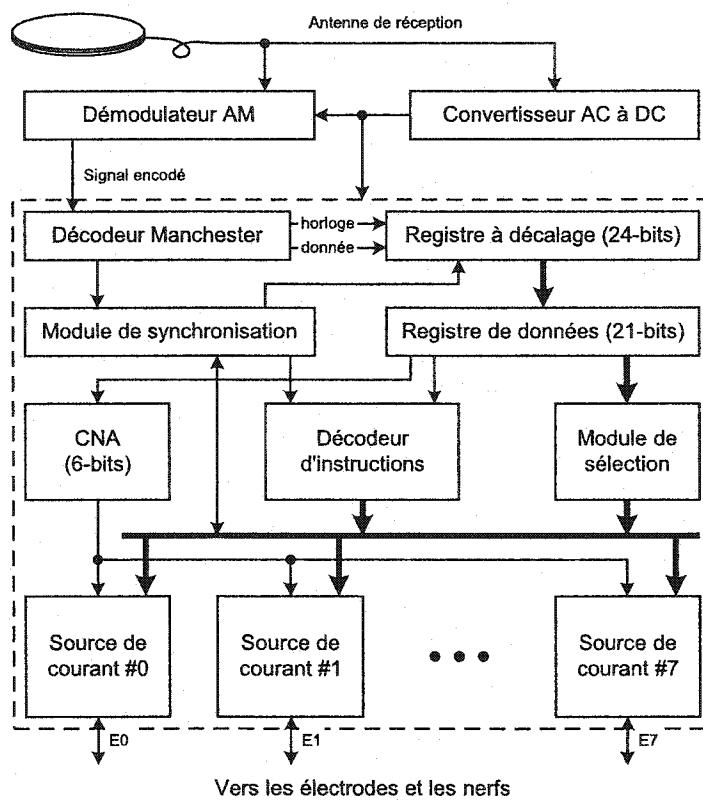

Le point de départ des neurostimulateurs dédiés à la récupération des fonctions vésicales de l'équipe PolySTIM est un système introduit par Sawan dans le cadre de sa thèse de doctorat<sup>[35]</sup>. Il s'agit d'un stimulateur implantable à 8 canaux monopolaires (ou 4 canaux bipolaires) construit à partir d'un microprocesseur dédié

à instructions de 24 bits et réalisé sur prédiffusé de  $4,0 \mu\text{m}$  (figure 2.1). Il offre une large gamme de fréquences et une amplitude maximale de  $3,0 \text{ mA}$ . L'énergie de l'implant est fournie par le contrôleur externe. Le patron de stimulation reste toutefois limité car l'amplitude pour chacun des canaux est envoyée en temps réel [38], [37], [36], [39].

Figure 2.1: Diagramme simplifié du neurostimulateur introduit par Sawan.

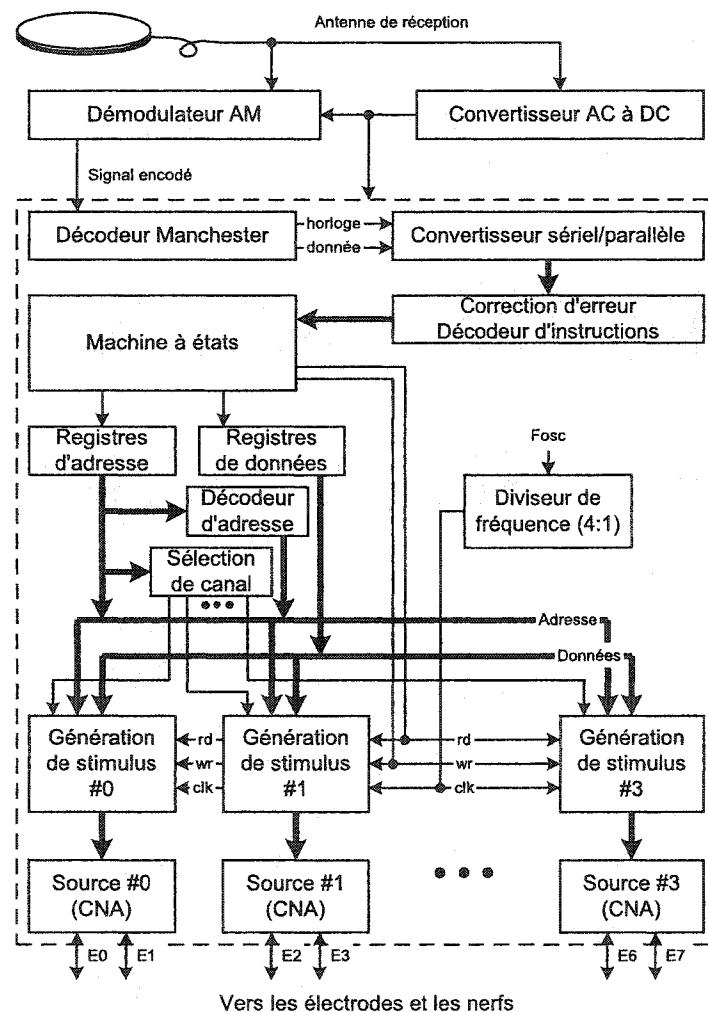

Un neurostimulateur conservant les principales caractéristiques du produit précédent et offrant, entre autres, une nouvelle fonction permettant la modulation en fréquence de stimuli a été réalisé par Arabi [4]. Ce circuit, conçu sur CMOS standard de  $1,2 \mu\text{m}$  et présenté à la figure 2.2, permet de détecter et de corriger

une erreur lors de la transmission d'un paramètre de stimulation. Les stimuli pour chacun des canaux (8 monopolaires ou 4 bipolaires) sont générés localement, à partir des paramètres reçus, par quatre instances d'un circuit numérique dédié à la génération des stimuli. Ce stimulateur, utilisé pour la vidange de la vessie par fatigue du sphincter, n'offre toutefois pas la flexibilité nécessaire à la stimulation selective.

Figure 2.2: Diagramme simplifié du neurostimulateur introduit par Arabi.

Pour combler les besoins nécessaires aux nouvelles techniques de stimulation, un microstimulateur neural sélectif (MSN) fut complété par Robin [33], [34]. Cet implant à un seul canal, réalisé à l'aide d'un FPGA et de composants discrets, produit un signal bipolaire composé de deux fréquences superposées (figure 2.3). Il offre un courant maximal de stimulation de 2,5 mA, une gamme de fréquences comprise entre 10 Hz et 1 kHz et une largeur d'impulsion allant jusqu'à 300  $\mu$ s. L'énergie nécessaire à la stimulation est fournie par un contrôleur externe dédié.

Figure 2.3: Schéma bloc du neurostimulateur introduit par Robin.

Les travaux qui ont suivi, menés par Schneider, ont donné lieu à deux nouvelles versions de ces stimulateurs implantables. Le premier, un neurostimulateur à lien bidirectionnel (NLB) introduit un outil de diagnosticque [40]. Il permet d'évaluer la composante résistive de l'interface nerf-électrode *in vivo* et d'envoyer les résultats de la mesure vers le contrôleur à l'aide du lien RF bidirectionnel. La télémesure utilise des courants inférieurs au seuil d'activation des fibres sympathiques et parasympathiques pour éviter la contraction de la vessie lors de la vérification de l'interface nerf-électrode. Les gammes des paramètres de stimulation restent sensiblement les

mêmes que pour le MSN soit un courant maximal de 2,0 mA, une sortie bipolaire multifréquence variant entre 18 Hz et 2 kHz et une largeur d'impulsion maximal de 210  $\mu$ s. Cet implant, réalisé avec un FPGA et d'autres composants discrets, récupère l'énergie nécessaire à son fonctionnement par le lien inductif.

Le second, un neurostimulateur sélectif et permanent (NSP), également basé sur le MSN, supporte deux modes de stimulation, soit la stimulation sélective pour la vidange de la vessie et une stimulation permanente pour aider à la rétention de l'urine [40]. Le NSP, réalisé à l'aide d'un FPGA, d'un microcontrôleur de la série PIC et d'autres composants discrets, reçoit l'énergie nécessaire à la stimulation sélective du contrôleur externe mais utilise une pile pour la stimulation permanente.

Le Tableau 2.1 résume les principales caractéristiques des stimulateurs électriques implantables développés par les membres de l'équipe PolySTIM.

Tableau 2.1: Résumé des caractéristiques des neurostimulateurs implantables.

| Stimulateur | Technologie | # canaux         | Fréquence  | Amplitude |

|-------------|-------------|------------------|------------|-----------|

| Sawan       | 4,0 $\mu$ m | 8/4 <sup>a</sup> | 1-500 Hz   | 3,0 mA    |

| Arabi       | 1,2 $\mu$ m | 8/4 <sup>a</sup> | 1-2000 Hz  | -         |

| Robin       | 0,8 $\mu$ m | 1 multifréquence | 10-1000 Hz | 2,5 mA    |

| Schneider   | discret     | 1 multifréquence | 18-2000 Hz | 2,0 mA    |

<sup>a</sup>8 canaux monopolaires ou 4 canaux bipolaires

## 2.4 Les contrôleurs externes

Bien que le mode de communication entre les stimulateurs implantables et leur contrôleur externe soit resté le même depuis les premières versions (i.e. modulation

ASK avec encodage Manchester), le format des trames, les gammes de chacun des paramètres et les options disponibles ont changé. Cette section présente brièvement les différents contrôleurs externes réalisés par l'équipe PolySTIM pour chacun des neurostimulateurs implantables. Ils sont présentés dans le même ordre que les implants de la section précédente, soit chronologiquement.

Le premier contrôleur externe destiné aux implants utilise un ordinateur personnel (PC) comme interface primaire. Un autre contrôleur, complété dans la même période et appelé processeur externe pour une prothèse urinaire (PEPU), inclus un microcontrôleur MC68HC805 de Motorola, un clavier de 20 touches, un écran LCD de 16 caractères ainsi qu'un système de régulation de l'alimentation pour produire les tensions nécessaires à son fonctionnement à partir de piles [37], [39]. Ce contrôleur offre le maximum de flexibilité pour la modification des paramètres de stimulation pour chacun des 8 canaux.

Un nouveau contrôleur externe, utilisant également un PC comme interface usager, fut développé pour le MSN [34]. Son architecture simplifiée, basée sur un FPGA, offre une flexibilité de programmation maximale grâce à l'utilisation du PC. Le contrôleur reçoit la trame de 64 bits du port parallèle du PC nécessaire à sa programmation et envoie les données à l'implant à travers le lien RF inductif.

Une version portative du contrôleur précédent, également destiné au MSN, permet de choisir parmi six ensembles de paramètres préprogrammés dans une mémoire morte de type EEPROM [34]. Ce contrôleur, basé sur une architecture utilisant un

FPGA, incorpore un écran LCD de 2 lignes et un clavier de 4 touches.

Conjointement avec le développement du NLB et du NSP, un contrôleur de test flexible utilisant un PC comme interface usager fut réalisé. Ce contrôleur, ayant la même architecture que le système développé pour le MSN, permet d'envoyer une trame de longueur variable pouvant contenir jusqu'à 88 bits [40].

Le besoin de systèmes moins encombrant pour une utilisation quotidienne a motivé le design d'un contrôleur portatif simplifié (CPS). Cette nouvelle architecture utilise un microcontrôleur PIC, quelques boutons et un écran LCD de 2 lignes [40].

La même architecture a donné lieu à une deuxième version du contrôleur avec une nouvelle programmation. Cette fois, un écran LCD de 4 lignes et des boutons de menu contextuel offrent une flexibilité accrue pour le choix des paramètres de stimulation. Ces systèmes sont également dédiés au NLB et au NSP.

Tableau 2.2: Résumé des caractéristiques des contrôleurs externes.

| Stimulateur | Interface               | Communication                    | Modulation |

|-------------|-------------------------|----------------------------------|------------|

| PEPU        | $\mu$ contrôleur        | Simplex                          | ASK        |

| Arabi       | PC<br>$\mu$ contrôleur  | Duplex simultané<br>RF - optique | ASK        |

| Robin       | FPGA                    | Simplex                          | ASK        |

| Schneider   | $\mu$ contrôleur<br>PIC | Duplex simultané<br>RF           | ASK        |

## 2.5 Les électrodes

Le système de stimulation neuromusculaire nécessite également une électrode pour acheminer les courants de stimulation entre l'implant et le nerf. Un bref

aperçu des types d'électrodes disponibles est donné plus bas. L'exercice ne vise que les électrodes à gaine (i.e. dont la forme entoure le nerf). Pour de plus amples détails, vous pouvez consulter les travaux de Crampon [17].

Un premier type d'électrodes à gaine cylindrique utilise des fils de sutures noués pour assurer le positionnement de l'électrode autour du nerf [25]. C'est le type d'électrodes le plus facile à réaliser. D'autres types d'électrodes utilisent les alliages à mémoire de forme (figure 2.5) pour retrouver et conserver leur forme cylindrique après leur installation. Enfin, on peut également trouver des électrodes en spirale, à gaines cylindriques concentriques ou hélicoïdales.

Figure 2.4: Électrode à gaine cylindrique avec armature en alliage à mémoire de forme réalisée par Crampon.

## 2.6 Conclusion

La revue des stimulateurs neuromusculaires existant permet de passer au cœur du mémoire, soit l'article «Implantable Selective Stimulator to Improve Bladder

Voiding: Design and Chronic Experiments in Dogs». Les données présentées dans cet article proviennent d'expérimentations en phase chronique réalisées sur 8 chiens à l'aide d'un microstimulateur implantable réalisé à partir de composants discrets.

## CHAPITRE 3

### SIMULATEUR IMPLANTABLE ET VALIDATION DE LA TECHNIQUE DE STIMULATION SÉLECTIVE EN PHASE CHRONIQUE

#### 3.1 Introduction à l'article publié dans «IEEE Transactions on Rehabilitation Engineering»

Le présent chapitre constitue le cœur de ce mémoire. Il s'agit d'un article publié dans la revue «IEEE Transactions on Rehabilitation Engineering» [9] qui passe en revue les sites de stimulation dédié à la récupération des fonctions vésicales ainsi que les techniques utilisées pour contourner les problèmes reliés à la dyssynergie de détrusor et du sphincter urétrale externe lors de la stimulation des racines sacrées. Il donne également une appréciation des résultats obtenus tant au niveau technique, avec la caractérisation des circuits fabriqués par l'équipe PolySTIM, qu'au niveau médical, en présentant les résultats d'essais en phase chronique sur huit chiens bâtards.

### **3.2 Article «Implantable Selective Stimulator to Improve Bladder Voiding: Design and Chronic Experiments in Dogs»**

#### **3.2.1 Abstract**

Among the treatments to enhance the bladder voiding, the sacral roots neuromodulation is one of the most promising techniques. The electrostimulation of sacral nerves provokes a simultaneous contraction of the detrusor muscle as well as the external urethral sphincter (EUS). A new simplified-architecture implantable stimulator with its wireless controller have been designed to investigate high-frequency inhibition stimulation strategies. This innovative technique based on high-frequency inhibition reduces sphincter activity during stimulation. Low-frequency current pulses also applied to the sacral roots induce contraction of the detrusor muscle resulting in low pressure voiding. Chronic experiments were carried out on ten male mongrel paraplegic dogs. One cuff electrode was implanted along with each stimulator for eight months. The animals were stimulated twice a day using the prototypes of our implantable selective stimulator while voided and residual urine volume were measured during the procedure. These experiments revealed that the proposed stimulation strategy enhances bladder voiding by more than 50% in comparison with low-frequency only stimulation. The residual urine volume was reduced to an average of 9% and low pressure micturition was achieved as shown by weekly cystourethrogram.

Keywords: Selective electrical stimulation, urinary bladder, implantable stimulator, chronic experiments, sacral roots.

### 3.2.2 Introduction

Several functional electrical stimulation (FES) techniques have been introduced to promote bladder voiding and prevent incontinence [8] [45] [50]. Clinical experiments as well as animal validation have been carried out to address the bladder voiding function. Four currently known stimulation sites (Fig. 3.1) have been investigated: the bladder wall (detrusor muscle), pelvic nerves, sacral roots and the spinal cord. Each one of these stimulation techniques presents its advantages and drawbacks [32] [39] [46] [47].

Figure 3.1: Possible stimulation sites and implantable stimulator position for high-frequency inhibition.

Bladder wall stimulation was the first investigated method to induce micturi-

tion [7]. Electrodes were sewn in the detrusor muscle and electrical stimulation was applied to induce detrusor muscle contraction but the movement of the detrusor muscle during bladder filling and emptying causes frequent electrode breakage while stimulation using high current amplitude increases impedance around the electrode and may cause damages [32] [46].

Electrostimulation by the right and left pelvic nerves could induce bladder voiding but many problems were reported. The external urethral sphincter was activated during excitation and resulted in impaired micturition. Complete emptying of the bladder was only obtained after section of the pudendal nerves [26]. Also, the surgery needed to expose the pelvic nerve is difficult compared to the surgery for other stimulation methods.

The third stimulation site to achieve micturition is the spinal cord. Using electrodes with exposed tips to reach beneath the spinal cord dorsal surface, selective activation of the detrusor muscle and external urethral sphincter relaxation can be obtained, producing low pressure bladder voiding [16] [21] [22] [27]. However, results were affected by electrode positioning and there was a high infection rate due to electrode insertion in the spinal cord [32] [46].

Regarding the fourth stimulation site, it is well established that sacral roots are the most promising electrode implantation sites to achieve bladder voiding functions [32] [39] [46]. Like the stimulation of the pelvic nerves, sacral roots excitation induces sphincter contraction which impairs micturition. Somatic fibers that supply

the urethral sphincter are more sensitive to electrical stimulation than autonomic fibers innervating the detrusor muscle. This means that a current large enough to provoke detrusor muscle contraction will inevitably activate the external urethral sphincter and interfere with micturition [5]. However, this site of stimulation shows the most encouraging results.

### 3.2.2.1 Neurostimulation Techniques of the Bladder

Currently, there are four main electrostimulation techniques used to overcome this dyssynergia and provoke micturition: poststimulus voiding in conjunction with dorsal rhizotomy, anodal block, sphincteric fatigue and selective stimulation by high-frequency inhibition [39].

1) *Poststimulus Voiding*: The poststimulus voiding technique is based on the fact that the striated sphincter muscle relaxes more rapidly than the smooth detrusor muscle. The sacral roots stimulation pattern consists of intermittent pulse trains (typically 3-6 seconds stimulation and 6-9 seconds pause) to allow bladder evacuation. An implantable stimulator designed by Brindley is presently one of the most clinically used systems to restore partial bladder functions. It has been used in over 700 patients with good clinical results [11] [48]. However, poststimulus voiding necessitates the transection of neural pathways (posterior rhizotomy) to impede reflex detrusor-sphincter dyssynergia (DSD) and allow voiding during the pause following stimulation as reported by Brindley [11]. The dorsal rhizotomy

also improves bladder compliance and capacity and prevents reflex incontinence. It does not affect stimulation-induced DSD but will abolish any reflex erection if previously present.

*2) Anodal Block:* This method of neurostimulation consists of preventing the propagation of the nerve action potential toward the external urethral sphincter using an anodal block technique. This technique uses hyperpolarization of the nerve membrane between the excitation application point and the external urethral sphincter [2] [20]. Acute animal experiments showed that the anodal blocking technique could decrease by more than 80% the stimulus-induced intraurethral pressure. Rijkhoff *et al.* also state that the technique can be applied to humans [32].

*3) Sphincteric Fatigue:* Urethral resistance can be reduced by stimulating pudendal nerves with high-frequency signals to induce sphincteric fatigue, while low-frequency current pulses are applied at the sacral root level, allowing micturition [28] [29] [39]. This technique, based on the fact that high-frequency stimulation rapidly provokes fatigue of the striated external urethral sphincter, was performed in both acute and chronic experiments on dogs. It achieved proper bladder emptying without performing neurectomy but necessitated surgery to reach the pudendal nerves. Results from the chronic experiments on dogs with the sphincteric fatigue stimulation strategy at the pudendal level were comparable to the results obtained on a control group with pudendal neurectomy [29].

*4) Selective Stimulation by High-Frequency Inhibition:* Recently, selective de-

trusor muscle activation has been obtained by performing stimulation of the sacral roots with a signal composed of two distinctive trains of bipolar-current pulses [41].

A high-amplitude, low-frequency train provokes detrusor muscle contraction while a low-amplitude, high-frequency train inhibits the external urethral sphincter contraction to allow micturition. This stimulation method, which is the subject of this article, allows bladder evacuation with a low-pressure voiding and low residual urine.

Previous attempts in primates to fatigue the sphincter with low-frequency (20 Hz) stimulation was not successful with poor voiding. The fatigued striated musculature sufficed for continence against maximal bladder contraction. However, the urethral pressure obtained with higher frequencies was significantly reduced resulting in better voiding [10].

### 3.2.2.2 Available Stimulators

Regarding the technical aspect, many devices are now available for neuromuscular stimulation but they lack important features:

1. a wide range of programmable parameters,

2. a high efficiency in energy transfer and data transmission,

3. a user-friendly interface,

4. high-frequency stimulus generation and,

5. waveform flexibility (monophasic, biphasic, anodic, etc.)

The two most frequently used commercially available stimulators for bladder control are :

- Medtronic: an implant programmable by two devices (physician full range programming and patient amplitude programmer). It also contains a telemetry circuit to confirm data validation and is limited to a maximum frequency of 130 Hz [1].

- NeuroControl Corporation: an implant designed by Brindley and composed of several identical receivers with their inductive couplings. Its maximum frequency is 300 Hz [10].

Several implantable multichannel stimulators and their external controllers were proposed by members of our team to fill the gaps and perform sacral roots and pudendal or sacral nerve stimulation [37] [36] [39]. These systems, validated in previous experiments, allowed to generate a wide range of stimuli through miniaturized implants [4] [37]. More recently, our team proposed a new stimulator based on a simplified architecture which is dedicated to selective stimulation applications. This device has been used in acute experiments and is validated in the current study. It can generate stimuli composed of two different bipolar-current trains of pulses with a high-frequency capability up to 1 kHz.

This paper details the combined sacral root stimulation of the bladder by low-frequency with high-frequency sphincter inhibition. The employed implantable stimulator is summarized in Section 3.2.3, the stimulation protocol and methods are described in Section 3.2.4, results of chronic experiments on 10 male mongrel dogs are reported in Section 3.2.5 and discussed in Section 3.2.6.

### 3.2.3 Description of the Stimulation System

Our stimulation system is composed of two main parts [34]:

- The external controller providing digital information, operating clock and energy to the implant through the skin;

- The implantable stimulator generating the current pulses through a bipolar cuff electrode which is wrapped around the sacral nerve.