**Titre:** Conception, réalisation et étude d'une plate-forme générique basée sur le protocole AMBA AHB

Title: [Conception, réalisation et étude d'une plate-forme générique basée sur le protocole AMBA AHB](#)

**Auteur:** Marc Bertola

Author: [Marc Bertola](#)

**Date:** 2003

**Type:** Mémoire ou thèse / Dissertation or Thesis

**Référence:** Bertola, M. (2003). Conception, réalisation et étude d'une plate-forme générique basée sur le protocole AMBA AHB [Mémoire de maîtrise, École Polytechnique de Montréal]. PolyPublie. <https://publications.polymtl.ca/7106/>

Citation: [Bertola, M. \(2003\). Conception, réalisation et étude d'une plate-forme générique basée sur le protocole AMBA AHB \[Mémoire de maîtrise, École Polytechnique de Montréal\]. PolyPublie. https://publications.polymtl.ca/7106/](#)

## Document en libre accès dans PolyPublie

Open Access document in PolyPublie

**URL de PolyPublie:** <https://publications.polymtl.ca/7106/>

PolyPublie URL: [https://publications.polymtl.ca/7106/](#)

**Directeurs de recherche:** Guy Bois

Advisors: [Guy Bois](#)

**Programme:** Non spécifié

Program: [Non spécifié](#)

In compliance with the

Canadian Privacy Legislation

some supporting forms

may have been removed from

this dissertation.

While these forms may be included

in the document page count,

their removal does not represent

any loss of content from the dissertation.

UNIVERSITÉ DE MONTRÉAL

CONCEPTION, RÉALISATION ET ÉTUDE D'UNE PLATE-FORME

GÉNÉRIQUE BASÉE SUR LE PROTOCOLE AMBA AHB

MARC BERTOLA

DÉPARTEMENT DE GÉNIE INFORMATIQUE

ÉCOLE POLYTECHNIQUE DE MONTRÉAL

MÉMOIRE PRÉSENTÉ EN VUE DE L'OBTENTION

DU DIPLÔME DE MAÎTRISE ÈS SCIENCES APPLIQUÉES

(GÉNIE ÉLECTRIQUE)

AVRIL 2003

National Library

of Canada

Acquisitions and

Bibliographic Services

395 Wellington Street

Ottawa ON K1A 0N4

Canada

Bibliothèque nationale

du Canada

Acquisitions et

services bibliographiques

395, rue Wellington

Ottawa ON K1A 0N4

Canada

*Your file* *Votre référence*

ISBN: 0-612-86381-6

*Our file* *Notre référence*

ISBN: 0-612-86381-6

The author has granted a non-exclusive licence allowing the National Library of Canada to reproduce, loan, distribute or sell copies of this thesis in microform, paper or electronic formats.

L'auteur a accordé une licence non exclusive permettant à la Bibliothèque nationale du Canada de reproduire, prêter, distribuer ou vendre des copies de cette thèse sous la forme de microfiche/film, de reproduction sur papier ou sur format électronique.

The author retains ownership of the copyright in this thesis. Neither the thesis nor substantial extracts from it may be printed or otherwise reproduced without the author's permission.

L'auteur conserve la propriété du droit d'auteur qui protège cette thèse. Ni la thèse ni des extraits substantiels de celle-ci ne doivent être imprimés ou autrement reproduits sans son autorisation.

# Canadä

UNIVERSITÉ DE MONTRÉAL

ÉCOLE POLYTECHNIQUE DE MONTRÉAL

Ce mémoire intitulé :

CONCEPTION, RÉALISATION ET ÉTUDE D'UNE PLATE-FORME

GÉNÉRIQUE BASÉE SUR LE PROTOCOLE AMBA AHB

présenté par : BERTOLA Marc

en vue de l'obtention du diplôme de : Maîtrise ès sciences appliquées

a été dûment accepté par le jury d'examen constitué de :

M. SAVARIA Yvon, Ph.D., président

M. BOIS Guy, Ph.D., membre et directeur de recherche

M. AUDET Yves, Ph.D., membre

## Remerciements

Ce travail a été accompli grâce aux contributions des personnes suivantes:

**Guy Bois** – D'abord et avant tout, merci à mon directeur de recherche qui m'a toujours soutenu, même lorsque l'inspiration n'était pas à son meilleur. Son support financier substantiel ainsi que les diverses conférences qu'il m'a payées m'ont mis en contact avec le domaine, me permettant de me développer rapidement. Merci!

**Hélène et Mario Bertola** – Mes parents, qui m'ont donné tant... je ne sais comment décrire leur générosité. Je suis éternellement reconnaissant, jusqu'au plus profond de moi, et j'espère pouvoir faire comme ils ont fait pour les miens plus tard... Merci!

**Luc Filion** – Mon compagnon en armes et soutien moral. Son amitié, sa bonté et sa générosité m'ont encouragé dans les moments creux où je ne voyais pas le bout du tunnel. Il était là pour faire évacuer la vapeur lorsque le cerveau surchauffait, mais aussi pour me rappeler à l'ordre lorsque mon cerveau devenait de la bouillie. Bref, un bon ami et parfois je regrette de ne pas avoir été suffisamment là pour lui. Merci!

**Yvon Savaria** – Pour les conseils techniques qui lui semblaient sans doute petits mais qui, pour moi, tenaient la clef pour déjouer mes problèmes. Merci!

**Geneviève Desaulniers** – La motivation pour en venir à bout... à notre beau futur, ma belle! Merci wooooooooooooo!

**Eric Yorke** – Cet homme exceptionnel a tenu les rênes de certaines tâches administratives de notre compilation musicale VARIA, me laissant la chance de finir mon mémoire. Merci!

## Résumé

Devant la croissance fulgurante de la densité des transistors, les concepteurs se voient obligés de modifier leurs méthodes de travail pour profiter adéquatement de ces nouvelles ressources. Certains se tournent vers la technique du raffinement progressif d'un modèle initialement très abstrait; d'autres tentent de recycler des modules d'un système à un autre, évitant ainsi d'avoir à re-concevoir un système à partir de zéro. Ce projet vient supporter la seconde approche: il s'agit de la conception d'une plate-forme modulaire et extensible, composée de divers modules qui permettent l'assemblage facile et rapide d'un système sur puce comportant un nombre arbitraire de maîtres de bus. Un second objectif du projet est de développer un bassin de connaissances sur le protocole AMBA AHB en l'utilisant comme standard de communication pour la plate-forme.

Avant de commencer la réalisation de la plate-forme, nous avons d'abord assimilé les diverses réalités de la conception par réutilisation de PI (propriété intellectuelle): La division des communications et du traitement, l'uniformisation des communications grâce aux protocoles de bus et la standardisation des interfaces (les recommandations de VCI). Nous avons ensuite étudié le protocole AMBA AHB pour nous assurer de bien comprendre tous ses aspects. Grâce au protocole, il a été possible de classer chacun des modules dans un de cinq rôles: maître, esclave, pont, arbitre et décodeur. Ce travail expose donc les résultats de cette étude sur AMBA AHB.

Plusieurs besoins ont influencé le développement de la plate-forme. Il fallait une architecture modulaire et configurable qui pouvait être générée automatiquement à l'aide d'outils informatiques. De plus, la plate-forme produite devait supporter un RTOS (système d'exploitation temps-réel) et fournir une bande passante maximale au microprocesseur qu'elle contient. Ainsi, les modules ont été regroupés ensemble dans un *bloc-processeur* qui comporte un seul bus: un microprocesseur ARM7TDMI, de la mémoire, un gestionnaire d'interruptions et une minuterie. Tous ces modules permettent le support et le bon fonctionnement d'un RTOS, tout en offrant un bus dédié au seul

maître (ARM7TDMI). Pour adapter les modules au protocole AHB, ces derniers ont été reliés au bus par des ponts (*wrappers*) qui effectuent la conversion. Afin d'étendre les fonctions du système, un pont a été ajouté afin de relier le bloc-processeur à un bus externe sur lequel se trouveraient les modules spécifiques à l'application (coprocesseurs, périphériques).

L'effort de conception a mené à l'émergence de certaines méthodologies de conception. Un outil a été créé pour générer un réseau d'interconnexion pour relier les divers modules. Cet ouvrage présente aussi les étapes pour créer des ponts pour des maîtres et des esclaves. On y trouve aussi des exemples d'arbitres.

Un système a été monté à l'aide de la plate forme. Il s'agit d'un détecteur de patrons. Le résultat du design a été très favorable: la structure modulaire permet beaucoup de flexibilité tout en offrant une performance égale aux designs *ad hoc* qui avaient été créés précédemment. Une analyse de performance présente l'effet du nombre de maîtres ou d'esclaves sur la surface et l'énergie dissipée par le réseau d'interconnexion.

Les travaux futurs incluent: l'amélioration du pont pour le ARM7TDMI, la conception d'un moyen d'initialisation réaliste pour le système et le développement de ponts reliant deux bus ayant des vitesses de fonctionnement différentes.

## Abstract

Faced with the incredible increases in transistor density, designers are forced to modify their methods in order to take advantage of these new resources efficiently. Some turn towards progressive refinement, the gradual detailing of an initially abstract model. Others attempt to transplant modules from existing systems, avoiding having to rebuild a system from scratch. This project supports the second approach: it consists of the development of a modular and expandable platform, composed of several modules that allow the rapid and easy assembly of an on-chip system containing an arbitrary number of bus masters. A secondary objective of the project is to develop know-how in the use of the AHB protocol, by using it as the standard for inter-module communication.

Before building the platform, it was necessary to assimilate the various concepts related to IP (intellectual property) reuse: the separation of communication and computation, the standardisation of communications through the use of bus protocols, and the adoption of standard interfaces (such as the VCI). It was then necessary to pick apart the AMBA AHB protocol in order to ensure that it was well understood. Thanks to the protocol, it was possible to categorize the various modules into five groups: master, slave, bridge (or wrapper), arbiter and decoder. This document presents the results of this interpretation of the specification.

Many needs influenced the development of the platform. It was necessary to create a modular and configurable architecture that could ideally be generated with the aid of software. The platform also had to support an RTOS (Real-Time Operating System) and supply a lot of bandwidth to the microprocessor that it contains. The modules were grouped into a larger module, a processor-block, containing a single bus: an ARM7TDMI processor, memory, an interrupt register and a timer. All of these modules allow the support and the proper functioning of the RTOS, while offering a dedicated bus to the only master (ARM7TDMI). The interfaces of the various modules are converted to AHB through the use of wrappers. In order to allow the system to expand, the processor-block

also contains a bridge that allows it to connect itself as the master of another AHB-compliant bus to which the custom coprocessors and peripherals are also connected.

The efforts that were invested in the design brought certain methodologies into being. A tool was created to automate the generation of the interconnection network for the bus. This document also presents a set of steps to aid the design of wrappers for masters and slaves. It also offers a few examples of arbiters.

A complete system was built, using the platform: a pattern-matching algorithm. The design results were quite encouraging: the modular structure offers a lot more flexibility while offering the same performance of older, custom, *ad hoc* designs. A performance analysis presents the effect of the number of masters and slaves on both the power consumption and area of the interconnection network.

Future work includes: improvements to the AR7TDMI-to-AHB wrapper, the implementation of a realistic boot-up mechanism and the development of bridges that connect bridges with different clock frequencies.

## Table des matières

|                                                                     |             |

|---------------------------------------------------------------------|-------------|

| <b>Remerciements .....</b>                                          | <b>iv</b>   |

| <b>Résumé .....</b>                                                 | <b>v</b>    |

| <b>Abstract.....</b>                                                | <b>vii</b>  |

| <b>Table des matières.....</b>                                      | <b>ix</b>   |

| <b>Liste des tableaux.....</b>                                      | <b>xiv</b>  |

| <b>Liste des figures.....</b>                                       | <b>xv</b>   |

| <b>Liste des acronymes .....</b>                                    | <b>xvii</b> |

| <b>Lexique.....</b>                                                 | <b>xix</b>  |

| <b>INTRODUCTION.....</b>                                            | <b>1</b>    |

| LES PROJETS ACTUELS DU CIRCUS .....                                 | 1           |

| <i>Picasso</i> .....                                                | 1           |

| <i>Syslib</i> .....                                                 | 2           |

| <i>Le détecteur de patrons</i> .....                                | 3           |

| OBJECTIF DU PROJET .....                                            | 4           |

| CONTRIBUTIONS DE CE MÉMOIRE .....                                   | 5           |

| PLAN DU MÉMOIRE.....                                                | 5           |

| <b>CHAPITRE 1: Revue de littérature.....</b>                        | <b>7</b>    |

| 1.1. L'ÉCART DE PRODUCTIVITÉ .....                                  | 7           |

| 1.1.1. <i>La "loi" de Moore</i> .....                               | 7           |

| 1.1.2. <i>L'écart de productivité</i> .....                         | 8           |

| 1.1.3. <i>Le raffinement progressif</i> .....                       | 9           |

| 1.1.4. <i>Réutilisation de la propriété intellectuelle</i> .....    | 10          |

| 1.2. ENJEUX DE LA RÉUTILISATION DE LA PROPRIÉTÉ INTELLECTUELLE..... | 10          |

| 1.2.1. <i>Gérer la complexité en modularisant</i> .....             | 11          |

|                                                        |           |

|--------------------------------------------------------|-----------|

| 1.2.2. Résister aux modifications en encapsulant ..... | 11        |

| 1.2.3. Ignorer la diversité en normalisant .....       | 12        |

| 1.3. LES PROTOCOLES DE BUS .....                       | 13        |

| 1.3.1. Bus sur puce vs. bus sur carte.....             | 13        |

| 1.3.2. AMBA.....                                       | 14        |

| 1.3.3. CoreConnect .....                               | 15        |

| 1.3.4. Wishbone.....                                   | 15        |

| 1.3.5. VCI.....                                        | 16        |

| 1.3.5. OCP.....                                        | 17        |

| 1.4. L'APPROCHE PLATE-FORME .....                      | 18        |

| <b>CHAPITRE 2 : Le protocole AMBA AHB.....</b>         | <b>19</b> |

| 2.1. LES ACTEURS DANS LES PROTOCOLES DE BUS .....      | 19        |

| 2.1.1. Maître.....                                     | 20        |

| 2.1.2. Esclave .....                                   | 20        |

| 2.1.3. Arbitre.....                                    | 21        |

| 2.1.4. Décodeur.....                                   | 21        |

| 2.1.5. Pont.....                                       | 21        |

| 2.2. LES FAMILLES DE PROTOCOLES AMBA .....             | 22        |

| 2.2.1. AMBA ASB .....                                  | 22        |

| 2.2.2. AMBA AHB .....                                  | 23        |

| 2.2.3. AMBA APB .....                                  | 25        |

| 2.3 LES SIGNAUX AHB .....                              | 25        |

| 2.3.1. Signaux communs.....                            | 26        |

| 2.3.2. Signaux de contrôle.....                        | 26        |

| 2.3.3. Signaux de données.....                         | 27        |

| 2.3.4. Signaux de sélection.....                       | 28        |

| 2.3.5. Signaux de réponse .....                        | 29        |

| 2.4. LES INTERACTIONS DANS LE PROTOCOLE AMBA AHB ..... | 31        |

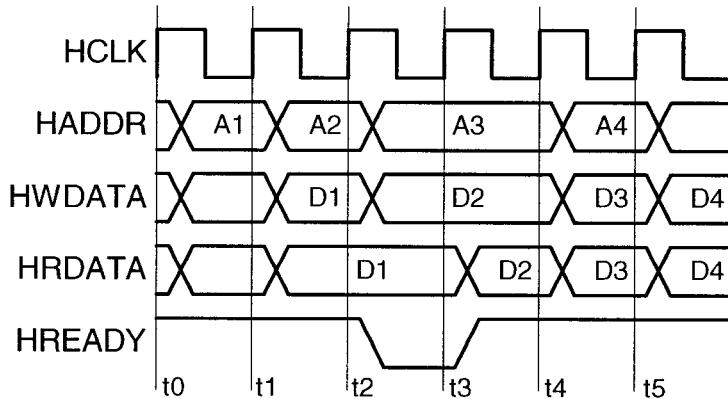

| 2.4.1. Les accès pipelinés.....                        | 32        |

|                                                                          |           |

|--------------------------------------------------------------------------|-----------|

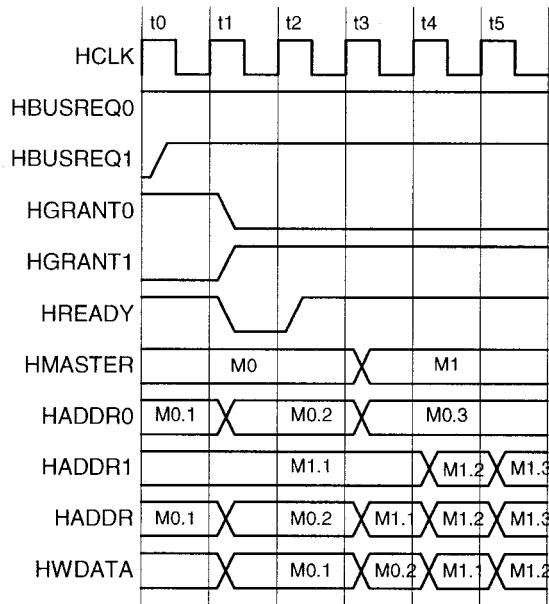

| 2.4.2. <i>L'arbitrage et la possession du bus</i> .....                  | 33        |

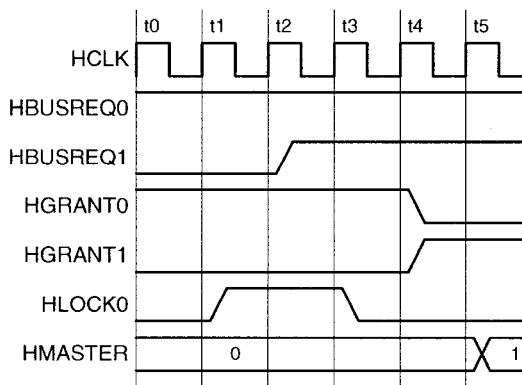

| 2.4.3. <i>Les accès atomiques</i> .....                                  | 35        |

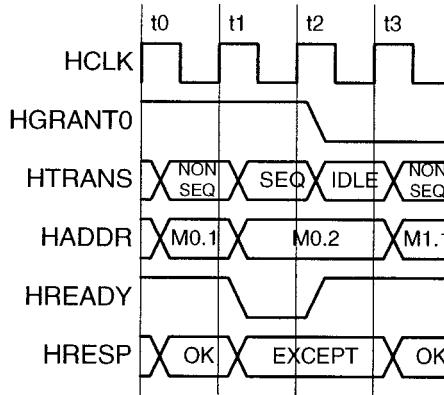

| 2.4.4. <i>La gestion d'exceptions</i> .....                              | 36        |

| 2.4.5. <i>Maître factice et esclave par défaut</i> .....                 | 37        |

| 2.5. CONSIDÉRATIONS SUR LA BANDE PASSANTE .....                          | 38        |

| 2.5.1. <i>Augmentation de la fréquence de l'horloge sur le bus</i> ..... | 38        |

| 2.5.2. <i>Division en sous-bus</i> .....                                 | 38        |

| 2.5.3. <i>Multiplication des canaux</i> .....                            | 39        |

| 2.5.4. <i>Utilisation d'une cache et d'un tampon d'écriture</i> .....    | 40        |

| 2.5.5. <i>AHB lite et Multi-Layer AHB</i> .....                          | 41        |

| <b>CHAPITRE 3 : Description de l'architecture .....</b>                  | <b>42</b> |

| 3.1. BESOINS DE LA PLATE-FORME .....                                     | 42        |

| 3.1.1. <i>Plate-forme cible pour Picasso</i> .....                       | 42        |

| 3.1.2. <i>Support d'un RTOS et de mécanismes de raffinement</i> .....    | 43        |

| 3.1.3. <i>Utilisation d'un protocole connu</i> .....                     | 43        |

| 3.1.4. <i>Maximisation de l'utilisation du processeur</i> .....          | 44        |

| 3.1.5. <i>Choix architecturaux pour répondre aux besoins</i> .....       | 44        |

| 3.2. LA DESCRIPTION DES MODULES.....                                     | 46        |

| 3.2.1. <i>Le réseau d'interconnexion</i> .....                           | 46        |

| 3.2.2. <i>Le processeur ARM7TDMI</i> .....                               | 47        |

| 3.2.3. <i>Les mémoires SSRAM</i> .....                                   | 49        |

| 3.2.4. <i>La minuterie programmable</i> .....                            | 50        |

| 3.2.5. <i>Le gestionnaire d'interruptions</i> .....                      | 51        |

| 3.2.6. <i>Le pont AHB-AHB</i> .....                                      | 53        |

| 3.2.7. <i>L'arbitre</i> .....                                            | 54        |

| 3.2.8. <i>Le décodeur</i> .....                                          | 55        |

| <b>CHAPITRE 4 : Méthodologies de conception pour AHB.....</b>            | <b>56</b> |

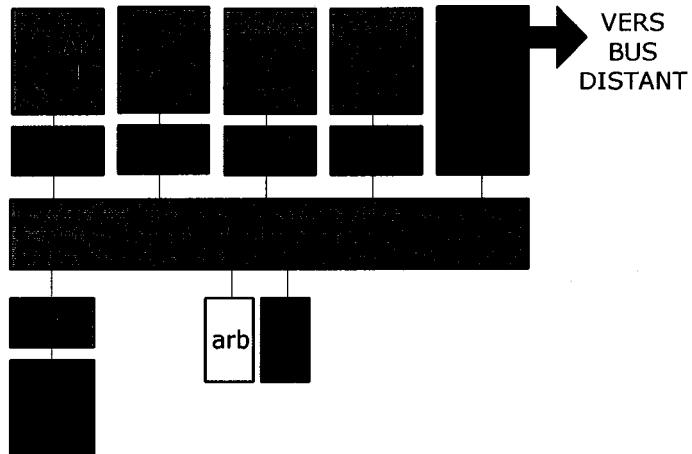

| 4.1. GÉNÉRATION AUTOMATIQUE D'UN RÉSEAU D'INTERCONNEXION.....            | 56        |

|                                                                   |           |

|-------------------------------------------------------------------|-----------|

| 4.1.1. <i>Génération des ports</i> .....                          | 57        |

| 4.1.2. <i>Maître factice et esclave par défaut</i> .....          | 58        |

| 4.1.3. <i>Multiplexeurs</i> .....                                 | 59        |

| 4.1.4. <i>Signaux HSPLIT</i> .....                                | 60        |

| 4.2. STRUCTURE D'UN PONT AHB POUR UN MAÎTRE.....                  | 60        |

| 4.2.1. <i>Responsabilités d'un maître AHB</i> .....               | 61        |

| 4.2.2. <i>Établir des correspondances</i> .....                   | 61        |

| 4.2.3. <i>Raffinement progressif de la machine à états</i> .....  | 62        |

| 4.3. STRUCTURE D'UN PONT AHB POUR UN ESCLAVE .....                | 69        |

| 4.3.1. <i>Les responsabilités des esclaves AHB</i> .....          | 69        |

| 4.3.2. <i>Raffinement progressif de la machine à états</i> .....  | 70        |

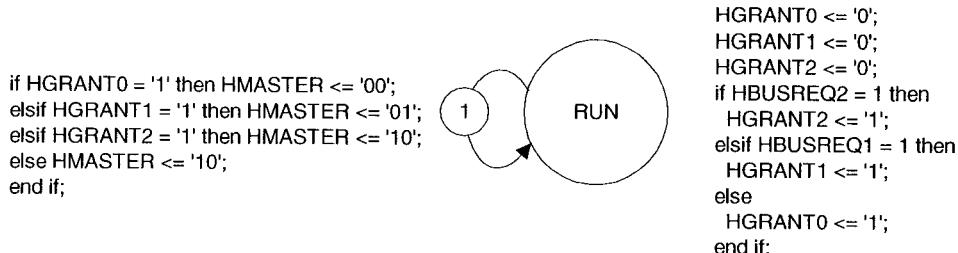

| 4.4. STRUCTURE D'UN ARBITRE.....                                  | 71        |

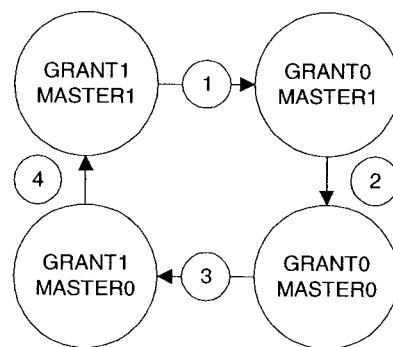

| 4.4.1. <i>Arbitre pour un maître et le maître factice</i> .....   | 72        |

| 4.4.2. <i>Arbitre utilisant une priorité statique</i> .....       | 73        |

| 4.4.3. <i>Arbitre avec respect des rafales</i> .....              | 73        |

| <b>CHAPITRE 5 : Expérimentation avec la plate-forme.....</b>      | <b>75</b> |

| 5.1. LE DÉTECTEUR DE PATRONS.....                                 | 75        |

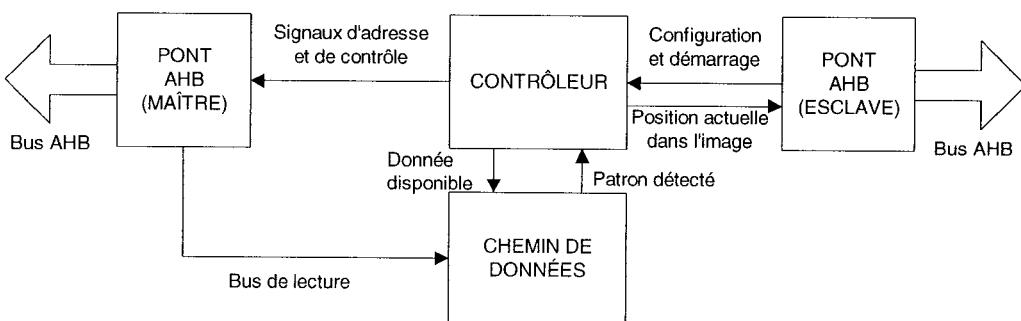

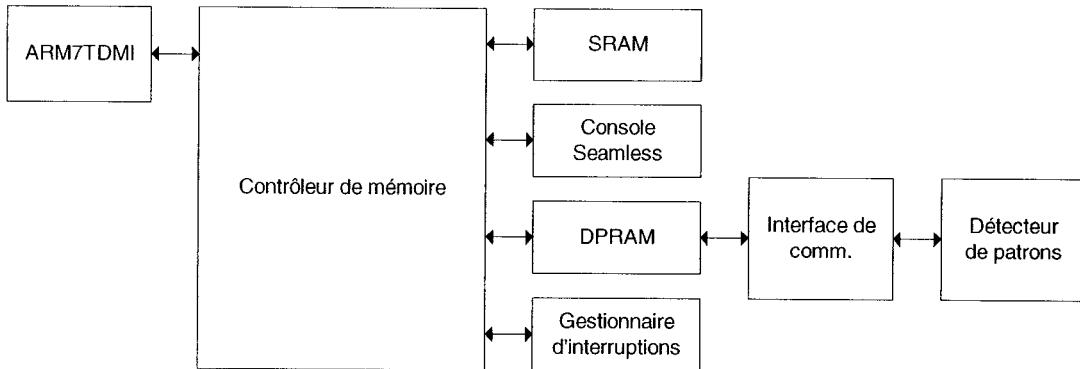

| 5.2. COMMUNICATION PROCESSEUR-COPROCESSEUR.....                   | 78        |

| 5.2.1. <i>Interactions du processeur et du coprocesseur</i> ..... | 78        |

| 5.2.2. <i>Architecture choisie</i> .....                          | 79        |

| 5.3. COMPARAISON AVEC LA VERSION ANTÉRIEURE .....                 | 80        |

| 5.3.1. <i>Modularité de la structure</i> .....                    | 80        |

| 5.3.2. <i>L'utilisation d'un protocole de bus</i> .....           | 82        |

| 5.4. IMPLANTATION D'UN NOUVEAU SCHÈME DE COMMUNICATION .....      | 83        |

| 5.4.1. <i>L'utilisation d'interruptions dans le système</i> ..... | 83        |

| 5.4.2. <i>Modifications à apporter au système</i> .....           | 84        |

| 5.4.3. <i>Avantages par rapport au système précédent</i> .....    | 84        |

| <b>CHAPITRE 6: Analyse de performance et discussions.....</b>     | <b>85</b> |

|                                                                         |            |

|-------------------------------------------------------------------------|------------|

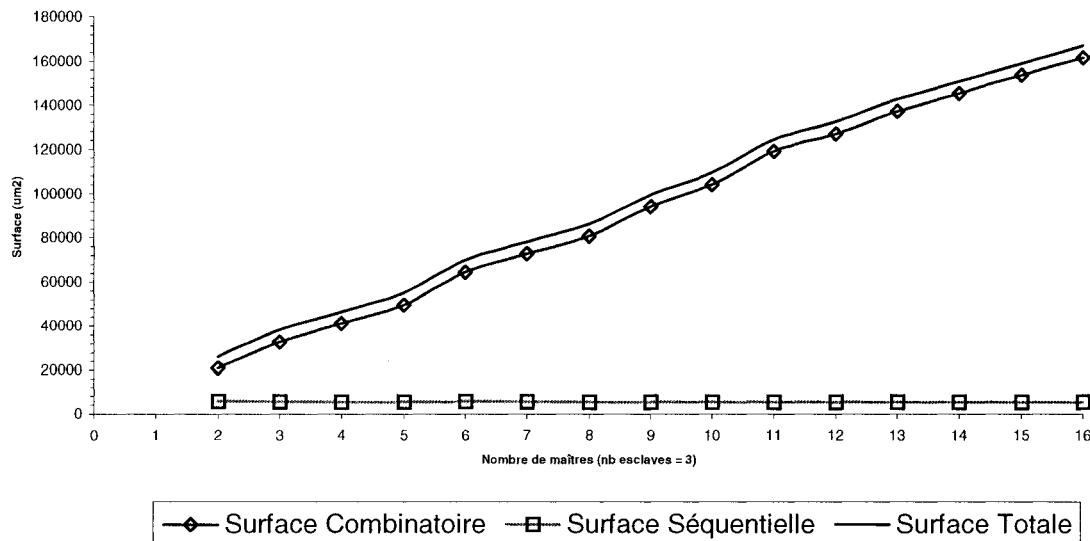

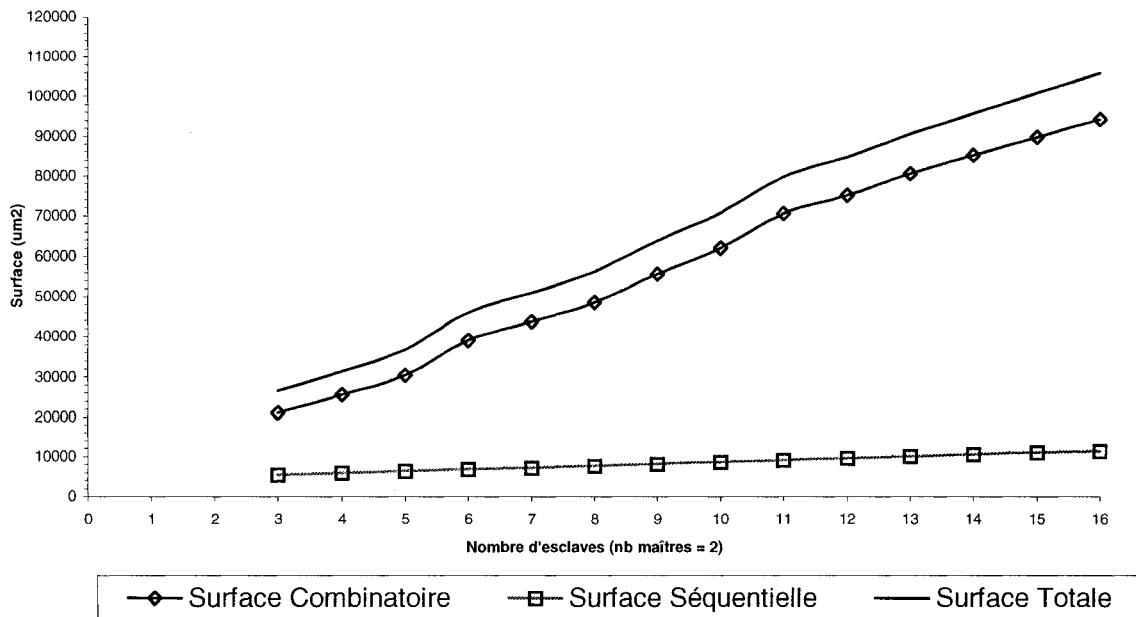

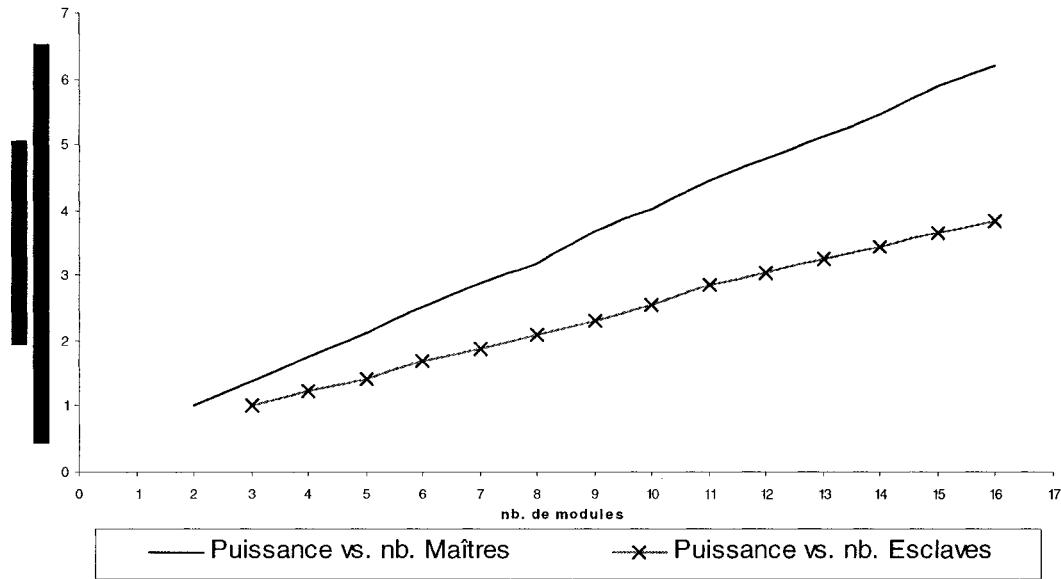

| 6.1. ANALYSE DU RÉSEAU D'INTERCONNEXION.....                            | 85         |

| 6.1.1. <i>Surface</i> .....                                             | 85         |

| 6.1.2. <i>Consommation de puissance</i> .....                           | 87         |

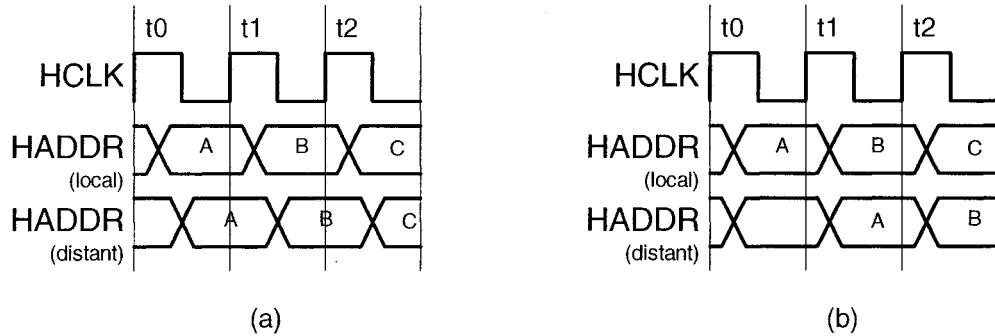

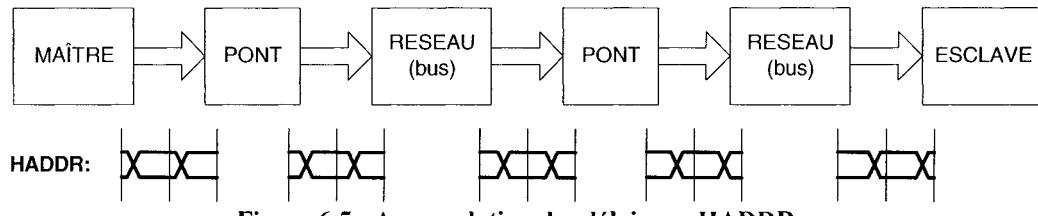

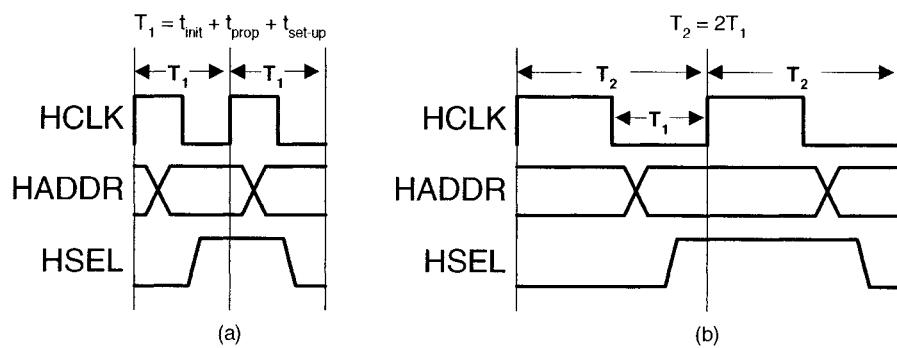

| 6.2. ANALYSE DU PONT AHB-AHB.....                                       | 88         |

| 6.2.1. <i>La structure du pont AHB-AHB</i> .....                        | 89         |

| 6.2.2 <i>Autres considérations concernant le pont AHB-AHB</i> .....     | 90         |

| 6.3 AMÉLIORATION DU PONT ARM7TDMI-AHB.....                              | 91         |

| <b>Conclusion .....</b>                                                 | <b>94</b>  |

| RÉSUMÉ DU TRAVAIL ACCOMPLI.....                                         | 94         |

| TRAVAUX FUTURS ET AMÉLIORATIONS .....                                   | 96         |

| <i>Initialisation du système</i> .....                                  | 96         |

| <i>Ponts ayant des domaines temporels différents</i> .....              | 97         |

| <i>Structures alternatives de bus</i> .....                             | 97         |

| CONSIDÉRATIONS FINALES.....                                             | 98         |

| <b>RÉFÉRENCES.....</b>                                                  | <b>99</b>  |

| <b>Annexe A : Génération du réseau d'interconnexion.....</b>            | <b>104</b> |

| <b>Annexe B : Exemple de code pour le réseau d'interconnexion .....</b> | <b>115</b> |

| <b>Annexe C : Code du pont AHB-AHB.....</b>                             | <b>126</b> |

| <b>Annexe D : Code du pont ARM7TDMI-AHB .....</b>                       | <b>133</b> |

| <b>Annexe E : Résultats de la synthèse .....</b>                        | <b>141</b> |

## Liste des tableaux

|                                                     |     |

|-----------------------------------------------------|-----|

| Tableau 2.1 : Les signaux de contrôle .....         | 26  |

| Tableau 2.2 : Les signaux de données .....          | 27  |

| Tableau 2.3 : Les signaux de sélection .....        | 28  |

| Tableau 2.4 : Les signaux de réponse .....          | 30  |

| Tableau 3.1 : Les registres de la minuterie .....   | 50  |

| Tableau 3.2 : Associations adresse-esclave .....    | 55  |

| Tableau 4.1 : Ports générés par rôle .....          | 58  |

| Tableau 4.2 : Les responsabilités d'un maître ..... | 61  |

| Tableau E.1: Résultats de la synthèse .....         | 141 |

## Liste des figures

|                                                                     |    |

|---------------------------------------------------------------------|----|

| Figure 1.1 : L'allure de la loi de Moore .....                      | 8  |

| Figure 1.2 : L'écart de productivité .....                          | 8  |

| Figure 1.3 : Le raffinement progressif .....                        | 10 |

| Figure 1.4 : Les raffinements facilitant la réutilisation .....     | 13 |

| Figure 1.5 : Les interfaces VCI .....                               | 17 |

| Figure 2.1 : Un module qui est à la fois maître et esclave .....    | 20 |

| Figure 2.2 : Le réseau d'interconnexion du protocole AMBA ASB ..... | 22 |

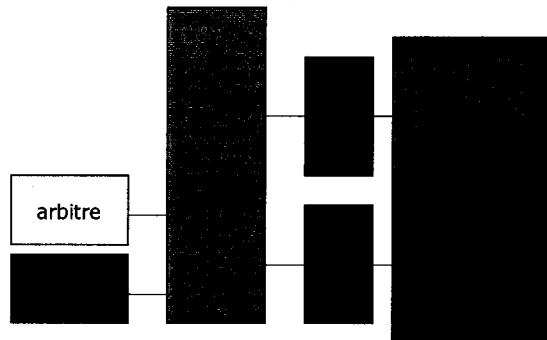

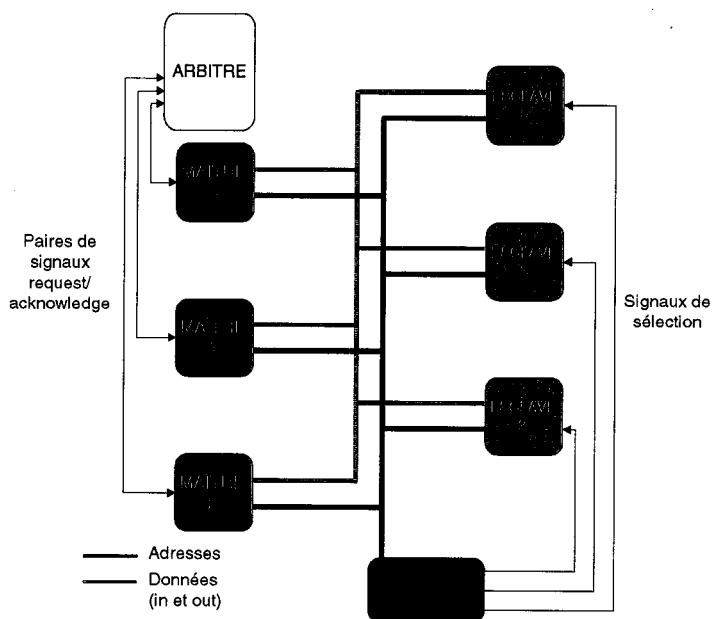

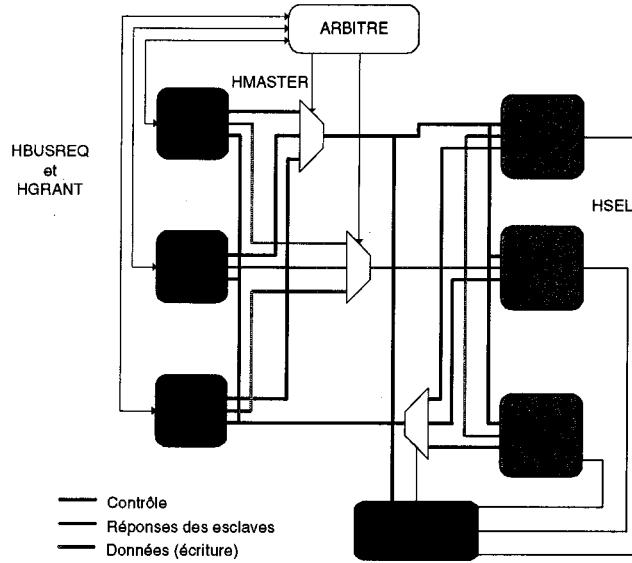

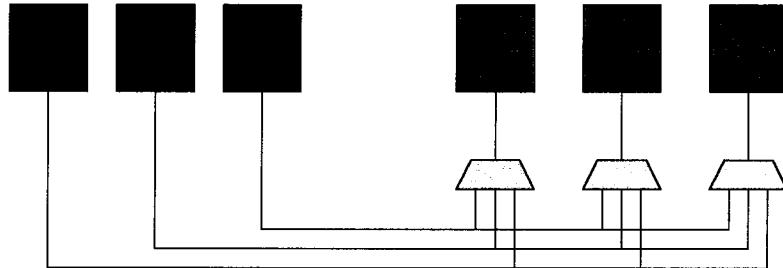

| Figure 2.3 : Le réseau d'interconnexion de AMBA AHB .....           | 24 |

| Figure 2.4 : Accès pipelinés .....                                  | 32 |

| Figure 2.5 : Exemple d'arbitrage .....                              | 34 |

| Figure 2.6 : Exemple d'accès atomique .....                         | 35 |

| Figure 2.7 : Gestion d'exceptions de HRESP(1:0) .....               | 37 |

| Figure 2.8 : La division en sous-bus .....                          | 39 |

| Figure 2.9 : La multiplication des canaux .....                     | 40 |

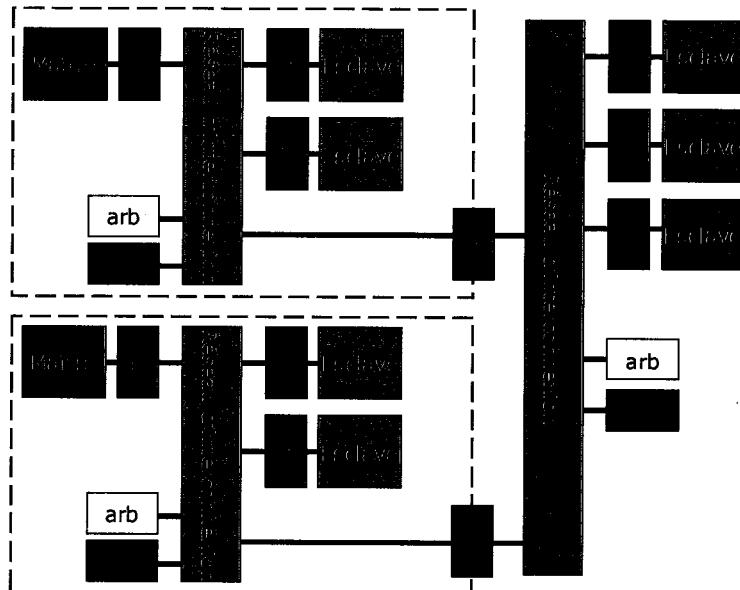

| Figure 3.1 : Le bus local du bloc-processeur .....                  | 46 |

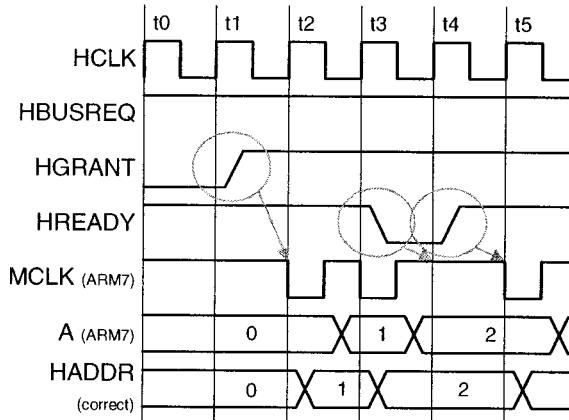

| Figure 3.2 : Le comportement du pont du ARM7TDMI .....              | 48 |

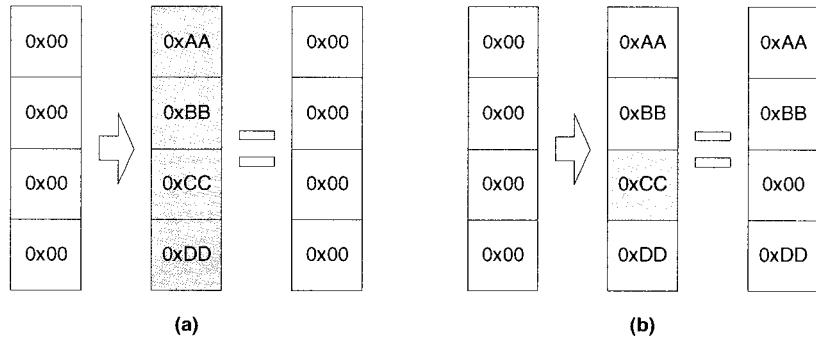

| Figure 3.3 : L'utilité de BWE_N .....                               | 50 |

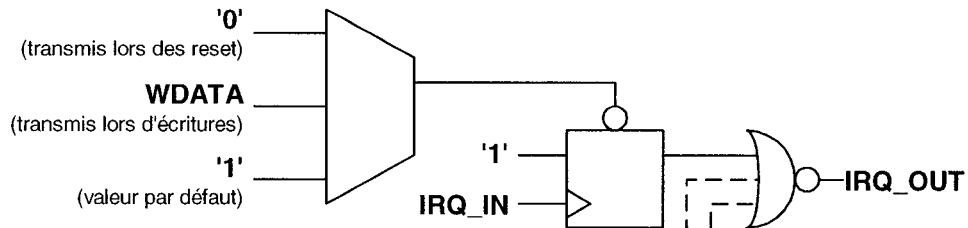

| Figure 3.4 : Structure d'un canal d'interruption .....              | 52 |

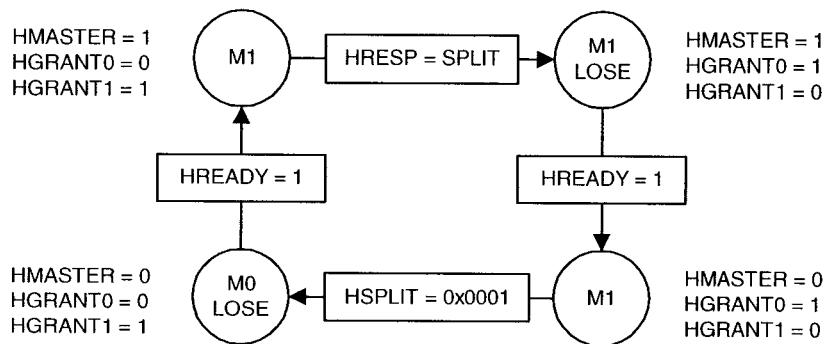

| Figure 3.5 : Le fonctionnement de l'arbitre .....                   | 54 |

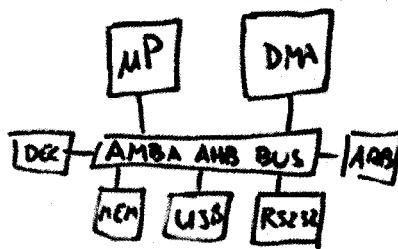

| Figure 4.1 : Croquis de concept .....                               | 56 |

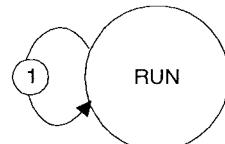

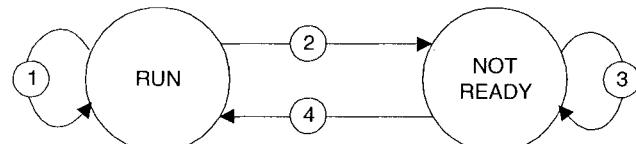

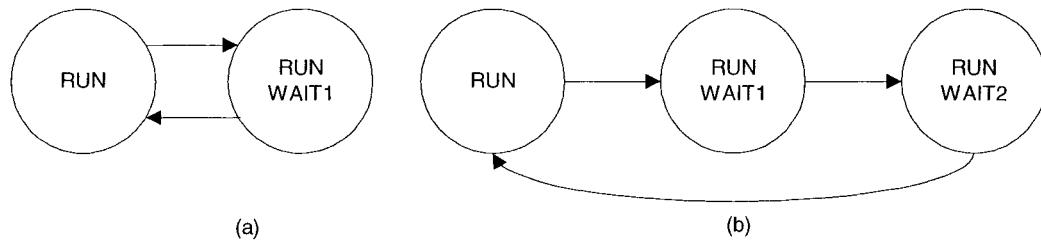

| Figure 4.2 : L'état de base .....                                   | 62 |

| Figure 4.3 : L'ajout d'un état d'attente .....                      | 63 |

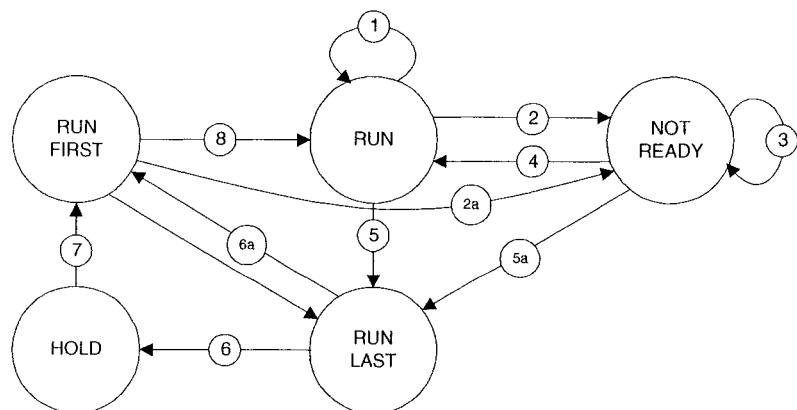

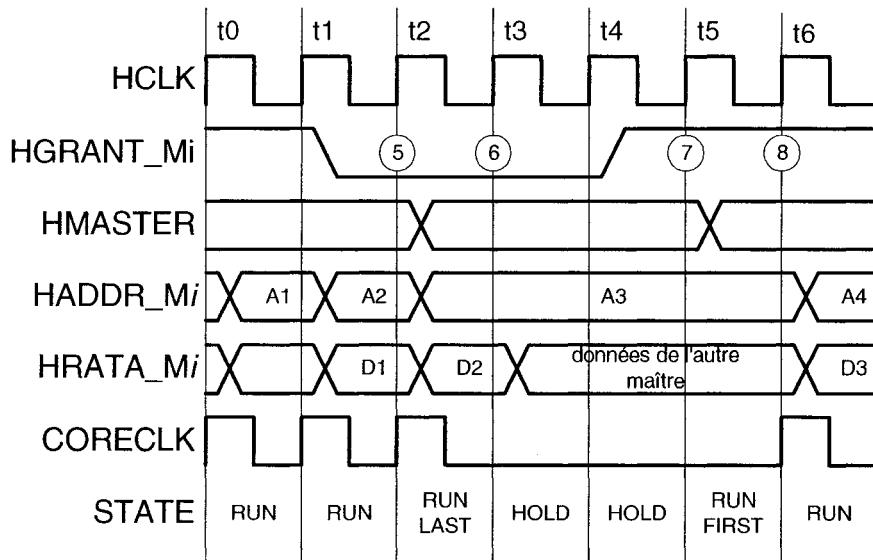

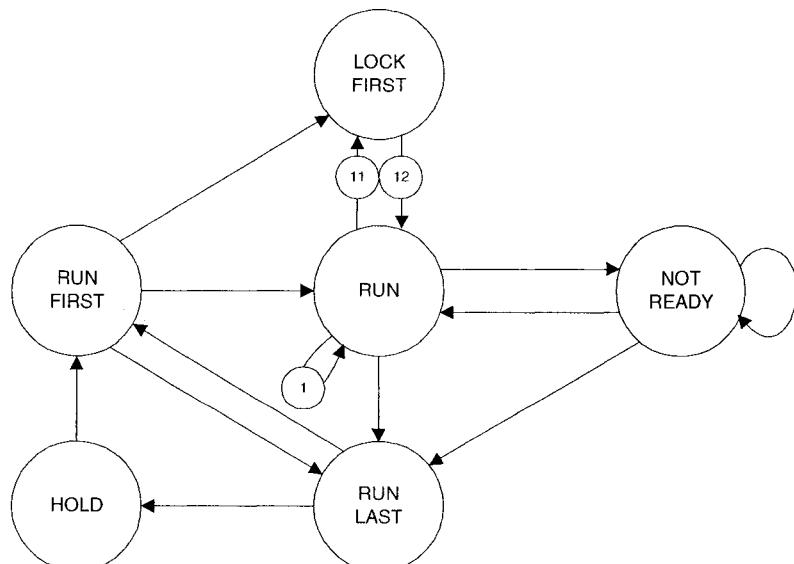

| Figure 4.4 : La gestion de l'arbitrage .....                        | 63 |

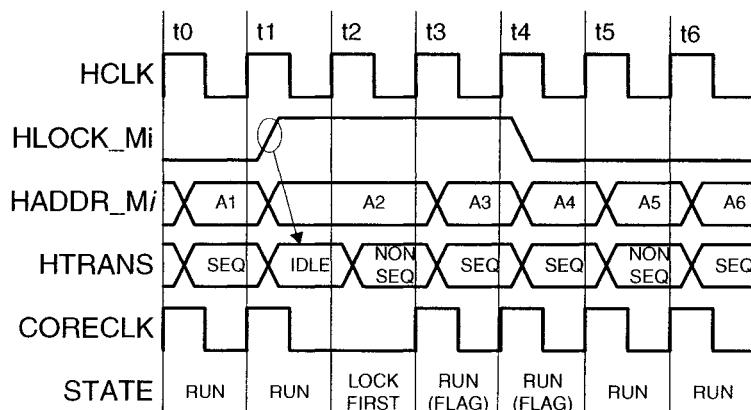

| Figure 4.5 : Le chronogramme de l'arbitrage .....                   | 64 |

| Figure 4.6 : Solution pour le problème des accès atomiques .....    | 65 |

|                                                                                    |    |

|------------------------------------------------------------------------------------|----|

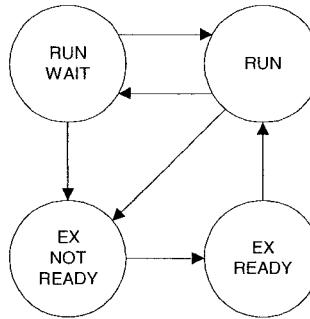

| Figure 4.7 : Intégration à la fig. 4.4 de la règle des accès atomiques .....       | 66 |

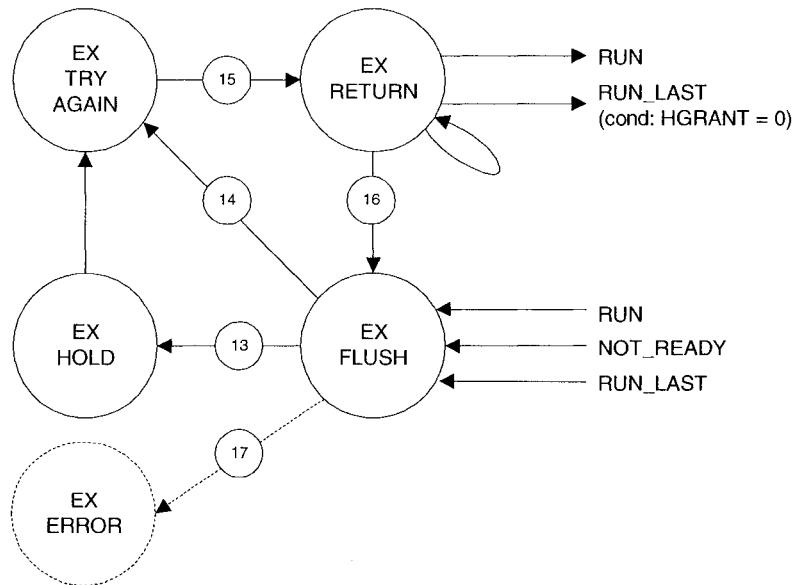

| Figure 4.8: Fragment qui s'occupe des exceptions .....                             | 67 |

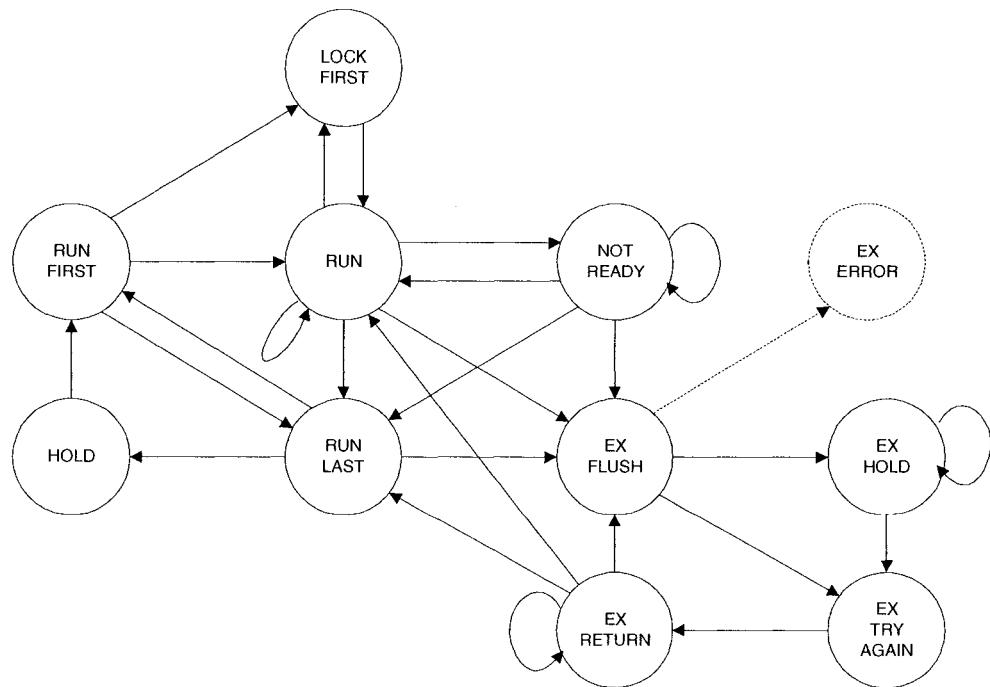

| Figure 4.9: La machine à états complète .....                                      | 68 |

| Figure 4.10 : Deux exemples d'états d'attente.....                                 | 70 |

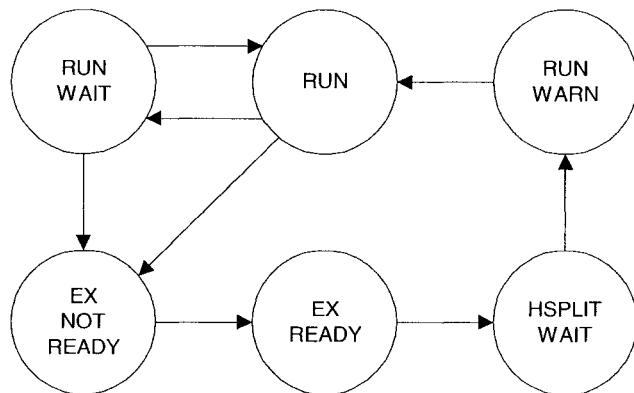

| Figure 4.11 : Ajout de la gestion d'interruptions à l'esclave .....                | 71 |

| Figure 4.12 : Ajout à la fig. 4.11 de la fonction permettant des accès SPLIT ..... | 71 |

| Figure 4.13 : Arbitre pour un seul maître .....                                    | 72 |

| Figure 4.14 : Arbitre avec priorité statique.....                                  | 73 |

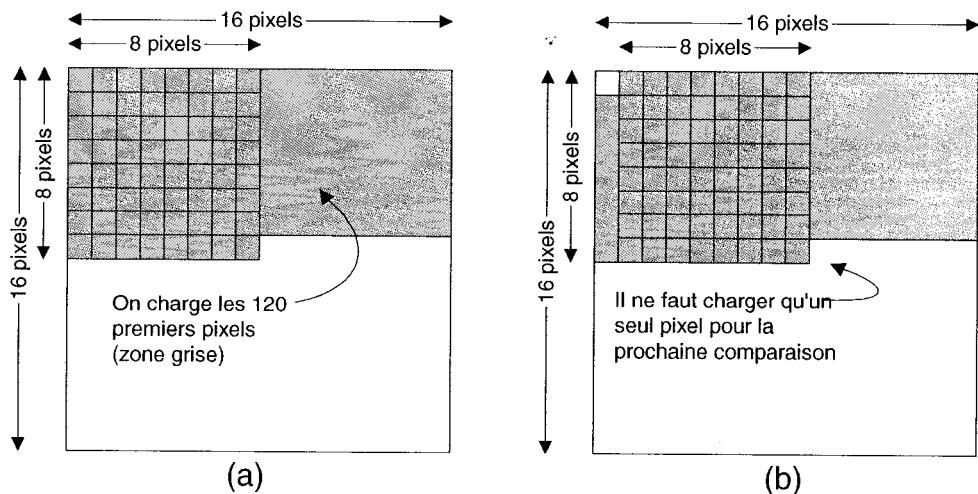

| Figure 5.1 : Pré-chargement de pixels .....                                        | 76 |

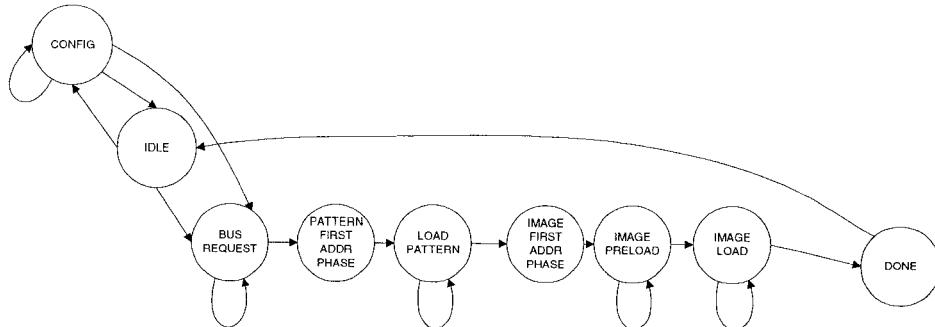

| Figure 5.2 : La machine à états du contrôleur.....                                 | 77 |

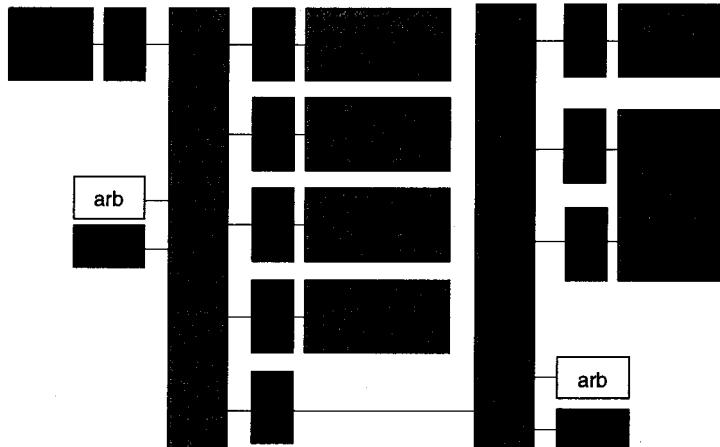

| Figure 5.3 : Diagramme-bloc du détecteur de patrons.....                           | 77 |

| Figure 5.4 : Le système complet.....                                               | 80 |

| Figure 5.5 : Diagramme-bloc de la version précédente du système .....              | 81 |

| Figure 6.1 : Surface occupée en fonction du nombre de maîtres.....                 | 86 |

| Figure 6.2 : Surface occupée en fonction du nombre d'esclaves .....                | 87 |

| Figure 6.3 : Analyse de puissance du réseau d'interconnexion.....                  | 88 |

| Figure 6.4 : Les deux options pour le pont AHB-AHB .....                           | 89 |

| Figure 6.5 : Accumulation des délais sur HADDR.....                                | 90 |

| Figure 6.6: Différences de période.....                                            | 91 |

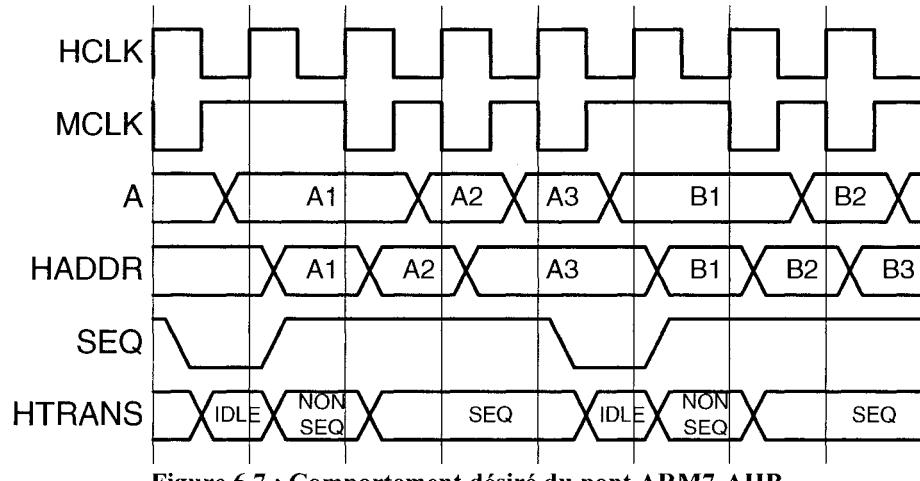

| Figure 6.7 : Comportement désiré du pont ARM7-AHB .....                            | 93 |

## Liste des acronymes

|                 |                                                  |

|-----------------|--------------------------------------------------|

| <b>AMBA</b>     | <b>Advanced Microcontroller Bus Architecture</b> |

| <b>AMBA AHB</b> | <b>Advanced High-speed Bus</b>                   |

| <b>AMBA APB</b> | <b>Advanced Peripheral Bus</b>                   |

| <b>AMBA ASB</b> | <b>Advanced System Bus</b>                       |

| <b>BCA</b>      | <b>Bus Cycle Accurate</b>                        |

| <b>BP</b>       | <b>Bloc-Processeur</b>                           |

| <b>CVE</b>      | <b>Co-Verification Environment</b>               |

| <b>DMA</b>      | <b>Direct Memory Access</b>                      |

| <b>DPRAM</b>    | <b>Dual-Port Random Access Memory</b>            |

| <b>DRAM</b>     | <b>Dynamic Random-Access Memory</b>              |

| <b>DSP</b>      | <b>Digital Signal Processor</b>                  |

| <b>FTP</b>      | <b>File Transfer Protocol</b>                    |

| <b>MPEG</b>     | <b>Motion Pictures Expert Group</b>              |

| <b>PCI</b>      | <b>Peripheral Component Interconnect</b>         |

| <b>PI</b>       | <b>Propriété Intellectuelle</b>                  |

| <b>RTL</b>      | <b>Register Transfer Level</b>                   |

| <b>RTOS</b>     | <b>Real-Time Operating System</b>                |

|              |                                                   |

|--------------|---------------------------------------------------|

| <b>SoC</b>   | <b>System on Chip</b>                             |

| <b>SMC</b>   | <b>Société Canadienne de la Microélectronique</b> |

| <b>SRAM</b>  | <b>Static Random-Access Memory</b>                |

| <b>SSRAM</b> | <b>Synchronous Static Random-Access Memory</b>    |

| <b>TF</b>    | <b>Timed Functional</b>                           |

| <b>UTF</b>   | <b>UnTimed Functional</b>                         |

| <b>VCI</b>   | <b>Virtual Component Interface</b>                |

| <b>VHDL</b>  | <b>VLSI Hardware Description Language</b>         |

| <b>VSIA</b>  | <b>Virtual Socket Interface Alliance</b>          |

## Lexique

|                       |                                                                                                                                                                                                                     |

|-----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>Accès</b>          | <i>Voir Transaction</i>                                                                                                                                                                                             |

| <b>Arbitre</b>        | Ce module cède l'accès au bus à un maître lorsque plusieurs le demandent.                                                                                                                                           |

| <b>AMBA</b>           | <b>Advanced Microcontroller Bus Architecture:</b> Spécification comportant trois protocoles de bus servant à des systèmes SoC.                                                                                      |

| <b>AMBA AHB</b>       | <b>Advanced High-speed Bus:</b> Protocole de la spécification AMBA servant pour les bus à haute performance. Ce protocole sert généralement pour relier des modules comme des microprocesseurs au reste du système. |

| <b>AMBA APB</b>       | <b>Advanced Peripheral Bus:</b> Protocole de la spécification AMBA servant pour des bus à basse performance. Les possibilités d'interconnexion sont moindres, mais la complexité de la conception est plus simple.  |

| <b>AMBA ASB</b>       | <b>Advanced System Bus:</b> Protocole de la spécification AMBA servant pour des bus à haute performance. Maintenant remplacé par AHB.                                                                               |

| <b>Architecture</b>   | Agencement particulier de modules dans un système. Certains protocoles proposent des architectures afin de normaliser la structure des systèmes qui les respectent.                                                 |

| <b>Bandé Passante</b> | Débit maximal de transfert de données en une unité de temps.                                                                                                                                                        |

|                        |                                                                                                                                                                                                                                                                                                                      |

|------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>BCA</b>             | <b>Bus Cycle Accurate:</b> Niveau d'abstraction d'un système où seules les transactions sur le bus marquent le passage du temps (leurs durées réelles sont ignorées)                                                                                                                                                 |

| <b>BP</b>              | <b>Bloc-Processeur:</b> Module conçu dans ce projet de maîtrise. Il contient un microprocesseur, de la mémoire, un gestionnaire d'interruptions, une minuterie et un pont permettant de relier le bus local à un autre bus. Vu de l'extérieur, le bloc processeur ressemble à un maître qui peut de relier à un bus. |

| <b>Bus</b>             | Ensemble de signaux reliant plusieurs modules ensemble, généralement selon un protocole donné.                                                                                                                                                                                                                       |

| <b>Circuit imprimé</b> | Circuit dont les fils sont imprimés sur une carte.                                                                                                                                                                                                                                                                   |

| <b>CIRCUS</b>          | Division du Groupe de recherche en microélectronique de l'École polytechnique de montréal qui se spécialise dans le domaine des systèmes sur puce.                                                                                                                                                                   |

| <b>CVE</b>             | <b>Co-Verification Environment:</b> Environnement de co-vérification. Outil permettant la simulation simultanée de matériel et de logiciel.                                                                                                                                                                          |

| <b>Décodeur</b>        | Module qui observe l'adresse émise par un maître et qui active l'esclave correspondant.                                                                                                                                                                                                                              |

| <b>DMA</b>             | <b>Direct Memory Access:</b> Un module DMA permet un transfert de données entre deux esclaves sans passer par le microprocesseur.                                                                                                                                                                                    |

| <b>DPRAM</b>           | <b>Dual-Port Random Access Memory:</b> Mémoire vive caractérisée par le fait qu'elle possède deux ports de communication. Deux accès peuvent être effectués sur elle simultanément.                                                                                                                                  |

|                     |                                                                                                                                                                                                                                                         |

|---------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>DRAM</b>         | <b>Dynamic Random-Access Memory:</b> Mémoire vive dynamique. Ne requiert qu'un seul transistor, mais perd sa valeur à cause des courants de fuite si elle n'est pas rafraîchie souvent.                                                                 |

| <b>DSP</b>          | <b>Digital Signal Processor:</b> Un microprocesseur spécialisé dans le calcul et un haut débit de données.                                                                                                                                              |

| <b>Esclave</b>      | Module qui répond aux transactions initiées par un ou plusieurs <i>maîtres</i> .                                                                                                                                                                        |

| <b>Exception</b>    | Situation anormale dans un système. Requiert généralement un traitement spécial.                                                                                                                                                                        |

| <b>FTP</b>          | <b>File Transfer Protocol:</b> Protocole permettant la transmission de fichiers sur un réseau (comme l'Internet).                                                                                                                                       |

| <b>Interface</b>    | Ensemble des signaux d'un module qui sont présentés au monde extérieur. Lorsqu'un protocole impose une interface, il exige que certains signaux soient présents.                                                                                        |

| <b>Interruption</b> | Signal provoquant une réaction d'un microprocesseur. Ce dernier traite une interruption en activant une fonction de gestion, qui sauvegarde généralement le contenu des registres, effectue un traitement spécial, puis revient à la tâche interrompue. |

| <b>Java</b>         | Langage de programmation interprété, conçu par Sun Microsystems, qui est indépendant du système d'exploitation sur lequel il est exécuté.                                                                                                               |

| <b>Maître</b>       | Module qui initie des transactions sur un bus (ex: microprocesseur)                                                                                                                                                                                     |

| <b>Module</b>       | Ensemble de fonctions regroupées de façon logique.                                                                                                                                                                                                      |

|                             |                                                                                                                                                                                                                                                      |

|-----------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>MPEG</b>                 | <b>Motion Pictures Expert Group:</b> Groupe d'experts en imagerie vidéo et la compression de celle-ci. MPEG désigne aussi les divers formats de compression que le groupe a créés.                                                                   |

| <b>Niveau d'abstraction</b> | Ensemble de caractéristiques d'un modèle donné: plus le niveau d'abstraction est élevé, moins on considère de détails d'implantation.                                                                                                                |

| <b>Noyau</b>                | Bloc de matériel qui effectue un traitement.                                                                                                                                                                                                         |

| <b>PCI</b>                  | <b>Peripheral Component Interconnect:</b> Protocole de communication surtout utilisé pour l'ajout de périphériques dans les ordinateurs personnels.                                                                                                  |

| <b>Périphérique</b>         | Module autre qu'un processeur, coprocesseur ou mémoire. Les périphériques sont généralement des esclaves.                                                                                                                                            |

| <b>PI</b>                   | <b>Propriété Intellectuelle:</b> Dans le contexte de la réutilisation des modules, la propriété intellectuelle représente des modules de matériel pouvant être échangés, vendus ou transplantés dans un système.                                     |

| <b>Pipeline</b>             | Structure matérielle divisant une opération en sous-opérations dont les résultats intermédiaires sont stockés dans des registres. Un pipeline peut généralement fonctionner à une cadence d'horloge plus élevée qu'un circuit combinatoire complexe. |

| <b>Plate-forme</b>          | Ensemble de blocs de propriété intellectuelle (PI) conçus pour fonctionner ensemble, servant généralement de base à laquelle un concepteur peut greffer ses propres blocs.                                                                           |

|                  |                                                                                                                                                                                                                                          |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>Pont</b>      | Module reliant deux bus distincts. Un pont reliant un bus contenant qu'un seul module à un autre bus s'appelle parfois <i>adaptateur</i> ou <i>wrapper</i> .                                                                             |

| <b>Port</b>      | Signal d'un module qui communique avec le monde extérieur                                                                                                                                                                                |

| <b>Protocole</b> | Ensemble de règles régissant la communication entre divers modules. Tous les modules qui respectent un protocole donné peuvent donc communiquer ensemble sans modification.                                                              |

| <b>RTL</b>       | <b>Register Transfer Level:</b> Niveau d'abstraction bas, représentant les détails des données transmises d'un registre à l'autre. Précède le niveau <i>portes</i> , où le fonctionnement est décrit comme une suite de portes logiques. |

| <b>RTOS</b>      | <b>Real-Time Operating System:</b> Système d'exploitation temps-réel. Permet la gestion de plusieurs processus s'exécutant en parallèle sur un microprocesseur.                                                                          |

| <b>Signal</b>    | Information transmise sur un canal. Dans le contexte de ce travail, tension sur un fil.                                                                                                                                                  |

| <b>SoC</b>       | <b>System on Chip:</b> Système informatique dont tous les modules ou presque sont contenus sur une seule puce.                                                                                                                           |

| <b>SMC</b>       | <b>Société Canadienne de la Microélectronique</b>                                                                                                                                                                                        |

| <b>SRAM</b>      | <b>Static Random-Access Memory:</b> Mémoire vive statique. Ce type de mémoire demande un grand nombre de transistors, mais garde sa valeur tant qu'elle est alimentée.                                                                   |

|                         |                                                                                                                                                                                     |

|-------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>SSRAM</b>            | <b>Synchronous Static Random-Access Memory:</b> Mémoire vive statique dont les transferts de données s'effectuent sur des coups d'horloge.                                          |

| <b>Système sur Puce</b> | <i>Voir SoC</i>                                                                                                                                                                     |

| <b>TF</b>               | <b>Timed Functional:</b> Se dit d'un niveau d'abstraction élevé où seuls l'algorithmique et la séquence des événements sont considérées.                                            |

| <b>Transaction</b>      | Le fait de transmettre ou de demander une donnée à un esclave via un bus.                                                                                                           |

| <b>UTF</b>              | <b>UnTimed Functional:</b> Se dit d'un niveau d'abstraction très élevé où seule la dimension algorithmique d'un système est considérée.                                             |

| <b>VCI</b>              | <b>Virtual Component Interface:</b> Ensemble d'interfaces normalisées proposées par la VSIA pour le design de modules de matériel. Facilite grandement la réutilisation de modules. |

| <b>VHDL</b>             | <b>VLSI Hardware Description Language.</b> Langage très populaire servant à décrire des modules matériels en utilisant du code.                                                     |

| <b>VSIA</b>             | <b>Virtual Socket Interface Alliance:</b> Alliance d'entreprises et de chercheurs dont la mission est de faciliter la réutilisation de propriété intellectuelle (PI)                |

## INTRODUCTION

Ce projet consiste à développer un ensemble de modules VHDL pouvant servir au prototypage rapide d'un système. Dans les sections qui suivent, le travail est situé dans le contexte des autres projets du groupe de recherche, puis les objectifs du projet sont énoncés. Les diverses sections du mémoire seront ensuite présentées brièvement.

### ***Les projets actuels du CIRCUS***

Ce projet vient répondre aux besoins de plusieurs projets au sein du CIRCUS [CIRC01], le laboratoire de recherche sur le co-design logiciel/matériel de l'École Polytechnique de Montréal. Cette section fait état des travaux qui étaient en cours au début du projet et qui ont influencé son développement.

#### **Picasso**

Au début de ce projet, le travail sur l'outil Picasso battait son plein. Le problème de la gestion de l'écart de productivité (discuté dans la section 1.1.2) a attiré beaucoup d'attention vers le domaine de la conception de systèmes sur puce (SoC, pour system on chip) qui servent au domaine des systèmes embarqués.

Picasso est un outil de co-design permettant à un concepteur d'automatiser une partie du développement d'un système embarqué. Le concepteur dessine des blocs, qui représentent divers modules soit matériels, soit logiciels et les relie ensemble comme s'ils étaient de la même nature. Les modules ont des ports qui sont reliés par des signaux. Pour chacun des blocs, le concepteur écrit soit une fonction en C, soit une description en VHDL. Pour simuler le système, Picasso prend chacun des liens, selon sa nature (matériel-matériel, matériel-logiciel, etc.), et génère automatiquement du code VHDL ou C pour réaliser des mécanismes de communication (bus direct pour les communications M-M, registres accessibles via le système de mémoire pour les communications L-M, etc.). Ainsi, le concepteur n'a pas à se soucier des détails de communication : il peut se concentrer sur les aspects fonctionnels de son système. De plus, il n'a pas à fournir de modèle matériel

pour le microprocesseur : le concepteur spécifie le nombre et le modèle des microprocesseurs, puis assigne les divers modules logiciels aux processeurs ainsi choisis. Le tout est ensuite simulé à l'aide de Seamless CVE [MeGr97], l'outil de co-vérification de Mentor Graphics.

Un problème dans la méthodologie de la première version de Picasso était qu'il ne fonctionnait que sous le système d'exploitation Windows, tandis que Seamless ne fonctionne que sous UNIX. Il fallait donc transmettre les fichiers générés par FTP au serveur UNIX, puis effectuer la simulation. Il était donc nécessaire de passer d'une machine à l'autre pour chaque modification du système, ce qui était fastidieux.

La deuxième version de Picasso a été entamée. Afin d'unifier toutes les étapes du processus de design sous un environnement de travail, l'outil a été codé en Java. Ce langage de programmation est disponible pour toutes les plates-formes principales et offre des primitives de programmation d'interfaces graphiques, simplifiant la tâche de développer une interface usager. Picasso pouvait donc fonctionner sous UNIX.

Également, on voulait ajouter un mécanisme pour effectuer l'exploration du partitionnement matériel-logiciel. En effet, le fait de coder des modules en VHDL ou en C impose immédiatement un partitionnement dès le début. L'idée d'un langage unifié pour décrire les deux a donc été proposée. Une partie du groupe de recherche s'est alors tournée vers Syslib, une méthodologie de conception système. Finalement, une architecture cible a été développée, puis éprouvée dans le cadre de la conception d'un détecteur de patrons.

## **Syslib**

Pour permettre l'exploration du partitionnement du système, il faut être capable de décrire un comportement tout en faisant abstraction de son implantation finale. La méthodologie habituelle pour cette approche est de commencer à un niveau d'abstraction très élevé : la description du comportement se fait au niveau purement algorithmique : on ne parle donc pas de fonctions, de tâches, de jeux d'instructions, d'architectures matérielles ou de

modèle de microprocesseur. Le travail se limite à décrire seulement le comportement désiré, sans imposer de contraintes de performance. Le concepteur peut ajouter des détails par la suite en raffinant le modèle algorithmique.

Plusieurs langages permettant cette méthodologie existent maintenant, comme SystemC et SpecC, mais à l'époque, ils n'étaient pas encore suffisamment développés. Des membres du CIRCUS se sont alors tournés vers le développement de Syslib, une méthodologie qui se démarquerait par l'utilisation d'un ensemble de fonctions implantées à divers niveaux de raffinement. Ainsi, on peut développer un système à un niveau très abstrait en utilisant les primitives de communication de Syslib, puis passer à des niveaux plus raffinés en modifiant très peu le code et en associant les primitives de communication à d'autre code plus raffiné et précisé.

Au niveau le plus bas de la méthodologie, on trouve la réalisation matérielle : le système est alors appliqué à une architecture modèle, une plate-forme, qui contient tout ce qu'il faut pour utiliser un système d'exploitation. Cependant, la plate-forme qui avait été suggérée initialement pour la deuxième version de Picasso avait des lacunes. Celles-ci sont mises en relief dans la prochaine section.

### **Le détecteur de patrons**

Pour mettre la plate-forme à l'épreuve, un système détectant un patron dans une image a été développé. Un microprocesseur ARM7TDMI génère une image et un patron, puis active un coprocesseur qui cherche le patron dans l'image. Une fois que le patron a été détecté, le coprocesseur retourne la réponse au ARM7TDMI. On assiste donc à des communications de tous les types : logiciel-matériel (écriture en mémoire des données, activation du coprocesseur), matériel-matériel (coprocesseur-mémoire), matériel-logiciel (coprocesseur-processeur) et enfin logiciel-logiciel (interaction entre divers processus sur le ARM7TDMI).

Le fonctionnement du système a été validé: les primitives de communication ont fait leur travail. Cependant, des lacunes plus sournoises ont fait surface : la difficulté de modifier

le système, notamment au niveau des mécanismes de communication. L'architecture de la plate-forme n'était tout simplement pas assez robuste aux modifications. Le changement du type de processeur aurait exigé de grosses modifications au niveau de l'architecture. L'ajout ou le retrait de modules comme des mémoires aurait le même effet.

## ***Objectif du projet***

L'objectif du travail est de développer une plate-forme matérielle configurable et hautement modulaire qui sert de cible pour Picasso et Syslib. Le modèle est codé en VHDL et a été co-simulé avec Seamless CVE.

La plate-forme doit aussi servir de laboratoire pour éprouver les principes de la réutilisation de la propriété intellectuelle, une approche envisagée pour tirer profit de la fulgurante avance des technologies. Ainsi, elle doit avoir une architecture régulière où les modules sont reliés ensemble sur un bus. Un protocole spécifique de communication a été adopté: AMBA AHB, une spécification qui permet de normaliser les interfaces des divers modules afin qu'ils puissent s'intégrer facilement à un nouveau design. Afin de convertir les interfaces non-standard des divers modules vers AHB, on aura recours à des adaptateurs, ou *ponts*. Ces modules se placent entre le module et le bus, assurant une compatibilité.

L'étude de cas du détecteur de patrons sera ensuite effectuée sur la plate-forme afin de l'étudier et de vérifier de manière informelle son comportement. L'expérience servira à souligner l'importance de certaines considérations de design. Cette expérience de conception permettra aussi de développer certaines méthodes de travail. Le texte de ce mémoire est donc aussi important que le code VHDL produit au cours du projet: C'est une chose de faire du code, mais la compréhension et l'interprétation des spécifications constitue une partie importante du travail. On peut même dire que la plate-forme a servi de prétexte pour apporter du savoir-faire dans le domaine des architectures SoC au groupe de recherche.

## ***Contributions de ce mémoire***

Ce projet de maîtrise a apporté les contributions suivantes:

- Un savoir-faire concernant les architectures de bus en général et le protocole AHB en particulier.

- Un modèle VHDL d'une plate-forme matérielle pouvant servir à la conception de prototypes de systèmes embarqués. La plate-forme peut aussi être utilisée dans un contexte didactique.

- Une méthodologie pour la conception des *wrappers* ou ponts pour les maîtres de bus AMBA.

## ***Plan du mémoire***

Le mémoire est divisé en six chapitres. Le chapitre 1, la revue de littérature, situe le projet dans le contexte actuel de la conception des systèmes sur puce. La problématique de l'écart de productivité est présentée. Une discussion suit sur les divers moyens de contrer cet écart. Enfin, on choisit une des techniques, puis on montre comment elle est appliquée au projet.

Le chapitre 2 porte sur le protocole AMBA. Plus qu'une simple transcription des spécifications, ce chapitre tente de défricher le protocole pour souligner les liens entre les signaux et d'éclaircir les intentions de certaines règles qui sembleraient un peu obscures au premier abord. Le chapitre 3 présente le contenu de la plate-forme. On cite d'abord les besoins à combler à l'aide de la plate-forme, puis on présente les divers modules qui en font partie.

Le chapitre 4 rapporte des expériences de design développées lors de la conception. On voit comment générer automatiquement un réseau d'interconnexion AHB. Des méthodologies de conception, ainsi que des exemples de machines à états complètent le chapitre.

Le chapitre 5 décrit une expérience de conception assistée de la plate-forme, soit l'implantation du détecteur de patrons. Une comparaison est établie entre l'ancienne plate-forme et la nouvelle.

Le chapitre 6 présente certains résultats de synthèse et commente qualitativement le design d'un module critique, soit le pont AHB-AHB.

## CHAPITRE 1: Revue de littérature

Tout travail de recherche est provoqué par le contexte scientifique de son époque. Avant d'entrer dans le vif du sujet, il est important de situer le travail par rapport aux problématiques actuelles afin de bien cerner en quoi il vient faire une contribution.

Le système développé dans le cadre de ce projet est la réalisation d'un modèle en VHDL d'une plate-forme de base pour le développement de systèmes qui seront implantés sur une seule puce. Cette approche sert particulièrement dans le domaine des systèmes embarqués, où l'espace occupé par les composantes est un facteur critique. En effet, ces appareils sont généralement portatifs et doivent donc être petits, légers et peu énergivores (afin de réduire la taille de la source d'alimentation, comme la pile).

Le présent chapitre présente donc les enjeux actuels de ce domaine. La section 1.1 présente le problème du fossé de la productivité. La section 1.2 montre comment réduire l'effort de conception en réutilisant des morceaux judicieusement codés de systèmes précédents.

### ***1.1. L'écart de productivité***

L'enjeu actuel du domaine de la conception de systèmes sur puce est que la technologie avance trop vite pour les concepteurs qui ne peuvent utiliser efficacement toutes les ressources qui sont à leur disposition. Cette section décrit ce problème, puis montre quelques approches de conception qui servent à le résoudre.

#### **1.1.1. La "loi" de Moore**

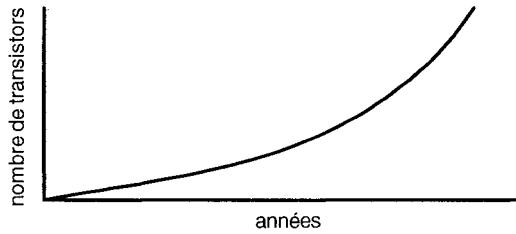

Gordon Moore, un des co-fondateurs de Fairchild et de Intel, énonça ce principe selon lequel la densité des transistors sur une puce double à tous les 18 mois. Ce nombre croissant de transistors permet l'intégration d'un nombre croissant de fonctions sur une même puce. L'allure de cette augmentation est schématisée dans la figure 1.1.

Figure 1.1 : L'allure de la loi de Moore

Cette croissance exponentielle de la densité permet de rapprocher les transistors et d'accélérer les interactions entre eux: on atteint donc des vitesses plus grandes, mais aussi une augmentation de la puissance dissipée.

### 1.1.2. L'écart de productivité

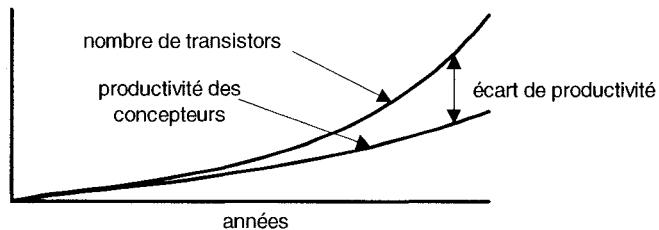

Pour pouvoir profiter de ces avances technologiques, il faut avoir des méthodologies de travail qui permettent de gérer un nombre aussi grand de transistors. Or, un écart existe actuellement entre le nombre de transistors disponibles et le nombre de transistors utilisables efficacement par les concepteurs. La figure 1.2 illustre ce phénomène nommé *écart de productivité*.

Figure 1.2 : L'écart de productivité

Beaucoup de facteurs expliquent cet écart. Dans [Nepp98], on remarque que les outils de conception assistée par ordinateur ne sont tout simplement pas assez puissants pour traiter des systèmes comportant des dizaines de millions de transistors. On note aussi qu'il n'existe pas de moyen efficace pour faire la vérification d'un système aussi complexe.

Ajouter du personnel n'aide plus après un certain seuil: trop de main-d'œuvre peut ralentir la progression d'un projet par le simple fait d'avoir à maintenir un réseau de

communication entre les membres de l'équipe de conception: c'est en quelque sorte la loi d'Amdahl appliquée à la gestion de personnel [Pres97], [Broo95].

Les méthodes de conception *ad hoc* ne tiennent plus la route. La complexité des systèmes est maintenant tellement grande que les concepteurs doivent se plier à des nouvelles méthodes. Ces techniques ne sont pas toujours les plus faciles à respecter, mais une discipline s'impose si on veut surmonter les difficultés liées aux systèmes modernes. Il est certain que la conception *ad hoc*, lorsqu'elle est appliquée à la création d'un petit système, peut donner des résultats quasi optimaux. Cependant, comme dans le domaine du placement-routage, les systèmes atteignent un niveau de complexité qui oblige le concepteur à utiliser des méthodes possiblement moins efficaces, mais plus structurées afin de réussir [GZDG00].

### 1.1.3. Le raffinement progressif

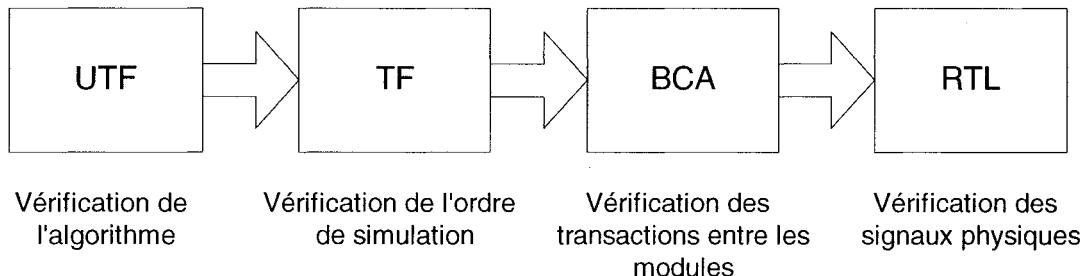

Deux techniques attirent actuellement l'attention des chercheurs [Fili02]. La première, le *raffinement progressif*, prône le développement sur plusieurs niveaux successifs d'abstraction. On fait abstraction des spécificités de l'implantation pour se concentrer sur un seul problème à la fois. Au niveau dit *fonctionnel* (*untimed functional* ou UTF, en anglais) aucune notion de temps n'est considérée, ce qui permet au concepteur de se concentrer uniquement sur la validité de l'algorithme à planter. On passe ensuite au niveau *comportemental* (*timed functional*, ou TF), où une certaine notion de temporalité est introduite: l'ordre des opérations devient important et les modules doivent se synchroniser de façon réaliste.

On passe ensuite au niveau *transactionnel* (*bus cycle accurate*, BCA) où la granularité du modèle est raffiné au point de décrire abstrairement les transactions entre les modules. Enfin on trouve le niveau *horloge*, qui exprime le niveau le plus élevé de détail avant la synthèse proprement dite. C'est à ce niveau qu'il existe suffisamment de détails pour voir l'effet de l'horloge. La figure 1.3 récapitule les diverses étapes.

Figure 1.3 : Le raffinement progressif

Plusieurs langages de description spécialisés existent pour supporter cette technique de design. Les deux plus connus sont SystemC [OSCI02] et SpecC [GZDG00], mais il est aussi possible d'utiliser des langages comme C++ ou Java pour les niveaux d'abstraction plus élevés.

#### 1.1.4. Réutilisation de la propriété intellectuelle

La seconde technique de conception, soit la *réutilisation de propriété intellectuelle*, suggère plutôt l'assemblage d'un système à partir d'une bibliothèque de modules matériels existants. Ces modules peuvent provenir du concepteur ou d'un fournisseur de modules de propriété intellectuelle (PI), qui vend des blocs de matériel accomplissant une tâche précise. La tâche de conception est donc réduite à celle de l'intégration qui, à ce niveau de complexité, demeure une tâche formidable, notamment au plan de la vérification. C'est cette approche qui est explorée dans ce travail.

Ces deux techniques ne sont pas mutuellement exclusives, et peuvent s'imbriquer: un fournisseur de modules de propriété intellectuelle peut offrir des modèles à tous les niveaux d'abstraction.

#### 1.2. Enjeux de la réutilisation de la propriété intellectuelle

La réutilisation de modules de manière *ad hoc*, c'est-à-dire sans utilisation d'une norme, n'est pas en soi une solution. On veut effectuer une intégration qui requiert le moins de modifications possibles aux modules qui composent le système. Des modules mal conçus ainsi qu'une architecture mal choisie mènent à des pertes de temps causées par la ré-

ingénierie de certaines parties du système. Cette section présente les philosophies de design qui permettent de faciliter le processus d'intégration.

### 1.2.1. Gérer la complexité en modularisant

À la base, pour permettre la réutilisation, il faut savoir diviser le système en divers modules. De nos jours, la conception de matériel se fait à l'aide de langages de description. La logique est donc représentée par du code qui peut par la suite être simulé. Il est un fait connu dans le domaine du génie logiciel que plus on modifie du code, plus on risque d'insérer des défauts [Pres97].

La stratégie à adopter est donc de découper le système en morceaux qui ont une fonction propre, qui forment "un tout", comme les registres et la logique de contrôle d'une mémoire, par exemple. Ainsi, lorsqu'on apporte une modification au module, on ne risque pas d'introduire des erreurs dans d'autres parties du système qui n'ont aucun lien avec lui.

C'est la première étape. Généralement, les langages de description obligent le concepteur à diviser son système ainsi. C'est le cas des *entity* en VHDL.

### 1.2.2. Résister aux modifications en encapsulant

Un module matériel a toujours une *fonction* bien précise. En mathématique, une *fonction* est une opération effectuée sur des opérandes et qui produit un résultat. Ainsi, un module reçoit des paramètres en entrée, les traite, et donne une réponse. Les entrées proviennent d'ailleurs et la réponse est utilisée par un autre module (ou est fournie ultimement à l'utilisateur). On remarque donc qu'un module a deux aspects: un aspect *traitement* (l'opération sur les données) et l'aspect *communication* (le moyen avec lequel le module reçoit et transmet des données).

Il est intéressant de noter que ces deux aspects sont relativement indépendants: quel que soit le moyen de communication choisi, l'opération effectuée sur les données en entrée ne change pas. Puisqu'il existe une infinité de moyens pour faire communiquer deux modules, l'adaptation d'un module vers un autre système risque d'exiger certaines

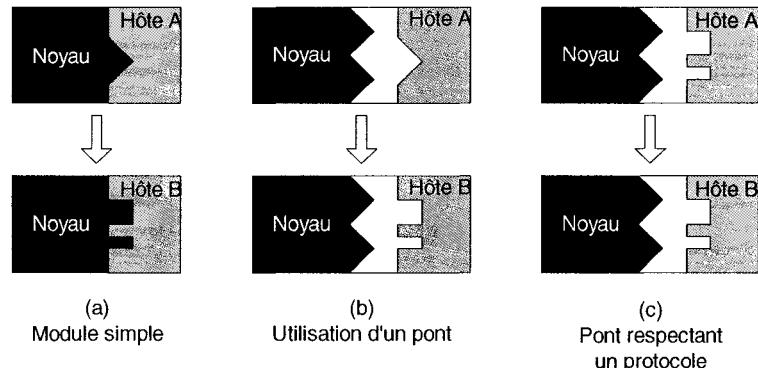

modifications à l'aspect *communication*. Puisqu'on ne veut pas insérer accidentellement des défauts dans la partie *traitement*, il est intéressant de diviser les deux aspects en des modules séparés. On obtient donc le *noyau*, qui effectue le traitement et le *pont* (*wrapper* en anglais) qui s'occupe de communiquer avec le reste du système.

Ces principes ont été fortement encouragés dans la littérature, notamment dans le développement de SpecC [GZDG00] et de VCI [VSIA00].

### 1.2.3. Ignorer la diversité en normalisant

Bien que la division en noyau et pont soit une technique bien utile, les concepteurs doivent néanmoins produire un nouveau pont pour chaque système, qui n'est pas toujours une petite tâche en soi. Il devient alors intéressant d'établir des *protocoles de communication*, soit des règles qui normalisent les communications inter-modules. Ainsi, un module ayant un pont qui respecte un protocole donné peut être transplanté facilement vers un autre système qui respecte le même protocole.

Un fournisseur de propriété intellectuelle peut ainsi garantir l'utilité de ses noyaux en fournissant une batterie de ponts respectant les divers protocoles standards pour chacun d'entre eux. L'utilisation d'un protocole peut aussi aider dans la vérification d'un module: il existe des outils de validation pour la plupart des protocoles [NiGo01].

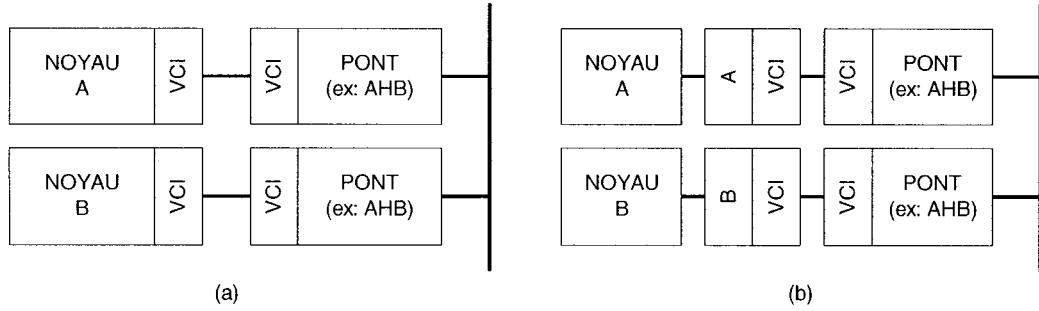

On remarque donc une nette amélioration par rapport à la structure initiale. La figure 1.4 récapitule l'évolution de la philosophie de conception. En (a), on voit que le noyau au complet doit être modifié pour l'adapter à un nouveau système hôte. En (b), on ajoute un pont (en blanc) qui est le seul module à être modifié lors du passage au nouveau système. Finalement en (c), on observe que l'utilisation d'un protocole de bus permet d'éviter complètement d'apporter des modifications aux modules.

**Figure 1.4 : Les raffinements facilitant la réutilisation**

### **1.3. Les protocoles de bus**

Dans la section précédente, on a soulevé l'importance des protocoles de communication. Il est donc tout naturel d'en choisir un pour ce projet de maîtrise. Cette section contient une revue des protocoles les plus populaires. Ce sont des protocoles *de bus*, c'est-à-dire des protocoles qui utilisent un bus pour transmettre des données.

Bien que les divers rôles des modules soient présentés à la section 2.1, il est important ici de résumer rapidement les concepts de base des protocoles de bus. Il existe des modules maîtres, qui initient des transferts via le bus, et des esclaves qui réagissent aux requêtes des maîtres. Pour communiquer avec un esclave précis, le maître indique l'identité du destinataire à l'aide du signal d'adresses. Généralement, il existe un module nommé décodeur qui interprète cette adresse et qui active l'esclave correspondant. Ce dernier réagit ensuite à la requête, soit en saisissant ou soit en émettant une donnée.

### 1.3.1. Bus sur puce vs. bus sur carte

On pourrait se demander pourquoi il existe des protocoles spécifiques au domaine des bus sur puce. En effet, des protocoles de bus comme PCI existent depuis bien longtemps pour les circuits imprimés, pourquoi ne pas les utiliser?

L'idée ici est que les bus pour les SoC ne sont pas tenus de respecter les mêmes contraintes que les bus pour les cartes (circuits imprimés). Sur les cartes, les bus relient plusieurs puces dont le coût est fortement influencé par le nombre d'entrées et de sorties

(de "pattes") qu'elles possèdent. On tente donc de minimiser le nombre de signaux et de pattes requis, permettant une plus grande densité de composantes sur la carte, et donc une carte plus petite [Cord99]. C'est pour cela que dans ces conditions, plusieurs modules voulant accéder à un signal y sont reliés directement, se mettant en haute impédance lorsqu'ils n'y ont pas accès. Un exemple classique est celui du bus d'adresses: seul le module qui a le droit de se servir du bus à un moment donné peut transmettre une valeur sur le bus. Tous les autres se mettent en haute impédance pour ne pas nuire au signal.

Les bus SoC modernes n'ont pas les mêmes contraintes que les bus sur cartes: la contrainte principale est celle des tests lors de la production. Puisque toutes les composantes sont intégrées sur une même puce, il devient difficile de faire des tests: on doit utiliser des méthodes automatiques de test. Or, ces méthodes ne sont pas compatibles avec l'utilisation de la haute impédance: les modèles de fautes se servent des valeurs "0" ou "1", pas "Z". De plus, les bus SoC n'ont pas les mêmes contraintes quant au coût des composants: le nombre de ports sur un module n'est pas un facteur aussi important au niveau coût que pour les bus sur circuit imprimé.

Les protocoles suivants sont donc mieux adaptés aux réalités des SoC.

### 1.3.2. AMBA

Depuis 1999, ARM propose la spécification AMBA [ARM00] en tant que norme pour les systèmes sur puce. Cette spécification offre trois protocoles qui peuvent être utilisés selon les besoins: Le premier, le *Advanced High-speed Bus* (AHB) est spécialement adapté pour les communications à haute vitesse requises par des modules performants. Le deuxième, le *Advanced System Bus* (ASB), est un protocole désuet qui avait été inspiré par les protocoles de bus sur carte et est en cours de disparition. Il a été supplanté par AHB. Enfin, il existe le *Advanced Peripheral Bus* (APB), qui sert pour les modules périphériques qui n'ont pas besoin de la performance du AHB. La simplicité du APB permet d'avoir des interfaces moins complexes et plus faciles à créer et à tester.

Le protocole AHB permet la gestion de plusieurs maîtres sur un même bus. Un algorithme d'arbitrage permet de choisir un maître à la fois afin d'éviter les collisions sur le bus. Il a été retenu pour ce projet car il est bien documenté et suffisamment flexible sans toutefois être trop compliqué. Il est aussi un des protocoles les plus populaires, étant supporté par la vaste gamme de processeurs de la société ARM. Une description détaillée se trouve au chapitre 2 du présent ouvrage.

### 1.3.3. CoreConnect

CoreConnect [IBM00] est un protocole conçu par IBM. Il ressemble beaucoup à AMBA. En effet, il possède lui aussi deux niveaux de complexité: le PLB (*Processor Local Bus*, l'homologue de AHB) et le OPB (*On-chip Peripheral Bus*, l'équivalent de APB). Il permet aussi les mêmes sortes de transactions. Il se différencie par certaines fonctions qui lui sont propres. Il est, notamment, possible d'effectuer une lecture et une écriture simultanément en utilisant les deux bus de données.

Le désavantage avec CoreConnect est que la structure proposée est trop lourde pour la plupart des applications actuelles. Souvent, les fonctions spécifiées par le protocole n'ont pas suffisamment d'utilité pour justifier l'effort de les planter. De plus, la documentation est lourde, difficile à déchiffrer et aride. Il est donc difficile de l'apprendre. La société IBM, consciente de ce problème, offre la possibilité d'accéder à des "boîtes à outils" logicielles qui permettent la génération automatique du bus et la vérification de la conformité des modules qui y sont reliés.

### 1.3.4. Wishbone

OpenCores.org, un site Web d'où l'on peut télécharger des noyaux de code VHDL gratuitement, a choisi le protocole Wishbone comme norme. Cette spécification, publiée par la société Silicore [Sili01], propose un ensemble minimal de signaux pour permettre des accès via un bus.

Pour qu'un module soit certifié compatible avec Wishbone, la spécification exige que de la documentation soit produite pour le module (un "Wishbone Datasheet"). La

documentation nécessaire doit respecter un certain format et contenir certaines informations précises. Cette approche est intéressante: elle impose une discipline au concepteur, le forçant à documenter son travail. La réutilisation du module en est simplifiée parce que l'intégrateur n'a pas à deviner son fonctionnement.

Une autre particularité du protocole est qu'il énonce sous formes de règles précises les spécifications à respecter. En parcourant la liste des règles, on peut cerner rapidement si un module respecte la spécification ou non. Cette liste claire des règles permet au concepteur d'apprendre le protocole rapidement.

Un désavantage de cette spécification est qu'elle permet au concepteur de changer le nom des signaux qu'elle définit, dans la mesure où ces changements sont bien documentés dans la fiche technique. De plus, ce protocole ne possède pas de décodeur: il laisse aux esclaves la tâche de vérifier l'adresse afin de savoir s'ils sont sélectionnés. Si jamais les correspondances esclave-адresses doivent être changées, il faut alors modifier tous les esclaves.

### 1.3.5. VCI

VCI, la *Virtual Component Interface* produite par l'Alliance VSI, n'est pas exactement un protocole de bus. Il s'agit plutôt d'un protocole de communication point à point pour la communication entre un noyau et son pont. Il définit donc une interface standard pour les maîtres (*Initiators*, dans la nomenclature VCI) et les esclaves (*Targets*). Ainsi, au lieu de produire une batterie de ponts pour chaque noyau, on crée un pont par protocole de bus qui sert à tous les noyaux qui veulent s'y relier. Pour les noyaux qui précèdent VCI, la spécification propose de fournir un autre pont pour adapter leur interface à celle exigée par VCI. La figure 1.5 présente l'allure des modules qui utilisent VCI. On voit en (a) deux noyaux qui respectent le protocole VCI. Ils utilisent le même pont pour accéder au bus. En (b), on voit comment adapter des noyaux non-conformes à VCI grâce à des ponts noyau-VCI (A-VCI et B-VCI).

Figure 1.5 : Les interfaces VCI

La communication point à point s'effectue en envoyant des paquets. L'initiateur envoie un paquet de requête (*request*) et attend une réponse (*response*) de la part de la cible. Selon un des trois protocoles de spécification, des signaux de contrôle sont utilisés pour synchroniser les transferts.

En effet, dire "le protocole VCI" est une grossière simplification: il existe plusieurs protocoles dans la spécification, chacun ayant un degré de complexité différent. Le protocole PVCI (*Peripheral VCI*) est le plus simple, permettant des accès composés d'une requête et d'une réponse. BVCI (*Basic VCI*) permet de faire des accès éclatés, c'est à dire de transmettre plusieurs requêtes sans attendre de réponse. Enfin, le AVCI (*Advanced VCI*) apporte un nombre de fonctionnalités qui permettent d'exploiter les optimisations qu'offrent certains modèles de processeurs et de DSP: les réponses aux accès peuvent revenir en désordre et les paquets reçus peuvent avoir une taille différente de ceux qui ont été envoyés.

### 1.3.5. OCP

OCP est une extension du protocole VCI. Il contient encore les trois niveaux de complexité mentionnés au paragraphe précédent, mais l'effort semble être une concrétisation des idées proposées par VSIA: Il existe une suite d'outils pour vérifier la conformité de modules à OCP.