|                         | Analysis and characterisation of design for testability methodologies for bipolar current mode logics                                                                                                                                                                                 |  |

|-------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Auteur: Author:         | Padmapriya Kumar                                                                                                                                                                                                                                                                      |  |

| Date:                   | 2002                                                                                                                                                                                                                                                                                  |  |

| Type:                   | Mémoire ou thèse / Dissertation or Thesis                                                                                                                                                                                                                                             |  |

| Référence:<br>Citation: | Kumar, P. (2002). Analysis and characterisation of design for testability methodologies for bipolar current mode logics [Mémoire de maîtrise, École Polytechnique de Montréal]. PolyPublie. <a href="https://publications.polymtl.ca/7098/">https://publications.polymtl.ca/7098/</a> |  |

# Document en libre accès dans PolyPublie Open Access document in PolyPublie

| URL de PolyPublie:<br>PolyPublie URL:    | https://publications.polymtl.ca/7098/ |

|------------------------------------------|---------------------------------------|

| Directeurs de<br>recherche:<br>Advisors: | Yvon Savaria                          |

| <b>Programme:</b><br>Program:            | Non spécifié                          |

#### UNIVERSITÉ DE MONTRÉAL

# ANALYSIS AND CHARACTERISATION OF DESIGN FOR TESTABILITY METHODOLOGIES FOR BIPOLAR CURRENT MODE LOGICS

# PADMAPRIYA KUMAR DÉPARTEMENT DE GÉNIE ÉLECTRIQUE ÉCOLE POLYTECHNIQUE DE MONTRÉAL

MÉMOIRE PRÉSENTÉ EN VUE DE L'OBTENTION DU DIPLÔME DE MAÎTRISE ÈS SCIENCES APPLIQUÉES (GÉNIE ÉLECTRIQUE) JUILLET 2002

© Padmapriya KUMAR, 2002.

National Library of Canada

Acquisitions and Bibliographic Services

395 Wellington Street Ottawa ON K1A 0N4 Canada Bibliothèque nationale du Canada

Acquisitions et services bibliographiques

395, rue Wellington Ottawa ON K1A 0N4 Canada

Your file Votre référence

Our file Notre référence

The author has granted a nonexclusive licence allowing the National Library of Canada to reproduce, loan, distribute or sell copies of this thesis in microform, paper or electronic formats.

The author retains ownership of the copyright in this thesis. Neither the thesis nor substantial extracts from it may be printed or otherwise reproduced without the author's permission.

L'auteur a accordé une licence non exclusive permettant à la Bibliothèque nationale du Canada de reproduire, prêter, distribuer ou vendre des copies de cette thèse sous la forme de microfiche/film, de reproduction sur papier ou sur format électronique.

L'auteur conserve la propriété du droit d'auteur qui protège cette thèse. Ni la thèse ni des extraits substantiels de celle-ci ne doivent être imprimés ou autrement reproduits sans son autorisation.

0-612-81710-5

## UNIVERSITÉ DE MONTRÉAL

## ÉCOLE POLYTECHNIQUE DE MONTRÉAL

#### Ce mémoire intitulé:

# ANALYSIS AND CHARACTERISATION OF DESIGN FOR TESTABILITY METHODOLOGIES FOR BIPOLAR CURRENT MODE LOGICS

présenté par: KUMAR Padmapriya

en vue de l'obtention du diplôme de: Maîtrise ès sciences appliquées

a été dûment accepté par le jury d'examen constitué de:

M. BRAULT Jean-Jules, Ph.D., président

M. SAVARIA Yvon, Ph.D., membre et directeur de recherche

M. SAWAN Mohamad, Ph.D., membre

#### **ACKNOWLEDGEMENTS**

I sincerely thank Dr. Yvon Savaria for the excellent guidance given throughout the project. His continuous encouragement and feedback has been of great value in accomplishing this task. He has been quite supportive in both the professional and personal aspects of my life. I express my sincere thanks to him for changing my life for the better.

I wish to express my sincere thanks to Dr. Pieter Trouborst of Nortel Networks, for the excellent guidance and valuable feedback given throughout the project. He was available whenever I needed him. Thank you for the excellent support, Sir. Also thanks for providing me the opportunity to work as a coop student at Nortel Networks.

I thank Bernard Antaki for mentoring me at the initial stage of my work. I would like to thank Ginette Monté for developing tools that enabled quick completion of the task on hand. I would like to thank the Canadian Microelectronics Corporation (CMC) for their tool supply and support. I would like to thank my colleagues at GRM for all the useful discussions we have had.

I extend my special thanks to friends and family for their continuous support, without whom this may not have been possible.

#### RÉSUMÉ

Le test des familles CMOS a largement retenu l'attention de la communauté scientifique En effet les CMOS constituent la technologie dominante à cause de sa faible consommation de puissance et de sa grande densité d'intégration. Cependant, les familles logiques en mode courant (Current Mode Logic, CML) implémentées avec des technologies bipolaires, ont continuellement occupé des secteurs lucratifs tels que celui des circuits très rapides. L'évolution technologique a permi la réalisation de procédés bipolaires de basse puissance et haute densité. Ceux-ci, combinés avec la propriété d'opération à haute vitesse des circuits logiques CML bipolaires, en fait un excellent choix pour les applications qui opèrent à très haute vitesse. Comme aucun procédé de fabrication n'est parfait, le test de ces circuits est indispensable. Mentionnons que très peu de documentation existe sur les méthodes de test applicable aux technologies ECL ou CML. Les méthodes de test proposées pour des procédés CMOS ne peuvent souvent pas être directement transférées aux procédés CML bipolaires. Par conséquent, il est important d'étudier la testabilité des logiques CML bipolaires. L'objectif principal est d'éviter le recours aux tests à pleine vitesse, jugés coûteux. La conception pour la testabilité (Design For Testability, DFT) est utilisée pour réduire les coûts de génération de tests et augmenter la couverture de pannes.

Une équipe de recherche précédente a déjà identifié des défauts possibles avec la famille logique CML bipolaire, et a proposé des méthodes de test pour les détecter. Ce mémoire

étudie la propagation des défauts et la dégradation de performance de la famille logique CML bipolaire. Nous avons choisi un type de défectuosité appelé pont qui a un impact fort sur le comportement d'une porte logique CML et nous avons analysé la manière par laquelle elle se propage à travers les chaînes de portes. Cette étude nous a permis de saisir à quel point ces défauts peuvent dégrader la performance des portes CML.

Ce mémoire étudie aussi en détail deux des méthodes de test déjà publiées, afin de déterminer leur compatibilité avec les logiques CML bipolaires. La première méthode de test diminue le rendement. Réciproquement, il se peut qu'elle n'identifie pas les circuits défectueux. En effet, nous montrons pourquoi ce n'est pas une technique pratique pour les procédés CML bipolaires. La deuxième technique de DFT ne peut pas être directement appliquée à cause des contraintes de conception. Nous discutons également des manières de surmonter ces obstacles, afin de rendre ces techniques de DFT faisables. Un ensemble de règles de conception est conçu pour améliorer la testabilité des logiques CML bipolaires. En mode test, nous analysons les effets des méthodes de DFT et des facteurs environnementaux sur la tension de sortie des CML bipolaires.

Une puce de test conçue par une équipe précédente et fabriquée par Nortel est examinée. La génération de vecteurs de test pour cette puce de test est discutée, ainsi que certains résultats de tests préliminaires déjà disponibles. Cette puce est considérée une plateforme d'évaluation des techniques de DFT proposées et appliquées aux portes CML bipolaires. Des méthodes de test, déjà proposées et mises en application dans la puce de

test par l'équipe précédente, ont été modifiées sur la base de nos travaux de recherche. Cependant, les principes de base des méthodes de DFT appliquées demeurent toujours inchangées. Par conséquent, les résultats de test de la puce de test sont très importants, dans la mesure ou ils permettent l'évaluation de la performance des structures DFT. La performance des portes CML bipolaires, en présence des défauts de fabrication, est bien caractérisée dans cette étude. En outre, on propose un ensemble de règles de conception pour la testabilité de ces portes CML bipolaires.

#### **ABSTRACT**

CMOS logics have had much of the scientific communities' attention owing to their low-power and high-density characteristics. However CML logic families implemented with bipolar technologies have continuously occupied lucrative niches such as very high-speed circuits. Advancements in technology have lead to the realisation of high-density, low power bipolar processes. This combined with the high-speed property of bipolar Cols, makes them an excellent choice for high-speed applications. Since no manufacturing process is perfect, testing these logics is important. Very little specific literature exists on the testability of bipolar CML gates. Design For Testability (DFT) methods proposed for CMOS processes cannot be directly transferred to bipolar CML processes. Therefore, it is important to study the testability of bipolar CML logics. The main objective is to obviate the need for expensive at-speed testers. DFT is used to reduce test generation costs and enhance the fault coverage of tests.

A previous research team has reported defects possible with bipolar CML logic families, and test techniques to detect these defects. This thesis studies fault propagation and performance degradation for a bipolar CML logic family. We chose a bridging defect type that has strong impact on the behaviour of a CML logic gate, and we analysed how it propagates through gate chains. This study helped us understand how defects can degrade CML gates' performance.

This thesis also studies two of the reported test techniques in greater detail to determine their suitability for bipolar CML logics. The first test method decreases the yield. Conversely, it may also not be able to identify defective circuits. We show why this is not a practical DFT technique for bipolar CML processes. The second DFT technique cannot be directly applied due to design constraints. We also discuss ways to overcome these obstacles, thus developing practically feasible DFT techniques. A set of design guidelines is devised to enhance the testability of bipolar CML logics. In the test mode, we analyse the impact on the output voltage of bipolar CML by the DFT method due to changes in environmental factors.

A test chip designed by a previous team has been fabricated by Nortel and is being tested. Test pattern generation for this test chip is discussed, together with some of the preliminary test results available. This chip is an evaluation vehicle for the proposed DFT techniques for bipolar CML gates. Test techniques, originally proposed and implemented in the test chip by a previous team, have been modified based on our research. However, the basic principles of the implemented DFT methods still remain the same. Therefore, the test results from the test chip are useful in gauging the performance of the DFT structures. The performance of bipolar CML gates in the presence of manufacturing defects is well characterised in this study. Also a set of design rules is proposed for the testability of bipolar CML gates.

#### CONDENSÉ EN FRANÇAIS

Historiquement, les familles logiques CMOS ont dominé grâce à leurs particularités de présenter une haute densité d'intégration ainsi qu'un faible consommation de puissance. Avec l'évolution technologique, les tailles des éléments bipolaires sont devenues de plus en plus faibles, et dans les applications qui opèrent à haute vitesse, la dissipation de puissance dynamique des portes bipolaires est devenue comparable à celles de type CMOS [27]. Les portes CML bipolaires sont utilisées dans les applications à haute vitesse, telles que le traitement des signaux, les communications par satellite, et les émetteurs/récepteurs de télécommunications.

L'utilisation avec succès des portes CML bipolaires dans les circuits VLSI complexes, nécessite l'application de méthodes de tests permettant de détecter leurs défauts de fabrication. Mentionnons que très peu de documentation existe sur leurs méthodes de test applicables aux familles bipolaires ECL ou CML. Les techniques de testabilité qui sont appropriées aux familles logiques CMOS sont moins adéquates pour les portes CML bipolaires [4, 29]. Étant donné qu'aussi bien les ECL que les CML, font parties des familles de logique non-saturées, certaines méthodes de testabilité proposées pour ECL peuvent être appliquées aux CML bipolaires.

La division microélectronique de Nortel Networks étudie la testabilité des portes CML bipolaires. La bibliothèque de conception NT25<sup>TM</sup> exploite un procédé bipolaire à haute performance. Dans la première phase du projet, Serge Patenaude et Bernard Antaki ont étudié les types de défauts possibles avec les portes CML bipolaires, et ont proposé aussi des méthodes de conception pour la testabilité (Design For Testability, DFT) qui permettent la détection de tels défauts. Cette thèse constitue une continuation de leurs travaux. Ginette Monté participe également à ces travaux.

Les techniques de conception par la testabilité (DFT) sont des méthodes de conception spécialement utilisées pour garantir la testabilité d'un dispositif. L'objectif principal de cette recherche est d'étudier la manière dont les défauts se propagent dans la famille CML bipolaire afin de déterminer leur contribution à la dégradation de la performance des portes CML bipolaires, et par conséquent, de concevoir des techniques de DFT permettant la détection de ces défauts de fabrication. Nous étudions, en détail, deux méthodes de test proposées par Patenaude et Antaki, qui sont applicables aux portes CML bipolaires. Un procédé de génération de vecteurs de test, qui utilise le flot de conception de Nortel et qui permet de tester une puce en appliquant toutes les méthodes de DFT qu'ils ont proposées, est décrit en détail. Certains résultats de test, déjà disponibles, sont présentés. Une des principales idées derrière la conception de telles méthodes de test pour les portes CML bipolaires est d'éviter, d'une part, le recours aux tests à pleine vitesse, qui sont coûteux, et d'autre part, l'utilisation d'un banc de tests fonctionnels à basse vitesse pour la détection des défauts de fabrication [9].

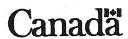

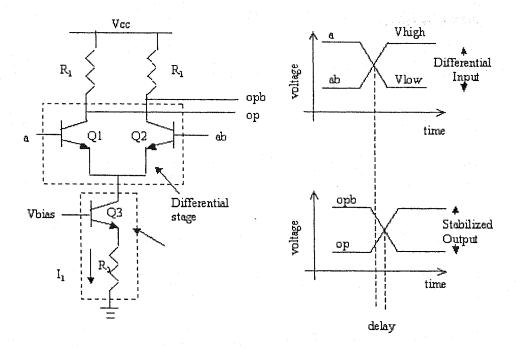

#### Portes bipolaires CML

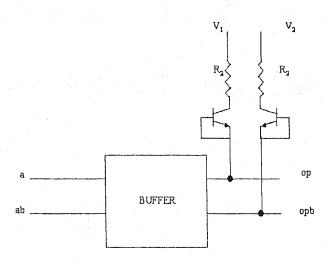

La structure des portes bipolaires CML est définie au chapitre 1. La bipolaire CML est une famille de logique non saturée, purement différentielle. Un inverseur en logique CML bipolaire est présenté à la figure1. Un courant I<sub>1</sub> traverse le transistor Q<sub>1</sub> lorsque l'entrée 'a' est au niveau haut, et par conséquent, la sortie 'op' est portée au niveau bas, comme illustré dans le graphe associé. Lorsque l'entrée complémentaire 'ab' est au niveau haut, le même courant I<sub>1</sub> traverse Q2, et par conséquent, la sortie 'op' est portée au niveau haut. Ainsi, ce circuit fonctionne comme un inverseur.

Figure 1. La porte tampon-inverseur en CML et sa réponse temporelle

Certains défauts peuvent transformer la nature différentielle de la porte. En effet, lorsqu'un court circuit de basse impédance, est inséré entre les entrées complémentaires 'a' et 'ab' ou 'b' et 'bb', d'une porte à 2-entrées, les deux lignes d'entrée ne sont plus

complémentaires l'une à l'autre. Cette défectuosité a fait l'objet d'études intensives tout au long de ce mémoire.

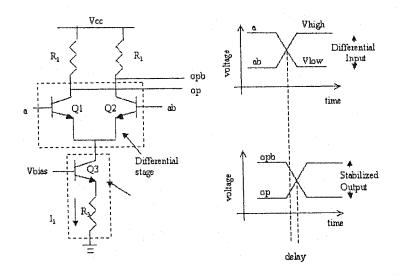

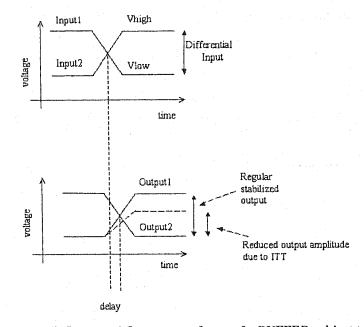

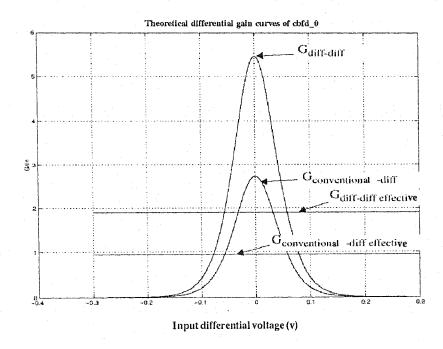

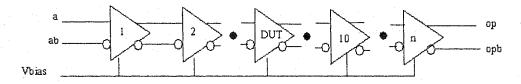

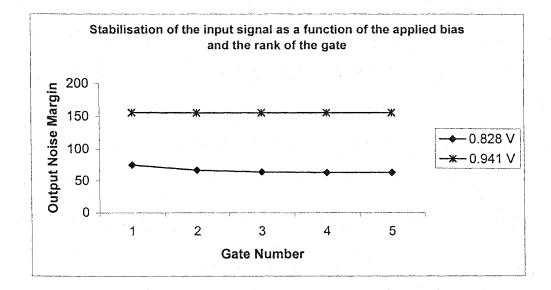

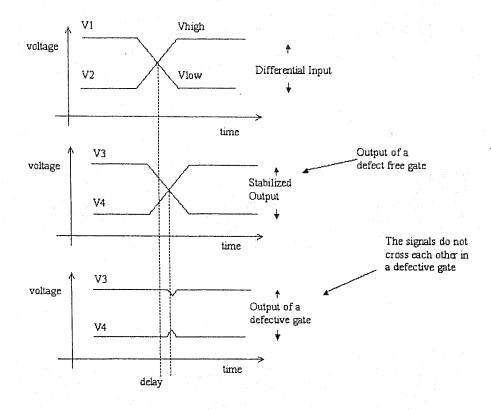

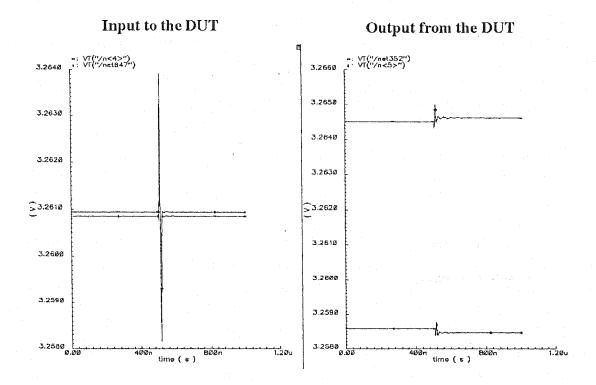

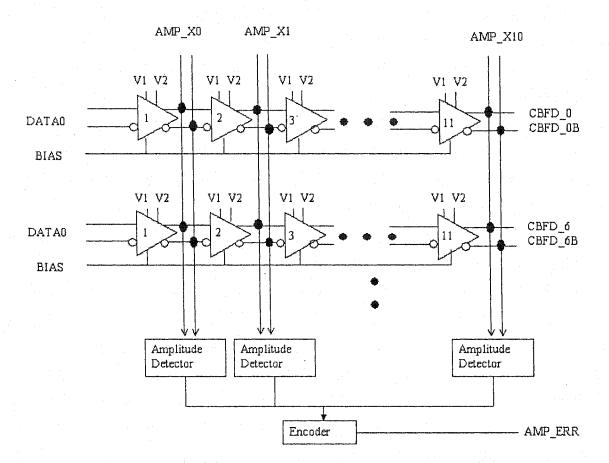

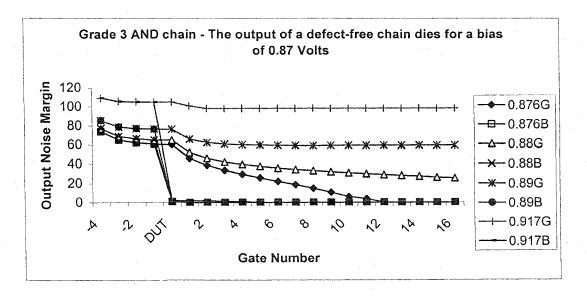

#### Technique de modification du gain par réduction de la polarisation (BAS)

La modification du gain par réduction de la polarisation est une technique qui consiste en l'application d'une phase de stress à un circuit en mode de test, par réduction de la polarisation qui lui est appliquée, afin de détecter des défauts de fabrication. La réduction de la polarisation appliquée à une porte réduit son gain (voir la figure 2.1 pour la courbe de gain). Par conséquent, une porte sans défaut produit une marge de bruit réduite. Par contre, lorsqu'un tel stress est imposé à un circuit défectueux, il rend plusieurs classes de pannes observables, ce qui se traduit par une forte dégradation de l'amplitude du signal de sortie. Lorsque plusieurs portes sont reliées en série pour former un environnement de simulation comme celui de la figure 2, les portes suivantes dans la chaîne n'ont pas assez de gain pour régénérer le rendement produit par une porte défectueuse. Dans ce cas, l'environnement de simulation commence à présenter le comportement d'un collage. Cependant, ces portes peuvent amplifier un signal de sortie de faible amplitude, produit par une porte sans défaut. Les détecteurs insérés à intervalles réguliers et qui sont conçus pour avoir un seuil approprié, peuvent identifier la présence d'un défaut de fabrication. Ainsi, cette technique identifie efficacement une porte défectueuse de celle sans défaut.

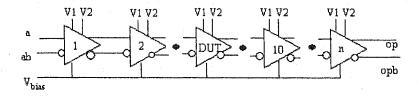

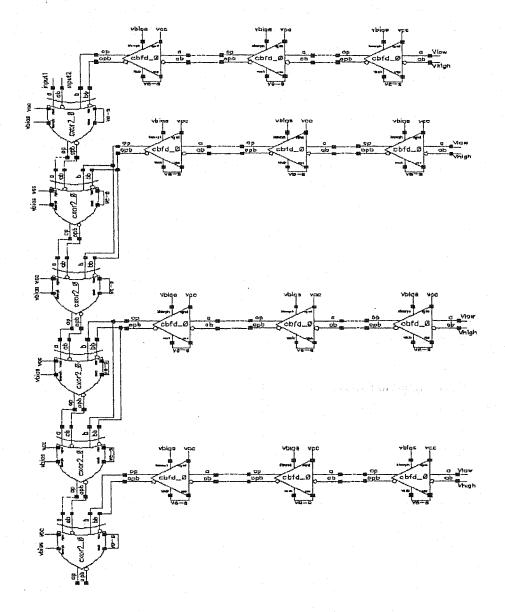

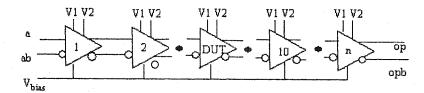

Figure 2. Environnement de simulation pour l'étude de la réduction de la polarisation (DUT: *Device Under Test*)

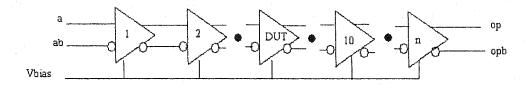

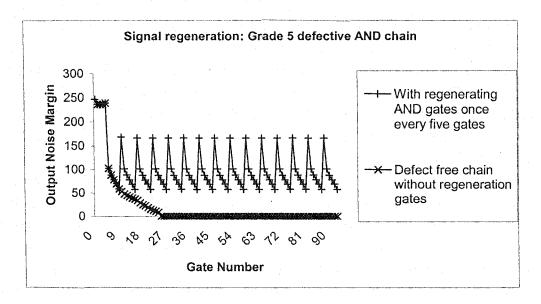

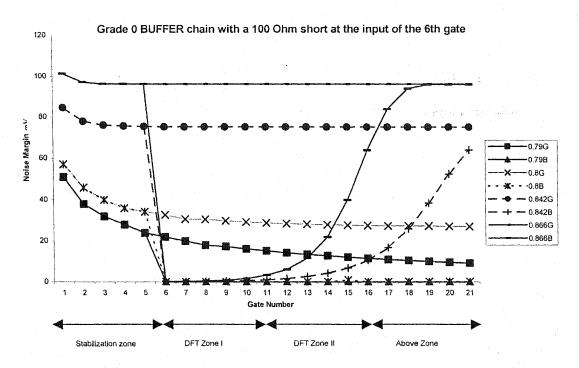

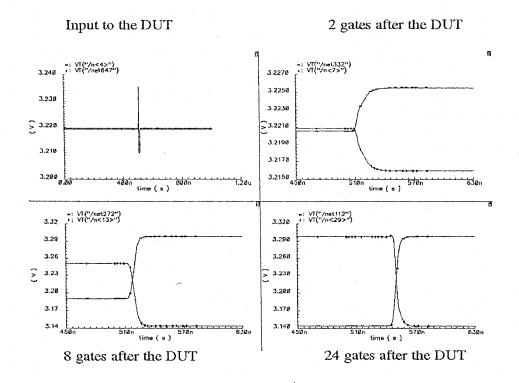

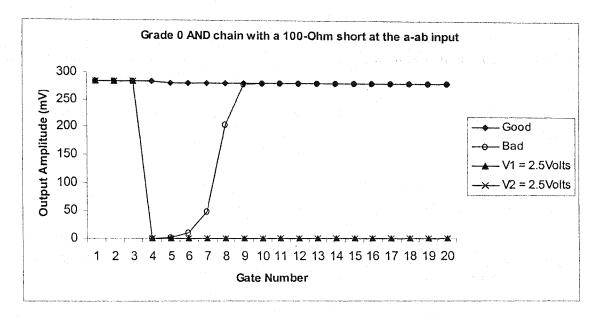

Lorsque la polarisation appliquée est trop faible, les portes n'ont pas assez de gain pour régénérer le signal de sortie produit par la porte sans défaut. Par contre, lorsque la polarisation appliquée est suffisamment élevée, les portes ont assez de gain pour régénérer même un signal de sortie de très faible amplitude produit par une porte défectueuse. Ceci est illustré à l'aide du circuit de la figure 3 pour une chaîne de tampon de grade 0 (la famille logique étudiée est disponible en 7avec un court circuit de 100 ohms à l'entrée de la 6ème porte.

Figure 3. Amplitude à la sortie à travers une chaîne de tampon de classe 0 pour différentes polarisations

Dans la figure 3, l'amplitude à la sortie de chaque porte de l'environnement de simulation est tracée pour différentes polarisations, aussi bien pour les chaînes défectueuses que celles sans défaut. G désigne une chaîne sans défaut (Good) et B désigne une chaîne défectueuse (Bad). L'amplitude de sortie change avec la tension de polarisation. Alors qu'une bonne chaîne fournit une amplitude faible, due à une polarisation réduite dans les premiers niveaux; une chaîne défectueuse produit, soit une amplitude très faible, soit une sortie nulle. Le signal se dégrade rapidement à l'entrée du dispositif sous test (DUT). Quatre zones peuvent être identifiées dans la figure 3 pour la technique de BAS. Dans la zone de stabilisation, le signal d'entrée est passé à travers quelques tampons avant de se stabiliser. La différence dans la marge de bruit restante entre les portes défectueuses et celles sans défauts est élevée dans la zone 'DFT Zone I', ce qui rend cette zone très utile

pour la détection de défauts. Cependant, la différence dans la marge de bruit restante entre les bonnes et les mauvaises chaînes est basse dans la zone 'DFT Zone II', car les portes tendent à amplifier, dans cette zone, des signaux de faible amplitude. Dans la zone 'Above Zone', le signal produit par la chaîne défectueuse est entièrement régénéré. Le nombre de portes dans la chaîne qui se collent dans chacune de ces zones, dépend de la profondeur de la chaîne, du type et du temps de réponse de la porte, ainsi que de la tension de polarisation appliquée.

Cette technique a été étudiée pour des tampons, des portes ET, et des XOR. Avec les contraintes utilisées et la méthodologie adoptée, la gamme utilisable de la marge de bruit de toutes les portes était simplement de 2 mV. Cette valeur est susceptible de changer en raison des variations de procédé. Cette amplitude restante est insuffisante, et par conséquent, elle ne peut pas être utilisée pour identifier une porte défectueuse. Plusieurs méthodes ont été exploitées afin d'améliorer la marge de bruit restante utilisable, mais n'ont pas fourni de résultats satisfaisants. Par conséquent, notre recherche démontre que cette méthode n'est pas pratique pour tester les portes CML bipolaires.

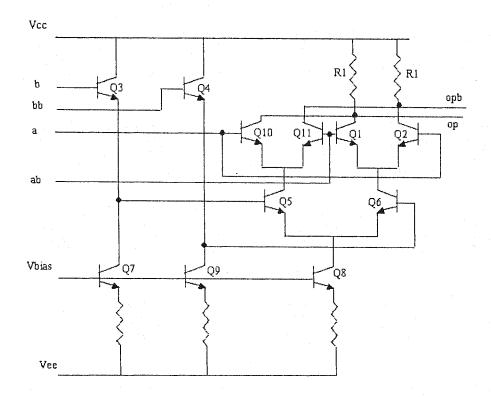

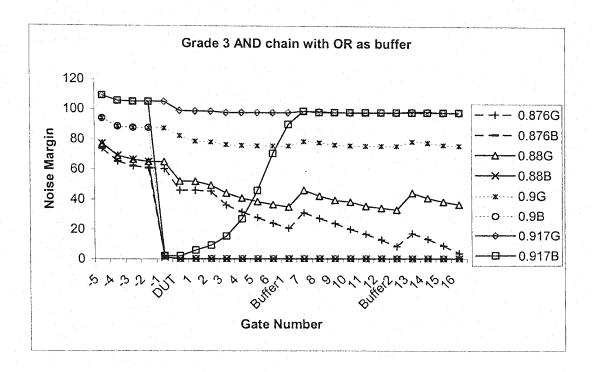

#### Le test de débalancement (ITT)

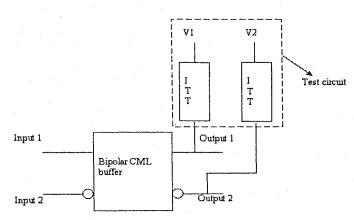

Pour assurer une couverture complète de tous les défauts possibles dans des portes CML, une méthode de test, proposée pour ECL par Anderson [29] et breveté par GERSBACH, E. de J., et MOSER, J.J., [19], est étudiée. Elle porte le nom de 'méthode de test de déséquilibre' (Imbalance Testing Technique, ITT). Cette méthode de test consiste en

l'application d'une phase de stress au circuit entier, afin de provoquer son déséquilibre, et par conséquent, tous les signaux marginaux sont suffisamment dégradés de façon à causer des erreurs logiques. La méthode de test de déséquilibre pour la famille CML bipolaire est étudiée dans cet ouvrage.

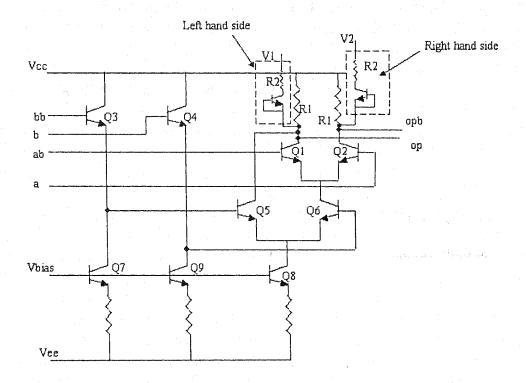

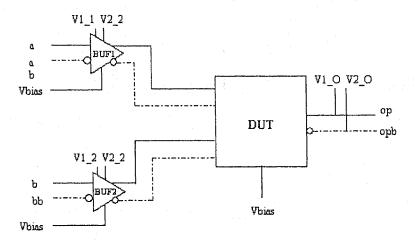

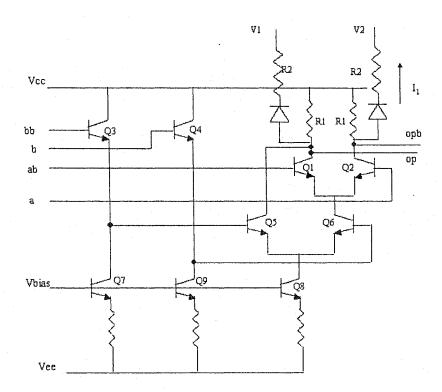

Figure 4. La circuiterie pour le test de débalancement

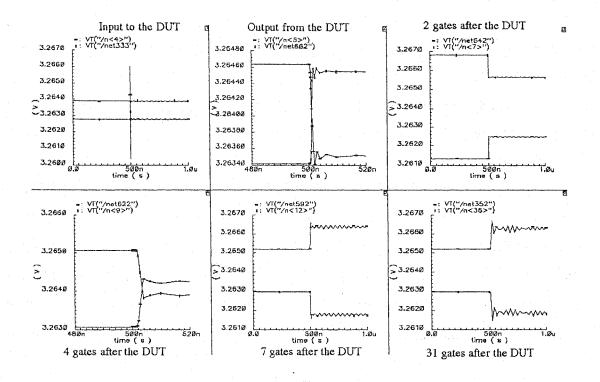

La figure 4 montre les circuits de test de déséquilibre connectés à chacune des lignes de sortie du tampon. En mode normal,  $V_1$  et  $V_2$  sont reliés à  $V_{cc}$ . En effet, la sortie de l'étage différentiel est déséquilibrée seulement si l'une des lignes de test est portée à un potentiel inférieur à  $V_{cc}$ . Lorsque  $V_1$  ou  $V_2$ , est inférieur à  $V_{cc}$ , un courant traverse la diode, ce qui entraı̂ne une réduction de la tension de sortie, et par conséquent, la diminution de la marge de bruit restante en sortie. Avec un déséquilibre convenablement appliqué, et pour le banc d'essai représenté à la figure 5, un circuit défectueux présente le comportement d'un collage.

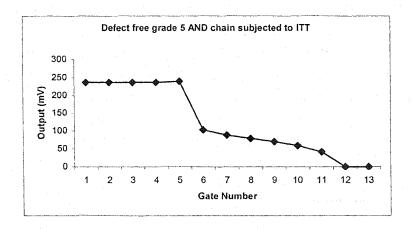

Figure 5. Environnement de simulation pour l'étude du test de débalancement

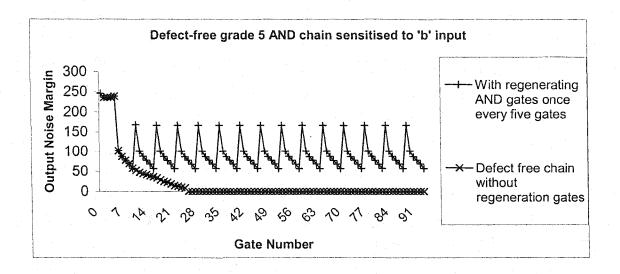

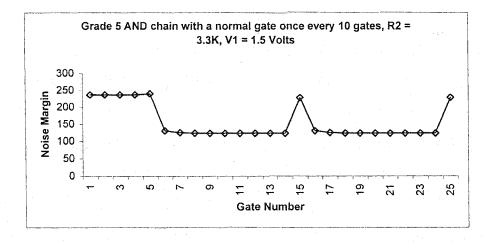

Lorsqu'un déséquilibre élevé est appliqué, une porte ET sans défauts présente le comportement d'un collage. Ce phénomène est appelé « accumulation de débalancement » ou « accumulation de stress ». Il a été démontré que la dissymétrie dans le schéma au niveau transistor de la porte ET, en est la cause. Afin de surmonter le problème d'accumulation, les portes placées à intervalles réguliers dans la chaîne ne doivent pas être déséquilibrées. Par conséquent, leurs gains demeurent inchangés, et elle sont capables de régénérer un signal de faible amplitude sur leurs entrées. Ceci est montré à la figure 6, où une porte normale est placée à la fin de chaque groupement de 5 portes. Ainsi, l'ITT parvient à identifier efficacement les éléments avec des défauts de fabrication. Le fait de soumettre, simultanément, la ligne de sortie et les lignes d'entrée multiples d'une porte à une contrainte de déséquilibre contribue aussi à une accumulation de débalancement. Un certain groupe de lignes déséquilibrées simultanément ne provoque pas l'accumulation, alors que d'autres la provoquent. Ces deux groupes sont identifiés, et des règles de conception sont présentées pour surmonter l'accumulation.

Figure 6. Processus de récupération: La sortie est sensible à l'entrée 'b'

#### Analyse de sensibilité

Les effets de variation de plusieurs paramètres tels que la résistance, la température, etc., sur l'ITT, et par conséquent, sur les portes CML bipolaires, sont analysés en détail. Une recherche dans ce sens a montré que le fait d'insérer deux diodes dans le banc de test de déséquilibre, peut minimiser l'impact de l'accumulation de débalancement. (Voir les tableaux 3.5 à 3.8 au chapitre 3). Ainsi, l'équation en tension est donnée par,

$$V_{cc} - I_1 R_1 - (n \cdot V_{be}) - I_1 R_2 - V_1 = 0$$

La sensibilité de  $V_{out}$ , relativement aux variations dans  $V_{be}$ ,  $R_1$  et  $R_2$ , respectivement, est donnée par les équations suivantes:

$\partial V_{out}^{\Delta} = n \cdot \frac{R_1}{R_1 + R_2} \partial V_{be}^{\Delta}$ , où 'n' est le nombre de diodes,  $\partial V_{be}^{\Delta}$  est la variation de la

$$\partial V_{out} = I_1 \cdot \frac{R_2}{R_1 + R_2} \cdot \partial R_1$$

, où  $\partial R_1$  est la variation de  $R_1$ .

$$\partial V_{out} = I_1 \cdot \frac{R_1}{R_1 + R_2} \cdot \partial R_2$$

, où  $\partial R_2$  est la variation de  $R_2$ .

Dans tous les cas cités ci-dessus, R<sub>2</sub> doit être augmentée ou diminuée, afin de minimiser l'impact des variations sur la tension de sortie. C'est au concepteur de choisir le nombre approprié de diodes ainsi que les bonnes valeurs pour R<sub>2</sub> et V<sub>1</sub>. Avec un degré de liberté si élevé, cette technique peut facilement être modifiée afin d'être compatible avec les contraintes d'utilisation, afin d'obtenir une meilleure couverture des défauts.

#### Testabilité du boîtier de test

tension de diode.

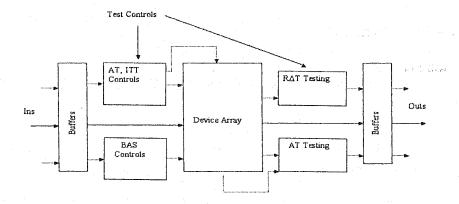

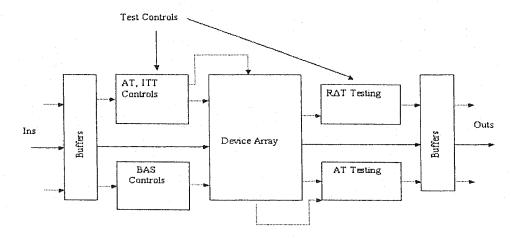

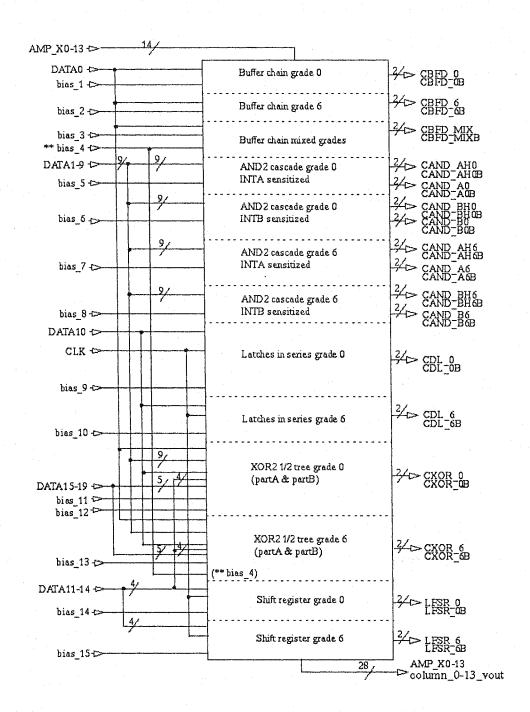

Une puce de test qui implémente les méthodes de testabilité a été proposée et conçue par Patenaude et Antaki. Cette puce de test est composée de deux principaux blocs: une matrice de portes comportant les structures de DFT proposées et le bloc des commandes de test, qui sont intercalés afin de former une architecture matricielle, tel qu'illustré à la figure 7 ci-dessous. Les deux blocs forment les lignes et les colonnes de la matrice, respectivement (voir les figures 5.2 et 5.3). Cette architecture permet de tester facilement n'importe quelle porte choisie

Figure 7. Diagramme bloc de la puce d'évaluation

Le matrice de cellules est composée de portes logiques de différents temps de réponse, connectées entre elles de façon à former des fonctions logiques très simples. Des chaînes des tampons, des blocs combinatoires composés de XOR et de ET, et des machines d'états re-configurables sont présentes dans la matrice de cellules. Les méthodes de test : 'Amplitude Testing' (AT), 'Imbalance Testing Technique' (ITT), 'Bias Alteration Stressing' (BAS), et 'Reduced Delta Testing' (RΔT) sont implémentées dans la puce de test.

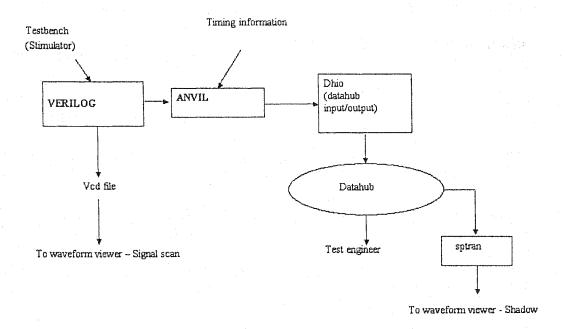

Les tests appliqués à la puce sont suffisamment simples pour permettre de tester complètement les fonctions de toutes les portes. Ils exploitent la structure des commandes des méthodes DFT, lesquelles permettent l'identification de plusieurs défauts dans la puce. Les structures de test sont réalisées avec des modèles de test faits sur commande et générés par l'outil de flot de Nortel. Un vecteur de test se compose de deux parties: a) les stimulus qui sont appliqués aux entrées de la puce, et b) les valeurs désirées aux sorties de la puce. Chaque ligne de la matrice du dispositif possède un générateur de polarisation

programmable dédié (Programmable Bias Generator, PBG), qui permet l'étude de chaque ligne possible, d'une façon indépendante.

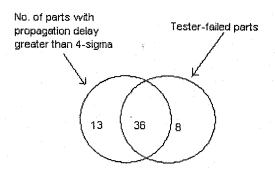

Les éléments défectueux sont identifiés en utilisant (a) des modèles fonctionnels et/ou (b) les techniques de DFT proposées. Les différents tests effectués sur la puce de test, sont énumérés comme suit: le test de continuité, le test de tension, le test de propagation du délai, le test d'amplitude, le test de déséquilibre, et finalement le test de BAS. Le test de propagation de délai est utilisé comme une référence par rapport aux techniques de DFT proposées, afin d'identifier les éléments défectueux. L'objectif est de comparer leur couverture respective, et d'identifier les défauts correspondants afin d'évaluer leur signification qualitative.

De tous les tests effectués avec les vecteurs de test que nous avons développé, 11.4% des éléments manufacturés ont été trouvés défectueux. Quand les résultats de quelques tests seront disponibles, d'autres analyses seront nécessaires afin de tirer des conclusions finales sur l'efficacité des méthodes de test proposées, et ceci est laissé pour des travaux futurs.

#### Conclusion

Nos travaux ont porté sur les validations de méthodes de DFT pour des portes CML bipolaires. Ils sont concluants dans la mesure où les techniques de DFT proposées parviennent à identifier avec succès les éléments défectueux d'un lot manufacturé. Un

ensemble de règles de conception est aussi présenté pour la méthode de test de déséquilibre. La sensibilité de la tension de sortie provoquée par les circuits de test dans l'ITT, due à des divers facteurs environnementaux, est aussi discutée. Une des méthodes de test proposées par une équipe précédente a été considérée invalide à cause de la limitation de l'environnement de test. Ce travail constitue une contribution au domaine du test des portes CML bipolaires. Ce travail peut servir de base pour des travaux futurs sur le sujet.

## TABLE OF CONTENTS

| BACKGROUND INFORMATION AND LITERATURE REVIEW               |    |

|------------------------------------------------------------|----|

| 1.1 Introduction                                           | 5  |

| 1.2 Emitter Coupled Logic                                  | 6  |

| 1.3 Bipolar CML gates                                      | 6  |

| 1.3.1 Inverter                                             | 7  |

| 1.3.2 Bipolar CML OR gate                                  | 9  |

| 1.4 VersArray Technology                                   | 11 |

| 1.5 The importance of testing                              | 11 |

| 1.6 Design For Testability                                 | 12 |

| 1.7 Significance of developing DFT methods for bipolar CML | 13 |

| 1.8 Faults and Defects                                     | 13 |

| 1.9 Fault modelling & Defect modelling for bipolar CML     | 14 |

| 1.9.1 Fault modelling.                                     | 14 |

| 1.9.2 Defects possible with bipolar CML & Defect modelling | 17 |

| 1.10 Types of test                                         | 19 |

| 1.11 Studied DFT techniques                                | 20 |

| 1.11.1 Bias Alteration Stressing Technique                 | 20 |

| 1.11.2 Imbalance Testing Technique                         | 20 |

| 1.12 Summary                                               | 22 |

| BIAS ALTERATION STRESS TECHNIQUE                           | 23 |

| 2.1 Introduction                                                       | 23  |

|------------------------------------------------------------------------|-----|

| 2.2 Test bench setup for characterising BAS technique                  | 24  |

| 2.3 Simulation results                                                 | 34  |

| 2.4 Observations                                                       | 36  |

| 2.5 Methods attempted to increase the usable range of bias voltages    | 46  |

| 2.6 Simulations taking process variations into account                 | 47  |

| 2.7 Summary and Conclusions on BAS testing.                            | 50  |

| IMBALANCE TESTING TECHNIQUE & STRESS ACCUMULATION  3.1 Introduction    |     |

| 3.2 Functionality of AND gates                                         | 52  |

| 3.3 Imbalance Test Technique                                           |     |

| 3.4 Imbalance Types and Limits                                         | 63  |

| 3.5 Analysis of stuck at behaviour observed in defect-free AND gates   | 68  |

| 3.6 Characterisation of ITT on one gate                                |     |

| 3.7 Overcoming stress accumulation                                     |     |

| 3.7.1 Signal regeneration                                              |     |

| 3.7.2 Low imbalance levels                                             | 80  |

| 3.7.3 Different imbalance levels                                       | 83  |

| 3.8 Conclusions                                                        | 83  |

| SENSITIVITY ANALYSIS                                                   |     |

| 4.1 Introduction                                                       |     |

| 4.2 Overview of the proposed testing technique                         | * . |

| 4.3 Deriving the sensitivity of V <sub>out</sub> to various parameters | 87  |

| 4.3.1 Sensitivity of the output voltage to $V_{bc}$ variations | 87  |

|----------------------------------------------------------------|-----|

| 4.3.2 Sensitivity of the output voltage to R <sub>1</sub>      | 88  |

| 4.3.3 Sensitivity of the output voltage to R <sub>2</sub>      | 90  |

| 4.3.4 Power Consumption                                        | 91  |

| 4.4 Analysis                                                   | 92  |

| 4.5 Case study                                                 | 93  |

| 4.5.1 Sensitivity of the output voltage to Vbe variations      | 93  |

| 4.5.2 Variation in R <sub>1</sub>                              | 93  |

| 4.5.3 Variation in R <sub>2</sub>                              | 94  |

| 4.5.4 Power consumed in the test circuit                       | 94  |

| 4.6 Environmental factors                                      | 95  |

| 4.6.1 Impact of chip warming up                                | 96  |

| 4.6.2 Effect of cooling                                        | 96  |

| 4.6.3 Other factors                                            | 96  |

| 4.7 Conclusions                                                | 97  |

| THE TESTING OF THE TEST CHIP                                   |     |

| 5.1 Introduction                                               | 98  |

| 5.2 The Test Chip                                              | 99  |

| 5.3 Device Array Block                                         | 99  |

| 5.3.1 BUFFER                                                   | 103 |

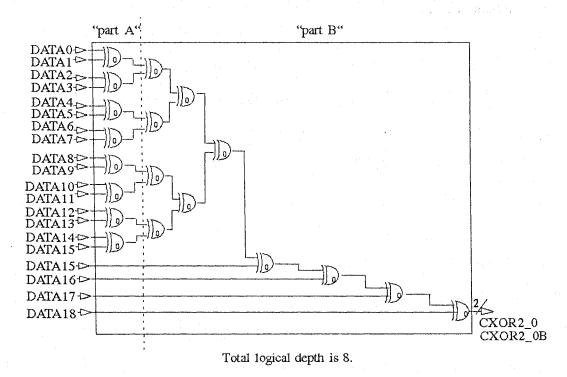

| 5.3.2 XOR                                                      | 103 |

| 5.3.3 AND                                                      | 104 |

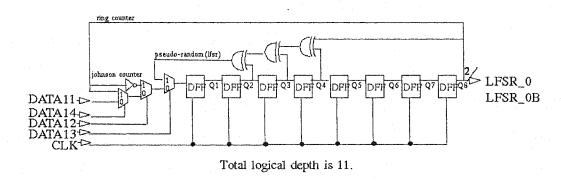

| 534LATCH                                                       | 104 |

| 5.4 Test control block                                      | 105  |

|-------------------------------------------------------------|------|

| 5.4.1 Bias Alteration Stressing (BAS) Technique             |      |

| 5.4.2 Imbalance Testing Technique (ITT)                     | 106  |

| 5.4.3 Amplitude Testing                                     | 106  |

| 5.4.4 Reduced Delta Testing (RΔT)                           | 107  |

| 5.5 Test pattern generation flow and the Testing process    | 108  |

| 5.6 Test pattern generation and the testing of the test chi | p110 |

| 5.6.1 Voltage test                                          | 113  |

| 5.6.2 Propagation Delay test                                | 113  |

| 5.6.3 Amplitude test                                        | 114  |

| 5.6.4 Imbalance test                                        | 115  |

| 5.6.5 BAS test                                              |      |

| 5.7 Test results                                            | 116  |

| 5.8 Summary                                                 | 120  |

# LIST OF TABLES

| BACKGROUND INFORMATION AND LITERATURE REVIEW5                                             |

|-------------------------------------------------------------------------------------------|

| Table 1.1 Truth table of an inverter   7                                                  |

| Table 1.2 Truth table of bipolar CML OR gate                                              |

| Table 1.3 Fault model definitions                                                         |

| Table 1.4 Defect modelling, excerpted from [29]                                           |

| Table 2.1 Truth table of bipolar CML XOR gate                                             |

| Table 2.2 Grade 3 BUFFER chain. Differential voltages representing a signal in mV as a    |

| function of the bias and rank in a defect-free chain when a 250 mV input                  |

| signal is applied to the chain                                                            |

| Table 2.3 Output amplitude (in mV) produced by a grade 0 AND chain with a 100 Ohm         |

| short at the a-ab input of the DUT                                                        |

| Table 2.4 Output amplitude (in mV) produced by a grade 0 AND chain with a 100 Ohm         |

| short at the b-bb input of the DUT41                                                      |

| Table 2.5 Useful bias voltage ranges for fault detection using BAS technique for a 30     |

| gate deep chain43                                                                         |

| Table 2.6 Usable range of bias voltages for BAS testing, for a 10 gate deep chain45       |

| Table 2.7 Usable range of bias voltages for BAS testing, for 15 gate deep chain45         |

| Table 2.8 Usable range of bias voltages for a 10 gate deep chain subjected to random      |

| variations47                                                                              |

| Table 2.9 Usable range of bias voltages for a 15 gate deep chain subjected to random      |

| variations48                                                                              |

| Table 2.10 Output amplitude (in mV) produced by a grade 3 XOR gate chain taking           |

| process variations into account and with a defect at the b-bb input of the                |

| DUT49                                                                                     |

| Table 3.1 Truth table of AND gate and the switching transistors53                         |

| Table 3.2 Grade 0 AND chain with a 100 ohm short at a - ab input, $R_2 = 1.5 \text{ K}59$ |

| Table 3.3 Grade 0 AND chain with a 100 ohm short at b-bb, $R_2 = 1.5 \text{ K}$ 61        |

| Table 3.4 Defect free grade 5 AND chain, $V_1 = 1.5V$ , $R_2 = 3.94K$ , one diode         |

| Table 3.5 Smallest resistance (in KOhms) that causes stuck-at behaviour in a fault free   |

|-------------------------------------------------------------------------------------------|

| 10-gate deep chain, when one diode is used in the test circuitry66                        |

| Table 3.6 Smallest resistance (in KOhms) that causes stuck-at behaviour in a fault free   |

| 20-gate deep chain, when one diode is used in the test circuitry66                        |

| Table 3.7 Smallest resistance that causes stuck-at behaviour in a fault free 10-gate deep |

| chain when two diodes are used in the test circuitry67                                    |

| Table 3.8 Smallest resistance that causes stuck-at behaviour in a fault free 20-gate deep |

| chain when two diodes are used in the test circuitry67                                    |

| Table 3.9 Eight imbalance patterns resulting in very low output noise margins75           |

| Table 3.10 One normal AND gate once in every five imbalanced AND gates, $V_1$ =1.5 V,     |

| R <sub>2</sub> =2.5 K81                                                                   |

| Table 5.1 Modes of operation of the re-configurable shift register105                     |

| Table 5.2 Propagation delay – mean and sigma values                                       |

## LIST OF FIGURES

| Figure 1.1 Bipolar CML Inverter                                                   |     |

|-----------------------------------------------------------------------------------|-----|

| Figure 1.2 Schematic of bipolar CML OR gate                                       | 10  |

| Figure 1.3 BUFFER with Imbalance test circuitry                                   | 21  |

| Figure 1.4 Input and Output waveforms of a BUFFER subject to ITT                  | 21  |

| Figure 3.1 Schematic of Bipolar CML AND gate with imbalance test circuit          | 54  |

| Figure 3.2 BUFFER test bench employed for ITT                                     | 56  |

| Figure 3.3 Output of a defective chain with & without ITT                         | 60  |

| Figure 3.4 Defect-free grade 5 AND chain outputs s-@-f when subjected to ITT      | 62  |

| Figure 3.5 Setup employed to characterise the ITT on one gate                     | 71  |

| Figure 3.6 Imbalance Analyser simulation results                                  | 72  |

| Figure 3.7 Signal regeneration: Output amplitude with & without regenerating gate | s79 |

| Figure 3.8 Periodic behaviour of the AND chain during signal restoration          | 81  |

| Figure 3.9 Steady output of defect-free AND chain for low imbalance voltages      | 82  |

| Figure 4.1 ITT as applied to a bipolar CML AND gate                               | 86  |

| Figure 5.1 Block Diagram of the Test Chip                                         | 99  |

| Figure 5.2 Block diagram of the device array                                      | 101 |

| Figure 5.3 Matrix architecture                                                    | 102 |

| Figure 5.4 XOR half tree                                                          |     |

| Figure 5.5 Re-configurable shift register.                                        | 105 |

| Figure 5.6 Test pattern generation tool flow                                      | 110 |

| Figure 5.7 Venn diagram of the tester-failed and sigma deviation parts            | 119 |

#### ABBREVIATIONS

AT Amplitude Testing

ATE Automatic Test Equipment

ATPG Automatic Test Pattern Generation

B Bad

BAS Bias Alteration Stressing

BSU Basic Step Unit

CML Current Mode Logic

CMOS Complementary Metal Oxide Semiconductor

DFT Design For Testability

DUT Device Under Test

ECL Emitter Coupled Logic

G Good

IC Integrated Circuit

IFA Inductive Fault Analysis

i/p input

ITT Imbalance Test Technique

NM Noise Margin

o/p Output

PBG Programmable Bias Generator

RΔT Reduced Delta Testing

RNM Remaining Noise Margin

TPG Test Pattern Generation

VCD Value Change Dump

VLSI Very Large Scale Integration

# LIST OF APPENDICES

| APPENDIX I   | <br>132 |

|--------------|---------|

| APPENDIX II  | <br>133 |

| APPENDIX III | <br>135 |

| APPENDIX IV  | <br>139 |

#### INTRODUCTION

Historically, MOS logic families have dominated due to their high density and low power consumption characteristics. However, ECL and CML logic families implemented with bipolar technologies have continuously occupied lucrative niches such as very high-speed circuits. The evolution of technology has lead to the realisation of high-speed circuits. Switching speeds up to 50 Gb/s and gate delays far below 1ns have been reported in [33]. CML gates are used in high-speed applications like telecommunications, transmitters, receivers, microwave digital processing, satellite communications, etc.

CML gates have maintained their popularity owing to their high speed and high gain characteristics. In order to successfully use these gates for complex VLSI circuits, it is imperative to test them for manufacturing defects. Very little specific literature exists on the testability of bipolar CML gates, as discussed in chapter 1. The dominance of MOS technologies has had for consequence that ECL and CML technologies have received little attention. Due to the technological evolution, area of bipolar devices has decreased significantly, and the dynamic power dissipation of bipolar gates favourably compares with CMOS in very high-speed applications [27]. Several testability techniques suitable for CMOS families are less appropriate for bipolar CML gates [4, 29]. Since both ECL and CML are non-saturating logic families, some of the testing techniques proposed for ECL may be applicable to bipolar CML as well.

The microelectronic division of Nortel Networks was studying the testability of bipolar CML gates, for their technology. NT25<sup>TM 1</sup> design kit is based on a high performance bipolar process. In the first phase of the project, Patenaude and Antaki studied the possible defects with bipolar CML gates, and also proposed DFT methods to detect such defects. This master thesis is a continuation of their work. Monté is also presently studying complementary related issues.

The main purpose of the work reported here is to determine how defects propagate in this logic family, and also to study how these defects degrade the performance of bipolar CML gates. We also study some of the potential testing techniques proposed by Patenaude and Antaki, as applicable to Bipolar CML gates. Certain testing techniques used in combination to improve fault coverage, were analysed in a test chip designed by Patenaude and Antaki [4, 29, 28]. One of the main ideas behind devising testing techniques for Bipolar CML gates was to obviate the need for expensive at-speed testers and use de-testing to detect manufacturing defects [9].

The first chapter of the thesis presents the basic concepts of bipolar CML gates and briefly describes the NT25<sup>TM</sup> VersArray technology. Some of the benefits of these gates are listed, and the importance of testing and design-for-testability is highlighted. Possible faults with these gates are also listed. This chapter also reviews some relevant literature. We also give a notion of the testing techniques that have been studied in this work.

I donain a dia me

NT25 is a trademark of Nortel Networks.

The second chapter studies one of the testing techniques, called the Bias Alteration Stressing (BAS) technique in detail. This testing technique enables the study of fault propagation in bipolar CML gates and also helps analyse the performance degradation of these gates. With this knowledge, it becomes easier to understand the characteristics of these gates and further devise suitable testing techniques for them. The results obtained for some of the gates studied are presented and analysed.

In the third chapter, we extend a testing technique studied for ECL gates to bipolar CML gates. We call this the Imbalance Testing Technique (ITT). Our analysis of this technique uncovers performance degradations in bipolar CML gates. The limitations imposed by these gates due to their design on ITT are also studied. We also present some useful methods to overcome the uncovered limitations. We finally present a set of design rules to avoid the limitations.

The fourth chapter discusses the sensitivity of the test circuitry proposed in chapter three to various parameters like noise, temperature, process variations, etc. These are some of the important factors to be taken care of while implementing the testing technique in an actual circuitry.

The fifth chapter discusses the test vectors generated for testing the test chip that implements some of the testing techniques studied by the previous team in the project. We also present some results obtained using these vectors. This chapter analyses the

efficiency of the testing techniques, and the fault coverage obtained by independent and combined study of different test techniques.

### **CHAPTER 1**

## BACKGROUND INFORMATION AND LITERATURE REVIEW

#### 1.1 Introduction

Complementary Metal Oxide Semiconductor (CMOS) technologies posses several advantages that largely stem from the low static power dissipation of some logic families they allow to integrate. It became the dominant technology and its testability was deeply studied. However, the testability of bipolar logic gates received very little attention from the scientific community due to their low density and high power consumption characteristics. Current Mode Logic (CML) devices using bipolar technology has long been the technology of choice in applications requiring logic functions at multi-gigahertz rates, where switching speed is more important than power dissipation and cost [4, 29, 19, 30, 32, 26, 27]. With the achievement of low power, high speed and high density, CML can find a variety of applications [27, 35]. In today's world, there is a strong interest in high-speed electronic technologies [26, 27].

In order to successfully use bipolar CML gates in circuits, it becomes imperative to study their testability. Their testability is a rarely studied topic. In order to fill this gap, and to be able to use these gates, we studied the testability of Nortel Networks' NT25<sup>TM</sup> bipolar CML technology combined with the VersArray technology that comprise a cell library and a set of technology files [6]. This bipolar CML logic family is similar to Emitter

Coupled Logic (ECL) families [4, 29]. Hence, we first briefly discuss ECL logic families, before focusing on CML.

## 1.2 Emitter Coupled Logic

Emitter Coupled Logic (ECL) is a non-saturated digital logic family. ECL is based on the use of a multi-input differential amplifier to amplify and combine digital signals, and emitter followers to adjust the dc voltage levels. They operate by diverting the current from one path to another rather than by switching the transistors 'on' and 'off'. The transistors remain entirely within their active operating regions at all times. Hence, the transistors have a much reduced charge storage time to contend with, and can change states much more rapidly. Therefore, it is possible to achieve propagation delays of 300 ps [27, 11]. Thus, the main advantage of this type of logic gates is their extremely high speed.

## 1.3 Bipolar CML gates

Bipolar CML gates are low power, high gain, and high-speed gates, operating in the low GHz frequency range. Like ECL, bipolar CML families operate by switching current between conducting and non-conducting branches of the gates. Bipolar CML gates are purely differential; using low voltage swings (250 mV) that lead to faster circuits and reduced power consumption [6]. Differential signalling reduces EMI (electromagnetic interferences), and is also less sensitive to cross talk, and offers high noise immunity.

In order to study the testability of a particular logic, it is important to understand its functionality. To orient the reader, in this section, we describe how bipolar CML logics are implemented in the VersArray NT25<sup>TM</sup> technology and also explain the operation of a simple inverter [6]. Then we also explain the operation of a two-level OR gate. Antaki [4] developed a set of Boolean equations for the outputs of Nortel's bipolar CML logic gates.

## 1.3.1 Inverter

Bipolar CML inverter is a simple logic gate using only one differential transistor pair as shown in the figure below. The output waveform of the inverter and its truth table are presented.

Table 1.1 Truth table of an inverter

| A    | ab   | ор   | Opb  |

|------|------|------|------|

| High | Low  | Low  | High |

| Low  | High | High | Low  |

Figure 1.1 Bipolar CML Inverter

In figure 1.1,  $V_{bias}$  is the bias voltage applied to the gate. The current  $I_1$  is supplied using a current source transistor. Input 'ab' is the complement of input 'a'. Similarly, outputs 'opb' and 'op' are complementary.

- When input 'a' is high, current I<sub>1</sub> flows through Q1, lowering the output voltage 'op'. On the other hand, no current flows through Q2, and therefore, 'opb' is high. Thus, when 'a' is high, 'op' is low; 'opb' is high, and the gate functions as an inverter.

- When 'ab' is high, the current I<sub>1</sub> flows through the transistor Q2, lowering the voltage 'opb'. When 'a' is low, being the complement of 'ab', no current flows through transistor Q1. Hence, 'op' is high and again the gate functions as an inverter.

The same circuit can be used as a buffer by simply switching the differential output lines, 'op' and 'opb' [4, 29, 6].

## 1.3.2 Bipolar CML OR gate

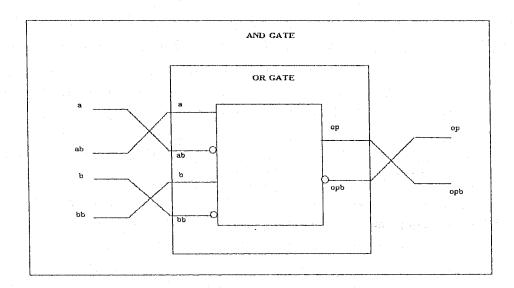

In this thesis, we also focus our attention on gates like OR, AND, and XOR. Bipolar CML AND gates and OR gates have received special attention in our study, for reasons that will become evident in chapters 2, 3 and 4 of this thesis. The operation of the OR gate is explained here, and the schematic of the XOR gate is given in figure 2.3.

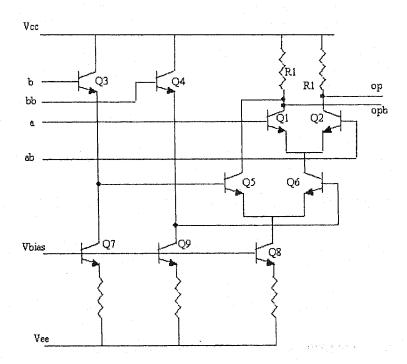

Figure 1.2 shows the schematic of a bipolar CML OR gate. The two input OR gate has two differential transistor pairs, one for each set of complementary inputs. The number of differential pairs in a circuit is equal to the number of complementary input signals [4, 6]. Each of the additional differential pairs uses level shifters to avoid saturation. In this schematic Q3 and Q4 are used for level shifting. For a two input circuit to function as an OR gate, when both the inputs are low, the output should be low, and it should be high otherwise [19]. In the schematic of figure 1.2,

- When the inputs 'a' and 'b' are high, the current flows through transistors Q1 and Q5, driving 'opb' low and 'op' high.

- When 'a' is high, and 'b' is low, the current flows through transistors Q1 and Q6, driving 'opb' low and 'op' high.

- When both 'a' and 'b' are low, the current flows through Q6 and Q2, driving 'op' low and 'opb' high.

- When 'a' is low and 'b' is high, the current flows through Q5, and the upper differential pair receives no current, even though the transistor Q2 can conduct.

Thus, 'opb' is driven low and 'op' is driven high.

The truth table of bipolar CML OR gate is given below. This table lists the transistors that conduct for a given signal value.

Figure 1.2 Schematic of bipolar CML OR gate

Figure 1.3

Table 1.2 Truth table of bipolar CML OR gate

| A | ab | b | bb | Conducting transistors | ор | opb |

|---|----|---|----|------------------------|----|-----|

| 0 | 1  | 0 | 1  | Q2, Q6                 | 0  | 1   |

| 1 | 0  | 1 | 0  | Q1, Q5                 | 1  | 0   |

| 1 | 0  | 0 | 1  | Q6, Q1                 | 1  | 0   |

| 0 | 1  | 1 | 0  | Q5, Q2                 | 1  | 0   |

# 1.4 VersArray Technology

Nortel Networks' VersArray technology is a gate array technology [6]. It consists of an array of Basic Step Units (BSU). Each basic step unit consists of two transistors and a resistor. These transistors and resistors are then connected together to form the desired logic. This technology offers seven speed grades by varying the value of the resistor R<sub>1</sub> and the applied bias. The right speed grade can be chosen based on the speed/power requirements. The functionality and architecture of NT25<sup>TM</sup> bipolar CML has been discussed so far. The following sections discuss the importance of testing, different design for testability methods and fault modelling for bipolar CML.

## 1.5 The importance of testing

During the fabrication of an IC, physical defects could occur [34]. Examples of physical defects are: improper contact windows, oxide breakdown, surface impurities, thin metal wire, etc. Testing of a system is an experiment in which the system is exercised and its

resulting response is analysed to ascertain whether it behaved correctly [2]. Testing is used to isolate the defective parts from a manufactured lot. Testing is important to ascertain the quality of a manufactured part. An undetected defect may fail the chip later on in the field due to various factors like high current, voltage, or environmental attributes. Detecting and discarding a defective chip at an early stage is more economic than detecting a defective board used in a system, in spite of the testing costs involved.

## 1.6 Design For Testability

Design For Testability (DFT) techniques are design methods specifically employed to ensure that a device is testable. *Controllability, observability* and *predictability* are the three most important factors that determine the complexity of deriving a test for a circuit.

- Controllability is the ability to establish a specific signal value at each node in a circuit by setting values on circuit's inputs.

- Observability is the ability to determine the signal value at any node in a circuit by controlling the circuit's inputs and observing its outputs.

- Predictability is the ability to obtain known output values in response to a given input stimuli.

DFT is used to reduce test generation costs and enhance the quality (fault coverage) of tests. For structured DFT techniques, tests are generated automatically, increasing the quality and substantially decreasing the test development time. This significantly affects the time to market of a product and hence its commercial success. Hence, it is important

to have a structured DFT methodology in place for any type of logic family. References [2] and [8] are excellent textbooks on testing and DFT. Significance of developing DFT methods for bipolar CML

In conventional digital testing, the Automatic Test Equipment (ATE) applies test vectors at the primary inputs of the circuit, measures the signals at the primary outputs of the circuit, and compares this against the expected output values to determine if the chip is defective. Due to the high gain of bipolar CML gates, these gates tend to mask noise margin faults, as reported in [4, 29, 19, 31, 32]. Classical digital testing techniques do not detect a good proportion of these faults, as the faults are not propagated to the primary outputs of the circuit (not *observable*). Therefore, it is important to develop DFT methods to detect such defects. This is the main objective of our study. We study two DFT techniques in detail to determine their suitability for bipolar CML. Proper modelling of the faults is essential to obtain high fault coverage. The following sections discuss the difference between defects and faults, their coverage, and modelling. The studied DFT techniques are also briefly described in this chapter.

#### 1.8 Faults and Defects

A defect in an electronic system is the unintended difference between the implemented hardware and its intended design. Examples are: unintended shorts between nets, an open in a net, etc. A representation of a 'defect' at the abstract function level is called a fault. The difference between a defect and a fault is that they are imperfections in the hardware and function, respectively.

Fault coverage is defined as the ratio of the number of detected faults to that of faults in the initial fault list. Defect coverage is the probability with which the test detects any defect that occurs on the chip.

# 1.9 Fault modelling & Defect modelling for bipolar CML

In order to design bipolar CML gates for their testability, it is important to understand the defects possible with this logic family. Patenaude [29] and Antaki [4] carried out an extensive study of the defects possible in bipolar CML. They developed a fault dictionary for CML gates and also proposed a few DFT techniques to detect some of these defects [5, 30]. They developed fault models for bipolar CML gates, and developed tools for Inductive Fault Analysis (IFA) and also to test CML gates [30, 31, 32]. In the following sections, we discuss the different types of fault modelling and defect modelling relevant to bipolar CML.

#### 1.9.1 Fault modelling

Physical faults do not allow direct mathematical testing and diagnosis. Logical faults are a convenient representation of the effect of the physical faults on the operation of the system. A fault is detected by observing the error caused by it. The basic assumptions regarding the nature of logical faults are referred to as a "fault model". Fault models are used to provide a fault list for test generation and test verification [2, 8]. Therefore, the

Commercial Garage

fault list, and hence the fault model used to generate it, play a key role in determining what test set is generated and its perceived effectiveness [12].

Esonu et al. [10] have reported a detailed study of fault models for shorts, stuck-at, truth table, delay, and Iddq faults for bipolar ECL. Some of the relevant fault models available in the literature are briefly described in table 1.3. While most of the fault models are described in [2, 8], additional references are provided for each model in the table. Menon et al. [26, 21, 23] analysed faults in simple logic circuits and suggested that transistor level testing provides a higher coverage of faults compared to that at the gate level. It is necessary to study the effects of failures at the transistor level and develop accurate fault models at this level [1]. The major fault models at transistor level are stuck-at faults, and bridging faults [7]. Bridging faults are reported to be the major failure modes in ICs in [27]. Certain bridging faults manifest as stuck-at faults [15]. Bridging faults are reported to be up to 30% of all the faults in [12] and up to 50% of all the faults in [20].

Table 1.3 Fault model definitions

| Fault model                   | Definition                                                                                                                                                                                                                                                                                                                                                              | References                   |

|-------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|

| Bridging fault                | A physical short between two signal lines is referred to as a bridging fault.                                                                                                                                                                                                                                                                                           | 18, 19, 20, 31               |

| Delay fault                   | These faults cause the combinational delay of a circuit to exceed the clock period. Specific delay faults are transition faults, gate-delay faults, line-delay faults, segment-delay faults, and path-delay faults.                                                                                                                                                     | 18, 30, 31                   |

| Like fault                    | A fault that forces both outputs of a differential circuit to identical values for certain input combinations, without causing any of the outputs to be stuck-at.                                                                                                                                                                                                       | 17, 29, 33                   |

| Path delay fault              | This fault causes the cumulative propagation delay of a combinational path to increase beyond some specified time duration. "Propagation delay" is defined as the propagation of a signal transition through a given path. Thus, for each combinational path there are two path-delay faults, which correspond to the rising and the falling transitions, respectively. | 21, 22, 30, 31               |

| Parametric fault              | Such a fault changes the values of electrical parameters of active or passive devices from their nominal or expected values                                                                                                                                                                                                                                             | 2, 4, 31, 32                 |

| Reduced Noise<br>Margin fault | A fault that reduces the remaining output noise margin.                                                                                                                                                                                                                                                                                                                 | 3, 4, 5, 12,<br>13, 14       |

| Stuck-at fault                | This fault is modelled by assigning a fixed (0 or 1) value to the input or output of a logic gate. Single stuck-at faults have 2 faults per line, stuck-at-1 and stuck-at-0.                                                                                                                                                                                            | 2, 17, 18,<br>20, 27, 31, 32 |

| Transition fault              | The gate delay of a given gate, usually an increase over the nominal value, is assumed to be large enough to prevent a passing transition from reaching any output within the clock period, even when the transition propagates through the shortest path. Possible transition faults of a gate are slow-to-rise and slow-to-fall types.                                | 3, 4, 14, 15,<br>32          |

| Truth-table fault             | A fault that produces an output of a logic gate that is different from the expected value for a given input.                                                                                                                                                                                                                                                            | 3, 4, 14, 15,<br>31          |

The most widely used fault model is that of a single line (wire) being permanently

<sup>&</sup>quot;stuck" at a logic value. Single-stuck fault model is a classical or standard fault model,

as it has been widely studied in the literature. A non-classical fault, in general refers to a fault other than a stuck-at fault. When choosing a fault model, it is important to select a model whose faults are generally dominated by faults of other fault models, because a test set detecting the faults of the chosen model will also detect many other faults that are not even explicitly considered. The best fault model representing many different physical faults is the single-stuck fault model [2, 8]. Tests that detect classical faults detect many non-classical faults as well [2].

Stuck-at faults at the gate level are the most popular fault models in digital testing. Automatic Test Pattern Generation (ATPG) tools support classical stuck-at fault models for structured tests. ATPG tools greatly reduce the test generation time and cost. If we could model most of the defects present in the bipolar CML family as stuck-at faults, then the process of test pattern generation can be automated. Therefore, in this study we use stuck-at faults models. Anderson [3] has proposed a DFT technique for ECL that forces stuck-at behaviour in defective gates. We study this method in detail in Chapter 3.

#### 1.9.2 Defects possible with bipolar CML & Defect modelling

In this section we study how the different physical defects possible with bipolar CML are mapped to fault models. A defect such as a short between a net and ground can be modelled as a 'stuck-at' fault. This 'short' is modelled by connecting a very low resistance in series between the net and the ground. Other defect models are discussed in

in a la Miner

table 1.4, excerpted from [29]. Proper fault modelling is required to obtain high fault coverage.

Table 1.4 Defect modelling, excerpted from [29]

| Defect type                                               | Definition                                                                                                                                                  | Model                                                                                                                                                      | References                   |

|-----------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|

| Short-circuit<br>between<br>different<br>transistor nodes | Used to model any defect causing an undesired interconnection between two terminals of a transistor.                                                        | Modelled using a small resistance or a direct connection between the two nodes.                                                                            | 3, 13, 17, 24,<br>23, 10, 18 |

| Open-circuit in a transistor terminal                     | Used to model any defect breaking a transistor node.                                                                                                        | Modelled using a high resistance, normally above 1 Mohms (some times in parallel with a small capacitor) in series with the terminal of the transistor.    | 3, 13, 17, 26,<br>10, 24, 18 |

| Pipe between collector and emitter                        | Used to model any defect causing an abnormal behaviour in a bipolar transistor (normally an abnormally high current between the collector and the emitter). | Modelled using a resistance connected in parallel between the collector and the emitter (the value of this resistance varies from 400 Ohms to a few KOhms) | 3, 13, 17, 10,<br>18         |

| Bridge between<br>two nodes                               | Used to model any short-<br>circuit between two<br>unspecified nodes.                                                                                       | Modelled by using a resistor between 400-Ohms and a few Kohms.                                                                                             | 17, 27, 12,<br>10, 25, 18    |

| Open                                                      | Used to model any open on an unspecified node.                                                                                                              | Modelled by using a resistor<br>above 1MOhms (sometimes in<br>parallel with a small capacitor)                                                             | 9, 17, 18                    |

We are interested in characterising the fault propagation and the performance degradation of bipolar CML gates. In a differential circuit, when one of the two differential inputs is defective and is shorted to the other, the output signals should not complement each other, as described by Menon et al. in [27, 14]. The differential output lines will exhibit stuck-at fault. Therefore, the differential output amplitude is zero. Such a defect should

be easy to detect, and hence it is used in our study. The effect of such a defect is described in detail in Chapter 2.

## 1.10 Types of test

In general, each chip is subjected to two types of tests, parametric and functional tests, as described below. These tests are further discussed in Chapter 5.

Parametric tests: DC parametric tests include shorts test, opens test, maximum current test, leakage test, output drive current test, and threshold levels test. AC parametric tests include propagation delay test, setup and hold test, functional speed test, access time test, refresh and pause time test, and rise and fall time test. These tests are usually technology dependant.

Functional tests: These consist of the input vectors and the corresponding responses. They check for proper operation of a verified design by testing the internal chip nodes. Functional tests cover a very high percentage of modelled faults (e.g., stuck-type).

Testing combinational and sequential circuits: Combinational circuits are tested by applying a sequence of test vectors and by comparing the output response with the expected output response. The tests in the sequence may be applied in any order. Almost, all digital systems of any significant size are realised as sequential circuits [2, 8]. Testing sequential circuits is considerably more difficult than testing combinational circuits. To detect a fault a test sequence is usually required, rather than a single input vector, and the response of a sequential circuit is a function of its initial state.

## 1.11 Studied DFT techniques

Some of the testing techniques proposed by Patenaude and Antaki [4, 29] are studied in detail to determine if they can be successfully used for bipolar CML gates [5, 28, 19, 30, 31, 32]. These techniques are briefly described below. In this study, we also uncovered some roadblocks and showstoppers. We discuss means to circumvent the problems found with these techniques. Therefore, some of these DFT methods can be used for bipolar CML family, as reported in [19].

## 1.11.1 Bias Alteration Stressing Technique

The first technique that we study is called the Bias Alteration Stressing (BAS) technique, in which the bias applied to the gate is altered to stress the gate [4, 29, 16]. With reduced bias, the gain of the gate is altered and a good gate outputs low amplitude, while a defective gate outputs very low amplitude or exhibits stuck-at behaviour.

## 1.11.2 Imbalance Testing Technique

The second technique is called the Imbalance Testing Technique (ITT) and was originally proposed for ECL gates by Anderson [3, 4, 29]. In ITT, a DFT circuitry is added to each of the two output lines of the gate. The idea is to reduce the output voltage of one of the complementary signals by dropping some voltage across the corresponding test circuit shown in figure 1.3. The gate is partially imbalanced by stressing one output line at a time. When only one output line is imbalanced, the differential output amplitude is lower than in a normal gate. This is shown in figure 1.4. By contrast, defective gates are often

led to exhibit stuck-at behaviour, leading to detection of defects on the biased side of the gate. Similarly, the other output line is imbalanced, after the first one has been restored to its original state. Therefore, ITT is a two-pass testing method.

Figure 1.4 BUFFER with Imbalance test circuitry

Figure 1.5 Input and Output waveforms of a BUFFER subject to ITT

We also study in detail the effect of variation of various parameters like resistance, temperature, etc., on the imbalance testing technique. The test chip implementing the test methods suggested by Patenaude and Antaki was fabricated [28]. We also discuss how we generated functional test patterns for this test chip. The testing of the test chip is not fully completed yet, and Ginette Monté is analysing the results available so far.

## 1.12 Summary

Evidently, very little literature exists on the testability of bipolar CML logics. Bipolar CML gates find extensive applications in high-speed digital circuits. We discussed about fault modelling and different types of faults possible with them. Bridging faults contribute to a major portion of the total faults. Bridging faults cover a wide variety of shorts. Menon's research on bipolar emitter coupled logics has been useful to successfully position our study on bipolar current mode logics. Some of the testing techniques already proposed by Patenaude and Antaki are studied in much detail in this thesis to find their suitability for the bipolar CML family.

#### **CHAPTER 2**

### BIAS ALTERATION STRESS TECHNIQUE

#### 2.1 Introduction

CML gates are growing in popularity owing to their high speed, high gain and relatively low power consumption characteristics. Due to their high gain, even a small signal output produced by a defective gate is quickly regenerated by other defect-free gates in the circuit as explained by the gate's gain coupled to their differential nature in figure 2.1 The classical definition for gain, G<sub>diff-diff</sub> is defined as the ratio of the differential output voltage to the differential input voltage. Other gain definitions can be found in [29]. CML gates tend to mask noise margin faults due to their high gain. Such defects could be detected, by altering the gain of the gate, degrading the performance of the gate. Bias Alteration Stressing (BAS) is a technique in which the circuit is stressed in the test mode by reducing the bias applied to it, to detect such defects [29]. The basic principle of operation of BAS is that when the bias is altered, the gain of the gate is altered, as seen from the figure excerpted from [29]. CML gates have a lower gain when reduced bias is applied. A defective gate present in the circuit often outputs very low amplitude or exhibits stuck-at behaviour. With a suitably reduced bias, normal gates that are present at the output of a defective gate do not have enough gain to regenerate, in a few levels, the signals of amplitude lower than some target threshold.

The objective of the BAS technique is to ensure that a detector designed to detect a very low amplitude signal, even when it is several levels after the defective gate, would have the ability to differentiate a fault-free circuit from a faulty one. To study the effect of bias variation and masking, a test bench was developed as described in the following section.

Figure 2.1 Theoretical differential gain curve of CML grade 0 BUFFER, excerpted from [29]

## 2.2 Test bench setup for characterising BAS technique

To study the effects of defects in bipolar CML gates, a number of gates of the same type and of the same speed grade are connected in series to form an appropriately biased chain. BUFFERs, as well as two input AND, and XOR gates are analysed. AND, and OR gates have the same schematic, (see the schematic of the bipolar CML OR gate presented in figure 1.2, chapter 1), with the exception that the input and output lines of

the OR gate are reversed to obtain an AND function, as shown in figure 2.2 [4, 6]. AND gates are analysed here. The functionality of bipolar CML OR gate is explained in chapter 1.

Figure 2.2 Bipolar CML AND gate from bipolar CML OR gate