|                   |                                                                                                                                                    |

|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>Titre:</b>     | Génération de tests robustes pour les circuits analogiques linéaires                                                                               |

| Title:            |                                                                                                                                                    |

| <b>Auteur:</b>    | Abdessatar Abderrahman                                                                                                                             |

| Author:           |                                                                                                                                                    |

| <b>Date:</b>      | 1997                                                                                                                                               |

| <b>Type:</b>      | Mémoire ou thèse / Dissertation or Thesis                                                                                                          |

| <b>Référence:</b> | Abderrahman, A. (1997). Génération de tests robustes pour les circuits analogiques linéaires [Thèse de doctorat, École Polytechnique de Montréal]. |

| Citation:         | PolyPublie. <a href="https://publications.polymtl.ca/7062/">https://publications.polymtl.ca/7062/</a>                                              |

## Document en libre accès dans PolyPublie

Open Access document in PolyPublie

|                           |                                                                                           |

|---------------------------|-------------------------------------------------------------------------------------------|

| <b>URL de PolyPublie:</b> | <a href="https://publications.polymtl.ca/7062/">https://publications.polymtl.ca/7062/</a> |

| PolyPublie URL:           |                                                                                           |

|                                 |                 |

|---------------------------------|-----------------|

| <b>Directeurs de recherche:</b> | Bozena Kaminska |

| Advisors:                       |                 |

|                   |              |

|-------------------|--------------|

| <b>Programme:</b> | Non spécifié |

| Program:          |              |

## INFORMATION TO USERS

This manuscript has been reproduced from the microfilm master. UMI films the text directly from the original or copy submitted. Thus, some thesis and dissertation copies are in typewriter face, while others may be from any type of computer printer.

**The quality of this reproduction is dependent upon the quality of the copy submitted.** Broken or indistinct print, colored or poor quality illustrations and photographs, print bleedthrough, substandard margins, and improper alignment can adversely affect reproduction.

In the unlikely event that the author did not send UMI a complete manuscript and there are missing pages, these will be noted. Also, if unauthorized copyright material had to be removed, a note will indicate the deletion.

Oversize materials (e.g., maps, drawings, charts) are reproduced by sectioning the original, beginning at the upper left-hand corner and continuing from left to right in equal sections with small overlaps.

ProQuest Information and Learning

300 North Zeeb Road, Ann Arbor, MI 48106-1346 USA

800-521-0600

UMI<sup>®</sup>

UNIVERSITÉ DE MONTRÉAL

**GÉNÉRATION DE TESTS ROBUSTES

POUR LES CIRCUITS ANALOGIQUES

LINÉAIRES**

par

Abdessatar ABDERRAHMAN

DÉPARTEMENT DE GÉNIE ÉLECTRIQUE ET DE GÉNIE INFORMATIQUE

ÉCOLE POLYTECHNIQUE DE MONTRÉAL

THÈSE PRÉSENTÉE EN VUE DE L'OBTENTION

DU DIPLÔME DE PHILOSOPHIAE DOCTOR (Ph.D)

(GÉNIE ÉLECTRIQUE)

OCTOBRE 1997

© Abdessatar Abderrahman 1997.

National Library

of Canada

Acquisitions and

Bibliographic Services

395 Wellington Street

Ottawa ON K1A 0N4

Canada

Bibliothèque nationale

du Canada

Acquisitions et

services bibliographiques

395, rue Wellington

Ottawa ON K1A 0N4

Canada

Your file Votre référence

Our file Notre référence

**The author has granted a non-exclusive licence allowing the National Library of Canada to reproduce, loan, distribute or sell copies of this thesis in microform, paper or electronic formats.**

**L'auteur a accordé une licence non exclusive permettant à la Bibliothèque nationale du Canada de reproduire, prêter, distribuer ou vendre des copies de cette thèse sous la forme de microfiche/film, de reproduction sur papier ou sur format électronique.**

**The author retains ownership of the copyright in this thesis. Neither the thesis nor substantial extracts from it may be printed or otherwise reproduced without the author's permission.**

**L'auteur conserve la propriété du droit d'auteur qui protège cette thèse. Ni la thèse ni des extraits substantiels de celle-ci ne doivent être imprimés ou autrement reproduits sans son autorisation.**

0-612-73437-4

Canada

UNIVERSITÉ DE MONTRÉAL

ÉCOLE POLYTECHNIQUE DE MONTRÉAL

Cette thèse intitulée:

**GÉNÉRATION DE TESTS ROBUSTES

POUR LES CIRCUITS ANALOGIQUES

LINÉAIRES**

présentée par: ABDERRAHMAN Abdessatar

en vue de l'obtention du diplôme de: Philosophiae Doctor

a été dûment acceptée par le jury d'examen constitué de:

M. SAVARIA Yvon, Ph.D., président

Mme KAMINSKA Bozena, Ph.D., membre et directrice de recherche

M. CERNY Eduard, Ph.D., membre et codirecteur de recherche

M. ABOULHAMID Mostapha, Ph.D., membre

M. THIBEAULT Claude, Ph.D., membre

## **DÉDICACE**

**A l'âme de mon père, à ma mère.**

**à ma femme et à mes enfants.**

## Remerciements

Je désire, en premier lieu, témoigner ma reconnaissance à ma directrice de recherche Madame Bozena Kaminska, professeur à l'École Polytechnique de Montréal, et à mon codirecteur Monsieur Eduard Cerny, professeur à l'Université de Montréal, dont la supervision a permis de mettre en oeuvre ce travail. Je remercie ma directrice pour ses conseils précieux, ses encouragements et son support financier, ainsi que la confiance qu'elle a mise en moi pour accomplir ce travail. Je remercie mon codirecteur pour ses sages directives, l'encadrement fructueux dont j'ai bénéficié, son support financier, ainsi que ses qualités professionnelles et humaines que j'ai admirées.

J'aimerais remercier l'organisme "Groupe Inter-Universitaire en Architecture des Ordinateurs et VLSI (GRIA0)" pour le support financier dont j'ai bénéficié durant l'accomplissement de cette thèse.

Je tiens à remercier tout particulièrement ma mère, Fatma, pour ses sacrifices sans limites, ma femme, Sayda, pour son appui persévérant, et mes filles Maroua, Mona, Safa et Ela pour le temps que je leur dois.

Je voudrais remercier Monsieur Yvon Savaria d'avoir accepté de présider la commission de jury. J'aimerais également remercier Monsieur Mostapha Aboulhamid et Monsieur Claude Thibeault d'avoir accepté de faire partie de cette commission. Je remercie aussi Monsieur Guy Bois d'avoir fait partie du jury de mon examen général de synthèse.

## RÉSUMÉ

Les circuits analogiques sont traditionnellement testés par la vérification de leur fonctionnalité. Or, ce genre de test est reconnu très coûteux. En effet, le coût de test analogique peut représenter jusqu'à 30% du coût total de fabrication. De plus, dans certaines applications, une proportion de 95% du coût total de test est dépensée dans le test analogique et 5% seulement dans le test de la partie numérique, alors que la puce est constituée dans une proportion de 95% de circuits numériques et 5% seulement de circuits analogiques. En outre, dans ce type de test les circuits sont sur-testés ou sous-testés puisqu'il n'y a pas de critère d'arrêt. Il en résulte, qu'afin de minimiser le coût de test de production, il est nécessaire de développer des techniques de génération de tests basées sur des modèles de défaut. En général, on distingue dans les circuits analogiques deux catégories de défauts: défauts paramétriques et défauts catastrophiques.

Dans cette thèse nous proposons une méthode de génération de tests basée sur ces modèles de défaut. Cette méthode vise à générer un ensemble minimal de tests robustes permettant d'assurer pour chacun des composants (paramètres) du circuit sous test une observabilité maximale de pannes. Cet ensemble de tests permettra de distinguer les circuits défectueux de ceux qui sont bons. Un ensemble de tests est dit robuste s'il est en mesure de détecter les défauts paramétriques et catastrophiques sous la contrainte d'effet maximal de masquage dû à la tolérance des composants du circuit. En effet, seulement dans ce cas, la qualité d'un test peut être correctement mesurée et garantie. La génération

d'un ensemble de tests ayant de telles spécifications en particulier, et le test des circuits analogiques en général, sont des problèmes difficiles. Cette difficulté émane de la complexité naturelle de ces circuits qui présentent un spectre continu de défauts. Cela provient de la continuité des variations dans le temps des grandeurs physiques qui caractérisent les circuits analogiques. Les effets de masquage causés par les tolérances des paramètres ainsi que l'incertitude que ces derniers induisent sur les caractéristiques de ces circuits compliquent encore plus le problème du test analogique. En outre, la non-linéarité de ces caractéristiques ainsi que le manque d'accessibilité aux noeuds internes rendent ce problème plus complexe.

Nous avons élaboré dans cette thèse une méthode de génération de tests multifréquences pour détecter les pannes paramétriques et catastrophiques dans les circuits analogiques linéaires. L'originalité de cette méthode réside dans le fait que le problème de génération de tests est formulé comme une série de problèmes d'optimisation. Étant donné un ensemble de performances (spécifications du circuit sous-test) et une plage de fréquences, la méthode proposée sélectionne les fréquences de tests qui maximisent l'observabilité des déviations d'un paramètre défectueux du circuit, observées à travers une performance, sous la contrainte de masquage maximal induit par les autres paramètres.

Initialement, nous avons résolu les problèmes d'optimisation formulés à l'aide d'une méthode de programmation non-linéaire, en l'occurrence la programmation quad-

ratique séquentielle (SQP) disponible dans l'outil de mathématiques MATLAB. Cependant de telles méthodes d'optimisation ne peuvent pas garantir que la solution trouvée est globale. Cela peut donc conduire à une sélection erronée de tests affectant ainsi la qualité de l'ensemble de tests générés. De plus, ces méthodes ne sont pas automatiques et dépendent de plusieurs paramètres qui doivent être choisis par un usager expérimenté. Nous avons alors élaboré une nouvelle méthode basée sur la programmation logique à contraintes, qui permet de résoudre les problèmes d'optimisation formulés comme une série de problèmes de satisfaction à contraintes. Cette méthode est automatique et génère des bornes étroites, infaillibles et garanties à l'intérieur desquelles se trouve les optimums (minimum et maximum) globaux d'une fonction non-linéaire. Cette qualité d'etroitesse et d'infaillibilité de ces bornes trouve son origine dans les propriétés de l'arithmétique relationnelle des intervalles sur laquelle est basée la programmation logique à contraintes (CLP) qu'on a utilisée pour réaliser ce travail. Parmi ces propriétés figurent la propriété d'inclusion des intervalles, le rétrécissement systématique de ces derniers à travers la propagation des contraintes, l'exactitude de ce processus, ainsi que l'arrondissement vers l'extérieur des résultats des calculs.

Nous illustrons l'efficacité de la méthode proposée sur des fonctions mathématiques non-linéaires reconnues difficiles. Puis, nous l'appliquons à des circuits électriques d'essai dans le contexte de la génération de tests.

Cette méthode est aussi utilisée pour résoudre le problème d'analyse de tolérance des performances d'un circuit dans le pire des cas. Cette analyse de tolérance joue un rôle important dans le domaine de vérification de design. Ce problème est efficacement traité ici comme une composante du problème de génération de tests. La méthode proposée est également utilisée pour analyser la testabilité des circuits analogiques linéaires, en vue d'augmenter l'observabilité des pannes grâce à la technique de design orienté testabilité (DFT).

Dans le premier chapitre nous mettrons en évidence l'importance du test analogique dans la mise en oeuvre des produits électroniques modernes, et la nécessité de mise au point de nouvelles méthodes de génération de tests plus performantes et plus économiques. Le sujet ainsi que les objectifs de cette thèse sont également définis dans le chapitre 1. Dans le chapitre 2, nous situerons ce sujet par rapport à la discipline dans laquelle il s'inscrit, et nous passerons en revue différents travaux accomplis dans le domaine du test analogique. L'analyse et la formulation du problème de génération de tests, ainsi que certains résultats expérimentaux et leur validation seront présentés dans le chapitre 3. La méthode d'optimisation globale proposée pour résoudre le problème de génération de tests et celui d'analyse de tolérance est décrite dans le chapitre 4. Le chapitre 5 est consacré à l'analyse et l'amélioration de la détectabilité des pannes dans les circuits analogiques linéaires. Enfin, nous concluons dans le chapitre 6.

## Abstract

Analog circuits are traditionally tested by verifying their function, which is known to be costly. Indeed, the estimated cost of analog testing may represent 30% of the total manufacturing cost. Furthermore, in some applications, 95% of total testing costs are spent in testing of analog circuits and 5% in testing of digital circuits, while 95% of the chip are digital and 5% are analog. Moreover, in this type of analog testing there is a lack of quantitative measure of a test quality. As a result, the circuits are over-tested or under-tested. Consequently, to minimize the test time and thus the cost of production testing of analog circuits, test generation techniques based on fault-models are required. In general, faults in analog circuits can be classified into catastrophic and parametric faults. A robust test set for analog circuits has to detect faults under maximal masking effects due to variations of circuit parameters in their tolerance box. Indeed, only in this case the quality of a test set may be correctly measured and guaranteed. In this thesis we elaborated a multifrequency test generation method (TPG) for detecting parametric and catastrophic faults in linear analog circuits. The originality of this method stems from the formulation of analog test generation problem as a series of optimization problems. Given a set of performances and a frequency range, our approach selects the test frequencies that maximize the observability of a parameter deviation on a circuit performance under the worst masking effects of normal variations of the other parameters. Initially, we solved these optimization problems by Sequential Quadratic Programming (SQP), a non-linear programming method available in MATLAB. Such optimization

methods use local information and consequently cannot guarantee a global optimum. Furthermore, they are not automatic and depend on various parameters which must be selected by an experienced user. We thus developed a new method based on Constraint Logic Programming(CLP) that solves the optimization problems in TPG as a series of Constraint Satisfaction Problems (CSPs). The TPG method is fully automatic and provides tight and guaranteed bounds on the global optima of a nonlinear function. This quality of tightness and correctness of the bounds as assured by our technique stems from the inclusion properties of intervals, outward rounding, and the correctness of narrowing on which is based CLP implemented using the Relational Interval Arithmetic (RIA). The TPG method was implemented in CLP(BNR) Prolog. We first illustrate the effectiveness of our approach on a number of nonlinear functions known to be difficult, and then we apply it to a realistic electronic circuit in the context of TPG.

Our method may also be used to solve worst-case tolerance analysis of circuit performances problem which plays an important role in design verification. This problem is efficiently tackled here as part of the test generation. Moreover, our approach is useful to analyze the testability of linear analog circuits, and thus permits to enhance the fault detectability thanks to design for testability.

The importance of analog testing and the need to develop new efficient and less costly methods are shown in Chapter 1. The objectives of the thesis are also defined in this chapter. Some important results on analog testing are reviewed in Chapter 2. Analy-

sis and formulation of the test generation problem are developed in Chapter 3. The test generation algorithm, some experimental results, and the test set validation are also described in Chapter 3. The new global optimization method based on CLP for solving the test generation and worst-case tolerance analysis problems are outlined in Chapter 4. The application of the proposed test generation method to analyze the testability of linear analog circuits is illustrated in Chapter 5. Finally, some conclusions are drawn in Chapter 6.

## TABLE DES MATIÈRES

|                                               |          |

|-----------------------------------------------|----------|

| DÉDICACE .....                                | iv       |

| REMERCIEMENTS .....                           | v        |

| RÉSUMÉ .....                                  | vi       |

| ABSTRACT .....                                | x        |

| TABLE DES MATIÈRES .....                      | xiii     |

| LISTE DES FIGURES .....                       | xx       |

| LISTE DES TABLEAUX.....                       | xxii     |

| <br>                                          |          |

| <b>Chapitre 1 -Introduction .....</b>         | <b>1</b> |

| 1.1 Objectifs de la thèse .....               | 4        |

| 1.2 Analyse du problème .....                 | 5        |

| <br>                                          |          |

| <b>Chapitre 2 -Revue de littérature .....</b> | <b>9</b> |

|                                                                      |    |

|----------------------------------------------------------------------|----|

| 2.1 Concepts de base .....                                           | 9  |

| 2.1.1 Test et diagnostic .....                                       | 9  |

| 2.1.2 Défauts physiques .....                                        | 9  |

| 2.1.3 Modélisation .....                                             | 11 |

| 2.1.4 Simulation .....                                               | 12 |

| 2.1.5 Modèle de défaut .....                                         | 12 |

| 2.1.6 Evaluation d'un test et simulation de pannes .....             | 15 |

| 2.2 Méthodes de test .....                                           | 16 |

| 2.2.1 Méthode de test en temps réel (On-line testing) .....          | 16 |

| 2.2.2 Méthode d'auto-contrôle de design (Self-checking design) ..... | 17 |

| 2.2.3 Méthode d'auto-test incorporé (Built-In Self Testing).....     | 17 |

| 2.2.4 Méthode de test à sonde guidée .....                           | 18 |

| 2.2.5 Méthode de test en circuit (In_circuit testing) .....          | 19 |

| 2.2.6 Méthode de test par comparaison .....                          | 19 |

| 2.2.7 Méthode de test par compression de la réponse .....            | 19 |

| 2.3 Modèle de défaut et simulation de pannes .....                   | 19 |

|                                                                    |    |

|--------------------------------------------------------------------|----|

| 2.4 Design orienté testabilité (Design For Testability: DFT) ..... | 22 |

| 2.4.1 Approche ad hoc .....                                        | 24 |

| 2.4.2 Approches structurées: Techniques de balayage ) .....        | 25 |

| 2.5 Diagnostic .....                                               | 29 |

| 2.6 Génération de tests .....                                      | 31 |

|                                                                                                             |           |

|-------------------------------------------------------------------------------------------------------------|-----------|

| <b>Chapitre 3 -Algorithme de génération de tests robustes pour les circuits analogiques linéaires .....</b> | <b>40</b> |

| 3.1 Introduction .....                                                                                      | 43        |

| 3.2 The proposed approach.....                                                                              | 45        |

| 3.2.1 Objectives .....                                                                                      | 45        |

| 3.2.2 Problem analysis .....                                                                                | 46        |

| 3.2.3 Problem formulation .....                                                                             | 47        |

| 3.2.3.1 Valid range determination .....                                                                     | 47        |

| 3.2.3.2 Minimum observable parameter deviatio .....                                                         | 48n       |

| 3.3 Test generation algorithm .....                                                                         | 51        |

|                                     |    |

|-------------------------------------|----|

| 3.4 Experimental Results .....      | 54 |

| 3.4.1 An illustrative example ..... | 54 |

| 3.4.2 A Realistic Application.....  | 58 |

| 3.4.3 Test set validation .....     | 62 |

| 3.5 Conclusions .....               | 65 |

|                                                                                                                                                                          |           |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|

| <b>Chapitre 4 -Algorithmes de recherche de solution globale des<br/>problèmes de génération de tests et d'analyse de tolérance, basés sur la<br/>technique CLP .....</b> | <b>73</b> |

| 4.1 Introduction .....                                                                                                                                                   | 77        |

| 4.2 Problem formulation .....                                                                                                                                            | 81        |

| 4.2.1 Objectives .....                                                                                                                                                   | 81        |

| 4.2.2 Problem Formulation .....                                                                                                                                          | 81        |

| 4.2.2.1 Worst-case tolerance analysis .....                                                                                                                              | 82        |

| 4.2.2.2 Minimum observable parameter deviation [12].....                                                                                                                 | 84        |

|                                                                         |     |

|-------------------------------------------------------------------------|-----|

| 4.3 Constraint Satisfaction Problems .....                              | 86  |

| 4.3.1 Constraint Logic Programming .....                                | 86  |

| 4.3.1.1 Functional Interval Arithmetic .....                            | 86  |

| 4.3.1.2 Relational Interval Arithmetic (RIA) .....                      | 88  |

| 4.3.1.3 Constraint Satisfaction Problems .....                          | 89  |

| 4.4 Proposed CLP-based approach for solving optimization problems ..... | 91  |

| 4.4.1 Worst-case tolerance analysis .....                               | 91  |

| 4.4.1.1 The basic approach .....                                        | 92  |

| 4.4.1.2 Description of the Optimization Algorithm .....                 | 94  |

| 4.4.1.3 Numerical Examples .....                                        | 97  |

| 4.4.2 Finding optima (max and min) of observable parameter values ..... | 99  |

| 4.5 Experimental Results .....                                          | 103 |

| 4.5.1 Example 1 .....                                                   | 103 |

| 4.5.2 Finding optima (max and min) of observable parameter values ..... | 99  |

|                                                                                |            |

|--------------------------------------------------------------------------------|------------|

| <b>4.6 Experimental Results .....</b>                                          | <b>103</b> |

| 4.6.1 Example 1 .....                                                          | 103        |

| 4.6.2 Example 2 .....                                                          | 106        |

| 4.6.3 Test quality .....                                                       | 108        |

| 4.6.3.1 Effects of tester resolution .....                                     | 109        |

| 4.6.3.2 Effects of parameter tolerances .....                                  | 110        |

| <b>4.7 Acceleration techniques .....</b>                                       | <b>112</b> |

| 4.7.1 Monotonicity test .....                                                  | 112        |

| 4.7.1.1 Computation of the worst-case circuit response .....                   | 112        |

| 4.7.1.2 Computation of observable parameter values .....                       | 113        |

| 4.7.2 Mean-value form .....                                                    | 114        |

| 4.7.3 Reducing search space of parameters .....                                | 116        |

| <b>4.8 Conclusions .....</b>                                                   | <b>117</b> |

| <b>Chapitre 5 -Analyse et amélioration de la détectabilité des pannes. 123</b> |            |

| 5.1 Introduction .....                                                         | 123        |

| 5.2 Définitions .....                                                          | 125        |

|                                                                     |            |

|---------------------------------------------------------------------|------------|

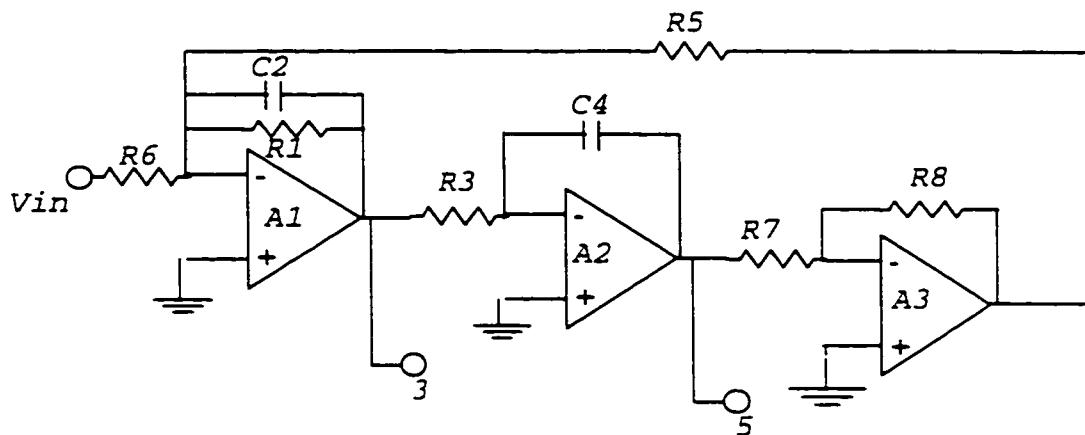

| 5.3 Analyse de détectabilité du filtre biquadratique .....          | 128        |

| 5.3.1 Observation des gains V3 et V5 .....                          | 128        |

| 5.3.2 Observation des phases aux noeuds 3 et 5 .....                | 130        |

| 5.3.3 Observation du facteur Q .....                                | 130        |

| 5.3.4 Application de la technique DFT .....                         | 131        |

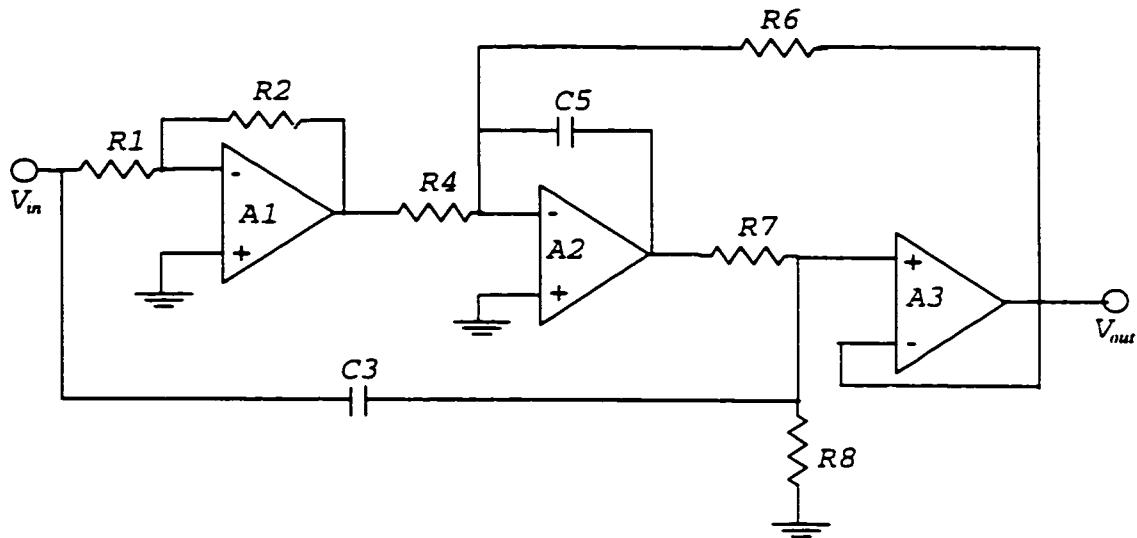

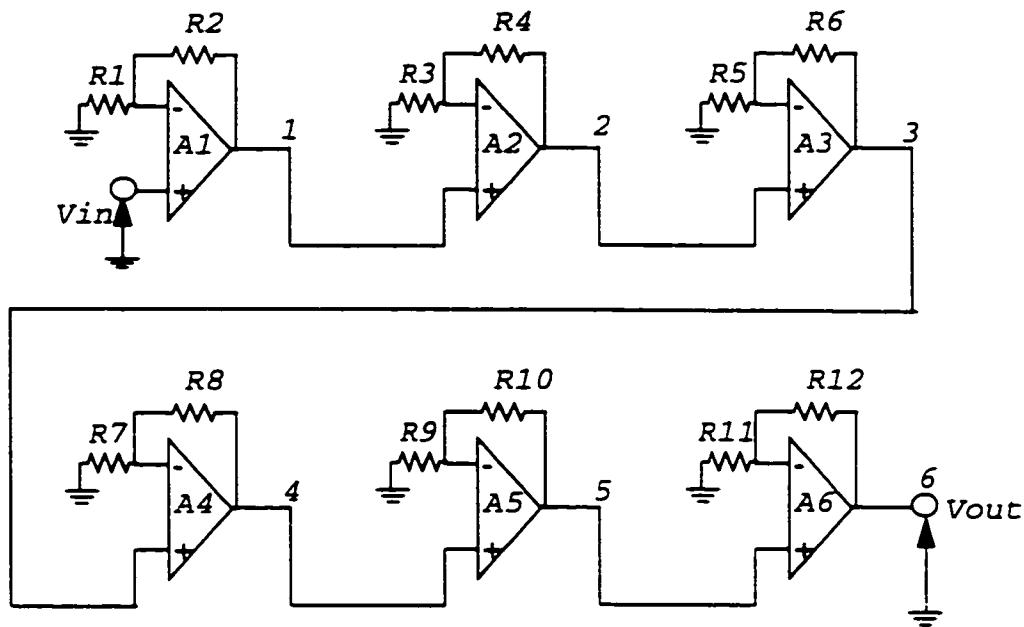

| 5.4 Analyse de détectabilité d'un amplificateur à large bande ..... | 135        |

| 5.4.1 Amplificateurs opérationnels de gain infini .....             | 135        |

| 5.4.2 Amplificateurs opérationnels de gain fini .....               | 136        |

| 5.4.3 Amplis opérationnels de gain dépendant de la fréquence .....  | 137        |

| 5.4.4 Application des techniques DFT .....                          | 139        |

| 5.5 Conclusion .....                                                | 142        |

| <b>Chapitre 6 -Conclusion Générale .....</b>                        | <b>143</b> |

| <b>BIBLIOGRAPHIE.....</b>                                           | <b>148</b> |

## LISTE DES FIGURES

|                                                                                                                                                                                                                                           |    |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

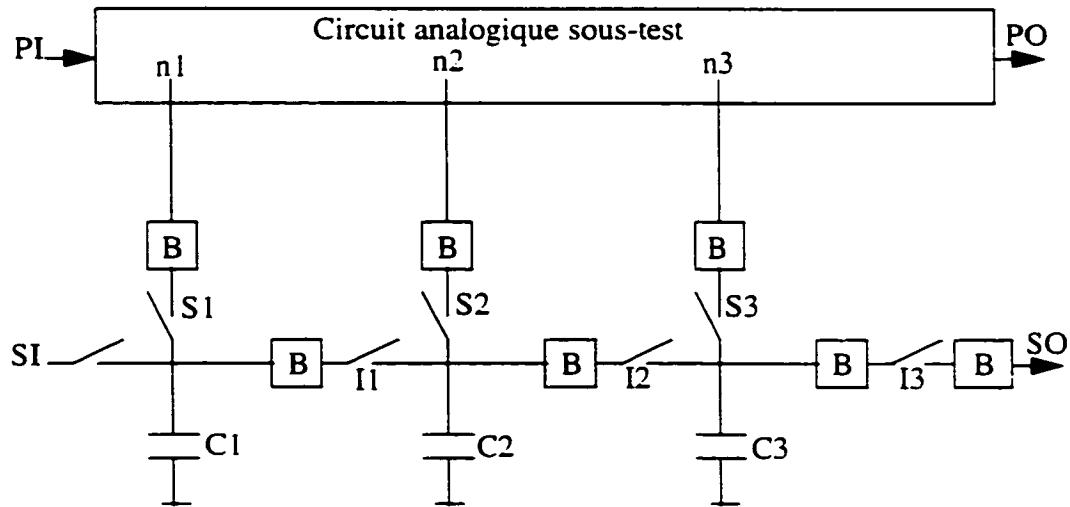

| <b>Figure 2.1:Chaîne de balayage analogique .....</b>                                                                                                                                                                                     | 26 |

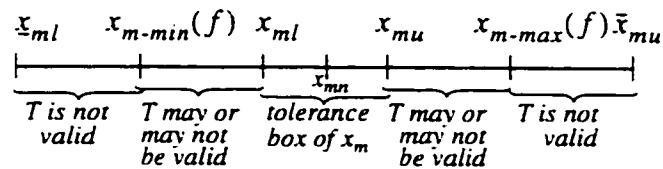

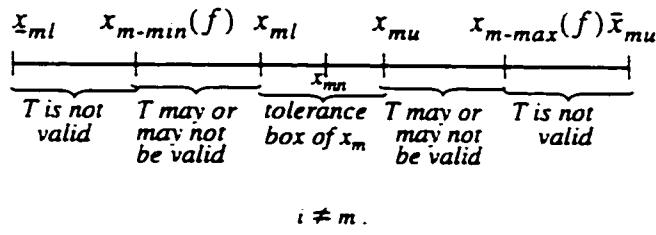

| <b>Figure 3.1:Total possible range of a parameter <math>x_m</math> under normal variations of <math>x_i</math> .....</b>                                                                                                                  | 48 |

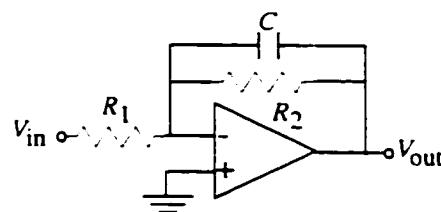

| <b>Figure 3.2:Low-pass filter .....</b>                                                                                                                                                                                                   | 55 |

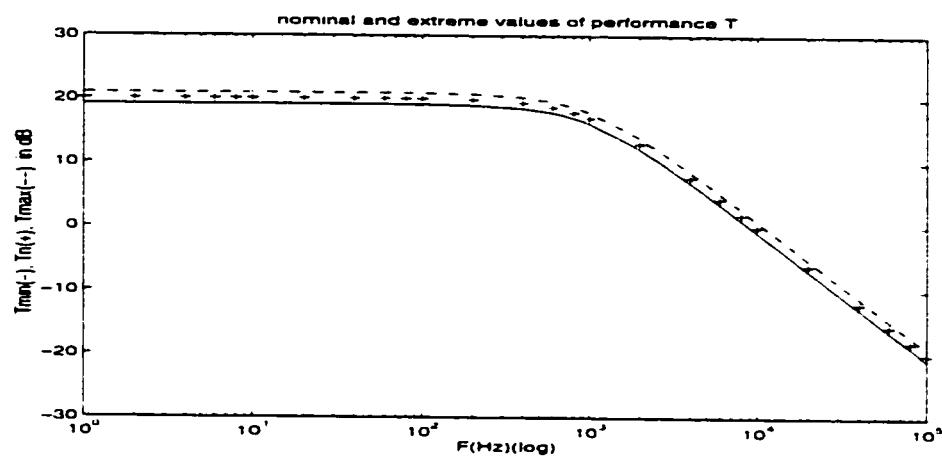

| <b>Figure 3.3:Extreme values <math>T_{\max}, T_{\min}</math> of pass-low filter gain .....</b>                                                                                                                                            | 57 |

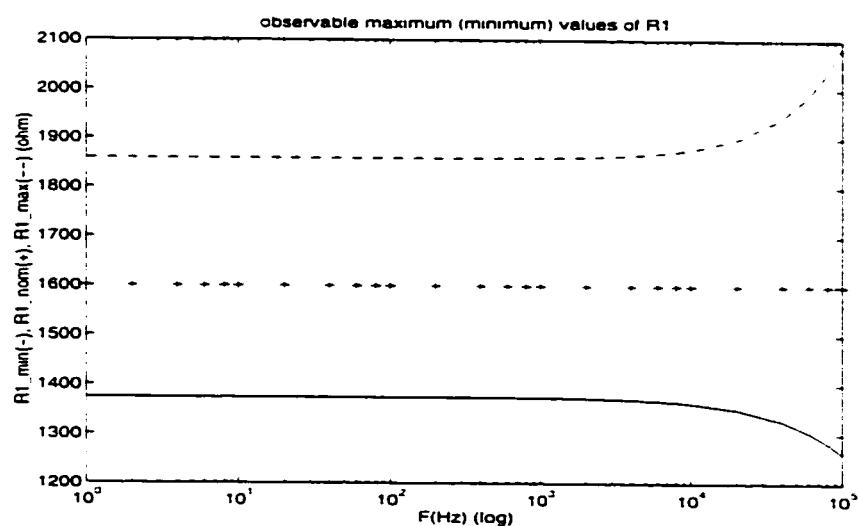

| <b>Figure 3.4:Observable minimum (maximum) deviation of parameter <math>R_1</math> .....</b>                                                                                                                                              | 57 |

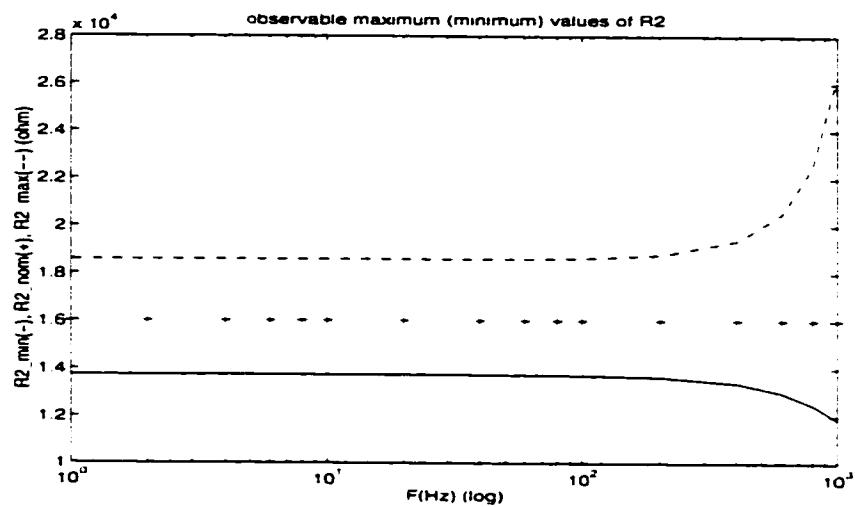

| <b>Figure 3.5:Observable minimum (maximum) deviation of parameter <math>R_2</math> .....</b>                                                                                                                                              | 58 |

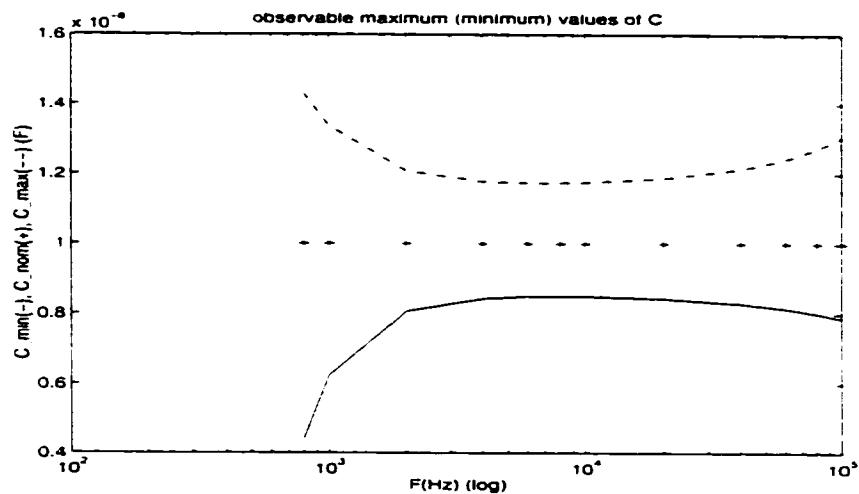

| <b>Figure 3.6:Observable minimum (maximum) deviation of parameter <math>C</math> .....</b>                                                                                                                                                | 58 |

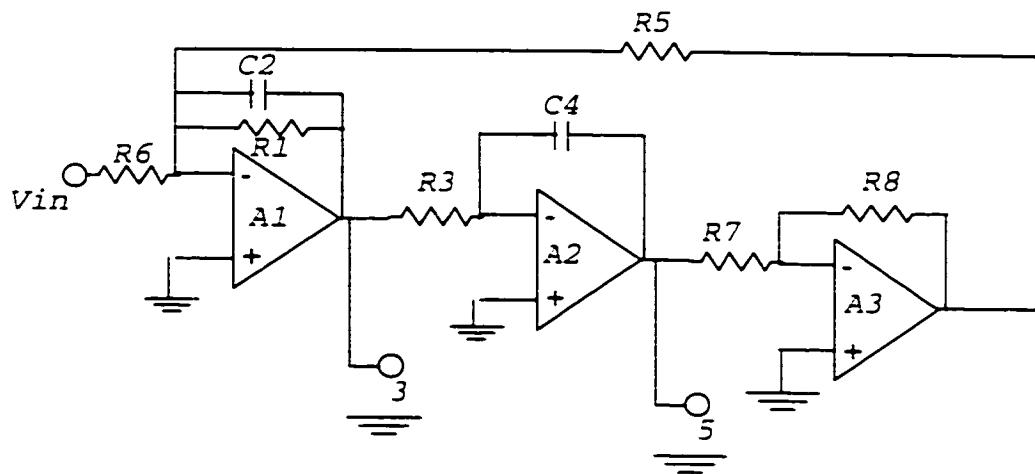

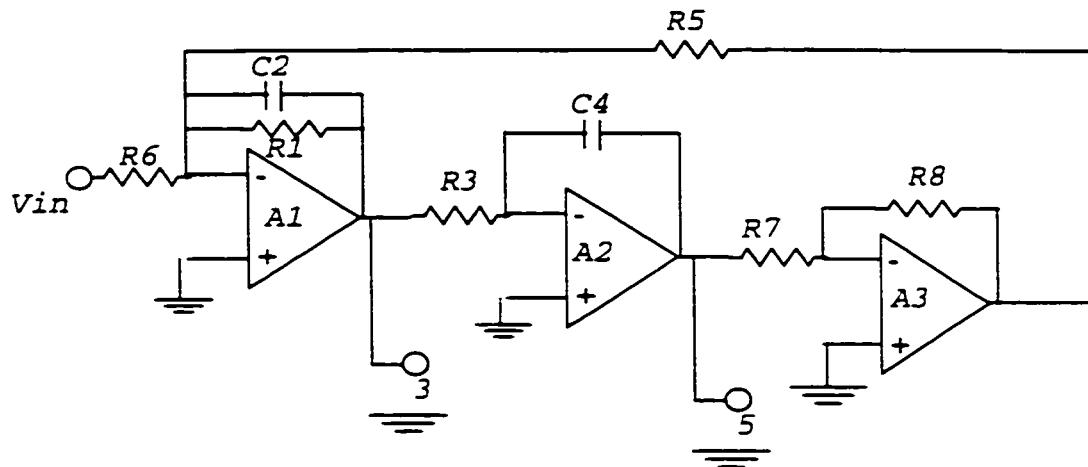

| <b>Figure 3.7:biquadratic filter .....</b>                                                                                                                                                                                                | 60 |

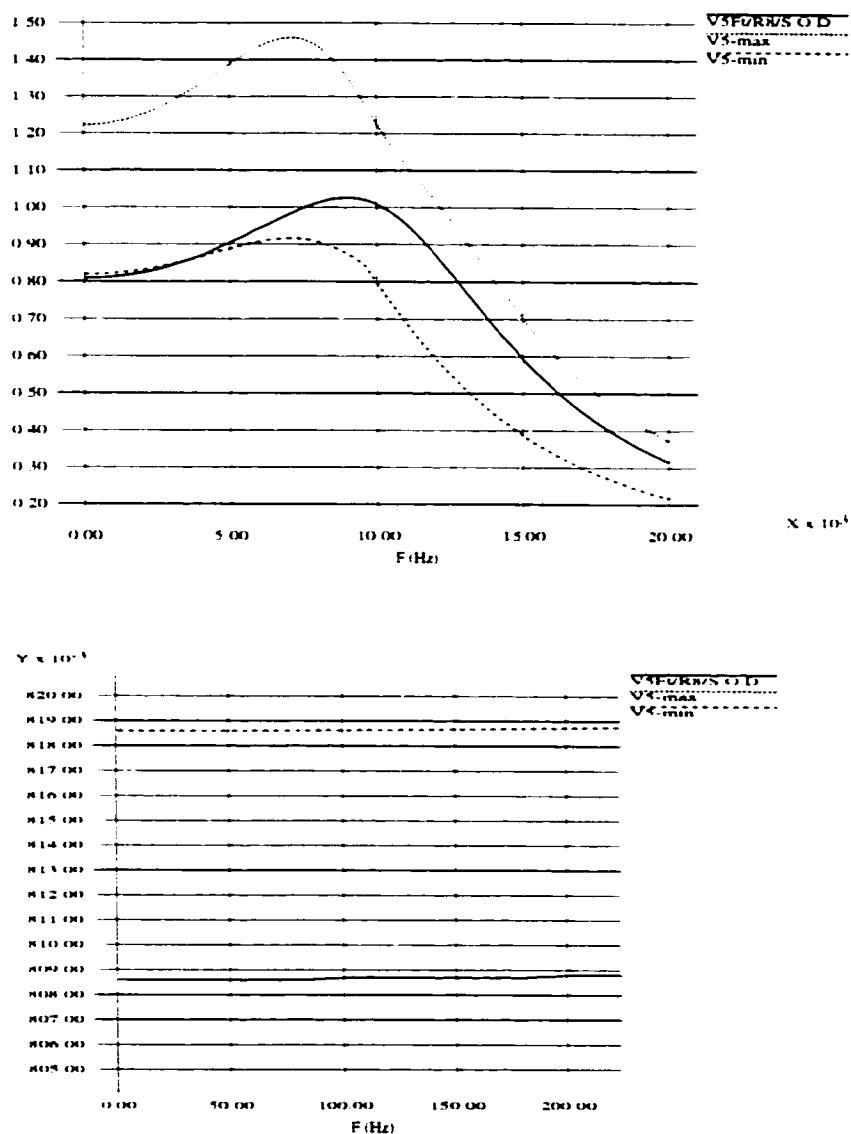

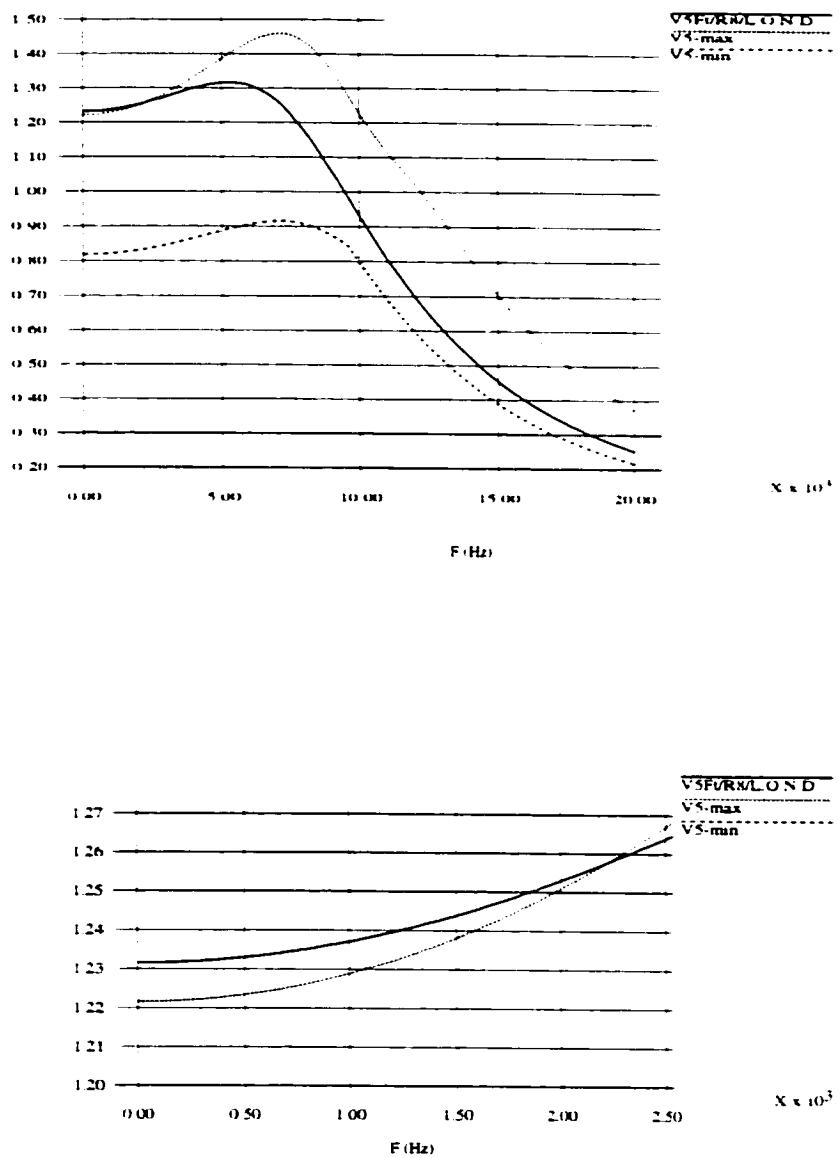

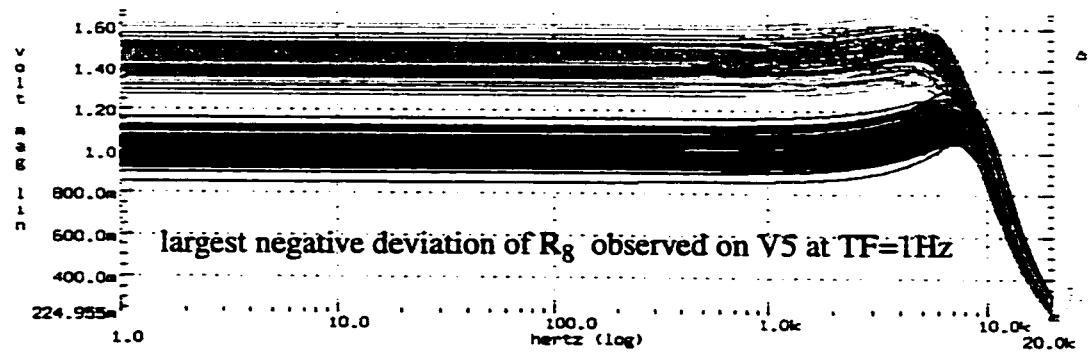

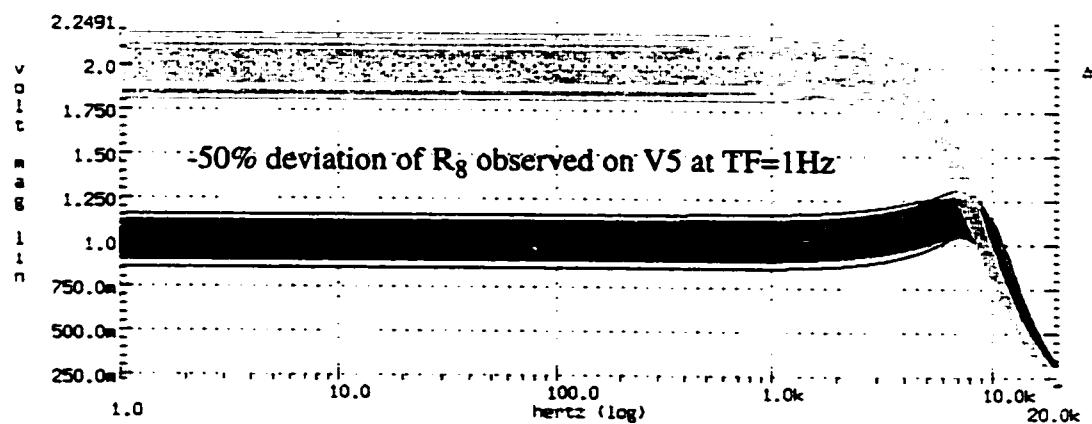

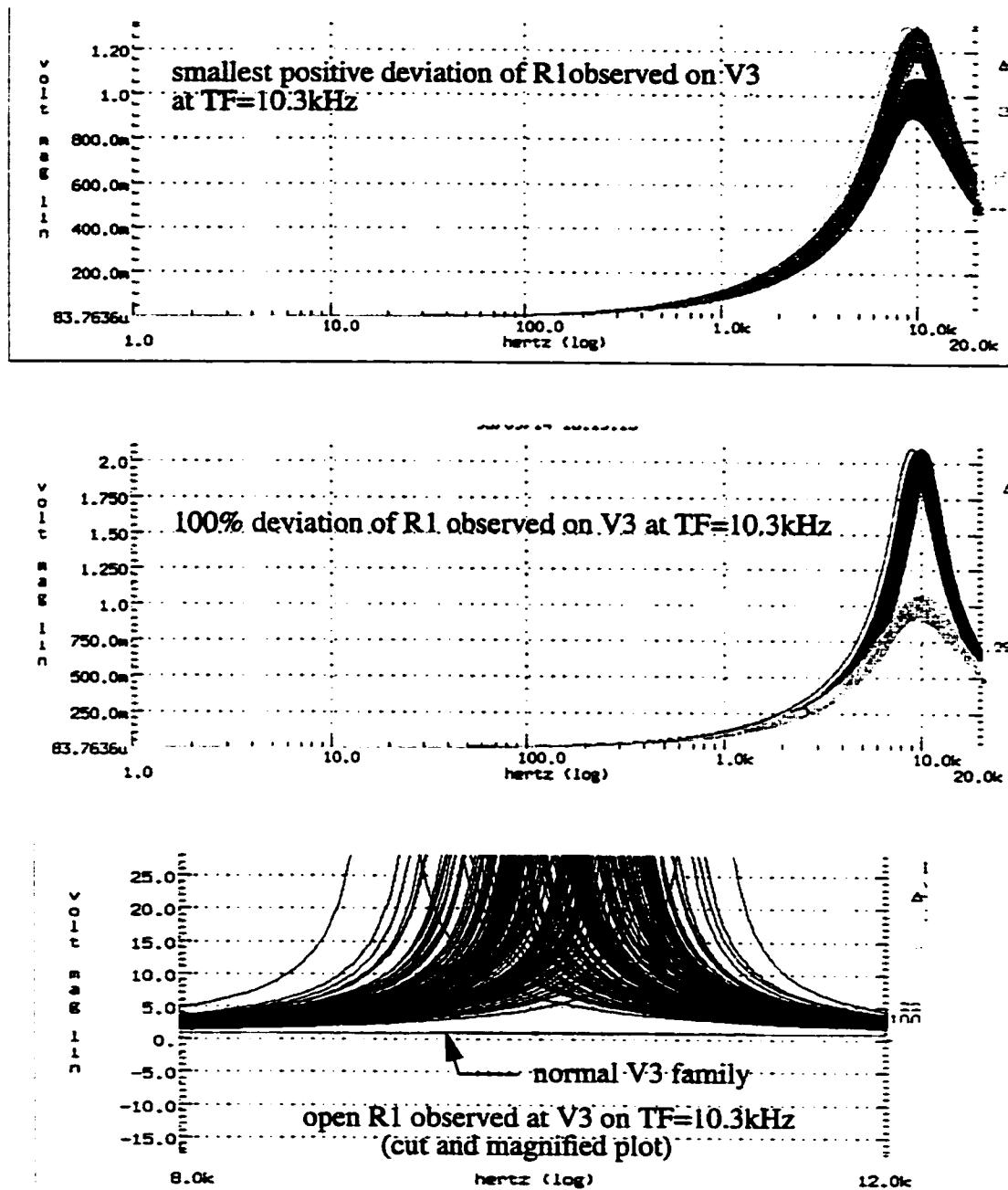

| <b>Figure 3.8:Faulty response <math>V5Ft</math> observed under the smallest observable positive deviation (S.O.P.D) of <math>R_8</math>, compared to the envelope of the normal range (<math>V5\text{-min}, V5\text{-max}</math>) ...</b> | 66 |

| <b>Figure 3.9:Faulty response <math>V5Ft</math> observed under the largest observable negative deviation (L.O.N.D) of <math>R_8</math>, compared to the envelope of the normal range (<math>V5\text{-min}, V5\text{-max}</math>) ...</b>  | 67 |

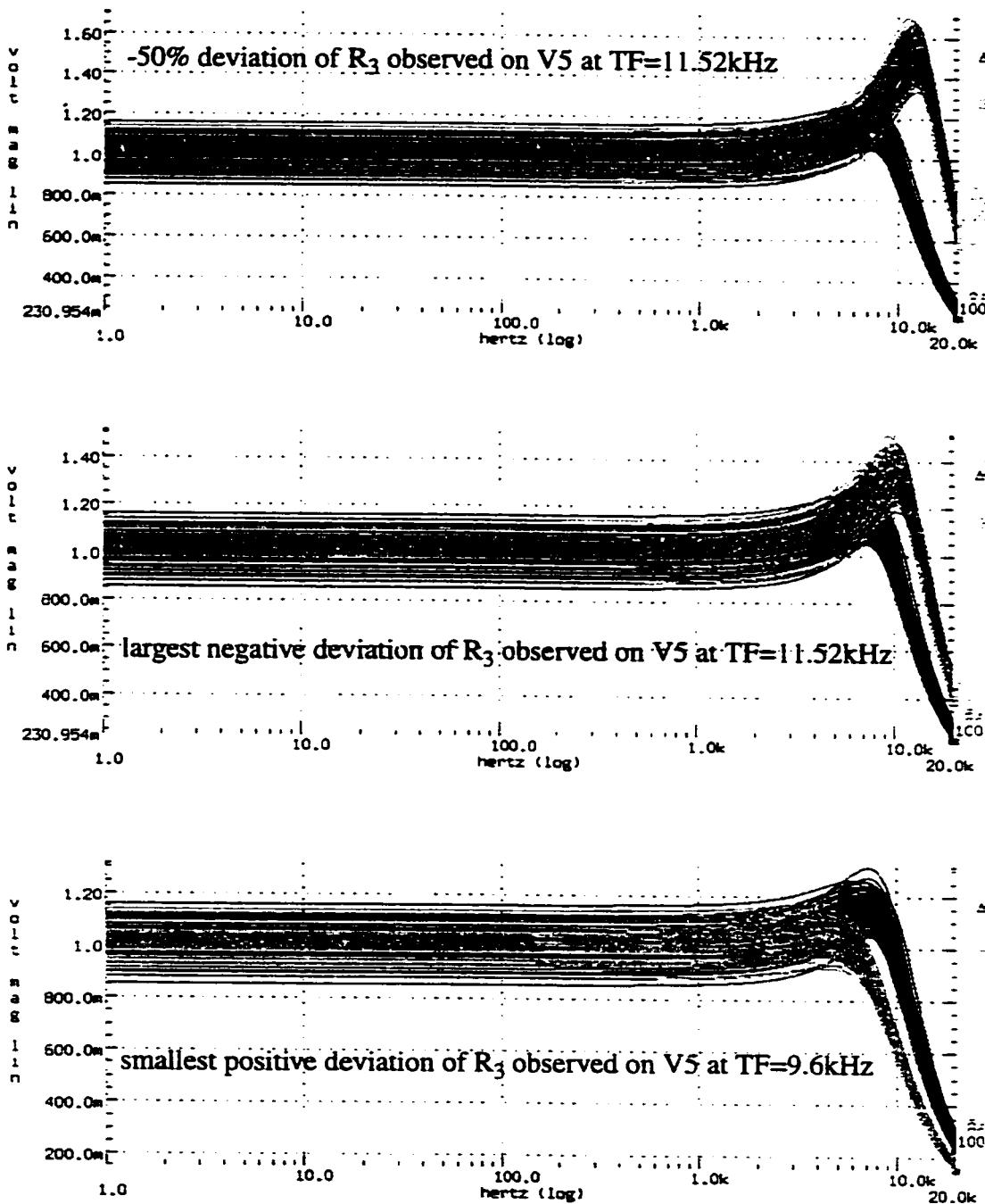

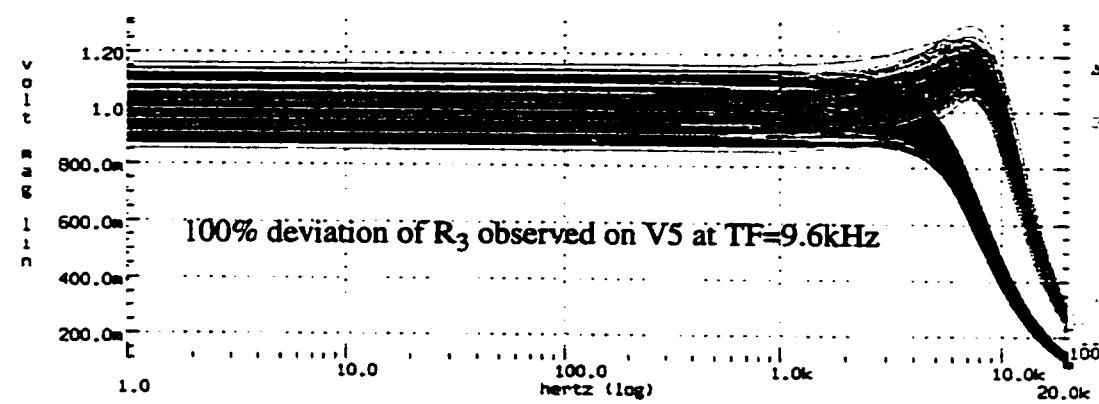

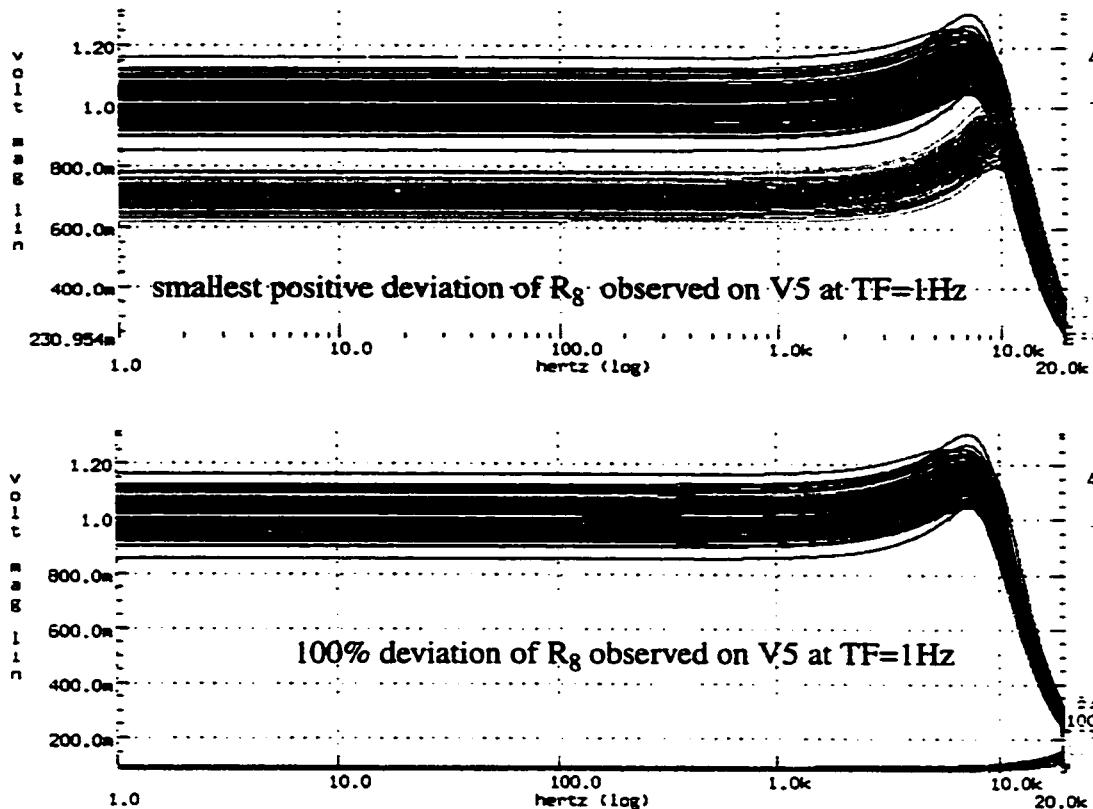

| <b>Figure 3.10:Faulty and good response families under faulty <math>R_3</math> and the other parameters varied randomly .....</b>                                                                                                         | 69 |

|                                                                                                                                           |     |

|-------------------------------------------------------------------------------------------------------------------------------------------|-----|

| <b>Figure 3.11:Faulty and good response families under faulty <math>R_8</math> and the other parameters varied randomly .....</b>         | 70  |

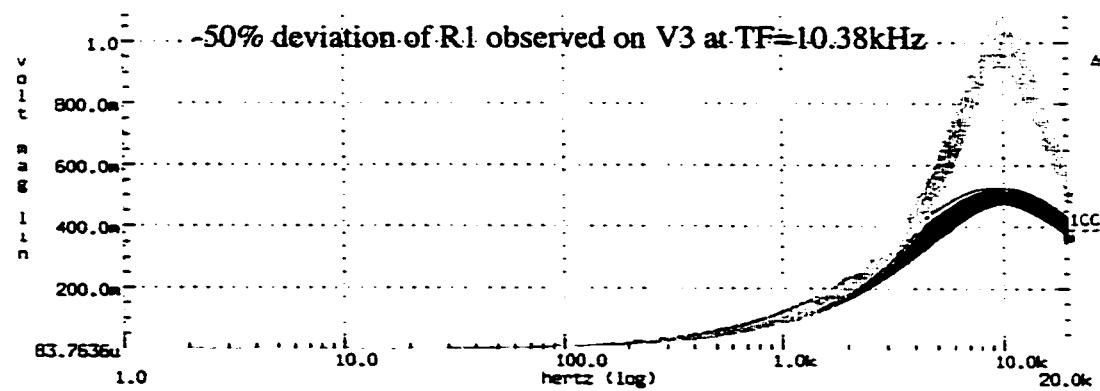

| <b>Figure 3.12:Faulty and good family responses under a faulty parameter <math>R_1</math> and other random parameter variations .....</b> | 71  |

| <b>Figure 4.1: A biquadratic filter .....</b>                                                                                             | 105 |

| <b>Figure 4.2: A notch filter .....</b>                                                                                                   | 108 |

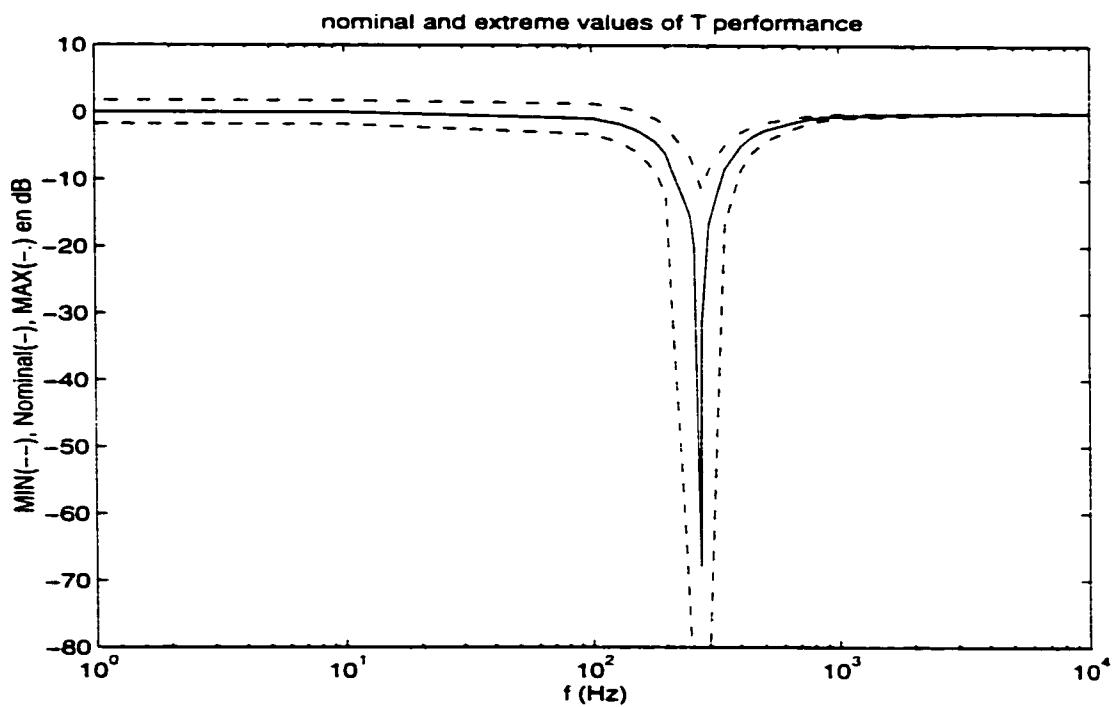

| <b>Figure 4.3:Nominal and worst-case magnitude of notch filter .....</b>                                                                  | 108 |

| <b>Figure 5.1:Filtre biquadratique .....</b>                                                                                              | 128 |

| <b>Figure 5.2:Amplificateur à large bande en cascade .....</b>                                                                            | 136 |

## LISTE DES TABLEAUX

|                                                                                                    |     |

|----------------------------------------------------------------------------------------------------|-----|

| <b>TABLE 3.1 : Computed and simulated results .....</b>                                            | 59  |

| <b>TABLE 3.2 : Computed results .....</b>                                                          | 62  |

| <b>TABLE 4.3 : Range of three-hump-camel function .....</b>                                        | 98  |

| <b>TABLE 4.4 : Range of six-hump-camel function .....</b>                                          | 99  |

| <b>TABLE 4.5 : Range of a composed function .....</b>                                              | 100 |

| <b>TABLE 4.6 : Results for biquadratic filter .....</b>                                            | 106 |

| <b>TABLE 4.7 : Results for notch filter .....</b>                                                  | 109 |

| <b>TABLE 4.8 : Tester resolution impact on parameter detectability .....</b>                       | 111 |

| <b>TABLE 4.9 : parameter tolerances impact on parameter detectability .....</b>                    | 112 |

| <b>TABLE 4.10 : Effect of monotonicity test .....</b>                                              | 114 |

| <b>TABLE 4.11 : Speeding-up the computation of SOPD and LOND values of biquad parameters .....</b> | 117 |

| <b>TABLEAU 5.1 : Résultats obtenus en observant les gains V3 et V5 .....</b>                       | 130 |

| <b>TABLEAU 5.2 : Résultats obtenus en observant les phases aux noeuds 3 et 5.....</b>              | 131 |

|                                                                                                         |     |

|---------------------------------------------------------------------------------------------------------|-----|

| <b>TABLEAU 5.3 : Résultats obtenus en observant V3 .....</b>                                            | 133 |

| <b>TABLEAU 5.4 : Résultats obtenus pour des gains d'amplis infinis .....</b>                            | 137 |

| <b>TABLEAU 5.5 : Résultats obtenus pour des gains d'amplis op.finis .....</b>                           | 138 |

| <b>TABLEAU 5.6 : Résultats obtenus pour des gains d'amplis op. finis dépendant de la fréquence.....</b> | 140 |

| <b>TABLEAU 5.7 : Résultats obtenus avec le circuit modifié .....</b>                                    | 142 |

# Chapitre 1

## Introduction

Depuis l'avènement des circuits intégrés, la densité d'intégration des transistors et les performances des circuits VLSI (Very Large Scale Integration) ne cessent de s'améliorer. Cette croissance rapide de la complexité des circuits VLSI, atteignant déjà quelques millions de transistors, et la prolifération sans précédent des circuits mixtes ont rendu le test de ces circuits une tâche ardue et très coûteuse. Alors que dans l'univers numérique plusieurs algorithmes et outils CAO de test sont de nos jours couramment utilisés dans l'industrie électronique, l'univers de test analogique accuse un certain retard. En effet, le test des circuits analogiques n'a été l'objet d'une attention accrue et intense que tout récemment. Cet intérêt si important trouve son origine dans l'augmentation considérable du nombre d'applications analogiques et mixtes. En fait, depuis l'avènement des circuits multipuces, il est devenu possible d'intégrer sur un même substrat des circuits analogiques et numériques et de les interconnecter. Par conséquent, depuis cet avènement on assiste à une prolifération sans précédent des circuits mixtes dans des nombreuses applications industrielles, plus particulièrement dans le traitement des signaux et des images. Cette nouvelle tendance a introduit de nouveaux défis dans le test des circuits mixtes provenant essentiellement de la difficulté de tester la partie analogique. Cette tâche est rendue plus compliquée par une accessibilité limitée aux noeuds internes de ces circuits et un nombre restreint de broches. En conséquence, le temps nécessaire de mise en marché des circuits analogiques

et mixtes devient dominé par le développement d'algorithmes et de programmes de test de la partie analogique.

L'un des problèmes importants dans le domaine du test est de pouvoir évaluer un ensemble de tests en termes d'efficacité et de qualité. Autrement dit, si l'on applique un ensemble de tests à un circuit, qu'est-ce qui nous permet de dire que ce circuit est correctement testé? L'évaluation d'un ensemble de tests se fait dans le cadre d'un modèle de défaut. Dans le cas des circuits numériques la qualité d'un ensemble de tests est mesurée par une quantité bien connue, à savoir la couverture des défauts. Celle-ci est souvent définie comme le pourcentage de défauts "collés à" détectés par l'ensemble de tests, divisé par le nombre total des défauts "collés à" qui peuvent se produire. La mesure de la qualité d'un ensemble de tests nous permet aussi de connaître les défauts non détectés et de modifier le circuit en conséquence pour augmenter sa testabilité (et de pratiquer ainsi du design orienté testabilité "DFT"). Par contre, dans l'univers analogique il est plus difficile d'évaluer et de garantir la qualité d'un test analogique. Cela provient du fait qu'il n'existe pas de modèle analogique universel et adéquat de défaut, tel que c'est établi dans l'univers numérique. Seules les défauts catastrophiques présentent une certaine analogie au modèle numérique "collé à". Dans ce cas, la simulation de défauts peut être utilisée pour quantifier la qualité d'un test en évaluant sa couverture de défauts. Il est aussi possible dans ce cas, de construire des dictionnaires de défauts pour le diagnostic des circuits analogiques. Il est clair, que le manque d'un modèle analogique de défaut approprié, plus particulièrement dans le cas de défauts paramétriques, constitue un handicap sérieux qui affecte le développement du test analogique.

Les circuits analogiques sont traditionnellement testés par la vérification de leur fonctionnalité. Or, ce genre de test est reconnu très coûteux. En effet, le coût de test analogique peut représenter jusqu'à 30% du coût total de fabrication. De plus, dans ce type de test les circuits sont sur-testés ou sous-testés puisqu'il n'y a pas de mesure quantitative de qualité permettant de disposer d'un critère d'arrêt. Il en résulte qu'afin de minimiser le coût de test de production, il est nécessaire de développer des techniques de génération de tests basées sur des modèles de défaut. Dans les circuits analogiques les défauts sont classifiés comme paramétriques s'ils altèrent les performances du circuit, ou catastrophiques s'ils causent la perte totale du bon fonctionnement du circuit. Nous nous proposons donc, dans cette thèse, de mettre au point une méthode de test pour les circuits analogiques linéaires basée sur ces modèles de défaut. Cette méthode vise à générer un ensemble minimal de tests robustes permettant d'assurer à chacun des composants (paramètres) du circuit une détectabilité maximale de défauts. Cet ensemble de tests permettra de distinguer les circuits défectueux de ceux qui sont bons. Un circuit est déclaré défectueux si un test parmi l'ensemble de tests sélectionnés amène une performance du circuit en dehors de sa plage de tolérance. Un ensemble de tests est dit robuste s'il est en mesure de détecter les défauts paramétriques et catastrophiques sous la contrainte d'effet maximal de masquage dû à la tolérance des paramètres du circuit. En effet, seulement dans ce cas, la qualité d'un test peut être correctement mesurée et garantie. La génération d'un ensemble de tests ayant de telle spécification en particulier, et le test des circuits analogiques en général, sont des problèmes difficiles. Cette difficulté émane de la complexité naturelle de ces circuits qui présentent un spectre continu de défauts. La variation continue dans le temps des quantités physiques qui caractérisent ces circuits est à l'origine de la conti-

nuité de ce spectre. Par conséquent, il y a absence de modèle adéquat équivalent au modèle numérique “collé à 0 ou à 1”, puisque les sorties analogiques ne peuvent être considérées comme des états hauts ou des états bas. En outre, le manque d’accessibilité aux noeuds internes et plus particulièrement la non-linéarité des caractéristiques de ces circuits, ainsi que l’effet de masquage dû au problème de tolérance, rendent le problème de test analogique plus complexe.

Tel qu’il a été mentionné ci-dessus, nous assistons aujourd’hui à une prolifération sans précédent des applications des circuits analogiques et mixtes. Il est donc urgent de pouvoir tester efficacement les produits de ces applications. Autrement, leur fiabilité est compromise.

## 1.1 Objectifs de la thèse

Dans cette thèse, nous nous proposons de mettre en oeuvre une méthode de génération de test multifréquences pour détecter les défauts paramétriques et catastrophiques dans les circuits analogiques linéaires. Etant donné un ensemble de performances d’un circuit et une plage de fréquences, l’objectif visé est de déterminer les valeurs des plus petites déviations (en valeur absolue) observables d’un paramètre défectueux du circuit, et de sélectionner les fréquences de test qui maximisent la détectabilité de ces déviations sous les contraintes de variations, dans le pire des cas<sup>1</sup>. des autres paramètres dans leur plage de tolérance.

---

1. le pire des cas correspond à la configuration où les valeurs prises par les autres paramètres produisent un effet maximal de masquage empêchant les déviations du paramètre défectueux d’être détectées jusqu’à une certaine limite.

L'originalité de cette thèse réside principalement dans la génération de tests robustes de qualité garantie. En effet, cette garantie trouve son origine dans le fait que l'approche proposée permet de déterminer d'une manière optimale les valeurs des plus petites déviations (en valeur absolue) des paramètres du circuit à partir desquelles toute déviation de ces paramètres est assurée d'être détectée. En outre, elle permet de sélectionner la meilleure fréquence qui maximise l'observation (déttection) de ces valeurs limites. L'originalité de cette approche émane aussi de la formulation du problème de génération de tests comme une série de problèmes d'optimisation. Enfin, cette originalité trouve sa racine dans la mise en oeuvre d'une méthode, fondée sur la programmation logique à contraintes, qui permet d'obtenir une solution globale à ces problèmes d'optimisation.

## 1.2 Analyse du problème

Dans l'univers analogique, une fonction élémentaire est réalisée par un groupe de composants interconnectés. A titre d'exemple, un transistor peut participer à la génération de plusieurs fonctions différentes dépendamment des composants avec lesquels il est interconnecté. A cause des fluctuations des paramètres du procédé de fabrication, un composant est réputé bon si sa valeur est comprise dans la plage de tolérance autour de sa valeur nominale. Il est important de mettre l'accent sur le fait que la valeur nominale n'est qu'une possibilité parmi une infinité de valeurs que peut

prendre un paramètre correct. Il en résulte que les effets de tolérance des paramètres induisent aussi un effet de tolérance sur la fonction (réponse de sortie, performance) associée. Par conséquent, deux circuits réputés bons réalisant la même fonction peuvent produire des réponses différentes à une même excitation, tout en restant dans la plage de tolérance. Autrement dit, les variations des paramètres se traduisent par des effets de variations des performances du circuit. Il s'en suit qu'un circuit est déclaré défectueux si la valeur de l'une de ses performances se trouve en dehors de sa plage de tolérance. Par conséquent, toute déviation d'un paramètre qui amène l'une des performances du circuit en dehors de sa plage de tolérance, est détectable en observant (mesurant) cette performance. Si l'on choisit un ensemble de performances tel que chaque paramètre du circuit est couvert par au moins l'une d'elles, alors l'observation de ces performances nous permet de distinguer les circuits défectueux de ceux qui sont bons. Naturellement, à ce stade plusieurs questions s'imposent à l'esprit parmi lesquelles: Selon quel critère faut-il sélectionner les performances à observer? Suivant quelle base peut-on sélectionner le test à appliquer? Comment garantir que les tests générés sont robustes (de meilleure qualité)?

Pour garantir la qualité d'un test, il faut nécessairement tenir compte des effets de tolérance des paramètres dans le pire des cas. En effet, supposons qu'un seul paramètre du circuit est défectueux (c'est une analyse de défaut simple). Et supposons aussi qu'on a pu observer l'effet de sa déviation en observant l'une des performances

du circuit sous la contrainte des variations des autres paramètres dans leur plage de tolérance dans le pire des cas. On en déduit que pour détecter cette déviation, il a fallu qu'elle soit suffisamment grande pour contrer d'une part, les effets de variations normales des autres paramètres dans le pire des cas et amener d'autre part, la performance observée en dehors de sa plage de tolérance. Autrement dit, le pire des cas correspond au masquage maximal, produit par les effets de tolérance des paramètres, qui empêche les variations d'un paramètre défectueux d'être détectées. à travers la performance observée, jusqu'à une certaine valeur limite au delà de laquelle toute déviation devient détectable. Il est clair qu'un ensemble de tests ne peut être robuste que s'il est en mesure de détecter les défauts paramétriques et catastrophiques sous la contrainte d'effet maximal de masquage dû à la tolérance des paramètres du circuit. C'est seulement dans ce cas que la qualité d'un test peut être mesurée et garantie. La génération d'un tel test s'avère un problème difficile puisque les circuits analogiques présentent un spectre continu de défauts. En outre, la non linéarité des performances de ces circuits complique davantage le problème du test analogique. La non linéarité se traduit par le fait que si la valeur d'un paramètre varie d'un certain facteur, les performances affectées par cette variation ne varient pas du même facteur. En d'autres termes, la relation  $T_k = T(x_1, \dots, x_m)$  liant les performances  $T_k$ ,  $k=1, \dots, n$ , du circuit et les paramètres  $x_i, i=1, \dots, m$ , est non linéaire. Par conséquent, le problème du test analogique touche à un problème mathématique non linéaire multidimensionnel dans un espace continu, problème reconnu très complexe et très difficile mettant en oeuvre

beaucoup de temps de calcul. Dans cette thèse on se propose de formuler ce problème et de mettre au point une méthode d'optimisation globale pour le résoudre.

Avant de procéder à l'analyse et à la résolution du problème posé, il est important de passer en revue différents travaux accomplis dans le domaine du test analogique, afin de mieux situer le problème étudié dans cette thèse et de clarifier le cadre dans lequel il s'inscrit.

## Chapitre 2

# Revue de littérature

### 2.1 Concepts de base

La plupart des concepts de base utilisés dans le domaine du test des circuits analogiques sont empruntés à l'univers numérique. Dans cette section, nous rappelons certains concepts fondamentaux tout en mettant l'accent, quand c'est nécessaire, sur les spécificités qui caractérisent et distinguent l'univers analogique.

#### 2.1.1 Test et diagnostic

Le processus de test peut être défini comme une procédure efficace d'extraction d'informations pertinentes concernant le système sous-test. En général, cette procédure est traduite par l'expérience dans laquelle le système est excité et sa réponse est analysée pour s'assurer de son bon fonctionnement. Si un comportement incorrect est détecté, alors l'objectif suivant est d'en localiser ou de diagnostiquer la cause et d'en déterminer la valeur.

### 2.1.2 Défauts physiques

Les défauts physiques sont à l'origine du fonctionnement incorrect d'un système. Ils sont détectés en observant les erreurs qu'ils produisent. Les défauts physiques peuvent être dûs à des erreurs de conception, des erreurs de fabrication, des défectuosités de fabrication ou des pannes physiques [5].

Les erreurs de conception sont dues à des spécifications incorrectes ou incomplètes, des violations des règles de conception, ou une incohérence entre les différents niveaux de conception. Les erreurs de fabrication peuvent être dues à une mauvaise sélection de composants, des connexions incorrectes ou à des court-circuits causés par des soudures mal faites. Par contre, les défectuosités physiques sont inhérentes à l'imperfection du procédé de fabrication, et ne sont pas par conséquent attribuables à des erreurs humaines. A titre indicatif, les court-circuits et les circuit-ouverts sont des défectuosités courantes du procédé de fabrication des circuits MOS LSI (Large Scale Integrated). Un profil de dopage incorrect et des erreurs d'alignement des masques sont aussi des exemples de défectuosités physiques. Il est à remarquer que la localisation précise des défectuosités physiques est un facteur pertinent permettant d'améliorer et de rendre mature un procédé de fabrication. Quant aux pannes physiques, elles peuvent se produire durant la vie d'un système et sont dues à l'effet de l'usure et à l'influence des facteurs d'environnement. À titre d'exemple, les connecteurs d'aluminium à l'intérieur d'un boîtier de circuit intégré s'amincent au fil du temps et peu-

vent casser sous le phénomène de l'électromigration et de la corrosion. Les facteurs tels que la température, l'humidité et les vibrations contribuent à l'accélération du vieillissement des composants. Des radiations cosmiques et des particules  $\alpha$  peuvent induire des pannes physiques dans les puces de mémoire à accès aléatoire (RAM) à haute densité. Certaines pannes physiques appelées "défauts de jeunesse" peuvent apparaître tôt après la fabrication.

Les défauts physiques peuvent être permanents s'ils sont toujours présents, ou intermittents s'ils apparaissent pendant certains intervalles de temps, ou transitoires (causés par exemple par un changement temporaire d'un facteur environnemental). En général, la considération des défauts physiques ne permet pas un traitement mathématique direct des problèmes de test et de diagnostic. La solution réside dans le traitement des quantités, maniables mathématiquement, et qui représentent les effets des défauts physiques sur les opérations du système. Ces quantités peuvent être des défauts logiques dans les circuits numériques. Alors que dans les circuits analogiques, elles peuvent être des défauts catastrophiques (similaire au modèle "collé à") ou des défauts paramétriques altérant les performances de ces circuits.

### 2.1.3 Modélisation

La modélisation joue un rôle primordial dans la conception, la fabrication et le test des systèmes électroniques. La façon avec laquelle nous représentons le système

conditionne la manière et les résultats de sa simulation pour vérifier sa conformité avec les spécifications. En outre, le modèle choisi pour représenter un système a également d'importantes conséquences sur la manière avec laquelle on construit les modèles de défauts, sur la simulation des défauts ainsi que sur la façon de générer les tests.

On distingue le modèle comportemental, le modèle fonctionnel et le modèle structurel. Le modèle fonctionnel d'un système numérique est une représentation de sa fonction logique (en l'occurrence sa table de vérité) abstraction faite des relations temporelles (diagrammes de temps). Le modèle comportemental est une combinaison du modèle fonctionnel et des relations temporelles. Cette distinction entre les deux modèles est importante du moment qu'elle permet à deux systèmes ayant la même fonction logique et des diagrammes de temps différents de partager un même modèle fonctionnel. Elle permet également aux deux aspects fonctionnel et temporel d'être traités séparément sur le plan vérification de la conception et génération de tests. Quant au modèle structurel, c'est une description hiérarchique dans laquelle chaque niveau est une collection d'éléments interconnectés, et tel que le niveau le plus bas est constitué d'éléments primitifs dont on connaît le modèle fonctionnel ou comportemental.

#### **2.1.4 Simulation**

Traditionnellement, les concepteurs ont utilisé un prototype pour la vérification d'un nouveau design. L'avantage principal d'un prototype est de pouvoir fonctionner à la vitesse de travail spécifiée. Par contre, il coûte cher et demande beaucoup de temps de mise en oeuvre. La simulation permet de remplacer le prototype par un modèle logiciel facilement modifiable et qu'on peut analyser sans difficulté. La simulation consiste à exciter le modèle avec une représentation des signaux d'entrée, et à déterminer l'évolution de la réponse de ce modèle en fonction du temps. Dans ce contexte, la simulation est une forme de test de vérification du design. Ce genre de test consiste à s'assurer que le design accomplit bien le comportement spécifié par comparaison des résultats obtenus par simulation à ceux attendus (spécifiés).

#### **2.1.5 Modèle de défaut**

Un modèle de défaut représente l'effet des défauts physiques sur le comportement d'un système modelisé. La modélisation des défauts physiques permet de réduire efficacement la complexité du problème d'analyse des défauts puisque plusieurs défauts physiques peuvent être modélisés par un même modèle de défaut. En outre, l'un des objectifs majeurs de la modélisation des défauts est de construire des modèles de défaut indépendants de la technologie utilisée. Autrement dit, un même modèle de défaut peut être appliqué à plusieurs technologies différentes. Il en résulte

que les méthodes de test et de diagnostic développées dans le cadre d'un modèle de défaut restent valables quand on change de technologie.

La modélisation de défauts est reliée étroitement au modèle construit pour représenter le système. En effet, on distingue les défauts<sup>1</sup> structurels dans le cas d'un modèle structurel, et les défauts fonctionnels dans le cas d'un modèle fonctionnel.

En général, dans l'univers numérique, les modèles de défauts structurels suppose que les éléments sont bons et que seulement les interconnexions peuvent être affectées. Les défauts typiques affectant les interconnexions sont des court-circuits et des circuit-ouverts. Dans l'univers numérique, le modèle structurel "collé à" est très répandu et a montré une très bonne efficacité représentative d'une large classe des défauts.

Par contre, dans le monde analogique il n'existe pas de modèle universel de défaut pour représenter les défauts analogiques. Différents facteurs sont à l'origine de ce sérieux handicap. En effet, les caractéristiques des circuits analogiques sont souvent non linéaires et le spectre de leurs valeurs est continu et assez large (à cause du problème de tolérance). Il en résulte que les méthodes déterministes sont souvent inefficaces pour modéliser ces circuits [6][7]. Les circuits analogiques sont aussi caractérisés par un spectre continu des défauts possibles. Par conséquent, il est très difficile de construire des modèles discrets simples et capables de couvrir tous (ou une large classe) les défauts possibles de ces circuits. En outre, les distributions statisti-

ques des défauts analogiques ne sont pas encore bien connues. Il s'en suit que les modèles probabilistes ne sont pas suffisamment efficaces.

Dans les circuits analogiques on distingue fondamentalement deux catégories de défauts: les défauts catastrophiques et les défauts paramétriques. Les défauts catastrophiques sont souvent le résultat des défauts aléatoires. Ces défauts peuvent être des déviations importantes des valeurs des composants ou des court-circuits et des circuit-ouverts [8]. Les défauts paramétriques sont causés par les fluctuations des paramètres du procédé de fabrication.

Aux difficultés mentionnées ci-dessus s'ajoute la question de savoir quel est le modèle de défaut qui domine et qu'on pourra utiliser? Malheureusement, il n'y a pas de consensus dans la communauté de test analogique concernant ce problème. En effet, certains travaux [9] mentionnent que 80 à 90% des défauts analogiques sont causés par des défauts catastrophiques tels que des composants (résistances, capacités, transistors) en court-circuits ou en circuit-ouverts, et que les défauts multiples sont peu probables (comme c'est le cas dans les circuits numériques). Par contre, d'autres travaux [10] mentionnent que la perte de rendement du procédé est causée par des phénomènes multiples. En particulier, la perte due aux défauts catastrophiques paraît insignifiante dans le cas des circuits analogiques bipolaires. Quant au procédé BICMOS, il n'est pas encore suffisamment mature. Mais les premières études mon-

trent que les défauts multiples catastrophiques et paramétriques existent dépendamment de l'implementation de la circuiterie analogique [11].

### **2.1.6 Evaluation d'un test et simulation de défauts**

Il est important de pouvoir évaluer l'efficacité et la qualité d'un test. L'évaluation d'un test est souvent effectuée dans le cadre d'un modèle de défaut. La qualité d'un test est mesurée par la couverture de défauts calculée comme le rapport du nombre des défauts que le modèle peut détecter au nombre total des défauts supposés possibles. L'évaluation d'un test se fait à l'aide de la simulation de défauts dans laquelle la réponse du modèle (représentant le circuit défectueux) est calculée. Un défaut est détecté s'il produit une réponse différente de celle produite par le modèle représentant le circuit réputé bon.

L'absence de modèle universel de défaut analogique, le problème de tolérance et la non linéarité des caractéristiques des circuits analogiques rendent les tâches de génération de tests, de diagnostic et de simulation de défauts extrêmement difficiles. Comme conséquence de la variation des paramètres du procédé, deux circuits, dont le fonctionnement est correct, peuvent produire des réponses différentes à une même excitation tout en restant dans la plage spécifiée. Cela provient du fait qu'à cause des fluctuations du procédé, les paramètres peuvent prendre une infinité de valeurs. Il en résulte, que contrairement au monde numérique, il n'est pas possible d'énumérer les

défauts analogiques possibles d'un modèle de défaut puisque leur spectre est continu. Par conséquent, compte tenu de la continuité du spectre des valeurs que peuvent prendre les paramètres bons (dans leur plage de tolérance) ou erronés (ayant dévié de cette plage), et de la non linéarité des caractéristiques (performances), un nombre extrêmement grand de simulations de défauts est requis pour assurer une évaluation correcte d'un test ou pour rendre efficace les méthodes de diagnostic basées sur la simulation de défauts (telle que l'approche de diagnostic à dictionnaire de défauts).

## 2.2 Méthodes de test

Compte tenu du fait que la plupart des principes des méthodes de test des circuits analogiques sont adoptés de l'univers numérique, il est intéressant de décrire brièvement les fondements de ces méthodes [5].

### 2.2.1 Méthode de test en temps réel (On-line testing)

Dans ce mode, le test est effectué dans les conditions normales de fonctionnement du système. Cette méthode suppose que le stimuli et la réponse du système ne sont pas connus à l'avance. En fait le stimuli est fourni en temps réel par les séquences générées par le système en fonctionnement. La méthode repose sur l'exploitation de certaines propriétés de la réponse, qui restent invariantes durant le fonctionnement correct (en l'absence de défauts) du système. Ces propriétés invariantes sont produites

par des techniques de design fiables permettant de les contrôler facilement durant le fonctionnement en temps réel. Les méthodes d'auto-vérification intégré (*Built\_In Self-Test*) et d'auto-contrôle de design (*Self\_checking design*) sont des méthodes de test qui peuvent être appliquées en temps réel.

### **2.2.2 Méthode d'auto-contrôle de design (*Self-checking design*)**

Tel que mentionné précédemment, cette méthode est basée sur le contrôle de certaines propriétés invariantes de la réponse. Autrement dit, elle implique l'utilisation des codes de détection des erreurs (tel que le contrôle de parité, le code de Berger,...) et des techniques spécifiques de design. La fonction de contrôle est assurée par un circuit de contrôle (*checker*).

### **2.2.3 Méthode d'auto-vérification intégré (*Built\_In Self Testing*)**

La méthode d'auto-vérification intégré (*Built\_In Self\_Test: BIST*) est une technique de design dans laquelle une partie du circuit est utilisée pour assurer l'auto-vérification du circuit. On distingue les différents types de BIST suivants:

-Le BIST concurrent en mode normal qui est une forme de test appliquée simultanément avec les opérations normales du système. Cette technique de test est souvent implementée en utilisant des techniques de codage ou bien la technique de duplication et de comparaison.

-Le BIST non-concurrent en mode normal est appliqué quand le système est dans un état de repos (état d'attente). Cette technique utilise des routines programmées (ou bien des routines ineffaçables écrites à l'usine) de diagnostic. Le processus de test peut être interrompu à tout moment pour permettre au système de rentrer en fonctionnement quand il est requis.

-Le BIST en mode test (*Off-line BIST*) met en œuvre des générateurs de motifs de test (*Test-pattern generator: TPG*) et des analyseurs de réponse de sortie incorporés sur la puce ou la carte imprimée. Il va de soi que cette technique ne détecte pas les défauts en temps réel. Le BIST fonctionnel en mode test est basé sur une description fonctionnelle du circuit et utilise un modèle de défaut fonctionnel. Alors que le BIST structurel est basé sur l'usage d'un modèle de défaut structurel, et pour lequel la couverture de défauts est calculée sur la base des défauts structurels détectés.

Le BIST peut être utilisé pour tester les systèmes montés dans leur environnement de travail sans avoir recours à des équipements de test sophistiqués et coûteux. Cette méthode est basée sur la détection des défauts au niveau unités (telles que les cartes des circuits imprimés). A titre d'exemple, l'armée américaine a adoptée une politique de maintenance à deux niveaux [5]. Le système doit s'auto-tester pour détecter automatiquement l'unité défectueuse. Celle-ci est remplacée sur le terrain et l'unité défectueuse est rejetée ou envoyée pour réparation (second niveau de test).

#### **2.2.4 Méthode de test à sonde guidée**

C'est une technique utilisée au niveau des cartes imprimées. Durant la première phase du test, la détection des défauts se fait au niveau des broches de bord de la carte selon le test go/no go. Dans la deuxième phase, si le défaut est détecté le testeur décide quelle ligne interne de la carte doit être commandée, et demande à l'opérateur d'y placer la sonde. Ensuite, le test est appliqué de nouveau et la procédure continue de cette manière jusqu'à la localisation du défaut. Certains testeurs possèdent une monture sous forme de lit de clous permettant de commander toutes les lignes accessibles (en général les broches de circuit intégré) en une seule étape.

#### **2.2.5 Méthode de test en circuit (*In-circuit testing*)**

L'objectif de cette méthode est de tester les composants déjà montés sur un circuit imprimé. Son principe de fonctionnement est d'isoler le circuit intégré à tester du reste de son environnement et d'y appliquer des motifs d'entrée générés par un testeur externe. Ensuite, les réponses de ce circuit sont analysées.

#### **2.2.6 Méthode de test par comparaison**

Dans cette méthode la réponse du circuit sous-test est comparée à la réponse attendue (spécifiée). Celle-ci peut être générée par un circuit réputé bon (appelé unité

en or) ou bien par émulation en temps réel de l'unité sous-test. Cette méthode qui est basée sur la comparaison est en réalité utilisée par plusieurs autres méthodes de test.

### **2.2.7 Méthode de test par compression de la réponse**

Cette méthode est basée sur la comparaison des signatures du circuit sous-test et celle de l'unité en or. En fait, au lieu de contrôler la réponse  $R$  du circuit sous-test, il s'agit de contrôler seulement une certaine fonction  $f(R)$  dérivée de cette réponse. La fonction  $f(R)$  est une représentation compressée appelée signature. A titre d'exemple, on peut compter le nombre des 1 (ou le nombre de transitions de 0 à 1 ou de 1 à 0) contenus dans la réponse du circuit sous-test et le comparer au nombre des 1 (ou des transitions) contenus dans la réponse du circuit réputé bon. Cette méthode est principalement utilisée dans la méthode d'auto-vérification intégré (BIST).

## **2.3 Modèle de défaut et simulation de défauts**

Tel que mentionné précédemment, le manque de modèle analogique universel, le problème de tolérance et de non linéarité, de spectre continu de défauts rendent la simulation de défauts au niveau du circuit (c.à.d au niveau composants) très difficile, voir impraticable.

Idéalement, un circuit analogique peut avoir un ensemble infini de défauts. Afin de réduire cet énorme espace de défauts possibles et d'aboutir à une liste restreinte de

défauts qu'on peut simuler [12], il est nécessaire d'utiliser un simulateur de défectuosités tel que VLASIC (*VLSI Layout Simulation for Integrated Circuits*) [13] [14] qui est basé sur la technique d'analyse inductive de défauts (IFA) [15]. L'application de la technique IFA au dessin de masques (*Layout*) nécessite la connaissance des statistiques des défectuosités du procédé de fabrication. VLASIC utilise la méthode de Monte Carlo pour insérer les défectuosités du procédé dans le dessin de masques en respectant leur statistique. La technique IFA permet d'identifier une liste restreinte de défauts qui reflètent les effets du plus grand nombre possibles de défectuosités injectées (cent milles utilisées dans [16] et un million dans [17]). Bien que cette manière de procéder réduit considérablement le nombre de défauts à considérer, la liste de défauts obtenue peut être encore assez longue et le temps de simulation correspondant est important. Afin d'accélérer le processus de simulation et de diminuer en conséquence le temps de traitement requis, différents travaux ont été réalisés utilisant la modélisation à des niveaux d'abstraction plus élevés. Ces travaux sont classifiés en deux catégories. Dans la première, les défauts sont modélisés au niveau circuit, et le comportement de la macro-cellule défectueuse est saisi à un niveau d'abstraction approprié grâce à un simulateur analogique [12] [17] [18] [19] [20]. A titre d'exemple, dans [17] et [20] la macro-cellule (amplis opérationnels, comparateurs, filtres, etc...) contenant le défaut injecté, est décrite au niveau circuit (sous forme de liste de noeuds en SPICE), alors que les autres parties non défectueuses du circuit sont remplacées par leur modèle comportemental correspondant au niveau d'abstraction

approprié. Dans cette méthode, la plus grande partie du temps de simulation est consacrée à la partie sous évaluation (macro-cellule défectueuse). Il s'en suit que le temps de simulation devient presque indépendant de la taille du circuit.

Par contre, dans la deuxième catégorie, les défauts ne sont pas modélisés au niveau circuit. Le comportement d'une macro-cellule est saisi au niveau fonctionnel (Les valeurs des éléments du macro-modèle sont calculés à l'aide des équations de design qui peuvent être des équations différentielles et/ou des fonctions mathématiques décrivant les relations entre les composants du circuit) [21] [22]. De même, si les macro-cellules non défectueuses sont aussi simulées au niveau fonctionnel, le temps de simulation utilisant SPICE est réduit considérablement.

Les auteurs de [16] [23] ont développé une approche hiérarchique pour produire des modèles de défaut à des niveaux d'abstraction supérieurs en se basant sur l'amplificateur opérationnel comme élément primitif.

Pour modéliser les effets de variations des paramètres du procédé de fabrication certains auteurs ont utilisé une enveloppe, de valeur constante, autour des réponses nominales et des réponses des circuits défectueux [19] [24] [25]. Cela ne reflète pas nécessairement la réalité et peut affecter la précision des résultats puisque les valeurs limites constituant l'enveloppe, peuvent varier avec le test appliqué, le degré de non-linéarité des réponses du circuit, etc.

## 2.4 Design orienté testabilité (*Design For Testability: DFT*)

Le coût de test d'un système est devenu une composante majeure du coût de design, de production et de la maintenance d'un système. Il est le reflet de plusieurs facteurs tels que le coût de génération de test, le temps requis pour le test, le coût de l'équipement de test automatique (ATE), etc... En outre, pour minimiser ce coût il est important de détecter les défauts le plus tôt possible [26]. En effet, un même défaut détecté au niveau carte coûtera beaucoup plus cher que s'il décelé au niveau composant. Il coûtera encore plus cher s'il est détecté chez le client.

La technique de design orienté testabilité (DFT) a connu un essor important ces dernières années. L'objectif de cette technique est de réduire le coût de test en introduisant des critères de testabilité suffisamment tôt dans les différentes étapes du design. L'objectif fondamental de la technique DFT consiste à augmenter la contrôlabilité et l'observabilité du circuit de telle manière à en assurer la testabilité. La contrôlabilité est la facilité de contrôler un noeud du circuit et de lui attribuer une certaine valeur. Alors que l'observabilité est la facilité de propager un défaut d'un noeud vers une sortie primaire. La mesure de la contrôlabilité et de l'observabilité dépendent du générateur de vecteurs de test utilisé. Par exemple, dans le cas d'un générateur aléatoire un noeud a une faible contrôlabilité si l'établissement de son état nécessite une longue séquence de vecteurs d'entrée. Un circuit a une faible

observabilité aléatoire s'il nécessite une longue séquence de vecteurs d'entrée pour pouvoir propager l'état d'un ou de plusieurs noeuds vers les sorties du circuit.

Par contre, dans l'univers analogique, il n'est pas aussi simple de contrôler et de propager des signaux (et d'effectuer les simulations et les calculs associés) comme c'est le cas dans les circuits numériques. Cela provient de la complexité naturelle des circuits analogiques qui présentent des problèmes de tolérance, de non linéarité de leurs caractéristiques et de la continuité de leurs spectres de défauts.

Plusieurs travaux accomplis lient la mesure de testabilité des circuits analogiques au degré de solvabilité du système d'équations de diagnostic décrivant les relations entre les performances mesurées et les paramètres du circuit [27] [28] [29]. Dans [30] l'observabilité d'un défaut associé au composant  $x_i$  est définie comme la sensibilité d'une performance  $T_i$  du circuit aux variations de la valeur de ce composant. Elle peut être déterminée par le calcul de la sensibilité de la performance (fonction de transfert par exemple) au noeud de test, relative à la variation de la valeur du composant considéré.

La plupart des méthodes DFT requièrent des modifications du circuit et affectent certains facteurs tels que la surface de silicium, le nombre de broches d'entrées-sorties et la vitesse de fonctionnement du circuit. Les valeurs de ces facteurs ont tendance à augmenter suite à l'usage de la technique DFT. Or, augmenter la surface et la complexité des puces VLSI a pour effet d'augmenter la puissance consommée, de

diminuer le rendement du procédé de fabrication, et d'augmenter ainsi le coût de ces circuits. Par conséquent, un compromis doit être trouvé permettant d'atteindre un bon rendement et de rendre bénéfique l'ajout de la circuiterie de DFT.

On distingue principalement deux méthodes DFT: l'approche structurée basée sur les techniques de balayage (*Scan techniques*) et l'approche ad hoc.

#### 2.4.1 Approche ad hoc

L'approche ad hoc essaie d'apporter une solution spécifique au problème de test d'un circuit donné. Afin d'augmenter la contrôlabilité et l'observabilité de certains noeuds non accessibles, on procède à la modification du design. Cette modification est réalisé par le (re)partitionnement du circuit permettant ainsi d'accéder directement ou indirectement à ces noeuds. La méthode de partitionnement la plus utilisée est basée sur le partitionnement en blocs fonctionnels. On procède ensuite, à l'ajout des points de test (contacts métalliques) pour augmenter l'observabilité. Pour réduire le nombre des points de test et le nombre de broches associées on utilise le multiplexage. On peut aussi utiliser des commutateurs incorporés implementés avec des portes de transmission et des multiplexeurs permettant ainsi d'accéder à plusieurs noeuds au moyen des signaux de contrôle numériques [31] [32].

Par contre, il est plus difficile d'augmenter la contrôlabilité d'un noeud puisqu'il faut isoler l'entrée (noeud) de l'étage courant de la sortie de l'étage précédent.

dent. Pour éviter d'effectuer l'isolation d'une manière destructive (couper la liaison au moyen des faisceaux électroniques par exemple) on procède à l'usage des portes de transmission et des multiplexeurs [31] [32]. L'ajout des commutateurs incorporés présente les inconvénients d'augmenter la surface et le temps de design. La nécessité des signaux de contrôle, ainsi que l'atténuation des signaux due aux portes de transmission et aux longs fils conduisant aux multiplexeurs et aux sorties primaires, constituent également d'autres désavantages.

Enfin, il est d'usage d'utiliser des interrupteurs analogiques permettant de briser les boucles des circuits analogiques pour pouvoir prendre convenablement les mesures. Cette façon de procéder permet d'éviter les coupures destructives des liaisons.

#### **2.4.2 Approches structurées: Techniques de balayage (Scan techniques)**

La méthode fondée sur la chaîne de balayage est plus répandue que la méthode ad hoc. Elle est appliquée durant la phase de design sous forme de directives à suivre ou comme des règles de design à respecter. Bien qu'il existe différentes méthodes, une technique de base pour augmenter la testabilité des noeuds consiste à les connecter à un registre de décalage. La question qui en découle est de savoir si l'on peut commander (à l'aide des signaux d'horloge) adéquatement le registre à décalage. Autrement dit, peut-on assurer la bande-passante, l'impédance, le niveau des signaux

nécessaires à la bonne conduite des mesures. Deux dispositifs bien connus qui fonctionnent comme un système d'échantillonnage et qui peuvent jouer le rôle des registres analogiques à décalage sont: le dispositif à transfert de charge (basé sur l'accumulation des charges dans des puits de potentiel) et le dispositif à transfert de charge réalisé à l'aide des transistors et des capacités (*Bucket-Brigade Device*). Ce dernier type de registre à décalage analogique a été utilisé dans [33] pour construire une chaîne de balayage analogique. Celle-ci est illustrée par la figure 2.1.

Figure 2.1: Chaîne de balayage analogique

Les signaux des noeuds n1, n2 et n3 sont échantillonnés grâce aux interrupteurs S1, S2 et S3, puis stockés dans les capacités C1, C2 et C3 qui sont isolées les unes des

autres par les suiveurs de tension B (amplificateur d'impédance d'entrée élevée et d'impédance de sortie faible). L'ensemble forme un échantillonneur-bloqueur. En mode normal, tous les interrupteurs sont ouverts coupant ainsi toute liaison entre les noeuds à tester et le registre à décalage. En mode test, les interrupteurs I1, I2 et I3 restent ouverts isolant ainsi les étages les uns des autres, alors que les interrupteurs S1 S2 et S3 se ferment pour permettre aux données des noeuds n1, n2 et n3 d'être échantillonnés en parallèle et stockées dans les capacités C1, C2 et C3. Ensuite l'interrupteur I3 est fermé (I2 et I1 restent ouverts) pour permettre au signal stocké dans C3 d'être transféré à la sortie SO. Puis, I2 est fermé (I1 reste ouvert) permettant au signal stocké dans C2 d'être transféré à son tour à la sortie. Enfin, le signal de C1 est transféré vers la sortie d'une façon similaire et l'opération entière se répète d'une manière cyclique. Durant ces opérations, la commande des interrupteurs peut être assurée par un simple registre à décalage numérique.

Cette chaîne de balayage analogique introduit des capacités parasites (intrinsèques aux amplificateurs) limitant ainsi la réponse en fréquence, plus particulièrement dans le cas des signaux à fréquences élevées. En outre, la circuiterie additionnelle peut être assez importante dépendamment du nombre des points de test requis.