**Titre:** Analyse, implantation et intégration d'une bibliothèque pour la spécification des systèmes embarqués dans une méthodologie de codesign

Title:

**Auteur:** Luc Filion

Author:

**Date:** 2002

**Type:** Mémoire ou thèse / Dissertation or Thesis

**Référence:** Filion, L. (2002). Analyse, implantation et intégration d'une bibliothèque pour la spécification des systèmes embarqués dans une méthodologie de codesign

Citation: [Master's thesis, École Polytechnique de Montréal]. PolyPublie.

<https://publications.polymtl.ca/7033/>

## Document en libre accès dans PolyPublie

Open Access document in PolyPublie

**URL de PolyPublie:** <https://publications.polymtl.ca/7033/>

PolyPublie URL:

**Directeurs de recherche:** Guy Bois, & El Mostapha Aboulhamid

Advisors:

**Programme:** Unspecified

Program:

UNIVERSITÉ DE MONTRÉAL

**ANALYSE, IMPLANTATION ET INTÉGRATION D'UNE

BIBLIOTHÈQUE POUR LA SPÉCIFICATION DES SYSTÈMES

EMBARQUÉS DANS UNE MÉTHODOLOGIE DE CODESIGN**

LUC FILION

DÉPARTEMENT DE GÉNIE ÉLECTRIQUE

ET DE GÉNIE INFORMATIQUE

ÉCOLE POLYTECHNIQUE DE MONTRÉAL

MÉMOIRE PRÉSENTÉ EN VUE DE L'OBTENTION DU DIPLÔME

DE MAÎTRISE ÈS SCIENCES APPLIQUÉES

(GÉNIE ÉLECTRIQUE)

DÉCEMBRE 2002

© Luc Filion, 2002

National Library

of Canada

Acquisitions and

Bibliographic Services

395 Wellington Street

Ottawa ON K1A 0N4

Canada

Bibliothèque nationale

du Canada

Acquisitions et

services bibliographiques

395, rue Wellington

Ottawa ON K1A 0N4

Canada

Your file Votre référence

Our file Notre référence

The author has granted a non-exclusive licence allowing the National Library of Canada to reproduce, loan, distribute or sell copies of this thesis in microform, paper or electronic formats.

L'auteur a accordé une licence non exclusive permettant à la Bibliothèque nationale du Canada de reproduire, prêter, distribuer ou vendre des copies de cette thèse sous la forme de microfiche/film, de reproduction sur papier ou sur format électronique.

The author retains ownership of the copyright in this thesis. Neither the thesis nor substantial extracts from it may be printed or otherwise reproduced without the author's permission.

L'auteur conserve la propriété du droit d'auteur qui protège cette thèse. Ni la thèse ni des extraits substantiels de celle-ci ne doivent être imprimés ou autrement reproduits sans son autorisation.

0-612-81546-3

Canada

**UNIVERSITÉ DE MONTRÉAL**

**ÉCOLE POLYTECHNIQUE DE MONTRÉAL**

Ce mémoire intitulé :

**«ANALYSE, IMPLANTATION ET INTÉGRATION D'UNE

BIBLIOTHÈQUE POUR LA SPÉCIFICATION DES SYSTÈMES

EMBARQUÉS DANS UNE MÉTHODOLOGIE DE CODESIGN»**

présenté par : FILION Luc

en vue de l'obtention du diplôme de : Maîtrise ès sciences appliquées

a été dûment accepté par le jury d'examen constitué de :

M. SAVARIA Yvon, Ph.D., président

M. BOIS Guy, Ph.D., membre et directeur de recherche

M. ABOULHAMID El Mostapha, Ph.D., membre et codirecteur de recherche

M. BOYER François-Raymond, Ph.D., membre

## Remerciements

Je tiens d'abord à remercier mon directeur de recherche Guy Bois pour l'enthousiasme qu'il a apporté à ce projet. M. Bois aura mis beaucoup de temps, de mots, d'insistance, de confiance et d'encouragement pour le développement de la bibliothèque. Sans son soutien personnel, ce projet n'existerait pas. J'aimerais également remercier mon codirecteur Mostapha Aboulhamid, qui répondit avec intérêt à mes nombreuses questions. Je remercie inéluctablement les gens qui m'ont subventionné, d'abord mon directeur de recherche Guy Bois, puis le ReSMiQ pour la bourse qu'il m'a octroyée. Je me vois également fort reconnaissant envers mes collègues qui ont directement aidé à la réalisation de ce projet, à la rédaction d'articles ou qui m'ont personnellement supporté : Marc Bertola, Jérôme Chevalier, Geneviève Cyr, mais aussi les autres étudiants du CIRCUS et membres du personnel qui m'ont apporté soutien, conseils et sourires. Certaines gens ont contribué d'une façon intéressante à ce mémoire en travaillant sur des projets de fins d'études au baccalauréat et je les remercie de bonne foi : Jean-Philippe Richer et Hugo Lefrançois.

Et dans ces moments les plus décourageants, que reste-t-il donc? Ma chère copine Laurence qui ne cessa de m'encourager. Mais encore, mes fabuleux brownies devant lesquels je m'incline et qui m'ont manifestement revigoré à plusieurs reprises! C'est avec joie que je vous les recommande !

## Résumé

Les méthodes utilisées aujourd’hui pour la conception de systèmes embarqués deviennent de moins en moins efficaces à cause de la complexité grandissante des circuits. Pour éviter une diminution de la productivité lors de la spécification des systèmes, un mouvement vers les langages orientés objets est essentiel. C'est avec des concepts tels la réutilisation et le raffinement progressif des spécifications que cette diminution sera évitée. Quelques groupes de recherche et compagnies ont opté pour cette voie, mais les bibliothèques disponibles sur le marché ne répondent pas à tous les besoins. Il est important que les concepteurs de systèmes comprennent bien ces nouvelles idées parce qu'ils feront face à un changement drastique dans leurs méthodes de design.

Nous avons d'abord revu l'entrée des spécifications dans les méthodologies existantes et avons examiné les langages et bibliothèques disponibles afin d'établir une liste des lacunes qu'elles possèdent. De là, nous avons proposé une méthodologie de conception des systèmes embarqués (ou méthodologie de codesign) qui utilise pour spécifications une bibliothèque système appelée *Syslib*. Cette bibliothèque, couvrant un niveau d'abstraction sans notion de temps (*untimed functional*), est programmée en C++ orienté objet pour faciliter le raffinement progressif vers des solutions finales d'implantation (matériel ou logiciel). Pour démontrer les possibilités de *Syslib*, un exemple de routeur de paquets producteur/consommateur est présenté. Nous discutons ensuite des techniques de raffinement. La spécification vers le matériel se fait à l'aide de la bibliothèque de modélisation *Cynlib*. Un exemple illustrant les difficultés de cette technique est présenté. Pour le raffinement vers le logiciel, on réutilise au maximum les spécifications *Syslib*.

Une fois la bibliothèque *Syslib* de niveau fonctionnel terminée, nous avons procédé à l'implantation de différents exemples de design pour démontrer les possibilités de la bibliothèque, question de bien la situer parmi l'ensemble des bibliothèques existantes. Les exemples présentés comprennent un décodeur JPEG, un contrôleur mémoire, un

*BlockMatcher*, un additionneur simple, de même que le routeur de paquets. Tous ces exemples ont été programmés à un niveau d'abstraction fonctionnel sans notion de temps en utilisant Syslib et SystemC, la bibliothèque « standard » de l'industrie. Les exemples sont comparés de façon quantitative mais aussi qualitative. Une analyse des résultats montre que la bibliothèque Syslib est plus performante pour des échanges de données intensifs. Aussi, les fichiers produits sont beaucoup plus petits et mieux adaptés pour l'embarquement des spécifications sur une plate-forme cible. De plus, nous avons démontré que Syslib est tout aussi simple à utiliser que SystemC (ou toute autre bibliothèque).

Les résultats de cette recherche démontrent que si l'on se dirige vers le développement d'un système en utilisant une méthodologie à raffinement progressif, Syslib apparaît comme un choix intéressant qui diminue le temps de conception d'un système.

## Abstract

The embedded systems design methods in use today are becoming less and less efficient because of the growing complexity of integrated circuits. A movement towards high level and object-oriented languages (C++ for instance) for system design is necessary to avoid productivity loss. It is by supporting concepts such as component re-using and the progressive refinement of the specifications that this productivity loss will be prevented. Several research groups and companies chose this way, but the libraries available on the market do not fulfil all the needs. Moreover, system designers will have to better understand these new ideas to cope with drastic changes in design methodologies and languages.

First of all, we review the specification capture phase of many existing methodologies and looked at the available languages and programming libraries to list their features and gaps. From this point, we propose a methodology for embedded systems design (or co-design methodology), which integrates a system-level library we called *Syslib*. The *Syslib* library is programmed in object-oriented C++ to facilitate progressive refinement towards a final implementation solution (hardware or software). *Syslib* covers the untimed functional level of abstraction. To demonstrate *Syslib*'s possibilities, a detailed example of a producer-consumer system called *PacketRouter* is explained. Then, we discuss about progressive refinement techniques. Hardware refinement is accomplished with the use of the modelling library *Cynlib*. For software aspects, we re-use the maximum of the *Syslib* specifications.

Once the *Syslib* library implemented, we developed various examples of design to situate the library amongst those existing. The examples presented include a JPEG decoder, a memory controller, a block matcher, a simple adder and finally the packet router presented above. To obtain comparative results (quantitative and qualitative), all these examples have been programmed at an untimed functional level of abstraction using

Syslib and SystemC (*de facto* industry standard). The results show that the Syslib library is more powerful with data-oriented applications and that the generated files are much smaller and more adapted for embedding at the architectural level. Moreover, we noticed that Syslib is as simple to use as SystemC (or others).

The results of this research demonstrate that the move towards system development using a progressive refinement methodology and a library like Syslib appears to be an interesting choice, which decrease the time of design.

## Table des matières

|                                                              |             |

|--------------------------------------------------------------|-------------|

| <b>REMERCIEMENTS .....</b>                                   | <b>IV</b>   |

| <b>RÉSUMÉ .....</b>                                          | <b>V</b>    |

| <b>ABSTRACT .....</b>                                        | <b>VII</b>  |

| <b>TABLE DES MATIÈRES .....</b>                              | <b>IX</b>   |

| <b>LISTE DES TABLEAUX.....</b>                               | <b>XIII</b> |

| <b>LISTE DES FIGURES .....</b>                               | <b>XIV</b>  |

| <b>LISTE DES ACRONYMES.....</b>                              | <b>XVII</b> |

| <b>LEXIQUE.....</b>                                          | <b>XX</b>   |

| <b>LISTE DES ANNEXES .....</b>                               | <b>XXIV</b> |

| <b>INTRODUCTION .....</b>                                    | <b>1</b>    |

| <b>CHAPITRE 1 : REVUE DE LA CONCEPTION DES SOC .....</b>     | <b>8</b>    |

| 1.1.    APPROCHES DE CONCEPTION .....                        | 8           |

| 1.1.1.    Approche par raffinement progressif .....          | 9           |

| 1.1.2.    Approche plate-forme.....                          | 9           |

| 1.2.    SÉMANTIQUE ET NORMALISATION .....                    | 11          |

| 1.2.1.    Accellera .....                                    | 11          |

| 1.2.2.    VSIA .....                                         | 11          |

| 1.3.    CONTRIBUTION DU LOGICIEL ET DE L'ORIENTÉ OBJET ..... | 13          |

| 1.3.1.    Évolution de l'utilisation du logiciel.....        | 13          |

| 1.3.2.    L'orienté objet .....                              | 15          |

| 1.4.    MODÈLES DE CALCUL.....                               | 17          |

| 1.4.1.    Définition .....                                   | 17          |

| 1.4.2.    Quelques modèles connus .....                      | 17          |

| 1.4.3.    Modèles de performance .....                       | 18          |

| 1.4.4.    Discussion sur les modèles.....                    | 19          |

|                                                         |                                                                  |           |

|---------------------------------------------------------|------------------------------------------------------------------|-----------|

| 1.5.                                                    | LANGAGES/BIBLIOTHÈQUES APPLICABLES À LA CONCEPTION DES SOC ..... | 20        |

| 1.5.1.                                                  | C/C++/Java .....                                                 | 21        |

| 1.5.2.                                                  | SystemC .....                                                    | 21        |

| 1.5.3.                                                  | SpecC .....                                                      | 23        |

| 1.5.4.                                                  | Cynlib.....                                                      | 24        |

| 1.5.5.                                                  | OCAPI-xl.....                                                    | 26        |

| 1.5.6.                                                  | UML.....                                                         | 26        |

| 1.5.7.                                                  | SDL .....                                                        | 27        |

| 1.5.8.                                                  | Rosetta et ALC .....                                             | 27        |

| 1.6.                                                    | MÉTHODOLOGIES DE CONCEPTION .....                                | 28        |

| 1.6.1.                                                  | Méthodologies basées sur le C++ .....                            | 28        |

| 1.6.2.                                                  | VCC Ciero de Cadence .....                                       | 29        |

| 1.6.3.                                                  | Gigascale Hub de Forte Design Systems .....                      | 30        |

| 1.6.4.                                                  | CoCentric de Synopsys.....                                       | 31        |

| 1.6.5.                                                  | Méthodologie basée sur Renoir 2000, Seamless CVE & C-Bridge..... | 32        |

| 1.7.                                                    | RÉTROSPECTIVE .....                                              | 33        |

| <b>CHAPITRE 2 : MÉTHODOLOGIE DE DÉVELOPPEMENT .....</b> |                                                                  | <b>35</b> |

| 2.1.                                                    | MÉTHODOLOGIE SYSLIB.....                                         | 35        |

| 2.2.                                                    | ANALYSE PRÉLIMINAIRE DE SYSLIB.....                              | 38        |

| 2.2.1.                                                  | Niveau fonctionnel ou Syslib <sup>FL</sup> .....                 | 38        |

| 2.2.2.                                                  | Niveau comportemental ou Syslib <sup>BL</sup> .....              | 39        |

| 2.2.3.                                                  | Niveau architectural ou Syslib <sup>LL</sup> .....               | 39        |

| 2.3.                                                    | DÉCISIONS D'IMPLANTATION.....                                    | 39        |

| 2.3.1.                                                  | Reprise du code de Cynlib.....                                   | 40        |

| 2.3.2.                                                  | Orientation générale .....                                       | 40        |

| 2.3.3.                                                  | Modules.....                                                     | 40        |

| 2.3.4.                                                  | Ports et canaux .....                                            | 41        |

| 2.3.5.                                                  | Communications, événements et données .....                      | 42        |

| 2.3.6.                                                  | Assemblage du tout .....                                         | 42        |

| 2.4.                                                    | EXEMPLE DE SYSTÈME .....                                         | 43        |

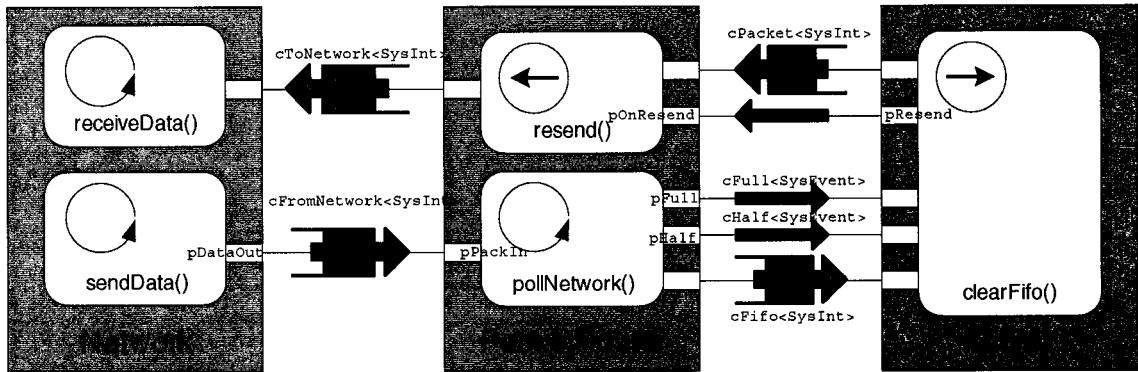

| 2.4.1.                                                  | Le <i>PacketRouter</i> .....                                     | 43        |

|                                                    |                                                   |           |

|----------------------------------------------------|---------------------------------------------------|-----------|

| 2.4.2.                                             | Fichier de structure des modules.....             | 45        |

| 2.4.3.                                             | Fichier d'implantation des modules.....           | 46        |

| 2.4.4.                                             | Fichier global du système.....                    | 49        |

| 2.5.                                               | IMPLANTATION DE LA BIBLIOTHÈQUE .....             | 50        |

| 2.5.1.                                             | Environnement.....                                | 50        |

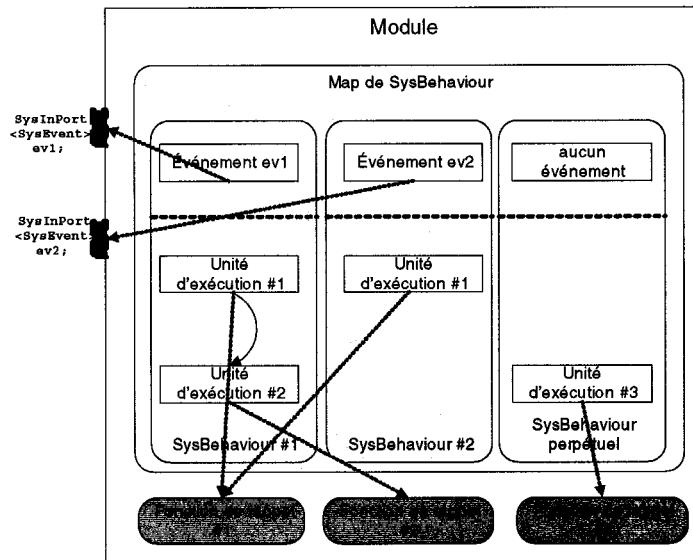

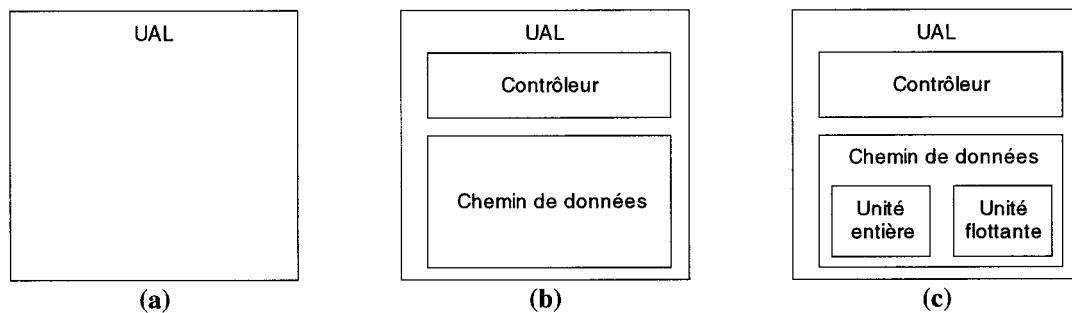

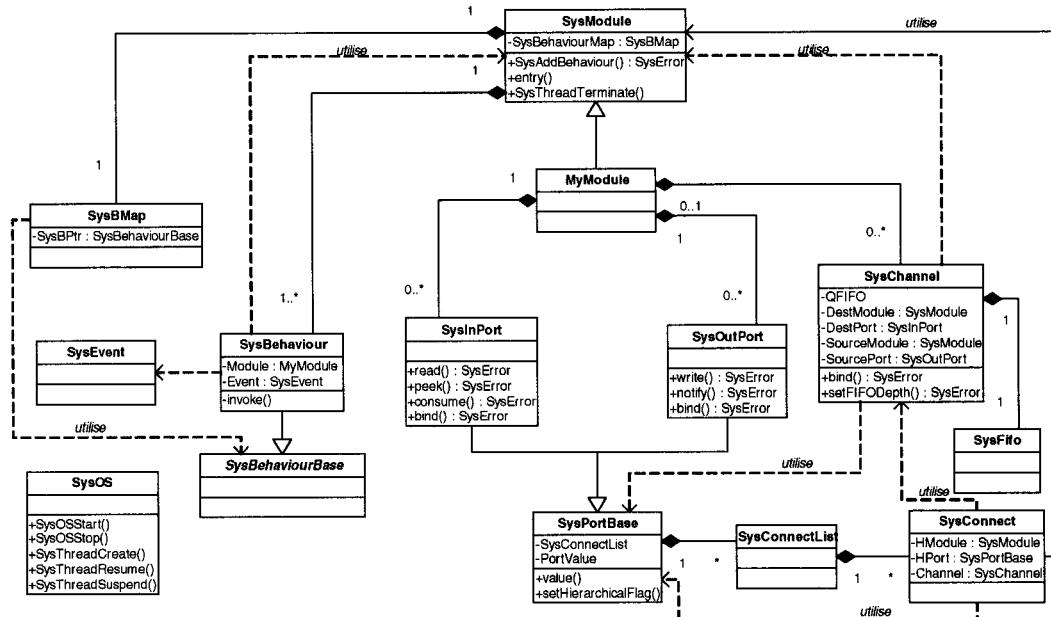

| 2.5.2.                                             | Structure interne d'un module.....                | 51        |

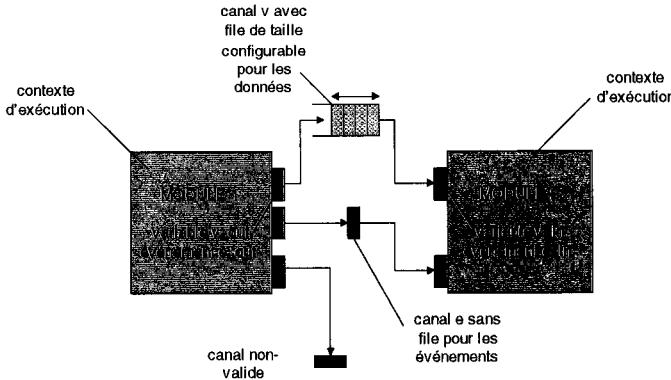

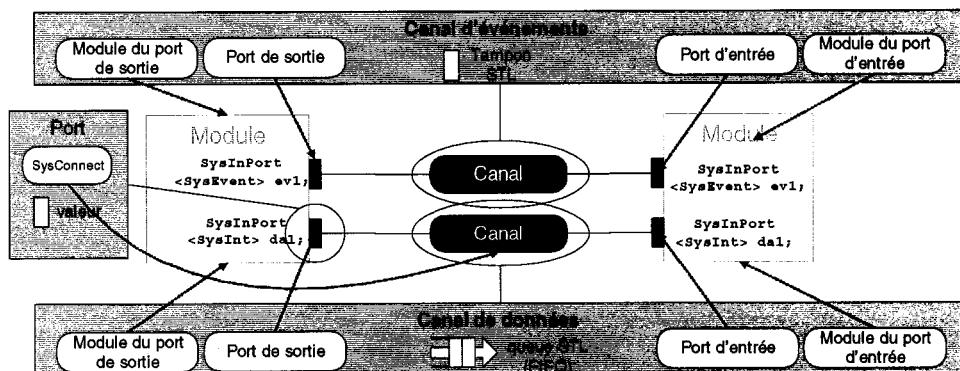

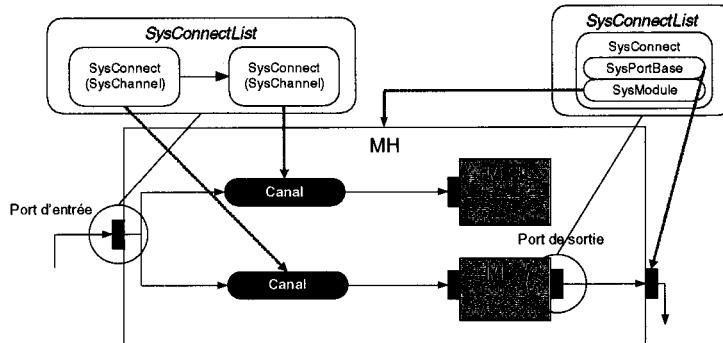

| 2.5.3.                                             | Structure interne des ports et canaux .....       | 52        |

| 2.5.4.                                             | Types de données abstraits .....                  | 54        |

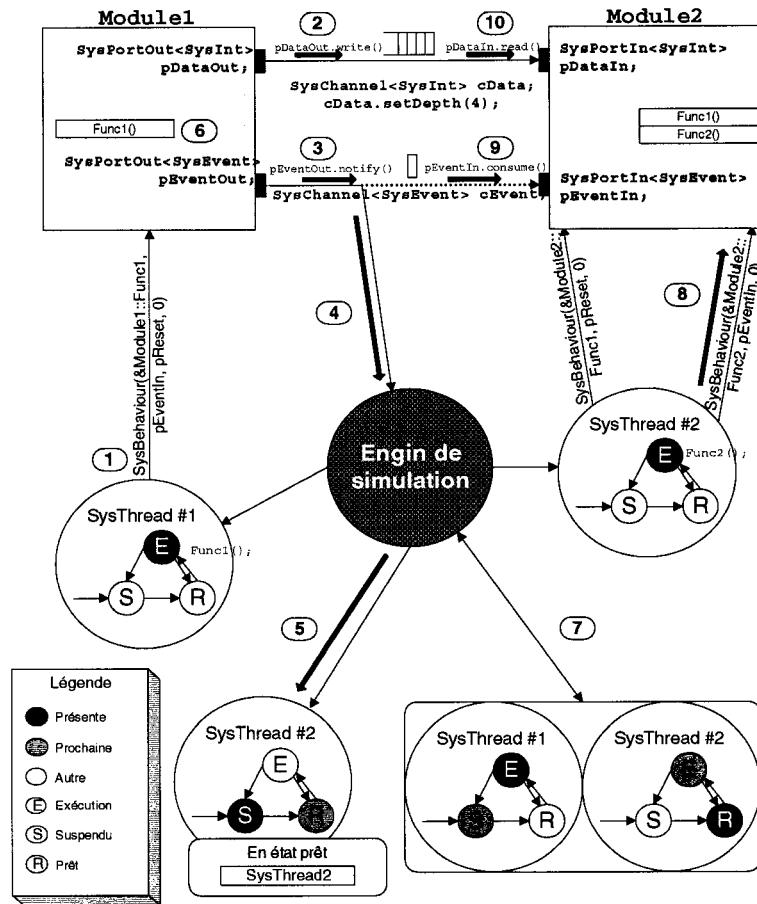

| 2.5.5.                                             | Engin de simulation Syslib.....                   | 54        |

| 2.5.6.                                             | Fonctions de rappels .....                        | 56        |

| 2.5.7.                                             | Support de la hiérarchie de modules .....         | 56        |

| 2.5.8.                                             | Vue détaillée de l'implantation .....             | 59        |

| 2.6.                                               | HIÉRARCHISATION DE L'EXEMPLE .....                | 63        |

| <b>CHAPITRE 3 : ANALYSE DE L'IMPLANTATION.....</b> |                                                   | <b>66</b> |

| 3.1.                                               | APPORT DE SYSLIB AU DESIGN DE SYSTÈMES .....      | 66        |

| 3.1.1.                                             | Design non bloquant.....                          | 66        |

| 3.1.2.                                             | Ordonnancement.....                               | 69        |

| 3.2.                                               | RAFFINEMENT D'UNE SPÉCIFICATION .....             | 70        |

| 3.3.                                               | RAFFINEMENT À NIVEAUX MULTIPLES .....             | 71        |

| 3.3.1.                                             | Vers le niveau temporisé (TF).....                | 72        |

| 3.3.2.                                             | Vers le logiciel.....                             | 75        |

| 3.3.3.                                             | Vers le niveau transactionnel (BCA) .....         | 76        |

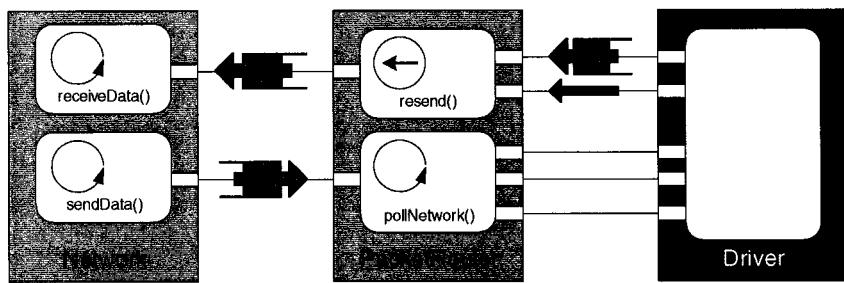

| 3.3.4.                                             | Vers le niveau matériel (PCA) .....               | 76        |

| 3.3.5.                                             | Exemple de raffinement matériel avec Cynlib ..... | 76        |

| <b>CHAPITRE 4 : ANALYSE DES RÉSULTATS .....</b>    |                                                   | <b>80</b> |

| 4.1.                                               | PROCÉDURES .....                                  | 81        |

| 4.1.1.                                             | Mesures de performance.....                       | 81        |

| 4.1.2.                                             | Gabarits .....                                    | 81        |

| 4.2.                                               | EXEMPLE #1 : L'ADDITIONNEUR SIMPLE.....           | 82        |

| 4.2.1.                                             | Implantation .....                                | 82        |

|        |                                                 |            |

|--------|-------------------------------------------------|------------|

| 4.2.2. | Différences avec SystemC.....                   | 82         |

| 4.3.   | EXEMPLE #2 : LE ROUTEUR DE PAQUETS.....         | 83         |

| 4.3.1. | Différences avec SystemC.....                   | 83         |

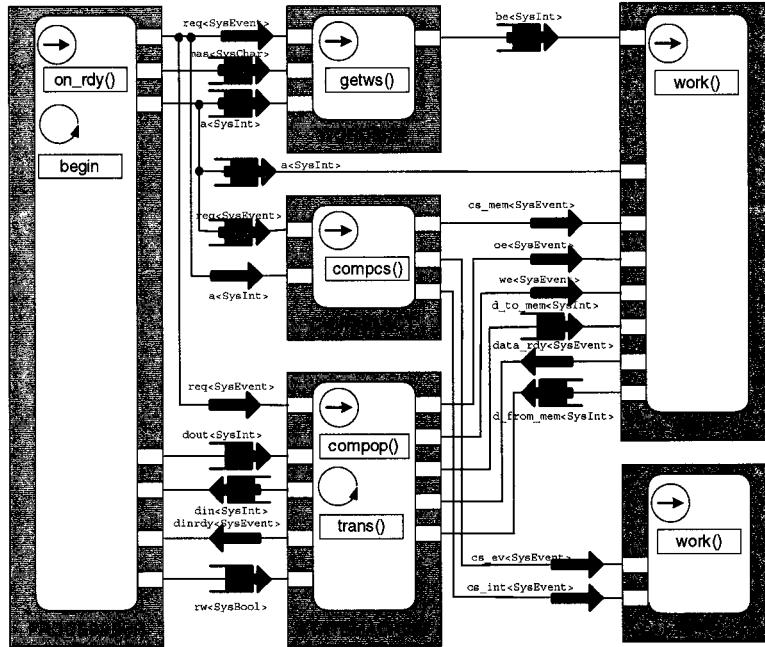

| 4.4.   | EXEMPLE #3 : LE CONTRÔLEUR MÉMOIRE.....         | 84         |

| 4.4.1. | Implantation .....                              | 84         |

| 4.4.2. | Différences avec SystemC.....                   | 85         |

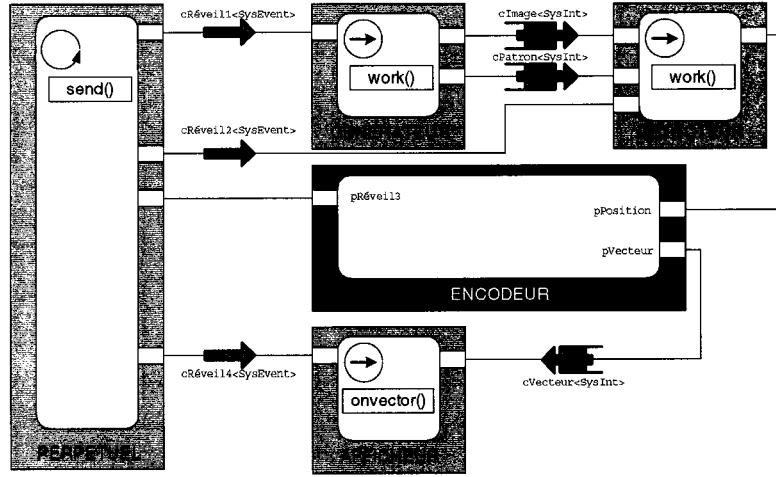

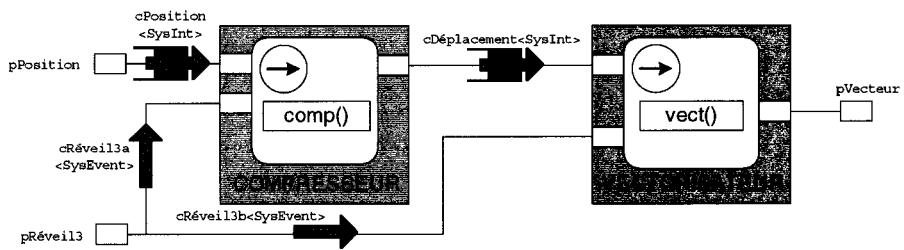

| 4.5.   | EXEMPLE #4 : LE <i>BLOCKMATCHER</i> .....       | 86         |

| 4.5.1. | Implantation .....                              | 87         |

| 4.5.2. | Différences avec SystemC.....                   | 88         |

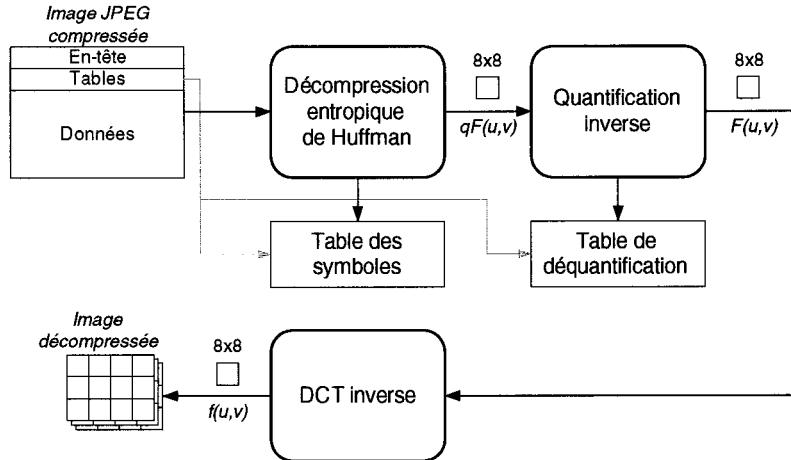

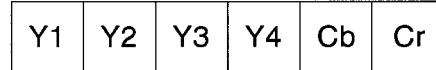

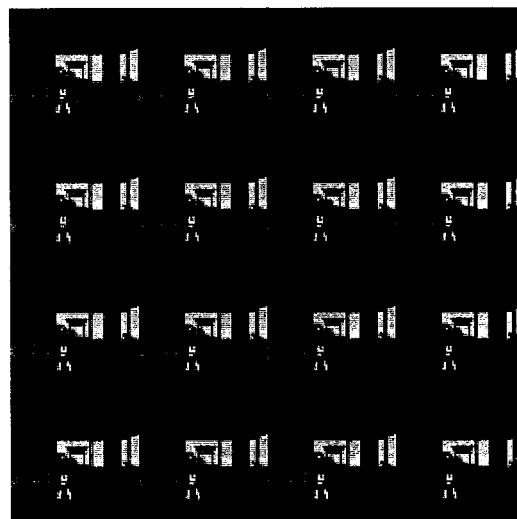

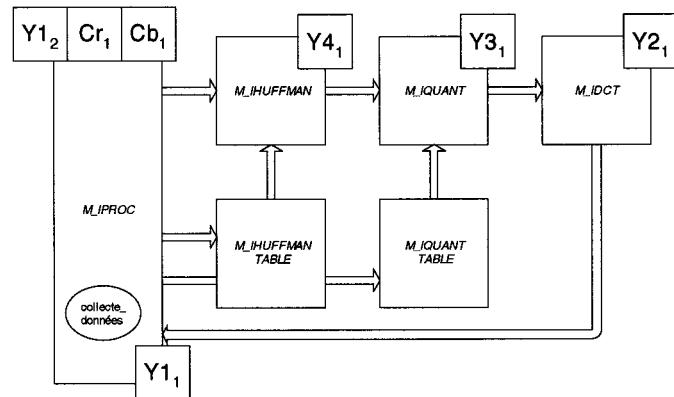

| 4.6.   | EXEMPLE #5 : LE DÉCODEUR JPEG .....             | 89         |

| 4.6.1. | Première version d'implantation .....           | 91         |

| 4.6.2. | Deuxième version d'implantation .....           | 92         |

| 4.6.3. | Différences avec SystemC.....                   | 93         |

| 4.7.   | RÉSULTATS QUANTITATIFS.....                     | 95         |

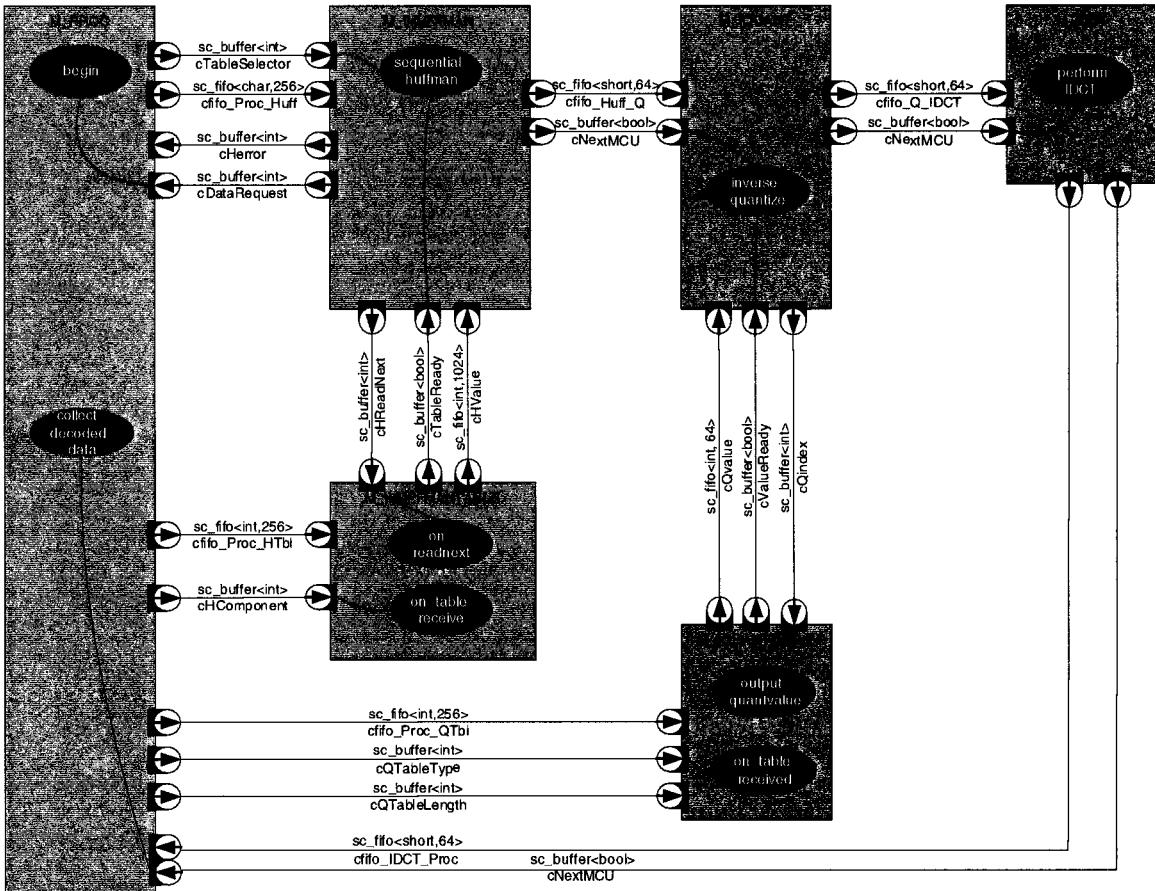

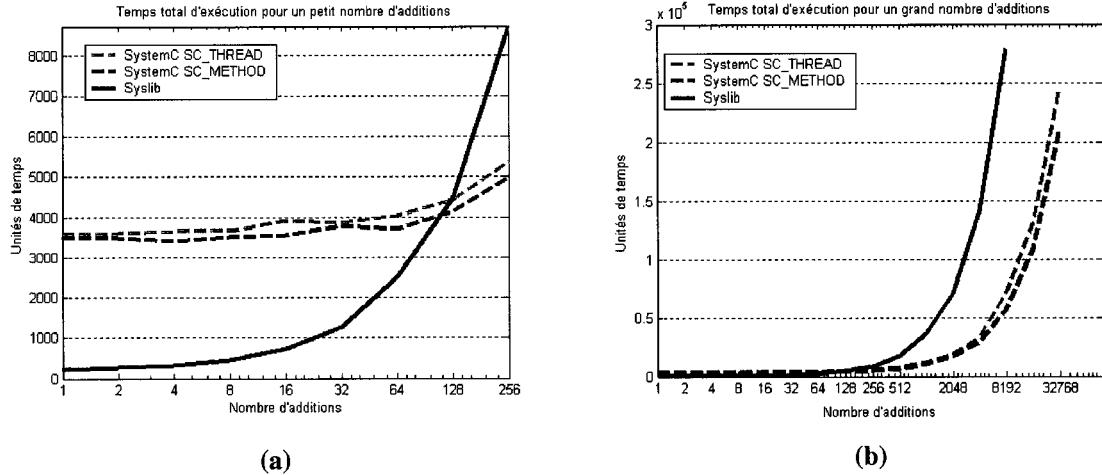

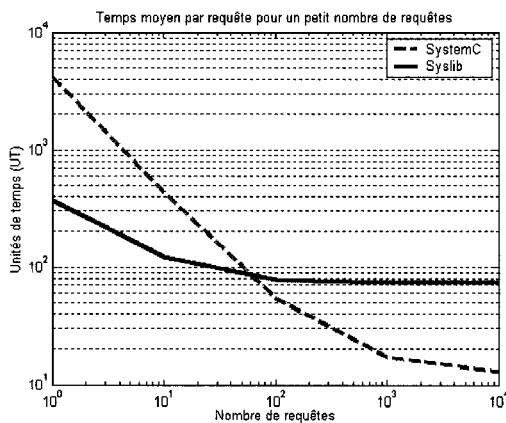

| 4.7.1. | Additionneur et contrôleur mémoire.....         | 96         |

| 4.7.2. | Décodeur JPEG.....                              | 98         |

| 4.7.3. | Routeur de paquets et <i>BlockMatcher</i> ..... | 101        |

| 4.7.4. | Taille des fichiers.....                        | 102        |

| 4.7.5. | Analyse des résultats .....                     | 102        |

| 4.8.   | RÉSULTATS QUALITATIFS .....                     | 104        |

| 4.8.1. | Considérations syntaxiques .....                | 104        |

| 4.8.2. | Styles de programmation.....                    | 106        |

| 4.9.   | AMÉLIORATIONS .....                             | 107        |

|        | <b>CONCLUSION ET TRAVAUX FUTURS.....</b>        | <b>109</b> |

|        | <b>REFERENCES .....</b>                         | <b>113</b> |

## Liste des tableaux

|                                                                                |     |

|--------------------------------------------------------------------------------|-----|

| TABLEAU 1 : EXEMPLES DE SYSTÈMES EMBARQUÉS .....                               | 1   |

| TABLEAU 2.1 : LÉGENDE DU GABARIT DE DESIGN SYSLIB .....                        | 44  |

| TABLEAU 2.2 : TYPES ABSTRAITS DANS SYSLIB .....                                | 54  |

| TABLEAU 2.3 : ÉNUMÉRATION DES CAS DE CONNEXIONS VALIDES .....                  | 58  |

| TABLEAU 2.4 : CLASSES DU PROJET SYSLIB .....                                   | 61  |

| TABLEAU 3.1 : RÉPERTOIRE DES OPÉRATIONS AVEC LEUR TEMPS D'EXÉCUTION ESTIMÉ ... | 75  |

| TABLEAU 4.1 : TEMPS D'EXÉCUTION POUR L'ADDITIONNEUR .....                      | 96  |

| TABLEAU 4.2 : TEMPS D'EXÉCUTION PAR REQUÊTE POUR LE CONTRÔLEUR MÉMOIRE .....   | 97  |

| TABLEAU 4.3 : TEMPS D'EXÉCUTION POUR LE DÉCODEUR JPEG .....                    | 99  |

| TABLEAU 4.4 : RAPPORT DE TEMPS D'EXÉCUTION POUR LE DÉCODEUR JPEG .....         | 100 |

| TABLEAU 4.5 : TAILLE DES FICHIERS POUR LES EXEMPLES PRÉSENTÉS.....             | 102 |

| TABLEAU 4.6 : STYLE DE PROGRAMMATION AVEC SYSLIB .....                         | 107 |

| TABLEAU 4.7 : TEMPS MOYEN MESURÉ POUR LES MÉTHODES IMPLANTÉES AVEC STL ...     | 108 |

| TABLEAU A.1 : PERFORMANCE DES LECTURES/ECRITURES POUR SYSLIB ET SYSTEMC...     | 127 |

| TABLEAU B.1 : RÉSULTATS COMPLETS POUR LE DÉCODEUR JPEG .....                   | 128 |

| TABLEAU C.1 : RACCOURCIS UTILISÉS POUR LA TRACE DU PIPELINE .....              | 131 |

| TABLEAU D.1 : TYPES DE DONNEES A TRANSFORMER.....                              | 135 |

| TABLEAU D.2 : PORTS A TRANSFORMER .....                                        | 135 |

## Liste des figures

|                                                                                     |    |

|-------------------------------------------------------------------------------------|----|

| FIGURE 1 : EXEMPLE CLASSIQUE D'UN SYSTÈME EMBARQUÉ .....                            | 2  |

| FIGURE 2 : MÉTHODOLOGIE GÉNÉRALE DE CODESIGN .....                                  | 3  |

| FIGURE 3 : MÉTHODOLOGIE DE CONCEPTION DE SYSTEMC .....                              | 5  |

| FIGURE 1.1 : LES CONCEPTS DE NORMALISATION PROPOSÉS PAR VSIA .....                  | 13 |

| FIGURE 1.2 : ÉVOLUTION DE L'UTILISATION DU C/C++ POUR LA CRÉATION DE SOC .....      | 14 |

| FIGURE 1.3 : SPÉCIFICATIONS ET SIMULATIONS MULTI-NIVEAUX AVEC SYSTEMC.....          | 22 |

| FIGURE 1.4 : NIVEAUX D'ABSTRACTION DE SYSTEMC .....                                 | 23 |

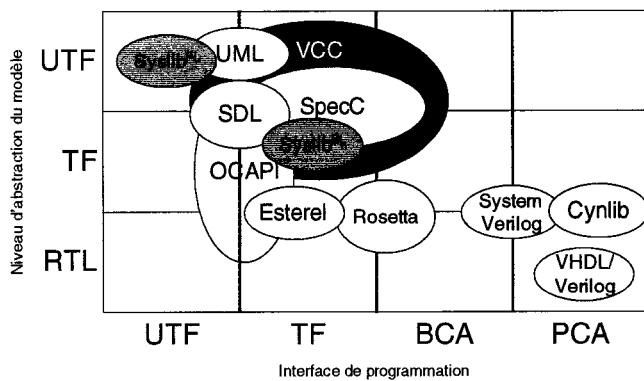

| FIGURE 1.5 : FLOT DE CONCEPTION CYNLIB .....                                        | 25 |

| FIGURE 1.6 : MAPPING DE LA FONCTION À L'ARCHITECTURE DANS VCC CIERTO.....           | 30 |

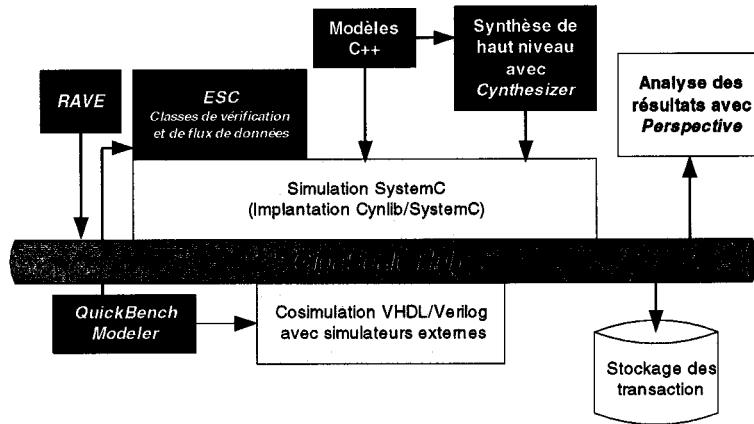

| FIGURE 1.7 : LA MÉTHODOLOGIE GIGASCALE HUB DE FORTE DESIGN SYSTEMS .....            | 31 |

| FIGURE 1.8 : COMPARAISON DES DIFFÉRENTS LANGAGES ET MÉTHODOLOGIES .....             | 33 |

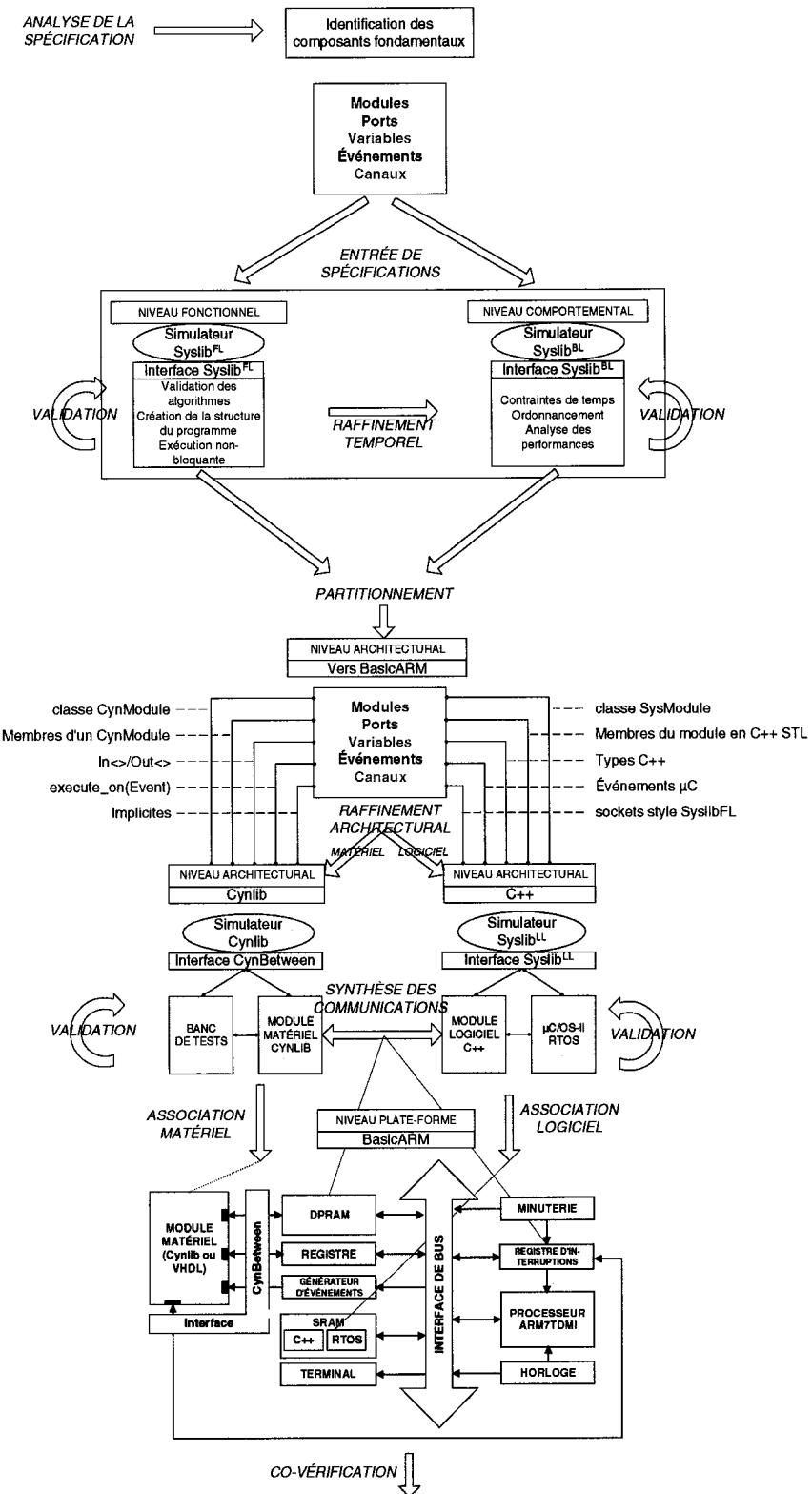

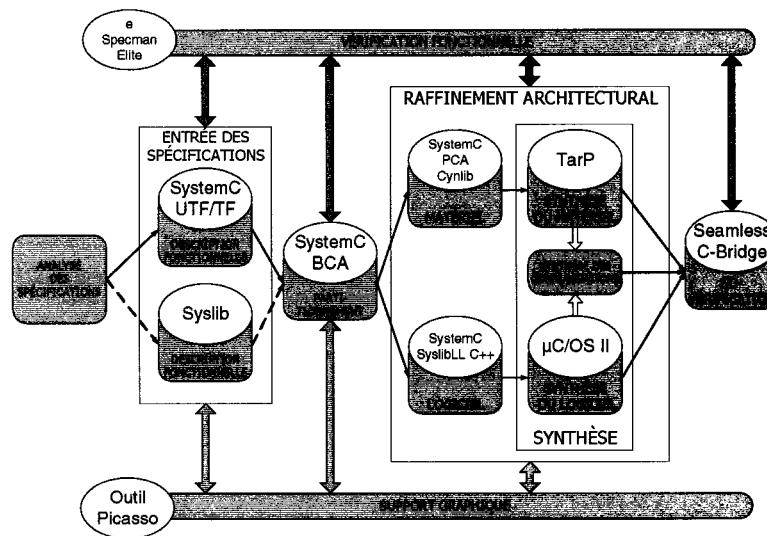

| FIGURE 2.1 : MÉTHODOLOGIE DE CODESIGN SYSLIB.....                                   | 36 |

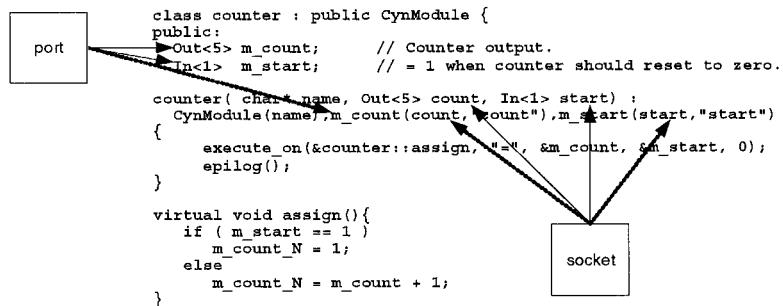

| FIGURE 2.2 : NOTIONS DE PORTS ET DE SOCKETS DANS CYNLIB .....                       | 41 |

| FIGURE 2.3 : LES CONCEPTS STRUCTURELS DE SYSLIB .....                               | 43 |

| FIGURE 2.4 : EXEMPLE DU <i>PACKETROUTER</i> .....                                   | 44 |

| FIGURE 2.5 : FICHIER DE STRUCTURE (.H) DU MODULE <i>PACKETROUTER</i> .....          | 46 |

| FIGURE 2.6 : FICHIER D'IMPLANTATION (.CPP) POUR LE MODULE <i>PACKETROUTER</i> ..... | 47 |

| FIGURE 2.7 : FICHIER GLOBAL ( <i>MAIN</i> ) DE L'EXEMPLE <i>PACKETROUTER</i> .....  | 49 |

| FIGURE 2.8 : STRUCTURE D'UN MODULE SYSLIB .....                                     | 51 |

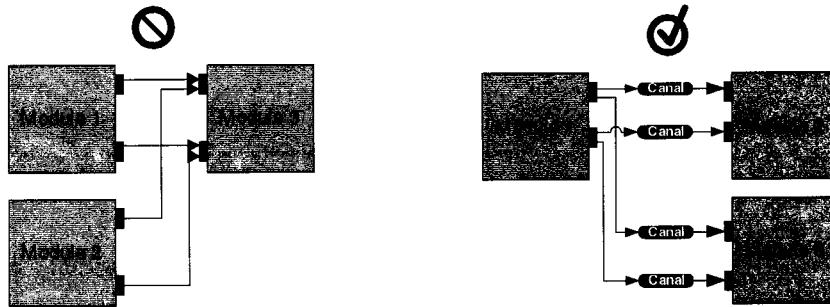

| FIGURE 2.9 : CONNEXIONS NON PERMISES ET PERMISES AVEC SYSLIB .....                  | 53 |

| FIGURE 2.10 : STRUCTURE DES PORTS ET DES CANAUX SYSLIB.....                         | 53 |

| FIGURE 2.11 : COMPORTEMENT DE L'ENGIN DE SIMULATION DE SYSLIB .....                 | 55 |

| FIGURE 2.12 : HIÉRARCHIE STRUCTURELLE.....                                          | 57 |

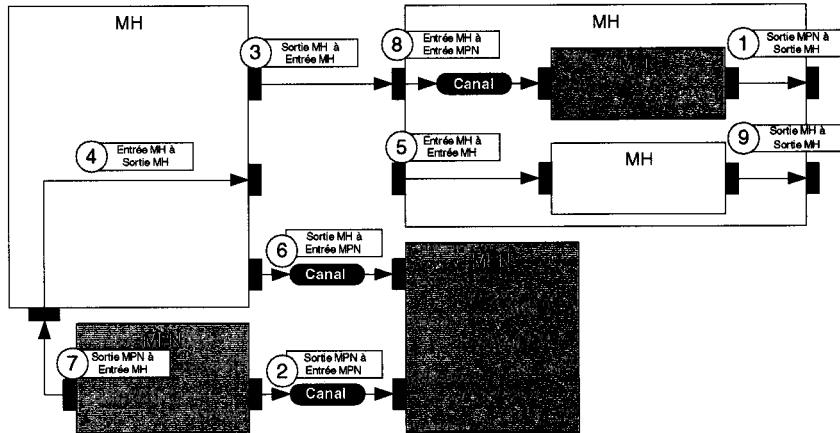

| FIGURE 2.13 : LES 9 TYPES DE CONNEXIONS VALIDES AVEC SYSLIB .....                   | 59 |

| FIGURE 2.14 : EXTENSION DES <i>SYSCONNECTS</i> .....                                | 59 |

| FIGURE 2.15 : SCHÉMA DES CLASSES UML DE SYSLIB .....                                | 60 |

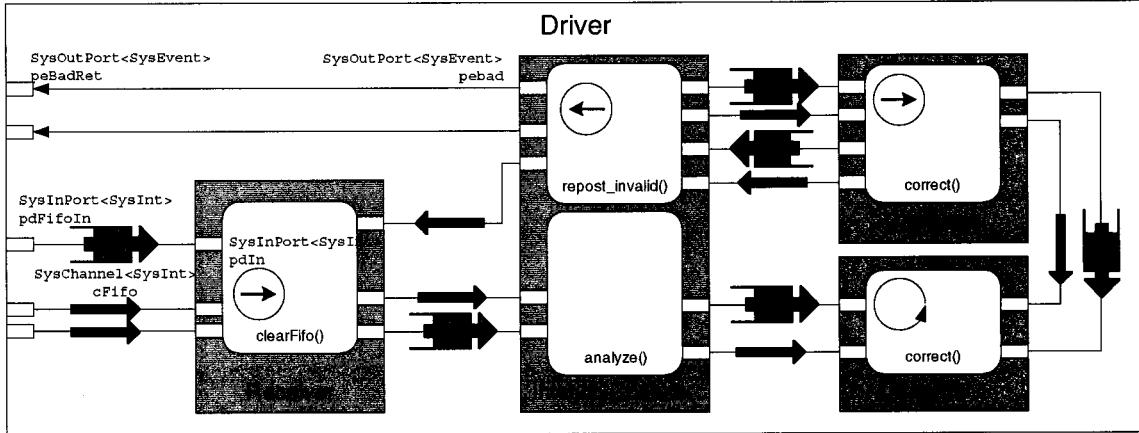

| FIGURE 2.16 : LE MODULE HIÉRARCHIQUE <i>DRIVER</i> .....                            | 63 |

|                                                                                 |     |

|---------------------------------------------------------------------------------|-----|

| FIGURE 2.17 : CONTENU DU MODULE HIÉRARCHIQUE <i>DRIVER</i> .....                | 64  |

| FIGURE 2.18 : EXEMPLE DE CODE POUR L'IMPLANTATION D'UN MODULE HIÉRARCHIQUE .    | 64  |

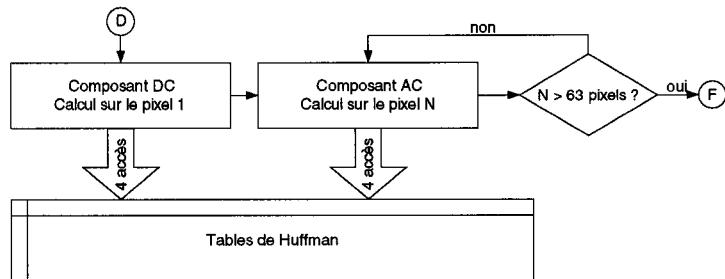

| FIGURE 3.1 : ALGORITHME GÉNÉRAL DE LA DÉCOMPRESSION DE HUFFMAN .....            | 67  |

| FIGURE 3.2 : EXEMPLES D'ALGORITHMES BLOQUANT ET NON BLOQUANT.....               | 68  |

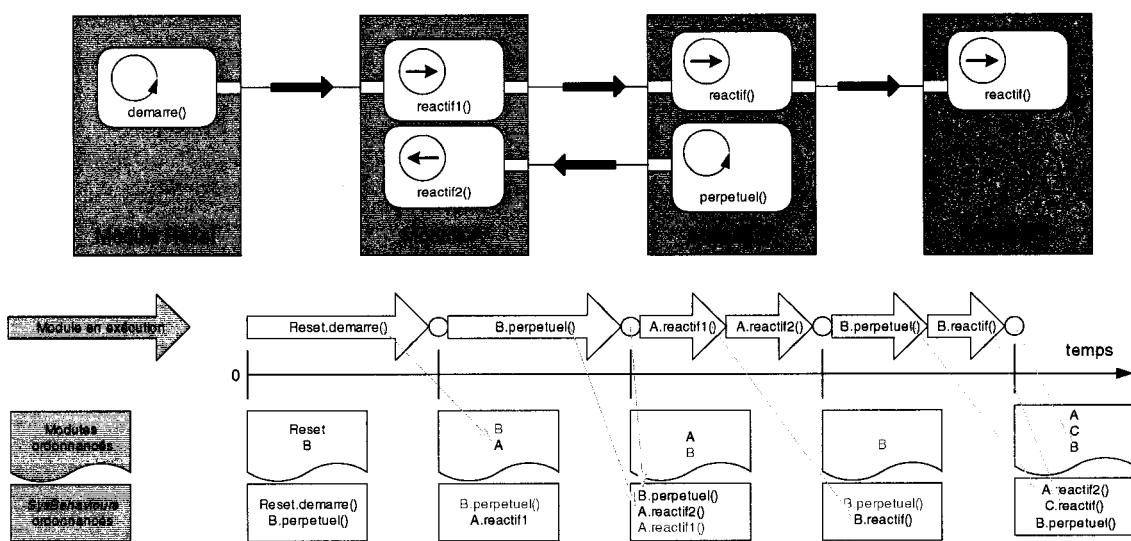

| FIGURE 3.3 : ORDONNANCEMENT DES MODULES ET <i>SysBEHAVIOURS</i> .....           | 69  |

| FIGURE 3.4 : CHEMINS POSSIBLES DE RAFFINEMENT.....                              | 72  |

| FIGURE 3.5 : PARTITIONNEMENT D'UN DÉCODEUR JPEG SUR LA PLATE-FORME TARP ....    | 74  |

| FIGURE 3.6 : STRUCTURES SYSLIB ET CYNLIB DU MODULE <i>PACKETROUTER</i> .....    | 77  |

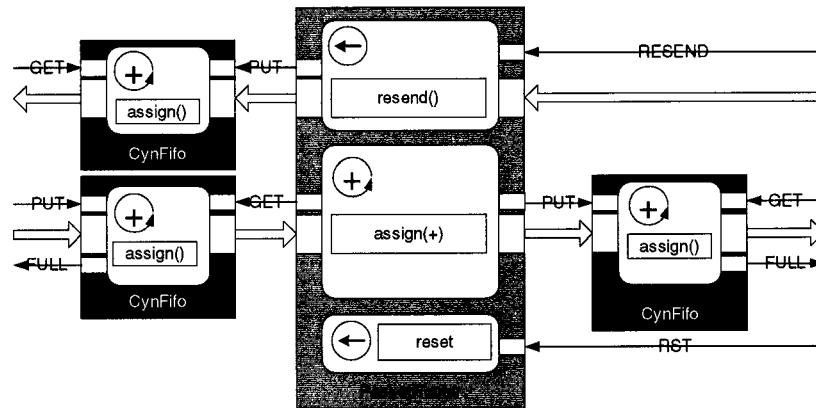

| FIGURE 3.7 : UTILISATION DES <i>CYNFIFOS</i> LORS DU RAFFINEMENT MATÉRIEL ..... | 79  |

| FIGURE 4.1 : GABARIT SYSTEMC .....                                              | 81  |

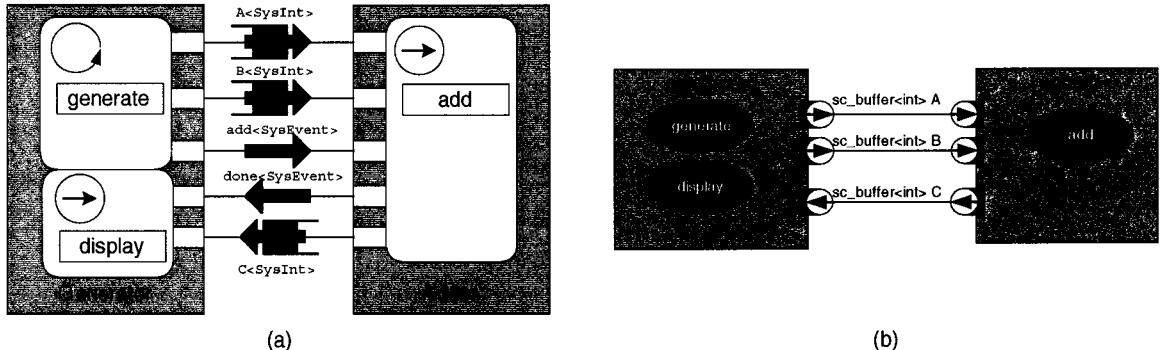

| FIGURE 4.2 : EXEMPLE DE L'ADDITIONNEUR SIMPLE AVEC SYSLIB ET SYSTEMC .....      | 83  |

| FIGURE 4.3 : EXEMPLE DU CONTRÔLEUR MÉMOIRE .....                                | 85  |

| FIGURE 4.4 : EXEMPLE DU <i>BLOCKMATCHER</i> .....                               | 88  |

| FIGURE 4.5 : DÉTAILS DU MODULE <i>ENCODEUR</i> DU <i>BLOCKMATCHER</i> .....     | 88  |

| FIGURE 4.6 : ALGORITHME DE DÉCODAGE JPEG .....                                  | 90  |

| FIGURE 4.7 : FORMAT D'IMAGE YUV 4:2:0.....                                      | 90  |

| FIGURE 4.8 : STRUCTURE SYSTEMC DU DÉCODEUR JPEG .....                           | 92  |

| FIGURE 4.9 : IMPLANTATION DU NOYAU DU DÉCODAGE AVEC SYSTEMC .....               | 94  |

| FIGURE 4.10 :IMPLANTATION DU NOYAU DU DÉCODAGE AVEC SYSLIB .....                | 95  |

| FIGURE 4.11 : RÉSULTATS POUR L'ADDITIONNEUR .....                               | 97  |

| FIGURE 4.12 : RÉSULTATS POUR LE CONTRÔLEUR MÉMOIRE.....                         | 98  |

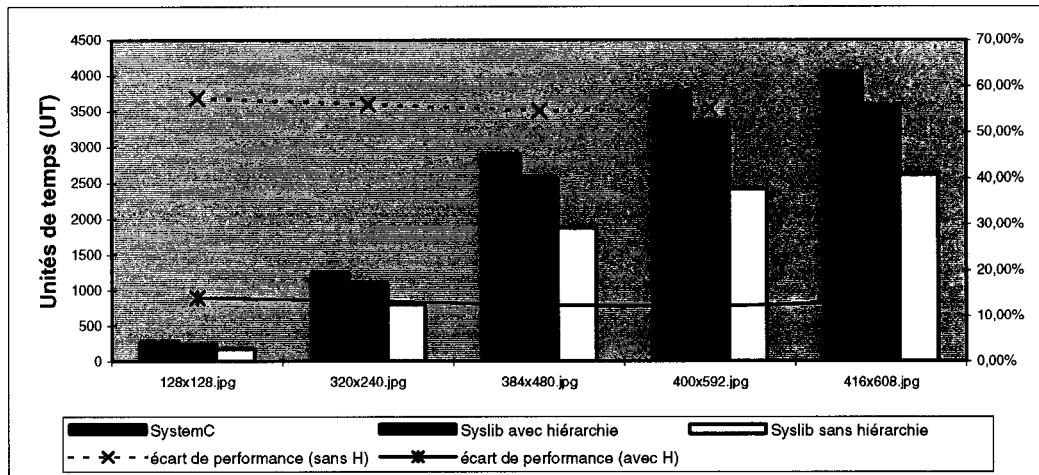

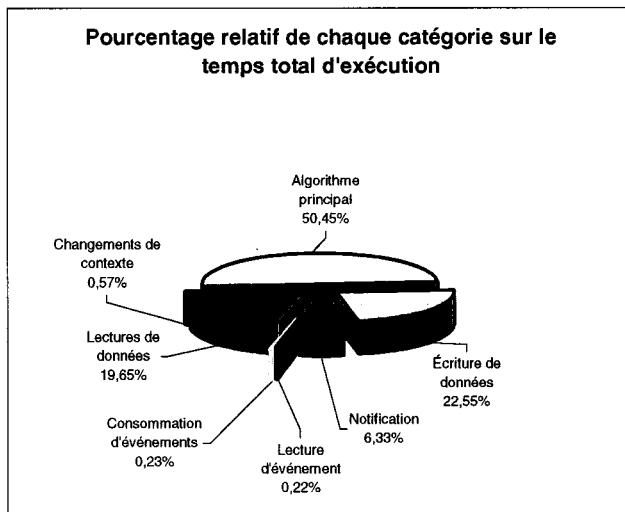

| FIGURE 4.13 : RÉSULTATS POUR LE DÉCODEUR JPEG.....                              | 99  |

| FIGURE 4.14 : POIDS PAR CATÉGORIE POUR LE DÉCODEUR JPEG EN SYSLIB .....         | 101 |

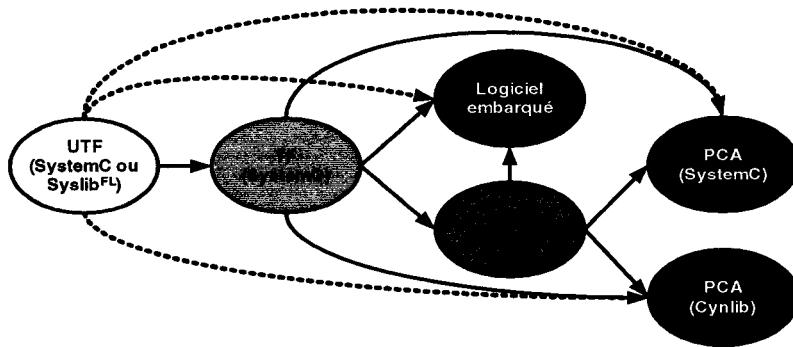

| FIGURE 4 : MÉTHODOLOGIE DE CODESIGN DU CIRCUS .....                             | 111 |

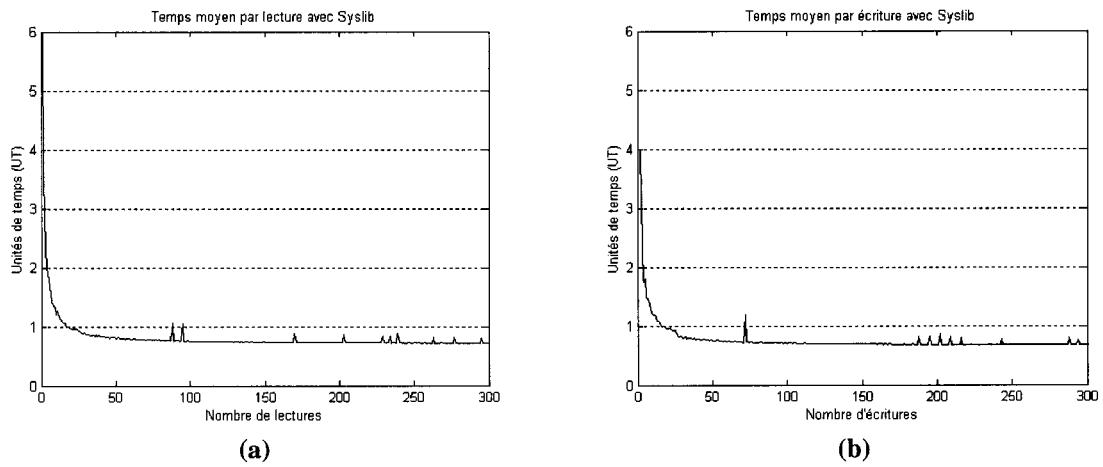

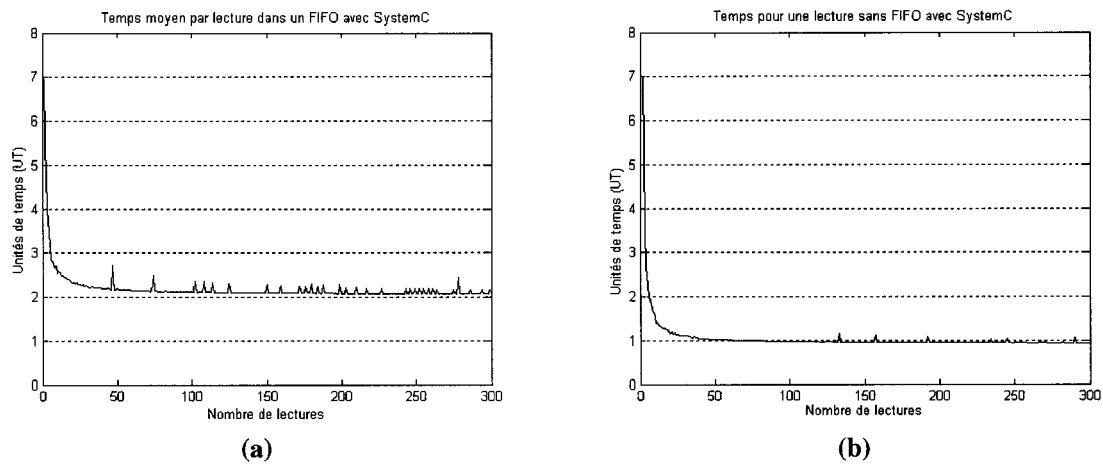

| FIGURE A.1 : TEMPS MOYENS POUR DES LECTURES ET ECRITURES AVEC SYSLIB .....      | 126 |

| FIGURE A.2 : TEMPS MOYENS POUR DES LECTURES AVEC SYSTEMC .....                  | 126 |

| FIGURE A.3 : TEMPS MOYENS POUR DES ECRITURES AVEC SYSTEMC .....                 | 127 |

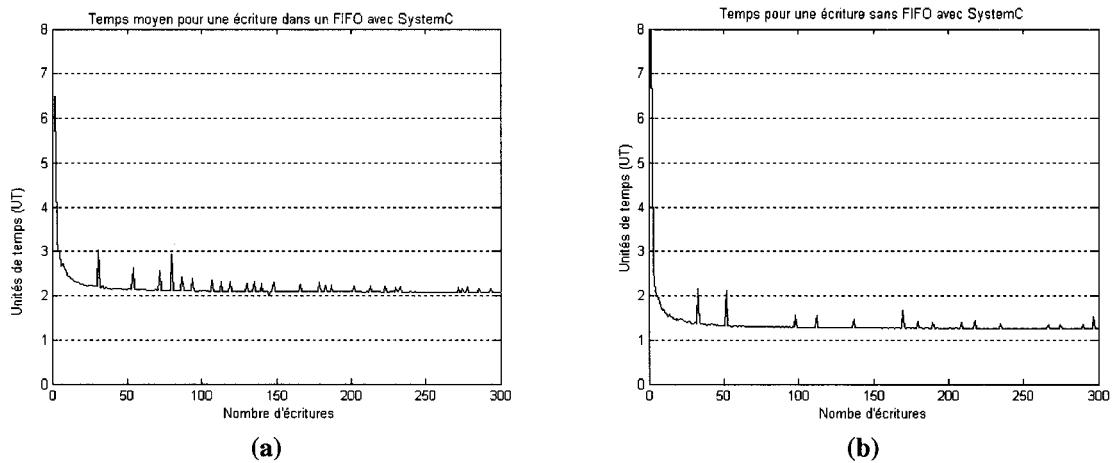

| FIGURE B.1 : IMAGE AVEC UN PATRON TUILÉ.....                                    | 129 |

| FIGURE C.1 : PIPELINAGE PARFAITEMENT BALANCÉ DU DÉCODEUR JPEG .....             | 130 |

|                                                                           |     |

|---------------------------------------------------------------------------|-----|

| FIGURE C.2 : SÉQUENCE DE LECTURE DES TABLES .....                         | 131 |

| FIGURE C.3 : SÉQUENCE DE LECTURE DE L'IMAGE .....                         | 132 |

| FIGURE C.4 : DIAGRAMME PIPELINÉ POUR LA LECTURE DE L'IMAGE .....          | 133 |

| FIGURE C.5 : DIAGRAMME PIPELINÉ OPTIMISÉ POUR LA LECTURE DE L'IMAGE ..... | 133 |

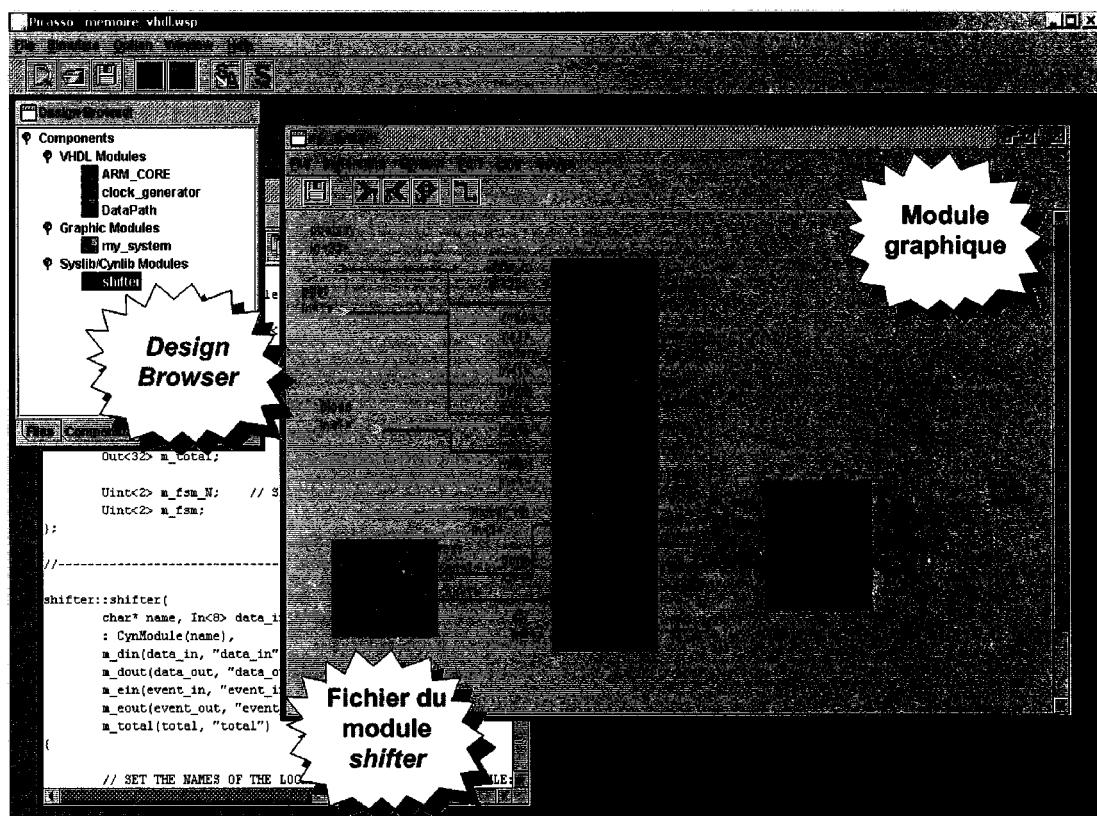

| FIGURE E.1 : ENTRÉE DE SPÉCIFICATIONS VHDL-CYNLIB AVEC PICASSO .....      | 145 |

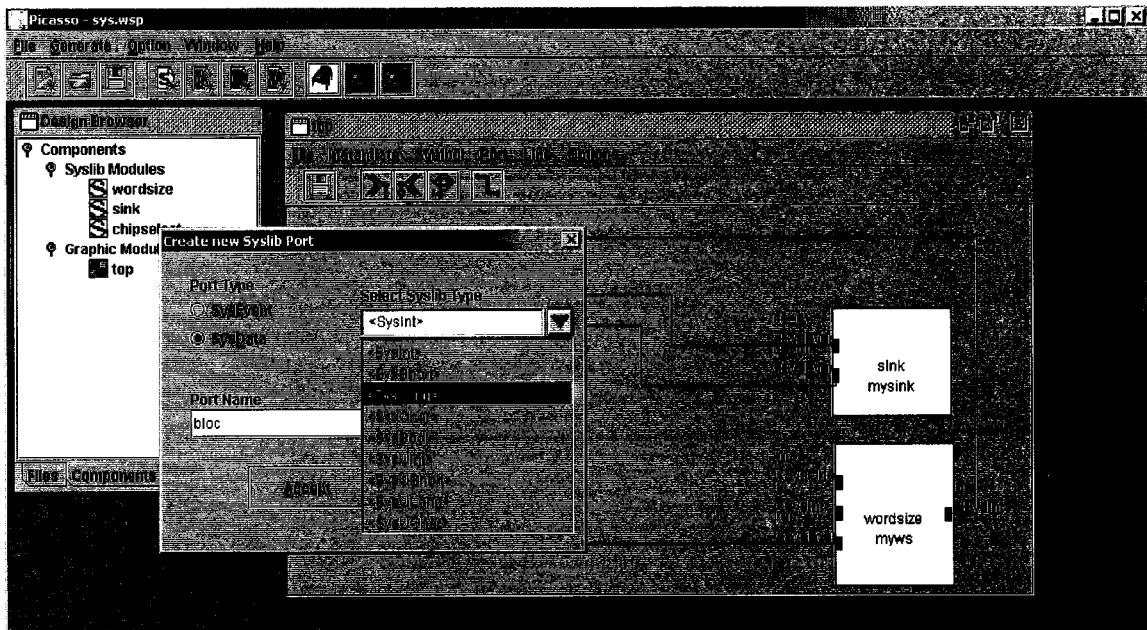

| FIGURE E.2 : CRÉATION D'UN SYSTÈME EN SYSLIB .....                        | 146 |

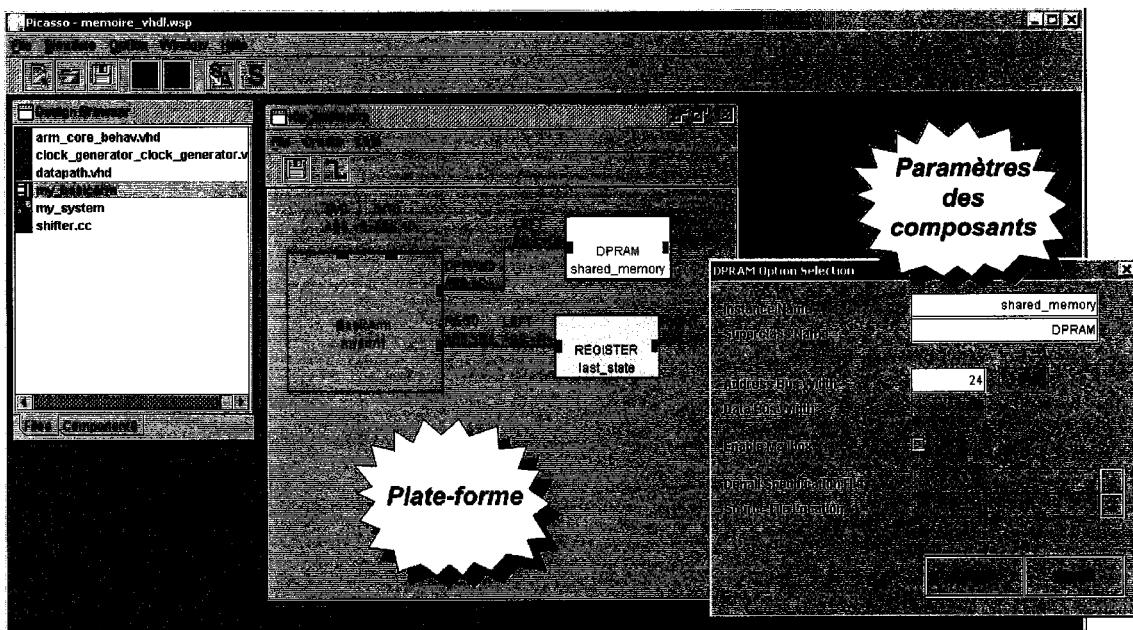

| FIGURE E.3 : CRÉATION D'ARCHITECTURE AVEC PICASSO .....                   | 147 |

## Liste des acronymes

|              |                                                                         |

|--------------|-------------------------------------------------------------------------|

| <b>AC</b>    | <i>Alterning Current</i> ou courant alternatif                          |

| <b>AHB</b>   | <i>Advanced High-performance Bus</i>                                    |

| <b>AMBA</b>  | <i>Advanced Microcontroller Bus Architecture</i>                        |

| <b>APB</b>   | <i>Advanced Peripheral Bus</i>                                          |

| <b>API</b>   | <i>Application Programming Interface</i>                                |

| <b>ASB</b>   | <i>Advanced System Bus</i>                                              |

| <b>ASIC</b>  | <i>Application Specific Integrated Circuit</i> ou circuit intégré dédié |

| <b>BCA</b>   | <i>Bus Cycle Accurate</i>                                               |

| <b>BL</b>    | <i>Behavioural Level</i> ou niveau comportemental                       |

| <b>CBC</b>   | <i>Constraint-Based Codesign</i>                                        |

| <b>CDFG</b>  | <i>Control Data Flow Graph</i>                                          |

| <b>CFSM</b>  | <i>Codesign FSM</i>                                                     |

| <b>DC</b>    | <i>Direct Current</i> ou courant continu                                |

| <b>DCT</b>   | <i>Discrete Cosine Transform</i>                                        |

| <b>DE</b>    | <i>Discrete Event</i>                                                   |

| <b>DPRAM</b> | <i>Dual Port RAM</i>                                                    |

| <b>DSP</b>   | <i>Digital Signal Processor</i>                                         |

| <b>ESC</b>   | <i>Extended SystemC</i>                                                 |

| <b>FIFO</b>  | <i>First In First Out</i>                                               |

| <b>FL</b>    | <i>Functional Level</i> ou niveau fonctionnel                           |

| <b>FLI</b>   | <i>Foreign Language Interface</i>                                       |

| <b>FPGA</b>  | <i>Field Programmable Gate Array</i>                                    |

| <b>FSM</b>   | <i>Finite State Machine</i>                                             |

| <b>HCFSM</b> | <i>Hierarchical Concurrent FSM</i>                                      |

| <b>HDL</b>   | <i>Hardware Description Language</i>                                    |

| <b>IP</b>    | <i>Intellectual Property</i>                                            |

| <b>ISS</b>   | <i>Instruction Set Simulator</i>                                        |

|             |                                                          |

|-------------|----------------------------------------------------------|

| <b>JPEG</b> | <i>Joint Photographic Experts Group</i>                  |

| <b>KPN</b>  | <i>Kahn Process Network</i>                              |

| <b>L-L</b>  | Logiciel-Logiciel                                        |

| <b>L-M</b>  | Logiciel-Matériel                                        |

| <b>MCU</b>  | <i>Minimal Component Unit</i>                            |

| <b>MH</b>   | Module hiérarchique                                      |

| <b>M-L</b>  | Matériel-Logiciel                                        |

| <b>M-M</b>  | Matériel-Matériel                                        |

| <b>MOC</b>  | <i>Model of Computation</i>                              |

| <b>MPEG</b> | <i>Moving Picture Expert Group</i>                       |

| <b>MPN</b>  | Module de premier niveau                                 |

| <b>OCL</b>  | <i>Object Constraint Language</i>                        |

| <b>OO</b>   | <i>Object Oriented</i> ou orienté objet                  |

| <b>OSCI</b> | <i>Open SystemC Initiative</i>                           |

| <b>PCA</b>  | <i>Pin Cycle Accurate</i>                                |

| <b>PLI</b>  | <i>Programming Language Interface</i>                    |

| <b>PSP</b>  | <i>Processor Support Package</i> ou paquetage processeur |

| <b>RAM</b>  | <i>Random Access Memory</i>                              |

| <b>RGB</b>  | <i>Red Green Blue</i>                                    |

| <b>ROM</b>  | <i>Read-Only Memory</i>                                  |

| <b>RPC</b>  | <i>Remote Procedure Call</i>                             |

| <b>RTL</b>  | <i>Register Transfer Level</i>                           |

| <b>RTOS</b> | <i>Real-Time Operating System</i>                        |

| <b>SDF</b>  | <i>Static DataFlow</i>                                   |

| <b>SLDL</b> | <i>System-Level Design Language</i>                      |

| <b>SoC</b>  | <i>System-on-Chip</i>                                    |

| <b>SR</b>   | <i>Synchronous Reactive</i>                              |

| <b>SRAM</b> | <i>Static RAM</i>                                        |

| <b>STL</b>  | <i>Standard Template Library</i>                         |

|                            |                                                                                                              |

|----------------------------|--------------------------------------------------------------------------------------------------------------|

| <b>Syslib<sup>BL</sup></b> | <i>Syslib Behavioural Level</i> ou Syslib niveau comportemental                                              |

| <b>Syslib<sup>FL</sup></b> | <i>Syslib Functional Level</i> ou Syslib niveau fonctionnel                                                  |

| <b>Syslib<sup>LL</sup></b> | <i>Syslib Lower Level</i> ou Syslib de niveau architectural                                                  |

| <b>TarP</b>                | <i>Target Platform</i>                                                                                       |

| <b>TF</b>                  | <i>Timed Functional</i>                                                                                      |

| <b>UML</b>                 | <i>Unified Modeling Language</i>                                                                             |

| <b>USB</b>                 | <i>Universal Serial Bus</i>                                                                                  |

| <b>UT</b>                  | Unités de temps                                                                                              |

| <b>UTF</b>                 | <i>Untimed Functional</i>                                                                                    |

| <b>VC</b>                  | <i>Virtual Component</i>                                                                                     |

| <b>VCI</b>                 | <i>Virtual Component Interface</i>                                                                           |

| <b>VHDL</b>                | <i>VHSIC Hardware Description Language</i>                                                                   |

| <b>VHSIC</b>               | <i>Very High Scale Integrated Circuit</i>                                                                    |

| <b>VSIA</b>                | <i>Virtual Socket Interface Alliance</i>                                                                     |

| <b>YUV</b>                 | <b>Y</b> = luminance, <b>U</b> = bleu-Y, <b>V</b> = rouge-Y<br>(YUV $\cong$ 0,3·Rouge + 0,6·Vert + 0,1·Bleu) |

## Lexique

|                              |                                                                                                                                                                                                                                                               |

|------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>Bibliothèque</b>          | Assortiment logiciel regroupant des services pour fins de programmation. En français, on dira souvent, à tort par anglicisme, librairie.<br><b>Anglais</b> : library                                                                                          |

| <b>Binding</b>               | Opération d'association des ports aux canaux ou à des ports hiérarchiques.<br><b>Français</b> : association.                                                                                                                                                  |

| <b>Burst Mode</b>            | Mode de transmission de données sur un bus dont le protocole est d'envoyer une seule adresse pour une série de données.<br><b>Français</b> : mode rafale ou transaction éclatée.                                                                              |

| <b>Byte enable</b>           | Sur une mémoire, signal servant à la sélection du bon octet.                                                                                                                                                                                                  |

| <b>Chip select</b>           | Sur une mémoire, signal servant à l'activation de celle-ci.                                                                                                                                                                                                   |

| <b>Chrominance</b>           | En télévision, signaux portant la composition de couleur d'une image.                                                                                                                                                                                         |

| <b>Codesign</b>              | Art de concevoir des systèmes logiciel-matériel fortement liés, des systèmes embarqués ou des systèmes sur puce.<br><b>Français</b> : co-spécification est une traduction correcte, mais comme « design » est reconnu en français, on emploiera « codesign ». |

| <b>Datapath</b>              | <b>Français</b> : chemin de données.                                                                                                                                                                                                                          |

| <b>Espace colorimétrique</b> | <b>Anglais</b> : color space.                                                                                                                                                                                                                                 |

| <b>Event-driven</b>          | Contrôlé par un événement, par un signal.                                                                                                                                                                                                                     |

| <b>Flag</b>                  | Variable indiquant un état particulier.<br><b>Français</b> : drapeau.                                                                                                                                                                                         |

| <b>Handler</b>               | Sous-programme qui permet la gestion de certaines opérations à l'intérieur du système.<br><b>Français</b> : gestionnaire.                                                                                                                                     |

|                             |                                                                                                                                                                                                                                            |

|-----------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b><i>Handshaking</i></b>   | Protocole de communication nécessitant au cours duquel deux entités doivent échanger des signaux, jusqu'à ce qu'ils soient parfaitement synchronisés et prêts à communiquer entre eux.<br><b>Français</b> : protocole de poignée de mains. |

| <b><i>Lookup Table</i></b>  | Tableau de références contenant des valeurs pré-calculées permettant d'établir une relation entre deux séries de valeurs.<br><b>Français</b> : table de conversion.                                                                        |

| <b>Luminance</b>            | En télévision, signaux décrivant la distribution de luminosité d'une image.                                                                                                                                                                |

| <b>Macro</b>                | Séquence d'instructions enregistrée sous un nom, qu'on peut rappeler et exécuter par le nom qui lui a été attribué.                                                                                                                        |

| <b><i>Map</i></b>           | En STL, structure de données de type conteneur associatif qui permet de lier à tout objet qui y est inséré une clef unique.<br><b>Français</b> : ensemble.                                                                                 |

| <b>Micronoyau</b>           | Système d'exploitation simplifié n'offrant que les concepts de bases.<br><b>Anglais</b> : Microkernel.                                                                                                                                     |

| <b><i>multi-thread</i></b>  | À plusieurs processus élémentaires.                                                                                                                                                                                                        |

| <b>Mutex</b>                | Sémaphore binaire.                                                                                                                                                                                                                         |

| <b><i>Netlist</i></b>       | Énumération des connexions entre les différents composants ou blocs fonctionnels d'un circuit.<br><b>Français</b> : liste d'interconnexions.                                                                                               |

| <b><i>Output enable</i></b> | Sur une mémoire, signal servant à valider les sorties de lecture.                                                                                                                                                                          |

| <b><i>Parser</i></b>        | Outil qui analyse des textes à partir de la reconnaissance d'unités syntaxiques à partir d'une grammaire hors contexte.<br><b>Français</b> : analyseur syntaxique.                                                                         |

| <b>Pipeline</b>             | Architecture structurelle qui permet de séparer un traitement en plusieurs étages d'exécution et de recouvrir simultanément l'exécution de chaque étage.                                                                                   |

| <b><i>Pixel</i></b>         | Élément graphique élémentaire caractérisé par une couleur et une intensité.                                                                                                                                                                |

|                                  |                                                                                                                                                                                                                                                                           |

|----------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b><i>Polling</i></b>            | Mode de traitement dans lequel l'entité chargée du contrôle des échanges sur un réseau interroge régulièrement chaque élément branché, afin de savoir si elle a des données à émettre ou si elle est prête à en recevoir.<br><b>Français :</b> interrogation, scrutation. |

| <b><i>Port-Socket</i></b>        | Voir <i>socket</i> .<br><b>Français :</b> capsule                                                                                                                                                                                                                         |

| <b>Préemption</b>                | Mode d'opération d'ordonnancement d'un système d'exploitation qui permet de retirer une tâche en exécution pour la remplacer par une autre plus prioritaire.                                                                                                              |

| <b><i>Reset</i></b>              | Remise d'un processus ou d'un système dans son état standard de démarrage.<br><b>Français :</b> réinitialisation.                                                                                                                                                         |

| <b><i>Socket</i></b>             | Interface de connexion ou connecteur logiciel permettant de communiquer d'une entité à une autre.                                                                                                                                                                         |

| <b><i>Template</i></b>           | En C++, superclasse définissant un composant logiciel fortement paramétré.<br><b>Français :</b> Modèle ou classe générique.                                                                                                                                               |

| <b><i>Testbench</i></b>          | Ensemble des tests utilisés pour valider une spécification.<br><b>Français :</b> banc d'essai.                                                                                                                                                                            |

| <b><i>Thread</i></b>             | Processus élémentaire.                                                                                                                                                                                                                                                    |

| <b><i>Timer</i></b>              | Dispositif qui permet aux entités d'établir les intervalles de temps désirés pour divers tâches.<br><b>Français :</b> temporisateur.                                                                                                                                      |

| <b><i>Timing</i></b>             | Correspondance exacte de temps entre des impulsions servant à la synchronisation.<br><b>Français :</b> minutage.                                                                                                                                                          |

| <b><i>Untimed functional</i></b> | Niveau fonctionnel sans notion de temps ou sans minutage.                                                                                                                                                                                                                 |

| <b><i>Watchdog</i></b>           | Dispositif qui surveille un signal afin de déceler l'absence d'une action à la fin d'une période déterminée pour effectuer un traitement compensatoire.<br><b>Français :</b> chien de garde.                                                                              |

|                                           |                                                                                                                                                         |

|-------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|

| <i>Watching</i><br><i>(local, global)</i> | Surveillance des signaux servant à l'établissement d'un système de traitement d'exceptions.<br><b>Français</b> : surveillance, horloge de surveillance. |

| <i>Wrapper</i>                            | Entité permettant d'en adapter une autre pour assurer une compatibilité au niveau des échanges de données.<br><b>Français</b> : enveloppe, adaptateur.  |

| <b>YUV</b>                                | Espace colorimétrique vidéo utilisé dans la télévision.                                                                                                 |

## Liste des annexes

|                                                                   |            |

|-------------------------------------------------------------------|------------|

| <b>ANNEXE A : PERFORMANCE DES LECTURES ET DES ECRITURES .....</b> | <b>125</b> |

| <b>ANNEXE B : RESULTATS DU DECODEUR JPEG.....</b>                 | <b>128</b> |

| <b>ANNEXE C : EXECUTION PIPELINEE DU DECODEUR JPEG .....</b>      | <b>130</b> |

| <b>ANNEXE D : TRANSFORMATION DE CODE AUTOMATISEE .....</b>        | <b>134</b> |

| <b>ANNEXE E : PICASSO .....</b>                                   | <b>143</b> |

| <b>ANNEXE F : CODE DE L'EXEMPLE DU PACKETROUTER .....</b>         | <b>150</b> |

## Introduction

Un système est qualifié d'embarqué lorsqu'il est dédié à une tâche informatique spécifique dans un environnement donné. Souvent, les systèmes embarqués seront implantés sur une puce unique que l'on nomme *system-on-chip* ou *SoC*. Ces systèmes sont séparés en deux catégories distinctes: des systèmes orientés pour le contrôle et des systèmes orientés pour le traitement des données. Des systèmes peuvent très bien être un mélange des deux. Des exemples de chacune de ces catégories sont donnés au tableau 1.

**Tableau 1 : Exemples de systèmes embarqués**

| Systèmes orientés contrôle                                                                                                                                         | Systèmes orientés traitement de données                                                                                                                           |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <ul style="list-style-type: none"> <li>• Contrôleur de freins ABS</li> <li>• Four à micro-ondes</li> <li>• Contrôleur de lance-missiles sur un chasseur</li> </ul> | <ul style="list-style-type: none"> <li>• Décodeur vidéo MPEG4</li> <li>• Téléphonie cellulaire</li> <li>• Commutateur dans les grands réseaux Internet</li> </ul> |

Que les systèmes soient contraints à opérer dans des environnements particuliers apporte son lot de difficultés. Par exemple, la consommation de puissance de certains de ces systèmes doit être réduite. Le cas du téléphone cellulaire en est un exemple évident. Par ailleurs, le système doit également répondre en temps réel aux stimuli externes auxquels il est soumis. Le temps réel indique qu'un système doit fournir une réponse aux stimuli dans un temps suffisamment petit et prévisible pour répondre au monde physique qui l'entoure. De plus amples informations et exemples sont présentés dans [BuWe97].

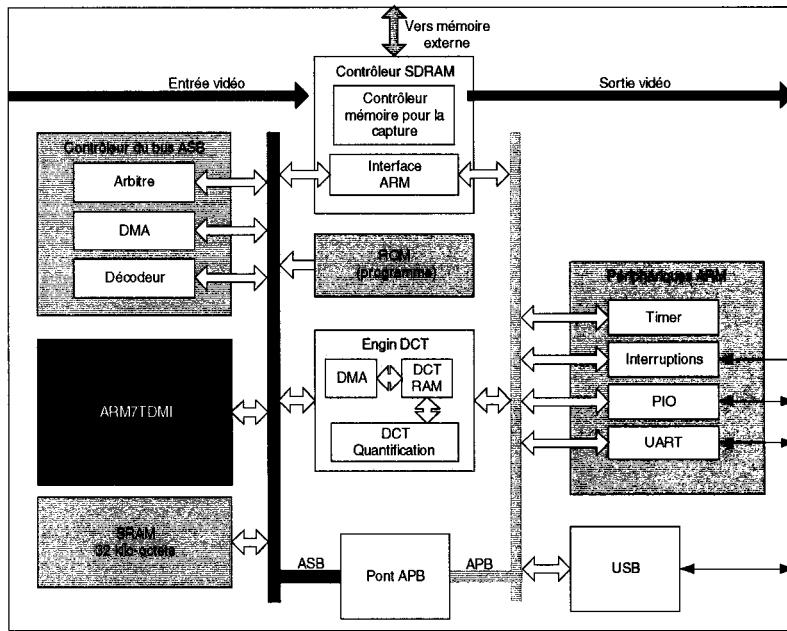

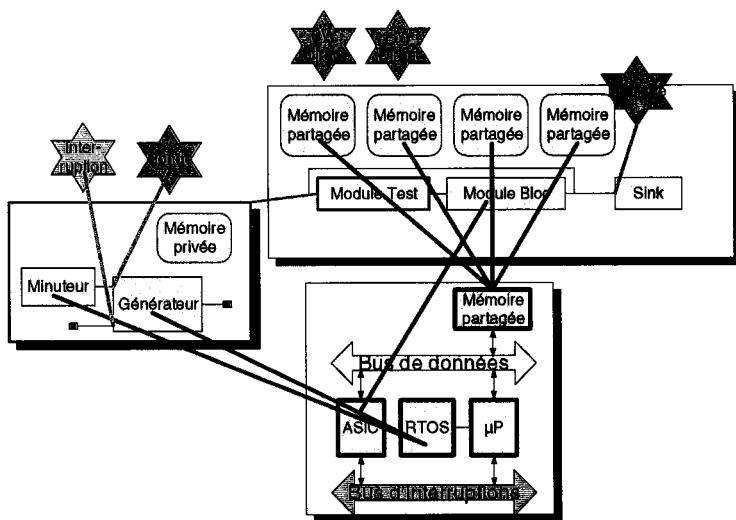

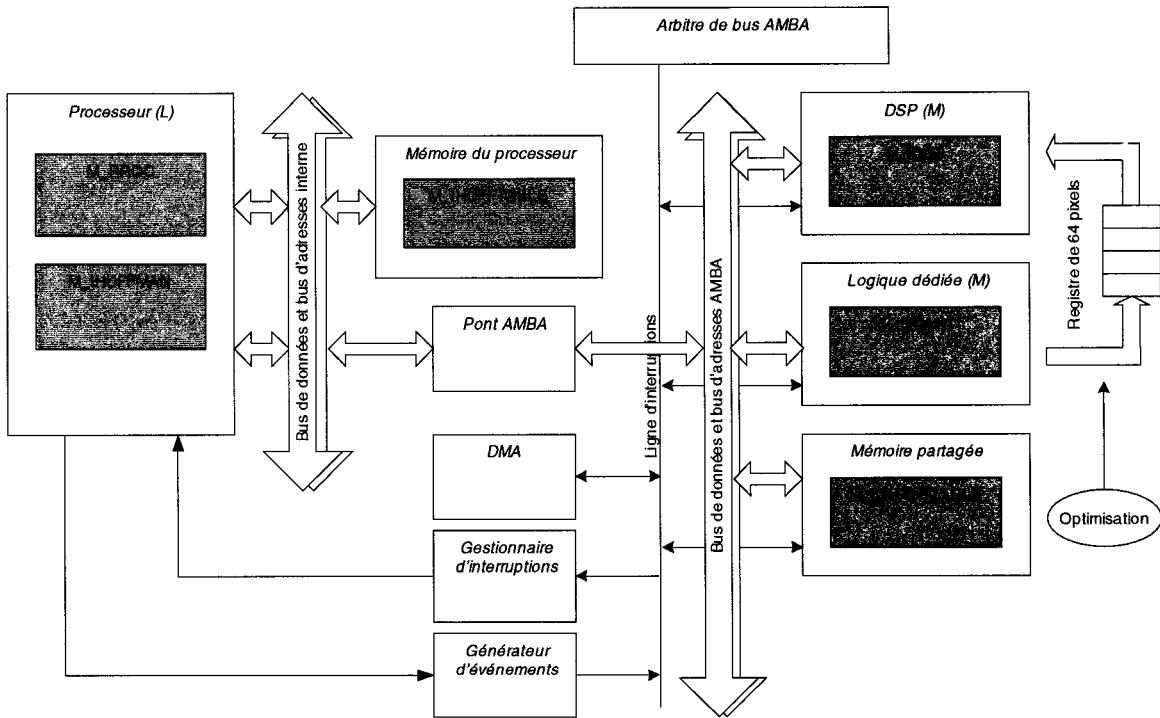

Techniquement, un système embarqué comprend une partie « matérielle », composée de circuits logiques dédiés ou ASIC, de DSP et FPGA, de mémoires. Également, ces systèmes sont munis d'une partie « logicielle » composée de programmes stockés en ROM s'exécutant sur des microprocesseurs dédiés. Des bus et interfaces de communication relient les deux mondes. Un exemple complexe de système embarqué est donné à la figure 1 où l'on voit la structure d'une caméra numérique.

Figure 1 : Exemple classique d'un système embarqué

Dans cet exemple, nous voyons à gauche, le microprocesseur de type ARM7TDMI branché à un bus normalisé AMBA (ASB). À ce même bus sont reliés des mémoires SRAM (qui contiennent entre autre le programme à exécuter), des contrôleurs ainsi que des circuits logiques dédiés, comme l'engin DCT. Un bus de périphériques à droite (APB) permet de brancher le système au monde extérieur (par exemple un magnétoscope).

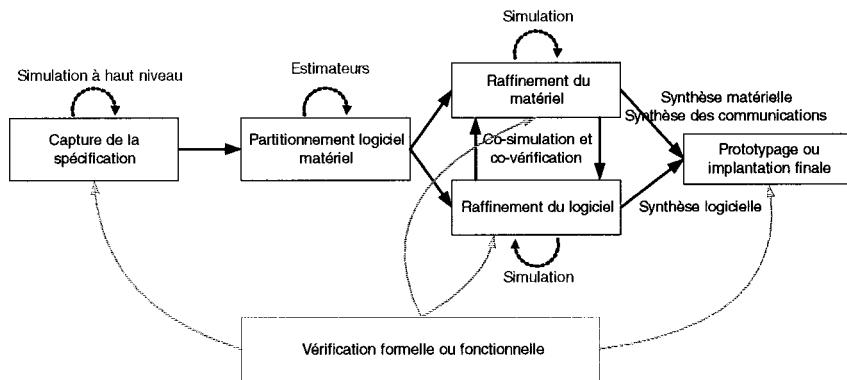

Le codesign se définit comme l'art de concevoir des systèmes sur lesquels le logiciel et le matériel sont intimement liés. On définira une méthodologie de codesign comme les multiples étapes nécessaires à la conception d'un SoC ou un PCB. En voici les principales étapes (tirées de [BCGH97]) représentées à la figure 2. On débute généralement avec la capture de la spécification grâce à des langages de haut niveau. On valide la spécification à l'aide de plusieurs simulations. Une fois la spécification validée, le concepteur passe à l'étape du partitionnement logiciel/matériel : il identifie les parties d'un système qui seront implantées en logiciel et quelles autres le seront en matériel. Une

façon formelle de parvenir à cette fin consiste en l'utilisation d'estimateurs, qui calculeront les coûts du logiciel (taille du code, temps d'exécution, surcoût rattaché au système d'exploitation, etc.) et les coûts du matériel (nombre de portes logiques, dissipation de puissance, nombre d'entrées-sorties, etc.) Une fois le partitionnement complété, on procède à un raffinement du matériel et du logiciel. Une fois les modules raffinés, on passe à la simulation conjointe du logiciel et du matériel ou co-simulation. Finalement, le système passe par une étape de synthèse pour transformer le comportement du matériel en circuit synthétisable (*netlist*) et pour compiler le logiciel (code machine) qui sera placé en ROM sur l'architecture. Il s'agit ensuite de valider les prototypes générés et de fabriquer la version finale du système sur une puce physique. Il va de soi que, si l'une des étapes révèle une insatisfaction en terme de performance ou de comportement, les concepteurs peuvent revenir en arrière.

**Figure 2 : Méthodologie générale de codesign**

La tendance veut qu'à plusieurs (voire toutes) étapes de la méthodologie, on procède à une vérification fonctionnelle du système spécifié. La vérification fonctionnelle tente de prouver que le système programmé est bel et bien celui qui a été spécifié. Elle se sépare en deux catégories complémentaires. Il y a la vérification formelle, qui utilise des modèles théoriques et mathématiques représentant la spécification pour prouver les aspects fonctionnels d'un système. La vérification fonctionnelle par simulation, quant à elle, cherche entre autre à balayer le plus de chemins d'exécution possibles (lors de

simulations) du système en design pour en vérifier la fonctionnalité. La vérification conjointe du matériel et du logiciel se nomme co-vérification. Le présent mémoire ne couvre pas les aspects de vérification, mais pour plus d'information, le lecteur peut se référer à [VSIA01], [RPS01] et [Berg00].

### **Problématique**

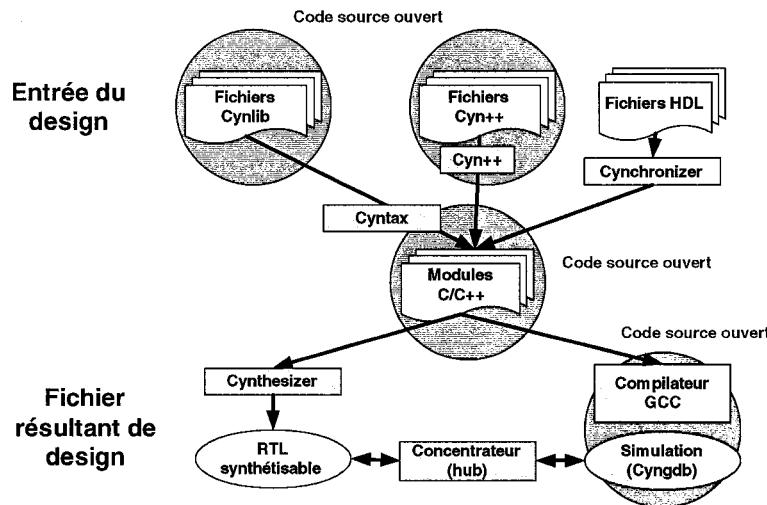

Depuis quelques années, l'étape de la capture des spécifications est de plus en plus réalisée à l'aide de langages de spécification de niveau d'abstraction élevé : C, C++, Java, etc. dont certains offrent le concept de l'orienté objet. Ces langages requièrent malheureusement une transformation syntaxique et comportementale complète pour passer aux étapes de codesign subséquentes. Certains groupes étendent ces langages en des bibliothèques permettant la conception orientée système, afin d'abstraire les éléments d'un système embarqué pour effectuer des simulations à un niveau le plus élevé possible. Dans certains cas, il est possible d'effectuer des simulations de matériel grâce à ces bibliothèques, ce qui diminue le temps de raffinement des spécifications et augmente la performance des simulations. Par exemple, des bibliothèques C++ reconnues telles SystemC [Swan01], SpecC [GZDG00] et Cynlib [FDS00a] se révèlent comme des propositions intéressantes. Ces bibliothèques, liées à une méthodologie solide, deviennent des outils puissants de conception.

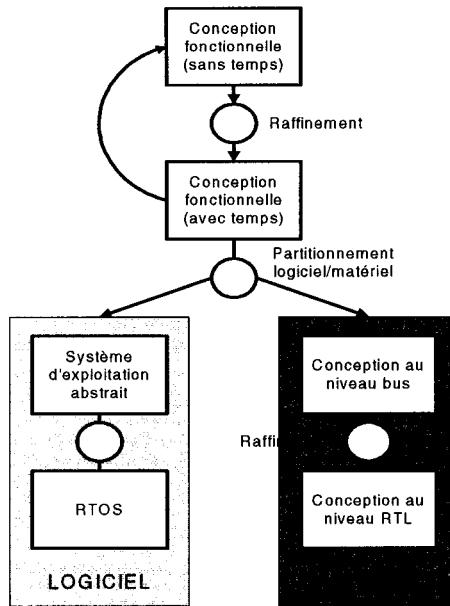

Toutefois, ces bibliothèques existantes ne répondent pas tout à fait aux besoins de conception des SoC sous plusieurs aspects. D'abord, très peu d'entre elles se lient à une méthodologie complète, ce qui ampute leur efficacité; tel est le cas de SystemC présentée à la figure 3 qui ne schématisise que grossièrement les directions à prendre pour concevoir un système et qui ne propose aucune solution concrète pour le partitionnement, la description du logiciel, les liens avec un système d'exploitation, ainsi que les communications entre les modules matériel et logiciel. Des versions futures sont cependant attendues.

SpecC propose quant à elle une méthodologie complète pour les SoC. Cependant, un problème majeur surgit: l'utilisation d'un langage non standardisé limite son utilisation aux seuls outils fournis par SpecC, à moins qu'on développe ses propres outils, ce qui est un travail long et fastidieux. Finalement, Cynlib propose un support flexible et simple pour le matériel. Toutefois, aucun support pour le logiciel ou aucune vision système n'est supportée, ce qui restreint ses possibilités.

**Figure 3 : Méthodologie de conception de SystemC**

### Objectifs

L'objectif principal de ce travail est d'intégrer une bibliothèque orientée objet de conception de systèmes embarqués dans une méthodologie complète de codesign. Définir une bibliothèque à tous les niveaux est un travail ardu et c'est pourquoi il importe de s'inspirer des travaux existants. Comme Cynlib n'est utile que pour la modélisation de matériel, on y superposera Syslib, notre bibliothèque de niveau système, en C++ orienté objet, qui complémera les besoins système de Cynlib. Il importe également de prouver qu'on peut utiliser sans tracas la bibliothèque Syslib pour programmer des exemples de design. Enfin, on voudra s'assurer que la bibliothèque programmée est performante et efficace en la comparant à une bibliothèque existante, en l'occurrence SystemC.

## **Méthodologie**

Il faut établir les besoins de la bibliothèque Syslib pour qu'elle puisse bien s'intégrer à une méthodologie de codesign. Une méthodologie complète est effectivement complexe et il apparaît évident que seulement quelques étapes seront couvertes dans ce mémoire. La bibliothèque sera implantée à un niveau d'abstraction élevé sans notion de temps (voir figure 3). Les autres étapes feront parti de travaux futurs au sein du CIRCUS<sup>1</sup>. Pour vérifier le bon fonctionnement de la bibliothèque, nous avons développé des exemples de design pouvant être capturées à haut niveau selon différents types de traitements (orienté contrôle, flôt de données, etc.). Il est par le fait même important de démontrer que le raffinement vers Cynlib se fait sans encombre et nous en donnons un exemple simple. Finalement, mentionnons qu'au cours de la réalisation de ce projet, SystemC sortit une version 2 de sa bibliothèque couvrant les aspects système en plus des aspects de matériel. Une comparaison entre les possibilités et performances de Syslib et SystemC sera donc présentée.

## **Originalité et contribution**

L'originalité de ce travail est démontrée par l'avantage d'avoir Syslib à sa portée. Cette bibliothèque fournit tous les outils nécessaires à la modélisation rapide d'un système embarqué. Cynlib ne possède aucun niveau système et puisque aucun n'est prévu par ses concepteurs, la combinaison Syslib/Cynlib est une solution intéressante pour la conception de systèmes. Cette liaison est supportée par la méthodologie de codesign proposée, ce que très peu de bibliothèques proposent. Syslib utilise également une approche de conception différente en proposant des concepts intéressants qu'on ne retrouve pas à ce jour dans les autres bibliothèques.

---

<sup>1</sup> Le CIRCUS est un sous-groupe du GRM (Groupe de Recherche en Microélectronique de l'École Polytechnique de Montréal) qui s'intéresse à la recherche sur le codesign.

De plus, ce travail est accompagné d'un outil graphique se nommant Picasso, permettant de faciliter l'entrée des spécifications, entre autre en générant automatiquement les connexions d'un système complexe. L'utilisation de moyens graphiques facilite le travail du concepteur en réduisant le temps nécessaire à l'entrée des spécifications [HePa96]. Il n'est cependant pas obligatoire d'utiliser Picasso pour l'entrée des spécifications. Syslib est indépendant de Picasso.

Également, ce projet a mené à la publication de plusieurs articles. D'abord [FiBA02a] a présenté notre méthodologie de codesign et l'outil Picasso au 70<sup>e</sup> congrès de l'ACFAS. Ensuite, [FiBA02b] a présenté la bibliothèque Syslib ainsi qu'un exemple de design à la 11<sup>e</sup> conférence HDLCon. Enfin, [FCBA02] a expliqué la méthodologie utilisée pour le design de la bibliothèque et l'engin de simulation au 2<sup>e</sup> atelier IWSOC. Toutes ces publications sont disponibles sur le site Internet du laboratoire de recherche sur le codesign de l'École Polytechnique, le CIRCUS [CIRC02].

### **Distribution des chapitres**

Ce mémoire est distribué en quatre chapitres. Le chapitre 1 survole les méthodologies de conception des systèmes embarqués, les langages ou bibliothèques de haut niveau utilisés pour développer des systèmes et l'apport de l'orienté objet dans la conception de systèmes. Le chapitre 2 présente la bibliothèque Syslib et sa méthodologie de codesign, son implantation et un exemple de système. Les problèmes rencontrés et les solutions choisies y sont aussi présentés. Le chapitre 3 traite de raffinement, une étape essentielle lors de tout design de système. Nous verrons les endroits où le raffinement s'impose et les principales étapes à suivre. Enfin, le chapitre 4 présente les résultats obtenus de quelques exemples de design de systèmes ainsi qu'une comparaison de ces mêmes exemples programmés avec SystemC.

# CHAPITRE 1

## Revue de la conception des SoC

Les systèmes embarqués s'intègrent dans de plus en plus d'applications de la vie quotidienne. Ce nouveau marché en croissance mènera l'industrie à redéfinir ses méthodes et techniques de conception pour répondre à l'extraordinaire demande qui surviendra aux cours des prochaines années. Pour mieux comprendre vers où les méthodes de conception se dirigent, on se doit également de comprendre d'où elles proviennent. Ce chapitre survole plusieurs aspects des outils, approches et méthodologies de conception existants des systèmes embarqués. Depuis des années, ces techniques et technologies ont évolué et ont progressé vers l'abstraction des descriptions, rendant possible la manipulation des systèmes complexes d'aujourd'hui. Les méthodologies les plus importantes et les plus pertinentes seront présentées. Nous verrons donc une partie des plus récents travaux en matière de spécification des systèmes embarqués. Nous nous attarderons particulièrement à la toute nouvelle vague de l'utilisation de l'orienté objet pour définir des systèmes en étudiant les principaux langages et bibliothèques de programmation qui attirent les industries et les groupes de recherche.

### 1.1. Approches de conception

Les ingénieurs de l'industrie utilisent plusieurs approches ou empruntent plusieurs voies pour concevoir un système embarqué. Une première voie consiste à intégrer des spécifications de matériel et de logiciel validées sur une plate-forme d'exécution. La plate-forme existe, pour fins de simulation, en langage de modélisation de matériel, tels VHDL ou Verilog. Le logiciel, sous forme de bibliothèques compilées, s'exécute sur un processeur embarqué. Il s'agit de l'approche plate-forme très prisée et diversifiée pour servir des marchés distincts. Une seconde approche consiste à modéliser un système complet au moyen d'un langage de haut niveau incluant les spécifications de l'application et la plate-forme d'exécution. Une simulation de haut niveau est effectuée pour valider le comportement du système, puis on raffine ensuite la spécification vers des niveaux

d'implantation, mais en conservant le même langage : c'est l'approche par raffinements progressifs. Dans les deux cas, une fois le système complètement validé, on passera à la synthèse du matériel, du logiciel et des communications. Il est évident qu'un mélange de ces deux approches est légitime.

### **1.1.1. Approche par raffinement progressif**

Cette approche est amenée par un langage spécialisé ou encore une bibliothèque de programmation qu'un programmeur inclut dans son code. Il est souvent question de langage orienté objet, par exemple C++, qui offre beaucoup de flexibilité pour ce genre de pratique.

Parmi les approches à raffinements progressifs, une d'entre-elles consiste à transformer des spécifications fonctionnelles vers des modèles architecturaux prédéfinis, principalement pour les communications et les ressources disponibles. Ces raffinements se tiennent dans les étapes de partitionnement et d'allocation des ressources [GoGB97]. Cette approche offre peu de flexibilité, par contre, la simplicité et l'efficacité du design obtenu est un avantage assuré.

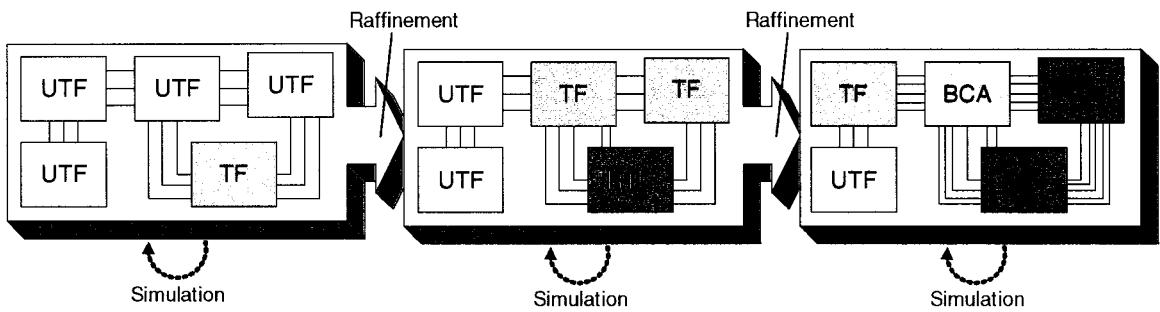

Une autre solution consiste à utiliser des bibliothèques de conception orientées objet qui permettent de décrire un système complet à plusieurs niveaux d'abstraction et de raffiner les spécifications jusqu'au niveau final d'implantation [Swan01]. Les spécifications débutent à un niveau fonctionnel et sont raffinées vers un niveau matériel tout en conservant la même bibliothèque. Les concepteurs ont le choix ou non d'inclure les détails de l'architecture dans les spécifications pour obtenir des résultats plus variés. Les possibilités sont infinies, mais le tout doit se faire manuellement.

### **1.1.2. Approche plate-forme**

On utilise souvent le terme architecture d'un système ou seulement architecture pour décrire l'organisation interne du système, i.e. la structure qui le compose. Le terme ne doit pas être confondu avec le concept d'architecture d'un ordinateur (ou d'un

microprocesseur) qui correspond non seulement à sa structure, mais également à son jeu d'instructions. Dans [HePa96], on différencie longuement ces concepts. Le terme plate-forme ne représente donc pas l'architecture du système en soi, mais plutôt une structure de base utilisée par les ingénieurs pour construire une nouvelle application de système embarqué. La grande majorité des compagnies qui conçoivent des SoC réutilisent en tout ou en partie la plate-forme d'un produit précédent, ce qui diminue le temps de conception du nouveau produit par la réutilisation de plusieurs composants ou modules déjà validés.

On parlera souvent de conception orientée plate-forme (*Platform-Based Design*) dans la littérature [CCHM99]. Cette solution permet de modéliser un SoC à partir d'une plate-forme d'exécution sur laquelle on insérera des blocs prédefinis en fonction de l'application à concevoir. Une multitude de systèmes sont possibles, par contre, une normalisation des interfaces de communication est requise, de même que la disponibilité des blocs à insérer respectant cette norme.

Des compagnies proposent d'intégrer leurs microprocesseurs sur des plates-formes qu'ils ont eux-mêmes conçues. Par exemple, la compagnie ARM [ARM00a], fabricant d'une famille de microprocesseurs dédiés aux systèmes embarqués, propose une plate-forme basée sur une norme de bus nommée AMBA [ARM00b] sur laquelle plusieurs bus et protocoles de communication s'adaptent à tout design. Également, IBM propose sa plate-forme CoreConnect adaptée à son processeur PowerPC [BeLe00]. Plusieurs outils sont fournis avec la plate-forme ce qui en fait un produit intéressant pour les ingénieurs. D'autres produits commerciaux basés sur l'approche plate-forme existent, notamment Platform Express de Mentor Graphics [Ment02a]. Le but de cet outil est de créer rapidement une plate-forme à l'aide d'une banque de blocs prédefinis (processeurs ARM7, ARM9, mémoire, DMA, USB, IP de tiers partis) basée sur les produits ARM et la norme de bus AMBA. Une fois la plate-forme générée, il est possible de la simuler avec les outils de Mentor Graphics.

## 1.2. Sémantique et normalisation

L'importance d'avoir une définition exacte pour tous les composants d'un système à tous ses niveaux est capitale. Avant de fixer des normes pour la création de système, il importe d'en établir la sémantique. La sémantique – du grec *sēmantikos* (qui signifie) – d'une chose, c'est l'étude scientifique et théorique d'un concept, qui le définit intégralement et dont toute interprétation personnelle est écartée. Puisque des milliers de compagnies et groupes de recherche développent des systèmes et composants, il s'ensuit l'établissement de normes à tous les niveaux de conception qui facilitent la compréhension et l'intégration des composants de même que leur interaction dans un système complet.

### 1.2.1. Accellera

Le groupe Accellera [Acce02] est composé de plusieurs industries et groupes de recherche qui ont pour but commun d'établir la sémantique dans la conception des systèmes embarqués : le tout permettra éventuellement d'établir des normes dans l'industrie. Un travail est déjà entrepris au niveau RTL [BaGa01]. Il a été appliqué à SystemVerilog [Suth02], une nouvelle extension à Verilog 2001 pour supporter la vérification et les communications de niveau architectural entre les modules. Il s'agit d'un pas vers le niveau système.

### 1.2.2. VSIA

Par ailleurs, une autre alliance industrielle et universitaire a déjà accompli beaucoup de travail pour normaliser la conception des systèmes. *Virtual Socket Interface Alliance* ou VSIA [VSIA02] énonce des normes pour inciter l'industrie à opter progressivement pour l'adoption d'un modèle de conception de systèmes basé sur l'exploration architecturale et l'échange de composant virtuels ou VC [VSIA97]. En d'autres termes, VSIA prône l'échange de composants protégés ou IP entre compagnies. En supposant que tous ces IP soient bâtis selon la même norme, leur intégration se fera théoriquement sans souci sérieux. VSIA propose de normaliser à trois endroits où un besoin se fait particulièrement sentir [LSJH00] :

- (1) l'utilisation des principes de communication communs ;

- (2) l'utilisation d'un format de design commun ;

- (3) l'usage d'une approche unifiée pour analyser les performances et la qualité du système.

Une proposition pour une norme supportant l'interopérabilité est également à l'étude. L'interopérabilité permet de mélanger des VC provenant d'environnements différents [DGOS01]. Plusieurs travaux de VSIA en cours sont résumés dans ce qui suit.

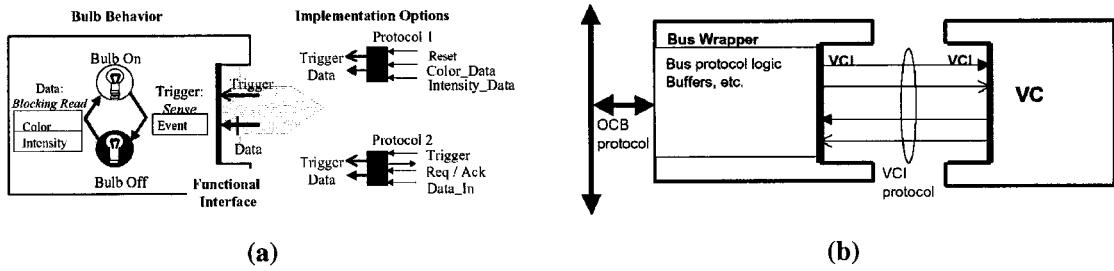

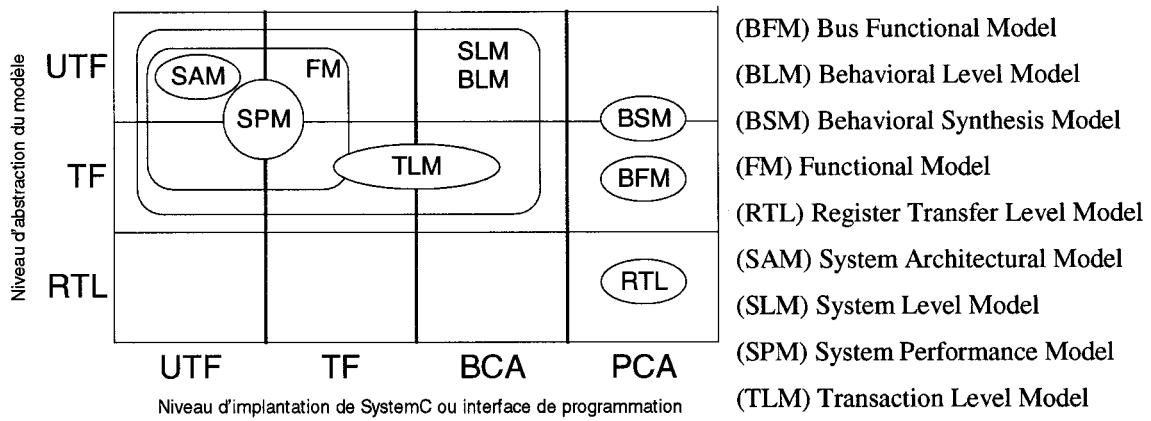

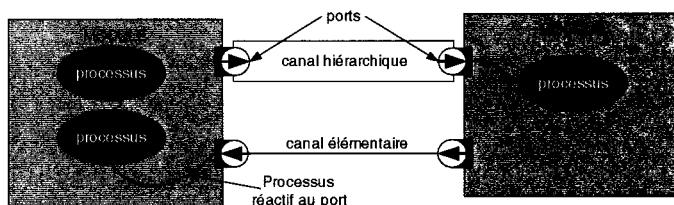

*System-Level Interface Behavioral* (SLIF) [VSIA00a] permet de mieux gérer l'intégration des VC entre eux. Un principe de conception basé sur les interfaces s'effectue en séparant le protocole de communication des comportements internes aux VC. On peut observer ce phénomène à la figure 1.1a, alors que deux protocoles s'attachent à l'interface d'un module. On arrive ainsi à créer une orthogonalité des VC et des protocoles qu'ils utilisent. La description des VC se fait sur un ensemble de couches représentant les différents niveaux d'abstraction de ce VC. Le protocole est exprimé grâce à une série de règles de transactions basées sur le flux de contrôle et de données fonctionnant avec des tampons et des queues, bloquant ou non avec ou sans priorité.

*On-Chip Bus Standard* (OCB VCI) [VSIA00b] offre un ensemble de signaux logiques ainsi que des protocoles flexibles pour transférer de l'information sur un bus entre deux points. On observe à la figure 1.1b un VC branché sur un bus par l'intermédiaire d'un adaptateur (*bus wrapper*) simple pour se conformer à la norme du bus. OCB VCI offre trois niveaux de complexité selon les besoins du concepteur: un niveau de base (*Basic VCI*), un niveau avancé (*Advanced VCI*) et un niveau pour les périphériques (*Peripheral VCI*). Ces normes offrent les fonctionnalités typiques d'un bus telles les transactions séparées (*split transactions*), les rafales (*burst*), le pipelinage et l'envoi de paquets.

Figure 1.1 : Les concepts de normalisation proposés par VSIA

Enfin, *System-Level Data-Types Standard* [LSJH00] propose des types de données normalisés. La norme propose entre autre de ne rien supposer quant à la taille des types au niveau des compilateurs ou encore d'affecter une valeur par défaut lors de la déclaration de variables. La proposition couvre aussi bien les types de haut niveau tels les entiers signés ainsi que les types de bas niveau comme les vecteurs de bits.

### 1.3. Contribution du logiciel et de l'orienté objet

Les méthodologies employées pour la conception des systèmes embarqués aujourd’hui ne répondent plus et ne résisteront pas à la complexité grandissante des systèmes. La densité de transistors par puce augmente au rythme de 60% par année selon la loi de Moore [VaGi02]. Cette forte augmentation crée des systèmes fort complexes ayant des besoins accrus en terme de performance de simulation et de vérification des circuits. Les méthodes pour construire ces systèmes doivent également se renouveler, sans quoi elles deviendront des obstacles majeurs dans leur fabrication.

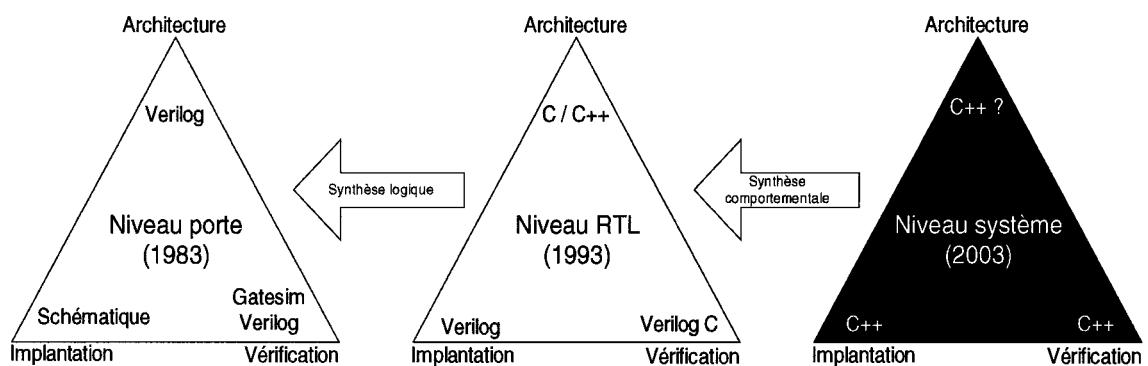

#### 1.3.1. Évolution de l'utilisation du logiciel

En regardant la façon dont un système est développé, on constate trois éléments clefs où l’entrée de code est requise: à l’implantation même des algorithmes et des fonctions, à la description de l’architecture utilisée et enfin, lors de la création de plans de vérification. La figure 1.2 proposée par [DaCl02] illustre ce principe. Le triangle de gauche montre qu’au début des années 1980, trois langages (ou concepts) différents étaient utilisés pour créer un système, à l’époque, de quelques centaines de milliers de portes logiques. Avec