**Titre:** Intégration d'une jonction six-port en technologie MMIC et son utilisation pour la conception d'un récepteur QPSK

Title: utilisation pour la conception d'un récepteur QPSK

**Auteur:** Éric Marsan

Author:

**Date:** 2003

**Type:** Mémoire ou thèse / Dissertation or Thesis

**Référence:** Marsan, É. (2003). Intégration d'une jonction six-port en technologie MMIC et son utilisation pour la conception d'un récepteur QPSK [Master's thesis, École Polytechnique de Montréal]. PolyPublie. <https://publications.polymtl.ca/6988/>

Citation:

## Document en libre accès dans PolyPublie Open Access document in PolyPublie

**URL de PolyPublie:** <https://publications.polymtl.ca/6988/>

PolyPublie URL:

**Directeurs de recherche:** Rénato Bosisio, & Ke Wu

Advisors:

**Programme:** Unspecified

Program:

UNIVERSITÉ DE MONTRÉAL

INTÉGRATION D'UNE JONCTION SIX-PORT EN TECHNOLOGIE MMIC ET

SON UTILISATION POUR LA CONCEPTION D'UN RÉCEPTEUR QPSK

ÉRIC MARSAN

DÉPARTEMENT DE GÉNIE ÉLECTRIQUE

ÉCOLE POLYTECHNIQUE DE MONTRÉAL

MÉMOIRE PRÉSENTÉ

POUR APPROBATION DU SUJET DE RECHERCHE DANS LE

CADRE DU DIPLÔME DE MAÎTRISE ÈS SCIENCES APPLIQUÉES

(GÉNIE ÉLECTRIQUE)

AVRIL 2003

National Library

of Canada

Acquisitions and

Bibliographic Services

395 Wellington Street

Ottawa ON K1A 0N4

Canada

Bibliothèque nationale

du Canada

Acquisitions et

services bibliographiques

395, rue Wellington

Ottawa ON K1A 0N4

Canada

Your file Votre référence

Our file Notre référence

The author has granted a non-exclusive licence allowing the National Library of Canada to reproduce, loan, distribute or sell copies of this thesis in microform, paper or electronic formats.

L'auteur a accordé une licence non exclusive permettant à la Bibliothèque nationale du Canada de reproduire, prêter, distribuer ou vendre des copies de cette thèse sous la forme de microfiche/film, de reproduction sur papier ou sur format électronique.

The author retains ownership of the copyright in this thesis. Neither the thesis nor substantial extracts from it may be printed or otherwise reproduced without the author's permission.

L'auteur conserve la propriété du droit d'auteur qui protège cette thèse. Ni la thèse ni des extraits substantiels de celle-ci ne doivent être imprimés ou autrement reproduits sans son autorisation.

0-612-81553-6

Canadâ

UNIVERSITÉ DE MONTRÉAL

ÉCOLE POLYTECHNIQUE DE MONTRÉAL

Ce mémoire intitulé:

INTÉGRATION D'UNE JONCTION SIX-PORT EN TECHNOLOGIE MMIC ET

SON UTILISATION POUR LA CONCEPTION D'UN RÉCEPTEUR QPSK

présenté par: MARSAN Éric

en vue de l'examen oral pour l'approbation du sujet

de recherche dans le cadre du diplôme de: Maîtrise ès science appliquées

a été dûment accepté par le jury d'examen constitué de:

M. AKYEL Cevdet, D.Sc.A., président

M. BOSISIO Renato G., M.Sc.A., membre et directeur de recherche

M. WU Ke, Ph.D., membre et codirecteur de recherche

M. DEMERS Yves, Ph.D., membre

À ma famille et mes amis(es),

Merci pour tout.

## REMERCIEMENTS

Tout d'abord, je voudrais remercier M. Renato G. BOSISIO pour avoir accepté de me diriger dans mes travaux de maîtrise. Son support a grandement été apprécié, ainsi que celui de mon codirecteur M. Ke WU.

Les travaux décrits dans ce mémoire n'auraient pas été possibles sans l'appui de M. Gailon BREHM et *Triquint Semiconductor* puisqu'ils ont permis la fabrication du prototype en technologie MMIC sur GaAs.

Un grand merci à M. Jules GAUTHIER et M. Jean-Frédéric GAGNÉ pour leur aide indispensable tout au long de mes travaux et à M. Traian ANTONESCU pour la photographie. Merci également à M. Steve DUBÉ et M. Roch BRASSARD pour la fabrication et le montage des prototypes et à M. René ARCHAMBAULT pour son support au niveau logiciel. Merci à tous les étudiants concernés de la communauté "poly-gramoise" pour les échanges, les opinions et les conseils relatifs à mes travaux.

Finalement, merci à mes parents qui m'ont encouragé et aidé à poursuivre mes études universitaires.

## RÉSUMÉ

Le présent mémoire traite essentiellement de l'intégration d'une jonction six-port en technologie monolithique micro-ondes intégrée (MMIC) sur arsénure de gallium (GaAs) pour la réalisation d'un récepteur sans fil utilisant la modulation "quadrature phase shift keying" (QPSK) et réalisant un taux de transfert de données rapide de quelques dizaines de mégabits par seconde. Le besoin pour de tels récepteurs coïncide, entre autre, avec l'émergence de nouvelles applications tels les communications personnelles et le multimédia mais impose d'importantes contraintes de coûts et de dimensions, d'où l'intérêt pour l'intégration. Ce mémoire se veut la poursuite de précédents travaux réalisés au centre de recherche Poly-Grames de l'École Polytechnique de Montréal ayant démontré la pertinence de l'utilisation du circuit six-port dans la conception de récepteurs numériques sous de nombreuses conditions d'opération. Dans ces récepteurs, le principe du circuit six-port est utilisé en remplacement des mélangeurs en quadrature communs à plusieurs architectures et permet une conversion homodyne.

Originalement, le circuit six-port était conçu sous forme planaire à l'aide de lignes de transmission micro-ruban pour réaliser des coupleurs hybrides et Wilkinson dont les dimensions sont inversement proportionnelles à la fréquence d'utilisation. Aux fréquences élevées, ce type de réalisation pose donc moins de problèmes mais peut sérieusement compromettre l'intégration à des fréquences inférieures puisque les dimensions requises signifieraient d'importants coûts en plus d'être peu pratiques. La jonction six-port décrite dans ce mémoire est conçue sous forme discrète pour un récepteur opérant dans la bande ISM (Industrielle-Scientifique-Médicale) non-réglementée de 5,8 GHz et vise à paver la voie vers la réalisation d'un récepteur complet à puce unique utilisant le principe du six-port. La jonction est intégrée en technologie MMIC sur GaAs par une collaboration de recherche avec la fonderie américaine *Triquint Semiconductor* et jointe à un circuit en bande de base analogique

conçu selon un principe similaire aux précédents prototypes, soit par des comparateurs et amplificateurs opérationnels, pouvant ultimement être intégrés.

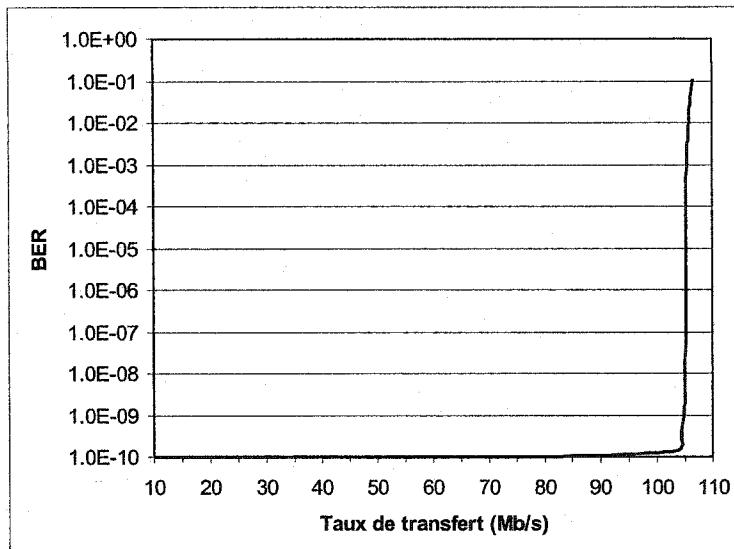

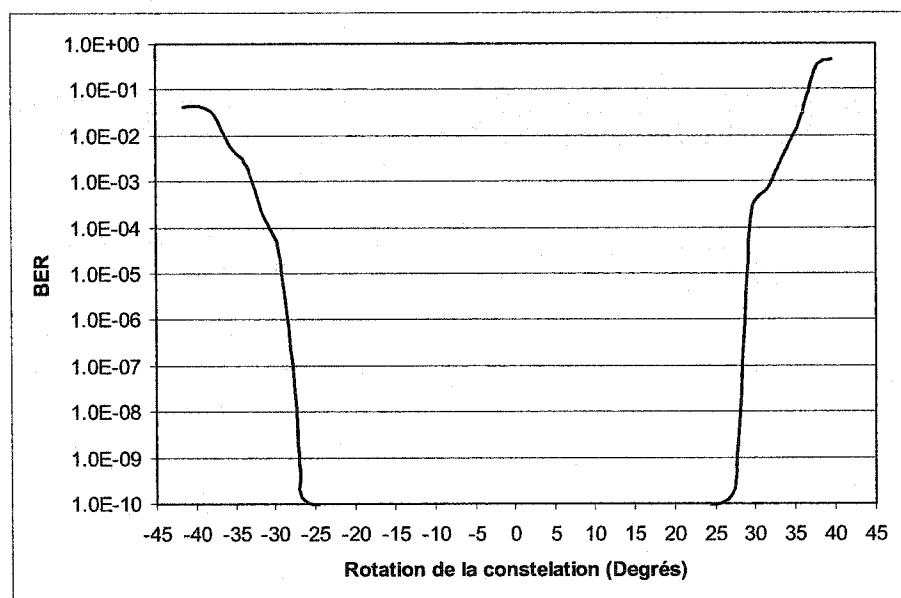

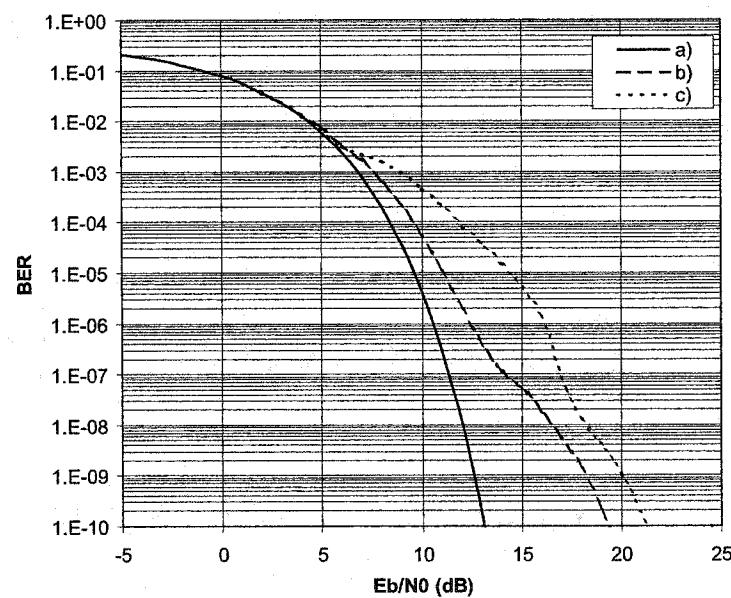

Différentes avenues pour la conception de la jonction sont d'abord abordées pour être ensuite confrontées aux réalités physiques des procédés de fabrication. Vu l'inexpérience avec le procédé et la fonderie, l'emploi de transistors est délibérément évité pour obtenir un circuit entièrement passif à l'exception de détecteurs RF réalisés avec des diodes Schottky. La conception est réalisée en utilisant le logiciel "Advanced Design System (ADS)" d'*Agilent Technologies*, les modèles ainsi que quelques données de mesures fournies par *Triquint Semiconductor*, la fonderie utilisée pour la fabrication. La jonction est mesurée en terme de paramètres S et comparée avec les données de simulation. Un retour sur la conception permet alors d'identifier quelques variations et valider ou invalider certains choix de conception. Par la suite, la jonction est jointe au circuit en bande de base pour former un récepteur sans circuit de récupération de la porteuse, la porteuse étant générée à même le banc de mesures dont la conception est également décrite. Trois indicateurs de performance sont mesurés et leurs valeurs comparées à celles obtenues pour des prototypes réalisés en technologie planaire. Ces trois indicateurs sont : le taux d'erreur en fonction du taux de transfert de données, le taux d'erreur en fonction d'une rotation de la constellation pour un taux de transfert de 40 Mb/s et le taux d'erreur en fonction du rapport de l'énergie par bit sur le bruit ( $E_b/N_0$ ) toujours pour un taux de 40 Mb/s. Les résultats obtenus sont très similaires aux résultats des précédents prototypes.

Finalement, le problème de la récupération de la porteuse est abordé en ayant à l'esprit la compatibilité avec d'autres types de modulation plus complexes et le maintien des principaux avantages apportés par la jonction six-port dont l'élimination des mélangeurs. Différentes méthodes sont passées en revue pour en venir à la proposition d'une architecture. L'architecture proposée est alors soutenue par divers résultats de simulation. Une étude expérimentale de cette architecture n'a pu être complétée dû à des contraintes de temps et des problèmes de fabrication.

## ABSTRACT

This thesis essentially studies the integration of a six-port junction using a Monolithic Microwave Integrated Circuit (MMIC) process on gallium arsenide (GaAs) to realize a wireless receiver. The receiver uses Quadrature Phase Shift Keying (QPSK) modulation and is designed for data rates of several megabits per second, needed for emerging applications such as personal communications and multimedia. However, these applications also bring important constraints on cost and size, paving the way for innovative receiver architectures. This thesis follows research done at the PolyGrames research center of *École Polytechnique de Montréal* which have demonstrated the relevance of using the six-port principle for the realization of digital receiver under many operating conditions. These receivers use a six-port junction in replacement of the mixers in quadrature very common to many receiver architectures to achieve homodyne conversion.

Originally, the six-port used in earlier receiver prototypes was designed in the planar form with the use of microstrip transmission lines to realize hybrid and Wilkinson couplers having dimensions inversely proportional to their center frequency of operation. At millimeter wave frequency, this type of six-port can be integrated quite easily but another method of design is required for lower frequencies as distributed elements would implicate dimensions leading to high cost and impractical sizes. The six-port junction described in this thesis is realized using lumped elements to be used in a receiver operating in the unrulled ISM (Industrial-Scientific-Medical) band of 5.8 GHz and is meant as a first step toward the design of a receiver on a chip using six-port principle. A research collaboration with the american foundry *Triquint Semiconductor* allowed the fabrication of the junction in MMIC technology, which is then joined to an analog baseband circuit made of high speed comparators and operational amplifiers. The baseband circuit is designed in such a way to allow it's integration in a further step.

Different solutions for the design of the six-port junction are first introduced and then confronted to the physical realities of the fabrication processes. Because of the inexperience with the foundry and the process, it was chosen to avoid any transistor on this first fabrication run to obtain a fully passive six-port with the exception of Schottky diodes used to realize RF detectors. The design of the junction is done using the software *Advanced Design System (ADS)* of *Agilent Technologies*, the models and some measurement data provided by the foundry. The junction is measured in terms of S parameters and compared to simulation data to identify variations, validate or invalidate design decisions. The six-port junction is then mounted on the baseband circuit to form the receiver without carrier recovery circuit and is operated in three conditions while the carrier is generated by the test bench. The operating conditions reproduced from earlier prototypes are the bit error rate (BER) function of the data rate, the BER function of constellation rotation at data rate of 40 Mb/s and BER function of the bit energy on noise ratio ( $E_b/N_0$ ) also at 40 Mb/s. Most of the results collected are in agreement with earlier prototypes.

Finally, the carrier recovery problem is studied having in mind the compatibility with more complex modulation schemes and to maintain the main advantages brought by the use of the six-port as the elimination of mixers for example. Different carrier recovery methods are first reviewed to propose an architecture followed by simulation results and, as time and fabrication constraints limited the study, the incomplete realization of a vector signal generator (modulator) using the same six-port. This last section brings more questions than answers but introduces a new application of the six-port circuit, even though the proposed architecture would be hard to realize completely for a single student in the prescribed delays as most of the carrier recovery techniques reviewed.

## TABLE DES MATIÈRES

|                                                                         |              |

|-------------------------------------------------------------------------|--------------|

| <b>DÉDICACE . . . . .</b>                                               | <b>iv</b>    |

| <b>REMERCIEMENTS . . . . .</b>                                          | <b>v</b>     |

| <b>RÉSUMÉ . . . . .</b>                                                 | <b>vi</b>    |

| <b>ABSTRACT . . . . .</b>                                               | <b>viii</b>  |

| <b>TABLE DES MATIÈRES . . . . .</b>                                     | <b>x</b>     |

| <b>LISTE DES FIGURES . . . . .</b>                                      | <b>xiii</b>  |

| <b>LISTE DES TABLEAUX . . . . .</b>                                     | <b>xvii</b>  |

| <b>LISTE DES SIGLES ET ABRÉVIATIONS . . . . .</b>                       | <b>xviii</b> |

| <b>INTRODUCTION . . . . .</b>                                           | <b>1</b>     |

| <b>CHAPITRE 1 INTRODUCTION ET RAPPEL DES CONCEPTS .</b>                 | <b>4</b>     |

| 1.1 Rappel sur la modulation M-PSK . . . . .                            | 4            |

| 1.2 Récepteurs à conversion directe et superhétéodyne . . . . .         | 7            |

| 1.2.1 Décalage CC . . . . .                                             | 10           |

| 1.2.2 Bruit de scintillement ("flicker noise") . . . . .                | 11           |

| 1.2.3 Fuites de l'oscillateur local . . . . .                           | 11           |

| 1.3 Le discriminateur de phase six-port et la modulation QPSK . . . . . | 11           |

| <b>CHAPITRE 2 LE SIX-PORT DISCRET . . . . .</b>                         | <b>17</b>    |

| 2.1 Les éléments RLC . . . . .                                          | 18           |

| 2.2 Le déphaseur . . . . .                                              | 24           |

| 2.2.1 Configurations A et C . . . . .                                   | 26           |

|                                                                         |                                                                                    |           |

|-------------------------------------------------------------------------|------------------------------------------------------------------------------------|-----------|

| 2.2.2                                                                   | Configurations B et D . . . . .                                                    | 29        |

| 2.3                                                                     | Le diviseur de puissance . . . . .                                                 | 29        |

| 2.4                                                                     | Coupleurs directionnels discrets . . . . .                                         | 32        |

| 2.4.1                                                                   | Coupleur COD . . . . .                                                             | 33        |

| 2.4.2                                                                   | Coupleur CTD . . . . .                                                             | 34        |

| 2.4.3                                                                   | Coupleur TRD . . . . .                                                             | 36        |

| 2.5                                                                     | Le détecteur RF . . . . .                                                          | 37        |

| <b>CHAPITRE 3 CONCEPTION DU SIX-PORT DISCRET ET RÉSULTATS . . . . .</b> |                                                                                    | <b>43</b> |

| 3.1                                                                     | Choix du procédé . . . . .                                                         | 43        |

| 3.2                                                                     | Conception du coupleur en quadrature . . . . .                                     | 47        |

| 3.3                                                                     | Conception du diviseur de puissance . . . . .                                      | 53        |

| 3.4                                                                     | Le six-port sans détecteurs . . . . .                                              | 55        |

| 3.5                                                                     | Conception des condensateurs . . . . .                                             | 57        |

| 3.6                                                                     | Conception du détecteur . . . . .                                                  | 58        |

| 3.7                                                                     | Le six-port avec détecteurs : performances globales . . . . .                      | 64        |

| <b>CHAPITRE 4 LE RÉCEPTEUR SIX-PORT ET LE BANC DE MESURES . . . . .</b> |                                                                                    | <b>67</b> |

| 4.1                                                                     | Le décodeur-comparateur . . . . .                                                  | 67        |

| 4.2                                                                     | Montage de mesure . . . . .                                                        | 71        |

| 4.3                                                                     | Performances du récepteur . . . . .                                                | 76        |

| <b>CHAPITRE 5 RÉCUPÉRATION DE LA PORTEUSE . . . . .</b>                 |                                                                                    | <b>83</b> |

| 5.1                                                                     | Caractérisation des méthodes de récupération propices au QPSK . . .                | 83        |

| 5.2                                                                     | Présentation de méthodes de récupération de la porteuse adaptées au QPSK . . . . . | 85        |

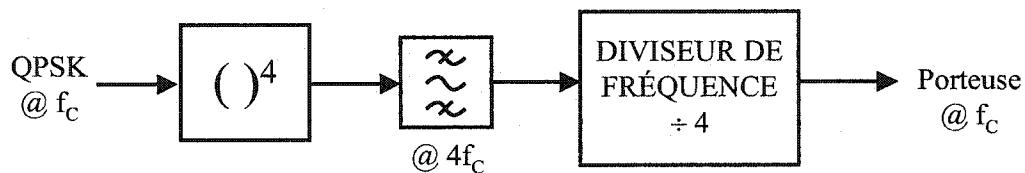

| 5.2.1                                                                   | Mise à la puissance quatre . . . . .                                               | 85        |

|                             |                                                                   |            |

|-----------------------------|-------------------------------------------------------------------|------------|

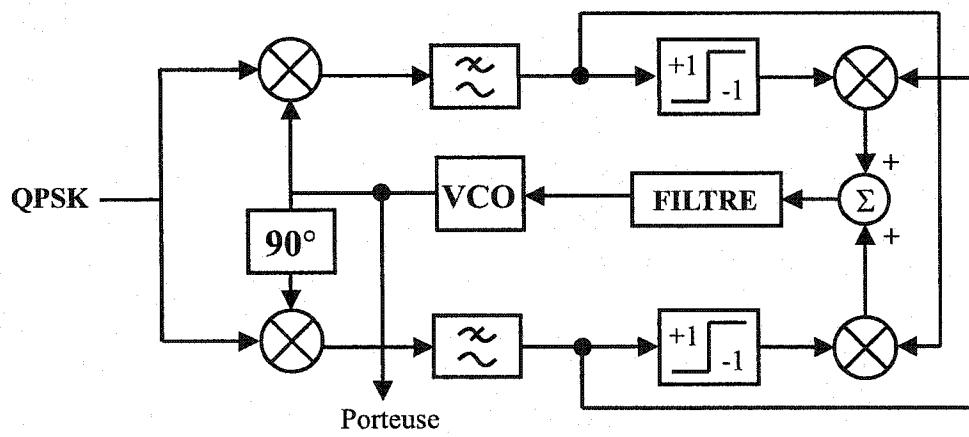

| 5.2.2                       | Boucle de Costas . . . . .                                        | 87         |

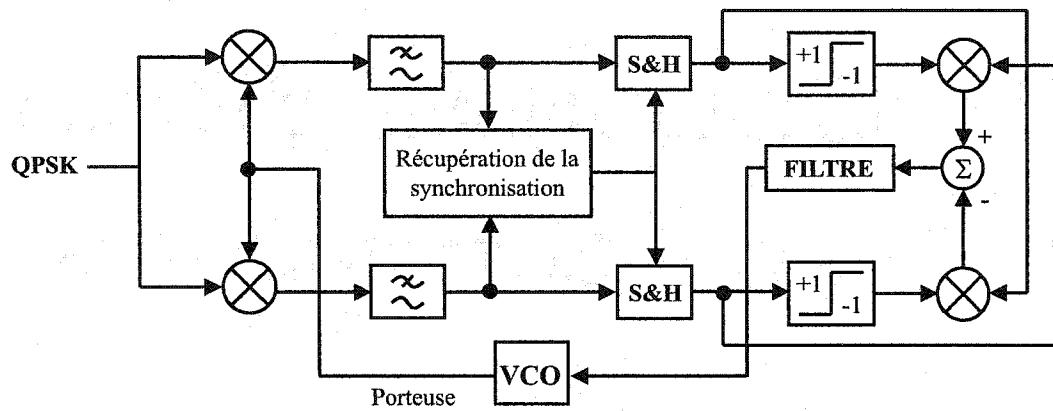

| 5.2.3                       | Boucle de contre-réaction de décision . . . . .                   | 88         |

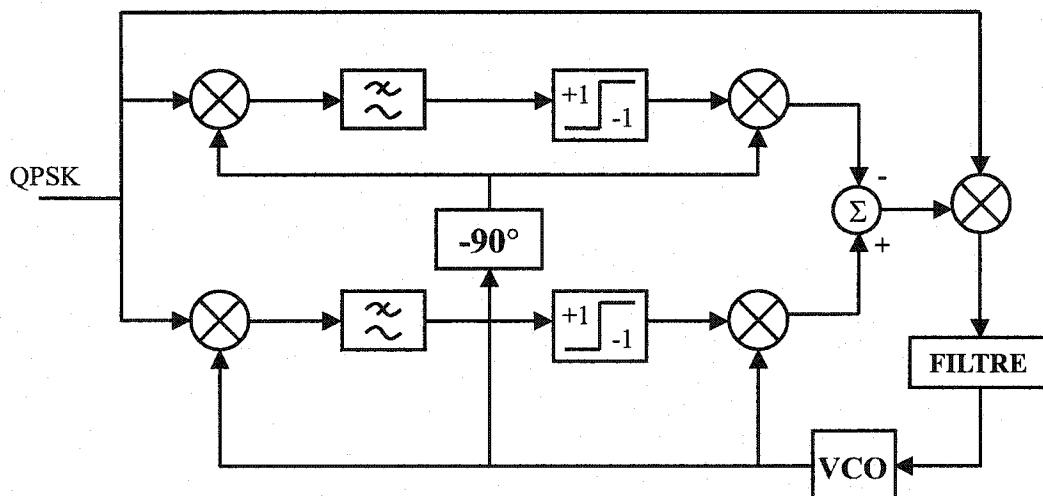

| 5.2.4                       | Démodulation-Remodulation . . . . .                               | 89         |

| 5.3                         | Proposition d'un circuit de récupération de la porteuse . . . . . | 91         |

| 5.4                         | Réalisation d'un prototype de modulateur six-port QPSK . . . . .  | 98         |

| <b>CONCLUSION . . . . .</b> |                                                                   | <b>105</b> |

| <b>RÉFÉRENCES . . . . .</b> |                                                                   | <b>108</b> |

## LISTE DES FIGURES

|           |                                                                                                                  |    |

|-----------|------------------------------------------------------------------------------------------------------------------|----|

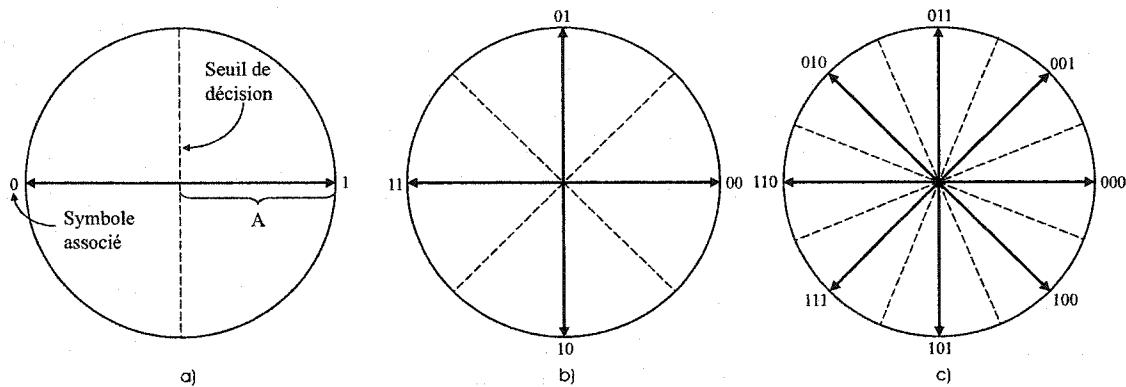

| FIG. 1.1  | Quelques constellations PSK : a) $M=2$ (BPSK), b) $M=4$ (QPSK),<br>c) $M=8$ . . . . .                            | 5  |

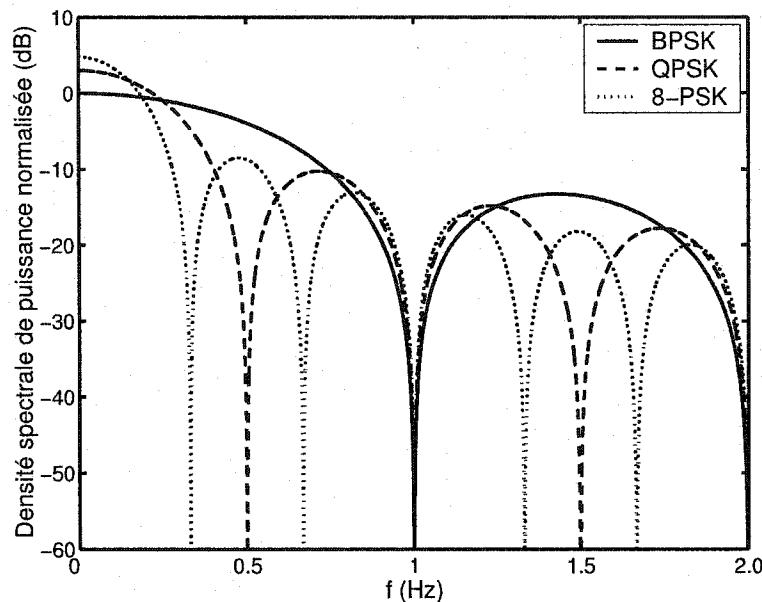

| FIG. 1.2  | Spectres PSK pour un taux de données constant ( $M=2,4,8$ et<br>$f_c = 0$ ) . . . . .                            | 6  |

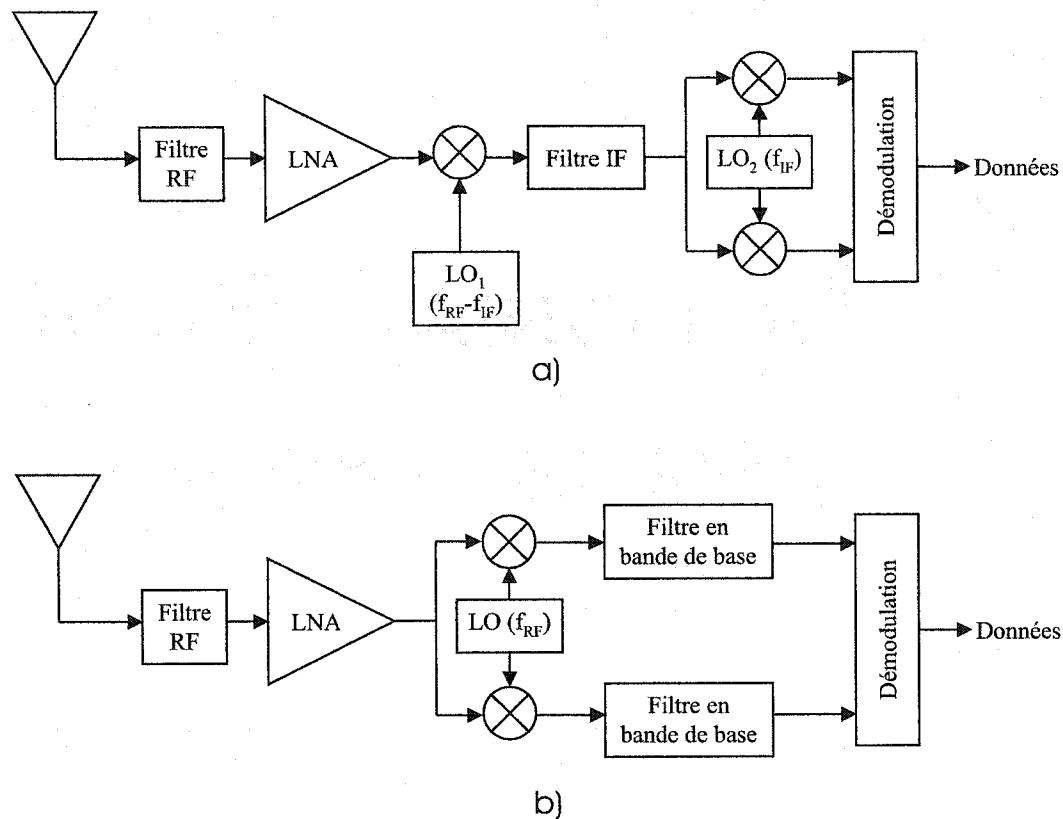

| FIG. 1.3  | Architecture de récepteurs : a) Superhétérodyne, b) Conversion directe . . . . .                                 | 8  |

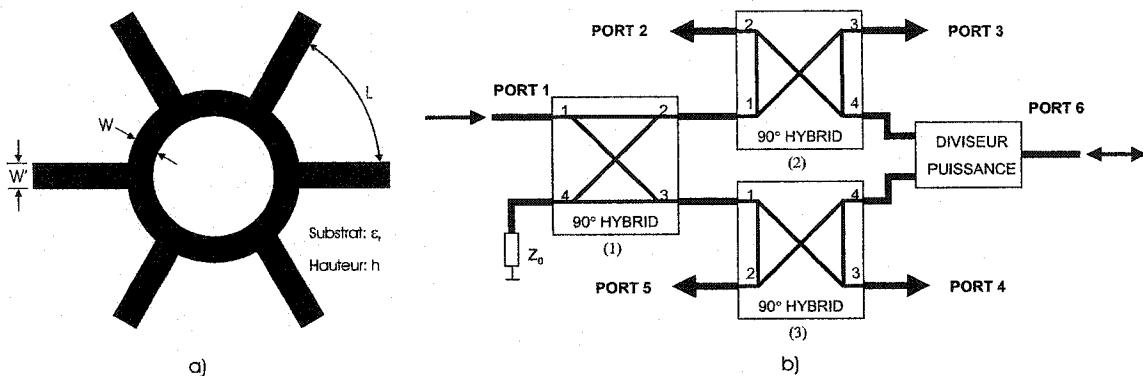

| FIG. 1.4  | Formes de réalisation des SP : a) anneau, b)coupleurs (Polytel)                                                  | 13 |

| FIG. 1.5  | Schémas bloc d'un récepteur SP . . . . .                                                                         | 16 |

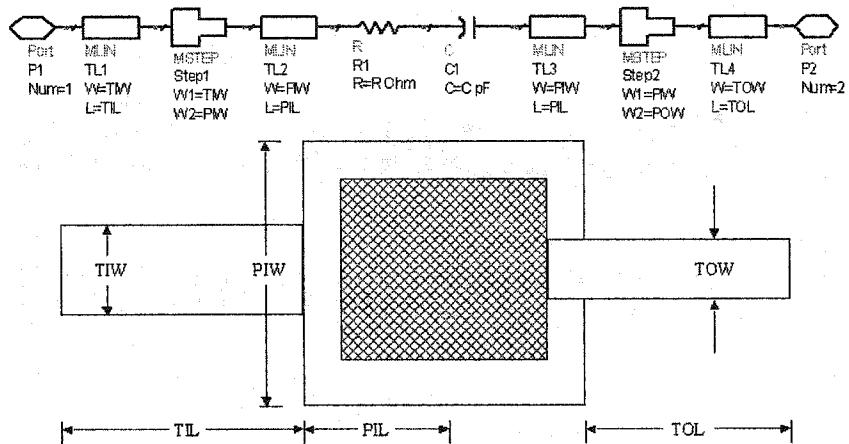

| FIG. 2.1  | Modèle d'une ligne de transmission ; a) ligne micro-ruban, b)<br>modèle équivalent . . . . .                     | 18 |

| FIG. 2.2  | Modèle d'une inductance série . . . . .                                                                          | 19 |

| FIG. 2.3  | Comparaison entre les résultats simulés (ADS-Momentum) et<br>mesurés d'une inductance MMIC . . . . .             | 21 |

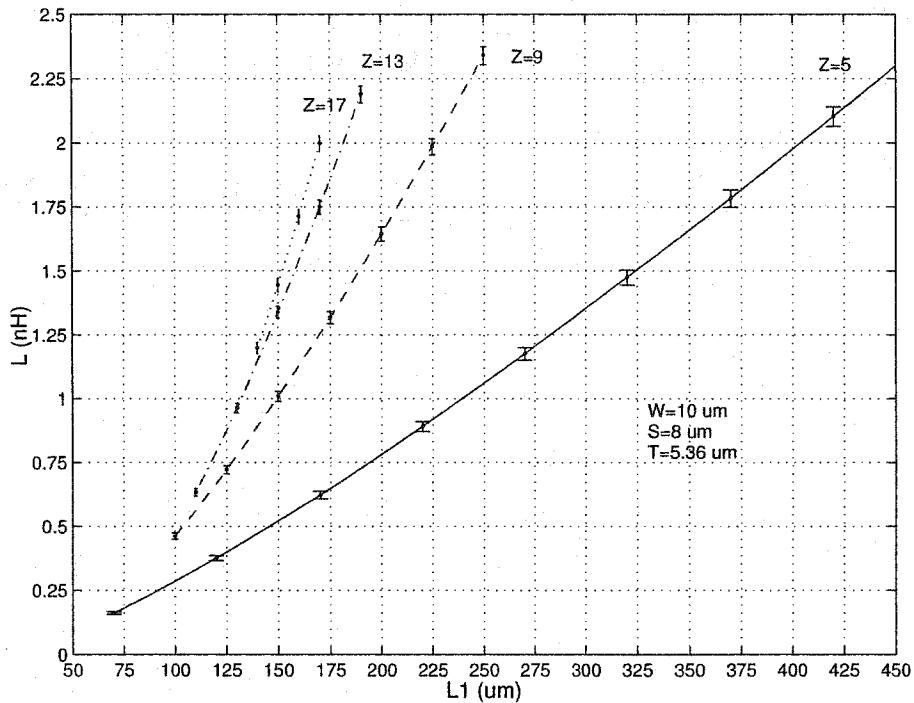

| FIG. 2.4  | Inductance en fonction du nombre de segments ( $Z$ ) et de la<br>longueur du premier segment ( $L_1$ ) . . . . . | 23 |

| FIG. 2.5  | Modèle de la capacité série . . . . .                                                                            | 24 |

| FIG. 2.6  | Modèle de la capacité parallèle . . . . .                                                                        | 25 |

| FIG. 2.7  | Modèle de la résistance série . . . . .                                                                          | 26 |

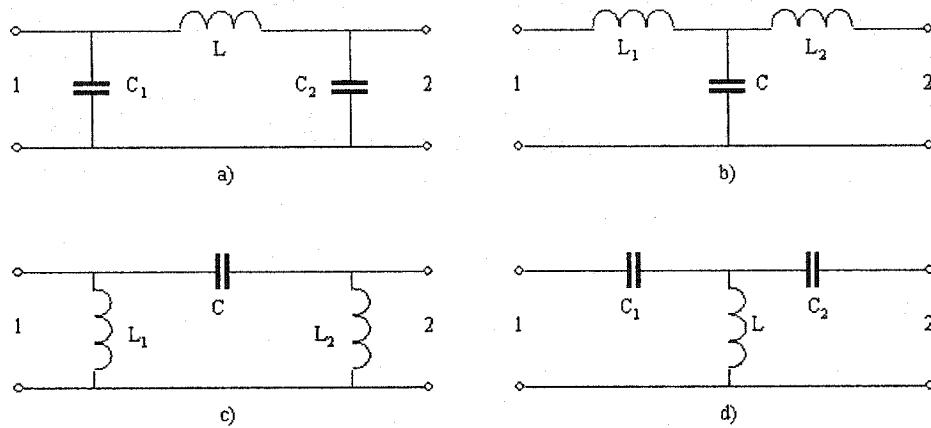

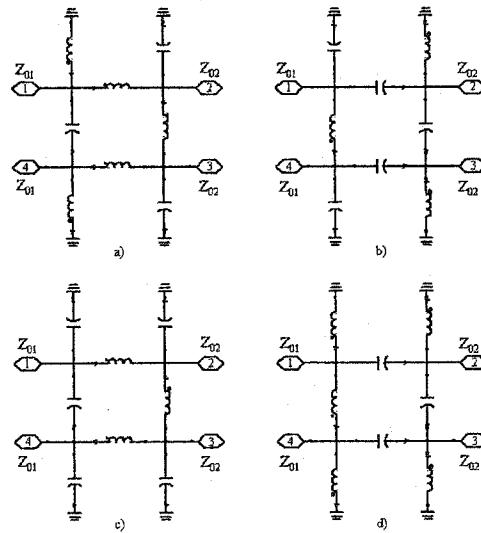

| FIG. 2.8  | Déphaseurs de base en éléments discrets . . . . .                                                                | 27 |

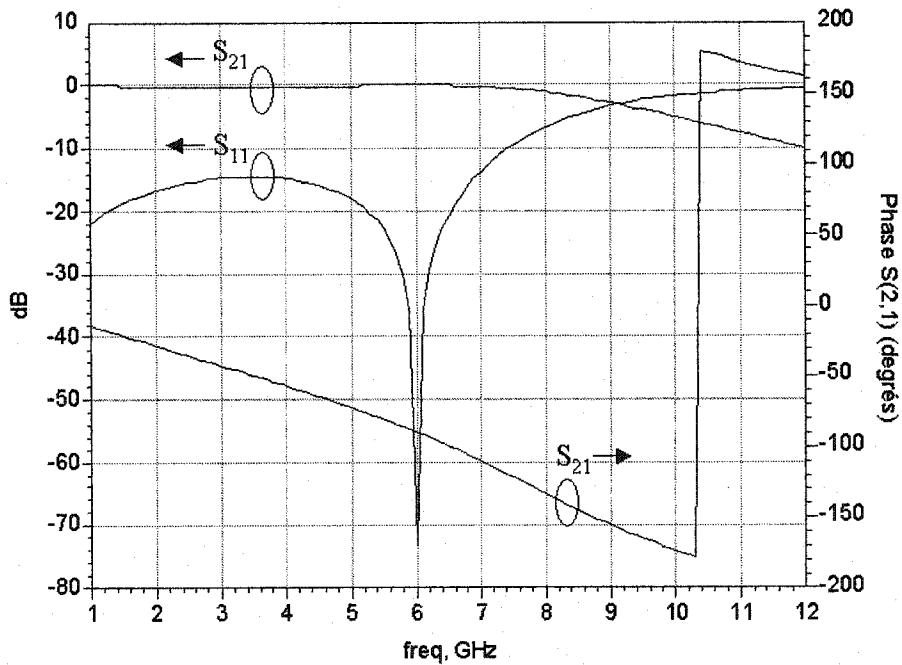

| FIG. 2.9  | Réponse en fréquence théorique du déphaseur A . . . . .                                                          | 28 |

| FIG. 2.10 | Réponse en fréquence théorique du déphaseur D . . . . .                                                          | 30 |

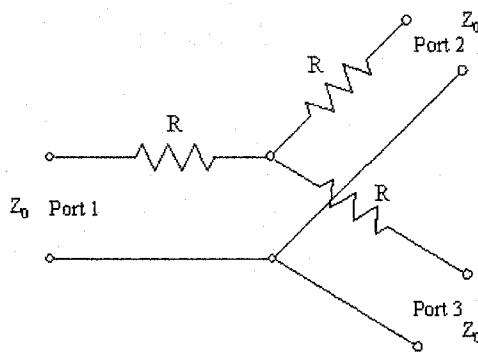

| FIG. 2.11 | Schéma du diviseur résistif . . . . .                                                                            | 31 |

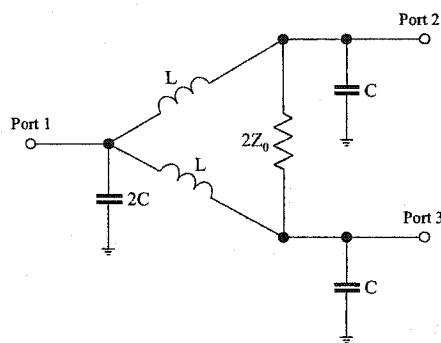

| FIG. 2.12 | Schéma du diviseur Wilkinson discret . . . . .                                                                   | 31 |

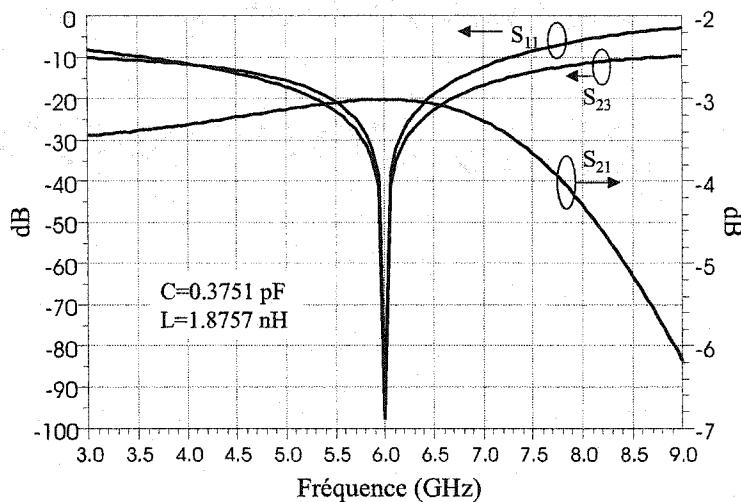

| FIG. 2.13 | Réponse en fréquence typique du diviseur Wilkinson Discret .                                                     | 32 |

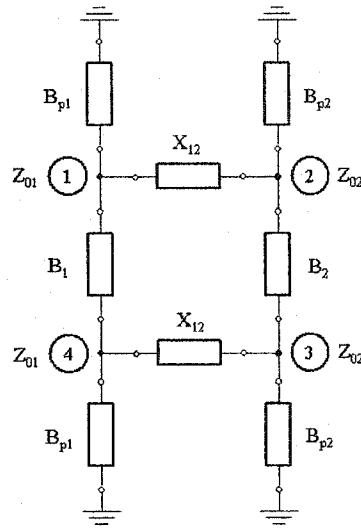

| FIG. 2.14 | Circuit équivalent d'un coupleur directionnel discret . . . . .                                                  | 33 |

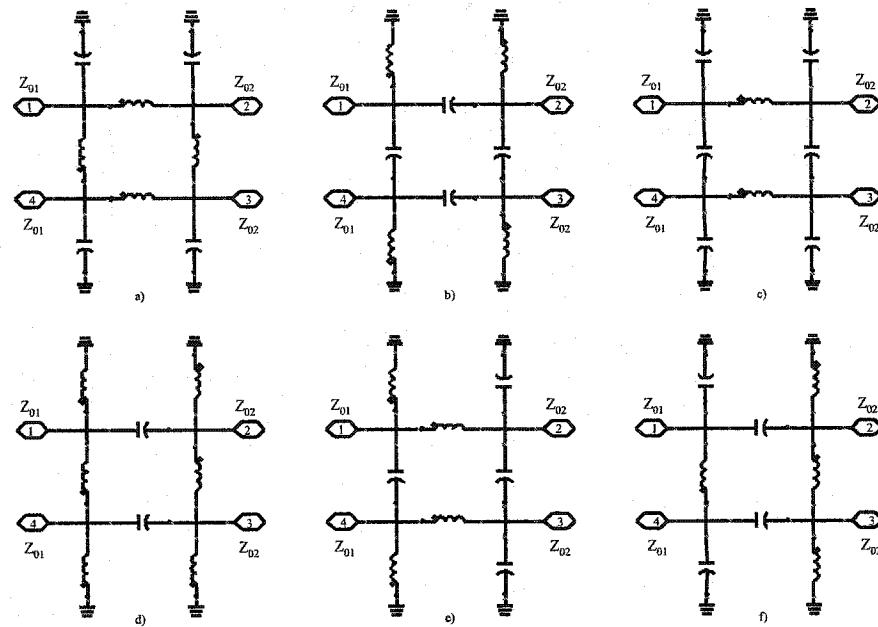

| FIG. 2.15 | Coupleurs COD en éléments discrets . . . . .                                                                     | 35 |

|           |                                                                                                                         |    |

|-----------|-------------------------------------------------------------------------------------------------------------------------|----|

| FIG. 2.16 | Coupleurs CTD en éléments discrets . . . . .                                                                            | 36 |

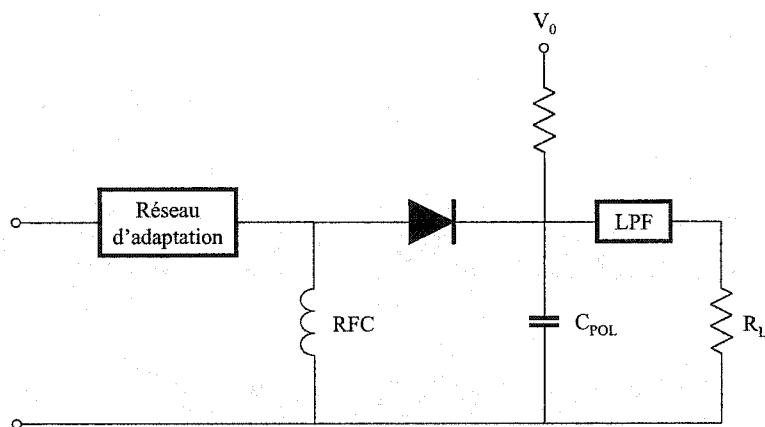

| FIG. 2.17 | Schémas de base d'un détecteur . . . . .                                                                                | 37 |

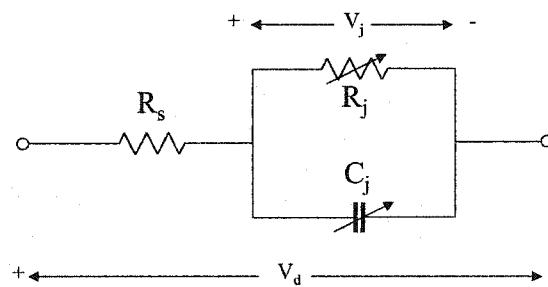

| FIG. 2.18 | Modèle équivalent simplifié de la diode . . . . .                                                                       | 39 |

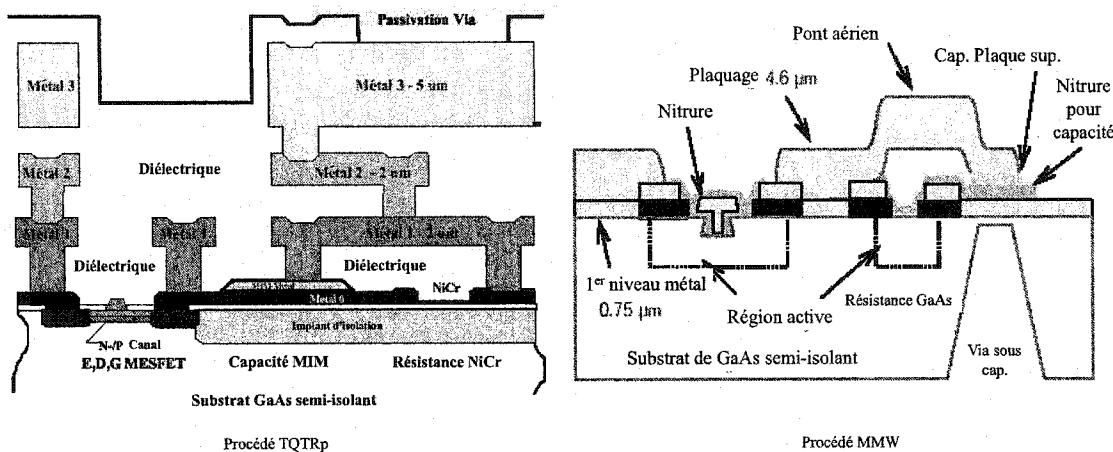

| FIG. 3.1  | Vue de coupe des procédés TQTRp et MMW (source : TQT) .                                                                 | 45 |

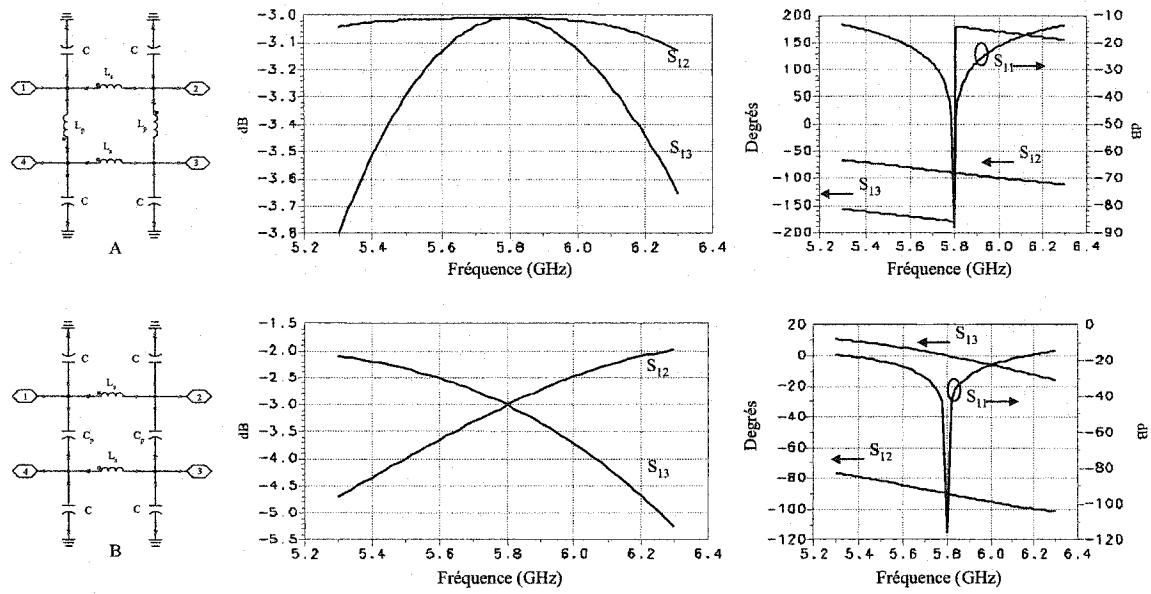

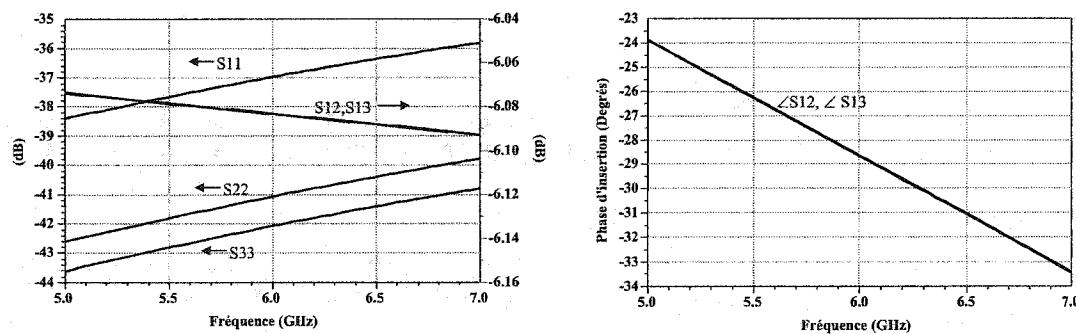

| FIG. 3.2  | Comparaison des performances théoriques des coupleurs A et B                                                            | 48 |

| FIG. 3.3  | Pertes de retour du coupleur A avec balayage des composants                                                             | 51 |

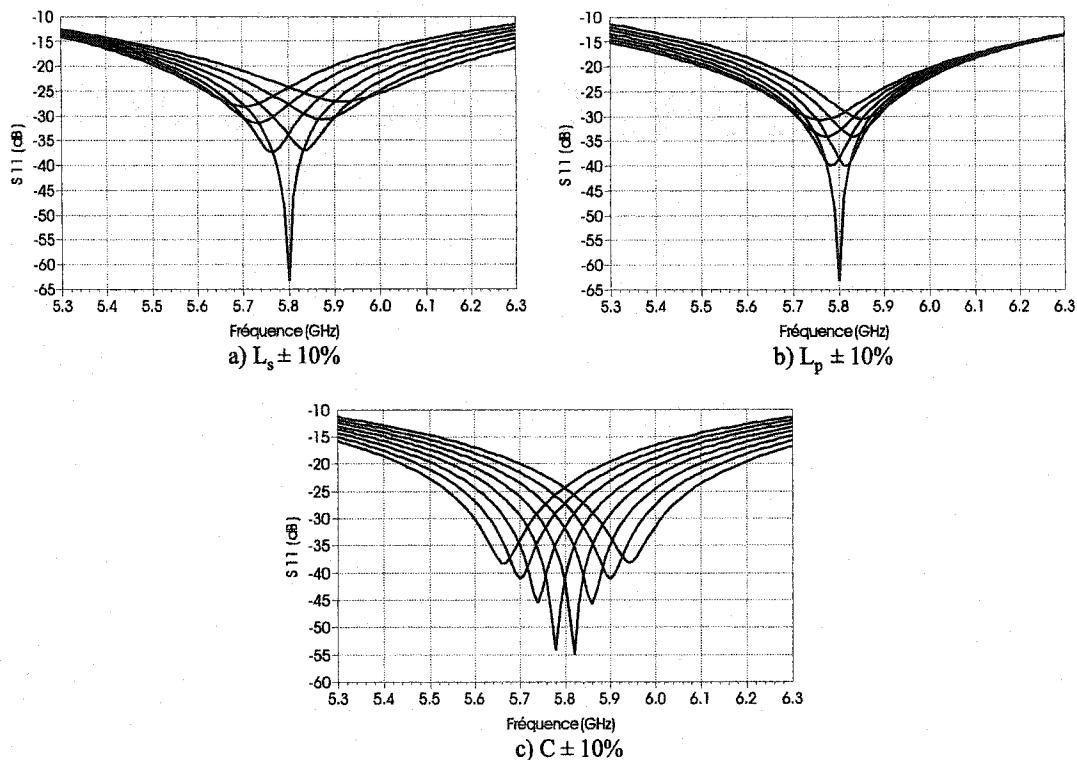

| FIG. 3.4  | Variation en fréquence des inductances sélectionnées, IND4 et<br>IND8 . . . . .                                         | 52 |

| FIG. 3.5  | Performances simulées du coupleur en quadrature conçu . .                                                               | 53 |

| FIG. 3.6  | Performances simulées du diviseur de puissance résistif conçu .                                                         | 54 |

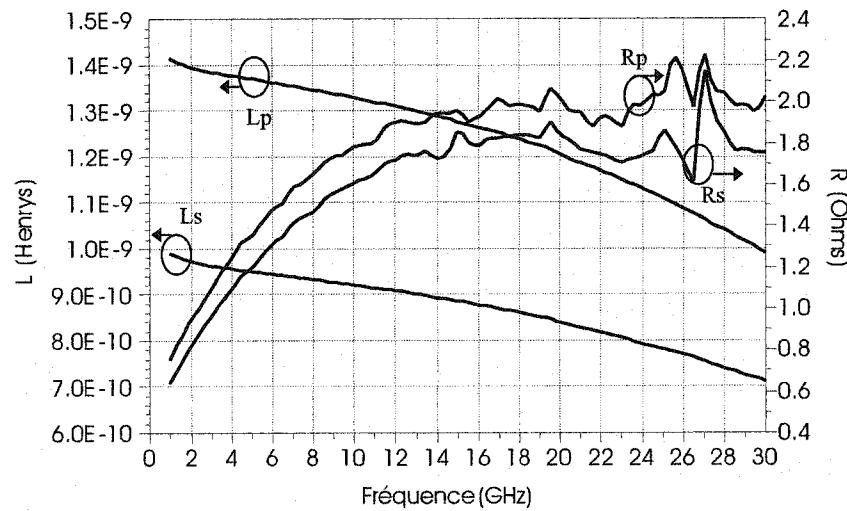

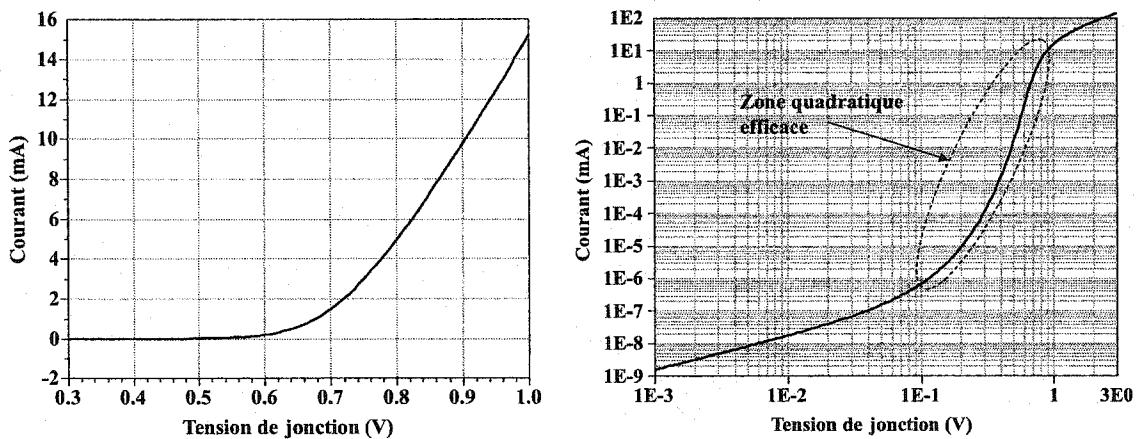

| FIG. 3.7  | Performances simulées du six-port conçu (sans détecteurs) .                                                             | 56 |

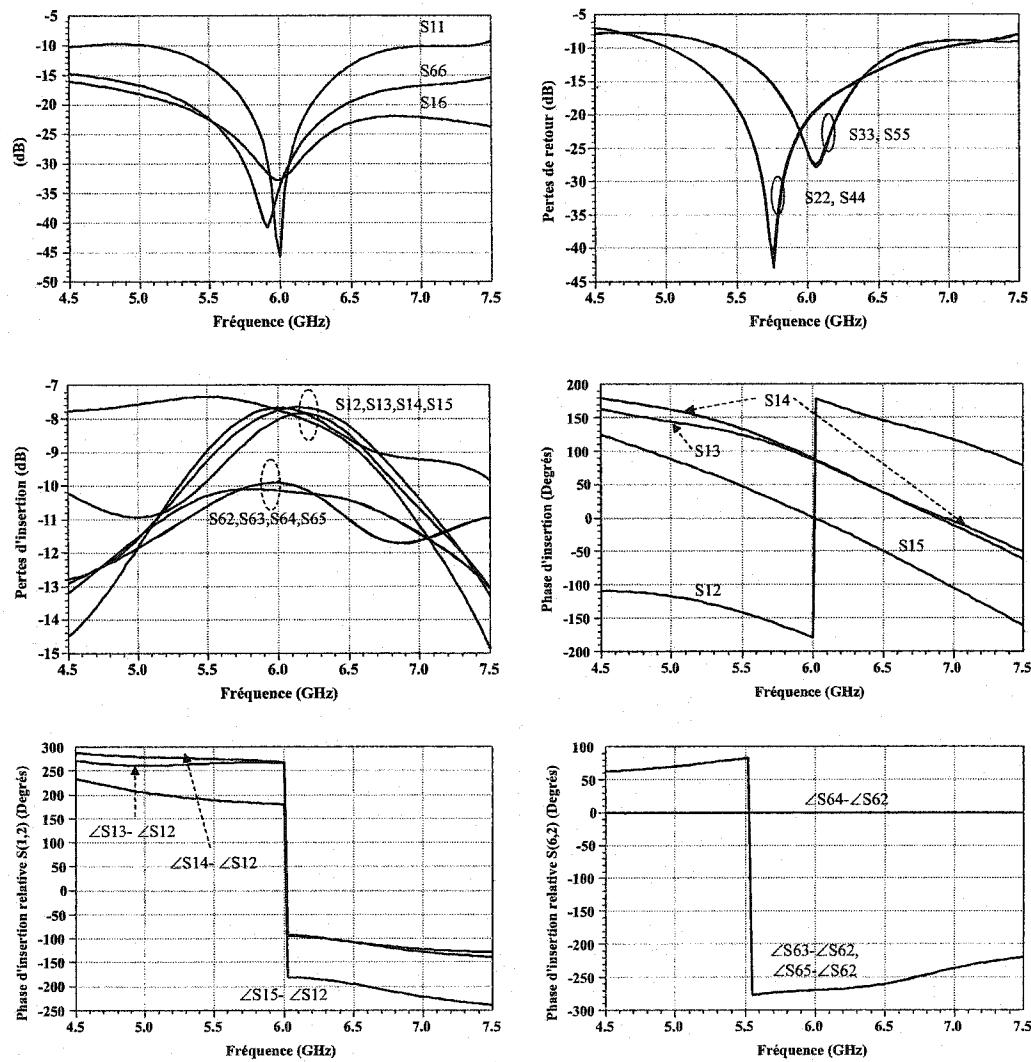

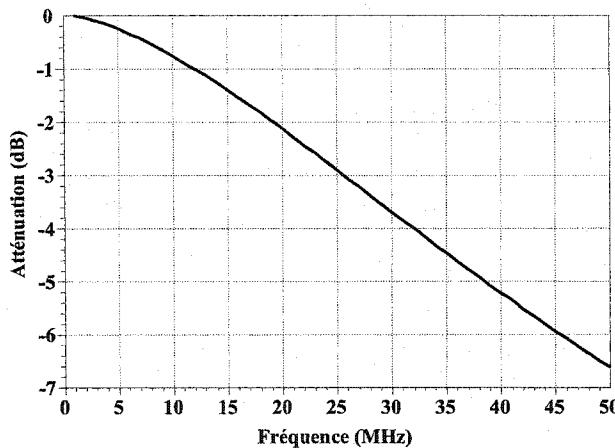

| FIG. 3.8  | Courbes I-V de la diode Schottky H2-38 $\mu\text{m}$ utilisée, échelles<br>linéaires et logarithmiques . . . . .        | 59 |

| FIG. 3.9  | Réponse en fréquence du détecteur . . . . .                                                                             | 61 |

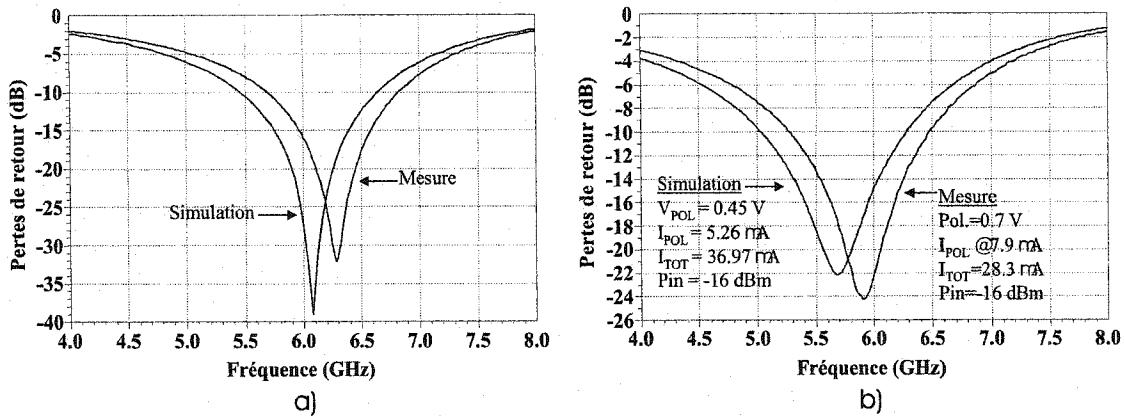

| FIG. 3.10 | Pertes de retour du détecteur : a) sans polarisation ( $\text{Pin}=-4$<br>dBm), b) avec polarisation . . . . .          | 63 |

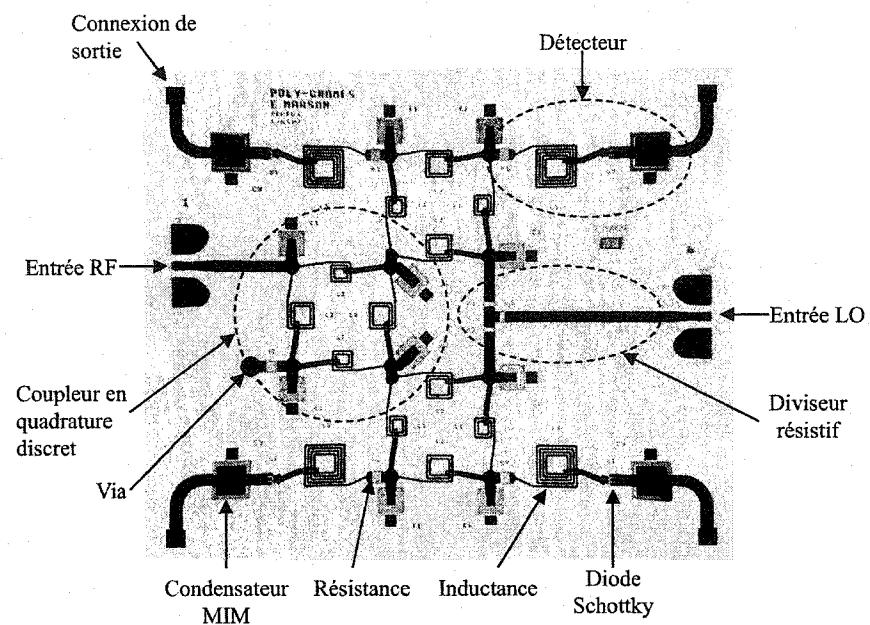

| FIG. 3.11 | Microphotographie du circuit MMIC fabriqué ( $3,58 \times 3,01 \text{ mm}^2$ )                                          | 65 |

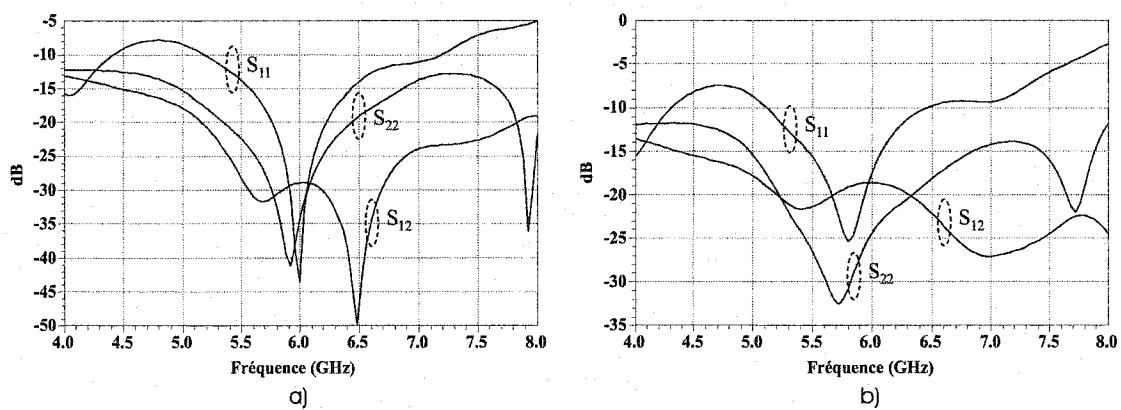

| FIG. 3.12 | Réponse en fréquence simulée (a) et mesurée (b) du six-port<br>complet . . . . .                                        | 65 |

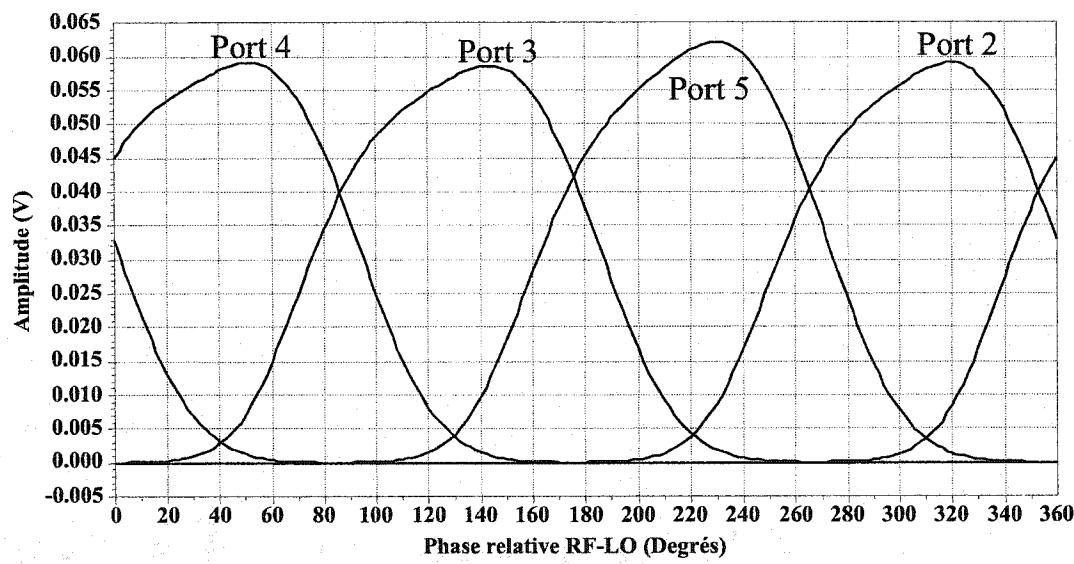

| FIG. 3.13 | Tensions de sorties pour un balayage de la phase relative entre<br>les signaux d'entrée LO et RF (simulation) . . . . . | 66 |

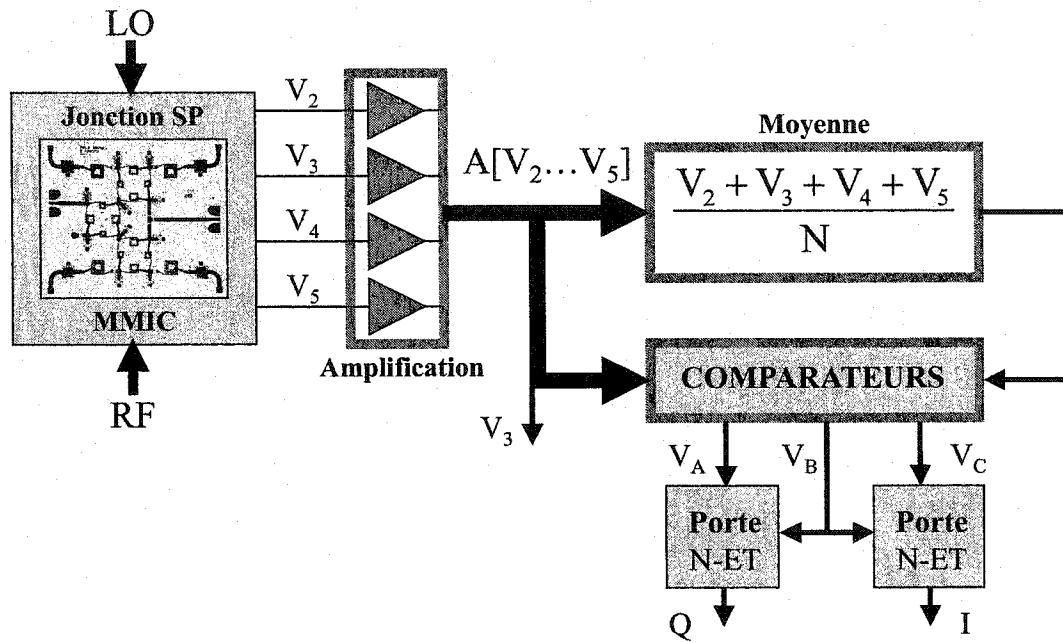

| FIG. 4.1  | Architecture du circuit en bande de base . . . . .                                                                      | 68 |

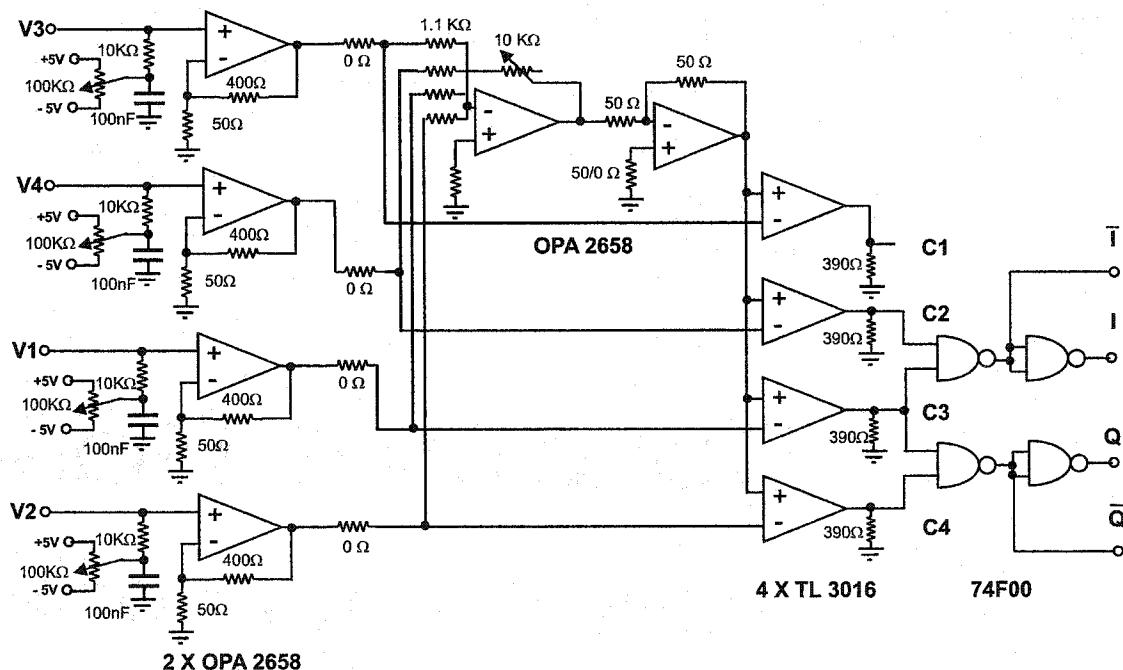

| FIG. 4.2  | Schéma électrique complet du circuit en bande de base . . . .                                                           | 70 |

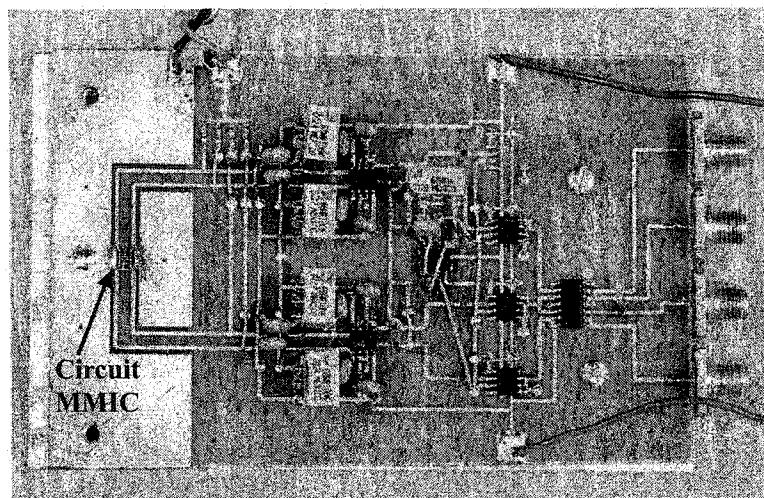

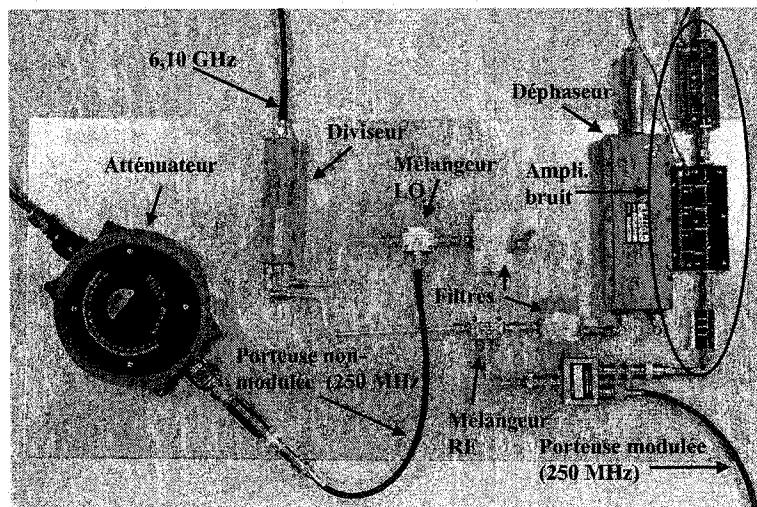

| FIG. 4.3  | Photographie du prototype . . . . .                                                                                     | 71 |

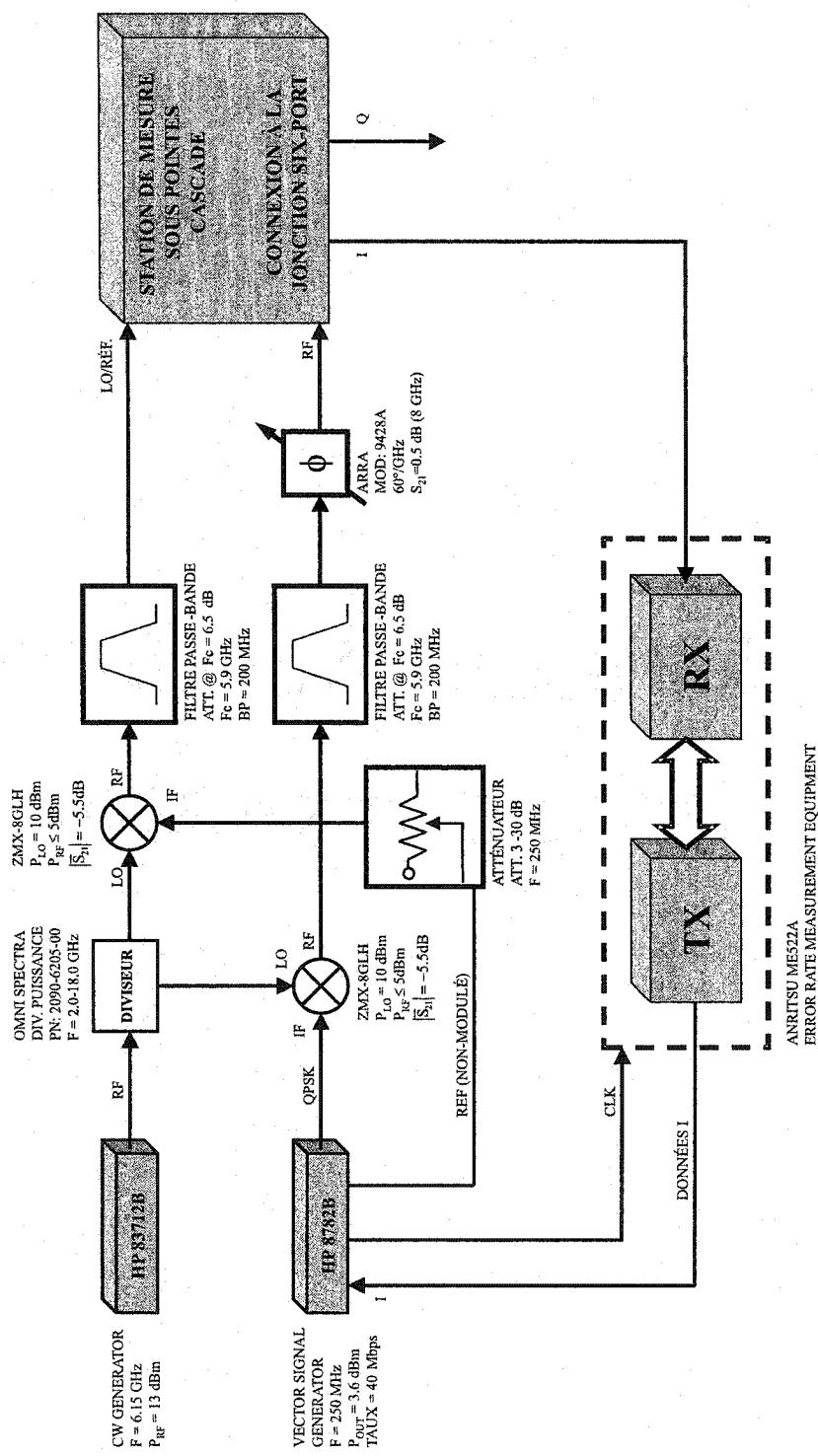

| FIG. 4.4  | Architecture du montage de mesure . . . . .                                                                             | 73 |

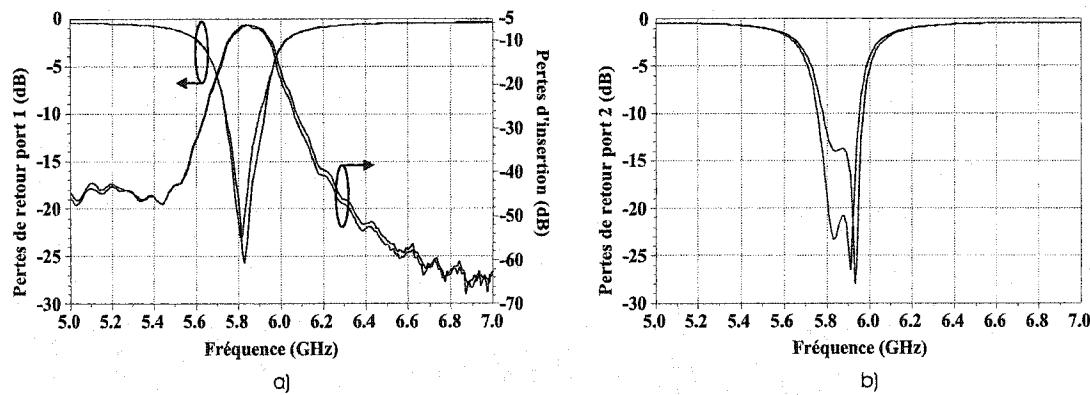

| FIG. 4.5  | Performances mesurées des deux filtres : a) $S_{11}$ et $S_{21}$ , b) $S_{22}$ .                                        | 75 |

| FIG. 4.6  | Circuit d'élévation en fréquence . . . . .                                                                              | 76 |

|           |                                                                                                                                                                                                                    |    |

|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

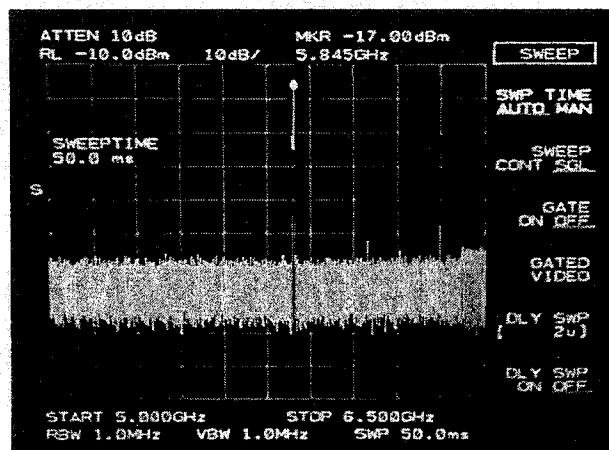

| FIG. 4.7  | Spectre à l'entrée LO du SP incluant une perte de 4 dB par rapport au niveau réel . . . . .                                                                                                                        | 77 |

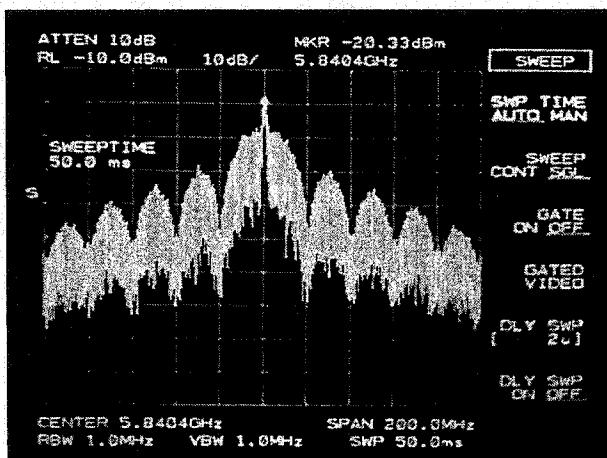

| FIG. 4.8  | Spectre à l'entrée RF du SP incluant une perte de 4 dB par rapport au niveau réel . . . . .                                                                                                                        | 78 |

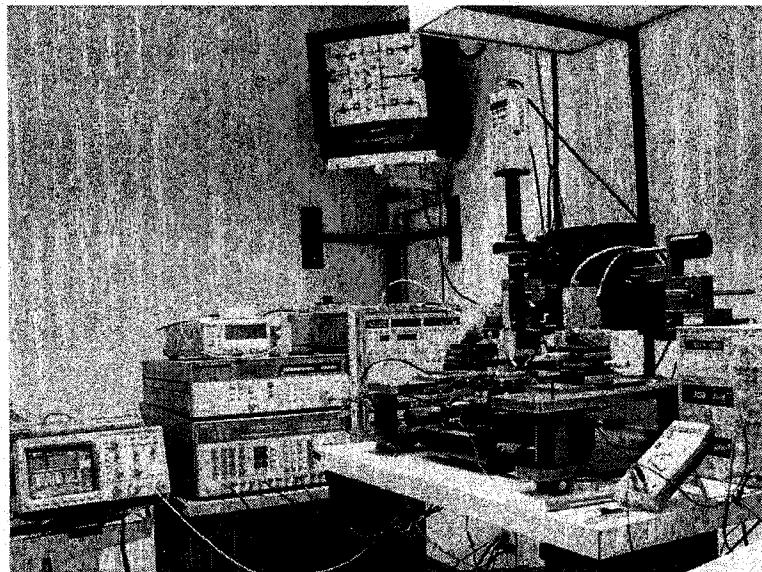

| FIG. 4.9  | Photographie du banc de mesure . . . . .                                                                                                                                                                           | 79 |

| FIG. 4.10 | Taux d'erreur en fonction du taux de transfert de données . .                                                                                                                                                      | 80 |

| FIG. 4.11 | Taux d'erreur en fonction de la rotation de la constellation à 40 Mb/s . . . . .                                                                                                                                   | 81 |

| FIG. 4.12 | Taux d'erreur en fonction du rapport de l'énergie par bit et de la densité spectrale du bruit pour un taux de 40 Mb/s :<br>a)Théorie QPSK, b)Précédent prototype [39], c)Récepteur avec jonction SP MMIC . . . . . | 82 |

| FIG. 5.1  | Circuit quadrupleur . . . . .                                                                                                                                                                                      | 85 |

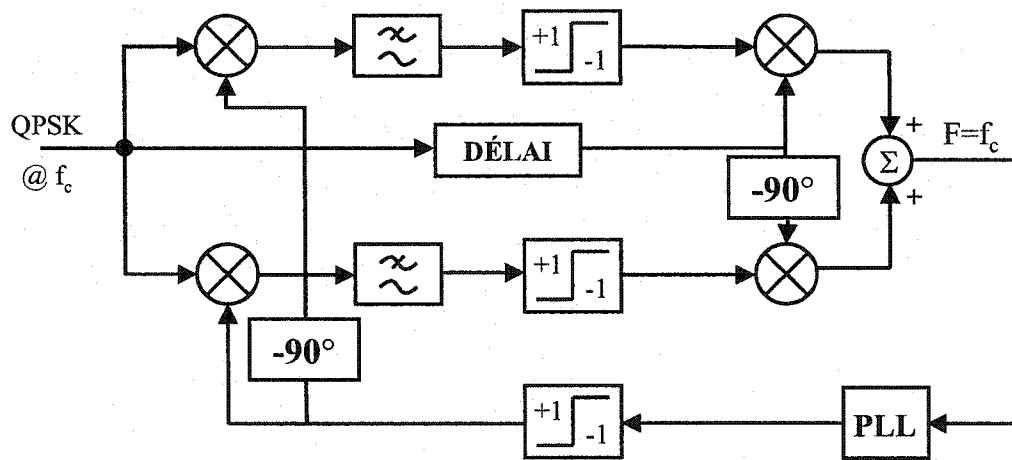

| FIG. 5.2  | Boucle de Costas . . . . .                                                                                                                                                                                         | 88 |

| FIG. 5.3  | Boucle de contre-réaction de décision . . . . .                                                                                                                                                                    | 89 |

| FIG. 5.4  | Démodulation-Remodulation . . . . .                                                                                                                                                                                | 90 |

| FIG. 5.5  | Modulation inverse . . . . .                                                                                                                                                                                       | 91 |

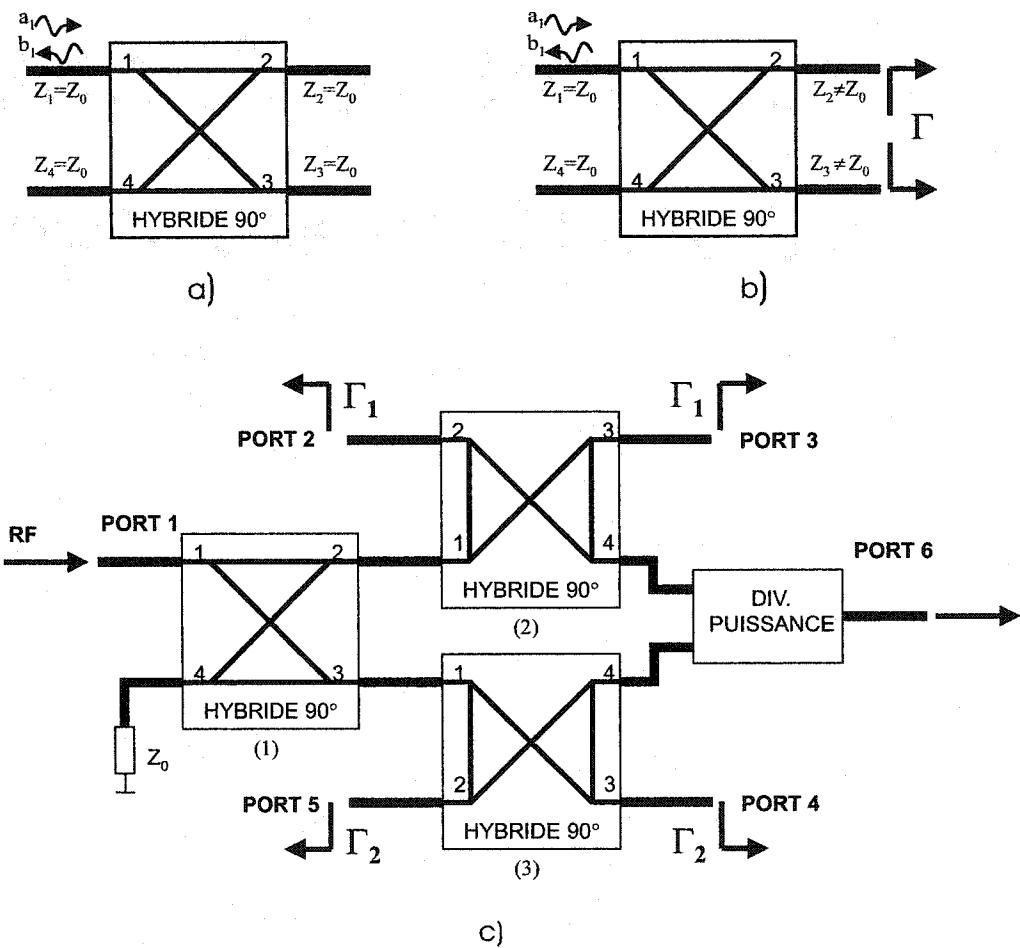

| FIG. 5.6  | a) coupleur hybride adapté, b) coupleur hybride avec réflexions aux ports 2 et 3, c) Modulateur six-port . . . . .                                                                                                 | 93 |

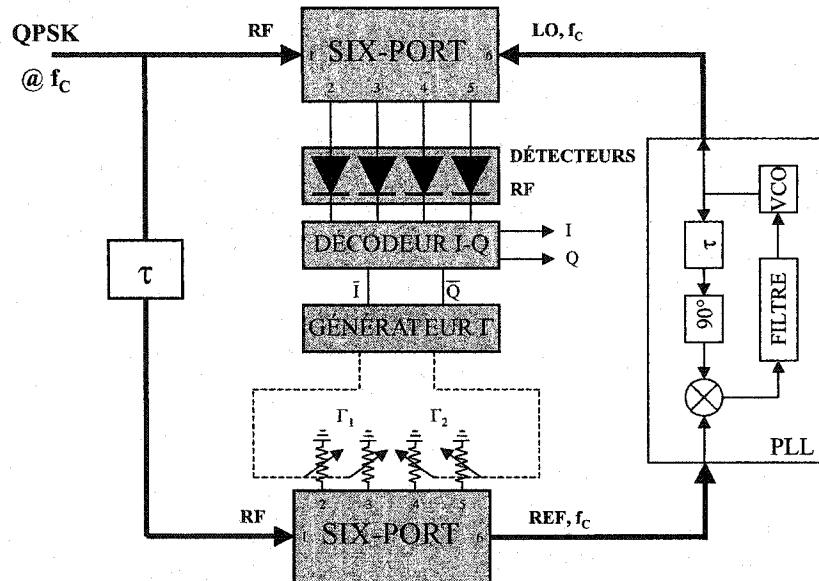

| FIG. 5.7  | Architecture proposée du récepteur . . . . .                                                                                                                                                                       | 95 |

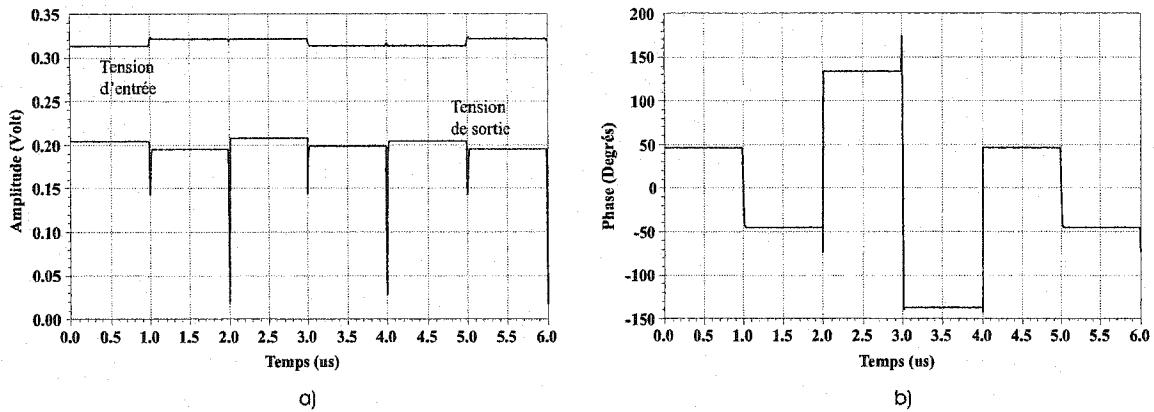

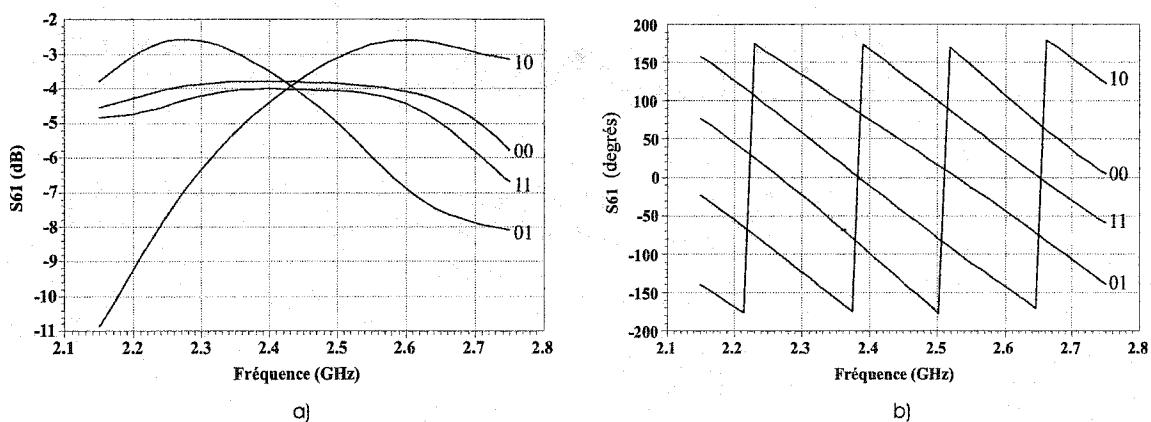

| FIG. 5.8  | Résultats de simulation du modulateur SP théorique : a)variations d'amplitude, b)variations de phase . . . . .                                                                                                     | 96 |

| FIG. 5.9  | Comportement en fréquence du modulateur SP modélisé : a)variation d'amplitude, b)variation en phase . . . . .                                                                                                      | 96 |

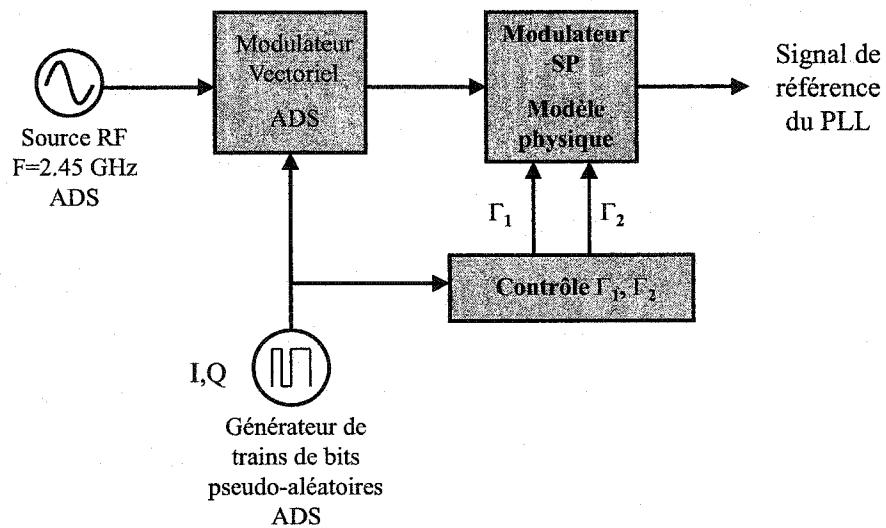

| FIG. 5.10 | Schéma de simulation pour la récupération de la porteuse sous ADS . . . . .                                                                                                                                        | 97 |

|           |                                                                                                                                                                                                           |     |

|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

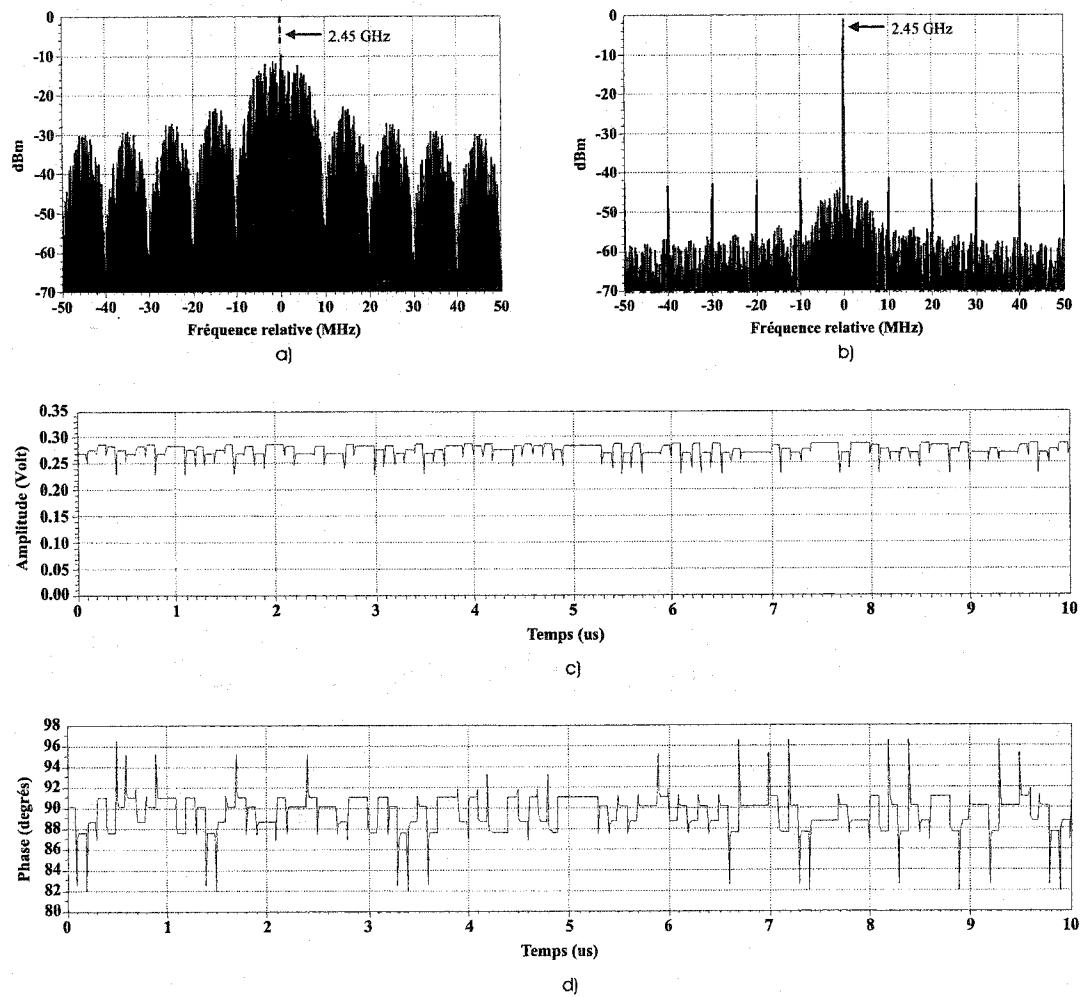

| FIG. 5.11 | Résultats de simulation de la récupération de la porteuse avec modulateur SP : a)spectre d'entrée, b)spectre à la sortie, c)variation d'amplitude à la sortie, d)variation de phase à la sortie . . . . . | 99  |

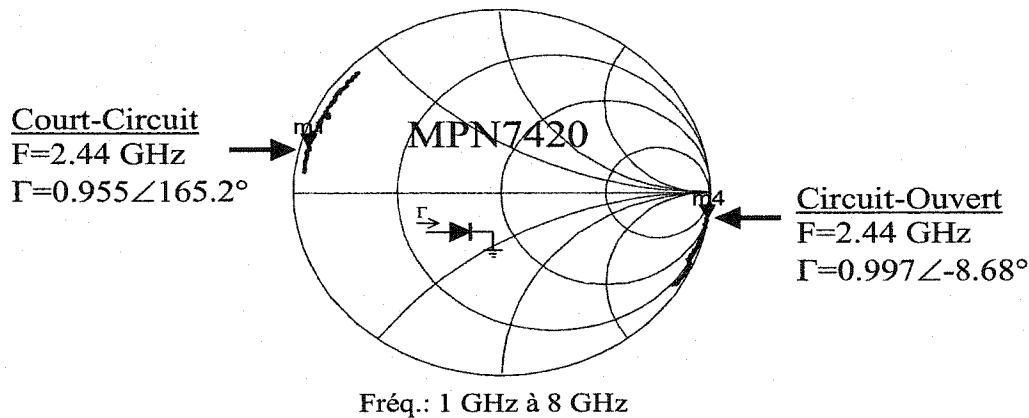

| FIG. 5.12 | Caractérisation de la diode MPN7420 . . . . .                                                                                                                                                             | 100 |

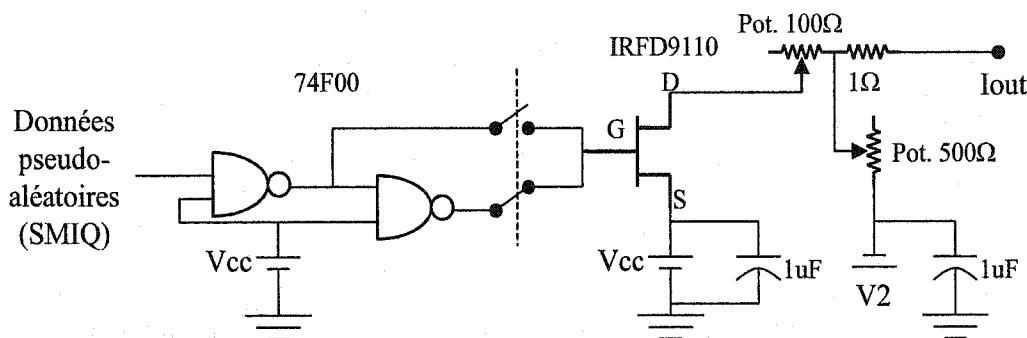

| FIG. 5.13 | Circuit de commutation des diodes . . . . .                                                                                                                                                               | 100 |

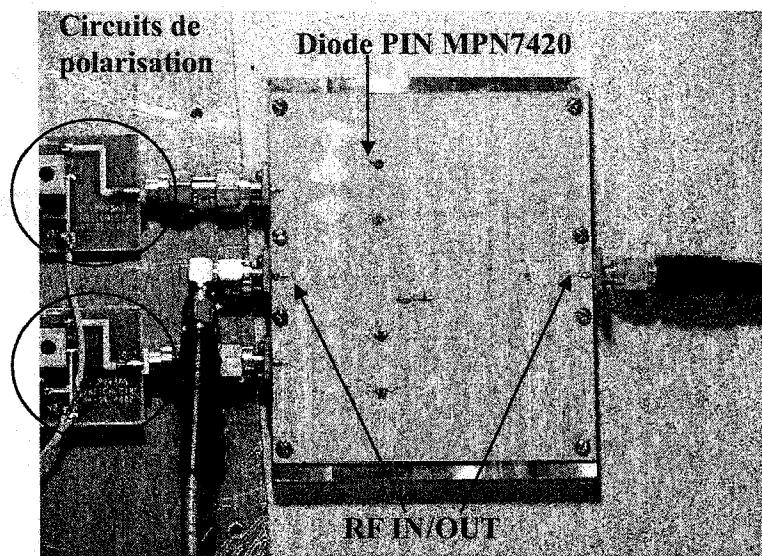

| FIG. 5.14 | Prototype du modulateur SP à 2,45 GHz en éléments distribués                                                                                                                                              | 101 |

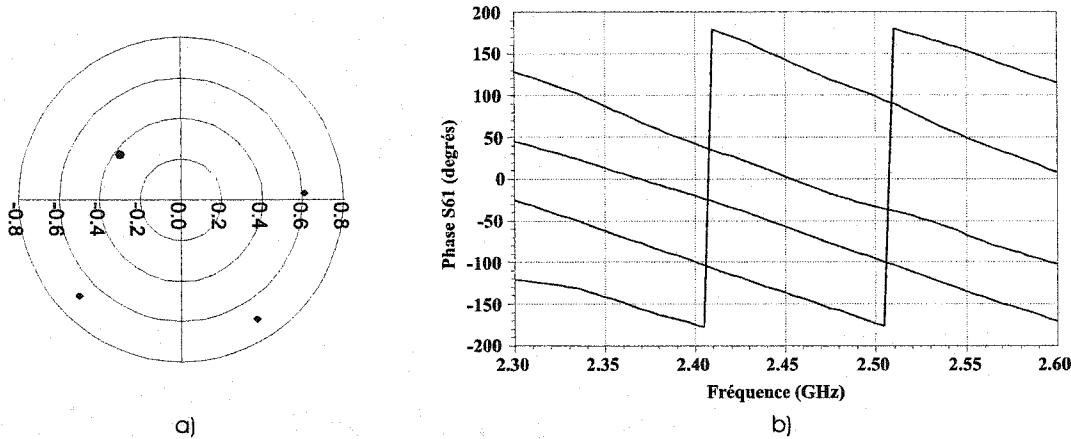

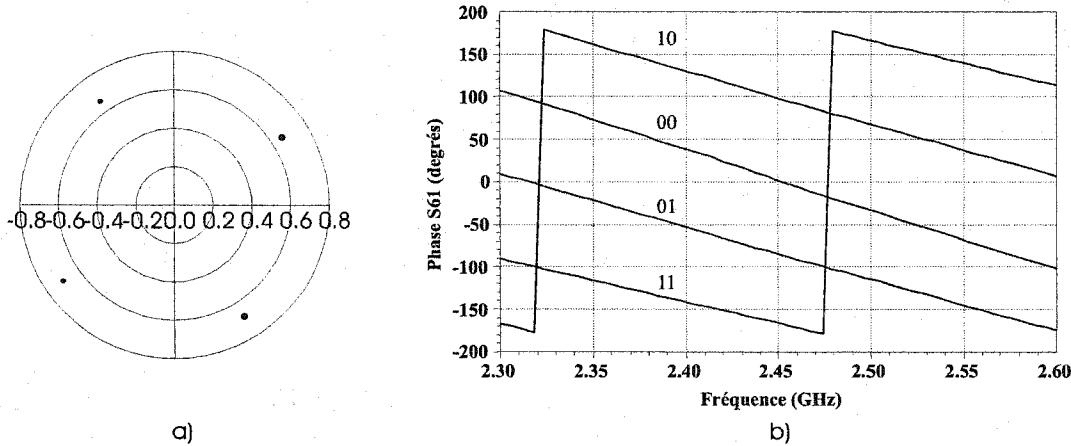

| FIG. 5.15 | États générés par le prototype : a) Diagramme polaire des états à 2,45 GHz (volt), b) Phase des états en fonction de la fréquence                                                                         | 102 |

| FIG. 5.16 | Correction du problème de fabrication par simulation : a) Diagramme polaire (volt), b) Relations de phase pour un balayage en fréquence . . . . .                                                         | 103 |

**LISTE DES TABLEAUX**

|          |                                                                                                 |    |

|----------|-------------------------------------------------------------------------------------------------|----|

| TAB. 1.1 | Amplitudes aux quatre ports de sortie selon l'état de modulation                                | 15 |

| TAB. 3.1 | Caractéristiques générales des procédés de TQT . . . . .                                        | 44 |

| TAB. 3.2 | Variation des condensateurs pour le procédé MMW . . . . .                                       | 50 |

| TAB. 3.3 | Variation entre le calcul, le modèle et la mesure de capacités témoins du procédé MMW . . . . . | 58 |

| TAB. 3.4 | Écarts des éléments discrets entre conception et mesure à 6 GHz                                 | 61 |

| TAB. 4.1 | Table de vérité associée au schéma de la figure 4.1 . . . . .                                   | 68 |

## LISTE DES SIGLES ET ABRÉVIATIONS

|       |                                                                         |

|-------|-------------------------------------------------------------------------|

| ADS   | <i>Advanced Design System</i> de Agilent Technologies                   |

| BER   | <i>Bit Error Rate</i> : taux d'erreur binaire                           |

| BPSK  | <i>Biphase Phase Shift Keying</i>                                       |

| ISM   | Industrielle-Scientifique-Médicale                                      |

| LO    | Oscillateur local                                                       |

| MMIC  | <i>Monolithic Microwave Integrated Circuit</i>                          |

| MHMIC | <i>Miniature Hybrid Microwave Integrated Circuit</i>                    |

| NRZ   | <i>Non-return to zero</i>                                               |

| PLL   | <i>Phase Locked Loop</i> : boucle à verrouillage de phase               |

| PSK   | <i>Phase Shift Keying</i>                                               |

| QAM   | <i>Quadrature Amplitude Modulation</i>                                  |

| QPSK  | <i>Quadrature Phase Shift Keying</i>                                    |

| RF    | Porteuse modulé                                                         |

| SNR   | Rapport signal sur bruit                                                |

| SP    | circuit Six-Port                                                        |

| TOS   | Taux d'onde stationnaire (VSWR)                                         |

| TQT   | <i>Triquint Semiconductor (Texas)</i>                                   |

| VCO   | <i>Voltage Controlled Oscillator</i> : oscillateur contrôlé par tension |

## INTRODUCTION

Depuis quelques années nous assistons à l'émergence de plusieurs applications nécessitant des équipements de communication personnels sans fil, miniatures et abordables. En conséquence, les sections basses du spectre électromagnétique propices à ces applications deviennent rares, trop restreintes et entraînent une migration vers des fréquences supérieures. Pour réduire les coûts de fabrication à ces fréquences, plusieurs recherches ont délaissé le récepteur superhétérodyne, de loin le plus répandu actuellement, et fait renaître la conversion homodyne [2] en raison de solutions techniques maintenant devenues possibles par intégration. Récemment, de nouvelles applications tel le multimédia ont de plus ajouté aux premiers critères énoncés un besoin croissant pour la transmission de données à haut débit. Dans le cas de la modulation QPSK, une modulation numérique à efficacité de puissance élevée souvent utilisée pour les hauts débits, cela se traduit en des canaux de communication plus larges et donc une réduction des contraintes de sélectivité avantageant la conversion homodyne. Le présent mémoire traite de l'utilisation et de l'intégration de la technologie six-port pour la réalisation d'un récepteur numérique homodyne QPSK à haut débit et se veut la poursuite de travaux initiés en [14, 26, 27, 43].

Les travaux portant sur l'utilisation d'un circuit six-port (SP) pour la démodulation de signaux numériques ont commencé en 1995 [27] au Poly-Grames ; le centre de recherche de l'école Polytechnique de Montréal consacré au domaine des hyperfréquences. Depuis, plusieurs prototypes de récepteurs à base de SPs ont vu le jour autant au sein du centre qu'ailleurs dans le monde [1, 22, 21, 29] et opèrent à des fréquences allant de 0,5 à 30 GHz. Pour être viable en tant que récepteur, le SP doit être compact et ses performances hautement répétables, d'où l'intérêt pour l'intégration. L'objectif final de ces travaux est le développement d'un récepteur sur puce unique fiable et abordable. Avant le début des travaux décrits dans le présent mémoire, le dernier prototype du Poly-Grames a été fabriqué sous forme planaire

en technologie intégrée hybride (MHMIC) et a démontré des performances justifiant la réalisation d'un prototype par une technologie de fabrication de circuits intégrés plus avancée (MMIC). Le principal avantage de cette technologie est de permettre l'intégration de composants actifs, étape essentielle pour obtenir une miniaturisation optimale et améliorer les performances. L'accès à cette technologie de fabrication a été possible grâce à une collaboration avec *Triquint Semiconductor* (TQT), une fonderie américaine oeuvrant dans la fabrication de circuits intégrés micro-ondes. Cette collaboration est très avantageuse en raison de l'expérience de l'entreprise dans le domaine et de la grande répétabilité de leurs procédés industriels.

Le présent projet consiste en la réalisation d'un prototype de récepteur QPSK à conversion directe à base de SP en technologie MMIC sur GaAs opérant dans la bande non-réglementée Industrielle-Scientifique-Médicale (ISM) de 5,8 GHz tout en reproduisant ou améliorant les performances obtenues par des circuits MHMIC. Les performances à maintenir par rapport aux prototypes précédents sont un débit de données rapide (environ 40 Mb/s), une bonne isolation entre les deux ports d'entrée et une courbe du taux d'erreur binaire (BER) en fonction du bruit très près de la courbe théorique. Le récepteur doit être de type matériel ("hardware-receiver") pour éviter la complexité reliée au traitement numérique des signaux. Ceci a pour conséquence de limiter le récepteur à la modulation QPSK alors que l'architecture peut, théoriquement, accommoder des modulations de phase plus complexes mais permet de le simplifier par une conception entièrement analogique. Puisqu'aucune fabrication de circuits SP en MMIC n'a été faite au Poly-Grames, ce travail vise également à investiguer la compatibilité du SP et de son architecture avec la technologie MMIC. Les chapitres 2 et 3 illustrent d'ailleurs l'impact important de la fréquence d'opération sur la conception du SP. De plus, il est souhaité d'augmenter le niveau d'intégration du SP. Les détecteurs sont donc fabriqués à même le circuit intégré alors qu'ils étaient auparavant externes. Ceci permet d'éviter les connexions haute fréquence de sorties. Puisque cette fabrication est la première avec cette fonderie, une certaine

inquiétude quant à la fidélité des performances réelles face aux modèles fournis a motivé l'exclusion volontaire de tout transistor du premier (et dernier) prototype. Ceci permet d'éviter les complications reliées à la polarisation et la caractérisation de ces dispositifs. Le dernier objectif principal concernant le prototype consiste à maximiser sa largeur de bande d'opération. Le chapitre 4 présente le récepteur, le banc de mesure et donne quelques résultats sur les performances obtenues. Finalement, un objectif secondaire consiste à étudier le problème de récupération de la porteuse au niveau du récepteur puisque les avantages de son architecture pour plusieurs types de modulation de phase ne correspondent pas clairement aux techniques de récupération actuelles. Par exemple, le SP permet d'éliminer les mélangeurs du récepteur alors que la majorité des méthodes de récupération utilisent cet élément. Le chapitre 5 porte sur ce sujet.

## CHAPITRE 1

### INTRODUCTION ET RAPPEL DES CONCEPTS

Ce premier chapitre à pour but d'introduire ou rappeler quelques concepts nécessaires à la compréhension du présent mémoire.

#### 1.1 Rappel sur la modulation M-PSK

La modulation consiste essentiellement à modifier les propriétés (amplitude, phase ou fréquence) d'une porteuse. Le M-PSK est une modulation numérique qui modifie la phase d'une porteuse selon "M" états de phase distincts. Ce type de signal a pour propriété une amplitude constante et une largeur de bande infinie si aucun filtrage n'est appliqué. Dans les systèmes de communication réels, les données numériques sont généralement filtrées avant la modulation pour diminuer le débordement spectral, mais cette analyse dépasse l'objectif de cette introduction. Un signal M-PSK peut se décrire mathématiquement par

$$\begin{aligned} s(t) &= A \cos [\omega_c t + \theta_n] \\ \theta_n &= \frac{2\pi(n-1)}{M}, \quad \text{où } n = 1, 2, \dots, M \end{aligned} \tag{1.1}$$

La séparation entre les états de phase adjacents est alors de  $2\pi/M$ . Par exemple, pour le 4-PSK (QPSK) la séparation est de  $\pi/2$  alors qu'elle est de  $\pi/4$  pour le 8-PSK. Une méthode souvent utilisée pour la représentation de ces signaux est le diagramme polaire par l'entremise de phaseurs dont les pointes représentent la constellation. Tel qu'illustré à la figure 1.1, le module du phaseur représente l'amplitude du signal et son angle l'état de phase. Puisqu'un signal M-PSK est d'amplitude constante, les différents états se situent sur un seul cercle. Les pointillés de la figure 1.1 indiquent les seuils de décision des différents états. Le récepteur doit donc déterminer lequel

des états se situe à l'intérieur de la limite de  $\pm\pi/M$  par rapport à la phase reçue et associer le symbole correspondant.

**FIG. 1.1:** Quelques constellations PSK : a)  $M=2$  (BPSK), b)  $M=4$  (QPSK), c)  $M=8$

Une autre méthode pour représenter la modulation M-PSK et les autres modulations de phase similaires est la représentation par signaux en quadrature. En effet, l'utilisation d'expansions trigonométriques permet de ré-écrire l'équation 1.1 de la façon suivante :

$$s(t) = A[p_n \cos \omega_c t + q_n \sin \omega_c t] \quad (1.2)$$

où  $p_n = \cos \theta_n$  et  $q_n = \sin \theta_n$ . Puisque les termes en  $\cos \omega_c t$  et  $\sin \omega_c t$  sont orthogonaux dans un diagramme de vecteurs, ils sont dits en quadrature. Le coefficient  $p_n$  est alors représenté sur l'axe horizontal et est appelé *in-phase* (en phase) ou *I* alors que  $q_n$  représente l'axe vertical et s'appelle le signal *quadrature* ou *Q*.

Le spectre de la porteuse pour des données numériques aléatoires s'exprime par

$$S(f) = A^2 T \left( \frac{\sin[(f - f_c)\pi T]}{(f - f_c)\pi T} \right)^2 \quad (1.3)$$

où  $f$  est la fréquence de symbole,  $f_c$  la fréquence de la porteuse et  $T$  la période de

symbole. La figure 1.2 illustre la forme caractéristique de trois spectres PSK générés par des données aléatoires où l'ordonnée correspond à la fréquence de la porteuse.

**FIG. 1.2:** Spectres PSK pour un taux de données constant ( $M=2,4,8$  et  $f_c = 0$ )

Un paramètre important des modulations numériques est la probabilité d'erreur. Elle permet de comparer les différents types de modulation entre elles, elle est fonction du rapport signal sur bruit (S/N) et elle assume un canal ajoutant un bruit blanc gaussien. Pour faciliter la comparaison des modulations et récepteurs, le S/N est habituellement exprimé en fonction de l'énergie par bit ( $E_b$ ), de la densité spectrale du bruit ( $N_0$ ), de temps de symbole ( $T$ ) et de la largeur de bande du système ( $B$ ) par la relation

$$\frac{S}{N} = \frac{E_s/T}{N_0B} = \frac{E_b \log_2(M)/T}{N_0B} \quad (1.4)$$

Cette dernière relation est valide pour les cas théorique et pratique puisqu'elle tient compte de la largeur de bande du récepteur et non de la largeur de bande minimale

de Nyquist ( $B=1/2T$ ). La probabilité d'erreur du QPSK est donnée par

$$P(e) = 2 \operatorname{erfc} \sqrt{\frac{E_s}{N_0}} \left(1 - \frac{1}{4}\right) \operatorname{erfc} \sqrt{\frac{E_s}{N_0}} \quad (1.5)$$

et le bruit entraîne une erreur si la phase détectée au récepteur sort de la région délimitée par

$$\theta_n - \frac{\pi}{4} \leq \phi < \theta_n + \frac{\pi}{4} \quad (1.6)$$

Puisqu'une probabilité ne peut être mesurée, il est nécessaire d'introduire un paramètre équivalent permettant la comparaison des systèmes par mesures : le taux d'erreur (BER). En théorie, une erreur survient si le récepteur détecte un des  $M - 1$  symboles autre que celui transmis. Cependant, dans le cas du PSK, un état adjacent est beaucoup plus probable d'être retenu. De plus, puisque le code Gray est normalement utilisé pour ce type de modulation (les états adjacents ne varient que d'un seul bit), il est plus probable qu'un seul bit ne soit erroné. Donc pour les rapports S/N élevés,

$$BER \approx \frac{P(e)}{\log_2 M} \quad (1.7)$$

## 1.2 Récepteurs à conversion directe et superhétérodyne

La grande majorité des récepteurs numériques sont conçus selon une architecture dite "superhétérodyne" (SH) en raison de sa sensibilité et sa sélectivité. Récemment, de nouveaux objectifs de conception tels un faible coût, une faible dissipation de puissance et une réduction des dimensions physiques des récepteurs RF a fait renaître une autre architecture ayant auparavant échouées étant révélée peu pratique auparavant : la conversion directe (CD)[2]. Le regain d'intérêt pour la CD s'explique premièrement par une plus grande facilité d'intégration que l'architecture SH. Deuxièmement, il est maintenant possible de supprimer ou contrôler certains désavantages que présente cette architecture par rapport à l'architecture SH avec les circuits intégrés.

Pour bien illustrer les avantages de la CD, il est d'abord nécessaire de résumer le fonctionnement de l'architecture SH.

**FIG. 1.3:** Architecture de récepteurs : a) Superhétérodyne, b) Conversion directe

Tel qu'illustré à la figure 1.3a, le signal RF est d'abord filtré, amplifié et amené à une fréquence intermédiaire par un premier oscillateur local. Généralement cette conversion en fréquence est réalisée par plus d'un étage mais un seul est ici considéré pour ne pas alourdir inutilement l'analyse. Le signal est ensuite filtré et normalement amplifié (non-illustré) avant d'être amené en bande de base pour être démodulé. L'amplification à la fréquence intermédiaire requiert une polarisation et un filtrage additionnel augmentant la dissipation de puissance du récepteur. Un autre problème est le signal image d'entrée se trouvant à  $\omega_{RF} - 2\omega_{IF}$ . Cette image doit être filtrée

puisque'elle se superposera au signal désiré à la sortie du premier mélangeur à la fréquence  $\omega_{IF} = \omega_{LO} - \omega_{RF}$ . Cette opération requiert un filtre RF analogique très sélectif (et très dispendieux) difficiles, sinon impossibles, à planter avec les technologies de fabrication de circuits intégrés actuelles. Les récepteurs utilisent donc des filtres externes tel un filtre à ondes acoustiques de surface (SAW) et plusieurs étages IF pour diminuer les contraintes de filtrage au prix d'une complexité accrue.

La CD ou sous une autre appellation, la conversion homodyne<sup>1</sup>, est une approche plus naturelle pour ramener un signal en bande de base. En fait, elle est similaire à l'architecture SH si l'on modifie le schéma de cette dernière pour une fréquence IF nulle. Malgré cette similitude, la conception et la réalisation du récepteur sont très différentes. Premièrement, l'étage IF est éliminé et remplacé par un filtrage en bande de base normalement de type passe-bas, ce qui permet d'éliminer les filtres SAW. Deuxièmement, l'image n'est plus un problème puisqu'il n'y a plus de fréquence intermédiaire. Finalement, le récepteur peut être intégré en entier éliminant ainsi les composants externes requis dans l'architecture SH. Par contre, la CD présente quelques faiblesses moins critiques ou inexistantes dans l'architecture SH. Parmi celles-ci, la distorsion de deuxième ordre et le débalancement des signaux IQ ne sont pas traités en détail puisque de bonnes techniques de conception peuvent les rendre négligeables assez facilement comparativement aux autres problèmes. La distorsion de deuxième ordre reste cependant problématique pour les applications où un fort signal de perturbation peut être envoyé au récepteur pour le rendre inopérant, mais cette situation n'est pas considérée. En bref, la distorsion de deuxième ordre peut se produire au niveau du LNA et des mélangeurs et produit un battement à très basse fréquence des signaux en bande de base. Le débalancement des signaux IQ, quant à lui, se traduit en une constellation en bande de base non-symétrique et peut

---

<sup>1</sup>Un récepteur à CD est dit homodyne lorsque son oscillateur local est synchronisé en phase avec le signal RF reçu.

potentiellement accroître le BER. Les sous-sections suivantes traitent avec plus de détails des autres faiblesses importantes de la CD.

### 1.2.1 Décalage CC

Un récepteur à conversion directe convertit directement le signal modulé en un signal en bande de base incluant le CC (fréquence nulle). La présence d'une tension de décalage CC une fois en bande de base peut donc corrompre les données ou saturer les étages subséquents diminuant la plage dynamique du récepteur. Le décalage CC origine de plusieurs phénomènes que peut illustrer la figure 1.3. Premièrement, l'isolation entre les ports d'un mélangeur est imparfaite. Une certaine portion du signal LO se mélange donc avec lui-même ce qui produit une tension CC. De plus, un signal provenant de l'oscillateur local (LO) peut fuir vers l'entrée du LNA ou tout simplement à l'espace libre et retourner à l'antenne suite à une réflexion par un obstacle quelconque. Ce phénomène peut, par exemple, résulter d'un couplage capacitif ou d'un couplage par le substrat si les composants sont intégrés sur une même puce. Un effet identique peut être produit à l'inverse par une forte interférence amplifiée par le LNA et se couplant à la seconde entrée du mélangeur. Le problème du décalage CC est important puisqu'il peut varier dans le temps, être fonction de l'environnement du récepteur et implique des tensions dépassant largement le niveau du signal d'intérêt à la sortie des mélangeurs.

Il est possible de résoudre ce problème par plusieurs méthodes. La méthode la plus simple est le *couplage CA* (filtrage passe-haut) des signaux à la sortie des mélangeurs. Par contre, certaines modulations dont le QPSK ont une composante spectrale en CC lorsqu'ils sont générés par des données pseudo-aléatoires. À cet effet, une étude par simulations indique que la dégradation causée par un filtrage passe-haut à fréquence de coupure inférieure à 0,1% du taux de données est négligeable [37], mais entraîne l'utilisation de grandes capacités et peut impliquer la perte de données lorsque la transmission est interrompue momentanément. Une autre méthode est l'*annulation*.

Le décalage CC peut en effet être détecté et compensé dans le temps. Cette solution est idéale pour les systèmes de communication par salves puisque le décalage CC peut être détecté lors d'un "silence". Le principal problème de cette méthode est qu'il est possible que des interférences s'ajoutent au niveau CC lors de la détection.

### **1.2.2 Bruit de scintillement ("flicker noise")**

Le bruit  $1/f$  ou bruit de scintillement est un phénomène de bruit intrinsèque aux dispositifs semiconducteurs. Tel que suggéré par sa définition, la densité spectrale du bruit de ces dispositifs varie proportionnellement à l'inverse de la fréquence. Or, un récepteur à CD convertit immédiatement le signal modulé en bande de base aux environs du CC. Le bruit de scintillement est donc plus élevé et affecte d'autant plus le récepteur qu'il sera amplifié par les amplificateurs en bande de base. Le récepteur SH est moins sujet à cette interférence car une bonne partie de l'amplification est réalisée en fréquence intermédiaire où le niveau de bruit  $1/f$  est normalement inférieur.

### **1.2.3 Fuites de l'oscillateur local**

Les fuites de l'oscillateur local ne provoquent pas uniquement un décalage CC. L'émission du signal LO par l'intermédiaire d'un couplage à l'antenne génère une interférence pour les autres récepteurs. Le problème est moins sévère pour les récepteurs SH puisque la fréquence de leur oscillateur local est normalement à l'extérieur de la bande de réception. Une attention particulière pour minimiser le couplage à l'antenne est donc essentielle.

## **1.3 Le discriminateur de phase six-port et la modulation QPSK**

Le six-port (SP) est un circuit passif originellement utilisé pour la mesure de circuits micro-ondes. Introduit au départ au domaine micro-ondes par Engen en 1977 [9] pour mesurer les paramètres S, il a depuis évolué sous différentes formes et

diverses applications allant de la réflectométrie aux récepteurs radar et numérique. Tel que son nom l'indique, le SP est un réseau de lignes de transmission originellement composé de six ports d'entrée-sortie. Il est cependant plus approprié de référer au principe SP puisque l'on retrouve d'autres versions avec un nombre réduit de ports mais fonctionnant selon le même principe. Le principe ou la technique de mesure par SP consiste à établir différentes relations de phases et d'amplitudes entre deux signaux : un signal inconnu et une référence (connue) où chacune des sorties du circuit se distingue habituellement par sa propre relation de phase. Le niveau RF aux sorties est ensuite mesuré par des détecteurs RF et les valeurs ainsi obtenues sont reliées aux caractéristiques du signal inconnu par une équation mathématique dont les coefficients ont été obtenus par une précédente étape de calibration. La calibration varie selon l'application et a fait l'objet de plusieurs travaux au Poly-Grames [15] et ailleurs . Les SP sont réalisés principalement sous deux formes : l'anneau ou un agencement de coupleurs (figure 1.4). L'anneau est la forme la plus simple où tous les ports sont placés sur un anneau commun et les ports de sortie séparés des deux ports d'entrée par les distances  $l_{i1}$  et  $l_{i2}$  introduisant un déphasage unique, fonction de la longueur d'onde guidée. Un tel circuit est évidemment très sélectif en fréquence. L'agencement de coupleurs permet de réaliser un SP moins sélectif mais complique quelque peu sa conception. Les diverses relations de phase sont alors obtenues en déphasant distinctement, par les coupleurs, les deux signaux d'entrée de sorte que chaque sortie ait une relation de phase unique. Peu importe la forme (anneau ou coupleur), les deux ports d'entrée sont normalement positionnés pour être isolés l'un de l'autre.

De nombreux travaux de recherche sur les SP et leurs applications ont été réalisés au Poly-Grames par le professeur Bosisio dès les années 1980 [28]. En 1994, le circuit SP est pour la première fois proposé pour la démodulation numérique [26, 27], une application qui a depuis été un important moteur de recherche. En 2000, l'architecture du SP a été revue et simplifiée pour ne discriminer que la phase [51]. Cette

FIG. 1.4: Formes de réalisation des SP : a) anneau, b) coupleurs (Polytel)

nouvelle architecture, nommée *Polytel* et illustrée par la figure 1.4b, comporte trois coupleurs hybrides et un diviseur de puissance Wilkinson. Le SP Polytel est plus approprié pour les récepteurs numériques PSK et ne nécessite pas obligatoirement l'obtention de coefficients par une technique de calibration quelconque à condition que le signal à démoduler et le signal de référence (LO) soient de même puissance.

$$[S]_{Hyb.} = \begin{pmatrix} 0 & -j\sqrt{2} & -1/\sqrt{2} & 0 \\ -j\sqrt{2} & 0 & 0 & -1/\sqrt{2} \\ -1/\sqrt{2} & 0 & 0 & -j\sqrt{2} \\ 0 & -1/\sqrt{2} & -j\sqrt{2} & 0 \end{pmatrix} \quad (1.8)$$

$$[S]_{Wil.} = \begin{pmatrix} 0 & -j\sqrt{2} & -j\sqrt{2} \\ -j\sqrt{2} & 0 & 0 \\ -j\sqrt{2} & 0 & 0 \end{pmatrix} \quad (1.9)$$

En supposant des coupleurs hybrides et Wilkinson sans perte représentés à leur fréquence centrale par les matrices S 1.8 et 1.9 respectivement, on peut calculer les

paramètres S du SP et obtenir :

$$[S]_{SP} = \begin{pmatrix} 0 & -1/2 & j/2 & 1/2 & j/2 & 0 \\ -1/2 & 0 & 0 & 0 & 0 & j/2 \\ j/2 & 0 & 0 & 0 & 0 & -1/2 \\ 1/2 & 0 & 0 & 0 & 0 & -1/2 \\ j/2 & 0 & 0 & 0 & 0 & j/2 \\ 0 & j/2 & -1/2 & -1/2 & j/2 & 0 \end{pmatrix} \quad (1.10)$$

Pour discriminer la phase, les signaux à comparer sont appliqués au SP par les ports 1 et 6 alors que les ports 2 à 5 sont les sorties. Puisque le but ultime est la conception d'un récepteur, le port 1 recevra le signal modulé et est nommé RF alors que le port 6 recevra le signal provenant d'un oscillateur local et porte le nom LO. Supposons deux signaux d'entrée de même fréquence décrits par

$$S_{RF} = A \cos(\omega t + \theta_{RF}) = \Re [A e^{j\theta_{RF}} e^{j\omega t}] \quad (1.11)$$

$$S_{LO} = B \cos(\omega t + \theta_{LO}) = \Re [B e^{j\theta_{LO}} e^{j\omega t}] \quad (1.12)$$

où les angles  $\theta$  représentent l'état de phase du signal à l'entrée du SP. La notation par phaseurs est utilisée et le terme en  $e^{j\omega t}$  par la suite supprimé par souci de simplicité. Puisque les ports RF et LO sont isolés ( $S_{16} = 0$ ), ces signaux se propageront uniquement aux sorties du SP où il se superposeront mais selon des relations de phases uniques. Les signaux sortant aux ports 2 à 5 se décrivent par

$$b_i = S_{RF} S_{i1} + S_{LO} S_{i6} = \frac{A}{2} e^{j\Delta\phi_i} + \frac{B}{2} \quad (1.13)$$

$$\Delta\phi_i = \phi_{RF} - \phi_{LO} + \angle S_{i1} - \angle S_{i6}, \quad i = 2, 3, 4, 5 \quad (1.14)$$

où  $S_{RF}$  est ré-exprimé relativement au signal de référence (LO). L'amplitude du

signal résultant, proportionnel à la puissance, est alors donné par

$$|b_i| = \sqrt{\left(\frac{A}{2}\right)^2 + \left(\frac{B}{2}\right)^2 + \frac{AB}{2} \cos \Delta\phi_i} \quad (1.15)$$

Si les deux signaux d'entrée sont de même puissance ( $A = B$ ), que le signal  $S_{RF}$  est modulé QPSK et que  $\phi_{RF} - \phi_{LO} = n\pi/2$  où  $n$  est un entier entre 0 et 3 représentant l'état de modulation, l'équation 1.15 se simplifie pour donner

$$|b_i| = \frac{A}{\sqrt{2}} \sqrt{\left[1 + \cos\left(\frac{n\pi}{2} + \angle S_{i1} - \angle S_{i6}\right)\right]}, \quad n = 0, 1, 2, 3; \quad i = 2, 3, 4, 5 \quad (1.16)$$

L'équation 1.16 exprime alors l'ensemble des amplitudes possibles aux sorties du SP selon les conditions mentionnées. Le tableau 1.1 illustre les amplitudes aux quatre ports selon l'état de modulation  $n$ . On constate qu'il est possible de démoduler un signal QPSK par une simple lecture de puissance en détectant un minima ou un maxima à l'un des ports de sortie sans passer par les signaux intermédiaires habituels IQ. Cette détection des états peut se faire par traitement de signal analogique en raison de sa simplicité ou par l'utilisation de convertisseurs analogique-numérique jumelés à un DSP pour les modulations plus complexes. Un récepteur à base de SP

**TAB. 1.1:** Amplitudes aux quatre ports de sortie selon l'état de modulation

| État (n) | Port 2       | Port 3       | Port 4       | Port 5       |

|----------|--------------|--------------|--------------|--------------|

| 0        | $A/\sqrt{2}$ | $A/\sqrt{2}$ | 0            | $A$          |

| 1        | 0            | $A$          | $A/\sqrt{2}$ | $A/\sqrt{2}$ |

| 2        | $A/\sqrt{2}$ | $A/\sqrt{2}$ | $A$          | 0            |

| 3        | $A$          | 0            | $A/\sqrt{2}$ | $A/\sqrt{2}$ |

est donc de type CD et aura essentiellement les mêmes avantages et inconvénients énoncés plus tôt à l'exception du débalancement des signaux classiques IQ puisque ces derniers sont absents et ne peuvent être générés qu'artificiellement. En effet, le détecteur RF génère facilement un décalage CC puisque toute puissance RF à

son entrée et dans sa bande d'opération sera convertie à la sortie. Par exemple, un décalage CC est généré dans le cas où les deux signaux atteignant le détecteur ne sont pas de puissance identique ce qui rend impossible l'annulation illustrée au tableau 1.1. Ces problèmes appliqués au récepteur SP ne seront pas traités dans ce mémoire mais ont déjà fait l'objet de travaux au Poly-Grames [48, 49].

D'autres architectures de SP ont aussi été analysées dans le but de sélectionner une architecture propice à l'intégration [1]. Cependant des simulations indiquent qu'aucune ne permet de surpasser l'isolation RF-LO obtenue par l'architecture présentée en utilisant que des éléments passifs. L'utilisation d'éléments actifs permettrait d'autres architectures plus compactes mais cela dépasse les objectifs énoncés.

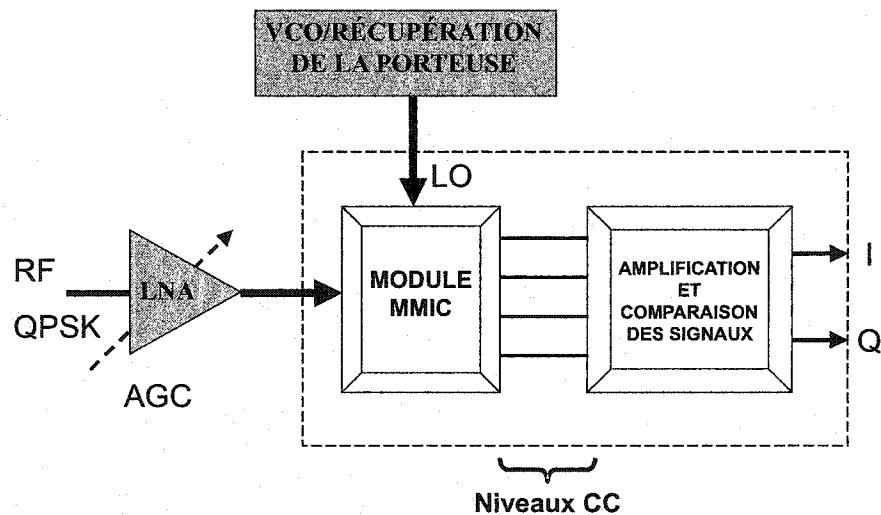

La figure 1.5 illustre l'architecture de base d'un récepteur à CD à base de SP avec traitement de signal analogique où les blocs ombragés sont réservés pour une seconde étape de fabrication. Le module MMIC contient le SP et ses détecteurs alors que le circuit en bande de base interprète les niveaux CC détectés et y associe le symbole correspondant.

FIG. 1.5: Schémas bloc d'un récepteur SP

## CHAPITRE 2

### LE SIX-PORT DISCRET

Au chapitre précédent, le six-port a été introduit et son comportement lorsque soumis à un signal modulé en phase a été présenté. Originalement, le six-port étant utilisé dans les bandes de fréquences micro-ondes (ou millimétriques), celui-ci est réalisé sous forme planaire à l'aide de lignes de transmission. Cependant, ce type de réalisation peut s'avérer peu pratique, volumineux et surtout très coûteux selon la technologie de fabrication utilisée et la fréquence d'opération. En effet, les dimensions d'un six-port réalisé à l'aide de lignes de transmission varient à l'inverse de sa fréquence d'opération alors que les coûts de fabrication augmentent généralement avec la superficie du circuit. Pour cette étude, l'objectif est d'intégrer le six-port en technologie MMIC sur GaAs pour une bande d'opération ISM allant de 5,725 GHz à 5,85 GHz. De plus, par soucis d'uniformité et d'efficacité, les fonderies réalisant ce type de circuit imposent une limite quant à la dimension maximale de ceux-ci. Cette limite peut être justifiée par les contraintes au niveau des équipements de fabrication, par des aspects économiques ou simplement pour maintenir un haut taux de succès de fabrication. En effet, les gaufres, sorte de matière première pour la fabrication de circuits intégrés, présentent des défectuosités locales ayant surtout un impact important lors de la réalisation de circuits actifs. Or, la probabilité de rencontrer l'une de ces défectuosités augmente avec l'accroissement du nombre de transistors ou des dimensions du circuit. À titre d'exemple, la fabrication du prototype d'un circuit chez *Triquint Semiconductor* a pour dimensions maximales 4 mm X 4 mm et coûte présentement 29 900 USD pour un procédé 0,25- $\mu$ m pHEMT. On peut donc rapidement constater l'importance de minimiser les dimensions du circuit. C'est ce que permettra l'utilisation d'éléments discrets.

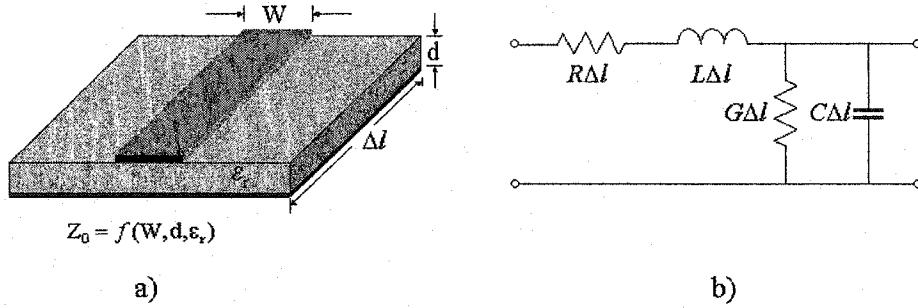

Tel qu'illustré par la figure 2.1, les lignes de transmission peuvent être modélisées

**FIG. 2.1:** Modèle d'une ligne de transmission ; a) ligne micro-ruban, b) modèle équivalent

par des éléments discrets. On peut donc porter les structures distribuées au domaine discret pour réaliser le même comportement, mais les différences au niveau des parasites imposent certaines limites. Quelles sont les implications de l'utilisation de ces éléments discrets dans la conception d'un six-port ? Quelles sont les contraintes au niveau de sa réalisation ? De quelle façon peut-on porter les structures réalisées par des éléments distribués dans le domaine discret ? C'est à ces questions que répondra ce chapitre.

## 2.1 Les éléments RLC

Les lignes de transmission sont modélisées en utilisant des éléments idéaux, ce qui n'est en fait qu'un artifice nous permettant une analyse mathématique simplifiée. Ou, selon un autre point de vue, les éléments discrets de cette modélisation ne sont que l'expression des parasites de la ligne de transmission. Or, les éléments discrets réels ont aussi leurs propres parasites influençant plus ou moins leur comportement selon la fréquence à laquelle ils sont utilisés. Ils peuvent être raisonnablement bien caractérisés sous forme de pertes et de fréquence de résonance. La fréquence de résonance d'un élément est la fréquence où il se produit un changement au niveau de la nature de son comportement. Par exemple lorsqu'une inductance se comporte telle

un condensateur. Les éléments discrets présentent normalement davantage de pertes que les lignes de transmission. Il est donc raisonnable de penser que la réalisation d'un six-port en éléments discrets présentera davantage de pertes qu'une réalisation équivalente sous forme d'éléments distribués ou de lignes de transmission. Il est cependant difficile de quantifier l'augmentation des pertes hors du contexte réel de ces éléments.

Il existe aussi une importante relation entre la fréquence de résonance et la valeur nominale de l'élément. En effet, la fréquence de résonance tend à décroître avec l'augmentation de la valeur nominale. Par exemple, une inductance de 5 nH entrera en résonance à une fréquence considérablement plus basse qu'une autre de 0,5 nH. On peut observer le même comportement, quoique moins prononcé, au niveau des condensateurs. En transposant cette réalité au six-port, on constate qu'il doit y avoir un certain compromis entre la fréquence d'opération et la valeur nominale des éléments discrets obtenus par calculs. En effet, un calcul pour une fréquence d'opération donnée pourrait signifier la réalisation d'un élément opéré au delà de sa fréquence de résonance, ce qui rend toute réalisation discrète impossible pour ce cas particulier. Ici sont présentés les modèles utilisés pour la caractérisation des éléments discrets. Par souci d'uniformité avec les chapitres ultérieurs, ces modèles sont équivalents à ceux utilisés par *Triquint Semiconductor* (TQT).

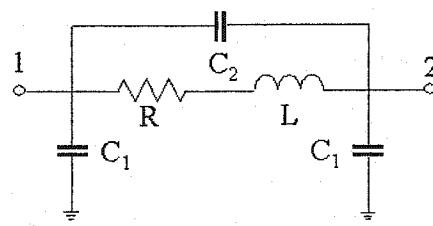

**FIG. 2.2:** Modèle d'une inductance série

La figure 2.2 illustre un modèle simple d'une inductance. L'élément inductif est normalement de l'ordre du nH et les condensateurs de l'ordre du fF. L'élément résistif

est, quand à lui, fonction du nombre de tours, de la dimension de l'inductance mais aussi de la fréquence bien que le modèle ne tienne pas compte de ce dernier paramètre. L'inductance est normalement l'élément discret présentant le plus de pertes. En plus d'être très sensible au couplage et très volumineux, cet élément présente une très forte relation entre la fréquence de résonance et sa valeur nominale. En effet, l'inductance est potentiellement l'élément le plus susceptible d'influencer négativement les performances d'un six-port discret ou même de rendre impossible sa réalisation. Il serait donc judicieux de minimiser leur nombre et leur valeur nominale. L'inductance est aussi plus complexe à réaliser au niveau du dessin ("layout"). Normalement réalisée à l'aide d'une fine ligne de transmission en spirale, il est difficile d'établir une relation précise entre le nombre de tours, les différents espacements et la valeur nominale obtenue et ce, même par l'utilisation de logiciels de simulation sophistiqués tel ADS-Momentum et HFSS.

Voici un exemple illustrant les différences pouvant survenir entre les résultats obtenus par simulation sous ADS-Momentum et les résultats mesurés après la fabrication de l'inductance. La simulation a été réalisée en utilisant les paramètres physiques de la fonderie au niveau des différentes couches composant une inductance de deux tours (ou 9 segments) définie par TQT pour une valeur nominale de 0,75 nH (l'élément inductif dans le modèle à la figure 2.2). Pour une raison de simplicité, quelques couches secondaires ont été retirées pour ne conserver que les couches conductrices et les couches diélectriques essentielles. Les résultats de simulation et de mesure sont ensuite interprétés en ne considérant que les sous-éléments résistifs et inductifs de l'inductance à l'aide d'une conversion des paramètres S du réseau à deux ports vers le paramètre B (ABCD). En d'autres termes, le réseau à deux ports a été considéré tel une impédance série Z composée de deux éléments, soit une résistance et une inductance série. L'inductance s'exprime donc par

$$L(f) = \Im\left\{\frac{Z(\omega)}{2\pi f}\right\} \quad (2.1)$$

où

$$Z(\omega) = Z_0 \frac{[1 + S_{11}(\omega)][1 + S_{22}(\omega)] - S_{12}(\omega)S_{21}(\omega)}{2S_{21}(\omega)}. \quad (2.2)$$

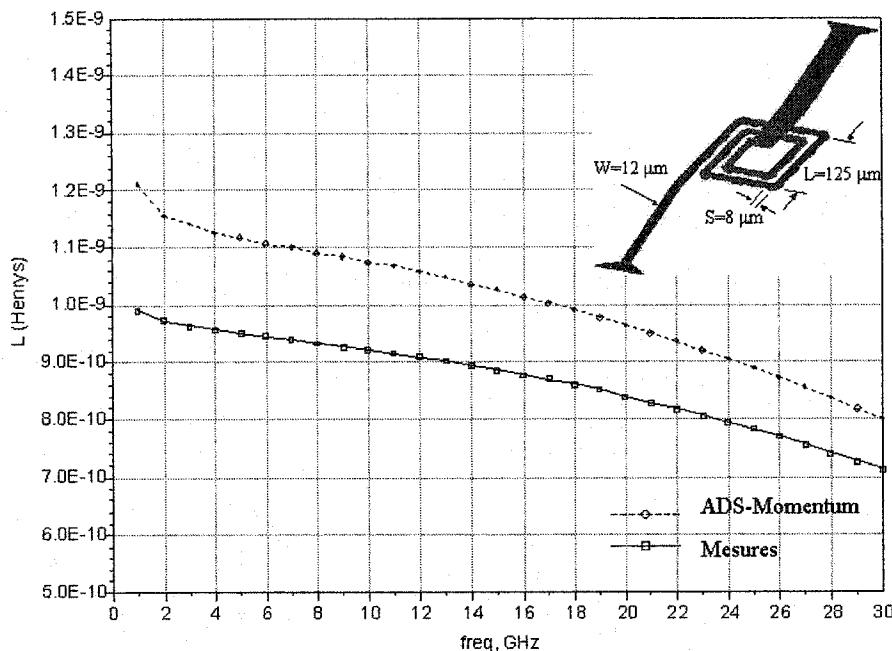

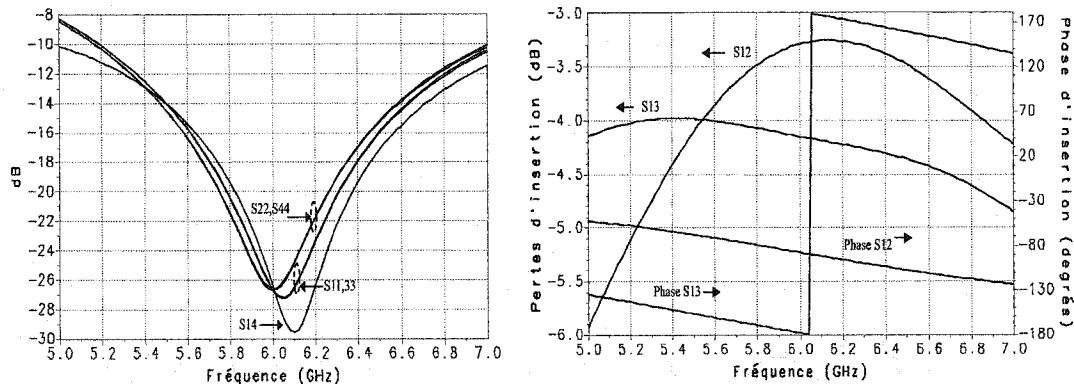

FIG. 2.3: Comparaison entre les résultats simulés (ADS-Momentum) et mesurés d'une inductance MMIC

On constate à la figure 2.3 que la précision de la simulation, bien qu'acceptable considérant la complexité du problème, reste insuffisante pour la précision requise à la construction d'un six-port discret. Ceci implique donc la construction d'une bibliothèque d'inductances où chacune est associée à un fichier de mesure. Cette approche peut devenir très laborieuse selon la base des variations de fabrication que l'on désire prendre en compte (ie.gaufre-gaufre, cycle-cycle, etc). L'écart entre les résultats simulés et mesurés peut être justifié par la difficulté de réaliser un modèle simulable entièrement fidèle à chacune des couches de sorte que leurs propriétés et l'interaction entre elles se rapprochent davantage de la réalité. On constate également que

la fréquence de résonance se situe au delà de 30 GHz ce qui se justifie par la faible valeur nominale de l'inductance utilisée pour cet exemple.

En plus des difficultés de simulation, il est relativement ardu de faire la conception d'inductances sous ces logiciels puisque celles-ci doivent être simulées par une méthode essai-erreur, l'optimisation étant très limitée pour ce type de simulation physique. Les simulations sont donc longues et le temps requis pour la modification des dessins considérable. Pour limiter l'effort de conception, évaluer l'effet de chaque dimension ou du moins fournir des dimensions de départ, un fichier "script" simple a été réalisé sous le logiciel MATLAB. Celui-ci permet de fournir une prédition de la valeur nominale de l'inductance en fonction de ses dimensions. La méthode est basée sur le calcul de l'inductance mutuelle des différents segments de l'inductance spirale-carrée et a été inspirée de l'article en [19]. Puisqu'il sagit d'une implantation statique, le logiciel n'est cependant pas en mesure de prédire la fréquence de résonance. À titre d'exemple, la figure 2.4 illustre le résultat de calculs réalisés en variant le nombre de tours et les dimensions de l'inductance en tenant compte de la plage de variation de la valeur nominale entraînée par les variations au niveau du procédé de fabrication de circuits sur GaAs de TQT. Les marges d'erreur illustrées à la figure ont été calculées en sachant que le procédé utilisé pour la fabrication (MMW) présente des variations au niveau de la largeur des lignes de l'ordre de  $\pm 1,5 \mu\text{m}$  dû à la photolithographie et de  $1,25 \mu\text{m}$  dû à l'alignement. On remarque d'ailleurs que la valeur nominale L selon les dimensions de l'inductance définie précédemment (figure 2.3) est très près de 0,75 nH bien que la largeur de ligne W soit légèrement modifiée de  $12 \mu\text{m}$  à  $10 \mu\text{m}$ .

Les figures 2.5 et 2.6 représentent deux modèles pour une capacité MIM (Métal-Isolant-Métal) selon qu'elle se trouve en configuration série ou parallèle. On remarque que ces modèles sont beaucoup plus près de la réalisation physique de la capacité. Cela s'explique par le fait que les capacités sont plus simples à caractériser en fonction de leurs dimensions. Les pertes d'un tel élément sont moins élevées et presque

**FIG. 2.4:** Inductance en fonction du nombre de segments ( $Z$ ) et de la longeur du premier segment ( $L_1$ )

négligeable face à celles d'une inductance à certaines fréquences assez basses. La valeur de la capacité est principalement fonction de sa surface et il est facile d'y inclure l'effet capacitif ajouté de structures secondaires nécessaires à sa fabrication tel les ponts aériens. Il est donc possible de prédire la valeur nominale de la capacité de façon relativement précise à l'aide de données sur la fonderie. Les fonderies fournissent généralement les paramètres nécessaires au calcul de la capacité. À titre indicatif, la valeur nominale des capacités est de l'ordre du pF et la résistance parasite de l'ordre de  $100 \text{ m}\Omega$ . En ce qui concerne la figure 2.6, on remarque l'ajout d'une inductance et d'une résistance parasite juste au-dessus de la mise à la terre. Ces parasites sont dues à la présence d'un via sous la plaque inférieure de la capacité parallèle. La valeur de ces parasites est fonction de la dimension et du type de via (plaqué ou non). Dans le cas d'un via de  $50 \mu\text{m}$  de diamètre, la résistance de celui-ci est de l'ordre de  $20 \text{ m}\Omega$ .

**FIG. 2.5:** Modèle de la capacité série

alors que l'inductance est d'environ 0,01 nH. De plus amples détails sur les capacités seront fournis dans un chapitre ultérieur.

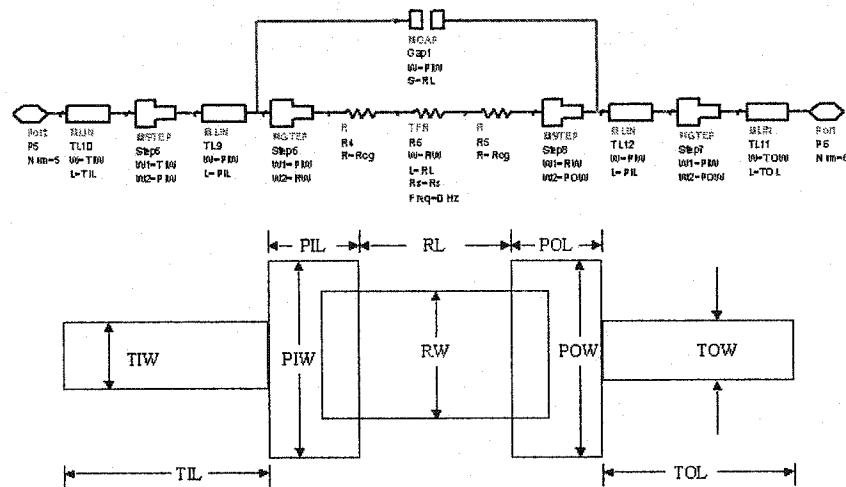

Le dernier élément discret est évidemment la résistance. Les parasites de cet élément ne présentent qu'un effet négligeable au niveau de la technologie de fabrication envisagée et de la fréquence d'opération. En technologie MMIC, la résistance est normalement réalisée à l'aide d'un film épais ("Thick film resistor") de nitrule de tantalum (TaN) ou de nichrome (NiCr) et sa valeur est fonction du rapport largeur/longueur de ce film. Cet élément pourrait donc être considéré tel une résistance idéale dans le cadre de cette étude. Par soucis de rigueur et pour inclure les paramètres des couches entrant dans sa fabrication, le modèle de la figure 2.7 est utilisé. La boîte centrale représente le film épais responsable de l'effet résistif alors que les boîtes de chaque côté représentent des structures de contact. Les structures de contact peuvent aussi contribuer à la résistance selon leur composition.

## 2.2 Le déphasageur

La modification de la phase d'un signal par l'utilisation d'éléments distribués se fait habituellement en utilisant une ligne de transmission de longueur bien définie.

FIG. 2.6: Modèle de la capacité parallèle

Le déphasage est alors fonction de la fréquence du signal et, dans le cas d'une ligne de transmission de type micro-ruban, s'exprime par

$$\phi = \beta l = \sqrt{\epsilon_e} \kappa_0 l \quad (2.3)$$

où

$$\kappa_0 = \frac{2\pi f}{c},$$

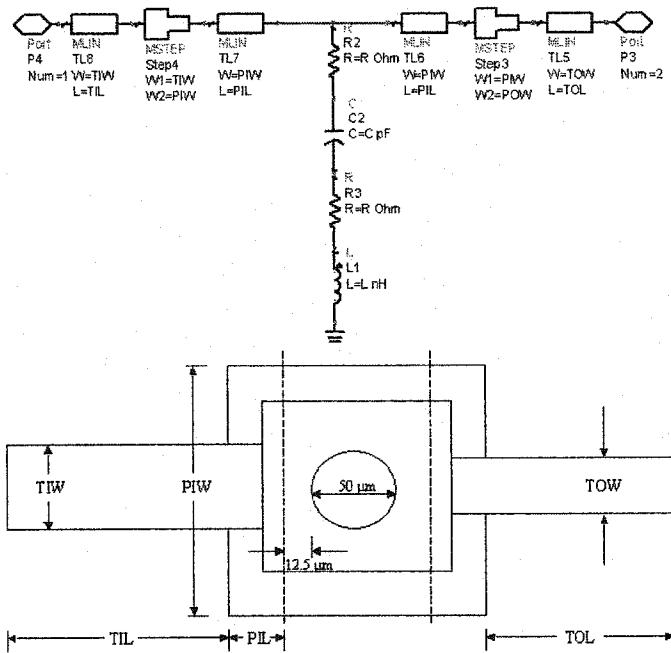

$c$  est la vitesse de la lumière et  $\epsilon_e$  est la constante diélectrique effective. À basse fréquence cette méthode est utile pour générer de petits déphasages, mais s'avère très peu efficace en terme des dimensions requises pour des déphasages plus importants. Il est possible de réaliser le même type de fonction par des circuits simples composés d'éléments discrets. La figure 2.8 illustre quatre configurations de base d'un tel déphaseur utilisant des éléments passifs.

FIG. 2.7: Modèle de la résistance série

### 2.2.1 Configurations A et C

En supposant des impédances caractéristiques d'entrée et de sortie identiques ( $Z_{01} = Z_{02}$ ) nous avons  $C_1 = C_2 = C$  et le circuit A (figure 2.8) s'exprime en paramètres de transmission telle l'équation 2.4.

$$\begin{pmatrix} A & B \\ C & D \end{pmatrix} = \begin{pmatrix} 1 & 0 \\ Y_C & 1 \end{pmatrix} \cdot \begin{pmatrix} 1 & Z_L \\ 0 & 1 \end{pmatrix} \cdot \begin{pmatrix} 1 & 0 \\ Y_C & 1 \end{pmatrix} = \begin{pmatrix} 1 + Z_L Y_C & Z_L \\ Z_L Y_C^2 + 2Y_C & Z_L Y_C + 1 \end{pmatrix} \quad (2.4)$$

FIG. 2.8: Déphasateurs de base en éléments discrets

Sachant que

$$S_{11} = \frac{A + B/Z_0 - CZ_0 - D}{A + B/Z_0 + CZ_0 + D} \quad (2.5)$$

$$S_{21} = \frac{2}{A + B/Z_0 + CZ_0 + D} \quad (2.6)$$

$$Z_L = jX_L \quad (2.7)$$

$$Y_C = jB_C \quad (2.8)$$

et en appliquant les conditions  $S_{11} = 0$  et  $\phi = \arg(S_{21})$ , on obtient la valeur des composants L et C par la solution du système d'équation suivant :

$$Z_0 X_L B_C^2 - 2Z_0 B_C + X_L/Z_0 = 0 \quad (2.9)$$

$$-\arctan\left(\frac{1}{2} \frac{X_L/Z_0 + 2Z_0 B_C - Z_0 X_L B_C^2}{1 - X_L B_C}\right) = \phi \quad (2.10)$$

Ce type de réseau permet l'obtention d'une phase de  $0$  à  $-90^\circ$  sans trop d'atténuation. Par exemple, la solution du réseau d'équation pour une impédance caractéris-

tique  $Z_0 = 50\Omega$  et une phase de  $-90^\circ$  à une fréquence de 5,8 GHz donne

$$\begin{aligned} B_C &= \frac{1}{Z_0} \Rightarrow C = 0,5488 \text{ pF} \\ X_L &= Z_0 \Rightarrow L = 1,372 \text{ nH}. \end{aligned} \quad (2.11)$$

La réponse en fréquence résultante est illustrée à la figure 2.9. On y constate l'obtention des conditions désirées, un déphasage négatif et une augmentation des pertes de conversion pour les fréquences supérieures à 6 GHz. Le circuit C peut être résolu à l'aide du même système d'équation en inversant les définitions des composants ( $X_L \rightarrow X_C$ ) et il en résultera en une réponse en fréquence également inversée.

FIG. 2.9: Réponse en fréquence théorique du déphaseur A

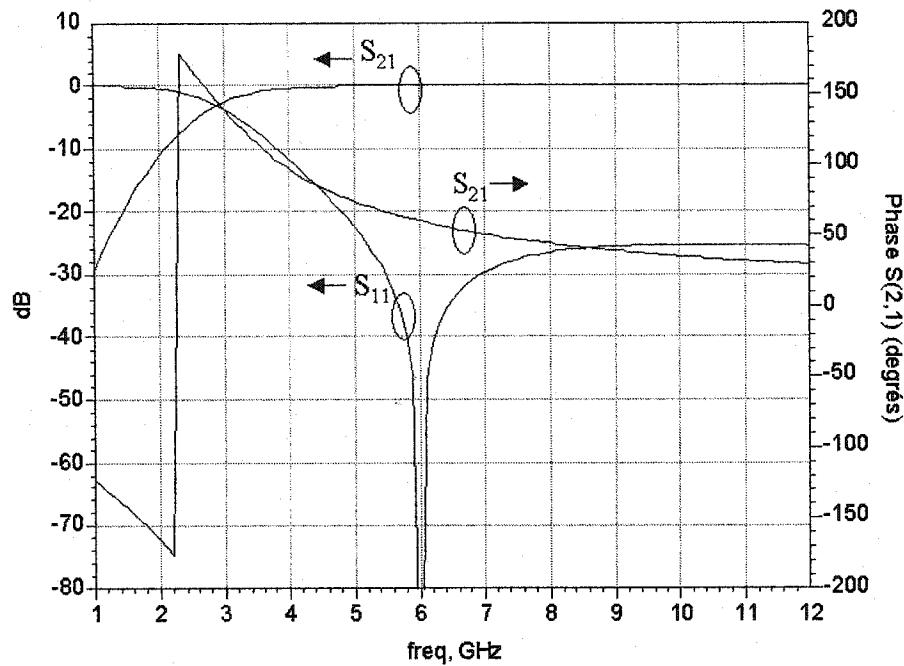

### 2.2.2 Configurations B et D

Selon les définitions et conditions de la sous-section 2.2.1, on obtient pour le déphasageur en configuration D (figure 2.8) le système d'équation suivant :

$$B_L X_C^2 - 2X_C + B_L Z_0^2 = 0 \quad (2.12)$$

$$-\arctan\left\{\frac{2X_C + 2B_L Z_0^2 - B_L X_C^2}{2Z_0(1 - B_L X_C)}\right\} = \phi \quad (2.13)$$

En solutionnant ce système d'équation pour une impédance caractéristique  $Z_0 = 50\Omega$  et une phase de  $60^\circ$  à une fréquence de 6 GHz on obtient