**Titre:** Une méthode de dérivation de modèles de processeurs embarqués dédiés à une application

Title: [Une méthode de dérivation de modèles de processeurs embarqués dédiés à une application](#)

**Auteur:** Olivier Hébert

Author: [Olivier Hébert](#)

**Date:** 2001

**Type:** Mémoire ou thèse / Dissertation or Thesis

**Référence:** Hébert, O. (2001). Une méthode de dérivation de modèles de processeurs embarqués dédiés à une application [Mémoire de maîtrise, École Polytechnique de Montréal]. PolyPublie. <https://publications.polymtl.ca/6957/>

Citation: [Hébert, O. \(2001\). Une méthode de dérivation de modèles de processeurs embarqués dédiés à une application \[Mémoire de maîtrise, École Polytechnique de Montréal\]. PolyPublie. https://publications.polymtl.ca/6957/](#)

## Document en libre accès dans PolyPublie

Open Access document in PolyPublie

**URL de PolyPublie:** <https://publications.polymtl.ca/6957/>

PolyPublie URL: [https://publications.polymtl.ca/6957/](#)

**Directeurs de recherche:** Yvon Savaria

Advisors: [Yvon Savaria](#)

**Programme:** Non spécifié

Program: [Non spécifié](#)

UNIVERSITÉ DE MONTRÉAL

UNE MÉTHODE DE DÉRIVATION DE MODÈLES DE PROCESSEURS

EMBARQUÉS DÉDIÉS À UNE APPLICATION

OLIVIER HÉBERT

DÉPARTEMENT DE GÉNIE ÉLECTRIQUE ET DE GÉNIE INFORMATIQUE

ÉCOLE POLYTECHNIQUE DE MONTRÉAL

MÉMOIRE PRÉSENTÉ EN VUE DE L'OBTENTION

DU DIPLÔME DE MAÎTRISE ÈS SCIENCES APPLIQUÉES

(GÉNIE ÉLECTRIQUE)

MARS 2001

National Library

of Canada

Acquisitions and

Bibliographic Services

385 Wellington Street

Ottawa ON K1A 0N4

Canada

Bibliothèque nationale

du Canada

Acquisitions et

services bibliographiques

385, rue Wellington

Ottawa ON K1A 0N4

Canada

Your file Votre référence

Our file Notre référence

**The author has granted a non-exclusive licence allowing the National Library of Canada to reproduce, loan, distribute or sell copies of this thesis in microform, paper or electronic formats.**

**L'auteur a accordé une licence non exclusive permettant à la Bibliothèque nationale du Canada de reproduire, prêter, distribuer ou vendre des copies de cette thèse sous la forme de microfiche/film, de reproduction sur papier ou sur format électronique.**

**The author retains ownership of the copyright in this thesis. Neither the thesis nor substantial extracts from it may be printed or otherwise reproduced without the author's permission.**

**L'auteur conserve la propriété du droit d'auteur qui protège cette thèse. Ni la thèse ni des extraits substantiels de celle-ci ne doivent être imprimés ou autrement reproduits sans son autorisation.**

**0-612-65580-6**

**Canada**

## **Identification des membres du jury**

UNIVERSITÉ DE MONTRÉAL

ÉCOLE POLYTECHNIQUE DE MONTRÉAL

Ce mémoire intitulé:

UNE MÉTHODE DE DÉRIVATION DE MODÈLES DE PROCESSEURS

EMBARQUÉS DÉDIÉS À UNE APPLICATION

présenté par: HÉBERT Olivier

en vue de l'obtention du diplôme de: Maîtrise ès sciences appliquées

a été dûment acceptée par le jury d'examen constitué de:

M. BOIS Guy, Ph.D., président

M. SAVARIA Yvon, Ph.D., membre et directeur de recherche

M. Aboulhamid El Mostapha, Ph.D., membre

## Remerciements

J'aimerais tout d'abord remercier les organismes subventionnaires qui m'ont soutenu financièrement au cours de mes études de maîtrise et de la réalisation du projet décrit dans le présent mémoire. Ceux-ci sont le Conseil de recherche en sciences naturelles et en génie du Canada (CRSNG) ainsi que la compagnie MiroTech Microsystems.

J'aimerais remercier les gens qui m'ont guidé tout au long de ce projet de recherche, soient mon directeur de recherche, le professeur Yvon Savaria de l'École Polytechnique de Montréal, ainsi que M. Ivan C. Kraljic, ingénieur chez MiroTech Microsystems. Également, mes professeurs qui m'ont éclairé sous différents sujets, soient les professeurs Guy Bois de l'École Polytechnique de Montréal et El Mostapha Aboulhamid de l'Université de Montréal.

J'aimerais aussi remercier les gens avec qui j'ai travaillé ou que j'ai côtoyé tout au long de mes travaux. Ceux-ci sont M. Alexandre Fortin (avec qui j'ai directement travaillé sur le projet), M. Frédéric Doucet, Mme Geneviève Cyr, M. Jean-Marc Tremblay et M. Patrice Vado.

Finalement, j'aimerais remercier mes parents et amis qui m'ont supporté pendant toute la durée de mes études.

## Résumé

Le temps de développement de systèmes embarqués étant de plus en plus court, et ceux-ci étant d'une complexité toujours grandissante, les concepteurs doivent maintenant utiliser des méthodologies nouvelles pour arriver à réaliser à temps leurs projets. Parmi les méthodes utilisées, la réutilisation de composantes disponibles sous la forme de blocs de propriété intellectuelle (IP) est très populaire. Toutefois, une implantation directe de composantes sans tenir compte de l'application qui est ciblée va produire des circuits qui ne seront pas optimaux. Ainsi, plusieurs parties des composantes pourraient ne pas être utilisées par l'application et être quand même implantées. On assisterait alors à un gaspillage des ressources disponibles.

Ce mémoire décrit une méthode de dérivation de processeurs dédiés permettant d'optimiser les circuits synthétisés en fonction de l'application que l'on cible. Ainsi, en introduisant une étape d'optimisation avant la synthèse finale du circuit, on peut extraire l'information contenue dans le microcode de l'application et optimiser le processeur pour l'exécution de cette application particulière. On décrit également le développement d'un modèle de processeur de traitement de signal parallèle destiné à implanter la méthode de dérivation. Celui-ci a été développé de façon à être fortement configurable et optimisable et ce, de façon automatique. Des expérimentations avec la méthode et le modèle de processeur sont également discutées. Elles permettent de prouver la validité de la méthode de dérivation de modèles de processeurs dédiés à une application.

## Abstract

With the time to market constraints for the development of embedded systems getting more rigid and shorter, and those systems getting increasingly complex, the designers must now use new methodologies in order to deliver their projects on time. Among the new methods now used, the reuse of components, available in the form of intellectual property (IP) blocs is very popular. However, the direct implementation of components, without any regards to the target application will lead to circuits that are sub-optimal. That is, many parts of the components may not be used at all by the application, but are implemented nonetheless. This would lead to a waste of available physical resources.

This master thesis presents a method to derive application-specific embedded processors that optimizes the circuits synthesized according to the target application. By introducing an extra step of optimization prior to final synthesis of the circuit, we can extract information from the application microcode, and optimize the processor for the execution of this specific application. We also describe the development of a parallel digital signal processor core designed to implement the derivation method. It has been developed to be highly configurable and optimizable, in an automatic way. Experiments with the method and the processor core are also presented, which prove the validity of the method for the derivation of application-specific embedded cores.

## Table des matières

|                                                                                                       |            |

|-------------------------------------------------------------------------------------------------------|------------|

| <b>IDENTIFICATION DES MEMBRES DU JURY .....</b>                                                       | <b>III</b> |

| <b>REMERCIEMENTS .....</b>                                                                            | <b>IV</b>  |

| <b>RÉSUMÉ .....</b>                                                                                   | <b>V</b>   |

| <b>ABSTRACT .....</b>                                                                                 | <b>VI</b>  |

| <b>TABLE DES MATIÈRES.....</b>                                                                        | <b>VII</b> |

| <b>LISTE DES TABLEAUX.....</b>                                                                        | <b>XI</b>  |

| <b>LISTE DES FIGURES .....</b>                                                                        | <b>XII</b> |

| <b>INTRODUCTION.....</b>                                                                              | <b>1</b>   |

| <b>CHAPITRE 1 .....</b>                                                                               | <b>6</b>   |

| <b>REVUE DE LITTÉRATURE ET RÉALISATIONS INDUSTRIELLES.....</b>                                        | <b>6</b>   |

| 1.1 PROCESSEUR XTENSA .....                                                                           | 7          |

| 1.2 ARC .....                                                                                         | 11         |

| 1.3 IMPROV SYSTEMS .....                                                                              | 13         |

| 1.4 DÉRIVATION DE PROCESSEURS POUR LA TOLÉRANCE AUX FAUTES .....                                      | 16         |

| 1.5 DÉRIVATION DE CIRCUITS À PARTIR D'UN ÉMULATEUR.....                                               | 19         |

| <b>CHAPITRE 2 .....</b>                                                                               | <b>24</b>  |

| <b>LA MÉTHODE DE DÉRIVATION DE MODÈLES DE PROCESSEURS<br/>EMBARQUÉS DÉDIÉS À UNE APPLICATION.....</b> | <b>24</b>  |

|                                                             |           |

|-------------------------------------------------------------|-----------|

| 2.1 INTRODUCTION .....                                      | 25        |

| 2.2 MOTIVATIONS .....                                       | 27        |

| 2.3 MÉTHODES DE DESIGN TRADITIONNELLES .....                | 29        |

| 2.4 OUTIL D'ANALYSE DU MICROCODE .....                      | 32        |

| 2.4.1 <i>Décodage des instructions</i> .....                | 32        |

| 2.4.2 <i>Statistiques d'utilisation</i> .....               | 34        |

| 2.5 ÉTUDE DE CAS : LE PROCESSEUR PULSE V1 .....             | 35        |

| 2.5.1 <i>Suite d'applications de test</i> .....             | 36        |

| 2.5.2 <i>Résultats d'analyses de la suite de test</i> ..... | 36        |

| 2.5.3 <i>Optimisations manuelles initiales</i> .....        | 39        |

| 2.6 OPTIMISATIONS DU MODÈLE .....                           | 40        |

| 2.6.1 <i>Élimination de ressources</i> .....                | 43        |

| 2.6.2 <i>Propagation de signaux constants</i> .....         | 44        |

| 2.6.3 <i>Tables de constantes locales</i> .....             | 45        |

| 2.6.4 <i>Recodage de champs</i> .....                       | 46        |

| 2.6.5 <i>Autres optimisations</i> .....                     | 46        |

| <b>CHAPITRE 3 .....</b>                                     | <b>48</b> |

| <b>ARCHITECTURE PRODSP .....</b>                            | <b>48</b> |

| 3.1 ARCHITECTURE PULSE .....                                | 49        |

| 3.1.1 <i>Description</i> .....                              | 49        |

| 3.1.2 <i>Réalisations</i> .....                             | 51        |

| 3.2 PRODSP .....                                            | 51        |

|                                                                    |           |

|--------------------------------------------------------------------|-----------|

| 3.2.1 <i>Description</i> .....                                     | 52        |

| 3.2.2 <i>Jeu d'instructions et architecture du microcode</i> ..... | 53        |

| 3.2.3 <i>Contrôleur</i> .....                                      | 55        |

| 3.2.4 <i>Configuration et État</i> .....                           | 59        |

| 3.2.5 <i>Communication et Entrées/Sorties</i> .....                | 60        |

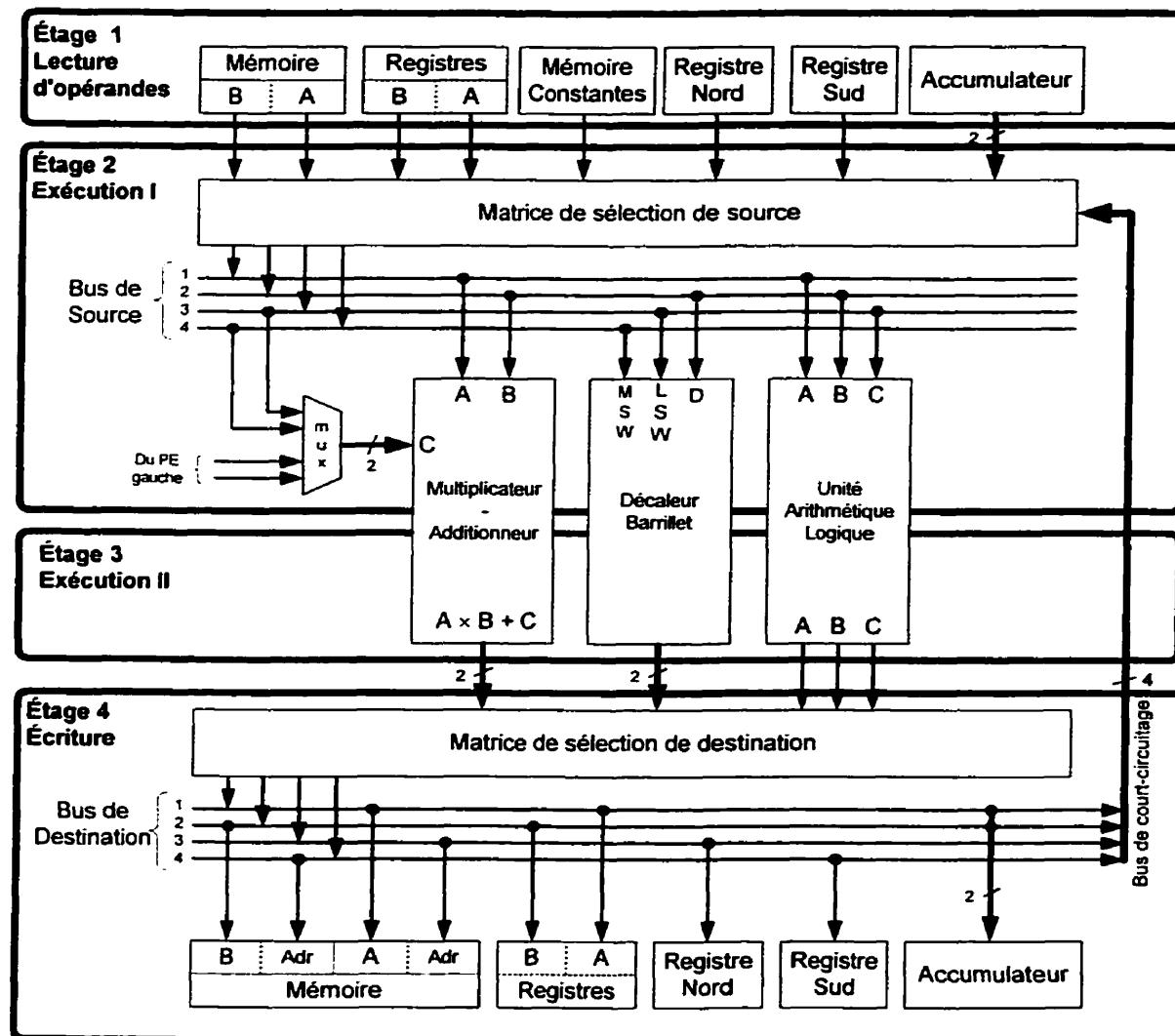

| 3.2.6 <i>Élément de calcul (PE)</i> .....                          | 63        |

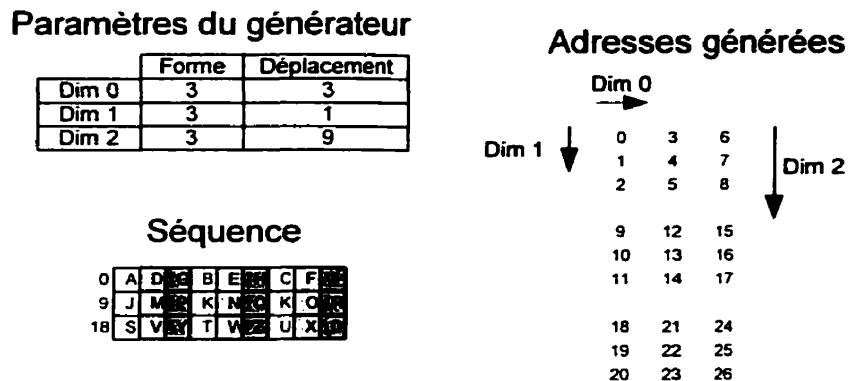

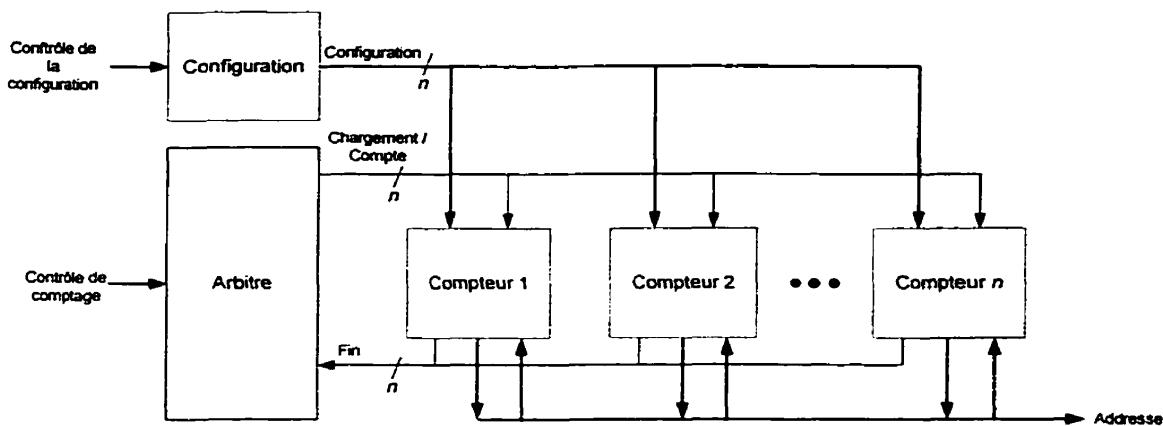

| 3.2.7 <i>Générateurs d'adresses externes</i> .....                 | 67        |

| 3.3 MÉTHODOLOGIE ET STYLE DE CODAGE .....                          | 70        |

| 3.3.1 <i>Paramètres et modules génériques</i> .....                | 71        |

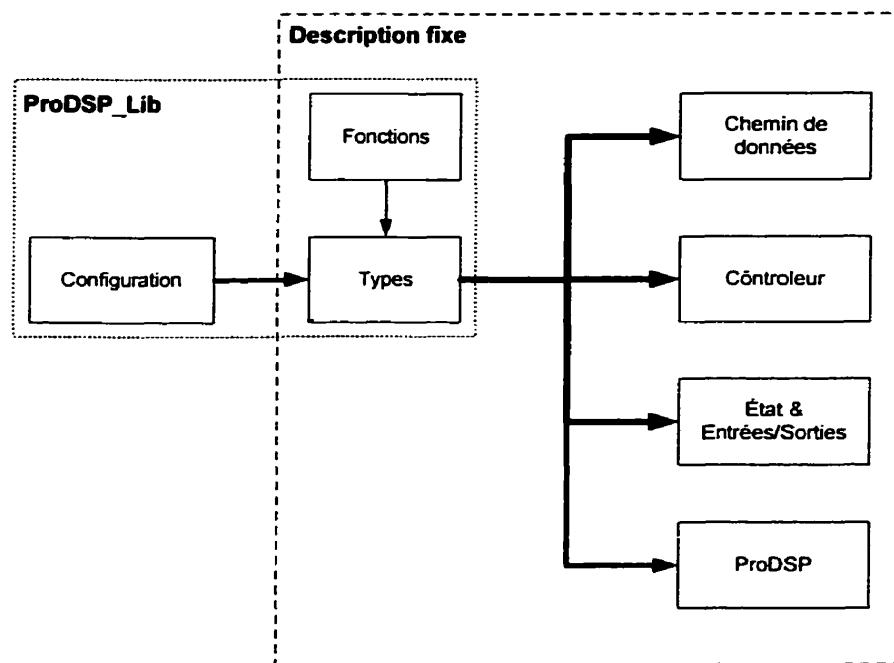

| 3.3.2 <i>Types et configuration</i> .....                          | 73        |

| 3.4 VALIDATION .....                                               | 79        |

| 3.5 OUTILS LOGICIELS.....                                          | 82        |

| 3.5.1 <i>Simulation</i> .....                                      | 82        |

| 3.5.2 <i>Synthèse</i> .....                                        | 83        |

| 3.5.3 <i>Problèmes rencontrés</i> .....                            | 84        |

| <b>CHAPITRE 4 .....</b>                                            | <b>85</b> |

| <b>OPTIMISATION DU MODÈLE .....</b>                                | <b>85</b> |

| 4.1 CONFIGURABILITÉ DU MODÈLE .....                                | 86        |

| 4.1.1 <i>Options de configuration</i> .....                        | 87        |

| 4.2 MODIFICATIONS DU MODÈLE .....                                  | 88        |

| 4.2.1 <i>Modifications du contrôleur</i> .....                     | 89        |

| 4.2.2 <i>Modifications du chemin de données</i> .....              | 90        |

|                                                            |            |

|------------------------------------------------------------|------------|

| <b>4.3 OUTIL D'OPTIMISATION .....</b>                      | <b>92</b>  |

| <i>4.3.1 Analyse du microcode.....</i>                     | <i>93</i>  |

| <i>4.3.2 Génération du modèle.....</i>                     | <i>93</i>  |

| <i>4.3.2.1 Constructions en langage HDL.....</i>           | <i>94</i>  |

| <i>4.3.2.2 Générateur de code HDL .....</i>                | <i>96</i>  |

| <i>4.3.2.3 Générateur de modèle ProDSP .....</i>           | <i>97</i>  |

| <i>4.3.3 Recodage du microcode.....</i>                    | <i>98</i>  |

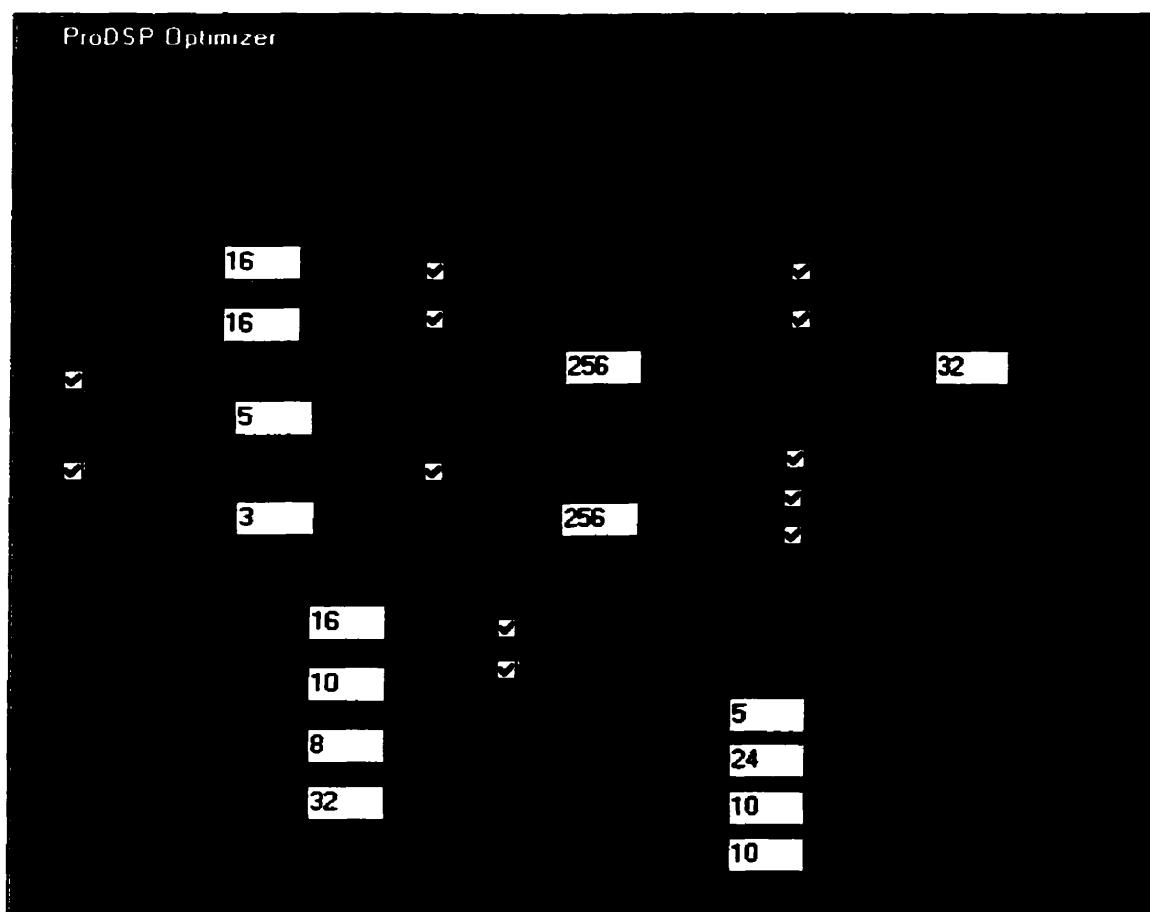

| <b>4.4 INTERFACE-USAGER ET EXEMPLE D'UTILISATION .....</b> | <b>99</b>  |

| <b>4.5 ÉTUDES DE CAS.....</b>                              | <b>101</b> |

| <i>4.5.1 Applications de test.....</i>                     | <i>101</i> |

| <i>4.5.2 Configurations de test.....</i>                   | <i>102</i> |

| <i>4.5.3 Synthèse des modèles de test.....</i>             | <i>103</i> |

| <i>4.5.4 Résultats des optimisations.....</i>              | <i>104</i> |

| <b>CONCLUSION .....</b>                                    | <b>108</b> |

| <b>RÉFÉRENCES.....</b>                                     | <b>114</b> |

## Liste des tableaux

|                                                                                                         |     |

|---------------------------------------------------------------------------------------------------------|-----|

| Tableau 1.1 Résultats quantitatifs de synthèse du contrôleur de processeur (Pflanz et al., 1998) .....  | 19  |

| Tableau 1.2 Utilisation globale des ressources pour différents algorithmes (Kraljic et al., 1996) ..... | 23  |

| Tableau 2.1 Utilisation des signaux de contrôle pour la suite d'applications de test .....              | 37  |

| Tableau 3.1 Modes d'adressage de la mémoire de l'architecture ProDSP .....                              | 77  |

| Tableau 3.2 Modes d'adressage de la mémoire pour un exemple d'application .....                         | 77  |

| Tableau 4.1 Options de configuration du processeur ProDSP .....                                         | 87  |

| Tableau 4.2 Configuration du modèle ProDSP pour les différentes applications .....                      | 103 |

| Tableau 4.3 Résultats de synthèse pour les différentes applications .....                               | 105 |

## Liste des figures

|                                                                                                                          |    |

|--------------------------------------------------------------------------------------------------------------------------|----|

| Figure I.1 Complexité des designs et productivité des concepteurs (SEMATECH, 1999) .....                                 | 3  |

| Figure 1.1 Flot de conception d'un processeur Xtensa (Tensilica, 2000) .....                                             | 8  |

| Figure 1.2 Flot d'information pour la conception d'un processeur avec la technologie<br>Tensilica (Tensilica, 2000)..... | 10 |

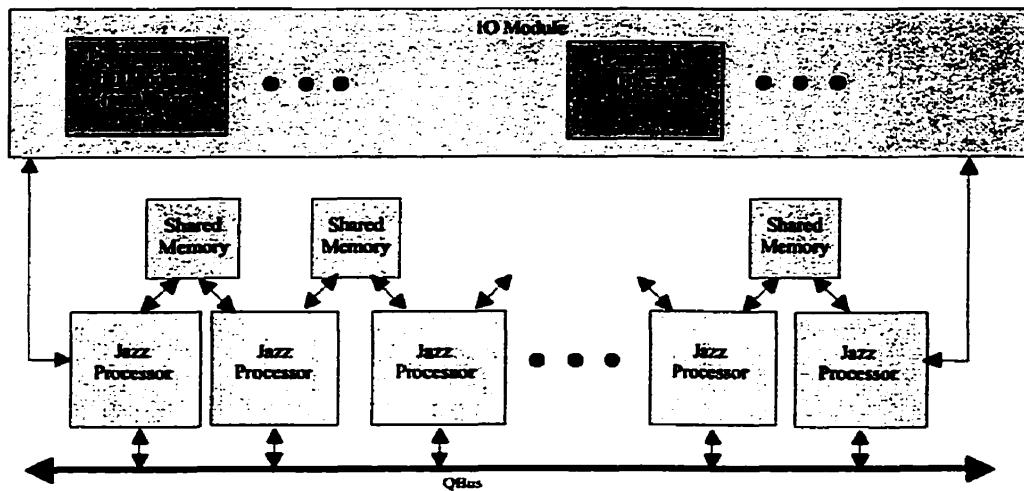

| Figure 1.3 Architecture du processeur Jazz (Improv, 2000).....                                                           | 14 |

| Figure 1.4 Architecture de la plate-forme de Improv (Improv, 2000).....                                                  | 15 |

| Figure 1.5 Flot de design pour la synthèse spécifique à une application (Pflanz et al.,<br>1998) .....                   | 18 |

| Figure 1.6 Architecture du processeur de flot de données (Kraljic et al., 1996) .....                                    | 20 |

| Figure 1.7 Portion du processeur active pour l'opérateur d'addition (Kraljic et al., 1996) .....                         | 21 |

| Figure 1.8 Flot de design pour la dérivation à partir des résultats d'émulation (Kraljic et<br>al.,1996) .....           | 22 |

| Figure 2.1 Méthode traditionnelle de synthèse d'un processeur embarqué pour une<br>implantation SOC.....                 | 31 |

| Figure 2.2 Dérivation de modèles de processeurs embarqués dédiés à une application<br>spécifique .....                   | 42 |

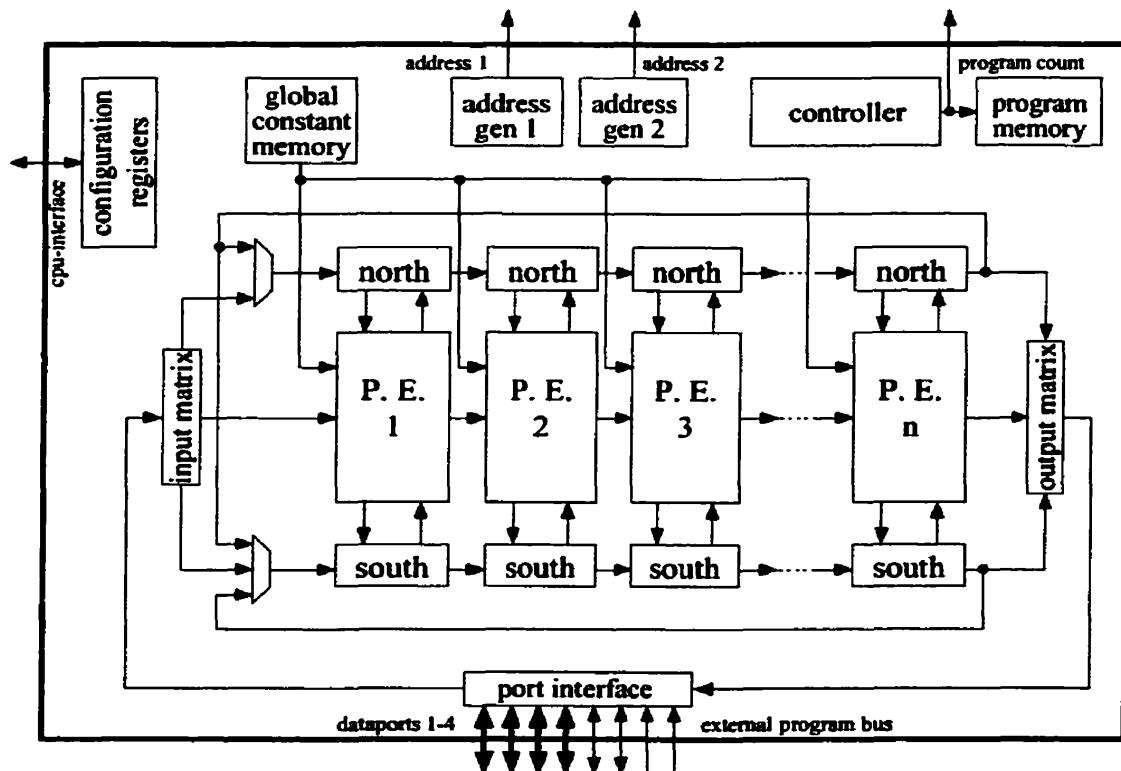

| Figure 3.1 Architecture PULSE simplifiée (Marriott et al., 1998) .....                                                   | 50 |

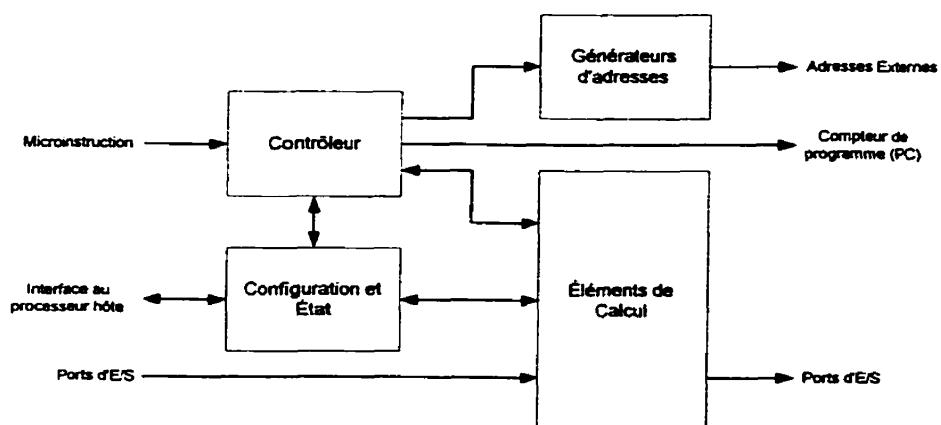

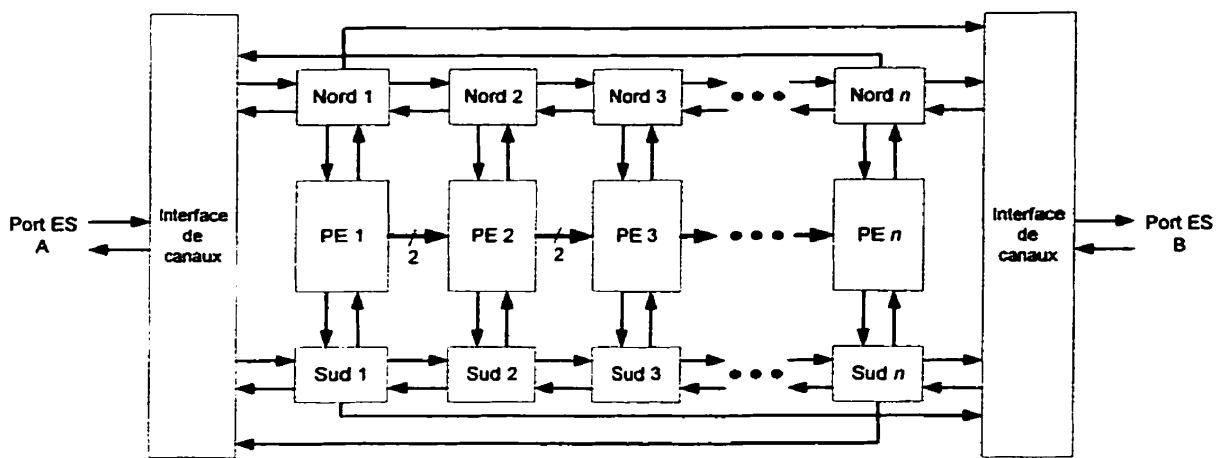

| Figure 3.2 Diagramme bloc de l'architecture ProDSP.....                                                                  | 52 |

| Figure 3.3 Diagramme bloc du Contrôleur ProDSP .....                                                                     | 55 |

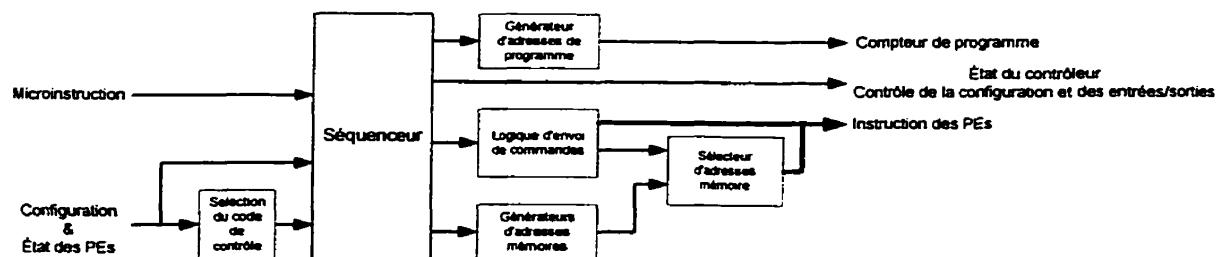

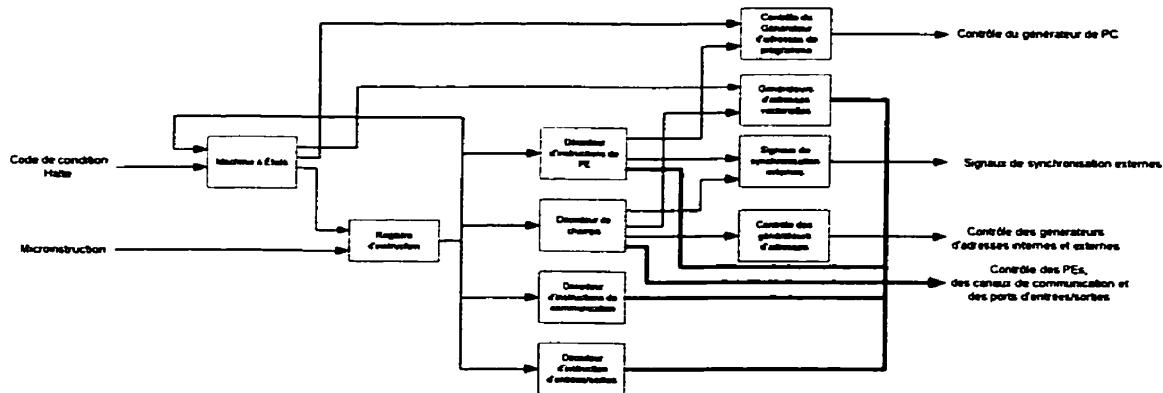

| Figure 3.4 Diagramme bloc du Séquenceur.....                                                                             | 56 |

|                                                                                     |     |

|-------------------------------------------------------------------------------------|-----|

| Figure 3.5 Diagramme bloc des canaux de communication .....                         | 61  |

| Figure 3.6 Pipeline du chemin de données de ProDSP .....                            | 64  |

| Figure 3.7 Exemple de génération d'adresses .....                                   | 68  |

| Figure 3.8 Diagramme bloc du générateur d'adresses linéaires à $n$ dimensions ..... | 69  |

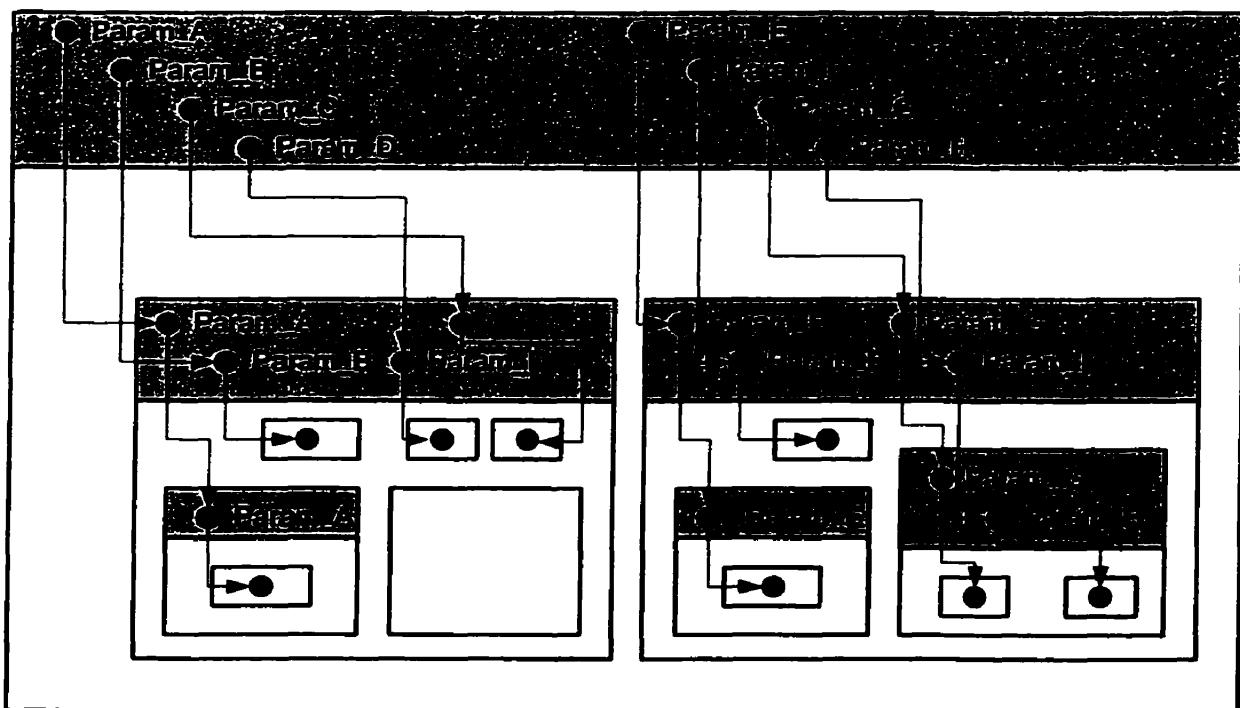

| Figure 3.9 Passage de paramètres par clauses génériques .....                       | 72  |

| Figure 3.10 Génération et propagation des types .....                               | 78  |

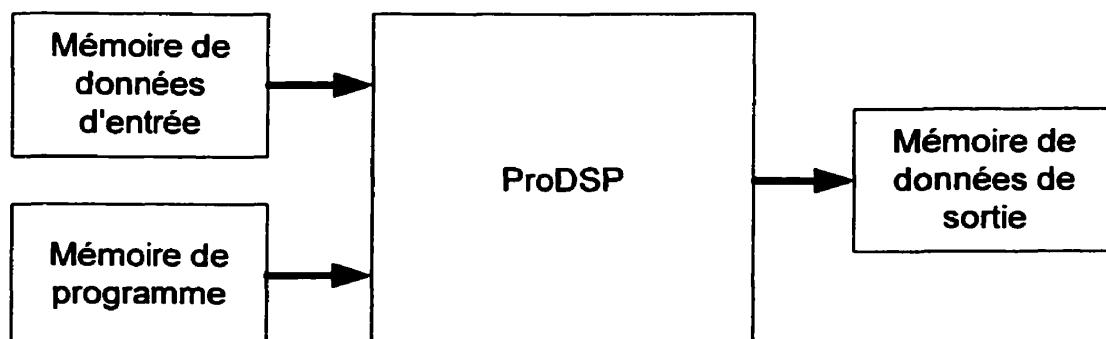

| Figure 3.11 Banc de test du modèle ProDSP .....                                     | 81  |

| Figure 4.1 Exemple de code sans modification pour granularité fine .....            | 91  |

| Figure 4.2 Exemple de code avec modifications pour granularité fine .....           | 92  |

| Figure 4.3 Interface-usager de l'optimiseur .....                                   | 100 |

## Introduction

Au cours des dernières années, la technologie de fabrication de dispositifs électroniques a connu une évolution fulgurante. De ce fait, on a vu apparaître des systèmes électroniques d'une très grande complexité dans les domaines traditionnels d'utilisation de tels systèmes, tels l'informatique et les télécommunications. On a également assisté à une prolifération de systèmes électroniques embarqués, dans un grand nombre d'appareils fort diversifiés, allant de la voiture au grille-pain.

D'autres facteurs ont contribué à la popularité rapidement grandissante de ces systèmes embarqués. Tout d'abord, la démocratisation des réseaux de communication, en particulier Internet, ont favorisé une adoption rapide d'items reliés aux technologies de l'information. Par ailleurs, on assiste présentement à un fort développement de l'industrie des communications sans fil, notamment par les réseaux cellulaires numériques (SCP : Système de communication personnel).

La tendance actuelle est à la convergence de toutes ces technologies, notamment par l'intégration de l'accès réseau aux divers appareils. On a d'ailleurs commencé à voir apparaître des téléphones cellulaires permettant d'accéder à Internet, ainsi que des appareils domestiques se connectant sur le réseau pour effectuer leurs fonctions (*internet applicances.*)

Toute cette intégration de service requiert des systèmes électroniques particulièrement puissants et complexes. Toutefois, comme ce sont des systèmes embarqués, ils sont soumis à une multitude de contraintes immuables. Celles-ci sont notamment la performance du système, la dissipation de puissance, le coût de production et finalement l'intégration des composantes qui forment le système.

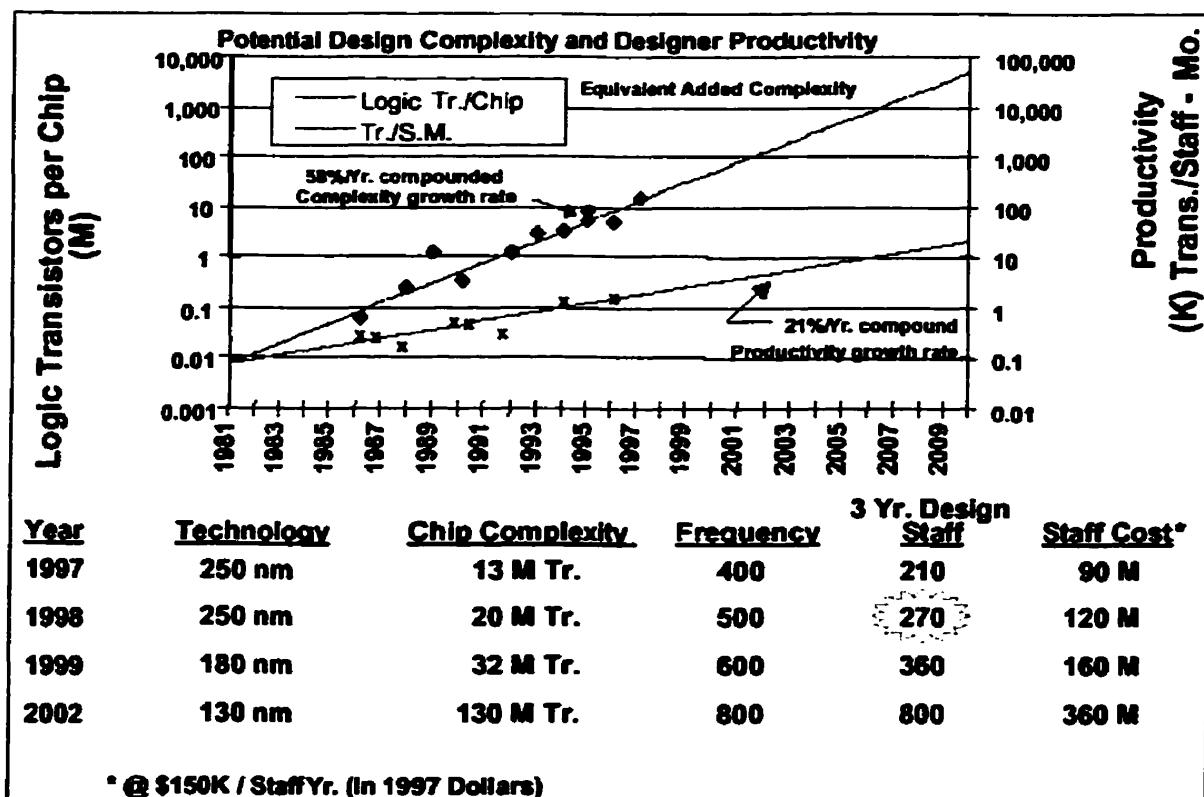

Avec la disponibilité de plate-formes cibles disposant de plusieurs millions de portes logiques équivalentes, tant sous la forme de logique programmable (FPGA : *Field Programmable Gate Arrays*) que de circuits intégrés à application spécifique (ASIC : Application Specific Integrated Circuit), on a vu apparaître une nouvelle façon de réaliser des systèmes embarqués : des systèmes sur une puce (SOC : *System-on-a-chip*). Toutefois, bien que la technologie soit capable de supporter des systèmes de plus en plus complexes, le temps et les ressources nécessaires pour réaliser de tels systèmes embarqués deviennent de plus en plus importants également. Ainsi, la productivité des concepteurs avec les méthodologies et les outils actuels ne suit pas la complexité possible des circuits intégrés. Ainsi, d'après (SEMATECH, 2000), un design de circuit de 32 millions de transistors en 1999 coûte environ 160 millions de dollars, et requiert 360 personnes pendant trois ans. Toutefois, un design de 130 millions de transistors (en suivant la capacité de fabrication) en 2002, coûterait 360 millions de dollars, et demanderait un personnel de 800 personnes. Ainsi, la complexité des designs augmente de 58% par année, alors que la productivité des concepteurs n'augmente que de 21% par année. Ceci est illustré à la figure I.1.

Pour tenter de vaincre cette disparité entre la productivité et la capacité de production, de nouvelles méthodologies de design sont apparues et continuent d'être développées. Ainsi, on tente d'introduire la réutilisation de composantes sous forme de blocs de propriété intellectuelle, tel que décrit en détails dans (Keating et al., 1999). Une autre méthodologie actuellement en développement est le codesign simultané des composantes logicielles et matérielles. Toutefois, ceci n'est pas encore suffisamment mature pour une utilisation industrielle courante.

**Figure I.1 Complexité des designs et productivité des concepteurs (SEMATECH, 1999)**

La dérivation de modèles est une autre méthode, qui est essentiellement une forme de réutilisation de composantes, mais qui optimise la composante en fonction de l'utilisation que l'on va en faire. Dans le cas d'un processeur, en connaissant à l'avance l'application qui devra être exécutée sur celui-ci, on peut optimiser les circuits qui forment le processeur de façon à obtenir un processeur optimal pour l'application spécifique qui est visée.

Ce mémoire expose les travaux qui ont été effectués dans le cadre du développement d'une méthodologie de dérivation de modèles processeurs embarqués dédiés à une application spécifique. On élaborera également sur le développement d'un modèle de processeur capable d'implanter la méthodologie de dérivation.

Ainsi, le premier chapitre de ce mémoire est essentiellement une revue des réalisations commerciales et de la littérature en ce qui a trait au domaine des processeurs configurables, ainsi que des méthodes de dérivation de processeurs. Il existe encore bien peu de modèles de processeurs configurables disponibles commercialement. En fait, seules deux compagnies sont des joueurs majeurs dans cette industrie pour l'instant. Pour ce qui est des méthodologies de dérivation, bien peu de recherche a été effectuée, et on retrouve que deux méthodes dans la littérature : une ayant pour but la minimisation de la complexité des circuits dans le but de réaliser des systèmes redondants, alors que l'autre est basée sur une méthodologie de dérivation à partir de résultats d'émulation de circuits.

Le deuxième chapitre présente la méthodologie de dérivation. À partir des flots de conception actuels, on élaborera sur le contexte d'utilisation de la méthode. Puis, on expliquera la justification du développement d'une telle méthode. On présentera par la suite un outil d'analyse de microcode permettant d'effectuer les premières analyses pour valider l'utilité de la méthode. On présentera ensuite l'étude de cas qui a été réalisée avec l'analyseur de microcode. Finalement, on détaillera la méthode automatique d'optimisation que l'on propose.

Le troisième chapitre présente le modèle de processeur qui a été développé pour implanter la méthode de dérivation. Ainsi, on expliquera d'abord l'architecture PULSE qui était l'architecture d'origine. Puis les parties importantes du processeur seront décrites. La méthodologie et le style de codage du modèle de processeur seront détaillés. Finalement, on discutera de la validation, ainsi que des outils utilisés tout au long de la réalisation de ce modèle de processeur.

Le quatrième et dernier chapitre présente le travail qui a été réalisé pour automatiser l'optimisation du modèle de processeur en fonction d'une application spécifique. On commencera par présenter les modifications que l'on a faites au modèle de processeur et la configurabilité de celui-ci. Puis, on présentera l'outil d'optimisation lui-même en discutant des options et des compromis. Un exemple d'utilisation, avec l'interface-usager et les différentes options sera présenté. Finalement, les résultats de quelques études de cas seront détaillés.

## Chapitre 1

### Revue de littérature et réalisations industrielles

Ce chapitre a pour but de présenter les diverses réalisations qui ont été effectuées dans des champs d'intérêts qui s'apparentent aux travaux décrits dans le présent mémoire. En effet, il existe bien peu de recherche et de travaux qui ont été réalisés sur la dérivation de processeurs ou l'optimisation de processeurs en fonction d'applications spécifiques.

On commencera par présenter les modèles de processeurs configurables les plus populaires, soient ceux des compagnies Tensilica, ARC Cores et Improv Systems. Le modèle de cette dernière compagnie est particulièrement intéressant, puisqu'il accompagne une méthode de développement de systèmes à partir d'un concept de plate-forme.

Finalement, on présentera une méthode de dérivation de processeur qui a été proposée pour générer des processeurs tolérants aux fautes, ainsi qu'une autre qui permettait de générer des automates de vision numérique à l'aide d'un émulateur matériel.

## 1.1 Processeur Xtensa

Une des compagnies majeures dans le domaine des modèles de processeurs configurables est Tensilica. Celle-ci est un fournisseur de blocs de propriété intellectuelle, principalement des processeurs de type RISC (*Reduced Instruction Set Computing*). L'architecture du processeur Xtensa, le principal produit de Tensilica, est une architecture de type 32 bits, entièrement nouvelle, qui correspond davantage aux besoins des systèmes embarqués d'aujourd'hui, comparativement aux modèles de processeurs similaires, qui avaient été conçus à la base pour une utilisation dans des stations de travail. Les caractéristiques de base du processeur sont les suivantes :

- Complexité d'environ 25 000 portes logiques, ce qui donne une utilisation d'environ  $0.7 \text{ mm}^2$  de surface de silicium, pour une implantation en technologie  $0.18\mu\text{m}$ .

- Haute performance : Plus de 220 MIPS (Millions d'instructions par seconde) pour une fréquence d'horloge de 200 MHz.

- Faible consommation de puissance : 0.4 mW/MHz pour une configuration typique, avec une implantation en technologie  $0.18 \mu\text{m}$ .

Une des particularités intéressantes de la technologie de Tensilica est la façon dont sont produits les modèles de processeurs. En effet, le modèle de processeur est configurable et peut être adapté en fonction d'une application spécifique. Ainsi, le concepteur dispose

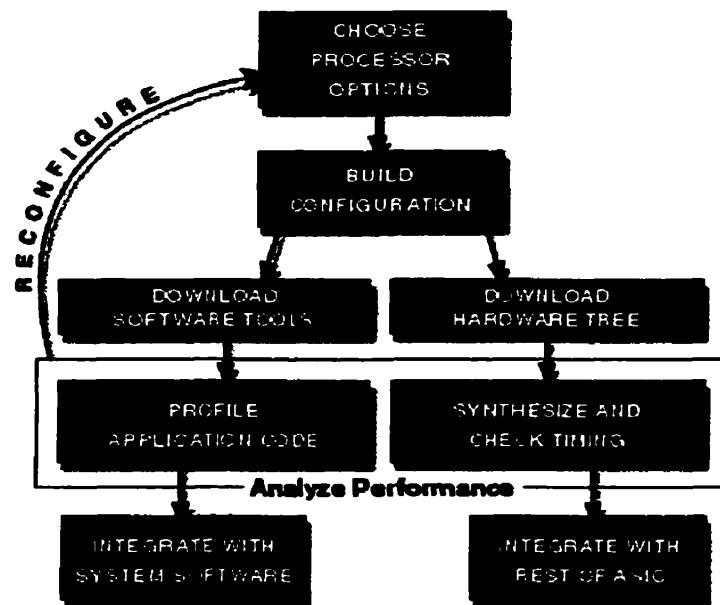

d'un grand nombre d'options pour générer un processeur dédié à application. Tout d'abord, on peut spécifier certains paramètres plus généraux, comme par exemple la fréquence d'opération ciblée, la complexité globale du processeur, le compromis entre la performance et la faible consommation de puissance, etc. Puis, une série d'options plus spécifiques, comme par exemple l'inclusion d'instructions spécifiques (i.e.: *min.* *max*) ou d'éléments de calcul (multiplicateur-additionneur). De plus, on doit choisir la taille des mémoires caches, ainsi que la fonctionnalité des interruptions. Finalement, on peut également rajouter des instructions au processeurs, en les décrivant dans un langage appelé TIE (*Tensilica Instruction Extension*). Tout ceci correspond à la première étape du flot de conception, illustré à la figure 1.1.

Figure 1.1 Flot de conception d'un processeur Xtensa (Tensilica, 2000)

Une fois les options de configuration choisies, on peut procéder à générer le modèle en langage HDL (*Hardware Description Language*), ainsi que les outils logiciels. Puis, on peut procéder à effectuer le profilage du code de l'application pour déterminer si le modèle est bien adapté à l'application que l'on vise. On peut également procéder à la synthèse du processeur et vérifier si celui-ci répond aux spécifications. Si ce n'est pas le cas, on peut retravailler la configuration et rajouter des instructions spécifiques de façon à améliorer le temps d'exécution de l'application. Finalement, on procède à intégrer le logiciel et le processeur avec le reste du système.

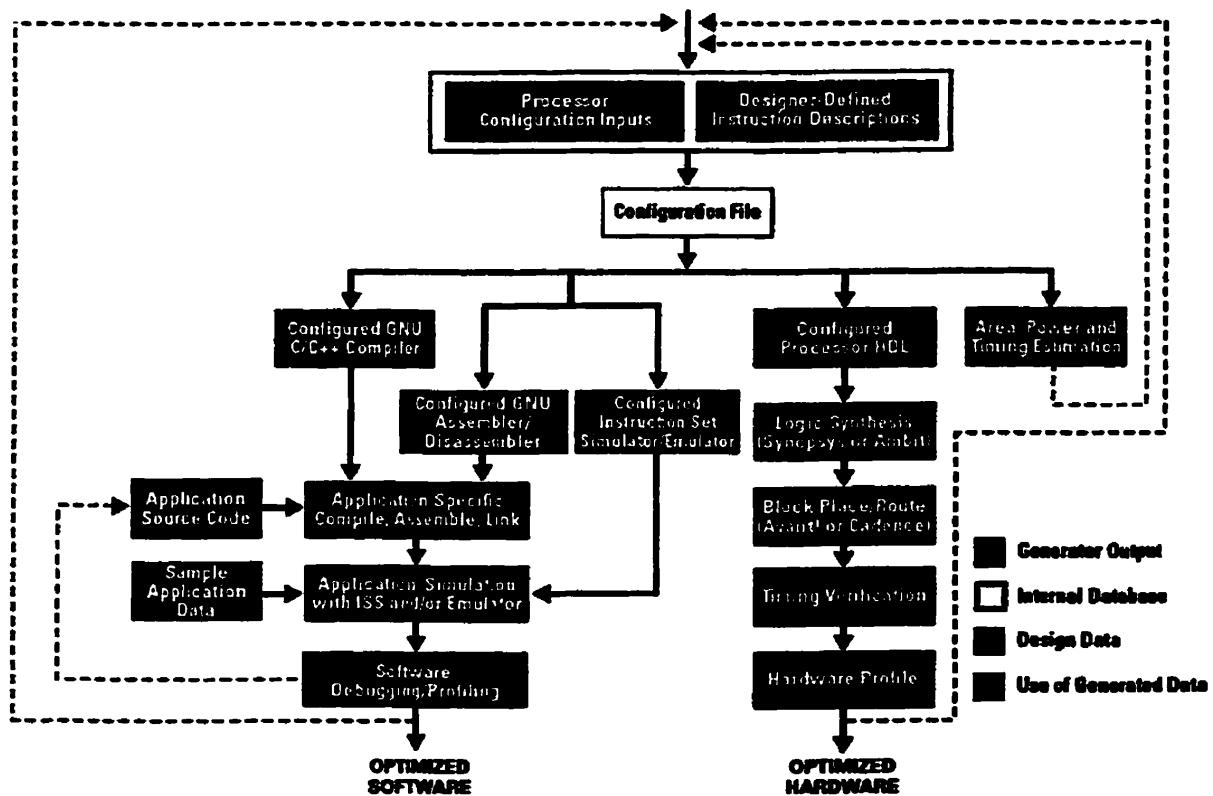

Une des particularités intéressantes de la technologie de Tensilica est le fait que les outils logiciels spécifiques au modèle de processeur dédié soient générés automatiquement. La figure 1.2 illustre le flot complet de l'information lors de la réalisation d'un modèle de processeur. On voit qu'en plus du modèle de processeur HDL et les estimations de *timing*, surface et consommation de puissance, on obtient la suite d'outils GNU pour le développement logiciel.

Ainsi, le compilateur C/C++, l'assembleur/désassembleur ainsi que le simulateur au niveau instruction sont générés automatiquement. Ceux-ci sont adaptés à l'architecture spécifique de la configuration du processeur que l'on conçoit. Ceci facilite grandement le développement du logiciel. De plus, le processeur est supporté par les systèmes d'exploitation temps-réel, ainsi que les outils de simulation de codesign logiciel/matériel les plus populaires.

Finalement, la compagnie propose maintenant un coprocesseur appelé Vectra, qui est construit de la même façon. Celui-ci a été conçu de façon à s'intégrer avec le modèle de processeur Xtensa. Il permet de réaliser de façon efficace des opérations de traitement de signal qui requièrent une puissance de calcul importante. L'architecture du coprocesseur est un croisement entre une architecture SIMD (*Single Instruction Multiple Data*) et un processeur vectoriel standard.

**Figure 1.2 Flot d'information pour la conception d'un processeur avec la technologie Tensilica**

(Tensilica, 2000)

## 1.2 ARC

La seconde compagnie importante dans le domaine des modèles de processeurs configurables est en fait celle qui fut la première à lancer son produit sur le marché, soit la compagnie ARC Cores Ltd. en 1997.

L'architecture proposée par la compagnie est de type RISC à 32 bits. Celle-ci a été optimisée de façon à pouvoir être fortement configurable. Les performances sont relativement similaires à celles du processeur Xtensa de la compagnie Tensilica. Ainsi, le processeur peut atteindre une fréquence d'opération supérieure à 200 MHz pour une implantation en technologie CMOS de 0.18 µm. La complexité dépend quant à elle des différentes options de configuration. En effet, une configuration minimale ne requiert qu'environ 8000 portes logiques, alors qu'une configuration maximale, avec les extensions pour le traitement de signal numérique, puisse demander plus de 100 000 portes logiques. Pour ce qui est de la consommation de puissance, l'architecture peut être optimisée de façon à minimiser celle-ci, notamment en utilisant des portes pour contrôler le passage de l'horloge dans certaines parties du processeur (*gated clocks*).

Le processus de réalisation d'un modèle de processeur ARC est relativement similaire à celui d'un processeur Xtensa. Toutefois, le nombre d'options de configuration disponibles est plus élevé. Ainsi, le processeur ARC est plus facilement configurable et optimisable que le processeur Xtensa. De plus, de la même façon que pour le processeur Xtensa, on effectue le choix de la configuration que l'on va utiliser pour une application

en trois étapes : on commence par sélectionner les options de configuration. Puis, on génère les fichiers de configuration des différents outils, ainsi que le modèle de processeur. On effectue ensuite un profilage de l'application, de façon à déterminer si le logiciel peut s'exécuter tout en respectant les spécifications, et si le modèle de processeur se synthétise selon les spécifications. Si ce n'est pas le cas, on devra alors procéder à modifier le logiciel ou les choix de configuration du processeur et on recommencera le processus.

Les options de configuration sont relativement similaires à celles du processeur Xtensa, mais dans le cas de ARC, on offre davantage de possibilités et de flexibilité. Tout le travail de la sélection de la configuration est effectué à l'aide d'un environnement graphique intitulé ARChitect. Celui-ci sert à générer le modèle de processeur ainsi que les fichiers de configuration pour les outils et la documentation appropriée pour le processeur dédié.

Contrairement à la technologie de Tensilica, les outils de développement logiciels ne sont pas inclus gratuitement. Ceux-ci doivent être achetés de la compagnie MetaWare. Celle-ci offre une suite complète d'outils de développement, qui permettent de supporter les différentes configurations, ainsi que les instructions que le concepteur pourrait décider de rajouter à son processeur.

### 1.3 *Improv Systems*

Ce que la compagnie Improv Systems propose comme produit n'est pas un modèle de processeur configurable, mais plutôt une plate-forme configurable, à partir de laquelle on construit un système complet. En effet, la technologie est disponible sous deux formes : soit sous des blocs d'IP que l'on peut synthétiser et intégrer dans un système (comme par exemple le processeur Jazz) ou bien sous la forme d'un circuit intégré contenant toute la plate-forme configurable.

C'est cette dernière version qui distingue la technologie de cette compagnie des autres. En effet, la plate-forme configurable est une nouvelle approche pour la réalisation de systèmes embarqués. Une plate-forme configurable comprend une série de processeurs, de blocs de mémoires et de ports d'entrées/sorties configurable, un peu de la même façon qu'un FPGA (*Field Programmable Gate Array*) consiste en une série de tables de vérités et d'éléments de mémoire. La différence avec la plate-forme configurable est que le niveau d'abstraction est beaucoup plus élevé.

Le bloc principal de l'architecture de Improv est le processeur Jazz. Celui-ci est un processeur avec un mot d'instruction de type VLIW (*Very Long Instruction Word*) qui permet d'exploiter le parallélisme au niveau des instructions. Le processeur dispose de plusieurs unités de calcul lui permettant d'effectuer un grand nombre d'opérations en parallèle. Celui-ci est illustré à la figure 1.3.

Figure 1.3 Architecture du processeur Jazz (Improv, 2000)

Le processeur peut fonctionner à une fréquence de 150 MHz pour une implantation en 0.18 µm. Comme il peut exécuter entre 7 et 14 instructions par cycle d'horloge, on obtient une performance d'environ 1.5 milliards d'opérations par seconde (BOPS : *Billions of operations per second*).

La plate-forme proposée par Improv consiste en une série de processeurs Jazz, interconnectés entre eux par des mémoires partagées, ainsi qu'un bus. De plus, on dispose de mémoires globales, ainsi que d'un module d'entrées/sorties. L'architecture est illustrée à la figure 1.4 :

Figure 1.4 Architecture de la plate-forme de Improv (Improv, 2000)

Ainsi, on peut voir que chaque processeur est connecté à son voisin immédiat par une mémoire partagée. En plus, chaque processeur peut communiquer avec n'importe quel autre processeur via un bus partagé. Selon la compagnie, ce type d'architecture, qui ressemble à une architecture à flot de données (les données sont traitées en file par chacun des processeurs) se prête bien à des applications en télécommunication ou en électronique de consommation.

Ce qui est intéressant chez Improv est la façon dont sont développées les applications et donc le système. En effet, celles-ci sont décrites dans un langage de haut niveau : le Java. Une suite d'outils permet le développement et la vérification du code Java. Une fois l'application fonctionnelle, on utilise un compilateur qui va effectuer le partitionnement de l'application pour la distribuer sur les différents processeurs. De plus, il va gérer les communications, tant inter-processeurs, qu'avec les ports d'entrées/sorties. Ceci permet

un développement très rapide d'un système, puisque le concepteur n'a qu'à le décrire dans un langage de haut-niveau. En aucun cas le concepteur ne doit construire des modules en matériel ou écrire des routines en assembleur.

Les avantages de l'utilisation de telles plate-formes sont nombreux. Parmi ceux-ci on note :

- Le volume de production de circuits intégrés n'est pas dépendant du nombre de projets différents, puisqu'on utilise toujours la même plate-forme.

- Les outils de compilation sophistiqués permettent au concepteur de demeurer à un niveau d'abstraction élevé.

- Un environnement de développement unifié pour l'ensemble du système embarqué.

- La possibilité de configurer l'ensemble des composantes de la plate-forme.

- Aucun système d'exploitation n'est nécessaire.

#### **1.4 Dérivation de processeurs pour la tolérance aux fautes**

Une méthode de dérivation de processeurs dans le cadre de la réalisation de systèmes tolérants aux fautes a été proposée par un groupe de recherche de l'université de Cottbus en Allemagne (Pflanz et al., 1998).

L'approche proposée pour réaliser des systèmes tolérants aux pannes consiste à dupliquer les structures effectuant les opérations de calcul (comme les processeurs) et à utiliser un système de votation pour s'assurer qu'une majorité des structures donnent le même résultat.

Comme on désirait implanter un tel système de redondance en utilisant des circuits de logique programmable, on devait réduire la complexité des circuits, de façon à pouvoir générer plusieurs instances de chaque circuit dans un seul circuit programmable. Pour ce faire, les auteurs ont développé une méthodologie permettant d'effectuer la synthèse de processeurs spécifiques à une application.

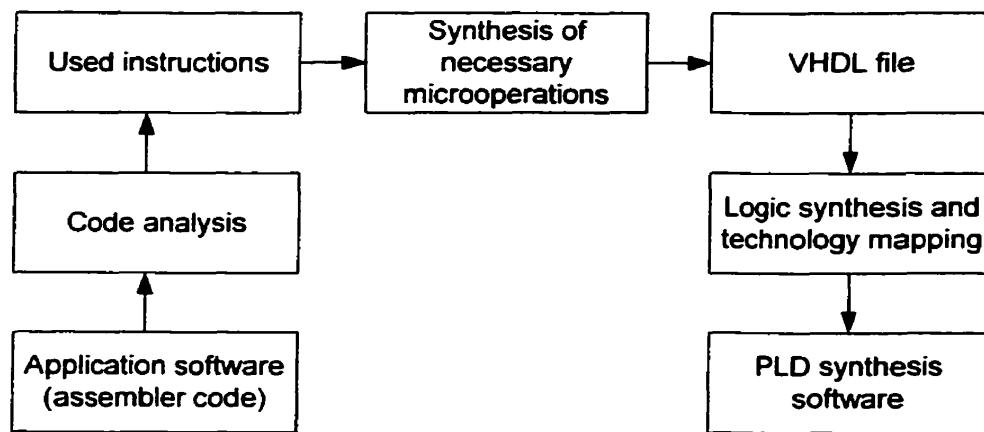

Ainsi, pour effectuer la réduction de la complexité du processeur à synthétiser, on commence par analyser les instructions qui sont utilisées par l'application. Chaque instruction requiert une certaine quantité de circuits qui doivent être implantés pour pouvoir supporter l'instruction. Ainsi, lorsque l'on a déterminé l'ensemble des instructions qui sont utilisées, on peut déterminer les circuits que l'on devra synthétiser pour pouvoir exécuter le code de l'application. Le modèle de processeur est décrit dans une forme structurelle en langage HDL. De cette façon, on peut facilement rajouter ou éliminer certains circuits du processeur. Le flot de design utilisé est illustré à la figure

1.5.

Figure 1.5 Flot de design pour la synthèse spécifique à une application (Pflanz et al., 1998)

Pflanz et al. ont implanté un processeur de type 8085, capable d'exécuter environ 60 microinstructions. L'ensemble du processeur, en excluant la mémoire interne, était d'une complexité d'environ 2500 portes logiques.

Ils ont effectué la synthèse du *contrôleur* de leur processeur pour différents programmes qui servaient d'exemples. Les programmes sont en fait des fonctions fort simples qui permettent d'effectuer des opérations simples avec le processeur. Les résultats qu'ils ont obtenus sont illustrés dans le tableau 1.1. Comme on peut le constater, les résultats de synthèse pour le *contrôleur* permettent de voir une réduction importante des circuits lorsque l'on élimine certaines instructions. De plus, il faut également tenir compte des structures opératives qui vont également être éliminées lorsque l'on retire des instructions.

**Tableau 1.1 Résultats quantitatifs de synthèse du contrôleur de processeur (Pflanz et al., 1998)**

| Fonction                           | Nombre de portes logiques | Nombre de nœuds |

|------------------------------------|---------------------------|-----------------|

| <b>Logique de contrôle entière</b> | <b>258</b>                | <b>332</b>      |

| ADD                                | 42                        | 150             |

| LOOP                               | 24                        | 135             |

| ADDSUB                             | 30                        | 138             |

| MULT                               | 43                        | 152             |

| LOGIC                              | 34                        | 139             |

| CONTR1                             | 52                        | 155             |

| CONTR2                             | 53                        | 156             |

Toute cette méthode de synthèse spécifique de processeurs permet de générer des circuits plus simples, qui vont pouvoir être implantés de façon redondante dans des circuits logiques programmables.

### **1.5 Dérivation de circuits à partir d'un émulateur**

Une dernière méthode de dérivation de processeurs a été proposée dans le cadre de la génération d'automates pour la vision numérique (Kraljic et al., 1996). Le principe est basé sur l'utilisation d'émulateurs matériels, qui permettent de simuler plus rapidement le fonctionnement d'un circuit en développement. Les émulateurs sont utilisés puisqu'ils permettent de diminuer les coûts reliés à la validation et à la simulation d'un circuit.

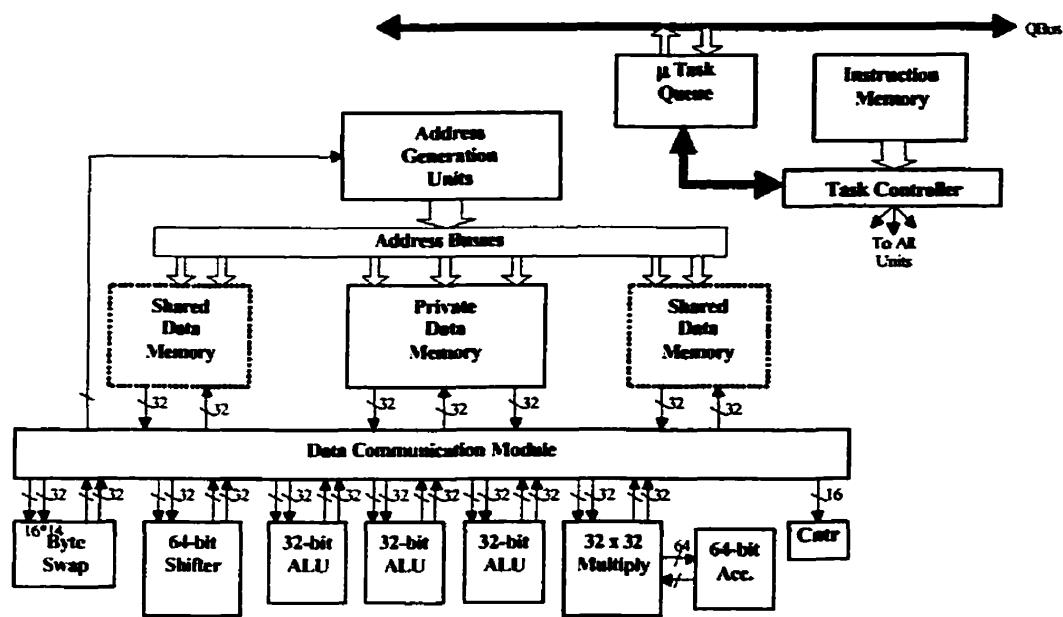

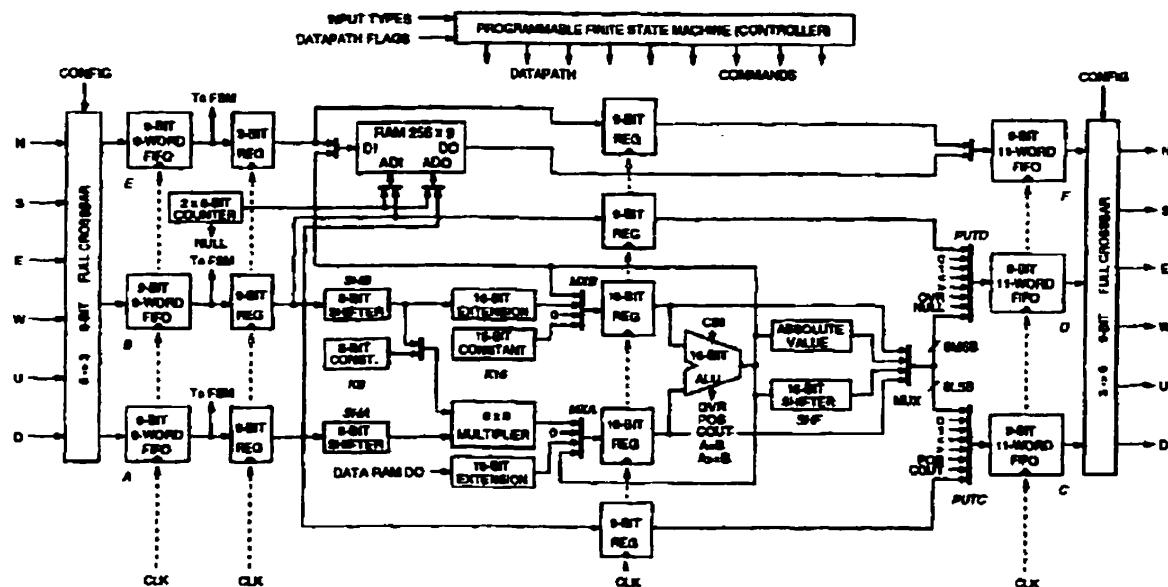

Ainsi, dans ce projet de recherche, la dérivation est faite à partir d'un processeur de flot de données (*data-flow processor*). Ainsi, l'émulateur consiste en fait en un vecteur tri-dimensionnel de processeurs de flot de données, chacun implantant un opérateur effectuant un traitement sur les données. L'architecture d'un tel processeur est donné à la figure 1.6. La configuration de chacun de ces processeurs permet de déterminer l'application qui va être implanté par l'ensemble du système.

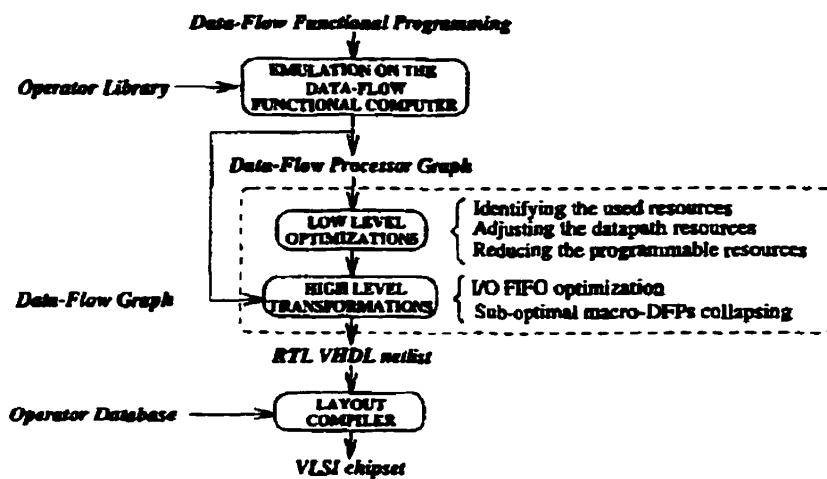

**Figure 1.6 Architecture du processeur de flot de données (Kraljic et al., 1996)**

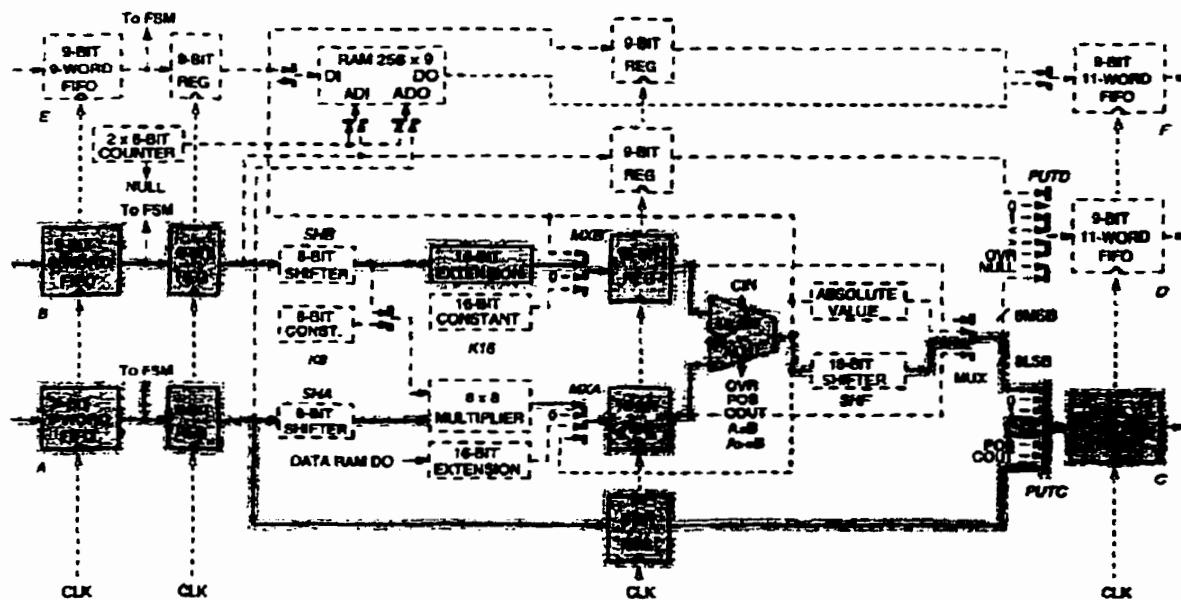

Une fois l'application décrite, on peut l'exécuter sur l'émulateur, de façon à valider le comportement de celle-ci. Lorsque le fonctionnement de l'application a été validé, on peut procéder à optimiser le circuit pour la synthèse finale du ASIC (*Application Specific*

*Integrated Circuit*) qui va planter l'application. En effet, comme les ressources de chaque processeur ne seront sûrement pas toutes utilisées pour l'implantation d'un opérateur, on peut procéder à effectuer une série d'optimisations de façon à réduire la complexité finale du circuit, tout en conservant la fonctionnalité. Par exemple, les éléments actifs dans le cas d'une opération d'addition sont illustrés à la figure 1.7 (éléments en gris).

Figure 1.7 Portion du processeur active pour l'opérateur d'addition (Kraljic et al., 1996)

Une série d'optimisations possibles, tant de haut niveau (en retravaillant le graphe de flot de données) que de bas niveau sont décrites dans l'article. Celles-ci permettent de réduire la complexité du circuit qui va être synthétisé. Le flot complet de design, incluant ces optimisations, est illustré à la figure 1.8.

Figure 1.8 Flot de design pour la dérivation à partir des résultats d'émulation (Kraljic et al., 1996)

Des études quantitatives ont été effectuées pour vérifier l'utilité de la méthode. Ainsi, les auteurs ont développé six applications et ont utilisé la méthode de dérivation pour obtenir des circuits optimisés dédiés pour les applications spécifiques. Le tableau 1.2 donne les résultats d'utilisation des ressources globales des processeurs en fonction des différentes applications qui ont été implantées. Comme on peut le constater, l'utilisation des ressources excède rarement utilisées plus de 50% et ce, pour l'ensemble des applications. Ceci fait en sorte que l'on peut facilement optimiser les circuits pour obtenir des circuits synthétisés beaucoup plus petits. Ces résultats vont être particulièrement utiles dans le cadre du projet décrit dans le présent mémoire.

**Tableau 1.2 Utilisation globale des ressources pour différents algorithmes (Kraljic et al., 1996)**

| Name                  | Edge<br>detector | 3 × 3<br>convolver | 2048<br>word<br>LUT | Nagao-<br>like | Defect<br>detector | Erosion<br>filter |

|-----------------------|------------------|--------------------|---------------------|----------------|--------------------|-------------------|

| <b>Operating DFPs</b> | 13               | 22                 | 25                  | 86             | 94                 | 110               |

| I/O ports %           | 41               | 43                 | 51                  | 50             | 45                 | 47                |

| Input FIFOs %         | 46               | 56                 | 70                  | 63             | 56                 | 62                |

| Output FIFOs %        | 35               | 31                 | 32                  | 36             | 34                 | 33                |

| Multiplier %          | 0                | 41                 | 0                   | 0              | 8                  | 0                 |

| True ALU op %         | 23               | 36                 | 0                   | 37             | 39                 | 43                |

| Data RAM %            | 15               | 18                 | 32                  | 13             | 12                 | 10                |

| Counter %             | 30               | 54                 | 0                   | 41             | 9                  | 54                |

| Prog RAM size %       | 3                | 8                  | 0                   | 9              | 5                  | 10                |

## Chapitre 2

### **La méthode de dérivation de modèles de processeurs embarqués dédiés à une application**

Ce chapitre présente la méthode de dérivation de processeurs embarqués spécifiques à une application, qui constitue la motivation principale du projet décrit dans le présent mémoire. On présentera dans le prochain chapitre l'architecture du processeur qui a été développé pour permettre d'utiliser la méthode décrite dans ce chapitre. Le dernier chapitre, quant à lui, présentera l'outil d'optimisation utilisé et les détails d'implantation pour appliquer la méthode sur le modèle de processeur développé.

On commencera par présenter le contexte dans lequel la méthode peut s'appliquer. Ainsi, certaines particularités dans le flot de conception actuel de systèmes ont permis de justifier une telle méthode. Puis, la motivation derrière le développement d'une telle méthode sera élaborée et on établira un lien avec des expérimentations antérieures. Ensuite, le flot traditionnel de design utilisé en industrie sera présenté, pour ensuite pouvoir le comparer avec notre méthode.

Un outil d'analyse de microcode sera ensuite décrit. Celui-ci nous a permis d'effectuer les premières analyses pour valider l'utilité de la méthode. On présentera ensuite l'étude de cas qui a été réalisée avec l'analyseur de microcode. Celle-ci est basée sur l'architecture de processeur PULSE qui va être présentée à la section 3.1. On détaillera le résultat des études préliminaires d'optimisations manuelles sur l'architecture PULSE, avant d'élaborer sur la méthode automatique d'optimisation que l'on propose. Celle-ci sera expliquée en détails, et on énumérera les différentes optimisations possibles.

## 2.1 *Introduction*

La vaste majorité des systèmes embarqués modernes disposent d'au moins un microprocesseur ou, d'un processeur de traitement de signal numérique (*DSP* : *Digital Signal Processor*). De plus, il est maintenant courant de retrouver plusieurs microprocesseurs ou DSP dans un système embarqué moyen. Par ailleurs, des plate-formes cibles disposant de plusieurs millions de portes logiques équivalentes sont maintenant couramment disponibles et ce, tant sous la forme de logique programmable (*FPGA* : *Field Programmable Gate Arrays*) ou de circuits intégrés à application spécifique (*ASIC* : *Application Specific Integrated Circuit*). Grâce à ces technologies, la possibilité de créer des systèmes sur une puce (*SOC* : *System-on-a-chip*) est maintenant une réalité. De plus, le temps disponible pour lancer un produit sur le marché (*time to market*) étant de plus en plus court, les concepteurs n'ont d'autre choix que d'effectuer de

la réutilisation de blocs déjà conçus. Ces blocs sont souvent disponibles sous la forme de blocs de propriété intellectuelle (IP : *Intellectual property*). Ainsi, un grand nombre de processeurs utilisés dans les systèmes embarqués, qui sont souvent utilisés pour exécuter de petits programmes à répétition sont, la majorité du temps, implanté à partir de blocs IP obtenus de différents fournisseurs.

Toutefois, même si de nos jours le nombre de portes logiques disponibles pour l'implantation des circuits est considéré comme étant plus qu'abondant, les exigences des systèmes embarqués font en sorte que le design de tels systèmes est toujours un défi. En effet, ceux-ci ont des besoins particuliers en ce qui a trait à la performance, la dissipation de puissance, l'intégration globale du système et surtout, les coûts de production. Ceci est encore le cas avec les SOC, où les techniques de design traditionnelles avec des blocs d'IP rigides (*hard IP cores*) n'utilisent pas de façon optimale les ressources disponibles. En effet, la plupart des applications n'utilisent pas toutes les composantes et fonctionnalités disponibles pour un modèle de processeur particulier. Ceci se produit notamment parce que le procédé de synthèse du processeur n'est pas lié à l'application spécifique qui va être exécuté sur le processeur dans le système en question.

C'est pourquoi, au cours des deux dernières années, on a vu apparaître de nouveaux types de blocs IP, comme les modèles configurables de processeurs (*soft cores*), tel que présenté dans le chapitre 1. Ces nouveaux types d'IP tentent d'exploiter davantage la flexibilité de la plate-forme SOC, et d'éliminer certains problèmes rencontrés avec les

blocs d'IP rigides, en permettant aux concepteurs de systèmes de configurer leur modèle de processeur pour les besoins de leur application-cible. Mais, encore une fois, l'optimisation réalisée est encore trop peu liée à l'application, et le modèle de processeur ainsi généré ne sera encore une fois pas optimal pour l'utilisation qu'on en fera.

C'est pourquoi une étape d'optimisation pourrait être introduite juste avant l'étape de synthèse. Cette optimisation permettra d'exploiter les particularités de l'application cible pour générer un processeur dédié à cette application. On aurait alors une méthode de dérivation de modèles de processeurs embarqués dédiés à une application.

## 2.2 Motivations

Un ensemble de facteurs a motivé le développement de ce projet. Tout d'abord, le temps de développement est maintenant un des obstacles majeurs auxquels sont confrontés les concepteurs. Les périodes de développement raccourcissent et la complexité des projets augmente constamment. Il devient alors impératif d'effectuer la réutilisation de certains blocs qui composent un système. Toutefois, il est toujours plus long de concevoir un module particulier à une application à partir de zéro ou en utilisant des bibliothèques de composants, que de dériver automatiquement un modèle spécifique à partir d'un modèle à utilisation générale.

Le temps nécessaire à la validation est particulièrement coûteux. En effet, celui-ci peut facilement accaparer plus des deux tiers du temps nécessaire pour la réalisation d'un système. La dérivation d'un modèle spécifique à partir d'un modèle générique permet de construire un modèle qui est correct par construction. Ainsi, un modèle ne comportant qu'un sous-ensemble de modules d'un modèle complet préalablement validé devrait normalement être fonctionnel, et ne requérir que très peu de validation pour s'assurer de son bon fonctionnement.

Finalement, les modèles dédiés à une application sont plus simples que les modèles à usage général. Ceci est dû au fait que bien souvent une bonne partie de la fonctionnalité non-utilisée est éliminée. À cause de cela, les circuits synthétisés vont être plus simples. Ces circuits plus simples vont être plus performants, dissiper moins de puissance et nécessiter moins de portes logiques (et donc moins de ressources) à l'implantation.

Un projet de recherche antérieur avait prouvé la validité de la méthode de dérivation dans le design d'automates de vision numérique à flot de donnés (Kraljic et al., 1996). Ainsi, dans ce projet de recherche, une application de traitement d'image était en premier lieu implantée et validée en temps-réel sur un émulateur disposant de 1024 processeurs. Ensuite, une description RTL (*Register Transfer Level*) qui représentait l'architecture minimale nécessaire à l'implantation de l'application était extraite en langage VHDL, à partir du graphe de processeurs de l'application.

La méthode de dérivation décrite dans le présent mémoire améliore celle proposée par Kraljic (1996), puisque les modèles de processeurs dédiés seront dérivés directement à partir d'un modèle VHDL validé. De plus, aucune architecture spécifique n'est vraiment visée, bien que dans le cadre de notre projet, un processeur de traitement de signal numérique de type SIMD (*Single Instruction Multiple Data*) sera notre cible initiale. Ainsi, le champ d'application visé dépasse les applications de vision numérique. Finalement, aucun émulateur matériel, coûteux et rapidement obsolète, n'est nécessaire. Seulement les outils traditionnels de design et de simulation, en plus de quelques outils spécifiques simples à développer.

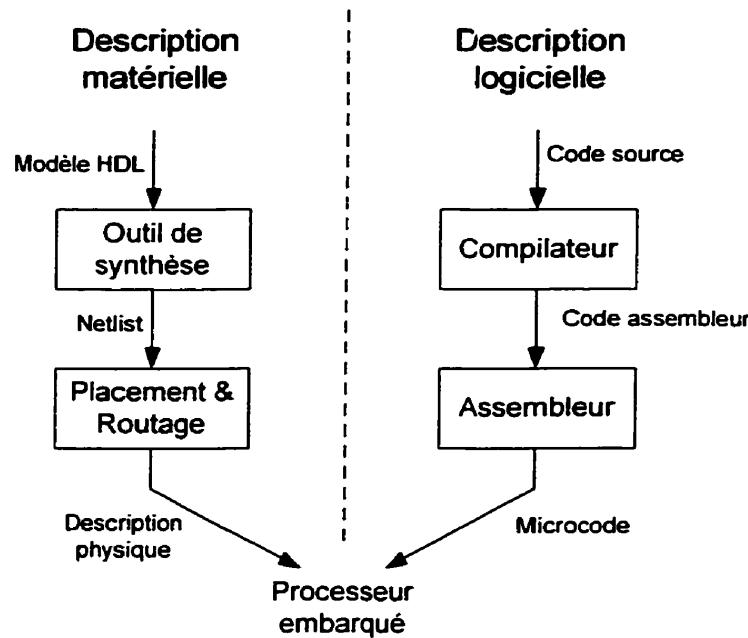

### **2.3 Méthodes de design traditionnelles**

Les méthodes de design traditionnelles de systèmes embarqués, qui impliquent l'utilisation de blocs de propriété intellectuelle (IP) pour implantation sur un système-sur-une-puce, comportent habituellement deux phases distinctes et pratiquement indépendantes, soit le design du matériel et le développement du logiciel. Habituellement, le développement du matériel n'implique que le choix du modèle de processeur qui va disposer du jeu d'instruction, de la puissance de calcul et des périphériques nécessaires pour l'application que l'on désire implanter. Le modèle de processeur, généralement disponible sous la forme d'un modèle rigide (*hard core*), est habituellement décrit avec un sous-ensemble synthétisable d'un langage de description de matériel (HDL : *Hardware Description Language*), comme le VHDL ou le Verilog, ou bien sous la forme

d'une liste de portes logiques et d'interconnexions (*netlist*). Le développement du logiciel est effectué normalement après le choix du modèle de processeur, de façon à pouvoir exploiter les particularités du modèle de processeur choisi. Cet échange d'information (développement du logiciel en fonction du type de processeur) est le seul qui aura lieu entre les flots de design matériel et logiciel et ce, pour toute la durée de la conception du système.

Ainsi, lorsque les parties matérielles et logicielles du système sont complétées, et que les deux ont été simulées et validées en profondeur, le système est alors synthétisé et intégré. Ceci est habituellement réalisé avec des outils de synthèse et de placement et routage dans le cas de la partie matérielle, et un compilateur et un assembleur (et possiblement un éditeur de liens (*linker*)) pour la partie logicielle. Les deux processus sont effectués indépendamment l'un de l'autre, tel qu'illustré à la figure 2.1.

**Figure 2.1 Méthode traditionnelle de synthèse d'un processeur embarqué pour une implantation SOC**

Cette division du design entre les parties logicielles et matérielles va produire un modèle de processeur embarqué qui va être sous-optimal en fonction de l'application ciblée. En effet, l'outil de synthèse ne peut exploiter aucune information concernant l'application qui va être exécutée sur le processeur de façon à pouvoir éliminer certaines composantes du circuit et en optimiser d'autres.

Les outils de synthèses modernes sont maintenant très puissants, et ils peuvent éliminer ou simplifier efficacement les circuits qui ne sont pas utilisés, en tout ou en partie. Toutefois, ces outils ne peuvent optimiser les circuits pour lesquels ils ne connaissent pas à l'avance les valeurs qui vont en alimenter les entrées. Ainsi, en analysant ce qui va être

donné en entrée au modèle de processeur, on pourra déterminer quels signaux vont permettre l'optimisation de quels circuits, et si ces optimisations sont valables et utiles.

## 2.4 Outil d'analyse du microcode

Pour déterminer la pertinence d'un couplage serré entre la synthèse d'un modèle de processeur et l'application logicielle qui va être exécutée, un outil d'analyse était nécessaire. Cet outil, une fois complété, peut également servir de base pour l'outil d'optimisation qui est nécessaire pour supporter la méthode.

L'outil d'analyse va utiliser la prédictibilité des signaux d'entrée au modèle de processeur pour réaliser son analyse. Il exploite le fait qu'il connaît à l'avance le microcode qui va être exécuté sur le processeur, puisque le développement de l'application est réalisé avant la synthèse finale du processeur. Ainsi, quand le code de l'application est terminé (que l'on va désigner comme du *firmware*, puisqu'il ne change pas aussi souvent que du logiciel ou *software*), il peut être analysé pour déterminer quelles composantes du processeur vont être utilisées. Le processeur peut donc être optimisé en fonction du *firmware* qu'il va avoir à exécuter et ce, avant la synthèse finale.

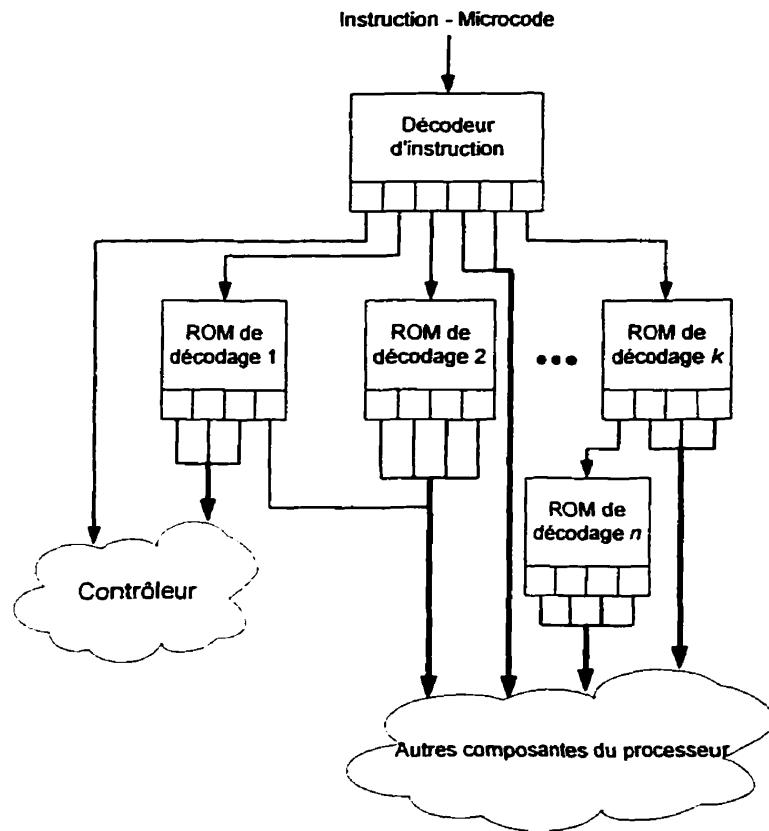

### 2.4.1 Décodage des instructions

On a conçu l'outil d'analyse de microcode pour identifier les ressources non-utilisées par une application spécifique. L'outil en question a été développé pour une architecture en

particulier, soit le processeur PULSE, décrit à la section 3.1. Toutefois, il peut être adapté à n'importe quelle architecture de décodage similaire à celle illustrée à la figure 2.2. L'outil décode une instruction du microcode de la même façon que cela se fait à l'intérieur du processeur visé. Ainsi, les différentes instructions sont décodées en des listes de champs de bits, en fonction du patron d'encodage des différents types d'instructions. Ensuite, certains champs sont passés en entrée à un autre ensemble de décodeurs. Ceux-ci émulent les nombreuses ROM (*Read Only Memory*) de décodage qui sont imbriquées à l'intérieur du processeur. La majorité des signaux qui vont alimenter les autres sections du processeur sont les sorties de ces émulateurs de ROM de décodage. Il est à noter que les optimisations proposées par la méthode décrite dans ce mémoire est également applicable pour les processeurs qui utilisent de la logique câblée (*hardwired logic*) plutôt que des ROM de décodage, même si dans ce cas-ci on ne vas considérer qu'une implantation à base de ROM.

L'analyseur a été conçu pour être aussi générique et indépendant de l'architecture ciblée que possible. Toute l'information concernant la structure des décodeurs d'instructions, des ROMs de décodage et des différents champs de bits sont définis dans des tables contenues dans des fichiers textes. Pour ce qui est des ROMs de décodage, elles sont extraites directement du code VHDL synthétisable, de façon à assurer un décodage authentique. Ainsi, pour porter l'outil d'une architecture de processeur à une autre, on n'a qu'à réécrire les différentes tables décrivant l'architecture, et possiblement modifier quelques portions du code source.

Figure 2.2 Décodage du microcode par l'outil d'analyse

#### 2.4.2 Statistiques d'utilisation

La seconde fonction de l'outil d'analyse est d'accumuler les différentes valeurs que vont prendre les signaux décodés pour toutes les instructions d'un programme en particulier. Lorsqu'un programme en question a été décodé et traité, l'analyseur peut déterminer les valeurs de chaque signal qui sont effectivement utilisées par l'application. Ainsi, pour chaque champ (ou signal) décodé, l'analyseur va fournir le nombre de valeurs réellement utilisées, les valeurs elles-mêmes, ainsi que le nombre de fois qu'elles sont utilisées. Il

calcule également le nombre de bits minimal pour coder un champ, en fonction du nombre de valeurs utilisées.

L'outil permet d'effectuer l'analyse de groupes de signaux. Ainsi, des statistiques relatives aux signaux contrôlant une composante en particulier, comme par exemple une unité arithmétique et logique, peuvent être générées. Ceci permet alors au concepteur d'avoir une bonne idée des ressources qui sont requises par son application. Ces statistiques pourront ensuite être utilisées de façon à optimiser la structure du modèle de processeur, tel qu'expliqué à la section 2.6.

## **2.5 Étude de cas : Le processeur PULSE V1**

Pour réaliser des mesures sur un processeur réel, l'analyseur de microcode a été adapté pour le processeur PULSE (*Parallel Ultra Large Scale Engine*) V1. Celui-ci est un processeur de type SIMD dédié à des applications de traitement d'images numériques en temps réel. Ce processeur a été choisi parce qu'on disposait de son modèle VHDL synthétisable et validé. De plus, un prototype avait été construit avec succès à partir de ce même modèle. Le design du processeur PULSE était d'une complexité d'environ 250 000 portes logiques. De plus, on disposait d'une suite d'applications qui avaient été écrites pour ce processeur.

### 2.5.1 Suite d'applications de test

Tel que mentionné, une série d'applications a été écrite pendant le développement du processeur PULSE V1. Un ensemble représentatif de programmes typiques pour cette architecture a été choisi pour servir de données de tests pour effectuer des mesures d'utilisations des différentes composantes du processeur. La suite d'application était la suivante :

- CONV3X3 : Une convolution bidimensionnelle  $3 \times 3$  générique.

- CONVMED : Une convolution bidimensionnelle  $3 \times 3$  générique suivie d'un filtre médian.

- EDGE : Un filtre de détection de contours.

- HISTO : Une analyse d'image en histogramme.

- IDEA : L'*International Data Encryption Algorithm* (IDEA), utilisé notamment par *Pretty Good Privacy* (PGP), tel que décrit dans Schneier (1995).

- MEDIAN3X3 : Un filtre d'image médian  $3 \times 3$ .

- RSA : Encryptage et décryptage RSA.

- SHRINK : Morphologie mathématique : réduction binaire d'une image.

### 2.5.2 Résultats d'analyses de la suite de test

Deux ensembles de signaux ont été mesurés pour nos applications de test : le microcode, ainsi que les signaux de contrôle de différents modules de l'élément de calcul de

l'architecture. Les résultats fournis au tableau 2.1 indiquent la taille minimale du microcode nécessaire pour encoder toutes les informations requises à l'exécution de l'application. Ceux-ci incluent l'impact recodage des différents champs, où les indices et les adresses sont optimisés pour minimiser le nombre de bits nécessaires. Ceci est expliqué plus en détails dans la section 2.6 qui décrit les différentes optimisations.

Pour les autres signaux de contrôle, il n'y a ni adresse, ni indexe dans les listes. Ces signaux contrôlent le comportement des différents modules. Les nombres indiqués entre parenthèses dans l'entête correspondent à la largeur des champs dans la structure de processeur originale alors que ceux contenus dans le tableau correspondent aux nombres de signaux de contrôle qui changent durant l'exécution de l'application. Un signal qui ne change pas indique qu'une ou plusieurs fonctionnalités ou mode d'opération d'un module ne sont pas utilisés.

**Tableau 2.1 Utilisation des signaux de contrôle pour la suite d'applications de test**

| Application | Microcode<br>(66) | Contrôle de<br>l'accumulateur<br>(5) | Contrôle de<br>l'ALU<br>(27) | Contrôle du décaleur-<br>barrillet (8) |

|-------------|-------------------|--------------------------------------|------------------------------|----------------------------------------|

| CONV3X3     | 17 (26 %)         | 2 (40 %)                             | 7 (26 %)                     | 3 (38 %)                               |

| CONVMED     | 24 (37 %)         | 2 (40 %)                             | 20 (75 %)                    | 7 (88 %)                               |

| EDGE        | 16 (25 %)         | 0 (0 %)                              | 9 (33 %)                     | 0 (0 %)                                |

| HISTO       | 14 (22 %)         | 0 (0 %)                              | 7 (26 %)                     | 0 (0 %)                                |

| IDEA        | 20 (31 %)         | 0 (0 %)                              | 15 (66 %)                    | 6 (75 %)                               |

| MEDIAN3X3   | 22 (33 %)         | 2 (40 %)                             | 19 (71 %)                    | 5 (63 %)                               |

| RSA         | 20 (31 %)         | 0 (0 %)                              | 12 (45 %)                    | 5 (63 %)                               |

| SHRINK      | 22 (33 %)         | 0 (0 %)                              | 6 (23 %)                     | 0 (0 %)                                |

**Tableau 2.1 Utilisation des signaux de contrôle pour la suite d'applications de test (suite)**

| Application      | Contrôle des canaux d'E/S<br>(14) | Contrôle du multiplicateur-additionneur(6) | Contrôle des mémoires<br>(17) | Contrôle des registres<br>(11) |

|------------------|-----------------------------------|--------------------------------------------|-------------------------------|--------------------------------|

| <b>CONV3X3</b>   | <b>6 (43 %)</b>                   | <b>2 (40 %)</b>                            | <b>2 (12 %)</b>               | <b>3 (28 %)</b>                |

| <b>CONVMED</b>   | <b>6 (43 %)</b>                   | <b>4 (67 %)</b>                            | <b>11 (65 %)</b>              | <b>11 (100 %)</b>              |

| <b>EDGE</b>      | <b>4 (29 %)</b>                   | <b>0 (0 %)</b>                             | <b>2 (12 %)</b>               | <b>10 (91 %)</b>               |

| <b>HISTO</b>     | <b>3 (22 %)</b>                   | <b>0 (0 %)</b>                             | <b>5 (30 %)</b>               | <b>0 (0 %)</b>                 |

| <b>IDEA</b>      | <b>6 (43 %)</b>                   | <b>4 (67 %)</b>                            | <b>14 (83 %)</b>              | <b>10 (91 %)</b>               |

| <b>MEDIAN3X3</b> | <b>6 (43 %)</b>                   | <b>4 (67 %)</b>                            | <b>11 (65 %)</b>              | <b>11 (100 %)</b>              |

| <b>RSA</b>       | <b>4 (29 %)</b>                   | <b>5 (84 %)</b>                            | <b>10 (59 %)</b>              | <b>10 (91 %)</b>               |

| <b>SHRINK</b>    | <b>4 (29 %)</b>                   | <b>0 (0 %)</b>                             | <b>14 (83 %)</b>              | <b>0 (0 %)</b>                 |

La première chose que l'on peut observer est que le microcode peut être recodé de façon à être beaucoup plus petit, une fois que l'on applique les optimisations proposées. Ceci nous donne en moyenne un microcode d'une largeur équivalente à environ un tiers de la taille du microcode original.

Pour ce qui est des signaux de contrôle des différents modules de l'élément de calcul, on peut déterminer que ce ne sont pas toutes les applications qui utilisent l'ensemble de ces modules, puisque plusieurs (tous, dans certains cas) signaux demeurent constants durant toute l'exécution de l'application. Par exemple, l'accumulateur n'est utilisé que dans trois des neuf applications de la suite de test. Et pour les modules qui sont effectivement utilisés par les applications, il est rare que la fonctionnalité d'un module soit effectivement entièrement exploitée. Ainsi, pour la suite de test, on peut déterminer que

plusieurs sections des modules de l'élément de calcul ne sont pas utilisées. Ceci nous indique que l'on pourrait facilement éliminer certaines sections sans modifier le comportement du processeur pour une application ciblée. Dans le cas du processeur PULSE V1, ceci pourrait être particulièrement intéressant puisqu'il y a quatre éléments de calcul dans l'architecture, l'élimination d'un composant est en fait répétée quatre fois.

### 2.5.3 Optimisations manuelles initiales

Une adaptation de l'architecture PULSE V1 pour une implantation sur un FPGA Virtex (Xilinx Inc., 2000) de la compagnie Xilinx a été effectuée. Le *Contrôleur* occupait 3934 *slices*<sup>1</sup> et le chemin de données 6772 *slices*. Des optimisations manuelles ont été effectuées de façon à réduire la complexité de l'architecture du processeur, dans le cas où celui-ci n'est utilisé que comme une machine dédiée à des opérations de multiplication-accumulation (MAC : multiply-accumulate) sur 8-bits. Par exemple, ce type de machine pourrait être utilisé pour implanter des opérations de traitement de signal tels des filtres à réponse impulsionnelle finie (FIR : Finite Impulse Response) ou des convolutions. Des optimisations plutôt simples ont été effectuées, comme par exemple l'ajustement de la largeur du chemin de données à la largeur des données traitées, l'élimination de composantes non-utilisées dans le chemin de données et la réduction de la profondeur des ROM de décodage. Même si ces optimisations étaient plutôt simples, le *Contrôleur* a été

---

<sup>1</sup> *Slice* : Structure élémentaire d'un FPGA Virtex, comprenant 2 tables de vérité (LUT : Look up table), deux bascules et de la logique de retenue et de contrôle.

réduit considérablement de taille (1330 *slices*). Même chose dans le cas du chemin de données, qui a été réduit à une taille de 1066 *slices*. L'optimisation globale du processeur a permis de réduire d'environ 75% sa taille. Ces résultats nous ont indiqué que par des optimisations automatiques, on pourrait obtenir de meilleurs résultats en appliquant des optimisations complexes, difficiles à réaliser manuellement.

## 2.6 Optimisations du modèle

Avec l'utilisation de systèmes-sur-une-puce pour intégrer et optimiser la performance et la dissipation de puissance des systèmes embarqués, ainsi que la disponibilité de plate-formes cibles disposant de plusieurs millions de portes logiques équivalentes, de nouvelles options sont maintenant disponibles pour le concepteur de systèmes embarqués. Notamment, on a vu apparaître des systèmes-sur-une-puce configurables, qui sont une combinaison d'un microprocesseur traditionnel, de logique programmable, de bus dédiés et de mémoire sur une même puce. Ce type de circuit permet d'implanter un système complet facilement, puisque l'ensemble des composantes de base sont déjà implantées (Triscend Inc., 2000)

Un autre type de modèle de processeur est apparu ces dernières années : le modèle de processeur configurable (*soft processor cores*). Ces modèles de processeurs permettent au concepteur de configurer leur processeur en choisissant le jeu d'instructions, les tailles des mémoires caches, et des registres. Ils peuvent aussi permettre l'addition de nouvelles

instructions, registres spéciaux et extensions multimédia. (Levy, 1999), (Burksy, 1999), (Xtensa Application Specific Microprocessor Solutions Overview Handbook. Tensilica Inc.)

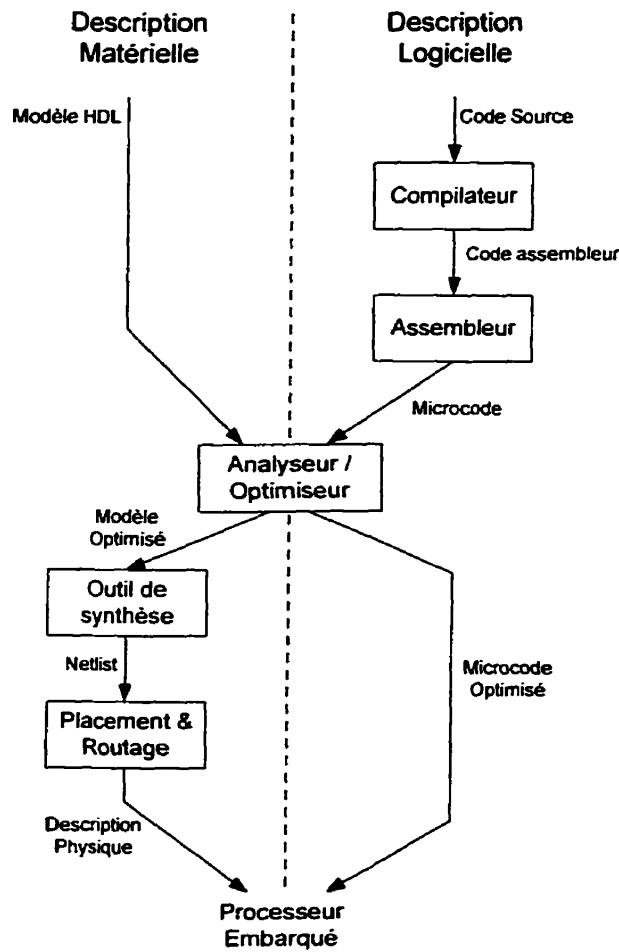

Toutefois, bien que ces nouveaux types de modèles de processeurs et les outils logiciels qui les accompagnent offrent davantage de flexibilité au concepteur, ils ne permettent pas une optimisation du modèle de processeur en fonction de l'application ciblée dans le système. En utilisant les statistiques concernant une application cible, comme celles produites par l'outil présenté à la section 2.4, on peut réaliser des optimisations sur le modèle HDL du processeur, ainsi que sur le microcode et ce, avant la synthèse finale. Ceci va donc nous donner la dérivation de modèles de processeurs embarqués, dédiés à une application spécifique. La figure 2.3 illustre cette nouvelle étape dans le flot de design.

Figure 2.2 Dérivation de modèles de processeurs embarqués dédiés à une application spécifique

Ainsi, dans notre approche, l'application est décrite en écrivant le logiciel qui cible un processeur complet. Puis, durant la phase d'optimisation avant synthèse, le sous-ensemble minimal requis du modèle de processeur est extrait et optimisé, ce qui nous donne une synthèse dédiée à une application. Comme mentionné à la section 1.4, une telle forme de synthèse dédiée a été proposée dans le contexte de processeurs tolérants aux pannes (Pflanz et al., 1998). Ainsi, comme on synthétisait des processeurs plus simples, on pouvait en produire davantage, et ainsi introduire de la redondance.

Les statistiques recueillies sur une application par l'outil d'analyse permettent de réaliser certaines optimisations simples, dont certaines seront décrites ci-bas.

### 2.6.1 Élimination de ressources

Quand on a pu déterminer qu'un composant en particulier n'est pas utilisé tout au long d'une application spécifique, on peut l'éliminer de la description du modèle de processeur avant de procéder à la synthèse de celui-ci. Par exemple, si le signal indiquant au module de multiplication-addition d'écrire son résultat sur le bus de destination de l'unité arithmétique et logique n'est jamais activé, alors le module de multiplication-addition peut être éliminé, économisant ainsi sur les ressources requises.

Il y a deux façons d'effectuer cela : la première est décrite dans la prochaine section, et implique simplement d'utiliser les capacités de l'outil de synthèse pour éliminer ces ressources inutilisées. La seconde stratégie est utilisée quand l'outil de synthèse ne peut effectuer automatiquement cette optimisation. Ceci peut se produire sous différentes conditions, une d'entre elles est la présence d'un tampon à trois-états qui est toujours en haute-impédance. Certains outils de synthèse n'éliminent pas le circuit qui a comme entrée un tampon à trois-états toujours en haute-impédance. Il faut donc procéder à éliminer ces sections de code avant d'envoyer le modèle à l'outil de synthèse. Ceci peut être facilement réalisé avec des clauses d'inclusion dans le modèle HDL (par exemple, en utilisant des constructions `if [...] generate` en VHDL), qui peuvent être sélectionnées par l'optimiseur. Ceci requiert un modèle HDL codé dans ce but : ainsi, il

faut pouvoir éliminer certains circuits sans que cela n'ait un impact sur la fonctionnalité de l'ensemble du reste du processeur.

### **2.6.2 Propagation de signaux constants**

Tel que spécifié précédemment, les outils de synthèse modernes sont très efficaces quand vient le temps d'optimiser des circuits logiques ou d'éliminer ces circuits quand des valeurs constantes sont données en entrées. Ainsi, quand on peut déterminer que des signaux demeurent constants pour toute l'exécution d'une application durant la phase d'analyse du microcode, on peut ainsi propager ces constantes dans le code, aux entrées des modules appropriés. L'outil de synthèse va alors procéder à remplacer tous les modules inutilisés par des valeurs constantes à leurs sorties. Ceci permet une économie de ressources, tel que présenté à la section précédente. Toutefois, ceci ne requiert pas un modèle codé spécifiquement pour ce type d'optimisation, puisque l'outil de synthèse se charge d'effectuer tout le travail. On n'a qu'à lui donner des valeurs constantes aux entrées.

De plus, cette méthode permet non seulement d'éliminer des circuits inutilisés, mais également de simplifier ceux dont toute la fonctionnalité n'est pas utilisée. Ainsi, si par exemple dans une unité arithmétique et logique on n'utilise qu'une partie des opérations arithmétiques, alors certains signaux de contrôle vont demeurer constants, et l'outil de synthèse va pouvoir optimiser le circuit pour ne conserver que les opérations réellement utilisées.

### 2.6.3 Tables de constantes locales