|                   |                                                                                                                                                                                                                                                                                                                                              |

|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>Titre:</b>     | Conception et réalisation d'un échantillonneur de grande vitesse en technologie higfet (transistor à effet de champ avec hétérostructure et grille isolée)                                                                                                                                                                                   |

| <b>Auteur:</b>    | Mihai Tazlauanu                                                                                                                                                                                                                                                                                                                              |

| <b>Date:</b>      | 1997                                                                                                                                                                                                                                                                                                                                         |

| <b>Type:</b>      | Mémoire ou thèse / Dissertation or Thesis                                                                                                                                                                                                                                                                                                    |

| <b>Référence:</b> | Tazlauanu, M. (1997). Conception et réalisation d'un échantillonneur de grande vitesse en technologie higfet (transistor à effet de champ avec hétérostructure et grille isolée) [Thèse de doctorat, École Polytechnique de Montréal]. PolyPublie. <a href="https://publications.polymtl.ca/6838/">https://publications.polymtl.ca/6838/</a> |

| Citation:         |                                                                                                                                                                                                                                                                                                                                              |

## Document en libre accès dans PolyPublie

Open Access document in PolyPublie

**URL de PolyPublie:** <https://publications.polymtl.ca/6838/>

PolyPublie URL:

**Directeurs de recherche:** John F. Currie

Advisors:

**Programme:** Non spécifié

Program:

UNIVERSITÉ DE MONTRÉAL

CONCEPTION ET RÉALISATION D'UN ÉCHANTILLONNEUR DE GRANDE

VITESSE EN TECHNOLOGIE HIGFET (TRANSISTOR À EFFET DE CHAMP

AVEC HÉTÉROSTRUCTURE ET GRILLE ISOLÉE)

MIHAI TAZLAUANU

DÉPARTEMENT DE GÉNIE PHYSIQUE

ÉCOLE POLYTECHNIQUE DE MONTRÉAL

THÈSE PRÉSENTÉE EN VUE DE L'OBTENTION

DU DIPLOME DE PHILOSOPHIAE DOCTOR (PH.D.)

(GÉNIE PHYSIQUE)

NOVEMBRE 1997

National Library

of Canada

Acquisitions and

Bibliographic Services

395 Wellington Street

Ottawa ON K1A 0N4

Canada

Bibliothèque nationale

du Canada

Acquisitions et

services bibliographiques

395, rue Wellington

Ottawa ON K1A 0N4

Canada

Your file Votre référence

Our file Notre référence

The author has granted a non-exclusive licence allowing the National Library of Canada to reproduce, loan, distribute or sell copies of this thesis in microform, paper or electronic formats.

The author retains ownership of the copyright in this thesis. Neither the thesis nor substantial extracts from it may be printed or otherwise reproduced without the author's permission.

L'auteur a accordé une licence non exclusive permettant à la Bibliothèque nationale du Canada de reproduire, prêter, distribuer ou vendre des copies de cette thèse sous la forme de microfiche/film, de reproduction sur papier ou sur format électronique.

L'auteur conserve la propriété du droit d'auteur qui protège cette thèse. Ni la thèse ni des extraits substantiels de celle-ci ne doivent être imprimés ou autrement reproduits sans son autorisation.

0-612-33031-1

Canada

UNIVERSITÉ DE MONTRÉAL

ÉCOLE POLYTECHNIQUE DE MONTRÉAL

Cette thèse intitulée:

CONCEPTION ET RÉALISATION D'UN ÉCHANTILLONNEUR DE GRANDE

VITESSE EN TECHNOLOGIE HIGFET (TRANSISTOR À EFFET DE CHAMP

AVEC HÉTÉROSTRUCTURE ET GRILLE ISOLÉE)

présentée par: TAZLAUANU, Mihai

en vue de l'obtention du diplôme de: Philosophiae Doctor

a été dûment acceptée par le jury d'examen constitué de:

M. YELON, Arthur, Ph.D., président

M. CURRIE, John F., Ph.D., membre et directeur de recherche

M. MASUT, Remo A., Ph.D., membre

M. AKTIK, Çetin, Ph.D., membre

## Remerciements

La soutenance de la thèse de doctorat marque une étape importante dans la formation technique et scientifique d'un ingénieur. Je voudrais donc profiter de cette occasion pour remercier plusieurs personnes qui ont eu un impact majeur sur mon activité de recherche.

Je voudrais, tout d'abord, remercier le professeur John F. Currie pour m'avoir accueilli dans son groupe de recherche du laboratoire LISA et pour avoir dirigé, avec compétence et enthousiasme, pendant toute la période nécessaire à l'élaboration de la thèse, mon activité de recherche. Je me considère privilégié d'avoir eu Dr. Currie comme directeur de recherche.

Je remercie très sincèrement le professeur Arthur Yelon pour les discussions techniques et le support scientifique. Ses remarques sont toujours pertinentes et son aide et conseils ont été inestimables.

Je remercie également le professeur Remo Masut pour sa disponibilité et pour les nombreux conseils techniques. Cela m'a permis de découvrir des nouveaux défis de recherche et de mieux résoudre les problèmes courants.

Je remercie très sincèrement le professeur Çetin Aktik d'avoir accepté de faire partie du jury d'examen de cette thèse.

Mes remerciements s'adressent tout aussi aux professeurs Michel Wertheimer, Michel Meunier, et Fadhel Ghannouchi pour leur aide dans ma formation scientifique.

Pendant tout le déroulement de la thèse j'ai côtoyé Dr. Chetlur Sundararaman, à l'époque associé de recherche dans le groupe de recherche du professeur Currie. Son expérience et son aide ont été un grand atout pour moi.

La recherche expérimentale est, en général, un travail d'équipe. Cette thèse a nécessité l'aide et l'effort d'un grand nombre de scientifiques, étudiants et techniciens. Je partage donc les réalisations de ce projet avec ceux dont j'ai eu l'occasion de collaborer au cours des dernières années au laboratoire LISA: Dr. Petru Ciureanu, Dr. Dentcho Ivanov, M. Pierre Mihelich, M. Tudor Sавescu, M. Robert Antaki, M. Mario Caron, M. Gino Turcotte, M. Normand Gravel, M. André Lecours, M. Christoph Huller, M. Luc Pouliot et Dr. Raymond Yip.

Je veux aussi mentionner, particulièrement, l'aide offerte par le groupe du professeur Masut qui a assuré la croissance des échantillons utilisés dans cette thèse. Je remercie donc Dr. Ahmed Bensaada, Dr. Mario Beaudoin, Dr. Zahia Bougrioua et M. Laurent Isnard.

## Résumé

Le but principal de cette thèse est de développer une nouvelle technologie pour la fabrication des circuits intégrés à haute vitesse. Les travaux réalisés ont touché toutes les étapes nécessaires pour la mise au point du produit, incluant la modélisation des dispositifs, la simulation des circuits fonctionnels, la conception des circuits intégrés, la fabrication des structures, et la caractérisation microphysique et électrique au niveau du flux de fabrication et du produit final. La stratégie considérée pour obtenir les meilleurs résultats est de répéter séquentiellement le cycle modélisation, conception, fabrication, et caractérisation électrique jusqu'à l'atteinte de la qualité prévue des circuits et la robustesse suffisante des procédés technologiques.

L'élément fondamental de cette technologie est le transistor à effet de champ avec hétérostructure et grille isolée, HIGFET. L'utilisation de la hétérostructure épitaxiale InP/InGaAs assure une mobilité élevée des porteurs de charge et, implicitement, la capacité des dispositifs de fonctionner à une fréquence élevée, inaccessible aux composants fabriqués sur silicium. La structure du transistor avec le canal de conduction enterré (la grille isolée) préserve un niveau élevé des tensions de claquage et élimine, au moins partiellement, les problèmes technologiques reliés à l'interface semi-conducteur-diélectrique.

En partant des résultats rapportés dans la littérature et de l'expérience existante au laboratoire LISA concernant la technologie de fabrication sur un substrat d'InP, nous avons développé et optimisé une structure de HIGFET appropriée à l'intégration des circuits intégrés numériques et des circuits d'échantillonnage-blocage.

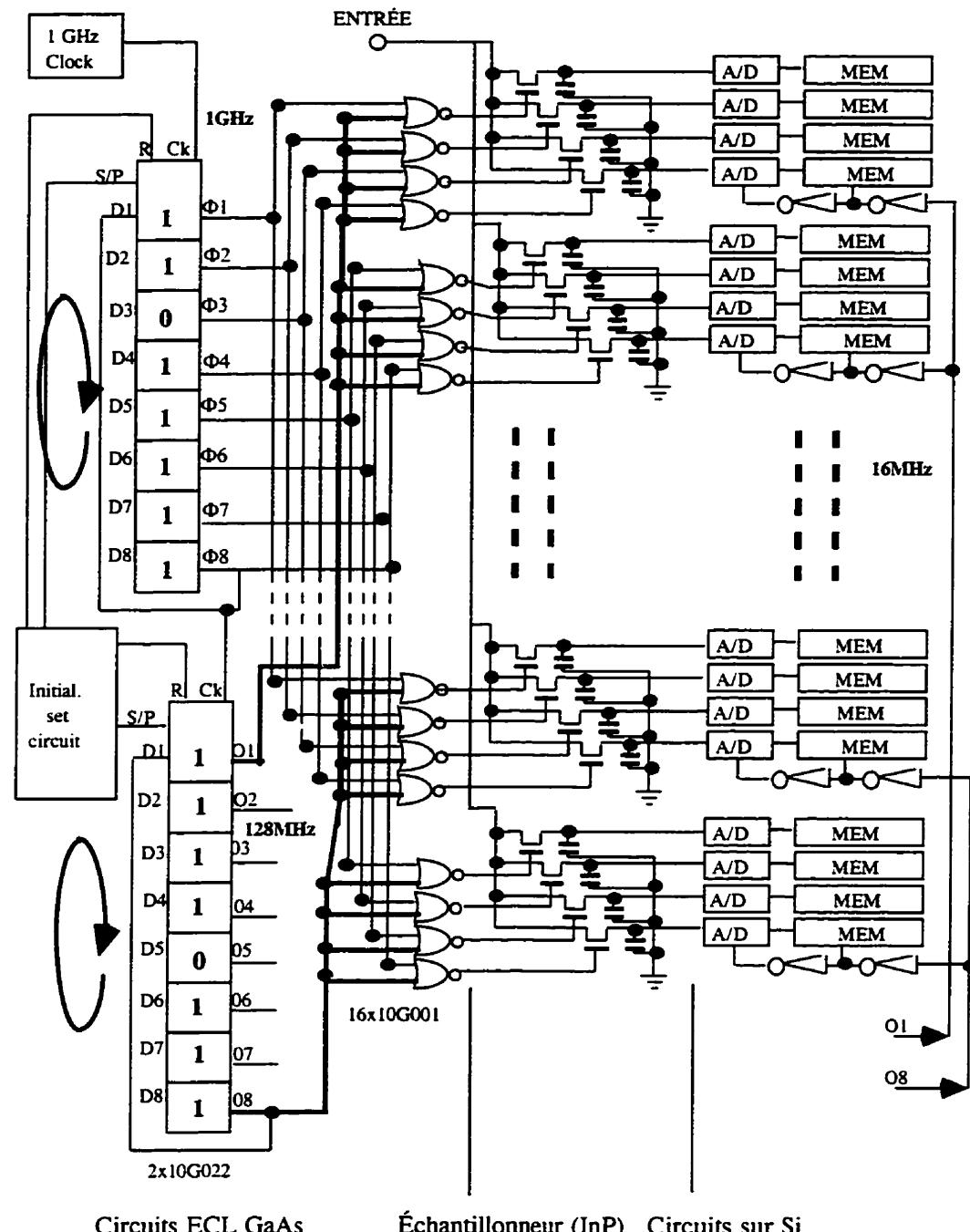

Le but final du projet est la fabrication d'un système d'acquisition de données basé sur un circuit d'échantillonnage-blocage. Deux architectures du système ont été essayées: 1° la structure avec le générateur des signaux d'horloge intégré sur le dé d'InP; et 2° le générateur des signaux d'horloge externe produit à partir de circuits ECL sur GaAs.

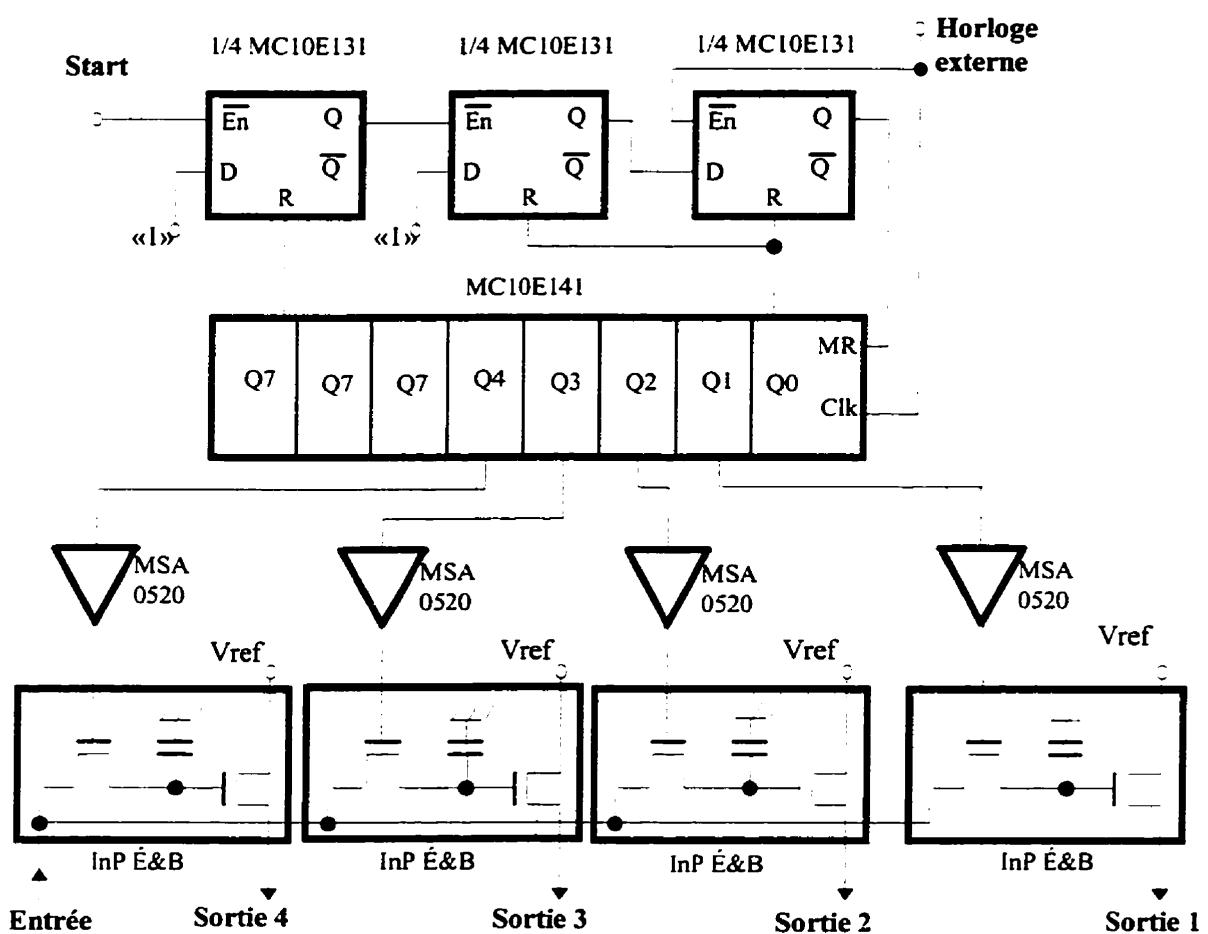

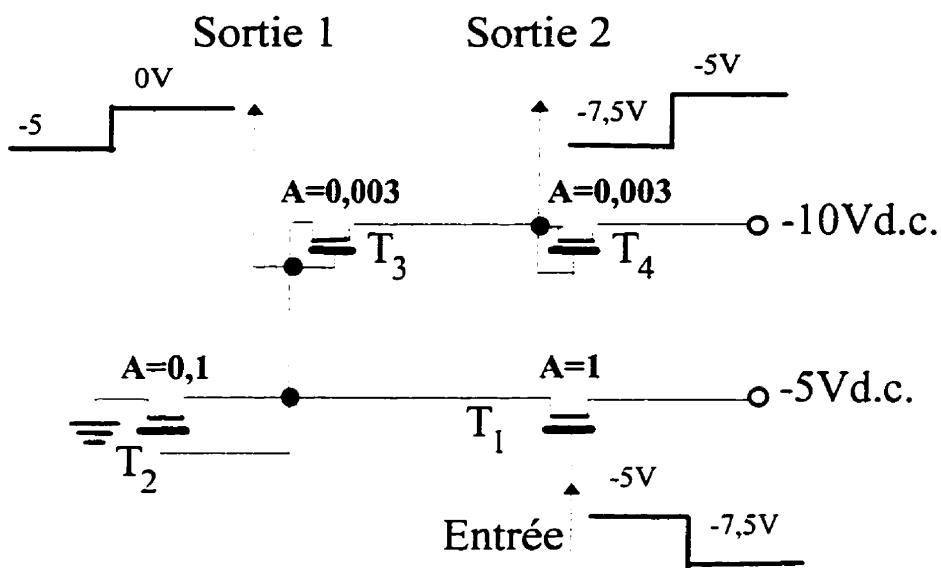

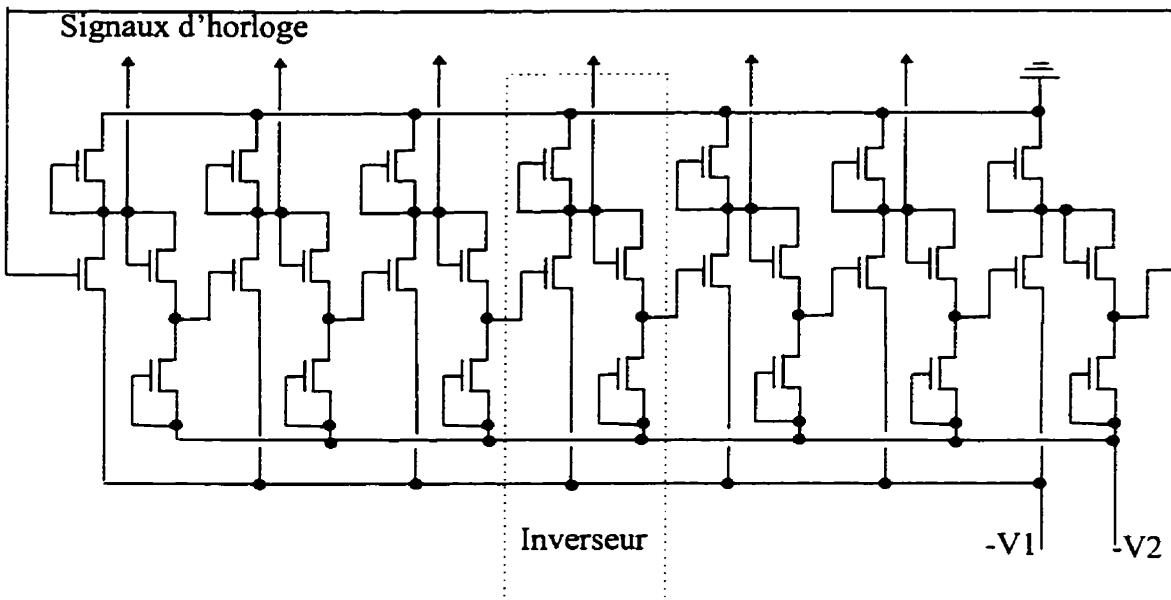

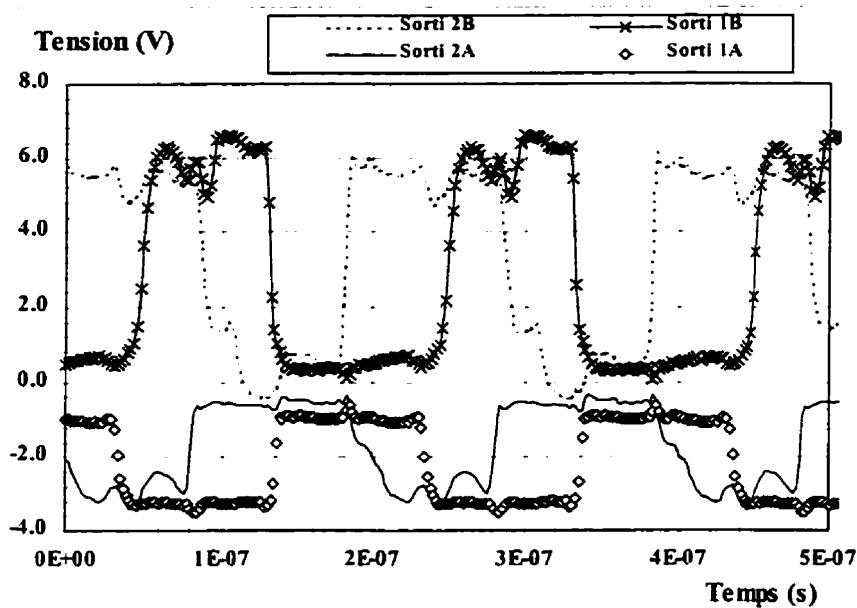

Pour générer les signaux d'horloge sur le même dé avec les circuits d'échantillonnage, nous avons développé une famille de circuits numériques basée sur un circuit inverseur original, adapté à une technologie NMOS avec les transistors fonctionnant en régime d'appauvrissement. Ce circuit a été utilisé pour la conception des amplificateurs tampon et des oscillateurs en anneau. Pour assurer les signaux d'horloge dans le domaine des GHz, nous avons proposé un circuit original générateur d'échelons. La conception optimale du circuit et les résultats de la simulation du fonctionnement ont été validés par les mesures des circuits générateurs d'échelons fabriqués. Nous avons obtenu un train d'impulsions équidistantes à une fréquence de 1 GHz.

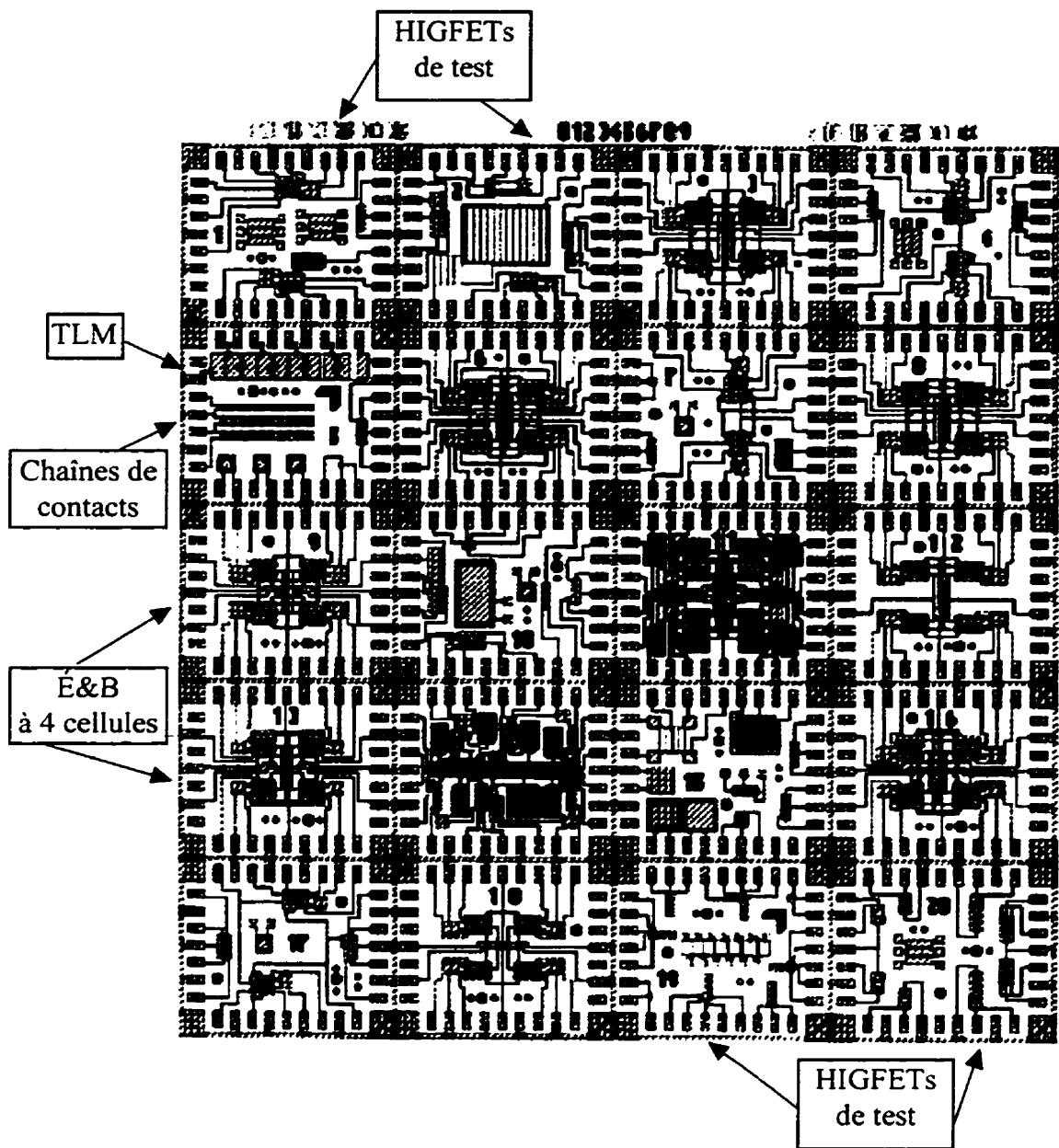

Quatre jeux de masques, réalisés dans l'environnement Cadence, ont permis la fabrication des dispositifs de test et des circuits fonctionnels. Chaque nouvelle génération de masques a reflété les acquis antérieurs et a implémenté des nouvelles structures et techniques de circuit. La surface allouée aux structures de test a dépassé 30 % de la surface totale des dés pour chaque jeu de masques et a permis non seulement le contrôle technologique, mais aussi une étude statistique de la variabilité spatiale des performances physiques et électriques.

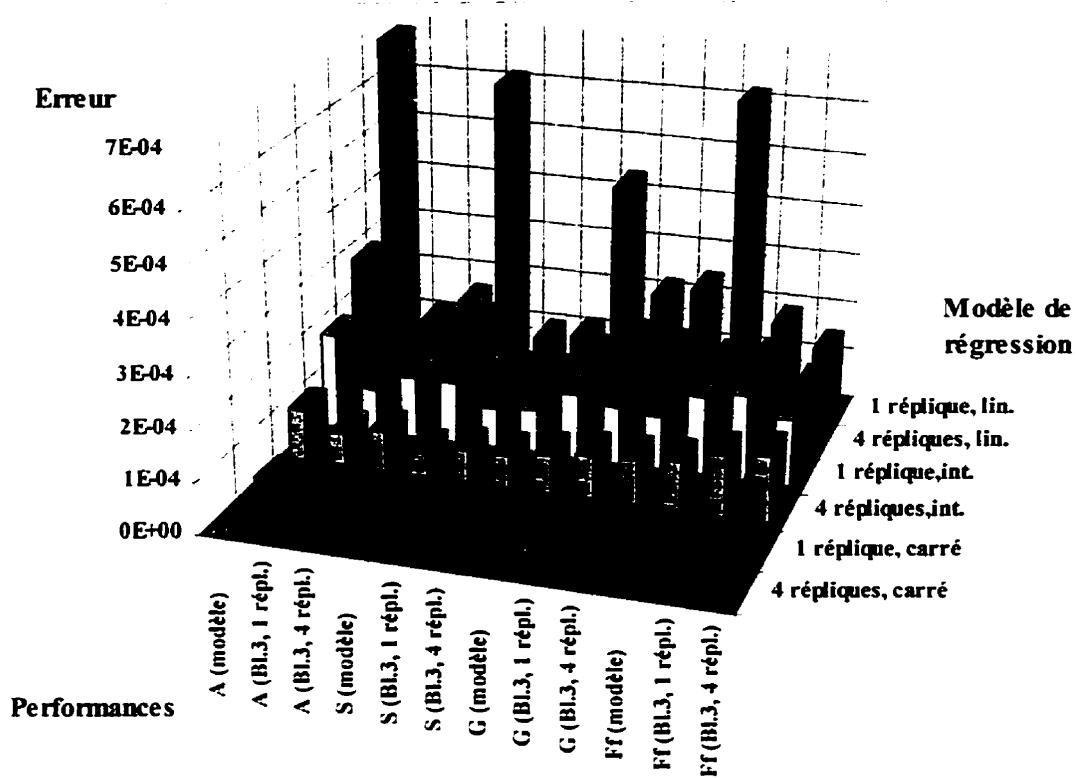

La technologie de fabrication a été soumise à des modifications et raffinements successifs, en vue d'optimiser le fonctionnement des dispositifs. Une attention particulière a été accordée à la robustesse technologique. L'étude exhaustive pour la simulation statistique des procédés technologiques a été réalisée en utilisant le

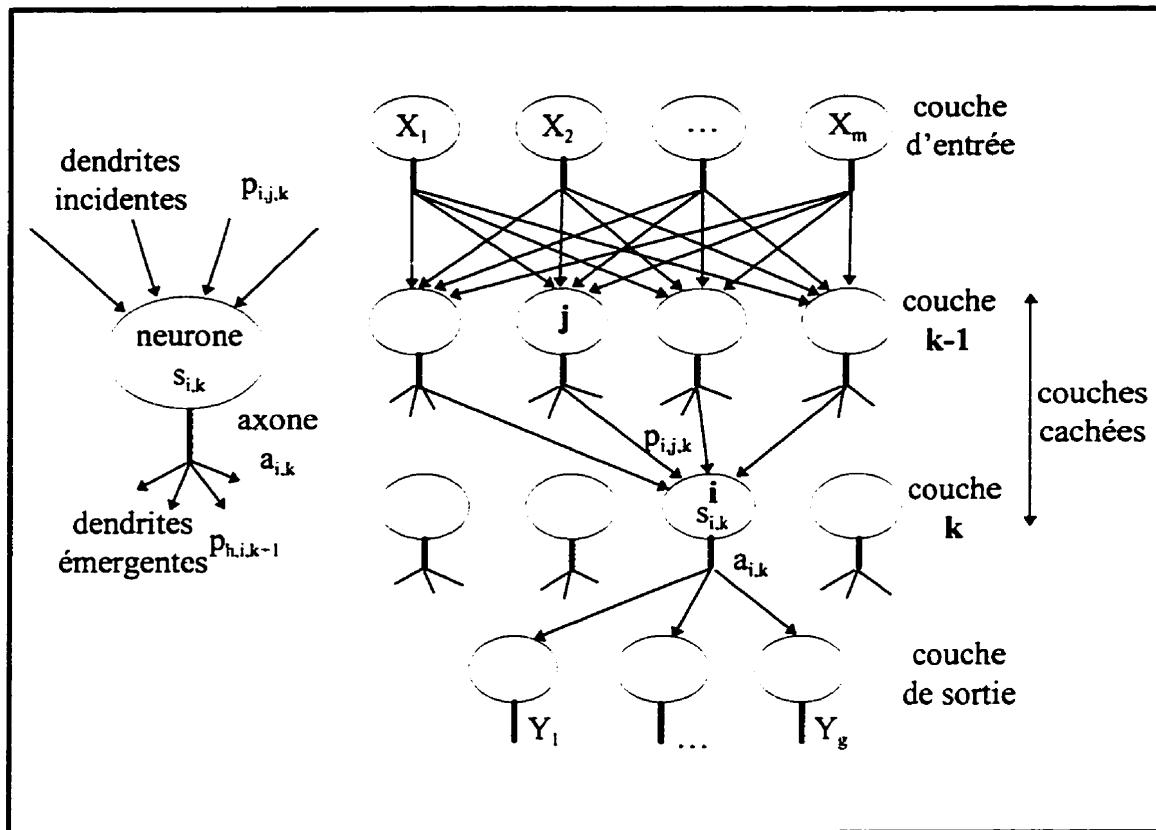

processus de gravure assistée par plasma (RIE). Nous avons proposé un nouveau modèle de simulation technologique, basé sur l'utilisation d'un réseau neural artificiel, qui assure une excellente exactitude de l'estimation des performances technologiques à partir d'un entraînement par exemple relativement réduit.

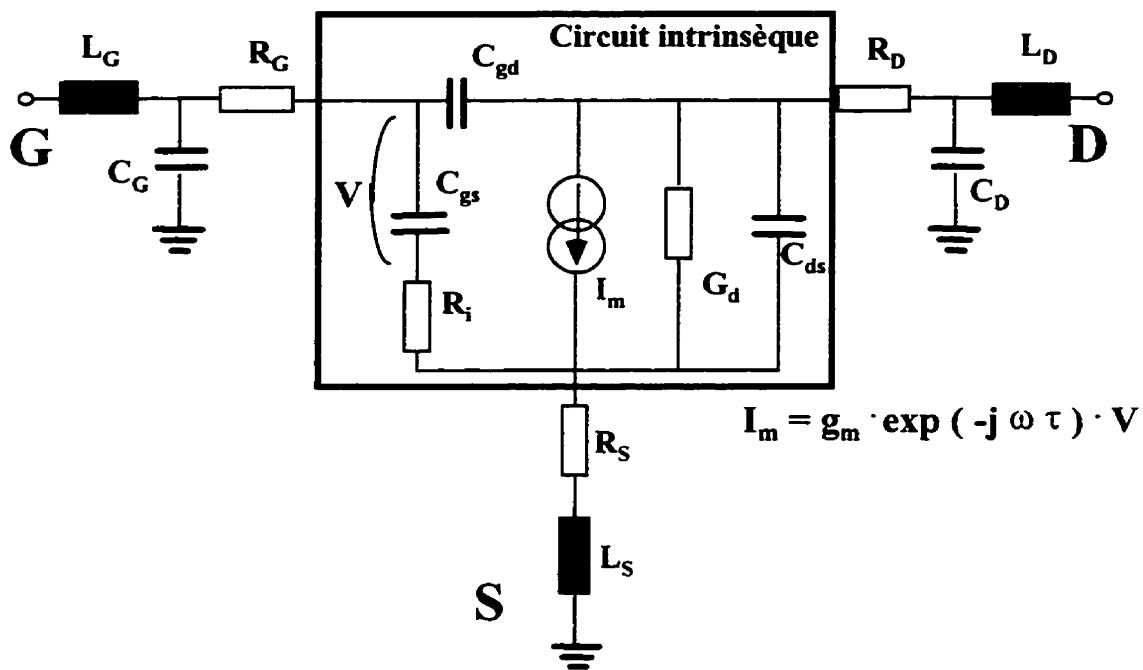

Les mesures électriques, effectuées sur les lots expérimentaux, ont permis la modélisation des dispositifs, la correction des certains problèmes technologiques et l'amélioration de la conception des circuits. À partir des valeurs mesurées des paramètres S du transistor, nous avons proposé un circuit équivalent des HIGFETs. La validation du modèle a été étudiée sur un domaine large de fréquences (30 MHz à 3 GHz) et l'effet du niveau des signaux c.c. a été analysé par le calcul des éléments du circuit équivalent pour tout le domaine d'intérêt de la polarisation de grille et de drain.

Les mesures électriques réalisées sur des structures de test dédiées, pendant le cycle de fabrication, ont permis l'identification et la correction de certains problèmes technologiques (contacts ohmiques, fuites de courant, intégrité des interconnexions, et instabilités thermiques). Les mesures correctives ont été validées par des expériences consacrées aux problèmes étudiés dont l'effort expérimental a été optimisé par l'utilisation des techniques statistiques (conception factorielle fractionnée).

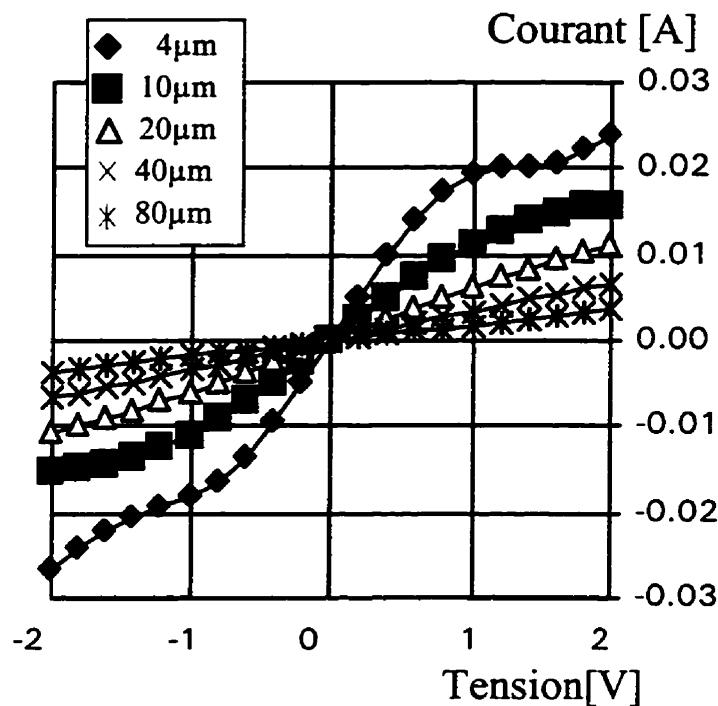

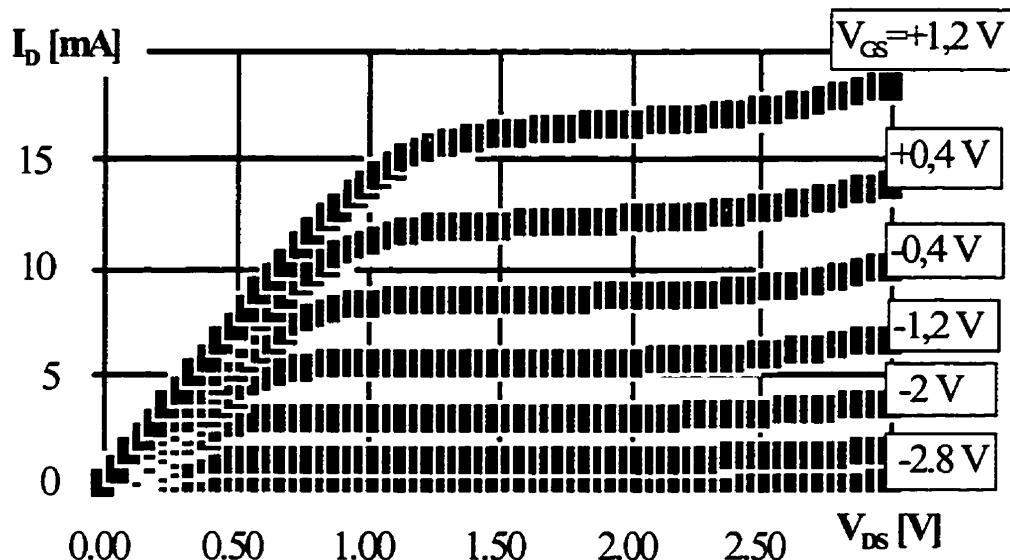

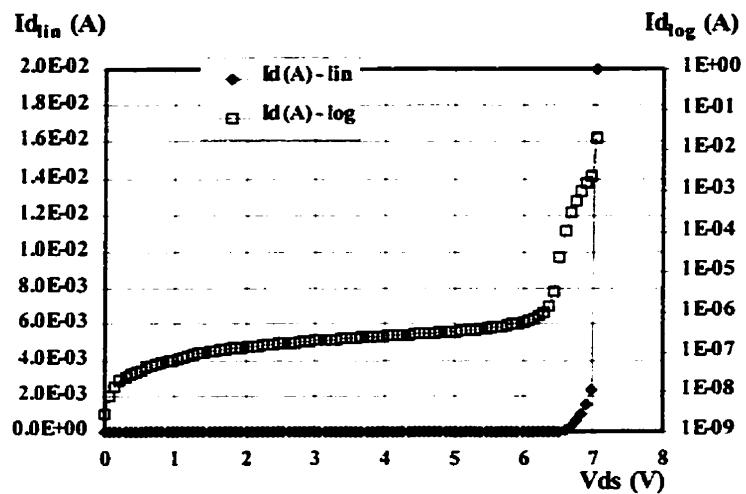

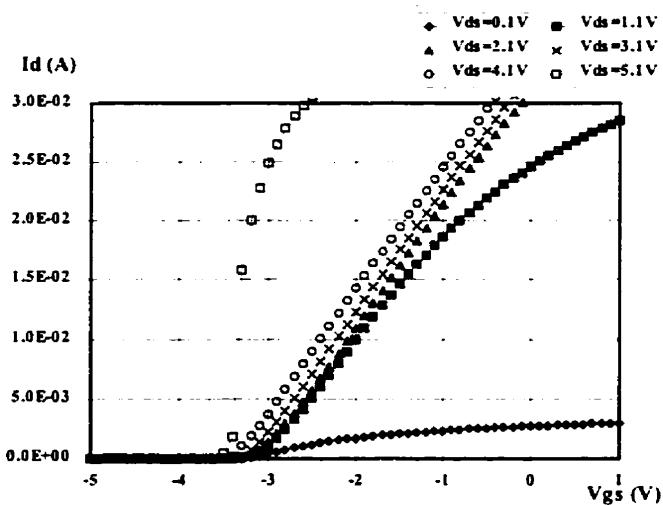

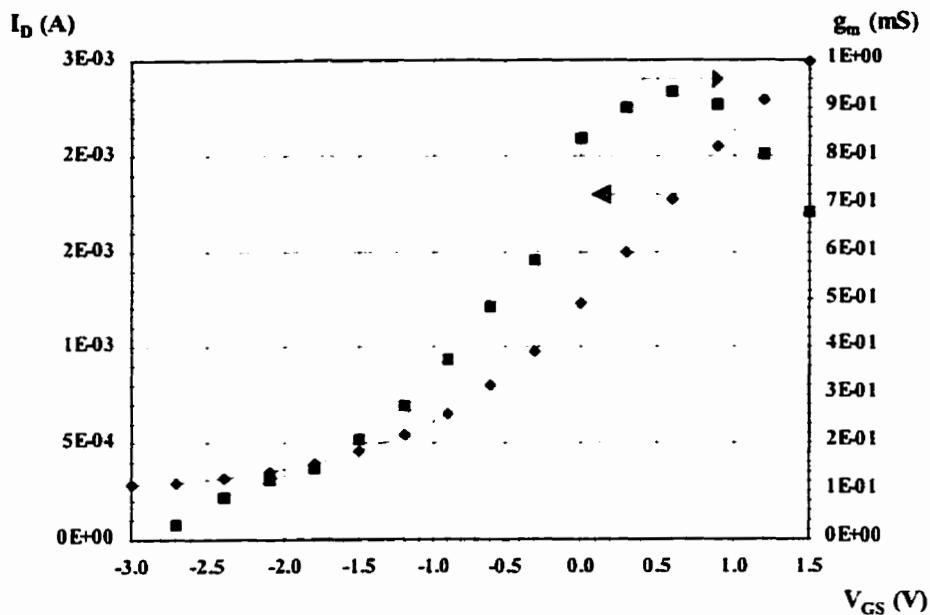

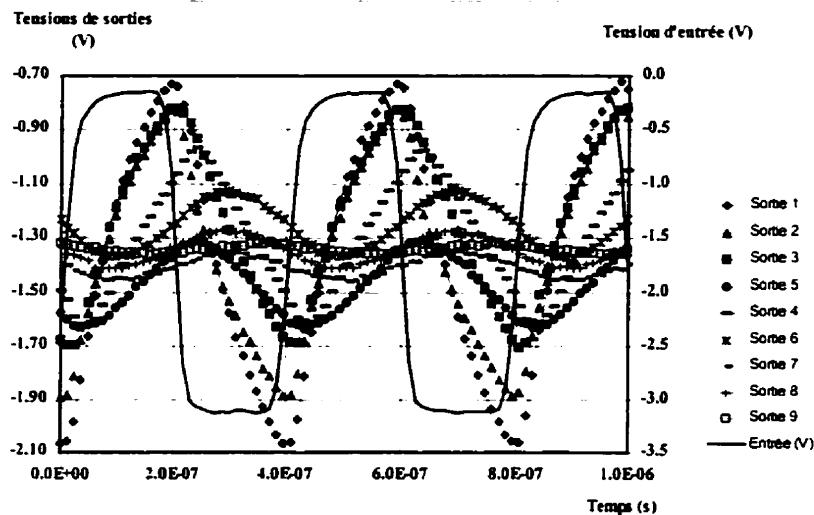

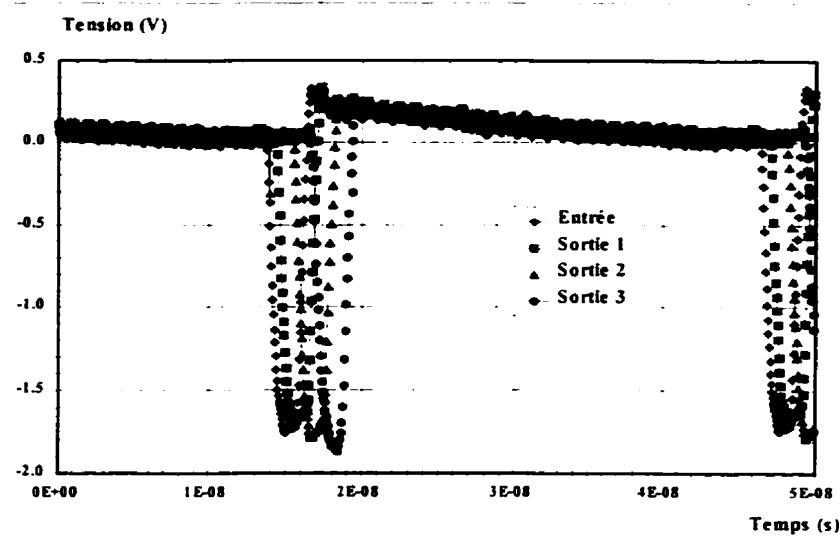

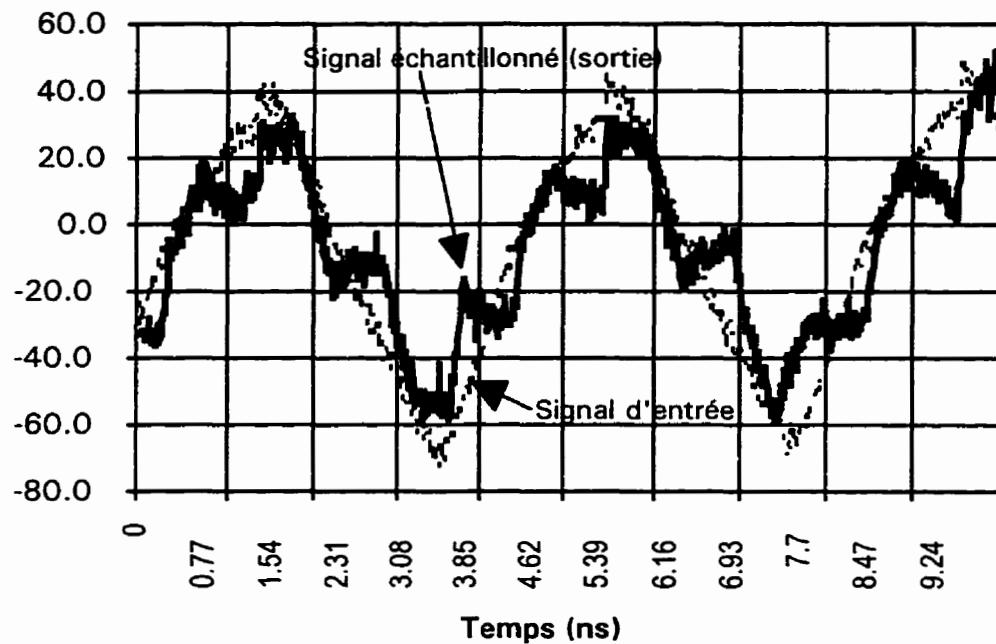

La caractérisation électrique des dispositifs fabriqués a montré des bonnes performances c.c. et c.a. Les HIGFETs ont un courant de drain maximal de 100 mA/mm, une transconductance de 50 mS/mm et un rapport  $I_{ON}/I_{OFF}$  de plus de  $10^5$ . La tension de seuil, pour les différents types de structures, a été comprise entre -1 V et -3,5 V, avec une bonne reproductibilité sur le même échantillon. La grille présente une fuite de moins de 1 nA pour une variation de tension de  $\pm 5$  V. La fréquence de coupure  $f_T$  est de l'ordre de 10 GHz. Les transistors ont montré un gain de 5 dB à 3 GHz et ont permis un échantillonnage correct jusqu'à 2 GHz.

## Abstract

The research work reported in this thesis details a new fabrication technology for high speed integrated circuits in the broadest sense, including original contributions to device modeling, circuit simulation, integrated circuit design, wafer fabrication, micro-physical and electrical characterization, process flow and final device testing as part of an electrical system. In most areas we were able to repeat at least once the steps involving modeling, design, fabrication and electrical characterization until the intended quality of the circuits and robustness of the fabrication technology were obtained. The integrated circuits are used to make a sample and hold data acquisition system.

The primary building block of this technology is the heterostructure insulated gate field effect transistor, HIGFET. We used an InP/InGaAs epitaxial heterostructure to ensure a high charge carrier mobility and hence obtain a higher operating frequency than that currently possible for silicon devices. We designed our transistor structures with a buried channel (insulated gate) to guarantee a high breakdown voltage and to eliminate the technological problems arising at the semiconductor-dielectric interface.

We designed and built integrated circuits with two system architectures. The first architecture integrates the clock signal generator with the sample and hold circuitry on the InP die, while the second is a hybrid architecture of an InP sample and hold assembled with an external clock signal generator made with ECL circuits on GaAs.

To generate the clock signals on the same die with the sample and hold circuits, we developed a digital circuit family based on an original inverter, appropriate for depletion

mode NMOS technology. We used this circuit to design buffer amplifiers and ring oscillators. To ensure clock signals at GHz frequencies, we proposed an original edge generator circuit. The optimal design of this circuit, as well as the simulated performances, were validated by measurements on the experimental edge generator circuits. We obtained equal spaced pulses at 1 GHz operating frequency.

Four mask sets produced in a Cadence environment, have permitted the fabrication of test and working devices. Each new mask generation has reflected the previous achievements and has implemented new structures and circuit techniques. For each mask set, the surface intended for test structures was more than 30 % of the total die area, and has allowed not only process control, but also a statistical study of the spatial variability of the physical and electrical performances.

The fabrication technology has undergone successive modifications and refinements to optimize device manufacturing. Particular attention has been paid to the technological robustness. The plasma enhanced etching process (RIE) had been used for an exhaustive study for the statistical simulation of the technological steps. We proposed a new technological simulation model, based on an artificial neural network that has ensured an excellent estimation accuracy of the process performances starting from a relative reduced training by examples.

Electrical measurements, performed on the experimental samples, have permitted the modeling of the devices, technological processing to be adjusted and circuit design improved. Starting from the measured values of the transistor S parameters, we proposed an equivalent circuit of the HIGFET. We validated our models over a large frequency range (30 MHz to 3 GHz). The DC voltage effects have been analyzed by computing the equivalent circuit elements for the entire domain of gate and drain bias.

Electrical measurements performed on dedicated test structures, during the fabrication cycle, allowed the identification and correction of some technological problems (ohmic contacts, current leakage, interconnection integrity, and thermal instabilities). Feedback corrections were validated by dedicated experiments with the experimental effort optimized by statistical techniques (factorial fractional design).

The electrical characterization of the fabricated devices shows good d.c. and a.c. performances. The HIGFETs have a maximum drain current of 100 mA/mm, a transconductance of 50 mS/mm and an ION/IOFF ratio larger than 105. The threshold voltage, for different types of structures, varies between -1 V and -3.5 V and has a good reproducibility on the same die. Gate leakage is less than 1nA for a voltage swing of  $\pm 5V$ . The cutting frequency,  $f_T$ , is on the 10 GHz range. Transistors show a gain of 5 dB at 3 GHz and allow a correct sampling up to 2 GHz.

# Table des matières

|                                              |      |

|----------------------------------------------|------|

| <b>Remerciements</b> .....                   | IV   |

| <b>Résumé</b> .....                          | VI   |

| <b>Abstract</b> .....                        | IX   |

| <b>Table des matières</b> .....              | XII  |

| <b>Liste des tableaux</b> .....              | XV   |

| <b>Liste des figures</b> .....               | XVI  |

| <b>Liste des symboles et acronymes</b> ..... | XXII |

| <b>Liste des annexes</b> .....               | XXVI |

| <br><br><br>                                 |      |

| <b>Chapitre 1</b>                            |      |

| <b>Introduction</b> .....                    | 1    |

| 1.1    Objectifs de la thèse .....           | 5    |

| 1.2    Organisation de la thèse .....        | 7    |

| <br>                                         |      |

| <b>Chapitre 2</b>                            |      |

| <b>Dispositif HIGFET</b> .....               | 11   |

| 2.1    Structure du HIGFET .....             | 11   |

| 2.2    Physique de la structure HIGFET ..... | 18   |

| 2.3    Modélisation du HIGFET idéal .....    | 21   |

| 2.4    Transistor HIGFET réel .....          | 25   |

**Chapitre 3**

|                                                                                 |    |

|---------------------------------------------------------------------------------|----|

| <b>Modélisation du HIGFET .....</b>                                             | 28 |

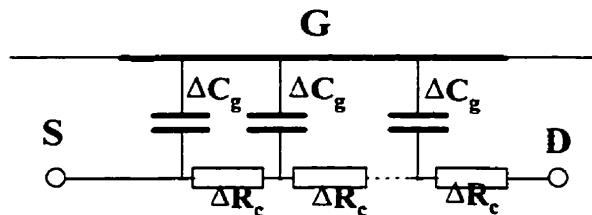

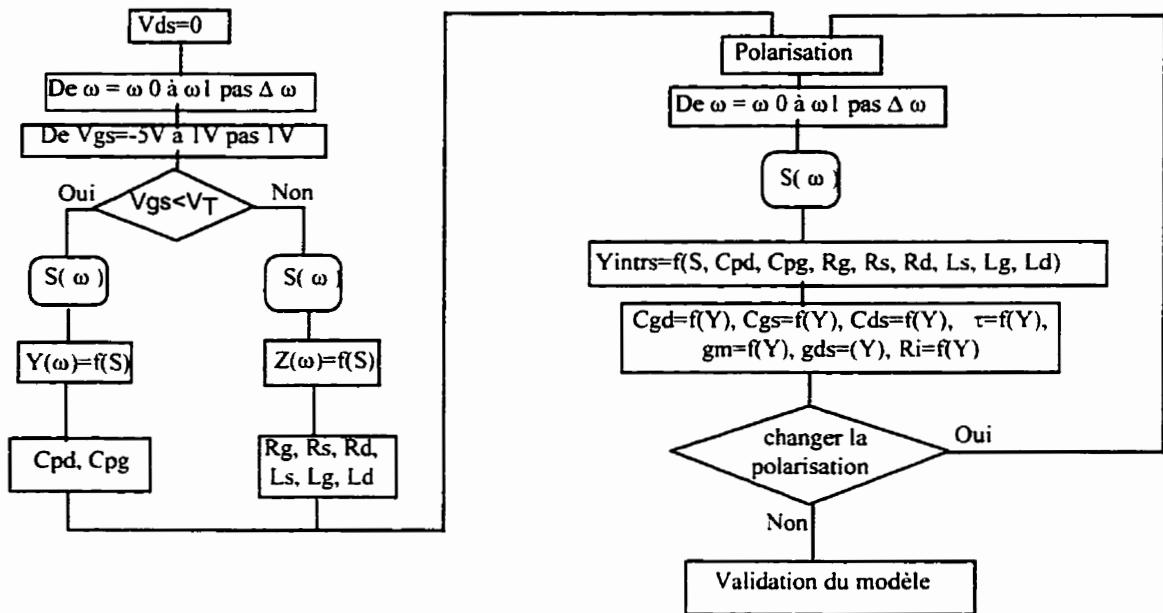

| 3.1 Modèle petit signal du HIGFET .....                                         | 29 |

| 3.2 Méthodologie d'évaluation du circuit équivalent extrinsèque .....           | 31 |

| 3.2.1 Calcul des résistances et des inductances parasites ( $V_{GS}=0$ ) .....  | 31 |

| 3.2.2 Calcul des capacités parasites ( $V_{GS}=-5V$ ) .....                     | 33 |

| 3.3 Calcul des paramètres intrinsèques .....                                    | 34 |

| 3.4 Influence de la polarisation et fréquence sur les éléments du circuit ..... | 40 |

| 3.5 Impédance d'entrée et de sortie du HIGFET .....                             | 52 |

**Chapitre 4**

|                                                                                    |    |

|------------------------------------------------------------------------------------|----|

| <b>Conception des circuits d'échantillonnage-blocage .....</b>                     | 56 |

| 4.1 Acquisition des données basée sur des circuits d'échantillonnage-blocage ..... | 56 |

| 4.2 Architecture du système É&B .....                                              | 65 |

| 4.3 Conception des circuits numériques .....                                       | 70 |

| 4.4 Conception des jeux de masques .....                                           | 75 |

**Chapitre 5**

|                                                 |     |

|-------------------------------------------------|-----|

| <b>Processus de fabrication .....</b>           | 85  |

| 5. 1. Introduction .....                        | 85  |

| 5. 2. Fabrication des dispositifs HIGFET .....  | 86  |

| 5.2.1 Photolithographie .....                   | 86  |

| 5.2.2 Métallisation .....                       | 88  |

| 5.2.3 Procédés chimiques .....                  | 90  |

| 5.2.4 Dépôt de $Si_3N_4$ .....                  | 91  |

| 5.2.5 Gravure par plasma (RIE) .....            | 92  |

| 5.3 Contrôle technologique .....                | 96  |

| 5.4 Simulation empirique du processus RIE ..... | 100 |

|                                  |                                                           |     |

|----------------------------------|-----------------------------------------------------------|-----|

| 5.4.1                            | Simulation statistique du processus RIE .....             | 101 |

| 5.4.2                            | Utilisation des réseaux neuraux artificiels (RNA) .....   | 104 |

|                                  | pour la modélisation du processus RIE                     |     |

| <b>Chapitre 6</b>                |                                                           |     |

| <b>Mesures électriques</b> ..... | 110                                                       |     |

| 6.1.                             | Introduction .....                                        | 110 |

| 6.2.                             | Contrôle technologique .....                              | 112 |

| 6.2.1                            | Résistance de contact et la résistance feuille .....      | 113 |

| 6.2.2                            | Résistance des couches métalliques et des contacts .....  | 124 |

| 6.3                              | Mesures des HIGFETs en courant continu .....              | 126 |

| 6.4                              | Performances électriques des circuits numériques .....    | 133 |

| 6.5                              | Mesures électriques à haute fréquence .....               | 137 |

| 6.5.1                            | Mesure de l'amplification et de la largeur de bande ..... | 138 |

| 6.5.2                            | Analyse des distorsions .....                             | 140 |

| 6.5.3                            | Caractérisation des régimes transitoires .....            | 143 |

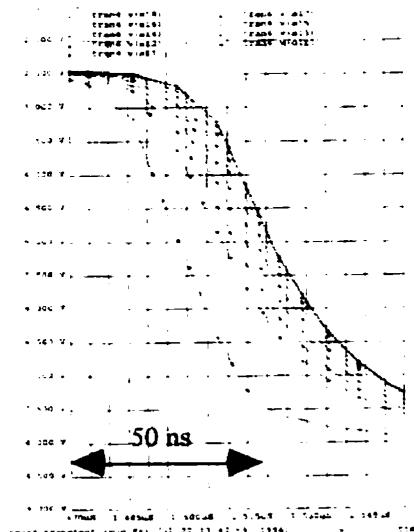

| 6.5.4                            | Échantillonnage à 1 GHz .....                             | 145 |

| <b>Chapitre 7</b>                |                                                           |     |

| <b>Conclusions</b> .....         | 147                                                       |     |

| <b>Références</b> .....          | 153                                                       |     |

| <b>Annexes</b> .....             | 163                                                       |     |

## Liste des tableaux

|              |                                                                  |     |

|--------------|------------------------------------------------------------------|-----|

| Tableau 3.1: | Valeurs moyennes des éléments du circuit équivalent .....        | 40  |

| Tableau 4.1: | Valeurs cible des performances du HIGFET .....                   | 65  |

| Tableau 5.1: | Comparaison entre les performances des modèles empiriques .....  | 108 |

|              | de simulation                                                    |     |

| Tableau 5.2: | Simulation du RSB par les modèles empiriques de simulation ..... | 108 |

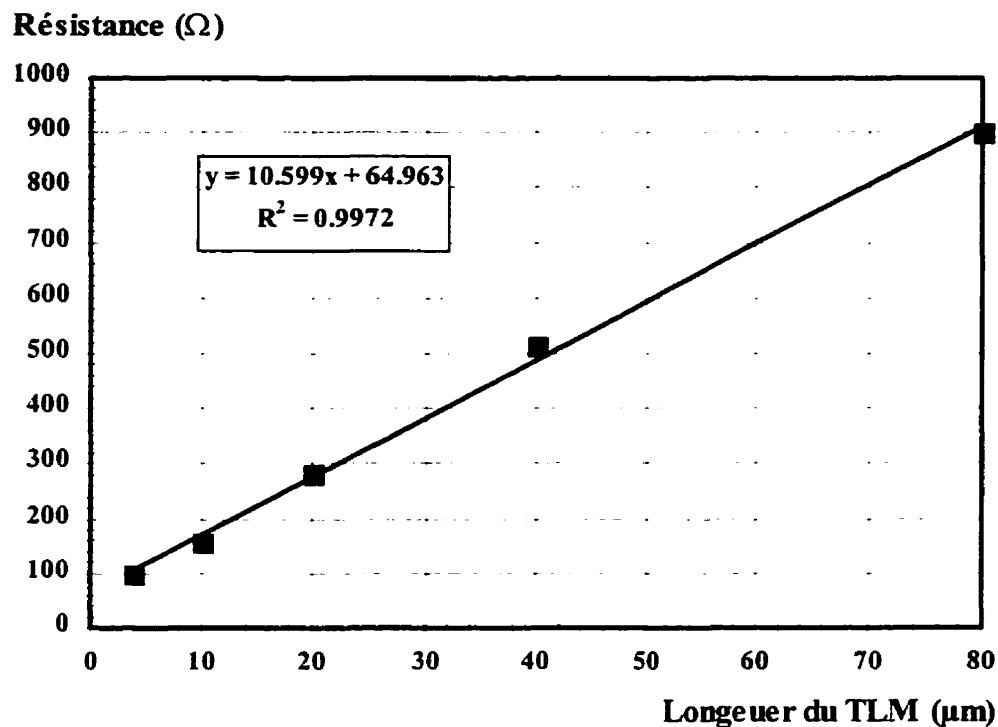

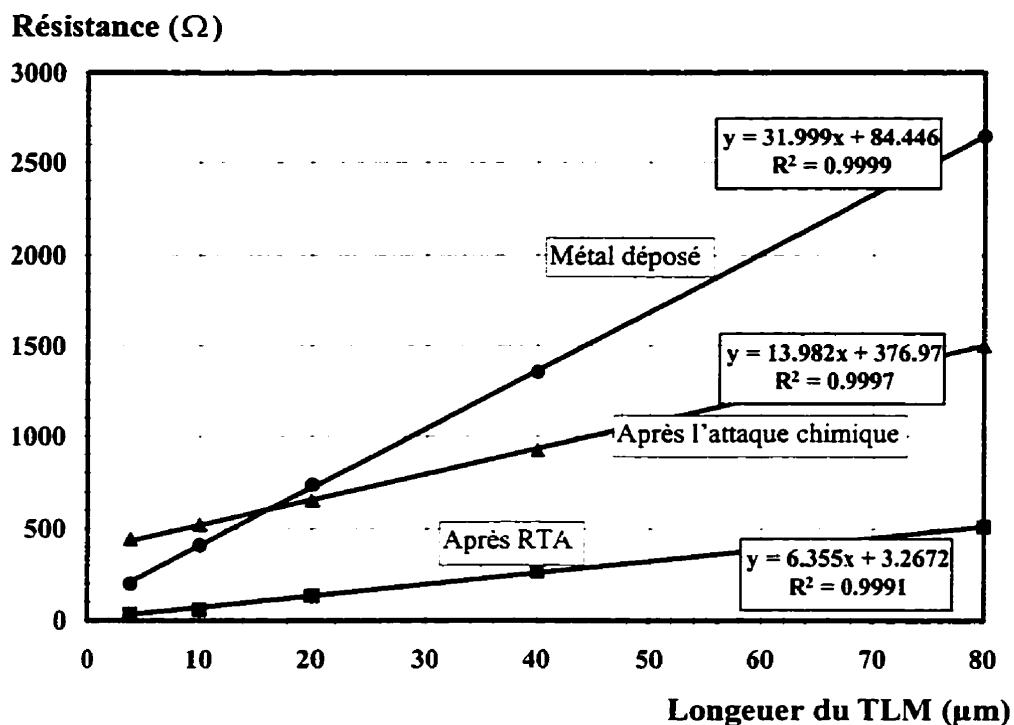

| Tableau 6.1: | Influence technologique sur les performances des TLMs .....      | 119 |

| Tableau 6.2: | Résistances des couches métalliques et des contacts .....        | 125 |

## Liste des figures

|             |                                                                         |    |

|-------------|-------------------------------------------------------------------------|----|

| Figure 1.1: | Déroulement des travaux présentés dans la thèse .....                   | 7  |

| Figure 2.1: | Section transversale dans le HIGFET .....                               | 13 |

| Figure 2.2: | Épaisseurs des couches qui forment la structure HIGFET .....            | 16 |

| Figure 2.3: | Hétérostructure InAlAs/InGaAs/InP .....                                 | 17 |

| Figure 2.4: | Diagrammes énergétiques de la bande de conduction à l'équilibre: ..     | 19 |

|             | (a) Tension de grille plus grande que la tension de seuil;              |    |

|             | (b) Tension de grille plus petite que la tension de seuil.              |    |

| Figure 2.5: | Diagrammes de la bande de conduction au long du canal dans .....        | 20 |

|             | le régime stationnaire: (a) Canal fermé; (b) Canal ouvert.              |    |

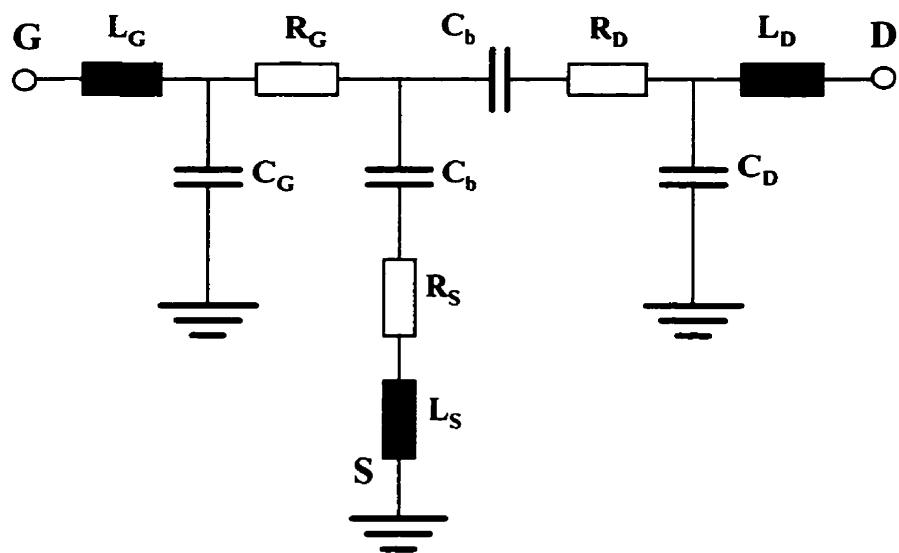

| Figure 3.1: | Circuit équivalent petit signal du HIGFET .....                         | 30 |

| Figure 3.2: | Circuit extrinsèque pour $V_{DS}=V_{GS}=0$ .....                        | 31 |

| Figure 3.3: | Circuit équivalent pour $V_{DS}=0$ et $V_{GS} < V_T$ .....              | 33 |

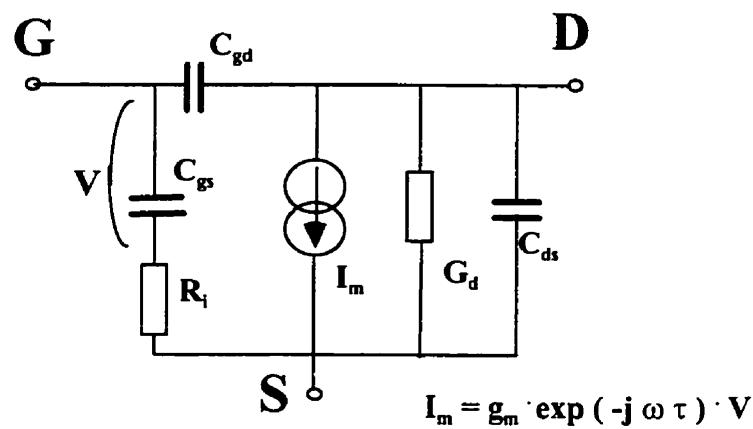

| Figure 3.4: | Circuit équivalent intrinsèque .....                                    | 34 |

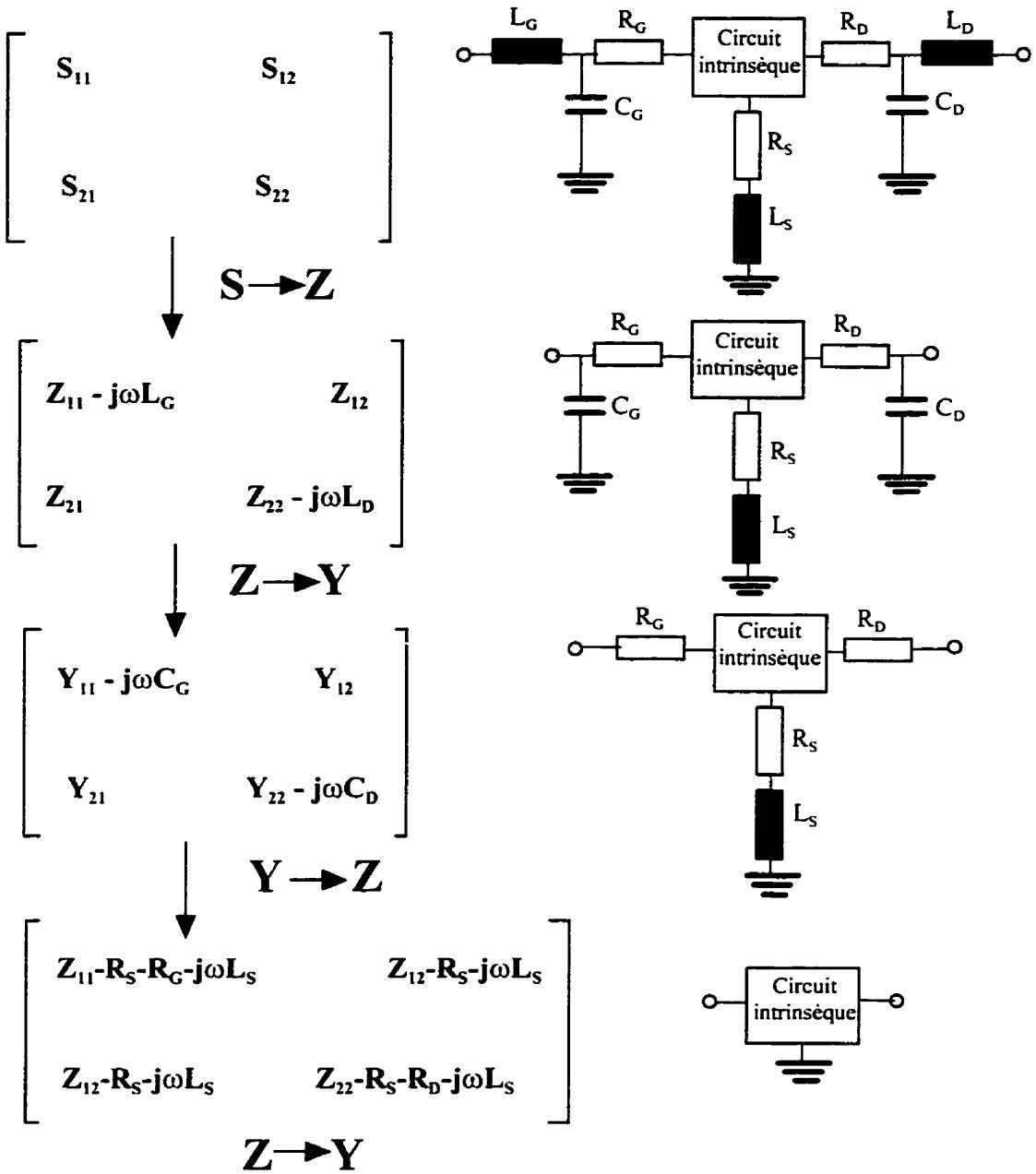

| Figure 3.5: | Extraction des paramètres extrinsèques .....                            | 36 |

| Figure 3.6: | Déduction expérimentale du modèle du HIGFET .....                       | 38 |

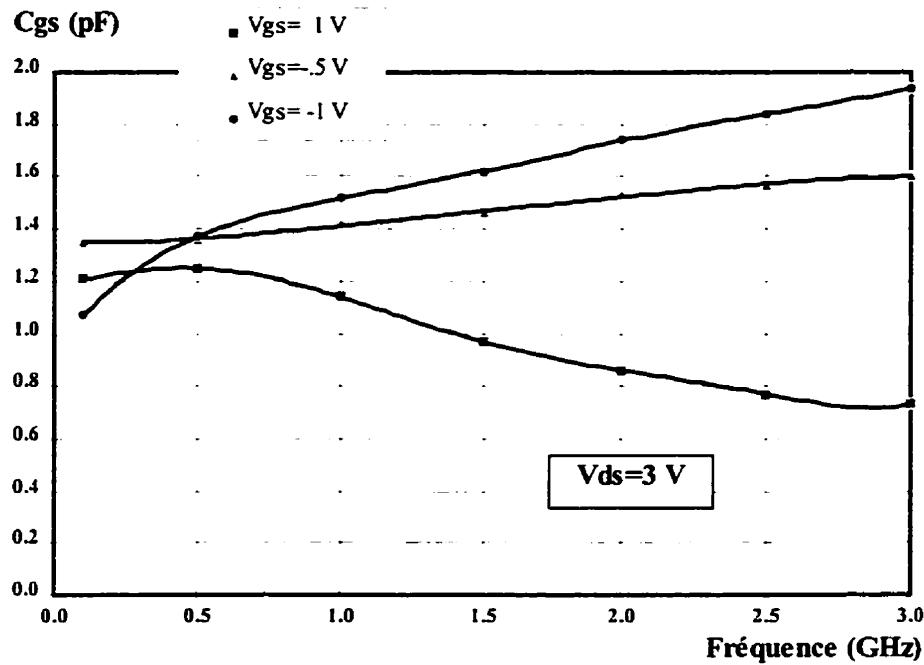

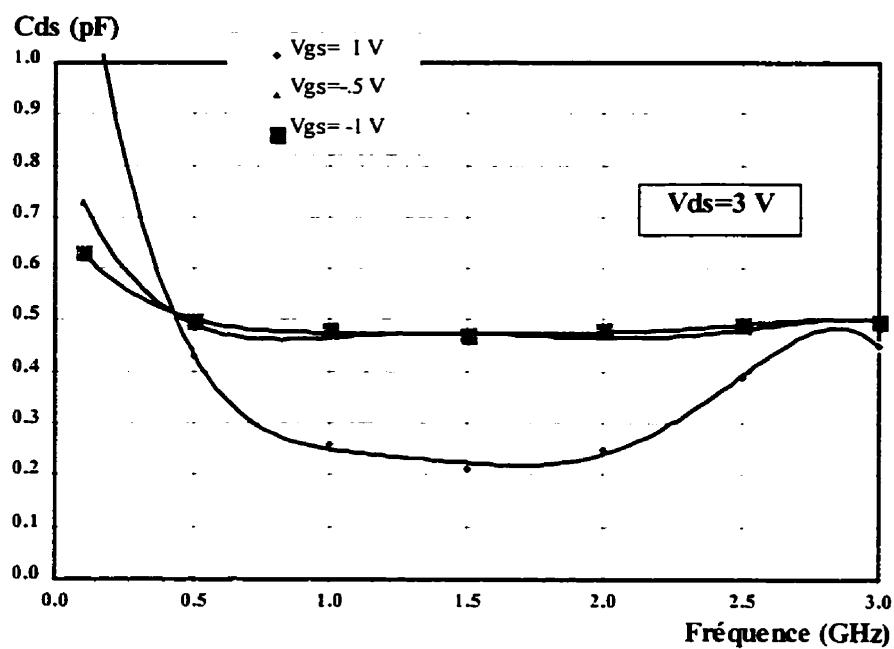

| Figure 3.7: | Influence de la fréquence et de la tension de grille sur $C_{gs}$ ..... | 42 |

| Figure 3.8: | Influence de la fréquence et de la tension de drain sur $C_{gs}$ .....  | 42 |

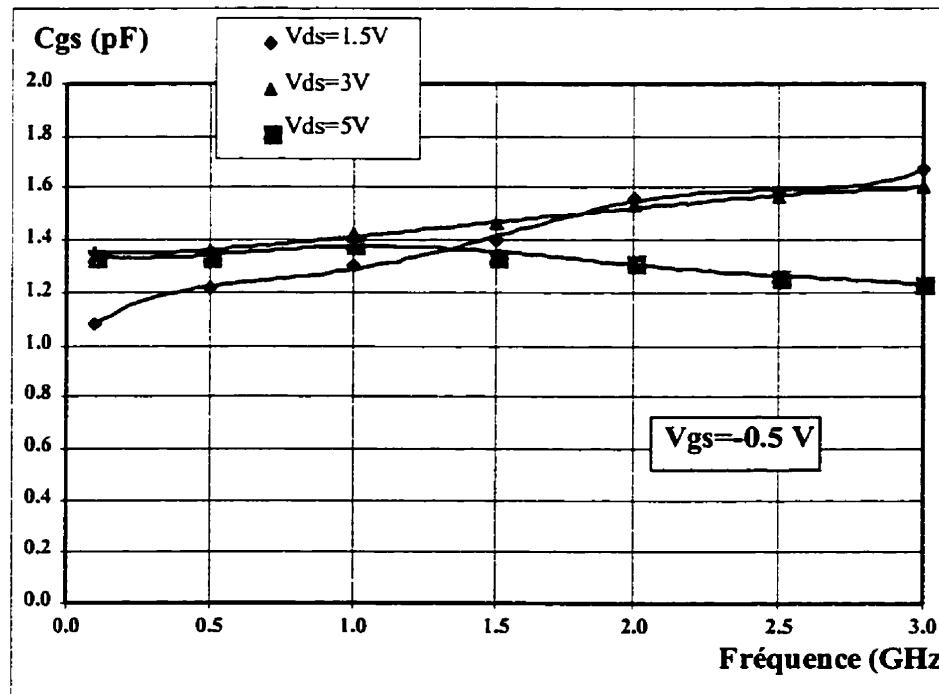

| Figure 3.9: | Influence de la fréquence et de la tension de grille sur $C_{gd}$ ..... | 44 |

|              |                                                                   |    |

|--------------|-------------------------------------------------------------------|----|

| Figure 3.10: | Influence de la fréquence et de la tension de drain sur $C_{gd}$  | 44 |

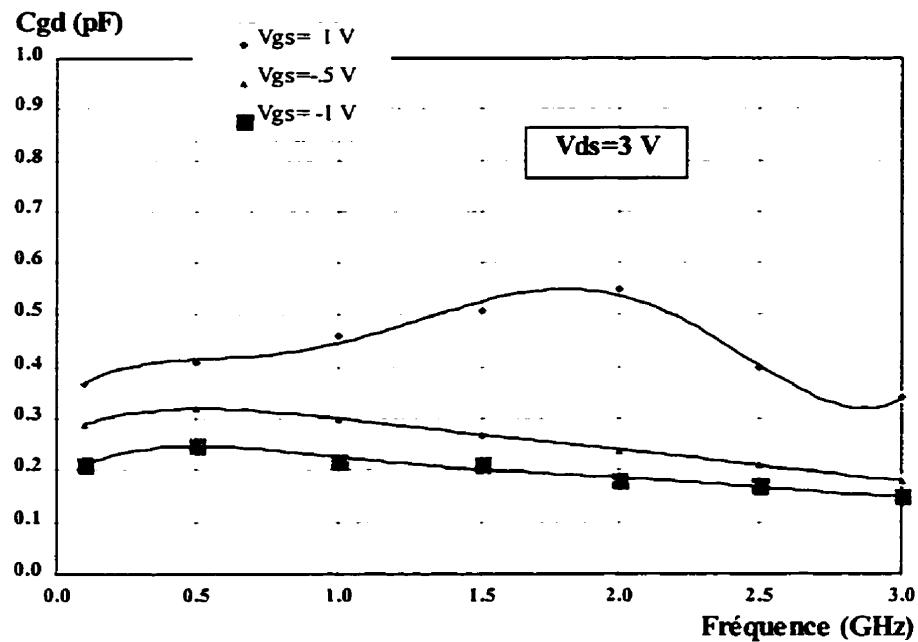

| Figure 3.11: | Influence de la fréquence et de la tension de grille sur $C_{ds}$ | 45 |

| Figure 3.12: | Influence de la fréquence et de la tension de drain sur $C_{ds}$  | 46 |

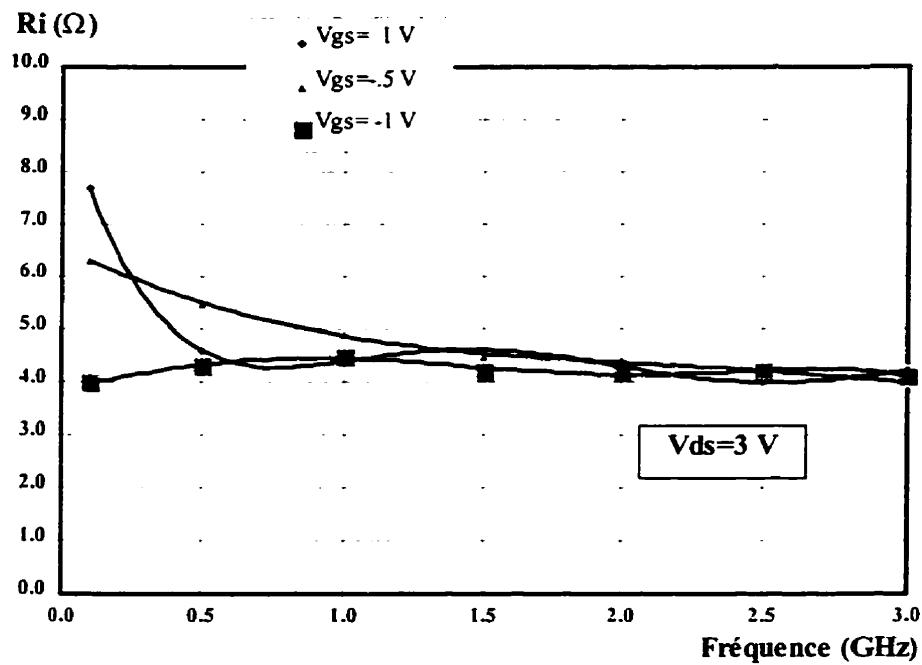

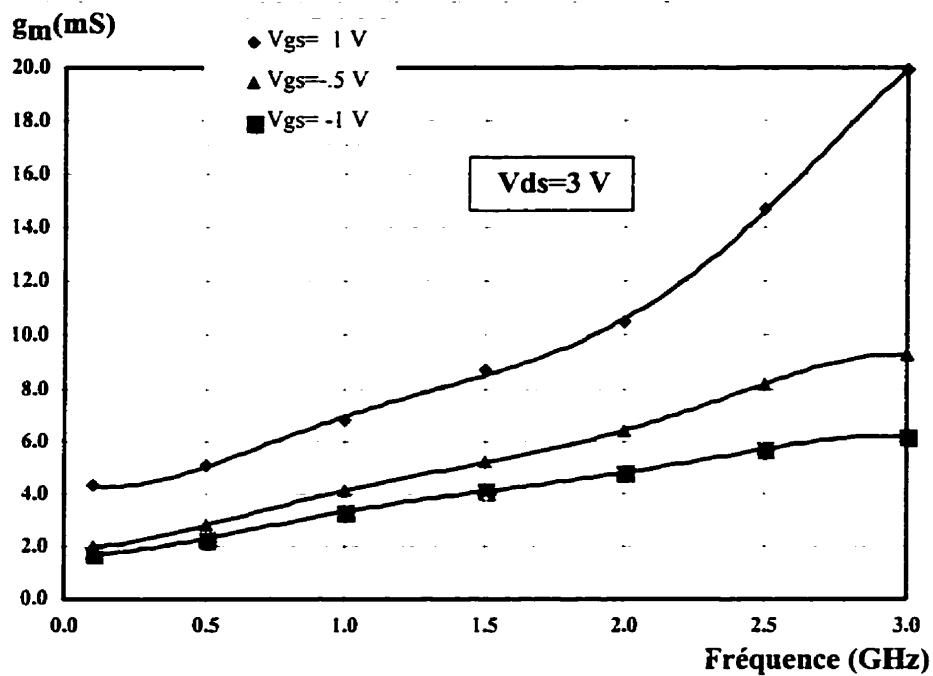

| Figure 3.13: | Influence de la fréquence et de la tension de grille sur $R_i$    | 47 |

| Figure 3.14: | Influence de la fréquence et de la tension de drain sur $R_i$     | 47 |

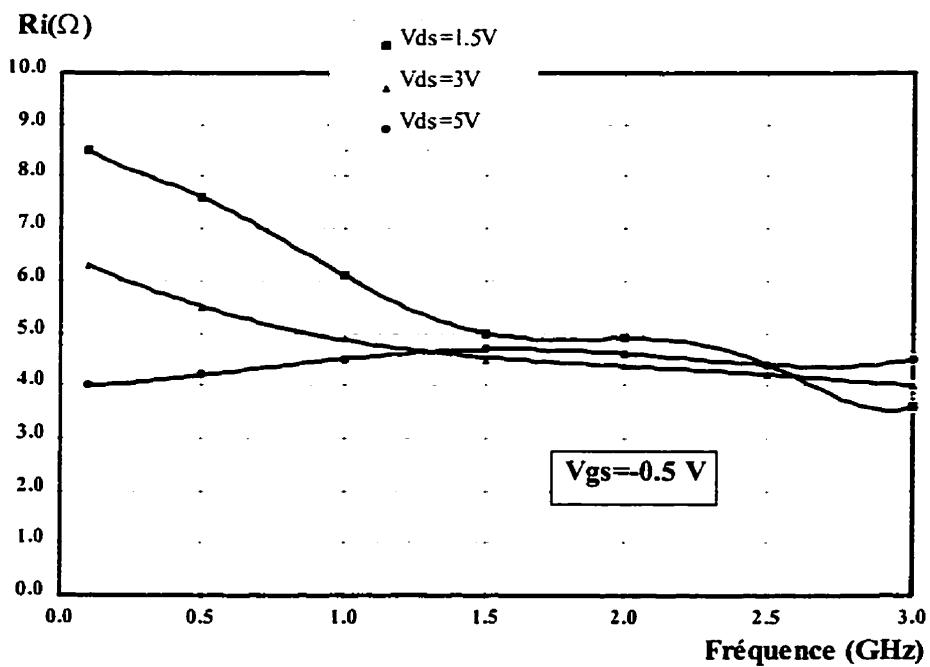

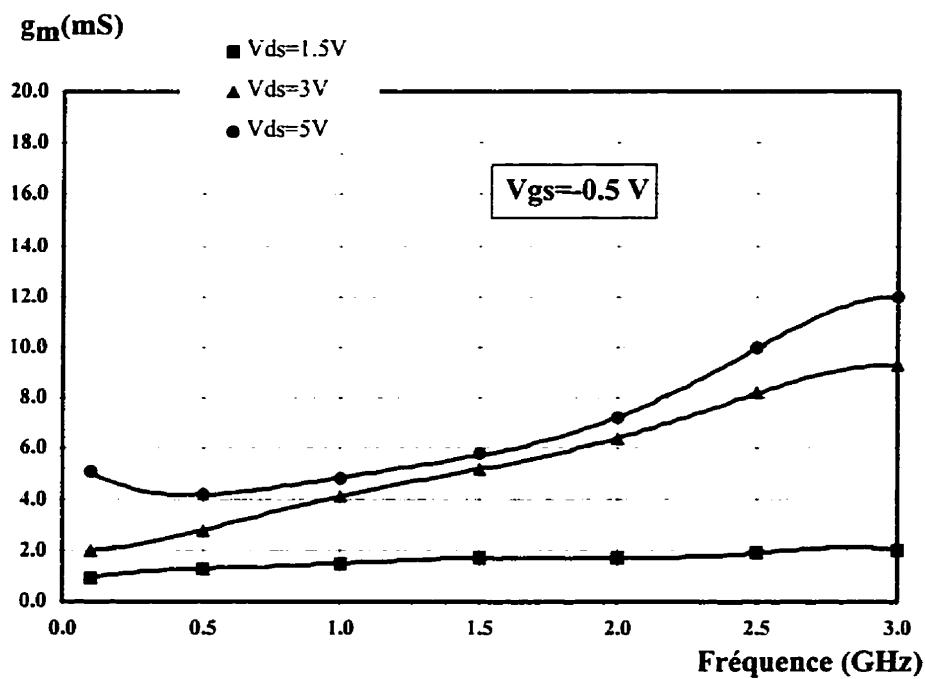

| Figure 3.15: | Influence de la fréquence et de la tension de grille sur $g_m$    | 49 |

| Figure 3.16: | Influence de la fréquence et de la tension de drain sur $g_m$     | 49 |

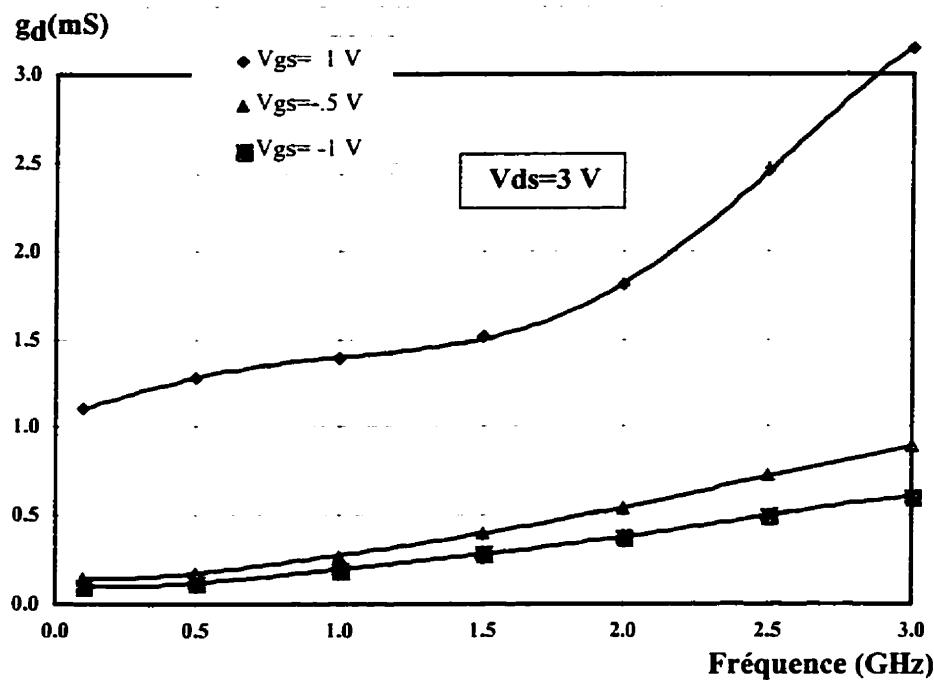

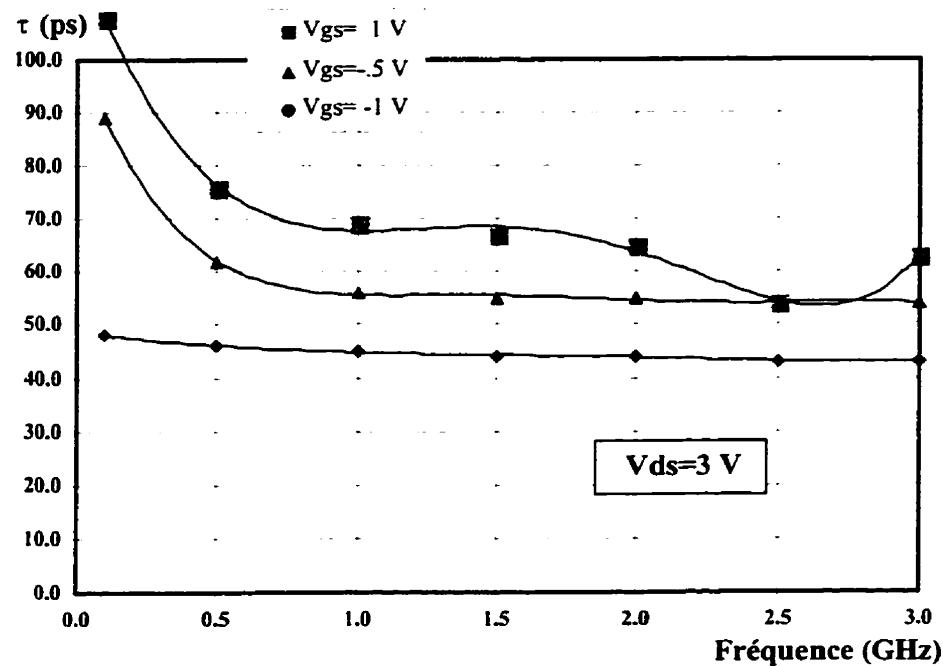

| Figure 3.17: | Influence de la fréquence et de la tension de grille sur $g_d$    | 50 |

| Figure 3.18: | Influence de la fréquence et de la tension de drain sur $g_d$     | 50 |

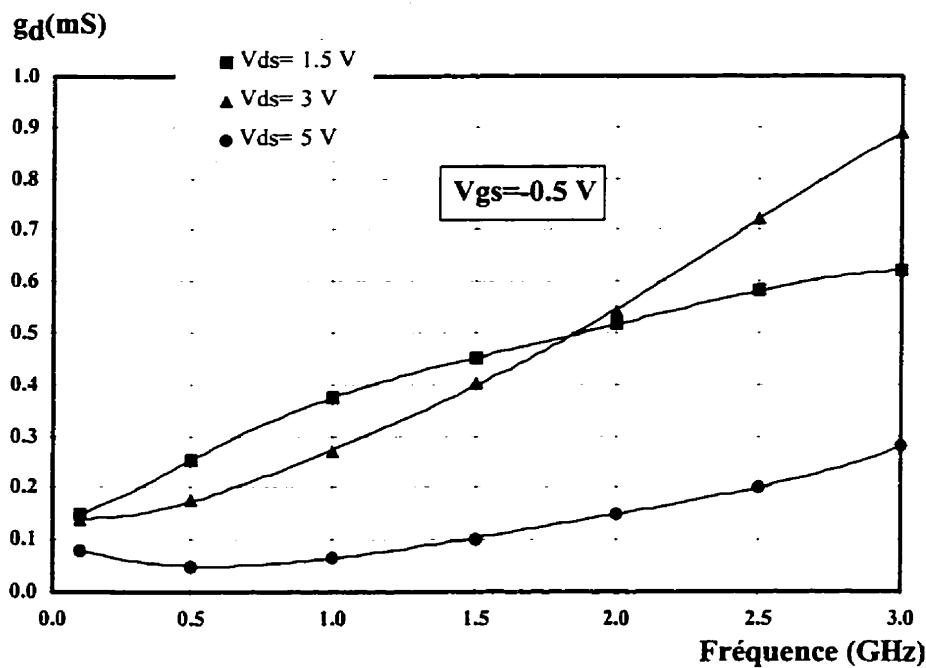

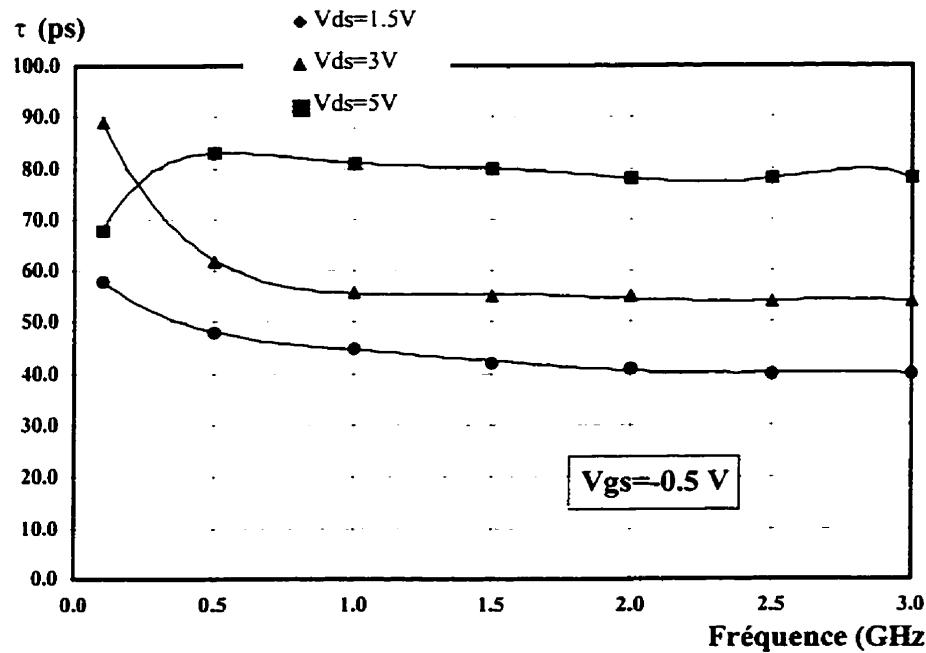

| Figure 3.19: | Influence de la fréquence et de la tension de grille sur $\tau$   | 51 |

| Figure 3.20: | Influence de la fréquence et de la tension de drain sur $\tau$    | 51 |

| Figure 3.21: | Modèle réduit du HIGFET                                           | 52 |

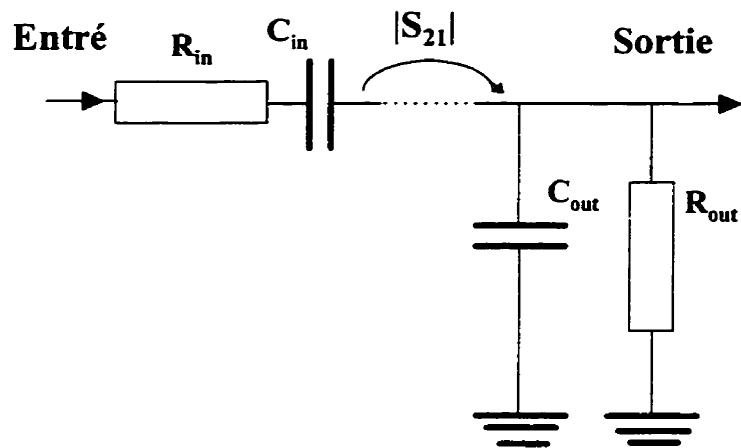

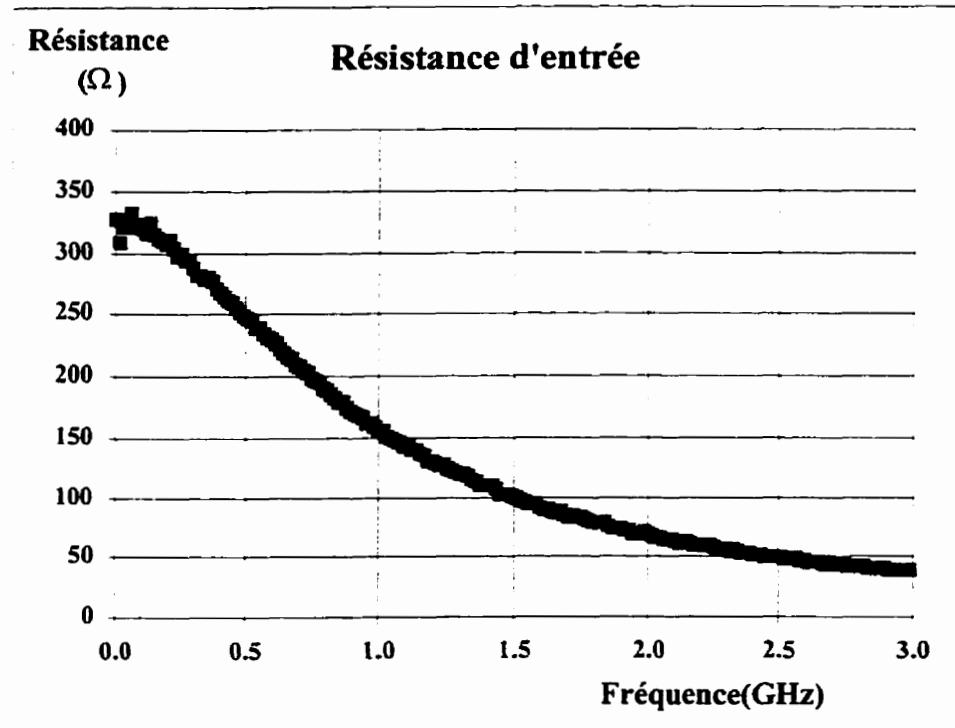

| Figure 3.22: | Variation avec la fréquence de la résistance d'entrée             | 53 |

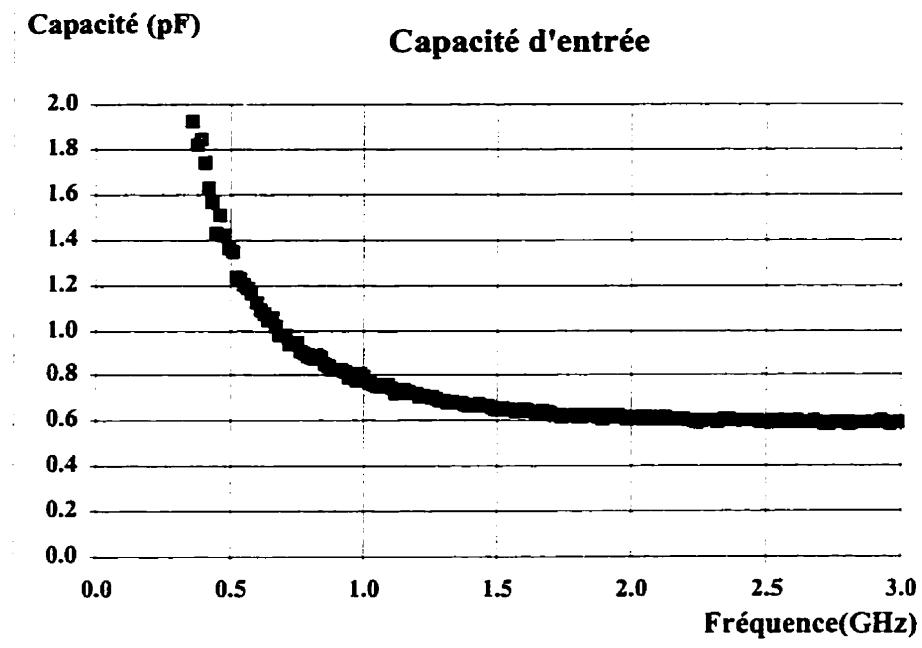

| Figure 3.23  | Variation avec la fréquence de la capacité d'entrée               | 54 |

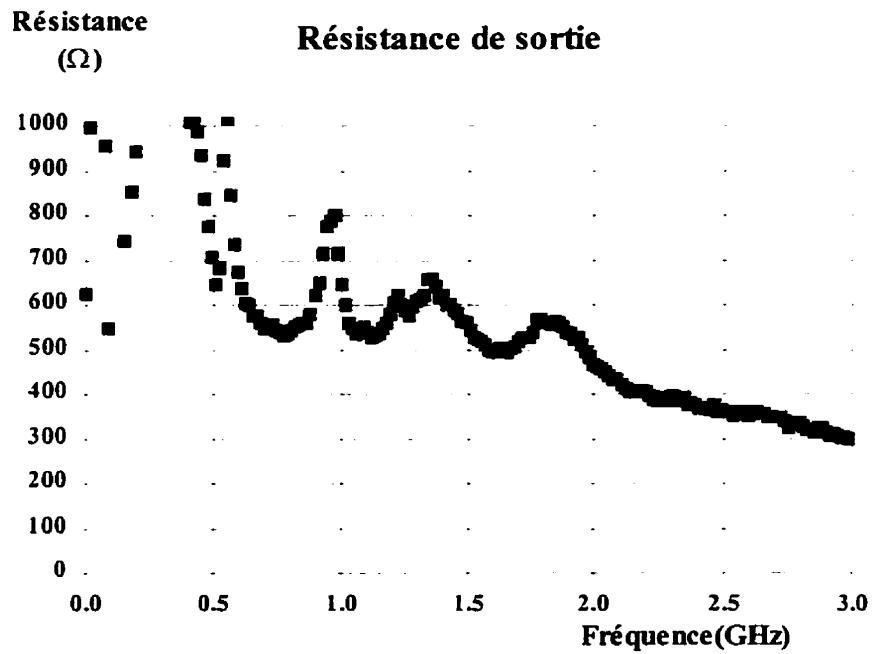

| Figure 3.24  | Variation avec la fréquence de la résistance de sortie            | 54 |

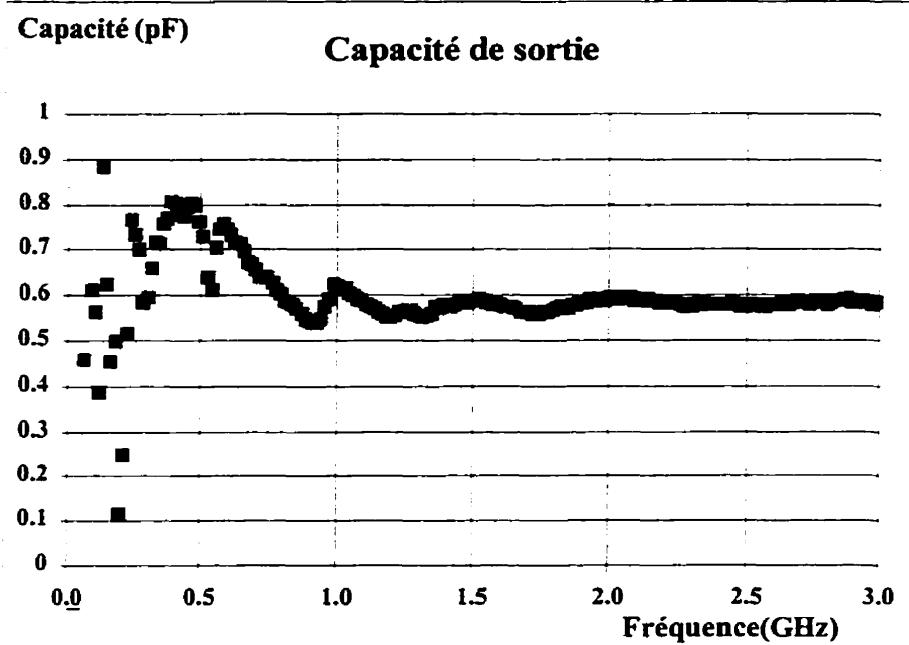

| Figure 3.25  | Variation avec la fréquence de la capacité de sortie              | 55 |

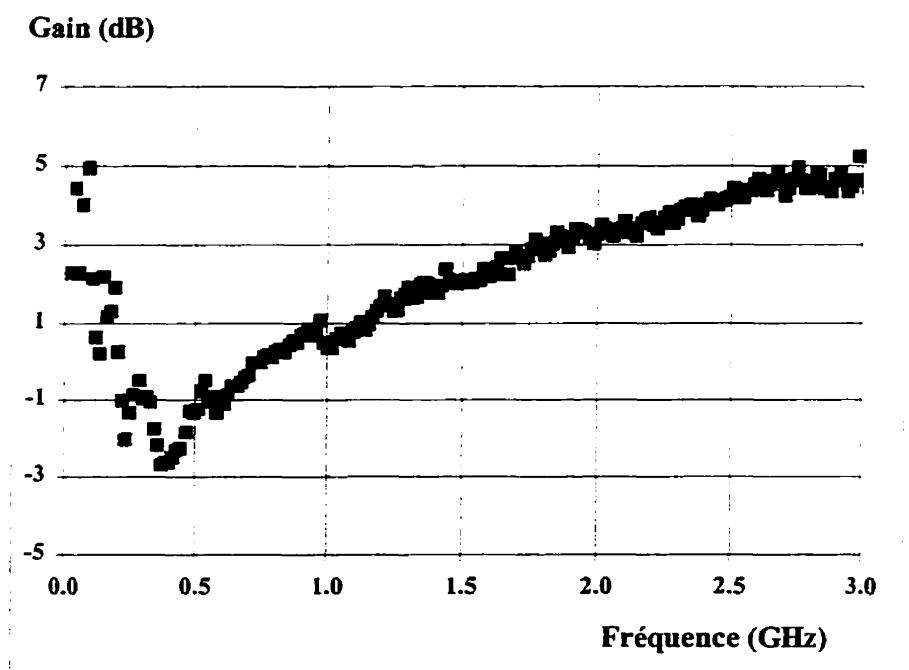

| Figure 3.26  | Variation avec la fréquence du gain                               | 55 |

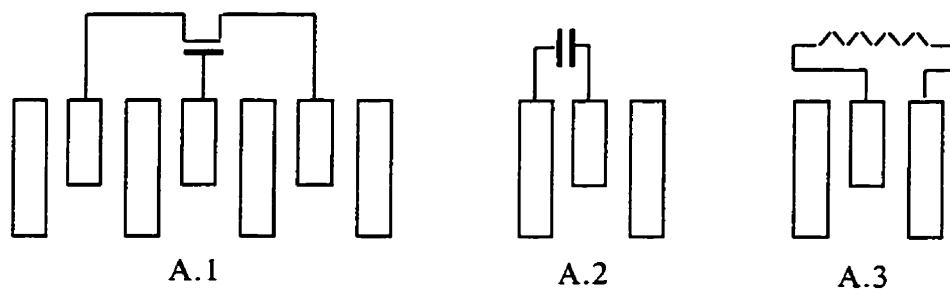

| Figure 4.1:  | Acquisition de données avec des circuits É&B                      | 57 |

| Figure 4.2:  | Architecture du système d'acquisition des données                 | 59 |

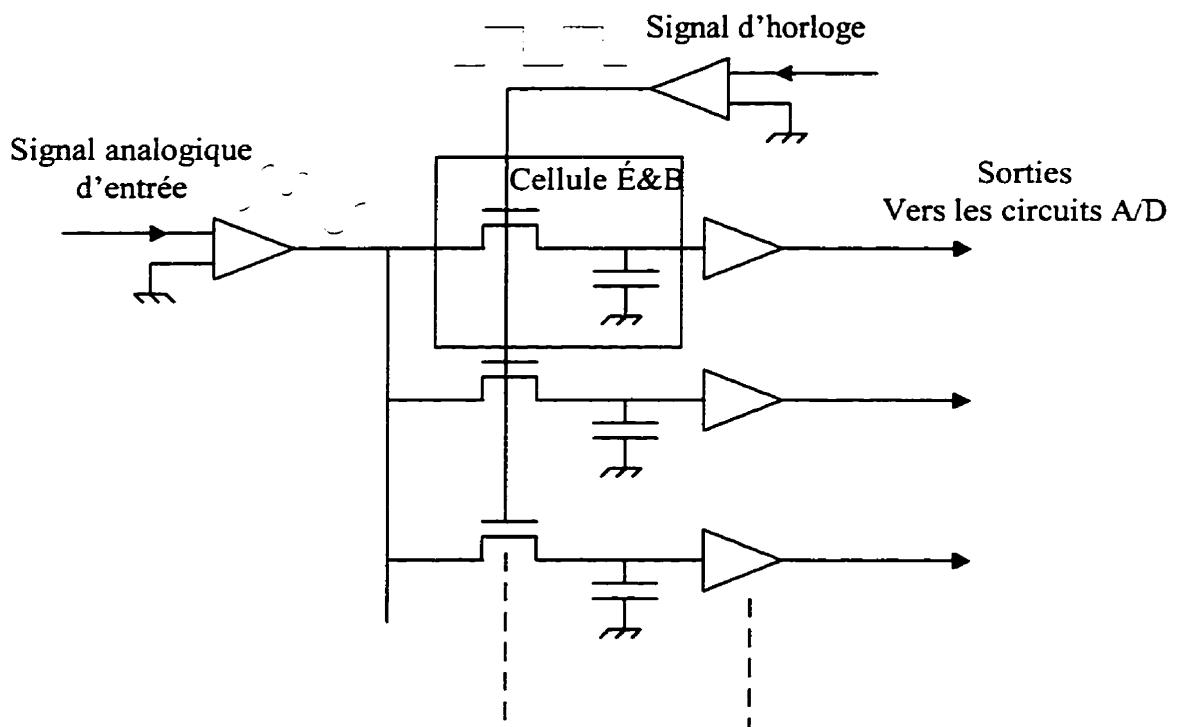

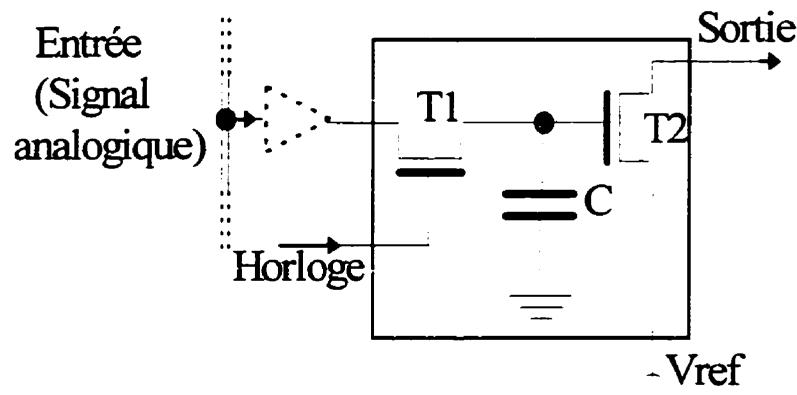

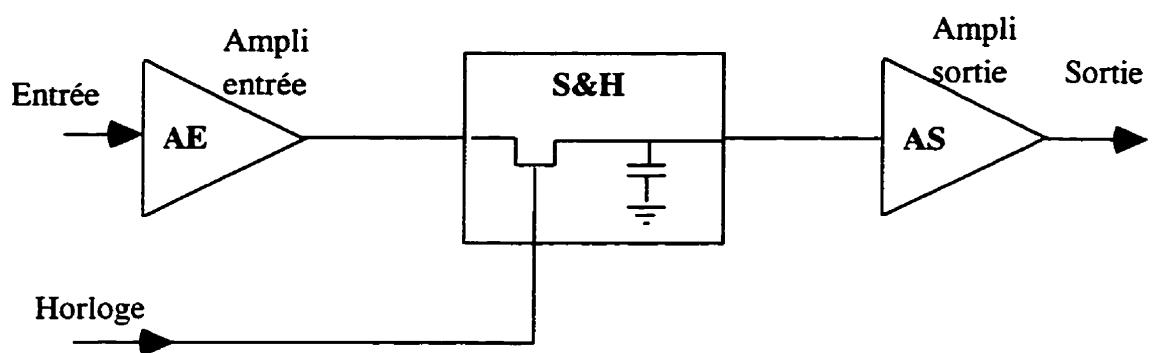

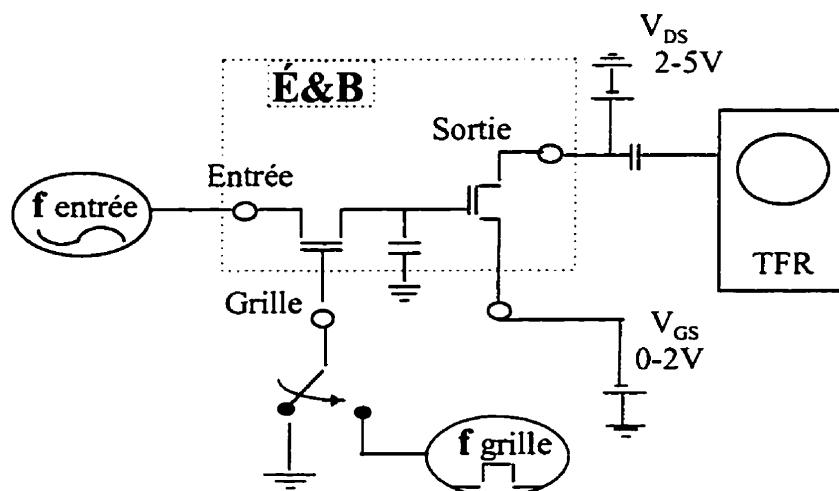

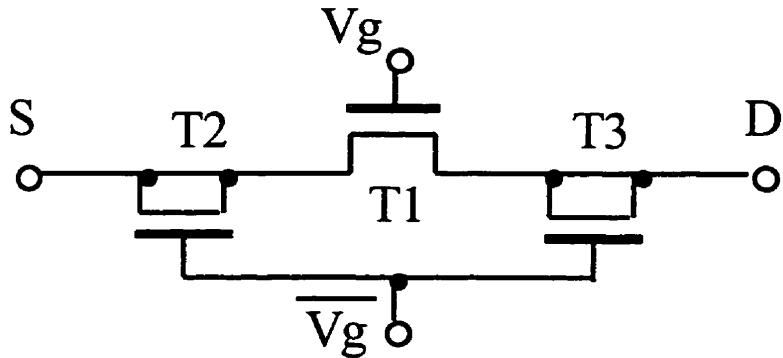

| Figure 4.3:  | Schéma de principe d'une cellule d'échantillonnage-blocage        | 66 |

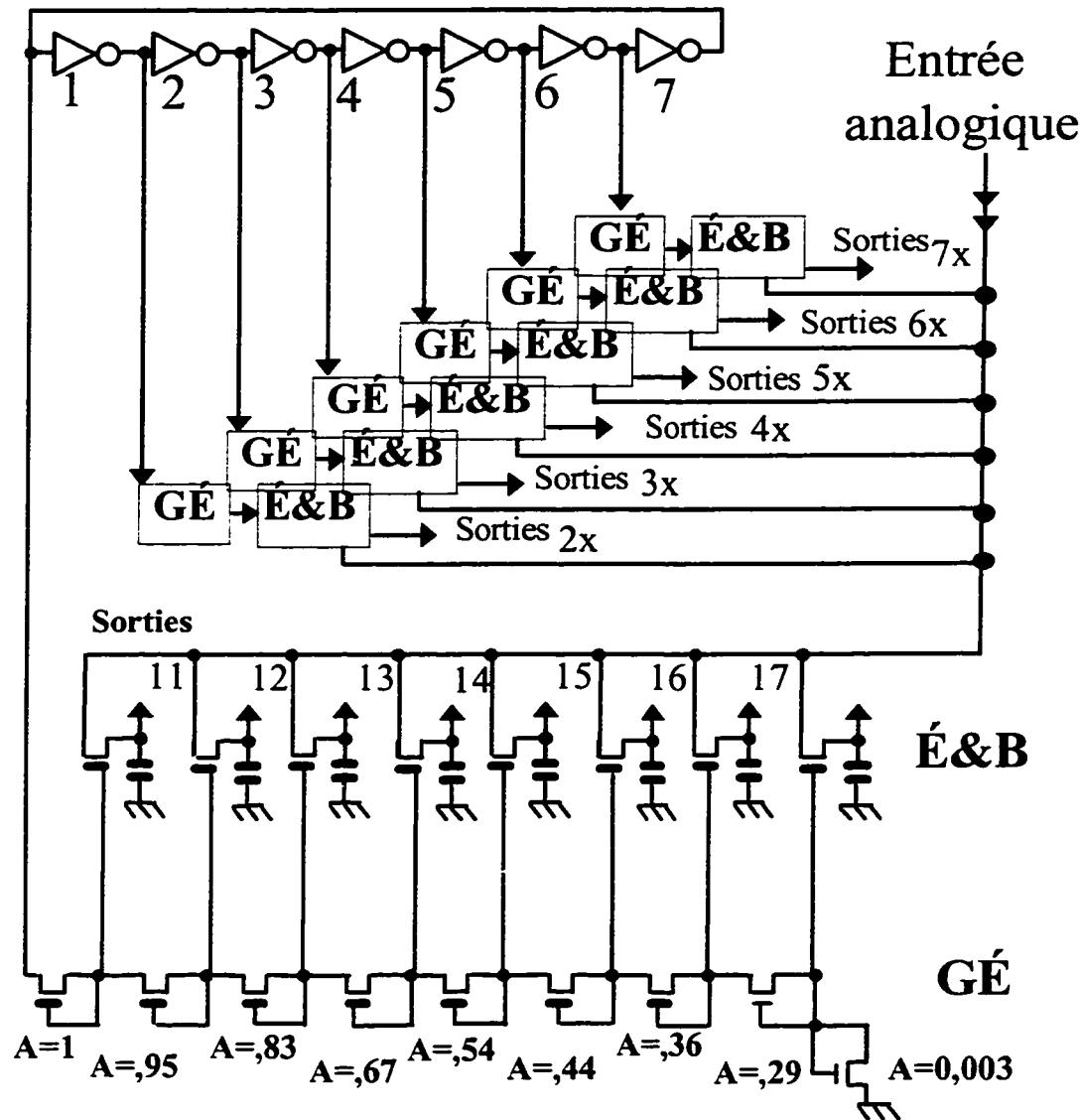

| Figure 4.4:  | Système É&B avec le circuit d'horloge intégré                     | 67 |

|               |                                                                           |    |

|---------------|---------------------------------------------------------------------------|----|

| Figure 4.5:   | Diagramme des signaux du système É&B avec le circuit<br>d'horloge intégré | 68 |

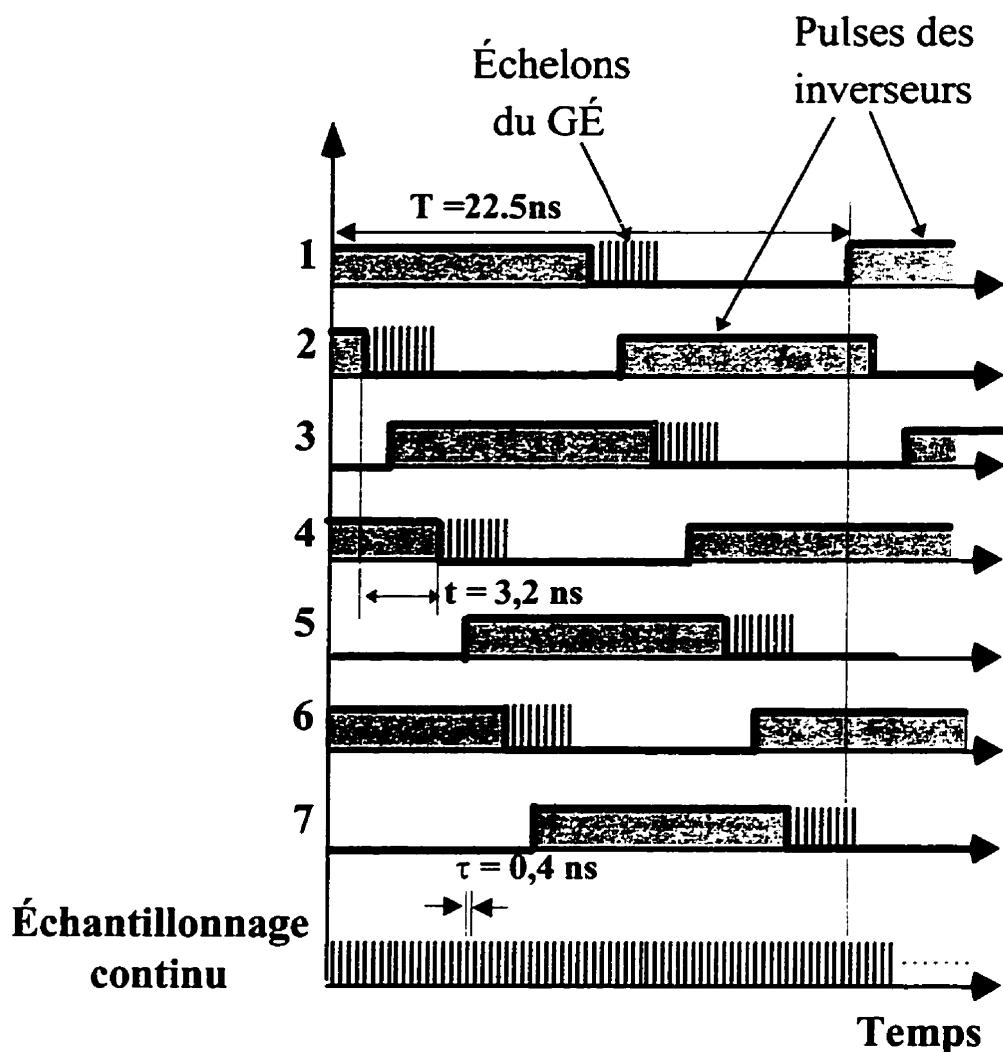

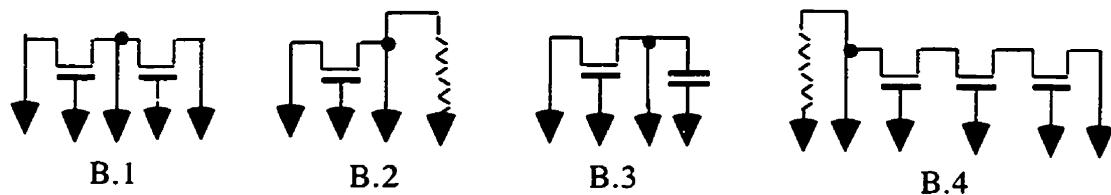

| Figure. 4.6 : | Circuit échantillonneur-bloqueur avec circuit d'horloge externe           | 69 |

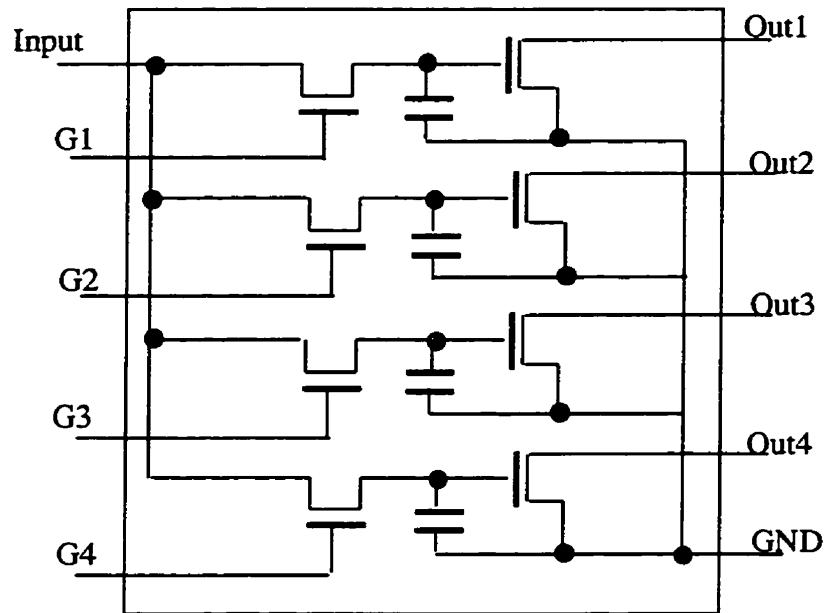

| Figure 4.7:   | Circuit intégrés avec quatre cellules É&B                                 | 70 |

| Figure 4.8 :  | Schéma d'un inverseur                                                     | 71 |

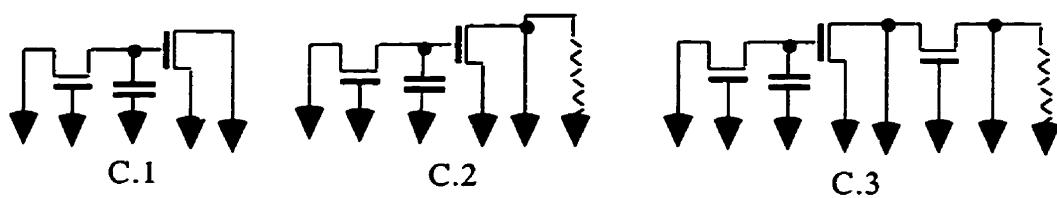

| Figure 4.9:   | Schéma électrique d'un oscillateur à 7 inverseurs                         | 73 |

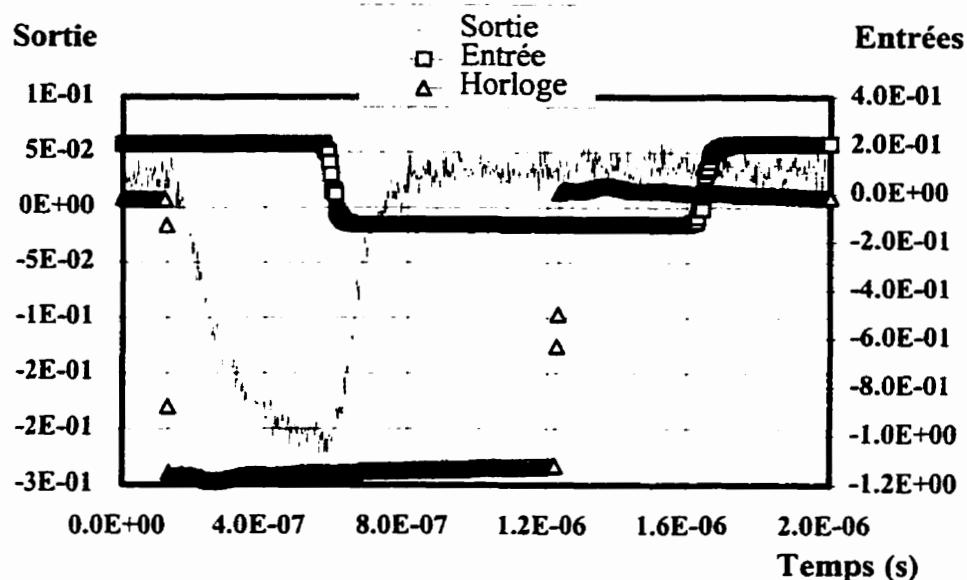

| Figure 4.10 : | Simulation de signaux générés par le circuit GÉ                           | 74 |

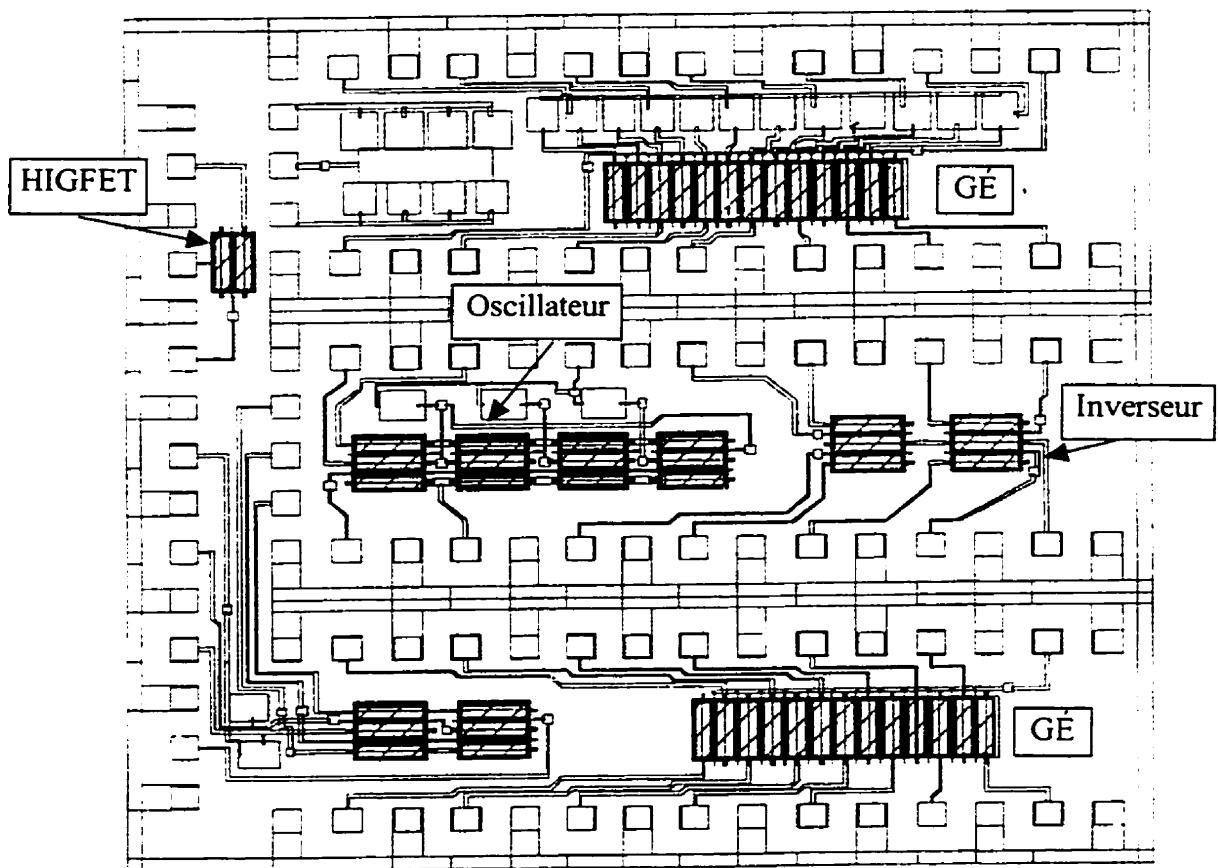

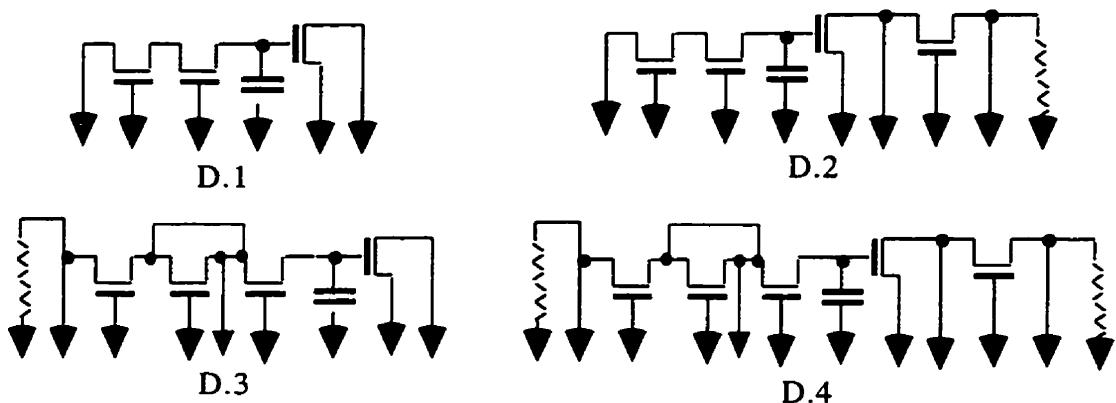

| Figure 4.11   | Jeu de masques SH1                                                        | 76 |

| Figure 4.12   | Jeu de masques SH2                                                        | 77 |

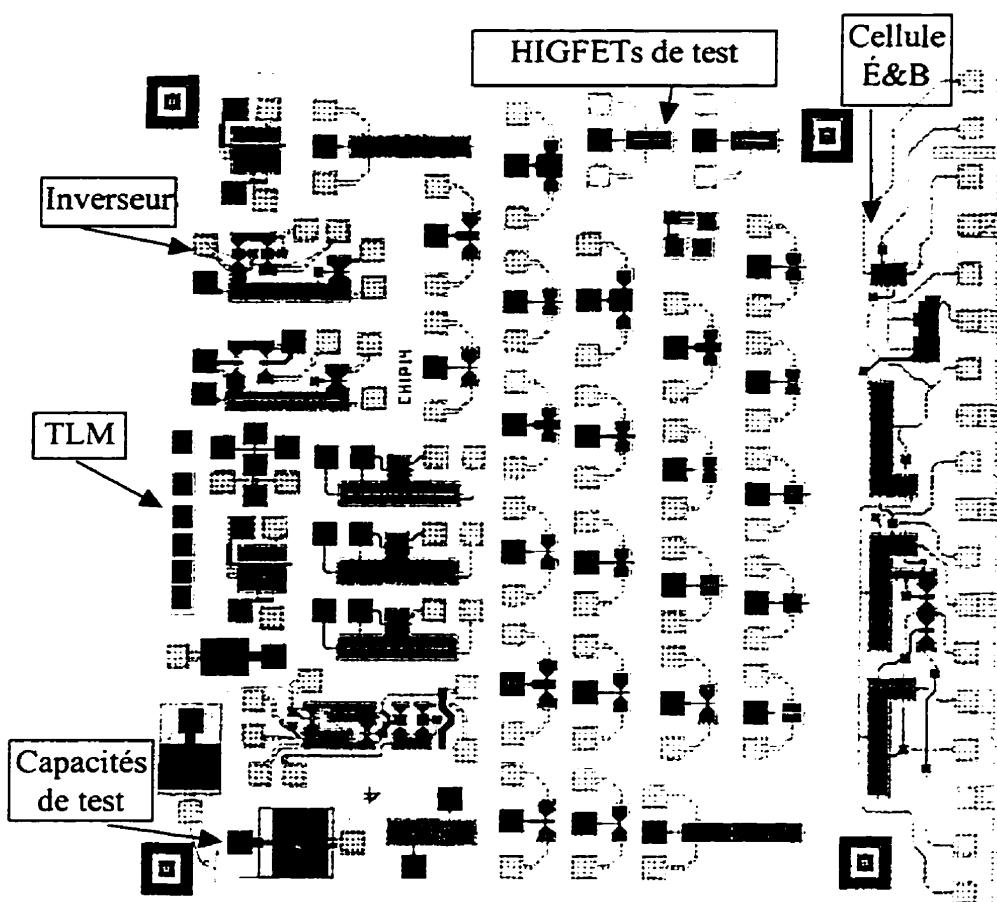

| Figure 4.13   | Jeu de masques SH3                                                        | 78 |

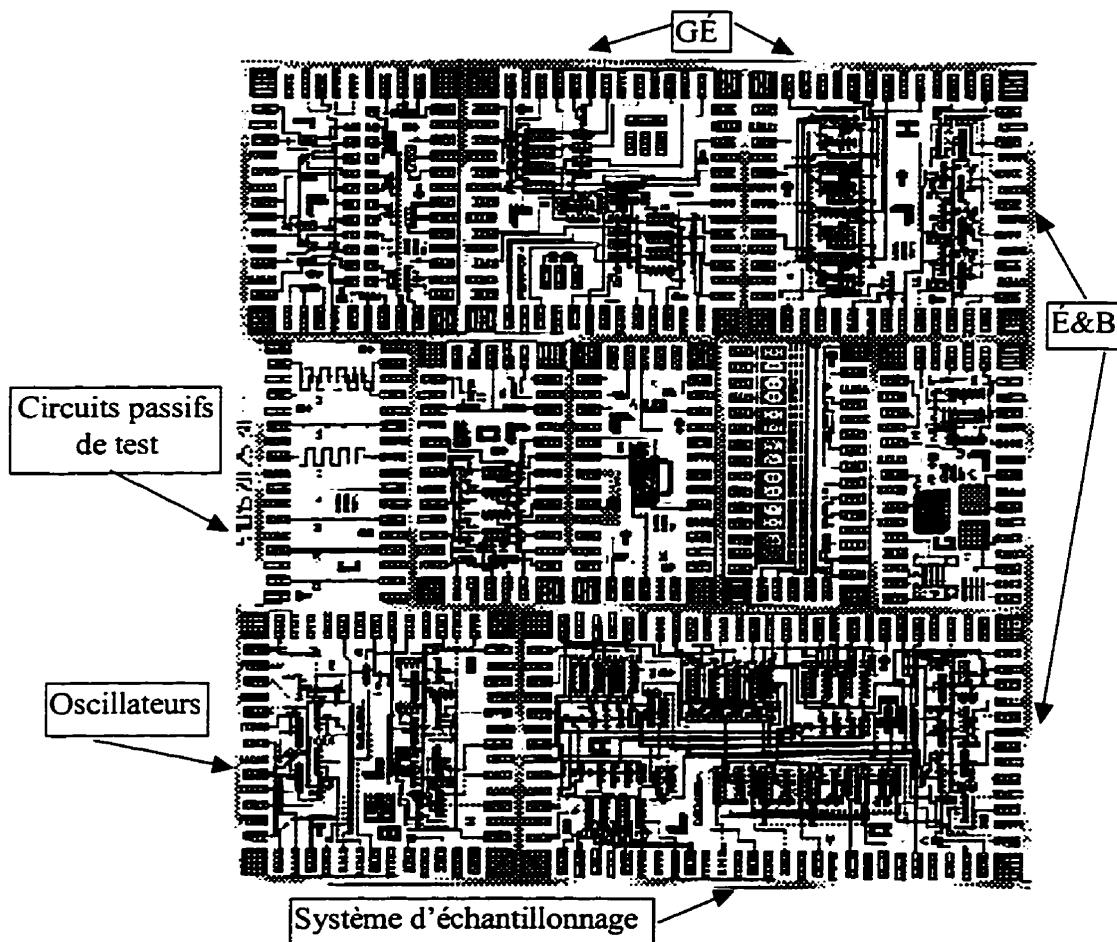

| Figure 4.14   | Jeu de masques SH4                                                        | 80 |

| Figure 4.15:  | Structure d'une cellule de l'échantillonneur                              | 82 |

| Figure 4.16:  | Structure de test pour les éléments discrets                              | 82 |

| Figure 4.17:  | Structure de test pour les circuits de base                               | 82 |

| Figure 4.18   | Structures d'échantillonneur avec amplificateur de sortie                 | 83 |

| Figure 4.19   | Structures d'échantillonneur avec amplificateur d'entrée<br>et de sortie  | 83 |

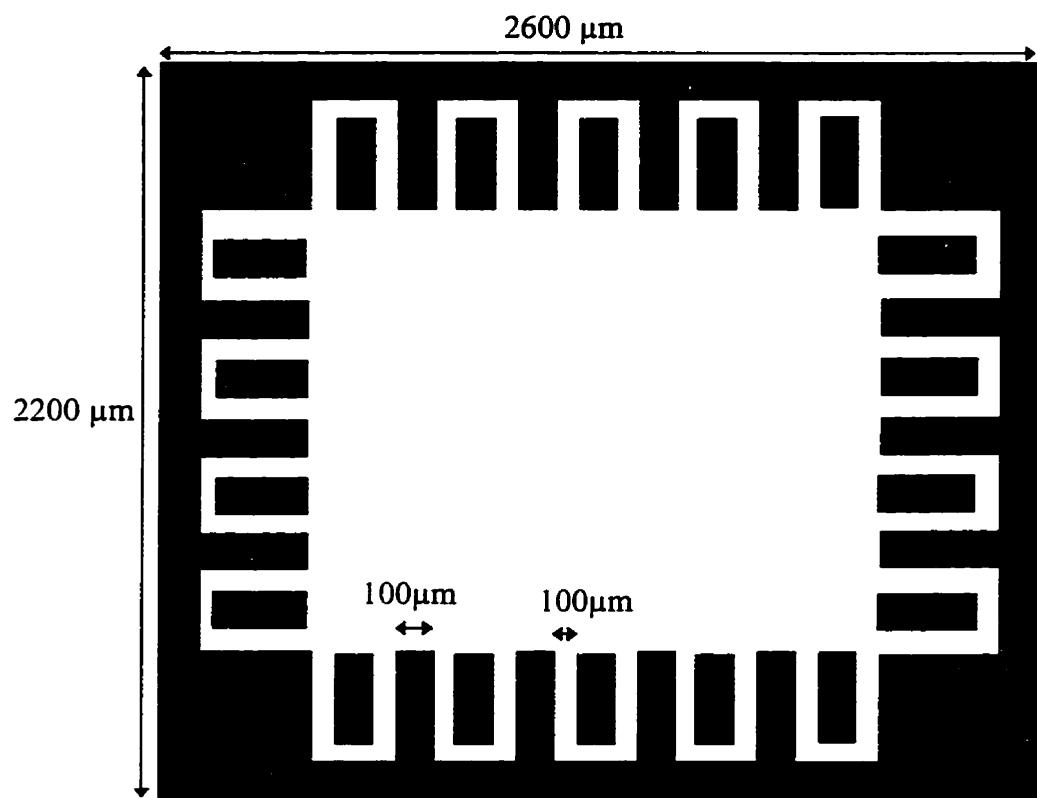

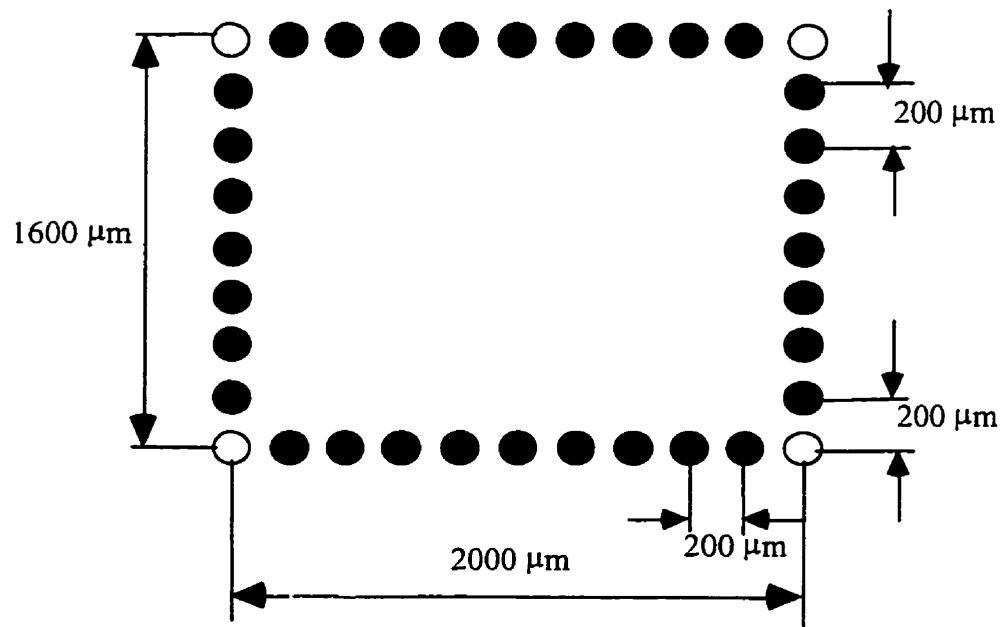

| Figure 4.20:  | Pads de mesure haute fréquence                                            | 84 |

| Figure 4.21:  | Pads de mesure pour courant continu et basse fréquence.                   | 84 |

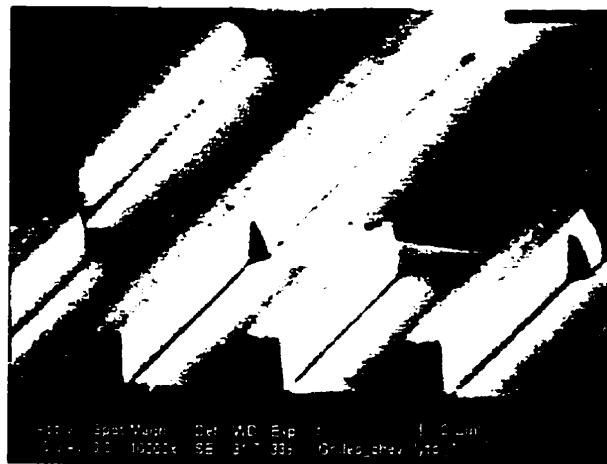

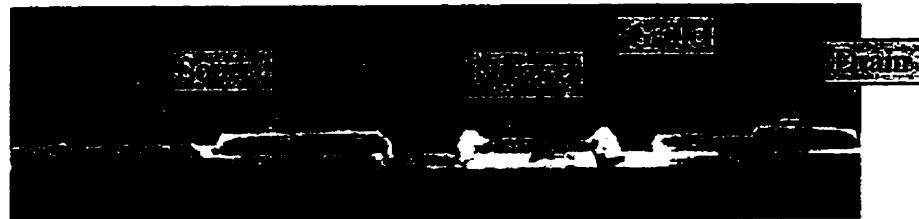

| Figure 5.1:   | Lithographie de grilles ( $0,8\mu\text{m}$ )                              | 87 |

| Figure 5.2:   | Lithographie de source et drain                                           | 88 |

|              |                                                                       |     |

|--------------|-----------------------------------------------------------------------|-----|

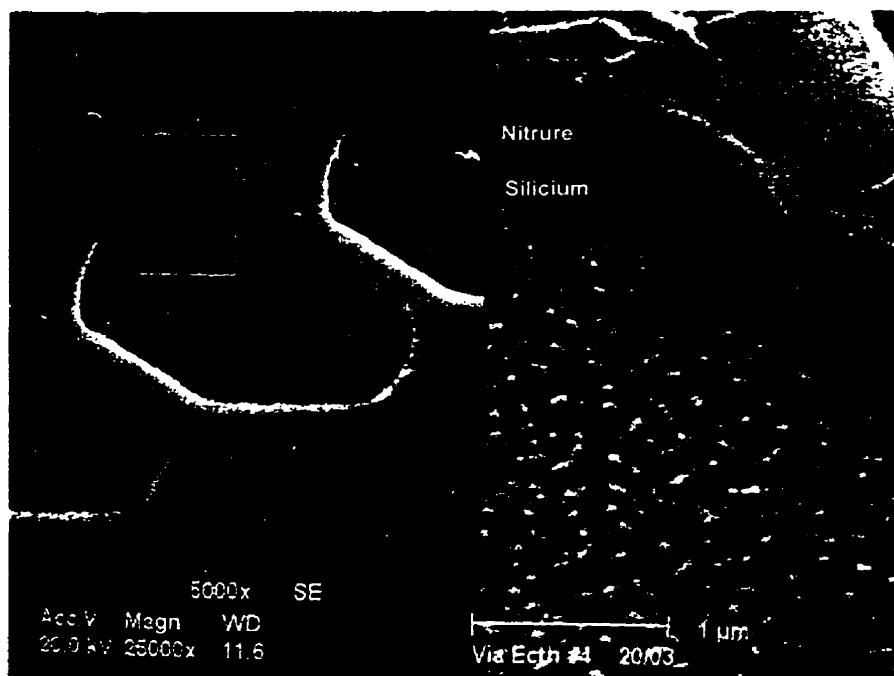

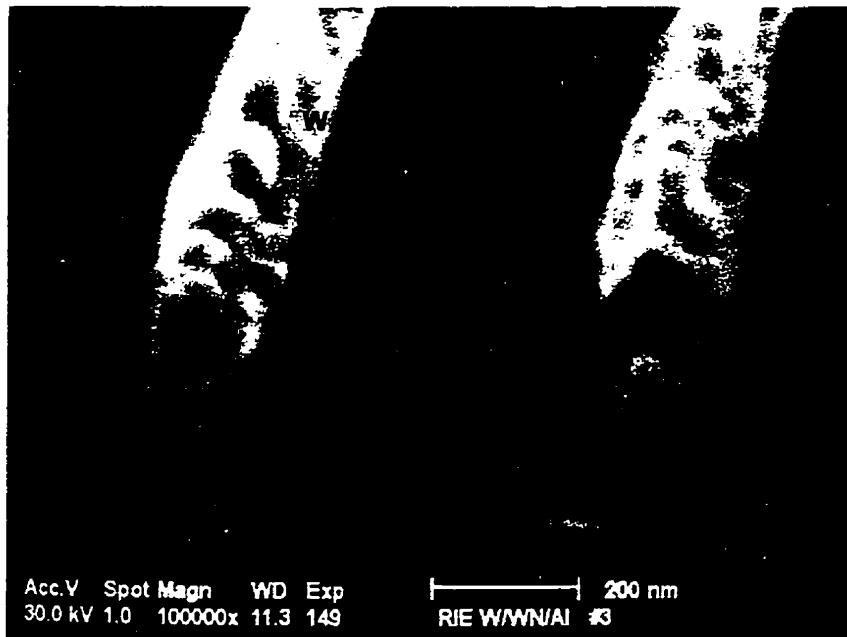

| Figure 5.3:  | Fenêtres de contact définies par RIE .....                            | 93  |

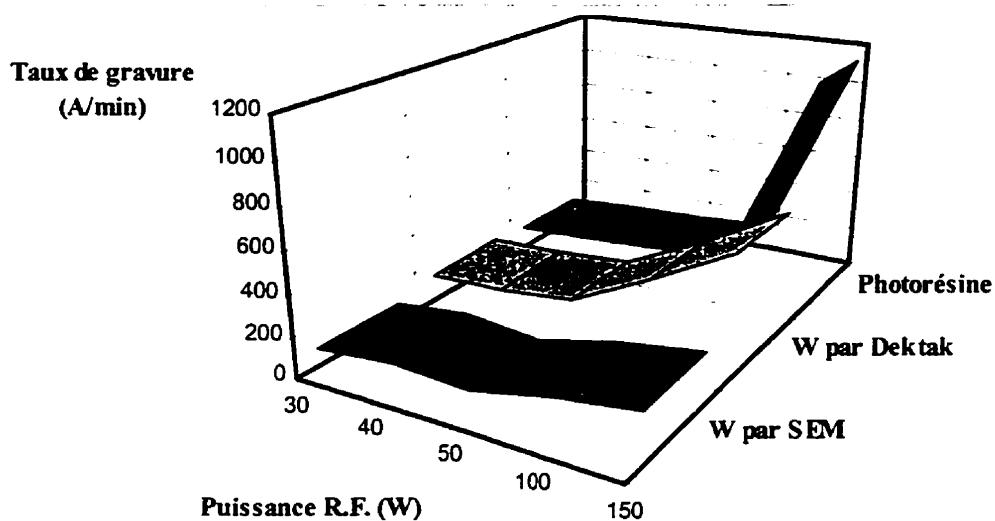

| Figure 5.4:  | Taux de gravure du W en fonction de la puissance R.F.....             | 94  |

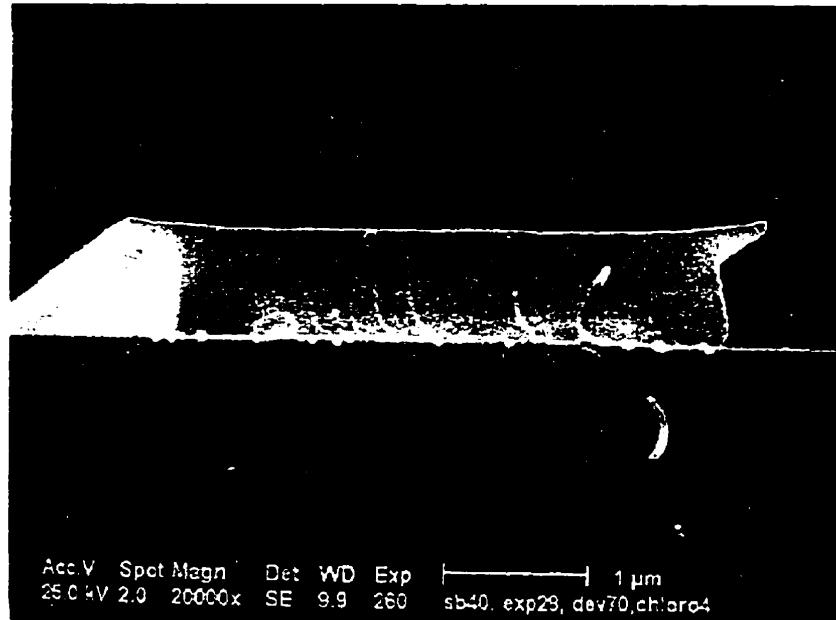

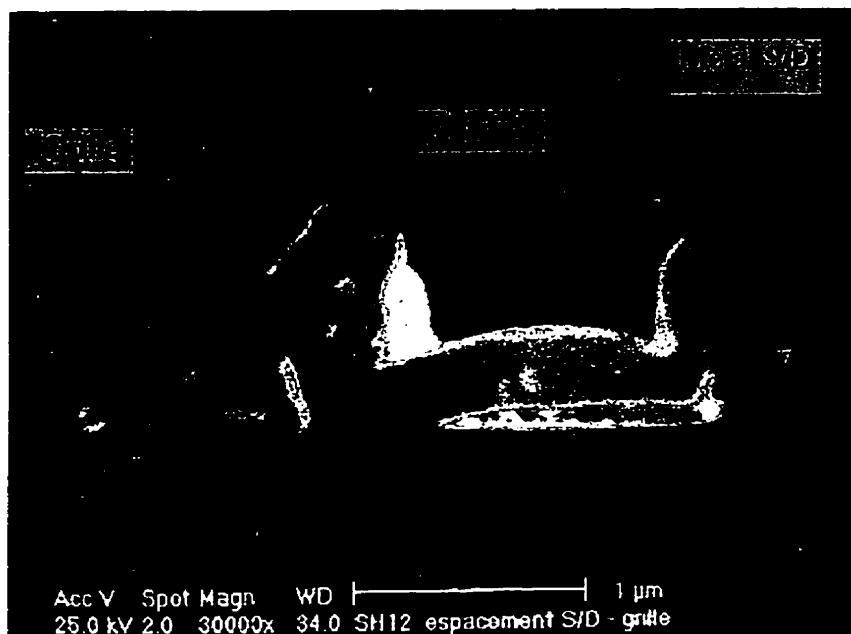

| Figure 5.5:  | Grille avec profile en forme de T .....                               | 95  |

| Figure 5.6:  | Grilles de tungstène avec longueur minimale .....                     | 95  |

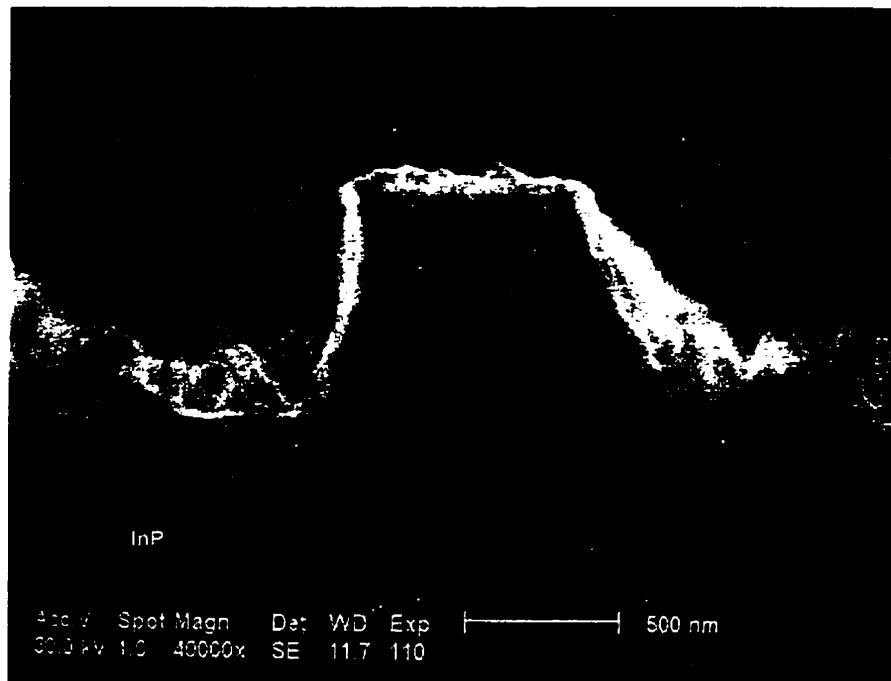

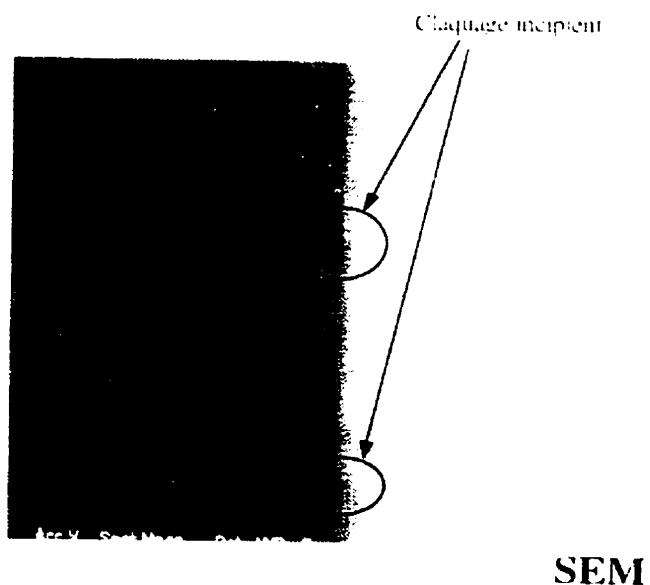

| Figure 5.8:  | Analyse SEM en section du HIGFET.....                                 | 98  |

|              | (a) Image d'ensemble; (b) Grille avec "moustaches"                    |     |

| Figure 5.9:  | Gravure RIE de W avec rédéposition accentuée.....                     | 101 |

| Figure 5.10: | Erreur carrée moyenne pour différents modèles de régression .....     | 103 |

| Figure 5.11: | Structure du RNA de type FFEBP .....                                  | 105 |

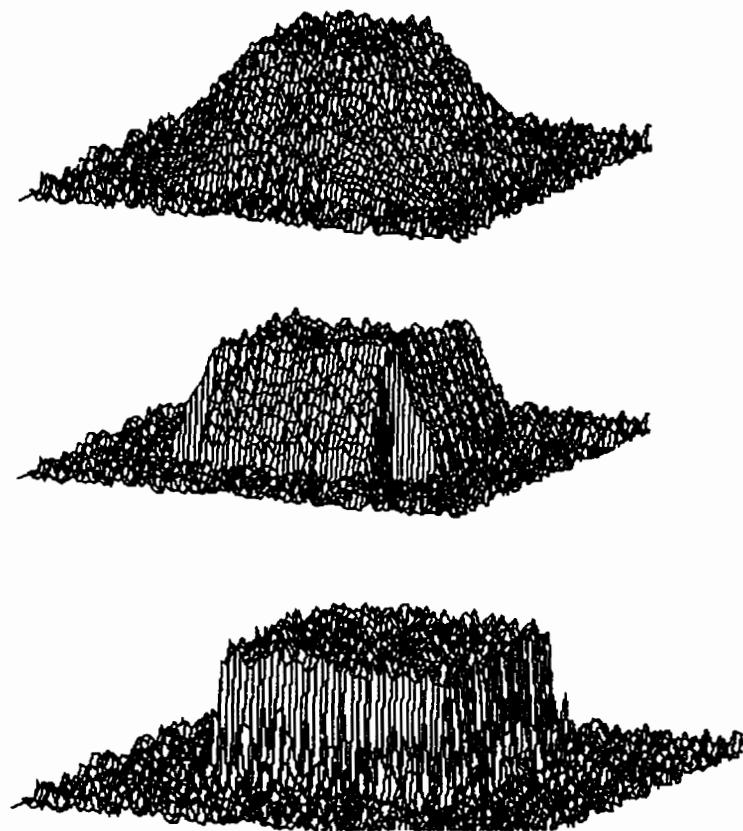

| Figure 5.12: | Effet de la géométrie de masque sur le profil simulé de gravure ..... | 109 |

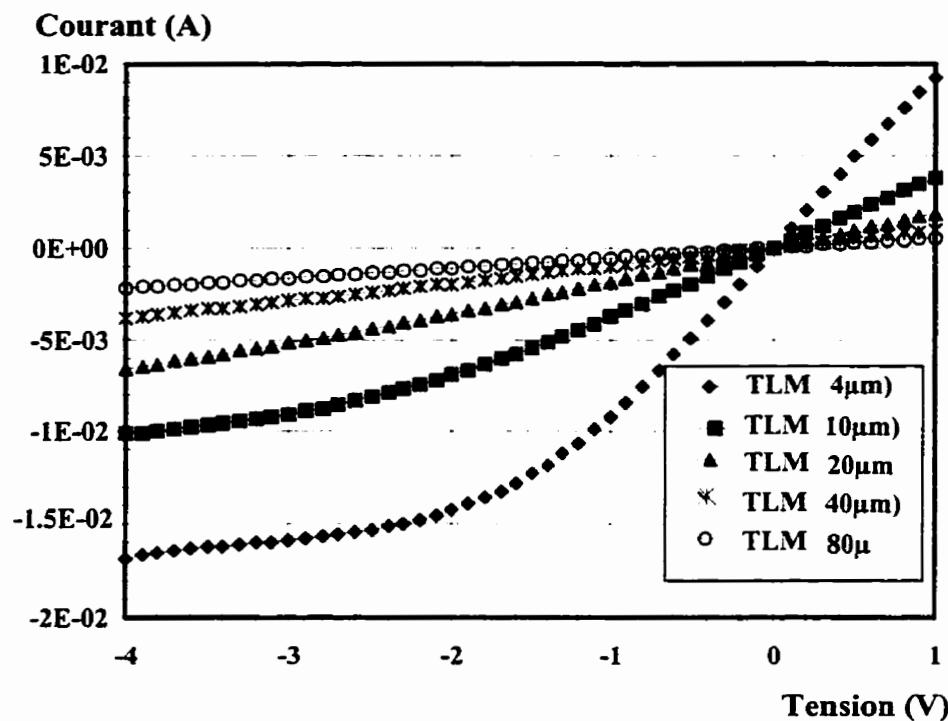

| Figure 6.1:  | Caractéristique I-V typique du TLM .....                              | 114 |

| Figure 6.2:  | Caractéristique I-V de la structure TLM .....                         | 115 |

| Figure 6.3:  | Dépendance de tension de la résistance des cellules TLM .....         | 114 |

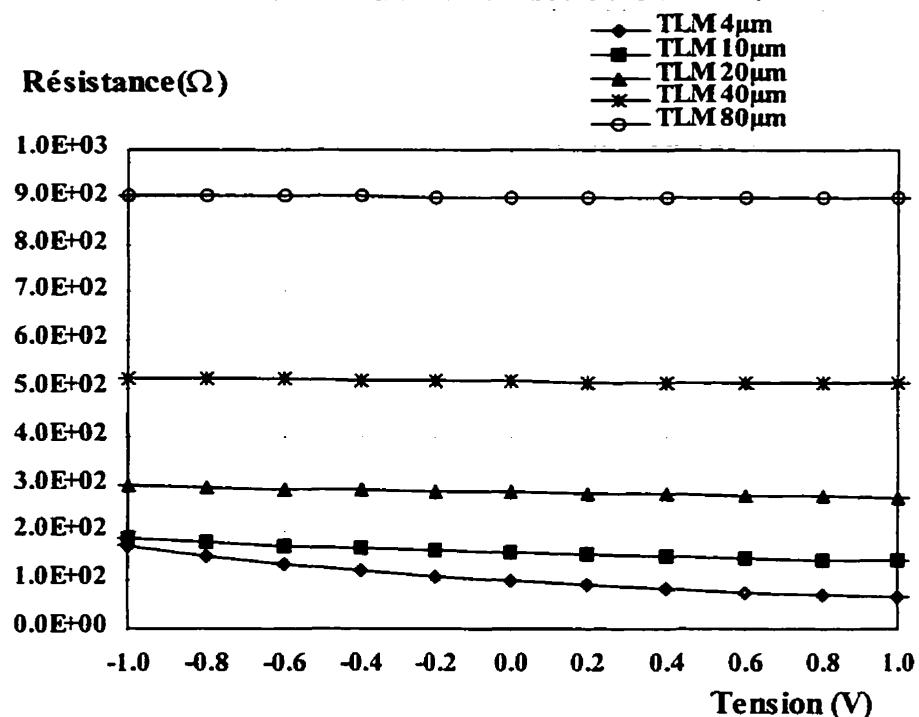

| Figure 6.4:  | Régression linéaire des résistances du TLM .....                      | 117 |

| Figure 6.5:  | Régression linéaire des résistances TLM après différentes .....       | 118 |

|              | étapes de fabrication                                                 |     |

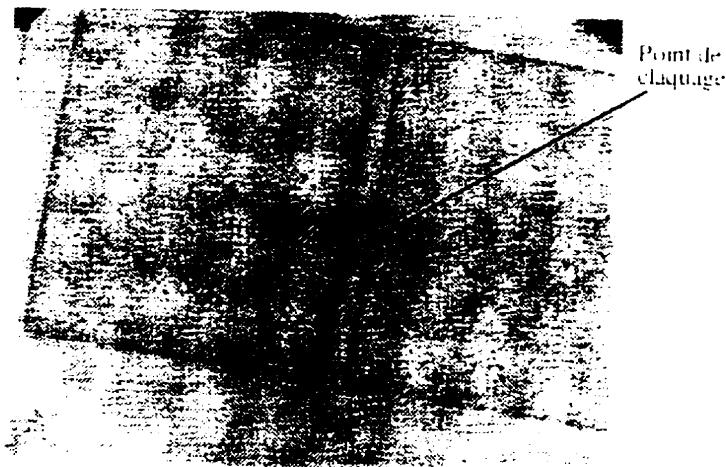

| Figure 6.6:  | Analyse par microscopie optique et SEM du phénomène .....             | 121 |

|              | de claquage                                                           |     |

| Figure 6.7:  | Structure TLM après 25 cycles I-V .....                               | 122 |

| Figure 6.8:  | Structure TLM après 50 cycles I-V .....                               | 123 |

| Figure 6.9:  | Structure TLM après 75 cycles I-V .....                               | 123 |

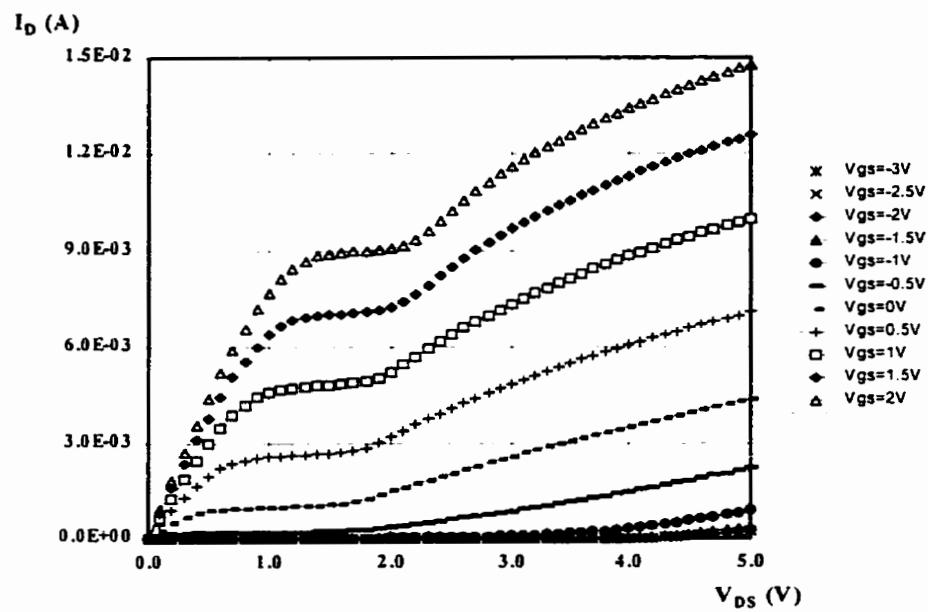

| Figure 6.10: | Caractéristique $I_D$ - $V_{DS}$ du HIGFET.....                       | 127 |

|                                                                                                                                       |     |

|---------------------------------------------------------------------------------------------------------------------------------------|-----|

| Figure 6.11: Caractéristique de claquage ( $V_{GS} = -3.5$ V) .....                                                                   | 128 |

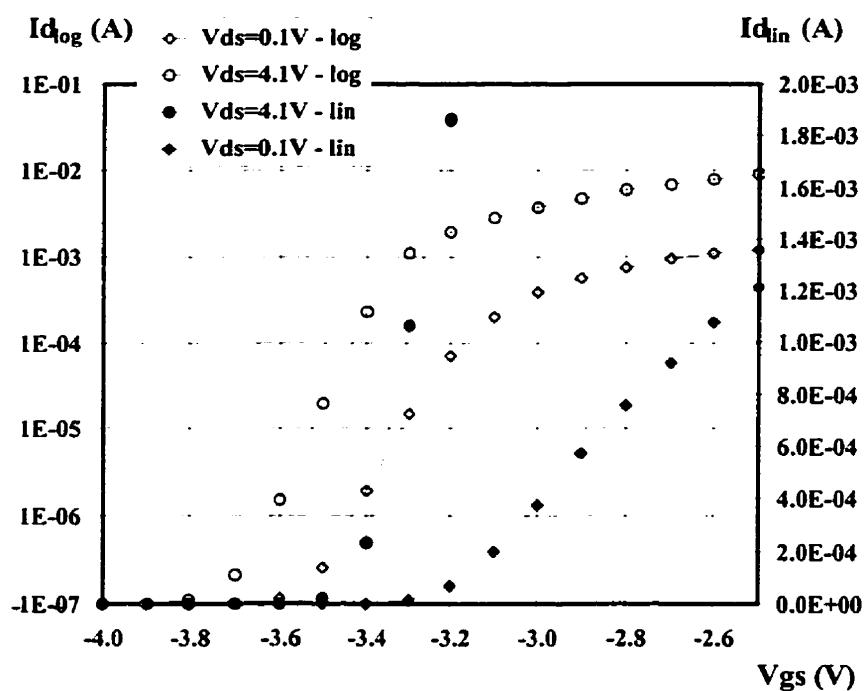

| Figure 6.12: Caractéristiques de transfert .....                                                                                      | 128 |

| Figure 6.13: Caractéristiques de transfert linéaire et de saturation .....                                                            | 129 |

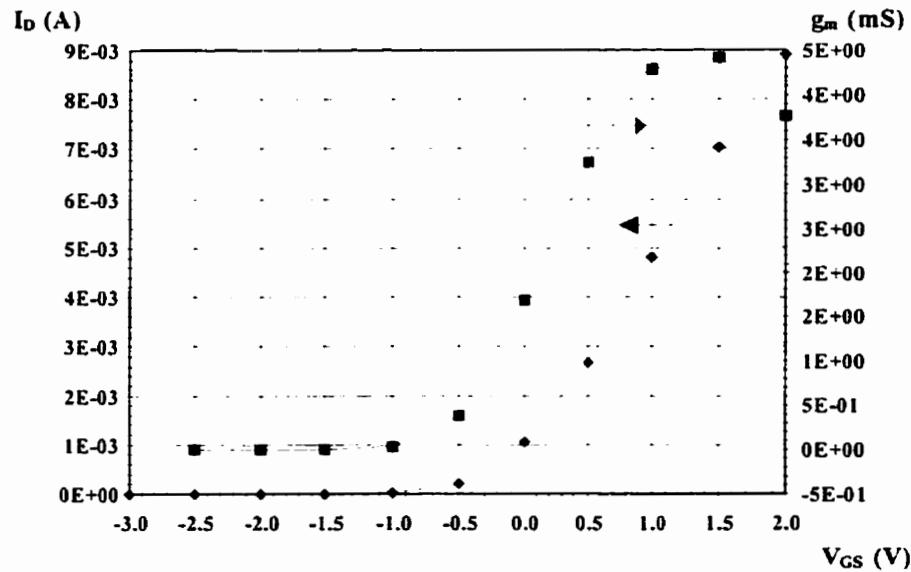

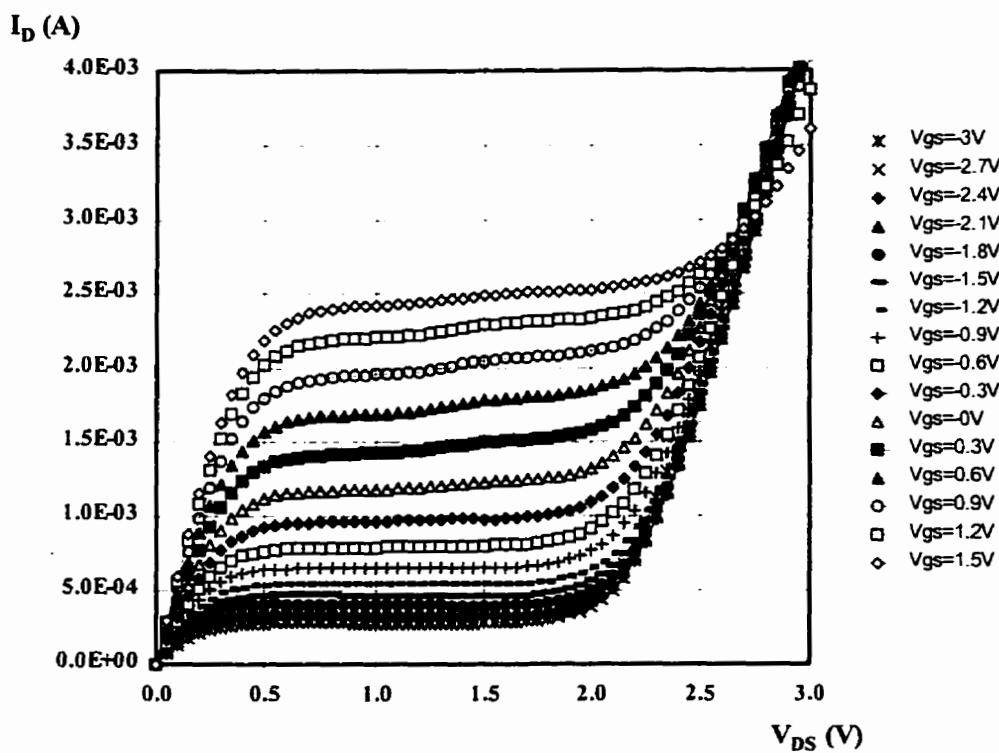

| Figure 6.14: Caractéristiques de sortie d'un HIGFET avec conduction parasite du canal .....                                           | 131 |

| Figure 6.15: Caractéristiques de transfert et de transconductance du HIGFET avec conduction parasite ( $V_{DS} = 1,5$ V) .....        | 131 |

| Figure 6.16: Caractéristiques de sortie d'un HIGFET avec fuites du courant de drain .....                                             | 132 |

| Figure 6.17: Caractéristiques de transfert et de transconductance du HIGFET avec fuites du courant de drain ( $V_{DS} = 1,5$ V) ..... | 133 |

| Figure 6.18: Formes d'onde d'un oscillateur en anneau .....                                                                           | 134 |

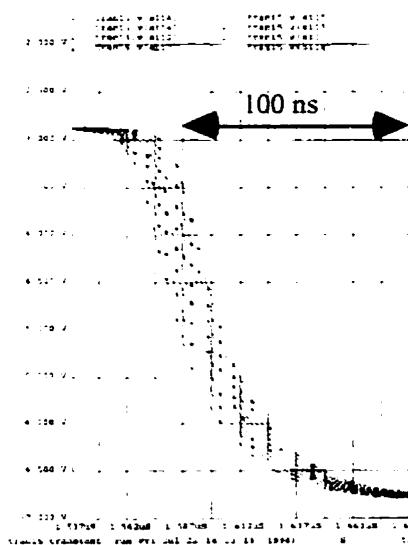

| Figure 6.19: Formes d'onde d'un circuit GÉ non-optimisé .....                                                                         | 135 |

| Figure 6.20: Formes d'onde d'un circuit GÉ optimisé .....                                                                             | 136 |

| Figure 6.21: Retard des signaux de sortie du GÉ optimisé .....                                                                        | 136 |

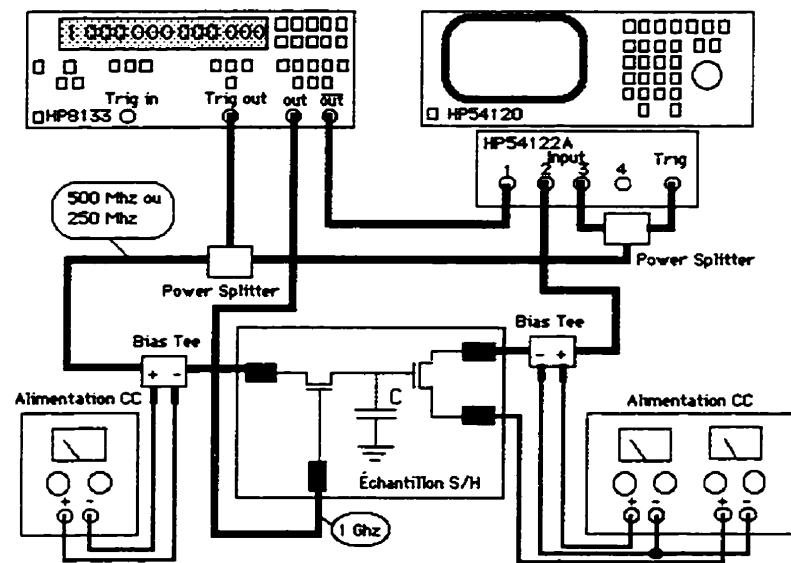

| Figure 6.22 : Système de mesure haute-fréquence .....                                                                                 | 138 |

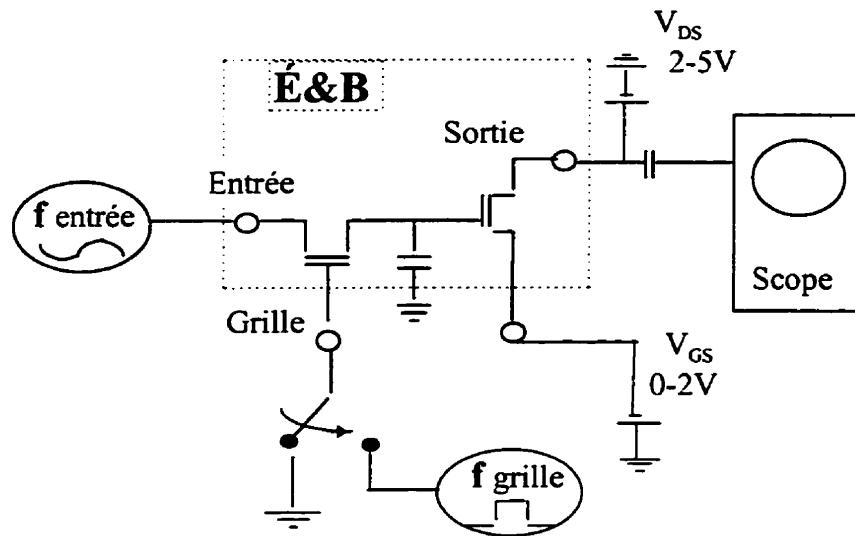

| Figure 6.23: Circuit de test pour mesurer l'amplification et la largeur de bande .....                                                | 139 |

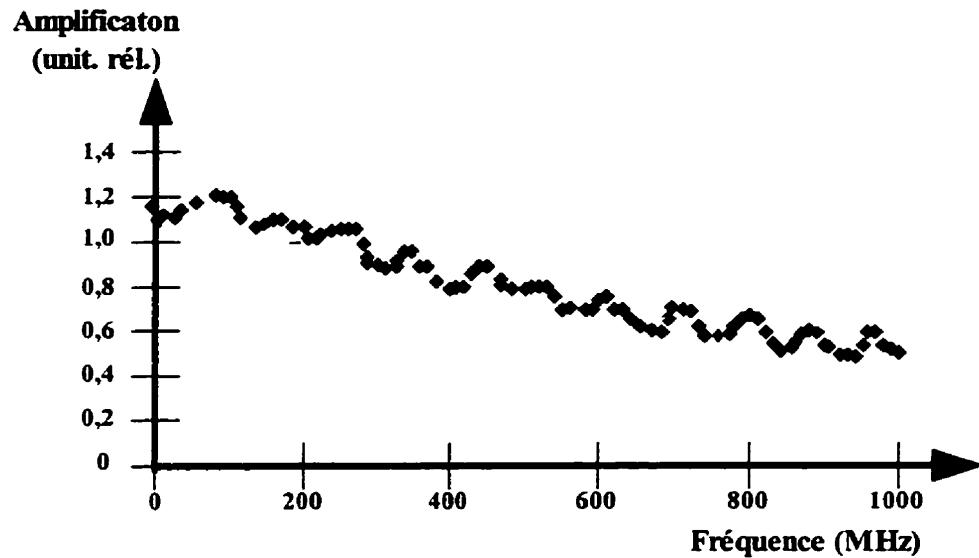

| Figure 6.24: Caractéristique de l'amplification relative .....                                                                        | 140 |

| Figure 6.25: Circuit de test pour l'analyse des distorsions .....                                                                     | 140 |

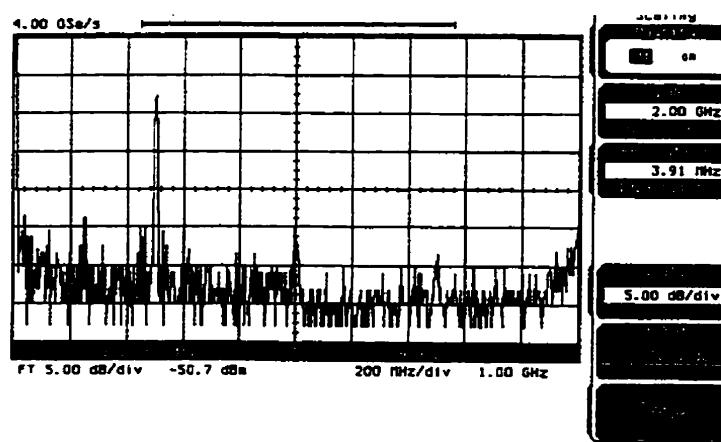

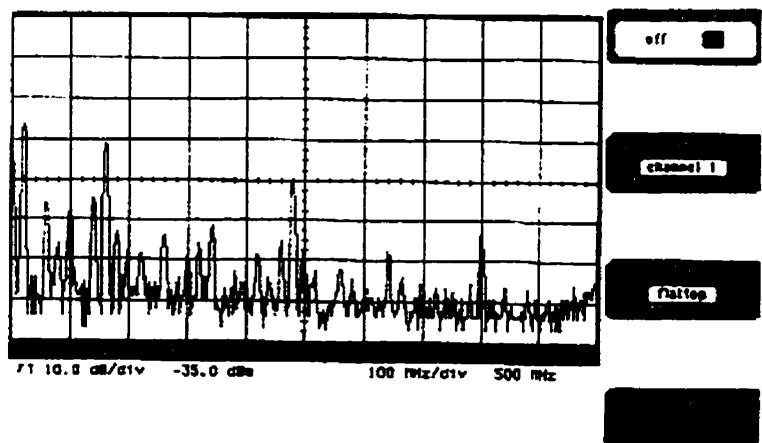

| Figure 6.26 : Spectre du signal avec l'entrée sinusoïdale de 500 MHz (sans horloge) .....                                             | 141 |

|                                                                                                                                            |     |

|--------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Figure 6.27 : Spectre du signal avec l'entrée sinusoïdale de 500 MHz .....<br>(horloge de 1 GHz)                                           | 141 |

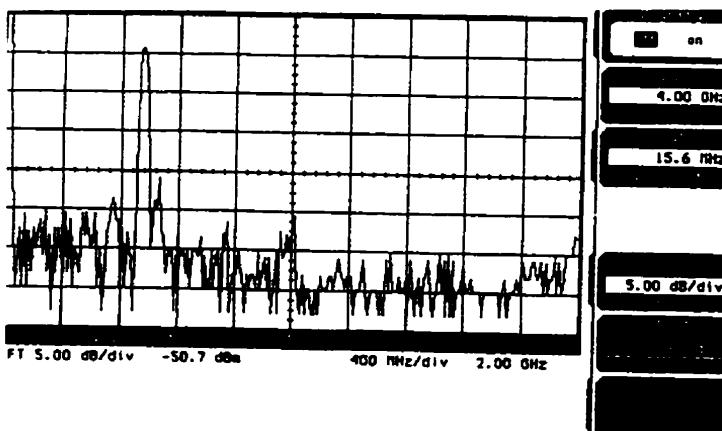

| Figure 6.28 : Réponse en fréquence pour un signal rectangulaire .....<br>a. Spectre du signal à l'entrée: b. Spectre du signal à la sortie | 142 |

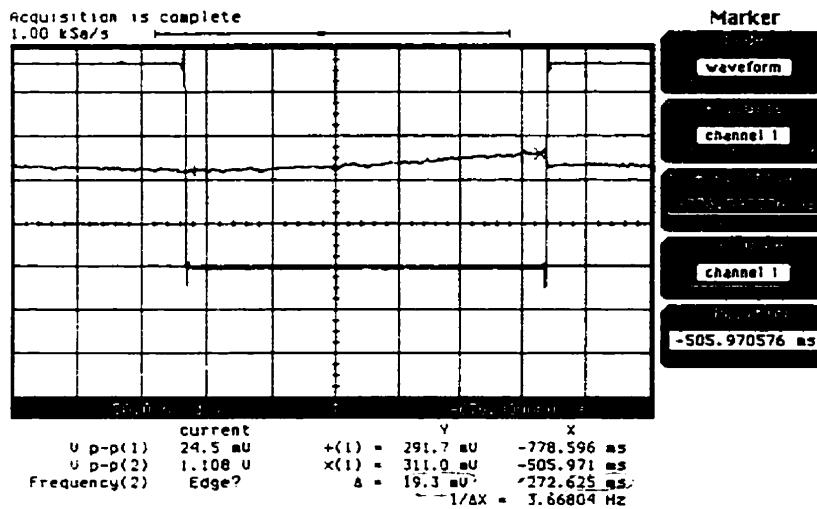

| Figure 6.29: Mesure de la période de stockage .....                                                                                        | 143 |

| Figure 6.30: Estimation de la période d'établissement .....                                                                                | 144 |

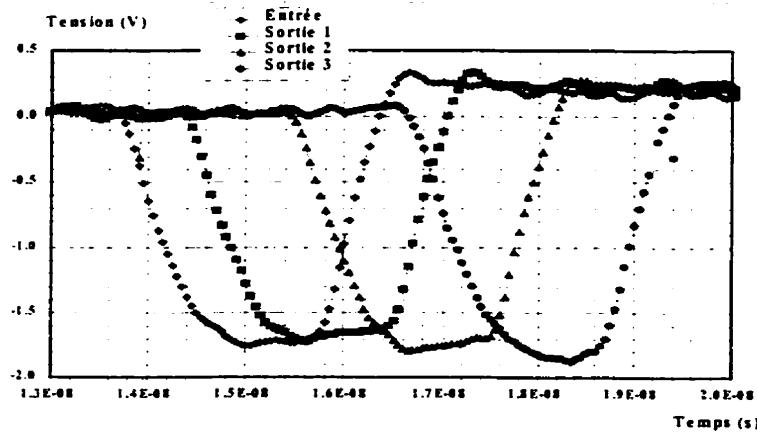

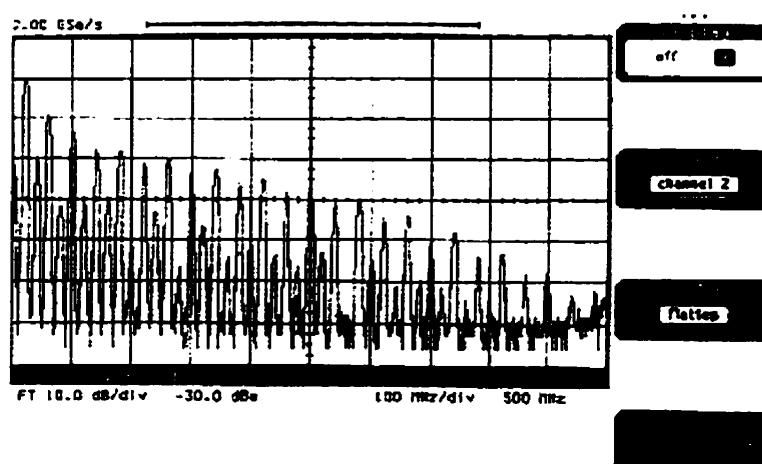

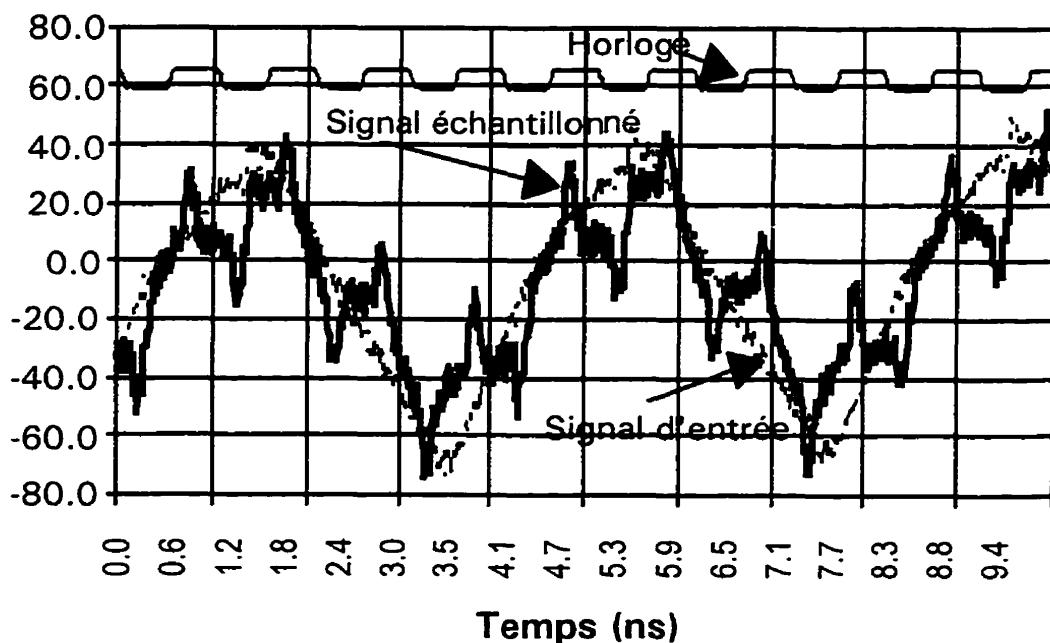

| Figure 6.31: Échantillonnage à 1 GHz sur SH9 .....                                                                                         | 145 |

| Figure 6.32: Échantillonnage à 1 GHz sur SH18 .....                                                                                        | 146 |

| Figure 7.1: Compensation du régime transitoire .....                                                                                       | 151 |

## Liste de symboles et acronymes

### Acronymes

|        |                                                           |

|--------|-----------------------------------------------------------|

| 2DEG   | Two dimensional electron gas                              |

| c.a.   | Courant alternatif                                        |

| c.c.   | Courant continu                                           |

| CCC    | Programme central circonscrit composé                     |

| CCD    | Charge Coupled Device                                     |

| CI     | Circuits intégrés                                         |

| CMOS   | Complementary Metal Oxide Semiconductor                   |

| É&B    | Échantillonneur-Bloqueur                                  |

| ECL    | Emitter Collector Logic                                   |

| ECR    | Electron Cyclotron Resonance                              |

| EDX    | Energy Dispersive X-Ray                                   |

| FET    | Field Effect Transistor                                   |

| FFEBP  | (Feed-Forward Error Back-Propagation )                    |

| GS     | Grille/Source                                             |

| GÉ     | Générateur d'échelons                                     |

| HEMT   | High electron mobility transistor                         |

| HIGFET | Heterojonction Insulated Gate Field-Effect Transistor     |

| I-V    | Courant - tension                                         |

| LISA   | Laboratoire pour l'Intégration des Senseurs et Actuateurs |

| MESFET | MEtal-Semiconductor Field-Effect Transistor               |

| MISFET | Metal-Insulator-Semiconductor Field-Effect Transistor     |

| MOCVD  | Metalorganic Chemical Vapor Deposition                    |

|        |                                           |

|--------|-------------------------------------------|

| MODFET | MOdulation-Doped Field-Effect Transistor  |

| MOS    | Metal Oxide Semiconductor                 |

| PECVD  | Plasma Enhanced Chemical Vapor Deposition |

| RIE    | Reactive Ion Etching                      |

| RNA    | Réseau neuronal artificiel                |

| RSB    | Rapport signal/bruit                      |

| RTA    | Rapid Thermal Annealing                   |

| S/D    | Source/Drain                              |

| SEM    | Scanning Electron Microscopy              |

| SHx    | Le lot no. x de fabrication               |

| TLM    | Transmission Line Measurement             |

## Symboles

|                          |                                       |

|--------------------------|---------------------------------------|

| A                        | Facteur géométrique de conception     |

| $a_{i,k}$                | Fonction de sortie associée à l'axone |

| b                        | Nombre de bits de résolution          |

| $C_{(V)}$                | Capacité de l'hétérojonction          |

| $C_{ds}$                 | Capacité drain-source équivalente     |

| $C_g$                    | Capacité de grille                    |

| $C_{gd}$                 | Capacité grille-drain équivalente     |

| $C_{gs}$                 | Capacité grille-source équivalente    |

| $C_{GS}, C_{DS}, C_{GD}$ | Capacités parasites                   |

| $\epsilon$               | Permitivité                           |

| e                        | -1,6 $10^{-19}$ C                     |

| E                        | Erreure                               |

|                 |                                                          |

|-----------------|----------------------------------------------------------|

| $E_c$           | Énergie de la bande de conduction                        |

| $\Phi_{F_i}$    | Travail de sortie                                        |

| $\Phi_i$        | Distance entre le niveau Fermi et la bande de conduction |

| $F_I$           | Facteur d'instruction                                    |

| $f_r$           | Fréquence de lecture                                     |

| $f_s$           | Fréquence d'échantillonnage                              |

| $g$             | Conductance                                              |

| $g_0$           | Conductance de sortie                                    |

| $g_D$           | Conductance de drain                                     |

| $g_{ds}$        | Conductance drain/source équivalente                     |

| $g_m$           | Transconductance                                         |

| $I_D$           | Courant de drain                                         |

| $I_{DSS}$       | Courant de drain maximum                                 |

| $I_G$           | Courant de grille.                                       |

| $k$             | Constante de Boltzman                                    |

| $\lambda$       | Affinité électronique,                                   |

| $l$             | Longueur de la résistance de Cermet                      |

| $L$             | Longueur de la grille                                    |

| $L_S, L_D, L_G$ | Inductances parasites,                                   |

| $\mu$           | Mobilité des porteurs de charge,                         |

| $n$             | Facteur d'idéalité,                                      |

| $n_s$           | Densité des porteurs de charge du canal                  |

| $N_{it}$        | Densité des charges d'interface                          |

| $N_{\square}$   | Nombre des carrés                                        |

| $p$             | Pente de la caractéristique TLM                          |

| $p_{i,j,k}$     | Pondérations du RNA                                      |

| $Q_C$           | Charge totale des électrons                              |

| $Q_{S(x)}$      | Densité superficielle de charge du semi-conducteur       |

|                   |                                                   |

|-------------------|---------------------------------------------------|

| $Q_{\text{spat}}$ | Charge spatiale                                   |

| $R_0$             | Ordonnée de la caractéristique TLM                |

| $R_C$             | Résistance de contact,                            |

| $\rho_C$          | Résistivité de contact,                           |

| $R_F$             | Résistance feuille,                               |

| $R_i$             | Résistance équivalente                            |

| $R_S, R_G, R_D$   | Résistances parasites                             |

| $s_{i,k}$         | État (l'entrée) du neurone                        |

| $\tau$            | Constante de temps                                |

| $\tau_0$          | Délai                                             |

| $T$               | Température                                       |

| $T_i$             | Transistor I                                      |

| $V_{(y)}$         | Potentiel du semi-conducteur                      |

| $V_d$             | Différence de potentiel de la hétérostructure     |

| $V_D$             | Tension de drain                                  |

| $V_{DS(y)}$       | Polarisation drain-source,                        |

| $V_{DSbd}$        | Tension de claquage                               |

| $V_G$             | Tension de grille                                 |

| $V_s$             | Tension de source                                 |

| $V_T$             | Tension de seuil                                  |

| $w$               | Largeur de la résistance de Cermet                |

| $W$               | Largeur de la région de charge spatiale ou du TLM |

| $\omega$          | $2\pi$ .fréquence                                 |

| $\{X_i\}$         | Vecteur d'entrée du RNA                           |

| $\{Y_i\}$         | Vecteur des valeurs mesurées des performances     |

| $Z$               | Largeur de la grille                              |

| $Z_g$             | Impédance équivalente de grille                   |

## Liste des annexes

### Annexe 1

**Flux de fabrication et contrôle du HIGFET .....** 163

### Annexe 2

**Paramètres pour la caractérisation du processus RIE .....** 165

# Chapitre 1

## Introduction

L'évolution de l'industrie de la micro-électronique au cours des dernières années a connu des changements majeurs et une dynamique accentuée, aussi bien au niveau de la conception des circuits intégrés et les technologies de fabrication, qu'en ce qui concerne les matériaux utilisés. L'univers de la micro-électronique est toujours dominé par le silicium et le but majeur du développement de cette industrie reste la miniaturisation qui assure un plus grand niveau d'intégration et une fréquence maximale plus élevée.

Malgré les avantages théoriques évidents, les semi-conducteurs composés n'ont pas creusé la brèche attendue au niveau global du marché, bien que certaines catégories de dispositifs soient essentiellement basées sur des composants III-V. Les dispositifs optoélectroniques sont typiquement réalisés sur un substrat d'InP et utilisent des couches ternaires et même quaternaires. Les transistors destinés au domaine des micro-ondes sont fabriqués sur GaAs et la structure MESFET est la plus souvent utilisée. Des nouvelles possibilités sont apparues avec les matériaux composés II-VI ou SiGe.

Les transistors à effet de champ réalisés sur les composants III-V ont des avantages intrinsèques, concernant la vitesse de travail, face aux dispositifs MOS sur silicium, ce qui les rendent très attractifs pour la fabrication des circuits intégrés de haute fréquence. Les technologies développées sur GaAs ont, à présent, le plus grand impact sur le marché [13], [27]. Malgré une vitesse élevée des électrons et une plus grande

conductivité thermique, l'extension des dispositifs réalisés sur InP a été empêchée, essentiellement à cause des instabilités à court et longue terme induites par les phénomènes complexes d'interface [19], [46].

Le MODFET<sup>1</sup>, basé sur le confinement à deux dimensions du gaz électronique à l'interface d'une hétérostructure, est le dispositif le plus étudié pour les applications numériques à haute fréquence [45], [68]. Ses avantages, face aux dispositifs MESFET<sup>2</sup>, sont liés à la plus grande vitesse des porteurs, à une barrière Schottky plus élevée et à un plus grand potentiel pour réaliser les structures complémentaires sur le même substrat [49]. La structure HIGFET<sup>3</sup> combine les avantages d'une plus grande tension de claquage associée avec les MISFET<sup>4</sup> et le gain élevé des dispositifs à hétérostructure [16], [6], [23]. C'est la raison pour choisir le HIGFET comme l'élément de base dans ce projet.

Deux approches ont été considérées pour l'hétérostructure, soient: 1° InAlAs / InGaAs [8] qui élimine la nécessité du dépôt d'une couche diélectrique et 2° InP / InGaAs [36], [37]. Le développement des dispositifs utilisant un pseudo-isolant (InAlAs) vient de la densité élevée et difficile à contrôler des pièmes à l'interface InP / diélectrique [47]. Le problème principal avec l'utilisation d'un semi-conducteur à large bande interdite comme couche isolante est la structure Schottky qui limite l'excursion positive de la tension à environ 1,2 V et la fuite assez importante du courant de grille. La réduction de la densité des pièmes à l'interface semi-conducteur/diélectrique par une couche ultra-mince (30 Å) de In<sub>2</sub>S<sub>3</sub>, technique de passivation développée dans le laboratoire LISA [61], [62], a permis la fabrication des dispositifs HIGFET avec une structure SiN<sub>x</sub> / InP / n-InGaAs / InP avec des bonnes performances c.c. ( $I_G \sim 10 \text{ nA}$  pour  $\Delta V_{GS} = \pm 5V$ ,  $I_{DSS} \sim$

---

<sup>1</sup> MODFET MODulation-Doped Field-Effect Transistor

<sup>2</sup> MESFET MEtal-Semiconductor Field-Effect Transistor

<sup>3</sup> HIGFET Heterojonction Insulated Gate Field-Effect Transistor

<sup>4</sup> MISFET Metal-Insulator-Semiconductor Field-Effect Transistor

150 mA/mm et  $g_m \sim 100$  mS/mm) et c.a. ( $f_T \sim 5\text{-}6$  GHz, gain en puissance de 14.2 dB à 3 GHz).

Les travaux effectués dans le cadre de ce projet couvre non seulement la conception et réalisation d'un dispositif HIGFET performant en terme de caractéristiques électriques et paramètres de fiabilité, mais aussi le développement des circuits intégrés (C.I.) basés sur cette technologie. Comme véhicule de test pour démontrer la faisabilité d'une famille des C.I. sur InP, nous avons choisi un circuit Échantillonneur-Bloqueur (É&B) destiné à l'implémentation d'un système rapide d'acquisition des données. Une telle application implique un bon fonctionnement du dispositif HIGFET tant dans un régime analogique (petit et grand signal) que numérique (commutation).

Il n'existe pas une littérature directement reliée à la réalisation des systèmes rapides d'acquisition des données basés sur une technologie HIGFET. Un système parallèle de commutateurs, réalisé dans une technologie Si CMOS, a été rapporté et commercialisé par Analytek [33]. La fréquence du système est de 130 MHz, limite déjà prévue pour la technologie Si CMOS [18]. Les systèmes d'acquisition des données réalisés dans une technologie MESFET sur GaAs fonctionnent entre 100 MHz [28] et 1Ghz avec une résolution de 6 bits [54]. Des meilleures performances ont été obtenues pour les échantillonneurs réalisés dans une technologie HEMT sur GaAs [13]. Des limitations importantes concernant les instabilités de courant pendant le temps ou la faible isolation de grille n'ont pas permis à cette technologie de s'imposer à l'échelle industrielle.

La plupart des systèmes d'acquisition à haute vitesse, présentement sur le marché, se servent d'un convertisseur analogique/numérique avec mémoire pour l'emmagasinage des résultats.

Nous avons considéré deux approches pour une telle acquisition de données. La première est une approche serielle, utilisant un dispositif à transfert de charge (CCD<sup>5</sup>) basé sur la conversion du signal d'entrée en paquets de charge équivalents. La deuxième est une approche parallèle, où un groupe de FETs à grande vitesse, agissant en interrupteurs, échantillonnent un signal d'entrée et mémorisent cette information en chargeant des capacités se trouvant sur le composant.

Des limitations technologiques rendent la fabrication des circuits CCD difficile dans des conditions de laboratoire, ce qui a conduit à choisir le circuit d'échantillonnage-blocage comme solution pour développer le système d'acquisition des données.

Les circuits É&B ont été utilisés pour développer le système d'acquisition de donné, l'élément de base étant le transistor HIGFET. L'architecture du système comprend les cellules É&B (transistor et capacité) aussi que les circuits numériques d'horloge et de contrôle. La cellule É&B, aussi que son circuit tampon de sortie, fonctionnent comme circuits analogiques grand signal, pendant que les circuits d'horloge et contrôle sont des circuits numériques en régime de commutation. En ajoutant les exigences concernant la fréquence maximale et la bande de passage, on obtient une image des performances électriques que la technologie HIGFET doit offrir.

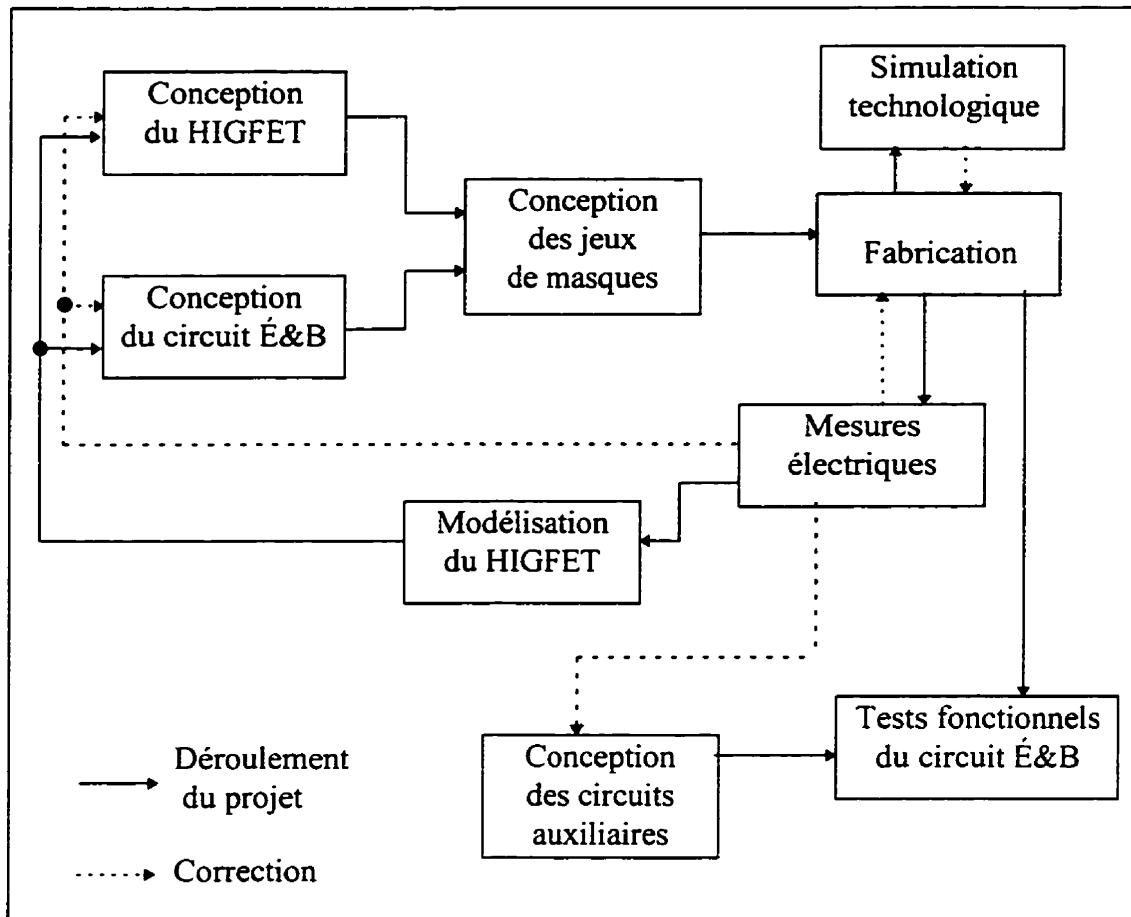

La stratégie considérée pour la mise au point du dispositif HIGFET et le développement des circuits intégrés dans cette technologie est de répéter, séquentiellement, le cycle modélisation, conception, fabrication, caractérisation électrique jusqu'à l'atteinte de la qualité prévue des circuits et la robustesse suffisante des procédés technologiques. La réaction offerte par les mesures électriques doit permettre les corrections et raffinements technologiques, les optimisations au niveau de la conception et l'amélioration des modèles utilisés pour les dispositifs HIGFET pour différentes conditions de travail.

---

<sup>5</sup> CCD Charge Coupled Device

## 1.1 Objectifs de la thèse

Les travaux présentés dans cette thèse représentent les contributions pour le développement d'une nouvelle technologie pour la fabrication des circuits intégrés à grande vitesse. Deux objectifs majeurs sont poursuivis dans ce projet.

- (a) La conception et fabrication d'un transistor de type HIGFET sur InP avec un bon fonctionnement dans le domaine des micro-ondes (1-10 GHz) et une bonne stabilité pendant le temps.

- (b) La conception et fabrication d'un circuit intégré Échantillonneur-Bloqueur, basé sur la technologie HIGFET.

Pour ce faire, nous avons choisi des objectifs spécifiques pour chaque des deux objectifs majeurs. Comme nous l'avons déjà mentionné, la poursuite des objectifs majeurs requiert un déroulement séquentiel des étapes de modélisation, conception, fabrication et caractérisation électrique. Chacun des sous-objectifs aborde un aspect particulier du cycle de développement du projet. Pour la fabrication des structures HIGFET ils sont:

- (a.1) conception de la structure HIGFET;

- (a.2) conception des jeux de masques pour réaliser les dispositifs et les structures de test technologique;

- (a.3) simulation statistique des processus technologiques complexes;

- (a.4) caractérisation microphysique et électrique.

Les principaux sous-objectifs pour la fabrication du circuit d'échantillonnage-blocage intégré sont:

- (b.1) modélisation des HGFETs pour les conditions spécifiques de fonctionnement;

- (b.2) conception du système d'acquisition de données;

- (b.3) conception des jeux de masques pour réaliser les circuits d'échantillonnage-blocage intégrés;

- (b.4) conception et réalisation des circuits électroniques auxiliaires (circuit d'horloge, interface avec le système de traitement de données, etc.)

- (b.5) tests fonctionnels des circuits d'échantillonnage-blocage.

## 1.2 Organisation de la thèse

La présentation de cette thèse suit généralement les objectifs spécifiques énoncés à la section précédente. Le sujet de cette thèse, le développement et mise au point d'une nouvelle technologie, est un travail complexe. La mise au point de la fabrication des C.I. en utilisant des nouveaux matériaux et processus technologiques peut dépasser le cadre d'une thèse de doctorat. En effet, pour accomplir les objectifs de ce projet nous avons utilisé les résultats des travaux d'autres chercheurs et étudiants du département. C'est le motif pour lequel certains aspects, surtout concernant les étapes de fabrication, seront seulement brièvement décrits. Nous nous sommes cependant efforcés de rendre la présentation aussi uniforme que possible. La figure 1.1 donne un aperçu des travaux réalisés et présentés dans la thèse.

Le chapitre 2 présente des aspects reliés à la structure et physique des dispositifs HIGFET. Ce chapitre présente les principes de base de la conception des transistors à hétérostructure en soulignant leurs performances dans le contexte des dispositifs à effet de champ réalisés sur des semi-conducteurs III-V. Nous analysons les critères de conception aussi que les principales structures de HIGFET réalisées dans le cadre du projet.

Le troisième chapitre est dédié à la simulation des dispositifs HIGFET. Cette étape marque un cycle complet pendant le déroulement du projet. Si la conception de la structure du HIGFET, analysé dans le deuxième chapitre, est le début du cycle, le modèle du transistor est développé à partir des résultats expérimentaux obtenus après la fabrication des dispositifs. En même temps, un modèle viable du HIGFET est une condition essentielle pour la conception des dispositifs et circuits et un moyen de validation de la structure initiale. A partir d'un nouveau modèle, le cycle conception, fabrication et caractérisation peut être repris et optimisé.

**Figure 1.1:** Déroulement des travaux présentés dans la thèse

La conception des circuits É&B et des circuits numériques afférents (inverseurs, circuits tampon, oscillateurs en anneau, générateurs d'échelons, etc.), aussi que l'architecture du système d'acquisition des données [11] en entier, sont abordées dans le chapitre 4. La comparaison entre les résultats expérimentaux et simulés pour différents circuits assure la validation des modèles et offre une estimation réaliste des performances de circuit qui peuvent être obtenues avec cette technologie. Une place à part est allouée à la conception et réalisation des circuits de test, tant pour le contrôle technologique que pour la

caractérisation électrique. Quatre jeux de masques, représentant les différents niveaux atteints pendant le déroulement du projet, englobent les résultats des étapes de conception.

La fabrication des circuits HIGFET est présentée dans le chapitre 5. L'analyse des différentes étapes de fabrication présente les critères qui ont conduit au choix des techniques de processus et l'investigation des différentes contraintes technologiques et de conception. L'accent est mis sur les différents types de problèmes apparus pendant le déroulement du projet et les méthodes utilisées pour optimiser et raffiner le flux de fabrication.

Une attention à part a été donnée à l'optimisation et contrôle des processus technologiques complexes qui ne peuvent pas être analysés par un modèle analytique. Le processus de gravure assistée par le plasma (RIE<sup>6</sup>) a été considéré comme véhicule de test pour rédiger des modèles technologiques empiriques. Une analyse comparative des techniques statistiques et d'une technique originale, basée sur des éléments d'intelligence artificielle, montre les avantages apportés par les réseaux neuraux artificiels dans la simulation des processus de fabrication complexes et dans l'assurance de la robustesse technologique.

Le chapitre 6 présente les principaux résultats expérimentaux obtenus avec différentes générations des transistors et circuits intégrés qui ont été fabriqués. Les mesures en courant continue sont plutôt utiles dans la caractérisation technologique et la validation des changements structurales et de conception. Les mesures à haute fréquence (100 MHz jusqu'à 3 GHz), réalisées autant en temps réel que par échantillonnage, donnent l'image exacte des performances des dispositifs et circuits HIGFET. Les mesures dans le

---

<sup>6</sup> RIE Reactive Ion Etching

domaine de fréquence sont essentiellement utilisées pour la modélisation des dispositifs, modélisation présentée dans le chapitre 3. Toutefois, certains paramètres importants de dispositif, comme le gain en tension ou puissance, ou la fréquence de coupure, sont déduits à partir des paramètres S du transistor HIGFET.

La synthèse des principaux résultats obtenus pendant le déroulement des travaux est présentée au chapitre 7. Une analyse critique des ces résultats situe nos travaux dans le contexte des technologies actuelles des dispositifs de haute fréquence. Finalement, des recommandations sur la poursuite des travaux et des directions pour améliorer les performances des dispositifs numériques réalisés sur l'InP, complètent ce document.

## Chapitre 2

### Dispositif HIGFET

#### 2.1 Structure du HIGFET

Le transistor HIGFET combine les avantages d'une tension de claquage plus grande, associée avec les structures MISFET, et le gain plus élevé des dispositifs à hétérostructures. Une telle structure apparaît comme la solution idéale pour développer une technologie numérique dans le domaine des hautes fréquences. C'est la raison pour le choix de la structure HIGFET comme élément de base dans ce projet. Les références sur la fabrication de telles structures sont assez rares comparativement au dispositifs MESFET ou HEMT, même si pendant les années '90 les efforts pour la fabrication des HIGFETs sont bien plus significatifs [9], [36], [37].

Danneville et al. [12] présentent un dispositif HIGFET fabriqué sur GaAs, dont la conduction 2DEG est générée à l'interface AlGaAs/GaAs. La couche d'AlGaAs, ayant aussi le rôle d'isolant de grille, a une fraction molaire de l'aluminium de 0,45. L'hétérostructure est crue par MOCVD avec les couches actives non dopées. Les dispositifs peuvent être utilisés aux applications micro-ondes jusqu'à 20 GHz mais, pour une polarisation de grille positive de plus de 1 V et une tension de drain plus grande que 0,7 V, la caractéristique I-V montre une résistance différentielle négative. L'effet est dû au réchauffement des électrons du gaz bidimensionnel par la tension source-drain. Ils

peuvent être transférés dans le semi-conducteur à bande interdite plus large et collectés au contact de grille.

En utilisant une hétérojonction InAlAs/InGaAs, Chan et al. [8] obtiennent une réduction significative du courant de grille du HIGFET, due à l'augmentation de la hauteur de la barrière des bandes de conduction. La hauteur de la barrière pour l'AlGaAs/GaAs est de presque 0.3 V et augmente jusqu'à 0.5 V pour l'hétérostructure  $\text{In}_{0.52}\text{Al}_{0.48}\text{As}/\text{In}_{0.53}\text{Ga}_{0.47}\text{As}$ . Pour les mêmes conditions de polarisation, le courant de grille peut diminuer de 1000 fois.

Martin et al. [38] annoncent une structure HIGFET sur InP avec une hétérostructure InP/InGaAs crue en accord de maille, et qui utilise comme diélectrique de grille une couche de  $\text{SiO}_2$  déposée par PECVD. Les régions de source et drain sont réalisées par implantation de silicium. Les transistors montrent une transconductance maximale de 240 mS/mm et un bon fonctionnement jusqu'à 5 GHz. Des instabilités du courant touchant les 20% affectent surtout le fonctionnement en courant continu des dispositifs.

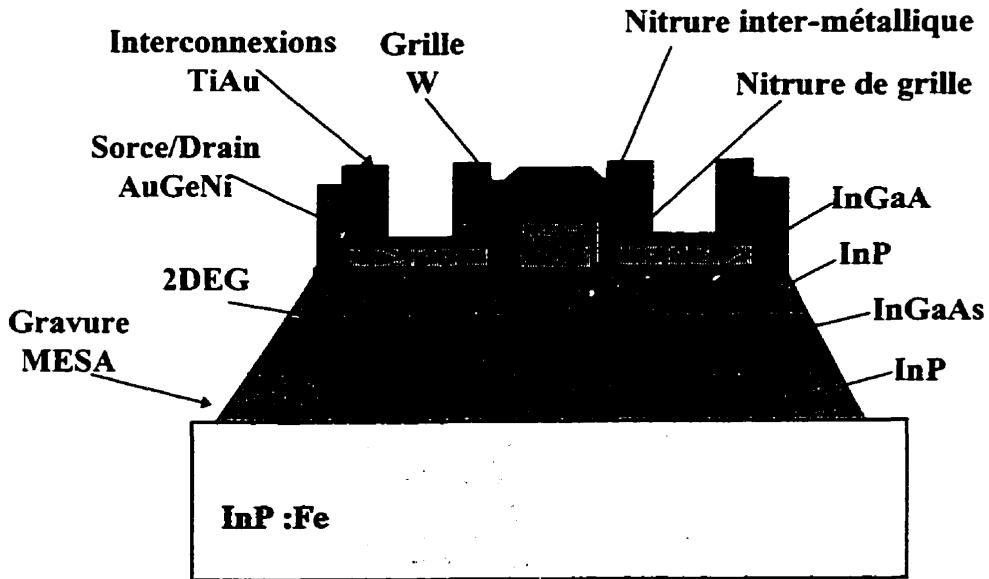

Le schéma de la structure de principe du HIGFET réalisée dans ce projet est présenté à la figure 2.1.

Figure 2.1: Section transversale dans le HIGFET

L'hétérostructure a été réalisée par croissance épitaxiale MOCVD sur un substrat de InP. Une couche d'In<sub>x</sub>Ga<sub>1-x</sub>As crue en accord de maille ( $x=0.53$ ) sur un substrat d'InP semble un excellent choix pour le canal du transistor. La mobilité des électrons, à la température ambiante, excède  $8000 \text{ cm}^2/\text{Vs}$  et la vitesse maximale des électrons est près de  $2,5 \times 10^7 \text{ cm/s}$ . Les résultats sont consistants avec ceux présentés dans la littérature [1], [20], [27].

Une couche tampon d'InP, interposée entre le substrat semi-isolant (dopé à Fe), et la couche d'InGaAs gardent les performances physiques du canal. L'interface entre la couche d'InGaAs et le tampon d'InP est crue en-situ et l'effet de l'ex-diffusion du Fe est éliminé. Une couche épitaxiale d'InP assure l'isolation du canal. La bande interdite plus large de l'InP induit, à l'interface avec le canal d'InGaAs, la couche de conduction 2DEG.

La dernière déposition épitaxiale est une couche sacrificielle d'InGaAs non-dopée. Cette couche est destinée à améliorer les contacts ohmiques de source et drain et elle est enlevée dans la région active du dispositif, sous la grille.

La fabrication des structures débute par une gravure chimique MESA qui réalise l'isolation des transistors. Pour réaliser le dispositif à effet de champ, nous avons déposé, par PECVD, une couche de  $\text{Si}_3\text{N}_4$  sur la hétérostructure. Elle est imposée par la faible hauteur de la barrière Schottky des métaux usuels sur l'InP avec un dopage non-intentionnel de type N (environ 0,2 eV). Pour réduire la densité des états d'interface, avant la déposition du nitre, la surface du semi-conducteur a été passivée par une couche très mince d'In<sub>2</sub>S<sub>3</sub>, [23], [61], [62].

Les contacts ohmiques de source et drain sont assurés par la déposition d'un système Au-Ge-Ni et la diffusion produite d'un traitement thermique rapide (RTA<sup>1</sup>), [60]. La grille est formée par une couche de W ou Ti/Au [10]. Après la déposition d'une deuxième couche de nitre et l'ouverture des fenêtres de contact, une couche d'Au est déposée et les interconnexions sont définies par la technique lift-off.

Le transistor implanté par cette structure est un dispositif qui fonctionne en régime d'appauvrissement à canal enfoui. Dans la conception initiale du transistor toutes les couches épitaxiales étaient non-dopées. Dans cette situation, la conduction est assurée essentiellement par la couche 2DEG formée à l'interface du canal InGaAs et de la couche couvercle d'InP. La discontinuité dans la bande de conduction, d'environ 0,2 eV, est presque 8 fois plus grande que l'énergie thermique ( $kT \sim 0.026$  eV) à la température de la pièce. Cela implique un bon confinement des électrons et, par conséquent, un bon contrôle de la caractéristique de transfert avec une tension de seuil relativement réduite ( $V_T \sim -1$  à -3 V).

---

<sup>1</sup> RTA Rapid Thermal Annealing

Les difficultés technologiques reliées au processus d'implantation ionique pour définir les régions de source et drain, aussi que les excellents contacts ohmiques réalisés par l'optimisation de la structure du système Ni-Ge-Au et du cycle RTA, ont imposé une structure non auto-alignée.

Les limitations photo-lithographiques d'alignement imposent une distance minimale entre la grille et les régions de source et drain d'environ 1 à 2 μm. C'est dans ces régions où, expérimentalement, nous avons aperçu une faiblesse électrique et technologique des dispositifs. La résistance série supplémentaire devient importante, surtout pour les applications micro-ondes. En plus, ces régions, non protégées par la grille, montrent une dégradation importante de la qualité de la surface semi-conductrice pendant le processus de gravure assistée par le plasma (RIE) de la grille [39] et une sensibilité accentuée due aux états d'interface induits par la déposition du nitre par PECVD. Tous ces problèmes d'interface conduisent à des instabilités de court et long terme dans le courant de drain [24]. Dans le pire des cas nous avons observé une disparition complète de la conduction, quelques mois après la fabrication des structures.

Le remplacement de la gravure RIE de grille par un processus lift-off et l'utilisation du procédé ECR<sup>2</sup> [51] au lieu du PECVD pour la déposition du nitre de grille, ont réduit substantiellement les instabilités en courant. Toutefois, pour augmenter la capacité en courant de la structure, essentielle pour les applications en régime de commutation, et réduire la résistance série, nous avons dopé la couche canal d'InGaAs avec Si. L'épaisseur et la concentration ont été optimisées pour maximiser le courant de saturation tout en gardant une grande mobilité des porteurs. Pour une concentration du Si de  $2.5 \times 10^{16} \text{ cm}^{-3}$  les mesures de la mobilité par effet Hall (trèfle de Van der Pauw avec

---

<sup>2</sup> ECR - Electron Cyclotron Resonance

une zone efficace de 2 mm) ont montré une mobilité d'environ  $10.000 \text{ cm}^2/\text{Vs}$ . Avec un dopage de l'ordre de  $3 \cdot 10^{17} \text{ cm}^{-3}$  la mobilité a diminué à  $8.000 \text{ cm}^2/\text{Vs}$ .

La validation finale du HIGFET, avec le canal dopé, a été réalisée par les mesures électriques qui ont montré une bonne transconductance, une tension de seuil acceptable et une haute fréquence de coupure des transistors. Pour garder la qualité de l'interface entre le canal et la couche couvercle et éliminer le dopage résiduel de la couche couvercle, une couche très mince d'InGaAs non-dopée a été intercalée entre le canal et la couche supérieure d'InP. La structure finale de l'hétérostructure et les épaisseurs de toutes les couches semi-conductrices qui forment le dispositif HIGFET sont présentées à la figure 2.2.

|                                       |           |                                                             |

|---------------------------------------|-----------|-------------------------------------------------------------|

| $\text{In}_x\text{Ga}_{1-x}\text{As}$ | $x=0.53$  | $200\text{\AA}$ non dopé                                    |

| InP                                   | couvercle | $200\text{\AA}$ non-dopé                                    |

| $\text{In}_x\text{Ga}_{1-x}\text{As}$ | espaceur  | $x=0.53$                                                    |

| $\text{In}_x\text{Ga}_{1-x}\text{As}$ | canal     | $x=0.53$                                                    |

| InP                                   | tampon    | $300\text{\AA}$ $N_d = 3 \cdot 10^{17} \text{ cm}^{-3}$ (P) |

| <b>Substrat InP Semi-Isolant (Fe)</b> |           |                                                             |

Figure 2.2: Épaisseurs des couches qui forment la structure HIGFET

Pendant les travaux effectués, nous avons essayé deux types de semi-conducteurs comme couche couvercle : l'InAlAs et l'InP. L'InAlAs a une bande interdite plus large et peut assurer le rôle d'isolant de grille. Il élimine aussi les problèmes d'interface isolant-

semi-conducteur, difficulté critique dans la technologie du InP avec un diélectrique de grille déposé après la croissance épitaxiale. Toutefois, l'interface entre le métal de grille et la couche d'InAlAs reste un contact Schottky qui limite l'excursion dans le domaine des tensions positives de grille. C'est finalement une couche d'InP qui a été choisie comme couche couvercle. On doit préciser que la réduction du nombre des différents types de semi-conducteurs utilisés dans la fabrication des structures améliore la robustesse technologique et, de toute façon, l'installation de croissance épitaxiale par MOCVD ne permet pas la déposition de couches contenant de l'aluminium. Dans une première période du déroulement du projet, nous avons utilisé des gaufres d'InP avec la croissance épitaxiale du système InAlAs/InGaAs/InP réalisée par un fabricant externe renommé, Epitaxial Products International Ltd. Cardiff, UK. La figure 2.3 présent la structure de cette hétérostructure.

|                                             |                   |                                       |

|---------------------------------------------|-------------------|---------------------------------------|

| $\text{In}_{0.53}\text{Ga}_{0.47}\text{As}$ | 100 Å             | $\text{Nd} = 10^{18} \text{ cm}^{-3}$ |

| $\text{In}_{0.52}\text{Al}_{0.48}\text{As}$ | 400 Å             | non-dopé                              |

| $\text{In}_{0.53}\text{Ga}_{0.47}\text{As}$ | 1000 Å            | non-dopé                              |

| $\text{In}_{0.52}\text{Al}_{0.48}\text{As}$ | 2000 Å            | non-dopé                              |

| Substrat InP semi-isolant                   | 600 $\mu\text{m}$ | Fe                                    |

Figure 2.3: Hétérostructure InAlAs/InGaAs/InP

Les dispositifs fabriqués dans cette structure ont montré une valeur élevée du courant de drain ( $I_{DSS} > 30 \text{ mA}$ ) et une bonne transconductance ( $g_m > 100 \text{ mS/mm}$ ). La fabrication des premiers HIGFETs dans cette structure a permis le raffinement des certains procédés technologiques et une première évaluation des performances des transistors HIGFET. Malheureusement, les substrats de faible qualité, supposés semi-isolants, ont montré une importante fuite de courant. En conséquence, la tension de seuil était élevée ( $V_T > |-5V|$ )

avec des courants résiduels inacceptables en état fermé des transistors. Comme les problèmes de qualité du substrat et de croissance des hétérostructures n'ont pas pu être résolus, nous avons abandonné cette structure et nous avons focalisé tous les efforts sur les hétérostructures InP/InGaAs/InP crues par le groupe MOCVD de l'École Polytechnique.

## 2.2 Physique de la structure HIGFET

Deux semi-conducteurs différents, mis en contact, généreront une différence de potentiel,  $V_d$ , induite par la différence de travail de sortie,  $e\Phi_i$ , ( $i = 1, 2$ ), des deux matériaux [32], [67]. Cette différence de potentiel produira une diffusion des électrons du semi-conducteur à plus faible travail de sortie vers l'autre. À l'équilibre thermodynamique, la différence des énergies des bandes de conduction des régions neutres des deux semi-conducteurs, loin de la jonction,  $\Delta E_c$ , est donnée par la différence entre les énergies  $e\Phi_{Fi}$ , qui représentent les distances entre le niveau Fermi et la bande de conduction de chaque semi-conducteur. Pour des matériaux caractérisés par l'affinité électronique,  $\chi_i$ , nous pouvons écrire:

$$\Phi_{Fi} = \Phi_i - \chi_i \quad (2.1)$$

$$V_d = \Phi_1 - \Phi_2 \quad (2.2)$$

$$\Delta E_c = e\Phi_{F2} - e\Phi_{F1} = -eV_d - (e\chi_2 - e\chi_1) \quad (2.3)$$

La relation (2.3) montre que la différence d'énergie entre les bandes de conduction est produite par un terme dépendant seulement de la nature du semi-conducteur,  $\chi_i$ , et la tension de diffusion, qui est influencée par le dopage du semi-conducteur.

À l'interface de l'hétérojonction, en raison de la continuité du potentiel, le terme  $-eV_d$  disparaît et la différence d'énergie entre les bandes de conduction se réduit à:

$$\Delta E_{c0} = -e(\chi_2 - \chi_1) \quad (2.4)$$

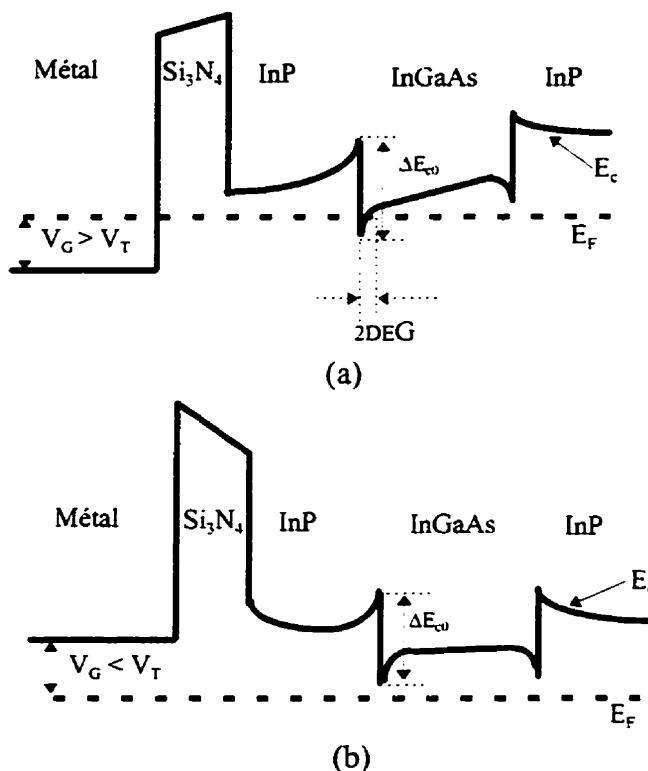

Dans le cas où  $\Phi_2 > \Phi_1$  et  $\chi_2 > \chi_1$ , le régime d'équilibre s'établit par la diffusion des électrons du semi-conducteur 1 vers le semi-conducteur 2. Comme  $\Delta E_{c0}$  est plus grande que  $\Delta E_c$ , le saut dans la bande de conduction à l'interface des deux matériaux favorise l'accumulation des électrons. Quand le niveau Fermi dépasse le niveau de la bande de conduction, il produit une dégénérescence locale du semi-conducteur 2. La figure 2.4 montre les diagrammes de la bande de conduction pour un transistor avec une telle structure de l'hétérojonction pour différentes polarisations de grille.

Figure 2.4: Diagrammes énergétiques de la bande de conduction à l'équilibre:

- (a) Tension de grille plus grande que la tension de seuil;

- (b) Tension de grille plus petite que la tension de seuil.

Pour une tension de grille assez négative pour dépasser la tension de seuil, une barrière énergétique est générée dans la bande de conduction, sous la grille. La dégénérescence locale de la couche d'InGaAs est enlevée et il n'y a plus de circulation de courant. Le dispositif est dans l'état de canal fermé.

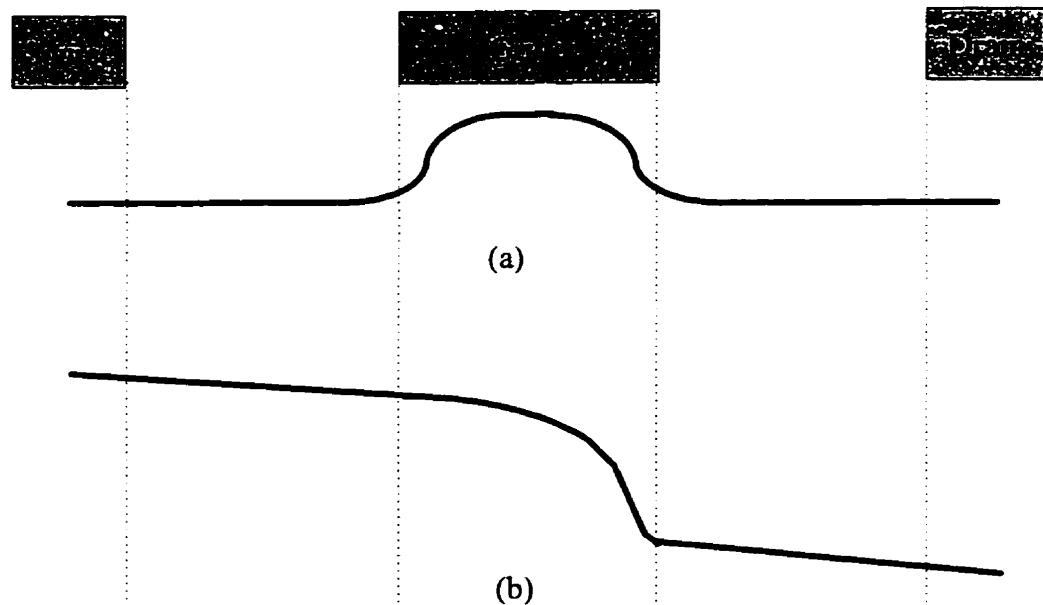

Pour une tension de grille plus grande que  $V_T$ , avec une tension appliquée entre la source et le drain du HIGFET, les électrons sont injectés dans le canal et on établit un courant électrique à travers le dispositif. Le transistor est dans l'état canal ouvert. La figure 2.5 présente les diagrammes de la bande de conduction au long du canal dans le régime stationnaire pour le dispositif fermé (a) et ouvert (b).

Figure 2.5: Diagrammes de la bande de conduction au long du canal dans le régime stationnaire:

(a) Canal fermé; (b) Canal ouvert.

Pour un transistor ouvert, avec  $V_G > V_T$ , et pour des valeurs réduites de la tension source-drain, le courant est proportionnel à la tension, avec une conduction ohmique du canal 2DEG dont la résistance diminue avec l'augmentation de la tension de grille (régime linéaire).

Lorsque la tension de drain augmente, le potentiel du semi-conducteur produit une augmentation de la barrière énergétique près du drain, et presque toute la chute de tension se retrouve dans cette région, comme suggère la figure 2.5 (b). La résistance du canal augmente au voisinage du drain et la caractéristique I-V devient non-linéaire.

Quand la tension de drain augmente jusqu'au seuil qui enlève la dégénérescence locale du canal, le régime de pincement est atteint, le canal 2DEG est fermé côté drain, et le transistor entre dans le régime de saturation.

### 2.3 Modélisation du HIGFET idéal

Le fonctionnement du transistor HIGFET est semblable au dispositif MOSFET en régime d'appauvrissement. En effet, pour une couche couvercle idéale, le HIGFET peut être traité comme un dispositif MOS avec un diélectrique composé des deux couches: nitrate et InP. Dans cette section nous développons un modèle analytique simplifié du HIGFET et dans la section suivante nous analyserons les différences observées dans le fonctionnement du transistor réel.

Comme le couvercle d'InP est non-intentionnellement dopé N, une région de charge spatiale, de largeur W, prend naissance au voisinage de l'interface avec le canal. L'intégration de l'équation de Poisson, pour une tension de grille  $V_G$  et en supposant le régime de déplétion, donne une estimation pour la largeur W de: