| <b>Titre:</b> Title:    | Low power low voltage sigma-delta modulators                                                                                                                             |

|-------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>Auteur:</b> Author:  | Zhijun Lu                                                                                                                                                                |

| Date:                   | 2004                                                                                                                                                                     |

| Туре:                   | Mémoire ou thèse / Dissertation or Thesis                                                                                                                                |

| Référence:<br>Citation: | Lu, Z. (2004). Low power low voltage sigma-delta modulators [Mémoire de maîtrise, École Polytechnique de Montréal]. PolyPublie.<br>https://publications.polymtl.ca/6660/ |

# Document en libre accès dans PolyPublie Open Access document in PolyPublie

URL de PolyPublie:

PolyPublie URL:

Directeurs de recherche:

Advisors:

Programme:

Program:

Non spécifié

## **NOTE TO USERS**

This reproduction is the best copy available.

#### UNIVERSITÉ DE MONTRÉAL

#### LOW POWER LOW VOLTAGE SIGMA-DELTA MODULATORS

# ZHIJUN LU DÉPARTEMENT DE GÉNIE ÉLECTRIQUE ÉCOLE POLYTECHNIQUE DE MONTRÉAL

MÉMOIRE PRÉSENTÉ EN VUE DE L'OBTENTION

DU DIPLÔME DE MAÎTRISE ÈS SCIENCES APPLIQUÉES

(GÉNIE ÉLECTRIQUE)

**AOÛT 2004**

Library and Archives Canada

Published Heritage Branch

395 Wellington Street Ottawa ON K1A 0N4 Canada Bibliothèque et Archives Canada

Direction du Patrimoine de l'édition

395, rue Wellington Ottawa ON K1A 0N4 Canada

> Your file Votre référence ISBN: 0-612-97965-2 Our file Notre référence ISBN: 0-612-97965-2

#### NOTICE:

The author has granted a non-exclusive license allowing Library and Archives Canada to reproduce, publish, archive, preserve, conserve, communicate to the public by telecommunication or on the Internet, loan, distribute and sell theses worldwide, for commercial or non-commercial purposes, in microform, paper, electronic and/or any other formats.

The author retains copyright ownership and moral rights in this thesis. Neither the thesis nor substantial extracts from it may be printed or otherwise reproduced without the author's permission.

#### **AVIS:**

L'auteur a accordé une licence non exclusive permettant à la Bibliothèque et Archives Canada de reproduire, publier, archiver, sauvegarder, conserver, transmettre au public par télécommunication ou par l'Internet, prêter, distribuer et vendre des thèses partout dans le monde, à des fins commerciales ou autres, sur support microforme, papier, électronique et/ou autres formats.

L'auteur conserve la propriété du droit d'auteur et des droits moraux qui protège cette thèse. Ni la thèse ni des extraits substantiels de celle-ci ne doivent être imprimés ou autrement reproduits sans son autorisation.

In compliance with the Canadian Privacy Act some supporting forms may have been removed from this thesis.

While these forms may be included in the document page count, their removal does not represent any loss of content from the thesis.

Conformément à la loi canadienne sur la protection de la vie privée, quelques formulaires secondaires ont été enlevés de cette thèse.

Bien que ces formulaires aient inclus dans la pagination, il n'y aura aucun contenu manquant.

## UNIVERSITÉ DE MONTRÉAL

## ÉCOLE POLYTECHNIQUE DE MONTRÉAL

#### Ce mémoire intitulé:

#### LOW POWER LOW VOLTAGE SIGMA-DELTA MODULATORS

Présenté par: ZHIJUN LU

en vue de l'obtention du diplôme de : Maîtrise ès sciences appliquées

a été dûment accepté par le jury d'examen constitué de :

M. AUDET, Yves,

Ph.D., président

M. SAWAN, Mohamad, Ph.D., membre et directeur de recherche

M. FAYOMI, Christian, Ph.D., membre

## **DEDICATION**

To all my friends

## **ACKNOWLEDGEMENTS**

I sincerely thank my supervisor, Professor Mahamad Sawan, for his excellent supervision and guidance throughout the course of this master thesis work. His kindness, patience and encouragement during my master degree study at Ecole Polytechnique deserve my deepest gratitude. His guidance and insight ensured our project's success. It was both an honor and privilege to work with him.

I would like to thank Professor Yves Audet for reading my thesis, Professor Christian Fayomi for his fruitful discussion and warm encouragement, and both of them for participating as members of the jury for this master thesis.

I appreciate the kind cooperation of members in Professor Sawan's PolySTIM laboratory for their friendship and all of their help over the years. I am very grateful to Yamu Hu for his numerous valuable discussions and constant assistance at various stages. He was a valuable resource and friend to me. I appreciate Abdelouahab Djemouai for listening to my ideas and providing feedback. Furthermore, I would like to thank Hany Ghattas, Jonathan Coulombe, Abdallah Kassem, Marc Belleau and Réjean Lepage for their friendship and kind help.

Finally, I wish to express my special gratitude to my family for their love, understanding and unyielding encouragement during the good and the difficult times encountered along the way.

This work was supported by the Natural Sciences and Engineering Research Council of Canada (NSERC). In addition, Canadian Microelectronics Corporation (CMC) offered all design and chip fabrication support.

## RÉSUMÉ

Les techniques de modulation de sur-échantillonnage et de filtrage de bruit sont devenues très populaires dans le domaine des convertisseurs analogiques-numériques (CAN) de haute résolution, et des générateurs de signaux. Le sur-échantillonnage et le filtrage de bruit représentent les techniques de base des CAN sigma-delta ( $\Sigma\Delta$ ). La popularité de ces techniques découle du fait que leur implémentation n'est pas reliée beaucoup à la précision des modules analogiques et du gain des amplificateurs. Ceci est principalement dû à l'utilisation des modules de traitement de signal numérique. De nos jours, les modulateurs  $\Sigma\Delta$  sont intégrés en utilisant des techniques de capacités commutées, qui sont bien adaptées pour le traitement de signaux en technologies CMOS standard. Une des caractéristiques importantes des circuits à capacités commutées est que leur précision ne dépend pas de la valeur absolue des capacités mais de la valeur de rapport de capacités.

Le but de ce mémoire de maîtrise est la conception de modulateurs analogique à numérique de très faible puissance. En plus de la faible puissance, ces modulateurs devront opérer à de basses tensions d'alimentation et posséder de larges plages dynamiques d'entrée et de sortie. Ces conditions sont principalement dictées par les applications visées, qui se situent dans le domaine des systèmes électroniques implantables.

Deux modulateurs  $\Sigma\Delta$  à faible puissance et basse tension d'alimentation sont développés, l'un de deuxième ordre et l'autre de quatrième ordre. Les deux modulateurs sont réalisés en utilisant un intégrateur à capacité-commutée de demi-délai, qui est basé sur la technique d'amplificateur opérationnel à transconductance (OTA) à commutation. L'utilisation de ce genre d'intégrateur permet de réduire la consommation de puissance et de surmonter les problèmes reliés aux commutateurs, qui nécessitent des tensions élevées indispensables pour les faire fonctionner à basse tension. Outre cet intégrateur, nous avons utilisé un multiplicateur de tension pour alimenter l'étage d'entrée de l'amplificateur OTA. Ce multiplicateur sert à doubler les tensions au niveau de l'étage d'entrée de l'OTA dans le but d'améliorer la plage dynamique des modulateurs. Ces modulateurs fonctionnent avec une basse tension d'alimentation (0.9V) et possèdent de larges plages dynamiques de mode commun d'entrée (0-1.2V) et de sortie (0.05V-0.85V).

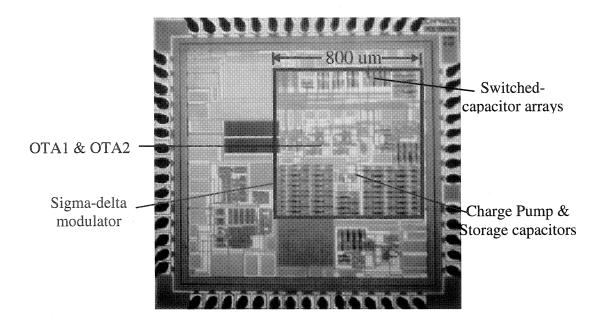

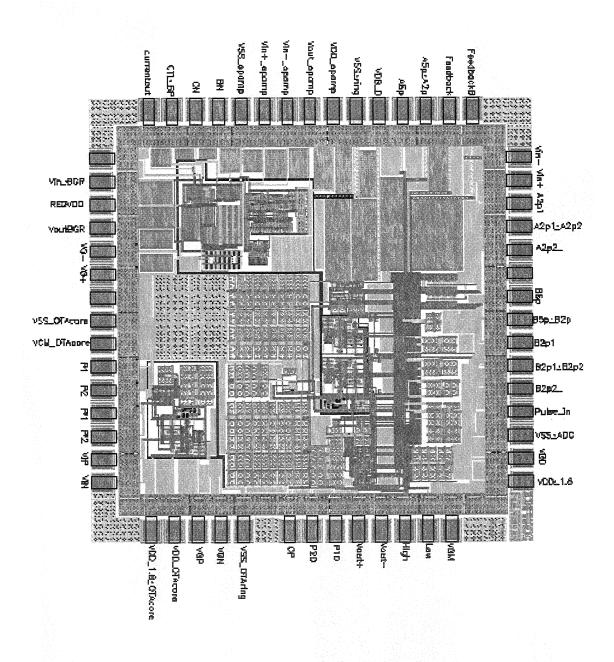

Le modulateur  $\Sigma\Delta$  deuxième ordre est fabriqué en technologie CMOS 0.18 um de TSMC disponible à travers la société canadienne de microélectronique (SCM). Sa surface active est de  $800\mu\text{m}\times800\mu\text{m}$ . Les résultats de simulation démontrent que le rapport signal sur bruit (Signal-to-Noise Ratio, SNR) de ce modulateur est égal à 74 dB dans la plage de fréquences de 0 à 10 KHz. La valeur mesurée du SNR est de l'ordre de 65 dB. La dissipation totale de puissance estimée par simulation est égale à 38  $\mu$ W en utilisant le calculateur de l'outil de Cadence et celle mesurée est égale à 66  $\mu$ W. De plus, le modulateur  $\Sigma\Delta$  de quatrième ordre proposé a été implémenté et caractérisé. Ses résultats

de simulation montrent une consommation de puissance de  $86~\mu W$  et un SNR de 90~dB dans la même bande de fréquence d'intérêt. Le modulateur a été originalement conçu pour des applications biomédicales, mais il peut être utilisé dans toute application nécessitant une conversion analogique à numérique dans les basses fréquences.

#### ABSTRACT

The oversampling and noise shaping modulation techniques are becoming popular to design high resolution analog-to-digital converters (ADCs) and signal generators. Oversampling and noise shaping are the two key techniques employed in the sigma-delta ( $\Sigma\Delta$ ) ADCs. The reason for their popularity comes from their implementations, which rely less on the matching of analog components and amplifier gains, and more on digital signal processing. Nowadays, switched-capacitor technique has been a popular method of implementing analog signal processing circuits in standard CMOS technologies. One of the important reasons for the success of switched-capacitor circuits is that the accuracy of signal processing function is proportional to the accuracy of capacitor ratios.

The aim of this master thesis is to design very low power analog-to-digital modulators. The proposed circuits work under low supply voltages since they are designed for implantable sensing applications. Under low voltage supply, the required modulators should have wide signal input and output swing ranges.

Two low power low voltage analog-to-digital  $\Sigma\Delta$  modulators are implemented. The first one is a second-order modulator, and the second is a fourth-order. Both of them are designed by using half delay switched-capacitor integrator based on switched-opamp technique. Also, we used voltage multiplier to boost the voltage in order to power up the input stage of the operational transconductance amplifier (OTA). A half delay integrator,

based on switched-opamp technique, is used to save power and solve low voltage switch driving problem. Voltage multiplier provides boosted voltage to OTA input pair to guarantee the operation of the modeling with rail-to-rail signal swing, thus enlarge dynamic range of modulators. The modulators work under low voltage supply (0.9V) with a wide input (0-1.2V) and output (0.05-0.85V) voltage ranges.

The proposed  $2^{nd}$ -order modulator, has been implemented and fabricated using the 0.18  $\mu$ m CMOS technology offered by Taiwan Semiconductor Manufacturing Co.,LTD (TSMC), which achieves a simulated peak SNR of 74 dB with the signal bandwidth 10 kHz and measured value is 65 dB. The simulated total power dissipation is around 38  $\mu$ W and the measured value gives 66  $\mu$ W. The chip core area is  $800\mu$ m× $800\mu$ m. In addition, the proposed  $4^{th}$ -order modulator has been implemented and characterized. Its simulation result gives a power dissipation of 86  $\mu$ W and a SNR of 90 dB within the same bandwidth. The modulator, originally designed for biomedical sensing applications, can be used for any low pass analog-to-digital conversion applications.

## CONDENCÉ EN FRANÇAIS

#### I. INTRODUCTION

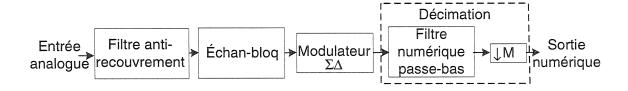

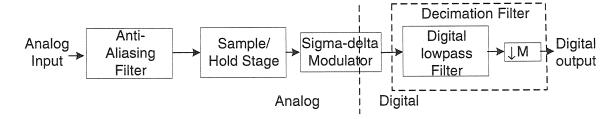

La croissance rapide du marché des systèmes électroniques portatifs a créé un grand besoin pour le développement de convertisseurs analogique-numérique (CAN) de haute résolution, de basse tension d'alimentation, et de faible puissance. La modulation sigmadelta ( $\Sigma\Delta$ ) représente un moyen promoteur pour le développement de ce genre de CAN. La figure 1 montre un schéma bloc simplifié d'un CAN  $\Sigma\Delta$  composé principalement d'un filtre anti-recouvrement, d'un échantillonneur-bloqueur, d'un modulateur  $\Sigma\Delta$  et d'un filtre passe-bas numérique de décimation de valeurs obtenues.

Figure 1 Schéma bloc d'un CAN  $\Sigma\Delta$ .

Comme le modulateur  $\Sigma\Delta$  est basé sur la technique de sur-échantillonnage, l'utilisation de filtre anti-recouvrement est non nécessaire. Selon le théorème d'échantillonnage de Nyquist, il est possible d'éviter le problème de recouvrement si la technique de sur-échantillonnage est utilisée. Dans de tels cas, l'échantillonnage est effectué, d'une manière inhérente, par un circuit modulateur  $\Sigma\Delta$  basé sur la technique de capacités-

commutés (CC), qui comprend des amplificateurs opérationnels (amp-op), des condensateurs, des commutateurs, et des horloges sans recouvrement.

La frontière entre la partie analogique et la partie numérique du convertisseur se situe à la sortie du modulateur  $\Sigma\Delta$  pour les modulateurs simples à une seule boucle. Le bloc de décimation comprend un filtre passe-bas et un sous-échantillonneur, qui constituent la partie numérique du modulateur. Le rôle de ce filtre consiste à éliminer le bruit de quantification en dehors de la bande passante.

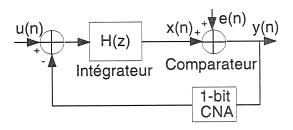

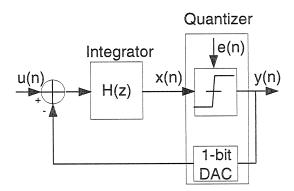

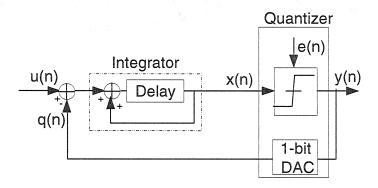

La figure 2 montre le schéma fonctionnel de base d'un modulateur  $\Sigma\Delta$  composé d'un intégrateur, un comparateur, et un convertisseur numérique à analogique (CNA) de rétroaction de 1-bit.

Figure 2 Schéma fonctionnel linéaire de base d'un modulateur  $\Sigma\Delta$

La fonction de transfert  $S_{TF}(z)$  de ce système et celle du bruit  $N_{TF}(z)$  sont données par les équations suivantes :

$$S_{TF}(z) \equiv \frac{Y(z)}{U(z)} = \frac{H(z)}{1 + H(z)}$$

(1)

$$N_{TF}(z) \equiv \frac{Y(z)}{E(z)} = \frac{1}{1 + H(z)}$$

(2)

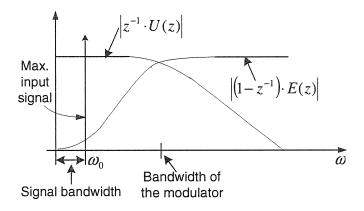

À partir de l'équation (2), on peut déduire que le zéro de la fonction de transfert du bruit  $N_{TF}(z)$  est égale au pole de H(z). En d'autres termes, si H(z) s'approche à l'infini, la valeur de  $N_{TF}(z)$  devient égale à zéro. Dans le domaine fréquentiel, la fonction de transfert du modulateur  $\Sigma\Delta$  peut être exprimée par l'équation suivante:

$$Y(z) = S_{TF}(z)U(z) + N_{TF}(z)E(z)$$

(3)

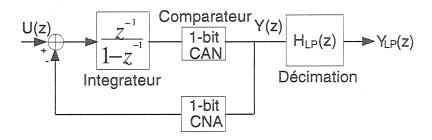

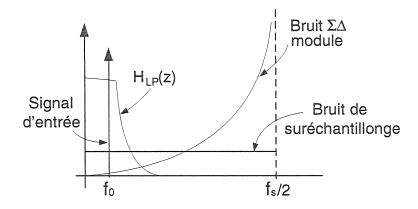

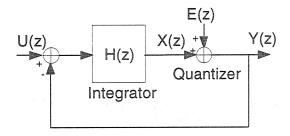

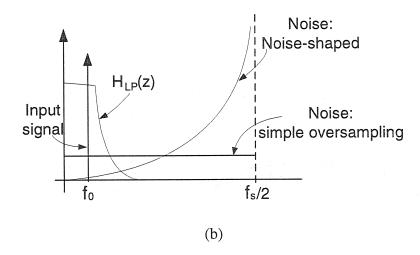

Pour minimiser le bruit de quantification, le module de H(z) devrait être très grand dans la bande de fréquence qui s'étend de 0 à  $f_0$ . Une grande valeur de H(z) permet aux fonctions de transfert  $H_{TF}(z)$  et  $N_{TF}(z)$  de prendre respectivement les valeurs approximativement 1 et 0 dans la bande de fréquence d'intérêt, et par conséquent, elle permet de réduire le bruit de quantification. Comme, la rétroaction du modulateur ne permet pas de filtrer le bruit de hautes fréquences, le convertisseur  $\Sigma\Delta$  nécessite un filtre additionnel passe-bas numérique. Le principe de base du modulateur  $\Sigma\Delta$  peut être bien expliqué à l'aide des figures 3 et 4.

Figure 3 Diagramme bloc du modulateur  $\Sigma\Delta$

Figure 4 Principe de sur-échantillonnage et filtrage de bruit

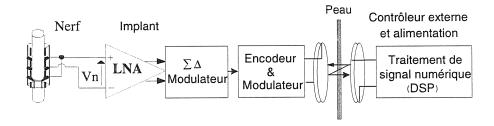

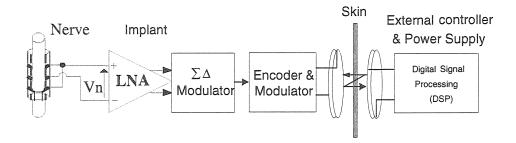

Le travail présenté dans ce mémoire consiste à développer un modulateur  $\Sigma\Delta$  de basse tension d'alimentation et de faible consommation de puissance. Ce travail s'inscrit dans le cadre des travaux de recherche en bioélectronique de notre équipe de recherche PolySTIM, qui est axé sur la réalisation de systèmes électroniques implantables (SEI) de hautes performances. Parmi les applications de ces systèmes, on trouve la stimulation fonctionnelle électrique (SFE) qui permet la restauration de la fonctionnalité des organes paralysés chez les humains [18]. La stimulation fonctionnelle électrique nécessite tout d'abord, la détection et la mesure du signal bioélectrique du nerf. Ce signal est ensuite amplifié et converti en données numériques qui sont transmises à un contrôleur externe par l'intermédiaire d'un lien inductif, puis traitées par un module de traitement de signal spécifique. Le modèle de base d'une application typique de SFE est illustré sur la figure 5. Nous proposons un modulateur  $\Sigma\Delta$  de  $2^{\text{éme}}$ -order pour réaliser la conversion analogique à numérique de signaux mesurés en raison de ses multiples avantages. En premier lieu, elle permet la réalisation de conversion de haute résolution avec de faible

consommation de puissance pour des applications à basses fréquences. En second lieu, sa modulation du rapport-cyclique (PWM) est très adéquate pour la transmission de données sans fil. Comme l'énergie totale, nécessaire au fonctionnement de l'implant, est transférée par le lien inductif à travers la peau, et que le modulateur  $\Sigma\Delta$  doit fonctionner sur une longue durée, le circuit résultant ne doit pas consommer très peu d'énergie.

Figure 5 Diagramme bloc d'une chaîne implantable de mesure de signaux bioélectriques

Le modulateur  $\Sigma\Delta$  présente aussi les avantages suivants: simplification du filtre antirecouvrement [6], simple programmation (contrôle du SNR par la modification du OSR ou par le changement de l'ordre du modulateur), et sa monotonicité inhérente [33]. Pour des considérations de faible puissance et de basse tension d'alimentation, un modulateur  $\Sigma\Delta$  deuxième ordre est tout d'abord favorisé pour réaliser un modulateur de 4<sup>ème</sup> ordre. Le modulateur proposé est axé principalement sur un faible consommation puissance, une basse tension d'alimentation, et finalement, une large gamme dynamique.

# II. IMPLEMEMTATION DU CIRCUIT À BASSE TENSION D'ALIMENTATION ET À FAIBLE CONSOMMATION DE PUISSANCE

Les modulateurs  $\Sigma\Delta$  proposés sont de deuxième et de quatrième ordres et sont mis en oeuvre par l'intermédiaire de deux techniques. Ces dernières sont un intégrateur à demidélai basé sur un amplificateur opérationnel commuté (amp-op-C) et un doubleur de tension. Ainsi, la première technique est utile pour la dissipation de puissance et la réduction du nombre de commutateurs critiques. Quant à la deuxième technique, elle est indispensable pour atteindre la gamme dynamique de « rail-to-rail » et pour concevoir un bon commutateur conductif.

#### 1. Conception des différents blocs de circuit

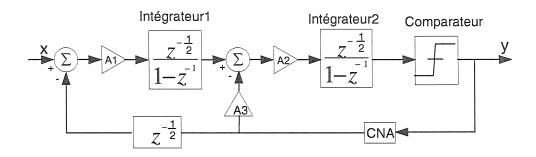

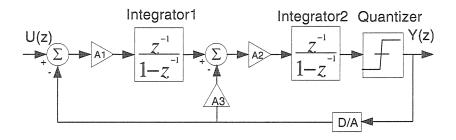

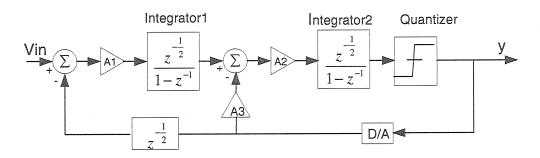

Le diagramme bloc d'un modulateur ΣΔ de deuxième ordre est montré à la figure 6. Ceci est constitué de deux intégrateurs à demi-délai, d'un comparateur et d'un CNA à 1 bit. Le circuit de capacités commutées est exploité pour mettre en application l'intégrateur grâce à sa précision élevée et à sa caractéristique inhérente d'échantillonnage. Trois différentes unités de gain (A1~A3) sont présentées et ajustées dans le chemin direct et dans la boucle de rétroaction respectivement. Ceci réduit la possibilité de saturation de l'intégrateur et améliore la linéarité du CAN.

Figure 6 Diagramme bloc du modulateur  $\Sigma\Delta$  de second ordre basé sur des intégrateurs à demi-délai

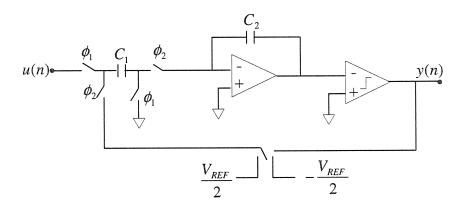

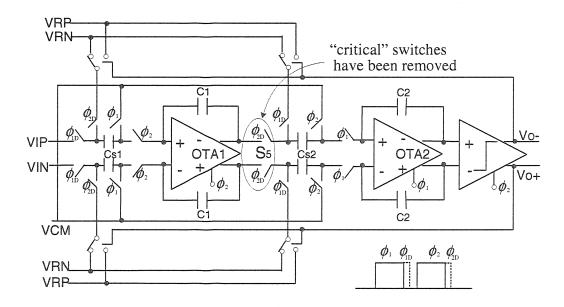

#### 2. Intégrateur à demi-délai

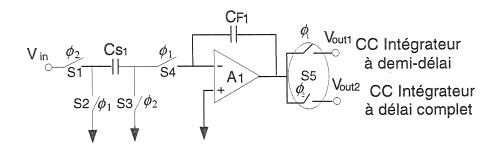

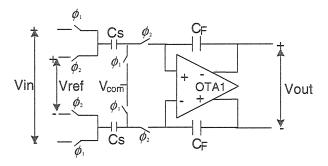

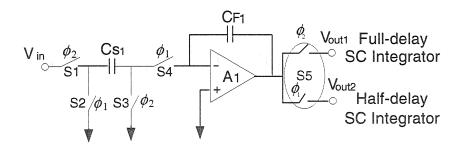

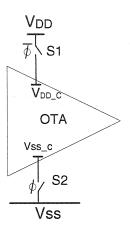

La technique de l'amp-op commuté s'est avérée une solution prometteuse pour opérer à basse tension et la moins coûteuse pour réaliser des circuits de capacités commutées avec la technologie standard CMOS. Cette technique élimine fondamentalement les commutateurs critiques garantissant ainsi une tension d'alimentation minimale nécessaire au fonctionnement à basse tension du circuit à condensateurs commutés sans problème de fiabilité [33]. La figure 7 illustre un intégrateur conventionnel, peu sensible, basé sur la technique de capacités commutées. Il est à noter que la sortie de l'intégrateur conventionnel est disponible à tout moment pour être traitée à l'étape suivante. En conséquence, premièrement, la sortie de l'intégrateur à demi-délai est disponible au circuit de l'étage suivant pendant la phase de la mise en veilleuse (Idle)  $\Phi_2$  de d'intégrateur. L'amp-op est fondamentalement en état de veilleuse pendant la phase  $\Phi_2$  après avoir exécuté la phase d'intégration ( $\Phi_1$ ). Deuxièment, la sortie de l'intégrateur à demi-délai est prise par le circuit de l'étage suivant durant sa phase d'intégration ( $\Phi_2$ ).

Figure 7 Intégrateur conventionnel basé sur des capacités commutées (CC)

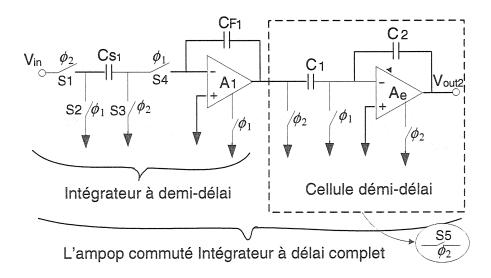

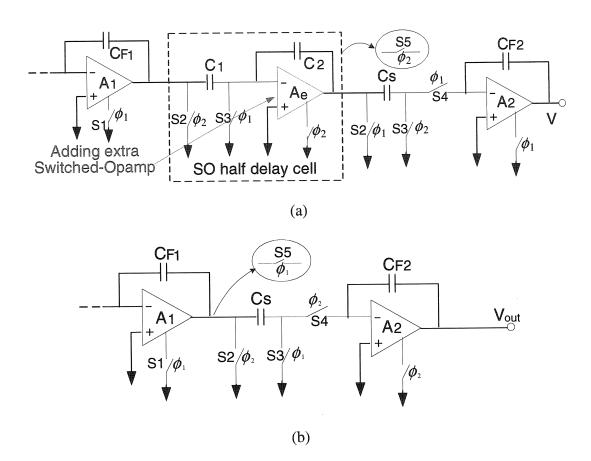

La figure 8 illustre un intégrateur basé sur l'amp-op commuté qui est équivalent à l'intégrateur conventionnel et il est réalisé par des capacités commutées. Cet intégrateur à délai complet est mis en oeuvre avec un amp-op commuté en ajoutant une cellule additionnelle au circuit à demi-délai. Cette cellule est réalisée avec un amp-op commuté supplémentaire (A<sub>e</sub>).

Figure 8 L'intégrateur basé sur l'amp-op commuté

Nous avons choisi de réaliser l'intégrateur basé sur l'amp-op commuté à demi-délai sans utiliser la cellule «switched-opamp» à demi-délai (amp-op commuté supplémentaire). La fonction de la cellule à demi-délai a été remplacée par la fonction marche et arrêt de l'amp-op commuté (A1). Cette structure équivaut à l'intégrateur conventionnel de demi-délai réalisé par des capacités commutées. De plus, la puissance dissipée d'un intégrateur basé sur l'amp-op commuté à demi-délai est réduite de 50% comparé à un intégrateur conventionnel basé sur les condensateurs commutés. La raison est que l'amp-op A1 arrête de fonctionner après la phase d'intégration.

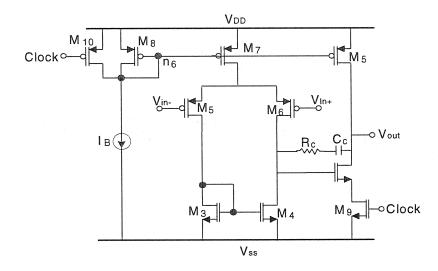

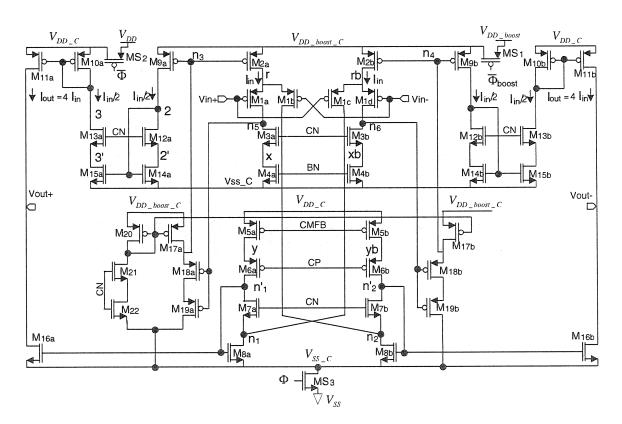

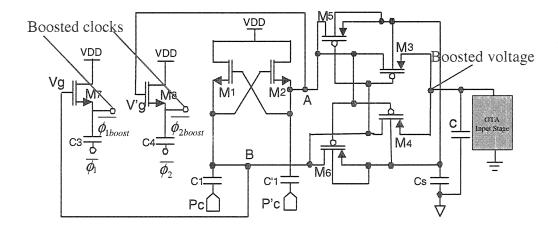

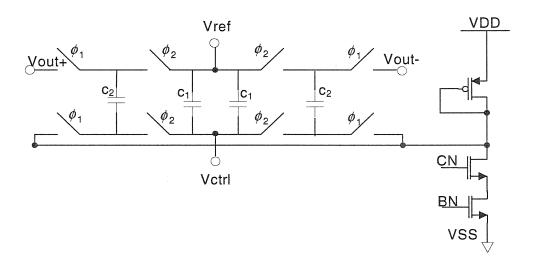

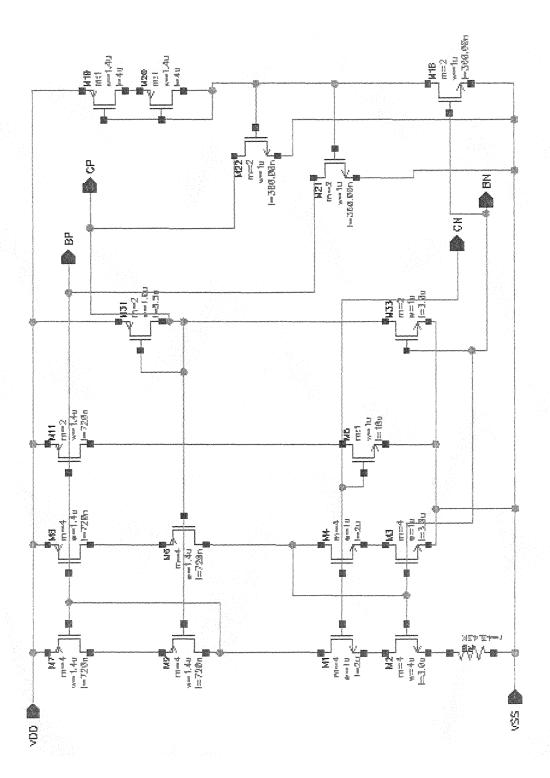

Il est à noter que le mode entièrement différentiel est adopté pour réduire les harmoniques paires causées par la distorsion. De plus, une rétroaction du mode commun (CMFB) est indispensable pour fixer la tension DC du nœud de sortie. Afin de réaliser une opération «rail-to-rail» de classe AB avec une basse tension d'alimentation, il est nécessaire de fournir un doubleur de tension aux deux branches d'entrée de l'OTA. Les branches de sortie fonctionnent toujours sous une basse tension d'alimentation afin de réduire la puissance dissipée.

#### 3. Le circuit doubleur de tension

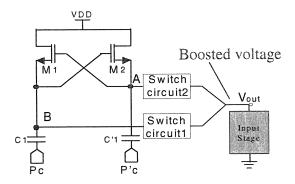

Nous avons conçu un modulateur  $\Sigma\Delta$  fonctionnant à une basse tension d'alimentation de 900 mV. Afin de maximiser la gamme de traitement des signaux, comme il a été mentionné ci-dessus, un doubleur de tension sur puce est introduit. D'une part, il produit la tension amplifiée ainsi que les horloges amplifiées aux deux branches d'entrée de

l'OTA et d'autre part, la faible tension d'alimentation ainsi que la transconductance du commutateur en technologie CMOS peuvent être sensiblement altérées. Afin de permettre l'opération en basse alimentation, le doubleur de tension sur puce produit une tension élevée entre la grille et la source du commutateur pour améliorer sa transconductance.

#### 4. Autres modules importants

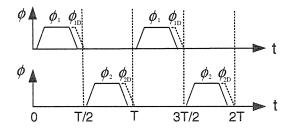

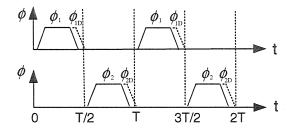

Le générateur d'horloge fournit des signaux sans recouvrement avec des horloges complémentaires et d'autres avec délai, qui commandent les portes de transmission. Ces horloges avec délai réduisent l'injection de charge (clock feedthrough). Ces signaux d'horloges sont montrés à la figure 9.

Figure 9 Horloges sans recouvrement typiques ainsi que les horloges avec délai.

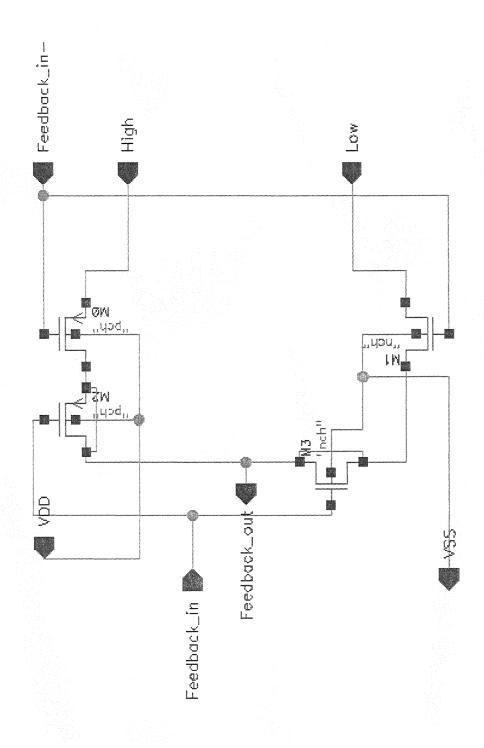

Considérant la linéarité du quantificateur, le circuit de rétroaction du CNA à un bit est mis en oeuvre à l'aide d'un commutateur CMOS commandé par la sortie du comparateur. Les tensions de références de rétroaction  $V_{low}$  et  $V_{high}$  dépendent de la gamme dynamique du signal de sortie.

## III. SIMULATION ET RÉSULTATS EXPÉRIMENTAUX

Le modulateur  $\Sigma\Delta$  de deuxième ordre a été fabriqué en technologie CMOS 0.18 um de TSMC disponible par le biais de la Société canadienne de microélectronique (SCM). De plus, le modulateur  $\Sigma\Delta$  de quatrième ordre proposé a été implémenté et caractérisé. D'abord, nous montrons les résultats de la simulation ainsi que les résultats expérimentaux du modulateur  $\Sigma\Delta$  de deuxième ordre respectivement. Ensuite, nous présenterons les résultats de simulation du modulateur  $\Sigma\Delta$  quatrième ordre.

#### 1. Simulation et résultats expérimentaux du modulateur $\Sigma\Delta$ de deuxième ordre

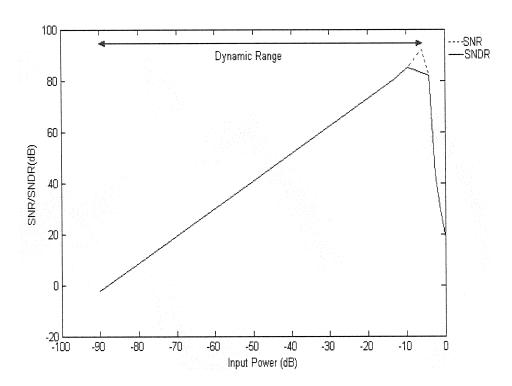

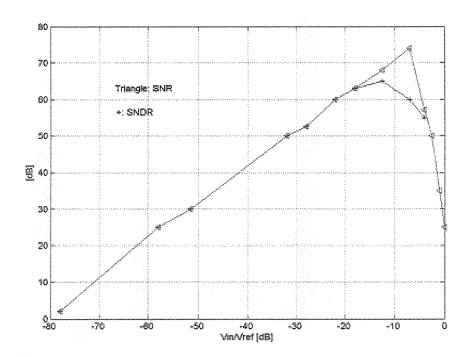

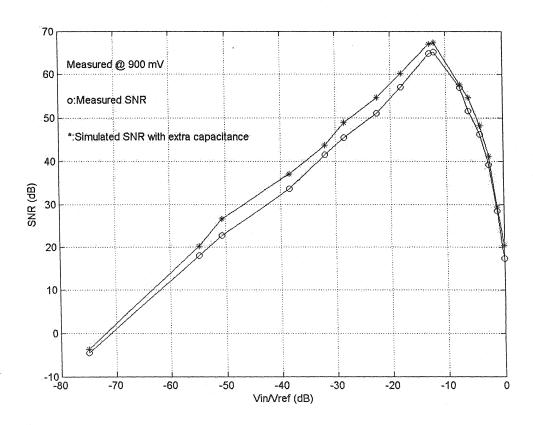

Le modulateur  $\Sigma\Delta$  de deuxième ordre et de faible puissance a été simulé. Il a réalisé une gamme dynamique de 78 dB, un SNR maximale de 74 dB et un SNDR de 65 dB en considérant une largeur de bande de signal de 10 KHz. Aussi, la puissance dissipée totale (dynamique et statique) est de 38  $\mu$ W. L'aire totale du modulateur  $\Sigma\Delta$  de deuxième ordre est de 800  $\mu$ m x 800  $\mu$ m. Les résultats expérimentaux indiquent que ce modulateur réalise un SNR de 65 dB et un SNDR de 46 dB. La différence entre les résultats de simulation et les résultats expérimentaux est due aux effets de la capacité additionnelle de chaque « pad » ainsi que la capacité du « wire-bonding ».

#### 2. Résultats de simulation du modulateur $\Sigma\Delta$ de quatrième ordre

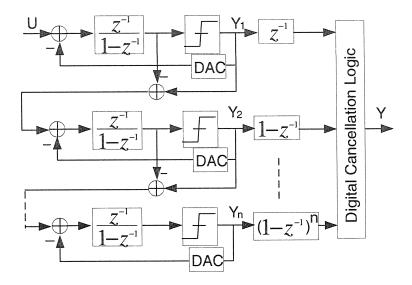

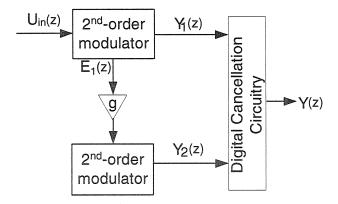

Le modulateur  $\Sigma\Delta$  de quatrième ordre proposé est basé sur l'architecture de « MASH » qui est composée de deux modulateurs  $\Sigma\Delta$  de deuxième ordre avec un circuit numérique

d'annulation. Les résultats de simulation montrent une consommation de puissance de 86  $\mu W$  et un SNR de 90 dB dans la même bande de fréquence.

#### IV. CONCLUSION

Les modulateurs proposés, qui utilisent des intégrateurs à demi-délai, basés sur la technique de l'amplificateur opérationnel commuté dissipent moins de puissance et réduisent au minimum le nombre de commutateurs critiques. Un doubleur de tension a été utilisé pour pouvoir atteindre la gamme dynamique « rail-to-rail » ainsi que pour avoir un bon commutateur conducteur. La puissance dissipée du modulateur de deuxième ordre est à peu près de 38 µW. Les valeurs maximales simulées de SNR et de SNDR sont de 74 dB et de 65 dB respectivement. Les résultats expérimentaux ont montré que le SNR et le SNDR par rapport à ce modulateur sont de 65 dB et de 46 dB respectivement dans une charge capacitive sur chaque pin. Bien qu'il y ait des différences entre les résultats de simulation et les résultats expérimentaux, nous avons pu démontrer la faisabilité de la conception d'un modulateur  $\Sigma\Delta$  à basse tension et à faible puissance dissipée en ayant recours à la technique de l'amp-op commuté avec un doubleur de tension intégré sur la puce. Le modulateur qui était à l'origine conçu pour des applications biomédicales, peut être utilisé pour toutes les applications de basse fréquence de conversion analogique à numérique.

## TABLE OF CONTENTS

| DEDICATION                                    | IV     |

|-----------------------------------------------|--------|

| ACKNOWLEDGEMENTS                              | V      |

| RÉSUMÉ                                        | VII    |

| ABSTRACT                                      | X      |

| CONDENCÉ EN FRANÇAIS                          | XII    |

| TABLE OF CONTENTS                             | XXIV   |

| LIST OF FIGURES                               | XXVIII |

| LIST OF TABLES                                | XXXII  |

| LIST OF ABBREVIATIONS                         | XXXIII |

| LIST OF APPENDIXES                            | XXXV   |

| CHAPTER 1 INTRODUCTION                        |        |

| 1.1 Motivation                                | 1      |

| 1.2 Research goals                            |        |

| 1.3 Master thesis organization                | 6      |

| CHAPTER 2 FUNDAMENTALS OF ΣΔ MODULATORS       | 8      |

| 2.1 Introduction                              | 8      |

| 2.2 Sigma-delta modulator performance metrics |        |

| 2.2.1 Dynamic range and peak SNR/SNDR         | 9      |

| 2.2.2 Oversampling ratio and Nyuist rate      | 10     |

| 2.2.3 Power consumption                       | 11     |

| 2.3 Sigma-delta modulators                    | 11     |

| 2.3.1 Principle of sigma-delta modulators                             |  |

|-----------------------------------------------------------------------|--|

| 2.3.2 First-order $\Sigma\Delta$ modulator with one-bit DAC feedback  |  |

| 2.3.3 Second-order $\Sigma\Delta$ modulator with one-bit DAC feedback |  |

| 2.3.4 Higher-order sigma-delta modulators                             |  |

| 2.3.5 Architecture tradeoff                                           |  |

| CHAPTER 3 LOW VOLTAGE ANALOG CIRCUIT DESIGN TECHNIQUES 28             |  |

| 3.1 Introduction                                                      |  |

| 3.2 Fundamental power limits29                                        |  |

| 3.3 Dynamic analog circuit and low voltage limits31                   |  |

| 3.3.1 MOSFET switch                                                   |  |

| 3.3.2 Charge injection errors                                         |  |

| 3.3.3 Voltage requirements of analog circuit                          |  |

| 3.4 Low voltage circuit techniques40                                  |  |

| 3.4.1 Voltage multiplier                                              |  |

| 3.4.2 Switched-capacitor integrators and switched-opamp technique     |  |

| 3.5 Recently reported design techniques45                             |  |

| CHAPTER 4 LOW VOLTAGE SECOND-ORDER ΣΔ MODULATOR 48                    |  |

| 4.1 Introduction 48                                                   |  |

| 4.2 Low voltage $\Sigma\Delta$ modulator                              |  |

| 4.3 Improved second order $\Sigma\Delta$ modulator 50                 |  |

| 4.3.1 System consideration                                            |  |

| 4.3.2 Rail-to-rail class AB OTA                                       |  |

| 4.3.3 Clock generation                                       | 55 |

|--------------------------------------------------------------|----|

| 4.3.4 Voltage doubler and its effect on SNR                  | 55 |

| 4.3.5 Common mode feedback                                   | 59 |

| 4.3.6 Bias circuit design                                    | 60 |

| 4.3.7 Comparator and D/A feedback circuits                   | 63 |

| 4.3.8 Reduction of charge injection effects                  | 66 |

| 4.4 Summary                                                  | 68 |

| CHAPTER 5 0.9 V LOW POWER FOURTH-ORDER ΣΔ MODULATOR          | 70 |

| 5.1 Introduction                                             | 70 |

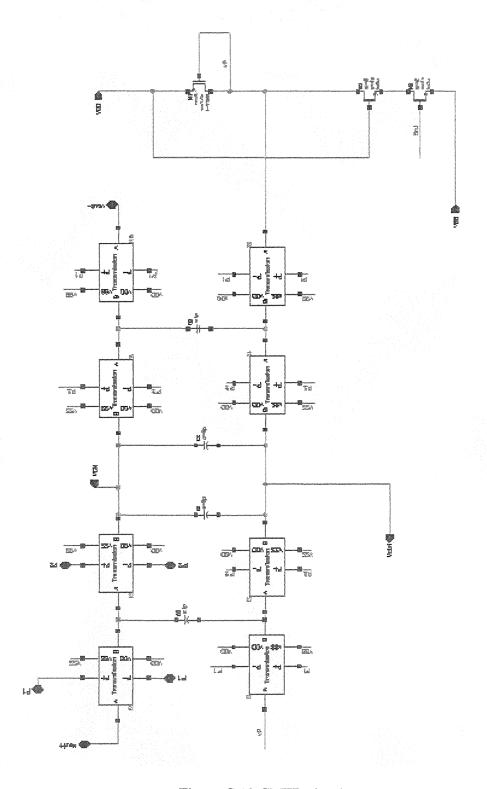

| 5.2 Fourth-order sigma-delta modulator                       | 71 |

| 5.2.1 System consideration                                   | 71 |

| 5.2.2 First and second loop circuitry                        | 73 |

| 5.2.3 Digital cancellation circuitry                         | 75 |

| 5.3 Sensitivity to mismatch                                  | 76 |

| 5.4 Summary                                                  | 77 |

| CHAPTER 6 SIMULATION & EXPERIMENTAL RESULTS                  | 78 |

| 6.1 Introduction                                             | 78 |

| 6.2 Simulated characteristics of the second-order modulator  | 78 |

| 6.3 Experimental results of 2 <sup>nd</sup> -order modulator | 84 |

| 6.4 Simulation results of 4 <sup>th</sup> -order modulator   | 87 |

| 6.5 Summary                                                  | 89 |

| CONCLUSION                                                   | Ω1 |

| REFERENCES | 94 |

|------------|----|

|            |    |

| APPENDIXES |    |

## LIST OF FIGURES

| Figure 1.1  | The simplified $\Sigma\Delta$ ADC system                                                     | 3  |

|-------------|----------------------------------------------------------------------------------------------|----|

| Figure 1.2  | Block diagram of a typical implantable monitoring chain                                      | 4  |

| Figure 2.1  | SNR and SNDR curves                                                                          | 10 |

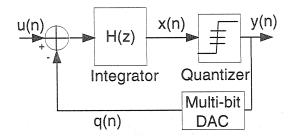

| Figure 2.2  | A simplified block diagram of a $\Sigma\Delta$ modulator with multi-bit quantizer            | 12 |

| Figure 2.3  | Linear model in time-domain of a $\Sigma\Delta$ modulator                                    | 12 |

| Figure 2.4  | Frequency domain of $\Sigma\Delta$ modulation                                                | 13 |

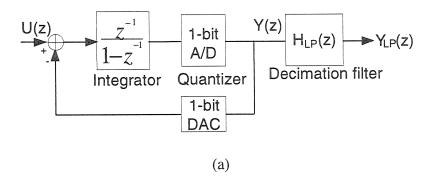

| Figure 2.5  | Principle of $\Sigma\Delta$ modulator (a) Diagram of $\Sigma\Delta$ program (b) Principle of |    |

|             | oversampling & noise shaping                                                                 | 14 |

| Figure 2.6  | A first-order $\Sigma\Delta$ modulation in time domain                                       | 15 |

| Figure 2.7  | Frequency response of the first-order $\Sigma\Delta$ modulator                               | 17 |

| Figure 2.8  | Implementation of a 1 <sup>st</sup> -order $\Sigma\Delta$ modulator                          | 18 |

| Figure 2.9  | Block Diagram of a second-order $\Sigma\Delta$ modulator                                     | 19 |

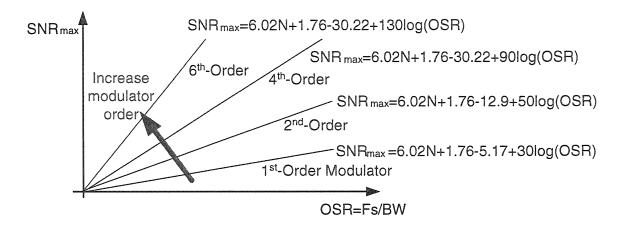

| Figure 2.10 | The SNR performance of different order $\Sigma\Delta$ modulators                             | 21 |

| Figure 2.11 | $\Sigma\Delta$ modulator block diagram                                                       | 22 |

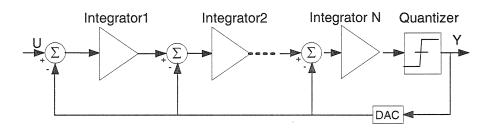

| Figure 2.12 | Multi-stage Nth-order MASH structure noise shaping modulator                                 | 23 |

| Figure 2.13 | Example of a 4 <sup>th</sup> -order 2-2 cascade (MASH) architecture                          | 25 |

| Figure 3.1  | Fully differential switched-capacitor integrator                                             | 29 |

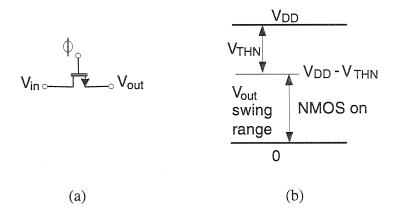

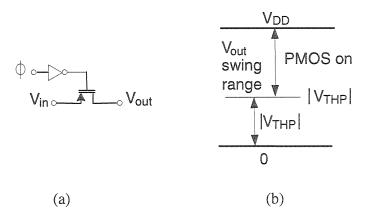

| Figure 3.2  | (a) NMOS switch, (b) Signal swing limitation of NMOS switch                                  | 32 |

| Figure 3.3  | (a) PMOS switch, (b) Signal swing limitation of PMOS switch                                  | 32 |

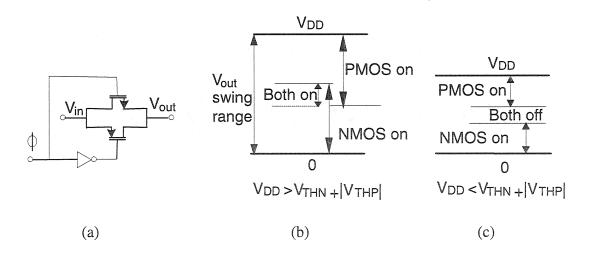

| Figure 3.4 (a) CMOS switch (b) Full signal swing range of CMOS switch, (c) The s           | ignal |

|--------------------------------------------------------------------------------------------|-------|

| swing limitation of CMOS switch at low voltage operation                                   | 33    |

| Figure 3.5 Charge injection in a n-channel transistor: (a) NMOS is on, (b) NMOS is         | off   |

|                                                                                            | 34    |

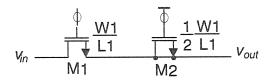

| Figure 3.6 Use of a half size dummy switch to cancel charge injection                      | 37    |

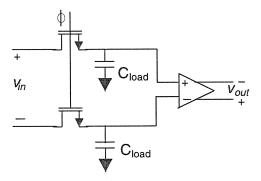

| Figure 3.7 Use of a fully differential circuit to minimize charge injection                | 37    |

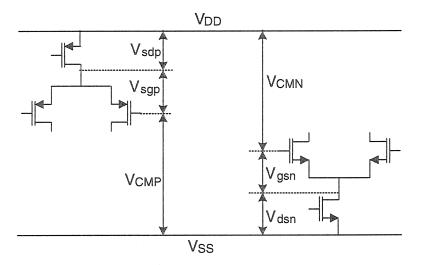

| Figure 3.8 Common mode voltage ranges of n- and p-channel pair-transistors                 | 39    |

| Figure 3.9 The voltage doubler circuit.                                                    | 40    |

| Figure 3.10 Conventional switched-capacitor integrator (SCI)                               | 41    |

| Figure 3.11 Switched-opamp technique: (a) Full delay SOI with extra switched-opa           | mp    |

| (b) Half delay SOI without extra switched-opamp                                            | 43    |

| Figure 3.12 Current switching method in the switched-opamp technique [9]                   | 44    |

| Figure 3.13 The voltage switching method.                                                  | 45    |

| Figure 4.1 Block diagram of 2nd-order $\Sigma\Delta$ modulator with half delay integrators | 49    |

| Figure 4.2 Half delay switched-OTA integrator cell with delayed clocks                     | 51    |

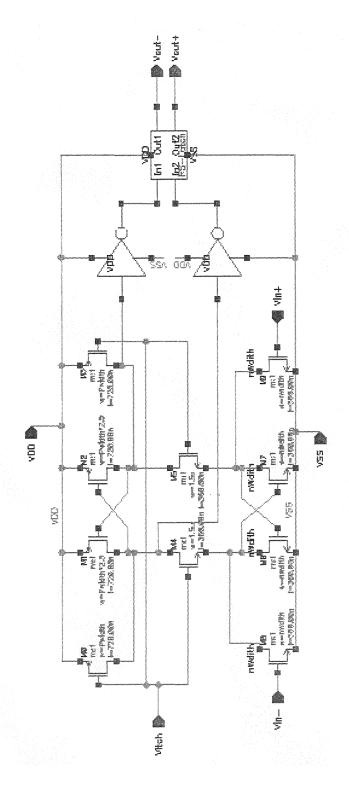

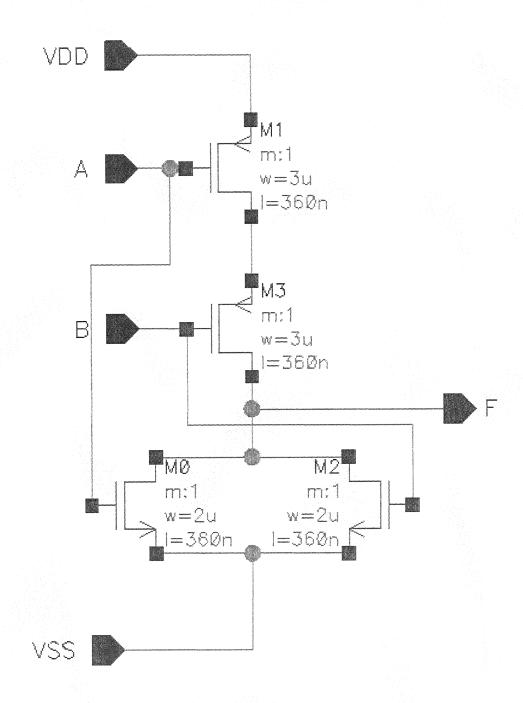

| Figure 4.3 The fully differential low-voltage class AB OTA                                 | 53    |

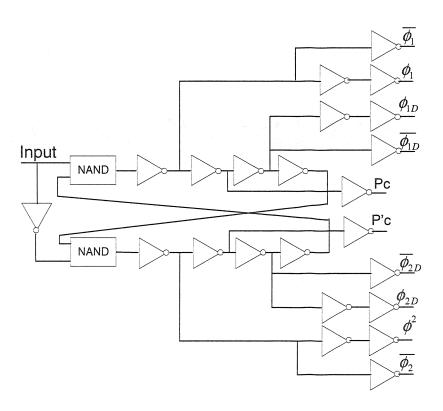

| Figure 4.4 Clocks generation circuit                                                       | 56    |

| Figure 4.5 Waveforms of a typical two-phase and nonoverlapping clock scheme                | 57    |

| Figure 4.6 Voltage doubler circuit                                                         | 57    |

| Figure 4.7 Common mode feedback circuit                                                    | 60    |

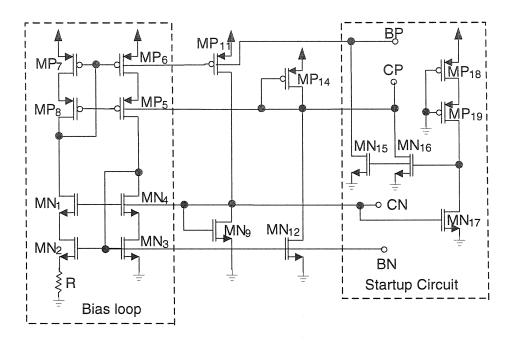

| Figure 4.8 A constant transconductance bias circuit                                        | 61    |

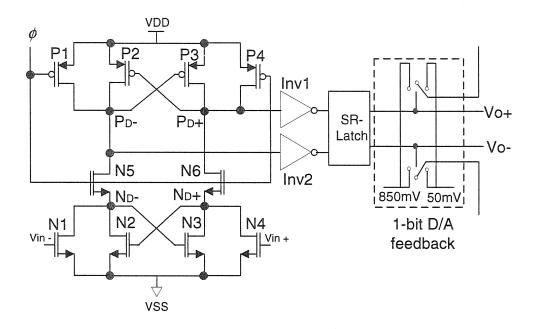

| Figure 4.9. Schematic of comparator with one-bit DAC                                       | 64    |

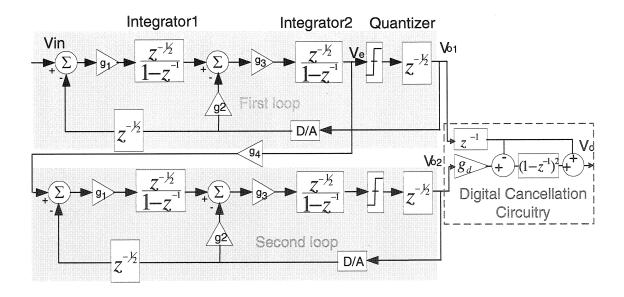

| Figure 5.1 Block diagram of 4th-order $\Sigma\Delta$ modulator with half delay integrator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 71    |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

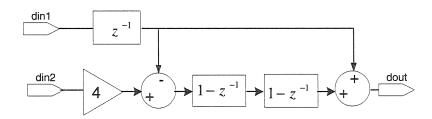

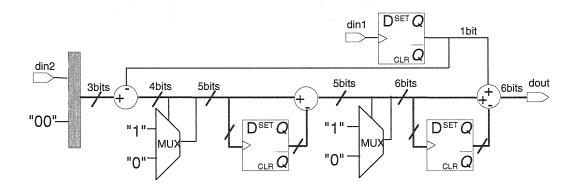

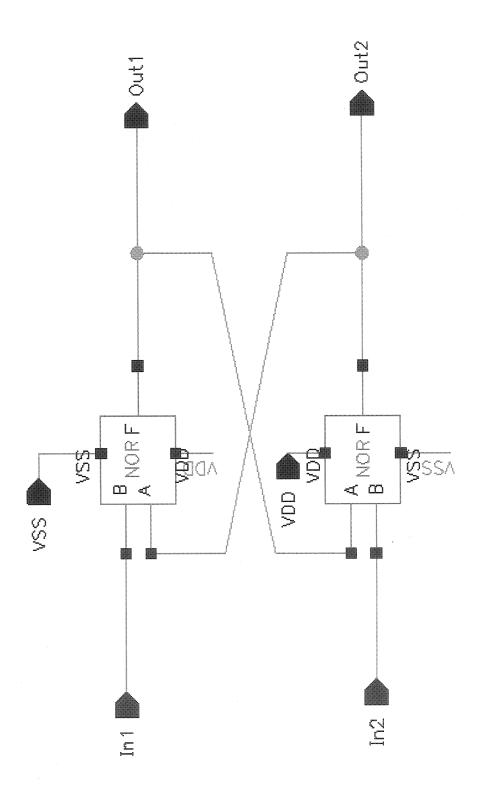

| Figure 5.2 Block scheme of DCC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 76    |

| Figure 5.3 DCC implementation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 76    |

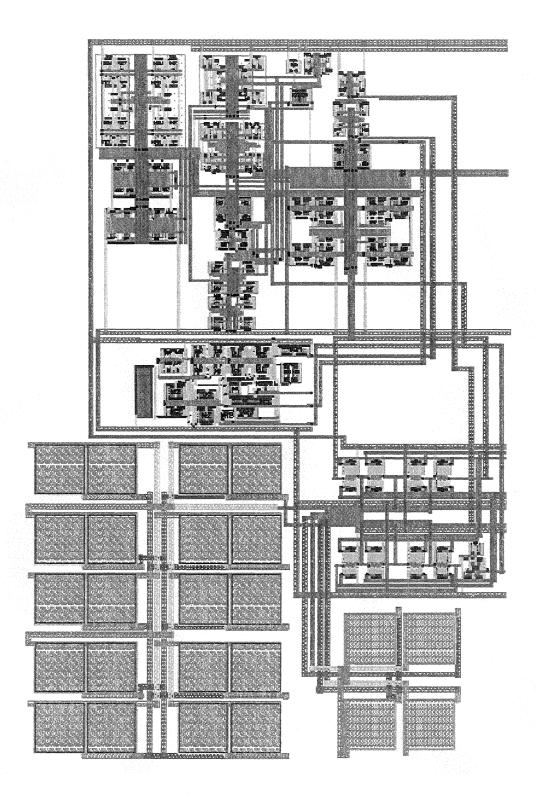

| Figure 6.1 Photograph of the 2 <sup>nd</sup> -order modulator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 79    |

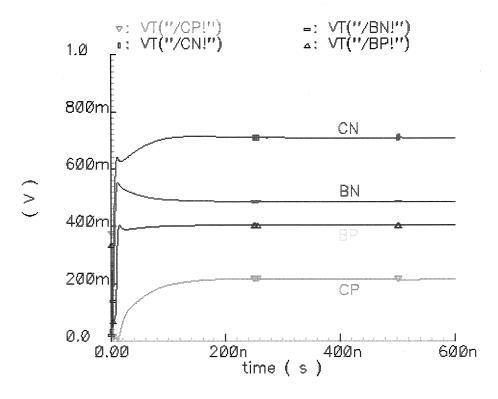

| Figure 6.2 Bias Voltages                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 79    |

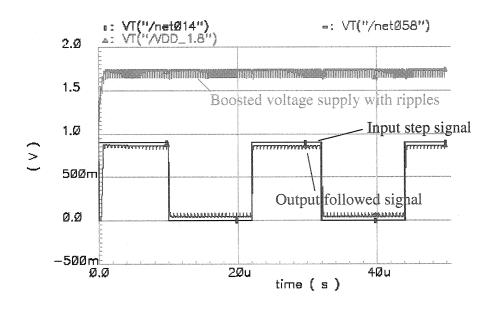

| Figure 6.3 Transient behavior of the OTA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 80    |

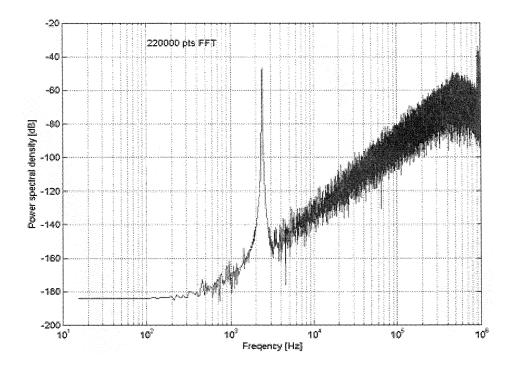

| Figure 6.4 $2^{nd}$ -order $\Sigma\Delta$ modulator simulated output spectrum                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 82    |

| Figure 6.5 Simulated SNR versus the input signal power                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 82    |

| Figure 6.6 Measured SNR & Simulated SNR with extra load capacitors in each page 1.5 Figure 6.6 Measured SNR & Simulated SNR with extra load capacitors in each page 1.5 Figure 6.6 Measured SNR & Simulated SNR with extra load capacitors in each page 1.5 Figure 6.6 Measured SNR & Simulated SNR with extra load capacitors in each page 1.5 Figure 6.6 Measured SNR & Simulated SNR with extra load capacitors in each page 1.5 Figure 6.6 Measured SNR & Simulated SNR with extra load capacitors in each page 1.5 Figure 6.6 Measured SNR & Simulated SNR with extra load capacitors in each page 1.5 Figure 6.6 Measured SNR & Simulated SNR with extra load capacitors in each page 1.5 Figure 6.6 | ad 86 |

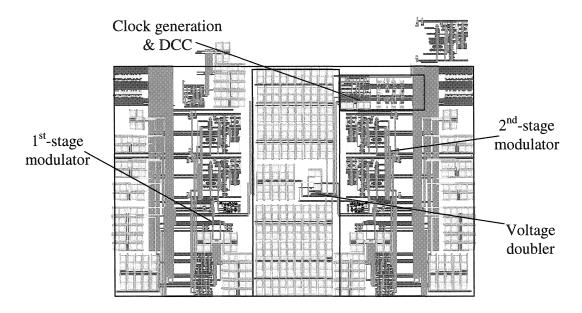

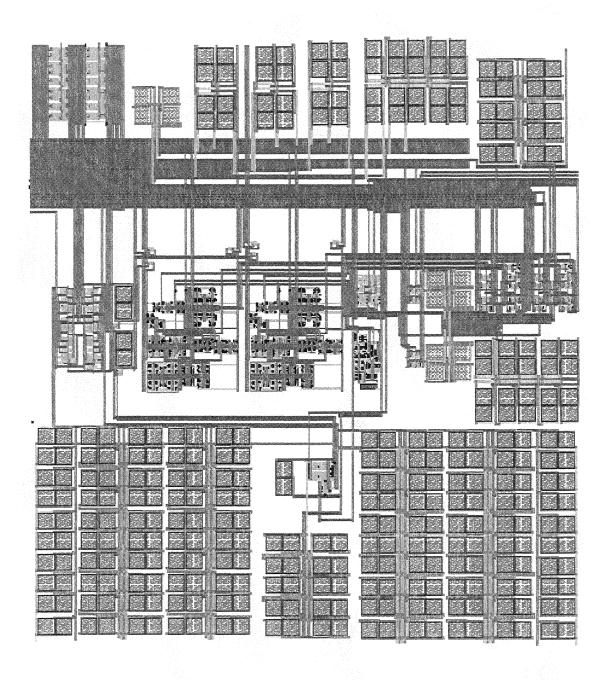

| Figure 6.7 Layout of the proposed $4^{th}$ -order $\Sigma\Delta$ modulator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 88    |

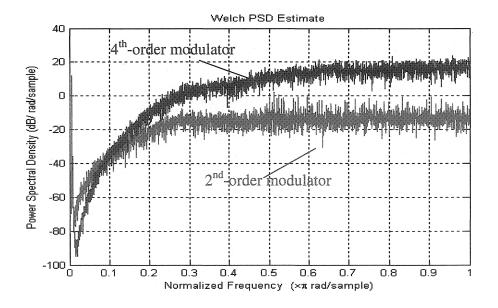

| Figure 6.8 SNR figures of the proposed $\Sigma\Delta$ modulators                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 88    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |       |

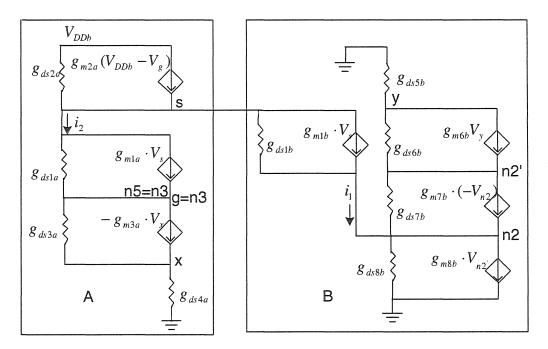

| Figure A5.1 Equivalent small signal model for the input stage of OTA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 107   |

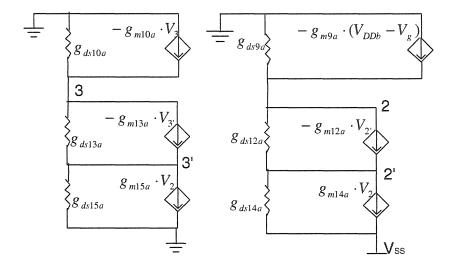

| Figure A5.2 Simplified equivalent small signal model for current mirror circuit o                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | f OTA |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 109   |

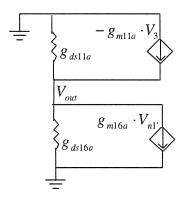

| Figure A5.3 Simplified equivalent small signal model for output stage of OTA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 110   |

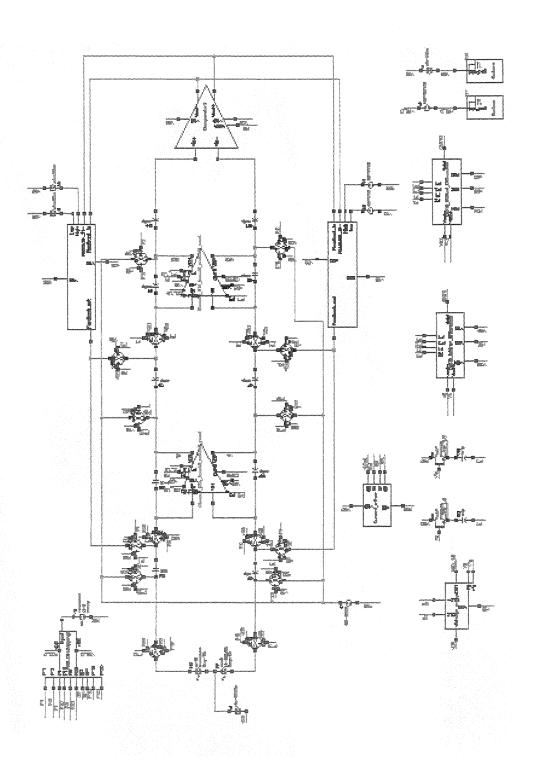

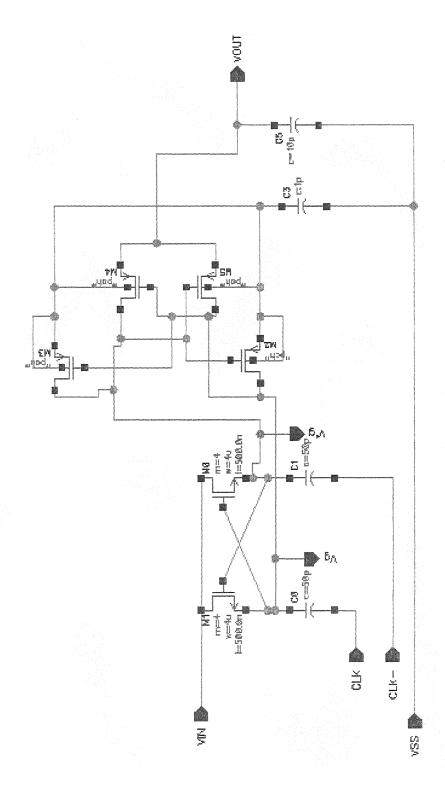

| Figure C.1 2 <sup>nd</sup> -order sigma-delta modulator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 113   |

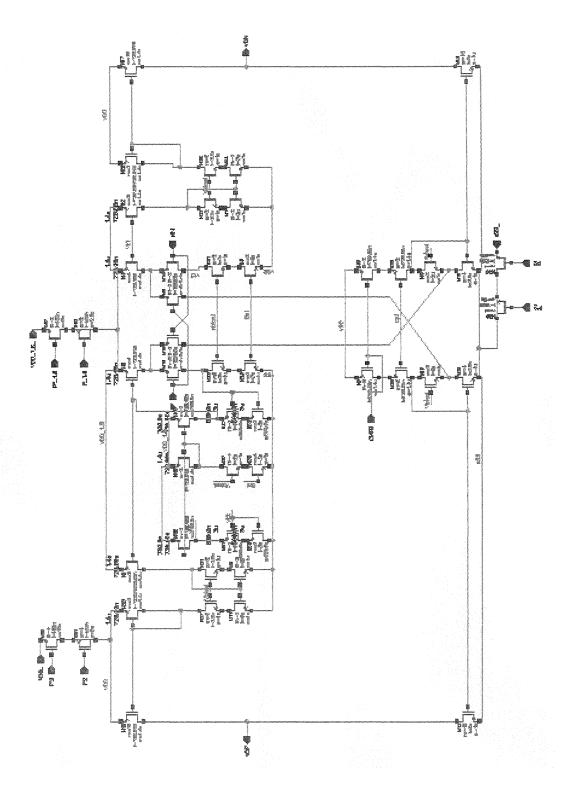

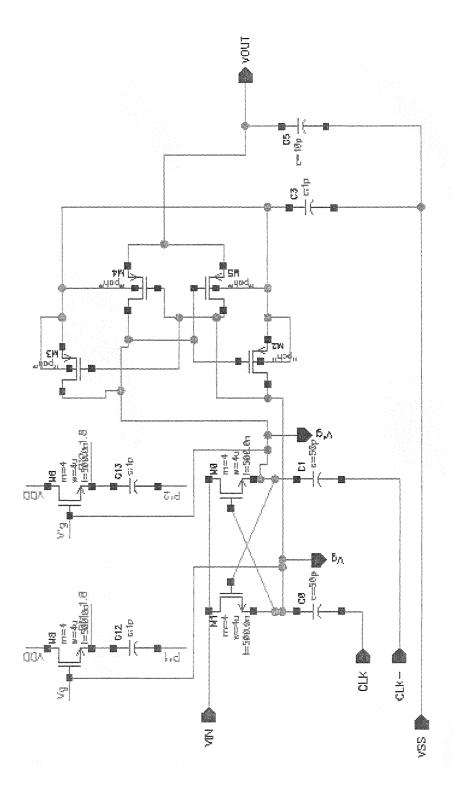

| Figure C.2 OTA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 114   |

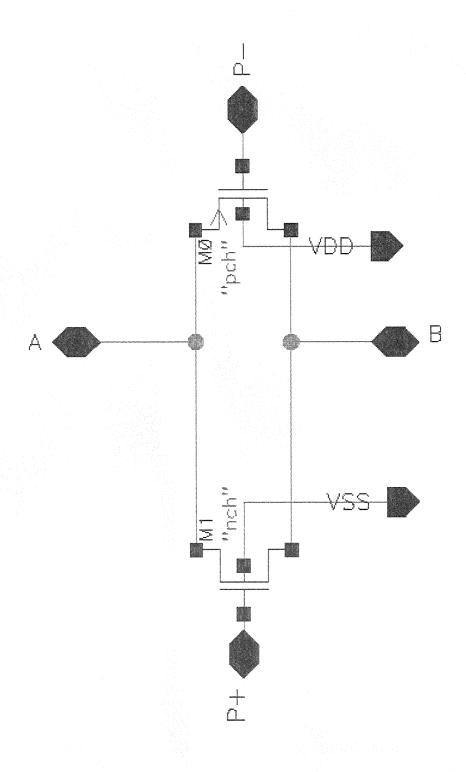

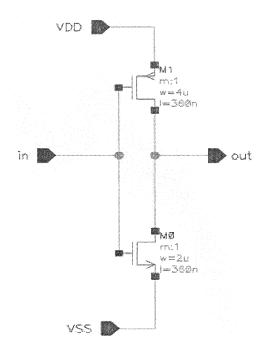

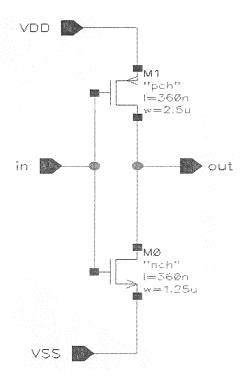

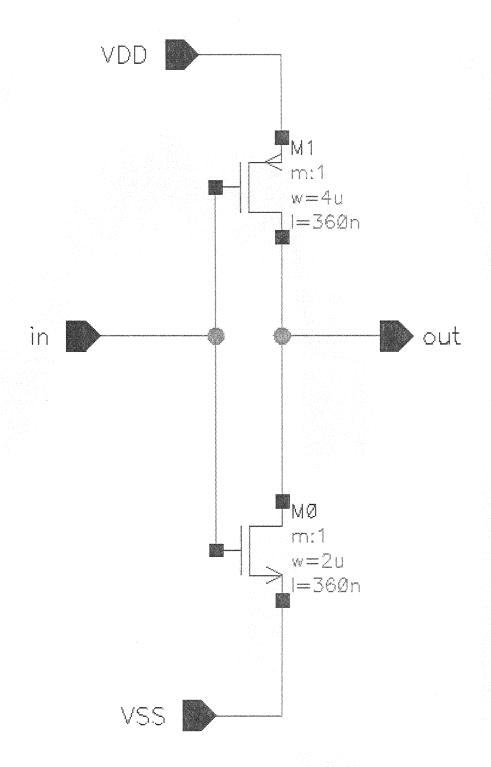

| Figure C.3 CMOS switch of switched-capacitor circuit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 115   |

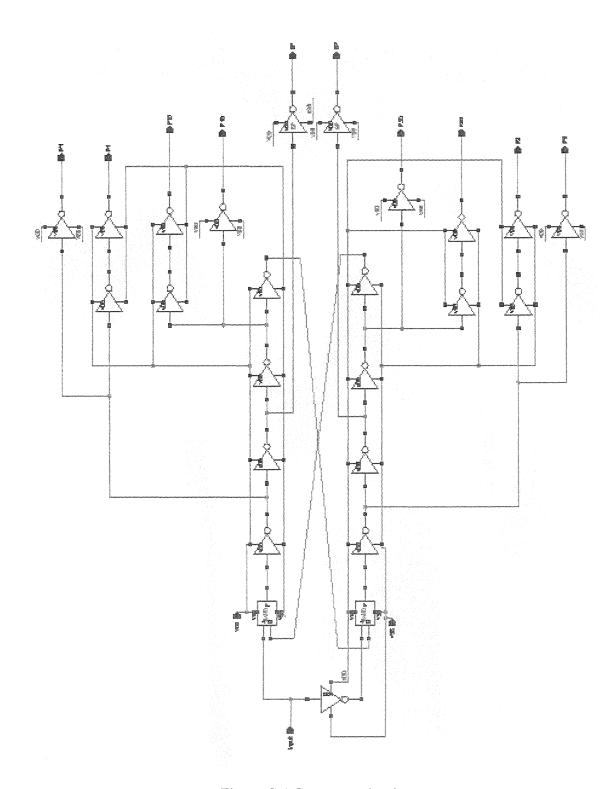

| Figure C.4 Generator circuit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 116   |