**Titre:** Matrices cellulaires reconfigurables en point flottant dédiées au

Title: traitement des signaux

**Auteur:** Nabil El Ghali

Author:

**Date:** 2011

**Type:** Mémoire ou thèse / Dissertation or Thesis

**Référence:** El Ghali, N. (2011). Matrices cellulaires reconfigurables en point flottant dédiées

au traitement des signaux [Mémoire de maîtrise, École Polytechnique de

Montréal]. PolyPublie. <https://publications.polymtl.ca/650/>

Citation:

## Document en libre accès dans PolyPublie

Open Access document in PolyPublie

**URL de PolyPublie:** <https://publications.polymtl.ca/650/>

PolyPublie URL:

**Directeurs de

recherche:** Michael J. Corinthios

Advisors:

**Programme:** génie électrique

Program:

UNIVERSITÉ DE MONTRÉAL

**MATRICES CELLULAIRES RECONFIGURABLES EN POINT

FLOTTANT DÉDIÉES AU TRAITEMENT DES SIGNAUX**

NABIL EL GHALI

DÉPARTEMENT DE GÉNIE ÉLECTRIQUE

ÉCOLE POLYTECHNIQUE DE MONTRÉAL

MÉMOIRE PRÉSENTÉ EN VUE DE L'OBTENTION

DU DIPLÔME DE MAÎTRISE ÈS SCIENCES APPLIQUÉES

(GÉNIE ÉLECTRIQUE)

AOÛT 2011

UNIVERSITÉ DE MONTRÉAL

ÉCOLE POLYTECHNIQUE DE MONTRÉAL

Ce mémoire intitulé :

**MATRICES CELLULAIRES RECONFIGURABLES EN POINT

FLOTTANT DÉDIÉES AU TRAITEMENT DES SIGNAUX**

Présenté par : EL GHALI Nabil

en vue de l'obtention du diplôme de : Maîtrise ès Sciences Appliquées

a été dûment accepté par le jury d'examen constitué de :

M. DAVID Jean Pierre, Ph. D., président

M. CORINTHIOS Michael J., Ph. D., membre et directeur de recherche

M. BRAULT Jean-Jules, Ph. D., membre

## DÉDICACE

*À mes parents et ma famille...*

## REMERCIEMENTS

Je tiens tout d'abord à exprimer ma gratitude envers le professeur Michael Corinthios, que je remercie de m'avoir encadré et offert cette idée de recherche comme sujet de mémoire. Je lui adresse aussi un grand merci pour m'avoir introduit à la publication d'articles scientifiques. Je remercie le professeur Corinthios pour l'excellence et le niveau très élevé de son enseignement qui repoussent sans cesse les frontières du savoir connu et permet ainsi aux étudiants de contribuer de manière significative à la recherche.

Mes remerciements vont aussi aux membres du jury, le professeur Jean Pierre David, et le professeur Jean-Jules Brault qui en ayant l'amabilité d'accepter d'évaluer ce travail m'ont fourni un enseignement précieux et de très haute qualité. Je tiens également à exprimer ma reconnaissance et mes remerciements au professeur Saydy Lahcen dont l'aide a été très précieuse et essentielle. Mes remerciements vont aussi au professeur Hoang Le-Huy, ainsi que le professeur Gilles Roy, le professeur Michel A. Duguay et le professeur Roland Malhamé.

J'adresse aussi mes remerciements à Nathalie Levesque, Ginette Desparois, Anne-Marie Bourret, Thomas Martinuzzo, Morgan Guitton et Marie-Hélène Dupuis. Je salue aussi le travail de tous les membres du personnel de l'École Polytechnique Montréal, les secrétaires et techniciens du département de Génie Électrique qui offrent quotidiennement aux étudiants un environnement de travail exceptionnel.

Mes remerciements vont aussi à mes proches Souad, Mustapha, Kais, Skander, Chiraz, Rania, Yasmine, Driss, Rayan, Sirine, Adnen.

## RÉSUMÉ

Les processeurs scalaires sont majoritairement utilisés de nos jours, pour le traitement des signaux numériques, par comparaison aux processeurs matriciels qui offrent pourtant plus de vitesse de calcul due à leur architecture parallèle traitant de nombreuses données en temps réel. Il existe une multitude d'architectures de matrices cellulaires. Cependant la grande majorité est très spécialisée pour le calcul d'une ou deux fonctions de traitement de signaux et seuls quelques processeurs matriciels sont reconfigurables afin de traiter la plupart des fonctions de traitement de signaux.

Ce mémoire présente l'architecture d'un processeur matriciel construit à partir de cellules complexes de calcul appelé "Module de Traitement Universel" (UPM). Ce processeur peut servir comme un module de propriété intellectuelle (IP block) destiné à être utilisé dans un FPGA pour le traitement des signaux. Des mêmes matrices d'UPMs sont reconfigurées en vue d'effectuer la plupart des opérations de Traitement Numérique des Signaux DSP incluant des fonctions de filtrage adaptatif récursives ou non et des fonctions d'analyse spectrale. Ce processeur peut être reconfiguré pour appliquer diverses transformées, filtres adaptatifs, filtres en treillis, en générations de fonctions, corrélations et en calcul de fonctions récursives qui peuvent être exécutées à grande vitesse. Pour une plus grande précision la conception est faite de manière à traiter les données en arithmétique point flottant. Afin de permettre le calcul de fonctions récursives l'unité de traitement UPM est construite avec un module de contrôle de récursivité. En outre l'UPM est conçu de manière à être mis en cascade afin d'augmenter l'ordre des opérations de traitement.

La conception logicielle de matrice 2x2 UPMs et 6x4 UPMs, qui sont programmées en langage Verilog-HDL, est simulée et testée avec les mêmes cellules reconfigurées en plusieurs fonctions telles que le filtrage adaptatif, l'analyse spectrale et le calcul de fonctions récursives. La même matrice de cellules a été simulée sur Matlab *Simulink* sous différentes configurations.

Les tests montrent que ce processeur offre une certitude de calcul acceptable pour tous les algorithmes proposés et une vitesse de calcul qui est limitée uniquement par la fréquence de l'horloge point flottant qui est au maximum de 100 *MHz*. Cependant les matrices cellulaires offrent une de performance de vitesse qui croît avec le nombre de cellules et qui est supérieure à celle offerte par les processeurs scalaires, aux *Duo Cores*, et des performances du même ordre de grandeur que les processeurs DSP les plus récents.

## ABSTRACT

Scalar processors are commonly used today in contrast with array processors which offer a higher computation speed due to their parallel architecture dealing with a great number of data in real time. Several cellular arrays architectures exist. However, the vast majority is highly specialized for the computation of one or two signal processing functions and only a few are reconfigurable to handle most of the of signal processing functions.

This thesis presents the architecture of an array processor constructed using building blocks which are complex computation cells named Universal Processing Module (UPM). This array processor may serve as an intellectual property (IP block) to be used in FPGA technology and dedicated to signal processing. The same UPMs matrices are reconfigured to perform most of digital signal processing DSP operations including adaptive recursive and non recursive filtering, and spectral analysis functions. This processor can be reconfigured in order to compute transforms, adaptive filters, lattice filters, function generations, correlations and recursive functions, all performed at high speed. For greater accuracy the processor is constructed in floating point arithmetic. In order to enable computation of recursive functions, the UPM is built with a recursion control module. This processing element can also be indefinitely with the intention to increase filtering order.

The software design of a 2x2 UPMs and a 6x4 UPMs arrays which is programmed in Verilog-HDL language, is simulated and tested using same cells reconfigured in order to compute DSP algorithms such as adaptive filtering, spectral analysis and recursive functions. The same matrix of cell is simulated on Matlab *Simulink* through different configuration.

The processor is tested with all proposed reconfigurations and offers an acceptable computing precision. The computational speed is reduced only by the floating point clock frequency which maximum is 100 *MHz*. However, cellular arrays speed performance increases with the number of cells and is superior to those offered by scalar processors, *Duo Cores* processors and at the same range of order with performances offered by recent DSP processors.

## TABLE DES MATIÈRES

|                                                                                |      |

|--------------------------------------------------------------------------------|------|

| DÉDICACE.....                                                                  | III  |

| REMERCIEMENTS .....                                                            | IV   |

| RÉSUMÉ.....                                                                    | V    |

| ABSTRACT .....                                                                 | VI   |

| TABLE DES MATIÈRES .....                                                       | VII  |

| LISTE DES TABLEAUX.....                                                        | XI   |

| LISTE DES FIGURES .....                                                        | XII  |

| LISTE DES SIGLES ET ABRÉVIATIONS .....                                         | XV   |

| LISTE DES ANNEXES.....                                                         | XVII |

| INTRODUCTION.....                                                              | 1    |

| CHAPITRE 1 REVUE DE LITTÉRATURE ET PROPOSITION DE RECHERCHE .....              | 2    |

| 1.1    Revue de littérature .....                                              | 2    |

| 1.1.1    Les processeurs Scalaires et Super Scalaires .....                    | 2    |

| 1.1.2    Les Processeurs Vectoriels ou Matrices cellulaires spécialisées ..... | 3    |

| 1.1.3    Les Matrices Cellulaires multifonctionnelles.....                     | 6    |

| 1.2    Question de recherche énoncée .....                                     | 8    |

| 1.3    Objectif général .....                                                  | 8    |

| 1.4    Objectifs spécifiques .....                                             | 8    |

| 1.5    Hypothèses Scientifiques Originales de Recherche .....                  | 9    |

| 1.6    Méthodologie employée .....                                             | 10   |

| 1.6.1    Phases du projet.....                                                 | 10   |

| 1.6.2    Méthodologie utilisée .....                                           | 11   |

| 1.7    Échéancier détaillé .....                                               | 12   |

|                                                                                  |    |

|----------------------------------------------------------------------------------|----|

| CHAPITRE 2 ÉTUDE ET CONCEPTION THÉORIQUE.....                                    | 13 |

| 2.1 Le Filtre à Réponse Impulsionnelle Finie (FIR) .....                         | 13 |

| 2.2 Le Filtre à Réponse Impulsionnelle Infinie (IIR).....                        | 15 |

| 2.3 Le Multiplieur et l'Additionneur Complex.....                                | 17 |

| 2.4 Le Module Universel de Traitement (UPM) .....                                | 20 |

| 2.5 Filtrage en Treillis .....                                                   | 27 |

| 2.5.1 Le Filtre en Treillis All-Zero à un étage .....                            | 27 |

| 2.5.2 Les Filtres en Treillis All-Zero à deux étages et $s$ étages.....          | 30 |

| 2.5.3 Le Filtre All-Pole .....                                                   | 31 |

| 2.5.4 Le Filtre Pole-Zero .....                                                  | 33 |

| 2.6 Corrélation et Intercorrelation .....                                        | 34 |

| 2.7 La transformée de Hilbert .....                                              | 36 |

| 2.8 La Transformée de Hartley Discrète .....                                     | 37 |

| 2.9 La Transformée de Cosinus Discrète (DCT).....                                | 38 |

| 2.10 La Transformée de Fourier Rapide (FFT).....                                 | 40 |

| 2.11 La Transformée de Walsh-Généralisée .....                                   | 44 |

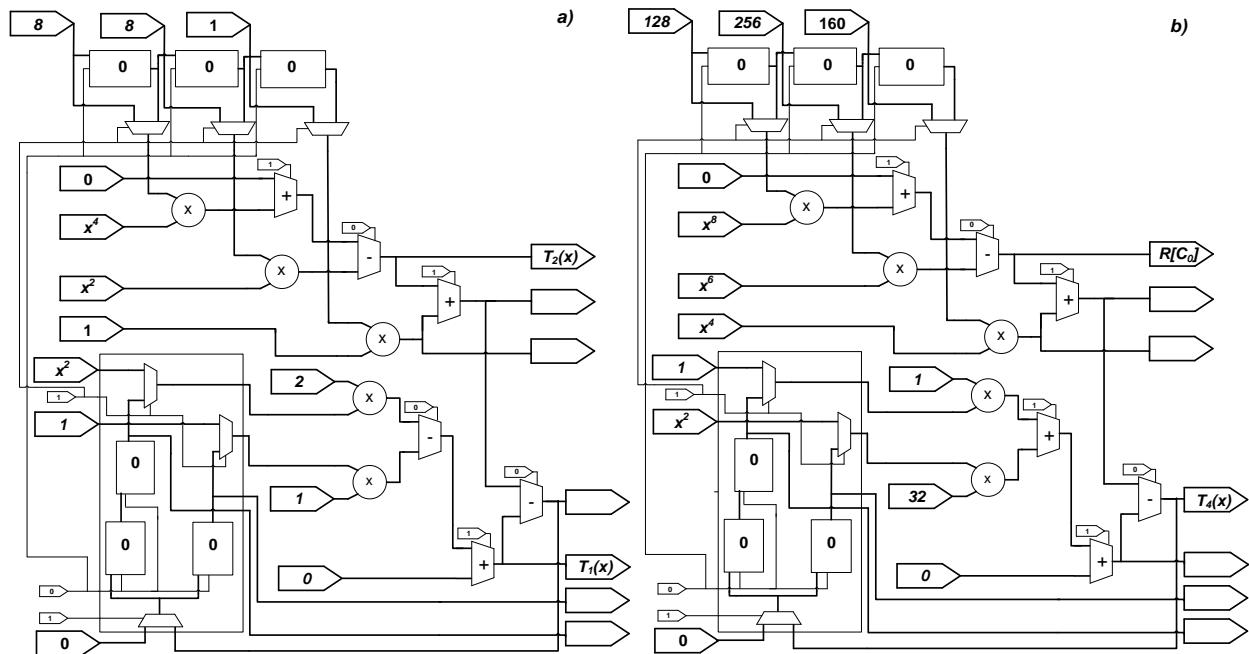

| 2.12 Génération de fonctions à l'aide de la série d'expansion de Chebyshev ..... | 44 |

| 2.12.1 Génération de la fonction de puissance de $x$ .....                       | 44 |

| 2.12.2 Génération des polynômes de Chebyshev .....                               | 45 |

| 2.12.3 Génération de fonctions par les séries d'expansion de Chebyshev .....     | 48 |

| 2.13 La Transformée Discrète de Hankel.....                                      | 51 |

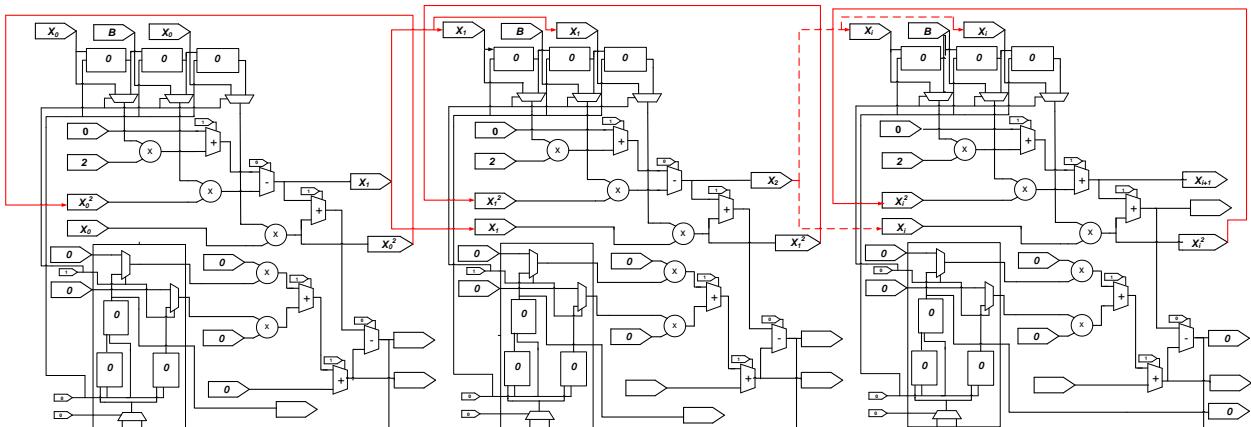

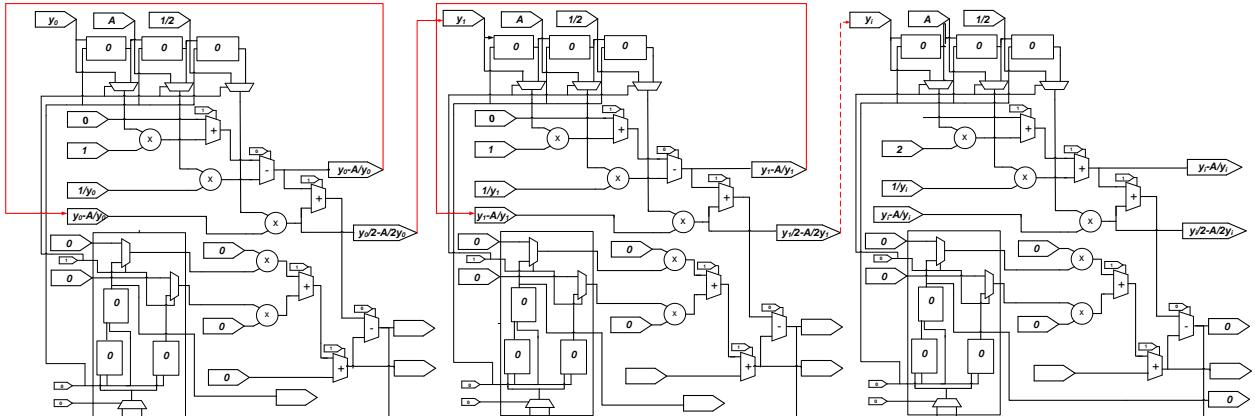

| 2.14 La Division par convergence selon Newton-Raphson .....                      | 52 |

| 2.15 L'évaluation de la $n^{eme}$ racine selon Newton-Raphson .....              | 53 |

| 2.16 Conclusion.....                                                             | 55 |

|                                                                                         |     |

|-----------------------------------------------------------------------------------------|-----|

| CHAPITRE 3 CONCEPTION LOGICIELLE .....                                                  | 56  |

| 3.1    Programmation de l'UPM et des sous-fonctions sur FPGA .....                      | 56  |

| 3.1.1    Outils de conception .....                                                     | 56  |

| 3.1.2    Génération de sous-fonctions par l'environnement de programmation .....        | 58  |

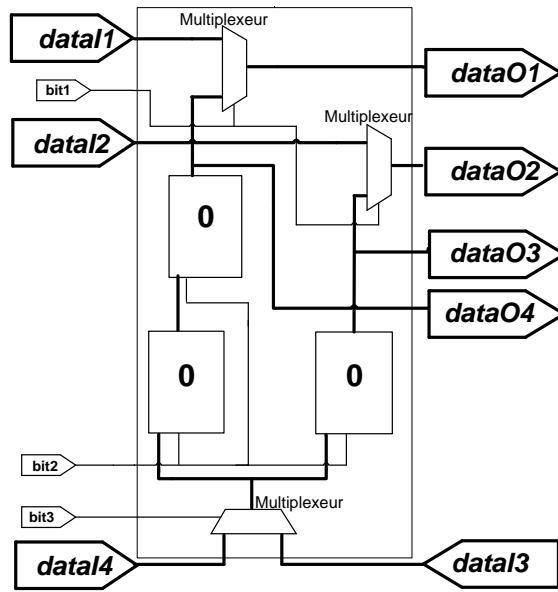

| 3.1.3    Construction du Module de Récursivité .....                                    | 58  |

| 3.1.4    Construction de l'UPM .....                                                    | 58  |

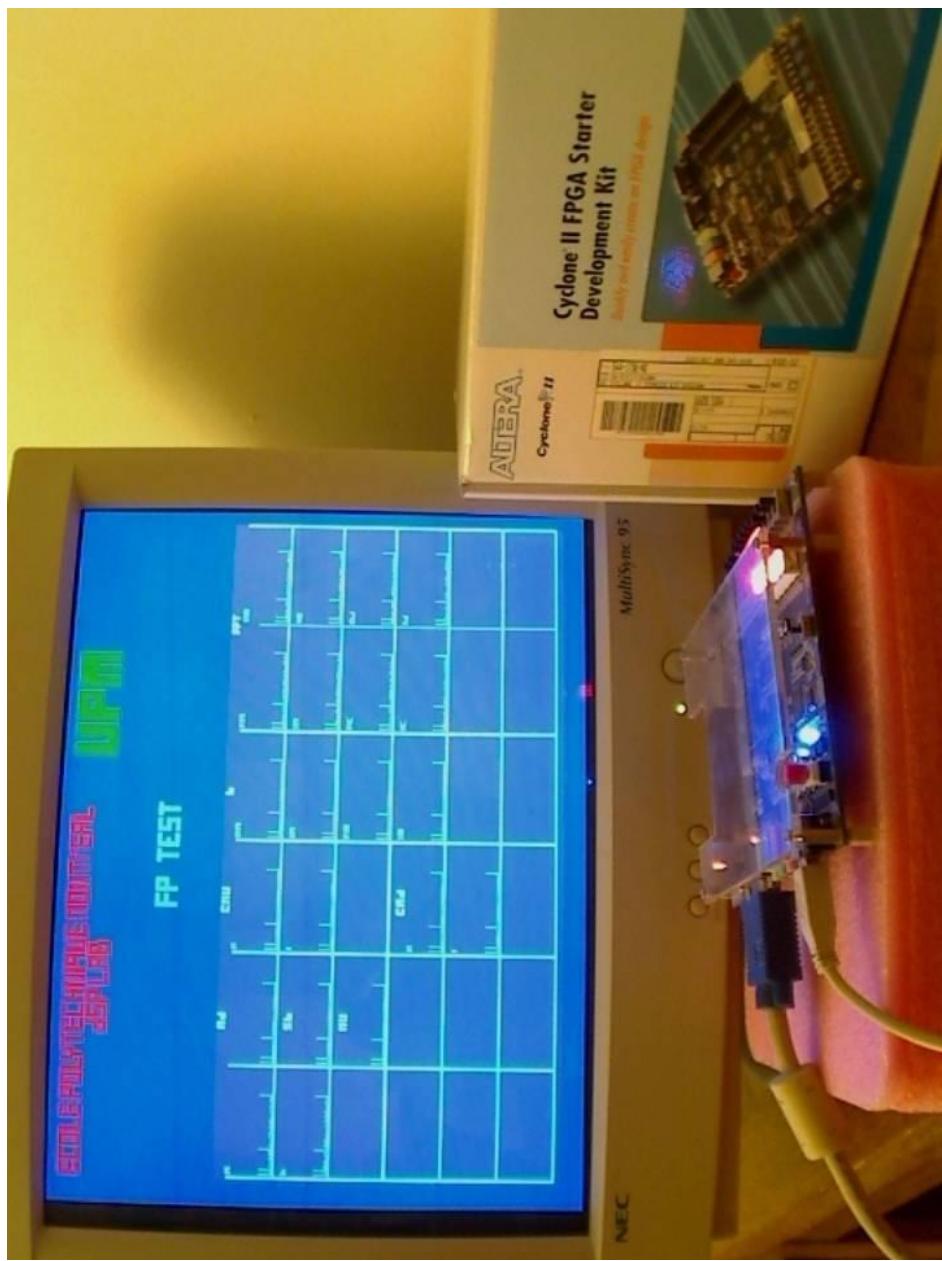

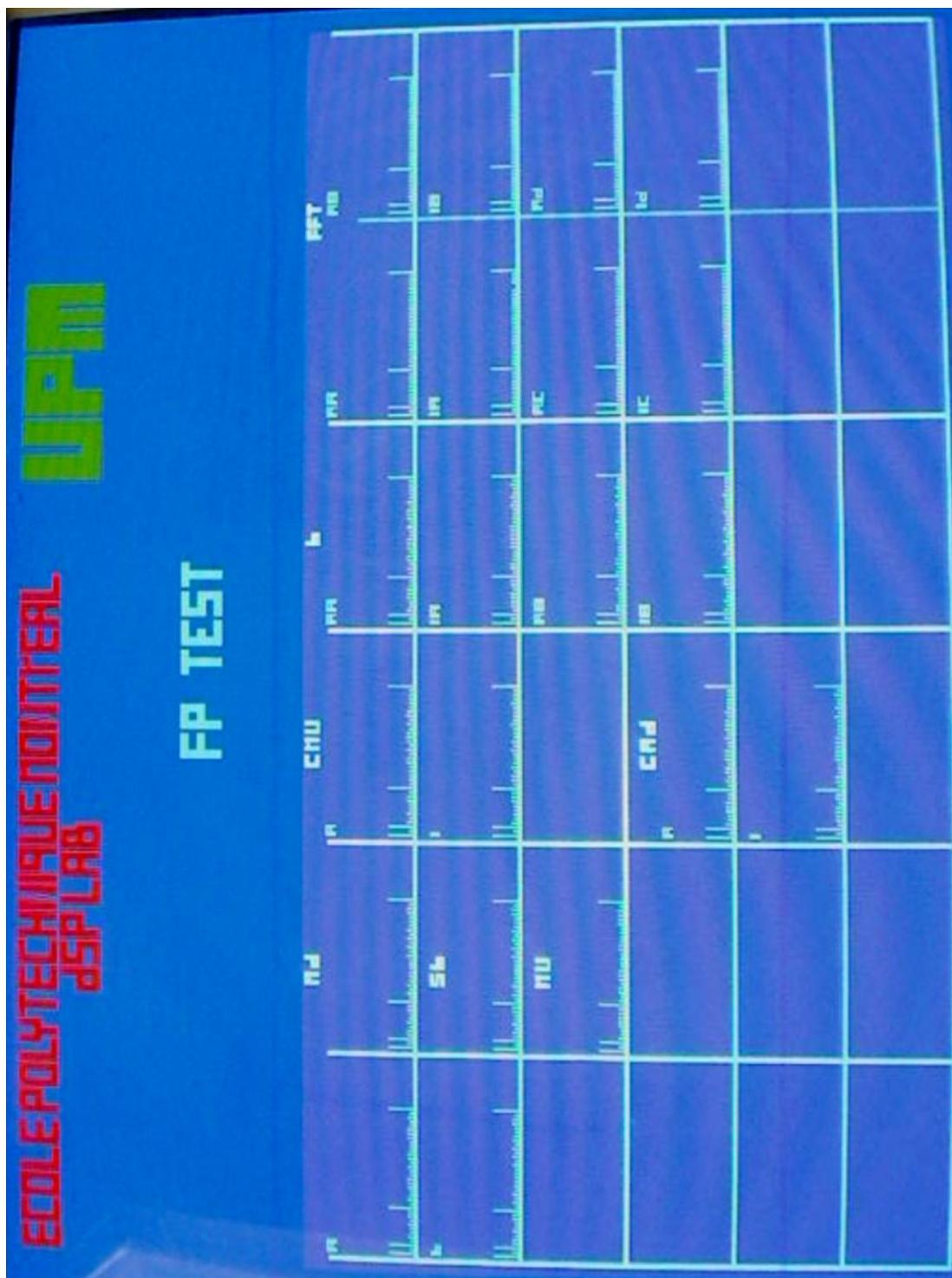

| 3.1.5    Conception du programme test sur écran VGA .....                               | 59  |

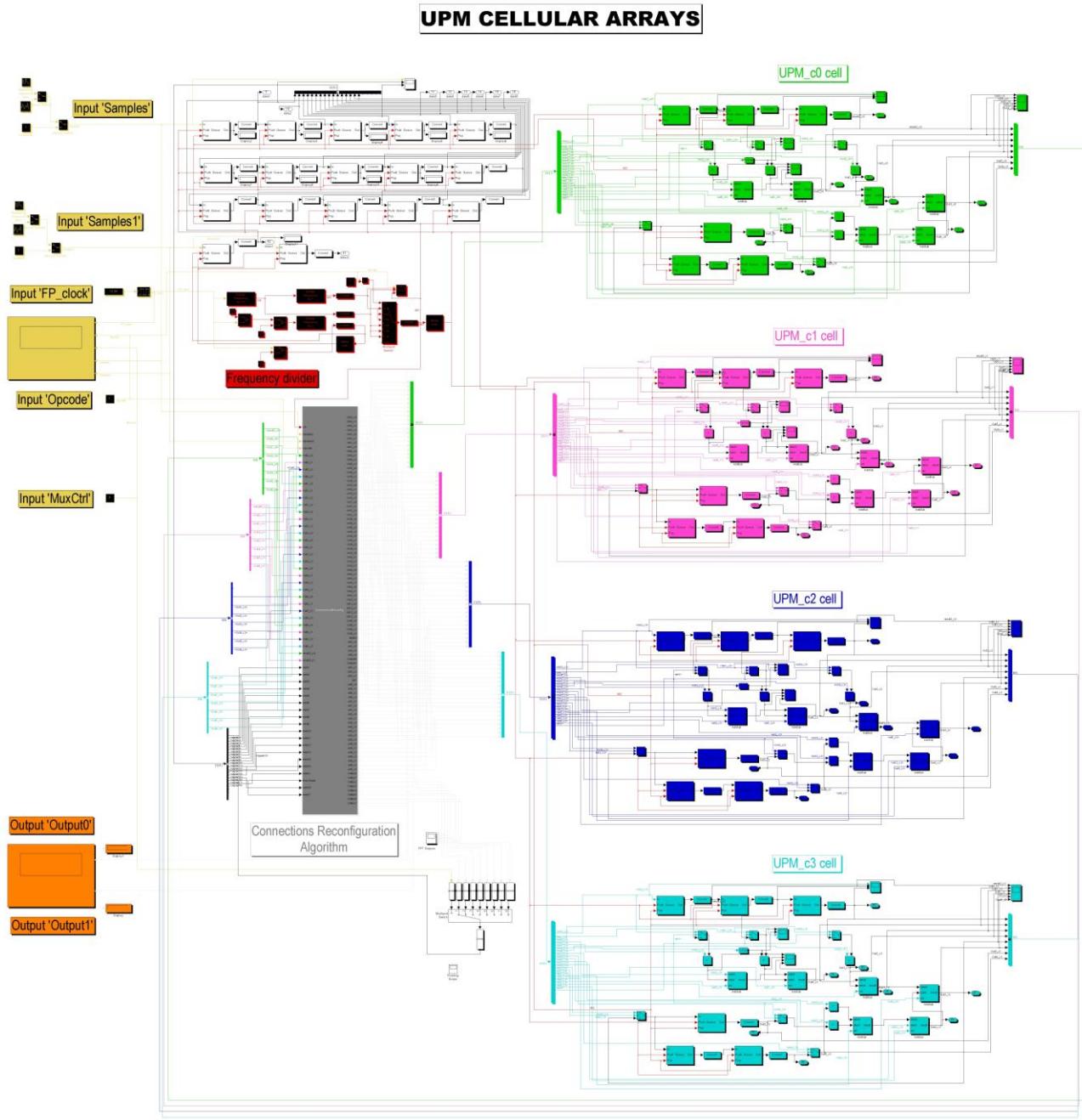

| 3.2    Conception de matrices d'UPMs reconfigurables sur FPGA.....                      | 63  |

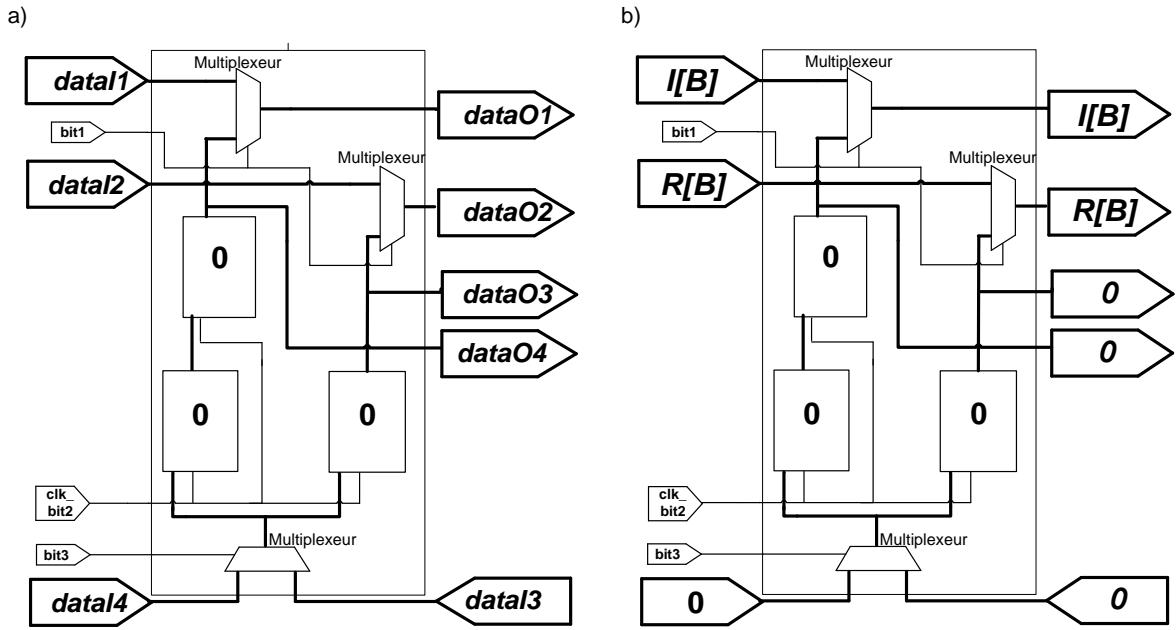

| 3.2.1    Configuration des ports d'entrées et sorties du processeur matriciel 2x2 ..... | 64  |

| 3.2.2    Contrôle temporel du processeur matriciel .....                                | 69  |

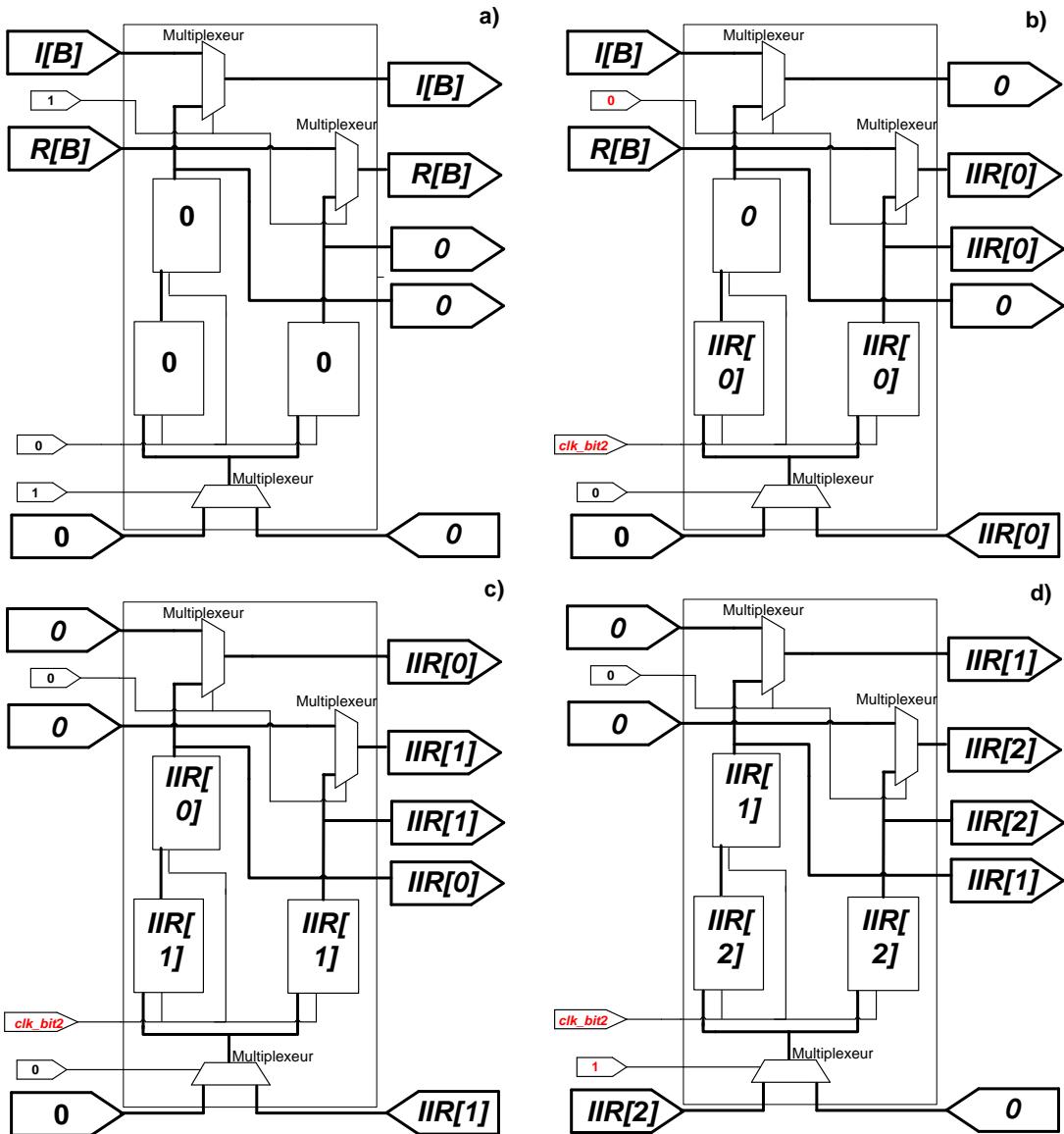

| 3.2.3    La reconfiguration des connexions internes entre les cellules .....            | 72  |

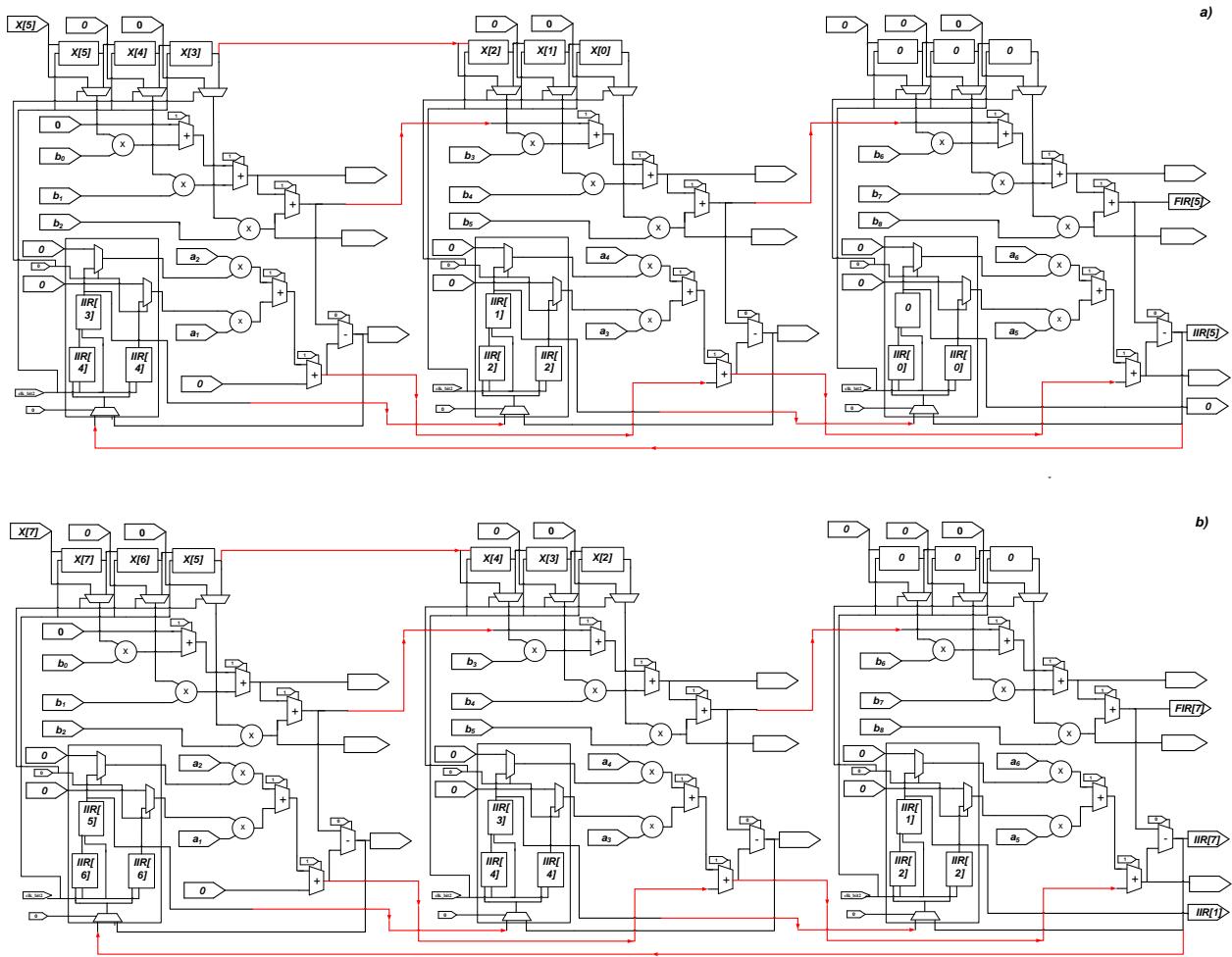

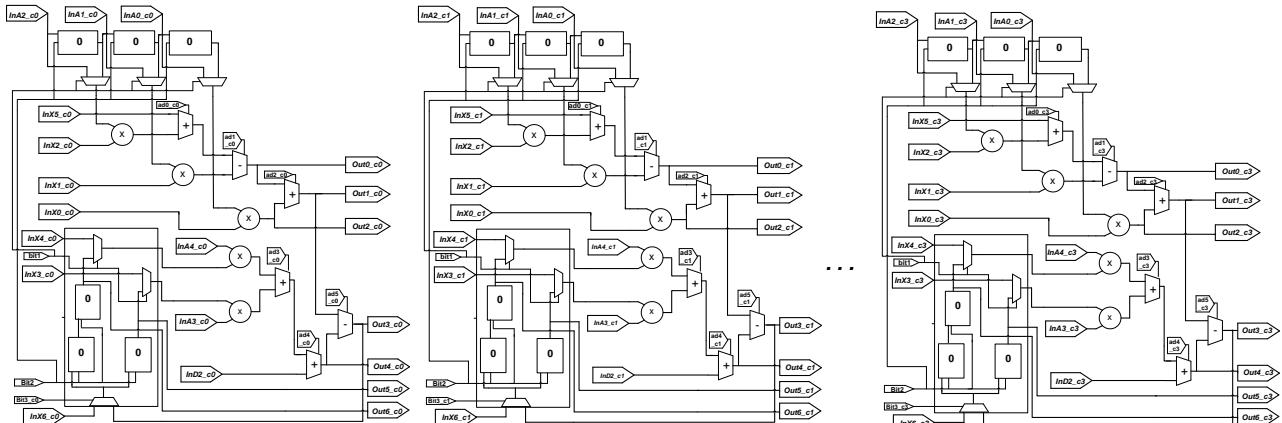

| 3.2.4    Conception sur FPGA d'une matrice cellulaire 6x4. ....                         | 85  |

| •    Filtrage FIR/IIR d'ordre $n=20$ .....                                              | 87  |

| •    Filtrage All-Pole d'ordre $s=10$ . ....                                            | 88  |

| •    Filtrage All-Zero d'ordre $s=10$ .....                                             | 89  |

| •    Filtrage FIR $n=30$ .....                                                          | 90  |

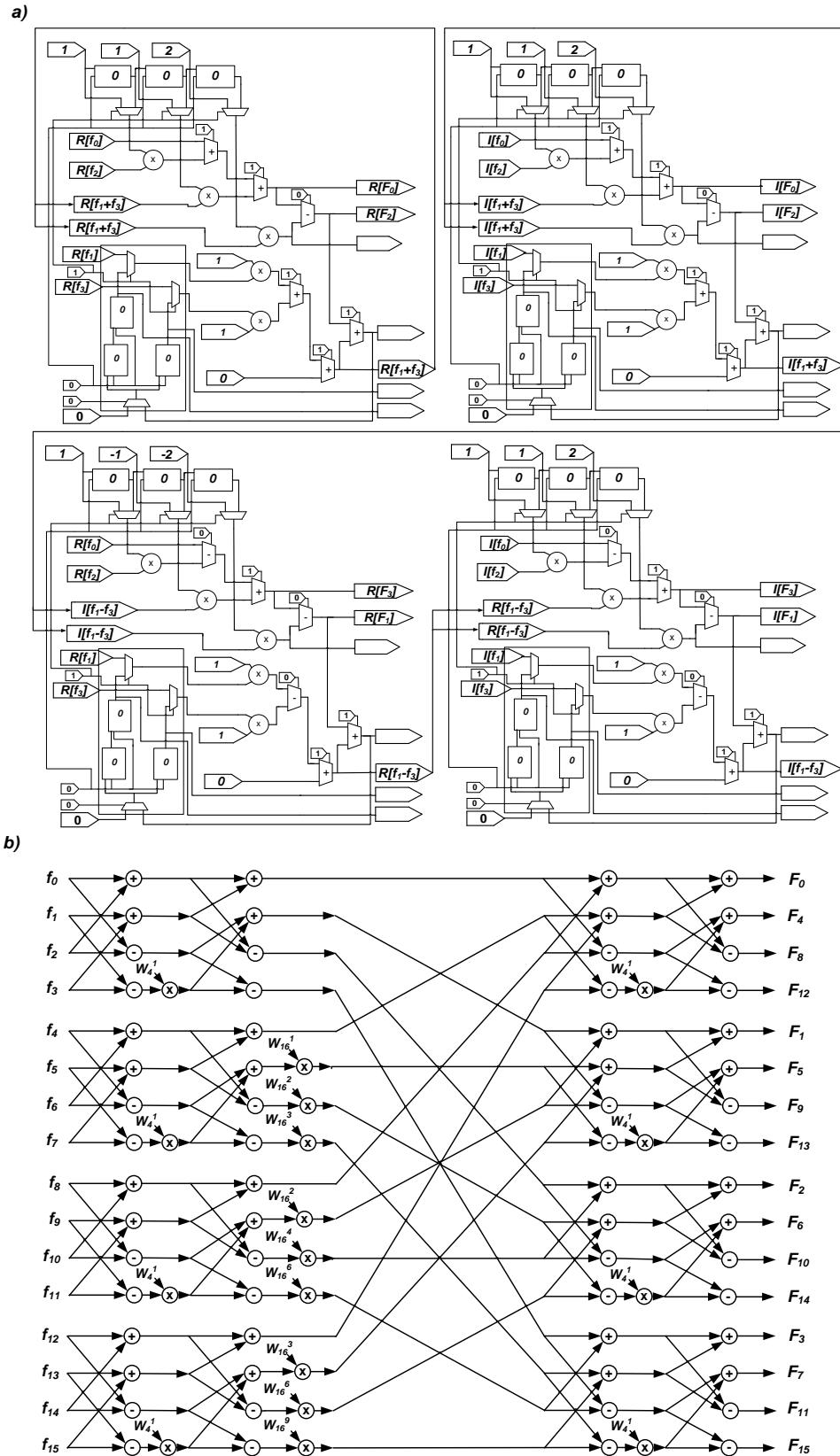

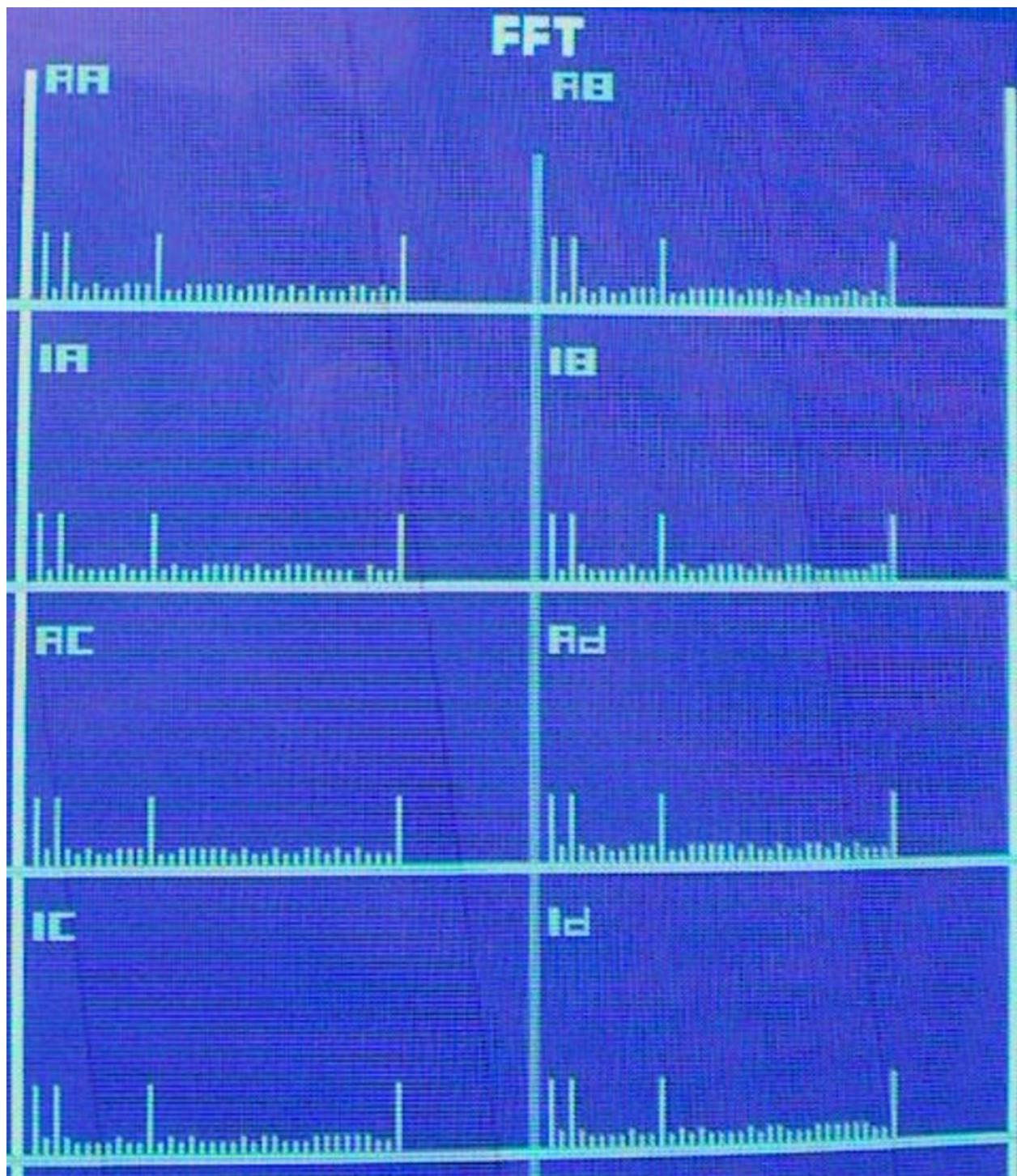

| •    FFT radical 4 d'ordre $N=16$ . ....                                                | 90  |

| 3.3    Conception de matrices d'UPMs reconfigurables sur <i>Simulink</i> .....          | 93  |

| 3.3.1    Contrôle des entrées et sorties de données de la matrice cellulaire. ....      | 93  |

| 3.3.2    Contrôle temporel de la matrice. ....                                          | 95  |

| 3.3.3    Conception des cellules UPMs sur Matlab. ....                                  | 97  |

| 3.3.4    Contrôle de la reconfiguration des connexions entre les cellules. ....         | 99  |

| 3.4    Conclusion.....                                                                  | 101 |

| CHAPITRE 4 TESTS ET PERFORMANCES DES MATRICES CELLULAIRES .....                         | 102 |

|       |                                                           |     |

|-------|-----------------------------------------------------------|-----|

| 4.1   | Tests des algorithmes programmés .....                    | 102 |

| 4.1.1 | Tests sur écran VGA et tests des sous-fonctions.....      | 102 |

| 4.1.2 | Tests des matrices cellulaires .....                      | 102 |

| 4.2   | Performances en termes d'espace logique des matrices..... | 103 |

| 4.3   | Performances de vitesse des matrices cellulaires .....    | 104 |

| 4.4   | Comparaison des performances de vitesse .....             | 106 |

| 4.5   | Conclusion.....                                           | 111 |

|       | CONCLUSION .....                                          | 112 |

|       | BIBLIOGRAPHIE ET REFERENCES .....                         | 116 |

## LISTE DES TABLEAUX

|                                                                                                               |     |

|---------------------------------------------------------------------------------------------------------------|-----|

| Tableau 1 : Polynômes de Chebyshev pour $0 \leq n \leq 8$ .....                                               | 48  |

| Tableau 3 : Coefficient d'expansion de Chebyshev des fonctions Exponentielles, Logarithmiques et Gamma. ..... | 49  |

| Tableau 4 : Coefficient d'expansion de Chebyshev des fonctions Bessel. ....                                   | 49  |

| Tableau 5 : Mode de transfert des données pour chaque mode de reconfiguration. ....                           | 68  |

| Tableau 6 : Tableau montrant les tests effectués sur les algorithmes DSP et leurs certitudes....              | 104 |

| Tableau 7 : Fréquences maximum des horloges générées par <i>TimeQuest</i> d' <i>Altera</i> .....              | 108 |

| Tableau 9 : Temps de calcul de l'algorithme FFT pour différents ordres.....                                   | 109 |

| Tableau 10 : Temps de calcul des algorithmes FIR/IIR et All-Pole. ....                                        | 109 |

| Tableau 11 : Comparaison des performances des matrices cellulaires avec d'autres processeurs. ....            | 110 |

| Tableau 12 : Comparaison de l'UPM avec l'UPE. ....                                                            | 115 |

## LISTE DES FIGURES

|                                                                                                                             |    |

|-----------------------------------------------------------------------------------------------------------------------------|----|

| Figure 1-1 : Exemple de matrices d'UPE [10].....                                                                            | 4  |

| Figure 1-2 : Architecture d'une transformée de Walsh-Paley Généralisée ordre, $N=27$ , [29]. .....                          | 5  |

| Figure 1-3 : Exemple de configuration de l'UPE [10].....                                                                    | 7  |

| Figure 1-4 : Configuration de matrices d'UPEs en DFT/Cherstenson [10].....                                                  | 7  |

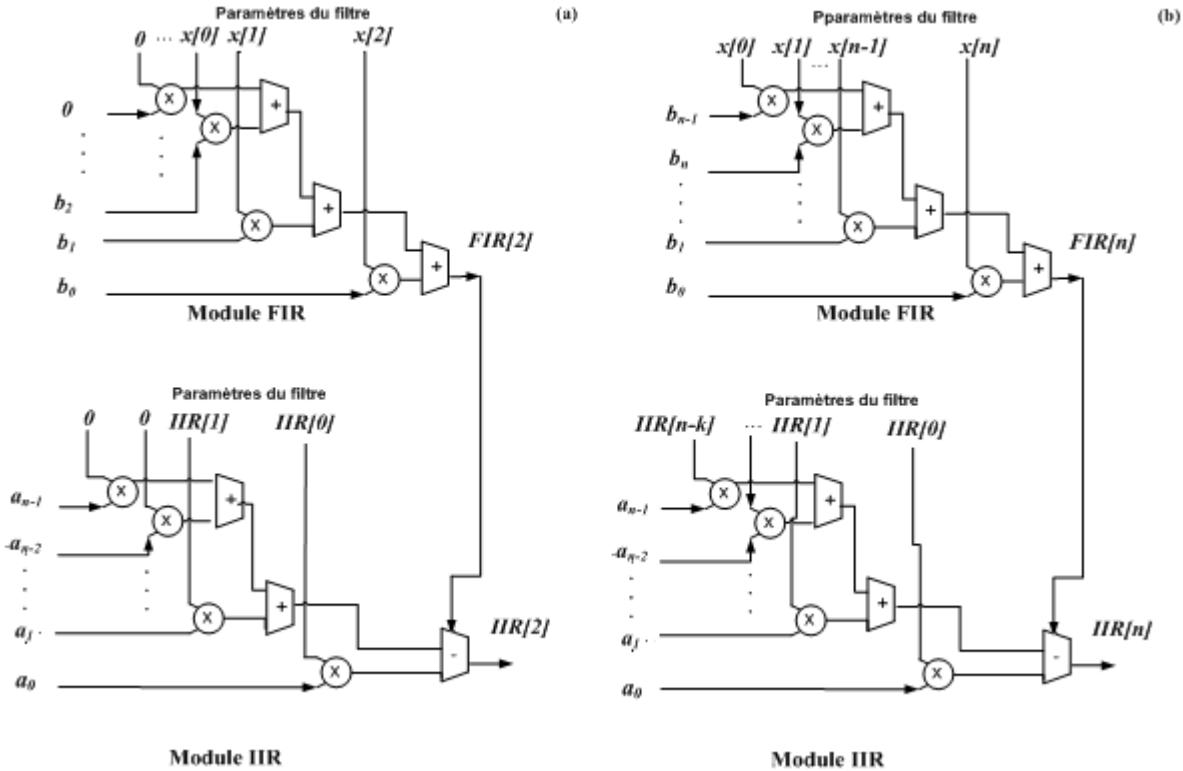

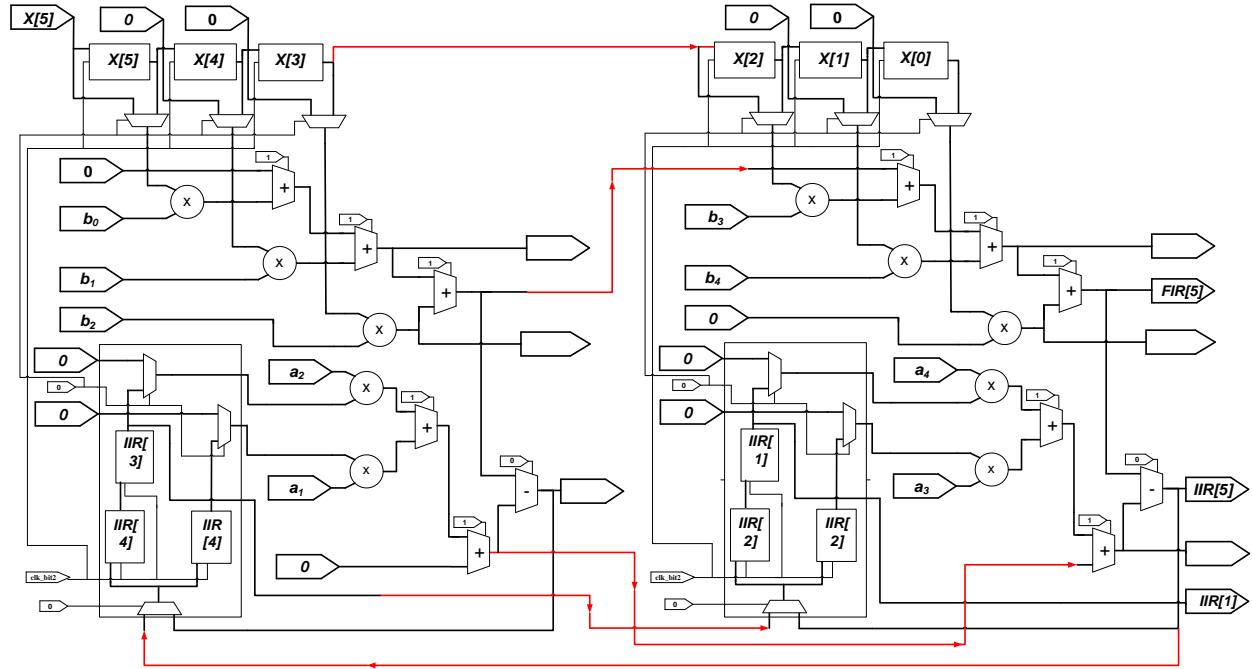

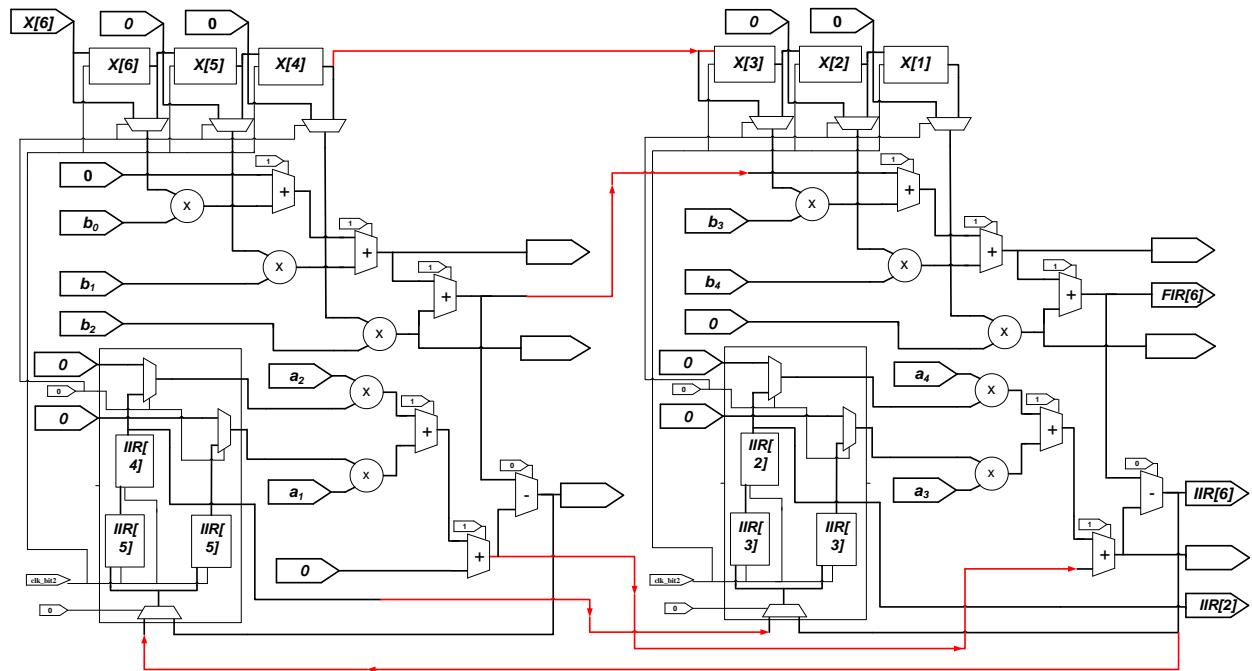

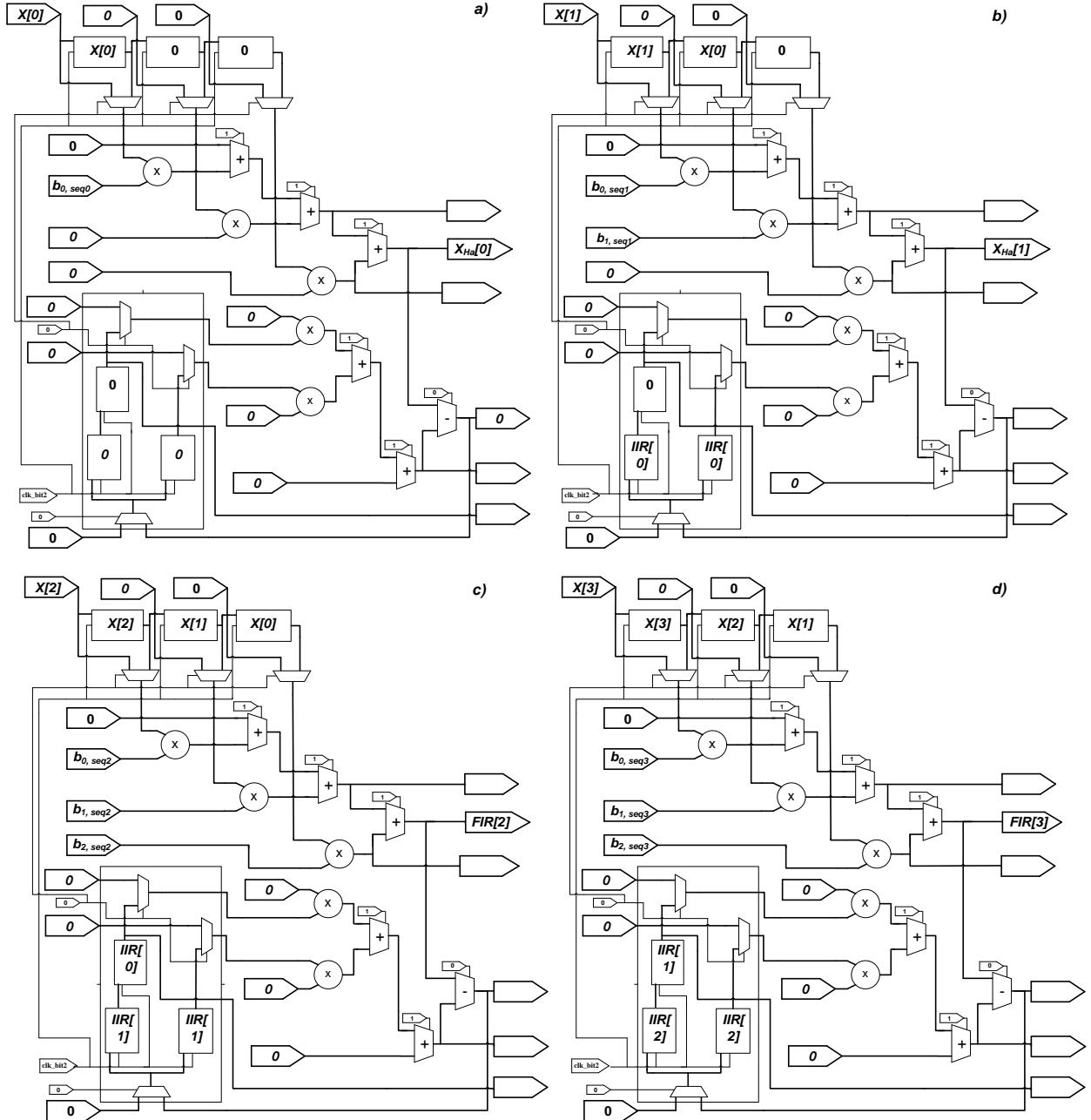

| Figure 2-1 : Schéma théorique du filtrage FIR <i>séquence 0 a)</i> et <i>séquence 1 b)</i> .....                            | 14 |

| Figure 2-2 : Schéma théorique du filtrage FIR <i>séquence 2 a)</i> et <i>séquence n b)</i> .....                            | 15 |

| Figure 2-3 : Schéma théorique du filtrage IIR <i>séquence 0 a)</i> et <i>séquence 1 b)</i> .....                            | 16 |

| Figure 2-4 : Schéma théorique du filtrage IIR <i>séquence 2 a)</i> et <i>séquence n b)</i> .....                            | 17 |

| Figure 2-5 : Multiplication complexe.....                                                                                   | 18 |

| Figure 2-6 : Module de contrôle de récursivité a) noms des entrées et sorties b) configuration en multiplieur complexe..... | 19 |

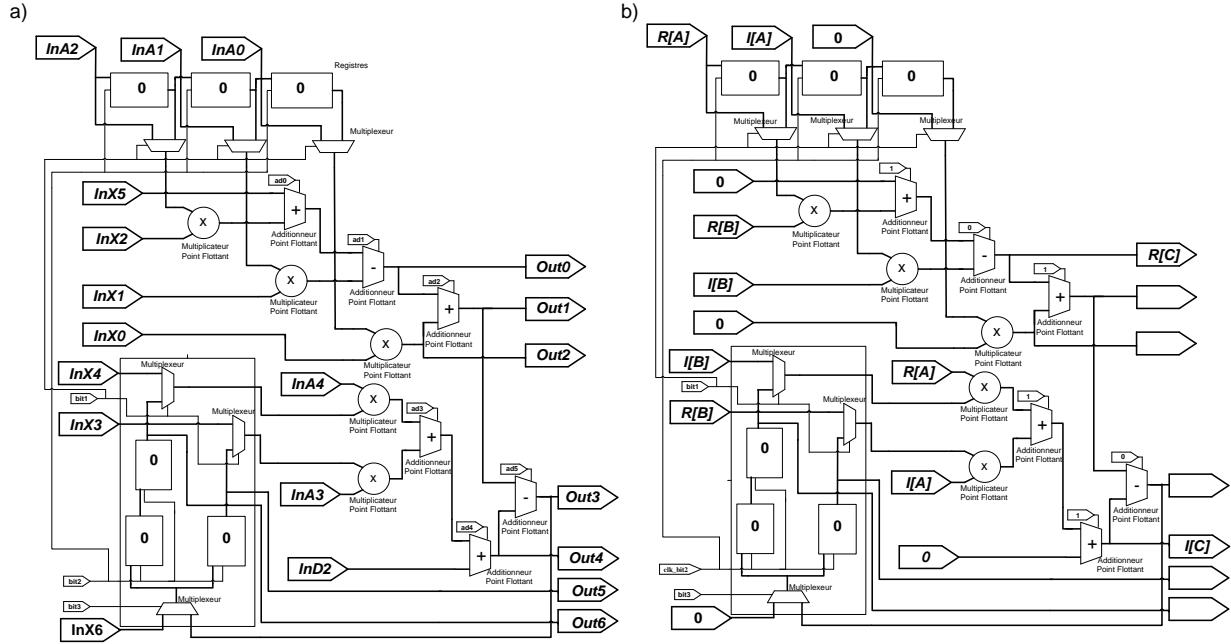

| Figure 2-7 : Module de récursivité en mode Multiplication Complex a) et Filtrage b), c), d).....                            | 20 |

| Figure 2-8 : a) Entrées et sorties de l'UPM b) UPM configuré en Multiplieur Complex.....                                    | 21 |

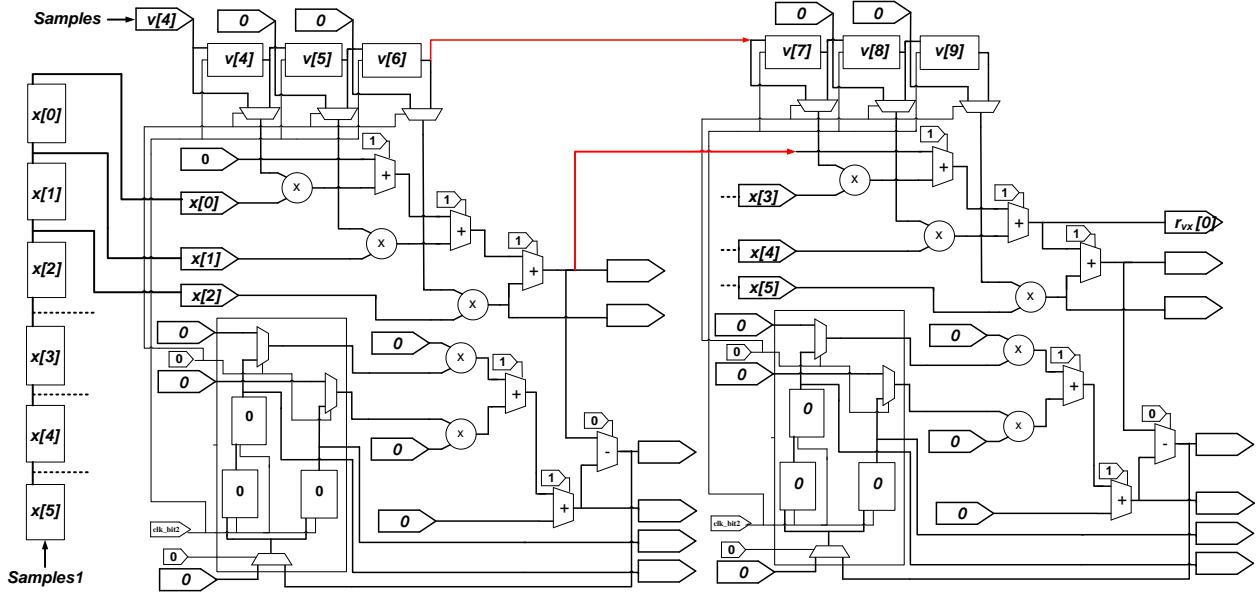

| Figure 2-9 : UPM en mode FIR/IIR ordre $N=2$ <i>séquence 0 a), séquence 1 b), séquence 2 c) et séquence 3 d)</i> .....      | 24 |

| Figure 2-10 : Cascade de deux UPMs en mode filtrage FIR/IIR ordre $N=4$ , <i>séquence 3</i> .....                           | 25 |

| Figure 2-11 : Cascade de deux UPMs en mode filtrage FIR/IIR ordre $N=4$ , <i>séquence 4</i> .....                           | 25 |

| Figure 2-12 : Cascade de deux UPMs en mode filtrage FIR/IIR ordre $N=4$ , <i>séquence 5</i> .....                           | 26 |

| Figure 2-13 : Cascade de deux UPMs en mode filtrage FIR/IIR ordre $N=4$ , <i>séquence 6</i> .....                           | 26 |

| Figure 2-14 : Configuration filtrage FIR/IIR ordre $N=6$ , <i>séquence 5 a) et séquence 7 b)</i> .....                      | 27 |

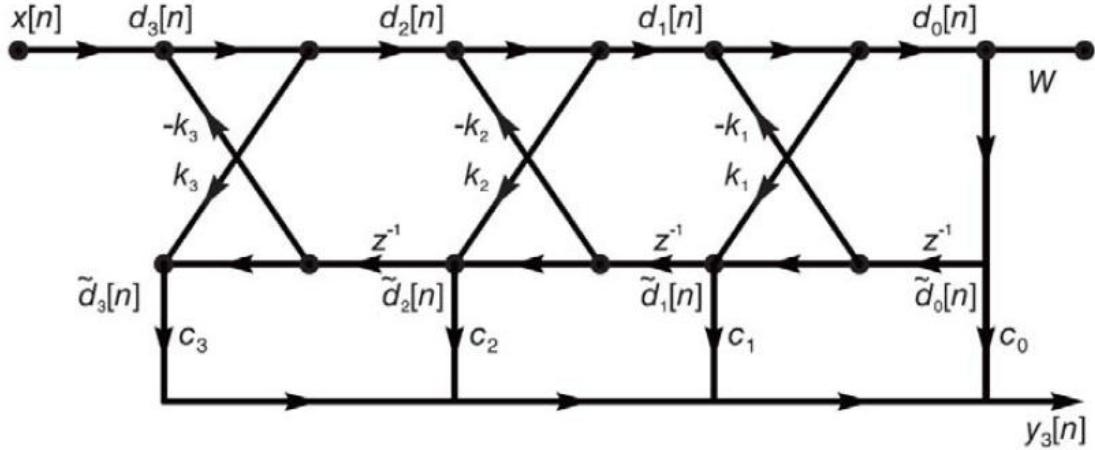

| Figure 2-15 : Filtre en treillis All-Zero trois étages, [1] p 767.....                                                      | 29 |

| Figure 2-16 : UPM configurée en Filtre en Treillis All-Zero, un étage. ....                                                 | 29 |

| Figure 2-17 : UPM configurée en Filtre en Treillis All-Zero, deux étages.....                                               | 30 |

| Figure 2-18 : Vecteur d'UPMs configurée en Filtre en Treillis All-Zero, $s$ étages. ....                                    | 31 |

|                                                                                                                                                                       |    |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Figure 2-19 : Vecteurs d'UPM configurée en Filtre en Treillis All-Pole, $s$ étages.....                                                                               | 32 |

| Figure 2-20 : Filtres en Treillis Pole-Zero <sup>5</sup> [1] p775. ....                                                                                               | 34 |

| Figure 2-21 : Vecteur d'UPMs configurée en corrélation ordre $N=5$ .....                                                                                              | 35 |

| Figure 2-22 : Vecteur d'UPMs configurée en Transformée de Hilbert, ordre $N=6$ , séquence 4 ...                                                                       | 38 |

| Figure 2-23 : Configuration en Transformée de Hartley $N=2$ , <i>séquence 0</i> en a), <i>séquence 1</i> en b),<br><i>séquence 2</i> en c) et <i>3</i> en d). ..      | 39 |

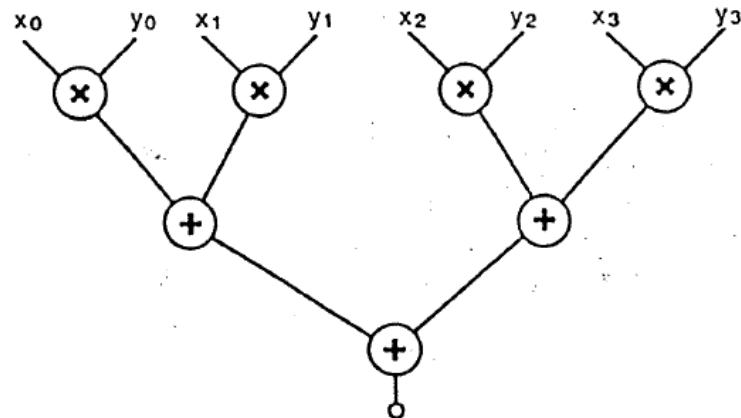

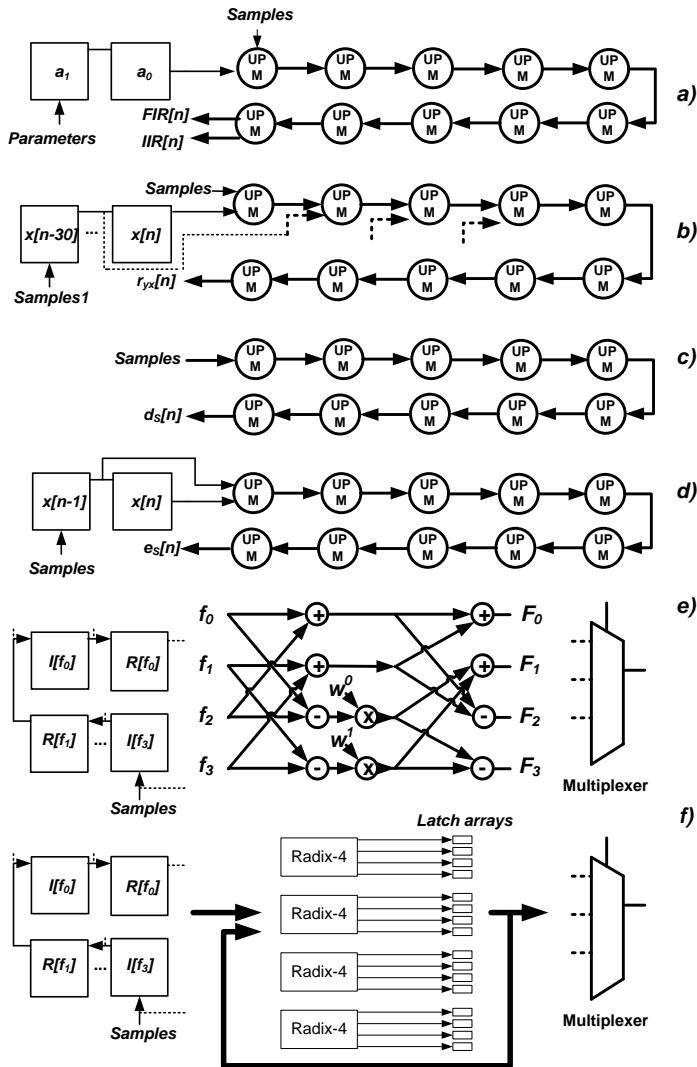

| Figure 2-24 : Processeur FFT parallèle haute vitesse radical-4. ....                                                                                                  | 40 |

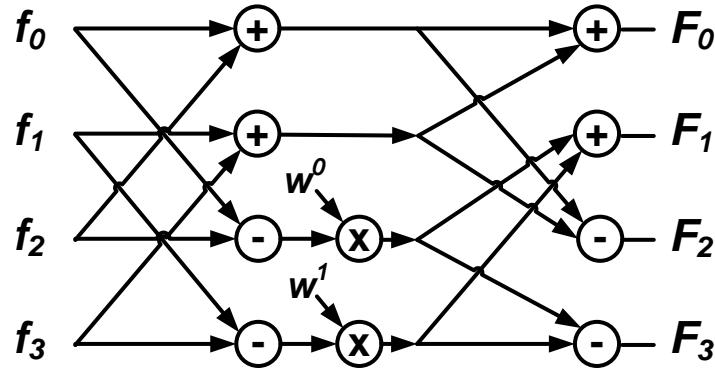

| Figure 2-25 : Matrices d'UPM effectuant une FFT (OIOO) $N=4$ . ....                                                                                                   | 41 |

| Figure 2-26 : Deux UPMs configurés en opérateur " <i>Butterfly</i> ". ....                                                                                            | 41 |

| Figure 2-27 : Configuration en opérateur " <i>Butterfly</i> " radical 4 a) et FFT, ordre $N=16$ . ....                                                                | 43 |

| Figure 2-28 : Transformées de Walsh-Paley et de Walsh-Kaczmarz Généralisées [29]. ....                                                                                | 45 |

| Figure 2-29 : Architecture optimale utilisant un UPE utilisé en a) base 5 p-optimal et b) les deux premiers étages d'un base 5 $p^2$ -optimal avec pipeline [29]..... | 46 |

| Figure 2-30 : Processeur d'image à géométrie constante parallèle utilisant un UPE base 2 [10]..                                                                       | 46 |

| Figure 2-31 : Génération de $x^2$ , $x^3$ et $x^4$ .....                                                                                                              | 47 |

| Figure 2-32 : Génération des polynômes de Chebychev $T_1(x)$ et $T_2(x)$ et $T_4(x)$ .....                                                                            | 47 |

| Figure 2-33 : Vecteur d'UPMs reconfigurés en calcul de division.....                                                                                                  | 52 |

| Figure 2-34 : Matrice d'UPMs reconfigurés en calcul de racine carrée. ....                                                                                            | 54 |

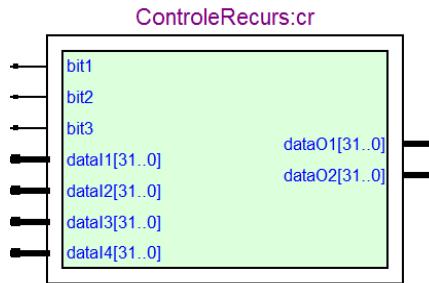

| Figure 3-1 : Noms des entrées et sorties du Module de contrôle de la récursivité.....                                                                                 | 59 |

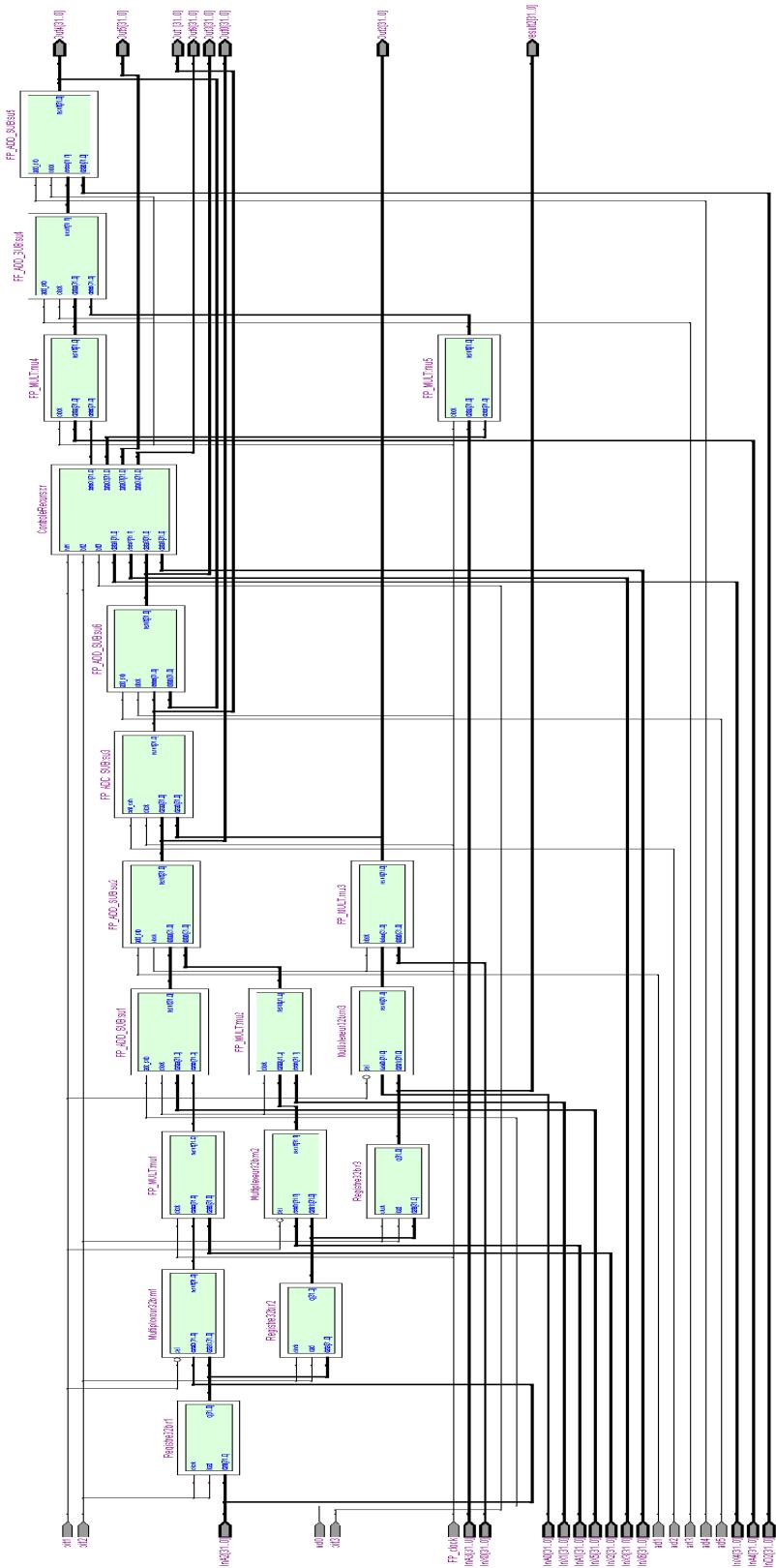

| Figure 3-2 : Diagramme RTL du Module de contrôle de la récursivité.....                                                                                               | 59 |

| Figure 3-3 : Entrées et sorties de l'UPM.....                                                                                                                         | 60 |

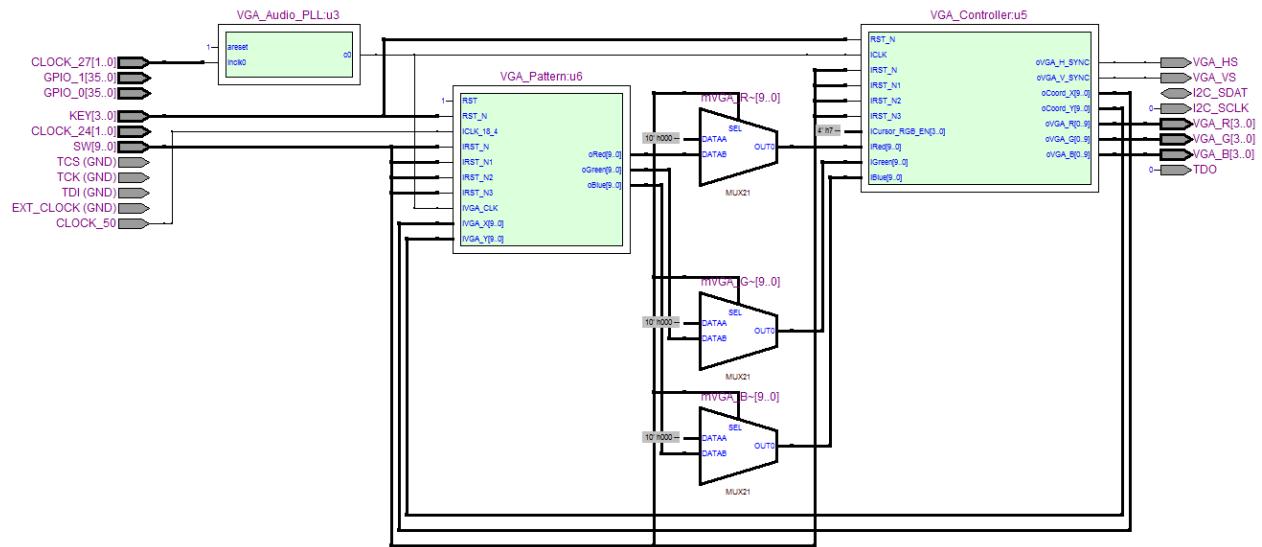

| Figure 3-4 : Diagramme interne du module " <i>CII_Starter_Default</i> ". .....                                                                                        | 61 |

| Figure 3-5 : Configuration des connexions pour différents algorithmes programmés. ....                                                                                | 66 |

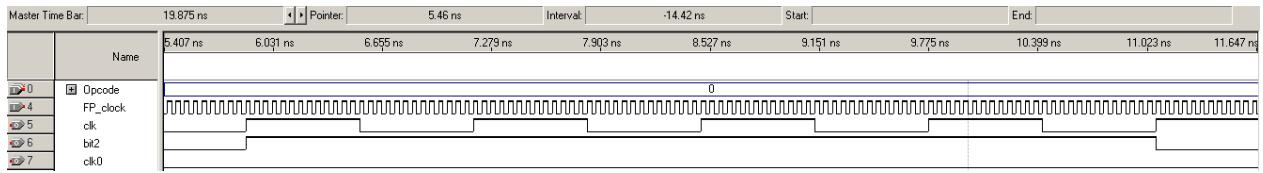

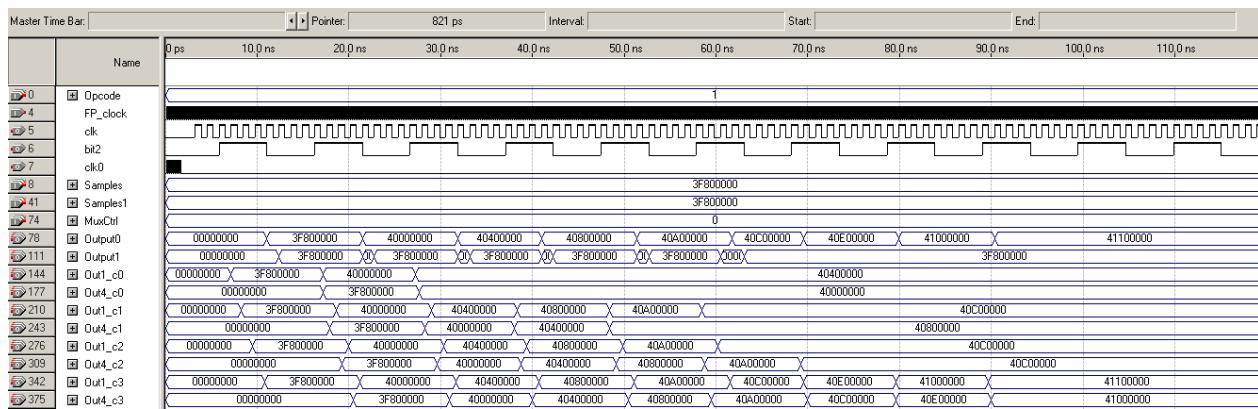

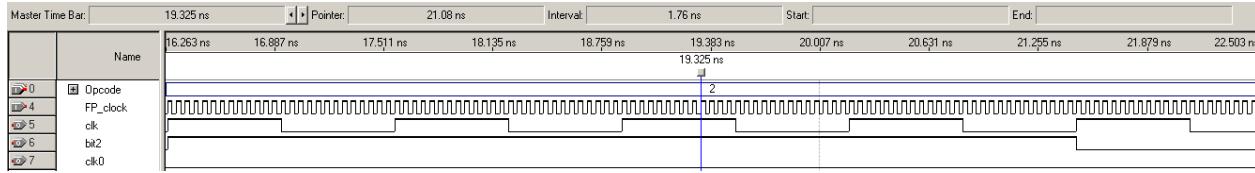

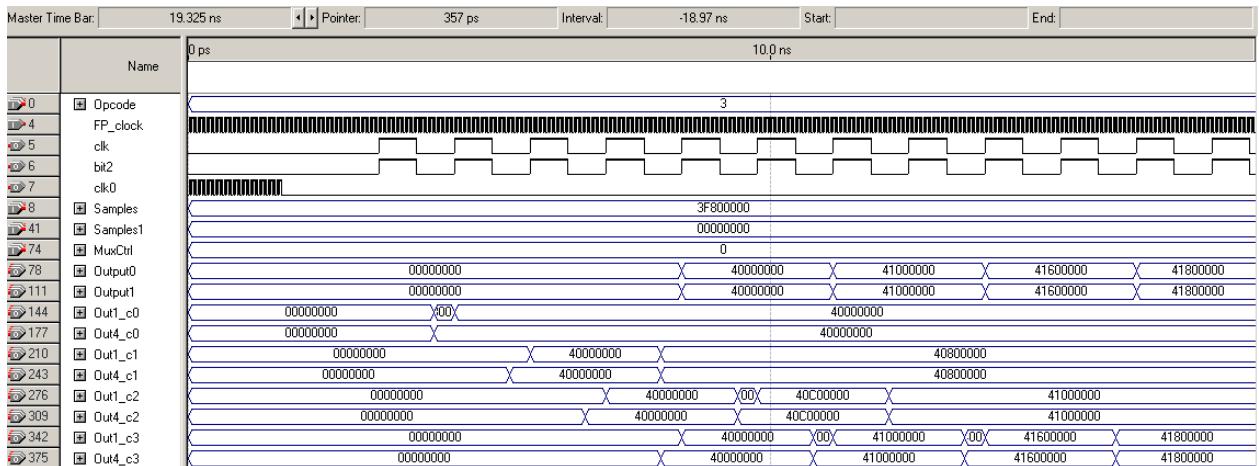

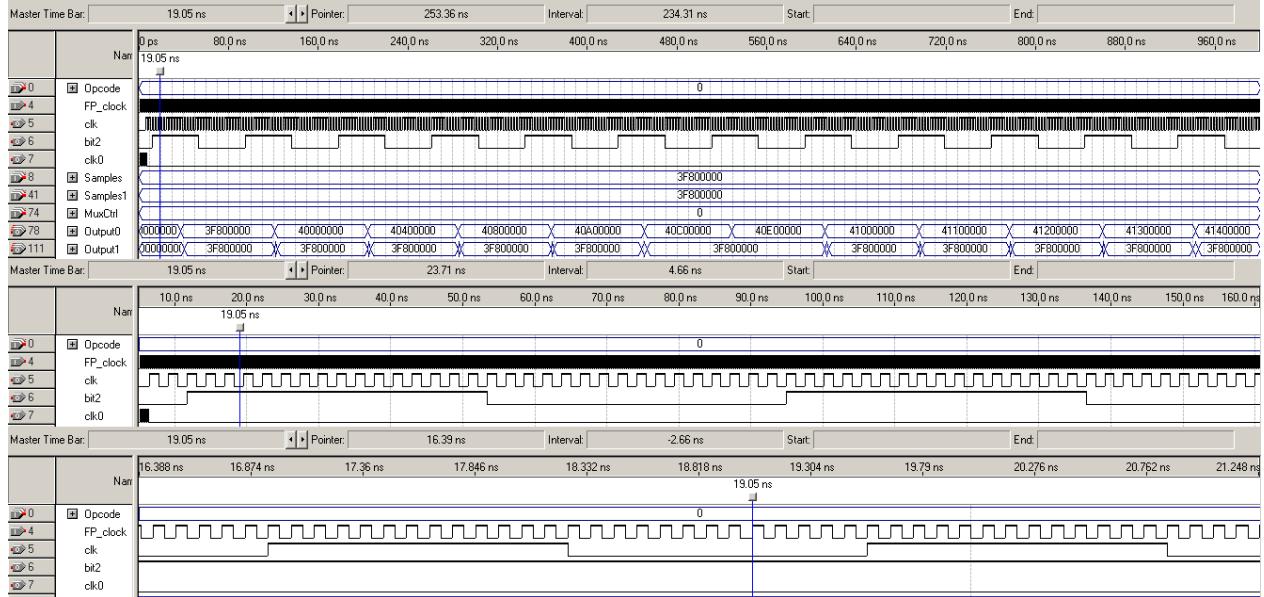

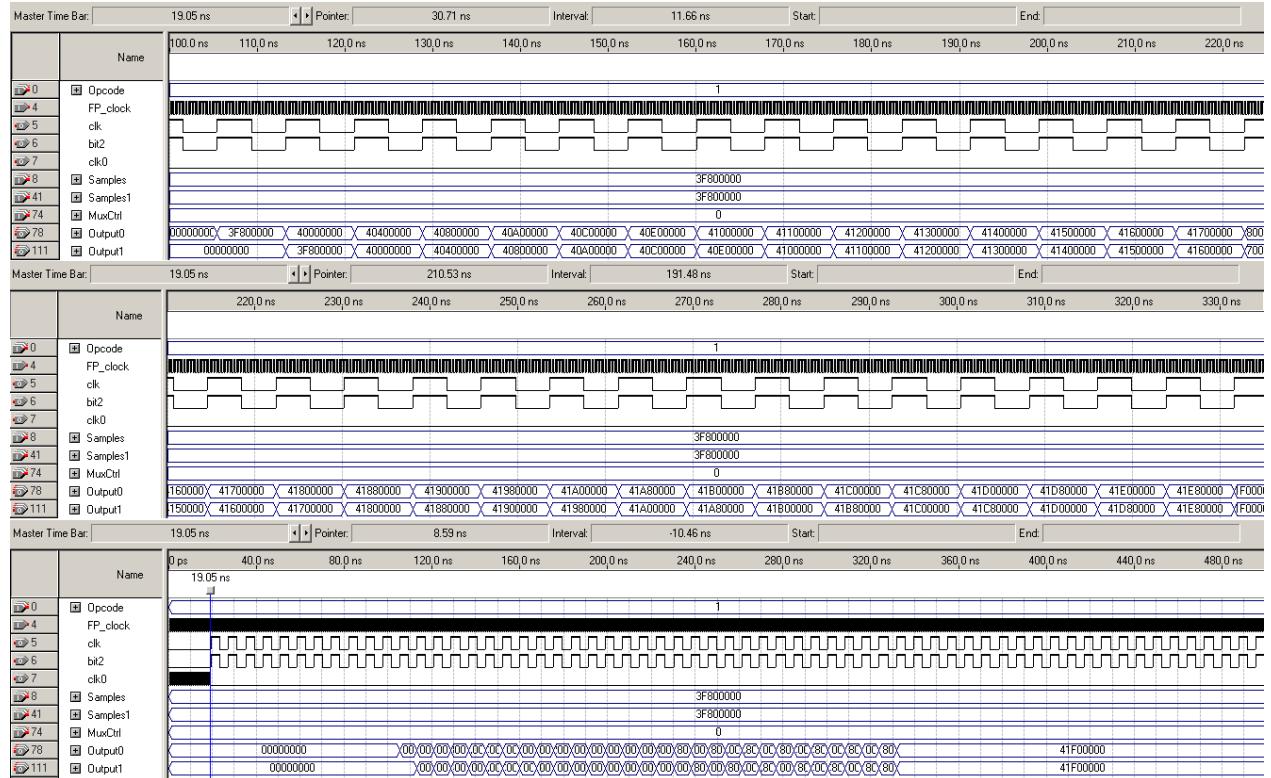

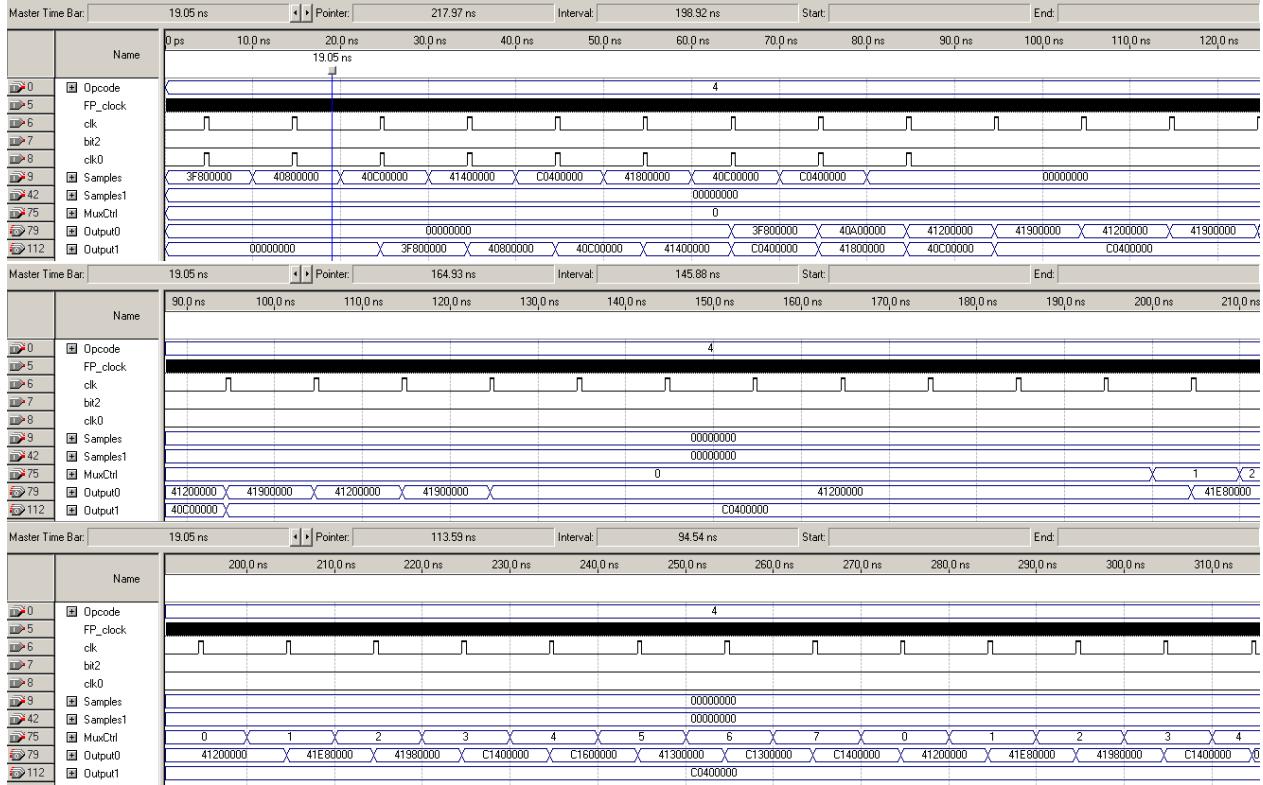

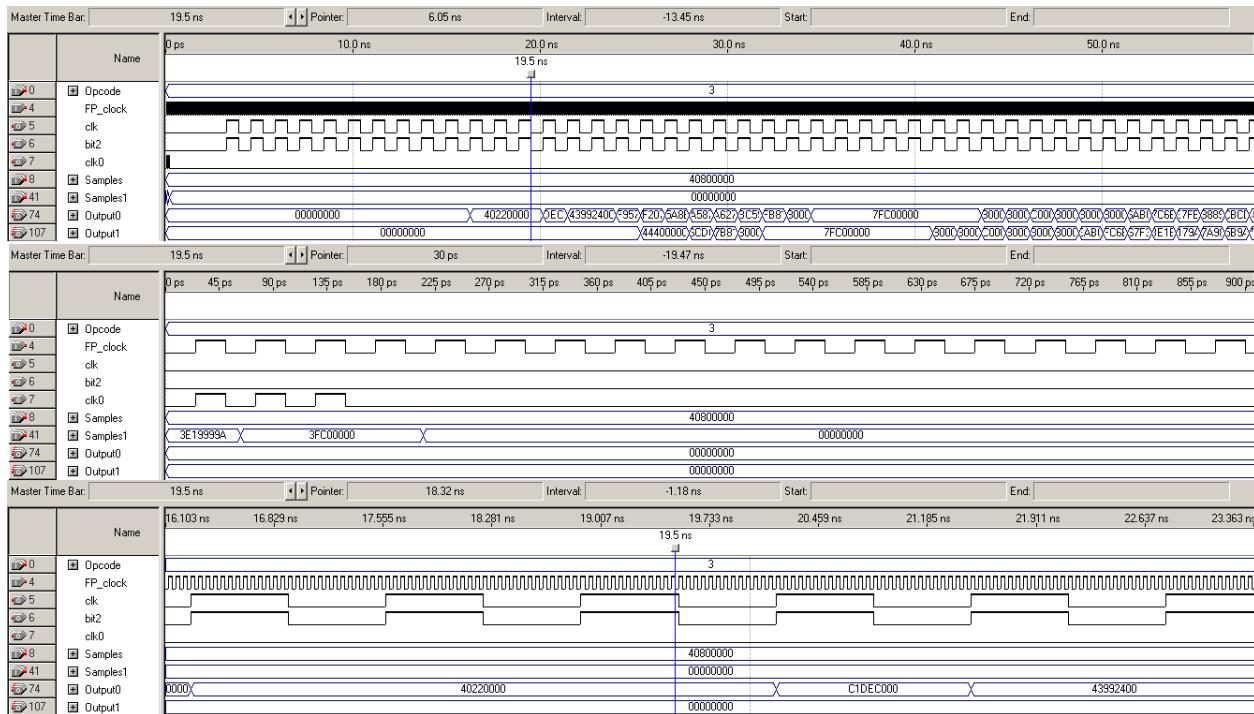

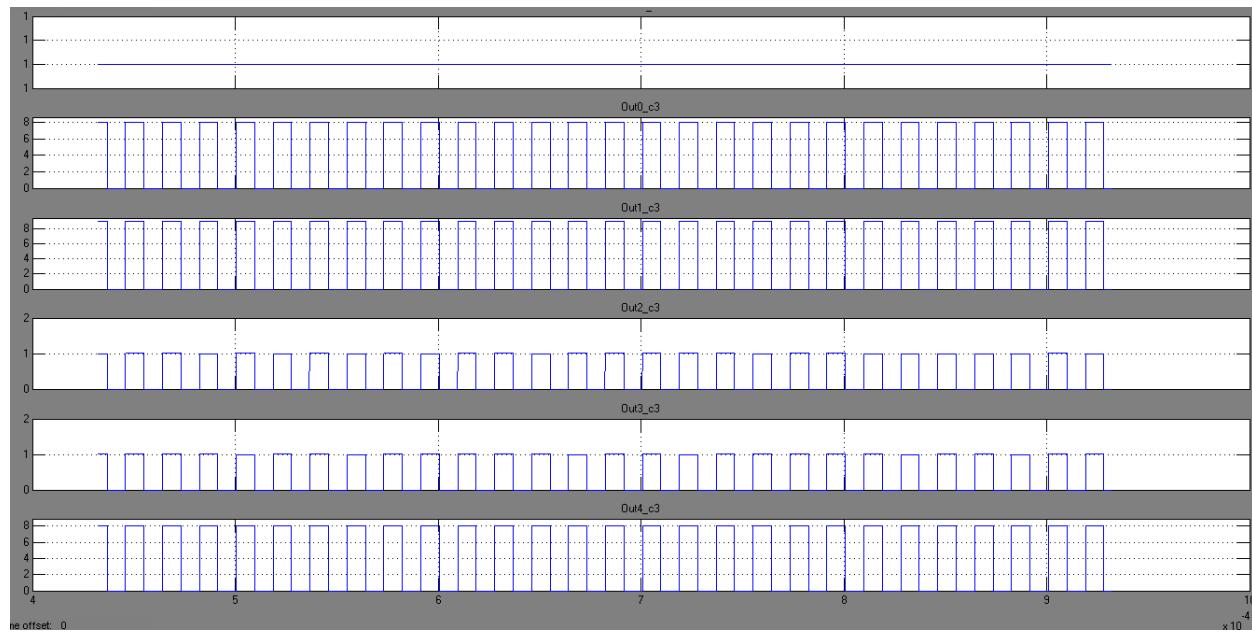

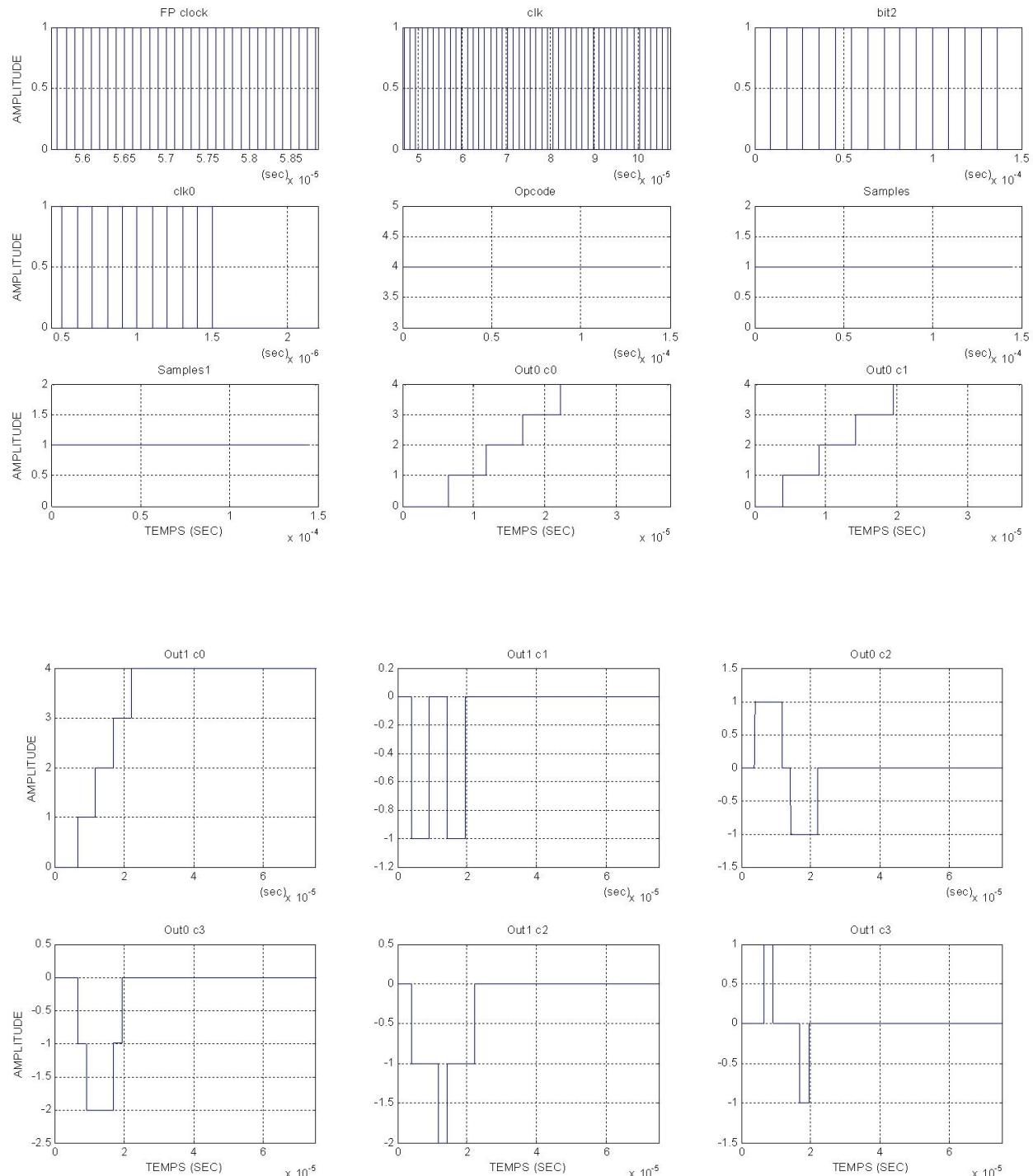

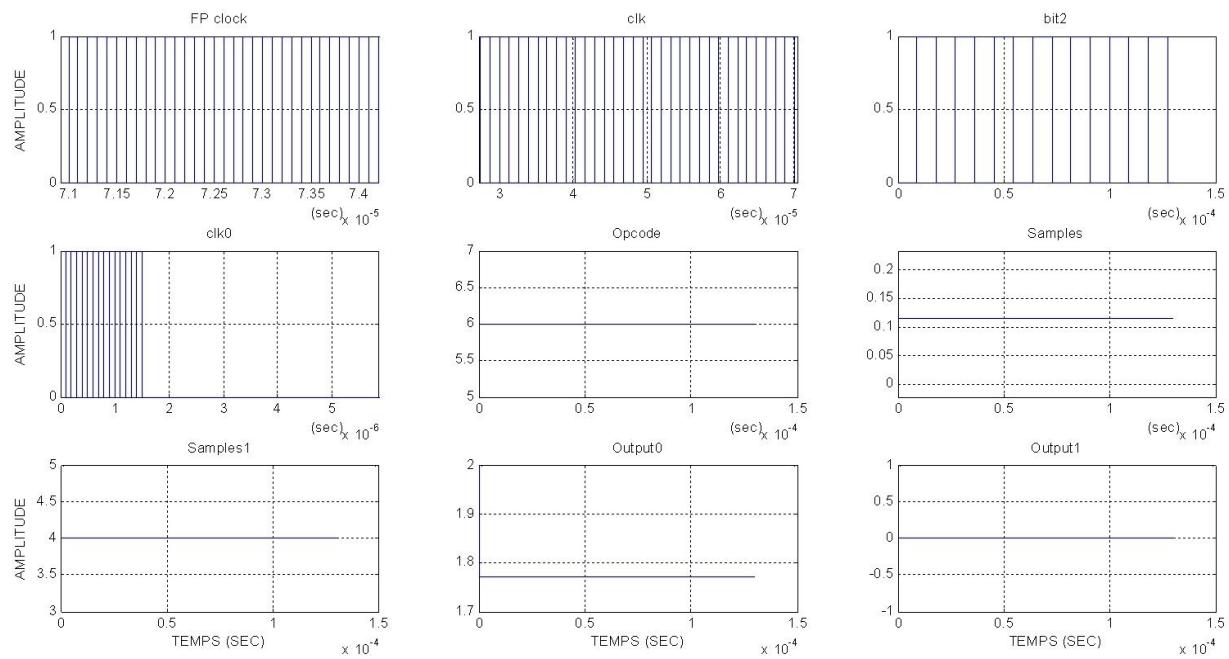

| Figure 3-7 : Diagramme temporel des horloges de contrôle du mode FIR/IIR non adaptatif. ....                                                                          | 75 |

| Figure 3-8 : Contrôle temporel du mode FIR/IIR non adaptatif. ....                                                                                                    | 75 |

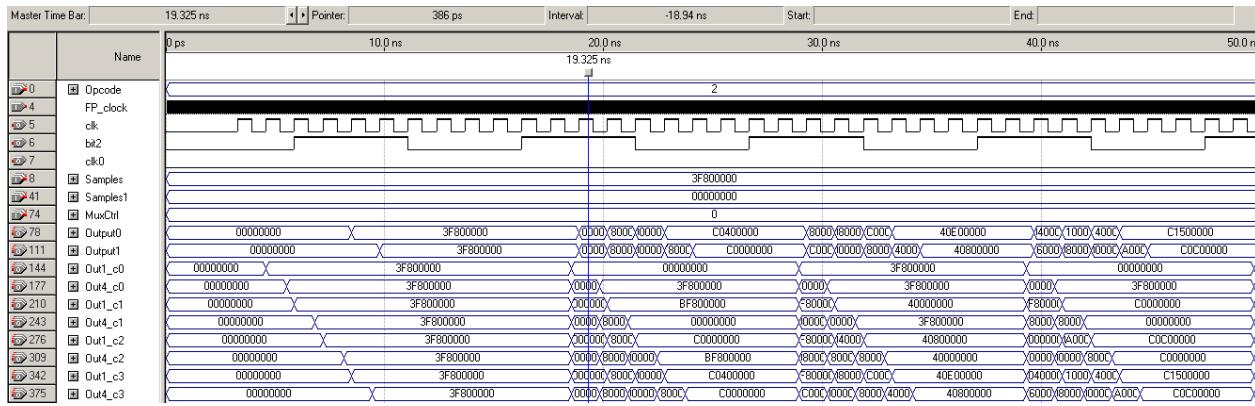

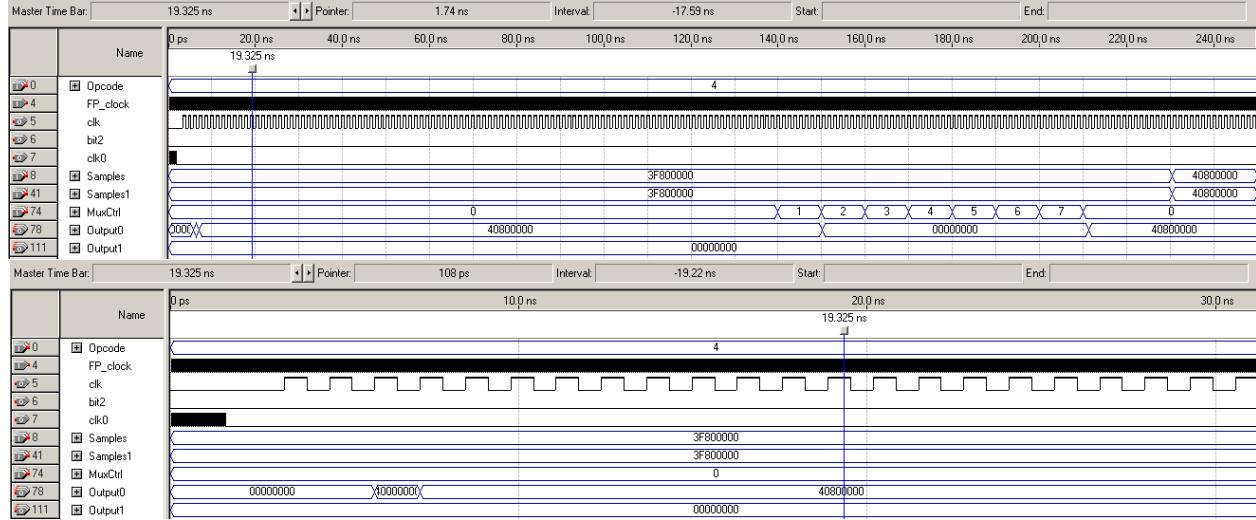

|                                                                                                                |     |

|----------------------------------------------------------------------------------------------------------------|-----|

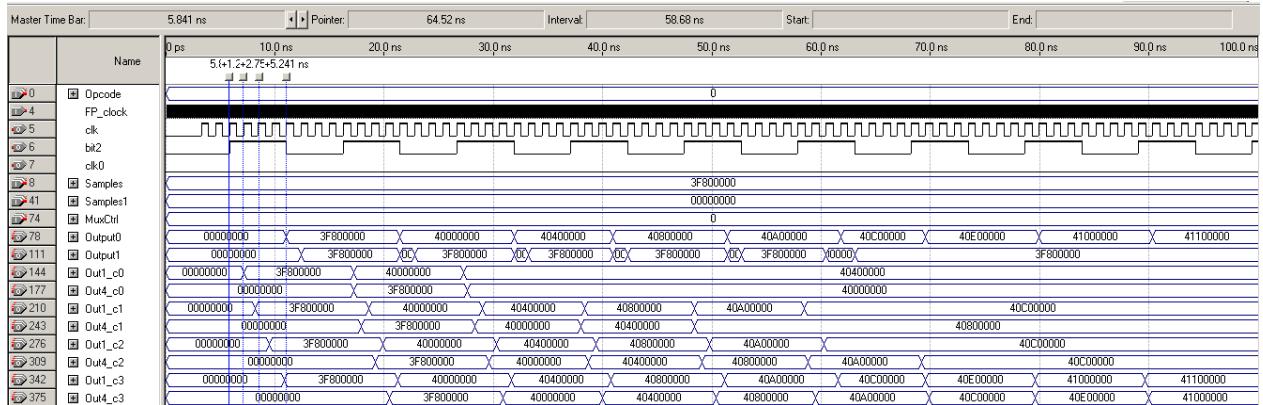

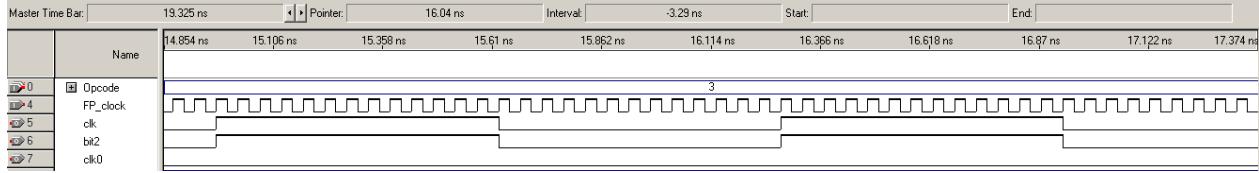

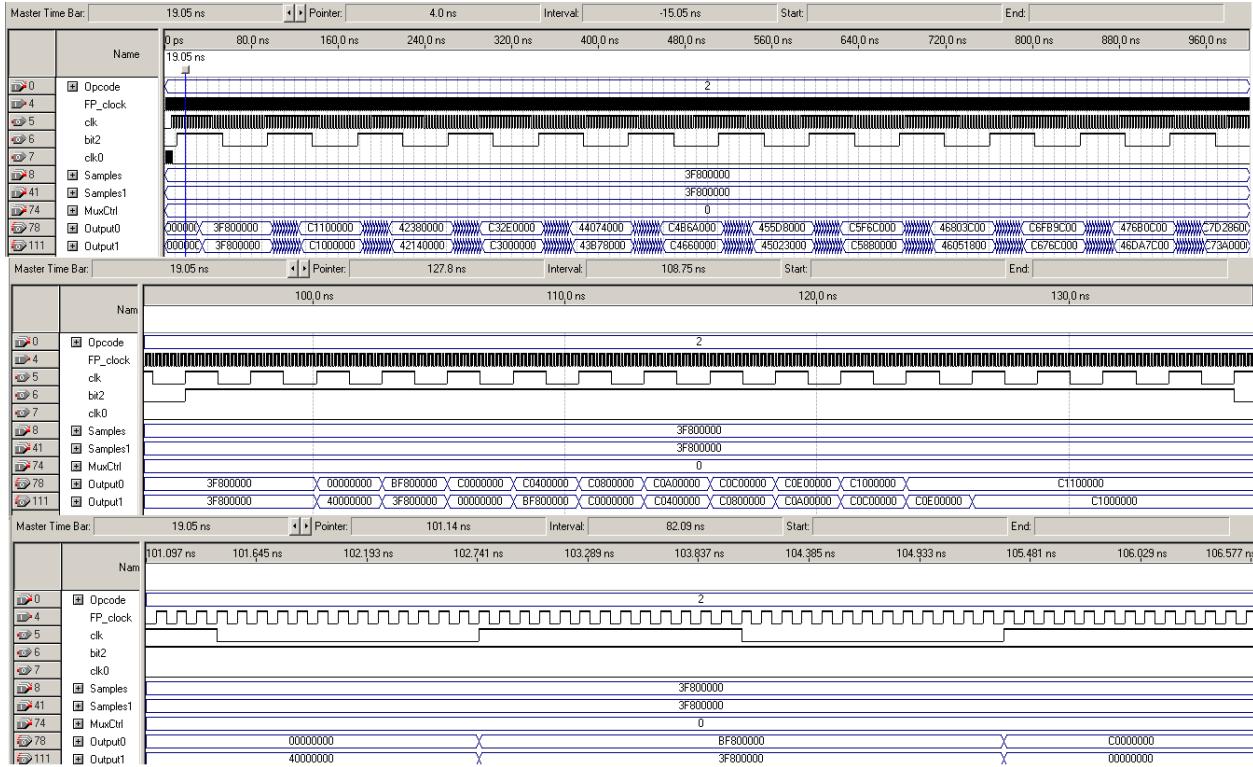

| Figure 3-9 : Diagramme temporel des horloges de contrôle du mode FIR/IIR adaptatif. ....                       | 77  |

| Figure 3-10 : Contrôle temporel du mode FIR/IIR adaptatif. ....                                                | 77  |

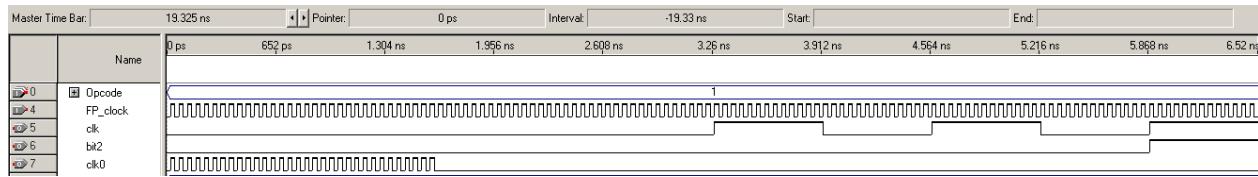

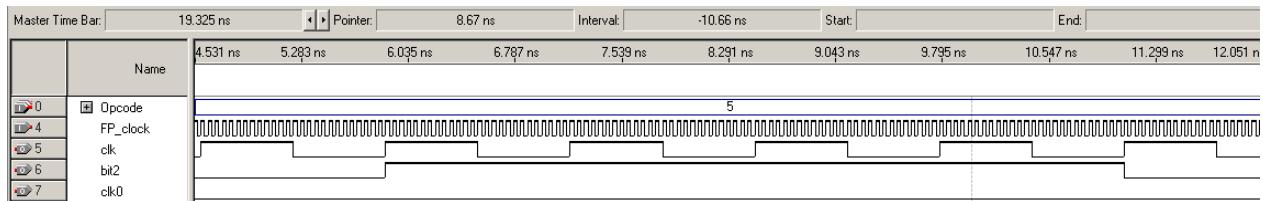

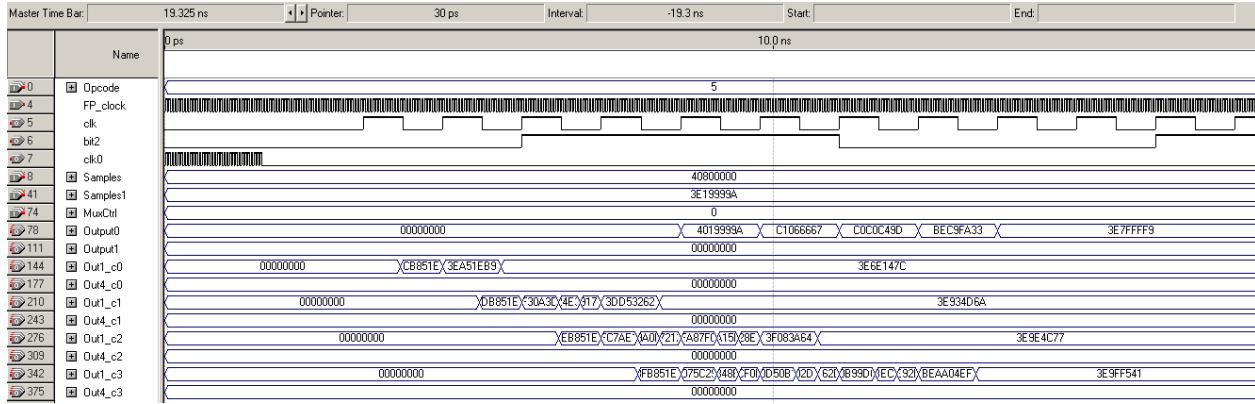

| Figure 3-11 : Diagramme temporel des horloges de contrôle du filtre en treillis All-Pole.....                  | 79  |

| Figure 3-12 : Contrôle temporel du filtre en treillis All-Pole. ....                                           | 79  |

| Figure 3-13 : Diagramme temporel des horloges de contrôle du filtre en treillis All-Zero. ....                 | 81  |

| Figure 3-14 : Contrôle temporel du filtre en treillis All-Zero. ....                                           | 81  |

| Figure 3-15 : Contrôle temporel de l'opérateur FFT radical 4.....                                              | 83  |

| Figure 3-16 : Diagramme des horloges de l'algorithme de division selon Newton-Raphson. ....                    | 84  |

| Figure 3-17 : Contrôle temporel du filtre de l'algorithme de division selon Newton-Raphson. ....               | 85  |

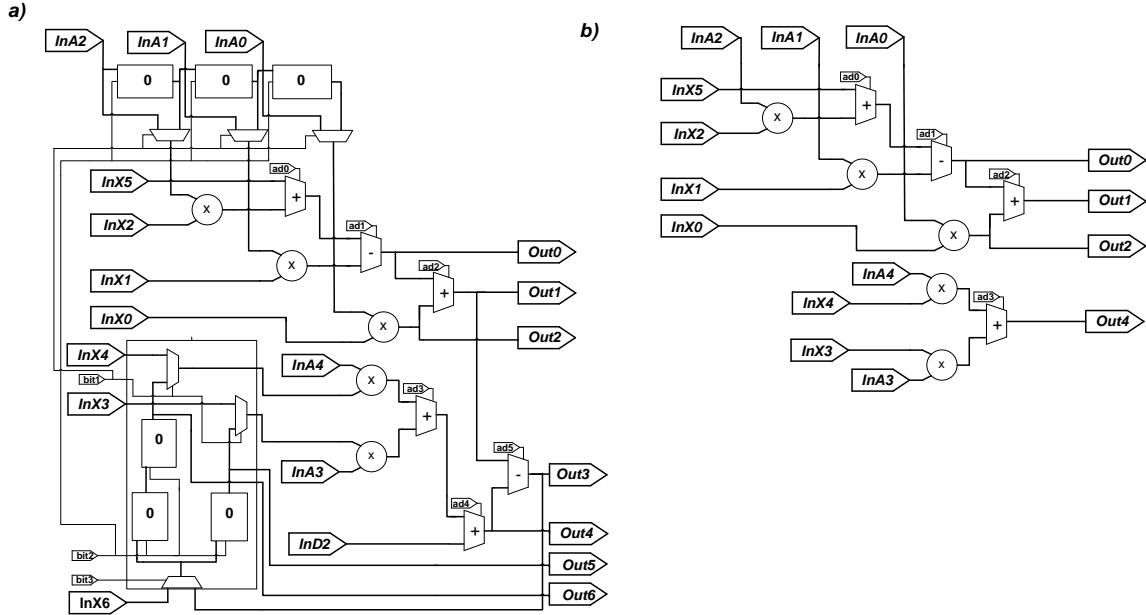

| Figure 3-18 : UPM avec contrôle de récursivité <i>UPMR.v</i> a) et sans contrôle <i>UPM.v</i> b).....          | 87  |

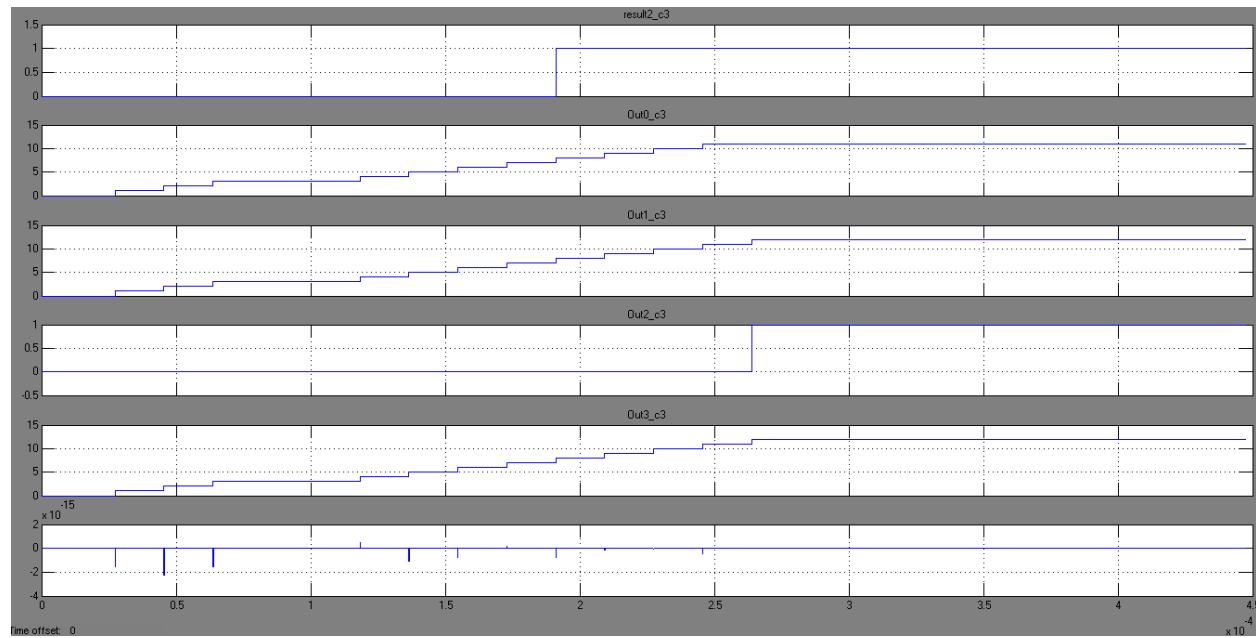

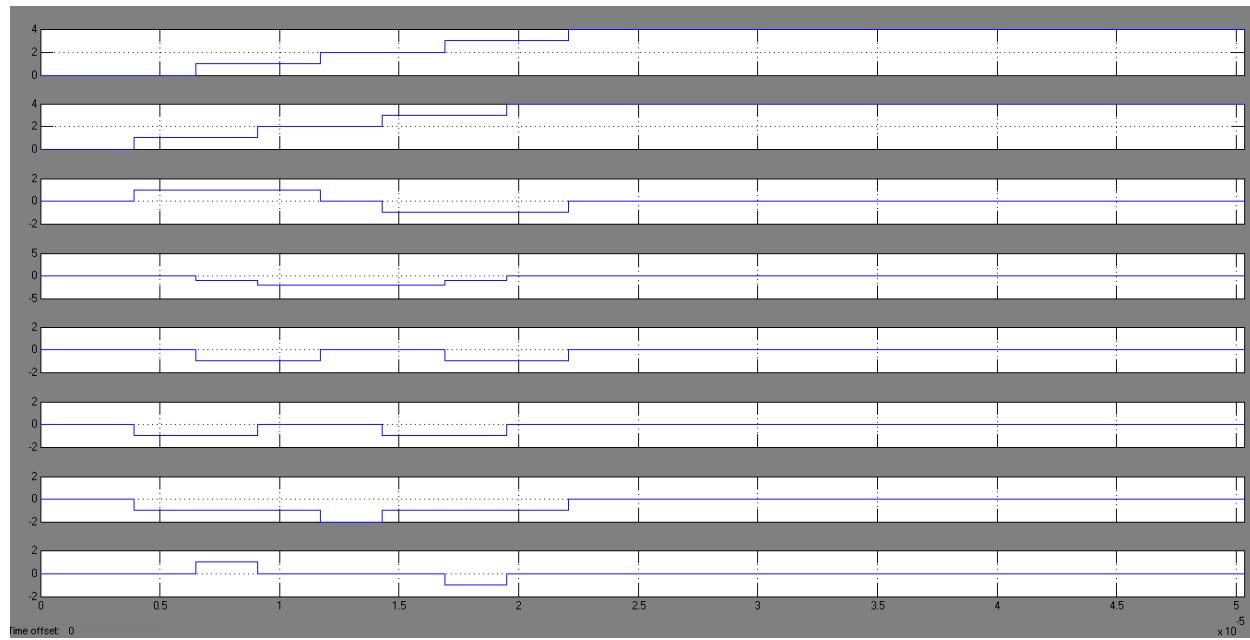

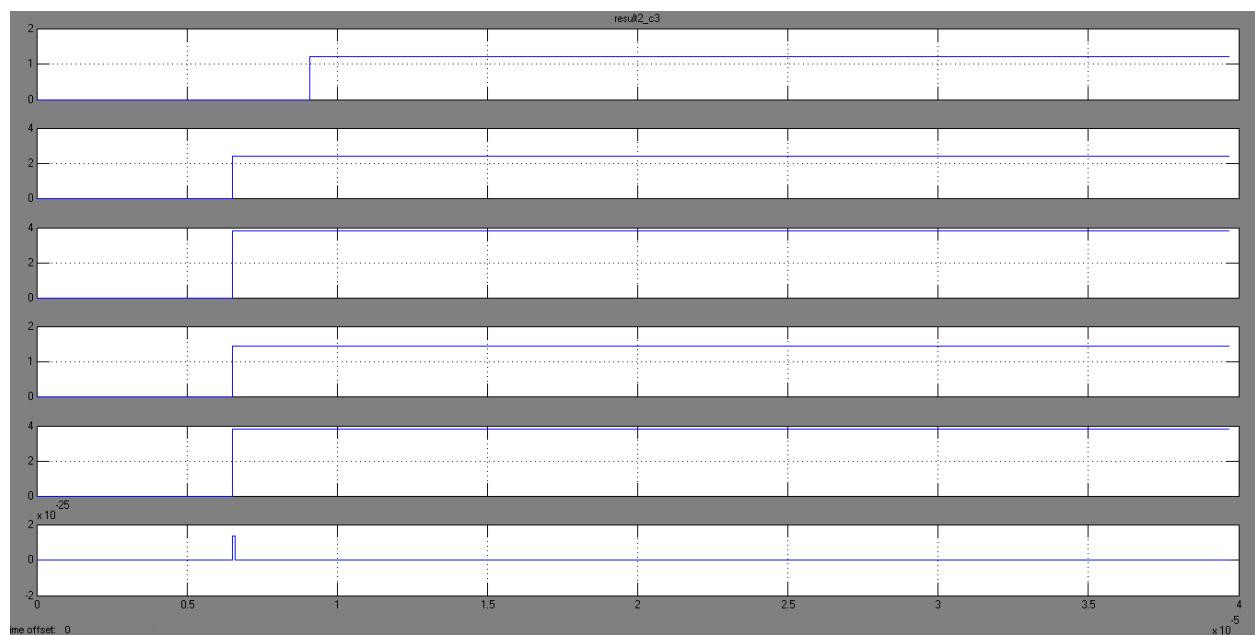

| Figure 3-19 : Diagramme temporel du Filtrage FIR/IIR, ordre $N=20$ . ....                                      | 88  |

| Figure 3-20 : Diagramme temporel du filtre de l'algorithme All-Pole $s=10$ . ....                              | 89  |

| Figure 3-21 : Diagramme temporel du filtre de l'algorithme All-Zero, $s=10$ .....                              | 90  |

| Figure 3-22 : Contrôle temporel du filtre de l'algorithme FIR, $N=30$ . ....                                   | 91  |

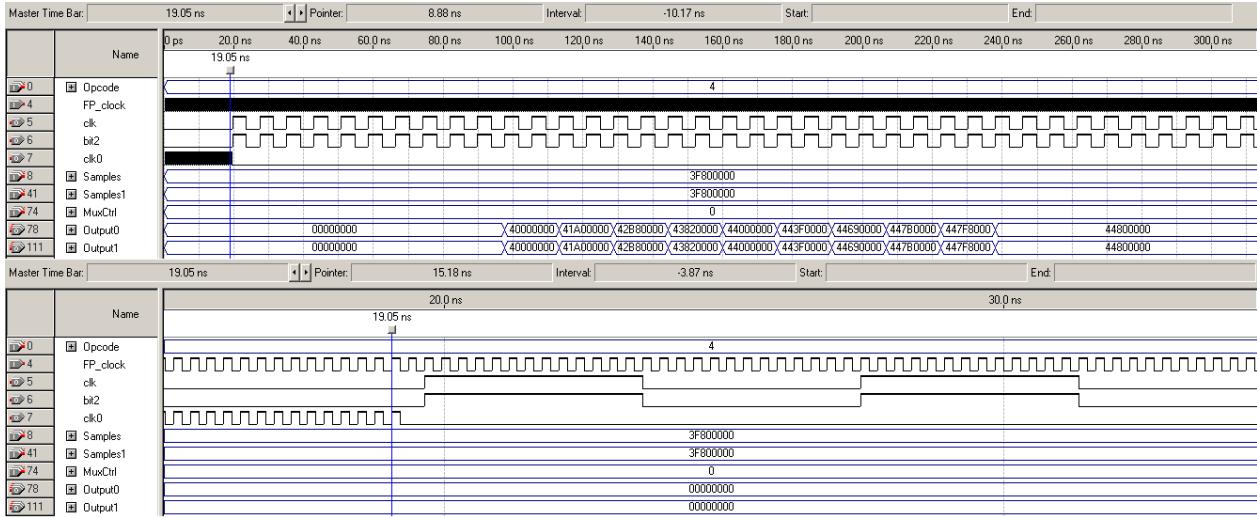

| Figure 3-23 : Contrôle temporel de l'algorithme FFT radical-4, ordre $N=16$ .....                              | 92  |

| Figure 3-24 : Contrôle temporel du filtre de l'algorithme de calcul de racine selon newton-Raphson $N=9$ ..... | 93  |

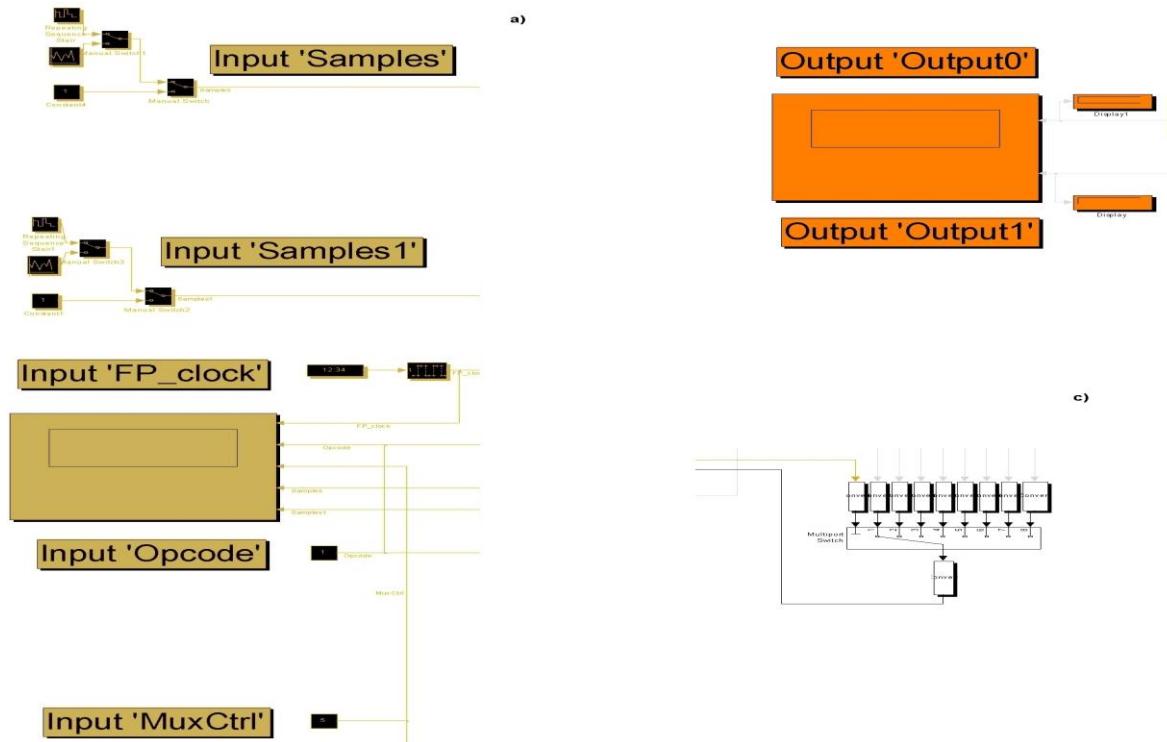

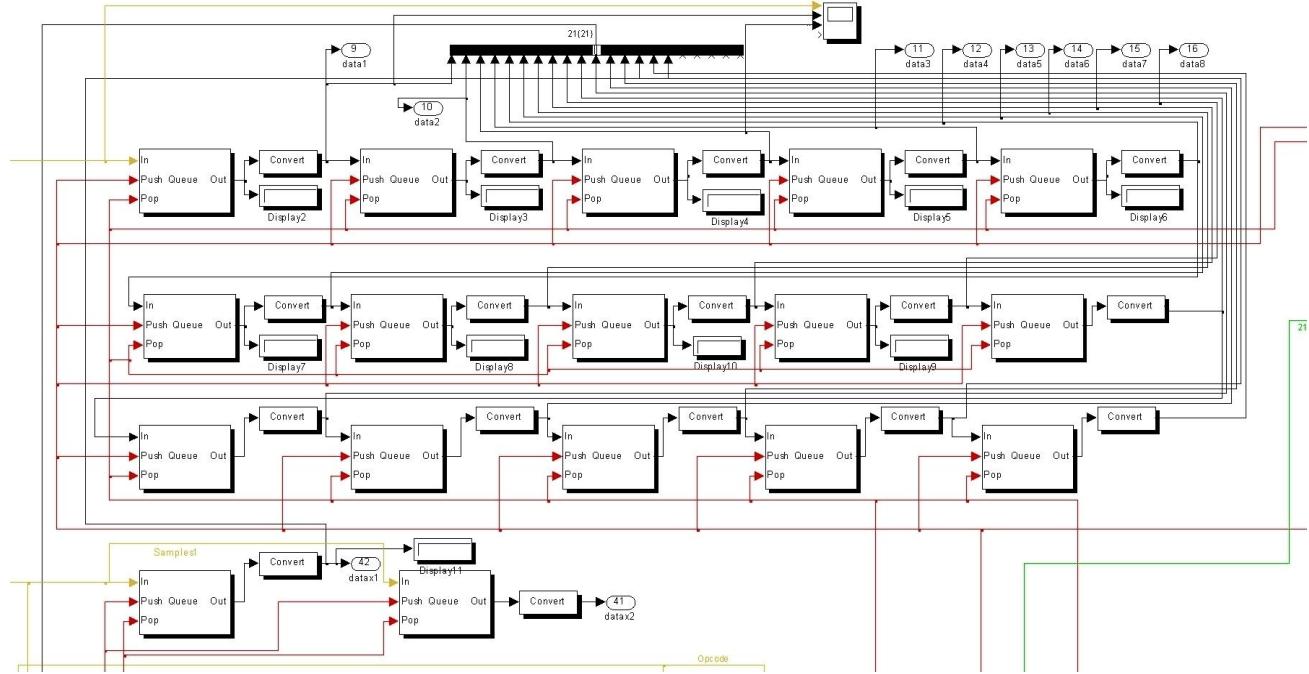

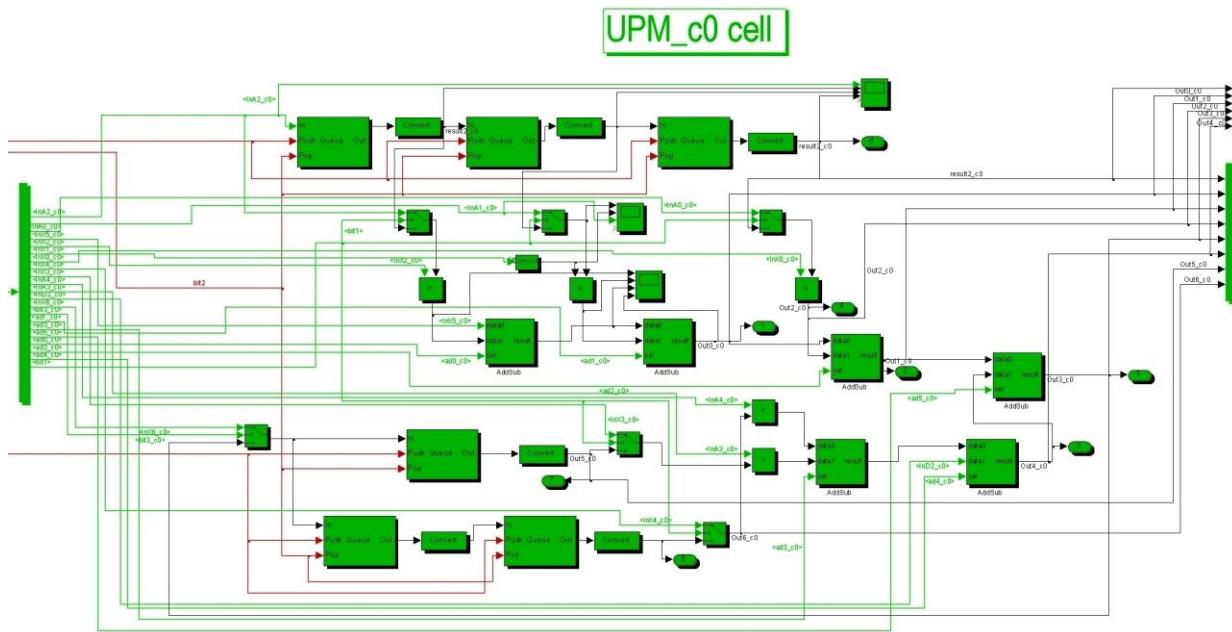

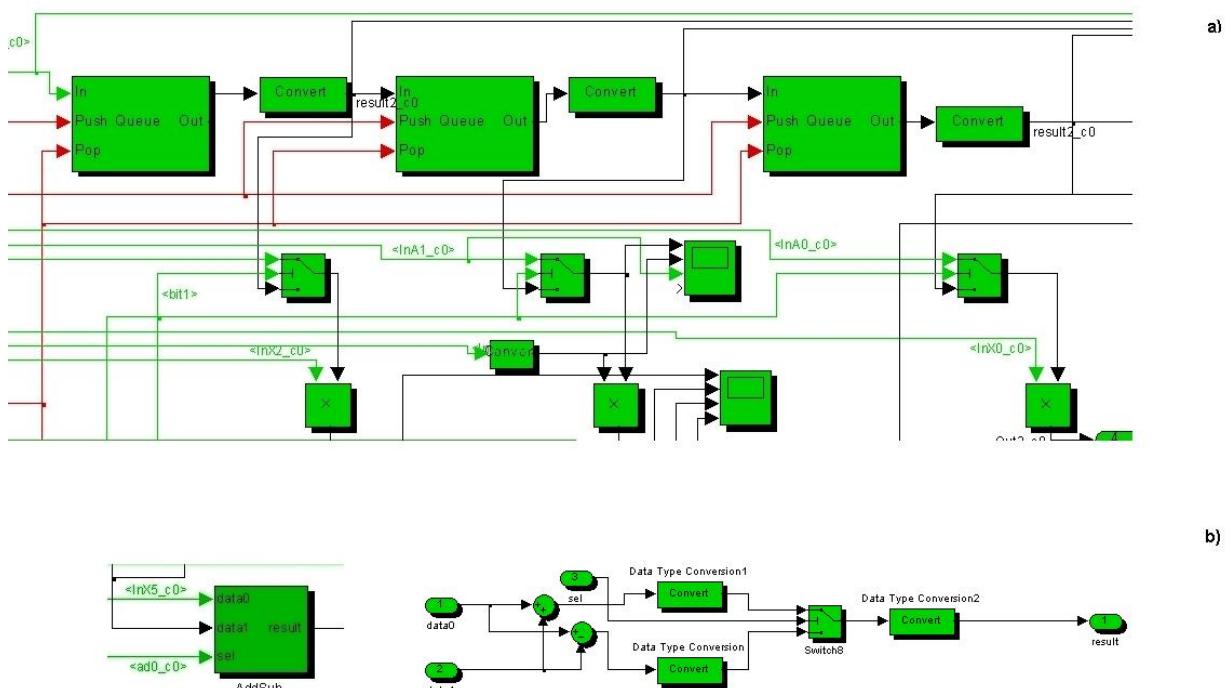

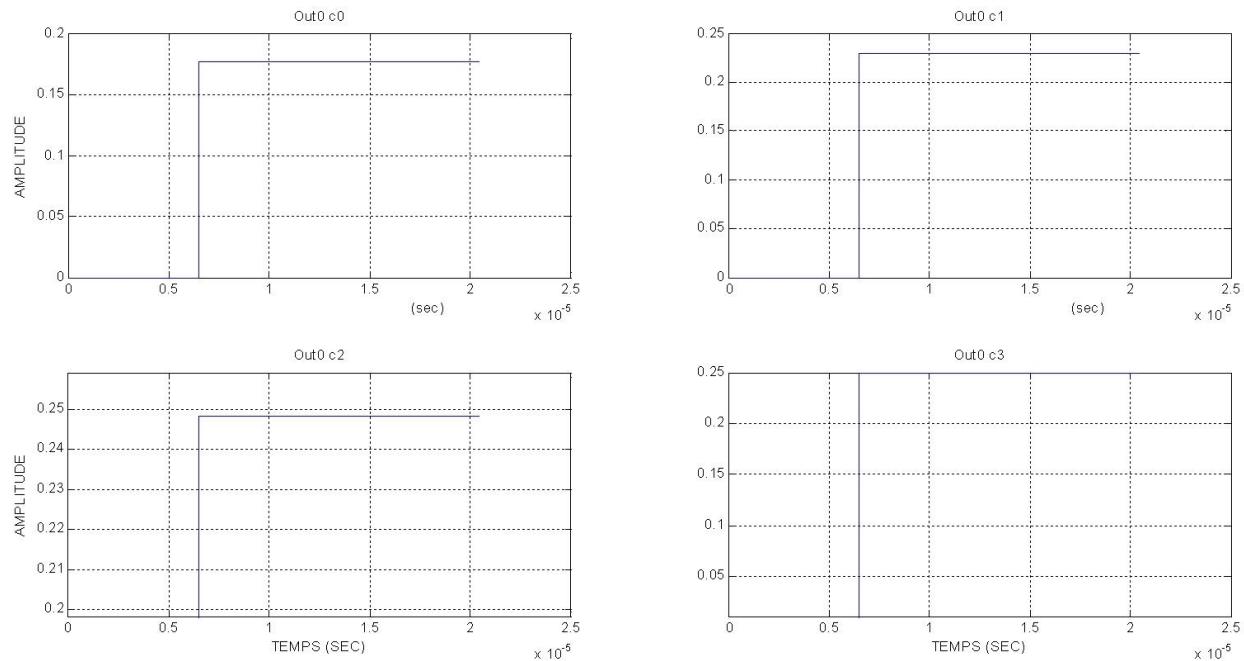

| Figure 3-25 : Modèle <i>Simulink</i> d'une matrice cellulaire $2x2$ .....                                      | 94  |

| Figure 3-26 : Modèle <i>Simulink</i> des entrées et sorties du processeur.....                                 | 95  |

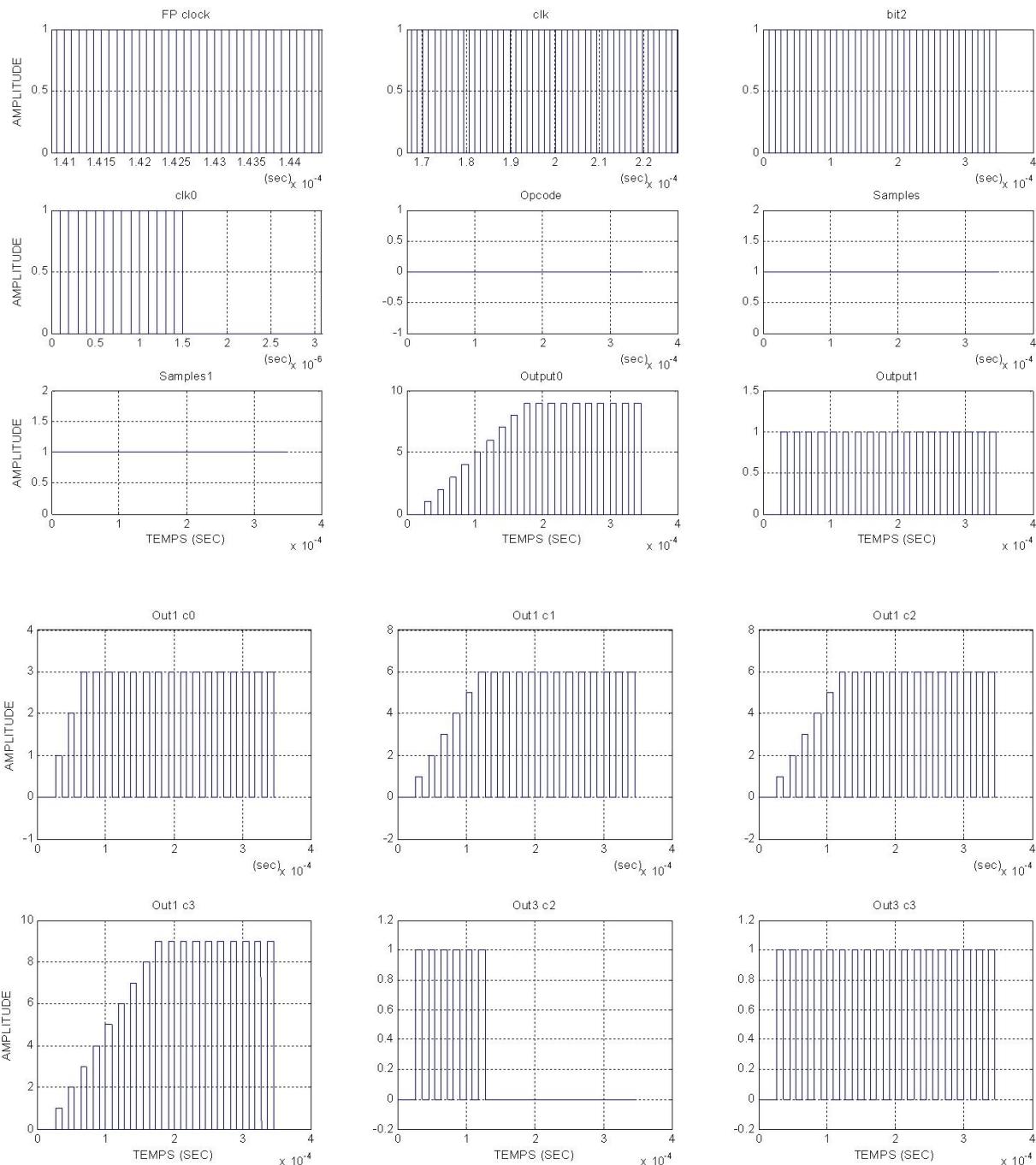

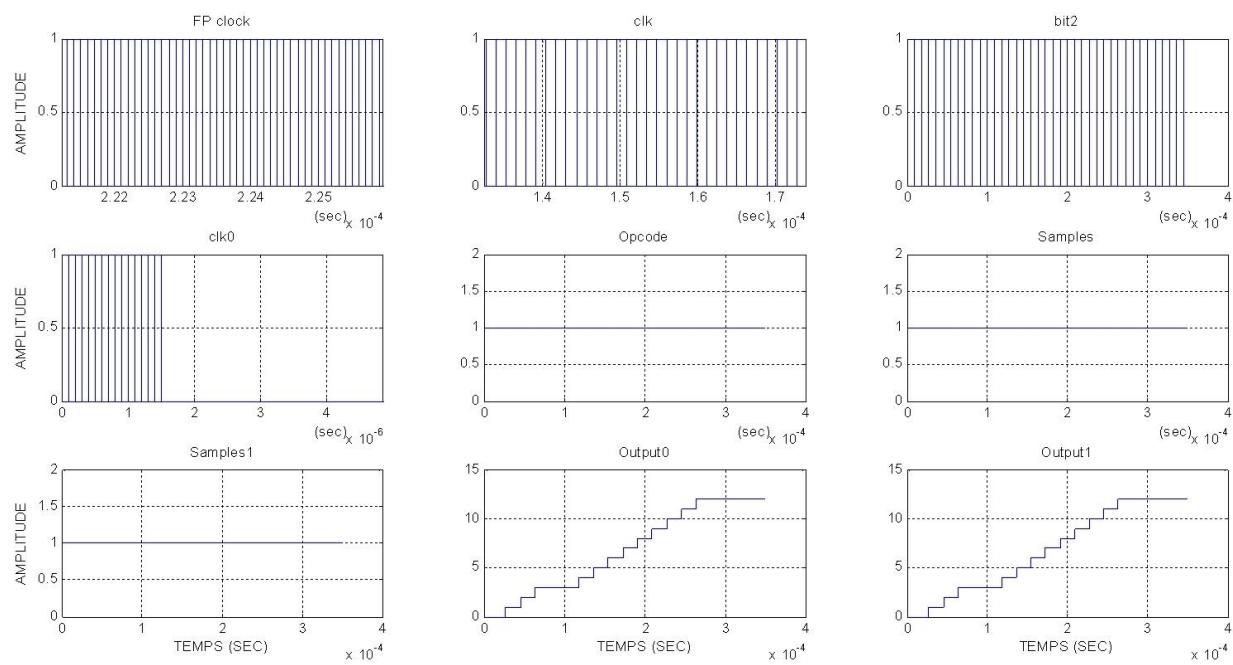

| Figure 3-27 : Modèle <i>Simulink</i> d'une série de registres à décalage. ....                                 | 96  |

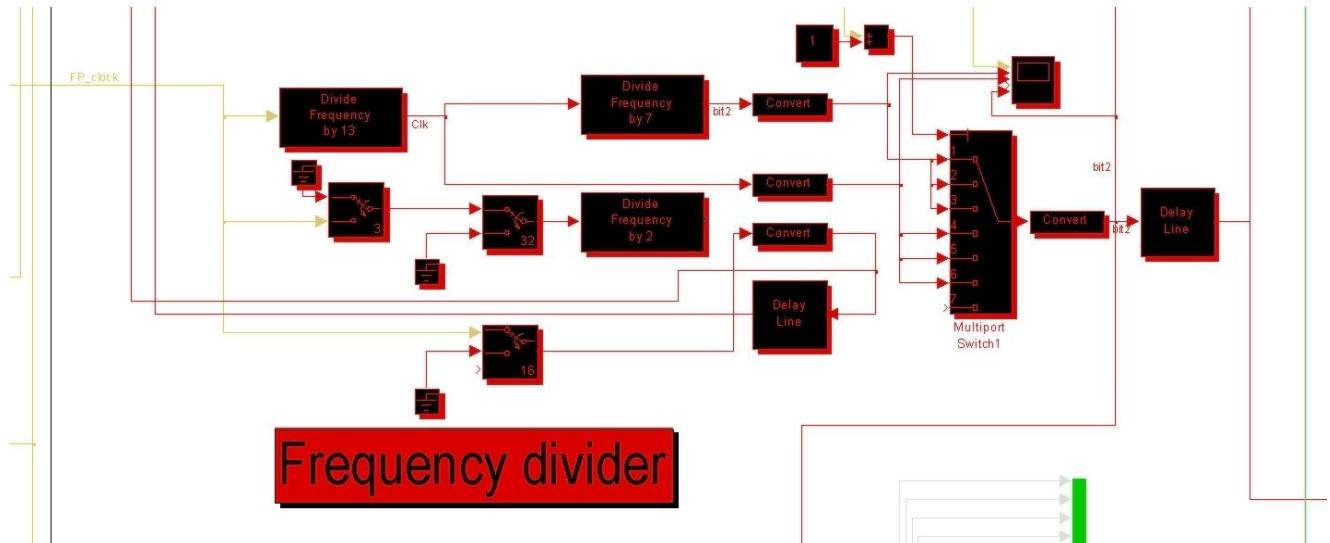

| Figure 3-28 : Modèle <i>Simulink</i> du contrôle temporel de la matrice.....                                   | 96  |

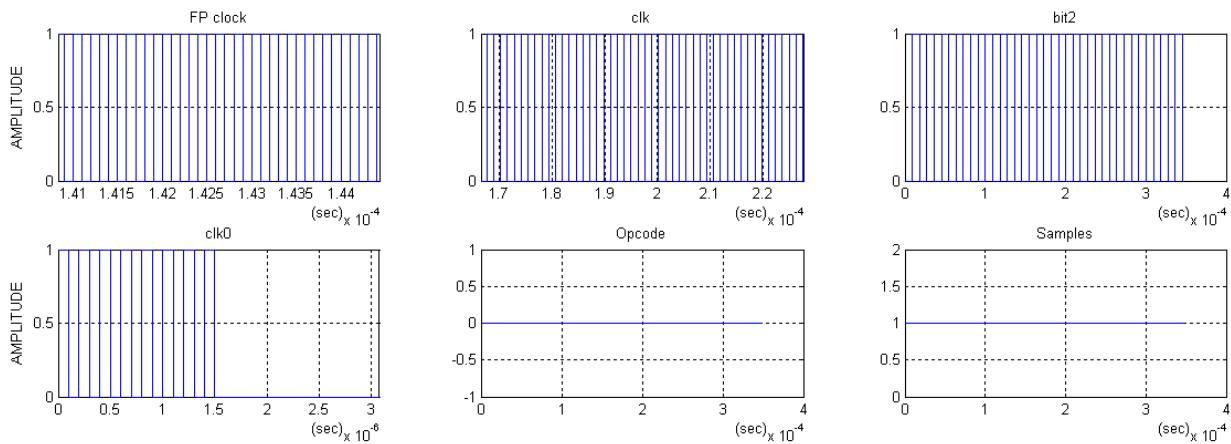

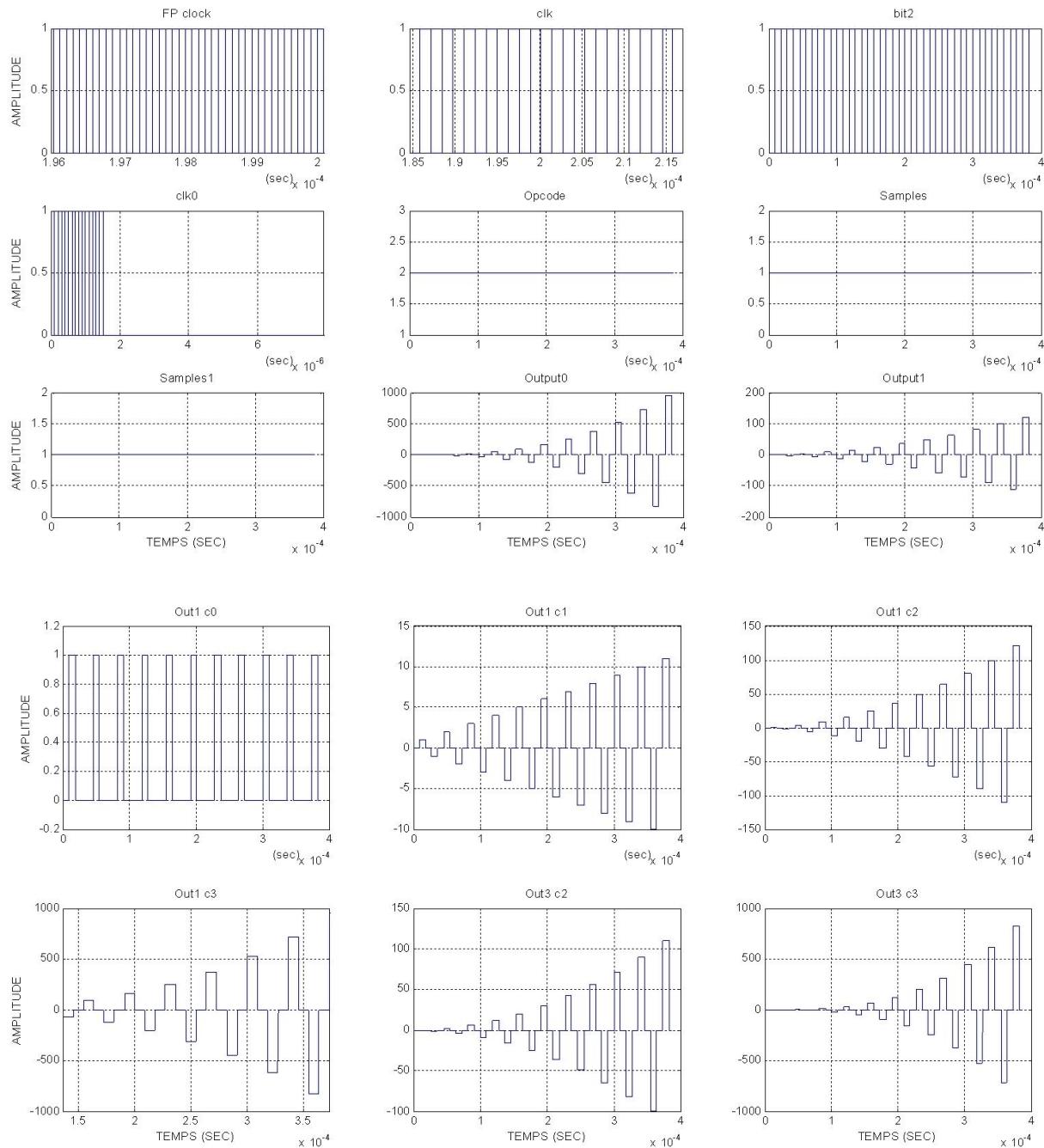

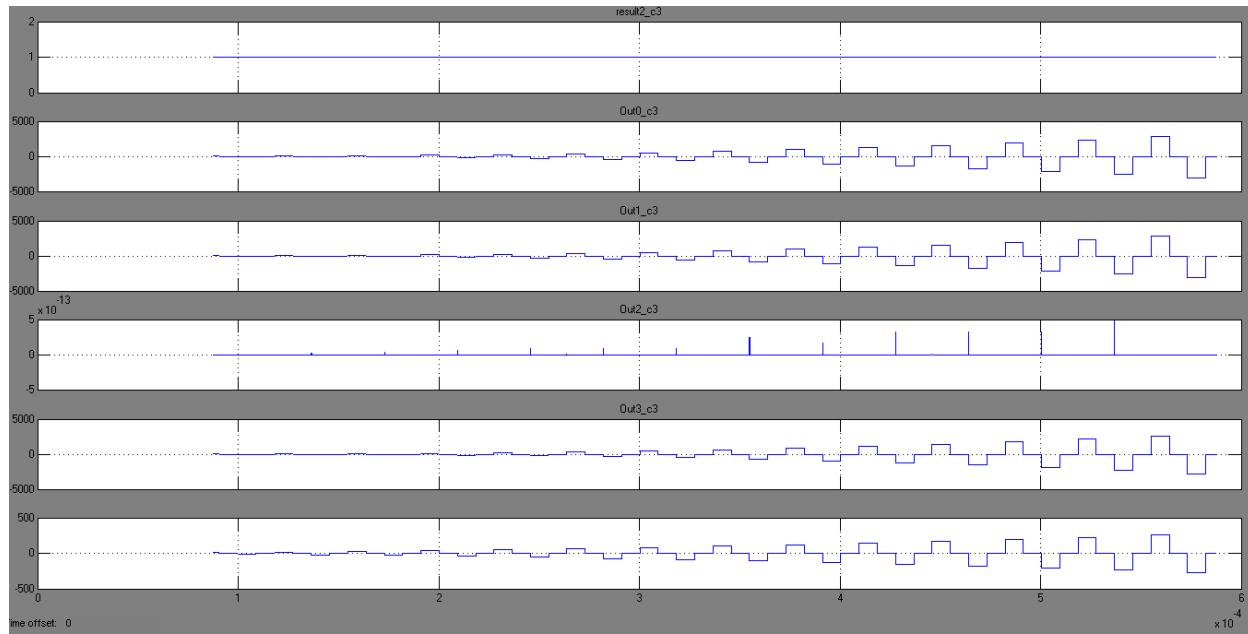

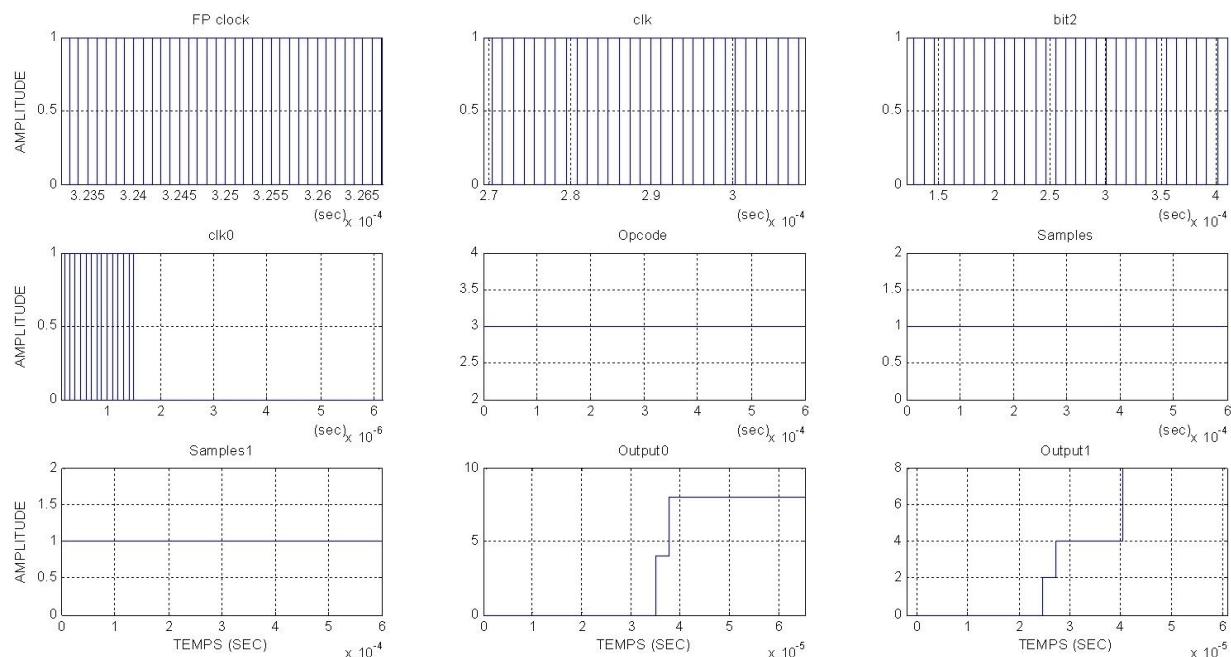

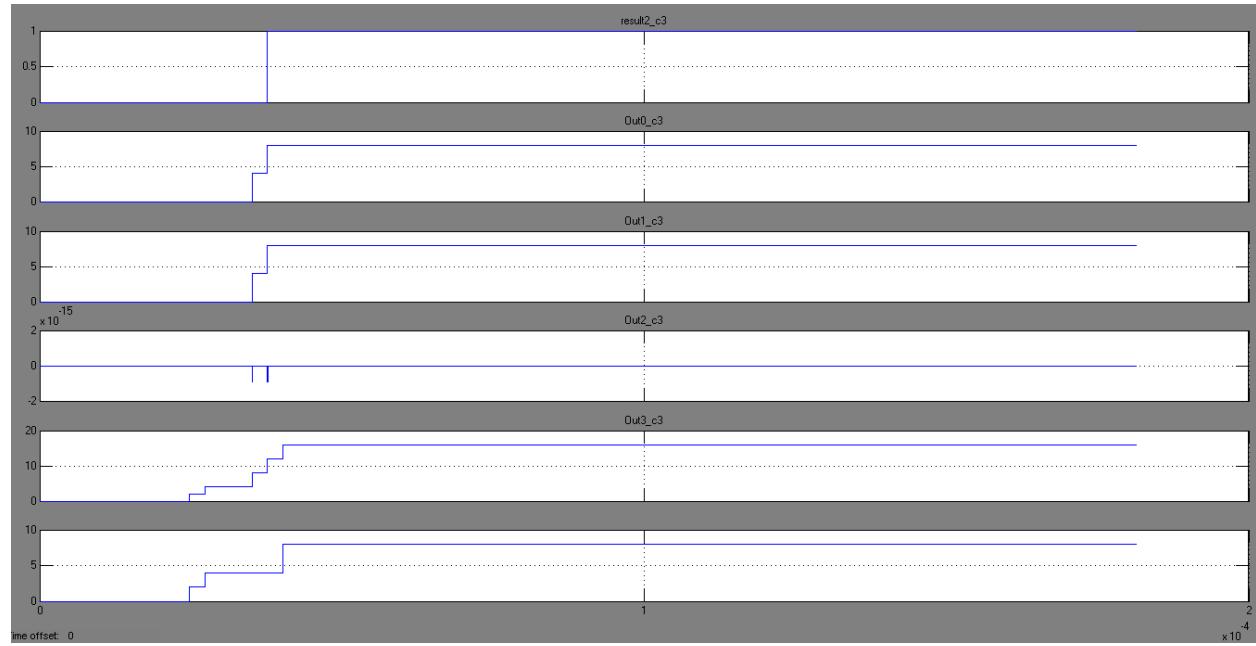

| Figure 3-29 : Horloges de contrôle générées par <i>Simulink</i> à partir de l'entrée <i>FP_clock</i> .....     | 97  |

| Figure 3-30 : Modèle <i>Simulink</i> d'une cellule UPM. ....                                                   | 98  |

| Figure 3-31 : Modèle <i>Simulink</i> d'une série de registres a) de l'additionneur/soustracteur b). ....       | 98  |

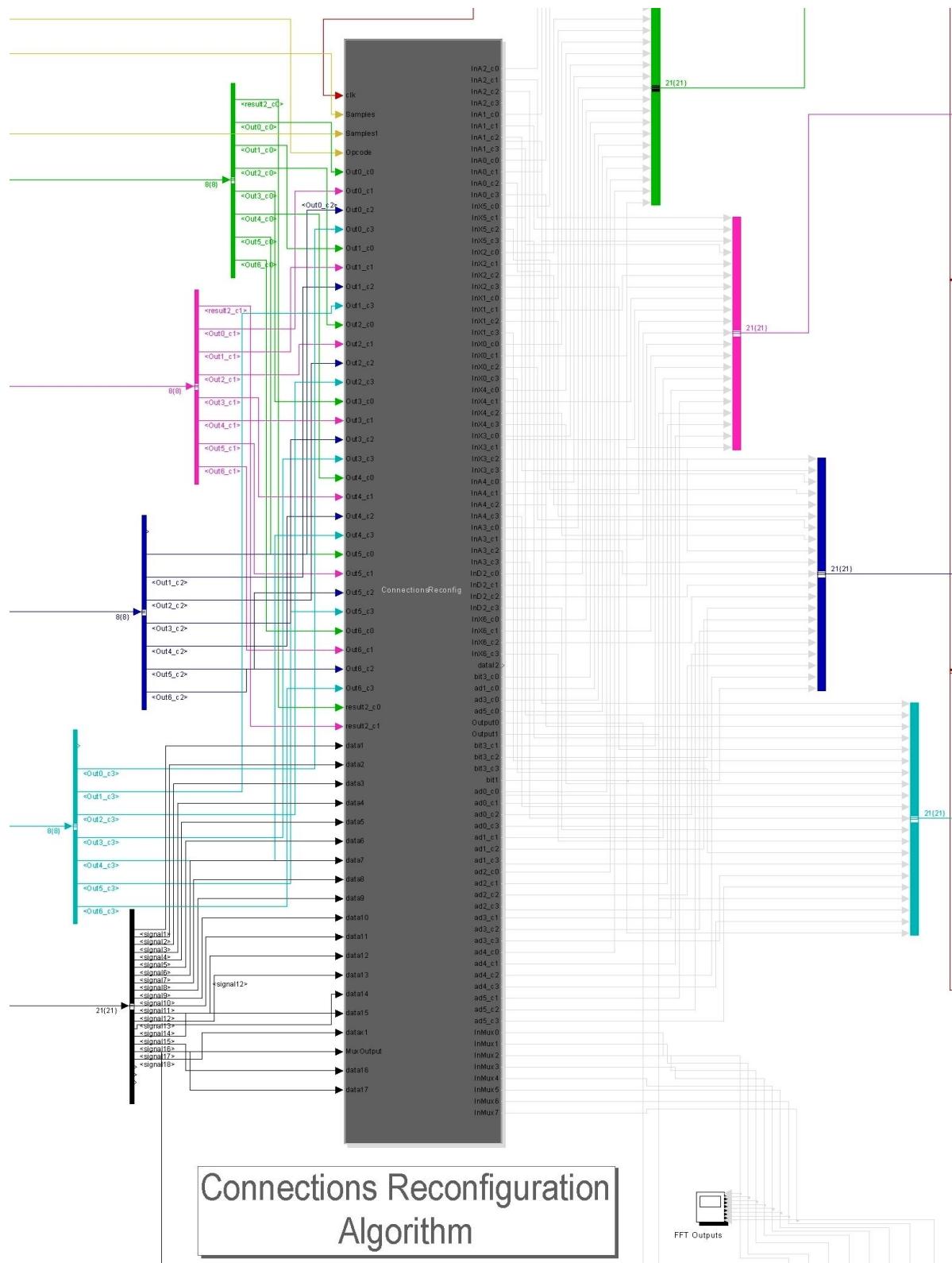

| Figure 3-32 : Modèle <i>Simulink</i> de l'algorithme de reconfiguration des connexions. ....                   | 100 |

## LISTE DES SIGLES ET ABRÉVIATIONS

|        |                                                   |

|--------|---------------------------------------------------|

| 1D     | Une Dimension                                     |

| 2D     | Deux dimensions                                   |

| ALU    | Arithmetic Logical Unit                           |

| ASIC   | Application Spécific Integrated Circuit           |

| CLB    | Configurable Logic Block                          |

| CORDIC | Coordinate Rotation Digital Computer              |

| DCT    | Discrete Cosine Transform                         |

| DHT    | Discrete Hartley Transform                        |

| DSP    | Digital Signal Processing                         |

| GOPS   | Giga Octet Par Seconde                            |

| HDL    | Hardware Description Language                     |

| HD-TV  | High Definition Television                        |

| IDCT   | Inverse Discrete Cosine Transform                 |

| IEEE   | Institute of Electrical and Electronics Engineers |

| IIR    | Infinite Impulse Response                         |

| IQ     | Inverse Quantization                              |

| FFT    | Fast Fourier Transform                            |

| FHT    | Fast Hartley Transform                            |

| FIR    | Finite Impulse Response                           |

| FPGA   | Field Gate Programmable Array                     |

| FPU    | Floating Point Unit                               |

| FWT    | Fast Walsh-Hadamard Transform                     |

|      |                                        |

|------|----------------------------------------|

| HTC  | Hilbert Transform Correlator           |

| LAB  | Logic Array Block                      |

| LE   | Logic Element                          |

| LMS  | Least Mean Square                      |

| MAC  | Multiply Accumulate                    |

| MC   | Motion Compensation                    |

| MIMD | Multiple Instructions Multiple Data    |

| MIPS | Million Instruction Per Second         |

| MUSE | Multiple Sub-Nyquist Sampling Encoding |

| NTSC | National Television System Committee   |

| OIOO | Ordered Input Ordered Output           |

| PLL  | Phase-Locked Loop                      |

| PE   | Processing Element                     |

| RAM  | Random Access Memory                   |

| RLS  | Recursive Least Square                 |

| RTL  | Register Transfert Level               |

| SIMD | Single Instruction Multiple Data       |

| UPE  | Universal Processing Element           |

| UPM  | Universal Processing Module            |

| VGA  | Video Graphic Array                    |

| VPE  | Vidéo Processing Element               |

## LISTE DES ANNEXES

|                                                                             |     |

|-----------------------------------------------------------------------------|-----|

| ANNEXE 1 – Diagramme de Gantt du projet.....                                | 121 |

| ANNEXE 2 – Code Verilog-HDL du Module de Contrôle de Récursivité.....       | 122 |

| ANNEXE 3 – Diagramme interne du Module de Contrôle de Récursivité.....      | 123 |

| ANNEXE 4 – Code Verilog-HDL de L’UPM.....                                   | 124 |

| ANNEXE 5 – Diagramme interne de L’UPM.....                                  | 125 |

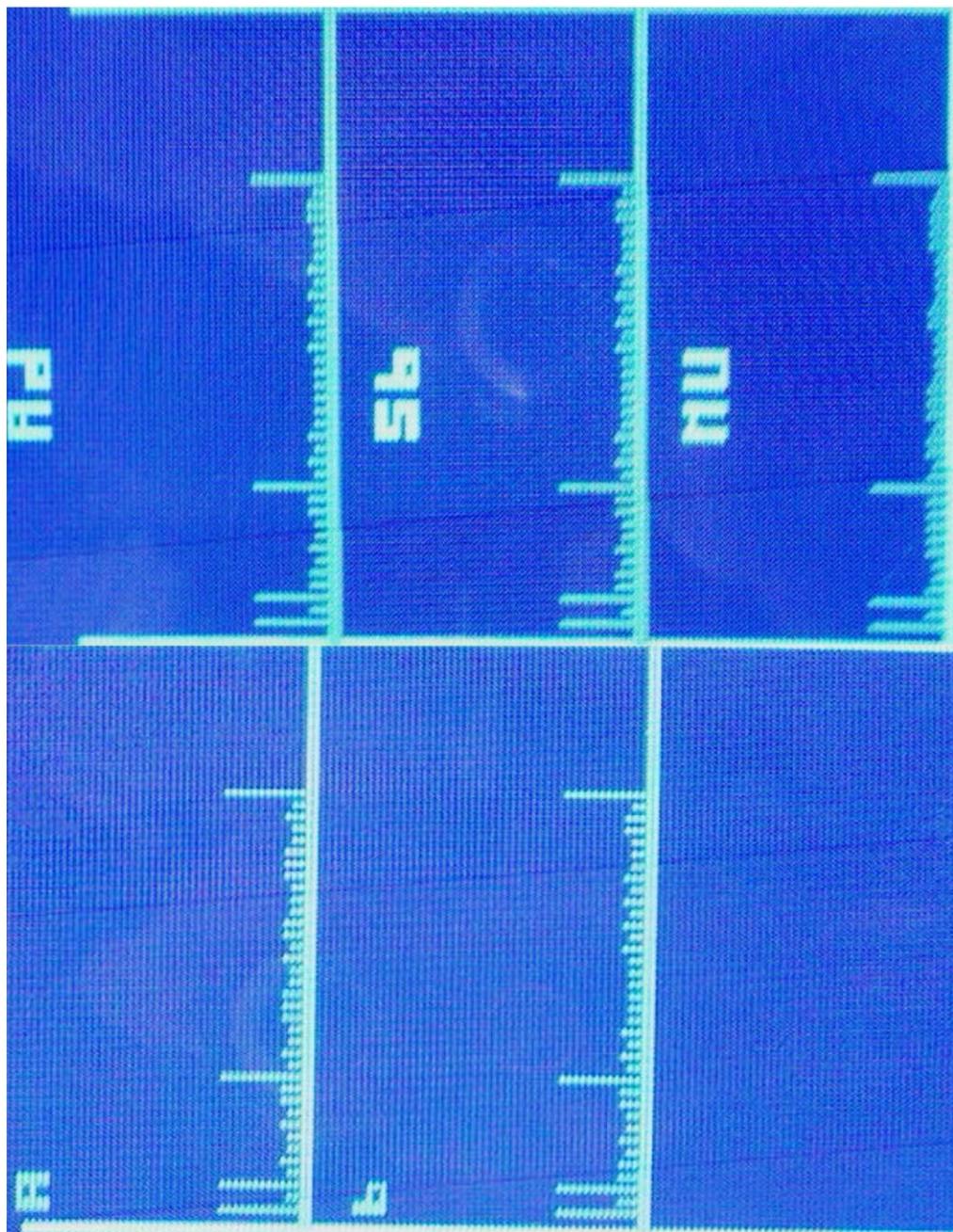

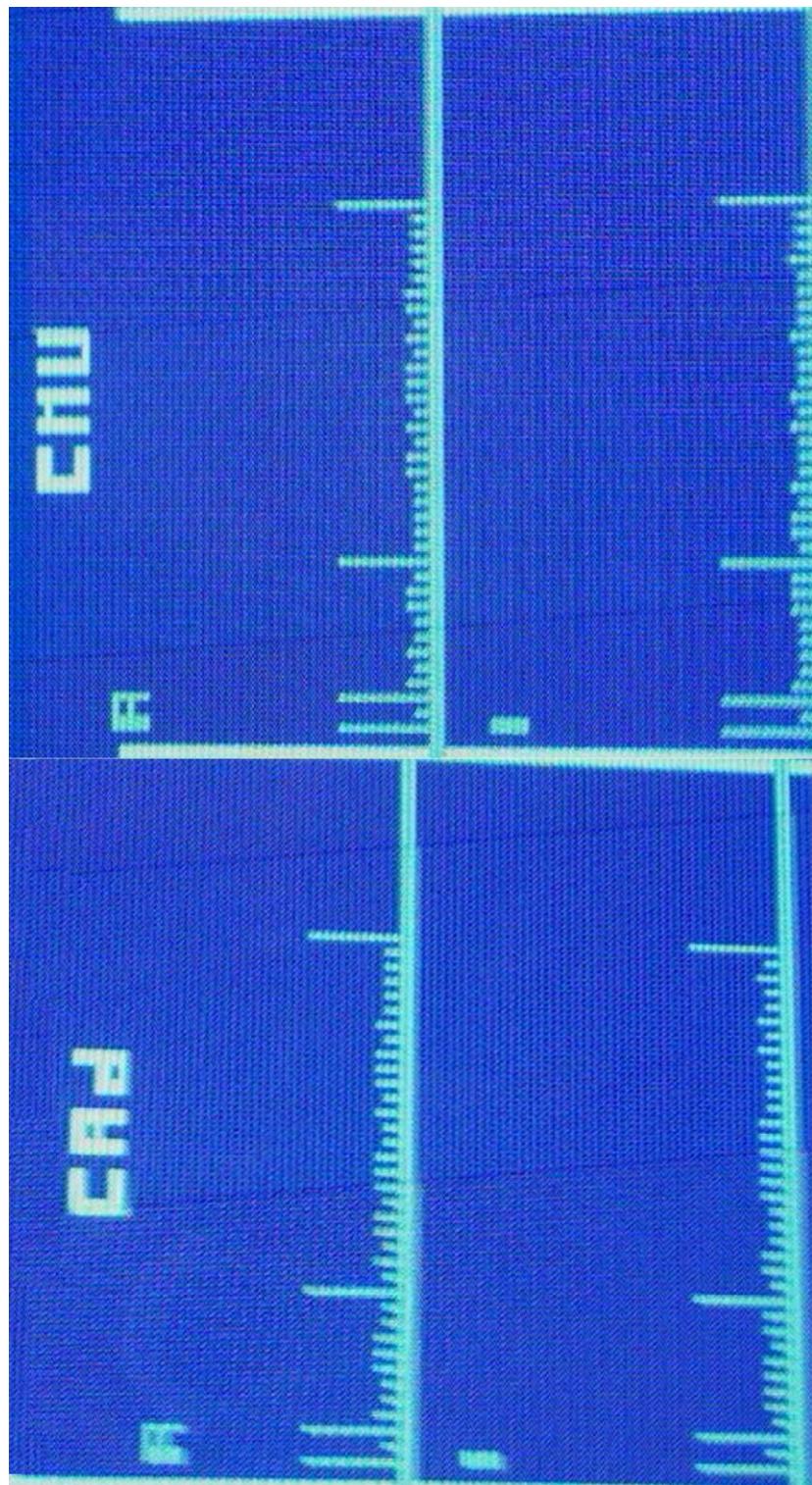

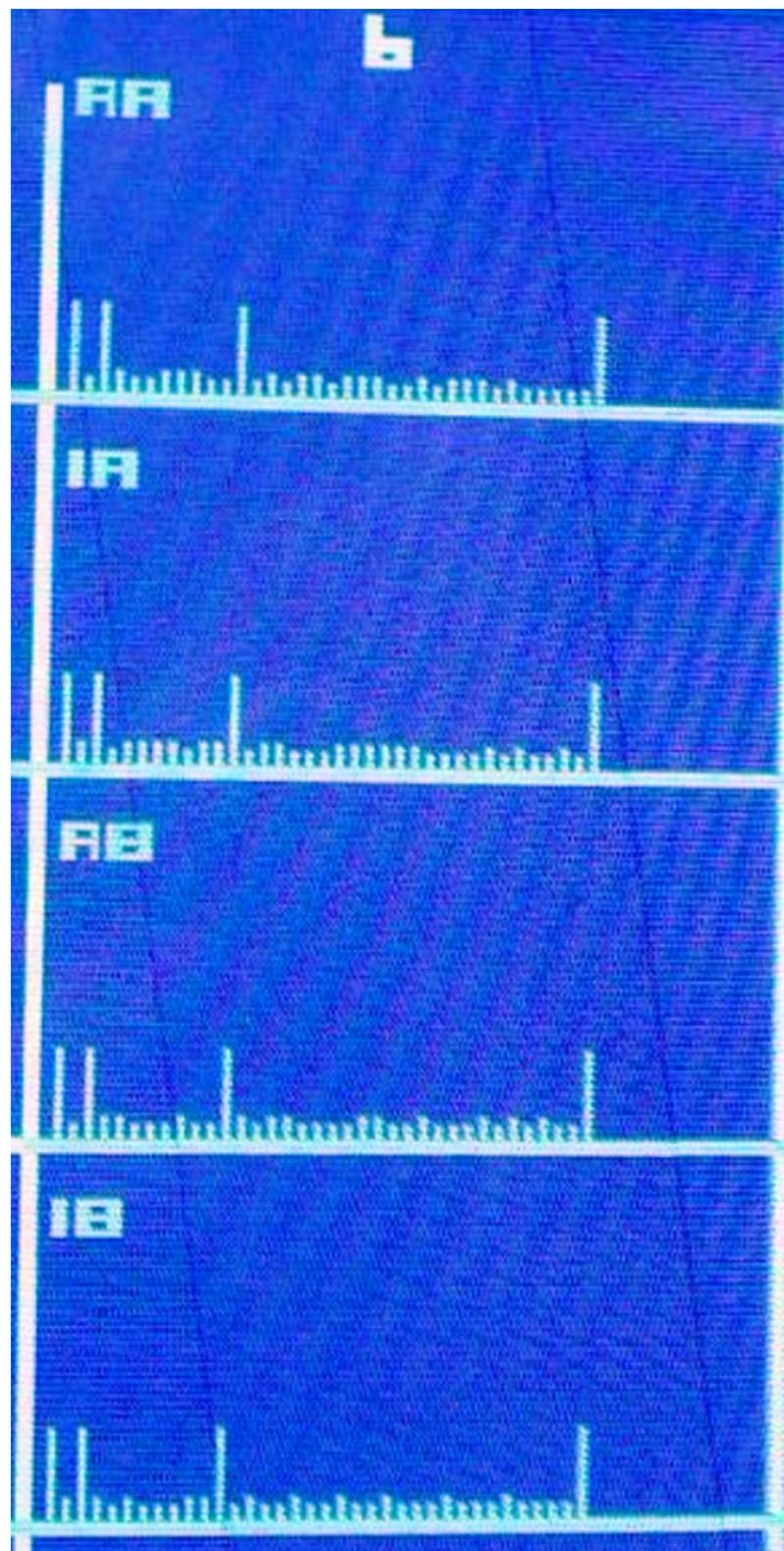

| ANNEXE 6 – Image des outils de tests sur écran VGA.....                     | 126 |

| ANNEXE 7 – Code du Module Top d'affichage VGA (1).....                      | 127 |

| ANNEXE 8 – Code du Module Top d'affichage VGA (2).....                      | 128 |

| ANNEXE 9 – Code de la fonction d'affichage " <i>VGA_Pattern</i> " (1).....  | 129 |

| ANNEXE 10 – Code de la fonction d'affichage " <i>VGA_Pattern</i> " (2)..... | 130 |

| ANNEXE 11 – Code de la fonction d'affichage " <i>VGA_Pattern</i> " (3)..... | 131 |

| ANNEXE 12 – Image de l'affichage des tests.....                             | 132 |

| ANNEXE 13 – Algorithme du processeur matriciel 2x2 UPMs (1).....            | 133 |

| ANNEXE 14 – Algorithme du processeur matriciel 2x2 UPMs (2).....            | 134 |

| ANNEXE 15 – Algorithme du processeur matriciel 2x2 UPMs (2).....            | 135 |

| ANNEXE 16 – Algorithme du processeur matriciel 2x2 UPMs (3).....            | 136 |

| ANNEXE 17 – Algorithme du processeur matriciel 2x2 UPMs (4).....            | 137 |

| ANNEXE 18 – Algorithme du processeur matriciel 2x2 UPMs (5).....            | 138 |

| ANNEXE 19 – Algorithme du processeur matriciel 6x4 UPMs (1).....            | 139 |

| ANNEXE 20 – Algorithme du processeur matriciel 6x4 UPMs (2).....            | 140 |

| ANNEXE 21 – Algorithme du processeur matriciel 6x4 UPMs (3).....            | 141 |

| ANNEXE 22 – Algorithme du processeur matriciel 6x4 UPMs (4).....            | 142 |

|                                                                            |     |

|----------------------------------------------------------------------------|-----|

| ANNEXE 23 – Algorithme du processeur matriciel 6x4 UPMs (5).....           | 143 |

| ANNEXE 24 – Algorithme du processeur matriciel 6x4 UPMs (6).....           | 144 |

| ANNEXE 25 – Algorithme du processeur matriciel 6x4 UPMs (7).....           | 145 |

| ANNEXE 26 – Algorithme du processeur matriciel 6x4 UPMs (8).....           | 146 |

| ANNEXE 27 – Algorithme du processeur matriciel 6x4 UPMs (9).....           | 147 |

| ANNEXE 28 – Algorithme du processeur matriciel 6x4 UPMs (10).....          | 148 |

| ANNEXE 29 – Algorithme du processeur matriciel 6x4 UPMs (11).....          | 149 |

| ANNEXE 30 – Algorithme du processeur matriciel 6x4 UPMs (12).....          | 150 |

| ANNEXE 31 – Algorithme du processeur matriciel 6x4 UPMs (13).....          | 151 |

| ANNEXE 32 – Algorithme du processeur matriciel 6x4 UPMs (14).....          | 152 |

| ANNEXE 33 – Algorithme du processeur matriciel 6x4 UPMs (15).....          | 153 |

| ANNEXE 34 – Algorithme du processeur matriciel 6x4 UPMs (16).....          | 154 |

| ANNEXE 35 – Algorithme du processeur matriciel 6x4 UPMs (17).....          | 155 |

| ANNEXE 36 – Algorithme du processeur matriciel 6x4 UPMs (18).....          | 156 |

| ANNEXE 37 – Algorithme de la fonction UPMR.v.....                          | 157 |

| ANNEXE 38 – Algorithme de la fonction UPM.v .....                          | 158 |

| ANNEXE 39 – Algorithme Matlab de reconfiguration des connections (1) ..... | 159 |

| ANNEXE 40 – Algorithme Matlab de reconfiguration des connections (2) ..... | 160 |

| ANNEXE 41 – Algorithme Matlab de reconfiguration des connections (3) ..... | 161 |

| ANNEXE 42 – Algorithme Matlab de reconfiguration des connections (4) ..... | 162 |

| ANNEXE 43 – Algorithme Matlab de reconfiguration des connections (5) ..... | 163 |

| ANNEXE 44 – Algorithme Matlab de reconfiguration (6).....                  | 164 |

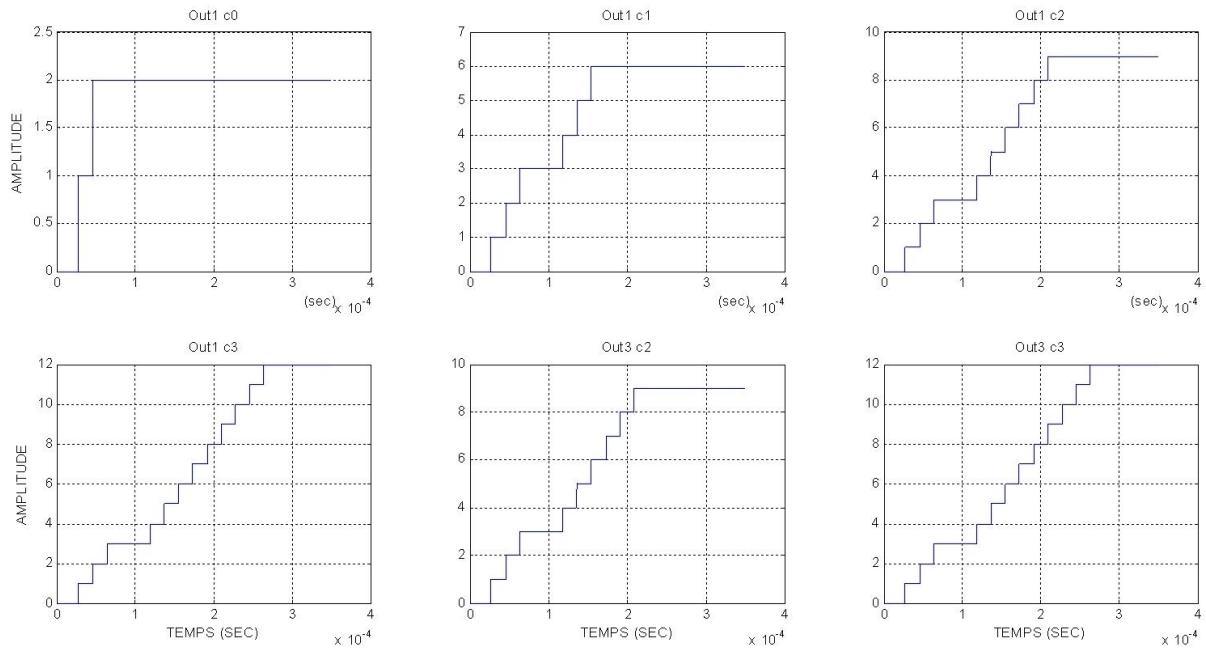

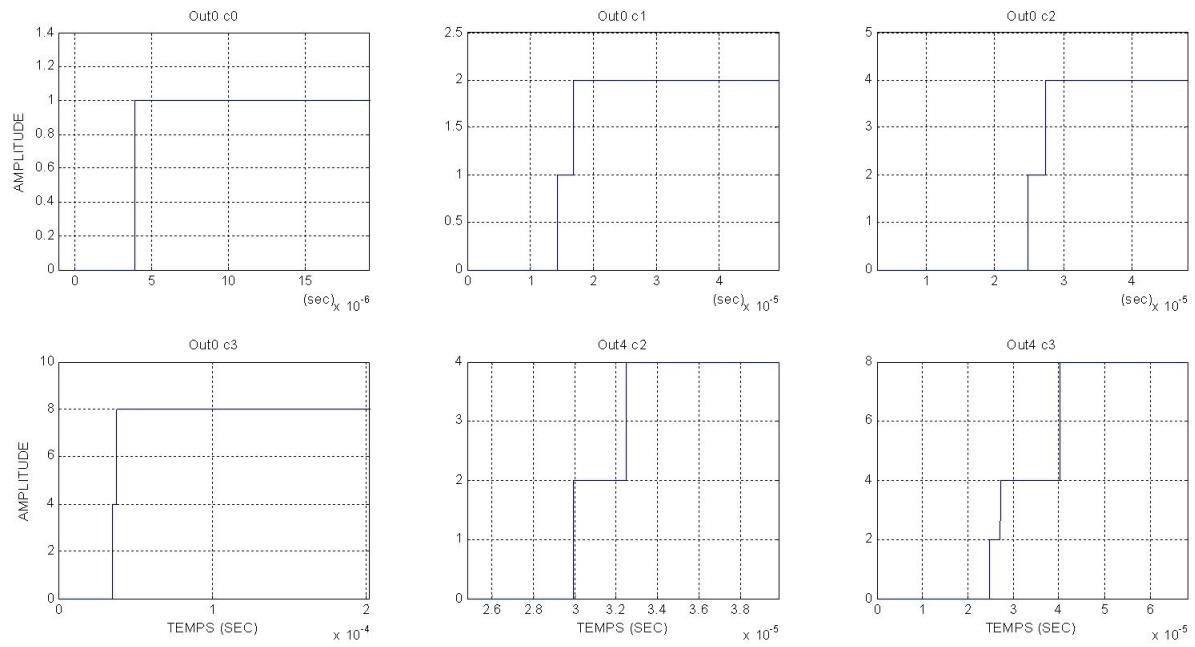

| ANNEXE 45 – Simulation du filtrage FIR/IIR, $N=8$ sur Matlab.....          | 166 |

| ANNEXE 46 – Simulation du filtrage FIR, $N=12$ sur Matlab.....             | 167 |

|                                                                                  |     |

|----------------------------------------------------------------------------------|-----|

| ANNEXE 47 – Simulation du filtre All-Pole, $s=4$ sur Matlab. ....                | 169 |

| ANNEXE 48 – Simulation du filtre All-Zero, $s=4$ sur Matlab. ....                | 170 |

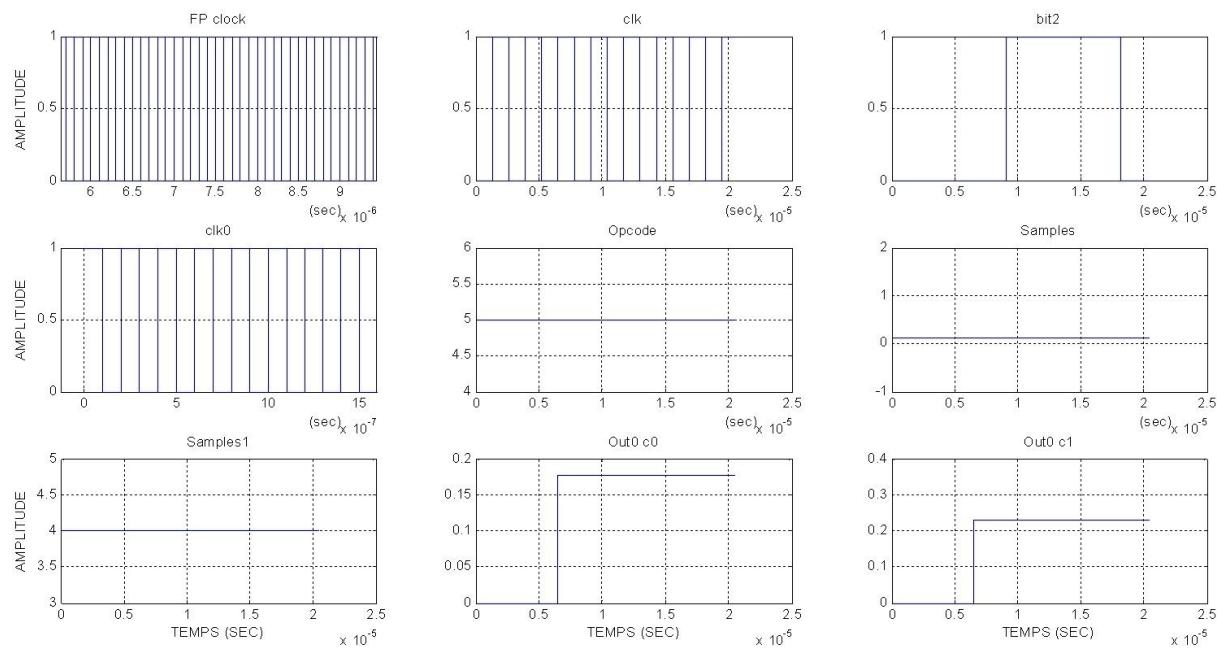

| ANNEXE 49 – Simulation de la FFT radical-4 sur Matlab. ....                      | 172 |

| ANNEXE 50 – Simulation de la division sur Matlab. ....                           | 173 |

| ANNEXE 51 – Simulation de la racine carrée sur Matlab. ....                      | 175 |

| ANNEXE 52 – Test des opérations Point Flottant sur écran VGA. ....               | 176 |

| ANNEXE 53 – Test VGA de la multiplication et addition complexe. ....             | 177 |

| ANNEXE 54 – Test VGA d'un opérateur " <i>Butterfly</i> " radical 2. ....         | 178 |

| ANNEXE 55 – Test VGA d'une FFT, ordre $N=4$ . ....                               | 179 |

| ANNEXE 56 – Performances de vitesse des opérateurs point flottant sur FPGA ..... | 180 |

| ANNEXE 57 – Ressources logiques utilisées par l'UPM.....                         | 181 |

| ANNEXE 58 – Ressources utilisées par les matrices cellulaires 6x4.....           | 182 |

## INTRODUCTION

La théorie du traitement de signal est basée sur une multitude de fonctions mathématiques et d'algorithmes qui sont utilisés dans des domaines comme le filtrage, le codage, la détection, l'analyse, l'enregistrement, la reconnaissance, la reproduction et bien d'autres [1]. Dans la majorité de ces applications, des processeurs numériques ou microprocesseurs sont utilisés.

Les microprocesseurs et les processeurs scalaires utilisent pour leurs calculs des ALUs (Unité Arithmétique Logique) ou des FPUs (Unité Point Flottant) qui sont des circuits logiques utilisés pour des opérations simples telles que la multiplication, l'addition, l'inversion et d'autres calculs basiques. Néanmoins l'utilisation des microprocesseurs implique que ces fonctions mathématiques soient programmées et compilées de manière séquentielle, avec un certain nombre d'instructions, ce qui apporte un délai d'exécution. Les processeurs superscalaires utilisent quelques ALUs et FPUs additionnels par rapport aux processeurs scalaires, ce qui leurs donne une plus grande vitesse d'exécution des instructions et donc une plus grande vitesse de calcul. Il existe aussi des processeurs vectoriels qui sont plus rapides car ils traitent plusieurs données en parallèle et en temps réel. Cependant ces processeurs vectoriels sont trop spécialisés et n'offrent en général qu'une ou deux fonctions de traitement de signal.

Ce mémoire souligne les concepts détaillés qui ont été mis en œuvre dans la recherche et la conception d'un module de propriété intellectuelle (IP block) destiné à être utilisé dans un FPGA pour le traitement numérique des signaux. Ce module appelé UPM (Module Universel de Traitement) est dédié aux processeurs vectoriels ou matrices cellulaires et leurs permettent d'être reconfigurables en vue d'offrir une multitude d'opérations de traitement en parallèle et en point flottant pour avoir une grande précision de calcul.

# CHAPITRE 1 REVUE DE LITTÉRATURE ET PROPOSITION DE RECHERCHE

Cette revue de littérature porte sur les différents processeurs scalaires et vectoriels dédiés au Traitement Numérique des Signaux. La question de recherche, l'objectif général et les objectifs spécifiques y sont énoncés ainsi que les hypothèses scientifiques originales de recherche. La méthodologie de recherche employée y est décrite ainsi que les phases du projet et son échéancier.

## 1.1 Revue de littérature

Les processeurs scalaires et vectoriels spécialisés dédiés au traitement numérique des signaux qui ont fait l'objet de recherches et qui sont actuellement employés sont exposés dans cette section. Néanmoins il sera montré que le concept d'élément de traitement universel des signaux dédié aux processeurs vectoriels existe déjà.

### 1.1.1 Les processeurs Scalaires et Super Scalaires

Les processeurs scalaires peuvent être définis comme des processeurs qui traitent une ou deux données (en point fixe ou point flottant) par cycle d'horloge car ils ne contiennent généralement qu'une ou deux unités arithmétiques logiques ALUs et une unité point flottant FPU pour effectuer des calculs. Les processeurs scalaires ont fait l'objet de recherches qui ont abouti à la création de processeurs superscalaires qui sont constitués d'au moins quatre ALUs et deux FPUs permettant ainsi d'augmenter le nombre d'instructions exécutées en parallèle. Ces processeurs sont majoritairement utilisés dans l'implémentation des algorithmes de traitement numérique des signaux DSP, tels que les processeurs *Pentium* d'Intel ou le *Nios* l'Altera [2-5]. En effet le processeur scalaire, du fait de son architecture qui traite d'un nombre limité de données à la fois et de sa nature séquentielle, permet la programmation de la majorité des algorithmes de DSP. D'autres processeurs scalaires sont plus spécifiques et spécialement utilisés pour les traitements

de signaux comme le *TMS320* de Texas Instruments et le processeur *SHARC* d'Analog devices [6,7].

### 1.1.2 Les Processeurs Vectoriels ou Matrices cellulaires spécialisées

Par opposition aux processeurs scalaires, les processeurs vectoriels (ou Matrices Cellulaires ou Matrices Systoliques) traitent un vecteur de données en parallèle offrant ainsi une plus grande vitesse de calcul par coup d'horloge. Les processeurs vectoriels sont apparus dans les années 1970s et ont formé la base de la plupart des supers ordinateurs jusqu'aux années 1980s et 1990s [8]. Le développement des processeurs scalaires a entraîné le déclin des processeurs vectoriels traditionnels. Cependant, la plupart des processeurs scalaires comprennent aujourd'hui des modules de traitements vectoriels tels que les processeurs à une instruction et multiple données SIMD qu'on peut retrouver dans les cartes de jeux vidéo, les accélérateurs graphiques, les communications spatiales, l'imagerie biomédicale et les applications nécessitant une haute vitesse de calcul, utilisant de multiples données en parallèle. La conception des processeurs vectoriels a pour point de départ la recherche d'idées de systèmes spécifiques à une application donnée [9]. En effet, les processeurs vectoriels, qui sont spécialisés pour une application donnée, ont attiré l'attention des chercheurs pour des implémentations d'une ou deux fonctions spécifiques de traitements numériques tels que le filtrage à Réponse Finie/Infinie FIR/IIR, la Transformée de Cosinus Discrète DCT/IDCT, la Transformée Discrète de Hartley DHT, la Transformée Discrète de Hilbert, le filtrage en Treillis, la Transformée de Fourier Rapide FFT, les fonctions de corrélation et bien d'autres.

- Le Filtrage FIR/IIR et la transformée DCT/IDCT

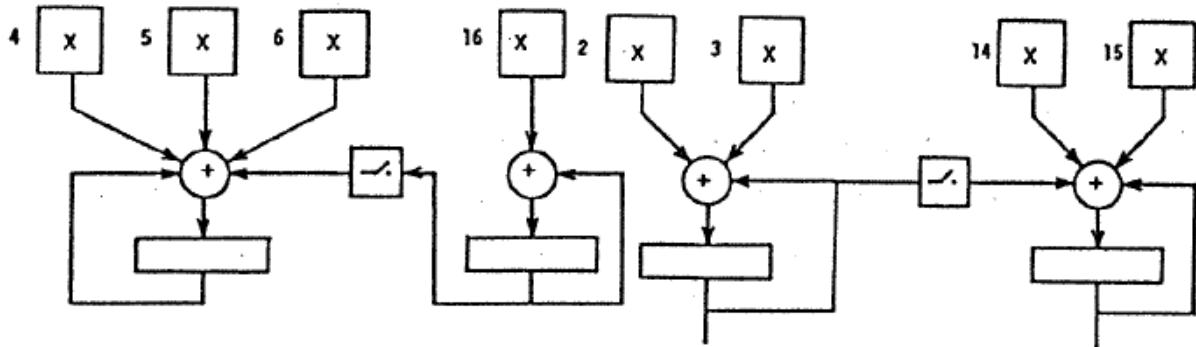

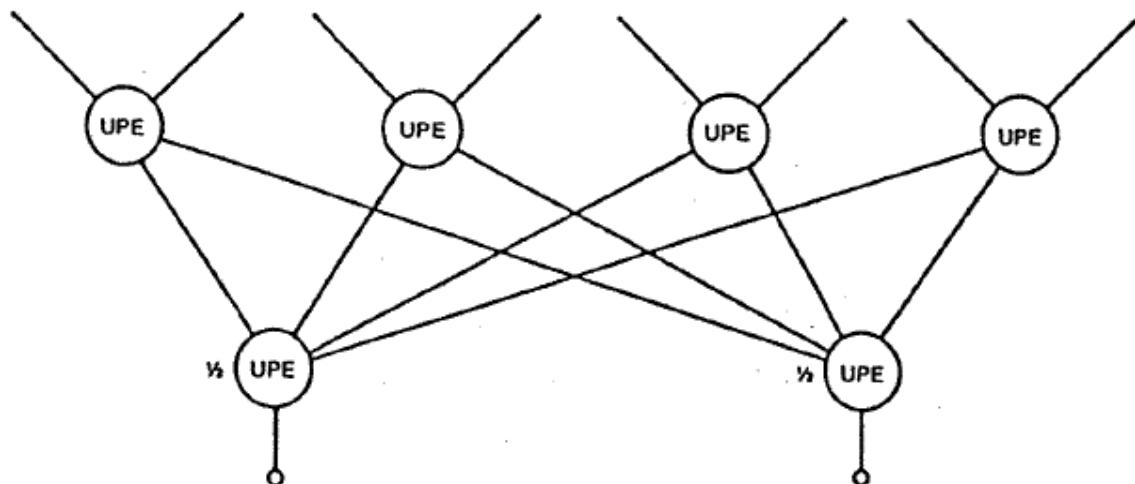

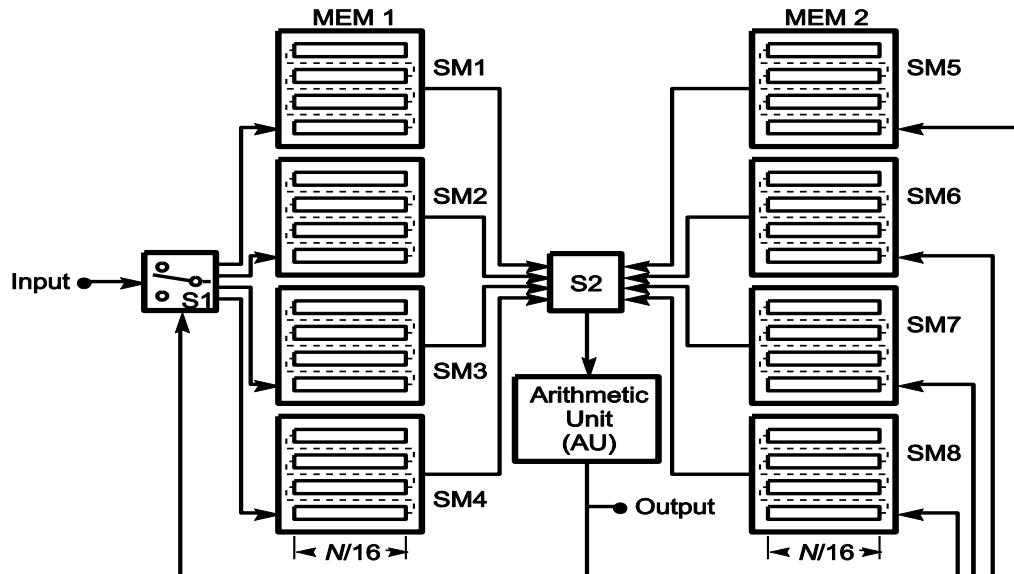

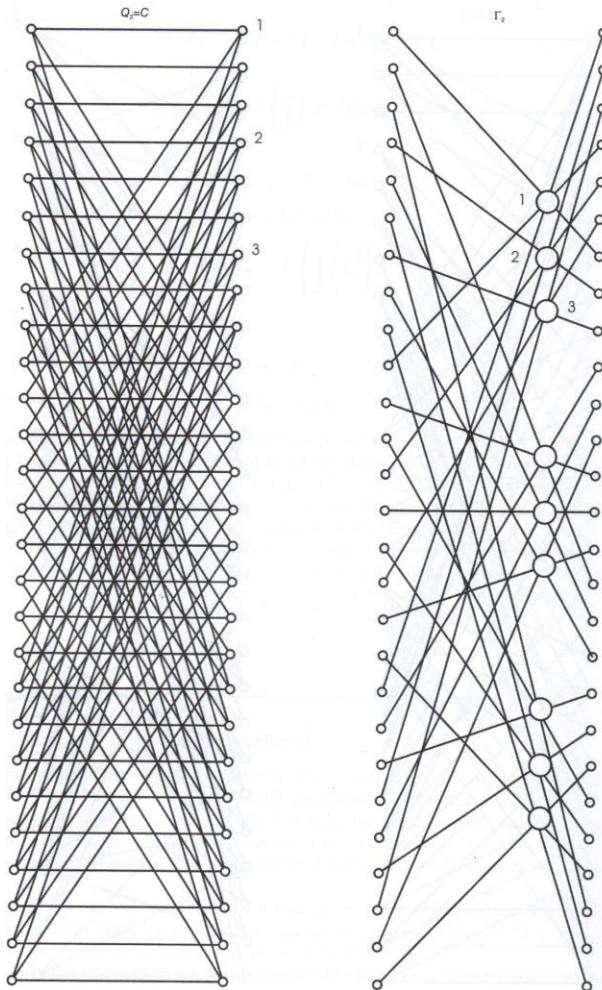

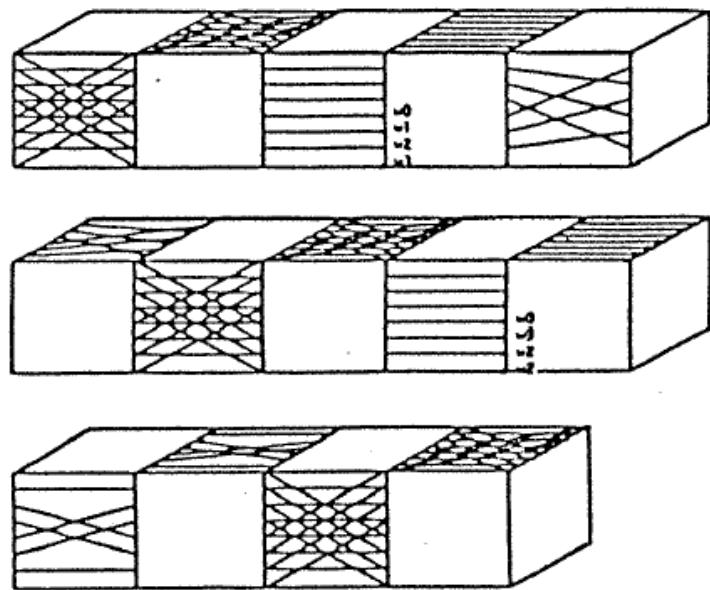

Plusieurs processeurs vectoriels [10,15] ont été conçus pour le filtrage des signaux numériques en une dimension et ont une architecture principalement constituées d'un vecteur de multiplicateurs accumulateurs appelé MACet de registres. Les multiplicateurs accumulateurs MACs sont aussi employés dans le filtrage adaptatif en deux dimensions 2D [10] qui est principalement utilisé dans le traitement numérique des images. Plus particulièrement, le filtrage FIR 2D [10] et [16,18], peut être implémenté avec un processeur vectoriel constitué de vecteurs ou matrices d'éléments de traitement (Processing Element) PE pour le filtrage des images. La figure 1-1 montre l'exemple d'une architecture de processeur dédié aux convolutions, corrélations et filtrage [10]. Des processeurs vectoriels ont été proposés pour des applications de traitement vidéo où des

cellules de traitement en point fixe sont mises en cascade indéfiniment pour effectuer des transformées de cosinus discrètes DCT/IDCT 2D [19,21].

FIGURE 7

MAP CELLS  $C_1$ ,  $C_2$ ,  $C_3$ , and  $C_{11}$

FIGURE 8

MAP CELLS  $C_2$ ,  $C_3$ ,  $C_{11}$ , and  $C_{12}$

FIGURE 9

MAP CELLS  $C_{11}$ ,  $C_{12}$ ,  $C_1$ , and  $C_2$

Figure 1-1 : Exemple de matrices d'UPE [10].

- Le Filtrage en treillis

Le filtrage en treillis est utilisé dans le traitement des signaux pour des applications telles que l'égalisation de canaux (channel equalization), l'identification de systèmes, les banques de filtrage et l'analyse de la voix et d'autres applications de filtrage [22,25]. Dans ces implémentations chaque cellule est caractérisée par la structure en treillis constituée de deux multiplicateurs, deux additionneurs et d'au moins un registre de décalage temporel.

- La Transformée de Fourier rapide FFT et de Walsh-Hadamard FWT

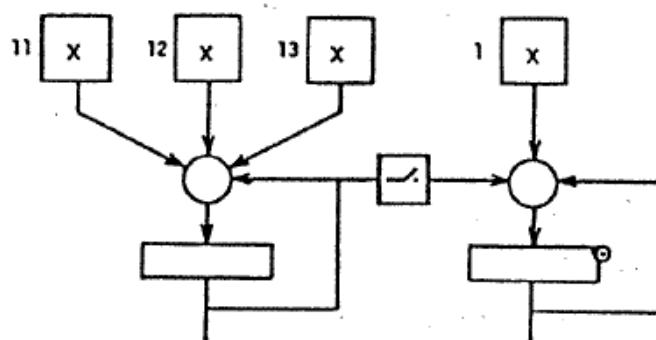

La transformée de Fourier rapide FFT qui, permet une évaluation spectrale des signaux en temps réel, est très utilisée dans le traitement numérique des signaux. Des matrices de multiplicateurs complexes et d'additionneurs complexes sont employées comme cellules pour effectuer une transformée de Fourier rapide FFT telles que les architectures proposées par le professeur Corinthios [10], [26,28]. Il est aussi possible d'utiliser des multiplicateurs et additionneurs complexes afin de construire un processeur dédié aux transformées rapides de Walsh-Hadamard FWT [10], [29,30] en ordre naturel, dyadique et séquentiel mais aussi pour des transformées de Walsh généralisées telles que la transformée de Walsh-Paley Généralisée dont l'architecture est illustrée sur la figure 1-2 pour un ordre  $N=27$ .

**Fig. 1. Operators  $Q_0$ ,  $Q_1$  and  $Q_2$  of the factorization of the GWP transformation matrix with  $N = 27$ ,  $p = 3$ .**

Figure 1-2 : Architecture d'une transformée de Walsh-Paley Généralisée ordre,  $N=27$ , [29].

- La Transformée de Hilbert et de Hankel

Des processeurs vectoriels sont aussi utilisés pour effectuer des transformées de Hilbert HTC dans lesquels chaque vecteur est constitué d'un multiplicateur, un additionneur, une série de registre à décalage et de diviseurs [31,33].

- La Transformée de Hartley

Plusieurs études récentes ont été portées sur l'implémentation de la transformée de Hartley Rapide FHT sur des processeurs vectoriels appelés aussi circuits systoliques [34,39]. Dans la plupart de ces réalisations les matrices ou vecteurs d'éléments de traitements sont constitués d'additionneurs, multiplicateurs de registre et d'un module de calcul numérique de rotation des coordonnées CORDIC qui sert au calcul des fonctions trigonométriques et hyperboliques.

- La séquence d'autocorrélation

Pour l'évaluation de la séquence d'autocorrélation des vecteurs de multiplicateurs accumulateurs sont utilisés [40,41].

### 1.1.3 Les Matrices Cellulaires multifonctionnelles

- Le concept d'Élément de Traitement Universel (UPE)

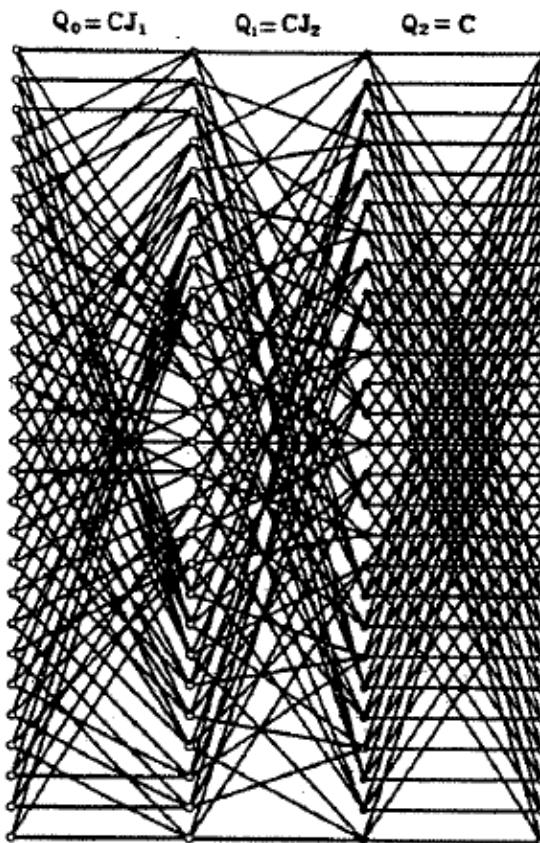

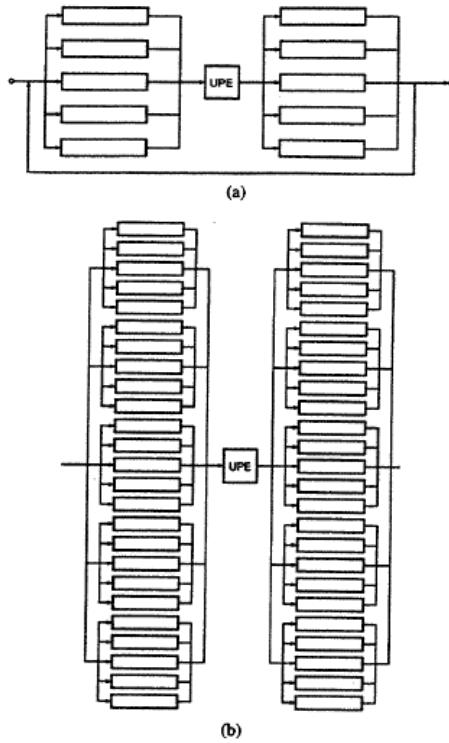

L'idée d'un élément de traitement PE universel a déjà été mentionnée pour la première fois par le Professeur Corinthios qui, dans ses travaux [10] datant de 1985 et dans son article [29] de 1994, est le premier à introduire le concept d'un élément de traitement universel qui pourrait être mis en cascade afin de calculer plusieurs algorithmes de traitement de signaux avec une très grande vitesse de calcul. En effet, dans ce chapitre [10], après avoir discuté des algorithmes à géométrie constante pour l'analyse spectrale généralisée, le Professeur Corinthios propose un modèle d'unité universelle de traitement appelé UPE dont le schéma est montré sur les figure 1-3 et 1-4, capable de traiter des algorithmes qui peuvent être vus comme une multiplication matricielle (convolution, filtrage, corrélation). Cet UPE correspond à un arbre d'additionneur 3D, [10] p 2, qui pourrait incorporer des multiplicateurs et additionneurs point flottant, [10] p 47. Les matrices cellulaires d'UPEs pourraient possiblement effectuer des calculs matriciels des multiplications accumulations et inversions de matrices  $p \times p$  [10] p 47 et incluraient un réseau de permutation et de mémoires externes partitionnées, le tout destiné à l'analyse spectrale et au filtrage FIR et IIR.

En outre l'UPE est un concept d'architecture pour une cellule universelle de traitement contrairement à l'UPM conçu dans ce mémoire sous forme d'un module de propriété intellectuelle (IP block) destiné à être utilisé dans un FPGA.

Fig. 8 (a) Side view of UPE and TATE, (b) A configuration example of UPE

Figure 1-3 : Exemple de configuration de l'UPE [10].

Fig. 9 Transform kernel using UPE's

Figure 1-4 : Configuration de matrices d'UPEs en DFT/Cherstenson [10].

- Brevets :

Des brevets ont été émis pour des processeurs vectoriels spécialisés tels que [42,46] qui montrent les types de processeurs les plus rencontrés dans l'industrie du traitement des signaux, effectuant des FFT, des multiplications accumulations et des opérateurs "butterfly".

## 1.2 Question de recherche énoncée

Est-il possible de concevoir un Module de Traitement des signaux multifonctionnel, reconfigurable par modification des connexions entre les mêmes cellules afin de calculer la plupart des fonctions de traitement des signaux tel que le filtrage FIR/IIR, le filtrage en treillis et les transformations spectrales? Plus particulièrement, pouvant être employés dans la construction de matrices cellulaires en point flottant dédiées à l'analyse spectrale, au filtrage FIR et IIR, au filtrage en treillis, à l'arithmétique complexe, aux calculs d'algorithmes récursifs, qui pourrait être mis en cascade afin d'augmenter l'ordre et la vitesse des opérations de traitement des signaux?

## 1.3 Objectif général

Concevoir théoriquement et tester sur FPGA (Field Programmable Gate Array) un Module Universel de Traitement UPM et les matrices cellulaires associées, en point flottant reconfigurables pour effectuer une multitude de fonctions DSP avec une architecture servant simultanément d'analyse spectrale, de filtrage adaptatif.

## 1.4 Objectifs spécifiques

- **Circuit numérique reconfigurable multifonctionnel**

Concevoir théoriquement un circuit numérique, appelé "*Module Universel de Traitement*" ou "*Cellule*", qui effectue les opérations de traitement suivantes [1]:

- Le Filtrage à réponse finie FIR.

- Le Filtrage à réponse infinie IIR.

- La Multiplication complexe.

- La Transformée Discrète de Hilbert.

- La Transformée Discrète Hankel.

- La Transformée Discrète de Hartley.

- La Transformée de Cosinus Discrète.

- La Corrélation et une Intercorrelation.

- Le Filtrage en treillis All-Pole, All-Zero et Zero-Pole.

- La Génération de fonctions trigonométriques, exponentielles, logarithmiques, Gamma et Bessel.

- La Transformée FFT.

- La Transformée de Walsh-Hadamard.

- La fonction Division utilisant l'algorithme de Newton-Raphson.

- La fonction racine carré utilisant l'algorithme de Newton-Raphson.

- **Matrices cellulaires**

Concevoir le module de traitement universel UPM pouvant être mis en cascade indéfiniment afin d'augmenter l'ordre de l'opération de traitement et de telle sorte qu'il puisse former un processeur Vectoriel ou des Matrices Cellulaires.

- **Point Flottant**

Concevoir l'Élément de Traitement de manière à ce qu'il effectue des calculs en point flottant afin d'augmenter la précision.

- **Programmation Test et Implémentation**

Programmer, tester et implémenter l'UPM sur circuit FPGA. Programmer et simuler des matrices cellulaires.

## 1.5 Hypothèses Scientifiques Originales de Recherche

La recherche proposée ici présente plusieurs hypothèses de contributions en termes de vitesse d'exécution, de nombre de fonctions offertes et en termes de précision:

- *Hypothèse 1:*

Si les matrices d'UPMs sont reconfigurables, offriront-elles un très grand nombre d'algorithmes de traitement des signaux? Réfutabilité: Si trop fonctionnalités sont incluses, il se pourrait que le circuit numérique prenne trop d'espace logique.

- *Hypothèse 2:*

Si ce même module UPM pouvait être mis en cascade, cela permettrait-il d'augmenter le nombre d'opérations effectuées en un seul coup d'horloge et ainsi cela donnerait-il plus de parallélisme et donc plus de vitesse exprimée en  $MHz$  ? Réfutabilité: Si un grand nombre d'UPM est mis en cascade, il se pourrait que cela prenne trop d'espace logique.

- *Hypothèse 3:*

Si le format point flottant IEEE 754 est utilisé les calculs seront-ils beaucoup plus précis ?

Réfutabilité : les opérateurs en point flottant prennent beaucoup d'espace et souffrent d'une latence de plusieurs cycles d'horloge, ce qui est problématique lorsqu'on ne peut pas utiliser le pipeline. La réalisation de cette cellule en point fixe donnerait une latence plus faible et ferait gagner de l'espace logique.

## 1.6 Méthodologie employée

### 1.6.1 Phases du projet

#### a) Phase 1: Activités théoriques

- 1- Conception du circuit de filtrage FIR: Étude théorique des équations de filtrage FIR, IIR et schématisation du circuit numérique à partir des équations et en utilisant des multiplicateurs et des additionneurs [1].

- 2- Conception du circuit Multiplieur Complex: Étude théorique de l'équation Multiplieur complexe et schématisation du circuit à partir de l'équation et en utilisant le circuit précédent.

- 3- Ajout du Filtrage en Treillis All-Pole, All-Zero et Zero-Pole.

- 4- Ajout des fonctionnalités Corrélations et d'Intercorrelations.

- 5- Ajout de la Transformée Discrète de Hilbert.

- 6- Ajout de la Transformée Discrète de Hartley.

- 7- Ajout de la Transformée Discrète de Cosinus.

- 8- Ajout des Générations de fonctions trigonométriques, exponentielles, logarithmiques, Gamma et Bessel.

- 9- Ajout de la Transformée Discrète de Hankel.

- 10- Ajout de la fonction division.

11-Ajout de la fonction racine carré.

**b) Phase 2: Programmation et implémentation sur FPGA**

Programmation, simulation et implémentation de la Cellule sur FPGA en utilisant une carte de développement FPGA *Cyclone II* d'*Altera* et en utilisant l'environnement de développement logiciel *Quartus v9.1* et *Quartus v10.1*. Programmation et simulation de matrices d'UPMs sous différentes reconfigurations.

**c) Phase 3: Test des sous-systèmes et du système.**

- 1- Test par simulation des sous-fonctions de l'UPM en utilisant le Simulateur de *Quartus II*.

- 2- Test par simulation de l'UPM et de vecteurs d'UPMs sous différentes configurations.

- 3- Obtenir une estimation des performances

- 4- Implémentation de l'UPM sur FPGA et test avec écran VGA.

**d) Phase 4: Rédaction d'article**

Rédaction d'un article publié à une conférence.

**e) Phase 5: Rédaction de mémoire**

- 1- Rédaction de mémoire.

- 2- Soumission et présentation du mémoire.

### 1.6.2 Méthodologie utilisée

La méthodologie employée ici consiste à étudier, en premier lieu, les équations théoriques des opérations de traitement de signal à concevoir. Puis il s'agit ensuite de schématiser ces équations sous forme de circuits logiques à l'aide de multiplicateurs et additionneurs point flottant. Pour se faire un filtre FIR/IIR et un multiplicateur complexe sont conçus théoriquement. Les deux opérations sont ensuite rassemblées dans un seul module. De la même manière, les autres fonctionnalités sont schématisées à partir de leurs équations en modifiant le module afin qu'il effectue chaque fonctionnalité en prenant soin de minimiser l'espace pris par l'UPM et aussi en rajoutant du parallélisme afin de gagner de la vitesse.

Sur le plan pratique, l'architecture de l'UPM est programmée sur FPGA en Verilog-HDL en utilisant l'environnement de programmation *Quartus II* d'*Altera*. Des simulations, de plusieurs configurations de l'UPM et de vecteurs d'UPMs, sont réalisées par l'intermédiaire du simulateur

de *Quartus II*. La carte de test *Cyclone II* d'*Altera* est utilisée pour effectuer l'implémentation sur FPGA de l'UPM dont les résultats de tests sont affichés sur écran VGA.

## 1.7 Échéancier détaillé

Le diagramme de Gantt dans l'ANNEXE 1 décrit l'échéancier détaillé du projet.

## CHAPITRE 2 ÉTUDE ET CONCEPTION THÉORIQUE

Les conceptions théoriques d'un élément de traitement, et les matrices cellulaires associées, reconfigurables dans le but d'effectuer la plupart des calculs de fonctions DSP en utilisant les mêmes cellules, sont présentées dans ce chapitre. À cet effet un module de contrôle de la récursivité, l'UPM et des matrices d'UPMs sont construits de telle manière à ce que les mêmes UPMs puissent être réutilisées et reconfigurées en filtres à Réponse Impulsionnelle Finie FIR, filtres à Réponse Impulsionnelle Infinie IIR. Pour se faire un module qui sert au calcul des fonctions récursives est construit et intégré à deux arbres de multiplicateurs accumulateurs. D'autres reconfigurations permettent à ces mêmes cellules de fonctionner en mode filtre en treillis All-Pole, All-Zero et Pole-Zero. Des matrices de corrélations sont montrées comme des possibles implémentations en utilisant ces mêmes éléments de traitement. L'architecture parallèle de ces matrices cellulaires mène vers une évaluation rapide et efficace de la plupart des transformées telle que la transformée discrète de Fourier, la transformée discrète de Hilbert, la transformée discrète de Hartley, la transformée discrète de cosinus et la transformée discrète de Hankel [1]. La transformée rapide de Fourier, rapide de Walsh-Hadamard, rapide généralisée de Walsh-Hadamard et d'autres analyses spectrales généralisées sont aussi implémentées ainsi que d'autres réalisations comprenant la génération de fonctions qui emploie les polynômes de Chebyshev pour générer des fonctions trigonométriques, trigonométriques inverses, exponentielles, logarithmiques, Gamma et Bessel. La technique récursive de Newton-Raphson est utilisée pour construire des matrices cellulaires effectuant simultanément plusieurs itérations des fonctions division et racine carrée [1].

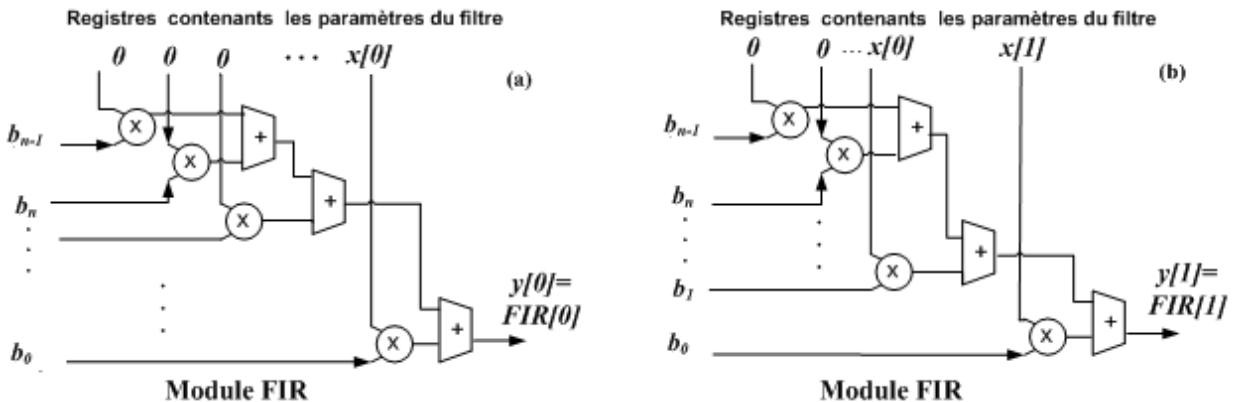

### 2.1 Le Filtre à Réponse Impulsionnelle Finie (FIR)

D'après le livre "*Signals, Systems, Transforms and Digital Signal Processing with MATLAB*"<sup>1</sup>, le Filtre à Réponse Impulsionnelle Finie FIR est un filtre numérique qui a une réponse impulsionnelle nulle entre les intervalles de chaque prise d'échantillons dont le nombre est fini.

---

<sup>1</sup> Voir la Référence [1] p374.

Le filtre FIR est caractérisé par une réponse  $y[n]$  basée uniquement sur les valeurs du signal d'entrée  $x[n]$ , il est donc non récursif. D'autre part, la forme temporelle du filtre peut être vue comme la convolution du signal d'entrée  $x[n]$  avec les coefficients  $b_k$ , telle que représenté dans l'équation suivante :

$$FIR[n] = y[n] = \sum_{k=0}^{N-1} b_k x[n-k] \quad (2.1)$$

Cette équation décrit le filtrage FIR, qui est similaire à celle représentant la convolution temporelle. Le filtre FIR est aussi une moyenne pondérée de points. L'équation (2.1) peut être schématisée par la figure 2-1 a) dans laquelle la *séquence 0* du filtrage FIR a pour équation :

$$y[0] = b_0 x[0]$$

La figure 2-1 b) illustre la *séquence 1* qui s'écrit :

$$y[1] = b_0 x[1] + b_1 x[0]$$

Des registres à décalage sont utilisés pour stocker les paramètres du filtre et les échantillons à filtrer. Cette figure montre la série de multiplicateurs et d'additionneurs point flottant qui permet de faire une convolution de manière parallèle. De même, sur la figure 2-2, les *séquences 2* en a) et b), sont illustrées et peuvent être vues comme une convolution de données point flottant, décalées à chaque séquence. L'équation de la séquence 2 se formule comme suit :

$$y[2] = b_0 x[2] + b_1 x[1] + b_2 x[0]$$

De même que la *séquence*  $n$  s'écrit :

$$y[n] = \sum_{k=0}^{N-1} b_k x[n-k] \quad (2.1)$$

Figure 2-2 : Schéma théorique du filtrage FIR *séquence 2* a) et *séquence n* b).

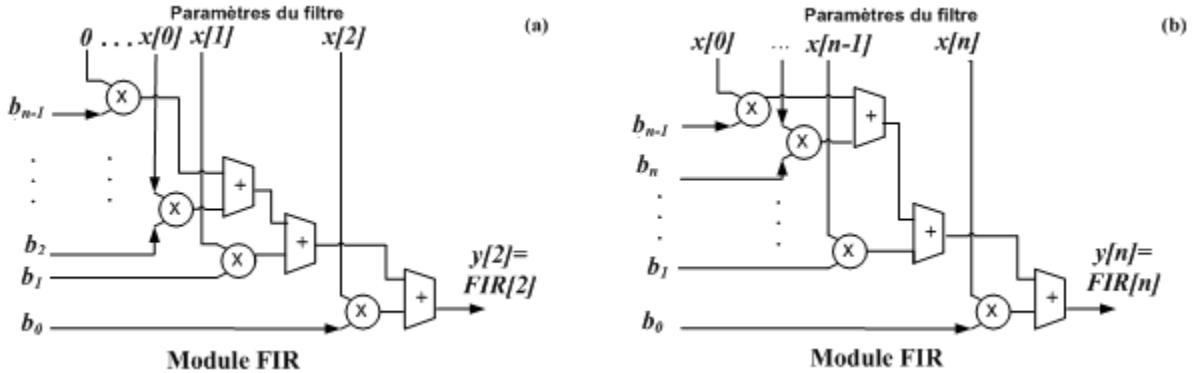

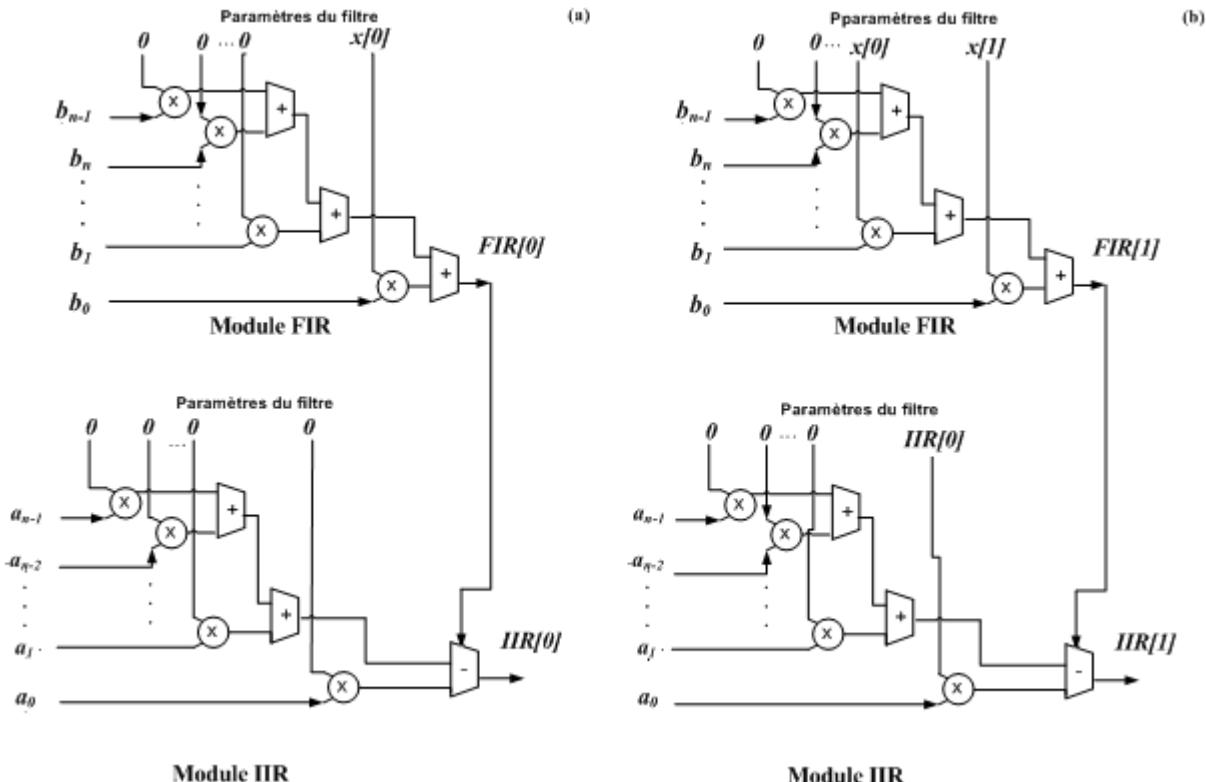

## 2.2 Le Filtre à Réponse Impulsionnelle Infinie (IIR)

Le filtre numérique IIR peut être décrit par l'équation suivante, [1] p374 :

$$IIR[n] = y[n] = \sum_{k=0}^M b_k x[n-k] - \sum_{k=1}^N a_k y[n-k] \quad (2.2)$$

Ce filtre est caractérisé par une réponse  $y[n]$  basée sur les valeurs du signal d'entrée  $x[n]$  ainsi que des valeurs antérieures de cette même réponse  $y[n-k]$ , il est donc récursif. D'autre part, la forme temporelle du filtre est représentée par l'équation (2.2) dans laquelle le signal d'entrée est  $x[n]$  et les coefficients  $b_k$ , sont les paramètres d'une convolution. Une autre convolution implique les paramètres  $a_k$  et la réponse antérieure  $y[n-k]$ . On remarque aussi que l'expression  $\sum_{k=0}^M b_k x[n-k]$  équivaut à un filtrage FIR. Deux modules FIR peuvent donc être utilisés pour effectuer cette opération :

$$IIR[n] = y[n] = FIR[n] - \sum_{k=1}^N a_k y[n-k] \quad (2.2)$$

La figure 2-3 a) illustre la *séquence* 0 dans laquelle deux modules de filtrage FIR sont utilisés d'une part pour le calcul de  $FIR[0]$  et d'autre part pour la convolution de  $a_k$  et de  $y[n-k]$  qui est soustraite à  $FIR[0]$ , ce qui donne le résultat du filtrage  $IIR[0]$  en sortie.

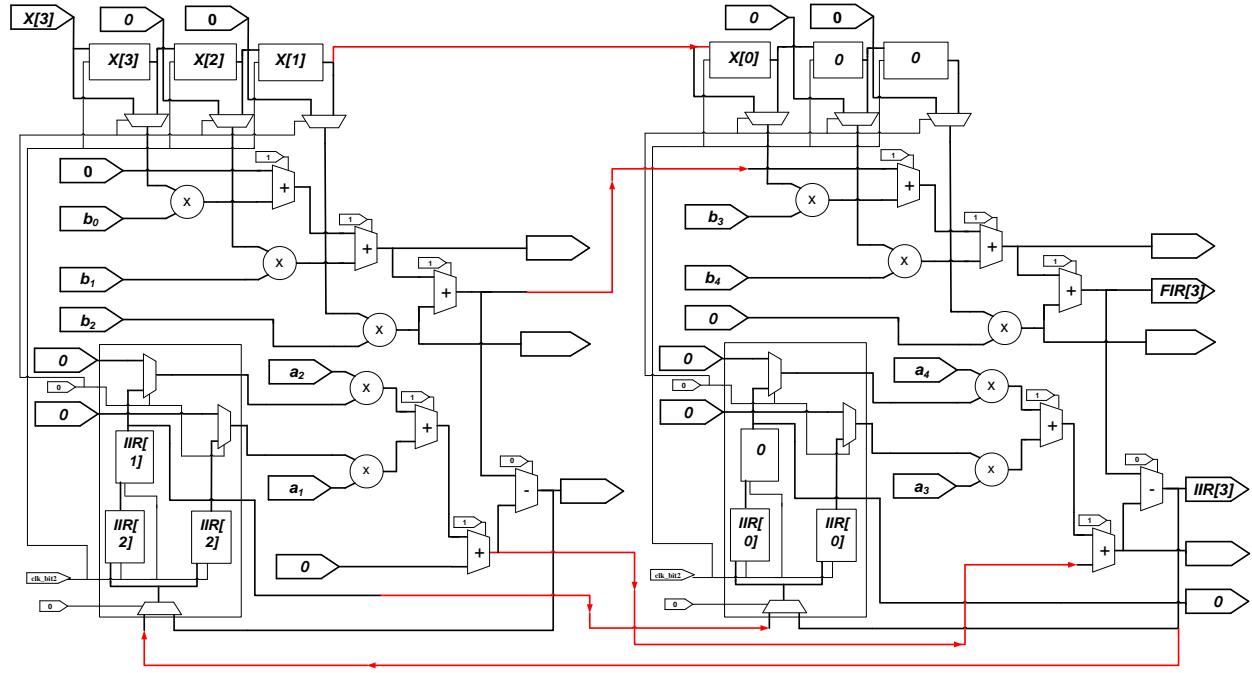

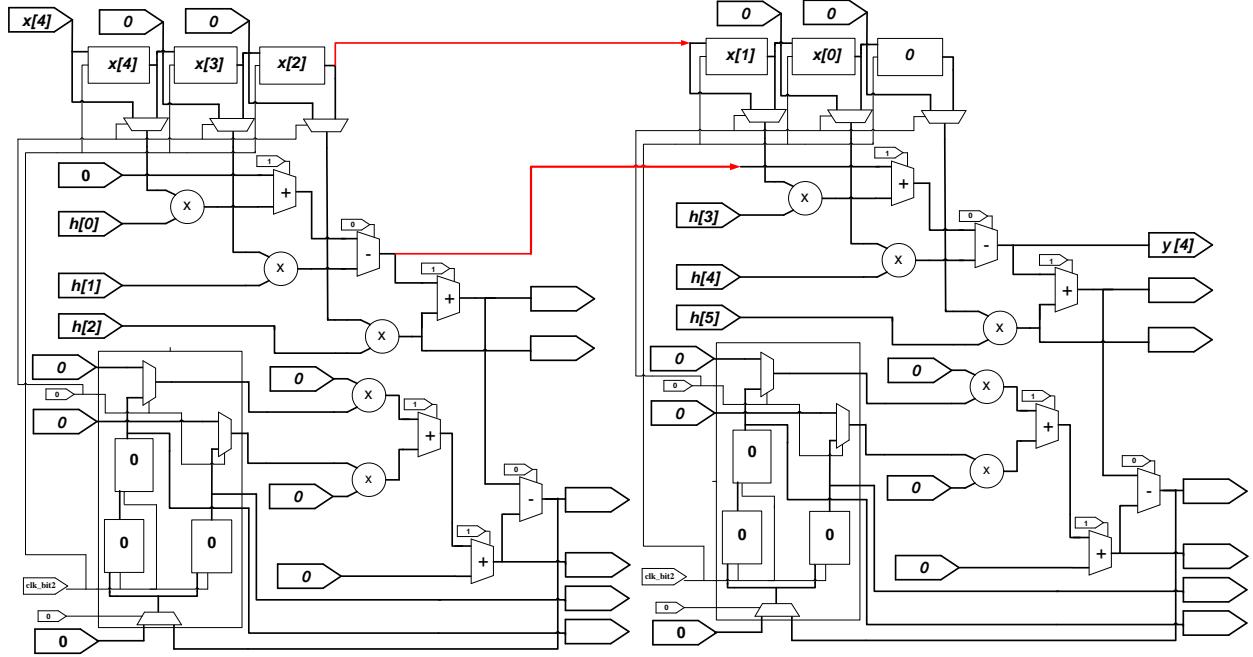

Figure 2-3 : Schéma théorique du filtrage IIR *séquence 0* a) et *séquence 1* b).

En reprenant l'équation (2.2), la *séquence 0* s'exprime de cette manière :

$$IIR[0] = y[0] = b_0 x[0] - 0 = FIR[0]$$

La *séquence 1*, qui est représentée sur la figure 2-3 b), s'écrit :

$$IIR[1] = y[1] = b_0 x[1] + b_1 x[0] - a_1 y[0] = FIR[1] - a_1 y[0]$$

La *séquence 2*, qui est illustrée sur la figure 2-4 a), peut être formulée de la sorte :

$$IIR[2] = y[2] = FIR[2] - a_1 y[1] - a_2 y[0]$$

La *séquence n*, sur la figure 2-4 b), s'écrit de cette façon :

$$y[n] = FIR[n] - \sum_{k=1}^N a_k y[n-k]$$

Figure 2-4 : Schéma théorique du filtrage IIR séquence 2 a) et séquence n b).

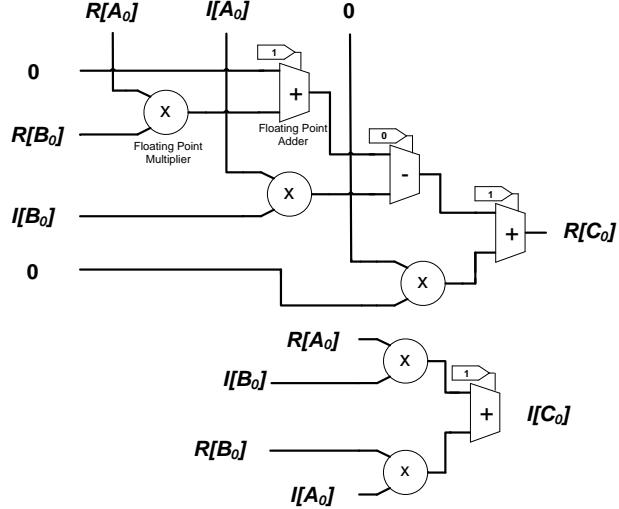

## 2.3 Le Multiplieur et l'Additionneur Complex

Les nombres complexes ont été imaginés et conçus au XVI<sup>ème</sup> siècle par le mathématicien italien Gerolamo Cardano. Les règles de multiplication, d'addition, de soustraction et de division ont, par la suite, été établies par le mathématicien italien Rafael Bombelli au même siècle. Soit deux nombres complexes  $A$  et  $B$ , et  $C$  le résultat de leur multiplication qui est donné par l'équation (2.3).

$$\begin{aligned}

& (\Re\{A\} + j\Im\{A\}) * (\Re\{B\} + j\Im\{B\}) \\

&= \Re\{A\}\Re\{B\} - \Im\{A\}\Im\{B\} + j(\Re\{A\}\Im\{B\} + \Im\{A\}\Re\{B\}) = \Re\{C\} + j\Im\{C\}

\end{aligned} \tag{2.3}$$

Dans la figure 2-5, le module IIR est modifié de sorte qu'il effectue les opérations de multiplications complexes. Ainsi deux multiplications sont calculées en parallèle en une seule séquence, le module du haut donne les parties réelles des résultats tandis que celui du bas, les

parties imaginaires. Cette architecture peut être reconfigurée afin d'effectuer des additions et soustractions complexes.

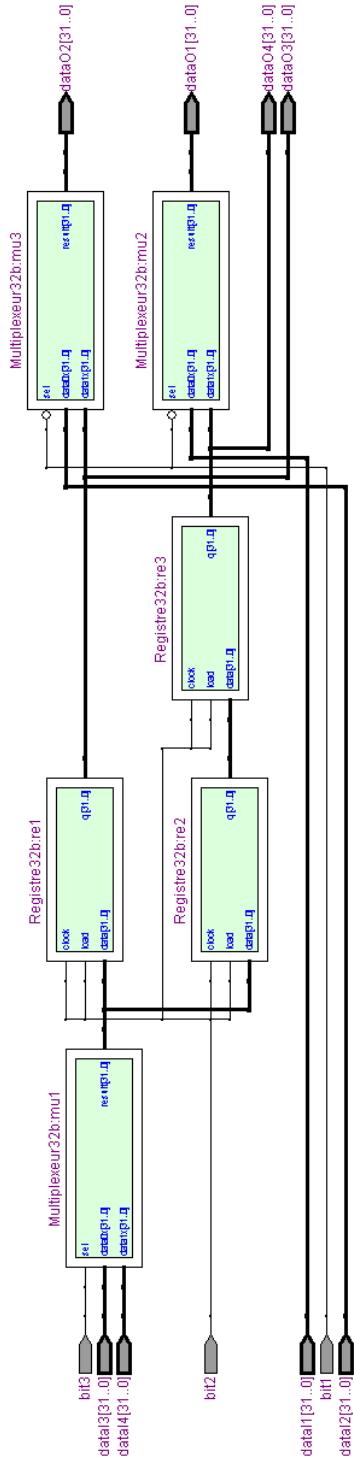

Figure 2-5 : Multiplication complexe

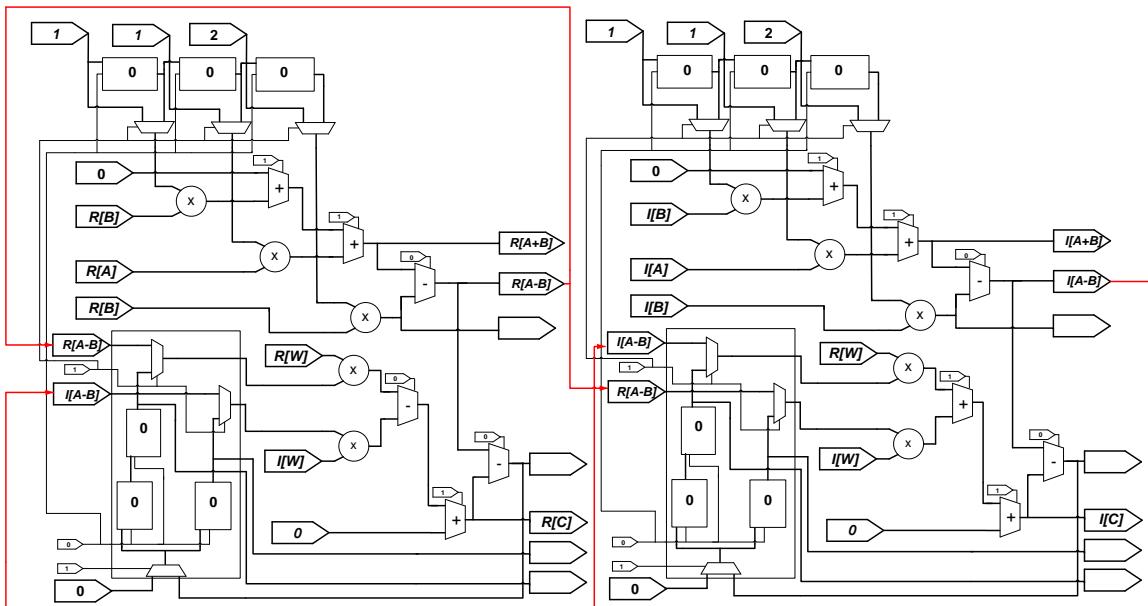

Afin de permettre à l'UPM d'effectuer des calculs récursifs et du filtrage IIR, un module, appelé *Module de Contrôle de Récursivité* est introduit. Ce module permet d'effectuer des calculs récursifs, de contrôler le choix entre la multiplication complexe et le filtrage IIR et de choisir la sélection de l'entrée IIR récursive. Ce module est montré dans la figure 2-6 dans laquelle les noms des entrées et sorties de ce module sont donnés en a) ainsi que sa configuration en multiplicateur complexe en b). Ce module est construit avec trois multiplexeurs, trois registres à décalage et comprend quatre entrées de 32-bits, trois entrées de contrôle de 1-bit et trois sorties de 32-bits. Sur cette figure l'entrée "bit1" sert à contrôler le choix entre le mode multiplicateur complexe et filtrage, l'horloge "clk\_bit2" sert à contrôler les registres à décalage et l'entrée "bit3" sert à sélectionner l'entrée IIR récursive.

Figure 2-6 : Module de contrôle de récursivité a) noms des entrées et sorties b) configuration en multiplicateur complexe.

La figure 2-7 a) illustre le module de contrôle de récursivité configuré en mode "Multiplication Complexe". La figure 2-7 b) indique la configuration du mode IIR pour la *séquence*  $n=0$ , la figure 2-7 c) pour  $n=1$  et la figure 2-7 d) pour  $n=2$ . Le "bit1", qui contrôle deux multiplexeurs, permet la sélection entre les données complexes et les résultats passés du calcul IIR provenant des registres à décalage. Ces trois registres à décalage servent à enregistrer les valeurs passées du filtrage IIR. Si l'horloge "clk\_bit2" de contrôle des registres à décalage est à 1, les données sont enregistrées et utilisées comme entrées des deux multiplexeurs du haut. Un troisième multiplexeur, dans le bas de la figure, sert à sélectionner l'entrée IIR par l'intermédiaire du "bit3". Si ce bit est à 1, le module prend comme entrée IIR les résultats provenant d'autres UPMs, et dans le cas contraire le module prend comme entrée IIR les résultats provenant du même UPM.

Figure 2-7 : Module de récursivité en mode Multiplication Complexe a) et Filtrage b), c), d).

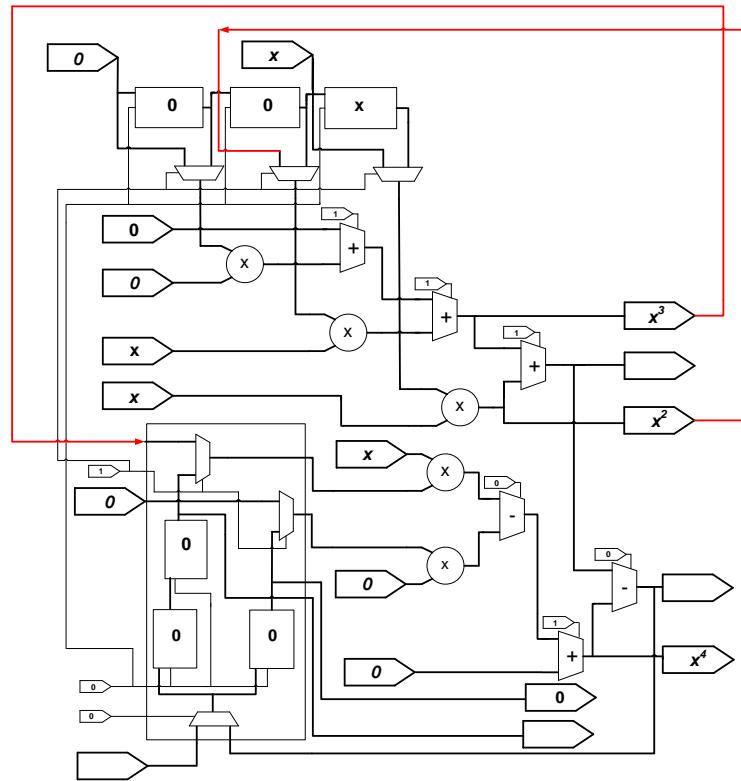

## 2.4 Le Module Universel de Traitement (UPM)

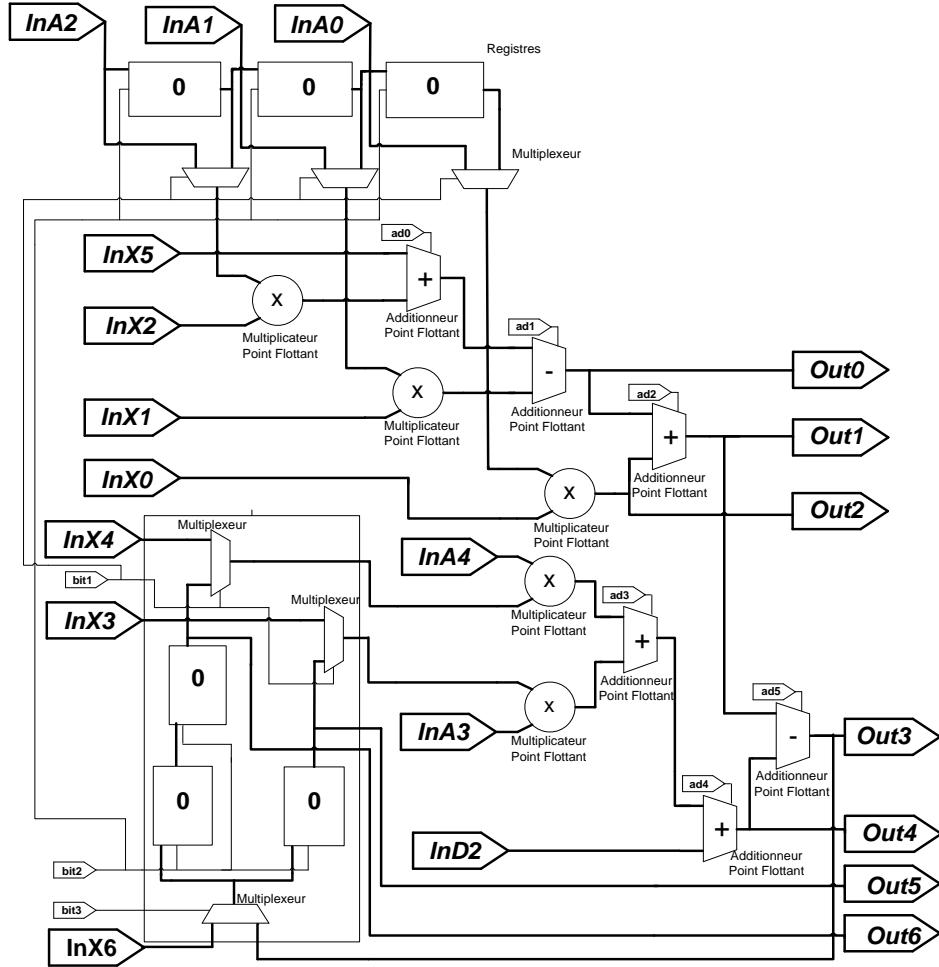

Le Module Universel de Traitement, qui est schématisé dans la figure 2-8, est constitué de cinq multiplieurs, six additionneurs en point flottant et d'un module de contrôle de récursivité. Les additionneurs peuvent effectuer une soustraction grâce à un bit de contrôle du signe de l'opération représenté par une entrée avec un  $1$  pour l'addition ou un  $0$  pour la soustraction. Les entrées de signes des additionneurs sont représentés de cette manière dans le schéma suivant.

Cette cellule comprend treize entrées et sept sorties de données de 32-bits, trois entrées de 1-bit pour le contrôle du module de récursivité et six entrées de 1-bit pour le contrôle des additionneurs. La partie supérieure de l'UPM est construite avec trois registres à décalage et trois multiplexeurs. Afin de permettre le fonctionnement en mode filtrage, une des entrées de la partie supérieure a été connectée à une série de registres à décalage qui sert à décaler temporellement les données provenant de cette entrée. Des multiplexeurs sont utilisés pour permettre à l'UPM de fonctionner en deux modes : filtrage et opération complexe.

Tel qu'illusté sur la figure 2-8, le "bit1" est mis à 1 afin de contrôler les données en entrée de telle sorte que l'UPM fonctionne en mode multiplieur complexe. Ce mode est aussi montré sur la figure 2-7 a). Dans cette configuration les calculs se font en une seule séquence et le résultat apparaît en sortie. Les équations arithmétiques (2.4) à (2.10) du circuit UPM expriment chaque sortie,  $Out0, Out1, Out2, Out3, Out4, Out5$  et  $Out6$  en fonction des entrées de données, de 32-bit, nommées sur la figure 2-8.

Soit la fonction  $mux(test, X, Y)$  qui retourne  $X$  lorsque  $test$  est vrai sinon elle retourne  $Y$ .

$$\begin{aligned} Out0 = & \text{mux}\left(\text{bit1}, \text{InA2} * Z^{-1}, \text{InA2}\right) * \text{InX2} \\ & + \text{InX5} + \text{mux}\left(\text{bit1}, \text{InA2} * Z^{-2}, \text{InA1}\right) * \text{InX1} \end{aligned} \quad (2.4)$$

$$Out1 = Out0 + Out2 \quad (2.5)$$

$$Out2 = \text{mux}\left(\text{bit1}, \text{InA2} * Z^{-3}, \text{InA0}\right) * \text{InX0} \quad (2.6)$$

$$Out3 = Out1 + Out4 \quad (2.7)$$

$$Out4 = \text{mux}\left(\text{bit1}, \text{Out6}, \text{InX4}\right) * \text{InA4} + \text{mux}\left(\text{bit1}, \text{Out5}, \text{InX3}\right) * \text{InA3} + \text{InD2} \quad (2.8)$$

$$Out5 = \text{mux}(\text{bit3}, \text{Out3}, \text{InX6}) * Z^{-1} \quad (2.9)$$

$$Out6 = \text{mux}(\text{bit3}, \text{Out3}, \text{InX6}) * Z^{-2} \quad (2.10)$$

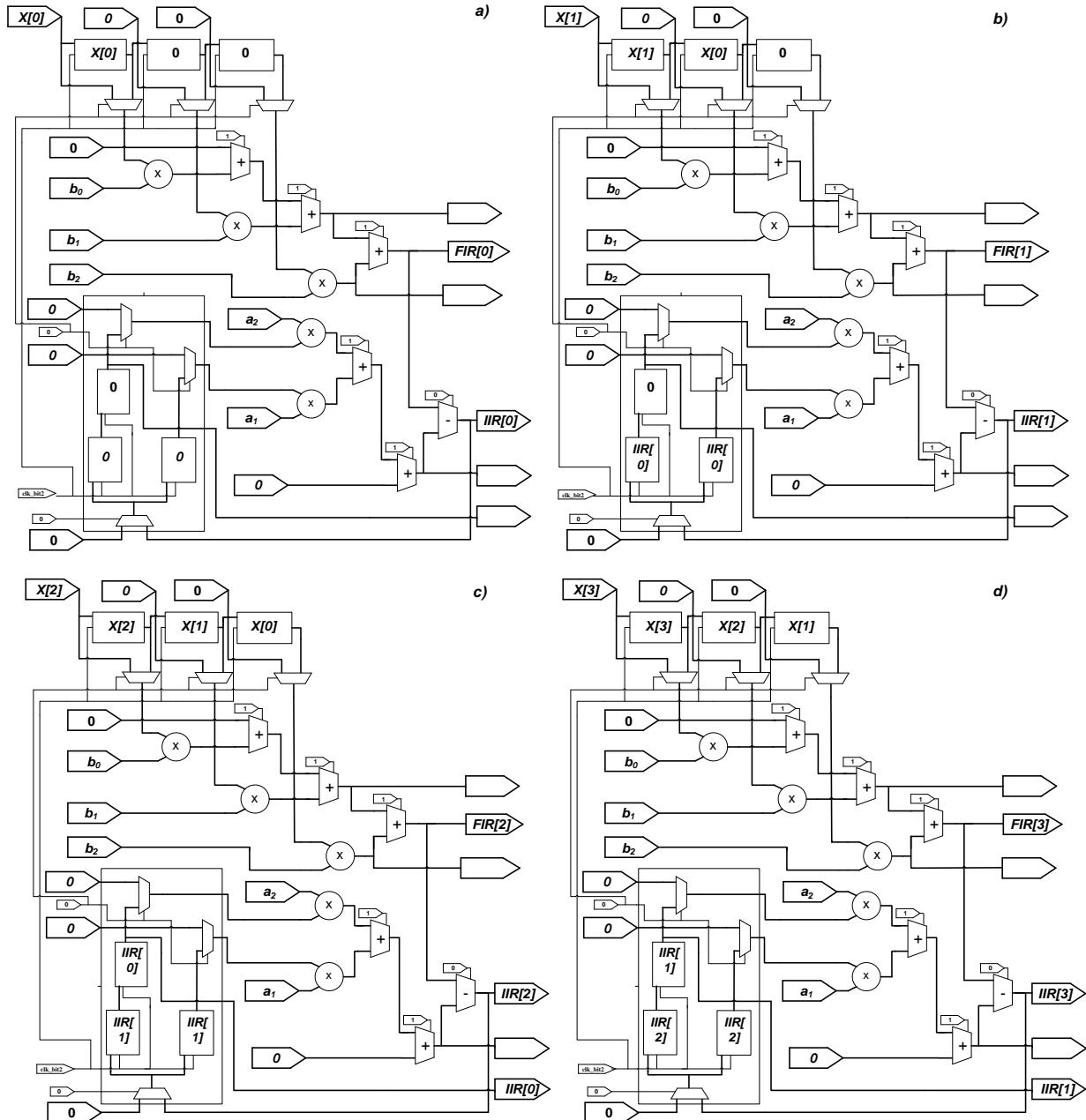

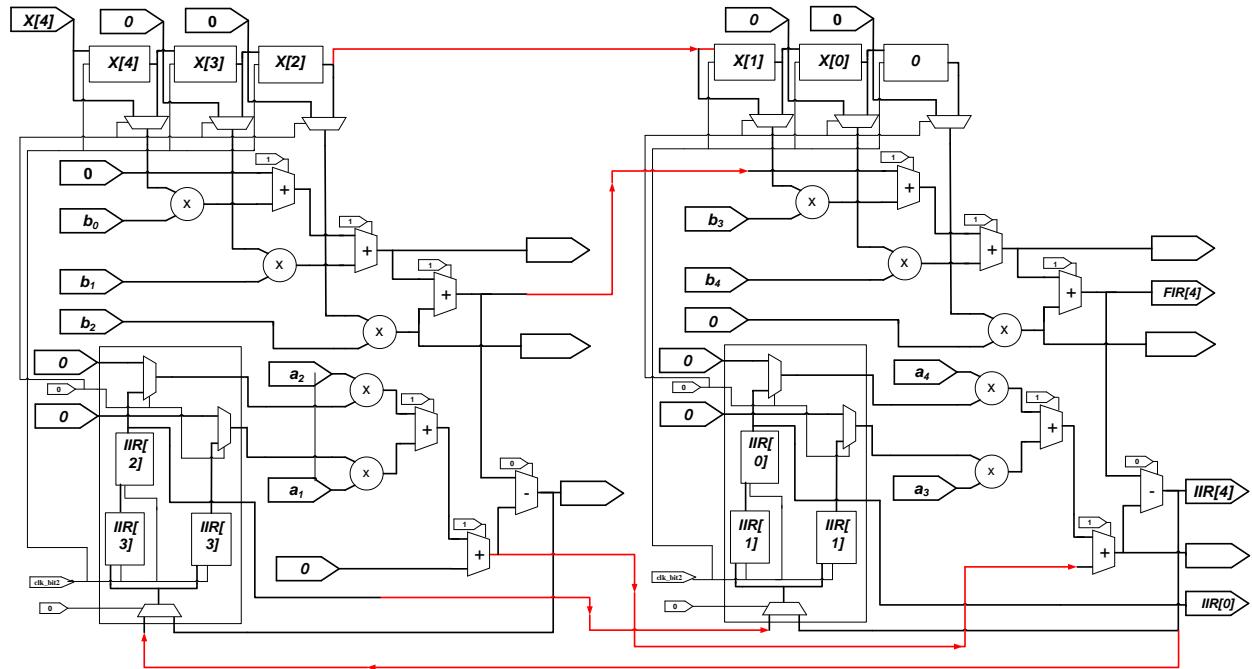

Le filtrage FIR/IIR est illustré sur la figure 2-9 pour les *séquences 0*, *séquences 1*, *séquences 2* et *séquences 3*. Dans ce mode, le bit "bit1" de contrôle des multiplexeurs est mis à zéro et l'horloge "clk\_bit2" permet de contrôler les registres à décalage et ainsi de décaler temporellement les données. Le "bit3" peut être utilisé pour changer l'entrée l'IIR du module de récursivité comme illustré sur la figure 2-9 d). En effet cette entrée sert à mettre en cascade plusieurs UPMs afin d'augmenter l'ordre du filtrage tel que montré sur les figures 2-10, 2-11, 2-12, 2-13 qui illustrent respectivement les *séquences 3*, *4*, *5* et *6* de deux UPMs configurés en cascade afin de faire du filtrage FIR/IIR  $N=4$ . De même, la figure 2-14 montre deux UPMs mis en cascade pour effectuer du filtrage FIR/IIR ordre  $N=6$ , *séquences 5* et *7*. Les équations arithmétiques (2.4) à (2.10) sont utilisées pour représenter un UPM configuré en filtrage FIR/IIR (Fig. 2-9) à l'aide des équations (2.11) à (2.17), en posant la valeur de l'entrée de données *InA2* de l'UPM égale à la valeur de

l'entrée du processeur matriciel "*Samples*". La valeur de *bit1* est mise égale à 0 en binaire et la valeur de *bit3* égale à 1 en binaire. Les valeurs respectives de *ad0*, *ad1*, *ad2*, *ad3*, *ad4*, *ad5* sont prises égales à 1, 1, 1, 1, 1, 0 en binaire et les valeurs des entrées de données *InA0*, *InA1*, *InX5*, *InX3*, *InX4* et *InD2* égales à 0, ce qui donne :

$$Out0 = InA2 * Z^{-1} * InX2 + InA2 * Z^{-2} * InX1 \quad (2.11)$$

$$Out1 = Out0 + Out2 \quad (2.12)$$

$$Out2 = InA2 * Z^{-3} * InX0 \quad (2.13)$$

$$Out3 = Out1 - Out4 \quad (2.14)$$

$$Out4 = Out6 * InA4 + Out5 * InA3 \quad (2.15)$$

$$Out5 = Out3 * Z^{-1} \quad (2.16)$$

$$Out6 = Out3 * Z^{-2} \quad (2.17)$$

Ces équations sont valables pour la (Fig. 2-9), cependant pour une matrice cellulaire comprenant *n* UPMs (Fig. 2-10 et Fig. 2-14), la sortie *Out3*, du *n*<sup>eme</sup> UPM, est connectée à l'entrée *InX6* du premier UPM du vecteur, tandis que pour les autres cellules du vecteur les sorties *Out1*, *Out4*, *Out6* de chaque UPM sont respectivement connectées aux entrées *InX5*, *InD2*, *InX6* de l'UPM suivant dans le vecteur.

Figure 2-9 : UPM en mode FIR/IIR ordre  $N=2$  séquence 0 a), séquence 1 b), séquence 2 c) et séquence 3 d).

Figure 2-10 : Cascade de deux UPMs en mode filtrage FIR/IIR ordre  $N=4$ , séquence 3.

Figure 2-11 : Cascade de deux UPMs en mode filtrage FIR/IIR ordre  $N=4$ , séquence 4.

Figure 2-12 : Cascade de deux UPMs en mode filtrage FIR/IIR ordre  $N=4$ , séquence 5.

Figure 2-13 : Cascade de deux UPMs en mode filtrage FIR/IIR ordre  $N=4$ , séquence 6.

Figure 2-14 : Configuration filtrage FIR/IIR ordre  $N=6$ , séquence 5 a) et séquence 7 b).

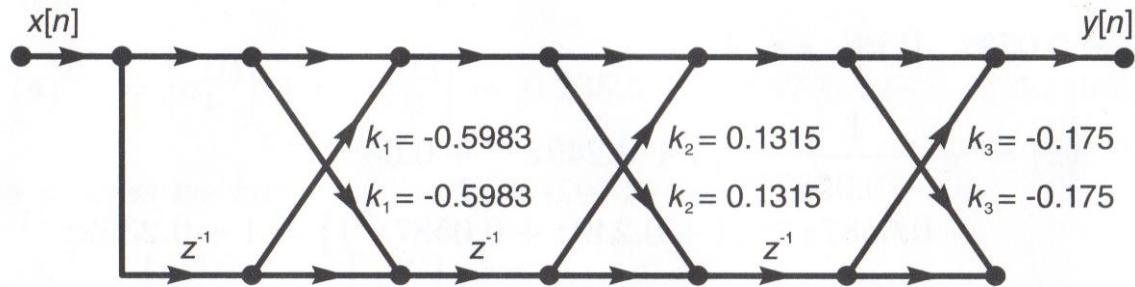

## 2.5 Filtrage en Treillis

### 2.5.1 Le Filtre en Treillis All-Zero à un étage

Les filtres en treillis (Lattice Filters) sont très utilisés dans le traitement numérique vocal et dans l'implémentation des filtres adaptatifs, [1], p760-775. Le filtre en treillis All-Zero à un étage est décrit par les équations suivantes :

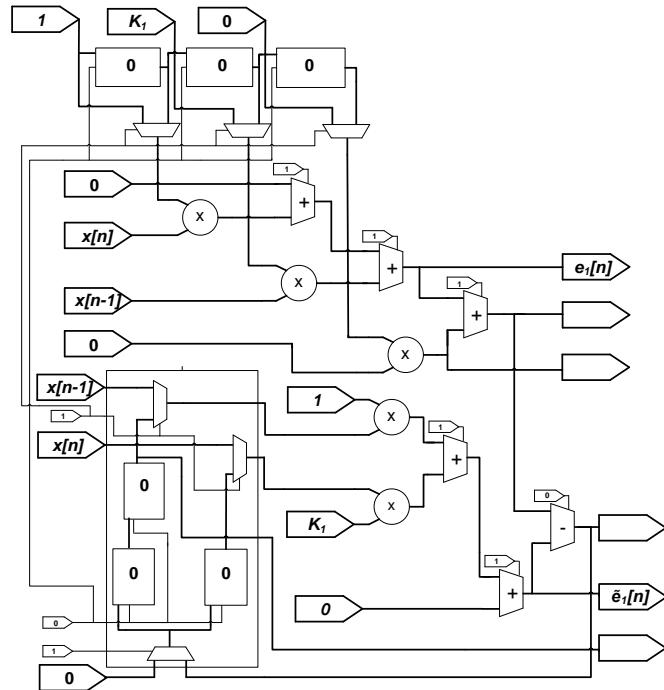

$$\begin{aligned} e_1[n] &= x[n] + k_1 x[n-1] \\ \tilde{e}_1[n] &= x[n-1] + k_1 x[n] \end{aligned} \quad (2.18)$$

La figure 2-15 illustre le schéma théorique d'un filtrage en treillis All-Zero à trois étages tiré de [1] p 767, et la figure 2-16 montre un UPM configuré en filtrage All-Zero à un étage, dans lequel  $e_1[n]$  et  $\tilde{e}_1[n]$  sont les sorties du filtre,  $x[n]$  est la séquence à filtrer et  $k_1$  le coefficient de réflexion du filtre. Les équations (2.4) à (2.10) peuvent être réécrites pour représenter un UPM configuré en filtrage All-Zero (Fig. 2-16) à l'aide des équations (2.19) à (2.25), en posant que les valeurs des entrées de données  $InX2$ ,  $InX3$  de l'UPM sont égales à la valeur de l'entrée du processeur matriciel "Samples". Les valeurs des entrées de données  $InA0$ ,  $InX0$ ,  $InD2$  et  $InX5$  sont mises égales à 0 et les valeurs de  $InX1$ ,  $InX4$  de l'UPM sont posées égales à la valeur de l'entrée du processeur matriciel "Samples"  $* Z^{-1}$  qui est retardée de 1. La valeur de  $bit1$  est initialisée égale à 1 en binaire ainsi que la valeur de  $bit3$ . Les valeurs respectives de  $ad0$ ,  $ad1$ ,  $ad2$ ,  $ad3$ ,  $ad4$ ,  $ad5$  sont mises égales à 1, 1, 1, 1, 1, 1 en binaire. Pour un vecteur d'UPMs (Fig. 2-17 et 2-18) le premier UPM prend les mêmes valeurs de configuration discutées dans la phrase précédente. Cependant la sortie  $Out4$  de chaque UPM est connectée à l'entrée  $InX6$  du même UPM; de même que pour chaque UPM (excepté celle du premier UPM du vecteur) la sortie  $Out0$  est connectée aux entrées de données  $InX2$  et  $InX3$  de l'UPM suivant, la sortie  $Out5$  de chaque UPM est connectée aux entrées  $InX1$  et  $InX4$  de l'UPM suivant :

$$Out0 = InA2 * Samples + InA1 * Samples * Z^{-1} \quad (2.19)$$

$$Out1 = Out0 + Out2 \quad (2.20)$$

$$Out2 = 0 \quad (2.21)$$

$$Out3 = Out1 + Out4 \quad (2.22)$$

$$Out4 = Samples * Z^{-1} * InA4 + Samples * InA3 \quad (2.23)$$

$$Out5 = Out4 * Z^{-1} \quad (2.24)$$

$$Out6 = Out4 * Z^{-2} \quad (2.25)$$

Figure 2-15 : Filtre en treillis All-Zero trois étages, [1] p 767.

Figure 2-16 : UPM configurée en Filtre en Treillis All-Zero, un étage.

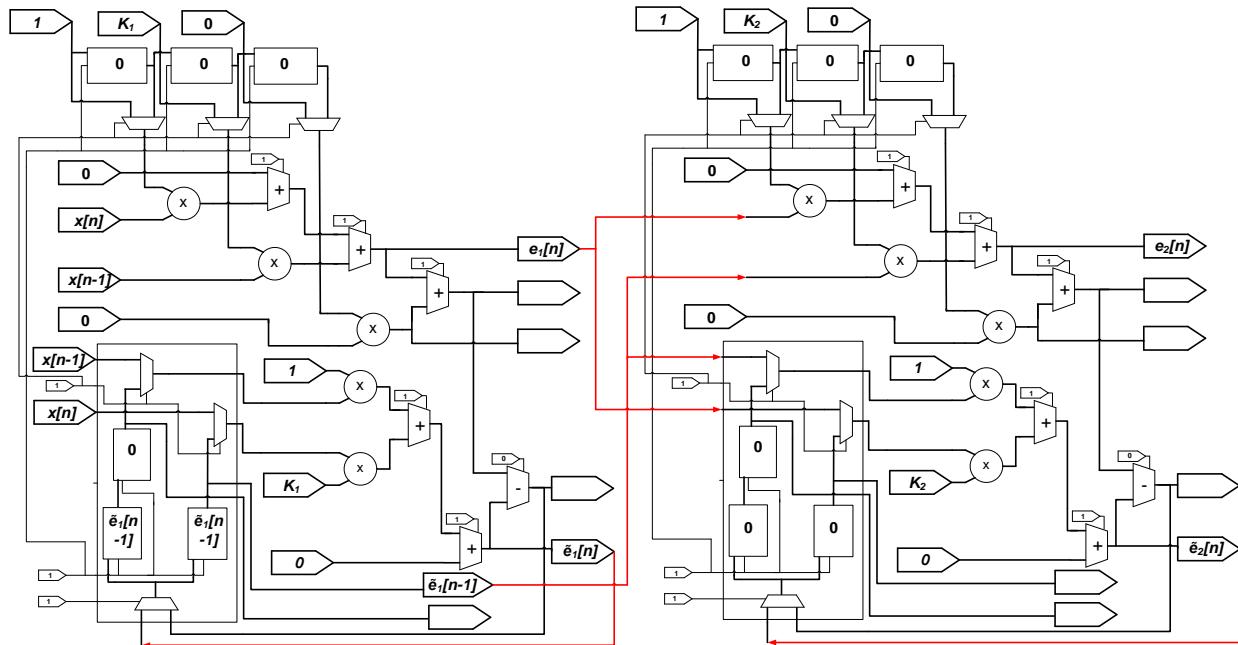

### 2.5.2 Les Filtres en Treillis All-Zero à deux étages et $s$ étages

De la même manière que le filtre en treillis d'ordre 1, le deuxième étage peut être représenté par l'expression suivante :

$$\begin{aligned} e_2[n] &= e_1[n] + k_2 \tilde{e}_1[n-1] \\ \tilde{e}_2[n] &= \tilde{e}_1[n-1] + k_2 e_1[n] \end{aligned} \quad (2.26)$$

Il est possible de mettre en cascade plusieurs filtres All-Zero de sorte que les entrées de l'étage 2,  $e_1[n]$  et  $\tilde{e}_1[n]$ , correspondent aux sorties de l'étage 1. Les résultats  $e_2[n]$  et  $\tilde{e}_2[n]$  sont les sorties du second étage et  $k_2$  le coefficient de réflexion du second étage. L'équation du filtre All-Zero d'ordre général s'écrit comme en (2.27). Ce filtre est illustré sur la figure 2-17.

$$\begin{aligned} e_s[n] &= e_{s-1}[n] + k_s \tilde{e}_{s-1}[n-1] \\ \tilde{e}_s[n] &= \tilde{e}_{s-1}[n-1] + k_s e_{s-1}[n] \end{aligned} \quad (2.27)$$

Figure 2-17 : UPM configurée en Filtre en Treillis All-Zero, deux étages.

La figure 2-18 représente le filtrage en treillis All-Zero à  $s$  étages. Tout comme les équations (2.18) et (2.26), l'équation (2.27) est récursive et dépend des valeurs passées de  $\tilde{e}_s[n]$ . Le module de récursivité est utilisé à cet effet, comme schématisé sur les figures 2-17 et 2-18. La valeur de  $\tilde{e}_s[n]$  est mise en entrée dans le module de récursivité et un registre à décalage permet d'enregistrer  $\tilde{e}_s[n-1]$ . Une sortie transfère la valeur de  $\tilde{e}_s[n-1]$  vers l'entrée du deuxième étage du filtre en treillis. Il est ainsi possible de créer un vecteur de filtrage en treillis dont le nombre d'étage est très élevé.

Figure 2-18 : Vecteur d'UPMs configurée en Filtre en Treillis All-Zero,  $s$  étages.

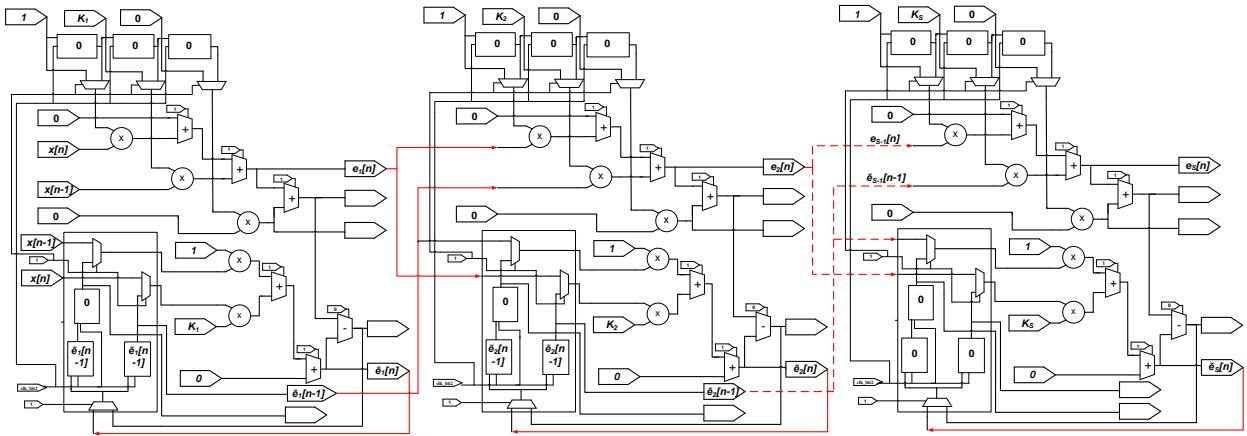

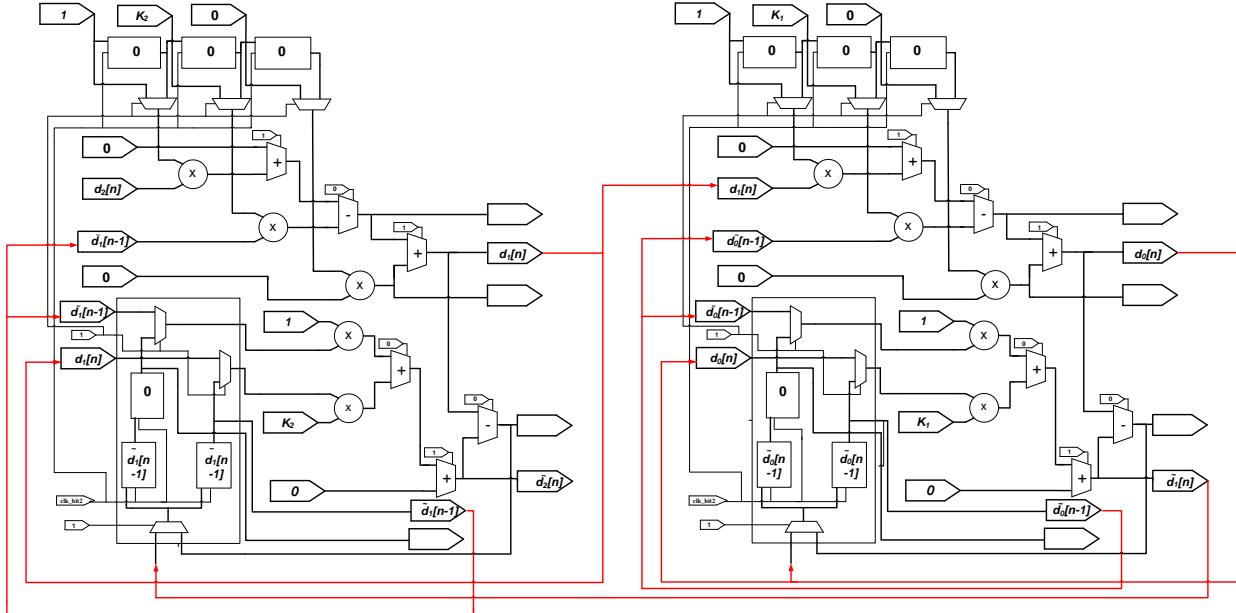

### 2.5.3 Le Filtre All-Pole

Le filtre en treillis All-Pole d'ordre général, [1] p770-773, a pour équation (2.28). À chaque  $s^{ème}$  étage, la sortie  $d_{s-1}[n]$  dépend du paramètre  $k_s$ , de l'entrée  $d_s[n]$  et de  $\tilde{d}_{s-1}[n-1]$  qui représente une valeur passé de  $\tilde{d}_{s-1}[n]$ .

$$\begin{aligned} d_{s-1}[n] &= d_s[n] - k_s \tilde{d}_{s-1}[n-1] \\ \tilde{d}_s[n] &= \tilde{d}_{s-1}[n-1] + k_s d_{s-1}[n] \end{aligned} \quad (2.28)$$

Cette configuration permet donc d'effectuer un calcul de filtrage All-Pole d'ordre indéfini avec un vecteur d'UPMs. En outre la sortie  $\tilde{d}_s[n]$  dépend de la valeur présente  $d_{s-1}[n]$  et passée

$\tilde{d}_{s-1}[n-1]$ . La figure 2-19 représente la cellule reconfigurée en filtre en treillis All-Pole au  $s^{\text{ème}}$  étage. Comme représenté, le module de récursivité est utilisé pour enregistrer la valeur passée de  $\tilde{d}_{s-1}[n]$  qui est  $\tilde{d}_{s-1}[n-1]$ .

Figure 2-19 : Vecteurs d'UPM configurée en Filtre en Treillis All-Pole,  $s$  étages.

Les équations (2.4) à (2.10) peuvent être réécrites pour représenter un UPM configuré en filtrage All-Pole (Fig. 2-19) à l'aide des équations (2.29) à (2.35), en posant que la valeur de l'entrée de données *InX2* du premier UPM du vecteur égale à la valeur de l'entrée du processeur matriciel "Samples". Les valeurs des entrées de données *InA0*, *InX0*, *InD2* et *InX5* sont mises égales à 0. Tous les UPMs du vecteur excepté le premier UPM ont une valeur de *InX2* qui est égale à la sortie *Out1* de l'UPM précédent. Pour toutes les cellules, la valeur de *bit1* est mise égale à 1 en binaire et la valeur de *bit3* est posée égale à 1 en binaire. Les valeurs respectives de *ad0*, *ad1*, *ad2*, *ad3*, *ad4*, *ad5* sont mises égales à 1, 0, 1, 1, 1, 0 en binaire. La sortie *Out5* de chaque UPM est connectée aux entrées *InX1* et *InX4* du même UPM. Pour chaque UPM la sortie *Out1* est connectée à *InX3* et la sortie *Out1* de chaque UPM (excepté le premier UPM du vecteur) est connectée à l'entrée *InX6* du même UPM :

$$Out0 = Samples * InX2 - InA1 * Out5 \quad (2.29)$$

$$Out1 = Out0 + Out2 \quad (2.30)$$

$$Out2 = 0 \quad (2.31)$$

$$Out3 = Out1 - Out4 \quad (2.32)$$

$$Out4 = Out5 * InA4 + Out1 * InA3 \quad (2.33)$$

$$Out5 = Out4 * Z^{-1} \quad (2.34)$$

$$Out6 = Out4 * Z^{-2} \quad (2.35)$$

#### 2.5.4 Le Filtre Pole-Zero

Le circuit précédent est utilisé pour construire un filtre Pole-Zero. En effet le filtre Pole-Zero est la somme pondérée des résultats du filtrage All-Pole avec un gain  $C_s$  qui varie à chaque étage, [1] p775. L'équation (2.36) du filtre Pole-Zero est schématisée par la figure 2-20. La sortie  $\tilde{d}_s[n]$  du filtre All-Pole est multipliée à chaque étage par une constante  $C_s$ . La sortie du pôles-zéros,  $y_s[n]$ , est le résultat de  $\tilde{d}_s[n]$  multipliée par le paramètre  $C_s$ .

$$y_s[n] = \sum_{s=0}^k c_s \tilde{d}_s[n] \quad (2.36)$$

Figure 2-20 : Filtres en Treillis Pole-Zero<sup>5</sup> [1] p775.

## 2.6 Corrélation et Intercorrelation

La fonction de corrélation est décrite par l'équation suivante où  $v[n]$  et  $x[n]$  sont les séquences d'entrées [1] p357-360:

$$r_{vx}[n] = \sum_{m=-\infty}^{\infty} v[n+m]x[m] \quad (2.37)$$