**Titre:** High-Efficiency Low-Voltage Rectifiers for Power Scavenging Systems

**Auteur:** Seyed Saeid Hashemi Aghcheh Body

**Date:** 2011

**Type:** Mémoire ou thèse / Dissertation or Thesis

**Référence:** Hashemi Aghcheh Body, S. S. (2011). High-Efficiency Low-Voltage Rectifiers for Power Scavenging Systems [Thèse de doctorat, École Polytechnique de Montréal].

Citation: PolyPublie. <https://publications.polymtl.ca/649/>

## Document en libre accès dans PolyPublie

Open Access document in PolyPublie

**URL de PolyPublie:** <https://publications.polymtl.ca/649/>

PolyPublie URL:

**Directeurs de recherche:** Mohamad Sawan, & Yvon Savaria

Advisors:

**Programme:** génie électrique

Program:

UNIVERSITÉ DE MONTRÉAL

# High-Efficiency Low-Voltage Rectifiers for Power Scavenging Systems

SEYED SAEID HASHEMI AGHCHEH BODY

DÉPARTEMENT DE GÉNIE ÉLECTRIQUE

ÉCOLE POLYTECHNIQUE DE MONTRÉAL

THÉSE PRÉSENTÉE EN VUE DE L'OBTENTION

DU DIPLÔME DE PHILOSOPHIAE DOCTOR (PH.D.)

(GÉNIE ÉLECTRIQUE)

AOÛT 2011

UNIVERSITÉ DE MONTRÉAL

ÉCOLE POLYTECHNIQUE DE MONTRÉAL

Cette Thèse intitulée:

# High-Efficiency Low-Voltage Rectifiers for Power Scavenging Systems

Présentée par : HASHEMI AGHCHEH BODY Seyed Saeid

en vue de l'obtention du diplôme de : Philosophiae Doctor

a été dûment accepté par le jury d'examen constitué de :

M. AUDET Yves, Ph. D., président

M. SAWAN Mohamad, Ph. D., membre et directeur de recherche

M. SAVARIA Yvon, Ph. D., membre et codirecteur de recherche

M. BRAULT Jean-Jules, Ph. D., membre

M. SHAMS Maitham, Ph. D., membre externe

## **DEDICATION**

*Dedicated to my parents*

*And*

*To my wife and sons*

## **ACKNOWLEDGEMENTS**

My thanks are due, first and foremost, to my supervisor, Professor Mohamad Sawan, for his patient guidance and support during my long journey at École Polytechnique de Montréal. It was both an honor and a privilege to work with him. His many years of circuit design experience in biomedical applications have allowed me to focus on the critical and interesting issues.

I would like to also thank Professor Yvon Savaria, whom I enjoyed the hours of friendly and stimulating technical discussions. His insightful comments, support, and timely advice was instrumental throughout the course of this work. He has been an invaluable source of help for my thesis and all the other submitted papers for publication.

I owe much gratitude to my wife, Mahboubeh, not only for taking care of our children, but also for her love, devotion, support, and patience during these many years, and for believing me every time I said I would graduate the “next year”.

My special thanks go to my departed parents, whom I miss so much. They offered me their unconditional love, and encouraged me throughout my studies. I wish they could see this day. May the Great God bless their souls.

I would also like to thank my sons, Hossein, Hamid and Mahdi for not complaining about my absence in many of their life events because to my studies. I specially appreciate Hossein, for listening to my ideas and providing valuable feedback and help.

Last but not least, my special gratitude goes to all fellow students, technicians, and staff of Polystim and GRM, in the past and present, for constructive discussions, friendship, and all the help they offered me over the years. I cannot list their names as they are many but I enjoyed the pleasant atmosphere they created in our research group. I would like to specifically thank Sami Hached, Ahmed Zargari, and Mohamed Zargari for their valuable time helping me in French translation of the summary section of this thesis.

I would like to thank the Natural Science and Engineering Research Council of Canada (NSERC), Canada Research Chair in Smart Medical Devices, and the Canada Research Chair in

Advanced Microelectronics Design for their financial support. I would also like to thank CMC Microsystems for providing access to design tools, technologies, and chip fabrication facilities.

## ABSTRACT

Rectifiers are commonly used in electrical energy conversion chains to transform the energy obtained from an AC signal source to a DC level. Conventional bridge and gate cross-coupled rectifier topologies are not sufficiently power efficient, particularly when input amplitudes are low. Depending on their rectifying element, their power efficiency is constrained by either the forward-bias voltage drop of a diode or the threshold voltage of a diode-connected MOS transistor. Advanced passive rectifiers use threshold cancellation techniques to effectively reduce the threshold voltage of MOS diodes. Active rectifiers use active circuits to control the conduction angle of low-loss MOS switches.

In this thesis, an active rectifier with a gate cross-coupled topology is proposed, which replaces the diode-connected MOS transistors of a conventional rectifier with low-loss MOS switches. Using the inherent characteristics of MOS transistors as comparators, dynamic biasing of the bulk of main switches and small pull-up transistors, the proposed self-supplied active rectifier exhibits smaller voltage drop across the main switches leading to a higher power efficiency compared to conventional rectifier structures for a wide range of operating frequencies in the MHz range. Delivery of high load currents is another feature of the proposed rectifier.

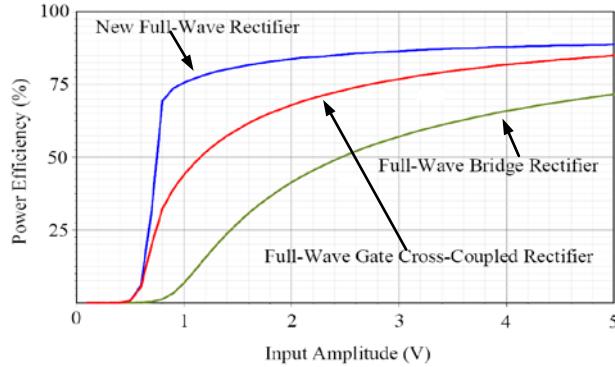

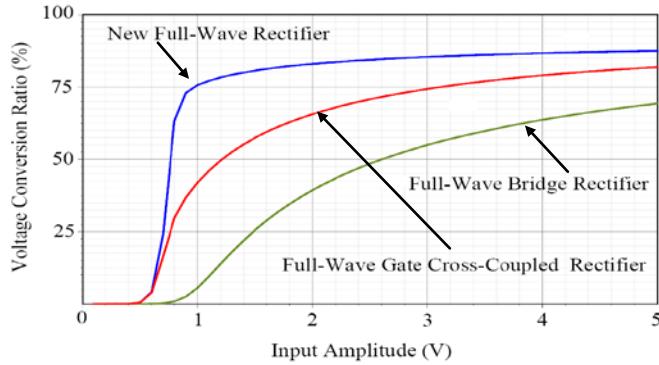

Using the bootstrapping technique, single- and double-reservoir based rectifiers are proposed. They present higher power and voltage conversion efficiencies compared to conventional rectifier structures. With a source amplitude of 3.3 V, when compared to the gate cross-coupled topology, the proposed active rectifier offers power and voltage conversion efficiencies improved by up to 10% and 16% respectively. The proposed rectifiers, using the bootstrap technique in double- and single-reservoir schemes, are well suited for very low input amplitudes. They present power and voltage conversion efficiencies of 75% and 76% at input amplitude of 1.0V and maintain their high efficiencies over input amplitudes greater than 1.0V. Single-reservoir bootstrap rectifier also reduces die area by 70% compared to its double-reservoir counterpart.

Different bulk biasing techniques for the various transistors are proposed. Short auxiliary

paths use the parasitic diffusion-bulk junction of the main pass switches in place of diode-connected pMOS transistors in the auxiliary paths. A flow-back current free scheme is also introduced in which, a smart control circuit selectively regulates the conduction angle of main pass transistors and prevents reverse currents. A close-track scheme using the parasitic diffusion-bulk junction diode of the charging transistor is also proposed. The resulting configuration has a relatively simple structure and produces the best performance among all double-reservoir structures for a wide range of input peak voltages. All the proposed rectifiers were fabricated in a 0.18  $\mu$ m 6-Metal/2-Poly TSMC 3.3 V standard CMOS process.

## RESUMÉ

Les redresseurs sont couramment utilisés dans de nombreux systèmes afin de transformer l'énergie électrique obtenue à partir d'une source alternative en une alimentation continue. Les topologies traditionnelles telles que les ponts de diodes et les redresseurs se servant de transistors à grilles croisées-couplées ne sont pas suffisamment efficaces en terme d'énergie, en particulier pour des signaux à faibles amplitudes. Dépendamment de leur élément de redressement, leur efficacité en termes de consommation d'énergie est limitée soit par la chute de tension de polarisation directe d'une diode, soit par la tension de seuil du transistor MOS. Les redresseurs passifs avancés utilisent une technique de conception pour réduire la tension de seuil des diodes MOS. Les redresseurs actifs utilisent des circuits actifs pour contrôler l'angle de conduction des commutateurs MOS à faible perte.

Dans cette thèse, nous avons proposé un redresseur actif avec une topologie en grille croisée-couplée. Elle utilise des commutateurs MOS à faible perte à la place des transistors MOS connectés en diode comme redresseurs. Le circuit proposé utilise des caractéristiques intrinsèques des transistors MOS pour les montages comparateurs et une polarisation dynamique des substrats des commutateurs principaux supportés par de petits transistors de rappel. Le redresseur proposé présente de faibles chutes de tension à travers le commutateur principal menant à une efficacité de puissance plus élevée par rapport aux structures d'un redresseur conventionnel pour une large gamme de fréquences de fonctionnement de l'ordre des MHz. La conduction des courants de charge élevée est une autre caractéristique du redresseur proposé.

En utilisant la méthode de *bootstrap*, des redresseurs à simple et à double réservoirs ont proposés. Ils présentent une efficacité de puissance et un rapport de conversion de tension élevés en comparaison avec les structures des redresseurs conventionnels. Avec une amplitude de source de 3,3 V, le redresseur proposé offre des efficacités de puissance et de conversion de tension améliorées par rapport aux circuits à transistors croisés couplés. Ces améliorations atteignent 10% et 16% respectivement. Les redresseurs proposés utilisent la technique de *bootstrap*. Ils sont bien adaptés pour des amplitudes d'entrée très basses. À une amplitude

d'entrée de 1,0 V, ces derniers redresseurs présentent des rendements de conversion de puissance et de tension de 75% et 76%. Le redresseur à simple réservoir réduit également l'aire de silicium requise de 70% par rapport à la version à double-réservoir.

Ajoutons que différentes techniques de polarisation du substrat pour les divers transistors sont également suggérées. Des chemins auxiliaires courts utilisent la diffusion parasite au niveau des jonctions des deux transistors commutateurs de passage principaux à la place des transistors pMOS connectés en diode dans ces chemins. Un chemin de retour du courant est également introduit. Ce chemin exploite un circuit de commande intelligent qui régule de manière sélective l'angle de conduction des transistors de passage principaux et qui bloque les courants inverses. Aussi, un circuit réalisé à l'aide d'une diode de diffusion à jonction parasite du transistor de charge est également proposé. La configuration qui en résulte a une structure relativement simple et elle affiche la meilleure performance parmi toutes les structures à réservoir double pour une large gamme de signaux de tension d'entrée. Tous les redresseurs proposés ont été simulés, implémentés et fabriqués avec la technologie CMOS 0.18  $\mu$ m 3.3V CMOS de Taiwan Semiconductor Manufacturing Company (TSMC).

## CONDENSÉ EN FRANÇAIS

### 1. Introduction

Les avancées technologiques dans le domaine des communications sans fil ont mené au développement des circuits intégrés à faible voltage et à basse consommation de puissance. Ces derniers sont nécessaires au bon fonctionnement et à l'atteinte des performances désirées dans les systèmes embarqués. Parmi les classes de systèmes qui nous intéressent, on peut citer les réseaux de capteurs [4,30,37], les étiquettes d'identification par radio fréquence (RFID) [11,134] et les dispositifs biomédicaux intelligents [57,81]. Plusieurs techniques d'alimentation incluant les batteries embarquées et les transmissions transcutanées sont relativement limitées en densité d'énergie, durée de vie, risque potentiel, intégration et en dimensions physiques.

D'un autre côté, les techniques de récupération d'énergie sont des procédés qui permettent de récupérer l'énergie disponible dans l'environnement (incluant le corps humain) et de la convertir en énergie électrique exploitables. Plusieurs travaux dédiés au développement de ces techniques montrent qu'elles peuvent être peu coûteuses, hautement intégrables et capables d'afficher des niveaux de puissance élevés. Néanmoins, ces techniques n'ont pas encore été considérées fiables et réalisables, bien que la recherche est en constante progression [41,155]. Ainsi, fournir l'énergie nécessaire et suffisante pour alimenter les implants électroniques demeure un défi.

La plupart des sources d'énergie, y compris les circuits à alimentation par induction et les systèmes au to alimentés grâce aux techniques de récupérations d'énergie sont de sources alternatives (AC) et doivent être converties en sources continues (DC). On a aussi rapporté que les liens à couplage inductif souffrent d'une faible efficacité de transfert de puissance due au mauvais couplage et à une bande passe étroite. Il est donc crucial d'utiliser un redresseur à haute efficacité à l'interface du système de transmission de puissance.

Dans une structure de redresseur alimenté par liaison inductive, les transistors MOS qui partagent le même substrat et dont les sources sont connectées à la bobine secondaire, sont sujets

à de grandes variations de tension. Par conséquent, cela peut induire d'importants courants de fuite au niveau du substrat, ce qui mène à une situation qui peut provoquer de *latch-up* dans un circuit intégré alimenté par un lien inductif. Ce phénomène pourrait entraver l'efficacité de la puissance du circuit et compromettre sa fiabilité. Par conséquent, la tension de seuil des transistors principaux MOS doit être contrôlée avec précision et les polarisations fixes [54,119] ou les techniques de commutation dynamique du substrat (DBS) [16-20] sont à considérer. Ces dernières (DBS) réduisent aussi l'effet du substrat sur les transistors MOS de rectification.

## 1.1 Implémentation des diodes

Une des parties essentielles d'un redresseur de puissance est l'élément de redressement, appelé aussi diode qui fournit un chemin unidirectionnel pour le courant circulant de la source vers la charge. Toutefois, dans certains procédés CMOS standard, il est impossible d'intégrer des diodes avec d'autres composants. Par conséquent, les diodes sont couramment implémentées en utilisant soit des diodes parasites d'une jonction P-N, ou des transistors connectés en diode. Ils sont tous deux limités par la chute de tension intrinsèque d'une diode ou par la chute de tension directe du transistor (0.4-0.6 V). Les transistors MOS connectés en diode (grâce à la courte connexion entre leur grille et leur drain) opèrent dans la région de saturation, ce qui entraîne une consommation d'énergie élevée.

Par ailleurs, dans les redresseurs à base de transistors connectés en diode,  $V_{GS}$  est modulée par  $V_{DS}$ . Pour les tensions autour de la tension de seuil ( $V_{Th}$ ), ce paramètre change légèrement d'une conduction directe en conduction inverse. Par conséquent, les commutateurs sont lents et ne peuvent être activés et désactivés complètement. Ceci a sujetti la structure à de fuites importantes, ce qui conduit à une faible efficacité de rectification.

La chute de tension dans un MOS connecté en diode dépend de la tension de seuil et de la surtension sur la grille nécessaire pour la circulation du courant. La chute de tension provoque une importante perte de puissance au sein du redresseur, qui affecte l'efficacité globale de puissance et diminue la tension délivrée aux modules précédents. D'autre part, l'usage des diodes Schottky à chute de tension faible (0.3 V) est possible [92,108,174] mais leur

implémentation est coûteuse, en raison de ses étapes de fabrication supplémentaires nécessaires et qui ne sont pas disponibles dans les procédés CMOS standard.

## 1.2 Performances et classification des redresseurs

Il y a de nombreux paramètres, tels que : l'efficacité de conversion de puissance (PCE), le rapport de conversion de tension (VCR), la tension moyenne de sortie (DC), la tension d'entrée minimale, et le courant moyen de charge qui peuvent être utilisés pour la caractérisation des redresseurs. Le PCE est défini comme le rapport de la puissance moyenne de sortie sur la puissance RF d'entrée. Le VCR est défini comme étant le rapport de la tension moyenne (DC) de sortie sur l'amplitude crête à l'entrée. La tension d'entrée minimale est la tension minimale qui pourrait être détectée par le redresseur. Ces tensions maximales et minimales déterminent la plage dynamique du redresseur.

Les redresseurs de puissance sont classés selon la méthode avec laquelle la diode est implémentée. Les circuits redresseurs utilisant des composants passifs comme diode ou les transistors MOS connectés en diode sont appelés redresseurs passifs. Les redresseurs actifs sont une autre catégorie de redresseurs dans lesquels la diode est implantée en utilisant des diodes actives, principalement composée de commutateurs MOS, de comparateurs et de circuits périphériques. Récemment, les redresseurs passif-actif ont également été introduits où le redresseur utilise une configuration à multi-étage, combinée de phases actives et passives.

## 2. Les redresseurs passifs à structures conventionnelles

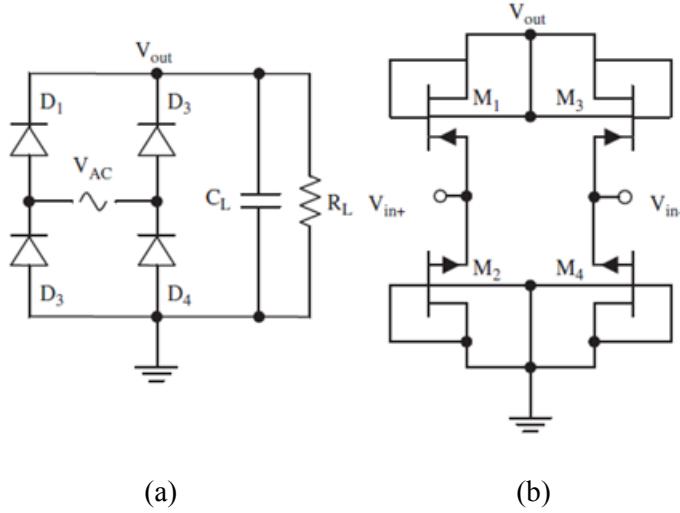

Les redresseurs demi-onde ne sont pas assez efficaces et leurs performances en termes de PCE et VCR sont limitées par une chute de tension dans les diodes. Les redresseurs en pont sont la version populaire des redresseurs pleine onde, où l'arrangement est constitué de quatre diodes (Figure 2.2). Une paire de diodes est responsable de la rectification dans chaque cycle du signal. Lorsque la tension d'entrée est supérieure à la tension de sortie, une diode est conductrice, ce qui permet de délivrer de la puissance à la charge. Dans ce cas l'autre diode régit le chemin du courant de la charge à l'amasse. Bien que la structure, par rapport à un pont

de demi-onde, bénéficie d'une efficacité de puissance plus élevée, de plus petites ondulations de sortie et d'une tension de claquage inverse plus élevée [1,83]. Elle souffre cependant d'une chute de tension de deux diodes en cascade à chaque cycle du signal.

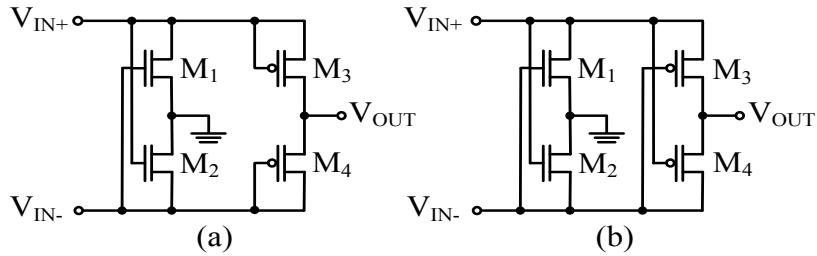

## 2.1 Les rectificateurs passifs à grille partiellement croisée-couplée

Les rectificateurs passifs à grille partiellement croisée-couplée (PGCCR) utilisent dans leur configuration une seule paire de transistors MOS à couplage croisé (Figure 2.4) [60,126]. Dans chaque cycle du signal de ce circuit, le  $V_{Th}$  d'un transistor MOS connecté en diode, est remplacé par la chute de tension efficace à travers un interrupteur MOS. Par rapport à un transistor connecté en diode, la chute de tension d'un interrupteur MOS dans la région triode, est négligeable. Cela réduit effectivement la chute de tension dans le redresseur à un seul  $V_{Th}$  par opposition aux configurations basées sur la chute de tension de deux transistors connectés en diode. L'autre avantage de ce redresseur est de commander la grille du transistor MOS avec une plage de tension plus élevée que celle des structures de transistors montés en diodes, ce qui réduit les fuites provoquées par les commutateurs et améliore leur conductivité. Le redresseur résultant affiche une plus grande efficacité de puissance comparée aux structures conventionnelles (FWDR), cependant, à chaque cycle de la source, il utilise les transistors MOS connectés en diode pour les connexions de charge et souffre donc de chutes de tension associées.

Comme les sources de tous les transistors MOS dans la structure PGCCR sont connectés aux bornes d'entrée, ils subissent de grandes variations de tension provoquant à haute fréquence. La protection de ce circuit contre le *latch-up* et les courants de fuite au niveau du substrat est cruciale. La technique de commutation dynamique du substrat (DBS) est utilisée avantageusement pour polariser dynamiquement les substrats des transistors [16-20].

## 2.2 La topologie à grille complètement croisé-couplée

Le problème associé à la tension de seuil de n'importe quel transistor MOS connecté en

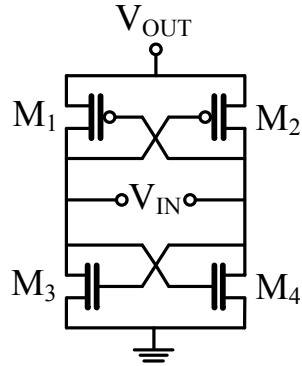

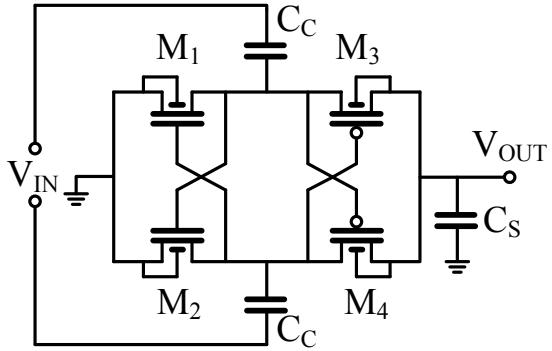

diode suivant une configuration PGCCR est surmonté avec l'utilisation de l'architecture à grille complètement croisé-couplée (FGCCR), où chaque paire de commutateurs MOS dans la topologie de type pont est connectée en croisé (Figure 4.1b) [13,44,111]. En topologie FGCCR, les transistors MOS agissent comme des commutateurs et le circuit n'est donc plus limité par la tension de seuil des transistors MOS connectés en diode, mais plutôt par la chute de tension drain source des interrupteurs.

Cependant, à chaque cycle, il existe une période où le potentiel du nœud de sortie est supérieur à celui du nœud d'entrée pour une durée considérable. Lorsque cela arrive, les paires croisées couplées peuvent ne pas être complètement désactivées, provoquant ainsi une fuite de charge du condensateur de sortie du à la source d'entrée. La fuite de charge dégrade alors l'efficacité d'épuissance. En outre, le circuit redresseur n'a pas une tension d'alimentation stable qui peut garantir le plus haut potentiel dans le système. Par conséquent, si les substrats du pMOS sont statiquement liés à des potentiels fixes, la diode entre la source et le substrat (ou drain et substrat) du transistor peut être polarisée directement.

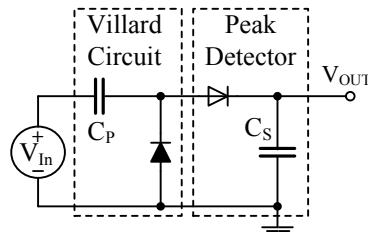

### 2.3 Les redresseurs à base de pompe à charge

Les circuits typiques de pompe de charge AC-DC utilisés dans les systèmes de collecte de puissance et dans les circuits RFID se composent de plusieurs cellules de redresseur dans une configuration en cascade [40,83,163,177]. La pompe de charge de Graetz (Figure 2.6) est souvent utilisée comme cellule de redresseur, qui se compose de diodes et de condensateurs afin de transférer des quantités de charge à travers les commutateurs cadencés de la source vers le condensateur de réservoir à la sortie. Cependant, la puissance de sortie de cette famille de redresseurs est souvent limitée à de faibles niveaux en raison des contraintes imposées pour la quantité des charges transférées et la taille du condensateur de sortie [173-174]. Aussi, ces redresseurs souffrent généralement de grandes ondulations à la sortie. Cela les rend incompatibles avec les applications où un courant élevé de charge et/ou une tension de sortie stable est nécessaire.

Les redresseurs de pompes de charges à multi-étages (Figure 2.8) sont souvent utilisés pour générer de tensions DC sez él evées à partir des f aibles amplitudes d'entrée [39,86,108,173]. Dans cette configuration, les entrées RF sont alimentées en parallèle dans chaque étage grâce à des condensateurs de pompage. Les tensions de sorties sont additionnées en série, afin de produire la tension de sortie finale. Cependant, comparé aux structures à un seul étage, l'efficacité globale de puissance et l'impédance d'entrée de l'étage subit une réduction.

Le problème commun associé aux redresseurs basés sur les multiplificateurs de tension est qu'ils fournissent du courant au nœud de sortie pendant le demi-cycle positif de l'entrée (phase de transfert d'échange). Au cours du demi-cycle négatif (phase de clamping), la diode en parallèle aide à la pré-décharge de la capacité de stockage vers la masse. Ce phénomène réduit l'efficacité globale de conversion de puissance (PCE) de ces types de redresseurs [137].

Les redresseurs à pompe de charge avancée basés sur des commutateurs MOS à seuil dynamiques (DTMOS) [166], ou sur des diodes de puissance ultra-faible (ULPD) (Figure 2.12b) [58,142] sont mises en œuvre à travers le processus Silicium-sur-Isolant (SOI). Le redresseur de type commutateur seulement [137] et ses versions avancées, à polarisation inversée (*bias-flip*) [137-138], et à résonnance [22,64,110,141,159] sont également introduites. Ils se composent d'un commutateur et d'une bobine qui sont connectés à travers la source d'entrée pilotant un redresseur en pont. On a rapporté que ces nouvelles configurations présentent une efficacité de puissance nettement supérieure à celle des redresseurs en pont conventionnel ou au doubleur de tension. Cependant, leur application est limitée par la disponibilité du procédé SOI, par une fréquence d'opération très basse et par la nécessité d'utiliser de grandes inductances.

### 3. Les techniques d'annulation de seuil

La tension de seuil est un paramètre dépendant du processus, qui dépend du choix de l'oxyde et de son épaisseur. La tension de seuil des principaux commutateurs MOS entraîne une dissipation de puissance constante au sein du redresseur et diminue la tension moyenne de sortie (DC). L'effet du substrat affecte la situation en imposant son effet délétère sur la tension de

seuil. L'utilisation de transistors à faible seuil, disponibles dans certains procédés CMOS avancés, peut sembler être une solution prometteuse au problème. Cependant, leur disponibilité n'est pas encore généralisée et les dispositifs implantés sont soumis à des fuites significatives à cause du grand dopage du canal menant à une consommation de puissance excessive et à des problèmes de fiabilité.

Il existe d'autres solutions qui emploient différentes techniques de circuits pour atténuer l'impact de la tension de seuil des transistors MOS.

### 3.1 La technique de la grille flottante

La technique de la grille flottante (FG) a été suggérée pour réduire de façon passive la tension de seuil des transistors MOS en injectant quelques charges dans la couche d'oxyde de la grille du transistor [23,100]. La charge programmée est emprisonnée pour des années sur la grille flottante et complètement isolée (environ 0.1% en 10 ans @ 100°C). Cette technique a été appliquée aux commutateurs MOS à grille croisée partiellement et entièrement couplée [111,128] et aux topologies de redresseurs à base de pompe de charge [100].

En général, les compromis des redresseurs à grille flottante compromettent la tension de seuil du transistor avec une augmentation de la capacité d'entrée. La grille flottante doit être programmée au moins une fois, pour tenir compte de charges résiduelles inconnues accumulées aux grilles flottantes de transistors après la fabrication du circuit intégré (effet d'antenne) [16,100]. Par ailleurs, le processus de programmation est lent, requiert souvent des tensions élevées fournies hors-puce, et présente un impact potentiel sur la fiabilité des circuits [42,111]. D'autre part, la performance du circuit redresseur peut diminuer légèrement avec la fuite de charges de la grille flottante et avec le changement de la température et du temps [16,100].

### 3.2 Techniques d'annulation statique du seuil

Avec ces techniques, une tension DC statique est générée durant une phase de repos du circuit pour être utilisée comme tension de polarisation à tout moment, indépendamment

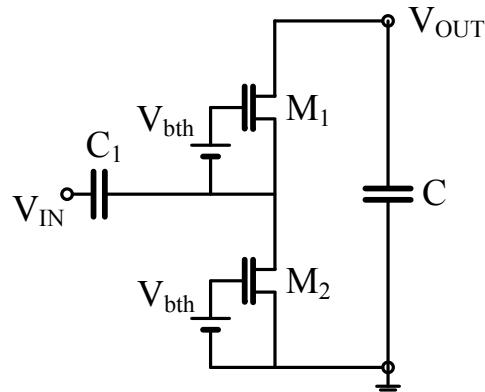

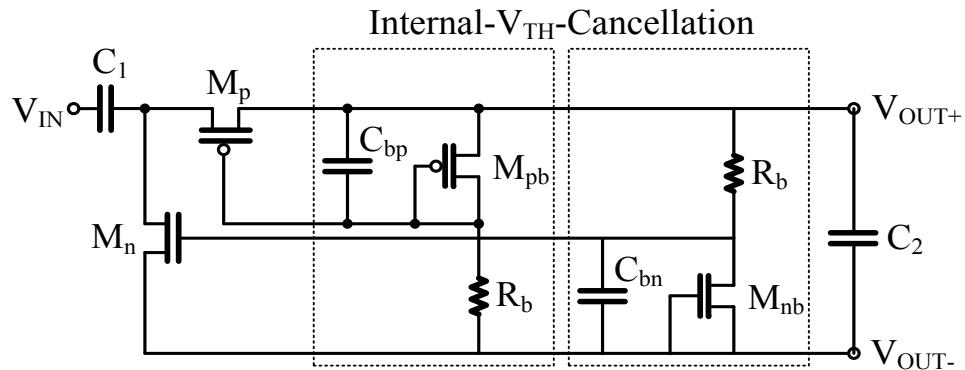

de l'amplitude instantanée du signal d'entrée RF et à la fin d'éliminer ou de réduire l'effet de la tension de seuil des dispositifs MOS sur la phase de travail. La tension DC statique peut être générée à partir des sources internes ou externes. Par conséquent, les différentes techniques, y compris l'élimination externe de  $V_{Th}$  (EVC) (Figure 2.9) [161] et l'élimination interne de  $V_{Th}$  (IVC) (Figure 2.10 et 2.11) [121,169,175,178] sont introduits. D'autre part, ces techniques de polarisation peuvent être appliquées sur les connexions grille et drain [161] ou substrat et source (effet du substrat) des transistors connectés en diode. Malheureusement, toutes les techniques citées consomment beaucoup d'énergie. Néanmoins, la réalisation d'une réduction simultanée de la résistance du canal ( $R_{ON}$ ) et du courant de fuite inverse pour les commutateurs MOS n'est pas possible [92].

### 3.3 Technique de courant commandé par le substrat

La technique de courant commandé par le substrat utilise un courant constant forcé de la connexion au substrat du transistor MOS, afin d'abaisser sa tension de seuil [103]. En utilisant cette technique, la contrainte de tension possible, la consommation de puissance accrue et le couplage du bruit associé à une pompe de charge sont à éviter. De plus, la mise en œuvre de cette technique exige de grands efforts au niveau de l'élaboration du circuit et du dessin des masques.

### 3.4 Technique de condensateur de *bootstrap*

Une autre technique permet la réduction du seuil en utilisant des condensateurs *bootstrap* [79-80,118]. Avec cette technique, la tension de seuil effective d'un transistor MOS connectée en diode est réduite à la différence entre deux tensions de seuil (Figure 2.14) [99]. Parmi les techniques actuellement connues, c'est la mieux adaptée aux procédés standards CMOS avancés, dans lesquels l'implémentation des condensateurs intégrés est faisable.

Avec une tension de seuil du transistor MOS classique, l'utilisation de cette technique pourrait entraîner une augmentation de la plage de tension de sortie pour une source de tension d'entrée donnée. Cette technique a été appliquée à une configuration classique de

redresseur demi-onde construite en utilisant une structure doubleur de tension [99]; cependant, la structure n'a pas affiché les améliorations de performance attendues.

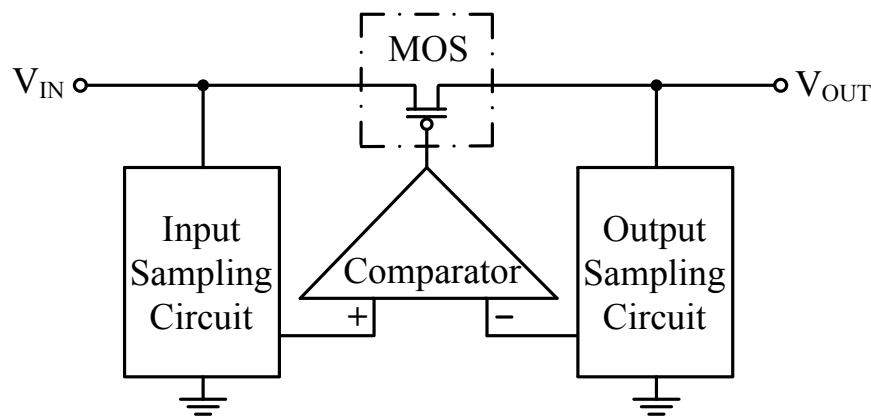

## 4. Redresseurs de puissance actifs (synchrone)

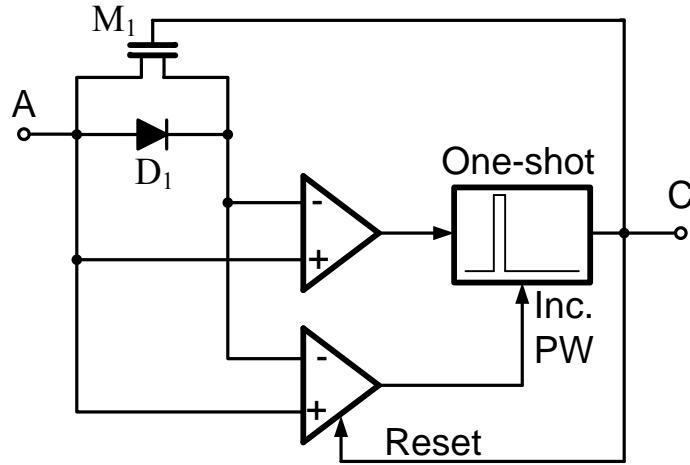

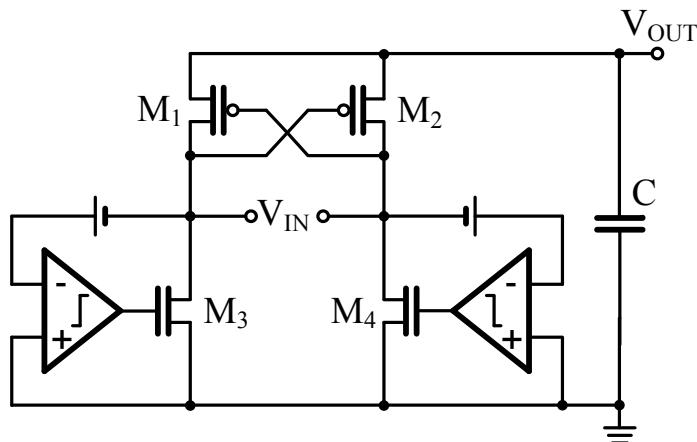

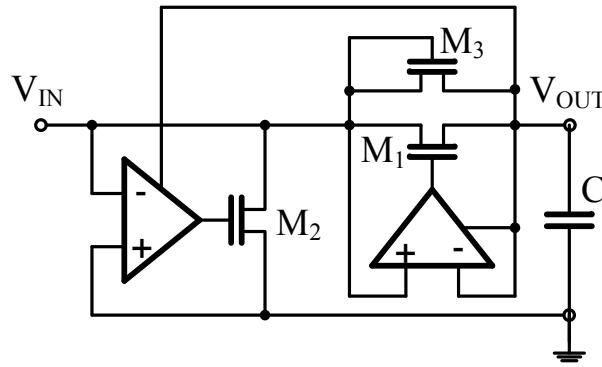

Les redresseurs de puissance actifs (synchrone) se basent sur la diode active, à la place de diodes ou transistors connectés en diode, pour atteindre des performances élevées (Figures 2.15 ou 4.1). Les diodes activent fonctionne presque comme une diode idéale, avec une chute de tension négligeable (généralement aux alentours de 20 mV) en conduction directe et un blocage de courant inverse presque parfait. La diode active se compose généralement de commutateurs, des comparateurs, et dans certains cas de rétroactions. Lorsque la tension d'entrée du redresseur est supérieure à sa tension de sortie, la sortie du comparateur passe au rail d'alimentation positive et active le commutateur pour permettre la recharge du condensateur de sortie. Inversement, lorsque la tension d'entrée du redresseur synchrone est inférieure à la tension de sortie, la sortie du comparateur passe au niveau bas, le commutateur est désactivé et le circuit de la conduction directe est déconnecté. En comparaison avec les structures de redresseurs passifs, cela fait d'appliquer une tension d'entraînement de grille plus élevée sur la base du transistor permet d'améliorer la conductivité du commutateur et l'efficacité de puissance en conséquence.

Généralement, les redresseurs actifs, comparativement aux redresseurs passifs, offrent une commutation ON/OFF plus rapide, utilisent une tension d'entraînement de grille plus élevée améliorant la conductivité des commutateurs, et permettent de réduire les fuites. Par conséquent, ils sont considérablement plus efficaces que leur homologue, en termes de tension de sortie et d'efficacité énergétique [21,97,104,130] pour des fréquences d'utilisation faibles et moyennes. Cependant, cet avantage est obtenu au prix de pertes statiques et de commutation. Les pertes statiques sont dues à l'état statique des circuits actifs, tandis que les pertes de commutation sont principalement associées aux grandes capacités parasites du commutateur.

Le nom bre, la structure et les caractéristiques (retard intrinsèque, la consommation de puissance, vitesse, tension d'alimentation) des comparateurs pourraient affecter considérablement les performances d'un redresseur en termes de courant de fuite inverse, la consommation de

puissance, la génération du courant de charge, la fréquence d'opération, l'ondulation de sortie, et l'efficacité de puissance. Généralement, un commutateur rapide dont la courbe d'hystérésis à faible consommation d'énergie est utilisée et d'autres caractéristiques telles que le gain unitaire de l'abondante pression, le gain en boucle ouverte et le temps de montée sont adaptés dépendamment de l'application. L'utilisation des boucles de rétroactions avec le commutateur sont également utilisées afin d'améliorer les performances (stabilité), ou introduire une tension arbitraire de décalage à leurs entrées [97]. Néanmoins, si ces pertes sont excessives, la réduction de la chute de tension de l'onde de vaste observable. Ainsi, les redresseurs actifs sont principalement mis en œuvre pour les applications dont les fréquences de fonctionnement sont relativement faibles et les plages de tension d'entrée sont supérieures à 1.5 V [128-129].

D'autres inconvénients associés aux redresseurs actifs sont le nombre élevé de composants et la complexité de conception. En général, des conceptions plus complexes comprenant plusieurs composants ont une consommation élevée de puissance et de grande surface.

Les redresseurs actifs utilisent soit l'alimentation d'appoint ou de la tension non régulée et déformée due au condensateur de sortie, pour alimenter leurs circuits actifs. Les redresseurs actifs autoalimentés utilisent soit un circuit de démarrage ou un chemin auxiliaire de chargement pour leur démarrage. Dans certains cas, un transistor MOS connecté en diode permet de charger le condensateur de sortie à partir de la source.

## 4.1 Architectures actives classiques

Le concept d'utilisation de structures actives, pour remplacer les diodes classiques dans les redresseurs passifs, pourrait être appliqué à toutes les structures passives. Il comprend un pont classique [149-150], des structures qui utilisent partiellement ou entièrement la grille croisée-couplée (Figures 2.16, 2.17 et 2.18) [47,56,63,97,104,144], ainsi que des architectures basées sur des pompes de charges (Figure 2.19) [80,113,152].

## 4.2 Redresseurs actifs avancés

Les redresseurs actifs avancés utilisent des commutateurs *phase-lead* [16-19] ou prédictifs

[87] pour améliorer les performances du comparateur et compenser son délai intrinsèque. Bien que ces techniques sont destinées à améliorer significativement la PCE du redresseur, les deux approches sont limitées par la complexité du circuit de temporisation et celle du système de surveillance de tension de sortie, ainsi que par leur sensibilité aux paramètres de conception.

Les redresseurs actifs basés sur une résonance pulsée sont introduits pour être utilisés avec des générateurs d'alimentation, ce qui rend leurs performances considérablement limitées par l'impédance capacitive interne [123,171-172]. Dans cette topologie, la commutation se produit à très basses fréquences (10 Hz à 1 kHz), afin de réduire les pertes de commutation. L'efficacité de puissance du redresseur est signalée être significativement plus élevée que celle des circuits classiques actifs, mais au prix d'utiliser une inductance élevée.

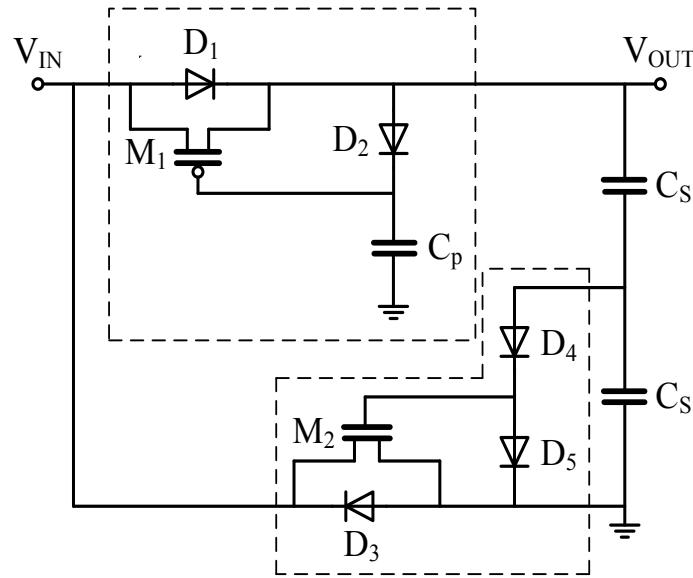

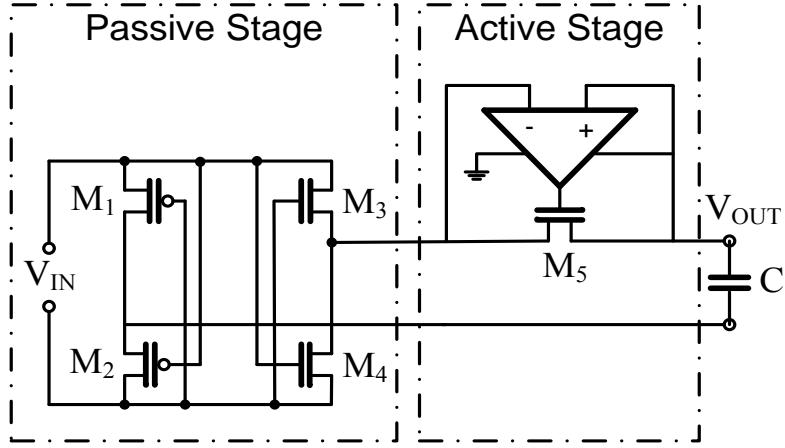

## 5. Les structures de redresseurs de puissance actif-passif

Il y a des topologies de redresseurs où les étages actifs et passifs sont utilisées [105,127,130-133]. Le redresseur se compose de deux étages (Figure 2.20). Le premier étage est un circuit complètement passif et utilisé pour convertir la moitié négative de l'onde sinusoidale, reçue à l'entrée, en une onde positive avec presque pas de chute de tension. Cette conversion est faite avec seulement quatre transistors CMOS standard et sans consommation importante de courant. La chute de tension dans cet étage est également limitée à la chute de tension drain-source des deux commutateurs MOS. Le deuxième étage est une diode active, y compris le commutateur MOS commandé par un comparateur qui utilise la connexion de substrat comme entrée, un biais de bêta-multiplicateur et un chemin auxiliaire pour le démarrage. Le redresseur expose une efficacité de tension et de puissance significativement plus élevée, par rapport aux solutions passives.

## 6. Contributions

### 6.1 Un redresseur actif

Pour améliorer l'efficacité de la conversion de puissance (PCE) et augmenter la tension de

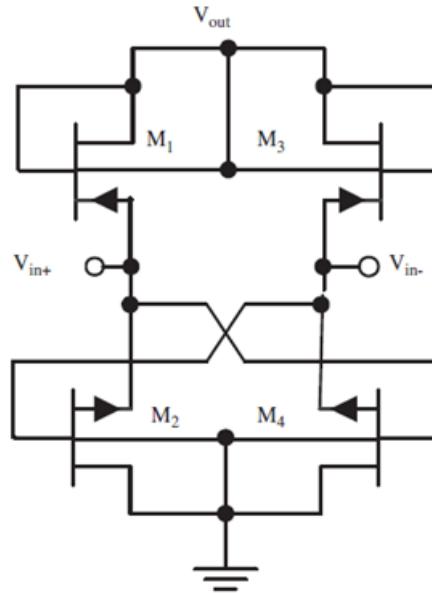

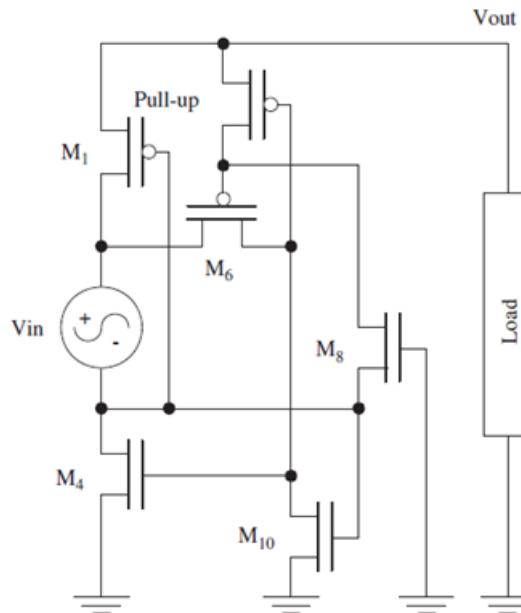

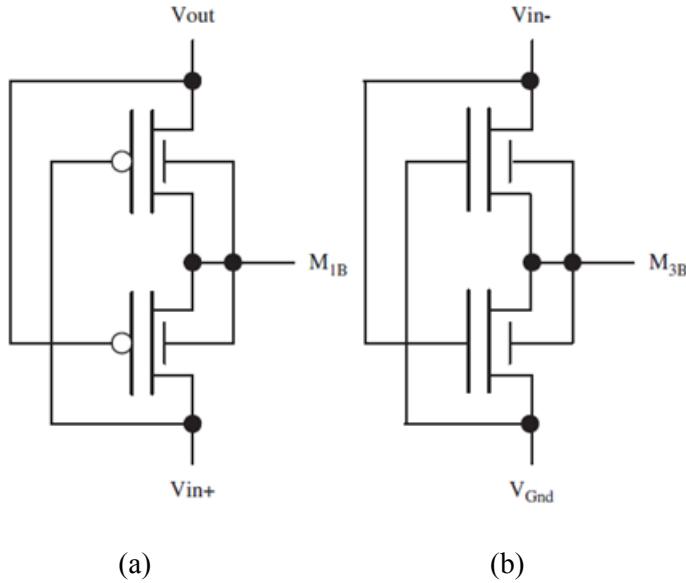

sortie, nous proposons un nouveau redresseur actif à pleine-onde (FWAR) dans lequel les commutateurs MOS remplacent toutes les diodes ou les MOS connectées en diode dans un redresseur de type pont conventionnel (FWBR) ou un redresseur en croisé-couplé (GCCR) structures (Figure 3.4) [71]. Le redresseur utilise des transistors de pMOS en forme de la grille croisée-couplée avec des transistors nMOS jouant le rôle de commutateurs à faible perte dans leur région triode, où ils peuvent présenter une chute de tension très faible à travers leurs terminaux drain-source. Les tensions les plus élevées disponibles dans le circuit sont appliquées de manière dynamique aux commutateurs à transistors afin de maximiser leur transconductance et minimiser, par conséquent, leur résistance de canal. Ainsi, ils n'introduisent pas de chute de tension à cause de  $V_{Th}$  dans le chemin direct de la source à charge. Les fuites à travers le substrat sont également minimisées par la polarisation dynamique de N-puits de pMOS avec la tension la plus élevée possible. Le design ne nécessite ni une source d'énergie interne, ni un chemin de signal auxiliaire pour la livraison de puissance au démarrage.

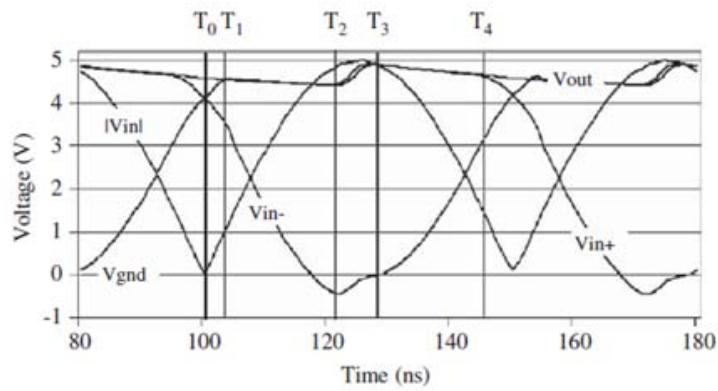

Le circuit proposé utilise un système à schéma double de contrôle symétrique pour les cycles positifs et négatifs. Il fonctionne de sorte que, pour chaque cycle d'entrée et sous des conditions adéquates de source et de charge (Tableau 3.1), une paire de transistors en chemin principal conduit. La conduction simultanée des commutateurs ferme le chemin du courant de la source vers la charge, et charge le condensateur de sortie. Les transistors pMOS de *pull-up* sont également utilisés pour aider à prévenir les grilles flottantes. Les courants de fuite et court-circuits sont également évités. En choisissant des transistors relativement plus larges que le minimum, on a, en partie, pu fournir un bon «timing» et optimiser des performances.

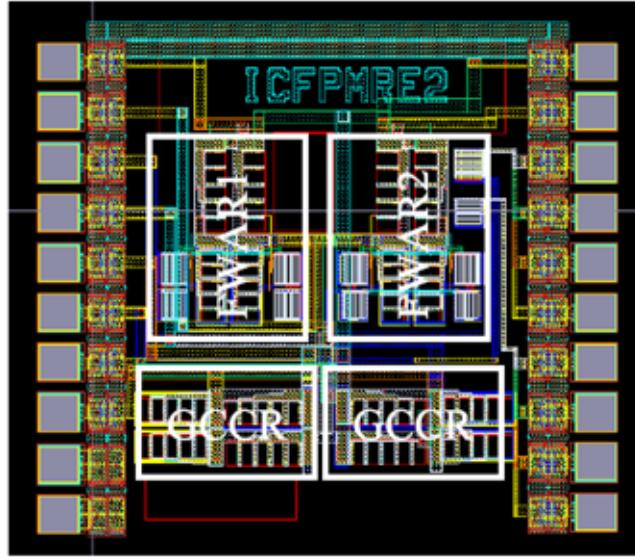

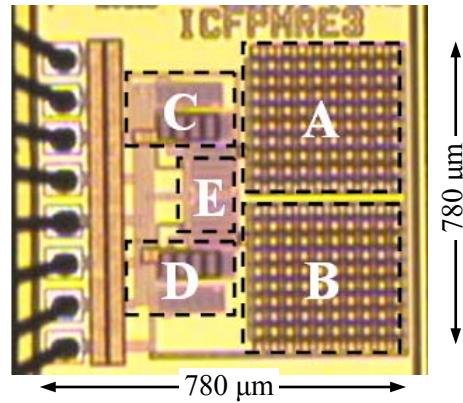

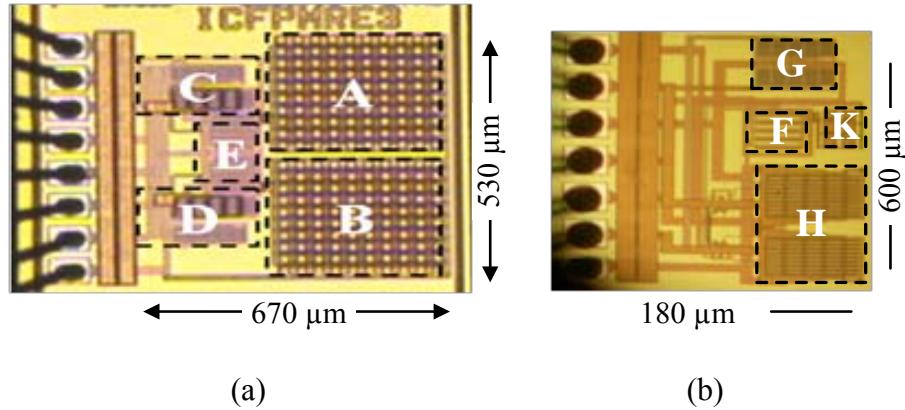

Le projet de redresseur actif à pleine-onde a été soigneusement menagé pour avoir une structure symétrique minimisant un déséquilibre potentiel dans les capacités parasites entre les connexions d'entrée. Il a été fabriqué en technologie 0.18  $\mu$ m 6-Métal/2-Poly TSMC 3.3V CMOS (Figure 3.11). La puce mesure une superficie de 1594×1080  $\mu$ m<sup>2</sup>.

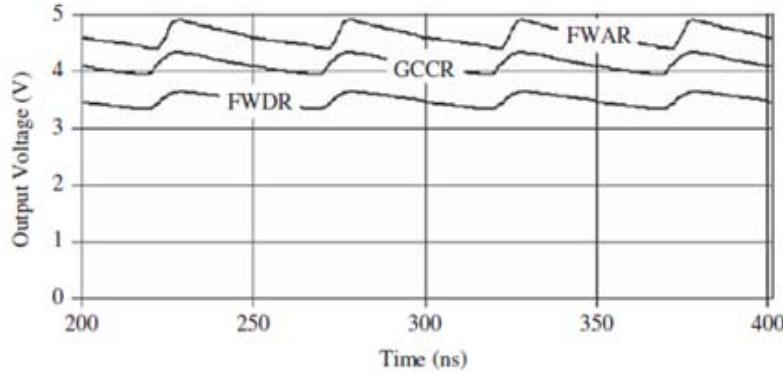

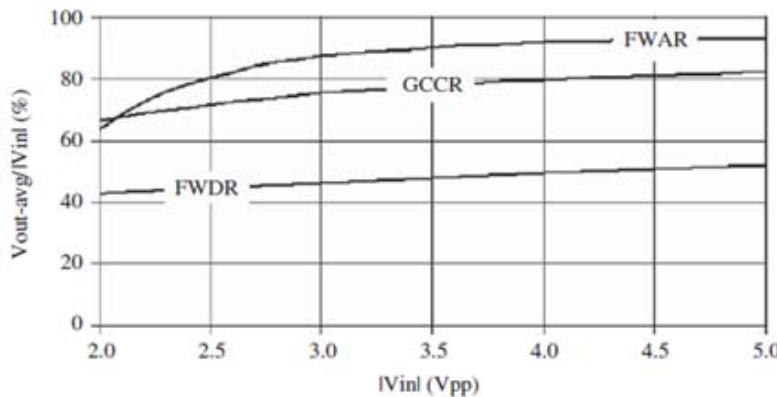

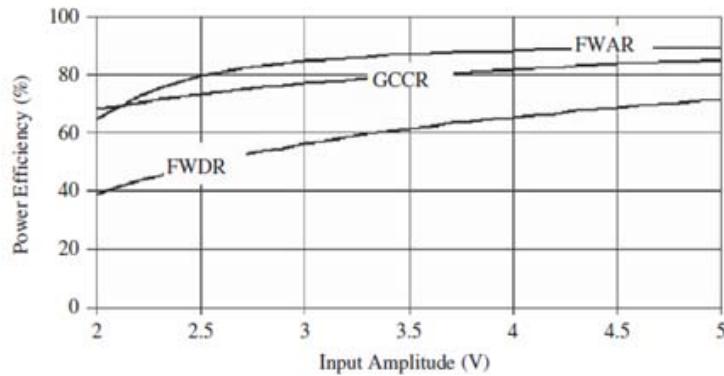

Basé sur les résultats de simulations, le redresseur actif à pleine-onde (FWAR) produit des tensions de sortie, des efficacités de puissance et des V<sub>CR</sub> sensiblement plus élevés en comparaison avec un redresseur en diode de type pont et redresseur à grille croisée-couplée

(GCCR) (Figures 3.8, 3.9 et 3.10). Les résultats de simulation confirment que la nouvelle structure est capable de générer des courants de charge élevés avec une petite dégradation de l'efficacité de puissance.

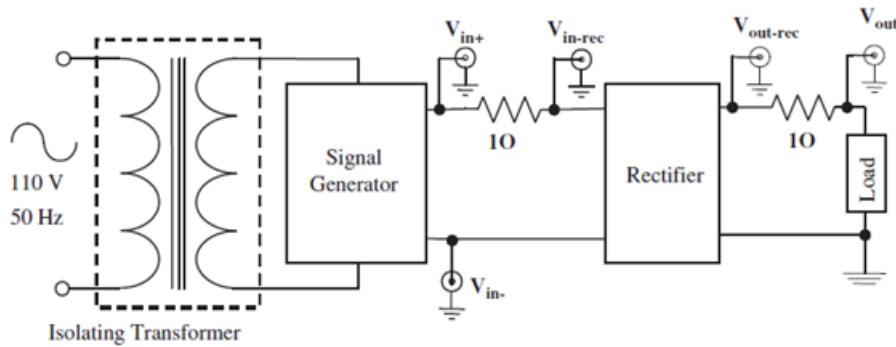

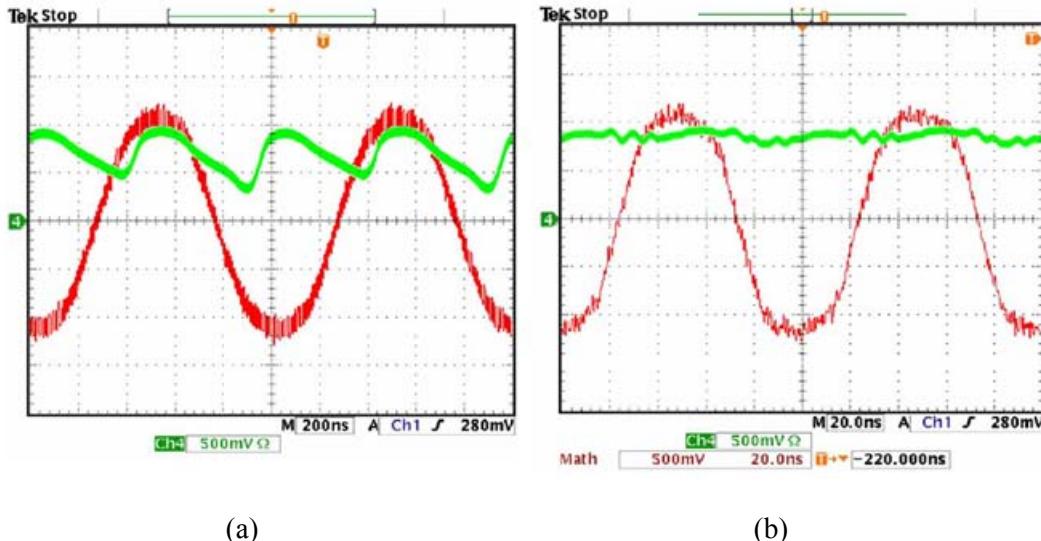

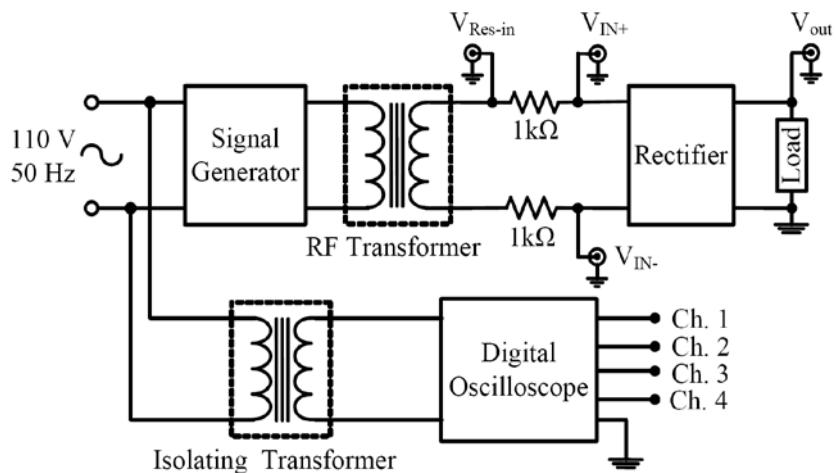

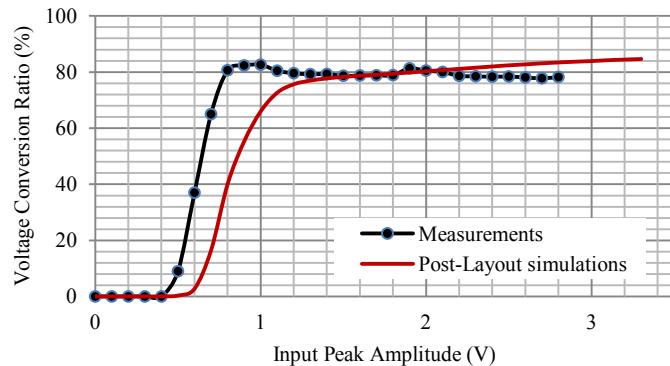

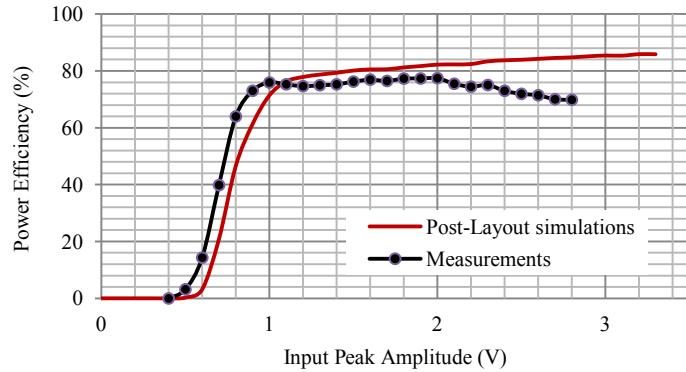

Pour mesurer les performances du redresseur, une plateforme a été développée (Figure 3.12) se servant d'un transformateur d'isolement (1:1) qui est utilisé pour découpler l'oscilloscope de la masse commune. Cette isolation permet d'éviter les boucles de terre dans l'installation et permet de référencer le signal de sortie à des tensions autre que la terre. Les tensions d'entrée et de sortie ainsi que le courant ont été mesurés pour calculer le PCE et le VCR. A partir des mesures, en accord étroit avec les résultats de la simulation, le redresseur proposé offre des tensions de sortie, une efficacité de tension et de puissance, remarquablement élevés par rapport à des structures FWBR et GCCR lorsqu'ils sont utilisés dans des applications à basse tension et courant élevé.

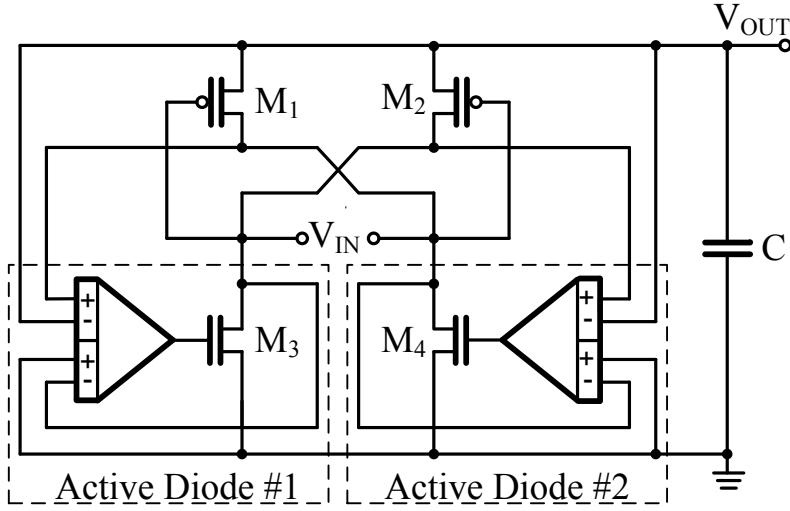

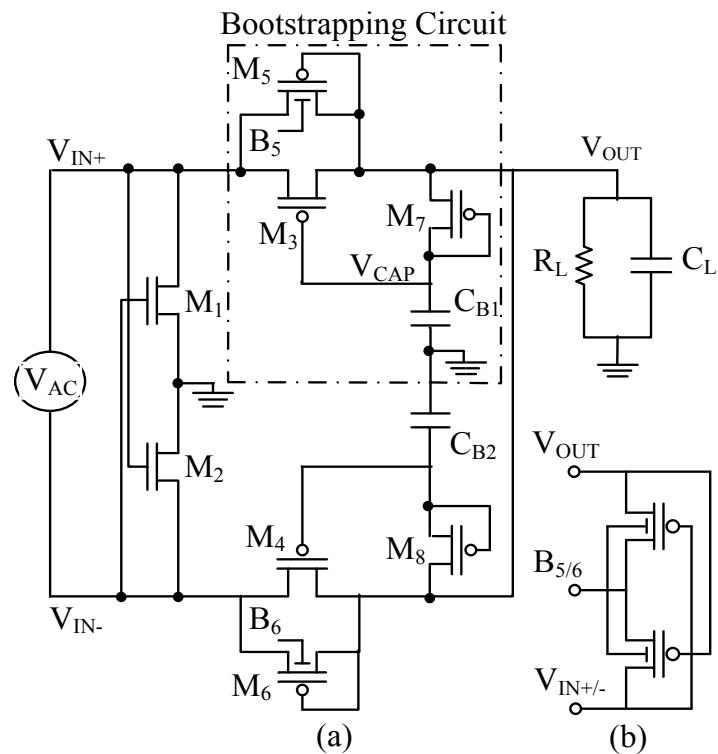

## 6.2 Redresseur de *bootstrap* à double-réservoir

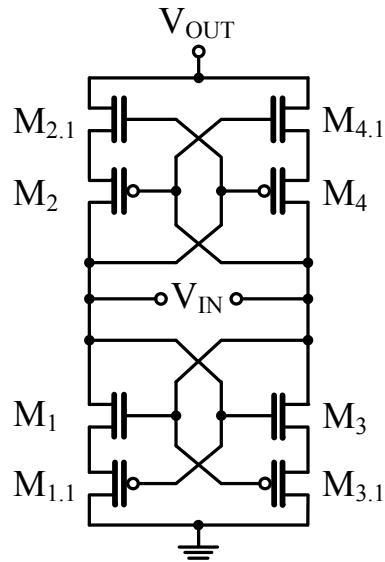

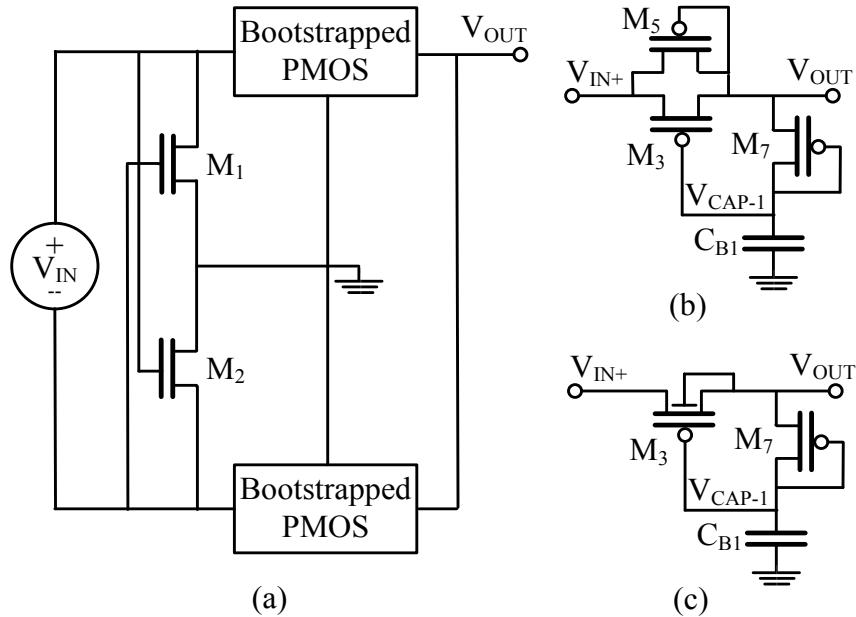

Nous proposons aussi un redresseur intégré pleine-onde (FWNR), ce qui est approprié pour de nombreuses applications y compris les implants intelligents biomédicaux et des étiquettes RFID (Figure 4.3a). La structure ne nécessite pas des techniques complexes de conception de circuits. Il bénéficie des avantages de la structure à large crête-couplée utilisée sur des transistors MOS sélectionnés.

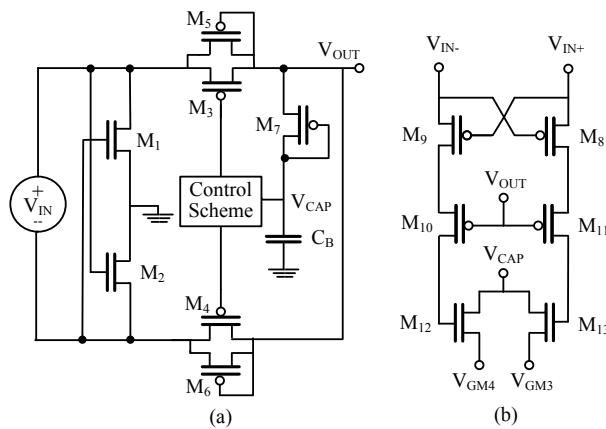

Il intègre également une paire d'interrupteurs pMOS avec une tension efficace de seuil très basse pour remplacer les diodes ou transistors pMOS connectés en diode dans les structures précédemment citées. Une combinaison de transistors pMOS connectés en diode avec le petit condensateur de *bootstrap* fournit la polarisation qui réduit la tension effective de seuil du transistor principal. Par conséquent, le redresseur est constitué de deux circuits pour la réduction du seuil, chacun contrôlé l'un des interrupteurs principaux. Un autre avantage de la nouvelle architecture est sa compatibilité avec les procédés CMOS standard, qui permet l'intégration des gros condensateurs sur la puce. L'architecture utilise la technique de commutation dynamique de substrat (DBS) pour polariser les substrats des transistors sélectionnés (Figure 4.3b), à fin de réduire les fuites de courant à travers le substrat et d'éliminer l'effet de substrat.

Il a été constaté que l'application de la technique DBS aux substrats de transistors principaux réduit de manière significative l'efficacité globale de puissance du redresseur. Par conséquent, les substrats de transistors principaux étaient reliés à  $V_{Out}$  ainsi que la plus haute tension disponible pendant la majorité du temps de fonctionnement du redresseur en raison de la présence du réservoir de sortie.

Le redresseur modifié fonctionne comme un redresseur à la grille croisée-couplée. Pendant chaque cycle d'entrée, une branche du circuit (chemin auxiliaire) qui comprend le transistor pMOS connectés en diode est insérée pour fournir un chemin entre l'entrée et la sortie pour charger le condensateur *bootstrap*. Cependant, la conduction simultanée des transistors pMOS dans les chemins principaux et auxiliaires contribue au courant de sortie.

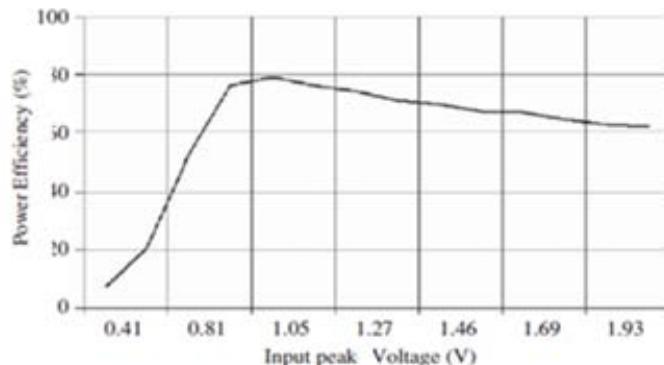

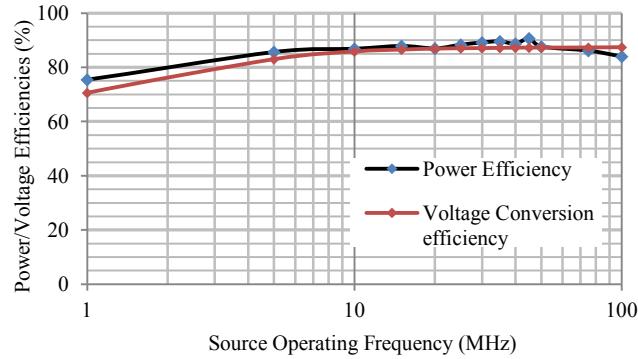

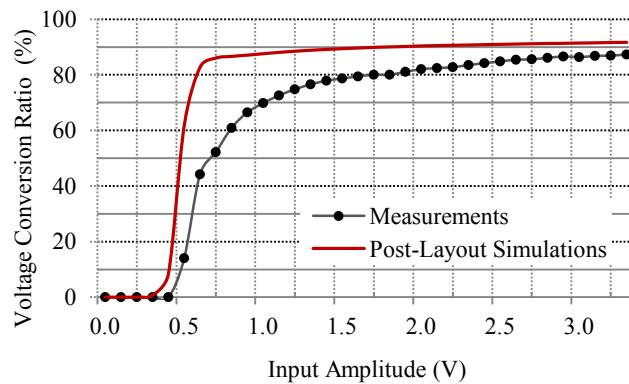

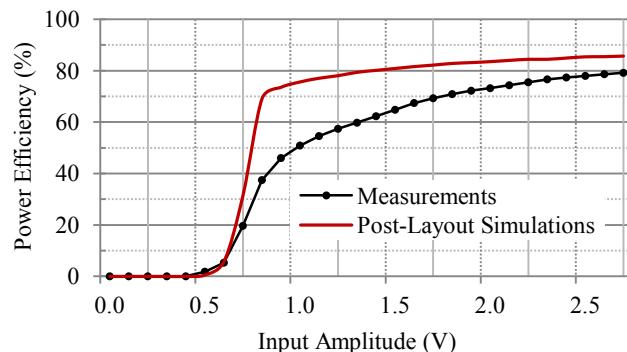

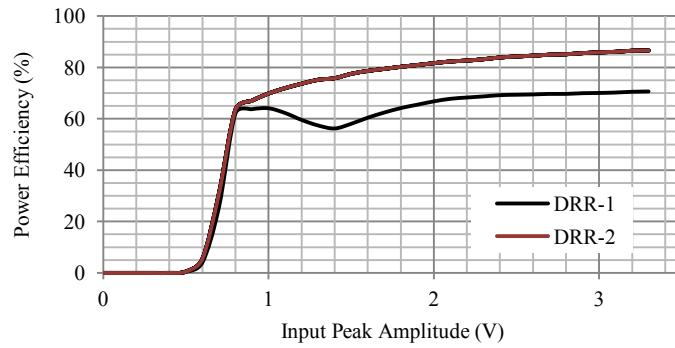

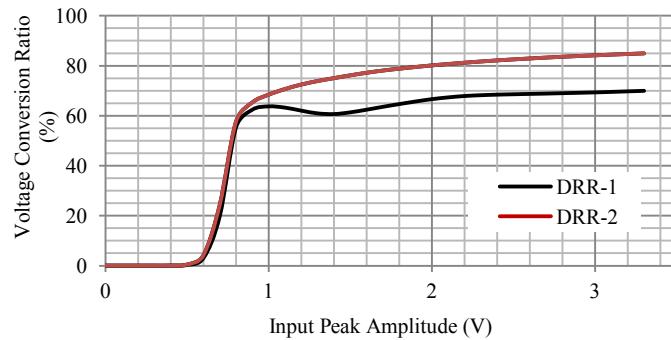

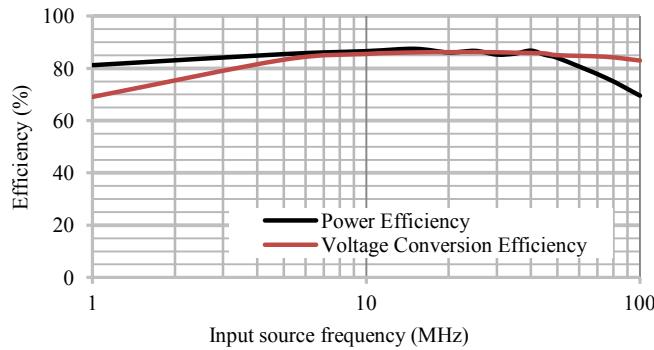

Les résultats obtenus à partir des simulations (Figures 4.4 et 4.5) montrent que le PCE et le VCR pour la structure proposée (FWNR) permettent d'atteindre rapidement des valeurs élevées pour des amplitudes de source très faible, et reste nettement plus élevé pour les tensions d'entrée plus large, par rapport aux structures de redresseur en pont classique (FWBR) et de la grille croisée-couplée (FWGR). Il a également été montré dans [70] que la tension de sortie moyenne de FWNR est significativement plus élevée que celle des autres topologies. Par conséquent, on peut s'attendre à ce que le nouveau circuit puisse être applicable à la mise en œuvre de redresseurs à l'aide de nouvelles technologies CMOS submicroniques où la tension d'alimentation nominale est inférieure à 1 V. Il a été noté que, comme prévu, les fréquences élevées de la source produisent de plus grandes PCE et de tension moyenne de sortie, dont il résulte des grandes VCR (Figure 4.9). Diverses simulations montrent que la nouvelle topologie du redresseur peut fonctionner sur une large gamme de fréquences jusqu'à 60 MHz à condition de faire les optimisations adéquates.

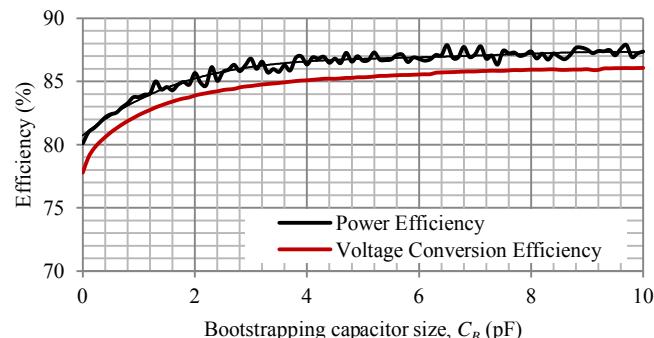

Le PCE et le VCR pour la structure FWNR varient avec la taille du condensateur d'amorçage (Figure 4.6). Toutefois, sur une large gamme de capacité, la performance du redresseur n'est pas très dépendante de la taille des condensateurs intégrés. Les résultats confirment que le nouveau redresseur fonctionne très bien avec un condensateur de 50 pF qui sont réalisables avec les procédés CMOS standard.

Le projet de redresseur pleine-onde (FWNR) a été soigneusement aménagé pour avoir une structure symétrique minimisant le déséquilibre du potentiel dans les capacités parasites entre les connexions de source et fabriqué en utilisant la procédé CMOS standard  $0.18 \mu m$  6-Métal/2-Poly TSMC 3.3V (Figure 4.7). Cette puce mesure  $780 \mu m \times 780 \mu m$  et elle possède 40 broches à double rangée. Les substrats locaux, nécessaires pour utiliser la technique DBS, ont été mis en œuvre en utilisant la couche «*deep n-well*». Tous les commutateurs principaux sont entourés par des anneaux de protection pour les isoler des cellules adjacentes.

Basé sur des observations distinctes, les mesures confirment que l'efficacité de puissance diminue avec le courant de charge. Le redresseur proposé génère une meilleure tension de sortie et une meilleure efficacité de puissance par rapport aux résultats rapportés par d'autres travaux en particulier lors du fonctionnement à partir de tensions de sources faibles. Le redresseur proposé, même avec des éléments mis en œuvre en utilisant la technologie d'intégration CMOS sous-micronique, est capable de supporter des courants de charge importants allant jusqu'à quelques mA.

### 6.3. Redresseurs de *bootstrap* à double-réservoir améliorées

Des améliorations s'appliquant à un redresseur intégré de pleine onde à double-réservoir (DRR-1) sont présentées [75]. Elles améliorent considérablement les performances en termes d'efficacité de conversion de puissance et de tension en réduisant le courant de retour de fuite tout en éliminant les chemins auxiliaires.

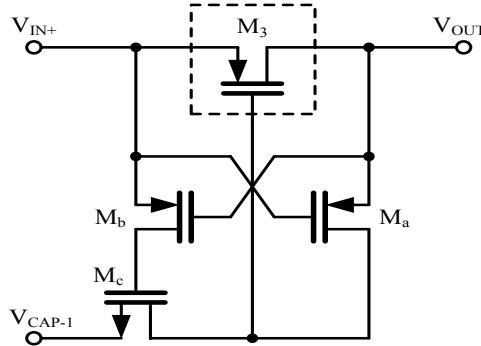

#### 6.3.1 Court chemin auxiliaire

Un court chemin auxiliaire, proposé pour la structure de la DRR-1 où les parasites de la jonction P-N de diffusion-substrat des commutateurs du chemin principal, est utilisé pour remplacer les transistors pMOS connectés en diode dans les chemins auxiliaires (DRR-2). La configuration proposée permet simultanément à polariser le substrat des commutateurs du passage principal, tout en fournissant des pistes auxiliaires de l'entrée au condensateur *bootstrap* (Figure 5.1c). Il est réalisé par la connexion du terminal du substrat des transistors du passage principal à  $V_{Out}$ . Il est à noter que le substrat du transistor pMOS dans les chemins de la charge est

toujours polarisé en utilisant la technique DBS.

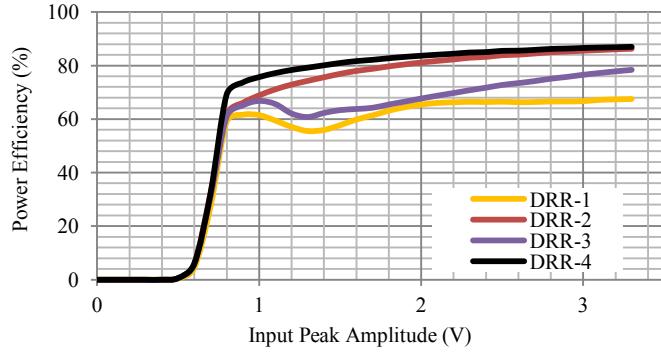

Basé sur les résultats des simulations schématique avec des conditions sur la charge appliquée, le redresseur proposé (DRR-2) présente une PCE et VCR significativement plus élevés que le DRR-1 (Figures 5.2 et 5.3). Les améliorations augmentent significativement pour les sources ayant des amplitudes plus élevées. On a également observé que le temps d'établissement du circuit de DRR-2 est plus court que celle de la DRR-1.

### 6.3.2 Les redresseurs sans courant de retour

Pendant le fonctionnement normal d'une structure de la DRR, la tension d'entrée à la chaîne de conversion de puissance et la tension de sortie varient dans le temps. Par conséquent, il existe des intervalles de temps, durant lesquels le flux de courant s'inverse dans les transistors pMOS principaux. Dans la structure utilisée avec des conditions variables sur la source et la charge, ce courant de retour peut considérablement dégrader les performances du redresseur d'un point de vue efficacité de puissance.

### 6.3.3. Système de contrôle pour limiter le flux de courant de retour

Pour résoudre le problème ci-dessus, nous proposons d'utiliser soit un système de contrôle (Figure 5.4) ou bien polariser les substrats des transistors de charge (Figure 5.6b). Dans le cas de la première solution, chaque transistor du passage principal est équipé du circuit de commande proposé (DRR-3). Dans une structure DRR-3, lors de chaque cycle d'entrée, ce circuit de commande compare en permanence les tensions d'entrées et de sortie, et connecte la plaque supérieure des condensateurs *bootstrap* à la grille des commutateurs du passage principal, lorsque les conditions appropriées sont réunies. Ainsi, il conduit finalement à un transfert de charge de la source d'entrée vers la charge que lorsque la tension d'entrée est supérieure à la tension de sortie, et elle bloque le courant de fuite inverse qui pourraient autrement passer via des interrupteurs principaux dans d'autres conditions. Des circuits de contrôle double doivent donc être utilisés de la même manière entre chaque condensateur *bootstrap* et la grille du transistor passage principal correspondant, pour annuler le courant d'écoulement de retour dans les cycles de source à la fois positifs et négatifs.

Nous proposons également d'utiliser les diodes parallèles de la diffusion-substrat de la jonction P-N des transistors de charge pour limiter les fuites de courant inverse à travers les transistors du passage principal. En utilisant cette technique, la tension sur la plaque supérieure des condensateurs *bootstrap* étroitement lié à la tension de sortie et la différence entre ces tensions est limitée à la chute de tension d'une diode polarisée en direct. Cette technique, appelée aussi “*close-track*” (Figure 5.6c), est mise en œuvre en connectant les substrats des transistors de charge à la tension de sortie (DRR-4). Cela réduit la complexité du circuit, et l'espace perdu de silicium sur la puce.

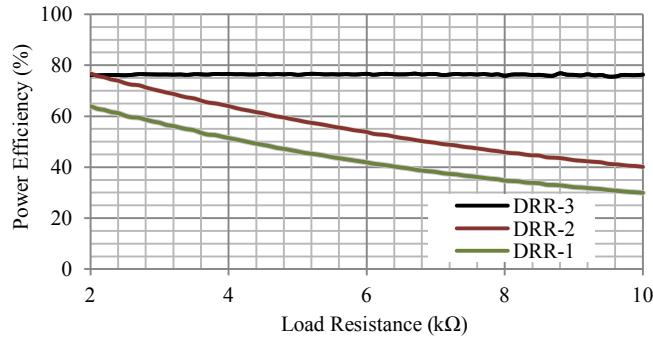

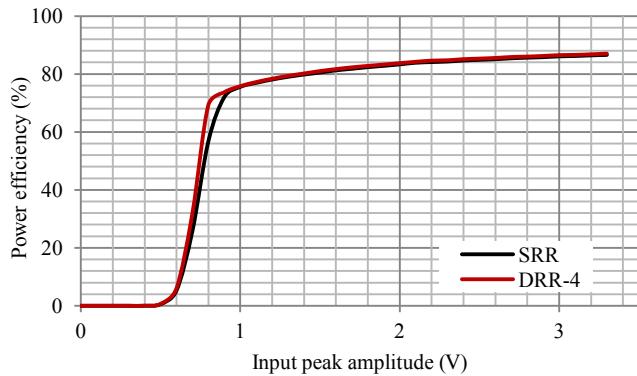

Les résultats des simulations (Figure 5.5) montrent que la structure DRR-3 proposée présente un PCE significativement plus élevé que les deux autres structures de la DRR sur une large plage de résistance de sortie. L'amélioration de l'efficacité est plus évidente avec des résistances de charge plus grandes. Le redresseur DRR-3, en accord avec nos attentes, offre un rendement énergétique plus élevé que la topologie de la DRR-2 avec des amplitudes crêtes à source inférieures à 1.0 V (Figure 5.7). Cependant, pour des amplitudes d'entrée plus grandes que 1.0 V, le rendement énergétique global est légèrement dégradé. La configuration de la DRR-4 a une structure relativement simple et produit la meilleure performance parmi toutes les structures à double-réservoir pour une large gamme d'amplitudes crêtes d'entrée.

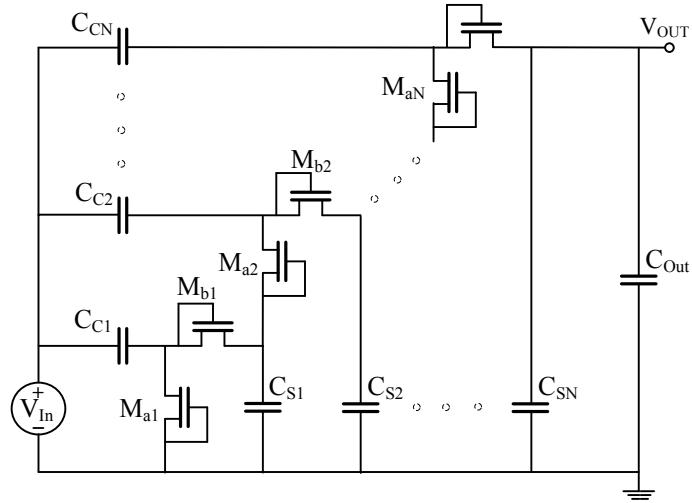

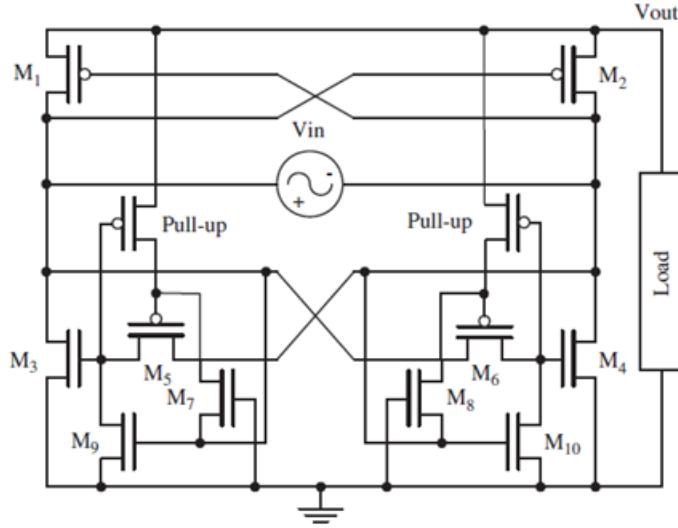

#### 6.4. Redresseur *bootstrap* à faible surface

L'utilisation de deux condensateurs de valeur relativement grande avec un grand transistor MOS de charge connecté en diode, qui est le cas pour les structures de DRR, peut limiter leur utilisation lorsque l'espace de silicium est limité. Afin d'économiser la surface de silicium, tout en bénéficiant des avantages offerts par la technique *bootstrap*, nous proposons une nouvelle structure de redresseur mono-réservoir pleine-onde (SRR). La structure (Figure 5.8a) a une grille à couplage croisé-couplé en plus d'un système de contrôle de polarité sélectif. Un système de contrôle a amélioré conduisant les transistors du passage principal avec les plus hautes tensions disponibles dans le circuit et utilisé pour connecter un seul condensateur *bootstrap* aux commutateurs du passage principal.

Le réservoir *bootstrap* peut être nettement plus petit que la taille totale des condensateurs dans les diverses structures de DRR. Les petits condensateurs *bootstrap*, par rapport aux structures de DRR différents, impliquent de plus petits transistors de charge que les composants correspondant dans les structures de la DRR. La symétrie dans le circuit proposé assure qu'il peut traiter la distorsion du signal d'entrée. Ainsi, le redresseur proposé maintient sa haute efficacité de puissance, si les amplitudes crêtes positives et négatives sont différentes.

Le substrat du transistor de charge est connecté au nœud de sortie pour réduire le courant de retour de fuite de la charge à la source. Cependant, les substrats des transistors de chemins principaux et auxiliaires sont connectés au nœud de sortie, car il correspond au nœud où est la tension plus élevée pendant la plupart de la période d'utilisation du redresseur.

Différentes simulations des circuits en schématique montrent que la nouvelle topologie des redresseurs peut fonctionner sur une large plage de fréquences jusqu'à 50 MHz (Figure 5.9). Les résultats (Figure 5.10) montrent également que sur une plage spécifique de capacité, la performance de la structure en termes de PCE et VCR n'est dépendante pas de la taille des condensateurs intégrés. On note aussi que la structure de SRR offre un rendement proche de sa valeur maximale avec un condensateur de 4 pF lorsqu'il est intégré à un processus CMOS standard. L'utilisation d'un condensateur *bootstrap* plus petit implique aussi de temps plus court pour le chargement proche de la tension de crête. La configuration de SRR permet d'obtenir des efficacités de puissance aussi élevées que la structure DRR-4 pour une large plage d'amplitudes l'entrée du circuit.

La SRR proposée a été étudiée et fabriquée en utilisant un processus CMOS standard 0.18  $\mu\text{m}$  6-Métal/2-Poly TSMC 3,3V. La puce mesure  $180 \times 600 \mu\text{m}^2$ . En comparant la surface de silicium utilisée par les circuits SRR et DRR-1, quand l'intégration de transistors de dimensions comparables, montre une économie de près de 70% dans la zone perdue de la puce.

## 7. Conclusions

Les redresseurs sont des circuits qui sont utilisés pour transformer l'énergie obtenue à partir de la plupart des sources d'énergie en une alimentation DC. Basé sur le type d'élément de

rectification, les circuits de redresseur sont classés comme actifs et passifs. La topologie grille croisée-couplée passive peut remplacer une ou deux diodes de redresseur en pont conventionnels par des commutateurs MOS et donc elle présente une plus grande efficacité de puissance. Les redresseurs actifs utilisent des circuits actifs pour contrôler les commutateurs MOS. Ils présentent généralement une efficacité énergétique plus élevée que le redresseur passif pour les fréquences de fonctionnement faibles ou moyennes. Ils sont cependant limités par les pertes de commutation, la complexité et les difficultés de conception. Nous avons proposé une nouvelle structure de redresseur pleine-onde intégrée qui utilise les qualités intrinsèques des transistors MOS sélectionnés comme comparateurs fonctionnant dans la région triode, pour atteindre une efficacité de puissance accrue et une chute de tension réduite. Le design ne nécessite ni une source d'énergie interne, ni un chemin de signal auxiliaire pour produire de la puissance au démarrage.

Il a également été montré qu'avec un transistor MOS classique qui a une tension de seuil régulière, l'application simultanée de la structure croisée-couplée et les techniques de réduction du seuil permettent d'obtenir une chute de tension très faible dans les commutateurs de passage principal. Cela engendre des efficacités de puissance et de tension significativement plus élevées comparées aux redresseurs avec les structures conventionnelles en pont et à grille croisée-couplée.

Différents redresseurs passifs basés sur la technique *bootstrap* ont également été proposés. Ils utilisent des condensateurs simples ou doubles d'amorçage pour réduire le seuil effectif des commutateurs du passage principal. La structure mono-réservoir économise la surface requise sur la puce par rapport à la topologie à double réservoir.

L'utilisation de diodes parasites des jonctions, disponibles dans le procédé CMOS standard ainsi que d'une technique de polarisation à courts chemins auxiliaires et de circuit "close-track" ont été introduits. Ils simplifient le redresseur, tout en maintenant son efficacité de puissance à un niveau élevé.

Avec une amplitude de source de 3,3 V et par rapport à la porte croisée couplée topologie, le redresseur proposé offre une puissance améliorée et une efficacité de conversion de tension

allant jusqu'à 10% et 16% de plus respectivement. Le redresseur proposé utilise la technique bootstrap, y compris les doubles et simples réservoirs. Ils sont bien adaptés pour des amplitudes d'entrée très basses. Ils présentent des rendements de conversion de puissance et de tension de 75% et 76% à l'amplitude d'entrée de 1,0 V et ils permettent de maintenir des rendements élevés sur les amplitudes d'entrée supérieure à 1.0V. Le redresseur à simple réservoir permet également d'économiser 70% de l'aire requise pour intégrer un redresseur double-réservoir. Tous les redresseurs ont été mis en œuvre en utilisant la technologie CMOS 0,18  $\mu$ m et ils sont conçus pour produire un courant de charge de plus de 2 mA lorsqu'ils opèrent dans la bande ISM jusqu'à 50 MHz.

## TABLE OF CONTENTS

|                                |       |

|--------------------------------|-------|

| DEDICATION .....               | III   |

| ACKNOWLEDGEMENTS .....         | IV    |

| ABSTRACT .....                 | VI    |

| RESUMÉ .....                   | VIII  |

| CONDENSÉ EN FRANÇAIS .....     | X     |

| TABLE OF CONTENTS .....        | XXX   |

| LIST OF TABLES .....           | XXXV  |

| LIST OF FIGURES .....          | XXXVI |

| LIST OF ABBREVIATIONS .....    | XL    |

| LIST OF SYMBOLS .....          | XLII  |

| CHAPTER 1 : INTRODUCTION ..... | 1     |

| 1.1 Motivation .....           | 1     |

| 1.2 Research Problems .....    | 1     |

| 1.3 Research Objectives .....  | 2     |

|                                                                               |           |

|-------------------------------------------------------------------------------|-----------|

| <b>1.4 Research Contributions .....</b>                                       | <b>3</b>  |

| <b>1.5 Thesis Organization .....</b>                                          | <b>6</b>  |

| <br>                                                                          |           |

| <b>CHAPTER 2 : INTEGRATED HIGH-EFFICIENCY LOW-VOLTAGE CMOS</b>                |           |

| <b>RECTIFIERS FOR WIRELESSLY POWERED APPLICATIONS: PAST AND PRESENT .....</b> | <b>8</b>  |

| <br>                                                                          |           |

| <b>2.1 Introduction .....</b>                                                 | <b>8</b>  |

| <br>                                                                          |           |

| <b>2.2 Design and Implementation Challenges for Passive Rectifiers .....</b>  | <b>10</b> |

| 2.2.1 Size of Main Switches .....                                             | 10        |

| 2.2.2 Operating Frequency .....                                               | 11        |

| 2.2.3 Output Ripples .....                                                    | 11        |

| 2.2.4 Threshold Voltage .....                                                 | 11        |

| 2.2.5 Load Current .....                                                      | 13        |

| 2.2.6 Bulk Biasing .....                                                      | 14        |

| <br>                                                                          |           |

| <b>2.3 Performance Metrics and Classification of Power Rectifiers .....</b>   | <b>15</b> |

| 2.3.1 Diode Implementations .....                                             | 16        |

| 2.3.1.1 P-N Junction Diode .....                                              | 16        |

| 2.3.1.2 Schottky Diode .....                                                  | 16        |

| 2.3.1.3 Diode-Connected MOS .....                                             | 17        |

| 2.3.2 Conventional Topologies for Passive Rectifiers .....                    | 18        |

| 2.3.2.1 Half-Wave Topology .....                                              | 18        |

| 2.3.2.2 Full-Wave Bridge Topology .....                                       | 19        |

| 2.3.3 Advanced Passive Bridge Rectifiers .....                                | 20        |

| 2.3.3.1 Partially Gate Cross-Coupled Topology .....                           | 20        |

| 2.3.3.2 Fully Gate Cross-Coupled Topology .....                               | 22        |

| 2.3.3.3 Charge-Pump Based Rectifiers .....                                    | 24        |

| <br>                                                                          |           |

| <b>2.4 Rectifiers with Threshold Cancellation Techniques .....</b>            | <b>27</b> |

| 2.4.1 Rectifiers Based on the Floating-Gate Technique .....                   | 28        |

| 2.4.2 Static $V_{Th}$ Cancellation Techniques .....                           | 30        |

| 2.4.2.1 External $V_{Th}$ Cancellation Technique .....                        | 30        |

|                                                                                                 |                                                         |           |

|-------------------------------------------------------------------------------------------------|---------------------------------------------------------|-----------|

| 2.4.2.2                                                                                         | Internal $V_{Th}$ Cancellation Technique .....          | 31        |

| 2.4.2.3                                                                                         | Self- $V_{Th}$ -Cancellation Technique .....            | 34        |

| 2.4.3                                                                                           | Differential $V_{Th}$ Cancellation Technique .....      | 35        |

| 2.4.4                                                                                           | Bulk-Drive Technique.....                               | 36        |

| 2.4.5                                                                                           | Bootstrapped Capacitor Technique.....                   | 37        |

| <b>2.5</b>                                                                                      | <b>Analysis and Modeling of Passive Rectifiers.....</b> | <b>37</b> |

| <b>2.6</b>                                                                                      | <b>Active (Synchronous) Power Rectifiers .....</b>      | <b>40</b> |

| 2.6.1                                                                                           | Active Diode Concept .....                              | 41        |

| 2.6.2                                                                                           | Main Challenges in Design of Active Rectifiers.....     | 41        |

| 2.6.3                                                                                           | Active Rectifiers with Conventional Topology .....      | 43        |

| 2.6.4                                                                                           | Active Rectifiers with a Charge-Pump Structure .....    | 47        |

| <b>2.7</b>                                                                                      | <b>Active-Passive Power Rectifier Structures.....</b>   | <b>49</b> |

| <b>CHAPTER 3 : A NOVEL LOW-DROP CMOS ACTIVE RECTIFIER.....</b>                                  |                                                         | <b>52</b> |

| <b>A NOVEL LOW-DROP CMOS ACTIVE RECTIFIER FOR RF-POWERED DEVICES: EXPERIMENTAL RESULTS.....</b> |                                                         | <b>53</b> |

| <b>3.1</b>                                                                                      | <b>Introduction .....</b>                               | <b>53</b> |

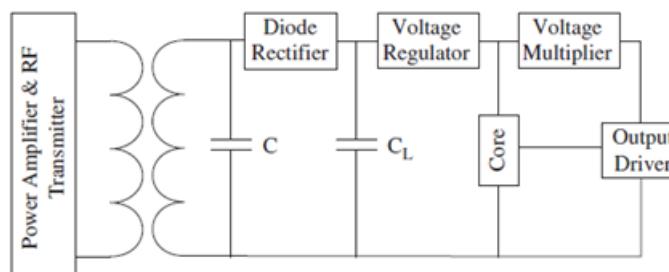

| <b>3.2</b>                                                                                      | <b>Power Conversion Chain.....</b>                      | <b>54</b> |

| 3.2.1                                                                                           | Rectifier Implementation .....                          | 55        |

| 3.2.2                                                                                           | CMOS Bridge Rectifiers.....                             | 55        |

| <b>3.3</b>                                                                                      | <b>New Proposed Active Rectifier .....</b>              | <b>59</b> |

| <b>3.4</b>                                                                                      | <b>Performance Metrics and Simulation Results .....</b> | <b>65</b> |

| <b>3.5</b>                                                                                      | <b>Measurement Results.....</b>                         | <b>67</b> |

| <b>3.6</b>                                                                                      | <b>Conclusion .....</b>                                 | <b>71</b> |

|                                                                            |            |

|----------------------------------------------------------------------------|------------|

| <b>3.7 References.....</b>                                                 | <b>71</b>  |

| <br>                                                                       |            |

| <b>CHAPTER 4 : A DOUBLE-RESERVOIR BOOTSTRAP RECTIFIER .....</b>            | <b>75</b>  |

| <b>A HIGH-EFFICIENCY LOW-VOLTAGE CMOS RECTIFIER FOR HARVESTING ENERGY</b>  |            |

| <b>IN IMPLANTABLE DEVICES</b>                                              |            |

| <br>                                                                       |            |

| <b>4.1 Introduction .....</b>                                              | <b>76</b>  |

| <br>                                                                       |            |

| <b>4.2 Rectifier Topologies and Threshold Cancellation Techniques.....</b> | <b>78</b>  |

| 4.2.1 CMOS Rectifier Implementation.....                                   | 78         |

| 4.2.2 Threshold Cancellation Techniques.....                               | 80         |

| <br>                                                                       |            |

| <b>4.3 The Proposed Rectifier .....</b>                                    | <b>83</b>  |

| <br>                                                                       |            |

| <b>4.4 Simulation and Measurement Results .....</b>                        | <b>85</b>  |

| 4.4.1 Simulation results .....                                             | 86         |

| 4.4.2 Measurement Results.....                                             | 88         |

| 4.4.3 Measurement Setup and Test Protocol.....                             | 89         |

| <br>                                                                       |            |

| <b>4.5 Conclusions.....</b>                                                | <b>96</b>  |

| <br>                                                                       |            |

| <b>4.6 References.....</b>                                                 | <b>96</b>  |

| <br>                                                                       |            |

| <b>CHAPITRE 5 : LOW-AREA BOOTSTRAP RECTIFIERS .....</b>                    | <b>100</b> |

| <br>                                                                       |            |

| <b>LOW-AREA AND FLOW-BACK CURRENT FREE CMOS INTEGRATED RECTIFIERS</b>      |            |

| <b>FOR POWER SCAVENGING DEVICES</b>                                        |            |

| <br>                                                                       |            |

| <b>5.1 Introduction .....</b>                                              | <b>102</b> |

| <br>                                                                       |            |

| <b>5.2 Bootstrapped-Capacitor Based Rectifiers.....</b>                    | <b>103</b> |

| 5.2.1 Short Auxiliary Paths.....                                           | 105        |

| <br>                                                                       |            |

| <b>5.3 Flow-Back Current Free Rectifiers.....</b>                          | <b>108</b> |

| 5.3.1 Control Scheme to Limit Flow-Back Current .....                      | 109        |

|                                                                                    |            |

|------------------------------------------------------------------------------------|------------|

| 5.3.2 Close-Track Scheme for Flow-Back Current Reduction .....                     | 111        |

| <b>5.4 Low-Area Bootstrapped Rectifier.....</b>                                    | <b>113</b> |

| 5.4.1 Control Circuit.....                                                         | 114        |

| <b>5.5 Conclusions.....</b>                                                        | <b>123</b> |

| <b>5.6 References.....</b>                                                         | <b>123</b> |

| <br>CHAPTER 6 : GENERAL DISCUSSION .....                                           | 127        |

| <b>6.1 Active Rectifier .....</b>                                                  | <b>128</b> |

| <b>6.2 Bootstrap Passive Rectifiers.....</b>                                       | <b>128</b> |

| 6.2.1 Double-Reservoir Bootstrapped Rectifier .....                                | 128        |

| 6.2.2 Improvements in Double-Reservoir Bootstrapped Rectifier .....                | 129        |

| 6.2.2.1 Short-Auxiliary Paths.....                                                 | 129        |

| 6.2.2.2 Flow-back Free Scheme .....                                                | 130        |

| <b>6.3 Single-Reservoir Bootstrapped Rectifier .....</b>                           | <b>130</b> |

| <b>6.4 Test and measurement setup .....</b>                                        | <b>131</b> |

| <br>CHAPTER 7 : CONCLUSIONS AND RECOMMENDATIONS .....                              | 132        |

| <b>7.1 Contributions of This Research .....</b>                                    | <b>132</b> |

| <b>7.2 Directions/Recommendations for Future Work.....</b>                         | <b>134</b> |

| 7.2.1 Single-Reservoir Bootstrapped Rectifier with Asymmetrical Input Cycles ..... | 134        |

| 7.2.2 Circuit Reliability Test .....                                               | 135        |

| 7.2.3 Input Matching Network Analysis .....                                        | 135        |

| 7.2.4 Modified Passive-Active Rectifier .....                                      | 135        |

| 7.2.5 Active Rectifier with Low Effective Switching Frequency.....                 | 136        |

| <br>BIBLIOGRAPHIE .....                                                            | 137        |

## LIST OF TABLES

|                                                                                  |     |

|----------------------------------------------------------------------------------|-----|

| <b>Table 3.1.</b> Rectifier switching states for positive cycle.....             | 63  |

| <b>Table 3.2.</b> Summary of measured power efficiency for cited rectifiers..... | 71  |

| <b>Table 4.1.</b> Post-layout and measurement results.....                       | 94  |

| <b>Table 4.2.</b> Comparison with most advanced rectifier characteristics.....   | 94  |

| <b>Table 5.1.</b> Circuit parameters for rectifier topologies.....               | 106 |

| <b>Table 5.2.</b> Comparison with most advanced rectifier characteristics.....   | 122 |

## LIST OF FIGURES

|                                                                                                                                    |    |

|------------------------------------------------------------------------------------------------------------------------------------|----|

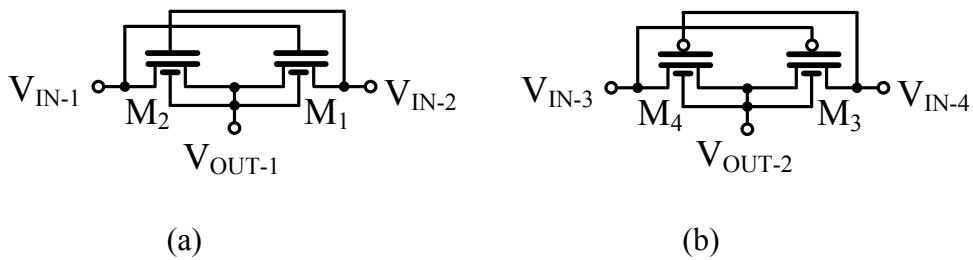

| <b>Figure 2.1.</b> Dynamic bulk switching scheme: (a) for nMOS transistors, (b) for pMOS transistors.                              | 14 |

| .....                                                                                                                              |    |

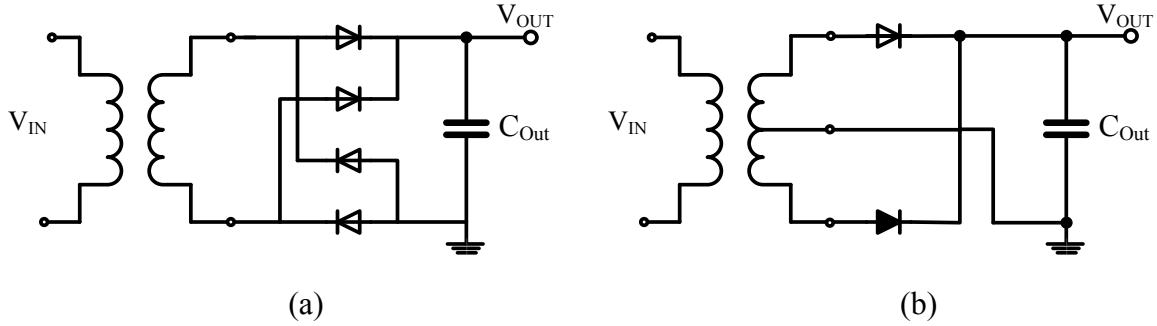

| <b>Figure 2.2.</b> Circuit diagram for a full-wave rectifier: (a) bridge, (b) center-tapped.                                       | 19 |

| .....                                                                                                                              |    |

| <b>Figure 2.3.</b> Circuit diagram for a full-wave nMOS-based bridge rectifier.                                                    | 20 |

| .....                                                                                                                              |    |

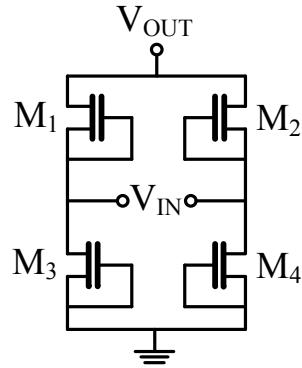

| <b>Figure 2.4.</b> Circuit diagram for a gate cross-coupled rectifier.                                                             | 21 |

| .....                                                                                                                              |    |

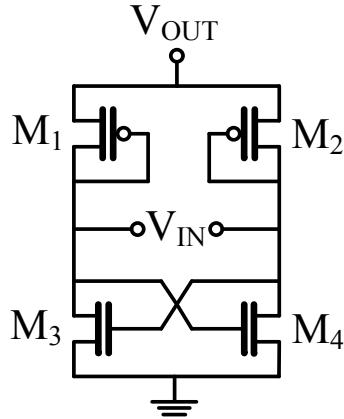

| <b>Figure 2.5.</b> Circuit diagram for a fully gate cross-coupled rectifier in [43].                                               | 23 |

| .....                                                                                                                              |    |

| <b>Figure 2.6.</b> Circuit diagram for a fully gate cross-coupled rectifier in [160].                                              | 23 |

| .....                                                                                                                              |    |

| <b>Figure 2.7.</b> Schematic of a Greinacher charge pump.                                                                          | 24 |

| .....                                                                                                                              |    |

| <b>Figure 2.8.</b> Schematic of a N-stage charge pump rectifier.                                                                   | 25 |

| .....                                                                                                                              |    |

| <b>Figure 2.9.</b> Circuit diagram for an external $V_{Th}$ cancellation technique in [161].                                       | 30 |

| .....                                                                                                                              |    |

| <b>Figure 2.10.</b> Circuit diagram for an internal $V_{Th}$ cancellation technique in [121].                                      | 31 |

| .....                                                                                                                              |    |

| <b>Figure 2.11.</b> Circuit diagram for an internal $V_{Th}$ cancellation technique in [169].                                      | 33 |

| .....                                                                                                                              |    |

| <b>Figure 2.12.</b> Circuit diagram for a Villard rectifier: (a) conventional diode-connected MOS, (b) ULPD-connected MOS in [94]. | 35 |

| .....                                                                                                                              |    |

| <b>Figure 2.13.</b> Circuit diagram for a rectifier cell using differential $V_{Th}$ cancellation technique.                       | 36 |

| ..                                                                                                                                 |    |

| <b>Figure 2.14.</b> Circuit diagram for a Villard charge-pump based rectifier using the bootstrapping capacitor technique [99].    | 38 |

| .....                                                                                                                              |    |

| <b>Figure 2.15.</b> Block diagram of typical active (synchronous) rectifier.                                                       | 40 |

| .....                                                                                                                              |    |

| <b>Figure 2.16.</b> Circuit diagram for active rectifier in [97].                                                                  | 44 |

| .....                                                                                                                              |    |

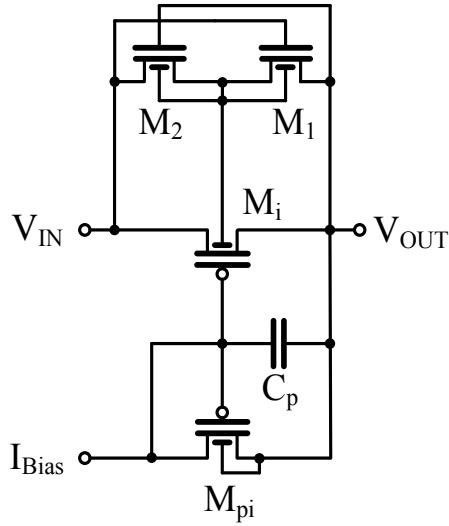

| <b>Figure 2.17.</b> Circuit diagram for active rectifier in [104].                                                                 | 45 |

| .....                                                                                                                              |    |

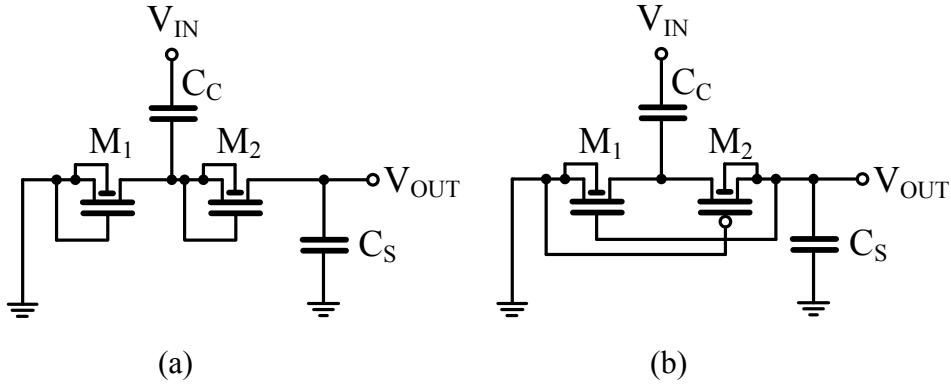

| <b>Figure 2.18.</b> Circuit diagram for active rectifier in [63].                                                                  | 46 |

| .....                                                                                                                              |    |

| <b>Figure 2.19.</b> Circuit diagram for active rectifier in [113].                                                                 | 48 |

|                                                                                                                                                          |    |

|----------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| <b>Figure 2.20.</b> Circuit diagram for active-passive rectifier in [133]. .....                                                                         | 50 |

| <b>Figure 3-1.</b> Block diagram of a typical PCC.....                                                                                                   | 54 |

| <b>Figure 3.2.</b> Schematic of a full-wave bridge rectifier: (a) diode implementation, (b) MOS diode-connected implementation.....                      | 56 |

| <b>Figure 3.3.</b> Gate cross-coupled rectifier [12]. .....                                                                                              | 57 |

| <b>Figure 3.4.</b> Schematic of the proposed full-wave rectifier.....                                                                                    | 60 |

| <b>Figure 3.5.</b> Schematic of the active parts during the positive half cycle .....                                                                    | 60 |

| <b>Figure 3.6.</b> Simulated result of the FWAR over one period. .....                                                                                   | 62 |

| <b>Figure 3.7.</b> Schematic of dynamic bulk biasing for main switches: (a) $M_1$ and (b) $M_3$ .....                                                    | 64 |

| <b>Figure 3.8.</b> Simulated output voltage of FWDR, GCCR and FWAR.....                                                                                  | 66 |

| <b>Figure 3.9.</b> Simulated VCRs for various rectifier structures.....                                                                                  | 66 |

| <b>Figure 3.10.</b> Simulated power efficiency versus input amplitude.....                                                                               | 67 |

| <b>Figure 3.11.</b> Photomicrograph of the prototype chip. ....                                                                                          | 68 |

| <b>Figure 3.12.</b> Voltage and power measurement setup. ....                                                                                            | 69 |