**Titre:** Définition, spécification et génération automatique d'architectures de modules réseau ciblant des FPGA

Title: de modules réseau ciblant des FPGA

**Auteur:** Rajat Singh Rajput

Author:

**Date:** 2025

**Type:** Mémoire ou thèse / Dissertation or Thesis

**Référence:** Singh Rajput, R. (2025). Définition, spécification et génération automatique d'architectures de modules réseau ciblant des FPGA [Mémoire de maîtrise, Polytechnique Montréal]. PolyPublie. <https://publications.polymtl.ca/62574/>

Citation:

## Document en libre accès dans PolyPublie

Open Access document in PolyPublie

**URL de PolyPublie:** <https://publications.polymtl.ca/62574/>

PolyPublie URL:

**Directeurs de recherche:** François-Raymond Boyer, & Yvon Savaria

Advisors:

**Programme:** Génie électrique

Program:

**POLYTECHNIQUE MONTRÉAL**

affiliée à l'Université de Montréal

**Définition, spécification et génération automatique d'architectures de modules

réseau ciblant des FPGA**

**RAJAT SINGH RAJPUT**

Département de génie électrique

Mémoire présenté en vue de l'obtention du diplôme de *Maîtrise ès sciences appliquées*

Génie électrique

Janvier 2025

**POLYTECHNIQUE MONTRÉAL**

affiliée à l'Université de Montréal

Ce mémoire intitulé :

**Définition, spécification et génération automatique d'architectures de modules

réseau ciblant des FPGA**

présenté par **Rajat SINGH RAJPUT**

en vue de l'obtention du diplôme de *Maîtrise ès sciences appliquées*

a été dûment accepté par le jury d'examen constitué de :

**Tarek OULD-BACHIR**, président

**François-Raymond BOYER**, membre et directeur de recherche

**Yvon SAVARIA**, membre et codirecteur de recherche

**Guy BOIS**, membre

## DÉDICACE

*Merci à mes proches pour le support...*

## REMERCIEMENTS

Je tiens à exprimer ma sincère gratitude à tous ceux qui m'ont aidé ou encouragé au cours de deux dernières années. J'aimerais remercier mon directeur de recherche, Yvon Savaria, ainsi que mon codirecteur, François-Raymond Boyer de m'avoir soutenu et aidé tout au long de ce projet. Je voudrais également remercier les membres du laboratoire pour l'aide aux installations d'appareils et les discussions. Je remercie Bill Pontikakis pour son aide dans l'orientation du projet.

De plus, je dois mes plus sincères remerciements à ma famille bien-aimée pour un support financier et moral.

## RÉSUMÉ

L'utilisation des langages de programmation pour optimiser toutes sortes de travaux complexes est la norme. Le langage P4 a besoin d'un tel support pour se développer avec l'aide de langages de haut niveau tel que le C++ et Python. En effet, il est présentement compliqué de réaliser des communications accélérées sur circuit logique programmable (FPGA) sans une seule manipulation manuelle du code en langage de description matériel (HDL). Dans cette étude, nous présentons une méthode de communication plus simple pour tous les utilisateurs d'externes des processeurs de paquets (P4). Notre objectif est d'utiliser des interfaces Python générées par une architecture personnalisée de P4. La génération automatique des interfaces va simplement permettre au programmeur de haut niveau d'avoir accès à des fonctionnalités de bas niveau sans avoir à programmer du HDL. C'est important, car généralement les programmeurs P4 ne connaissent pas ou ne veulent pas manipuler le HDL. La génération et l'interconnectivité des modules matériels pour les pipelines P4 sont effectuées sur une base automatique pour les utilisateurs d'externes qui veulent avoir plus de fonctionnalités dans leur réseau de communication. Les interfaces générées incluent l'accès direct à la mémoire (DMA) et l'interconnexion des composants périphériques, permettent la mise en œuvre de pont de communication multipériphériques flexibles. Les résultats de simulation valident la véritable fonctionnalité de notre méthodologie d'interface de pointe. En effet, une fonction externe au programme P4 a été connectée à l'aide d'interface générée automatiquement. Cette fonction externe communique avec le pipeline P4 à travers les modules matériels générés. En plus d'améliorer l'efficacité de développement, ce projet a une faible consommation de ressources matérielles et la solution est fonctionnelle dans l'industrie, car celle-ci est validée par les outils d'Intel. La compilation avec Quartus des modules matériels générés à partir du compilateur d'Intel et celles générées par l'outil Python montre une utilisation de ressources de 1,81 % de la logique (table de recherche ou LUT) pour une puce Arria10. De plus, les ressources sont limitées à 1,62 % pour la mémoire (bloc de RAM) et 0,96 % pour les bascules (registres). La différence avec le pipeline sans interface générée est de 281 registres et 194 LUT, donc une différence de 1,64 % et de 4,54 % pour le nombre de registres et le nombre d'unités logique (LUT) respectivement. La méthode proposée est efficace pour l'utilisateur et améliore la flexibilité du langage P4.

## ABSTRACT

Optimizing and automating complex tasks is crucial in this world of fast advancement. Indeed, existing software-only programmable switches offer low performance, and those based on complex ASICs lack flexibility. The solution to this scientific concern was the arrival of the P4 packet processing language. Once again, developing networking hardware using traditional hardware description language is complex and time-consuming. P4 is a domain-specific language proposed to facilitate network equipment development and programmable switches. Software developers still consider the language to be missing some important external functions. This thesis proposes a simple communication method to extend software and ASIC-based switches to improve the performance of software switches and the flexibility of ASIC switches. The best way to visualize this scenario for a packet processing language like P4 is to have a flexible autogenerated communication procedure. The desired functionality is assumed to be expressed using the P4 language for all users of external packet processors (P4). We aim to use Python interfaces generated by a custom architecture in P4 and Python tools. Auto-generation of interfaces is proposed to reduce the development effort required from application developers to obtain hybrid solutions leveraging FPGAs. It is important because, generally, P4 programmers do not know or do not want to manipulate a hardware description language (HDL). The generation and interconnectivity of hardware modules for P4 pipelines are performed automatically. The proposed solution exploits direct memory access (DMA) and peripheral component interconnection interfaces to implement flexible multi-peripheral communication bridges. Simulation results validate the proper functionality of our state-of-the-art P4 interface methodology. Indeed, an external function to the P4 program was connected using an autogenerated interface. In addition to improving development efficiency, this project has low consumption of hardware resources, and the solution is functional in the industry because Intel tools validate it. Compiling with Quartus the hardware modules generated by Intel's compiler and those generated by the Python tool show a resource usage of 1.81 % of the logic (lookup table or LUT) for an Arria10 chip. Additionally, resources are limited to 1.62 % for memory (RAM block) and 0.96 % for flip-flops (registers). The proposed method is efficient for the user and improves the flexibility of the P4 language. The difference with the pipeline without generated interface is 281 registers and 194 LUTs, so a difference of 1.64 % and 4.54 % for the number of registers and the number of logical units (LUT) respectively. The proposed method is efficient for the user and improves the flexibility of the P4 language.

## TABLE DES MATIÈRES

|                                                                           |       |

|---------------------------------------------------------------------------|-------|

| DÉDICACE . . . . .                                                        | iii   |

| REMERCIEMENTS . . . . .                                                   | iv    |

| RÉSUMÉ . . . . .                                                          | v     |

| ABSTRACT . . . . .                                                        | vi    |

| TABLE DES MATIÈRES . . . . .                                              | vii   |

| LISTE DES TABLEAUX . . . . .                                              | ix    |

| LISTE DES FIGURES . . . . .                                               | x     |

| LISTE DES SIGLES ET ABRÉVIATIONS . . . . .                                | xi    |

| LISTE DES ANNEXES . . . . .                                               | xii   |

| <br>CHAPITRE 1 INTRODUCTION . . . . .                                     | <br>1 |

| 1.1 Contexte . . . . .                                                    | 1     |

| 1.2 Problématique . . . . .                                               | 2     |

| 1.3 Objectifs de recherche . . . . .                                      | 3     |

| 1.4 Contributions . . . . .                                               | 3     |

| 1.5 Vérification . . . . .                                                | 4     |

| 1.6 Organisation du mémoire . . . . .                                     | 4     |

| 1.7 Langage P4 . . . . .                                                  | 4     |

| 1.7.1 Trois composants du plan de donné P4 . . . . .                      | 4     |

| 1.7.2 Architecture P4 . . . . .                                           | 5     |

| 1.7.3 Externe en P4 . . . . .                                             | 5     |

| <br>CHAPITRE 2 REVUE DE LA LITTERATURE . . . . .                          | <br>7 |

| 2.1 HDL en Python . . . . .                                               | 7     |

| 2.1.1 Compatibilité de Python . . . . .                                   | 7     |

| 2.2 HDL générée par les outils Python . . . . .                           | 8     |

| 2.3 Interfaces dans les réseaux de communication . . . . .                | 10    |

| 2.3.1 PCIe (Interconnexion de composants périphériques Express) . . . . . | 10    |

|                                                                    |                                                                      |           |

|--------------------------------------------------------------------|----------------------------------------------------------------------|-----------|

| 2.3.2                                                              | DMA (module d'accès direct à la mémoire) . . . . .                   | 10        |

| 2.3.3                                                              | AXI (interface extensible avancée) . . . . .                         | 10        |

| 2.4                                                                | Interfaces P4 . . . . .                                              | 11        |

| 2.5                                                                | Interface pour le projet Pegasus . . . . .                           | 12        |

| 2.6                                                                | Synthèse de la littérature . . . . .                                 | 14        |

| <b>CHAPITRE 3 ARCHITECTURE DE L'ENVIRONNEMENT DES INTERFACES .</b> |                                                                      | <b>15</b> |

| 3.1                                                                | Pipeline P4 d'Intel . . . . .                                        | 15        |

| 3.1.1                                                              | Architecture du pipeline de traitement P4 d'Intel . . . . .          | 15        |

| 3.2                                                                | Génération automatique d'interfaces avec PyXHDL . . . . .            | 17        |

| 3.2.1                                                              | Module DMA . . . . .                                                 | 18        |

| 3.2.2                                                              | Module PCIe . . . . .                                                | 24        |

| 3.3                                                                | Compilation des Interfaces . . . . .                                 | 26        |

| 3.3.1                                                              | Compilation du code de l'externe C++ . . . . .                       | 27        |

| 3.3.2                                                              | Les bits de l'externe P4 . . . . .                                   | 28        |

| 3.3.3                                                              | Le code HLS pour la table d'action P4 . . . . .                      | 29        |

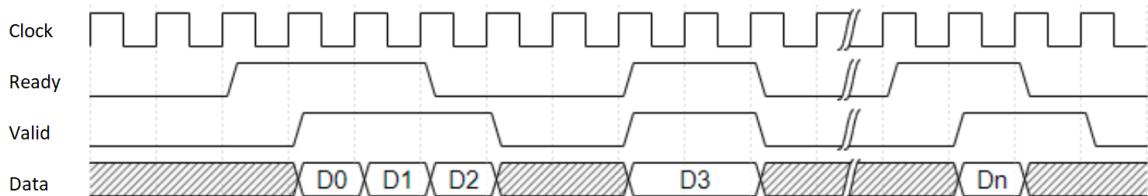

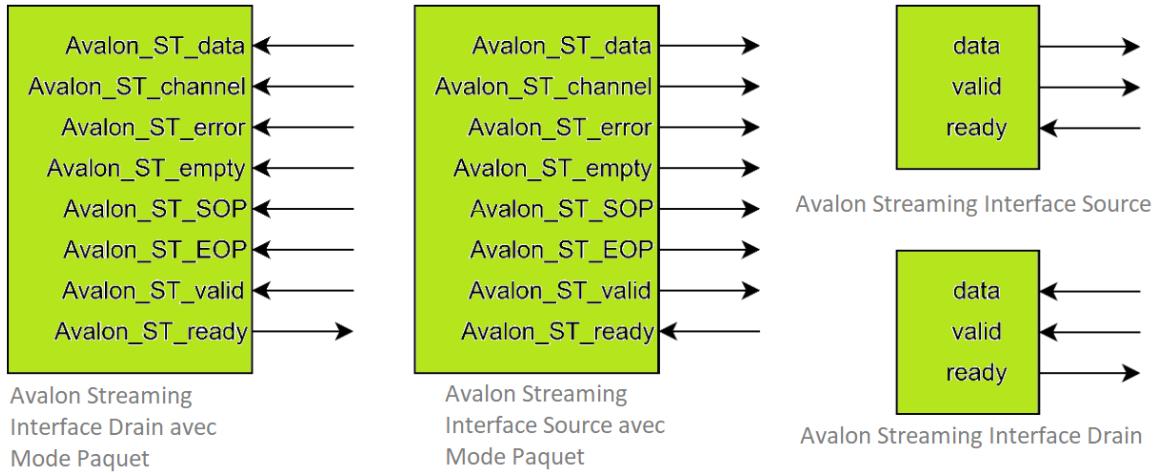

| 3.3.4                                                              | Avalon Stream . . . . .                                              | 30        |

| 3.3.5                                                              | La génération de l'interface . . . . .                               | 30        |

| 3.3.6                                                              | Ajustements supplémentaires aux dossiers de l'interface . . . . .    | 32        |

| 3.4                                                                | Composition du réseau . . . . .                                      | 33        |

| 3.4.1                                                              | Synthèse de la solution proposée . . . . .                           | 34        |

| <b>CHAPITRE 4 EXPERIMENTATIONS ET RESULTATS .</b>                  |                                                                      | <b>36</b> |

| 4.1                                                                | Test et fonctionnement . . . . .                                     | 36        |

| 4.1.1                                                              | Préparation à l'extraction du résultat de l'externe de P4 . . . . .  | 36        |

| 4.2                                                                | Résultats obtenus avec l'interface générée automatiquement . . . . . | 37        |

| 4.3                                                                | Discussion des résultats . . . . .                                   | 40        |

| <b>CHAPITRE 5 CONCLUSION ET RECOMMANDATIONS .</b>                  |                                                                      | <b>44</b> |

| 5.1                                                                | Synthèse des travaux . . . . .                                       | 44        |

| 5.2                                                                | Limitations et contraintes . . . . .                                 | 44        |

| 5.3                                                                | Travaux Futurs . . . . .                                             | 45        |

| <b>RÉFÉRENCES .</b>                                                |                                                                      | <b>46</b> |

| <b>ANNEXES .</b>                                                   |                                                                      | <b>49</b> |

**LISTE DES TABLEAUX**

|             |                                                                                                                             |    |

|-------------|-----------------------------------------------------------------------------------------------------------------------------|----|

| Tableau 2.1 | Utilisation de Python comme langage de programmation pour le matériel RTL . . . . .                                         | 9  |

| Tableau 3.1 | Génération de la logique combinatoire et de la logique séquentielle à partir de l'outil PyXHDL . . . . .                    | 23 |

| Tableau 4.1 | Ressources utilisées par l'architecture P4 modifié après synthèse sur Quartus pour le FPGA Arria10 . . . . .                | 40 |

| Tableau 4.2 | Différence des ressources utilisées par l'architecture P4 modifié après synthèse sur Quartus pour le FPGA Arria10 . . . . . | 41 |

| Tableau 4.3 | L'utilisation des ressources par entités matériels (synthèse Quartus) . .                                                   | 43 |

## LISTE DES FIGURES

|            |                                                                                                      |    |

|------------|------------------------------------------------------------------------------------------------------|----|

| Figure 2.1 | Le processus de compilation du programme P4 d'Intel jusqu'à déploiement de gauche à droite . . . . . | 11 |

| Figure 2.2 | La distribution de charges au niveau du projet Pegasus . . . . .                                     | 12 |

| Figure 3.1 | Fonctionnalités exprimées avec un module externe au pipeline P4 . .                                  | 16 |

| Figure 3.2 | Génération du chemin jusqu'au CPU . . . . .                                                          | 17 |

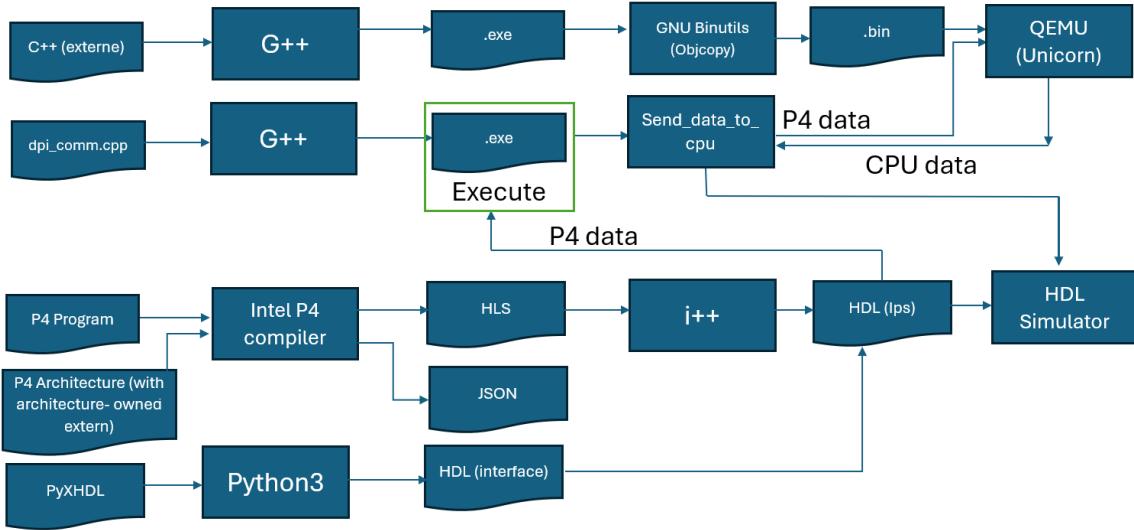

| Figure 3.3 | Flot de données complet pour l'implémentation et le test de solutions en P4 . . . . .                | 18 |

| Figure 3.4 | Lecture de données par une application P4 arrivant d'un module externe                               | 28 |

| Figure 3.5 | Symbole de l'exécutable de l'externe C++ de l'utilisateur . . . . .                                  | 29 |

| Figure 3.6 | Le Chronogramme du fonctionnement d'un Avalon Stream . . . . .                                       | 30 |

| Figure 3.7 | Les ports importants de l'Avalon Stream d'Intel . . . . .                                            | 31 |

| Figure 3.8 | L'architecture P4 n'accepte pas les réponses de l'externe P4 . . . . .                               | 31 |

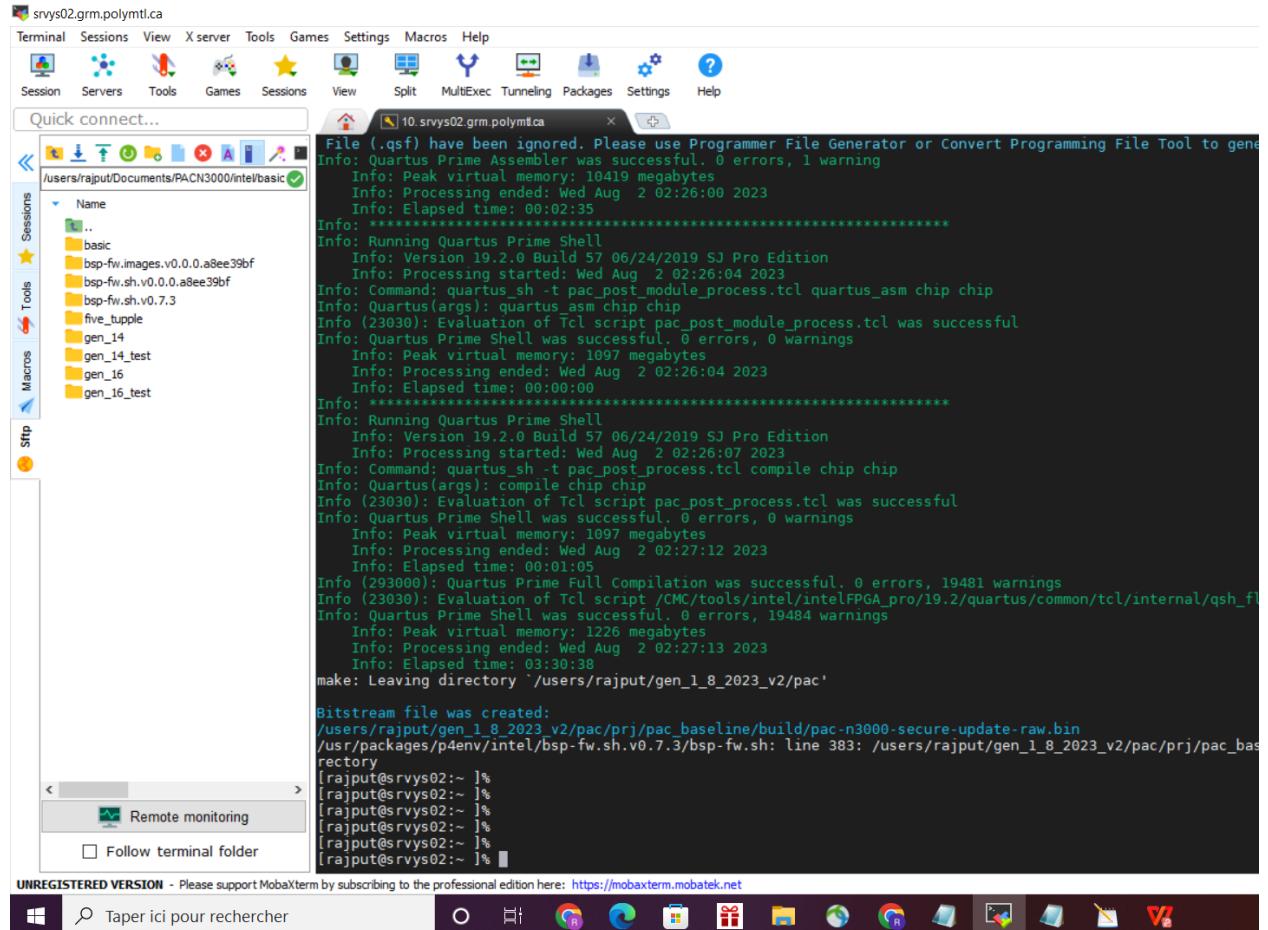

| Figure 4.1 | Génération de l'interface avec le nouveau compilateur . . . . .                                      | 37 |

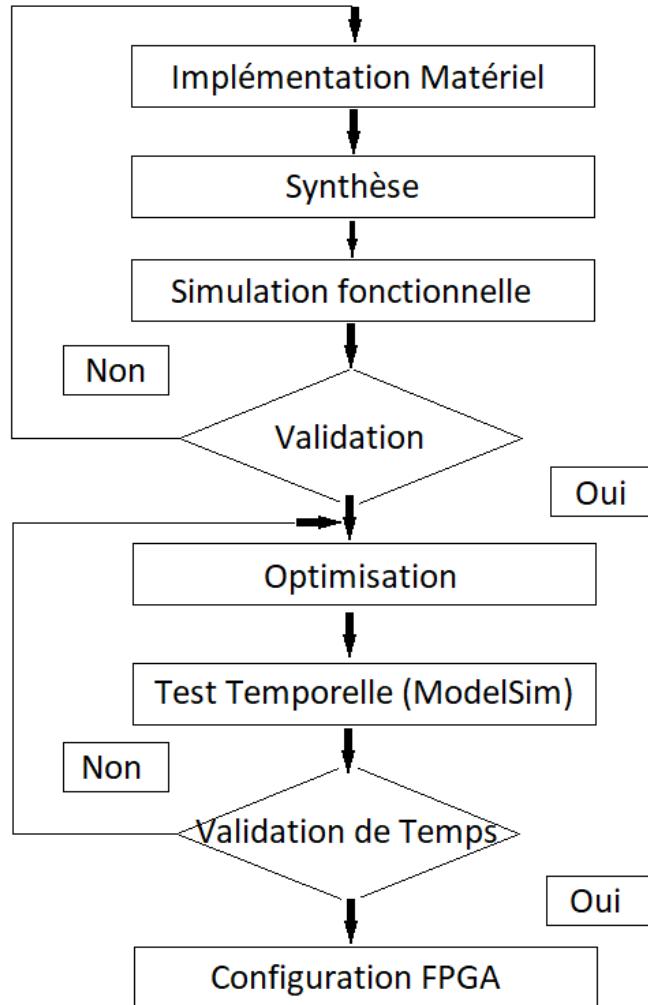

| Figure 4.2 | Étape d'implantation de matériel dérivé de P4 . . . . .                                              | 39 |

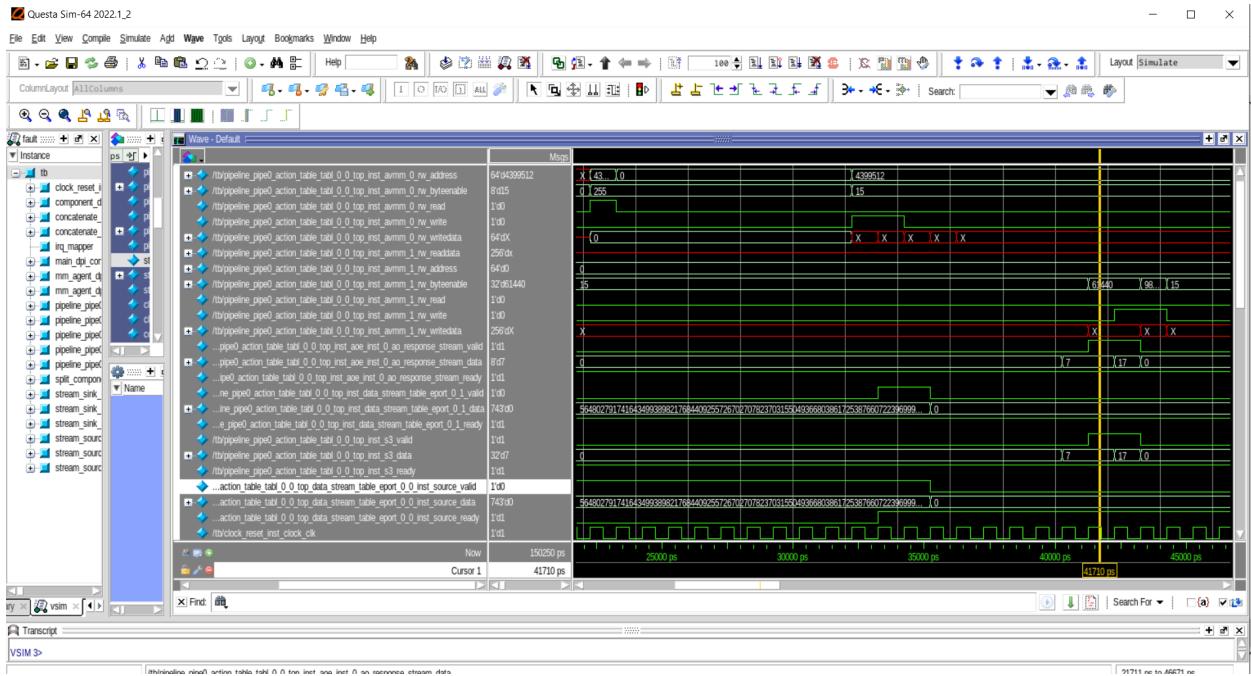

| Figure 4.3 | La validation du fonctionnement des interfaces . . . . .                                             | 40 |

| Figure A.1 | Génération de bitstream avec l'ancien compilateur . . . . .                                          | 50 |

## LISTE DES SIGLES ET ABRÉVIATIONS

|           |                                                                  |

|-----------|------------------------------------------------------------------|

| ALM       | Adaptive Logic Module                                            |

| AMBA      | Advanced Microcontroller Bus Architecture                        |

| AOE       | Architecture-Owned Extern                                        |

| API       | Application Programming Interface                                |

| ARM       | Advanced RISC Machine                                            |

| AXI       | Advanced Extensible Interface                                    |

| BRAM      | Block Random Access Memory                                       |

| CPU       | Central Processing Unit                                          |

| DFA       | Deterministic Finite Automaton                                   |

| DMA       | Direct Memory Access                                             |

| DRAM      | Dynamic Random Access Memory                                     |

| DUT       | Device Under Test                                                |

| EOP       | End Of Packet                                                    |

| FIFO      | First In First Out                                               |

| FPGA      | Field Programmable Gate Arrays                                   |

| HDL       | Hardware Description Language                                    |

| HLS       | High Level Synthesis                                             |

| IP        | Intellectual Property                                            |

| LUT       | Look-Up Tables                                                   |

| NIC       | Network Interface Card                                           |

| PAC N3000 | Programmable Acceleration Card N3000                             |

| PCIe      | Peripheral Component Interconnect express                        |

| PIE       | Position-Independent Executables                                 |

| P4        | Programming Protocol-independent Packet Processors               |

| RTL       | Register Transfer Level                                          |

| SDN       | Software-Defined Networking                                      |

| SOC       | System-on-a-Chip                                                 |

| SOP       | Start Of Packet                                                  |

| VHDL      | Very High-Speed Integrated Circuit Hardware Description Language |

**LISTE DES ANNEXES**

|          |                                         |    |

|----------|-----------------------------------------|----|

| Annexe A | Fichier Python de compilation principal | 49 |

|----------|-----------------------------------------|----|

## CHAPITRE 1 INTRODUCTION

### 1.1 Contexte

Le matériel utilisé dans les réseaux de données, également appelé équipement réseau ou périphériques du réseau informatiques, est un appareil électronique nécessaire à la communication et à l'interaction entre les appareils d'un réseau informatique. Plus précisément, ces équipements assurent la transmission de données dans un réseau de données informatique. Les unités qui sont le dernier récepteur ou celles qui génèrent des données sont appelées hôtes, systèmes finaux ou équipements terminaux de données. Dans une perspective plus large, les téléphones mobiles, les tablettes et les appareils associés à l'Internet des objets peuvent également être considérés comme du matériel de réseau. À mesure que la technologie progresse et que les réseaux IP sont intégrés aux infrastructures des bâtiments et aux services publics domestiques, le terme matériel réseau devient ambigu en raison du nombre considérablement croissant de points finaux compatibles avec le réseau.

Les applications réseau se développent rapidement en raison de la demande de vitesses de transfert de données plus élevées et les marchés des serveurs et de l'infonuagique. En conséquence, les centres de données continuent d'évoluer pour répondre à ces demandes. Ils optent pour une solution qui est plus universelle, comme le langage P4, qui spécifique. Les programmes P4 sont conçus pour être indépendants de l'implémentation, donc ils peuvent être compilés sur de nombreux types de support matériels tels que des processeurs à usage général, des FPGA, des systèmes sur puce, des processeurs réseau et des ASIC. Les périphériques réseau jouent un rôle essentiel en facilitant la communication entre les ordinateurs et les réseaux Internet.

Le marché des réseaux continue d'exiger une transmission de données plus fluide et de nombreux défis sont propres au marché des réseaux comme la perte de canal et la compensation de perte de canal sur la ligne de transmission. Cependant, dans certains systèmes, le délai de traitement peut être assez important, en particulier lorsque les routeurs exécutent des algorithmes de chiffrement complexes et examinent ou modifient le contenu des paquets [1]. L'inspection approfondie des paquets effectuée par certains réseaux examine le contenu des paquets pour des raisons de sécurité, juridiques ou autres, ce qui peut entraîner des retards très importants et n'est donc effectuée qu'à des points d'inspection sélectionnés. Le langage P4 n'est pas la solution au déchargement du réseau lors de ces situations. Dans le cas où le nombre de calculs est important, il n'est essentiellement pas possible de faire le déchargement vers un processeur ou FPGA de haute performance et augmenter le parallélisme avec d'autres

équipements du réseau ou périphériques du réseau informatiques.

En fait, le réseau est composé des interfaces comme le PCIe, l'AXI et SPI ou l'I2C qui relient les composants de la topologie très efficacement. La communication peut se faire pour la distribution de fonctionnalité qui n'est pas réalisable en P4 ou celle qui demande plus de matériel. Cette fonctionnalité peut être transférée à un autre composant comme FPGA ou le CPU de l'hôte [2]. En effet, les interfaces sont programmables en matériel et elles permettent l'échange d'informations à l'aide des ports en entrées et en sorties. Elles sont très visibles, dans le marché, configurées en Verilog (HDL).

## 1.2 Problématique

Le problème avec les interfaces configurées en langage matériel est la consommation de temps et d'énergie. Des études montrent que les programmeurs des langages matériels consacrent beaucoup de temps dans la conception du matériel exact sans problème ou bogue [3]. Tout simplement parce qu'il n'est pas possible de valider le code matériel sans les déploiements en matériel et sans effectuer une vérification avec le logiciel adéquat. Les modules programmés en matériel sont accessibles au logiciel et font des échanges de données pour effectuer la logique du matériel implémenté. Il est à noter que les FPGA favorisent l'implémentation flexible du matériel. Les interfaces qui sont utilisées pour communiquer l'information d'un FPGA à l'autre ou vers un hôte sont aussi programmées en HDL (RTL) [2].

Par conséquent, ce principe de fonctionnement n'est pas favorable pour les langages descriptifs comme le P4 qui désirent avoir accès à la configuration des interfaces matérielles. Les limites de P4 font en sorte qu'il n'est pas possible de programmer les interfaces flexibles directement en P4 en passant simplement par l'architecture de celle-ci.

Ces interfaces sont possibles si un module décrit en P4 collabore avec une autre langue de haut niveau comme le C++ ou le Python. D'ailleurs, Python est utilisé de plus en plus dans la programmation et l'automatisation, car il favorise la simplicité de développement pour le programmeur.

Bref, le problème vient du fait que les compilateurs applicables au programme P4 sont toujours dépendants des langages comme le VHDL et le Verilog pour la configuration des interfaces. Il est aussi vrai que les interfaces sont parfois pré-implémentées et disponible dans une bibliothèque que le compilateur consulte pour la synthèse des interfaces. Donc pour interconnecter un pipeline P4 avec le réseau, tenter de le faire avec des interfaces préimplémentées est très limité.

### 1.3 Objectifs de recherche

Ce mémoire a pour objectif premier de proposer un outil permettant d'étendre l'accessibilité du langage P4. Les applications écrites en HDL venant du compilateur P4 auront accès aux interfaces flexibles. Ces modules HDL devront faire la communication à une fonctionnalité externe au travers d'un code d'interface codé d'un langage de haut niveau au lieu d'être dans un langage de bas niveau (VHDL, Verilog). Les programmes P4 peuvent, quant à eux, avoir un code qui permet l'utilisation des externes.

Les externes personnalisés interconnectés avec le pipeline P4 dans l'architecture du programme P4 permettent plus de fonctionnalité aux actions des tableaux P4. Les actions ayant une fonction externe favorisent l'encapsulation et la conception de code modulaire en permettant de spécifier et d'implémenter différents comportements séparément. Cela accélère les temps de compilation, car apporter une petite modification nécessite uniquement de recompiler cette unité de traduction et de recréer les liens, et non de recompiler l'intégralité de la base de code.

D'ailleurs, il est aussi possible de voir, lors de la compilation, que le code P4 compilé, dans ce projet, utilise le compilateur HLS pour générer le code HDL pour des tableaux P4.

La déclaration de fonctions via un externe sera visible en langage matériel, après la compilation du code P4, la fonction externe sera accessible dans le code HDL à travers les IPs HDL du tableau P4 du programme P4 de l'utilisateur. Donc, ce code HDL peut, à ce moment-là, être connecté aux interfaces provenant d'un autre langage de haut niveau comme le C++ ou le Python.

### 1.4 Contributions

La principale contribution de ce projet est un générateur d'interface qui étend un langage pour la description du plan de données P4. Premièrement, le code P4 est utilisé pour générer des modules matériels pour une application réseau. Ensuite, ce projet permet de générer automatiquement les interfaces pour cette application P4 à l'aide de l'outil de Python «PyXHDL». Deuxièmement, l'environnement réalise les interconnexions avec ces interfaces aux externes de l'utilisateur. Un externe peut être écrit en C++ et peut faire un retour de la valeur calculée à travers ces interfaces générées pour la fonctionnalité de l'externe. La gestion de ces interfaces est sous le contrôle du script Python d'Intel.

## 1.5 Vérification

L'environnement de vérification est basé sur l'utilisation d'un externe personnalisé dans le code P4. Cet externe sera utilisé pour automatiquement générer des interfaces codées en PyXHDL. Ce projet utilise Python et la simulation matérielle pour illustrer le bon fonctionnement des externes communiquant avec le pipeline P4.

Les interfaces permettent des échanges à partir du module de la mémoire BRAM et en communiquant avec le processeur émulé à travers le module DPI-C utilisés en SystemVerilog.

## 1.6 Organisation du mémoire

La suite de ce mémoire est organisée comme suit. Tout d'abord, une revue des travaux sur les recherches existantes est résumée dans le chapitre II. Par la suite, le programme P4 pour le compilateur d'Intel et l'interface Python sont exposés dans le chapitre III. Dans le chapitre IV, une discussion est présentée sur les résultats du transfert de données. Finalement, le chapitre V conclut ce mémoire et propose des travaux futurs dans le but de favoriser le développement matériel (bas niveau). Avant tout, faisons un petit aperçu de la composition du langage P4 à la section suivante.

## 1.7 Langage P4

Cette section présente les notions préliminaires concernant le projet. Il s'agit de la nouvelle structure et le langage de programmation de réseaux en P4, la logique des externes ainsi que les méthodes utilisées pour l'autogénération par la programmation de haut niveau.

L'émergence des commutateurs programmables a gagné du terrain parmi les principaux fournisseurs de réseaux. L'autogénération de modules de bas niveau utilisant un langage de haut niveau comme P4 a révolutionné la conception des systèmes de communication et les générations d'IP [2]. Dans ce type de gestion, l'utilisation de Python a constitué une avancée majeure dans la synthèse moderne de bas niveau.

### 1.7.1 Trois composants du plan de donné P4

Le langage P4 décrit le comportement de la procédure de traitement des paquets en trois parties. La première partie est liée à l'extraction de l'en-tête du paquet lors de l'étape de l'analyseur [4].

La deuxième partie est associée à la logique de contrôle des paquets lors de la phase de correspondance et d'action. Ici, les en-têtes de paquets sont utilisés pour créer des clés de

recherche en utilisant des champs de paquets ou des métadonnées calculées.

La troisième partie principale implique l'inverse de l'analyse, à savoir la construction de paquets.

### 1.7.2 Architecture P4

Le fichier d'architecture P4 sert de descripteur principal pour les interfaces P4 à générer par le compilateur P4. Ce fichier est valide pour tous les blocs et externes de P4 [4]. Les connexions actuelles pour les externes sont rendues possibles via un bus déjà disponible en HDL, tel que l'AXI [2]. Les modules d'interface sont instanciés par le compilateur pour établir la connexion au pipeline P4. L'architecture peut être différente pour différents FPGA et ceci est aussi valide pour différentes versions de P4 comme le P4<sub>16</sub>.

Listing 1.1 La définition de mon externe dans un architecture P4

```

1 #include <core.p4>

2 extern Custom_Extern_Component{

3     Custom_Extern_Component();

4     void update(in bit<256> data)

5 }

```

### 1.7.3 Externe en P4

Comme les unités de somme de contrôle et bien d'autres, le langage P4 possède différents éléments externes qui rendent le langage performant. Ces externes sont utilisés dans le langage P4 pour exécuter des API définies. Leurs comportements internes sont fixes. Un objet externe définit un ensemble de méthodes accessibles aux programmes P4, offrant un moyen d'interagir avec ces composants spécifiques à l'architecture sans exposer les détails internes de leurs implémentations internes [4, 5]. Ce code 1.1 est la définition d'externe dans le fichier d'architecture P4. Cela inclut l'utilisation du type «extern» pour définir le constructeur d'objet externe personnalisé Custom\_Extern\_Component() comme en C++ puis une déclaration de la méthode externe nommée update().

Comme dans le code 1.2 la déclaration de la méthode Custom\_Architecture<Header, Metadata>(), crée l'instance de l'objet externe Custom\_Extern\_Component(). Il est alors possible de faire un appel à l'instance externe (comme une fonction en C++) dans les actions du bloc de contrôle du programme P4 illustrés au code 1.3. L'objet Custom\_Pipeline<Header, Metadata>() déclare la structure du pipeline comme faisant partie d'une entité en utilisant un type tel que «package». Il en va de même pour l'entité de niveau supérieur de l'architec-

ture, `Custom_Architecture<Header, Metadata>()`, qui inclut désormais l'instance externe de l'utilisateur (`custom_extern`) ainsi que l'instance d'objet de ce pipeline appelée `pipe0`.

Listing 1.2 La liaison de l'externe au pipeline P4 dans l'architecture P4

```

1 package Custom_Pipeline<Header, Metadata>(

2   Parser<Header, Metadata> parser,

3   Ingress<Header, Metadata> ingress,

4   Deparser<Header> deparser

5 );

6 package Custom_Architecture<Header, Metadata> (

7   Custom_Pipeline<Header, Metadata> pipe0,

8   Custom_Extern_Component custom_extern = Custom_Extern_Component()

9 );

```

Listing 1.3 Utilisation l'externe dans l'action P4

```

1 action port_ctrl(bit<8> eport) {

2   md_intr.egress_port = eport;

3   bit<256> AOE_data= 7;

4   aoe_inst.update(AOE_data);

5 }

```

## CHAPITRE 2 REVUE DE LA LITTERATURE

Dans ce chapitre, nous mettons en évidence certaines découvertes importantes liées à ce projet. Donc, cette section abordera les sujets suivants : la génération de HDL à l'aide d'outils Python, les interfaces dans les réseaux de communication, l'interface P4, ainsi que les interfaces du projet Pegasus.

### 2.1 HDL en Python

Les langages de haut niveau facilitent la génération des langages matériels comme VHDL [6]. Python a connu un regain de popularité pour plusieurs raisons. Facilité d'apprentissage et d'utilisation comme la syntaxe de Python est claire et intuitive, ce qui la rend facile à apprendre et à utiliser pour les débutants. Il permet aux développeurs d'écrire moins de code pour accomplir plus de tâches par rapport à de nombreux autres langages de bas niveau RTL [7].

Python prend en charge plusieurs paradigmes de programmation, notamment la programmation procédurale, orienté objet et fonctionnelle. Il a une large gamme d'applications utilisées dans le développement Web, l'analyse de données, l'intelligence artificielle, le calcul scientifique, l'automatisation, etc. Python dispose d'une vaste bibliothèque standard et d'un riche écosystème de bibliothèques tierces pour pratiquement toutes les applications. De plus, une communauté vaste et active contribue à une richesse de ressources, de documentation et de support.

Python peut facilement s'interfacer avec des langages comme C/C++ (via des extensions) et Java (via Jython). Idéal pour le prototypage en raison de sa nature de haut niveau et de son cycle de développement rapide. Pour la science des données et apprentissage automatique, c'est le langage préféré des scientifiques grâce à des bibliothèques telles que NumPy, pandas, TensorFlow et scikit-learn.

#### 2.1.1 Compatibilité de Python

Python est indépendant de la plate-forme et peut fonctionner sous Windows, macOS et Linux. Python gagne également du terrain dans le domaine de la conception matérielle, notamment en tant qu'outil de génération RTL. Python permet aux concepteurs d'écrire des descriptions abstraites de haut niveau du matériel qui peuvent ensuite être converties en RTL. Les constructions de haut niveau et les fonctionnalités orientées objet permettent un

code réutilisable et maintenable.

La nature interprétative et la syntaxe concise de Python facilitent le prototypage et l’itération rapides des conceptions matérielles. Les outils de débogage robustes de Python facilitent l’identification et la résolution des problèmes dès le début du processus de conception [8].

Python peut s’intégrer aux outils EDA (Electronic Design Automation) existants, facilitant ainsi un flux de travail transparent.

Des bibliothèques telles que MyHDL, PyMTL et Chisel (qui utilisent Scala mais ont un objectif similaire) permettent aux concepteurs de décrire le matériel en Python ou dans des langages de haut niveau similaires, qui sont ensuite convertis en Verilog/VHDL. Entrée de conception flexible avec ces outils qui offrent une entrée de conception plus flexible et expressive par rapport au DSL (Domain Specific Language) HDL traditionnel.

## 2.2 HDL généré par les outils Python

Les interfaces dans certains autres projets utilisent aussi python, mais avec les librairies telles que le PyHDL ou le MyHDL. Ces librairies permettaient un accord parfait prédéfini pour la génération de code matériel. Bref, il y a plusieurs outils qui favorisent l’utilisation du langage de haut niveau (Python) pour faire la génération du code en bas niveau (RTL). Les outils et leurs environnements sont tous différents les uns des autres, ainsi que les communautés les supportant impactent grandement la flexibilité et l’extensibilité des outils, voire la table 2.1. L’outil PyXHDL est considéré faible pour la catégorie de Soutien communautaire, car son développement n’est pas fait par un grand nombre de personnes. Il est considéré de qualité moyenne pour la flexibilité, l’extensibilité et ainsi que pour la performance et l’efficacité. Cet outil gratuit est assez puissant, rapide et facile à utiliser malgré son apparition récente sur le marché.

En effet, PyXHDL prend avantage d’être compatible avec les outils EDA existants. Cet outil de l’environnement Python permet aussi, comme le Chisel une bonne prise en charge de la vérification et des tests.

Les outils comme le MyHDL permettent d’avoir pratiquement les mêmes fonctionnalités que les autres de la liste, donc de faire la génération du code matériel avec un langage de haut niveau [9]. Plus spécifiquement, les générateurs MyHDL sont similaires aux blocs «Always» dans Verilog et aux processus en VHDL. Un module matériel (appelé bloc dans la terminologie MyHDL) est modélisé comme une fonction qui renvoie des générateurs. Cette approche facilite la prise en charge de fonctionnalités telles que la hiérarchie arbitraire, l’association de ports, les tableaux d’instances et l’instanciation conditionnelle. De plus, MyHDL propose des classes

TABLEAU 2.1 Utilisation de Python comme langage de programmation pour le matériel RTL

| Outils    | Soutien communautaire | Flexibilité et extensibilité | Performance et efficacité | Licence et coût |

|-----------|-----------------------|------------------------------|---------------------------|-----------------|

| MyHDL     | Moyen                 | Élevé                        | Élevé                     | gratuite        |

| PyMTL     | Moyen                 | Élevé                        | Élevé                     | gratuite        |

| PHDL      | Faible                | Moyen                        | Moyen                     | gratuite        |

| Migen     | Moyen                 | Élevé                        | Élevé                     | gratuite        |

| Chisel    | Élevé                 | Élevé                        | Élevé                     | gratuite        |

| SpinalHDL | Moyen                 | Élevé                        | Élevé                     | gratuite        |

| NGEN      | Faible                | Moyen                        | Moyen                     | gratuite        |

| HWT       | Faible                | Moyen                        | Moyen                     | gratuite        |

| PyXHDL    | Faible                | Moyen                        | Moyen                     | gratuite        |

qui implémentent les concepts traditionnels de description du matériel. Il fournit une classe de signaux pour prendre en charge la communication entre les générateurs, une classe pour prendre en charge les opérations orientées bits et une classe pour les types d'énumération.

D'un autre côté, en PyMTL le concepteur commence par développer une conception sous test (DUT «Device Under Test») au niveau fonctionnel et un banc de test entièrement en Python. Ensuite, le DUT est affiné de manière itérative au niveau du cycle et au niveau du transfert de registre, ainsi que par la vérification et l'évaluation à l'aide d'une simulation basée sur Python et du même banc de test. Le concepteur peut, après la traduction d'un modèle PyMTL en Verilog et utiliser le même banc de test pour la cosimulation. Notez que les concepteurs peuvent également co-simuler le code source SystemVerilog existant avec un banc de test PyMTL.

D'ailleurs, Chisel (Constructing Hardware In a Scala Embedded Language) est un langage de construction de matériel intégré dans le langage de programmation de haut niveau Scala [10]. Chisel est une bibliothèque de définitions de classes spéciales, d'objets prédéfinis et de conventions d'utilisation au sein de Scala. Ainsi, lors de la conception du Chisel, le programmeur écrit en réalité un programme Scala qui construit un graphe matériel.

Enfin, le HWT est le pont entre HLS et HDL. Il offre un style de codage comme HLS, mais en même temps il vous permet de manipuler des objets HDL [11]. Cela signifie qu'il est un peu plus lent d'écrire un prototype que dans HLS, mais vous savez toujours quoi, comment et pourquoi se passe. HWT utilise le «netlist» de haut niveau pour la représentation interne de la conception cible. Les «netlist» optimisées sont générées à partir d'instructions de code habituelles, d'appels de fonctions, d'instructions, etc. Les processus matériels sont automatiquement résolus. Cette «netlist» est facile à utiliser et facile à modifier ou à analyser

par l'utilisateur s'il manque quelque chose dans la bibliothèque principale. Les modes de sérialisation permettent également de modifier le comportement du composant pendant la sérialisation.

Tous les outils présentés dans cette section sont très semblables. Ils permettent de faire la génération du code de bas niveau en utilisant les langages de haut niveau comme le Python. Ces outils n'ont pas les mêmes plates-formes de fonctionnement et ne sont pas sous la gestion du même propriétaire et sont compatibles avec de différents composants comme les FPGA, les CPU ainsi que divers logiciels. Alors, une comparaison de fiabilité dépend surtout sur la méthode de l'implémentation et les besoins en matière de fonctionnalité (le besoin d'un code simple, efficace et facile à comprendre).

### 2.3 Interfaces dans les réseaux de communication

Dans les réseaux et les systèmes numériques, une interface fait référence à une méthode standardisée permettant aux composants de communiquer entre eux. Ces interfaces définissent les règles et protocoles de transfert de données, garantissant l'interopérabilité entre les différents appareils et systèmes.

#### 2.3.1 PCIe (Interconnexion de composants périphériques Express)

PCIe est une interface de communication haute vitesse utilisée pour connecter des composants haute vitesse telle que des cartes graphiques, des SSD et des cartes réseau à la carte mère. Ayant une bande passante élevée, faible latence, prend en charge plusieurs voies (x1, x4, x8, x16) pour des performances évolutives [12, 13].

#### 2.3.2 DMA (module d'accès direct à la mémoire)

Les DMA permettent aux périphériques matériels de transférer des données vers/depuis la mémoire sans impliquer le processeur, libérant ainsi les ressources du processeur. Les DMA sont capables d'effectuer le transfert de données à grande vitesse. Ils sont efficaces pour les transferts de données volumineux et ils réduisent la surcharge du processeur [13].

#### 2.3.3 AXI (interface extensible avancée)

AXI fait partie de la spécification ARM AMBA (Advanced Microcontroller Bus Architecture), utilisée pour le transfert de données à grande vitesse dans les SoC (System on Chips).

Performant de haute performance et à débit élevé, les bus AXI prennent en charge plusieurs transactions en cours, longueurs de rafale flexibles.

## 2.4 Interfaces P4

Dans le contexte de notre recherche, les interfaces servent de conduits intégraux permettant d'isoler le réseau P4 par rapport au plan de données. Une interface est définie comme un point de communication facilitant l'interaction entre des entités distinctes au sein des modules P4 [4]. Il faut noter ici que chaque entité est supposée fonctionner indépendamment selon l'architecture définie par l'utilisateur. Les interfaces permettent aux diverses entités de d'échanger des données sur des mécanismes de connexion reconnus tels que le PCIe exploitée dans notre projet. Traditionnellement, P4 fait des connexions en utilisant des interfaces AXI.

Les interfaces en P4 découlent directement du code P4 dans le fichier de son architecture [4,5]. Le fichier comme expliqué auparavant est lié au «core» du code P4 et permet de former les liens en utilisant des liens possibles dans les fichiers du compilateur. Le code P4 est compilé traditionnellement à une version JSON pour la partie de l'application logicielle du plan de contrôle, mais les compilateurs modernes génèrent aussi les modules matériels.

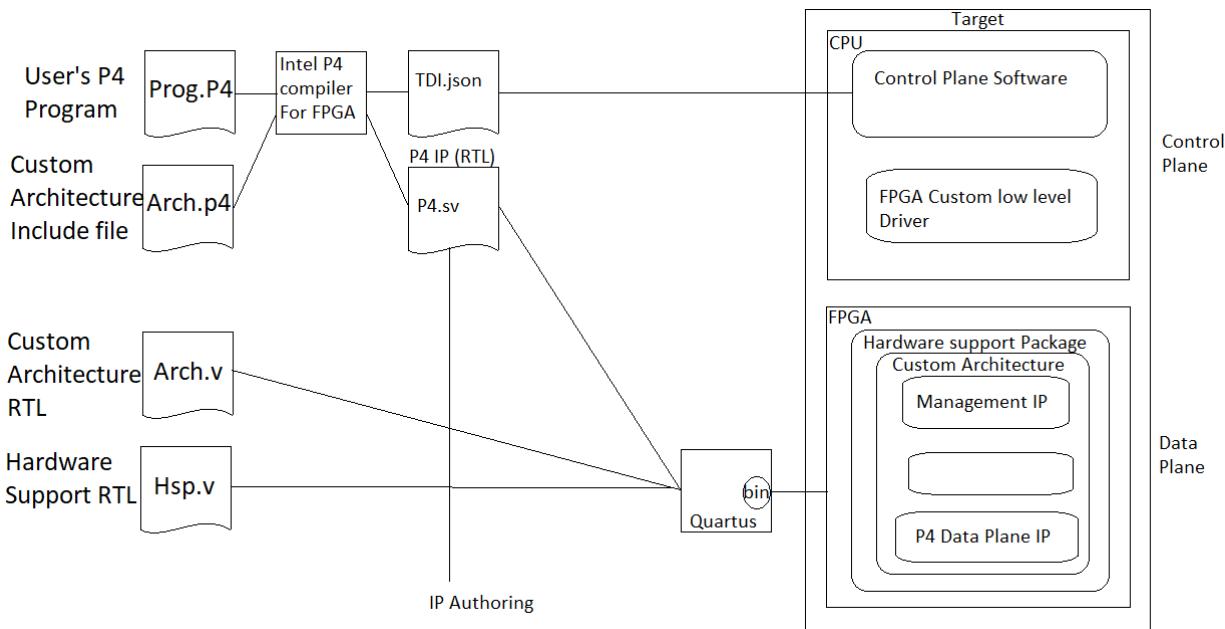

FIGURE 2.1 Le processus de compilation du programme P4 d'Intel jusqu'à déploiement de gauche à droite

Les compilateurs d'Intel et de Xilinx ont le pouvoir de prendre les bibliothèques à leur disposition pour traduire un code P4 en HDL en utilisant le passage par HLS comme pour le

projet eHDL [14]. Ceci permet de minimiser le temps de compilation ainsi que cette nouvelle façon de faire permet de réduire le stress d'écrire du code RTL. Dans ce projet, il est question d'utiliser l'architecture du FPGA Arria10 d'Intel (PAC N3000). Le compilateur d'Intel tente de faire un alignement simple pour le passage du code P4 à du code HDL [15]. La bonne structure de compilation du compilateur P4 d'Intel est visible à la figure 2.1. Le FPGA est la cible de l'implémentation pour le pipeline P4 une fois convertie en HDL après la synthèse Quartus.

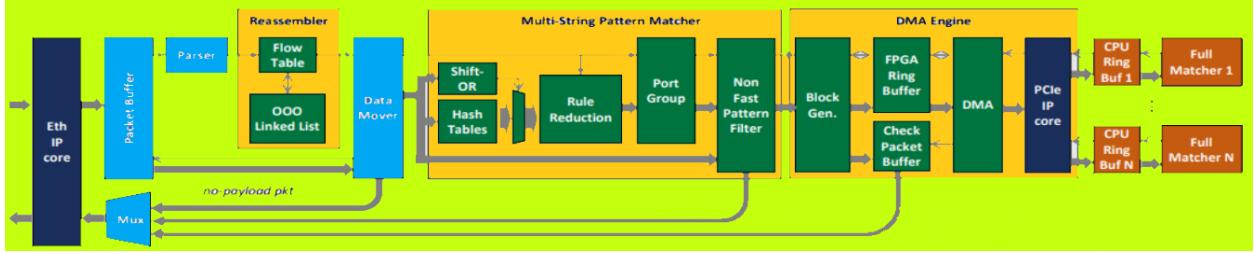

FIGURE 2.2 La distribution de charges au niveau du projet Pegasus

## 2.5 Interface pour le projet Pegasus

Les interfaces ont été implémentées avec Python dans le projet de Pegasus [2]. Dans ce projet, l'équipe a utilisé les templates Jinja2 comme à l'exemple du code 2.1 pour faire la génération automatique d'interfaces HDL comme VHDL et Verilog. Pegasus avait comme objectif de rendre le processus plus rapide pour coder les modules HDL de la détection de l'intrusion [16]. De plus, le projet utilise ses interfaces générées pour distribuer la charge d'un FPGA sur d'autres composants de la topologie comme un deuxième FPGA ou l'hôte de la communication du réseau (voir figure 2.2). Le projet a réussi à implémenter la logique de la détection d'intrusion à l'aide de Python et pouvait atteindre des vitesses atteignant 100 Gbps.

Listing 2.1 «Template» de Jinja2 en Python

```

1 Hallo {{ nom }}!

2

3 Dans le test d'aujourd'hui {{ nom_du_test }}.

4 Tu as obtenu {{ note }} points pour {{ note_max }}.

5

6 Salut,

7 Rajat

8

9

```

```

10

11 from jinja2 import Environment, FileSystemLoader

12

13 note_max = 100

14 nom_du_test = "Externe en C++"

15 participants = [

16     {"nom": "Jean", "note": 100},

17     {"nom": "Fred", "note": 87},

18     {"nom": "Luis", "note": 92},

19 ]

20

21 environment = Environment(loader=FileSystemLoader("templates/"))

22 template = environment.get_template("message.txt")

23

24 for participants in participants:

25     filename = f"message_{participants['nom'].lower()}.txt"

26     content = template.render(

27         participants,

28         note_max=note_max,

29         nom_du_test=nom_du_test

30     )

31     with open(filename, mode="w", encoding="utf-8") as message:

32         message.write(content)

33         print(f"... wrote {filename}")

```

Pegasus a utilisé le Python pour toute sa plate-forme de conception et de génération de codes HDL ainsi que pour la simulation des différentes configurations de tests en utilisant le système de détection et de prévention des intrusions.

Le projet Pegasus est basé sur l'utilisation de l'architecture du FPGA Startix10. Ce FPGA est utilisé comme une première ligne de défense, en étant considéré comme une ressource de détection d'intrusion pour les premiers processus de filtrage, avant même l'intervention du CPU dans la méthode traditionnelle, comme illustré à la figure 2.2. Le partage de tâches entre le CPU et le FPGA est notamment viable dans d'autres applications. Le projet de [17] utilise la reconnaissance par automates finis déterministes (DFA) avec des performances élevées de prétraitement. Le projet de [18] permet la reconfiguration pour répondre aux demandes d'inférence de réseaux neuronaux profonds en temps réel sur un SmartNIC photonique-électronique. Plus proche de notre utilité est le projet de [19], qui traite du calcul hybride FPGA et CPU à l'aide de leur outil Spork («hybrid computing scheduler») pour exploiter les avantages en termes d'efficacité énergétique des FPGA pour ce type de charges de travail à un coût raisonnable. Par ailleurs, de nouvelles méthodologies permettent d'atteindre les objectifs de

télécommunications issus de la 5G [20].

Alors, les paquets entrent en contact avec le FPGA directement sans passer par le processeur d'hôte. Quoique, au besoin (selon le fonctionnement du réseau) ceux-ci sont dirigés vers un deuxième FPGA ou l'hôte. Il est aussi important de noter que cette transition est aussi possible pour des paquets qui n'ont pas été tout à fait décodés.

## 2.6 Synthèse de la littérature

Lors de cette section, il était question de faire une revue de la littérature pour le choix des outils de génération automatique de code HDL pour les interfaces (DMA, PCIe). La comparaison des outils de génération a été effectuée sur la performance et la facilité d'utilisation des outils comme MyHDL. D'ailleurs, le projet de référence Pegasus avait aussi été présenté dans ce chapitre. Pegasus est un projet d'extension de pipeline de détection d'intrusion utilisant le « *Jinja template* » de Python. Il faut savoir que l'outil est un bon choix pour générer du matériel pour FPGA [21]. Bref, nous verrons dans la prochaine section que l'utilisation du langage P4 est destinée à la génération de pipeline P4, mais peut aussi servir à déclarer une fonction externe pour étendre le pipeline P4.

## CHAPITRE 3 ARCHITECTURE DE L'ENVIRONNEMENT DES INTERFACES

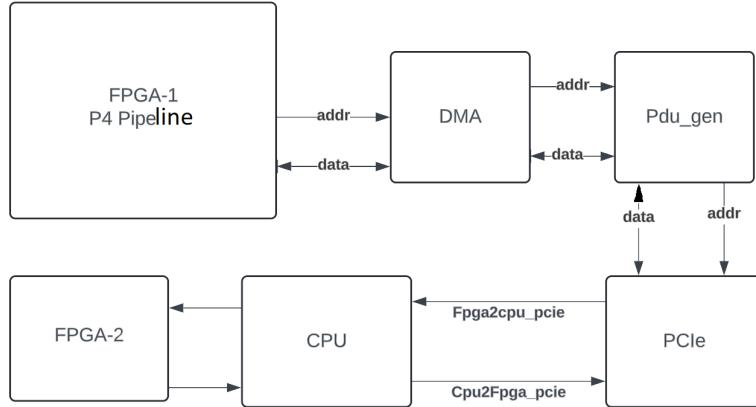

La mise en œuvre de certaines fonctionnalités dans les programmes P4 nécessite l'utilisation de modules appelés externes. De cette façon, le programme P4 du plan de données («Data Plane») devient plus efficace. Un FPGA peut avoir des périphériques comme d'autres FPGA. Les externes vont communiquer avec ces périphériques au travers d'interfaces. Alors, l'exécution de l'externe prend place sur d'autres FPGA ou processeurs. L'objet de ce mémoire est la génération automatique de ces interfaces. Une interface comme le PCIe permet une communication entre divers périphériques comme les FPGA, le CPU, etc. Ce chapitre traitera des thèmes suivants : les outils de développement pour le P4 offerts par Intel, la génération automatique d'interfaces avec PyXHDL, la compilation des interfaces, ainsi qu'une analyse de haut niveau des réseaux.

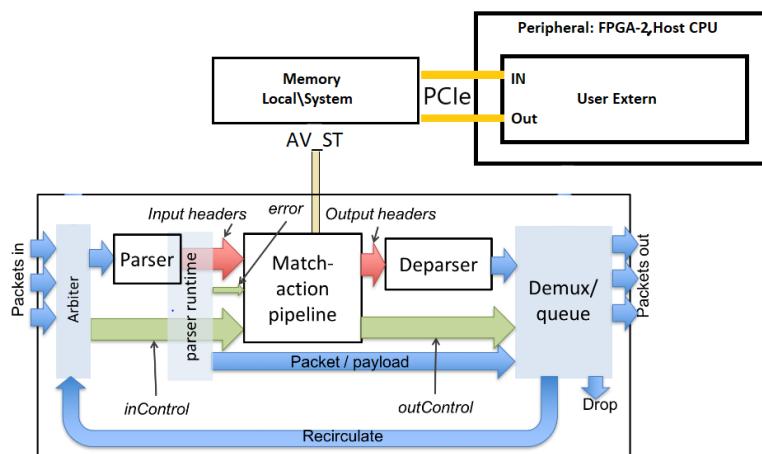

### 3.1 Pipeline P4 d'Intel

La conception des interfaces commence par l'écriture d'un programme P4 qui utilise des blocs fonctionnels, souvent appelés modules IP externes. C'est la fonctionnalité de cet externe qui peut être déployée sur un autre périphérique. Un système exploitant cette organisation est illustré à la figure 3.1. Le compilateur d'Intel propose un modèle différent de celui offert par le BMv2 («Behavioral Model version 2»). Une différence importante vient du fait qu'il accepte des IP externes. L'autre différence, c'est qu'il génère une description de matériel exprimée en HDL pour le programme P4 fourni par l'utilisateur. De plus, certaines différences importantes sont à la base de l'écriture de l'architecture du programme P4. Plus spécifiquement, dans les deux prochaines sections, il sera question de faire une analyse du code P4 d'Intel qu'il est essentiel de compiler pour faire fonctionner un externe avec l'interface générée.

#### 3.1.1 Architecture du pipeline de traitement P4 d'Intel

Premièrement, pour qu'une interface soit compatible en matériel avec le programme d'utilisateur à la fin de la compilation, il faut un programme P4 compatible au compilateur d'Intel. Le programme P4 accepté par le compilateur d'Intel et celui accepté par le compilateur BMv2 ont aussi des similitudes comme les blocs P4 traditionnellement disponibles dans le langage. Par exemple, le programme P4 doit contenir les éléments essentiels pour le fonctionnement d'un pipeline de traitement de paquets («parser», «match&action», «deparser»). Le

programme P4 compatible au compilateur d'Intel est essentiellement le même que le P4<sub>16</sub> de la communauté P4 [4]. La principale différence est qu'il est maintenant possible d'y ajouter plus de composant comme des IP externes dans les blocs «action» et «table». Ceci facilite l'ajout de l'interface qui permet de faire des transferts tels qu'illustré à la figure 3.2. L'interface est un module matériel, donc écrite dans un langage comme le VHDL ou Verilog qu'il sera possible de connecter au pipeline P4.

Deuxièmement, pour qu'une interface soit compatible en matériel avec l'architecture P4 personnalisée, cette architecture doit être compatible au compilateur d'Intel. L'architecture P4 d'Intel doit être utilisée avec des outils de liaison des externes d'utilisateur exprimée par des annotations spécifiées via la syntaxe @. L'architecture personnalisée est une conception conventionnelle pour FPGA compatible au P4 et une couche d'adaptateur logiciel. Une fois que l'architecture personnalisée est créée, le système mis en œuvre dans un FPGA ressemble à un dispositif P4 programmable conventionnel. Le concepteur d'architecture P4 personnalisée a la même flexibilité qu'un concepteur qui développe du matériel pour un FPGA lorsqu'il est nécessaire de personnaliser les parties non programmables en P4 de la couche matérielle («Data Plane»).

Le concepteur d'architecture personnalisée peut instancier les IP du plan de données P4 sans connaître le code P4 source fourni par le concepteur de l'application. Cela fonctionne parce que le compilateur P4 d'Intel pour FPGA infère les noms de module IP du plan de données P4 à partir du fichier d'architecture personnalisée. La figure 3.1 montre un pipeline P4 qui accède à un module externe élaboré par un utilisateur à travers une interface dont la conception sera l'objet de la prochaine sous-section.

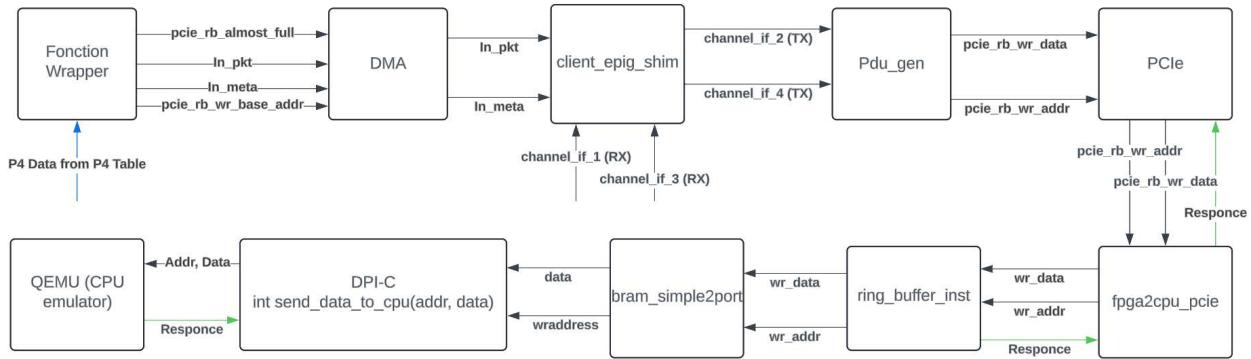

FIGURE 3.1 Fonctionnalités exprimées avec un module externe au pipeline P4

FIGURE 3.2 Génération du chemin jusqu’au CPU

La figure 3.1 met aussi en évidence le lien qui est utile pour faire fonctionner une interface avec un pipeline P4 et avec les périphériques exploitant la fonctionnalité de l’externe. L’interface prend son accès au pipeline principal à partir du bloc d’action, là où se trouvent les tables de comparaison P4. Comme mentionné, l’architecture joue le rôle de gérer les bonnes liaisons au pipeline P4. Une fois la compilation terminée, il est possible de faire le lien entre l’architecture et ses composants à l’aide d’un langage de haut niveau comme le Python.

Donc, ayant le programme P4 et l’architecture P4 personnalisée dans une bonne forme permet de faciliter l’utilisation du code matériel généré par le compilateur d’Intel pour le connecter à l’interface générée à l’aide de l’outil PyXHDL exploité dans le présent projet.

Un important élément d’originalité du présent projet réside dans l’utilisation d’un programme P4 avec du code matériel généré automatiquement par un langage de haut niveau (Python et HLS). Ce mémoire introduit des extensions à un programme P4 applicable dans le contexte du compilateur d’Intel pour les SmartNIC utilisant les pipelines P4.

### 3.2 Génération automatique d’interfaces avec PyXHDL

L’outil PyXHDL génère du code HDL compatible avec divers langages de description de matériel cibles populaires tel que le VHDL, le Verilog, le SystemVerilog. Il est à noter que les sections précédentes ont permis d’identifier l’outil PyXHDL comme un outil flexible (section 2.2 du chapitre précédent) et facile d’utilisation à cause de sa syntaxe facile à comprendre. La programmation d’une interface est effectuée à l’aide des classes héritant de celles de l’outil PyXHDL introduit dans le code 3.1 par exemple.

La figure 3.3 montre le chemin des ressources que parcourt l’ensemble de données de ce

FIGURE 3.3 Flot de données complet pour l’implémentation et le test de solutions en P4

projet. La propagation se fait, normalement, de gauche vers la droite et plus spécifiquement selon le sens des flèches. Les blocs courbés représentent les données et les blocs rectangulaires représentent les processus. D’abord, il est possible de voir le programme P4, l’architecture P4 et l’outil PyXHDL pour la génération d’interface. En effet, cette partie de bas de la figure 3.3 montre l’implémentation des interfaces et l’emplacement de l’interconnectivité (bloc HDL compilé à travers le code HLS) avec l’interface. La partie du haut montre le cas de la validation de l’interface à l’aide du code DPI-C (dpi\_comm.cpp), qui fait le lien entre l’émulateur exécutant l’externe et la simulation RTL.

### 3.2.1 Module DMA

La toute première étape du processus proposé pour la génération d’interface entre un programme P4 et ses externes, effectuée avec l’outil PyXHDL, exploite le code HDL pour un module DMA cité plus tôt (listing 3.1).

Cette approche se distingue de celle adoptée dans Pegasus [2] que l’on utilise comme projet de référence. C’est une méthode qui se distingue de la génération de code HDL avec «Jinja Template», car l’utilisateur peut aussi faire des modifications à haut niveau en Python.

De cette façon, il est possible de voir le passage d’un code Python vers un code matériel Verilog. Donc, l’utilisateur peut comprendre la provenance des générations du code de ce projet ce qui est aussi utile pour les concepteurs électronique. Pegasus utilise la génération d’IP pour ses pipelines en HDL à travers les «Jinja Template» de Python et utilise les modules

DMA et PCIe comme interface entre ses périphériques (FPGA, hôte). Cette solution permet de faire un accès rapide aux données des ressources externes (calculs C++) à Pegasus.

L’interface générée automatiquement dans ce projet est le DMA et le PCIe, illustrés à la figure 3.2 par le bloc mémoire et les deux canaux jaunes respectivement. De plus, le code HLS permet de générer un «Avalon Stream» qui est directement lié au DMA (bloc mémoire), et qui sera discuté à la section 3.3.3. Compte tenu du caractère central du module DMA cité pour la méthode de génération d’interfaces proposée, il est important de bien le comprendre. Le module DMA, visible à la figure 3.2 est relié à la mémoire. Ceci favorise un échange de données avec le CPU sans l’alourdir. Le module DMA fait le pont entre le pipeline de traitement P4 et les périphériques liés à l’aide de l’interface PCIe. Cette dernière peut faire des liens selon l’adresse attribuée (pour le FPGA et le CPU). La flexibilité offerte par ce modèle vient notamment du fait que les bus PCIe sont connectés avec la mémoire vers laquelle pointe le DMA.

Le code fourni au listing 3.1 illustre un cas où le générateur de PyXHDL génère le code RTL pour le module DMA. Cet exemple est une des éléments clés du présent projet. Ce module écrit en Python est directement lié avec le compilateur HDL d’Intel. Donc, la génération d’interface effectuée de cette façon doit simplifier la création de ponts entre le langage Python et le langage matériel. Le langage matériel dans lequel le module DMA sera généré est le Verilog. Ce choix est principalement dû à l’intégration aux modules IPs Verilog déjà disponible après la compilation du programme P4 avec le compilateur d’Intel. Il est à noter que la génération automatique des interfaces dans ce projet est pleinement généralisable pour des applications de transferts de paquets. L’interface peut avoir un usage plus spécifique comme pour la détection d’instruction (Pegasus [2]). Alors, ces interfaces sont personnalisées pour l’application du transfert de données respective. En effet, l’interface sera utile pour la connexion à l’externe généré par le programme P4 d’Intel fourni par l’utilisateur.

Avant d’aller dans les détails de la conception du module DMA à l’aide de l’outil PyXHDL, il est important de mentionner que le code matériel (HDL) généré par cet outil est synthétisable et multi-usage. Un utilisateur peut apporter des modifications au code Python de l’outil PyXHDL et le code sera toujours synthétisable. Il est donc possible de faire des changements sur les ports d’entrée ou de sortie ainsi que sur différentes variables, tout en maintenant la compatibilité du code pour diverses applications. Il faudra également modifier les autres modules dépendants dans le pipeline P4 (ou dans toute autre application) pour assurer la compatibilité. C’est pourquoi le protocole de communication PCIe-DMA est universel à travers différents systèmes embarqués, en réseau ou autre.

Listing 3.1 Classe de PyXHDL pour l'implémentation des modules d'interface HDL

```

1  class DMA(X.Entity):

2      PORTS = 'Clk, Rst_n, =pcie_rb_wr_data, =pcie_rb_wr_addr,

3              =pcie_rb_wr_en, \

4              pcie_rb_base_addr, pcie_rb_almost_full, =pcie_rb_update_valid,

5              =pcie_rb_update_size, \

6              disable_PCIE, pdumeta_cpu_data, pdumeta_cpu_valid,

7              pdumeta_cpu_ready, \

8              =pdumeta_cpu_csr_readdata, =ddr_wr_req_data, =ddr_wr_req_valid,

9              ddr_wr_req_almost_full, \

10             =ddr_rd_req_data, =ddr_rd_req_valid, ddr_rd_req_almost_full,

11             ddr_rd_resp_data, \

12             ddr_rd_resp_valid, =ddr_rd_resp_almost_full, \

13             in_pkt, in_meta, in_usr, nomatch_pkt'

14

15

16     @X.hdl_process(kind=X.ROOT_PROCESS)

17     def run():

18

19

20         lis = []

21         lis2 = []

22

23         for i in range(6):

24             lis.append(vs.mkwire(ExternIP_channel_if(

25                 _P=dict(WIDTH=512)), "channel_if_"+str(i+1)))

26

27         for i in range(2):

28             lis2.append(vs.mkwire(ExternIP_channel_if(

29                 _P=dict(WIDTH=388)), "channel_if_"+str(i+7)))

30

31

32         A = Clk

33         QQ = vs.mkwire(tp.UInt(1))

34

35         ...

36

37         ExternIP_unified_fifo(in_clk = A,

38             in_reset = B,

39             out_clk = EEE,

40             out_reset = EEE,

41             in_data = pdumeta_cpu_data,

42             in_valid = pdumeta_cpu_valid,

43             in_ready = pdumeta_cpu_ready,

44             out_data = MM,

45             out_valid = NN,

46             out_ready = OO,

47             fill_level = PP,

48             almost_full = EEE,

49

50

51

52

53

54

55

56

57

58

59

60

61

62

63

64

65

66

67

68

69

70

71

72

73

74

75

76

77

78

79

80

81

82

83

84

85

86

87

88

89

90

91

92

93

94

95

96

97

98

99

100

101

102

103

104

105

106

107

108

109

110

111

112

113

114

115

116

117

118

119

120

121

122

123

124

125

126

127

128

129

130

131

132

133

134

135

136

137

138

139

140

141

142

143

144

145

146

147

148

149

150

151

152

153

154

155

156

157

158

159

160

161

162

163

164

165

166

167

168

169

170

171

172

173

174

175

176

177

178

179

180

181

182

183

184

185

186

187

188

189

190

191

192

193

194

195

196

197

198

199

200

201

202

203

204

205

206

207

208

209

210

211

212

213

214

215

216

217

218

219

220

221

222

223

224

225

226

227

228

229

230

231

232

233

234

235

236

237

238

239

240

241

242

243

244

245

246

247

248

249

250

251

252

253

254

255

256

257

258

259

259

260

261

262

263

264

265

266

267

268

269

270

271

272

273

274

275

276

277

278

279

279

280

281

282

283

284

285

286

287

288

289

289

290

291

292

293

294

295

296

297

298

299

299

300

301

302

303

304

305

306

307

308

309

309

310

311

312

313

314

315

316

317

318

319

319

320

321

322

323

324

325

326

327

328

329

329

330

331

332

333

334

335

336

337

338

339

339

340

341

342

343

344

345

346

347

348

349

349

350

351

352

353

354

355

356

357

358

359

359

360

361

362

363

364

365

366

367

368

369

369

370

371

372

373

374

375

376

377

378

379

379

380

381

382

383

384

385

386

387

388

389

389

390

391

392

393

394

395

396

397

398

399

399

400

401

402

403

404

405

406

407

408

409

409

410

411

412

413

414

415

416

417

418

419

419

420

421

422

423

424

425

426

427

428

429

429

430

431

432

433

434

435

436

437

438

439

439

440

441

442

443

444

445

446

447

448

449

449

450

451

452

453

454

455

456

457

458

459

459

460

461

462

463

464

465

466

467

468

469

469

470

471

472

473

474

475

476

477

478

479

479

480

481

482

483

484

485

486

487

488

489

489

490

491

492

493

494

495

496

497

498

499

499

500

501

502

503

504

505

506

507

508

509

509

510

511

512

513

514

515

516

517

518

519

519

520

521

522

523

524

525

526

527

528

529

529

530

531

532

533

534

535

536

537

538

539

539

540

541

542

543

544

545

546

547

548

549

549

550

551

552

553

554

555

556

557

558

559

559

560

561

562

563

564

565

566

567

568

569

569

570

571

572

573

574

575

576

577

578

579

579

580

581

582

583

584

585

586

587

588

589

589

590

591

592

593

594

595

596

597

597

598

599

599

600

601

602

603

604

605

606

607

608

609

609

610

611

612

613

614

615

616

617

618

619

619

620

621

622

623

624

625

626

627

628

629

629

630

631

632

633

634

635

636

637

638

639

639

640

641

642

643

644

645

646

647

648

649

649

650

651

652

653

654

655

656

657

658

659

659

660

661

662

663

664

665

666

667

668

669

669

670

671

672

673

674

675

676

677

678

679

679

680

681

682

683

684

685

686

687

688

689

689

690

691

692

693

694

695

696

697

697

698

699

699

700

701

702

703

704

705

706

707

708

709

709

710

711

712

713

714

715

716

717

718

719

719

720

721

722

723

724

725

726

727

728

729

729

730

731

732

733

734

735

736

737

738

739

739

740

741

742

743

744

745

746

747

748

749

749

750

751

752

753

754

755

756

757

758

759

759

760

761

762

763

764

765

766

767

768

769

769

770

771

772

773

774

775

776

777

778

778

779

779

780

781

782

783

784

785

786

787

787

788

789

789

790

791

792

793

794

795

796

797

797

798

799

799

800

801

802

803

804

805

806

807

808

809

809

810

811

812

813

814

815

816

817

817

818

819

819

820

821

822

823

824

825

826

827

828

828

829

829

830

831

832

833

834

835

836

837

837

838

839

839

840

841

842

843

844

845

846

847

847

848

849

849

850

851

852

853

854

855

856

857

857

858

859

859

860

861

862

863

864

865

866

867

867

868

869

869

870

871

872

873

874

875

876

876

877

877

878

879

879

880

881

882

883

884

885

886

886

887

888

888

889

889

890

891

892

893

894

894

895

895

896

896

897

897

898

898

899

899

900

901

901

902

902

903

903

904

904

905

905

906

906

907

907

908

908

909

909

910

910

911

911

912

912

913

913

914

914

915

915

916

916

917

917

918

918

919

919

920

920

921

921

922

922

923

923

924

924

925

925

926

926

927

927

928

928

929

929

930

930

931

931

932

932

933

933

934

934

935

935

936

936

937

937

938

938

939

939

940

940

941

941

942

942

943

943

944

944

945

945

946

946

947

947

948

948

949

949

950

950

951

951

952

952

953

953

954

954

955

955

956

956

957

957

958

958

959

959

960

960

961

961

962

962

963

963

964

964

965

965

966

966

967

967

968

968

969

969

970

970

971

971

972

972

973

973

974

974

975

975

976

976

977

977

978

978

979

979

980

980

981

981

982

982

983

983

984

984

985

985

986

986

987

987

988

988

989

989

990

990

991

991

992

992

993

993

994

994

995

995

996

996

997

997

998

998

999

999

1000

1000

1001

1001

1002

1002

1003

1003

1004

1004

1005

1005

1006

1006

1007

1007

1008

1008

1009

1009

1010

1010

1011

1011

1012

1012

1013

1013

1014

1014

1015

1015

1016

1016

1017

1017

1018

1018

1019

1019

1020

1020

1021

1021

1022

1022

1023

1023

1024

1024

1025

1025

1026

1026

1027

1027

1028

1028

1029

1029

1030

1030

1031

1031

1032

1032

1033

1033

1034

1034

1035

1035

1036

1036

1037

1037

1038

1038

1039

1039

1040

1040

1041

1041

1042

1042

1043

1043

1044

1044

1045

1045

1046

1046

1047

1047

1048

1048

1049

1049

1050

1050

1051

1051

1052

1052

1053

1053

1054

1054

1055

1055

1056

1056

1057

1057

1058

1058

1059

1059

1060

1060

1061

1061

1062

1062

1063

1063

1064

1064

1065

1065

1066

1066

1067

1067

1068

1068

1069

1069

1070

1070

1071

1071

1072

1072

1073

1073

1074

1074

1075

1075

1076

1076

1077

1077

1078

1078

1079

1079

1080

1080

1081

1081

1082

1082

1083

1083

1084

1084

1085

1085

1086