|                         | Improving the Efficiency of Deep Learning Model Implementations<br>Using Hardware Aware Design Techniques                                                                                                                                                                              |

|-------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Auteur: Author:         | Mobin Vaziri                                                                                                                                                                                                                                                                           |

| Date:                   | 2024                                                                                                                                                                                                                                                                                   |

| Type:                   | Mémoire ou thèse / Dissertation or Thesis                                                                                                                                                                                                                                              |

| Référence:<br>Citation: | Vaziri, M. (2024). Improving the Efficiency of Deep Learning Model<br>Implementations Using Hardware Aware Design Techniques [Mémoire de maîtrise,<br>Polytechnique Montréal]. PolyPublie. <a href="https://publications.polymtl.ca/61861/">https://publications.polymtl.ca/61861/</a> |

# Document en libre accès dans PolyPublie Open Access document in PolyPublie

| URL de PolyPublie:<br>PolyPublie URL:    | https://publications.polymtl.ca/61861/ |

|------------------------------------------|----------------------------------------|

| Directeurs de<br>recherche:<br>Advisors: | Pierre Langlois, & Shervin Vakili      |

| <b>Programme:</b><br>Program:            | Génie informatique                     |

# POLYTECHNIQUE MONTRÉAL

affiliée à l'Université de Montréal

| Improving | the                    | Efficiency | of Deep  | Learning  | Model In | nplementat | tions |

|-----------|------------------------|------------|----------|-----------|----------|------------|-------|

|           | $\mathbf{U}\mathbf{s}$ | ing Hardw  | vare Awa | re Design | Techniqu | ies        |       |

#### MOBIN VAZIRI

Département de génie informatique et génie logiciel

Mémoire présenté en vue de l'obtention du diplôme de Maîtrise ès sciences appliquées Génie informatique

Décembre 2024

# POLYTECHNIQUE MONTRÉAL

affiliée à l'Université de Montréal

Ce mémoire intitulé :

Improving the Efficiency of Deep Learning Model Implementations

Using Hardware Aware Design Techniques

présenté par Mobin VAZIRI

en vue de l'obtention du diplôme de *Maîtrise ès sciences appliquées* a été dûment accepté par le jury d'examen constitué de :

François-Raymond BOYER, président

Pierre LANGLOIS, membre et directeur de recherche

Shervin VAKILI, membre et codirecteur de recherche

François LEDUC-PRIMEAU, membre

# **DEDICATION**

Dedicated to my family, and to the one who gives meaning to infinity...

#### ACKNOWLEDGEMENTS

I am profoundly thankful to Prof. Pierre Langlois, my supervisor, for his unwavering support, guidance, and the vast knowledge he has generously imparted throughout my research. Prof. Langlois significant expertise in the field has been instrumental in developing my research work, guiding me in setting research objectives, developing solutions, and experimenting with new ideas. His encouragement and inspiration have been invaluable, and I am sincerely grateful for his mentorship.

My heartfelt thanks go to my co-supervisor, Prof. Shervin Vakili, whose unwavering dedication to excellence and meticulous attention to detail have significantly shaped the quality of my work. His guidance and constructive feedback have been crucial to my success, and I consider myself fortunate to have such a knowledgeable advisor. Prof. Vakili's contributions to my research have been immense, and I genuinely appreciate his support.

I sincerely thank NSERC for their financial support and the GR2M lab for providing the necessary processing resources. Their support was essential to the completion of this work.

Lastly, I want to express my sincere appreciation to my family for their selflessness, unwavering belief in me, and constant encouragement throughout my journey. I hope I have made them proud.

# RÉSUMÉ

Avec la croissance rapide de la génération de données et la complexité croissante des tâches en apprentissage automatique, cryptographie et traitement en temps réel, le besoin de matériel performant et efficace augmente. Les CPU traditionnels, bien que polyvalents, peinent à répondre aux exigences de traitement parallèle, entraînant une consommation d'énergie élevée, une latence accrue et un débit réduit. Bien que les GPU gèrent mieux les grandes quantités de données et les algorithmes complexes, leur forte consommation énergétique et leur manque d'extensibilité limitent leur efficacité dans des environnements contraints comme le calcul en périphérie et les appareils IoT. Ainsi, la conception de circuits dédiés sur FPGA et ASIC s'avère essentielle pour atteindre performance, efficacité énergétique et adaptabilité.

Les FPGA, offrant flexibilité post-fabrication et parallélisme, équilibrent performance et adaptabilité, tandis que les ASIC, optimisés pour des tâches spécifiques, offrent une efficacité énergétique supérieure mais manquent de reconfigurabilité. La demande croissante pour l'IA en temps réel a encouragé des techniques de compression de modèles comme l'élagage et la quantification, qui réduisent les besoins en calcul et en mémoire des réseaux neuronaux, rendant ces modèles adaptés aux dispositifs limités. Par ailleurs, les réseaux de neurones artificiels (ANN) remplacent de plus en plus les méthodes de calcul traditionnelles dans des domaines comme la cryptographie et les systèmes de contrôle, offrant des alternatives plus efficaces pour des applications en temps réel, telles que la communication sécurisée.

Cette thèse présente trois contributions : DyRecMul: a novel low-cost approximate multiplier for FPGAs, pour une multiplication efficace dans les accélérateurs d'IA; Optimized Deep Learning Architectures for Efficient Automatic Modulation Recognition, qui réduit la complexité des modèles de deep learning pour les systèmes de communication; et HENNC: Efficient FPGA Core Generation for ANN-Based Chaotic Oscillators Using High-Level Synthesis, qui utilise des modèles ANN pour des applications cryptographiques sur du matériel économe en énergie. Ces contributions offrent des solutions innovantes pour des systèmes de calcul avancés sur des plateformes matérielles contraintes.

#### **ABSTRACT**

As data generation surges and computational tasks in areas like machine learning, cryptography, and real-time processing grow more complex, the need for hardware that balances performance and efficiency has increased. Traditional CPUs, though versatile, struggle with the parallel processing demands of these tasks, leading to higher energy consumption, increased latency, and reduced throughput. GPUs offer significant improvements in handling large datasets and complex algorithms, but their high energy use and scalability issues limit their effectiveness in resource-constrained environments, such as edge computing or IoT devices. To achieve real-time performance, enhanced energy efficiency, and adaptability, designing and implementing dedicated computational circuits on FPGAs and ASICs has proven effective and often essential. FPGAs combine post-fabrication flexibility with scalable parallelism, offering a balanced trade-off between performance and adaptability. In contrast, ASICs, while highly optimized for specific tasks, provide superior performance and energy efficiency but lack reconfigurability. Furthermore, the growing demand for real-time AI has also spurred the development of model compression techniques, such as pruning and quantization, which reduce the computational and memory requirements of neural networks, making them suitable for devices with limited processing power. Pruning removes unnecessary parameters, streamlining models without significantly affecting accuracy, while quantization reduces the precision of weights and activations to improve efficiency on hardware like FPGAs and ASICs. Additionally, Artificial Neural Networks (ANNs) are increasingly replacing traditional computational methods in fields such as cryptography and control systems, providing more efficient alternatives to resource-intensive numerical methods for simulating complex systems. This shift is particularly beneficial for real-time applications, such as secure communication, where ANN-based models offer faster, more efficient performance.

This thesis builds on these advancements in hardware efficiency and presents three key contributions: "DyRecMul: a novel low-cost approximate multiplier for FPGAs", which tackles the challenge of hardware-efficient multiplication for AI accelerators; "Optimized Deep Learning Architectures for Efficient Automatic Modulation Recognition", which applies pruning and quantization to reduce the complexity of deep learning models for real-time communication systems; and "HENNC: Efficient FPGA Core Generation for ANN-Based Chaotic Oscillators Using High-Level Synthesis", which replaces traditional numerical simulations with ANN-based models for cryptographic applications, enabling secure systems on low-cost, energy-efficient hardware. These contributions provide innovative solutions for deploying advanced computational systems on constrained hardware platforms.

# TABLE OF CONTENTS

| DEDICATION                                                        | iii |

|-------------------------------------------------------------------|-----|

| ACKNOWLEDGEMENTS                                                  | iv  |

| RÉSUMÉ                                                            | V   |

| ABSTRACT                                                          | vi  |

| TABLE OF CONTENTS                                                 | vii |

| LIST OF TABLES                                                    | X   |

| LIST OF FIGURES                                                   | xi  |

| LIST OF SYMBOLS AND ACRONYMS                                      | xii |

| CHAPTER 1 INTRODUCTION                                            | 1   |

| CHAPTER 2 BACKGROUND                                              | 5   |

| 2.1 Neuron Model and Artificial Neural Networks                   | 5   |

| 2.2 Deep Neural Networks                                          | 6   |

| 2.3 Model Compression Techniques                                  | 7   |

| 2.3.1 Pruning                                                     | 7   |

| 2.3.2 Quantization                                                | 8   |

| 2.4 FPGA Architecture                                             | 9   |

|                                                                   | 10  |

|                                                                   | 11  |

| CHAPTER 3 ARTICLE 1: DYRECMUL: FAST AND LOW-COST APPROXIMATE      |     |

| MULTIPLIER FOR FPGAS USING DYNAMIC RECONFIGURATION                | 12  |

| 3.1 Introduction                                                  | 13  |

| 3.2 Analytical Description                                        | 15  |

| 3.3 DyRecMul for INT8 Multiplication: Architecture and Components | 16  |

| · · · · · · · · · · · · · · · · · · ·                             | 17  |

|                                                                   | 18  |

|                                                                   | 21  |

|       | 3.3.4 Two's Complement Logic                                             | 21 |

|-------|--------------------------------------------------------------------------|----|

| 3.4   | Generalized DyRecMul                                                     | 22 |

|       | 3.4.1 Hardware Cost Estimation                                           | 22 |

|       | 3.4.2 Accuracy Considerations                                            | 25 |

| 3.5   | Reconfiguration Time and Rapidly Reconfigurable DyRecMul                 | 26 |

| 3.6   | Target Applications                                                      | 28 |

|       | 3.6.1 Low-cost Hardware Accelerators for Updatable Supervised Learning . | 28 |

|       | 3.6.2 Deep Reinforcement Learning Hardware                               | 28 |

|       | 3.6.3 DL Hardware Accelerators With Weight-Stationary Dataflows          | 29 |

|       | 3.6.4 Updatable Digital Filters                                          | 30 |

| 3.7   | Results                                                                  | 30 |

|       | 3.7.1 Error Analysis and Evaluation                                      | 30 |

|       | 3.7.2 Hardware Implementation Results                                    | 31 |

|       | 3.7.3 Accuracy in Deep Learning Computation                              | 34 |

| 3.8   | Conclusion                                                               | 37 |

| CHAPT | ΓER 4 ARTICLE 2: ACCURACY-AWARE LOW-COMPLEXITY DEEP LEAR                 | N- |

| ING   | G MODELS FOR AUTOMATIC MODULATION RECOGNITION                            | 38 |

| 4.1   | Introduction                                                             | 39 |

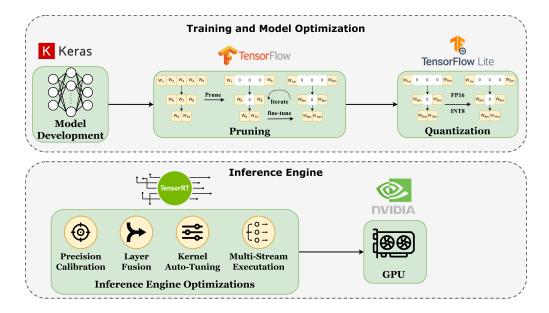

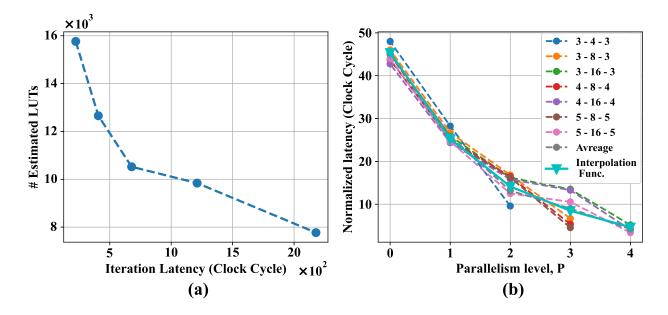

| 4.2   | Proposed Design Flow                                                     | 40 |

|       | 4.2.1 Model Development                                                  | 41 |

|       | 4.2.2 Structural Pruning                                                 | 43 |

|       | 4.2.3 Post-training Dynamic Range Quantization                           | 43 |

| 4.3   | Experimental Results                                                     | 44 |

| 4.4   | Conclusion & Future Work                                                 | 45 |

| CHAPT | TER 5 ARTICLE 3: HENNC: HARDWARE ENGINE FOR ARTIFICIAL                   |    |

| NEU   | URAL NETWORK-BASED CHAOTIC OSCILLATORS                                   | 47 |

| 5.1   | Introduction                                                             | 48 |

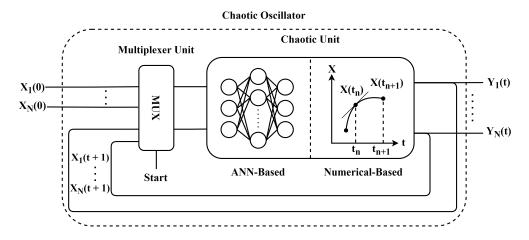

| 5.2   | ANN-based Chaotic Oscillator                                             | 49 |

| 5.3   | Proposed Framework                                                       | 51 |

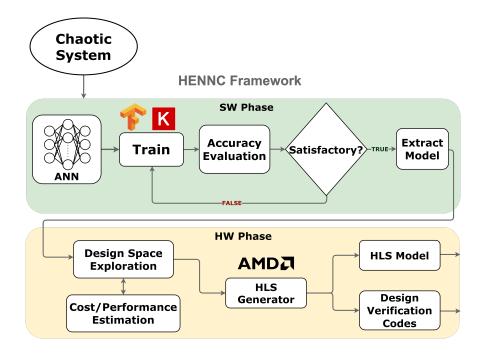

|       | 5.3.1 Software Phase                                                     | 52 |

|       | 5.3.2 Hardware Phase                                                     | 53 |

| 5.4   | Results                                                                  | 55 |

| 5.5   | Conclusion                                                               | 57 |

| CHAP  | TER 6 GENERAL DISCUSSION                                                 | 58 |

| СНАРТ | TER 7 CONCLUSION | 61 |

|-------|------------------|----|

| 7.1   | Summary of Works | 61 |

| 7.2   | Limitations      | 62 |

| 7.3   | Future Research  | 63 |

| REFER | RENCES           | 64 |

# LIST OF TABLES

| Table 3.1 | Error Analysis and Comparisons                                     | 32 |

|-----------|--------------------------------------------------------------------|----|

| Table 3.2 | Implementation Costs and Performance Comparison for INT8 and UINT8 | ,  |

|           | datatypes                                                          | 34 |

| Table 3.3 | Implementation Costs and Performance Comparison for $INT/UINT12$   |    |

|           | and INT/UINT16 Multipliers                                         | 35 |

| Table 3.4 | Inference Accuracy and Hardware Metrics Comparison With Previous   |    |

|           | Studies                                                            | 35 |

| Table 4.1 | Summary of The Models' Parameters                                  | 41 |

| Table 4.2 | Summary of The Training Hyperparameters                            | 42 |

| Table 4.3 | Comparison Between Performance of Baseline Models and Optimized    |    |

|           | Models                                                             | 45 |

| Table 5.1 | Number of Operations in an ANN with 8 Neurons in the Hidden Layer, |    |

|           | and in RK-4 with Chen Chaotic System                               | 52 |

| Table 5.2 | Hyperparameters and Performance of ANN-based Model                 | 52 |

| Table 5.3 | Hardware Costs for HENNC Candidate Designs and Existing Works.     | 57 |

|           |                                                                    |    |

# LIST OF FIGURES

| Figure 3.1 | DyRecMul architecture for INT8 multiplication of $Z = X \times W$ , using      |    |

|------------|--------------------------------------------------------------------------------|----|

|            | float(1,2,5) internal floating-point format                                    | 17 |

| Figure 3.2 | INT8 to $float(1, 2, 5)$ encoder: LUT mapping and corresponding truth          |    |

|            | tables                                                                         | 18 |

| Figure 3.3 | 5-bit dynamically reconfigurable multiplier with 3-bit result using CFG-       |    |

|            | LUT5 primitives. The second operand, $Op2=23$ in this example                  | 20 |

| Figure 3.4 | $float\left(1,2,5\right)$ to INT8 decoder: LUT mapping and corresponding truth |    |

|            | tables                                                                         | 21 |

| Figure 3.5 | Architecture of RR_DyRecMul utilizing a ping-pong scheme to reduce             |    |

|            | the reconfiguration latency.                                                   | 27 |

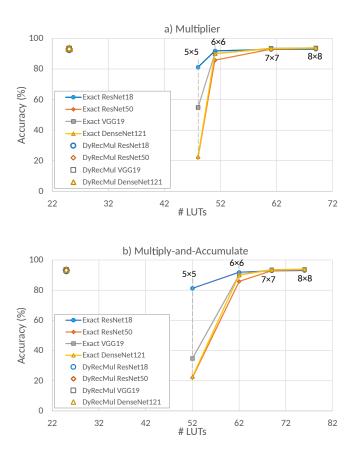

| Figure 3.6 | Trade-offs between hardware utilization and inference accuracy when            |    |

|            | running four benchmark CNNs using DyRecMul and standard exact                  |    |

|            | multipliers of different sizes: (a) signed multiplier results, and (b) MAC     |    |

|            | results                                                                        | 36 |

| Figure 4.1 | Proposed design flow                                                           | 40 |

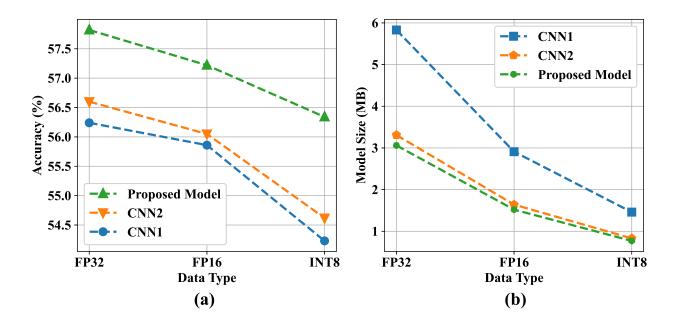

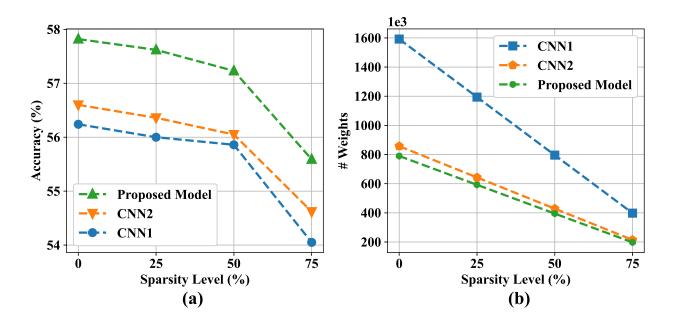

| Figure 4.2 | Quantizing models with different bitwidths vs (a) accuracy (b) model           |    |

|            | size                                                                           | 43 |

| Figure 4.3 | Pruning models with different sparsity vs (a) accuracy (b) the number          |    |

|            | of weights                                                                     | 44 |

| Figure 5.1 | Architecture of chaotic oscillators                                            | 49 |

| Figure 5.2 | HENNC framework design flow                                                    | 51 |

| Figure 5.3 | (a) Estimated cost and latency for the 3-16-3 ANN. (b) Normalized              |    |

|            | actual latencies and the interpolation curve when utilizing DSP resources.     | 54 |

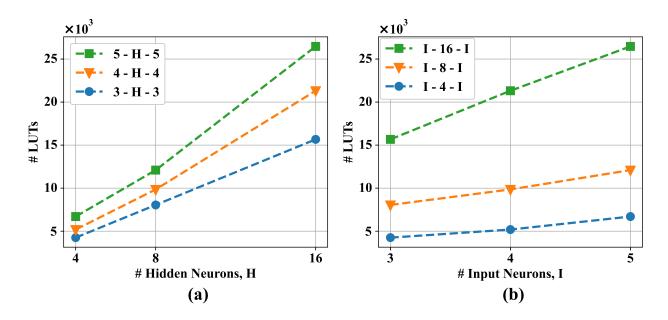

| Figure 5.4 | Post-synthesis number of LUTs as a function of the number of neurons           |    |

|            | in the (a) hidden layer, (b) input and output layers                           | 55 |

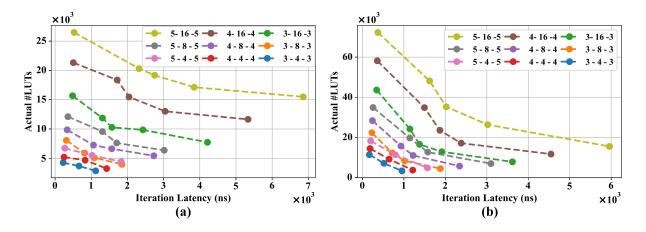

| Figure 5.5 | Post-synthesis hardware cost and latency of the design space explored          |    |

|            | by HENNC for different ANN sizes in two modes: (a) with DSP uti-               |    |

|            | lization, and (b) without DSP utilization                                      | 56 |

#### LIST OF SYMBOLS AND ACRONYMS

AI Artificial Intelligence

AMR Automatic Modulation Recognition

ANN Artificial Neural Network

ASIC Application-Specific Integrated Circuit

BRAM Block RAM

CFGLUT5 Configurable Lookup Tables

CNN Convolutional Neural Network

CPU Central Processing Unit

DNN Deep Neural Network

DL Deep Learning

DSP Digital Signal Processing

FPGA Field-Programmable Gate Array

FLOP Floating-Point Operation GPU Graphics Processing Unit

HLS High-Level Synthesis

LUT Lookup Table

MAC Multiply-Accumulate

ML Machine Learning

NLP Natural Language Processing

PRNG Pseudo-Random Number Generator

PTQ Post-Training Quantization QAT Quantization-Aware Training

RK Runge-Kutta

SNR Signal-to-Noise Ratio

TPU Tensor Processing Unit

#### CHAPTER 1 INTRODUCTION

With the rapid evolution of Machine Learning (ML) and Deep Learning (DL) applications, the demand for specialized hardware that combines high performance with energy efficiency has surged in modern computing systems. An increasing range of application domains, including Computer Vision [1], Natural Language Processing (NLP) [2], Speech Processing [3], and Healthcare and Biomedical fields [4], are increasingly dependent on Artificial Neural Networks (ANNs). These networks often contain millions of parameters and require efficient, real-time processing of large datasets. While traditional processors like Central Processing Units (CPUs) are versatile, they often struggle with the high demands of ML and DL tasks, which benefit significantly from massive parallel computing to achieve high throughput and low latency.

CPUs are effective at sequentially handling diverse tasks but face limitations with the large-scale computations of ML and DL models. Graphics Processing Units (GPUs) have emerged as a popular choice for accelerating these computations, providing extensive parallelism that enables faster execution of core neural network operations, such as matrix multiplications and convolutions, outperforming CPUs in speed and efficiency for these workloads. While GPUs deliver high throughput, they can be power-inefficient when scaled for real-time edge applications [5]. To overcome these limitations, reconfigurable hardware, such as Field-Programmable Gate Arrays (FPGAs) and Application-Specific Integrated Circuits (ASICs), has proven effective in achieving the enhanced efficiency necessary for real-time ML and DL inference.

FPGAs are particularly valued for their flexibility, as they can be reprogrammed after fabrication to implement various digital circuits. This reconfigurability makes FPGAs ideal for real-time applications where tasks may evolve or require custom optimization, such as in ML/DL inference and signal processing algorithms. By enabling the design of custom datapaths and control logic, FPGAs offer a unique balance between the high performance of dedicated hardware and the adaptability of software-defined solutions. For instance, in ML inference, an FPGA can be configured to efficiently handle specific neural network models or operations, often achieving lower latency and greater energy efficiency than GPUs. However, FPGAs have limitations compared to GPUs or ASICs, especially in terms of raw computational power. Additionally, designing optimized configurations for FPGAs can be complex and time-consuming, often requiring expertise in Hardware Description Languages (HDLs)

like VHDL or Verilog. Despite these challenges, FPGAs are an effective solution when reprogrammability and high efficiency through customized computing circuits are prioritized.

ASICs, unlike FPGAs, are fixed-function circuits designed for specific tasks. Once manufactured, they cannot be reprogrammed; however, this fixed nature allows them to achieve the highest levels of performance and energy efficiency for their intended function. Properly designed ASIC hardware accelerators for ML/DL computing can often outperform CPUs, GPUs, and even FPGA-based accelerators in terms of speed and power consumption. This makes ASICs ideal for large-scale deployments of deep learning inference when the task is well-defined and remains stable over time. Examples of DL accelerators primarily designed for ASIC implementation include Google's Tensor Processing Units (TPUs) [6], NVIDIA's Deep Learning Accelerator (NVDLA) [7], MIT's Eyeriss [8], and Berkeley's Gemmini [9], all of which provide significant inference performance with enhanced energy efficiency.

In both FPGA and ASIC implementations, constraints in logic and memory resources, as well as limited energy budgets, restrict the maximum achievable performance. Consequently, these devices often face challenges in real-time computing for large ML and DL models, which can contain millions or even billions of parameters. To address this, model compression techniques have become essential, enabling these devices to handle large models more efficiently while maintaining high performance.

Model compression techniques are crucial for reducing the computational and memory demands of deep learning models, enabling their deployment on devices with limited processing power and energy resources. One of the most widely adopted model compression techniques is pruning, which reduces the size of a neural network by removing less important weights and connections. Neural networks often contain a large number of redundant parameters, especially in deep architectures where certain neurons or filters contribute little to the overall accuracy. Pruning techniques identify these redundancies and eliminate them, effectively shrinking the parameters and operations without significantly affecting its accuracy [10]. Pruning can be performed at different granularities, such as unstructured weight pruning, where individual weights are removed, or structured pruning, where entire filters, channels, or layers are pruned. Structured pruning is particularly advantageous for hardware deployment because it results in a regularized model that is easier to map onto hardware resources [11]. By reducing the number of active neurons or filters, pruning not only saves memory but also reduces the number of computations required during inference, making it especially valuable for real-time Artificial Intelligence (AI) applications where low latency and power efficiency are crucial.

Another important model compression technique is quantization, which reduces the precision

of the weights and activations in a neural network. Instead of using single-precision 32-bit floating-point representations, quantization reduces these values to lower-precision formats, such as 8-bit integers. This reduction in precision significantly decreases the amount of memory needed to store the model and reduces the cost and latency of arithmetic circuits in DL hardware accelerators. There are two main quantization approaches: Post-Training Quantization, which applies quantization after the model is trained, and Quantization-Aware Training, where quantization is incorporated during the training process, allowing the model to adapt and maintain accuracy [12]. Modern hardware, such as GPUs and FPGAs, are optimized to perform low-precision computations more efficiently, further enhancing the performance gains from quantization. Quantized models have become the standard for deploying deep learning on mobile and embedded devices, where power and memory constraints are strict [13].

ANNs themselves can sometimes serve as a form of hardware optimization by replacing traditional computational methods. Thanks to the Universal Approximation Theorem [14], which states that neural networks can approximate any continuous function to a desired accuracy, ANNs can effectively substitute complex algorithms with simpler, more hardware-friendly models. This approach reduces the computational load and enables more efficient processing in certain applications. Beyond their primary use in machine learning, ANNs are increasingly being applied to replace traditional computational methods, particularly in solving complex differential equations. For example, chaotic systems, which are often modeled using differential equations solved by computationally intensive methods like the Runge-Kutta (RK) algorithm [15], can instead be approximated using ANNs [16]. ANNs can efficiently replicate the behavior of these systems. This substitution results in significantly reduced computational and hardware requirements compared to traditional numerical methods. As a result, ANNs offer a faster and more efficient alternative for solving differential equations in real-time applications, enabling more optimized hardware utilization without sacrificing accuracy.

The discussions above on hardware efficiency, model compression, and the replacement of traditional computational methods with ANNs establish the foundation for the contributions presented in this thesis. Specifically, this thesis introduces the following three contributions in the field of optimized machine learning computing:

• DyRecMul: a fast and low-cost approximate multiplier for FPGAs using dynamic reconfiguration, addresses the need for hardware-efficient multiplication in machine learning, where the need for rapid matrix multiplication is paramount. By leveraging approximate computing, this work proposes a new multiplier that significantly reduces the

hardware cost compared to exact multipliers, offering a scalable solution for FPGA-based AI accelerators [17].

- The second contribution presents an accuracy-aware, low-complexity deep learning model designed for Automatic Modulation Recognition (AMR), a task of relevance in certain wireless communication scenarios where modulation classification is required in real-time. To reduce model complexity for real-time applications, pruning and quantization techniques are applied, enabling the deployment of highly accurate models on edge devices without the excessive power and memory demands of traditional architectures. [18].

- Finally, HENNC, a hardware engine for ANN-based chaotic oscillators, is introduced as a fast, computer-aided platform that automatically generates efficient hardware cores for these oscillators. HENNC facilitates the deployment of ANNs as replacements for traditional numerical methods for realizing chaotic systems, with a particular emphasis on cryptographic applications. This work demonstrates the feasibility of implementing secure communication systems on low-cost, energy-efficient hardware by replacing computationally intensive numerical methods with cost-effective ANN-based models [19].

#### The thesis is organized as follows:

- Chapter 2 introduces key concepts such as ANNs, chaotic systems, FPGAs, pruning, and quantization, serving as a foundation for the methods explored in the following chapters.

- Chapter 3 explains DyRecMul, an FPGA-based approximate multiplier optimized for machine learning, achieving significant hardware efficiency with minimal accuracy loss.

- Chapter 4 describes pruning and quantization techniques in DL models for AMR and introduces a new model, balancing accuracy and parameters.

- Chapter 5 covers HENNC, showing how ANNs replace traditional numerical methods for efficient cryptographic system simulation on hardware.

- Chapter 6 highlights the contributions to hardware efficiency and model optimization, promoting scalable and resource-efficient solutions in modern computing.

- Chapter 7 summarizes the results, emphasizing the impact of the proposed methods and suggesting future work directions.

#### CHAPTER 2 BACKGROUND

This chapter provides the essential background for this thesis. Section 2.1 covers neuron models and ANNs, followed by an overview of Deep Neural Networks in Section 2.2. Model compression techniques for hardware optimization are presented in Section 2.3, while Section 2.4 details FPGA architecture. Section 2.5 introduces chaotic systems and their applications in cryptography. The chapter concludes with a summary in Section 2.6, integrating these concepts as a foundation for the research.

#### 2.1 Neuron Model and Artificial Neural Networks

ANNs are modeled after the concept of biological neurons described in [20]. A neuron consists of inputs, weights, a bias, and an activation function. The output y of a neuron is computed by summing the weighted inputs and adding a bias term, then passing the result through a non-linear activation function:

$$y = f\left(\sum_{i=1}^{n} w_i x_i + b\right) \tag{2.1}$$

where n is the number of inputs to the neuron,  $x_i$  represents the input,  $w_i$  the weights, and b the bias term. The activation function f introduces non-linearity, enabling the network to learn complex patterns.

ANNs are foundational to modern deep learning and typically consist of three types of layers: input, hidden, and output. These layers enable the network to model complex data relationships by processing inputs through weighted sums, activation functions, and passing results to subsequent layers. Connectivity patterns vary by architecture, from fully connected to more specialized structures. The core operation driving this process is the Multiply-Accumulate (MAC) operation, which involves multiplying inputs by weights and summing the results. Each MAC counts as two Floating-Point Operations (FLOPs): one for multiplication and one for addition. For instance, in a fully connected NN with L layers, the total number of MACs can be computed as:

$$\#MACs = \sum_{i=2}^{L} n_i \times n_{i-1}$$

(2.2)

where  $n_i$  is the number of neurons in the  $i^{th}$  layer.

#### 2.2 Deep Neural Networks

Deep Neural Networks (DNNs) are a subset of ANNs that incorporate multiple hidden layers, allowing the network to learn more abstract representations of data. While traditional ANNs typically consist of a few hidden layers, DNNs can have hundreds or even thousands of layers. This depth enables DNNs to learn hierarchical features, making them particularly effective in tasks like image recognition and NLP. Convolutional Neural Networks (CNNs) are a specialized type of DNN designed for tasks involving grid-like data structures, such as images. Unlike fully connected networks, CNNs take advantage of the spatial structure of data, significantly reducing the number of parameters by using local connections and shared weights [21]. The key operation in a CNN is the convolution, where a two-dimensional filter (or kernel) is applied to local regions of the input data. This operation produces a feature map that highlights specific patterns in the data. The convolution operation is given by:

$$Y[c_{out}, i, j] = \sum_{c_{in}=0}^{C_{in}-1} \sum_{m=0}^{K_h-1} \sum_{n=0}^{K_w-1} X[c_{in}, i \cdot S_h + m - P_h, j \cdot S_w + n - P_w] \cdot W[c_{out}, c_{in}, m, n]$$

(2.3)

where X is the input feature map, W is the filter, Y is the output feature map,  $C_{in}$  and  $C_{out}$  are the number of input and output channels,  $K_h$  and  $K_w$  are the height and width of the filter, and  $S_h$ ,  $S_w$ ,  $P_h$ , and  $P_w$  are the strides and padding along height and width, respectively.

CNNs consist of several types of layers, including convolutional layers, pooling layers (which reduce the spatial dimensions of the feature maps), and fully connected layers, typically used at the final stages of classification tasks. In each convolutional layer, multiple filters are applied to the input data to extract a diverse set of features that capture different patterns, such as edges, textures, and shapes. These learned features are progressively abstracted as the network deepens. The number of MACs in a convolutional layer can be calculated as:

$$#MACs = H_o \cdot W_o \cdot K_h \cdot K_w \cdot C_{in} \cdot C_{out}, \qquad (2.4)$$

where  $H_o$  and  $W_o$  are output feature size and can be obtained as:

$$H_o = \left| \frac{\text{Input Height} - K_h + 2P_h}{s_h} \right| + 1, \quad W_o = \left| \frac{\text{Input Width} - K_w + 2P_w}{s_w} \right| + 1. \quad (2.5)$$

#### 2.3 Model Compression Techniques

Model compression techniques reduce the computational and memory needs of DNNs without significantly affecting accuracy. Two of the most popular methods for achieving this are pruning and quantization, each focusing on different aspects of the network. This section discusses both methods and compares them.

#### 2.3.1 Pruning

Pruning is a key model compression technique designed to reduce the number of parameters in DNNs while maintaining model accuracy. This is critical in deploying models on resource-constrained environments, where computational and storage efficiency are paramount. Pruning strategies can be broadly classified into unstructured, structured, and semi-structured methods.

Unstructured pruning involves removing individual weights from the neural network based on some importance criteria, typically targeting weights with low magnitudes [10]. The objective of unstructured pruning is to minimize the loss function  $\mathcal{L}(w)$ , subject to a sparsity constraint on the weights:

$$\min_{w} \mathcal{L}(w; D) = \min_{w} \frac{1}{N} \sum_{i=1}^{N} \ell(w; (x_i, y_i)),$$

(2.6)

s.t.

$$||w||_0 \le k$$

where w represents the network weights, and  $D = \{(x_i, y_i)\}_{i=1}^N$  is the dataset consisting of input data  $x_i$  and corresponding labels  $y_i$  for N samples. The pruning process removes weights with small magnitudes, thereby simplifying the model but typically requiring specialized hardware to exploit sparsity for speed improvements [22].

Structured pruning eliminates entire filters, channels, or even layers, resulting in a more compact and hardware-friendly network. Unlike unstructured pruning, it preserves the regular structure of the model. For a given prune ratio and a neural network with  $P = \{p_1, p_2, \ldots, p_L\}$ , where  $p_i$  denotes the set of channels, filters, neurons, or attention heads in layer i, the goal of structured pruning is to find  $P' = \{p'_1, p'_2, \ldots, p'_L\}$ , minimizing performance loss while enhancing speed under the defined prune ratio. Here,  $p'_i \subseteq p_i$  for  $i \in \{1, \ldots, L\}$ . Structured pruning facilitates hardware acceleration by removing entire elements, such as

filters, channels, or layers, leading to a reduced model size and improved computational efficiency.

While structured pruning focuses on maintaining regularity in the network, semi-structured pruning introduces a balance between unstructured and structured pruning. It applies predefined sparsity patterns within layers, keeping some level of structure while still allowing for more fine-grained pruning than structured methods. This makes semi-structured pruning more adaptable to hardware acceleration while retaining the flexibility of unstructured pruning. One example of semi-structured pruning is the 2:4 (2-out-of-4) sparsity pattern, where two weights out of every four consecutive weights are pruned. This pattern allows semi-structured pruning to take advantage of specialized hardware accelerators like NVIDIA Ampere GPU's sparse tensor cores, which are optimized for specific sparsity patterns [23]. Semi-structured pruning offers the flexibility to achieve high pruning rates like unstructured methods but without the irregularity that can hinder practical speedups. It strikes a balance, making it effective for both accuracy preservation and computational efficiency.

#### 2.3.2 Quantization

Quantization is a model compression technique that reduces the precision of the weights and activations in a neural network from full precision, typically 32-bit floating-point numbers, to lower precision formats such as 16-bit, 8-bit, or even 4-bit integers. By reducing the bit-width of the data used in DNNs, quantization significantly lowers memory usage and computational complexity, making DNNs more efficient for deployment on hardware-constrained applications such as mobile devices and edge computing platforms. This efficiency gain often comes with minimal impact on model accuracy when appropriately applied, making quantization a highly effective technique for real-time inference applications [12].

The process of uniform quantization can be described as mapping a real-valued vector x to a discrete grid of integers using the following transformation for each element:

$$x_{\text{int}} = \text{clip}\left(\left\lfloor \frac{x}{s} \right\rfloor + z, L, U\right),$$

(2.7)

where s is the scaling factor, z is the zero point, and  $\lfloor \cdot \rfloor$  denotes the round-to-nearest-integer operator. The clip function ensures that the quantized values lie within the quantization range [L, U], where L and U depend on whether the quantization is signed or unsigned [12]. Quantization methods can be categorized into two main approaches: post-training quantization (PTQ) and quantization-aware training (QAT).

PTQ is a method where a pre-trained model is quantized without further training. PTQ typically converts the weights and activations of a full-precision model into lower precision after the model has been fully trained. This method is fast and straightforward, requiring minimal computational resources as it avoids retraining. However, PTQ can lead to a notable drop in accuracy, especially for larger, more complex models, or when aggressive quantization (such as 4-bit) is applied. Despite these challenges, PTQ remains widely used since it does not require additional training [12].

QAT integrates quantization directly into the training process. During QAT, the model is trained with simulated low-precision operations, allowing it to adapt to the quantization noise introduced by the lower bit-width representations. QAT generally results in better performance and accuracy retention compared to PTQ because the model can learn to compensate for the reduced precision. The downside of QAT is that it requires additional training time and computational resources, which may not always be feasible in real-world applications, particularly for large-scale models. Nevertheless, QAT is preferred when high accuracy is crucial in low-precision deployments [24].

#### 2.4 FPGA Architecture

The architecture of an FPGA consists of four primary components: Logic Elements (LEs), programmable interconnects, Input/Output (I/O) blocks, and embedded memory. These components work together to provide a flexible and reconfigurable platform for custom digital logic designs. AMD-Xilinx FPGAs utilize higher-level units called Configurable Logic Blocks (CLBs), each containing multiple LEs or slices. At the core of FPGA architecture, CLBs are configured to implement arbitrary logic circuits using programmable Lookup Tables (LUTs), flip-flops, multiplexers, and carry logic. In modern AMD-Xilinx FPGAs, each CLB is divided into slices, with each slice containing four 6-input LUTs and eight flip-flops. The 6-input LUTs can implement combinational logic functions or serve as distributed memory, providing versatility for both computation and localized storage needs.

To connect these CLBs and other on-chip resources, programmable interconnects are used, forming the essential pathways for signal routing. Configured through a switch matrix, these interconnects provide the flexibility to dynamically route signals based on the specific design, helping to minimize delays and ensuring smooth communication across the FPGA. This seamless routing architecture enhances the overall efficiency and adaptability of the device.

Supporting external communication, I/O blocks manage data transfer between the FPGA and external systems. These blocks are configurable to accommodate a wide variety of

communication standards, making it possible for the FPGA to interface with numerous external components and systems.

Focusing on the latest AMD-Xilinx FPGA families [25], this architecture includes specialized resources like Digital Signal Processing (DSP) slices and Block RAM (BRAM), which complement the core elements. DSP slices are optimized for high-speed arithmetic operations, such as MAC, making them indispensable for tasks involving heavy computation. Meanwhile, BRAM provides on-chip memory, configurable as single-port or dual-port RAM, allowing high-throughput data access during complex operations. Enhancing flexibility further, modern FPGAs supports partial reconfiguration, allowing specific regions of the FPGA to be updated without interrupting the operation of the entire device. This feature is especially valuable in dynamic environments that demand continuous operation while adapting to changing conditions.

#### 2.5 Chaotic Systems

Chaotic systems are deterministic systems that display highly unpredictable behavior due to their sensitivity to initial conditions, often called the "butterfly effect" [26]. These systems, governed by nonlinear differential equations, are deterministic but exhibit complex and seemingly random behavior over time.

One notable example of a chaotic system is the Lorenz system [26], described by the following set of three-dimensional differential equations:

$$\frac{dx}{dt} = \sigma(y - x), \quad \frac{dy}{dt} = x(\rho - z) - y, \quad \frac{dz}{dt} = xy - \beta z \tag{2.8}$$

where x, y, and z are system state variables, and  $\sigma$ ,  $\rho$ , and  $\beta$  are system parameters. When  $\sigma = 10$ ,  $\rho = 28$ , and  $\beta = 8/3$ , the system exhibits chaotic behavior, where small changes in initial conditions lead to vastly different trajectories.

Due to the complexity of chaotic systems, they are typically solved using numerical methods such as Euler's method or higher-order Runge-Kutta methods [16]. These techniques approximate the system's state over time by discretizing time into small steps and iteratively solving the equations, though this can become computationally expensive, particularly over long simulation times or in real-time applications. ANNs offer an efficient alternative by learning the system's dynamics directly, enabling future state predictions based on current inputs without the need for iterative equation solving. This reduces computational demands

and allows for faster predictions, beneficial in scenarios requiring rapid or resource-efficient processing.

Chaotic systems are widely used in generating Pseudo Random Number Generators (PRNGs) [27]. The deterministic yet unpredictable nature of chaos makes them suitable for certain cryptographic applications and simulations. By evolving a chaotic system from a specific seed (initial condition), a sequence of numbers that mimic randomness can be generated. However, due to statistical weaknesses and predictability concerns, additional post-processing techniques are often required to make chaotic PRNGs suitable for secure encryption systems [28].

#### 2.6 Chapter Summary

This chapter established the foundational concepts that drive the thesis. Starting with the principles of neural networks, we examined how ANNs and DNNs model complex data. Model compression techniques, such as pruning and quantization, were introduced to demonstrate efficient optimization for hardware constraints. FPGA architecture was then discussed as an ideal platform for deploying these optimized networks, thanks to its reconfigurable resources. Finally, chaotic systems were explored for their utility in secure computations. Together, these topics form a cohesive framework for efficient, hardware-accelerated neural network deployment in resource-limited applications, setting the stage for the work that follows.

# CHAPTER 3 ARTICLE 1: DYRECMUL: FAST AND LOW-COST APPROXIMATE MULTIPLIER FOR FPGAS USING DYNAMIC RECONFIGURATION

Authors: Mobin Vaziri, Shervin Vakili, Amirhossein Zarei, and J.M. Pierre Langlois.

Published in: ACM Transactions on Reconfigurable Technology and Systems (2024).

Submitted: 21 December 2023 Published: 02 May 2024

#### **Abstract**

Multipliers are widely-used arithmetic operators in digital signal processing and machine learning circuits. Due to their relatively high complexity, they can have high latency and be a significant source of power consumption. One strategy to a lleviate these limitations is to use approximate computing. This paper thus introduces an original FPGA-based approximate multiplier specifically optimized for machine learning computations. It utilizes dynamically reconfigurable L UT primitives in A MD-Xilinx technology to realize the core part of the computations. The paper provides an in-depth analysis of the hardware architecture, implementation outcomes, and accuracy evaluations of the multiplier proposed in INT8 precision. The paper also facilitates the generalization of the proposed approximate multiplier idea to other datatypes, providing analysis and estimations for hardware cost and accuracy as a function of multiplier parameters. Implementation results on an AMD-Xilinx Kintex Ultrascale+ FPGA demonstrate remarkable savings of 64% and 67% in LUT utilization for signed multiplication and multiply-and-accumulation configurations, respectively when compared to the standard Xilinx multiplier core. Accuracy measurements on four popular deep learning benchmarks indicate a minimal average accuracy decrease of less than 0.29% during post-training deployment, with the maximum reduction staying less than 0.33%. The source code of this work is available on GitHub<sup>1</sup>.

<sup>&</sup>lt;sup>1</sup>https://github.com/INRS-ECCoLe/DyRecMul

#### 3.1 Introduction

Computational circuits may become a bottleneck in wireless communications, digital signal processing, multimedia, image processing, machine learning, etc., due to their high energy consumption, long delay, and large circuit area utilization. Applications such as neural networks have inherent error resilience, which presents an opportunity to use approximation techniques for enhancing their efficiency [29, 30]. Multiplication is a fundamental operation in computations, and, to enhance its efficiency, various approximate multipliers have been proposed. These multipliers aim to reduce delay, energy consumption, and area [31]. In 1962, Mitchell [32] introduced the first logarithm-based multiplier. This multiplier converted multiplications into addition operations, and it deployed approximation methods to calculate logarithmic expressions. Since then, there have been significant advancements in logarithm-based approximate multipliers [33–36]. Liu et al. used approximate adders to improve accuracy and reduce power consumption compared to conventional logarithm-based multipliers [33]. Given that two-variable multiplication is a nonlinear operation, several works proposed methods to use linearization for approximate multiplication [37,38]. An approximate linearization algorithm, called ApproxLP [37], utilized comparators to separate different sub-domains and allocate a proper linear function to each one instead of a nonlinear multiplication. This method, however, requires additional comparators to increase accuracy and reduce sub-domain size, which can result in longer delays and increased area [31]. Chen et al. introduced an Optimally Approximate Multiplier (OAM) [38] to improve linearization and minimize the number of comparators, resulting in lower delay and improved performance. Other studies suggest utilizing a combination of accurate and approximate multipliers with varying precision levels to achieve the necessary accuracy, but this may come at the cost of higher energy consumption and circuit area [39,40].

In non-logarithmic multiplication, the approximation can be introduced at four distinct stages: data input, partial product generation, accumulation, and Booth encoding [31]. Truncating input data is often used to reduce bitwidth, and it can be done through methods such as the Dynamic Segment Method (DSM) and Static Segment Method (SSM) [41–44]. DSM keeps a specified number of bits from the most significant '1' in an *n*-bit operand but requires more hardware resources than SSM. SSM has limited and pre-determined options for truncating input data, resulting in more redundant bits [31,41]. Some works have introduced approximations in the partial product generation stage [45–48]. However, the most beneficial stage to introduce approximation is during partial product accumulation, which typically requires the largest circuit area and computation time.

Compressors can be used for counting ones in tree-based partial product accumulations [31],

such as the Wallace tree [49] and Dadda tree [50]. Instead of exact compressors, a variety of approximate compressors have been introduced to decrease circuit area and delay [46, 47, 51–62]. These include the approximate 1-bit half adder, approximate 1-bit full adder, and approximate 4-2 compressors [54, 55, 58, 60]. To further decrease energy consumption, delay, and hardware utilization, high-order approximate compressors with more than five inputs have been proposed [51, 53, 59, 61]. Mahdiani et al. proposed a technique that removes the least significant partial products from the partial product matrix to decrease circuit area and delay, although it comes with some degree of error which can be adjusted by modifying the truncation level [56].

The existing approximate methods, which have been mainly designed to reduce energy consumption and area utilization in ASIC implementations, may not be as effective in FPGAs. This is because FPGA reconfigurable logic fabrics are typically based on fixed-size LUTs. Modern AMD-Xilinx and Intel FPGAs have hardwired DSP multipliers that offer faster and more energy-efficient multiplication than soft implementation on general-purpose LUT fabrics. The DSP-based multipliers are valuable resources that are situated in specific locations, which can result in long routing delays. On the other hand, LUTs are spread out across the chip, making them more easily routable. Moreover, there is a limitation on the number of DSP-based multipliers available. One solution is to deploy approximation methods to enhance the efficiency of LUT-based multiplication, in terms of speed, energy/power consumption, and hardware utilization. Ullah et al. [63, 64] implemented an optimization technique by truncating the least significant partial product of a  $4 \times 2$  multiplier to reduce LUT utilization. Van Toan et al. [65] designed compact 3-2 and 4-2 compressors for use in different approximate multipliers with varying levels of accuracy. Kumm et al. [66] proposed dynamically reconfigurable FIR filters in Xilinx FPGAs using Configurable Look-up Tables (CFGLUT5s).

This paper introduces DyRecMul, a cost-effective dynamically reconfigurable approximate multiplier for FPGAs. It is optimized for machine learning computation, has a short critical path, and uses a small number of LUTs. DyRecMul utilizes AMD-Xilinx technology's reconfigurable LUT primitives to approximate multiplication without significant accuracy degradation, even in post-training inference. To preserve dynamic range, DyRecMul utilizes a cost-effective encoder that transforms a fixed-point operand into a floating-point format, and a decoder to revert the result back to fixed-point. The paper presents the design details and evaluation results of an INT8 version of DyRecMul since INT8 is a popular datatype in cost-effective machine learning computing. The multiplier introduces negligible accuracy loss while reducing significantly the number of required LUTs in FPGAs compared to the standard exact multiplier. Additionally, DyRecMul boasts very low latency, which allows for a faster

clock frequency than that of typical AMD-Xilinx multiplier cores. The key contributions of this paper are summarized below.

- Utilization of dynamically reconfigurable LUTs in AMD-Xilinx FPGAs to make a low-cost and fast short-bitwidth multiplier.

- Internal conversion of fixed-point to a floating-point format to preserve dynamic range that is beneficial for machine learning and deep learning applications.

- For an INT8 case study, illustration of the design detail of a highly optimized encoder circuit to convert INT8 to 8-bit floating-point (FP8) format and a low-cost decoder to convert FP8 to INT8.

#### 3.2 Analytical Description

A precise N-bit signed integer multiplication of two operands, X and W, can be represented by:

$$Z = s_z. \sum_{i=0}^{2N-2} z_i.2^i = s_x. \sum_{i=0}^{N-2} x_i.2^i \times s_w. \sum_{i=0}^{N-2} w_i.2^i$$

(3.1)

where  $x_i$ ,  $w_i$  and  $z_i$  denote the  $i^{th}$  bit of operand X and W and the result Z, respectively.  $s_x$  takes the value of -1 when X is negative, and 1 otherwise. The same logic applies to  $s_z$  and  $s_y$ . In INT8 representation, N = 8. When using multipliers in a computing system that only supports a single datatype, the output Z must be expressed in the same format as the input operands. This can be done using techniques like truncation.

The proposed approach utilizes an encoder to convert the first operand, X, to a floating-point representation,  $\hat{X}_{float}$ , of format:

$$float (sign_{BW}, exp_{BW}, mnt_{BW}),$$

$sign_{BW} \in \{0, 1\}, exp_{BW} > 0, mnt_{BW} < N - 1$

$$(3.2)$$

where  $sign_{BW}$ ,  $exp_{BW}$ , and  $mnt_{BW}$  denote the bitwidth of the sign, exponent, and mantissa elements, respectively. In this section, centered on signed multiplication, a single bit is designated to represent the sign, i.e.,  $sign_{BW} = 1$ . To enable covering the entire dynamic range of X,  $exp_{BW}$  and  $mnt_{BW}$  must fulfill the following:

$$2^{exp_{BW}} + mnt_{BW} > N - 1. (3.3)$$

The mantissa is a segment of  $mnt_{BW}$  bits from |X|, with the leftmost bit in |X| that contains '1' being the most significant bit. Since the mantissa is shorter than the magnitude bits of X, this conversion involves an approximation. The conversion can be expressed as:

$$\hat{X}_{float} = \left[ \hat{X}_{sign}, \ \hat{X}_{exp}, \ \hat{X}_{mnt} \right]$$

(3.4)

$$\begin{cases} \hat{X}_{sign} = x_{N-1}, \\ \hat{X}_{exp} = N - i \text{ where } \begin{cases} 2^i < |X| \le 2^{i-1}, \ X \ge 2^{mnt_{BW}} \\ 0, \ X < 2^{mnt_{BW}}, \end{cases} \\ \hat{X}_{mnt} = Round\left(\frac{|X|}{2^{exp}}\right) \end{cases}$$

The mantissa  $\hat{X}_{mnt}$  is then multiplied by |W| to generate the mantissa of the result. To keep the result in the format of Eq. 3.2, the product is quantized to  $mnt_{BW}$  bits using:

$$\hat{Z}_{mnt} = Q\left(\hat{X}_{mnt} \times |W|, \ mnt_{BW}\right), \tag{3.5}$$

where Q is the quantization function. The result must be converted back to integer format. For this purpose, the (N-1)-bit absolute value of Z is first calculated by:

$$|Z| = 2^{\hat{X}_{exp}} \times \hat{Z}_{mnt} \tag{3.6}$$

The result, Z, in integer format is obtained by applying a two's complement function when Z is negative. The sign of Z is determined by XORing the sign bits of X and W.

$$Z = s_z. |Z|, \begin{cases} s_z = +1, \ x_{N-1} \oplus w_{N-1} = 0\\ s_z = -1, \ x_{N-1} \oplus w_{N-1} = 1 \end{cases}$$

$$(3.7)$$

#### 3.3 DyRecMul for INT8 Multiplication: Architecture and Components

INT8 quantization is a supported feature in machine learning frameworks such as TensorFlow Lite and PyTorch, as well as hardware toolchains like AMD-Xilinx DNNDK. Moreover, INT8 is a popular datatype in machine learning hardware accelerators and ML-optimized GPUs designed for embedded and edge applications [67], [68]. The INT8 DyRecMul described in this section can be used in place of INT8 multipliers for pre- or post-training inference. This multiplier is intended primarily for single-datatype INT8 architectures, meaning that it calcu-

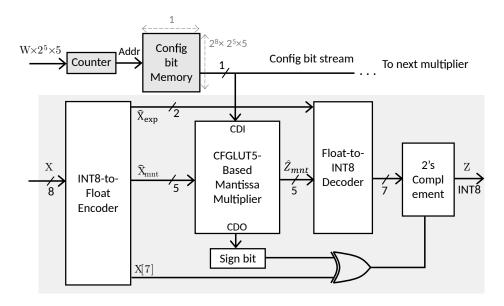

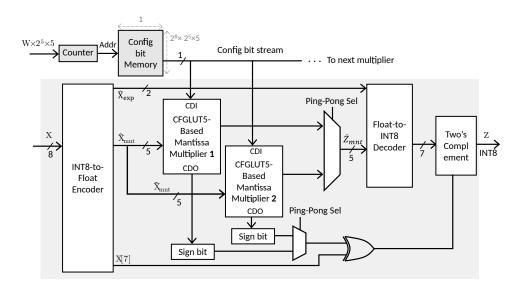

Figure 3.1 DyRecMul architecture for INT8 multiplication of  $Z = X \times W$ , using float (1, 2, 5) internal floating-point format.

lates  $Z = X \times W$ , where X, W and Z are all INT8. Fig. 3.1 depicts its architecture, which consists of four main components: (1) a cost-effective INT8 to floating-point encoder; (2) an ultra-low-cost mantissa multiplier using dynamically reconfigurable LUTs; (3) a floating-point to INT8 decoder; (4) a two's complement logic. The following subsections describe each component in detail.

#### 3.3.1 Integer to Floating-Point Encoder

The proposed architecture converts its first operand, X, from INT8 to float (1,2,5) representation, where 1, 2, and 5 indicate the number of allocated bits to the sign, exponent, and mantissa, respectively. This conversion corresponds to Eq. 3.4 in Section 3.2. The mantissas are multiplied and the exponents are added, and this conversion limits the binary multiplication to five bits while maintaining the dynamic range, which is crucial for accurate DL computations. As will be discussed later, DyRecMul deploys a CGFLUT5-based unsigned multiplier in which one operand must be five bits wide to achieve optimal efficiency. When this multiplier is used in a weight stationary DL accelerator, input feature maps are fed as the first operand, X, to the multipliers. Without a floating-point conversion, the feature maps would need to be directly quantized to five bits. That would significantly limit the supported dynamic range, which could cause important accuracy loss for small activation values and ultimately lead to a prohibitive level of inaccuracy in ML inference. More precisely, such a quantization would limit the range of supported values to  $[-2^5, 2^5 - 1]$ , while float (1, 2, 5)

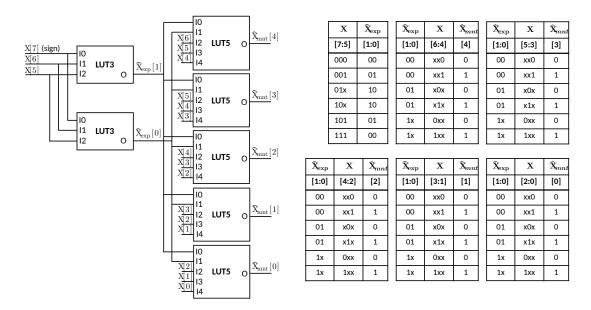

Figure 3.2 INT8 to float(1,2,5) encoder: LUT mapping and corresponding truth tables.

expands the range to  $[-2^3 \times 2^5, 2^3 \times 2^5 - 1]$  and demands the same unsigned multiplier size for mantissa multiplication. The experimental results in Section 3.7.3 demonstrate that this conversion greatly helps in maintaining the precision of DL calculations.

The conversion logic from INT8 to float(1,2,5) is designed to be low-cost and efficient, requiring only seven LUT5 elements. Fig. 3.2 depicts the truth tables and the corresponding LUT5 allocations for this encoder. The 2-bit exponent is acquired from the sign bit and the two most significant bits, while each mantissa bit is obtained from the exponent and three corresponding input bits. The encoder's critical path consists of two LUT5 units and their corresponding routing circuits.

#### 3.3.2 Dynamically Reconfigurable Mantissa Multiplier

This component implements mantissa multiplication according to Eq. 3.5. The mantissa multiplier which serves as the core component of DyRecMul, is a cost-effective unsigned integer multiplier based on AMD-Xilinx CFGLUT5 primitives. CFGLUT5 offers a distinctive capability allowing the logical function of the LUT5 to be altered during circuit operation. This reconfiguration is achieved by programming new configuration bits into the LUT5, enabling it to adopt a new logic function with a maximum of 5-bit inputs and one output. The design subsystem controls the programming of new configuration bits, and this reconfiguration process does not necessitate external partial or complete reprogramming of the FPGA, ensuring uninterrupted operation. The programming of new configurations is carried out

serially through a single-bit CDI input port, while CDI/CDO ports facilitate the cascading of multiple CFGLUT5 units in a chain.

In the mantissa multiplier, the logic circuit for multiplication with the second operand is programmed into CFGLUT5 units. Whenever the second operand, W, undergoes changes, the CFGLUT5 units within the mantissa multiplier are reconfigured to establish a constant multiplication logic with the updated value. The first operand is fed into the 5-bit input port of CFGLUT5s. Hardcoding the multiplication logic for the second operand directly into the LUTs, instead of employing a traditional double-operand multiplier, significantly reduces the hardware cost of the multiplication circuit.

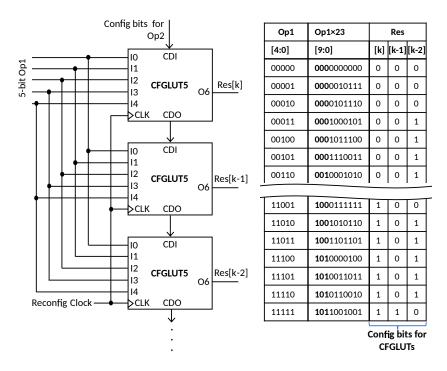

Fig. 3.3 illustrates the LUT mapping and configuration bits for an example 5-bit unsigned multiplier. The output consists of the quantized k most significant bits of the result. This means that only k CFGLUT5s are needed, each generating one output bit. In this example, a value of 23 is assumed for the second operand, W, configuring the CFGLUT5s to realize the logic circuit of a constant multiplier calculating the product of a 5-bit quantized first operand, and 23. Fig. 3.3 depicts the process of calculating the configuration bits for three CFGLUT5s which produce the three most significant bits of the product. Rounding is used in these calculations to minimize quantization error. The configuration bits are loaded into the CFGLUT5s serially through a cascaded CDI and CDO chain. As the bitwidth of the first operand surpasses five, the number of CFGLUT5s required for each output bit grows exponentially. More precisely, the required number of CFGLUT5s is:

$$#CFGLUT5 = 2^{b_1 - 5} \times k \tag{3.8}$$

where  $b_1$  and k denote the bitwidth of the first operand, X, and the result, Z, respectively.

As an example, implementing an exact  $8 \times 8$  unsigned multiplier requires  $2^3 \times 16 = 128$  CFGLUT5s. Although the LUT utilization may appear to be high, a more serious obstacle lies in the significant number of reconfiguration bits - a total of 4096 ( $128 \times 2^5$ ). In order to fully exploit the CFGLUT5s while minimizing their quantity, we limited the first operand, to five bits, resulting in one CFGLUT5 utilization per result bit. Thus, using k parallel CFGLUT5s allows for calculating the k-bit result of a 5-bit multiplication. If the bitwidth is shorter, some CFGLUT5s may remain partially unused, while increasing it to over five bits will exponentially increase the number of CFGLUT5s. Additionally, for the INT8 DyRecMul, we set the result bitwidth k to five, restricting the number of CFGLUT5s to only five units and the number of reconfiguration bits to 160. When this multiplier is used in a weight stationary DL accelerator, weights are translated into the configuration bits in CFGLUT5s, and input feature maps are fed as operands to the multipliers. As there is no interdependence

Figure 3.3 5-bit dynamically reconfigurable multiplier with 3-bit result using CFGLUT5 primitives. The second operand, Op2 = 23 in this example.

between CFGLUT5 elements, they can operate entirely in parallel, resulting in a short critical path of just one CFGLUT5.

The configuration bits for CFGLUT5s are stored in a shared BRAM-based memory, as illustrated in Fig. 3.1. This memory functions like a read-only memory, storing all configuration bits for every possible  $2^N$  value of the second operand. A counter generates the read address for the configuration memory during reconfiguration. When the second operand, W, changes, this counter is initialized to the address of the first configuration bit corresponding to the new W. The counter then increments with each clock cycle, and during each cycle, it programs one bit into the chain of CFGLUT5s inside the mantissa multiplier through CDI/CDO pins. In the case of the INT8 DyRecMul, this process continues for 160 clock cycles to write all 160 new configuration bits.

When multiple DyRecMuls are utilized in a design, the reconfiguration BRAM can be dual-ported to facilitate the parallel reprogramming of two DyRecMuls. Furthermore, a single reconfiguration memory can be employed for the sequential reprogramming of more than two DyRecMuls, albeit at the expense of a longer reconfiguration time. The reconfiguration time is an important factor in the efficiency of DyRecMul. As previously mentioned, DyRecMul is most suitable for applications where one of the operands does not change frequently. In other words, DyRecMac gains an edge when one of the operands remains unchanged

significantly longer than the reconfiguration time. The influence of reconfiguration time on the overall processing time primarily relies on the dataflow and architecture of the DL accelerator. Section 3.6 will review some of the main target applications that can effectively take advantage of DyRecMul.

#### 3.3.3 Floating-point to Integer Decoder

In deep learning computing, multiplication operations are often followed by addition or subtraction. However, a significant drawback of floating-point representations is the high hardware cost of their adder/subtractor circuits, which limits overall efficiency. To address this issue and enable subsequent addition or subtraction in integer format, DyRecMul converts the result back to integer form using decoder and two's complement components.

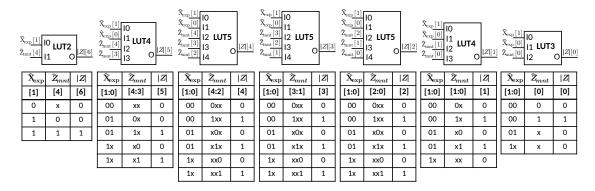

The decoder converts the result of mantissa multiplication along with the exponent of the first operand into a 7-bit unsigned format. The decoder needs seven LUT5 units, with each unit producing one output bit using two exponent bits and a maximum of three mantissa bits. The truth table of each output bit is shown in Fig. 3.4. Since all LUT5 units function in parallel, the critical path is only one LUT5.

### 3.3.4 Two's Complement Logic

The output of the decoder is the absolute value of the result. As described in Section 3.2, the sign of the product can be obtained by exclusive OR operation between the sign bit of the two operands. If the product is negative, a two's complement function must be applied. Two's complement logic can be realized using eight LUT5 units. The carry signal is expected to be a major source of latency in this multiplier. To create an unsigned version of DyRecMul, we only need to remove the two's complement stage, modify the floating-point format to

Figure 3.4 float (1, 2, 5) to INT8 decoder: LUT mapping and corresponding truth tables.

float(0,2,5), and make slight adjustments to the encoder and decoder stages. The results in section 3.7 indicate that the unsigned version is more efficient than the signed version. This is because the two's complement stage, which consumes a significant amount of hardware resources, is present only in the signed DyRecMul.

#### 3.4 Generalized DyRecMul

Section 3.3 detailed the design of an INT8 multiplier with internal float(1,2,5) conversion. A crucial question arises regarding the effectiveness of DyRecMul with other data types and floating-point formats. The cost and accuracy of a DyRecMul multiplier depend on four key parameters:  $mnt_{BW}$ , the mantissa bitwidth in the floating-point encoding of Op1;  $exp_{BW}$ , the exponent bitwidth;  $m\hat{X}_{exp} = max\left(\hat{X}_{exp}\right) + 1$ , the maximum value that the exponent may attain plus one; and  $\hat{Z}_{BW}$ , the number of mantissa product bits generated by the mantissa multiplier unit. Altering these parameters results in different trade-offs between hardware cost and accuracy. The main task in designing a DyRecMul multiplier entails selecting suitable values for these parameters. This section provides an estimation of the hardware cost and accuracy of an  $N \times N$  DyRecMul as a function of these four parameters. These estimation functions provide insight into the overall efficiency of the DyRecMul method and facilitate the process of designing DyRecMul multipliers for various data types.

#### 3.4.1 Hardware Cost Estimation

In this section, we provide a conservative estimation of the hardware cost for three crucial components of unsigned DyRecMul—namely, the encoder, mantissa multiplier, and decoder—measured in terms of the number of utilized LUT5 units. To establish a uniform metric, we estimate the number of LUT5s, striving to map all logic onto LUT5 resources, excluding other elements such as F7, F8, and F9 MUX primitives in AMD-Xilinx FPGA technology [69]. Since each LUT6 in modern AMD-Xilinx technology consists of two LUT5 units, the estimations provided in this section can be converted to LUT6 utilization by dividing the estimated number of LUT5s by two. Moreover, the estimations can be readily extended to the signed DyRecMul by applying minor modifications and incorporating the LUT utilization for the two's complement component.

#### Integer to Floating-Point Encoder

As illustrated in Fig. 3.2 for the INT8 case, the integer to floating-point encoder comprises two components: (1) an exponent identifier circuit, and (2) mantissa extractor.

The exponent identifier examines the  $m\hat{X}_{exp}$  most significant bits to determine the  $exp_{BW}$  bits of the exponent. This is realized by a circuit that bears similarities to a  $m\hat{X}_{exp}$ -to- $exp_{BW}$  priority encoder. As long as  $m\hat{X}_{exp} \leq 5$ , each output bit can be generated by a single LUT5. However, when  $m\hat{X}_{exp}$  exceeds 5, a conservative and simplified estimation approach involves dividing the exponent identifier into two steps. The first step employs a logic circuit to convert the  $m\hat{X}_{exp}-1$  most significant bits, retaining only the most significant '1' bit and masking other less significant bits to zero. This step requires almost  $m\hat{X}_{exp}-1$  LUTs. The second step resembles a binary decoder with  $exp_{BW}$  output bits. In decoders, each output bit typically depends on a maximum of  $2^{exp_{BW}}/2$  input bits. One LUT5 is adequate to process a maximum of five input bits in this stage. Since  $exp_{BW}$  is not supposed to be too large in DyRecMul, we can estimate that  $\lceil 2^{exp_{BW}}/10 \rceil$  LUT5s are required for each output bit. In summary, the estimated total number of LUT5s for the exponent identifier can be expressed as:

$$exp_{LUT5} = \begin{cases} exp_{BW}, & m\hat{X}_{exp} \le 5, \\ \left\lceil \frac{2^{exp_{BW}}}{10} \right\rceil \times exp_{BW} + m\hat{X}_{exp} - 1, & m\hat{X}_{exp} > 5. \end{cases}$$

(3.9)

Recalling that  $m\hat{X}_{exp} = max(\hat{X}_{exp}) + 1$ , the exponent bitwidth,  $exp_{BW}$ , is directly derived from  $m\hat{X}_{exp}$  as follows:

$$exp_{BW} = \left[\log_2\left(m\hat{X}_{exp}\right)\right]. \tag{3.10}$$

The mantissa extractor functions as a multiplexer, with the exponent acting as its selector and  $m\hat{X}_{exp}$  bits of the first operand as its input. Each bit of the mantissa is derived from the  $exp_{BW}$ -bit exponent and  $m\hat{X}_{exp}$  bits of the input, X. As long as  $m\hat{X}_{exp} + exp_{BW} \leq 5$ , each output bit can be generated by one LUT5. However, if  $m\hat{X}_{exp} + exp_{BW}$  exceeds 5, a multilayer tree of LUTs implements this multiplexer. Every  $4\times1$  multiplexer can be implemented within a single LUT6 or two LUT5. Thus, we conservatively estimate the number of LUT5 in the first layer as  $\left\lceil m\hat{X}_{exp}/4 \right\rceil \times 2$ . Every four LUTs from the first layer, along with two exponent bits, feed one LUT6 in the second layer. Therefore, we estimate the number of LUT5s in the second layer as  $\left\lceil m\hat{X}_{exp}/4 \right\rceil \times 2$ . A third layer will be needed only when  $m\hat{X}_{exp}$  exceeds 16 and will need more than one LUT when it exceeds 64, which is too large to consider. Hence, for simplicity, we discard the third layer here. Overall, the obtained estimation for LUT5 utilization in the mantissa extractor will be as follows:

$$mnt_{LUT5} = \begin{cases} mnt_{BW}, & m\hat{X}_{exp} < 4, \\ mnt_{BW} \times 2, & m\hat{X}_{exp} = 4, \\ \left( \left\lceil \frac{m\hat{X}_{exp}}{4} \right\rceil + \left\lceil \frac{m\hat{X}_{exp}}{16} \right\rceil \right) \times 2 \times mnt_{BW}, & m\hat{X}_{exp} > 4. \end{cases}$$

(3.11)

The total estimated number of LUT5 units required for integer to floating-point encoding is:

$$encoder_{LUT5} = exp_{LUT5} + mnt_{LUT5}$$

(3.12)

# Floating-Point to Integer Decoder

The decoder converts the product result to integer format. Similar to the mantissa extractor in the encoder, the decoder operates as a multiplexer, with each output bit chosen from one of the  $m\hat{X}_{exp}$  mantissa product bits,  $\hat{Z}_{exp}$ . Consequently, each output bit of the decoder requires a multiplexer, employing the exponent as the selector to choose among  $m\hat{X}_{exp}$  bits of the mantissa product. As long as  $m\hat{X}_{exp} + exp_{BW} \leq 5$ , a single LUT5 is sufficient for implementing the multiplexer of each bit. If it exceeds 5, a similar approximation to Eq. 3.11 is applied. The resulting estimation function for the total number of LUT5s for the decoder is as follows:

$$decoder_{LUT5} = \begin{cases} N, & m\hat{X}_{exp} < 4, \\ N \times 2, & m\hat{X}_{exp} = 4, \\ \left( \left\lceil \frac{m\hat{X}_{exp}}{4} \right\rceil + \left\lceil \frac{m\hat{X}_{exp}}{16} \right\rceil \right) \times N \times 2, & m\hat{X}_{exp} > 4. \end{cases}$$

(3.13)

For the signed version, Eq. 3.13 needs to be adjusted by replacing N with N-1.

#### CFGLUT5-Based Mantissa Multiplier

As detailed in Section 3.3.2, an estimate of the required number of LUT5 units for mantissa multiplication can be obtained as follows:

$$mnt\_multiply_{LUT5} = \begin{cases} \left[ \hat{Z}_{BW} \right], & mnt_{BW} \leq 5, \\ \left[ 2^{mnt_{BW} - 5} \times \hat{Z}_{BW} \right], & mnt_{BW} > 5. \end{cases}$$

(3.14)

Increasing  $\hat{Z}_{\rm BW}$  enhances accuracy at the expense of a larger mantissa multiplication unit and an extended reconfiguration time.

As an example, for a UINT8 DyRecMul multiplier with float(0, 2, 5) internal floating-point format, and the parameter values of N=8,  $exp_{BW}=2$ ,  $mnt_{BW}=5$ ,  $m\hat{X}_{exp}=4$ , and  $\hat{Z}_{BW}=5$ , the estimated total number of LUT5s using Eq. 3.12, 3.13, and 3.14 is as follows:

$$total_{LUT5} = encoder_{LUT5} + decoder_{LUT5} + mnt_multiply_{LUT5} = 12 + 16 + 5 = 33 \quad (3.15)$$

From Eq. 3.15, the estimated number of LUT6 units required for this UINT8 DyRecMul is approximately 17. It is worth noting that the synthesizer tools typically have the capability to reduce LUT utilization through optimization.

### 3.4.2 Accuracy Considerations