**Titre:** Systèmes de distribution d'énergie robustes exploitant des convertisseurs CC-CC efficaces

Title: convertisseurs CC-CC efficaces

**Auteur:** Nader El Zarif

Author:

**Date:** 2024

**Type:** Mémoire ou thèse / Dissertation or Thesis

**Référence:** El Zarif, N. (2024). Systèmes de distribution d'énergie robustes exploitant des convertisseurs CC-CC efficaces [Thèse de doctorat, Polytechnique Montréal].

Citation: PolyPublie. <https://publications.polymtl.ca/61603/>

## Document en libre accès dans PolyPublie

Open Access document in PolyPublie

**URL de PolyPublie:** <https://publications.polymtl.ca/61603/>

PolyPublie URL:

**Directeurs de recherche:** Yvon Savaria, & Christian Fayomi

Advisors:

**Programme:** Génie électrique

Program:

**POLYTECHNIQUE MONTRÉAL**

affiliée à l'Université de Montréal

**Systèmes de distribution d'énergie robustes exploitant des convertisseurs

CC-CC efficaces**

**NADER EL ZARIF**

Département de génie électrique

Thèse présentée en vue de l'obtention du diplôme de *Philosophiæ Doctor*

Génie électrique

Décembre 2024

**POLYTECHNIQUE MONTRÉAL**

affiliée à l'Université de Montréal

Cette thèse intitulée :

**Systèmes de distribution d'énergie robustes exploitant des convertisseurs

CC-CC efficaces**

présentée par **Nader EL ZARIF**

en vue de l'obtention du diplôme de *Philosophiæ Doctor*

a été dûment acceptée par le jury d'examen constitué de :

**Yves AUDET**, président

**Yvon SAVARIA**, membre et directeur de recherche

**Christian FAYOMI**, membre et codirecteur de recherche

**Tarek OULD-BACHIR**, membre

**Frederic NABKI**, membre externe

## DÉDICACE

*À mes parents bien-aimés Rahih et Sabah,*

*À ma femme bien-aimée Faten,*

*À mes frères Nizar et Abdel Rahman,*

*À ma famille... .*

## REMERCIEMENTS

Je tiens à exprimer ma plus profonde gratitude et reconnaissance à mes directeurs de thèse, le Prof. Yvon Savaria et le Prof. Christian Jesus B. Fayomi, pour les suivis inébranlables, leurs encouragements et leur soutien tout au long de mon parcours doctoral. Leurs précieux conseils et leur expertise ont été essentiels dans l'orientation de mes recherches, et leur mentorat a joué un rôle déterminant dans mon développement académique et personnel. Je suis également profondément reconnaissant envers le Prof. Mohamed Sawan, qui m'a initialement intégré à ce projet et m'a offert l'opportunité de travailler avec des individus aussi remarquables.

Je tiens à adresser mes remerciements particuliers au Prof. Ahmad Hassan et au Dr. Mohamed Ali, dont l'amitié et le mentorat ont été inestimables tout au long de ce parcours. Vos conseils et votre soutien ont été d'une grande importance pour moi durant cette période.

À ma famille bien-aimée — ma mère, Sabah ; mon père, Rabih ; mes frères, Nizar et Abdel Rahman ; et ma chère épouse, Faten — aucun mot ne saurait exprimer la profondeur de mon amour et de ma reconnaissance envers chacun de vous. Votre soutien indéfectible, votre patience et vos encouragements ont été la base qui m'a permis de poursuivre et d'atteindre mes rêves. Merci d'avoir été à mes côtés à travers chaque défi et d'avoir cru en moi, même dans les moments les plus difficiles.

Je tiens également à exprimer ma gratitude sincère à mes collègues de l'université qui sont devenus de proches amis. Mostafa Amer, Ahmed Abuelnasr, Isa Altoobaji, Akram Rifaii, Hussein Assaf et Ibrahim Housseini, votre collaboration, vos conseils et votre amitié ont non seulement enrichi mon expérience académique, mais ont aussi grandement contribué à ma réussite. Je suis reconnaissant d'avoir partagé ce parcours avec vous et d'avoir créé ensemble un environnement d'apprentissage et de soutien mutuel.

Enfin, je suis éternellement reconnaissant envers toutes les personnes qui ont contribué à mon parcours doctoral. Votre soutien, vos encouragements et votre amitié ont été inestimables, et je vous dédie cette réussite à chacun d'entre vous.

## RÉSUMÉ

L'essor de l'électrification et l'intégration des énergies renouvelables dans les secteurs industriels et automobiles modernes ont intensifié la demande de systèmes de gestion de l'énergie performants et efficaces. Les convertisseurs DC-DC jouent un rôle fondamental dans des applications telles que les véhicules électriques, les systèmes industriels et l'électronique grand public, en stabilisant et optimisant le flux d'énergie sous des charges variables et dans des conditions environnementales fluctuantes. Cette thèse apporte une contribution significative dans le domaine en abordant les défis techniques des convertisseurs DC-DC. Elle y parvient en concevant des systèmes efficaces et thermiquement intelligents via l'intégration de contrôleurs basés sur des boucles à verrouillage de phase (BVP), une modélisation précise des composants, et des capteurs thermiques avancés.

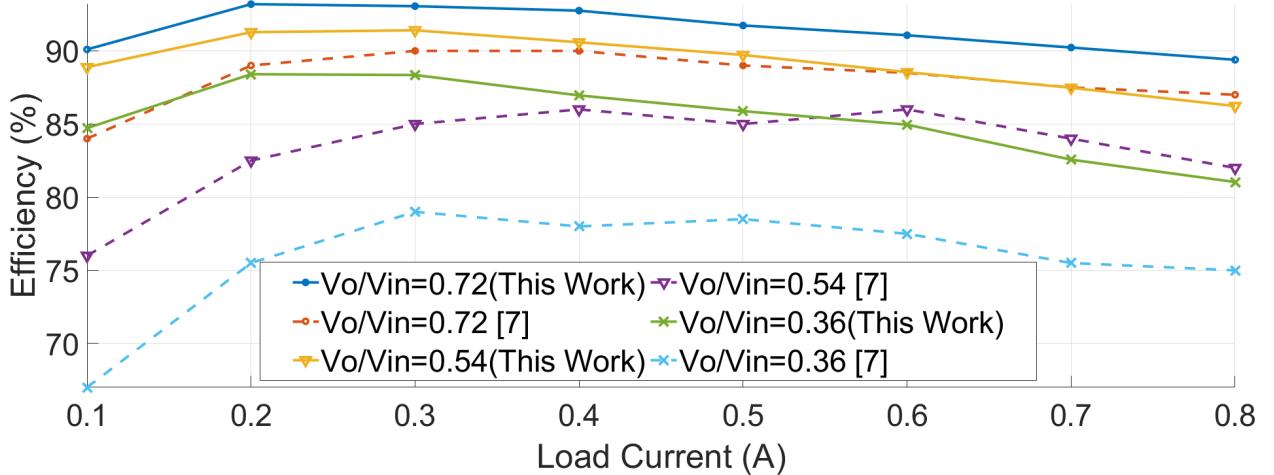

Les recherches ont débuté par la conception de contrôleurs BVP adaptés aux convertisseurs abaisseurs (Buck) et Zeta, visant à fournir des temps de réponse rapides et une stabilité robuste même sous des conditions de charge fluctuantes. Les résultats expérimentaux obtenus pour le convertisseur abaisseur, présentés lors de la conférence LASCAS, ont démontré un rendement maximal de 93,5%, avec une ondulation de tension réduite à 35 mV dans des conditions d'exploitation typiques. Ce résultat est notable, car il dépasse le rendement actuel des convertisseurs abaisseur de pointe, contribuant ainsi à l'avancement de l'électronique de puissance. Par ailleurs, le convertisseur Zeta, détaillé dans un article soumis à *IEEE Access*, a atteint une sortie stable avec une régulation de charge inférieure à 0,1% pour une large gamme de variations d'entrée, tout en maintenant une efficacité de 94% sous des charges nominales. Ces résultats soulignent la robustesse et l'adaptabilité des contrôleurs conçus, caractéristiques essentielles pour les applications réelles où une régulation de tension constante est cruciale.

En plus de l'amélioration des techniques de contrôle, cette recherche aborde les limitations des modèles de composants conventionnels qui négligent souvent des éléments tels que la résistance série de l'inducteur et la résistance en conduction des MOSFET, ce qui entraîne des inexactitudes dans les simulations. La nouveauté de cette recherche réside dans l'intégration exhaustive de ces paramètres dans le modèle, qui a démontré une forte fidélité avec les performances réelles, améliorant ainsi la précision de la prévision des réponses transitoires et stationnaires sous des charges de forte intensité par rapport aux modèles traditionnels. Cette approche de modélisation avancée permet de mieux aligner les résultats de simulation avec les mesures pratiques, offrant ainsi un cadre de conception de convertisseurs plus fiable et de haute précision.

Une contribution importante de cette thèse réside dans l'intégration de capteurs de température basés sur un oscillateur en anneau au sein du système de convertisseur DC-DC, permettant un suivi thermique précis en temps réel des composants critiques, tels que les MOSFET et les inducteurs. Présenté initialement lors de la conférence NEWCAS, ce travail a démontré la faisabilité de l'utilisation de ces capteurs pour fournir des données thermiques en temps réel, jetant ainsi les bases pour de futures stratégies de contrôle adaptatif pouvant exploiter ces données pour atténuer le stress thermique. Développé davantage dans un article publié dans le journal MDPI, ce travail étend la portée avec une calibration détaillée et une implémentation physique du capteur à oscillateur en anneau, atteignant une précision de  $\pm 0,5^\circ\text{C}$  dans diverses conditions de fonctionnement. Ce niveau de précision souligne la fiabilité des capteurs et leur potentiel pour une intégration dans des boucles de rétroaction capables de gérer activement le stress thermique, contribuant ainsi à prolonger la durée de vie des composants et à renforcer la résilience du système dans des applications à haute densité de puissance.

En somme, cette recherche établit une approche systématique pour relever les défis électriques et thermiques associés aux convertisseurs DC-DC à haute efficacité. Les solutions développées, comprenant le contrôle basé sur BVP, une modélisation précise des composants, et la surveillance thermique en temps réel autonome, jettent non seulement les bases de systèmes d'alimentation adaptatifs et résilients, mais ouvrent également des perspectives passionnantes pour de futures intégrations. Bien que les capteurs thermiques aient été mis en œuvre de manière indépendante dans ce travail, ils fournissent des informations critiques pour une intégration potentielle dans de futurs designs de convertisseurs, où les données thermiques en temps réel pourraient être utilisées activement pour optimiser le contrôle et atténuer le stress thermique. Cette recherche répond aux besoins des applications actuelles et ouvre la voie à une nouvelle génération de systèmes d'électronique de puissance, positionnant ainsi les futurs systèmes pour tirer parti des données en temps réel pour améliorer les performances, en accord avec les exigences croissantes des solutions modernes de gestion de l'énergie.

## ABSTRACT

The drive toward electrification and renewable energy integration in modern industrial and automotive sectors has intensified the demand for efficient, high-performance power management systems. DC-DC converters are fundamental in electric vehicles, industrial systems, and consumer electronics applications, stabilizing and optimizing power flow under variable loads and environmental conditions. This thesis significantly contributes to the field by addressing the technical challenges of DC-DC converters. It does so by designing high-efficiency, thermally aware systems through integrating Phase-Locked Loop (PLL)-based controllers, precise component modeling, and advanced thermal sensing.

The research began with designing PLL-based controllers tailored for both Buck and Zeta converters, aiming to deliver rapid response times and robust stability even under fluctuating load conditions. The experimental results from the Buck converter, presented at the LASCAS conference, demonstrated a peak efficiency of 93.5% with significantly reduced voltage ripple, measuring only 35 mV under typical operating conditions. This result is significant as it surpasses the current state-of-the-art efficiency for Buck converters, thereby contributing to the advancement of power electronics. Moreover, the Zeta converter, detailed in the IEEE Access submission, achieved a stable output with load regulation of less than 0.1% across a wide range of input variations, maintaining an efficiency of 94% under nominal loads. These results are significant as they demonstrate the robustness and adaptability of the designed controllers, which is crucial for real-world applications. These PLL-based controllers minimized transient overshoot and improved steady-state stability, supporting high-power-density applications where consistent voltage regulation is critical.

In addition to advancing control techniques, this research addresses limitations in conventional component modeling, which often neglects elements such as inductor series resistance and MOSFET ON resistance, leading to simulation inaccuracies. The novelty of this research lies in the comprehensive incorporation of these parameters into the model, which has shown high fidelity with real-world performance, improving accuracy in predicting transient and steady-state responses under high-current loads compared to traditional models. This enhanced modeling approach aligns simulation outcomes with practical measurements, offering a more reliable framework for high-precision converter designs.

An important contribution of this thesis is integrating ring oscillator-based temperature sensors within the DC-DC converter system, enabling precise real-time monitoring of critical components such as MOSFETs and inductors. Initially presented at the NEWCAS con-

ference, this work demonstrated the feasibility of using these sensors to provide real-time thermal data, laying the foundation for future adaptive control strategies that could leverage this data to mitigate thermal stress. Building on this, the MDPI journal expands the work with a detailed calibration and physical implementation of the ring-oscillator sensor, achieving an accuracy of  $\pm 0.5^{\circ}\text{C}$  across diverse operating conditions. This level of precision underscores the sensors' reliability. It highlights their potential for integration into feedback loops that actively manage thermal stress, ultimately contributing to increased component longevity and enhanced system resilience in high-power-density applications.

This research establishes a systematic approach to tackling high-efficiency DC-DC converters' electrical and thermal challenges. The developed solutions, encompassing PLL-based control, precise component-specific modeling, and standalone real-time thermal monitoring, lay the groundwork for adaptable and resilient power systems and open up exciting possibilities for future integration. While the thermal sensors were implemented independently in this work, they provide critical insights for potential integration in future converter designs, where real-time thermal data could be actively utilized for enhanced control and stress mitigation. This research addresses the needs of current applications. It paves the way for next-generation power electronics, positioning future systems to leverage real-time data for improved performance in line with the advancing demands of modern power management solutions.

## TABLE DES MATIÈRES

|                                                                              |     |

|------------------------------------------------------------------------------|-----|

| DÉDICACE . . . . .                                                           | iii |

| REMERCIEMENTS . . . . .                                                      | iv  |

| RÉSUMÉ . . . . .                                                             | v   |

| ABSTRACT . . . . .                                                           | vii |

| TABLE DES MATIÈRES . . . . .                                                 | ix  |

| LISTE DES TABLEAUX . . . . .                                                 | xiv |

| LISTE DES FIGURES . . . . .                                                  | xv  |

| LISTE DES SIGLES ET ABRÉVIATIONS . . . . .                                   | xix |

| LISTE DES ANNEXES . . . . .                                                  | xxi |

| <br>                                                                         |     |

| CHAPITRE 1 INTRODUCTION . . . . .                                            | 1   |

| 1.1 Contexte et motivation . . . . .                                         | 1   |

| 1.2 Énoncé du problème . . . . .                                             | 4   |

| 1.3 Importance de la recherche et originalité . . . . .                      | 6   |

| 1.4 Objectifs de recherche et aperçu . . . . .                               | 7   |

| 1.4.1 <b>O-1</b> :Objectif principal . . . . .                               | 7   |

| 1.4.2 Objectifs spécifiques . . . . .                                        | 8   |

| 1.5 Impacts environnementaux et avantages économiques . . . . .              | 9   |

| 1.6 Publications et contributions aux objectifs de recherche . . . . .       | 10  |

| 1.6.1 Circuits intégrés fabriqués . . . . .                                  | 12  |

| 1.7 Organisation de la thèse . . . . .                                       | 13  |

| <br>                                                                         |     |

| CHAPITRE 2 REVUE DE LITTÉRATURE . . . . .                                    | 15  |

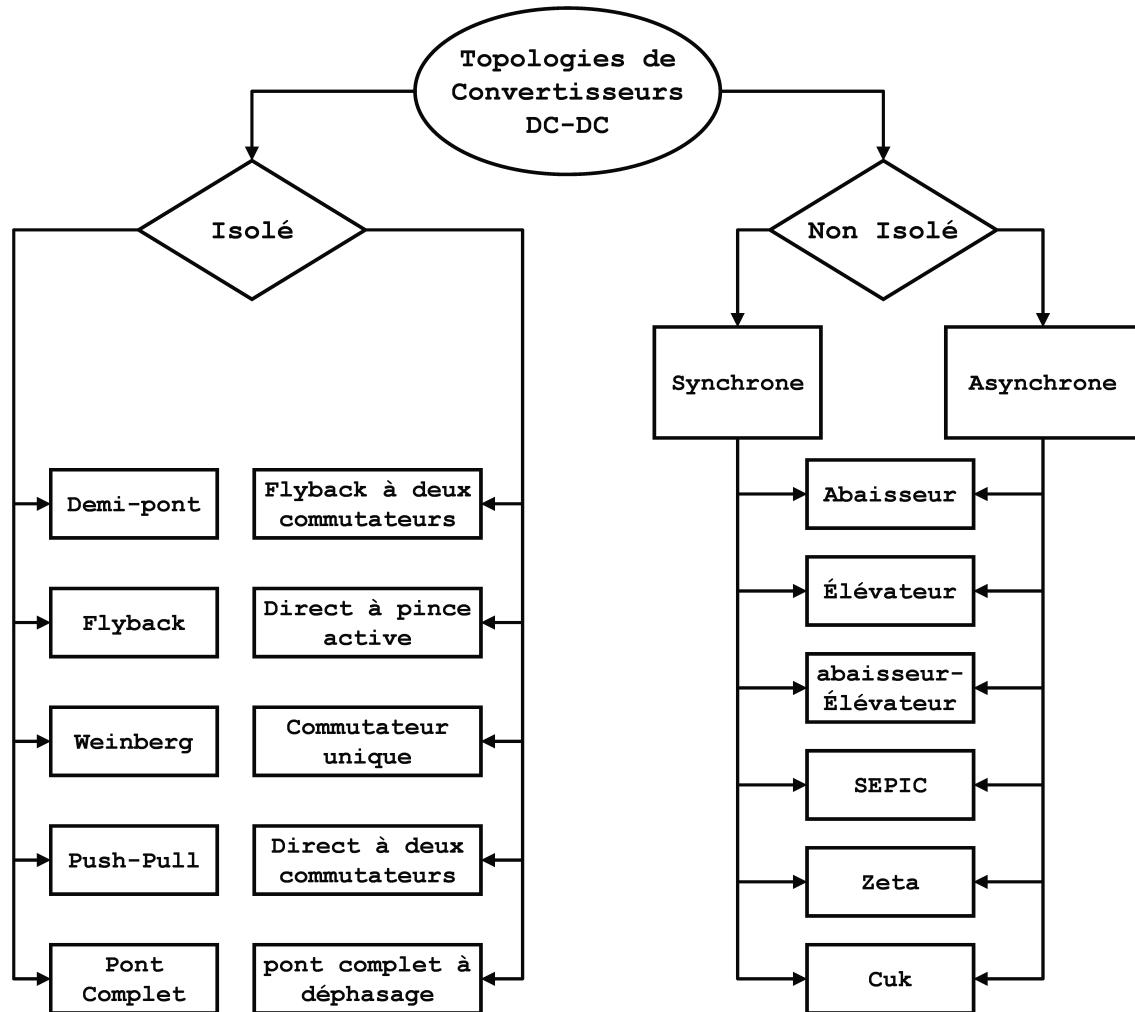

| 2.1 Classification architecturale des convertisseurs CC-CC . . . . .         | 16  |

| 2.1.1 Vue d'ensemble des types de convertisseurs CC-CC . . . . .             | 16  |

| 2.1.2 Classification par topologie . . . . .                                 | 17  |

| 2.2 Commande analogique vs. commande numérique pour les convertisseurs CC-CC | 21  |

| 2.2.1 Comparaison entre la commande analogique et la commande numérique      | 21  |

|                                                                                                                                      |                                                                          |           |

|--------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------|-----------|

| 2.2.2                                                                                                                                | Schémas de commande en boucle fermée . . . . .                           | 22        |

| 2.3                                                                                                                                  | Commande en mode tension vs. commande en mode courant . . . . .          | 23        |

| 2.3.1                                                                                                                                | Commande en mode tension . . . . .                                       | 23        |

| 2.3.2                                                                                                                                | Commande en mode courant . . . . .                                       | 26        |

| 2.3.3                                                                                                                                | Commande en mode courant . . . . .                                       | 26        |

| 2.3.4                                                                                                                                | Résumé de la comparaison . . . . .                                       | 29        |

| 2.3.5                                                                                                                                | Résumé comparatif . . . . .                                              | 30        |

| 2.4                                                                                                                                  | Contrôle PID et variantes avancées . . . . .                             | 31        |

| 2.4.1                                                                                                                                | Vue d'ensemble de la commande PID . . . . .                              | 31        |

| 2.4.2                                                                                                                                | Implémentations avancées de la commande PID . . . . .                    | 32        |

| 2.4.3                                                                                                                                | Améliorations récentes des convertisseurs CC-CC contrôlés par PID .      | 34        |

| 2.4.4                                                                                                                                | Types de compensateurs pour la stabilité et les performances . . . . .   | 35        |

| 2.5                                                                                                                                  | Techniques de commande avancées pour les convertisseurs CC-CC . . . . .  | 37        |

| 2.5.1                                                                                                                                | Commande par anticipation . . . . .                                      | 37        |

| 2.5.2                                                                                                                                | Commande en mode coulissant . . . . .                                    | 39        |

| 2.6                                                                                                                                  | Travaux les plus apparentés aux contributions de la thèse . . . . .      | 41        |

| 2.6.1                                                                                                                                | Modélisation des convertisseurs CC-CC . . . . .                          | 41        |

| 2.6.2                                                                                                                                | Commande basée sur le temps pour les convertisseurs CC-CC . . . .        | 42        |

| 2.6.3                                                                                                                                | Avancées dans les convertisseurs CC-CC basés sur la BVP . . . . .        | 43        |

| 2.7                                                                                                                                  | Capteurs thermiques et leur rôle dans les convertisseurs CC-CC . . . . . | 43        |

| 2.7.1                                                                                                                                | Besoin de capteurs thermiques dans les convertisseurs CC-CC . . . .      | 43        |

| 2.7.2                                                                                                                                | Impact de la température sur les composants des convertisseurs CC-CC     | 44        |

| 2.7.3                                                                                                                                | Stratégies de gestion thermique activées par les capteurs . . . . .      | 45        |

| 2.7.4                                                                                                                                | Étapes de calibration et d'intégration des capteurs thermiques . . . .   | 45        |

| 2.7.5                                                                                                                                | Applications dans la gestion thermique dynamique . . . . .               | 46        |

| 2.7.6                                                                                                                                | Conclusion et perspectives . . . . .                                     | 46        |

| <b>CHAPITRE 3 ARTICLE 1 : A HIGH EFFICIENCY AND FAST RESPONSE PLL<br/>BASED BUCK CONVERTER : IMPLEMENTATION AND SIMULATION . . .</b> |                                                                          | <b>47</b> |

| 3.1                                                                                                                                  | Abstract . . . . .                                                       | 47        |

| 3.2                                                                                                                                  | Introduction . . . . .                                                   | 47        |

| 3.3                                                                                                                                  | Proposed PLL Based Buck Converter . . . . .                              | 48        |

| 3.4                                                                                                                                  | PWM Controller . . . . .                                                 | 50        |

| 3.4.1                                                                                                                                | PWM Topology . . . . .                                                   | 50        |

| 3.4.2                                                                                                                                | Voltage Controlled Delay Line . . . . .                                  | 51        |

| 3.5                                                                                                                                  | Simulation Results . . . . .                                             | 54        |

|                                                                                                                                             |     |

|---------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 3.6 Conclusion . . . . .                                                                                                                    | 56  |

| <br>                                                                                                                                        |     |

| CHAPITRE 4 ARTICLE 2 : A SYSTEMATIC APPROACH FOR PLL-BASED ZETA POWER CONVERTER CONTROL . . . . .                                           | 57  |

| 4.1 Abstract . . . . .                                                                                                                      | 57  |

| 4.2 Introduction . . . . .                                                                                                                  | 57  |

| 4.3 Background Information . . . . .                                                                                                        | 59  |

| 4.4 Power Stage Analysis of the Zeta Converter . . . . .                                                                                    | 62  |

| 4.4.1 Power Stage Transfer Function . . . . .                                                                                               | 62  |

| 4.4.2 Effects of Parasitic Resistances . . . . .                                                                                            | 63  |

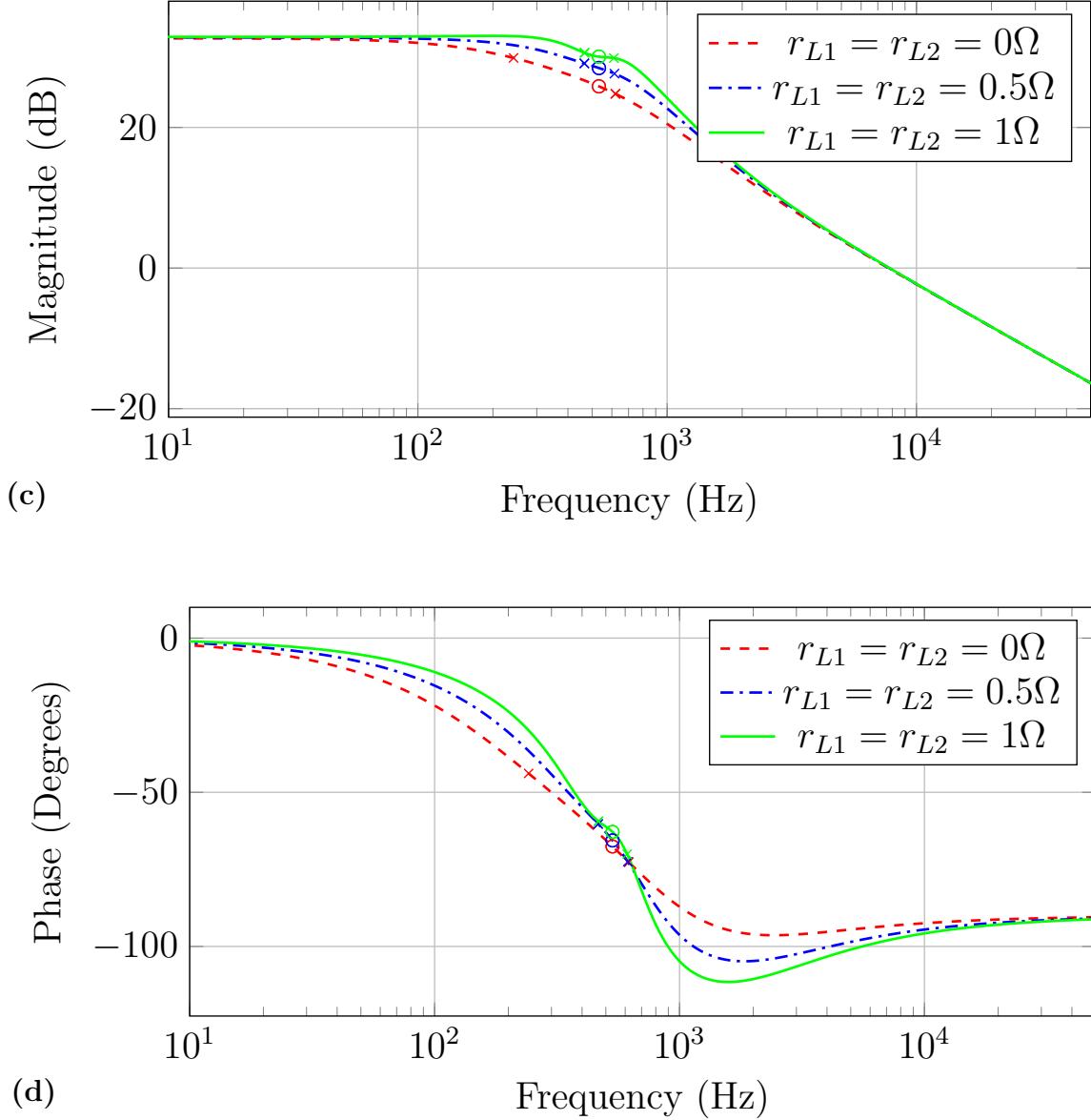

| 4.5 PLL-Based Controller . . . . .                                                                                                          | 65  |

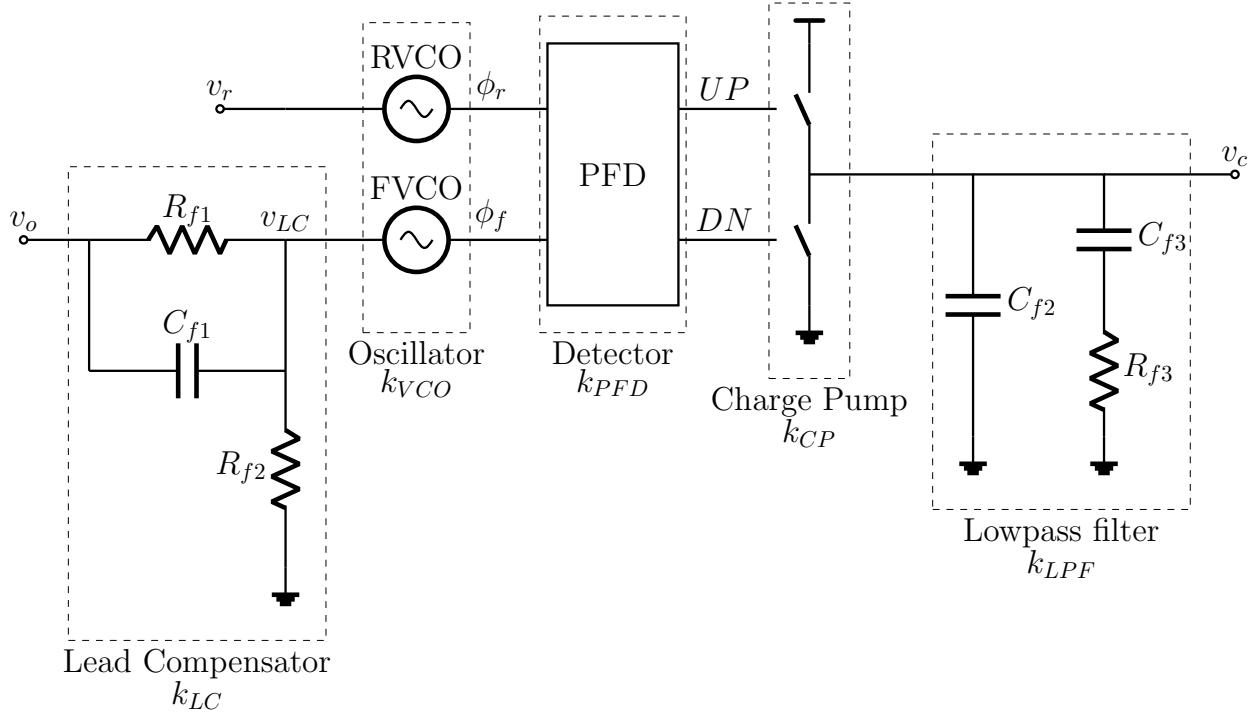

| 4.5.1 Circuit Implementation . . . . .                                                                                                      | 69  |

| 4.6 Phase Margin Graphical Approach . . . . .                                                                                               | 72  |

| 4.7 Experimental Setup and Measurement Results . . . . .                                                                                    | 72  |

| 4.7.1 Parameter Selection and Transfer Function . . . . .                                                                                   | 73  |

| 4.7.2 Experimental Setup . . . . .                                                                                                          | 76  |

| 4.7.3 Measurement Results . . . . .                                                                                                         | 78  |

| 4.8 Conclusion . . . . .                                                                                                                    | 88  |

| <br>                                                                                                                                        |     |

| CHAPITRE 5 Intégration des modèles thermiques dans les convertisseurs CC-CC pour une conception sensible à la température . . . . .         | 90  |

| 5.1 Introduction . . . . .                                                                                                                  | 90  |

| 5.2 Capteurs thermiques pour gérer l'incertitude et les variations de température . . . . .                                                 | 91  |

| 5.2.1 Gestion thermique dans les convertisseurs CC-CC . . . . .                                                                             | 92  |

| 5.2.2 Gestion thermique des inducteurs . . . . .                                                                                            | 94  |

| 5.3 Travail expérimental : analyse du diagramme de Bode avec variations de température . . . . .                                            | 96  |

| 5.3.1 Analyse des marges de gain et de phase . . . . .                                                                                      | 97  |

| 5.4 Analyse de la réponse temporelle . . . . .                                                                                              | 99  |

| 5.4.1 Scénario optimal . . . . .                                                                                                            | 100 |

| 5.4.2 Pire scénario . . . . .                                                                                                               | 101 |

| 5.4.3 Impact des variations sur les performances du système . . . . .                                                                       | 102 |

| 5.5 Conclusion . . . . .                                                                                                                    | 103 |

| <br>                                                                                                                                        |     |

| CHAPITRE 6 ARTICLE 3 : INVESTIGATION OF DIFFERENT INTEGRATED TEMPERATURE MONITORING SENSORS FOR HIGH-VOLTAGE SOC DC-DC CONVERTERS . . . . . | 104 |

|                                                                                                                                       |                                                                                                     |     |

|---------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------|-----|

| 6.1                                                                                                                                   | Abstract . . . . .                                                                                  | 104 |

| 6.2                                                                                                                                   | Introduction . . . . .                                                                              | 104 |

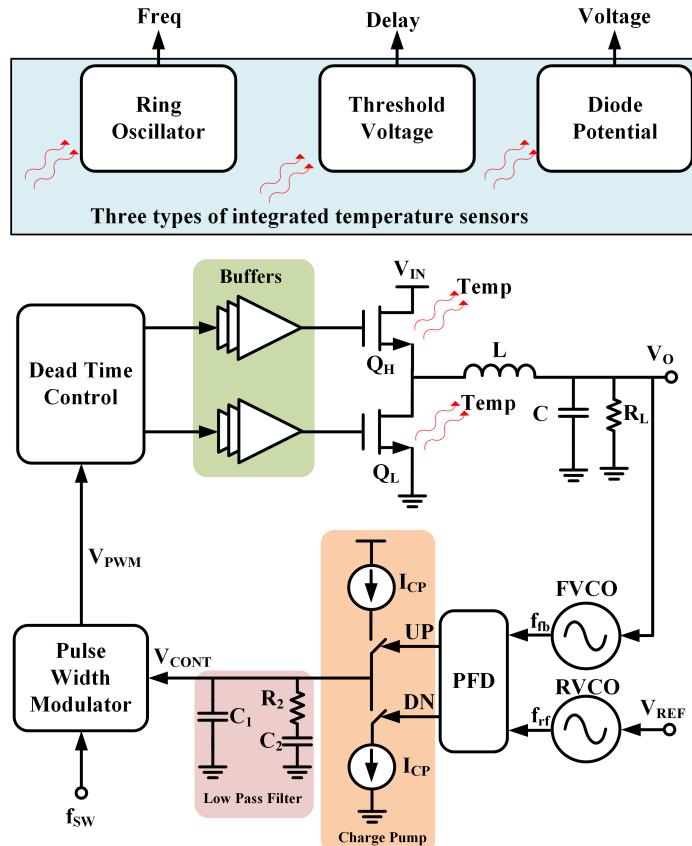

| 6.3                                                                                                                                   | Phase-Locked Loop-based Buck Converter . . . . .                                                    | 106 |

| 6.3.1                                                                                                                                 | System Overview . . . . .                                                                           | 106 |

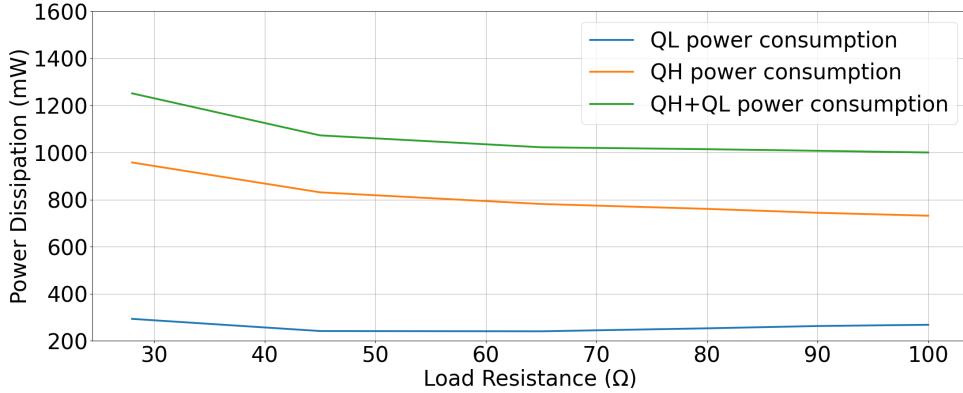

| 6.3.2                                                                                                                                 | Power Dissipation . . . . .                                                                         | 107 |

| 6.4                                                                                                                                   | On-chip Thermal Monitoring Techniques . . . . .                                                     | 108 |

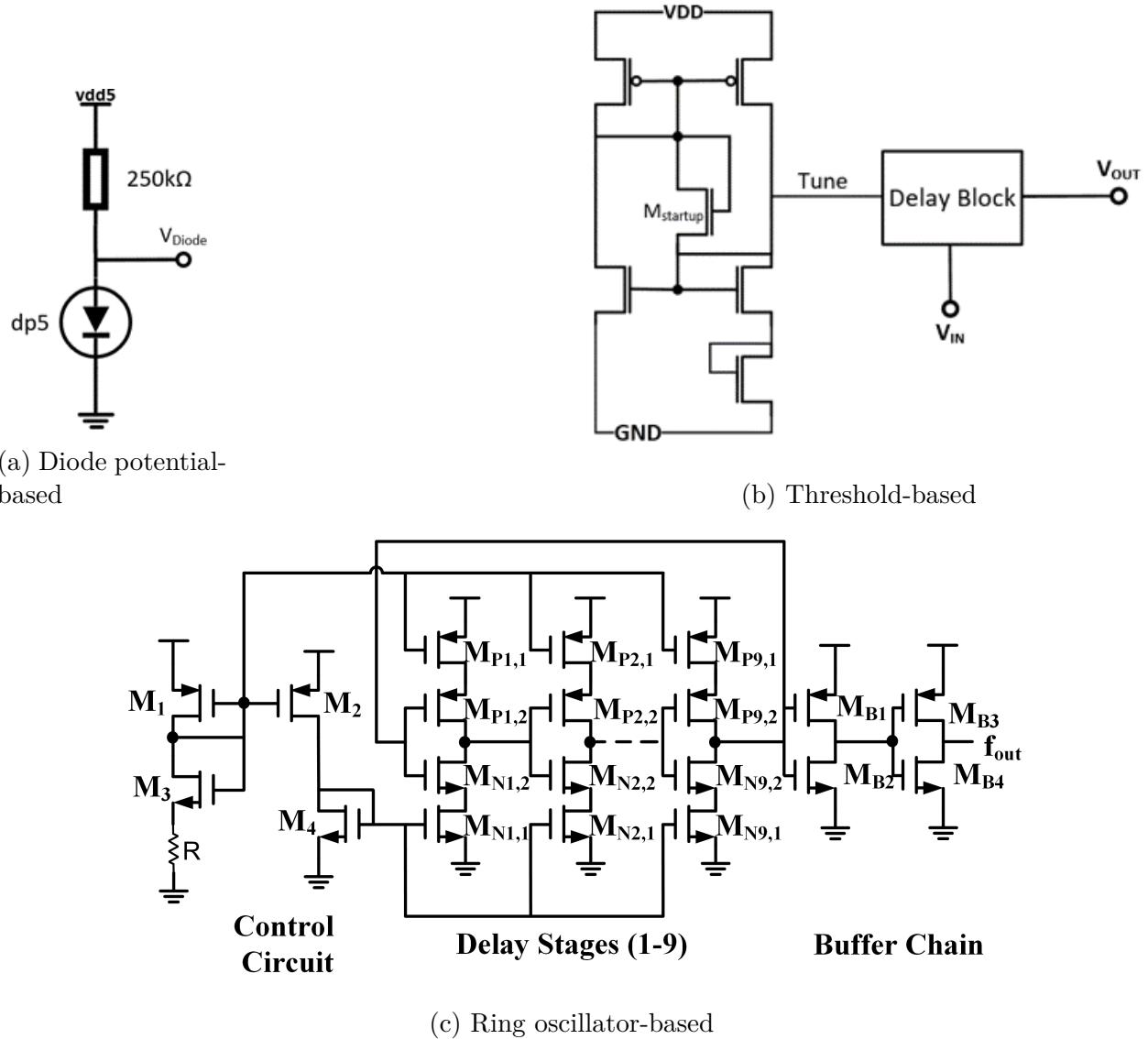

| 6.4.1                                                                                                                                 | Diode Potential-based Temperature Sensor . . . . .                                                  | 108 |

| 6.4.2                                                                                                                                 | Threshold Voltage-based Temperature Sensor . . . . .                                                | 108 |

| 6.4.3                                                                                                                                 | Ring Oscillator-based Temperature Sensor . . . . .                                                  | 109 |

| 6.4.4                                                                                                                                 | Temperature Readings . . . . .                                                                      | 110 |

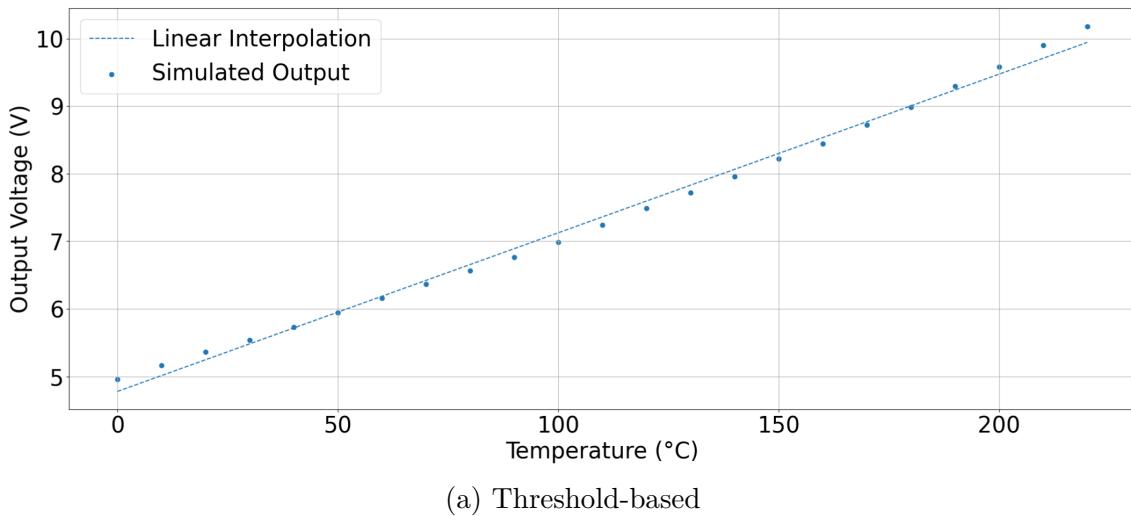

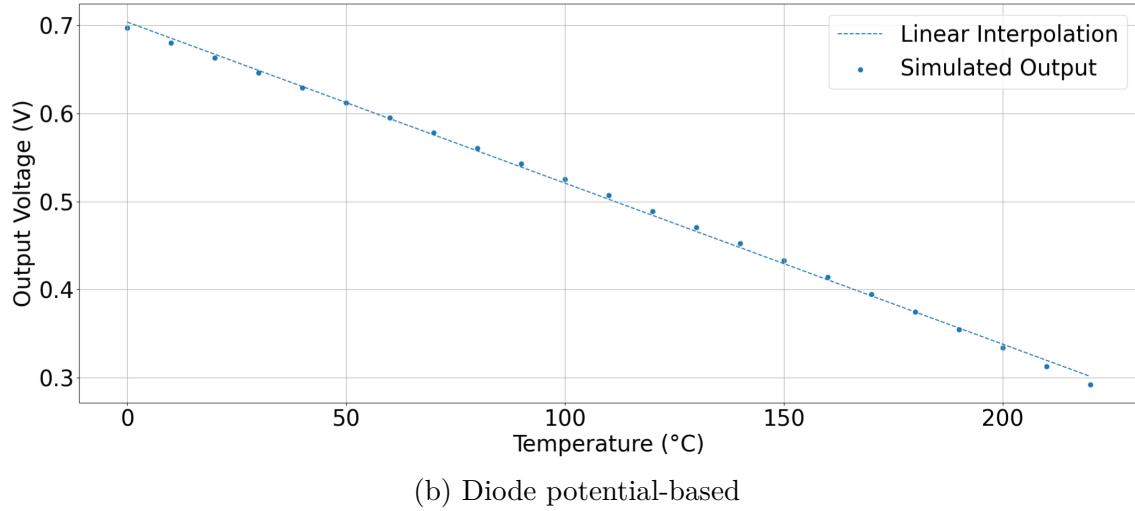

| 6.5                                                                                                                                   | Simulation Results . . . . .                                                                        | 110 |

| 6.6                                                                                                                                   | Conclusion . . . . .                                                                                | 113 |

| <br>CHAPITRE 7 ARTICLE 4 : CALIBRATION OF RING OSCILLATOR-BASED INTEGRATED TEMPERATURE SENSORS FOR POWER MANAGEMENT SYSTEMS . . . . . |                                                                                                     | 115 |

| 7.1                                                                                                                                   | Abstract . . . . .                                                                                  | 115 |

| 7.2                                                                                                                                   | Introduction . . . . .                                                                              | 115 |

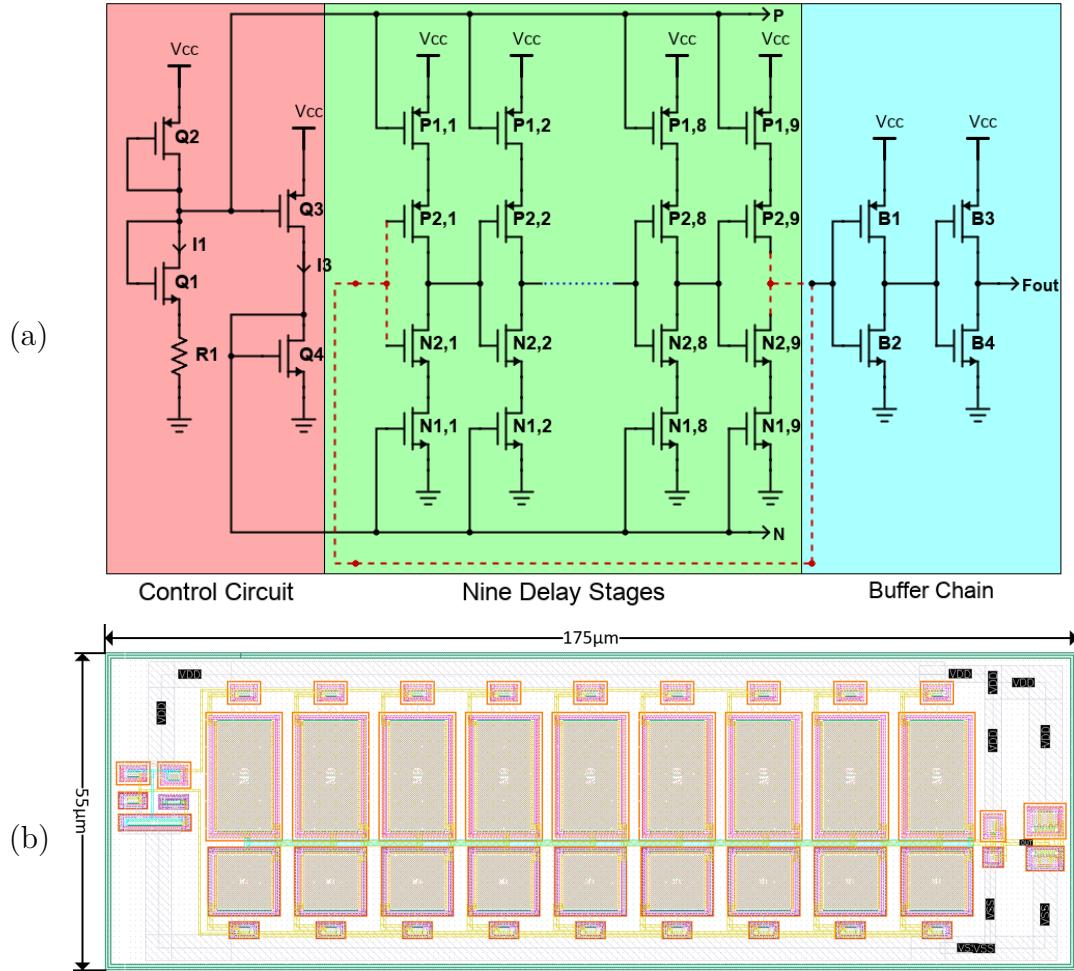

| 7.3                                                                                                                                   | Ring Oscillator-based Temperature Sensor : Design, Implementation and Evaluation Criteria . . . . . | 119 |

| 7.3.1                                                                                                                                 | Design and Implementation : . . . . .                                                               | 119 |

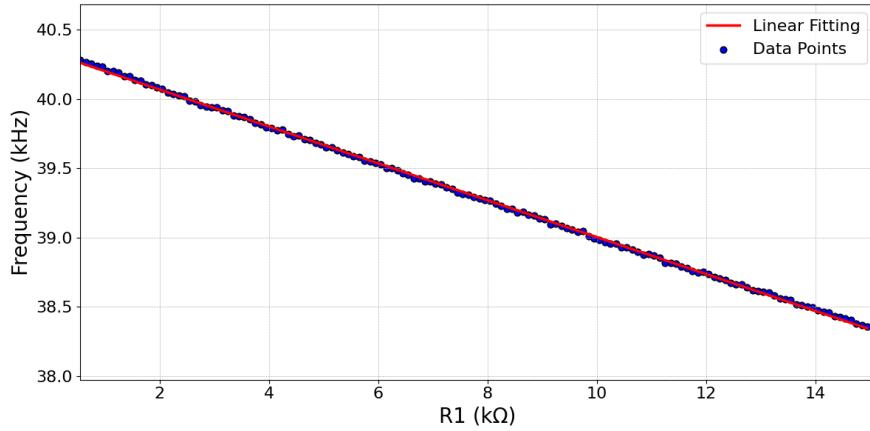

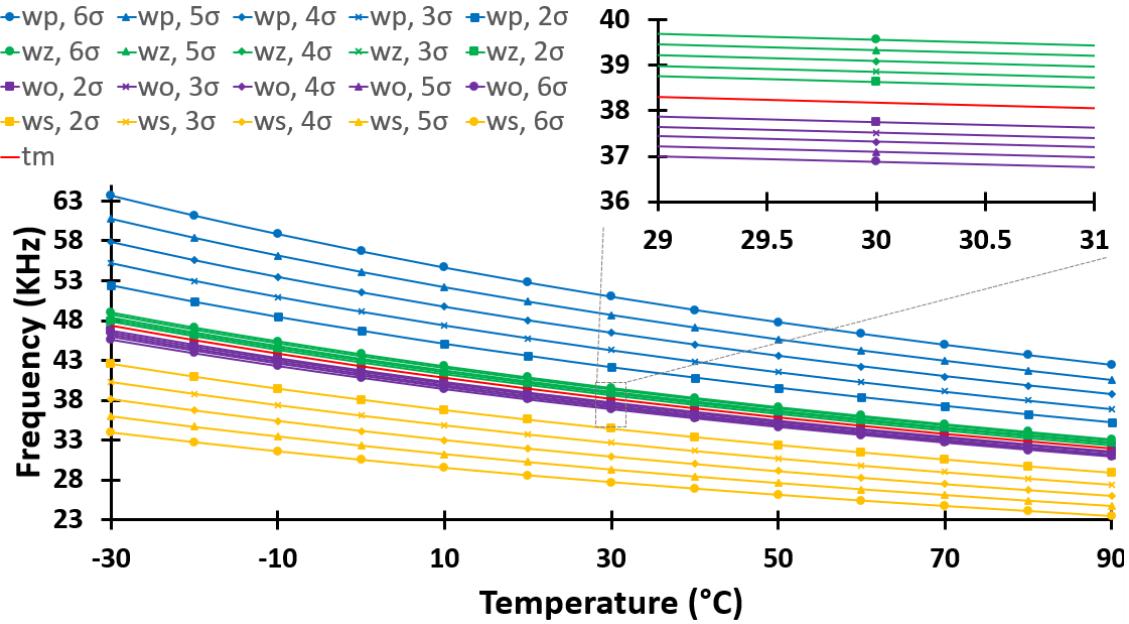

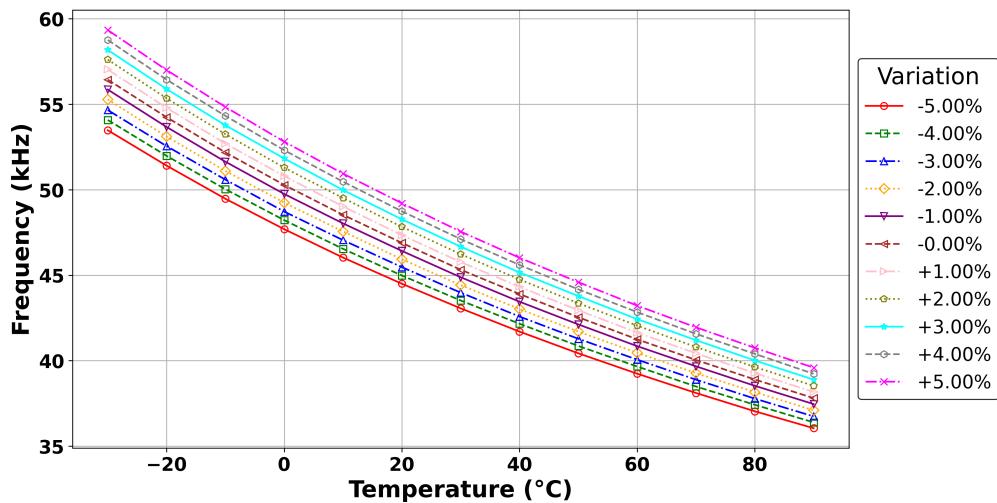

| 7.3.2                                                                                                                                 | Evaluation Criteria : . . . . .                                                                     | 123 |

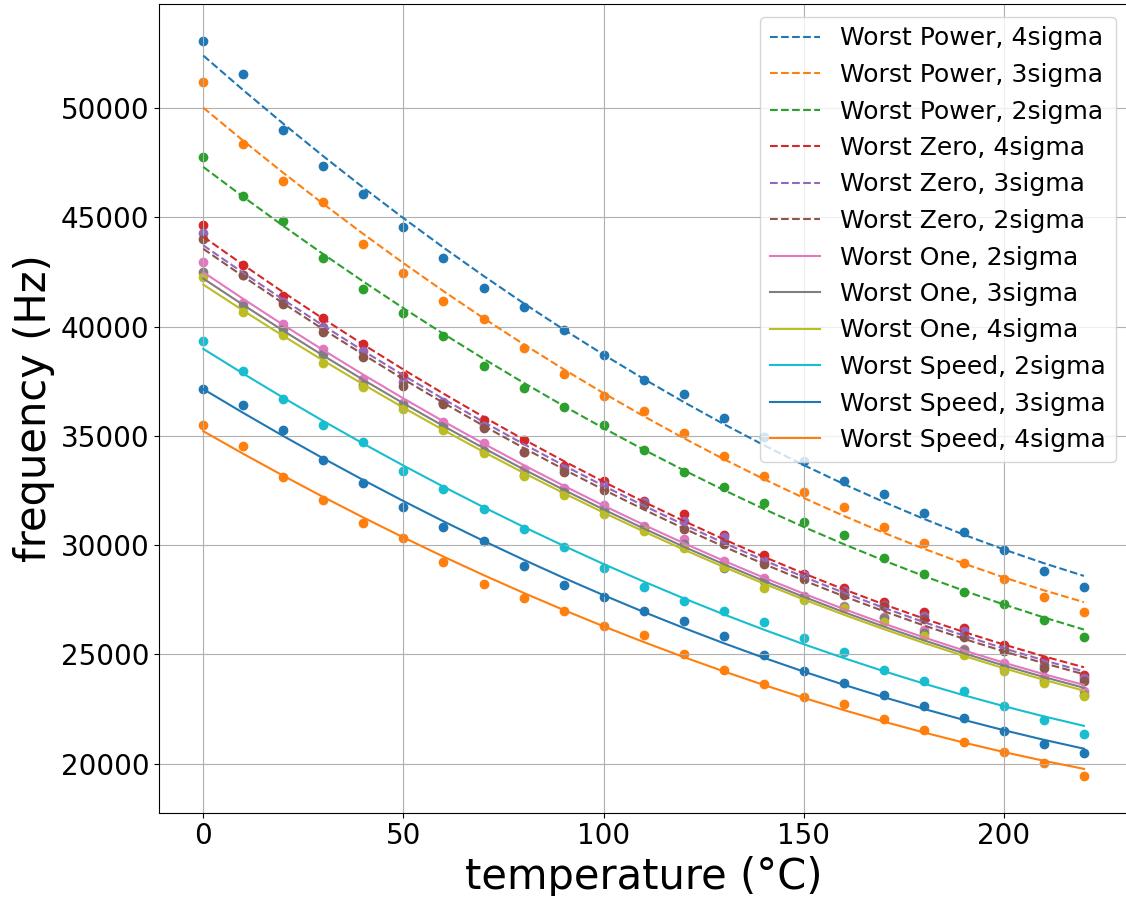

| 7.4                                                                                                                                   | Experimental Setup and Measurement Results . . . . .                                                | 127 |

| 7.4.1                                                                                                                                 | Chip Testbench and Measurements . . . . .                                                           | 127 |

| 7.4.2                                                                                                                                 | Evaluation Criteria . . . . .                                                                       | 129 |

| 7.4.3                                                                                                                                 | Fitting & Measurement Results . . . . .                                                             | 130 |

| 7.5                                                                                                                                   | Conclusion . . . . .                                                                                | 136 |

| <br>CHAPITRE 8 DISCUSSION . . . . .                                                                                                   |                                                                                                     | 137 |

| 8.1                                                                                                                                   | Atteinte des objectifs de recherche . . . . .                                                       | 137 |

| 8.1.1                                                                                                                                 | Conception et développement de contrôleurs BVP pour les convertisseurs abaisseur et Zeta . . . . .  | 137 |

| 8.1.2                                                                                                                                 | Modélisation des composants clés des convertisseurs pour une précision améliorée . . . . .          | 138 |

| 8.1.3                                                                                                                                 | Validation expérimentale et comparaison des performances des convertisseurs . . . . .               | 138 |

|                                 |                                                                                                                     |     |

|---------------------------------|---------------------------------------------------------------------------------------------------------------------|-----|

| 8.1.4                           | Intégration et utilisation de capteurs de température en temps réel pour une gestion thermique adaptative . . . . . | 139 |

| 8.2                             | Implications et importance . . . . .                                                                                | 139 |

| 8.3                             | Comparaison avec la littérature existante . . . . .                                                                 | 140 |

| 8.4                             | Limitations et perspectives de travaux futurs . . . . .                                                             | 141 |

| 8.4.1                           | Intégration systémique et modélisation thermique . . . . .                                                          | 141 |

| 8.4.2                           | Développement d'un contrôleur sensible à la température . . . . .                                                   | 142 |

| 8.4.3                           | Élargissement des applications du contrôleur . . . . .                                                              | 142 |

| 8.4.4                           | Commande par anticipation . . . . .                                                                                 | 143 |

| 8.4.5                           | Conception de convertisseurs en cascade . . . . .                                                                   | 143 |

| CHAPITRE 9 CONCLUSION . . . . . |                                                                                                                     | 144 |

| 9.1                             | Résumé des points principaux . . . . .                                                                              | 144 |

| 9.2                             | Rappel des objectifs de recherche . . . . .                                                                         | 145 |

| 9.3                             | Validation des hypothèses . . . . .                                                                                 | 146 |

| 9.4                             | Synthèse avec les discussions . . . . .                                                                             | 147 |

| 9.5                             | Importance et contribution au domaine . . . . .                                                                     | 148 |

| 9.6                             | Déclaration de clôture . . . . .                                                                                    | 149 |

| 9.7                             | Diffusion des connaissances . . . . .                                                                               | 150 |

| RÉFÉRENCES . . . . .            |                                                                                                                     | 153 |

| ANNEXE . . . . .                |                                                                                                                     | 171 |

## LISTE DES TABLEAUX

## LISTE DES FIGURES

|             |                                                                                                                                  |    |

|-------------|----------------------------------------------------------------------------------------------------------------------------------|----|

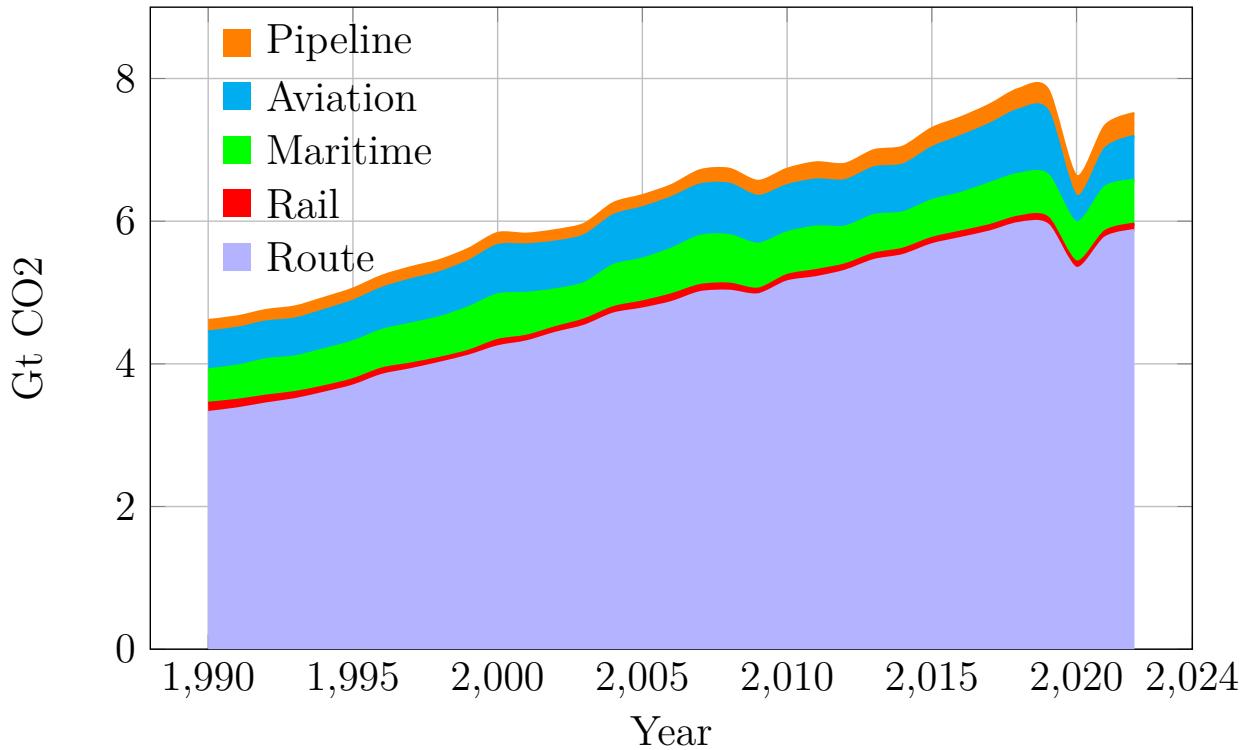

| Figure 1.1  | Émissions mondiales de CO <sub>2</sub> par secteur (1990-2030) . . . . .                                                         | 2  |

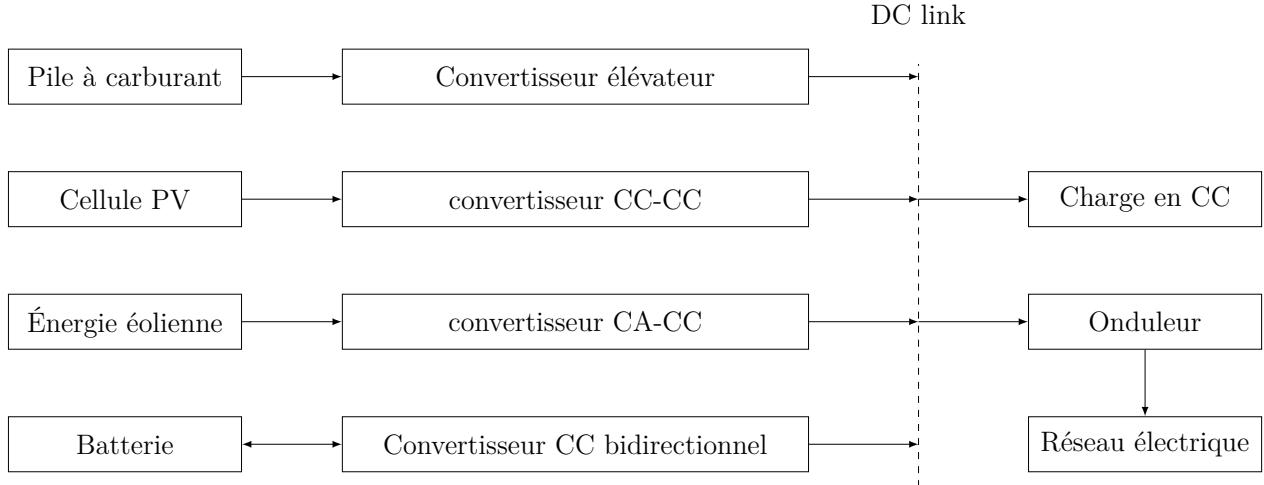

| Figure 1.2  | Système énergétique hybride avec interface de batterie . . . . .                                                                 | 3  |

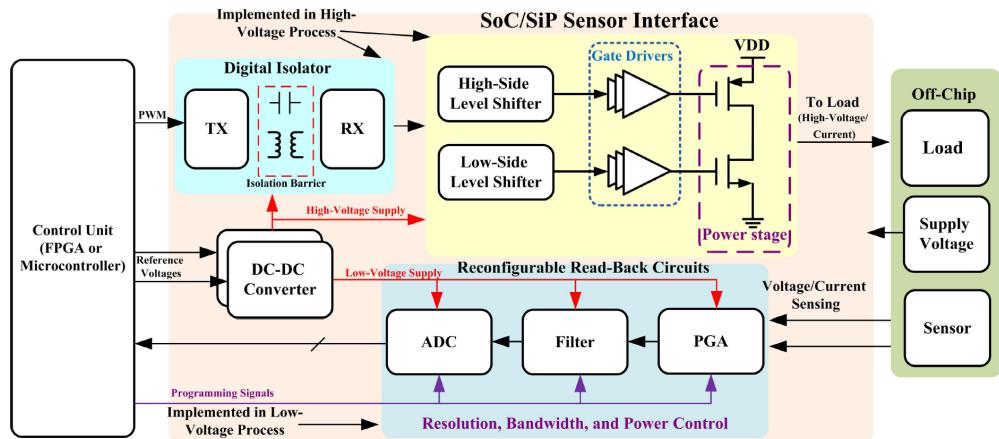

| Figure 1.3  | Schéma fonctionnel de l'interface polyvalente du capteur SsP/SdB où le convertisseur CC-CC a été implanté, tiré de [1] . . . . . | 4  |

| Figure 2.1  | Classification des convertisseurs CC-CC. . . . .                                                                                 | 18 |

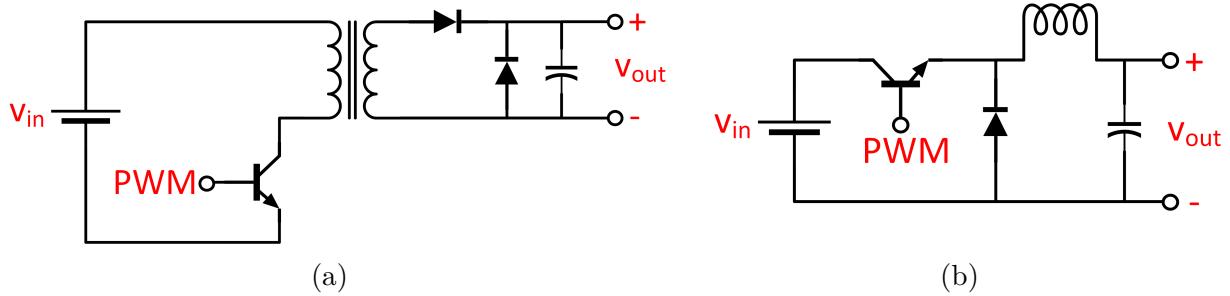

| Figure 2.2  | Exemples de circuits avec topologies isolée (a) et non isolée (b). . . . .                                                       | 19 |

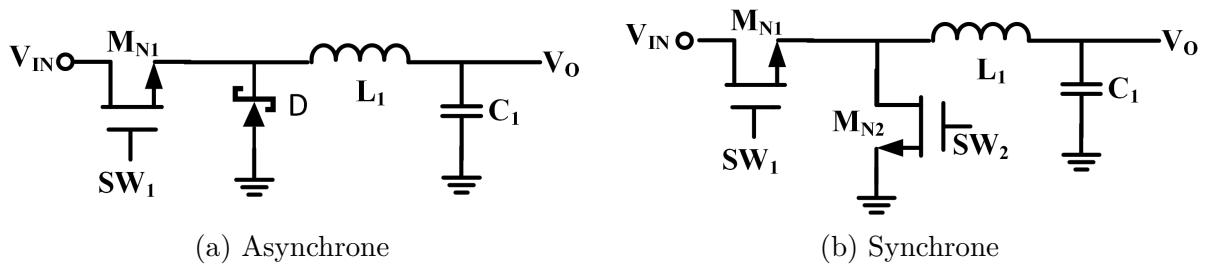

| Figure 2.3  | Topologie asynchrone (a) et implémentation en topologie synchrone (b). . . . .                                                   | 20 |

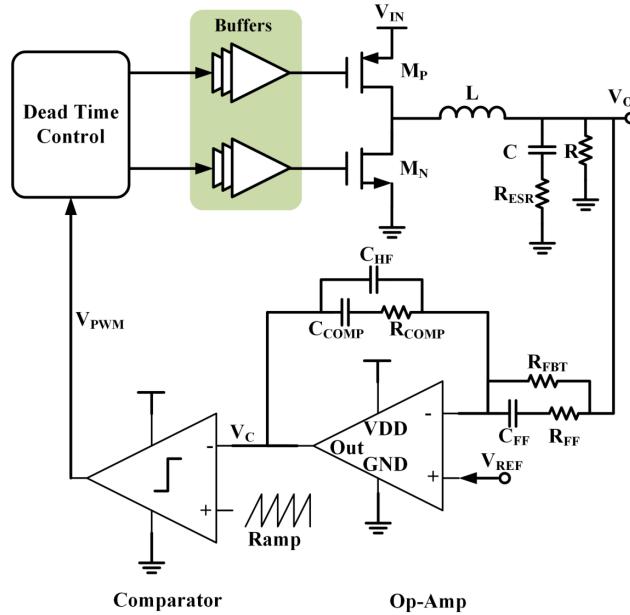

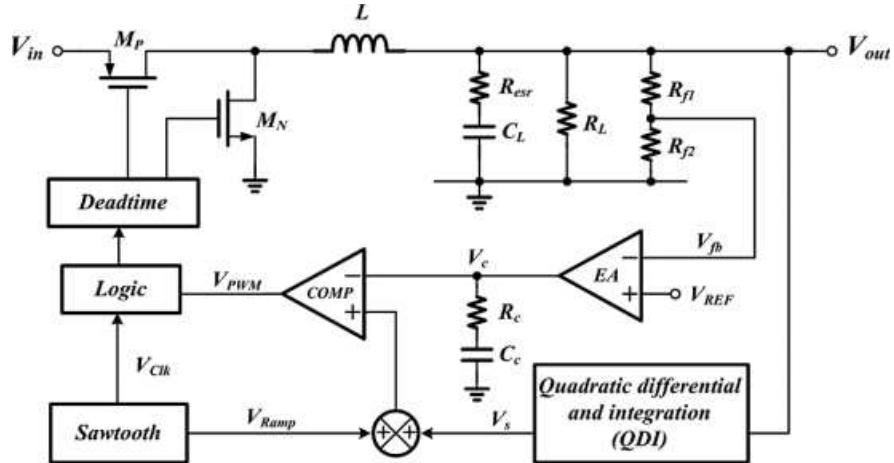

| Figure 2.4  | Schéma de commande en mode tension pour un abaisseur. . . . .                                                                    | 25 |

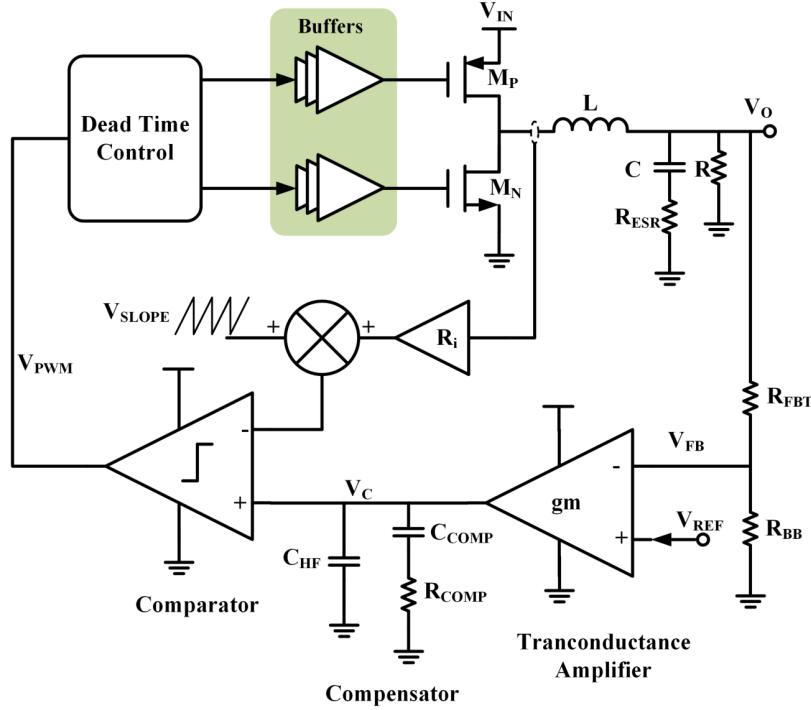

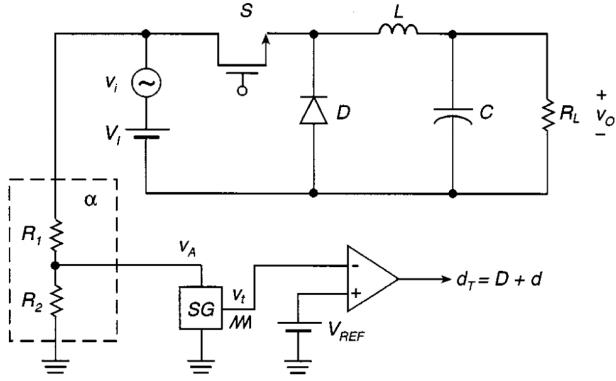

| Figure 2.5  | Schéma de commande en mode courant pour un Buck. . . . .                                                                         | 29 |

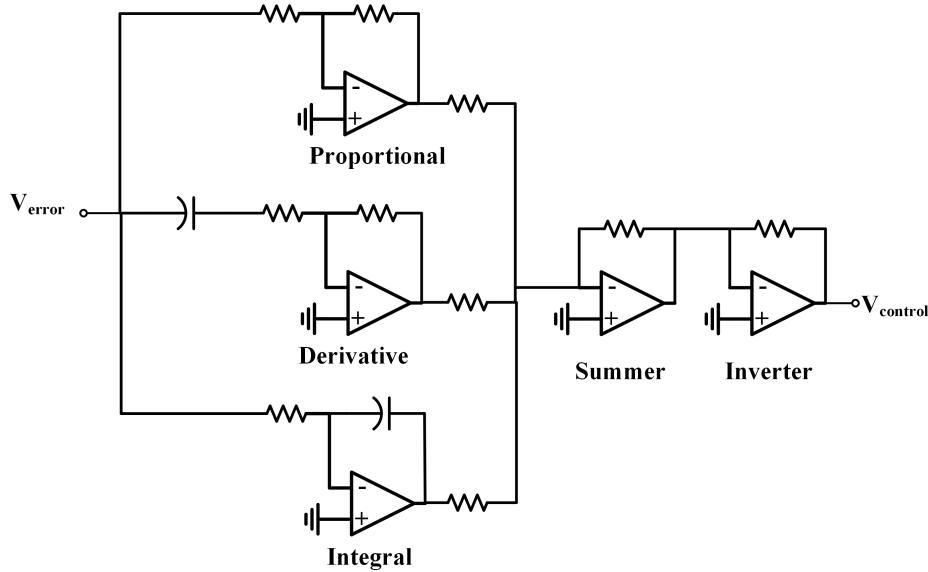

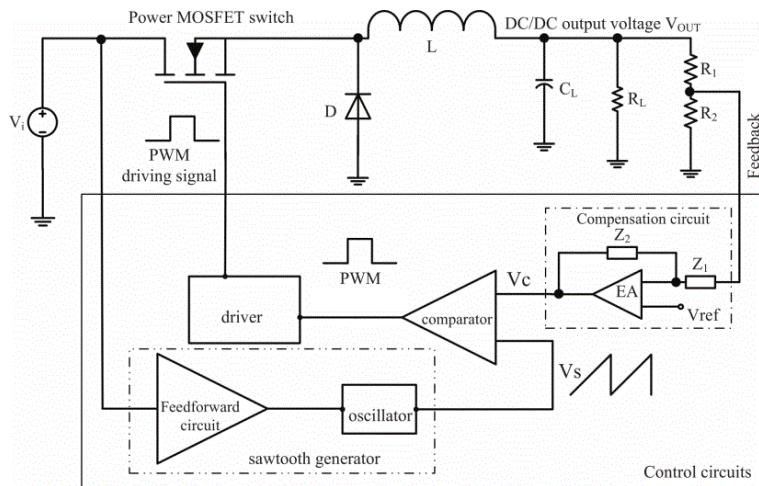

| Figure 2.6  | Schéma générique d'un contrôleur PID. . . . .                                                                                    | 32 |

| Figure 2.7  | Diagramme du circuit PID basé sur AOT. . . . .                                                                                   | 33 |

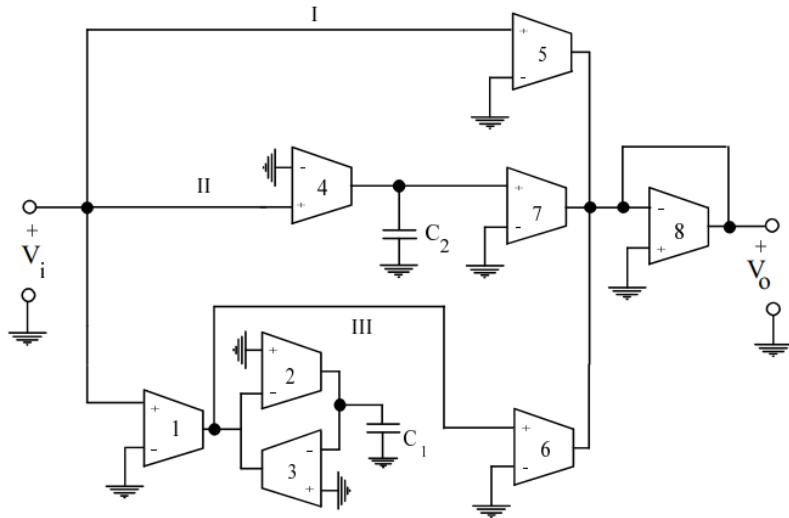

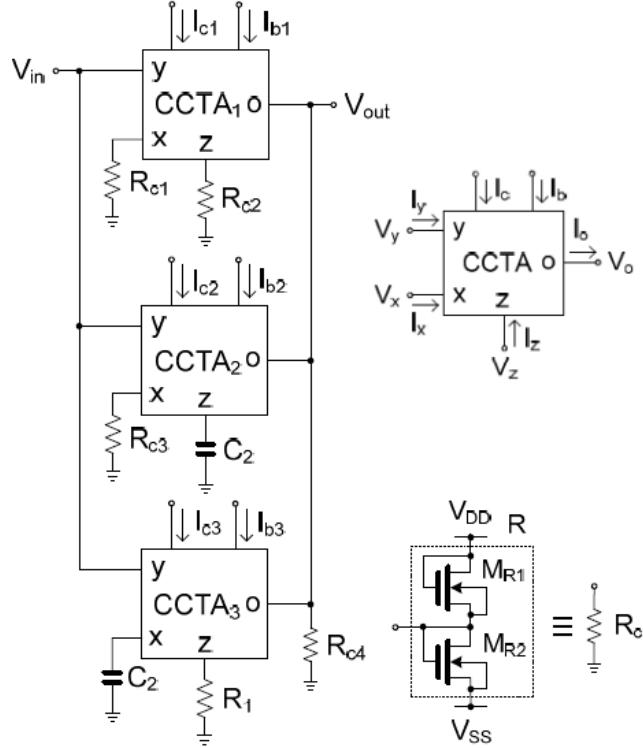

| Figure 2.8  | Contrôleur PID programmable utilisant un ATCC. . . . .                                                                           | 34 |

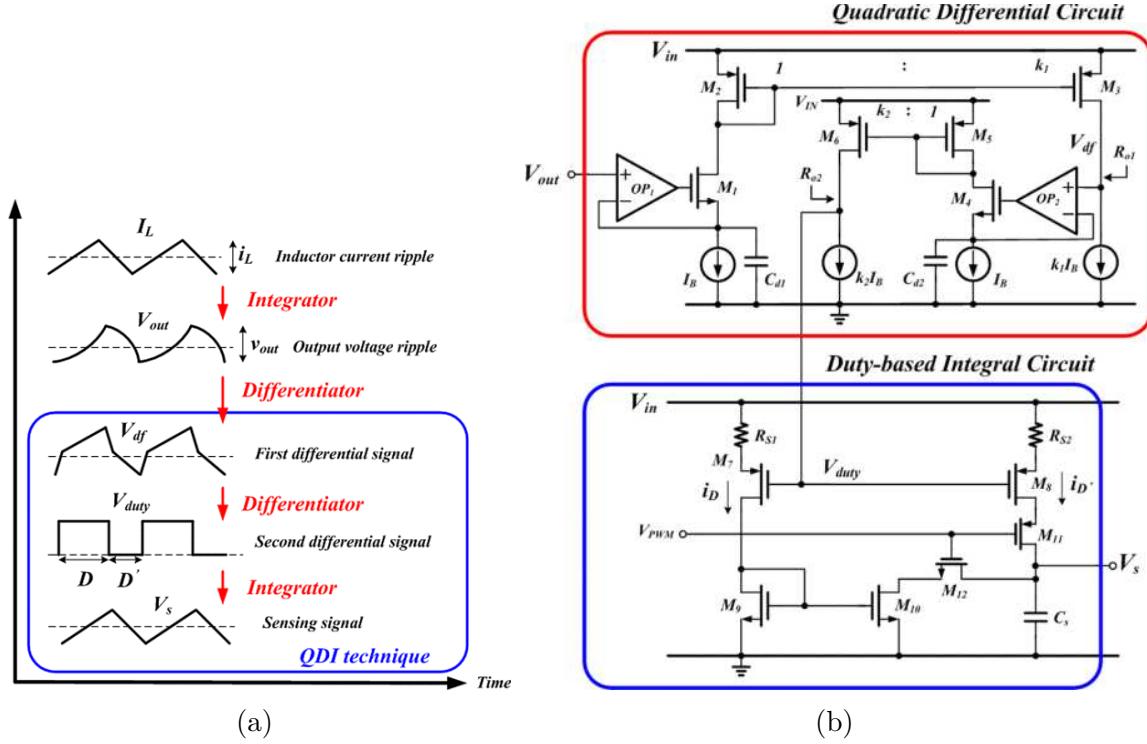

| Figure 2.9  | Concept DQI (a) et implémentation circuit (b). . . . .                                                                           | 35 |

| Figure 2.10 | Diagramme de blocs avec DQI. . . . .                                                                                             | 35 |

| Figure 2.11 | Commande par anticipation en boucle ouverte pour un convertisseur abaisseur. . . . .                                             | 38 |

| Figure 2.12 | Commande par anticipation en boucle fermée pour un convertisseur abaisseur. . . . .                                              | 38 |

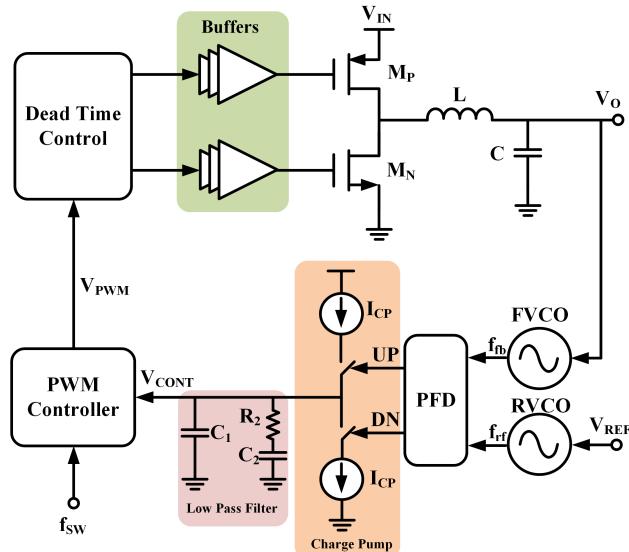

| Figure 3.1  | Block diagram of the proposed PLL based buck converter. . . . .                                                                  | 49 |

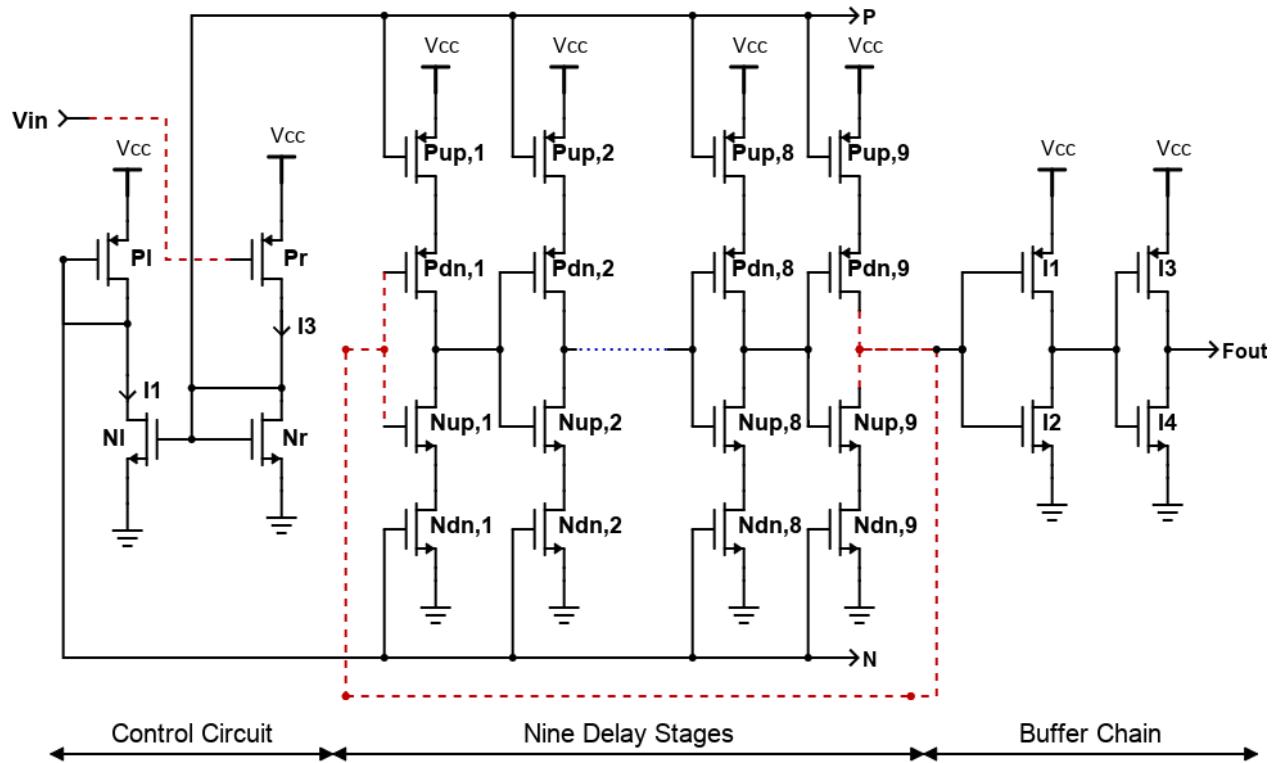

| Figure 3.2  | Current starved VCO circuit implementation used in FVCO and RVCO. . . . .                                                        | 50 |

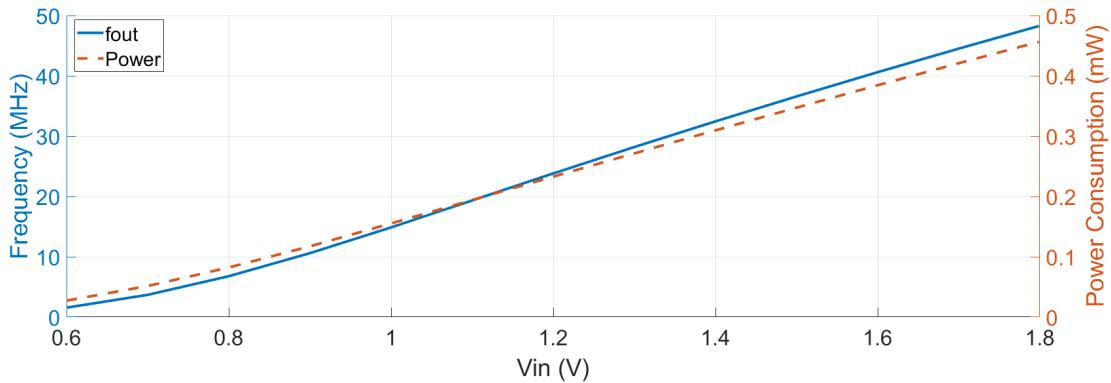

| Figure 3.3  | Linear Voltage - Frequency relation of the current starved VCO. . . . .                                                          | 50 |

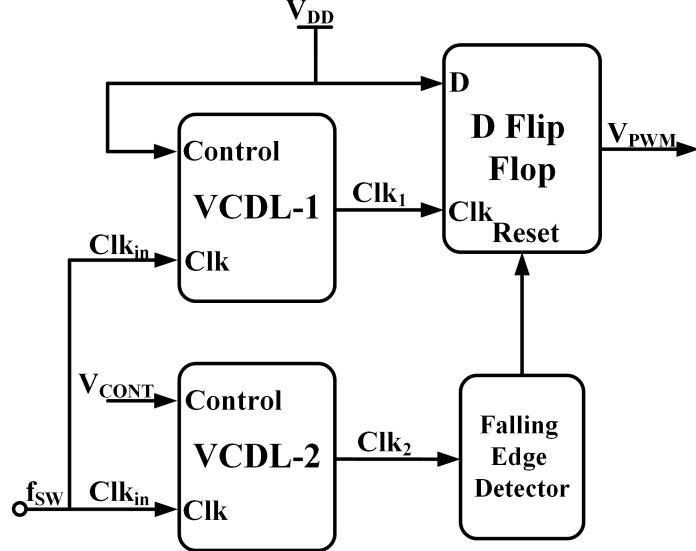

| Figure 3.4  | Block diagram of the proposed PWM. . . . .                                                                                       | 51 |

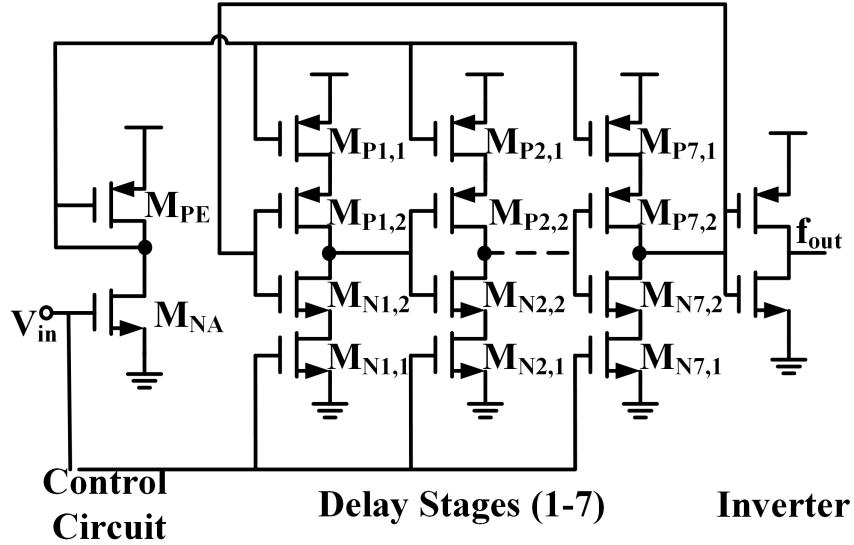

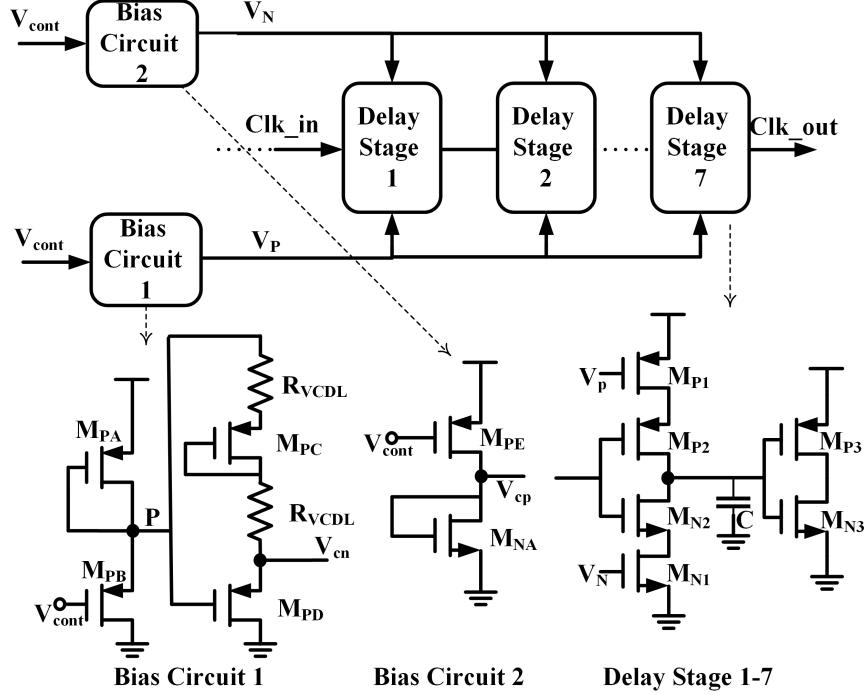

| Figure 3.5  | Block diagram of the VCDL and the circuit implementation of the building blocks. . . . .                                         | 52 |

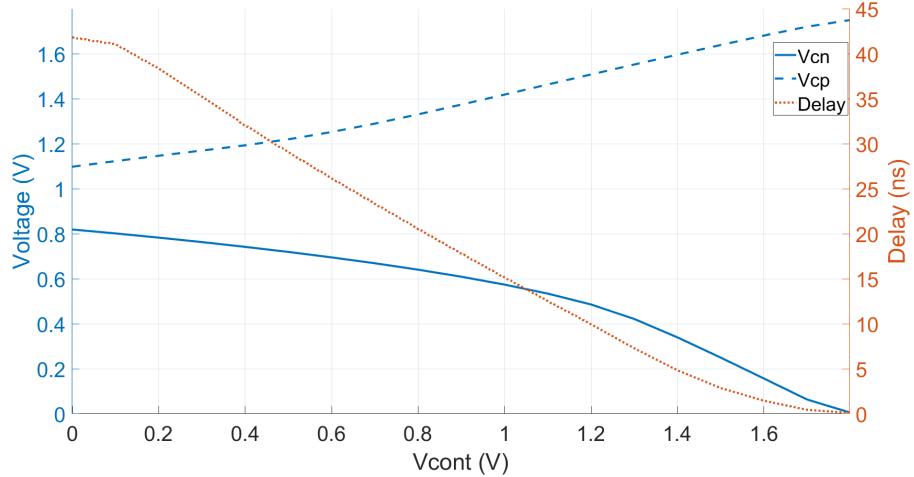

| Figure 3.6  | The generated bias voltages that provide a linear delay for each VCDL stage. . . . .                                             | 53 |

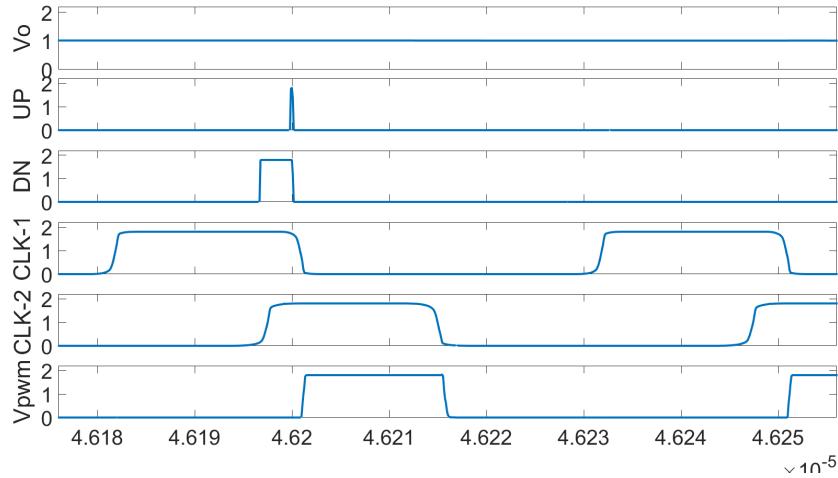

| Figure 3.7  | Steady state performance of the proposed converter for $V_{ref} = 1V$ . . . . .                                                  | 53 |

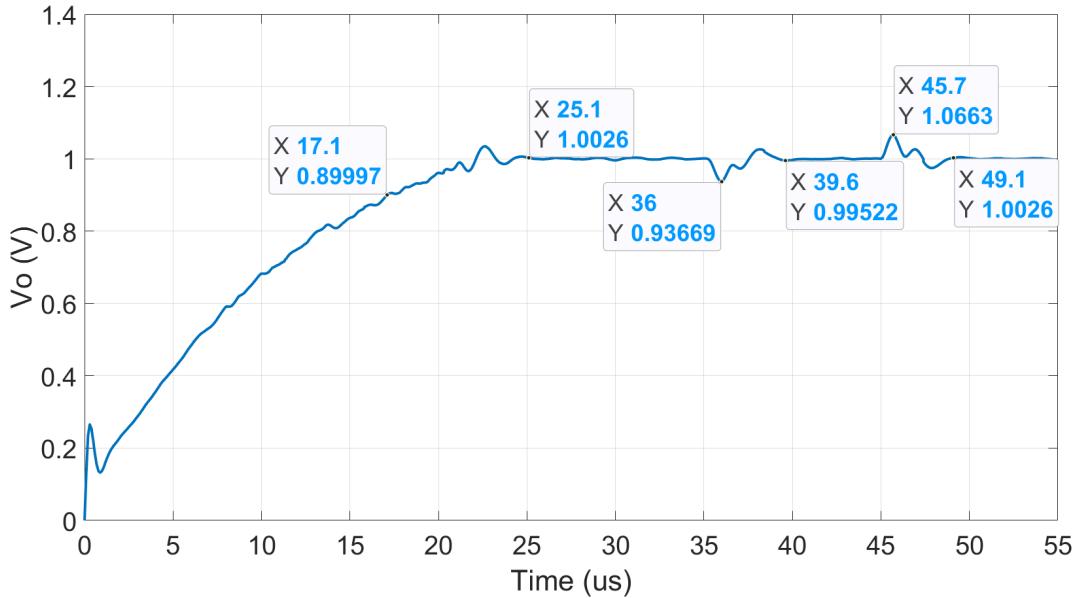

| Figure 3.8  | System transient response to step current increase (at t=35μS) and step current decrease (at t=45μS) of 0.4A. . . . .            | 54 |

| Figure 3.9  | Simulated system efficiency over wide range of reference voltages and load currents. . . . .                                     | 55 |

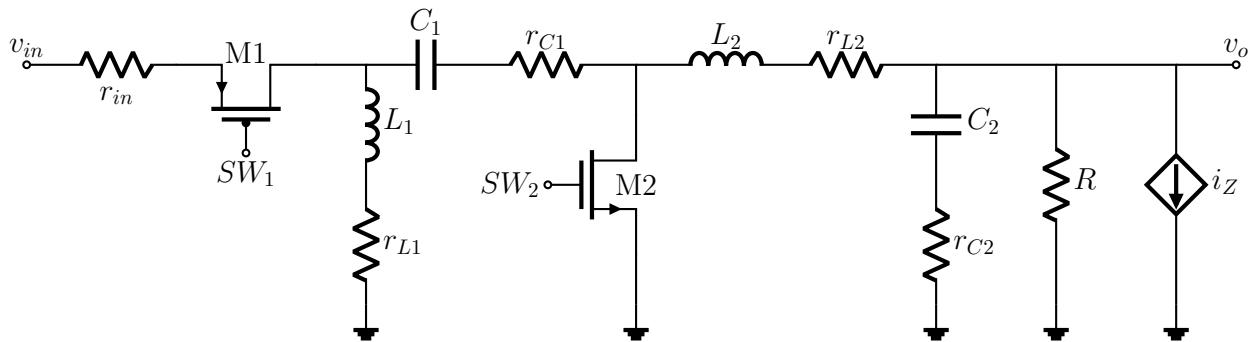

| Figure 4.1  | Zeta converter circuit used in the steady-state average technique. . . . .                                                       | 62 |

|             |                                                                                                                                                                                                                                                                                                                               |    |

|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

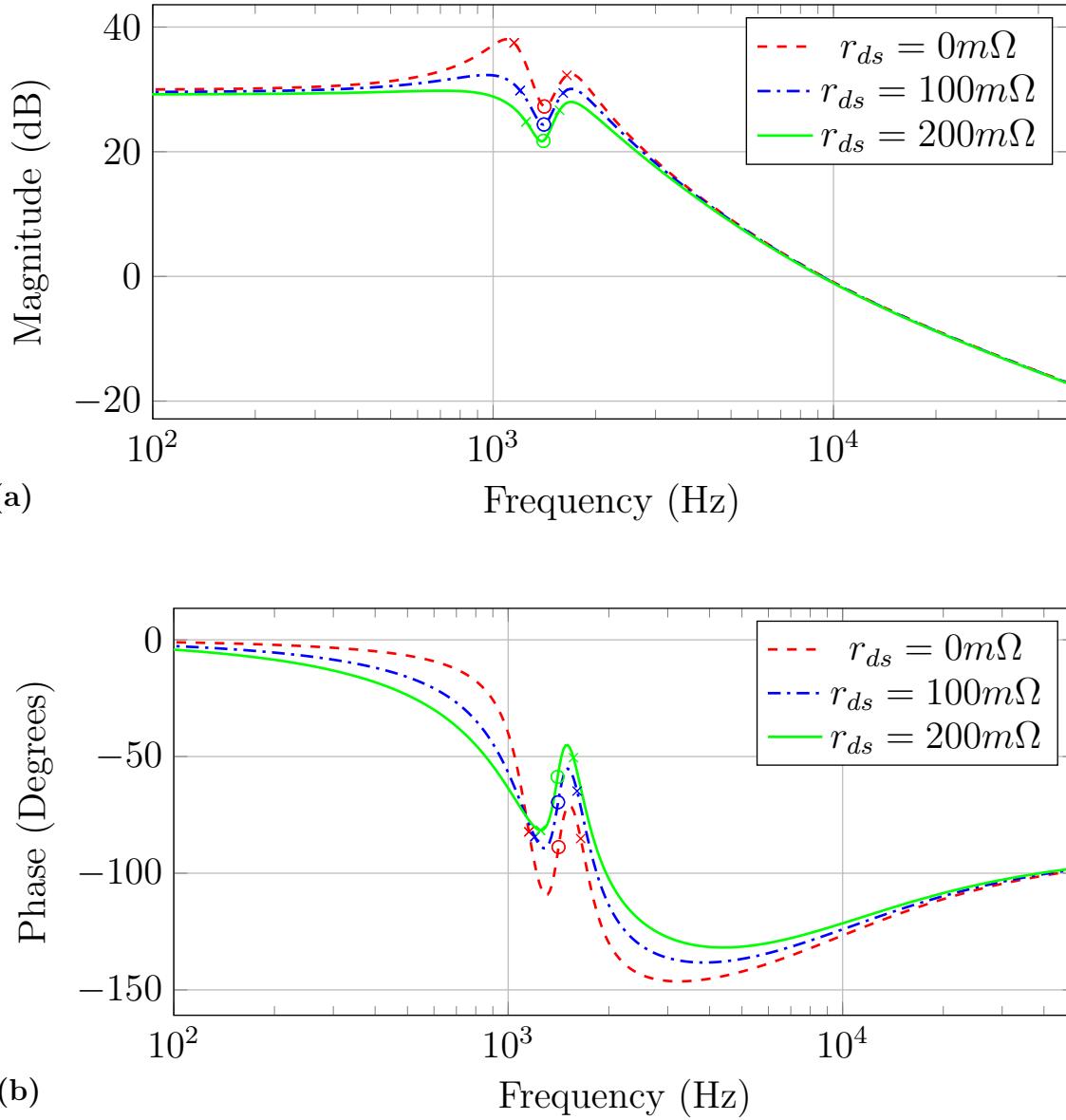

| Figure 4.2  | Bode plot analysis of the transfer function $v_{od}$ . The plots characterize the effects of the power transistors ON resistances on (a) the magnitude and (b) the phase of the transfer function and the effects of the inductor resistance on (c) the magnitude and (d) the phase of the transfer function.                 | 65 |

| Figure 4.3  | Block Diagram of the proposed controller.                                                                                                                                                                                                                                                                                     | 67 |

| Figure 4.4  | Voltage-controlled oscillator circuit implementation.                                                                                                                                                                                                                                                                         | 70 |

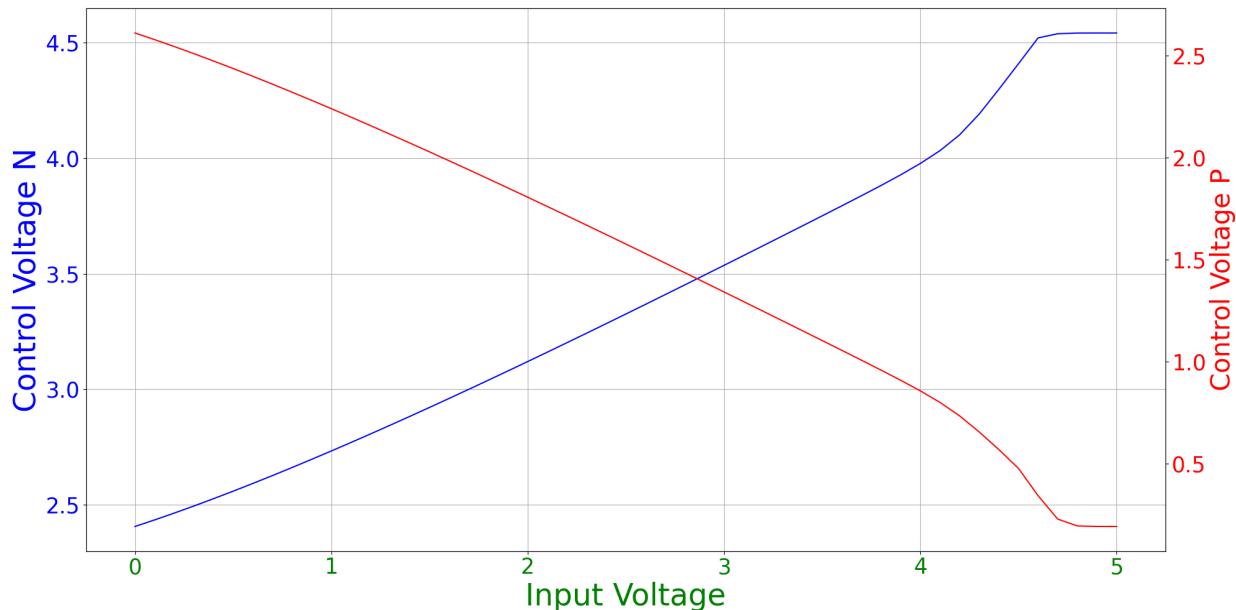

| Figure 4.5  | Variations of the control voltages P and N to the input voltage $V_{IN}$ .                                                                                                                                                                                                                                                    | 70 |

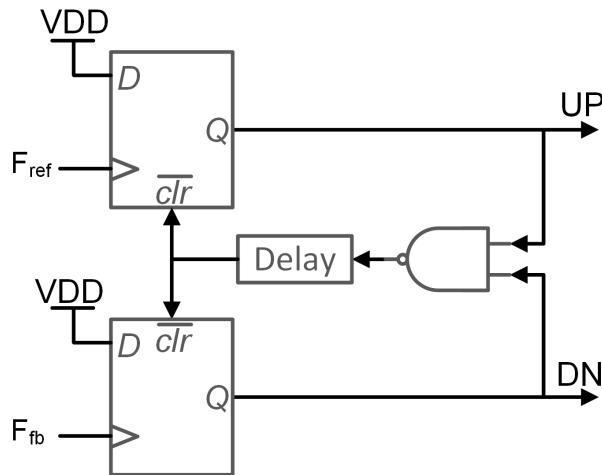

| Figure 4.6  | Circuit Implementation of the phase frequency detector.                                                                                                                                                                                                                                                                       | 71 |

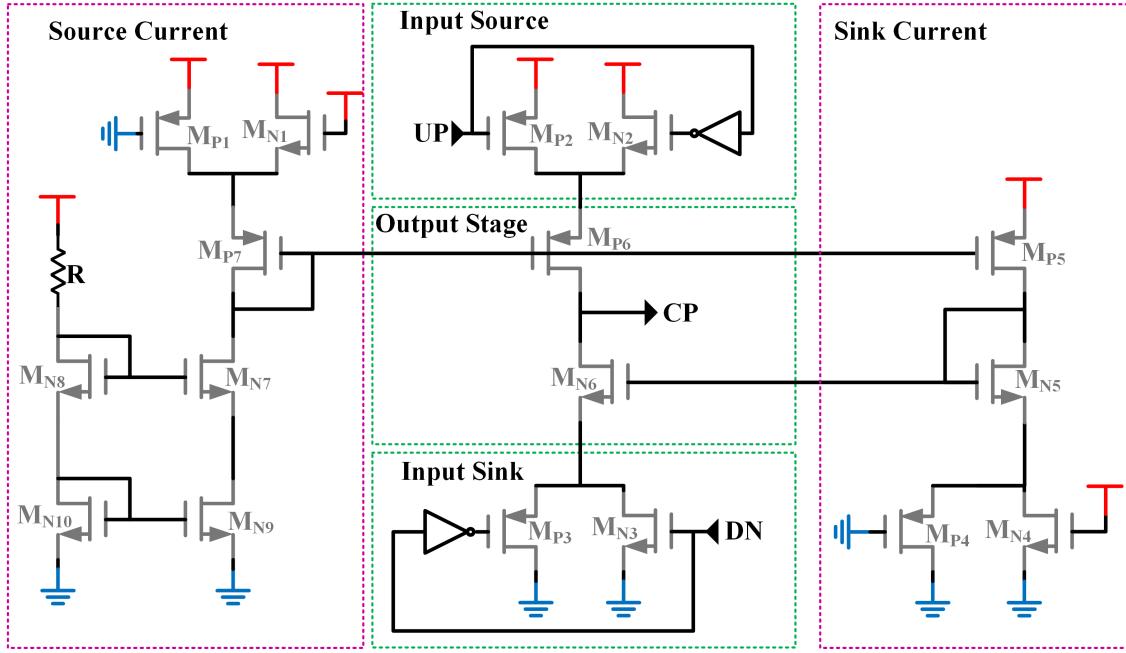

| Figure 4.7  | Charge pump transistor-level implementation.                                                                                                                                                                                                                                                                                  | 73 |

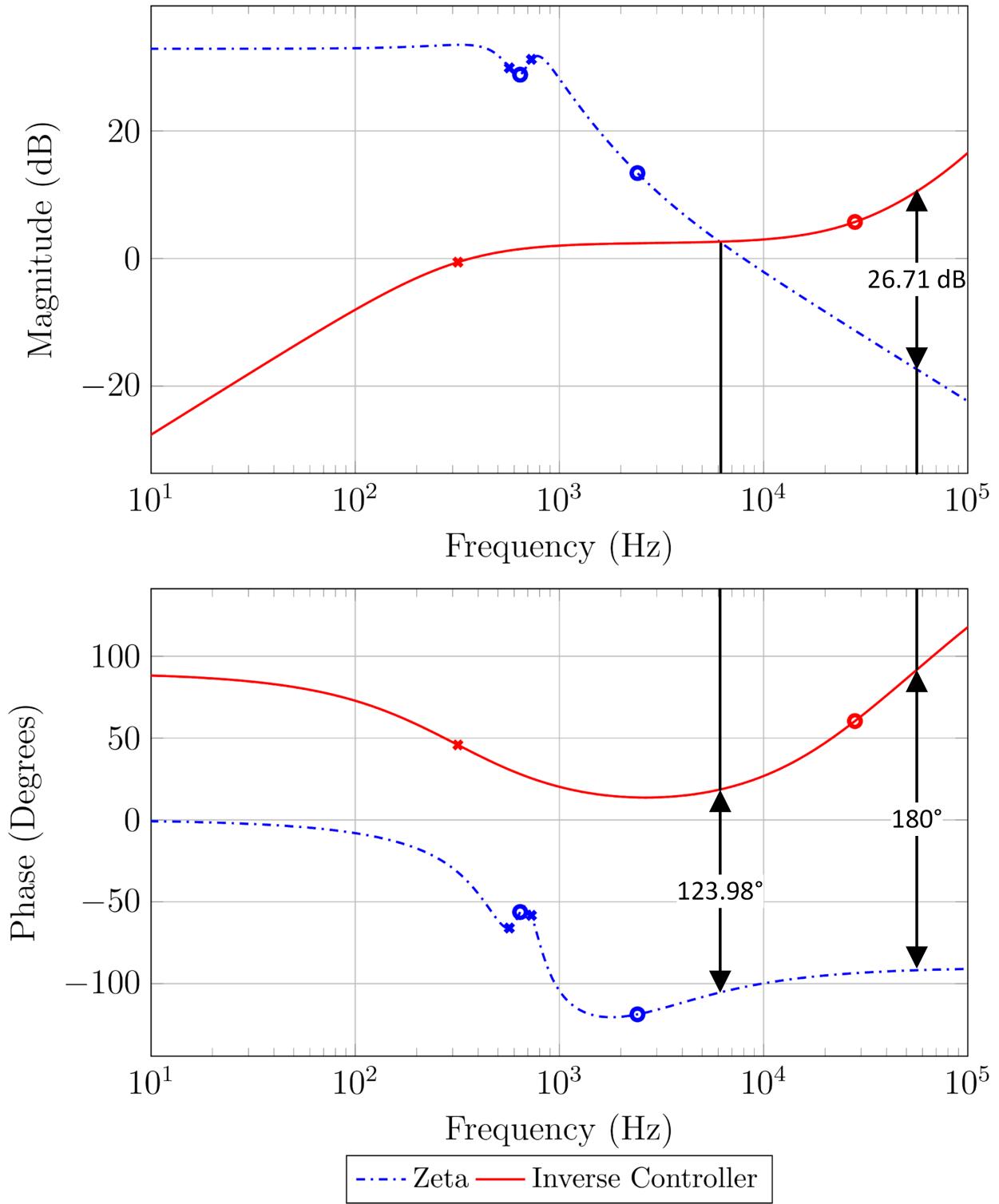

| Figure 4.8  | Graphical analysis of the closed-loop system. Bode plot of the Zeta converter (dashed blue) and the inverse controller (red). From this approach, the gain margin is 26.71 dB, and the phase margin is $180^\circ - 123.98^\circ = 56.02^\circ$ .                                                                             | 75 |

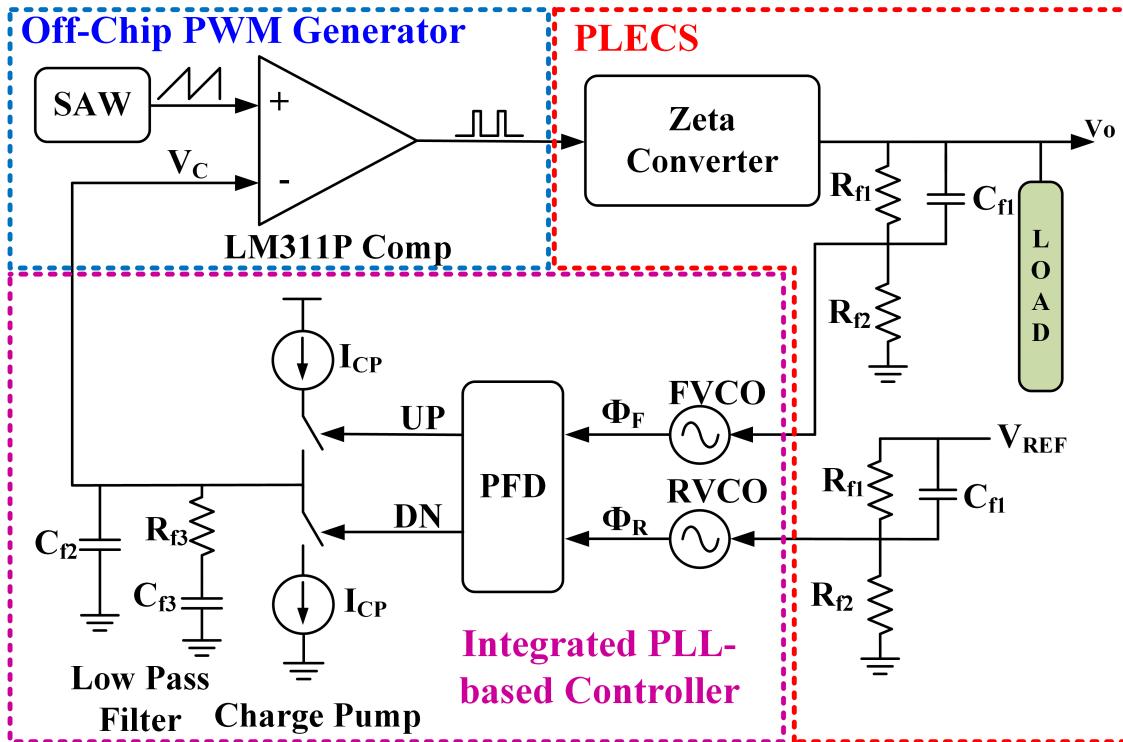

| Figure 4.9  | Block diagram of the proposed closed-loop Zeta converter system implementation                                                                                                                                                                                                                                                | 77 |

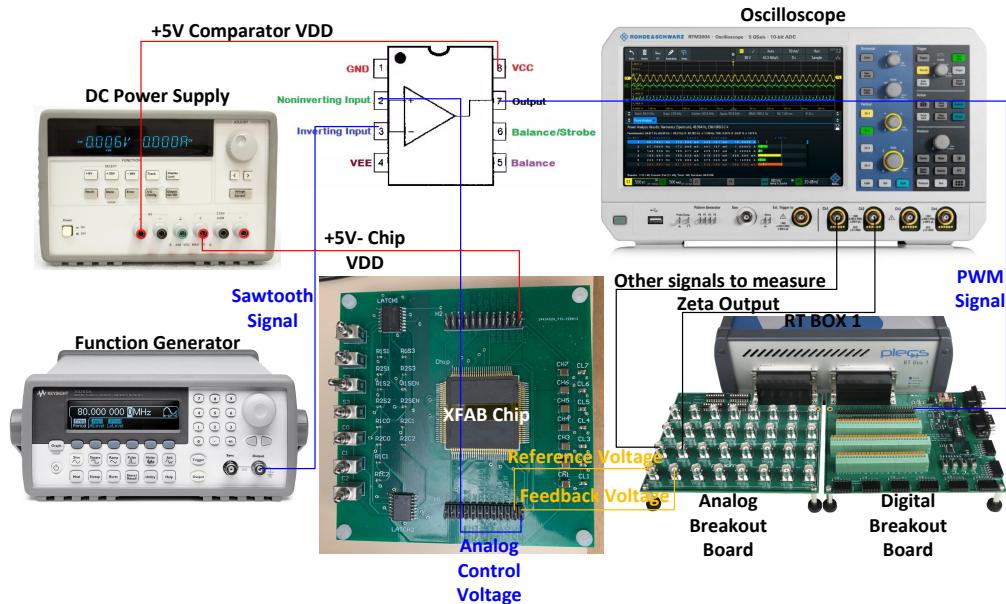

| Figure 4.10 | Testbench Setup                                                                                                                                                                                                                                                                                                               | 77 |

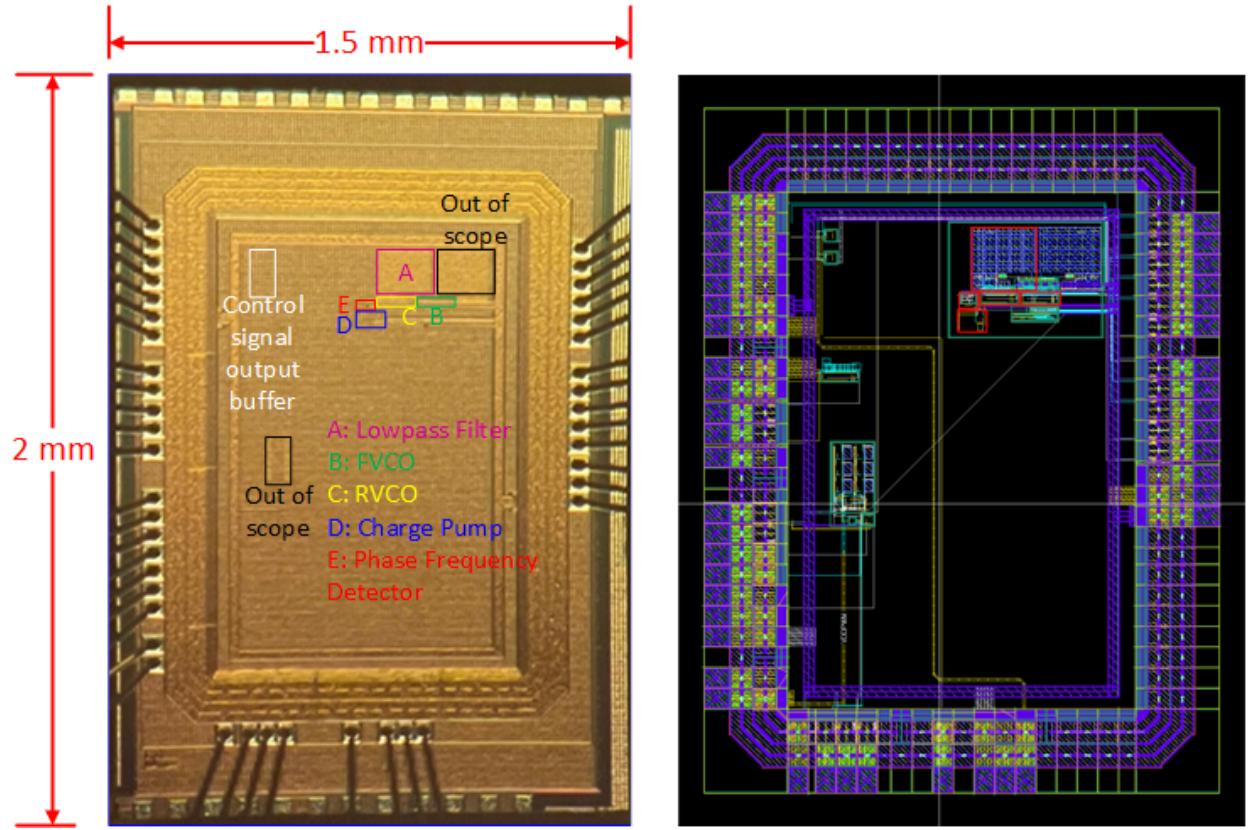

| Figure 4.11 | Micrograph of the fabricated chip (left) and its layout implementation (right).                                                                                                                                                                                                                                               | 78 |

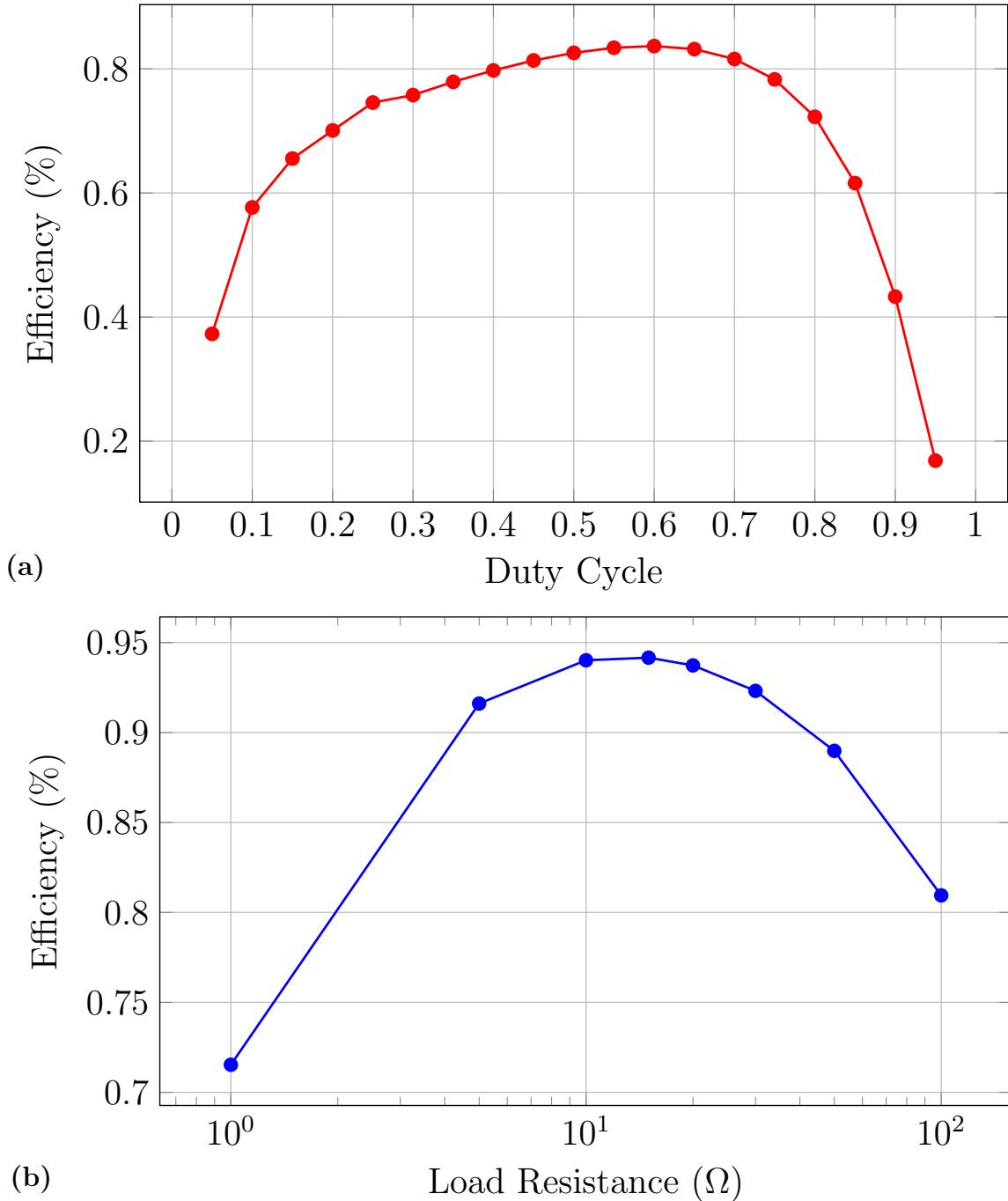

| Figure 4.12 | Effects of (a) the duty cycle and (b) the load resistance on the system's efficiency.                                                                                                                                                                                                                                         | 79 |

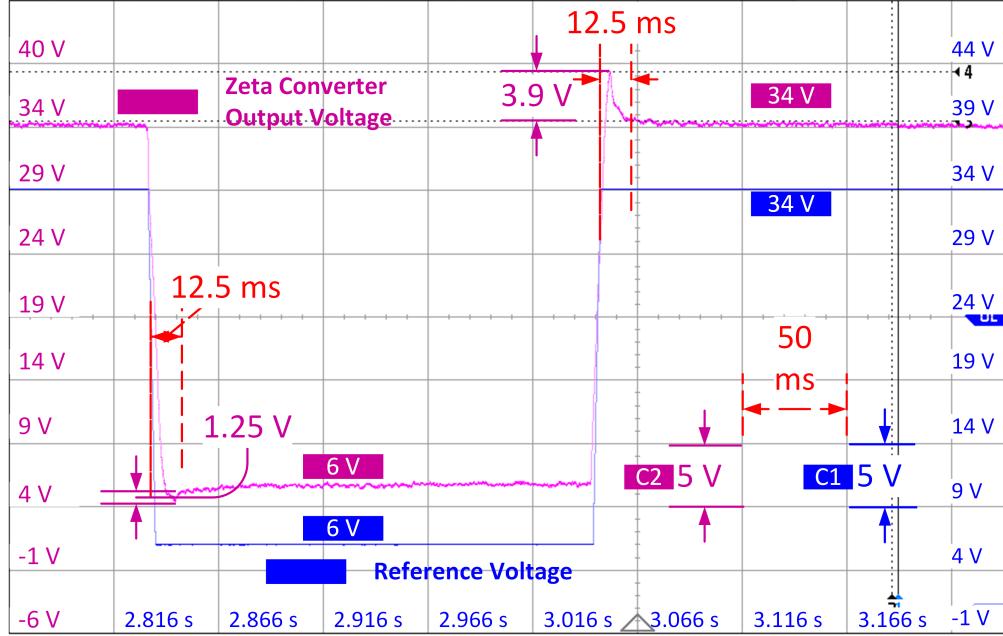

| Figure 4.13 | System responses for a Zeta converter : (a) reference tracking showing both buck and Zeta modes (pink curve - left y-axis, blue curve - right y-axis), and (b) startup response (light blue curve - left y-axis, dark blue curve - right y-axis).                                                                             | 81 |

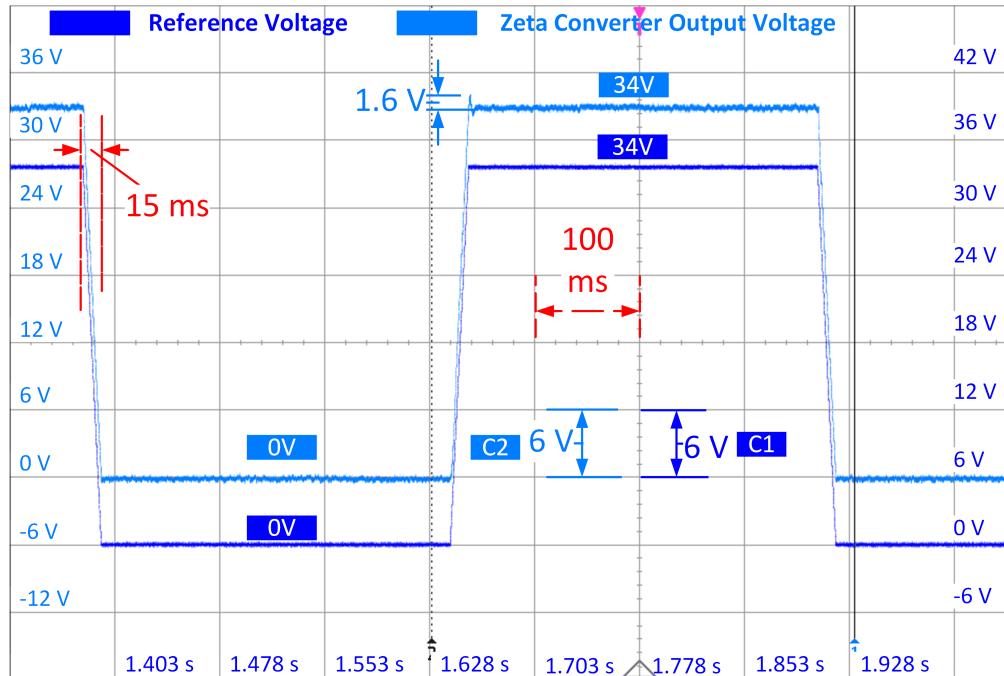

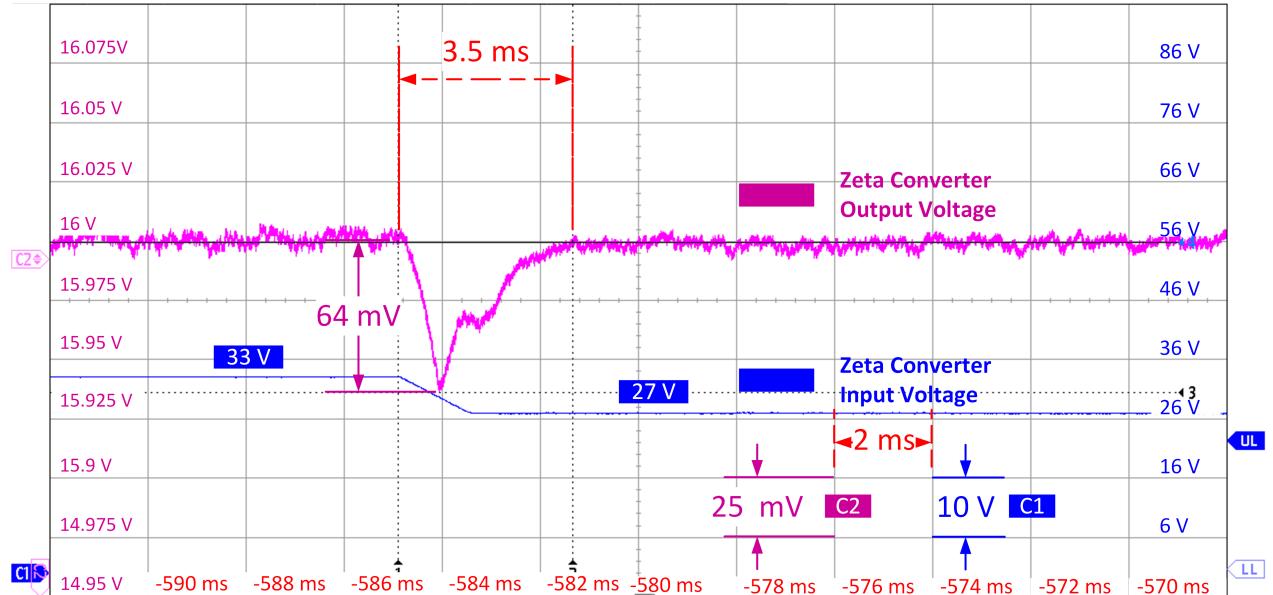

| Figure 4.14 | Closed-loop transient line regulation for a Zeta converter response to a 6V change in input voltage : (a) with source changing from 27V to 33V (pink curve and left y-axis, blue curve, and right y-axis) and (b) source changing from 33V to 27V, with a 16V reference voltage and load resistance of $100 \Omega$ .         | 82 |

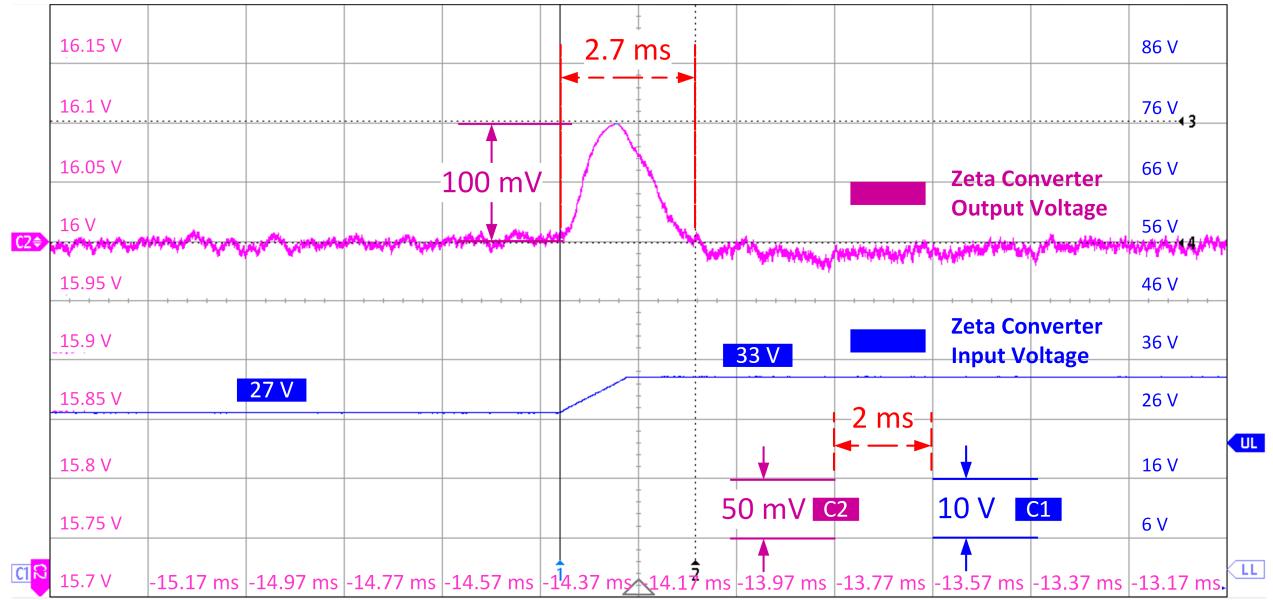

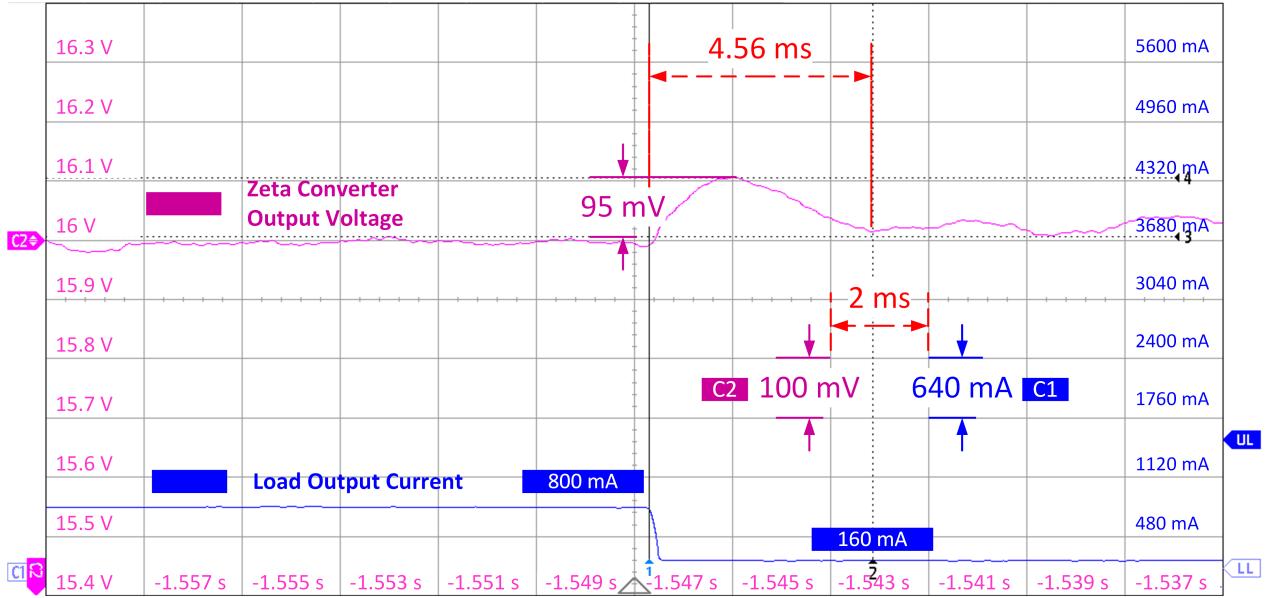

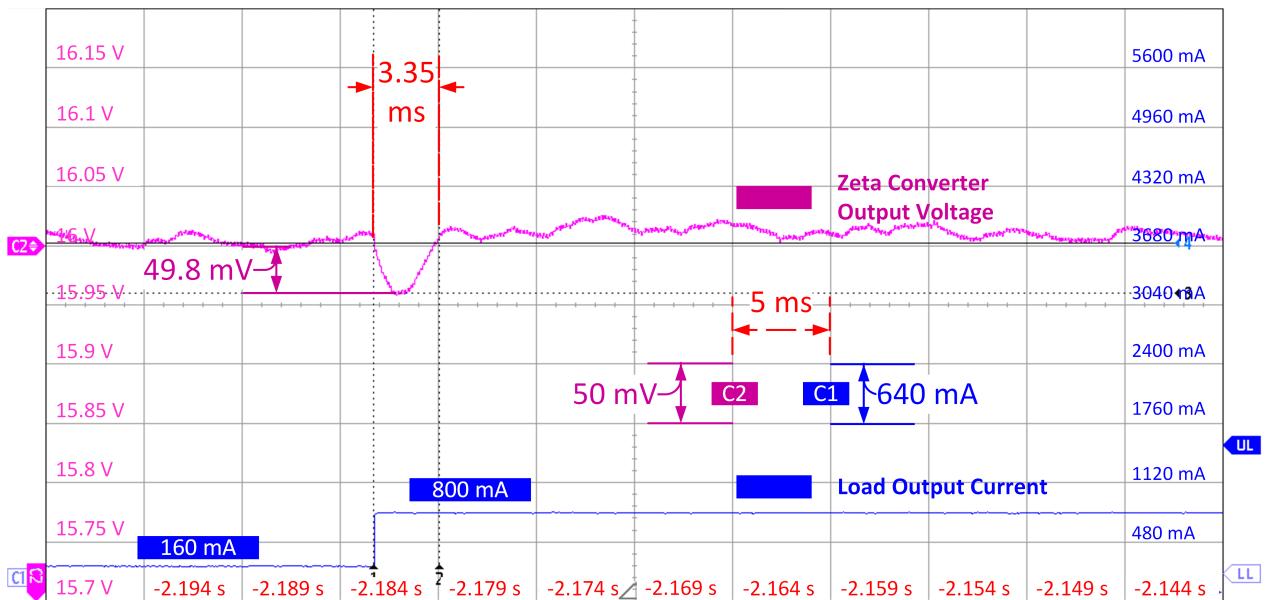

| Figure 4.15 | Closed-loop transient load regulation for a Zeta converter response to a 640mA change in load current : (a) with current changing from 800mA to 160mA (pink curve and left y-axis, blue curve, and right y-axis) and (b) load current changing from 160mA to 800mA, with a 16V reference voltage and an input voltage of 28V. | 84 |

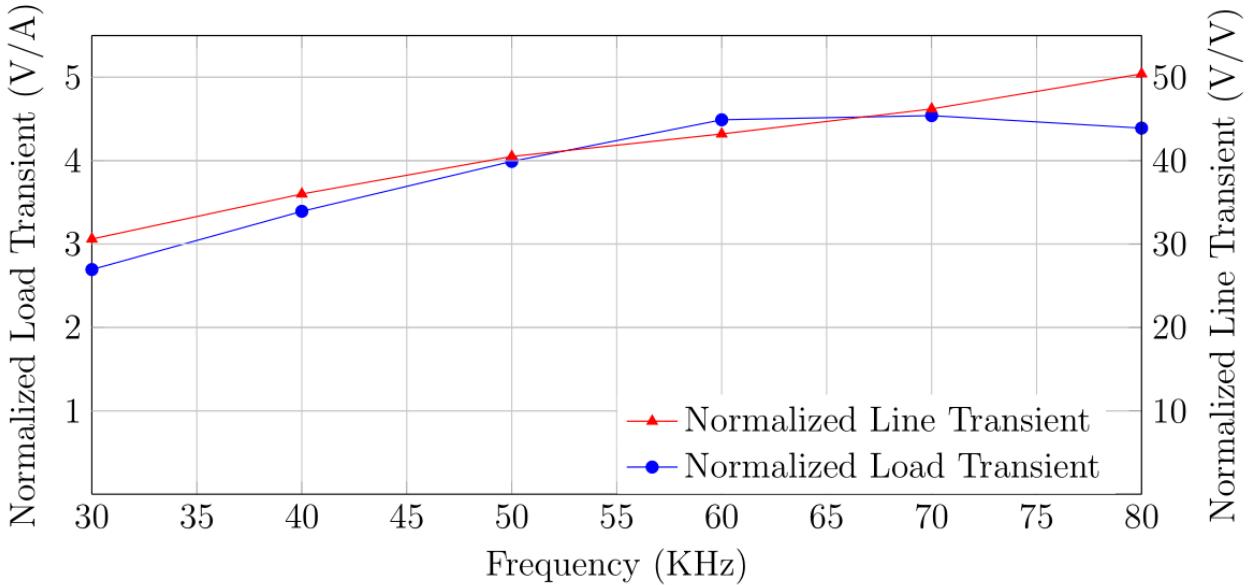

| Figure 4.16 | Normalized Line and Load Transient (NLT) values of the Zeta converter under various frequencies.                                                                                                                                                                                                                              | 86 |

|            |                                                                                                                                                                                                                                                                                                                                                                                                |     |

|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

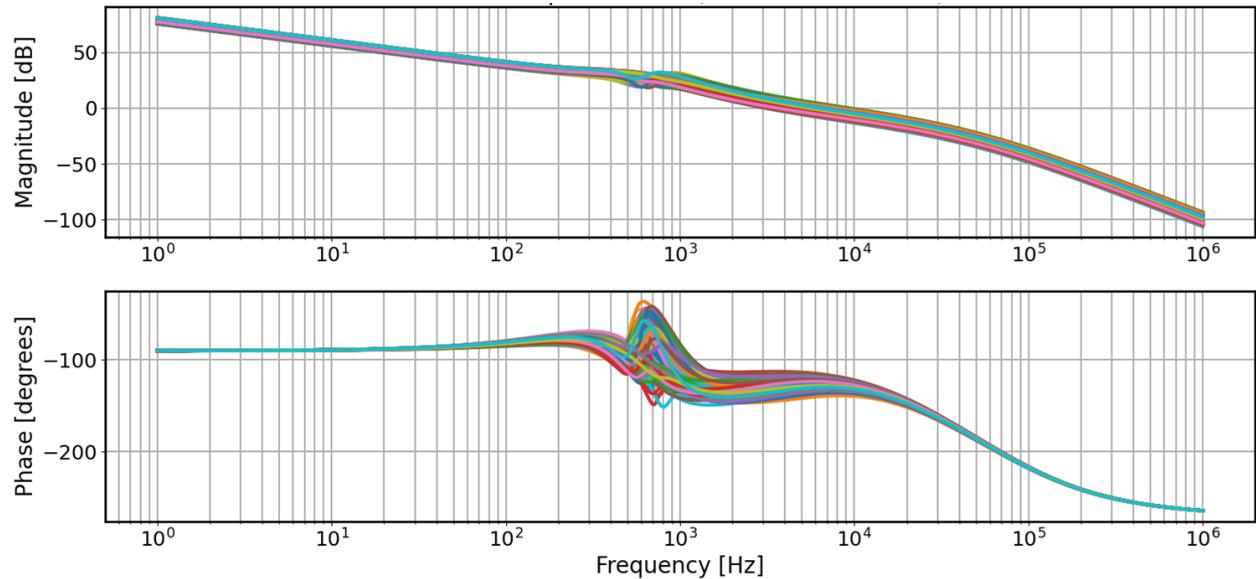

| Figure 5.1 | Effet de $\pm 20\%$ d'incertitude sur le diagramme de Bode en boucle ouverte                                                                                                                                                                                                                                                                                                                   | 98  |

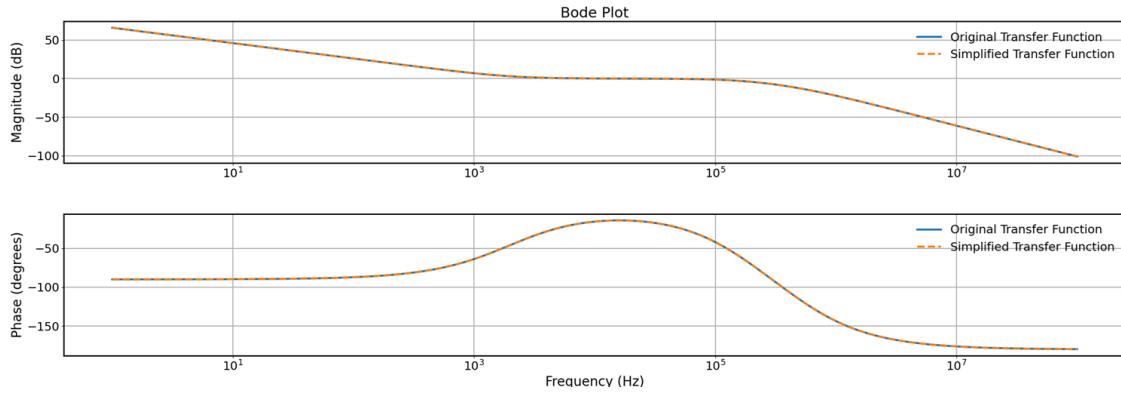

| Figure 5.2 | Comparaison des diagrammes de Bode entre les fonctions de transfert originales et simplifiées du contrôleur.                                                                                                                                                                                                                                                                                   | 100 |

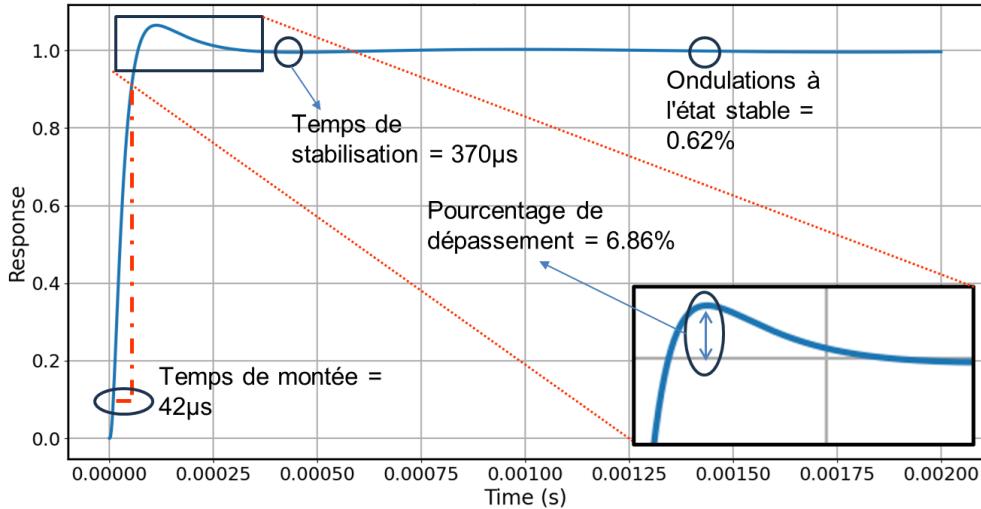

| Figure 5.3 | Réponse temporelle pour le scénario optimal montrant un faible dépassement et un temps de stabilisation rapide.                                                                                                                                                                                                                                                                                | 101 |

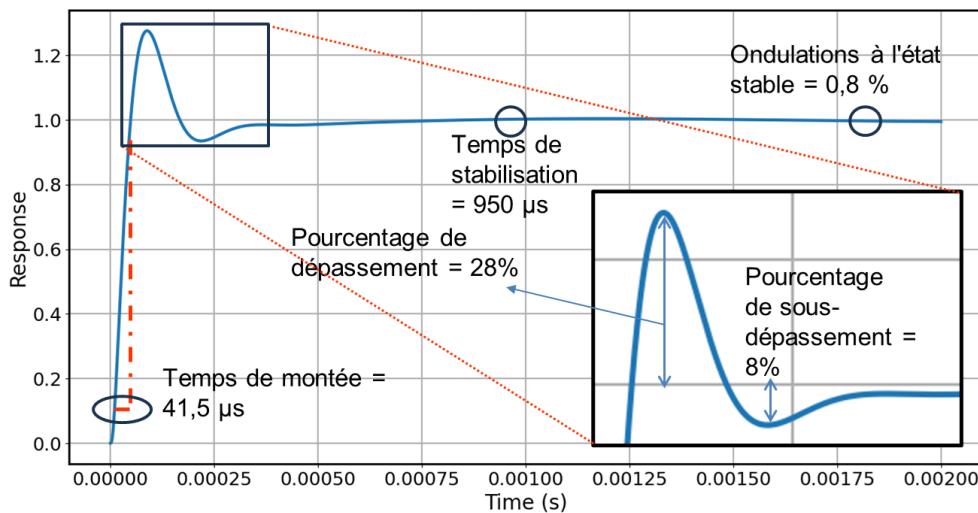

| Figure 5.4 | Réponse temporelle pour le pire scénario montrant un dépassement et un sous-dépassement plus importants.                                                                                                                                                                                                                                                                                       | 102 |

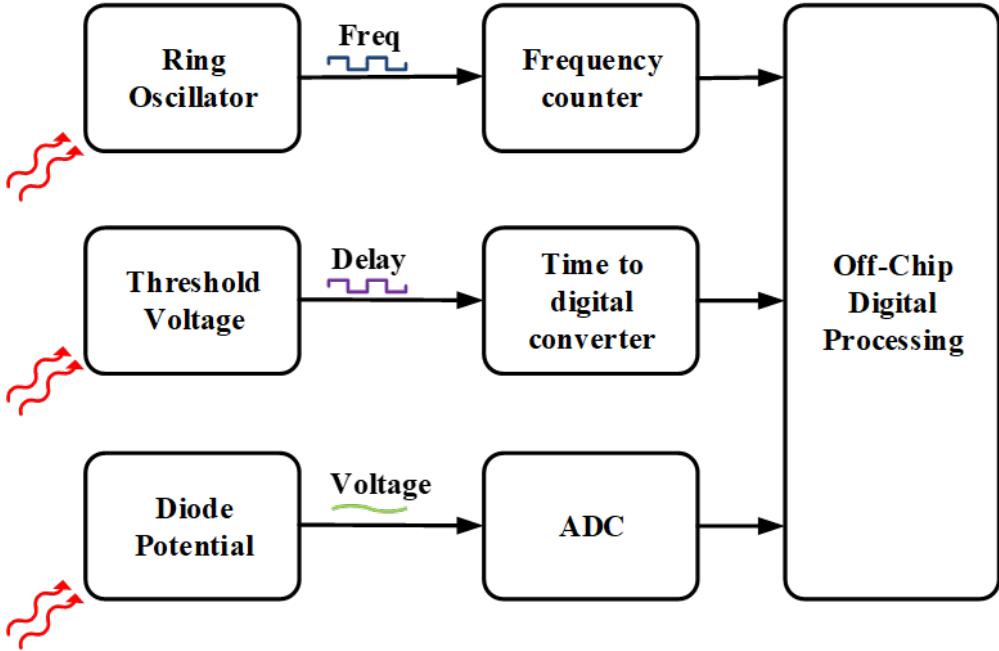

| Figure 6.1 | Block diagram of a proposed phase-locked loop-based Buck converter with integrated temperature sensors.                                                                                                                                                                                                                                                                                        | 105 |

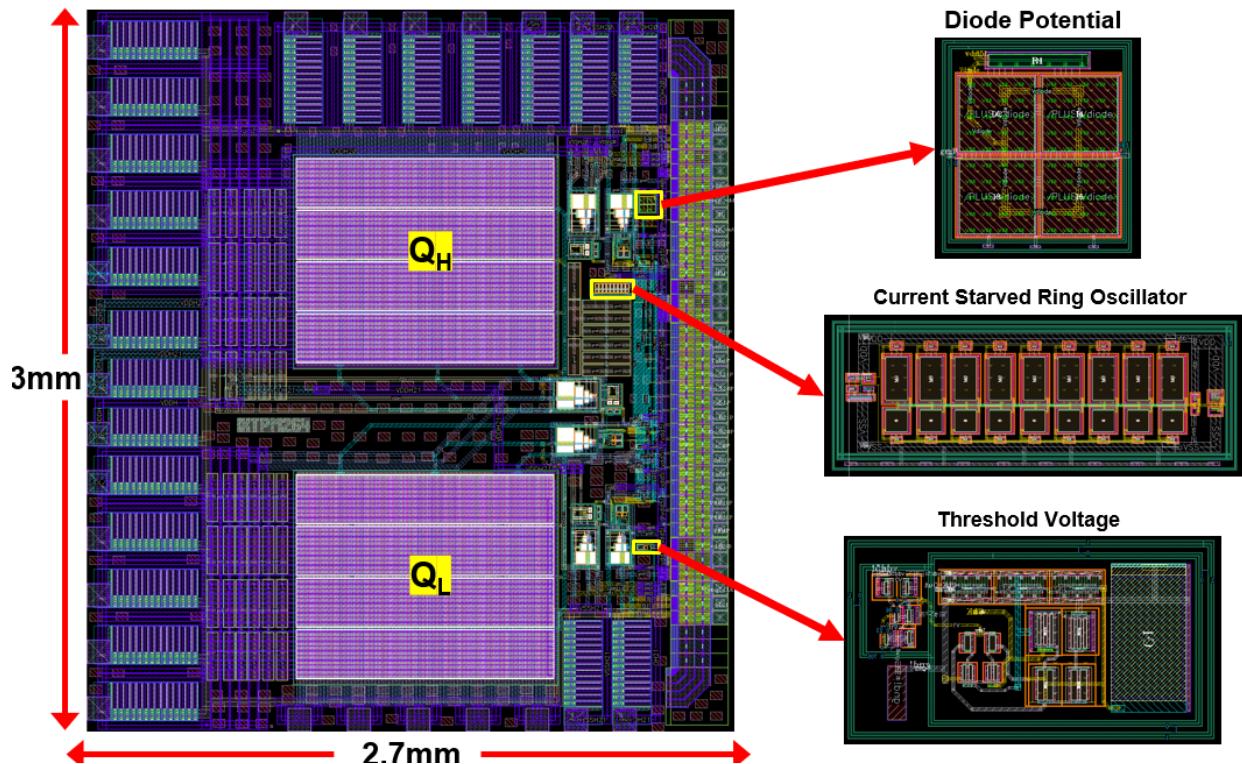

| Figure 6.2 | Layout implementation of the buck converter and the thermal sensors.                                                                                                                                                                                                                                                                                                                           | 107 |

| Figure 6.3 | Power consumption of the low side NMOS ( $Q_L$ ), high side NMOS ( $Q_H$ ) in a DC-DC converter, as a function of its load resistance at 28 V output voltage.                                                                                                                                                                                                                                  | 108 |

| Figure 6.4 | Circuit diagrams of the three implemented temperature sensors.                                                                                                                                                                                                                                                                                                                                 | 109 |

| Figure 6.5 | Temperature reading by FPGA interface.                                                                                                                                                                                                                                                                                                                                                         | 110 |

| Figure 6.6 | Simulation results over temperature changes for : (a) Threshold-based, (b) Diode potential-based, and (c) Ring oscillator.                                                                                                                                                                                                                                                                     | 112 |

| Figure 7.1 | Implementation of the ROTs : (a) Transistor-level (top) and (b) Layout level (bottom).                                                                                                                                                                                                                                                                                                         | 121 |

| Figure 7.2 | Simulated output frequency of the ROTs as a function of $R_1$ (typical process parameters at $27^\circ\text{C}$ ).                                                                                                                                                                                                                                                                             | 122 |

| Figure 7.3 | Post-layout simulation performance of the ROTs over process corners : typical (tm), worst-one (wo : fast-n, slow-p), worst-zero (wz : slow-n, fast-p), worst-power (wp : fast-n, fast-p), and worst-speed (ws : slow-n, slow-p), each at $2\sigma$ , $3\sigma$ , $4\sigma$ , $5\sigma$ , and $6\sigma$ .                                                                                       | 123 |

| Figure 7.4 | Analysis of the ROTs power supply sensitivity across the typical process corners spanning $-30^\circ\text{C}$ to $90^\circ\text{C}$ temperature range.                                                                                                                                                                                                                                         | 124 |

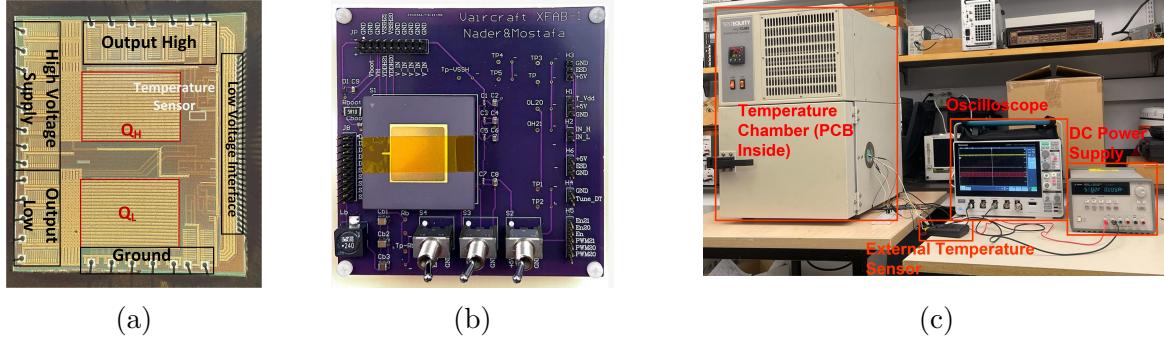

| Figure 7.5 | (a) Microphotograph of the fabricated XFAB chip prototype detailing the DC-DC converter configuration and the strategic placement of the ROTs near the high-power transistor $Q_H$ , (b) Custom printed circuit board (PCB) designed for chip testing with a user-friendly external interface, and (c) Testbench setup employed for the characterization of the fabricated temperature sensor. | 129 |

|            |                                                                                                                                                                                                                                                                                        |     |

|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

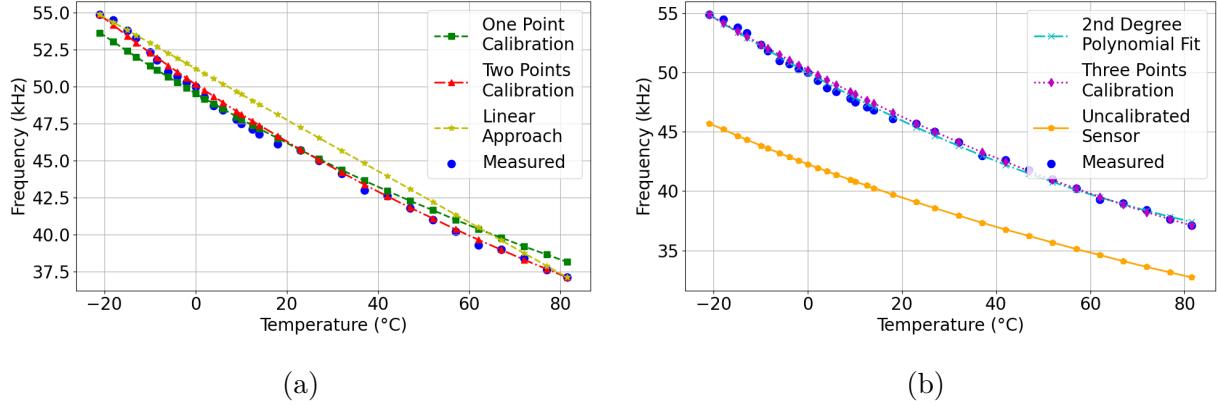

| Figure 7.6 | Performance evaluation of various calibration techniques : (a) Comparisons between One-Point Calibration, Two-Point calibration, and Linear Calibration, and (b) Comparisons among Three-Point calibration, 2nd Degree Polynomial Fit (Best-fit), and the uncalibrated sensor. . . . . | 133 |

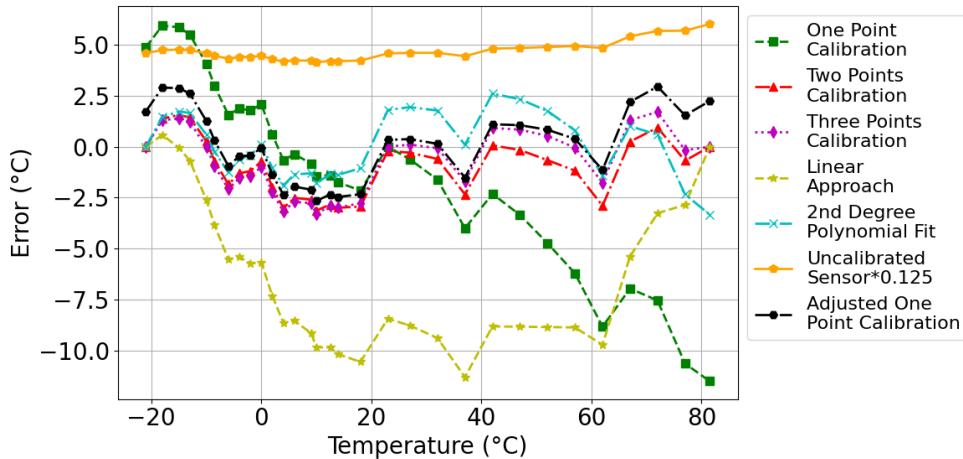

| Figure 7.7 | Temperature errors of different calibration techniques. . . . . . . . .                                                                                                                                                                                                                | 134 |

## LISTE DES SIGLES ET ABRÉVIATIONS

|       |                                                                                                               |

|-------|---------------------------------------------------------------------------------------------------------------|

| AICA  | Alimentation des Interfaces de Capteur et Actuateurs (Power Sensor Interface - PSI)                           |

| AOT   | Amplificateur Opérationnel à Transconductance (Operational Transconductance Amplifier - OTA)                  |

| APE   | Avions plus électriques (More Electric Aircraft - MEA)                                                        |

| ATCC  | Amplificateur de Transconductance à Convoyeur de Courant (Current Conveyor Transconductance Amplifier - CCTA) |

| BVP   | Boucle à verrouillage de phase (Phase-Locked Loop - PLL)                                                      |

| CAN   | Convertisseurs analogique-numérique (Analog to digital converter - ADC)                                       |

| CC-CC | Courant Continu à Courant Continu (Direct Current to Direct Current - DC-DC)                                  |

| CeMC  | Commande en mode coulissant (Sliding-Mode Control - SMC)                                                      |

| CMC   | Commande en mode courant (Current-Mode Control - CMC)                                                         |

| CMCDO | Contrôleur de mode coulissant de deuxième ordre (Second Order Sliding Mode Controller - SOSMC)                |

| CMP   | Composant magnétique planaire (Planar Magnetic Component - PMC)                                               |

| CMT   | Commande en Mode Tension (Voltage-Mode Control - VMT)                                                         |

| CNA   | Convertisseurs numérique-analogique (Digital to analog converter - DAC)                                       |

| CPA   | Contrôle Prédictif Adaptatif (Adaptive Model Predictive Control - AMPC)                                       |

| CPE   | Commercial prêt à l'emploi (Commercial off-the-shelf - COTS)                                                  |

| CRI   | Commande de réinitialisation intégrale (Reset-Integral Control - RIC)                                         |

| CTA   | Contrôle thermique actif (Active Thermal Control - ATC)                                                       |

| CTEA  | Contrôle de la tension d'entrée par anticipation (Input-Voltage Feed-forward Control - IVFF)                  |

| CUC   | Contrôle en un cycle (One-Cycle Control - OCC)                                                                |

| DP    | Détecteur de phase (Phase Detector - PD)                                                                      |

| DPZ   | Détecteur de passage à zéro (Zero Crossing Detector - ZCD)                                                    |

| DQI   | Différentielle quadratique et intégration (Quadratic Differential and Integration - QDI)                      |

| DT    | Diffusivité Thermique (Thermal Diffusivity - TD)                                                              |

|      |                                                                              |

|------|------------------------------------------------------------------------------|

| ERLA | Écrêteur de roue libre actif (Active Clamp Flyback - ACF)                    |

| FPB  | Filtre Passe-Bas (Low Pass Filter - LPF)                                     |

| GES  | Gaz à effet de serre (Greenhouse Gas - GHG)                                  |

| ICP  | Interface de Capteur de Puissance (Power Sensor Interface - PSI)             |

| LRCT | Ligne à retard commandée en tension (Voltage Controlled Delay Line - VCDL)   |

| MCC  | Mode de Conduction Continue (Continuous Conduction Mode - CCM)               |

| MCOS | Mode coulissant d'ordre supérieur (Higher Order Sliding Mode - HOSM)         |

| MFI  | Modulateur de fréquence d'impulsion (Pulse Frequency Modulator - PFM)        |

| MLI  | Modulateur de Largeur d'Impulsion (Pulse Width Modulator - PWM)              |

| MRP  | Moyenne en Régime Permanent (Steady State Average - SSA)                     |

| OCC  | Oscillateur commandé par courant (Current Controlled Oscillator - CCO)       |

| OCT  | Oscillateur commandé par tension (Voltage Controlled Oscillator - VCO)       |

| PC   | Pompe de Charge (Charge Pump - CP)                                           |

| PID  | Proportionnelle-Intégrale-Dérivée (Proportional-Integral-Derivative - PID)   |

| PSN  | Processeurs de signaux numériques (Digital Signal Processor - DSP)           |

| RDE  | Réseau de distribution électrique (Electric Power Distribution Grids - EPDG) |

| RMC  | Rétroaction en mode courant (Current-Mode Feedback - CFB)                    |

| RSE  | Résistance en série effective (Effective Series Resistance - ESR)            |

| SdB  | Système dans un boîtier (System-in-Package - SiP)                            |

| SsP  | Système sur puce (System-on-Chip - SoC)                                      |

| VE   | Véhicules électriques (Electric Vehicles - EV)                               |

**LISTE DES ANNEXES**

|          |                                                                                           |     |

|----------|-------------------------------------------------------------------------------------------|-----|

| Annexe A | ARTICLE 2 : A SYSTEMATIC APPROACH FOR PLL-BASED ZETA<br>POWER CONVERTER CONTROL . . . . . | 171 |

|----------|-------------------------------------------------------------------------------------------|-----|

## CHAPITRE 1 INTRODUCTION

### 1.1 Contexte et motivation

Les secteurs des transports et de l'industrie évoluent rapidement pour répondre aux exigences croissantes en matière d'efficacité, de durabilité et de conformité environnementale. Ces secteurs contribuent de manière significative aux émissions mondiales de gaz à effet de serre (GES), avec le transport représentant 27% des émissions nationales de GES aux États-Unis en 2022 [2]. À l'échelle mondiale, le secteur des transports est responsable de près de 24% des émissions directes de CO<sub>2</sub> issues de la combustion de carburants, les véhicules routiers contribuant à environ les trois quarts de ce total, comme indiqué dans la figure 1.1 [3]. Cela souligne l'urgence de stratégies telles que l'électrification pour atténuer les impacts environnementaux de la consommation de combustibles fossiles. Bien que le secteur automobile ait déjà adopté substantiellement les véhicules électriques (VE), des innovations similaires émergent dans les applications industrielles, augmentant l'efficacité opérationnelle et réduisant considérablement la consommation de carburant et les émissions [4, 5].

Les transports électrifiés sont considérés comme une approche clé pour réduire l'empreinte carbone dans divers secteurs, y compris l'aviation, le transport maritime et l'industrie automobile. Le passage des systèmes basés sur les combustibles traditionnels à des alternatives électriques offre de nombreux avantages, notamment une meilleure efficacité, une fiabilité accrue, une réduction du poids des systèmes, des coûts de maintenance et d'exploitation réduits et, surtout, une diminution des émissions de GES [6–8]. Cependant, le succès de cette transition dépend fortement de la performance et de la résilience des réseaux de distribution électrique (RDE), qui constituent l'épine dorsale des systèmes de véhicules électrifiés. Les RDE gèrent la distribution d'énergie provenant de diverses sources, telles que les batteries, les panneaux solaires photovoltaïques et les générateurs AC thermoélectriques, vers différentes charges, y compris les moteurs électriques et les composants électroniques [1], [9]. Assurer un fonctionnement efficace et fiable dans des conditions variées est essentiel pour le succès global des stratégies d'électrification.

À mesure que les secteurs avancent vers l'électrification et l'intégration des énergies renouvelables, une gestion efficace de l'énergie devient de plus en plus cruciale. Les convertisseurs CC-CC jouent un rôle essentiel dans le maintien d'un flux d'énergie stable entre les sources d'énergie et les systèmes de stockage. Dans les systèmes hybrides d'énergie renouvelable intégrant plusieurs sources, telles que l'éolien et le solaire, comme présenté dans la figure 1.2, les convertisseurs CC-CC gèrent efficacement les fluctuations de puissance causées par les

FIGURE 1.1 Émissions mondiales de CO2 par secteur (1990-2030)

conditions environnementales variables. Par exemple, les convertisseurs connectés aux cellules photovoltaïques régulent la sortie pour répondre aux besoins du système ou recharger les batteries. Cela permet un flux d'énergie bidirectionnel qui améliore les capacités de stockage pendant les périodes de faible demande et fournit de l'énergie lorsque la génération renouvelable est insuffisante. Cette adaptabilité assure un fonctionnement continu dans les contextes industriels, optimisant l'utilisation de l'énergie et réduisant les interruptions ; dans les véhicules électriques, elle facilite le stockage d'énergie et un transfert efficace lors du freinage régénératif et de la recharge.

Les cadres industriels modernes intègrent de plus en plus de capteurs, d'actionneurs et de systèmes de contrôle électronique, augmentant considérablement la complexité de l'infrastructure et la demande énergétique. Ces systèmes nécessitent des solutions de gestion de l'énergie robustes pour garantir une haute performance et une fiabilité, notamment dans des environnements dynamiques et fluctuants. Pour répondre à ces besoins croissants, les technologies de système sur puce (SsP) et de système dans un boîtier (SdB) sont explorées pour miniaturiser les systèmes traditionnels, accroître l'adaptabilité et réduire l'impact environnemental. Ces technologies sont particulièrement précieuses dans les applications exigeant une distribution d'énergie efficace et flexible, car elles permettent une personnalisation pour

FIGURE 1.2 Système énergétique hybride avec interface de batterie

répondre aux exigences spécifiques des capteurs et actionneurs.

Cependant, les convertisseurs CC-CC traditionnels sont souvent encombrants et ont du mal à s'adapter efficacement à des conditions d'entrée variables. Cette recherche répond à ces limitations en développant deux convertisseurs CC-CC optimisés : un convertisseur abaisseur pour une régulation fiable de la tension abaissée et un convertisseur Zeta pour la gestion des environnements avec des tensions d'entrée fluctuantes. Le convertisseur abaisseur est conçu pour une réduction de tension stable, tandis que le convertisseur Zeta offre un ajustement bidirectionnel de la tension, permettant à la fois des opérations de montée et de descente sous des conditions variables [10]. Cette approche raffinée vise à améliorer les performances des convertisseurs, à réduire les pertes d'énergie et à augmenter l'adaptabilité pour les applications industrielles exigeantes, en exploitant les technologies avancées de semi-conducteurs et les pratiques de gestion thermique innovantes.

L'objectif de cette recherche est double : concevoir et développer des convertisseurs CC-CC compacts et hautement efficaces répondant aux divers besoins énergétiques industriels, et créer un capteur thermique autonome permettant de surveiller la température des composants critiques. Bien que le capteur thermique soit développé indépendamment, il pose les bases pour une future intégration avec les convertisseurs CC-CC. Cette intégration permettra de créer des convertisseurs thermiquement adaptatifs capables de répondre dynamiquement aux variations de température, renforçant ainsi la fiabilité et l'efficacité du système.

## 1.2 Énoncé du problème

Cette thèse doctorale s'inscrit dans le cadre d'une initiative de recherche plus vaste visant à développer des interfaces de capteurs intégrées et reconfigurables. L'objectif principal de cette recherche est de concevoir et de mettre en œuvre un système pour l'Alimentation des interfaces de capteur et actuateurs (AICA) basée sur des convertisseurs CC-CC avancé optimisé. Ces AICA doivent soutenir le fonctionnement et la commande de divers types de charges dans les applications industrielles, telles que les isolateurs, les convertisseurs analogiques-numérique et les amplificateurs. Le système AICA comprend une architecture complexe de signaux mixtes, combinant des composants de circuits haute et basse tension, y compris des pilotes de portes, des décaleurs de niveaux, des amplificateurs, des comparateurs et des contrôleurs [1, 9].

FIGURE 1.3 Schéma fonctionnel de l'interface polyvalente du capteur SsP/SdB où le convertisseur CC-CC a été implanté, tiré de [1]

En plus de l'intégration du système AICA, cette recherche se concentre sur la performance en boucle fermée à travers le développement d'un contrôleur robuste. Ce contrôleur est essentiel pour maintenir un fonctionnement fiable et gérer efficacement les surtensions dans la source d'alimentation, en particulier dans des environnements dynamiques tels que les systèmes de véhicules. La gestion de ces défis implique de concevoir des stratégies de contrôle capables de stabiliser la distribution de puissance vers les actionneurs, même en présence de fluctuations de tension, améliorant ainsi la résilience et l'efficacité du système AICA dans les environnements industriels. Plusieurs défis de recherche critiques ont été identifiés dans ce contexte. Ils sont résumés ci-dessous :

*Problème 1 : Limitations des composants standard* : Les modules AICA couramment utilisés

dans des secteurs comme l'automobile et les transports reposent sur des composants standards souvent encombrants, coûteux et inefficaces en termes de consommation d'énergie. Ces composants manquent de reconfigurabilité suffisante pour s'interfacer facilement avec divers actionneurs, ce qui accroît la complexité de conception. Cette complexité entraîne des défis économiques et impacte le délai de mise sur le marché [1, 9, 11]. De plus, des problèmes découlant du câblage et la surcharge de refroidissement contribuent au poids du système et introduisent des inefficacités parasites et thermiques, affectant finalement la fiabilité du système. Le développement d'un système AICA intégré utilisant des technologies CMOS haute tension présente des avantages significatifs, y compris une polyvalence accrue pour la reconfiguration en fonction des spécifications des actionneurs et la possibilité de compensation intégrée avec des parasitismes réduits. Cela peut permettre des fréquences de fonctionnement plus élevées et des composants passifs plus petits [12].

*Problème 2 : Vulnérabilités environnementales et aux surtensions :* Le système AICA est régulièrement exposé à des RDE et à des conditions environnementales difficiles, le rendant vulnérable aux variations de température, aux interruptions d'alimentation et aux surtensions transitoires. Les surtensions peuvent augmenter rapidement les niveaux d'alimentation au-delà des valeurs nominales (allant de 36 V ou 28 V à des valeurs aussi élevées que 115 V) ou les faire chuter sous les valeurs nominales (jusqu'à 14 V) en quelques millisecondes. Cette situation nécessite des contrôleurs robustes capables de gérer les variations de ligne et de charge pour garantir des opérations sûres, efficaces et fiables [13, 14]. Bien que des techniques de commande existantes, telles que la rétroaction en mode courant (RMC), la commande en mode coulissant (CeMC), la commande en un cycle (CUC), la commande de réinitialisation intégrale (CRI) et la commande de la tension d'entrée par anticipation (CTEA), aient été proposées pour répondre à ces défis, elles rencontrent toutes des limitations, y compris des instabilités conditionnelles, des complexités de mise en œuvre, des harmoniques imprévisibles, une dégradation des performances et des problèmes de couplage de bruit [15].

*Problème 3 : Manque de modélisation précise pour la conception du contrôleur :* Une modélisation précise est essentielle pour concevoir des contrôleurs pour les convertisseurs CC-CC, fournissant des informations cruciales sur le comportement du système dans diverses conditions de fonctionnement. Les méthodes de modélisation traditionnelles, telles que la technique de moyenne en régime permanent (MRP), simplifient l'analyse, mais négligent souvent des facteurs critiques en s'appuyant sur des hypothèses qui linéarisent et moyennent le système. Bien que la modélisation MRP puisse inclure des composants parasites clés, tels que la résistance série de l'inducteur et la résistance à l'état passant des transistors de puissance, elle reste limitée dans sa capacité à capturer les non-linéarités inhérentes du système et ses comportements variables dans le temps. Ce décalage entre les modèles théoriques simplifiés et les

performances réelles des convertisseurs nécessite des approches de modélisation améliorées qui puissent réduire l'écart entre les simulations et les applications pratiques.

*Problème 4 : Absence de gestion thermique intégrée :* Les variations thermiques ont un impact considérable sur la performance et la fiabilité des convertisseurs CC-CC, en particulier dans les applications à haute densité de puissance où une chaleur excessive peut dégrader le comportement des composants et les performances globales du système. De nombreuses stratégies de commande actuelles ne tiennent pas adéquatement compte des conditions thermiques en temps réel, rendant les convertisseurs vulnérables à la surchauffe, aux pertes d'efficacité et aux pannes potentielles du système. Bien que des avancées aient été réalisées pour optimiser l'efficacité et la réponse dynamique, peu de stratégies intègrent des données thermiques en temps réel dans les boucles de rétroaction de contrôle. Ce travail aborde ce manque en mettant en œuvre des capteurs de température pour une surveillance en temps réel, jetant les bases de conceptions futures de convertisseurs CC-CC thermiquement adaptatifs, qui améliorent la résilience face aux conditions environnementales fluctuantes et assurent une performance et une longévité constantes.

### 1.3 Importance de la recherche et originalité

Cette recherche est importante, car elle fait progresser le développement de convertisseurs CC-CC efficaces, fiables et compacts, particulièrement adaptés aux applications à haute performance telles que les véhicules électriques, les systèmes industriels et l'électronique grand public. Ce travail répond à plusieurs défis critiques dans le domaine de l'électronique de puissance en intégrant des stratégies de commande novatrices et des technologies de capteurs avancées, établissant les bases pour des développements futurs en gestion thermique et en adaptabilité dynamique des systèmes.

L'originalité de cette recherche se manifeste dans plusieurs aspects clés. Par exemple, l'introduction de contrôleurs basés sur la boucle à verrouillage de phase (BVP) dans les convertisseurs abaisseurs et Zeta propose une perspective unique et des améliorations novatrices de la réponse dynamique et de la stabilité globale du système. Cette approche, qui se distingue des méthodes traditionnelles comme le commande en mode de tension (CMT), présente le potentiel de surmonter plusieurs limitations rencontrées dans les stratégies précédentes, suscitant ainsi un intérêt pour l'exploration plus approfondie des possibilités offertes par cette recherche.

De plus, bien que la gestion thermique ne soit pas l'objectif principal de ce travail, la modélisation et l'intégration de capteurs de température dans le système de convertisseur CC-CC