**Titre:** Conception et intégration d'un circuit haute tension reconfigurable

Title: pour l'interfaçage de capteurs

**Auteur:** Timothée Matéo Trembly

Author:

**Date:** 2024

**Type:** Mémoire ou thèse / Dissertation or Thesis

**Référence:** Trembly, T. M. (2024). Conception et intégration d'un circuit haute tension reconfigurable pour l'interfaçage de capteurs [Mémoire de maîtrise, Polytechnique Montréal]. PolyPublie. <https://publications.polymtl.ca/59049/>

Citation:

## Document en libre accès dans PolyPublie Open Access document in PolyPublie

**URL de PolyPublie:** <https://publications.polymtl.ca/59049/>

PolyPublie URL:

**Directeurs de recherche:** Ahmad Hassan, & Yvon Savaria

Advisors:

**Programme:** Génie électrique

Program:

**POLYTECHNIQUE MONTRÉAL**

affiliée à l'Université de Montréal

**Conception et intégration d'un circuit haute tension reconfigurable pour

l'interfaçage de capteurs**

**TIMOTHÉE MATEO TREMBLY**

Département de génie électrique

Mémoire présenté en vue de l'obtention du diplôme de *Maîtrise ès sciences appliquées*

Génie électrique

Août 2024

**POLYTECHNIQUE MONTRÉAL**

affiliée à l'Université de Montréal

Ce mémoire intitulé :

**Conception et intégration d'un circuit haute tension reconfigurable pour

l'interfaçage de capteurs**

présenté par **Timothée Matéo TREMBLY**

en vue de l'obtention du diplôme de *Maîtrise ès sciences appliquées*

a été dûment accepté par le jury d'examen constitué de :

**Tarek OULD-BACHIR**, président

**Ahmad HASSAN**, membre et directeur de recherche

**Yvon SAVARIA**, membre et codirecteur de recherche

**Mostafa DARVISHI**, membre

## DÉDICACE

*À Albane, pour avoir toujours cru en moi.*

## REMERCIEMENTS

Avant toute chose, je tiens à exprimer ma profonde gratitude à mes superviseurs, les professeurs Ahmad Hassan et Yvon Savaria, pour l'opportunité exceptionnelle qu'ils m'ont offert de réaliser ma maîtrise sous leur direction. Je leur suis reconnaissant pour leur soutien constant, leur motivation inébranlable et la confiance qu'ils m'ont accordée tout au long de mes études. J'adresse également mes remerciements au Docteur Mostafa Amer pour ses conseils précieux et son écoute attentive.

Je souhaite remercier les membres du comité, les professeurs Tarek Ould-Bachir et Mostafa Darvishi, pour avoir accepté d'évaluer ce travail de maîtrise. Leurs retours constructifs ont incontestablement enrichi ce compte-rendu de mes travaux.

Je suis également reconnaissant envers tous les membres du projet VairCRAFT, qui ont contribué à donner un sens profond à mon travail. Un merci particulier à Réjean Lepage pour son assistance précieuse, m'ayant permis un accès constant aux logiciels nécessaires à mon travail. Surtout, je tiens à remercier Justin Pabot, mon interlocuteur le plus proche et ami fidèle durant ces deux années de maîtrise, toujours présent dans les bons comme dans les mauvais moments.

Je suis reconnaissant à MITACS et au CRSNG pour leur soutien financier tout au long de ma maîtrise. Merci également à CMC Microsystems et au CNR pour l'accès à leurs outils de conception et à leurs usines de fabrication.

Enfin, je souhaite adresser mes remerciements les plus sincères à ma famille, à mes amis et à tous ceux qui ont croisé mon chemin pour les belles choses qu'ils m'ont apportées. Merci à Lucas, Thomas, Justin, Michel, Boris, Abélia, Luc, Valérie et Chloé. Ces travaux ne seraient pas ce qu'ils sont aujourd'hui sans la force que vous m'avez insufflée.

## RÉSUMÉ

Depuis quelques années, l'industrie du transport connaît un important essor des solutions électriques, qui pourraient représenter une solution viable et durable pour réduire l'impact environnemental et social de cette industrie. Cette transition vers l'électrique induit également une augmentation du volume d'électronique embarquée installée dans les véhicules pour améliorer leur performance et leur consommation.

Cependant, de tels circuits sont coûteux et complexes à mettre en place, en particulier dans des solutions industrielles qui doivent maintenir de bons niveaux de performance en milieu hostile et sous des niveaux de tensions élevés, supérieurs à ceux usuellement présentés dans la littérature. Pour répondre à cette problématique de complexité de conception, ce mémoire contribue au développement d'une interface de capteurs reconfigurable, adaptée à une grande variété d'applications de précision haute tension.

L'interface de capteurs doit amplifier et filtrer les signaux analogiques des capteurs avant leur conversion et traitement numériques. Les amplificateurs à gain programmable (AGP) sont essentiels pour ajuster le niveau de signal à une plage optimale pour les convertisseurs analogique-numérique (CAN), tandis que les filtres anti-repliement (FAR) sont cruciaux pour éliminer les fréquences indésirables avant l'échantillonnage. Ce mémoire se propose de développer des solutions avancées pour ces deux composants en se concentrant sur une structure d'AGP à rétroaction négative, ainsi qu'un FAR continu, dont la fréquence de coupure sera reconfigurable. Ces deux circuits bénéficieront d'une conception en mode-courant, qui a su montrer dans la littérature récente de nombreux avantages pour les interfaces de précision.

L'objectif principal est d'imaginer une interface de capteurs offrant une haute précision et une robustesse remarquable face aux variations environnementales dans un environnement haute tension, tout en garantissant sa versatilité pour pouvoir l'adapter à une multitude d'applications sans devoir repasser par de coûteuses étapes de conception.

La revue de littérature explore les travaux existants sur les AGP et les FAR, en mettant l'accent sur les architectures actuelles les plus pertinentes face aux contraintes de conception liées à la haute tension. En particulier, ce manuscrit argumente sur les avantages et inconvénients des AGP basés sur une transconductance contrôlée et sur une rétroaction négative, et justifie le choix de cette seconde technique pour une application haute tension nécessitant précision, linéarité et stabilité sur de larges plages de fonctionnement.

En ce qui concerne les FAR, la revue couvre les différentes techniques de conception de

filtres, y compris les filtres actifs et passifs, et leurs performances en termes de réjection des fréquences indésirables dans les bandes de fréquences basses. Les FAR doivent être robustes aux variations de processus, de tension et de température (PVT), et ce mémoire évalue les approches reconfigurables qui permettent une adaptation dynamique des caractéristiques du filtre en fonction des conditions opérationnelles.

Les travaux décrits dans ce mémoire comprennent la conception détaillée, la simulation et l'implémentation de l'AGP et du FAR. Pour l'AGP, une structure à rétroaction négative a été choisie et optimisée. Une structure innovante et résiliente aux variations de procédé et de température est également proposée pour permettre la conversion à la volée d'un domaine de tension bipolaire vers un domaine de tension unipolaire. La conception inclut des simulations post-layout pour vérifier les performances en termes de linéarité, de bruit, d'impédance d'entrée et de sortie et de réjection du mode commun. Une attention particulière a été portée à la stabilité du gain sur une large gamme de températures et de variations de procédé.

Le FAR développé dans ce mémoire utilise une approche reconfigurable continue pour s'adapter aux changements de fréquence des signaux parasites dans une multitude d'applications. La solution proposée se base sur la modélisation et le contrôle des éléments parasites des éléments actifs utilisés. Tout comme pour l'AGP, la performance du FAR est vérifiée à travers des simulations post-layout, sur une large gamme de températures et de variations de procédé.

Les résultats montrent que l'AGP conçu présente une faible erreur de gain, une haute impédance d'entrée et une faible impédance de sortie, ce qui est crucial pour maintenir l'intégrité des signaux des capteurs. Les tests ont démontré une excellente stabilité de gain pour tout signal dans la plage d'amplitude et de fréquence d'entrée, et pour une large gamme de températures et de variations de procédé.

Le FAR reconfigurable a quant à lui démontré une grande précision sur le contrôle de sa fréquence de coupure par rapport à la modélisation mathématique. Les simulations post-layout ont pu démontrer la résilience du FAR aux variations de procédé, mais également sa vulnérabilité aux variations de température. Ce manuscrit présente également de multiples pistes d'amélioration pour le système présenté, afin notamment d'améliorer la résilience du FAR aux variations de température, et d'améliorer la précision de l'AGP pour le rendre compétitif par rapport aux solutions industrielles discrètes existantes sur le marché.

En conclusion, cette recherche propose une solution avancée pour les interfaces de capteurs des véhicules électriques, combinant un AGP à rétroaction négative et un FAR reconfigurable. Il s'agit d'un système innovant, combinant dans un seul dé monolithique un AGP et un FAR en mode-courant ainsi qu'un convertisseur de tension bipolaire/unipolaire. Le dé est également

capable de fonctionner avec des plages de tensions élevées, atteignant  $\pm 10$  V, ce qui est encore absent de la littérature pour ce niveau de performance.

Les composants présentés offrent des performances prometteuses en termes de précision et de robustesse, démontrant la pertinence de nos choix de conception. Les travaux futurs se concentreront sur l'optimisation des sous-systèmes de circuit, afin d'amener leur performance au niveau des puces industrielles présentes sur le marché.

Ce mémoire de maîtrise contribue significativement au domaine des interfaces de capteurs, en proposant des solutions innovantes qui répondent aux exigences strictes des systèmes électroniques industriels modernes. Les résultats obtenus ouvrent la voie à de nouvelles recherches et développements dans ce domaine, avec des implications potentielles pour une large gamme d'applications technologiques.

## ABSTRACT

In recent years, the transportation industry has experienced a significant rise in adopting electric vehicles, which could represent a viable and sustainable option to reduce this industry's environmental and social impact. This transition to electric vehicles also increases the volume of embedded electronics installed in these vehicles to improve their performance and efficiency.

However, such circuits are expensive and complex to implement, particularly in industrial solutions that must maintain high-performance levels in harsh environments and under high-voltage conditions that exceed those usually presented in the literature. To address this design complexity, this thesis contributes to developing reconfigurable sensor interfaces suitable for a wide range of high-precision, high-voltage applications.

The sensor interface must amplify and filter the analog signals from the sensors before their digital conversion and processing. Programmable gain amplifiers (PGAs) are essential for adjusting the signal level to an optimal range for analog-to-digital converters (ADCs). At the same time, anti-aliasing filters (AAFs) are crucial for eliminating unwanted frequencies before sampling. This thesis aims to develop advanced solutions for these two components, focusing on a negative feedback PGA structure and a continuous AAF with reconfigurable cutoff frequency. Both circuits will benefit from a current-mode design, which has shown numerous advantages for precision interfaces in recent literature.

The primary objective is to design a sensor interface that offers high precision and remarkable robustness against environmental variations in a high-voltage environment, while ensuring versatility for adoption in multiple applications without requiring costly redesigns.

The literature review explores existing works on PGAs and AAFs, emphasizing the most relevant current architectures regarding high-voltage design constraints. Specifically, this manuscript discusses the advantages and drawbacks of PGAs based on controlled transconductance and negative feedback, justifying the choice of the latter technique for high-voltage applications requiring precision, linearity, and stability over wide operating ranges.

Regarding AAFs, the review covers various filter design techniques, including active and passive filters, and their performance in rejecting unwanted frequencies in low-frequency bands. AAFs must be robust to process, voltage, and temperature (PVT) variations, and this thesis evaluates reconfigurable approaches that allow dynamic adaptation of the filter's characteristics based on operating conditions.

The work in this thesis includes the detailed design, simulation, and implementation of the PGA and AAF. For the PGA, a negative feedback structure was chosen and optimized. An innovative structure resilient to process and temperature variations is also proposed to enable on-the-fly conversion from a bipolar voltage domain to a unipolar voltage domain. The design includes post-layout simulations to verify performance in linearity, noise, input and output impedance, and common-mode rejection. Particular attention was given to gain stability over a wide range of temperatures and process variations.

The AAF developed in this thesis uses a continuous reconfigurable approach to adapt to changes in the frequency of parasitic signals across various applications. The proposed solution is based on modeling and controlling the active components' parasitic elements. Similarly to the PGA, the performance of the AAF is verified through post-layout simulations over a wide range of temperatures and process variations.

The results show that the designed PGA exhibits low gain error, high input impedance, and low output impedance, which are crucial for maintaining the integrity of sensor signals. Tests have demonstrated excellent gain stability for any signal within the input amplitude and frequency range, and across a wide range of temperatures and process variations.

The reconfigurable AAF demonstrated high accuracy in controlling its cutoff frequency compared to mathematical modeling. Post-layout simulations showed the AAF's resilience to process variations, but also its vulnerability to temperature variations. This manuscript also presents several paths for improvement for the proposed system, particularly to enhance the AAF's resilience to temperature variations and to improve the PGA's accuracy to make it competitive with existing discrete industrial solutions on the market.

In conclusion, this research proposes an advanced solution for sensor interfaces in electric vehicles, combining a negative feedback PGA and a reconfigurable AAF. This innovative system combines a PGA, a current-mode AAF, and a bipolar/unipolar voltage converter in a single monolithic die. The die can also operate with high voltage ranges, reaching  $\pm 10$  V, which is not yet present in the literature at this performance level.

The components proposed and validated in this thesis offer promising performance in terms of precision and robustness, demonstrating the relevance of our design choices. Future work will focus on optimizing the circuit subsystems to bring their performance to the level of industrial chips available on the market.

This master's thesis significantly contributes to sensor interfaces by proposing innovative solutions that meet the stringent requirements of modern industrial electrical systems. The reported results pave the way for further research and development, with potential implica-

tions for various technological applications.

## TABLE DES MATIÈRES

|                                                                 |        |

|-----------------------------------------------------------------|--------|

| DÉDICACE . . . . .                                              | iii    |

| REMERCIEMENTS . . . . .                                         | iv     |

| RÉSUMÉ . . . . .                                                | v      |

| ABSTRACT . . . . .                                              | viii   |

| TABLE DES MATIÈRES . . . . .                                    | xi     |

| LISTE DES TABLEAUX . . . . .                                    | xiv    |

| LISTE DES FIGURES . . . . .                                     | xv     |

| LISTE DES SIGLES ET ABRÉVIATIONS . . . . .                      | xviii  |

| LISTE DES ANNEXES . . . . .                                     | xix    |

| <br>CHAPITRE 1 INTRODUCTION . . . . .                           | <br>1  |

| 1.1 Contexte . . . . .                                          | 1      |

| 1.2 Problématiques et motivations . . . . .                     | 2      |

| 1.3 Objectifs de recherche . . . . .                            | 3      |

| 1.4 Contributions . . . . .                                     | 4      |

| 1.5 Plan du mémoire . . . . .                                   | 4      |

| <br>CHAPITRE 2 REVUE DE LITTÉRATURE . . . . .                   | <br>6  |

| 2.1 Les amplificateurs à gain programmable . . . . .            | 6      |

| 2.1.1 Structures à transconductance contrôlée . . . . .         | 8      |

| 2.1.2 Structures à rétroaction négative . . . . .               | 15     |

| 2.2 Les filtres anti-repliement . . . . .                       | 20     |

| <br>CHAPITRE 3 ARCHITECTURE DE L'INTERFACE DE CAPTEURS PROPOSÉE | <br>26 |

| 3.1 Le convoyeur de courant de seconde génération . . . . .     | 28     |

| 3.1.1 Le suiveur en tension . . . . .                           | 29     |

| 3.1.2 Les miroirs de courant . . . . .                          | 30     |

| 3.2 L'Amplificateur Opérationnel . . . . .                      | 31     |

|                                              |                                                                      |    |

|----------------------------------------------|----------------------------------------------------------------------|----|

| 3.3                                          | L'étage d'entrée haute tension . . . . .                             | 33 |

| 3.3.1                                        | Les interrupteurs haute tension . . . . .                            | 33 |

| 3.3.2                                        | L'étage de conversion tension/courant . . . . .                      | 37 |

| 3.4                                          | Le filtre anti-repliement . . . . .                                  | 38 |

| 3.4.1                                        | La source de courant contrôlée en tension . . . . .                  | 39 |

| 3.5                                          | L'étage de sortie . . . . .                                          | 41 |

| 3.5.1                                        | Conversion courant/tension . . . . .                                 | 41 |

| 3.5.2                                        | Conversion bipolaire/unipolaire . . . . .                            | 43 |

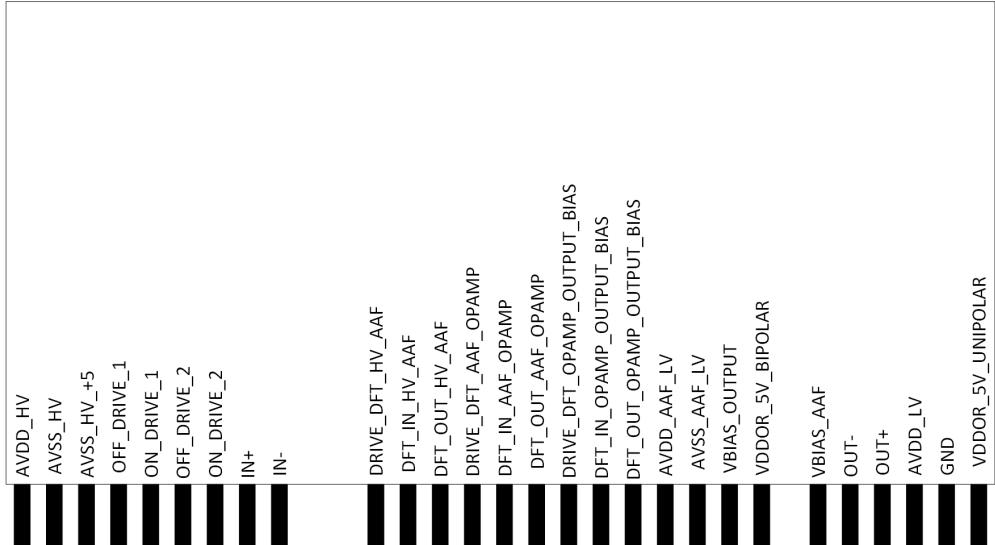

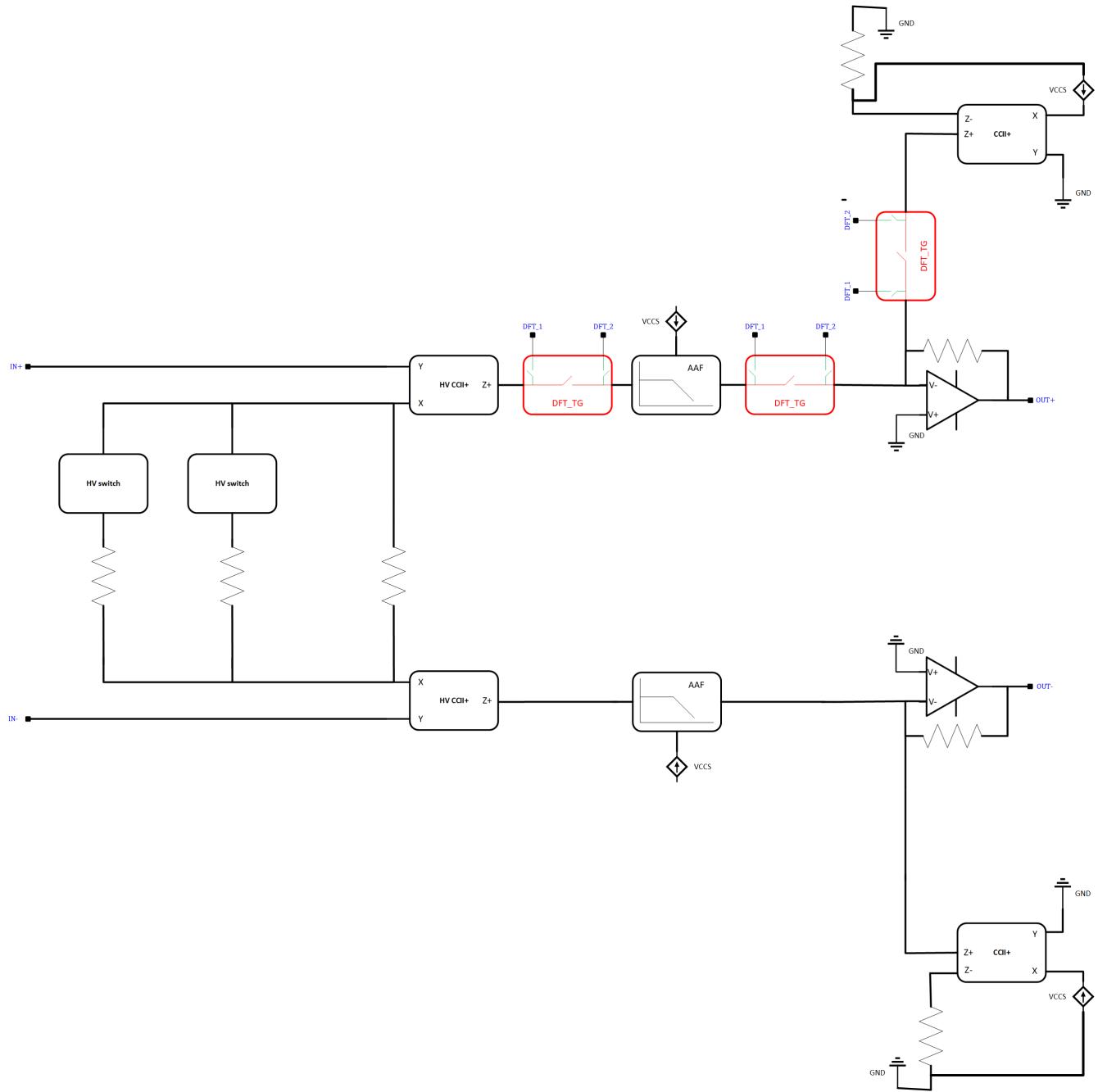

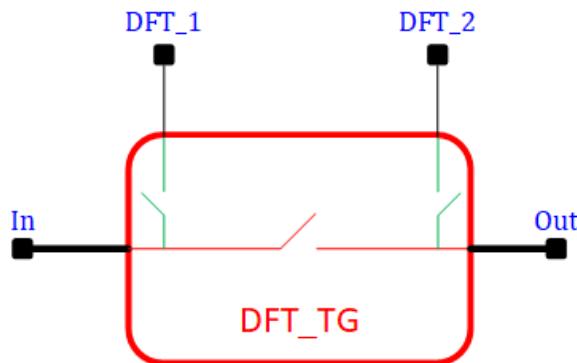

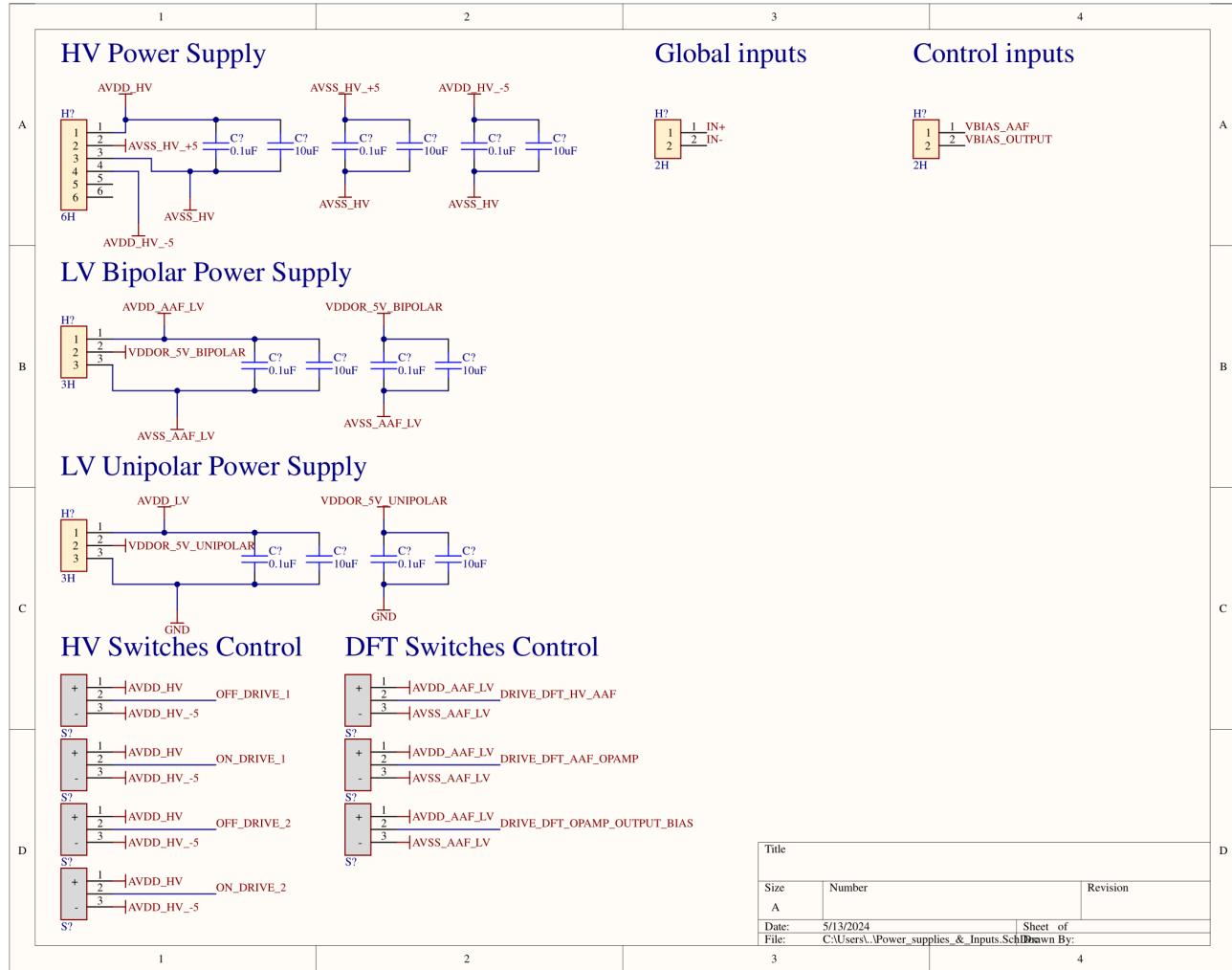

| 3.6                                          | Conception pour la testabilité . . . . .                             | 45 |

| CHAPITRE 4 RÉSULTATS EXPÉRIMENTAUX . . . . . |                                                                      | 47 |

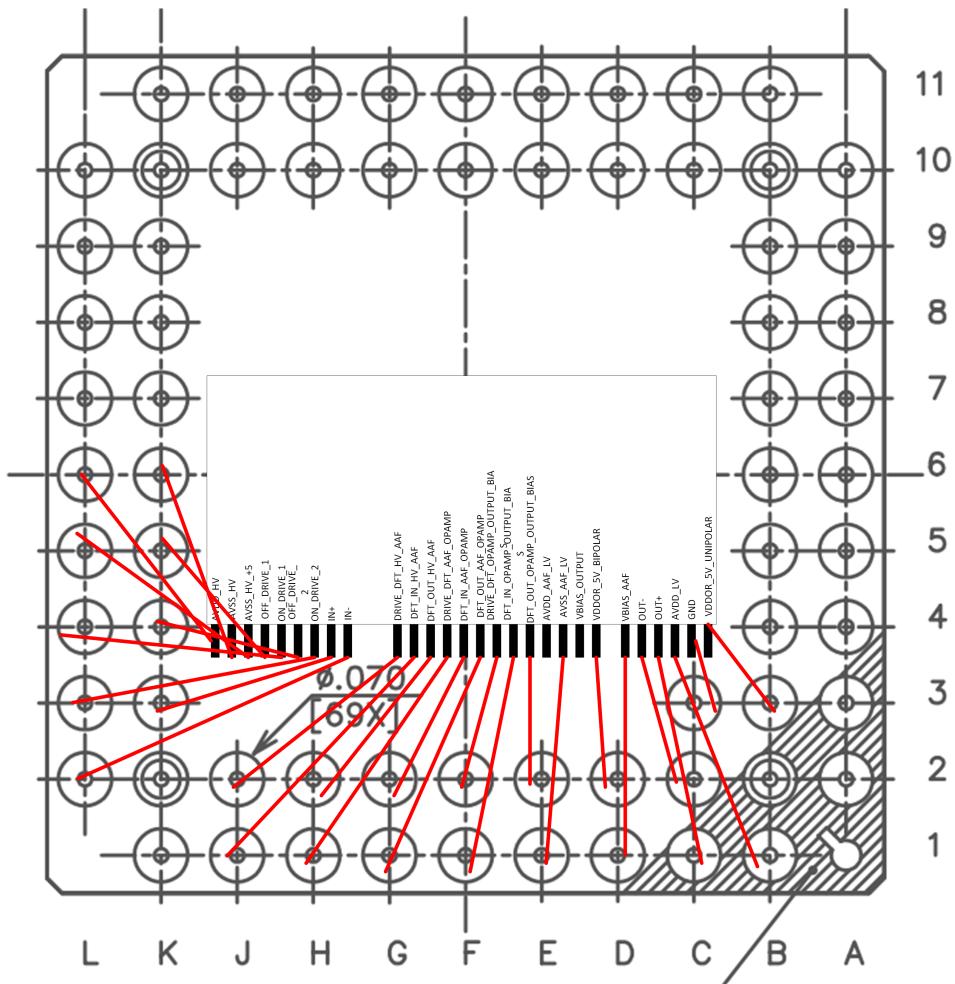

| 4.1                                          | Layout de la puce . . . . .                                          | 47 |

| 4.1.1                                        | Layout général des circuits et dimensionnement des passifs . . . . . | 47 |

| 4.1.2                                        | Invariance en température des résistances . . . . .                  | 48 |

| 4.2                                          | Résultats de simulation post-layout : AGP . . . . .                  | 51 |

| 4.2.1                                        | Erreur et non-linéarité du gain . . . . .                            | 52 |

| 4.2.2                                        | Impédance d'entrée et de sortie . . . . .                            | 53 |

| 4.2.3                                        | TRMC du système . . . . .                                            | 55 |

| 4.2.4                                        | Invariance aux variations PVT . . . . .                              | 56 |

| 4.3                                          | Résultats de simulation post-layout : FAR . . . . .                  | 56 |

| 4.3.1                                        | Contrôle de la SCCT et du FAR . . . . .                              | 57 |

| 4.3.2                                        | Analyse fréquentielle de la reconfigurabilité . . . . .              | 58 |

| 4.3.3                                        | Résistance aux variations PVT . . . . .                              | 58 |

| 4.3.4                                        | Mesures supplémentaires . . . . .                                    | 60 |

| CHAPITRE 5 DISCUSSION . . . . .              |                                                                      | 61 |

| 5.1                                          | Fonctionnalité . . . . .                                             | 61 |

| 5.2                                          | Précision du gain . . . . .                                          | 61 |

| 5.3                                          | Impédances d'entrée et de sortie du système . . . . .                | 62 |

| 5.4                                          | TRMC du système . . . . .                                            | 63 |

| 5.5                                          | Reconfigurabilité du FAR . . . . .                                   | 63 |

| 5.6                                          | Comparaison avec la littérature . . . . .                            | 65 |

| CHAPITRE 6 CONCLUSION . . . . .              |                                                                      | 67 |

| 6.1                                          | Synthèse des travaux . . . . .                                       | 67 |

| 6.2                                          | Limitations de la solution proposée . . . . .                        | 67 |

| 6.3                                          | Améliorations futures . . . . .                                      | 68 |

|                      |    |

|----------------------|----|

| RÉFÉRENCES . . . . . | 70 |

| ANNEXES . . . . .    | 74 |

**LISTE DES TABLEAUX**

|             |                                                                                                                          |    |

|-------------|--------------------------------------------------------------------------------------------------------------------------|----|

| Tableau 3.1 | Spécifications souhaitées du circuit envisagé . . . . .                                                                  | 26 |

| Tableau 4.1 | Fréquence de coupure (kHz) du FAR avec variations de procédé et de température ( $I_{bias} = 10 \mu\text{A}$ ) . . . . . | 59 |

| Tableau 5.1 | Spécifications souhaitées du circuit envisagé et résultats obtenus . . .                                                 | 61 |

| Tableau 5.2 | Performance du FAR en comparaison avec la littérature . . . . .                                                          | 65 |

## LISTE DES FIGURES

|             |                                                                                                                                                                                                                |    |

|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

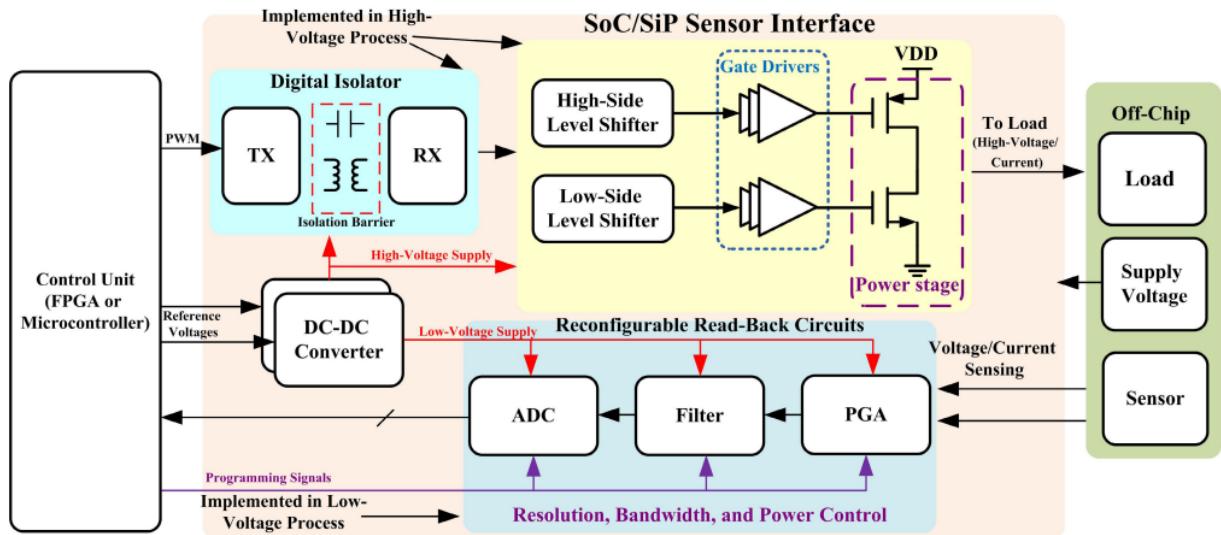

| Figure 1.1  | Schéma-bloc de l'interface de capteurs versatile proposée . . . . .                                                                                                                                            | 2  |

| Figure 2.1  | Un APG basique en boucle fermée (a) et en boucle ouverte (b) . . . . .                                                                                                                                         | 7  |

| Figure 2.2  | Un AGP basique en boucle ouverte, basé sur un réseau de résistances . . . . .                                                                                                                                  | 8  |

| Figure 2.3  | Schéma conceptuel (a) et au niveau transistor (b) de l'AGP à dégénération active . . . . .                                                                                                                     | 10 |

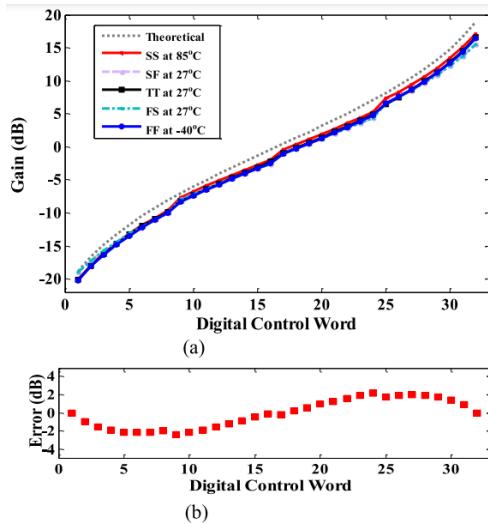

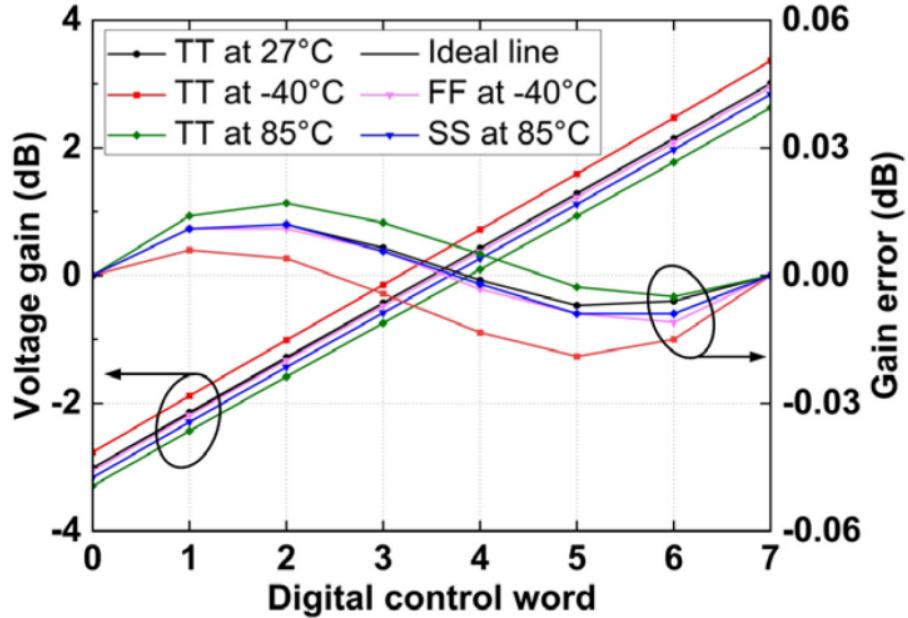

| Figure 2.4  | Comparaison du gain théorique et simulé pour différents 'coins' du domaine paramétrique ou 'corners' (a) et la courbe d'erreur sur le gain pour le corner typique (b) de l'AGP à dégénération active . . . . . | 10 |

| Figure 2.5  | AGP à commutation de transistors . . . . .                                                                                                                                                                     | 11 |

| Figure 2.6  | Erreur de gain dB-linéaire (a) et échelons de gain dB-linéaire (b) en fonction de $k_1$ pour l'AGP à commutation de transistors . . . . .                                                                      | 11 |

| Figure 2.7  | Schéma de principe (a) et schéma au niveau transistor (b) de l'AGP à rétroaction positive active- $g_m$ (b) . . . . .                                                                                          | 12 |

| Figure 2.8  | Erreur de gain pour de multiples valeurs de gain et corners pour l'AGP à rétroaction positive active- $g_m$ . . . . .                                                                                          | 13 |

| Figure 2.9  | Schéma de la cellule élémentaire pour l'AGP à cellules cascadées . . . . .                                                                                                                                     | 14 |

| Figure 2.10 | Erreur de gain en fonction de la température (a) et linéarité du gain en fonction du corner de procédé (b) pour l'AGP à cellules cascadées . . . . .                                                           | 14 |

| Figure 2.11 | AGP à AOP simple avec rétroaction résistive . . . . .                                                                                                                                                          | 15 |

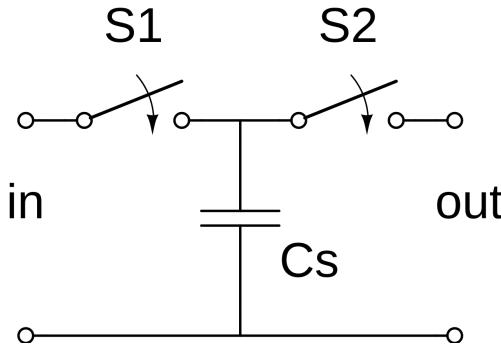

| Figure 2.12 | Capacité commutée . . . . .                                                                                                                                                                                    | 16 |

| Figure 2.13 | AGP à amplificateurs cascades . . . . .                                                                                                                                                                        | 17 |

| Figure 2.14 | Courbe d'erreur pour les différents étages de l'AGP à amplificateurs cascades . . . . .                                                                                                                        | 18 |

| Figure 2.15 | Un amplificateur d'instrumentation . . . . .                                                                                                                                                                   | 19 |

| Figure 2.16 | AGP en Mode-Courant . . . . .                                                                                                                                                                                  | 20 |

| Figure 2.17 | Filtre passe-haut de Sallen-Key . . . . .                                                                                                                                                                      | 22 |

| Figure 2.18 | Circuit de multiplication de capacité . . . . .                                                                                                                                                                | 23 |

| Figure 2.19 | FAR en courant à rétroactions multiples . . . . .                                                                                                                                                              | 23 |

| Figure 2.20 | FAR à résistance active . . . . .                                                                                                                                                                              | 24 |

| Figure 2.21 | FAR à base de CCII . . . . .                                                                                                                                                                                   | 25 |

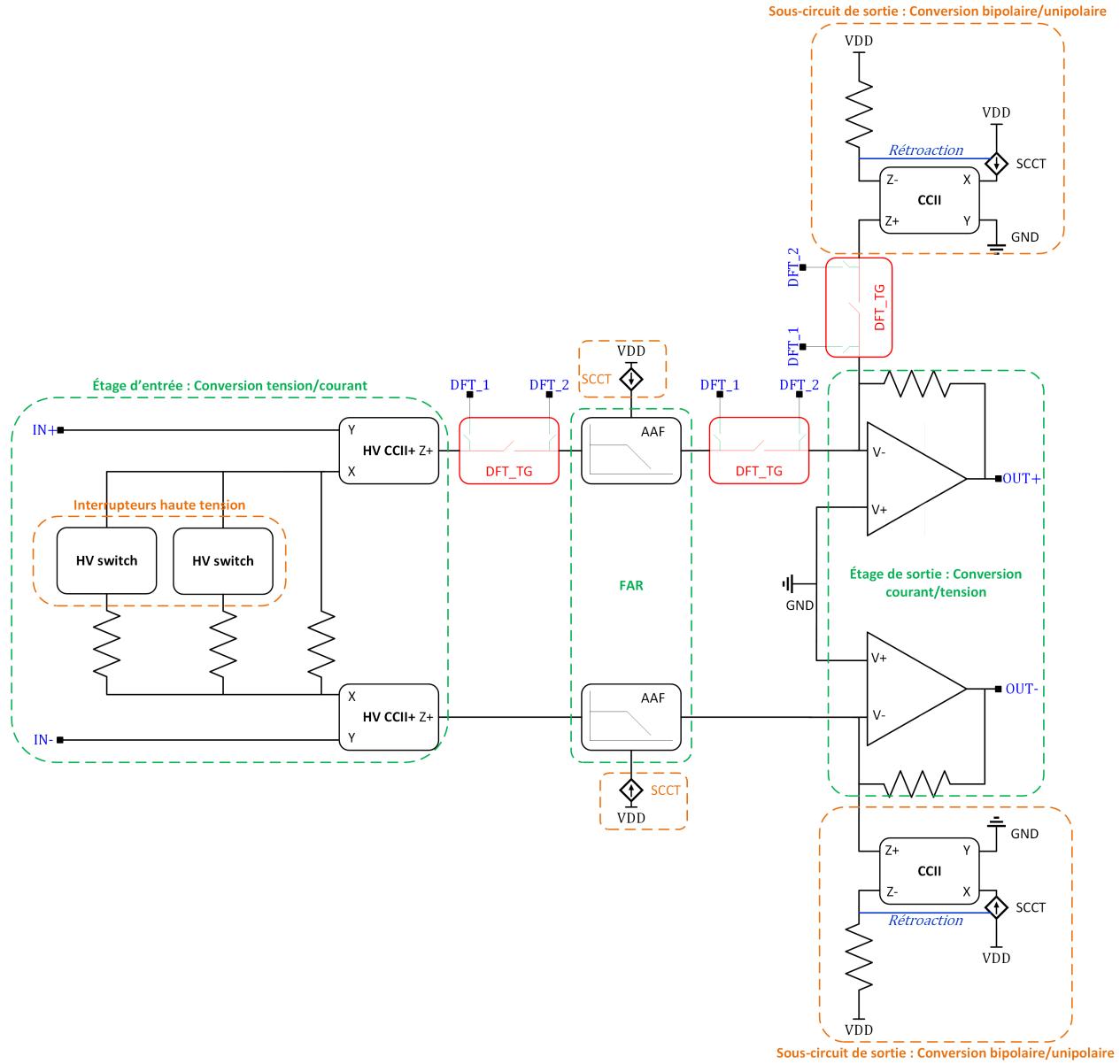

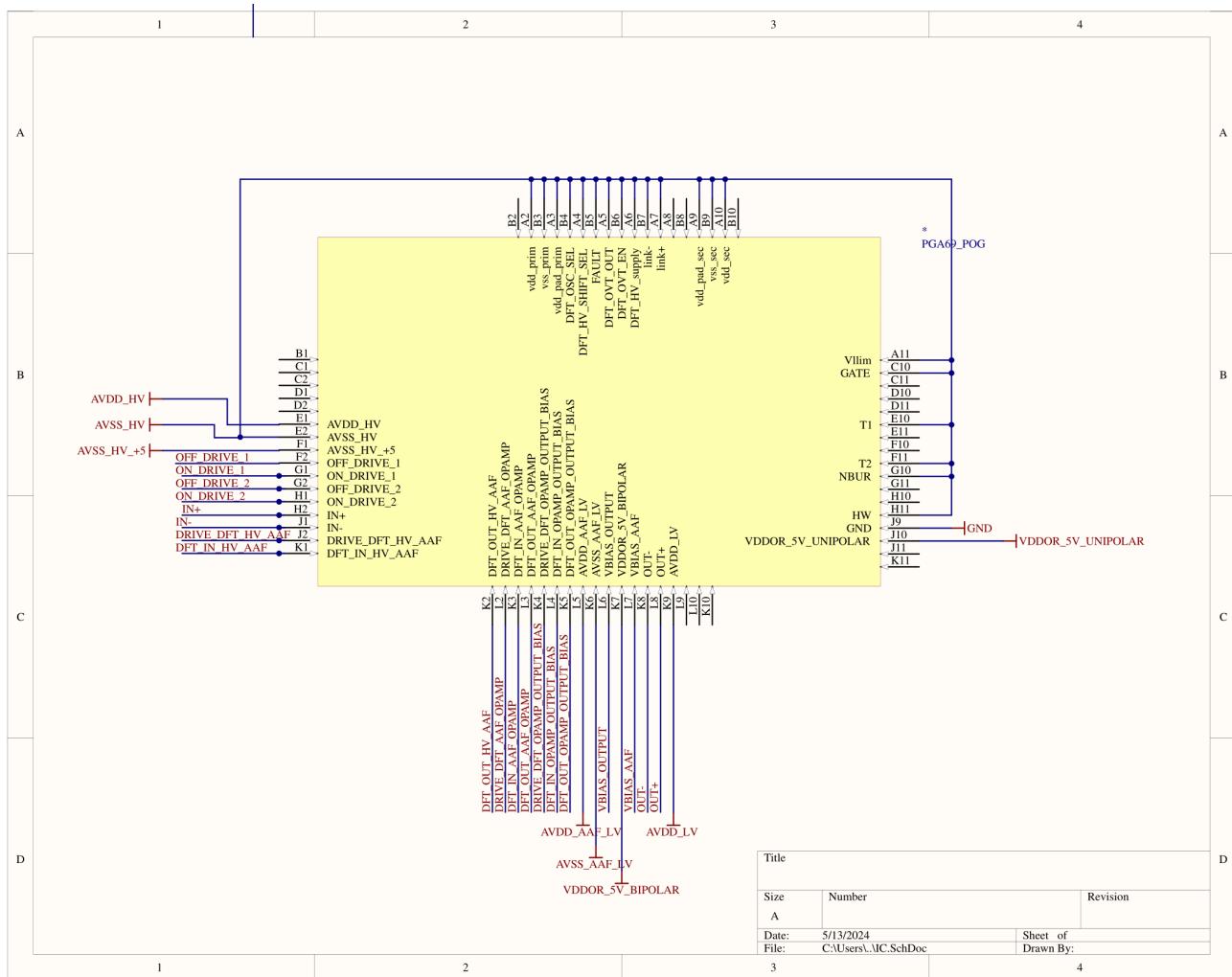

| Figure 3.1  | Circuit haute tension d'interfaçage pour une interface de capteurs reconfigurable proposé . . . . .                                                                                                            | 27 |

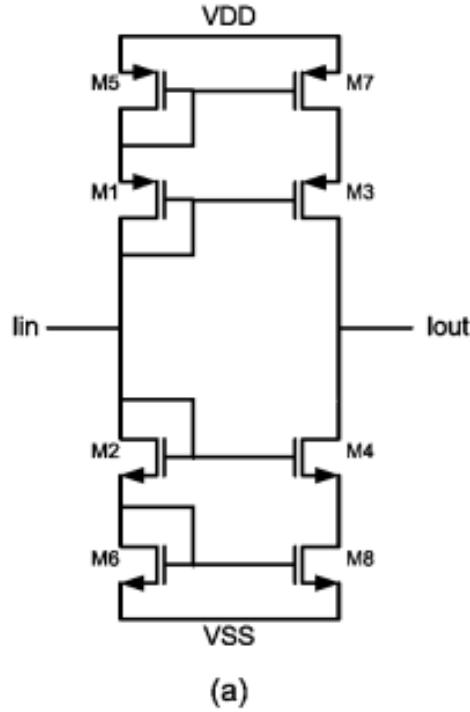

| Figure 3.2  | Un CCII contrôlé en courant (CCCI) . . . . .                                                                                                                                                                   | 29 |

|             |                                                                                                                                                                                 |    |

|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Figure 3.3  | Un DFVF . . . . .                                                                                                                                                               | 30 |

| Figure 3.4  | Un miroir de courant cascode . . . . .                                                                                                                                          | 31 |

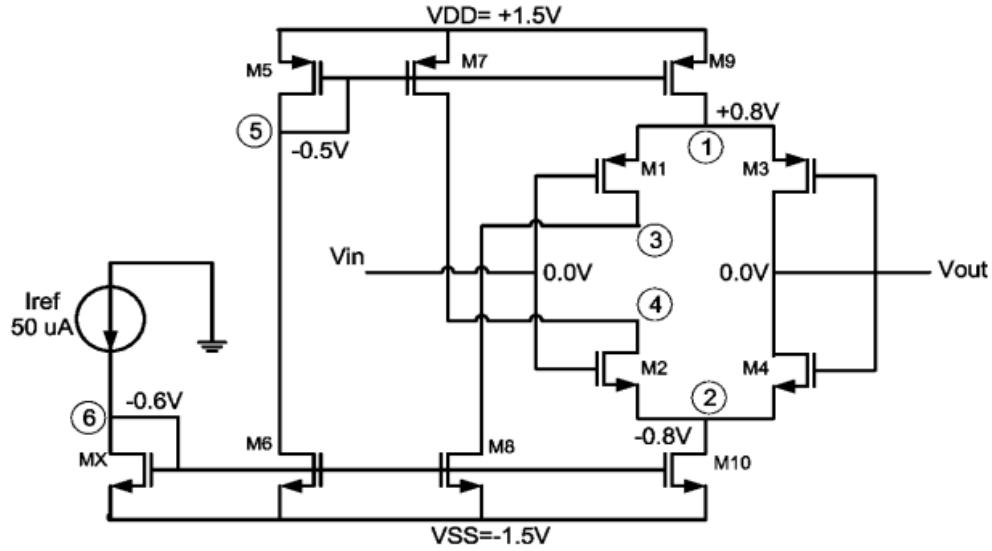

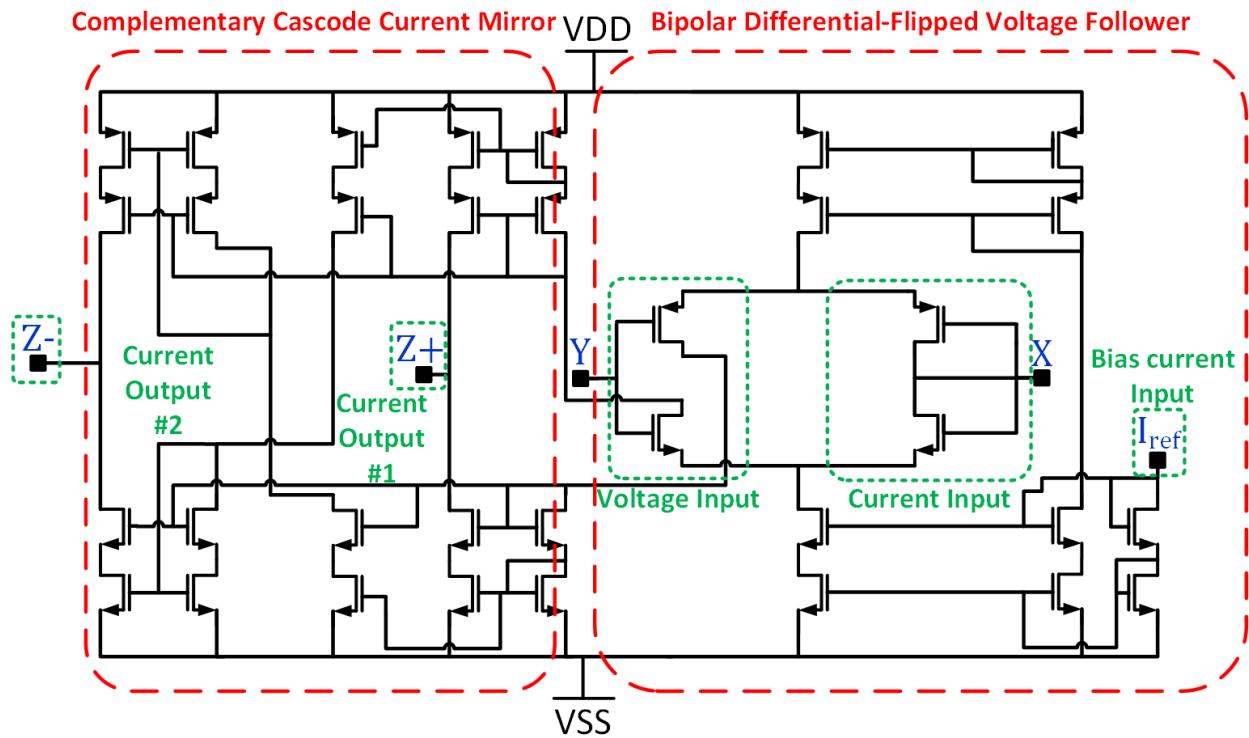

| Figure 3.5  | Le CCCII proposé . . . . .                                                                                                                                                      | 32 |

| Figure 3.6  | L'AOP utilisé . . . . .                                                                                                                                                         | 32 |

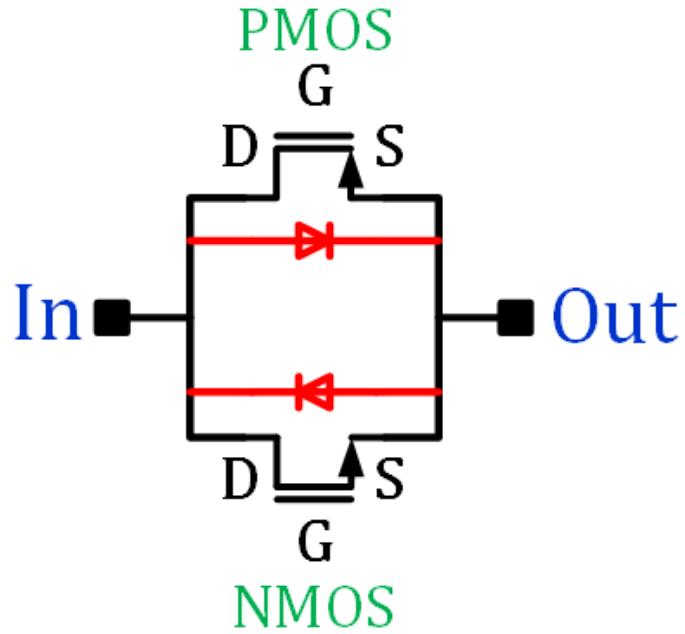

| Figure 3.7  | Une porte de transmission impossible à fermer avec des DEMOS HT                                                                                                                 | 34 |

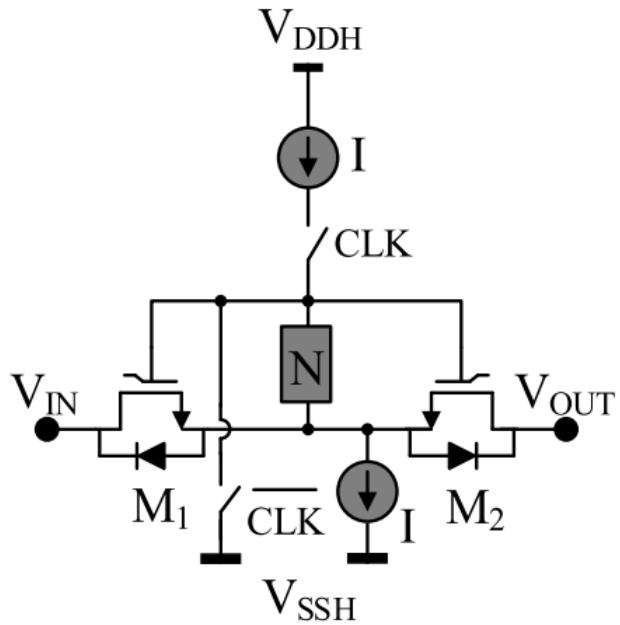

| Figure 3.8  | Première version de l'interrupteur haute tension employé . . . . .                                                                                                              | 35 |

| Figure 3.9  | Seconde version de l'interrupteur haute tension employé . . . . .                                                                                                               | 36 |

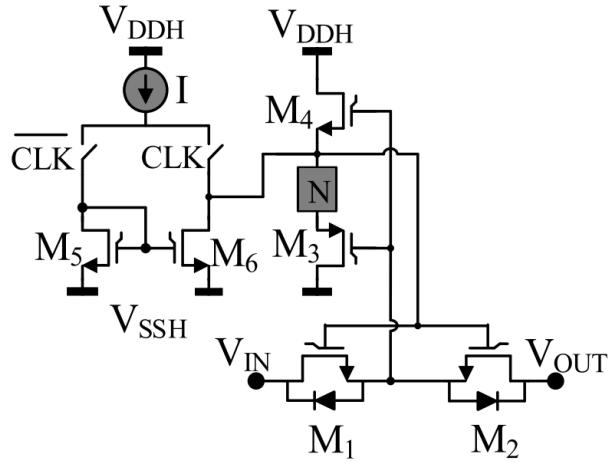

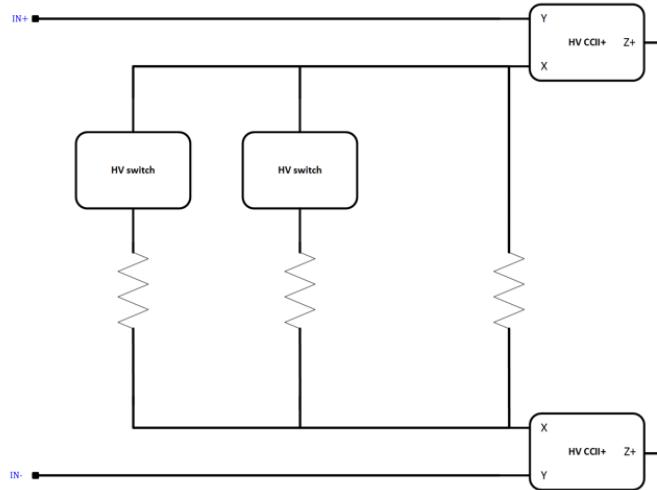

| Figure 3.10 | Le CCCII HT proposé . . . . .                                                                                                                                                   | 37 |

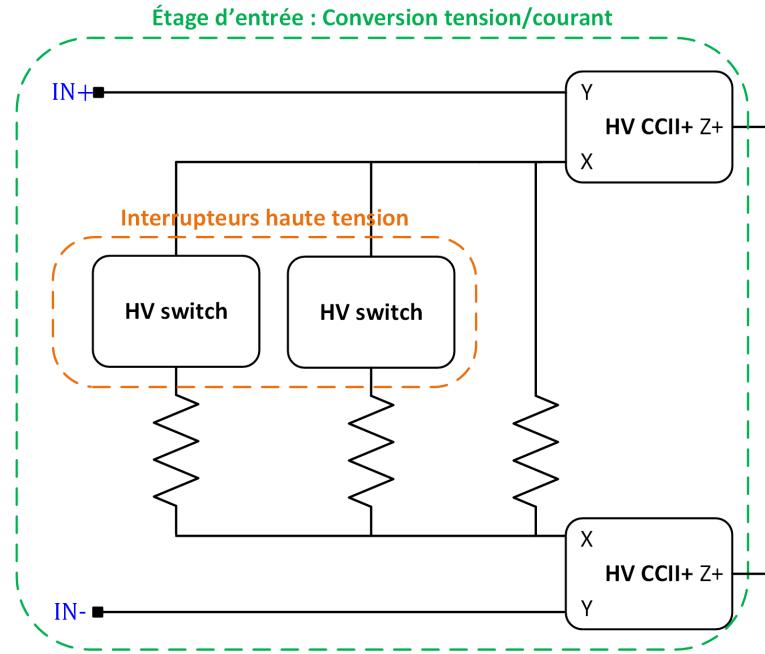

| Figure 3.11 | L'étage d'entrée HT . . . . .                                                                                                                                                   | 38 |

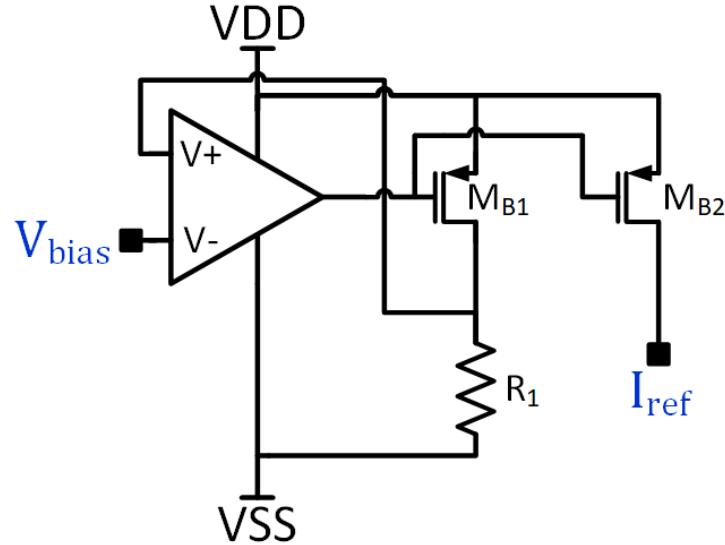

| Figure 3.12 | La source de courant contrôlée en tension . . . . .                                                                                                                             | 39 |

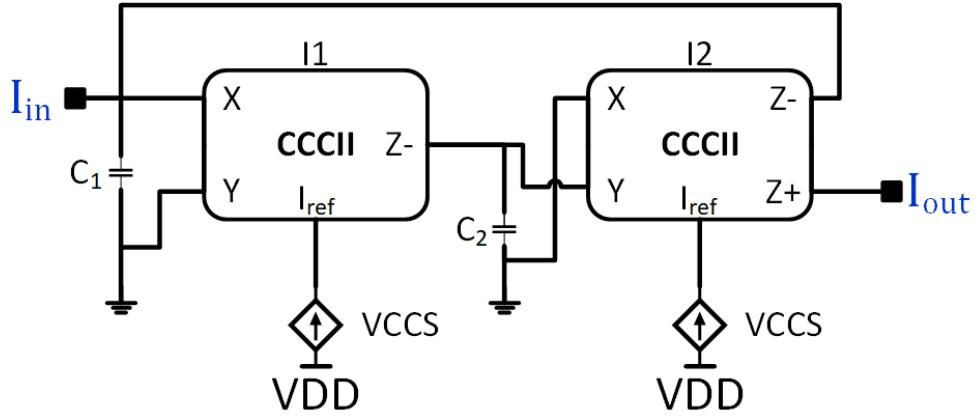

| Figure 3.13 | Le filtre anti-repliement proposé . . . . .                                                                                                                                     | 40 |

| Figure 3.14 | Circuit équivalent du FAR proposé . . . . .                                                                                                                                     | 41 |

| Figure 3.15 | Étage de sortie à AOP . . . . .                                                                                                                                                 | 42 |

| Figure 3.16 | SCCT avec rétroaction pour l'étage de sortie . . . . .                                                                                                                          | 44 |

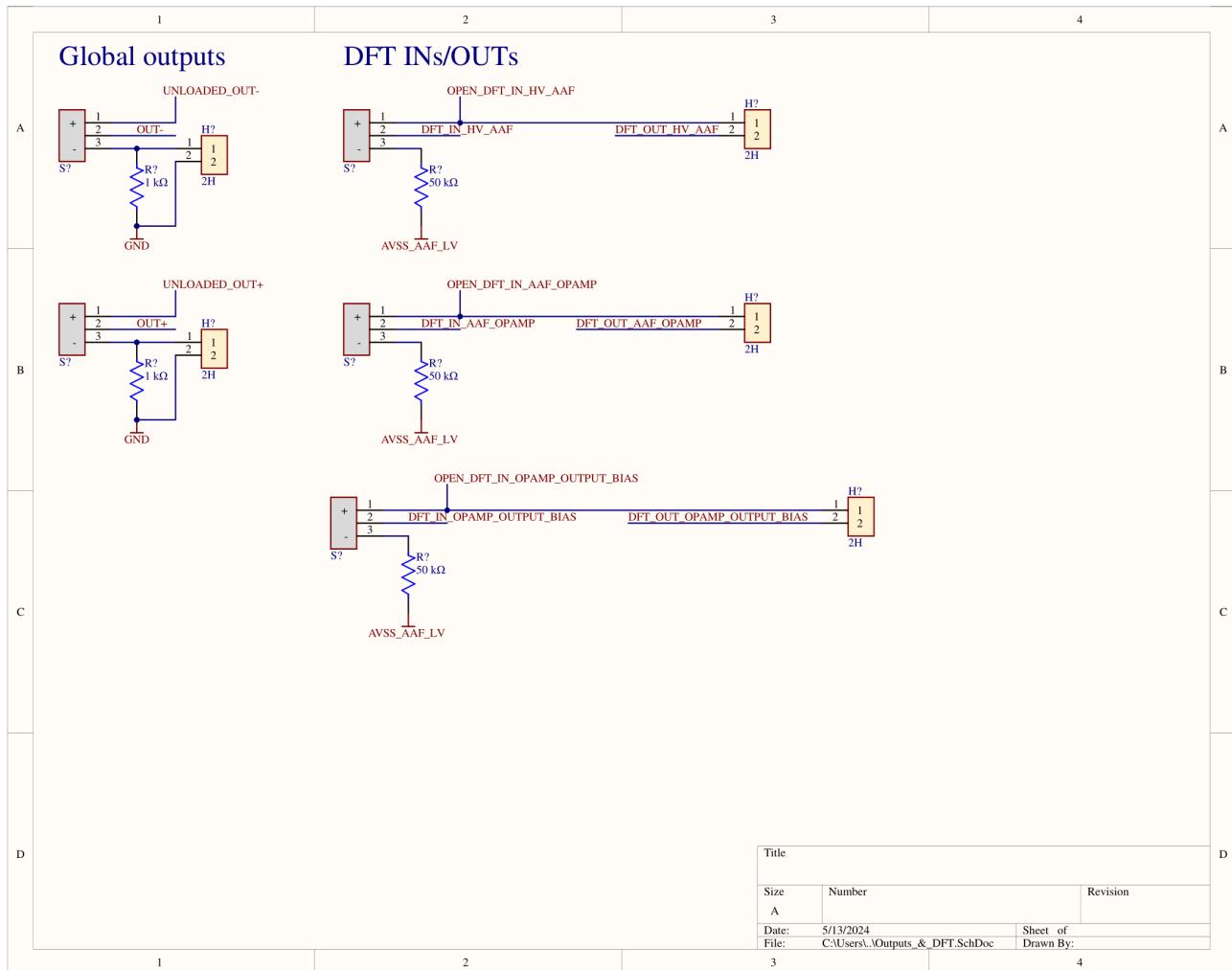

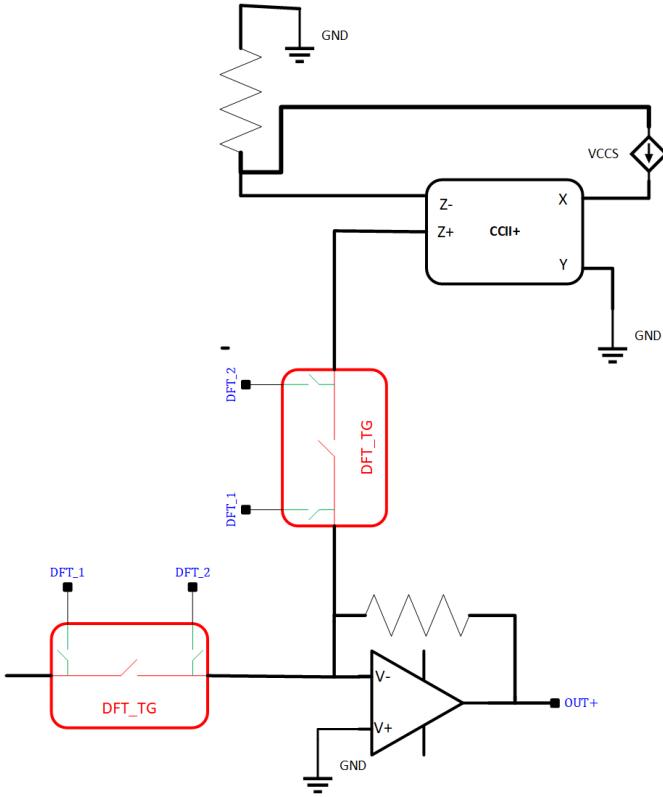

| Figure 3.17 | Schéma-bloc du DFT proposé . . . . .                                                                                                                                            | 45 |

| Figure 3.18 | DFT proposé . . . . .                                                                                                                                                           | 46 |

| Figure 4.1  | Layout de la puce envoyée pour fabrication . . . . .                                                                                                                            | 47 |

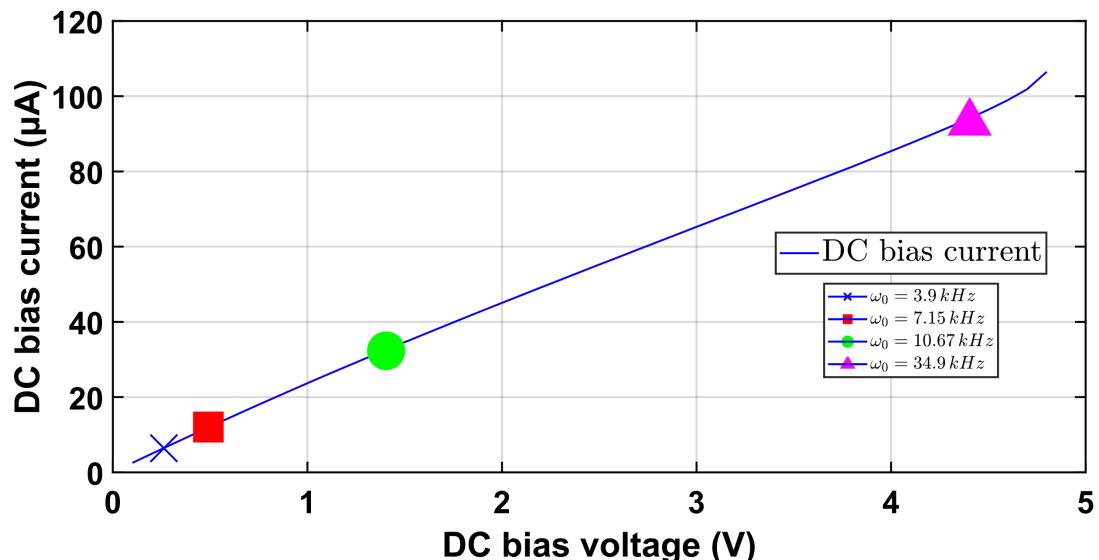

| Figure 4.2  | Courant généré par la SCCT ( $\mu$ A) en fonction de la valeur de la tension de polarisation (V) . . . . .                                                                      | 50 |

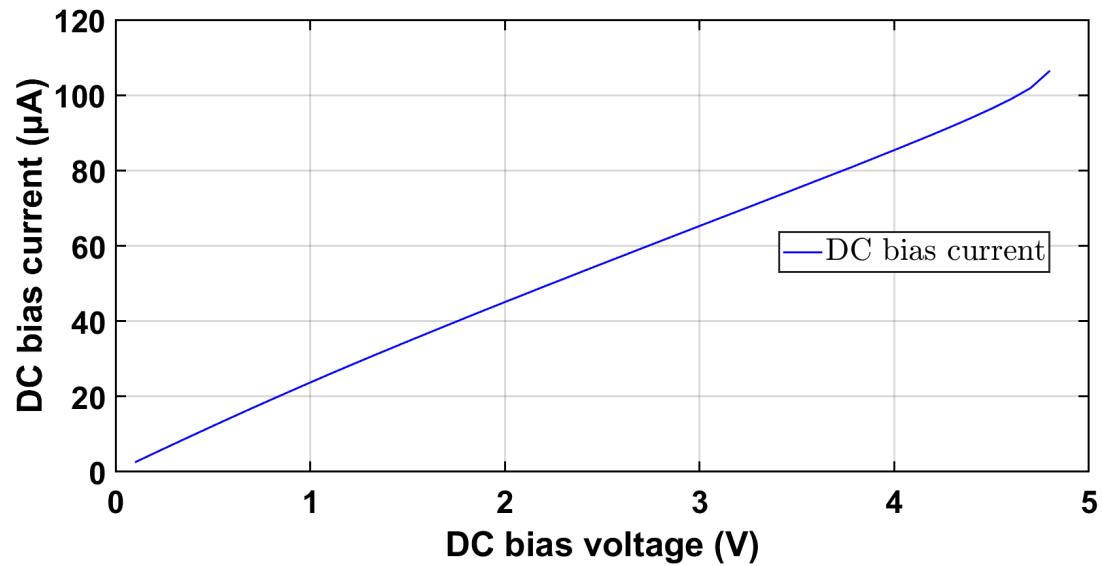

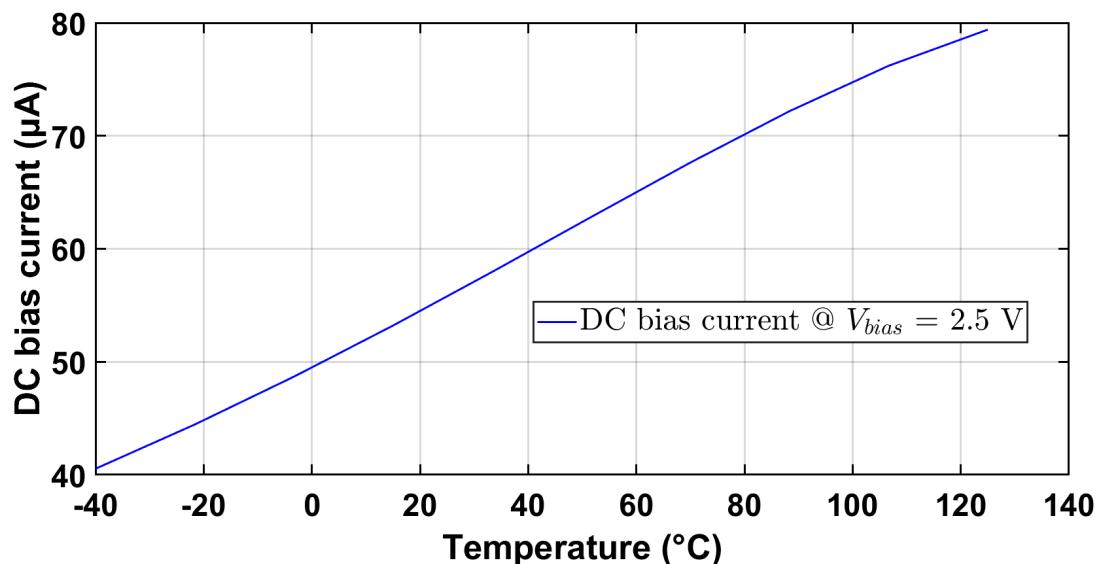

| Figure 4.3  | Courant généré par la SCCT ( $\mu$ A) en fonction de la température ( $^{\circ}$ C) pour $V_{bias} = 2.5$ V . . . . .                                                           | 50 |

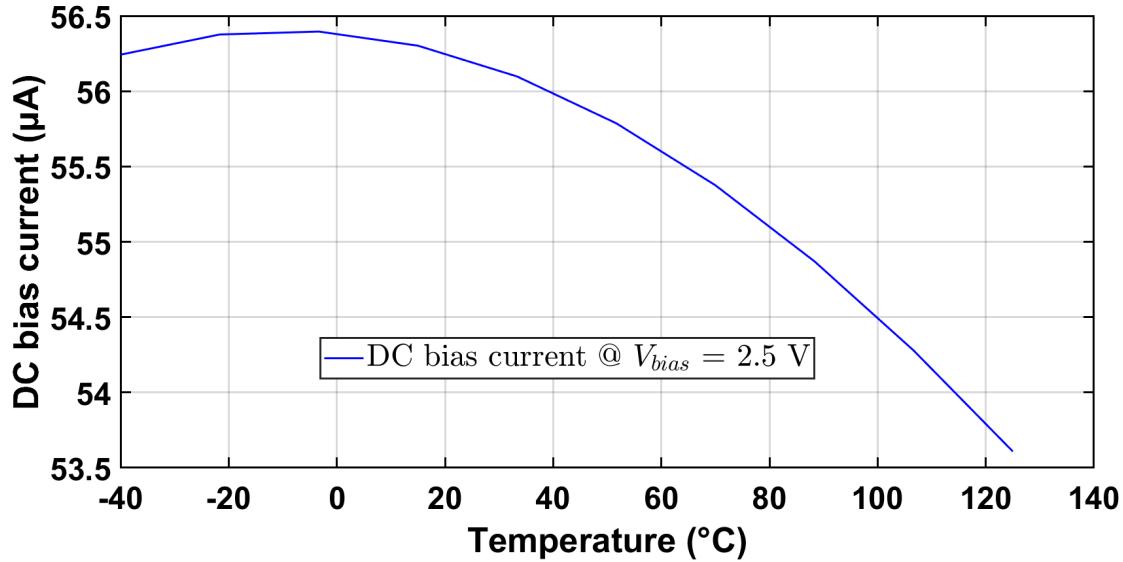

| Figure 4.4  | Courant généré par la SCCT ( $\mu$ A) en fonction de la température ( $^{\circ}$ C) pour $V_{bias} = 2.5$ V avec la compensation en température . . . . .                       | 51 |

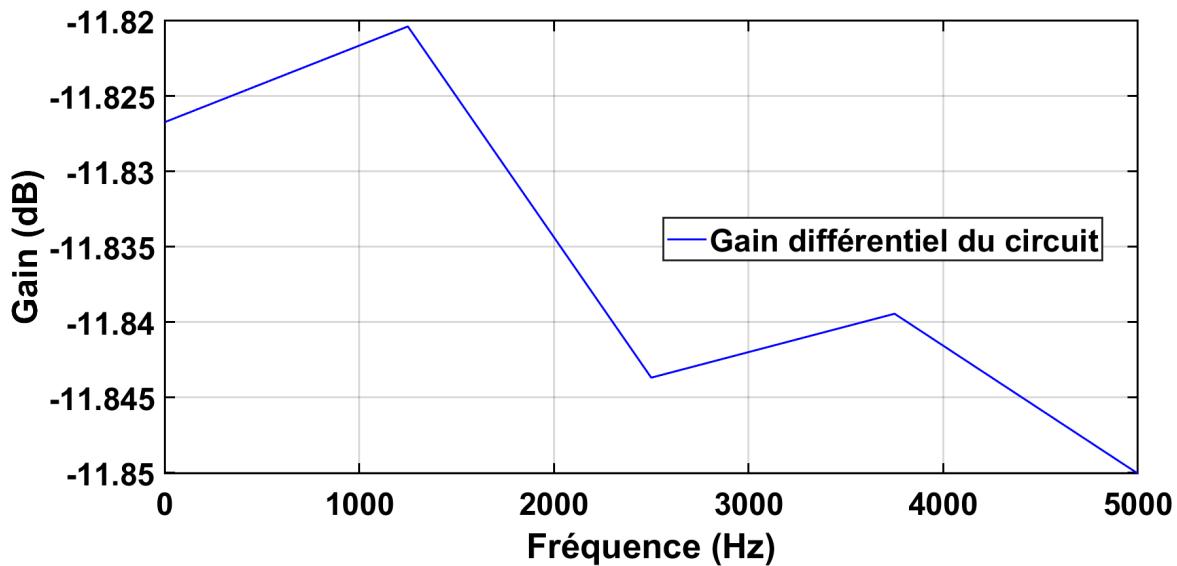

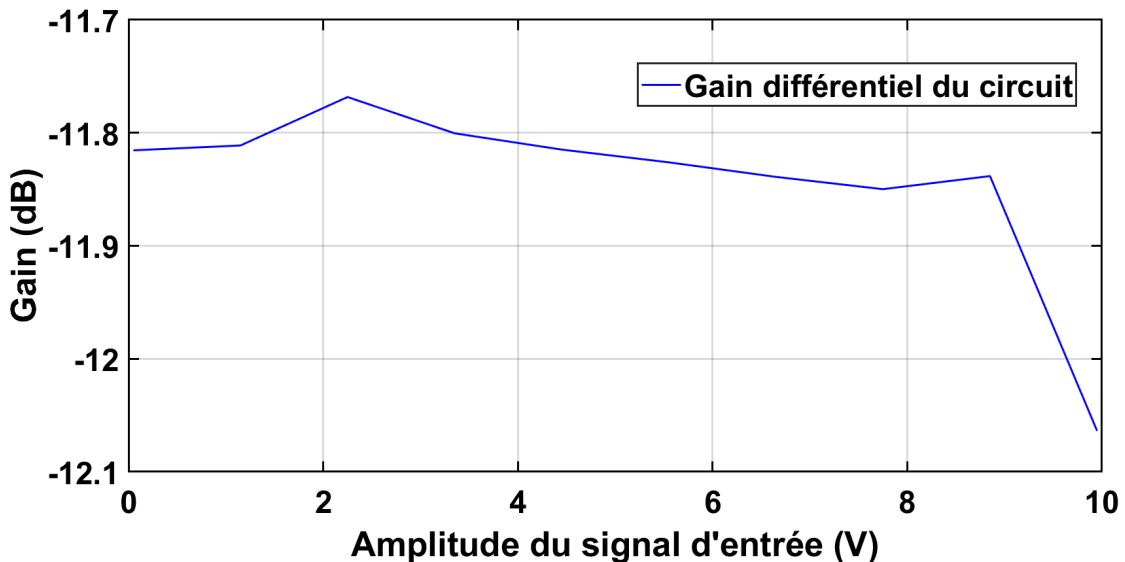

| Figure 4.5  | Non-linéarité du gain par rapport à la fréquence du signal d'entrée, pour un gain théorique de -12.0412 dB (0.25), et un signal d'entrée sinusoïdal d'amplitude 8 V . . . . .   | 52 |

| Figure 4.6  | Non-linéarité du gain par rapport à l'amplitude du signal d'entrée, pour un gain théorique de -12.0412 dB (0.25), et un signal d'entrée sinusoïdal de fréquence 5 kHz . . . . . | 53 |

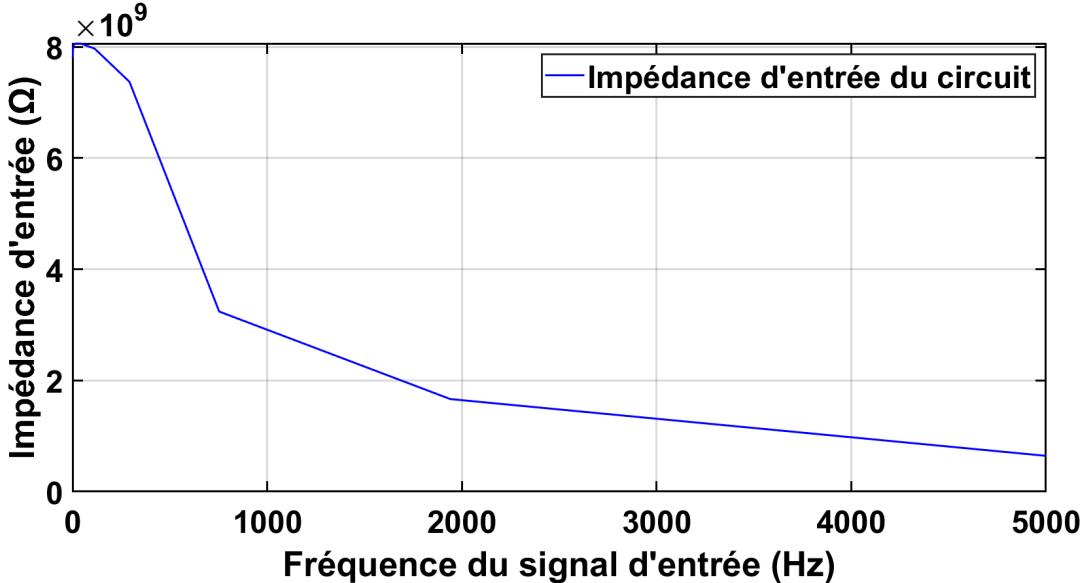

| Figure 4.7  | Impédance d'entrée du système, en fonction de la fréquence du signal d'entrée . . . . .                                                                                         | 54 |

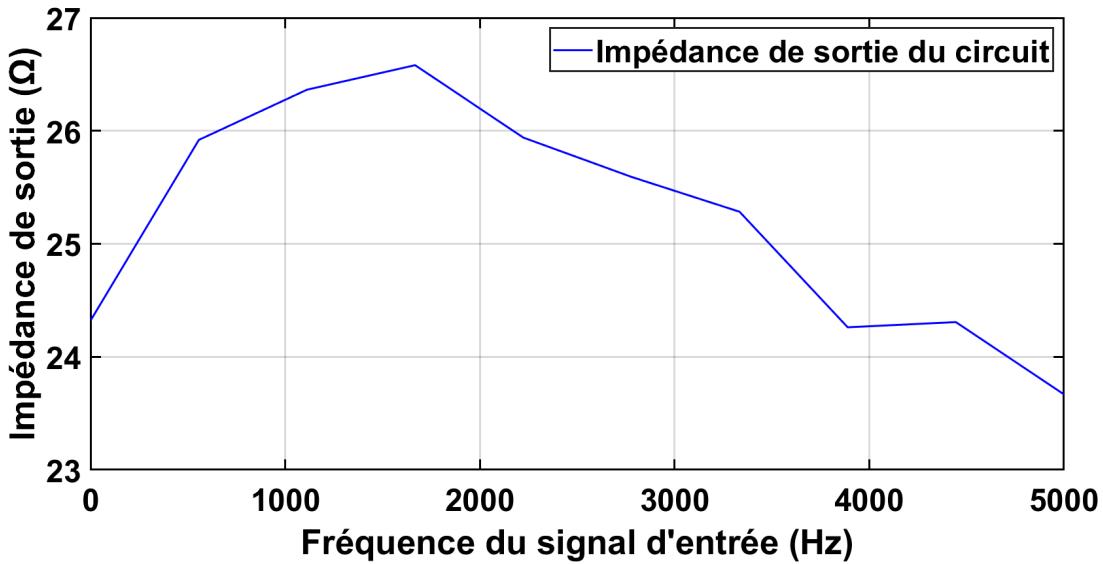

| Figure 4.8  | Impédance de sortie du système, en fonction de la fréquence du signal d'entrée . . . . .                                                                                        | 55 |

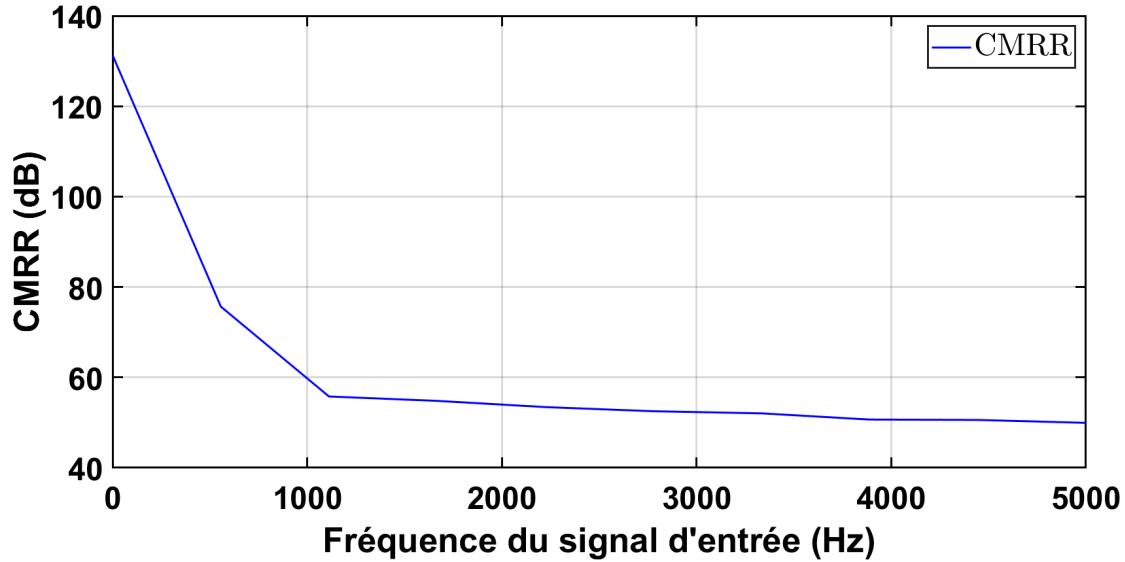

| Figure 4.9  | Taux de Réjection de Mode Commun du système en fonction de la fréquence, pour $G = 0.25$ . . . . .                                                                              | 56 |

|             |                                                                                                                        |    |

|-------------|------------------------------------------------------------------------------------------------------------------------|----|

| Figure 4.10 | Courant généré par la SCCT en fonction de la tension de polarisation avec fréquences de coupure équivalentes . . . . . | 57 |

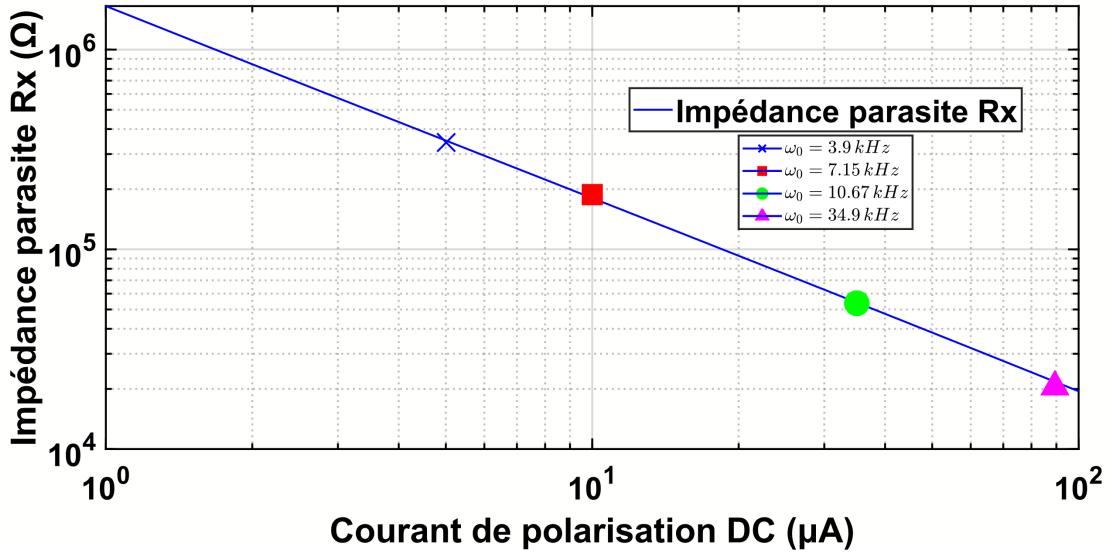

| Figure 4.11 | Impédance parasite du CCII basse tension en fonction de son courant de polarisation . . . . .                          | 58 |

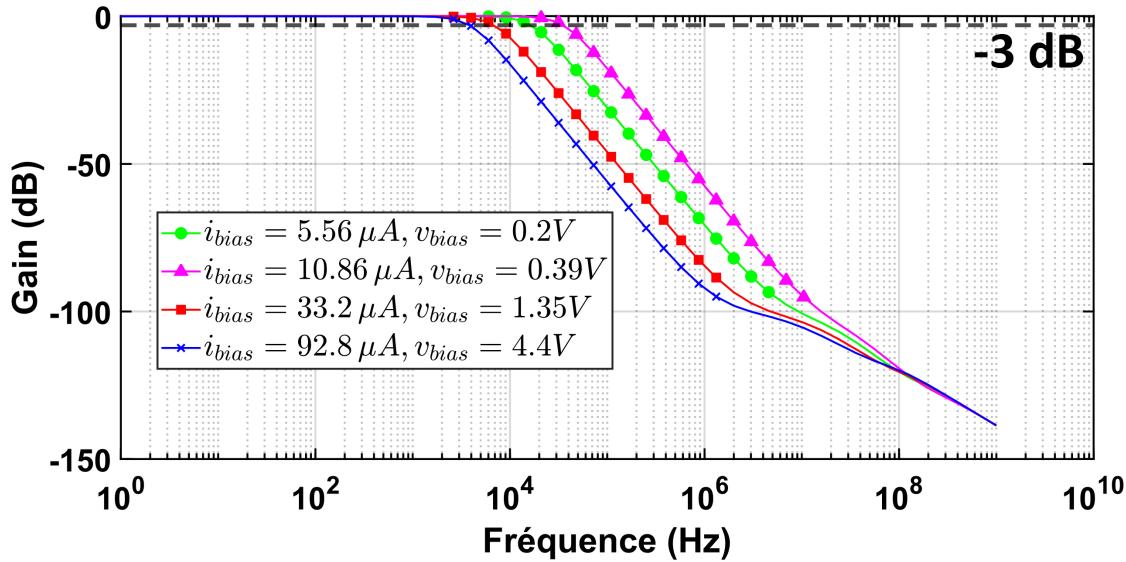

| Figure 4.12 | Analyse fréquentielle du comportement du FAR en fonction du courant de polarisation des CCIIs . . . . .                | 59 |

## LISTE DES SIGLES ET ABRÉVIATIONS

|        |                                                                |

|--------|----------------------------------------------------------------|

| AGP    | Amplificateur à Gain Programmable                              |

| AGV    | Amplificateur à Gain Variable                                  |

| AOP    | Amplificateur Opérationnel                                     |

| CAN    | Convertisseur Analogique/Numérique                             |

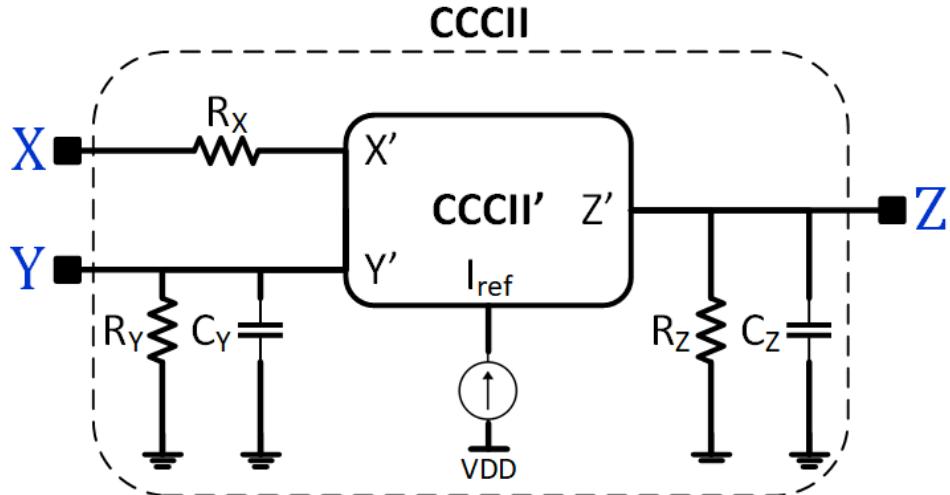

| CCCII  | Convoyeur de Courant de Seconde Génération Contrôlé en courant |

| CCII   | Convoyeur de Courant de Seconde Génération                     |

| CMRR   | Taux de Réjection de Mode Commun                               |

| FAR    | Filtre Anti-Repliement                                         |

| HT     | Haute Tension                                                  |

| DEMOS  | Transistor MOS à drain étendu                                  |

| MC     | Mode-Courant                                                   |

| QFGMOS | MOS à Grille Quasi-Flottante                                   |

| SiP    | System-in-Package                                              |

| SoC    | System-on-Chip                                                 |

| TRMC   | Taux de Réjection de Mode Commun                               |

**LISTE DES ANNEXES**

|          |                                   |    |

|----------|-----------------------------------|----|

| Annexe A | Plan de test de la puce . . . . . | 74 |

|----------|-----------------------------------|----|

## CHAPITRE 1 INTRODUCTION

### 1.1 Contexte

Depuis les dernières décennies, l'industrie du transport a connu un développement exponentiel, tant pour le transport de marchandises que de personnes [1]. Bien que ce développement soit un élément essentiel du système économique et social mondial, il suscite de nombreuses interrogations concernant son impact économique et social. En effet, les émissions de gaz à effet de serre générées par l'industrie du transport constituent une part importante de la pollution mondiale. D'après l'Agence pour la Protection de l'Environnement, l'industrie du transport représente en effet 28 % des émissions de gaz à effet de serre des États-Unis en 2021, soit 6340 millions de tonnes de CO<sub>2</sub> [2]. Cela en fait le premier contributeur national à ces émissions. De plus, il est important de souligner que 2.1 millions de personnes meurent chaque année en raison de ces émissions [3]. L'accès très inégal à ces moyens de transports, la pénurie en ressources naturelles et l'impact de cette industrie sur l'être humain sont tout autant de facteurs soulignant le besoin urgent de développer des solutions durables, tant sur le plan environnemental que social.

Le passage à l'électrique des véhicules a sur le papier de nombreux avantages, à condition que l'électricité soit produite de manière durable. Avec la nouvelle tendance de passage à l'électrique vient la possibilité d'introduire de plus en plus d'électronique embarquée, ce qui permet d'améliorer encore plus le rendement des véhicules, et donc leur performance, leur fiabilité et leur consommation énergétique. Cette avancée technologique offre également l'opportunité de réduire les coûts de maintenance à long terme et d'augmenter la durée de vie des véhicules.

Les interfaces de capteurs jouent un rôle crucial dans cette nouvelle dynamique. En effet, leur optimisation améliore significativement la performance du système. Cependant, ce sujet est complexe, car le haut niveau de spécialisation des systèmes industriels rend souvent un système obsolète d'un véhicule à l'autre. Compte tenu des coûts de fabrication élevés des circuits spécialisés (ASIC), il est essentiel de proposer des architectures intégrées reconfigurables, capables de répondre à une multitude de problèmes et d'applications tout en conservant des performances compétitives.

Ce mémoire de maîtrise s'inscrit dans le cadre des travaux d'un groupe de recherche plus large, visant à développer des interfaces de capteurs intelligentes, reconfigurables et performantes, viables en milieu hostile [4].

En particulier, ce mémoire se concentre sur les éléments fondamentaux d'un circuit dit de read-back, à savoir les Amplificateurs à Gain Programmable (AGP) et les Filtres Anti-Repliement (FAR).

## 1.2 Problématiques et motivations

Comme mentionné précédemment, ce mémoire s'inscrit dans une dynamique de recherche plus large, visant à proposer une interface de capteurs reconfigurable adaptée à une multitude d'applications industrielles en milieu hostile [5], comme présenté en Figure 1.1.

FIGURE 1.1 Schéma-bloc de l'interface de capteurs versatile proposée [5]

Les travaux présentés ici s'appuient sur le contexte et les études déjà décrits dans [6], s'attaquant plus particulièrement à la partie "Reconfigurable Read-Back Circuits" présentée dans la Figure 1.1. L'article [5] présente les besoins spécifiques de cette interface. Un premier élément essentiel est une isolation électrique, permettant de séparer la charge, potentiellement soumise à de hauts niveaux de tension, de l'unité de contrôle qui souhaite en extraire de l'information. Dans l'exemple de la Figure 1.1 tiré de [5], cette dernière est mise en œuvre dans un FPGA.

Présenté dans [6], un amplificateur de tension isolé avec gain programmable a déjà été proposé. Cet amplificateur répond aux normes et besoins usuellement rencontrés en milieu industriel hostile [7]. Basés sur une isolation inductive et un capteur à effet Hall, les travaux présentés dans [6] offrent une solution innovante et adaptée à une multitude d'interfaces de capteurs industriels haute tension en milieu hostile. L'amplificateur isolé présenté permet

d'obtenir un circuit de Read-Back haute tension depuis la charge, avec une plage d'entrée de  $\pm 10$  V tout en supportant des tensions de mode commun de plusieurs centaines de volts.

Bien que l'isolation à partir de capteurs à effet Hall soit indubitablement adaptée et pertinente dans ce mémoire, certains éléments restent manquants et/ou peu satisfaisants pour le développement d'une interface de capteurs modulaire, flexible et performante telle que présentée dans la Figure 1.1. Particulièrement, le dé fabriqué n'inclut pas de FAR, un composant absolument fondamental de toute interface de capteurs. En effet, le FAR permet le bon échantillonnage du signal par un Convertisseur Analogique/Numérique (CAN) afin d'éviter le repliement de spectre lors de la conversion numérique du signal pour lecture par un processeur. De plus, l'AGP proposé est très sensible aux variations du procédé de fabrication et de la température, ce qui limite fortement la précision d'interfaces de capteurs exploitant ce circuit.

### 1.3 Objectifs de recherche

On cherche ainsi à compléter l'interface de capteurs développée dans [6], afin de compléter la proposition initiale énoncée dans [4]. En particulier, l'intégrabilité et la performance de l'AGP et du FAR laissent encore à désirer. Afin de pouvoir poursuivre l'intégration de l'interface de capteurs dans un System-in-Package (SiP), l'intégration des composants nouvellement développés sera faite dans un System-on-Chip (SoC), afin de maximiser les possibilités d'intégration du système global.

Le système doit être complètement différentiel afin de pouvoir gérer simultanément des mesures simples et des mesures différentielles, permettant ainsi la mesure de tensions, mais aussi de courant à l'aide d'une résistance de shunt. Compte tenu de l'application industrielle haute tension envisagée, le système devra être capable de gérer des tensions différentielles allant jusqu'à  $\pm 10$  V, et sera intégré à l'aide d'un procédé haute tension (HT).

L'accent devra également être mis sur la résilience aux variations paramétriques du procédé, de tension d'alimentation et de température, afin de garantir une solution performante dans toutes les situations. La solution se doit d'être conçue à l'aide de procédés CMOS et/ou bipolaires afin de faciliter son intégration avec le reste de l'interface.

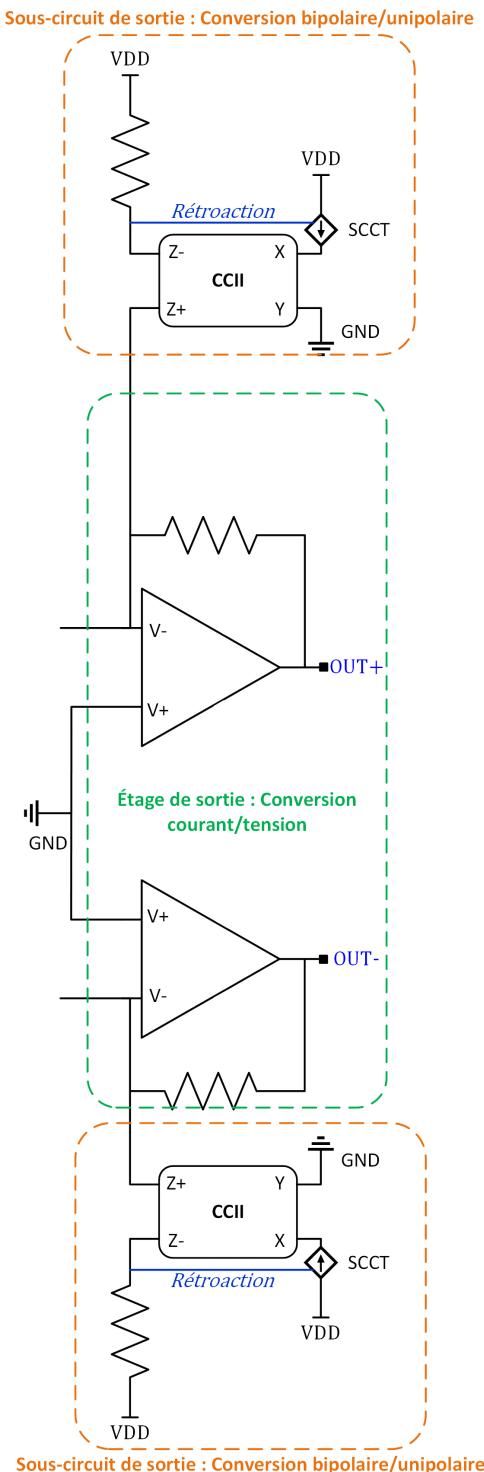

Les circuits proposés devront être hautement reconfigurables, afin encore une fois de proposer une solution facilement adaptable au plus grand nombre possible d'applications. En particulier, il sera important pour l'AGP de proposer une conversion d'un domaine de tension bipolaire vers un domaine de tension unipolaire, la norme des circuits de contrôle digitaux. On souhaite également pouvoir déterminer la fréquence de coupure du FAR, avec la possibilité

d'atteindre des fréquences de coupure très basses, dans l'ordre de grandeur des kHz.

Enfin, le système devra présenter une bonne résistance au bruit, une excellente linéarité et avoir la possibilité de travailler sur la plus grande plage de fréquence possible afin de garantir la versatilité de l'interface et de minimiser les modifications à mettre en place pour l'installer sur différents appareils.

## 1.4 Contributions

Ce mémoire présente une architecture innovante d'amplificateur d'instrumentation à base de convoyeurs de courant de seconde génération (CCII). Incluant un AGP et un FAR, le circuit proposé permet de convertir un signal dans une plage de tension bipolaire,  $\pm 10$  V, vers une plage de tension unipolaire 5 V. Le système exploite les nombreux avantages de la conception en mode courant : 1) indépendance du gain et de la bande passante, 2) plus grande plage dynamique, 3) meilleur Taux de Réjection du Mode Commun (TRMC), 4) excellente linéarité, 5) sensibilité réduite aux éléments parasites, au bruit, aux variations de procédé et de température [8].

En particulier, ce mémoire présente trois sous-systèmes innovants :

- Une architecture de CCII haute tension, encore absente de la littérature, pour l'étage d'entrée de l'amplificateur d'instrumentation.

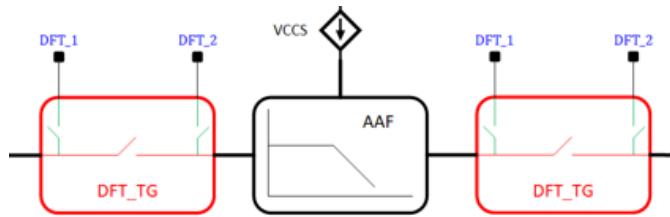

- Un AAF en mode courant basé sur des CCII, directement intégré à l'intérieur de l'amplificateur d'instrumentation, profitant de l'approche en mode courant, avec un contrôle intégré de la fréquence de coupure sans complexifier le circuit. Ce contrôle se base sur la modélisation et le contrôle des éléments parasites inhérents aux CCII.

- Un étage de sortie permettant de reconfigurer à la volée le niveau DC correspondant au 0 en sortie, entre 0 V et 5 V. Le design inclut une boucle de rétroaction, permettant une grande résilience aux variations de procédé et de température, même en l'absence d'appariement ou de compensation des éléments passifs définissant le gain de l'étage.

Un article de conférence a également été soumis à la conférence ICECS2024, portant sur le FAR proposé.

## 1.5 Plan du mémoire

Ce mémoire est organisé comme suit. Dans un premier temps, le chapitre 2 détaille l'état de l'art actuel concernant les différents éléments du système proposé, à savoir l'AGP et le FAR. La solution proposée est détaillée dans le chapitre 3. Les résultats de simulation post-

layout obtenus sont présentés dans le chapitre 4. La pertinence des résultats obtenus et leur positionnement par rapport à la littérature sont évoqués dans le chapitre 5. Enfin, le chapitre 6 résume la proposition énoncée par le présent mémoire, met en lumière les performances obtenues avec la solution proposée ainsi que ses limitations, et suggère des pistes de recherche ultérieure.

## CHAPITRE 2 REVUE DE LITTÉRATURE

### 2.1 Les amplificateurs à gain programmable

Dans le contexte d'une interface de capteurs, il est presque toujours indispensable d'utiliser un AGP pour ajuster l'amplitude du signal d'entrée à la plage d'amplitude du CAN. En effet, un CAN compare le signal d'entrée à une référence de tension interne, en général 1.8 V [9], 3.3 V [10] ou 5 V [11]. Pour atteindre la résolution maximale de mesure d'un CAN, le signal d'entrée devrait s'approcher le plus possible de la valeur maximale de sa plage de mesure [12]. Cependant, en fonction du type de signal à l'entrée de l'interface, il peut être nécessaire d'augmenter l'amplitude du signal, ou bien au contraire de la réduire pour éviter une saturation du CAN. Les AGP répondent à ce besoin de programmabilité du gain à l'entrée d'un CAN. Usuellement, cette programmabilité se fait à l'aide d'une tension DC ou d'une entrée digitale [12].

Les principaux indicateurs de la performance d'un AGP considérés sont les suivants :

- **La précision du gain**, usuellement mesurée en pourcentage. La précision du gain détermine l'écart entre la valeur réelle du gain et la valeur que l'on devrait obtenir à partir de l'équation théorique sans tenir compte des sources d'erreur.

- **La linéarité du gain**, encore une fois usuellement mesurée en pourcentage. Elle représente les variations de la valeur du gain sur une plage de valeurs du signal d'entrée, ainsi que sur la plage de valeurs du gain.

- **La bande passante**, qui représente la plage de fréquences sur laquelle la réponse de l'AGP reste constante.

- **Le décalage (offset)**, correspondant à la quantité de tension DC parasite non souhaitée que l'on retrouve rapportée comme un signal additif en entrée de l'AGP.

- **La consommation de puissance** du circuit.

- **Les effets des variations de température et de procédé**, qui vont modifier la valeur du gain, de la linéarité et du décalage en fonction de l'environnement du circuit.

On distingue dans un premier temps deux types d'amplificateurs à gain programmable : les circuits en boucle ouverte, et les circuits en boucle fermée [13]. Les circuits en boucle fermée ont l'avantage d'avoir une excellente linéarité et un contrôle simple du gain. Traditionnellement, ces circuits se basent soit sur une impédance d'entrée variable, soit sur une impédance variable dans une rétroaction négative. Les deux architectures les plus populaires pour réaliser cette impédance sont un réseau de résistances interchangeables avec des inter-

rupteurs, ou bien des résistances équivalentes à base de capacités commutées. Cependant, cette excellente performance se paie par une plus forte consommation de puissance, et une limitation en fréquence due au produit gain-bande inhérent aux structures basées sur un Amplificateur OPérationnel (AOP). À l'inverse, les structures en boucle ouverte ouvrent une plus grande variété de techniques de commande, modifiant généralement une transconductance variable, c'est-à-dire le  $g_m$  d'un transistor, ou une impédance variable au niveau de la charge. Les structures boucle ouverte ont l'avantage d'occuper beaucoup moins de place, et d'avoir une consommation de puissance bien moindre. Ces solutions ont une bien meilleure tenue en fréquence, mais ont une moins bonne linéarité, et le contrôle du gain est souvent plus complexe.

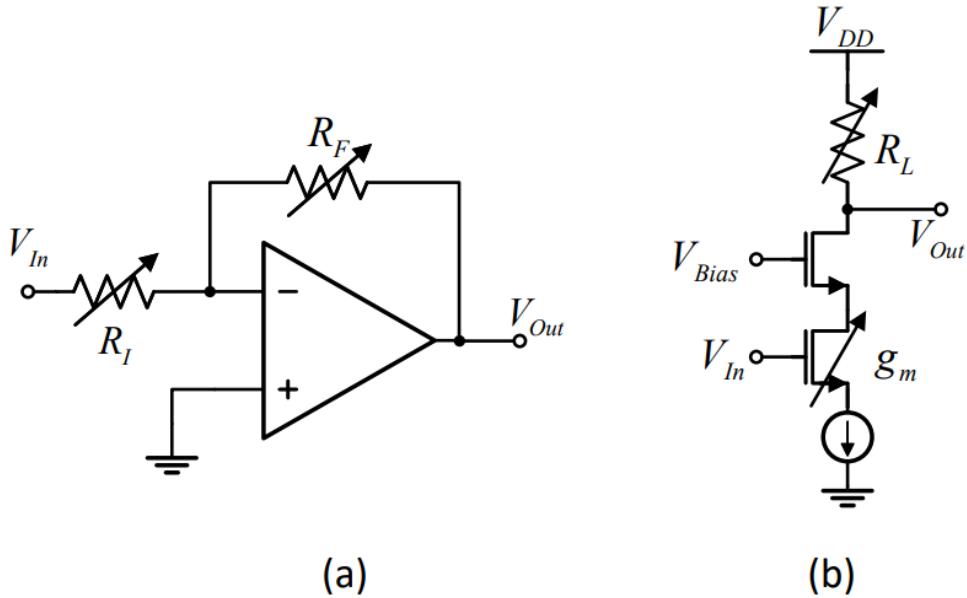

FIGURE 2.1 Un APG basique en boucle fermée (a) et en boucle ouverte (b) [14]

Il est également important de souligner une différence de vocabulaire fondamentale dans la littérature. Il faut faire la distinction entre les Amplificateurs à Gain Variable (AGV) (VGA dans la littérature), et les Amplificateurs à Gain Programmable (AGP) (PGA dans la littérature). La différence entre ces deux types de circuits tient au type de contrôle proposé. Les AGV proposent un contrôle continu du gain, tandis que les AGP proposent un contrôle discret. Compte tenu encore une fois du contexte industriel de précision envisagé [4], [5], la présente revue de littérature se concentre sur les AGPs. En effet, ces derniers permettent de connaître exactement la valeur de gain demandée, ce qui élimine le facteur d'erreur sur la mesure ajoutée par la commande continue.

### 2.1.1 Structures à transconductance contrôlée

Intéressons-nous dans un premier temps aux possibilités offertes par les structures à transconductance contrôlée.

Comme présenté en Figure 2.1, l'approche la plus classique en boucle ouverte pour réaliser un AGP est une architecture à réseau de résistances.

FIGURE 2.2 Un AGP basique en boucle ouverte, basé sur un réseau de résistances [15]

Conceptuellement, l'idée est d'exploiter l'équation fondamentale pour un MOSFET, définissant son  $g_m$  en fonction du courant de drain :

$$g_m = \frac{\delta I_D}{\delta V_{GS}} \quad (2.1)$$

En modifiant la résistance de polarisation au niveau du drain, on modifie la valeur du courant de drain. Cela permet de linéairement contrôler le  $g_m$  de la cellule, et par extension le gain de l'AGP [15]. Il est possible d'atteindre un contrôle similaire en utilisant des résistances

pour dégénérer la source du transistor [16], ou en mettant en parallèle des transistors de même longueur, mais de largeur variable pour interagir directement avec le  $g_m$  intrinsèque du transistor équivalent [17]. Ces deux dernières variations ont récemment été citées comme très prometteuses dans la littérature. Par rapport à l'architecture standard présentée en Figure 2.2, ces architectures présentent une excellente résilience aux variations de procédé et de température.

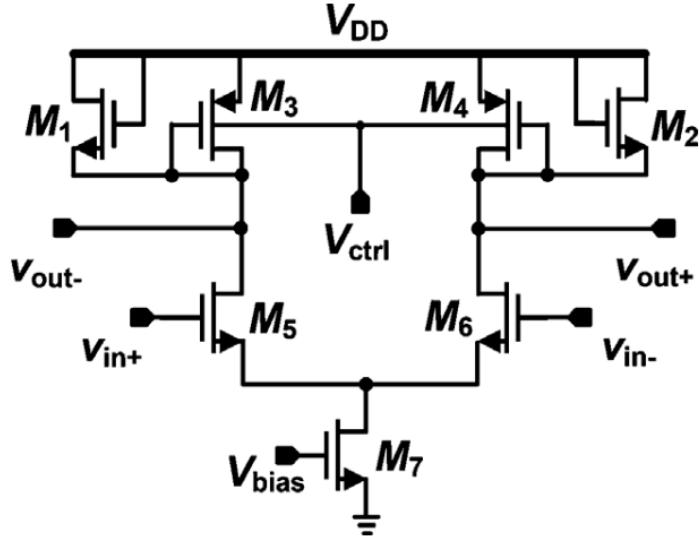

La Figure 2.3 présente une architecture récente proposée dans la littérature basée sur la dégénération active, simultanément au niveau de la source et de la charge. Les principaux avantages présentés pour cette architecture sont une consommation de puissance indépendante du gain, ainsi qu'une excellente invariance aux variations de procédé. Le circuit démontre également une excellente linéarité du gain sur l'entièreté de la bande passante du circuit.

Comme on peut le voir sur la Figure 2.4, cet AGP présente comme évoqué précédemment une grande résilience aux variations de procédé et de température. Cependant, on observe également une erreur sur le gain non négligeable (jusqu'à 3 dB) comparé au gain linéaire attendu, ce qui est loin d'être négligeable. De plus, le gain du circuit est intrinsèquement limité par le  $g_m$  des transistors, ce qui peut être limitant en fonction du niveau de performance à disposition, ce qui peut rapidement devenir limitant lorsque l'on utilise un procédé HT comme dans notre application [4]. Une solution pour régler ce problème serait de cascader plusieurs étages, mais cela implique une augmentation linéaire avec le nombre d'étages de l'erreur sur la précision du gain.

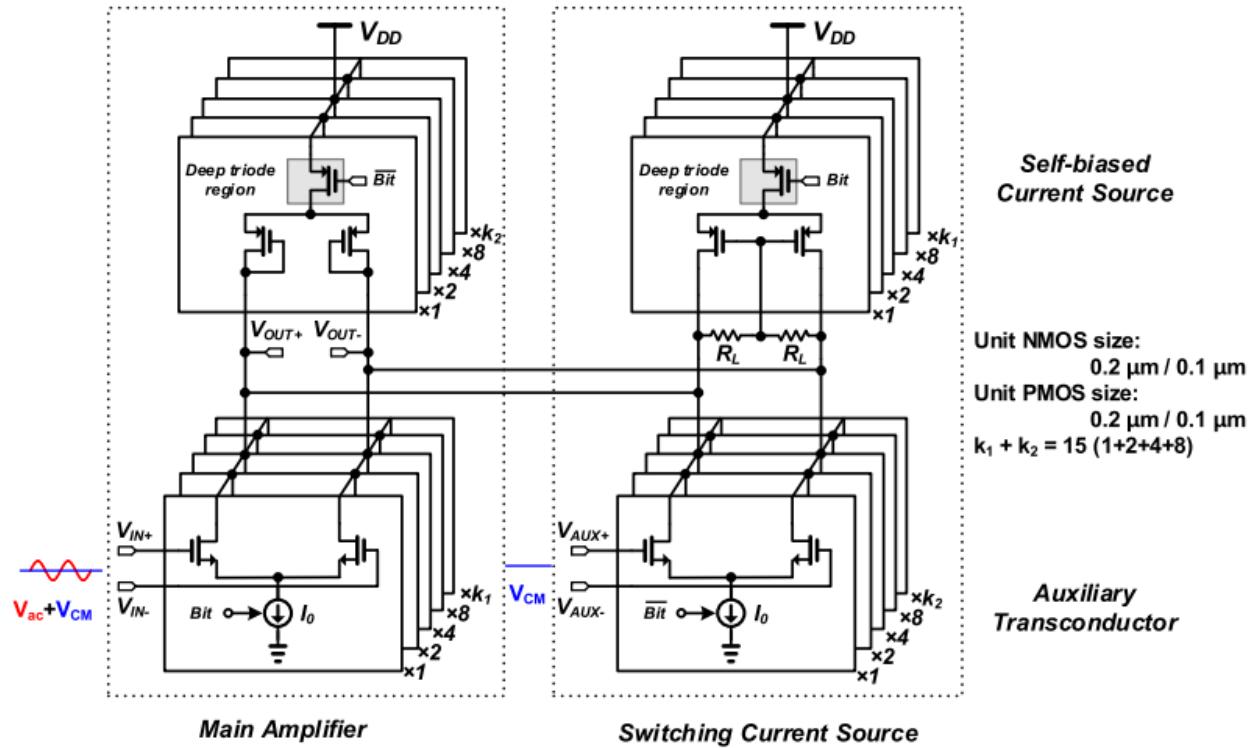

Comme évoqué précédemment, l'alternative est de modifier directement la largeur équivalente des transistors, ce qui est l'approche présentée dans [17], et présentée dans la Figure 2.5. Par rapport à l'architecture à dégénération active proposée précédemment, cette architecture permet de limiter l'influence de la cascade d'étages successifs sur la précision du gain, avec une croissance reportée comme étant plus lente qu'une croissance linéaire [17].

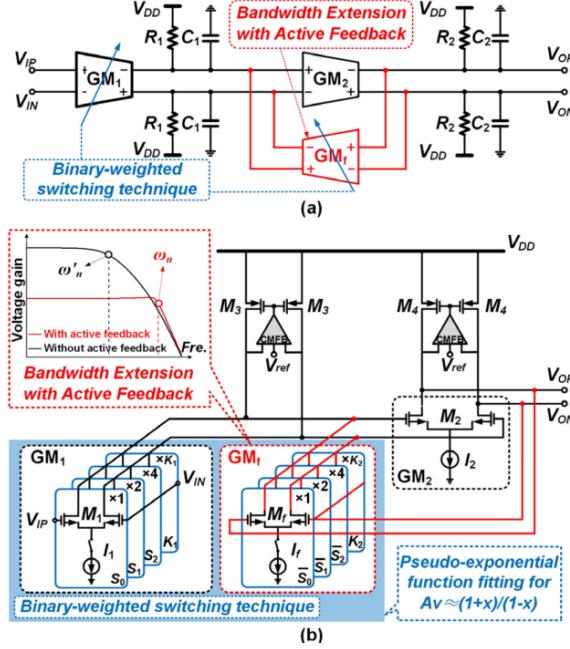

Si cette solution permet d'efficacement contourner le problème de limitation du gain lié au  $g_m$  des transistors, cette architecture a malgré tout d'autres limitations. Il est évoqué dans [17] que la valeur de l'échelon de gain et l'erreur sur ce même gain sont liés à un facteur  $k_1$ , qui correspond à la longueur équivalente de transistor qui est toujours active (donc sans aucun transistor ajouté en parallèle), comme on peut le voir sur la Figure 2.5. Les résultats expérimentaux mettent en avant une relation en forme de U entre ce facteur  $k_1$  et l'échelon de gain, ainsi que l'erreur sur le gain, comme présenté dans la Figure 2.6.

On observe ainsi très clairement grâce à la Figure 2.6 que l'échelon et la précision du gain sont fonction de la valeur choisie pour  $k_1$ . Cela rend ardu l'adaptation d'une telle architecture à une interface versatile pour une grande variété d'applications. Une telle architecture nécessiterait

FIGURE 2.3 Schéma conceptuel (a) et au niveau transistor (b) de l'AGP à dégénération active [16]

FIGURE 2.4 Comparaison du gain théorique et simulé pour différents corners (a) et courbe d'erreur sur le gain pour le corner typique (b) de l'AGP à dégénération active [16]

FIGURE 2.5 AGP à commutation de transistors [17]

FIGURE 2.6 Erreur de gain dB-linéaire (a) et échelons de gain dB-linéaire (b) en fonction de  $k_1$  pour l'AGP à commutation de transistors [17]

un moyen de modifier également le facteur  $k_1$ , ce qui complexifie le contrôle du gain. On note cependant que la tenue en fréquence du circuit et sa consommation de puissance sont très attractives.

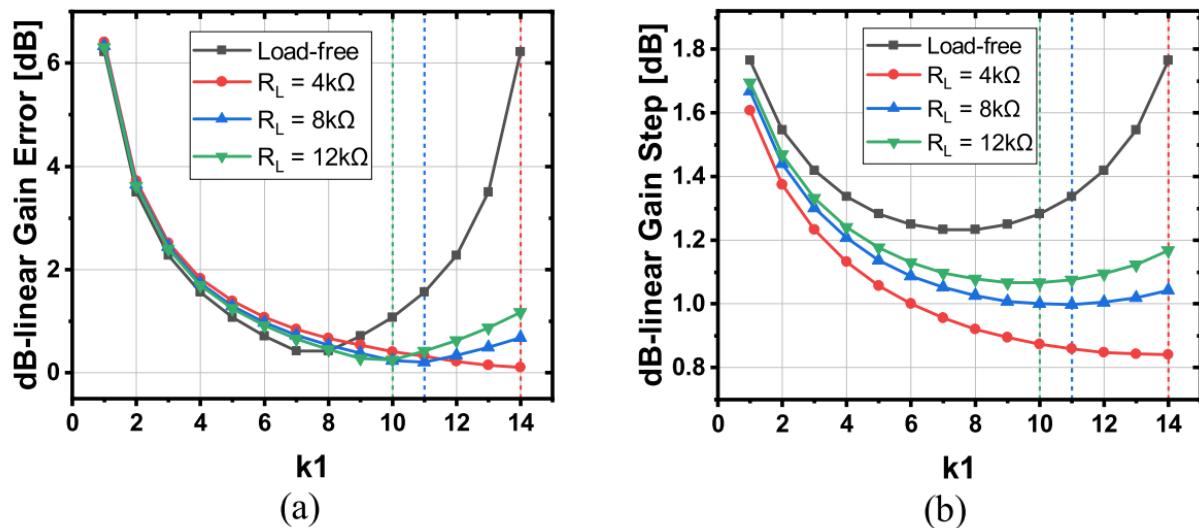

[18] propose une nouvelle fois une amélioration de l'architecture présentée précédemment, en introduisant cette fois-ci une rétroaction positive à l'aide d'un élément de transconductance.

FIGURE 2.7 Schéma de principe (a) et schéma au niveau transistor (b) de l'AGP à rétroaction positive active- $g_m$  (b) [18]

On observe sur la partie (a) de la Figure 2.7 le schéma de principe de ce nouveau circuit. On observe ainsi bien un premier bloc de transconductance, construit sur le même principe que précédemment, suivi par un second bloc à gain fixe, sur lequel on fixe une rétroaction à transconductance variable. Cela a de nombreux avantages, notamment une extension de la bande passante du système, une réduction de la distorsion engendrée par le système et un meilleur contrôle du gain du système. En effet, le gain peut à présent être exprimé sous la forme d'un simple rapport :

$$A_{V_0} = \frac{G_{m1}G_{m2}R_1R_2}{1 + G_{mf}G_{m2}R_1R_2} \quad (2.2)$$

Considérant encore une fois des paramètres  $k_1$  et  $k_2$  pour le rapport des tailles des transistors 'always on' dans le système, la Figure 2.8 présente les améliorations sur le contrôle du gain.

On observe ainsi que cette technique permet de limiter l'erreur de gain à 0.015 dB contre 1.6

FIGURE 2.8 Erreur de gain pour de multiples valeurs de gain et corners pour l'AGP à rétroaction positive active- $g_m$  [18]

dB précédemment en pire cas (sur charge), et donc de garantir une excellente linéarité du système. Le système possède également une excellente robustesse aux variations de procédé et de température, comme le montre la Figure 2.8.

Cette itération d'AGP à transconductance contrôlée semble être un candidat de bonne facture pour notre solution. Cependant, se basant purement sur des paires différentielles, il risque de fortement souffrir du passage à un procédé HT, avec des transistors MOS Laterally-diffused, asymétriques et avec des parasites affectant bien plus fortement le comportement du transistor. Nous risquons donc de ne pas pouvoir atteindre d'aussi bonnes performances sur la linéarité du gain.

La dernière approche populaire consiste à cascader des cellules élémentaires. Au lieu de se consacrer sur la réduction de l'erreur et l'amélioration de la linéarité du gain d'un AGP complexe, cette architecture cherche à agressivement optimiser une cellule élémentaire, avec donc d'excellentes performances, et à la cascader pour augmenter la plage de gain et la rendre convenable [19]. Une telle cellule est présentée dans la Figure 2.9.

Encore une fois, le design présente une grande robustesse aux variations de procédé et de température, ainsi qu'une excellente erreur maximale sur le gain de 0.2 dB, comme présenté

FIGURE 2.9 Schéma de la cellule élémentaire pour l'AGP à cellules cascadées [19]

à la Figure 2.10.

FIGURE 2.10 Erreur de gain en fonction de la température (a) et linéarité du gain en fonction du corner de procédé (b) pour l'AGP à cellules cascadées [19]

Malheureusement, cette technique n'est encore une fois pas très bien adaptée à notre situation. Notamment, considérant que nous ciblons un procédé HT, nous ne disposerons pas de transistors avec un bas niveau d'alimentation, 1.8 V ou inférieur, permettant d'atteindre des performances compétitives. Les parasites vont par définition encore une fois limiter les performances de notre cellule élémentaire, et donc par extension les performances d'un tel AGP dans notre cas si nous voulions l'implémenter.

### 2.1.2 Structures à rétroaction négative

Pour pallier les problèmes inhérents aux circuits à transconductance contrôlée, il est possible de plutôt utiliser un circuit disposant d'une rétroaction négative pour fixer le gain du système, à l'aide de composants passifs. Comme évoqué précédemment, ces circuits bénéficient d'une très grande linéarité et d'une excellente précision, souvent au prix de l'espace occupé par le système ainsi que de la consommation de puissance. En effet, ces circuits emploient des composants actifs comme des AOP, dont la consommation est non négligeable, d'autant plus lorsque la fréquence d'opération augmente.

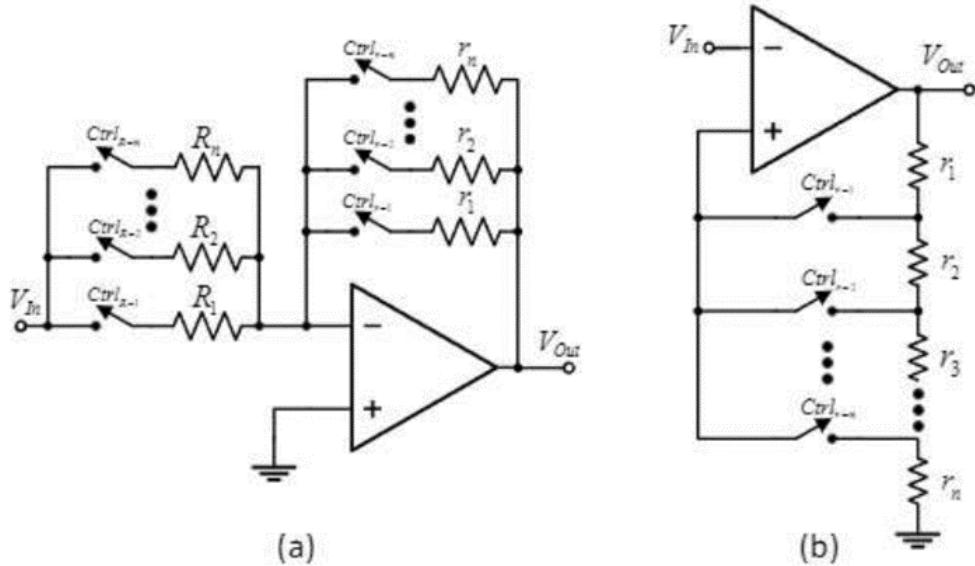

Nous avons pu voir jusqu'à présent les limitations des architectures basées sur la transconductance d'une paire différentielle. L'alternative populaire dans la littérature est une architecture à base d'AOP, qui permet d'obtenir plus facilement une très grande précision et linéarité. Présente depuis longtemps dans la littérature [20] [21], ce type de circuit utilise une impédance de rétroaction négative avec un AOP afin de régler le gain du système. Le réglage de cette impédance se fait le plus souvent à travers un réseau réglable à l'aide d'interrupteurs, ou à l'aide de capacités commutées.

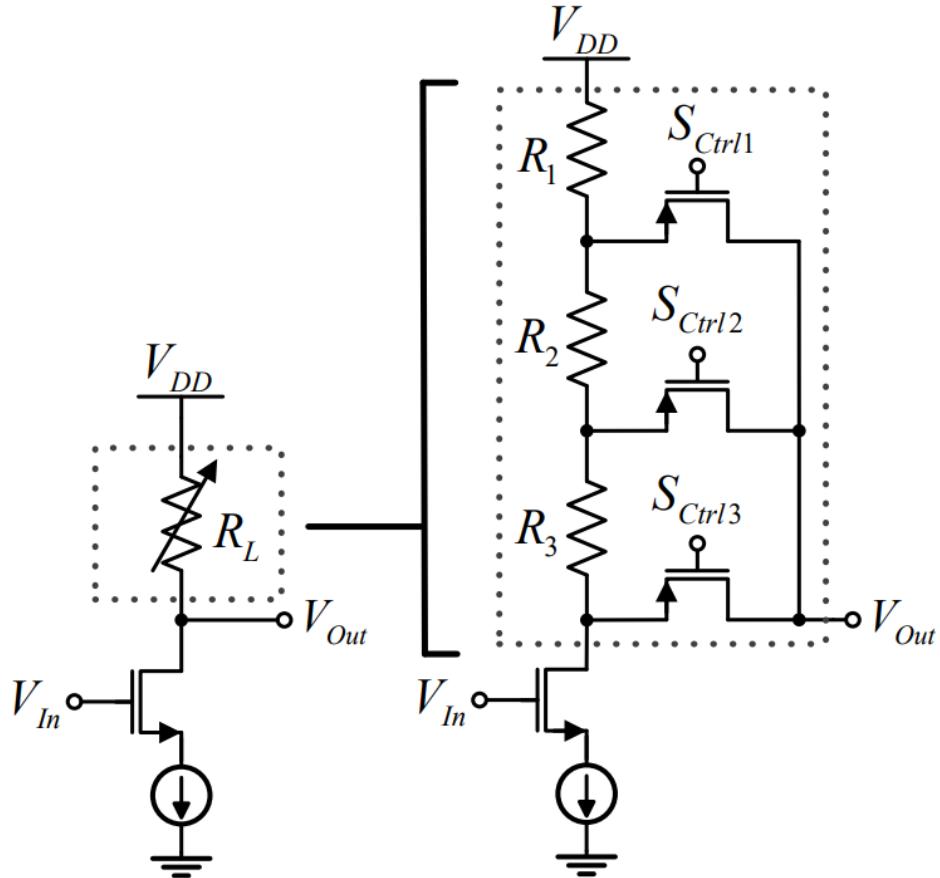

FIGURE 2.11 AGP à AOP simple avec rétroaction résistive [20]

Comme on peut le voir sur la Figure 2.11, le moyen le plus simple d'implémenter dans ce cas de figure une résistance variable est d'utiliser un réseau de résistances, que l'on vient commuter avec des interrupteurs. Comme on peut le voir sur la Figure 2.11 (a), ce réglage peut s'effectuer aussi bien au niveau de la résistance d'entrée que de la résistance de rétroaction.

Le principal inconvénient de ce type d'architecture est que le gain est limité par la précision de la résistance en elle-même. La résistance des interrupteurs (traditionnellement réalisés à l'aide d'une porte de transmission CMOS) peut elle aussi influer sur la valeur du gain. La Figure 2.11 (b) présente une architecture alternative, permettant de minimiser l'influence de la résistance parasite  $R_{on}$  des interrupteurs.

Ce type d'AGP est usuellement employé pour des systèmes ne nécessitant que peu de réglages de gain. En effet, les composants passifs sont des éléments volumineux, qui prennent beaucoup de place si intégrés dans un SoC.

L'alternative usuelle est d'employer des capacités commutées pour obtenir des résistances équivalentes [22]. L'idée est de tirer profit du concept des capacités commutées, qui affirme que selon l'architecture présentée sur la Figure 2.12, la capacité deviendra équivalente à une résistance, dont la valeur sera égale à l'équation suivante, avec  $f$  la fréquence de commutation des interrupteurs :

$$R_{eq} = \frac{1}{C_S f} \quad (2.3)$$

FIGURE 2.12 Capacité commutée

Cela a plusieurs avantages, notamment la réduction de l'espace occupé, puisque que la solution nécessite alors bien moins de condensateurs que de résistances précédemment. De plus, les procédés récents permettent généralement un appariement de qualité supérieure entre les condensateurs par rapport aux résistances. Le principal inconvénient de cette technique est l'injection de charge dans le circuit liée aux commutations successives des interrupteurs, qui peut nuire à la précision du système. Il peut également parfois être complexe de garantir très précisément la fréquence du signal de contrôle, ce qui amène une complexité supplémentaire dans la conception. Enfin, le signal de sortie passe du domaine continu au domaine discret, ce qui implique de limiter la fréquence de commutation à des valeurs bien supérieures à celle du signal qui est traité. Cela introduit également la problématique du repliement de spectre.

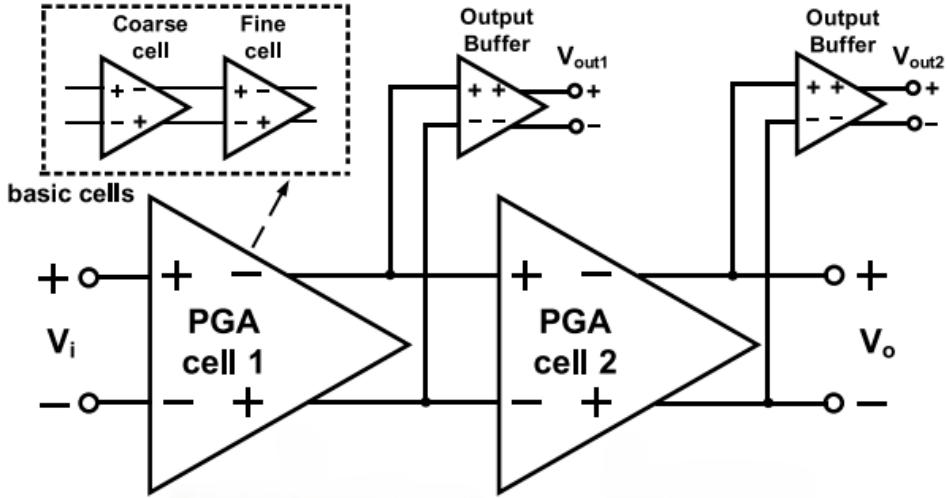

Afin de compenser les sources d'erreurs intrinsèques aux AGP à AOP simples (liées aux non-idealités des composants et aux problématiques évoquées ci-avant), une première approche consiste à cascader plusieurs amplificateurs, tout en décalant les courbes d'erreurs des différents étages, afin de faire en sorte qu'elles se compensent [23]. Une telle architecture est présentée dans la Figure 2.13.

FIGURE 2.13 AGP à amplificateurs cascadés [23]

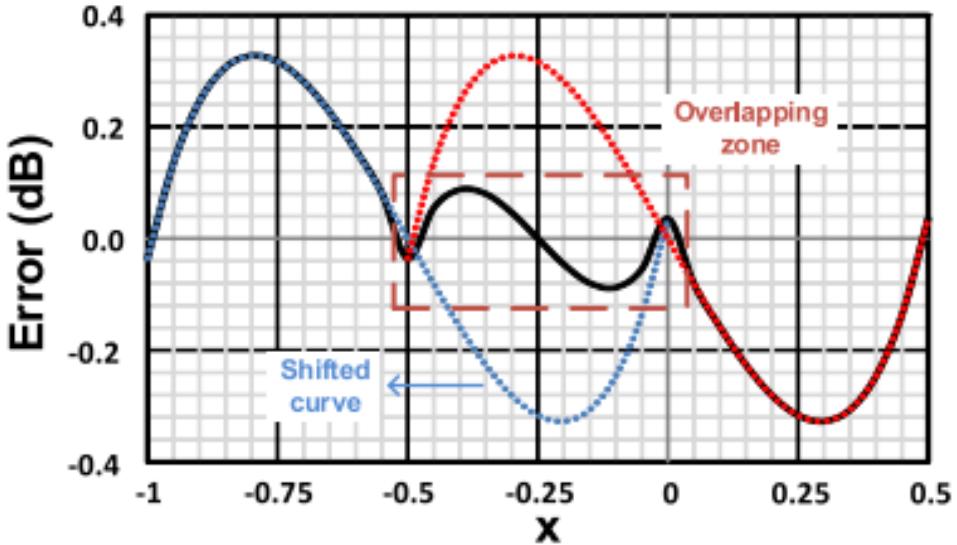

La Figure 2.14 présente ainsi un exemple de compensation d'erreur en utilisant un AGP à deux étages [23].

Pour la puce présentée dans [23], cette technique permet de réduire l'erreur du système de 0.118 dB pour un étage simple à 0.07 dB pour le système global.

Cependant, cette architecture reste limitée pour des applications HT, car le plus faible gain des étages individuels introduit des problématiques de saturation des étages successifs. Dans le cas de notre application, cela reviendrait à alimenter de multiples étages avec une alimentation haute tension, ce qui consommerait énormément d'énergie. Dans le cas présenté [23], le système consomme plus de 7 mW pour une alimentation de seulement 1.8 V. De plus, ce type d'architecture reste vulnérable aux variations de procédé et de température, qui peuvent intervenir sur les différents étages de façon asymétrique, détruisant ainsi le schéma de compensation. Étant donné la taille importante des composants passifs, et le nombre d'étages à cascader (jusqu'à 8 dans [23]), il paraît complexe d'obtenir un appariement compétitif sur un SoC à vocation industrielle, avec donc un fort rendement demandé lors de la production.

Jusqu'à présent, toutes les solutions présentées sont pertinentes et intéressantes pour des applications de recherche spécialisées, mais peinent à se généraliser à une large variété d'ap-

FIGURE 2.14 Courbe d'erreur pour les différents étages de l'AGP à amplificateurs cascades [23]

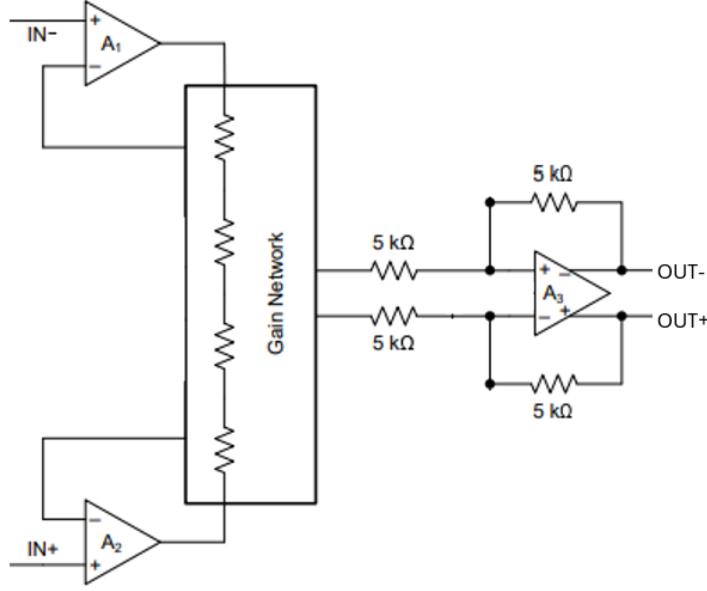

pllications industrielles HT. Quand on s'intéresse aux techniques utilisées pour les AGP standards dans ce milieu, on se rend compte assez rapidement que le standard est l'amplificateur d'instrumentation [24]. En effet, posséder un AOP dédié à chaque entrée permet de garantir une forte impédance d'entrée pour tout signal dans la plage d'entrée de mode commun, ainsi qu'un chemin continu vers la sortie pour celui-ci. Le gain est usuellement contrôlé par la valeur d'un ratio de résistances, garantissant une bonne résistance aux variations de procédé et de température. Les architectures récentes développées d'AOP avec stabilisation par hachage permettent d'atteindre d'excellentes performances du point de vue de la linéarité et de la précision du gain. La Figure 2.15 présente un schéma classique d'amplificateur d'instrumentation, implémenté dans un AGP HT de Texas Instruments.

En revanche, ces systèmes possèdent également des limitations. Pour ces architectures, il est important que le gain programmable se fasse au niveau de l'étage d'entrée [25] pour assurer les meilleures performances en termes de bruit et de précision. Le fait d'avoir une amplification en tension au niveau de l'étage d'entrée réduit la plage de signal admissible en entrée pour de fortes valeurs de gain, sous peine de saturation. De plus, le Taux de Réjection de Mode Commun (TRMC) devient ici limité non plus par la performance individuelle des AOP, mais plutôt par l'appariement des résistances au niveau de l'amplificateur de sortie [25], ce qui le limite à environ 80 dB pour les procédés modernes. Étant donné qu'il est primordial de rejeter autant que faire se peut le bruit de mode commun lors d'une mesure différentielle, c'est une limitation importante de ce type d'architecture.

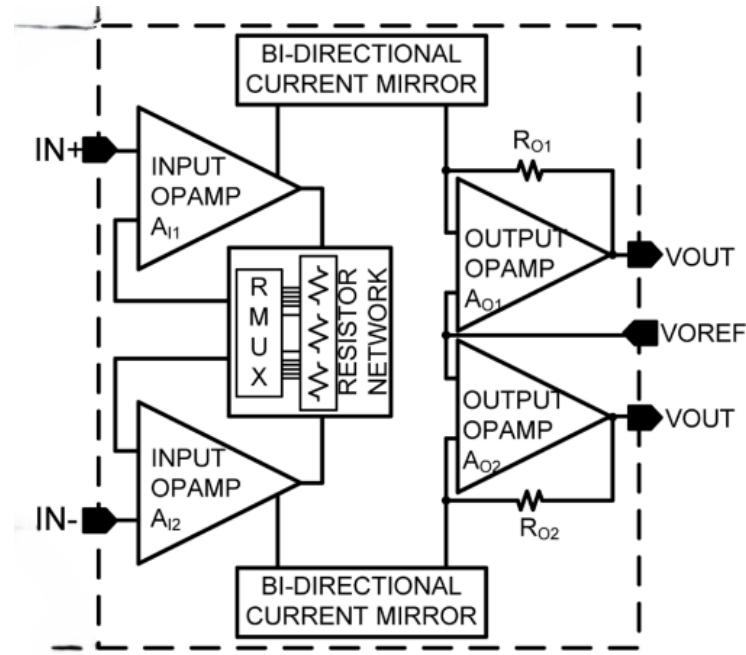

FIGURE 2.15 Un amplificateur d'instrumentation [24]

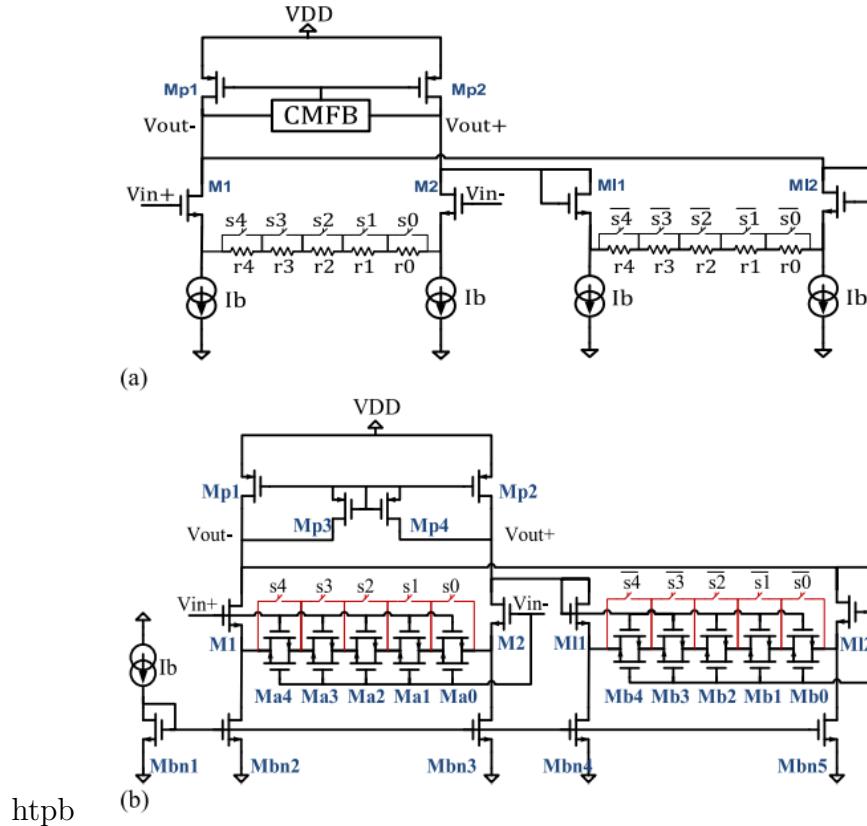

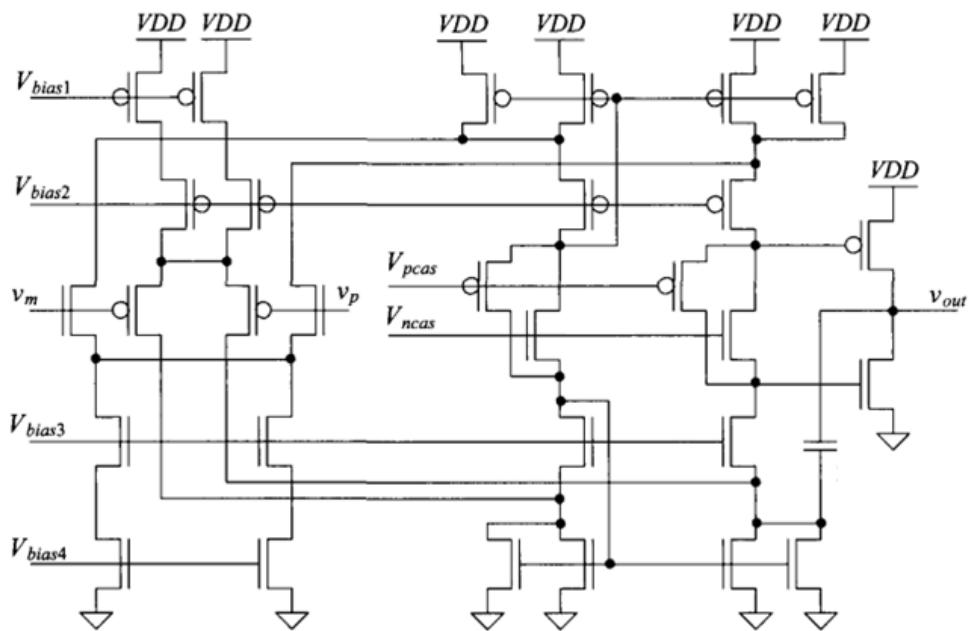

Il existe de nombreux exemples dans la littérature d'architectures exploitant le Mode-Courant (MC) pour obtenir des performances de grande qualité pour des AGP en tension [26], [25]. Adapter ce mode de conception aux amplificateurs d'instrumentation est un moyen très intéressant de répondre aux limitations du modèle présenté jusqu'à présent.

Ce type de structure, présenté en Figure 2.16, reprend le schéma classique de l'amplificateur d'instrumentation, et y introduit un étage intermédiaire en mode courant. On obtient ainsi une plus grande plage d'entrée pour le signal et un grand TRMC, tout en conservant les avantages de la structure précédente, à savoir une haute impédance d'entrée, et d'excellentes performances au niveau de la précision et de la linéarité.

Ce type de circuit fonctionne comme suit : tout d'abord, les amplificateurs d'entrée transmettent la tension d'entrée à travers un réseau variable de résistances. La tension induite sur les résistances produit en retour un courant, miroir de la tension d'entrée selon la loi d'Ohm. Ce même courant est alors copié par un miroir de courant, et transmis à l'étage de sortie, où il est re-converti en tension. On évite ainsi les problèmes de saturation évoqués précédemment grâce à la conversion en courant. De plus, le TRMC est maintenant limité par le mésappariement des AOP au niveau de la résistance de sortie, du gain en boucle ouverte et du TRMC, ce qui ouvre beaucoup plus de possibilités d'optimisation.

On choisira cette topologie comme point de départ pour notre AGP, en tant que solution répondant le mieux à nos problématiques de conception dans la littérature. Il s'agit également

FIGURE 2.16 AGP en Mode-Courant [25]

d'une structure usuelle dans les systèmes industriels, à l'efficacité prouvée.

On notera toutefois que puisque nous avons besoin d'un amplificateur HT, il sera nécessaire de se pencher soigneusement sur la conception des amplificateurs pour la conversion tension/courant et courant/tension, afin de s'assurer de la bonne performance du système même avec des transistors HT possédant des éléments parasites non négligeables.

## 2.2 Les filtres anti-repliement

Un filtre anti-repliement (FAR) est un type de filtre passe-bas utilisé pour prévenir les effets de repliement de spectre qui surviennent lors de l'échantillonnage d'un signal continu, généralement au niveau d'un convertisseur analogique-numérique (CAN). Ce filtre est donc essentiel dans une interface de capteur, garantissant l'intégrité du signal durant l'échantillonnage.

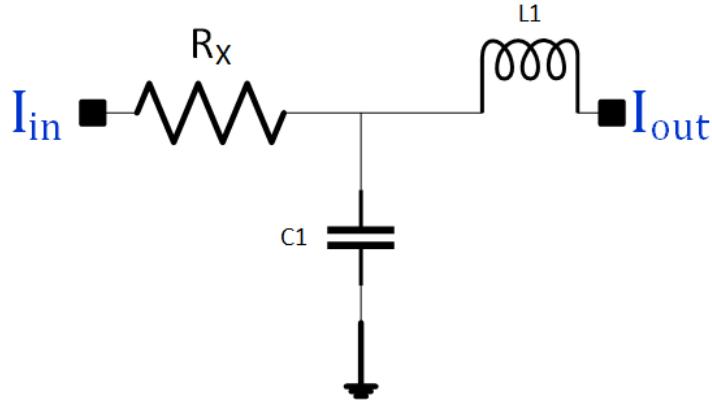

Concrètement, un FAR élimine les fréquences élevées du signal à l'aide de pôles et de zéros. Les pôles représentent des fréquences qui rendent le dénominateur de la fonction de transfert du FAR égal à zéro, et entraînent une réduction de la pente de la fonction de transfert du système. Les zéros représentent des fréquences qui rendent le numérateur d'une fonction de transfert égal à zéro et entraînent une augmentation de la pente de la fonction de transfert du système. Le comportement du filtre est déterminé par la position de ces pôles et zéros

dans le plan complexe, influençant ainsi la réponse en fréquence du filtre. L'ordre du filtre, défini par le nombre de pôles, détermine la pente de la coupure de fréquence et donc son efficacité à atténuer les hautes fréquences.

Dans ce contexte, le nombre d'éléments réactifs, tels que les inductances et les capacités, détermine le nombre de pôles du filtre. Ces éléments forment des circuits résonants qui contribuent à la réponse en fréquence souhaitée. La littérature propose une variété de configurations de filtres, que ce soit en mode courant ou en mode tension, chacun ayant ses propres avantages en termes de performance et d'implémentation.

Dans le cadre de notre application [4], le principal défi réside dans la nécessité d'une reconfigurabilité élevée de la fréquence de coupure du filtre, afin de pouvoir s'adapter à une grande variété d'applications. Cela requiert une architecture intégrée capable de répondre efficacement à des fréquences de coupure potentiellement de l'ordre du kHz. Atteindre de telles fréquences peut s'avérer complexe en raison des grandes constantes RC nécessaires et de la taille conséquente des composants passifs intégrés. Si la littérature propose une immense variété d'architectures, nous nous concentrerons ici plus spécifiquement sur celles ayant démontré une capacité à performer dans des bandes de fréquences basses avec une bonne reconfigurabilité, afin de se concentrer sur des cas similaires à notre application. Les principaux indicateurs de la performance d'un FAR considérés sont les suivants :

- **L'ordre du filtre**, qui définit la pente dans la zone de transition, et donc à quel point le FAR se rapproche d'un filtre idéal, qui rejette parfaitement toutes les fréquences dépassant la fréquence de coupure.

- **Le gain du filtre** dans la bande passante, qui devrait idéalement être parfaitement unitaire.

- **Les ondulations** du filtre dans la bande passante, qui introduisent des non-linéarités dans la réponse du filtre lorsque son gain théorique devrait être parfaitement unitaire.

- **La reconfigurabilité du filtre**, soit le nombre de décades sur lequel la fréquence de coupure du filtre peut être contrôlée.

- **La précision du contrôle du filtre**, définissant à tout instant à quel point la fréquence de coupure effective du filtre est proche de sa valeur théorique.

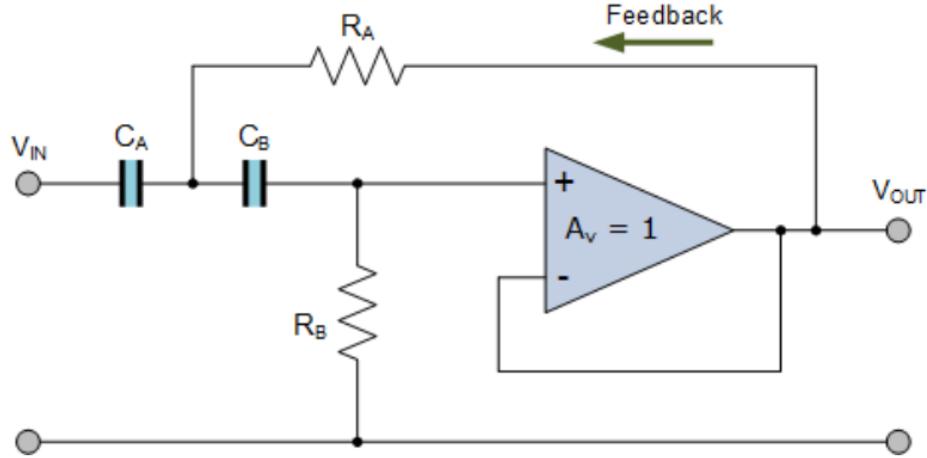

La structure la plus commune pour obtenir une réponse passe-bas ou passe-haut d'ordre 2 ou plus dans la littérature est le filtre dit "de Sallen-Key", qui utilise un AOP pour améliorer les structures élémentaires uniquement composées d'éléments passifs, dont la performance reste très limitée, particulièrement dans un contexte d'intégration où la performance des composants passifs en eux-mêmes n'est pas du tout compétitive par rapport à des composants discrets [27]. Cette architecture est présentée dans la Figure 2.17.

FIGURE 2.17 Filtre passe-haut de Sallen-Key [28]

Il est possible de moduler la fréquence de coupure en modifiant la valeur des composants passifs, que l'on pourrait alors imaginer externes dans notre cas. En effet, la fréquence de coupure d'un tel circuit est défini de la façon suivante :

$$f_{coupure} = \frac{1}{2\pi R_1 R_2 C_1 C_2} \quad (2.4)$$

Cependant, changer la valeur de composants passifs n'est pas toujours chose aisée lorsque la précision est un critère de performance primordial, comme on a pu le voir dans la partie de cette revue dédiée aux AGP. Utiliser un réseau de résistance et/ou de capacités peut introduire des éléments résistifs parasites, et une technique implémentant des capacités commutées peut encore une fois introduire de l'injection de charge à cause des commutations, ce qui peut être un problème de taille dans un filtre dont le rôle est typiquement d'éliminer les composantes parasites du signal.

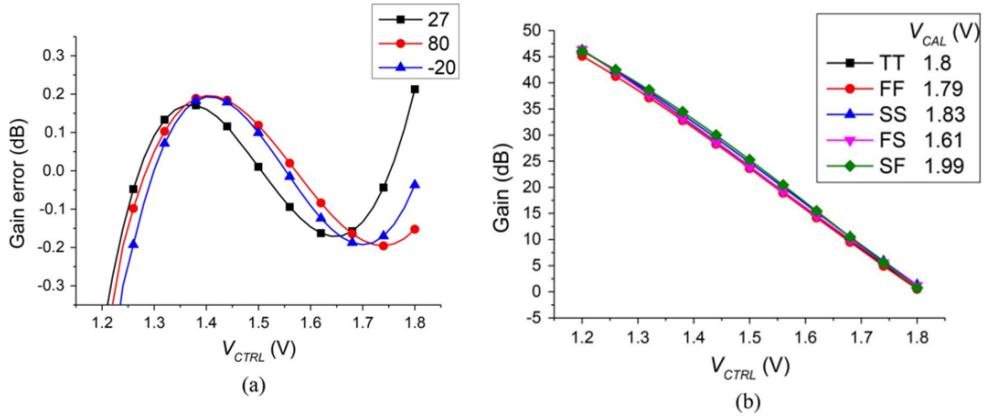

Une alternative présentée dans la littérature est la multiplication de capacité [29], qui permettrait ainsi de modifier à la volée la valeur équivalente des condensateurs sans directement interagir avec les composants passifs. Un tel circuit est présenté dans la Figure 2.18.

Cependant, on peut voir que ce genre de circuit est loin d'être trivial, et nécessite de nombreux composants, qui peuvent tous être amenés à être plus ou moins sensibles aux variations de procédé et de température, ce qui rend plus complexe l'obtention d'un très grand niveau de précision avec ce type de structure. Même si l'on décide d'apparier les condensateurs entre eux, leur valeur absolue a toujours une importance directe dans la réponse du filtre, et l'erreur sur cette valeur ne peut qu'être amplifiée par une multiplication.

FIGURE 2.18 Circuit de multiplication de capacité [29]

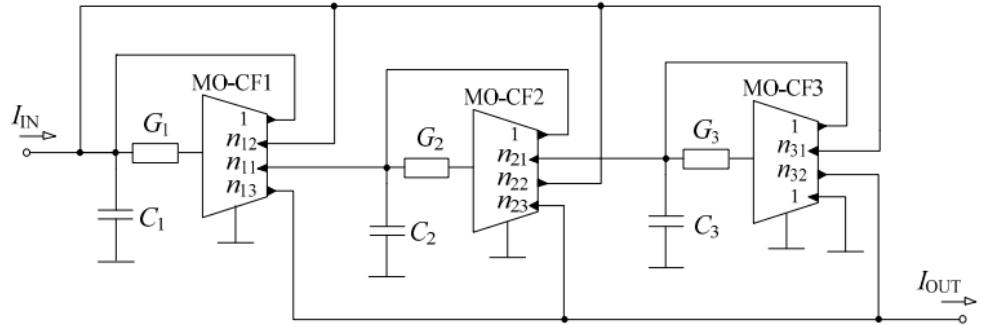

Intéressons-nous donc à présent à des architectures alternatives présentant spécifiquement des résultats compétitifs dans les bandes de fréquence basses dans la littérature. Une première alternative est d'utiliser un filtre en courant, avec des rétroactions multiples, comme présenté dans [30].

FIGURE 2.19 FAR en courant à rétroactions multiples [30]

Ce type d'architecture, présenté en Figure 2.19, cherche à contrôler le gain de chaque rétroaction en courant pour venir contrôler la réponse en fréquence du circuit. Cependant, on observe encore une fois que de nombreux blocs sont nécessaires, tous avec des gain indépendants. Cela nécessite donc une attention toute particulière à la robustesse des différents blocs aux variations de procédé et de température, ainsi qu'à leur appariement. Cela peut donc se révéler délicat à contrôler avec précision dans le cadre d'une application en milieu hostile.

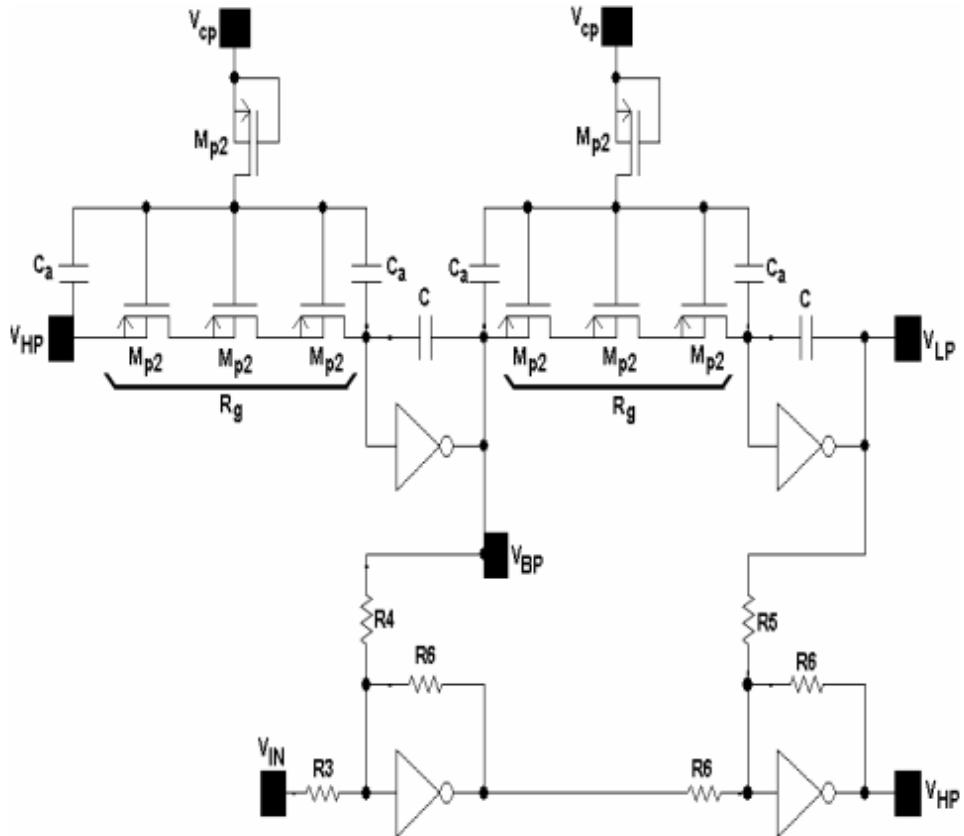

Une autre alternative standard dans la littérature est l'emploi de composants actifs pour simuler une impédance résistive très grande, ce qui permet ainsi d'atteindre les fortes constantes

RC nécessaires à des fréquences de coupure très basses [31]. Cette architecture est présentée dans la Figure 2.20.

FIGURE 2.20 FAR à résistance active [31]

Si ce type de circuit permet très efficacement de générer des impédances résistives très élevées, les composants résistifs actifs ainsi générés sont souvent sujets à des non-linéarités, et ont bien souvent une mauvaise invariance en température [27]. Le bruit de scintillation lié aux transistors est particulièrement prononcé à basse fréquence, ce qui peut poser des problèmes d'injection de bruit en l'absence d'un circuit de compensation approprié.

Pour résoudre ces problèmes, des architectures à base de MOS à grille quasi-flottante (QFG-MOS dans la littérature) ont été proposées dans la littérature [31], [32]. Cependant, il s'agit d'un type de composant très spécialisé, qui n'est pas offert dans tous les procédés CMOS, et notamment pas dans le procédé HT à notre disposition. De plus, les circuits à base de QFGMOS ont besoin de calibrations périodiques pour assurer leur performance, à cause des effets de vieillissement qui leurs sont associés, et sont particulièrement difficiles à intégrer aux côtés de circuits CMOS standards.

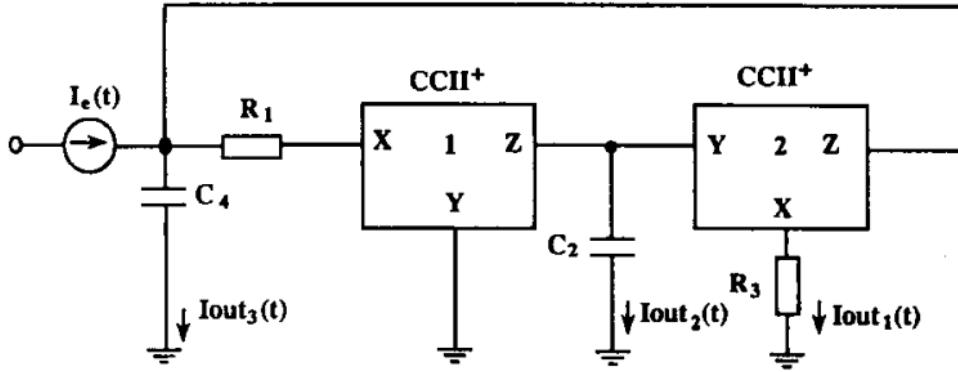

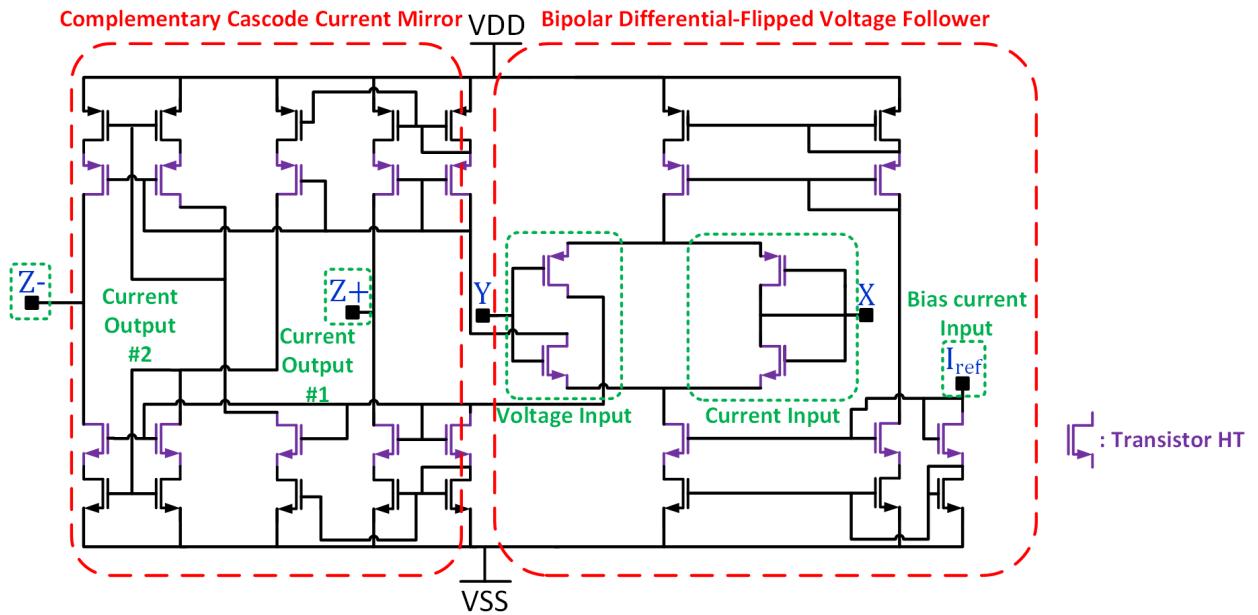

Il existe enfin une dernière architecture qui a su faire ses preuves, les filtres à base de convoyeurs de courant, et particulièrement de convoyeurs de courant de seconde génération (CCII) [33]. Il s'agit encore une fois d'un filtrage en courant. Un exemple de ce type d'architecture est présenté dans la Figure 2.21.

FIGURE 2.21 FAR à base de CCII [34]

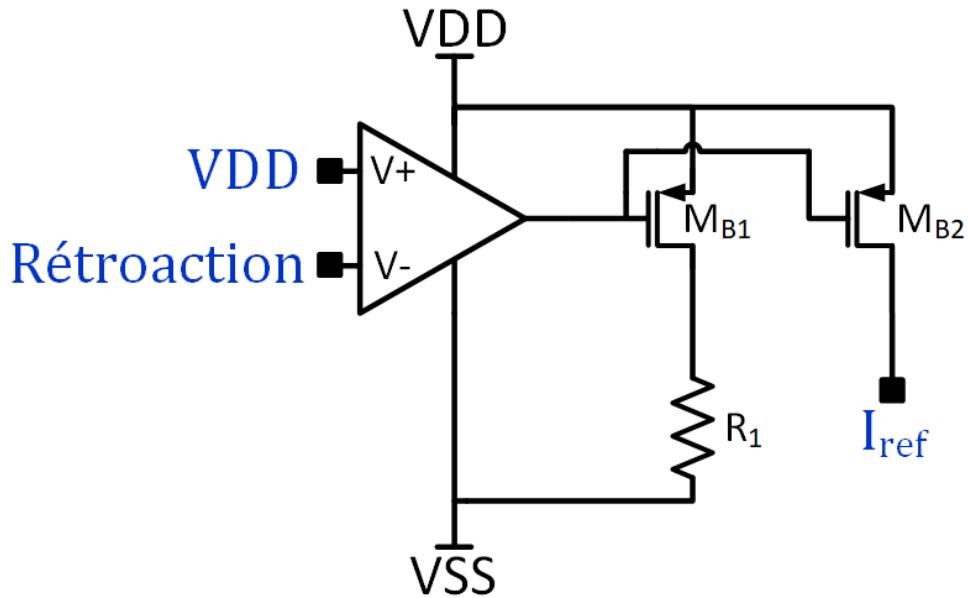

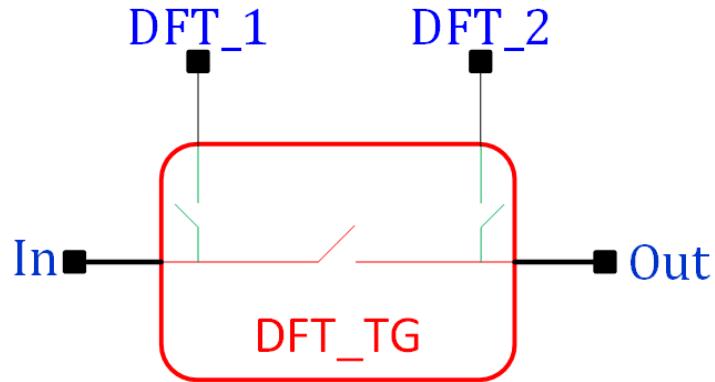

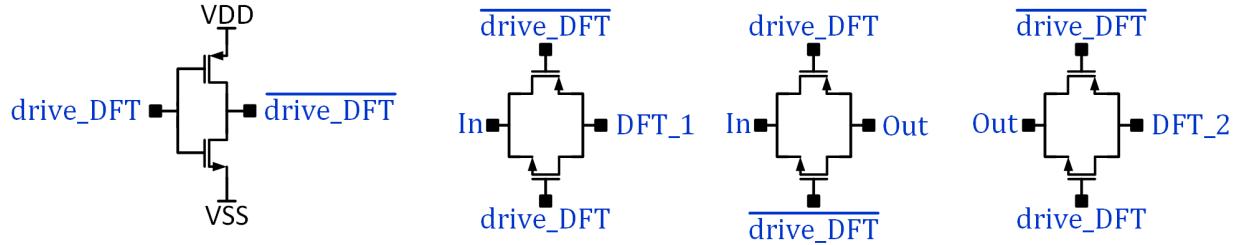

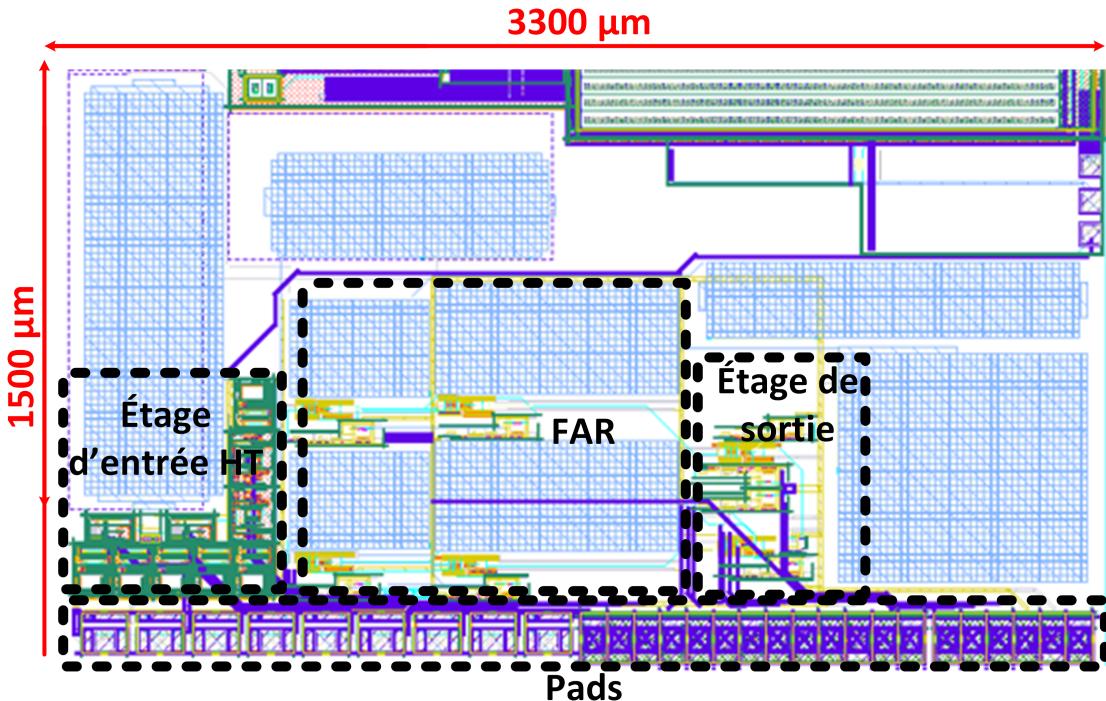

L'intérêt principal des CCII est leur robustesse intrinsèque aux effets parasites des transistors, ce qui fait de ce type d'architecture un excellent candidat pour une intégration dans un procédé HT comme le nôtre, où nous n'avons dans tous les cas pas accès aux transistors les plus performants du marché. De plus, l'approche en courant permet d'utiliser des transistors basse tension, qui ont naturellement une meilleure performance. Enfin, le contrôle de la fréquence de coupure du filtre peut facilement être contrôlée par l'impédance résistive au niveau du port d'entrée X des CCII [33], [34].