|                         | Self-aligned insulated gate FET technology for InP : an interface engineering approach                                                                                                                                                                                 |

|-------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Auteur:<br>Author:      | Chetlur S. Sundararaman                                                                                                                                                                                                                                                |

| Date:                   | 1993                                                                                                                                                                                                                                                                   |

| Туре:                   | Mémoire ou thèse / Dissertation or Thesis                                                                                                                                                                                                                              |

| Référence:<br>Citation: | Sundararaman, C. S. (1993). Self-aligned insulated gate FET technology for InP: an interface engineering approach [Thèse de doctorat, Polytechnique Montréal]. PolyPublie. <a href="https://publications.polymtl.ca/57987/">https://publications.polymtl.ca/57987/</a> |

|                         |                                                                                                                                                                                                                                                                        |

# Document en libre accès dans PolyPublie Open Access document in PolyPublie

| URL de PolyPublie:<br>PolyPublie URL:    | https://publications.polymtl.ca/57987/ |

|------------------------------------------|----------------------------------------|

| Directeurs de<br>recherche:<br>Advisors: |                                        |

| <b>Programme:</b><br>Program:            | Non spécifié                           |

### UNIVERSITÉ DE MONTRÉAL

# SELF - ALIGNED INSULATED GATE FET TECHNOLOGY FOR InP: AN INTERFACE ENGINEERING APPROACH

par

# Chetiur S.SUNDARARAMAN DÉPARTEMENT DE GÉNIE PHYSIQUE ÉCOLE POLYTECHNIQUE

# THÈSE PRÉSENTÉ EN VUE DE L'OBTENTION DU GRADE DE PHILOSOPHIAE DOCTOR (Ph.D.)

(GÉNIE PHYSIQUE)

Mai 1993

<sup>©</sup> droits réservés de Chetlur S. SUNDARARAMAN 1993

Acquisitions and Bibliographic Services Branch

395 Wellington Street Ottawa, Ontario K1A 0N4 Bibliothèque nationale du Canada

Direction des acquisitions et des services bibliographiques

395, rue Wellington Ottawa (Ontario) K1A 0N4

Your file Votre référence

Our tile Notre référence

The author has granted an irrevocable non-exclusive licence allowing the National Library of Canada to reproduce, loan, distribute or sell copies of his/her thesis by any means and in any form or format, making this thesis available to interested persons.

L'auteur a accordé une licence irrévocable et non exclusive Bibliothèque permettant à la nationale du Canada reproduire, prêter, distribuer ou vendre des copies de sa thèse de quelque manière et sous quelque forme que ce soit pour mettre des exemplaires de cette thèse à disposition la personnes intéressées.

The author retains ownership of the copyright in his/her thesis. Neither the thesis nor substantial extracts from it may be printed or otherwise reproduced without his/her permission. L'auteur conserve la propriété du droit d'auteur qui protège sa thèse. Ni la thèse ni des extraits substantiels de celle-ci ne doivent être imprimés ou autrement reproduits sans son autorisation.

ISBN 0-315-86560-1

ne C. S. SUNDARA RAMAN

extation Abstracts International is arranged by broad, general subject categories. Please select the one subject which most ly describes the content of your dissertation. Enter the corresponding four-digit code in the spaces provided.

SUBJECT CODE

### ject Categories

#### **E HUMANITIES AND SOCIAL SCIENCES**

| MUNICATIONS AND THE A lecture istory na                                                                                                                        | .0729<br>.0377<br>.0900<br>.0378<br>.0357<br>.0723<br>.0391<br>.0399<br>.0708<br>.0413                                     |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|

| ATION ral                                                                                                                                                      | .0515<br>.0514<br>.0516                                                                                                    |

| ual and Multicultural ess nunity College culum and Instruction Childhood entary ce ance and Counseling h er y of e Economics trial uage and Literature ematics | .0273<br>.0282<br>.0688<br>.0275<br>.0727<br>.0518<br>.0524<br>.0277<br>.0519<br>.0680<br>.0745<br>.0520<br>.0278<br>.0521 |

| ophy of<br>cal                                                                                                                                                 | .0523                                                                                                                      |

| Psychology Reading Religious Sciences Secondary Social Sciences Sociology of Special Teacher Training Technology Tests and Measurements Vocational                                        | .0535<br>.0527<br>.0714<br>.0533<br>.0534<br>.0340<br>.0529                                                       |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------|

| LANGUAGE, LITERATURE AND LINGUISTICS                                                                                                                                                      |                                                                                                                   |

| Language General Ancient Linguistics Modern Literature                                                                                                                                    | .0289                                                                                                             |

| General Classical Comparative Medieval Modern African American Asian Canadian (English) Canadian (French) English Germanic Latin American Middle Eastern Romance Slavic and East European | .0294<br>.0295<br>.0297<br>.0298<br>.0316<br>.0591<br>.0305<br>.0352<br>.0355<br>.0593<br>.0311<br>.0312<br>.0315 |

| PHILOSOPHY, RELIGION AND THEOLOGY                                                                                    |                                                             |

|----------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|

| Philosophy<br>Religion                                                                                               | .0422                                                       |

| General Biblical Studies Clergy History of Philosophy of Theology                                                    | .0319<br>.0320<br>.0322                                     |

| SOCIAL SCIENCES                                                                                                      |                                                             |

| American Studies                                                                                                     | .0323                                                       |

| Anthropology Archaeology Cultural Physical Business Administration                                                   | .0326                                                       |

| General Accounting Banking Management Marketing Canadian Studies                                                     | .0310<br>.0272<br>.0770<br>.0454                            |

| Economics General Agricultural Commerce-Business Finance History Labor Theory Folklore Geography Gerontology History | .0503<br>.0505<br>.0508<br>.0509<br>.0510<br>.0511<br>.0358 |

| General                                                                                                              | .0578                                                       |

|                                                                                                                      |                                                             |

| Ancient                                                                                                                            | 0581<br>0582<br>0328<br>0331<br>0332<br>0334<br>0335<br>0336<br>0333<br>0337<br>0585 |

|------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|

| Political Science GeneralInternational Law and                                                                                     | 0615                                                                                 |

| Relations                                                                                                                          | 0616<br>0617<br>0814                                                                 |

| Sociology General Criminology and Penology Demography Ethnic and Racial Studies Individual and Family Studies Industrial and Labor |                                                                                      |

| Relations<br>Public and Social Welfare<br>Social Structure and                                                                     | 0629<br>0630                                                                         |

| Development                                                                                                                        | 0700<br>0344<br>0709<br>0999<br>0453                                                 |

|                                                                                                                                    |                                                                                      |

### ENCES AND ENGINEERING

| DGICAL SCIENCES                                       |       |

|-------------------------------------------------------|-------|

| interel                                               | 0.472 |

|                                                       | 04/3  |

| gronomy<br>nimal Culture and                          | .0285 |

| inimal Culture and                                    | 0 475 |

| Nutrition                                             | .04/5 |

| nimal Pathology                                       | 0476  |

| nimal Pathology                                       |       |

| Technology                                            | 0359  |

| orestry and Wildlite                                  | .0478 |

| lant ( illture                                        | 114/9 |

| lant Pathology                                        | 0480  |

| lant Physiology                                       | 0817  |

| lant Physiology<br>ange Management<br>Vood Technology | .0777 |

| Vood Technology                                       | 0746  |

| gy                                                    |       |

| ženeral                                               | 0306  |

| natomy                                                |       |

| iostatistics                                          | 0308  |

| otany                                                 | 0300  |

| iell                                                  | 0307  |

| cology                                                | 0377  |

| ntomology                                             | 0353  |

| enetics                                               |       |

| zenerics                                              | 0307  |

| imnology                                              | 0/93  |

| Nicrobiology                                          | 0410  |

| Nolecular                                             |       |

| leuroscience                                          | 031/  |

| Dceanography<br>Hysiology                             | 0416  |

| hysiology                                             | 0433  |

| adiation                                              | 0821  |

| adiation<br>eterinary Science                         | 0778  |

| oology                                                | 0472  |

| hysics                                                |       |

| Seneral                                               |       |

| Nedical                                               | 0760  |

|                                                       |       |

| TH SCIENCES                                           |       |

| eochemistry                                           | 0425  |

| chemistry                                             | 0996  |

|                                                       |       |

| peophysics yidrology Aineralogy aleobotany aleoecology aleontology aleozoology aleozoology alynology hysical Geography hysical Oceanography IEALTH AND ENVIRONMENTA                                                                                                                                                                      | 0388<br>0411<br>0345<br>0426<br>0418<br>0985<br>0427<br>0368<br>0415                                                                         |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|

| CIENCES                                                                                                                                                                                                                                                                                                                                  | •                                                                                                                                            |

| nvironmental Sciences                                                                                                                                                                                                                                                                                                                    | 0768                                                                                                                                         |

| lealth Sciences General Audiology Chemotherapy Dentistry Education Hospital Management Human Development Immunology Medicine and Surgery Mental Health Nursing Nutrition Obstetrics and Gynecology Occupational Health and Therapy Ophthalmology Pathology Pharmacology Pharmacology Physical Therapy Public Health Radiology Recreation | 0300<br>0992<br>0567<br>0350<br>0769<br>0758<br>0982<br>0564<br>0347<br>0569<br>0380<br>0354<br>0381<br>0571<br>0419<br>0572<br>0573<br>0574 |

| Speech Pathology                                                                                                               | .0460<br>.0383<br>.0386                                     |

|--------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|

| PHYSICAL SCIENCES                                                                                                              |                                                             |

| Pure Sciences Chemistry General Agricultural Analytical Biochemistry Inorganic Nuclear Organic Pharmaceutical Physical Polymer | .0749<br>.0486<br>.0487<br>.0488<br>.0738<br>.0490<br>.0491 |

| Radiation                                                                                                                      | 0754                                                        |

| Physics General Acoustics Astronomy and                                                                                        | 0605<br>0986                                                |

| Astrophysics                                                                                                                   | .0606<br>.0608<br>.0748<br>.0607                            |

| Elementary Particles and High Energy Fluid and Plasma Molecular Nuclear Optics Radiation Solid State Statistics                | .0609<br>.0610<br>.0752<br>.0756<br>.0611                   |

| Applied Sciences Applied Mechanics Computer Science                                                                            | 0346                                                        |

| Engineering General Aerospace Agricultural Automotive Biomedical Chemical Civil Electronics and Electrical Heat and Thermodynamics Hydraulic Industrial Materials Science Mechanical Metallurgy Mining Nuclear Packaging Petroleum Sanitary and Municipal System Science Geotechnology Operations Research Plastics Technology Cestile Technology Captivery      | 0540<br>0541<br>0542<br>0543<br>0544<br>0348<br>0545<br>0546<br>0547<br>077<br>07551<br>0552 |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|

| PSYCHOLOGY           General         0           Behavioral         0           Clinical         0           Clinical         0           Experimental         0           Industrial         0           Personality         0           Psychobiology         0           Psychobiology         0           Psychometrics         0           Social         0 | 0384<br>0622<br>0620<br>0623<br>0624<br>0625<br>0989<br>0349                                 |

### **UNIVERSITÉ DE MONTRÉAL**

### **ÉCOLE POLYTECHNIQUE**

### Cette thèse intitulée

# SELF - ALIGNED INSULATED GATE FET TECHNOLOGY FOR Inp: AN INTERFACE ENGINEERING APPROACH

présenté par: <u>Chetlur S. SUNDARARAMAN</u> en vue de l'obtention du grade de: <u>Philosophiae doctor</u> a été dûment accepté par le jury d'examen constitué de:

- M. MASUT Remo., Ph. D., président

- M. CURRIE John F., Ph. D., membre et directeur de recherche

- M. MEYYAPPAN Meyya, Ph. D., membre

- M. AKTIK Çetin, Ph. D., membre

Man ought to act

There is freedom only in action

-Bhagavad Gita-

To My Parents

C.R.Srinivasan and Amirtha Srinivasan

### SUMMARY

The technologies based on InP and associated ternary and quaternary alloys are being pursued vigorously in the emerging areas of optoelectronics, and high frequency electronics. Fabrication of insulated gate FET structures on InP is hampered by the poor quality of the InP/insulator interface. InP does not have a stable native oxide and deposited insulators are normally used. However, the InP surface degrades during even modest thermal annealing 150-300°C, similar to that used for dielectric deposition, with the formation of surface phosphorus (VP) vacancy traps. These traps reduce the transconductance and cause the drain current to drift with time. Thermal degradation is especially serious for self-aligned gate (SAG) structures that use a high temperature implant anneal in the fabrication process and there are no reports of a reproducible SAGFET technology for InP to date.

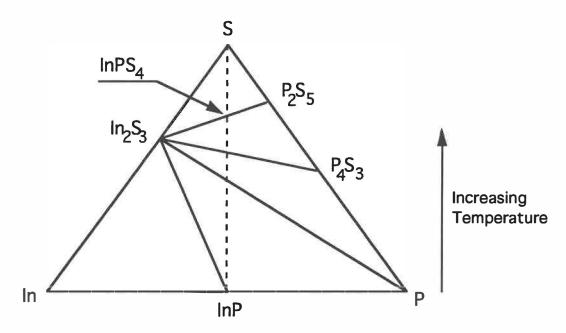

In this study, we present a new approach by combining a novel indirect plasma deposition technique with sulfur (S) surface passivation to engineer a low trap interface that shows good high temperature stability and a highly reproducible SAGFET technology has been developed that shows promise. The first phase of this study concentrates on the nature of S passivation of InP by PL and XPS measurements. The results clearly show thermal S passivation leads to the formation of a 30Å In<sub>2</sub>S<sub>3</sub> layer that prevents P out-diffusion from the InP surface, thereby decreasing the VP deep level emission intensity from the passivated samples. Latter a universal model for the formation of sulfide layers on InP from monolayer coverage to thick sulfide layers is proposed. Monolayer In-S coverage is explained as a photo electrochemical interaction between deposited neutral S° atoms and acceptor-like In dangling bonds while thicker

sulfide layers are due to S reacting with the InP substrate according to the In-P-S ternary equilibrium phase diagram.

S passivated Metal/silicon nitride/InP (MIS) capacitors with near ideal C-V characteristics, negligible hysterisis and midgap interface state density in the low 10<sup>11</sup>cm<sup>-2</sup>.eV<sup>-1</sup>have been fabricated for the first time. The passivated capacitors exhibit good high temperature stability upto 700°C thermal annealing and show promise for a self-aligned gate FET technology for InP. The complete process technology, viz. mesa isolation, implantations, implant activation, indirect plasma nitride, gate and contact metallization, has been developed including a novel implant annealing technique and the new indirect plasma deposition technique. A exclusive copyright test chip using 5 mask levels is designed to fabricate the SAGFETs and to evaluate their characteristics. Accumulation and inversion type passivated SAG MISFETs and InP/InGaAs/InP SAG HIGFETs are fabricated and tested. This is the first report of passivated SAGFETs in literature and the technology is extremely reproducible. The FETs exhibit excellent transistor characteristics with low output conductance ( $g_0 = 0.05-0.38$  mS/mm) and performance comparable to nonself-aligned FETs. The measured peak transconductances are 10-12 mS/mm and 30 mS/mm for MISFETs and HIGFETs respectively. The drain current drift in these devices is guite small (6%) and upward over a period of 10<sup>4</sup> seconds indicating the absence of V<sub>D</sub> related traps. Device performance is mainly limited by high gate leakage due to S incorporation into the insulator and the passivation process is also found to be quite non-uniform. Suggestions are made to reduce gate leakage and a novel epitaxial interface engineering technique is proposed to improve uniformity.

The study clearly reveals the advantages of using interface engineering techniques for next generation insulated gate high speed devices for InP and is expected to inspire the development of a mature interface engineering technology for III-V semiconductors.

### RÉSUMÉ

Les techniques de passivation deviennent de plus en plus populaires pour les dispositifs à base de semi-conducteurs III-V et leurs développements promet une amélioration des performances des dispositifs à grande mobilité actuels et mènera vers de nouvelles structures de dispositifs. En particulier, l'ingénierie d'interface à base de souffre (S) promet des structures à grille isolante basées sur l'InP, comme par exemple les HIGFET. Dernièrement, des études ont montré que la passivation InP/SiO2 avec du souffre (S) donnait une faible densité d'états d'interface et que les MISFET à grille non-auto-alignée passivés ont des courants de dérive de drain négligeables. Malgré les aspects bénéfiques de la passivation à base de souffre (S) qui ont été rapportés, la nature exacte du mécanisme de passivation, sa stabilité en température et son application au procédé de grille auto-alignée ne sont pas connus. Ces importants résultats sont cruciaux pour le développement des futurs transistors à effet de champ à grille isolante (FET) sur InP.

Dans ce travail, on a étudié en détail la passivation de la surface de l'InP avec du souffre et on a expliqué comment se produit la passivation thermique avec du souffre, on a proposé un modèle universel sur la formation des couches de sulfure sur l'InP. On a réussi à appliquer le procédé de passivation pour la première fois au nitrure de silicium déposé par PECVD, utilisé comme grille isolante et ainsi démontré l'efficacité de la technique de passivation à base de souffre afin de contrôler la densité de défauts à l'interface InP/nitrure de silicium.

La surface passivée est stable jusqu'à T=700°C et la technique est appliquée pour la première fois afin de fabriquer des structures Métal-isolant-semi-conducteur (MIS) FET à grilles isolantes auto-alignées et des hétérojonctions à grilles isolantes (HIG) FET InP/InGaAs/InP. Un procédé technologique complet, convenable pour la passivation de grille métallique, incluant quelques nouvelles techniques de traitement a été développé. Un module (chip) de diagnostic a été mis au point afin d'évaluer les différents procédés, le dispositif et les paramètres du circuit. Les structures FET à grilles isolantes auto-alignées non passivées n'exhibent pas les caractéristiques d'un transistor, par contre ceux passivées au souffre possèdent une excellente caractéristique DC mais de modestes performances. Ce travail montre l'importance des techniques de passivation à l'interface pour les structures à grilles isolantes à base d'InP.

La passivation thermique de la surface de l'InP avec du souffre est étudiée en détail en utilisant des techniques analytiques telles que la photoluminescence (PL), la spectroscopie de photo électron à rayon X (XPS) et l'XPS à résolution angulaire. À partir des mesures PL, il a été observé que la passivation réduit les lacunes de phosphore qui sont liées à l'émission des niveaux profonds dans la gamme de température 150-300°C. La dissociation du phosphore à la surface durant le recuit thermique conduit à la formation des lacunes de surface, qui sont très importantes pour les dispositifs à base d'InP. À partir des mesures XPS, on a montré que durant le recuit le souffre réagit avec le substrat d'InP selon le diagramme de phase ternaire In-P-S et forme une couche tampon In2S3 de 30 Å d'épaisseur. La diffusion du souffre S et la formation d'une couche de sulfure à la surface empêchent la diffusion du

phosphore P de la surface de l'InP, minimisant ainsi les niveaux profonds associés aux états vacants de P. Ayant identifié le mécanisme exacte du procédé de passivation thermique de l'InP, on a proposé un modèle universel de passivation portant sur la formation des différentes couches de sulfure, des monocouches jusqu'aux couches épaisses qui sont rapportées dans la littérature.

Le modèle proposé classifie les couches de sulfure en a) interaction photoélctrochimique de surface entre les atomes neutres de souffre S déposés à partir d'une solution et les états accepteurs associés à la surface d'atomes In conduisant à une monocouche S servant de couverture; b) réactions à l'équilibre du diagramme de phase assistées thérmiquement/plasma entre l'InP et S conduit à la formation d'une couche épaisse de sulfure. Ces dernières réactions sont divisées en régime de sulfurisation faible, intermédiaire et fort. Il a été remarqué que la passivation thermique entre 150-300°C correspond au faible régime de sulfurisation. La densité d'états d'interface à l'interface InP/nitrure est évaluée par des mesures C-V à haute fréquence sur des structures MIS passivées et non-passivées. Afin de fabriquer des capacités MIS, une nouvelle technique de dépôt du diélectrique a été développée, c'est la méthode par plasma indirect, qui est non coûteuse et évite d'endommager le substrat par le plasma. Les capacités MIS de InP/Si3N4, passivées exhibent à haute fréquence des caractéristiques C-V idéales avec un hystéresis négligeable (< 0.1 V) et une densité d'états d'interface de 1x10<sup>11</sup> cm<sup>-2</sup>.eV<sup>-1</sup> et une densité égale à 8x10<sup>10</sup> cm<sup>-2</sup>.eV<sup>-1</sup> au milieu de la bande interdite. Par contre, les courbes C-V correspondant aux échantillons nonpassivés montrent de large hystéresis ainsi qu'une augmentation de la densité d'états d'interface à 0.15 eV en dessous de l'extrémité la bande de conduction.

Une étude préliminaire par spectroscopie transitoire des niveaux profonds (DLTS) a été effectuée pour évaluer l'énergie d'activation et la section efficace de capture des pièges d'interface à l'interface passivée au souffre. La passivation d'interface utilisant le souffre S montre une bonne stabilité thermique car les structures MIS conservent leurs caractéristiques C-V idéales même après un recuit allant jusqu'à 700°C. La passivation avec du souffre apparaît comme étant un bon candidat pour réaliser des structures à grilles auto-alignées sur InP.

Pour fabriquer les SAGFET passivés, on a développé un procédé technologique complet, comprenant l'évaluation du substrat, le nettoyage de la gaufre, l'isolation mésa, le dépôt par plasma indirect de la couche isolante Si3N4, l'implantation, son activation et la métallisation grille/contact. Les techniques rapportées dans la littérature ont été modifiées et de nouveaux procédés ont été développés. En particulier, une nouvelle méthode de recuit à lampe, à rampe lente (SRLA) et une nouvelle technique de déposition par plasma indirect. Une variété d'instruments de caractérisation sont utilisés pour optimiser ces procédures. un module de diagnostic avec des structures de test spéciales est crée pour vérifier la compatibilité de l'intégration des séquences du nouveau procédé,les différents matériaux, le procédé et les paramètres du dispositif. L'ensemble de test intégré utilise 5 niveaux de masques dont la dimension minimale d'un motif est de 1µm.

En utilisant les procédés de fabrication mentionnés et l'ensemble de masques, les premiers SAG MISFET et HIGFET passivés ont été fabriqués. Le

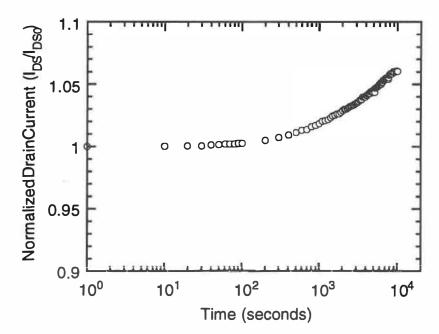

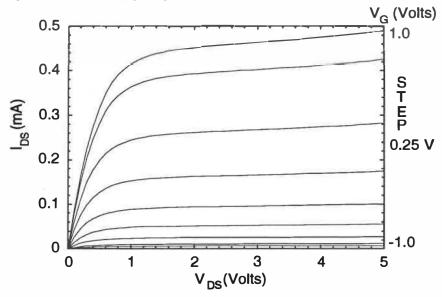

test des dispositifs a montré des caractéristiques de transistors bien définies, exhibant une faible conductance de sortie (go=0.05-0.38 mS/mm) et des performances modestes. Les MISFET du type accumulation et inversion ont exhibé une transconductance maximale (gmo) de 10-12 mS/mm et 2-3 mS/mm respectivement tandis que pour les HIGFET la valeur maximale était de 30 mS/mm. Par contre, les FET non passivés mais fabriqués en utilisant le même procédé n'ont montré aucune propriété de transitor; ce qui implique que l'ingénierie d'interface à base de S est l'étape qui a permis d'obtenir des SAGFET et cela indique l'importance d'utilisation de ces techniques pour la fabrication de dispositifs à base d'InP. De plus, les MISFET à accumulation montrent un faible courant de dérive de drain (<6%) positif (DCD) sur une période de 10<sup>4</sup> secondes, comparable au courant de dérive négatif qui est associé à l'interface et aux pièges vacants de phosphore P. L'augmentation du courant de drain dans les expériences de (DCD) indique que la passivation contrôle la formation des sites vacants de P à l'interface.

Le recuit après fabrication a un impact important sur le procédé et les caractéristiques du dispositif. Un recuit à 400°C durant 30 minutes améliore les caractéristiques électriques des MISFET de type accumulation par contre cela dégrade les performances de ceux en mode d'inversion. À partir des mesures de lignes de transmission (TLM) on a pu estimer des valeurs minimales de résistivité de contact de 15  $\mu\Omega$ .cm² pour les MISFET et HIGFET et des résistances de couches implantées correspondantes de 2-5 k $\Omega$ / $\neg$  et 40  $\Omega$ / $\neg$  respectivement.

Le problème majeure est l'incorporation du souffre S dans la grille isolante durant le traitement à haute température, causant un courant de fuite

de grille élevé, ce qui limite les performances des FET. De plus, le traitement de passivation chimique utilisé dans cette étude est assez non-uniforme et l'interface passivée présente des rugosités ce qui cause la réduction de la mobilité dans le canal. En utilisant un diélectrique plus dense et une autre couche épitaxiale servant d'interface, par exemple une couche sous contrainte de GaP, à large bande interdite, qui remplace la couche protectrice de sulfure d'indium, on pourra résoudre les problèmes de fuite et de non-uniformité et améliorer ainsi les performances du transistor. Néanmoins, l'étude révèle l'importance des techniques d'interface pour les prochaines générations de dispositifs à grilles isolantes et à grande vitesse. Il est attendu à ce que ce travail contribue à de sérieux travaux scientifiques et conduit au développement de techniques d'interfaces pour les semi-conducteurs III-V.

### **ACKNOWLEDGMENTS**

Many individuals have participated and infused this work with scientific suggestions, technical help and more importantly their enthusiasm and cheer.

I am greatly indebted to,

- Prof. John F. Currie, for his excellent guidance, his good cheer and above all for his patience and support through tough times. I have been fortunate to have this real "gentleman" as advisor.

- Prof. Carl W.Wilmsen of Colorado State University, for accepting me in his research group and for introducing me to this research area.

- Prof. Richard Leonelli of the University of Montreal, for the PL measurements and for interesting discussions on S passivation.

- Prof. Arthur Yelon and Dr. Edward Sacher for extending the XPS facility and for many insightful discussions on the mechanisms of monolayer S coverage on InP.

- Prof. Çetin Aktik of the University of Sherbrooke, for the Si implantations, the DLTS measurements and for his encouragement.

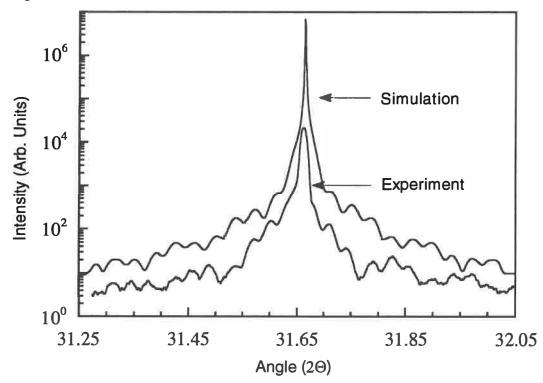

- Prof. Remo Masut for the HXRD measurements and for many technical discussions and encouragement.

- Prof. Meyya Meyyappan of Scientific Research Associates for taking time-off to participate as a jury member and for many long distance scientific discussions.

- Dr. Subash Gujrathi for the ERD measurements and for many technical discussions and encouragement.

- Dr. Martinu Ludvik for his advice on the modifications of the PECVD system for indirect plasma deposition.

- Dr. Carla Miner of BNR for the scanning PL measurement of the heterostructure wafer.

- Mme Suzie Poulin for the numerous XPS measurements including many last minute experiments and for her pleasing demeanor.

- Dr. Ravi Iyer of Colorado State University, for his enthusiastic assistance and many technical discussions.

- Dr. Mario Beaudoin for the PECVD system training, efforts to keep it up and running and for excellent comradeship.

- Dr. Ye Tao of NRC for many discussions on surface passivation.

- Pierre Mihelich for the C-V frequency dispersion measurements and comradeship

- René Lacoursière, François Rigano and Carole Painchaud for their help in maintaining the MODFAB equipment.

- Hughes Bouchard for generously sharing his office space and good humor.

- Mme. Lucille Rozon for her administrative help with a smile.

- Amtout Abdenour for the french resumé and Fouad Benkhelifa for his help in preparing this manuscript and their excellent comradeship.

- Dr. V.Kalyanaraman, Viji, Dr. Ajai Jain, Renu, Dr. V.Chandrashekar, Srinath and Shashank for their support during some tough personal times.

- Lourdes Desouza for her enthusiasm and humor and for typing the references.

- My parents, C.R.Srinivasan and Amirtha Srinivasan and my sisters Vijaya, Vasudha and Vidya for their love, support and sacrifice.

# TABLE OF CONTENTS

| DEDICATION    | lV                                                          |

|---------------|-------------------------------------------------------------|

| SUMMARY       | v                                                           |

| RESUMÉ        | viii                                                        |

| ACKNOWLE      | DGMENTSxiv                                                  |

| TABLE OF C    | CONTENTSxvi                                                 |

| LIST OF FIGUR | RESxxi                                                      |

| LIST OF TAE   | BLESxxviii                                                  |

| OTHER ILLUS   | TRATIONSxxix                                                |

| LIST OF ANNE  | <b>XES</b> xxx                                              |

| INTRODUCT     | ION1                                                        |

| CHAPTER 1     | - SURFACE PASSIVATION                                       |

| 1.1 Intr      | oduction13                                                  |

| 1.2 The       | ermal S passivation of InP15                                |

| 1.2.1         | The passivation procedure14                                 |

| 1.2.2         | Photoluminescence experiments17                             |

| 1.2.3         | X-ray photoelectron spectroscopy25                          |

| 1.2.          | 3.1 Chemical nature of the surface28                        |

| 1.2.          | 3.2 Thickness of the sulfide layer34                        |

| 1.2.3         | The Passivation mechanism36                                 |

| 1.3 A u       | niversal model for the formation of sulfide layers on InP39 |

| 1.3.1         | Surface interactions40                                      |

| 1.3.2         | Bulk interactions48                                         |

| 1.3.3         | Conclusions49                                               |

| CH  | APTE  | R 2  | - FA   | BRICATION TECHNOLOGY FOR SAG FETS |    |

|-----|-------|------|--------|-----------------------------------|----|

|     | 2.1   | Intr | oduc   | ion                               | 52 |

|     | 2.2   | Wa   | fer ch | naracterization                   | 53 |

|     | 2.3   | Che  | emica  | I cleaning and etching            | 60 |

|     | 2.3   | 3.1  | The    | cleaning cycle                    | 60 |

|     | 2.3   | 3.2  | lodic  | acid                              | 61 |

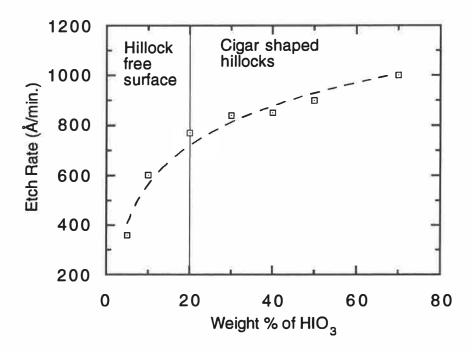

|     |       | 2.3. | .2.1   | Etch rate with concentration      | 62 |

|     |       | 2.3. | .2.2   | Etch rate with temperature        | 63 |

|     |       | 2.3. | .2.3   | Surface and profile               | 66 |

|     | 2.3   | 3.3  | The    | phosphoric-peroxide mixture       | 69 |

|     | 2.4   | The  | gate   | insulator                         | 72 |

|     | 2.4   | l.1  | Limit  | ations and solutions              | 72 |

| 2.4 |       | 1.2  | Indir  | ect plasma nitride                | 74 |

|     |       | 2.4. | 2.1    | The indirect plasma system        | 74 |

|     |       |      | 2.2    | Conditions for nitride deposition | 75 |

|     |       |      | 2.3    | The Si/nitride interface          | 76 |

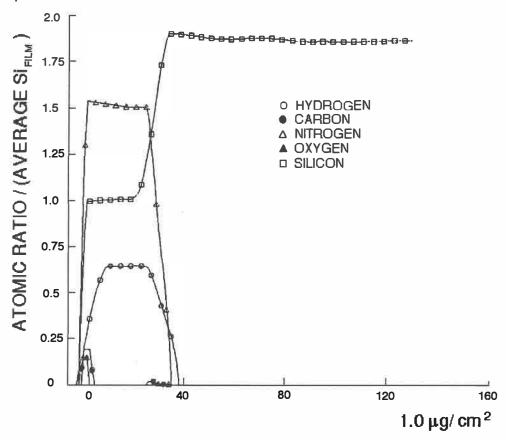

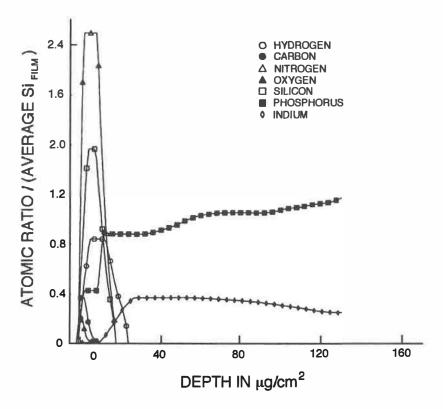

|     |       | 2.4. | 2.4    | Stoichiometry of the nitride      | 77 |

|     | 2.5   | Ion  | Impla  | ntation                           | 80 |

|     | 2.5   | 5.1  | Gene   | eral considerations               | 80 |

|     | 2.5   | 5.2  | TRIM   | simulations                       | 81 |

|     | 2.5.3 |      | Pola   | ron measurements                  | 82 |

|     | 2.5   | 5.4  | Rapid  | d thermal activation              | 83 |

|     | 2.5   | .5   | Slow   | Ramp Lamp Anneal (SRLA)           | 84 |

|     |       | 2.5. | 5.1    | Polaron profiles                  | 85 |

|     | 2.6   | Con  | tacts. |                                   | 87 |

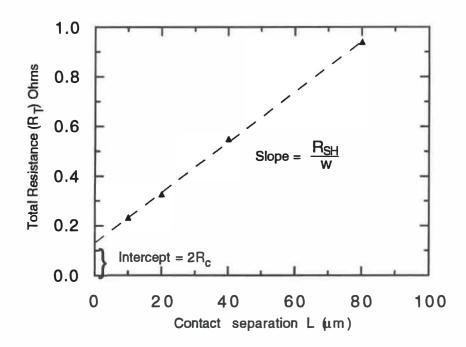

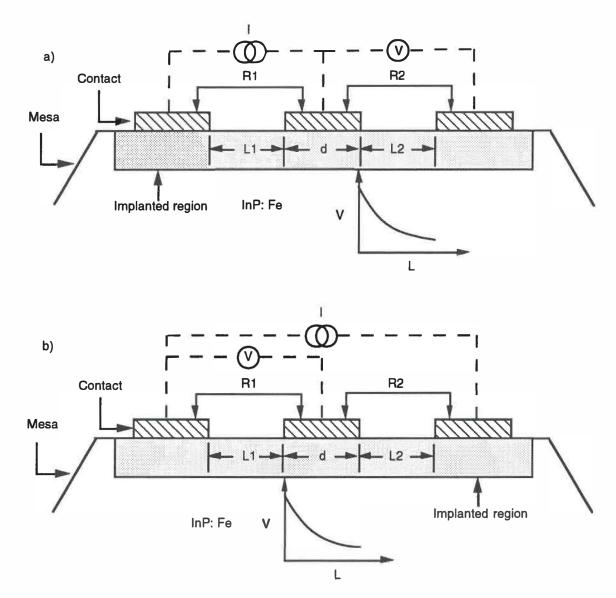

|     | 2.6   | 6.1   | Transmission line model                          | 89  |

|-----|-------|-------|--------------------------------------------------|-----|

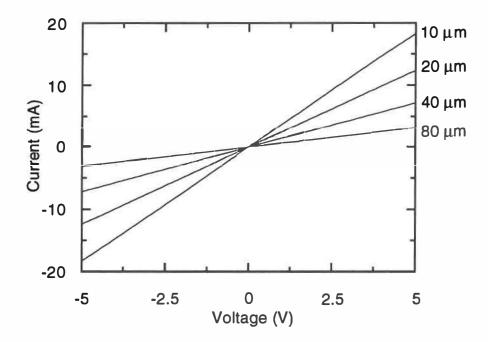

|     | 2.6   | 6.2   | Contact resistivity measurements                 | 92  |

| CHA | APTER | 3     | - INTERFACE ENGINEERED MIS DIODES                |     |

|     | 3.1   | Intr  | oduction                                         | 94  |

|     | 3.2   | Fat   | orication of Interface engineered MIS capacitors | 95  |

|     | 3.3   | The   | e dielectric on S treated InP                    | 97  |

|     | 3.4   | Die   | electric leakage                                 | 97  |

|     | 3.4   | .1    | I-V characteristics                              | 97  |

|     | 3.5   | The   | e InP/nitride interface                          | 99  |

|     | 3.5   | .1    | C-V characteristics                              | 99  |

|     | 3.5   | .2    | Experimental results                             | 102 |

|     | 3.5   | .3    | Surface state density                            | 104 |

|     | 3.6   | Inte  | erface trap characteristics                      | 107 |

|     | 3.6   | .1    | Deep level transient spectroscopy                | 107 |

|     | 3.6   | .2    | Experimental results                             | 109 |

|     | 3.7   | Ten   | mperature stability of the passivated capacitors | 113 |

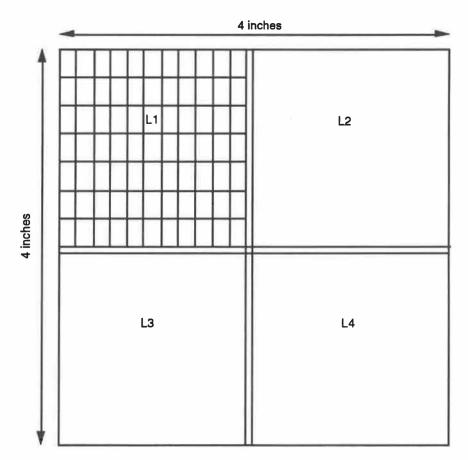

| CHA | PTER  | 4     | - MASK SET DESIGN                                |     |

|     | 4.1   | Intr  | oduction                                         | 118 |

|     | 4.2   | Crit  | eria for diagnostic chip design                  | 118 |

|     | 4.3   | Des   | sign considerations                              | 121 |

|     | 4.4   | Tes   | st structures                                    | 122 |

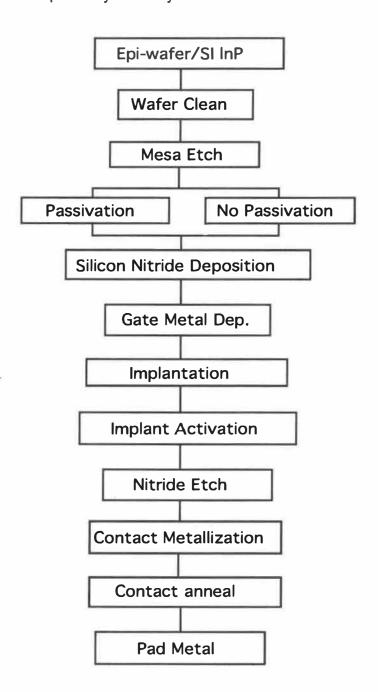

| CHA | PTER  | 5     | - DEVICE FABRICATION                             |     |

|     | 5.1   | Intro | oduction                                         | 125 |

|     | 5.2   | Sar   | nples                                            | 125 |

|     | 5.3   | Che   | emical cleaning                                  | 125 |

|     | 5.4  | Device isolation                           | 29 |

|-----|------|--------------------------------------------|----|

|     | 5.5  | Passivation1                               | 30 |

|     | 5.6  | Gate dielectric deposition                 | 31 |

|     | 5.7  | Gate metal lift-off                        | 31 |

|     | 5.8  | Post metallization anneal1                 | 33 |

|     | 5.9  | Implantation                               | 33 |

|     | 5.10 | Implant activation1                        | 34 |

|     | 5.11 | Contact metallization                      | 35 |

| СНА | PTER | R 6 - DC ELECTRICAL PERFORMANCE            |    |

|     | 6.1  | Introduction14                             | 40 |

|     | 6.2  | Performance of MISFETs14                   | 40 |

|     | 6.2  | .1 Accumulation type MISFETs1              | 40 |

|     |      | 6.2.1.1 Current- Voltage characteristics14 | 40 |

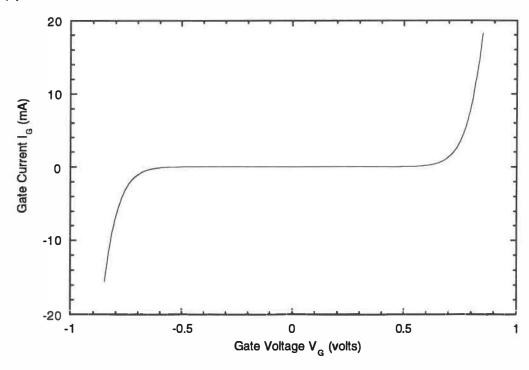

|     |      | 6.2.1.2 Gate leakage14                     | 41 |

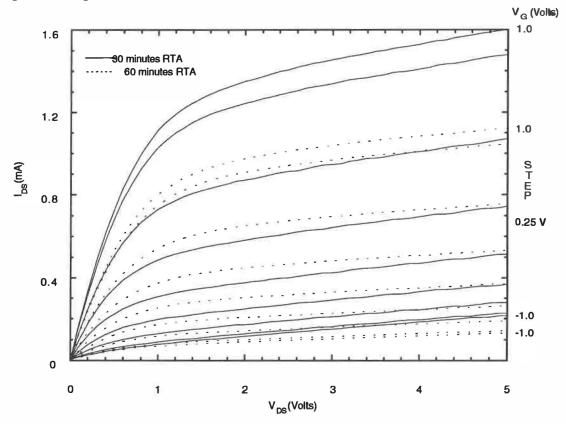

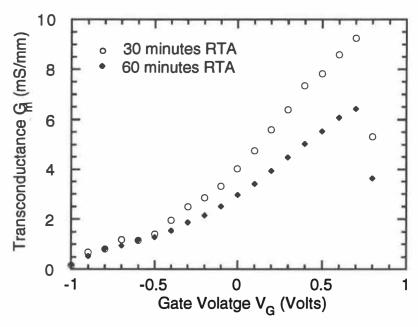

|     |      | 6.2.1.3 Effect of annealing                | 43 |

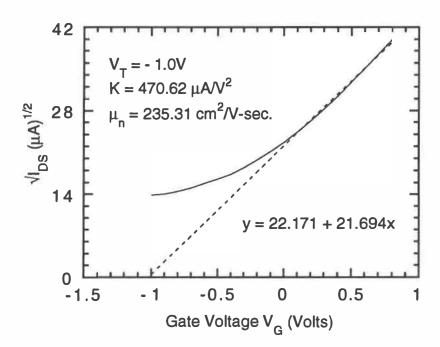

|     |      | 6.2.1.4 Channel mobility14                 | 44 |

|     |      | 6.2.1.5 Uniformity                         | 45 |

|     |      | 6.2.1.6 Drain current drift                | 47 |

|     | 6.2  | .2 Inversion Type MISFETs14                | 48 |

|     |      | 6.2.2. Figure of merit                     | 49 |

|     | 6.2  | .3 Unpassivated MISFETs15                  | 51 |

|     | 6.2  | .4 Conclusions15                           | 52 |

|     | 6.3  | HIGFETS                                    | 53 |

| CON | CLUS | SIONS AND RECOMMENDATIONS15                | 57 |

| REF | EREN | NCES16                                     | 33 |

| ANNEXES       | <br>77 |

|---------------|--------|

| THE TEST CHIP |        |

### **LIST OF FIGURES**

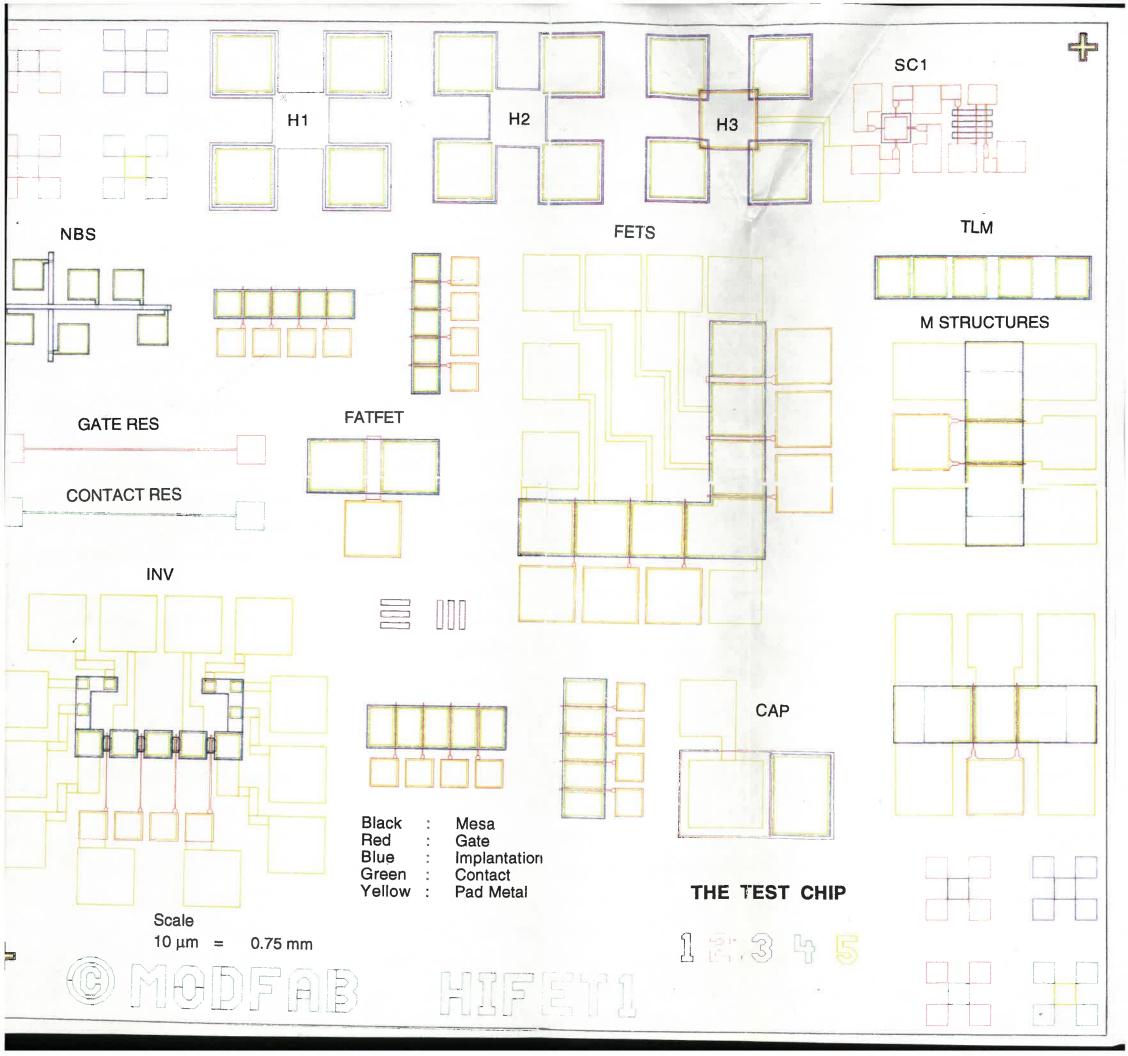

| Figure 1   | Cross-section of a non-self-aligned MISFET. Note the     |

|------------|----------------------------------------------------------|

|            | overlap of the gate with the source / drain regions      |

| Figure 2   | Cross-section of a conventional non-self-aligned HIGFET  |

|            | with gate/source and gate/drain overlap. 2DEG refers to  |

| я          | the two dimensional electron gas channel that is formed  |

|            | at the heterojunction interface5                         |

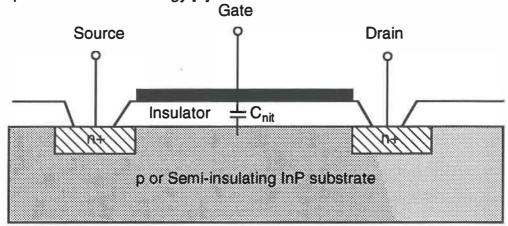

| Figure 3   | Cross-section of a self-aligned gate MISFET. Note that   |

|            | the source / drain regions are perfectly aligned to gate |

|            | and the gate does not overlap these regions8             |

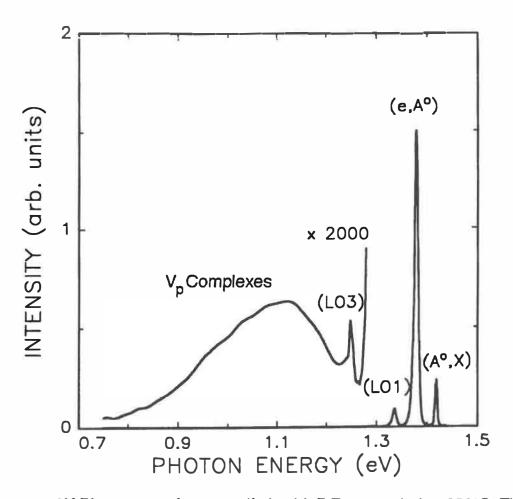

| Figure 1.1 | 8K PL spectrum from unsulfurized InP:Zn                  |

|            | annealed at 250°C18                                      |

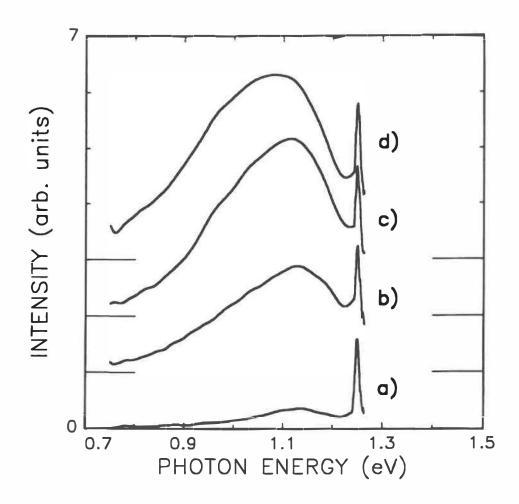

| Figure 1.2 | A selective representative PL spectra of the             |

|            | deep level emission from (a) as-received InP:Zn and      |

|            | unsulfurized InP:Zn and annealed at                      |

|            | temperatures of (b) 150, (c) 250 and (d) 300°C           |

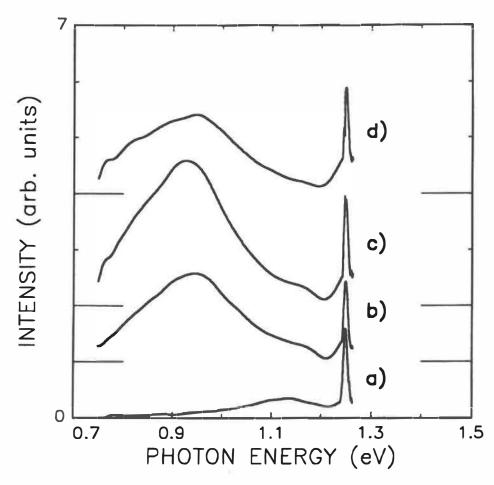

| Figure 1.3 | PL spectra from (a) as-received InP:Zn and               |

|            | sulfurized InP:Zn annealed at temperatures of            |

|            | (b) 150, (c) 250 and (d) 300°C21                         |

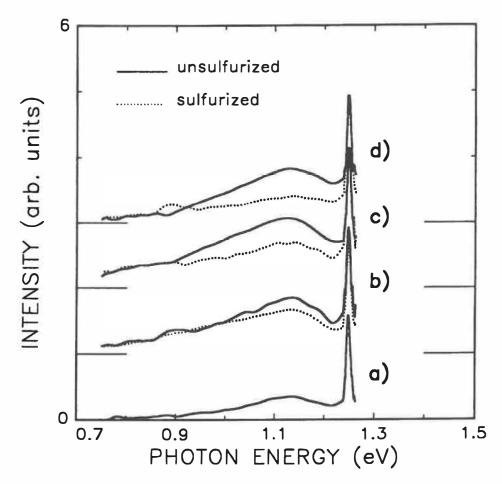

| Figure 1.4 | PL spectra of (a) as-received InP and from untreated and |

|            | S passivated InP:Zn samples that are annealed at         |

|            | temperatures of (b) 150, (c) 250 and (d) 300°C, and      |

|            | etched to remove the top 20Å surface layers 23           |

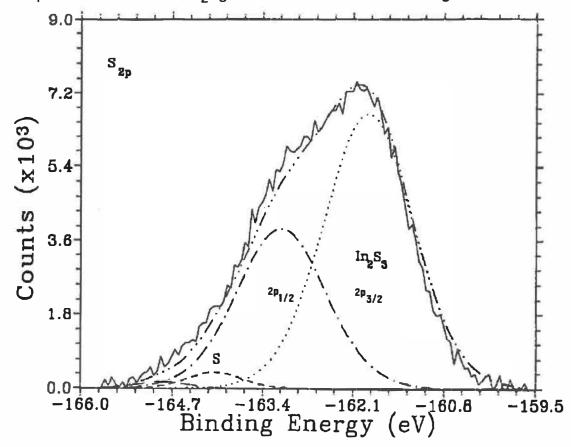

| Figure 1.5 | Representative curve fitted S2p line from a sulfurized   |

|            | sample annealed at 250°C for 30 minutes                  |

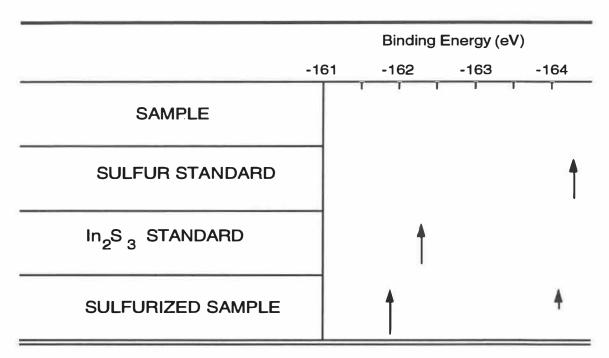

| Figure 1.6  | Sulfur peak positions for standards and sulfurized        |

|-------------|-----------------------------------------------------------|

|             | samples                                                   |

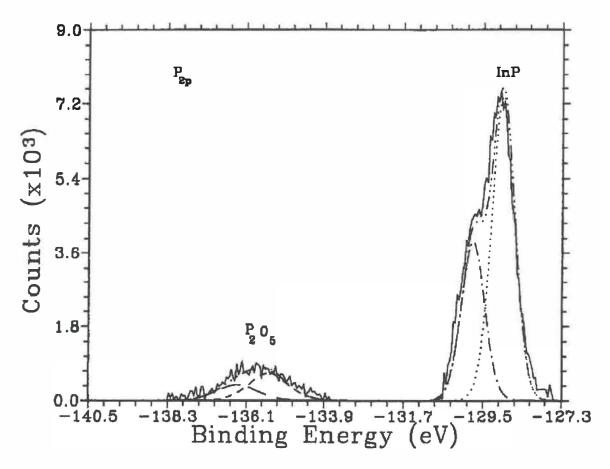

| Figure 1.7  | The curve fitted P2p line from a sulfurized sample        |

|             | annealed at 250°C for 30 minutes                          |

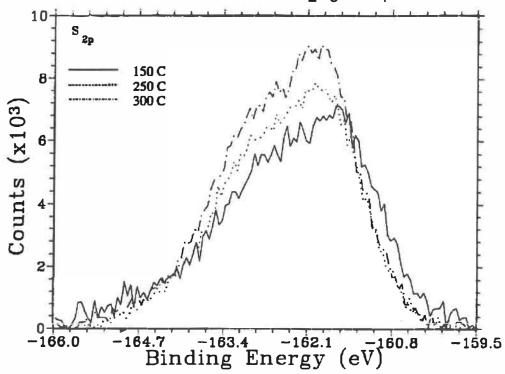

| Figure 1.8  | Comparison of the S2p spectra from sulfurized samples     |

|             | annealed at 150, 250, and 300°C                           |

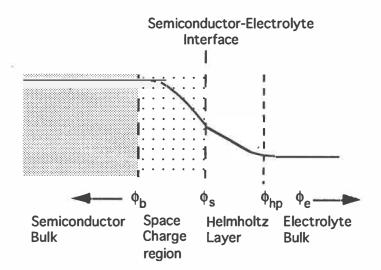

| Figure 1.9  | The semiconductor-electrolyte junction depicting the      |

|             | distribution of charge and electric potential 41          |

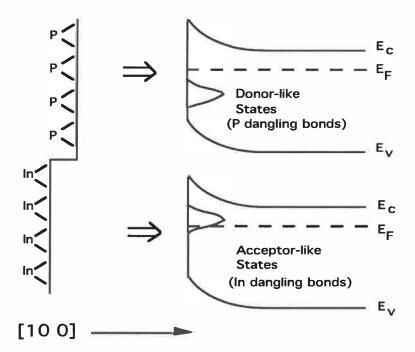

| Figure 1.10 | A perspective view of the (100) InP surface with In and P |

|             | dangling bonds giving rise to acceptor and donor states   |

|             | in the band gap                                           |

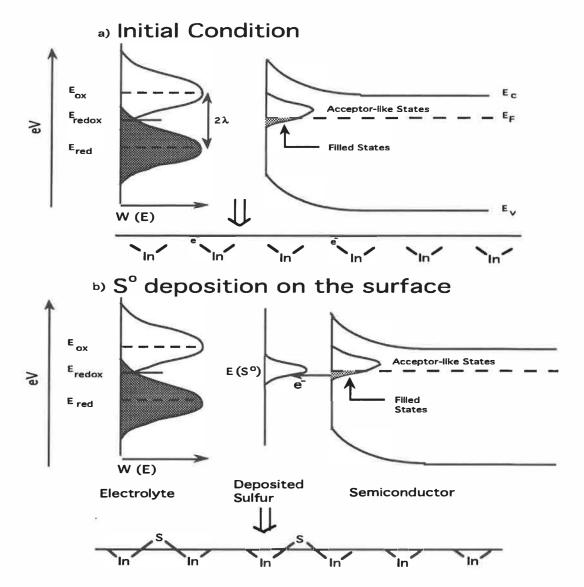

| Figure 1.11 | Schematic of a) the energy band diagram of the            |

|             | electrolyte - n InP interface with partly filled acceptor |

|             | surface states and b) creation of S° states at the        |

|             | interface following S deposition and the formation of     |

|             | In-S bonds due to charge sharing between filled           |

|             | acceptor states and the S° states                         |

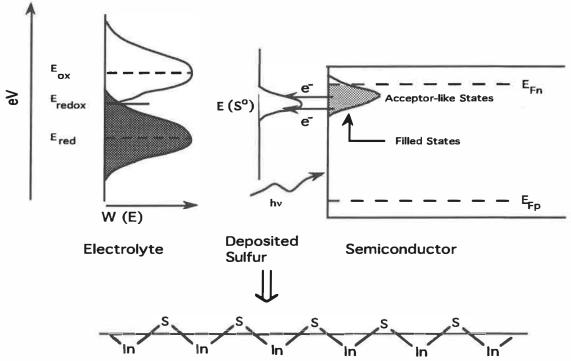

| Figure 1.12 | Schematic diagram showing the formation of improved       |

|             | In-S coverage under high intensity above bandgap          |

|             | illumination. EFn and EFp represent the quasi-Fermi       |

|             | levels for electrons and holes respectively 46            |

| Figure 1.13 | The In-P-S ternary phase diagram showing the various      |

|             | compounds that are formed for T < 408°C 48                |

| Figure 2.1  | Measured mismatch in parts per million (ppm) over the     |

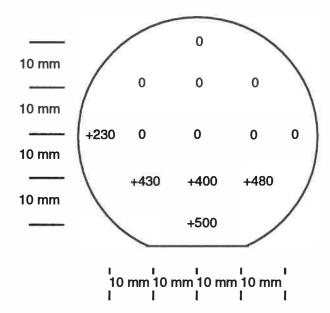

|             | entire wafer55                                            |

| Figure 2.2   | High resolution X-ray diffraction fringe pattern of the                    |

|--------------|----------------------------------------------------------------------------|

|              | epitaxial wafer56                                                          |

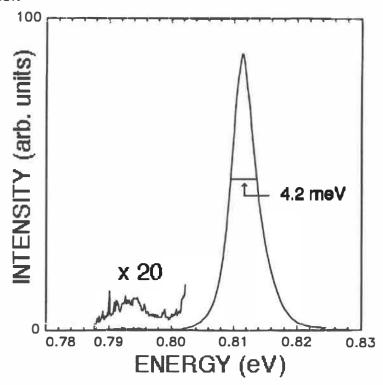

| Figure 2.3a  | 7K band edge PL spectrum of the InGaAs channel layer                       |

|              | lattice matched to InP                                                     |

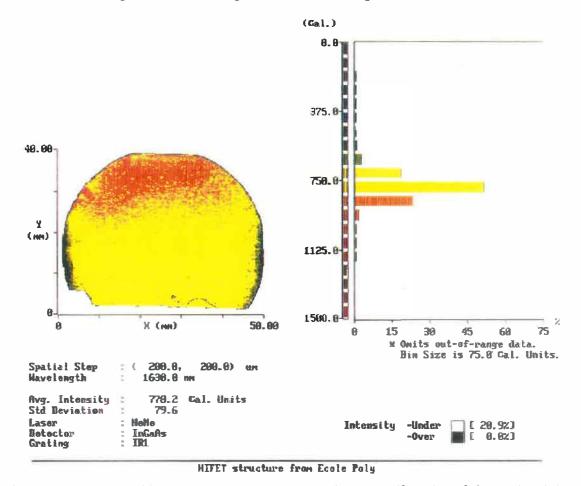

| Figure 2.3b  | Scanning PL measurement to estimate uniformity of the                      |

|              | epitaxial layers over the 2" heterostructure wafer 59                      |

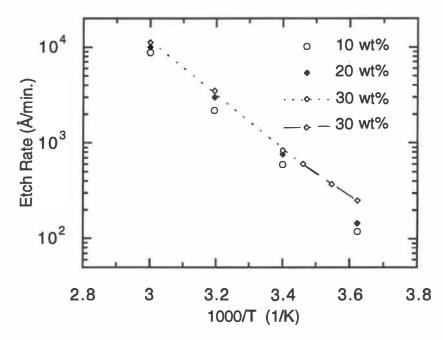

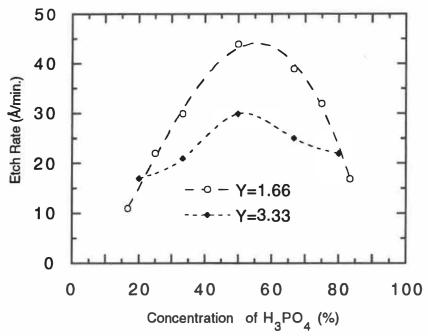

| Figure 2.4   | Variation of etch rate with wt. % concentration (C) 63                     |

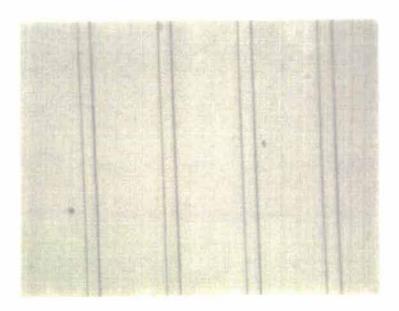

| Figure 2.5a. | Photomicrograph of the surface quality of a p-InP sample                   |

|              | etched in 5 wt.% HIO364                                                    |

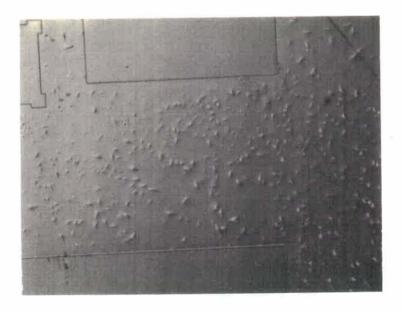

| Figure 2.5b. | Photomicrograph of the p-InP surface quality following a                   |

|              | etch in 30% HIO <sub>3</sub>                                               |

| Figure 2.6   | Variation of etch rate with temperature for different                      |

|              | wt % of HIO365                                                             |

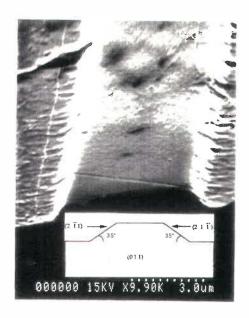

| Figure 2.7a. | SEM profile of the (100) p-InP sample etched in 20 wt.%                    |

|              | HIO3 along the [0 1 1] direction 68                                        |

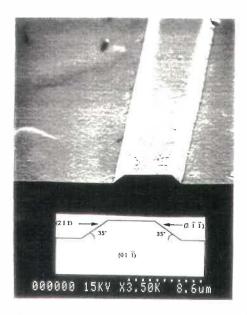

| Figure 2.7b. | SEM profile of the (100) p-InP sample etched in 20 wt%                     |

|              | HIO3 along the [0 1 $\overline{1}$ ] direction68                           |

| Figure 2.8.  | Variation of etch rate with relative concentration of                      |

|              | H <sub>3</sub> PO <sub>4</sub> 70                                          |

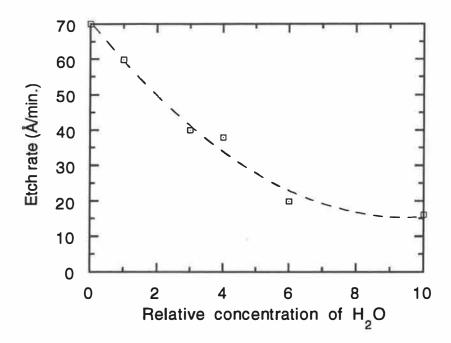

| Figure 2.9.  | Variation of etch rate with dilution for a 1:1:H3PO4:H2O2                  |

|              | solution71                                                                 |

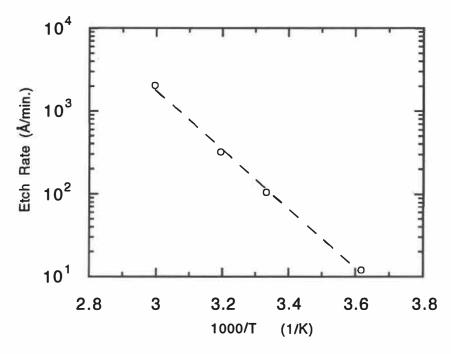

| Figure 2.10. | Variation of etch rate with temperature for a                              |

|              | 1:1:H <sub>3</sub> PO <sub>4</sub> :H <sub>2</sub> O <sub>2</sub> solution |

| Figure 2.11. | Schematic drawing of the floating potential indirect                       |

|              | plasma PECVD deposition apparatus used in the study 74                     |

| Figure 2.12. | Capacitance-voltage curves of Al/ Silicon nitride/ p-Si              |       |

|--------------|----------------------------------------------------------------------|-------|

|              | direct and Indirect plasma MIS structures                            | 77    |

| Figure 2.13. | ERD depth profile of indirect plasma nitride on Si                   |       |

|              | substrate                                                            | 78    |

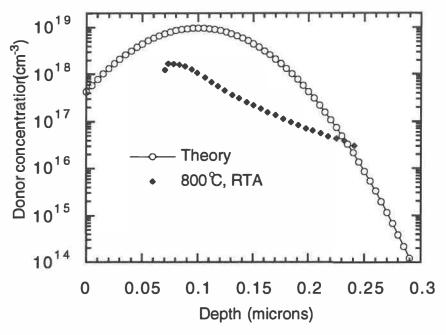

| Figure 2.14  | Polaron dopant depth profile of the 1x1014/ cm <sup>2</sup> , 80 keV |       |

|              | Si implantation activated by a 800°C RTA                             | 83    |

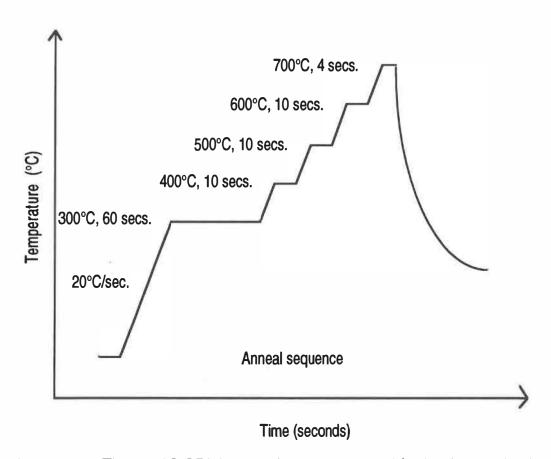

| Figure 2.15  | The 700°C SRLA anneal sequence used for implant                      |       |

|              | activation.                                                          | 84    |

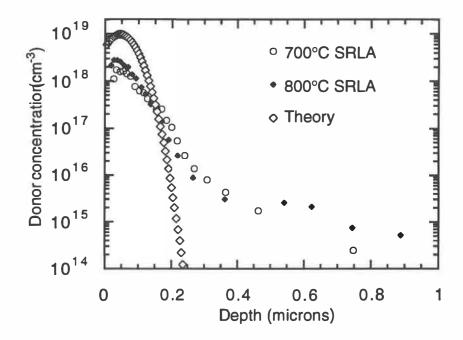

| Figure 2.16  | Polaron dopant depth profile of the 1x1014/ cm <sup>2</sup> , 80 keV |       |

|              | Si implantation activated by a 800°C RTA                             | 86    |

| Figure 2.17  | Plot of total resistance (RT) with contact length                    | 89    |

| Figure 2.18. | a) Potential variation with separation of the unloaded               |       |

|              | contact and b) potential variation within a contact                  | 91    |

| Figure 2.19  | I-V characteristics of the Au-Ge-Ni contacts to a Si                 |       |

|              | implanted and mesa isolated region arranged in a TLM                 |       |

|              | structure with different contact separations                         | 92    |

| Figure 3.1   | ERD depth profile of indirect plasma silicon nitride on              |       |

|              | InP                                                                  | 96    |

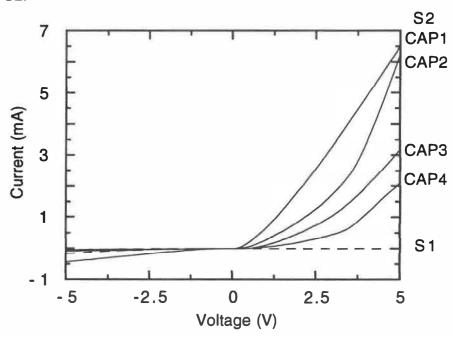

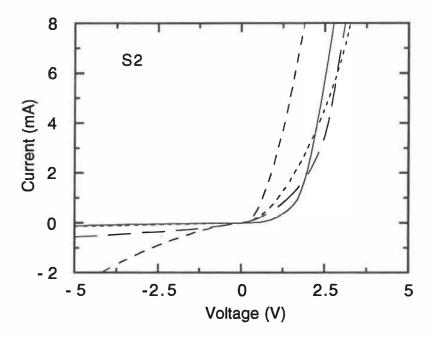

| Figure 3.2.  | Leakage current Vs voltage characteristics of a) mildly              |       |

|              | sulfurized (S1) and b) strongly sulfurized (S2)                      |       |

|              | Au/Ti/Silicon Nitride/undoped InP MIS diodes                         | 98    |

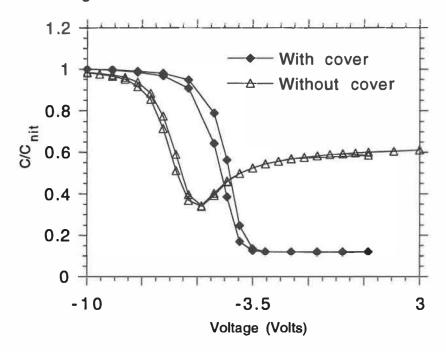

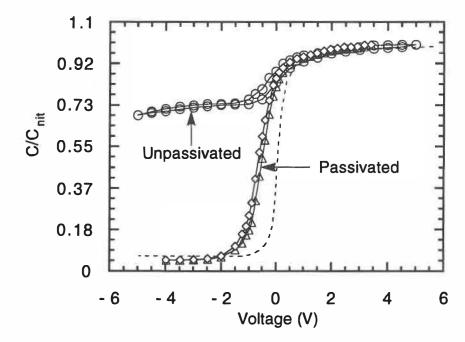

| Figure 3.3.  | High frequency (100 KHz) C-V curves of sulfur                        |       |

|              | passivated and unpassivated Ti/Au/Si3N4/undoped InP                  |       |

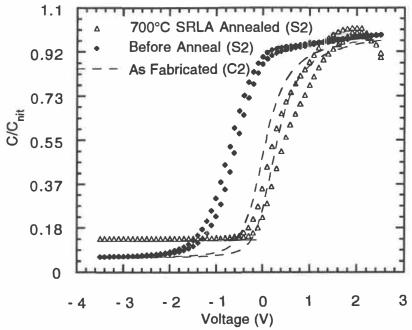

|              | MIS capacitors.                                                      | . 102 |

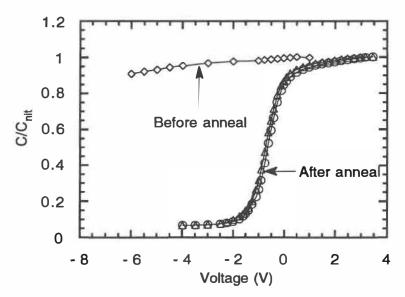

| Figure 3.4   | The high frequency capacitance-voltage curves before                 |       |

|             | and after the 300°C anneal in forming gas                       |

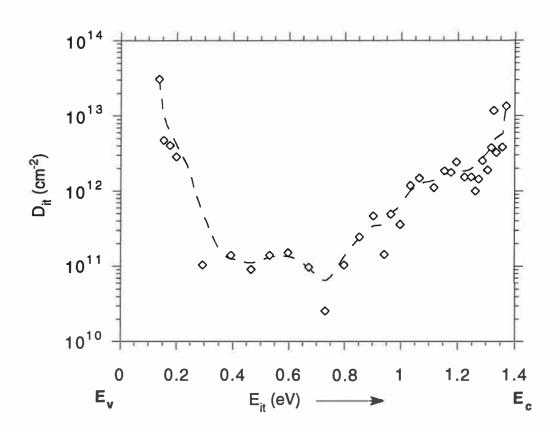

|-------------|-----------------------------------------------------------------|

| Figure 3.5. | Variation of interface state density with energy in the InP     |

|             | bandgap calculated by the high frequency C-V                    |

|             | (Terman) method for a sulfur passivated MIS diode 104           |

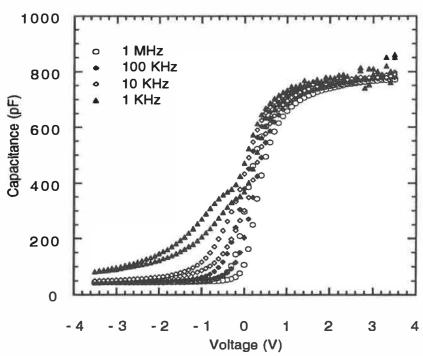

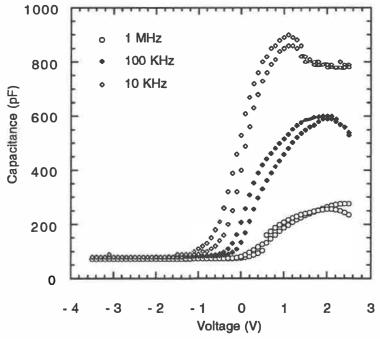

| Figure 3.6. | Sulfur passivated MIS capacitor exhibiting small                |

|             | frequency dispersion and hysterisis in its C(f) - V             |

|             | characteristics                                                 |

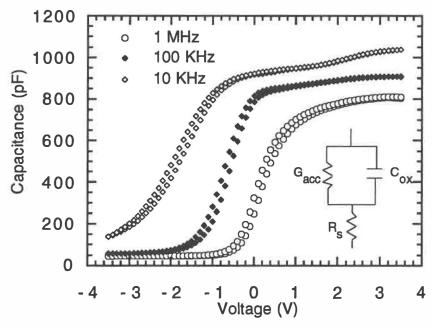

| Figure 3.7. | Sulfur passivated MIS capacitor exhibiting frequency            |

|             | dispersion due to extra parasitic resistance R <sub>S</sub> 106 |

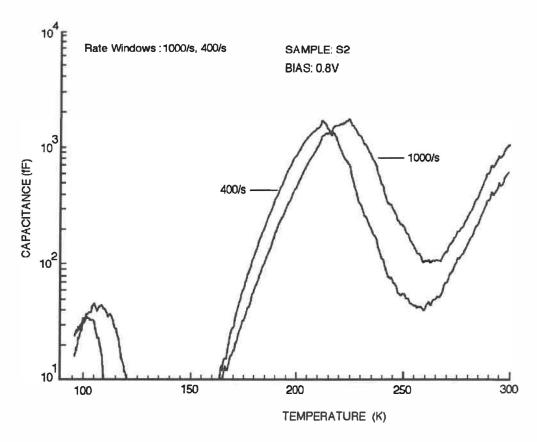

| Figure 3.8. | Typical DLTS spectrum of a S interface engineered MIS           |

|             | diode for two different rate windows                            |

| Figure 3.9  | Leakage characteristics of S passivated MIS diode               |

|             | following a 700°C SRLA anneal                                   |

| Figure 3.10 | High frequency C-V characteristics of a passivated MIS          |

|             | diode subjected to a 700°C SRLA anneal                          |

| Figure 3.11 | Frequency dispersion of passivated MIS diode (S2)               |

|             | after SRLA anneal                                               |

| Figure 4.1. | Layout of the 4 level mask                                      |

| Figure 5.1. | Flow chart of the device fabrication sequence for               |

|             | SAGFETs126                                                      |

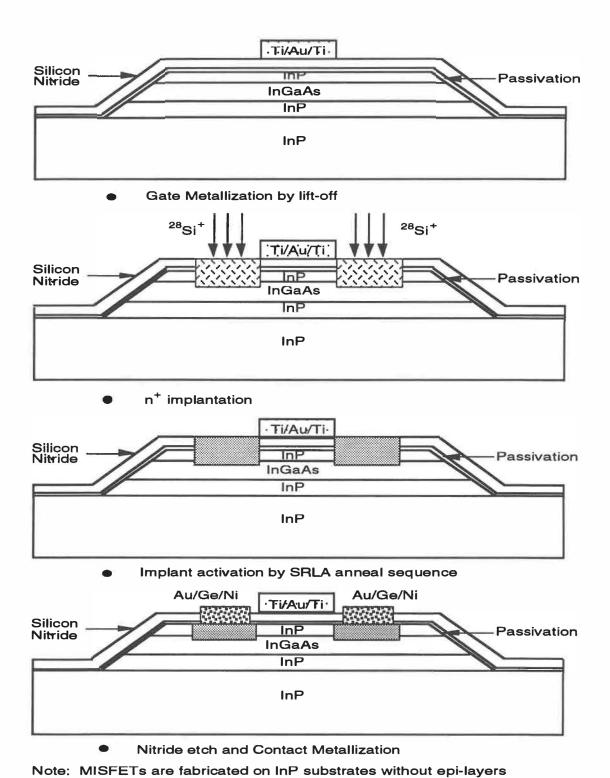

| Figure 5.2. | Schematic view of the wafer cross-section during                |

|             | different stages of processing                                  |

| Figure 5.3. | Photomicrograph of the amorphised silicon nitride               |

|             | regions and the gate metal following implantation               |

| Figure 5.4  | A 1μm gate and the implanted silicon nitride regions                |

|-------------|---------------------------------------------------------------------|

|             | following activation a 700°C SRLA anneal                            |

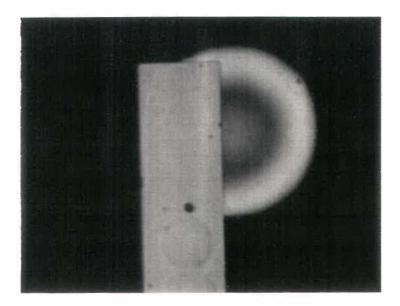

| Figure 5.5  | Photomicrograph of the S out-diffusion near the edge of             |

|             | a 3 µm gate on a post implant annealed sample 13                    |

| Figure 5.6  | Photomicrograph of the completed HIGFET showing the                 |

|             | gate and source/drain metallizations 13                             |

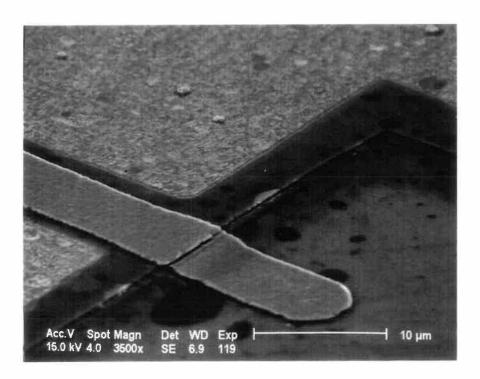

| Figure 5.7  | SEM photograph of the completed HIGFET showing the                  |

|             | gate, source/drain and contact metallizations                       |

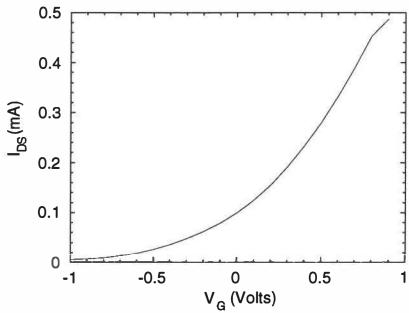

| Figure 6.1  | Drain I-V characteristics of a 5x200 μm <sup>2</sup> accumulation   |

|             | MISFET after annealing14                                            |

| Figure 6.2. | Gate leakage characteristics of the MISFETs 142                     |

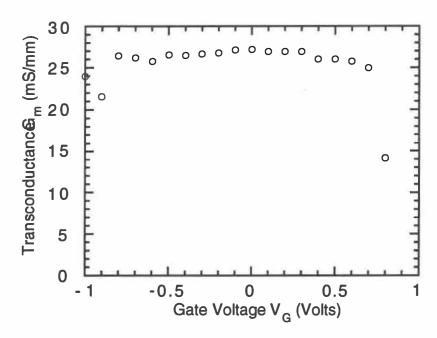

| Figure 6.3. | Effect of annealing on MISFET transconductance 143                  |

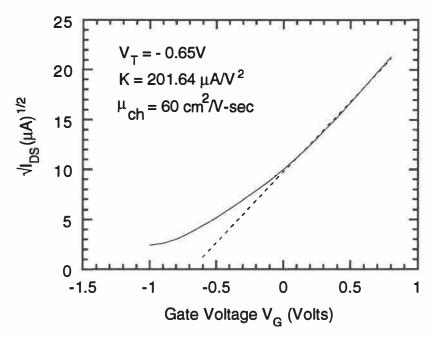

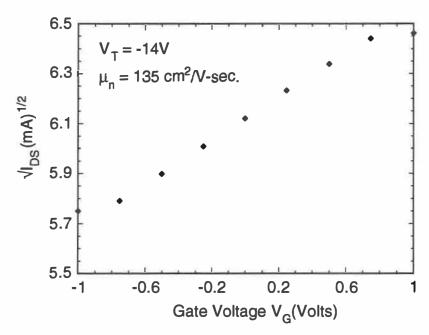

| Figure 6.4. | The √IDS Vs VG plot to estimate channel mobility and                |

|             | threshold voltage144                                                |

| Figure 6.5. | Drain current drift of the accumulation type MISFET                 |

|             | annealed at 400°C for 30 minutes                                    |

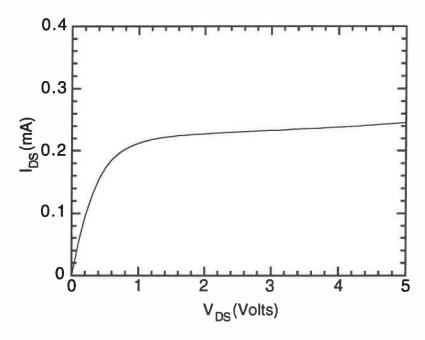

| Figure 6.6. | Drain current-voltage curves of an as-fabricated                    |

|             | $3x200 \ \mu m^2$ inversion type MISFET showing excellent           |

|             | linear and saturation regions 149                                   |

| Figure 6.7. | IDS Vs VG curve of the as-fabricated inversion MISFET.              |

|             | The curve indicates that leakage sets in before strong              |

|             | inversion is achieved                                               |

| Figure 6.8. | The $\sqrt{\text{IDS}}$ Vs VG plot to estimate channel mobility and |

|             | threshold voltage                                                   |

| Figure 6.9.    | Drain current-voltage characteristics of an unpassivated           |       |

|----------------|--------------------------------------------------------------------|-------|

|                | MISFET. The characteristics do not change with gate                |       |

|                | voltage (VG)                                                       | . 151 |

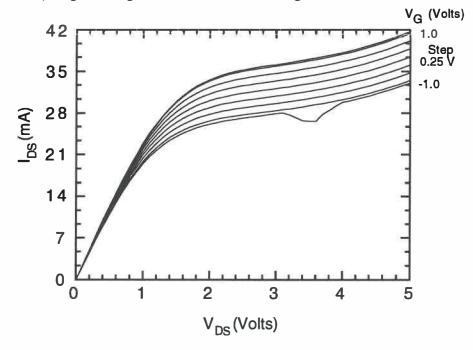

| Figure 6.10.   | Drain I-V characteristics of an as-fabricated 2x200μm <sup>2</sup> |       |

|                | HIGFET                                                             | . 153 |

| Figure 6.11.   | Variation of transconductance with gate voltage of                 |       |

|                | as-fabricated HIGFET                                               | . 154 |

| Figure 6.12.   | The √IDS Vs VG plot to estimate channel mobility and               |       |

|                | threshold voltage.                                                 | . 154 |

| The Test Chin  |                                                                    |       |

| THE LEST LININ |                                                                    |       |

# LIST OF TABLES

| Table 1.1  | Ratio of the integrated intensity of the deep level                 |     |

|------------|---------------------------------------------------------------------|-----|

|            | emission in treated InP                                             | 20  |

| Table 1.2. | Parameters used for fitting the XPS peaks                           | 29  |

| Table 1.3  | Measured and calculated values of R and overlayer                   |     |

|            | thickness for different temperatures                                | 35  |

| Table 2.1  | Bulk wafer specifications of manufacturer                           | 54  |

| Table 2.2  | Manufacturer supplied material specifications for                   |     |

|            | heterostructure wafer                                               | 54  |

| Table 2.3a | Peak positions of the P2p and In3d5/2 spectra                       | 66  |

| Table 2.3b | Atomic ratios of the etched surface                                 | 66  |

| Table 2.4  | TRIM simulated range and straggle values for different              |     |

|            | material combinations for ion energies used in this                 |     |

|            | study                                                               | 81  |

| Table 3.1  | Position of DLTS peaks for different rate windows and               |     |

|            | gate bias                                                           | 112 |

| Table 3.2  | Measured activation energies and capture cross-                     |     |

|            | sections of interface states in the InP band gap for a S            |     |

|            | passivated MIS capacitor                                            | 112 |

| Table 5.1  | Parameters used for electron beam metal evaporation                 | 132 |

| Table 6.1  | Transconductance ( $G_m$ ), sheet resistance ( $R_{sh}$ ) of        |     |

|            | implanted regions and contact resistivity ( $p_{\rm C}$ ) values of |     |

|            | enhancement and inversion type, as-fabricated and                   |     |

|            | thermally annealed, FETs monitored on sample dies                   | 146 |

### OTHER ILLUSTRATIONS

| The test chip |

|---------------|

|---------------|

# LIST OF ANNEXES

| ANNEXE I:   | Single overlayer model                               | xxxi   |

|-------------|------------------------------------------------------|--------|

| ANNEXE II:  | Capacitance - Voltage relationships for an ideal MIS |        |

|             | capacitor                                            | xxxiii |

| ANNEXE III: | Small pulse MIS DLTS analysis                        | xxxv   |

#### INTRODUCTION

In order to understand the motivation for a work like this, we have to look beyond this narrow effort at the larger perspective. The one that defines the basic nature of human beings: the need to evolve. Evolution is a fundamental property of human beings. Except for periods of lethargy in history, we are constantly attempting to speed up this process in a systematic fashion. To what end-nobody knows, but let's hope it stays coherent and under control. The evolutionary process like any other in nature has matured in character from an urge to survive to a desire to understand the properties and order of the universe and engineer them to our advantage. Such comprehension and management requires effective communication coupled to information gathering and processing. As a result we have witnessed a steady increase in speed and volume in these areas. The modern day communication and information systems have a strong under-pinning in electronics and opto-electronics technologies that are semiconductor based. It is therefore natural for us to seek newer and faster semiconductor technologies.

III-V semiconductors such as Gallium Arsenide (GaAs), Indium Phosphide (InP) and their alloys are especially attractive since carrier transport is faster in these materials with higher peak electron velocities and mobilities than Silicon (Si). In addition, most of the III-V materials of interest possess a direct bandgap with the alluring possibility of assembling electronic and optical components on the same chip. The initial attempts to develop a bulk III-V technology by applying the techniques used in Si technology did not succeed for various reasons like material degradation during high temperature processing, difficulty to control

dopant diffusion, lack of a stable native oxide, surface Fermi level pinning etc. [1]. It became obvious that new technological strategies have to be adopted to address these issues. Such adaptations led to the development and maturity of the GaAs based MEtal Semiconductor Field Effect Transistor (MESFET) technology. The advent of advanced epitaxial techniques such as molecular beam epitaxy offered a new impetus to the III-V area by allowing lattice matched or strained growth of different binary, ternary and quaternary crystalline layers on a bulk single crystal substrate. A multitude of new exotic heterostructure devices immediately followed. Devices with tunable band gaps, strain layer superlattices, hot electron transistors, quantum well structures, wave guides and optical modulators based on refractive index variations, heterostructure lasers etc. The list is quite long and we are just exploring the tip of the iceberg. Although the immediate impact in terms of application is quite limited, these developments are expected to revolutionize the area of opto-electronics. This trend also saw the emergence of InP based heterostucture lasers and detectors that operate in the low loss 1.2-1.3 μm wavelength range suitable for optical communications. It was therefore highly desirable to develop a InP based FET technology to provide some amount of on-chip electronic circuitry with the optoelectronic components.

The major problem hindering a suitable MESFET technology was the low Schottky barrier height (~0.2-0.3V) on n-type InP. One solution is to deposit/ grow a thin (~50 -100 Å) tunnel oxide that increases the barrier height [2]. The most promising approach is to grow a epitaxial layer of a material that has a large Schottky barrier over the high mobility channel layer. Depletion type Metal Insulator Doped channel (MID)FETs fabricated using this approach show great potential and were first demonstrated by S.Bahl and J.Del Alamo of MIT [3,4].

However, leakage is still a problem and limits this approach for applications that demand a large dynamical voltage range and for low noise, low power requirements. For these purposes we need a Metal-Insulator-Semiconductor (MIS) type Insulated gate FET technology on InP.

As mentioned earlier, InP does not have a stable native oxide and attempts to grow one have failed miserably (1). Deposited insulators are used instead, but the InP/insulator interface is quite rough with a large concentration of

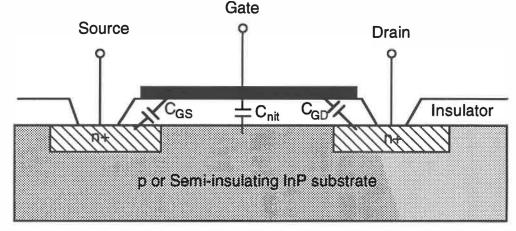

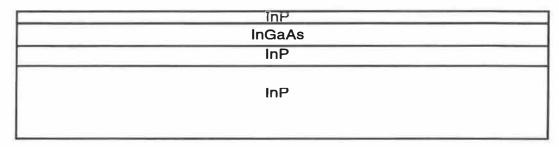

Figure 1 Cross-section of a non-self-aligned MISFET. Note the overlap of the gate with the source / drain regions.

interface states (> 10<sup>13</sup> cm<sup>-3</sup>) that reduce the channel carrier mobility [1]. Thus the advantages of using a high mobility material is lost. Another important consideration is the poor stability of InP to thermal anneals and plasma exposure. InP surface degrades quite easily even at moderate processing temperatures with the formation of Phosphorus (P) vacancies [1,5,6]. In fact, we show in chapter 1.2.2 that formation of P vacancies is inescapable during insulator deposition. In addition, high temperature processing causes the InP/insulator interface to degrade and become unusable. The first reports on InP MISFETs therefore used a non-self- aligned gate approach, shown in figure 1, that

deliberately avoids subjecting the interface to high temperature process cycles [6-8]. Although some groups reported impressive performance, slow traps at the interface cause the drain current to drift as high as 80% and the long term reliability of these devices is in question [9,10]. This drawback has been addressed and solved by R.Iyer and D.L.Lile [6,11]. Prompted by the success of Sulfur (S) passivation techniques that dramatically reduced the surface recombination velocity in GaAs [12], they applied this technique to achieve InP/SiO<sub>2</sub> interface with low surface state density and effectively suppress drift in non-self-aligned FETs without loss of performance. The mechanism responsible for this improvement is presumed by Wilmsen et. al. to be due to S filling up the surface P vacancies [13]. We study the passivation mechanism in detail and offer direct evidence in chapter 1 that S treatment reduces surface P vacancies. We show that passivation is due to the formation of a cap indium sulfide layer that suppresses P out-diffusion from the near surface regions of InP. However, it is generally believed that the S treated interface is guite rough and there are no reports of mobility enhancement in passivated surface channel devices to date and the uniformity of the passivation process is poor [6,11].

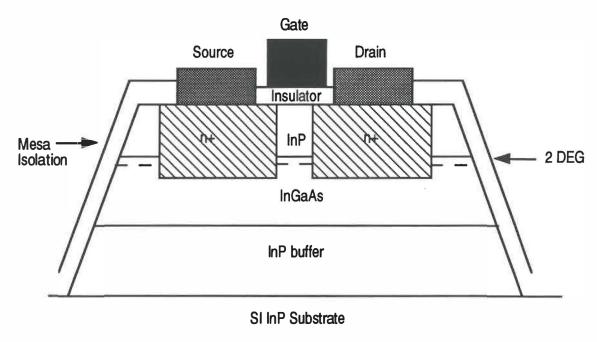

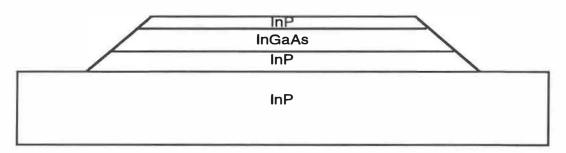

Figure 2. Cross-section of a conventional non-self-aligned HIGFET with gate/source and gate/drain overlap. 2DEG refers to the two dimensional electron gas channel that is formed at the heterojunction interface.

A parallel trend in III-V FETs has therefore been the development of Heterojunction Insulated Gate Field Effect Transistors (HIGFETs), where electron transport occurs at a high mobility heterojunction interface and the channel is physically separated from the low mobility insulator/semiconductor interface [14,15]. The cross-section of the HIGFET is shown in figure 2. The state-of-the-art technology is to use epitaxial insulators such as InAlAs that possess a larger band gap than the channel material, e.g. InGaAs [16,17]. The main requirements of epitaxial dielectrics are a large conduction band discontinuity ( $\Delta E_c$ ) and high resistivity. The lattice matched InAlAs technology offers a  $\Delta E_c$  of 0.51 eV that restricts the maximum gate source voltage typically to 1.0-1.25 volts. In comparison, the barrier height of a conventional insulator is about 5-7 eV. The lower barrier heights of epitaxial insulators also restrict the high temperature operation and reduce the maximum charge holding capacity of CCD type

structures. The ideal solution is to epitaxially grow a lattice matched or strained layer of a high resistivity, large band gap insulator like BN or diamond like carbon etc. This is a technological challenge and has not been adequately realized yet. Lacking such a epitaxial insulator technology, use of conventional dielectrics for HIGFETs is still of interest. Recently, Martin et. al. demonstrated a non-selfaligned buried channel InP/InGaAs ( $\Delta E_c = 0.3 \text{ eV}$ ) HIGFET using SiO<sub>2</sub> as the gate insulator [14]. Charge confinement in these devices is determined by the large insulator barrier while the confinement of the carriers in the channel is decided by the  $\Delta E_c$  barrier. These devices show large transconductance due to carrier transport at the high mobility heterojunction interface and a large allowable (> ± 5V) input voltage swing. However a 20% Drain Current Drift (DCD) over 10<sup>4</sup> seconds at 300°K and considerable hysterisis in the C-V characteristics indicate a significant amount of traps at the insulator/InP interface. Lowering the interface state density at the top semiconductor/ insulator will lower DCD and result in better modulation of the channel charge and increase the small signal response [18,19].

The other aspect to this picture is that if compound semiconductor technologies have to become a viable alternative, they have to out-perform the ever shrinking Si electronics which increases in speed on a daily basis [20]. The pressure is even greater with the emergence of newer technologies such as Multi-Chip Modules (MCMs) that mount chips of different technologies close to each other eliminating parasitics that the different circuits appear to be part of the same Integrated Circuit (IC), for e.g. a MCM with a Si IC driving a III-V laser diode for all purposes is similar to a silicon IC with a on-chip laser diode. It is important to stress that these trends will effectively terminate interest in III-V

FETs if they don't catch-up. However, in favor of compound semiconductors we find that the electron mobility at the hetero-interface is much larger than the channel mobility at the Si/SiO<sub>2</sub> interface and III-V technologies such as HEMTs, HIGFETs etc., dominate Si in high frequency response [18,21]. The major advantage of Si MOSFETs is that the gate is aligned to the drain and source regions with minimum overlap and therefore minimum parasitic capacitance. Please refer to figure 3 for the cross-section of a self-aligned gate FET. So a decrease in channel length with other parameters unchanged will lead to a increase in speed and a larger cut-off frequency (f<sub>t</sub>) given by [5]

$$f_t = \frac{g_m}{2\pi (C_{nit} + C_{GS} + C_{GD})}$$

(1)

where  $g_m$  represents the transconductance,  $C_{nit}$  the insulator capacitance,  $C_{GS}$  the gate to source parasitic capacitance and  $C_{GD}$  the gate to drain parasitic capacitance.  $C_{GS}$  and  $C_{GD}$  are negligible for a self-aligned gate FET.

In contrast, since surface degradation of InP is a major concern, almost all InP based III-V devices reported in the available literature follow the non-self-aligned approach that avoids high temperature anneal cycles once the gate dielectric is deposited [6,7,10,14,22,23]. In non-self-aligned FETs the gate metallization has a minimum overlap of about 1 micron over the drain and source regions for alignment purposes as shown in figure 1. This overlap causes the parasitic capacitances  $C_{\rm GS}$  and  $C_{\rm GD}$  to dominate when device geometry shrinks to a micron or below and offsets any gain in performance. In addition, there are many associated process problems in fabricating non-self-aligned short channel

FETs and realization of self-aligned FETs would be essential for the future development of this technology [5].

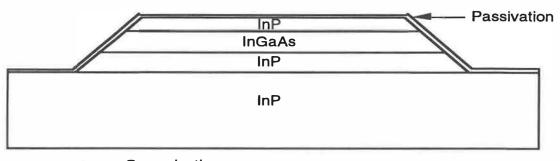

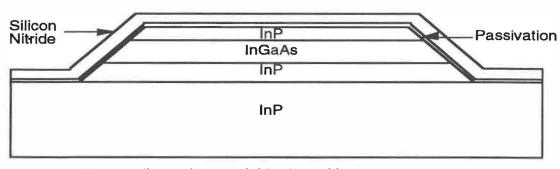

Figure 3. Cross-section of a self-aligned gate MISFET. Note that the source / drain regions are perfectly aligned to gate and the gate does not overlap these regions.

Very little work has been done to date to fabricate self-aligned structures on InP. There are only two reports in the available literature on self-aligned FETs on InP [24,25]. Both follow an approach very similar to the Si MOSFET technology with metal gates. The first report is by D.C.Cameron et. al. in 1982 [24]. They use a SiO<sub>2</sub> gate insulator and a Mo gate which also serves as the implant mask. They report impressive FET characteristics with channel mobilities of 1700-2400 cm<sup>2</sup>V<sup>-1</sup>s<sup>-1</sup>. The second report is by K.Oigawa et. al. in 1987, who use a similar approach with W gates and silicon nitride as the gate insulator [25]. The 10μm gate length devices exhibit large transconductances of 55 mS/mm but show non-linear I-V characteristics. As pointed out in a review article by J.F.Wager et. al., these efforts could not be reproduced by other groups [5]. They mention that interfacial considerations have to be taken into account and observe that a high temperature anneal increases the InP/insulator interface density to an unacceptably large value and results in a large negative shift in the flatband

voltage. As seen in chapters 4&7, our own work shows that the Fermi level is pinned at the interface for such unpassivated self-aligned devices, probably due to an increase in interface state density associated with P vacancies. There are no reports to date on the fabrication of a InP/InGaAs Self-Aligned Gate (SAG) FET presumably due to such interfacial problems.

It is clearly obvious, that the next generation self-aligned gate HIGFET requires a technology strategy that should allow high temperature processing while maintaining a low defect density insulator/InP interface and a high mobility heterojunction interface [5,18]. In this report we propose, for the first time, that interface engineering based fabrication schemes are essential for this purpose and that such techniques open the door to self-aligned gate HIGFETs using conventional dielectrics. The term "interface engineering" refers to any fabricational procedure that conditions the interface to modify or ameliorate its electrical, thermal, microstructural, mechanical and optical properties. The III-V epitaxial technology abounds with such techniques. Some common examples are, buffer layers to stop substrate dislocations and provide a smooth interface [14], superlattices (SLS) to relieve interfacial stress [26] and trap carriers and large bandgap tunnel layers to increase Schottky barrier heights [2]. We would like to point out that interface passivation that usually alters the electrical or chemical nature of the surface is a subset of interface engineering [27]. As mentioned before, we are chiefly concerned about engineering a low trap density interface and increase its high temperature stability. The idea is motivated by our initial work to investigate the S passivation mechanism of InP, an enigma at that time [28,29]. The study identified that crucial to the passivation technique is the formation of a thin In<sub>2</sub>S<sub>3</sub> layer that effectively checks P out-diffusion from the

substrate, especially at higher temperatures. In<sub>2</sub>S<sub>3</sub> is a large bandgap material with better high temperature stability than InP. Our experiments show that this layer can stabilize the InP surface from degradation at temperatures as high as 300°C. It is quite possible that by depositing an insulator on top of the cap layer we should be able to protect the cap indium sulfide layer and the InP/insulator interface from thermal degradation at even higher temperatures. This logically translates into potential high temperature operation and a SAG process. We therefore proceeded to develop a SAG technology based on S interface engineering of the InP surface.