| <b>Titre:</b><br>Title: | Transient free switching of capacitor banks                                                                                                                                    |

|-------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Auteur:<br>Author:      | Gordon P. Mack                                                                                                                                                                 |

| Date:                   | 1990                                                                                                                                                                           |

| Туре:                   | Mémoire ou thèse / Dissertation or Thesis                                                                                                                                      |

| Référence:<br>Citation: | Mack, G. P. (1990). Transient free switching of capacitor banks [Mémoire de<br>maîtrise, Polytechnique Montréal]. PolyPublie.<br><u>https://publications.polymtl.ca/57036/</u> |

# **Document en libre accès dans PolyPublie** Open Access document in PolyPublie

| URL de PolyPublie:<br>PolyPublie URL:    | https://publications.polymtl.ca/57036/ |

|------------------------------------------|----------------------------------------|

| Directeurs de<br>recherche:<br>Advisors: | Guy Olivier                            |

| Programme:<br>Program:                   | Génie électrique                       |

UNIVERSITE DE MONTREAL

TRANSIENT FREE SWITCHING OF CAPACITOR BANKS

par

Gordon P. MACK DEPARTEMENT DE GENIE ELECTRIQUE ECOLE POLYTECHNIQUE

RAPPORT DE PROJET PRESENTE EN VUE DE L'OBTENTION

DU GRADE DE MAITRE EN INGENIERIE (M. Ing)

GENIE ELECTRIQUE

Mars 1990

c Gordon P. Mack 1990

*CA2PQ* UP 9 1990 M153

#### UNIVERSITE DE MONTREAL

#### ECOLE POLYTECHNIQUE

## Ce rapport de projet intitulé

# TRANSIENT FREE SWITCHING OF CAPACITOR BANKS

présenté par: Gordon P. MACK en vue de l'obtention du grade de: M. Ing. a été dûment accepté par le jury d'examen constitué de:

M. Georges-Emile April, M. Sc.M. Guy Olivier, Ph.D., directeur de projet

#### SOMMAIRE

Le but de cette étude est de démontrer qu'il est possible de commuter des banques de condensateurs sans transitoires. Six topologies différentes de commutateur triphasés à thyristor ont été analysées au moyen de la transformé de Laplace. Par la suite quatre de ces six topologies ont été mises à l'essai au laboratoire avec une charge de 7 kvar. Dans chaque cas, la banque de condensateur a été commutée avec succès sans aucune transitoire de cour-La conclusion le plus importante de cette étude est ant. la suivante: les thyristors, qui constituent les éléments principaux des commutateurs, doivent être amorcés seulement quand la tension à leurs bornes est nulle. De plus, il a été démontré que des banques de condensateurs peuvent être commutées sans transitoires à l'aide d'un commutateur constitué de seulement trois thyristors.

#### ABSTRACT

The purpose of this study was to demonstrate that it is possible to switch banks of capacitors without transients. Six different configurations of three phase thyristor switches were analyzed using Laplace Transforms. Subsequently, four of the six configurations were tested in the laboratory, with a 7 kvar load. In each case the capacitor bank was successfully switched without inrush cur-The most important conclusion of this study is rents. the thyristors, of which the thyristor switch is this: composed, should only be fired when the voltage across them Furthermore, it was demonstrated that transient is zero. free switching could be achieved with a thyristor switch made with only three thyristors.

#### ACKNOWLEDGEMENTS

There are many people who have encouraged and supported me throughout these last ten months. I would now like to thank them publicly.

Guy Olivier has surpassed all my expectations of what a supervisor could be. I began my masters with the notion that supervisors were often the modern day equivalent of slave drivers, Guy has been anything but. He has been a good friend and an excellent teacher, so much so that many things that I had "learned" in the past finally started making sense after I began working with Guy. His manner with students is exemplary if not remarkable; how Guy manages to service so many interrupts without losing synchronism or his sense of humour baffles me - maybe he operates at a higher clock rate than the rest of us.

I am really thankful that the project required me to work in the lab, for it is there that I got to know Stephane Poulin and Daniel Lefebvre. Apart from giving me timely technical advice, they were a tremendous moral support, sympathizing with me when my circuits and software were plagued with bugs and celebrating with me when things worked. They both are quick with a joke, and although it meant that I always had to beware of booby traps, it made for a great work atmosphere. Other members of the Polytechnique family that deserve special recognition are Rosaire Deslierres and Jean-Luc Sheink, who do much to cultivate good relations within the section (even with anglophones), and my fellow graduate students Ngandui Eloi and Mohand Ouhrouche who have taken an interest in me and my work.

My own family's support should not go unmentioned. For years now they have given me much love and encouragement, which in turn has given me the confidence to take on new challenges. My parents deserve a special thanks for they have been loving mentors; the fact that I am an engineer is due in large part to my desire emulate my father.

This masters has required a fair amount of sacrifice. Unfortunately I have not been the one who has had to bear most of the sacrifice. That lot fell on my fiancé Anne. She has come to realize that when people refer to me as her "futur", it is because I can't be her "present" because I have to go off and work in the lab. Certainly, I do regret that this project has taken longer than I expected, because it has often meant that I have not been able to do what I enjoy most, spend time with Anne.

Finally, it is exciting to realize that I have learned a tremendous amount here at Polytechnique and that I can now embark on new ventures a little "moins niaiseux" than when I came.

# TABLE OF CONTENTS

×

| I                                                 | Page |

|---------------------------------------------------|------|

| SOMMAIRE                                          | iv   |

| ABSTRACT                                          | v    |

| ACKNOWLEDGEMENTS                                  | vi   |

| LIST OF FIGURES AND TABLES                        | xii  |

| LIST OF OSCILLOGRAMS                              | xvi  |

| INTRODUCTION                                      | 1    |

| CHAPTER ONE - PRELIMINARY INFORMATION             | 5    |

| 1.1 - Literature Review                           | 5    |

| 1.2 - Description of Test Setup                   | 8    |

| CHAPTER TWO - THE SINGLE PHASE AC CONTROLLER USED |      |

| AS A SWITCH                                       | 13   |

| 2.1 - Introduction                                | 13   |

| 2.2 - Analysis of a Single Phase AC Controller .  | 14   |

| 2.3 - Predictions of Circuit Behavior             | 16   |

| 2.4 - Computer Plots of Expected Circuit Behavior | 17   |

| 2.5 - Experimental Results                        | 20   |

-

ix

CHAPTER THREE - THREE-WIRE BRANCH-CONTROLLER WITH DELTA-CONNECTED LOAD . . . . . . 22 22 22 3.3 - Predictions of Circuit Behavior . . . . 26 3.4 - Computer Plots of Expected Circuit Behavior 27 3.5 - Experimental Results . . . . . . . . . . . 30 CHAPTER FOUR - THREE-WIRE LINE-CONTROLLER WITH DELTA-CONNECTED LOAD . . . . . . 35 35 4.2 - Predictions of Circuit Behavior . . . . 36 4.3 - Computer Plots of Expected Circuit Behavior 38 CHAPTER FIVE - THREE-WIRE ASYMMETRICAL LINE-CONTROLLER WITH DELTA-CONNECTED LOAD . . . . . 41 41 41 5.3 - Predictions of Circuit Behavior .... 46 5.4 - Computer Plots of Expected Circuit Behavior 48 5.5 - Experimental Results . . . . . . . . . . . . 51

ix

CHAPTER SIX - THREE-WIRE LINE-CONTROLLER WITH

| WYE-CONNECTED LOAD                                | 55 |

|---------------------------------------------------|----|

| 6.1 - Introduction                                | 55 |

| 6.2 - Predictions of Circuit Behavior             | 56 |

| 6.3 - Computer Plots of Expected Circuit Behavior | 58 |

CHAPTER SEVEN - THREE-WIRE ASYMMETRICAL LINE-CONTROLLER

| WITH WYE-CONNECTED LOAD                           | 61 |

|---------------------------------------------------|----|

| 7.1 - Introduction                                | 61 |

| 7.2 - Analysis                                    | 61 |

| 7.3 - Predictions of Circuit Behavior             | 66 |

| 7.4 - Computer Plots of Expected Circuit Behavior | 68 |

| 7.5 - Experimental Results                        | 71 |

CHAPTER EIGHT - THREE-WIRE NEUTRAL POINT-CONTROLLER

| WITH WYE-CONNECTED LOAD                           | 75 |

|---------------------------------------------------|----|

| 8.1 - Introduction                                | 75 |

| 8.2 - Analysis                                    | 75 |

| 8.3 - Predictions of Circuit Behavior             | 82 |

| 8.4 - Computer Plots of Expected Circuit Behavior | 84 |

| 8.5 - Experimental Results                        | 88 |

| CHAPTER NINE - DISCUSSION                                                           | 92  |

|-------------------------------------------------------------------------------------|-----|

| 9.1 - Introduction                                                                  | 92  |

| 9.2 - Comparison of the "Thyristor Switches"                                        | 92  |

| 9.3 - Common Evaluation                                                             | 95  |

| 9.4 - Problems and Suggested Solutions                                              | 100 |

| CONCLUSION                                                                          | 102 |

| BIBLIOGRAPHY                                                                        | 103 |

| APPENDIX A - REACTIVE POWER CONTROL AND THE USE OF<br>THYRISTOR SWITCHED CAPACITORS | 105 |

| APPENDIX B - ELECTRONIC SWITCHES                                                    | 118 |

| APPENDIX C - STANDARD AND DEFINITIONS AND REQUIREMENT                               | S   |

| FOR THYRISTOR AC POWER CONTROLLERS                                                  | 120 |

| APPENDIX D - DERIVATION OF THE LAPLACE TRANSFORM                                    |     |

| FOR A SINUSOIDAL VOLTAGE SOURCE                                                     | 125 |

| APPENDIX E - ZERO CROSSING AND GATING LOGIC CIRCUITS                                | 126 |

xi

# LIST OF FIGURES AND TABLES

| FIGU | RES |                                              | Page |

|------|-----|----------------------------------------------|------|

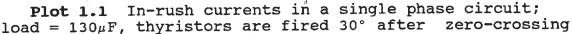

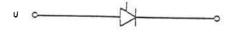

| 1.1a | -   | The Single Phase AC Controller               | 9    |

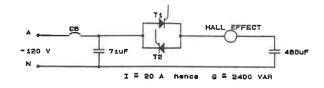

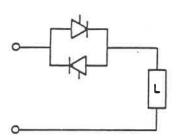

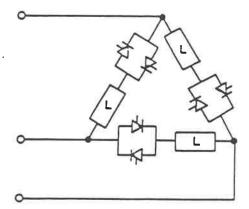

| 1.1b | -   | The Three-Wire Branch-Controller with        |      |

|      |     | Delta-Connected Load, W33AA                  | 9    |

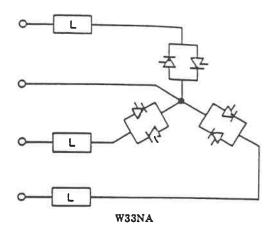

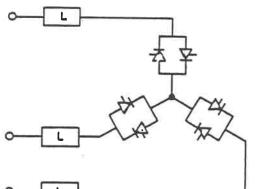

| 1.1c | -   | The Three-Wire Asymmetrical Line-Controller  |      |

|      |     | with Delta-Connected Load, W32AD             | 10   |

| 1.1d | -   | The Three-Wire Asymmetrical Line-Controller  |      |

|      |     | with Wye-Connected Load, W32AY               | 10   |

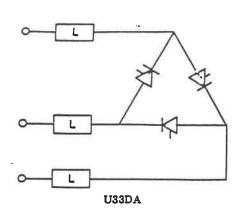

| 1.1e | -   | The Three-Wire Neutral Point-Controller      |      |

|      |     | with Wye-Connected Load, U33DA               | 10   |

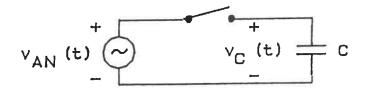

| 2.1  | -   | An equivalent circuit for a Single Phase     |      |

|      |     | AC Controller with a capacitive load         | 13   |

| 2.2  | -   | Switching in the Single Phase AC Controller  | 17   |

| 2.3  | -   | Switching out the Single Phase AC Controller | 18   |

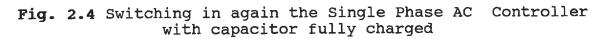

| 2.4  | -   | Switching in again the Single Phase AC       | 19   |

| 3.1  | -   | Circuit diagram of a Three-Wire Branch-      |      |

|      |     | Controller with a Delta-Connected Load       | 22   |

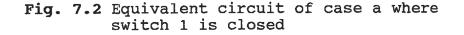

| 3.2  | -   | Equivalent circuit of case a                 | 22   |

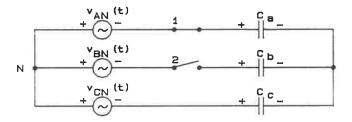

| 3.3  | -   | Equivalent circuit of case b                 | 23   |

| 3.4  | -   | Equivalent circuit of case c                 | 24   |

| 3.5  | -   | Switching in a Three-Wire Branch-Controller  |      |

|      |     | with a Delta-Connected Load                  | 27   |

| 3.6  | -   | Switching out a Three-Wire Branch-Controller |      |

|      |     | with a Delta-Connected Load                  | 28   |

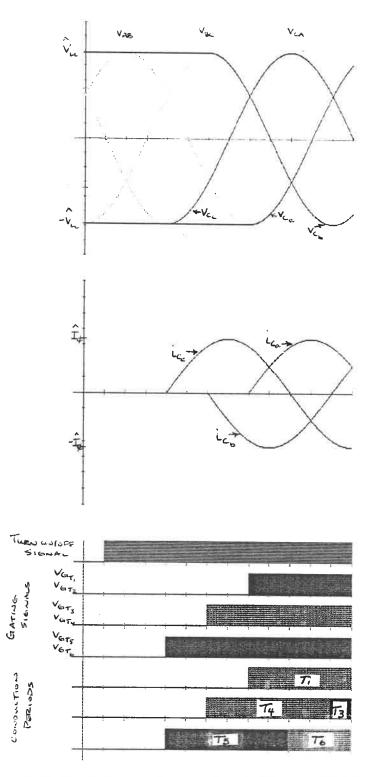

| 3.7 | - | Switching in again a Three-Wire Branch-        |

|-----|---|------------------------------------------------|

|     |   | Controller with a Delta-Connected Load 29      |

| 4.1 | - | Circuit diagram of a Three-Wire Line-          |

|     |   | Controller with a Delta-Connected Load 35      |

| 4.2 | - | Switching in a Three-Wire Line-Controller      |

|     |   | with a Delta-Connected Load 38                 |

| 4.3 | - | Switching out a Three-Wire Line-Controller     |

|     |   | with a Delta-Connected Load                    |

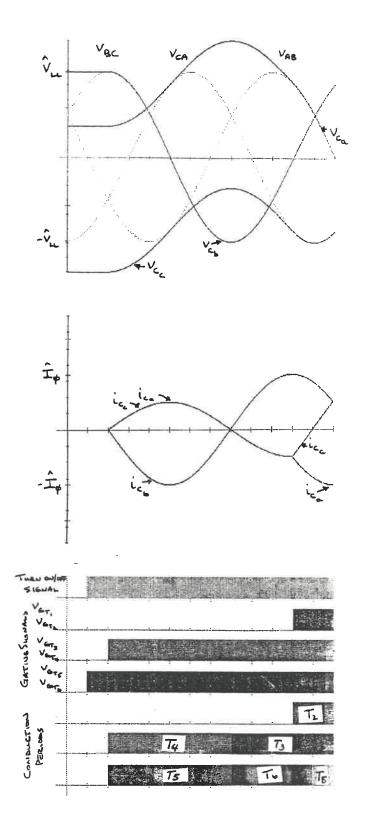

| 4.4 | - | Switching in again a Three-Wire Line-          |

|     |   | Controller with a Delta-Connected Load 40      |

| 5.1 | - | Circuit diagram of a Three-Wire Asymmetrical   |

|     |   | Line-Controller with a Delta-Connected Load 41 |

| 5.2 | - | Equivalent circuit of case a 41                |

| 5.3 | - | Equivalent circuit of case b 43                |

| 5.4 | - | Switching in a Three-Wire Asymmetrical         |

|     |   | Line-Controller with a Delta-Connected Load 48 |

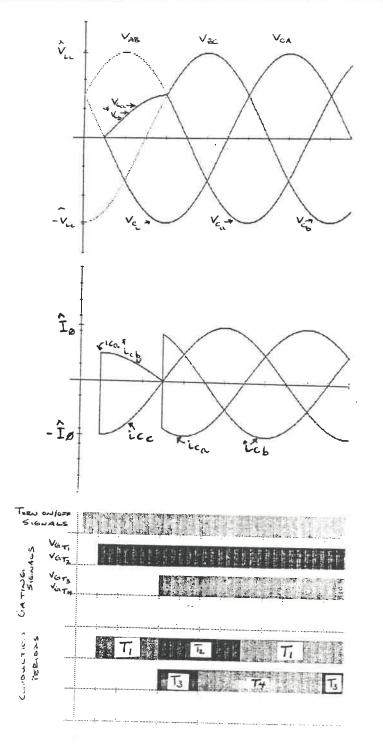

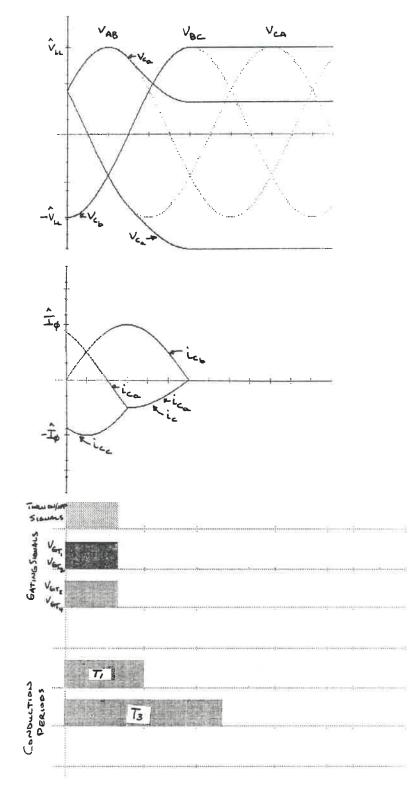

| 5.5 | - | Switching out a Three-Wire Asymmetrical        |

|     |   | Line-Controller with a Delta-Connected Load 49 |

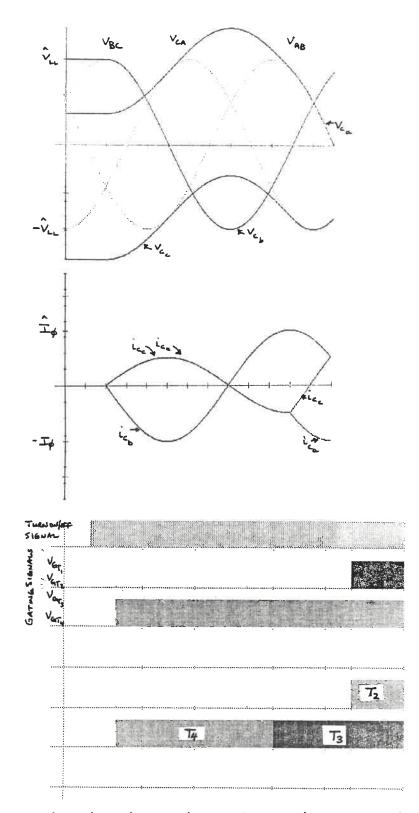

| 5.6 | - | Switching in again a Three-Wire Asymmetrical   |

|     |   | Line-Controller with a Delta-Connected Load 5  |

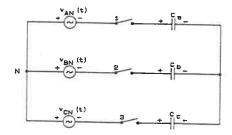

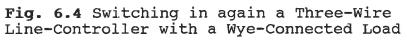

| 6.1 | - | Circuit diagram of a Three-Wire Line-          |

|     |   | Controller with a Wye-Connected Load 55        |

| 6.2 | - | Switching in a Three-Wire Line-Controller      |

|     |   | with a Wye-Connected Load                      |

| 6.3 | - | Switching out a Three-Wire Line-Controller     |

|     |   | with a Wye-Connected Load 59                   |

xiii

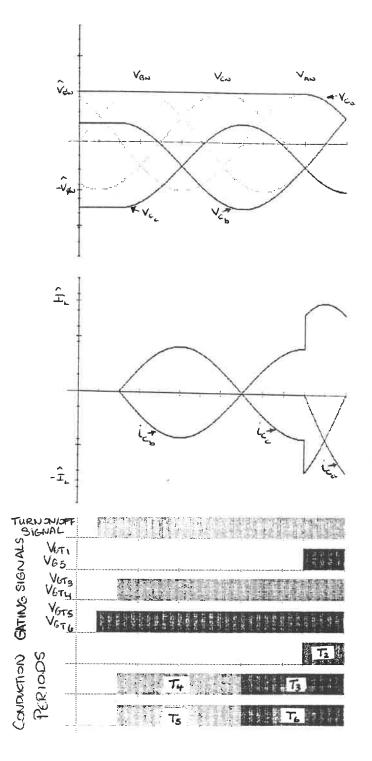

| 6.4 | - | Switching in again a Three-Wire Line-        |    |

|-----|---|----------------------------------------------|----|

|     |   | Controller with a Delta-Connected Load       | 60 |

| 7.1 | - | Circuit diagram of a Three-Wire Asymmetrical |    |

|     |   | Line-Controller with a Wye-Connected Load .  | 61 |

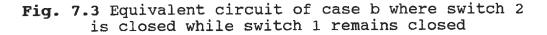

| 7.2 | - | Equivalent circuit of case a                 | 61 |

| 7.3 | - | Equivalent circuit of case b                 | 62 |

| 7.4 | - | Switching in a Three-Wire Line-Controller    |    |

|     |   | with a Wye-Connected Load                    | 68 |

| 7.5 | - | Switching out a Three-Wire Line-Controller   |    |

|     |   | with a Wye-Connected Load                    | 69 |

| 7.6 | - | Switching in again a Three-Wire Line-        |    |

|     |   | Controller with a Wye-Connected Load         | 70 |

| 8.1 | - | Circuit diagram of a Three-Wire Neutral      |    |

|     |   | Point-Controller with a Wye-Connected Load   | 75 |

| 8.2 | - | Equivalent circuit of case a                 | 75 |

| 8.3 | - | Equivalent circuit of case b                 | 77 |

| 8.4 | - | Switching in a Three-Wire Neutral Point-     |    |

|     |   | with a Wye-Connected Load                    | 84 |

| 8.5 | - | Switching out a Three-Wire Neutral Point-    |    |

|     |   | Controller with a Wye-Connected Load         | 85 |

| 8.6 | - | Switching in again a Three-Wire Neutral      |    |

|     |   | Point-Controller with a Wye-Connected Load   | 86 |

| 8.7 | - | Currents flowing in a Three-Wire Neutral     |    |

|     |   | Point-Controller with a Wye-Connected Load   | 87 |

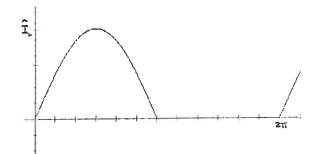

| 9.1 | - | A half-wave rectified sinusoidal current .   | 97 |

xiv

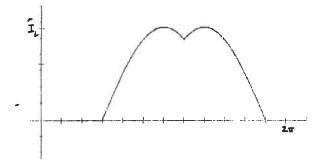

| 9.2   | - | Thyristor current in a Neutral Point-   |

|-------|---|-----------------------------------------|

|       |   | Controller with a Wye-Connected Load 98 |

| 9.3   | - | Current spike caused by noise 101       |

| TABLE | s | Page                                    |

xv

# LIST OF OSCILLOGRAMS

| PLOTS |   | Page                                           |  |

|-------|---|------------------------------------------------|--|

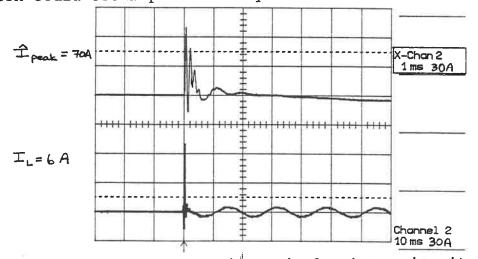

| 1.1   | - | In-rush currents in a single phase circuit 7   |  |

| 1.2   | - | Output from the zero-crossing detector 12      |  |

| 2.1   | - | Switching in the Single Phase AC Controller 20 |  |

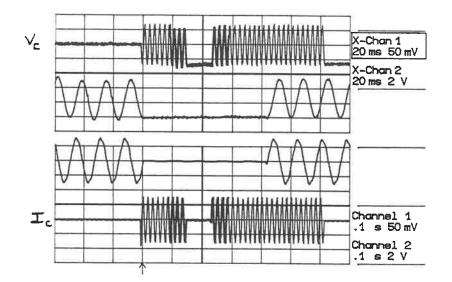

| 2.2   | - | Switching in, out and in again the Single      |  |

|       |   | Phase AC Controller                            |  |

| 3.1   | - | Switching in a Three-Wire Branch-Controller    |  |

|       |   | with a Delta-Connected Load                    |  |

| 3.2   | - | The capacitor currents when switching in a     |  |

|       |   | Three-Wire Branch-Controller 31                |  |

| 3.3   | - | Switching in, out and in again a Three-Wire    |  |

|       |   | Branch-Controller                              |  |

| 3.4   | - | Line currents when switching in a Three-Wire   |  |

|       |   | Branch-Controller                              |  |

| 3.5   | _ | Phase currents when switching in a Three-Wire  |  |

|       |   | Branch-Controller                              |  |

| 3.6   | - | Capacitor voltages when switching a Three-Wire |  |

|       |   | Branch-Controller                              |  |

| 5.1   | - | Switching in a Three-Wire Asymmetrical Line-   |  |

|       |   | Controller with a Delta-Connected Load 51      |  |

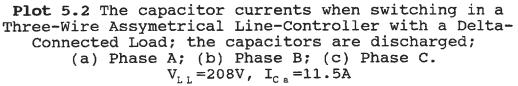

| 5.2   | - | The capacitor currents when switching in a     |  |

|       |   | Three-Wire Asymmetrical Line-Controller 52     |  |

| 5.3   | - | Switching in, out and in again a Three-Wire    |  |

|       |   | Asymmetrical Line-Controller 53                |  |

| 5.4 | - | Phase currents when switching in a Three-Wire  |

|-----|---|------------------------------------------------|

|     |   | Asymmetrical Line-Controller 54                |

| 5.5 | - | Capacitor voltages when switching a Three-Wire |

|     |   | Asymmetrical Line-Controller 54                |

| 7.1 | - | Switching in a Three-Wire Asymmetrical Line-   |

|     |   | Controller with a Wye-Connected Load 71        |

| 7.2 |   | The capacitor currents when switching in a     |

|     |   | Three-Wire Asymmetrical Line-Controller 72     |

| 7.3 | - | Switching in, out and in again a Three-Wire    |

|     |   | Asymmetrical Line-Controller 73                |

| 7.4 | - | Phase currents when switching in a Three-Wire  |

|     |   | Asymmetrical Line-Controller 74                |

| 7.5 | - | Capacitor voltages when switching a Three-Wire |

|     |   | Asymmetrical Line-Controller 74                |

| 8.1 |   | Switching in a Three-Wire Neutral Point-       |

|     |   | Controller with a Wye-Connected Load 88        |

| 8.2 | - | The capacitor currents when switching in a     |

|     |   | Three-Wire Neutral Point-Controller 89         |

| 8.3 |   | Switching in, out and in again a Three-Wire    |

|     |   | Neutral Point-Controller 90                    |

| 8.4 | - | Phase currents when switching in a Three-Wire  |

|     |   | Neutral Point-Controller 91                    |

| 8.5 | - | Capacitor voltages when switching a Three-Wire |

|     |   | Neutral Point-Controller 91                    |

#### INTRODUCTION

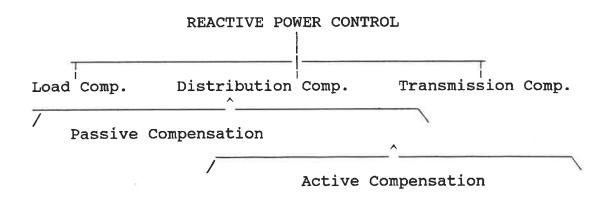

Switching banks of capacitors in and out of power systems is becoming increasingly common, largely because there is a growing interest in reactive power control. High energy prices coupled with the difficulties in extending transmission networks due to high interest rates and the occasional problems in obtaining right of way oblige utilities to look for ways to operate existing power systems more efficiently. Reactive power control is one such scheme that enables the system to operate at or very near unity power factor.

Reactive power control is based on the fact that when the reactive power demanded by the load is supplied locally the generating source need only produce the real power demanded. Consequently losses can be reduced by minimizing the total flow of reactive power.

However most industries constitute inductive loads and as result operate at lagging power factor. Because of the high cost of supplying reactive power most utilities penalize customers if their power factor falls below a fixed value. The purpose of penalty tariffs for low power factor is to encourage industry to share the power utility's enthusiasm for reactive power control, or as it is more commonly referred to, power factor correction.

There are different ways that the vars can be supplied at the load. Synchronous condensers were common in the past but increasingly power capacitors are becoming the preferred choice. The demise of PCBs during the 1970's resulted in a considerable amount of research into capacitor technology and subsequently several important advances. As a result, it is now possible to install large, reliable and highly efficient banks of capacitors in a relatively small space and at a modest price.

Power capacitors connected in shunt are usually installed in one of three ways: as fixed capacitance connected directly across the load; in banks of capacitors which can be switched into or out of a particular system or as part of a continuously controlled static compensator usually called a TSC (Thyristor Switched Capacitor).

Whether the capacitors are installed in a fixed, switched or continuously controlled configuration will depend mostly on the type of compensation involved. In load compensation the objectives [4] are such that one can afford a slower response, so either fixed or switched capacitance will normally be sufficient. However, in transmission compensation the speed of response is critical so switched or preferably continuously controlled capacitors are used.

2.

Capacitors have traditionally been switched using mechanical contactors. The most serious problem which results is that of switching transients, otherwise known as in-rush currents. The transients occur whenever there is a potential difference between the load and the source voltages at the moment that the switch is closed. Because contactors, by their very construction, are closed in a random fashion one cannot predict the magnitude of the transient that will result. Frequently they can exceed 10 pu. [3] and the resulting wear is such that the switching life of the contactor is quite limited.

The second drawback of mechanical contactors is that they are slow. The fastest available mechanical switches [4] take 2 cycles to close or open whereas the more conventional capacitor switches can take anywhere between six and thirty cycles.

Replacing conventional mechanical contactors with three phase thyristor switches would solve both these problems. The fact that thyristors can be "turned on" almost instantaneously (0.9  $\mu$ sec) means that the response would be less than 2 cycles and better still, it means that the capacitor bank could be switched in without transients. Appendix A explores in greater detail the subject of reactive power control and the use of thyristor switched capacitors.

3.

The objectives of this project are two-fold:

- 1) Demonstrate that it is possible to switch banks of capacitors without transients using thyristors.

- 2) Conduct a preliminary characterization study of suitable three phase thyristor switches.

research was pursued through three different The The first was a review of currently available litstages. This was carried out primarily at CISTI (Canadian erature. Institute for Scientific and Technical Information) in The second stage was that of the theoretical ana-Ottawa. The different thyristor configurations were analysis. lyzed using Laplace transforms. The final stage was one of experimentation in the laboratory to ensure that our calculations were correct.

The report is divided into nine chapters. Chapter one provides preliminary information helpful in understanding the work that follows. Chapters two through eight present the six different three phase thyristor switches as well as the single phase thyristor switch. Chapter nine is a discussion of the results and a comparison of the different configurations.

#### CHAPTER ONE

#### PRELIMINARY INFORMATION

#### 1.1 - Literature Review

There is very little published information on the use of ac controllers in switching banks of capacitors since most of the literature concerning ac controllers focuses on ways to control R-L loads (i.e. induction motors, heaters Of the dozen or so publications concerning thyrisetc.). tor-switched capacitors, most approach the problem from the utility's perspective, namely: how can one improve the power system's performance? To our knowledge there are two publications [1], [2] which approach the problem of switching banks of capacitors from an industrial perspective, what is the most economical solution? However, namely: while these texts give a very comprehensive treatment of the capacitor aspects of the problem, they tend to give only a cursory treatment of the power electronic aspects.

When actual thyristor configurations are presented in the literature the accompanying analysis usually only describes the single phase controller or at best the threephase controller in delta, which is simply three single phase controllers joined together. To my knowledge there is no publication which details how capacitor banks can be switched with less than six thyristors. One can, nonetheless, glean some information from the literature.

Generally it is agreed that the ideal instant for transient-free switching is when  $dv_s/dt = 0$  and  $V_{c_a} = v_s(0)$ . This implies that the capacitors are charged to the peak voltage and that the thyristors are only gated when the source voltage peaks. Consequently the thyristors begin conducting at the instant that the current passes through zero. However, if the thyristors are fired at any instant other than when the source voltage equals the load voltage, switching transients will result. It is therefore critical to monitor the voltage across the thyristor switch and to only fire the thyristors when the voltage across the thyristors passes through zero. This switching condition is derived in chapter two.

In order to quantify the seriousness of the problem we decided to reproduce switching transients in the single phase case. This was accomplished by delaying the thyristor firing signal. Plot 1.1 shows the in-rush currents, in excess of 11 p.u., which occurred when the thyristors were fired 30 electrical degrees after the voltage across the thyristors passed through zero. The switching transients got worse as this delay was increased. In the event that the capacitors were discharged the most serious transients would occur if the thyristors were fired when the source voltage was at its peak. However, even worse transients could be expected if the capacitors were left fully charged to the negative peak voltage and the thyristors were then fired when the source was at its positive peak voltage. With conventional switch gear it is possible that this situation could occur periodically.

Switching transients can shorten the life of both the capacitor bank and the switching apparatus. In the case of thyristor switches the thyristors can be destroyed if the di/dt of the in-rush currents exceed the thyristor ratings. Traditionally there have been two solutions to the problem of switching transients. The first solution, a precharger, is rather elaborate and requires that the capacitors be pre-charged to their peak value of the source voltage. In a sense, this method attempts to create the ideal conditions for switching since the resulting current will be zero if the thyristors are fired when the source voltage passes through its peak. However, this solution is both costly and slow. The second solution consists of adding an inductance in series. The inductance is rated so that in the worst case the di/dt will still be less than what the thyristor is rated for. While simpler than the pre-charger solution, it would be better if the series inductance could be eliminated completely: this would be the case if the inherent inductance of the circuit could safely limit the di/dt.

Given the lack of information on ways in which thyristors can be used to switch capacitors, we felt it would be worthwhile to conduct a practical study examining different configurations of thyristors that could be used to switch banks of capacitors without transients. The questions we wanted to address included: 1) Is it possible to switch capacitors without transients? 2) Can the traditionally included series inductors and pre-chargers be eli-3) What is the minimum number of thyristors that minated? can be used to switch a three-phase capacitor bank?

#### 1.2 - Description of Test Setup

Upon completion of the literature review the analysis stage began. The various results of the analysis stage are presented in chapters two through ten, so we will not discuss them here but rather jump ahead to look at how each configuration was tested in the laboratory.

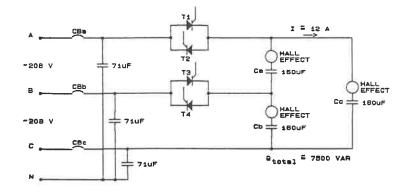

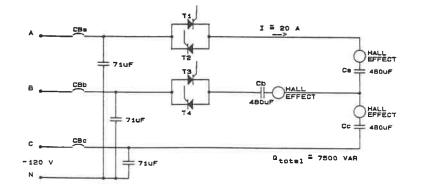

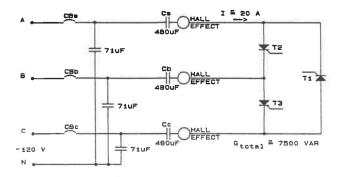

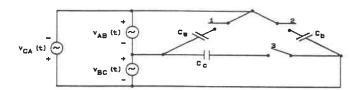

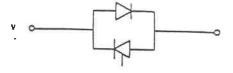

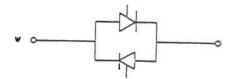

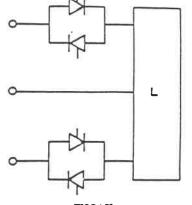

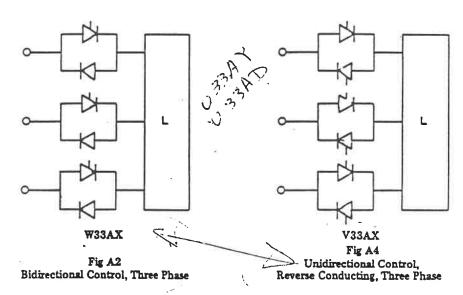

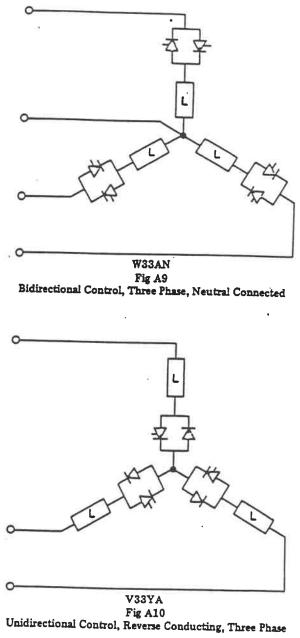

The wiring diagrams for each of the tested configurations are given below (see Fig. 1.1). Each configuration has been named and coded. The names are slightly modified versions of the names that Shepherd gave to these configurations of ac controllers [3]. The codes, however, conform to the IEEE Standard P428/D2 entitled "Standard Definition and Requirements for Thyristor AC Controllers".[6] Relevant sections of this standard are included in Appendix C.

Note that W33AY and W33AD were not tested as they behave the same as W32AY and W32AD respectively.

Fig. 1.1a The Single Phase AC Controller

Fig. 1.1b The Three-Wire Branch-Controller with Delta-Connected Load, W33AA

Fig. 1.1c The Three-Wire Asymmetrical Line-Controller with Delta-Connected Load, W32AD

Fig. 1.1d The Three-Wire Asymmetrical Line-Controller with Wye-Connected Load, W32AY

Fig. 1.1e The Three-Wire Neutral Point-Controller with Wye-Connected Load, U33DA

A few explanations will help clarify why we chose these particular test setups.

1) The 71uF connected across the source was meant to ensure that if there were any transients, we would see them as this source capacitance would try to transfer any excess charge instantaneously to the load capacitance. We chose 71uF because that was the largest capacitance we could connect across each phase with the material we had available.

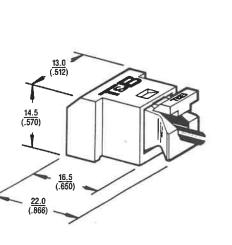

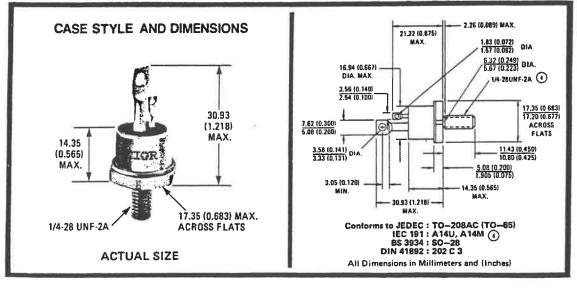

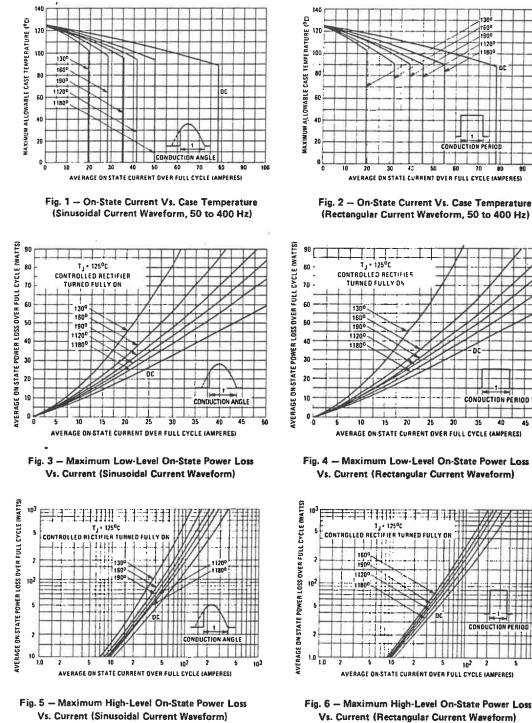

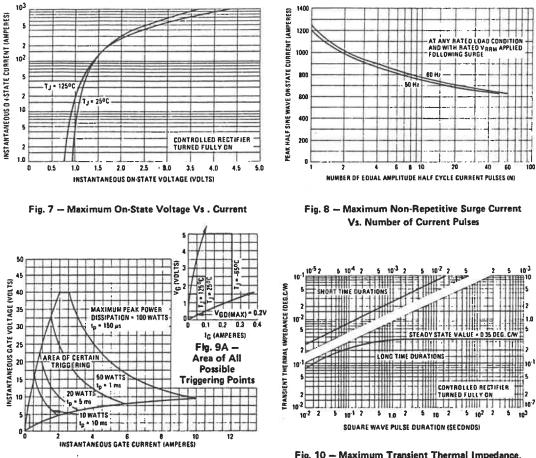

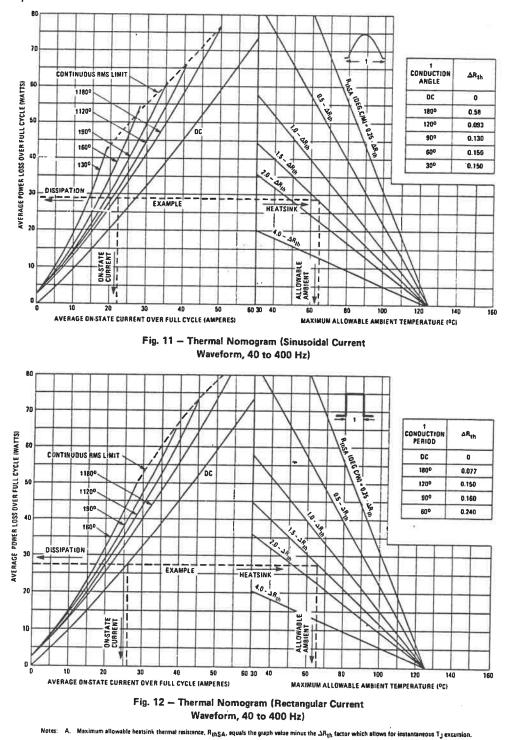

2) The thyristors used in the experiment are International Rectifier, 50RIA Series, 80 A rms. Each thyristor was mounted on its own heatsink and has its own snubber (R=15  $\Omega$ , C=1uF). The thyristor specifications are given in Appendix E.

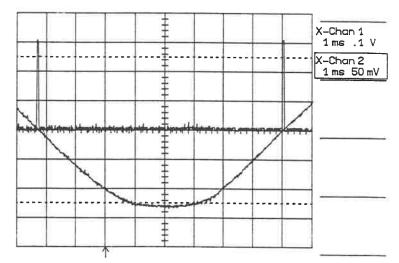

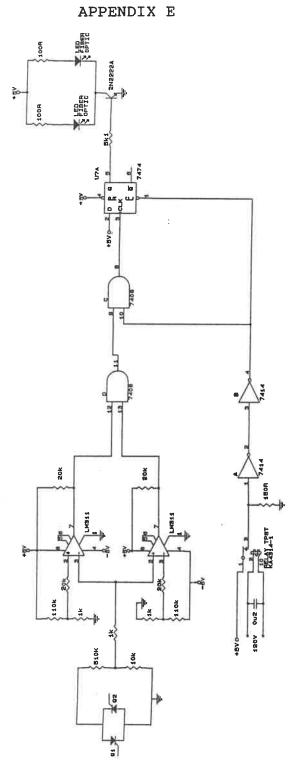

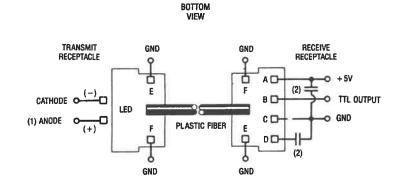

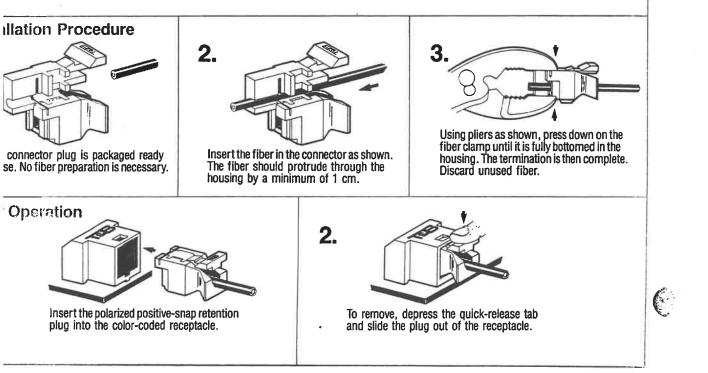

3) The thyristors are fired by means of a fibre optic gate amplifier circuit developed by Ecole Polytechnique. The signal to gate the thyristor is basically the output of a two input AND gate where INPUT 1 is the 'Turn-on' signal and INPUT 2 is the output of the zero crossing detector circuit (see Plot 1.2). The circuit diagram for the logic circuits is given in Appendix F.

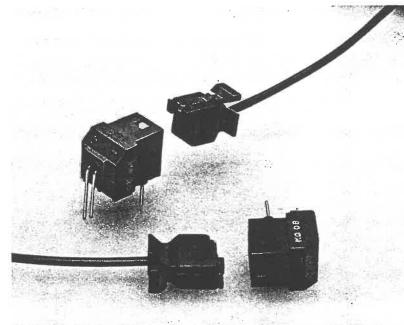

4) The use of fibre optic triggered gate amplifiers was necessary since the opto-thyristors, which we initially used to fire the thyristors, introduced delay thus causing switching transients. 5) The current is monitored by means of Hall Effect current sensors.

6) The source voltage is governed by the ac controller configuration (i.e. W33AD requires  $V_{LL}$  whereas W33AY requires  $V_{LN}$ ).

7) The load varies according to the line current. As the circuit breaker was rated for 20 A, the load would either be 480uF or 160uF so as to ensure the maximum line current.

Plot 1.2 Output from the zero-crossing detector

#### CHAPTER TWO

#### THE SINGLE PHASE AC CONTROLLER USED AS A SWITCH:

#### 2.1 - Introduction

Having completed a review of published literature, the analysis stage began. It consisted of analyzing, by means of Laplace Transforms, the various equivalent circuits for each configuration. The analysis of the single phase case is very helpful in understanding subsequent analyses of three phase circuits since many of the results found in the single phase case can be applied directly.

It is worth noting that the experimental results for the single phase case are presented later in this chapter. It was felt that for the sake of clarity the experimental results of each configuration should be presented in the same chapter as the configuration's analysis.

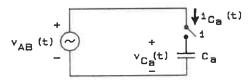

Fig. 2.1 An equivalent circuit for a Single Phase AC Controller with a capacitive load.

2.2 - Analysis of a Single Phase AC Controller

Given that the sinusoidal ac supply voltage is:

$V_{s} = V_{max} \sin(\omega_{o}t + \alpha)$

The corresponding Laplace transform is (see Appendix D for derivation):

$$L\{V_{s}\} = V_{max} \left( \frac{s \cdot \sin \alpha + \omega_{o} \cdot \cos \alpha}{s^{2} + \omega_{o}^{2}} \right)$$

Using the circuit of Fig. 2.1, we see that after the switch has been closed, Kirchhoff's voltage law requires that:

$$V_{s} = \frac{1}{C} \int_{0}^{t} i dt + v_{c} (0^{-})$$

Transforming this equation into the s-domain and solving for I(s) yields:

$$I(s) = C \left[ V_{max} \left( \frac{s_2 \cdot \sin \alpha + \omega_0 s \cdot \cos \alpha}{s_2 + \omega_0^2} \right) - V_c \left( 0^- \right) \right]$$

[eq. 2.1]

After ensuring that all factors of the equation are expressed as proper rational polynomials (i.e. the denominator is of a higher order than the numerator) we can find the Inverse Laplace Transform:

$$i(t) = L^{-1} \{I(s)\}$$

= C{  $V_{max} \sin \alpha - v_{c}(0^{-}) \} \delta(t)$

+  $C\omega_{o}V_{max} \cos(\omega_{o}t + \alpha)$  [eq. 2.2]

This equation shows that the optimal moment for firing the thyristors is when the voltage across the thyristor switch is zero, namely when  $V_{max} \sin \alpha = v_c (0^-)$ . It is possible to switch the capacitor in without transients at this instant because the impulse component of the current expression is zero.

With an understanding of how thyristor switches open, one can predict the final conditions of the system. The thyristors block after the gate triggering signals have been removed, and the current flowing through their anode declines to zero. Since the current in a capacitor leads the voltage by 90°, the current passes through zero when the voltage is at its peak value  $V_{max}$ . In other words, whenever the switch is opened the capacitor is left charged to its maximum value.

15.

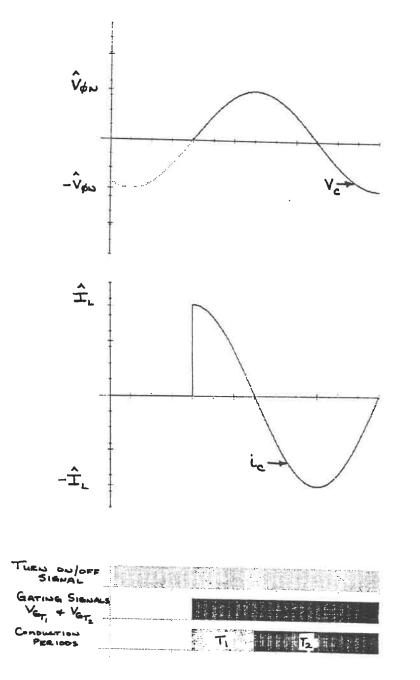

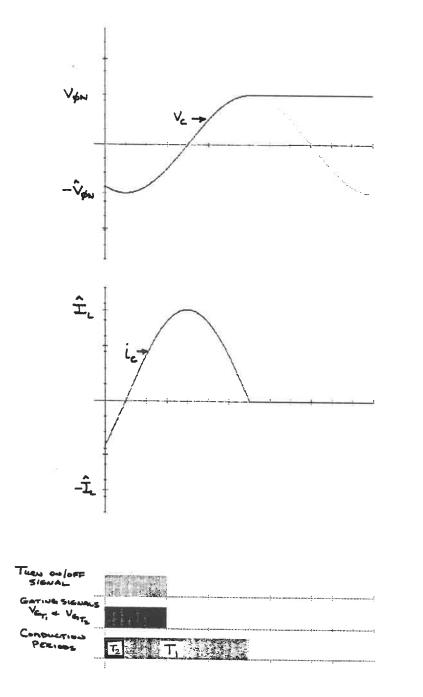

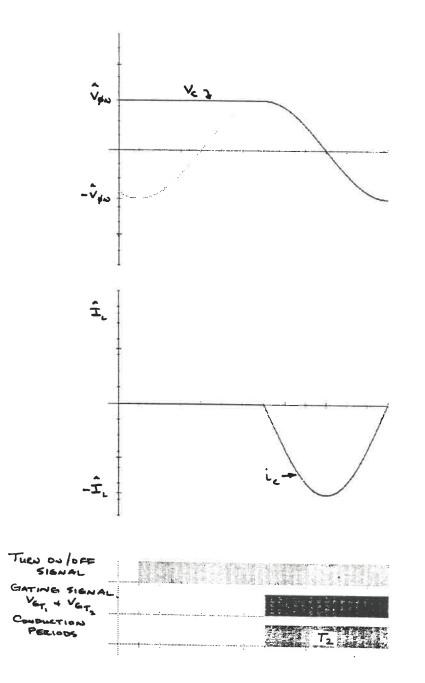

#### 2.3 - Predictions of Circuit Behavior:

With this information we can predict how the circuit will perform in the stages of operation that interest us: 1) switching in a discharged capacitor; 2) switching out the capacitor; 3) switching in the charged capacitor.

1) SWITCHING IN A DISCHARGED CAPACITOR: Thyristors should be gated at  $V_c = v_s (0^-) = 0$ (i.e. when the voltage across the thyristors is zero) Corresponding current  $i(t) = C\omega_o V_{max} \cos(\omega_o t + \alpha)$

2) SWITCHING OUT THE CAPACITOR: Thyristor stops conducting at  $i_c(t)=0$ resulting capacitor voltage  $V_c = \pm V_{max}$

3) SWITCHING IN CHARGED CAPACITOR: Thyristors should be gated at  $V_c = v_s (0^-) = V_{max}$ (i.e. when the voltage across the thyristors is zero) Corresponding current at  $i(0^+)=0$

### 2.4 - Computer Plots of Expected Circuit Behavior:

Fig. 2.2 Switching in the Single Phase AC Controller with the capacitor discharged

Fig. 2.3 Switching out the Single Phase AC Controller

18.

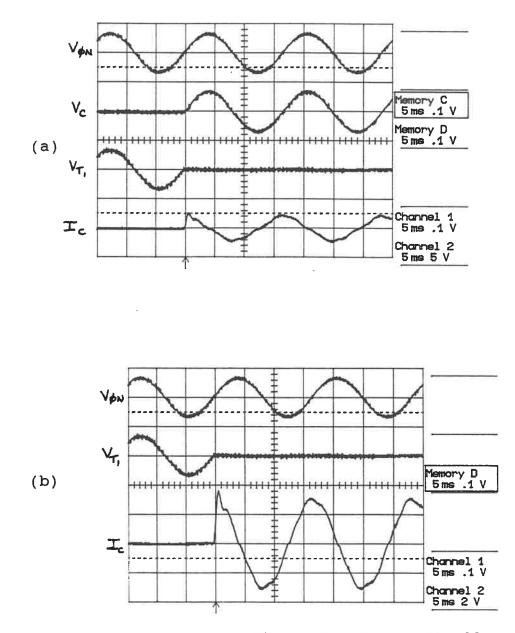

**Plot 2.1** Switching in the Single Phase AC Controller with the capacitor is discharged. (a) Oscillogram including the voltage across the thyristors; (b) Oscillogram showing a magnified current waveform.  $V_{\Phi N} = 120V$ ,  $I_c = 21A$

## CHAPTER THREE

### THREE-WIRE BRANCH-CONTROLLER WITH DELTA-CONNECTED LOAD:

## 3.1 - Introduction:

In this configuration, three separate switches must be closed before the capacitive load is fully connected to the source. Hence we have three different cases to analyse in order to determine how this configuration behaves.

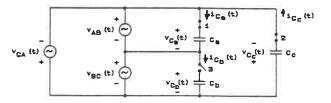

Fig. 3.1 Circuit diagram of a Three-Wire Branch-Controller with a Delta-Connected Load

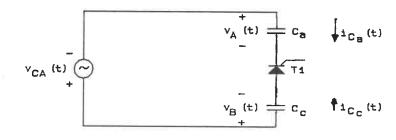

3.2 - Analysis:

Case a: Close switch 1

Fig. 3.2 Equivalent circuit of case a where switch 1 is closed

The equivalent circuit of this case is shown in Fig. 3.2. By analogy with the single phase circuit we can write directly:

$$i_{AB}(t) = C_{a} \{V_{ABmax} \sin \theta_{AB} - V_{Ca}(0)\} \delta(t) + C_{a} \omega_{o} V_{ABmax} \cos(\omega_{o} t + \theta_{AB})$$

where  $V_{ABmax} = \sqrt{3}V_{ANmax}$  and  $\theta_{AB} = \alpha_A + 30^{\circ}$

hence

$$i_{AB}(t) = C_{a} \{ \overline{J3} \cdot V_{ANmax} \sin(\alpha_{A} + 30^{\circ}) - V_{Ca}(0^{-}) \} \delta(t)$$

+  $C_{a}\omega_{o} \overline{J3} \cdot V_{ANmax} \cos(\omega_{o}t + \alpha_{A} + 30^{\circ})$

Condition to switch without transients:

$V_{ABmax} \sin \theta_{AB} = V_{Ca} (0^{-})$

This shows that switch 1 should be closed when the voltage across it is zero.

Case b: Close switch 2

Fig. 3.3 Equivalent circuit of case b where switch 2 is closed while switch 1 remains closed

The equivalent circuit of this case is shown in Fig. 3.3. As both loops are independent, this case can be viewed as two independent single phase ac circuits. The current in the inner loop remains unchanged from the steady state current of case a. Hence

$i_{AB}(t)=C_{a}\omega_{o}V_{ABmax}\cos(\omega_{o}t+\Theta_{AB})$

The current in the outer loop can be written directly by analogy with the single phase circuit:

$$i_{CA}(t) = C_{c} \{V_{CAmax} \sin \theta_{CA} - V_{Cc}(0^{-})\} \delta(t) + C_{c} \omega_{o} V_{CAmax} \cos(\omega_{o} t + \theta_{CA})\}$$

where  $V_{CAmax} = \sqrt{3}V_{Cmax}$  and  $\theta_{CA} = \alpha_{C} + 30^{\circ}$

Condition to switch without transients:

$V_{CAmax}\sin\theta_{CA} = V_{Cc}(0)$

This shows that switch 2 should be closed when the voltage across it is zero.

Case c: Close switch 3

Fig. 3.4 Equivalent circuit of case c where switch 3 is closed while switches 1 & 2 remain closed

The equivalent circuit of this case is shown in Fig. 3.4. The parameter of interest to us is  $i_{BC}(t)$  when switch 3 is closed. This can be found by writing the differential equation for the current flowing through  $C_b$ .

$i_{BC}(t)=C_{b}dV_{BC}(t)/dt$

where  $V_{bc}(t) = V_{BCmax} \sin(\omega_{o}t + \theta_{BC})$

Transforming this equation into the s-domain yields:

$I_{BC}(s) = C \left[ V_{max} \left( \frac{s^2 \cdot \sin \alpha + \omega_0 s \cdot \cos \alpha}{s^2 + \omega_0^2} \right) - V_c(0^-) \right]$

As this is of the same form as eq. 2.1, we know that the time domain solution will be in the same form as eq. 2.2. Hence:

$$i_{BC}(t) = C_{b} \{V_{BCmax} \sin\theta_{BC} - V_{Cb}(0^{-})\}\delta(t) + C_{b}\omega_{o}V_{BCmax} \cos(\omega_{o}t + \theta_{BC})\}$$

where  $V_{BCmax} = \sqrt{3}V_{BCmax}$  and  $\theta_{BC} = \alpha_b + 30^\circ$

Condition to switch without transients:

$V_{BCmax}\sin\theta_{BC} = V_{Cb}(0^{-})$

This shows that switch 3 should be closed when the voltage across it is zero.

### 3.3 - Predictions of Circuit Behavior:

With this information, we can predict how the circuit will perform in the stages of operation that interest us: 1) switching in a discharged capacitor; 2) switching out the capacitor; 3) switching in the charged capacitor.

1) SWITCHING IN A DISCHARGED CAPACITOR:

Thyristors should be gated when the voltage across them is zero.

Corresponding current  $i(t)=\pm i_{max}$  .

2) SWITCHING OUT THE CAPACITOR:

Thyristor stops conducting at  $i_{\phi}(t)=0$ .

Resulting capacitor voltages:

$V_{Ca} = \pm V_{ABmax} = \pm 294 V$  $V_{Cb} = \pm V_{BCmax} = \pm 294 V$

$V_{C,c} = \pm V_{C,A,m,a,x} = \pm 294$  V

3) SWITCHING IN CHARGED CAPACITOR:

Thyristors should be gated when the voltage across them is zero.

Corresponding current:  $i(0^{-})=0$ .

# 3.4 - Computer Plots of Expected Circuit Behavior:

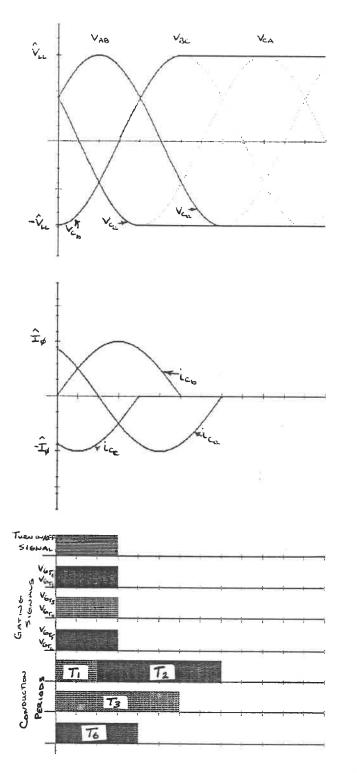

Fig. 3.5 Switching in a Three-Wire Branch-Controller with a Delta-Connected Load; the capacitors are discharged

Fig. 3.6 Switching out a Three-Wire Branch-Controller with a Delta-Connected Load

## 3.5 - Experimental Results:

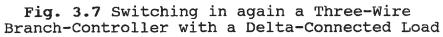

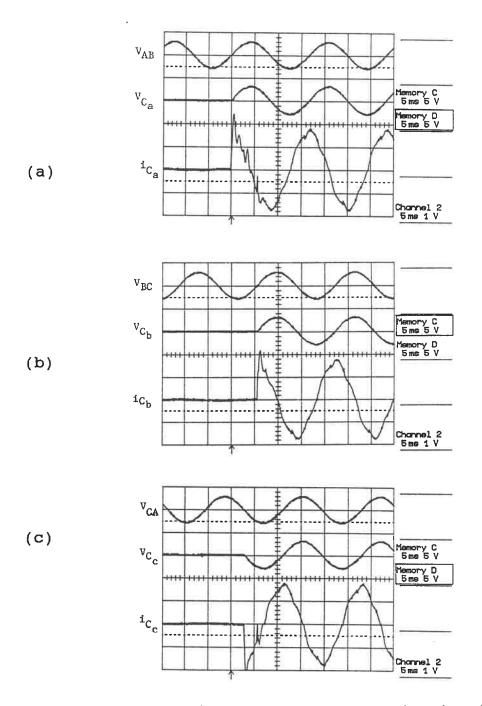

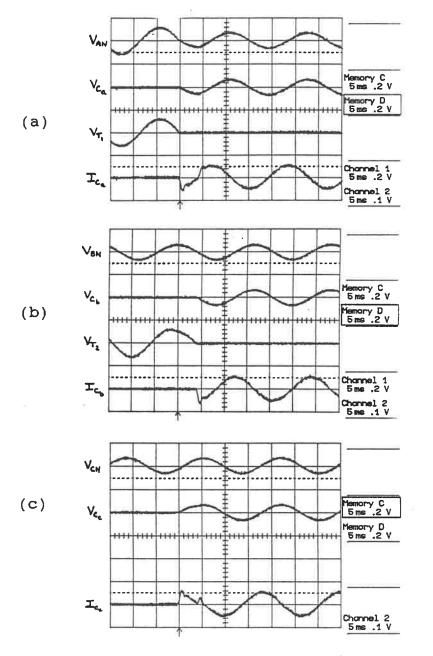

Plot 3.1 Switching in a Three-Wire Branch-Controller with a Delta-Connected Load; the capacitors are discharged (a) Phase A; (b) Phase B; (c) Phase C.  $V_{LL}$ =208V,  $I_{Ca}$ =11.5A

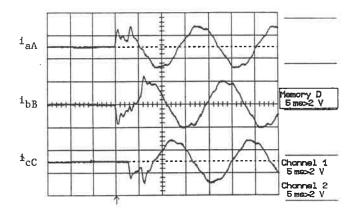

Plot 3.4 Line currents when switching in a Three-Wire Branch-Controller with a Delta-Connected Load;  $V_{LL} = 208V$ ,  $I_{Ca} = 11.5A$

Plot 3.5 Phase currents when switching in a Three-Wire Branch-Controller with a Delta-Connected Load;  $V_{L\,L} = 208V$ ,  $I_{C\,a} = 11.5A$

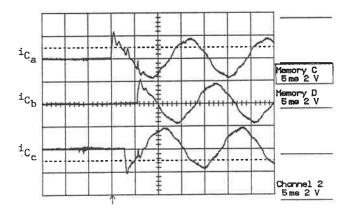

Plot 3.6 Capacitor voltages when switching a Three-Wire Branch-Controller with a Delta-Connected Load;  $V_{LL}$ =208V,  $I_{Ca}$ =11.5A

#### CHAPTER FOUR

### THREE-WIRE LINE-CONTROLLER WITH DELTA-CONNECTED LOAD

## 4.1 - Introduction:

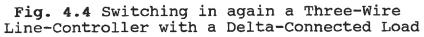

In this configuration three switches must be closed before the capacitive load is fully connected to the source. However, closing the first switch does not cause any current to flow, although it does connect one of the phases of the load to the source. Current only begins to flow when the second thyristor switch is closed, and a path for the current is created. As a result, this configuration behaves the same way as the Three-Wire Asymmetrical Line-Controller with a Delta-Connected Load. For the analysis of the circuit's behavior refer to chapter five.

Fig. 4.1 Circuit diagram of a Three-Wire Line-Controller with a Delta-Connected Load

### 4.2 - Predictions of Circuit Behavior:

Using the information found in the analyses of Chapter Five, we can predict how the circuit will perform in the stages of operation that interest us: 1) switching in a discharged capacitor; 2) switching out the capacitor; 3) switching in the charged capacitor.

1) SWITCHING IN A DISCHARGED CAPACITOR:

Thyristors should be gated when the voltage across them is zero.

The magnitude and direction of the current in the different phases depends on which switch is closed first and the polarity of the source voltage when the switch is closed. Nonetheless the magnitude of the largest current in the thyristors will not exceed:  $\pm i_{lmax}$ .

### 2) SWITCHING OUT THE CAPACITOR:

Thyristors stop conducting when the corresponding line current  $i_L(t)=0$ .

There are only four possible states that the capacitor bank could adopt after being switched off (this is because we have choosen to operate the W33AD as a W32AD by ensuring that switch 3 is always the last switch to turn off and the first switch to turn on).

To understand how these final states are arrived at it is useful to remember that after one of the three switches has been opened we no longer have a three phase source, but rather a single phase source. In addition, opening a switch causes one of the capacitors to be connected in parallel with the two other capacitors. Consequently, as the capacitor which is connected directly across the source is charged to its peak value, the two other capacitors see their voltage decrease. (For a more detailed discussion of the turn off process see chapter five.)

The four possible final states are:

an marco - an ar

|                 | А       | В       | С       | D       |

|-----------------|---------|---------|---------|---------|

| $V_{Ca}$        | 107.6V  | -401.6V | -107.6V | 401.6V  |

| $v_{\rm Cb}$    | 294.0V  | 107.6V  | -294.0V | -107.6V |

| V <sub>cc</sub> | -401.6V | 294.OV  | 401.6V  | -294.0V |

3) SWITCHING IN CHARGED CAPACITOR:

Thyristors should be gated when the voltage across them is zero.

Corresponding current:  $i(0^{-})=0$ .

# 4.3 - Computer Plots of Expected Circuit Behavior:

Fig. 4.2 Switching in a Three-Wire Line-Controller with a Delta-Connected Load; the capacitors are discharged

Fig. 4.3 Switching out a Three-Wire Line-Controller with a Delta-Connected Load

----

### CHAPTER FIVE

### THREE-WIRE ASYMMETRICAL LINE-CONTROLLER WITH DELTA-CONNECTED LOAD

## 5.1 - Introduction:

In this configuration, two switches must be closed before the capacitive load is fully connected to the source. Hence we have two different cases to analyze, in order to understand how this configuration behaves.

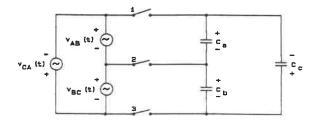

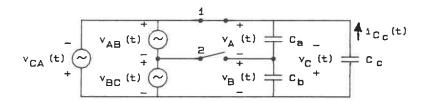

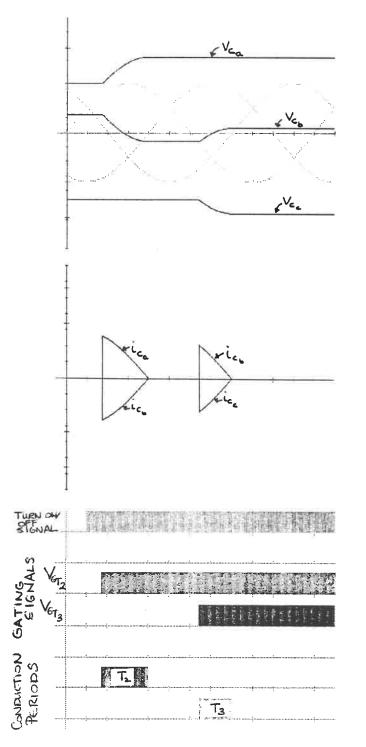

Fig. 5.1 Circuit diagram of a Three-Wire Assymmetrical Line-Controller with a Delta-Connected Load

5.2 - Analysis:

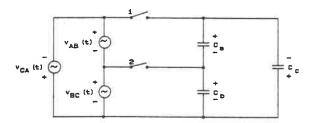

Case a: close switch 1

Fig. 5.2 Equivalent circuit of case a where switch 1 is closed

Using the circuit of Fig. 5.2 we see that after the switch has been closed, Kirchhoff's voltage law requires that:

$$v_{CA}(t) = \frac{1}{C_{a}} \int_{0}^{t} i_{Ca} \cdot dt + v_{Ca}(0^{-}) + \frac{1}{C_{b}} \int_{0}^{t} i_{Cb} \cdot dt + v_{Cb}(0^{-})$$

note that  $i_{Ca} = i_{Cb}$

After transforming, solving for  $I_{Ca}(s)$ , and then finding the inverse transform we see that:

$$i_{Ca}(t) = \frac{C_a \cdot C_b}{C_a + C_b} \left[ V_{CAmax} \sin \theta_{CA} - V_{Ca}(0^-) - V_{Cb}(0^-) \right] \delta(t) + \frac{C_a \cdot C_b}{C_a + C_b} \omega_0 V_{Camax} \cos(\omega_0 t + \theta_{Ca}) \right]$$

In like manner we can show that:

$$i_{Ca}(t) = C_{c} \left[ V_{CA} \sin \theta_{CA} - V_{Cc} (0^{-}) \right] \delta(t) + C_{c} \omega_{0} V_{CAmax} \cos(\omega_{0} t + \theta_{CA})$$

Conditions for switching without transients are:

$V_{CAmax} \sin\theta_{CA} = V_{Ca} (0^{-}) = V_{Cc} (0^{-})$

This shows that switch 1 should be closed when the voltage across it is zero.

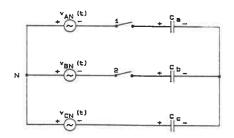

# Case b: close switch 2 with switch 1 remaining closed

Fig. 5.3 Equivalent circuit of case b where switch 2 is closed while switch 1 remains closed

The equivalent circuit is shown in Fig. 5.3. By Kirchhoff's voltage law we can show that:

$$v_{AB} = \frac{1}{C_a} \int_0^t i_{Ca} dt + v_{Ca} (0^-)$$

Transforming, solving for  $I_{c_a}(s)$  and then finding the inverse transform yields:

$$i_{Ca}(t) = C_{a}[V_{ABmax}\sin(\theta_{AB}) - V_{Ca}(0^{-})] + \delta(t) + C_{a}\omega_{0}V_{ABmax}\cos(\omega_{0}t + \theta_{AB})$$

In the same way we can show that:

$$i_{Cb}(t) = C_{b}[V_{BCmax}\sin\theta_{BC} - V_{Cb}(0^{-})] \delta(t) + C_{b}\omega_{0}V_{BCmax}\cos(\omega_{0}t + \theta_{BC})$$

Conditions for switching without transients are:

$$V_{ABmax} \sin \theta_{AB} = V_{Ca} (0^{-})$$

and  $V_{BCmax} \sin \theta_{BC} = V_{Cb} (0^{-})$

This shows that switch 2 should be closed when the voltage across it is zero.

### Turn Off:

It is important to remember that these equations can be used to determine the optimal moment for switching in a capacitor bank regardless of the capacitor voltage. Consequently, whether the capacitors are fully charged or fully discharged makes no difference; the optimal moment for switching in the capacitors is when the voltage across the thyristor switch is zero.

We will now exam the turning off process. Upon receiving the command to turn off the thyristors, the gate signal to each thyristor is removed. However, this does not mean that the thyristors are turned off. A thyristor only turns off when the current flowing through it decreases to zero. In this particular configuration it is the line current which must decline to zero before the thyristors will stop conducting. If we examine the same case that is depicted in Fig. 5.5, we note that when the line current is zero (i.e.  $i_{aA} = 0$ ), the corresponding capacitor voltages are:  $V_{Ca} = 0.866 \cdot V_{AB}$ ,  $V_{Cb} = 0$ ,  $V_{Cc} = -0.866 \cdot V_{CA}$ . (Remember that the line current lags the phase current by 30°.) Consequently, these are the conditions that exist immediately after switch 1 is opened.

As soon as switch 1 is opened the circuit topology changes; we no longer have a three phase source, but rather a single phase source connected directly across one capacitor  $C_b$ , and across the series connection of  $C_a$  and  $C_c$ . We note that at the instant that switch 1 is opened that the new source voltage  $V_{BC}$  equals the load voltage  $V_{Cb} = V_{Ca} + V_{Cc}$ , which equals zero. Kirchhoff tells us the sum of the load voltages must always equal zero. Therefore, as  $V_{Cb}$  is being charged to the peak line voltage,  $V_{Ca}$  has to decrease at the rate of half the source voltage  $V_{BC}$ . Likewise,  $V_{Cc}$  has to decrease at the same rate. If this does not happen the load voltages will not be balanced.

At the instant that  $V_{Cb}$  is charged to the peak line voltage, the corresponding line current  $i_{bB}$  will decline to zero. It is at this moment that we can consider the capacitor bank disconnected from the source. We note that the final voltages are:  $V_{Ca} = (0.866-0.5) \cdot V_{LLmax} = 107.6V;$  $V_{Cb} = V_{LLmax} = 294.0V; V_{Cc} = (-0.866-0.5) \cdot V_{LLmax} = -401.6V.$

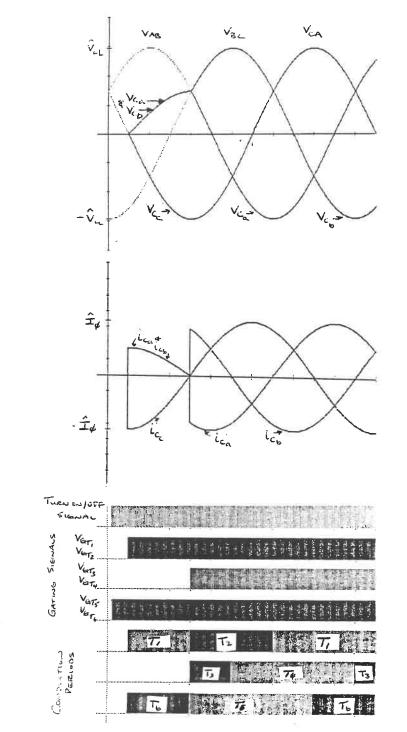

### 5.3 - Predictions of Circuit Behavior:

With this information we can predict how the circuit will perform in the stages of operation that interest us: 1) switching in a discharged capacitor; 2) switching out the capacitor; 3) switching in the charged capacitor.

1) SWITCHING IN A DISCHARGED CAPACITOR:

Thyristors should be gated when the voltage across them is zero.

The magnitude and direction of the current in the different phases depends on which switch is closed first and the polarity of the source voltage when the switch is closed. Nonetheless the magnitude of the largest current in the thyristors will not exceed:  $\pm i_{Lmax}$ .

### 2) SWITCHING OUT THE CAPACITOR:

Thyristors stop conducting when the corresponding line current  $i_{L}(t)=0$ .

There are only four possible states that the capacitor bank could adopt after being switched off. The four possible final states are:

|                  | A       | В       | С       | D       |

|------------------|---------|---------|---------|---------|

| $V_{Ca}$         | 107.6V  | -401.6V | -107.6V | 401.6V  |

| V <sub>Cb</sub>  | 294.0V  | 107.6V  | -294.0V | -107.6V |

| V <sub>c c</sub> | -401.6V | 294.OV  | 401.6V  | -294.0V |

3) SWITCHING IN CHARGED CAPACITOR:

Thyristors should be gated when the voltage across them is zero.

Corresponding current: i(0<sup>-</sup>)=0.

# 5.4 - Computer Plots of Expected Circuit Behavior:

Fig. 5.4 Switching in a Three-Wire Assymetrical Line-Controller with a Delta-Connected Load; the capacitors are discharged

## 5.5 - Experimental Results:

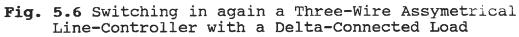

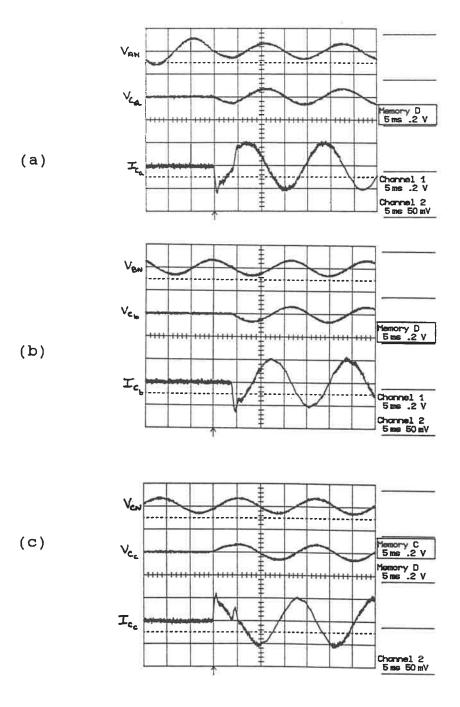

Plot 5.1 Switching in a Three-Wire Assymetrical Line-Controller with a Delta-Connected Load; the capacitors are discharged. (a) Phase A; (b) Phase B; (c) Phase C.  $V_{LL}$ =208V,  $I_{Ca}$ =11.5A

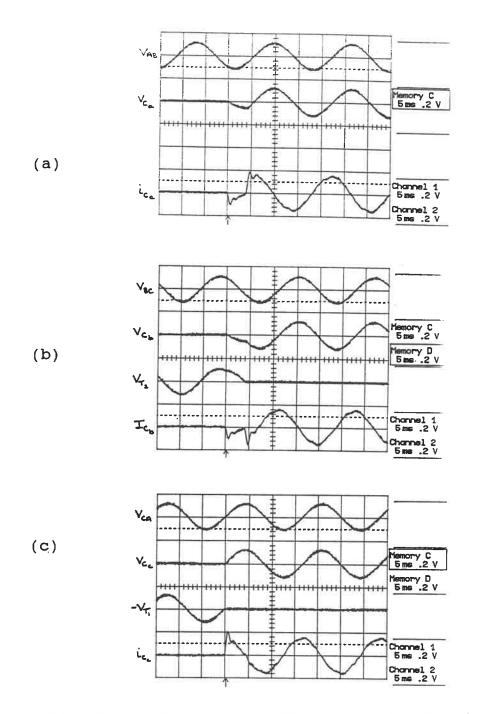

**Plot 5.4** Phase currents when switching in a Three-Wire Assymetrical Line-Controller with a Delta-Connected Load.  $V_{LL}$ =208V,  $I_{Ca}$ =11.5A

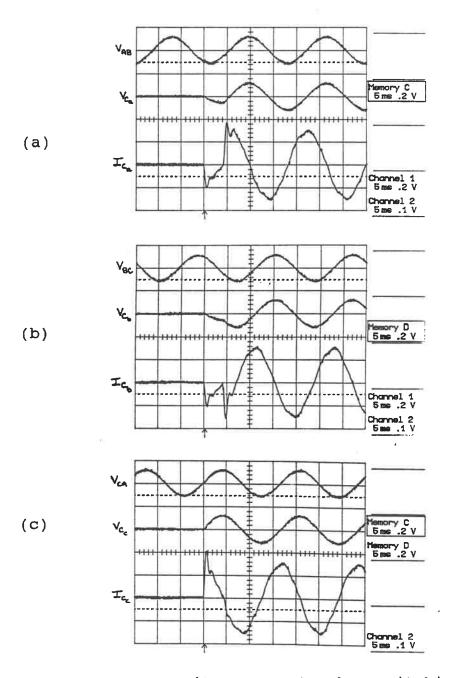

**Plot 5.5** Capacitor voltages when switching a Three-Wire Assymetrical Line-Controller with a Delta-Connected Load.  $V_{LL}$ =208V,  $I_{Ca}$ =11.5A

#### CHAPTER SIX

#### THREE-WIRE LINE-CONTROLLER WITH WYE-CONNECTED LOAD

#### 6.1 - Introduction:

In this configuration three switches must be closed before the capacitive load is fully connected to the source. However, closing the first switch does not cause any current to flow, although it does connect one of the phases of the load to the source. Current only begins to flow when the second thyristor switch is closed, and a path for the current is created. As a result, this configuration behaves the same way as the Three-Wire Asymmetrical Line-Controller with a Wye-Connected Load. For the analysis of the circuit's behavior refer to chapter seven.

the state of the second s

## 6.2 - Predictions of Circuit Behavior:

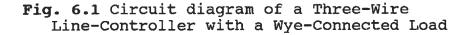

With this information we can predict how the circuit will perform in the stages of operation that interest us: 1) switching in a discharged capacitor; 2) switching out the capacitor; 3) switching in the charged capacitor.

1) SWITCHING IN A DISCHARGED CAPACITOR:

Thyristors should be gated when the voltage across them is zero.

The magnitude and direction of the current in the different phases depends on which switch is closed first and the polarity of the source voltage when the switch is closed. Nonetheless the magnitude of the largest current flowing through the thyristors will not exceed:  $\pm i_{\phi_{max}}$ .

#### 2) SWITCHING OUT THE CAPACITOR:

Thyristors stop conducting when the corresponding line current  $i_{\phi}(t)=0$ .

There are only four possible states that the capacitor bank could adopt after being switched off (this is because we have choosen to operate the W33AY as a W32AY by ensuring that switch 3 is always the last switch to turn off and the first switch to turn on).

To understand how these final states are arrived at it is useful to remember that after one of the three switches has been opened we no longer have a three

phase source, but rather a single phase source. In addition, opening a switch causes one of the capacitors to be disconnected while leaving the two other capaciconnected in series across the tors source. Consequently, the disconnected capacitor is left fully charged; the two other capacitors, while orginally charged to the same voltage, now see their voltage increase and decrease respectively as the source voltage climbs to its peak and the phase current declines (For a more detailed discussion of the turn to zero. off process see chapter seven.)

The four possible final states are:

|                  | А       | В       | С       | D       |

|------------------|---------|---------|---------|---------|

| V <sub>C a</sub> | 170.0V  | -232.2V | -170.0V | 232.2V  |

| V <sub>Cb</sub>  | 62.2V   | 170.0V  | -62.2V  | -170.0V |

| V <sub>cc</sub>  | -232.2V | 62.2V   | 232.2V  | -62.2V  |

3) SWITCHING IN CHARGED CAPACITOR:

Thyristors should be gated when the voltage across them is zero.

Corresponding current: i(0) = 0.

# 6.3 - Computer Plots of Expected Circuit Behavior:

Fig. 6.2 Switching in a Three-Wire Line-Controller with a Wye-Connected Load; the capacitors are discharged

Fig. 6.3 Switching out a Three-Wire Line-Controller with a Wye-Connected Load

#### CHAPTER SEVEN

#### THREE-WIRE ASYMMETRICAL LINE-CONTROLLER WITH WYE-CONNECTED LOAD

## 7.1 - Introduction:

In this configuration, two switches must be closed before the capacitive load is fully connected to the source. Hence we have two different cases to analyze, in order to understand how this configuration behaves.

Fig. 7.1 Circuit diagram of a Three-Wire Asymmetrical Line-Controller with a Wye-Connected Load

7.2 - Analysis:

Case a: close switch 1

Using the circuit of Fig. 7.2 we see that after the switch has been closed, Kirchhoff's voltage law requires that:

$$v_{CA}(t) = \frac{1}{C_{a}} \int_{0}^{t} i_{Ca} \cdot dt + v_{Ca}(0^{-}) + \frac{1}{C_{c}} \int_{0}^{t} i_{Cc} \cdot dt + v_{Cc}(0^{-})$$

note that  $i_{Cc} = -i_{Ca}$

After transforming, solving for  $I_{C_{c}}(s)$ , and then finding the inverse transform we see that:

$$i_{Cc}(t) = \frac{C_a \cdot C_c}{C_a + C_c} \left[ V_{CAmax} \sin \theta_{CA} - V_{Cc}(0^-) + V_{Ca}(0^-) \right] \delta(t) + \frac{C_a \cdot C_c}{C_a + C_c} \omega_0 V_{CAmax} \cos(\omega_0 t + \theta_{CA}) \right]$$

Conditions for switching without transients are:

$V_{CAmax} \sin \theta_{CA} = V_{Cc} (0^{-}) - V_{Ca} (0^{-})$

This shows that switch 1 should be closed when the voltage across it is zero.

Case b: close switch 2 with switch 1 remaining closed

the second second second second second second

The equivalent circuit is shown in Fig. 7.3. By Kirchhoff's current law we can show that:

$I_{aA} + I_{bB} + I_{cC} = 0$ where:  $I_{aA} = sC_{a} (v_{AN} - v_{0}) - C_{a} v_{AN} (0^{-})$  $I_{bB} = sC_{b} (v_{BN} - v_{0}) - C_{b} v_{BN} (0^{-})$  $I_{cC} = sC_{c} (v_{CN} - v_{0}) - C_{c} v_{CN} (0^{-})$

solving for  $v_0$  yields:

$$V_{0} = \frac{1}{3} \left[ (v_{A N} - \frac{v_{C a} (0^{-})}{s}) + (v_{B N} - \frac{v_{C b} (0^{-})}{s}) + (v_{C N} - \frac{v_{C c} (0^{-})}{s}) \right]$$

since  $C_{a} = C_{b} = C_{c}$

Transforming, solving for  $I_{Cb}(s)$  and then finding the inverse transform yields:

$$i_{Cb} = (C/3) \cdot \{ (V_{BCmax} \cdot \sin\theta_{BC} - V_{Cb}(0^{-}) + V_{Cc}(0^{-}) - V_{ABmax} \cdot \sin\theta_{AB} - V_{Cb}(0^{-}) + V_{ca}(0^{-}) \} \cdot \delta(t) + (C/3) \cdot \{ V_{BC}\omega_{o}\cos(\omega t + \theta_{BC}) - V_{AB}\omega_{o}\cos(\omega t + \theta_{AB}) \}$$

Conditions for switching without transients are:

$$V_{BNmax} \cdot \sin\theta_{BN} = V_{Cc}(0^{-}) + V_{Ca}(0^{-}) - 2 \cdot V_{Cb}(0^{-})$$

This shows that switch 2 should be closed when the voltage across it is zero.

63.

}

#### Turn Off:

It is

important to remember that these equations can be used to determine the optimal moment for switching in a capacitor bank regardless of the capacitor voltage. Consequently, whether the capacitors are fully charged or fully discharged makes no difference; the optimal moment for switching in the capacitors is when the voltage across the thyristor switch is zero.

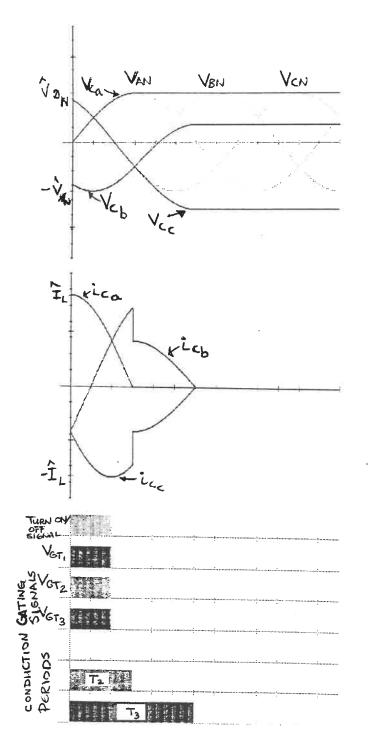

We will now exam the turning off process. Upon receiving the command to turn off the thyristors, the gate signal to each thyristor is removed. However, this does not mean that the thyristors are turned off. A thyristor only turns off when the current flowing through it decreases to zero. In this particular configuration it is the line current which must decline to zero before the thyristors will stop conducting. If we examine the same case that is depicted in Fig. 7.5, we note that when the line current is zero (i.e.  $i_{aA} = 0$ ), the corresponding capacitor voltages are:  $V_{Ca} = V_{AN}$ ,  $V_{Cb} = -0.5 \cdot V_{BN}$ ,  $V_{Cc} = -0.5 \cdot V_{CN}$ . Consequently, these are the conditions that exist immedi-

ately after switch 1 is opened.

As soon as switch 1 is opened the circuit topology changes; we no longer have a three phase source, but rather a single phase source connected directly across the series connection of  $C_{\rm b}$  and  $C_{\rm c}$ . We note that at the instant

switch 1 is opened that the new source voltage  $V_{BC}$  equals the load voltage  $V_{Cb} - V_{Cc}$ , which equals zero. Kirchhoff tells us the sum of the load voltages must always equal zero. Therefore, as  $V_{BC}$  rises to the peak line voltage,  $V_{Cb}$  has to increase at the rate of half the source voltage. Likewise,  $V_{Cc}$  has to decrease at the same rate. If this does not happen the load voltages will not be balanced.

At the instant that  $V_{Cb}$  is charged to the peak line voltage, the corresponding line current  $i_{bB}$  will decline to zero. It is at this moment that we can consider the capacitor bank disconnected from the source. We note that the final voltages are:

> $V_{Ca} = V_{LNmax} = 170.0V$  (as before);  $V_{Cb} = (-0.5+0.866) \cdot V_{LNmax} = 62.2V;$  $V_{Cc} = (-0.5-0.866) \cdot V_{LNmax} = -232.2V.$

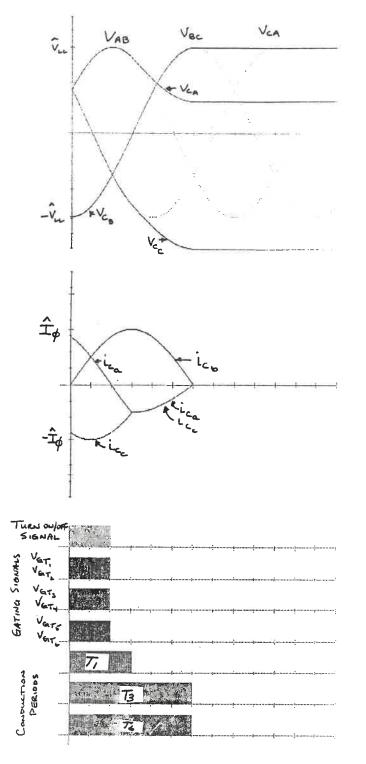

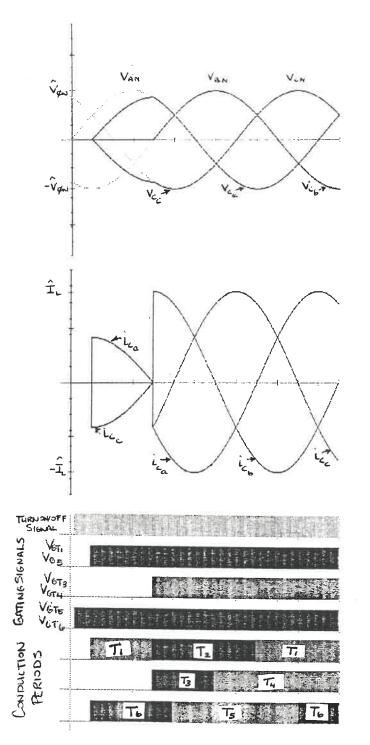

## 7.3 - Predictions of Circuit Behavior:

With this information we can predict how the circuit will perform in the stages of operation that interest us: 1) switching in a discharged capacitor; 2) switching out the capacitor; 3) switching in the charged capacitor.

1) SWITCHING IN A DISCHARGED CAPACITOR:

Thyristors should be gated when the voltage across them is zero.

The magnitude and direction of the current in the different phases depends on which switch is closed first and the polarity of the source voltage when the switch is closed. Nonetheless the magnitude of the largest current flowing through the thyristors will not exceed:  $\pm i_{0max}$ .

#### 2) SWITCHING OUT THE CAPACITOR:

Thyristors stop conducting when the corresponding line current  $i_{\phi}(t)=0$ .

There are only four possible states that the capacitor bank could adopt after being switched off. The four possible final states are:

|                  | A       | В       | C       | D       |

|------------------|---------|---------|---------|---------|

| V <sub>C a</sub> | 170.0V  | -232.2V | -170.0V | 232.2V  |

| $V_{\rm Cb}$     | 62.2V   | 170.0V  | -62.2V  | -170.0V |

| V <sub>C c</sub> | -232.2V | 62.2V   | 232.2V  | -62.2V  |

3) SWITCHING IN CHARGED CAPACITOR:

Thyristors should be gated when the voltage across them is zero.

Corresponding current:  $i(0^{-})=0$ .

Ficc

Î

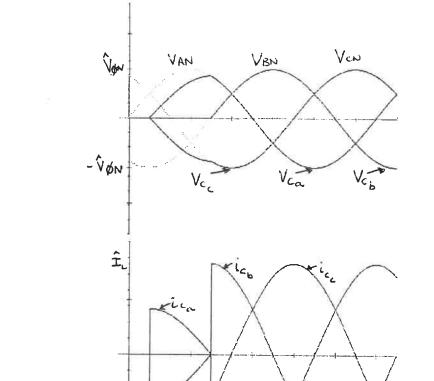

# 7.4 - Computer Plots of Expected Circuit Behavior:

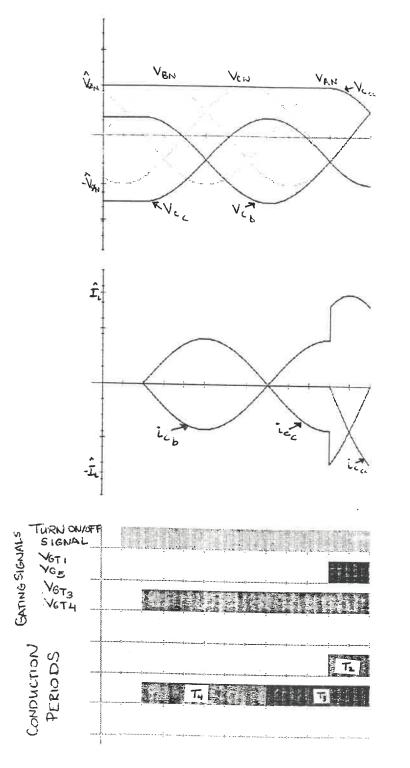

Fig. 7.4 Switching in a Three-Wire Line-Controller with a Wye-Connected Load; the capacitors are discharged

Fig. 7.5 Switching out a Three-Wire Line-Controller with a Wye-Connected Load

Fig. 7.6 Switching in again a Three-Wire Line-Controller with a Wye-Connected Load

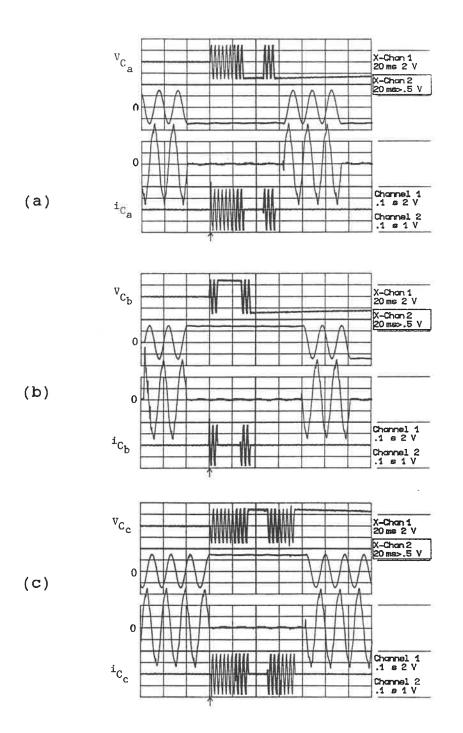

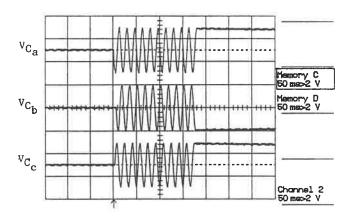

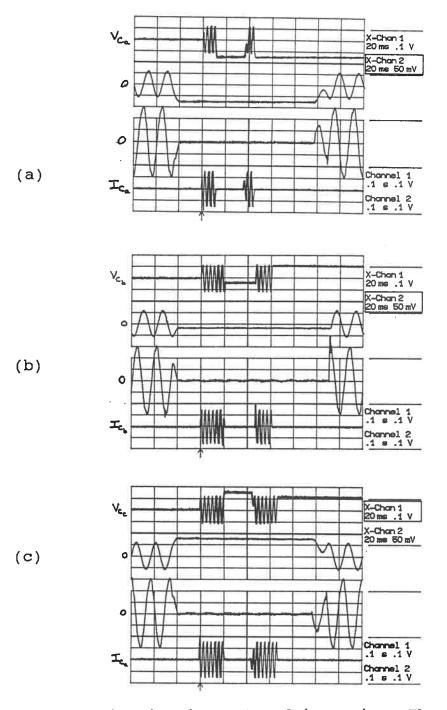

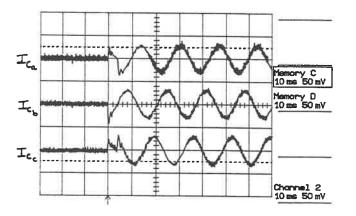

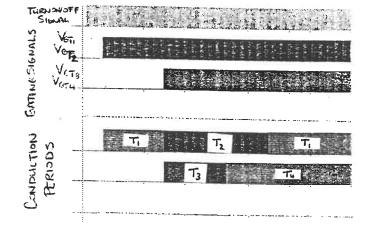

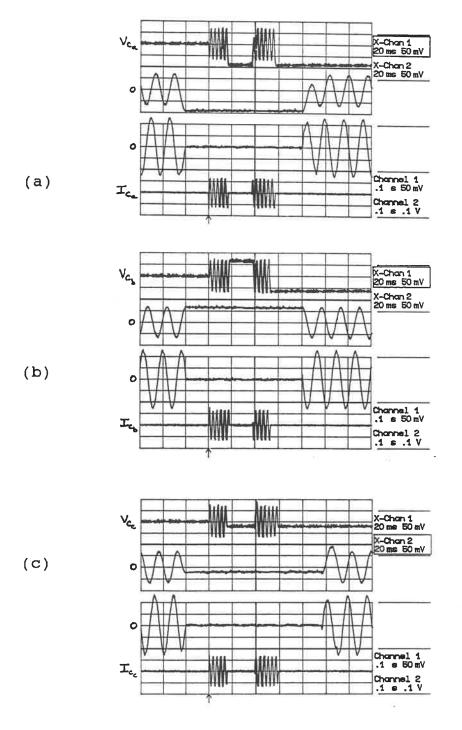

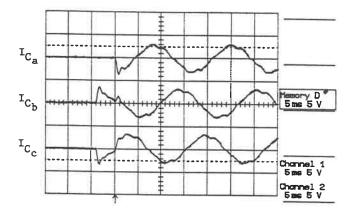

**Plot 7.1** Switching in a Three-Wire Asymmetrical Line-Controller with a Wye-Connected Load; the capacitors are discharged. (a) Phase A; (b) Phase B; (c) Phase C.  $V_{\Phi N} = 120V$ ,  $I_{Ca} = 21.5A$

**Plot 7.2** Capacitor currents in a Three-Wire Asymmetrical Line-Controller with a Wye-Connected Load. (a) Phase A; (b) Phase B; (c) Phase C.  $V_{\Phi N}$ =120V,  $I_{Ca}$ =21.5A

. .

- 10 C

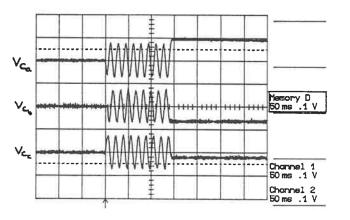

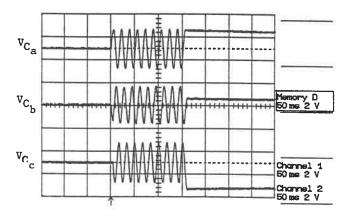

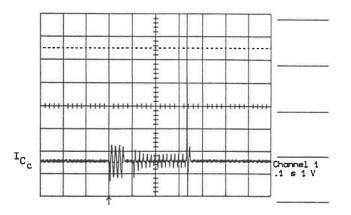

Plot 7.3 Switching in, out and in again a Three-Wire Branch-Controller with a Wye-connected Load (a) Phase A; (b) Phase B; (c) Phase C  $V_{\Phi N}$ =120V,  $I_{Ca}$ =21.5A

Plot 7.4 Phase currents when switching in a Three-Wire Branch-Controller with a Wye-Connected Load  $V_{\phi N}$ =120V,  $I_{Ca}$ =21.5A

**Plot 7.5** Capacitor voltages when switching a Three-Wire Branch-Controller with a Wye-Connected Load  $V_{\phi N}$ =120V,  $I_{Ca}$ =21.5A

#### CHAPTER EIGHT

#### THREE-WIRE NEUTRAL POINT-CONTROLLER WITH WYE-CONNECTED LOAD

#### 8.1 - Introduction:

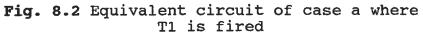

In this configuration, three thyristors must be fired before the capacitive load will be fully connected to the source. Two general cases present themselves:

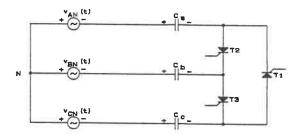

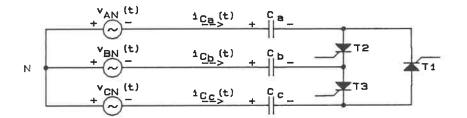

Fig. 8.1 Circuit diagram of a Three-Wire Neutral Point-Controller with a Wye-Connected Load

8.2 - Analysis:

<u>Case a</u>: fire T1

an set of an end of an end of the

So long as  $i_{c,c} > 0$ , we know that Kirchhoff's voltage law requires that:

$$\mathbf{v}_{Ca}(t) = \frac{1}{C_{A}} \int_{0}^{t} \mathbf{i}_{Cc} dt + \mathbf{v}_{Ca}(0^{-}) + \frac{1}{C_{c}} \int_{0}^{t} \mathbf{i}_{Cc} dt + \mathbf{v}_{Cc}(0^{-})$$

note that  $i_{Cc} = -i_{Ca}$

After transforming, solving for  $I_{c_c}(s)$ , and then finding the inverse transform we see that:

$$i_{C_{c}}(t) = \frac{C_{a} \cdot C_{b}}{C_{a} + C_{b}} \left[ \left( V_{CAmax} \sin \theta_{CA} + V_{Ca} \left( 0^{-} \right) - V_{Cc} \left( 0^{-} \right) \right] \cdot \delta(t) \right] \\ + \frac{C_{a} \cdot C_{b}}{C_{a} + C_{b}} \left[ V_{CAmax} \omega_{o} \cos(\omega t + \theta_{CA}) \right]$$

N.B.: this is only true so long as T1 is conducting i.e.  $t \le (\pi/2 - \theta_{CA})/\omega$ for  $t > (\pi/2 - \theta_{CA})/\omega$   $i_{CC} = 0$

Consequently the conditions for switching without transients are:

$$V_{CA} \sin \theta_{CA} = V_{Cc} (0^{-}) - V_{CA} (0^{-})$$

------

This shows that thyristor 1 should be fired when the voltage across T1 is zero.

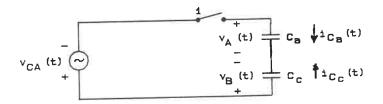

# <u>Case b</u>: fire thyristors T2 and T3 while T1 continues to be triggered.

This case is quite a bit more complex. We want to determine when T2 and T3 should be fired. It should be noted that while T1 is still being triggered, it may not be conducting. This would occur if the sum of the voltages stored across  $C_a$  and  $C_c$  is equal to the magnitude of the line voltage.

Fig. 8.3 Equivalent circuit of case b where T2 and T3 are fired while T1 continues to conduct

The equivalent circuit of case b is shown in Fig. 8.3. The question to be answered is: when can the various neutral points (currently separated by thyristors) be joined together without transients occurring?

We know that under balanced conditions:

$$I_{aA} + I_{bB} + I_{cC} = 0$$

where:  $I_{aA} = sC_a (V_{AN} - V_0) - C_a V_{AN} (0^{-})$

$I_{bB} = sC_b (V_{BN} - V_0) - C_b V_{BN} (0^{-})$

$I_{cC} = sC_c (V_{CN} - V_0) - C_c V_{CN} (0^{-})$

solving for  $\boldsymbol{v}_{\scriptscriptstyle 0}$  yields:

$$V_{0} = \frac{1}{3} \left[ (v_{A N} - \frac{v_{C a} (0^{-})}{s}) + (v_{B N} - \frac{v_{C b} (0^{-})}{s}) + (v_{C N} - \frac{v_{C c} (0^{-})}{s}) \right]$$

since  $C_{a} = C_{b} = C_{c}$

Transforming, solving for  $I_{Cb}(s)$  and then finding the inverse transform yields:

$$i_{Cb} = (C_b/3) \cdot \{ (V_{BCmax} \cdot \sin\theta_{BC} - V_{Cb}(0^-) + V_{Cc}(0^-) \\ - V_{ABmax} \cdot \sin\theta_{AB} - V_{Cb}(0^-) + V_{ca}(0^-) \} \cdot \delta(t) \\ + (C_b/3) \cdot \{ V_{BC}\omega_o\cos(\omega t + \theta_{BC}) - V_{AB}\omega_o\cos(\omega t + \theta_{AB}) \}$$

In like manner we find that:

$$i_{Ca} = (C_a/3) \cdot \{ (V_{ABmax} \cdot \sin\theta_{AB} - V_{Ca}(0^-) + V_{Cb}(0^-) \\ - V_{CAmax} \cdot \sin\theta_{CA} - V_{Cc}(0^-) + V_{Ca}(0^-) \} \cdot \delta(t) \\ + (C_a/3) \cdot \{ V_{BC}\omega_o\cos(\omega t + \theta_{BC}) - V_{AB}\omega_o\cos(\omega t + \theta_{AB}) \}$$

$$i_{Cb} = (C_c/3) \cdot \{ (V_{CAmax} \cdot \sin\theta_{CA} - V_{Cc}(0^-) + V_{Ca}(0^-) - V_{BCmax} \cdot \sin\theta_{BC} - V_{Cb}(0^-) + V_{Cc}(0^-) \} \cdot \delta(t) + (C_c/3) \cdot \{ V_{CA}\omega_o \cos(\omega t + \theta_{CA}) - V_{BC}\omega_o \cos(\omega t + \theta_{BC}) \}$$

Hence the conditions for switching without transients are:

$$V_{BCmax} \cdot \sin\theta_{BC} = V_{Cb} (0^{-}) - V_{Cc} (0^{-})$$

$$V_{ABmax} \cdot \sin\theta_{AB} = V_{Ca} (0^{-}) - V_{Cb} (0^{-}) \text{ and}$$

$$V_{CAmax} \cdot \sin\theta_{CA} = V_{Cc} (0^{-}) - V_{Ca} (0^{-})$$

It is important to note that when these conditions are satisfied, the voltages across T2 and T3 are zero. Consequently, this shows that T2 and T3 should be fired when the voltages across each of them are zero.

-----

}

## Turn Off:

We will now examine the turning off process. Upon receiving the command to turn off the thyristors, the gate signal to each thyristor is removed. However, this does not mean that the thyristors are turned off. A thyristor only turns off when the current flowing through it decreases to zero. In this particular configuration it is the line current which must decline to zero before the thyristors will stop conducting. If we examine the same case that is depicted in Fig. 8.5, we note that when the line current is zero (i.e.  $i_{aA} = 0$ ), the corresponding capacitor voltages are:  $V_{Ca} = V_{AN}$ ,  $V_{Cb} = -0.5 \cdot V_{BN}$ ,

$V_{cc} = -0.5 \cdot V_{CN}$ . Consequently, these are the conditions that exist immediately after thyristor 2 stops conducting.

As soon as T2 stops conducting the circuit topology changes; we no longer have a three phase source, but rather a single phase source connected directly across the series connection of  $C_b$  and  $C_c$ . We note that at the instant T2 stops conducting the new source voltage  $V_{BC}$  equals the load voltage  $V_{Cb} - V_{Cc}$ , which equals zero. Kirchhoff tells us the sum of the load voltages must always equal zero. Therefore, as  $V_{BC}$  rises to the peak line voltage,  $V_{Cb}$  has to increase at the rate of half the source voltage. Likewise,  $V_{Cc}$  has to decrease at the same rate. If this does not happen the load voltages will not be balanced.

At the instant that  $V_{Cb}$  is charged to the peak line voltage, the corresponding line current  $i_{bB}$  will decline to zero. It is at this moment that we can consider the capacitor bank disconnected from the source. We note that the final voltages are:

> $V_{Ca} = V_{LNmax} = 170.0V$  (as before);  $V_{Cb} = (-0.5+0.866) \cdot V_{LNmax} = 62.2V;$  $V_{Cc} = (-0.5-0.866) \cdot V_{LNmax} = -232.2V.$

#### Turning On Again:

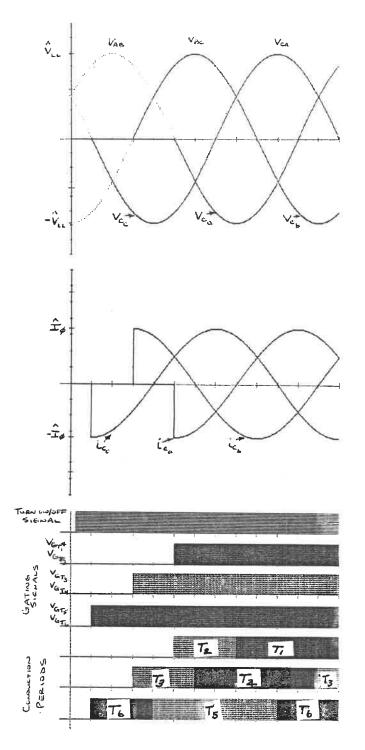

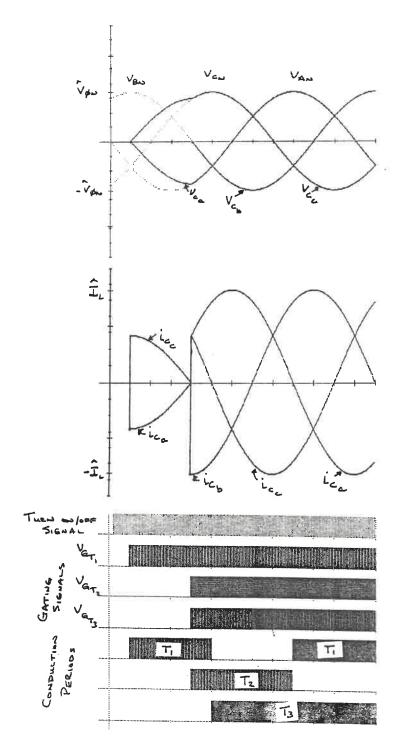

It is not possible to rapidly switch a Three-Wire Neutral Point-Controller with a Wye-Connected Load. What one has to do is to wait for the voltages across the phase capacitors to decay. In the lab we noticed that while the capacitors did not need to be fully discharged, the voltages across all capacitors had to be less that 170V.

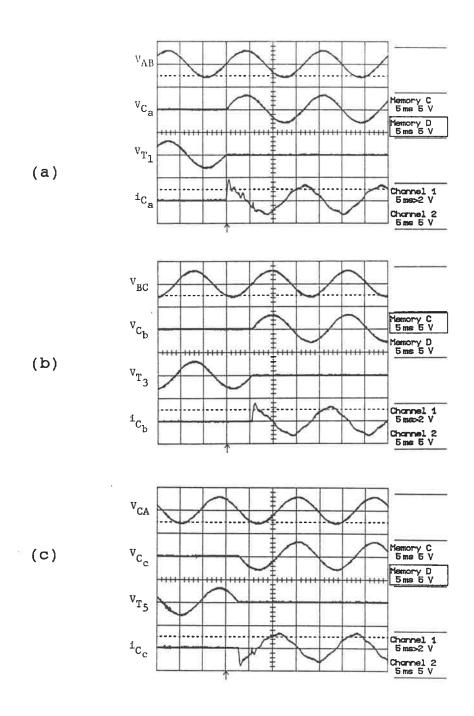

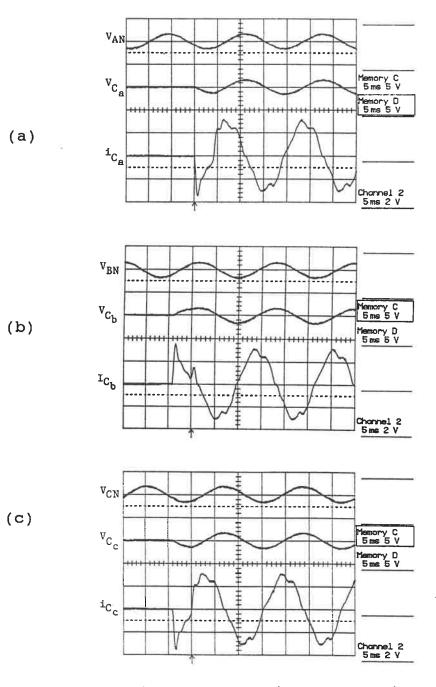

one attempts to rapidly switch the system on, off If and on again, which is what we show in Fig. 8.6 and Plot 8.3, the system will respond by charging two capacitors to the peak voltages and completely discharging the third The net result is that the delay is even loncapacitor. ger than if one had initially waited. As a result, in any practical realization of this configuration some sort of "fixed delay" would need to be installed to ensure that the system will not try to turn on again until the capacitors have discharged sufficiently. Some of the information that would be needed to calculate this "fixed delay" would be the amount of resistance in parallel with each capacitor (apparently the C.S.A. requires that all banks of capacitors have resistance connected in parallel across them to ensure that they will not remain fully charged) and the theoretical result indicating the earliest possible time that capacitors, with voltages decaying from their final values, can be switched in again.

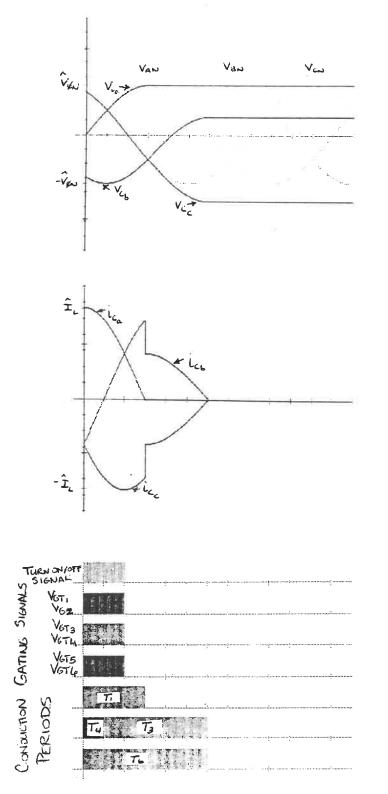

#### 8.3 - Predictions of Circuit Behavior:

With this information we can predict how the circuit will perform in the stages of operation that interest us: 1) switching in a discharged capacitor; 2) switching out the capacitor; 3) switching in the charged capacitor.

1) SWITCHING IN A DISCHARGED CAPACITOR:

Thyristors should be gated when the voltage across them is zero.

The magnitude and direction of the current in the different phases depends on which thyristor is fired first and the polarity of the source voltage when the switch is closed. Nonetheless the magnitude of the largest current flowing through the thyristors will not exceed:  $\pm i_{\phi_{max}}$ .

#### 2) SWITCHING OUT THE CAPACITOR:

Thyristors stop conducting when the corresponding line current  $i_{\phi}(t)=0$ .

There are only three possible states that the capacitor bank could adopt after being switched off. The three possible final states are:

|                 | A       | В       | С       |

|-----------------|---------|---------|---------|

| $V_{Ca}$        | 170.0V  | -232.2V | -232.2V |

| V <sub>Cb</sub> | 62.2V   | 170.0V  | 62.2V   |

| $v_{c c}$       | -232.2V | 62.2V   | 170.0V  |

#### 3) SWITCHING IN CHARGED CAPACITOR:

Thyristors should be gated when the voltage across them is zero. However, it is important to wait until the voltages across all the capacitors have decayed to voltages below 170V, before one fires any of the thyristors. If one does not wait the required time before sending the turn on signal, two of the thyristors will be able to conduct but the third be blocked indefinitely. This is the situation simulated in Fig. 8.6 and shown in Plot 8.3. We note that since only two thyristors can conduct the capacitor bank becomes charges to a new final state:  $V_{Ca} = -294V$ ;  $V_{Cb} = 294V$ ;  $V_{Cc} = 0V$ . In practise it is still possible to eventually reconnect the capacitor bank to the source, however the delay will be longer than the orginal delay.

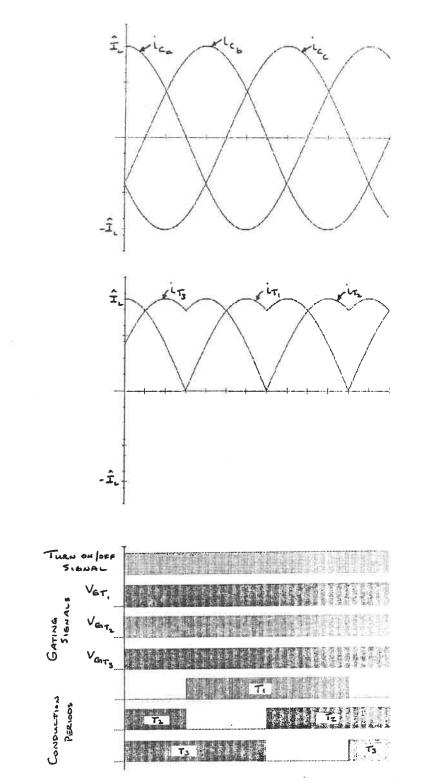

# 8.4 - Computer Plots of Expected Circuit Behavior:

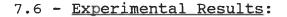

Fig. 8.4 Switching in a Three-Wire Neutral Point-Controller with a Wye-Connected Load; the capacitors are discharged

Fig. 8.5 Switching out a Three-Wire Neutral Point-Controller with a Wye-Connected Load

Fig. 8.6 Switching in again a Three-Wire Neutral Point-Controller with a Wye-Connected Load

Fig. 8.7 Currents flowing in a Three-Wire Neutral Point-Controller with a Wye-Connected Load

# 8.5 - Experimental Results:

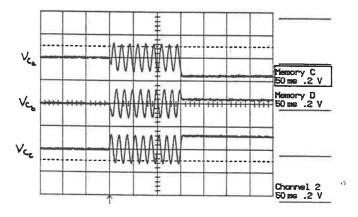

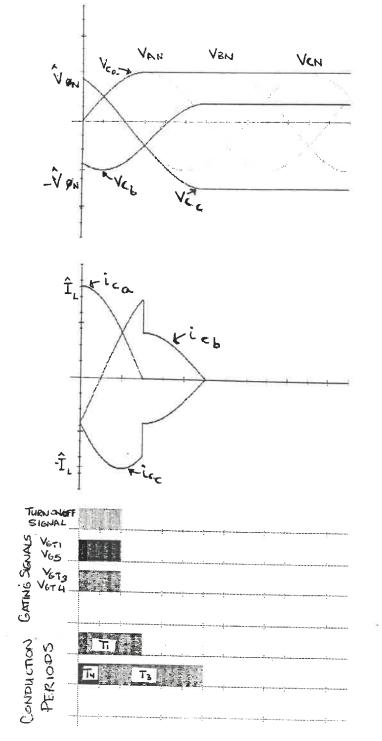

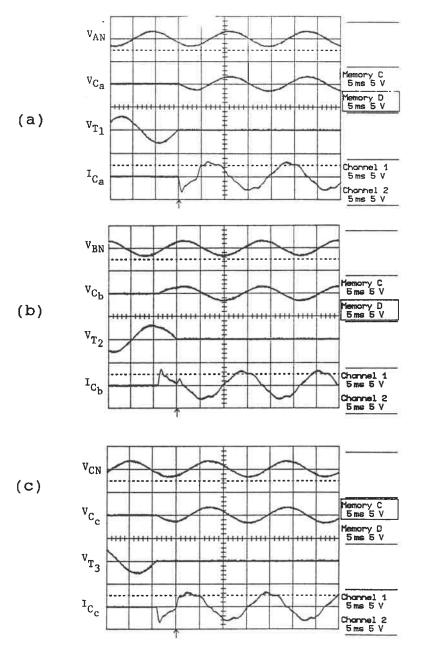

**Plot 8.1** Switching in a Three-Wire Neutral Point-Controller with a Wye-Connected Load; the capacitors are discharged. (a) Phase A; (b) Phase B; (c) Phase C.  $V_{\phi N}$ =120V,  $I_{Ca}$ =21.5A

**Plot 8.2** Capacitor currents in a Three-Wire Neutral Point-Controller with a Wye-Connected Load. (a) Phase A; (b) Phase B; (c) Phase C.  $V_{\phi N} = 120V$ ,  $I_{Ca} = 21.5A$

<sup>v</sup>c<sub>a</sub> AAAAA X-Chan 1 20 ms 1 V IVVVI X--Chan 2 20 ms 1 V 0 (a) 0 V Channel 1 .1 so1 V  $I_{C_a}$ WW Channel 2 .1 = 2 V v<sub>Cb</sub> ANAAAAA X-Chan 1 20 ms 1 V YYYYYYY X-Chan 2 20 ms 1 V 0 (b) 0 \*\*\*\*\*\* IC, Channel 1 .1 so 1 V Channel 2 .1 # 2 V v<sub>Cc</sub> X-Chan 1 20 ms 1 V VVVV X-Chan 2 20 ms 1 V (C) Ò V Ó. Channel 1 .1 s>1 V 'Cc Channel 2 .1 s 2 V WWW

- 25 A (25 - 3

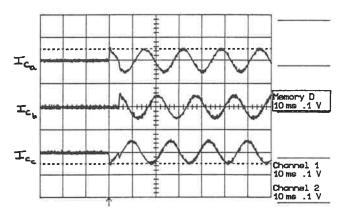

**Plot 8.4** Phase currents when switching in a Three-Wire Neutral Point-Controller with a Wye-Connected Load  $V_{\phi N}$ =120V,  $I_{Ca}$ =21.5A

**Plot 8.5** Capacitor voltages when switching a Three-Wire Neutral Point-Controller with a Wye-Connected Load  $V_{\Phi N}$ =120V,  $I_{Ca}$ =21.5A

#### CHAPTER NINE

#### DISCUSSION

#### 9.1 - Introduction:

Having presented the six different three phase "thyristor switches" in the preceding chapters, we will compare them in this chapter. Following the comparison, we will briefly detail some of the more difficult problems encountered during this research and suggest ways that they may be overcome in future work.

#### 9.2 - Comparison of the "Thyristor Switches":

#### Three-Wire Branch-Controller with Delta-Connected Load

ADVANTAGES: - Ease of control

- Switching phase current

- Rapid response

- Each phase is independent

DISADVANTAGES: - Six thyristors

- Thyristors must block line voltage

Three-Wire Line-Controller with Delta-Connected Load

- ADVANTAGES: Complete isolation of load when switch is open

- DISADVANTAGES: Six thyristors

- Thyristors must block line voltage

- Slower response

- Switching line current

#### Three-Wire Asymmetrical Line-Controller with Delta-Connected Load

- ADVANTAGES: Four thyristors

- DISADVANTAGES: Thyristors must block line voltage

- Slower response

- Switching line current

### Three-Wire Line-Controller with Wye-Connected Load

- ADVANTAGES: Complete isolation of load when switch is open

- Thyristors block phase voltage

- DISADVANTAGES: Six thyristors

- Slower response

93.

#### Three-Wire Asymmetrical Line-Controller with Wye-Connected Load

- ADVANTAGES: Four thyristors

- Thyristors block phase voltage

- DISADVANTAGES: Slower response

#### Three-Wire Neutral Point-Controller with Wye-Connected Load

- ADVANTAGES: Three thyristors

- DISADVANTAGES: Thyristors must block line voltage

- Thyristors conduct for 2\*T/3 & not T/2

- Switching line current

- Slower response

- the second second second second second

- Cannot be retriggered before all capaci-

tor voltages have decayed below 170V

9.3 - Common Evaluation:

A common evaluation of the six thyristor switches is presented in Table 9.1. It would therefore be helpful to examine the different criterion used in this evaluation.

Criterion 1: Number of Thyristors

This criterion is self evident.

<u>Criterion 2</u>: Repetitive Peak Voltage across capacitors This is the maximum voltage to which any one of the phases of the capacitor bank can be charged:

W33AA can be charged to maximum of  $12 \cdot V_{LL}$  (see pg. 26)

W33AD & W32AD can be charged to a maximum of

$(\sqrt{3/2} + 0.5) \cdot \sqrt{2 \cdot V_{LL}} = 1.932 \cdot V_{LL}$  (see pg. 44)

W33AY & W32AY can be charged to a maximum of  $(0.5 + \sqrt{3/2}) \cdot \sqrt{2 \cdot V_{LN}} = 1.115 \cdot V_{LL}$  (see pg. 64)

U33DA can be charged to a maximum of

$(0.5 + \sqrt{3/2}) \cdot \sqrt{2 \cdot V_{LN}} = 1.115 \cdot V_{LL}$  (see pg. 79)

Criterion 3: Repetitive Peak Voltage across thyristors

This is the maximum steady state voltage which the thyristors would have to block:

W33AA must be able to block the voltage resulting from a fully charged capacitor and the source voltage reaching the peak line voltage i.e.  $12 \cdot V_{LL} + 12 \cdot V_{LL} = 2.828 \cdot V_{LL}$

W33AD & W32AD must be able to block the voltage resulting from a fully charged capacitor and the source voltage reaching the peak line voltage

i.e.  $1.932 \cdot V_{LL} + \int 2 \cdot V_{LL} = 3.346 \cdot V_{LL}$

W33AY & W32AY must be able to block the voltage resulting from two fully charged capacitors and the source voltage reaching the peak line voltage. A worst case scenario for  $V_{T1}$  would exist with  $V_{Ca} = 170V$ ,  $V_{Cc} = -232.2V$ , and  $V_{CA} = -294V$  i.e.  $0.817 \cdot V_{LL} + 1.115 \cdot V_{LL} + 12 \cdot V_{LL} = 3.346 \cdot V_{LL}$

U33DA must be able to block the voltage resulting from two fully charged capacitors and the source voltage reaching the peak line voltage. A worst case scenario for  $V_{T1}$ would exist with  $V_{Ca} = 170V$ ,  $V_{Cc} = -232.2V$ , and  $V_{CA} = -294V$ i.e.  $0.817 \cdot V_{LL} + 1.115 \cdot V_{LL} + \downarrow 2 \cdot V_{LL} = 3.346 \cdot V_{LL}$

#### <u>Criterion 4</u>: RMS On-state Current (In one thyristor)