| <b>Titre:</b> Title:    | Detection of hard faults in combinational logic circuits                                                                                                                                                                                     |

|-------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Auteur: Author:         | David H. Stannard                                                                                                                                                                                                                            |

| Date:                   | 1989                                                                                                                                                                                                                                         |

| Type:                   | Mémoire ou thèse / Dissertation or Thesis                                                                                                                                                                                                    |

| Référence:<br>Citation: | Stannard, D. H. (1989). Detection of hard faults in combinational logic circuits [Master's thesis, École Polytechnique de Montréal]. PolyPublie. <a href="https://publications.polymtl.ca/56720/">https://publications.polymtl.ca/56720/</a> |

# Document en libre accès dans PolyPublie Open Access document in PolyPublie

| URL de PolyPublie:<br>PolyPublie URL:    | https://publications.polymtl.ca/56720/ |

|------------------------------------------|----------------------------------------|

| Directeurs de<br>recherche:<br>Advisors: | Bozena Kaminska                        |

| Programme: Program:                      | Génie électrique                       |

CH2P9 UP 8 1989 S784

### UNIVERSITE DE MONTREAL

#### DETECTION OF HARD FAULTS IN COMBINATIONAL LOGIC CIRCUITS

par

# David H. STANNARD DEPARTEMENT DE GENIE ELECTRIQUE ECOLE POLYTECHNIQUE

MEMOIRE PRESENTE EN VUE DE L'OBTENTION

DU GRADE DE MAITRE ES SCIENCES APPLIQUEES (M.Sc.A.)

**DECEMBRE 1989**

© David H. Stannard 1989

Bibliothèque nationale du Canada

Canadian Theses Service

Service des thèses canadiennes

Ottawa, Canada K1A 0N4

> The author has granted an irrevocable nonexclusive licence allowing the National Library of Canada to reproduce, loan, distribute or sell copies of his/her thesis by any means and in any form or format, making this thesis available to interested persons.

> The author retains ownership of the copyright in his/her thesis. Neither the thesis nor substantial extracts from it may be printed or otherwise reproduced without his/her permission.

L'auteur a accordé une licence irrévocable et non exclusive permettant à la Bibliothèque nationale du Canada de reproduire, prêter, distribuer ou vendre des copies de sa thèse de quelque manière et sous quelque forme que ce soit pour mettre des exemplaires de cette thèse à la disposition des personnes intéressées.

L'auteur conserve la propriété du droit d'auteur qui protège sa thèse. Ni la thèse ni des extraits substantiels de celle-ci ne doivent être imprimés ou autrement reproduits sans son autorisation.

ISBN 0-315-58199-9

### **UNIVERSITE DE MONTREAL**

### **ECOLE POLYTECHNIQUE**

#### Ce mémoire intitulé

#### DETECTION OF HARD FAULTS IN COMBINATIONAL LOGIC CIRCUITS

est présenté par: David H. Stannard en vue de l' obtention du grade de: Maitre es sciences appliquées (M.Sc.A.)

M. Bernard Lanctôt, Président, ing.M. Jean-Charles Bernard, Ph.D.Mme. Bozena Kaminska, Ph.D.M. Yvon Savaria, Ph.D.

### **ABSTRACT**

Integrated circuits have become increasingly complex while their users have become more stringent in their quality requirements and simultaneously exhibiting a larger appetite for newer products at a faster rate. Indeed, some integrated circuits resemble the statement of *systems on silicon* and are being designed by systems designers instead of the traditional IC designer.

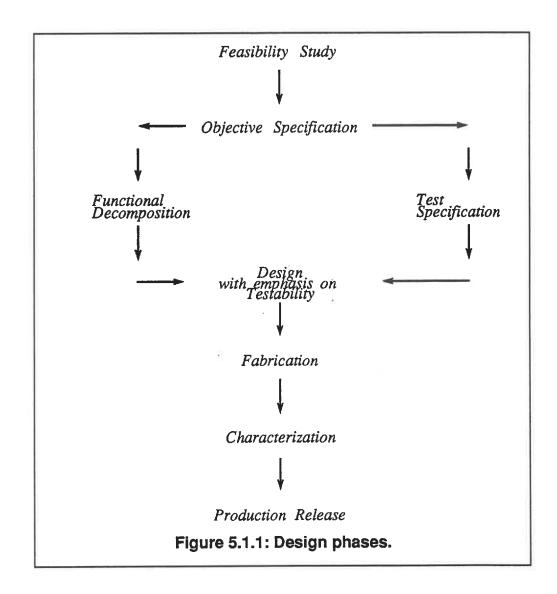

When one adds to these tough specifications the need for high reliability, the ability to be manufacturable, and the desire to provide a product ready for volume delivery within six months of defining of the circuit's objective specification, it becomes apparent that the current testing bottleneck can no longer be tolerated. It is desirable to provide a design environment which will allow the design team to identify testing difficulties such as those logic faults, due to circuit fabrication, which are hard to test. It is critical that these faults are identified as early in the design as possible, and that the necessary information describing their origins be provided to the design team thus allowing the appropriate design corrections to be made given knowledge of the design's constraints: cost, circuit performance, yield at the wafer level, test time, and time to market; all of these are known from the original objective specifications which form a contract on all the parties involved in the design process.

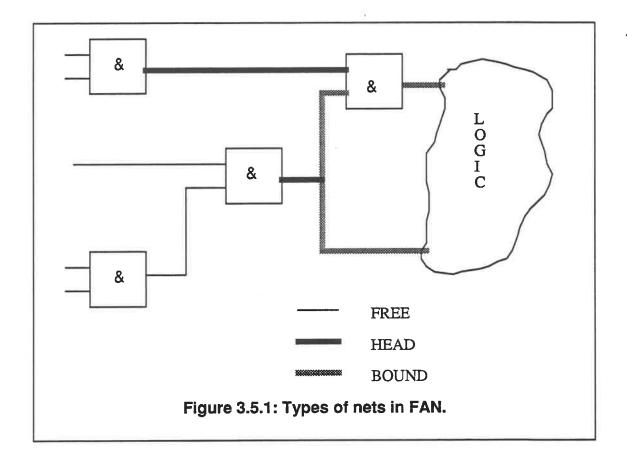

This thesis examines an approach to defining and indentifying hard to test faults contained within a combinational logic circuit based upon the use of cost constraints imposed upon the automatic test pattern generation (ATPG) process. This approach was used since past heuristic-based methods such as testability measures have not provided an accurate means of detecting the hard faults' presence. By coupling the concept of cost constraints to a variant of an efficient and extensible automatic test pattern generation tool (Fujiwara's FAN), it was hoped that one of the heuristic's past problems, the lack of coupling to the test generation effort, could be corrected.

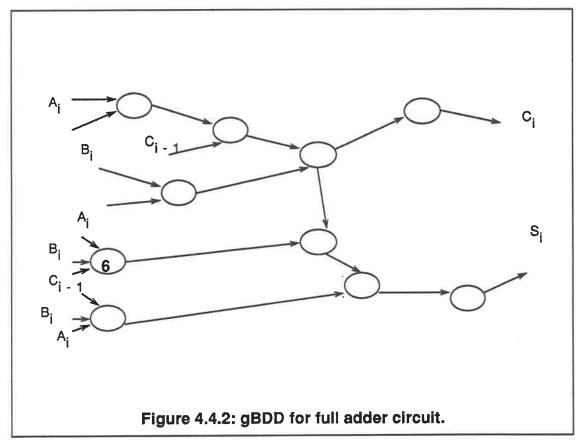

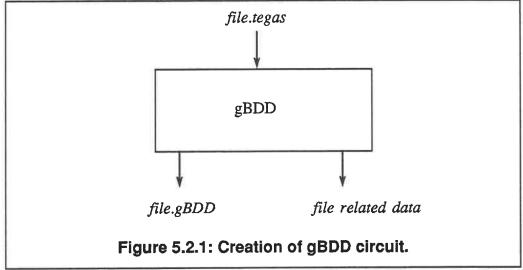

In addition to creating this tool, a new circuit modelling method was developed: graph binary decision diagrams (gBDD) which was created to provide a

means of including information about the circuit's functionality and structural aspects. A simple fault simulator, designed around the single stuck at fault model, was incorporated into the hard fault identifier HUB. HUB also provides feedback indicating the causes of the hard faults by indicating which ATPG phase is the most costly (according to time measurements), which ATPG phases cause backtracks to occur, and which logic elements can be clearly defined as the originators of the backtracks.

The results of this research have indicated that this approach has merit, but a problem is apparent: without circuit schematics for the circuit being evaluated, it is difficult to verify the preciseness of HUB's results and to allow meaningful analysis of the circuit. However, for the circuits evaluated and for which schematics were available, HUB provided information about the reasons for the redundant logic faults (not considered as hard faults in this thesis) identified by exhaustive searches of the circuit whose correctness was verified by comparision with the circuit's schematics. The cost information also shows the relative costs of the various ATPG phases and clearly identified that the majority of the backtracks are caused by the net justification phase.

The most significant result of this research is the creation of the new circuit modelling technique gBDD that allows the vertical integration of a wide variety of previous researchers' works in manipulating functional related circuit information and structural based circuit data. The ability to generate functional based tests (as opposed to tests built around a fault model such as the traditional stuck at fault) is made possible by the functional circuit information and is derived from the binary decision diagram portion of the gBDD circuit model. The manipulation of graph portion of the new circuit model, extracted from the circuit's structure, is useful for determining the placement of diagnostic test points derived from knowledge about the circuit's reconvergent fanout characteristics and for calculating testability metrics in hierarchically described circuits.

### **SOMMAIRE**

Une nouvelle méthode a été créée afin de découvrir la présence des défauts dans un circuit logique, combinatoire seulement, qui sont difficiles à détecter (HFs) avec des essais pour la vérification du circuit. On a proposé de les classer et de faire leur détection en utilisant des heuristiques fondées sur les coûts et les budgets de vérification pour le circuit pendant qu'un algorithme tente de générer des tests pour les défauts choisis. Cette méthode a été choisie afin de permettre l'intégration des contraintes de ressources, les heuristiques qui découlent, les vrais efforts requis pour la génération des vecteurs, et de ramasser des informations sur les causes de ces HFs. Grâce à l'algorithme de génération automatique des vecteurs de test FAN, qui sert comme fondation pour HUB (le système pour découvrir la présence des HFs), on peut même détecter s'il y a des HFs créés par la redondance lors de la conception du circuit.

Pour supporter HUB, une nouvelle méthode de modélisation du circuit a été créée - gBDD - (graph binary decision diagram): cette modélisation permet de combiner les avantages des informations structurelles, décrites par les graphes, ave les informations de comportement détaillées par les BDDs (binary decision diagrams).

HUB est un ensemble de logiciels qui permet de traduire une description du circuit en modélisation gBDD, qui génère des mesures afin de les utiliser avec des heuristiques pendant la phase de génération des vecteurs de test, et qui tente d'identifier la présence de ces défauts difficiles à détecter par l'algorithme de génération des vecteurs. HUB mesure les coûts de cette phase de génération et le logiciel garde ces données dans un fichier pour un traitement ultérieur par

l'usager. Les logiciels ont été faits pour que l'usager puisse modifier les contenus avec les logiciels commerciaux et en utilisant des commandes du système d'exploitation de l'ordinateur, surtout ceux d'UNIX. Donc cette recherche a créé un environnement de travail. L'usager peut se servir d'HUB comme simple générateur de vecteurs ou même pour apprendre comment ce genre de logiciel fonctionne.

HUB a été utilisé pour tenter d'identifier la présence des HFs dans des circuits combinatoires d'ISCAS 1985. Malgré que les principes de base permettent de découvrir et de définir ces défauts, selon la définition de coût et en absence des retours en arrière (en anglais, backtracks), HUB ne génère pas assez de données pour bien identifier les causes de ces HFs. Les résultats indiquent que HUB peut identifier les raisons pour les retours en arrière par l'identification du noeud responsable pour ce retour et que la majorité de ces retours sont causés par la phase de justification des noeuds à l'intérieur du circuit. HUB a réussi à mesurer les coûts de chaque phase majeure de la génération automatique des vecteurs de test malgré que le système d'UNIX semble avoir un problème à bien mesurer la quantité de temps. Pour permettre la future correction du circuit, HUB imprime des informations sur les heuristiques responsables des difficultés pendant les phases majeures de la générations de ces vecteurs.

Par contre, le modèle du circuit (gBDD) a fait ses preuves comme méthode pour aider la génération des vecteurs de test et est devenu le résultat le plus important de cette recherche. Ce modèle a permis la modification de la façon de générer les vecteurs de test et d'ajouter des nouvelles heuristiques. Ce modèle permet l'utilisation d'autres modèles de défauts avec des modifications au logiciel.

### **NOTES of THANKS**

During this period of research, many people have been instrumental in providing technical support, guidance, and the use of tools that would otherwise not be available:

A special note of thanks to my supervisor and mentor, Mme. Bozena Kaminska, for her support and efforts during the past two years. She has allowed me to experiment with ideas and concepts that were foreign to me before embarking down these paths and caused me to expand my horizons.

My wife and children also deserve an enormous recognition for their support and encouragement during the hectic times of university, full time employement, and the daily requirements of being a father in a family unit.

My employer, MITEL S.C.C. has graciously provided me with access to a multitude of computer and software tools, absences from my employment, and encouragement to forge ahead in the wonderful domain of integrated circuit technology.

To all the professors, administrative staff too numerous to list; you all know who you are - I thank you too.

### **Table of Contents**

| Abstr  | activ                                                          |

|--------|----------------------------------------------------------------|

| Somm   | airevi                                                         |

| Notes  | of Thanksviii                                                  |

| List o | f Tablesxii                                                    |

| List o | f Figuresxiv                                                   |

| List o | f Graphsxvii                                                   |

| List o | f Acronymsxviii                                                |

|        | of Appendicesxix                                               |

| 1.0    | Introduction 1                                                 |

| 2.0    | Previous Work in Identifying Hard to Test Faults (HFs) 5       |

| 2.1    | The effect of reconvergent fanout and redundancy 5             |

| 2.2    | Testability Measures (TMs) 8                                   |

| 2.2.1  | SCOAP - Sandia Controllability Observability Analysis Program. |

|        | 11                                                             |

| 2.2.2  | COP - Controllability Observability Program 14                 |

| 2.3    | Using of ATPGs to detect HFs17                                 |

| 2.4    | Previous use of cost in Testability Analysis 20                |

| 2.4.1  | Breuer's Sensitivity Functions 20                              |

| 2.4.2  | Random Test Cost Functions 21                                  |

| 2.4.3  | Sequential Test Cost Functions 23                              |

| 2.4.4  | Summary of Cost Functions 24                                   |

| 3.0   | Review of Automatic Test Pattern Generation (ATPG) 26             |

|-------|-------------------------------------------------------------------|

| 3.1   | Fault modelling 26                                                |

| 3.1.1 | Single stuck at fault model and 5 value logic 27                  |

| 3.2   | Single versus Multiple path sensitization 31                      |

| 3.3   | The Four ATPG phases of Deterministic Gate Level Test Generation. |

|       |                                                                   |

| 3.4   | Random Test Pattern Generation and Hybrid Methods 36              |

| 3.5   | Review of the FAN algorithm 39                                    |

| 3.6   | Backtrack reduction methods and the importance of heuristics.     |

| 3.7   | Summary 44                                                        |

| 4.0   | Mixed Graph - Binary Decision Diagram (gBDD) Circuit Model.       |

| 4.1   | Introduction 45                                                   |

| 4.2   | A Review of graph techniques 46                                   |

| 4.3   | A Review of binary decision diagrams (BDDs) techniques 49         |

| 4.4   | gBDD - Graph Binary Decision Diagrams 54                          |

| 4.5   | Summary 58                                                        |

| 5.0   | Detection of Hard Faults using HUB 59                             |

| 5.1   | Introduction to budgetary constraints 59                          |

| 5.2   | The HUB algorithm64                                               |

| 5.3   | Important HUB attributes 71                                       |

| 5.3.1 | ATPG control by Graph Node (GN)72                                 |

| 5.3.2 | pdcf Personality File                        | 74             |

|-------|----------------------------------------------|----------------|

| 5.3.3 | Fault model, fault collapsing and simulation | 75             |

| 5.3.4 | Interactive Mode and Information Feedback    | <b>78</b>      |

| 5.3.5 | Other HUB features                           | 30             |

| 5.3.6 | Hierarchy Provisions                         | 31             |

| 5.3.7 | Summary 8                                    | 32             |

| 6.0   | Results                                      | 33             |

| 6.1   | Circuit characteristics of used for results  | 35             |

| 6.2   | Comparison of gBDD                           | 35             |

| 6.2.1 | gBDD Temporal performance                    | 35             |

| 6.2.2 | File sizes.                                  | 38             |

| 6.3   | ATPG related results                         | 90             |

| 6.4   | Fault Simulation related results.            | <del>)</del> 1 |

| 6.5   | Hard Fault Detection                         | 93             |

| 6.5.1 | Extended example using Image                 | 93             |

| 6.5.2 | General Results10                            | )7             |

| 6.6   | Summary 11                                   | 12             |

| 7.0   | Conclusions                                  | <b>L4</b>      |

| 8.0   | Bibliography11                               | 17             |

### **List of Tables**

| Table 2.2.1.1: SCOAP initial conditions                                 |

|-------------------------------------------------------------------------|

| Table 2.1.1.2: SCOAP values for the full adder circuit                  |

| Table 2.2.2.1: COP initial conditions                                   |

| Table 2.2.2.2: COP values for the full adder circuit                    |

| Table 3.1.1.1: Rules for Difference intersection                        |

| Table 6.1.1: ISCAS and other test circuit characteristics               |

| Table 6.2.1.1: gBDD time distributions                                  |

| Table 6.2.2.1: Circuit Model File Requirements (k bytes)                |

| Table 6.3.1: Partial ATPG results - no simulation 90                    |

| Table 6.4.1: ATPG results with simulation vs fault simulation 92        |

| Table 6.5.1.1: Cumulative total cost distribution 104                   |

| Table 6.5.1.2: Cumulative propagation distribution                      |

| Table 6.5.1.3: Cumulative justification cost distribution               |

| Table 6.5.2.1: Justification backtrack information                      |

| Table 6.5.2.2: Mean of backtracks                                       |

| Table 6.5.2.3: Mean and standard deviation of total costs 109           |

| Table 6.5.2.4: Mean and standard deviation of propagation total costs   |

| Table 6.5.2.5: Mean and standard deviation of justification total costs |

| Table 6.5.2.6: Mean and standard deviation of backtrack total costs.    |

| Table 6.5.2.7: Mean and standard deviation of backtrace total costs. |     |

|----------------------------------------------------------------------|-----|

| •••••••••••••••••••••••••••••••••••••••                              | 111 |

| Table 6.5.2.8: Mean and standard deviation of implication total      |     |

| costs                                                                | 112 |

## **List of Figures**

| Figure 2.1.1: Example of reconvergent fanout               |

|------------------------------------------------------------|

| Figure 2.1.2a: Graph with reconvergent fanout              |

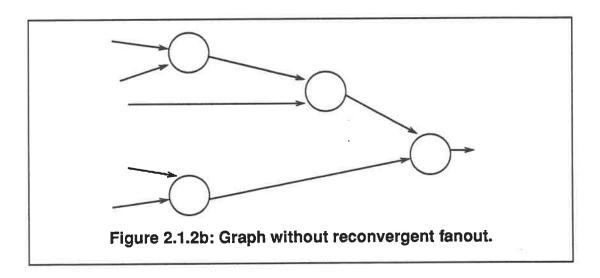

| Figure 2.1.2b: Graph without reconvergent fanout 8         |

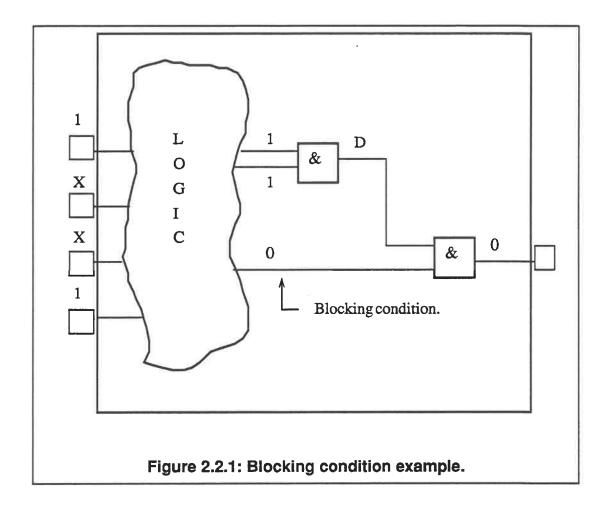

| Figure 2.2.1: Blocking condition example 10                |

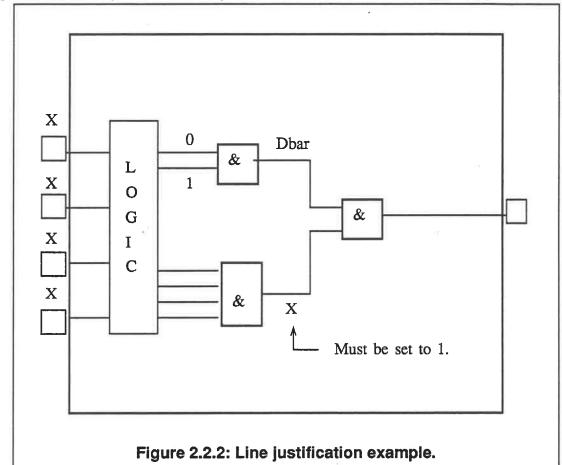

| Figure 2.2.2: Line justification example 11                |

| Figure 2.2.1.1: SCOAP pseudo code 12                       |

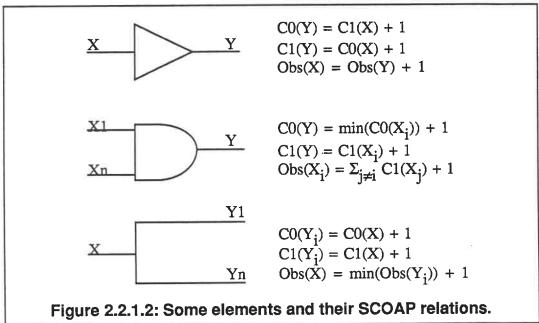

| Figure 2.2.1.2: Some elements and their SCOAP relations    |

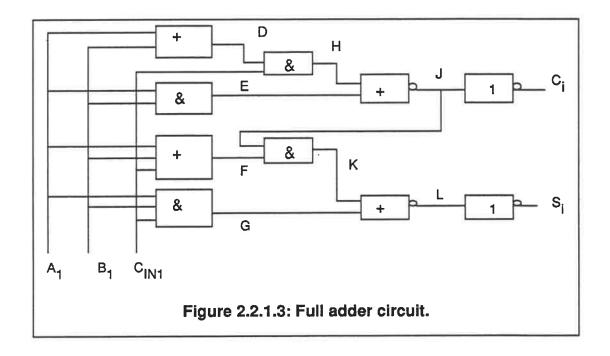

| Figure 2.2.1.3: Full adder circuit                         |

| Figure 2.2.2.1: COP pseudo code                            |

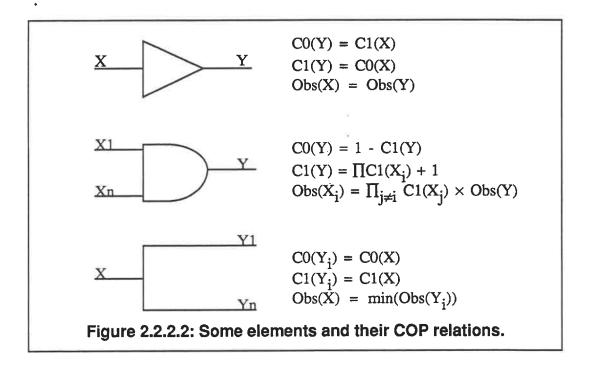

| Figure 2.2.2.2: Some elements and their COP relations      |

| Figure 2.4.2.1: ESPRIT pseudo code                         |

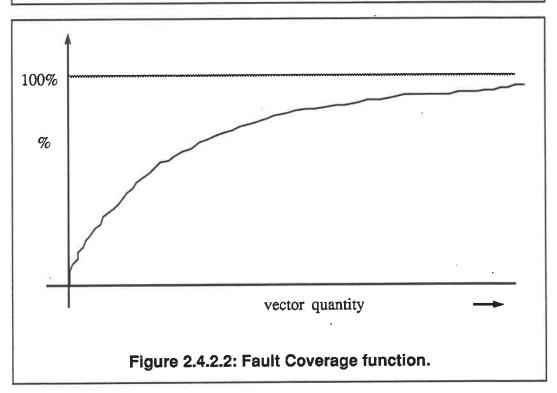

| Figure 2.4.2.2: Fault Coverage function                    |

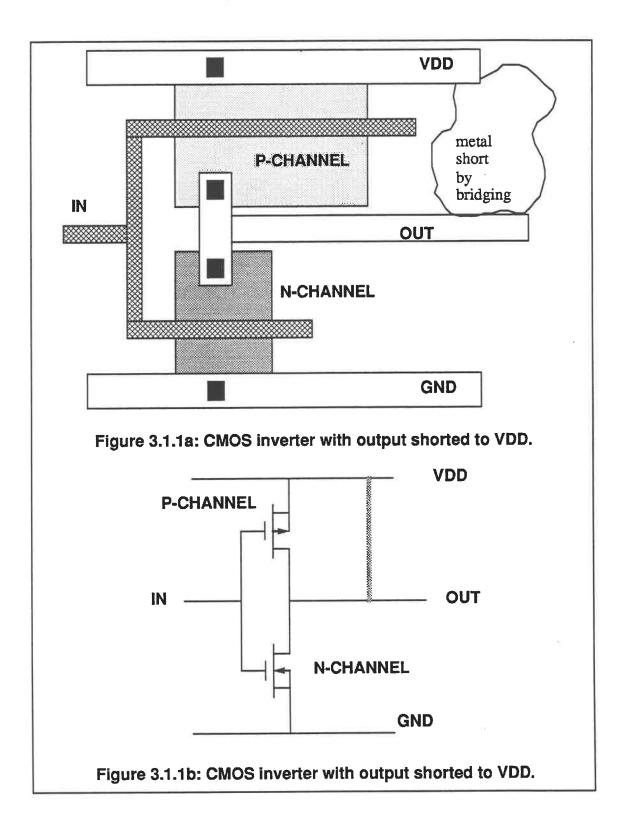

| Figure 3.1.1a: CMOS inverter with output shorted to VDD 28 |

| Figure 3.1.1b: CMOS inverter with output shorted to VDD 28 |

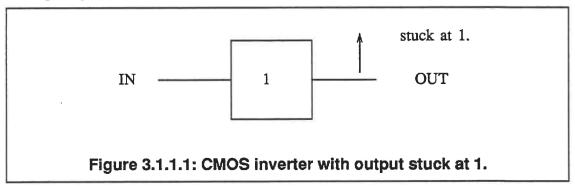

| Figure 3.1.1.1: CMOS inverter with output stuck at 1       |

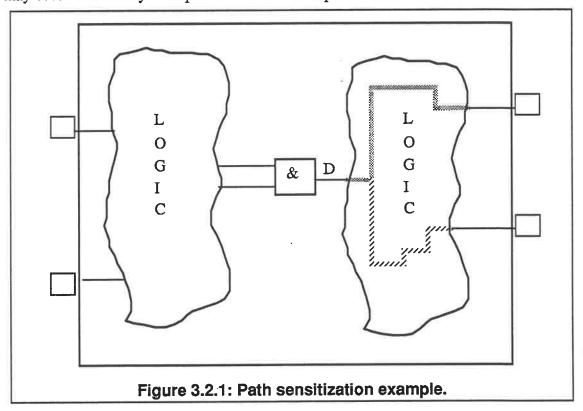

| Figure 3.2.1: Path sensitization example                   |

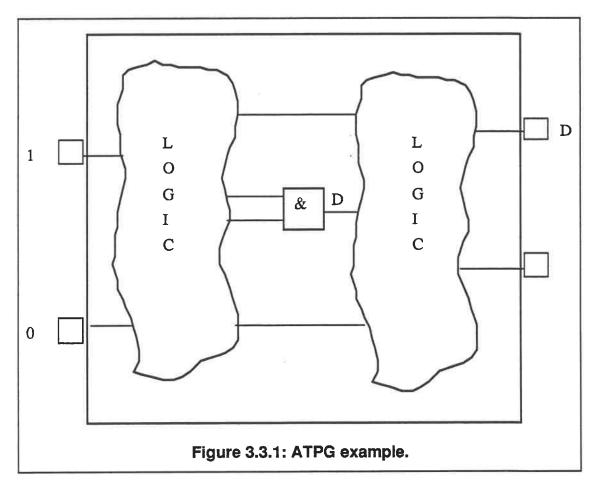

| Figure 3.3.1: ATPG example                                 |

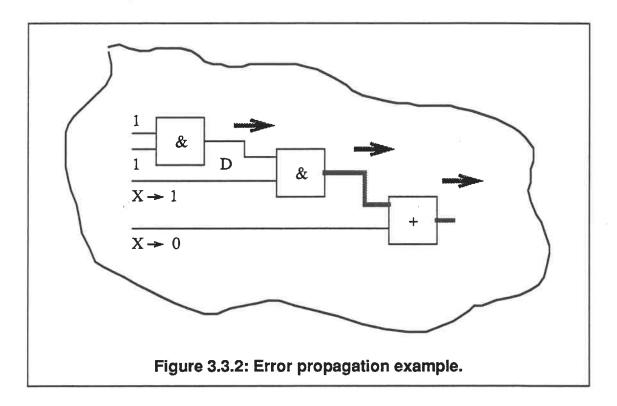

| Figure 3.3.2: Error propagation example                    |

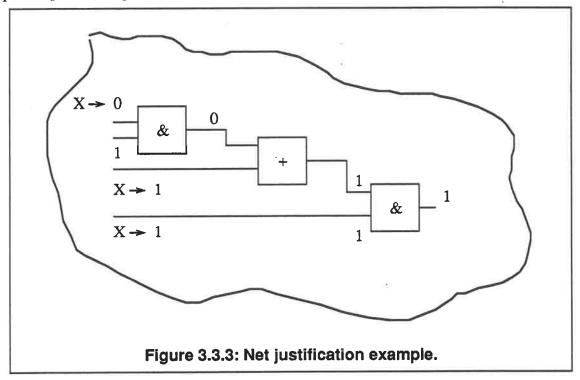

| Figure 3.3.3: Net justification example                    |

| Figure 3.3.4: A typical ATPG algorithm 36                  |

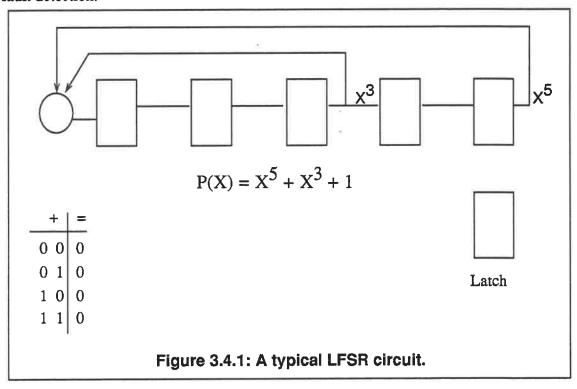

| Figure 3.4.1: A typical LESR circuit.                      |

| Figure 3.4.2: Random Test Pattern Generation             | 38   |

|----------------------------------------------------------|------|

| Figure 3.5.1: Types of nets in FAN                       | 41   |

| Figure 3.5.2: FAN pseudo code                            | 42   |

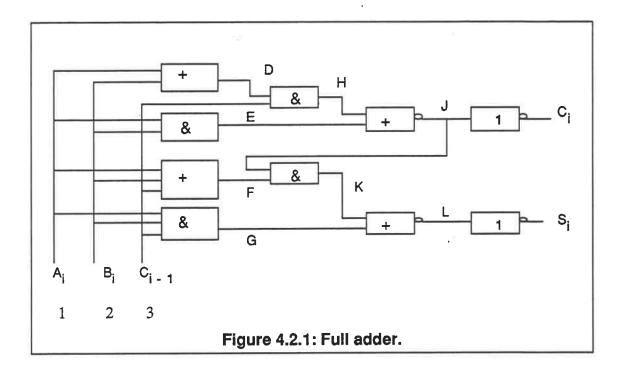

| Figure 4.2.1: Full adder                                 | 47   |

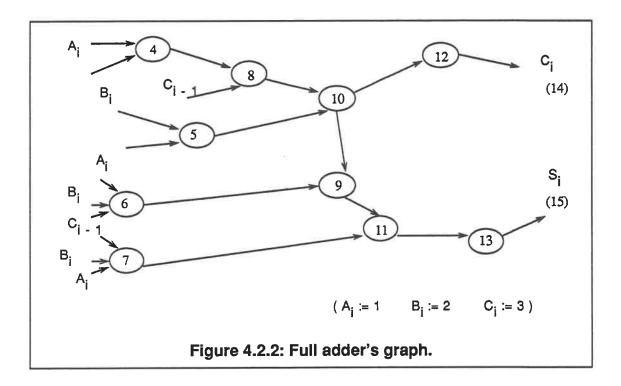

| Figure 4.2.2: Full adder's graph                         | 48   |

| Figure 4.2.3: Full adder's relation matrix.              | 50   |

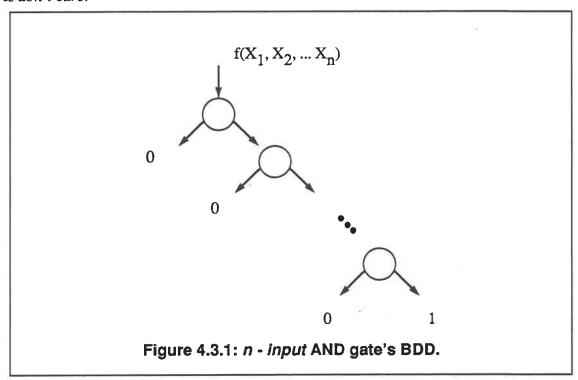

| Figure 4.3.1: n - input AND gate's BDD.                  | 51   |

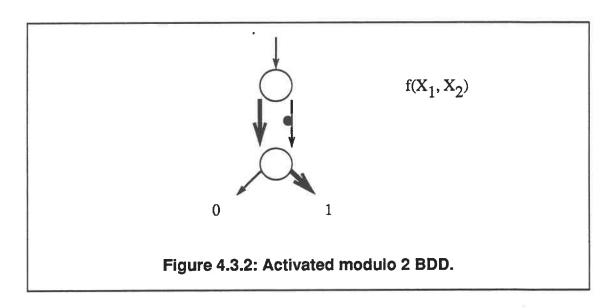

| Figure 4.3.2: Activated modulo 2 BDD.                    | 52   |

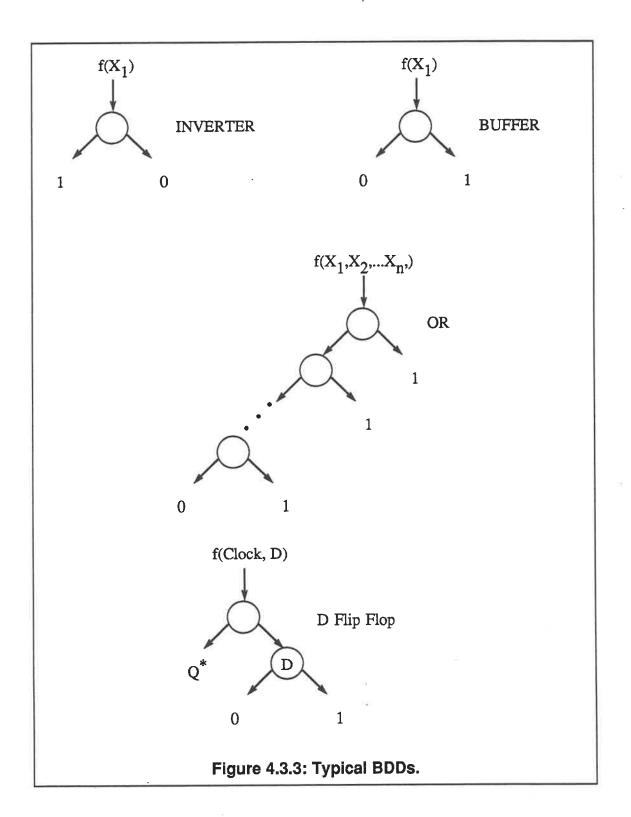

| Figure 4.3.3: Typical BDDs                               | 53   |

| Figure 4.4.1: Modified BDD for AND gate                  | 56   |

| Figure 4.4.2: gBDD for full adder circuit.               | 57   |

| Figure 4.4.3: Graph node and mBDD node data structures   | 58   |

| Figure 5.1.1: Design phases                              | 62   |

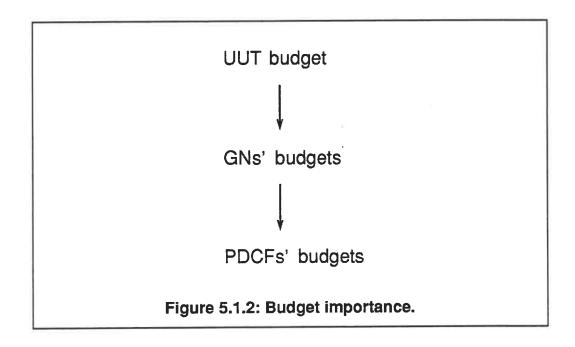

| Figure 5.1.2: Budget importance.                         | 63   |

| Figure 5.1.3: Budget formulae.                           | 64   |

| Figure 5.2.1: Creation of gBDD circuit                   | 65   |

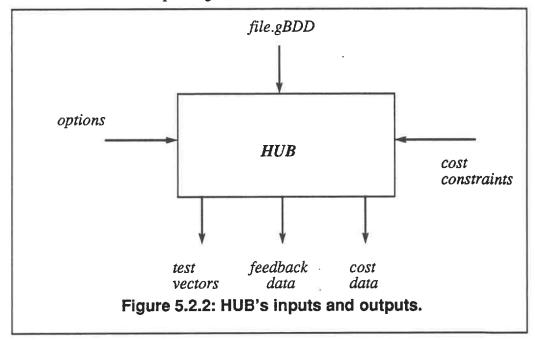

| Figure 5.2.2: HUB's inputs and outputs.                  | 66   |

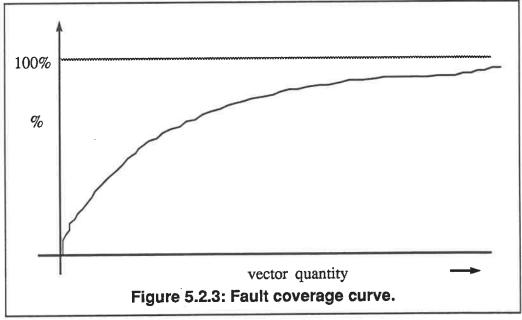

| Figure 5.2.3: Fault coverage curve.                      | 67   |

| Figure 5.2.4: HUB's pseudo code.                         | 68   |

| Figure 5.2.5: HUB ATPG's pseudo code                     | . 69 |

| Figure 5.2.6: HUB Cost Accounting Data Structure.        | . 70 |

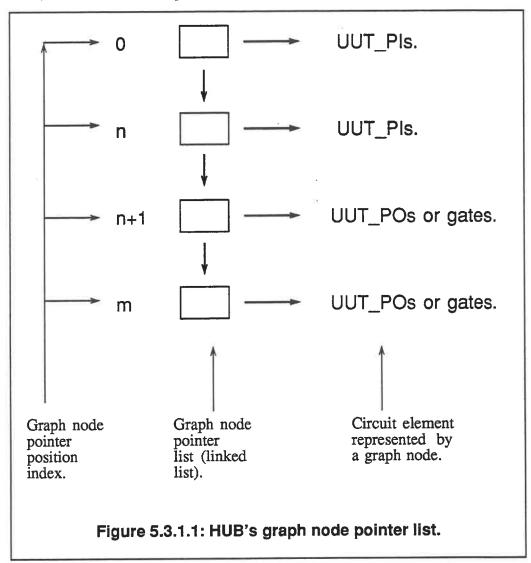

| Figure 5.3.1.1: HUB's graph node pointer list.           | . 73 |

| Figure 5.3.2.1: 2-input AND gate's pdcf personality file | . 74 |

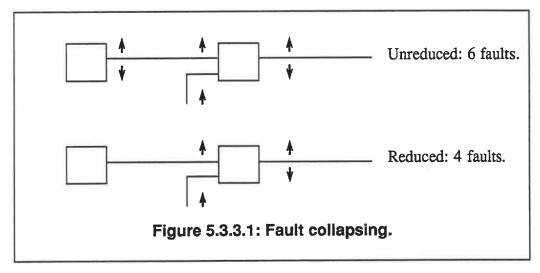

| Figure 5.3.3.1: Fault collapsing                       | 76  |

|--------------------------------------------------------|-----|

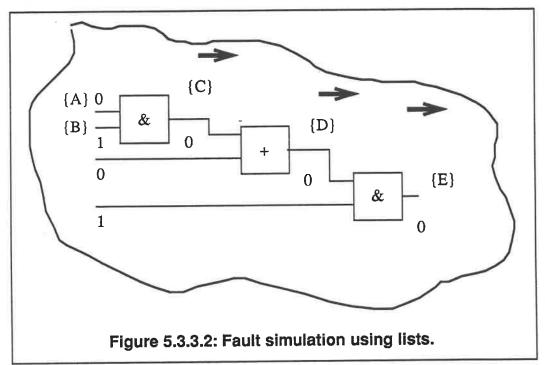

| Figure 5.3.3.2: Fault simulation using lists           | 77  |

| Figure 5.3.3.3: Fault simulation sample output data    | 79  |

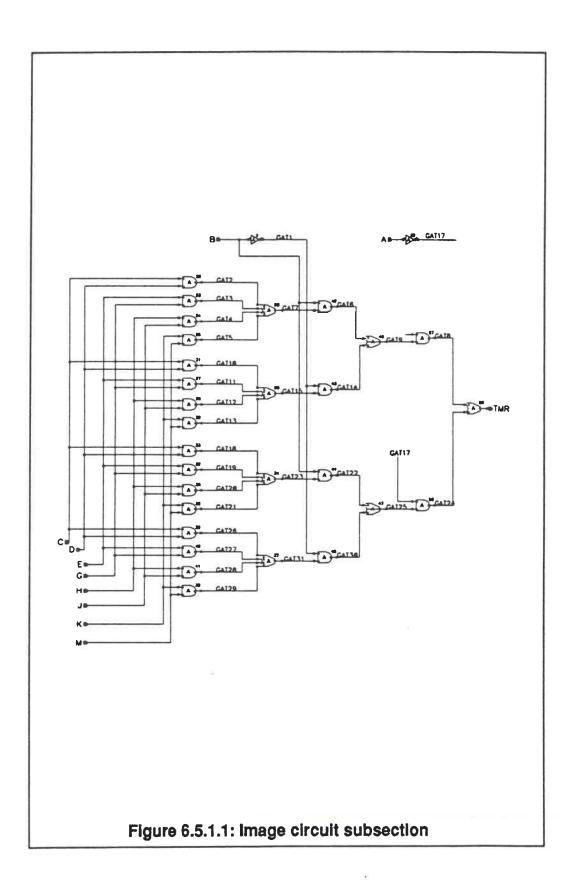

| Figure 6.5.1.1: Image circuit subsection               | 95  |

| Figure 6.5.1.2: Partial HUB hard fault data            | 107 |

| Figure A.1: HUB's options and syntax.                  | 124 |

| Figure A.2: HUB's data output.                         | 125 |

| Figure A.3b: HUB's SILOS II' vector output             | 126 |

| Figure A.3a: HUB's documented vector output            | 126 |

| Figure A.4: Neutral netlist syntax.                    | 127 |

| Figure A.5: Permissible element list                   | 127 |

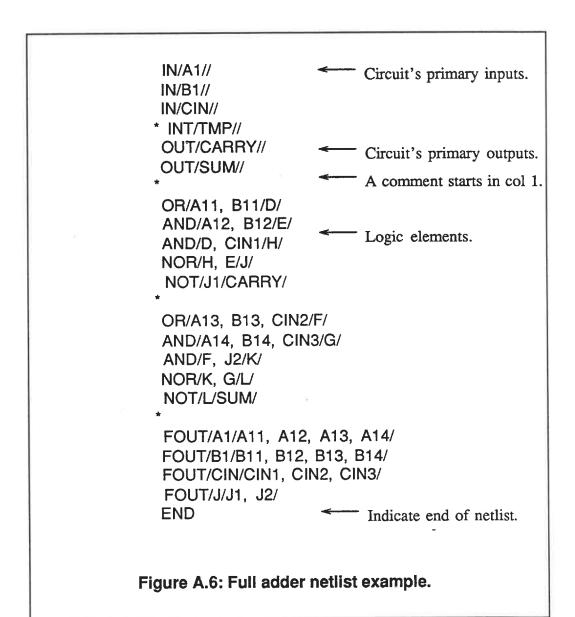

| Figure A.6: Full adder netlist example.                | 128 |

| Figure B.1: Listing of Image's graph node output names | 129 |

| Figure B.2: Example of HUB's accounting data           | 130 |

# **List of Graphs**

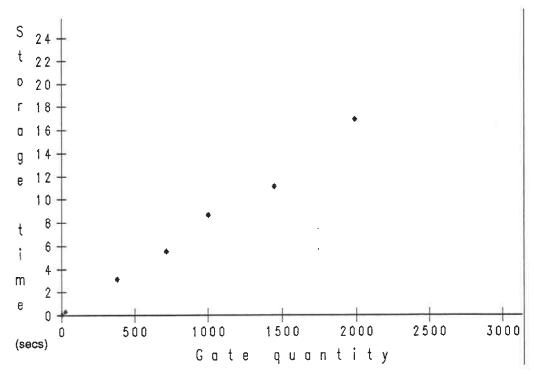

| Graph 6.2.1.1: gBDD file storage time 87                       |

|----------------------------------------------------------------|

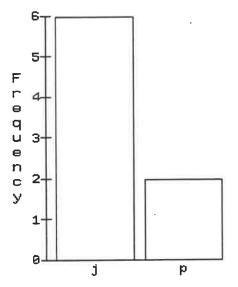

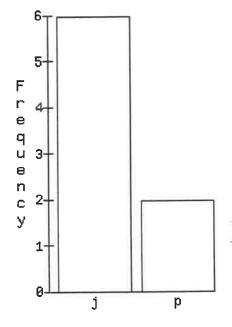

| Graph 6.5.1.1: Primary Backtrack Phases                        |

| Graph 6.5.1.2: Secondary Backtrack Phases                      |

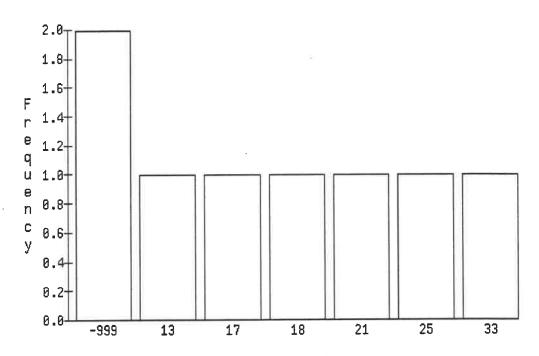

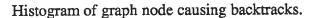

| Graph 6.5.1.3: Graph Node causing Backtrack Phase              |

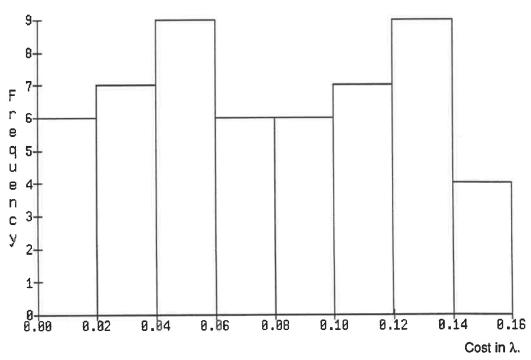

| Graph 6.5.1.4: Graph node number (reduced fault dictionary) 98 |

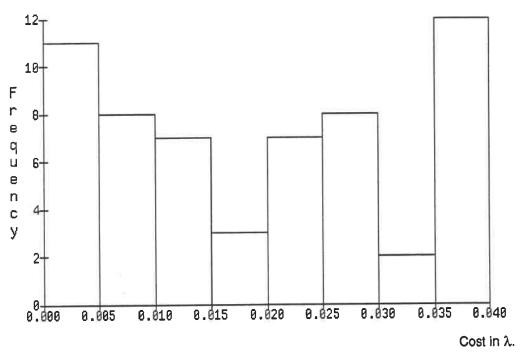

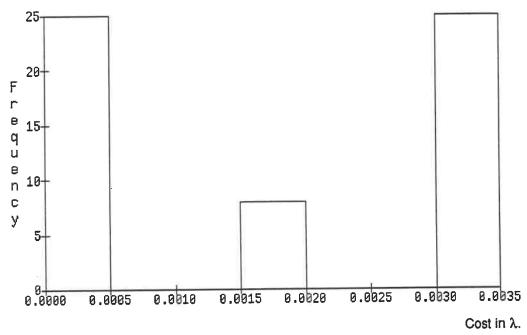

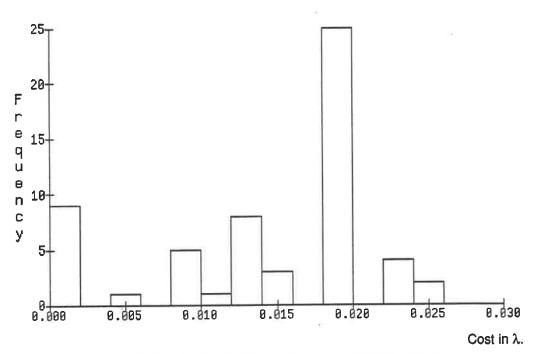

| Graph 6.5.1.5: Propagation phase cost histogram                |

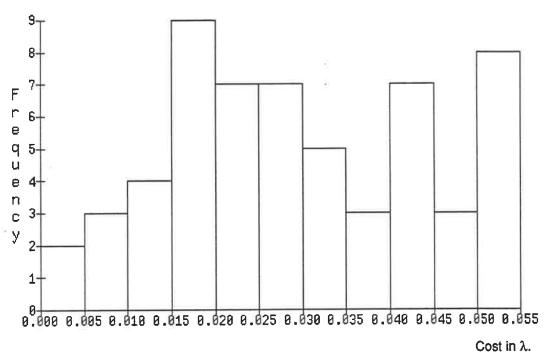

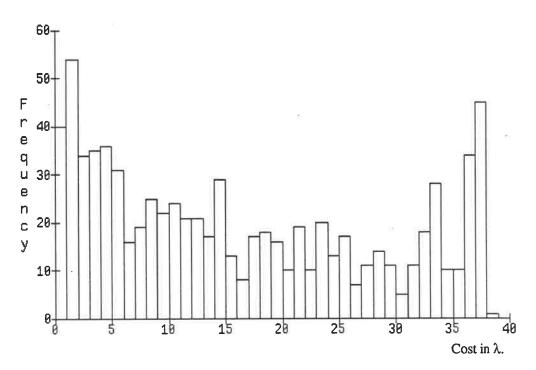

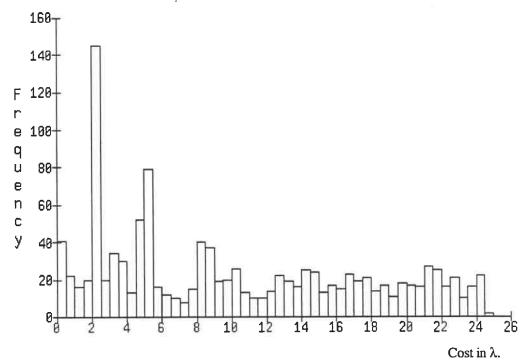

| Graph 6.5.1.6: Justification phase cost istogram               |

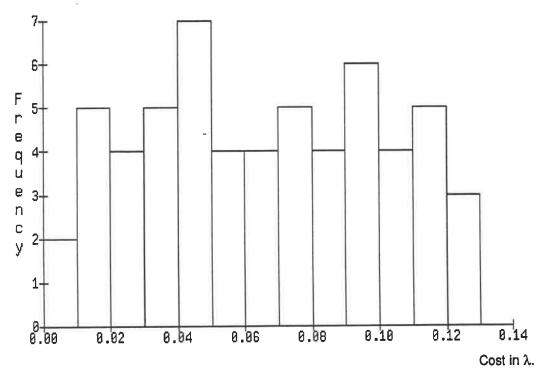

| Graph 6.5.1.7: Backtrace phase cost histogram 100              |

| Graph 6.5.1.8: Backtrack phase cost histogram 100              |

| Graph 6.5.1.9: Implication phase cost histogram 101            |

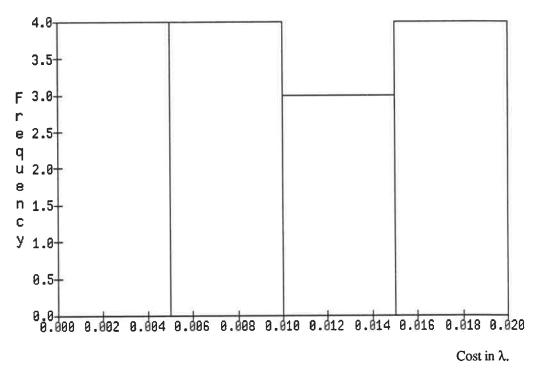

| Graph 6.5.1.10: Total cost histogram 101                       |

| Graph 6.5.1.11: Budget histogram                               |

| Graph 6.5.1.12: Total cost histogram (fault simulation)        |

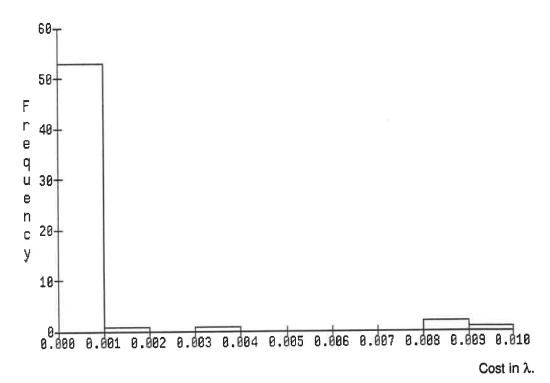

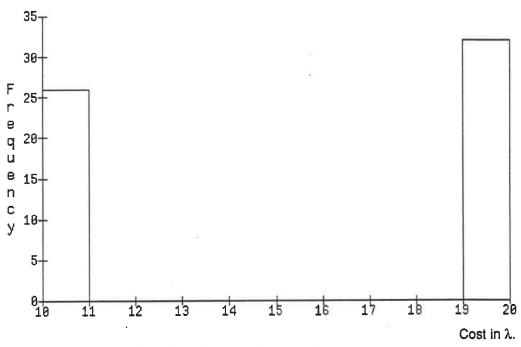

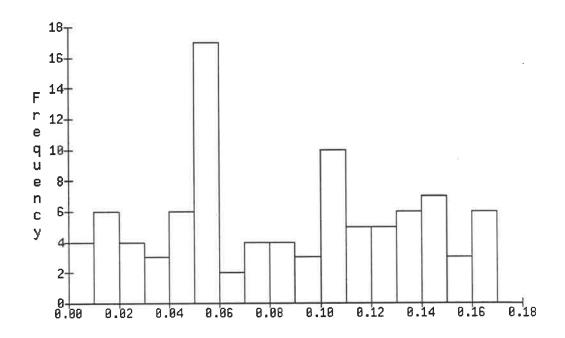

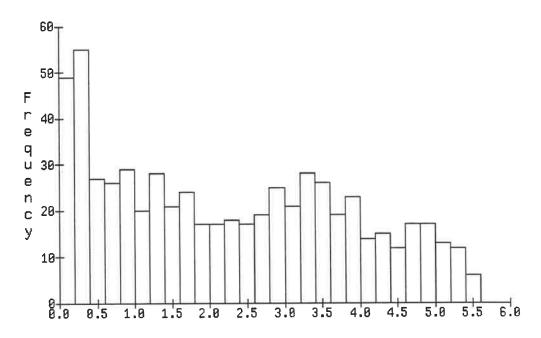

| Graph C.1: C17 total cost histogram                            |

| Graph C.3: C880 total cost histogram                           |

| Graph C.2: C95 total cost histogram                            |

| Graph C.5: C2670 total cost histogram                          |

| Graph C.4: C1908 total cost histogram                          |

| Graph C.6: Full adder total cost histogram                     |

### **List of Acronyms**

ATPG Automatic Test Pattern Generation.

BDD Binary Decision Diagram.

COP Controllability Observability Program.

CDP<sub>i</sub> Cummulative detection probability.

D Difference.

FAN FANout oriented ATPG.

FCE Fault Coverage Estimate.

gBDD graph BDD.

HUB Hard fault detection Using Budgetary constraints.

HF Hard Faults.

mBDD modified BDD.

pdcf primitive d cube of failure.

$Pd_{li}$  Probability of detecting net l stuck at i.

PI Primary Input.

PO Primary Output.

PODEM Path Oriented DEcisioin Making.

SCOAP Sandia Controllability Observability Analysis

Program.

TM Testability Measure.

UUT Unit Under Test.

UUT\_PI UUT's Primary Input.

UUT\_PO UUT's Primary Output.

VICTOR Vlsi Identifier of Controllability, Testability,

Observability and Redundancy.

# **List of Appendices**

| 9.0  | Appendix A | 124 |

|------|------------|-----|

| 10.0 | Appendix B | 129 |

| 11.0 | Appendix C | 131 |

#### 1.0 Introduction.

The continued increase in integrated circuit (IC) complexity, the tremendous pressure on reducing the time to market for these dense products coupled with the tumultuous drive to design products having inherently better quality and manufacturability with the first product revision has resulted - once again - in a heightened awareness of the testing bottleneck. Test and design engineers understand from their first hand experience, the conflicting interests caused by the requirements of high quality (expressed as a test metric), short test application times, the need for high yields - an ambiguously defined term - and reduced test costs.

The literature mentions that high test quality, such as 95% fault coverage metric using the single stuck at fault model, provides for more reliable products [McCluskey 88]. All testing, and hence the ensuing high quality, requires the ability to control the testing stimuli and observe the deterministic results. An IC design's controllability and observability are key aspects that have been addressed through the design methodology and grouped loosely under the monicker of Design For Test (DFT). Ad hoc techniques, such as those listed by Bardell [Bardell et al. 86], and the more formal DFT ideas, examples are listed in [McCluskey 86] [Bardell et al. 86], have been suggested as means to approach the testing problem from the hardware perspective. Even more recently, researchers have been working on synthesis which includes the designing of testable hardware as demonstrated in papers from [Devadas et al.][Sangio 88a] [Beenker et al. 89]. There has been a tendency to use these methods as the proverbial "silver bullet" intended to slay the testing monster. The negative effect of some DFT solutions on product yield, die size and even circuit performance has led to its use on an as needed basis in more recent years - as exemplified by the work on partial scan path [Agrawal et al. 88].

At the 1989 International Test Conference, the invited speaker, Dr. Tom Williams of the IBM corporation stressed the need for quality by stating that achieving the 100 ppm (parts per million) of defective units requires a minimum of 100% single stuck at

fault coverage and that the integrated circuits must be tested for delay faults. With the increasing demand of the computationally intense software verification activities such as fault simulation, one must design testable, manufacturable ICs using methods that relieve this tool-related burden [D&T 89] [Miczo 86].

Therein lies one of the fundamental problems facing the testing community identification of what is hard to test and what is easily tested. Much work in the field of estimating circuit testability, using the concept of testability measures (TMs), has met with limited success. Despite the introduction of many different TMs - SCOAP [Goldstein 79], COP [Brglez 85], VICTOR [Ratiu 82] - subsequent authors have shown that there is little confidence in the ability to correlate these static TMs with the reality of testing the circuits; this despite their use in guiding automatic test pattern generation (ATPG) for pruning the algorithm's decision search space. Even Ivanov's work using dynamic TMs [Ivanov 85] provided little extra benefit once the added computational loading was considered. The underlying difficulty appears to be the use of heuristics to create linear algorithms to approximate an NP complete problem.

The use of ATPGs to detect faults which are hard to test (HFs) is a definite possibility since, when an algorithm is employed, an exhaustive search will positively identify the presence of redundant logic and other HFs. ATPGs are known to be NP complete and their indiscriminate use can result in large computer run times. Guidance heuristics, such as TMs and backtrack limits, were introduced as attempts to reduce this excessive computer usage. However, as Fujiwara [Fujiwara 85] and Marlett [Marlett 89] indicate, it is important to reduce backtracks by making the correct decision and thus try to avoid labelling testable faults as HFs due to erroneous decisions. Ivanov suggested that the use of TMs actually causes the ATPG's failure [Ivanov 85] for certain conditions.

ATPGs and TMs suffer another limitation: they indicate that a fault is hard to test but fail to indicate the cause other than the fact that the backtrack limit has been exceeded (ATPG) or that the testability is deteriorating. In order to correct the

underlying problem, it is desirable to understand the HF's origins - is there no error propagation path? - is there a conflict due to the assignment of logic values to the nets?

This thesis proposes to identify the existence of HFs in logic circuits (restricted to combinational logic) based upon some new concepts which will be used to extend the previous work of other researchers. The concept of costs - and the budgetary constraints which arise from the cost of work - will be applied as a true measure of what type of fault is a hard fault. This is the primary direction taken by this paper. Cost accounting techniques will be applied to the various phases of an extended version of a well known ATPG (Fujiwara's FAN [Fujiwara 85]): these phases are the error propagation (difference or D propagation), net justification, the net implication (the simulation due to application of known values to the logic circuit's nets), the decision space creation (backtracing) and the re-evaluation of previous decisions (backtracking).

The concept of cost will be used to tie in design related knowledge - i.e. how much emphasis the designer wishes to place on the thorough testing of a given design - by allowing the designer to specify the total cost constraints for the unit under test (UUT). This will allow the use of an efficient algorithm to perform an exhaustive search in the worst case or unlimited budget, and to also examine the impact of severe budget considerations. Recent estimates indicate that fully one half of a large IC's development cost may be due to the impact of the IC's testing [Henckels 88a] [Henckels 88b].

In order to support this method, new heuristics have been developed and coupled with a new circuit modelling technique. These aid an extended FAN algorithm in arriving at a solution. The novel circuit model provides help in guiding the decision making process and provides for the future use of hierarchical circuit description in order to reduce the test generation time. It also permits the removal of the single stuck at fault model restriction.

This thesis is divided into 7 Chapters and has the following organization:

- Chapter 2.0 reviews previous research on identifying hard to test faults (HFs). Testability Measures (TMs), specifically SCOAP and COP, are discussed; the effect of reconvergence and fanout in circuits, and the previous use of cost in Testability Analysis are reviewed; and the means by which automatic test pattern generation have all been used to attempt to discover the presence of HFs at the various phases of circuit design are described.

- Chapter 3.0 provides a review of the key concepts involved with automatic test pattern generation (ATPG) required to introduce our method of hard fault identification - HUB. A summary of the basic single stuck at fault model, the internals of ATPG algorithms (specifically Fujiwara's FAN since this has served as a basis for HUB), and the basic framework of definitions is undertaken.

- Chapter 4.0 details the mixed graph and binary decision diagram circuit model which is required by HUB. Its ability to describe the circuit's functionality and structure, to provide hierarchical modelling of mixed combinational and sequential circuits, and to allow different fault models to be employed are presented.

- HUB Hard fault detection Using Budgetary constraints is explained in depth in Chapter 5.0.

- HUB's heuristics, the introduction of the budgetary constraint concept that is central to our HF identification tool, and a preview of how the circuit modelling technique will be closely coupled with to HUB, are described in Chapters 4.0 and 5.0

- The results of measurements obtained from HUB on some of the 1985 ISCAS combinational benchmark circuits are provided in Chapter 6.0; this data is also analysed and explained in this same chapter. Chapter 7.0 provides the conclusions.

### 2.0 Previous Work in Identifying Hard to Test Faults (HFs).

This chapter will provide insight into the existence of hard to test logic faults caused by the nature of the design methodologies and how various techniques have been employed to attempt the detection of their existence at various stages of the circuit design cycle.

The important effects of reconvergent fanout and logic redundancy in a logic circuit provides a review of some basic definitions and leads into the use of tools; specifically tools used to manipulate this information. Additional heuristic tools, used to estimate the vaguely defined circuit testability, are presented using two traditional testability measure sets: (1) SCOAP; and (2) COP which are linear approximation approaches to the NP complete test generation problem. Subsequently, the use of automatic test pattern generation tools in detecting HFs will be described including additional explications as to how the tool and its circuit environment can cause faults to become hard to test.

A review of sensitivity cost functions, random test cost functions, and sequential test cost functions introduce more fully the concept of applying cost measures in improving a circuit's testability. These sections will also provide insights into the diversity of techniques, metrics, and heuristics employed in testability analysis.

### 2.1 The effect of reconvergent fanout and redundancy.

The presence of reconvergent fanout definitely causes difficult to test faults - HFs. Bell states that backtracking operations within ATPGs, caused by redundancy and the decision making process, are caused by reconvergent fanout [Bell Taylor 88]. He also quotes Savir as indicating that reconvergent fanout [Savir 83] may cause the inability of TMs to correlate with the difficulty that ATPGs can experience in trying to generate a solution. Reconvergent fanout also prompted Fujiwara to develop the FAN ATPG algorithm [Fujiwara 85]. These HFs have driven several researchers to develop techniques which analyse the circuit's structure and indicate either the

points at which *test points* (used to increase the observability within a circuit) need to be inserted or whether the circuit is difficult to test - TMs.

Russell provided techniques, based upon graph theory, for determining the diagnostic resolution of faults within combinational logic circuits with application to the insertion of test points [Russell Kime 71]. These techniques only examined the circuit's structure without any consideration of the UUT's function or the function of the individual modules from which the UUT is composed. This work was specifically aimed at determining where test points - a structural change - could be inserted. They also wished to evaluate the network structure's contribution to the UUT's fault diagnosis properties. Batni later extended these principles to diagnostic test generation techniques [Batni Kime 76].

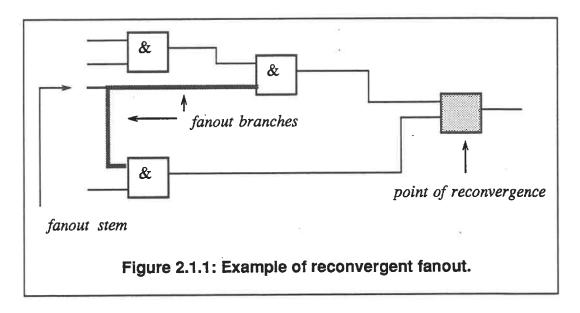

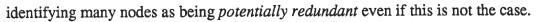

Reconvergence in a circuit exists when a signal, emanating from a common point known as the *fanout stem*, flows along more than one path each of which are referred to as *fanout branches*, and then arrive at a common circuit primitive - the *reconvergence point* [Kirkland Mercer 88]. Figure 2.1.1 shows a simple example with the appropriate points annotated. Note that the introduction of reconvergence alters the tree like structure of the circuit's associated graph. Figure 2.1.2a shows the circuit graph in the presence of reconvergent fanout and Figure 2.1.2b demonstrates the effect of replacing the fanout branches with two independent signal sources.

Redundancy can generate HFs also. A redundant fault is caused by a redundant connection - a connection, which when removed and replaced by a fixed logic value of 0 or 1 - does not alter the output functions of a circuit. A circuit that contains no redundant connections is called *irredundant*. A theorem [Miczo 86] follows from this definition.

THEOREM 2.1: All stuck at 0 and stuck at 1 faults contained in the combinational circuit UUT, are detectable if and only if the circuit is irredundant.

[Russell Kime 71] state that reconvergence is a necessary condition for redundancy. They extend theorem 2.1 to state the sufficient condition for detecting every fault within an irredundant circuit.

THEOREM 2.2: If a circuit is irredundant, then every stuck at 0 and stuck at 1 fault on a net and at a module's inputs and outputs in the network is detectable. If a network is irredundant, then the existence of a directed path from an element fault to a PO is a sufficient condition for that fault to be detectable at that PO

VICTOR (Vlsi Identifier of Controllability, Testability, Observability and Redundancy) [Ratiu 82] is an example of a 4 pass linear algorithm for combinational logic circuits which endeavours to determine an UUT's testability, identify redundancy, and attempt to generate test vectors. VICTOR flattens (levels) the circuit, calculates the zero and one controllabilities, obtains the observability values and then indicates redundancies while performing test generation. However McCluskey notes that VICTOR [McCluskey 86] tends to be a pessimistic procedure,

### 2.2 Testability Measures (TMs).

Several researchers have tried to identify the presence of faults which will be hard to test, (HFs), by establishing testability measures (TMs). The testability of a design is evaluated using these TMs prior to generating the set of test vectors used to detect a faulty circuit. Efforts have focused on the creation of linear algorithms

based upon heuristics in order to quantify the relative difficulty in generating the subsequent testing stimuli. These TMs are derived, in general, from metrics designed to quantify the *controllability* and the *observability* of the individual *nets* or *lines* within the UUT. The *controllability* is the ability to set a given *net l* to a known logic value  $v \in \{0, 1\}$  from values placed on the UUT's primary inputs (PIs). *Observability*, the counterpart of controllability, is the ability to observe the logic value on *net l* (typically with an error value impressed on it and not a logic 0 or logic 1) at a given UUT's primary output (PO). Observability is also a function of the nets' controllabilities as is shown below.

Poor controllability or observability hinders the ability to generate a test for a faulty circuit element. Lack of control can cause one or more of the following problems to occur:

- propagation of the error, caused by the faulty element, may be blocked due to a *blocking condition* on a logic gate: such as a logic 0 on one or more of an AND gate's inputs as shown in Figure 2.2.1;

- line justification may not be possible. Figure 2.2.2 shows a net with the current value of 'X' (don't care) and which requires setting to logic 1. In this example, a zero is more easily generated than a one, since only 1 of the 2<sup>4</sup> input combinations provides this logic 1;

- the actual sensitization of the error, local to the faulty logic element, may be difficult. The inability to generate an environment whereby the error condition is clearly evident may preclude the possibility of detecting the faulty circuitry.

Lack of observability can be related to the inability to control a net which would allow the error signal to be propagated to an UUT PO. The terms, *propagation*, sensitization and justification, will be explained in more detail as automatic test pattern generation is covered in Chapter 3.

Two examples of widely discussed TMs are presented: (1) SCOAP - Sandia Controllability Observability Analysis Program - which uses heuristics related to a circuit element's relative depth within the UUT; and (2) COP - Controllability Observability Program - that applies signal probability under the assumption of independent fanout branches for reconvergent fanout conditions. The overall advantage of these TMs is that they are O(n), linear, where n is the number of logic

gates contained by the circuit being examined.

#### 2.2.1 SCOAP - Sandia Controllability Observability Analysis Program.

Goldstein suggested that the relative depth of a logic gate within the UUT would provide a measure of the ease in testing a fault on a net associated with this gate. SCOAP [Goldstein 79] [Goldstein 80] was the computer implementation of the algorithm which calculates the 6 TMs. These 6 metrics are used to gauge the testability of the combinational and sequential circuitry; only the 3 combinational TMs will be described. Essentially the controllability is decreased, indicated by an integer value which increases by an fixed quantity (tending towards infinity or poor control), as one proceeds from the UUT's primary inputs (PIs) heading towards the UUT's primary outputs (POs) through the various gates in its cone of influence.

SCOAP first determines the nets' zero,  $C_0(\text{net }l)$ , and one,  $C_1(\text{net }l)$ , controllabilities. This information is required for calculating the nets' observability on the second pass. The observability also decreases as the TM's magnitude increases

```

Initialize all PIs, POs and internal nets.

C0 and C1 for PIs set to 1.

C0 and C1 for POs and nets set to ∞.

Obs for PIs and nets set to ∞.

Obs for POs set to 0.

for all logic elements in UUT {

Calculate C0.

Calculate C1.

}

for all logic elements in UUT {

Calculate Observability.

}

```

and is denoted by Obs(I); observabilities are independent of the value being observed. The SCOAP program's pseudo code is presented in Figure 2.2.1.1 makes use of the following relationships, only some are shown, and initial conditions in order to predict the testability. Some simple logic primitives, with their corresponding combinational controllability and observability equations, are shown in Figure 2.2.1.2. The same figure also provide the information for fanout stems, the net driving a fanout, and fanout branches. The initial conditions for the unit under test's primary inputs (PIs) and primary outputs (POs) are listed in Table 2.2.1.1. Agrawal has indicated in a past paper [Agrawal Mercer 82] the poor correlation between the predicted ease of testability and the reality.

A simple circuit, the full adder of Figure 2.2.1.3, is used as an example to show the combinational controllabilities and observabilities for every net in the

circuit; these values are found in Table 2.2.1.2. This same circuit is reused in the next section, where a different set of testability measures is calculated. Note that the values within the accolades are for the fanout branches. The value chosen is the minimum of the set.

| Parameters | Primary Inputs | Primary Outputs |

|------------|----------------|-----------------|

| СО         | 1              | 60              |

| C1         | 1              | 00              |

| Obs        | <b>∞</b>       | 0               |

Table 2.2.1.1: SCOAP initial conditions.

SCOAP's sequential TMs are not discussed here as many other techniques have been proposed and since this thesis is primarily concerned with combinational logic HF identification. The TMs based upon sequential path length, as established from a graph representation seem to be a more favoured approach.

### 2.2.2 COP - Controllability Observability Program.

Brglez suggested that a more correct method [Brglez 83] [Brglez 85] for determining a circuit's testability is to use signal probabilities in calculating the TMs. COP's controllability and observability metrics are restricted to only combinational circuitry resulting in a total of 3 measures. COP [Brglez 85] also requires two passes, highlighted in Figure 2.2.2.1, through a UUT to accomplish the testability analysis: the first pass is initiated from the UUT PIs and determines the controllabilities,  $C_0$ (net l) and  $C_1$ (net l) as the algorithm proceeds through the UUT towards the UUT POs; the second iteration determines the observability Obs(l) starting at the UUT POs and working towards the UUT PIs using the previously determined  $C_0$ (net l) and  $C_1$ (net l). The initial conditions are stated in Table 2.2.2.1 and some formulae are shown in Figure 2.2.2.2. The COP TMs, for the full adder circuit of Chapter 2.2.1, have been calculated and are found in Table 2.2.2.2.

| NET NAME | C0  | C1  | Obs              |

|----------|-----|-----|------------------|

| A1       | . 1 | 1   | 6 {8, 6, 13, 10} |

| B1       | 1   | 1   | 6 {8, 6, 13, 10} |

| CIN1     | 1   | 1   | 7 {7, 13, 10}    |

| D        | 3   | 2   | 6                |

| E        | 2   | 3 x | 4                |

| F        | 4   | 2   | 10               |

| G        | 2   | 4   | 7                |

| Н        | 2   | 4   | 4                |

| J        | 4   | 5   | 1                |

| К        | 5   | 8   | 4                |

| L        | 6   | 8   | 1                |

| CARRY    | 6   | 5   | 0                |

| SUM      | 9   | 7   | 0                |

Table 2.1.1.2: SCOAP values for the full adder circuit.

| Parameters | Primary Inputs | Primary Outputs |  |  |  |

|------------|----------------|-----------------|--|--|--|

| CO         | 0.5            | ∞               |  |  |  |

| C1         | 0.5            | ∞               |  |  |  |

| Obs        | ∞              | 1               |  |  |  |

Table 2.2.2.1: COP initial conditions.

Other TMs have been suggested, but Huissman has indicated in a recent paper that there is still a great deal of difficulty in predicting a circuit's testability [Huissman 88]. He also notes that despite the lack of a definitive TM, and their lack of success, that work should continue in this area.

```

Initialize all PIs and POs.

C0 and C1 for PIs set to 0.5.

C0 and C1 for POs and nets set to ∞.

Obs for PIs and nets set to ∞.

Obs for POs set to 1.

for all logic elements in UUT {

Calculate C0.

Calculate C1.

}

for all logic elements in UUT {

Calculate C5.

Figure 2.2.2.1: COP pseudo code.

```

Despite the inherent limitations of these TMs caused by the use of heuristics, their use in guiding automatic test generators has become commonplace. These guidance heuristics have not been limited to the COP and SCOAP TMs.

#### 2.3 Using of ATPGs to detect HFs.

Automatic Test Pattern Generation (ATPG) algorithms and procedures have been created to generate test vectors for a given fault set for a given circuit requiring testing. Algorithms, by their very nature, guarantee a solution (providing that there is at least one solution possible) if they are allowed to work until their natural termination point. However brute force methods such as the *D-algorithm* [Roth 67] may have a tendency to be highly inefficient for classes of logic circuits - and degrade to a time consuming exhaustive search of all the circuit's vector space. The assigning of decisions in a totally random manner lead to the development of improved techniques that prune the decision space: *PODEM* [Goel 81]. FAN [Fujiwara 83] used topological heuristics to reduce the decision space's size. PODEM and FAN

will become exhaustive searches in the limit should their pruning heuristics be useless, or of poor quality, for a particular circuit. Thus, an algorithmic ATPG can be used to decisively indicate an HF's presence.

As the ATPG works towards constructing a solution, it may encounter situations where a decision (arbitrary) is required; an incorrect choice is a costly effort as indicated by Fujiwara in his work on developing FAN [Fujiwara 83] [Fujiwara 85]. Reversing a previous decision - a backtrack operation on the decision space - requires that the ATPG perform much extra work. As such, many ATPGs will declare a fault as hard to test when the number of "backtracks", generated in the search for a solution, exceeds an arbitrary limit - such as 10. The fault may be incorrectly labelled since a generic heuristic has been arbitrarily imposed. This is, none the less, one additional method (above an exhaustive search) by which an ATPG can identify HFs - the metric of cost of effort. While the heuristic based result is not always precise, the exhaustive search is and one can safely assume that the cause is redundancy. A limit of 10 backtracks per test generation exercise for a selected fault appears to be a useful figure of merit. Researchers, such as Fujiwara, found that increasing this limit by 2 orders of magnitude does not significantly increase the quantity of detected faults. It would seem that the heuristics may be causing the ATPG failure. [Agrawal Seth 89] suggest that test generation is made difficult by factors other than the quantity of gates, the quantity of memory elements (sequential logic elements) and the circuit's sequential depth. Their list is augmented by Ivanov's suggestion that the heuristics [Ivanov 85] also compound the automatic test generator's quandary in finding a solution:

- poor initializability.

- poor controllability and observability for memory elements.

- structural dependencies (reconvergent fanout for example).

- cycles within the circuit.

- the guidance heuristics.

| NET NAME | C0    | C1    | Obs   |

|----------|-------|-------|-------|

| A1       | 0.500 | 0.500 | 0.312 |

| B1       | 0.500 | 0.500 | 0.312 |

| CIN1     | 0.500 | 0.500 | 0.562 |

| D        | 0.250 | 0.750 | 0.375 |

| E        | 0.750 | 0.250 | 0.625 |

| F        | 0.125 | 0.875 | 0.410 |

| G        | 0.875 | 0.125 | 0.560 |

| Н        | 0.625 | 0.375 | 0.750 |

| J        | 0.531 | 0.469 | 1.000 |

| K        | 0.590 | 0.410 | 0.875 |

| L        | 0.484 | 0.516 | 1.000 |

| CARRY    | 0.469 | 0.531 | 1.000 |

| SUM      | 0.516 | 0.484 | 1.000 |

Table 2.2.2: COP values for the full adder circuit.

#### 2.4 Previous use of cost in Testability Analysis.

#### 2.4.1 Breuer's Sensitivity Functions.

Breuer used the concept of cost [Breuer 83] in extending the testability measure concepts. His specific goal was to identify points within the UUT for the optimal and automatic insertion of test points for improved observability and gates for increased controllability (addition of AND gates for improving the zero controllability and OR gates for facilitating the one controllability). He identified the cost of controlling nets and observing nets by heuristics that had served as the basis for SCOAP. Breuer labels the zero controllability as  $\phi_0(l)$ , the one controllability as  $\phi_1(l)$ , and the observability as  $\phi_2(l)$ , for a given circuit net l. The UUT's costs are totalled by first summing each individual cost for L - the set of nets contained by the UUT - providing  $\phi_0$ ,  $\phi_1$ , and  $\phi_2$  as shown in equations 2.4.1.1 - 2.4.1.3. The total testability cost,  $\phi_1$ , is the result of the weighted sum of these addends.

$$\$_{0} = \sum_{1 \in L} \phi_{0}(l)$$

$$\$_{1} = \sum_{1 \in L} \phi_{1}(l)$$

$$\$_{2} = \sum_{1 \in L} \phi_{2}(l)$$

$$\$'_{1} = \sum_{1 \in L} k_{1} \$_{1}$$

$$2.4.1.3$$

$$2.4.1.4$$

Breuer then specified a sensitivity function used to calculate the reduction in costs (such as the improved zero controllability of a net l obtained by inserting an AND gate) generated by adding a test point at an arbitrary circuit net. Equation

2.4.1.5 specifies the sensitivity for a single modification to a net l.  $S_j$  is a binary variable used to indicate that the test point is activated ( $S_j = 1$ ) or that normal circuit functionality occurs ( $S_j = 0$ ). Breuer [Breuer 83] [Chen Breuer 85] implemented a program by which constraints could be applied - the maximum cost of modifications; upper bounds on individual nets within the UUT - to the UUT while automatically applying DFT.

$$\frac{\partial \$_{i}}{\partial \$_{j}(1)} = \frac{\left| \$_{i}(S_{j}(l) = 1) - \$_{i}(S_{j}(l) = 0) \right|}{1 - 0}$$

2.4.1.5

#### 2.4.2 Random Test Cost Functions.

Lisanke et al. also use a cost function - a testability cost function - while generating tests from randomly created patterns [Lisanke et al. 86] [Lisanke et al. 87]. Their program, ESPRIT, consists of the five modules indicated in the pseudo code shown in Figure 2.4.2.1.

```

Compute Input Signal Probabilities. /* 1 */

do{

Generate Vectors. /* 2 */

Fault Simulation. /* 3 */

Update Fault List. /* 4 */

Evaluate Fault Coverage Slope. /* 5 */

} until Fault Coverage Slope < User's Value.

Evaluate Fault Coverage Slope.

By until Fault Coverage Slope < User's Value.

Figure 2.4.2.1: ESPRIT pseudo code.

```

Costs are used for 2 of ESPRIT's "functions": (1) - the computation of input signal probabilities and (2) - by the decision making process for continuing to attempt to generate tests. The former is the most important part of ESPRIT and is based upon COP [Brglez 84]. Remembering that the probability of detecting a fault on a net l is:

$$Pd_{l/0} = C_1(l) * Obs(l)$$

2.4.2.1

$$Pd_{l/1} = (1 - C_1(l)) * Obs(l)$$

2.4.2.2

One can then determine the *cumulative detection probability*  $CPd_j$ , by random patterns, given n independent trials, with the expression:

$$CPd_{j}(l) = 1 - (1 - Pd_{j})$$

2.4.2.3

Lisanke et al. defined a fault coverage estimate (FCE) as a means to predict random test pattern generation costs for an UUT about which one knows the net list, fault set and input signal probabilities. The estimated fault coverage curve, a function of the number of independent trials is shown in Figure 2.4.2.2 and is the average of the cumulative detection probabilities over the fault set F as defined by:

FCE(n) =

$$\frac{1}{F}$$

$\sum_{j=1}^{F} \text{CPd}_{j}(l)$  2.4.2.4

That the estimated fault coverage approaches unity with an increasing number of trials is intuitive - as n approaches 2<sup>m</sup> (m primary inputs on the UUT) the testing becomes exhaustive.

The area above the curve described by FCE is proportional to the amount of effort required by the fault simulation phase, Since ESPRIT's run time costs (computer processing unit's - CPU - time or cost) is dominated by the fault

simulation phase, the authors created a cost function \$ that represents this area \$. This area is defined by the equation:

$$\$ = \sum_{n=0}^{\infty} [1 - FCE(n)]$$

2.4.10

The authors minimize the cost function \$ in order to produce the optimal input signal probabilities used during the vector generation phase. This is achieved by using a gradient optimization technique that provides information on how \$ changes due to input signal probability modifications.

# 2.4.3 Sequential Test Cost Functions.

Agrawal et al., in creating a new ATPG [Agrawal et al. 89], defined three (3) cost functions used in developing a generalized directed search methodology. (1) An initialization cost function is used during the circuit initialization phase of their ATPG. (2) A concurrent test generation cost function is employed for simultaneously

testing several faults, and (3) a single fault test generation cost function is used when testing a single fault while generating vectors. Each of these cost functions is applicable to one of the three independent ATPG phases.

The initialization phase is required to generate an initialization vector sequence where the number of unknown signals on flip flop logic elements increases the *initialization cost*. The user may specify a non-zero initialization target value instead of the default target of zero cost.

A distance metric, the shortest distance from any fault effect of that fault to any primary output, is used in selecting whether a vector candidate is to be accepted after its trial. Agrawal et al. contend that the smaller the cost, the closer the fault is to being detected - thus a detected fault has zero cost.

The third cost function - single fault test generation cost function - is similar to the concepts proposed by the SCOAP TM. This dynamic cost reflects the minimum number of primary inputs that must be changed and the minimum number of additional vectors to control a node's value. This cost must describe both the effort to sensitize the fault and to propagate the fault to a primary output. A weighting penalty may be assigned to the dynamic sequential controllability (DSC).

## 2.4.4 Summary of Cost Functions.

The above three methods are indicative of the segregated approach to the use of cost in the testability arena. Breuer used his cost metrics to indicate how design for testability could be automatically added to the UUT. However, Breuer's metrics were based upon SCOAP's predecessor and Agrawal [Agrawal Mercer 82] has previously demonstrated the limitations of SCOAP TMs. [Agrawal et al. 89] also rely heavily on heuristic cost measures although attempts were made to vertically integrate these measures into an ATPG system. Lisanke et al. attempted to unify the cost of test pattern generation, albeit randomly created test patterns, with TMs.

An improved technique would appear to be a properly formulated amalgamation of these seemingly disparate methods; testability measures,

heuristics, costs, automatic test pattern generation and user supplied constraints. Cost is a primordial consideration given that one cannot:

- increase the circuit size without reasonable justification;

- degrade system performance;

- monopolize computer capacity for ATPG;

- cause excessive test application times due to excessively long test patterns;

- allow poor quality product, determined by lower fault coverage values, to reach clients.

Many of these, if not all, cost related parameters can be used to define a more precise definition of device testability and may be applicable on a varying product by product basis. This shall be the thrust of this thesis - the identification of HFs based upon budgetary (cost) constraints.

# 3.0 Review of Automatic Test Pattern Generation (ATPG).

ATPG principles are reviewed in depth in this section, providing the foundation for the HF identification algorithm HUB. The traditional fault model, the single stuck at fault, and the use of the five valued logic - at the heart of the D calculus used for the D algorithm - are also presented. This section also reviews the differences between the single path and multiple path sensitization methodologies. The definitions of basic terms are interspersed throughout the section. An ATPG's use of heuristics is explained as are the trade-offs and additional features encountered during the creation of an automatic test pattern generator.

## 3.1 Fault modelling.

Dr. Tom Williams noted that the concept of testing structure instead of function, as proposed by R. Eldred, was responsible for the literal explosion of research into fault models and the accompanying automatic test pattern generation tools [Williams 89a]. Eldred described how structure could be verified based upon tests for specific faults under a fault model which accurately describes the realistic set of physical defects that occur within the structure [Eldred 59]. An underlying theme of fault models is the 3 abstraction levels associated with the concepts of defects, faults, and errors.

Defects refer to the physical aberration or anomaly which occurs during the manufacturing process. For integrated circuits, these may correspond to contaminants, metallization problems (voids or bridging), contact problems, etc.. These defects can have different defect densities and are often a function of the particular process [Galiay 80]. The defects may be modelled as having an influence over a relatively large area - known as global or clustered defects - or as very localized defects - point defects [Shen 85]. A metal bridging defect between the positive power supply and an inverter's output is shown at a layout representation level in Figure 3.1.1.a. This defect's effect could be represented at the transistor abstraction level by a fault such as the well known single-stuck-at-n,  $n \in \{0, 1\}$  as

shown in Figure 3.1.1.b.

In turn, the fault's presence causes the introduction of an *error* at a functional abstract level. As an example, if this inverter was one of an instructions ROM's outputs and was fed to the input of a signature register [Bardell *et al.* 86], one would obtain a *burst error* [Stallings 88].

There are several advantages in using a fault model. The following are some of those enumerated by [Miczo 86]:

- Create tests specifically for those faults most likely to occur;

- Compute a *test quality metric* by determining how many potential faults are caught by the test stimulus;

- Debug yield problems by relating defects to specific test patterns.

Considerable work has been done recently, using a technique known as Inductive Fault Analysis (IFA), in relating the fabrication process knowledge to the circuit layout in order to determine the fault types most likely to occur [Shen 85] [Ferguson 88].

#### 3.1.1 Single stuck at fault model and 5 value logic.

A typical defect in the *MOSFET* (Metal Oxide Surface Field Effect Transistor) technology occurs in the metallization [Galiay 80] e.g.: the bridging of two adjacent metal runs. This might cause a transistors output to be shorted to the power supply. Such a defect is typically represented by a *fault* such as the well known *single stuck* at n, s-a-n where  $n \in \{0, 1\}$  and it is assumed that only one such fault exists at any given time. Figure 3.1.1a. represents an inverter, in *CMOS* (Complementary MOS), which has its output shorted to the positive power supply. The corresponding fault at transistor and gate abstraction levels, a s-a-1, are indicated in Figure 3.1.1b and Figure 3.1.1.1.

One wishes to detect the presence of improper circuit fabrication in an efficient manner. The tendency has been to use a fault model - a wide variety exists - especially the single stuck at n fault model which was created around the late 1950s [Eldred 59] and whose use, correctly or otherwise, has continued into this age of *CMOS* and *BiCMOS* (Bipolar CMOS mixed technology process). It has been suggested repeatedly that the stuck at model is insufficient for CMOS technology and lead to the development of the *stuck open* [Wadsack 78]. However, simulators for the single stuck at fault model are seemingly the dominant factor. Automatic test pattern generation is typically constructed for *s-at-n* faults. It is important to note that stuck open faults appear to be correctable through proper design approaches [Soden 89], are apparently detectable when a high single stuck at fault coverage exists simultaneously with nodes that change states frequently - *high toggle activity*, and that their occurrence is not as high as the literature had previously suggested [Shen 85].

Indeed, it has been suggested that certain structures such as PLAs may not be adequately modelled by the s-a-n regardless of the process technology.

The presence of a stuck at fault is commonly indicated by the use of a 5 valued logic system where any net l within the circuit, can have the value  $v \in \{0, 1, X, D, Dbar\}$ . The D signifies the presence of a Difference between a correctly fabricated and an improperly manufactured circuit. The intersections producing D and Dbar are shown in Table 3.1.1.1. This table shows 2 important concepts: (1) - the presence of a fault can only be indicated by the detection of a difference; (2) - that the difference

is only specified for the logic values 0 and 1.

|                            | ( | GOOD CIRCUIT |     |

|----------------------------|---|--------------|-----|

| FA                         |   | 0            | . 1 |

| F A U L T Y C I            | 0 | 0            | D . |

| C<br>R<br>C<br>U<br>I<br>T | 1 | D            | 1   |

Table 3.1.1.1: Rules for Difference intersection.

To successfully create a test for a given fault, it is essential to cause the difference D or Dbar, to be visible on at least one of the unit under test's primary outputs. Thus the difference must exist at two levels: (1) *locally* - that is for the sub element within the UUT which is the target for a fault and (2) *globally* - that is visible external to the UUT. Failure to comply with either requirement will cause the fault to be untestable.

Given a circuit to be tested, UUT, a set of faults can be created - typically this is at a gate level representation. The fault list or fault dictionary F(UUT) is generally unranked [Shen 85] meaning that any relative importance for the different faults is ignored. This fault dictionary may not be minimally sized since faults may be collapsed (reduced) on local and global levels. Generally n-input logic primitives such as AND and OR gates have their fault quantity reduced from 2n + 2 to n + 2 faults on a local level [Miczo 86]. Further fault collapsing can be obtained by using fault dominance [McCluskey 86] and fault equivalence [Miczo 86] relationships. Indeed,

at the local level, many n-input combinational logic functions can further reduce their faults to n + 1.

#### 3.2 Single versus Multiple path sensitization.

For a given circuit, the difference value may arrive at a *fanout stem* (a net which controls more than one destination logic element) as effort is expended, to cause the difference to appear on a primary output (PO). This scenario is depicted in Figure 3.2.1. One could chose to provide a path from this fanout stem to an PO by selecting a unique path, known as *single path sensitization* (SPS), or by selecting several paths, known as *multiple path sensitization* (MPS). In the case of SPS, "all" that one need do is to pick the best path - minimum effort (easiest) or least costly - among the legitimate choices available. MPS typically attempts to drive the error towards the UUT's POs by all possible valid paths. Picking the winning route in SPS is usually done with the aid of heuristics - indeed the use of testability measures such as the COP observability measure. The original version of PODEM [Goel 81] used a distance metric similar to SCOAP while Ivanov used COP in a later version [Ivanov 85]. A gate with an "X" on its output and having an error signal on one of its inputs, is known as a *D Frontier*; this D Frontier is the starting point for the path sensitization phase.

## 3.3 The Four ATPG phases of Deterministic Gate Level Test Generation.

Given an arbitrary unit under test for a given fault, such as shown in Figure 3.3.1, the objective is to generate a test assuming the presence of a fault - for this example and the remainder of this thesis unless expressly stated to the contrary, all test generation shall assume the single stuck at fault model - which will detect its presence in an improperly fabricated circuit. The element, an 2 input AND logic gate, is selected as the target for a fault represented as D. Prior to the test all internal nets are assumed to be Xs as are the UUT's PIs and POs.

Any ATPG can be reduced to a set of four basic operations when generating a test for a given fault. The sensitization (or error activation) of a fault for the element

within the UUT is required to render the fault visible - by the presence of a difference. Although for simple logic primitives, such as ANDs, ORs etc., this will only be done once per trial due to the small fault sensitization set, the sensitization phase can conceptually occur repeatedly if one cannot subsequently create an environment within the UUT by which a valid test is created. Once the difference has been created, the three other phases are engaged: the *error propagation* using either single or multiple path sensitization; *justification* of the nets' values which are set during the various phases and the evaluation of net values or *implication* phase. These phases may occur in a variety of sequences - this is an implementation issue.

To sensitize the s-a-0 error on the AND gate's output, Figure 3.3.1, it is first necessary to generate the difference D requiring that the fault free AND gate produce a logic 1 - refer to Table 3.1.1.1. This dictates that all the AND gate's inputs must be set to logic 1 for both the fault free and the faulted circuit. This step is referred to as the error sensitization or activation phase.

Once a net's value has been uniquely assigned ( $l \in \{0, 1\}$ ), an *implication* phase may be invoked. Implication is simply an evaluation (simulation) of the net's effect on other logic elements within the circuit and within its cone of influence. Since no fanout of the AND gate's inputs occur in this example, no implication is required due to the error sensitization. This simulation may occur whenever a list of nets, whose values have changed, exists. This phase can discover the presence of conflicts - a node that must take inconsistent values simultaneously: 0 and 1; D and 1 or Dbar and 0.

It is necessary to propagate the error, using an *error propagation phase*, until the error appears on at least one of the UUT's POs. Either single or multiple path sensitization may be used, and possibly a mixture of both. Figure 3.3.2 shows how the error propagation might occur.

It is also required to justify the assignment of net values. Net values are assigned when the error is sensitized and as the error is propagated at each logic primitive en route to an UUT PO. Figure 3.3.3 indicates how a typical justification phase might occur.

Thus, in general, one could represent the ATPG's actions by the pseudo code of Figure 3.3.4. The simplified code does not consider how the search space is created or how reversing previous decisions is handled. Also, it is not necessarily true that this order is followed exactly as there may be a variety of implementations. It is possible to add a fault simulation phase to identify other faults detectable by the test vector (using the deterministically generated stimulus). Fault simulation is one method that allows a more compact test set by targeting easier faults and without reverting to the use of vector manipulation routines after the completion of the test generation phase. Previous authors have indicated that a good percentage of the

UUT's fault set may be easily detectable by random vector generation - this is suggested by the rapid rate of fault detection early in the ATPG; it has been suggested that this is roughly in the 65% to 85% fault coverage region [Agrawal Seth 88]. Even in the case of sequential test pattern generation, one can find these central phases [Marlett 88].

The ATPG works backwards in the circuit graph to build the *decision space* or the *tree* that represents the search space for the fault in question by a process known as *backtracing*. While the circuit graph is immutable for the whole circuit during the test generation process, the decision space depends upon the target fault and the search algorithms (or procedure in the case of a non algorithmic program implementation). Should a decision be unjustifiable or create a conflict, the decision must be changed through a technique called *backtracking*. Although different methods might be used, driven by complex heuristics, the general principle is to change the last unchanged decision which will eliminate the pending conflict and which will not generate any new conflicts. Should no choices remain, an explicit or implicit exhaustive search of the decision space has occurred; this determines that the fault is

untestable due to redundancy which was previously seen to be caused by the presence of reconvergent fanout. Large backtracks usually trigger a limit and abort the search for the targeted fault.

```

while (Faults remain in UUT){

Pick a fault.

Sensitize the fault.

while (No test && Choices remain){

Propagate fault to an UUT PO.

Justify all nets' assignments.

Implication of nets' assignments.

}

Simulate for other faults detected by this test.

}

Figure 3.3.4: A typical ATPG algorithm.

```

The decision space's size, if one considers the UUT as a black box with n PIs, could consist of n nodes which are a 1:1 mapping of the PIs and their state. This is precisely the case for PODEM [Goel 81] while the D algorithm's size can potentially include a node for every circuit net. A tuple placed on a stack can be effectively used to represent the search space in a computer representation.

## 3.4 Random Test Pattern Generation and Hybrid Methods.

It has been suggested that the first portion of deterministic test generation, where each vector may detect many additional faults (hence the use of fault simulation), is due to the *random easiness* of these faults. Therefore these faults could be detected by using randomly generated test vectors. Many authors have

worked on such techniques [Bardell et al. 86] especially since much work in the Built In Self Test (BIST) area is centered on the use of pseudo random stimulus created by using LFSRs (Linear Feedback Shift Registers) such as that in Figure 3.4.1. Further work on varying the outputs weighting has occurred in order to allow nearly 100% fault detection.

An additional approach has been to use a two phase methodology: detect the random easy faults using randomly generated test vectors - performing fault simulation on these vectors; then switch to a deterministic automatic test pattern generator to detect the remaining faults. This method is depicted by the pseudo code in Figure 3.4.2. A recent article [Abramovici 89] suggests that this hybrid technique is of little or no use. Their research shows that random test vectors detect the same faults found in the second phase.

```

while (Faults remain in UUT){

while (Random easy){

Create a random test vector.

Perform fault simulation.

}

while (Not random easy){

Deterministic ATPG.

}

}

Figure 3.4.2: Random Test Pattern Generation.

```

Another approach to test pattern generation was suggested by Chang et al. in a hierarchical test generator CHIEFS [Chang et al. 86]. This ATPG used a technology independent circuit representation called binary decision diagrams (BDDs) [Akers 78a] which also allowed test generation for circuits about which no detailed design knowledge was available. The tests were built around the ability of the BDDs to represent the logical function of the circuit, readily constructed from the circuit's truth table. These experiments were designed to elicit stimulus that tested for correct operation and to test that undesired functionality was not present. Although obtaining good test coverage using this new fault model, the fault coverage using the single stuck at fault model tended to suffer - albeit that from one implementation method to another for the same circuit more consistency was achieved than by predecessors [Abadir Reghbati 85] [Abadir Reghbati 86]. Chang noted that this traditional fault coverage improved with increased implementation knowledge. Note that a new simulator was required to support this circuit and fault model. Until recently, this has been one of the few attempts to generate tests where hierarchy has been exploited.