| <b>Titre:</b> Title:    | Architectural Exploration of KeyRing Self-Timed Processors                                                                                                                       |

|-------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Auteur: Author:         | Mickaël Fiorentino                                                                                                                                                               |

| Date:                   | 2020                                                                                                                                                                             |

| Type:                   | Mémoire ou thèse / Dissertation or Thesis                                                                                                                                        |

| Référence:<br>Citation: | Fiorentino, M. (2020). Architectural Exploration of KeyRing Self-Timed Processors [Thèse de doctorat, Polytechnique Montréal]. PolyPublie. https://publications.polymtl.ca/5552/ |

# Document en libre accès dans PolyPublie Open Access document in PolyPublie

| URL de PolyPublie:<br>PolyPublie URL:    | https://publications.polymtl.ca/5552/ |

|------------------------------------------|---------------------------------------|

| Directeurs de<br>recherche:<br>Advisors: | Yvon Savaria, & Claude Thibeault      |

| <b>Programme:</b><br>Program:            | Génie électrique                      |

# POLYTECHNIQUE MONTRÉAL

affiliée à l'Université de Montréal

| Architectural exploration of KeyRing self-timed processor | Architectural | exploration | of KevRing | self-timed | processors |

|-----------------------------------------------------------|---------------|-------------|------------|------------|------------|

|-----------------------------------------------------------|---------------|-------------|------------|------------|------------|

## MICKAEL FIORENTINO

Département de génie électrique

Thèse présentée en vue de l'obtention du diplôme de Philosophix Doctor Génie électrique

Décembre 2020

# POLYTECHNIQUE MONTRÉAL

affiliée à l'Université de Montréal

Cette thèse intitulée:

Architectural exploration of KeyRing self-timed processors

présentée par Mickael FIORENTINO

en vue de l'obtention du diplôme de Philosophi  $\alpha$  Doctor a été dûment acceptée par le jury d'examen constitué de :

Jean-Pierre DAVID, président

Yvon SAVARIA, membre et directeur de recherche

Claude THIBEAULT, membre et codirecteur de recherche

Pierre LANGLOIS, membre

Zeljko ZILIC, membre externe

# **DEDICATION**

À mon père...

#### ACKNOWLEDGEMENT

En premier lieu, je remercie chaleureusement mes directeurs de thèse Yvon Savaria et Claude Thibeault pour leur soutien indéfectible durant les 5 années de mon doctorat. J'ai bénéficié d'une très grande liberté dans mes directions de recherches et dans mes choix éditoriaux; je les remercie tout particulièrement d'avoir toujours encouragé et appuyé mes décisions.

Merci aux membres du jury ainsi qu'à Tom Awad d'Octasic d'avoir pris le temps de lire et d'évaluer cette thèse de doctorat.

Mes remerciements s'adressent ensuite à tous mes collègues du GRM pour leur bienveillance à mon égard et leur enthousiasme quotidien. Je tiens à remercier particulièrement Omar et Érika avec qui j'ai noué des liens d'amitié qui dépassent de loin le cadre du laboratoire. Je leur dois beaucoup, et je leur serai éternellement reconnaissant d'avoir été à mes côtés. Merci à Michel, Mathieu, Thibaut, Jefferson et Thomas pour nos franches rigolades et nos débats animés. Un grand merci également à Réjean pour sa disponibilité sans faille, mais aussi et surtout pour son amitié sincère.

Je profite de cette occasion pour remercier mes amis, Céline, Anders, Sabrina, Bastien, Jeanne, Arthur, Alexy, et Jean-Baptise avec qui j'ai partagé cette tranche de vie à Montréal et que je n'oublierai jamais.

Enfin, je remercie toute ma famille, en particulier ma sœur et mon père, pour leur soutien inconditionnel et leur amour salvateur. Surtout, merci à Juliette, ma compagne, mon amie, ma confidente, l'amour de ma vie; merci à elle de rendre ma vie merveilleuse.

## RÉSUMÉ

Les dernières décennies ont vu l'augmentation des performances des processeurs contraintes par les limites imposées par la consommation d'énergie des systèmes électroniques : des très basses consommations requises pour les objets connectés, aux budgets de dépenses électriques des serveurs, en passant par les limitations thermiques et la durée de vie des batteries des appareils mobiles. Cette forte demande en processeurs efficients en énergie, couplée avec les limitations de la réduction d'échelle des transistors—qui ne permet plus d'améliorer les performances à densité de puissance constante—, conduit les concepteurs de circuits intégrés à explorer de nouvelles microarchitectures permettant d'obtenir de meilleures performances pour un budget énergétique donné. Cette thèse s'inscrit dans cette tendance en proposant une nouvelle microarchitecture de processeur, appelée KeyRing, conçue avec l'intention de réduire la consommation d'énergie des processeurs.

La fréquence d'opération des transistors dans les circuits intégrés est proportionnelle à leur consommation dynamique d'énergie. Par conséquent, les techniques de conception permettant de réduire dynamiquement le nombre de transistors en opération sont très largement adoptées pour améliorer l'efficience énergétique des processeurs. La technique de clock-qating est particulièrement usitée dans les circuits synchrones, car elle réduit l'impact de l'horloge globale, qui est la principale source d'activité. La microarchitecture KeyRing présentée dans cette thèse utilise une méthode de synchronisation décentralisée et asynchrone pour réduire l'activité des circuits. Elle est dérivée du processeur AnARM, un processeur développé par Octasic sur la base d'une microarchitecture asynchrone ad hoc. Bien qu'il soit plus efficient en énergie que des alternatives synchrones, le AnARM est essentiellement incompatible avec les méthodes de synthèse et d'analyse temporelle statique standards. De plus, sa technique de conception ad hoc ne s'inscrit que partiellement dans les paradigmes de conceptions asynchrones. Cette thèse propose une approche rigoureuse pour définir les principes généraux de cette technique de conception ad hoc, en faisant levier sur la littérature asynchrone. La microarchitecture KeyRing qui en résulte est développée en association avec une méthode de conception automatisée, qui permet de s'affranchir des incompatibilités natives existant entre les outils de conception et les systèmes asynchrones. La méthode proposée permet de pleinement mettre à profit les flots de conception standards de l'industrie microélectronique pour réaliser la synthèse et la vérification des circuits KeyRing. Cette thèse propose également des protocoles expérimentaux, dont le but est de renforcer la relation de causalité entre la microarchitecture KeyRing et une réduction de la consommation énergétique des processeurs, comparativement à des alternatives synchrones équivalentes.

La principale contribution de cette thèse est le développement conjoint de la microarchitecture KeyRing et de la méthode de conception automatisée, qui permet l'exploration architecturale de circuits KeyRing. En particulier, cette dissertation présente i) une définition rigoureuse de la microarchitecture KeyRing; ii) la conception de circuits KeyRing, incluant plusieurs processeurs de complexité croissante, ainsi que leurs alternatives synchrones utilisées comme points de comparaison pour l'évaluation des performances et de la consommation d'énergie; iii) des méthodes de conception dédiées, et des contraintes temporelles adaptées, rendant les circuits KeyRing compatibles avec les outils de synthèse et de vérifications temporelles standards; et iv) l'élaboration de protocoles expérimentaux permettant de générer des résultats reproductibles.

Un premier processeur, appelé *Mini-Mips*, basé sur la technique de conception asynchrone ad hoc d'Octasic, a été conçu en suivant une approche empirique. Son étude met au jour les principes de conception à l'origine de la microarchitecture KeyRing. Le Mini-Mips implémente une version simplifiée du jeu d'instruction MIPS, et cible une implémentation sur plateforme d'émulation matérielle FPGA, où il est comparé avec une alternative synchrone classique (pipeline à 5 étages). Des expériences réalisées sur la plateforme FPGA—permettant de contrôler l'exécution de programmes de test sur les processeurs cibles tout en observant leur consommation d'énergie—valident le fonctionnement du Mini-Mips. Cette première expérience met également en lumière les limitations de l'approche empirique, en particulier s'agissant de la méthode de conception. Ces limites sont repoussées avec la microarchitecture KeyRing et la méthode de conception automatisée qui y est associée.

Les Key Unit (KU)—circuits responsables de la génération décentralisée d'horloges asynchrones—ainsi que le protocole KeyRing—un arrangement de KU ayant une topologie toroïdale—sont au coeur de la microarchitecture KeyRing. Des définitions sont dérivées de l'analyse du graphe modélisant le protocole KeyRing. Elles permettent de prédire des propriétés des circuits KeyRing (niveau de parallélisme, performances) à partir des paramètres de la microarchitecture. Le modèle est également le support de définitions formelles pour les contraintes temporelles des circuits KeyRing. Ces contraintes sont décrites au format SDC, et exploitées par le flot de conception standard. Spécifiquement, les circuits KeyRing sont synthétisés en technologie ASIC 65 nm en utilisant les outils de conception de Synopsys. La méthode de conception automatisée proposée dans cette thèse est validée en simulation post-synthèse, et par l'analyse des rapports de l'analyse temporelle.

La microarchitecture KeyRing et sa méthode de conception automatisée sont valorisées par la conception du processeur KeyV, qui implémente la variante RV32IM complète du jeu d'instructions RISC-V. La comparaison de deux microarchitectures de KeyV—deux variantes

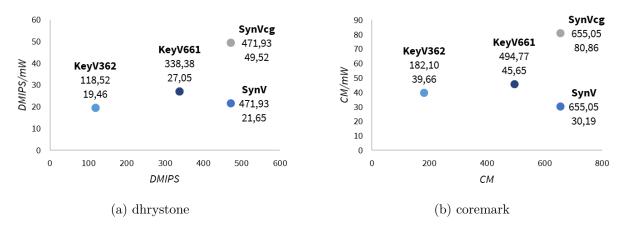

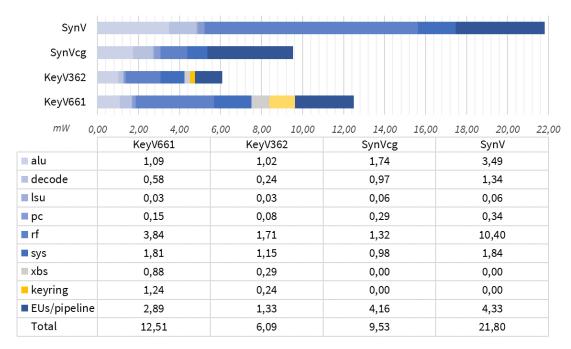

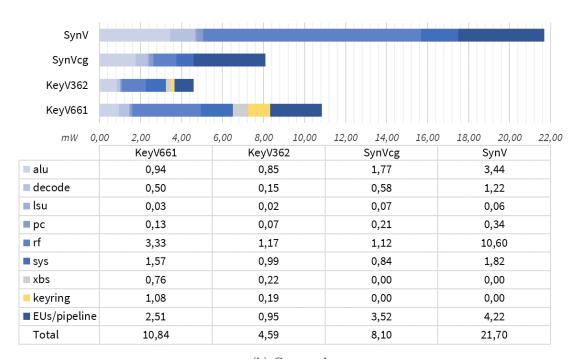

de la microarchitecture KeyRing—illustre les compromis de KeyRing entre résilience aux violations de contraintes temporelles, et performances. Un protocole expérimental basé sur les simulations post-synthèse des programmes de référence Dhrystone et Coremark, associées à l'analyse de puissance qui prend en compte l'activité des circuits en simulation, permet de comparer le processeur KeyV avec une alternative synchrone classique, appelée SynV (6 étages de pipeline), synthétisée avec et sans clock-gating. Les résultats montrent d'abord que les netlists de KeyV exécutent les programmes de références en simulation post-synthèse sans violations des contraintes temporelles. L'évaluation des performances et de la consommation d'énergie montre ensuite que KeyV possède une efficience énergétique entre celle de SynV avec clock-gating et celle de SynV sans clock-gating.

#### **ABSTRACT**

Over the last years, microprocessors have had to increase their performances while keeping their power envelope within tight bounds, as dictated by the needs of various markets: from the ultra-low power requirements of the IoT, to the electrical power consumption budget in enterprise servers, by way of passive cooling and day-long battery life in mobile devices. This high demand for power-efficient processors, coupled with the limitations of technology scaling—which no longer provides improved performances at constant power densities—, is leading designers to explore new microarchitectures with the goal of pulling more performances out of a fixed power budget. This work enters into this trend by proposing a new processor microarchitecture, called *KeyRing*, having a low-power design intent.

The switching activity of integrated circuits—i.e. transistors switching on and off—directly affects their dynamic power consumption. Circuit-level design techniques such as clock-gating are widely adopted as they dramatically reduce the impact of the global clock in synchronous circuits, which constitutes the main source of switching activity. The KeyRing microarchitecture presented in this work uses an asynchronous clocking scheme that relies on decentralized synchronization mechanisms to reduce the switching activity of circuits. It is derived from the AnARM, a power-efficient ARM processor developed by Octasic using an ad hoc asynchronous microarchitecture. Although it delivers better power-efficiency than synchronous alternatives, it is for the most part incompatible with standard timing-driven synthesis and Static Timing Analysis (STA). In addition, its design style does not fit well within the existing asynchronous design paradigms. This work lays the foundations for a more rigorous definition of this rather unorthodox design style, using circuits and methods coming from the asynchronous literature. The resulting KeyRing microarchitecture is developed in combination with Electronic Design Automation (EDA) methods that alleviate incompatibility issues related to ad hoc clocking, enabling timing-driven optimizations and verifications of KeyRing circuits using industry-standard design flows. In addition to bridging the gap with standard design practices, this work also proposes comprehensive experimental protocols that aims to strengthen the causal relation between the reported asynchronous microarchitecture and a reduced power consumption compared with synchronous alternatives.

The main achievement of this work is a framework that enables the architectural exploration of circuits using the KeyRing microarchitecture. Specifically, this work presents *i*) a rigorous definition of the KeyRing microarchitecture; *ii*) the design of KeyRing circuits, including several processors of increasing complexity, in combination with their synchronous alterna-

tives that can be used as baseline for performance and power consumption comparisons; iii) custom design flows and timing constraints enabling KeyRing circuits to benefit from timing-driven optimization and verification capabilities of standard EDA tools; and iv) the elaboration of experimental protocols that permit to generate reproducible results.

A first processor, called *Mini-Mips*, is designed with an Octasic-style asynchronous microarchitecture using an empirical approach. Its study allows to uncover the main design principles that are then used to define the KeyRing design style. The Mini-Mips implements a simplified version of the MIPS Instruction Set Architecture (ISA) and targets an Field Programmable Gate Array (FPGA) emulation platform. It is compared with a classical 5-stage synchronous pipeline microarchitecture having comparable characteristics. An EDA method is proposed for the timing-driven implementation of the asynchronous Mini-Mips on FPGA. It is validated by experimental results conducted on the emulation platform, which allows to control the execution of benchmarks on the processors while monitoring their power consumption. This first design attempt also demonstrates shortcomings of the design, and the EDA method, which are addressed in the KeyRing microarchitecture and the definitive EDA method.

At the core of the KeyRing microarchitecture are the Key Units (KUs), a self-timed clock controller, and the KeyRing protocol, an organization of KUs having a toroidal mesh topology. Definitions derived from the analysis of the KeyRing graph allow to predict the performances of KeyRing circuits, by establishing links between the parameters of the circuit, the level of parallelism, and the speed of self-timed clocks. Formal definitions of the timing constraints in KeyRing circuits are proposed. Their implementation in the standard SDC format is leveraged by a novel EDA method enabling the timing-driven synthesis of KeyRing circuits using industry-standard design flows. In particular, KeyRing circuits are synthesized using a 65 nm ASIC design kit and Synopsys EDA tools. The proposed EDA method is validated with post-synthesis timing simulations and the analysis of STA reports.

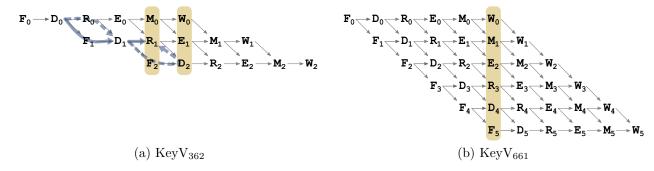

The KeyRing microarchitecture and the associated EDA method is showcased with the design of complete RV32IM RISC-V processor, called KeyV. Two KeyV microarchitectures are compared, illustrating trade-offs between robustness to timing-violations and performances. An experimental protocol based on post-synthesis timing simulations of the standard Dhrystone and Coremark benchmarks, combined with activity-aware power analysis, is proposed to compare KeyV processors with a 6-stage synchronous pipeline alternative, called SynV, synthesized with and without clock-gating. Results first show that the KeyV netlists successfully execute complex benchmarks in post-synthesis simulations without timing violations. Performance and power consumption evaluations then show that KeyV has a power efficiency in between SynV with clock-gating and SynV without clock-gating.

## TABLE OF CONTENTS

| DEDIC  | ATION  |                                                            | 111  |

|--------|--------|------------------------------------------------------------|------|

| ACKNO  | OWLEI  | OGEMENT                                                    | iv   |

| RÉSUM  | ſÉ     |                                                            | V    |

| ABSTR  | ACT    |                                                            | iii  |

| TABLE  | OF C   | ONTENTS                                                    | Х    |

| LIST O | F TAB  | LES                                                        | ciii |

| LIST O | F FIGU | URES                                                       | civ  |

| LIST O | F SYM  | BOLS AND ABBREVIATIONS                                     | vii  |

| СНАРТ  | TER 1  | INTRODUCTION                                               | 1    |

| 1.1    | Conte  | xt and Motivations                                         | 1    |

|        | 1.1.1  | Overview of energy-aware innovations in microprocessors    | 1    |

|        | 1.1.2  | Synchronous and asynchronous design paradigms              | 5    |

|        | 1.1.3  | Octasic ad hoc approach towards reducing power consumption | 9    |

| 1.2    | Object | 77                                                         | 13   |

| 1.3    | -      |                                                            | 16   |

| СНАРТ  | TER 2  | LITERATURE REVIEW                                          | 17   |

| 2.1    | Synch  | ronous and Asynchronous Circuits                           | 17   |

|        | 2.1.1  | Synchronization paradigms                                  | 17   |

|        | 2.1.2  | The elastic channel abstraction                            | 19   |

|        | 2.1.3  | Pipelining                                                 | 21   |

| 2.2    |        |                                                            | 23   |

|        | 2.2.1  | Micropipeline                                              | 24   |

|        | 2.2.2  | Mousetrap                                                  | 25   |

|        | 2.2.3  |                                                            | 26   |

| 2.3    | Octasi | ic ad hoc Asynchronous Design Style                        | 28   |

|        | 2.3.1  |                                                            | 28   |

|        | 2.3.2  |                                                            | 29   |

| 2.4   | Design | Automation                                                    | 33 |

|-------|--------|---------------------------------------------------------------|----|

|       | 2.4.1  | The standard synchronous design flow                          | 33 |

|       | 2.4.2  | Asynchronous design flows                                     | 34 |

| 2.5   | Static | Timing Analysis                                               | 37 |

|       | 2.5.1  | Timing constraints of synchronous and BD asynchronous designs | 38 |

|       | 2.5.2  | Relative Timing Constraints                                   | 40 |

|       | 2.5.3  | Integration of BD asynchronous circuits in standard STA tools | 41 |

| СНАРТ | TER 3  | MINI-MIPS: IMPLEMENTING A SIMPLE OCTASIC-STYLE ASYN-          |    |

| CHF   | RONOU  | JS PROCESSOR ON FPGA                                          | 44 |

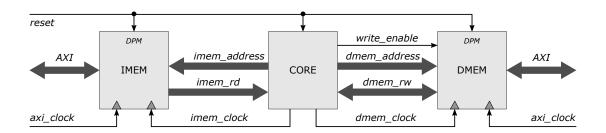

| 3.1   | Mini-N | Mips Architecture                                             | 45 |

| 3.2   | Top-le | vel and common building blocks                                | 45 |

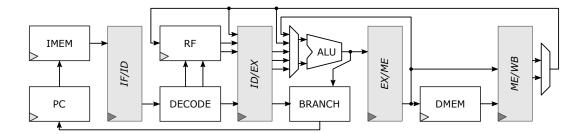

| 3.3   | The sy | vnchronous 5-stage pipeline microarchitecture                 | 46 |

| 3.4   | The O  | ctasic-style asynchronous microarchitecture                   | 48 |

|       | 3.4.1  | Overview                                                      | 49 |

|       | 3.4.2  | Instruction Level Parallelism                                 | 52 |

|       | 3.4.3  | Token Unit                                                    | 55 |

| 3.5   | FPGA   | Implementation Methodology                                    | 57 |

|       | 3.5.1  | Gate level design of asynchronous modules                     | 58 |

|       | 3.5.2  | Timing constraints                                            | 59 |

|       | 3.5.3  | Implementation flow                                           | 64 |

| 3.6   | Protot | syping Platform                                               | 65 |

| 3.7   | Experi | imental Results                                               | 68 |

|       | 3.7.1  | Resource utilization                                          | 69 |

|       | 3.7.2  | Post-implementation timing analysis                           | 69 |

|       | 3.7.3  | Runtime performance and power consumption                     | 73 |

| 3.8   | Limita | ations                                                        | 74 |

|       | 3.8.1  | Design                                                        | 75 |

|       | 3.8.2  | Simulations                                                   | 76 |

|       | 3.8.3  | Implementation methodology                                    | 78 |

| СНАРТ | TER 4  | MODELING THE KEYRING MICROARCHITECTURE                        | 80 |

| 4.1   | The T  | ribonacci Circuit                                             | 81 |

| 4.2   | Key U  | nits                                                          | 84 |

| 4.3   | In-Ord | ler KeyRing Systems                                           | 88 |

|       | 4.3.1  | General principles                                            | 89 |

|       | 4.3.2  | Predicting Performance                                        | 92 |

|       | 4.3.3  | Arbitrating the access to shared resources               | 94  |

|-------|--------|----------------------------------------------------------|-----|

| 4.4   | Static | Timing Analysis                                          | 95  |

|       | 4.4.1  | Relative Timing Constraints of KeyRing systems           | 96  |

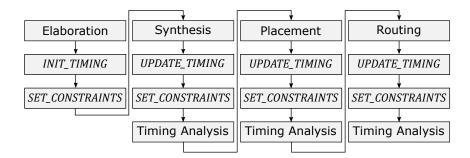

|       | 4.4.2  | Timing driven synthesis flow                             | 99  |

|       | 4.4.3  | The KeyRing Tcl library                                  | 101 |

| СНАРТ | TER 5  | KEY-V: ARCHITECTURAL EXPLORATION OF KEYRING RISC-        | V   |

| PRO   | CESSO  | ORS WITH A TIMING-DRIVEN ASIC DESIGN FLOW                | 104 |

| 5.1   | Softwa | re Ecosystem                                             | 105 |

|       | 5.1.1  | RISC-V ISA                                               | 105 |

|       | 5.1.2  | Toolchain                                                | 106 |

|       | 5.1.3  | Benchmarks                                               | 107 |

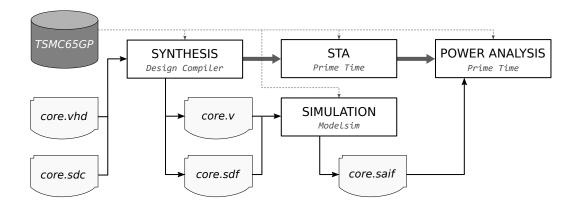

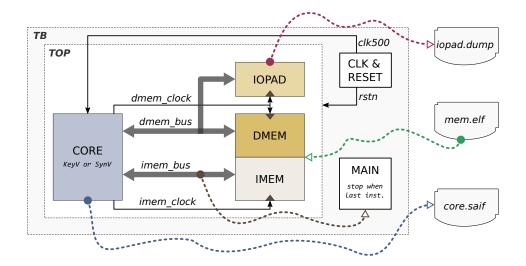

| 5.2   | EDA I  | Ecosystem                                                | 108 |

|       | 5.2.1  | Synthesis flow                                           | 109 |

|       | 5.2.2  | Simulation flow                                          | 110 |

| 5.3   | SynV:  | RISC-V Processor Based on a 6-stage Synchronous Pipeline | 111 |

| 5.4   | KeyV:  | RISC-V Processors Based on the KeyRing Microarchitecture | 113 |

|       | 5.4.1  | $KeyV_{362}$ & $KeyV_{661}$ microarchitectures           | 114 |

|       | 5.4.2  | Handling stalls                                          | 117 |

|       | 5.4.3  | Synchronization with synchronous modules                 | 119 |

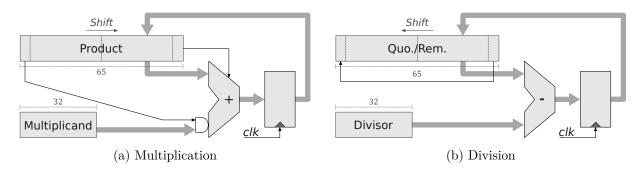

|       | 5.4.4  | Multiplier/Divider submodule inner-KeyRing               | 121 |

|       | 5.4.5  | Timing constraints                                       | 123 |

| 5.5   | Experi | imental Results                                          | 126 |

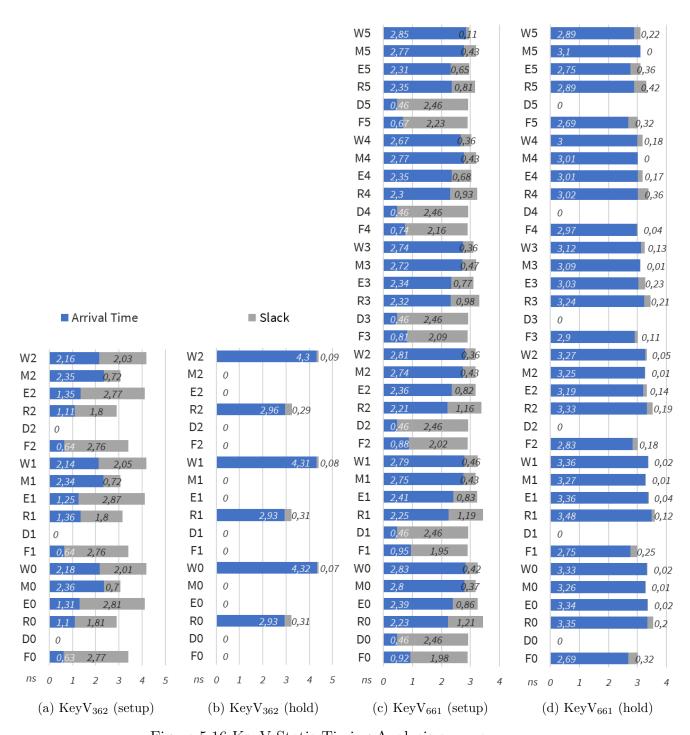

|       | 5.5.1  | Timing                                                   | 128 |

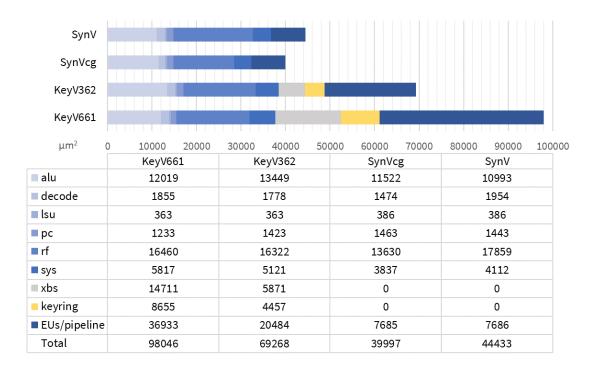

|       | 5.5.2  | Area                                                     | 135 |

|       | 5.5.3  | Performance                                              | 136 |

| СНАРТ | TER 6  | CONCLUSION                                               | 140 |

| 6.1   | Summ   | ary                                                      | 140 |

| 6.2   |        | tions                                                    | 143 |

| 6.3   |        | e Research                                               | 144 |

| REFER | ENCES  | 5                                                        | 146 |

# LIST OF TABLES

| 3.1 | Resources utilization summary              | 69  |

|-----|--------------------------------------------|-----|

| 5.1 | KeyV DEs configurations                    | 126 |

| 5.2 | Summary of KeyV and SynV synthesis results | 127 |

# LIST OF FIGURES

| 1.1  | Levels of abstraction involved in solving problems with microprocessors |

|------|-------------------------------------------------------------------------|

| 1.2  | [3]                                                                     |

| 1.3  | Comparison of the AnARM performance                                     |

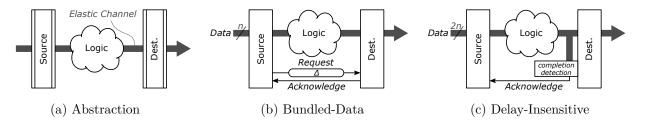

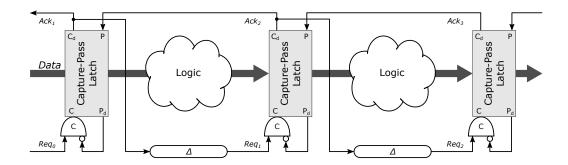

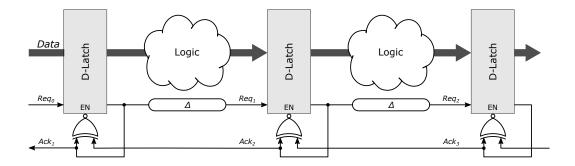

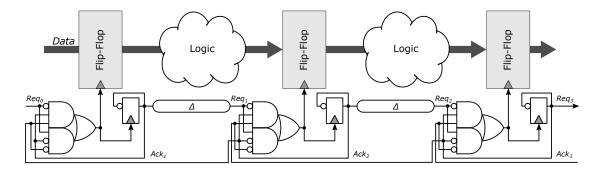

| 2.1  | Main sequential circuits synchronization paradigms                      |

| 2.2  | Asynchronous elastic channels                                           |

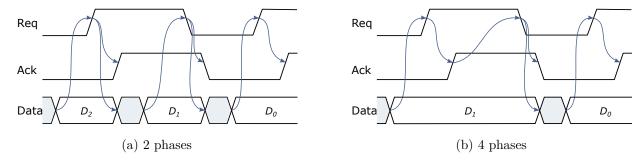

| 2.3  | Handshaking protocols                                                   |

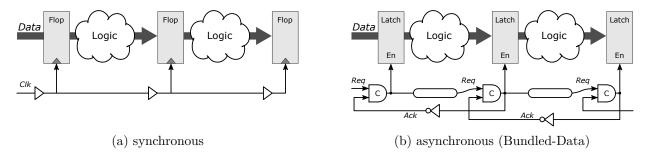

| 2.4  | Simple linear pipelines implementations                                 |

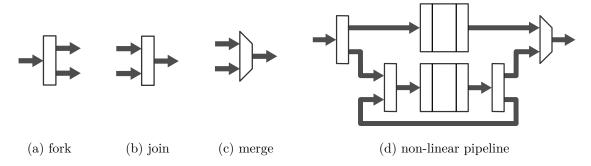

| 2.5  | Non-linear asynchronous pipeline components and example implemen-       |

|      | tation                                                                  |

| 2.6  | Micropipeline                                                           |

| 2.7  | Mousetrap                                                               |

| 2.8  | Click Elements                                                          |

| 2.9  | AnARM processor top-level organization                                  |

| 2.10 | Typical Execution Unit (EU) stages                                      |

| 2.11 | Illustration of Instruction Level Parallelism in the AnARM              |

| 2.12 | Timing of a typical synchronous pipeline stage                          |

| 2.13 | Timing of a typical Bundled-Data asynchronous pipeline stage 39         |

| 3.1  | Mini-Mips Top-Level                                                     |

| 3.2  | Overview of the Mini-Mips synchronous 5-stage pipeline microarchitec-   |

|      | ture                                                                    |

| 3.3  | Instruction Level Parallelism in the synchronous 5-stage pipeline 48    |

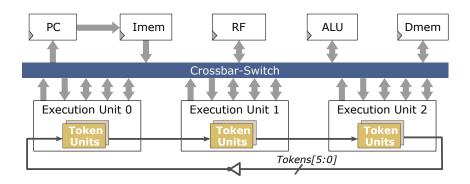

| 3.4  | Octasic-style asynchronous Mini-Mips core top-level organization 50     |

| 3.5  | Multicycle Execution Unit                                               |

| 3.6  | Organization of EU stages in the Octasic-style asynchronous microar-    |

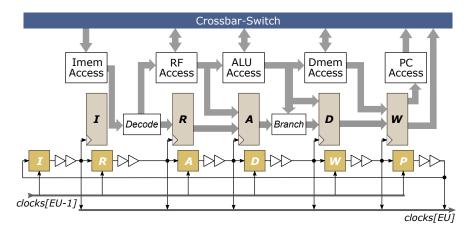

|      | chitecture                                                              |

| 3.7  | Instruction Level Parallelism (ILP) implementation trade-offs using the |

|      | Octasic-style asynchronous microarchitecture                            |

| 3.8  | Token Unit in the Mini-Mips                                             |

| 3.9  | Delay Element in the Mini-Mips                                          |

| 3.10 | VHDL code snippet of a DE stage mapped into one LUT of 7-series         |

|      | FPGAs                                                                   |

| 3.11 | VHDL code snippet of a typical EU stage                                 |

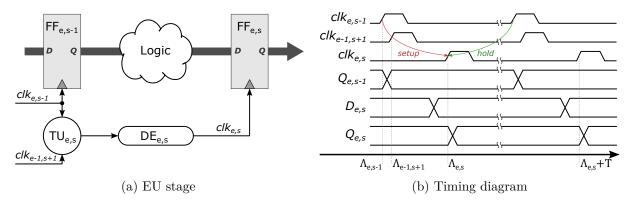

| 3.12 | Clocking scheme of a typical Octasic-style asynchronous EU stage              | 60  |

|------|-------------------------------------------------------------------------------|-----|

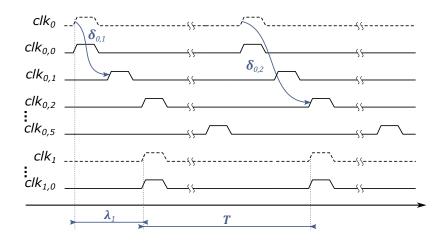

| 3.13 | Timing diagram showing how the clocks in the Octasic-style asyn-              |     |

|      | chronous Mini-Mips are defined in the timing constraints                      | 62  |

| 3.14 | Octasic-style asynchronous Mini-Mips FPGA implementation flow $$ .            | 65  |

| 3.15 | Prototyping platform for the Mini-Mips cores based on a Xilinx ZC706          |     |

|      | board                                                                         | 66  |

| 3.16 | Post-implementation STA and timing simulation results of the Octasic-         |     |

|      | style asynchronous Mini-Mips core implemented on a Xilinx 7-series            |     |

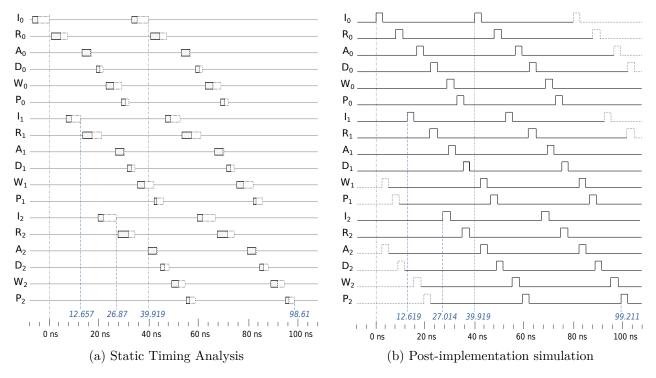

|      | FPGA                                                                          | 70  |

| 3.17 | STA results showing the benefits of the reported timing-driven imple-         |     |

|      | mentation methodology compared with a non timing-driven implemen-             |     |

|      | tation flow                                                                   | 72  |

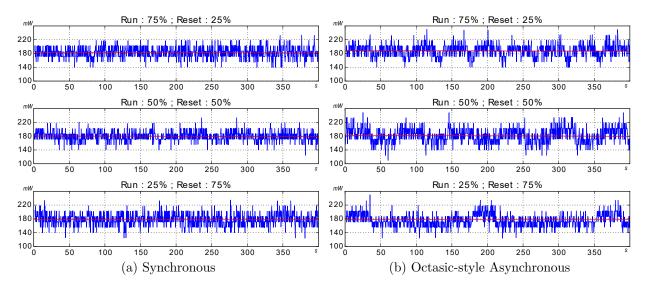

| 3.18 | Power consumption of the Mini-Mips processors                                 | 73  |

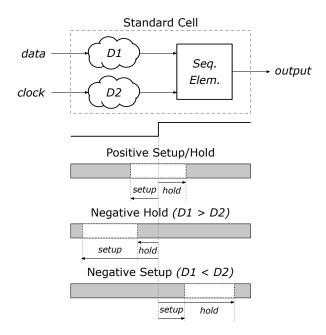

| 3.19 | Setup & Hold timing checks intervals used in timing simulations [103]         | 78  |

| 4.1  | Key<br>Ring sequential circuit implementing the Tribonacci sequence $\ \ .$ . | 81  |

| 4.2  | Execution flow of the Tribonacci KeyRing circuit                              | 83  |

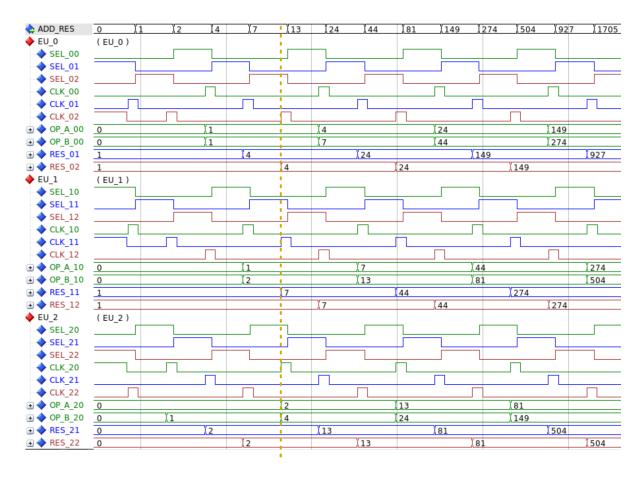

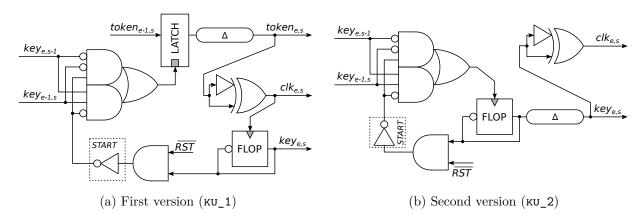

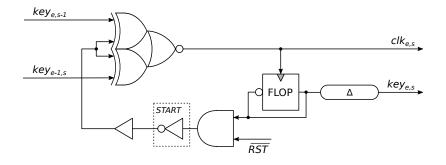

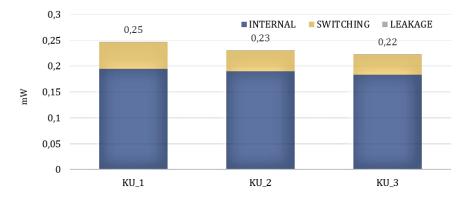

| 4.3  | Key Unit design iterations                                                    | 84  |

| 4.4  | Key Unit final version ( $\kappa u_3$ )                                       | 85  |

| 4.5  | Comparison of the KeyRing power consumption                                   | 86  |

| 4.6  | A generic KeyRing circuit                                                     | 88  |

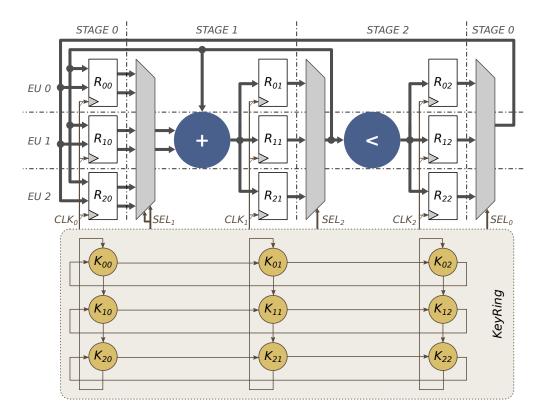

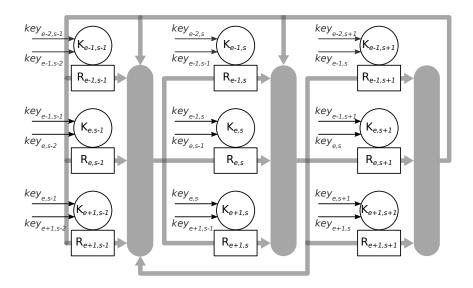

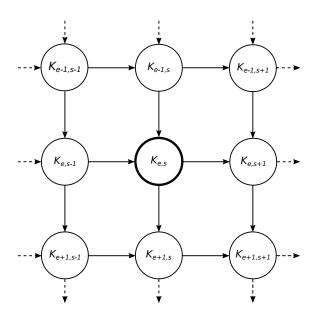

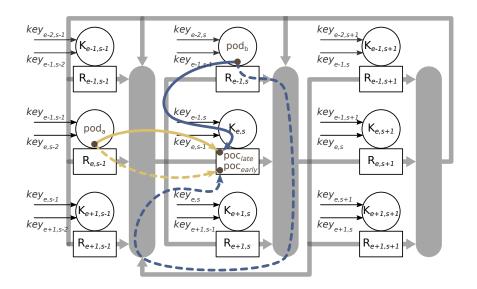

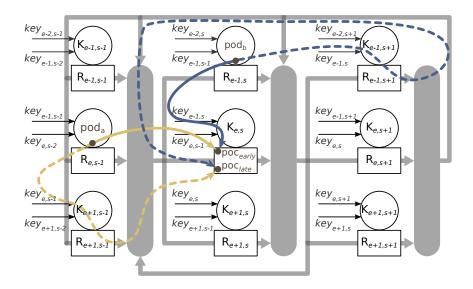

| 4.7  | The KeyRing protocol                                                          | 89  |

| 4.8  | Arbitration of resources access between Execution Units stages                | 95  |

| 4.9  | Protocol-level $setup$ RTCs definitions in a KeyRing circuit                  | 96  |

| 4.10 | Protocol-level $hold$ RTCs definitions in a KeyRing circuit                   | 97  |

| 4.11 | Code snippet from the KeyRing.tcl package showing the KeyRing                 |     |

|      | data structure                                                                | 103 |

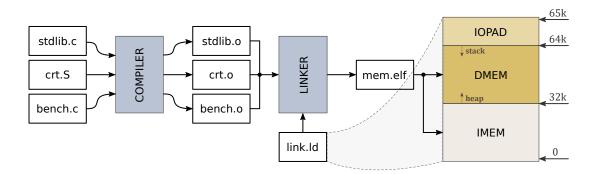

| 5.1  | Software environment used for the compilation of benchmarks into              |     |

|      | RV32IM binaries targeting KeyV and SynV processors                            | 106 |

| 5.2  | Code snippet from $\mathtt{crt.S}$ illustrating how programs start and end $$ | 107 |

| 5.3  | EDA environment used for the implementation, verification, and per-           |     |

|      | for<br>mance/power evaluation of KeyV and SynV processors                     | 108 |

| 5.4  | Overview of the simulation environment used to assess the perfor-             |     |

|      | mances and record the activity of KeyV and SynV processors while              |     |

|      | executing a benchmark                                                         | 110 |

| 5.5  | Overview of the SynV 6-stage pipeline microarchitecture                       | 111 |

| 5.6  | Multiplication & division Finite State Machines (FSMs)                        | 112 |

| 5.7  | Overview of KeyV processors microarchitecture                        | 113 |

|------|----------------------------------------------------------------------|-----|

| 5.8  | Branches                                                             | 115 |

| 5.9  | Comparison of Instruction Level Parallelism in KeyV processors       | 116 |

| 5.10 | Implementation of stalls in KeyV                                     | 117 |

| 5.11 | Synchronization of the (synchronous) cycle counter with the KeyRing  | 120 |

| 5.12 | Proposed circuits to clock the mul/div FSMs using a $(1,1,1)$ inner- |     |

|      | KeyRing, and to synchronize it with the main KeyRing                 | 121 |

| 5.13 | Simulation snapshot showing the use of the inner-KeyRing             | 122 |

| 5.14 | Setup Timing Report                                                  | 132 |

| 5.15 | Hold Timing Report                                                   | 133 |

| 5.16 | KeyV Static Timing Analysis summary                                  | 134 |

| 5.17 | Area comparison of KeyV and SynV                                     | 135 |

| 5.18 | Performance and power efficiency comparison of KeyV and SynV         | 136 |

| 5.19 | Comparison of KeyV and SynV power consumption broken down by         |     |

|      | modules                                                              | 139 |

#### LIST OF SYMBOLS AND ABBREVIATIONS

ALU Arithmetic and Logic Unit

ASIC Application Specific Integrated Circuit

BD Bundled-Data BM Burst Mode

BFS Breadth First Search

CAD Computer Aided Design

CCS Composite Current Source

CISC Complex Instruction Set Computing

CLB Configurable Logic Block

CSR Control Status Register

CTS Clock Tree Synthesis

DC Design Compiler

DE Delay Element

DI Delay-Insensitive

DPM Dual Port Memory

DSP Digital Signal Processor

DVFS Dynamic Voltage and Frequency Scaling

DVS Dynamic Voltage Scaling

EDA Electronic Design Automation

EU Execution Unit

FIFO First In First Out

FSM Finite State Machine

FPGA Field Programmable Gate Array

GALS Globally Asynchronous Locally Synchronous

GCC GNU Compiler Collection GPDK General Purpose Design Kit

HDL Hardware Description Language

ILP Instruction Level Parallelism

IoT Internet Of Things

IP Intellectual Property

ISA Instruction Set Architecture

ITRS International Technology Roadmap for Semiconductors

KU Key Unit

LCS Local Clock Set

LUT Look Up Table

LSU Load Store Unit

MIPS Millions Instructions Per Second

MMACS Millions of Multiply-and-Accumulate operations per Second

NRZ Non Return to Zero NoC Network on Chip

NTC Near Threshold Computing

PaR Place and Route PC Program Counter

PCB Printed Circuit Boards

PL Programmable Logic

PS Processing System

PVT Process, Voltage, and Temperature

QDI Quasi-Delay-Insensitive

RAW Read After Write

RF Register File

RISC Reduced Instruction Set Computing

RT Relative Timing

RTC Relative Timing Constraint RTL Register Transfer Level

RZ Return to Zero

SDC Synopsys Design Constraints

SDD Small-Delay Defect

SDF Standard Delay Format SNUG Synopsys User Group

SoC System On Chip

STA Static Timing AnalysisSTG Signal Transition GraphTDP Thermal Design Power

TLM Transaction Level Modeling

TU Token Unit

VLSI Very Large Scale Integration

WAR Write After Read

XBM eXtended Burst Mode

XDC Xilinx Design Constraints

#### CHAPTER 1 INTRODUCTION

#### 1.1 Context and Motivations

Improving the energy efficiency of Very Large Scale Integration (VLSI) circuits is the main driving force of the microelectronic industry [1]. As the most ubiquitous components of information systems, microprocessors are representative of this trend. Their wide range of applications require different trade-offs in the performance vs. power consumption space. On one hand, processors designed for wireless sensors found in the Internet Of Things (IoT) typically have ultra-low power requirements. On the other hand, processors designed for computational intensive tasks, as found in personal computers and servers, favor high performances. In between, processors designed for mobile and embedded devices are instances where the performance/power trade-offs are the most aggressively explored. Indeed, in recent years, mobile processors have benefited from tremendous improvements in performances while keeping their power envelope within tight boundaries, as dictated by the requirements of the mobile devices market: passive cooling, and day-long battery life [2]. Technologies, architectures, and design methods that enhance the energy efficiency of microprocessors are beneficial for the entire design space—low-power processors can have better performances, and high-performance processors can consume less power. Given the scale at which processors are deployed, even minor improvements can have huge impacts. Apart from power and performances, other challenges have been identified by the International Technology Roadmap for Semiconductors (ITRS), which include dealing with increased variability, aging, scalability, and fault rates, as the integration density of VLSI circuits continues to rise.

## 1.1.1 Overview of energy-aware innovations in microprocessors

Figure 1.1 Levels of abstraction involved in solving problems with microprocessors [3]

Patt presents in [3] a view of microprocessors in abstraction layers, as depicted in Figure 1.1. Problems, formulated by algorithms, are eventually solved in microprocessors by flows of electrons, controlled by an arrangement of transistors. The discipline of microprocessor design lie between the *program* and the *physics* abstractions. Architectures (also known as

Instruction Set Architectures (ISAs)) are the specifications of processors, which are implemented in microarchitectures by means of circuits. Each of these abstraction layers has an impact on the performance and the power consumption of microprocessors. For decades, improvements in performances of microprocessors were led by innovations in transistors architectures and manufacturing processes. But the sustained increase in transistor switching rates, as we moved from one transistor technology to the next, also led to an overall growth in power consumption [1]. For example, the *PowerPC 601*, launched by IBM in 1993, has a Thermal Design Power (TDP) of 6,5 W and operates at 75 MHz, while the *Power*?, released by IBM in 2010, has a TDP of 200 W and operates at 3.5 GHz [4]. Around the 2010's, the industry hit a power-wall—increasing the switching rates further would lead to TDPs that could not be properly handled by most systems. In the mean time, the semiconductor manufacturing industry—that is, the companies, called foundries, that fabricate the chips from silicon wafers based on circuits design—was facing technological challenges that slowed down Moore's law. New transistor architectures and innovative manufacturing processes require important investments, which results in Application Specific Integrated Circuits (ASICs) having ever increasing production costs. These two factors—the power wall and the manufacturing costs—have been the source of renewed interests in microarchitectural and circuits innovations, which today have a greater influence on the overall growth in energy efficiency of microprocessors. In this work, we focus on the microarchitectural aspect of microprocessors. CMOS VLSI circuits consume most of their energy in switching transistors. That is, the dynamic energy consumption due to transitions  $(0 \to 1 \text{ and } 1 \to 0)$ , has a greater influence than the static energy consumption due to on- and off-currents dissipations while the transistors are idle. The power  $P_{dynamic}$  required per transistor depends on the capacitive load  $C_{load}$  it drives, the voltage V, and the frequency of the transitions F [5]:

$$P_{dynamic} \propto C_{load} \times V^2 \times F \tag{1.1}$$

Dynamic power is first impacted by innovations in transistor architectures and manufacturing processes. Voltages have dropped from 5 V down to 1 V, and the load capacitance has decreased as we moved from one transistor technology node to the next, reducing power consumption. Higher integration density of transistors, coupled with higher switching frequencies, have, as a first approximation, increased power consumption as much as they have improved performances, thus having a moderated impact on energy. Alternative circuits logic style have been proposed as a way to reduce dynamic power or improve performances. For example, dynamic logic styles—such as domino logic, C<sup>2</sup>MOS, or pass-transistor logic, which were widely used in asynchronous circuits—were proposed as energy-efficient alterna-

tives to the static CMOS logic style [6,7]. But CMOS logic remains the de-facto choice for semi-custom design methodologies of VLSI circuits, because they compare favorably with respect to circuit speed and layout efficiency, and are robust against transistor downsizing and voltage scaling which allow efficient performance and power optimizations [8]. Indeed, in the last decade, the CMOS scaling paradigm has changed from "speed hungry" to "power thrifty" [9]. For example, operating transistors in the sub-threshold regime—a circuit design technique, called Near Threshold Computing (NTC) [10]—is of prevailing importance today. NTC is widely adopted in the ultra-low power design space because it is extremely effective to reduce energy, by scaling voltages down to 0,6 V, despite inducing performance penalties. An influential research project conducted at the ETH Zurich, called PULP, have recently demonstrated the effectiveness of this technique with a System On Chip (SoC) achieving 1 GOPS within a 10 mW power envelope [11].

On the opposite side of the microprocessor abstraction view, programs and architectures as well have an important impact on dynamic power. ISAs designed for the typical case, favoring fewer, and simpler, instructions—a paradigm known as Reduced Instruction Set Computing (RISC)—, are more energy efficient than Complex Instruction Set Computing (CISC) architectures alternatives [5]. Although CISC architectures can produce shorter programs, having more instructions that are more complex leads to microarchitectures with longer datapaths and bigger control structures, which results in an overall increase in power due to both a higher number of transistors and a higher switching activity. Compilers, often designed with microarchitectural aspects in mind, allow to optimize programs to reduce their size and improve their performance, thus improving the overall energy efficiency of the system.

Another key component enabling energy-aware designs is automation. Advances in software development, coupled with improvements of processors performances, enabled the advent of Electronic Design Automation (EDA) in the late 1980's [12]. Hardware Description Languages (HDLs), such as VHDL and Verilog, were created in combination with simulation engines, logic synthesis tools, and placement and routing algorithms, to automate the conception of VLSI circuits from high-level models. Computer Aided Design (CAD) tools have been responsible for a paradigm shift in the way integrated circuits are designed. Indeed, high-level modeling and simulations allow to design circuits that are more complex and less error prone; the synthesis of these models into optimized gate level circuits improves performance and power consumption, while lowering time-to-market; timing verifications and formal equivalence improve reliability, etc. For example, synthesis tools automatically size and organize the gates in a circuit according to user-defined constraints. Optimization algorithms balance constraints of conflicting purposes (e.g. performance and power)—for instance by choosing gates of varying sizes and drive strength—, to find the optimal design point.

Dynamic power can be reduced with system-level innovations, the most widely adopted of which are Dynamic Voltage Scaling (DVS) and clock-gating [13]. The DVS technique allows to alter the voltage of a circuit, or part of a circuit, as a function of its computation requirements. It is most effective in large circuits, where the chip can be split in independently powered island. The voltage of each island is dropped down when no computations are performed, thus saving power. The frequency of the processing islands can also be altered to improve the power savings, in which case the technique is referred to as Dynamic Voltage and Frequency Scaling (DVFS). The clock-gating technique only affects the switching frequency parameter F. Instead of altering the transistors switching rate, which, as we have seen, has a limited impact on energy, the idea is to limit the number of transistors switching, during the computation of a task, to the one being used for that computation. Clock-gating is performed by advantageously placing dedicated clock-gating cells on the clock-tree; a process mostly automated with modern EDA tools. These cells, dynamically controlled by the circuit, can block a clock signal reaching a group of registers, thus preventing the logic driven by these registers from switching. In large circuits, it can have huge impacts on the power consumption, while having virtually no impact on performances. The DVFS and the clockgating techniques are often used in combination. When used in smaller circuits, however, the power consumption overhead due to the added logic required to implement both techniques can dominate over the savings they induce by operating.

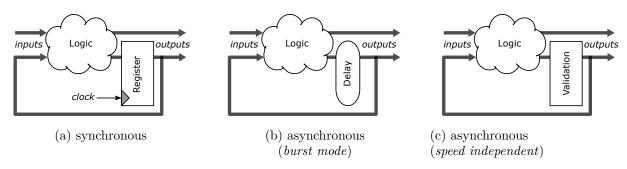

Finally, dynamic power is affected by the Register Transfer Level (RTL) design paradigm used in the system. There are two main competing branches: the synchronous design paradigm, in which data are sampled at a fixed rate using a global synchronization signal called a clock, and the asynchronous design paradigm, in which data are sampled at a dynamic rate using local synchronizations mechanisms [7,14,15]. Both design paradigms were born at the same time, in the 1950's, from the requirements of sequential circuits implementing Finite State Machines (FSMs)—that is, the need for synchronization methods allowing to update the logical states of FSMs, while preventing glitches due to propagation delays through combinational logic and feedback loops. When computers occupied the space of entire rooms, the delays involved in moving data favored designing with an asynchronous approach (the ILIAC is a famous example of such early processors built from asynchronous design principles). As computers scaled down to Printed Circuit Boards (PCBs), first, and to VLSI circuits then, in the 1970's, the delays decreased enabling synchronous circuits to thrive. The synchronous paradigm started to dominate, mainly because it is inherently simpler than its asynchronous competitor. The rise of EDA took place while the synchronous paradigm was mainstream. Over the years, the synchronous paradigm has driven the evolution of CAD tools towards meeting its design needs, thus solidifying its dominance.

## 1.1.2 Synchronous and asynchronous design paradigms

The synchronous paradigm is efficient. Having a single clock signal, with a fixed periodicity, dictating the pace of the circuit facilitates the design and eases automation. On one hand, the simplicity of synchronous designs enables repeatable structures, and generic communication channels that favor design reuse [16]. The different building blocks of a big circuit can be built and assembled independently, using synchronizers if the clocks frequencies do not match [17]; the knowledge of tow modules native frequency is enough to synchronize their contents. This had a great influence on the emergence of companies specializing in the design of reusable modules, called Intellectual Property (IP), intended to be used as part of bigger circuits. On the other hand, the simplicity of the timing conditions ensuring the correct operation of synchronous circuits—the rate at which logic states can be updated must be within the bounds of the clock frequency—are easy to enforce and validate. These timing conditions are translated into design constraints, which fuel EDA tools optimization algorithms and verification engines. This dual outcome of the synchronous paradigm simplicity—common design practices favoring design reuse, and simple timing requirements enabling the extensive use of design automation—is the backbone of its resilience and long-term dominance [1].

However, the synchronous paradigm suffers from performance and power limitations due to the distribution of the clock [18]. First, the distribution of a global clock signal throughout a VLSI chip—often performed using Clock Tree Synthesis (CTS)—becomes more difficult as the density of integration of VLSI circuits increases. Indeed, as circuits carry on with Moore's law, the relative distance between synchronization elements increases, and wire delays have a greater impact on the total delay of the logic. The skew induced by longer clock distribution networks—that is, the maximum delay between the occurrences of a clock edge in different locations of the circuit—has limited the performances of VLSI circuits to the point where, passed a certain complexity, it is now impossible to use a single clock signal for the entire design without seriously altering its performances. Furthermore, this trend is accentuated by the difficulty to achieve timing closure—that is, validating the correct operation of the circuit from a timing perspective—in face of increased Process, Voltage, and Temperature (PVT) variations induced by technology scaling. This is especially pronounced with synchronous circuits, which must account for the worst-case delays in the circuit to size the clocks. Then, in addition to the performance penalties induced by clock skews, the scaling of the clock distribution network has resulted in important power consumption issues. A famous example illustrating the impact of the clock tree on the power consumption of a microprocessor is the Alpha 21164. In a 1998 publication [19], the authors uncover the power breakdown of this high-performance processor, showing that the clocks are responsible of over 40 % of the total.

The asynchronous paradigm is elegant. Unlike the theory of synchronous circuits design, which is quite simple, the theoretical aspects of asynchronous circuits design is still an active research area. This field, which has seen significant development since the late 1980's, is derived from both the first asynchronous FSMs of the 1950's, with the influential work of Huffman and Muller, and the theory of concurrency developed in computer science. The formal models of the asynchronous paradigm, which are conceptualized at a level of abstraction close to fundamental mathematics, not only have direct implications when applied to real circuits, but also play a significant role in arousing the interest of the research community. Asynchronous theories are elegant—the mathematical term for beautiful—, and their study should be pursued out of sheer curiosity, which is the most noble aspect of research.

On a more practical note, asynchronous designs have the potential to address the shortcomings of synchronous circuits, with respect to power consumption, PVT variations, and noise, while having competitive performances and proving robust to faults and aging [20]. Indeed, asynchronous circuits use distributed synchronization mechanisms, as opposed to the centralized clock used in synchronous systems, which support, by design, the modular compositions of variability-tolerant systems. This allows to adapt dynamically the activity of the circuit based on the computation requirements of the task being processed, without extensive instrumented power management. The inherent elasticity of asynchronous circuits is the source of their versatility, which makes them suitable candidates for a variety of use cases [21]. In the high-performance design space, designers use the elasticity of fine-grain asynchronous pipelines to achieve high throughputs. Two projects, both published in 1997, have famously attempted to demonstrate the superiority of asynchronous microprocessors: the asynchronous MIPS R3000 from the California Institute of Technology [22], and the AMULET, an asynchronous ARM developed in the University of Manchester [23]. Of interest is also the development of RAPPID [24], an asynchronous instruction length decoder for the Intel Pentium II processor, which achieved a 3× better throughput, 2× better latency, while consuming  $2 \times$  less power within the same area footprint as the fastest commercial synchronous alternative fabricated on the same CMOS 0.25 µm process. In the low-power design space, designers exploit the distributed synchronization schemes of asynchronous systems to save power by reducing the switching activity of the circuit. A recent example illustrating this use-case is the asynchronous MSP430—a 16-bit Digital Signal Processor (DSP) from Texas Instruments (TI)—developed in the University of Utah in 2017, which exhibits a minimum of  $5 \times$  energy per instruction improvement over a synchronous alternative [25]. Finally, asynchronous circuits have proved successful in some niche applications, such as contactless secured smartcards used in banking, or passport applications, where, in addition to being robust to the voltages variations of the energy source, their properties are also exploited

to counter hardware attacks. Some companies have successfully made the asynchronous paradigm an industrial reality. To name a few that are still active today: *Achronix* develops Field Programmable Gate Arrays (FPGAs) based on high-speed asynchronous logic; *Fulcrum*—now part of Intel—produces high-speed asynchronous networking chips; *Tiempo* designs variability-tolerant asynchronous circuits for secured smartcards; and *Octasic* develops communication systems based on their custom asynchronous DSPs [15, 20].

However, it is clear that the adoption of asynchronous circuits has been limited, and that the vast majority of the circuits designed today still rely on the synchronous paradigm. This can be explained by a combination of factors [7, 15]. First, asynchronous design styles are plentiful. In contrast with the synchronous paradigm, in which a fairly small number of design guidelines are agreed-upon [16], there is a wide range of asynchronous design styles, which vary with respect to data encoding, synchronization protocols, circuits logic styles, etc. Although this is the result of a healthy and productive research environment—many avenues are explored, which uncover new design opportunities—, it has the side effect of preventing design reuse. Paradoxically, most asynchronous design styles, when taken alone, surpass the synchronous paradigm in terms of modularity (for example, it is possible to communicate between circuits in separated chips without synchronizers). But it is difficult—if possible at all—to interface asynchronous circuits having different design styles. This limited design reuse is worsened by the dominance of synchronous circuits, as commercial IPs are likely to be synchronous, making their integration within an otherwise asynchronous system more complex. In addition, having multiple asynchronous design styles, each with a steep learning curve, does not play in favor of a growing designer base. The second factor affecting the adoption of asynchronous circuits is their lack of support by standard EDA tools, and their limited compatibility with conventional design and verification flows. Indeed, the leaders in the EDA industry (Cadence, Synopsys, and Mentor in the ASIC world, and Xilinx and Altera—now part of Intel—in the FPGA world) never invested in asynchronous technologies. In addition, most asynchronous design styles rely on specific cells—the Muller C-element is a good example—that are typically not part of the standard cells provided by the foundries as part of a transistor technology design kit. Although this is manageable for companies having the resources to design their own standard cells, or for researchers staying at the prototyping phase, it is a major issue for smaller companies. If they were to commit to a non standard cells based asynchronous design style, they would have to reinvest the resources in designing these cells for each new transistor technology node, which, in addition to the need for custom design flow, becomes a competitive liability. That is why, alternative asynchronous design styles and implementation flows are actively explored to overcome these limitations. An important part of this work fits with these trends.

Alternative asynchronous design styles—also known as asynchronous templates—that solely rely on standard cells have been proposed in the past two decades. The most influentials of them are reviewed in chapter 2. Alternative design flows have followed two paths [15, 26, 27]. The first path is concerned with designing custom EDA environments, some of which are still in active development today. These include custom HDLs, dedicated synthesis tools, and even FPGAs targeting asynchronous circuits prototyping. But the multiplicity of asynchronous design styles contributes to spreading the efforts put in these directions. Although some asynchronous EDA tools are currently used in an industrial context (the Tiempo custom synthesis flow is a known example), they are reserved for niche usage, and may arguably perform worse than their synchronous counterparts. The second path that is extensively explored is concerned with finding new methods that can bridge the gap between the asynchronous paradigm and industry-standard, synchronous-oriented, EDA tools. The automated implementation of an asynchronous circuit using standard CAD tools and conventional design flows is of varying complexity depending on the asynchronous design style used in the system of interest. In particular, the abilities of synchronous EDA tools to optimize a circuit such that it meets the performance requirements set by the designer in the form of timing constraints—such optimizations are said to be timing-driven—, and to verify that, under the worst case scenario, the circuit is exempt of error due to the propagation delay of signals through the logic—a verification performed by means of Static Timing Analysis (STA)—are difficult to exploit with asynchronous designs. The research in this direction is of utmost interest because timing-driven optimizations, and STA, are key components of modern EDA tools effectiveness.

In practice, asynchronous circuits which tend to follow fairly purist design approaches are developed in relative isolation. Nevertheless, globally synchronous systems still suffer from strong limitations as technologies continue to scale down. A solution that has emerged, and that has been widely adopted in the past decade to design SoCs of important complexity, is based on an hybrid approach called Globally Asynchronous Locally Synchronous (GALS) [14,20,28]. It relies on asynchronous design principles to build interfaces between locally clocked synchronous processing modules—they interact asynchronously with a network through asynchronous/synchronous interfaces or pausible clocks—, thereby taking advantages of both worlds. GALS designs benefit from the design reuse of synchronous IPs, and the flexibility provided by elastic asynchronous interconnects. However, this design style is more adapted for multi-core designs; the synchronous/asynchronous discussion still prevails at the core level. This work deals with asynchronous RTL design techniques for the design of processor cores, in combination with EDA methods that enable timing-driven optimizations and verifications.

#### 1.1.3 Octasic ad hoc approach towards reducing power consumption

In this context, Octasic—a Montreal based company that has specialized in wireless and media processing systems based on their in-house DSPs—is developing a custom asynchronous design style with a low-power design intent. When they started the development of their DSPs, in the early 2000's, the strategy of Octasic to tackle the problem of the power consumption was to get rid of the clocks, which, as we have seen, represents a significant portion—close to half—of the total power budget in a synchronous VLSI circuit. Naturally, they considered the asynchronous paradigm. But the shortcomings of asynchronous circuits with respect to their integration with standard design flows were the main limitations that prevented Octasic from fully adopting the asynchronous paradigm. In particular, the need for designing custom cells specific to asynchronous circuits—typically not provided as part of standard design kits—was the biggest obstacle. Thus, instead of adopting existing asynchronous design techniques, they developed their own design style, that solely relies on standard cells, in combination with a dedicated design flow based on in-house CAD tools [29].

This led to the Opus family of asynchronous DSP cores: the Opus1 (used in the OCT1010) was released in 2008; the Opus2 (used in the OCT2200) was released in 2011; and the Opus3 (used in the OCT3032W) was released in 2018. They are used commercially and deployed in production telecommunication equipments sold by multiple companies worldwide. The details of their custom asynchronous design methodology was first revealed in two patents [30, 31]—filled in 2009 and respectively issued in 2012 and in 2014—, and the Opus2 microarchitecture was uncovered in a publication that appeared in the 2012 edition of the International Symposium on Asynchronous Circuits and Systems (ASYNC). In this publication, Octasic claims that the Opus2 DSP core delivers 2000 Millions of Multiply-and-Accumulate operations per Seconds (MMACS) with a power efficiency of 21 MMACS/mW when operating at 1 V. When compared in a similar 90 nm CMOS technology node, it is reported to be 3× better than the TI C64x+ synchronous DSP alternative—advertised by TI as the most power-efficient DSP at the time—, which delivers 4000 MMACS with a reported power efficiency of 7 MMACS/mw at 1 V. Moreover, it is of interest to note that the Opus DSPs have enjoyed a commercial success that is often cited as an example to illustrate the benefits of using asynchronous circuits [7, 20]. Finally, since the release of their publications, other companies have developed processors based on very similar design principles [32,33].

Following the success of the Opus DSP cores, Octasic decided to leverage its original asynchronous design technique to build a general-purpose processor targeting embedded applications. A project started in 2012 as a research collaboration between Octasic, École de Technologie Supérieures (ETS), and Polytechnique Montreal, with the goal of building a proces-

sor, called the *AnARM*, capable of achieving performances comparable to those of the ARM Cortex-A7—one of the most power-efficient core used in mobile SoCs at the time [34]—in a smaller power envelope. To achieve this goal, the idea was to build upon the asynchronous subsystems that were originally developed for the Opus DSPs. The AnARM implements the ARMv7 ISA, although it does not include the *Thumb* and *NEON* ISA extensions for simplicity. The circuit was designed and fabricated using the STMicroelectronics 28 nm FD-SOI technology, which was the most advanced transistor technology available that allowed prototyping at the time of the design. Post-fabrication results have been published in the 2019 edition of ASYNC [35].

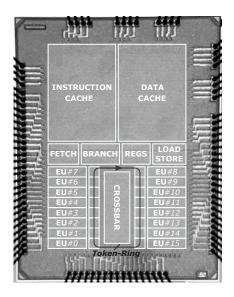

Figure 1.2 The AnARM die micrograph with an overlay representing its top-level organization. The core size is 0,78 mm  $\times$  1,13 mm (0,88 mm<sup>2</sup>) [35].

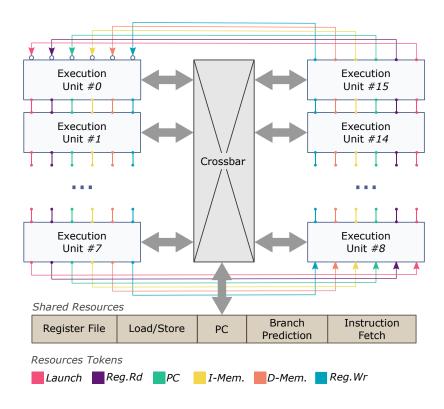

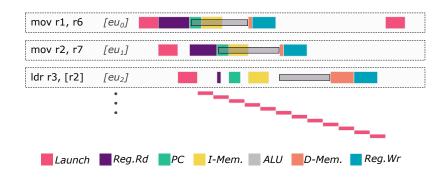

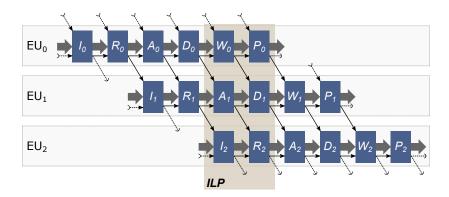

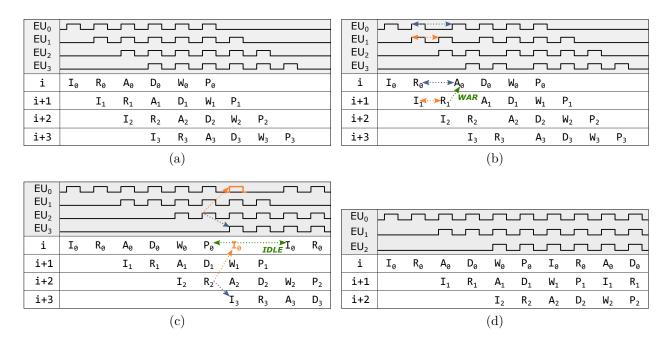

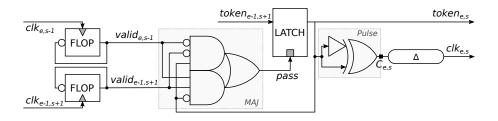

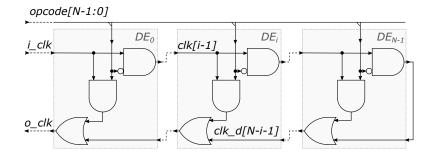

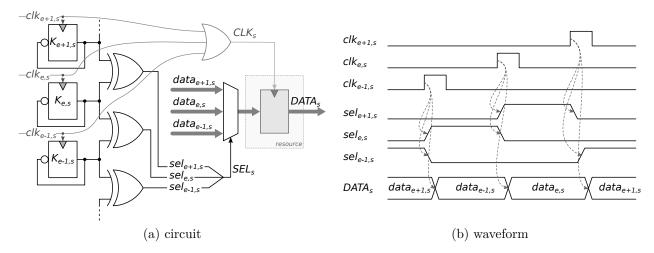

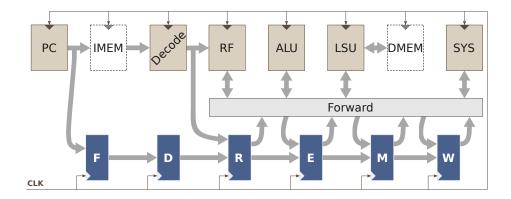

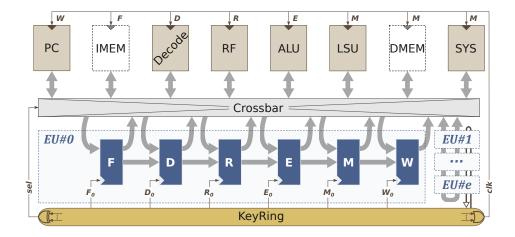

Figure 1.2 shows the die micrograph of the AnARM, with an overlay summarizing its top-level organization. In contrast with most synchronous or asynchronous processors, the AnARM makes no use of pipelining to exploit the inherent parallelism of a sequence of instructions. Instead of pipelining, the AnARM computes multiple instructions concurrently in multiple multicycle Execution Units (EUs). A typical EU provides all the functions that would normally be found at different stages of a pipeline, including instruction decoding, arithmetical and logical operations, etc. The duration of each cycle in an EU is modulated according to the delay of the instruction being executed—much like what is done with many asynchronous schemes—using Delay Elements (DEs). Clocks are created locally, using pulse generators, to trigger the registers in the EUs datapaths. This allows to use flip-flops as the main storage elements in the circuit, which eases the integration with standard EDA flows and test methods. The AnARM is composed of 16 EUs that are linked to one another via a crossbar

switch. The central section spanning the core comprises the register file (REGS), the memory access (LOAD/STORE), the instructions fetch (FETCH), and the branch prediction (BRANCH) sub-systems. These resources are shared among EUs, and their access are regulated using the token-ring, as illustrated in Figure 1.2. It serves the dual purpose of arbitrating the access to the shared resources, ensuring that a resource access is only granted to one EU at a time, and of synchronizing the transactions between resources and EUs. Instructions are issued to EUs in sequence following the program order. They are then processed out-of-order, before being completed in-order. Hence, the AnARM is an out-of-order processor with in-order instructions issue, out-of-order execution, and in-order completion.

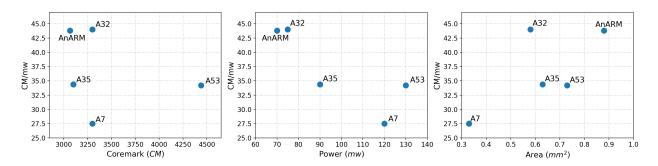

Figure 1.3 Comparison of the AnARM performance with synchronous ARM cores in the 28 nm CMOS technology node [35].

Figure 1.3 compares the AnARM with synchronous ARM cores implemented with comparable 28 nm CMOS technologies [35]. The processors are compared in terms of performance (the scores come from the Coremark (CM) benchmark), power consumption (the methods used to evaluate power are undisclosed in the references), and area. Each metric is plotted against the power efficiency (the performance-power ratio expressed in CM/mW), such that the relative ordering of the processors are always the same on the Y axis, and vary only on the X axis. The A7 (2011) [34] was the baseline when the project started. The A53 (2013) and A35 (2015) are the A7 successors [36]. Finally, the A32 (2017) is the most power-efficient ARM core in the Cortex-A family [37]. The AnARM achieves the design goal of 43,8 CM/mW. It is 1.6× more power-efficient than the A7 (27,5 CM/mW). It delivers 3 066 CM, close to the A35 and the A32, but consumes only 70 mW. It provides the same power efficiency as the A32, at a slightly lower performance/power design point. Also, it is worth mentioning that the AnARM achieves 1 806 Dhrystone MIPS (DMIPS) while consuming 80 mW (22,7 DMIPS/mW). Finally, the AnARM core occupies 0,88 mm<sup>2</sup>, compared with 0,33 mm<sup>2</sup> for the A7 and 0,73 mm<sup>2</sup> for the A53. This area overhead is expected due to the replication of computing resources in EUs.

The performance and the power consumption results of the Opus2 and of the AnARM suggest that the Octasic asynchronous design style leads to power efficient circuits. However, the comparison of complex SoCs is always a difficult task when circuits vary in features and design intent, while being implemented with different EDA flows, and fabricated using different CMOS technologies (albeit being at the same node). In addition, the reported advantages of Octasic processors compared to synchronous alternatives are mitigated by the opacity of the methods employed to estimate the results. Thus, the superiority of the Octasic design style [35] over the synchronous paradigm in terms of power efficiency has not been properly established yet. Such a demonstration would require more reliable experimental protocols. Nevertheless, it is manifest that the Octasic original asynchronous design techniques play a central role in the power-savings strategy employed in their processors. Furthermore, the power-efficiency figures exhibited by the Opus2 and the AnARM provide a clear indication that these processors are amongst the most power-efficient in their category.

But the Octasic asynchronous design principles are somewhat unorthodox. To paraphrase Michel Laurence, author of the Opus2 publication [29], they are the result of an empirical development process, rather than a research-oriented approach. The Octasic asynchronous design style is derived from ad hoc solutions—that is, solutions adapted for very specific needs—to the problem of eliminating the clock-tree to reduce the power consumption of the processors. But these ad hoc design principles lack of a theoretical background that would provide the generality and the justifications required to form a design paradigm. In addition, we will make the case in the following that the Octasic design style [35] diverges from existing asynchronous design styles. In particular, it does not belong to the conventional elastic asynchronous paradigm. The reason is that it does not use the elastic channel abstraction—a notion discussed in section 2.1—characteristic of most asynchronous designs. Instead, it adopts new methods to exploit parallelism among processing elements (which also differ from traditional pipelining), in which the self-timed clocking mechanism is tightly coupled with the arbitration of resources access. Finally, despite relying solely on standard cells, and despite using most of the design practices that are commonly found in synchronous circuits—for example using flip-flops as the main storage elements—, the Octasic design style [35] shares the shortcomings of asynchronous circuits with respect to their limited integration with standard EDA tools. Indeed, at first glance, the use of self-timed clocks makes the Octasic design style [35] incompatible with STA engines, and timing-driven optimization algorithms, of synchronous CAD tools. This prevents standard synthesis and Place and Route (PaR) tools from performing the optimization steps that automatically size and organize the circuit based on performance requirements, and prevents the use of standard STA tools when verifying the timing of the circuits, ensuring that it is correctly working under the worst case scenario.

## 1.2 Objectives and Contributions

This work took place within the broader context of the AnARM project. The AnARM processor has first served as a proof of concept to showcase the Octasic ad hoc asynchronous design technique, by comparing its characteristics (performance, power consumption, area) with other general purpose synchronous processors, as discussed in the previous section, and as reported in [35]. But the AnARM also provided a context to propose a novel architecture for asynchronous caches in [38], a new model for DVS in [39], and original test methods in [40–42]. In this work, we further explore the design trade-offs of the Octasic asynchronous design style uncovered with the Opus2 and the AnARM experiments.

We have seen that the Opus2 and the AnARM processors are more power-efficient than their synchronous alternatives, although we reckon with the limitations of the methodology leading to this conclusion. Consequently, this work relies on the research hypothesis that the Octasic asynchronous design principles lead to power-efficient circuits. In this work, we aim to strengthen the causal relation between the reported design style and a reduced power consumption, compared with the synchronous paradigm. To support this goal, we propose experimental protocols based on the design of a series of asynchronous processors, derived from the Octasic asynchronous design principles, that are compared with their synchronous alternatives. In particular, we first report the design of an asynchronous Mini-Mips processor and its synchronous counterpart. They implement a small subset of the MIPS ISA, and are implemented on a Xilinx 7-series FPGA. We then present the KeyV asynchronous processors, and compare their characteristics with the SynV synchronous alternatives. They implement the 32-bit variant of the RISC-V ISA (RV32IM) [43], and are synthesized with a 65 nm CMOS technology from TSMC. Their performances and power consumption are evaluated and compared, in simulations, using the Dhrystone and the Coremark benchmarks.

Furthermore, we have seen that the Octasic asynchronous design style relies on ad hoc principles, that were created as the result of an empirical development process. Hence, this rather unorthodox design style does not fit well within the existing synchronous and asynchronous design paradigms. In this work, we revisit the Octasic asynchronous design techniques, using circuits and methods coming from the asynchronous paradigm, with the objective of laying the foundations for a more rigorous definition of this unorthodox design style. The goal is to formally define generic design principles that can provide the theoretical background necessary to support a new paradigm. These principles should assist with the decision-making process of a design, and support the methods that enable design automation. Based on formalized design principles inspired by the Octasic design style [35] proposed in this thesis, we propose the *KeyRing* microarchitectures.

Here, it is important to emphasize that, in contrast with the out-of-order microarchitectures of the Opus2 and the AnARM, the KeyRing processors developed in this work are based on in-order microarchitectures. Indeed, as it will be discussed in Chapter 4, in the process of building the principles of the KeyRing design style, the decision was made to consider simpler microarchitectures first. Thus, the design of the KeyRing microarchitectures presented in this work result from an attempt to answer the question: How would a processor be designed, based on the Octasic asynchronous design style, if it was in-order?

Finally, we have seen that the Octasic asynchronous design style was created with the intent to comply with common design practices. In particular, it solely relies on standard cells. However, it still has a limited compatibility with standard EDA tools, which is mainly due to its clocking mechanism conflicting with the timing analysis, and timing optimizations, capabilities of the tools. In this work, we intend to further lower the barrier with standard EDA tools. To this end, the KeyRing design style is made compatible with timing-driven optimizations, and the Static Timing Analysis, capabilities of standard EDA tools. This is achieved using a combination of circuit design techniques and EDA methods.

To summarize, the main objective of this work can be stated as follows:

Develop a framework for the architectural exploration of processors derived from the KeyRing design style.

To achieve this main objective, we propose to complete the following secondary objectives:

- Define the formal principles behind the KeyRing microarchitecture that would serve as the basis for a generic design paradigm.

- Design KeyRing processors of reasonable—yet realistic—complexity, in combination with their synchronous alternatives.

- Develop custom design flows, and propose new circuits, that enable the timing-driven implementation and verification of KeyRing processors using standard EDA tools.

- Elaborate experimental protocols that allow to produce reproducible results and make fair comparisons between KeyRing processors and their synchronous alternatives, in terms of area, performance, and power consumption.

Each of these objectives led to the proposed solutions and methods that are claimed as contributions. Specifically, the contributions of this work are as follows:

- A deep analysis of the Octasic asynchronous design style, as implemented in the Opus2 and the AnARM processors.

- KeyRing, a generic microarchitecture derived from the Octasic asynchronous design style and novel circuit structures inspired from the asynchronous paradigm.

- A theoretical framework, based on a graph representation of the KeyRing microarchitecture, that lays the foundation for the KeyRing design paradigm, and that serves as the basis for balancing designs trade-offs, and enabling timing-driven EDA flows.

- A method to perform the Static Timing Analysis of KeyRing systems with standard EDA tools, based on the timing relations derived from the theoretical model, that enables timing-driven optimizations with synthesis tools, and timing verifications with STA engines.

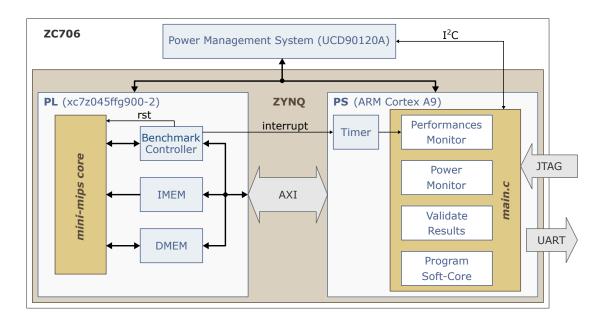

- A prototyping platform enabling the comparison of KeyRing processors with their synchronous alternatives on FPGA, that can measure the power consumption of the processors while they execute a benchmark.

- An ASIC development framework enabling the comparison of KeyRing processors with their synchronous alternatives, that can evaluate the performances and the power consumption of the processors while they execute a benchmark.

- Multiple implementations of the KeyRing microarchitecture, including Mini-Mips, a simple KeyRing processor implementing a subset of the MIPS ISA, and *Mini-Spim*, its synchronous alternative, implemented on FPGA; *KeyBonacci*, a sequential KeyRing circuit implementing the Tribonacci algorithm [44]; *KeyV*, a series of RISC-V processors, and *SynV*, their synchronous (clock-gated and non-clock-gated) alternatives, implemented with a timing-driven EDA flow using a 65 nm ASIC technology.

As of the date of writing this dissertation, the following papers related to this work have been published, or are about to be submitted:

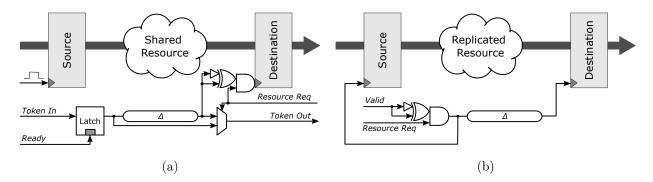

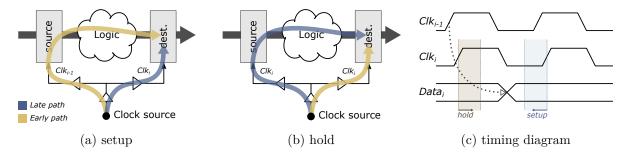

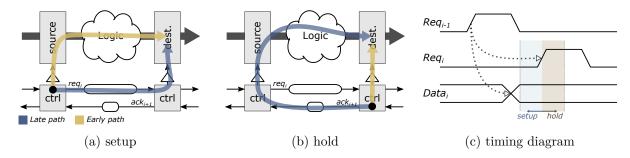

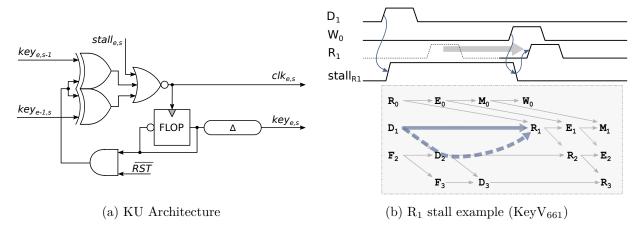

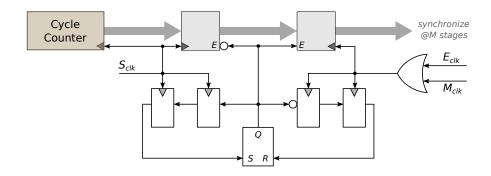

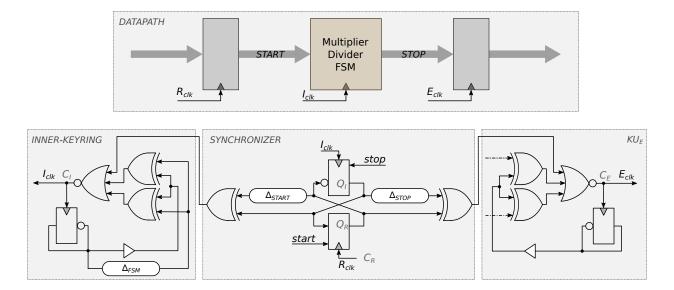

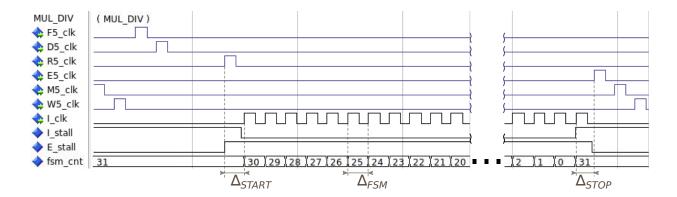

- Self-timed circuits FPGA implementation flow [45] published in NEWCAS (2015). This paper reports preliminary work discussed in Chapter 2.