---

|                   |                                                                                                                                                                                                                                                                                                                       |

|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>Titre:</b>     | Architecture matérielle logicielle pour l'exécution à latence réduite d'applications de télécommunications émergentes sur centre de données                                                                                                                                                                           |

| <b>Auteur:</b>    | Michel Gémieux                                                                                                                                                                                                                                                                                                        |

| <b>Date:</b>      | 2020                                                                                                                                                                                                                                                                                                                  |

| <b>Type:</b>      | Mémoire ou thèse / Dissertation or Thesis                                                                                                                                                                                                                                                                             |

| <b>Référence:</b> | Gémieux, M. (2020). Architecture matérielle logicielle pour l'exécution à latence réduite d'applications de télécommunications émergentes sur centre de données [Thèse de doctorat, Polytechnique Montréal]. PolyPublie.<br><a href="https://publications.polymtl.ca/5264/">https://publications.polymtl.ca/5264/</a> |

| Citation:         |                                                                                                                                                                                                                                                                                                                       |

---

## Document en libre accès dans PolyPublie

Open Access document in PolyPublie

---

**URL de PolyPublie:** <https://publications.polymtl.ca/5264/>

PolyPublie URL:

**Directeurs de recherche:** Yvon Savaria, Guchuan Zhu, & Jean Pierre David

Advisors:

**Programme:** génie électrique

Program:

**POLYTECHNIQUE MONTRÉAL**

affiliée à l'Université de Montréal

**Architecture matérielle logicielle pour l'exécution à latence réduite

d'applications de télécommunications émergentes sur centre de données**

**MICHEL GÉMIEUX**

Département de génie électrique

Thèse présentée en vue de l'obtention du diplôme de *Philosophiæ Doctor*

Génie électrique

Avril 2020

**POLYTECHNIQUE MONTRÉAL**

affiliée à l'Université de Montréal

Cette thèse intitulée :

**Architecture matérielle logicielle pour l'exécution à latence réduite

d'applications de télécommunications émergentes sur centre de données**

présentée par **Michel GÉMIEUX**

en vue de l'obtention du diplôme de *Philosophiæ Doctor*

a été dûment acceptée par le jury d'examen constitué de :

**Richard GOURDEAU**, président

**Yvon SAVARIA**, membre et directeur de recherche

**Guchuan ZHU**, membre et codirecteur de recherche

**Jean-Pierre DAVID**, membre et codirecteur de recherche

**Guy BOIS**, membre

**Bertrand GRANADO**, membre externe

## DÉDICACE

*À tous ceux qui n'ont pas arrêté de me dire :

“Tu es trop proche de la fin pour ne pas finir...”

Merci, vous aviez tous raison... .*

## REMERCIEMENTS

J'aimerais commencer par remercier les Professeurs Yvon Savaria, Guchuan Zhu et Jean-Pierre David qui m'ont accepté sous leur direction pour mener ce projet doctoral dans son entièreté. Je leur serais éternellement reconnaissant de m'avoir permis d'adhérer à un projet avec un partenaire industriel menant des projets de recherche à la pointe de la technologie. Un projet à travers lequel j'ai développé des compétences qui m'ont transformé en une ressource en demande dans l'industrie et qui m'ont valu une place dans une startup à la fine pointe de la technologie avec énormément de potentiel. Je voudrai aussi remercier Patrice Plante et Sébastien Regimbal avec qui ce projet a commencé durant à la maitrise et qui se concrétise en un travail doctoral. Un merci particulier à Richard Goudreau, Guy Bois et Bertrand Granado d'avoir accepté de donner de leurs temps afin de faire partie du jury qui évaluera le travail effectué tout au long de mon doctorat. Puis je tiens à remercier les personnes proches de moi, que ce soit du domaine personnel que professionnel, m'ayant soutenue à travers ce merveilleux, mais aussi tumultueux périple. Particulièrement à :

- Mes collègues et ami(e)s de laboratoire : Mickael Fiorentino, Erika Jolicoeur-Miller et Omar Al Terkawi.

- L'ensemble de l'administration du GRM et de Polytechnique, toujours prêt à aider les étudiants au meilleur de leurs habilités.

- L'ensemble de l'équipe technique du GRM, mais surtout à Rejean Lepage, un collègue et ami qui m'a supporté dans les bons et mauvais moments durant tout mon parcours à Polytechnique.

- Ma famille proche et lointaine ainsi que mes amis, pour leur soutien constant.

J'aimerais terminer en remerciant le conseil de recherches en sciences naturelles et en génie du Canada (CRSNG), Hydro-Quebec, et la Collectivité Territoriale de Martinique (CTM) pour le support financier, ainsi que Huawei Technologie Canada pour le support technique et financier.

## RÉSUMÉ

L'industrie des technologies de l'information et des communications fait face à une demande croissante de services sans fil et Internet omniprésents. Cette demande est alimentée par une explosion du nombre d'appareils mobiles riches en multimédia. Il a été estimé qu'à partir de cette année, 2020, le volume de trafic de données mobiles doublera chaque année pour plusieurs années. En conséquence, il en résulte une augmentation significative des dépenses en capital pour les systèmes construits sur les technologies actuelles de réseau d'accès radio qui sont essentiellement basées sur des architectures avec une structure fixe utilisant des plates-formes propriétaires et des mécanismes de contrôle et de gestion de réseau distribués. D'autre part, pour garantir la qualité de service requise, les sous-systèmes sont dimensionnés en fonction des demandes de pointe. Par conséquent, l'extension du réseau aura un impact considérable sur les dépenses d'exploitation. La recherche proposée vise à développer une architecture matérielle et logicielle adaptée à une grappe d'unités de traitement virtualisée pour les signaux en bande de base d'accès radio en nuage. Ce type d'architecture devra prendre en charge le traitement en temps réel avec des processeurs généralistes sur une plateforme hétérogène. Cela soulève deux défis principaux : la planification des tâches en temps réel et leur exécution d'une manière plus déterministe par rapport aux plates-formes généralistes existantes. Ainsi, les mécanismes d'allocation et de gestion des ressources dans les grappes informatiques doivent être revus. Le deuxième défi est d'obtenir un comportement à faible variance qui implique deux préoccupations majeures : le temps de calcul et le délai de communication. Essentiellement, la variation du temps de calcul est inhérente à tous les processeurs généralistes. Néanmoins, l'infrastructure de communication des grappes informatiques existantes ne fournit aucun soutien pour les communications à faible variance. La recherche proposée est divisée en deux principaux sujets :

- Le calcul dynamique, l'allocation et la gestion des ressources réseau dans une grappe informatique (hétérogène) : les algorithmes d'allocation dynamique des ressources et de planification des tâches en temps réel formeront la fonctionnalité de base prise en charge par le plan de contrôle. Afin de répondre aux fortes contraintes en temps réel de cette classe d'applications, une implémentation matérielle parallèle basée sur circuit logique programmable (FPGA) du plan de contrôle est proposée.

- La prise en charge des calculs et communications à faible variance avec un plan de contrôle implémenté en matériel : Data Plane Development Kit (DPDK) peut être combinée avec la technologie Quick Path Interconnect (QPI) pour fournir une pile de protocoles reposant sur des liaisons physiques haute performance conçues pour des

communications quasi déterministes. Nous montrons qu'en combinant une implémentation matérielle efficace avec la technologie QPI et la bibliothèque DPDK, il existe un fort potentiel pour réaliser des plans de contrôle haute performance.

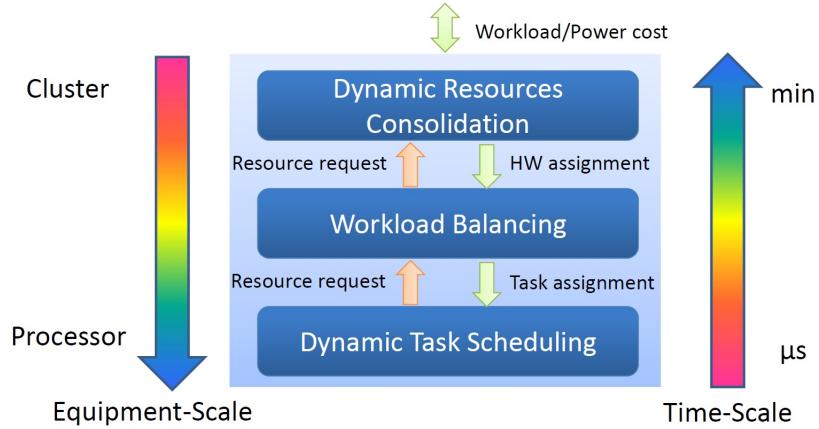

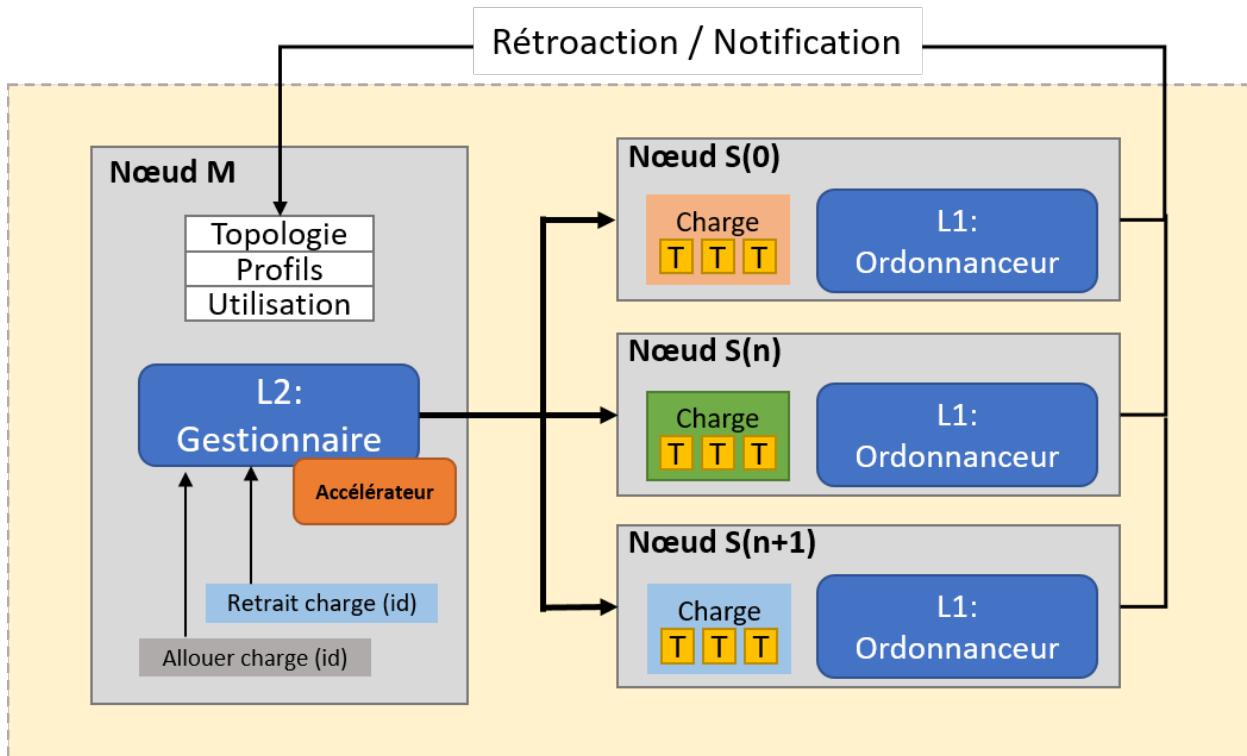

Afin de résoudre cette problématique, nous découpons la gestion des ressources en trois niveaux, l'ordonnancement qui représente la planification des tâches sur une unité de calcul (L1), la gestion des ressources (L2) qui gère les charges de travail à acheminer sur plusieurs noeuds d'unités de calcul, puis la consolidation des ressources (L3) qui s'assure de la gestion de la consommation d'énergie d'une grappe à travers le temps. Cette thèse se concentre et contribue sur les axes suivants :

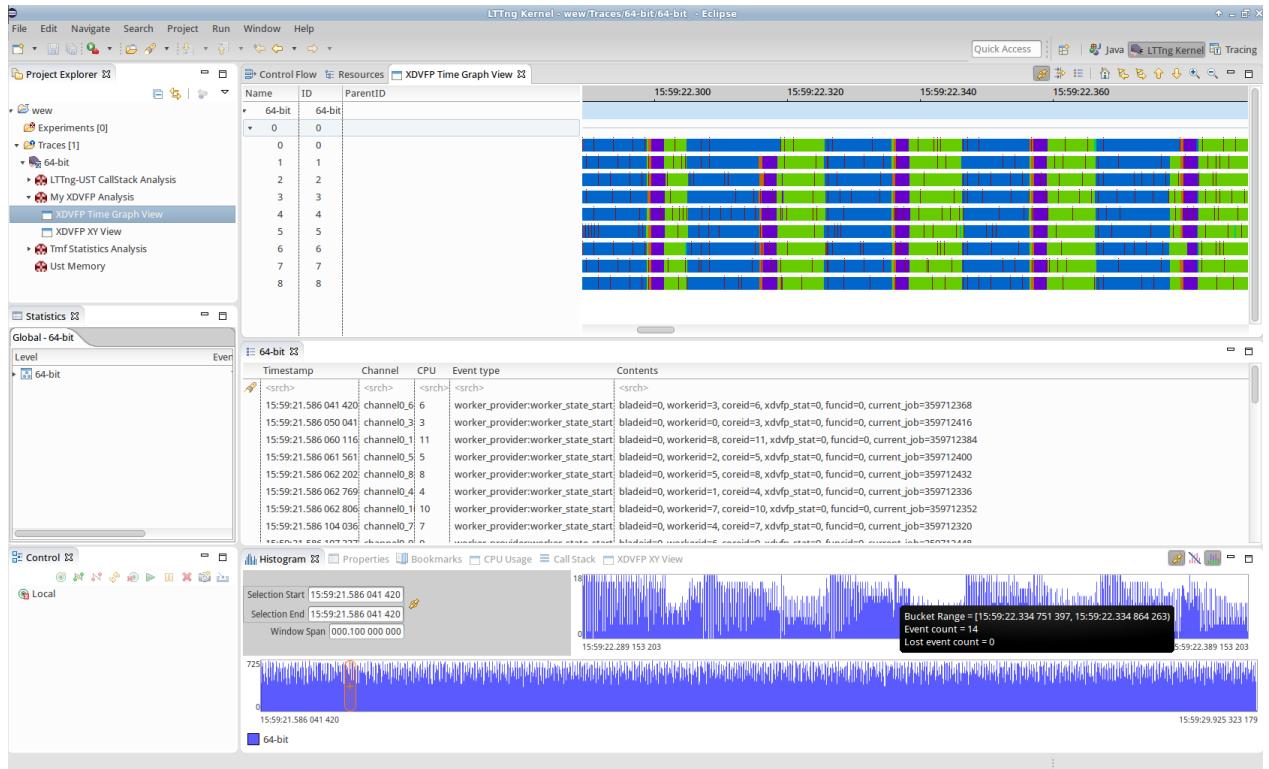

- Équilibrage de la charge de travail et ordonnancement dynamiques de tâches, où nous démontrons que notre plateforme et sa bibliothèque générique “3D Virtual Fabric Processors” (XDVFP) améliorent l'utilisation des unités de calcul de 80.5 à 99.6%.

- Calculs et communications à faible variance avec un plan de contrôle implémenté en matériel, dans lequel nous démontrons que nous réduisons la complexité de notre moteur de calcul d'allocation de tâche (L2) à une complexité  $O(1)$  grâce à l'utilisation d'un accélérateur matériel.

- Tâches à faible variance d'exécution sur un processeur multicœur à l'aide d'un plan de contrôle matériel, où nous utilisons ce même plan de contrôle énoncé plus haut, ce qui permet l'allocation de tâches jusqu'à 760 fois plus vite avec un haut déterminisme au sein de XDVFP.

- Caractérisation et validation du système, où nous explorons les capacités d'une nouvelle plateforme et proposons un ensemble de conseils aux futurs utilisateurs et concepteurs.

- Interconnexion à faible latence et à faible variance pour une grappe informatique en temps réel, où nous proposons et implémentons un nouveau type de communication en utilisant le dernier niveau de cache d'un processeur générique à partir d'un accélérateur matériel (FPGA).

Ce projet de thèse a donc pour principales contributions de :

- Démontrer qu'il est possible de virtualiser un protocole de télécommunication émergent en utilisant que des produits commercialement disponibles, tout en réduisant les coûts.

- Créer une plateforme hétérogène pouvant rencontrer les requis de basse latence et haut débit afin d'assurer la pérennité du système pour des futures normes de communication.

- Proposer et démontrer qu'un nouveau système de communication à faible variance, peu latent à haute bande passante entre les accélérateurs et les processeurs est possible et surtout viable.

## ABSTRACT

The Information and Communications Technology industry is facing an increasing demand for ubiquitous wireless and Internet services introduced by an explosion of multimedia-rich mobile devices. It is estimated that starting this year, 2020, the volume of mobile data traffics will double every year. Consequently, it results in significant increases of capital expenditures for systems built on the current Radio Access Network technologies, which are essentially based on architectures with a fixed structure (not reconfigurable) using proprietary platforms with distributed network control and management mechanisms. To ensure the required quality of service, subsystems are dimensioned with respect to the peak demands. Therefore, network expansion will considerably impact on operating expenditures. This thesis aims at developing an architecture at both hardware and software levels suitable for a virtualized Baseband Processing Unit pool in Cloud Radio Access Network in order to support real-time processing in a General Purpose Processor based platform. This raises two main challenges: scheduling tasks in real-time and executing them in a manner that is reduces variance compared to the existing General Purpose Processor based platforms. Real-time tasks from radio air interface in the Cloud Radio Access Network must be scheduled at a finer grain and must be completed within a given timeslot. Thus, mechanisms for resource allocation and management in computing clusters must be revisited. The second challenge is obtaining a behavior with reduced variability that involves two major concerns: computing time and communication delay. Nevertheless, the communication infrastructure of existing computing clusters does not provide any support for low variance communications. The proposed research is divided into the following main subjects:

- Adaptive computing and network resource allocation and management in (heterogeneous) computing clusters: The algorithms for dynamic resources allocation and real-time task scheduling will form the core functionality that the control plane will support. In order to meet the hard real-time constraints of that class of applications, a parallel Field Programmable Gate Array based hardware implementation of the control plane is proposed.

- Supporting low variance computations and communications with a hardware implemented control plane: Intel's Data Plane Development Kit can be combined with its Quick Path Interconnect technology to provide a protocol stack sitting over high performance physical links designed for low variance communications. A notable feature is the availability of a hardware core for the implementation of Quick Path Interconnect and its high performance differential Inputs and Outputs (IOs). By combining

an effective hardware implementation with the Quick Path Interconnect technology (core, physical link, and associated protocol stack) and the Data Plane Development Kit library, there is a strong potential to realize high performance control planes.

In order to solve this problem, we divide the ressource management application into three levels, the scheduling which represents the scheduling of tasks on a compute unit (L1), the load balancing of ressources (L2) which manages the workloads to be routed to one or several nodes of compute units, then ressource consolidation (L3) which manages the energy consumption of a cluster over time. This thesis focuses and contributes on the following topics:

- Dynamic workload balancing and task scheduling, where we demonstrate that our platform and its associated generic library “3D Virtual Processors ” (XDVF) improve the use of computing units by more than 200%.

- Low variance computation and communication enabled by a hardware implemented control plane, in which we demonstrate that we reduce the complexity of our load balancer’s task cost engine (L2) to  $O(1)$ .

- Low variance tasks execution on a multicore processor using a hardware implemented control plane, which allows tasks to be running up to 760 times faster with high determinism within XDVF.

- System characterization and validation, where we explore the capabilities of a new platform and offer insight to future users and designers.

- Low latency and low variance interconnection for real-time computing in a cluster, where we offer and implement a new type of communication using the last level of cache of a generic processor from a hardware accelerator (FPGA).

The main contributions of this thesis are to:

- Prove and demonstrate that it is possible to virtualize an emerging telecommunication protocol using only commercially available products, while reducing costs.

- Create a heterogeneous platform that can meet the requirements of low latency and high speed to ensure the sustainability of a system for future communication standards.

- Propose and demonstrate that a new low variance, low-latency high-bandwidth communication system between accelerators and processors is possible and also viable.

## TABLE DES MATIÈRES

|                                                                                                                        |       |

|------------------------------------------------------------------------------------------------------------------------|-------|

| DÉDICACE . . . . .                                                                                                     | iii   |

| REMERCIEMENTS . . . . .                                                                                                | iv    |

| RÉSUMÉ . . . . .                                                                                                       | v     |

| ABSTRACT . . . . .                                                                                                     | vii   |

| TABLE DES MATIÈRES . . . . .                                                                                           | ix    |

| LISTE DES TABLEAUX . . . . .                                                                                           | xii   |

| LISTE DES FIGURES . . . . .                                                                                            | xiii  |

| LISTE DES SIGLES ET ABRÉVIATIONS . . . . .                                                                             | xiv   |

| <br>CHAPITRE 1 INTRODUCTION . . . . .                                                                                  | <br>1 |

| 1.1 Cadre théorique . . . . .                                                                                          | 2     |

| 1.1.1 <i>Runtime</i> . . . . .                                                                                         | 3     |

| 1.1.2 Grappe de calcul . . . . .                                                                                       | 3     |

| 1.1.3 Allocation de ressources . . . . .                                                                               | 4     |

| 1.2 Problématique et questions de recherche . . . . .                                                                  | 5     |

| 1.3 Objectifs . . . . .                                                                                                | 6     |

| 1.4 Contributions . . . . .                                                                                            | 6     |

| 1.5 Structure de la thèse . . . . .                                                                                    | 7     |

| <br>CHAPITRE 2 ACCÉLÉRATEURS ET ALLOCATION DE RESSOURCE DANS LE<br>DOMAINE DES TÉLÉCOMMUNICATIONS ÉMERGENTES . . . . . | <br>9 |

| 2.1 Contexte général du projet de recherche . . . . .                                                                  | 9     |

| 2.2 Cloud Radio Access Networks . . . . .                                                                              | 9     |

| 2.3 Accélérateurs en informatique reconfigurable haute performance (HPRC) . .                                          | 11    |

| 2.3.1 Le paradigme HPC . . . . .                                                                                       | 11    |

| 2.3.2 Pertinence de l'utilisation de FPGA dans HPC . . . . .                                                           | 13    |

| 2.3.3 Accélération d'exécution logicielle . . . . .                                                                    | 14    |

| 2.3.4 L'allocation des ressources . . . . .                                                                            | 19    |

| 2.4 Sommaire de la revue de littérature . . . . .                                                                      | 20    |

|                                                                                                                          |    |

|--------------------------------------------------------------------------------------------------------------------------|----|

| CHAPITRE 3 DÉMARCHE, HYPOTHÈSES DE RECHERCHE ET OBJECTIFS . . . . .                                                      | 21 |

| 3.1 Partenariat Polytechnique-Industrie . . . . .                                                                        | 21 |

| 3.2 Méthodologie et axes de recherche . . . . .                                                                          | 21 |

| 3.3 Hypothèses de recherches . . . . .                                                                                   | 24 |

| 3.3.1 Thèmes principaux . . . . .                                                                                        | 24 |

| 3.3.2 Thèmes complémentaires . . . . .                                                                                   | 27 |

| 3.4 Expérimentation . . . . .                                                                                            | 28 |

| CHAPITRE 4 XDVFP : UNE PLATEFORME POUR LA GESTION DE RESSOURCES<br>RÉSEAU DYNAMIQUE BASÉE SUR DPDK . . . . .             | 29 |

| 4.1 Plateforme XDVFP . . . . .                                                                                           | 29 |

| 4.1.1 Gestion et allocation de ressources au niveau des cabinets de serveurs                                             | 29 |

| 4.1.2 Architecture générale . . . . .                                                                                    | 30 |

| 4.1.3 Modèle d'allocation et gestions de ressources sur XDVFP . . . . .                                                  | 31 |

| 4.2 XDVFP sur DPDK . . . . .                                                                                             | 34 |

| 4.2.1 Bibliothèques de programmation parallèle . . . . .                                                                 | 34 |

| 4.2.2 Modèle de programmation : StreamIt sur DPDK . . . . .                                                              | 35 |

| 4.2.3 Une application exécutée sur XDVFP . . . . .                                                                       | 38 |

| 4.3 Résultats . . . . .                                                                                                  | 41 |

| 4.4 Discussion et améliorations possibles . . . . .                                                                      | 44 |

| CHAPITRE 5 ARTICLE 1 : A CACHE-COHERENT HETEROGENEOUS ARCHI-<br>TECTURE FOR LOW LATENCY REAL TIME APPLICATIONS . . . . . | 47 |

| 5.1 Abstract . . . . .                                                                                                   | 47 |

| 5.2 Introduction . . . . .                                                                                               | 48 |

| 5.3 Related Works . . . . .                                                                                              | 50 |

| 5.3.1 FPGAs in HPCs . . . . .                                                                                            | 50 |

| 5.3.2 Software runtime . . . . .                                                                                         | 51 |

| 5.4 Context and Proposed Architecture . . . . .                                                                          | 52 |

| 5.4.1 Overall System Architecture . . . . .                                                                              | 52 |

| 5.4.2 Proposed Hardware Architecture - The CCHA . . . . .                                                                | 55 |

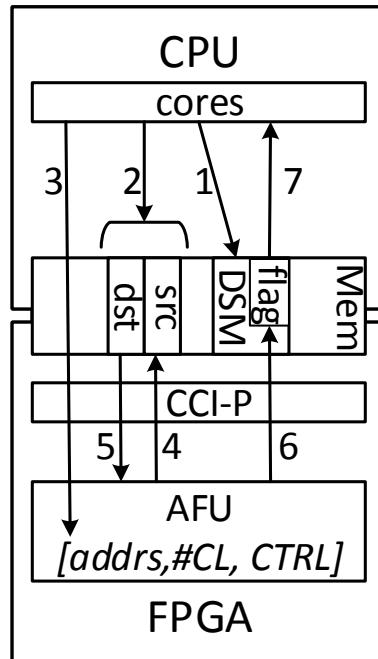

| 5.5 A Case Study . . . . .                                                                                               | 57 |

| 5.5.1 Max-Min Algorithm . . . . .                                                                                        | 57 |

| 5.5.2 Software Tests . . . . .                                                                                           | 57 |

| 5.5.3 FPGA Max-Min Implementation . . . . .                                                                              | 59 |

| 5.6 Results and Discussion . . . . .                                                                                     | 61 |

| 5.6.1 Resource Utilization . . . . .                                                                                     | 61 |

|                                                                                                                             |                                                                                        |    |

|-----------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|----|

| 5.6.2                                                                                                                       | Latency Analysis . . . . .                                                             | 63 |

| 5.7                                                                                                                         | Conclusion and Future Work . . . . .                                                   | 64 |

| 5.8                                                                                                                         | Acknowledgements . . . . .                                                             | 65 |

| <br>CHAPITRE 6 ARTICLE 2 : A HYBRID ARCHITECTURE WITH LOW LATENCY<br>INTERFACES ENABLING DYNAMIC CACHE MANAGEMENT . . . . . |                                                                                        | 66 |

| 6.1                                                                                                                         | Abstract . . . . .                                                                     | 66 |

| 6.2                                                                                                                         | Introduction . . . . .                                                                 | 67 |

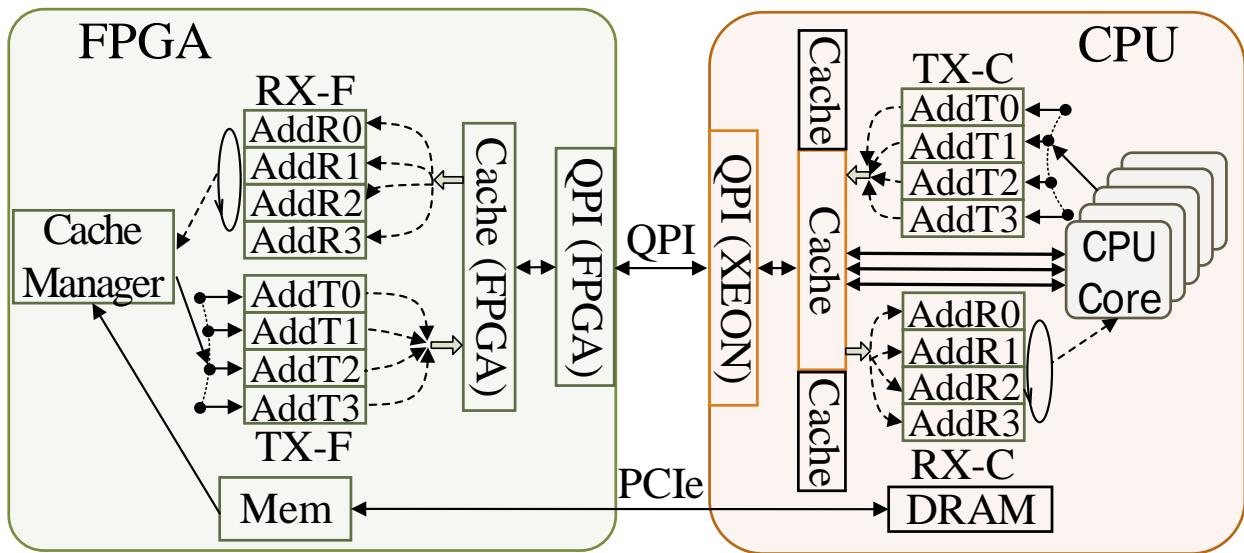

| 6.3                                                                                                                         | Background . . . . .                                                                   | 69 |

| 6.3.1                                                                                                                       | Microarchitectures . . . . .                                                           | 69 |

| 6.3.2                                                                                                                       | Real-Time Resource Allocation . . . . .                                                | 72 |

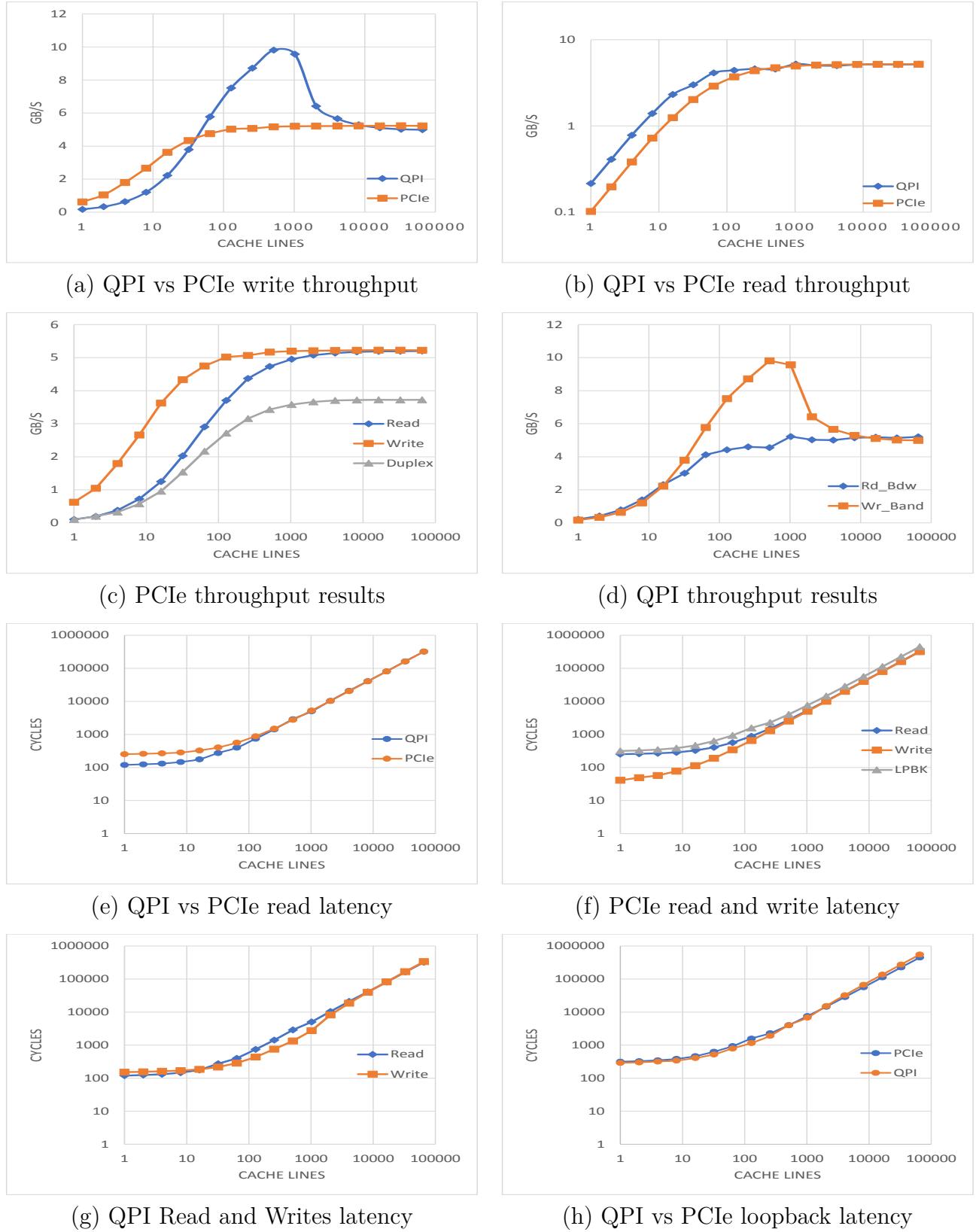

| 6.4                                                                                                                         | Characterization of Low Latency Interfaces on a Hybrid CPU-FPGA Architecture . . . . . | 72 |

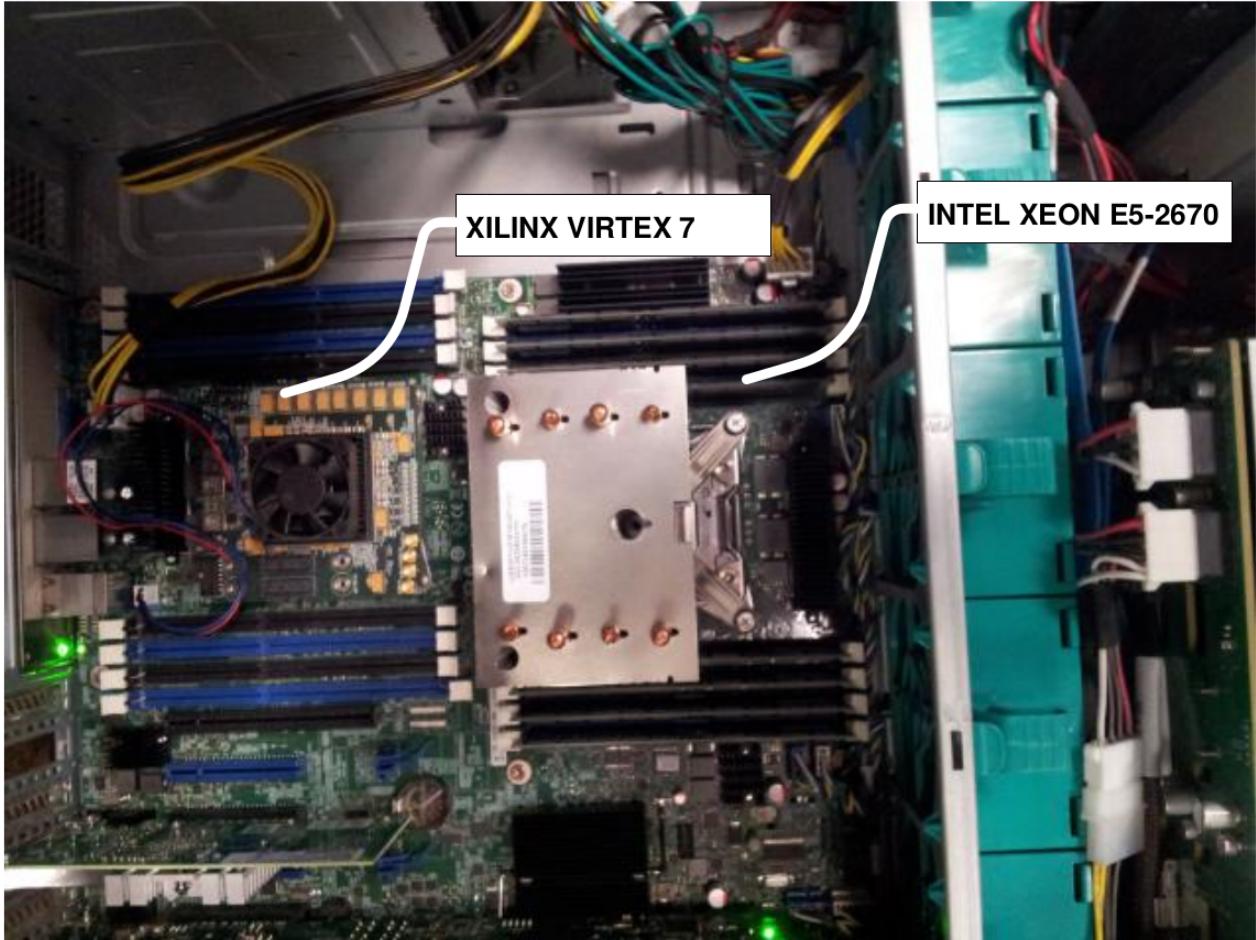

| 6.4.1                                                                                                                       | Hardware Configuration . . . . .                                                       | 72 |

| 6.4.2                                                                                                                       | Characterization Approach of Low Latency Interfaces . . . . .                          | 73 |

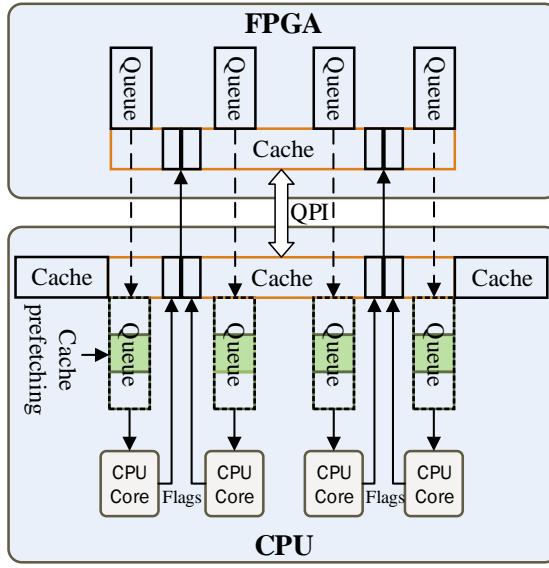

| 6.5                                                                                                                         | Performance Improvements with Queue-Based Cache Management on an MCP                   | 76 |

| 6.6                                                                                                                         | Validation of Low Latency Communication and Case Study of Cache Management . . . . .   | 79 |

| 6.6.1                                                                                                                       | Characterization Results of Low Latency Interfaces . . . . .                           | 79 |

| 6.6.2                                                                                                                       | A Case Study - Merkle Tree Acceleration . . . . .                                      | 85 |

| 6.6.3                                                                                                                       | Implementation of Merkle Tree and Experiment Results . . . . .                         | 86 |

| 6.7                                                                                                                         | Conclusion and Future Work . . . . .                                                   | 90 |

| <br>CHAPITRE 7 DISCUSSION GÉNÉRALE . . . . .                                                                                |                                                                                        | 92 |

| 7.1                                                                                                                         | Synthèse des travaux . . . . .                                                         | 92 |

| 7.2                                                                                                                         | Impact de la recherche . . . . .                                                       | 94 |

| 7.3                                                                                                                         | Limitations de la solution proposée . . . . .                                          | 95 |

| <br>CHAPITRE 8 CONCLUSION ET RECOMMANDATIONS . . . . .                                                                      |                                                                                        | 97 |

| 8.1                                                                                                                         | Conclusion . . . . .                                                                   | 97 |

| 8.2                                                                                                                         | Améliorations futures . . . . .                                                        | 97 |

| 8.2.1                                                                                                                       | Interconnexion réseau . . . . .                                                        | 98 |

| 8.2.2                                                                                                                       | Consolidation dynamique des ressources . . . . .                                       | 98 |

| <br>RÉFÉRENCES . . . . .                                                                                                    |                                                                                        | 99 |

**LISTE DES TABLEAUX**

|             |                                                                                     |    |

|-------------|-------------------------------------------------------------------------------------|----|

| Tableau 2.1 | Berkeley's 13 dwarfs . . . . .                                                      | 12 |

| Tableau 4.1 | Résultats de XDVFP avec des systèmes d'Allocation de ressource différents . . . . . | 42 |

| Tableau 5.1 | 5G expected requirements . . . . .                                                  | 49 |

| Tableau 5.2 | HRA Area report . . . . .                                                           | 61 |

| Tableau 6.1 | Communication Interfaces . . . . .                                                  | 72 |

| Tableau 6.2 | Useful AALSDK API Functions . . . . .                                               | 75 |

| Tableau 6.3 | MCP access latency . . . . .                                                        | 79 |

| Tableau 6.4 | Typical Memory Hierarchy Access times . . . . .                                     | 89 |

## LISTE DES FIGURES

|             |                                                                         |    |

|-------------|-------------------------------------------------------------------------|----|

| Figure 1.1  | Architecture système vue à haut niveau . . . . .                        | 3  |

| Figure 2.1  | Exemples de graphes de flot de traitement parallèles et séquentiels . . | 15 |

| Figure 2.2  | Pipelining logiciel à grosse granularité . . . . .                      | 16 |

| Figure 3.1  | Architecture système multi niveaux . . . . .                            | 22 |

| Figure 4.1  | Architecture système de XDVFP . . . . .                                 | 31 |

| Figure 4.2  | Moteur d'allocation de ressources . . . . .                             | 33 |

| Figure 4.3  | Exécution de tâche + données . . . . .                                  | 36 |

| Figure 4.4  | Pipeline logiciel à granularité élevée . . . . .                        | 37 |

| Figure 4.5  | Ordonnancement sur 4 coeurs . . . . .                                   | 37 |

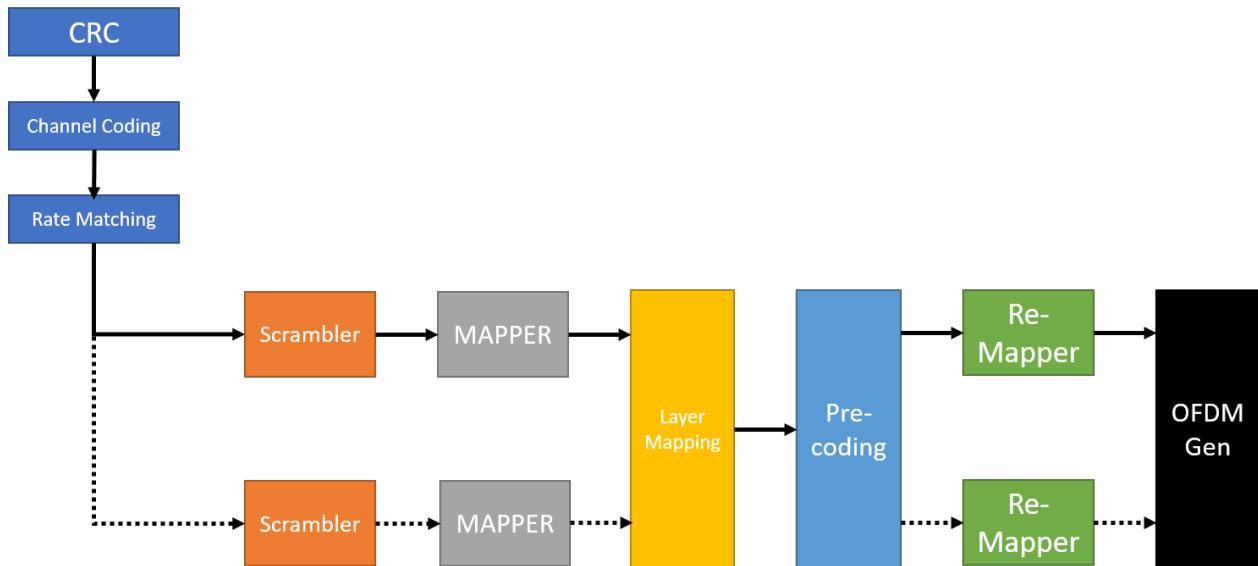

| Figure 4.6  | Partitionnement des tâches de liaison descendante . . . . .             | 41 |

| Figure 4.7  | Trace de l'application LTE utilisant XDVFP sur un noeud . . . . .       | 43 |

| Figure 4.8  | Moteur d'allocation de ressources accéléré . . . . .                    | 45 |

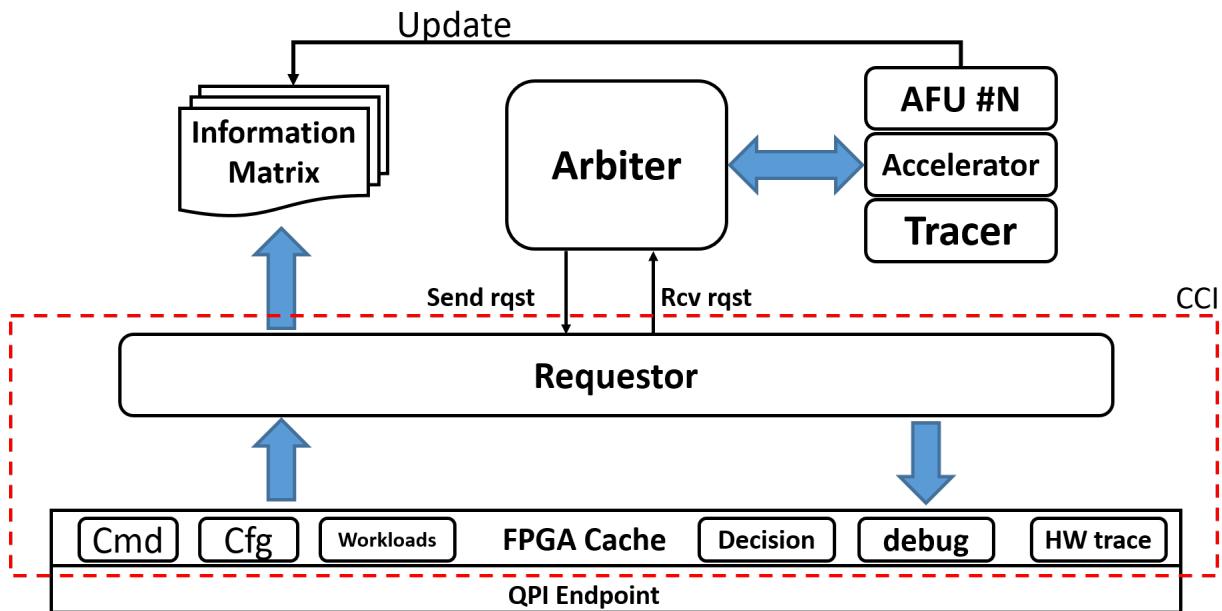

| Figure 5.1  | CCHA Platform Architecture . . . . .                                    | 53 |

| Figure 5.2  | CCHA Platform Picture . . . . .                                         | 54 |

| Figure 5.3  | Proposed Architecture - Block diagram . . . . .                         | 55 |

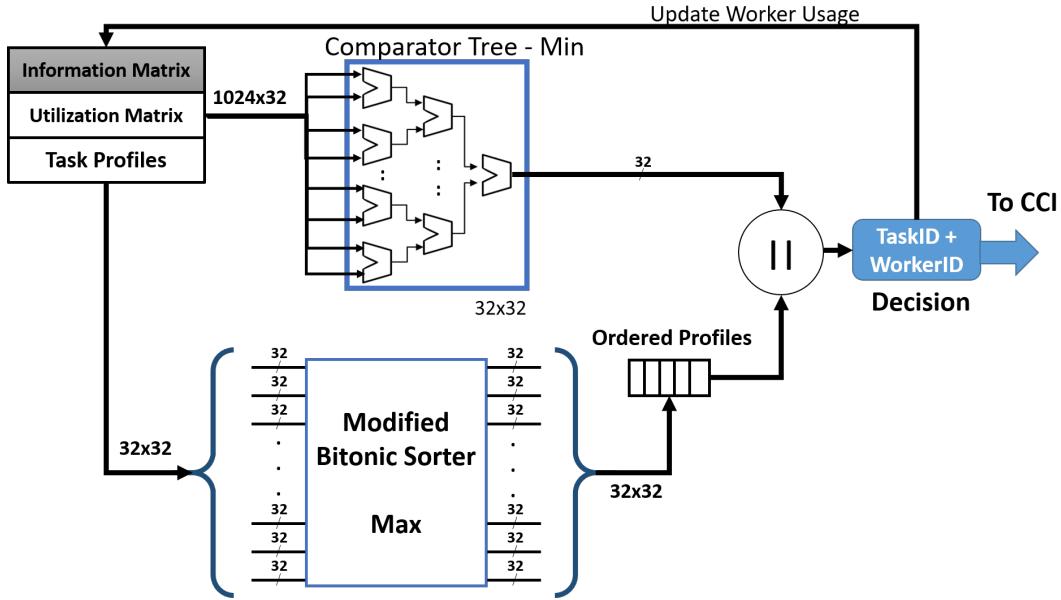

| Figure 5.4  | Max-Min block architecture. . . . .                                     | 59 |

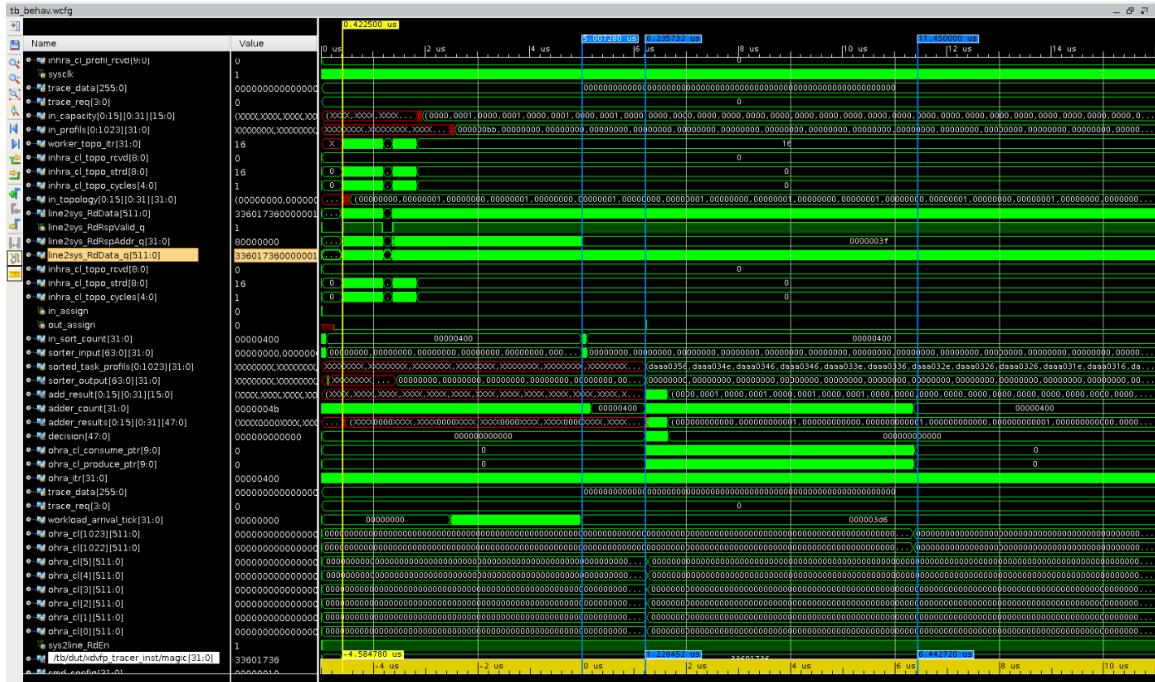

| Figure 5.5  | Simulation Results . . . . .                                            | 62 |

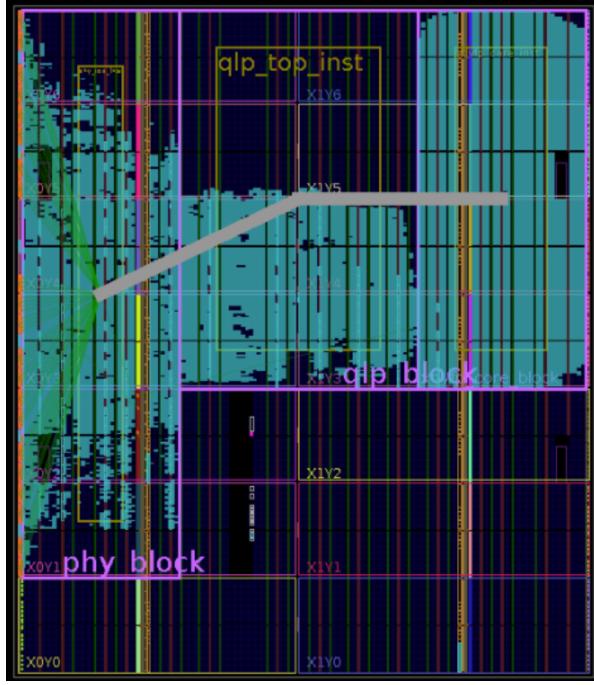

| Figure 5.6  | Implementation Results . . . . .                                        | 63 |

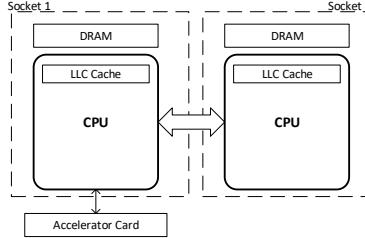

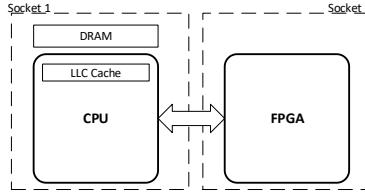

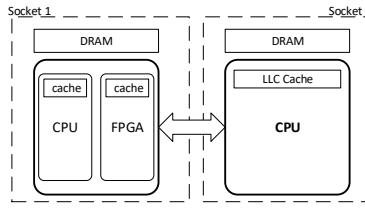

| Figure 6.1  | Accelerator Card . . . . .                                              | 67 |

| Figure 6.2  | Socketed FPGA . . . . .                                                 | 67 |

| Figure 6.3  | MCP . . . . .                                                           | 67 |

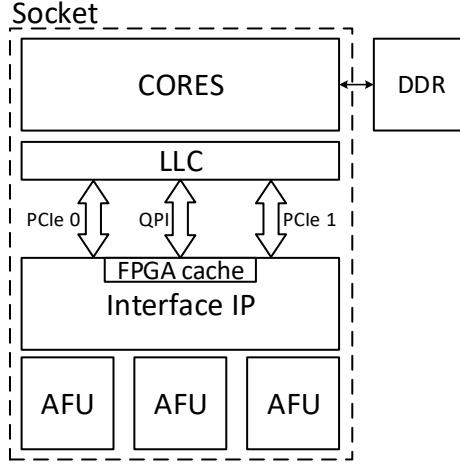

| Figure 6.4  | Accelerator Architectures . . . . .                                     | 67 |

| Figure 6.5  | QPI and PCIe connections between CPUs and FPGA. . . . .                 | 73 |

| Figure 6.6  | The loop back application . . . . .                                     | 74 |

| Figure 6.7  | Proposed hybrid architecture composed of CPUs and an FPGA. . . .        | 77 |

| Figure 6.8  | Queue-based cache management. . . . .                                   | 78 |

| Figure 6.9  | Cold cache characterization results . . . . .                           | 81 |

| Figure 6.10 | Warmed cache characterization results . . . . .                         | 82 |

| Figure 6.11 | Merkle Tree in Blockchain applications. . . . .                         | 85 |

## LISTE DES SIGLES ET ABRÉVIATIONS

|        |                                          |

|--------|------------------------------------------|

| IETF   | Internet Engineering Task Force          |

| OSI    | Open Systems Interconnection             |

| ACK    | Acknowledge                              |

| ASIC   | Application Specific Integrated Circuit  |

| BBU    | Base Band Unit                           |

| BRAM   | Bloc RAM                                 |

| BS     | Base Station                             |

| CAPEX  | Capital Expenses                         |

| CAPI   | Coherent Accelerator Processor Interface |

| CCI    | Cache Coherent Interface                 |

| CPRI   | Common Public Radio Interface            |

| CPU    | Central Processing Unit                  |

| CRAN   | Cloud Radio Access Network               |

| DAG    | Directed Acyclic Graph                   |

| DDR    | Double Data Rate                         |

| DPDK   | Data Plane Development Kit               |

| eNodeB | Evolved NodeB                            |

| FDMA   | Frequency Division Multiple Access       |

| FFT    | Fast Fourier Transform                   |

| FPGA   | Field Programmable Gate Array            |

| GDDR   | Graphics Double Data Rate                |

| GPP    | General Purpose Processor                |

| GSM    | Global System/Standard Mobile            |

| HPC    | High Performance Computing               |

| IP     | Intellectual Property                    |

| LLC    | Last Level of Cache                      |

| LTE    | Long Term Evolution                      |

| MAC    | Media Access Control                     |

| MIC    | Many Integrated Core                     |

| MIMO   | Multiple Input, Multiple Output          |

| MKL    | Math Kernel Library                      |

| NFV    | Network Function Virtualization          |

| NIC    | Network Interface Controller             |

|       |                                            |

|-------|--------------------------------------------|

| OBSAI | Open Base Station Architecture Initiative  |

| OFDM  | Orthogonal Frequency-Division Multiplexing |

| OPEX  | Operation Expenses                         |

| PCIe  | Peripheral Component Interconnect Express  |

| PHY   | Physical Layer                             |

| QPI   | Quick Path Interconnect                    |

| RAN   | Radio Access Network                       |

| RRH   | Remote Radio Head                          |

| RRU   | Remote Radio Unit                          |

| SDN   | Software Defined Network                   |

| SIMD  | Single Instruction on Multiple Data        |

| TBB   | Threading Building Blocks                  |

| WAN   | Wide Area Network                          |

| WCET  | Worst Case Execution Time                  |

## CHAPITRE 1 INTRODUCTION

L'industrie des technologies de l'information et des communications (TIC) fait face à une demande croissante de services sans-fil et internet omniprésents, provoquée par l'explosion du nombre d'appareils mobiles intelligents. Il a été estimé qu'à partir de cette année, 2020, le volume des trafics de données mobiles doublera chaque année pour plusieurs années à venir [1]. Pour augmenter la capacité globale du système, il est nécessaire de diviser le réseau avec des cellules plus petites, ce qui nécessite l'installation de nouveaux sites et équipements et, par conséquent, entraîne une augmentation significative des dépenses en capital (CAPEX) pour la mise en oeuvre des réseaux d'accès radio (RAN). Les technologies sous-jacentes reposent essentiellement sur des architectures à structure fixe utilisant des plateformes propriétaires et des mécanismes de contrôle et de gestion des réseaux distribués. D'autre part, pour garantir la qualité de service (QoS) requise, les sous-systèmes (stations de base) sont dimensionnés en fonction des demandes. Par conséquent, l'extension du réseau aura un impact considérable sur les dépenses d'exploitation (OPEX). De plus, la consommation d'énergie électrique représente une part importante des coûts d'exploitation [2]. Par conséquent, l'expansion du réseau dans une architecture RAN traditionnelle avec des ressources sur l'approvisionnement est un fardeau pour les systèmes énergétiques, ce qui augmentera considérablement l'empreinte carbone des TIC. De nos jours, l'industrie des TIC est sous une pression énorme pour développer de nouvelles technologies RAN qui peuvent répondre au besoin d'une densité de capacité sans cesse croissante, tout en réduisant les CAPEX, OPEX, ainsi que l'impact environnemental. Pour relever ce défi, un grand effort a été fait par l'industrie ces dernières années et il est reconnu que l'une des solutions viables consiste à permettre une intégration plus étroite des infrastructures informatiques et des systèmes de télécommunications, traditionnellement séparés, pour former un réseau unifié [1]. Conformément à cette vision, le China Mobile Research Institute a introduit le concept de réseaux d'accès radio basé sur le nuage (C-RAN), renforcé par le traitement centralisé du signal et des données, la radio coopérative, le nuage et une infrastructure propre (plus verte) [3]. Contrairement aux RAN conventionnels, un C-RAN dissocie l'unité de traitement en bande de base (BBU) de la radiocommande (RRH), permettant une opération centralisée des BBU et un déploiement évolutif des RRH sous forme de petites cellules. L'électronique des stations de base numérique conventionnelle peut ensuite être déplacée vers des centres de données hébergeant des processeurs à usage général (GPP) de haute performance, c'est-à-dire le bassin BBU. Grâce à la virtualisation et au contrôle (logique) du réseau centralisé, le C-RAN permet le calcul dynamique et la gestion des ressources réseau en matière de répartition et de gestion active de la consommation

d'énergie, conduisant à des solutions économies en énergie et rentables, avec une utilisation globale améliorée du réseau. En tant que grand fournisseur mondial de solutions TIC, le partenaire industriel du projet investit dans le développement de technologies liées au C-RAN visant à ouvrir la voie vers les réseaux mobiles de prochaine génération (5G). Néanmoins, bien que certains efforts aient été déployés par les secteurs universitaire et industriel pour faire avancer le paradigme C-RAN [4] [5], cette technologie est encore à ses balbutiements et il existe de nombreux problèmes en suspens devant être résolu avant que le réseau de mobilité 5G ne devienne réalité. En ce qui concerne cet ultime objectif, l'une des priorités du partenaire industriel vise le développement de stations de base qui sont déployables avec les technologies actuellement disponibles.

La recherche effectuée dans cette thèse explore des solutions pour l'informatique dynamique et l'allocation des ressources réseau, ainsi que pour la gestion des bassins BBU C-RAN fonctionnant sur une grappe de calcul informatique dans des infrastructures telles que les centres de données. Les solutions explorées comprennent des implémentations exploitant des circuits intégrés composés d'un réseau de cellules programmables (FPGA) pour l'allocation dynamique des ressources et des algorithmes de planification en temps réel. La recherche caractérise également la variabilité et l'amélioration des performances possibles sur un prototype C-RAN assurant la gestion du tampon, le verrouillage de la cache et la gestion des communications entre processeurs, pour permettre la virtualisation de différentes normes de communication sans fil, telles que Long-Term-Evolution (LTE) et ultimement la 5G.

L'objectif principal de cette thèse est de développer des solutions économies en énergie et rentables pour la gestion des ressources informatiques, de stockage et de mise en réseau (allocation des ressources 3D) des grappes informatiques dans le contexte d'applications pour le C-RAN. Les algorithmes, solutions et outils de prototypage développés dans cette thèse sont validés avec la plate-forme *3D Virtual Fabric Processors* développé conjointement avec le partenaire industriel de ce projet, qui a permis une intégration transparente des résultats obtenus avec les processus de développement d'ingénierie de pointe du partenaire industriel. Ce projet a contribué non seulement à la stratégie de développement à long terme du partenaire industriel, mais elle représente également un pas en avant significatif pour l'équipe impliquée dans ce projet en fournissant un contexte à cette recherche.

## 1.1 Cadre théorique

Afin d'avoir une bonne compréhension du travail effectué, certains concepts doivent être définis. Les concepts élaborés ci-dessous expliquent à haut niveau les thèmes sur lesquels cette thèse s'appuie.

### 1.1.1 Runtime

Pour une meilleure compréhension, nous devons définir le concept de *Runtime* et les systèmes d'exécution. Un système d'exécution est la collection de tous les mécanismes logiciels et matériels qui permettent à un programme de s'exécuter sur une plate-forme donnée. Lorsque l'exécution est mentionnée dans ce projet de thèse, elle fait référence aux systèmes logiciels et matériels, qui servent à la gestion de la mémoire et des ressources, ainsi qu'à l'accélération matérielle pour l'exécution des tâches. Il ne faut pas confondre le système d'exécution proposé avec un environnement d'exécution similaire à JAVA (*Java Runtime Environment*), qui fournit plutôt un espace de développement et d'exécution.

### 1.1.2 Grappe de calcul

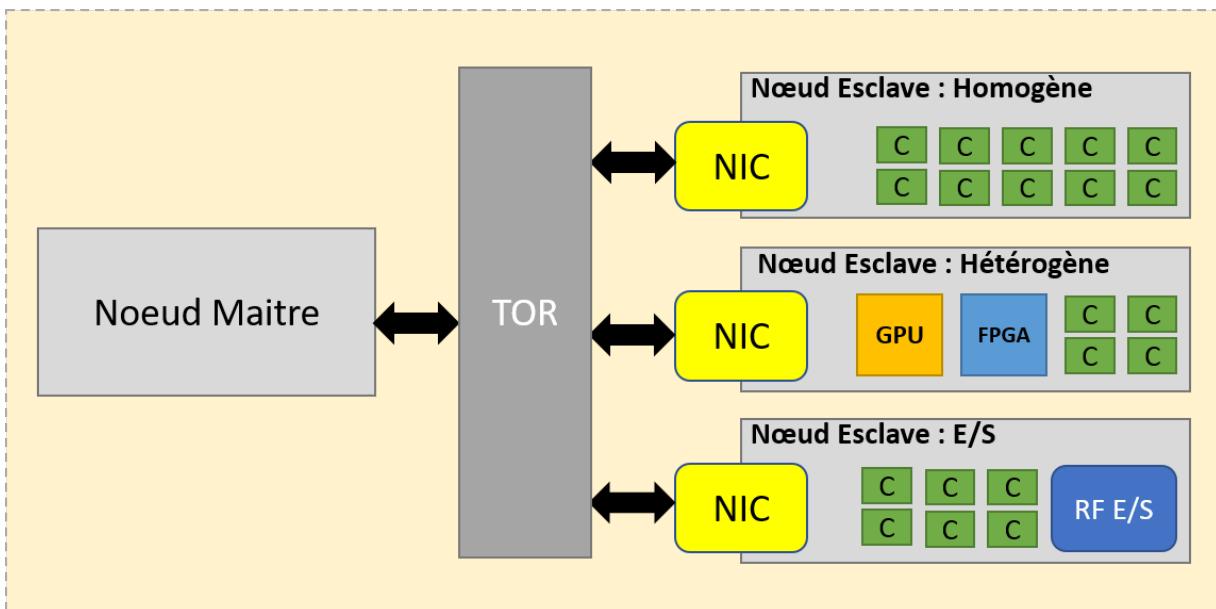

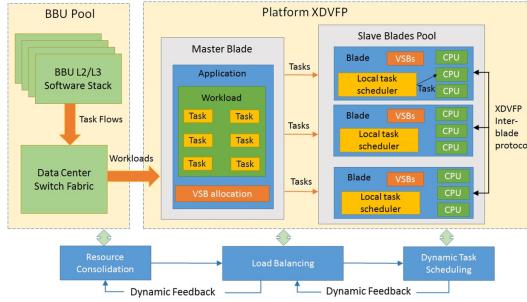

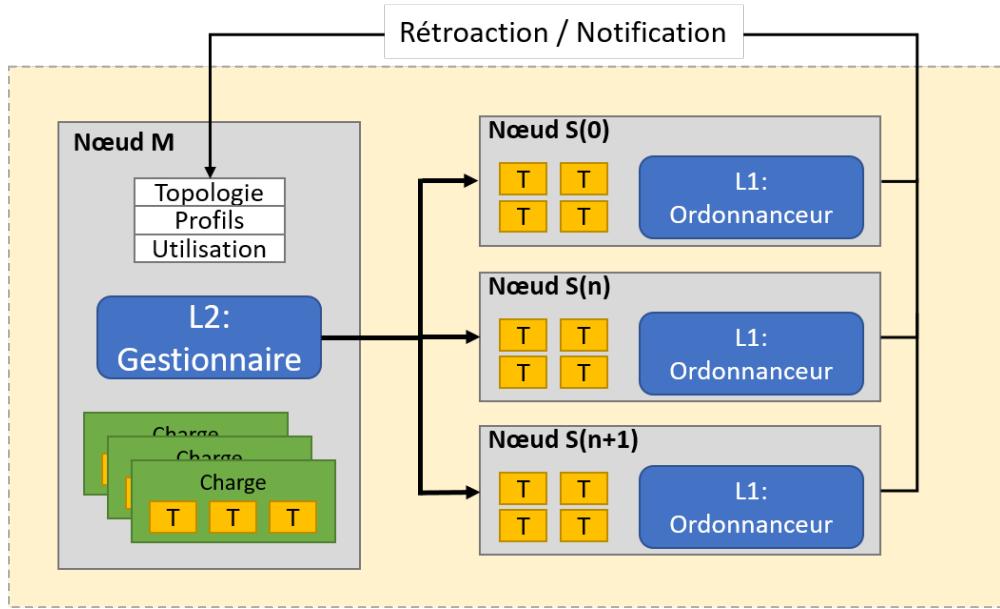

Afin de comprendre quelle technologie permet les contributions de cette thèse, une description de notre plateforme informatique s'impose. Cette section présente brièvement l'architecture globale d'une grappe de calcul informatique. Comme le montre la Figure 1.1, la grappe est constituée de plusieurs lames de serveur organisées dans une configuration maître-esclave, connectées ensemble avec un commutateur à faible latence et à large bande passante. Une lame sert de nœud maître, tandis que les autres lames esclaves servent de nœuds de calcul. Un tel système pourrait prendre différentes configurations, rendant l'ensemble du système hétérogène.

Figure 1.1 Architecture système vue à haut niveau

En raison du contexte d'application, certains esclaves pourraient être dédiés au calcul de l'interface aérienne (*Common Public Radio Interface* pour les applications LTE), tandis que le reste pourrait fournir différents types de ressources de calcul, telles que les unités de traitements graphique à usage général (GPU), les FPGA et différentes saveurs d'unités centrales de traitement x86 (CPU).

### 1.1.3 Allocation de ressources

L'ordonnancement est la méthode par laquelle on donne accès aux ressources de la machine ainsi qu'aux processus (ensemble de tâches) de calcul d'une application donnée. Le principal but est de pouvoir adéquatement équilibrer l'utilisation des ressources afin que les processus s'effectuent le plus efficacement que possible. De cette façon, un ordonnanceur est le mécanisme qui s'occupe de gérer quel processus peut avoir accès aux ressources de la plateforme et quand. Dans notre cas, nous parlerons d'un ordonnanceur de tâches, aussi nommé "*task scheduler*". Dans le contexte LTE un bon ordonnanceur doit tenir compte des contraintes temps réel, car la norme nous impose une borne stricte sur le temps de traitement par usager de 10ms [6]. Ce dernier doit donc prendre en considération :

- Les échéances pour assurer que chaque processus respecte la plage de temps qui lui est allouée.

- La latence, premièrement le délai d'exécution, c'est-à-dire le temps entre la réception de la requête et sa complétion. Puis le temps de réponse entre l'envoi de la première requête et la réception de la première réponse ("*acknowledge*").

- L'utilisation des CPU, afin ne pas sur-utiliser un processeur, alors que d'autres le sont peu.

- Le débit, qui correspond au nombre d'exécutions de processus par unité de temps.

Afin que l'ordonnanceur puisse gérer les contraintes de temps imposées par le contexte de télécommunication, les tâches seront acheminées avec des descriptifs. Les plus utilisés sont :

- Le temps de relâchement (*Release time*), qui est le temps auquel une tâche est prête à être exécutée.

- Le délai minimum, qui est le minimum de temps permis au début de l'exécution d'une tâche et après sa complétion.

- Le délai maximal, qui est le maximum de temps permis au début de l'exécution d'une tâche et après sa complétion.

- Le WCET (*Worst Case Execution Time*), qui est le plus long temps d'exécution que peut prendre une tâche.

- Le *Runtime* (Notez que le terme Runtime prend plusieurs sens dans cette thèse. Ces

sens sont clairs par le contexte), qui représente le temps pris pour accomplir une tâche sans interruption.

- Le poids ou priorité, qui est souvent le niveau d'urgence de la tâche.

- La mémoire consommée, cela pourrait être la mémoire nécessaire pour exécuter une tâche ou même les espaces requis pour exécuter une fonction reliée à la tâche.

Une fois toutes ces caractéristiques prises en compte, il faut avoir un ordonnancement adéquat, qui nous permettra d'atteindre la qualité de service voulue. Dans les domaines du “*Cloud Computing*” et du “*High Performance Computing (HPC)*”, un ordonnancement efficace des tâches d'un processus est primordial afin d'avoir la plus grande performance possible. Il existe une abondante littérature sur le sujet de l'ordonnancement de tâches, ce que nous pouvons en retirer est qu'il n'existe pas une solution parfaite qui a la capacité de résoudre tous les problèmes. Ainsi, au lieu de s'efforcer à trouver l'ultime solution d'ordonnancement, les concepteurs se fient à des algorithmes ou stratégies, qu'ils choisissent en fonction des caractéristiques de l'application. Il existe de nombreux algorithmes d'ordonnancement disponibles dans la littérature [7].

## 1.2 Problématique et questions de recherche

La recherche dans ce projet vise à développer une architecture à la fois matérielle et logicielle adaptée à un bassin (*pool*) BBU virtualisé en C-RAN afin de prendre en charge le traitement en temps réel dans une plateforme basée sur GPP. Cela soulève deux défis principaux : la planification des tâches en temps réel et leur exécution d'une manière moins variable par rapport aux plates-formes GPP existantes. La planification habituelle des tâches dans les grappes de calcul ne se fait pas de façon fine et elle n'est en aucun cas spécialisée. D'autre part, les tâches en temps réel à partir de l'interface radioélectrique dans le C-RAN doivent être planifiées à un niveau plus fin et elles doivent être achevées dans un intervalle de temps donné. En outre, la consolidation des tâches (sur les cœurs de CPU) doit être envisagée afin d'optimiser l'utilisation du CPU et de minimiser les frais de communication. Ainsi, les mécanismes d'allocation et de gestion des ressources dans les grappes informatiques doivent être revus. Le deuxième défi est d'obtenir un comportement à faible variance qui implique deux préoccupations majeures : le temps de calcul et le délai de communication. Essentiellement, la variation du temps de calcul est inhérente à tous les GPP. Une étude préliminaire indique que le DPDK [8] semble fournir une infrastructure capable de gérer la variation du temps de calcul à des niveaux acceptables. Néanmoins, l'infrastructure de communication des grappes informatiques existantes ne fournit aucun support pour les communications à faible variance.

### 1.3 Objectifs

Concrètement, cette thèse vise à développer une architecture matérielle générique pour l'accélération d'applications s'exécutant sur des grappes HPC hétérogènes. L'objectif visé était de réduire la latence du HPC grâce à l'accélération matérielle des systèmes d'allocation et de gestion des ressources informatiques dynamiques à plusieurs échelles de temps. L'une des applications cibles est la plate-forme de calcul pour prendre en charge des normes de communication sans fil telles que LTE et 5G. Une partie essentielle du projet de thèse consiste à développer et caractériser des algorithmes pour répartir les charges de travail sur les lames de serveur de manière équilibrée dans le but de maximiser l'utilisation des processeurs dans la grappe de calcul et de garantir la bande passante pour le transfert de données entre les nœuds de calcul et la mémoire cache réservée pour permettre l'exécution des tâches avec une faible variance. La charge de travail répartie entre les lames de serveur doit ensuite être planifiée à une échelle plus fine afin de minimiser la durée requise pour terminer les exécutions de tâches. Les étapes franchies pour atteindre les objectifs cités ont consisté à :

- Proposer et implémenter un cadre d'allocation des ressources efficace pour les grappes de HPC hétérogènes.

- Proposer et implémenter une architecture matérielle reconfigurable pour l'accélération des services du centre de données.

- Implémenter un allocateur de ressources matérielles multi-domaines (niveaux) pour les grappes hétérogènes.

Les résultats de cette recherche seront précieux pour les praticiens de l'industrie, ainsi que pour les fournisseurs de logiciels associés dans le développement de meilleures pratiques et d'outils pour la gestion des contraintes et la planification prévisionnelle. Les travaux effectués auront un impact sur l'avenir du HPC et, éventuellement, sur la plupart des processeurs à usage général.

### 1.4 Contributions

L'atteinte des objectifs cités nous amène à revendiquer pour principales contributions :

- Une démonstration qu'il est possible de virtualiser un protocole de télécommunications emergent en n'utilisant que du matériel commercialement disponible (COTS) et ce en réduisant les coûts d'OPEX et CAPEX d'un futur opérateur de télécommunications.

- La création d'une plateforme hétérogène pouvant rencontrer les requis de basse latence et haut débit des normes de communication émergentes.

- La proposition et la démonstration qu'un nouveau système de communication à faible

variance, peu latent à haute bande passante entre accélérateur et processeur est possible et surtout viable.

En plus de ces principales contributions, cette thèse offre aussi une solution viable et expensible à notre partenaire industriel. En effet, la bibliothèque 3D Virtual Fabric Processors (XDVFP) n'est pas seulement un élément essentiel d'une plateforme pour l'implémentation de futures normes de communications, mais elle est aussi une bibliothèque générique permettant l'exécution de tâches avec une faible variabilité et efficace (haute bande passante) sur des plateformes hétérogènes multinoeuds. Nous proposons notre nouvelle approche d'allocation de ressources dynamique dans une grappe de calcul haute performance. Nous nous baserons sur de nouveaux systèmes logiciels couplés avec des améliorations structurelles proposées, menant à la création de notre bibliothèque générique XDVFP. Nous démontrons ensuite que nous pouvons avoir une exécution à faible variance des tâches avec une meilleure utilisation des unités de calcul disponibles, grâce à l'introduction d'accélérateurs matériels. Les résultats de cette contribution ont été publiés dans un article intitulé « A Cache-Coherent Heterogeneous Architecture for Low Latency Real Time Applications ». Puis, nous avons aussi eu l'opportunité d'avoir accès à des plateformes CPU-FPGA d'avant-garde sur lesquelles nous avons pu expérimenter nos résultats de caractérisation et élaborer un ensemble de conseils pour ceux qui voudraient utiliser ou construire ce type de plateforme dans le futur. Nous utilisons ces nouvelles plateformes en socle pour implémenter une nouvelle technique de gestion dynamique et efficace du dernier niveau de cache d'un CPU. Les résultats de la caractérisation et des performances obtenus grâce à notre nouvelle technique de gestion de cache sont exposés dans l'article de revue « A Hybrid Architecture with Low Latency Interfaces Enabling Dynamic Cache Management ». Nous sommes aussi pionniers dans l'exploration et l'élaboration de différentes techniques de communication à travers le dernier niveau de cache d'un CPU à partir d'un accélérateur matériel, rendant cette thèse une des publications fondatrices d'un nouveau domaine de recherche prometteur.

## 1.5 Structure de la thèse

Cette thèse est organisée comme suit. Le Chapitre 2 est consacré à l'état de l'art pertinents, incluant les cadres logiciels associés, les techniques et architectures utilisées dans le domaine du HPC appliqués aux télécommunications. Le Chapitre 3 décrit notre méthodologie de recherche et explique le processus de génération de pistes de recherche, d'identification des problèmes, des éléments exploitables, des étapes spécifiques et des résultats éventuels en termes de documents de recherche. Il présente une vue d'ensemble du corps de cette thèse. Nous nous dirigeons ensuite vers le corps central du projet de thèse qui a été présenté comme

un chapitre exploré en profondeur et deux articles.

Nous présentons tout d'abord une architecture logicielle et matérielle, ainsi que les résultats préliminaires de la solution proposés avant l'incorporation d'accélérateurs. Le tout constitue le Chapitre 4 de cette thèse.

Un premier article traite des nouvelles techniques d'accélération d'allocation de ressources sur FPGA dans le cadre de grappe de calcul haute performance pour application nécessitant une basse latence. Cet article est intitulé «*A Cache-Coherent Heterogeneous Architecture for Low Latency Real Time Applications*», exposé dans le cadre du 2017 IEEE 20th International Symposium on Real-Time Distributed Computing (ISORC) et est présenté dans le Chapitre 5 de la thèse.

Notre deuxième article présente une nouvelle technique de gestion dynamique du dernier niveau de cache (LLC) de CPU avec un accélérateur matériel. Cet article est intitulé «*A Hybrid Architecture with Low Latency Interfaces Enabling Dynamic Cache Management*» et il a été présenté dans l'édition du mois d'octobre 2018 de la revue IEEE Access. Cet article est reproduit comme Chapitre 6 dans cette thèse.

Enfin, au Chapitre 7, nous présentons un résumé et une discussion de nos contributions au monde de la recherche, de leur impact sur l'écosystème des HPC et nous formulons des recommandations pour les travaux futurs qui pourraient être menés dans ce domaine.

## CHAPITRE 2 ACCÉLÉRATEURS ET ALLOCATION DE RESSOURCE DANS LE DOMAINE DES TÉLÉCOMMUNICATIONS ÉMERGENTES

Ce chapitre servira de fondation sur laquelle se base une bonne partie des concepts utilisés et étudiés dans cette thèse. Il vise à résumer l'état de l'art, ainsi qu'à démontrer le potentiel de recherche de cette thèse.

### 2.1 Contexte général du projet de recherche

Afin de mieux situer la revue de l'état de l'art, le contexte global du projet de thèse doit être mis en perspective. Ce projet doctoral a commencé au sein d'un projet plus vaste soutenu par un partenaire industriel. La ligne directrice du projet était l'accélération de grappe de calcul pour les technologies émergentes, tel que la 5G. En effet, pour le cas de la 5G, il est estimé que l'architecture soutenant éventuellement le protocole devra avoir 10-100x la bande passante de la technologie précédente, LTE, tout en réduisant de 10x la latence [7]. Une des techniques proposées par l'industrie est connue sous l'appellation Cloud Radio Access Networks (C-RAN), dans le cadre de laquelle une ou un petit ensemble de grappe serviraient de zone de traitement "nuagique" plus proche des utilisateurs pour pallier aux besoins de performances des protocoles. Le principal problème est qu'afin de rencontrer les requis de bande passante, latence et efficacité énergétique dans des petits centres de HPC, les architectures existantes sont inadéquates. Au sein de ce projet, nous visons à introduire une architecture système et une bibliothèque logicielle générique pour satisfaire ces besoins. Nous proposons d'utiliser des accélérateurs au sein de la grappe pour, à la fois augmenter la quantité de traitements possibles tout en diminuant le besoin en énergie. Puis notre bibliothèque logicielle fournira un environnement propice pour l'implémentation de diverses applications nécessitant une accélération. Nous proposons aussi une infrastructure logicielle utilisant les accélérateurs matériels disponibles dans la grappe pour une gestion dynamique des ressources permettant d'améliorer la capacité de calcul tout en réduisant grandement la latence globale de traitement.

### 2.2 Cloud Radio Access Networks

L'architecture d'un C-RAN se compose de trois éléments clés [5] [6] ; les unités d'accès radio distribuées (RAU) sur le site distant d'une petite cellule ; un bassin de BBU dans un nuage de centre de données, géré par des processeurs généraux à haute performance offrant une

virtualisation en temps réel ; et un réseau de transport optique à large bande passante et à faible latence reliant les BBU et les RAU. La séparation des RAU du traitement en bande de bases permet de migrer le traitement des signaux et des données vers une entité centralisée et, par conséquent, elle embrasse les technologies émergentes des centres de données et du traitement nuagique (*Cloud Computing*) et enfin elle permet des infrastructures plus vertes, une réduction des CAPEX et OPEX, un équilibrage de charge efficient pour soutenir un grand trafic et des services flexibles [9] [10]. Le projet proposé se concentre principalement sur les questions liées aux BBU, en particulier le concept d'Infrastructure-as-a-Service (IaaS) activé par la technologie des centres de données.

L'un des sujets centraux liés aux nuages IaaS est de savoir comment allouer dynamiquement des ressources aux grappes de calcul pour minimiser les coûts d'exploitation tout en respectant les contraintes de QoS. Dans la littérature, l'une des solutions les plus populaires pour trouver le meilleur compromis entre ces deux objectifs contradictoires modélise l'allocation des ressources en tant que problème de bien-être social ("social welfare") exprimé par une fonction d'utilité appropriée [11]. Ces dernières années, ce paradigme a été largement adopté dans l'ingénierie du trafic sous le nom de *Network Utility Maximization* (NUM) [12] et la gestion de l'énergie dans le *Smart Grid* [13]. De nombreux modèles et algorithmes ont été développés. Ils peuvent être facilement appliqués aux affectations de ressource dynamiques dans les grappes informatiques avec des adaptations adéquates. Une autre solution viable est l'application de technologies des systèmes de commande, en particulier le *Model Predictive Control* (MPC) [14], ce qui revient à trouver une solution optimale compromettant les performances souhaitées et le coût requis. L'allocation dynamique des ressources peut également être formulée comme un problème de contrôle par rétroaction [15], auquel des outils de la théorie des systèmes de commande peuvent être appliqués à la conception d'algorithmes de commande en temps réel. Néanmoins, une formulation appropriée des problèmes de commande permettant une maximisation de l'utilité conjointe de la qualité de service et des coûts de consommation d'énergie est encore nécessaire [16]. En effet, l'allocation dynamique des ressources à différents niveaux du traitement nuagique est un sujet de recherche très actif dans la littérature [17].

Pour réduire davantage les coûts d'exploitation dus à la consommation d'énergie, les solutions au niveau du cabinet d'équipements informatique consistent à mettre hors tension les serveurs inactifs à l'aide de composants matériels de bas niveau pour prendre en charge une mise à l'échelle des performances proportionnelle à la consommation d'énergie. La réduction du sourcoût introduit par le basculement entre différents états d'alimentation et les ressources physiques (par exemple, les serveurs, les configurations de base, etc.) peut également faire progresser considérablement la gestion des ressources écoénergétiques [18].

L'intérêt de la mise en œuvre de systèmes C-RAN sur les nuages informatiques était clairement compris. Par contre, même si le maximum de puissance de traitement qui est disponible dans un grand centre de données permet en principe des solutions par la force brute, les récentes tentatives industrielles de le faire de façon économiquement acceptables n'ont pas donné les résultats souhaités. Un facteur clé qui a entravé ces initiatives est la latence entre les fils de coopération rencontrés avec les systèmes d'exploitation de centre de données gérés par un Linux typique. Une solution à ce problème a été élaborée par Intel, le fournisseur de la grande majorité des processeurs au cœur des centres de données. Le Data Plane Development Kit (DPDK) [19] a été spécifiquement proposé à cet effet.

## 2.3 Accélérateurs en informatique reconfigurable haute performance (HPRC)

L'informatique reconfigurable haute performance est considérée comme la prochaine étape du HPC [20]. Actuellement à l'ère de l'informatique hétérogène, l'ajout de matériel reconfigurable [21], similaire aux FPGA, révolutionne la façon dont nous faisons des calculs, avec l'arrivée de "FPGA intégrés" [22]. Les sections suivantes explorent l'état actuel du HPC et l'évolution vers l'informatique hétérogène pour finir avec un argument pour les FPGA dans les environnements HPC.

### 2.3.1 Le paradigme HPC

Afin de mettre en place correctement cette recherche, nous devons comprendre le but et les principaux algorithmes exécutant une plate-forme HPC donnée. Le calcul haute performance consiste à utiliser plusieurs unités de calcul parallèles, dans le cas de nos serveurs lames, pour exécuter et résoudre des problèmes scientifiques. L'unité informatique peut s'étendre de la petite lame à processeur unique aux serveurs multiprocesseurs haute performance connectés via des liaisons à haut débit. Une grappe HPC typique contient des millions de cœurs actifs, comme le plus grand système connu qui contient 10 649 600 cœurs [23]. Les applications typiques roulant sur des HPC sont la résolution d'équations complexe, la simulation large (génome) et le rendu de calculs hautement techniques. Ces types d'applications à grande échelle mettent l'accent sur l'analyse massive de données [24]. Jusqu'à présent, la plupart des puissants systèmes HPC étaient basés sur un processeur. Cependant, l'analyse massive des données étant la nouvelle application principale des systèmes HPC, l'homogénéité des systèmes est coûteuse pour un propriétaire de centre HPC. En effet, la consommation électrique et la génération de chaleur sont proportionnelles à la vitesse d'horloge des processeurs. Cette combinaison a un impact négatif sur le coût de possession d'un système HPC [25]. Afin d'obtenir un meilleur coût de performance, l'alternative viable aux HPC conventionnels est

la migration vers des architectures hétérogènes de HPC. L'informatique hétérogène n'est pas nouvelle et à de nombreuses architectures différentes. Dans le domaine CPU, vous pouvez trouver une plate-forme multicœur asymétrique [26] avec la même architecture, deux unités de calcul cadencées différentes, elle est appelée architecture Big.LITTLE. L'informatique hétérogène est lorsque plusieurs architectures ou matériels informatiques sont utilisés dans un système donné pour exécuter des applications spécifiques ou très spécifiques. Habituellement, le HPC hétérogène implique l'utilisation d'accélérateurs matériels différents du conventionnel (CPU) utilisés dans les lames de serveur. Cependant, différents accélérateurs ont des forces différentes. Pour pouvoir répondre aux besoins d'un type d'accélérateur spécifique, nous devons mieux définir les applications fonctionnant sur les systèmes HPC. Afin de comparer précisément un système, D. Patterson de l'Université de Berkley a classé les principaux types d'algorithmes qui fonctionnent sur les HPC, il les a nommés, les 13 nains [27]. Le tableau ci-dessous définit chaque nain. Nous observons 4 groupes principaux du Tableau 5.2 :

- calculs arithmétiques complexes combinés à un accès régulier à la mémoire est plus efficace sur les **GPU** ;

- calculs arithmétiques complexes combinés à un accès irrégulier à la mémoire est plus efficace sur les **FPGA** ;

- calculs arithmétiques simple nécessitant une gestion complexe de la mémoire, favorisent les architectures **Multicoeurs** ;

- calculs arithmétiques simple utilisant des opérations matérielles spécifiques, favorise les **FPGA**.

Tableau 2.1 Berkeley's 13 dwarfs

| Dwarf                                    | Application             | Accelerator |

|------------------------------------------|-------------------------|-------------|

| <b>DLA</b> : Dense Linear Algebra        | dense matrices          | GPU         |

| <b>SLA</b> : Sparse Linear Algebra       | sparse matrice          | FPGA        |

| <b>SM</b> : Spectral Methods             | FFT-based methods       | GPU         |

| <b>NBM</b> : N-Body Methods              | Particle interactions   | GPU         |

| <b>SG</b> : Structured Grids             | Fluid dynamics          | FPGA        |

| <b>UG</b> : Unstructured Grids           | Adaptive mesh FEM       | FPGA        |

| <b>MR</b> : Map Reduce                   | Monte Carlo integration | Multicore   |

| <b>CL</b> : Combinational Logic          | Logic gates             | FPGA        |

| <b>GT</b> : Graph Traversal              | Searching, selection    | Multicore   |

| <b>DP</b> : Dynamic Programming          | Tower of Hanoi problem  | Multicore   |

| <b>BB</b> : Backtrack and Branch-n-Bound | Global optimization     | Multicore   |

| <b>GM</b> : Graphical Models             | Probabilistic networks  | Multicore   |

| <b>FSM</b> : Finite State Machines       | TTL counter             | FPGA        |

La principale information à tirer du Tableau 5.2 est que la plupart des applications HPC

impliquent le traitement d'une grande quantité d'informations. La latence semble être une pensée d'après-coup. C'est là que nos recherches revendiquent l'une de ses contributions, à savoir améliorer la latence des HPC hétérogènes, en ce qui a trait à la satisfaction de contraintes de latence et de variabilité réduite d'exécution. Cette proposition vise à résoudre le problème avec l'utilisation de la prise en charge FPGA (*offload*). La section suivante expliquera plus en détail la viabilité du FPGA dans HPC.

### 2.3.2 Pertinence de l'utilisation de FPGA dans HPC

Nous pouvons déduire du Tableau 5.2 que le FPGA est mieux adapté à l'application de diffusion. Des travaux similaires à Inta et al dans [28] exposent les FPGA comme accélérateurs de fonctions. Dans le cas d'une application ou une fonction donnée s'exécute sur le FPGA et renvoie ses résultats à une unité de traitement principale.

Deux problèmes principaux peuvent être dérivés de l'utilisation des FPGA. Le premier, c'est sa courbe d'apprentissage. Il est bien connu que pour utiliser la majeure partie de la puissance de traitement FPGA exposée par Escobar et al dans [29], le développeur doit également avoir une bonne connaissance de l'architecture matérielle. Pour le rendre facile à utiliser, des cadres et outils de programmation de haut niveau ont été introduits, communément appelés outils HLS [30], [31]. La plupart des HPC contenant des FPGA connectent tous les accélérateurs via PCIe. PCIe est principalement conçu pour favoriser la bande passante par rapport à la latence.

De nombreuses études et systèmes utilisent un protocole de communication basé sur PCIe [32] [33]. L'utilisation d'accélérateurs FPGA via la communication PCIe n'est pas nouvelle dans le domaine HPC [34]. De grands acteurs comme Intel et Microsoft [35] ont réussi à intégrer l'accélération FPGA dans leur flux de traitement pour une analyse massive des données de leur moteur de recherche Bing. Peu d'attention a été accordée aux problèmes de latence dans HPC pour favoriser le traitement massif des données. Nous explorerons le problème de latence dans les applications de flux *streaming* dans la prochaine section de cette revue de la littérature. C'est là que les FPGA à fiches (*in-socket*) entrent en action. Considérés comme la prochaine étape importante du HPRC, comme le montre le professeur Chow dans [36] le professeur Ling dans [37], ils permettent des communications à faible latence entre l'unité de traitement. Certains diront que ce n'est pas nouveau en raison des "processeurs logiciels" déjà disponibles sur les plates-formes FPGA, comme Nios [38], Microblazes [39] et Zynq avec processeurs ARM [40] "dur". Le problème avec ces implémentations est toujours la difficulté de les intégrer dans une grappe HPC tout en utilisant un protocole à latence plus faible. Pour résoudre ce problème, le FPGA en prise (*in-socket*) a réduit la latence de communication avec

l'utilisation du bus frontal [41]. La communication point à point entre le CPU et le FPGA a permis aux développeurs d'avoir un meilleur accès à la mémoire système [22]. Même si elle était 6 fois moins latente que la communication PCI-X, elle est encore trop élevée pour compenser la virtualisation 5G. Afin de répondre aux exigences de la 5G les implémentations de [41] et [22] manquaient d'une fonctionnalité spécifique, une interface cohérente de cache (CCI).

La première communication FPGA / CPU cohérente en cache a été introduite par Intel, avec le bus Quick Path Interconnect [22]. L'utilisation de ces avancées permet à cette recherche de contribuer au domaine d'étude. Une CCI permet des communications via la mise en cache. La latence des communications serait équivalente au temps requis pour écrire et lire un point de données dans le cache. Dans les fiches (*socket*), les FPGA permettent un traitement à faible latence et à haut débit d'avoir un répartiteur de ressources multiniveaux efficaces. Notre travail étant à la jonction entre deux domaines, nous comparerons les gains d'efficacité au HPC avec les accélérateurs FPGA et les allocateurs de ressources matérielles. Malheureusement, peu de travaux ont été publiés dans notre créneau, en raison de la faible disponibilité de la plate-forme FPGA QPI en fiche. Nous sommes quelques-uns à avoir cette opportunité.

Notre architecture matérielle permettra le déploiement des algorithmes de programmation complexes [42] et d'allocation des ressources. Ce qui accélérera finalement les temps d'exécutions d'un HPC hétérogène. La section suivante explique en détail ce que nous appelons un “*Runtime*”.

### 2.3.3 Accélération d'exécution logicielle

La manière typique d'obtenir un système moins latent consiste à utiliser des “systèmes d'exploitation en temps réel (RTOS)”, tels que FreeRTOS [43]. Laplante et al dans [44] expliquent comment ils réduisent la latence induite par la gestion des ressources avec des insertions d'assemblages intelligents au niveau du noyau. Cependant, un problème associé à RTOS est leur rigidité et le manque de support pour les nouvelles bibliothèques de calcul. Les rendant moins adaptés aux nouvelles applications, en particulier les applications de type HPC. En dehors de l'utilisation de RTOS, les moyens courants pour accélérer l'exécution sont les suivants :

- une meilleure gestion de la mémoire ;

- un algorithme de planification spécifique à l'application et un schéma d'allocation des ressources ;

- une nouvelle méthodologie et l'architecture.

Pour les systèmes hétérogènes, il existe des alternatives logicielles qui utilisent des ensembles

de bibliothèques pour des applications spécifiques. Pour les applications CPU, le cadre d'exécution OPENCL [45] est fréquemment utilisé pour obtenir une utilisation plus efficace des processeurs multicoeurs et comme langage pour intégrer des accélérateurs dans le système (language pour plateforme hétérogènes). Plus récemment, Augonnet et al [46] ont présenté StarPU une bibliothèque de programmation de tâches pour les architectures hybrides, une bibliothèque qui prend en charge les problèmes d'exécution pour les architectures hétérogènes. StarPU facilite l'utilisation d'accélérateurs et simplifie la mise en œuvre de communications, de transferts de données et de gestion de mémoire plus efficaces entre les multiples unités de traitement d'une grappe (plates-formes hybrides).

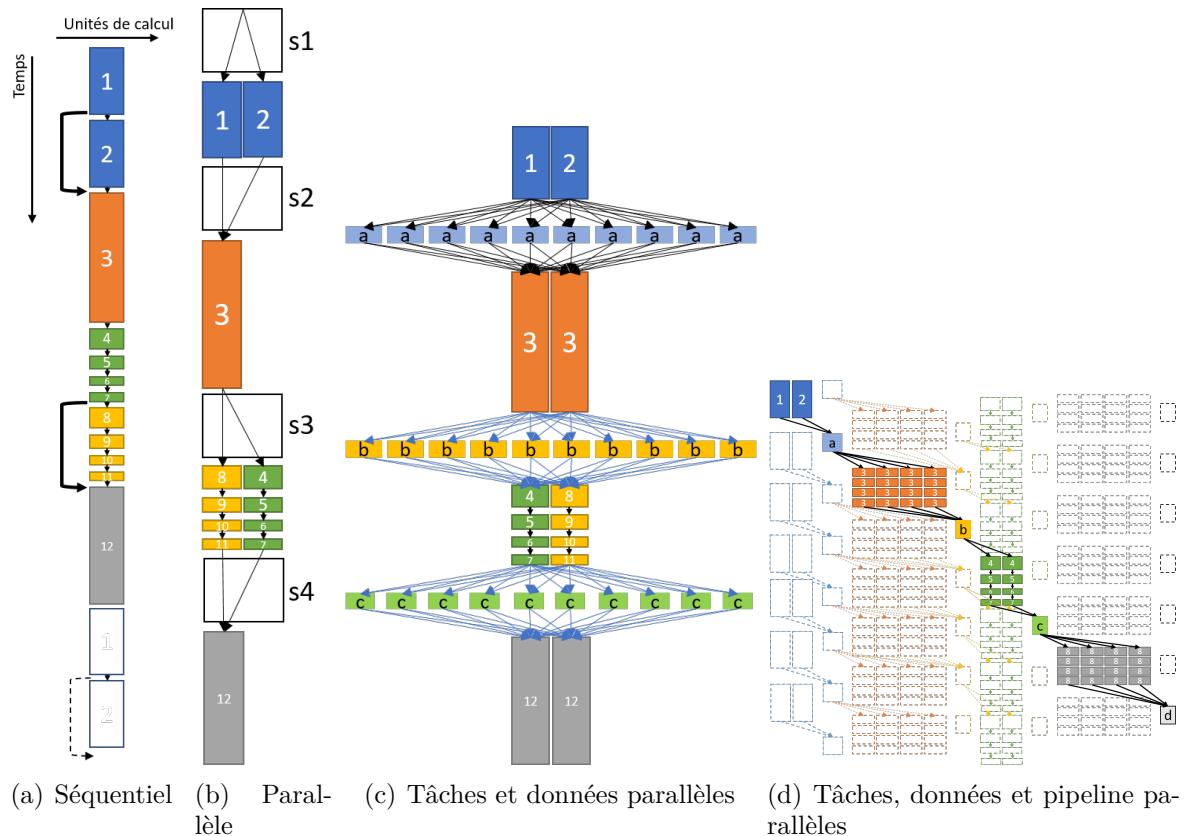

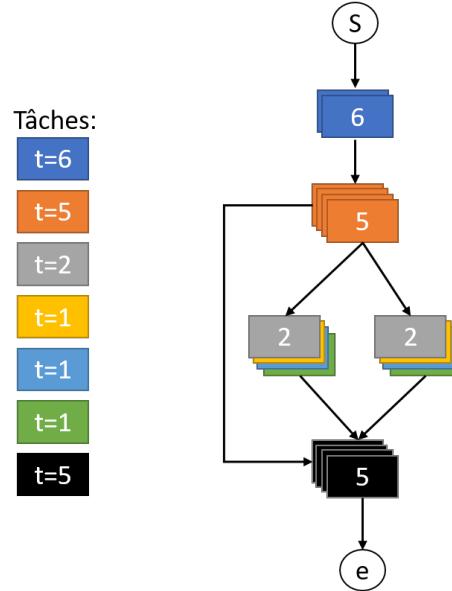

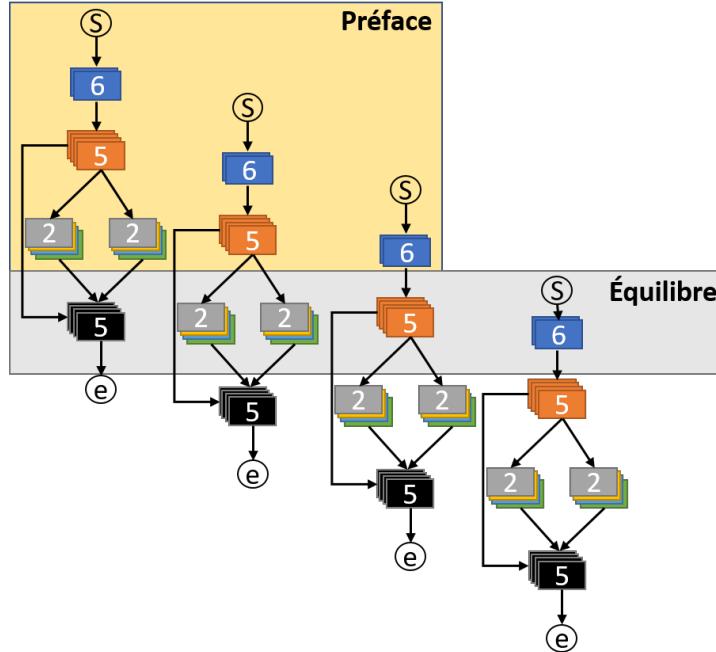

Ces bibliothèques exploitent généralement un système de programmation par tâches afin d'obtenir des exécutions parallèles. Examinons donc les différents modèles d'exécution parallèle (aussi appelé modèle de synchronisation) étudiés dans cette thèse en référant à la Figure 2.1. Dans cette figure, (a) représente un programme séquentiel tandis que (b) exécute des tâches en parallèle. En (b), certaines tâches nécessitent l'achèvement de leurs prédecesseurs afin de préserver la cohérence séquentielle du programme. La première synchronisation prise en

Figure 2.1 Exemples de graphes de flot de traitement parallèles et séquentiels

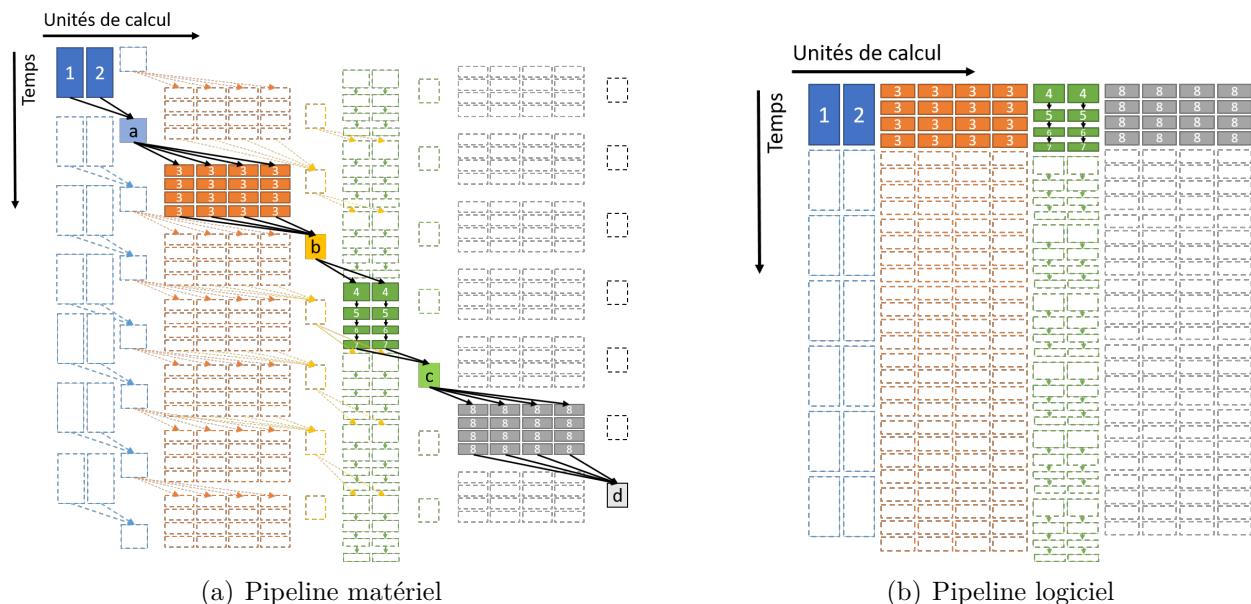

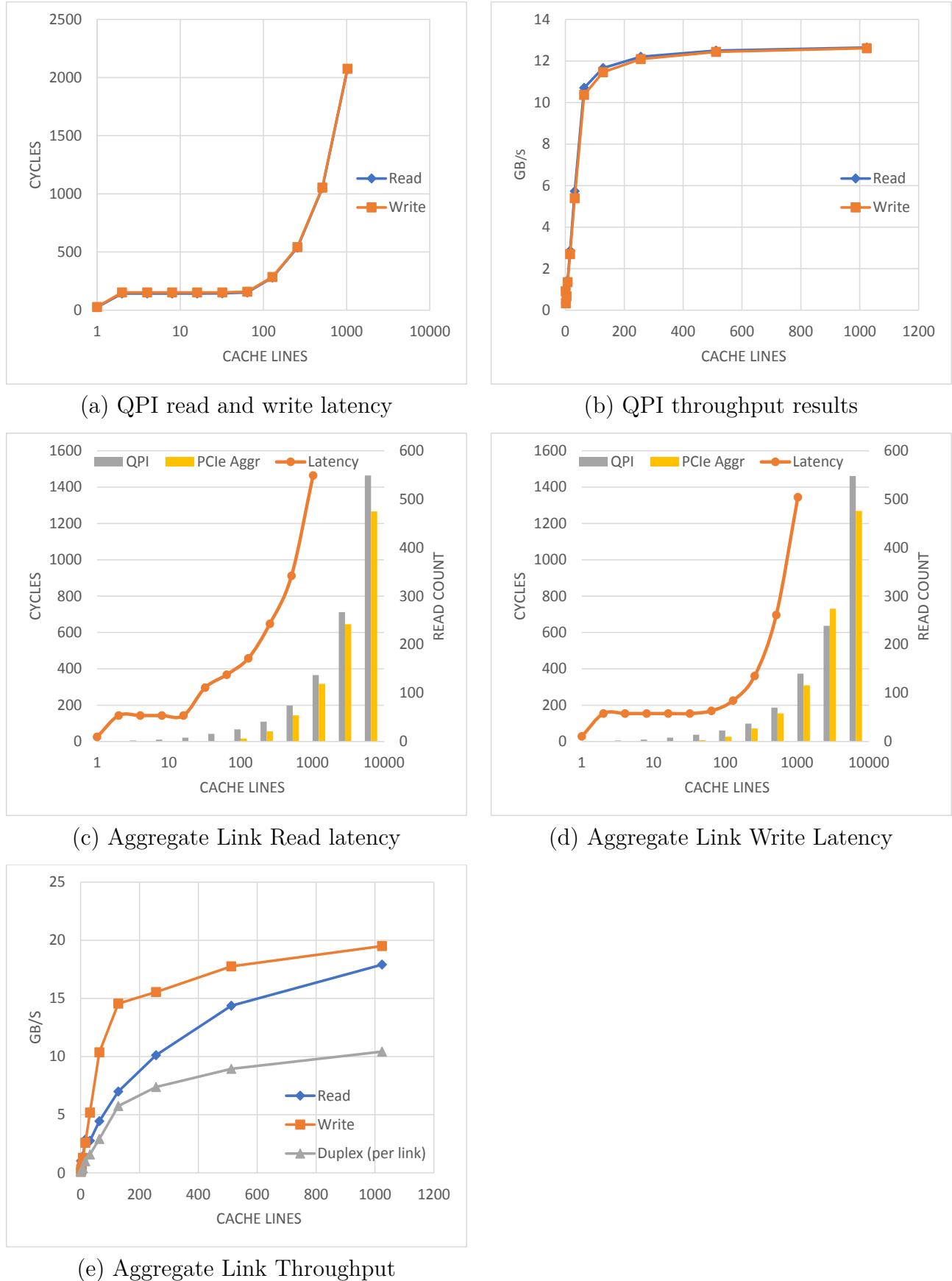

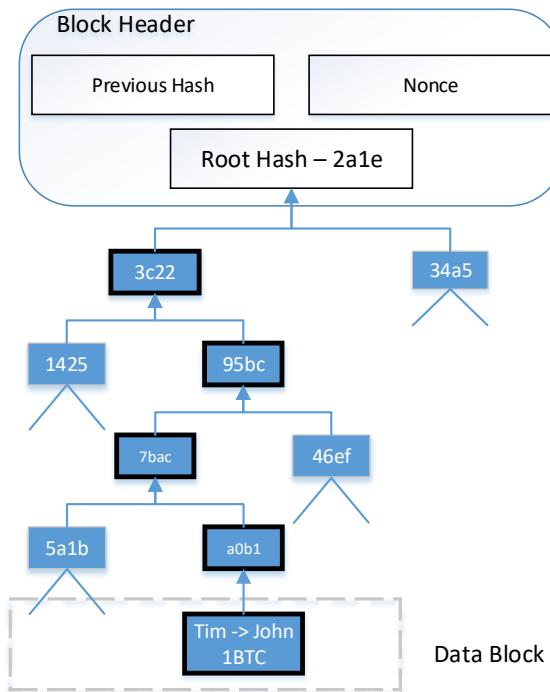

charge par nos premiers résultats exposé au Chapitre 4 est : **Parallélisme explicite des tâches** : dans ce mode, les dépendances ne sont pas gérées par le *runtime* et l'application attendra explicitement l'achèvement d'un ensemble de tâches avant d'envoyer une autre charge de travail qui consomme des données produites par une charge de travail précédente. Le cas présenté en (c) correspond à un parallélisme au niveau des données. Le runtime XDVFP que nous proposons ne fait rien à ce niveau. Cependant, cela est largement utilisé dans les tâches LTE par l'utilisation d'instructions *Intel Single Instruction Multiple Data* (SIMD). (d) présente comment les tâches dépendantes et indépendantes peuvent être canalisées dans un système lorsque les dépendances sont gérées par le *runtime*. La diagonale illustrée en (d) correspond au cas du traitement d'un bloc de transport LTE. Puis dans le Chapitre 4 nous explorons le mode de synchronisation du **Parallélisme des tâches piloté par les données**. Dans ce mode, nous pourrions répartir les tâches d'une sous-trame LTE complète et nous synchronisons au niveau de la sous-trame. Le niveau suivant consiste à briser la limite de la sous-trame pour permettre le traitement des sous-trames en parallèle. Nous appelons ce mode **Pipelining logiciel à gros grains** : la Figure 2.2 aide à visualiser la différence entre le pipelining matériel et logiciel.