|                                            | Analog Compressive Sensing for Multi-Channel Neural Recording:  Modeling and Circuit Level Implementation                                                                                                                                                                                     |  |  |

|--------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Auteur:  Author: Fereidoon Hashemi Noshahr |                                                                                                                                                                                                                                                                                               |  |  |

| Date:                                      | nte: 2020                                                                                                                                                                                                                                                                                     |  |  |

| Type:                                      | Mémoire ou thèse / Dissertation or Thesis                                                                                                                                                                                                                                                     |  |  |

| Référence:<br>Citation:                    | Hashemi Noshahr, F. (2020). Analog Compressive Sensing for Multi-Channel<br>Neural Recording: Modeling and Circuit Level Implementation [Thèse de doctorat,<br>Polytechnique Montréal]. PolyPublie. <a href="https://publications.polymtl.ca/5248/">https://publications.polymtl.ca/5248/</a> |  |  |

# Document en libre accès dans PolyPublie Open Access document in PolyPublie

| <b>URL de PolyPublie:</b><br>PolyPublie URL: | https://publications.polymtl.ca/5248/ |

|----------------------------------------------|---------------------------------------|

| Directeurs de recherche: Advisors:           | Mohamad Sawan                         |

| Programme:                                   | génie électrique                      |

## POLYTECHNIQUE MONTRÉAL

affiliée à l'Université de Montréal

# ANALOG COMPRESSIVE SENSING FOR MULTI-CHANNEL NEURAL RECORDING: MODELING AND CIRCUIT LEVEL IMPLEMENTATION

### FEREIDOON HASHEMI NOSHAHR

Département de génie électrique

Thèse présentée en vue de l'obtention du diplôme de Philosophiæ Doctor Génie électrique  $Avril \ 2020$

<sup>©</sup> Fereidoon Hashemi Noshahr, 2020.

# POLYTECHNIQUE MONTRÉAL

affiliée à l'Université de Montréal

Cette thèse intitulée :

ANALOG COMPRESSIVE SENSING FOR MULTI-CHANNEL NEURAL RECORDING: MODELING AND CIRCUIT LEVEL IMPLEMENTATION

présentée par **Fereidoon HASHEMI NOSHAHR** en vue de l'obtention du diplôme de *Philosophiæ Doctor* a été dûment acceptée par le jury d'examen constitué de :

Yvon SAVARIA, président

Mohamad SAWAN, membre et directeur de recherche

Guchuan ZHU, membre

Frédéric NABKI, membre externe

# **DEDICATION**

To my beloved parents, wife, son, brothers, and friends . . .

#### ACKNOWLEDGEMENTS

I would like to express my sincere gratitude to my supervisor Prof. Mohamad Sawan for giving me the opportunity to pursue my Ph.D. program under his supervision, and his continuous support and motivation. I also highly appreciate him for his mentoring and helping me in my research. I express my sincere thanks and gratitude to Dr. Yvon Savaria, Dr. Guchuan Zhu, and Dr. Frédéric Nabki for agreeing to be members of the examination board of my Ph.D. thesis.

My appreciation also goes to all my colleagues and friends in Polystim Neurotech Lab. including but not limited to Morteza Nabavi, Mohammad Noghabaei, Mohammad Honarparvar and Armin Najarpour for their valuable interactions in my journey. Likewise, I would like to thank Réjean Lepage and Laurent Mouden for their constant technical helps and supports that backed me to demonstrate my ideas as well as Marie-Yannick Laplante for her kind helps in the administrative level. I also appreciate Dr. Kolta Arlette at the faculty of Dentistry at University of Montreal for performing the neural recordings in an in vitro experiment on the slices of a mouse brain by our prototype neural amplifier.

I am dedicating my thesis to my parents for their endless love and support along the way and I am thankful of my wife and son for their patience and non-stop encouragement towards higher achievements. In the end, my thank goes for CMC Microsystems for supporting me with their design tools and integrated circuits manufacturing facilities.

## RÉSUMÉ

Dans cette thèse, nous présentons la conception d'un implant d'enregistrement neuronal multicanaux avec un échantillonnage compressé mis en oeuvre avec un procédé de fabrication CMOS à 65 nm.

La réduction de la technologie affecte à la baisse les paramètres des amplificateurs neuronaux couplés en AC, comme la fréquence de coupure basse, en raison de l'effet de canal court des transistors MOS.

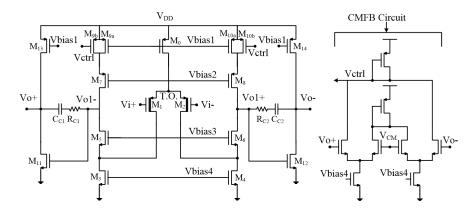

Nous analysons la fréquence de coupure basse et nous constatons que l'origine de ce problème, dans les technologies avancées, est la diminution de l'impédance d'entrée de l'amplificateur opérationnel de transconductance (OTA) en raison de la fuite d'oxyde de grille à l'entrée des OTA. Nous proposons deux solutions pour réduire la fréquence de coupure basse sans augmenter la valeur des condensateurs de rétroaction de l'étage d'entrée. La première solution est appelée rétroaction positive croisée et la deuxième solution utilise des PMOS à oxyde épais dans la paire de l'entrée différentielle de l'OTA. Il est à noter que pour compresser le signal neuronal, nous utilisons le CS dans le domaine analogique.

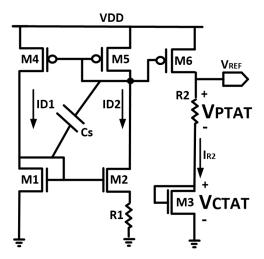

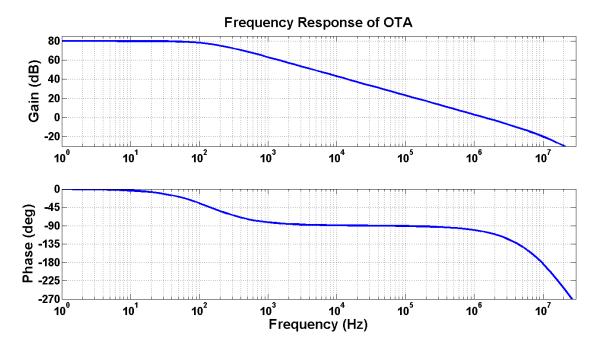

Pour la réalisation, un intégrateur à capacité commutée est requis. Les paramètres non idéaux de l'OTA utilisé dans cet intégrateur, tels que le gain fini, la bande passante, la vitesse de balayage et le changement rapide de la sortie. Toutes ces imperfections induisent des erreurs et réduisent le rapport signal sur bruit (SNR) total. Nous avons simulé ces imperfections sur Matlab et Simulink pour définir les spécifications de l'OTA requis. Aussi, pour concevoir les circuits analogiques correspondant aux interfaces neuronales requises, tels qu'un amplificateur neuronal, une référence de tension compacte et à faible consommation d'énergie est requise. Nous avons proposé une référence de tension de faible consommation d'énergie sans utiliser le transistor bipolaire parasite de la technologie CMOS pour diminuer la surface de silicium requise. Finalement, nous avons complété l'encodeur de CS et un convertisseur analogique-numérique à approximation successive (SAR ADC) requis pour la chaine d'enregistrement des signaux neuronaux dans ce projet.

### **ABSTRACT**

In this thesis we present the design of a multi-channel neural recording implant with analog compressive sensing (CS) in 65 nm process.

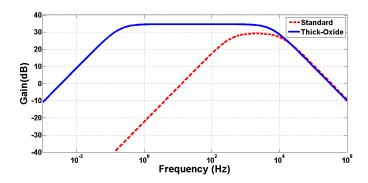

Scaling down technology demotes the parameters of AC-coupled neural amplifiers, such as increasing the low-cutoff frequency due to the short-channel effects of MOS transistors.

We analyze the low-cutoff frequency and find that the main reason of this problem in advanced technologies is decreasing the input resistance of the operational transconductance amplifier (OTA) due to the gate oxide static current leakage in the input of the OTA. In advanced technologies, the gate oxide is thin and some electrons can penetrate to the channel and cause DC current leakage. We proposed two solutions to reduce the low-cutoff frequency without increasing the value of the feedback capacitors of the front-end neural amplifier. The first solution is called cross-coupled positive feedback, and the second solution is utilizing thick-oxide PMOS transistors in the input differential pair of the OTA. Compress the neural signal, we utilized the CS method in analog domain.

For its implementation, a switched-capacitor integrator is required. Non-ideal specifications of OTA of CS integrator such as finite gain, bandwidth, slew rate and output swing induce error and reduce the total signal to noise ratio (SNR). We simulated these non-idealities in Matlab and Simulink and extracted the specification of the required OTA. Also, to design analog circuits such as neural amplifier a low power and compact voltage reference is required. We implemented a low-power band-gap reference without utilizing parasitic bipolar transistor to decrease the silicon area. At the end, we completed the CS encoder and successive approximation architecture analog-to-digital converter (SAR ADC).

# TABLE OF CONTENTS

| DEDICATION                                                    |

|---------------------------------------------------------------|

| ACKNOWLEDGEMENTS iv                                           |

| RÉSUMÉ                                                        |

| ABSTRACT                                                      |

| TABLE OF CONTENTS vii                                         |

| LIST OF TABLES                                                |

| LIST OF FIGURES                                               |

| LIST OF SYMBOLS AND ACRONYMS xv                               |

| CHAPTER 1 INTRODUCTION                                        |

| 1.1 Motivation and Objectives                                 |

| 1.2 Contributions                                             |

| 1.3 Thesis Organization                                       |

| CHAPTER 2 LITERATURE REVIEW                                   |

| 2.1 Introduction                                              |

| 2.2 Neural Signals                                            |

| 2.3 Neural Recording Architectures                            |

| 2.4 Neural Amplifiers                                         |

| 2.4.1 Neural Amplifier Topologies                             |

| 2.4.2 Multistage Amplifiers                                   |

| 2.4.3 Noise Reduction Techniques                              |

| 2.4.4 Advanced Neural-signal Amplifiers                       |

| 2.5 Analog to Digital Converters                              |

| 2.6 Data Compression                                          |

| 2.7 Conclusion                                                |

| CHAPTER 3 SYSTEMATIC DESIGN OF ANALOG COMPRESSIVE SENSING EN- |

| CODERS                                                        |

| 3.1   | Introd                                  | uction                                           |  |

|-------|-----------------------------------------|--------------------------------------------------|--|

| 3.2   | CS Background and Neurorecording System |                                                  |  |

| 3.3   | System                                  | n Level Simulations                              |  |

|       | 3.3.1                                   | Finite Gain Effect                               |  |

|       | 3.3.2                                   | Finite Bandwidth and Slew Rate Effect            |  |

|       | 3.3.3                                   | Finite Output Swing Effect                       |  |

| 3.4   | CS Co                                   | ore with iEEG Input                              |  |

| 3.5   | Variab                                  | ble Compression                                  |  |

| 3.6   | Progra                                  | amable Gain CS Core                              |  |

| 3.7   | Discus                                  | sion and Conclusion                              |  |

| СНАРТ | TER 4                                   | NEURAL AMPLIFIER AND REFERENCE CIRCUIT DESIGN 50 |  |

| 4.1   | Neura                                   | l Amplifier Design                               |  |

|       | 4.1.1                                   | Introduction                                     |  |

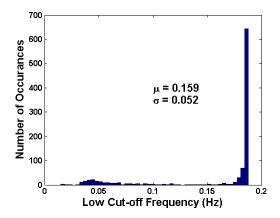

|       | 4.1.2                                   | Low-Cutoff Frequency Analysis                    |  |

|       | 4.1.3                                   | Proposed Solutions                               |  |

|       | 4.1.4                                   | Thick Oxide Differential Pair                    |  |

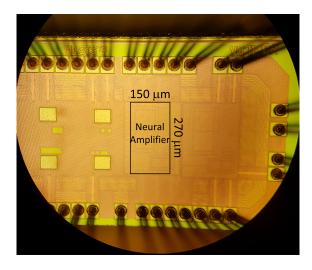

|       | 4.1.5                                   | Measurement and In Vitro Results                 |  |

|       | 4.1.6                                   | Conclusion                                       |  |

| 4.2   | Voltag                                  | ge Reference Design                              |  |

|       | 4.2.1                                   | Introduction                                     |  |

|       | 4.2.2                                   | Fundamentals of Voltage Reference Design         |  |

|       | 4.2.3                                   | Proposed Design                                  |  |

|       | 4.2.4                                   | Conclusion                                       |  |

| CHAPT | TER 5                                   | CS ENCODER AND ADC DESIGN                        |  |

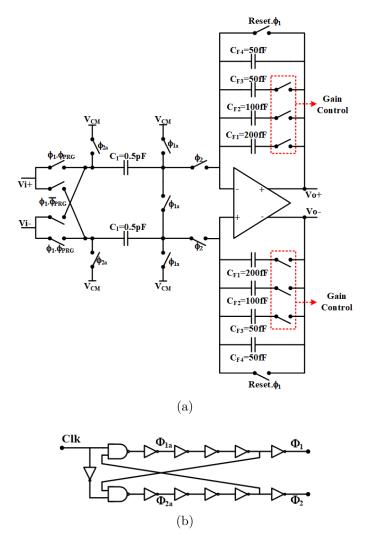

| 5.1   | CS En                                   | coder Design                                     |  |

|       | 5.1.1                                   | Pseudorandom Number Generator                    |  |

|       | 5.1.2                                   | Implementation of CS Core and PGA                |  |

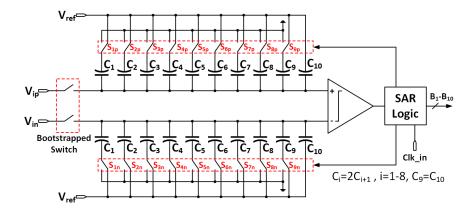

| 5.2   | ADC :                                   | Design                                           |  |

|       | 5.2.1                                   | SAR ADC Architecture                             |  |

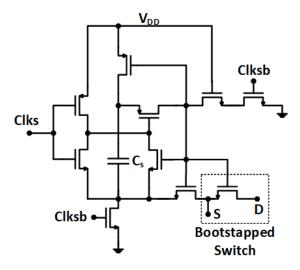

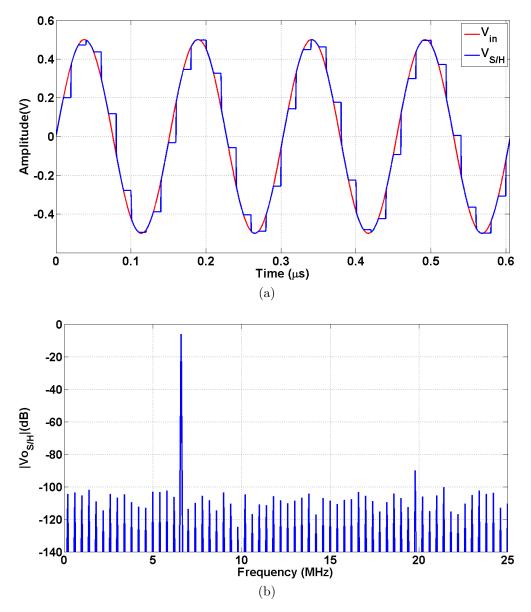

|       | 5.2.2                                   | S/H Circuit Design                               |  |

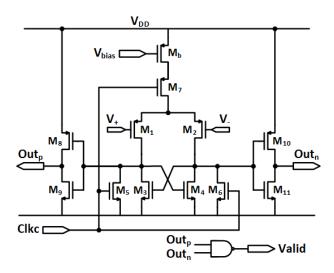

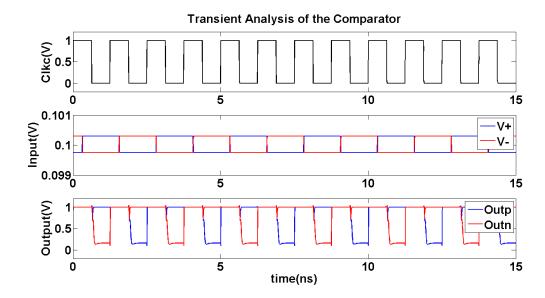

|       | 5.2.3                                   | Dynamic Comparator                               |  |

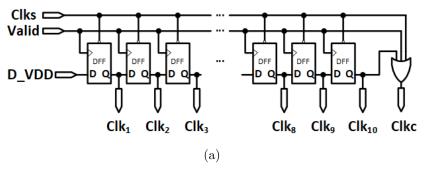

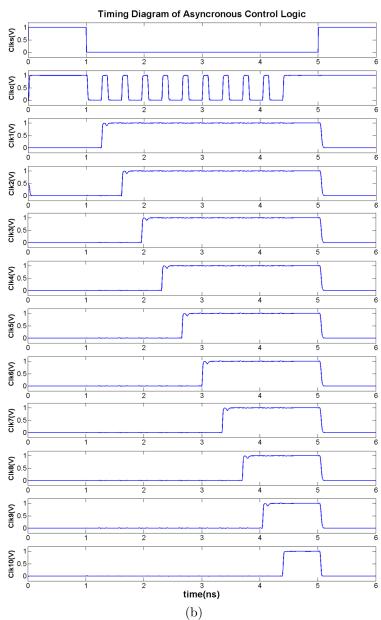

|       | 5.2.4                                   | SAR Asynchronous Control Logic                   |  |

| СНАРТ | TER 6                                   | CONCLUSION                                       |  |

| 6.1   | Contri                                  | butions                                          |  |

| 1 | X |

|---|---|

|   |   |

| 6.2    | Summary of Works | 91 |

|--------|------------------|----|

| 6.3    | Future Research  | 92 |

| DIDITO |                  |    |

| BIBLIO | OGRAPHY          | 93 |

# LIST OF TABLES

| 2.1 | NEURAL SIGNAL PARAMETERS                            | 10 |

|-----|-----------------------------------------------------|----|

| 2.2 | COMPARISON BETWEEN DIFFERENT TOPOLOGIES OF NEU-     |    |

|     | RAL AMPLIFIERS                                      | 31 |

| 3.1 | FINITE BANDWIDTH SIMULATION RESULT                  | 44 |

| 4.1 | EXPERIMENTAL AND SIMULATION CHARACTERISTICS OF NEU- | -  |

|     | RAL AMPLIFIER                                       | 63 |

| 4.2 | COMPARISON OF FULLY INTEGRATED NEURAL AM-           |    |

|     | PLIFIERS                                            | 64 |

| 4.3 | COMPARISON OF MAIN PARAMETERS OF CHOSEN VOLTAGE     |    |

|     | REFERENCES                                          | 74 |

| 5.1 | CONFIGURATION OF ADC RESOLUTION                     | 89 |

# LIST OF FIGURES

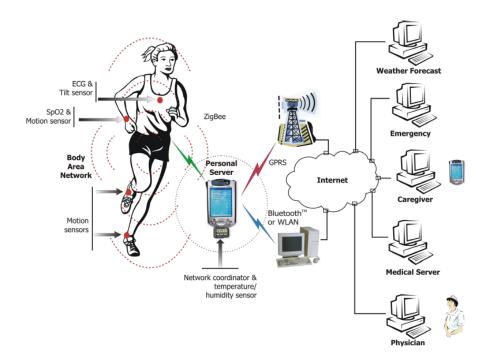

| Wireless Body Area Network                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

|---------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

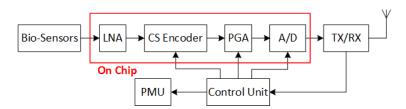

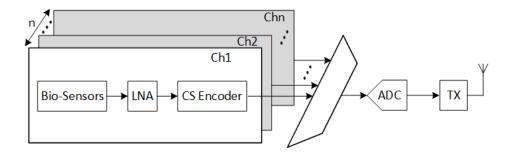

| Simplified block diagram of a neural recording implant with CS encoder    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

| for one channel                                                           | 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |

| Block diagram of different multi-channel neural recording architec-       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

| tures. (a) This architecture shares an ADC among all of the chan-         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

| nels. (b) This architecture utilizes an ADC for each channel. (c) This    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

| architecture shares an ADC at each column                                 | 11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |

| Implementing a high-pass pole using a low-pass filter in the feedback.    | 14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |

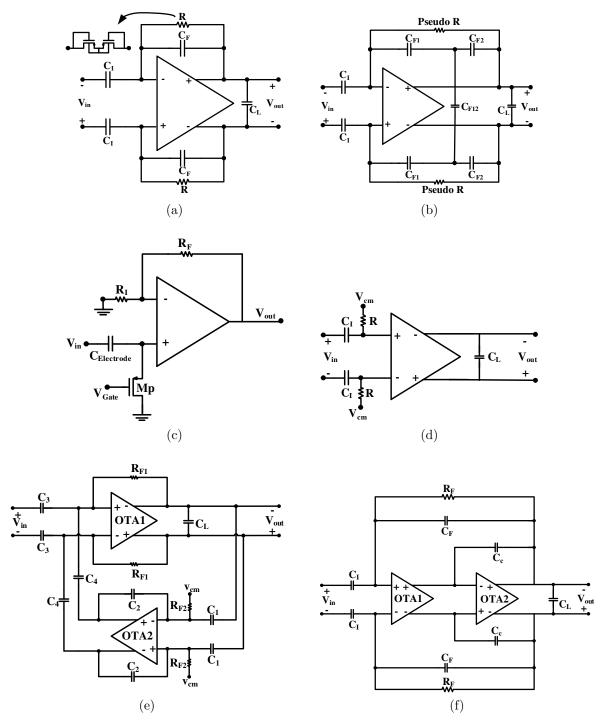

| AC-coupled neural amplifier topologies. (a) Conventional capacitive-      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

| feedback network (CFN) topology. (b) CFN amplifier using T-capacitor      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

| feedback network topology. (c) AC-coupling utilizing the electrode ca-    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

| pacitance and a resistive element. (d) Open loop network (OLN) topol-     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

| ogy. (e) Capacitive amplifier feedback network (CAFN) topology. (f)       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

| Miller compensated CFN (MCCFN) topology                                   | 15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |

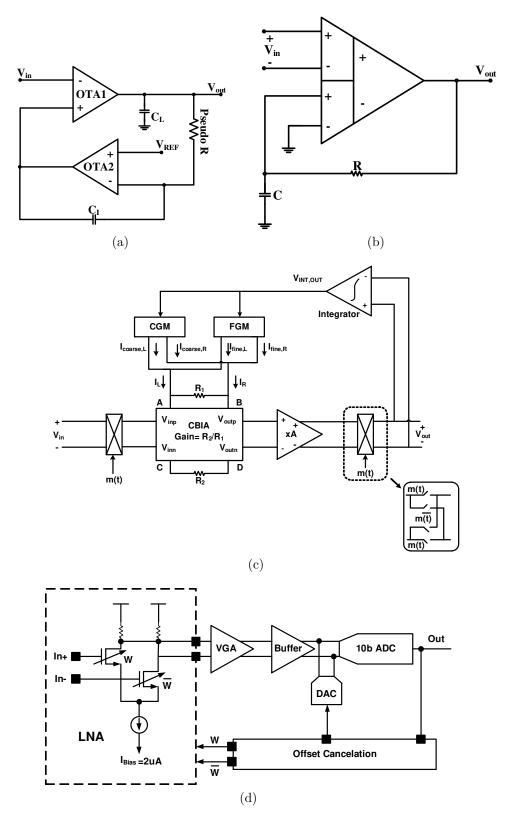

| DC-coupled neural amplifiers utilizing (a) an analog active LPF. (b)      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

| an analog passive LPF and a differential difference amplifier, (c) analog |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

| and digital DC servo loops (DSL), and (d) input differential pair width   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

| modulation by an offset cancellation feedback                             | 18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |

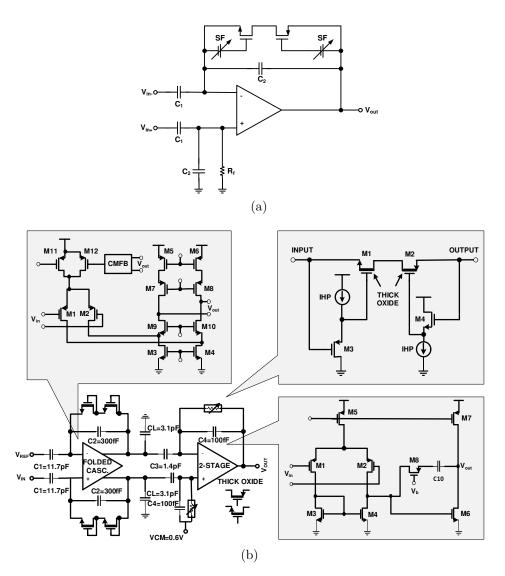

| Improving the linearity of CFN amplifier utilizing (a) source-followers   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

| (SF). (b) two gain stages with employing the proper NMOS and PMOS         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

| pseudoresistor and SFs                                                    | 21                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |

| (a) Schematic of a three-stage amplifier, (b) Second-stage amplifier      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

| tunes the high and low-cutoff frequency                                   | 22                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |

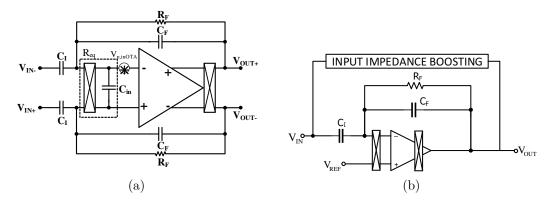

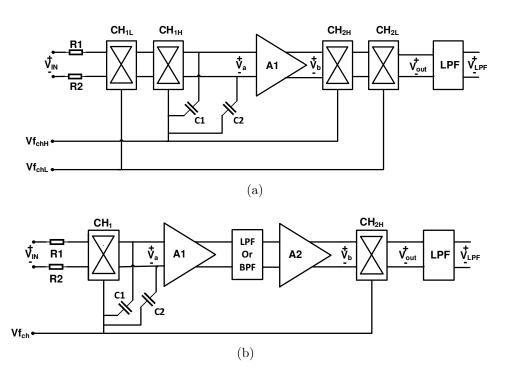

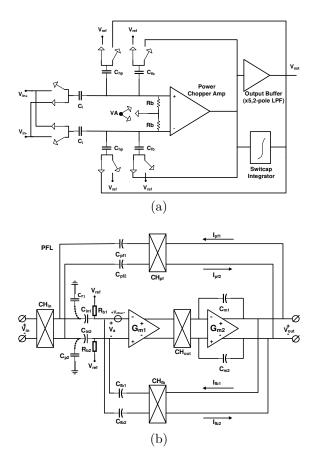

| CHS technique in the CFN neural amplifiers. (a) Noise model of neural     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

| amplifier when the first chopper is placed in front of the OTA. (b) Uti-  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

| lizing an impedance boosting feedback circuit to increase the amplifier   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

| input impedance                                                           | 25                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |

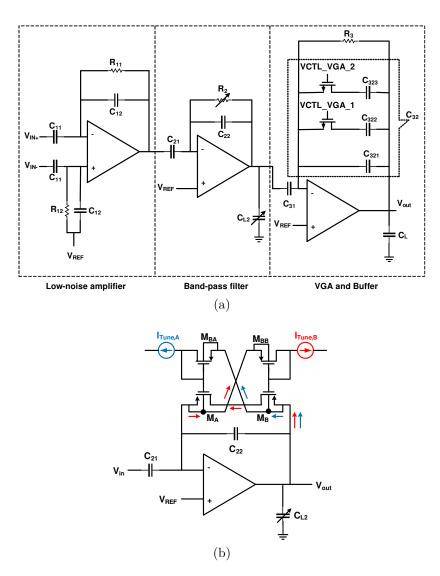

| (a) Schematic of nested chopper amplifier technique. (b) Schematic of     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

| Spike filtering technique                                                 | 27                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |

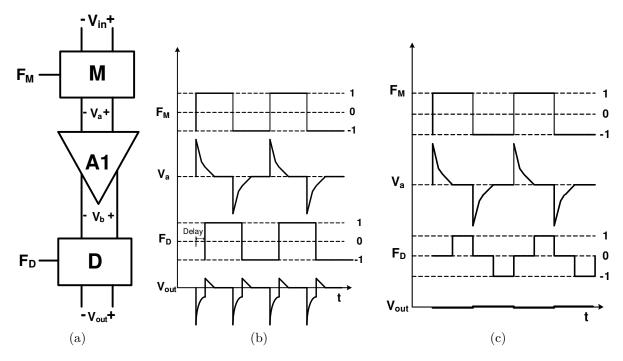

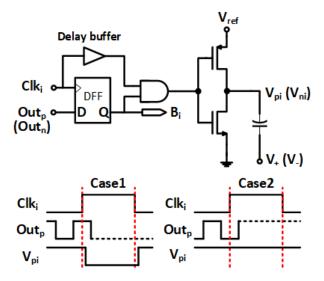

| (a) Delayed modulation technique, (b) delayed demodulation clock di-      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

| agram, (c) dead band clock diagram                                        | 27                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |

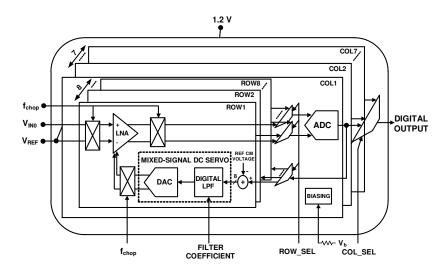

|                                                                           | Simplified block diagram of a neural recording implant with CS encoder for one channel.  Block diagram of different multi-channel neural recording architectures. (a) This architecture shares an ADC among all of the channels. (b) This architecture utilizes an ADC for each channel. (c) This architecture shares an ADC at each column.  Implementing a high-pass pole using a low-pass filter in the feedback. AC-coupled neural amplifier topologies. (a) Conventional capacitive-feedback network (CFN) topology. (b) CFN amplifier using T-capacitor feedback network topology. (c) AC-coupling utilizing the electrode capacitance and a resistive element. (d) Open loop network (OLN) topology. (e) Capacitive amplifier feedback network (CAFN) topology. (f) Miller compensated CFN (MCCFN) topology.  DC-coupled neural amplifiers utilizing (a) an analog active LPF. (b) an analog passive LPF and a differential difference amplifier, (c) analog and digital DC servo loops (DSL), and (d) input differential pair width modulation by an offset cancellation feedback.  Improving the linearity of CFN amplifier utilizing (a) source-followers (SF). (b) two gain stages with employing the proper NMOS and PMOS pseudoresistor and SFs.  (a) Schematic of a three-stage amplifier, (b) Second-stage amplifier tunes the high and low-cutoff frequency.  CHS technique in the CFN neural amplifiers. (a) Noise model of neural amplifier when the first chopper is placed in front of the OTA. (b) Utilizing an impedance boosting feedback circuit to increase the amplifier input impedance.  (a) Schematic of nested chopper amplifier technique. (b) Schematic of Spike filtering technique. |  |

| 2.10 Chopper switches placed in front of the AC-coupling capacitors. |                                                                               |    |  |  |

|----------------------------------------------------------------------|-------------------------------------------------------------------------------|----|--|--|

|                                                                      | Circuit architecture of neural amplifier, illustrating two loop feedback      |    |  |  |

|                                                                      | paths to define the midband gain and high pass corner, (b) Schematic          |    |  |  |

|                                                                      | of the capacitively-coupled LNA with the positive feedback loop for           |    |  |  |

|                                                                      | input impedance boosting.                                                     | 28 |  |  |

| 2.11                                                                 | Block diagram of the 56-channel neural recording implant utilizing DC-        |    |  |  |

|                                                                      | coupled FEA and digital DSL                                                   | 28 |  |  |

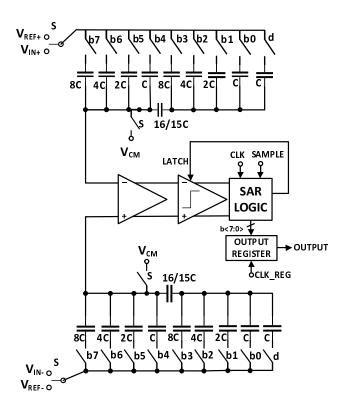

| 2.12                                                                 | Differential 8-bit SAR ADC                                                    |    |  |  |

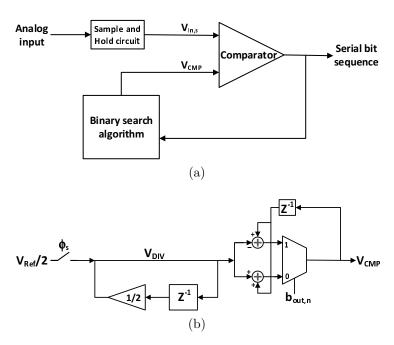

| 2.13                                                                 | Modified SAR ADC for single-channel application. (a) Block diagram            |    |  |  |

|                                                                      | of the modified SAR ADC. (b) Schematic of binary search algorithm.            | 34 |  |  |

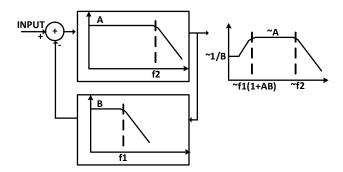

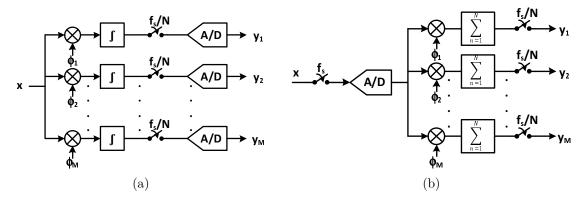

| 2.14                                                                 | Block diagram of CS core of (a) an analog implantation (b) a digital          |    |  |  |

|                                                                      | implantation                                                                  | 36 |  |  |

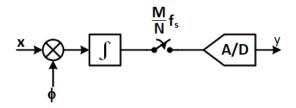

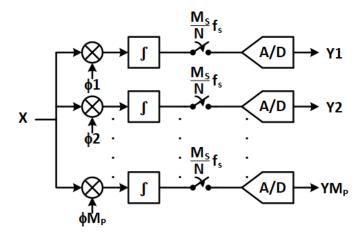

| 3.1                                                                  | Block diagram of neural recording system with the CS in analog domain.        | 40 |  |  |

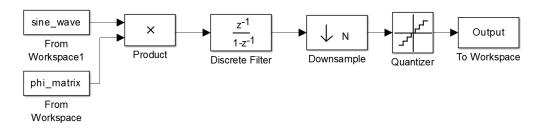

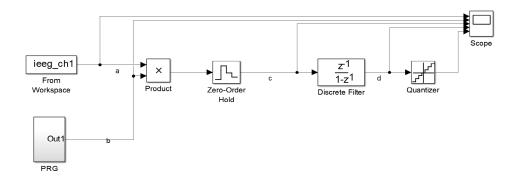

| 3.2                                                                  | Simulink simulation of the CS Encoder                                         | 41 |  |  |

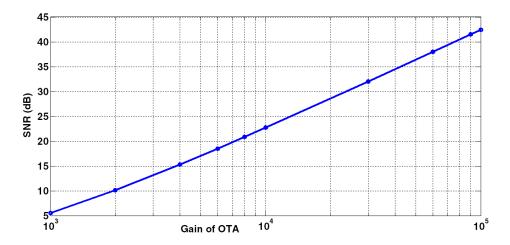

| 3.3                                                                  | SNR of reconstructed signal versus the gain of the OTA                        | 42 |  |  |

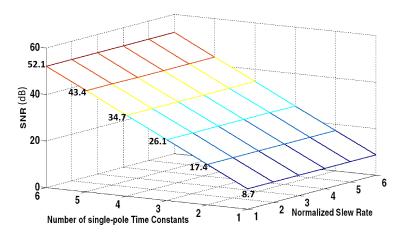

| 3.4                                                                  | Total SNR as a function of slew rate and settling time                        | 43 |  |  |

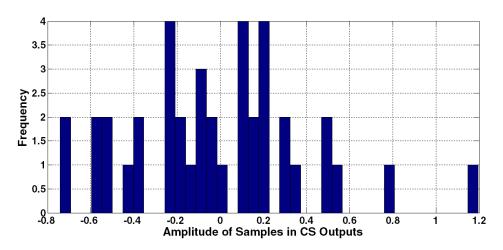

| 3.5                                                                  | Histogram of M samples of CS outputs (M=40)                                   | 44 |  |  |

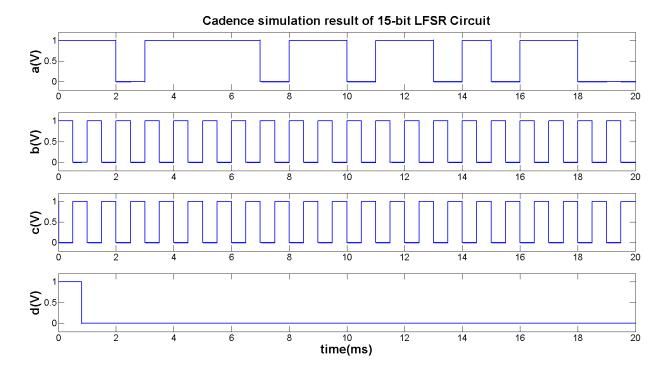

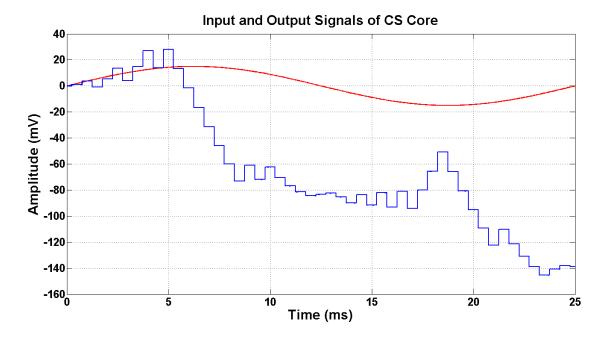

| 3.6                                                                  | Simulink simulation of CS core block diagram in MATLAB                        | 45 |  |  |

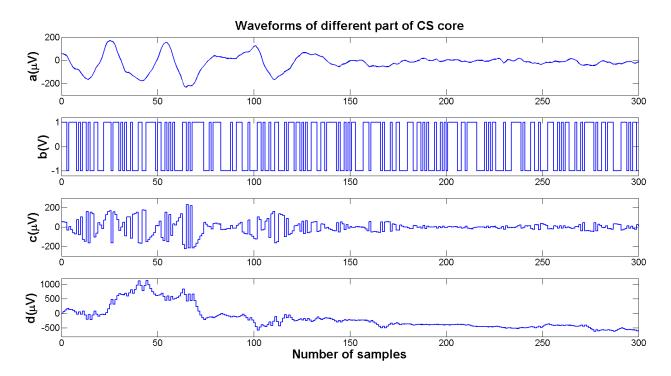

| 3.7                                                                  | .7 Waveforms of Simulink Scope of Figure 3.6: (a) The original iEEG sig-      |    |  |  |

|                                                                      | nal, (b) Random $\pm 1$ generated by Pseudo-Random Generator (PRG),           |    |  |  |

|                                                                      | (c) Multiplication result of signal a and b, and (d) Integration of signal c. | 46 |  |  |

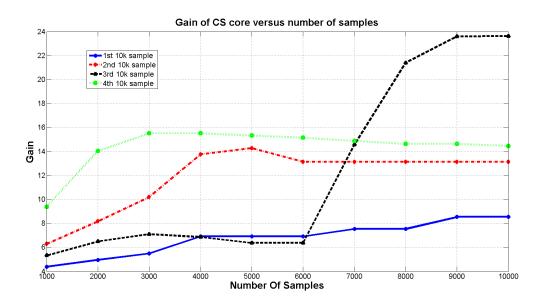

| 3.8                                                                  | Gain of CS core versus the number of sequences                                | 46 |  |  |

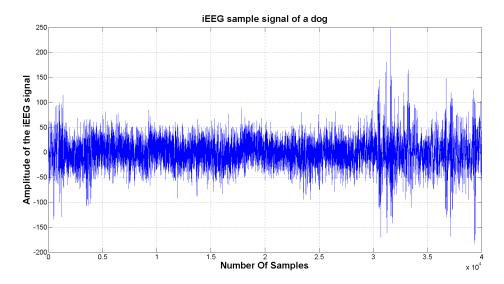

| 3.9                                                                  | iEEG signal of a dog                                                          | 47 |  |  |

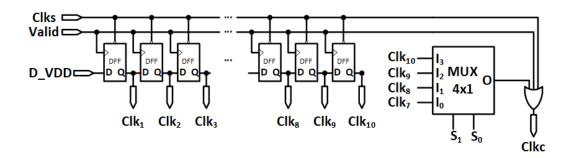

| 3.10                                                                 | The CS core with series sequences                                             | 48 |  |  |

| 3.11                                                                 | The CS core with parallel-series sequences                                    | 48 |  |  |

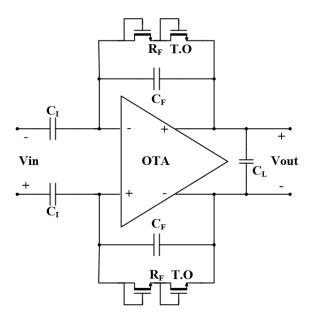

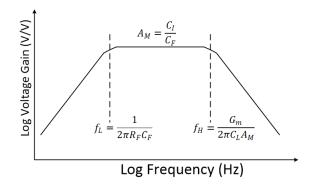

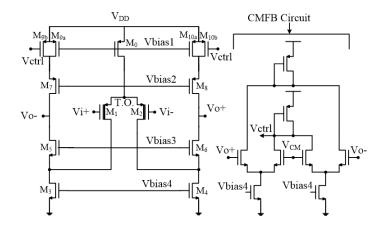

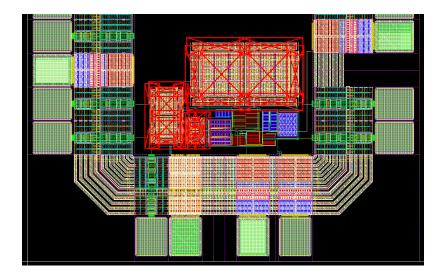

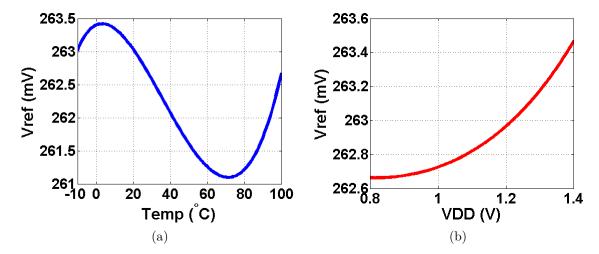

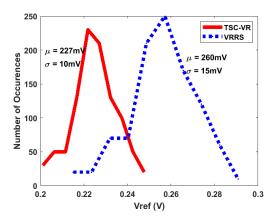

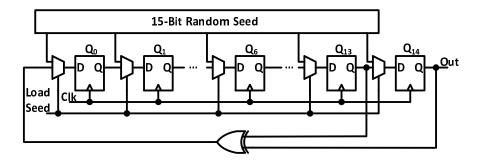

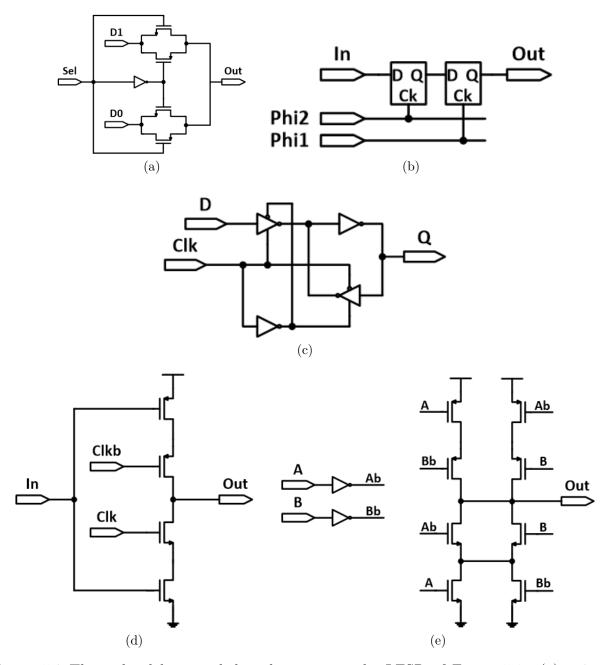

| 4.1                                                                  | Fully differential capacitive feedback network neural amplifier               | 52 |  |  |

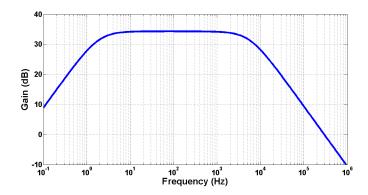

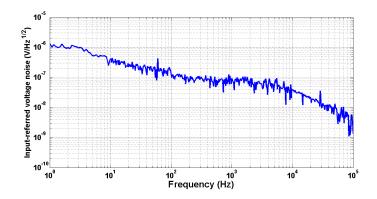

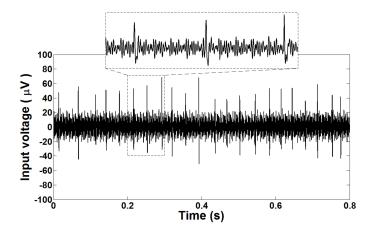

| 4.2                                                                  | Frequency response of the amplifier                                           | 53 |  |  |

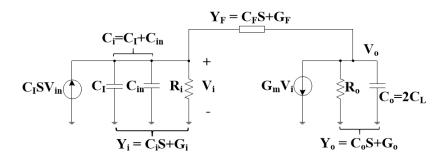

| 4.3                                                                  | Small signal equivalent of the half-circuit of the neural amplifier           | 53 |  |  |

| 4.4                                                                  | Frequency response of a neural amplifier with various amounts of $R_i$ .      | 54 |  |  |

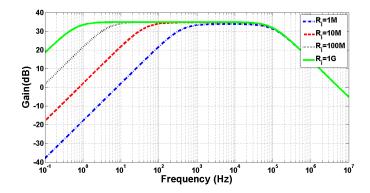

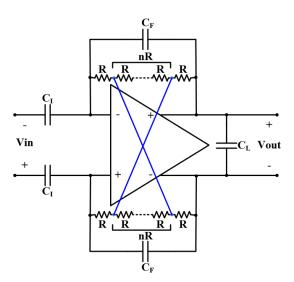

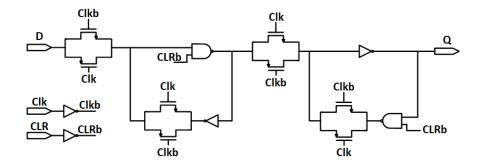

| 4.5                                                                  | The neural amplifier with cross-coupled positive feedback architecture.       | 55 |  |  |

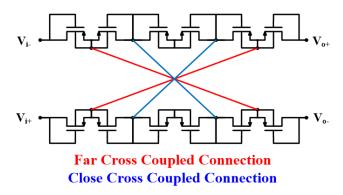

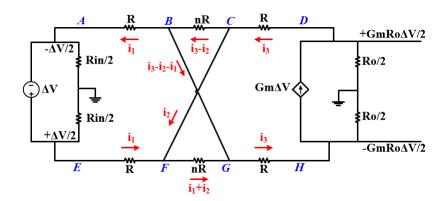

| 4.6                                                                  | Cross-coupled positive feedback connections                                   | 56 |  |  |

| 4.7                                                                  | Small signal equivalent circuit of the neural amplifier with a CCPF           |    |  |  |

|                                                                      | connection                                                                    | 56 |  |  |

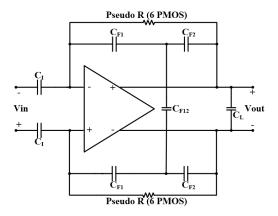

| 4.8                                                                  | T-capacitor feedback network architecture with CCPF                           | 58 |  |  |

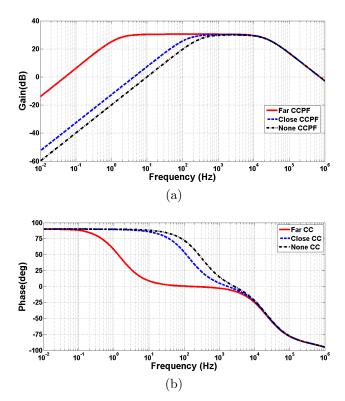

| 4.9                                                                  | Frequency response of the amplifier of Figure 4.8 with far, close and         |    |  |  |

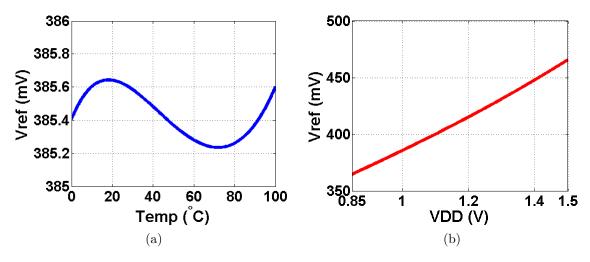

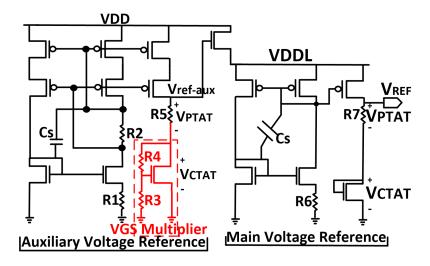

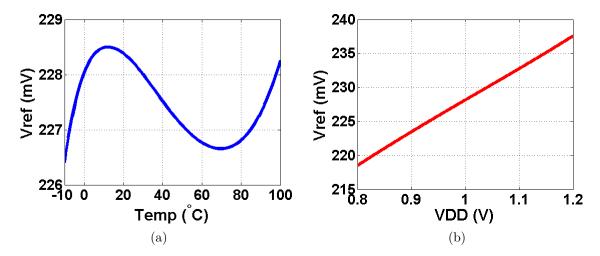

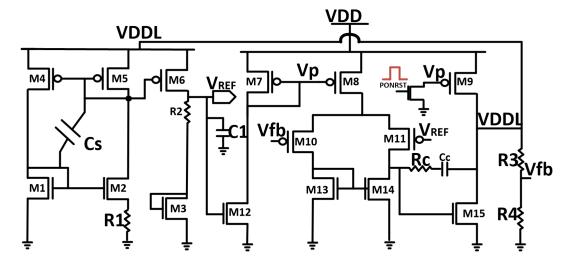

|                                                                      | no CCPF connection. (a) gain, and (b) phase                                   | 58 |  |  |