| <b>Titre:</b> Title:    | Fully Programming the Data Plane: A Hardware/Software Approach                                                                                                                                                                                  |

|-------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                         | Jeferson Santiago da Silva                                                                                                                                                                                                                      |

| Date:                   | 2020                                                                                                                                                                                                                                            |

| Type:                   | Mémoire ou thèse / Dissertation or Thesis                                                                                                                                                                                                       |

| Référence:<br>Citation: | Santiago da Silva, J. (2020). Fully Programming the Data Plane: A Hardware/Software Approach [Thèse de doctorat, Polytechnique Montréal]. PolyPublie. <a href="https://publications.polymtl.ca/5215/">https://publications.polymtl.ca/5215/</a> |

# Document en libre accès dans PolyPublie Open Access document in PolyPublie

| URL de PolyPublie:<br>PolyPublie URL:    | https://publications.polymtl.ca/5215/           |

|------------------------------------------|-------------------------------------------------|

| Directeurs de<br>recherche:<br>Advisors: | François-Raymond Boyer, & J. M. Pierre Langlois |

| <b>Programme:</b><br>Program:            | Génie informatique                              |

# POLYTECHNIQUE MONTRÉAL

affiliée à l'Université de Montréal

| T 11  | ъ .         |          | T-1    | TT 1       | 100 0     |          |

|-------|-------------|----------|--------|------------|-----------|----------|

| Fully | Programming | the Data | Plane: | a Hardware | /Software | Approach |

# JEFERSON SANTIAGO DA SILVA

Département de génie informatique et génie logiciel

Thèse présentée en vue de l'obtention du diplôme de Philosophiæ Doctor Génie informatique

Avril 2020

# POLYTECHNIQUE MONTRÉAL

affiliée à l'Université de Montréal

Cette thèse intitulée:

Fully Programming the Data Plane: a Hardware/Software Approach

présentée par **Jeferson SANTIAGO DA SILVA** en vue de l'obtention du diplôme de *Philosophiæ Doctor* a été dûment acceptée par le jury d'examen constitué de :

Alejandro QUINTERO, président

Pierre LANGLOIS, membre et directeur de recherche

François-Raymond BOYER, membre et codirecteur de recherche

Guy BOIS, membre

Otmane AIT MOHAMED, membre externe

# **DEDICATION**

To the  $\heartsuit \heartsuit$  of my life: Clara  $\clubsuit$  and Sophie  $\P$ .

#### **ACKNOWLEDGEMENTS**

Premièrement, je souhaiterais remercier mon directeur de recherche, Pierre. Je pense sincèrement que c'est une personne dont tout le monde a besoin dans sa vie. Pierre a été un directeur exceptionnel, patient et calme, mais qui a su me motiver lorsque cela était nécessaire. Son optimisme est contiagieux! Ses remarques positives et bienveillantes m'ont toujours motivé et m'ont permis de me sentir bien même dans les moments où j'étais « down ». Merci Pierre!

Deuxièmement, je veux exprimer toute ma gratitude à mon codirecteur FRB, avec qui je m'estime chanceux d'avoir eu l'opportunuité de travailler. Je pense sincèrement qu'il est très fort techniquement, du matériel au logiciel. Par ailleurs, nos discussions portant sur le langage C++ et le « clean code » vont me manquer.

J'aimerais aussi remercier l'ensemble des professeurs et du personnel de Polytechnique avec qui j'ai eu l'honneur de travailler, notamment Yvon Savaria et Normand Bélanger.

I'd like to thank my labmates. A few have already left us, but you still remain in my thoughts. Merci Ahmed, Bachir, Imad. Les mots me manquent pour remercier Thomas et Thibaut, que je considère comme de vrais amis, et non simplement comme des collègues de laboratoire. Les gars, merci pour les super bons moments, pour les blagues, pour les discussions, pour les conseils...

My thanks also go to the folks of Kaloom who have been awesome during my internship there. At Kaloom I was able to link my research to real-world problems. Also, I thank Mitacs/Canada and CNPq/Brazil for providing me the funds to conduct this research.

Não poderia esquecer da minha família no Brasil: mãe, pai, irmã, sobrinhas, tios e avós. Sem o apoio de vocês, este desafio jamais se concretizaria. Obrigado por sempre me apoiarem, desde que decidi sair de casa para estudar engenharia em Porto Alegre!

Como sobremesa, o melhor vem no final: Clara e Sophie. Minha esposa Clara merece não só meus agradecimentos mas meu sincero pedido de desculpas. Obrigado por aceitar me acompanhar nessa jornada, por aguentar meu mal humor, por ouvir minhas lamentações, sempre me incentivando com o seu famoso jargão: "vai dar tudo certo". E perdão, principalmente pelo tempo juntos que este trabalho nos furtou.

Obrigado princesa Sophie! Obrigado pelas risadinhas, pelas sonequinhas juntinhos, pelos momentinhos que brincamos, que por vezes aliviaram a pressão que um doutorado impõe. Sophie, papai não é a doutora brinquedos, mas agora também é doutor!

# RÉSUMÉ

Les réseaux définis par logiciel — en anglais Software-Defined Networking (SDN) — sont apparus ces dernières années comme un nouveau paradigme de réseau. SDN introduit une séparation entre les plans de gestion, de contrôle et de données, permettant à ceux-ci d'évoluer de manière indépendante, rompant ainsi avec la rigidité des réseaux traditionnels. En particulier, dans le plan de données, les avancées récentes ont porté sur la définition des langages de traitement de paquets, tel que P4, et sur la définition d'architectures de commutateurs programmables, par exemple la Protocol Independent Switch Architecture (PISA).

Dans cette thèse, nous nous intéressons a l'architecture PISA et évaluons comment exploiter les FPGA comme plateforme de traitement efficace de paquets. Cette problématique est étudiée a trois niveaux d'abstraction : microarchitectural, programmation et architectural.

Au niveau microarchitectural, nous avons proposé une architecture efficace d'un analyseur d'entêtes de paquets pour PISA. L'analyseur de paquets utilise une architecture pipelinée avec propagation en avant — en anglais feed-forward. La complexité de l'architecture est réduite par rapport à l'état de l'art grâce a l'utilisation d'optimisations algorithmiques. Finalement, l'architecture est générée par un compilateur P4 vers C++, combiné à un outil de synthèse de haut niveau. La solution proposée atteint un débit de 100 Gb/s avec une latence comparable à celle d'analyseurs d'entêtes de paquets écrits à la main.

Au niveau de la programmation, nous avons proposé une nouvelle méthodologie de conception de synthèse de haut niveau visant à améliorer conjointement la qualité logicielle et matérielle. Nous exploitons les fonctionnalités du C++ moderne pour améliorer à la fois la modularité et la lisibilité du code, tout en conservant (ou améliorant) les résultats du matériel généré. Des exemples de conception utilisant notre méthodologie, incluant pour l'analyseur d'entête de paquets, ont été rendus publics.

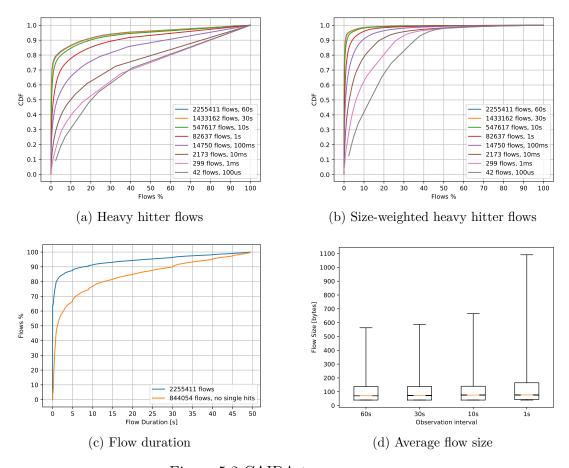

Au niveau architectural, nous avons proposé une méthode de cache pour une architecture de plan de données programmable hétérogène, pour laquelle le débit de traitement peut être inégal entre les différentes plateformes utilisées. Pour ce faire, nous avons caractérisé une trace provenant d'un centre de données afin d'identifier les propriétés des paquets pouvant être exploitées par la cache. Ces propriétés ont ensuite été utilisées pour concevoir des politiques d'éviction et de promotion. Une plateforme de simulation a été développée, et permet de démontrer qu'une politique de promotion aléatoire combinée à une politique de promotion heuristique basée sur la fréquence atteint un taux de succès élevé ( $\sim 90\%$ ) avec des tailles de caches relativement petites ( $8\,\mathrm{k}$  entrées).

## **ABSTRACT**

Software-Defined Networking (SDN) has emerged in recent years as a new network paradigm to de-ossify communication networks. Indeed, by offering a clear separation of network concerns between the management, control, and data planes, SDN allows each of these planes to evolve independently, breaking the rigidity of traditional networks. However, while well spread in the control and management planes, this de-ossification has only recently reached the data plane with the advent of packet processing languages, e.g. P4, and novel programmable switch architectures, e.g. Protocol Independent Switch Architecture (PISA).

In this work, we focus on leveraging the PISA architecture by mainly exploiting the FPGA capabilities for efficient packet processing. In this way, we address this issue at different abstraction levels: i) microarchitectural; ii) programming; and, iii) architectural.

At the microarchitectural level, we have proposed an efficient FPGA-based packet parser architecture, which is a major PISA's component. The proposed packet parser follows a feed-forward pipeline architecture in which the internal microarchitectural has been meticulously optimized for FPGA implementation. The architecture is automatically generated by a P4-to-C++ compiler after several rounds of graph optimizations. The proposed solution achieves 100 Gb/s line rate with latency comparable to hand-written packet parsers. The throughput scales from 10 Gb/s to 160 Gb/s with moderate increase in resource consumption. Both the compiler and the packet parser codebase have been open-sourced to permit reproducibility.

At the programming level, we have proposed a novel High-Level Synthesis (HLS) design methodology aiming at improving software and hardware quality. We have employed this novel methodology when designing the packet parser. In our work, we have exploited features of modern C++ that improves at the same time code modularity and readability while keeping (or improving) the results of the generated hardware. Design examples using our methodology have been publicly released.

At the architectural level, we have proposed a heterogeneous match table caching scheme to alleviate the memory capacity/performance trade-off of current programmable dataplanes. To this end, we have characterized a real-world data center trace to derive caching premises. These premises have been the basis for novel network-aware cache eviction and promotion policies. Our work also includes an open-source simulation and implementation viability analysis of the proposed solution. The results indicate that a simple random promotion policy combined with a heuristic frequency-based promotion policy achieves a high hit ratio  $(\sim 90\%)$  with relatively small cache sizes (8 k entries).

# TABLE OF CONTENTS

| DEDICATION                                  | iii |

|---------------------------------------------|-----|

| ACKNOWLEDGEMENTS                            | iv  |

| RÉSUMÉ                                      | v   |

| ABSTRACT                                    | vi  |

| TABLE OF CONTENTS                           | ⁄ii |

| LIST OF TABLES                              | х   |

| LIST OF FIGURES                             | xi  |

| LIST OF SYMBOLS AND ACRONYMS                | cii |

| CHAPTER 1 INTRODUCTION                      | 1   |

| 1.1 Context and Motivation                  | 1   |

| 1.2 Problem Statement                       | 3   |

| 1.3 Research Objectives and Contributions   | 4   |

| 1.4 Research not Included in this Thesis    | 6   |

| 1.5 Thesis Outline                          | 6   |

| CHAPTER 2 BACKGROUND AND LITERATURE REVIEW  | 7   |

| 2.1 Programmable Networks                   | 7   |

| 2.1.1 The Long Way to Programmable Networks | 7   |

|                                             | 8   |

|                                             | 10  |

|                                             | 11  |

|                                             | 12  |

|                                             | 16  |

|                                             | 16  |

|                                             | ۱7  |

|                                             | 19  |

|                                             | 19  |

|       | 2.4.2  | FPGAs                                                              | 20 |

|-------|--------|--------------------------------------------------------------------|----|

| 2.5   | Chapte | er Conclusion                                                      | 21 |

|       |        |                                                                    |    |

| СНАРТ |        | ARTICLE 1: P4-COMPATIBLE HIGH-LEVEL SYNTHESIS OF LOW               |    |

|       |        | 100 Gb/s STREAMING PACKET PARSERS IN FPGAS                         | 22 |

| 3.1   |        | uction                                                             | 22 |

| 3.2   |        | d Work                                                             | 23 |

| 3.3   | Design | Methodology                                                        | 24 |

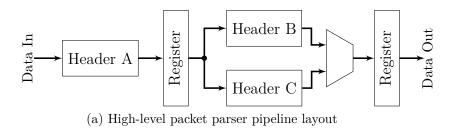

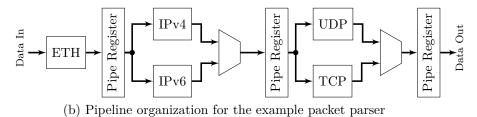

|       | 3.3.1  | High-Level Architecture                                            | 25 |

|       | 3.3.2  | Microarchitectural Aspects                                         | 26 |

|       | 3.3.3  | Pipeline Layout Generation                                         | 30 |

| 3.4   | Experi | imental Results                                                    | 32 |

| 3.5   | Conclu | asion                                                              | 35 |

| СНАРТ | TD 1   | ARTICLE 2: MODULE-PER-OBJECT: A HUMAN-DRIVEN METHOD-               |    |

|       |        | OR C++-BASED HIGH-LEVEL SYNTHESIS DESIGN                           | 37 |

| 4.1   |        | uction                                                             | 38 |

| 4.2   |        | d Work                                                             | 40 |

| 4.2   | 4.2.1  | QoR Improvements in HLS-based Design                               | 40 |

|       | 4.2.1  | Raising the Abstraction Level in HLS                               | 41 |

|       | 4.2.3  | High-Level Languages (HLLs) as Intermediate Representation in FPGA | 41 |

|       | 4.2.3  | Design                                                             | 42 |

| 4.3   | MnO 1  | HLS Methodology                                                    | 42 |

| 4.0   | 4.3.1  |                                                                    | 42 |

|       | 4.3.1  | Overview of the MpO Methodology                                    | 44 |

|       | 4.3.3  |                                                                    |    |

|       |        |                                                                    | 44 |

|       | 4.3.4  | Specializing Operands with constexpr                               | 47 |

|       | 4.3.5  | Exploiting STL Constructs                                          | 47 |

|       | 4.3.6  | Inheritance and Static Polymorphism                                | 48 |

| 4 4   | 4.3.7  | Smart Constructors                                                 | 50 |

| 4.4   |        | s-parser Generation from P4                                        | 50 |

|       | 4.4.1  | Top-Level Pipeline                                                 | 50 |

|       | 4.4.2  | Adapting MpO to Current HLS tools                                  | 51 |

| 4.5   |        | Imental Results                                                    | 52 |

|       | 4.5.1  | Experimental Setup                                                 | 52 |

|       | 4.5.2  | Results                                                            | 52 |

|       | 4.5.3  | Analysis and Discussions                                           | 56 |

| 4.6                              | Concl   | usion                                              | 57 |

|----------------------------------|---------|----------------------------------------------------|----|

| СНАРТ                            | TER 5   | ARTICLE 3: VIRTUALLY INFINITE MATCH TABLES ON PRO- |    |

| GRA                              | AMMA    | BLE DATAPLANES                                     | 58 |

| 5.1                              | Introd  | uction                                             | 58 |

| 5.2                              | Backg   | round                                              | 60 |

|                                  | 5.2.1   | Cache Replacement Algorithms                       | 60 |

|                                  | 5.2.2   | Constraints of Programmable Dataplanes             | 61 |

| 5.3                              | Learni  | ing from the Traffic                               | 62 |

| 5.4                              | Traffic | e-aware Cache Policies                             | 63 |

|                                  | 5.4.1   | Cache Eviction                                     | 64 |

|                                  | 5.4.2   | Cache Promotion                                    | 65 |

| 5.5 Evaluating Cache Performance |         | ating Cache Performance                            | 65 |

|                                  | 5.5.1   | Experimental Setup                                 | 65 |

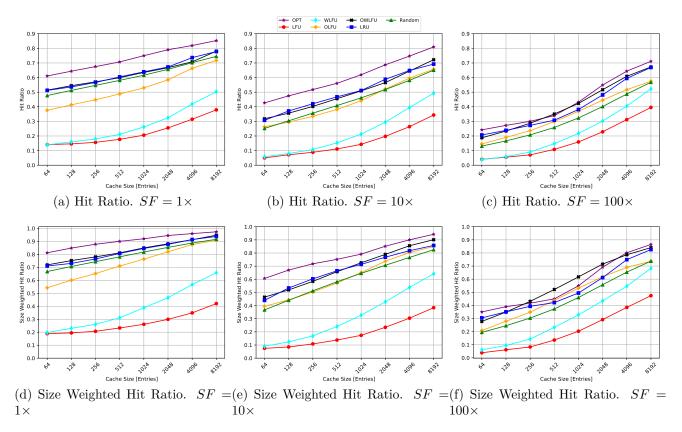

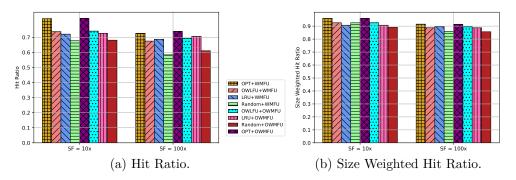

|                                  | 5.5.2   | Simulation Results                                 | 66 |

|                                  | 5.5.3   | Discussions                                        | 67 |

|                                  | 5.5.4   | Limitations                                        | 69 |

| 5.6                              | Relate  | ed Work                                            | 70 |

| 5.7                              | Concl   | usion                                              | 71 |

| СНАРТ                            | TER 6   | GENERAL DISCUSSION                                 | 72 |

| СНАРТ                            | TER 7   | CONCLUSION                                         | 75 |

| 7.1                              | Summ    | ary of Works                                       | 75 |

| 7.2                              | Limita  | ations                                             | 76 |

| 7.3                              | Future  | e Research                                         | 77 |

| REFER                            | ENCES   |                                                    | 78 |

# LIST OF TABLES

| Table 3.1 | Parser results comparison                 | 33 |

|-----------|-------------------------------------------|----|

| Table 4.1 | Summary of C++ features used in this work | 43 |

| Table 4.2 | Packet parser results. Adapted from [10]  | 53 |

| Table 4.3 | Flow-based TM results                     | 54 |

| Table 4.4 | Digital up-converter HW QoR results       | 55 |

| Table 4.5 | Digital up-converter SW quality results   | 56 |

| Table 5.1 | Experimental parameters                   | 66 |

# LIST OF FIGURES

| Figure 2.1 | SDN vs regular computing systems. Adapted from [25]                  | 10 |

|------------|----------------------------------------------------------------------|----|

| Figure 2.2 | PISA internal architecture. Adapted from [4]                         | 13 |

| Figure 2.3 | Parser graph representation and parser abstract machine              | 14 |

| Figure 3.1 | High-level architecture                                              | 26 |

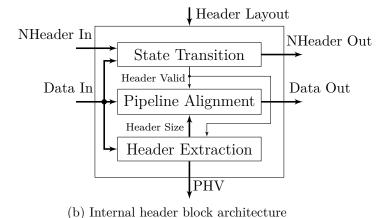

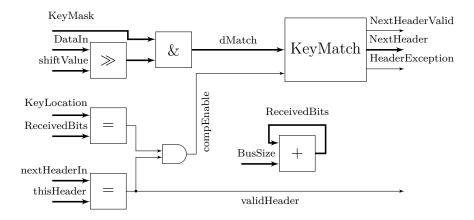

| Figure 3.2 | Station transition block                                             | 28 |

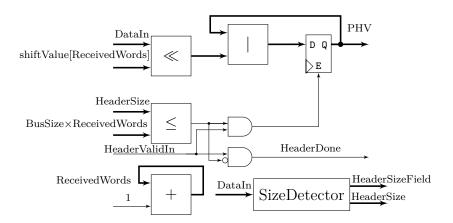

| Figure 3.3 | Header extraction block                                              | 28 |

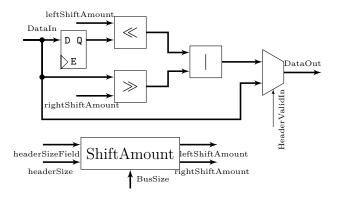

| Figure 3.4 | Pipeline alignment block                                             | 29 |

| Figure 3.5 | Parser pipeline generation                                           | 30 |

| Figure 3.6 | Parser graph transformation                                          | 31 |

| Figure 3.7 | Synthesis results for multiple data rate parsers                     | 35 |

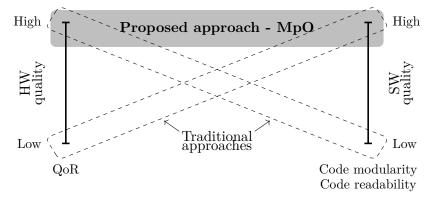

| Figure 4.1 | HLS design approaches                                                | 39 |

| Figure 4.2 | Representation of a packet parser                                    | 45 |

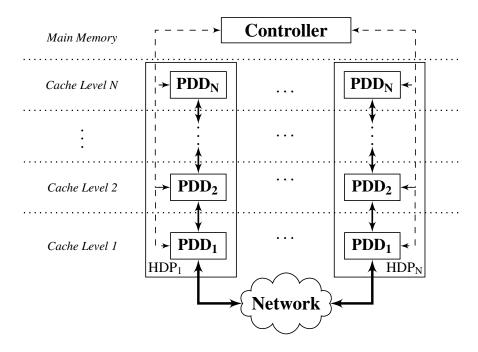

| Figure 5.1 | Reference caching system                                             | 60 |

| Figure 5.2 | CAIDA trace summary                                                  | 63 |

| Figure 5.3 | Cache performance evaluation when no promotion policy implemented    | 67 |

| Figure 5.4 | Cache performance evaluation when promotion policies are implemented | 68 |

|            |                                                                      |    |

#### LIST OF SYMBOLS AND ACRONYMS

ALU Arithmetic Logical Unit

ASIC Application-Specific Integrated Circuits

ASM Abstract State Machine BPF Berkeley Packet Filter

CLI Command Line Interface

CPU Central Processing Unit

CRTP Curiously Recurring Template Pattern

DAG Directed Acyclic Graph

DC Data Center

DPI Deep Packet InspectionDRY Don't Repeat Yourself

DSA Domain Specific Architecture

DSE Design Space Exploration

DSL Domain Specific Language

eBPF extended Berkeley Packet Filter

eLOC Equivalent Lines of Code

FE Forwarding Element

FF Flip-Flop

FIS Flow Instruction Set

FPGA Field-Programmable Gate Array HDL Hardware Description Language

HDP Heterogeneous Data Plane

HLL High-Level Language

HLS High-level Synthesis

HW Hardware

IC Integrated Circuit

LLVM Low Level Virtual Machine

LOC Lines of Code

LPM Longest Prefix Match

LUT Lookup Table

MAT Match-Action Table

MMT Multiple Match Tables

MpO Module-per-Object

NCL Network Classification Language

NP Network Processor

NPL Network Programming Language

ONF Open Networking Foundation

OS Operating System

PDD Programmable Dataplane Device

PHV Packet Header Vector

PISA Protocol Independent Switch Architecture

QoR Quality of Results

QoS Quality of Service

RISC Reduced Instruction Set Computer

RMT Reconfigurable Match Tables

ROM Read-Only Memory

RTL Register-Transfer Level

SDN Software-Defined Networking

SMT Single Match Table

SPMD Single Program Multiple Data

STL Standard Template Library

SW Software

TCAM Ternary Content-Addressable Memory

TM Traffic Manager

VHDL Very High Speed Integrated Circuit Hardware Description Language

VLIW Very Long Instruction Word

VM Virtual Machine

#### CHAPTER 1 INTRODUCTION

#### 1.1 Context and Motivation

Over the last decade, Software-Defined Networking (SDN) [1] has emerged to break the rigidity of computer networks by allowing network administrators to manage the network in a softwarized fashion. Indeed, SDN has decoupled the data and control planes, allowing both to evolve independently. Hence, complex network protocols and algorithms are implemented in software in a centralized controller while data plane devices only execute a series of configurable actions. The SDN paradigm has also changed key abstractions of the networking domain. Instead of a stack of protocols as in traditional network deployments, SDN is based on a clear separation of concerns. These concerns are straightforward:

- Users develop network applications by defining networking rules in a management plane based on the network status reported central entity.

- A centralized controller (control plane) collects network status (congestion status, connectivity). It also communicates with the data plane to install forwarding rules.

- The data plane forwards packets using predefined forwarding rules.

To consolidate the SDN paradigm, McKeown et al. [2] proposed OpenFlow in 2008. Open-Flow defines a standard interface between the controller and the OpenFlow switch<sup>1</sup> and it uses this interface to configure pre-determined actions in data plane devices. This standardization has thus made OpenFlow the *de facto* SDN protocol.

However, recent advances in programmable data plane devices and languages have the potential to undermine OpenFlow's hegemony. Since OpenFlow is standardized, new network applications and protocols cannot be deployed until a new standard revision takes place. Besides, when a new revision is released, switch vendors need to develop new chips, which increases not only the cost but time to market.

To deal with OpenFlow limitations, the P4 language was proposed in 2014 [3]. P4 is a Domain Specific Language (DSL) in which users can arbitrarily specify protocol-agnostic packet processing behavior. In P4, users can arbitrarily define the set of matching fields and the associated actions in case of a match. Also, network programmers can reformat packet headers in any fashion, allowing the development of custom and novel data plane algorithms.

The PISA [4] is a general and realistic abstraction to process P4 programs. PISA is made

<sup>&</sup>lt;sup>1</sup>The term *switch* describes any network device that forwards data from an input to an output port.

of a programmable packet parser, a pipeline of Match-Action Tables (MATs), optional user-defined external functions and objects, a packet scheduler, and a deparser. By 2013, commercial programmable Application-Specific Integrated Circuits (ASIC) PISA switches had already far crossed the Tb/s barrier [5]. However, such high throughput comes with a programmability cost. Thus, P4 programmers are innovation limited due to resource scarcity (internal memory for stateful applications) or fixed-function modules (preset scheduling algorithms). Indeed, state-of-the-art PISA switches have no more than a few hundreds of megabits of internal memory shared between match tables and stateful user-defined memories.

Current Data Center (DC) applications, such as machine learning and load balancing, demand at the same time high throughput and programmability. These applications have historically run in DC server clusters. However, servers are also responsible for implementing soft-switches to isolate their tenants' Virtual Machines (VMs) and containers. To improve server efficiency, a recent trend has been to employ Field-Programmable Gate Arrays (FPGAs) for DC server offloading [6], [7].

Recent work has also proposed mapping P4 programs to FPGAs [8] as an alternative to inflexible and memory-bound ASIC switches and performance-limited soft-switches. While FPGA-based solutions have augmented the degree of programmability and the memory bandwidth of PISA switches, the performance of FPGA-based switches is far lower than its ASIC counterparts. This is mainly due to the intrinsics of the FPGA microarchitecture which does not include hardwired associative memories (required for implementing match-tables) and the lack of FPGA specific compiler optimizations.

In this work, we show that there is no silver bullet in programmable packet processing. Throughout the next chapters, we study the limitations of current packet processing solutions while proposing enhancements to the state-of-the-art. These enhancements include microarchitectural and compiler optimizations for a PISA module implemented in FPGAs. This is accompanied by a software-friendly FPGA design methodology that can be extended outside the network domain. Also, we propose coupling programmable heterogeneous devices to exploit the potential of each component aiming for efficient packet processing. To make this heterogeneous switch architecture more attractive, we study how a caching scheme split between the data and control plane can minimize reaction time and increase the hit ratio.

#### 1.2 Problem Statement

SDN and OpenFlow have not directly dealt with the subject of data plane programming. Only recent efforts on packet processing languages, such as P4, have considered data plane devices are programmable platforms. Much of these efforts are due to state-of-the-art programmable switches that implement/emulate the PISA architecture.

However, current PISA switches limit the innovation potential brought by P4. Indeed, high-performance PISA switches trade-off programmability and throughput. In a computer architecture analogy, PISA is much like what a Reduced Instruction Set Computer (RISC) processor is: lean and fast. As for RISC, PISA fits the most of network applications, but a few ones suffer due to its limited instruction set.

As P4 is based on an explicit imperative match-action programming paradigm, P4-aware devices require fast associative memories to implement match-tables. Contrary to regular memory structures, associative memories, either Ternary Content-Addressable Memorys (TCAMs) or their algorithmic emulations, are expensive both in terms of silicon area and power. Thus, ASIC switches limit the amount of those memories. As a consequence, ASIC switches limit the number of active sessions which has a trend of increasing with the advent of next-generation mobile communications (>1 M).

This performance/memory trade-off, the infamous memory wall, has been observed since the beginnings of the computer era. Although not a new problem, solutions for it in the domain of programmable dataplanes have yet not been thoroughly studied.

More flexible architectures for packet processing have also been recently explored, such as memory-abundant soft-switches running on commodity servers [9] and FPGAs [8]. However, the benefits of soft-switches are overwhelmed by their low performance that is limited to a few dozens of Gb/s. For that reason, they are mainly used in data center servers for routing packets between the host Operating System (OS) and the tenants' VMs. FPGAs, on the other hand, are more limited than Central Processing Units (CPUs) in terms of programmability. However, FPGAs can outperform soft-switches by at least one order of magnitude in terms of throughput and many orders of magnitude for processing latency.

FPGAs seem a natural alternative for programmable ASIC switches. Nonetheless, the performance gap between FPGAs and ASIC switches ( $10 \times$  at best) needs to be reduced. This starts by investigating how packet processing blocks can be mapped into the FPGA fabric and how the intrinsic FPGA architecture can be leveraged to process packets.

However, widespread adoption of FPGAs is also limited because hardware designers have historically programmed FPGAs using Hardware Description Language (HDL), such as Ver-

ilog and VHDL. Such languages need verbose and explicit microarchitecture details, such as synchronization and pipelining. High-Level Synthesis (HLS) tools have simplified FPGA development by automatically generating HDL codes from behavioral C-based descriptions. Yet, no generalized design methodology and design patterns have been formally proposed to date targeting HLS design. As a consequence, the HLS adoption is mainly limited to hardware designers who understand in-depth methodologies for FPGA design, since one still needs to explicitly enforce microarchitectural details while using higher-abstracted languages.

FPGAs, however, will not scale in performance as modern programmable ASIC switches do. Also, the cost of state-of-the-art FPGAs limits their large scale deployment. Thus, heterogeneous switch architectures, comprising FPGAs and ASICs may be a solution to achieve high performance and programmability, besides their almost infinite pool of computing resources. Nonetheless, this coupling exposes a few challenges. First, the mismatched processing capabilities of these devices require careful mapping of applications to each device according to the processing requirements of each application. Second, a flow cache scheme is required to exploit the performance of programmable switches aiming at maximizing the matches on these devices. In this scenario, an FPGA is seen as the main memory to extend the limited amount of internal memory on programmable switches. Thus, a custom cache policer algorithm is required to coordinate flow migrations from one device to another.

## 1.3 Research Objectives and Contributions

In this work, we focus on leveraging FPGAs as part of a programmable packet processing system. We investigate the components of a packet processing pipeline and we identify those that are the best fit for FPGAs. In this research, we developed a few of these modules using a novel high-level HLS methodology targeting FPGAs. This methodology exploits high-level constructs of modern C++ to raise the design abstraction while improving performance and code modularity. To exploit the strengths of FPGAs for packet processing, we propose a heterogeneous packet processing pipeline using a programmable ASIC switch and an FPGA. To extract the maximum performance, a novel heterogeneous cache scheme was proposed.

In summary, this research led to three major published contributions:

- Jeferson Santiago da Silva, François-Raymond Boyer, and J.M. Pierre Langlois. "P4-compatible high-level synthesis of low latency 100 Gb/s streaming packet parsers in FPGAs." Proceedings of the 2018 ACM/SIGDA International Symposium on Field-Programmable Gate Arrays. 2018.

- 2. Jeferson Santiago da Silva, François-Raymond Boyer, and J.M. Pierre Langlois. "Module-

- per-Object: a human-driven methodology for C++-based high-level synthesis design." 2019 IEEE 27<sup>th</sup> Annual International Symposium on Field-Programmable Custom Computing Machines (FCCM). IEEE, 2019.

- 3. Jeferson Santiago da Silva, Thibaut Stimpfling, Thomas Luinaud, François-Raymond Boyer, and J.M. Pierre Langlois. "Virtually infinite match tables on programmable dataplanes." Submitted to the ACM SIGCOMM Computer Communication Review. 2020.

In our first contribution, we designed a programmable packet parser architecture directly derived from a P4 description (§3, [10]). We judiciously designed the parser's microarchitectural tecture to improve performance and reduce FPGA resource usage. The microarchitectural components were described in C++ that were further synthesized using an off-the-shelf HLS compiler. Moreover, we developed part of a P4-to-C++ back-end compiler to automatically generate HLS-oriented C++ class templates. Our compiler also performs a series of graph transformations to improve pipeline efficiency. The proposed packet parser architecture achieves a line-rate greater than 100 Gb/s with latency comparable to hand-written packet parsers and resource utilization similar to the state-of-the-art.

As a second research contribution, we developed a novel high-level and human-driven HLS methodology for FPGAs (§4, [11]). This methodology aims at raising the HLS design abstraction by employing well-known software engineering techniques. The proposed methodology is anchored in five coding style premises: class templates, const variables, Standard Template Library (STL) usage, inheritance and polymorphism, and smart class constructors. In addition to the proposed methodology, our work identified limitations on current HLS tools while providing hints to programmers in how to overcome these limitations. We demonstrated that the achieved hardware Quality of Results (QoR) using our methodology approaches and is sometimes superior to traditional HLS while significantly improving software quality.

As a final contribution, we proposed a novel caching scheme aiming at leveraging heterogeneous programmable dataplanes (§5, [12]). As traditional caching systems may not be directly applied to programmable dataplanes, either due to resource constraints or low performance, we developed novel cache policies based on a real-world data center traces. From the trace analysis, we derived caching premises based on temporal traffic locality, flow duration times, and flow sizes. The proposed caching policies hit ratio evaluation approach the state-of-the-art. We also discussed the feasibility of the proposed caching scheme in the context of current programmable dataplanes.

#### 1.4 Research not Included in this Thesis

Throughout this Ph.D. research, we have conducted several other research works that are not in the focus of this thesis. These supplementary works are summarized as follows:

- Support for P4 externs [13]. In this work, we have studied the P4 language and compiler to support P4 externs. We have implemented a header compression engine as P4 extern objects. We have added to the open-source P4 backend compiler the support for generating arbitrary P4 externs.

- Heterogenous Programmable Dataplanes [14]. We have proposed combining heterogeneous devices to emulate a single logical heterogeneous programmable dataplane. We have prototype such a dataplane made of an FPGA and a soft switch to evaluate its feasibility.

- Evaluation of FPGAs as programmable switches [15]. We have thoroughly studied the microarchitectural aspects of mapping PISA components to FPGAs. Our analyses have found that match tables implementation are the main performance bottleneck. In addition, we have identified the network applications that are suitable for the current FPGA architecture.

- Mapping P4 match tables to FPGAs [16]. In this work, we have exploited balanced binary trees to emulate P4-defined Longest Prefix Match (LPM) tables on FPGAs. We have also proposed a framework to automatically generate the LPM tables hardware which is optimized to improve post-implementation memory efficiency.

## 1.5 Thesis Outline

This paper-based thesis is organized into seven chapters. Chapter 2 presents a background and the literature review necessary to understand the context of this work. In this chapter, we review the history and the current status of programmable networks and programmable dataplanes. We also recap the DSLs used for packet processing and how data plane programs are compiled/mapped into real architectures. In Chapter 3, we present our first research contribution: an automatic packet parser generation from a P4 program. Chapter 4 describes the high-level HLS design methodology which the core of our second contribution. Chapter 5 presents the proposed caching scheme targeting high-speed heterogeneous programmable switches. In Chapter 6 we discuss the contributions of this thesis and its pertinence in the scope of programmable dataplanes. Finally, Chapter 7 concludes this work.

#### CHAPTER 2 BACKGROUND AND LITERATURE REVIEW

In this chapter, we provide the necessary background and the literature review for this work. We start by providing the background on programmable networks, from their origins up to the latest developments. We then review the state-of-the-art on programmable dataplanes, including common hardware-software (micro)architectures for packet processing. Then, we present a review of data plane programming languages with the focus on the prominent P4 language. We close this chapter by presenting techniques for mapping packet processing programs to real hardware architectures.

## 2.1 Programmable Networks

This section review important concepts on programmable networks. We start by presenting a historical recap on the evolution of programmable networks. Then, we present the key factors that contributed to consolidate the SDN paradigm in recent years.

## 2.1.1 The Long Way to Programmable Networks

Technological leaps do not happen by turning a switch on. It rather takes several, sometimes imperceptible, small steps in between. Rigid computer networks have not turned into flexible fully programmable networks in the blink of an eye. To illustrate this, in 2014, Feamster et al. [17] conducted a historic study from how we transitioned from rigid computer networks to SDN. The authors reviewed the evolution of programmable networks over the past 25 years. Their work identified three eras in programmable network history:

- i. The active networks era;

- ii. The control and data path separation; and

- iii. The OpenFlow era.

Active networks [18], [19] opened the first era of programmable networks. Active networks were precursors of network programmability by allowing users to run custom code in network appliances. To do so, programs executing in network equipment were encapsulated into packets and their execution was based on packet headers. As a consequence, active networks lowered the innovation barrier and paved the path to network virtualization and data plane programming. However, industry skepticism has almost life-sentenced active networks. This skepticism was well-grounded, especially with regards to security issues due to potentially malicious code running in network equipment in addition to the possible reduced performance.

The second era of programmable networks was marked by the separation of the control and data planes [20], [21]. Historically, network switches tightly coupled the control and data planes. However, the increasing demand for high throughput network devices pushed packet processing into dedicated hardware. Thus, complex control software could not directly interact with the packet processing logic. As a consequence, efforts for developing open interfaces between the control and data planes proliferated in the network community. Also, this decoupling led to pushing complex control software outside network switches in a centralized network-wise controller. Since no standardized control-data plane interface was defined at the time, a plethora of proprietary ones was developed, which were not necessarily compatible among different switch vendors.

To deal with the standardization issue, a group of researchers at Stanford's Computer Science department created the Ethane project [22]. The Ethane project was the basis for the development of OpenFlow [2], which started the third era in programmable networks. Open-Flow is based in a commodity Ethernet switch that uses flow tables for forwarding packets. OpenFlow also defines a standard user interface to provide means to configure the flow tables through a centralized controller. The OpenFlow specification [23], maintained by the Open Networking Foundation (ONF), defines the directives for OpenFlow-aware switches.

An OpenFlow switch has three parts: OpenFlow flow tables, OpenFlow channel, and OpenFlow protocol. Flow tables in OpenFlow switches are organized in a pipelined fashion divided in ingress and egress pipelines. A table matching triggers packet actions and statistics counters. The OpenFlow channel is an out-band link connecting OpenFlow switches to the controller. This channel is used to install forwarding rules on switches and to gather network statistics. The OpenFlow protocol defines the semantics of messages changed between an OpenFlow switch and the controller. The three main roles of an OpenFlow switch are selecting a forwarding rule from a flow table, updating flow statistics counters and applying actions over the packet according to the selected rule. Incoming packets that the switch is not able to process are eventually sent to the controller the slow path for further processing. More recently, advances in programmable switch architectures (PISA §2.2.2) packet processing languages (P4 §2.3.2) can potentially start a new programmable networks era: the programmable dataplanes era (§2.2).

#### 2.1.2 Consolidating the Software-defined Networking Paradigm

Historically, standard network hardware has defined network functionalities rather than user requirements. In today's fast-evolving Internet environment, traditional ASICs switches, which require a long design cycle, are no longer are a viable option. Users want to be able

to deploy new applications at any time using a software platform rather than ordering new switch chips as new requirements appear. Also, the development of new switch ASIC chips takes months to years while user applications change at a much fast pace.

The SDN paradigm emerged from this need. SDN [1] completely decouples the control and data planes in network devices. Therefore, SDN allows network programmability because the lower-level hardware implementations are abstracted for the user. Therefore, users only need to be concerned about developing their desired network applications. Thus, switches are also simplified, becoming a set of actions applied to the packets based on pre-defined matching rules. In SDN, network intelligence is logically centralized in a controller that is responsible for configuring and managing a set of SDN switches. The controller communicates with the switches using a simple and well-defined interface. The SDN paradigm is vendor and protocol agnostic and aims for high scalability, from the enterprise to the carrier level.

While the control and data plane decoupling can be seen as the core of SDN, many other ancient aspects of network research were incorporated into the SDN paradigm. As discussed in §2.1.1, active networks, standardized interfaces, and logically centralized control played a major role to push SDN networks further. Besides, SDN networks provide a global view of the network by managing global network state, which fairly simplifies the development of network applications by offering a "single big switch abstraction" to network administrators.

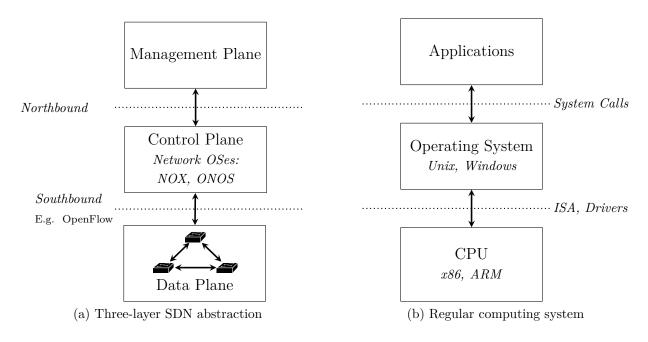

As Kreutz et al. state in [24], a cornerstone principle in SDN is the clear separation of concerns. These concerns, in turn, can be split into three abstraction layers: management plane, control plane, and data plane. The management plane is responsible for implementing network policies. The control plane distributes these policies to data plane devices that forward packets according to strict network policies. Figure 2.1 presents a graphic view of the three-layer SDN separation alongside its analog in regular computing systems.

As in regular computing systems, the heart of the SDN paradigm is the network operating system, also known as SDN controller [26]–[28]. Historically, managing networks was a difficult and error-prone task since it mainly relied on vendor-specific assembly language or, at best, vendor-specific Command Line Interfaces (CLIs). In contrast, with network OSes, network application developers have at their disposal an abstract view of forwarding devices through well defined and open programming interfaces. As SDN research has mainly focused on SDN controllers and network OSes, a plethora of these was developed in recent years [26]–[29]. These works tackled several key aspects, such as centralized vs distributed control, network state distribution and consistency, control plane resilience and scalability, among others.

Applications running in the management plane communicate with the network OS through

Figure 2.1 SDN vs regular computing systems. Adapted from [25]

a northbound interface. A myriad of network applications was developed in recent years for SDN networks. Interested readers should refer to a survey by Kreutz et al. [24] for more details. A standard northbound interface provides a common and vendor-agnostic abstraction for network applications accessing the network OS, similarly to what regular computer applications do using system calls. While several research efforts have proposed northbound interfaces [30], [31], to date, no standard northbound solution has been widely employed. In case of distributed controllers, east/westbound interfaces (not shown in Figure 2.1) are also required to guarantee network consistency among controllers. Similarly to the northbound, no consensus has been reached on standardized east/westbound interfaces.

On the other hand, OpenFlow [2] has recently been consolidated as the *de facto southbound interface*. Several other southbound interfaces have as well been proposed [32]–[34]. To date, however, none of them have gained the same attention as OpenFlow has. However, advances in programmable dataplanes [3] and data plane programming languages [4], [25] have the potential to changes this state of affairs (§2.2).

#### 2.2 The Programmable Dataplanes Era

SDN has emerged as a technology to break the rigidity of traditional computer networks. Indeed, with the clear separation of control and data planes, more complex network applications are developed at a fast pace in a software-oriented fashion. However, traditional deployments of SDN have mainly provided flexibility for control plane development. Open-Flow, the *de facto* standard for SDN deployments, has considered data plane equipment as "dumb" forwarding devices, forwarding packets based on pre-defined matching rules against packet header fields. As a consequence, even OpenFlow switches were still rigid switches in their concept. Recent developments on programmable dataplanes (§2.2.2) and packet processing languages [4], [25] promise to unleash the full power of programmable networks.

# 2.2.1 The Origins

Network Processors (NPs) have dominated the domain of programmable packet processing from the second half of the 1990s to the first half of the 2000s. A common NP architecture is a massively multi-core/multi-thread application-specific instruction-set processor. Many NPs have been commercially developed by several companies worldwide [35], [36]. Packets are normally assigned to a specific processor core and are treated in a run-to-completion fashion. Since NPs are normally implemented on top of Von Neumann machines, complex packet processing, such as Deep Packet Inspection (DPI) and packet classification, is allowed. Nonetheless, such processing flexibility comes with an inherent performance cost. First, packets assigned to different processor cores may undergo different treatments. Thus, packet reordering is common in NPs. Second, NPs cannot guarantee a predictable processing latency because it is a function of the type of treatment that a packet undergoes. Another limiting aspect of NPs is programmability which requires low-level assembly programming or, at best, subsets of the C idiom.

Fixed-function ASICs switches have also been proposed aiming for fast packet processing. In contrast to NPs, ASIC switches offer very high performance with an upper-bounded predictable latency [37]. State-of-the-art ASIC chips have surpassed dozens of Tb/s of aggregated packet switching capacity. As a consequence, these fixed-function devices impose even lower programming abstractions compared to NPs, mainly relying on proprietary user-exposed CLIs for device configuration. However, the main drawback of fixed-function ASIC chips is that these devices come with a preset of supported protocols that are "burned" in silicon. Thus, new protocols cannot be deployed in such switches until a new tape-out revision is released, which compromises time-to-market due to the time-consuming ASIC design flow.

Versatile soft-switches [9], [38] have also found their place in the context of programmable dataplanes. Although, soft-switches have mainly been deployed in data center servers to multiplex network traffic between tenant's VMs or containers. Traditional soft-switch imple-

mentations are developed on top of fast I/O management frameworks, such as DPDK [39], fd.io [40], and netmap [41], running in user-space. Some state-of-the-art soft-switches, such as the Open vSwitch [9], are OpenFlow-aware implementations largely deployed in data center networks. However, since soft-switches are implemented in commodity servers, their performance is limited to a few dozens of Gb/s.

## 2.2.2 The Protocol Independent Switch Architecture

In 2008, Casado et al. put in place the current view of modern packet forwarding hardware [42]. The authors discuss the lack of a sweet-spot in the tradeoff between hardware simplicity and flexibility in packet forwarding devices. Their work states three clear premises for hardware implementations of network switches:

- i. software (control-plane) and hardware (data-plane) must communicate through a clean interface;

- ii. the hardware needs to be simple to keep up with the increasing performance requirements; and

- iii. hardware and software should cooperate for flexible and efficient packet processing.

Casado's premises were consistent with the prominent OpenFlow development at the time. Besides, Casado et al. proposed the first sketch of a match-action packet processing approach that has dominated packet forwarding since then. Indeed, the OpenFlow's Single Match Table (SMT) switch architecture [2] is a generalization of Casado's work. In Casado's proposal, the hardware piece of the forwarding plane stores matching rules in a TCAM populated in software. Matched packets undergo actions (forward, drop, etc.) in hardware while the non-matched ones are treated in software.

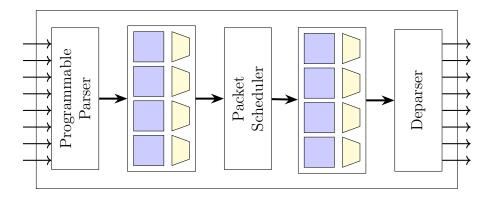

However, fully reconfigurable protocol-agnostic packet forwarding was not proposed until 2013 when Bosshart et al. proposed and implemented the Reconfigurable Match Tables (RMT) architecture [4]. RMT, also known as PISA, is a RISC-like programmable hardware architecture for software-defined packet processing. As shown in Figure 2.2, PISA is made up of a programmable parser, a pipeline of match-action tables, a packet scheduler, and a deparser. In the figure, blue squares represent match stages while yellow trapeziums are action stages.

The RMT architecture is a generalization of the Multiple Match Tables (MMT) architecture. The MMT architecture decomposes a single match table into multiple tables, which reduces hardware complexity by allowing wide and large tables to be implemented with multiple narrow and shallow ones. However, in MMT, the matching values are fixed header fields. In

Figure 2.2 PISA internal architecture. Adapted from [4]

contrast, RMT allows arbitrary matching. This is achieved by unique RMT's characteristics:

- i. the programmable parser for arbitrary header extraction;

- ii. the flexible logical match tables topology; and

- iii. configurable action engines for custom action definitions.

Throughout this section, the microarchitectural components of PISA are explained in details.

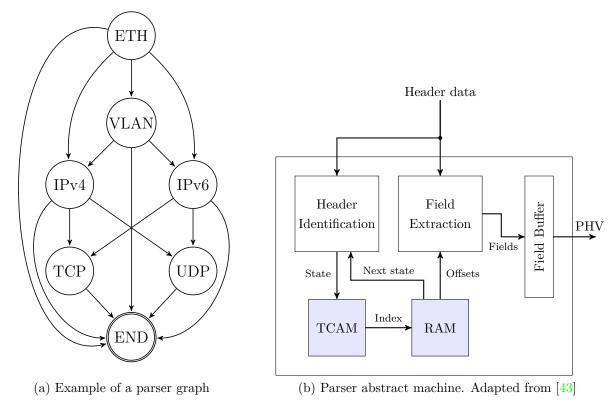

#### Packet Parser

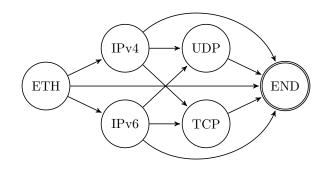

A packet parser identifies the set of protocols supported in a programmable dataplane and extracts header fields for further processing in the match-action stages. A common abstraction to represent a packet parser is through an Abstract State Machine (ASM), where each state represents a protocol while state transitions represent the protocols stack supported by the data plane device. As a result, a packet parser ASM can be graphically represented by Directed Acyclic Graph (DAG), as shown in Figure 2.3a.

Gibb [43] proposed design principles for modern hardware-based programmable packet parsing. Indeed, Gibb 's work is the basis for the packet parser described in the original PISA paper [4]. Gibb proposed an abstract parser machine for both fixed and programmable parsers, as shown in Figure 2.3b.

Fixed and programmable parsers share common modules: header identification, field extraction, and field buffer. The header identification module implements the parser ASM identifies the correct headers sequence. The field extraction module extracts specific header fields and stores them into the field buffer. The output of the field buffer is the Packet Header Vector (PHV) to be used in match-action stages. The blocks in blue, the TCAM and RAM modules, are specific to programmable parsers as they allow in-field parser reconfiguration.

Figure 2.3 Parser graph representation and parser abstract machine

Since Gibb 's proposal, a plethora of recent works have proposed hardware implementation of packet parsers for both FPGAs and ASICs [44]–[50].

## Match Stage

The programmable match-action stages are the core of the PISA model. In the matching part, packet header fields (or metadata) are matched against matching rules stored in a match table. For instance, a simple set of matching rules can be:

- Allow a packet entering the network if it is within a specific range of IP addresses.

- Deny access otherwise.

Match operations include exact, range, longest-prefix, and ternary (wildcard) matching. Exact matching exactly compares a search key against the set of keys stored in a table. Range matching checks if a search key is within a specified range of keys. LPM searches for a stored key that matches the maximum number of bits in the searched key. Ternary or wildcard matching allows searching a stored key that matches a wildcardly masked search key. Finally, in PISA, matching operations are agnostic to the table contents.

However, implementing hardware-based match tables is expensive since it requires to implement associative arrays. However, advances in cuckoo hashing [51], [52] improved the memory efficiency for the exact match operation. Cuckoo hash tables implement a series of N independent hash tables HT using N unique hash functions hf. A match for a given key k is detected when  $hf_j(k) \in HT_j, \forall j \in \{0, ..., N-1\}$ . Hash conflicts are resolved by recursively spreading keys throughout the tables. Bosshart et al. reported a 95% load factor for a cuckoo-based exact match table [4]. As a consequence, cuckoo hash tables became the  $de\ facto\ implementation$  for hardware-based exact match tables.

The other three search types (range, LPM, and ternary), however, still rely on TCAMs. TCAMs are known for being expensive and power-hungry devices. Indeed, TCAM memories exhaustively search entries in parallel in a table which increases power consumption. Moreover, because a search key may match multiple entries due to wildcard masking, a priority encoder is also required to resolve priority, which contributes to increasing power consumption and hardware resource usage. Although Arsovski et al. demonstrated a TCAM design with an overhead of only  $\approx 2.7 \times$  compared to an SRAM, real-world implementations report an overhead of  $6 \times \sim 7 \times [4]$ .

Therefore, due to power and area budget constraints, the amount of internal memory reserved for match operations is limited to a few hundreds of Mb. Algorithmic approaches for emulating content-agnostic lookup tables as well as rule caching schemes [54]–[57] have been (and are still being) proposed to minimize these limitations.

## **Action Stage**

Actions are commonly executed following a match operation. In the case of a match, the match table returns an action (or action identifier) and its parameters (when required). If a miss occurs, the table returns a default action to be executed.

Actions are similar to procedures in traditional computer programs. Actions are made of basic arithmetic, logical, bit-shift, and conditional operations. Actions are straightforwardly mapped to hardware in a format of ALUs. Indeed, the PISA architecture implements these Arithmetic Logical Units (ALUs) using configurable Very Long Instruction Word (VLIW) processors [4].

### Packet Scheduling

A packet scheduler decides at what times and in what order packets are sent. However, in PISA, scheduling algorithms cannot be programmable. Only a few preset scheduling

algorithms can be configured at compile time.

Thus, the push-in-first-out (PIFO) queue [58], [59] was proposed as an abstraction upon which a programmable packet scheduler can be built. More recently, the push-in-extract-out (PEIO) queue [60] extended PIFO to support more expressive packet scheduling algorithms, including non-conserving ones.

However, both PIFO and PEIO queues require using associative memories for selecting a packet candidate to be scheduled. As described in §2.2.2, the use of these scarce resources could jeopardize the practicality of programmable packet scheduling in high-speed switches.

### Deparser

The departer recombines the set of modified packet headers before sending a packet to an egress port. Little research efforts have focused on the design of packet departers. As a consequence, the departer is commonly referred as the packet parter's counterpart. Thus, the design of packet departers normally follow the premises of parter's implementations.

## 2.3 Packet Processing Languages

As in regular computing systems, the need for good programming abstractions was also required for packet processing. As data-plane processing became more complex, and as a consequence the hardware architectures running these applications, the network community introduced several packet processing languages over the last two decades. In this section, we first recap the history on packet processing languages then we introduce the P4 language.

#### 2.3.1 The Race for Abstractions

As discussed in §2.2.1, the dominant packet processing hardware at the beginnings of the SDN age was difficult to program, normally requiring low-level machine code.

Packet processing DSLs emerged to alleviate this programming burden. These languages contrast with regular general-purpose programming languages by exposing application-aware semantics that is normally associated with a particular Domain Specific Architecture (DSA).

The Network Classification Language (NCL) was one of the first DSLs designed for packet processing. NCL was a DSL designed by Intel for its IXA class of NPs. An NCL program defines a set of classification rules and the actions in case a match. In NCL, programmers specify packet headers and the parser state machine. Classification rules are defined as if-like statements. NCL supports table operations including match table creation and lookups.

Click [61] and its NP-Click [62] variation are other examples of packet processing DSLs. Click was initially intended to simplify router design. An IP router can be created by connecting basic blocks (elements) through a directed graph structure. Graph edges represent the packet flow throughout the router. Elements in Click are C++ objects, which are provided to the user as libraries. NP-Click is a Click variation tailored for NPs. NP-Click provides an intermediate programming model that exposes only the required underneath hardware details to the programmer. Both Click and NP-Click perform relatively well when compared to traditional lower-level implementations (less than 10% of performance overhead).

In 2009, Duncan and Jungck proposed packet [63], a C-based DSL tailored for packet processing. Packet C keeps the semantics of the standard C99 while introducing specifics for packet processing, such as packet types, databases, and searchsets. packet C follows a Single Program Multiple Data (SPMD) parallel programming model in which a program is executed across multiple threads that share memory. Although packet C eases the task of programming a network device, its abstraction is too low and close to the hardware.

In 2013, Song introduced POF [25], a protocol-oblivious packet processing language targeting network processors. In POF, the packet parser is configured by a controller. Table lookups are defined by simple  $\langle$  offset, length  $\rangle$  tuples to guarantee protocol independence. Moreover, POF explores a generic Flow Instruction Set (FIS) [31] to compose complex actions from basic instructions. In 2015, Song et al. [64] proposed an abstract forwarding model to expand the POF supportability to different hardware architectures.

Brebner and Jiang developed the PX language in 2014 [65]. PX is an object-oriented packet processing language targeting Xilinx FPGA devices. PX syntax and semantics resemble C++, however, PX also includes packet specific built-in classes, such as parsers, classifiers, and search engines.

#### 2.3.2 The P4 Language

By December of 2014, the OpenFlow standard version 1.5.0 [23] had already defined up to 44 header fields of several protocols that should be parsed in a network switch.

In this context, still in 2014, P4 [3] emerged as a protocol-agnostic alternative for describing packet processing. Today, the P4 consortium<sup>1</sup> is responsible for maintaining the P4 specification, the workgroups, and the open-source code base for the reference compiler.

P4 follows an imperative match-action-based programming model. In its first version, today known as P4<sub>14</sub>, the P4 execution model was based on a fixed abstract switch model similar to

<sup>1</sup>https://p4.org

PISA. The main components of a P4<sub>14</sub> program are the header definitions, the packet parser, the action definitions, the match tables, and control blocks.

In P4, packet headers are defined in structures similar to C structs. Each of these structures is made of header fields, defined as an arbitrary stream of bits. Similarly, per-packet metadata can be described using similar constructs.

The packet parser is defined as a parser state machine. This state machine evaluates header fields and/or metadata to derive the set of supported protocols as well as extracts header fields to be used in match-action tables.

Match tables have particular semantics in P4. A P4 program can only read from a match table. Table entries are populated and modified in-field using a run-time program that interfaces with the control plane. The user defines the search type (exact, range, LPM, and ternary), the search key made of one or more header fields (or metadata), and the list of actions to be executed following a match/miss. Optional parameters include the table size and a default action in case of a table miss.

Actions are similar to procedures in general purpose programming languages. Actions are made of basic P4 primitives, such as additions, subtractions, header field modifications. Actions may have execution parameters, either fixed or as a result of a match table lookup operation. Moreover, P4<sub>14</sub> does not allow conditionals in actions.

The control block manages the program control flow using imperative statements. Tables and actions are applied inside control blocks. Conditionals are allowed within control blocks in a form of if-else statements. Packet modifications are also permitted in control blocks, including header (in)validation. P4<sub>14</sub> has no specific semantics for packet deparsing. The deparsing logic is inferred from the parser graph.

The P4 compiler compiles a P4 program into two DAGs: a parser graph and a table dependency graph. The parser graph is derived from the parser state machine and it indicates the dependency between headers. The table dependency graph is generated by analyzing the program flow in control blocks and it indicates the order in which tables need to be applied.

In 2016, P4 underwent a major language review [66]. The newest P4 version, known as  $P4_{16}$ , strengthens the language semantics (stronger types, valid type casts) and completely separates the language from the architecture it is compiled into. However,  $P4_{16}$  broke backwards compatibility with  $P4_{14}$ . The enhancements brought by  $P4_{16}$  can be summarized as follows:

- Language conciseness: the number of keywords was reduced by a factor 2×;

- Language-architecture separation;

- Explicit deparsing logic through emit statements;

- Formal support for externs;

- Reference compiler refactoring.

The P4 consortium encourages P4 programmers to use P4<sub>16</sub>. P4<sub>16</sub> has better support for type checking, portability, and it has stronger semantics. The current compiler design includes several optimization passes, including life-time analysis and dead-code removal. As members of an open-source community, users are also encouraged to report bugs and propose modifications to the language/compiler.

# 2.4 Compiling Packet Processing Programs

This section cover recent research efforts on compiling packet processing programs. We start by presenting the mapping of these programs to CPUs and programmable switches. Then, we present recent works on mapping network applications to FPGAs.

# 2.4.1 CPUs and Programmable Switches

Soft-switches have been largely deployed in data centers for traffic forwarding between VMs in servers where OVS [9] has been consolidated as the OpenFlow-aware alternative. In 2016, Shahbaz et al. proposed PISCES [67], a protocol independent soft-switch. PISCES builds upon the classic OVS with specific back-end modifications to support P4. P4 programs are compiled into OVS-specific C code, replacing hardwired OVS software components (parser, match tables, and actions) by custom P4-derived code.

Berkeley Packet Filter (BPF) is a standard packet filtering mechanism employed in Unix-based systems. extended Berkeley Packet Filter (eBPF) is a BPF derivation for virtualized environments. Tu et al. proposed an eBPF back-end supporting P4 [68]. P4 programs are compiled into C code which is afterward compiled into eBPF programs using Low Level Virtual Machine (LLVM) back-end.

Mapping P4 programs to programmable PISA-like switches have mainly been done in the industry. Barefoot Tofino was the first proposed P4-aware programmable switch. P4 programs are compiled into a programmable parser and match-action pipelines. While the first Tofino<sup>TM</sup> version<sup>2</sup> achieves up to 6.4 Tb/s line rate and its second version achieves 12.8 Tb/s<sup>3</sup>, it has several architecture limitations that may limit the innovation potential of P4 programmers. First, the PHV is limited to a few hundred bytes, which limits the number of parsed headers (e.g. deep header encapsulation). Second, mapping a P4 program into Tofino<sup>TM</sup> is

<sup>&</sup>lt;sup>2</sup>https://www.barefootnetworks.com/products/brief-tofino/

<sup>3</sup>https://www.barefootnetworks.com/products/brief-tofino-2/

an ILP problem which means [69] that the program either compiles and runs at line rate or does not compile at all. Many factors may contribute to failing the compilation process. Table sizes and dependencies are such constraints directly exposed to programmers.

Cisco has recently released its new Cisco Silicon One<sup>TM</sup> Q100<sup>4</sup> switch which supports P4. Broadcom, on the other hand, has developed its own packet processing language called Network Programming Language (NPL)<sup>5</sup> for its new Trident 4 and Jericho 2 switch families<sup>6</sup>. At this moment, no much details regarding both Cisco or Broadcom architectures nor how packet processing programs are mapped into them are known. However, programmers are likely to face similar problems to ones observed in Tofino<sup>TM</sup>.

#### 2.4.2 FPGAs

Recent industrial and academic works proposed mapping data plane programs to FPGAs. Xilinx SDNet<sup>7</sup> is a proprietary tool that allows mapping PX programs [65] to Xilinx FPGAs. Recent versions of Xilinx SDNet [70] also support to P4 programs which are compiled into PX before being implemented on an FPGA. Ibanez et al. [71] used Xilinx SDNet to map P4 programs to the off-the-shelf NetFPGA board [72]. Netcope Technologies' P4-to-VHDL<sup>8</sup> is a similar commercial tool that automatically generates RTL descriptions from P4 programs.

P4FPGA [73] is an open-source P4-to-FPGA compiler. P4FPGA builds upon the open-source front-end compiler maintained by the P4 consortium while adding an FPGA-specific back-end. The back-end compiler generates BlueSpec System Verilog code which is further compiled into synthesizable Verilog. P4FPGA is vendor-independent and has been demonstrated in both Xilinx and Intel FPGAs. However, the performance of P4FPGA is limited to few dozens of Gb/s and relies on a proprietary BlueSpec compiler.

Recent works proposed specific microarchitectures for packet processing. Some of them were accompanied by frameworks for hardware generation from P4. Benácek et al. proposed P4-to-VHDL [44] for generating packet parsers from P4. P4-to-VHDL is an HLS-like tool that builds upon previous works on packet parser microarchitecture [74], [75]. Similarly, Benáček et al. extended P4-to-VHDL to also generate the packet deparser logic [76]. Also derived from [44], the work by Cabal et al. presented a packet parser architecture for terabit networks [77].

Mapping agnostic MATs on FPGAs were also proposed. Kekely et al. proposed a hybrid Cuckoo-tree approach for implementing exact and LPM tables. Pure exact match Cuckoo

<sup>&</sup>lt;sup>4</sup>https://www.cisco.com/c/en/us/solutions/service-provider/innovation/silicon-one.html

<sup>&</sup>lt;sup>5</sup>https://nplang.org/

<sup>&</sup>lt;sup>6</sup>https://www.broadcom.com/blog/trident4-and-jericho2-offer-programmability-at-scale

<sup>7</sup>https://www.xilinx.com/sdnet.html

<sup>8</sup>https://www.netcope.com/en/products/p4-to-vhdl

approaches were also proposed for high-speed networks achieving over terabit throughput [79], [80]. The generation of P4-based match-action tables were studied in [16], [81]. Pontarelli et al. proposed a RISC-like approach for implementing primitive actions on FPGAs [82].

Several other works have targeted data plane realization on FPGAs, although not P4 compatible. ReClick [83] is a Click-like language and compiler targeting network virtualization on FPGAs. Similarly, ClickNP [84] is also inspired in Click aiming at accelerating network functions. ClickNP is a C-like language and uses off-the-shelf HLS tools to generate FPGA-specific code. Emu [85] is a standard C# library for implementing network functions on FPGAs. Eran et al. [86] proposed a similar library for data plane acceleration on FPGAs but written in modern C++.

# 2.5 Chapter Conclusion

SDN beyond OpenFlow. Although OpenFlow has consolidated its place in SDN environments, advances in programmables dataplanes and languages, notably PISA and P4, may jeopardize its hegemony. The PISA+P4 combination is a powerful toolkit for describing agnostic packet processing at the data plane level, an aspect that OpenFlow had not yet covered. However, research regarding P4 is still maturing and many research avenues are yet to be explored.

P4 beyond PISA. PISA is indeed a realistic architecture for processing P4 programs at wire speed. However, the programming expressiveness allowed by P4 may be limited due to PISA's architectural constraints. Other devices, such as FPGAs and CPUs, have been recently explored for packet processing, however, a sweet spot for this has not yet been found. Heterogeneous data planes may be a potential solution to fill this gap. However, research regarding them is in preliminary research stages with many open questions, such as caching for heterogeneous match tables.

FPGAs beyond RTL. HLS tools and DSLs, such as P4, have made FPGAs accessible for a wider audience. Indeed, there is no more need for FPGA experts for developing and testing network applications. However, specialized FPGA microarchitectures, compilers, and good programming abstractions are still needed for more efficient P4-based packet processing.

# CHAPTER 3 ARTICLE 1: P4-COMPATIBLE HIGH-LEVEL SYNTHESIS OF LOW LATENCY 100 Gb/s STREAMING PACKET PARSERS IN FPGAS

Authors: Jeferson Santiago da Silva, François-Raymond Boyer, and J.M. Pierre Langlois. Published in: Proceedings of the 2018 ACM/SIGDA International Symposium on Field-Programmable Gate Arrays.

#### Abstract

Packet parsing is a key step in SDN-aware devices. Packet parsers in SDN networks need to be both reconfigurable and fast, to support the evolving network protocols and the increasing multi-gigabit data rates. The combination of packet processing languages with FPGAs seems to be the perfect match for these requirements.

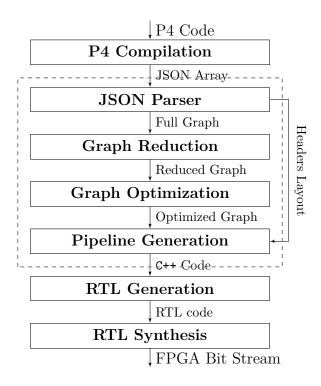

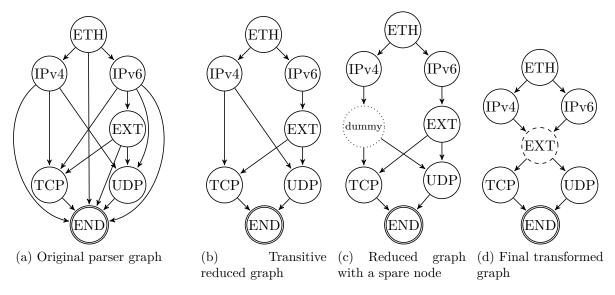

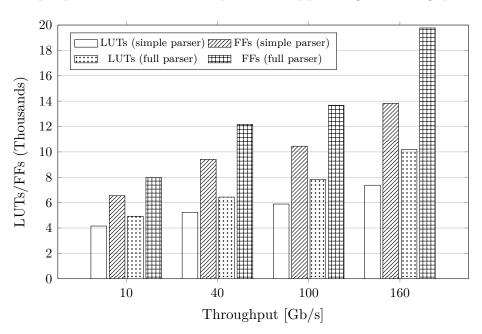

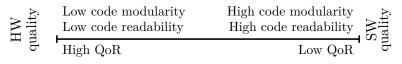

In this work, we develop an open-source FPGA-based configurable architecture for arbitrary packet parsing to be used in SDN networks. We generate low latency and high-speed streaming packet parsers directly from a packet processing program. Our architecture is pipelined and entirely modeled using templated C++ classes. The pipeline layout is derived from a parser graph that corresponds to a P4 code after a series of graph transformation rounds. The RTL code is generated from the C++ description using Xilinx Vivado HLS and synthesized with Xilinx Vivado. Our architecture achieves a 100 Gb/s data rate in a Xilinx Virtex-7 FPGA while reducing the latency by 45% and the LUT usage by 40% compared to the state-of-the-art.

#### 3.1 Introduction

The emergence of recent network applications have opened new doors to FPGA devices. Dataplane realization in Software-Defined Networking (SDN) [87] is an example [8], [88] of such applications. In SDN networks, the data and control planes are decoupled, and they can evolve independently of each other. When new protocols are deployed in a centralized intelligent controller, new forwarding rules are compiled to the data plane element without changing the underlying hardware. FPGAs, therefore, offer the right degree of programma-bility expected by these networks, by offering fine grain programmability with sufficient and power-efficient performance.

A standard SDN Forwarding Element (FE) is normally implemented in a pipelined-fashion [4]. Incoming packets are parsed in order to extract header fields to be matched in the

processing pipelines. These pipelines are organized as a sequence of match-action tables. In SDN FEs, a packet parser is expected to be programmable, and it can be reconfigured at run time whenever new protocols are deployed.

Recent packet processing programming languages, such as POF [25] and P4 [3], allow describing agnostic data plane forwarding behavior. Using such languages, a network programmer can specify a packet parser to indicate which header fields are to be extracted. He can as well define which tables are to be applied, and the correct order in which they will be applied.