| <b>Titre:</b> Title: | A reconfigurable low-voltage and low-power millimeter-wave dualband mixer in 65-nm CMOS                                                                    |

|----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Auteurs:<br>Authors: | Fang Zhu, Kuangda Wang, & Ke Wu                                                                                                                            |

| Date:                | 2019                                                                                                                                                       |

| Type:                | Article de revue / Article                                                                                                                                 |

| Référence:           | Zhu, F., Wang, K., & Wu, K. (2019). A reconfigurable low-voltage and low-power millimeter-wave dual-band mixer in 65-nm CMOS. IEEE Access, 7, 33359-33368. |

# Document en libre accès dans PolyPublie Open Access document in PolyPublie

https://doi.org/10.1109/access.2019.2903580

| <b>URL de PolyPublie:</b> PolyPublie URL:         | https://publications.polymtl.ca/5195/                                                  |

|---------------------------------------------------|----------------------------------------------------------------------------------------|

| Version:                                          | Version officielle de l'éditeur / Published version<br>Révisé par les pairs / Refereed |

| <b>Conditions d'utilisation:</b><br>Terms of Use: | IEEE Open Access Publishing Agreement                                                  |

## Document publié chez l'éditeur officiel Document issued by the official publisher

| <b>Titre de la revue:</b> Journal Title: | IEEE Access (vol. 7)                                                                                                                                                                                                                                                    |

|------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>Maison d'édition:</b><br>Publisher:   | IEEE                                                                                                                                                                                                                                                                    |

|                                          | https://doi.org/10.1109/access.2019.2903580                                                                                                                                                                                                                             |

| <b>Mention légale:</b><br>Legal notice:  | Translations and content mining are permitted for academic research only. Personal use is also permitted, but republication/redistribution requires IEEE permission. See http://www.ieee.org/publications_standards/publications/rights/index.html for more information |

Received February 17, 2019, accepted March 3, 2019, date of publication March 7, 2019, date of current version March 29, 2019.

Digital Object Identifier 10.1109/ACCESS.2019.2903580

## A Reconfigurable Low-Voltage and Low-Power Millimeter-Wave Dual-Band Mixer in 65-nm CMOS

FANG ZHU<sup>10</sup>, KUANGDA WANG<sup>10</sup>, (Member, IEEE), AND KE WU<sup>10</sup>, (Fellow, IEEE)

Poly-Grames Research Center, Department of Electrical Engineering, Polytechnique Montréal, Montreal, QC H3T 1J4, Canada

<sup>2</sup>School of Information Science and Engineering, Institute for Future Wireless Research, Ningbo University, Ningbo 315211, China

Corresponding author: Fang Zhu (fang.zhu@polymtl.ca)

This work was supported in part by the Natural Sciences and Engineering Research Council of Canada (NSERC) Discovery Grant, and in part by the NSERC Strategic Grant.

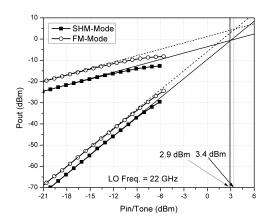

**ABSTRACT** In this paper, we propose, investigate, and demonstrate a reconfigurable low-voltage and low-power millimeter-wave mixer in a 65-nm CMOS, which can be switched as either a subharmonic mixer (SHM) or a fundamental mixer (FM) for the dual-band applications. Based on a modified Gilbert mixer topology, the proposed CMOS mixer can operate at a low supply voltage and low local oscillator (LO) pumping power while providing good performance in both SHM and FM modes. To the best of our knowledge, this is the first reported Gilbert SHM based on the stacked switching quads in a low-voltage CMOS technology. Under 1-V supply voltage and -3-dBm LO pumping power, the measured conversion gain (CG) of the proposed CMOS mixer is  $-4.8 \pm 1.5$  dB from 34 to 56 GHz and  $-0.1 \pm 1.5$  dB from 17 to 43 GHz in the SHM and FM modes, respectively. The measured double-sideband (DSB) noise figure (NF) is 18.5–20 dB from 37 to 49 GHz and 12.4–14 dB from 17 to 35 GHz in the SHM and FM modes, respectively. The measured input third-order intercept point (IIP3) is 2.9 and 3.4 dBm, respectively, for the SHM and FM modes at the LO frequency of 22 GHz. In addition, the total dc power consumption of the proposed mixer including output buffers is 7 mW in both the operation modes.

**INDEX TERMS** CMOS, dual-band mixer, fundamental mixer (FM), Gilbert mixer, low-power, low-voltage, millimeter-wave (mmW), reconfigurable, subharmonic mixer (SHM).

#### I. INTRODUCTION

Research and development of multi-band and multi- standard wireless communication systems have gained significant interest in recent years [1]-[3]. Traditional design strategies have adopted separate single-band radio-frequency (RF) front-ends, which can physically be arranged in parallel for multi-band operations [1]. The drawback in this case is that the number of RF blocks involved in the system development is multiplied by the number of frequency bands of interest, hence the development cost, physical size and power consumption of the system are all increased. Alternative approach is to design a multi-band transceiver system that reuses common RF blocks as much as possible among the multiple frequency bands [2]. This approach is also appealing for millimeter-wave (mmW) transceivers on silicon to

The associate editor coordinating the review of this manuscript and approving it for publication was Yang Yang.

increase the versatility, save the chip area, and reduce the power consumption.

A multi-band mixer is one of the key components in a multi-band transceiver. A switched dual-band mixer was proposed in [4], where a switched inductor matching network was used to select the frequency band of interest. By using a dual-band L-C matching network, the mixer proposed in [5] can operate in two desired frequency bands simultaneously. The concept of composite right/left-handed transmission lines was also used to implement a dual-band mixer [6]. All these mixers, however, require multiple local oscillators (LOs) for multi-band operations. By selecting either the fundamental or 2<sup>nd</sup> order harmonic output of the oscillator as the LO through a set of complementary switches, a dual-band self-oscillating mixer was proposed in [7]. Similarly, band selection was achieved by either mixing the input signal with the fundamental or 3<sup>rd</sup> order harmonic component of the LO in [8]. A reconfigurable passive subharmonic mixer (SHM) with a multi-stage injection locked ring oscillator as LO was

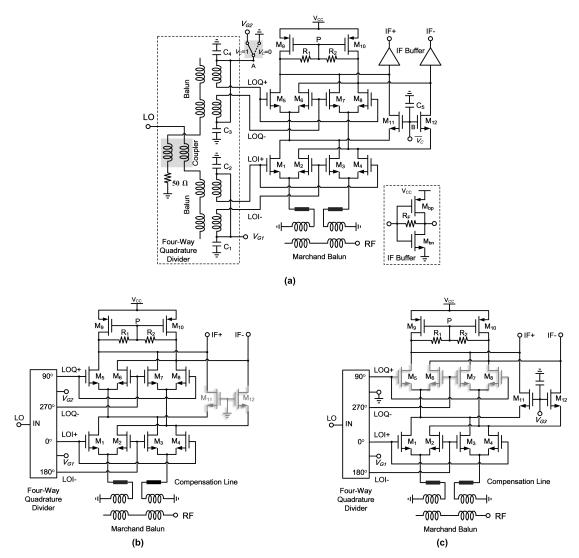

FIGURE 1. Schematic of the proposed reconfigurable dual-band CMOS mixer based on a modified Gilbert mixer topology.

(a) Complete circuit. (b) Proposed mixer in SHM mode (without IF buffers). (c) Proposed mixer in FM mode (without IF buffers).

proposed in [9] for dual-band applications. The multi-stage injection locked ring oscillator was used to generate multiple LO phases. By selecting appropriate LO phases, the mixer can be reconfigured between the fundamental and subharmonic operation modes.

In this paper, a reconfigurable low-voltage and low-power mmW dual-band mixer in 65-nm CMOS is proposed, studied and demonstrated. The proposed CMOS mixer can be switched as either a SHM or a fundamental mixer (FM) for dual-band applications. By using a modified Gilbert mixer topology [10] and an active load [11], the proposed CMOS mixer can operate at 1 V supply voltage and -3 dBm LO pumping power while maintaining a good performance in both SHM and FM modes. The 1V supply voltage and -3 dBm LO power make it suitable for low-voltage and low-power applications. To the best of our knowledge, this is the first proposed Gilbert SHM based on stacked switching quads [12] in CMOS technology. The rest of this paper

is organized as follows. The analysis and design of the proposed mixer in SHM and FM modes are presented in Section II (A) and (B), respectively. Section III provides the measured results and comparisons. Finally, Section IV summarizes this paper.

### II. ANALYSIS AND DESIGN OF THE PROPOSED RECONFIGURABLE DUAL-BAND MIXER

As the feature size of the CMOS transistor continues to shrink, a proportional downscaling in the supply voltage is mandatory to maintain gate-oxide reliability. Therefore, low-voltage CMOS mixers are highly required, which have to force many compromises between conversion gain (CG), LO power, linearity, noise figure (NF), port-to-port isolation, power consumption, and supply voltage.

Fig. 1(a) shows the schematic of the proposed CMOS mixer based on a modified Gilbert mixer topology, where the tail current source and the RF transconductance stage in

a conversional Gilbert mixer are replaced by a Marchand-balun-based RF stage to reduce the supply voltage [10]. In addition, an active load that is composed of two PMOS transistors ( $M_9$  and  $M_{10}$ ) and two common-mode feedback resistors ( $R_1$  and  $R_2$ ) is employed to provide a high load impedance [11].

The core of the mixer is composed of two stacked switching quads  $(M_1-M_8)$  and a common-gate differential pair  $(M_{11}-M_{12})$ . The bottom switching quad is composed of transistors  $M_1-M_4$ , whose gates are biased near the threshold voltage  $V_{\rm th}$ . The top switching quad is composed of transistors  $M_5-M_8$ , whose gates are biased at  $V_{\rm A}$ . The common-gate differential pair is composed of transistors  $M_{11}-M_{12}$ , whose gates are biased at  $V_{\rm B}$ . As shown in Fig. 1(a),  $V_{\rm A}$  and  $V_{\rm B}$  represent the dc voltage at node A and node B, respectively, whose values can be selected by the control voltage  $V_{\rm C}$  as

$$V_{\rm A} = \begin{cases} V_{\rm G2}, & \text{if } V_{\rm C} = 1\\ 0, & \text{if } V_{\rm C} = 0 \end{cases}$$

(1)

and

$$V_{\rm B} = \overline{V_{\rm C}}.\tag{2}$$

where  $V_{\rm G2}$  is the turn-on voltage of the top switching quad that is approximately equal to the sum of  $V_{\rm th}$  and the drain voltage of the bottom switching quad  $V_{\rm Db}$ , while  $\overline{V_C}$  is the complementary value of  $V_{\rm C}$ .

High impedance compensation lines are employed between the RF Marchand balun and the bottom switching quad, as shown in Fig. 1, to compensate the parasitic capacitances of the transistors  $M_1$ - $M_4$  [10]. A passive fourway quadrature divider, which is composed of a 90<sup>\*</sup> coupler and two Marchand baluns, is utilized to generate quadrature LO signals. The bottom and top switching quads are driven by the in-phase LO signal (LOI) and quadrature LO signal (LOQ), respectively. By adding four bypass capacitors  $(C_1-C_4)$  as shown in Fig. 1(a), the two LO Marchand baluns in the four-way quadrature divider could provide dc bias voltages  $(V_{G1} \text{ and } V_A)$  for the stacked switching quads without affecting the LO characteristics. Compared with a commonly used lumped poly-phase filter [12], [13], the passive four-way quadrature divider has a much lower insertion loss in the mmW range at the cost of a larger chip size. In addition, the transimpedance amplifier (TIA), which is composed of an NMOS transistor  $M_{\rm bn}$ , a PMOS transistor  $M_{\rm bp}$  and a feedback resistor  $R_{\rm F}$  (500  $\Omega$ ), is utilized as an intermediate-frequency (IF) output buffer [11].

As will be discussed below, the proposed mixer can be reconfigured for operation between the subharmonic and fundamental modes simply by changing its bias, as shown in Fig. 1(b) and 1(c), where the IF buffers are removed for simplicity.

#### A. PROPOSED MIXER IN SUBHARMONIC MODE

A SHM allows for the use of an LO operating at a frequency that is only a fraction of the LO frequency of a FM [12].

This is very attractive in mmW frequency range, where an LO source with low phase noise and high output power is not always available [14]. The most widely used SHM topologies include the anti-parallel diode pair (APDP) based SHMs [15]-[17], the FET resistive SHMs [18]-[20], and the transconductance SHMs [14], [21]-[23]. Three distinct Gilbert SHMs [24], including the stacked-LO SHM [12], [25]–[27], the top-leveled-LO SHM [28]–[31] and the bottom-leveled-LO SHM [24], [32], have also been proposed. Among these structures, the Gilbert stacked-LO SHM achieves the highest CG and port-to-port isolation, while requiring the lowest LO pumping power [24]. However, this topology usually needs a high supply voltage, such as 3.3 V in [12] and [25] and 4 V in [26], due to the stacked structure. Thus, it is not suitable for low-voltage applications, especially in CMOS technologies. To date, all the published Gilbert stacked-LO SHMs are based on bipolar technologies. On the other hand, the top-leveled-LO SHM, the bottom-leveled-LO SHM, as well as the double balanced passive SHM [33], [34], can operate with a lower supply voltage in CMOS technologies. However, they usually require much higher LO pumping power with lower CG and worse port-to-port isolation.

To operate an active SHM at low supply voltage and low LO pumping power while providing a good CG and high port-to-port isolation, a modified Gilbert stacked-LO SHM is proposed for the first time, as shown in Fig. 1(b), where  $V_{\rm A} = V_{\rm G2}$  and  $V_{\rm B} = 0$  V. Which means that the transistors  $M_5$ - $M_8$  in the top switching quad are biased near the turn-on voltage, while the common-gate devices  $M_{11}$ - $M_{12}$  are in offstate. During the positive excursions of LOQ,  $M_5$  and  $M_8$  are turned on, while  $M_6$  and  $M_7$  are turned off. On the contrary, during the negative excursions of LOQ,  $M_5$  and  $M_8$  are turned off, while  $M_6$  and  $M_7$  are turned on. In other words, the top switching quad is switched by LOQ. Meanwhile, the bottom switching quad is switched by LOI. The two stages of switching with 90r phase offset provide an effective doubling of the LO frequency [12]. Therefore, a subharmonic mixing is obtained. According to the simulation, the CG of the SHM is robust to phase errors in the quadrature LO signals [34], which eases the design of the LO quadrature divider.

Compared with the conventional Gilbert stacked-LO SHM [12], [25]–[27], the balun coupling in the proposed SHM reduces two stacking stages and mitigates the voltage headroom problem. The operation of the proposed SHM is provided in the following. Assuming the LO waveform is a square wave with 50% duty cycle and the switching transistors are operating as ideal switches, the mixing function and the output voltage of the SHM can be expressed as follows [26], [34]:

$$m_h(t) = \frac{4}{\pi} \sum_{n=0}^{\infty} \frac{1}{2n+1} \sin[2(2n+1)\omega_{LO}t]$$

(3)

$$v_{out} = A_{\nu}v_{in}(t)m_h(t) \tag{4}$$

where  $\omega_{LO}$  is the angular frequency of the LO signal,  $v_{in}(t)$  is the input voltage of the mixer, and  $A_v$  is the nonmixing

("amplifier-mode") voltage gain, which is exhibited when the mixer core is configured as a simple "cascode commongate" state by applying large dc bias voltages at the gates of the stacked switching quads [35]. Herein,  $A_v$  can be expressed as

$$A_{\nu} = g_m R_L \tag{5}$$

where  $g_{\rm m}$  is the transconductance of the transistors  $M_1$ - $M_4$ , and  $R_{\rm L}$  is the load impedance of the mixer.

Assuming

$$v_{in}(t) = v_{RF}(t) = V_{RF}\cos(\omega_{RF}t) \tag{6}$$

where  $V_{\rm RF}$  and  $\omega_{\rm RF}$  represent the voltage amplitude and the angular frequency of the RF input signal, respectively.

Substituting (3) and (6) into (4), we can obtain

$$v_{out}(t) = A_{\nu}V_{RF}\cos(\omega_{RF}t)\frac{4}{\pi}\sum_{n=0}^{\infty}\frac{1}{2n+1}\sin[2(2n+1)\omega_{LO}t]$$

$$= \frac{2}{\pi}A_{\nu}V_{RF}\sum_{n=0}^{\infty}\frac{1}{2n+1}\sin[\omega_{RF}t - 2(2n+1)\omega_{LO}t]$$

$$+ \frac{2}{\pi}A_{\nu}V_{RF}\sum_{n=0}^{\infty}\frac{1}{2n+1}\sin[\omega_{RF}t + 2(2n+1)\omega_{LO}t]. \quad (7)$$

As can be observed, a number of different frequency components ( $\omega_{RF} \pm (4n + 2)\omega_{LO}$ ) are obtained, but only the first term in (7) with n = 0 is the desired IF product with a frequency of  $\omega_{RF} - 2\omega_{LO}$ , whose amplitude can be expressed as

$$v_{IF}(t) = \frac{2}{\pi} A_{\nu} V_{RF} \sin[(\omega_{RF} - 2\omega_{LO})t]. \tag{8}$$

Therefore, the voltage conversion gain (VCG) and the power CG of the SHM can respectively be derived as

$$VCG_h = \frac{V_{IF}}{V_{RF}} = \frac{2}{\pi} A_v = \frac{2}{\pi} g_m R_L \tag{9}$$

and

$$CG_h = \frac{P_{IF}}{P_{RF}} = (VCG_h)^2 \frac{R_S}{R_L} = \frac{4}{\pi^2} g_m^2 R_L R_S$$

(10)

where  $V_{\rm IF}$  and  $P_{\rm IF}$  represent the voltage amplitude and power of the IF signal, respectively,  $P_{\rm RF}$  is the input power of the RF signal, and  $R_{\rm S}$  is the source impedance.

It should be noted that, for a passive SHM [34],  $A_v = 1$ , and the VCG is

$$VCG_{ph} = \frac{2}{\pi}. (11)$$

Therefore, the CG of the proposed SHM is higher than that of the passive SHM as long as  $g_{\rm m}R_{\rm L}>1$ .

To obtain a high CG, a large  $R_L$  and a high  $g_m$  are required. However, a larger  $R_L$  will cause a larger dc voltage drop on the IF load and therefore aggravates the voltage headroom problem. The active load, however, can provide a very high impedance in the differential-mode for high CG but a moderate impedance in the common-mode for low dc voltage drop.

By using the active load, a high CG can be obtained with a smaller dc voltage drop.

A higher  $g_{\rm m}$  can also result in a higher CG. Normally, larger devices have a higher  $g_{\rm m}$ . However, the larger the transistor size is, the larger the parasitic capacitances (e.g. the drain-bulk capacitance  $C_{\rm DB}$ , and the source-bulk capacitance  $C_{\rm SB}$ ) will be, which will provide high capacitive coupling paths to the lossy substrate, especially at mmW frequency range [34]. In addition, larger devices require higher LO pumping power and higher dc power [11]. Therefore, trade-offs between CG, dc power, and LO pumping power have to be concerned during device size selection. In this design, a total gate width of 20  $\mu$ m with a ten-finger transistor is selected to obtain sufficient CG with low LO power and low dc power.

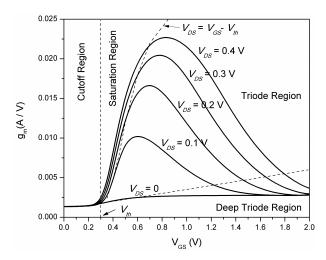

FIGURE 2. Simulated transconductance  $g_m$  of the NMOS transistor with gate width of 20  $\mu$ m versus  $V_{GS}$  and  $V_{DS}$ .

Fig. 2 shows the simulated  $g_{\rm m}$  of the selected NMOS transistor versus its gate-source voltage  $V_{\rm GS}$  and drain-source voltage  $V_{\rm DS}$ . For a given  $V_{\rm GS}$ ,  $g_{\rm m}$  decreases as  $V_{\rm DS}$  decreases. This explains why high supply voltage is normally required in the Gilbert mixer design [11], [24], [25]. It is interesting to note that, for a given  $V_{\rm DS}$ ,  $g_{\rm m}$  is a convex upward function versus  $V_{\rm GS}$ . Since  $V_{\rm GS}$  is determined by the voltage amplitude of the LO signal ( $V_{\rm LO}$ ) in this design, the CG of the SHM will also be a convex upward function versus  $V_{\rm LO}$ . Furthermore, if  $V_{\rm LO}$  is large enough, the transistors will be pushed into the deep triode region, as shown in Fig. 2, and the operation of the proposed SHM will be similar to the passive SHM proposed in [34].

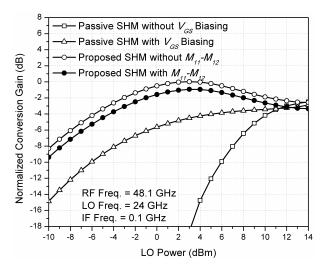

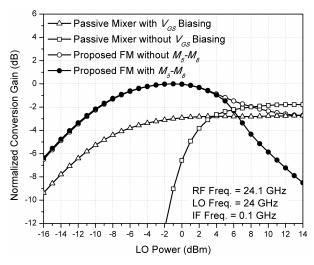

Fig. 3 simulates the normalized CGs of the proposed SHM, a passive SHM with optimized  $V_{\rm GS}$  biasing [34] and a passive SHM without  $V_{\rm GS}$  biasing, versus LO power. As can be observed, the passive SHM without  $V_{\rm GS}$  biasing requires the highest LO power (e.g. 12 dBm) for a reasonable CG. By adding an optimized  $V_{\rm GS}$  biasing, the CG of the passive SHM can be improved at low LO power region. The proposed SHM can further improve the CG with a lower LO power.

FIGURE 3. Simulated CGs of different SHMs versus LO power. The peak CG is normalized to 0 dB.

For example, to achieve a -4 dB of normalized CG, the passive SHM with optimized  $V_{\rm GS}$  biasing requires 4 dBm of LO pumping power while the proposed SHM only requires -6 dBm of LO power at the expense of 2 mW of dc power consumption. This is very attractive in the mmW frequency range, where the LO power is a valuable resource.

It should be mentioned that, the off-state transistors  $M_{11}$ - $M_{12}$  and the IF buffers are removed in the above simulation for fair comparison. The off-state transistors  $M_{11}$ - $M_{12}$ , however, may degrade the performance of the proposed SHM due to the parasitic loading. By adding the off-state transistors  $M_{11}$ - $M_{12}$ , the simulated CG of the proposed SHM degrades about 1 dB, as shown in Fig. 3. Additionally, the simulated NF also degrades about 1 dB. Fortunately, the RF bandwidth and the input third order intercept point (IIP3) are hardly affected according to the simulation.

#### B. PROPOSED MIXER IN FUNDAMENTAL MODE

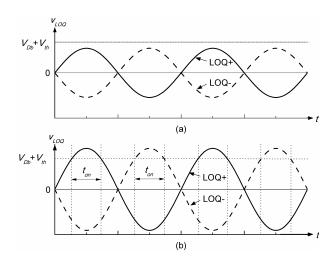

The proposed CMOS mixer can also be reconfigured as a FM by setting  $V_{\rm C}=0$  V. Therefore,  $V_{\rm B}=1$  V and  $V_{\rm A}=0$  V, which means that the gates of the transistors  $M_5$ - $M_8$  in the top switching quad are biased at 0 V, while the common-gate devices  $M_{11}$ - $M_{12}$  are activated, as shown in Fig. 1(c). If the voltage amplitude of LOQ ( $V_{\rm LOQ}$ ) is smaller than  $V_{\rm Db}+V_{\rm th}$ , as shown in Fig. 4(a), the transistors  $M_5$ - $M_8$  will be in offstate during both the positive and negative excursions of LOQ. In this case, the power of LOQ is wasted. Since only the bottom switching quad is switched by LOI, a mixing only happens in the bottom switching quad.

The operation of the proposed FM is provided in the following. Assuming the LO waveform is a square wave with 50% duty cycle and ideal switching, the mixing function of the FM can be expressed as

$$m_f(t) = \frac{4}{\pi} \sum_{n=0}^{\infty} \frac{1}{2n+1} \sin[(2n+1)\omega_{LO}t].$$

(12)

**FIGURE 4.** Voltages on the gates of  $M_5$ - $M_8$  in the FM mode. (a)  $V_{LOQ} < V_{Db} + V_{th}$ . (b)  $V_{LOQ} > V_{Db} + V_{th}$ .

Similarly, the output IF voltage and the CG of the FM can respectively be obtained as

$$v_{IF}(t) = \frac{2}{\pi} A_{\nu} V_{RF} \sin[(\omega_{RF} - \omega_{LO})t]$$

(13)

and

$$CG_f = \frac{P_{IF}}{P_{RF}} = \frac{4}{\pi^2} g_m^2 R_L R_S.$$

(14)

Comparing (10) and (14), it is noteworthy that the CG of the SHM is the same as that of the FM under ideal conditions. In practice, however, the CG of the SHM will be lower than that of the FM, due to a non-ideal square-wave switching and a higher parasitic capacitive coupling to the substrate at high frequencies [34].

Fig. 5 simulates the normalized CGs of the proposed FM, a passive ring mixer with an optimized  $V_{\rm GS}$  biasing and a passive ring mixer without  $V_{\rm GS}$  biasing, versus LO power.

FIGURE 5. Simulated CGs of different FMs versus LO power. The peak CG is normalized to 0 dB.

Although half of the LO power is wasted by LOQ, the simulated CG of the proposed FM is still higher than that of the passive ring mixer with an optimized  $V_{\rm GS}$  biasing at low LO power region. The simulated CG of the proposed FM equals to that of the passive ring mixer when the LO power is higher than 13 dBm, because the transistors in the proposed FM have been pushed into the deep triode region.

Similarly, the off-state transistors  $M_5$ - $M_8$  and the IF buffers are removed in the above simulation for fair comparison. The simulated CG of the proposed FM with  $M_5$ - $M_8$  is also plotted in Fig. 5, which is equal to that of the FM without  $M_5$ - $M_8$  when the LO power is lower than 4 dBm. However, when the LO power is higher than 4 dBm, the simulated CG of the FM with  $M_5$ - $M_8$  drops much faster than that of the FM without  $M_5$ - $M_8$ . This is because the transistors  $M_5$ - $M_8$  will be activated during the time  $t_{\rm on}$ , as shown in Fig. 4(b), when  $V_{\rm LOQ}$  is larger than  $V_{\rm Db} + V_{\rm th}$ . Thus, a part of IF currents at the drain of the bottom switching quad will be routed through the top switching quad and upconverted to other frequencies. Therefore, we should make sure  $P_{\rm LO} < 4$  dBm during the operation of the fundamental mixing mode.

According to the simulation, the performances of the proposed FM, including the CG, NF, RF bandwidth and IIP3, are hardly affected by the off-state transistors  $M_5$ - $M_8$  when  $P_{LO} < 4$  dBm. This is because the off-state transistors  $M_5$ - $M_8$  are connected to the IF stage, where the parasitic loading effects can be ignored.

#### **III. MEASURED RESULTS**

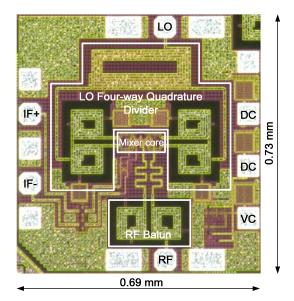

The proposed reconfigurable low-voltage and low-power mmW dual-band mixer is designed and fabricated in TSMC 65-nm CMOS technology. A die micrograph is shown in Fig. 6. The chip is measured via on-wafer probing. During the measurements, RF and LO signals of the mixer are provided by a vector network analyzer (Agilent N5245A) and a signal generator (Agilent E8257D), respectively, and the output spectrum is observed by a spectrum analyzer (Agilent N9030A). The complete circuit including the TIA buffers, draws 7 mA of dc current from a 1 V supply in both SHM and FM modes.

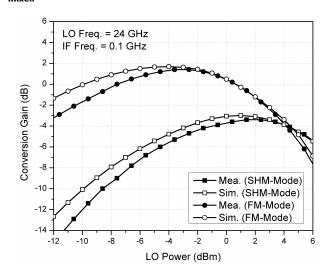

Fig. 7 shows the simulated and measured CG of the mixer in both SHM and FM modes versus the LO power. In the measurement, the LO frequency is 24 GHz and the IF frequency is 0.1 GHz. The corresponding RF frequencies are 48.1 GHz and 24.1 GHz for the SHM and FM modes, respectively. As shown in Fig. 7, the mixer in the SHM mode achieves a maximum CG of -3.3 dB at the LO power of 2 dBm, while the mixer in the FM mode achieves a maximum CG of 1.4 dB at the LO power of -3 dBm. When the LO power further increases, the measured CG of the mixer in both modes drops faster than that in Fig. 3 and Fig. 5. This is because a higher LO power reduces the dc voltage at the input port of the TIA, which drives the TIA into a low-gain operation [11]. This effect was not considered in the simulations in Section II, because the TIA buffers are removed in Fig.1(b) and (c) for fair comparison with the

FIGURE 6. Micrograph of the proposed reconfigurable dual-band CMOS

FIGURE 7. Simulated and measured CG versus the LO power for both SHM and FM modes.

passive mixers. In the following measurements, an LO power of -3 dBm is used for low LO drive.

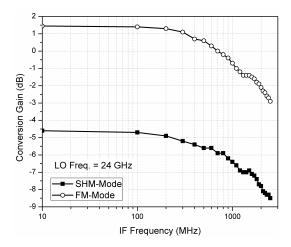

Fig. 8 shows the measured CG versus the IF frequency from 10 MHz to 2.5 GHz with an LO frequency of 24 GHz for both SHM and FM modes. The proposed mixer demonstrates a 3-dB IF bandwidth of 1.7 GHz for both modes.

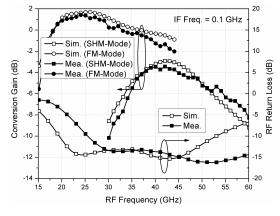

Fig. 9 shows the simulated and measured CG of the mixer in both modes versus the RF frequency with a fixed IF frequency of 0.1 GHz. The measured CG of the mixer is  $-4.8 \pm 1.5$  dB from 34 to 56 GHz and  $-0.1 \pm 1.5$  dB from 17 to 43 GHz for the SHM and FM modes, respectively. The measured RF return loss of the mixer is better than 10 dB from 20 to 60 GHz, which agrees well with the simulated result.

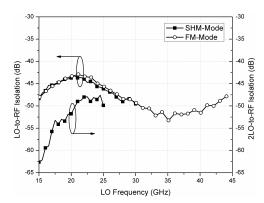

The measured LO-to-RF isolation of the mixer for both modes is better than 43 dB and the measured 2LO-to-RF isolation of the mixer in the SHM mode is better than 47 dB, as shown in Fig. 10. In the measurement of the 2LO-to-RF

TABLE 1. Comparisons of subharmonic mixers in various topologies and technologies.

| Ref.      | RF<br>Freq<br>(GHz) | CG (dB)     | DSB<br>NF<br>(dB) | LO<br>Power<br>(dBm) | V <sub>CC</sub> (V)<br>& dc<br>Power<br>(mW) | LO-to-RF<br>Isolation<br>(dB) | 2LO-to-RF<br>Isolation<br>(dB) | IIP3<br>(dBm) | Chip<br>Area<br>(mm²) | SHM Topology                      | Tech.                               |

|-----------|---------------------|-------------|-------------------|----------------------|----------------------------------------------|-------------------------------|--------------------------------|---------------|-----------------------|-----------------------------------|-------------------------------------|

| [17]      | 10-40               | -16.6 ± 1   | n/a               | 8                    | 0 & 0                                        | > 12                          | > 51                           | n/a           | 0.74                  | APDP                              | 0.18-μm<br>CMOS                     |

| [20]      | 28-50               | -10.3 ± 0.7 | n/a               | 7                    | 0 & 0                                        | > 37                          | > 33                           | 16            | 0.61                  | FET resistive                     | 0.13- <i>μ</i> m<br>CMOS            |

| [14]      | 9-31                | -9 ± 1      | n/a               | 9.7                  | 0 & 0                                        | > 18                          | > 28                           | 3             | 0.9                   | Transconductance<br>Source-pumped | 90-nm<br>CMOS                       |

| [22]      | 21-40               | -11.2 ± 3   | n/a               | 10.5                 | 1.3 &<br>74.6                                | > 50                          | > 47                           | n/a           | 0.97                  | Transconductance<br>Gate-pumped   | 0.18-μm<br>CMOS                     |

| [12]      | 1-2                 | 18.2 ± 1    | 7                 | 10                   | 3.3 & 9.2                                    | > 30                          | > 67                           | -7.5          | n/a                   | Gilbert<br>Stacked-LO             | Si/SiGe<br>HBT                      |

| [24]      | 5.2                 | 14.5        | 24                | -8                   | 3.3 &<br>13.2                                | > 50                          | > 75                           | -5            | 1.5                   | Gilbert<br>Stacked-LO             | 2- <i>µ</i> m<br>GaInP/Ga<br>As HBT |

| [24]      | 10                  | 0           | 24                | 12                   | 3.3 & 2.6                                    | > 23                          | > 32                           | 5             | 1                     | Gilbert<br>Bottom-LO              | 2-µm<br>GaInP/Ga<br>As HBT          |

| [24]      | 10                  | 13          | 22                | 12                   | 3.3 & 6.6                                    | > 32                          | > 59                           | -7.5          | 1                     | Gilbert<br>Top-LO                 | 2-µm<br>GaInP/Ga<br>As HBT          |

| [29]      | 35-65               | -7.5 ± 1.5  | 14.5              | 5                    | 3.3 &<br>45.4                                | > 45                          | > 50                           | 6             | 1*                    | Gilbert<br>Top-LO                 | 90-nm<br>CMOS                       |

| [30]      | 30-100              | -1.5 ± 1.5  | n/a               | 10                   | n/a & 58                                     | > 47                          | > 47                           | n/a           | 0.35                  | Gilbert<br>Top-LO                 | 90-nm<br>CMOS                       |

| This work | 34-56               | -4.8 ± 1.5  | 18.5              | -3                   | 1 & 7                                        | > 43                          | > 47                           | 2.9           | 0.5                   | Modified Gilbert<br>Stacked-LO    | 65-nm<br>CMOS                       |

<sup>\*</sup>Demodulator area

**FIGURE 8.** Measured CG versus the IF frequency for both SHM and FM modes.

isolation, the LO frequency is only swept from 15 to 25 GHz, therefore the output  $2\times LO$  frequency range is only from 30 to 50 GHz, which is limited by the maximum frequency of the spectrum analyzer (Agilent N9030A).

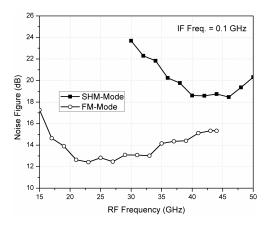

For double-sideband (DSB) NF measurements, the RF source is replaced by a noise source (Keysight 346CK01). Fig. 11 shows the measured DSB NF of the proposed mixer

**FIGURE 9.** Simulated and measured CG and RF port return loss versus the RF frequency for both SHM and FM modes.

for both modes after calibration. The lowest DSB NF is 18.5 and 12.4 dB for the SHM and FM modes, respectively.

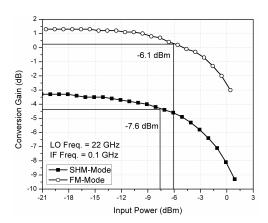

For large signal measurements, the RF source is replaced by a vector signal generator (Agilent E8267D), which can provide a higher output power and two-tone signals up to 44 GHz. Fig. 12 shows the measured CG versus the RF input power, where the LO frequency is 22 GHz and the IF frequency is 0.1 GHz. The input 1 dB power compression point (IP<sub>1dB</sub>) of the mixer is -7.6 dBm and -6.1 dBm for

| Ref.      | RF Freq<br>(GHz) | CG (dB)    | DSB<br>NF<br>(dB) | LO<br>Power<br>(dBm) | V <sub>CC</sub> (V) & dc Power (mW) | LO-to-RF<br>Isolation<br>(dB) | IP <sub>1dB</sub> (dBm) | IIP3 (dBm) | Chip<br>Area<br>(mm²) | FM Topology             | Tech.           |

|-----------|------------------|------------|-------------------|----------------------|-------------------------------------|-------------------------------|-------------------------|------------|-----------------------|-------------------------|-----------------|

| [36]      | 20-75            | 3 ± 2      | n/a               | 6                    | 3 & 93                              | > 30                          | 2.1                     | 11         | 0.3                   | Conventional<br>Gilbert | 90-nm<br>CMOS   |

| [37]      | 40-50            | $10 \pm 2$ | n/a               | 15                   | 0 & 0                               | > 49                          | 4.5                     | 15.5       | 0.83                  | Resistive Ring          | 45-nm SOI       |

| [38]      | 30-90            | -7.7 ± 1.5 | n/a               | 2.5                  | 1 & 0.6                             | > 30.2                        | 3                       | n/a        | 0.39                  | Drain/Gate<br>Pumped    | 90-nm<br>CMOS   |

| [39]      | 53-70            | 5.9 ± 1.5  | 13                | -6                   | 1.2 & 3                             | > 37                          | -16.6                   | -4         | 0.3                   | Source<br>Pumped        | 90-nm<br>CMOS   |

| [10]      | 31-96            | -3 ± 1.5   | n/a               | 0                    | 1.2 & 7.2                           | > 48                          | -4.7                    | n/a        | 0.5**                 | Modified<br>Gilbert     | 0.13-μm<br>CMOS |

| [11]      | 20-50            | 0 ± 2      | 13                | 0                    | 1.2 & 6                             | > 46                          | -1                      | 9.5        | 0.49                  | Modified<br>Gilbert     | 90-nm<br>CMOS   |

| This work | 17-43            | -0.1 ± 1.5 | 12.4              | < -6*                | 1 & 7                               | > 43                          | -7.6                    | 3.4        | 0.5                   | Modified<br>Gilbert     | 65-nm<br>CMOS   |

TABLE 2. Comparisons of fundamental mixers in various topologies and technologies.

<sup>\*</sup>The input LO power is -3 dBm, but half of the LO power (i.e. the power of LOQ) is wasted on the off-state transistors  $M_5$ - $M_8$ : \*Demodulator area.

FIGURE 10. Measured isolations for both SHM and FM modes.

FIGURE 11. Measured DSB NF for both SHM and FM modes.

the SHM and FM modes, respectively. The measured IIP3 of the proposed mixer in the SHM mode is 2.9 dBm for RF two-tone of 43.895 GHz and 43.905 GHz, and the measured IIP3 of the mixer in the FM mode is 3.4 dBm for RF two-tone of 22.095 GHz and 22.105 GHz, as shown in Fig. 13.

Table 1 compares the proposed mixer in SHM mode with some other previously published SHMs in various topologies

FIGURE 12. Measured CG versus the RF input power for both SHM and FM modes.

FIGURE 13. Measured IIP3 for both SHM and FM modes.

and technologies. The proposed CMOS mixer in the SHM mode achieves good CG, NF and linearity performance under low supply voltage, low dc power and low LO pumping power, at the expense of larger chip area due to the passive baluns and the quadrature coupler.

Table 2 compares the proposed mixer in FM mode with some other previously published FMs in various topologies and technologies [36]–[39]. The proposed CMOS mixer in the FM mode shows comparable performance with other modified Gilbert mixers, even though half of the LO power is wasted.

#### **IV. CONCLUSION**

In this paper, a reconfigurable low-voltage and low-power mmW dual-band CMOS mixer is proposed, studied and demonstrated. By changing its bias, the mixer can be reconfigured for operation between subharmonic and fundamental modes for dual-band applications. Based on a modified Gilbert mixer topology, the proposed CMOS mixer can operate at 1 V supply voltage and -3 dBm LO power while providing CG of  $-4.8 \pm 1.5$  dB from 34 to 56 GHz in the SHM mode and CG of  $-0.1 \pm 1.5$  dB from 17 to 43 in the FM mode. The measured IIP3 of the CMOS mixer is 2.9 dBm and 3.4 dBm for the SHM and FM modes, respectively, at LO frequency of 22 GHz. The total dc power consumption of the mixer is 7 mW for both states, including the output IF buffers. This circuit could be attractive in a mmW dual-band portable system where low-voltage and low-power are required.

#### **ACKNOWLEDGMENT**

The authors would like to thank CMC Microsystems, Kinston, ON, Canada, for their technical support, design tools, and chip fabrication. The authors also acknowledge and thank J. Gauthier, T. Antonescu, and D. Dousset, all with the Poly-Grames Research Center, for their help in measurements.

#### **REFERENCES**

- [1] B. Bakkaloglu, P. Fontaine, A. N. Mohieldin, S. Peng, S. J. Fang, and F. Dul, "A 1.5-V multi-mode quad-band RF receiver for GSM/EDGE/CDMA2K in 90-nm digital CMOS process," *IEEE J. Solid-State Circuits*, vol. 41, no. 5, pp. 1149–1159, May 2006.

- [2] V. Jain, F. Tzeng, L. Zhou, and P. Heydari, "A single-chip dual-band 22–29-GHz/77–81-GHz BiCMOS transceiver for automotive radars," *IEEE J. Solid-State Circuits*, vol. 44, no. 12, pp. 3469–3485, Dec. 2009.

- [3] W. Zhang, A. Hasan, F. M. Ghannouchi, M. Helaoui, Y. Wu, and Y. Liu, "Concurrent dual-band receiver based on novel six-port correlator for wireless applications," *IEEE Access*, vol. 5, pp. 25826–25834, 2017.

- [4] Y.-S. Hwang, S.-S. Yoo, and H.-J. Yoo, "A 2 GHz and 5GHz dual-band direct conversion RF frontend for multi-standard applications," in *Proc. IEEE Int. SOC Conf.*, Sep. 2005, pp. 189–192.

- [5] T. A. Abdelrheem, H. Y. Elhak, and K. M. Sharaf, "A concurrent dual-band mixer for 900-MHz/1.8 GHz RF front-ends," in *Proc. 46th Midwest Symp. Circuits Syst.*, vol. 3, Dec. 2003, pp. 1291–1294.

- [6] P. de Paco, R. Villarino, G. Junkin, O. Menendez, and E. Corrale, "Dual-band mixer using composite right/left-handed transmission lines," *IEEE Microw. Wireless Compon. Lett.*, vol. 17, no. 8, pp. 607–609, Aug. 2007.

- [7] B. R. Jackson and C. E. Saavedra, "A dual-band self-oscillating mixer for C-band and X-band applications," *IEEE Trans. Microw. Theory Techn.*, vol. 58, no. 2, pp. 318–323, Feb. 2010.

- [8] M. El-Nozahi, A. Amer, E. Sánchez-Sinencio, and K. Entesari, "A millimeter-wave (24/31-GHz) dual-band switchable harmonic receiver in 0.18-μm SiGe process," *IEEE Trans. Microw. Theory Techn.*, vol. 58, no. 11, pp. 2717–2730, Nov. 2010.

- [9] A. Mazzanti, M. B. Vahidfar, M. Sosio, and F. Svelto, "A low phase-noise multi-phase LO generator for wideband demodulators based on reconfigurable sub-harmonic mixers," *IEEE J. Solid-State Circuits*, vol. 45, no. 10, pp. 2104–2115, Oct. 2010.

- [10] J.-H. Tsai, "Design of 1.2-V broadband high data-rate MMW CMOS I/Q modulator and demodulator using modified Gilbert-cell mixer," *IEEE Trans. Microw. Theory Techn.*, vol. 59, no. 5, pp. 1350–1360, May 2011.

- [11] F. Zhu et al., "A broadband low-power millimeter-wave CMOS downconversion mixer with improved linearity," *IEEE Trans. Circuits Syst. II, Exp. Briefs*, vol. 61, no. 3, pp. 138–142, Mar. 2014.

- [12] L. Sheng, J. C. Jensen, and L. E. Larson, "A wide-bandwidth Si/SiGe HBT direct conversion sub-harmonic mixer/downconverter," *IEEE J. Solid-State Circuits*, vol. 35, no. 9, pp. 1329–1337, Sep. 2000.

- [13] R. C. Frye, S. Kapur, and R. C. Melville, "A 2-GHz quadrature hybrid implemented in CMOS technology," *IEEE J. Solid-State Circuits*, vol. 38, no. 3, pp. 550–555, Mar. 2003.

- [14] M. Bao, H. Jacobsson, L. Aspemyr, G. Carchon, and X. Sun, "A 9–31-GHz subharmonic passive mixer in 90-nm CMOS technology," *IEEE J. Solid-State Circuits*, vol. 41, no. 10, pp. 2257–2264, Oct. 2006.

- [15] C.-H. Lin, Y.-A. Lai, J.-C. Chiu, and Y.-H. Wang, "A 23–37 GHz miniature MMIC subharmonic mixer," *IEEE Microw. Wireless Compon. Lett.*, vol. 17, no. 9, pp. 679–681, Sep. 2007.

- [16] H.-K. Chiou, W.-R. Lian, and T.-Y. Yang, "A miniature Q-band balanced sub-harmonically pumped image rejection mixer," *IEEE Microw. Wireless Compon. Lett.*, vol. 17, no. 6, pp. 463–465, Jun. 2007.

- [17] C.-M. Lin, H.-K. Lin, Y.-A. Lai, C.-P. Chang, and Y.-H. Wang, "A 10–40 GHz broadband subharmonic monolithic mixer in 0.18μm CMOS technology," *IEEE Microw. Wireless Compon. Lett.*, vol. 19, no. 2, pp. 95–97, Feb. 2009.

- [18] M.-F. Lei, P.-S. Wu, T.-W. Huang, and H. Wang, "Design and analysis of a miniature W-band MMIC subharmonically pumped resistive mixer," in *IEEE MTT-S Int. Microw. Symp. Dig.*, Jun. 2004, pp. 235–238.

- [19] H.-J. Wei, C. Meng, P.-Y. Wu, and K.-C. Tsung, "K-band CMOS sub-harmonic resistive mixer with a miniature Marchand balun on lossy silicon substrate," *IEEE Microw. Wireless Compon. Lett.*, vol. 18, no. 1, pp. 40–42, Jan. 2008.

- [20] H.-K. Chiou and J.-Y. Lin, "Symmetric offset stack balun in standard 0.13-μm CMOS technology for three broadband and low-loss balanced passive mixer designs," *IEEE Trans. Microw. Theory Techn.*, vol. 59, no. 6, pp. 1529–1538, Jun. 2011.

- [21] J.-J. Hung, T. M. Hancock, and G. M. Rebeiz, "A 77 GHz SiGe sub-harmonic balanced mixer," *IEEE J. Solid-State Circuits*, vol. 40, no. 11, pp. 2167–2173, Nov. 2005.

- [22] S.-H. Hung, Y.-C. Lee, C.-C. Su, and Y.-H. Wang, "High-isolation millimeter-wave subharmonic monolithic mixer with modified quasicirculator," *IEEE Trans. Microw. Theory Techn.*, vol. 61, no. 3, pp. 1140–1149, Mar. 2013.

- [23] Y. Yan, M. Bao, S. E. Gunnarsson, V. Vassilev, and H. Zirath, "A 110–170-GHz multi-mode transconductance mixer in 250-nm InP DHBT technology," *IEEE Trans. Microw. Theory Techn.*, vol. 63, no. 9, pp. 2897–2904, Sep. 2015.

- [24] T.-H. Wu, S.-C. Tseng, C.-C. Meng, and G.-W. Huang, "GaInP/GaAs HBT sub-harmonic Gilbert mixers using stacked-LO and leveled-LO topologies," *IEEE Trans. Microw. Theory Techn.*, vol. 55, no. 5, pp. 880–889, May 2007.

- [25] K. Schmalz, W. Winkler, J. Borngraber, W. Debski, B. Heinemann, and J. C. Scheytt, "A subharmonic receiver in SiGe Technology for 122 GHz sensor applications," *IEEE J. Solid-State Circuits*, vol. 45, no. 9, pp. 1644–1656, Sep. 2010.

- [26] Y. Zhao, E. Ojefors, K. Aufinger, T. F. Meister, and U. R. Pfeiffer, "A 160-GHz subharmonic transmitter and receiver chipset in an SiGe HBT technology," *IEEE Trans. Microw. Theory Techn.*, vol. 60, no. 10, pp. 3286–3299, Oct. 2012.

- [27] E. Öjefors, B. Heinemann, and U. R. Pfeiffer, "Subharmonic 220- and 320-GHz SiGe HBT receiver front-ends," *IEEE Trans. Microw. Theory Techn.*, vol. 60, no. 5, pp. 1397–1404, May 2012.

- [28] M. Goldfarb, E. Balboni, and J. Cavey, "Even harmonic double-balanced active mixer for use in direct conversion receivers," *IEEE J. Solid-State Circuits*, vol. 38, no. 10, pp. 1762–1766, Oct. 2003.

- [29] J.-H. Tsai and T.-W. Huang, "35–65-GHz CMOS broadband modulator and demodulator with sub-harmonic pumping for MMW wireless gigabit applications," *IEEE Trans. Microw. Theory Techn.*, vol. 55, no. 10, pp. 2075–2085, Oct. 2007.

- [30] J.-H. Tsai, H.-Y. Yang, T.-W. Huang, and H. Wang, "A 30–100 GHz wideband sub-harmonic active mixer in 90 nm CMOS technology," *IEEE Microw. Wireless Compon. Lett.*, vol. 18, no. 8, pp. 554–556, Aug. 2008.

- [31] V. H. Le et al., "A CMOS 77-GHz receiver front-end for automotive radar," IEEE Trans. Microw. Theory Techn., vol. 61, no. 10, pp. 3783–3793, Oct. 2013

- [32] Z. Zhang, Z. Chen, L. Tsui, and J. Lau, "A 930 MHz CMOS DC-offset-free direct-conversion 4-FSK receiver," in *IEEE ISSCC Dig. Tech. Papers*, San Francisco, CA, USA, Feb. 2011, pp. 290–291.

- [33] H. C. Jen, S. C. Rose, and R. G. Meyer, "A 2.2 GHz sub-harmonic mixer for directconversion receivers in 0.13μm CMOS," in *IEEE ISSCC Dig. Tech. Papers*, San Francisco, CA, USA, Feb. 2006, pp. 1840–1849.

- [34] R. M. Kodkani and L. E. Larson, "A 24-GHz CMOS passive subharmonic mixer/downconverter for zero-IF applications," *IEEE Trans. Microw. The*ory Techn., vol. 56, no. 5, pp. 1247–1256, May 2008.

- [35] B. Gilbert, "The MICROMIXER: A highly linear variant of the Gilbert mixer using a bisymmetric class-AB input stage," *IEEE J. Solid-State Circuits*, vol. 32, no. 9, pp. 1412–1423, Sep. 1997.

- [36] J.-H. Tsai, P.-S. Wu, C.-S. Lin, T.-W. Huang, J. G. J. Chern, and W.-C. Huang, "A 25–75 GHz broadband Gilbert-cell mixer using 90-nm CMOS technology," *IEEE Microw. Wireless Compon. Lett.*, vol. 17, no. 4, pp. 247–249, Apr. 2007.

- [37] M. Parlak and J. F. Buckwalter, "A passive I/Q millimeter-wave mixer and switch in 45-nm CMOS SOI," *IEEE Trans. Microw. Theory Techn.*, vol. 61, no. 3, pp. 1131–1139, Mar. 2013.

- [38] Y.-C. Wu, C.-C. Chiong, J.-H. Tsai, and H. Wang, "A novel 30–90-GHz singly balanced mixer with broadband LO/IF," *IEEE Trans. Microw. The*ory Techn., vol. 64, no. 12, pp. 4611–4623, Dec. 2016.

- [39] W.-T. Li, H.-Y. Yang, Y.-C. Chiang, J.-H. Tsai, M.-H. Wu, and T.-W. Huang, "A 453-µW 53-70-GHz ultra-low-power double-balanced source-driven mixer using 90-nm CMOS technology," *IEEE Trans. Microw. Theory Techn.*, vol. 61, no. 5, pp. 1903–1912, May 2013.

**FANG ZHU** received the B.S. degree in electronics and information engineering from Hangzhou Dianzi University, Hangzhou, China, in 2009, and the M.S. and Ph.D. degrees in electromagnetic field and microwave technique from Southeast University, Nanjing, China, in 2011 and 2014, respectively.

From 2014 to 2016, he was a MMIC Designer with Nanjing Milliway Microelectronics Technology, Co., Ltd., Nanjing. He is currently a

Post-Doctoral Research Fellow with the Poly-Grames Research Center, École Polytechnique de Montréal, Montreal, QC, Canada. His current research interests include CMOS and GaAs monolithic microwave integrated circuits (MMICs), microwave and millimeter-wave components and transceiver systems, and their applications in communication, sensing, and tracking.

**KUANGDA WANG** (S'12–M'18) received the B.S. degree in mathematics and the M.E. degree in EM field and microwave technique from Southeast University, Nanjing, China, in 2009 and 2012, respectively, and the Ph.D. degree in electrical engineering from the École Polytechnique de Montréal, Montreal, QC, Canada, in 2018.

From 2017 to 2018, he was with the Antenna/OTA Design, Apple, Inc., Cupertino, CA, USA. Since 2019, he has been a Postdoctoral

Research Fellow with the Poly-Grames Research Center, École Polytechnique de Montréal. He is the inventor/co-inventor of five PCT or US patents. His current research interest includes the millimeter-wave components and systems for positioning and sensing in industrial and medical applications.

**KE WU** (M'87–SM'92–F'01) received the B.Sc. degree (Hons.) in radio engineering from the Nanjing Institute of Technology (Southeast University), China, in 1982, the D.E.A. degree (Hons.) in optics, optoelectronics, and microwave engineering from the Institut National Polytechnique de Grenoble (INPG), in 1984, and the Ph.D. degree (Hons.) in optics, optoelectronics, and microwave engineering from the University of Grenoble, France, in 1987.

He was the Founding Director of the Center for Radiofrequency Electronics Research of Quebec (Regroupement stratégique of FRQNT) and the Tier-I Canada Research Chair of RF and Millimeter-Wave Engineering. He is currently a Professor of electrical engineering and the NSERC-Huawei Industrial Research Chair of Future Wireless Technologies with Polytechnique Montréal (University of Montreal), QC, Canada. He has been the Director of the Poly-Grames Research Center. He is also with the School of Information Science and Engineering, Ningbo University, on leave from his home institution, leading a special 5G and future wireless research program there. He has held guest, visiting, and honorary professorships with many universities around the world. He has authored or co-authored over 1200 referred papers and a number of books/book chapters. He has filed more than 50 patents. His current research interests include substrate integrated circuits and systems, antenna arrays, field theory and joint field/circuit modeling, ultra-fast interconnects, wireless power transmission and harvesting, and MHz-through-THz technologies and transceivers for wireless sensors and systems, as well as biomedical applications. He is also interested in the modeling and design of the microwave and terahertz photonic circuits and systems.

Dr. Wu is a Fellow of the Canadian Academy of Engineering (CAE) and the Royal Society of Canada (The Canadian Academy of the Sciences and Humanities). He is also a member of the Electromagnetics Academy, Sigma Xi, URSI, and IEEE-Eta Kappa Nu (IEEE-HKN). He is also the inaugural representative of North America as a member of the European Microwave Association (EuMA) General Assembly. He was a recipient of many awards and prizes, including the first IEEE MTT-S Outstanding Young Engineer Award, the 2004 Fessenden Medal of the IEEE Canada, the 2009 Thomas W. Eadie Medal of the Royal Society of Canada, the Queen Elizabeth II Diamond Jubilee Medal in 2013, the 2013 FCCP Education Foundation Award of Merit, the 2014 IEEE MTT-S Microwave Application Award, the 2014 Marie-Victorin Prize (Prix du Quebec-the highest distinction of Québec in the natural sciences and engineering), the 2015 Prix d'Excellence en Recherche et Innovation of Polytechnique Montréal, and the 2015 IEEE Montreal Section Gold Medal of Achievement. He has held key positions in and has served on various panels and international committees, including the Chair of the Technical Program Committees, the International Steering Committees, and the international conferences/symposia. In particular, he was the General Chair of the 2012 IEEE Microwave Theory and Techniques (IEEE MTT-S) International Microwave Symposium (IMS). He was the Chair of the joint IEEE Montreal chapters of MTT-S/AP-S/LEOS and then the restructured the IEEE MTT-S Montreal Chapter, Canada. He has served the IEEE MTT-S and Administrative Committee (AdCom) as the Chair of the IEEE MTT-S Transnational Committee, the Member and Geographic Activities (MGA) Committee, the Technical Coordinating Committee (TCC), and the 2016 IEEE MTT-S President, among many other AdCom functions. He has served on the editorial/review boards of several technical journals, transactions, proceedings, and letters, as well as scientific encyclopedia, including as the Editor and the Guest Editor. He was an IEEE MTT-S Distinguished Microwave Lecturer, from 2009 to 2011.

• • •