**Titre:** Synthétiseur de fréquences RF destiné aux dispositifs médicaux implantables

Title: implantables

**Auteur:** Louis-François Tanguay

Author:

**Date:** 2010

**Type:** Mémoire ou thèse / Dissertation or Thesis

**Référence:** Tanguay, L.-F. (2010). Synthétiseur de fréquences RF destiné aux dispositifs médicaux implantables [Thèse de doctorat, École Polytechnique de Montréal].

Citation: PolyPublie. <https://publications.polymtl.ca/431/>

## Document en libre accès dans PolyPublie

Open Access document in PolyPublie

**URL de PolyPublie:** <https://publications.polymtl.ca/431/>

PolyPublie URL:

**Directeurs de recherche:** Mohamad Sawan, & Yvon Savaria

Advisors:

**Programme:** génie électrique

Program:

UNIVERSITÉ DE MONTRÉAL

SYNTHÉTISEUR DE FRÉQUENCES RF DESTINÉ AUX DISPOSITIFS MÉDICAUX

IMPLANTABLES

LOUIS-FRANÇOIS TANGUAY

DÉPARTEMENT DE GÉNIE ÉLECTRIQUE

ÉCOLE POLYTECHNIQUE DE MONTRÉAL

THÈSE PRÉSENTÉE EN VUE DE L'OBTENTION

DU DIPLÔME DE PHILOSOPHIÆ DOCTOR

(GÉNIE ÉLECTRIQUE)

DÉCEMBRE 2010

UNIVERSITÉ DE MONTRÉAL

ÉCOLE POLYTECHNIQUE DE MONTRÉAL

Cette thèse intitulée:

SYNTHÉTISEUR DE FRÉQUENCES RF DESTINÉ AUX DISPOSITIFS MÉDICAUX

IMPLANTABLES

présentée par: TANGUAY Louis-François

en vue de l'obtention du diplôme de: Philosophiæ Doctor

a été dûment acceptée par le jury d'examen constitué de:

M. BRAULT Jean-Jules, Ph.D., président

M. SAWAN Mohamad, Ph.D., membre et directeur de recherche

M. SAVARIA Yvon, Ph.D., membre et codirecteur de recherche

M. BLAQUIÈRE Yves, Ph.D., membre

M. KOUKI Ammar, Ph.D., membre externe

## **REMERCIEMENTS**

Je voudrais tout d'abord remercier sincèrement mon directeur de recherche, le professeur Mohamad Sawan, chez qui la rigueur et l'exigence invitent les autres au dépassement. Je tiens à lui exprimer ma gratitude pour sa grande disponibilité, sa patience, ainsi que pour la générosité avec laquelle il a su partager ses connaissances et conseils.

Je remercie également mon codirecteur de recherche, le professeur Yvon Savaria, pour son aide, ses encouragements, ainsi que pour les nombreuses discussions techniques stimulantes qui ont agrémenté ces années de recherche doctorale. Je suis aussi profondément redevant envers les membres du jury qui ont généreusement accepté d'investir de leur précieux temps et expertise afin d'évaluer cette thèse.

Dans le cadre de ce doctorat, j'ai eu la chance de côtoyer et de travailler avec des étudiants motivés et brillants. Je tiens à remercier tous les étudiants du groupe de recherche Polystim, pour leur support et leur enthousiasme dans le laboratoire. Je tiens également à remercier chaleureusement Réjean Lepage, Laurent Mouden et Gaétan Décarie pour leur support technique, tant au niveau des outils informatiques que de l'assemblage des puces et circuits imprimés.

Je remercie également Marie-Yannick Laplante et Ghislaine Carrier pour leur aide inestimable au niveau administratif. Je suis aussi très reconnaissant envers le Fonds Québécois de la Recherche sur la Nature et les Technologies (FQRNT) ainsi que Micronet R&D, pour le support financier sans lequel cette thèse n'aurait jamais vu le jour.

Enfin, je remercie profondément Anne qui m'a offert tout son support et n'a cessé de m'encourager jusqu'à la toute fin de la rédaction de cette thèse. Je suis un individu excessivement privilégié d'avoir une personne aussi merveilleuse et généreuse à mes côtés.

## RÉSUMÉ

Les microsystèmes biomédicaux implantables présentent un énorme potentiel pour la recherche médicale. Les dispositifs médicaux intelligents implantables, qui combinent des capteurs et/ou des actuateurs avec des circuits intégrés, ouvrent la voie à des applications fascinantes. Aujourd’hui, la possibilité d’utiliser la technologie CMOS pour intégrer des circuits RF, numériques, et même certains types de capteurs sur une même puce, suscite un vif intérêt dans un domaine nouveau : celui des réseaux de capteurs implantables, ou BSN (Body-Sensor Networks) et leurs applications en recherche biomédicale. L’implantation dans le corps de tels réseaux de capteurs sans-fil permettrait de surveiller, détecter ou même combattre différentes maladies, et ce de manière *in situ*.

Avec des dimensions minimales inférieures à 100 nm, la technologie CMOS représente un choix viable pour l’implémentation des blocs de bases des circuits intégrés radio-fréquences (Radio-Frequency Integrated Circuits - RFIC) à faible consommation de puissance. Toutefois, la réduction de la tension d’alimentation permise dans les procédés CMOS nanométriques, l’impédance de sortie limitée des transistors disponibles, ainsi que les variations de procédés ont pour conséquence que plusieurs architectures de circuits analogiques n’offrent plus les performances requises ou ne sont tout simplement plus applicables. Des méthodes de conception innovatrices doivent être utilisées et des compromis judicieux doivent être faits afin de maintenir les performances requises.

Dans un système de communication sans-fil, l’oscillateur local (*Local Oscillator - LO*) est l’un des modules les plus importants puisqu’il sert à générer la porteuse du lien RF qui sera par la suite modulée pour transmettre les données. Dans un contexte où la consommation de puissance doit être strictement minimisée, la génération d’une fréquence porteuse RF stable dans un procédé CMOS nanométrique présente des défis énormes. Dans cette optique, cette thèse se concentre sur la conception, l’analyse, ainsi que sur l’implémentation de circuits analogiques et RF à basse tension faisant partie d’un synthétiseur de fréquences à consommation ultra faible utilisant un procédé CMOS nanométrique.

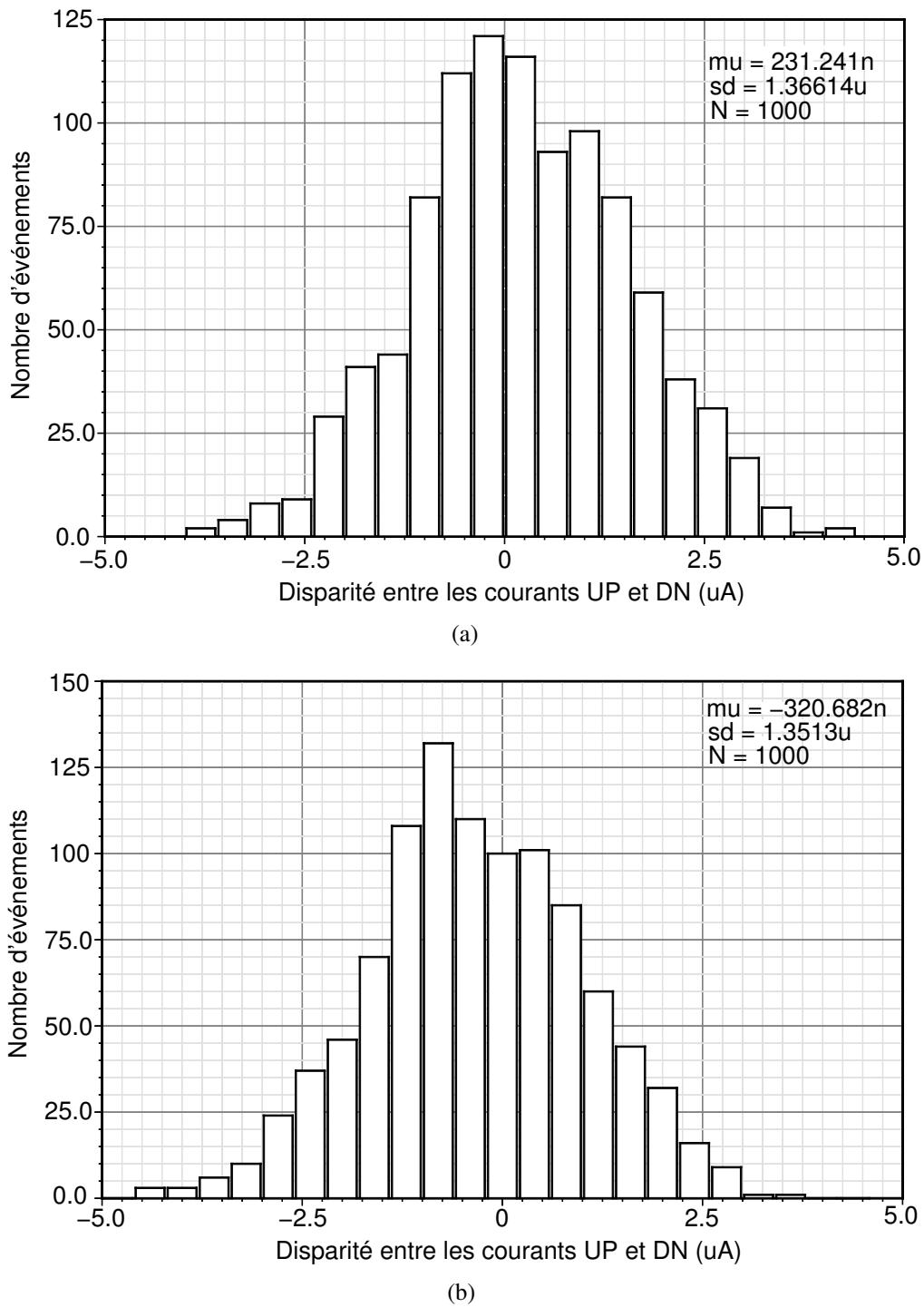

Tout d’abord, une nouvelle architecture de miroir de courant présentant une impédance de sortie très élevée destiné aux applications à faible tension d’alimentation est présentée. Ce miroir de courant de faible complexité présente une résistance de sortie très élevée et ce pour des tensions de sortie s’approchant des alimentations. Ensuite, une nouvelle architecture de pompe de charges CMOS destinée aux boucles à verrouillage de phase à faible tension et faible puissance est proposée afin de contourner les difficultés causées par la basse tension d’alimentation et la faible impédance de sortie des transistors nanométriques. La configuration de pompe de charges proposée résulte en un courant de sortie dont la magnitude est constante et le non-appariement entre les courants

$I_{UP}$  et  $I_{DOWN}$  est minimal, tout en minimisant la consommation de puissance et la complexité des circuits. Aussi, le niveau des impulsions de courant indésirables (*glitches*) lors de l'activation et la mise hors circuit des commutateurs est très faible dû au maintien de la tension aux grilles des transistors de sortie à une valeur pratiquement constante entre les différents états de la pompe de charges .

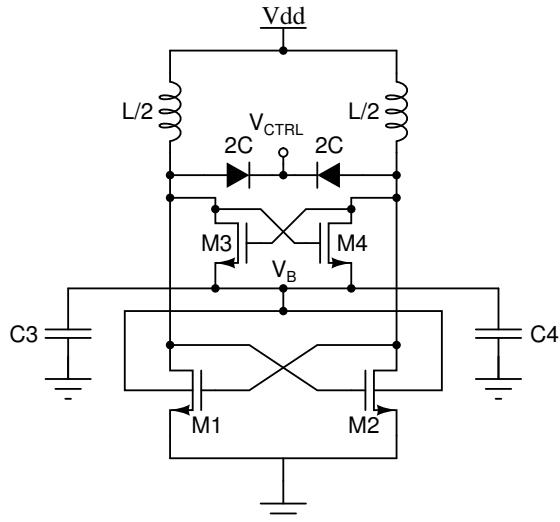

Un nouvel oscillateur contrôlé par tension avec résonateur LC (LC-VCO) minimisant l'impact des variations de procédé sur la consommation de puissance et le bruit de phase est ensuite étudié. L'architecture proposée permet d'assurer le démarrage du VCO, de diminuer la variabilité du bruit de phase et de minimiser la consommation de puissance, et ce peu importe le coin du procédé. L'approche utilisée consiste à alimenter le cœur du VCO à l'aide d'un régulateur de tension dont la valeur de la référence dépend des paramètres du procédé à l'endroit sur la puce où est situé le VCO. La conception et le processus d'optimisation de l'inductance utilisée dans le résonateur du LC-VCO sont également présentés.

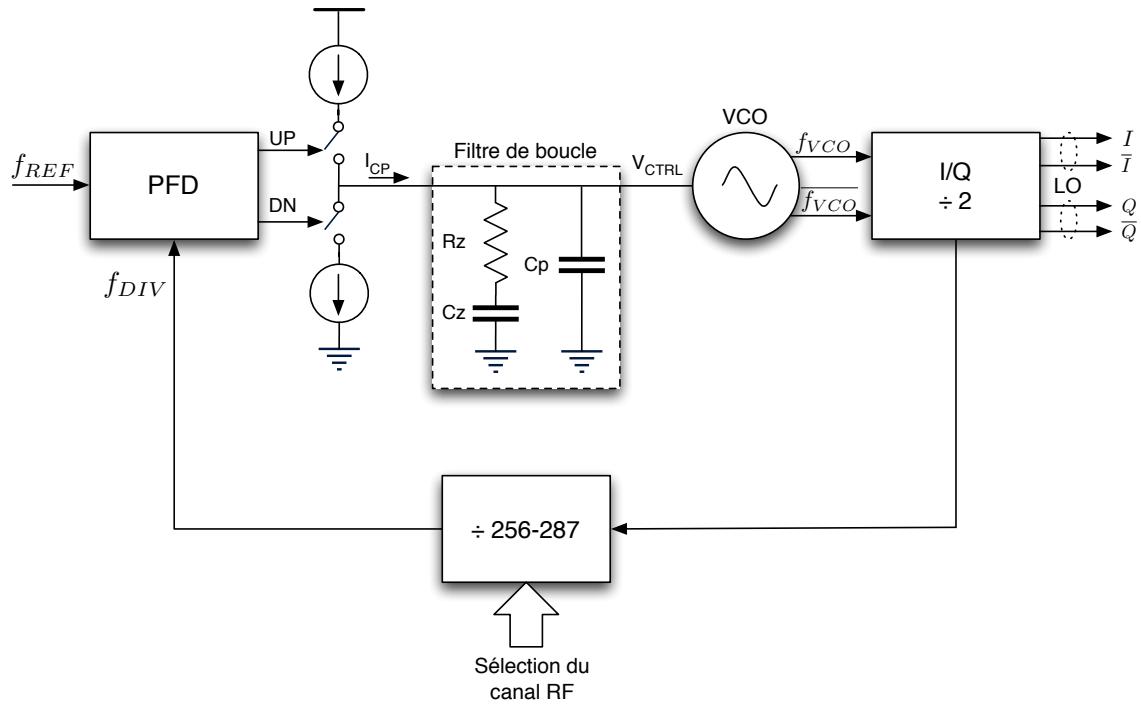

Un diviseur de fréquence programmable numérique à consommation ultra-faible a été conçu afin d'implémenter un synthétiseur de fréquences à diviseur entier N. Les bascules-D et les bistables de ce diviseur ont été soigneusement conçues de façon à minimiser leur consommation de puissance. Le synthétiseur résultant a été fabriqué en technologie CMOS 90-nm et opère dans la bande Industrielle, Scientifique et Médicale (ISM) de 902-928 MHz. Ce synthétiseur, basé sur une PLL, permet la sélection de 7 canaux de 3.4 MHz de bande passante dans la bande ISM et fournit les versions différentielles, I/Q des porteuses RF. La consommation totale mesurée du synthétiseur est de  $640 \mu\text{W}$ , soit environ un ordre de grandeur plus faible que celle des synthétiseurs d'architecture similaire récemment présentés dans la littérature.

## ABSTRACT

Implantable biomedical microsystems present a huge potential for medical research. The recent possibility to use CMOS technology to integrate radio-frequency (RF) circuits, baseband signal processing, and even sensors on a same chip has led to a tremendous growth of interest in wireless sensors and their applications. Such microsystems typically include a microprocessor and memory, an energy source, one or more sensors, an analog-to-digital converter (ADC), and a RF transceiver to communicate with a remote base-station or processing unit. In the biomedical field, it is expected that implanting such wireless sensing microsystems could greatly help the medical research community in learning about the progression of some diseases and assess degree of response to treatment.

With a minimum feature size that has reduced under 100 nm, CMOS technology has become a viable choice for the implementation of low-power radio-frequency integrated circuits (RFIC) building blocks. However, the reduction of the supply voltage combined with the low output impedance of nanometer transistors have caused many analog and RF circuit solutions to be unsuitable, or even unusable due to voltage headroom constraints. Therefore, new circuit techniques and innovative design approaches are needed in order to meet the required performance level while maintaining low power consumption.

In a wireless communications system, the local oscillator (LO) is one of the most important building blocks since it generates the RF carrier signal upon which data is modulated for transmission. In a context where power consumption must be strictly minimized, the generation of a stable RF carrier using a nanometer CMOS process presents huge challenges. In this regard, this thesis focuses on the design, the analysis and the implementation of low-voltage analog and RF circuits used to build an ultra-low power integer-N frequency synthesizer.

First, a new current mirror architecture dedicated to low-voltage, low-power applications is presented. The proposed current mirror offers a very high output resistance and an enhanced output voltage range in comparison with other current mirrors similar in architecture. Then, a novel charge pump dedicated to low-power low-voltage PLLs is proposed. The design of this circuit was motivated by the need of a nano-CMOS charge pump that would offer constant current magnitude and minimum current mismatch over a wide range of output voltage, while maintaining power consumption and complexity level as low as possible. A LC resonator-based voltage-controlled oscillator (LC-VCO) that implements a new technique to reduce the impact of process variation on phase noise and power consumption is presented. The LC-VCO uses a regulated supply voltage to set the bias current required for proper start-up of the oscillations. To mitigate the impact of process

variations, the output voltage of the regulator tracks process parameters at the location of the VCO on the die. In addition to ensuring proper start-up of the VCO, the proposed implementation has improved immunity to variations in phase noise and supply current under different process corners, and hence avoids worst-case design. The optimization process and design of the integrated inductor used in the LC-VCO are presented as well.

An ultra-low power digital programmable frequency divider was designed in order to implement an integer-N frequency synthesizer. The flip-flops and latches of this divider were carefully designed and layed out in order to minimize their power consumption. Fabricated in a 90-nm CMOS process from STMicroelectronics, the frequency synthesizer operates in the 902-928 MHz Industrial, Scientific and Medical (ISM) band. It allows the selection of 7 channels 3.4 MHz wide in the ISM band and provides the differential, I/Q versions of the RF carrier. The total measured power consumption of the frequency synthesizer is  $640 \mu\text{W}$ , about an order of magnitude lower than that of other synthesizers with a similar architecture recently presented in the litterature.

## TABLE DES MATIÈRES

|                                                                                            |           |

|--------------------------------------------------------------------------------------------|-----------|

| REMERCIEMENTS . . . . .                                                                    | iii       |

| RÉSUMÉ . . . . .                                                                           | iv        |

| ABSTRACT . . . . .                                                                         | vi        |

| TABLE DES MATIÈRES . . . . .                                                               | viii      |

| LISTE DES FIGURES . . . . .                                                                | xi        |

| LISTE DES ACRONYMES ET DES SYMBOLES . . . . .                                              | xiv       |

| LISTE DES TABLEAUX . . . . .                                                               | xvi       |

| LISTE DES ANNEXES . . . . .                                                                | xvii      |

| <br>                                                                                       |           |

| <b>CHAPITRE 1      INTRODUCTION . . . . .</b>                                              | <b>1</b>  |

| 1.1 Les microsystèmes implantables pour la recherche médicale . . . . .                    | 1         |

| 1.2 Liens RF à faible consommation de puissance pour les microsystèmes implantables        | 3         |

| 1.2.1 Communications sans fil aux fréquences UHF . . . . .                                 | 3         |

| 1.2.2 Génération des fréquences porteuses RF . . . . .                                     | 4         |

| 1.2.3 Transmetteurs/récepteurs existants . . . . .                                         | 6         |

| 1.3 Procédés CMOS nanométriques : opportunités et défis . . . . .                          | 7         |

| 1.4 Objectifs de la recherche . . . . .                                                    | 8         |

| 1.5 Contributions originales découlant de cette thèse . . . . .                            | 9         |

| 1.6 Organisation de la thèse . . . . .                                                     | 10        |

| <br>                                                                                       |           |

| <b>CHAPITRE 2      SYNTHÈSE DE FRÉQUENCE : LA BOUCLE À VERROUILLAGE DE PHASE . . . . .</b> | <b>12</b> |

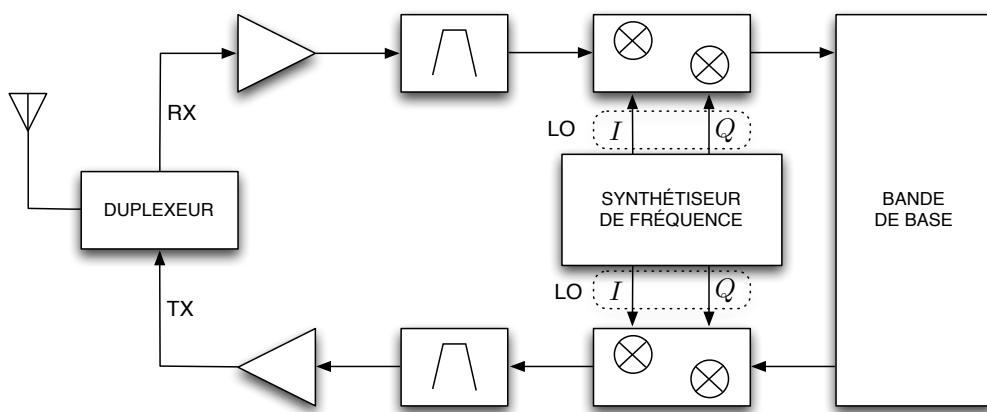

| 2.1 Rôle de l'oscillateur local (LO) dans un transmetteur/récepteur . . . . .              | 12        |

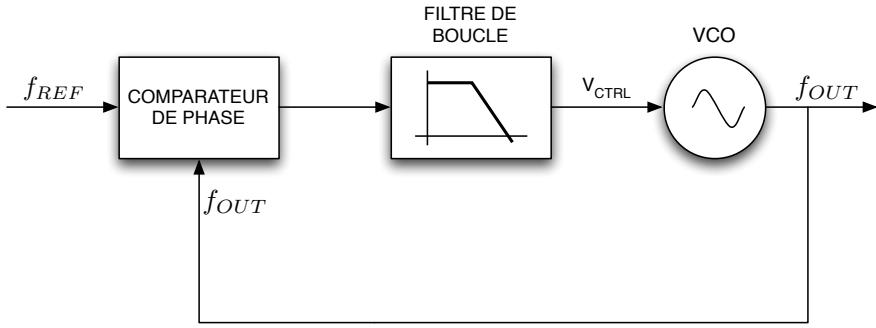

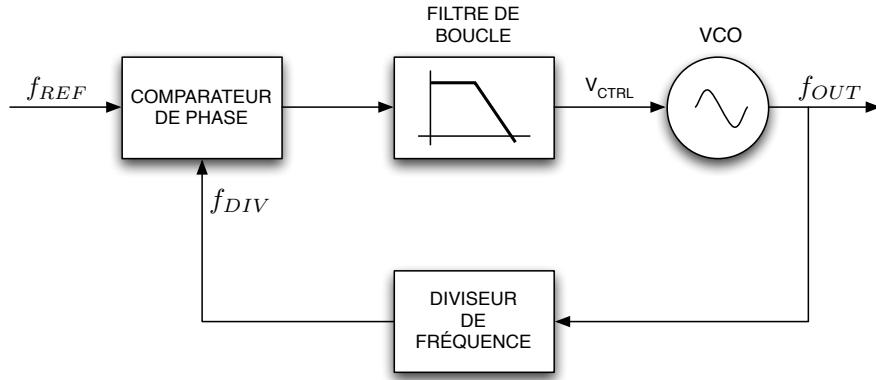

| 2.2 La boucle à verrouillage de phase pour la synthèse de fréquences . . . . .             | 13        |

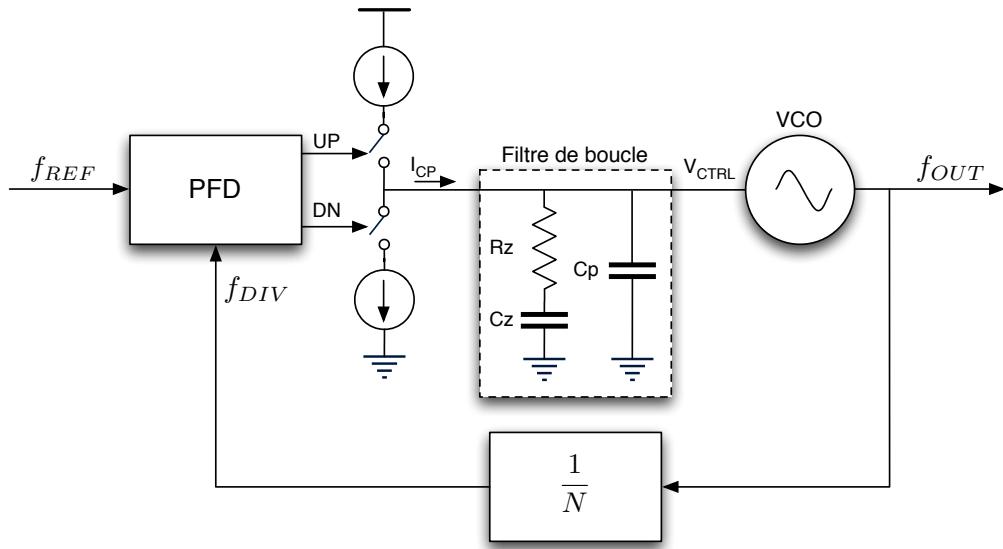

| 2.3 Synthétiseur de fréquences à pompe de charges . . . . .                                | 15        |

| 2.3.1 Oscillateur contrôlé par tension (VCO) . . . . .                                     | 16        |

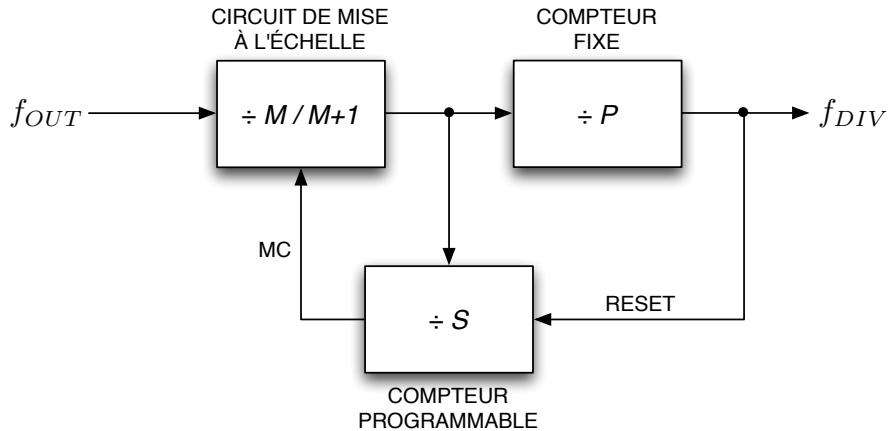

| 2.3.2 Diviseur de fréquence programmable . . . . .                                         | 17        |

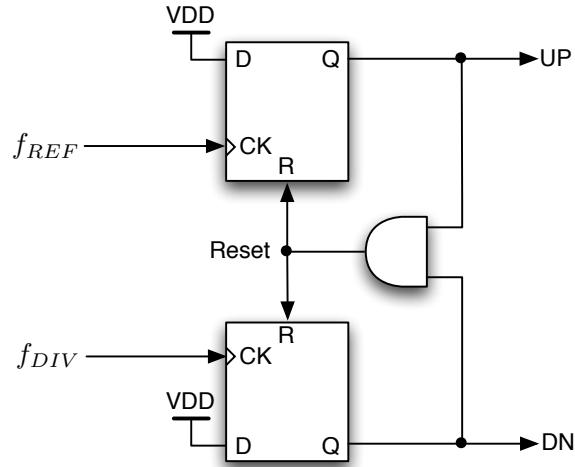

| 2.3.3 DéTECTEUR de phase/fréquence et pompe de charges . . . . .                           | 18        |

| 2.3.4 Filtre de boucle . . . . .                                                           | 20        |

|                                                                                                    |                                                                                        |           |

|----------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|-----------|

| 2.4                                                                                                | Modèle linéaire . . . . .                                                              | 21        |

| 2.4.1                                                                                              | Gain en boucle ouverte et marge de phase . . . . .                                     | 22        |

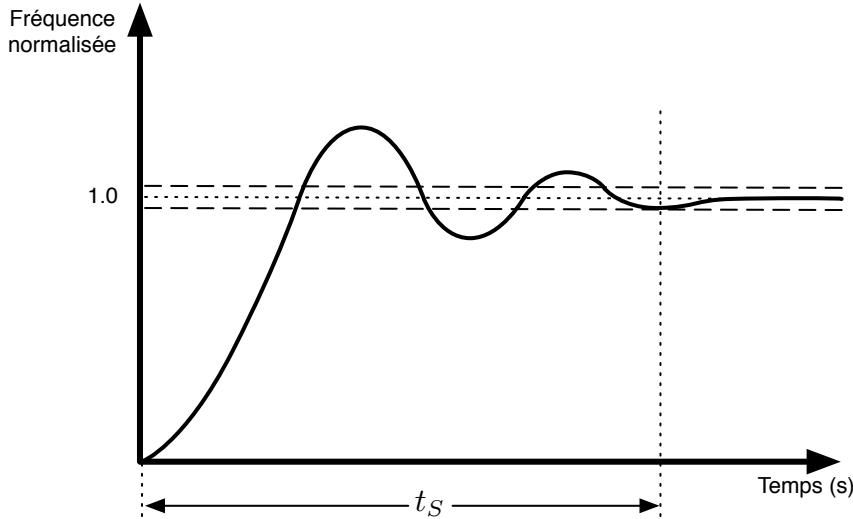

| 2.4.2                                                                                              | Temps de stabilisation et de démarrage . . . . .                                       | 24        |

| 2.5                                                                                                | Critères de performance des synthétiseurs . . . . .                                    | 25        |

| 2.5.1                                                                                              | Plage de syntonisation, résolution fréquentielle et précision . . . . .                | 25        |

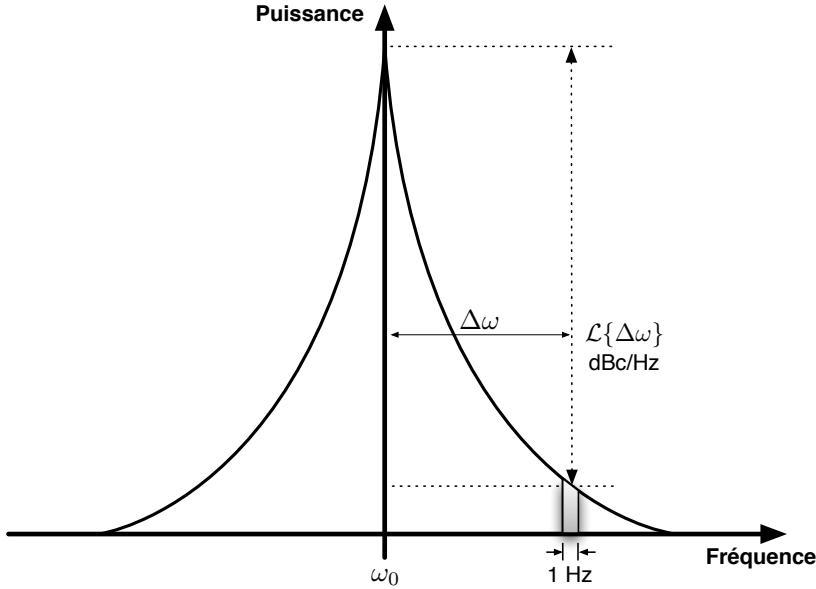

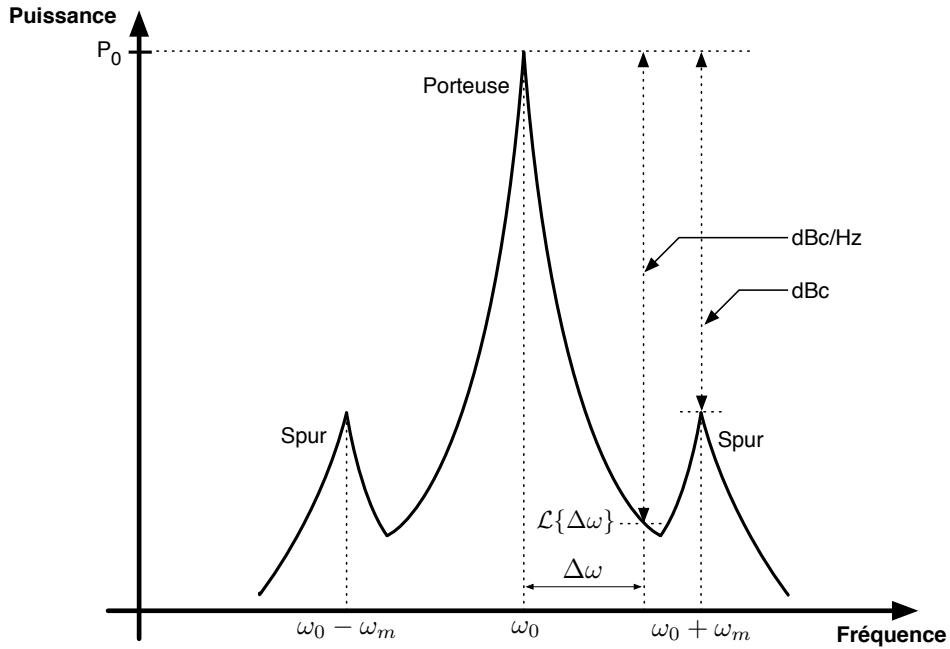

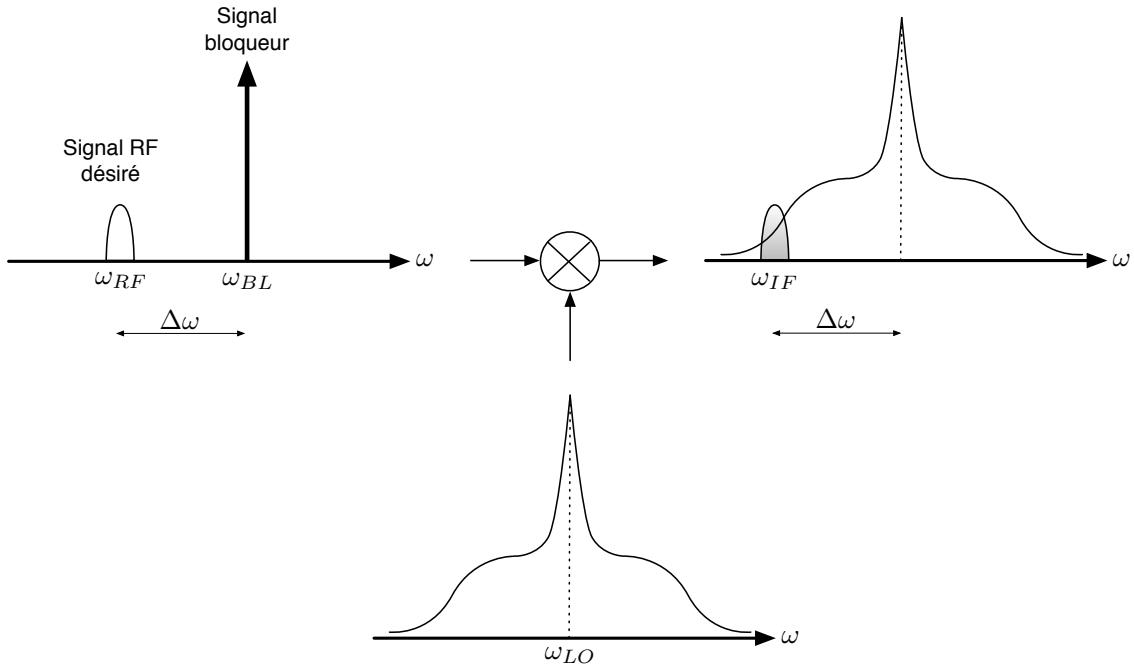

| 2.5.2                                                                                              | Bruit de phase et <i>spurs</i> . . . . .                                               | 26        |

| 2.6                                                                                                | Modèle mathématique du bruit de phase . . . . .                                        | 29        |

| 2.7                                                                                                | Survol des synthétiseurs récemment présentés dans la littérature . . . . .             | 30        |

| 2.8                                                                                                | Synthétiseur de fréquences proposé pour les microsystèmes implantables . . . . .       | 31        |

| 2.8.1                                                                                              | Spécifications du synthétiseur de fréquences . . . . .                                 | 32        |

| 2.8.2                                                                                              | Conception du synthétiseur de fréquences . . . . .                                     | 33        |

| <b>CHAPITRE 3 NOUVEAU MIROIR DE COURANT CMOS OPÉRANT À BASSE TENSION D'ALIMENTATION . . . . .</b>  |                                                                                        | <b>36</b> |

| 3.1                                                                                                | Miroirs de courant à haute impédance de sortie opérant à bas voltage . . . . .         | 37        |

| 3.2                                                                                                | Le degré de saturation d'un transistor . . . . .                                       | 39        |

| 3.2.1                                                                                              | Circuit de polarisation cascode . . . . .                                              | 40        |

| 3.3                                                                                                | Architecture et opération du miroir de courant proposé . . . . .                       | 41        |

| 3.3.1                                                                                              | Résistance de sortie incrémentale à basse fréquence . . . . .                          | 42        |

| 3.3.2                                                                                              | Plage dynamique de sortie . . . . .                                                    | 45        |

| 3.3.3                                                                                              | Choix du facteur d'échelle $K$ des sources de courant auxiliaires $I_{IN}/K$ . . . . . | 46        |

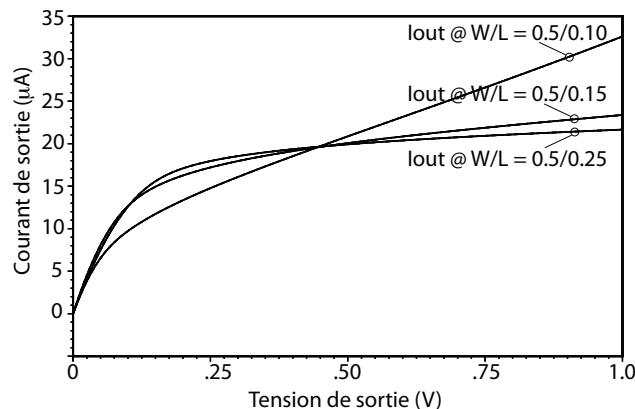

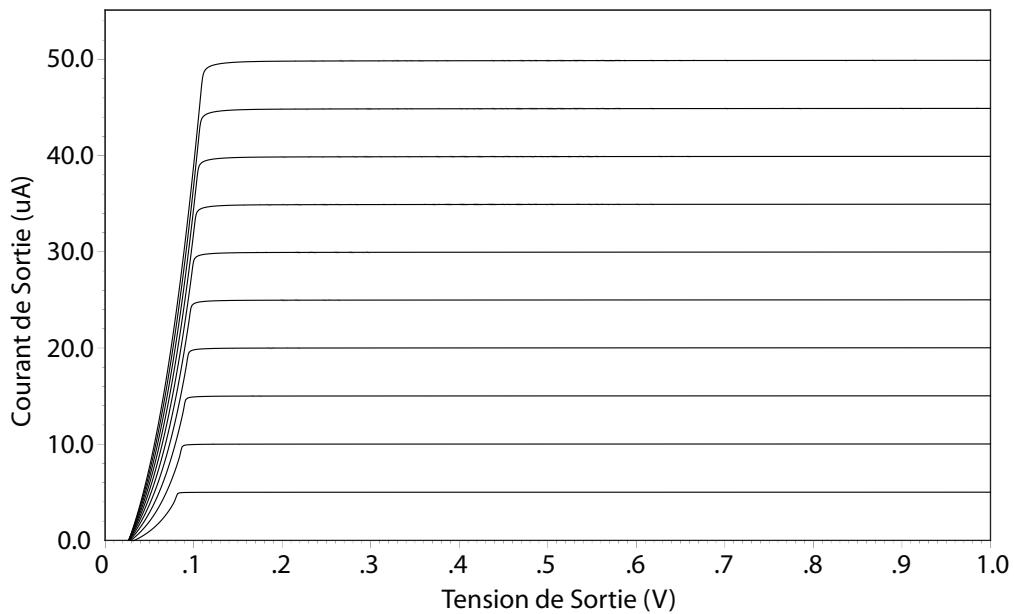

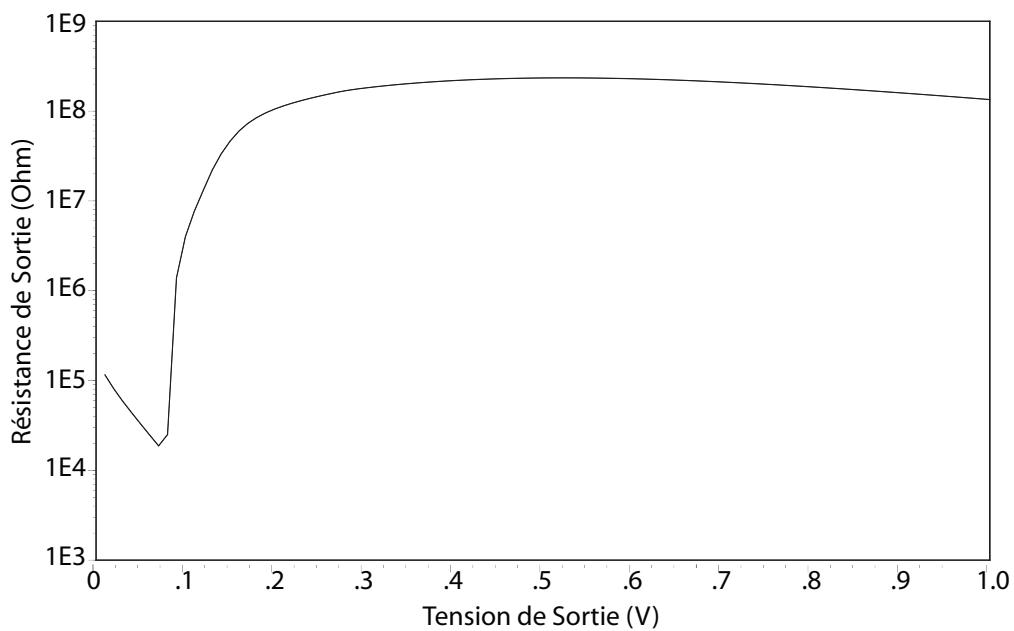

| 3.4                                                                                                | Illustration des performances du nouveau miroir de courant . . . . .                   | 46        |

| 3.5                                                                                                | Conclusion . . . . .                                                                   | 48        |

| <b>CHAPITRE 4 PFD ET NOUVELLE POMPE DE CHARGES CMOS . . . . .</b>                                  |                                                                                        | <b>50</b> |

| 4.1                                                                                                | Détecteur de phase et de fréquence (PFD) et pompe de charges (CP) . . . . .            | 50        |

| 4.1.1                                                                                              | Pompes de charges proposées dans la littérature . . . . .                              | 53        |

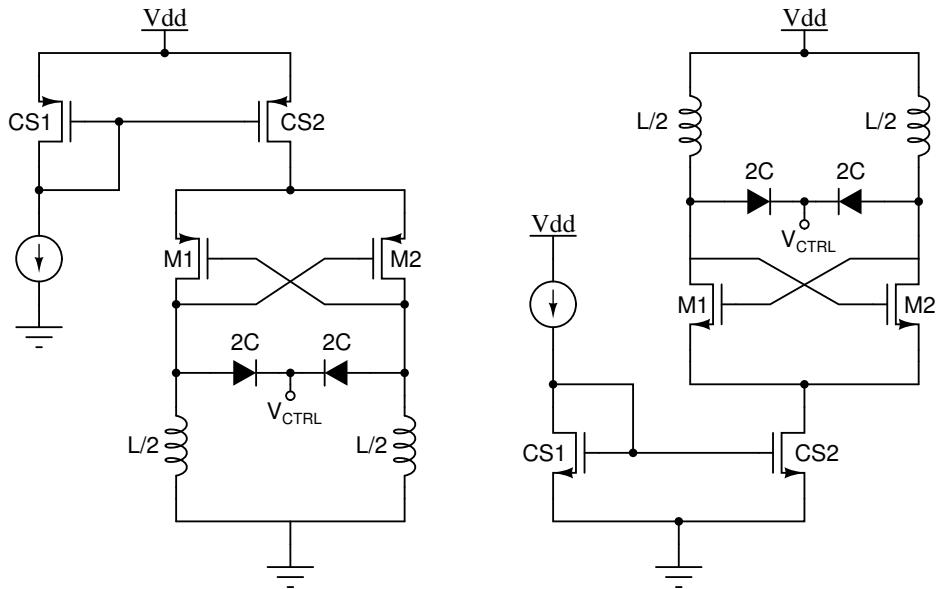

| 4.2                                                                                                | Nouvelle pompe de charges CMOS . . . . .                                               | 55        |

| 4.3                                                                                                | Fonctionnement de la pompe de charges proposée . . . . .                               | 56        |

| 4.4                                                                                                | Caractéristiques de la pompe de charges . . . . .                                      | 61        |

| 4.4.1                                                                                              | Résistance de sortie . . . . .                                                         | 61        |

| 4.4.2                                                                                              | Sources de courant auxiliaires $I_{CP}/K$ . . . . .                                    | 61        |

| 4.5                                                                                                | Implémentation détaillée et résultats . . . . .                                        | 62        |

| 4.6                                                                                                | Conclusion . . . . .                                                                   | 66        |

| <b>CHAPITRE 5 NOUVEAU LC-VCO CONTRÔLÉ PAR TENSION TOLÉRANT AUX VARIATIONS DE PROCÉDÉ . . . . .</b> |                                                                                        | <b>68</b> |

|                                                                                                                    |                                                                            |     |

|--------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------|-----|

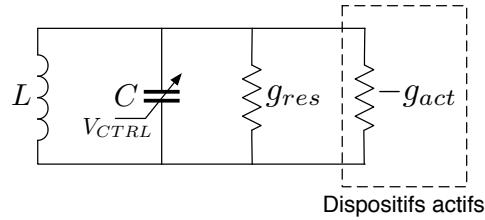

| 5.1                                                                                                                | Oscillateurs contrôlés par tension avec résonateur <i>LC</i>               | 69  |

| 5.2                                                                                                                | Impact de la variabilité                                                   | 69  |

| 5.3                                                                                                                | Solutions existantes pour mitiger l'impact de la variabilité sur un LC-VCO | 71  |

| 5.4                                                                                                                | Nouveau LC-VCO tolérant aux variations de procédé                          | 72  |

| 5.4.1                                                                                                              | Architecture du LC-VCO proposé                                             | 72  |

| 5.4.2                                                                                                              | Génération de la tension de référence $V_{REF}$                            | 74  |

| 5.5                                                                                                                | Conception des composants passifs du synthétiseur                          | 76  |

| 5.5.1                                                                                                              | Inductance intégrée                                                        | 76  |

| 5.5.2                                                                                                              | Varactors                                                                  | 80  |

| 5.6                                                                                                                | Implémentation en technologie CMOS 90-nm et résultats                      | 81  |

| 5.6.1                                                                                                              | Conception du VCO                                                          | 81  |

| 5.6.2                                                                                                              | Caractérisation de l'inductance                                            | 83  |

| 5.6.3                                                                                                              | Impact de la tension de polarisation adaptative du VCO                     | 85  |

| 5.7                                                                                                                | Conclusion                                                                 | 88  |

| <b>CHAPITRE 6      IMPLÉMENTATION DU SYNTHÉTISEUR DE FRÉQUENCES : DIVISEUR PROGRAMMABLE ET RÉSULTATS DE MESURE</b> |                                                                            | 90  |

| 6.1                                                                                                                | Diviseur de fréquence programmable                                         | 90  |

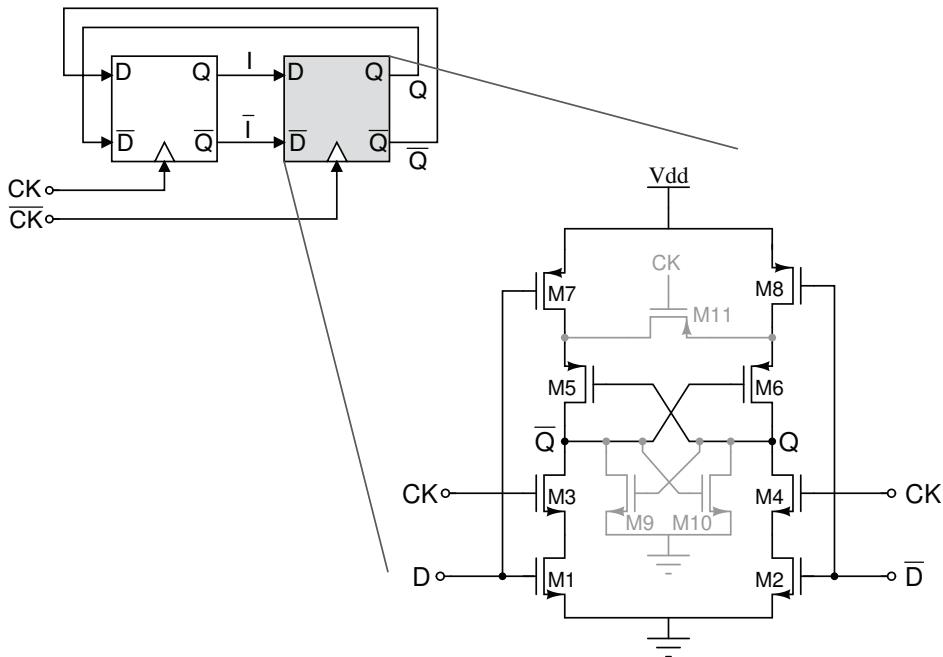

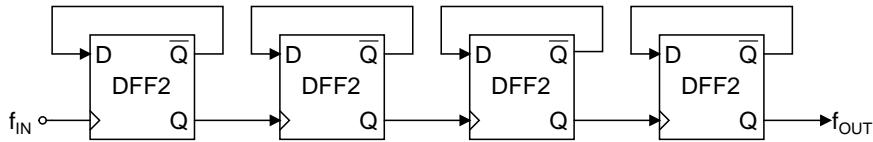

| 6.1.1                                                                                                              | Diviseur par 2 pour la génération des signaux <i>I/Q</i>                   | 91  |

| 6.1.2                                                                                                              | Diviseur de fréquence programmable                                         | 93  |

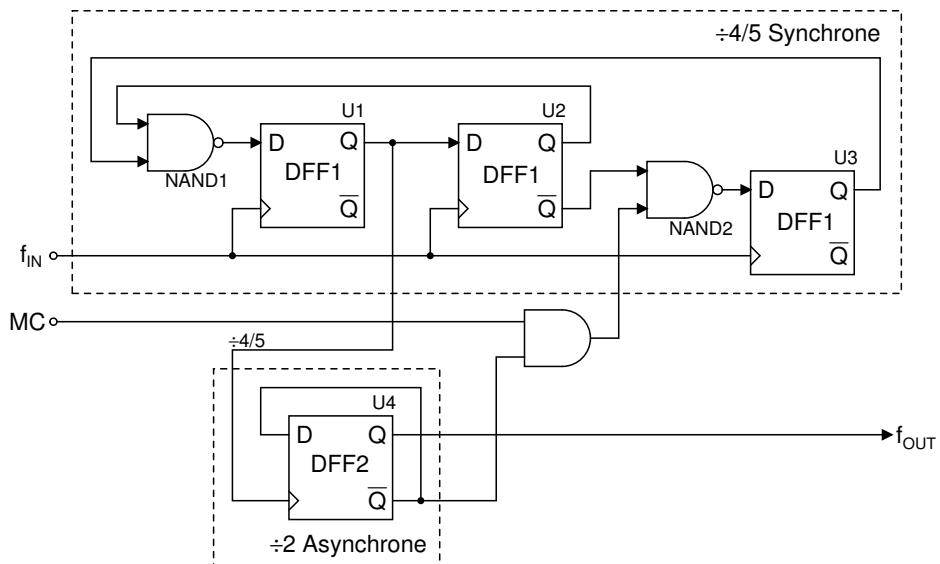

| 6.1.2.1                                                                                                            | Circuit de mise à l'échelle à double module et $\div 32$ fixe              | 95  |

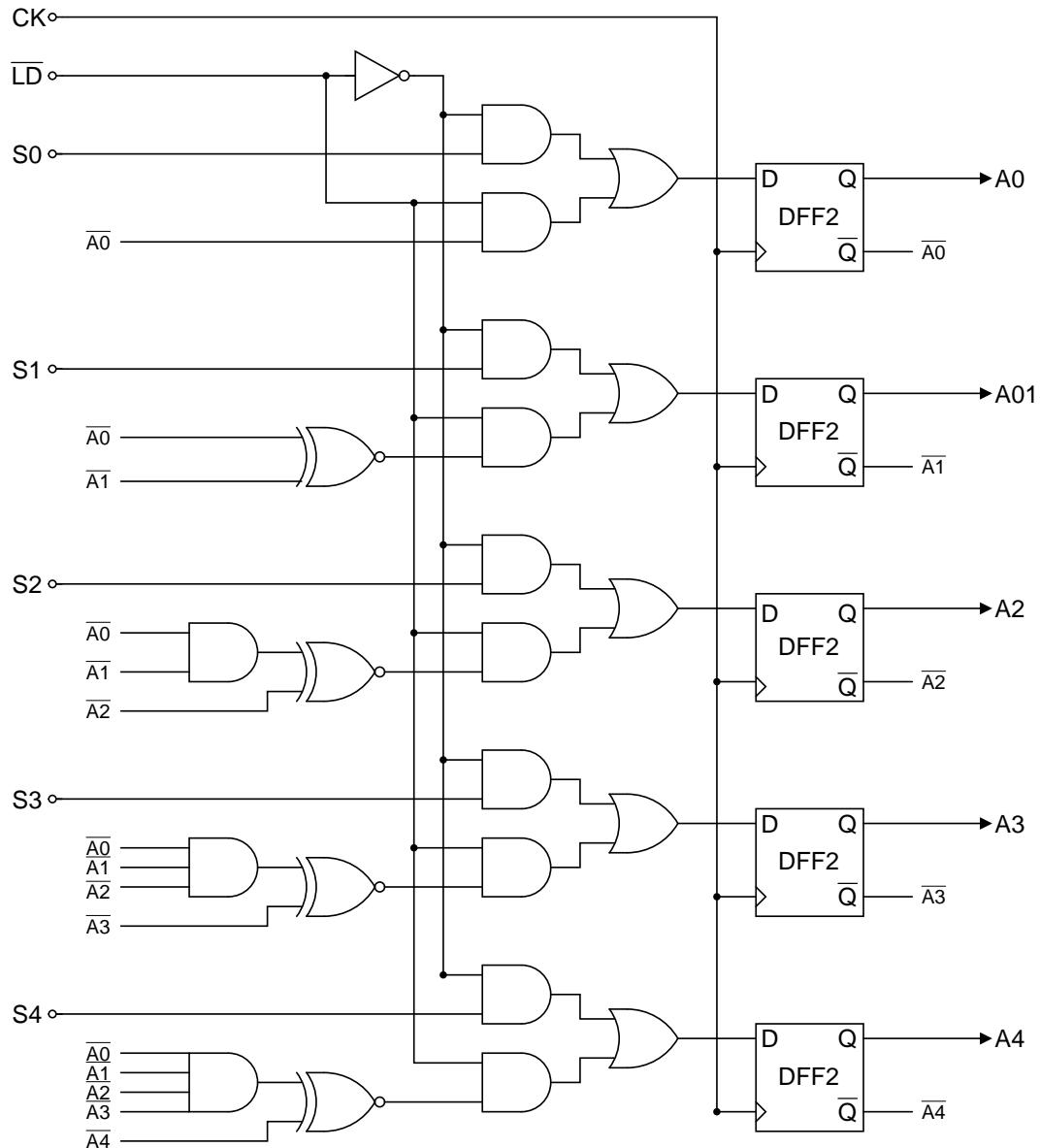

| 6.1.2.2                                                                                                            | Compteur à rebours programmable                                            | 95  |

| 6.1.2.3                                                                                                            | Conception des bascules-D                                                  | 97  |

| 6.2                                                                                                                | Résultats de simulation et de mesure du synthétiseur de fréquences         | 99  |

| 6.2.1                                                                                                              | Détails d'implémentation                                                   | 99  |

| 6.2.2                                                                                                              | Circuit imprimé de validation et équipement de test                        | 101 |

| 6.2.3                                                                                                              | Temps de démarrage et bruit de phase                                       | 102 |

| 6.2.4                                                                                                              | Améliorations potentielles                                                 | 104 |

| <b>CHAPITRE 7      CONCLUSION</b>                                                                                  |                                                                            | 107 |

| 7.1                                                                                                                | Synthèse des travaux                                                       | 107 |

| 7.2                                                                                                                | Travaux futurs                                                             | 108 |

| <b>PUBLICATIONS RELATIVES À CETTE THÈSE</b>                                                                        |                                                                            | 109 |

| <b>RÉFÉRENCES</b>                                                                                                  |                                                                            | 111 |

| <b>ANNEXES</b>                                                                                                     |                                                                            | 119 |

## LISTE DES FIGURES

|             |                                                                                              |    |

|-------------|----------------------------------------------------------------------------------------------|----|

| FIGURE 1.1  | Microsystème sans fil implantable pour la surveillance de paramètres biologiques. . . . .    | 2  |

| FIGURE 2.1  | Structure générique d'un transmetteur/récepteur RF. . . . .                                  | 12 |

| FIGURE 2.2  | Diagramme bloc d'une boucle à verrouillage de phase. . . . .                                 | 13 |

| FIGURE 2.3  | Diagramme bloc d'un synthétiseur de fréquences. . . . .                                      | 14 |

| FIGURE 2.4  | Diagramme bloc d'un synthétiseur de fréquences utilisant une pompe de charges. . . . .       | 15 |

| FIGURE 2.5  | Modèle d'un oscillateur à résonateur $LC$ dans le régime permanent. . . . .                  | 16 |

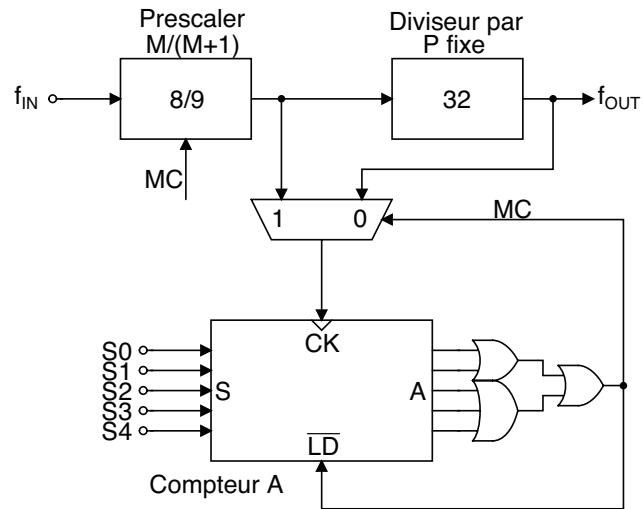

| FIGURE 2.6  | Diagramme bloc du diviseur de fréquence programmable. . . . .                                | 17 |

| FIGURE 2.7  | Détecteur de phase/fréquence. . . . .                                                        | 18 |

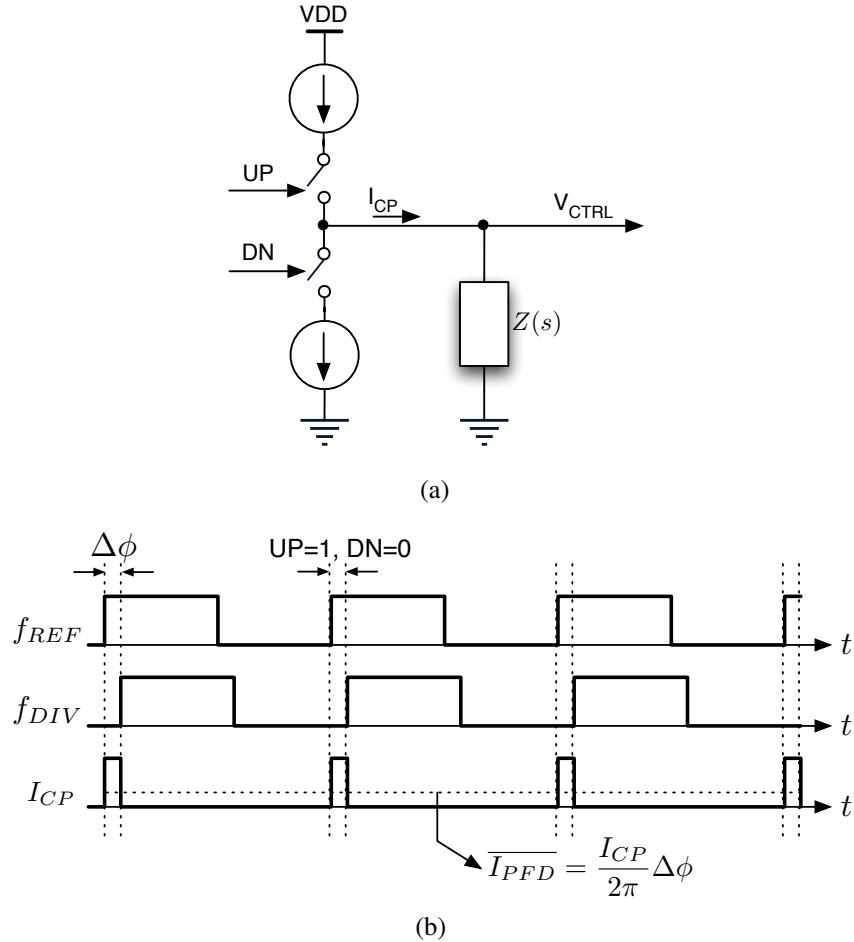

| FIGURE 2.8  | Pompe de charges et son diagramme temporel. . . . .                                          | 19 |

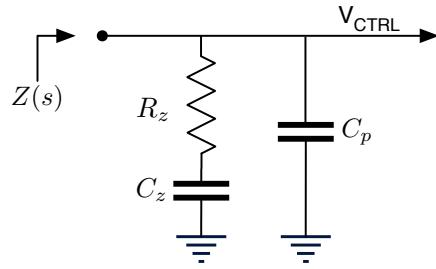

| FIGURE 2.9  | Filtre de boucle du synthétiseur de fréquences. . . . .                                      | 20 |

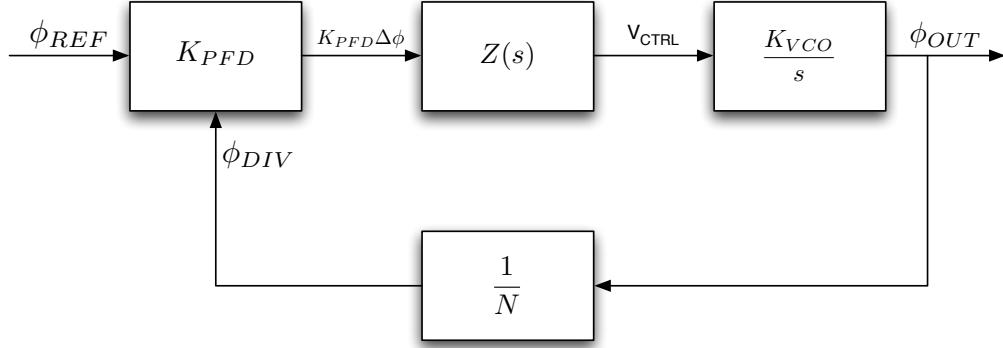

| FIGURE 2.10 | Modèle linéarisé d'un synthétiseur de fréquences. . . . .                                    | 21 |

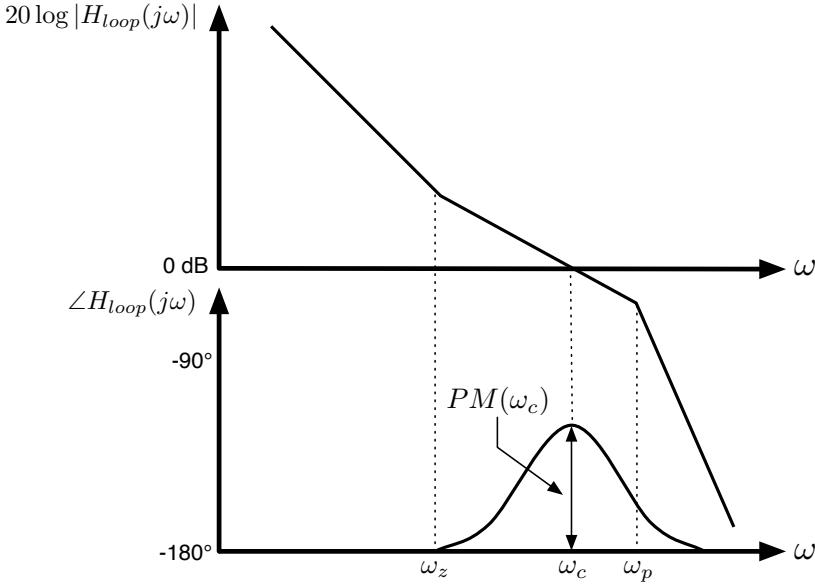

| FIGURE 2.11 | Diagramme de Bode du gain en boucle ouverte du synthétiseur de fréquences.                   | 23 |

| FIGURE 2.12 | Temps de stabilisation d'un synthétiseur de fréquences. . . . .                              | 24 |

| FIGURE 2.13 | Bruit de phase d'un oscillateur. . . . .                                                     | 26 |

| FIGURE 2.14 | Bruit de phase et modulations parasites ( <i>spurs</i> ) dans un oscillateur. . . . .        | 27 |

| FIGURE 2.15 | Abaissement de fréquence réciproque causé par le bruit de phase dans un oscillateur. . . . . | 28 |

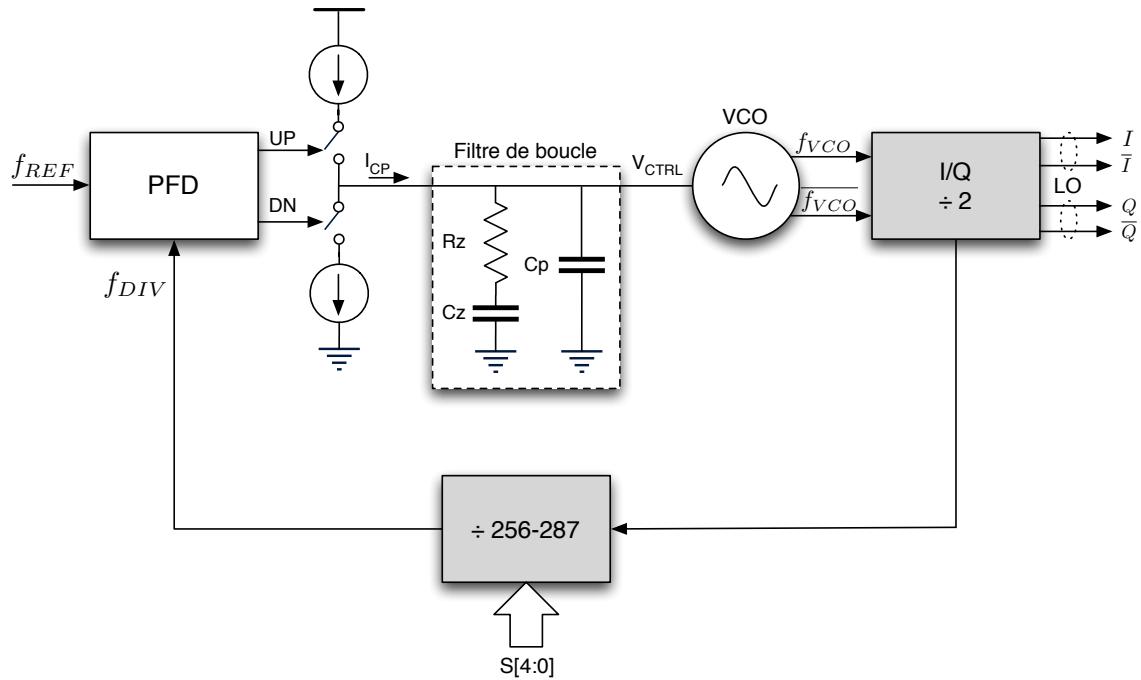

| FIGURE 2.16 | Architecture du synthétiseur proposé. . . . .                                                | 32 |

| FIGURE 3.1  | Courant à la sortie d'un miroir de courant simple NMOS. . . . .                              | 36 |

| FIGURE 3.2  | Miroir de courant avec tension de drain fixée à l'aide d'un ampli-op. . . . .                | 37 |

| FIGURE 3.3  | Miroir de courant entièrement cascode et miroir de courant high swing super-Wilson. . . . .  | 38 |

| FIGURE 3.4  | Composantes avant $I_F$ et inverse $I_R$ du courant de drain d'un MOSFET. .                  | 39 |

| FIGURE 3.5  | Circuit de polarisation cascode à bas voltage. . . . .                                       | 40 |

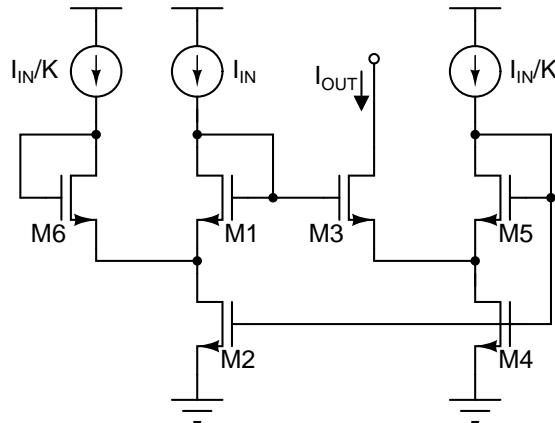

| FIGURE 3.6  | Construction du nouveau miroir de courant à haute impédance de sortie. .                     | 41 |

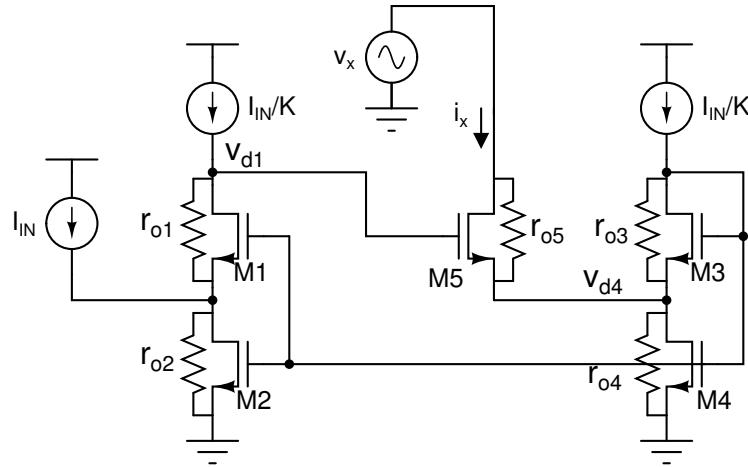

| FIGURE 3.7  | Miroir de courant proposé. . . . .                                                           | 42 |

| FIGURE 3.8  | Circuit utilisé pour le calcul de la résistance de sortie du miroir de courant.              | 43 |

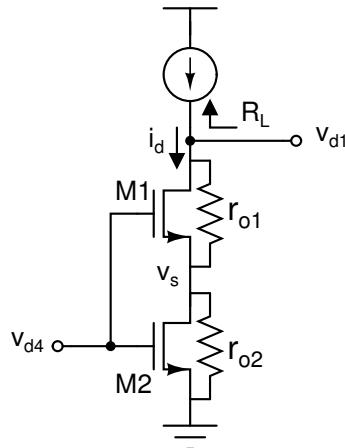

| FIGURE 3.9  | Calcul du gain à basse fréquence de l'étage auto cascode. . . . .                            | 44 |

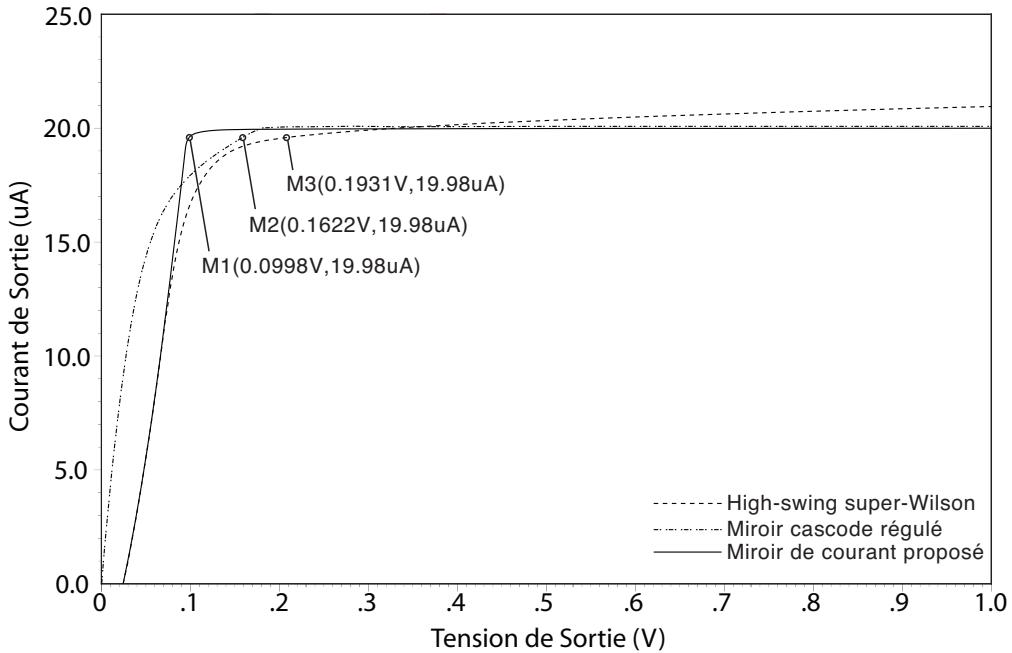

| FIGURE 3.10 | Variation du courant de sortie du miroir de courant proposé. . . . .                         | 47 |

| FIGURE 3.11 | Résistance de sortie du miroir de courant proposé. . . . .                                   | 47 |

| FIGURE 3.12 | Comparaison des performances du miroir de courant proposé. . . . .                           | 48 |

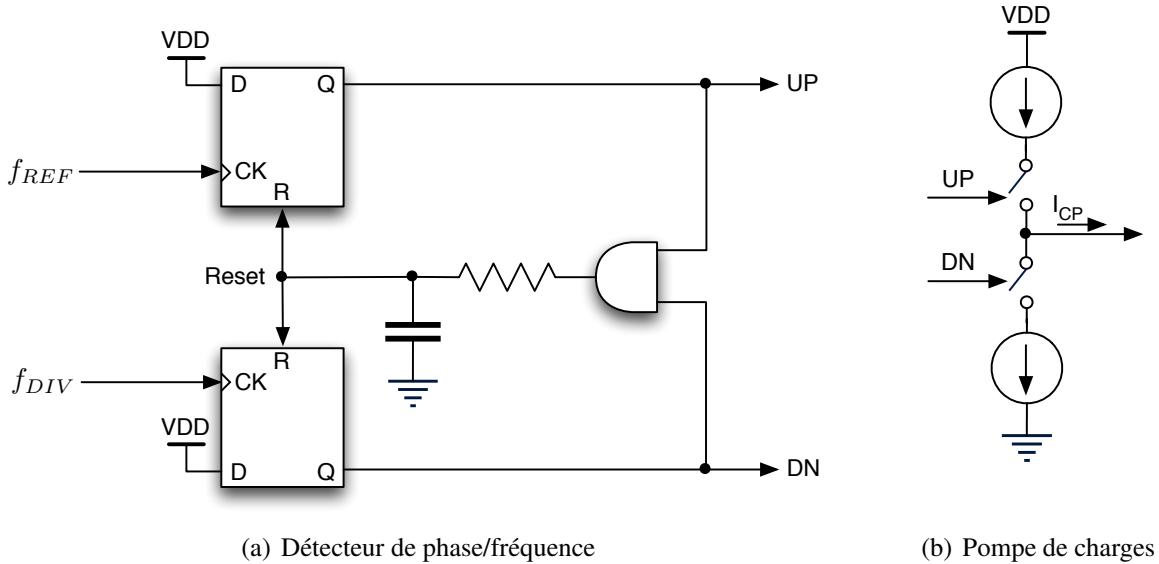

| FIGURE 4.1  | Détecteur de phase/fréquence (PFD) et pompe de charges (CP). . . . .                         | 51 |

|             |                                                                                                 |     |

|-------------|-------------------------------------------------------------------------------------------------|-----|

| FIGURE 4.2  | Élimination de la zone morte d'un PFD. . . . .                                                  | 52  |

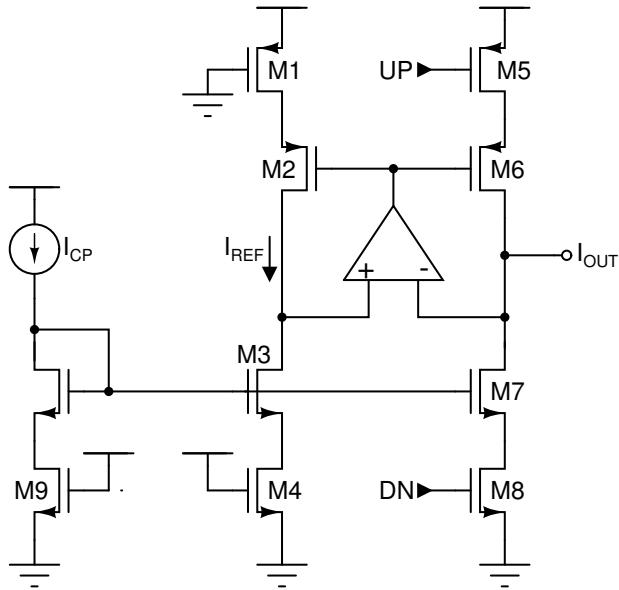

| FIGURE 4.3  | Utilisation d'un amplificateur opérationnel pour l'appariement des courants. . . . .            | 54  |

| FIGURE 4.4  | Pompe de charges à renforcement de gain. . . . .                                                | 55  |

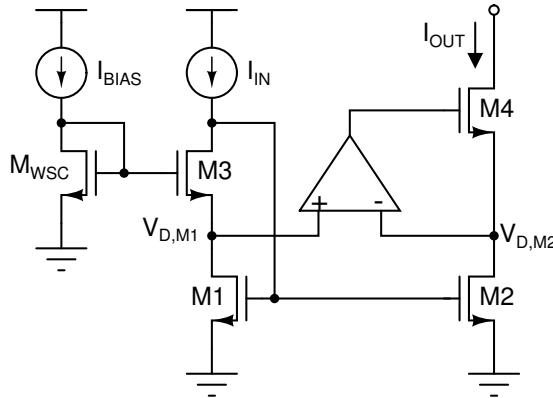

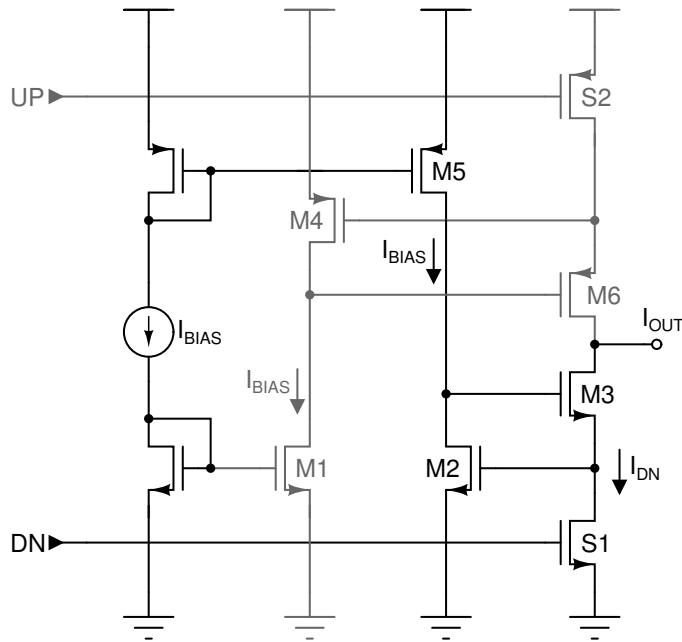

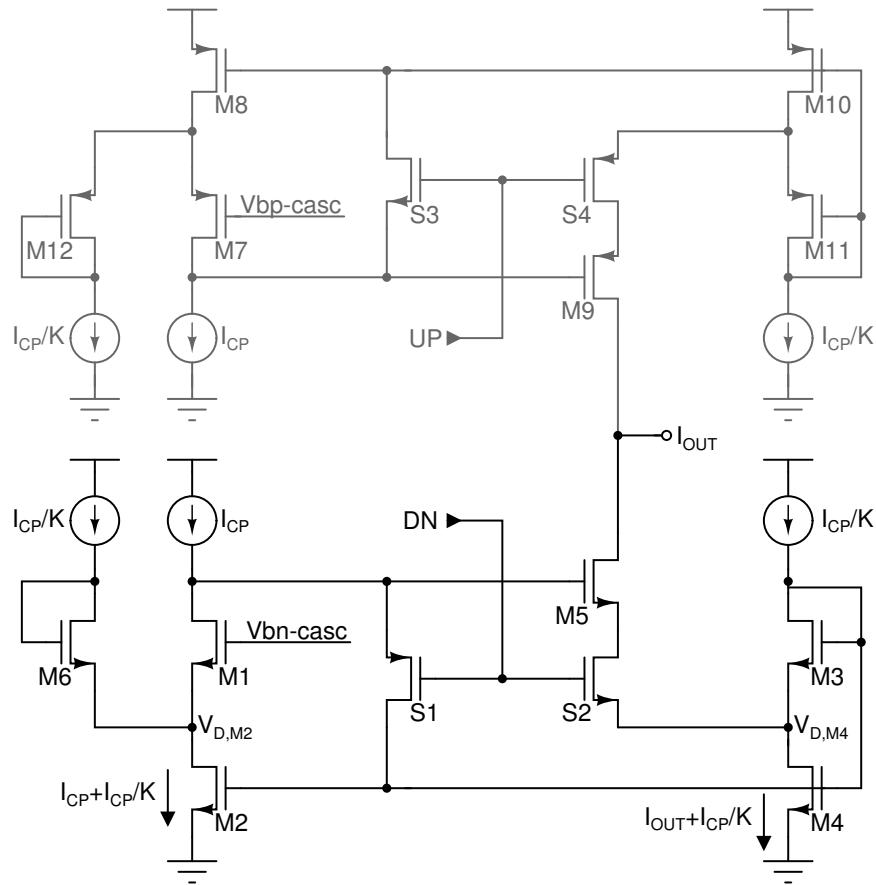

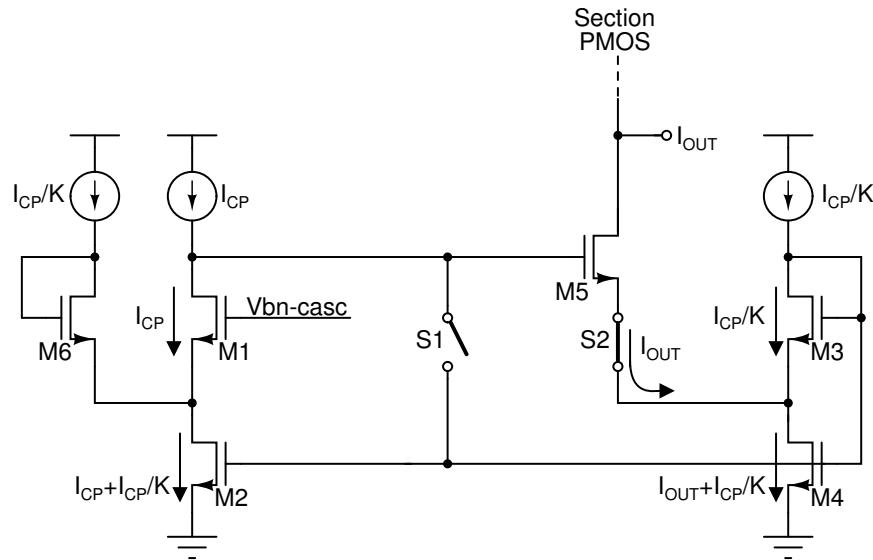

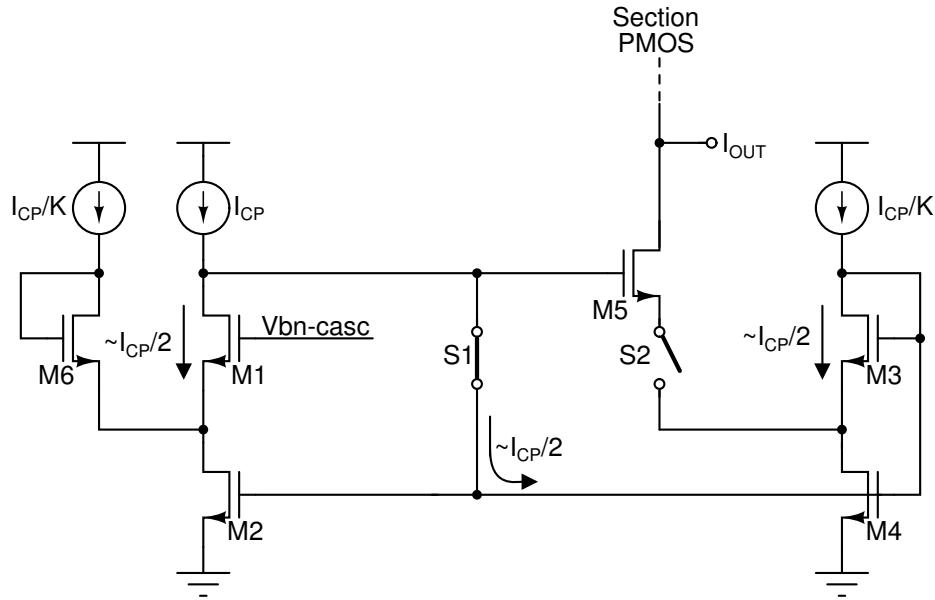

| FIGURE 4.5  | Schéma électronique de la pompe de charges CMOS proposée. . . . .                               | 56  |

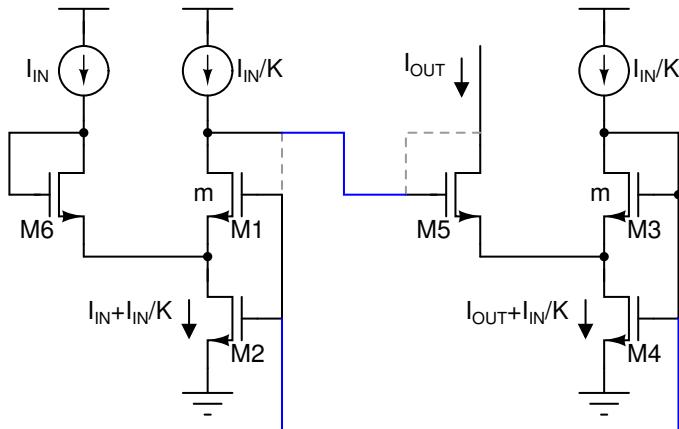

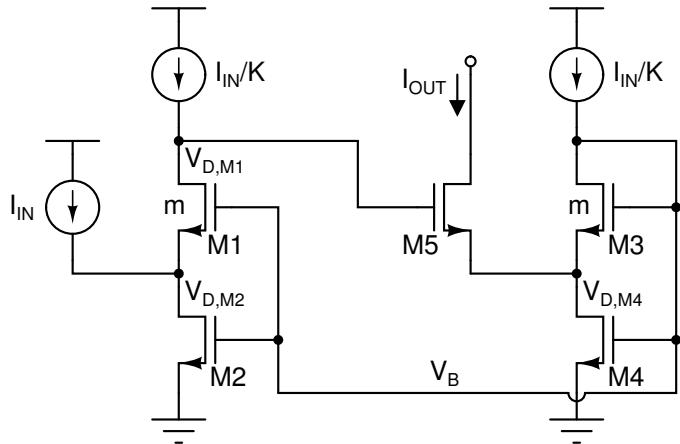

| FIGURE 4.6  | Courants dans la pompe de charges dans l'état actif. . . . .                                    | 57  |

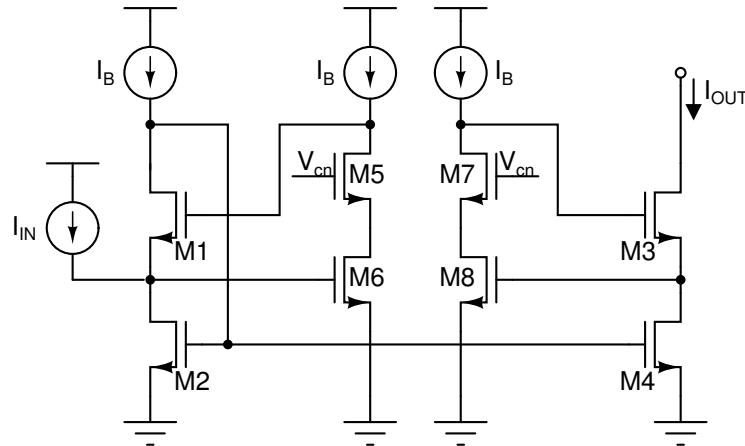

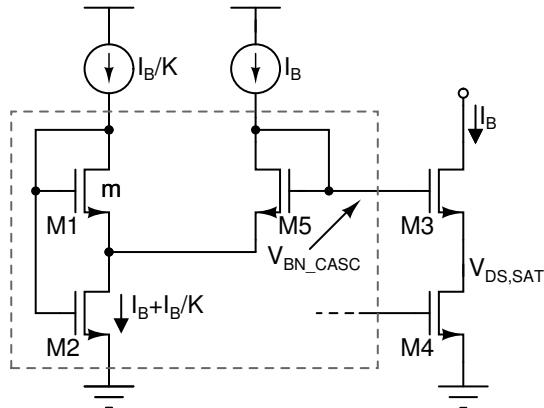

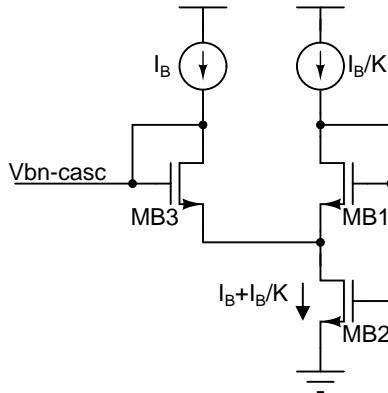

| FIGURE 4.7  | Circuit générant la tension de polarisation cascode. . . . .                                    | 58  |

| FIGURE 4.8  | Courants dans la pompe de charges lorsqu'elle est désactivée. . . . .                           | 60  |

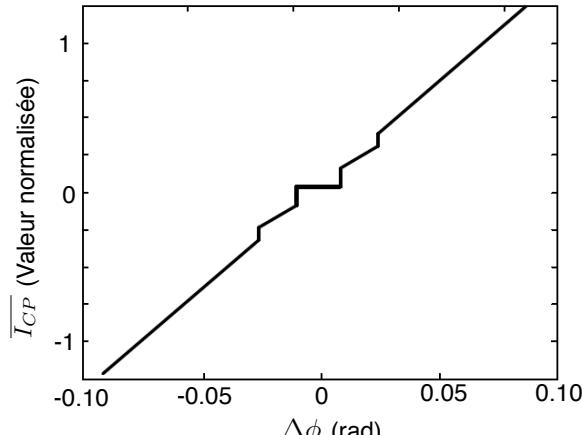

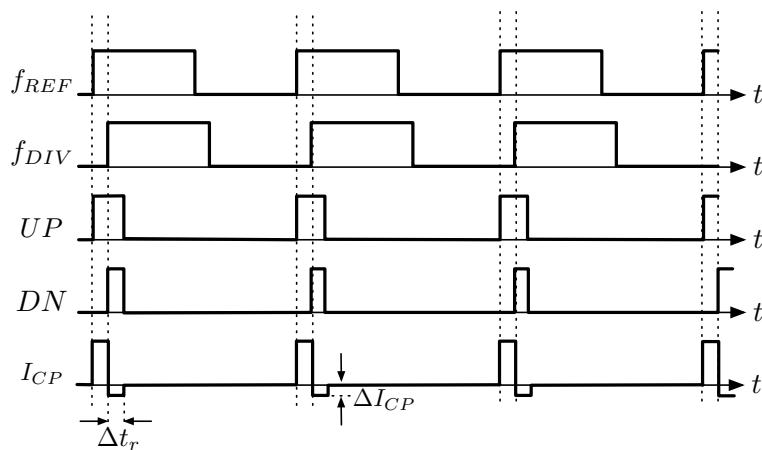

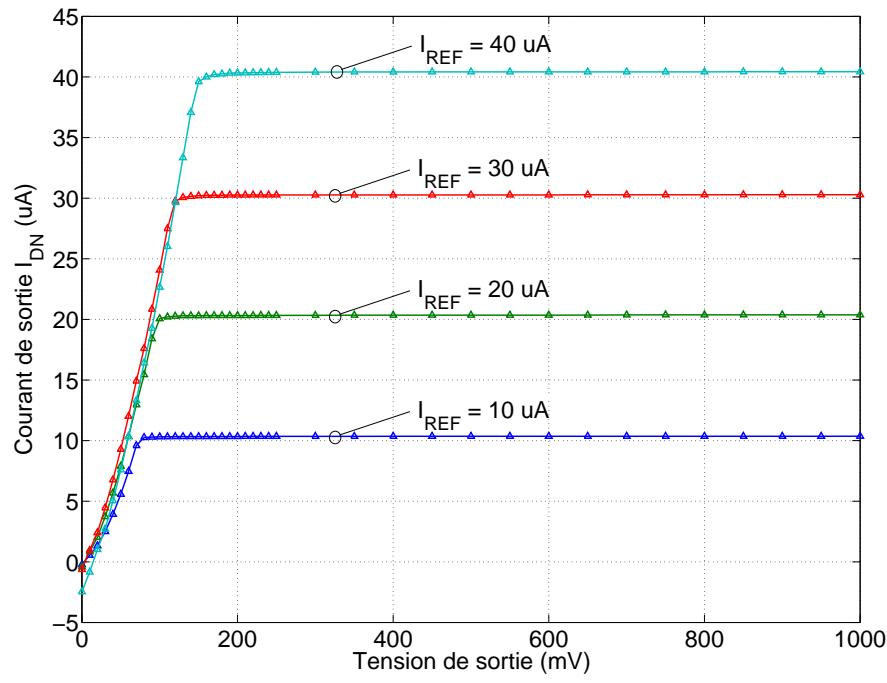

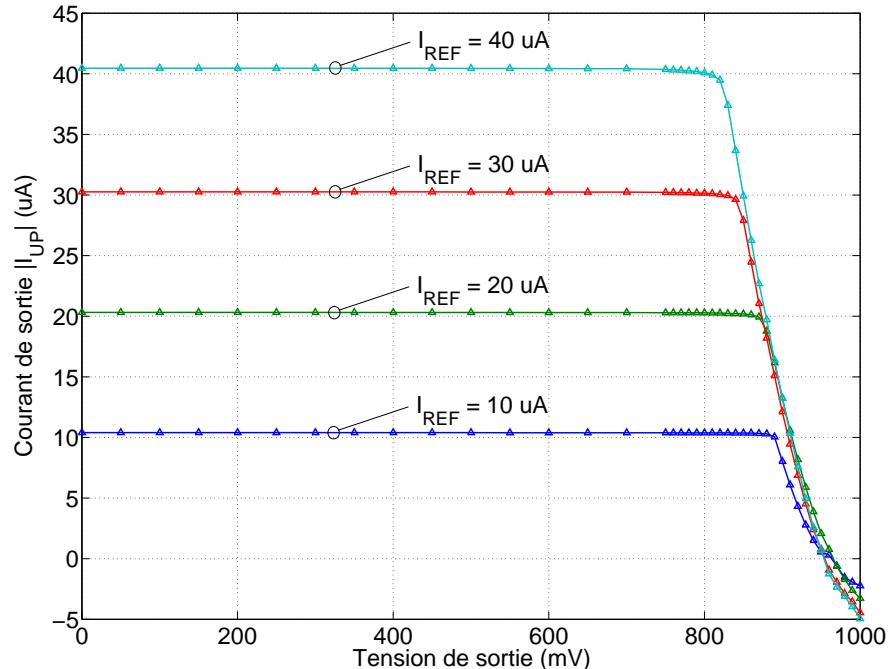

| FIGURE 4.9  | Courant mesuré à la sortie de la pompe de charges en fonction de $V_{OUT}$ . . . . .            | 63  |

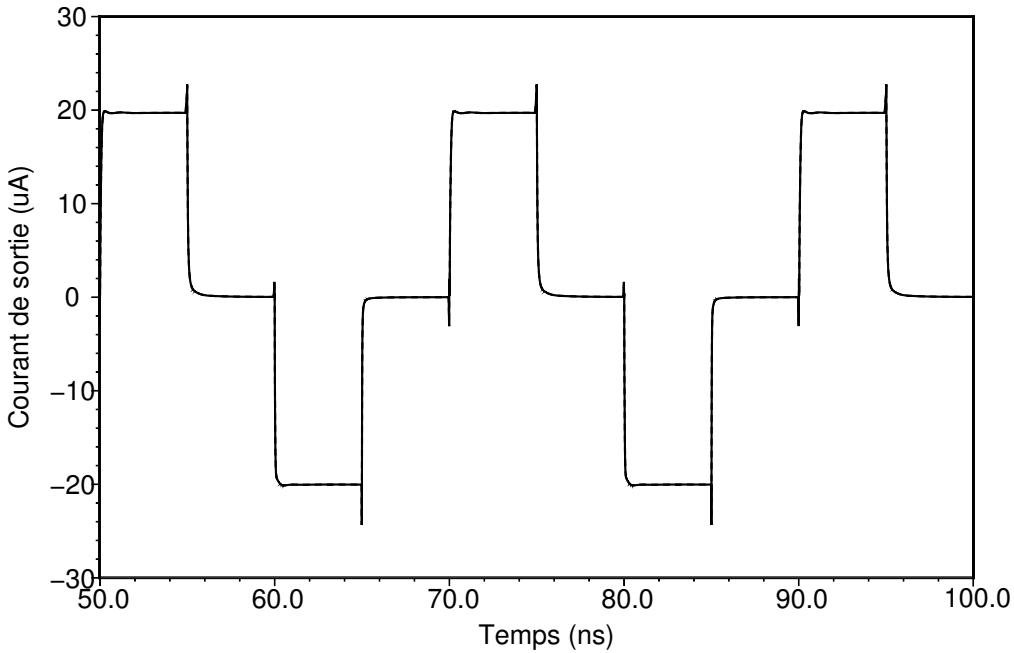

| FIGURE 4.10 | Réponse transitoire de la pompe de charges. . . . .                                             | 64  |

| FIGURE 4.11 | Simulation Monte Carlo de la pompe de charges. . . . .                                          | 65  |

| FIGURE 5.1  | LC-VCO utilisant une source de courant de queue pour fixer le courant de polarisation. . . . .  | 70  |

| FIGURE 5.2  | VCO tolérant aux variations de procédé grâce à une polarisation adaptative du substrat. . . . . | 71  |

| FIGURE 5.3  | VCO avec circuit de contrôle automatique de l'amplitude. . . . .                                | 72  |

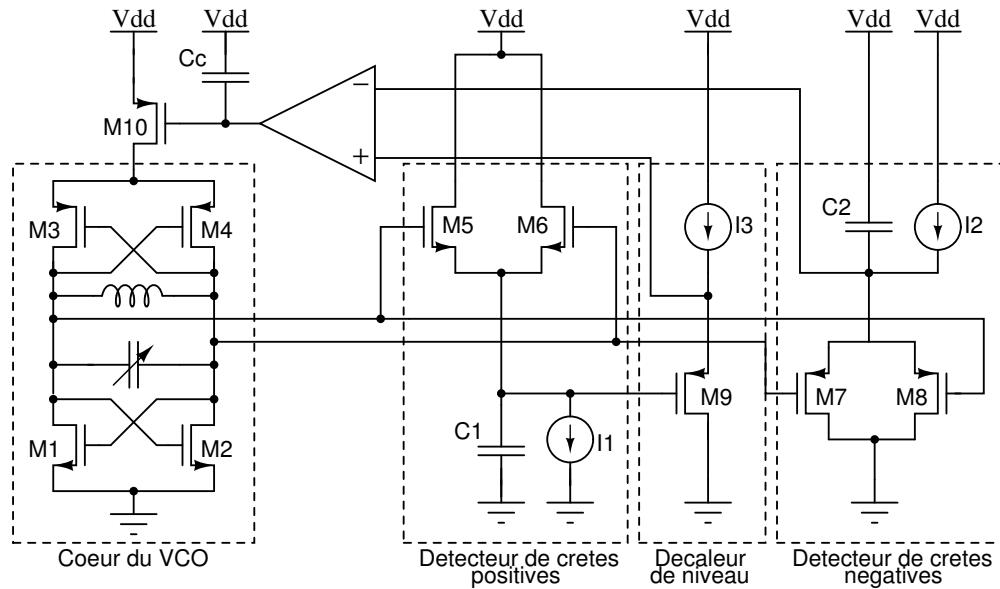

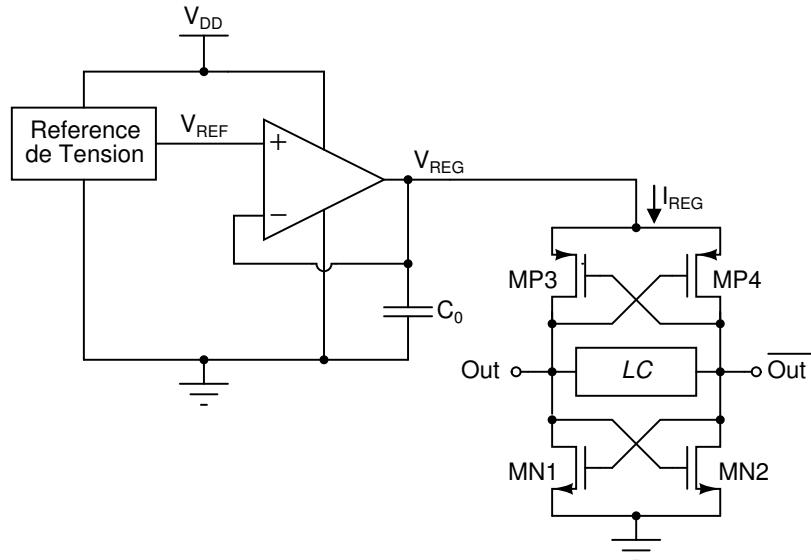

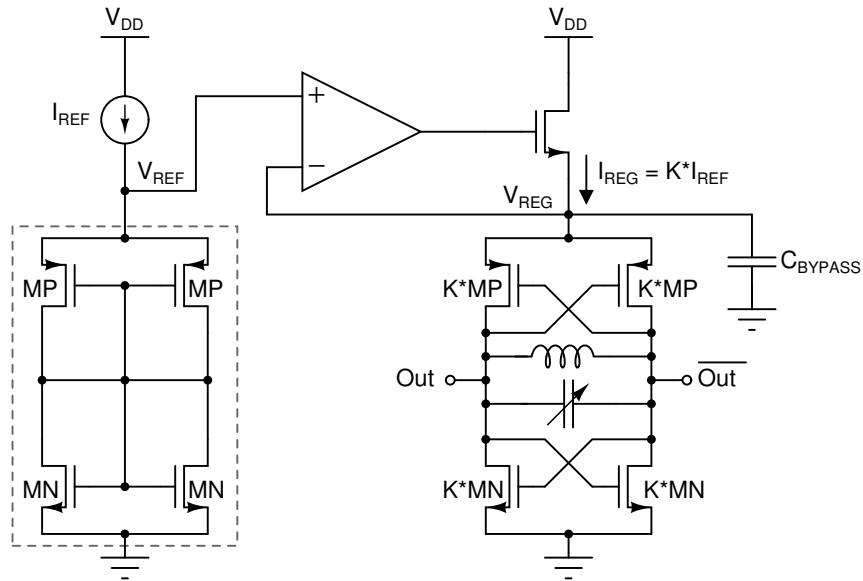

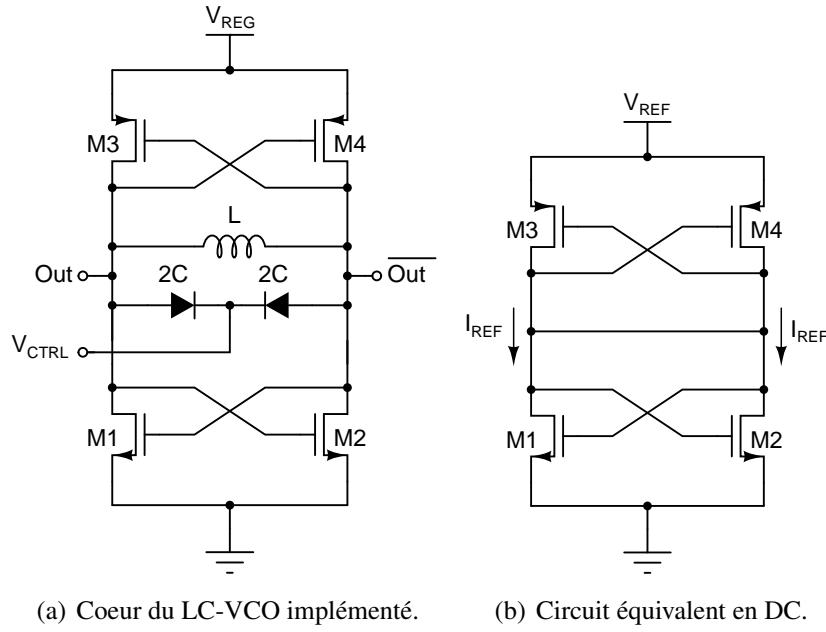

| FIGURE 5.4  | Diagramme bloc du LC-VCO proposé. . . . .                                                       | 73  |

| FIGURE 5.5  | Schéma du LC-VCO proposé avec circuit de génération de $V_{REF}$ . . . . .                      | 74  |

| FIGURE 5.6  | Circuit équivalent en DC du LC-VCO proposé. . . . .                                             | 75  |

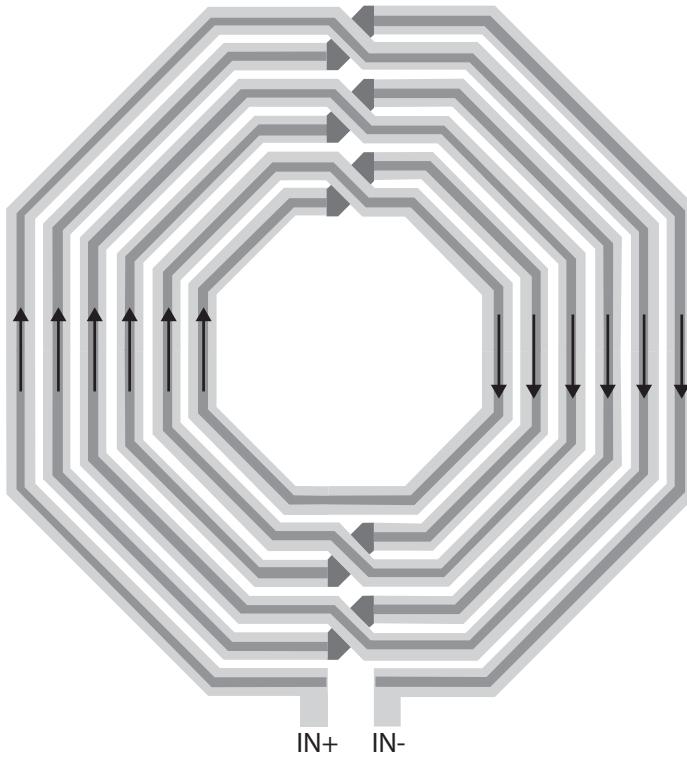

| FIGURE 5.7  | Inductance octogonale intégrée. . . . .                                                         | 77  |

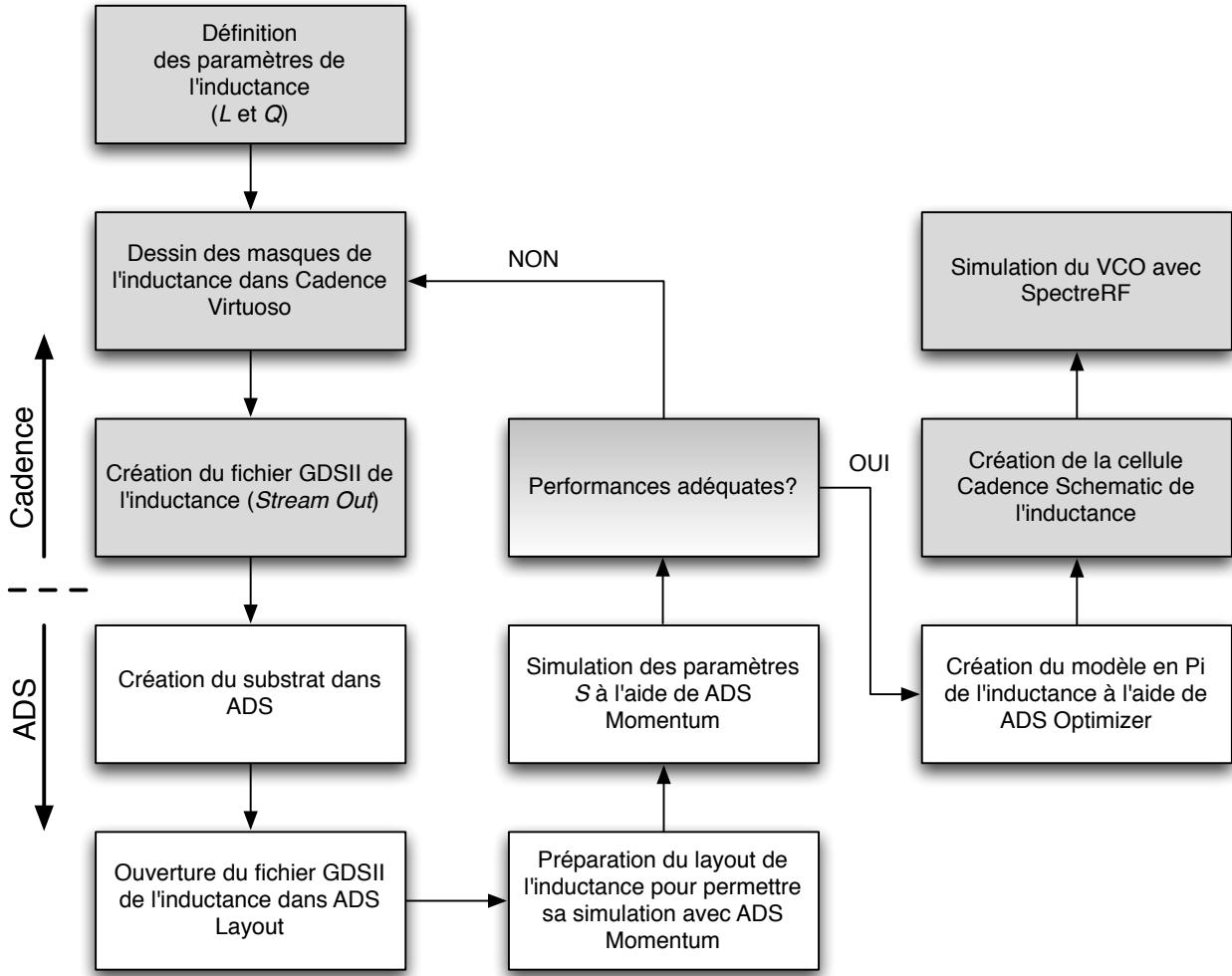

| FIGURE 5.8  | Étapes de conception de l'inductance intégrée. . . . .                                          | 78  |

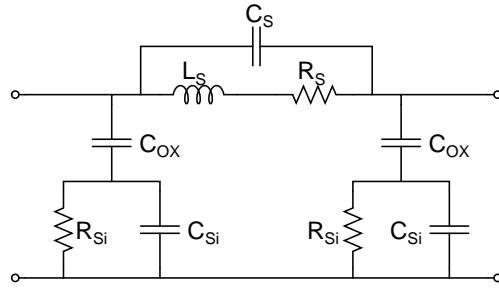

| FIGURE 5.9  | Modèle discret équivalent de l'inductance octogonale. . . . .                                   | 79  |

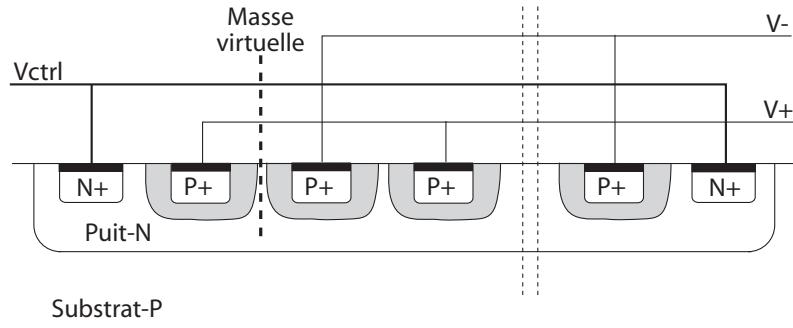

| FIGURE 5.10 | Vue en coupe d'un varactor à diode intégrée . . . . .                                           | 81  |

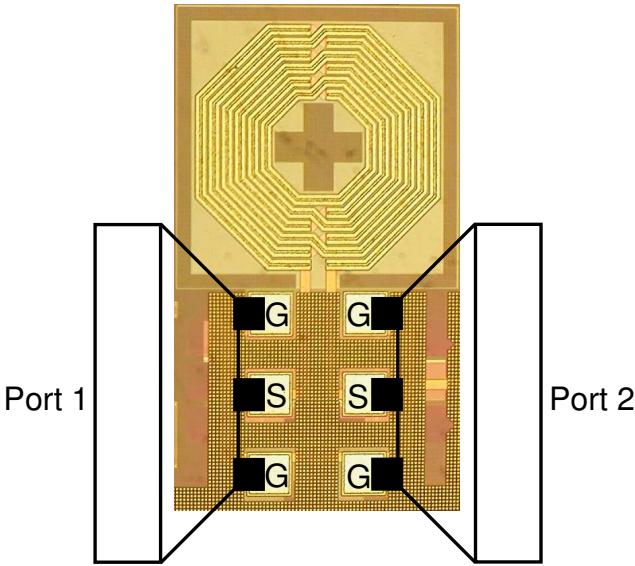

| FIGURE 5.11 | Banc d'essai de l'inductance octogonale. . . . .                                                | 83  |

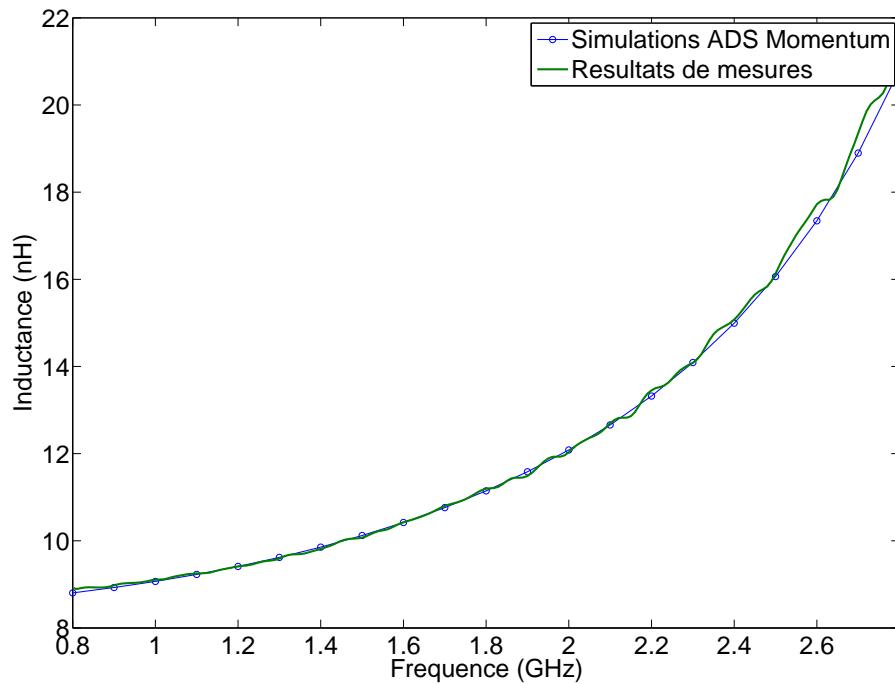

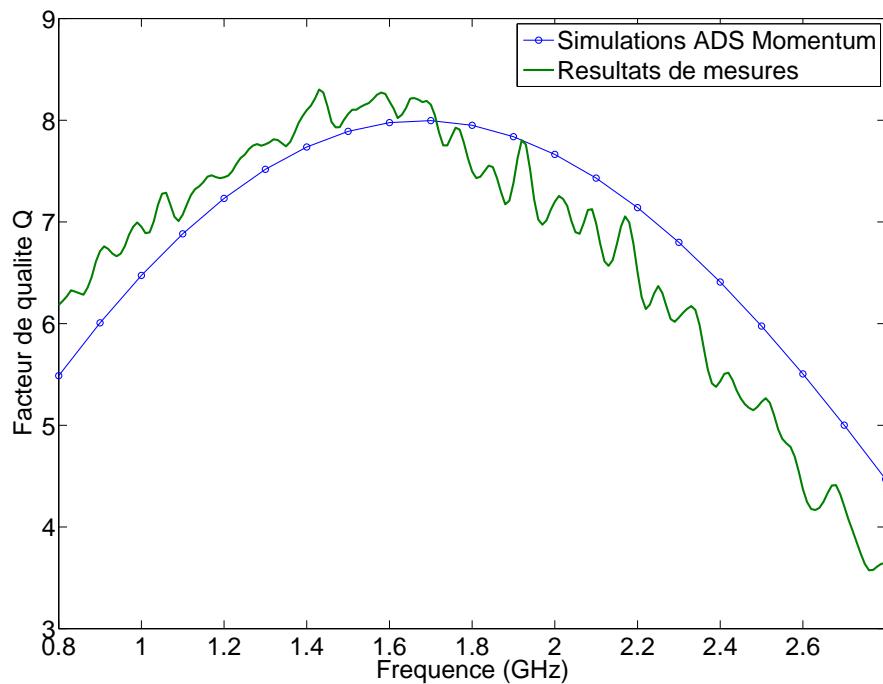

| FIGURE 5.12 | Caractérisation de l'inductance intégrée : simulations et résultats de mesure. . . . .          | 84  |

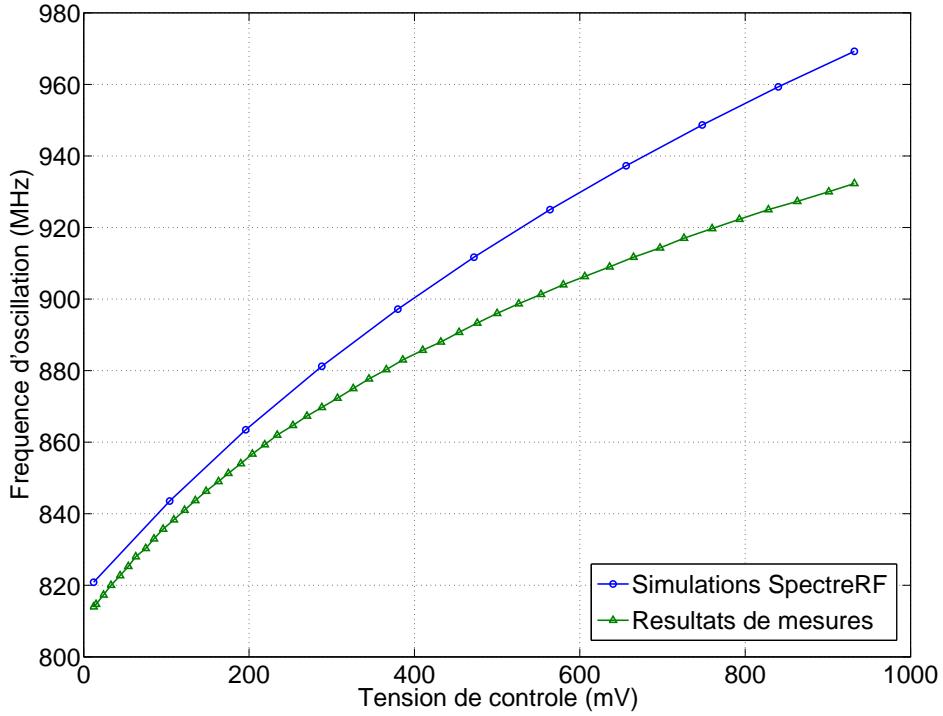

| FIGURE 5.13 | Plage de syntonisation simulée et mesurée du LC-VCO. . . . .                                    | 85  |

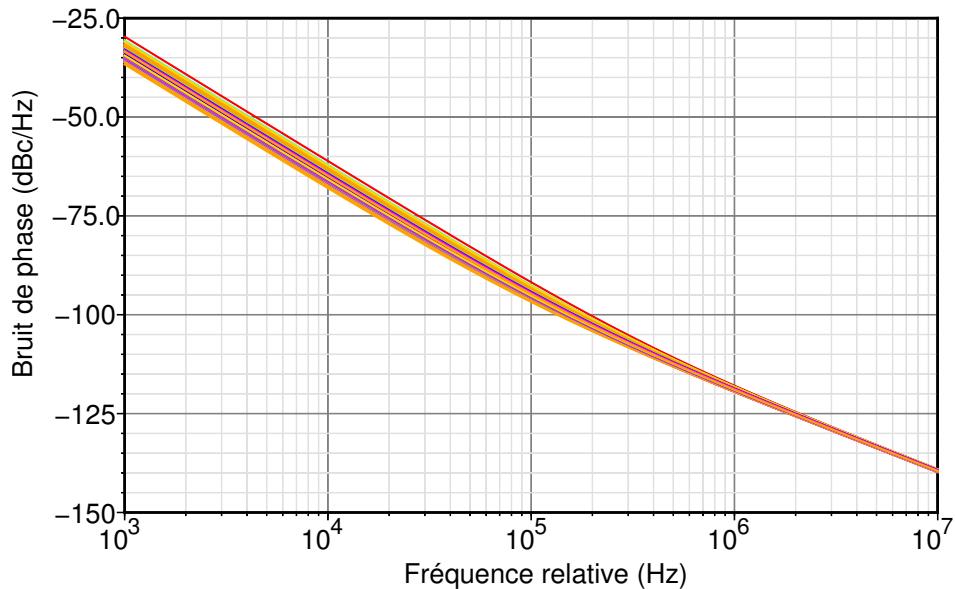

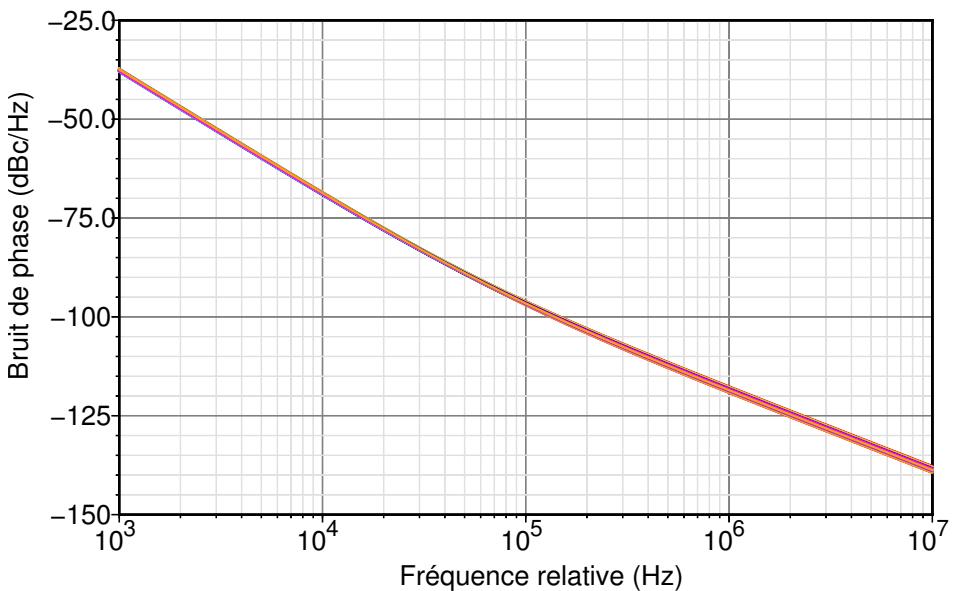

| FIGURE 5.14 | Performance en terme de bruit de phase du nouveau LC-VCO proposé. . . . .                       | 87  |

| FIGURE 6.1  | Place du diviseur programmable dans le synthétiseur proposé. . . . .                            | 91  |

| FIGURE 6.2  | Diagramme bloc et schéma électronique du diviseur par 2 $I/Q$ . . . . .                         | 92  |

| FIGURE 6.3  | Diagramme bloc du diviseur de fréquence programmable. . . . .                                   | 94  |

| FIGURE 6.4  | Circuit de mise à l'échelle à double module $\div 8/9$ . . . . .                                | 94  |

| FIGURE 6.5  | Diviseur par 32 asynchrone. . . . .                                                             | 95  |

| FIGURE 6.6  | Compteur à rebours programmable à 5-bit. . . . .                                                | 96  |

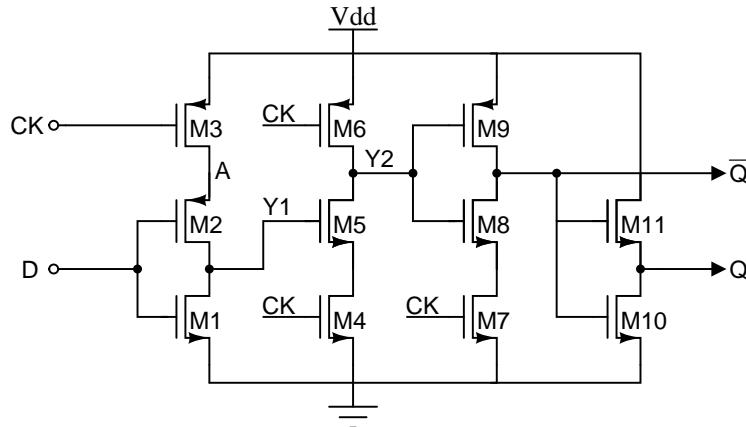

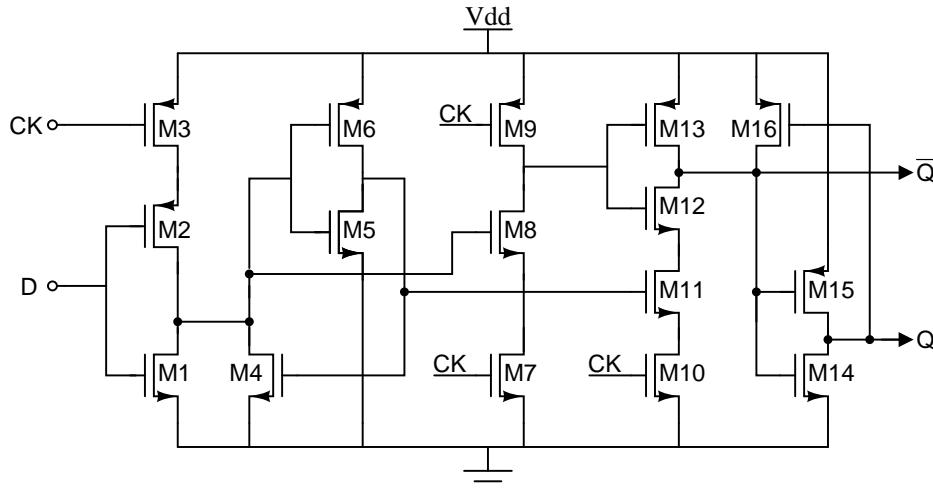

| FIGURE 6.7  | Bascule-D TSPC (DFF1). . . . .                                                                  | 98  |

| FIGURE 6.8  | Bascule-D TSPC optimisée pour opérer à basses fréquences (DFF2). . . . .                        | 99  |

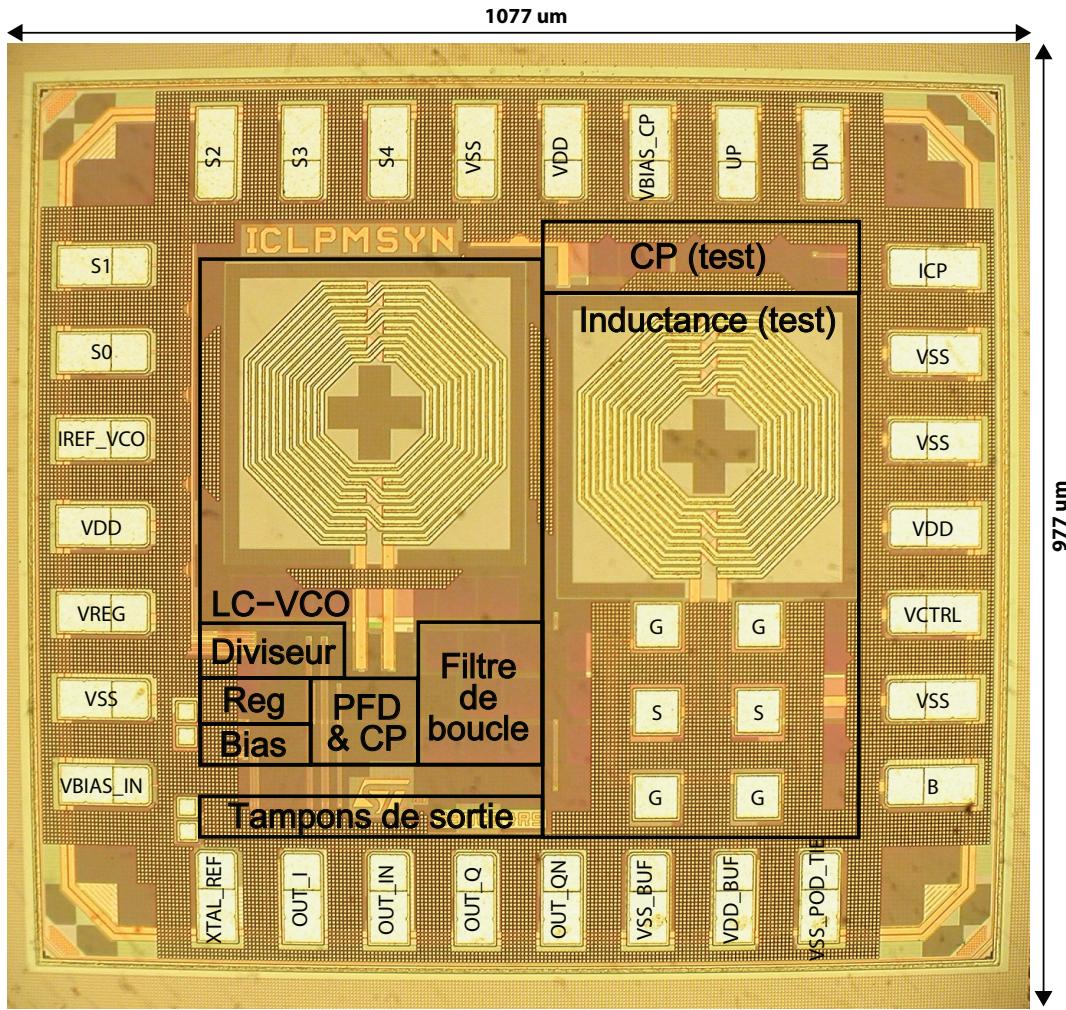

| FIGURE 6.9  | Microphotographie du circuit intégré du synthétiseur de fréquences. . . . .                     | 100 |

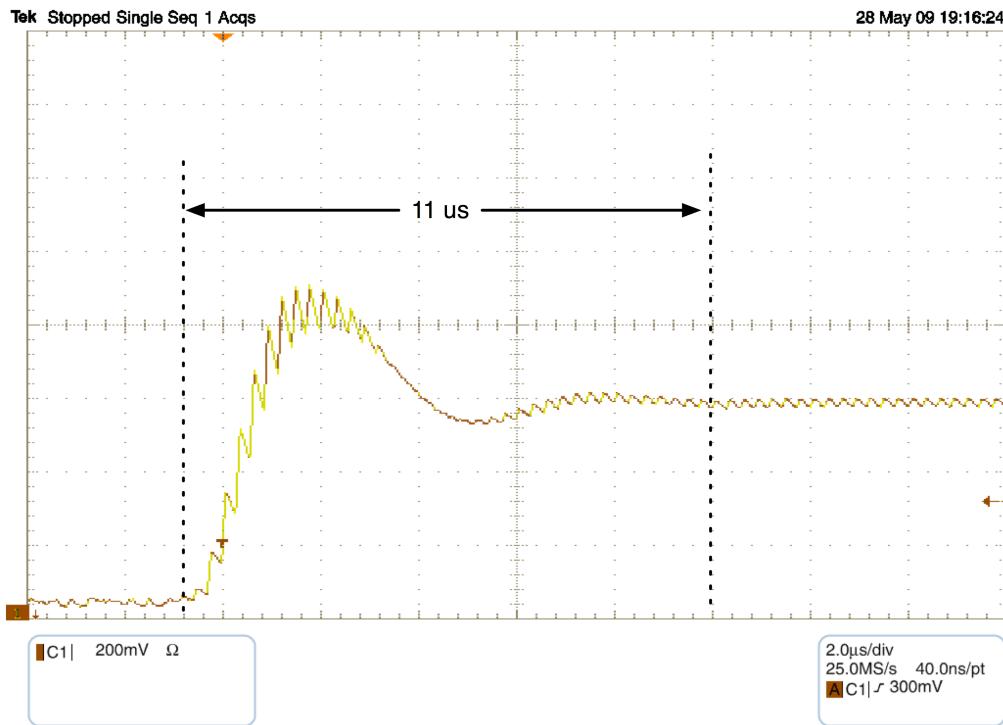

| FIGURE 6.10 | Tension $V_{CTRL}$ du synthétiseur suite à un saut de fréquence de 10 MHz. . . . .              | 103 |

|              |                                                                                                |     |

|--------------|------------------------------------------------------------------------------------------------|-----|

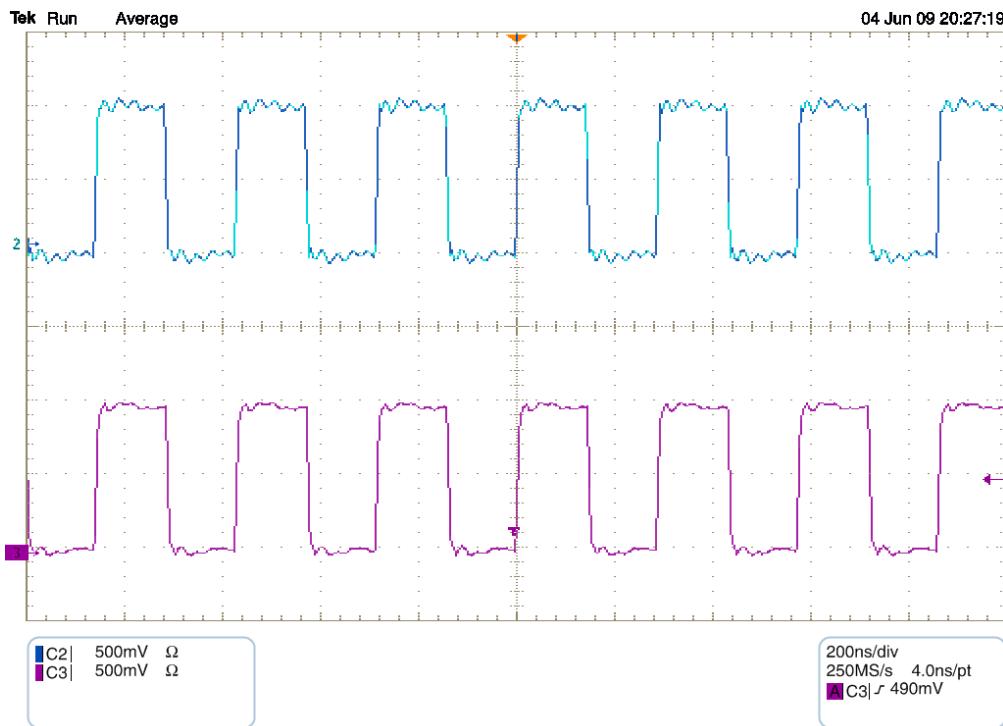

| FIGURE 6.11  | Signaux à l'entrée du PFD lorsque le synthétiseur est verouillé. . . . .                       | 103 |

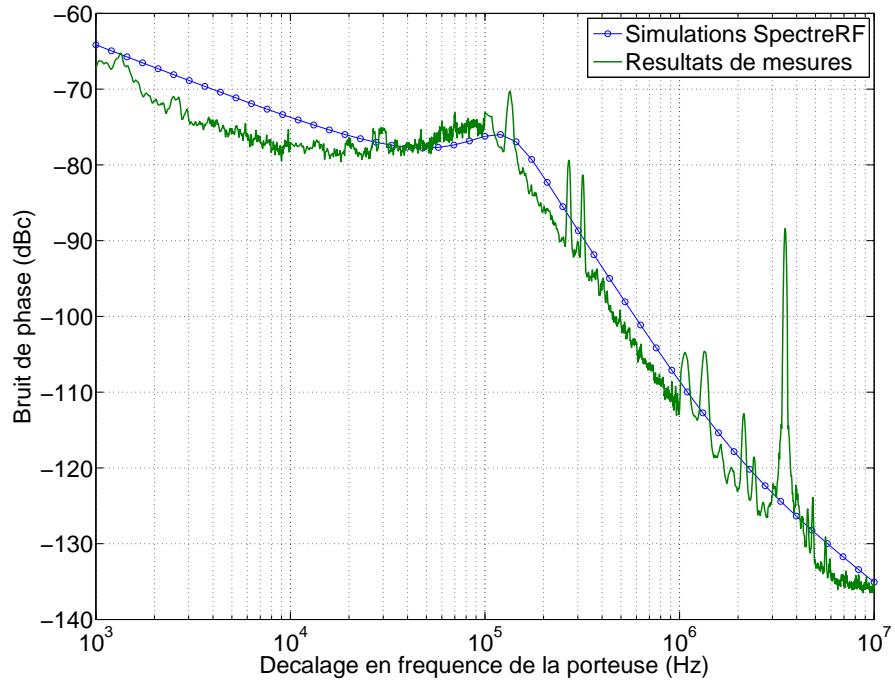

| FIGURE 6.12  | Bruit de phase simulé et mesuré du synthétiseur. . . . .                                       | 104 |

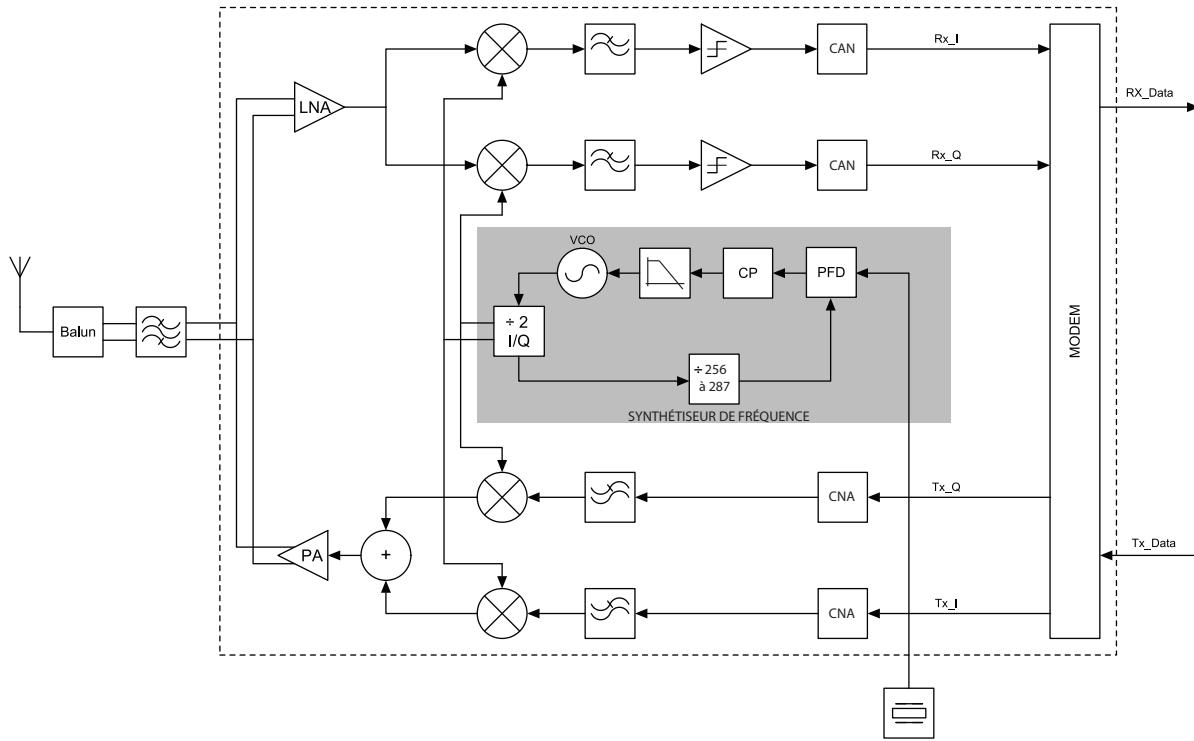

| FIGURE I.1   | Architecture proposée du transmetteur/récepteur RF implantable. . . . .                        | 123 |

| FIGURE II.1  | Efficacité de transconductance $g_m/I_D$ en fonction du coefficient d'inversion $IC$ . . . . . | 128 |

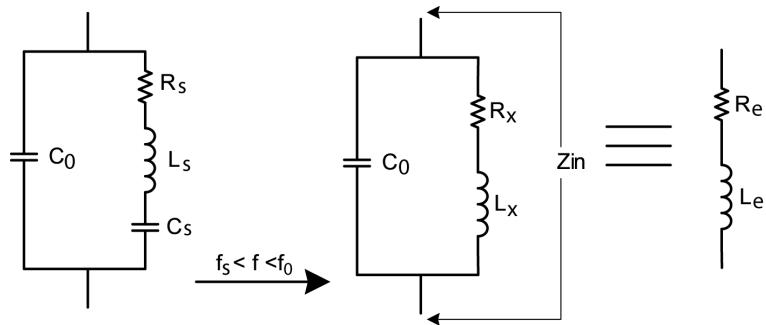

| FIGURE III.1 | Modèle électrique équivalent d'un résonateur SAW. . . . .                                      | 131 |

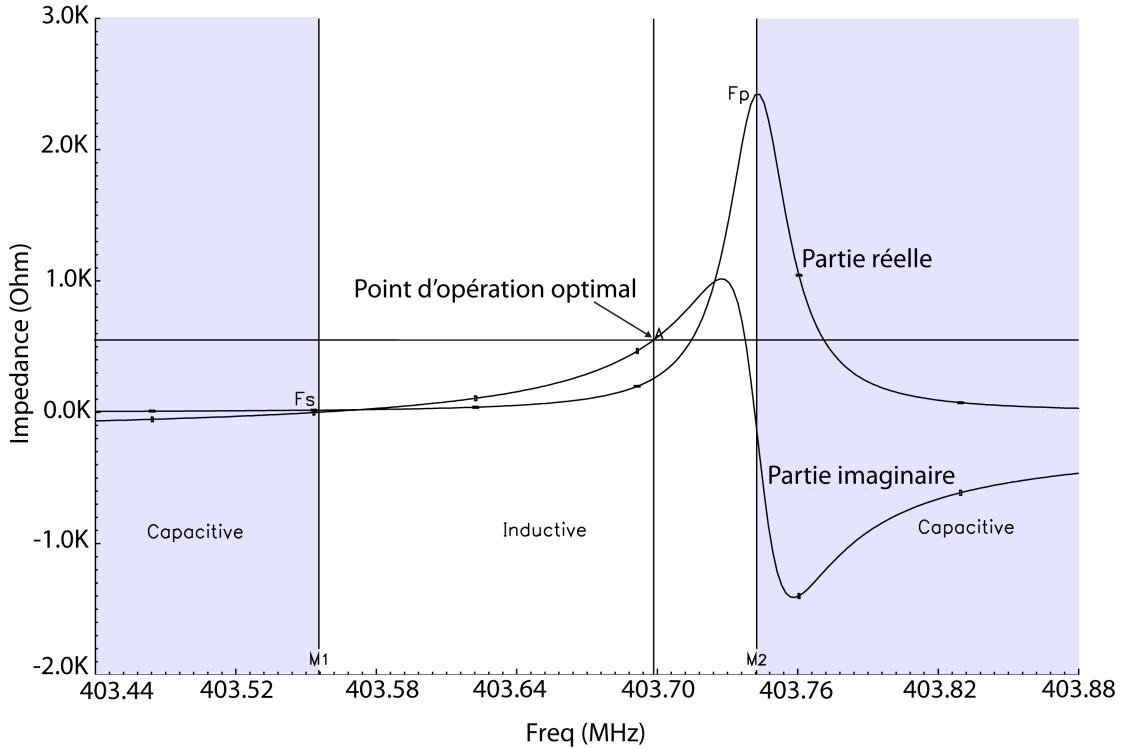

| FIGURE III.2 | Impédance différentielle du résonateur SAW. . . . .                                            | 132 |

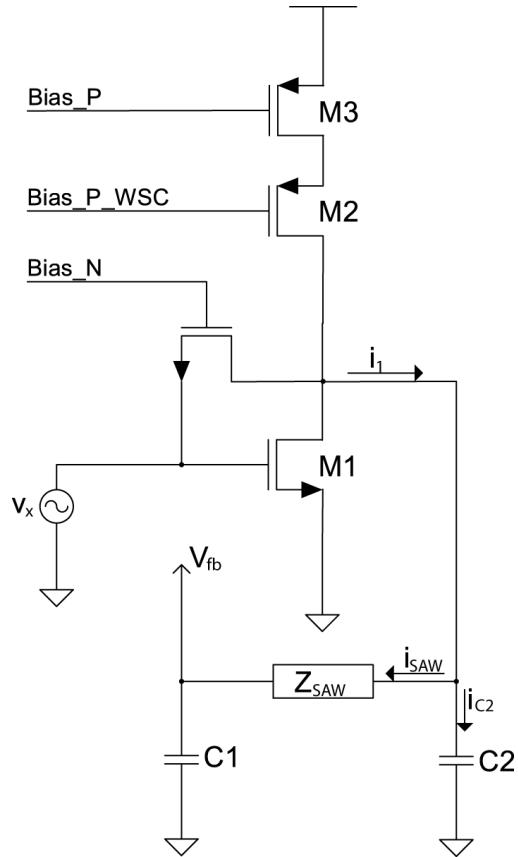

| FIGURE III.3 | Calcul du gain de boucle de l'amplificateur utilisé dans l'oscillateur de type Pierce. . . . . | 133 |

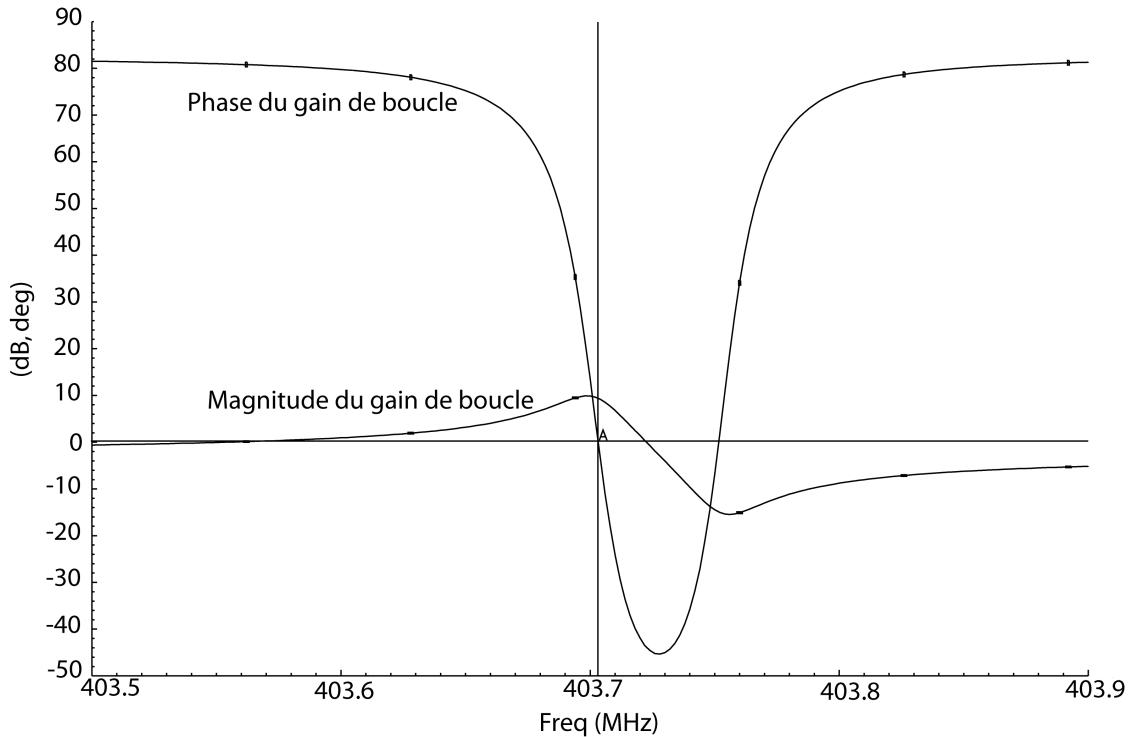

| FIGURE III.4 | Valeur absolue et phase du gain de boucle de l'oscillateur SAW. . . . .                        | 135 |

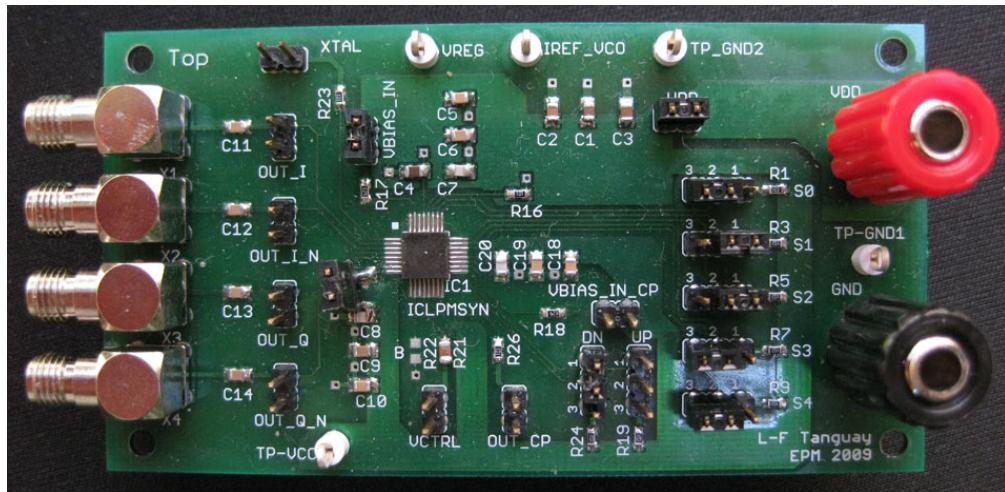

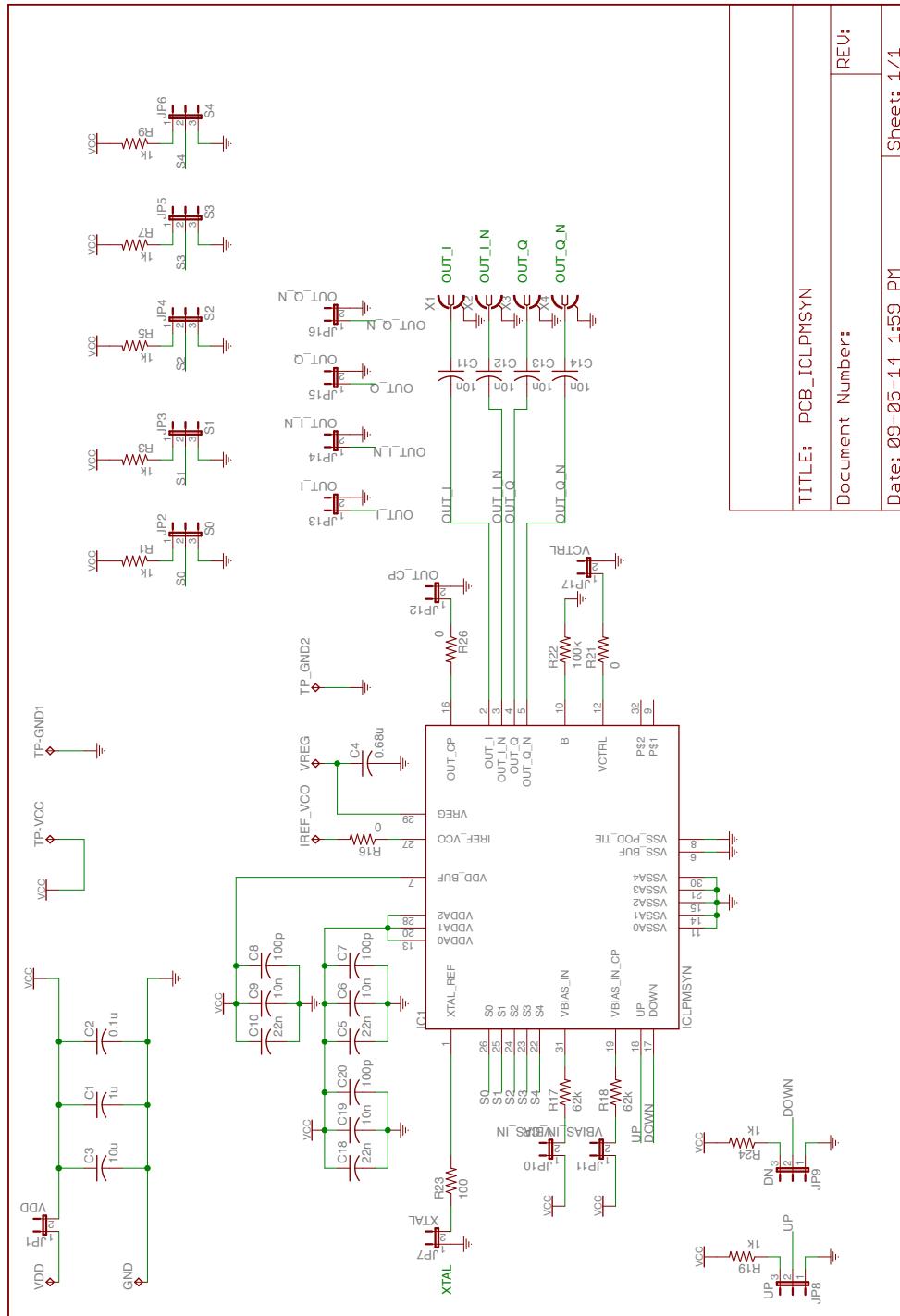

| FIGURE IV.1  | Circuit imprimé de validation du synthétiseur de fréquences. . . . .                           | 136 |

| FIGURE IV.2  | Schéma électrique du circuit imprimé de validation. . . . .                                    | 137 |

## LISTE DES ACRONYMES ET DES SYMBOLES

### **Acronymes**

|            |                                                              |

|------------|--------------------------------------------------------------|

| ASK        | Amplitude Shift Keying                                       |

| BAW        | Bulk Acoustic Wave                                           |

| BER        | Bit Error Rate                                               |

| BSN        | Body Sensor Networks                                         |

| CAN        | Convertisseur Analogique à Numérique                         |

| CML        | Current Mode Logic                                           |

| CMOS       | Complementary Metal-Oxide Semiconductor                      |

| CNA        | Convertisseur Numérique à Analogique                         |

| CP         | Pompe de charges                                             |

| DC         | Courant continu                                              |

| DECT       | Digital Enhanced Cordless Telecommunications                 |

| DIBL       | Drain Induced Barrier Lowering                               |

| EEG        | Electro-encéphalogramme                                      |

| FBAR       | Film Bulk Acoustic Resonator                                 |

| FM         | Modulation de fréquence                                      |

| FSK        | Frequency Shift Keying                                       |

| GMSK       | Gaussian Minimum Shift Keying                                |

| GSM        | Global System for Mobile communications                      |

| ICL        | Inductive Coupled Link                                       |

| IFP        | Interstitial Fluid Pressure                                  |

| ISM        | Industrielle, Scientifique et Médicale (Bande de fréquences) |

| <i>I/Q</i> | Composantes en phase et en quadrature                        |

| LSK        | Load Shift Keying                                            |

| LO         | Oscillateur Local                                            |

| MEMS       | Micro-electromechanical Systems                              |

| MHz        | Mégahertz                                                    |

| MICS       | Medical Implant Communication System                         |

| MOS        | Metal Oxide Semiconductor                                    |

| MSK        | Minimum Shift Keying                                         |

| OOK        | On-Off Keying                                                |

| PC         | Personal computer                                            |

| PFD        | Détecteur de Phase-Fréquence                                 |

|      |                                  |

|------|----------------------------------|

| PLL  | Phase-Locked Loop                |

| ppm  | Parties par Million              |

| PSK  | Phase Shift Keying               |

| RF   | Radiofréquence                   |

| RFIC | Circuit Intégré Radiofréquence   |

| RMS  | Root Mean Squared                |

| RX   | Récepteur                        |

| SAW  | Surface Acoustic Wave            |

| SNR  | Rapport signal à bruit           |

| TX   | Transmetteur                     |

| UHF  | Ultra-High Frequency             |

| VCO  | Oscillateur Contrôlé par Voltage |

## Symboles

|                    |                                                     |

|--------------------|-----------------------------------------------------|

| $\Delta\Sigma$     | Delta-Sigma                                         |

| $\epsilon_0$       | Permittivité du vide                                |

| $\epsilon_r$       | Permittivité relative                               |

| $f$                | Fréquence (Hz)                                      |

| $g_m$              | Transconductance d'un transistor MOS                |

| $K_{PFD}$          | Gain de la combinaison PFD/CP                       |

| $K_{VCO}$          | Gain du VCO                                         |

| $\lambda$          | Longueur d'onde                                     |

| $I_D$              | Courant de drain d'un transistor MOS                |

| $\mu_r$            | Perméabilité magnétique relative                    |

| $\mu_0$            | Perméabilité magnétique du vide                     |

| $PM$               | Marge de phase                                      |

| $Q$                | Facteur de qualité                                  |

| $S_\nu(\omega)$    | Densité spectrale de puissance du signal de tension |

| $S_\theta(\omega)$ | Densité spectrale de puissance du signal de phase   |

| $\omega$           | Fréquence angulaire                                 |

| $\omega_{-3dB}$    | Fréquence de -3 dB en boucle fermée                 |

## LISTE DES TABLEAUX

|             |                                                                                                                                                                          |     |

|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| TABLEAU 2.1 | Résumé des spécifications requises du synthétiseur de fréquences proposé.                                                                                                | 33  |

| TABLEAU 2.2 | Choix de conception du synthétiseur de fréquences. . . . .                                                                                                               | 34  |

| TABLEAU 4.1 | Performances de la pompe de charges proposée. . . . .                                                                                                                    | 66  |

| TABLEAU 5.1 | Valeurs des composants du modèle équivalent de l'inductance. . . . .                                                                                                     | 80  |

| TABLEAU 5.2 | Résultats des analyses Monte Carlo pour les deux implémentations de LC-VCO. . . . .                                                                                      | 88  |

| TABLEAU 5.3 | Comparaison des performances du LC-VCO tolérant aux variations de procédé proposé avec celles de LC-VCOs publiés récemment. . . . .                                      | 89  |

| TABLEAU 6.1 | Définition des ports d'entrées et sorties du circuit intégré. . . . .                                                                                                    | 101 |

| TABLEAU 6.2 | Résumé des performances du synthétiseur de fréquences. . . . .                                                                                                           | 105 |

| TABLEAU 6.3 | Comparaison de la puissance consommée par le synthétiseur proposé avec celle des synthétiseurs d'architecture similaire récemment présentés dans la littérature. . . . . | 106 |

| TABLEAU I.1 | Budget de puissance du lien RF proposé. . . . .                                                                                                                          | 121 |

## LISTE DES ANNEXES

|            |                                                                                                   |     |

|------------|---------------------------------------------------------------------------------------------------|-----|

| ANNEXE I   | <b>ANALYSE SYSTÈME . . . . .</b>                                                                  | 119 |

| I.1        | Bande de fréquence et méthode de modulation . . . . .                                             | 119 |

| I.1.1      | Bande de fréquence visée . . . . .                                                                | 119 |

| I.1.2      | Méthode de modulation . . . . .                                                                   | 120 |

| I.2        | Budget de puissance proposé pour le lien RF . . . . .                                             | 120 |

| I.2.1      | Rapport signal à bruit requis au récepteur . . . . .                                              | 122 |

| I.3        | Architecture de transmetteur/récepteur RF proposée . . . . .                                      | 122 |

| I.3.1      | Performances requises . . . . .                                                                   | 122 |

| I.3.2      | Figure de bruit . . . . .                                                                         | 123 |

| I.3.3      | Linéarité du récepteur . . . . .                                                                  | 124 |

| I.3.4      | Plage dynamique du récepteur . . . . .                                                            | 124 |

| I.3.5      | Bruit de phase . . . . .                                                                          | 125 |

| ANNEXE II  | <b>MÉTHODOLOGIE DE CONCEPTION DE CIRCUITS ANALOGIQUES ET RF À FAIBLE CONSOMMATION . . . . .</b>   | 126 |

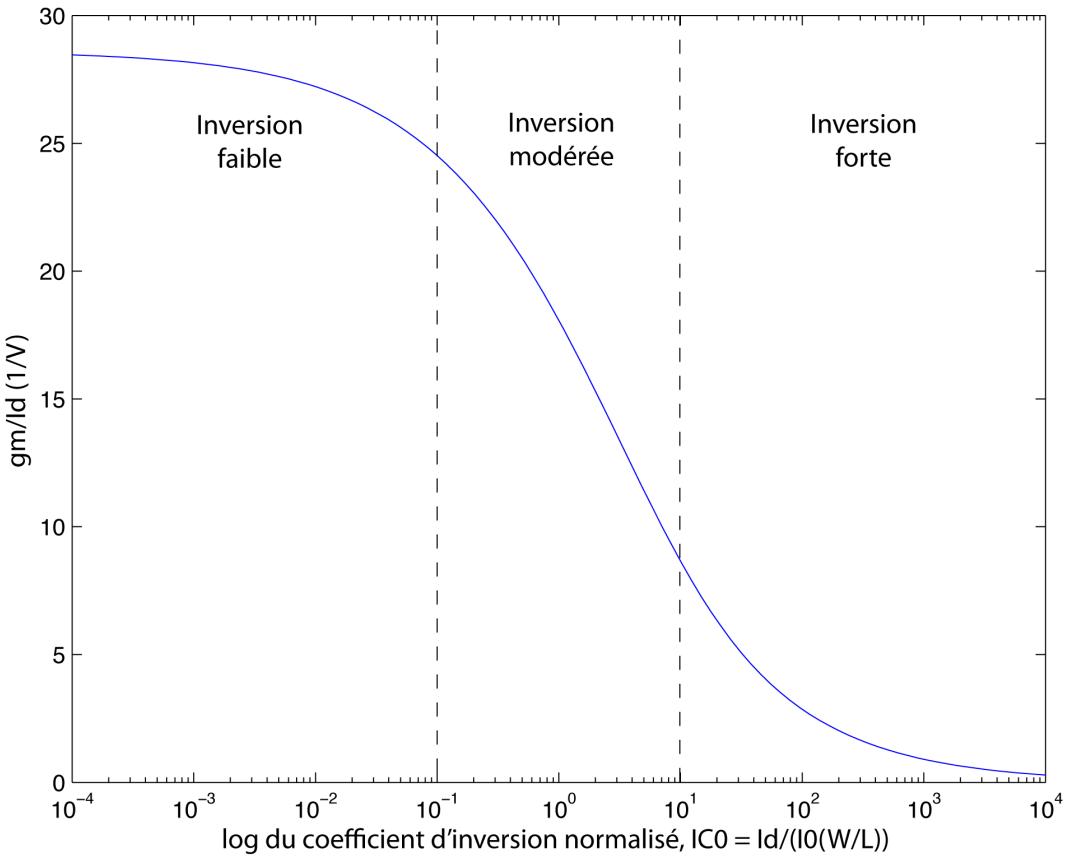

| II.1       | Méthodologie $g_m/I_D$ . . . . .                                                                  | 127 |

| II.1.1     | Reformulation des différents paramètres de conception . . . . .                                   | 129 |

| II.1.2     | Étapes de conception pour les circuits RF faible consommation . . . . .                           | 130 |

| ANNEXE III | <b>POINT D'OPÉRATION OPTIMAL D'UN RÉSONATEUR SAW DANS UN OSCILLATEUR DE TYPE PIERCE . . . . .</b> | 131 |

| III.1      | Conception d'un oscillateur de type Pierce basé sur un résonateur SAW . . . . .                   | 131 |

| III.2      | Résultats et conclusions . . . . .                                                                | 134 |

| ANNEXE IV  | <b>CIRCUIT IMPRIMÉ POUR LA CARACTÉRISATION DU SYNTHÉTISEUR . . . . .</b>                          | 136 |

| ANNEXE V   | <b>MODÈLES VERILOG-A DES MODULES DU SYNTHÉTISEUR DE FRÉQUENCES . . . . .</b>                      | 138 |

## CHAPITRE 1

### INTRODUCTION

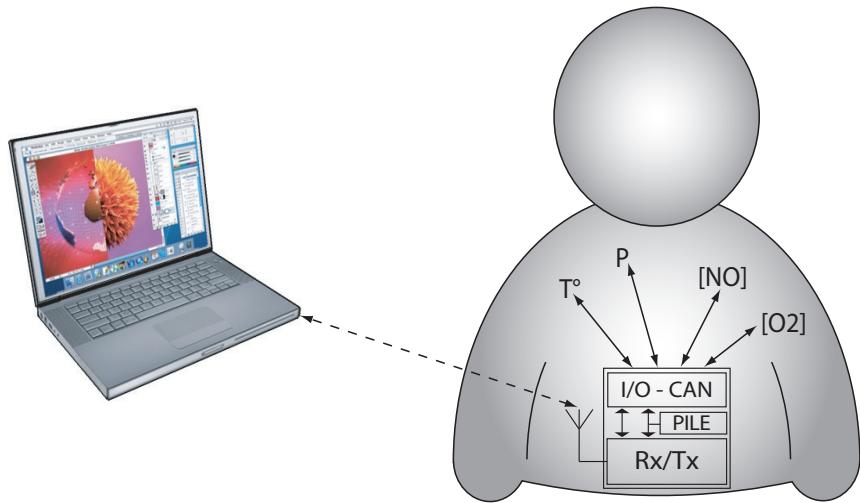

La possibilité d'utiliser la technologie CMOS pour intégrer des circuits analogiques et radiofréquences (RF), des modules de traitement de signal numériques, et même certains types de capteurs sur une même puce suscite depuis quelques années un vif intérêt dans le domaine des réseaux de capteurs et leurs applications [1]. Les noeuds de ces réseaux de capteurs intègrent généralement une source d'énergie, un microcontrôleur et de la mémoire, un convertisseur analogique-à-numérique (CAN), un ou plusieurs capteurs, ainsi qu'un transmetteur/récepteur sans fil afin de communiquer avec une station de traitement distante [2, 3]. Dans le domaine du génie biomédical, ces microsystèmes sans fil présentent un énorme potentiel pour la recherche médicale où leur implantation potentielle dans le corps humain ouvre la voie à des applications fascinantes. D'ailleurs, des progrès impressionnantes ont été accomplis dans l'utilisation conjointe de la technologie CMOS et des MEMS (*Microelectromechanical Systems*) pour la réalisation de biocapteurs intégrés [4]. En effet, les techniques de microfabrication récentes rendent possible la conception de biocapteurs de taille minimale présentant un potentiel certain pour la surveillance *in vivo* de paramètres biologiques tels que la température [5], la pression [6], le pH [7], les concentrations d'oxygène [8] et d'oxyde d'azote [9], pour ne nommer que ceux-ci.

#### 1.1 Les microsystèmes implantables pour la recherche médicale

La recherche sur l'arthrite et le cancer, qui font partie de la grande famille des maladies auto-immunes, bénéficierait grandement de la surveillance *in vivo* en temps réel de divers paramètres biologiques à l'aide d'un microsystème de capteurs implanté dans le corps, tel qu'illustré à la figure 1.1. La surveillance de ces paramètres au niveau de l'articulation ou même de l'intérieur d'une tumeur pourrait grandement contribuer à la compréhension de ces maladies et à l'évaluation du niveau de réponse à un traitement [10]. Parmi les paramètres d'intérêt pour la recherche médicale, mentionnons la concentration d'oxyde d'azote (NO), qui est reconnu pour jouer un rôle clé dans les fonctions physiologiques et pathologiques reliées à la réponse immunitaire des maladies inflammatoires telles que le cancer et l'arthrite rhumatoïde [11, 12]. De même, une meilleure évaluation du taux d'oxygénéation dans une tumeur pourrait mener à la découverte de marqueurs aidant au diagnostic de la maladie, et pour l'élaboration de nouvelles méthodes de thérapie [13]. Un autre paramètre dont la mesure *in vivo* serait d'intérêt est la température, car cela permettrait d'identifier

FIGURE 1.1 Microsystème sans fil implantable pour la surveillance de paramètres biologiques.

des changements localisés associés à l'inflammation d'une articulation ou d'une tumeur. De même, la mesure du pH permettrait d'identifier la présence de conditions pathologiques associées à un niveau de pH anormal, et la mesure du gradient de pH extra-cellulaire dans une tumeur aiderait à évaluer l'efficacité d'un médicament et l'évolution de la maladie [14]. La mesure de la pression serait également souhaitable car la présence d'une tumeur entraîne une augmentation anormale de la pression du fluide intersticiel (*Interstitial Fluid Pressure - IFP*), qui serait une barrière au transport de macromolécules de grande taille telles que les agents thérapeutiques utilisés lors des traitements [15]. Enfin, il a été démontré que les changements des propriétés des tissus affectés par une tumeur modifient leur impédance électrique. Ceci, encore une fois, pourrait résulter en un outil utile pour la surveillance de l'évolution de la maladie ou l'impact d'une médication [16].

La recherche sur l'épilepsie pourrait également profiter de ces microsystèmes sans-fil implantables, car ceux-ci pourraient permettre la détection, voire même la prévention du déclenchement d'une crise d'épilepsie [17, 18]. Un ou plusieurs noeuds de capteurs implantés enregistreraient l'EEG intracrânien en utilisant des sondes neuronales à titre de capteurs, et les données seraient recueillies par un système portable externe dans lequel serait implémenté un algorithme de détection de crise. Lorsqu'une crise serait sur le point de se déclencher, le ou les implants recevraient l'alerte et appliqueraient un traitement local approprié ; que ce soit une stimulation électrique, du refroidissement local, ou l'administration d'un médicament [19]. Enfin, la possibilité de construire de tels microsystèmes sans fil dédiés à la surveillance de paramètres biologiques serait un pas en avant vers l'implémentation de réseaux de capteurs implantables pour les soins de santé à domicile, comme par exemple les *Body Sensor Networks*, ou BSN [20]. Lorsque la technologie des capteurs utilisés pour la mesure de paramètres biologiques sera mature et que des systèmes de communication sans

fil à consommation ultra faible seront disponibles, il est raisonnable de croire que les BSN auront un impact considérable sur les services de soins de santé en général. Par exemple, les BSN pourront être utilisés pour effectuer le suivi post chirurgical ainsi que la prévention de maladies chez les patients à risque [21]. Toutefois, l'implémentation de tels réseaux de capteurs sans fil implantables présente des défis techniques énormes, que ce soit en termes d'autonomie énergétique, de niveau d'intégration, de fiabilité, ou encore de bio-compatibilité. Des multiples difficultés posées par un projet de cette envergure, celles reliées à l'implémentation d'un lien de communication sans fil à consommation ultra faible sont abordées dans le cadre de cette thèse, et des pistes de solutions sont présentées.

## 1.2 Liens RF à faible consommation de puissance pour les microsystèmes implantables

L'utilisation de câbles transcutanés entre le microsystème implanté et la station de traitement externe augmente significativement les risques d'infection en plus d'être encombrante pour le patient. L'utilisation d'un lien sans fil pour la transmission des données est donc fortement désirable. Toutefois, mesurer les paramètres biologiques *in situ* et transmettre les données à l'aide d'un lien sans fil présentent d'énormes défis techniques en termes d'intégration et de consommation d'énergie. Une solution qui est actuellement utilisée consiste à utiliser un lien inductif couplé (*Inductive Coupled Link - ICL*) entre le dispositif implanté et la station de traitement externe. Ce type de lien sans fil permet à la fois de fournir l'énergie à l'implant et d'établir un lien de communication bidirectionnel basé sur la modulation de charge (*Load Shift Keying - LSK*) [22]. Ces liens inductifs opèrent généralement dans la bande de fréquences Industrielle, Scientifique et Médicale (ISM) de 13.56 MHz. Ces systèmes sont robustes et fiables, mais la très courte portée du champ magnétique alternatif, combinée avec la quantité limitée de puissance disponible à l'implant, requiert souvent que le contrôleur soit placé directement au dessus de celui-ci, en contact direct avec la peau du patient [23].

### 1.2.1 Communications sans fil aux fréquences UHF

Dans le but de surmonter les limitations inhérentes à la courte portée d'opération des liens inductifs, tout en offrant l'opportunité d'utiliser des antennes beaucoup plus compactes et un taux transfert plus élevé, de plus en plus de systèmes implantables utilisent les bandes de fréquences UHF (*Ultra High Frequency*) MICS de 402-405 MHz, et les bandes ISM de 902-928 MHz et 2.4 GHz [24]. Typiquement, un lien RF destiné aux communications avec un microsystème implantable consiste en deux modules principaux : 1) une station de contrôle située à l'extérieur du corps du patient qui a

pour rôle de gérer les communications avec l'implant et de recevoir les données de celui-ci, et 2) un microsystème implantable qui effectue les mesures des paramètres biologiques et transmet celles-ci vers la base de traitement externe où elles seront éventuellement traitées et sauvegardées. Étant donné que le transfert d'énergie aux fréquences UHF est relativement inefficace, le microsystème implantable nécessite l'utilisation de piles miniatures, soit primaires ou rechargeables, et doit donc avoir une autonomie aussi prolongée que possible.

Dans les applications de réseaux de capteurs sans fil, ce sont les circuits RF qui déterminent la consommation de puissance totale du système et, par conséquent, la durée de vie des piles. Il est alors avantageux que le transmetteur/récepteur RF opère avec un facteur d'utilisation (*duty cycle*) minimal : c'est-à-dire que les paramètres biologiques d'intérêt soient mesurés et enregistrés à même le microsystème implanté, puis transmis vers la station externe par paquets et de façon sporadique. Le transmetteur/récepteur est alors désactivé la majorité du temps, et est activé lorsque des paquets de données doivent être transmis. Un débit de données de l'ordre de 100 kb/s est considéré comme étant optimal afin de diminuer la consommation de puissance en transmettant les données par paquets et donc minimiser la durée où l'amplificateur de puissance est activé [25]. Ce taux de transmission de données est très avantageux en terme de consommation de puissance si l'on considère le compromis entre le débit de données et le facteur d'utilisation du transmetteur/récepteur. Un débit très élevé de l'ordre du Mb/s implique une largeur de bande élevée et une consommation de puissance augmentant de façon considérable durant la transmission des paquets de données afin de maintenir un SNR suffisant au démodulateur. À l'opposé, pour une quantité de données égale à transmettre, un débit de donnée très faible requiert que l'amplificateur de puissance et l'oscillateur local soient actifs pratiquement en permanence, résultant en une consommation de puissance significative.

### 1.2.2 Génération des fréquences porteuses RF

Le transmetteur/récepteur du microsystème implantable doit opérer à une fréquence *exactement* égale à celle de la station de traitement externe afin qu'un lien de communication puisse être établi. L'utilisation d'une fréquence porteuse RF précise est un prérequis fondamental des radios à bande étroite. Par exemple, l'utilisation d'un oscillateur à résonateur *LC* oscillant librement sans être stabilisé à une fréquence de référence résulterait assurément en un lien de communication RF mal syntonisé en considérant les variations de procédé et de fabrication. Le taux d'erreurs de transmission sur les données (BER) introduit serait inacceptable, en supposant que le système réussisse à établir une communication. Les approches existantes pour la génération d'une fréquence porteuse RF stable sont les suivantes :

1. La porteuse est générée directement en RF à l'aide d'un oscillateur basé sur un résonateur micromachiné tel qu'un résonateur SAW (*Surface Acoustic Wave*), un résonateur BAW (*Bulk Acoustic Wave*), ou encore un résonateur microélectromécanique MEMS.

2. Une fréquence porteuse précise et stable est générée à l'aide d'un synthétiseur de fréquences qui stabilise la sortie d'un oscillateur RF sur la fréquence d'un oscillateur à cristal de référence.

La première approche permet d'atteindre des niveaux de consommation de puissance extrêmement faible selon le type de résonateur utilisé. Par exemple, un oscillateur à 1.9 GHz basé sur un microrésonateur FBAR (*Film Bulk Acoustic Resonator*) offrant une consommation de puissance inférieure à  $100 \mu\text{W}$  a été présenté par des chercheurs de l'Université de Californie à Berkeley [26]. Toutefois, ce type d'oscillateur ne génère qu'une fréquence unique et précise, fixée par le résonateur dont le facteur de qualité  $Q$  est très élevé, et cette fréquence ne peut être modifiée que de quelques ppm. Ceci signifie que seules des méthodes de modulation de faible performance comme OOK et ASK peuvent être utilisées. De plus, la fréquence de résonance de ces microrésonateurs ne concorde pas avec les bandes de fréquences actuellement disponibles pour les implants biomédicaux.

Les résonateurs microélectromécaniques dont la fréquence de résonance concorde avec la bande ISM de 902-928 MHz sont de type SAW (*Surface Acoustic Wave*). Le facteur de qualité très élevé laisse croire, à tort, qu'ils peuvent être utilisés pour concevoir des oscillateurs à consommation de puissance ultra faible. Nous avons implémenté un oscillateur de type Pierce basé sur un résonateur SAW durant la phase exploratoire de cette recherche, et nous avons établi une relation permettant de déterminer le point d'opération optimal en terme de consommation de puissance [27]. Une version abrégée de cet article est présentée à l'annexe III. Nous avons trouvé que la composante inductive à la résonance des résonateurs SAW est relativement faible, ce qui nécessite l'utilisation de condensateurs de grande valeur dans un oscillateur typique de type Pierce ou Colpitts, ce qui a un impact négatif sur la consommation de puissance. Même lorsque les résonateurs SAW sont utilisés à leur point d'opération optimal en terme de consommation de puissance, le courant minimal que doivent fournir les transistors pour soutenir les oscillations est supérieur à  $300 \mu\text{A}$ . En rappelant que l'utilisation de ce type de résonateur ne permet la génération que d'une seule fréquence et que celle-ci ne peut pas être modulée, cette solution s'avère peu attrayante.

La consommation de puissance d'un synthétiseur de fréquences est plus élevée étant donné le niveau de complexité supérieur, mais cette approche permet la génération de plusieurs fréquences différentes, ce qui risque de s'avérer une nécessité pour opérer dans une bande de fréquence très dense en utilisateurs telles que les bandes ISM. De plus, l'utilisation d'un synthétiseur de fréquences permet l'utilisation de méthodes de modulation de fréquence et de phase telles que FSK et QPSK qui sont nettement plus efficaces et robustes que la modulation d'amplitude, et qui per-

mettent aussi d'atteindre des débits de transmission largement supérieurs. Ainsi, il est raisonnable de supposer que la consommation de puissance *moyenne* d'un synthétiseur de fréquences utilisé dans un microsystème implantable dont le facteur d'utilisation de l'ordre de 1% pourrait même être inférieure à celle d'un oscillateur à résonateur FBAR devant opérer en permanence.

### 1.2.3 Transmetteurs/récepteurs existants

Les transmetteurs/récepteurs à basse consommation et à débit de données moyen destinés aux systèmes implantables et aux réseaux de capteurs requièrent des architectures qui diffèrent de celles retrouvées dans les systèmes haute performance destinés aux applications telles GSM et DECT. Malgré le fait que les domaines des microsystèmes implantables et des réseaux de capteurs en général soient relativement récents, un certain nombre d'architectures intéressantes de transmetteurs et de récepteurs RF à faible consommation ont été proposées. Dans le milieu académique, un transmetteur implantable sans-fil pour la transmission de signaux neuronaux a été présenté par des chercheurs de UCLA [19]. Leur système utilise un LC-VCO de 3.2 GHz modulé en fréquence de façon analogique à titre de transmetteur et un analyseur de spectre externe pour la réception et la démodulation des signaux FM. La portée de communication de leur système est de 1 m, et la consommation de puissance du système est d'environ 8 mW. Des chercheurs de l'université de l'Utah ont présenté un système d'enregistrement neuronal implantable qui utilise un transmetteur FM opérant à 433 MHz utilisant aussi un LC-VCO [17]. Le résonateur du LC-VCO utilise une inductance externe de 47 nH qui sert également d'antenne de transmission. Implémenté en technologie CMOS 0.5  $\mu$ m, le transmetteur consomme un total de 465  $\mu$ W.

Des chercheurs de l'Université de Californie à Berkeley ont présenté un transmetteur/récepteur FSK à faible fréquence intermédiaire (*Low IF*) à ultra faible consommation opérant à 900 MHz [28]. Le récepteur affiche une sensibilité de -94 dBm pour un débit de 20 kbps et une consommation de puissance de 1.2 mW. La puissance transmise est de 250  $\mu$ W, pour une consommation de 1.3 mW en transmission. Dans la même institution, d'autres chercheurs ont présenté un transmetteur/récepteur à canal unique à consommation ultra faible basé sur l'architecture à super régénération [29]. Le transmetteur utilise la modulation OOK, et consiste en un oscillateur de type Pierce stabilisé à l'aide d'un résonateur BAW afin de générer une porteuse très stable directement en RF. Un amplificateur classe C permet de transmettre une puissance de 375  $\mu$ W, pour une consommation de puissance en transmission de 1.6 mW. Le récepteur, basé sur l'architecture à super régénération, dissipe 400  $\mu$ W sous une alimentation de 1 V, et offre une sensibilité de -100.5 dBm à un débit de 5 kbps.

Un transmetteur/récepteur commercial à consommation ultra faible développé pour les réseaux

de capteurs implantables a été présenté par la compagnie Toumaz Technology [30]. Ce système, opérant dans la bande ISM européenne de 870/900 MHz, utilise un modulateur et démodulateur I/Q GMSK, et utilise un synthétiseur de fréquences verouillé à un oscillateur à cristal externe. Le débit maximal est de 160 kbps, la sensibilité du récepteur est de -86 dBm, la puissance de sortie est de -10 dBm, et le transmetteur/récepteur consomme 9 mW. Enfin, un autre transmetteur/récepteur commercial opérant dans les bandes 402-405 MHz MICS et 433 MHz ISM est offert pour les applications médicales implantables [31]. Le module de communication utilise un canal de réveil nécessitant un courant ultra faible (250 nA) opérant à 2.45 GHz. Le synthétiseur de fréquences permet de sélectionner 10 canaux dans la bande 402-405 MHz et 2 canaux dans la bande 433 MHz. Conçu en technologie CMOS 0.18  $\mu\text{m}$ , le transmetteur/récepteur permet un débit maximal de 800 kbps dans la bande ISM et une portée de 2 m, pour une consommation de courant inférieure à 5.5 mA sous une tension d'alimentation variant entre 2.1 V et 3.5 V.

### 1.3 Procédés CMOS nanométriques : opportunités et défis

Grâce à leur potentiel d'intégration sans égal et à la possibilité d'utiliser ces technologies pour réaliser des circuits consommant très peu d'énergie, les procédés CMOS nanométriques présentent maintenant une solution intéressante pour combiner les circuits analogiques, RF et numériques sur une même puce. La réduction d'échelle de la technologie CMOS résulte en une augmentation significative de la transconductance des transistors de même que des fréquences de transition supérieures à 100 GHz. Dans les noeuds technologiques antérieurs, les transistors utilisés dans les circuits RF devaient être polarisés en inversion forte afin d'obtenir une fréquence de transition  $f_t$  convenable avec, en conséquence, une efficacité de transconductance ( $g_m/I_D$ ) faible [32]. L'intérêt d'utiliser un procédé CMOS nanométrique pour les applications RF à ultra faible consommation réside dans le fait que  $f_t$  et  $f_{MAX}$  sont si élevées que les transistors peuvent être opérés en inversion faible et modérée au delà de 1 GHz, et ce avec un gain raisonnable. Les transistors ont donc une efficacité de transconductance  $g_m/I_D$  largement supérieure, nécessitant un courant de drain plus faible pour obtenir un gain de transconductance donné, ce qui résulte en une diminution significative de la puissance consommée.

Toutefois, la réduction d'échelle des procédés CMOS digitaux est aussi accompagnée d'une réduction importante de l'impédance de sortie des transistors et du gain de tension intrinsèque. Ceci est principalement dû à l'effet des implants halo utilisés pour contrôler l'effet canal court (*short-channel effect*) et l'effet DIBL (*Drain-Induced Barrier Lowering*) [33]. Alors que les circuits CMOS numériques en sont très peu affectés, la réduction de l'impédance de sortie des transistors combinée avec la diminution de la tension d'alimentation a un impact majeur sur les performances

des circuits analogiques, et par conséquent sur leur conception. Une autre problématique provient de la variabilité des propriétés électriques des transistors nanométriques causées par les limitations physiques fondamentales telles que les pertes de dopants, leur fluctuation statistique sur les dispositifs de taille minimale, ainsi que les variations de l'épaisseur d'oxyde de grille [33]. En fait, les variations statistiques des procédés CMOS ont empiré à chaque nouveau noeud technologique, et sont devenues un défi majeur dans les noeuds technologiques nanométriques [34]. Un des objectifs de cette thèse sous-jacent à l'utilisation d'un procédé CMOS nanométrique est l'implémentation de nouvelles architectures de circuits CMOS nanométriques analogiques et RF permettant de mitiger les difficultés mentionnées précédemment.

## 1.4 Objectifs de la recherche

Les travaux de cette thèse portent sur la conception et l'implémentation de topologies de circuits pour la synthèse de fréquence compatibles avec une consommation de puissance inférieure au mW et une tension d'alimentation très faible. Un synthétiseur de fréquences à diviseur entier sera implanté en utilisant un procédé CMOS nanométrique et une méthodologie de conception de circuits analogiques et RF développée spécialement pour les applications à basse consommation de puissance. De nouvelles architectures de composantes analogiques et RF telles que le VCO, l'inductance et le varactor intégrés, la pompe de charges et le diviseur de fréquence numérique seront étudiées. L'hypothèse de travail est que l'utilisation d'un procédé de fabrication CMOS nanométrique et l'application d'une méthodologie de conception dédiée aux circuits analogiques à consommation ultra faible permettra de réduire la consommation de puissance sous la barre de 1 mW. Nous profiterons de la fréquence de transition  $f_T$  très élevée des transistors nanométriques en opérant les transistors de tous les modules en inversion faible et modérée afin de minimiser la consommation de puissance, et ce de 0 Hz à 2 GHz.

Ce projet de recherche s'inscrit dans le cadre de la mise en oeuvre d'une plateforme RF micro puissance permettant d'établir un lien de communications sans fil entre un microsystème implantable et une station de traitement externe, tel qu'ilustré à la figure 1.1. L'analyse au niveau système de la plateforme RF implantable est présentée à l'annexe I. Un survol des contraintes particulières qui doivent être prises en compte lors de la conception des modules RF est présenté, et les choix de conception tels que la fréquence de la porteuse, le débit de données et le type de modulation y sont discutés. Un budget de puissance du lien RF est présenté et l'architecture d'un transmetteur/récepteur RF à consommation ultra faible est proposée. Finalement, les différents critères de performances de ce récepteur/transmetteur sont calculés.

## 1.5 Contributions originales découlant de cette thèse

Les travaux de recherche effectués dans le cadre de cette thèse ont permis de générer de nouvelles architectures de circuits analogiques et RF afin de limiter la consommation de puissance tout en mitigeant les difficultés associées à la conception de circuits analogiques dans un procédé CMOS nanométrique. De façon spécifique, nous pouvons identifier les contributions originales suivantes :

1. Conception et simulation d'un oscillateur à consommation de puissance ultra-faible à l'aide d'un résonateur à onde acoustique de surface (SAW) en technologie CMOS 90-nm. La relation mathématique décrivant le point d'opération optimal en terme de consommation de puissance d'un tel résonateur basé sur sa réponse en fréquence a été développée. Ce travail a été présenté dans le cadre d'une conférence invitée à APPCAS 2006, intitulée "*Low Power SAW-Based Oscillator for an Implantable Multisensor Microsystem*" [27].

2. Un nouveau miroir de courant présentant une impédance de sortie très élevée destiné aux applications à faible tension d'alimentation a été conçu et fabriqué en technologie CMOS 90-nm. L'impédance de sortie du miroir de courant proposé est de l'ordre de  $g_m^2 r_o^3$ , soit d'un facteur  $g_m r_o$  plus élevée que celle du miroir de courant super-Wilson, où  $g_m$  et  $r_o$  sont respectivement la transconductance et la résistance incrémentale drain-source d'un transistor MOS. Ce miroir de courant a été présenté dans le cadre d'une conférence invitée à APPCAS 2008, intitulée "*A Very-High Output Impedance Current Mirror for Very-Low Voltage Biomedical Analog Circuits*" [35].

3. Une nouvelle architecture de pompe de charges CMOS destinée aux PLL à faible tension et faible puissance a été proposée et implémentée en technologie CMOS 90-nm. La configuration de pompe de charges proposée résulte en un courant de sortie dont la magnitude est constante et le non-appariement entre le courant  $I_{UP}$  et  $I_{DOWN}$  est minimal, tout en minimisant la consommation de puissance et la complexité. Cette pompe de charges a été présentée dans un article intitulé "*A Very-High Output Impedance Charge Pump for Low-Voltage Low-Power PLLs*" dans la revue *Microelectronics Journal* [36].

4. Un oscillateur contrôlé par tension avec résonateur *LC* (LC-VCO) minimisant l'impact des variations de procédé sur la consommation de puissance et le bruit de phase a été conçu et implanté en technologie CMOS 90-nm. L'approche utilisée consiste à alimenter le cœur du VCO à l'aide d'un régulateur de tension dont la valeur de la référence dépend des paramètres du procédé à l'endroit sur le circuit intégré où est situé le VCO. Cette nouvelle technique permettant de réduire l'impact des variations de procédé sur un LC-VCO a été présentée dans le cadre d'une conférence invitée à ICSICT 2008, intitulée "*Process Variation Tolerant LC-VCO Dedicated to Ultra-Low Power Biomedical RF Circuits*" [37].

5. Implémentation et validation expérimentale d'un synthétiseur de fréquences à diviseur entier à consommation de puissance ultra faible opérant dans la bande ISM de 902-928 MHz. Il permet la syntonisation de 7 canaux de 3.4 MHz de largeur, fournit les versions différentielles  $I/Q$  de la porteuse et offre un temps de démarrage de l'ordre de  $10 \mu s$ . Un prototype a été fabriqué à l'aide du procédé digital CMOS 90-nm 7M2T de STMicroelectronics. La consommation de puissance totale mesurée du synthétiseur, en excluant les tampons de sortie de test, est de  $640 \mu W$ ; environ un ordre de grandeur inférieure à celle de synthétiseurs d'architecture similaire récemment présentés dans la littérature.

Les résultats préliminaires de ces travaux ont été présentés dans le cadre d'une conférence invitée à ISSCS 2007, intitulée "*A Fully-Integrated 580  $\mu W$  ISM-Band Frequency Synthesizer for Implantable Medical Devices*" [38], puis dans un article invité intitulé "*An Ultra-Low Power ISM-Band Integer-N Frequency Synthesizer Dedicated to Implantable Medical Microsystems*" dans la revue *Analog Integrated Circuits and Signal Processing* [39]. Enfin, les résultats expérimentaux de la version finale du synthétiseur de fréquences à consommation ultra faible ont été présentés dans le cadre d'une conférence invitée à NEWCAS 2010, intitulée "*A 640  $\mu W$  Frequency Synthesizer Dedicated to Implantable Medical Microsystems in 90-nm CMOS*" [40].

## 1.6 Organisation de la thèse

Un synthétiseur de fréquences est composé de plusieurs modules distincts tels le VCO, la pompe de charges, le diviseur de fréquence, etc. Chacun de ces modules nécessite une attention particulière lors de la conception et fait appel à des domaines de spécialisation variés, allant de la microélectronique analogique aux circuits numériques à haute vitesse, en passant par les circuits intégrés radiofréquences (RFIC). Pour cette raison et par souci de clarté, chacun des chapitres de cette thèse regroupe un ou des modules du synthétiseur selon leur rôle, et un survol de la littérature associée à ce ou ces modules spécifiques y est présenté.