|                         | Design and Implementation of Integrated High Efficiency Low-voltage CMOS DC-DC Converters                                                                                                                                                                                          |

|-------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Auteur: Author:         | Omar Al-Terkawi Hasib                                                                                                                                                                                                                                                              |

| Date:                   | 2010                                                                                                                                                                                                                                                                               |

| Type:                   | Mémoire ou thèse / Dissertation or Thesis                                                                                                                                                                                                                                          |

| Référence:<br>Citation: | Al-Terkawi Hasib, O. (2010). Design and Implementation of Integrated High Efficiency Low-voltage CMOS DC-DC Converters [Mémoire de maîtrise, École Polytechnique de Montréal]. PolyPublie. <a href="https://publications.polymtl.ca/425/">https://publications.polymtl.ca/425/</a> |

# Document en libre accès dans PolyPublie Open Access document in PolyPublie

| URL de PolyPublie:<br>PolyPublie URL:    | https://publications.polymtl.ca/425/ |

|------------------------------------------|--------------------------------------|

| Directeurs de<br>recherche:<br>Advisors: | Mohamad Sawan, & Yvon Savaria        |

| Programme: Program:                      | Génie Électrique                     |

#### UNIVERSITÉ DE MONTRÉAL

# DESIGN AND IMPLEMENTATION OF INTEGRATED HIGH EFFICIENCY LOW-VOLTAGE CMOS DC-DC CONVERTERS

OMAR AL-TERKAWI HASIB DÉPARTEMENT DE GÉNIE ÉLECTRIQUE ÉCOLE POLYTECHNIQUE DE MONTRÉAL

MÉMOIRE PRÉSENTÉ EN VUE DE L'OBTENTION DU DIPLÔME DE MAÎTRISE ÈS SCIENCES APPLIQUÉES (GÉNIE ÉLECTRIQUE) DÉCEMBRE 2010

### UNIVERSITÉ DE MONTRÉAL

### ÉCOLE POLYTECHNIQUE DE MONTRÉAL

Ce mémoire intitulé:

# DESIGN AND IMPLEMENTATION OF INTEGRATED HIGH EFFICIENCY LOW-VOLTAGE CMOS DC-DC CONVERTERS

présenté par : M. <u>AL-TERKAWI HASIB Omar</u> en vue de l'obtention du diplôme de : <u>Maîtrise ès Sciences Appliquées</u> a été dûment accepté par le jury constitué de :

- M. AUDET Yves, Ph.D., président

- M. SAWAN Mohamad, Ph.D., membre et directeur de recherche

- M. SAVARIA Yvon, Ph.D., membre et co-directeur de recherche

- M. ZHU Guchuan, Doct., membre

To my dear mother, I can't be grateful enough...

## Acknowledgments

Writing this part of the thesis might prove to be a very difficult task for me. To include all the people who are responsible for me being here in few lines is almost impossible. First, I would like to thank God the Merciful for providing me with such a wonderful opportunity, surrounding me with an amazing group of people and keeping me in a good health and well-being. Among those amazing people are my parents who raised me to never quit and to keep learning and to pursue my dreams with all my heart. I am especially grateful to my mother who loved me and supported me unconditionally during all these years. Thank you Mom! I also thank the rest of my family for their continuous love, support and encouragements.

I would not be writing this thesis if it weren't for my inspiring professors. I would like to start by thanking my current director Prof. Mohamad Sawan for accepting me as his student and giving me the chance to purse my master's degree. His guidance and support are greatly appreciated. I would also like to thank my co-director Prof. Yvon Savaria for the time and effort he put in helping me complete this work and for tolerating my mistakes and the ridiculous amount of typos that I make. I'm also grateful for the teaching and encouragement I received from my undergraduate professors, especially Prof. Mohamed Zribi and Dr. Nabil Khachab.

I appreciated the kindness that I've seen from the people in my research group (Polystim). A special thank to Fayçal Mounaim who has been a great lab mate and friend during the two past years. His help and experience was invaluable in completing this work. My gratitude also goes to Sébastien Ethier and Guillaume Simard for sharing their experience and knowledge with me. I would also like to extend my thanks to our technical support Réjean Lepage and our secretary Marie-Yannick Laplante.

I would like to thank all of my friends. Each of them have contributed in building my current personality. I start by thanking Ahmad Haider for pushing me to apply to École Polytechnique de Montréal despite my poor knowledge in French. I would like to thank Omar Al-Naggar for teaching me how to be systematic in learning and presenting my ideas. My thanks goes to Ali-Akbar Samadani, Khadige Abboud and their family for opening the door to both their hearts and homes for me. I'm also grateful to the group of friends who organized a welcoming party each time I visited Kuwait and to the people who sent me encouragement emails during difficult times. More importantly, I would like to thank Ali

Al-Naggar, Mohamad Adly, Ahmad Boland and Afrah Lutfi for supporting me and for being my good friends.

Finally, I would like to acknowledge the financial support from the Natural Sciences and Engineering Research Council of Canada (NSERC), the Resmiq research network supported by the Fonds Québecois de la Recherche sur la Nature et les Technologies, and the products and services provided by CMC Microsystems that facilitated this research, including CAD tools and fabrication services.

### Résumé

De nos jours, les appareils portatifs sont utilisés dans plusieurs applications. Ils utilisent en général une batterie qui doit être remplacée ou rechargée régulièrement. Dans le cas d'applications biomédicales, la durée de vie de la batterie est un paramètre critique. Pour un appareil implantable, une longue durée de vie est un objectif primordial. Cet objectif est généralement atteint en réduisant la consommation de puissance des circuits constituant l'implant. Parmi les diverses techniques existantes qui permettent la réduction de la consommation en puissance des circuits CMOS, on retrouve la technique d'ajustement dynamique de la tension (dynamic voltage scaling - DVS). En réduisant la tension d'alimentation, la consommation totale des circuits peut être diminuée. Cependant cette technique ne peut être implémentée sans faire appel à des circuit dédiés à une gestion intelligente de l'énergie. Dans ce contexte, l'utilisation de convertisseurs de tension DC-DC devient nécessaire pour économiser la charge de la batterie. Mais pour garantir une réduction effective de la consommation globale, des convertisseurs DC-DC de haute efficacité doivent être utilisés. A cette contrainte se rajoute la miniaturisation en utilisant des circuits hautement intégrés pour les applications telles que les implants biomédicaux. Le défi réside dans la conception d'un convertisseur DC-DC totalement intégré tout en assurant une haute efficacité sur une grande plage de tension de sortie. De plus, les appareils tels que les implants électroniques fonctionnet souvent en mode de veille pour réduire la consommation, entrainant ainsi des variations conséquentes de la charge du convertisseur DC-DC. Ceci rajoute un défi supplémentaire pour le maintient d'une haute efficacité de la conversion DC-DC à faible charge.

Dans ce mémoire, nous présentons la conception détaillée d'un convertisseur DC-DC hautement efficace et totalement intégré dans une technologie CMOS à faible tension. Nous proposons une implémentation originale et totalement intégrée d'un convertisseur DC-DC à capacités commutés (switched capacitor - SC) opérant avec un contrôle asynchrone. L'efficacité du convertisseur est maintenue élevée en ajustant sa topologie et sa fréquence d'opération selon la charge. Le convertisseur SC DC-DC proposé utilise trois topologies distinctes pour réaliser trois taux de conversion différents. Ainsi, le convertisseur maintient une haute efficacité à différents niveaux de tensions de sortie. De plus, afin de réduire les pertes d'énergie, le contrôle asynchrone adapte la fréquence d'opération aux diverses conditions de charge. Ce contrôle est également capable d'adapter la taille des interrupteurs du convertisseur SC DC-DC pour améliorer encore plus l'efficacité de la conversion. Les résultats expérimentaux de ce travail confirment la théorie et les simulations conduites lors de la conception. Une puce

de  $1.5 \times 1.5 mm^2$  contenant le convertisseur proposé a été fabriqué en utilisant la technologie IBM CMOS  $0.13 \mu m$ . Le convertisseur est capable d'atteindre une efficacité maximale de 80% en fournissant une tension de sortie entre 0.3V et 1.1V à partir d'une entrée à 1.2V. Le convertisseur utilise un ensemble de condensateurs intégré dont la capacité totale est de 350pF pour fournir une puissance de sortie maximale de  $230 \mu W$ , ciblant ainsi de nombreuses applications à très faible puissance.

### Abstract

Today, battery-powered portable devices are used in many applications. In applications like biomedical implants, the battery life is a major concern. Since replacing the battery of an implant needs a surgical procedure, a long battery life is a goal that all implants try to achieve. This is normally done by reducing the power dissipation in the implant's circuitry. One of the various techniques that exist for reducing the power consumption in CMOS circuitry is the dynamic voltage scaling (DVS) technique. By reducing the supply voltage, the overall power consumption of the circuits can be decreased. This technique cannot be implemented without power management blocks. The use of DC-DC converters becomes a must to save battery power. The overall power reduction can be improved by introducing high efficiency DC-DC converters. Moreover, to provide patients with the most comfort, small integrated circuits should be used in applications such as biomedical implants.

The challenging aspect of designing integrated DC-DC converters is keeping the efficiency high while providing an adjustable output voltage. Additionally, devices such as electronic implants go in and out of stand-by mode to reduce power consumption. From the perspective of the DC-DC converter, the output load power is varying according to the mode of operation of the implant. This adds another challenge of sustaining the DC-DC conversion efficiency high under various loading conditions. At very light loads, preserving a high conversion efficiency is a challenge.

In this master thesis, a detailed design of a high-efficiency low-voltage fully integrated DC-DC converter is presented. A unique structure of a fully integrated switched-capacitor (SC) DC-DC converter with asynchronous control is proposed. The efficiency of the converter is maintained high by adjusting the converter topology and operating frequency according to the loading conditions. The proposed SC DC-DC converter uses three different topologies to achieve three different conversion ratios. By doing so, the converter maintains high conversion efficiency at various output voltage levels. Also, an adaptive operating frequency is used by the asynchronous control to reduce efficiency losses at various loading conditions. Moreover, the applied control is able to change the size of the switches in the SC DC-DC converter when needed. This leads to further enhancement in the overall conversion efficiency. The simulations and experimental results of this work supported the theories of the design. The converter was fabricated on a  $1.5 \times 1.5 mm^2$  chip using IBM CMOS  $0.13 \mu m$  technology. Operating with an input voltage of 1.2V, the proposed DC-DC converter is able to provide

output voltages between 1.1V and 0.3V with a maximum efficiency of 80%. This design is aimed at ultra-low-power applications. It uses a total of 350pF on-chip capacitors to support a maximum output power of  $230\mu W$ .

## Condensé en français

### 1. Introduction

Au cours de la dernière décennie, la demande d'appareils portatifs a connu une augmentation constante. Grâce à la miniaturisation, aux multiples fonctionnalités et à la possibilité de les alimenter par batterie uniquement, ces appareils ont trouvé leur place dans de nombreuses applications y compris les implants biomédicaux. Dans de tels systèmes, la durée de vie de la batterie est un facteur crucial [35]. Il est donc nécessaire d'augmenter la durée de vie de la batterie et cela passe par la réduction autant que possible de la dissipation de puissance des composants électroniques.

L'ajustement dynamique de la tension (DVS) constitue la principale technique utilisée pour réduire la consommation d'énergie des circuits CMOS [47]. Celle-ci exploite le fait que la consommation d'énergie est reliée de manière quadratique à la tension d'alimentation (équation 1.1). Pour tirer avantage de la technique DVS, des convertisseurs DC-DC abaisseurs de tension qui peuvent fournir des sorties variables sont requis [10, 19, 26, 29, 30, 40]. De plus, il a été démontré que la technique DVS utilisée dans un système asynchrone peut réduire encore plus la consommation de puissance des circuits utilisés [24].

L'objectif de ce travail est de concevoir un convertisseur DC-DC hautement efficace, totalement intégré et dédié aux implants biomédicaux. Le type de convertisseur DC-DC proposé est à capacités commutées (switched capacitor- SC) avec un taux de conversion variable. Ce type de convertisseurs convient aux implants biomédicaux car il est efficace et peut être complètement intégré sur puce [29, 43]. Pour être capable d'appliquer la technique DVS, le convertisseur SC DC-DC doit varier la tension de sortie. Cependant, l'efficacité de conversion maximale que le convertisseur SC DC-DC puisse fournir dépend de la tension de sortie (équation 2.5). Heureusement, ce problème peut être résolu en ajustant le taux de conversion du SC DC-DC en fonction de la tension de sortie requise. Il existe différents types de pertes d'énergie qui contribuent à la réduction de l'efficacité (équation 2.8). L'une des principales pertes d'énergie est due aux commutations ( $E_{sw}$ ). Ces pertes dépendent de la fréquence de commutation. Afin de réduire ces pertes, le convertisseur SC DC-DC devrait commuter seulement quand c'est nécessaire. Or, un convertisseur SC DC-DC dépend en général d'une fréquence d'horloge constante. La puissance de sortie, l'efficacité de la conversion ainsi que le choix de la taille des condensateurs et des commutateurs au moment de la conception

dépendent de la fréquence de cette horloge.

La recherche d'une fréquence d'opération optimale qui maximiserait l'efficacité par rapport à la taille des condensateurs et des commutateurs peut être laborieuse. Ceci devient encore plus complexe quand le convertisseur SC utilise différentes topologies à différentes tensions de sortie. La conception présentée ici utilise un contrôleur totalement asynchrone qui varie la fréquence selon la topologie utilisée et selon le courant requis par la charge du convertisseur DC-DC. Le contrôleur réduit la commutation au minimum nécessaire et réduit ainsi les pertes de puissance associées à la commutation. De plus, afin de pouvoir opérer sur une large plage de tension de sortie tout en maintenant une bonne efficacité, le convertisseur SC DC-DC proposé bascule entre trois différentes topologies permettant les taux de conversions suivants :  $1,\frac{2}{3}$  et  $\frac{1}{3}$ .

### 2. Conception du convertisseur SC DC-DC proposé

### 2.1 Vue d'ensemble de la structure proposée

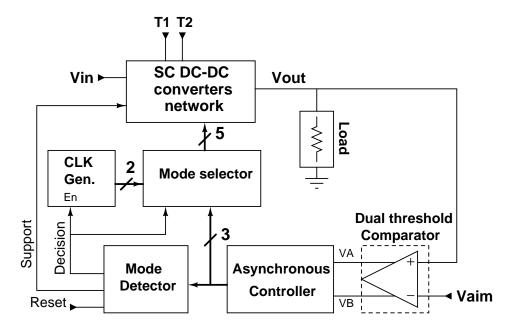

Un aperçu complet de la structure proposée est illustré à la Fig. 3.1. Le réseau du convertisseur (SC DC-DC converters network) a la possibilité de changer sa topologie en fonction des signaux numériques  $T_1$  et  $T_2$ . Les taux de conversion qui peuvent être réalisés par les topologies possibles sont 1,  $\frac{2}{3}$  et  $\frac{1}{3}$ . La quatrième combinaison de  $T_1$  et  $T_2$  désactive le convertisseur. La boucle de rétroaction est constituée d'un comparateur à deux tensions de seuil, d'un contrôleur asynchrone (Asynchronous Controller), d'un détecteur de mode (Mode Detector) et d'un sélecteur de mode (Mode Selector). Le comparateur génère deux signaux numériques,  $V_A$  et  $V_B$ .  $V_A$  est le résultat de la comparaison entre Vout et  $V_{aim}$ , alors que  $V_B$  est généré par un seuil inférieur à  $V_{aim}$  de près de 0.1V. La combinaison de  $V_A$  et de  $V_B$  crée trois valeurs d'entrée possibles utilisées par le contrôleur asynchrone.

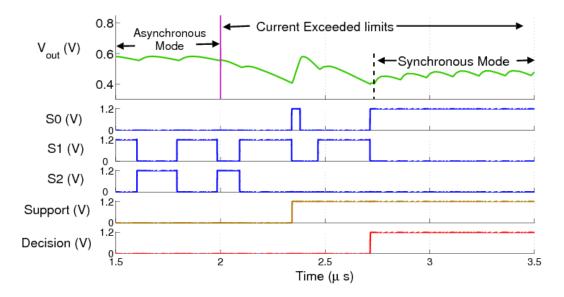

Le contrôleur asynchrone proposé génère trois signaux dont les largeurs d'impulsion et les fréquences sont ajustées en fonction de la charge. Ces signaux de commande sont transmis au réseau du convertisseur SC DC-DC par l'intermédiaire du sélecteur de mode, qui choisit entre deux modes d'opération : soit le mode asynchrone (Asynchronous Drive Mode) qui est le principal mode de fonctionnement, soit le mode synchrone (Synchronous Drive Mode) qui est un mode de repli disponible lorsque la charge dépasse la valeur attendue. En mode asynchrone, les signaux du contrôleur sont transmis au réseau du convertisseurs SC DC-DC, tandis que dans le mode synchrone, les signaux sont transmis à partir d'un générateur d'horloge.

Le sélecteur de mode choisit un signal pour piloter le réseau du convertisseurs en se basant sur le signal "Decision" issu du détecteur de mode. Pour des valeurs de charge régulières, le signal Decision est au niveau bas, ce qui désactive le générateur d'horloge et transmet les signaux du contrôleur asynchrone vers le réseau du convertisseurs SC DC-DC. Quand la charge de courant dépasse la capacité nominale du réseau de convertisseurs, le signal Decision passe au niveau haut et configure le convertisseur à un circuit synchrone en activant une horloge à 4 MHz pour opérer le convertisseur. La raison principale pour basculer vers le mode synchrone est de maintenir l'ondulation de la tension de sortie faible dans le cas de grands courants de charge. Ceci sera expliqué dans la section suivante.

Selon la taille des condensateurs et des commutateurs utilisés ainsi que la topologie choisie, il y a une limite de courant qui peut être délivré à la charge. Le détecteur de mode est le bloc qui détecte quand la limite de courant du réseau de convertisseurs est dépassée. Le processus de détection se fait par l'inspection du motif des signaux générés par le contrôleur asynchrone. Une fois que le motif régulier change, le détecteur de mode envoie le signal "Support" au réseau de convertisseurs. Ce signal active des commutateurs supplémentaires parallèles dans le convertisseur. Ce faisant, le convertisseur augmente la limite maximale du courant de charge d'une certaine valeur. Si cela s'avère insuffisant pour alimenter la charge, alors le détecteur passe le signal Decision au niveau haut mettant ainsi le convertisseur en mode synchrone.

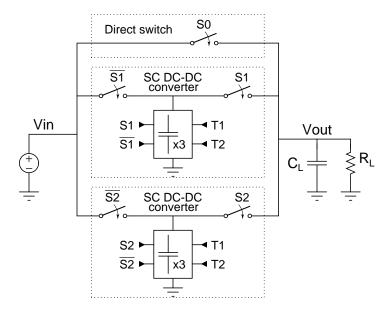

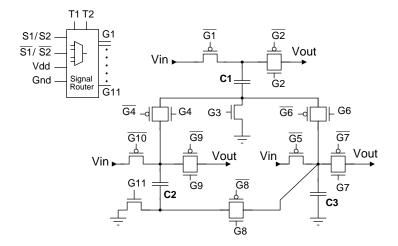

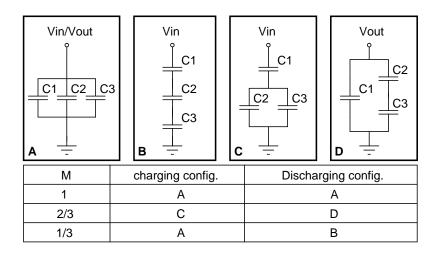

### 2.2 Stratégie de contrôle asynchrone

Le réseau de convertisseurs dans la structure présentée précédemment est constitué d'un commutateur direct et de deux convertisseurs SC DC-DC à topologie ajustable (Fig. 3.2). Le commutateur direct est utilisé pour initialiser la capacité de charge à la tension désirée, et les convertisseurs SC DC-DC gardent Vout à cette valeur. Cette opération donne au convertisseur non seulement un temps de montée rapide lors du basculement entre les topologies mais également une conversion efficace en régime permanent. Chacun des convertisseurs SC DC-DC est composé de trois condensateurs et de onze interrupteurs (Fig. 3.3). Selon les topologies utilisées, les interrupteurs sont réglés sur ON ou OFF, sous contrôle d'un signal ou de son complément (voir le tableau 4.3). L'arrangement illustré dans la Fig. 3.3 peut connecter les condensateurs dans quatre différentes combinaisons série-parallèle qui permettent trois taux de conversion possibles  $(1, \frac{2}{3}$  et  $\frac{1}{3}$ ).

Le contrôleur asynchrone est en réalité une machine à états asynchrone. Pour piloter le réseau de convertisseurs SC DC-DC de manière asynchrone, le contrôleur attend certains

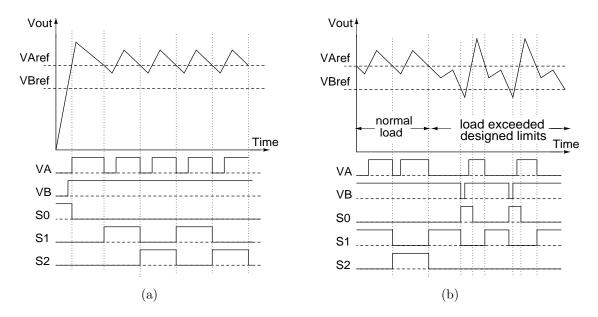

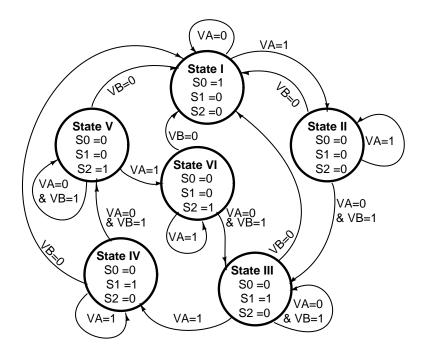

événements qui sont déclenchés par la tension de sortie. Ces événements sont détectés par le comparateur qui compare Vout à deux seuils  $V_{Aref}$  et  $V_{Bref}$ . Dans le circuit proposé,  $V_{Aref} = V_{aim}$ ,  $V_{Bref} = V_{aim} - 0.1V$  et  $V_{aim}$  est la tension de sortie désirée. De ces deux seuils,  $V_A$  et  $V_B$  sont générés par le comparateur. Le diagramme d'états qui définit la génération des signaux de contrôle  $S_0$ ,  $S_1$  et  $S_2$  par rapport à  $V_A$  et  $V_B$  est montré dans la Fig. 3.6. Le circuit complet du contrôleur asynchrone est donné sur la Fig. 4.2.

Lorsque le circuit démarre pour la première fois, le contrôleur détecte que Vout est inférieur aux deux seuils puis fournit les signaux de commande de manière à ce que la capacité de charge ainsi que les deux convertisseurs SC commencent à se charger. Aussitôt que la tension de sortie dépasse  $V_{Aref}$ , le contrôleur désactive le commutateur direct. La différence entre la constante de temps du mécanisme de charge RC et le retard dans la boucle de rétroaction entraine des dépassements de tension de sortie. Ensuite, le contrôleur va attendre que la tension de sortie descende en dessous de  $V_{Aref}$  pour connecter l'un des convertisseurs SC à la charge. Dans des conditions normales de charge, la charge stockée par le convertisseur va relever la tension au delà de  $V_{Aref}$ . Le convertisseur connecté fournira la tension de sortie nécessaire jusqu'à ce que toutes les charges disponibles soient consommées. Lorsque la tension de sortie redescend en dessous de  $V_{Aref}$ , le contrôleur connecte la sortie à l'autre convertisseur SC pendant que le précédent se recharge. A partir de là, le contrôleur continuera d'alterner les deux convertisseurs pour alimenter la charge. La Fig. 3.5(a) montre un chronogramme qui résume cette opération de contrôle en fonction de la tension de sortie.

Quand la charge devient supérieure à la valeur attendue, le convertisseur SC DC-DC ne sera pas en mesure d'élever Vout au dessus de  $V_{Aref}$  avant que la charge stockée soit consommée. La tension Vout commencera alors à baisser jusqu'à ce qu'elle atteigne  $V_{Bref}$  (Fig. 3.5(b)). À ce moment là, le contrôleur asynchrone activera l'interrupteur direct pour élever la tension de sortie. Cela remettra à zéro l'opération du contrôleur et ce dernier essayera de soutenir la charge de nouveau avec les convertisseurs. Si la charge reste élevée pendant un certain temps, le détecteur de mode activera des interrupteurs de sortie additionnels. Dans le cas où cela ne résoud pas le problème, le détecteur de mode décidera de passer au mode synchrone pour parvenir à une meilleure régulation.

#### 2.3 Détecteur de Mode et Sélecteur de Mode

Le bloc qui est chargé de déterminer si les convertisseurs SC sont en mesure de supporter la charge ou pas, est le détecteur de mode. Il peut indirectement déterminer si le courant de charge dépasse les capacités des convertisseurs SC en inspectant le motif du signal de commande généré par le contrôleur asynchrone. Comme vu précédemment sur la Fig. 3.5(b), le motif des signaux de commande  $S_0$ ,  $S_1$  et  $S_2$  change quand le convertisseur SC ne peut pas supporter la charge.

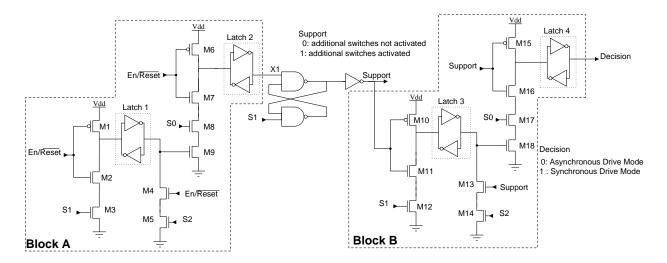

Le détecteur de mode illustré sur la Fig. 3.7 est conçu pour détecter ce motif. Initialement, le détecteur de mode est remis à zéro. Cela implique que toutes les bascules du circuit sont remise à zero et les signaux Support et Decision sont au niveau bas. Quand le détecteur de mode est activé, il désactivera tous les transistors de remise à zéro et activera  $M_2$ ,  $M_7$ ,  $M_{11}$  et  $M_{16}$ . Le motif normal débutera avec le passage à '1' de  $S_1$  alors que  $S_0$  et  $S_2$  sont à '0'.  $S_1$  activera le transistor  $M_3$  qui tire le courant de cette branche et bascule l'état de Latch1 pour appliquer finalement un niveau haut sur la grille de  $M_9$ .

Maintenant  $M_9$  est activé et il y a deux scénarios possibles : soit  $S_2$  passe à '1' alors que  $S_1$  passe à '0' (cas normal), soit  $S_0$  passe à '1' et  $S_1$  passe à '0' (si le courant de charge a dépassé la limite). Dans le premier cas,  $M_5$  sera activé et remettra Latch1 à son état initial qui désactive  $M_9$ . Alors que  $S_1$  et  $S_2$  s'alternent, Latch1 continuera à changer d'état et le signal Support restera bas. Dans le second cas,  $M_8$  sera activé et basculera l'état de Latch2, passant le noeud  $X_1$  au niveau haut. Pour éviter des erreurs dans le processus de détection, les portes NAND couplées par croisement garantiront que  $S_1$  a complètement atteint zéro avant de changer le signal Support à '1'.

Une fois que le signal Support est haut, des commutateurs supplémentaires dans les convertisseurs sont activés pour supporter le courant de charge élevée. Si cela n'était pas suffisant pour supporter la charge, le motif des signaux de commande sera répété. Le bloc B dans le détecteur de mode détectera la répétition du motif et délivrera le signal Decision. Lorsque le signal Decision est haut, le sélecteur de mode va basculer vers le mode synchrone. Fig. 4.4 montre le circuit du sélecteur de mode. La transition entre les deux modes d'opération ainsi que les signaux de commande du contrôleur asynchrone et du détecteur de mode sont montrés dans la Fig. 4.7.

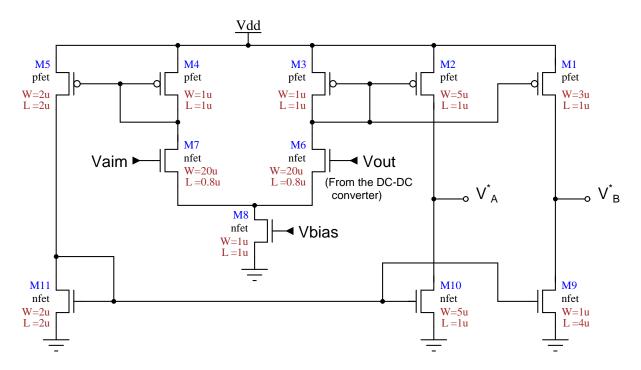

### 2.4 Comparateur à double seuils

Le comparateur qui a été utilisé pour ce convertisseur est montré sur la Fig. 4.5. Pour réduir la consommation d'énergie et la surface de silicium, nous avons conçu un comparateur à deux seuils plutôt que d'utiliser deux comparateurs. Ce comparateur est basé sur un amplificateur opérationnel à transconductance (OTA) et des miroirs de courant. Ceci a été inspiré du travail accompli par [16].

Le comparateur fonctionne comme suit.  $M_8$  est utilisé pour polariser le comparateur. La paire différentielle  $M_6$ - $M_7$  permettra de comparer la tension de sortie Vout du convertisseur DC-DC avec Vref qui est la tension désirée. Le résultat de la comparaison résultera en un courant dans l'une des branches de la paire différentielle. Le courant est ensuite acheminé à  $M_2$  et  $M_{10}$ . La différence entre les courants de drains de  $M_2$  et  $M_{10}$  va tirer  $V_A^*$  soit vers  $V_{dd}$  (1.2V) soit vers la masse. Les transistors  $M_2$  et  $M_{10}$  sont de dimensions telles que  $V_A^* = 0.6$  lorsque  $V_{out} = V_{aim}$ . En changeant la taille des transistors de sortie, le seuil peut être déplacé.  $M_1$  et  $M_9$  sont dimensionnés de sorte que  $V_B^*$  est généré à un seuil inférieur à  $V_A^*$  de 60mV. Pour générer  $V_A$  et  $V_B$  qui déclenchent le contrôleur asynchrone,  $V_A^*$  et  $V_B^*$  sont amplifiés par des inverseurs.

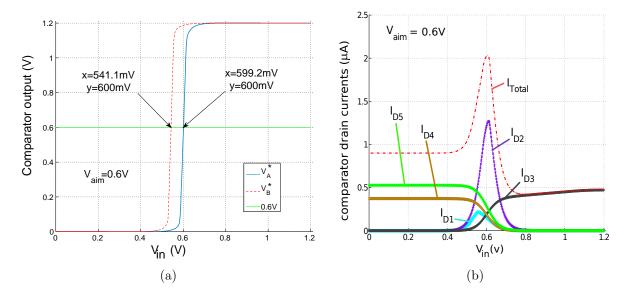

La Fig. 4.6 présente les résultats des analyses de simulation DC du comparateur montré sur la Fig. 4.5. Le balayage est fait avec  $V_{bias} = 0.2V$  et  $V_{aim} = 0.6V$ . Les résultats sur la Fig. 4.6(a) montrent la génération de  $V_A^*$  et  $V_B^*$ . Le seuil supérieur peut être mesuré à 599.2mV alors que le seuil inférieur est de 541.1mV. Quant à la consommation de puissance, ce comparateur ne consomme que  $2.4\mu W$  au maximum qui se produit lorsque  $V_{out} = V_{aim}$ . Fig. 4.6(b) montre le courant dans chaque branche du comparateur, ainsi que le courant total consommé.

### 3. Résultats

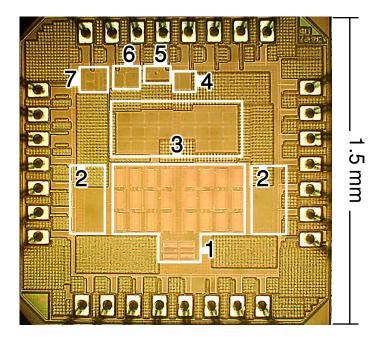

La conception présentée dans ce mémoire a été implémentée dans l'environnement Cadence avec la technologie CMOS  $0.13\mu m$  de IBM. La structure complète, excepté le générateur d'horloge, a été intégrée et une puce a été fabriquée. Fig. 3.8 montre une vue microscopique de la puce résultante. La superficie totale incluant les pads est de  $2.225mm^2$  mais seulement  $0.52mm^2$  de cette superficie est effectivement occupée par les circuit actifs. Celle-ci utilise des capacités intégrés MIM de 150pF pour chaque convertisseur, plus 50pF pour le condensateur de sortie. Le courant maximum qui peut être fourni est de  $240\mu A$ . Ceci peut être facilement augmenté en augmentant la taille des condensateurs utilisés. Le convertisseur fonctionne sur une alimentation de 1.2V et peut fournir des tensions de sortie de 300mV à 1.1V.

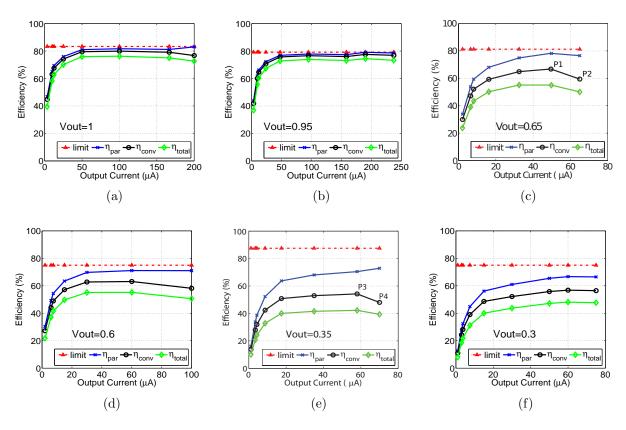

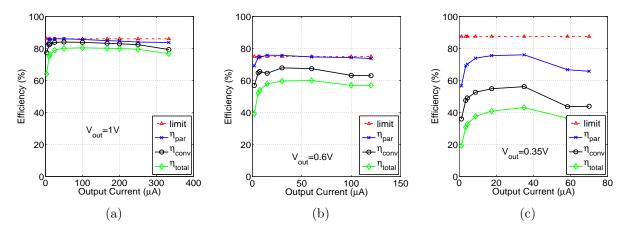

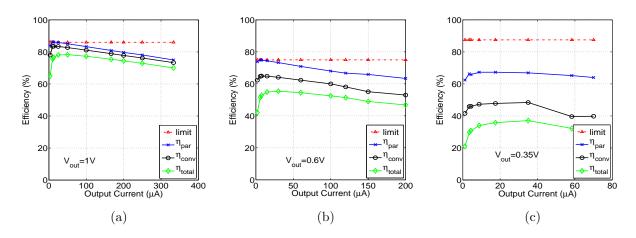

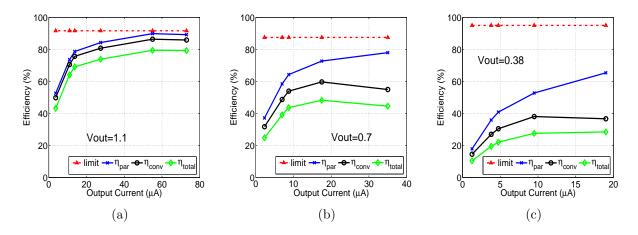

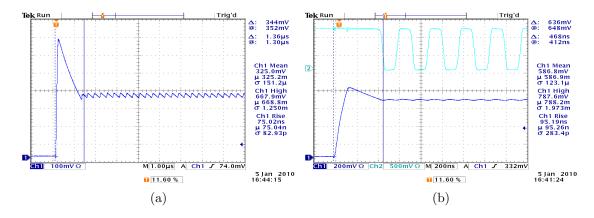

Les Fig. 3.9 et 4.11 montrent la régulation de la tension de sortie à des valeurs différentes. D'autre part, Fig. 3.10 et 4.8-4.10 montrent l'efficacité du convertisseur sous différentes topologies, différents courants de charge et différentes tensions de sortie. Dans les dernières figures, l'efficacité a été séparée en trois courbes nous permettant de voir la contribution des pertes liées aux composants parasites, celles dues à la commutation et à la conduction.

Les courbes d'efficacité présentée sont définies dans les équations (3.3-3.5). De plus, dans ces figures les courbes d'efficacité avec et sans les pertes de commutation sont presque parallèles, impliquant que celles-ci diminuent quand le courant de charge est réduit. En outre, à faible charge, les pertes dans les composants parasites et les fuites de courant réduisent l'efficacité de manière drastique. Enfin, la comparaison avec les récents travaux effectués sur les convertisseurs SC DC-DC montre que nous avons réussi à obtenir de bons résultats lorsque le convertisseur est commandé de manière asynchrone (tableau 3.1).

#### 4. Conclusion

L'importance de la durée de vie de la batterie pour les appareils portatifs et les implants biomédicaux a conduit les chercheurs à développer de nouvelles méthodes de réduction de la consommation de puissance. L'ajustement dynamique de la tension (DVS) est l'une des méthodes les plus connues pour réduire la consommation de puissance des circuits CMOS. Pour appliquer cette technique, des convertisseurs DC-DC à tension de sortie ajustable sont utilisés. À cette fin, nous avons conçu un convertisseur DC-DC qui serait approprié pour de telles applications.

Dans ce mémoire, nous avons conçu et démontré un convertisseur SC DC-DC hautement efficace et totalement intégré dans une structure capable de supporter des systèmes à très faible consommation d'énergie grâce à une tension de sortie ajustable et un fonctionnement asynchrone. Pour ce convertisseur, nous avons adopté une stratégie asynchrone pour minimiser les pertes d'énergie dues à la commutation et les pertes dynamiques des circuits logiques en adaptant la fréquence d'opération aux conditions de charge. En se basant sur la stratégie proposée de commande asynchrone, un processus de détection intelligent a été développé pour ajuster la taille des interrupteurs utilisés selon la puissance de sortie. En outre, un mode de repli synchrone a été incorporé pour rendre le convertisseur robuste en présence de conditions de charge inattendues. Enfin, les théories adoptées et les circuits conçus ont été vérifiés par des mesures expérimentales. Les résultats obtenus s'avèrent compétitifs avec les travaux récents dans ce domaine.

# Table of Contents

| Dedication                                                                        | 111  |

|-----------------------------------------------------------------------------------|------|

| Acknowledgments                                                                   | iv   |

| Résumé                                                                            | vi   |

| Abstract                                                                          | viii |

| Condensé en français                                                              | Х    |

| Table of Contents                                                                 | xvii |

| List of Tables                                                                    | XX   |

| List of Figures                                                                   | xxi  |

| List of Appendices                                                                | xxiv |

| List of Abbreviations and Symbols                                                 | XXV  |

| Chapitre 1 Introduction                                                           | 1    |

| 1.1 Motivation                                                                    | 1    |

| 1.2 Objectives and Challenges                                                     | 3    |

| 1.3 Contributions                                                                 | 5    |

| 1.4 Thesis Organization                                                           | 5    |

| Chapitre 2 Basic Switched-Capacitor Converters Principals And Literature Review . | 7    |

| 2.1 SC DC-DC Converters Fundamentals                                              | 7    |

| 2.1.1 Conversion Mechanism and the Conversion Ratio                               | 7    |

| 2.1.2 Efficiency of SC DC-DC converters                                           | 9    |

| 2.1.3 Drive Signal Requirements                                                   | 12   |

| 2.2 SC DC-DC Converters Control Methods                                           | 12   |

| 2.2.1 Open Loop Control                                                           | 13   |

| 2.2.2 Pulse Width Modulation (PWM) Control                                        | 14   |

| 2.2.3 Pulse Frequency Modulation (PFM) Control                                    | 14   |

| 2.3 Literature Review                                                             | 15   |

| 2.4     | Asynchronous Sequential Logic                                          | 19 |

|---------|------------------------------------------------------------------------|----|

|         | 2.4.1 An Overview                                                      | 19 |

|         | 2.4.2 An Example of a 2-bit Counter                                    | 21 |

|         | 2.4.3 Summary                                                          | 23 |

| Chapitr | e 3 A Low-Power Asynchronous Step-Down DC-DC Converter for Implantable |    |

| Dev     | ices                                                                   | 24 |

| 3.1     | Abstract                                                               | 24 |

| 3.2     | Introduction                                                           | 25 |

| 3.3     | Efficiency and Conversion Ratio                                        | 26 |

| 3.4     | Proposed DC-DC Converter                                               | 28 |

|         | 3.4.1 Structure overview of the converter circuit                      | 28 |

|         | 3.4.2 Asynchronous Control strategy                                    | 31 |

|         | 3.4.3 Load limits detection and operation mode selection               | 34 |

| 3.5     | Experimental Results                                                   | 36 |

|         | 3.5.1 Discussion                                                       | 40 |

|         | 3.5.2 Comparison with the latest reported results                      | 42 |

| 3.6     | Conclusion                                                             | 43 |

| Chapitr | e 4 Additional Circuits and Results                                    | 45 |

| 4.1     | Asynchronous Controller Circuit                                        | 45 |

|         | 4.1.1 Synthesis of the Asynchronous Controller                         | 45 |

| 4.2     | Signal Router Circuits                                                 | 47 |

| 4.3     | Mode Selector Circuits                                                 | 49 |

| 4.4     | Dual-Threshold Comparator Design                                       | 50 |

| 4.5     | Additional Measurement Results                                         | 52 |

|         | 4.5.1 Transition Between Driving Modes                                 | 52 |

|         | 4.5.2 Additional Efficiency Results                                    | 53 |

|         | 4.5.3 Additional Output Voltage Measurements                           | 55 |

|         | 4.5.4 Output Ripple Measurements                                       | 56 |

| 4.6     | Layout Precautions and Recommendations                                 | 57 |

|         | 4.6.1 Layout Protective Structures                                     | 57 |

| Chapitr | e 5 General Discussion                                                 | 60 |

| Chapitr | e 6 Conclusion                                                         | 63 |

| 6.1     | Achieved Results                                                       | 64 |

|                                         | xix |

|-----------------------------------------|-----|

| 6.2 Limitations and Future Improvements | 64  |

| References                              | 66  |

| Appendices                              | 70  |

# List of Tables

| Table 2.1 | Comparison of recent literature on step-down SC DC-DC converters.                    | 18 |

|-----------|--------------------------------------------------------------------------------------|----|

| Table 2.3 | 2-bit counter flow table                                                             | 22 |

| Table 2.4 | 2-bit counter excitation table                                                       | 22 |

| Table 3.1 | comparison with recently published results                                           | 42 |

| Table 4.1 | Asynchronous Controller flow table                                                   | 46 |

| Table 4.2 | Asynchronous Controller excitation table                                             | 46 |

| Table 4.3 | The signal router's output for each switch in the SC network according               |    |

|           | to the conversion ratio needed (set by $T_1$ and $T_2$ ). $\phi$ is one of the drive |    |

|           | signals, either $S_1$ or $S_2$ in the Asynchronous Drive Mode, or the clock          |    |

|           | signals $(CLK \text{ and } \overline{CLK})$ in the Synchronous Drive Mode            | 49 |

# List of Figures

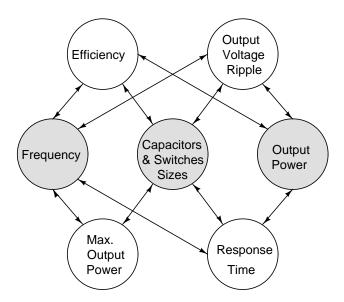

| Figure 1.1 | The SC DC-DC converter performance measurements and their depen-                                 |    |

|------------|--------------------------------------------------------------------------------------------------|----|

|            | dence on the operating frequency, output power (output voltage and                               |    |

|            | loading current) and sizes of the components                                                     | 4  |

| Figure 2.1 | An example of the operation of a SC series-parallel configuration in                             |    |

|            | stepping down an input voltage, (a) shows the complete network of ca-                            |    |

|            | pacitors and switches. $\Phi_1$ and $\overline{\Phi_1}$ are the control signals for the switches |    |

|            | (b) shows the equivalent circuit when the switches controlled by $\Phi_1$ are                    |    |

|            | ON, (b) shows the equivalent circuit when the switches controlled by                             |    |

|            | $\overline{\Phi_1}$ are ON                                                                       | 8  |

| Figure 2.2 | An example of a non-overlapping drive signals that should be used to                             |    |

|            | avoid overlapping drive signal currents                                                          | 12 |

| Figure 2.3 | A simplified model of a SC DC-DC converter consisting of a dependent                             |    |

|            | voltage source and a series resistance                                                           | 13 |

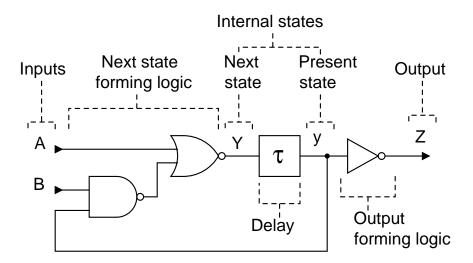

| Figure 2.4 | A simple asynchronous sequential circuit                                                         | 20 |

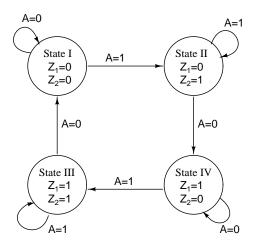

| Figure 2.5 | State flow graph for a 2-bit counter that is level triggered by the input                        |    |

|            | signal $A$                                                                                       | 21 |

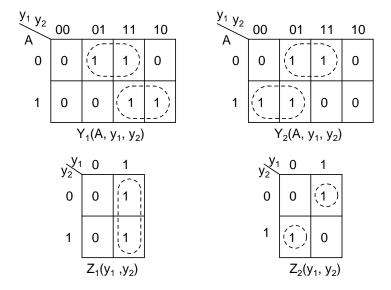

| Figure 2.6 | Karnaugh maps derived from the excitation table of the 2-bit counter.                            | 23 |

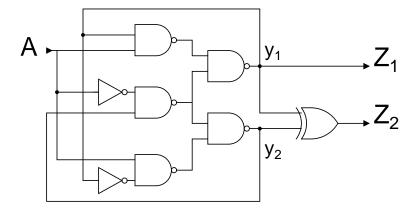

| Figure 2.7 | Circuit of the asynchronous 2-bit counter                                                        | 23 |

| Figure 3.1 | Overview of the structure of the proposed asynchronous DC-DC con-                                |    |

|            | verter                                                                                           | 29 |

| Figure 3.2 | Simplified architecture of the SC DC-DC converters network                                       | 30 |

| Figure 3.3 | Arrangement of switches and capacitors in the SC converter                                       | 30 |

| Figure 3.4 | Possible topologies that can be realized with the arrangement of ca-                             |    |

|            | pacitors and switches shown in Fig. 3.3. M represents the conversion                             |    |

|            | ratio achieved when switching between two of the shown arrangements.                             | 31 |

| Figure 3.5 | Timing diagram when the converter operates under: (a) regular load,                              |    |

|            | (b) load that exceeds the limits                                                                 | 32 |

| Figure 3.6 | The state-flow diagram of the asynchronous controller                                            | 33 |

| Figure 3.7 | The Mode Detector circuit showing all blocks and signals used in the                             |    |

|            | processes of issuing the signals Support and Decision                                            | 35 |

| Figure 3.8  | Photomicrograph of the proposed converter. The main building blocks are numbered as follows: (1) Capacitors, (2) Switches, (3) Signal router, |    |

|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------|----|

|             | (4) Mode detector, (5) Comparator, (6) Asynchronous controller and                                                                            |    |

|             | (7) Mode Selector                                                                                                                             | 37 |

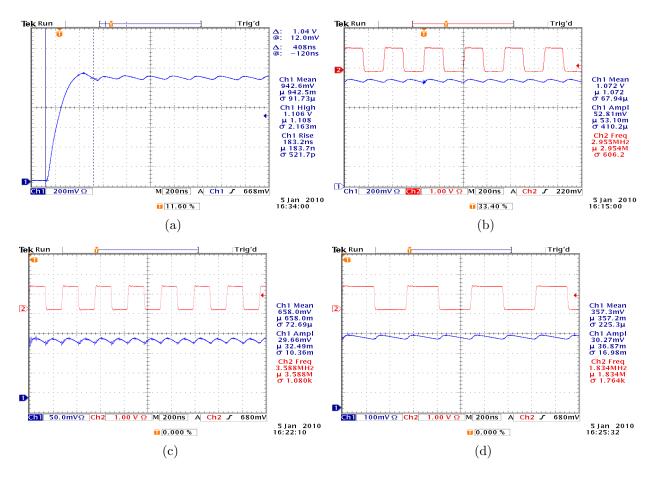

| Figure 3.9  | Measurement of the output voltage and the drive signal $S_1$ of the con-                                                                      |    |

| S           | verter while loaded with $10k\Omega$ and $100pF$ : (a) shows the output voltage                                                               |    |

|             | start up response from $0V$ to $0.95V$ with a settling time of $408ns$ , (b)                                                                  |    |

|             | presents the regulation at $V_{out} = 1.07V$ with a peak to peak output rip-                                                                  |    |

|             | ple of $53mV$ while the asynchronous drive signal frequency is $3MHz$ ,                                                                       |    |

|             | (c) presents the regulation at $V_{out} = 0.66V$ with a peak to peak out-                                                                     |    |

|             | put ripple of $36mV$ while the asynchronous drive signal frequency is                                                                         |    |

|             | $3.6MHz$ , (d) presents the regulation at $V_{out} = 0.36V$ with a peak                                                                       |    |

|             | to peak output ripple of $32mV$ while the asynchronous drive signal                                                                           |    |

|             | frequency is $1.9MHz$                                                                                                                         | 38 |

| Figure 3.10 | The graphs show results of the efficiency measurements versus the load                                                                        |    |

|             | current at different output voltages. The three types of efficiency de-                                                                       |    |

|             | fined in section 3.3 are shown in each subfigure:(a) presents the effi-                                                                       |    |

|             | ciencies at $V_{out} = 1V$ , (b) presents the efficiencies at $V_{out} = 0.95V$ , (c)                                                         |    |

|             | presents the efficiencies at $V_{out} = 0.65V$ , (d) presents the efficiencies at                                                             |    |

|             | $V_{out} = 0.6V$ , (e) presents the efficiencies at $V_{out} = 0.35V$ , (f) presents                                                          |    |

|             | the efficiencies at $V_{out} = 0.3V$                                                                                                          | 39 |

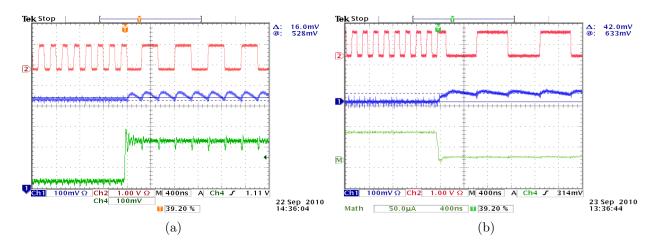

| Figure 3.11 | Measurement of (a) line regulation at an output voltage of $0.53V$ with                                                                       |    |

|             | an input step from $1V$ to $1.2V$ resulting in a $16mV$ change in the                                                                         |    |

|             | output voltage, (b) load regulation at an output voltage of $0.63V$ with                                                                      |    |

|             | a load step from $68\mu A$ to $1\mu A$ resulting in an $42mV$ change in the                                                                   |    |

|             | output voltage. In both measurements, the variations in the drive                                                                             |    |

|             | signal's frequency is apparent                                                                                                                | 40 |

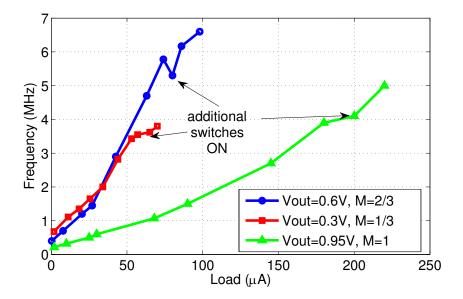

| Figure 3.12 | The graph shows the measurement results of the operating frequency                                                                            |    |

|             | at different output load values. These measurements are done at $V_{out}$ of                                                                  |    |

|             | $0.3V$ , $0.6V$ and $0.95V$ with conversion ratios of $\frac{1}{3}$ , $\frac{2}{3}$ and 1, respectively.                                      |    |

|             | The points at which additional switches are turned on are shown on                                                                            |    |

|             | the graph                                                                                                                                     | 41 |

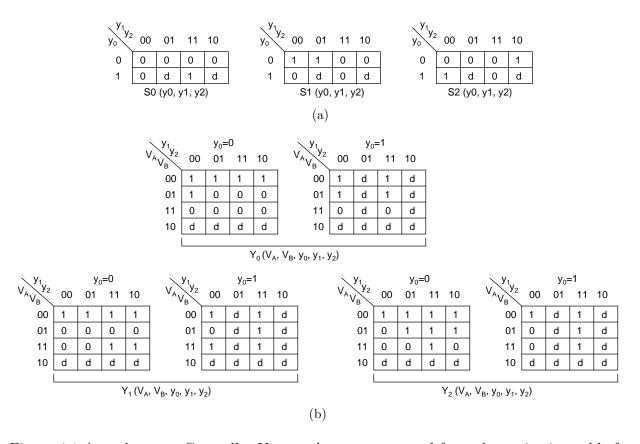

| Figure 4.1  | Asynchronous Controller Karnaugh maps extracted form the excitation                                                                           |    |

|             | table for: (a) the outputs $(S_0, S_1 \text{ and } S_2)$ , (b) next states $(Y_0, Y_1 \text{ and } S_2)$                                      |    |

|             | $Y_2$ )                                                                                                                                       | 48 |

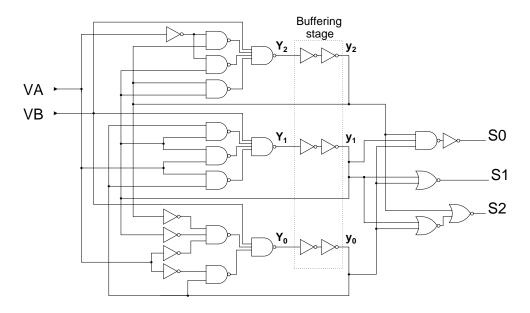

| Figure 4.2  | The full digital circuit of the Asynchronous Controller block that ap-               |    |

|-------------|--------------------------------------------------------------------------------------|----|

|             | pears in Fig 3.1                                                                     | 48 |

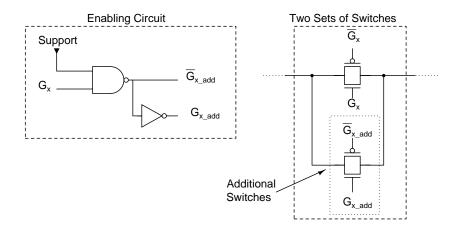

| Figure 4.3  | The enabling circuit within the Signal Router. When Support signal                   |    |

|             | is low $G_{X\_add} = GND$ . When Support signal is high $G_{X\_add} = G_X$           | 50 |

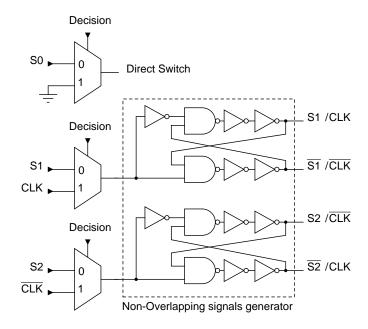

| Figure 4.4  | The Mode Selector circuit consisting of multiplexers and non-overlapping             |    |

|             | signal generators.                                                                   | 50 |

| Figure 4.5  | The dual threshold comparator based on OTA and 3 current mirrors.                    |    |

|             | $V_A^*$ and $V_B^*$ are the unbuffered outputs of the comparator                     | 51 |

| Figure 4.6  | The results of the DC analysis of the comparator: (a) Show the input-                |    |

|             | outputs voltage characteristic, (b) Shows the comparator drain currents              |    |

|             | Vs input voltage characteristics                                                     | 52 |

| Figure 4.7  | The transition from Asynchronous to Synchronous Drive Mode when                      |    |

|             | the load exceeds the limit                                                           | 53 |

| Figure 4.8  | Efficiency simulation results versus the load current at (a) $V_{out} = 1V$ ,        |    |

|             | (b) $V_{out} = 0.6V$ , (c) $V_{out} = 0.35V$ . The three types of efficiency defined |    |

|             | in section 3.3 are shown                                                             | 54 |

| Figure 4.9  | Efficiency PLS versus the load current at (a) $V_{out} = 1V$ , (b) $V_{out} =$       |    |

|             | $0.6V$ , (c) $V_{out} = 0.35V$ . The three types of efficiency defined in section    |    |

|             | 3.3 are shown                                                                        | 54 |

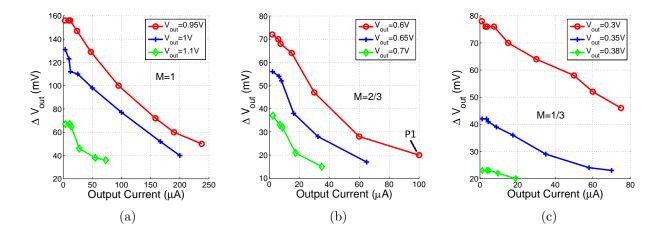

| Figure 4.10 | Additional efficiency experimental results versus the load current at (a             |    |

|             | $V_{out} = 1.1V$ , (b) $V_{out} = 0.7V$ , (c) $V_{out} = 0.38V$ . The three types of |    |

|             | efficiency defined in section 3.3 are shown                                          | 55 |

| Figure 4.11 | Additional measurements of the output voltage of the converter while                 |    |

|             | loaded with $10k\Omega$ and $100pF$ : (a) $V_{out}$ going from $0V$ to $0.35V$ in    |    |

|             | $1.36\mu s$ , (b) $V_{out}$ going from $0V$ to $0.64V$ in $468ns$                    | 56 |

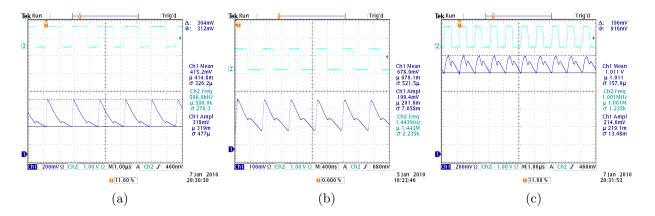

| Figure 4.12 | Output voltage when the load current exceeds the limits while the Mode               |    |

|             | Detector is deactivated: (a) when the converter is using a conversion                |    |

|             | ratio of $M = 1/3$ the ripple is $304mV$ , (b) when the converter is using a         |    |

|             | conversion ratio of $M=2/3$ the ripple is $200V$ , (c) when the converter            |    |

|             | is using a conversion ratio of $M=1$ the ripple is $196mV$                           | 56 |

| Figure 4.13 | Measurement of the output voltage ripple $(\Delta V_{out})$ versus the loading       |    |

|             | current at different conversion ratios $(M)$ : (a) $M=1$ , (b) $M=2/3$ ,             |    |

|             | (c) $M = 1/3$                                                                        | 57 |

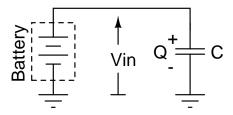

| Figure A.1  | Charging a capacitor from a DC supply (e.g. battery)                                 | 71 |

# List of Appendices

| APPENDIX A | Derivation | Of The | Linear | Efficiency | of SC | DC-DC | converters |  |  |  | 70 |

|------------|------------|--------|--------|------------|-------|-------|------------|--|--|--|----|

|------------|------------|--------|--------|------------|-------|-------|------------|--|--|--|----|

### List of Abbreviations and Symbols

#### Abbreviations:

ADM Asynchronous Drive Mode.

AFS Automatic Frequency Scaling.

AGPC Adaptive Gain-Pulse Control.

ASM Asynchronous State Machine.

CMOS Complementary Metal-Oxide-Semiconductor.

DC Direct Current.

DFS Dynamic Frequency Scaling.

DPWM Digital Pulse Width Modulation.

DVS Dynamic Voltage Scaling.

EMI Electromagnetic Interference.

MIM Metal-Insulator-Metal.

MOS Metal-Oxide-Semiconductor.

NMOS N-type Metal-Oxide-Semiconductor.

PFM Pulse Frequency Modulation.

PLS Post-Layout-Simulation.

PMOS P-type Metal-Oxide-Semiconductor.

PWM Pulse Width Modulation.

SC Switched Capacitor.

SDM Synchronous Drive Mode.

### **Symbols:**

$\Delta V_{out}$  Output voltage ripple.

$\eta$  Efficiency.

$\eta_{lin}$  Linear efficiency. Max. possible efficiency for a SC DC-DC converter.  $\eta_{par}$  Efficiency of a SC DC-DC converter including only losses in conduction

and parasitics (i.e. total efficiency without switching and control losses).

$\eta_{conv}$  Total efficiency of SC DC-DC converter without losses in control circuit.  $\eta_{total}$  Total efficiency of SC DC-DC converter including losses in control circuit.

C Capacitance.

E Energy.

$E_{cond}$  Energy lost during conduction.

$E_{ctrl}$  Energy consumed (lost) in control circuit.

$E_{in}$  Input energy.  $E_{out}$  Output energy.

$E_{par}$  Energy lost in parasitics.

$E_{sw}$  Energy lost in switching (operating the switches in the SC converter).

f Frequency.

L Length of the channel of a MOS transistor. M Conversion ration of a SC DC-DC converter.

P Power.

$P_{in}$  Input power.  $P_{out}$  Output power.

$P_{dynamic}$  Dynamic power consumption.  $P_{static}$  Static power consumption.

R Resistance.

$V_{DD}$  Supply voltage.  $V_{in}$  Input voltage.

$V_{NL}$  Output voltage at no load.

$V_{out}$  Output voltage.

W Width of the channel of a MOS transistor.

## Chapter 1

### Introduction

### 1.1 Motivation

Modern technologies have enabled engineers to integrate devices with various functionalities into silicon chips that are very compact. Nowadays these devices are part of our daily life. Among the key contributers to our luxurious life style are portable devices. They have affected our life style in many ways. With recent incorporation of portable devices in medicine, the way we think about treatment of patients has expanded. Biomedical implants have offered solutions to numerous medical problems [15].

In biomedical implants, the size of the device and the battery life-time are of great importance. Since a lot of the implants tackle chronicle or permanent health issues, the implants should be as convenient as possible for the patients to live with. That is to say, smaller and lighter implantable devices are more convenient for patients. The size of implants is reduced by integrating what can be integrated of the circuitry into a single chip. While, the prolongation of the battery life is done by minimizing the power consumption of the implant's circuits as much as possible [13, 14, 33, 34] and finding other alternative power sources [9, 12, 28, 39].

Most electronic devices nowadays are designed using the CMOS technology. The power consumption of CMOS circuits is given by [36]:

$$P = P_{static} + P_{dynamic} = \frac{V_{DD}^2}{R} + fCV_{DD}^2$$

$$\tag{1.1}$$

where  $V_{DD}$  is the power supply voltage, R is the equivalent resistance of the circuit between the power supply and ground, f is the operating frequency and C is the capacitance between the output of the circuit and ground. A very interesting fact can be seen in Eq. (1.1). The power consumption of CMOS circuits is proportional to the square of the power supply voltage. Hence, if we reduce  $V_{DD}$  by a certain amount, we reduce the power consumption of the circuit quadratically. What Eq. (1.1) does not tell us is that, reducing  $V_{DD}$  might affect other circuit performance measurements. For example in digital circuits, there is a trade-off between speed and  $V_{DD}$ . Reducing  $V_{DD}$  slows down the circuit. The other fact that can be seen in Eq. (1.1) is that, the frequency of operation is directly proportional to the dynamic power consumption. This implies that, reducing the frequency of operation of a system also reduces its power consumption. On the other hand, lower operating frequencies leads to slower systems.

Dynamic Voltage Scaling (DVS) and Dynamic Frequency Scaling (DFS) are two techniques that exploits the previously mentioned facts [25, 31, 47]. By adaptively adjusting the power supply voltage to the conditions of operation of a system, we can minimize power consumption. This is the basis of the DVS technique. Likewise in DFS, by adaptively adjusting the operating frequency of a system, or operating completely asynchronously [24], according to the workload of the system, the power consumption is minimized. These two techniques can be very helpful with extending the battery life-time in biomedical implants.

To implement the DVS technique under battery powered devices, DC-DC converters are used [10, 19, 22, 30, 40]. These converters are able to reproduce levels of DC voltages different than the input voltage (battery voltage is this case). There are various types of DC-DC converters that can be used to address the needs of the DVS technique, but since we are also considering the size of the device, we have to try to propose and demonstrate a DC-DC converter that is suitable for integration on-chip.

There are three main families of DC-DC converters: Resonant converters, Switched Capacitor (SC) converters and linear regulators [7]. The resonant DC-DC converter uses inductors and capacitors to achieve conversion. They are proven to be top notch when it comes to the conversion efficiency. However, on-chip inductors are huge, have a low quality factor, and can cause electromagnetic interference (EMI) problems [20, 44, 46]. On the other hand, linear regulators are very easy to design and integrate, But their conversion efficiency is considerably lower than the Resonant converters, especially when the output voltage is much lower than the input voltage [6, 17]. The last family of DC-DC converters is the SC DC-DC converters. It was shown in literature that this family of converters can be implemented completely on-chip while providing good conversion efficiency levels [11, 26, 29, 40, 43]. From this discussion we conclude that the most suitable family of DC-DC converters that adheres to our initial requirements is the SC DC-DC converters.

### 1.2 Objectives and Challenges

The DC-DC converter that we are designing here should handle battery powered devices, such as implants, that use DVS and/or DFS. Keeping that in mind, we will consider the following goals:

- In order to reduce the size and weight of portable device (implants), The DC-DC converter should be completely integrated on chip.

- Devices that operate with DVS requires from the DC-DC converter the ability to provide different levels of voltages from a single voltage source (in this case the battery). In addition, the change between the different levels of output voltage should be achieved as quick as possible.

- To extend the battery life-time of the powered device, the DC-DC converter should consume the lowest power possible. That implies that, the conversion efficiency under various operating conditions must be high.

- As we will explain in the coming chapters, to maximize the efficiency of a SC DC-DC converter, the operating frequency of the converter should be adapted to the loading conditions. A frequency control module should be implemented to take care of this task.

- To provide the best conversion efficiency at different levels of output voltage, the SC

DC-DC converter has to adjust its switching topology. This fact will be elaborated in later chapters.

- Finally, since the circuits in battery powered implants are of low power nature, the designed DC-DC converter must maximize the efficiency around such values of power.

The list of goals that we just established faces various challenges. To fully integrate a SC DC-DC converter we will need to use on-chip capacitors. The capacitance that the on-chip capacitors provide is not as high as the capacitance of external capacitors. This has two consequences on the performance of a SC DC-DC converter; the reduction of the maximum output power that can be supplied by the SC DC-DC converter and the increase in the output ripple. The latter can be reduced by using higher switching frequencies but that solution has side-effects on other performance measurements concerning efficiency and dynamic power loss. This reduction in the maximum output power is not a main concern since we are targeting low power applications.

Improving the response time of a SC DC-DC converter is yet another challenge. In SC DC-DC converters, the response time depends on the sizes of the capacitors and switches used as well as the frequency of operation and the output power. This means that, the

Figure 1.1 The SC DC-DC converter performance measurements and their dependence on the operating frequency, output power (output voltage and loading current) and sizes of the components

response time is also tied to a bundle of other performance measurements. In fact, all the other major performance measurements are dependent on the following parameters: the frequency of operation, output power (output voltage and loading current) and the sizes of the capacitors and switches. Note here that by "size of switches" we are referring to the width (W) and length (L) of the CMOS switches, which determines the ON resistance and the gate capacitance of the CMOS transistor.

Figure 1.1 illustrates which performance measurements depend on which parameters. This complex relationship between the performance measurements makes the design process of the SC DC-DC converter challenging. The frequency of operation and the size of components are design parameters, while the output power is a parameter that is determined solely by the load demand for power. Therefore, when trying to find an optimum, the designer have about three or more levels of sweeps. One sweep is done on the size of capacitors, and another one or two sweeps are done for determining the size of switches (NMOS, PMOS). Finally the frequency of operation is swept in a certain range to optimize the performance measurements. Furthermore, if for any reason some elements of the design changed, the optimization process might have to be redone.

The last challenge that faces this design is implementing an adaptive frequency control method. The control should consume the least amount of power while maintaining a good

level of conversion efficiency for the SC DC-DC converter. In addition, a promising strategy is to ensure that the control adapts automatically the frequency of operation to the operating conditions of the SC DC-DC converter.

#### 1.3 Contributions

In light of the goals that we have set and the challenges that have been mentioned, the contributions of this thesis are as follows:

- We have designed and implemented a new fully integrated asynchronous SC DC-DC converter structure that is capable of supporting ultra-low-power systems, such as biomedical implant circuitry, with an adjustable output voltage. This converter takes advantage of variable conversion ratio and scalable operating frequency to enhance the conversion efficiency under different operating conditions. To ensure robustness of the design, the SC DC-DC converter is equipped with a synchronous back-up mode that is triggered when the loading power exceeds the maximum load current.

- Moreover, in chapter 3 and 4 we developed an asynchronous controller capable of not only automatically scaling the operating frequency but also scaling the size of the switches used depending on the loading conditions. Both of these techniques help reducing the power losses in the charge transfer switches in the converter, as well as the dynamic power losses in the controller.

- We have also constructed a smart limit detection scheme in the control to allow a Mode Detector block to identify when the loading power exceeds the maximum output power. As we will explain in the coming chapters, to control the switches' sizes, we made use of the same smart detection scheme to allow the Mode Detector to turn ON additional parallel switches when needed. We also designed the Mode Detector so that it can be very easily expanded to support as many levels of additional parallel switches as desired. This is done by simply repeating (cascading) a basic block in the Mode Detector's circuitry.

### 1.4 Thesis Organization

This master's thesis is organized as follows. First, an introduction to fundamentals of conversion mechanism and efficiency in SC DC-DC converters as well as a literature review is presented in chapter 2. Chapter 3 discusses the design of a low-power asynchronous step-down DC-DC converter for implantable devices. Chapter 4 provides additional details and results for the proposed SC DC-DC converter. A general discussion about the complete

thesis is provided in chapter 5. Finally, the thesis is concluded and future improvements are suggested in chapter 6

### Chapter 2

# Basic Switched-Capacitor Converters Principals And Literature Review

### 2.1 SC DC-DC Converters Fundamentals

A brief look on the fundamental operation of a SC DC-DC converter will help the reader to better understand the topic discussed in this thesis. Terms such as: conversion ratio, conversion efficiency and drive signals are explained in this section. Moreover, some of the recent work on step-down SC DC-DC converters are reviewed. But before proceeding, two simple questions should be answered. What is a SC DC-DC converter? And how does it convert one voltage value to another?

#### 2.1.1 Conversion Mechanism and the Conversion Ratio

A switched-capacitor (SC) DC-DC converter (may also be known as a charge pump) is a block that takes an input voltage  $(V_{in})$  and outputs a different value of a voltage  $(V_{out})$ . This block consists of a network of capacitors and switches, and operates in two phases or more. If the output is higher in voltage than the input, the conversion is called a "step-up" conversion. Vice versa, if the output voltage was lower than the input, the conversion is called a "step-down" conversion. The type of conversion that we will be focusing on in this thesis is the step-down conversion.

Most of the SC DC-DC converters operate in two phases: a charging phase and a discharging phase. The charging phase takes place when a group of capacitors in the network are connected to the DC power source (input) to get charged, while the discharging phase starts when this group of capacitors are connected to the load (output) to discharge. Since these capacitors are responsible of transferring the charge from the input to the output, they are sometimes known as the charge-transfer capacitors [29, 45]. Likewise, some authors refers to them as the pumping capacitors because they "pump" the charge from the input to the output [11, 40].

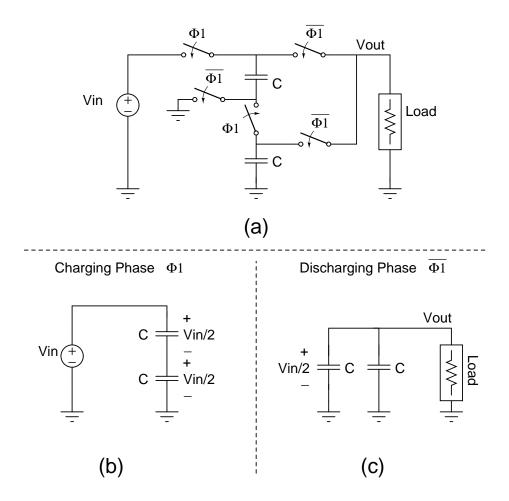

Figure 2.1 An example of the operation of a SC series-parallel configuration in stepping down an input voltage, (a) shows the complete network of capacitors and switches.  $\Phi_1$  and  $\overline{\Phi_1}$  are the control signals for the switches (b) shows the equivalent circuit when the switches controlled by  $\Phi_1$  are ON, (b) shows the equivalent circuit when the switches controlled by  $\overline{\Phi_1}$  are ON.

There maybe several different configurations of connecting the capacitors in each of these phases, and each configuration has its own characteristics. In this project, we adopted the "Series-Parallel" configuration. Not only is this configuration simple, but also it offers a better performance at lower switching frequencies [37]. The reason for pursuing lower switching frequencies will be explained soon.

An example of a series-parallel step-down SC DC-DC converter is presented in Fig. 2.1. Two capacitors and five switches are connected in a network, and the switches are controlled by two signals  $\Phi_1$  and  $\overline{\Phi_1}$  (Fig. 2.1(a)). In the first phase (charging phase),  $\Phi_1$  turns ON a set of switches which will connect the two capacitors in series (Fig. 2.1(b)). Since both capacitors have the same value of capacitance C, each will be charged to  $V_{in}/2$ . Assuming of

course that enough time was provided for the capacitors to be fully charged. In the second phase, the switches connected to  $\Phi_1$  turn OFF, while the ones connected to  $\overline{\Phi}_1$  turn ON. This will connect both capacitors in parallel with the output load resulting in an output voltage  $V_{out} = V_{in}/2$ . As current starts to flow in the load, the charge stored in the capacitors will deplete and the output voltage will drop.

In the previous example,  $V_{in}$  was converted to  $V_{in}/2$ . If the load was not connected, the output voltage would have remained at half the input. The ratio of the output voltage to the input voltage, when no load is connected, is called the conversion ratio (M).

$$M = \frac{V_{NL}}{V_{in}} \tag{2.1}$$

Notice that, the output voltage  $(V_{out})$  of a SC DC-DC converter with conversion ratio (M) cannot exceed the output voltage at no load  $(V_{NL})$ . For the last example, the conversion ratio M = 1/2 and  $V_{out}$  can have a maximum value of  $V_{NL} = V_{in}/2$ . Now that we explained how the conversion is carried out in a series-parallel SC DC-DC converter, let us see what effects the efficiency in the conversion process.

### 2.1.2 Efficiency of SC DC-DC converters

In general, the conversion efficiency of any DC-DC converter can be defined as the percentage of energy delivered to the load  $(E_{out})$  with respect to the energy taken from the supply  $(E_{in})$  [30]:

$$\eta = \frac{E_{out}}{E_{in}} \times 100\% \tag{2.2}$$

where,

$$E_{out} = \int_{T} P_{out} dt \tag{2.3}$$

$$E_{in} = \int_T P_{in} dt \tag{2.4}$$

From this definition, if we try to derive the efficiency of the circuit in Fig. 2.1, we will find that:

$$\eta_{lin} = \frac{1}{M} \frac{V_{out}}{V_{in}} \times 100\% \tag{2.5}$$

An interesting fact can be seen in Eq. (2.5). The conversion efficiency does not depend on the size of the capacitors nor on the resistance in the charging path. Rather, the efficiency of a SC DC-DC converter only depends on  $V_{out}$ ,  $V_{in}$  and the conversion ratio M. This equation is commonly known as the linear efficiency ( $\eta_{lin}$ ). It is considered as the maximum efficiency that a SC DC-DC converter can achieve [21, 29]. The name "linear efficiency" is given to this term because the efficiency drops linearly as  $V_{out}$  decreases. A detailed derivation of Eq. (2.5) is provided in Appendix A. To maximize the efficiency under different output voltages, the conversion ratio M should be adjusted accordingly. Moreover, by substituting Eq. (2.1) in Eq. (2.5), the linear efficiency would be written as:

$$\eta_{lin} = \frac{V_{out}}{V_{NL}} \times 100\% \tag{2.6}$$

This equation implies that the efficiency of a SC DC-DC converter is maximum when  $V_{out} = V_{NL}$ . Note that Eq. (2.5) represents the efficiency of transferring the charge (conduction) between the input and output in a SC DC-DC converter. In Eq. (2.2), If  $E_{in}$  was redefined as the sum of the energy delivered to the load ( $E_{out}$ ) and the energy wasted in the conversion process ( $E_{loss}$ ), the efficiency in Eq. (2.2) can be rewritten as:

$$\eta = \frac{E_{out}}{E_{out} + E_{loss}} \times 100\% \tag{2.7}$$

$E_{loss}$  is a combination of various kinds of loss mechanisms in a SC DC-DC converter. To enhance the efficiency of the converter, we should define these losses. in [30], Ramadass et Chandrakasan identified four different types of losses.

Conduction losses ( $E_{cond}$ ): The first type of losses,  $E_{cond}$ , is due to the power dissipated in internal voltage drops in the SC network. This term is the intrinsic loss that occurs when a capacitor charges from a battery (refer to Appendix A). It is the same loss that led to the definition of the linear efficiency in Eq. (2.5). It depends mainly on value of  $V_{out}$ ,  $V_{in}$  and the conversion ratio M. As discussed earlier, this loss is reduced by keeping  $V_{out}$  close to  $V_{NL}$  and using a SC DC-DC converter with variable conversion ratio.

Parasitic losses( $E_{par}$ ): The second term  $E_{par}$ , is the energy loss due to stray parasitic capacitances in the circuitry. Some parasitic capacitances for example, would store certain amount of energy from the source during the charging phase then discharge to ground during the discharge phase. The nature of this loss makes it very hard to control. It can depend on the technology, type of capacitors used and the configuration of the SC network. In addition, we can include current leakages in ESD protections circuitry (if any).

Switching losses( $E_{sw}$ ): The third loss term  $E_{sw}$ , is the energy used to operate the switches in the network. Since the switches used normally in a SC DC-DC converter are MOS switches, a certain amount voltage should be applied to the gates to turn them ON in one phase, and

then the gates are discharged to ground in the next phase. This is very similar to way the stray parasitic capacitance losses happen. One method to reduce these losses is by using smaller switches. This however increases the ON resistance of the switches, which can affect other performance measurements such as the maximum output voltage or current. A more reasonable approach is to vary the switches' size according to the load current. Another method of reducing this term is by reducing the switching frequency. Of course, since the frequency also affects other performance measurements, it suggests that potential benefits could be derived from a design based on a variable frequency approach.

Control losses ( $E_{ctrl}$ ): Finally,  $E_{ctrl}$  is the energy lost in the control circuitry. This term is the main reason why most new converters operate with digital control circuitry, which can be designed to have negligible static power consumption. The dynamic power consumption however is still an issue. Because all the current digital control circuits depend on a constant frequency clock, a certain amount of constant dynamic power loss exists. Traditionally, SC DC-DC converters were designed as open-loop converters where a control circuit was not needed. These kinds of losses may not be present in open-loop designs.

By combining all the losses that were mentioned above, the total conversion efficiency of the SC DC-DC converter becomes:

$$\eta_{total} = \frac{E_{out}}{E_{out} + E_{cond} + E_{par} + E_{sw} + E_{ctrl}} \times 100\%$$

(2.8)

Note that in Eq. (2.8), if  $E_{out}$  decreases while the energy losses are constant, the efficiency decreases rapidly. To maintain the efficiency high, the losses should also decrease as  $E_{out}$  decreases. In other words, the energy losses should scale with the output current (load). In this work we will design various techniques, such as complete asynchronous control and automatic switch size scaling, to make sure the energy losses scale with the output load. Unfortunately, the energy losses cannot be reduced indefinitely because there are some leakages and static power losses in CMOS circuits that are not avoidable.

Finally, we should mention here that the efficiency can be similarly defined using the average power instead of the energy. Both definitions will lead to the same result, but to be consistent with the analysis of the losses found in literature and the derivation of the linear efficiency presented in appendix A, the definition of the energy efficiency will be used throughtout this thesis.

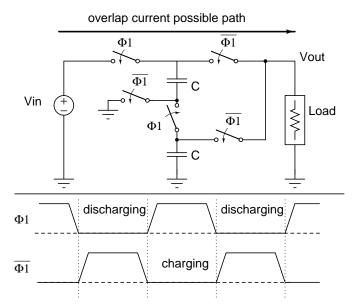

Figure 2.2 An example of a non-overlapping drive signals that should be used to avoid overlapping drive signal currents.

#### 2.1.3 Drive Signal Requirements

A drive signal is the signal that controls the MOS switches in the SC DC-DC converter. Alternating between 0V and  $V_{dd}$ , these signals turn ON and OFF the switches to change the connection of the capacitors in the charging and discharging phases. Typically, SC DC-DC converters operate with a drive signal and its complement. The most important requirement of these signals is to be non-overlapping. Fig. 2.2 shows an example of a SC DC-DC converter and the patten of a drive signal  $(\Phi_1)$  and its complement  $(\overline{\Phi_1})$  that should be used to drive it. If the drive signals overlap, currents may flow through undesired paths. The example in Fig. 2.2 shows one of the possible undesired paths of current that could happen if  $\Phi_1$  and  $\overline{\Phi_1}$  overlap. This path creates a connection between  $V_{in}$  and  $V_{out}$  leading to a current flowing directly form the input to the output, which reduces the conversion efficiency significantly and affects the output voltage regulation.

# 2.2 SC DC-DC Converters Control Methods

There are various control methods that exist in the literature for SC DC-DC converters. The main purpose of a control method is to regulate the output voltage at a desired level under different loading conditions. In this section, we will take a brief look at the main control methods for SC DC-DC converters, which are pulse width modulation (PWM) control and

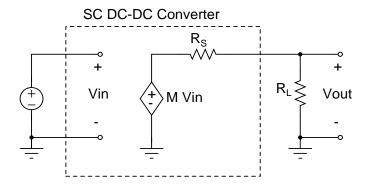

Figure 2.3 A simplified model of a SC DC-DC converter consisting of a dependent voltage source and a series resistance.