**Titre:** Implémentation d'une mémoire cache supportant la recherche IP

Title:

**Auteur:** Bachir Fradj

Author:

**Date:** 2019

**Type:** Mémoire ou thèse / Dissertation or Thesis

**Référence:** Fradj, B. (2019). Implémentation d'une mémoire cache supportant la recherche IP [Mémoire de maîtrise, Polytechnique Montréal]. PolyPublie.

Citation: <https://publications.polymtl.ca/4178/>

## Document en libre accès dans PolyPublie

Open Access document in PolyPublie

**URL de PolyPublie:** <https://publications.polymtl.ca/4178/>

PolyPublie URL:

**Directeurs de recherche:** Yvon Savaria

Advisors:

**Programme:** génie électrique

Program:

**POLYTECHNIQUE MONTRÉAL**

affiliée à l'Université de Montréal

**Implémentation d'une mémoire cache supportant la recherche IP**

**BACHIR FRADJ**

Département de génie électrique

Mémoire présenté en vue de l'obtention du diplôme de *Maîtrise ès sciences appliquées*

Génie électrique

Décembre 2019

**POLYTECHNIQUE MONTRÉAL**

affiliée à l'Université de Montréal

Ce mémoire intitulé :

**Implémentation d'une mémoire cache supportant la recherche IP**

présenté par **Bachir FRADJ**

en vue de l'obtention du diplôme de Maîtrise ès sciences appliquées

a été dûment accepté par le jury d'examen constitué de :

**Jean-Jules BRAULT**, président

**Yvon SAVARIA**, membre et directeur

**Pierre LANGLOIS**, membre

## **REMERCIEMENTS**

Tout d'abord, je tiens à remercier mon directeur de recherche, le Professeur Yvon Savaria, de m'avoir encouragé à réaliser une maîtrise en génie électrique et d'avoir dirigé mes travaux de recherche. Je le remercie également pour les ressources qu'il a mises à ma disposition et du cadre de travail très stimulant qui m'a été offert ; en m'intégrant au sein d'un laboratoire de recherche compétent et en créant des opportunités tout au long de ma maîtrise comme celle d'être en stage chez Kaloom, une entreprise très prometteuse.

Aussi, j'aimerai remercier mes collègues de laboratoire, Jeferson Santiago da Silva, Thibaut Stimpfling, Thomas Luinaud et Imad Benacer, de m'avoir intégré facilement à l'équipe, d'avoir développé mon sens de la réflexion scientifique et d'avoir été des exemples de travailleurs acharnés et passionnés.

Mais surtout, j'aimerai remercier Monsieur Normand Bélanger, assistant de recherche, bras droit de Monsieur Savaria, de m'avoir encadré et suivi durant mon apprentissage. Je le remercie pour tout le temps et l'énergie qu'il a investis pour suivre mon avancement, corriger mes lacunes et me guider face aux différents problèmes rencontrés. Je tiens à lui exprimer ma profonde gratitude pour la patience et la bienveillance dont il a fait part.

Mes remerciements sont également adressés à l'ensemble du corps enseignant ainsi qu'à tout le personnel de l'École Polytechnique de Montréal et tous ceux qui ont participé de près ou de loin au bon déroulement de cette maîtrise.

Enfin, je présente mes remerciements aux membres du jury pour leur participation à l'évaluation de ce mémoire.

## RÉSUMÉ

La croissance explosive du trafic Internet a été accompagnée d'une croissance exponentielle de la bande passante des liens de transmission des équipements de traitement de données, à savoir les routeurs, rendue possible par le déploiement de la fibre optique. Les routeurs sont devenus le principal goulot d'étranglement du traitement des paquets circulant dans le réseau. L'implémentation matérielle permet aux routeurs de satisfaire les exigences de performance d'un routeur à haute vitesse en exploitant l'abondant parallélisme disponible dans le traitement des paquets. Les ASIC (« Application-Specific Integrated Circuits »), qui sont des circuits intégrés spécialisés, sont alors utilisés pour leur performance. Ces circuits induisent cependant des coûts : comme les routeurs sont construits à partir de matériel spécialisé, ce sont des périphériques à fonction fixe qui ne peuvent pas être programmés.

Beaucoup d'efforts et de travaux ont été réalisés afin de rendre les ASIC plus programmables, cependant, cela est encore insuffisant pour exprimer de nombreux algorithmes. Dû à la nécessité de mieux contrôler les opérations du réseau et à la demande constante d'offrir de nouvelles fonctionnalités, la contrainte de la programmabilité des routeurs est devenue aussi importante que la performance.

Les routeurs logiciels sont considérés plus appropriés dans le contexte où la programmabilité prime sur la performance et ils peuvent bénéficier d'une performance intéressante, comme l'incarnent les processeurs de réseau. Les processeurs réseau utilisent des accélérateurs matériels pour implémenter des fonctions spécifiques comme l'utilisation des mémoires TCAM (« Ternary Content Addressable Memory ») pour effectuer des recherches de types LPM (« Longest Prefix Match »), nécessaires pour la transmission des paquets. La TCAM satisfait le requis de débit exigé par le LPM, qui est le facteur de performance le plus limitant dans la transmission de paquets au vu de sa complexité, et elle s'est imposée comme la solution standard dans l'industrie. Cependant, elle présente des inconvénients graves : sa consommation d'énergie élevée, sa faible flexibilité (opérations de mise à jour lente) et son coût financier (coût par bit plus élevé par rapport aux autres types de mémoire). La consommation d'énergie de la TCAM est critique dans les routeurs, qui ont des budgets de puissance énergétique limités.

La motivation de notre travail est d'explorer le concept d'une mémoire cache généralisée pouvant soutenir le LPM. La mémoire sur puce d'un processeur réseau joue le rôle de mémoire cache et est

implémentée en utilisant la technologie SRAM (« Static Random Access Memory) qui est une mémoire beaucoup moins couteuse que la mémoire TCAM. Afin d'accélérer le LPM, la mémoire cache enregistre les préfixes consultés récemment, afin de diminuer le temps d'accès à la table de routage.

Dans ce mémoire, une architecture de mémoires associatives-LPM est proposée. Elle repose sur des mémoires associatives (mémoire cache partiellement associative) implémentées grâce à des fonctions de hachage. Ces mémoires permettent d'associer des préfixes de tailles différentes à des adresses de la mémoire cache, s'affranchissant de la nature pleinement associative de la mémoire TCAM.

Puisque la transition d'IPv4 à IPv6 prend une importance croissante, ce travail cible le LPM pour IPv6. Nous avons utilisé un outil de synthèse de haut niveau (« High-Level Synthesis » - HLS) ciblant une carte FPGA (« Field-Programmable Gate Array ») ZC706 de Xilinx pour émuler la fonctionnalité de la mémoire cache. Nous montrons qu'une table de 26 000 préfixes de 128 bits s'insère dans une mémoire cache de 1 Mo et que le débit atteint permet de transmettre des paquets à un débit de 160 Gbps. La carte FPGA a servi de support pour concevoir une plateforme de prototypage configurable pour la conception et le test de fonctions de réseau.

## ABSTRACT

The Internet's traffic growth has been accompanied by an exponential growth in the bandwidth of the data processing equipment transmission links, made possible by the deployment of optical fiber. Routers have, therefore, become the main bottleneck in the packets processing speed across the network. The hardware implementation allows routers to meet performance requirements of a high-speed router by exploiting the abundant parallelism available in packet processing. ASICs (Application-Specific Integrated Circuit) are specialized integrated circuits used for their performance, but they have a cost: as routers are built from specialized hardware, they are fixed-function devices that do not cannot be programmed.

Much effort and work has been done to make ASICs more programmable, however, this is still insufficient to express many algorithms. Due to the need to better control network operations and the constant demand to support new features, the constraint of router programmability has become as important as performance. Hardware specification is the only way to achieve performance requirements for high-speed routers, however some contexts involve high computing requirements with lower link speeds. Software routers are considered more appropriate in the context where programmability takes precedence over performance and can benefit from interesting performance, as incarnated by network processors. Network processors use hardware accelerators to implement specific functions like TCAM (Ternary Content Addressable Memory) memories to perform LPM (Longest Prefix Match) lookup, required for packet transmission. The TCAM meets the speed required by the LPM, which is the most limiting performance factor in packet transmission due to its complexity, and has been an effective standard in the industry. However, TCAMs have some serious disadvantages: their high-power consumption, their poor scalability and their higher cost per bit compared to other memory types.

The motivation of our work is to explore the concept of a generalized cache memory that can support the LPM. The on-chip memory of a network processor acts as a cache memory and is implemented using SRAM technology (Static Random-Access Memory) which is a much less expensive memory than TCAM memory. In order to speed up LPM lookup, the cache memory stores the prefixes consulted recently, in order to reduce the access time to the routing table.

In this thesis, an architecture is proposed which relies on associative memories implemented by hash functions. As the transition from IPv4 to IPv6 becomes primordial, this work targets the LPM

for IPv6. We used HLS (High-Level Synthesis) tools targeting a Xilinx ZC706 FPGA (Field-Programmable Gate Array) to emulate the functionality of the cache. We show that a table of 26,000 prefixes is inserted in a 1 MB cache and the throughput achieved allows processing packets at wire speed over four 40Gb links. The FPGA is used as prototyping platform for designing and testing network functions, including our solution.

## TABLE DES MATIÈRES

|                                                               |      |

|---------------------------------------------------------------|------|

| REMERCIEMENTS .....                                           | III  |

| RÉSUMÉ .....                                                  | IV   |

| ABSTRACT.....                                                 | VI   |

| TABLE DES MATIÈRES .....                                      | VIII |

| LISTE DES TABLEAUX .....                                      | XI   |

| LISTE DES FIGURES .....                                       | XII  |

| LISTE DES SIGLES ET ABRÉVIATIONS .....                        | XIV  |

| CHAPITRE 1 INTRODUCTION.....                                  | 1    |

| CHAPITRE 2 NOTIONS FONDAMENTALES .....                        | 4    |

| 2.1    Introduction .....                                     | 4    |

| 2.2    Modèles .....                                          | 4    |

| 2.2.1    Modèle TCP/IP .....                                  | 5    |

| 2.2.2    Encapsulation .....                                  | 6    |

| 2.3    Réseaux de communication de données .....              | 7    |

| 2.3.1    Ethernet / Réseau local .....                        | 8    |

| 2.3.2    Internet / Réseau mondial .....                      | 9    |

| 2.4    Conclusion.....                                        | 12   |

| CHAPITRE 3 LES ROUTEURS.....                                  | 14   |

| 3.1    Introduction .....                                     | 14   |

| 3.2    Fonctionnalités d'un routeur.....                      | 14   |

| 3.3    Plan de données, de contrôle et de gestion .....       | 16   |

| 3.4    Architecture .....                                     | 18   |

| 3.4.1    Compromis entre performance et programmabilité ..... | 18   |

|                                                          |                                                         |    |

|----------------------------------------------------------|---------------------------------------------------------|----|

| 3.4.2                                                    | Révolution SDN.....                                     | 21 |

| 3.4.3                                                    | Travaux de recherche courants .....                     | 24 |

| 3.5                                                      | Conclusion .....                                        | 27 |

| CHAPITRE 4 RECHERCHE IP.....                             |                                                         | 29 |

| 4.1                                                      | La recherche (« lookup »).....                          | 29 |

| 4.2                                                      | LPM.....                                                | 30 |

| 4.2.1                                                    | Recherche IP —Contexte .....                            | 30 |

| 4.2.2                                                    | Adressage IPv6, routage et transmission de paquets..... | 31 |

| CHAPITRE 5 SYNTHÈSE DES SOLUTIONS DISPONIBLES .....      |                                                         | 41 |

| 5.1                                                      | Structures de données et algorithmes.....               | 41 |

| 5.1.1                                                    | Listes et tables.....                                   | 41 |

| 5.1.2                                                    | Structure arborescentes.....                            | 45 |

| 5.2                                                      | TCAM .....                                              | 47 |

| 5.3                                                      | Conclusion .....                                        | 52 |

| CHAPITRE 6 MÉMOIRE CACHE SUPPORTANT LA RECHERCHE IP..... |                                                         | 53 |

| 6.1                                                      | Mémoire cache de processeur.....                        | 53 |

| 6.1.1                                                    | Architecture de base de la mémoire cache .....          | 54 |

| 6.1.2                                                    | Opération du contrôleur de cache .....                  | 54 |

| 6.1.3                                                    | Types de correspondance.....                            | 55 |

| 6.1.4                                                    | Approche de conception .....                            | 58 |

| 6.2                                                      | Mémoire cache soutenant les recherches IP .....         | 60 |

| 6.2.1                                                    | Hachage groupé.....                                     | 60 |

| 6.2.2                                                    | Fonctions de hachage .....                              | 63 |

| 6.2.3                                                    | Architecture .....                                      | 67 |

|                                        |    |

|----------------------------------------|----|

| CHAPITRE 7 ÉVALUATION DE LA CACHE..... | 74 |

| 7.1 Résultats .....                    | 74 |

| 7.1.1 Structure de données .....       | 74 |

| 7.1.2 Latence et débit .....           | 77 |

| 7.1.3 Ressources physiques .....       | 78 |

| 7.2 Plateforme de prototypage.....     | 79 |

| CHAPITRE 8 CONCLUSION .....            | 84 |

| RÉFÉRENCES.....                        | 85 |

## **LISTE DES TABLEAUX**

|                                                                           |    |

|---------------------------------------------------------------------------|----|

| Tableau 4-1 : Format d'une adresse « unicast » globale .....              | 38 |

| Tableau 6-1 : Nombre de collisions maximal dans une case de hachage ..... | 61 |

| Tableau 6-2 : Nombres de cases de hachage par groupe de préfixes .....    | 63 |

| Tableau 6-3 : Matrice H1 .....                                            | 66 |

| Tableau 7-1 : Résultats temporels .....                                   | 78 |

| Tableau 7-2 : Consommation des ressources physiques .....                 | 78 |

| Tableau 7-3 : Signaux de l'interface AXI4-Stream.....                     | 80 |

## LISTE DES FIGURES

|                                                                                           |    |

|-------------------------------------------------------------------------------------------|----|

| Figure 2-2: Couche du modèle ISO/OSI .....                                                | 5  |

| Figure 2-3 : Couche du modèle TCP/IP .....                                                | 6  |

| Figure 2-4 : Mécanisme d'encapsulation.....                                               | 7  |

| Figure 2-5 : Transmission d'un paquet IP .....                                            | 11 |

| Figure 3-1 : Plan de données, de contrôle et de gestion [13].....                         | 17 |

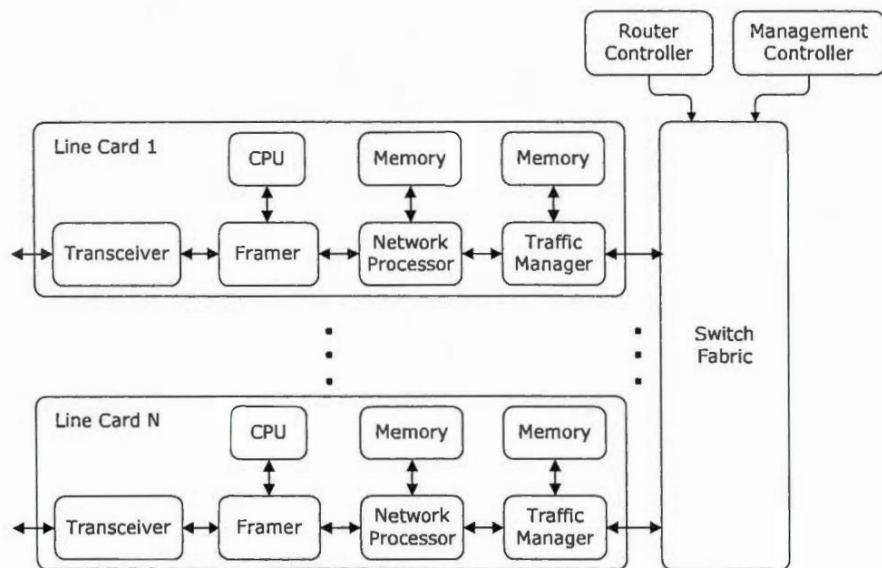

| Figure 3-2 : Architecture typique d'un NP [12].....                                       | 19 |

| Figure 3-3 : Évolution de la performance des routeurs [1].....                            | 20 |

| Figure 3-4 : Algorithmes de routeur [1] .....                                             | 21 |

| Figure 3-5 : Architecture SDN [13] .....                                                  | 22 |

| Figure 3-6: Routeur ASIC [21] .....                                                       | 25 |

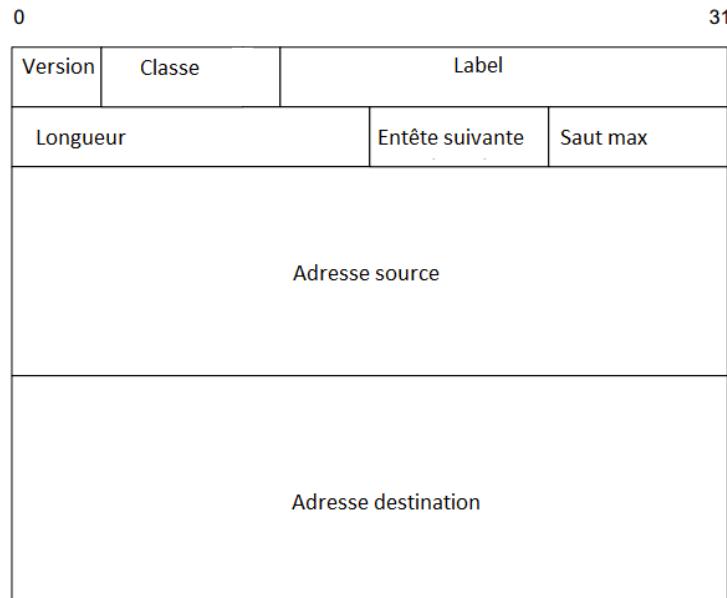

| Figure 4-1 : En-tête IPv6 [9] .....                                                       | 32 |

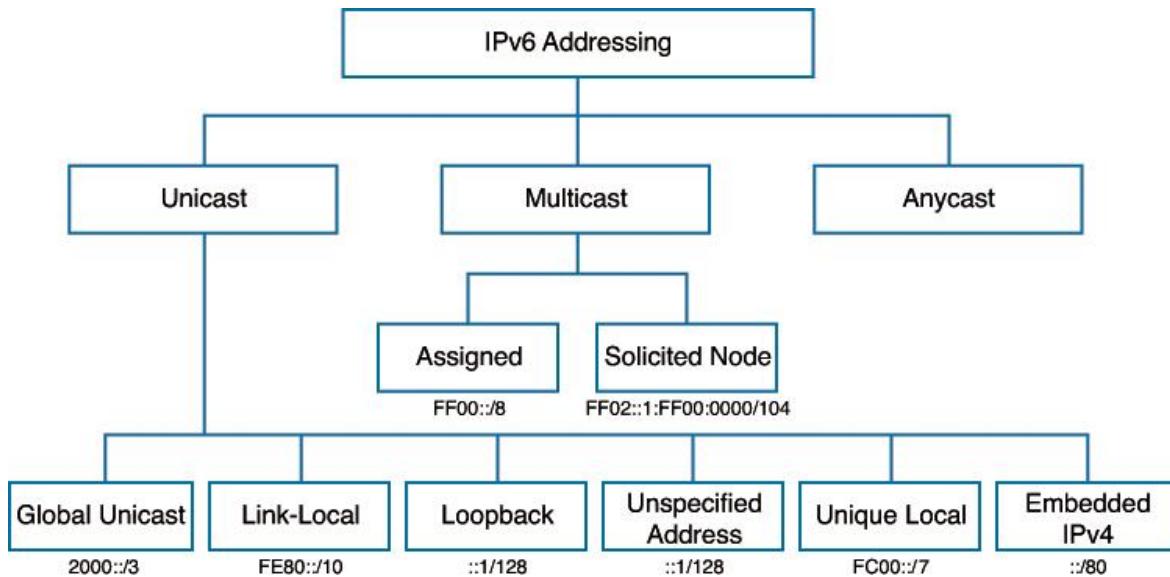

| Figure 4-2 : Types d'adresse IPv6.....                                                    | 36 |

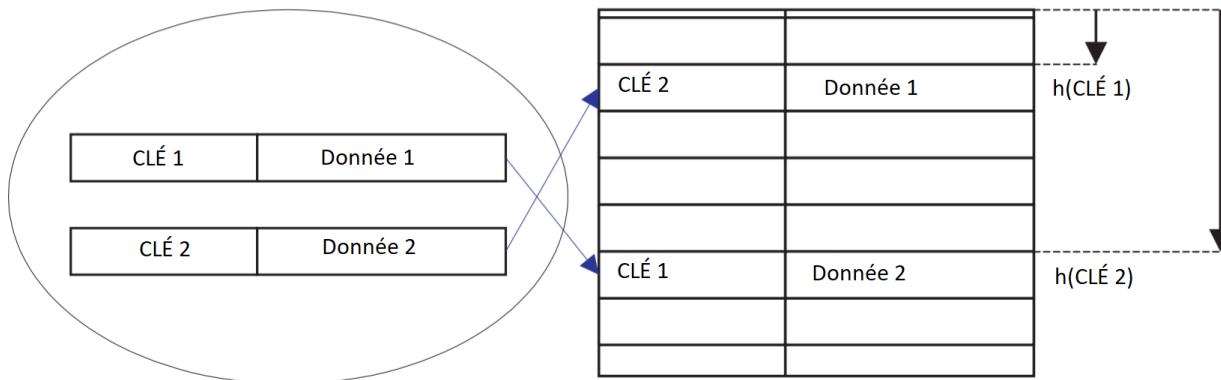

| Figure 5-1 : Correspondance du hachage .....                                              | 42 |

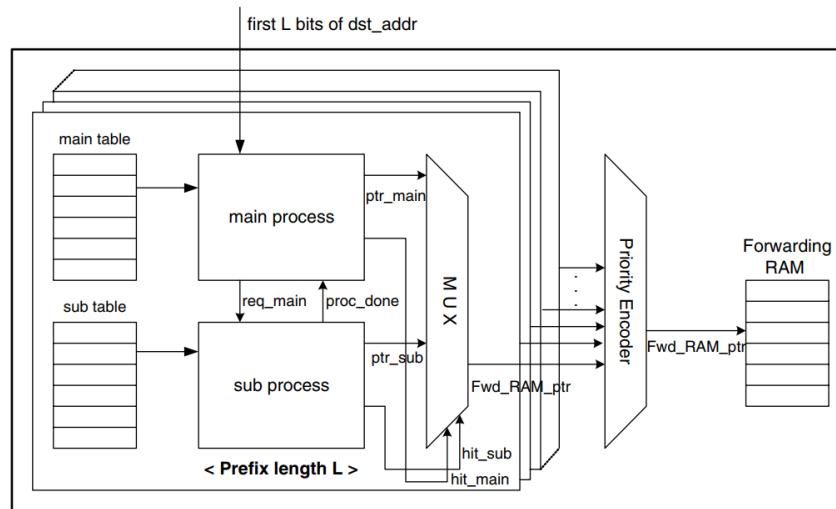

| Figure 5-2: Hachage parallèle [6].....                                                    | 43 |

| Figure 5-3: Implémentation du hachage parallèle grâce à l'extension des préfixes [7]..... | 44 |

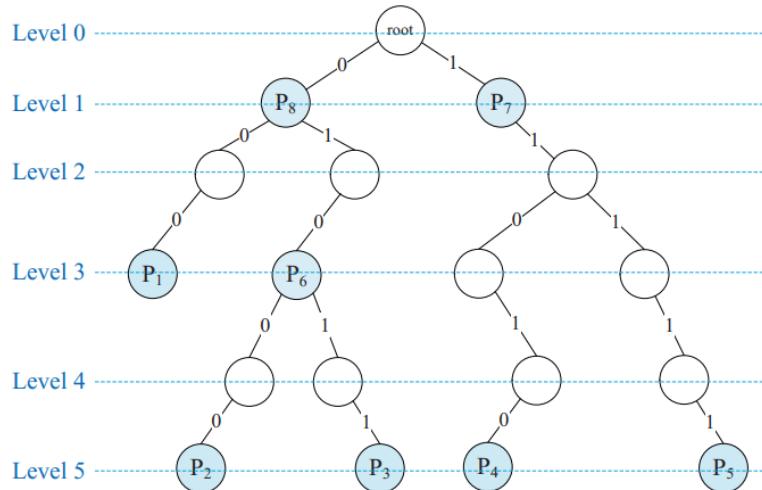

| Figure 5-4: Structure d'arborescence binaire [35] .....                                   | 46 |

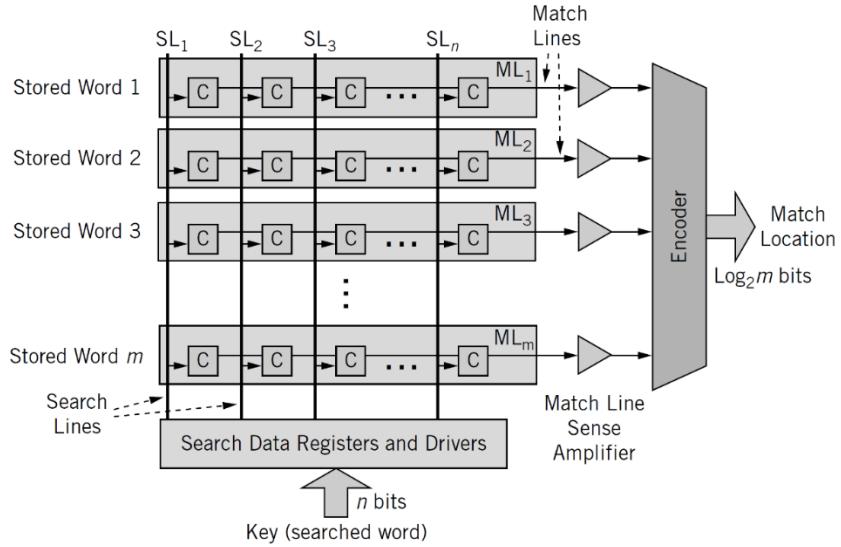

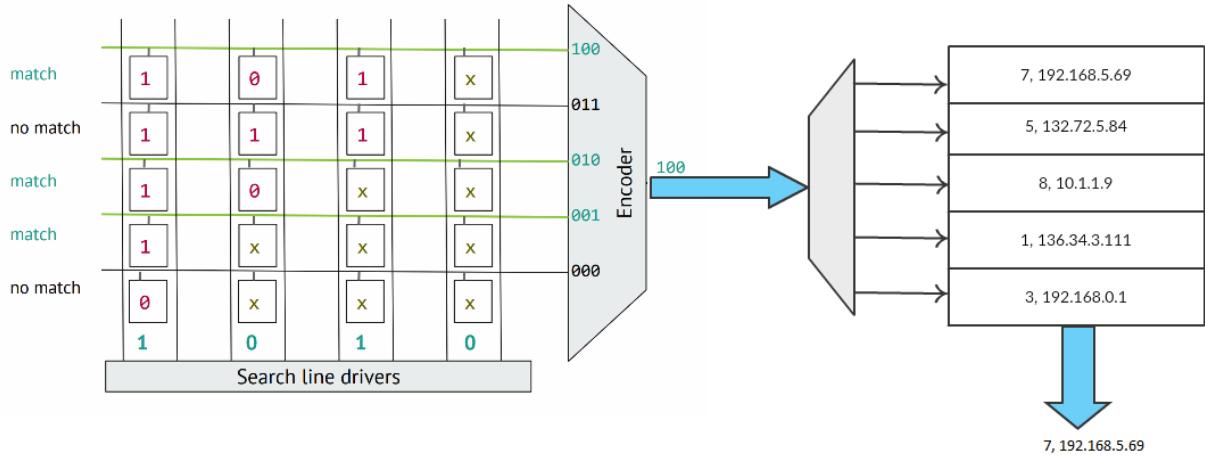

| Figure 5-5 : Structure de la mémoire CAM [9].....                                         | 48 |

| Figure 5-6: Implémentation basée sur une TCAM pour le LPM [8].....                        | 49 |

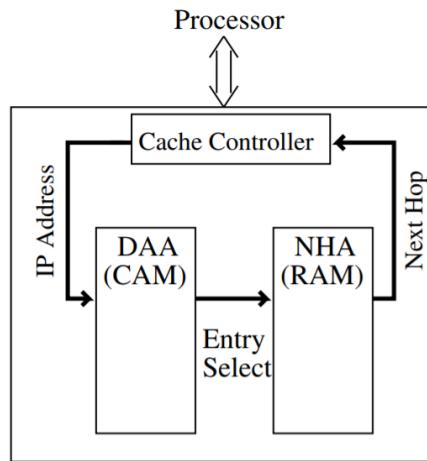

| Figure 5-7: Représentation fonctionnelle d'un cache pour la recherche IP [36] .....       | 50 |

| Figure 5-8: Routeur basé sur des processeurs réseau [39].....                             | 51 |

| Figure 6-1: Hiérarchie mémoire.....                                                       | 53 |

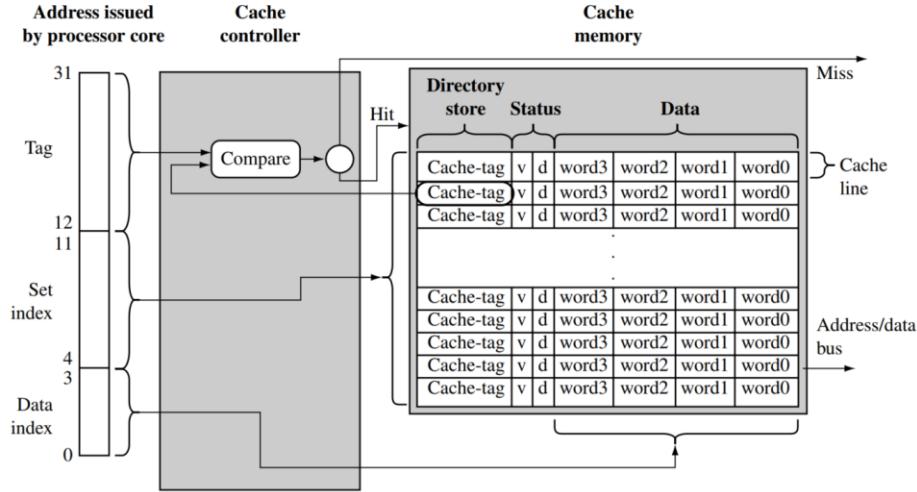

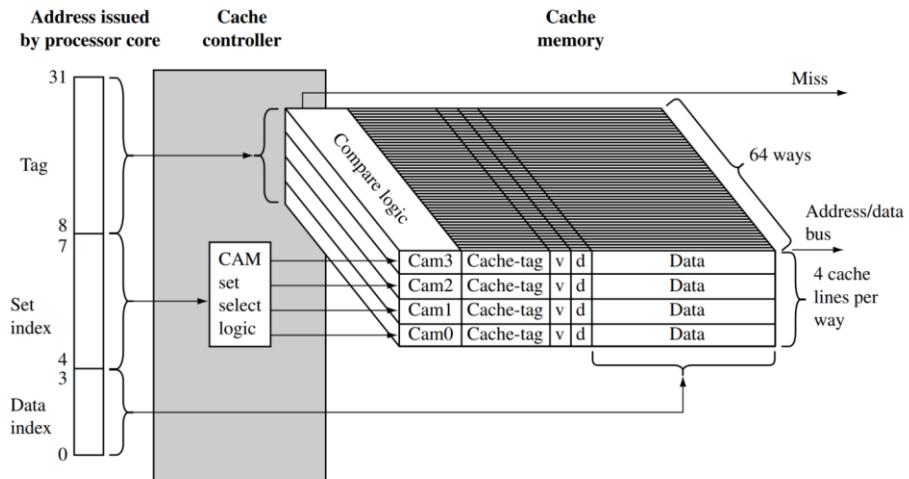

| Figure 6-2: Architecture d'une mémoire cache [47] .....                                   | 55 |

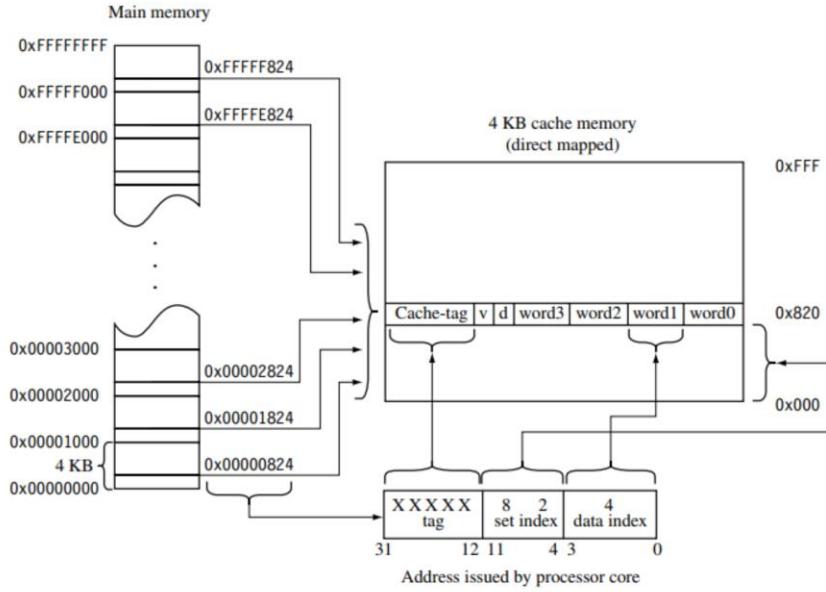

| Figure 6-3: Mémoire cache à correspondance préétablie [47].....                           | 57 |

|                                                                                          |    |

|------------------------------------------------------------------------------------------|----|

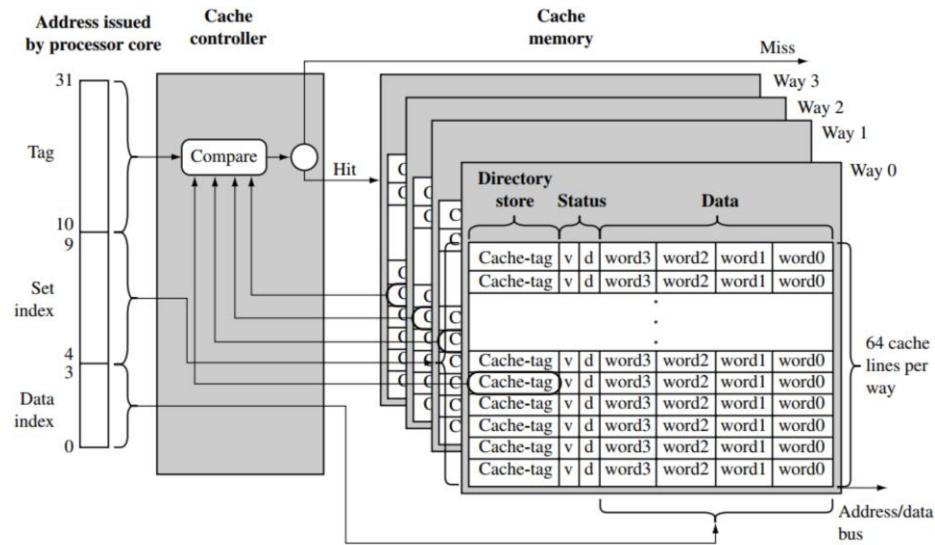

| Figure 6-4: Mémoire cache partiellement associative [47] .....                           | 58 |

| Figure 6-5: Schéma fonctionnel d'un cache ARM940T [47] .....                             | 59 |

| Figure 6-6: Groupes de préfixes.....                                                     | 62 |

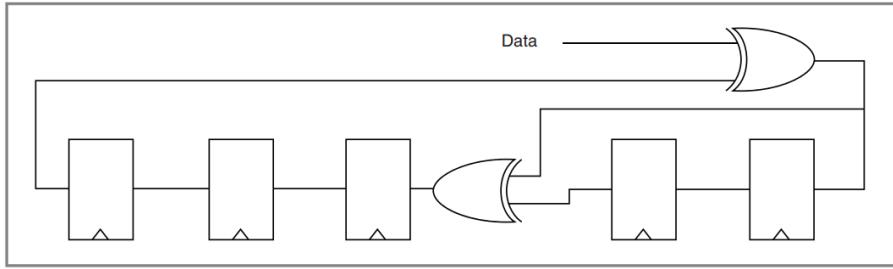

| Figure 6-7: Registre à décalage à rétroaction linéaire [44].....                         | 64 |

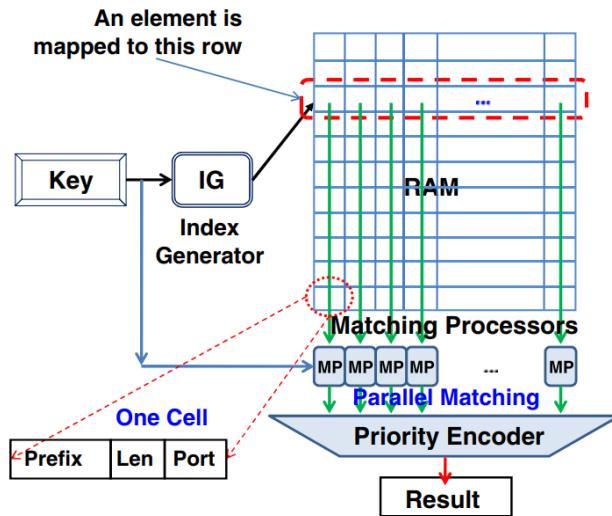

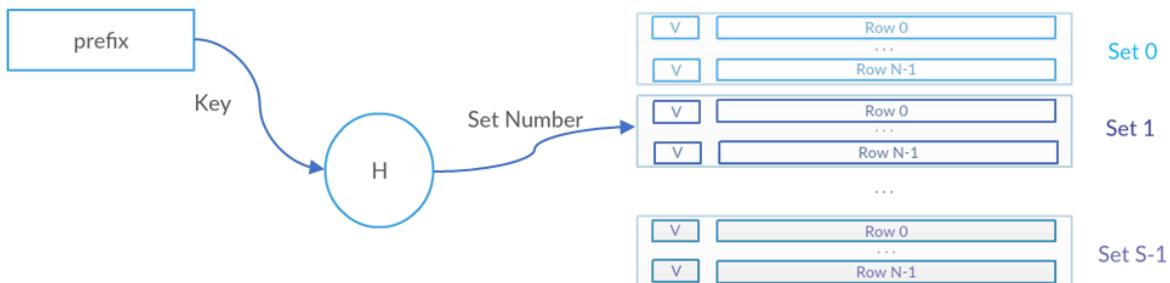

| Figure 6-8: Correspondance d'un préfixe .....                                            | 67 |

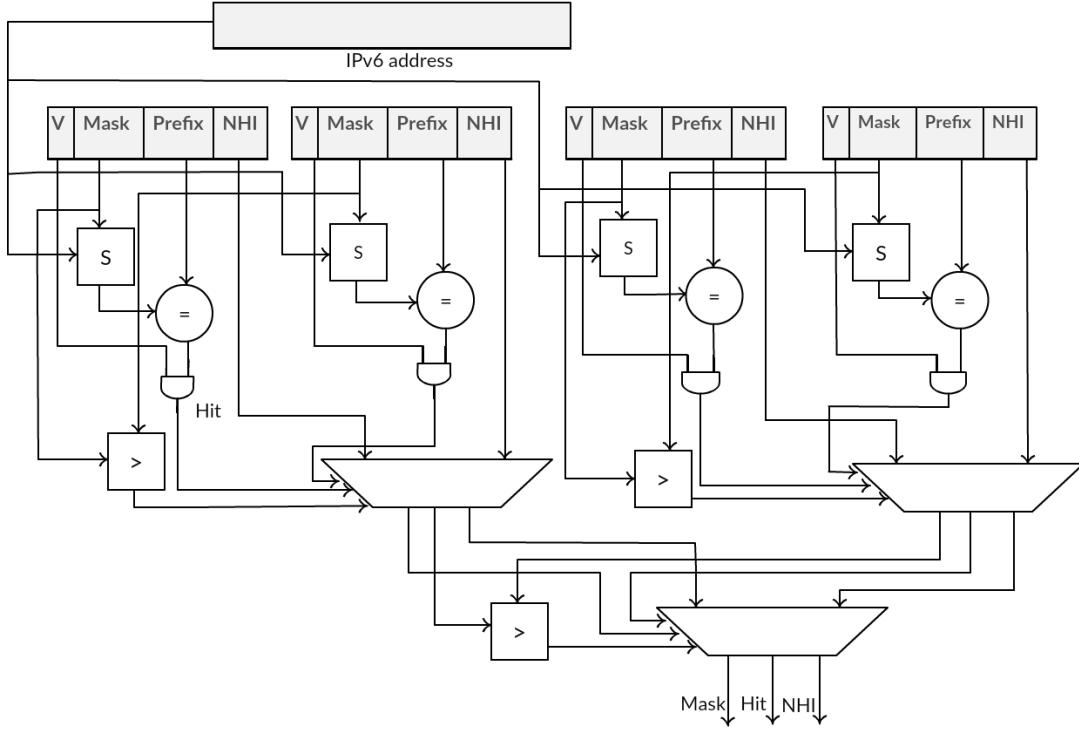

| Figure 6-9: Recherche IP dans un ensemble de cache .....                                 | 70 |

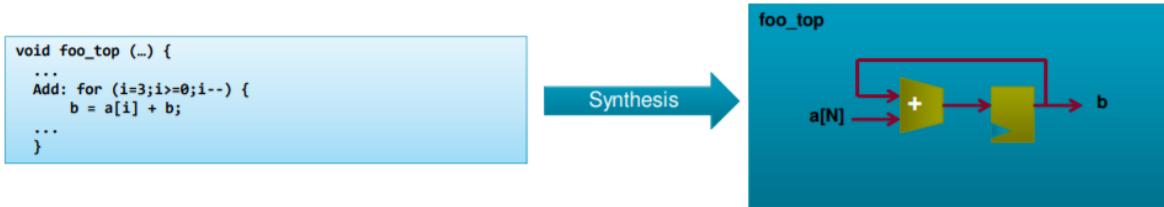

| Figure 6-10: Synthèse par défaut d'une boucle <i>for</i> [48].....                       | 71 |

| Figure 6-11: Optimisation d'une boucle <i>for</i> [48].....                              | 71 |

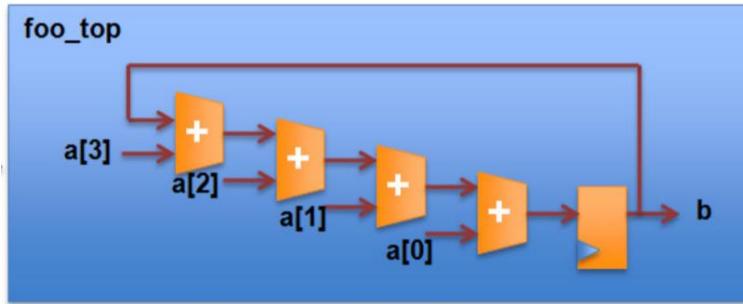

| Figure 6-12: Optimisation de la latence et du débit [49] .....                           | 72 |

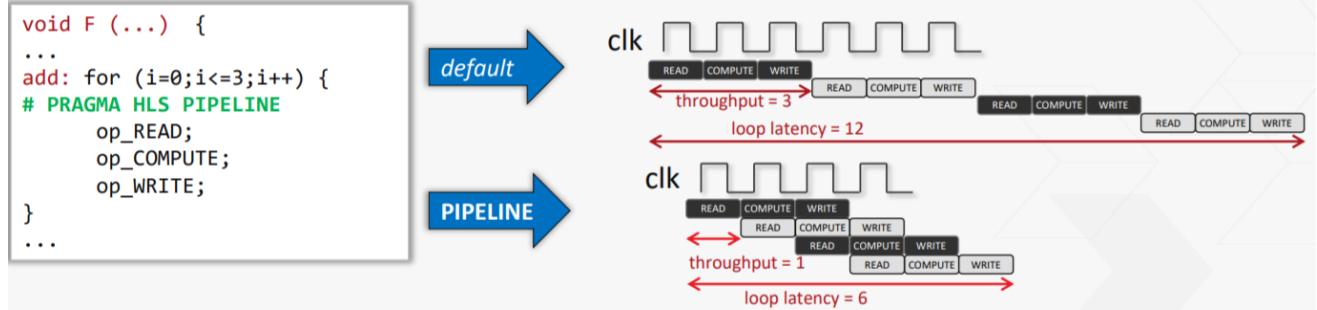

| Figure 6-13: Partitionnement de la mémoire [49].....                                     | 72 |

| Figure 6-14 : code original [50] .....                                                   | 73 |

| Figure 6-15 : code optimisé [50] .....                                                   | 73 |

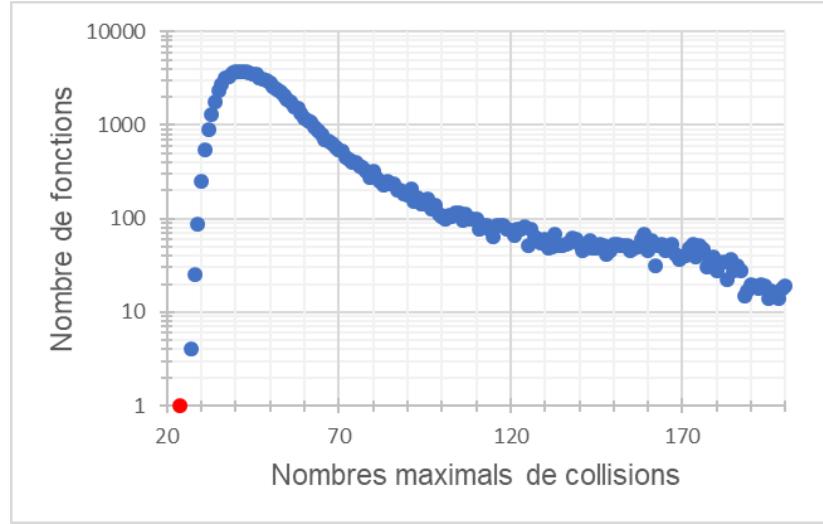

| Figure 7-1 : Collisions des fonctions de hachage universelles .....                      | 75 |

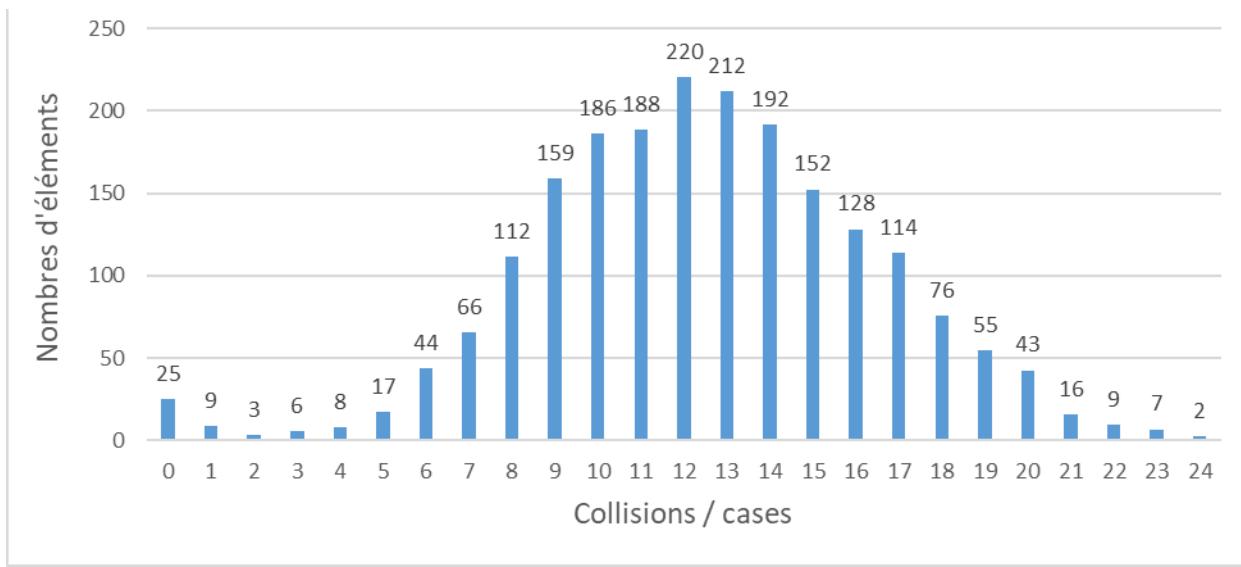

| Figure 7-2: Distribution de la fonction de hachage universelle la plus performante ..... | 75 |

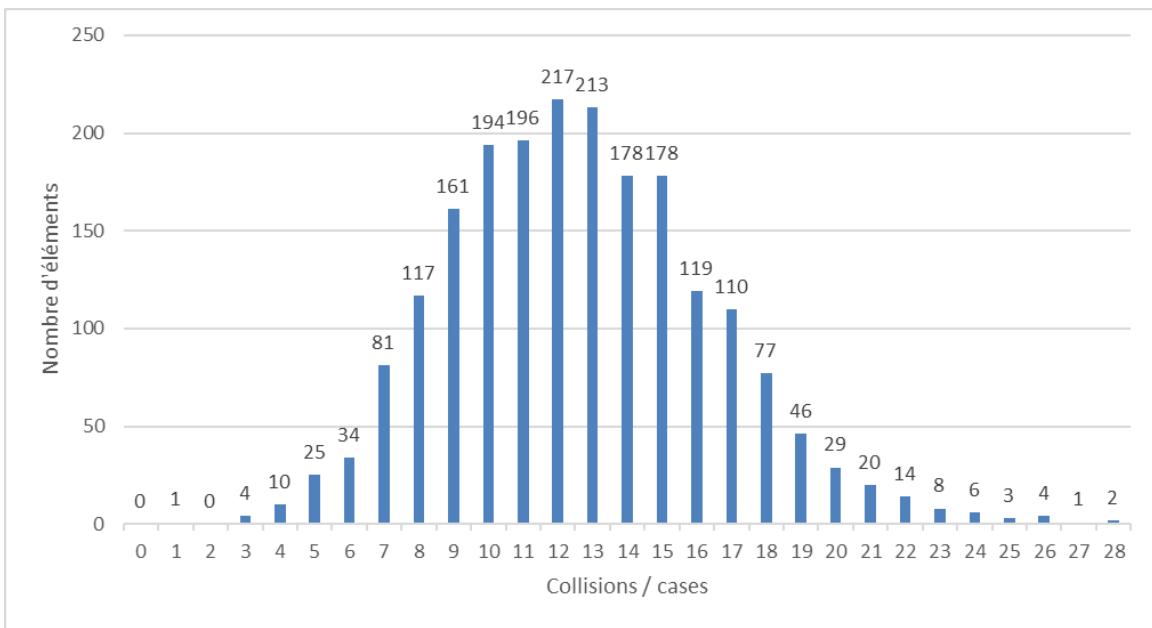

| Figure 7-3: Distribution de nos fonctions de hachage.....                                | 76 |

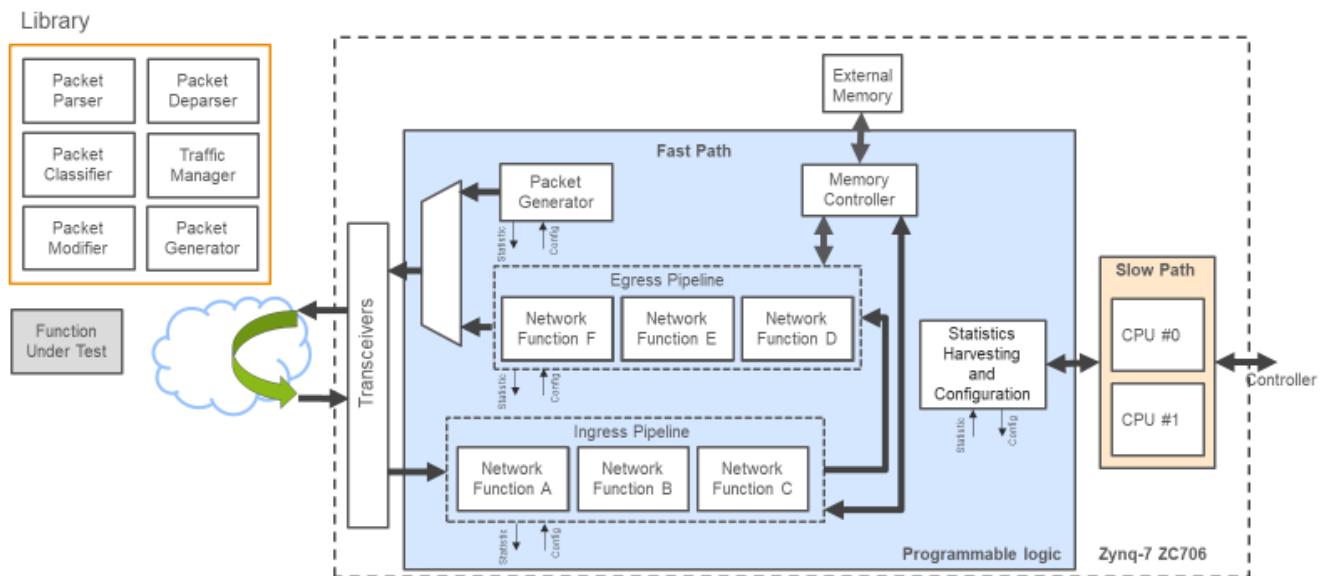

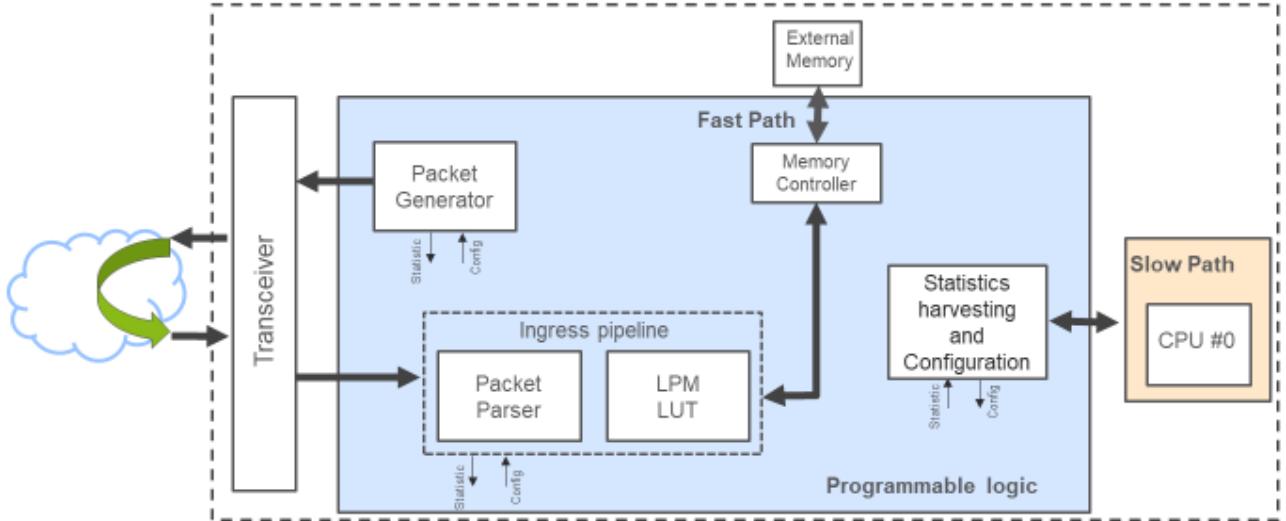

| Figure 7-4: Architecture de la plateforme de prototypage.....                            | 79 |

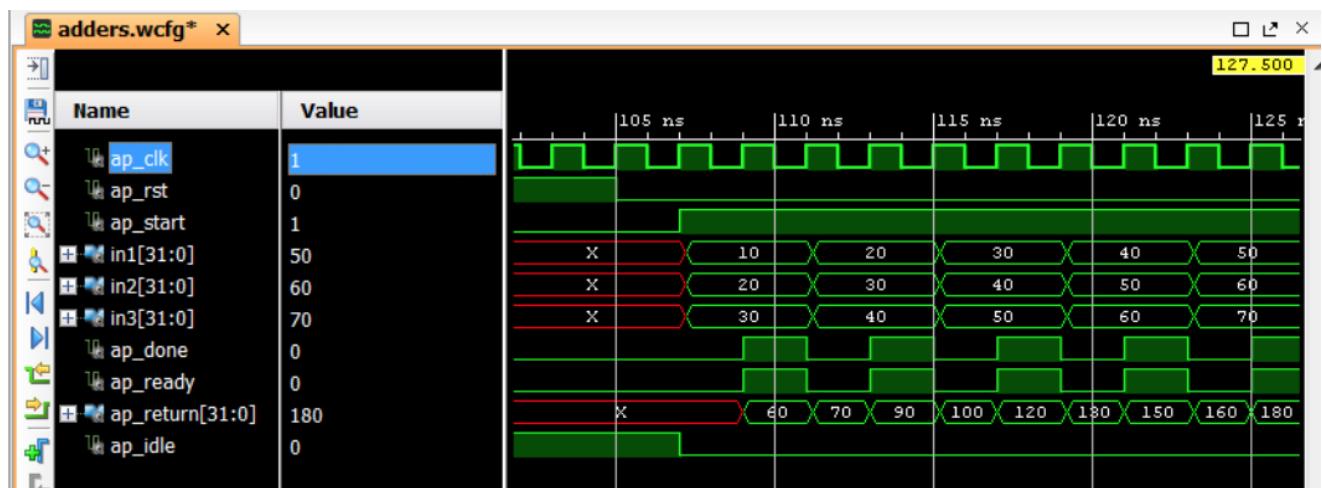

| Figure 7-5: Signaux du protocole ap_ctrl_hs.....                                         | 81 |

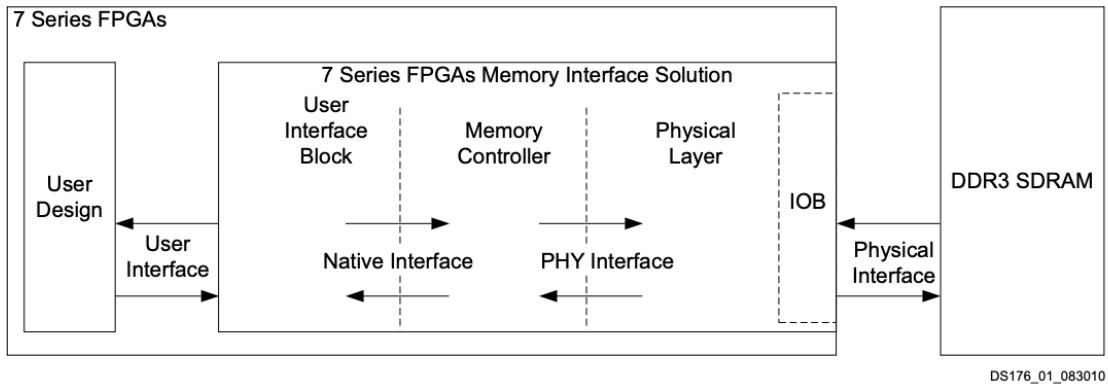

| Figure 7-6: Interface entre le FPGA et la DDR3 .....                                     | 82 |

| Figure 7-7: Architecture du banc d'essai fonctionnel .....                               | 83 |

## LISTE DES SIGLES ET ABRÉVIATIONS

|         |                                                        |

|---------|--------------------------------------------------------|

| ARP     | Address Resolution Protocol                            |

| AS      | Autonomous Systems                                     |

| ASIC    | Application Specific Integrated Circuits               |

| BGP     | Border Gateway Protocol                                |

| BRAM    | Block Random Access Memory                             |

| CAM     | Content Addressable Memory                             |

| CIDR    | Classless Inter-Domain Routing                         |

| CPU     | Central Processing Unit                                |

| CSMA/CD | Carrier Sense Multiple Access with Collision Detection |

| DoD     | Department of Defense                                  |

| DRAM    | Dynamic Random Access Memory                           |

| DHCP    | Dynamic Host Configuration Protocol                    |

| DWDM    | Dense Wavelength Division Multiplexing                 |

| EGP     | External Gateway Protocol                              |

| FIB     | Forwarding Information Base                            |

| FPGA    | Field-Programmable Gate Array                          |

| GPP     | General Purpose Processor                              |

| HTTP    | HyperText Transfer Protocol                            |

| IANA    | Internet Assigned Numbers Authority                    |

| ICANN   | Internet Corporation for Assigned Names and Numbers    |

| ICMP    | Internet Control Message Protocol                      |

| IGP     | Interior Gateway Protocol                              |

| IoT     | Internet of Things                                     |

|       |                                                            |

|-------|------------------------------------------------------------|

| IP    | Internet Protocol                                          |

| IPSec | Internet Protocol Security                                 |

| ISO   | International Standard Organization                        |

| LAN   | Local Area Networks                                        |

| LFSR  | Linear Feedback Shift Register                             |

| LIR   | Local Internet Registry                                    |

| LPM   | Longest Prefix Match                                       |

| MAC   | Media Access Control                                       |

| MTU   | Maximum Transmission Unit                                  |

| NAT   | Network Address Translation                                |

| NHI   | Next Hop Information                                       |

| NP    | Network Processor                                          |

| NVGRE | Network Virtualization using Generic Routing Encapsulation |

| OSI   | Open Systems Interconnection                               |

| OSPF  | Open Shortest Path Bridging                                |

| OTV   | Overlay Transport Virtualization                           |

| P4    | Programming Protocol-Independent Packet Processors         |

| PBB   | Provider Backbone Bridge                                   |

| PCI-E | Peripheral Component Interconnect Express                  |

| PDU   | Protocol Data Unit                                         |

| RAM   | Random-Access Memory                                       |

| RFC   | Requests For Comments                                      |

| RIR   | Regional Internet Registry                                 |

| RIP   | Routing Information Protocol                               |

|       |                                     |

|-------|-------------------------------------|

| RT    | Routing Table                       |

| SDN   | Software-Defined Networking         |

| SNMP  | Simple Network Management Protocol  |

| SoC   | System on a Chip                    |

| SRAM  | Static Random-Access Memory         |

| STT   | Stateless Transport Tunnelling      |

| TCAM  | Ternary Content Addressable Memory  |

| TCP   | Transmission Control Protocol       |

| TTL   | Time-To-Live                        |

| UDP   | User Datagram Protocol              |

| VHDL  | VHSIC Hardware Description Language |

| VoIP  | Voice over Internet Protocol        |

| VxLAN | Virtual Extensible LAN              |

## CHAPITRE 1 INTRODUCTION

Les systèmes réseau (« network systems ») sont conçus pour répondre aux exigences fonctionnelles spécifiées par les protocoles. Ils doivent également satisfaire des exigences de performance constamment croissantes; dues à l'augmentation du nombre d'utilisateurs d'Internet et l'émergence de nouvelles applications de plus en plus gourmandes en bande passante. Le déploiement de la fibre optique a entraîné une explosion des débits, soutenus par les liens de transmission, ce qui a conduit les routeurs à devenir le principal goulot d'étranglement de la performance actuelle d'Internet.

Un routeur implémente de nombreuses fonctionnalités, autres que la transmission de paquets, relatives à la sécurité, à la surveillance et à la performance. L'évolution des routeurs était principalement motivée par la performance des fonctions de traitement de paquets. En raison de la nécessité d'offrir de nouvelles fonctionnalités et le besoin constant d'évolutivité, la programmabilité des routeurs est devenue aussi importante que leur performance. L'équilibre entre la performance et la programmabilité imposent des compromis majeurs lors de la conception de systèmes réseau, car ces caractéristiques exigent des contraintes d'implémentation différentes.

Les routeurs basés sur des ASIC représentent la meilleure solution pour satisfaire les besoins de performance, car ils utilisent des fonctions matérielles dédiées et exploitent l'abondant parallélisme disponible dans le traitement des paquets. Cependant, ils présentent l'inconvénient d'avoir un temps de commercialisation élevé (« time-to-market »), d'une part, et d'être rigide d'autre part. Les routeurs logiciels [1], basés sur des plateformes programmables, sont plus adaptés aux applications nécessitant plus de flexibilité. Ces derniers ont évolué au cours des années pour offrir une performance intéressante, comme l'incarnent très bien les processeurs de réseau (« Network Processors »). Les processeurs de réseau implémentent certaines fonctions en logiciel et utilisent des accélérateurs matériels pour les fonctions dont les requis de performance sont importants.

La recherche IP [2] est souvent le goulot d'étranglement de la transmission de paquets. Le routeur doit faire correspondre l'adresse IP de destination de chaque paquet à une table de routage, qui peut contenir des millions d'entrées [3], pour déterminer le prochain saut du paquet vers sa destination finale. Les réseaux IP sont identifiés en utilisant la notation CIDR (« Classless Inter-Domain Routing »). Le routage inter-domaine sans classe permet de créer une hiérarchie d'adresses réseau

en définissant des sous-réseaux IP, où la partie de l'adresse IP utilisée pour le routage est le préfixe. La notation CIDR a permis de réduire la taille des tables de routage en spécifiant une large plage d'adresses dans une entrée de la table de routage grâce à un préfixe. Cependant, la recherche IP devient plus complexe ; le CIDR nécessite que les routeurs traitent des préfixes de taille variable, où plusieurs préfixes peuvent correspondre à l'adresse IP à rechercher. Le LPM est le critère de priorisation pour retourner la meilleure correspondance, où le préfixe le plus long représente le meilleur résultat de recherche. Puisque la transition d'IPv4 à IPv6 devient primordiale, nous ciblons le LPM pour IPv6.

Les mémoires TCAM [4] sont une solution standard et répandue en industrie pour effectuer la recherche IP de manière performante. Chaque cellule mémoire peut stocker un bit valant '0', '1' ou 'X' (« wildcard » ou entrées indifférentes) ; les entrées indifférentes permettent de faire des recherches masquées, où certains bits de la clé de recherche peuvent être ignorés. Chaque préfixe de la table de routage est stocké dans un mot complété par des « wildcards » et, lors d'une opération de recherche, la mémoire adressable par contenu compare simultanément l'adresse IP à tous les mots stockés. Parce qu'une TCAM effectue une recherche dans sa mémoire en un seul cycle d'horloge, elle est plus rapide que les autres types de mémoire dans toutes applications de recherche d'un contenu. Les TCAM constituent des accélérateurs matériels et elles peuvent s'interfacer avec un processeur de réseau comme une mémoire ordinaire. Elles sont également utilisées dans la conception de mémoire cache.

Certains routeurs utilisent un système de mise en cache [5] (« caching ») pour accélérer la recherche IP. La mémoire cache stocke les préfixes consultés récemment, afin de diminuer le temps d'accès à la table de routage.

En dépit de certaines propriétés fort intéressante, les TCAM présentent certains inconvénients graves : leur consommation d'énergie élevée, leur faible flexibilité et leur coût par bit supérieur par rapport aux autres types de mémoire. La motivation de notre travail est de concevoir une mémoire cache, pouvant supporter la recherche IP, en proposant une solution matérielle alternative à la TCAM et capable de satisfaire les besoins de performance.

Les solutions basées sur le hachage [6] sont utilisées pour effectuer une recherche IP dans un sous-ensemble de la table de routage au lieu de la totalité de la table, afin de réduire le nombre de préfixes à analyser. L'accès s'effectue par une fonction de hachage, qui, à partir de l'adresse IP à rechercher,

calcule une valeur qui indexe les éléments de la table de hachage (« buckets ») qui, contient les préfixes. Cependant, le hachage présente des défis majeurs. Le premier défi consiste à gérer les collisions générées par le hachage qui dégradent la performance. Une collision est produite quand deux clés de hachage différentes produisent le même résultat de hachage (pointent vers la même case de hachage). Ces collisions conduisent à des opérations de recherche supplémentaires sont nécessaires et une mauvaise distribution des préfixes conduit à une utilisation partielle et inefficace de la mémoire. Le deuxième défi concerne la taille variable des préfixes, qui pose des problèmes lors de la définition des clés de hachage (les clés doivent avoir une taille définie). Le hachage avec les « wildcards » peut être résolu par le hachage restreint (« restricted hashing ») ou le hachage groupé (« grouped hashing ») [7]. Dans le hachage groupé, les préfixes sont regroupés en fonction de leurs longueurs et une fonction de hachage différente est utilisée pour chaque groupe.

Le but de notre travail est de proposer une architecture qui repose sur des mémoires associatives (mémoire cache partiellement associative), implémentée grâce au hachage groupé, et qui permet d'associer des préfixes de tailles différentes à des adresses de la mémoire cache. Cette solution exploite l'implémentation des mémoires caches de processeurs, qui utilisent des mémoires SRAM, six fois moins couteuses que les mémoires TCAM [8]. Dans ce mémoire, nous visons à prouver la faisabilité d'une telle approche et de présenter des résultats de performance satisfaisants.

Ce mémoire est constitué de huit chapitres dont le premier représente l'introduction. Le deuxième chapitre vise à présenter les notions fondamentales sur lesquelles reposent les réseaux de communication. Le troisième chapitre présente les fonctionnalités d'un routeur, ses exigences de performance, ainsi que les architectures et les implementations dominantes. Le chapitre 4 est consacré à l'adressage IP pour permettre de comprendre la complexité et le défi que présente la recherche IP. Le chapitre 5 présente les différentes solutions matérielles et logicielles dominantes dans la littérature. Le chapitre 6 détaille la méthodologie et la conception de notre solution. Dans le chapitre 7, nous discutons des résultats obtenus et nous présentons une implementation concrète de notre solution. Enfin, le chapitre 8 clos ce mémoire.

## CHAPITRE 2 NOTIONS FONDAMENTALES

### 2.1 Introduction

Les réseaux de communication (« communication networks ») sont apparus sous forme de connexions physiques entre pairs (« peer-to-peer »), transportant d'abord des données en flux analogique, puis évoluant vers des connexions acheminant des données en flux numérique: les données de communications sont segmentées en paquets. Le paquet est l'unité de données qui est acheminée entre deux hôtes dans un réseau.

La croissance rapide des applications et des réseaux de communications est accompagnée d'une croissance exponentielle du nombre et du débit des paquets circulant dans le réseau, qui doivent être traités. Le traitement du flot des flots des données circulant sur le réseau concerne le traitement de paquets en fonction des protocoles, des demandes et du comportement du réseau. Il est donc essentiel de comprendre les notions fondamentales sur lesquelles reposent les réseaux de communication pour savoir comment un paquet est créé pour pouvoir l'analyser et le traiter.

### 2.2 Modèles

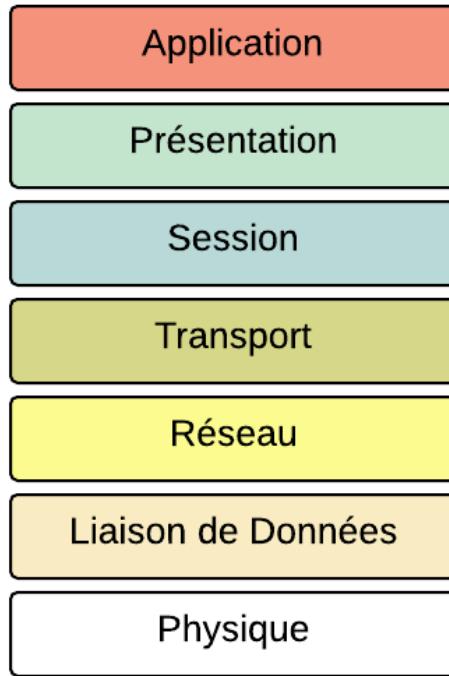

Au fur et à mesure que la programmation des réseaux de communication, des interfaces et des équipements réseaux devenaient de plus en plus sophistiqués, l'organisation internationale de normalisation (« International Standard Organization », ISO) proposait une architecture de réseau structurée en couches abstraites appelée OSI (Open Systems Interconnection). Ce modèle a pour but de permettre l'interconnexion de systèmes hétérogènes et de s'adapter à la croissance des flux de données à traiter en normalisant les communications. Le modèle ISO/OSI comporte sept couches, représentées à la figure 1-1, où chaque couche se rapporte à une fonction réseau bien précise, qu'on appelle *service*.

Les données à transmettre entre deux nœuds suivent un chemin défini : les données du nœud émetteur traversent d'abord la couche la plus abstraite (couche application, L7), avant de passer par les couches successives jusqu'à la couche la moins abstraite (couche physique, L1), pour être transmises (sous la forme de trames) au support de communication. Au niveau du nœud destinataire, les données traversent le chemin inverse (de la couche physique vers la couche application).

L'activité de chaque couche est codifiée selon un certain *protocole*. Un protocole est un ensemble de règles qui détermine le format et la transmission des données. Chaque couche prépare les données pour la couche suivante : deux couches superposées communiquent donc entre elles et partagent une *interface*. Enfin, la fonctionnalité d'une couche peut être réalisée par un équipement réseau différent de celui des autres couches.

Figure 2-1: Couches du modèle ISO/OSI

### 2.2.1 Modèle TCP/IP

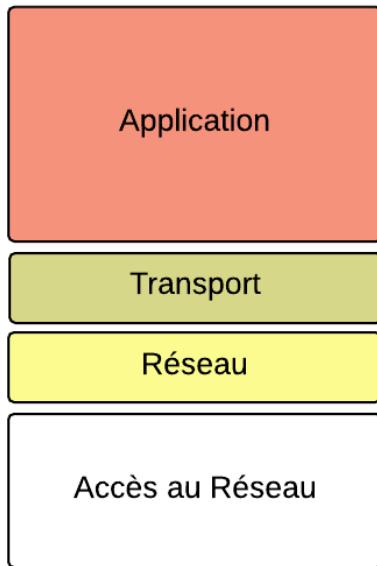

Le département américain de la Défense (« Department of Defense ») a proposé un autre modèle en couches axé sur la modélisation de réseau de données, plus simple et contenant moins de couches ; comme représenté dans la figure 1-2. Ce modèle, le TCP/IP, est fondé, tout comme le modèle ISO/OSI, sur le concept de **pile de protocoles indépendants**. Néanmoins, on remarque que les couches présentation et session ne sont plus présentes dans le modèle TCP/IP car elles semblaient peu utiles (peu utilisées).

La révolution du modèle TCP/IP réside dans la couche Internet (L3). Cette couche réalise l'interconnexion des réseaux (hétérogènes) distants **sans connexion**. Comme aucune connexion n'est présente, l'acheminement des paquets se fait de manière indépendante, ainsi les paquets

peuvent arriver dans le désordre. La couche Internet a une implémentation officielle : le protocole Internet (« Internet Protocol »). En effet, contrairement au modèle ISO/OSI, le modèle TCP/IP est né d'une implémentation : les protocoles TCP et IP. La normalisation est venue par la suite. Les couches situées au-dessus de l'IP sont responsables de la création de divers types de connexion pour de nombreuses applications (par exemple, l'application HTTP, pour la navigation sur le Web). Les deux types de protocoles définis dans la couche de transport (L4) sont les protocoles TCP et UDP.

Aujourd'hui, le modèle TCP/IP, plus souple, s'est imposé comme modèle de référence. Le modèle OSI, plus rigoureux, est principalement utilisé pour certaines applications critiques, ou pour garantir une qualité de service.

Figure 2-2 : Couches du modèle TCP/IP

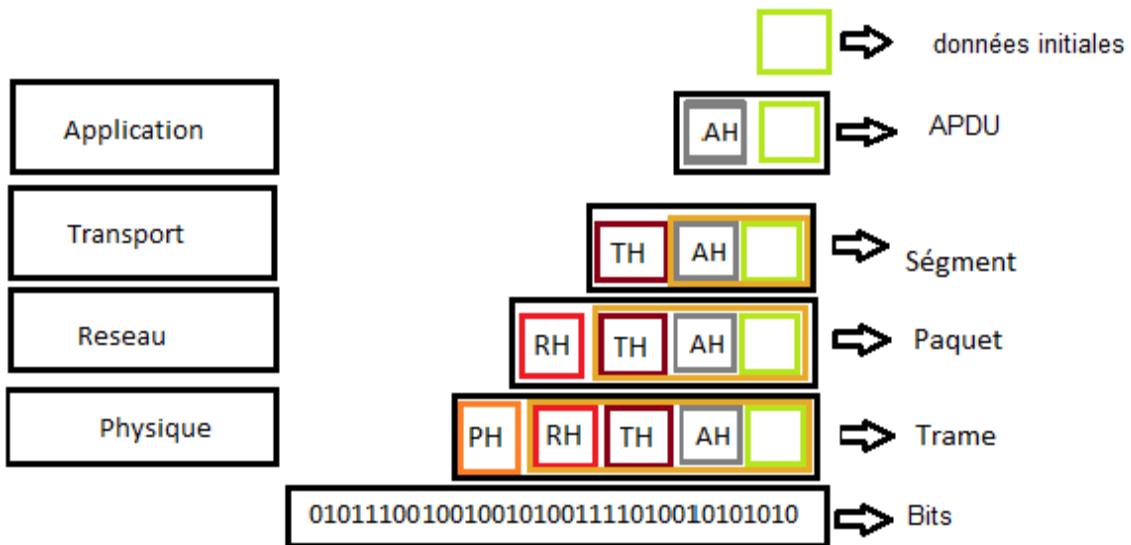

### 2.2.2 Encapsulation

Les deux modèles reposent sur le concept de pile de protocoles, grâce à un mécanisme d'*encapsulation*. Chaque couche ajoute son propre en-tête au paquet, avec des informations spécifiques à la couche en question (définies par le protocole), ce qui permet aux couches homologues du nœud récepteur de pouvoir interpréter correctement le paquet. Les données sont ainsi enveloppées à chaque couche et portent le nom de PDU et sont constituées de l'en-tête

spécifique à la couche courante et des données initiales auxquelles on a ajouté les en-têtes des couches qui la précédent.

La figure 1-3 illustre ce mécanisme d'encapsulation et représente les PDU associés aux couches application, réseau et physique. Ainsi, on définit une trame comme étant la structure de données transportée à travers un lien physique. Le paquet représente l'unité d'encapsulation transmise à travers l'interface entre la couche réseau et la couche liaison, représentant ainsi des données qui voyagent indépendamment sur le réseau et dont la taille est limitée. Enfin, un datagramme représente l'unité de donnée utilisée par les applications.

Figure 2-3 : Mécanisme d'encapsulation

Lors de la réception, l'en-tête spécifique à chaque couche est enlevé : les couches supérieures n'ont pas besoin des en-têtes des couches inférieures.

## 2.3 Réseaux de communication de données

Il existe de nombreux types de réseaux de données, ainsi que plusieurs topologies pour les catégoriser, utilisant des technologies différentes. Cependant, on distingue deux technologies très répandues : Ethernet et Internet.

### 2.3.1 Ethernet / Réseau local

La technologie Ethernet fut la première technologie à haut débit pour les réseaux locaux (« Local Area Networks », LAN). Elle a été conçue originellement pour une topologie physique et logique en bus, où les nœuds d'un réseau LAN sont reliés les uns aux autres par un canal de diffusion commun. Chaque machine a une adresse distincte et propre, permettant de l'identifier, appelée adresse MAC. Elle représente l'adresse physique d'un périphérique et est sensée être unique au monde. Cette topologie reposait sur le protocole CSMA/CD, qui permet d'accéder au support de transmission et de gérer les collisions de communications.

Ethernet fut ensuite adapté (norme 10BASE-T) pour utiliser des topologies physiques en étoile sur câbles à paires torsadées (équipés de connecteurs RJ45), les pairs étant rattachés à des concentrateurs (« hubs »). Néanmoins, la topologie logique reste le bus et le médium reste partagé (tout le monde reçoit toutes les trames), provocant des collisions potentielles. Pour résoudre les problèmes liés aux collisions, les commutateurs (« switches ») ont été développés afin de maximiser la bande passante disponible, en reprenant les câbles à paires torsadées (puis la fibre optique), permettant d'avoir des topologies plus souples : topologie logiques et physiques en étoile où les communications entre deux pairs donnés sont isolées.

Un commutateur transporte les trames qu'il reçoit vers un de ses ports, grâce à une table qui contient les adresses MAC de ses interfaces. L'usage de commutateurs permet de ne plus avoir de collisions et de construire des réseaux plus étendus géographiquement. Le commutateur est également utilisé pour relier des segments de réseaux subdivisés (un grand réseau peut être subdivisé pour une meilleure gestion du réseau).

Le protocole Ethernet intervient dans les couches liaison de données (niveau 2) et physique (niveau 1) du modèle ISO/OSI et il permet à deux (ou plus) hôtes de communiquer dans un réseau local en utilisant les adresses MAC associées à chaque hôte. Cependant, la mise en place d'un réseau constitué de commutateurs à l'échelle mondiale n'est pas réalisable, il est nécessaire d'utiliser des systèmes spécialement conçus pour assurer une connectivité globale. De plus, Ethernet est peu flexible, par exemple, à chaque fois qu'une application serveur ou une application client modifie son adresse MAC (par exemple, on remplace une plate-forme matérielle), une nouvelle adresse MAC doit être associée et distribuée à tous les pairs qui veulent communiquer avec elle. Pour résoudre ce problème, le protocole Internet (couche L3) utilise des adresses logiques IP qui peuvent

être facilement configurées. La couche L3 est efficace pour les réseaux locaux, mais elle est surtout nécessaire pour l'interconnexion de réseaux.

### **2.3.2 Internet / Réseau mondial**

#### **2.3.2.1 Vue d'ensemble**

Internet est un réseau informatique couvrant l'ensemble du globe, composé de milliers de réseaux LAN interconnectés (aussi bien publics que privés). Étant donné qu'Internet est en perpétuelle croissance et inclut des centaines de milliers de réseaux, une approche hiérarchique est utilisée pour découper le réseau en domaines appelés systèmes autonomes (« Autonomous Systems », AS), représentant ainsi des agrégations de réseaux. Chaque AS est identifié par un numéro unique (16 bits) alloué par la Société pour l'attribution des noms de domaine et des numéros sur Internet (« Internet Corporation for Assigned Names and Numbers », ICANN) et le registre Internet régional (« Regional Internet Registry », RIR). Le nombre de systèmes autonomes enregistrés est passé d'environ 10 000 en 2000 à plus de 60 000 en 2013 [10], ce qui est un bon indicateur de l'augmentation substantielle de la complexité d'Internet.

Internet s'appuie sur le modèle TCP/IP et repose sur un ensemble standardisé de protocoles. Le protocole IP est l'implémentation officielle de la couche réseau et est devenue la plateforme la plus commune pour les applications de communications de données et, également, pour plusieurs services de télécommunications comme la tété (IPTV). La quatrième génération du système de téléphonie cellulaire (4G) est également basée sur une infrastructure IP.

La fonctionnalité principale de la couche réseau consiste à fournir une connectivité de bout en bout entre deux hôtes, se trouvant dans le même réseau ou deux réseaux différents. Cette fonctionnalité est la base de la conception d'Internet. Les réseaux IP utilisent un mécanisme de routage par saut (« hop-by-hop ») à commutation de paquets et sont indépendants du matériel. Le routage est l'une des fonctionnalités de protocole importantes qui doivent être implémentées dans la couche réseau afin d'obtenir une connectivité de bout en bout. Le routage consiste à déterminer comment atteindre une interface réseau donnée et représente, avec l'adressage et la transmission de paquets, les trois notions importances pour comprendre la fonctionnalité de la couche réseau.

### 2.3.2.2 Adressage, routage et transmissions de paquets

L'abstraction des réseaux IP du matériel découle du mode d'adressage choisi : on affecte à chaque interface une adresse logique, qu'on appelle adresse IP, découlant de l'adresse du réseau auquel elle est connectée. Le protocole IP utilise des champs d'adresses de 32 bits pour la version IPv4 et 128 bits pour la version IPv6 et chaque hôte peut avoir une ou plusieurs adresses IP. La motivation d'utiliser des adresses IP de 128 bits est d'étendre l'espace d'adressage, qui s'épuise [11], afin d'assurer les besoins futurs. Dans cet ouvrage, nous nous intéressons à la version 6 du protocole IP. L'adressage IP sera discuté plus en détail au chapitre 3. Notons que d'autres mécanismes sont utilisés pour pallier les problèmes de la pénurie des adresses IP comme la traduction d'adresses réseau (« Network Address Translation », NAT) qui permet de faire correspondre une seule adresse externe publique visible sur Internet (adresse routable) à toutes les adresses d'un réseau privé (réseau intranet).

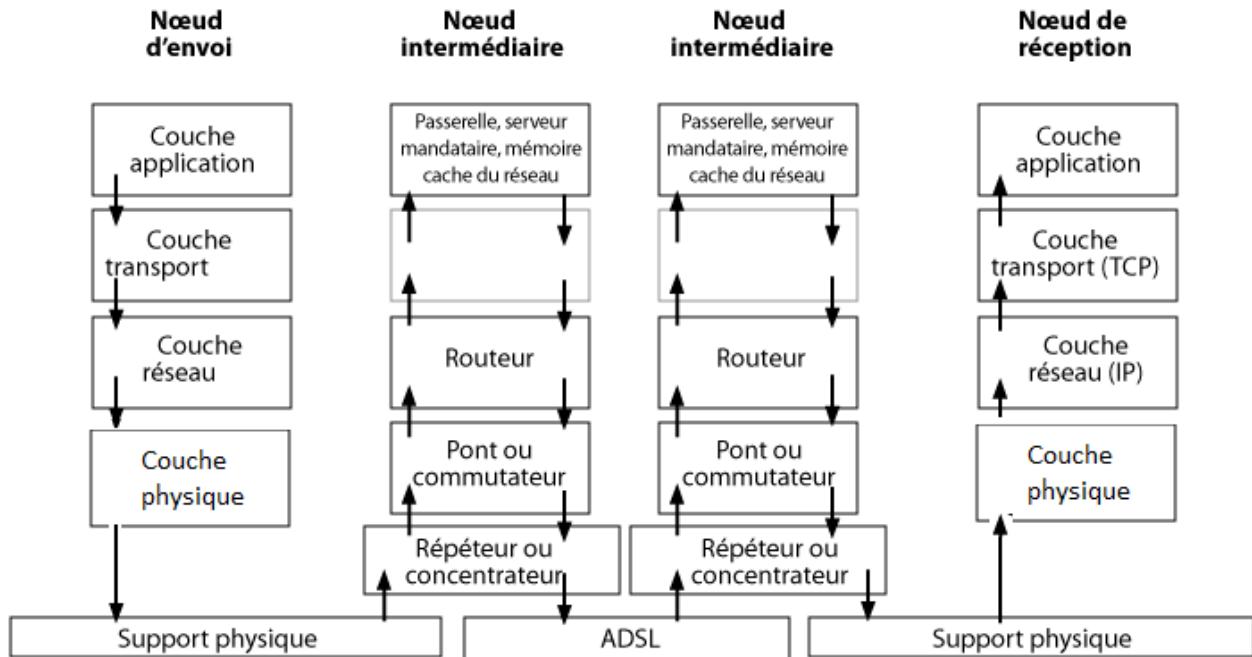

Le protocole Internet lie les adresses IP aux adresses MAC L2 (pour la transmission de paquets sur Ethernet L2) à l'aide du protocole ARP. L'hôte émetteur diffuse un paquet ARP en demandant l'adresse MAC L2 de l'hôte possédant l'adresse IP de destination. Si l'hôte se trouve dans le même réseau IP, l'adresse MAC de l'hôte destinataire est renvoyée, sinon, l'adresse MAC du routeur par lequel il est doit passer pour sortir du réseau est renvoyée. Le routeur est le dispositif responsable de faire transiter les paquets d'un réseau vers une autre car il dispose de plus d'une carte réseau dont chacune est reliée à un réseau différent.

Il est important de distinguer la notion de routage de paquets à celle de la transmission de paquet. Le routage détermine la route à suivre pour chaque paquet pour arriver à sa destination, alors que la transmission correspond à l'action d'acheminer un paquet d'une interface à une autre. Quand le routeur reçoit une trame provenant d'une machine connectée à un des réseaux auquel il est rattaché, il extrait l'adresse IP de destination de l'en-tête IP du paquet et une décision de transmission est prise en fonction de l'adresse IP de destination et de sa table de routage. La table de routage contient les adresses des réseaux attachés au routeur ainsi que les interfaces (adresses des cartes réseau) par lesquelles les paquets doivent être acheminés. Les tables de routage sont construites et maintenus notamment grâce au protocole de routage. Sur la base de cette décision, le paquet est acheminé vers le routeur du saut suivant ou vers sa destination. La figure 1-4 montre comment un paquet est acheminé entre deux nœuds dans deux réseaux différents.

La topologie hiérarchique présentée précédemment (systèmes autonomes) permet de gérer le routage de manière interne et indépendante : en utilisant des protocoles de routage appelés IGP, opérant dans un seul AS pour optimiser des routes utilisées dans sa propre structure (exemple : le protocole RIP) et ; en utilisant des protocoles de routage EGP pour échanger des informations de routages entre deux AS (exemple : le protocole BGP).

Figure 2-4 : Transmission d'un paquet IP

Cependant, à mesure que les routeurs deviennent plus centraux et ont de nombreuses adresses de destination (i.e. de nombreuses interfaces de sortie) à gérer, il peut s'avérer difficile de choisir parmi les interfaces possibles pour l'adresse de destination appropriée (correspondance optimale). En effet, un des mécanismes les plus répondus est le routage inter-domaines sans classe (« Classless Inter-Domain Routing », CIDR), qui permet à un réseau IP de se décomposer en plusieurs sous-réseaux (subdivision logique) pour divers intérêts comme la séparation des services, rendre le réseau plus flexible et limiter la propagation des « broadcast » (opération coûteuse qui consiste à diffuser les données à toutes les machines du réseau) ; il ajoute de la complexité et influence l'adressage, le routage et la transmission des paquets. Comme chaque entrée de la table de routage peut spécifier un sous-réseau, une adresse de destination peut correspondre à plusieurs entrées de table. Une stratégie de recherche appelée « Longest Prefix Match » (LPM) est utilisée pour trouver le port de sortie représentant la meilleure correspondance.

La transmission des paquets (« packets forwarding ») représente l'une des principales tâches de traitement de paquets. La transmission de paquets et ses exigences de performance et fonctionnelles seront couvertes dans les chapitres suivants. L'adressage, ainsi que d'autres sujets liés à la transmission de paquets seront discutés ; néanmoins, nous n'allons pas développer le sujet du routage. En effet, un algorithme de routage spécifique mis en œuvre ne prend pas en compte les exigences de transmission [12], tant que les paquets sont transférés vers les ports de sortie appropriés, tout algorithme de routage possible (y compris une table configurée de manière statique) est acceptable. Il s'agit donc de deux fonctions ayant deux implémentations propres et distinctes.

### **2.3.2.3 Évolution des routeurs**

Historiquement, l'objectif principal d'Internet consistait à interconnecter facilement une grande variété de réseaux existants (par exemple, réseaux longue distance, réseaux locaux, réseaux de satellites et réseaux radio) via un ensemble de routeurs entre ces réseaux. De ce fait, la plus grande partie de la complexité résidait dans les hôtes finaux, alors que les routeurs fonctionnaient selon le principe de « best-effort » [1] (faire au mieux) pour transmettre des paquets, n'assurant aucune fiabilité et limitant beaucoup de services comme : la hiérarchisation des paquets, les fonctions de sécurité permettant de détecter les défaillances du réseau, etc. Les premiers routeurs étaient donc singulièrement dédiés à la transmission de paquets. Aujourd'hui, quatre décennies après la publication des idées sous-jacentes à Internet, il est clair que les routeurs doivent faire beaucoup plus que la transmission de paquets et d'autres objectifs tels que la performance, la sécurité et la surveillance gagnent en importance. En conséquence, un routeur typique implémente aujourd'hui de nombreuses fonctionnalités au-delà de la transmission de paquets, relatives à la sécurité (par exemple, contrôle d'accès), à la surveillance (par exemple, compter le nombre de paquets appartenant à chaque flux) et à la performance (par exemple, files d'attente prioritaires). Nous discuterons dans le chapitre suivant de l'évolution des routeurs (architectures et implémentations), ainsi que des exigences de performance et fonctionnelles auxquels ils sont confrontés.

## **2.4 Conclusion**

Ce chapitre avait pour but de définir les concepts fondamentaux sur lesquels reposent les réseaux de communication de données. Un routeur possède plusieurs interfaces réseaux par lesquelles il

fait transiter les paquets IP qu'il reçoit. Un paquet IP est transporté de routeur en routeur, potentiellement, jusqu'à arriver à sa destination. Le routeur représente ainsi la pierre angulaire d'Internet. Cependant, aux vues des exigences exponentielles que nécessite le traitement de paquets, d'autre concepts et technologies ont vues le jour et on fait évoluer la manière dont on traite le réseau.

## CHAPITRE 3 LES ROUTEURS

### 3.1 Introduction

On distingue deux catégories de fonctions de traitement de paquets : les fonctions du plan de contrôle (« control plane ») et les fonctions du plan de données (« data plane » ou « forwarding plane »). Les fonctions de contrôle sont destinées à configurer l'équipement réseau alors que les fonctions du plan de données sont destinées à traiter les paquets et transporter le trafic en se basant sur la configuration de l'équipement réseau. Les fonctions du plan de contrôle s'exécutent relativement peu souvent en comparaison avec les fonctions du plan de données : de l'ordre d'une fois toutes les millisecondes, par opposition à une fois toutes les nanosecondes. Ce qui se traduit par des requis et des implémentations fort différentes.

Le traitement réseau désigne ainsi le traitement des paquets entrants dans le réseau selon un ensemble de règles qui gèrent leur transmission sur un lien de communication sortant. Les progrès récents en matière de technologie de réseau ont entraîné une explosion des débits soutenus par les équipements réseau. Disposant de la technologie de fibre optique rapide pour la transmission de données, les éléments de traitement de données, à savoir les routeurs, sont devenus le principal goulot d'étranglement [3] de la performance actuelle d'Internet.

Dans ce chapitre, nous allons présenter les fonctionnalités d'un routeur, ses exigences de performance, ainsi que les architectures et les implémentations dominantes. Ce chapitre a également pour but d'introduire l'objectif et l'intérêt du projet de recherche dans le cadre duquel cette recherche s'inscrit.

### 3.2 Fonctionnalités d'un routeur

Les exigences fonctionnelles pour un routeur IP sont déterminées par une série de documents officiels décrivant les aspects et spécifications techniques d'Internet (« Requests For Comments, RFC »). Un routeur implémente plusieurs tâches qui nécessitent différentes fonctions. Le processus de traitement de paquets peut se résumer à trois étapes [12] : le traitement d'entrée (opérant le traitement de la couche liaison pour recevoir un paquet IP), la transmission de paquet et le traitement de sortie (mise en file d'attente et ordonnancement des paquets ainsi que le traitement de la couche de liaison pour la transmission).

Les tâches de traitement de paquets impliquent essentiellement [9] :

- La mise en trame (« framing »)

- L'analyse et l'extraction des champs d'entête du paquet (« parsing »)

- La classification

- La recherche (« lookup »)

- La modification

- La compression et le cryptage

- La gestion du trafic (« traffic management » et « queueing »)

- La transmission des paquets (« forwarding »)

Le traitement des paquets commence par l'entrée du paquet sur un port d'entrée associé à une des interfaces de l'équipement réseau et sa mise en trame. Le « framing » garanti que les paquets sont reçus correctement et corrigé, dans certain cas, les bits incorrects du paquet. Par la suite, les paquets sont analysés et classés, en fonction des exigences de l'application. Ce tri est basé sur plusieurs champ de paquets, extraits durant le « parsing », qui seront comparés à un ensemble de règles contenues dans une ou plusieurs tables de classification. Traditionnellement, cinq champs (« 5-uplets ») sont utilisés : l'adresse IP Source, l'adresse IP Destination, le Protocole de transport, le Port Source et le Port de Destination. Une table de classification consiste, généralement, en une table de recherche qui exploite plusieurs stratégies de recherche (par exemple, la recherche de type « exact match »). Chaque règle a une action associée, qui sera effectuée si les champs utilisés pour la classification correspondent à cette règle. Une action consiste à un traitement appliqué au paquet.

La tâche de recherche (« lookup table») est une opération atomique impliquée dans d'autres tâches, comme la classification et la transmission de paquets. Puisque toutes les activités de traitement de paquets commencent par une recherche IP, le « lookup » est donc le traitement le plus fréquent et important dans le traitement de paquets. Étant donné son importance, le chapitre 3 sera dédié à la tâche de recherche (particulièrement, la recherche IP, « IP lookup »).

Lors de la phase de modification du paquet, le routeur peut supprimer ou modifier le paquet en cours de traitement, ou générer éventuellement de nouveaux paquets, selon l'application (une application de type « multicast », par exemple, duplique le paquet en cours de traitement). Certains

systèmes de traitement de paquets compressent et chiffrent les paquets avant qu'ils ne quittent le système, mais souvent les paquets transitent sans modification. Enfin, la transmission du paquet peut impliquer d'autres fonctions de mise en queue, de priorisation et de gestion de trafic pour s'assurer que le récepteur va recevoir le paquet selon le modèle de trafic attendu.

Afin de respecter les exigences fonctionnelles, différentes fonctions sont nécessaires [12] telles que :

- Le calcul de la somme de contrôle (« checksum ») : l'en-tête IP contient un « checksum » qui couvre les champs de l'en-tête pour s'assurer que ces champs importants n'ont pas été corrompus. Lors de la réception d'un paquet, tout système doit vérifier que cette somme de contrôle est toujours correcte.

- TTL (« Time-To-Live ») : il s'agit d'un compteur indiquant le nombre maximal de routeurs par lesquels le paquet peut transiter. Le compteur est décrémenté à chaque saut et le paquet est rejeté si ce compteur atteint la valeur zéro. Cette fonctionnalité garantit que les paquets qui ne peuvent atteindre leur destination seront rejettés pour ne pas traverser le réseau de manière indéterminée et infinie.

- Autres fonctions : un certain nombre d'autres opérations peuvent être effectuées (non standard, dépendamment de l'application). Un exemple de telles opérations est la fragmentation IP. Lorsque les datagrammes sont plus longs que ce que le réseau peut transférer directement, le datagramme doit être envoyé en plusieurs parties. Cela se produit lorsque le datagramme dépasse l'unité de transmission maximale (MTU). Une fois que le datagramme original a été fragmenté ou segmenté, il doit être réassemblé à la destination.

### **3.3 Plan de données, de contrôle et de gestion**

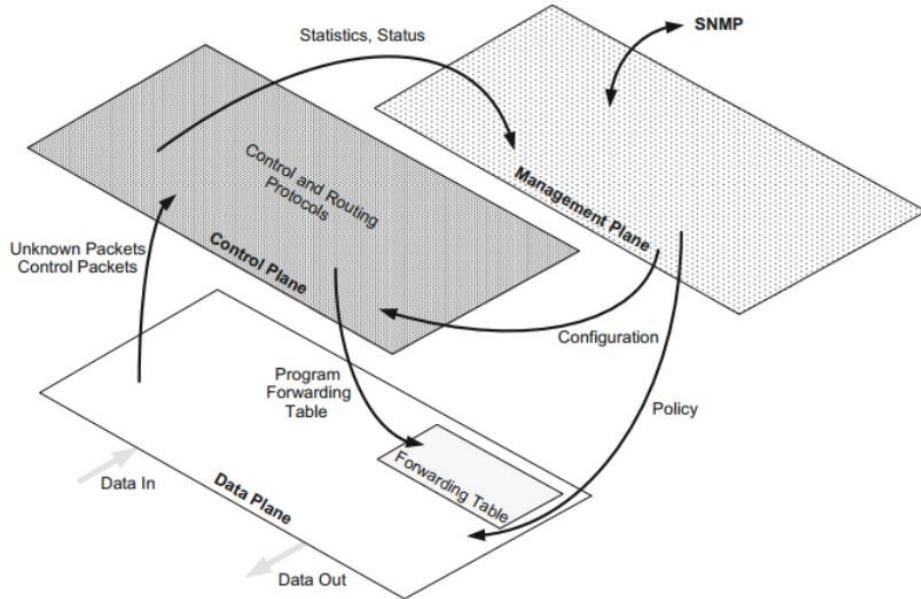

Les réseaux informatiques peuvent être divisés en trois plans de fonctionnalités [13] : les plans de données, de contrôle et de gestion (voir Figure 2-1). Le plan de contrôle est responsable de l'exécution de protocoles de routage, tels que RIP, OSPF ou BGP, afin de peupler et de maintenir à jour les tables de transmission (« forwarding tables »).

Le plan de données est responsable de l'acheminement des paquets, conformément aux tables de routage, et de diverses fonctions de traitement de paquets telles que la mise en mémoire tampon des paquets (« packet buffering »), l'ordonnancement des paquets (« packet scheduling ») et la

modification des en-têtes. Le plan de gestion inclut les services logiciels utilisés pour surveiller et configurer à distance la fonctionnalité de contrôle, tel que le protocole SNMP. Les administrateurs réseau définissent la politique du réseau via le plan de gestion alors que le plan de contrôle l'applique et que le plan de données l'exécute en transmettant les données en conséquence.

Figure 3-1 : Plan de données, de contrôle et de gestion [13]

Le plan de contrôle s'exécute généralement lorsque la topologie du réseau ou la stratégie du réseau change. Par conséquent, les fonctions de contrôle ne sont pas effectuées à l'arrivée de chaque paquet ; elles n'ont pas donc besoin d'autant de performance de la part du matériel. Cependant, les fonctions de « data plane » sont fréquentes, effectuées sur chaque paquet qui passe par le routeur, et nécessitent ainsi une implémentation performante.

Dans les réseaux IP traditionnels, les plans de contrôle et de données sont étroitement couplés et intégrés dans les mêmes dispositifs de réseau. Ce couplage était considéré comme important pour la conception d'Internet : c'était le meilleur moyen de garantir la résilience des réseaux [13], qui était l'objectif crucial de conception. Cependant, cela a rendu extrêmement difficiles diverses tâches de gestion du réseau [14], telles que déboguer les problèmes de configuration et prévoir ou contrôler le comportement de routage. C'est la raison fondamentale pour laquelle les réseaux traditionnels sont rigides et complexes à gérer et à contrôler, rendant l'innovation difficile. Au début des années 2000, le plan de contrôle des routeurs s'est vu donc séparé du plan de données.

Nous présentons, dans la section suivante, l'évolution des architectures des routeurs pour rencontrer les différents besoins de traitement de réseau. Nous discuterons également du concept SDN (« Software-Defined Networking »), qui est un modèle d'architecture réseau devenu un paradigme puissant et révolutionnaire. Avec SDN, il est possible de résoudre divers problèmes persistants dans le domaine du réseau en améliorant la séparation entre le plan de contrôle et le plan de données, permettant aussi d'introduire des technologies comme la virtualisation [15].

## 3.4 Architecture

### 3.4.1 Compromis entre performance et programmabilité

Historiquement, l'évolution des routeurs de réseau était principalement motivée par la performance des fonctions de traitement de paquets.

La performance d'un routeur peut être exprimée selon plusieurs dimensions [12] :

- Le débit de transmission : qui déterminent la quantité de données pouvant être transférée via le système par unité de temps.

- Le taux de paquets : étant donné que la plupart des opérations doivent être effectuées pour chaque paquet, les petits paquets entraînent une charge de travail plus importante pour un débit de données donné fixé.

- La consommation d'énergie électrique.

L'exigence de la vitesse de traitement de paquets peut être illustrée par un simple exemple : un routeur à haute vitesse actuel [1] est censé soutenir un débit de l'ordre du téribit par seconde ; supposons que ce dernier traite des paquets de 1000 bits et qu'il effectue 10 opérations par paquet, alors le routeur doit prendre en charge environ 10 milliards d'opérations par seconde.

En raison de la nécessité de mieux contrôler les opérations du réseau et de la demande constante de nouvelles fonctionnalités, la programmabilité des routeurs est devenue aussi importante que la performance. Elle peut être exprimée en fonction des algorithmes soutenus, en utilisant un modèle de programmation, et l'extensibilité. Cet équilibre entre la performance et la programmabilité représente un compromis majeur que rencontrent les opérateurs de réseau.

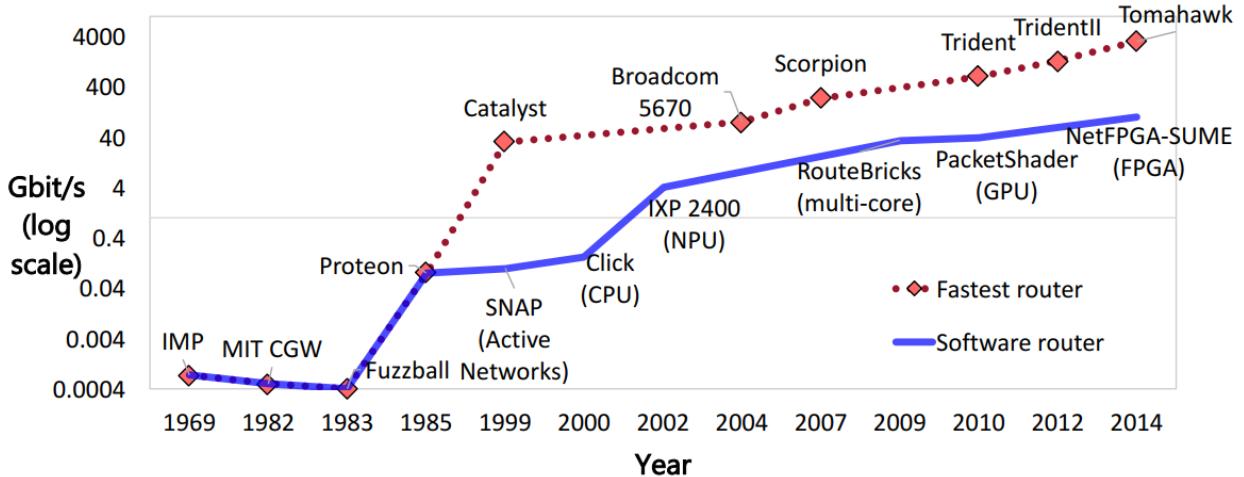

### 3.4.1.1 Routeurs logiciels

Initialement les routeurs étaient basés sur des processeurs à usage général (« General Purpose Processor », GPP), où les fonctions de réseaux étaient réalisées en logiciel. Ces derniers ont évolué au cours des années ; par exemple, en 2000, Click [16] utilisait un processeur avec un seul cœur. Au début des années 2000, Intel a lancé une gamme de processeurs spécifiques pour les applications réseaux, appelés processeurs de réseau, tels que le IXP2800 [17] en 2002. Il existe également des routeurs basés sur des processeurs graphiques (PacketShader [18], proposé en 2010) ou encore des circuits logiques programmables comme le FPGA dans l'implémentation présentée par NetFPGA-SUME [19] en 2014.

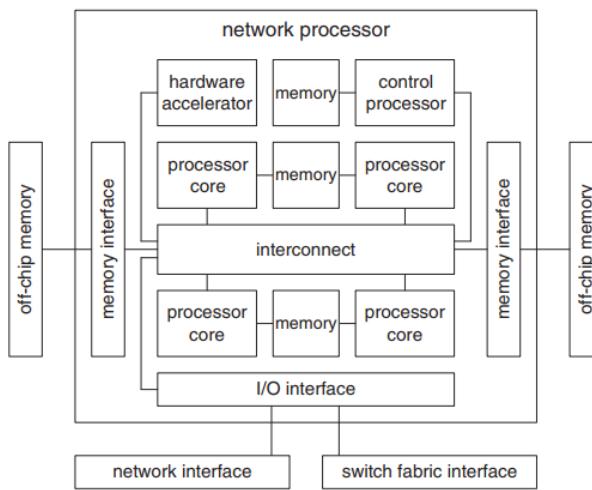

Cette évolution a permis aux routeurs logiciels d'être plus performant ; par exemple, les processeurs de réseaux bénéficient d'une performance intéressante grâce à l'utilisation de processeurs multicoeurs, de modules matériels dédiés pour les opérations réseaux courantes (accélérateurs), d'interfaces mémoire à haute vitesse et d'interfaces d'entrée/sortie à haut débit. Par exemple, le processeur de réseau NP-5 [20] de Mellanox soutient un débit de 240 Gb/s. La figure 2-2 illustre l'architecture typique d'un processeur de réseau. Ce dernier possède une interface avec un « switch fabric », responsable de déplacer les données entrant dans un nœud du réseau vers le nœud suivant.

Figure 3-2 : Architecture typique d'un NP [12]

L'avantage principale des routeurs logiciels reste la flexibilité : l'ajout de nouvelles fonctionnalités se fait facilement, permettant ainsi aux routeurs de prendre en charge différents services (pare-feu,

détection d'intrusion, proxy ...). D'ailleurs, la demande de soutenir différents services ne cesse de croître. Cependant, la croissance de la quantité de données à traiter, due à la croissance du débit des liens et des débits de transmission, exige des équipements plus performants. En effet, les routeurs logiciels ne sont pas en mesure de satisfaire les exigences de performance d'un routeur à haute vitesse (i.e. 1 Tb/s) [1].

### 3.4.1.2 Routeurs basés sur des ASIC

Comme mentionné précédemment, Le plan de contrôle des routeurs s'est vu séparé du plan de données. Utilisé moins fréquemment, le plan de contrôle est alors implémenté en logiciel, sur des processeurs à usage général pour être plus flexible ; alors que le plan de données est implémenté avec des entités matérielles plus performantes.

Figure 3-3 : Évolution de la performance des routeurs [1]

L'implémentation matérielle offre aux routeurs une amélioration de la performance (10 à 100 fois plus élevée par rapport aux routeurs logiciels, voir Figure 2-3) qui résulte de l'exploitation complète de l'abondant parallélisme disponible dans le traitement des paquets. La spécification matérielle permet de traiter simultanément différentes parties d'un même paquet (ou des paquets appartenant à des ports différents) et d'effectuer simultanément différentes opérations sur différents paquets.

Les ASIC, qui sont des circuits intégrés spécialisés, sont utilisés pour leur performance, mais ils possèdent un coût : comme les routeurs sont construits à partir de matériel spécialisé, ce sont des périphériques à fonction fixe qui ne peuvent normalement pas être programmés. Pour modifier une

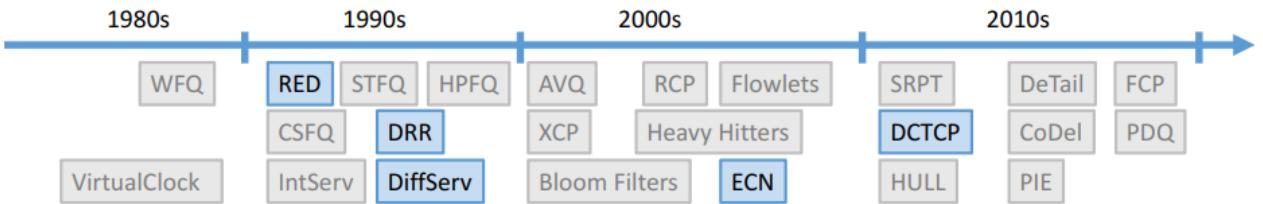

fonctionnalité, l'opérateur de réseau doit attendre, de 2 à 3 ans, la prochaine génération de routeur, ce qui crée un décalage entre la standardisation et la disponibilité de nouveaux protocoles ou de certaines nouvelles applications. En conséquence, les routeurs à haute vitesse sont limités dans leur capacité à intégrer des nouveaux algorithmes. La figure 2-4 présente une chronologie des principaux algorithmes de routeur mis au point depuis les années 1980. Seule une poignée (représentée en bleu) est disponible dans les routeurs les plus rapides du moment.

Figure 3-4 : Algorithmes de routeur [1]

### 3.4.2 Révolution SDN

Contrairement aux autres domaines de l'informatique, les réseaux informatiques sont difficiles à gérer et à faire évoluer. Pour prendre en charge de nouveaux services, les gestionnaires devaient configurer des milliers de périphériques, augmentant considérablement la complexité du réseau [22]. Puisque les équipements réseaux diffèrent d'un fournisseur à l'autre, seul un petit nombre d'interfaces externes est normalisé (par exemple, la transmission de paquets), ce qui limite la capacité des opérateurs de réseaux à adapter les réseaux à leurs environnements individuels et à améliorer leur matériel ou leurs logiciels.

Le plus gros inconvénient des approches traditionnelles est le faible niveau d'abstraction [15]. La réduction de la complexité des architectures exige certainement un niveau d'abstraction plus élevé. L'abstraction ne supprime pas toute la complexité du réseau, mais elle donne la possibilité d'encapsuler ou de masquer un certain degré de complexité. De plus, l'abstraction est l'une des conditions essentielles d'une conception modulaire efficace : elle offre la souplesse nécessaire pour effectuer le traitement dans différentes parties du réseau. Même si l'abstraction du plan de données est basée sur les couches du modèle TCP/IP (présenté précédemment), les interfaces sont mal implémentées et violent les principes de la modularité [15]. Ce constat a poussé les chercheurs et les industriels à penser le traitement du réseau différemment, faisant apparaître un nouveau paradigme, qui a défini les abstractions dont avait besoin le réseau, le SDN.

Le SDN repose sur plusieurs travaux antérieurs, notamment ceux qui avaient pour but la séparation entre le plan de contrôle et le plan de données, l'apprivoisement des réseaux de centre de données et la réorganisation de la gestion des réseaux. Le SDN permet aux opérateurs de programmer le plan de contrôle du réseau, en introduisant l'idée du contrôle centralisé : en déplaçant le plan de contrôle hors des équipements réseaux, le plan de contrôle entier pour le réseau pourrait être centralisé sur quelques serveurs (exécuté sur des processeurs performants). Ceci permet à ces serveurs de calculer des itinéraires pour l'ensemble du réseau avec l'avantage de la visibilité globale du réseau. Pour ce faire, le SDN avait besoin d'un mécanisme permettant au plan de contrôle d'alimenter le contenu des tables de routage, une fois que le plan de contrôle a calculé les itinéraires pour chaque routeur. Ces tables sont ensuite consultées par le plan de données lors de la transmission des paquets. Le plus connu de ces mécanismes était l'API OpenFlow, qui a exposé une interface entre le plan de contrôle et le plan de données.

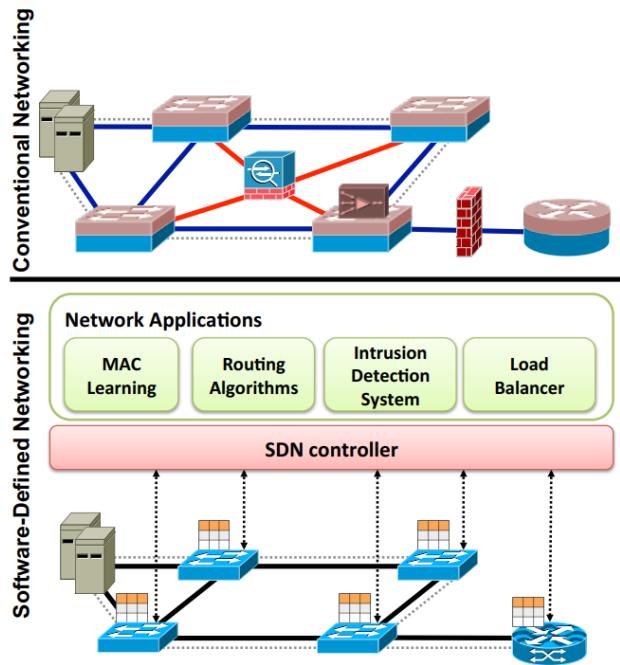

Figure 3-5 : Architecture SDN [13]

La figure 2-5 illustre la différence architecturale entre les réseaux traditionnels et les réseaux SDN. Avec SDN, la gestion devient plus simple. À noter que, puisque le plan de données est responsable principalement de transiter des paquets vers les interfaces appropriées, il est plus juste d'appeler la plateforme qui l'implémente un commutateur (« switch »); par exemple, un commutateur ASIC. Cependant, le terme routeur est souvent utilisé par abus de langage.

### 3.4.2.1 Traitement basé sur le flux

Avec SDN, le traitement du plan de données devient basé sur les flots (« flow-based »). Un flot est défini de manière générale par un ensemble de valeurs de champs de l'en-tête des paquets agissant comme critère de correspondance et auquel on associe un ensemble d'actions.

Dans le cas d'une implémentation OpenFlow, un commutateur a une ou plusieurs tables de flots, représentant les règles de transmission de paquets. Chaque règle est associée à une action spécifique que le routeur doit exécuter sur un paquet entrant si des champs d'en-tête particuliers du paquet correspondent à cette entrée (par exemple, 15 champs, allant de la couche 2 à la couche 4, pour un routeur supportant la version 1.1.0 d'OpenFlow). Par exemple, une règle pourrait indiquer au routeur de transmettre un paquet sur un port de sortie particulier (action) si le paquet a une certaine adresse IP de destination (correspondance). Le plan de données est chargé de lire les tables de correspondance et d'exécuter l'action appropriée sur chaque paquet (si le paquet correspond à une règle particulière). L'action [14] à exécuter peut consister, par exemple, à supprimer le paquet, le transmettre à une interface particulière, à modifier un champ d'en-tête etc. Ces tables de correspondance contiennent également un ensemble de compteurs (pour calculer le nombre d'octets et de paquets) et un mécanisme de priorité (pour lever toute ambiguïté si deux règles venaient à correspondre à un même paquet).

L'abstraction de flot permet d'unifier le comportement de différents types de périphériques réseau où tous les paquets d'un flot reçoivent un traitement identique.

### 3.4.2.2 Fonctionnalités clés de l'architecture SDN

Le SDN présente une abstraction pour la définition d'une architecture pour le plan de contrôle centralisé, pour découpler la topologie, le trafic et les dépendances entre les couches, pour avoir un réseau multicouche dynamique etc.

Mais surtout, SDN et OpenFlow ont révolutionné la manière dont on traite le réseau, en s'appuyant sur l'approche dite de « Match-Action » [24], qui consiste à exécuter une action en fonction de l'entrée des tables de correspondance, qui convient au paquet entrant. OpenFlow propose différents types d'instruction comme appliquer, effacer et écrire des actions, permettant d'avoir une flexibilité sans précédent (limitée néanmoins) pour les routeurs basés sur les ASIC (dans un routeur statique, toutes les tables de flots sont remplies manuellement).

### 3.4.3 Travaux de recherche courants

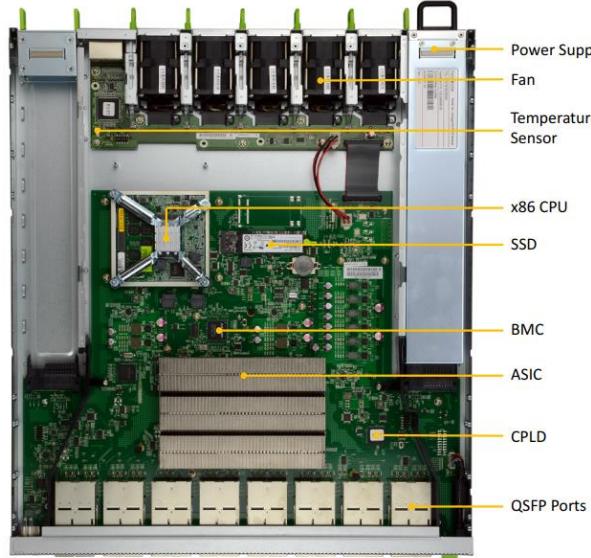

Comme vu précédemment, le seul moyen de satisfaire les besoins de performance élevée est d'utiliser un routeur basé sur un ASIC. La figure 2-6 représente un routeur typique de centre de données. Dans ces routeurs, les tables de flux sont souvent implémentées à partir de TCAM et SRAM, qui sont des mémoires rapides mais de capacité limitée (on discutera plus en détails de ces mémoires dans le chapitre 4). Le plan de contrôle, quant à lui, s'exécute sur une carte CPU, qui roule un micro-serveur. En plus de ces composants standards (RAM, support de stockage, etc.), une carte CPU dispose d'une interconnexion PCI-E au commutateur ASIC et la présence d'un processeur x86 permet l'installation de Linux, offrant les fonctionnalités générales d'un système d'exploitation.

Puisque l'implémentation ASIC est requise pour obtenir une grande performance, beaucoup de travaux de recherche se sont focalisé à rendre ces routeurs plus programmables.

#### 3.4.3.1 Évolution d'OpenFlow

Initialement, avec OpenFlow, l'ensemble des champs sur lesquels des correspondances pouvaient être effectuées était fixe et limité à un petit nombre. De même, les actions autorisées sur les en-têtes de paquet étaient limitées à un ensemble fixe d'actions. Les routeurs les plus récents (également les plus performants) utilisent un traitement de type « match-action » plus souple. Dans ces routeurs, un « parser programmable » [1] permet à l'utilisateur de spécifier un nouveau format de protocole car l'utilisateur est capable de spécifier les champs à extraire du paquet sans être contraint à un ensemble fixe de champs disponibles à des emplacements fixes dans l'en-tête du paquet. Également, pour surmonter la limite de la capacité mémoire des TCAM (en raison de leur coût), le traitement est fait à l'aide de plusieurs tables de flots en pipeline.

Figure 3-6: Routeur ASIC [21]

### 3.4.3.2 Routeur “programmable”

La communauté SDN a consacré beaucoup de travail de recherche à la programmation du plan de contrôle et elle cible aujourd’hui la programmation dans le plan de données. De ce fait, des travaux universitaires et industriels ont abouti au développement de routeurs dits programmables [1]. Ces routeurs ont un jeu d’instructions minimal qui permet à un opérateur de réseau d’exprimer des règles de transmission de type OpenFlow pour n’importe quel protocole. Cela contraste avec OpenFlow, qui ne prend en charge qu’un ensemble fixe d’actions (suppression, décrémentation, durée de vie, transfert, etc.)

Le langage de programmation P4 a émergé d’un effort de l’industrie et du milieu académique visant à mettre au point un langage de programmation standard pour ces routeurs. Les compilateurs P4 visent des architectures de routeurs “programmable” telles que l’architecture RMT et FlexPipe. P4 [25] permet de programmer le plan de données et les programmeurs utilisent des abstractions spécifiques à un domaine (« domain-specific abstractions »), et faisant partie du langage, pour mettre en œuvre diverses applications innovantes : notamment les outils de diagnostic réseau et de télémétrie, des systèmes d’équilibrage de charge (« load balancing »), et même des protocoles de consensus optimisés.

L’architecture RMT [24] (« Reconfigurable Match Tables ») permet la définition d’en-têtes et de séquences d’en-tête arbitraires, une correspondance arbitraire (de champs) par un nombre arbitraire

de tables (règles), une écriture arbitraire de champs d'en-tête de paquet (mais pas le corps du paquet) et une mise à jour de l'état du paquet, permettant ainsi de soutenir de nouveaux protocoles tels que PBB, VxLAN, NVGRE, STT et OTV [24].

Le Tofino [26] (produit de Barefoot Networks, en décembre 2016) est un des fruits de ces travaux. Il est présenté comme le commutateur programmable le plus rapide au monde, supportant 11 instructions et une vitesse atteignant les 6.5 Tb/s. PISA [26] (« Protocol Independent Switch Architecture ») est l'architecture du Tofino et elle découle du concept de RMT.

### 3.4.3.3 Limites des routeurs ASIC

#### 3.4.3.3.1 Flexibilité limitée

Beaucoup d'efforts et de travaux ont été réalisés afin de rendre les ASIC plus programmables. Cependant cela est encore insuffisant pour exprimer certains des algorithmes illustrés à la figure 2-4. En effet, les auteurs du papier introduisant l'architecture RMT [24] ont défini des restrictions de reconfigurabilité nécessaires afin de soutenir une vitesse de l'ordre du téribit par seconde, comme des restrictions matérielles (par exemple, le nombre d'étages de pipeline), la taille maximale d'un paquet pouvant être traité mais surtout des restrictions au niveau des actions possibles. Les instructions sont limitées à des opérations arithmétiques et logiques simples, permettant l'implémentation de certains protocoles, mais n'autorisant pas le cryptage des paquets ou le traitement des expressions régulières, par exemple. Également, ces instructions ne sont pas en mesure d'implémenter la fonctionnalité d'une machine à état, ce qui constitue un handicap quand il s'agit d'offrir de multiples algorithmes.

#### 3.4.3.3.2 Capacité mémoire limitée

Une autre limitation des ASIC (dans le domaine des réseaux) est la capacité mémoire. En effet, les exigences de performance nécessitent l'utilisation de mémoire TCAM ou SRAM pour implémenter les tables de correspondance (« match tables »), qui sont des mémoires rapides mais coûteuses. Puisque ces mémoires sont intégrées sur puce (« on-chip »), elles sont limitées à quelques dizaines de mégaoctets [27]. Par ailleurs, les tables de flots peuvent contenir la description des millions de flots [28] ce qui dépasse la capacité de ces mémoires.

### 3.5 Conclusion

Une mise en œuvre matérielle est le seul moyen d'atteindre les requis de performance pour les routeurs à haut débit. Néanmoins, certains scénarios ont des exigences en calculs élevées mais pour des débits plus faibles, par exemple, pour l'implémentation des algorithmes de couche MAC en Wifi et des algorithmes de traitement du signal dans la couche physique sans fil[1].