| <b>Titre:</b> Title:    | High Quality Delay Testing Scheme for a Self-Timed Microprocessor                                                                                                                                                                                 |

|-------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>Auteur:</b> Author:  | Omar Al-Terkawi Hasib                                                                                                                                                                                                                             |

| Date:                   | 2019                                                                                                                                                                                                                                              |

| Type:                   | Mémoire ou thèse / Dissertation or Thesis                                                                                                                                                                                                         |

| Référence:<br>Citation: | Al-Terkawi Hasib, O. (2019). High Quality Delay Testing Scheme for a Self-Timed Microprocessor [Thèse de doctorat, Polytechnique Montréal]. PolyPublie. <a href="https://publications.polymtl.ca/4011/">https://publications.polymtl.ca/4011/</a> |

# Document en libre accès dans PolyPublie Open Access document in PolyPublie

URL de PolyPublie:

PolyPublie URL:

Directeurs de recherche:

Advisors:

Programme:

Program:

génie électrique

# POLYTECHNIQUE MONTRÉAL

affiliée à l'Université de Montréal

| Ligh              | analita. | dolore | tosting | achomo | fon | _ | colf timed | microprocessor |

|-------------------|----------|--------|---------|--------|-----|---|------------|----------------|

| $\mathbf{n}_{10}$ | quantv   | aeiav  | testing | scheme | ior | a | sen-umea   | microprocessor |

## OMAR AL-TERKAWI HASIB

Département de génie électrique

Thèse présentée en vue de l'obtention du diplôme de Philosophiæ Doctor Génie Électrique

Août 2019

# POLYTECHNIQUE MONTRÉAL

affiliée à l'Université de Montréal

Cette thèse intitulée:

High quality delay testing scheme for a self-timed microprocessor

présentée par Omar AL-TERKAWI HASIB

en vue de l'obtention du diplôme de *Philosophiæ Doctor* a été dûment acceptée par le jury d'examen constitué de :

Yvon SAVARIA, membre et directeur de recherche Claude THIBEAULT, membre et codirecteur de recherche Yves BLAQUIÈRE, membre Benoit NADEAU-DOSTIE, membre externe

# **DEDICATION**

To my mother, without you this would not have been possible...

#### ACKNOWLEDGEMENTS

During these five years of my PhD, I have worked with many wonderful and intelligent people, and was surrounded by lots of love and support that made this journey bearable. I would like to start this section by giving thanks to God for facilitating this work and providing me with the means, time, health and capabilities to absorb all this knowledge, and for the motivation to continue this work to the end. Next, I would like to thank my family for being supportive and understanding during this long journey of higher education. I realize that I could have been much more helpful to them if I was working and making 3 times the money. So I appreciate their patience with me. Of course, I could not have made it this far if it wasn't for my mother, who supported me and encouraged me (in many different ways) to finish as soon as possible. I love you Mom!

I would also like to thank both of my supervisors, Yvon Savaria and Claude Thibeault. Yvon have encouraged me over the years, though I was reluctant, to continue my graduate studies and gave me a good financial incentive to go back and do this PhD. Claude was very generous in both knowledge and financial support. Delay testing is a hugely new domain to me and Claude's experience have helped me present my work in the most relevant way to the people in this research domain. I also must thank both my supervisors Yvon Savaria and Claude Thibeault for all the guidance and support that they provided me during these past five years. Not to mention, their effort into accommodating my need to finish this dissertation in time, and their patience in reviewing my papers and correcting my endless typos.

This journey would have been much more difficult if it wasn't for the great people that were around me. I would like to thank my desk neighbor and friend Mickael Fiorentino for listening to all my ranting about the research community and the difficulties of PhD, and for making time to discuss with me the different aspects of my work and idealistic ideas of how the world should be. I would like to also thank my other lab mates Michel Gemieux, Safa Berrima, and recently Erika Miller, for being great lab mates and putting up with all the noise that I made arguing with Mickael.

This work would not have been possible if it was not for the awesome help of my friend and great system admin Rejean Lepage. He put in extremely great effort to setup the proper environment and security measures to install the latest technologies on our servers. He also would cut time from his vacation to remote login and fix issues in the system so that our work would not be blocked. Thank you Rejean.

Being thousands of miles away from home meant that loneliness would be a common visitor for me. However, the great company of my friends in Montreal made it always much easier. I would like to thank first Ahmad Haidar and Mohammad Fathy. I cannot put in words how irreplaceable these friends are. I would also like to thank Faycal Mounaim, Maraym Tabtabai and Mahya Dehbozorgi for the endless fun we had during these years with the rest of the group and especially for inviting me to their houses and sharing heart-warming home made meals. I also shouldn't forget my online friends from back home. You guys on twitter have heard me rant more than anyone I know and still did not unfollow me. You also made me feel as if I never left home. Thank you.

Finally, I would like to thank CMC Microsystems and CMP for providing the CAD tools and access to the 28nm PDK, Octasic for providing financial support and scientific guidance, and the Natural Sciences and Engineering Research Council of Canada for providing partial funding. From Octasic, I would like to specifically thank Daniel Crepeau for taking the time to help me make the test in this work functional. Lastly, many thanks goes to CMC and professor Gordon Roberts (from McGill university) for the access to the Teradyne FLEX tester.

## RÉSUMÉ

La popularité d'internet et la quantité toujours croissante de données qui transitent à travers ses terminaux nécessite d'importantes infrastructures de serveurs qui consomment énormément d'énergie. Par conséquent, et puisqu'une augmentation de la consommation d'énergie se traduit par une augmentation des coûts, la demande pour des processeurs efficaces en énergie est en forte hausse. Une manière d'augmenter l'efficacité énergétique des processeurs consiste à moduler la fréquence d'opération du système en fonction de la charge de travail. Les processeurs endochrones et asynchrones sont une des solutions mettant en œuvre ce principe de modulation de l'activité à la demande. Cependant, les méthodes de conception non conventionnelles qui leur sont associées, en particulier en termes de testabilité et d'automation, sont un frein au développement de ce type de systèmes.

Ce travail s'intéresse au développement d'une méthode de test de haute qualité adressée aux pannes de retards dans une architecture de processeur endochrone spécifique, appelée AnARM. La méthode proposée consiste à détecter les pannes à faibles retards (PFR) dans l'AnARM en tirant profit des lignes à délais configurables intégrées. Ces pannes sont connues pour passer au travers des modèles de pannes de retards utilisés habituellement (les pannes de retards de portes). Ce travail s'intéresse principalement aux PFR qui échappent à la détection des pannes de retards de portes mais qui sont suffisamment longues pour provoquer des erreurs dans des conditions normales d'opération. D'autre part, la détection de pannes à très faibles retards est évitée, autant que possible, afin de limiter le nombre de faux positifs. Pour réaliser un test de haute qualité, ce travail propose, dans un premier temps, une métrique de test dédiée aux PFR, qui est mieux adaptée aux circuits endochrones, puis, dans un second temps, une méthode de test des pannes de retards basée sur la modulation de la vitesse des lignes à délais intégrés, qui s'adapte à un jeu de vecteurs de test préexistant.

Ce travail présente une métrique de test ciblant les PFR, appelée pourcentage de marges pondérées (PoMP), ainsi qu'un nouveau modèle de test pour les PFR (appelé test de PFR idéal). La métrique PoMP est construite de manière flexible, ce qui lui permet de s'adapter aux informations du circuit et de l'environnement de test disponibles. Ainsi, comme l'AnARM utilise plusieurs vitesses d'opérations pendant le test, le calcul de la PoMP est particulièrement sensible aux effets que la modulation de fréquence peut induire sur la qualité du test. En particulier, des mesures spéciales sont prises pour éviter le sur-test du circuit. Le surtest peut mener à la conclusion que le circuit à tester est défectueux, à cause de pannes

de retard qui sont en réalité trop courtes pour affecter ses fonctionnalités. Une infrastructure logicielle a été mise au point pour le calcul de la PoMP, permettant de la comparer avec d'autres métriques de la littérature sur de larges échantillons procédés-tensions-températures. Les simulations sont réalisées sur une sélection de circuits de références synthétisés en technologie 28 nm FD-SOI de STMicroelectronics. Les résultats montrent que la PoMP est la métrique la plus sensible aux changements qui affectent le test et le sur-test des PFR.

Ce travail propose une méthode d'optimisation du test des PFR basée sur la PoMP. La méthode associe des fréquences d'horloges de test avec des vecteurs de test préexistant pour maximiser la qualité du test. La méthode employée consiste, dans un premier temps, à classifier les meilleurs choix de test pour chaque panne dans le circuit, puis, dans un second temps, à grouper les pannes qui partagent les mêmes conditions de fonctionnement (i.e. fréquence d'horloges de test, vecteurs de tests, et masquage). Les techniques de groupement et de masquage permettent de significativement diminuer le nombre de vecteurs de test tout en conservant une bonne qualité de test des PFR. Sur une sélection de circuits de références, la méthode proposée est capable d'améliorer la valeur de la métrique PoMP jusqu'à 32.97% comparé à un test à vitesse nominale. Le test optimisé des PFR qui est proposé, ainsi que les tests à vitesse nominale développés précédemment, sont mis en œuvre sur les 25 puces AnARM fabriquées en technologie 28 nm FD-SOI de STMicroelectronics. L'AnARM inclut quatre fréquences d'horloges pour le test : une à vitesse nominale, et trois à vitesses supérieures. Comparé au test à vitesse nominale, l'optimisation du test des PFR améliore la qualité du test de l'AnARM, mesuré par la PoMP, de 60.03% à 69.71% en utilisant les lignes à délais intégrés, pour des vecteurs de test identiques. De plus, le nombre de vecteurs de test final n'augmente que d'un facteur 4 par rapport au test à vitesse nominale. Si la vitesse des lignes à délais variables est ajustée, la méthode d'optimisation peut atteindre une qualité de test de 89.01%. Les résultats post-fabrication obtenus par le test à vitesse nominale et le test optimisé des PFR sur les 25 puces de l'AnARM qui sont présentés dans ce travail, confirment l'efficacité de la méthode de test des PFR proposée.

#### ABSTRACT

The popularity of the Internet and the huge amount of data that is transfered between devices nowadays requires very powerful servers that demand lots of power. Since higher power consumptions mean more expenses to companies, there is an increase in demand for power efficient processors. One of the ways to increase the power efficiency of processors is to adapt the processing speeds and chip activity according the needed computation load. Self-timed or asynchronous processors are one of the solutions that apply this principle of activity on demand. However, their unconventional design methodology introduces several challenges in terms of testability and design automation.

This work focuses on developing a high quality delay test for a specific architecture of self-timed processors called the AnARM. The proposed delay test focuses on catching effective small-delay defects (SDDs) in the AnARM by taking advantage of built-in configurable delay lines. Those defects are known to escape one of the most commonly used delay fault models (the transition delay fault model). This work mainly focuses on effective SDDs which can escape transition delay fault testing and are large enough to fail the circuit under normal operating conditions. At the same time, catching very small delay defects is avoided, when possible, to avoid falsely failing functional chips. To build the high quality delay test, this work develops an SDD test quality metric that is better suited for circuits with adaptable speeds. Then, it builds a delay test optimizer that adapts the built-in delay lines speeds to a preexisting at-speed pattern set to create a high quality SDD test.

This work presents a novel SDD test quality metric called the weighted slack percentage (WeSPer), along with a new SDD testing model (named the ideal SDD test model). WeSPer is built to be a flexible metric capable of adapting to the availability of information about the circuit under test and the test environment. Since the AnARM can use multiple test speeds, WeSPer computation takes special care of assessing the effects of test frequency changes on the test quality. Specifically, special care is taken into avoiding overtesting the circuit. Overtesting will cause circuits under test to fail due to defects that are too small to affect the functionality of these circuits in their present state. A computation framework is built to compute WeSPer and compare it with other existing metrics in the literature over a large sets of process-voltage-temperature computation points. Simulations are done on a selected set of known benchmark circuits synthesized in the 28nm FD-SOI technology from STMicroelectronics. The results show that WeSPer is the most accurately sensitive metric

to changes that effect SDD test escapes and overtesting.

An SDD test optimization method based on WeSPer is proposed in this work. The method pairs test clock speeds with preexisting test patterns to maximize the delay test quality. This is done by listing the best choices to test each fault in the circuit, then grouping faults that share the same test conditions (i.e. test clock speed, patterns and masking). The grouping and masking techniques ensure that the final pattern count decreases without a significant decrease in the SDD test quality. The proposed SDD test optimization method can be applied to the AnARM structure, as well as synchronous systems that are compatible with faster-than-at-speed testing. On a set of benchmark circuits, the proposed technique is able to improve the WeSPer value by up to 32.97% (a relative increase of 60.98%) compared to classical at-speed testing using the same pattern set. The proposed optimized SDD test, along with a previously developed at-speed test, are applied on 25 AnARM chips fabricated in the 28nm FD-SOI technology from STMicroelectronics. The AnARM includes 4 levels of test clocks speeds: one at-speed and 3 faster-than-at-speed. Compared to at-speed testing, the optimization SDD test improved the SDD test quality of the AnARM, measured by WeSPer, from 60.03% to 69.71% using the built-in delay lines with the same at-speed test pattern set. Moreover, the final pattern count grows by no more than 4 times the initial at-speed test. If the built-in delay line speed are adjusted, the optimization technique is able to further increase the test quality to 89.01%. The post-silicon at-speed test results and post-silicon optimized SDD test for 25 AnARM chips are presented in this work. The results validate the effectiveness of the proposed SDD test.

Finally it is should be noted that, although the goal of this work is to develop a high quality delay test for the AnARM structure, the proposed metric (WeSPer) along with the proposed SDD test optimization method are not limited to this specific structure. Both WeSPer, and the proposed optimization method for SDD testing, can be applied to classical synchronous systems.

# TABLE OF CONTENTS

| DEDIC  | ATION iii                                               |

|--------|---------------------------------------------------------|

| ACKNO  | OWLEDGEMENTS iv                                         |

| RÉSUM  | IÉ                                                      |

| ABSTR  | ACT viii                                                |

| TABLE  | OF CONTENTS                                             |

| LIST O | F TABLES xiii                                           |

| LIST O | F FIGURES xiv                                           |

| LIST O | F SYMBOLS AND ACRONYMS                                  |

| LIST O | F APPENDICES                                            |

| СНАРТ  | TER 1 INTRODUCTION                                      |

| 1.1    | Overview and Motivation                                 |

| 1.2    | Delay Testing         1                                 |

| 1.2    | 1.2.1 Delay Fault Models                                |

|        | 1.2.2 Small Delay Defects: Definitions and Challenges   |

|        | 1.2.3 Scan Based Testing                                |

| 1.3    | The AnArm structure                                     |

| 1.4    | Objectives                                              |

| 1.5    | Work Organization                                       |

| СНАРТ  | TER 2 PRIOR WORKS ON SMALL-DELAY DEFECT TESTING AND AN- |

| ARN    | M AT-SPEED TESTING                                      |

| 2.1    | Overview on SDD Testing                                 |

| 2.2    | Pattern Generation for Small-Delay Defect Testing       |

| 2.3    | Dealing with PVT variations                             |

| 2.4    | Faster-Than-At-Speed Testing (FAST)                     |

|        | 2.4.1 Programmable Clock Generator for FAST             |

|        | 2.4.2 FAST optimization                                 |

| 2.5   | Small- | Delay Defect Test Quality Metrics                    |

|-------|--------|------------------------------------------------------|

|       | 2.5.1  | Delay Test Coverage (DTC)                            |

|       | 2.5.2  | Statistical Delay Quality Level (SDQL)               |

|       | 2.5.3  | Small Delay Defect Coverage (SDDC)                   |

|       | 2.5.4  | Quadratic Small Delay Defect Coverage (SDDC $^Q$ )   |

|       | 2.5.5  | Statistical Delay Fault Coverage (SDFC)              |

|       | 2.5.6  | Metrics Summary                                      |

| 2.6   | At-Spe | eed Testing of the AnARM                             |

|       | 2.6.1  | Test Structures                                      |

|       | 2.6.2  | Test Modes                                           |

|       | 2.6.3  | AnARM LOC Strategy                                   |

|       | 2.6.4  | Pattern Generation Considerations                    |

| 2.7   | Contri | butions and Publication Related to This Work         |

| СНАРТ | TER 3  | THE IDEAL SDD TEST MODEL AND THE WEIGHTED SLACK      |

| _     |        | AGE                                                  |

| 3.1   |        | leal SDD Test Model                                  |

| 3.2   |        | Veighted Slack Percentage (WeSPer) 37                |

|       | 3.2.1  | WeSPer for FAST                                      |

|       | 3.2.2  | Statistical WeSPer                                   |

| 3.3   | Multi  | PVT Point Metric Computation Flow                    |

| 3.4   |        | ation Results and Discussion                         |

|       | 3.4.1  | Single PVT results                                   |

|       | 3.4.2  | Multi-PVT Single Benchmark Analysis                  |

|       | 3.4.3  | Benchmark Circuits Results Summary                   |

|       | 3.4.4  | Metric Sensitivity                                   |

|       | 3.4.5  | Predictability                                       |

|       | 3.4.6  | Worst-Case PVT Point                                 |

|       | 3.4.7  | Statistical WeSPer                                   |

| 3.5   | Summ   | ary 59                                               |

| СНАРТ | TER 4  | OPTIMIZED SDD TEST BASED ON THE IDEAL TEST MODEL AND |

| WES   | SPER   |                                                      |

| 4.1   |        | Optimization                                         |

|       | 4.1.1  | Single Fault Optimization                            |

|       | 4.1.2  | Fault Grouping                                       |

|       | 4.1.3  | The Masking Strategy                                 |

| 4.2   | SDD Test Optimization Results                | 70  |

|-------|----------------------------------------------|-----|

|       | 4.2.1 Benchmark circuits results             | 71  |

| 4.3   | Summary                                      | 76  |

| СНАРТ | TER 5 POST-SILICON TEST RESULTS OF THE ANARM | 77  |

| 5.1   | Pre-Silicon Test Setup                       | 77  |

|       | 5.1.1 At-Speed Test Coverage                 | 78  |

|       | 5.1.2 Faster than At-Speed Setup             | 79  |

| 5.2   | Tester Setup                                 | 81  |

| 5.3   | Test Sequence                                | 83  |

| 5.4   | At-Speed Test Post-Silicon Results           | 84  |

| 5.5   | Optimized SDD Test Post-Silicon Results      | 84  |

| СНАРТ | TER 6 CONCLUSIONS AND RECOMMENDATIONS        | 88  |

| 6.1   | Summary of Works                             | 88  |

| 6.2   | Limitations                                  | 90  |

| 6.3   | Future Work and Possible Improvements        | 91  |

| REFER | RENCES                                       | 92  |

| APPEN | NDICES                                       | 101 |

# LIST OF TABLES

| Table 2.1 | Summary of test modes                                                      | 32  |

|-----------|----------------------------------------------------------------------------|-----|

| Table 3.1 | Benchmark circuit characteristics                                          | 44  |

| Table 3.2 | Metric results with the test clock speed indicated with respect to the     |     |

|           | system clock by (S) when it is $10\%$ slower , (A) when it is at-speed and |     |

|           | (F) when is $10\%$ faster                                                  | 46  |

| Table 3.3 | Single PVT overtesting results                                             | 48  |

| Table 3.4 | TAA pattern set results for metrics with respect to ATPG pattern set       |     |

|           | result. Values represent the $(\%)$ of improvement                         | 52  |

| Table 4.1 | Benchmark circuits characteristics                                         | 71  |

| Table 4.2 | Optimized SDD test quality comparison                                      | 72  |

| Table 4.3 | The quality and groups count for the optimized SDD test                    | 76  |

| Table 5.1 | Coverage results                                                           | 79  |

| Table 5.2 | Post-silicon test results of 25 AnARM chips at different test clock speeds | 85  |

| Table 5.3 | Number of failing endpoints when using faster-than-at-speed level 2        |     |

|           | test speed                                                                 | 85  |

| Table 5.4 | AnARM Mul-units and optimized SDD test characteristics                     | 86  |

| Table 5.5 | Test results of applying the optimized SDD test on the Mul-units           | 86  |

| Table B.1 | Grouping and directions of I/Os                                            | 116 |

| Table B.2 | Patterns size summary                                                      | 117 |

# LIST OF FIGURES

| Figure 1.1  | Synchronous circuit example                                                  | 2  |

|-------------|------------------------------------------------------------------------------|----|

| Figure 1.2  | Example explaining the different types of delay defects with respect to      |    |

|             | path delays though a given fault                                             | 6  |

| Figure 1.3  | Timing diagram of the classical LOS and LOC                                  | 8  |

| Figure 1.4  | Simplified schematic of the execution unit (EU)                              | 9  |

| Figure 1.5  | Timing diagram of the EU operation                                           | 9  |

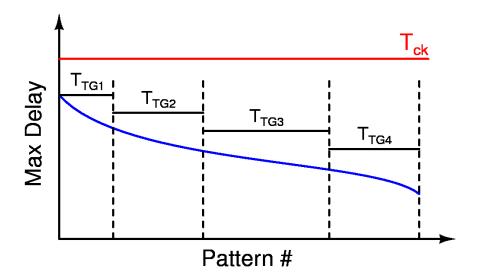

| Figure 2.1  | Example of probability of delay defect detection as defined by [54]          | 16 |

| Figure 2.2  | Example of pattern and path weight calculation based on [25]                 | 17 |

| Figure 2.3  | Grouping patterns based on the maximum delay achieved with each              |    |

|             | pattern and selecting the appropriate test clock period [49]                 | 19 |

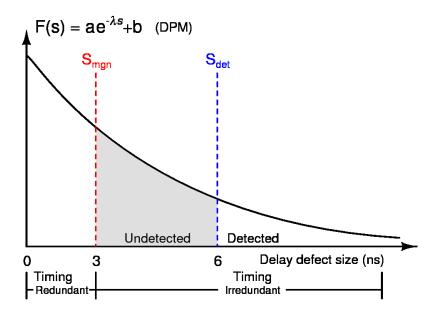

| Figure 2.4  | Example of delay defect distribution divided into regions based on the       |    |

|             | value of $S_{mgn}$ and $S_{det}$ [20]                                        | 23 |

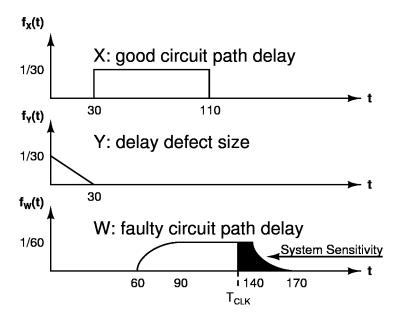

| Figure 2.5  | A small example on the calculation of the system sensitivity                 | 26 |

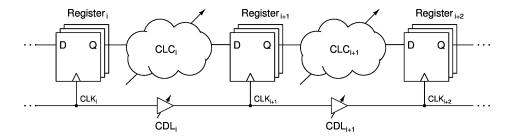

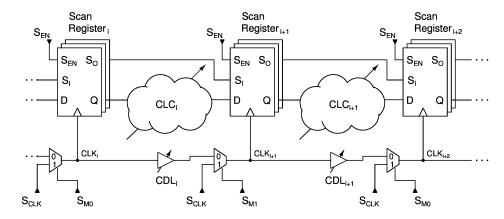

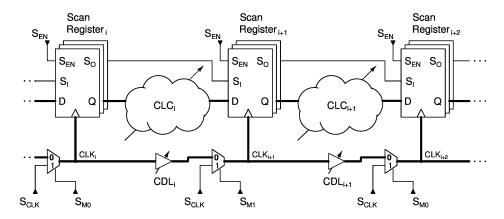

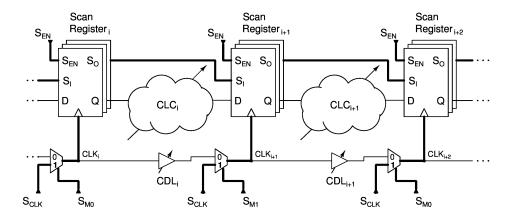

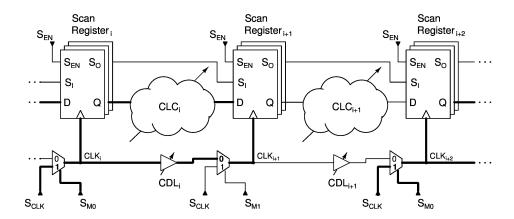

| Figure 2.6  | Generalized multi-stage self-timed structure using the Octasic design        |    |

|             | style                                                                        | 29 |

| Figure 2.7  | Test structures inserted into the targeted multi-stage self-timed structure. | 29 |

| Figure 2.8  | Multi-stage self-timed structure configured for regular operation            | 30 |

| Figure 2.9  | Multi-stage self-timed structure configured for shifting the test vectors    |    |

|             | synchronously                                                                | 30 |

| Figure 2.10 | Multi-stage self-timed structure configured for at-speed launch and cap-     |    |

|             | ture                                                                         | 30 |

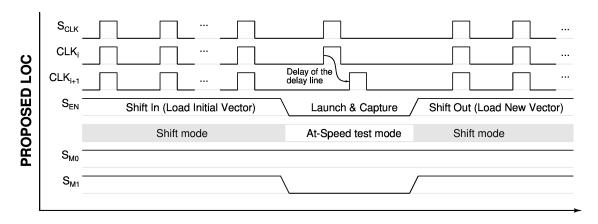

| Figure 2.11 | Timing diagram of the AnARM LOC strategy                                     | 32 |

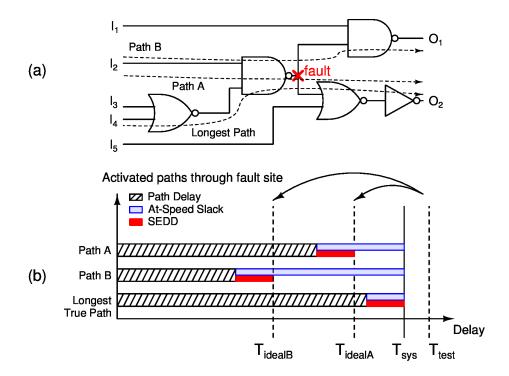

| Figure 3.1  | Example circuit with selected paths shown in (a) along with a path           |    |

|             | delay diagram shown in (b). In (b) the path delay diagram shows the          |    |

|             | smallest effective delay defect (SEDD) size of the marked fault and          |    |

|             | slack of each path along with their ideal test clock period                  | 37 |

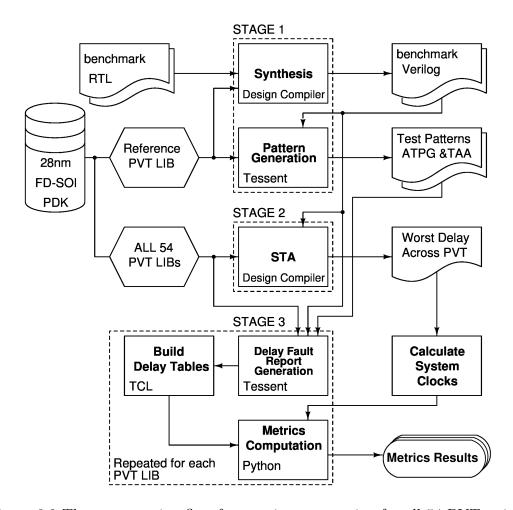

| Figure 3.2  | The computation flow for metric computation for all 54 PVT points.           | 41 |

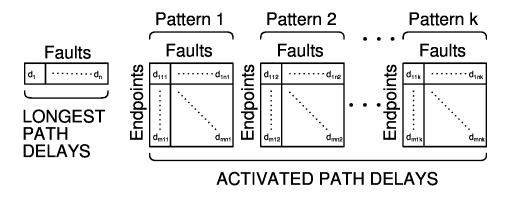

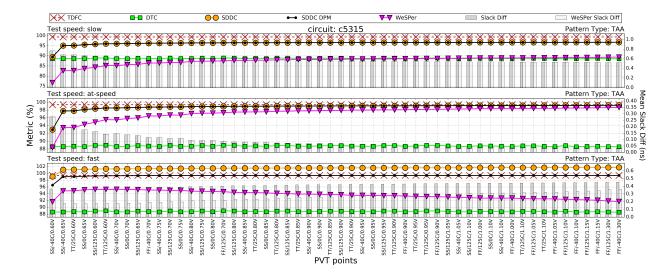

| Figure 3.3  | Path delay tables                                                            | 43 |

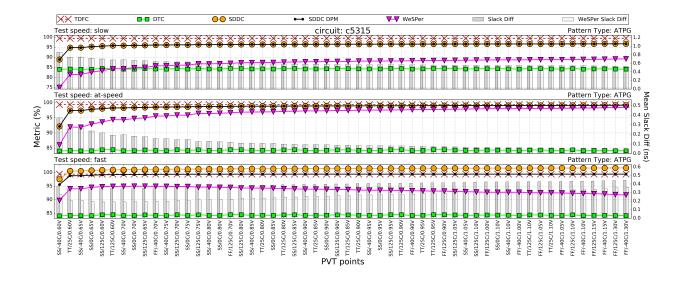

| Figure 3.4  | Metric results for all available PVT points for the c5315. The left Y-       |    |

|             | axis shows metric values while the right Y-axis shows the mean slack         |    |

|             | difference values. These results were obtained with a regular ATPG           |    |

|             | pattern set and are plotted for three test clock speeds: slow (top),         |    |

|             | at-speed (middle) and fast (bottom)                                          | 50 |

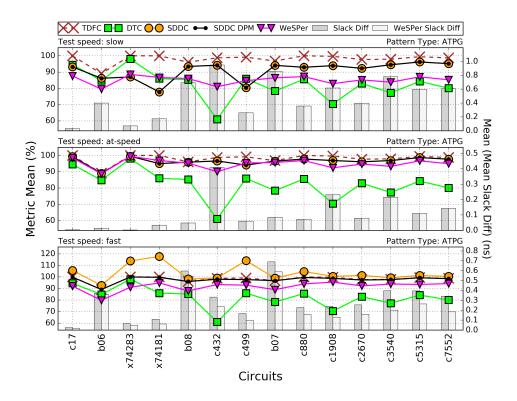

| Figure 3.5  | Metrics results summary for a test applied on the selected benchmark      |    |

|-------------|---------------------------------------------------------------------------|----|

|             | circuit set using a regular ATPG pattern set for three test clock speeds: |    |

|             | slow (top), at-speed (middle) and fast (bottom). The mean metric          |    |

|             | values across PVT points are plotted against the left Y-axis, whereas     |    |

|             | the right Y-axis plots the mean of the mean slack difference              | 51 |

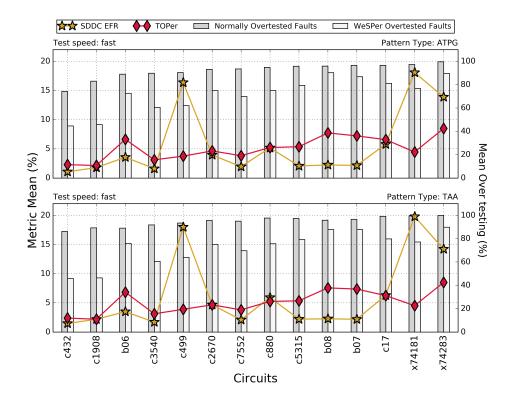

| Figure 3.6  | Overtesting results summary. The lines show the mean value for the        |    |

|             | overtesting metrics across all PVT points with respect to the left Y-     |    |

|             | axis. The right Y-axis along with the bars show the mean percentage of    |    |

|             | overtested faults with respect to the total number of faults for Weighted |    |

|             | Slack Percentage (WeSPer) and other metrics across all PVT points.        | 53 |

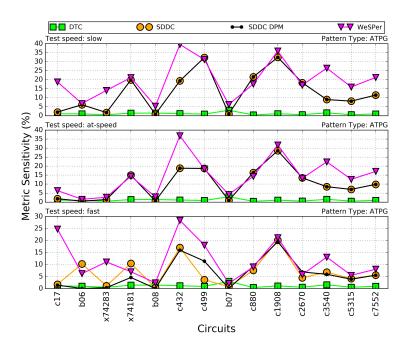

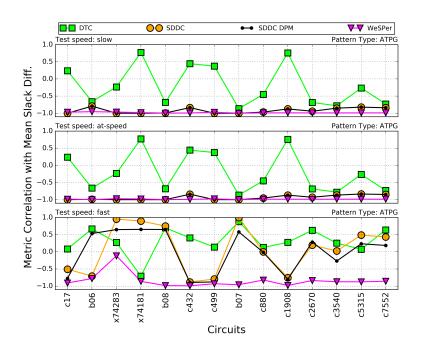

| Figure 3.7  | The sensitivity of each metric across PVT points plotted for three test   |    |

|             | clock speeds when using the ATPG pattern set                              | 55 |

| Figure 3.8  | Correlations between metric changes and MSD changes across PVT            |    |

|             | points for three test clock speeds: slow (top), at-speed (middle) and     |    |

|             | fast (bottom). Note that a negative correlation is expected, thus the     |    |

|             | closer the result is to -1 the better                                     | 55 |

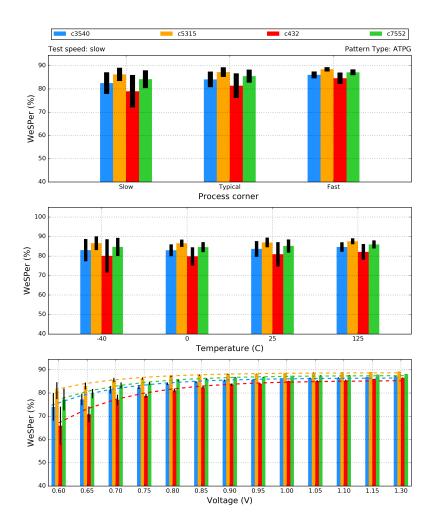

| Figure 3.9  | WeSPer values with the change of process point, temperature and volt-     |    |

|             | age for a selected set of circuits. The bars in the figure are ordered as |    |

|             | in the legend and represent the mean value. The standard deviation        |    |

|             | value is represented by the smaller black bars. The dashed line shows     |    |

|             | that a very good curve fit can be obtained with only 3 PVT points         |    |

|             | using the equation $a - b \exp(-cV)$                                      | 57 |

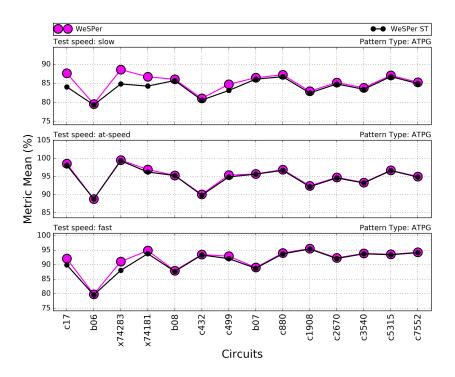

| Figure 3.10 | Comparison between non-statistical WeSPer and statistical WeSPer          |    |

|             | (WeSPer $_{ST}$ ) under an ATPG patter and three different clock speed    | 58 |

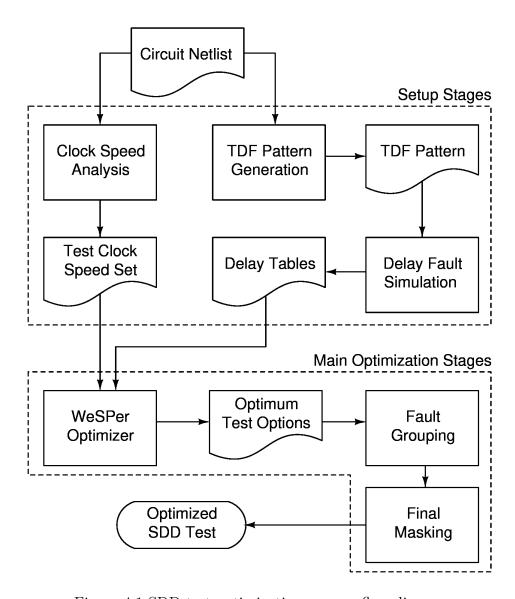

| Figure 4.1  | SDD test optimization process flow diagram                                | 61 |

| Figure 4.2  | Test options generation algorithm                                         | 63 |

| Figure 4.3  | Example of the process of generating a set of optimum test options        |    |

|             | for a given fault and pattern. Options that are under the limit are       |    |

|             | undertesting the fault whereas ones over the limit are overtesting it     | 65 |

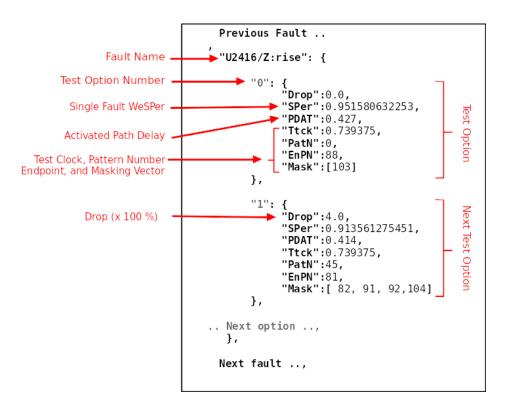

| Figure 4.4  | Optimum test options file structure written in JavaScript Object No-      |    |

|             | tation (JSON) format                                                      | 67 |

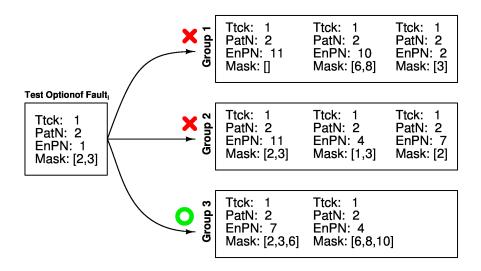

| Figure 4.5  | Fault grouping algorithm                                                  | 68 |

| Figure 4.6  | Example on fault grouping compatibility                                   | 69 |

| Figure 4.7  | Optimized SDD test file structure written in JSON format                  | 70 |

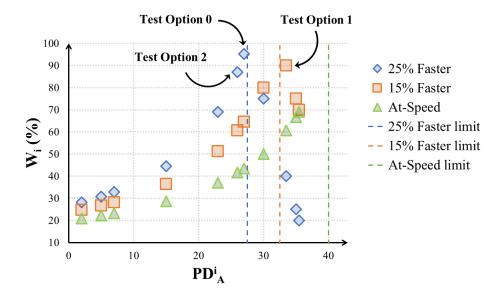

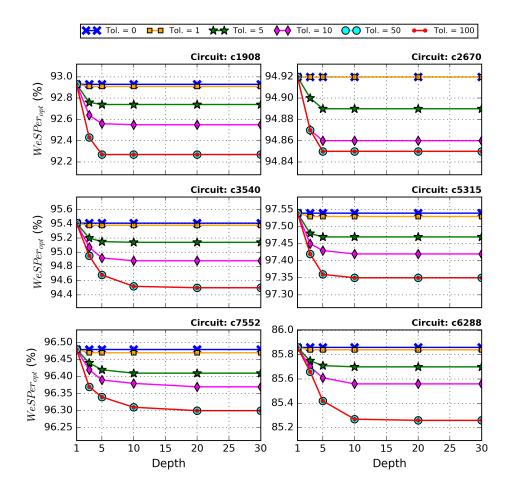

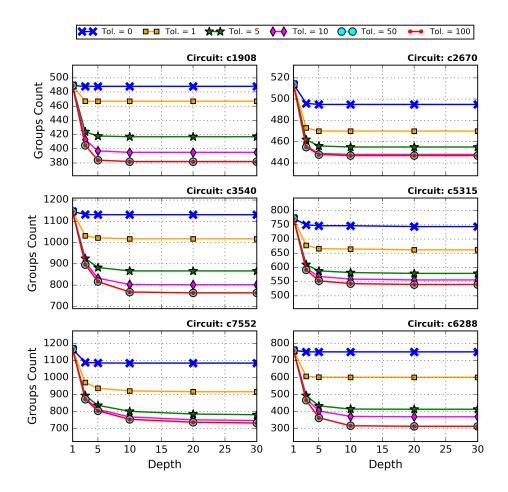

| Figure 4.8 | Fault grouping analysis on benchmark circuits. $WeSPer_{opt}$ versus the   |     |

|------------|----------------------------------------------------------------------------|-----|

|            | depth of the test options file and quality drop tolerance. This is for the |     |

|            | case of 4 test clocks, with non timing-aware pattern set while allowing    |     |

|            | overtesting. The results of the alternative cases is similar               | 73  |

| Figure 4.9 | Fault grouping analysis on benchmark circuits. Groups count versus         |     |

|            | the depth of the test option file and quality drop tolerance. This is      |     |

|            | for the case of 4 test clocks, with non timing-aware pattern set while     |     |

|            | allowing overtesting. The results of the alternative cases is similar      | 74  |

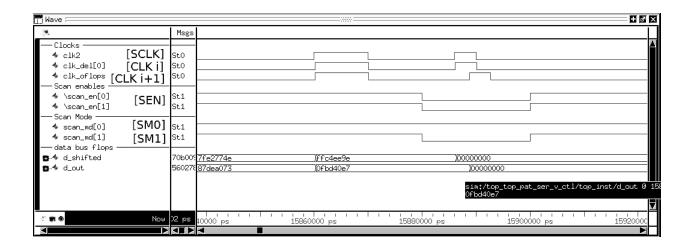

| Figure 5.1 | Post-synthesis simulation of the proposed LOC on the picoALU show-         |     |

|            | ing the transition from the shift mode to the at-speed test mode. The      |     |

|            | signal names, with reference to Fig. 2.11, are shown next to the original  |     |

|            | design names                                                               | 78  |

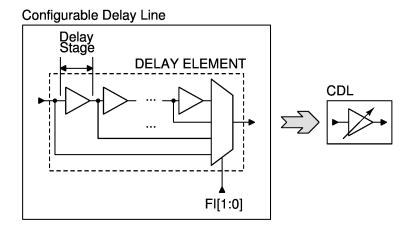

| Figure 5.2 | Configurable delay line (CDL) structure                                    | 80  |

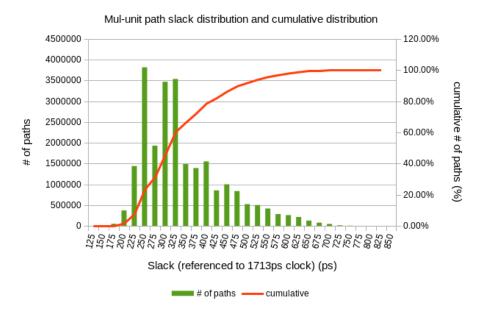

| Figure 5.3 | The slack timing report showing the path slack distribution of 200,000     |     |

|            | paths in the Mul-unit circuit. This report is generated at the expect      |     |

|            | process-voltage-temperature (PVT) point (TT/0.9V/25°C)                     | 80  |

| Figure 5.4 | Mul-unit delay lines connections to endpoints                              | 81  |

| Figure 5.5 | The test setup comprising of the FLEX tester with the PCB, socket          |     |

|            | and AnARM chip                                                             | 82  |

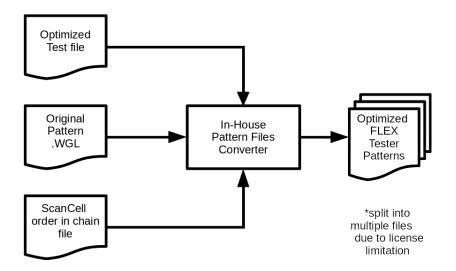

| Figure 5.6 | The pattern conversion process from the optimized SDD test file to the     |     |

|            | FLEX tester pattern                                                        | 83  |

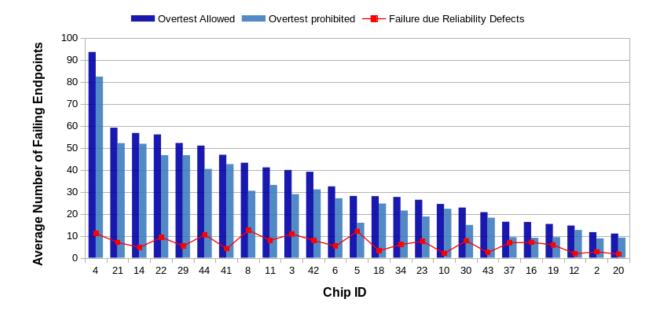

| Figure 5.7 | Optimized SDD test post-silicon test results                               | 87  |

| Figure A.1 | Metric results for all available PVT points for the c5315. The left Y-     |     |

|            | axis shows metric values while the right Y-axis shows the mean slack       |     |

|            | difference values. These results were obtained with a regular TAA          |     |

|            | pattern set and are plotted for three test clock speeds: slow (top),       |     |

|            | at-speed (middle) and fast (bottom)                                        | 101 |

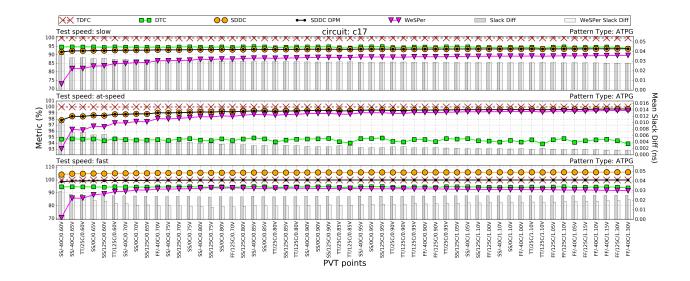

| Figure A.2 | Metric results for all available PVT points for the c17. The left Y-       |     |

|            | axis shows metric values while the right Y-axis shows the mean slack       |     |

|            | difference values. These results were obtained with a regular ATPG         |     |

|            | pattern set and are plotted for three test clock speeds: slow (top),       |     |

|            | at-speed (middle) and fast (bottom)                                        | 102 |

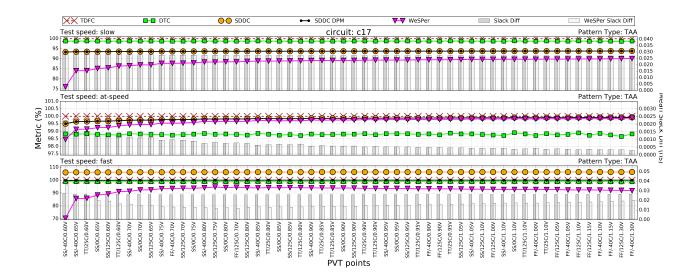

| Figure A.3 | Metric results for all available PVT points for the c17. The left Y-    |     |

|------------|-------------------------------------------------------------------------|-----|

|            | axis shows metric values while the right Y-axis shows the mean slack    |     |

|            | difference values. These results were obtained with a regular TAA       |     |

|            | pattern set and are plotted for three test clock speeds: slow (top),    |     |

|            | at-speed (middle) and fast (bottom)                                     | 102 |

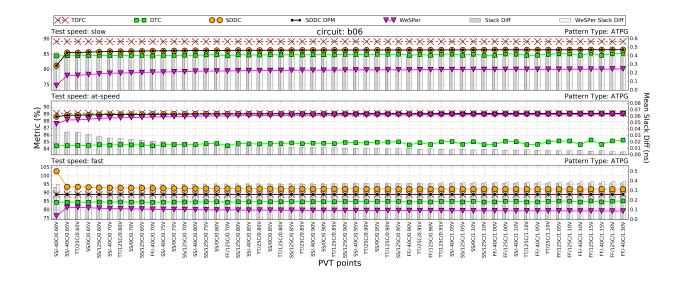

| Figure A.4 | Metric results for all available PVT points for the b06. The left Y-    |     |

|            | axis shows metric values while the right Y-axis shows the mean slack    |     |

|            | difference values. These results were obtained with a regular ATPG      |     |

|            | pattern set and are plotted for three test clock speeds: slow (top),    |     |

|            | at-speed (middle) and fast (bottom)                                     | 103 |

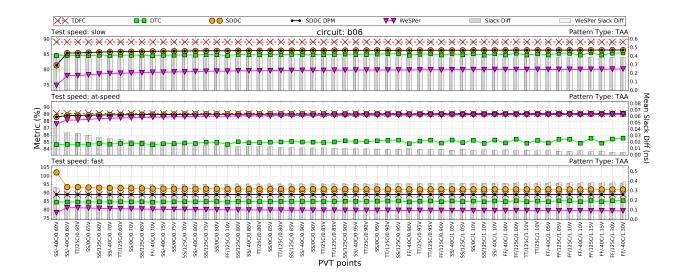

| Figure A.5 | Metric results for all available PVT points for the b06. The left Y-    |     |

|            | axis shows metric values while the right Y-axis shows the mean slack    |     |

|            | difference values. These results were obtained with a regular TAA       |     |

|            | pattern set and are plotted for three test clock speeds: slow (top),    |     |

|            | at-speed (middle) and fast (bottom)                                     | 103 |

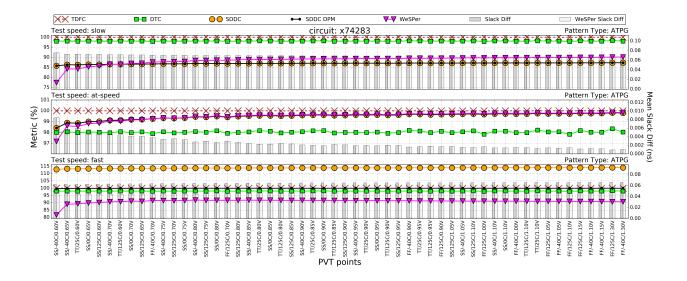

| Figure A.6 | Metric results for all available PVT points for the x74283. The left Y- |     |

|            | axis shows metric values while the right Y-axis shows the mean slack    |     |

|            | difference values. These results were obtained with a regular ATPG      |     |

|            | pattern set and are plotted for three test clock speeds: slow (top),    |     |

|            | at-speed (middle) and fast (bottom)                                     | 104 |

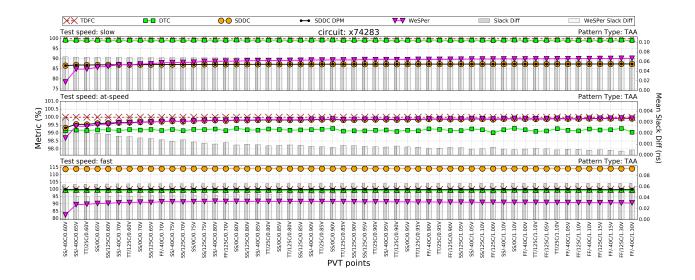

| Figure A.7 | Metric results for all available PVT points for the x74283. The left Y- |     |

|            | axis shows metric values while the right Y-axis shows the mean slack    |     |

|            | difference values. These results were obtained with a regular TAA       |     |

|            | pattern set and are plotted for three test clock speeds: slow (top),    |     |

|            | at-speed (middle) and fast (bottom)                                     | 104 |

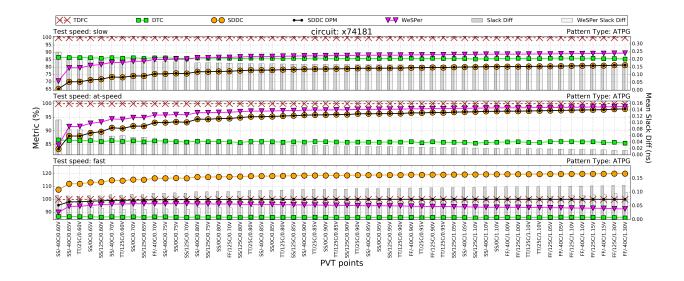

| Figure A.8 | Metric results for all available PVT points for the x74181. The left Y- |     |

|            | axis shows metric values while the right Y-axis shows the mean slack    |     |

|            | difference values. These results were obtained with a regular ATPG      |     |

|            | pattern set and are plotted for three test clock speeds: slow (top),    |     |

|            | at-speed (middle) and fast (bottom)                                     | 105 |

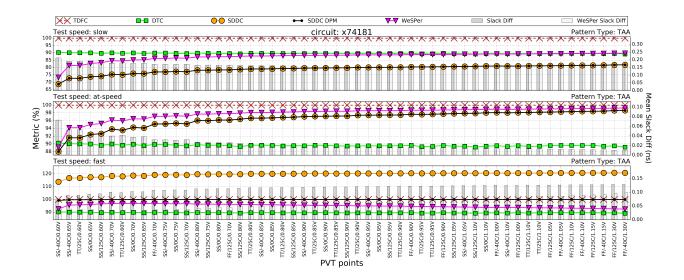

| Figure A.9 | Metric results for all available PVT points for the x74181. The left Y- |     |

|            | axis shows metric values while the right Y-axis shows the mean slack    |     |

|            | difference values. These results were obtained with a regular TAA       |     |

|            | pattern set and are plotted for three test clock speeds: slow (top),    |     |

|            | at-speed (middle) and fast (bottom)                                     | 105 |

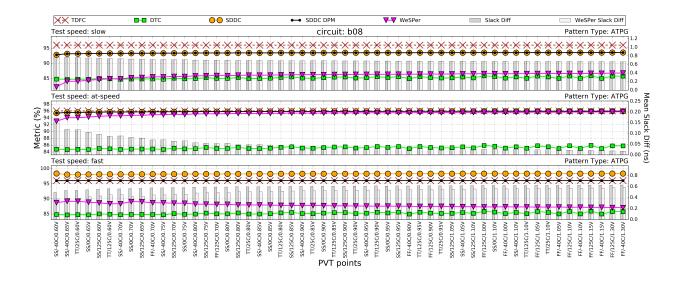

| Figure A.10 | Metric results for all available PVT points for the b08. The left Y-  |     |

|-------------|-----------------------------------------------------------------------|-----|

|             | axis shows metric values while the right Y-axis shows the mean slack  |     |

|             | difference values. These results were obtained with a regular ATPG    |     |

|             | pattern set and are plotted for three test clock speeds: slow (top),  |     |

|             | at-speed (middle) and fast (bottom)                                   | 106 |

| Figure A.11 | Metric results for all available PVT points for the b08. The left Y-  |     |

|             | axis shows metric values while the right Y-axis shows the mean slack  |     |

|             | difference values. These results were obtained with a regular TAA     |     |

|             | pattern set and are plotted for three test clock speeds: slow (top),  |     |

|             | at-speed (middle) and fast (bottom)                                   | 106 |

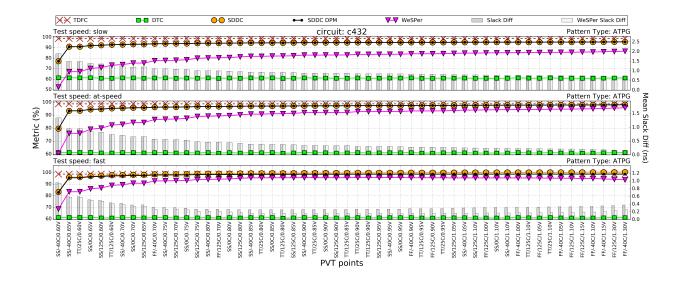

| Figure A.12 | Metric results for all available PVT points for the c432. The left Y- |     |

|             | axis shows metric values while the right Y-axis shows the mean slack  |     |

|             | difference values. These results were obtained with a regular ATPG    |     |

|             | pattern set and are plotted for three test clock speeds: slow (top),  |     |

|             | at-speed (middle) and fast (bottom)                                   | 107 |

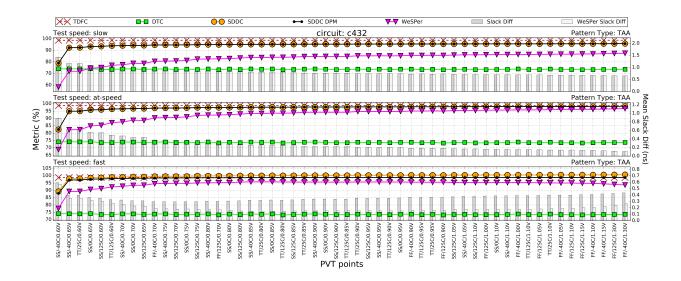

| Figure A.13 | Metric results for all available PVT points for the c432. The left Y- |     |

|             | axis shows metric values while the right Y-axis shows the mean slack  |     |

|             | difference values. These results were obtained with a regular TAA     |     |

|             | pattern set and are plotted for three test clock speeds: slow (top),  |     |

|             | at-speed (middle) and fast (bottom)                                   | 107 |

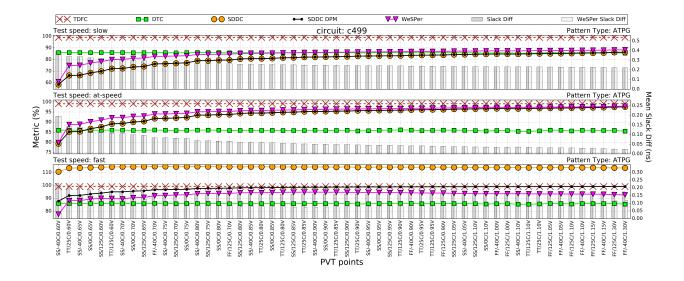

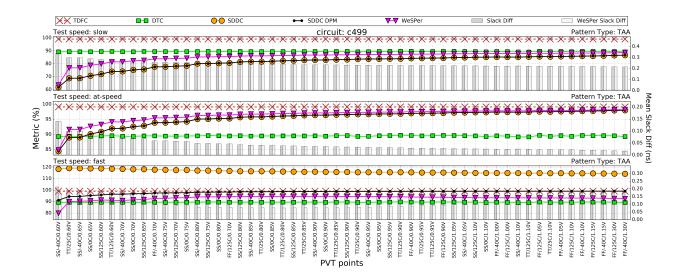

| Figure A.14 | Metric results for all available PVT points for the c499. The left Y- |     |

|             | axis shows metric values while the right Y-axis shows the mean slack  |     |

|             | difference values. These results were obtained with a regular ATPG    |     |

|             | pattern set and are plotted for three test clock speeds: slow (top),  |     |

|             | at-speed (middle) and fast (bottom)                                   | 108 |

| Figure A.15 | Metric results for all available PVT points for the c499. The left Y- |     |

|             | axis shows metric values while the right Y-axis shows the mean slack  |     |

|             | difference values. These results were obtained with a regular TAA     |     |

|             | pattern set and are plotted for three test clock speeds: slow (top),  |     |

|             | at-speed (middle) and fast (bottom)                                   | 108 |

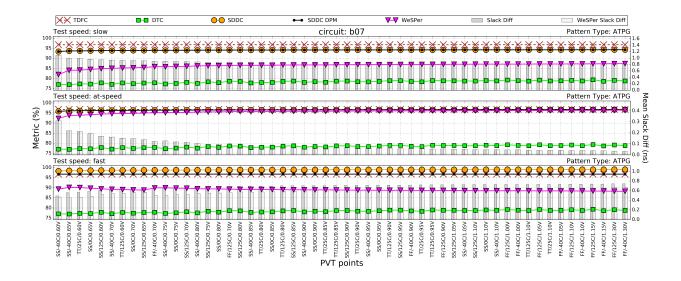

| Figure A.16 | Metric results for all available PVT points for the b07. The left Y-  |     |

|             | axis shows metric values while the right Y-axis shows the mean slack  |     |

|             | difference values. These results were obtained with a regular ATPG    |     |

|             | pattern set and are plotted for three test clock speeds: slow (top),  |     |

|             | at-speed (middle) and fast (bottom)                                   | 109 |

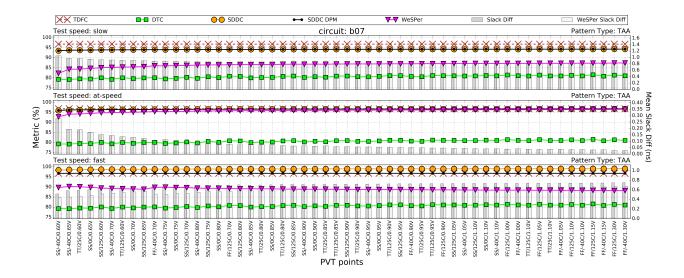

| Figure A.17 | Metric results for all available PVT points for the b07. The left Y-   |     |

|-------------|------------------------------------------------------------------------|-----|

|             | axis shows metric values while the right Y-axis shows the mean slack   |     |

|             | difference values. These results were obtained with a regular TAA      |     |

|             | pattern set and are plotted for three test clock speeds: slow (top),   |     |

|             | at-speed (middle) and fast (bottom)                                    | 109 |

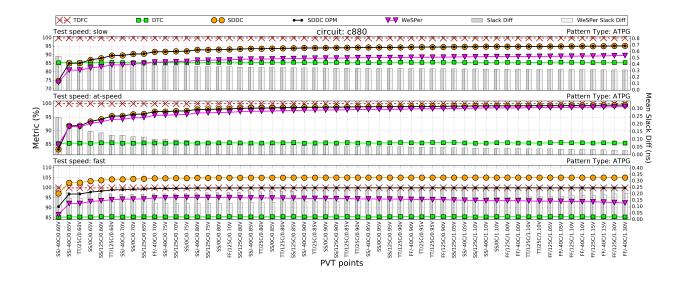

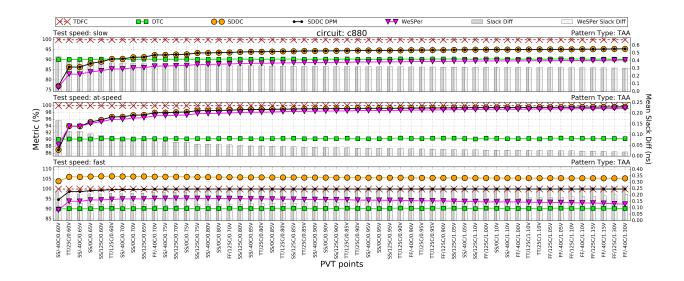

| Figure A.18 | Metric results for all available PVT points for the c880. The left Y-  |     |

|             | axis shows metric values while the right Y-axis shows the mean slack   |     |

|             | difference values. These results were obtained with a regular ATPG     |     |

|             | pattern set and are plotted for three test clock speeds: slow (top),   |     |

|             | at-speed (middle) and fast (bottom)                                    | 110 |

| Figure A.19 | Metric results for all available PVT points for the c880. The left Y-  |     |

|             | axis shows metric values while the right Y-axis shows the mean slack   |     |

|             | difference values. These results were obtained with a regular TAA      |     |

|             | pattern set and are plotted for three test clock speeds: slow (top),   |     |

|             | at-speed (middle) and fast (bottom)                                    | 110 |

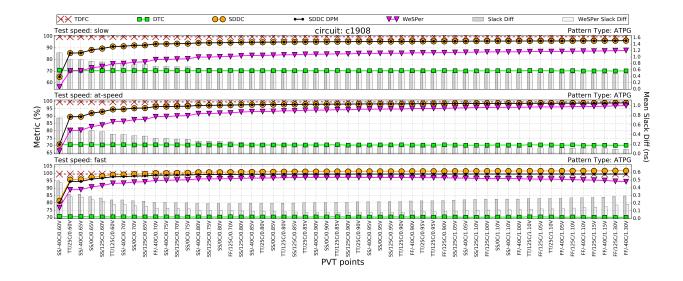

| Figure A.20 | Metric results for all available PVT points for the c1908. The left Y- |     |

|             | axis shows metric values while the right Y-axis shows the mean slack   |     |

|             | difference values. These results were obtained with a regular ATPG     |     |

|             | pattern set and are plotted for three test clock speeds: slow (top),   |     |

|             | at-speed (middle) and fast (bottom)                                    | 111 |

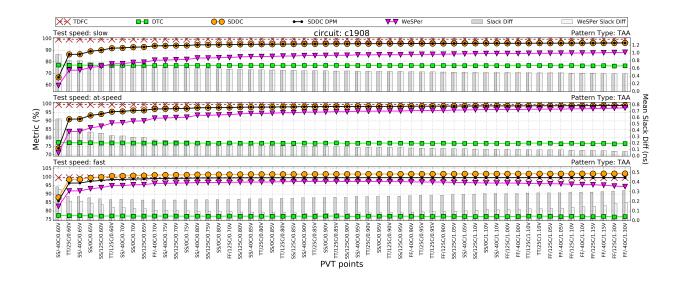

| Figure A.21 | Metric results for all available PVT points for the c1908. The left Y- |     |

|             | axis shows metric values while the right Y-axis shows the mean slack   |     |

|             | difference values. These results were obtained with a regular TAA      |     |

|             | pattern set and are plotted for three test clock speeds: slow (top),   |     |

|             | at-speed (middle) and fast (bottom)                                    | 111 |

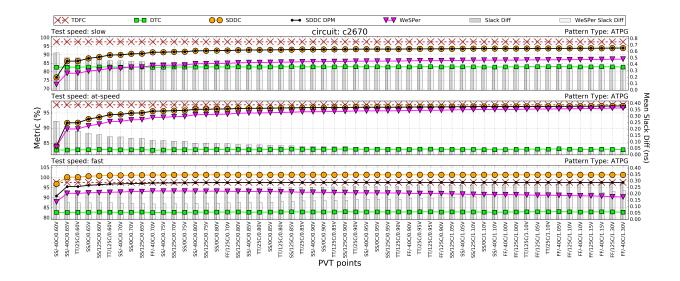

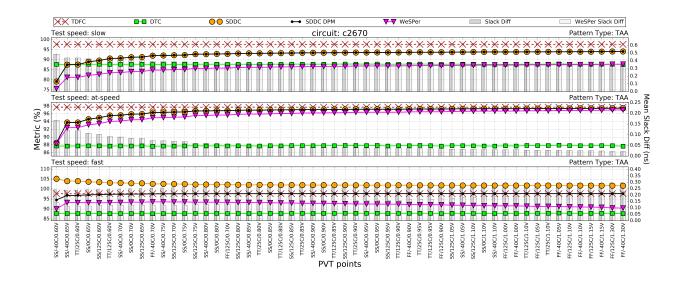

| Figure A.22 | Metric results for all available PVT points for the c2670. The left Y- |     |

|             | axis shows metric values while the right Y-axis shows the mean slack   |     |

|             | difference values. These results were obtained with a regular ATPG     |     |

|             | pattern set and are plotted for three test clock speeds: slow (top),   |     |

|             | at-speed (middle) and fast (bottom)                                    | 112 |

| Figure A.23 | Metric results for all available PVT points for the c2670. The left Y- |     |

|             | axis shows metric values while the right Y-axis shows the mean slack   |     |

|             | difference values. These results were obtained with a regular TAA      |     |

|             | pattern set and are plotted for three test clock speeds: slow (top),   |     |

|             | at-speed (middle) and fast (bottom)                                    | 112 |

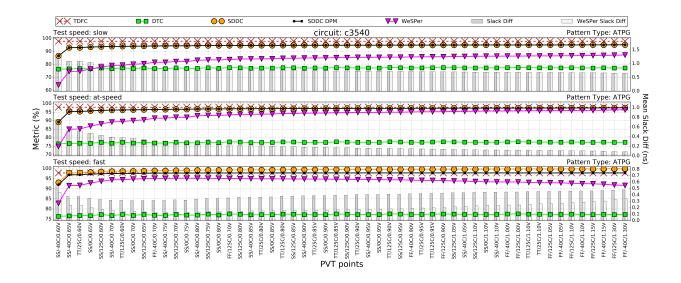

| Figure A.24 | Metric results for all available PVT points for the c3540. The left Y- |     |

|-------------|------------------------------------------------------------------------|-----|

|             | axis shows metric values while the right Y-axis shows the mean slack   |     |

|             | difference values. These results were obtained with a regular ATPG     |     |

|             | pattern set and are plotted for three test clock speeds: slow (top),   |     |

|             | at-speed (middle) and fast (bottom)                                    | 113 |

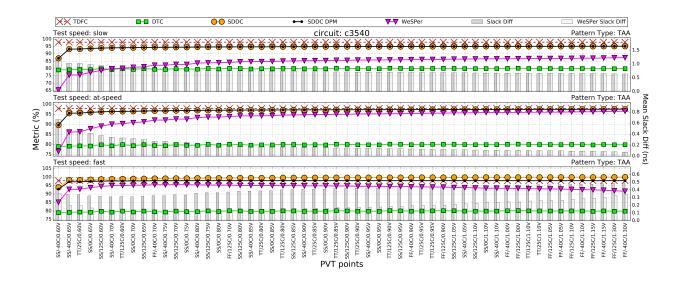

| Figure A.25 | Metric results for all available PVT points for the c3540. The left Y- |     |

|             | axis shows metric values while the right Y-axis shows the mean slack   |     |

|             | difference values. These results were obtained with a regular TAA      |     |

|             | pattern set and are plotted for three test clock speeds: slow (top),   |     |

|             | at-speed (middle) and fast (bottom)                                    | 113 |

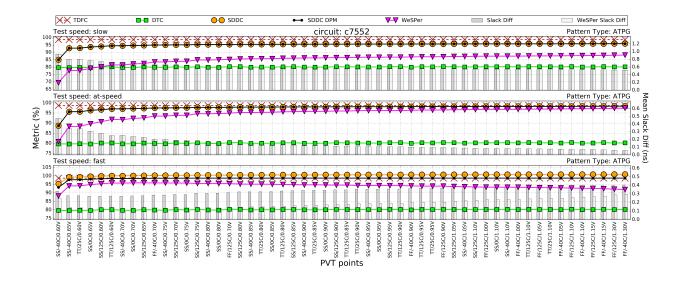

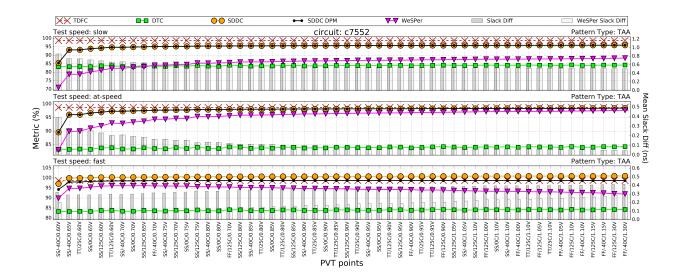

| Figure A.26 | Metric results for all available PVT points for the c7552. The left Y- |     |

|             | axis shows metric values while the right Y-axis shows the mean slack   |     |

|             | difference values. These results were obtained with a regular ATPG     |     |

|             | pattern set and are plotted for three test clock speeds: slow (top),   |     |

|             | at-speed (middle) and fast (bottom)                                    | 114 |

| Figure A.27 | Metric results for all available PVT points for the c7552. The left Y- |     |

|             | axis shows metric values while the right Y-axis shows the mean slack   |     |

|             | difference values. These results were obtained with a regular TAA      |     |

|             | pattern set and are plotted for three test clock speeds: slow (top),   |     |

|             | at-speed (middle) and fast (bottom)                                    | 114 |

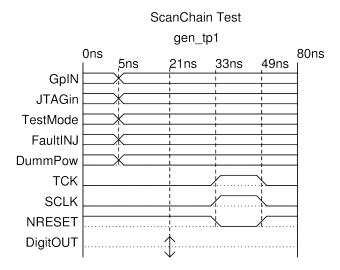

| Figure B.1  | The gen_tp1 time plate for the scan chain test                         | 118 |

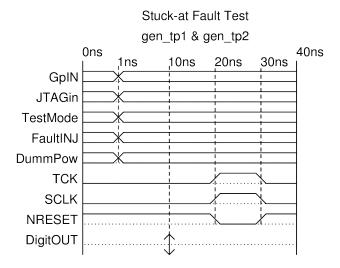

| Figure B.2  | The gen_tp1 time plate for the stuck-at fault test                     | 118 |

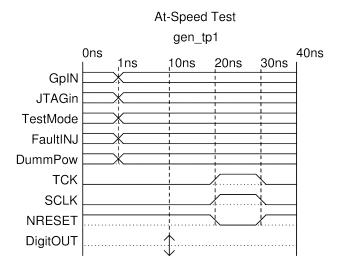

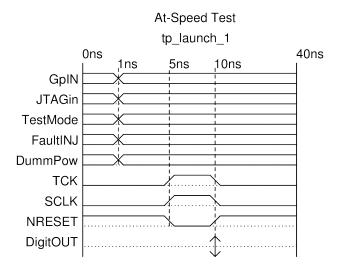

| Figure B.3  | The gen_tp1 time plate for the at-speed test                           | 119 |

| Figure B.4  | The launch time plate for the at-speed test                            | 119 |

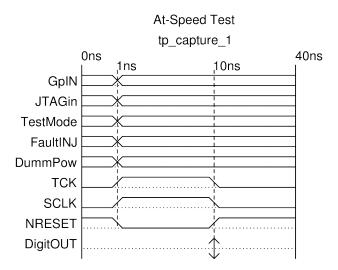

| Figure B.5  | The capture time plate for the at-speed test                           | 120 |

#### LIST OF SYMBOLS AND ACRONYMS

ATE Automatic test equipment

ATPG Automatic test pattern generation

CAD Computer-Aided DesignCDL Configurable delay lineCLC Configurable logic cloud

CL confidence level

CUT Circuit under test

DPM Defect per million

DTC Delay Test Coverage

DUT Device under test

EU Execution unit

FAST Faster-than-at-speed testing JSON JavaScript Object Notation

LOC launch-on-capture LOS launch-on-shift

MSD Mean slack difference PCB Printed circuit board

PDF Path delay fault

PDK Process design kit

PLL Phase-locked loop

PVT Process-voltage-temperature

SDDC Small-Delay Defect Coverage

SDD Small-Delay Defect

SDFC Statistical Delay Fault Coverage SDQL Statistical Delay Quality Level SDQM Statistical Delay Quality Model SEDD Smallest effective delay defect

STA Static Timing Analysis

TDFC Transition delay fault coverage

TDF Transition delay fault

TOPer Total Overtesting Percentage WeSPer Weighted Slack Percentage

# LIST OF APPENDICES

| Appendix A | Additional Metric Simulation Results | 101 |

|------------|--------------------------------------|-----|

| Appendix B | Test Setup Details                   | 115 |

#### CHAPTER 1 INTRODUCTION

#### 1.1 Overview and Motivation

In this era of mobile devices and very powerful servers that run the Internet, designs with high power efficiency are in demand. Classical synchronous systems that waste power on clock trees and constant circuit activity are an unattractive solution, from a power efficiency point of view, when compared to event-triggered asynchronous design methodologies. Synchronous designs are however, faster than standard asynchronous systems. This is due to the fact that most asynchronous designs waste time on managing the timing of operations (e.g. handshaking), and thus tend to be slower than their synchronous counterparts. One of the unique design methods which does not suffer from this problem is the self-timed (source-synchronous) design presented by Octasic for their digital signal processor (DSP) chip [1]. Their DSP design shows a comparable system performance in terms of speed, while having advantages in power efficiency and area consumption. It has been shown that clocks and their distribution networks can consume up to 40% of the total chip power [2]. Removing synchronous clocks to design an asynchronous system would definitely reduce the power consumption, but the unconventional design methodologies of such systems introduce several challenges in terms of design, testability and design automation with industrial tools [3]. Standard computer-aided design (CAD) softwares cannot be fully used to properly synthesis and test unconventional asynchronous designs without putting a great deal of effort into adapting them.

This work is a part of a bigger project that aims to design a highly testable self-timed microprocessor, called AnARM, which uses the Octasic self-timed architecture. This work targets specifically the development of high quality delay test methods to test small-delay defects (SDDs) taking advantage of the unique Octasic self-timed clocking structure. In this chapter, a general introduction to delay testing and the Octasic structure will be presented before further discussing the challenges and goals of this work.

#### 1.2 Delay Testing

Classical synchronous circuits are the base for most modern processors that are embedded in almost every smart device on the market. The correct operation of synchronous circuits relies on a timing relation between the processed data and the operating clock. Fig 1.1 shows a simplified example of a synchronous circuit. In order for a synchronous circuit to operate

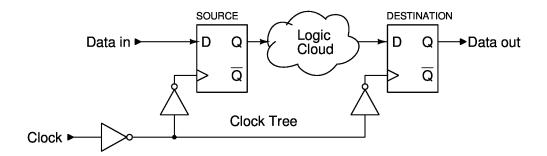

Figure 1.1 Synchronous circuit example.

correctly, there are two main timing constraints that need to be satisfied: the setup timing constraint, and the hold timing constraint [4]. These two constraints govern the delay of the logical cloud and clock network delays with respect to the operating clock period and flip-flop stability time requirements (setup time and hold time). With respect to the logic cloud delay, the setup constraint for circuit circuits can be written as:

$$t_{logic} \le T_{sys} - t_{setup} - t_{CK-Q} - t_{skew} \tag{1.1}$$

Whereas the hold constraint can be written as:

$$t_{logic} \ge t_{hold} - t_{CK-Q} + t_{skew} \tag{1.2}$$

Where  $t_{logic}$  is the combinational logic cloud delay,  $T_{sys}$  is the operating (system) clock period,  $t_{CK-Q}$  is the delay for the data to appear at the output of the flip-flop after the clock edge arrival,  $t_{setup}$  is the setup time for the output flip-flops,  $t_{hold}$  is the hold time for the output flip-flops and  $t_{skew}$  is the clock tree timing skew.

All of the delays in equations (1.1) and (1.2), except the external clock period, are susceptible to delay variation in CMOS circuits. There are many sources of delay variations, such as process variation, temperature variation, power supply variations, cross-talk and aging [5–8]. To account for most of these variations during the design stage, a static timing analysis (STA) tool is used to find the worst delay in a circuit in order to determine the operating frequency. After fabrication, the speed of the same circuit will vary due to process variations, and sometimes as a consequence, chips that contain no detected fault and that meet a minimum level of performance may be binned into speed categories. Speed variations in fabricated chips are expected and are modeled in the libraries that are provided from the foundry.

However, recent CMOS technologies are becoming extremely small and the fabrication process is becoming more complicated and more defect prone than before [9,10]. This brings an increase to the occurrence rate of defects that may not be catastrophic but that add undesirable delays to the circuit. Delay defects can be caused for example by weak connections (resistive short/opens) which lead to unexpected changes in the delays of a circuit [5,11]. These added delays cannot be predicted from the design stages and can be difficult to find with normal functional testing. Information on delay defects are not normally included in the standard process design kit (PDK).

The main reason for applying delay testing is to catch these unexpected delay increases that can happen due to inaccuracies in the fabrication process. Delay testing checks thoroughly that the timing constraints are not violated, and that the chip can operate at the rated speed. This is done by carefully selecting the input data, applying a test clock at a certain speed and comparing the results with the expect ones. With millions of transistors packed into modern high speed chips, the challenge in delay testing is to test the entire chip in a reasonable time without missing any defect that can cause the chip to fail in the field.

There are four main aspects that define a delay test: the delay fault model, the test clock speed, the test structure and the applied test pattern. The choice of delay fault model defines how the applied pattern will be generated, whereas the test clock speed defines test structures that need to be inserted into the circuit under test (CUT) and the requirements of the tester. We will introduce here briefly the delay fault models used in testing, how to apply an at-speed delay test using scan based testing, and discuss SDDs. As this work does not contribute to test pattern generation algorithms, we will not delve into the specifics of automatic test pattern generation (ATPG) for delay testing.

#### 1.2.1 Delay Fault Models

A fault is an abstract representation of the defect on a functional level. Delay faults in this case are represented as added delays to the circuit. The two main categories of delay fault models, that are well known in the literature, are the path delay fault (PDF) model [12] and the transition delay fault (TDF) model [13].

In the PDF model, the defect is assumed to be distributed along the path of the signal, and a fault is detected when the total delay along the path exceeds the testing clock period. The PDF model defines two types of faults per path, one for a falling transition and one for

a rising transition. This means that the numbers of delay faults in a given circuit is twice the number of paths in it. In addition, paths under the PDF model are categorized based on the ability to measure the delay of the path independently from other paths in the CUT [14]. The testable paths in PDF are generally categorized into robust, strong non-robust, weak non-robust and functional. This categorization is based on the ability to sensitize a path in a given way using the inputs. The conditions for proper sensitization of paths in PDF are very difficult to meet and so its application is limited to a small set of paths (normally critical paths) [14–17]. Moreover, the number of paths in a circuit can grow exponentially with the number of logic gates [18] making it difficult, if not impossible, to test all paths in a reasonable time. Nonetheless, the PDF based delay test is a very thorough test and is often used to check the critical paths of a circuit.

The other widely known model is the TDF model. The TDF model assumes a single defect on each node of a circuit. The defect (if it exists) is assumed to be big enough that it can be detected regardless of the slack of the sensitized path. This approximation makes the TDF model a much simpler model, and allows for the reuse of the ATPG from the common stuck-at-fault testing. In the stuck-at-fault model, a node is assumed to be stuck at a single value (0 or 1), which corresponds in a way to the two fault types that are defined under the TDF model, slow-to-rise or slow-to-fall. In contrast to the PDF model, in the TDF model, the number of faults to be tested grows linearly with the number of logic gates in the circuit [18]. The simplicity of the TDF model comes with a disadvantage that allows for some delay defects to remain undetected. The next subsection will elaborate on this point. Note that this work is built around the TDF model and will try to address some of those test escapes.

As we will indicate in the literature review, there are some attempts to create a hybrid model of the two delay fault models, as in [19]. However, this work is built on the TDF model due to its simplicity, popularity and compatibly with the existing test tools. Thus, from this point onward the text will focus on the TDF model.

#### 1.2.2 Small Delay Defects: Definitions and Challenges

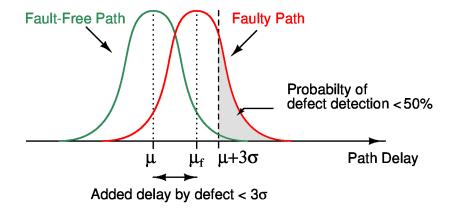

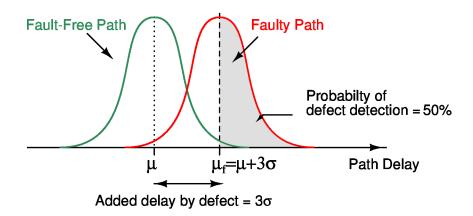

As mentioned previously, in the TDF model, the assumption is that the delay defect is large enough to be detected on a node regardless of the path used for testing. If the defect was not large enough, then it would escape the test undetected. The question here is whether catching such a small defect critical? The answer to the question depends on how small is

small, and how reliable the chip needs to be. Some defects can be large enough to fail the circuit under normal operation, yet small enough to pass a TDF based test. Others can be small enough to cause no observed failure today, but might grow in the near future to be a problem. Others can be so small that it would be difficult to distinguish them from delay variation induced by the process, cross-talk or supply noise. To better understand the work presented here, we will start by defining all the terms that will be frequently used in relation to delay defects and delay testing.

- **Normal operating conditions**: this refers to the system clock speed, temperature and supply voltage under which the CUT is expected to operate.

- *Gross delay defect*: A delay defect that will always be caught in a traditional TDF delay test if tested under normal operating conditions.

- **Small-delay defect (SDD)**: a delay defect that adds a small amount of delay to a path in a circuit and that can potentially escape traditional TDF delay testing and remain undetected.

- *SDD size*: the amount of added delay in nanoseconds (ns).

- **Tested defect size**: The smallest SDD size at a fault site that is tested with the applied test clock and pattern.

- Effective SDD: an SDD that is large enough to cause a failure in the circuit when operating at normal operating conditions, yet small enough to escape traditional TDF delay testing if tested with a short path under the same operating conditions.

- Smallest effective delay defect (SEDD): The smallest size of an SDD at a fault site that can cause a failure in the circuit at normal operating conditions.

- Reliability defect: An SDD that is smaller than the SEDD for the given fault, also known as a "timing-redundant" defect [20].

- *True path*: a path in a circuit through which a transition can propagate to an endpoint under a possible sensitization condition (i.e. input vector).

- **Test escape**: An SDD that escapes a TDF based delay test because it was not tested with the proper slack (defined by test path and operating conditions).

- *Overtesting*: In this work, overtesting refers to testing an SDD of a size smaller than the SEDD of that fault.

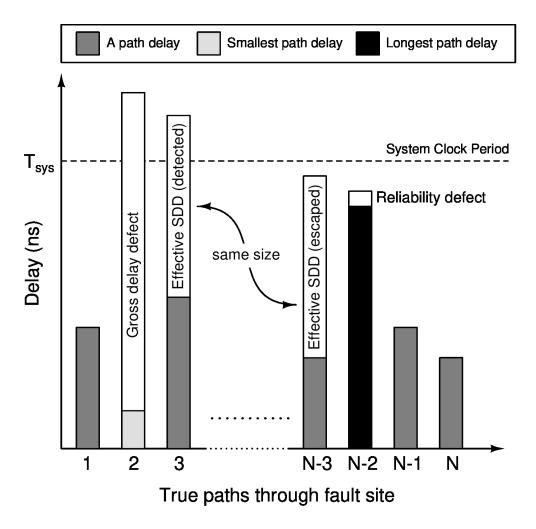

The simplified example in Fig.1.2 shows the different types of delay defects that were defined above on a given fault site and for a given transition (rise or fall), where the paths that can carry the transition through this fault site are enumerated. As shown, a gross delay defect adds enough delay to be detected through any path. By contrast, an effective SDD detection depends on the path through which it was tested. On the other hand, a reliability

Figure 1.2 Example explaining the different types of delay defects with respect to path delays though a given fault.

defect cannot be detected with at-speed testing, no matter which path tests it. Remember here that we are following the TDF model in defining a delay fault, and by doing so, we are modeling there delay faults as a single fault located solely at a fault site (a node in a circuit).

The small size of SDDs creates many challenges in testing it properly. The main challenge in SDD testing is the ability to avoid false detection of a fault, and to accurately estimate delays during test pattern generation. Since the size of the defect is small, it is important to take into account factors that can induce delay in the circuit. For example, it is well know that for a digital circuit there is a relationship between the supply voltage and the delay of a digital gate [4,21]. If for any reason, the supply voltage fluctuates during testing, it can cause a small variation in delay that could be falsely identified as an SDD [22]. For example, a 10% variation on  $V_{DD}$  can create a 30% delay variation in 90nm technology and it gets worse in

more advanced technology nodes. For instance, in the 32nm technology the delay variation is 83% for the same 10% variation on  $V_{DD}$  [23,24]. In addition, cross-talk and process variation on a chip make the determination of the path delay and path lengths difficult, thus making the choice of the best path to test a fault through a very difficult one [25]. Delay variation on a chip (due to process, temperature or voltage variations) can also induce hazards (glitches) in a reconverging path. For SDDs, these hazards can mask the detection of a valid SDD or falsely flag a circuit as faulty [26]. It is quite challenging to develop a method to determine the validity of SDDs during testing, and obviously, the validity of a test result is definitely related to how similar the test environment is to the environment of normal system operation.

### 1.2.3 Scan Based Testing

As circuits complexity grows, it is important to gain access to as many nodes in a circuit as possible in order to test it properly. The most common way to apply delay test is using what is called *scan based testing* [27]. Scan based testing is a testing method where the inputs and outputs of the CUT are launched and captured through a scan chain. This method allows for the flexibility to inject test inputs and detect test results as needed in the CUT. In addition, because scan-based testing is integrated in a chip, it enables at-speed testing (testing at the same speed as normal operation). In contrast to trying to control the test speed using external testers that are usually built in an older (slower) technology.

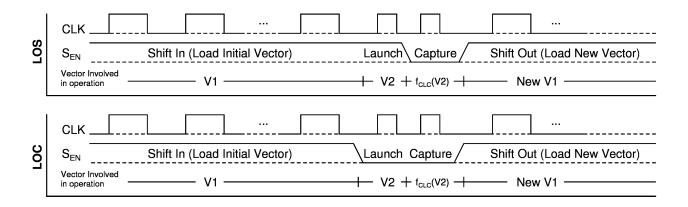

In literature, there are two standard scan based delay testing methods: launch-on-shift (LOS), also known as skewed-load [28], and launch-on-capture (LOC), also known as broadside test [29]. The LOS is done by applying an initial vector (V1) and waiting for the signals in the CUT to settle before applying a second vector (V2). V2 is applied by shifting in one more bit and switching quickly from scan mode to functional mode, then issuing the capture clock. The disadvantage of this method is that the scan-enable ( $S_{EN}$ ) signal needs to arrive at all the destination flops and settle before the capture clock edge occurs. This constraint becomes harder to meet as the test clock frequency increases (time between launch and capture decreases). On the other hand, the LOC does not have a timing constraint on the scan-enable signal. After applying V1, by scanning it in and waiting for the response to settle in the CUT, V2 will be ready at the inputs of the source flops waiting to be latched by the clock edge (launched). The test clock is pulsed twice, where the first pulse will launch V2 into the CUT, and the second pulse will capture the test result. The time between those two pulses define the speed of the test. The main limitation of LOC is the generation of V2. The classical approach is that V2 is the response from the CUT when V1 is applied to

Figure 1.3 Timing diagram of the classical LOS and LOC.

its inputs. This makes the possible pattern combination limited and thus the test coverage would be lower than LOS. The timing diagram of the LOS and LOC is shown in Fig.1.3. Notice that due to the timing constraint on LOS, it is difficult to have the test run at-speed, whereas it is easy in the case of LOC.

#### 1.3 The AnArm structure

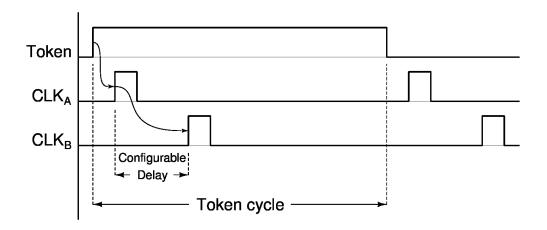

In [1], Octasic presented a single-rail bundled-data handshake-free (self-timed) asynchronous processor architecture. Those technical words simply imply that there is a single control line (clock) and that the data has to arrive to the destination before the clock [3]. The Octasic architecture uses mainly flip-flops rather than latches (which is common in asynchronous designs) and it was successfully used in several generations of commercialized ICs. The architecture of [1] uses 16 execution units (EUs) to build an ad-hoc like processing pipeline. Every EU can be configured to process any instruction in the processor. The processing steps, access to resources and timing are managed by token rings. In this system, tokens are signals that circulate in token rings between all EUs. There is one token ring for each shared resource (e.g. data/instruction cache). Once a token is acquired by an EU, the EU holds the token and starts processing the part of the instruction requiring this resource (e.g. fetch, read/write register banks) [30,31].

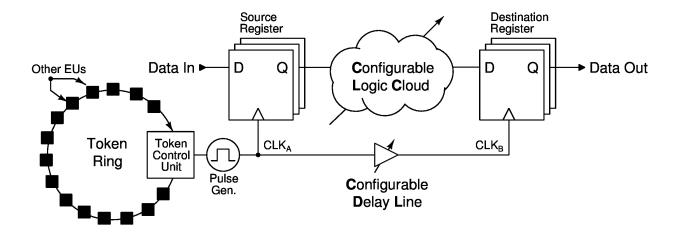

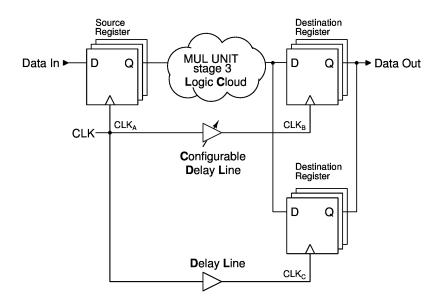

Fig. 1.4 presents a simplified schematic of an EU. When an EU acquires a token, a pulse is generated at node  $CLK_A$ . The pulse clocks the input flip-flops (source register) sending the data through the pre-configured combinational logic cloud. At the same time, the pulse travels through the delay line to the output flip-flops (destination register) and triggers the

Figure 1.4 Simplified schematic of the execution unit (EU).

Figure 1.5 Timing diagram of the EU operation.

capture of the result of the processed data. Since the EU is a group of multiple different processing clouds, the delay of the delay line is configured to match the delay of the selected processing cloud. The selection of the processing cloud depends on the operation that is being processed (i.e. the type of the token acquired). The diagram in fig. 1.5 shows timing of the operation of the simplified EU.

Since the EU structure has a race between the clock pulse and the data, there are two timing constraints that need to be satisfied for it to function correctly [31,32]: a setup time constraint and a hold time constraint. These constraints are similar to the synchronous circuits constraints. However, since this structure is self-timed and uses a configurable delay line (CDL), the setup and hold time constraints govern mainly the delay of the CDL with respect to the delays of the configurable logic cloud (CLC). The setup time constraints of the EU can be written as follows:

$$t_{CLC} \le t_{CDL} - t_{setup} - t_{CK-Q} \tag{1.3}$$

Where  $t_{CK-Q}$  is the delay for the data to appear at the output of the flip-flop after the clock edge arrival,  $t_{CLC}$  is the combinational cloud delay,  $t_{CDL}$  is the delay of the CDL and  $t_{setup}$  is the setup time for the output flip-flops. As can be seen from this equation, to ensure proper operation, the delay of the CDL needs to be appropriately selected. For the hold time constraint of the EU, two conditions need to be satisfied:

$$T_{token} \ge t_{CDL}$$

(1.4)

$$t_{CLC} \ge t_{hold} + (t_{CDL} - T_{token}) - t_{CK-Q} \tag{1.5}$$

Where  $T_{token}$  is the time for the token to circle around the token ring and come back to the same EU,  $t_{hold}$  is the hold time for the output flip-flops and the rest of the terms are as previously described in equation (1.3). The first condition in the hold constraint governs the relationship between the token ring delay and the CDL delay. This relationship is usually satisfied by the fact that the token ring is much longer than the CDL. However, this puts an upper limit on the delay of the CDL. The second constraint is similar to the synchronous hold time constraint, however, since a single pulse launches and captures the data, a hold violation is very unlikely to occur in this architecture if the first condition of the hold constraint is satisfied. Hence, the delay testing strategy will focus solely on checking the setup time constraint by testing the delays in the logic cloud against the delay of the CDL.

## 1.4 Objectives

As we discussed in the previous section, Octasic presented a unique structure for a self-timed processor. The AnARM chip that is developed in this project is a testable version of the Octasic structure. It was designed and fabricated in the STMicroelectronics 28nm FD-SOI technology, and it is based on the ARM instruction set. As will be discussed in the next chapter, a scan-based at-speed test strategy for the AnARM have been developed as part of the team efforts on this project. However, the at-speed test method was not applied on the AnARM chips as the AnARM was still in the final design stages. In this work, it was our responsibility to test the developed at-speed test strategy an reuse it to develop a high-quality SDD test method.

To summarize, the following is the main objective of this work.

• Develop a high-quality SDD test method that targets the Octasic self-timed EU structure by taking advantage of its unique clocking style.

The following are secondary objectives that by achieving them we will achieve the main objective:

- Propose an SDD test model and test quality metric that can take into consideration the unique clocking style of the EU.

- Develop an algorithm that adapts the CDL delay during pattern application to maximize the proposed SDD test quality metric.

- Validate previously developed at-speed test method and use the existing test structures to apply the developed high-quality SDD test.

The following are side objectives that are in-line with this work but have only been partially achieved due to the time limitation of this project:

- Study, and if possible include, the effect of PVT variations during the development of the SDD quality metric.

- Study the pros and cons of the Octasic EU clocking style, compared to classical synchronous clock trees, in terms of SDD testing.

Each of these objectives led to the proposed solutions and methods that are claimed as contributions. Considering the unconventional characteristics of the Octasic design style and the required literature background to understand the contributions of

this work, we elected to fully state the contributions of this work, in section 2.7, after fully reviewing prior works done in SDD testing and delay testing on the AnARM.

Finally, note that although the objectives of this work target the Octasic structure, the presented work and contributions can be expanded to conventional synchronous systems. For this reason, many of the coming sections do not specifically target the Octasic structure.

## 1.5 Work Organization

This dissertation is organized as follows. In chapter 2, the contributions of this work will be detailed after a review of literature. A novel SDD test model, and a SDD test quality metric that is derived from it, are presented in chapter 3 along with simulation results and discussions. Chapter 4 presents a method of building an optimized SDD test using the developed SDD test quality metric. Simulation results proving the validity of the presented technique are presented in the same chapter. The applied test results on silicon are presented and discussed in chapter 5. Finally, conclusions and recommendations for future work are listed in chapter 6.

Note that some parts of this work generate great amount of data and figures. In order not to distract the reader with too many figures, supplementary figures have been added in the appendices.

# CHAPTER 2 PRIOR WORKS ON SMALL-DELAY DEFECT TESTING AND ANARM AT-SPEED TESTING

As mentioned in the objectives (in section 1.4), the goal of the work presented in this dissertation is to develop a high-quality SDD delay defect test for the AnARM processor. In order to assess the contributions of this work, this chapter will present the most notable works done in the domain of SDD testing, and prior works done on developing a delay test for the AnARM. Then, at the end of this chapter, we conclude with a list of the contributions of this work.

Before proceeding with the review of prior works, it is important to note that in the literature, the term SDD is loosely defined as any delay defect that is small enough to escape delay testing. In order to be clear, we will indicate, when possible, the specific type of SDDs that the reviewed work is talking about with reference to the definitions previously listed in section 1.2.2.

## 2.1 Overview on SDD Testing

As mentioned in chapter 1, standard delay testing is based on one of two delay fault models: the path delay fault (PDF) model or the transition delay fault (TDF) model [8,12,13,27]. A PDF based delay test is an extensive search of all possible paths in a circuit for delay defects. Effective SDDs cannot escape detection if all paths in a CUT are tested with an at-speed speed clock under normal operating conditions. However, as the circuit complexity grows, the time to apply such a test can grow exponentially, and the conditions to correctly sensitize paths become more complicated [16,18]. On the other hand, a TDF based test applies test vectors to excite a transition (rising and falling) through each node in a circuit. It is less time consuming to apply a TDF based test than a PDF one. However, since not all paths are tested, it is possible to miss an SDD that can cause a chip to fail in the field.

To test for SDDs, most researchers have focused on building tests that enhance TDF based tests. The main idea in the majority of the literature is to reduce the slack window in which an SDD can escape during testing. This is either done by enhancing the ATPG algorithm to sensitize longer paths (in terms of delay) [17, 26, 33–44], or by applying a test clock that runs faster than the normal system clock [45–52]. In this case the test is referred to as faster-than-at-speed testing (FAST).

## 2.2 Pattern Generation for Small-Delay Defect Testing

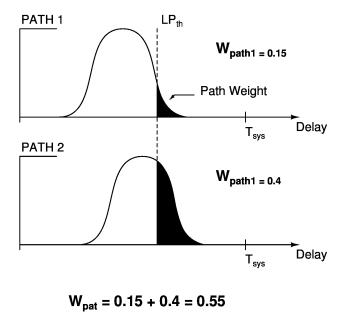

An ATPG is a software that is used to generate the stimulus (vectors) that test the CUT and define the expected results [4]. In the classical stuck-at fault model, only one vector is needed to test if a node is stuck-at a logical 0 or 1. In delay testing, a transition is needed to check for delay faults and so a pattern, which consists of two vectors, is needed. The group of all patterns generated to test a circuit is called a pattern set. Under the standard TDF model, these patterns are generated without considering path delays. Thus, as mentioned in the previous subsection, TDF based delay tests cannot detect effectively SDDs. Some researchers in the field of delay testing tried to enhance the ATPG techniques to address this problem by generating better delay test patterns.

Looking at the research that was done on SDD testing from the side of pattern generation and selection, we see that all the ideas are focused on generation and/or selecting patterns that reduce the slack the path through which a fault is tested [17, 33, 35–37, 39, 42, 53]. In this field of research there are two schools of thought: one is to construct a timing-aware ATPG (TAA), and the other is to use other non-timing driven techniques that reduces the probability of a test escapes.