| <b>Titre:</b> Cache Predictability and Performance Improvement in ARINC-<br>Title: Compliant Systems |                                                                                                                                                                                                                                                                           |

|------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Auteur:<br>Author:                                                                                   | Alexy Torres Aurora Dugo                                                                                                                                                                                                                                                  |

| Date:                                                                                                | 2019                                                                                                                                                                                                                                                                      |

| Type:                                                                                                | Mémoire ou thèse / Dissertation or Thesis                                                                                                                                                                                                                                 |

| Référence:<br>Citation:                                                                              | Torres Aurora Dugo, A. (2019). Cache Predictability and Performance<br>Improvement in ARINC-653 Compliant Systems [Mémoire de maîtrise,<br>Polytechnique Montréal]. PolyPublie. <a href="https://publications.polymtl.ca/3941/">https://publications.polymtl.ca/3941/</a> |

# Document en libre accès dans PolyPublie Open Access document in PolyPublie

| <b>URL de PolyPublie:</b> PolyPublie URL: | https://publications.polymtl.ca/3941/ |

|-------------------------------------------|---------------------------------------|

| Directeurs de recherche: Advisors:        | Gabriela Nicolescu                    |

| Programme:                                | Génie informatique                    |

# POLYTECHNIQUE MONTRÉAL

affiliée à l'Université de Montréal

| Cache predictability and performance improvement in ARIN | VC-653 | compliant |

|----------------------------------------------------------|--------|-----------|

| systems                                                  |        |           |

## ALEXY TORRES AURORA DUGO

Département de génie informatique et génie logiciel

Mémoire présenté en vue de l'obtention du diplôme de Maîtrise ès sciences appliquées Génie informatique

Juillet 2019

# POLYTECHNIQUE MONTRÉAL

affiliée à l'Université de Montréal

| Се | mémoire      | intitulé  | : |

|----|--------------|-----------|---|

|    | TITO TITO TE | 111010010 | • |

Cache predictability and performance improvement in ARINC-653 compliant systems

présenté par Alexy TORRES AURORA DUGO

en vue de l'obtention du diplôme de *Maîtrise ès sciences appliquées* a été dûment accepté par le jury d'examen constitué de :

Giuliano ANTONIOL, président

Gabriela NICOLESCU, membre et directrice de recherche

Michel DAGENAIS, membre

# **DEDICATION**

$I\ dedicate\ my\ work\ to\ my\ family\ and\ friends,$  thank you for supporting me

#### **ACKNOWLEDGEMENTS**

I would like to thank my research director Prof. Gabriela Nicolescu for her support and help during my master years. I am thankful toward Mannarino System and Softwares, especially Mr. Dahman Assal for all the support and advice they provided me. I would also like to thank all my laboratory colleagues for their help and the good times we had together. I am grateful for the help that Prof. Frédéric Pétrot provided me to find my way in the domain of computer science that is embedded systems. I would like to thank my family and friends that never ceased to support me during these past years. Finally, I would like to acknowledge Mitacs for the financial support they provided for this project and made it possible for me to conduct this research.

## RÉSUMÉ

Depuis les années 2000, les processeurs multi-coeurs sont développés afin de répondre à une demande croissante en performances et miniaturisation. Ces nouvelles architectures viennent remplacer les processeurs mono-coeurs, moins rentables sur le plan des performances et de la consommation énergétique. De par cette transition, les systèmes avioniques actuels se retrouvent face à un défi de taille. Ces systèmes critiques n'utilisent que des processeurs mono-coeurs, éprouvés et validés depuis des années afin de garantir la fiabilité du système. Cependant, les fabriquants de processeurs et autres microcontrôleur délaissent peu à peu ces architectures pour ne produire que des processeurs multi-coeurs. Afin de maintenir les systèmes avioniques critiques, les intégrateurs doivent alors se tourner vers ces nouveaux processeurs. Cependant, cette transition n'est pas sans défi. Outre le fait de devoir assurer la portabilité des applications mono-coeur dans un environnement multi-coeurs, l'utilisation de plusieurs coeurs permet leur exécution concurrente. Ce nouveau paradigme apporte aux systèmes des comportements qui peuvent entrainer, dans certains cas, un dysfonctionnement complet du système. De tels comportements ne sont pas acceptables dans ces systèmes où la moindre faute peut provoquer des pertes humaines. Les systèmes critiques suivent certaines règles afin de garantir leur intégrité. Le standard ARINC-653 définit un ensemble de règles et de recommandations afin de développer ce genre de systèmes. Le standard introduit le concept de système partitionné où chaque partition s'exécute indépendamment des autres et ne peut pas influer sur le comportement du système ou des autres partitions. Ainsi, si une partition vient à fonctionner anormalement, son exécution ne peut compromettre le bon fonctionnement des autres partitions. Le problème émergeant dans les architectures multicoeurs vient du fait que plusieurs partitions peuvent s'exécuter de manière parallèle. Cette nouvelle possibilité introduit de la concurrence sur les ressources du système, ce qui génère des comportements non prévisibles. Ces comportements, appelés interférences apparaissent lorsque plusieurs coeurs partagent les mêmes ressources. Lors d'un accès à ces ressources (mémoire, périphériques, etc.), un arbitrage doit être fait afin d'assurer l'intégrité des données. Cet arbitrage peut causer des délais dans l'accès à une ressource. De plus si plusieurs partitions accèdent à une même ressource, le concept d'isolation n'est plus respecté. Dans le cas des mémoires caches partagées, une partition peut évincer des données utilisées par une autre partition. Dans ce mémoire, nous étudions la possibilité d'empêcher l'évincement de données des caches privés d'un processeur. Cette méthode, appelée cache locking, permet de réduire le nombre de fautes de cache dans les caches privés et ainsi limiter les accès aux caches partagés. Cela permet de réduire les interférences liées aux caches partagés, non seulement

en termes de concurrence d'accès, mais aussi d'évincement non voulus de données dans ces caches. Ainsi nous introduisons un outil de profilage d'utilisation de la mémoire dans les systèmes partitionnés. Nous présentons aussi un algorithme associé à cet outil permettant de sélectionner le contenu des mémoires caches devant être empêché d'être évincé. Cet outil propose un processus complet de traitement des traces d'accès mémoire jusqu'à la création des fichiers de configuration. Nous avons validé notre approche par le biais de simulation et d'expérimentation sur matériel réel. Un système d'exploitation temps réel respectant la norme ARINC-653 a été utilisé afin de conduire nos expérimentations. Les résultats obtenus sont encourageants et permettent de comprendre l'impact des méthodes de caches locking pour les systèmes embarqués multi-coeurs.

#### **ABSTRACT**

Due to their energy efficiency and their capability to be miniaturized, multi-core processors have been developed to replace the less cost-effective single-core architectures. Since around year 2000, processor manufacturers slowly stopped producing single-core processors. This raised an issue for avionic system designers. In these critical systems, designers use processors that have proven their reliability through time. However, none of such processors are multi-core. To be able to keep their system up to date, aerospace system designers will have to make the transition to multi-core architectures. This transition brings a lot of challenges to system designers and integrator. Current single-core applications may not be fully portable to multi-core systems. Thus developers will have to make sure the transition is possible for such applications. Multi-core CPUs offer the ability to execute multiple tasks in parallel. From this ability, new behaviors may induce delays, bugs and undefined behaviors that may result in general system failure. In critical systems, where safety is crucial, such comportment is unacceptable. Safety critical systems have to comply with multiple standards and guidance to ensure their reliability. One of the standard Real Time Operating Systems developers may rely on is the ARINC-653. This standard introduces the concept of partitioned systems. In such systems, each partition runs independently and should never be able to modify or impact the behavior of another partition. This concept ensures that if one partition comes to misbehave, the system's integrity is not impacted. In multi-core systems, multiple applications can run in parallel and access hardware and software resources at the same time. This concurrence, if not correctly managed, will introduce delays in execution time, loss of performances and unwanted behaviors. We call interferences any behavior introduced by this concurrence on the resources shared by different cores or partitions. When concurrent accesses to shared components occur, arbitration has to be done to ensure the data integrity. In most cases, this arbitration is the cause of interferences. However, other sources of interference exist. For instance, if two partitions share the same cache, one partition may evict other partition data from the cache. This leads to unpredictable delays when the next partitions will need to access the evicted data. In this thesis, we explore methods to prevent cache line evictions in private processor caches. This work allows to reduce the number of cache misses occurring at the private level, which reduces the amount of access done to the lower memory levels and reduces interferences related to them. We call this method cache locking. We introduce a framework capable of profiling memory accesses done by applications and propose a cache content selection algorithm that selects cache lines to be locked to reduce cache misses in private caches. We present the toll and the associated processing pipeline, from the memory

profiling, to the cache locking configuration table generation. We validated our approach on simulated and actual hardware and used a proprietary ARINC-653 compliant system to conduct our experiments. The results obtained are encouraging and allow to understand the impact of private caches and cache locking methods to reduce multi-core interferences in safety-critical systems.

# TABLE OF CONTENTS

| DEDICA | ATION                                            |

|--------|--------------------------------------------------|

| ACKNO  | WLEDGEMENTS ir                                   |

| RÉSUM  | É                                                |

| ABSTR  | ACT vi                                           |

| TABLE  | OF CONTENTS in                                   |

| LIST O | F TABLES xi                                      |

| LIST O | F FIGURES xii                                    |

| LIST O | F SYMBOLS AND ACRONYMS                           |

| СНАРТ  | ER 1 INTRODUCTION                                |

| 1.1    | Context                                          |

| 1.2    | Research Challenges                              |

| 1.3    | Objectives                                       |

| 1.4    | Contribution                                     |

| СНАРТ  | ER 2 LITERATURE REVIEW                           |

| 2.1    | Interference in Multi-core Systems               |

| 2.2    | Memory Interference in Multi-core Systems        |

| 2.3    | Communication Interference in Multi-core Systems |

| 2.4    | Scheduling and WCET Analysis                     |

| СНАРТ  | ER 3 THEORETICAL BACKGROUND AND METHODOLOGY 12   |

| 3.1    | Definitions                                      |

| 3.2    | Methodology                                      |

| 3.3    | Basic Concepts                                   |

|        | 3.3.1 Cache Memories                             |

|        | 3.3.2 Address representation in the cache        |

|        | 3.3.3 Cache Locking and Partitioning             |

|        | 3.3.4 Integrated Modular Avionic                 |

|       | 3.3.5  | Design Assurance Levels                               | 1 |

|-------|--------|-------------------------------------------------------|---|

|       | 3.3.6  | ARINC-653 and Isolation                               | 2 |

|       | 3.3.7  | Interference in Multi-core Architectures              | 4 |

| CHAPT | ΓER 4  | CACHE LOCKING FRAMEWORK                               | 7 |

| 4.1   | Frame  | ework Goal                                            | 7 |

| 4.2   | Modu   | les Definition                                        | 8 |

| 4.3   | Input  | and Output Definitions                                | 2 |

| 4.4   | Memo   | bry Tracing                                           | 3 |

|       | 4.4.1  | Trace Definition                                      | 3 |

|       | 4.4.2  | The proposed approach for QEMU as a memory tracer     | 5 |

|       | 4.4.3  | QEMU Limitation and Proposed Solutions                | 7 |

| 4.5   | Design | n choices                                             | 7 |

|       | 4.5.1  | Programing Language                                   | 8 |

|       | 4.5.2  | Performance Improvements                              | 8 |

| CHAPT | ΓER 5  | ARTICLE 1: CACHE LOCKING CONTENT SELECTION ALGORITHMS | 3 |

| FOI   | R ARIN | IC-653 COMPLIANT RTOS                                 | 9 |

| 5.1   | Abstr  | act                                                   | 9 |

| 5.2   | Introd | luction                                               | 9 |

| 5.3   | Backg  | round and Context                                     | 1 |

|       | 5.3.1  | From Federated To IMA Architecture                    | 1 |

|       | 5.3.2  | ARINC-653 And Partitioned Systems                     | 2 |

|       | 5.3.3  | Caches Architecture                                   | 3 |

| 5.4   | Relate | ed Work                                               | 4 |

| 5.5   | Cache  | -Locking Algorithms                                   | 6 |

|       | 5.5.1  | Overview                                              | 7 |

|       | 5.5.2  | Greedy Selection Algorithm                            | 7 |

|       | 5.5.3  | Genetic Selection Algorithm                           | 1 |

| 5.6   | Result | ts                                                    | 5 |

|       | 5.6.1  | Benchmarks                                            | 5 |

|       | 5.6.2  | Algorithm Comparison                                  | 5 |

|       | 5.6.3  | Performance Improvement                               | 7 |

|       | 5.6.4  | Predictability Improvement                            | 9 |

|       | 5.6.5  | Overhead of the Solution                              | 1 |

|       | 5.6.6  | Comparison with previous work                         | 1 |

| 5.7   | Concl  | usion                                                 | 2 |

| 5.8   | Acknowledgments                        | 63 |

|-------|----------------------------------------|----|

| СНАРТ | ΓER 6 GENERAL DISCUSSION               | 64 |

| 6.1   | Considered Architectures               | 64 |

|       | 6.1.1 PowerPC e200/e500                | 64 |

|       | 6.1.2 x86 architecture                 | 64 |

| 6.2   | Benchmarks                             | 65 |

| 6.3   | Results Gathering and Methodology      | 65 |

| 6.4   | Results synthesis                      | 67 |

|       | 6.4.1 Simulated results                | 67 |

|       | 6.4.2 Results on MPC5777C architecture | 72 |

| СНАРТ | TER 7 CONCLUSION                       | 73 |

| 7.1   | Summary of the proposed contribution   | 73 |

| 7.2   | Limitations                            | 74 |

| 7.3   | Future Research                        | 74 |

| REFER | RENCES                                 | 76 |

# LIST OF TABLES

| Table 5.1 | Methods for cache locking                                              | 45 |

|-----------|------------------------------------------------------------------------|----|

| Table 5.2 | Instruction intensive applications                                     | 56 |

| Table 5.3 | Execution time for different trace sizes                               | 56 |

| Table 5.4 | Greedy algorithm based approach against genetic algorithm based ap-    |    |

|           | proach. Results are expressed in the percentage of avoided misses. The |    |

|           | greedy approach performs better in most cases                          | 58 |

| Table 5.5 | Cache miss increase on overlocked caches                               | 58 |

| Table 5.6 | Comparison between PLRU and PRR algorithms regarding the cache         |    |

|           | locked lines                                                           | 60 |

| Table 5.7 | Standard deviation of execution time (CPU cycles). Results show        |    |

|           | that we significantly reduce the execution time standard deviation by  |    |

|           | 97.29% on average                                                      | 60 |

| Table 6.1 | Cache architectures of the e200z7, e500v1 and Intel Atom N270 $$       | 65 |

|           |                                                                        |    |

## LIST OF FIGURES

| Figure 3.1  | Example of cache hierarchy                                                   | 15 |

|-------------|------------------------------------------------------------------------------|----|

| Figure 3.2  | Example of cache organization                                                | 16 |

| Figure 3.3  | Address representation as seen by the cache                                  | 19 |

| Figure 3.4  | Virtual memory address compared to cache representation address              | 20 |

| Figure 3.5  | Example of federated architecture                                            | 21 |

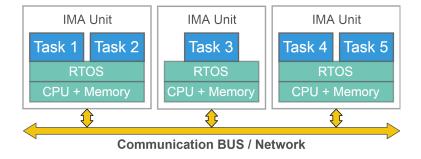

| Figure 3.6  | Example of IMA architecture                                                  | 21 |

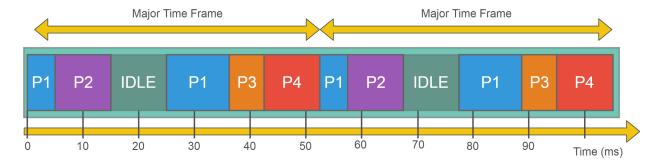

| Figure 3.7  | Example of a major time frame                                                | 23 |

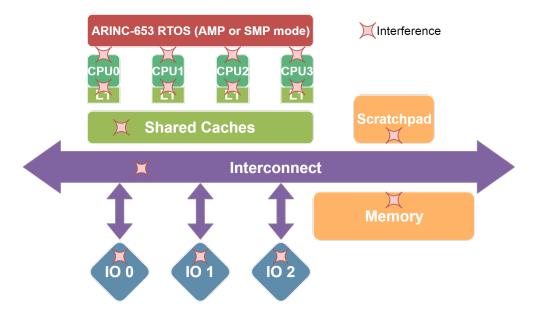

| Figure 3.8  | Interference-prone architecture                                              | 25 |

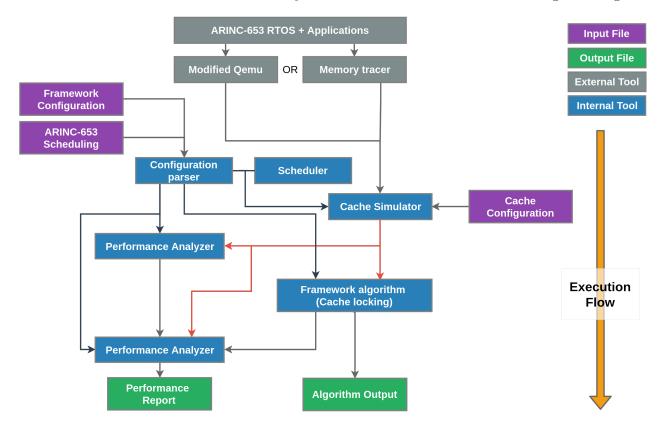

| Figure 4.1  | Cache Locking Framework                                                      | 28 |

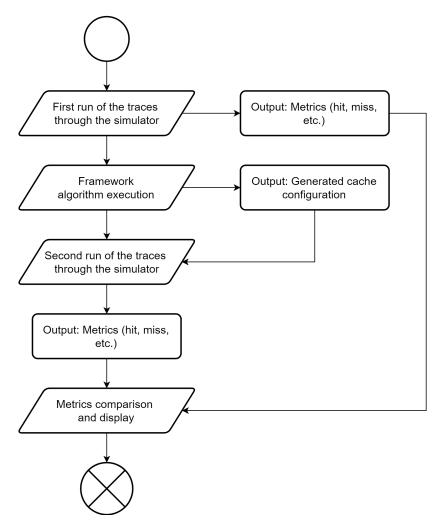

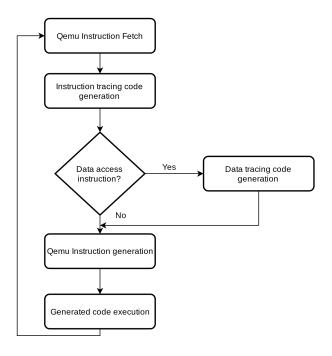

| Figure 4.2  | Performance Analyzer execution flow                                          | 31 |

| Figure 4.3  | Trace file representation                                                    | 33 |

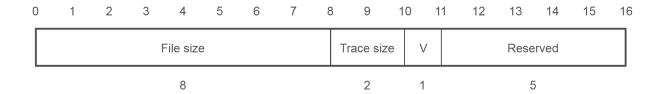

| Figure 4.4  | Trace format header                                                          | 34 |

| Figure 4.5  | Trace format definition                                                      | 35 |

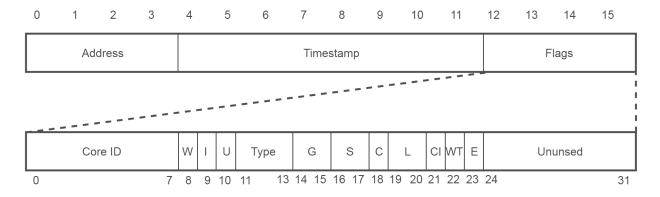

| Figure 4.6  | Qemu translation process                                                     | 37 |

| Figure 5.1  | IMA architecture example                                                     | 42 |

| Figure 5.2  | Partitioned RTOS major time frame example                                    | 43 |

| Figure 5.3  | 4-Way associative cache architecture                                         | 44 |

| Figure 5.4  | Greedy algorithm process flow                                                | 49 |

| Figure 5.5  | GA cache representation                                                      | 54 |

| Figure 5.6  | Crossover operator used in the genetic algorithm                             | 54 |

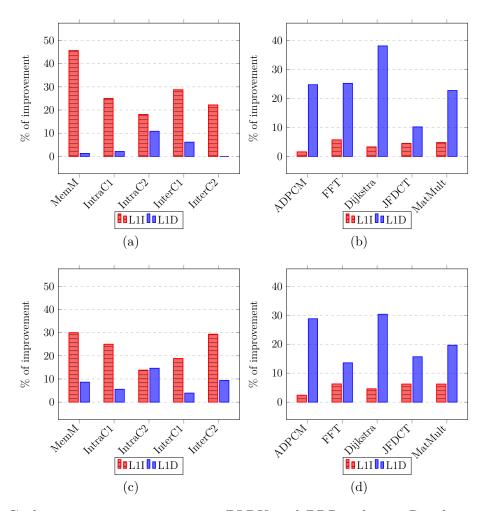

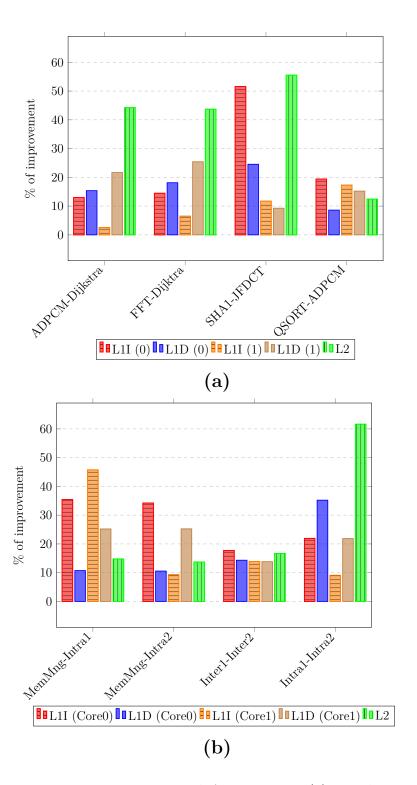

| Figure 5.7  | Cache miss improvement using PLRU and PRR policies. Results are              |    |

|             | shown for instruction intensive applications (a) with a reduction of miss    |    |

|             | up to $45\%$ and data intensive applications with a reduction of miss up     |    |

|             | to $38\%$ (b). Instruction intensive applications (c) with a miss reduction  |    |

|             | up to $30\%$ and data intensive applications with a miss reduction up to     |    |

|             | 31% (d)                                                                      | 57 |

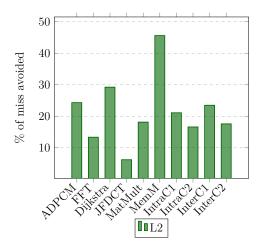

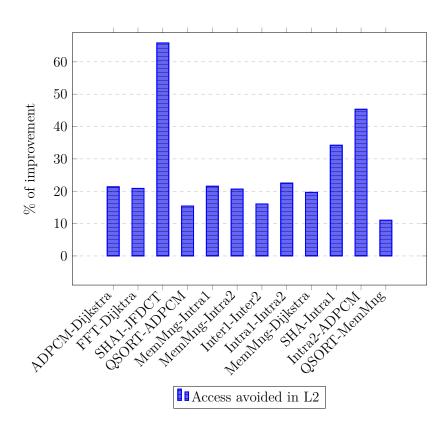

| Figure 5.8  | L2 accesses avoided for PRR policy. Our algorithm allows to reduce           |    |

|             | the workload on L2 cache by $45\%$ in some cases and of $31.5\%$ on average. | 59 |

| Figure 5.9  | Execution time comparison in CPU cycles. The overhead is comprised           |    |

|             | in the measure, meaning that our approach does not add execution             |    |

|             | time overhead when used                                                      | 60 |

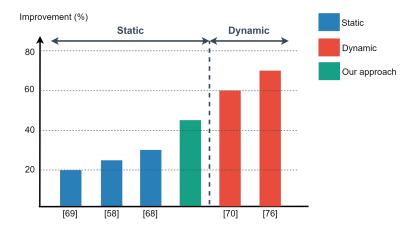

| Figure 5.10 | Comparison of our solution with previous work                                | 62 |

|             |                                                                              |    |

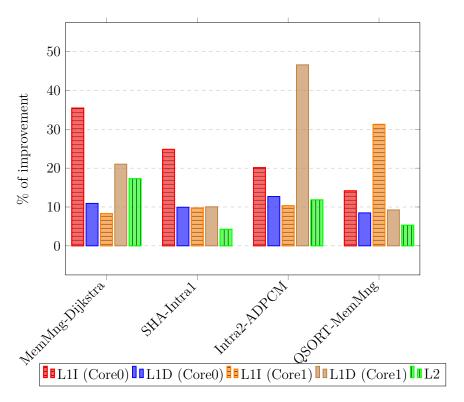

| Figure 6.1 | Cache miss improvement on Intel Atom N270. Results are shown for           |    |

|------------|----------------------------------------------------------------------------|----|

|            | co-running instruction and data-intensive applications with a miss re-     |    |

|            | duction up to $47\%$ in private L1 and $17.5\%$ in shared L2               | 68 |

| Figure 6.2 | Cache miss improvement on Intel Atom N270. (a) Results are shown           |    |

|            | for co-running data intensive applications with a miss reduction up to     |    |

|            | 51% in private L1 and $55%$ in shared L2. (b) Results are shown for        |    |

|            | co-running instruction intensive applications with a miss reduction up     |    |

|            | to 46% in private L1 and 62% in shared L2                                  | 69 |

| Figure 6.3 | L2 accesses avoided on Intel Atom N270. Results are shown for co-          |    |

|            | running applications. All accesses to the L2 are potential contention      |    |

|            | factors. Results show a reduction of $26.21\%$ on average with peaks up    |    |

|            | to 65.84%                                                                  | 70 |

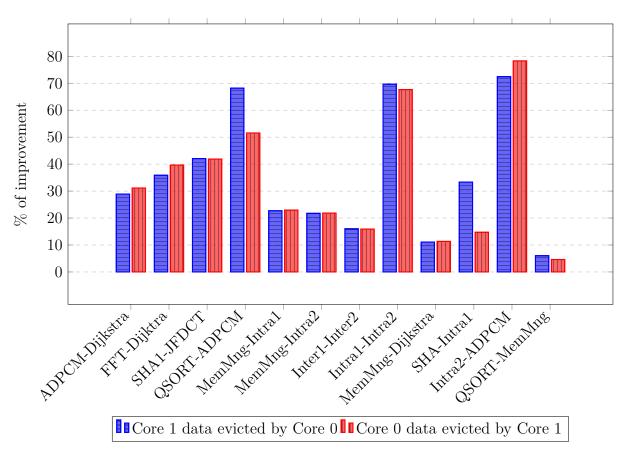

| Figure 6.4 | Percentage of indirect interferences avoided (cache line eviction). Our    |    |

|            | approach allows to reduce the amount of indirect interference of $33.22\%$ |    |

|            | on average with peaks up to 78.28%.                                        | 71 |

## LIST OF SYMBOLS AND ACRONYMS

**AER** Acquisition Execution Restitution

APEX Application EXecutive

**API** Application Programming Interface

**ARINC** Avionics Application Standard Software Interface

**CAST** Certification Authorities Software Team

**CPU** Central Processing Unit

**DMA** Direct Memory Access

EUROCAE European Organization for Civil Aviation Equipment

FPU Floating Point Unit

**HM** Health Monitor

IMA Integrated Modular Avionic

IO Input/Output

MMU Memory Management Unit

MPU Memory Protection Unit

**OS** Operating System

PMC Performance Monitoring Counters

RTCA Radio Technical Commission for Aeronautics

RTOS Real Time Operating System

SWaP Size Weight and Power

TDMA Time-Division Multiple Access

WCET Worst Case Execution Time

XML Extensible Markup Language

## CHAPTER 1 INTRODUCTION

This chapter presents the main challenges that avionics program manufacturers face when new multi-core architectures are integrated in avionic systems. We then introduce the objectives and contributions of this thesis.

#### 1.1 Context

Nowadays multi-core architectures are more and more present in embedded systems. Compared to single-core processors, these processors often have better performances and appear to be more energy efficient [1]. Therefore, processor manufactures are reducing the development of single-core processing units.

Multi-core processors allow different tasks to be extended in parallel. It is particularly appealing in systems where a lot of tasks have to execute in a limited amount of time. More and more computing intensive tasks appear in critical systems. Image processing, artificial intelligence and communications are some of these tasks. Enabling parallelism for processes will provide faster response time and, thus, improve safety of the system.

Actors in the aerospace domain only rely on proven architectures that have been used for years. PowerPC architectures, for instance, are often used for their reliability. However, looking at the current market of processors in critical embedded systems, ARM processors slowly replace PowerPC ones due to their lower prices and power consumption.

Avionics actors, being a small part of the processor market, will soon have to make the transition from single-core to multi-core processors if they want to keep their architectures up to date.

The criticality of aerospace applications enforces developers to design programs that comply to major standard such as ARINC-653 [2] standards or DO-178C [3] guidance documents. However such documents do not address multi-core architectures due to their lack of determinism and the multiple issues raised by their design. Recently, the Certification Authorities Software Team (CAST) released different papers about multi-core processors use in avionic systems. Most of the issues brought by multi-core processor are clearly stated but no actual mean of avoidance of such issues is defined.

To catch up with the multi-core tendency, one solution is to develop new Real Time Operating System (RTOS) capable of supporting such architectures while providing the same services and level of safety than single-core RTOS. The new RTOS will also have to take advantages of

the increase of performance brought by the multi-core architecture (parallel execution, load balancing). RTOS developers started to release new versions of their product to support multi-core platforms<sup>1</sup>. However these new RTOS do not fully address the challenges brought my the new architectures.

One of the strongest constraints in the avionics domain is task isolation. The isolation principle defines that one application cannot impact the behavior of another application in the system [2]. From a single-core point of view, this principle is ensured by spacial isolation. Peripherals and memory areas can be isolated to restrict their access to one or more applications. Timing isolation is inherently achieved executing one application at a time.

Multi-core architectures allows faster processing. Indeed, the gain of performances comes from the multiple processing units, executing software code in a parallel manner. Multiple paradigms can be used to take advantages of multi-core processors. One may take one application and modify its code to run multiple parts of the application in parallel. In aerospace systems, this is not the targeted option. Current avionic applications are not designed to run in parallel and the effort to update the code of each application is not worth the cost. However, future applications may take into account the possibility to achieve multiple tasks in parallel. The other way of updating the system to multi-core processors is to have multiple applications running at the same time. This option is more realistic in the current context of aerospace systems.

In multi-core processors, temporal isolation needs to be explicitly addressed as multiple applications execute in parallel at a certain moment. Thus, applications no longer have exclusive access to the resources but instead share them with other independent applications. The principle of isolating applications is called partitioning. Application partitioning is an execution model that ensures the exclusive use of internal resources [4](caches, memories, hardware accelerators, etc.) and external resources [5] (Input/Output (IO), peripherals, etc.) at a given moment. Concurrent accesses to these shared resources create interferences. These interferences can bring the system in an unstable state [6] (bug, crashes, etc.) when multiple applications modify the memory state or access a peripheral. In most current systems, memories, peripherals and other resources cannot satisfy multiple requests at the same time. Thus, an arbitration must be made between the different requests they receive. This arbitration may delay the access to the resource for the processors (or component) which sent the request. These delays will impact the responsiveness and the execution time of independent applications. From the multicore designer's viewpoint, interference occurrence

<sup>&</sup>lt;sup>1</sup>eg. DeOS (DDCI), VxWorks 653 (WindRiver)

is not a dysfunctional behavior, it is considered a performance bottleneck. However, for the avionics designers, interference occurrences are considered dysfunctional behaviors. In the avionics domain, where such non-deterministic behavior cannot be tolerated, as they can entail casualties, research has to be conducted to reduce the impact of interferences [7].

#### 1.2 Research Challenges

One of the most important challenges to face in the real-time embedded systems domain is the ability to compute the Worst Case Execution Time (WCET) of each application or tasks running on the system. This metric allows bounding the task's execution. Bounding tasks execution time allow the system designer to ensure that the system can schedule the tasks correctly [8]. Interferences entailed by the presence of multiple cores executing in parallel will prevent the developers from computing or even measuring the WCET correctly. X. Jean et al. [9] proposed methods to allow WCET computations in non-deterministic systems. However, the current literature does not always address interferences and prefers to propose solutions to take them into account instead of mitigating them<sup>2</sup>. P. Huyck [10] and H. Agrou et al. [11] highlight the importance of the different issues raised by the use of multi-core architectures in current avionic systems.

#### 1.3 Objectives

This section presents the global objective of this thesis as well as the detailed objectives defined during the conducted research.

Research Question In this master thesis, we answer the following question: How to reduce interferences and improve performance of private and shared caches in ARINC-653 compliant environments?

**Objectives** The global objective of the thesis is to develop a solution to mitigate interferences with focus on interferences caused by caches in multi-core processors. We propose new methods to optimize the resources (caches) usage while ensuring isolation between applications in the system. The solution is integrated in a proprietary RTOS certified for avionic use. The following specific objectives have been defined for the project:

<sup>&</sup>lt;sup>2</sup>For instance, one may compute WCET assuming that caches are disabled, thus, taking into account any cache-related interferences possible (as the worst case happens when all memory accesses produce a miss in the cache).

- to define, analyze and characterize interferences present in multi-core systems.

- to develop cache analysis tools to profile cache usage in the system.

- to design software solutions (algorithms) to mitigate the detected interferences.

- to integrate the developed method in the proprietary RTOS.

- to validate the approach and methods based on results gathered with the RTOS.

#### 1.4 Contribution

To solve cache interferences, the proposed contributions are:

- Propose a memory tracing framework, capable of analyzing memory accesses of realtime tasks. The framework embeds a memory tracing module integrated in the Qemu emulator. An ARINC-653 scheduler enables the framework to know the state of the system at any moment. We also integrated different memory trace based algorithms in the framework.

- 2. Define new approaches to select the cache lines to lock (prevent the lines from eviction)<sup>3</sup>. This selection can be based on multiple criteria;

- 3. Integrate cache locking mechanism in an ARINC-653 compliant RTOS;

$<sup>^3</sup>$ Cache locking concepts are defined later in this thesis.

#### CHAPTER 2 LITERATURE REVIEW

In this chapter, we present the related work conducted around interferences in multi-core architectures. We did not limit ourselves to cache related interferences and preferred to keep a large vision of what interferences are and where they occur in the system.

#### 2.1 Interference in Multi-core Systems

Since multi-core architectures have been introduced, extensive research has been conducted to use them in the avionic domain. However, the parallelism brought by such processors comes at the cost of interferences.

In [12], caches are said to be the most important and critical interference channel in the system. Multiple sources of interferences have been observed such as caches, memory, shared busses, etc.

In [13,14] interrupts are also shown to create interferences. Indeed, when multiple interrupts are routed to the same core, but not handled by this specific core, the core has to transfer the interrupts to the handling core(s). This leads to delay in execution and non-deterministic behavior if interrupts are not delivered with a fixed period. To avoid this, authors propose to disable interrupts usage from partitions and rely on the RTOS to enforce determinism on interrupts.

In [13, 15, 16], interference channels are classified and studied to quantify the impact they have on the system execution time. It is reported that even inside the CPU, interferences occur [15]. The Floating Point Unit (FPU) can be shared between multiple cores, which may lead to contention on this component. Other units such as the branch prediction unit will introduce non-deterministic behavior in the system.

Hyperthreading and cache coherence protocols have also been shown to introduce competition to resources that were supposedly private to a CPU core [17]. Other shared components of the system are categorized as interference channels. IOs are often considered as a part of the interference channels as they can modify the behavior of a partition. In [14] authors explain how a partition can steal execution time from another partition by using Direct Memory Access (DMA) transfers. Authors also show how a partition can lock the bus, stalling other cores of the processor and potentially leading to deadlines misses of other partitions. They propose to disable DMA interrupts for partitions and rely on polling to notify the partition when the transfer is complete. Interference mitigation has also been studied under multiple

forms. In [18], a framework is developed to deploy IMA applications. An offline analysis is done by the tool to compute the WCET of each application of the system. This analysis is done thanks to a single-core approach. The authors present a model that divides system resources in private areas that are only used by one core. Using this method, they expect the partitions to behave in the same way as if they executed in single-core environment. A scheduling method is also presented to allow the correct use and repartition of the resources in the system. However, even if multiple interferences are solved by this approach, contention on shared resources such as busses or memory still exists. Other methods lean toward detection of interference from application profiling [19]. A solution to avoid interferences is to deactivate all core of the CPU except one [20]. This solution would, however, remove all the advantages brought by the multi-core processors.

#### 2.2 Memory Interference in Multi-core Systems

We refer as memory interferences all interferences that occur in the memory hierarchy. This spans from the CPU's private caches to the central memory. Mass storage devices are considered as IOs and are excluded from this category. In this section we present different studies and mitigation efforts made to reduce memory interferences.

In [21], a suite of benchmarks is proposed. This suite allows to study the impact of shared cache interferences in the system. The presented methods consist in running the applications to test on N cores and to run the benchmark applications on the other cores. Benchmark applications will stress the shared resources and one can use probes such as Performance Monitoring Counters (PMC) to study the influence of interferences on the critical applications. Other works considering the same approach have been published such as the benchmarks proposed in [22].

As said earlier, shared caches are the component where most of the interferences occur. In [17], three cache-related interferences are defined.

The first interference type, also present in single-core systems, occurs when a partition evict data it does not own from the cache. In this case data that are being evicted are not owned by any partition currently executing in the system. Such interferences can be solved by invalidating the cache at each partition switch. This ensures that the state of the cache is always the same when the partition begins its execution.

The second type of interference is the same as the first but this time in multi-core systems. As many partitions can execute in parallel, a partition can evict data that are owned by another partition that currently executes in the system.

Finally, the third type of interference is cache contention. When multiple cores concurrently access the cache, the cache controller serializes the accesses. This has the effect to stall the cores waiting to access the cache and introduces delays in execution time. In [12] cache coherence protocols also induce interferences as a core can indirectly modify the content of another core's cache through the protocols. To mitigate such interferences, cache partitioning is one of the most effective solutions [23, 24]. In [25] a framework relies on cache coloring to divide the cache into multiple partitions. This method prevents partitions to evict from cache data they do not own. Authors rely on cache partitioning and task scheduling. Cache partitioning avoids cache-related interferences while task scheduling allows multiple partitions to use the same cache area: when two partitions use the same cache area, they will never be scheduled at the same time. Two mitigation methods are then possible:

- Partitions cannot evict data they do not own from the cache at any time. Each partition needs its private cache area.

- Two partitions can share the same cache area. They can evict each other's data, but will never be executed at the same time. If the two partitions flush and invalidate their cache area before executing, then no interference is possible.

In [26] an offline profiling framework is proposed to manage caches in multi-core systems. The goal of the tool is to determine the memory pages which are the most frequently accessed. The profiling data are compiled to generate a memory map which is used to generate an execution independent memory profile of the application. This profile is used to partition caches and thus avoid a partition from evicting another partition's data. Other partitioning approaches have been studied as in [27]. Authors use the memory manager of the Xen hypervisor to allocate pages in the system. This allows having multiple pools of addresses. Each pool refers to one or more partitions in the cache. Other sources of interferences are present in the cache such as cache writes buffers [28].

Locking caches has also been studied to reduce interferences in two ways. The first improvement brought by cache locking is the reduction of cache misses. Thus, locking data in private cache will reduce the amount of memory accesses in shared areas. In [29] static code analysis is explored to select which instruction data should be locked. However, such a method cannot be used for data as most data accesses are implicit and addresses are only known at run time. Using static analysis could not allow to determine which addresses are accessed. More methods for cache locking are studied in the literature review provided in Chapter 5 of this thesis.

Memory interferences also happen in DRAM memories. In [30] memory banks are allocated

to different applications. As for cache partitioning, this avoids having multiple applications or partitions using the same memory bank and reduce the number of interferences. Such methods could be applied by tweaking the virtual memory addresses as done for cache partitioning. Application scheduling is also used to optimize memory use and reduce performance impact when multiple applications try to access the memory at the same time [31]. DRAM caches known as row buffers are also considered as interference channels. In [32], interbank interferences and the intrabank interferences are studied. The authors propose to model generated interferences and apply memory bank partitioning and budgeted memory accesses to mitigate them. In [33] and [22] memory bus contention is shown to create interference when multiple cores access the main memory. In [33] performance monitoring counters are used to set bandwidth limitations to partitions to prevent them from accessing the memory and adding contention on the memory bus. This method does not remove interference but allows bounding them. Budget servers have also been studied to bound interferences generated by memory accesses [34]. One may associate a budget to a partition, a partition's process or a core of the processor. The recurrent method is to use performance monitoring counters to track budget. These counters are present in most architectures and allow monitoring multiple events such as cache misses, CPU clock cycles, page fault counter, etc.

#### 2.3 Communication Interference in Multi-core Systems

Contrary to memory interferences that occur in shared memory regions, communication interferences occur in shared communication channels. Multiple cores share busses, interconnects, IOs and other communications means. The most important part of communication interferences is due to contention on such components [35]. This issue is inevitable in multi-core systems; however, it is possible bound the effect of interference to ease the WCET measurement.

One type of communication interferences that the literature tries to tackle is IO interference. When multiple partitions try to access an IO or a peripheral, contention on the bus, communication ports and the IO itself occurs. In [36] a method to serialize accesses to IOs is proposed. In this approach a core is dedicated to IO management and all other cores are not allowed to provide any access to them. When a partition needs to access an IO, the access is serialized with other cores requests. The dedicated core can run one IO partition or more (for instance, one may choose to have one IO partition per regular partition). This method prevents the system from having multiple IO accesses occurring at the same time. However, IO partitions must be run with a high rate since many IO accesses can be done by a partition and should be quickly serviced.

To overcome the potentially high response time induced by the approach proposed in [36], research introduced hardware components to manage IO interferences. In [37] a framework is proposed to restrict partitions bandwidth usage. A virtualization system abstracts each peripheral in the systems. These virtual IOs are scheduled in a manner that tricks the partition that uses it into thinking it is executing in a single-core environment. Those virtual peripherals are scheduled thanks to an IO scheduler. This method relies on hardware components developed on FPGAs. These additional interfaces make a bridge between the system and the peripherals. The bridges allow monitoring peripheral traffic (income and outcome) and block any partition's traffic for which the budget has been exceeded.

Communication interferences are also introduced by hardware resources arbitration. It is important to consider different arbitration methods and study their impact on the system's behavior. In [35] a comparison between different resource sharing arbitration such as Time-Division Multiple Access (TDMA) is proposed. Associated with this contribution, the author defines a generalization of the WCET computing methods considering TDMA and Priority Division arbitration methods. Fair arbitration methods (Round Robin) and more complex schemes are studied (TDMA, Priority Division). The later methods associate priorities to requests on the components. The conducted experiments show that TMDA is the worst algorithm to use with at most 20% of total utilization while priority based and round robin schemes allow up to 65% of total utilization. Priority division, however, is in the middle and allows up to 45% of total utilization with 8 cores. Concerning the jitter introduced by arbitration schemes, results show that TDMA performs poorly, introducing up to 80% of jitter on 8 cores while the Priority based scheme introduces 40% of jitter. To optimize bus access arbitration, scheduling tables can be used to enforce the predictable bus access scheme for each partition or core [38].

#### 2.4 Scheduling and WCET Analysis

Execution models have also piked interest of researchers to mitigate interferences. In [39] a two-step execution model is introduced. The first step consists in loading the data in private memory components. By serializing these accesses, interferences are avoided. Each shared memory access time slice is defined by the system integrator in charge of configuring the system scheduling. Once the first step is finished, the partition can proceed to execute its tasks and process the data loaded in its private memory. The resulting system consists of two execution modes. The first is a sequential mode when all data are loaded in private partitions' memory component. The second is a parallel mode when all partitions executed their tasks. Once the partition finished its processing, it waits for its next loading slice to

push the data to shared memory and load new data. Both modes are not mutually exclusive as multiple partitions can process the data while a partition loads its own data. However, it is impossible to have more than one partition in the loading phase. Such models have also been studied by [40].

In [18] a method to deploy interference-free applications on multi-core platforms is proposed. The toolchain allows the developers to compute applications WCET thanks to single-core methods. Each application must be mapped on cores before the use of this tool. Another execution model is presented to separate shared data handling and private data processing. The Acquisition Execution Restitution (AER) execution model, proposed in [41], distinguishes three fundamental steps.

- The first step is data acquisition where the partition loads all the data needed for its execution from the shared memory. Only one partition at a time can enter the acquisition phase.

- Once the acquisition step finished, the execution step starts and the partition processes the data previously loaded. Multiple partitions can enter this phase at the same time. Since the execution phase does not require shared component accesses, no interference can happen.

- The final phase is the restitution phase. During this step, the partition writes back all the data to the shared memory. As for the acquisition phase, only one partition at a time executes the restitution step.

During acquisition phases, all partitions (excepted the one doing the acquisition) must be in the execution phase or waiting. Same goes for the restitution phase when only one partition can access the shared memory. However, multiple partitions can be in the execution phase.

Most of the previous work describes scheduling methods to overcome interference occurrence when hardware support is not present. The AER (acquisition, execution and restitution) model is proposed in [41]. Thanks to this model, the data are brought and written back to private memory sequentially (acquisition and restitution). Then, the execution phase can use the private memory to compute while other cores can access the shared memory to execute their acquisition or restitution phases.

\*\*\*

In this chapter, we presented previous work conducted to mitigate interferences in avionic systems. In this thesis we focus on private cache interferences. We choose this type of

interference because it is not widely represented in the literature and their mitigation profits both single-core and multi-core platforms. We also expect this work to take part of a more general research, which purpose is to treat the complete memory hierarchy.

#### CHAPTER 3 THEORETICAL BACKGROUND AND METHODOLOGY

In this chapter, we will introduce the basic concepts and definitions relative to our research topic. The notion of hard real-time systems and critical systems will be explained as well as the cache and memory aspects in multi-core systems.

#### 3.1 Definitions

RTOS (Real Time Operating System) A real Time operating systems (usually abbreviated RTOS) is a specific type of highly time constrained Operating System. Each tasks of a system must be executed in a certain amount of time, making the system fail if this requirement is not met.

**Periodic tasks** A task that has an execution period, thus starting its execution each time this period is elapsed. This type of task also has an execution deadline. The deadline is inferior or equal to the period.

**Aperiodic tasks** A task that has no particular period and can be triggered anytime in the system. Such tasks also have deadlines, relative to the start time of the task.

**Deadline miss** A deadline miss occurs when a task does not finish its execution before reaching its deadline.

Cache memory A fast but usually small memory, temporarily storing data to serve them faster the next time they are accessed.

Cache miss / cache hit A cache hit occurs when a data accessed by a program is present in the cache. A cache miss occurs when the data is not present in the cache and needs to be loaded from slower memory.

Cache replacement mechanism When the cache memory is full and a cache miss occurs, the replacement algorithm will select a "victim" in the cache to evict and be replaced by the newly loaded data.

Interference (in multi-core context) A hazardous system's behavior introducing non-determinism in tasks execution time (jitters, delays, etc.).

#### 3.2 Methodology

#### Interferences analysis in multi-core systems

The first phase of the project is based on a literature review on the subject of interferences and, more generally, on the subject of multi-core architecture in aeronautics. This phase will allow to familiarize with the very special subject of critical RTOS in multi-core environments. The study of published works will give a global point of view of the current state of the art in the domain. Gathering the information allows us to find issues to address in our research. We also expect to learn about ARINC-653, CAST-32 [42] and other standards used in aeronautics. The literature review will span into four steps:

- Global analysis of the problems encountered in multi-core architecture with RTOS;

- Categorize multi-core interferences present in multi-core architectures;

- Gather experimental metrics and measures to be taken into account during the research;

- List existing solutions and possible improvements to be made;

The project being in direct partnership with an industrial company<sup>1</sup>, a particular attention will be taken to report already existing patents.

#### Analysis of existing mitigation solutions

Multiple ARINC-653 compliant RTOS already exist on the market and some are DO-178 certified. These products embed different technologies to isolate resources and partitions (time and space partitioning). Some manufacturers also provide new methods to mitigate the presence of interferences in multi-core systems. However none of these RTOS are certified for multi-core use. The current solution to run on such systems is to deactivate the additional cores to limit the RTOS only to run on one core. A review of the state-of-the-art solutions for interference mitigation will be conducted. Where the first step of the methodology was to study interferences in multi-core systems, the second phase is to gather all the existing solutions to mitigate these interferences. This phase consists in providing an overview of the different mitigation means to the industrial partner. We will also gather the different metrics and results used to compare the solutions. Once this step completed, a suite of benchmarks will be developed to achieve this comparison. This suite will be reused to validate and compare our mitigation approaches. In this thesis, we focus on private and shared cache interferences.

<sup>&</sup>lt;sup>1</sup>MANNARINO Systems and Software

## Cache Interference Mitigation

The third phase of the proposed work is the development of cache interference mitigation means. Based on the preliminary literature review, we expect to develop a new approach to limit or mitigate interferences in private and shared caches. Several studies can be conducted to achieve that goal:

- Mitigation of isolation-related interference (e.g., modification of partition content by another partition);

- Mitigation of delays induced by contention of shared resources(e.g., cache contention);

- Interference aware memory management in multi-core systems (e.g., deterministic memory allocation);

For each developed method, experimentation will be done to compare our approach to other solutions. We may also produce different mitigation means. However we expect all these solutions to be independent. To validate and characterize the improvement brought by our solutions, we plan to use multiple ARINC-653 compliant operating systems such as VxWorks-653 [43], or the open source POK [44].

## Integration of the prototype solutions in an existing RTOS

Once the solution validated, we expect to implement our work in a proprietary RTOS developed by the industrial. During the development of such mitigation means, we will also support the company team to design the RTOS to support multi-core systems.

#### 3.3 Basic Concepts

In this section we present the basic concept related to our research. The notion of cache memory is introduced as well as cache locking and partitioning. We also explain the concepts of isolation defined by the ARINC-653 standard.

#### 3.3.1 Cache Memories

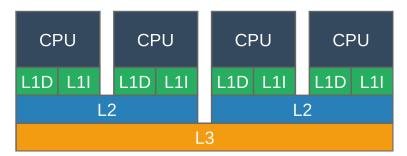

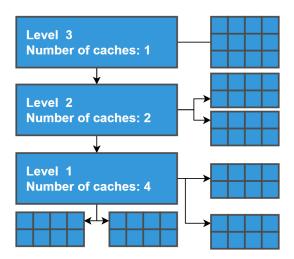

Caches were introduced to address the growing gap between memory speed and CPU speed [1]. They are small and fast memories attached to the CPU. Caches are organized by level, creating together with the main memory the memory hierarchy. The faster the cache, the more expensive it is. This leads to a cache of different sizes depending on the cache level. Figure 3.1 shows a generic cache memory hierarchy. The first level in the hierarchy, L1, is usually segregated into two different caches: one cache stores the instructions and the other the data. This is called the Harvard model. The next levels are usually unified caches, they store both instructions and data. Caches can be classified in two categories: private caches, which are only used by one core and shared caches that are used by multiple cores. A cache

Figure 3.1 Example of cache hierarchy

is in general modeled as a matrix where rows are called *cache sets*, columns are called *cache ways* and cells are called *cache lines*.

Cache associativity The mapping between memory addresses and cache lines can be achieved in different ways. The mean of mapping memory addresses to lines is called the cache associativity. Each address is mapped to a certain set. The way that will accept the data is determined by the cache replacement policy. The most used mapping policies are [45]:

• Direct mapping is the simplest mapping. The set of a line is computed by applying a modulo operation to the address. For a cache that contains n sets, the mapping operation is  $address \mod n$  where  $\mod$  is the modulo operation. Direct mapped

caches contain one unique way. If data from another address is contained in the cache line, it is evicted and replaced by the new data.

- N-Way associative caches are composed of N ways. As for direct-mapped caches, the set of an address is computed with the operation *address* mod n, where n is the number of sets in the cache. The way that will accept the new data is determined by the cache replacement policy, explained later in this section. Figure 3.2 shows a 4-way set associative cache.

- Fully associative caches are the most expensive caches to produce. Memory addresses can be mapped in any sets of the cache. These caches are actually composed of a unique set with multiple ways. Once again, the way that will be populated by the access depends on the cache replacement policy.

Other less popular policies exist such as N-Way skewed associative cache, pseudo-associative caches, etc [46].

Set 0 - Way 0 | Set 0 - Way 1 | Set 0 - Way 2 | Set 0 - Way 3

| ,             | ,             | ,             | ,             |  |  |  |

|---------------|---------------|---------------|---------------|--|--|--|

| Set 1 - Way 0 | Set 1 - Way 1 | Set 1 - Way 2 | Set 1 - Way 3 |  |  |  |

| Set 2 - Way 0 | Set 2 - Way 1 | Set 2 - Way 2 | Set 2 - Way 3 |  |  |  |

|               |               |               |               |  |  |  |

|               |               |               |               |  |  |  |

Figure 3.2 Example of cache organization

Set N-1 - Way 0 | Set N-1 - Way 1 | Set N-1 - Way 2 | Set N-1 - Way 3

**Coherency** In single-core CPUs cache lines can have two states.

- The valid state is used when the data has been loaded from the main memory and can be used by the CPU;

- The invalid state describes a line for which data needs to be loaded or reloaded;

At system startup, all lines of the cache are set to invalid. In multi-core systems coherency needs to be kept between the different private caches. Imagine the following scenario:

- Data A is loaded by CPU C1 and CPU C2;

- Data A is now contained in C1 private cache and C2 private cache;

- C1 modifies the value of data A, the modification occurs in its private cache;

- C2 now has an incorrect value of data A;

To avoid the case where a CPU's private cache contains incorrect data, cache coherence protocols were introduced. These protocols ensure a coherent state of the private caches. Shared caches must be kept coherent when not all CPUs of the system share the caches. This is the case for the level 2 (L2) caches in Figure 3.1. Multiple cache coherence protocols exist: MSI, MESI, MOESI, etc [47]. The description of such protocols is out of the scope of this thesis and will not be given.

Replacement Policy When all the ways of a set are used and a new data must be stored in the cache, the system needs to determine which way is to be replaced. This is the task that the replacement policy has to achieve. Multiple policies have been designed and each of them has a different goal [45]. Some of them may be used to increase memory reuse, others to decrease the impact of the replacement policy on determinism. In our approach, two replacement policies are used: Pseudo-Round-Robin and Pseudo-LRU. We choose to focus on these policies as they are the most commonly used [45].

Pseudo-Round-Robin is a simple and cost-effective replacement policy implemented in the PowerPC e200z7 processor. Thanks to a counter, the cache controller keeps track of the way to replace. When a cache miss occurs, the cache controller checks if the way pointed by the counter can be replaced (the way is eligible for replacement, i.e., it is not locked or disabled). The counter is increased until a replaceable way is encountered. If the counter reaches the maximal number of ways, it is set to 0. When the counter stops, it points to the way that will receive the new data. If no way to the set is replaceable, the cache is bypassed and the data retrieved from the main memory.

LRU (Least Recently Used) is a replacement policy that keeps records on the previously accessed ways. When a data needs to be loaded in the cache, the way that will be selected for replacement is the way that has been accessed the least recently. When ways are not eligible for replacement, they are not taken into account in the process of selecting the least recently accessed way.

**Pseudo LRU** is a variant of the LRU replacement policy. It aims to overcome the resource overhead that are needed by the LRU policy (counters to keep track of the least recently used way). This is an heuristic of the LRU algorithm based on binary search trees to lower the

resource overhead. Multiple other policies exist that are aimed to increase different metrics such as data throughput, power efficiency, resource usage, etc.

Write policy are different ways to allocate and manage the data in the cache and the memory. We can distinguish two categories of write policies. The first category is data write back to the memory. When a data needs to be written back to the main memory or lower level caches, the cache controller needs to know when to write back this data. Two choices are possible:

- Write through policy defines that in case of cache hit or miss, the data is modified in the cache (in certain cases, described later in this section) and directly written back in the memory.

- Copy-back policy tries to improve data throughput by only writing data back when needed. Data is copied to the main memory or lower cache levels when the line containing the data is evicted or when the cache coherence protocol needs it. When a data must be evicted, it is only written back when modified (also called dirty).

Associated with write policies, write allocation policies are different and can be used with any write policy. Again, two choices are available:

- No write-allocate policy do not allocate a cache line on write miss. When a write miss occurs, the data is directly written in the main memory or the lower cache levels.

- Allocate on write policy allocates a new line on write miss. The data is loaded in the cache and modified directly in it. The allocation policy is the same as data read or instruction fetches.

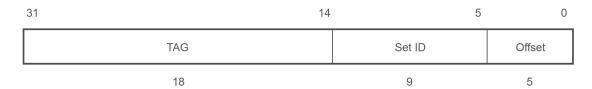

#### 3.3.2 Address representation in the cache

Caches have different representations of memory addresses compared to the CPU of the main memory. By separating an address in different blocks, one can compute in which set of the cache an address will be stored. Figure 3.3 shows how to separate an address in different parts. The first block, starting from bit 0 represents the offset of the address in a cache line. The size of this address block depends on the cache line size. In our example, 5 bits are used to represent the offset in the cache line since we have 32 bytes cache lines. The next part of the address is the set ID. This section starts at the end of the offset section and its size depends on the number of sets available in the cache. In the example we provide, the cache

has 512 sets, which makes the set ID section of the address of the size of 9 bits. The rest of the address is called the tag. The tag is used to decide if the address requested by the CPU is present in the cache or not. The cache hit detection mechanism is out of the scope of this thesis and will not be further explained.

Figure 3.3 Address representation as seen by the cache

#### 3.3.3 Cache Locking and Partitioning

Cache management methods give the user the possibility to modify how caches behave. This could be done to improve the system's performances, reduce non-deterministic behaviors or avoid data to be stored for different reasons. In this thesis we discuss two of them: cache locking and cache partitioning.

Cache locking consists in locking instructions or data in the cache. When a new data has to be loaded in the caches, locked lines are not taken into account in the set of candidates for eviction. This means a locked line will never be evicted from the cache until it is unlocked. Locking lines could be used to improve kernel services delivery time for instance. It has to be noted that a locked line can be invalidated. In that case the line will have to be reloaded from lower memory levels. Such a case can happen when two or more cores use the same data.

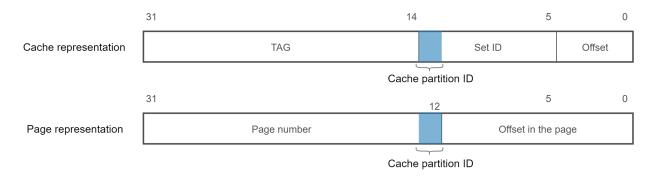

Cache coherency protocols are able to change lines coherency state without taking into account the line's lock state. Cache partitioning has a different impact on caches. Partitioning the cache is a more abstract concept and is usually managed by software means, contrary to cache locking that is hardware reliant. Partitioning the cache means allocating an area of it to one or multiple applications such that other applications cannot access this area. This is done by allocating specific virtual addresses to the different applications. Depending on the page size, a portion of the page number overlaps with the set index. The Operating System (OS) memory manager can tweak that portion of address to select in which sets the data contained in the page will be loaded. An example of the method is given in Figure 3.4. For this example, the cache has 512 sets and is 8-way associative. Cache lines contain 32 bytes of data. We are using 4 kilobytes pages. With this setting, bits 12 and 13 are contained

in both the cache set ID portion of the address and in the page number portion. This allows the memory manager to split the address space into four partitions. Partition 0 will store data of pages for which the page number ends with bits 00, partition 1 will receive data for which the page number ends with bits 01 and so on. Reducing the page size will allow the

Figure 3.4 Virtual memory address compared to cache representation address

user to segregate the cache in more than four partitions as the offset in the page portion of the address will be smaller. The same effect will be observed if the number of sets in the cache increases.

#### 3.3.4 Integrated Modular Avionic

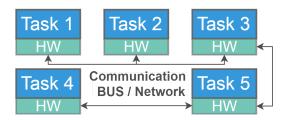

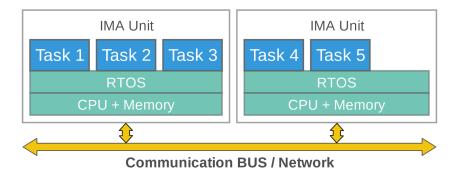

Integrated Modular Avionic (IMA) architectures have been developed since 1990. They were designed to solve multiple issues of the previous architectures called federated architectures. Federated architectures were designed such that each computer assisted features of a plane were deployed in separate units. These units were able to communicate through multiple networks of avionic buses. However this architecture is difficult to maintain and communications between the units became less efficient as the number of functionalities increased [48]. With the constant increase of computer-assisted features, federated architectures were not able to fulfill the needs of avionic system designers [48]. Figure 3.5 shows a simple federated architecture with five distinct tasks that execute on their own hardware. IMA is designed to regroup multiple functionalities of the plane in one single Line Replaceable Unit. Each functionality runs in a partitioned environment. This ensures that all the tasks executed by the system are independent and cannot interfere with each other. This architecture has the advantage of reducing the amount of equipment required in the plane, their weight and their power consumption [48]<sup>2</sup>. Communication between the different partitions is made through

<sup>&</sup>lt;sup>2</sup>This concept is known as Size Weight and Power (SWaP).

Figure 3.5 Example of federated architecture

shared memory, which increases the communication speed and reduce the workload on the avionic buses and networks. Figure 3.6 is an example of IMA architecture designed to make the transition from the federated architecture presented in Figure 3.5.

Figure 3.6 Example of IMA architecture

#### 3.3.5 Design Assurance Levels

Due to their criticality, avionic systems must be certified by competent authorities. These organizations base their work on multiple standard such as the DO-178 guideline document. This guidance is developed by the Radio Technical Commission for Aeronautics (RTCA) and the European Organization for Civil Aviation Equipment (EUROCAE) since 1992 and is regularly updated. The last revision of the document is DO-178C. DO-178 guidance describes a set of objectives in order to certify a product. Five criticality levels are defined to classify software by their level of criticality:

- Level A applications are defined as applications for which failure may lead to catastrophic events (possible crash of the aircraft, flight safety compromised, potential casualties, etc.);

- Level B applications failure may induce serious problems, leading to few casualties;

- Level C failure drastically drops in terms of severity compared to level B as failure of such application may provoke serious dysfunction to fundamental airplane functions, causing passenger discomfort or increase the crew workload;

- Level D failure is considered as minor;

- Level E failure does not impact safety;

When an RTOS is aimed to host mixed criticality software, the RTOS should be certified to the highest level of application the RTOS will host. Failures as described in the guidance are undefined behaviors, erroneous output, deadline misses, etc. For each DAL, a number of objectives are defined [49]:

- DAL A: 71 objectives defined;

- DAL B: 69 objectives defined;

- DAL C: 62 objectives defined;

- DAL D: 25 objectives defined;

- DAL E: 0 objectives defined;

The highest DO-178 levels enforce traceability in the software. This means that each line of code (and for higher DAL, each assembly instruction) must be traceable to a requirement of the system. The object code must be traceable to the source code, source code must be traceable to lower-level requirements which are traceable to higher-level requirements that are refined from specification documents.

#### 3.3.6 ARINC-653 and Isolation

The Avionics Application Standard Software Interface (ARINC)-653 standard is a guideline document to design partitioned systems. This document is used in avionics to isolate multiple applications that run on the same system. This has the advantage to avoid side effect when one application crashes. Each independent environment of the system is called a partition. A partition contains processes that execute as if they were the only processes in the system. Each process shares the same address space and are scheduled with real-time schedulers. An analogy can be made between POSIX systems and ARINC-653 systems: the ARINC partitions are POSIX processes and ARINC processes are POSIX threads. The standard defines how to achieve this partitioning [2] using the concepts of time partitioning, space partitioning, application executive and health monitor.

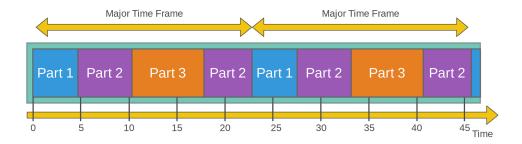

**Time partitioning** enforces the system's partitions to run during a limited amount of time at strictly defined periods. This principle allows the processes running in the partition to "think" they are the only ones running in the systems. Time partitioning defines the notion of time window and major time frame.

- A time window is a span of time during which an application runs. A partition can have multiple time windows of different lengths. During its execution, a partition has exclusive access to the CPU.

- The major time frame is a succession of time windows that repeats itself through time. It defines how partitions will execute and ensures no overlapping is possible.

Figure 3.7 shows an example of major time frame. In this setting, partition 1 has two time windows of 5 ms and 10 ms. The major time frame can contain gaps, during which no partition runs. This is the case from 15 ms to 25 ms. When the end of the major time frame is reached, the system repeats the pattern.

Figure 3.7 Example of a major time frame

Space partitioning or resource partitioning is the second aspect of partitioned systems. It allows reserving resources for each partition and isolates these resources from partitions that do not use them. This ensures that a partition can't access resources of another partition and modify its behavior. Resources can also be shared by different partitions when needed (e.g., screen, shared memory used to communicate, etc.). Resource partitioning applies to memory in the system. Memory isolation can be done by the use of Memory Management Unit (MMU), Memory Protection Unit (MPU) or other memory protection means. Other resources such as IOs or peripherals can be reserved for one or more partitions. To this end, some systems propose IO-MMU. One may consider bandwidth limitations as resource

partitioning. In single-core processors, only one partition can use any resource at a time. This ensures exclusive use of a resource during the partition's time window. However, in multi-core systems, this rule does not apply. Multiple partitions can execute in parallel, which means that two or more partitions can access a resource at the same time. This is obvious for the memory, but IOs and peripherals also suffer from this.

**APplication EXecutive (APEX)** also known as APEX is a set of standard interfaces with the RTOS. The Application Programming Interface (API) increases the portability of ARINC-653 compliant applications. Each function of the system can be used with the APEX such as process creation, IO and peripheral accesses, time management, synchronization primitives, inter and intra-partition communications, etc.

**Health Monitor (HM)** or HM is a background task that ensure the correct behavior of the system. The HM is in charge of handling errors and exceptions that occur when a partition is executed. It allows the user to associate a handler to each error that can occur. For instance, when a deadline miss is detected in a partition, the HM can restart the partition or trigger a routine to recover from the error.

#### 3.3.7 Interference in Multi-core Architectures

Interferences are defined as unwanted behavior caused by resource sharing in multi-core systems. Examples of such behavior are: time delays, execution time jitters or data corruption. This is indeed not acceptable in critical systems where timing must be ensured and execution time strictly bounded.

Interferences are present in both single-core and multi-core systems. An example of single-core interference is when two partitions evict each other's data in private caches. To avoid this interference, private caches can be flushed at each partition switch [50]. That way, the state of the cache when a partition is scheduled is always the same.

Multi-core platforms can execute multiple tasks in parallel. Each processing unit (or core) has its own execution environment and does not share its private resources such as CPU registers, private caches, etc. However multiple resources are shared between these cores. Shared caches are used by multiple cores at the same time. This allows faster inter-core communication and reduces the number of different components in the system. Buses are used by multiple cores to access the memory of the IOs, and the memory itself is shared among them. Figure 3.8 shows an example of interference-prone architecture where interferences are marked in red. Shared resources where interferences occur are called interference channels.

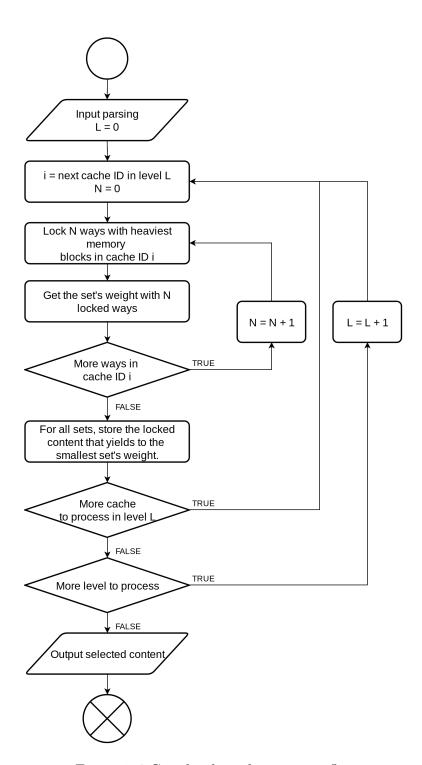

Most resources that are accessed concurrently cannot serve all the requests at the same time. Controllers are in charge of selecting the request to serve by sequencing all the requests. Selecting the next core to serve can be done in a fair way (e.g., first come first served) or unfair way (e.g., Core 0 always has the priority on other cores). Such strategies will enforce stalls on cores waiting for their request to be served. This is where one type of interference occurs. Core execution's gets delayed because of the contention on shared resources. A principle of partitioned systems is broken when this condition occurs. Interferences are evidences that a partition executing on a core can modify the behavior of a partition executing on another core.