|                         | Radio-Frequency Signal Synthesis and Digital Signal Processing<br>Technique for Software Defined Radar System                                                                                                                                                                        |

|-------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Auteur:<br>Author:      | Wen Rui Li                                                                                                                                                                                                                                                                           |

| Date:                   | 2010                                                                                                                                                                                                                                                                                 |

| Type:                   | Mémoire ou thèse / Dissertation or Thesis                                                                                                                                                                                                                                            |

| Référence:<br>Citation: | Li, W. R. (2010). Radio-Frequency Signal Synthesis and Digital Signal Processing Technique for Software Defined Radar System [Master's thesis, École Polytechnique de Montréal]. PolyPublie. <a href="https://publications.polymtl.ca/386/">https://publications.polymtl.ca/386/</a> |

# Document en libre accès dans PolyPublie Open Access document in PolyPublie

| URL de PolyPublie:<br>PolyPublie URL:    | https://publications.polymtl.ca/386/ |

|------------------------------------------|--------------------------------------|

| Directeurs de<br>recherche:<br>Advisors: | Ke Wu                                |

| <b>Programme:</b><br>Program:            | Génie électrique                     |

# UNIVERSITÉ DE MONTRÉAL

# RADIO-FREQUENCY SIGNAL SYNTHESIS AND DIGITAL SIGNAL PROCESSING TECHNIQUE FOR SOFTWARE DEFINED RADAR SYSTEM

# WEN RUI LI DÉPARTEMENT DE GÉNIE ÉLECTRIQUE ÉCOLE POLYTECHNIQUE DE MONTRÉAL

MÉMOIRE PRÉSENTÉ EN VUE DE L'OBTENTION

DU DIPLÔME DE MAÎITRISE ÈS SCIENCES APPLIQUÉES

(GÉNIE ÉLECTRIQUE)

AOÛT 2010

#### UNIVERSITÉ DE MONTRÉAL

# ÉCOLE POLYTECHNIQUE DE MONTRÉAL

#### Ce mémoire intitulé:

# RADIO-FREQUENCY SIGNAL SYNTHESIS AND DIGITAL SIGNAL PROCESSING TECHNIQUE FOR SOFTWARE DEFINED RADAR SYSTEM

présenté par: LI Wen Rui

en vue de l'obtention du diplôme de: Maîtrise ès sciences appliquées

à été dûment accepté par le jury d'examen constitué de :

- M. FRIGON Jean-François, Ph. D., président

- M. WU Ke, Ph. D., membre et directeur de recherche

- M. CARDINAL Christian, Ph. D., membre

# Dédicace

To my family

#### AKNOWLEDGEMENTS

First of all, I would like to give my sincerely thanks to my supervisor, Professor Ke Wu, for his guidance, support and encouragement throughout my studies, which is indispensable for me to finish this thesis. I am very grateful to have the opportunity to participate in this interesting project.

I would like to express my gratitude to my partner, Ph.D. Lin Li, for his continuous support, invaluable help and throughout the work involved in this thesis, which gave a lot of irreplaceable help and support. I would like to also thank to another partner, Ph.D. Xiaoping Chen, for his excellent work on antenna and unselfish help on everything.

I would like to also give my thanks also to my friend Liang Han who helps a lot in the correction of my thesis. This thesis was also made possible by my friends Bensalem Bilel and Bassel Youzkatli El Khatib, who contributed their valuable time on the French section of this thesis.

I would like to also thank to M. Jules Gauthier, M. Steve Dubé, and M. Traian Antonescu for their patient during the elaboration of the prototypes and their technical assistance, to M. Jean-Sebastien Décarie for his software support.

I appreciate the friendly help provided by Liang Han, Ning Yang, Fanfan He, Zhenyu Zhang, Pengyan Zhang, Yingrao Wei, Xingling Li, Boutayeb Halim and everyone in Poly-Grames.

# RÉSUMÉ

Cet ouvrage présente de façon concise l'exécution autonome d'un système économique de radar défini par logiciel, basé sur le design de Ph D. Hui Zhang. L'un des objectifs de cette mise en œuvre est la réalisation d'une version planaire miniaturisée d'un système de radar en utilisant la technique planaire du « guide d'onde intégré au substrat »(GIS).

Le rôle du système de radar défini par logiciel est de mesurer la vitesse, la portée et l'angle d'une cible à l'aide d'un appareil de radar planaire. Afin de mesurer ces paramètres, ce système de radar défini par logiciel combine deux types de fonctions incluant «l'onde continue à modulation fréquentielle» (OCMF) et «l'onde continue» (OC) dont l'aiguillage entre elles est contrôlé par un logiciel via un micro-processeur. Le synthétiseur de fréquence est démarré par un DDS qui peux générer un signal flexible comme OC et OCMF, et puis un PLL est utilisé pour augmenter la fréquence du signal DDS. À la sortie de DDS et PLL, un transmetteur est installé ayant pour rôle d'effectuer une nouvelle mise à niveau du signal avant de le transmettre à une antenne GIS. Avec une antenne GIS planaire ayant un gain élevé et une taille réduite, l'onde électromagnétique (OEM) est rayonnée dans un angle étroit.

Après que la cible rencontrée réfléchit l'OEM, l'antenne réceptrice à deux canaux reçoit le signal réfléchi et le transfère au récepteur. Selon l'Effet Doppler, la mesure de vitesse est effectuée par CO et ensuite, la portée est mesurée par FMCW. Finalement, ce radar obtient l'angle mesuré par la différence de phases entre les deux canaux d'antenne.

Le sous-ensemble suivant le récepteur est le système de traitement numérique du signal avec un convertisseur analogique-numérique (ADC en anglais). Ce ADC échantillonne le signal analogique avec une fréquence de 82KHz et une résolution de 8bit. Puis, un calcul FFT est effectué sur les données de formes d'ondes venant des deux canaux et l'information de la fréquence est cueillie sur la cible. Finalement, quelques algorithmes sont exécutés pour avoir la vitesse, la portée et l'information de l'angle de la cible.

À ce point, le système de radar avec la technique GIS est entièrement réalisé et fonctionnel, permettant ainsi de valider l'efficacité de la technique SIW rendant le système de radar plan et compact.

#### **ABSTRACT**

This work presents a complete hardware and standalone implementation of a cost-effective software-defined radar system based on the architecture proposed during the thesis work of Hui Zhang, a former Ph.D. student. One objective of this implementation is to realize the planarization and miniaturization of such a radar system by deploying the substrate integrated waveguide (SIW) technology.

The requirement of software-defined radar systems is to measure the speed, range and angle of a target by an integrated planar circuit platform. In order to satisfy this requirement, this developed software-defined radar system combines two functions, namely, frequency modulated continuous wave (FMCW) and continuous wave (CW), and the switching between them is controlled by software running in a micro-processor. In our implementation, the frequency synthesizer is configured by a direct digital synthesizer (DDS) which can flexibly generate various signals such as CW and FMCW. In addition, a phase-locked loop (PLL) is used to up-convert the signal from DDS to an upper frequency platform. Subsequently, the generated high frequency signal is transmitted by a power amplifier and radiated by an SIW antenna. Electromagnetic waves (EMW) are radiated in a narrow angle range thanks to attractive characteristics of the SIW antenna such as high gain, small size, and planar implementation.

Echoed by the target, the EMW are received by two receiving antennas and then they are sent to a receiver front-end. According to the use of Doppler Effect, the speed measurement is accomplished by using the CW waveform while the range is measured by the FMCW waveform. Moreover, the presented radar system yields the angle measured by using a phase difference between the two receiving channels.

The subsystem following the receiver is the digital signal processing unit with an analog digital converter (ADC) as the interface between the analog and the digital parts. The ADC samples the analog signal with a rate of 80 kHz and a resolution of 8 bit. Then FFT calculations are carried out to generate the waveform data from both channels and, the

frequency information about the target is found from which the speed, range and angle information of the target can be obtained.

The entire radar system integrated with the SIW technique is completely realized and verified. The presented system has successfully demonstrated the design and application of cost-effective planar radar.

## CONDENSE EN FRANÇAIS

#### 1. Introduction

Avec l'évolution continue des circuits intégrés et les technologies de communication sans fil, les applications radar deviennent omniprésentes. Bien que les technologies de radar ont été intensivement étudiés depuis plusieurs années, la plupart des implémentations pratiques radar ne peut être utilisé pour des applications spécifiques, telles que la prévention des collisions ou régulateur de vitesse adaptatif (ACC) des fonctions dans les systèmes de transport ou les applications de sécurité dans les deux secteurs militaires et civils. En outre, les technologies radar ont progressé énormément pour les applications de défense, mais ils ne sont toujours pas bien préparés et mis au point pour des applications commerciales civil.

Avec les progrès sans précédent de la technologie numérique et les logiciels, la radio définie par logiciel (SDR) technique a été proposée et développée [4]. De plus en plus les systèmes analogiques ont été remplacés par des systèmes numériques de toutes sortes. D'autre part, des modules de matériel programmable sont largement été utilisés dans les systèmes de radiodiffusion numérique à différents niveaux fonctionnels. L'un des objectifs de l'aide de la technologie RRL est de tirer parti de ces modules de matériel programmable et de construire des plates-formes flexibles basées sur le système de radio définie par logiciel. Dans le cadre d'une technique définie par logiciel, les techniques radars conventionnels ont également été déplacés de plus en plus vers des modules numérisés. Une plate-forme d'un système de radar définie par logiciel de a été développé par un travail de thèse précédent dans notre groupe. Avec ce nouveau concept, certaines lacunes du système de radar traditionnel sont résolues d'une certaine façon. Toutefois, le système proposé a été uniquement mis en œuvre avec les dispositifs discrets et la mesure de paramètres n'a été faite que dans l'environnement de laboratoire

Il est bien connu que la plupart des appareils radar et les systèmes sont directement conçus à partir d'architectures conventionnelles de la première version des radars militaires, qui ont un certain nombre de problèmes. Tout d'abord, un inconvénient évident est leur taille

volumineuse causée par une grande antenne qui n'est pas non plus facile à fabriquer. Le deuxième problème est que la plupart d'entre eux ont été élaborées pour des applications spécifiques, et donc il ya un manque de souplesse. La troisième est que la plupart des systèmes radar sont associés à un coût élevé et / ou avec une fonction inflexible.

Afin de réduire la taille et de la fabriquer facilement, le guide d'ondes intégré substrat (SIW) la technologie qui a été proposée ces dernières années offre une solution prometteuse [1]. La technique SIW appartient à la famille de substrat de circuits intégrés (SIC). Un des avantages bien documentés de la technologie SIW est une réduction de la taille importante de circuits par rapport aux structures de guides d'ondes classiques. Un autre avantage de SIW est que l'ensemble du circuit peut être construit ou intégré utilisant la norme carte de circuit imprimé (PCB) ou laser de forage et de traitement de métallisation.

Afin de fournir une série de fonctions souples, un nouveau concept de radar reconfigurable a été proposé et il est appelé radar définie par logiciel dans le Ph.D. projet de Hui Zhang. La particularité de ce radar définie par logiciel est sa flexibilité d'un logiciel synthétiseur de fréquence reconfigurable, frontal, l'architecture du système et un puissant système de traitement numérique du signal. De manière générale, le radar défini par logiciel est une sorte de plate-forme radar universel, dans lequel, une technique de génération de signal flexible est réalisée sur l'horloge ou entrée d'oscillateur de référence avec la capacité d'un logiciel configurable.

Enfin, l'équilibre entre coût et performance est obtenue par l'adoption d'un certain nombre de technologies. Dans le système présenté, antennes guide d'ondes classiques sont remplacés par les antennes SIW, et ce non seulement de réduire la taille de l'ensemble, mais diminue aussi le coût en raison d'une fabrication simplifiée artisanat contenant des BPC. En outre, avec l'aide de l'émetteur-récepteur reconfigurables et traitement numérique du signal (DSP), les performances et les fonctionnalités du prototype de radar sont améliorées. radars classiques réalisés à moindre coût que des fonctions limitées de mesures des paramètres tels que la mesure de la vitesse individuelle, mais la gamme et des

mesures d'angle sont généralement exclus. En combinant un synthétiseur flexible avec DSP technique de pointe, le radar défini par logiciel peut fournir l'occasion de mettre en œuvre de multiples fonctionnalités à un faible coût.

Dans ce projet de recherche, susmentionnées, trois technologies y compris l'antenne SIW, synthétiseur de fréquence reconfigurables et processeur de signaux numériques sont intégrés dans un système radar définie par logiciel multifonction et à faible coût. Afin de réaliser le synthétiseur de fréquence reconfigurable, le technique de synthèse digitale directe (DDS) est utilisée conjointement avec boucle verrouillée en phase (PLL). Le circuit DDS est contrôlé par une unité centrale de traitement (CPU) qui génère tous les signaux nécessaires tels que les ondes continues (CW) et en modulation de fréquence à onde continue (FMCW). Le signal de sortie de la DDS est injecté à la PLL pour faire une modulation de fréquence, et la fréquence généré signal modulé est transmis suivant les étapes d'un tripleur de fréquence et un amplificateur de puissance. Enfin, le signal haute fréquence est rayonnée par l'antenne SIW libérer de l'espace sous la forme d'EMW. Dans ce projet, le signal CW est utilisé pour mesurer la vitesse du déplacement de fréquence de détection induite par effet Doppler. Le signal FMCW fonctionne en collaboration avec le signal CW pour la plage de mesure. Malgré une seule antenne de transmission, une antenne de réception avec deux canaux est utilisée. Avec la plate-forme de l'antenne à deux canaux de réception, EMW traduit par cible arriver dans les deux canaux avec des phases différentes, ce qui permet de mesurer la direction ou l'angle d'arrivée de l'onde EM incidente, à savoir l'angle de la cible. Le système radar proposé reconfigurable est esquissé dans la figure 1.2.

Le système radar se compose essentiellement de sept parties: le module DSP, synthétiseur reconfigurable, module IF, émetteur, récepteur, antennes et les alimentations.

Cette thèse est organisée comme suit. Dans le chapitre 2, le principe du radar et techniques de base utilisées dans ce projet sont expliquées, ainsi que l'architecture du système et des paramètres de base. Le chapitre 3 présente la théorie de synthétiseurs de fréquence, y compris la DDS et des techniques de PLL. Par la suite, le chapitre 4 décrit l'unité de

traitement numérique dans le système et le module logiciel ainsi que l'organigramme. Le chapitre 5 donne des détails sur la structure de l'émetteur-récepteur en œuvre, qui comprend un émetteur, une antenne d'émission, à deux canaux antennes de réception, un récepteur, un filtre FI et d'un amplificateur. Les résultats simulés et mesurés sont également présentés et discutés dans le chapitre 5. Enfin, le chapitre 6 conclut ce projet et fournit des orientations de recherche futures dans le cadre de ce projet.

Comme tous les systèmes radar, le système radar définie par logiciel est utilisé pour positionner activement la cible avec la mesure des paramètres de cibles, y compris la vitesse et l'angle de rang. Le résultat de mesure doit satisfaire à l'exigence d'exactitude de base indiquée dans le tableau 2.1.

#### 2. Méthodologie

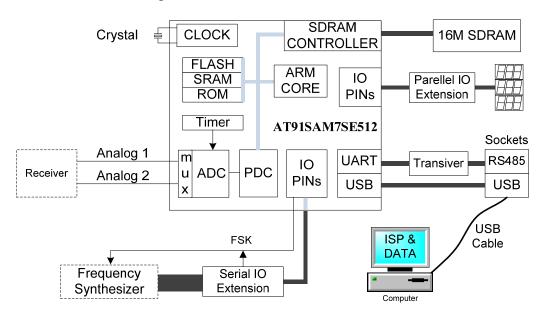

#### 2.1. Le principe de base

Effet Doppler, qui est un phénomène physique très connu, est très utile pour mesurer la vitesse le long de la ligne de visée (LOS) entre la cible et le radar. Cela signifie qu'un système de radar est en mesure de recevoir le signal réfléchi dont la fréquence est décalée si la vitesse de déplacement de la cible a une composante le long de la LOS. La direction de déplacement de fréquence dépend de la cible s'approche ou s'éloigne de l'écran radar. Quelle que soit la direction de cible le changement de fréquence est proportionnel à l'amplitude de la composante de vitesse LOS.

Outre la mesure de la vitesse, la plage de mesure est un autre problème dans le développement de la technologie radar. Une façon de mesurer la portée est l'utilisation du radar à impulsions modulées. Le radar à impulsions modulées mesure la gamme en mesurant le temps de trajet d'une impulsion très courte entre le radar et la cible. Comme il n'est pas facile à réaliser une largeur d'impulsion très étroite, il est difficile de donner une résolution supérieure de la fourchette. En remplacement, la modulation de fréquence à onde continue peut être utilisée dans le système de radar en vue d'obtenir une résolution plus élevée dans la plage de mesure. Modulation de fréquence à onde continue dispose

également d'un faible niveau de puissance, qui permet d'utiliser solides circuits micro-ondes État.

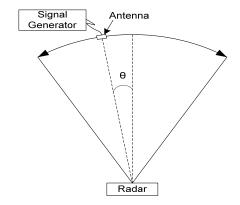

Angle measurement is another function that is always required to be implemented in radar system. We make use of two receiving antennas and the arriving angle of target can be calculated by measuring the phase difference between the EMW signals received by the two antennas.

#### 2.2 Structure du système

La principale caractéristique de ce système radar est sa capacité reconfigurable par logiciel. Les paramètres reconfigurables comprennent la fréquence de fonctionnement dans une certaine fourchette, le type de modulation de fréquence et de ses paramètres. D'exploitation à 35 GHz, le système radar proposé est essentiellement composé de six parties, y compris le module DSP, synthétiseur de fréquence configurable, émetteur, récepteur et antennes module IF

#### 2.3 Conception synthétiseurs de fréquence et de mise en œuvre

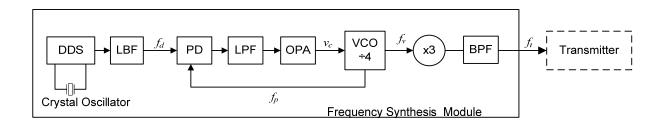

Fonctionnant à une fréquence de 35.1GHz et avec des caractéristiques reconfigurable, le radar comporte un synthétiseur de fréquence à ondes millimétriques qui est principalement composé de DDS, PLL, VCO et multiplicateur de fréquence. Selon la théorie de l'échantillonnage, un DDS peut produire presque n'importe quel signal de fréquence au sein de 100 MHz avec un oscillateur à quartz de 200 MHz sous le contrôle d'un MCU. Dans ce projet, DDS deux sorties signal de fréquence unique et avec une fréquence du signal FMCW désigné par fd, 45,7 ~ 46.4MHz. Le PLL serrures fp sortie du VCO à 64 \* fd. Puis, le signal hyperfréquence est multiplié par x3 multiplicateur de fréquence et nous générer le signal de transmission avec FT fréquence, 35GHz, ce qui est rayonnée dans l'espace par l'antenne émettrice.

#### 2.4 Traitement numérique du signal

La vitesse et la portée sont contenues dans le décalage de fréquence, à savoir le décalage de fréquence Doppler pour la vitesse et de déplacement de fréquence FMCW pour la gamme. En outre, pour la mesure de l'angle, l'information de phase est nécessaire pour les données d'origine. La FFT méthode la plus fondamentale est utilisé pour estimer la fréquence et de l'information de phase dans les signaux. Basé sur le spectre, les données cibles pourraient être calculées et enfin les paramètres de déplacement de cible peut être obtenu à partir du système de paramètres opérationnels pour les armes chimiques et FMCW.

Mais la FFT a une certaine faiblesse. La résolution de la fréquence est limitée par la période d'échantillonnage. Afin d'améliorer la résolution en fréquence, la FFT est utilisée par interpolation. La FFT, interpolation peut être utilisé pour obtenir le résultat plus de précision la fréquence en calculant le centre de l'énergie des points voisins.

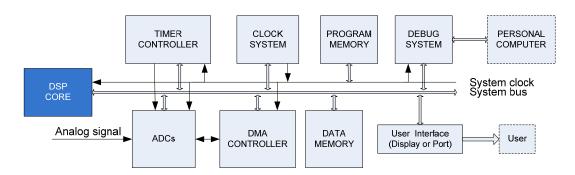

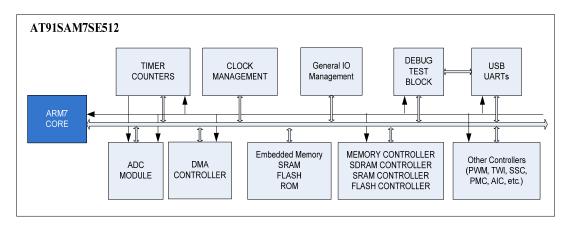

La machine avancée RISC (ARM) est utilisée comme unité DSP dans le système de radar définie par logiciel. ARM est en fait une sorte d'ordinateur d'instructions réduit (RISC) CPU. Les caractéristiques les plus remarquables de la puce ARM, c'est qu'il a de meilleures performances avec une consommation électrique beaucoup plus faible par rapport à la classique CPU, c.-à-x86 série. L'AT91SAM7SE512 puce DSP sélectionné intègre plusieurs blocs de mémoire, y compris la mémoire flash, SRAM et ROM. En plus de la mémoire embarquée, il intègre également d'autres périphériques nécessaires, y compris ADC, minuterie et un contrôleur DMA. Avec tous les composants d'un système intégré DSP peut être construit. Depuis la mémoire intégrée n'est pas assez grande, une SDRAM 16MByte est étendue dans le système pour stocker le code et les données d'échantillonnage AD.

Voici l'organigramme de données du système DSP. D'abord les deux canaux du signal analogique est échantillonné et converti en signal numérique par ADC et stockées dans la mémoire. La deuxième étape est que le noyau ARM exécute l'algorithme nécessaire, y compris la FFT, interpolation pour obtenir la fréquence et la phase d'information. Enfin, basée sur la fréquence et la phase d'information, de la vitesse de la cible, la portée et

l'angle est évalué et affiché ou transmis à un ordinateur par le port de communication UART ou USB.

#### 2.5 Mise en œuvre du système et de mesure

D'autres parties du système radar définie par logiciel comprennent émetteur, les antennes et le module IF, qui est terminé par le groupe de projet. Après le signal à ondes millimétriques est généré par le synthétiseur de fréquence, il est injecté à l'émetteur. Ensuite, il se transforme en onde électromagnétique rayonnée et libérer de l'espace par une antenne directionnelle avec un gain élevé. Dans le cas où la cible est dans la plage de fonctionnement du système radar, EMW serait réfléchi par la cible et une partie de l'énergie EMW serait reçu par les antennes de réception du système radar. Les informations de la cible sont contenues dans le transporteur du signal reçu. Le signal reçu est un transporteur très haute fréquence, 35.1GHz, certains types de diminuer la fréquence de conversion ou la transformation doit être réalisée par un récepteur en vue d'obtenir le signal en bande de base pour le système de traitement numérique du signal. Dans ce projet, la transformation comprend la démodulation, filtrage et d'amplification.

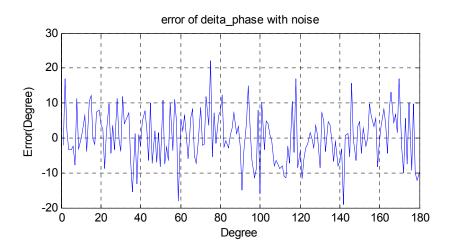

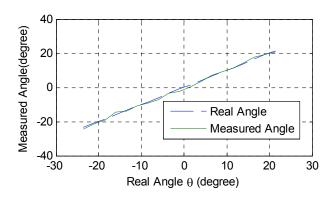

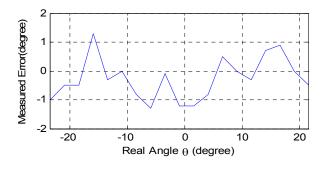

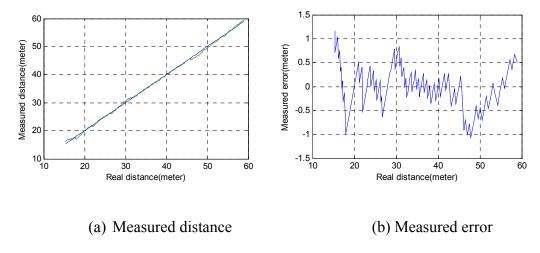

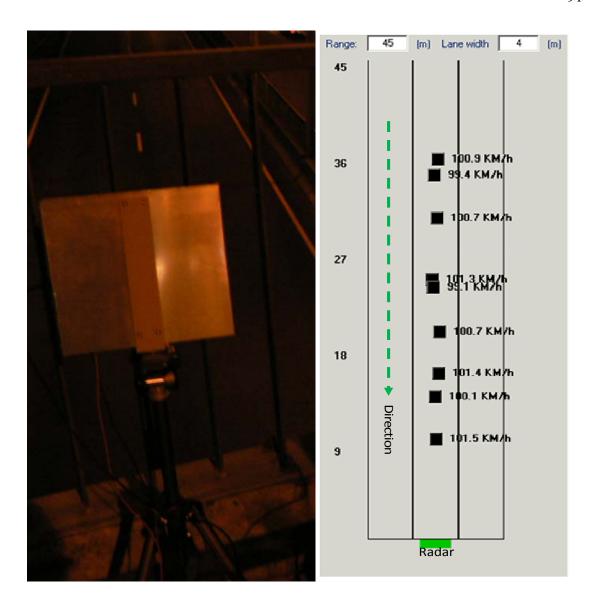

Enfin, certains simulation et la mesure est effectuée pour le système mis en œuvre. La simulation finis comprend l'estimation portée du radar, l'impact du bruit au résultat de la mesure, l'ambiguïté angle par l'écart entre les antennes de réception. La mesure est effectuée pour vérifier la spécification du système, y compris la mesure de l'angle, la plage de mesure et le test global sur une route. Enfin, le résultat de la mesure indique que le système est mis en œuvre avec succès et satisfait à l'objectif supposé au début.

#### 3. Conclusion

Dans cette thèse, un système défini par logiciel radar basé sur la synthèse de fréquence et les techniques de traitement numérique du signal a été analysé, développé et fabriqué. Une série de simulations et de mesures ont été faites, qui a vérifié les performances et les fonctionnalités du système proposé.

L'ensemble du système se compose essentiellement de quatre parties: le synthétiseur de fréquence, la fronde émetteur-end, le filtre FI et les circuits de l'amplificateur et le

système de traitement des signaux numériques. Ces pièces sont déjà intégrées dans une plate-forme unique qui peut fonctionner comme un prototype intégré. Les résultats des mesures montrent que le système a la capacité de mesurer la vitesse, l'angle et la distance relative d'une cible dans le cas où la direction de déplacement est connue.

Pour intégrer la CW et la fréquence FMCW balaie ensemble, DDS et PLL sont employés dans le système. Les performances et les caractéristiques du système de synthétiseur de fréquence sont analysées et simulés. Afin d'atteindre planarisation et de la miniaturisation, antennes planaires SIW sont utilisés. Pour réaliser la mesure de l'angle, deux antennes de réception et d'utilisation de deux récepteurs dans ce système. La fonction d'ambiguïté mesure d'angle du système de double antenne est analysée à travers des résultats de simulation.

Matériel du système de DSP à bord a été mis en œuvre basée sur le noyau ARM, dans lequel l'algorithme DSP basée sur FFT est réalisé. Certaines fonctions du système radar sont mises en œuvre et vérifié par le logiciel. Enfin, ce système est capable de mesurer la portée, la vitesse et l'angle de la cible telle que la surveillance de l'automobile.

Toutefois, certaines difficultés à réduire le rendement et les fonctionnalités du système. L'un d'eux est le problème multi-cibles et l'ambiguïté sens de déplacement mentionnés aux articles 2.6 et 6.2, respectivement. L'ambiguïté et la précision de mesure d'angle présente un autre problème à résoudre.

Dans l'environnement réel, des cas multi-cibles sont le plus souvent rencontrés et qu'ils sont censés mesurer. Par conséquent, l'ambiguïté multi-cible est un sujet principal à résoudre. Pour résoudre cette difficulté, un algorithme de gamme Doppler devrait être mis en œuvre pour les applications multi-cibles.

Afin de réaliser l'algorithme plus avancé, la puissance de calcul du système de DSP doit être améliorée aussi. D'autres technologies telles DSP dédié et FPGA sont des candidats possibles.

La précision du système actuel n'est pas assez élevée pour travailler dans certains

scénarios spécifiques qui requièrent des mesures avec une résolution très élevée. Une étude plus poussée devrait être fait pour améliorer la précision de mesure.

# **TABLE OF CONTENTS**

| Dédicace                                                  | iii   |

|-----------------------------------------------------------|-------|

| AKNOWLEDGEMENTS                                           | iv    |

| RÉSUMÉ                                                    | V     |

| ABSTRACT                                                  | Vii   |

| CONDENSE EN FRANÇAIS                                      | ix    |

| TABLE OF CONTENTS                                         | XVIII |

| LIST OF TABLES                                            | xxi   |

| LIST OF FIGURES                                           | XXii  |

| LIST OF NOTATIONS AND SYMBOLS                             | XXVi  |

| Introduction                                              | 1     |

| CHAPTER 1 Software Defined Radar System                   | 6     |

| 1.1. System Objectives and Requirement                    | 6     |

| 1.2. Basic Principle of Radar System                      | 6     |

| 1.3. Doppler Effect in Radar                              | 8     |

| 1.4. Frequency Modulated Continuous Wave                  | 10    |

| 1.5. Principle of Angle Measurement                       | 13    |

| 1.6. Radar Equation                                       | 14    |

| 1.7. Software-Defined Radar System                        | 16    |

| CHAPTER 2 Frequency Synthesizer Design and Implementation | 22    |

| 2.1. Brief description of Frequency Synthesizer Module    | 22    |

| 2.2. DDS                                                  | 23    |

| 2.2   | 2.1   | Introduction of DDS Device AD9854                    | 23 |

|-------|-------|------------------------------------------------------|----|

| 2.2   | 2.2   | Operating Modes of AD9854                            | 25 |

| 2.2   | 2.3   | Ramped FSK Mode for FMCW signal                      | 27 |

| 2.2   | 2.4   | Implement of AD9854 in Software Defined Radar System | 29 |

| 2.3.  | Pha   | se Locked Loop (PLL)                                 | 32 |

| 2.3   | 3.1   | The Transfer Function of PLL                         | 33 |

| 2.3   | 3.2   | Transient Response of PLL                            | 35 |

| 2.3   | 3.3   | Frequency Ramp Applied to the Reference Input        | 38 |

| 2.3   | 3.4   | PLL Design in our Project.                           | 40 |

| 2.3   | 3.5   | Phase noise influenced by PLL                        | 44 |

| 2.4.  | Exp   | periment Result                                      | 45 |

| СНАРТ | TER 3 | B Digital Signal Processing                          | 50 |

| 3.1.  | Fas   | t Fourier Transform                                  | 50 |

| 3.2.  | Gei   | neral Concept of DSP System                          | 56 |

| 3.3.  | DS    | P Device Selection                                   | 58 |

| 3.3   | 3.1   | Basic Considerations                                 | 58 |

| 3.3   | 3.2   | Selection of DSP Unit                                | 58 |

| 3.4.  | Per   | ipheral in AT91SAM7SE512                             | 61 |

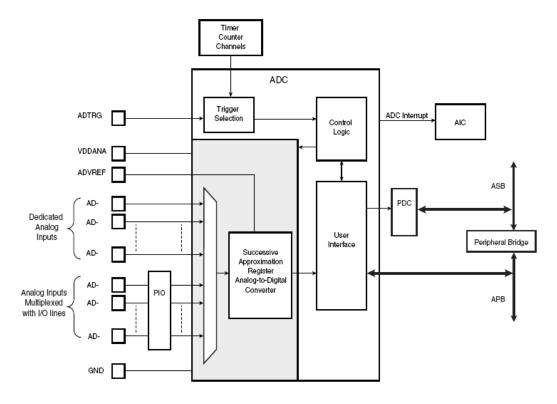

| 3.4   | 1.1   | The Analog Digital Convertor                         | 61 |

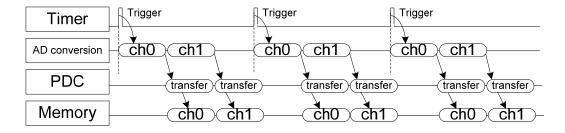

| 3.4   | 1.2   | Timer Counter and Peripheral DMA Controller          | 63 |

| 3.4   | 1.3   | USB and UART                                         | 64 |

| 3.5.  | Hai   | dware Implementation of DSP System                   | 65 |

| 3.6.  | Pro   | cessing of the ADC Sampling Result                   | 69 |

| 3.6     | 5.1  | Obtaining Frequency from FFT Results             | 69 |

|---------|------|--------------------------------------------------|----|

| 3.6     | 5.2  | Matching Frequency Results from the Two Channels | 72 |

| 3.6     | 5.3  | Matching Results from FMCW and CW                | 72 |

| 3.7.    | Sof  | tware Structure and Flowchart                    | 73 |

| СНАРТ   | ER 4 | System Implementation and Measurements           | 76 |

| 4.1.    | Tra  | nsmitter                                         | 76 |

| 4.2.    | Rec  | eiver                                            | 78 |

| 4.3.    | Exp  | periments and Simulation Results                 | 83 |

| СНАРТ   | ER 5 | 5 Conclusion and Future Work                     | 92 |

| 5.1.    | Cor  | nclusion                                         | 92 |

| 5.2.    | Futi | ure Work                                         | 93 |

| Referen | ce   |                                                  | 94 |

# LIST OF TABLES

| Table 2-1 System requirement                       | 6  |

|----------------------------------------------------|----|

| Table 2-2 Frequency shift in FMCW stage            | 20 |

| Table 3-1 Operating modes of AD9854                | 25 |

| Table 3-2 Initialization code of AD9854            | 32 |

| Table 3-3 Frequencies of the frequency synthesizer | 46 |

| Table 3-4 Phase Noise of 35GHz CW signal           | 47 |

| Table 4-1 Bit-reverse order for N=8 [26]           | 54 |

| Table 4-2 Some DSP units in the current market     | 58 |

| Table 4-3 Performance evaluation results           | 61 |

| Table 4-4 ADC performance of AT91SAM7SE512 [13]    | 63 |

| Table 4-5 Effects of interpolated FFT              | 71 |

| Table 5.5-1 System parameters                      | 83 |

# LIST OF FIGURES

| Figure 1.1 Structure of an SIW slot array antenna          | 2  |

|------------------------------------------------------------|----|

| Figure 1.2 Block diagram of the proposed system            | 4  |

| Figure 2.1 Two steps of radar operation                    | 7  |

| Figure 2.2 Example of the upcoming vehicle                 | 8  |

| Figure 2.3 Linear FMCW waveform                            | 11 |

| Figure 2.4 Principle of FMCW radar system                  | 11 |

| Figure 2.5 Angle measurement with phase difference         | 14 |

| Figure 2.6 Radar equation for transmission                 | 15 |

| Figure 2.7 Diagram of the proposed radar system            | 17 |

| Figure 2.8. Combination of CW and FMCW                     | 20 |

| Figure 3.1 Diagram of Frequency Synthesizer.               | 22 |

| Figure 3.2 Diagram of DDS operating principle              | 23 |

| Figure 3.3 Function block diagram of AD9854 [11]           | 24 |

| Figure 3.4 Single tone mode                                | 25 |

| Figure 3.5 Unramped FSK function [11]                      | 26 |

| Figure 3.6 Example of chirp mode [11]                      | 27 |

| Figure 3.7 Block diagram of ramped FSK function [11]       | 28 |

| Figure 3.8 An example of ramped FSK function [11]          | 28 |

| Figure 3.9 Ramped FSK mode for FMCW/CW waveform generation | 29 |

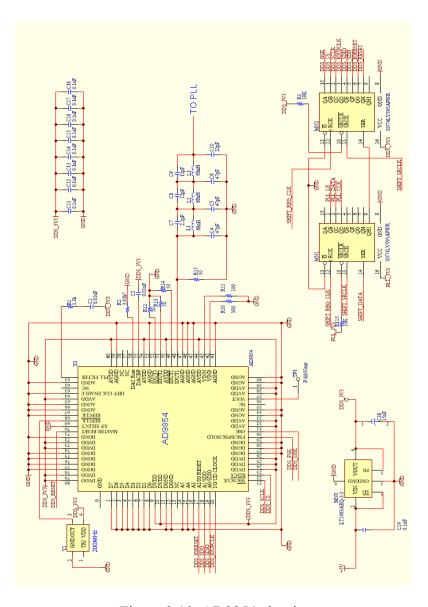

| Figure 3.10 AD9854 circuit.                                | 30 |

| Figure 3.11 Filter for DDS output in ADS                   | 31 |

| Figure 3.12 Simulation results of our DDS low pass filter  | 31 |

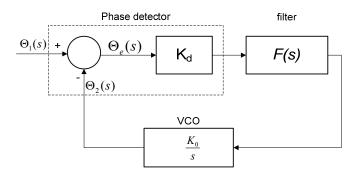

| Figure 3.13 Block diagram of PLL                                             | 33 |

|------------------------------------------------------------------------------|----|

| Figure 3.14 Active PI filter                                                 | 34 |

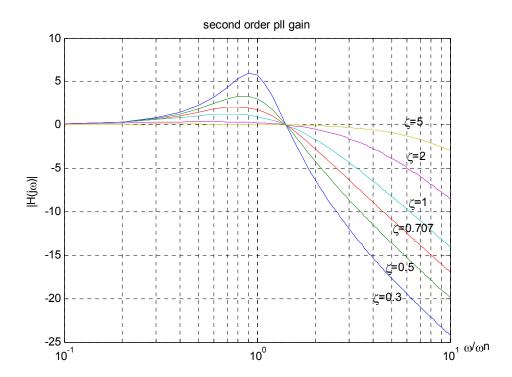

| Figure 3.15. Bode diagram of the phase-transfer function $H(j\omega)$ of PLL | 36 |

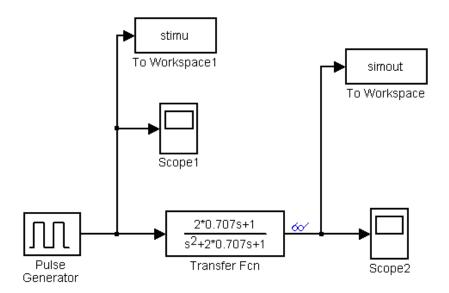

| Figure 3.16. Simulation mode1 of PLL transient response with Simulink        | 37 |

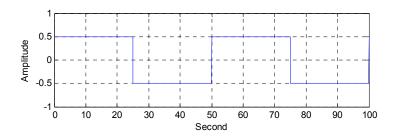

| Figure 3.17 Input of the 2 <sup>nd</sup> order system                        | 37 |

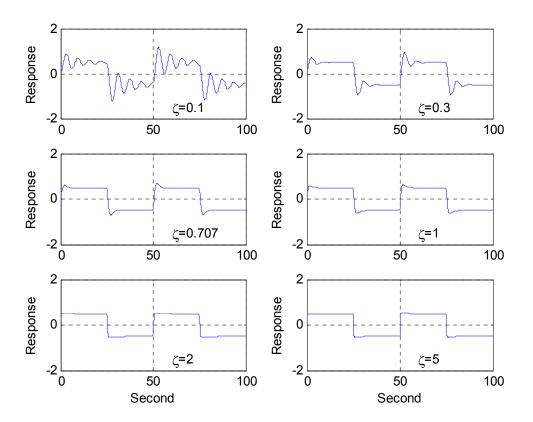

| Figure 3.18 Dynamic responses of the 2 <sup>nd</sup> order system            | 38 |

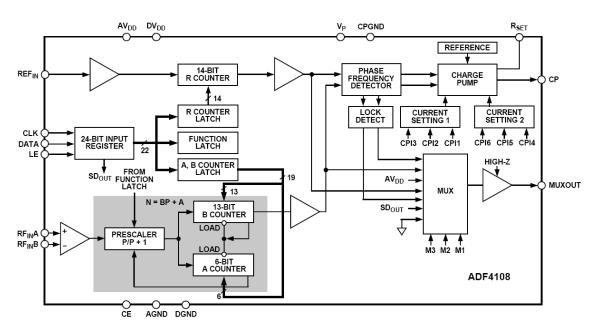

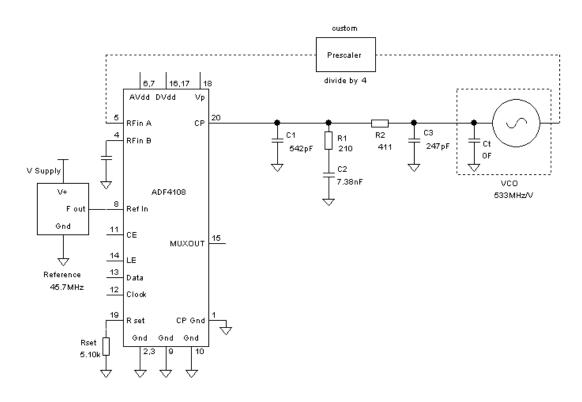

| Figure 3.19. Function block diagram of AD4108 [12]                           | 40 |

| Figure 3.20 PLL design model using AD4108 in ADIsimPLL                       | 41 |

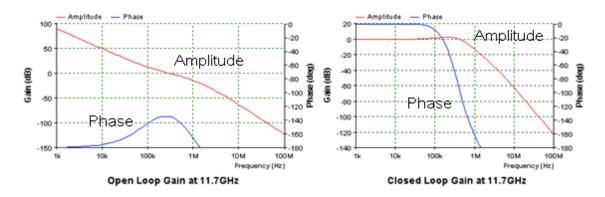

| Figure 3.21 Open and closed loop gain given by ADIsimPLL                     | 41 |

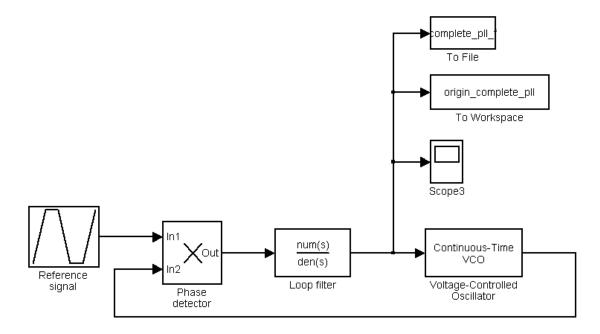

| Figure 3.22 Simulation model of PLL in Simulink of Matlab                    | 42 |

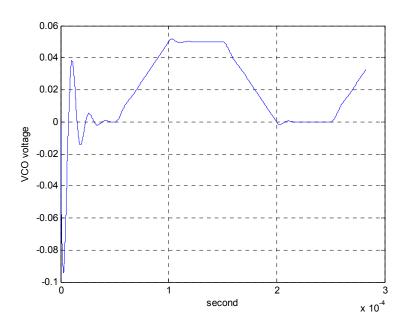

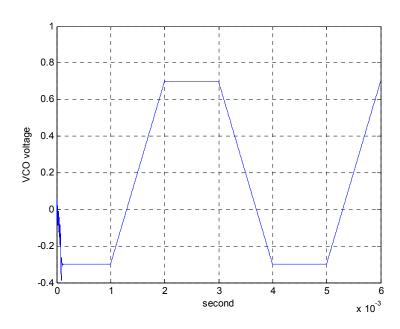

| Figure 3.23 Completely frequency response of PLL by using Simulink           | 43 |

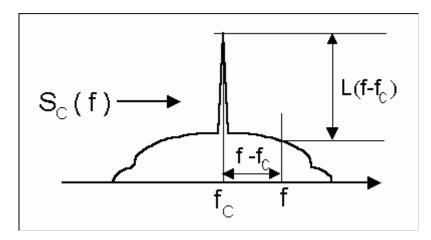

| Figure 3.24 Definition of phase noise spectrum [30]                          | 44 |

| Figure 3.25 Diagram of frequency synthesizer module                          | 46 |

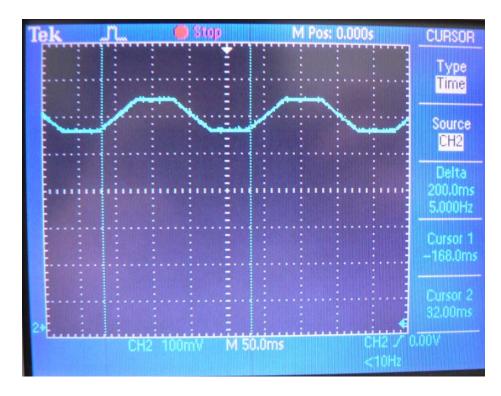

| Figure 3.26 Measured VCO modulation voltage signal                           | 47 |

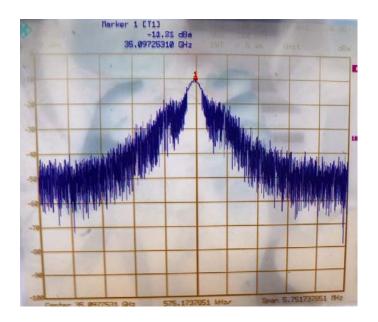

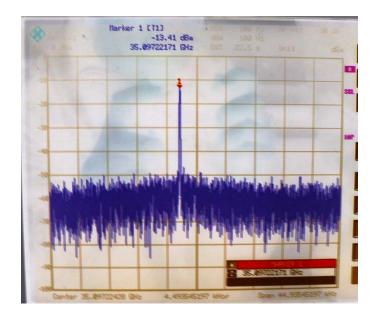

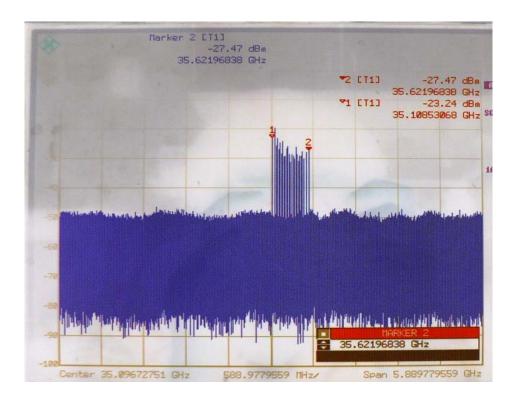

| Figure 3.27 Frequency spectrum of CW signal                                  | 48 |

| Figure 3.28 Frequency spectrum of FMCW signal.                               | 49 |

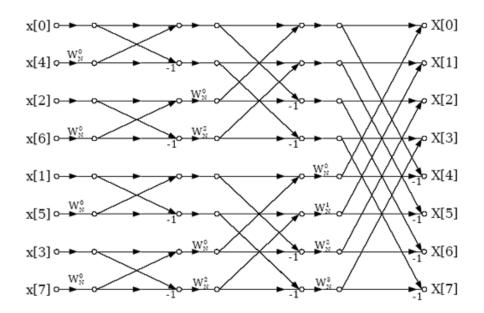

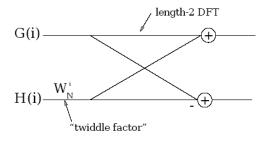

| Figure 4.1 Three stages in the computation of an N = 8-point DFT [26]        | 53 |

| Figure 4.2 Basic butterfly computation [26]                                  | 53 |

| Figure 4.3 C code for radix-2 FFT                                            | 55 |

| Figure 4.4 Basic function block diagram of a general DSP                     | 57 |

| Figure 4.5 Function block diagram of AT91SAM7SExxx                           | 60 |

| Figure 4.6 Function block diagram of ADC [13]                                | 62 |

| Figure 4.7 Relationship between ADC, Timer, PDC and memory                   | 63 |

| Figure 4.8 The architecture of the DSP system.                          | 65 |

|-------------------------------------------------------------------------|----|

| Figure 4.9 AT91 and SDRAM                                               | 67 |

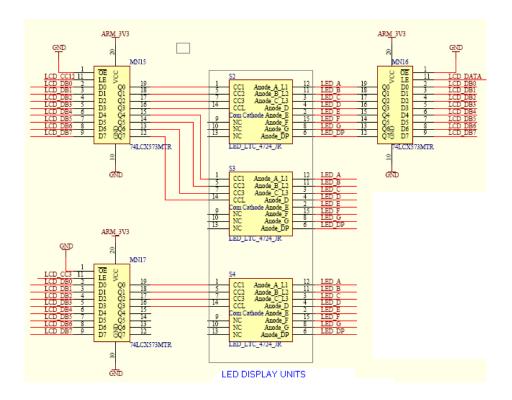

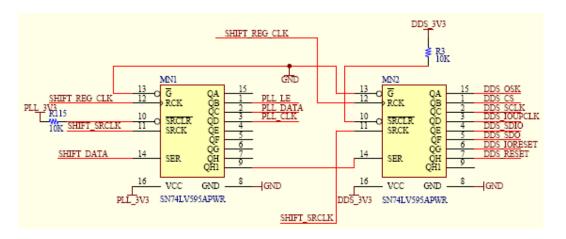

| Figure 4.10 IO extension for display                                    | 68 |

| Figure 4.11 IO extension for frequency synthesizer                      | 68 |

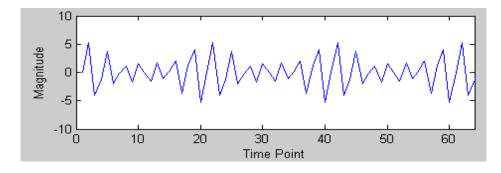

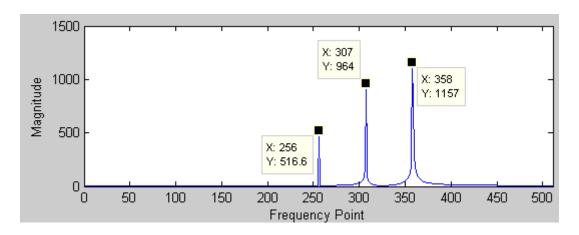

| Figure 4.12 Signal containing 3 components of different frequencies.    | 69 |

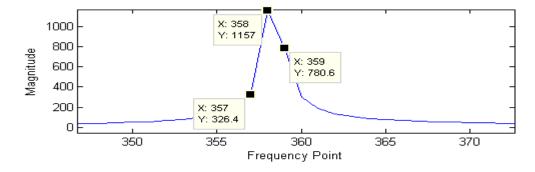

| Figure 4.13 FFT results of the signal containing 3 frequency components | 70 |

| Figure 4.14 Using Interpolated FFT.                                     | 71 |

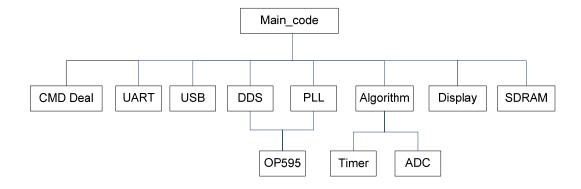

| Figure 4.15 Software Structure                                          | 74 |

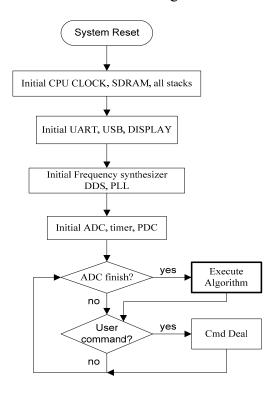

| Figure 4.16 Whole software flowchart                                    | 74 |

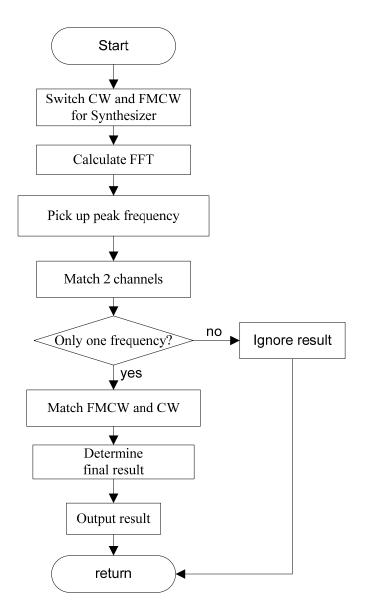

| Figure 4.17 Algorithm flowchart                                         | 75 |

| Figure 5.1 Transceiver module                                           | 77 |

| Figure 5.2 Photo of the antenna                                         | 77 |

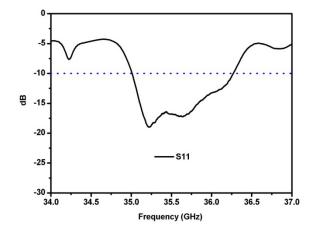

| Figure 5.3 Measured antenna return loss                                 | 78 |

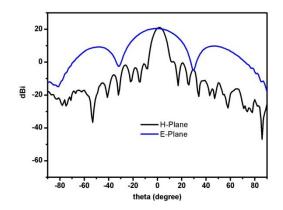

| Figure 5.4 Measured radiation pattern of antenna                        | 78 |

| Figure 5.5 Receiver Module                                              | 79 |

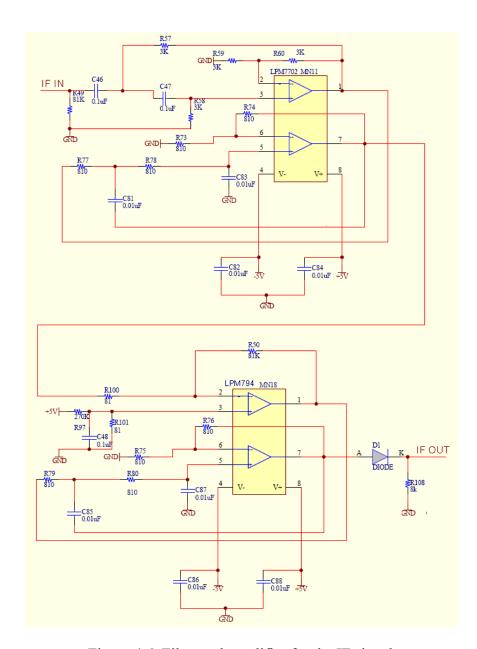

| Figure 5.6 Filter and amplifier for the IF signal.                      | 82 |

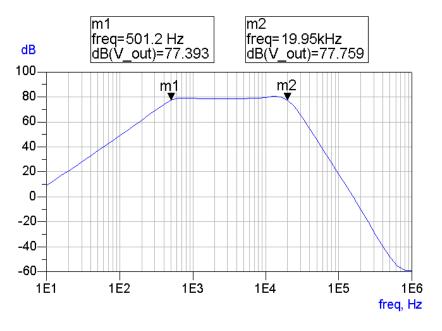

| Figure 5.7 Simulated results of the filter and amplifier for IF         | 83 |

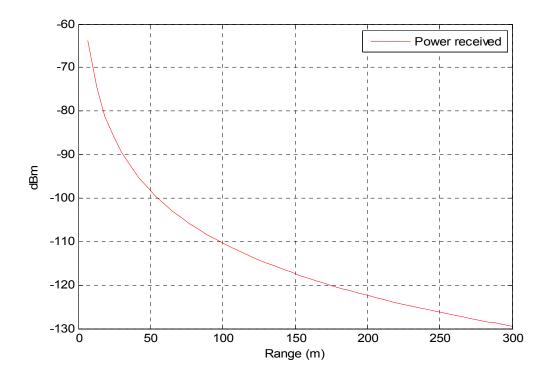

| Figure 5.8 Received power by radar vs. distance of target               | 84 |

| Figure 5.9 Final realized radar system                                  | 85 |

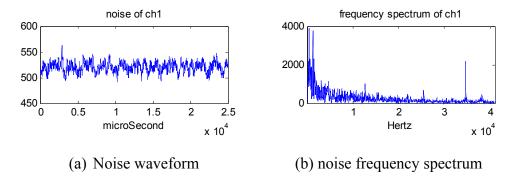

| Figure 5.10 Noise record.                                               | 86 |

| Figure 5.11 Simulation: angle measurement ambiguity                     | 86 |

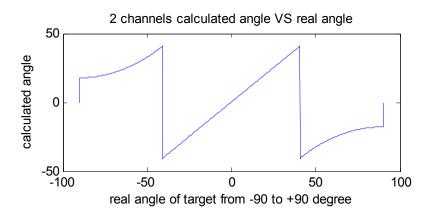

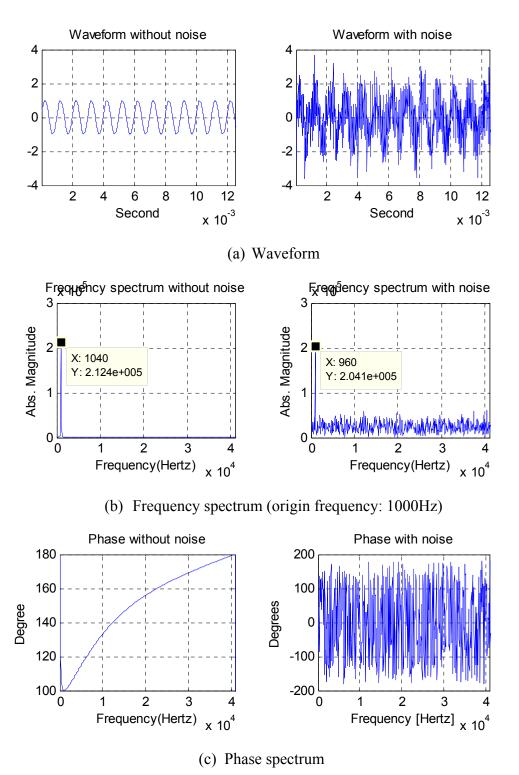

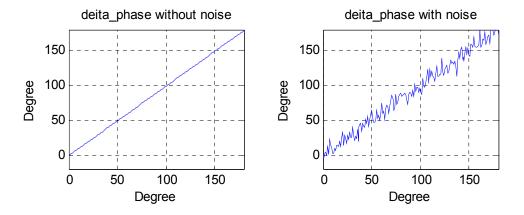

| Figure 5.12 Simulated noise's influence on angle measurement            | 88 |

| Figure 5.13 Angle measurement pattern                                   | 89 |

| Figure 5.14 | Angle measurement results                     | 89 |

|-------------|-----------------------------------------------|----|

| Figure 5.15 | Distance measurement results                  | 90 |

| Figure 5.16 | Experimental tests on highway and the results | 91 |

# LIST OF NOTATIONS AND SYMBOLS

ACC Adaptive Cruise Control

AD Analog to Digital

ADC Analog Digital Conversion/Convertor

AIC Advanced Interrupt Controller

ASM Assemble Language

BPF Band Pass Filter

BPSK Binary phase-shift keying

CPU Center Processing Unit

CW Continuous Wave

DDS Direct Digital Synthesis

DFT Discrete Fourier Transform

DMA Direct Memory Access

DSP Digital Signal Processing

EM Electromagnetic

EMW Electromagnetic Wave

FFT Fast Fourier Transform

FMCW Frequency Modulated Continuous Wave

FPGA Field Programable Gate Array

FSK Frequency-shift keying

IC Integrated Circuit

ISP In-System Programming

LNA Low Noise Amplifier

LPF Low Pass Filter

MCU Micro-Controller Unit

MIPS Million Instructions Per Second

PA Power Amplifier

PC Personal Computer

PDC Peripheral DMA Controller

PLL Phase-Locked Loop

PnP Plug and Play

SDR Software-Defined Radio

SIC Substrated Integrated Circuit

SIW Substrate Integrated Waveguide

UART Universal Asynchronous Receiver/Transmitter

UDP USB Device Port

USB Universal Serial Bus

VCO Voltage Controlled Oscillator

#### **INTRODUCTION**

With the continuous development of integrated circuits and wireless communication technologies, radar applications are becoming ubiquitous. Although radar technologies have intensively been investigated for more than a half century, most practical radar implementations can only be used for specific applications, such as collision avoidance or adaptive cruise control (ACC) functions in transportation systems or security applications in both military and civil sectors. Moreover, radar technologies have progressed enormously for defense applications but they are still not well prepared and developed for commercial applications [2].

With the unprecedented advancement of digital radio and software technology, the software-defined radio (SDR) technique was proposed and developed [4]. More and more analog radio systems have been replaced by digital radio systems of various kinds. On the other hand, programmable hardware modules have vastly been used in digital radio systems at different functional levels. One of the objectives of using the SDR technology is to take advantages of these programmable hardware modules and build up flexible platforms based on software-defined radio system [4]. In the framework of a software-defined technique, conventional radar techniques have also been moved towards more and more digitized functional modules. Software-defined radar system platform was developed by one previous thesis work in our group [2] [3]. With this new concept, certain shortcomings of traditional radar system are resolved in some way. However, the proposed system was only implemented with discrete devices and the parameter measurement was only done in the laboratory environment.

It is well known that most of the radar devices and systems are directly conceived from conventional architectures of the early version of military radars, which have a number of problems [2]. First of all, an obvious drawback is their bulky size caused by a large antenna which is also not easy to fabricate. The second problem is that most of them were developed only for specific applications, and therefore there is a lack of flexibility. The

third shortcoming is that most radar systems are associated with a high cost and/or with an inflexible function.

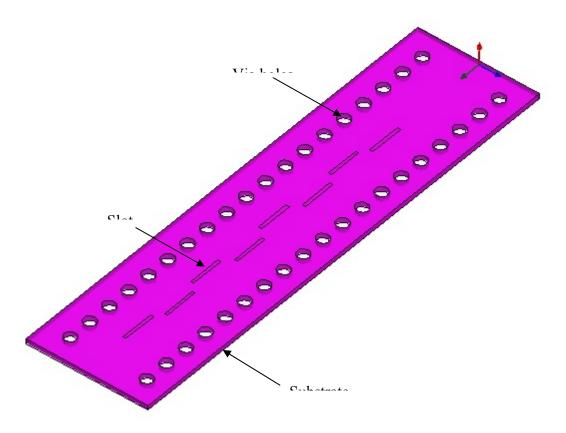

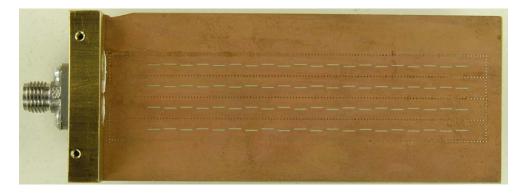

In order to shrink the size and make the fabrication easier, the substrate integrated waveguide (SIW) technology that was proposed in recent years provides a promising solution [1]. The SIW technique belongs to the family of substrate integrated circuits (SICs). One of the well-documented advantages of the SIW technology is a significant size reduction of circuits compared to conventional waveguide structures. Another advantage of SIW is that the whole circuit can be constructed or integrated using standard printed circuit board (PCB) or laser drilling and metallization processing [1]. The basic construction of an SIW slot array antenna is shown in Figure 0.1.

Figure 0.1 Structure of an SIW slot array antenna

In order to provide a series of flexible functions, a new type of re-configurable radar concept was proposed and it is called software-defined radar in the Ph.D. project of Hui

Zhang. The distinct feature of this software-defined radar is its flexibility of software reconfigurable frequency synthesizer, front-end, system architecture and powerful digital signal processing system. Generally speaking, the software-defined radar is a kind of universal radar platform, within which, a flexible signal generation technique is realized based on the clock or reference oscillator input together with a software configurable capability.

Finally, the balance between cost and performance is achieved by adopting a number of technologies. In the presented system, conventional waveguide antennas are replaced by SIW antennas, and this not only reduces the whole size, but also decreases the fabricating cost due to a simplified PCB craftwork. Moreover, with the help of the reconfigurable transceiver and digital signal processing (DSP) system, the performances and functionalities of the radar prototype are improved. Conventional radars realized at low cost only have limited functions of parameter measurements such as the sole velocity measurement, but the range and angle measurements are generally excluded. By combining a flexible synthesizer with advanced DSP technique, software-defined radars can provide an opportunity to implement multiple functionalities at low cost.

In this research project, the afore-mentioned three technologies including SIW antenna, reconfigurable frequency synthesizer and digital signal processor are integrated together in a software-defined radar system with multi-function and low cost. In order to realize the reconfigurable frequency synthesizer, direct digital synthesis (DDS) technique is used together with phase-locked loop (PLL). The DDS circuit is controlled by a central processing unit (CPU) that generates all required signals such as continuous wave (CW) and frequency modulated continuous wave (FMCW) waveforms. The output signal of the DDS is injected to the PLL for making a frequency modulation, and the generated frequency modulated signal is transmitted following the stages of a frequency tripler and a power amplifier. Finally, the high frequency signal is radiated by the SIW antenna to free space in the form of EMW. In this project, the CW signal is used for measuring the velocity from the detection frequency shift induced by Doppler Effect. The FMCW signal works together with the CW signal for range measurement. Despite a single

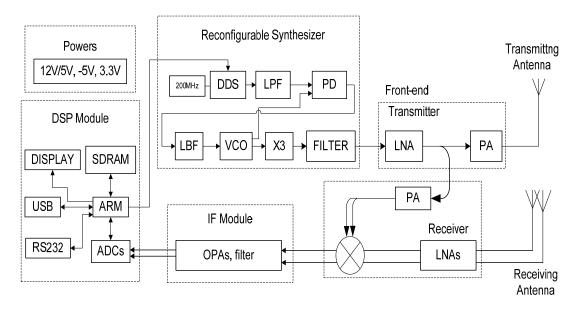

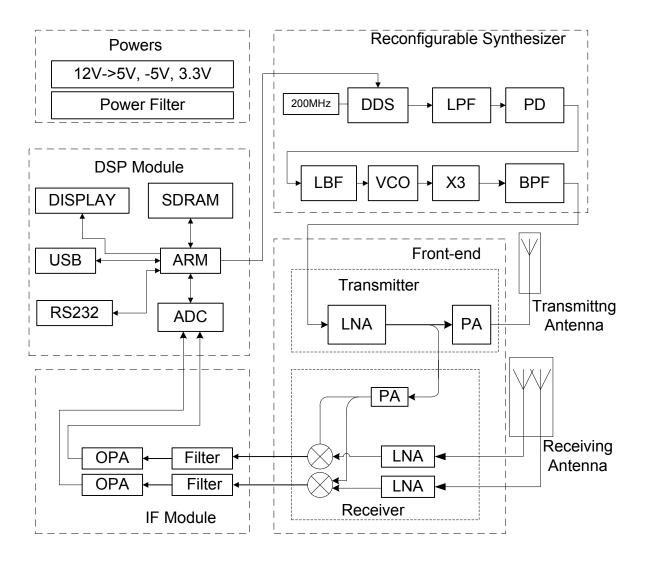

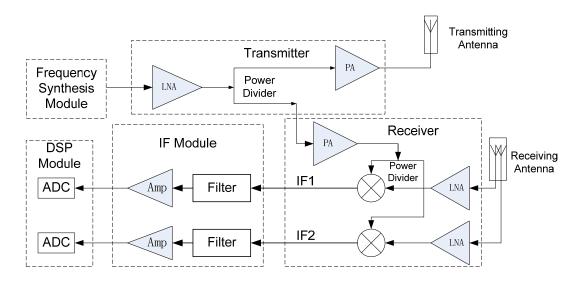

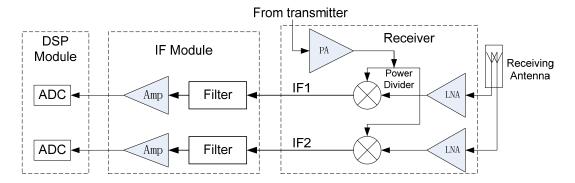

transmitting antenna, a receiving antenna with two channels is used. With the platform of the two-channel receiving antenna, EMW reflected by target arrive into the two channels with different phases, which allows for measuring the direction or the arrival angle of the incoming EM wave, namely the target's angle. The proposed reconfigurable radar system is sketched in Figure 0.2.

Figure 0.2 Block diagram of the proposed system

The whole radar system mainly consists of seven parts: DSP module, reconfigurable synthesizer, IF module, transmitter, receiver, antennas and power supplies.

This thesis is organized as follows. In chapter 2, the basic radar principle and techniques used in this project are explained as well as the system architecture and basic parameters. Chapter 3 presents the theory of frequency synthesizer including the DDS and PLL techniques. Subsequently, Chapter 4 describes the digital processing unit in the system and the software module as well as the flowchart. Chapter 5 gives structure details of the implemented transceiver, which includes a transmitter, a transmitting antenna, two-channel receiving antennas, a receiver, an IF filter and an amplifier. The simulated and measured results are also presented and discussed in Chapter 5. Finally, Chapter 6

concludes this project and provides future research directions in connection with this project.

#### CHAPTER 1 SOFTWARE DEFINED RADAR SYSTEM

### 1.1. System Objectives and Requirement

Like any radar system, the software-defined radar system is used to actively position the targets with measuring the parameters of targets including velocity rang and angle. The measurement result should meet the basic accuracy requirement shown in Table 1-1.

Value Items RF frequency: 35GHz Waveform type CW and FMCW Measurement speed > 10 times per second ADC sample frequency > 40kSPS (Sample per second) Velocity error < 1 km/hRange error < 1 mAngle error < 1 degree

Table 1-1 System requirement

# 1.2. Basic Principle of Radar System

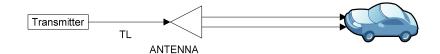

Generally speaking, a complete radar operation consists of two steps, which are shown in Figure 1.1. Figure 1.1a shows the first step which is the transmitting phase and Figure 1.1b presents the second step which is the receiving phase. In both figures, "TL" means microwave transmission line.

During the first step (transmitting phase), a transmitter produces a microwave signal which is fed into an antenna at the end of the front-end transmission. Then, the microwave signal is radiated by the antenna to the surrounding space in the form of a propagating

electromagnetic (EM) wave. Finally, some portion of the propagating wave energy travels in the direction of the object of interest, called target, for example, a running car.

(a) First step of radar operation: transmitting

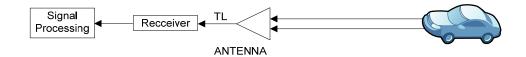

(b) Second step of radar operation: receiving

Figure 1.1 Two steps of radar operation

During the second step, once the traveling EM wave encounters the target, part of its energy is reflected back into the space in all possible direction depending on the target's scattering properties. Some of the reflected energy may arrive at the receiving antenna. Then the receiving antenna captures the EM wave and feeds it into receiver. At last, the signal out of receiver arrives into the signal processing unit and we can obtain the information about the target, for example, its speed and distance.

There are two situations regarding the relationship between the transmitting part and the receiving part, which construct two kinds of radar system. The first type of radar is called 'bistatic' radar in which the two parts are in different locations while the second type is called 'monostatic' radar in which the two parts are in the same location even integrated into one device. In this work, only the monostatic radar will be studied and discussed. Following a long-period development of radar technologies, a number of radar types have been developed. Continue wave Doppler and linear frequency modulated radar will be realized in the proposed system.

#### 1.3. **Doppler Effect in Radar**

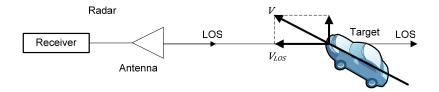

Doppler Effect, which is a very-known physical phenomenon, is very useful in measuring speed along the line of sight (LOS) between target and radar. This means that a radar system is able to receive the reflected signal whose frequency is shifted if the target's moving speed has a component along the LOS. The frequency shifting direction depends on whether the target is moving towards or away from the radar. Whatever the direction of target moves in, the shift of frequency is proportional to the magnitude of the LOS velocity component[5]. An example of the upcoming vehicle is shown in Figure 1.2.

Figure 1.2 Example of the upcoming vehicle

The transmitted continuous sinusoid wave  $S_t$  can be expressed as

$$s_t = A\cos(2\pi f_0 t + \varphi_0) \tag{2.1}$$

where A is magnitude of the signal,  $f_0$  is signal frequency in Hertz, t is time in second,  $\mathcal{R}$  is the initial phase of the sinusoid wave. After time delay  $\tau$ , the signal is reflected back to the antenna by the target which has a range of R(t), expressed by equation(2.2).

$$s_r = B\cos(2\pi f_0(t-\tau) + \varphi_0)$$

(2.2)

where B is magnitude of the reflected and attenuated signal, and the time delay  $\tau$  is

$$\tau = \frac{2R(t)}{c} \tag{2.3}$$

where c is the speed of light. Varying range R(t) is (assuming the target is moving towards to the radar)

$$R(t) = R_0 - v_{LOS}t (2.4)$$

where  $R_0$  is the initial range at time t=0,  $V_{LOS}$  is the velocity component of LOS. By substituting (2.3) and (2.4) into equation (2.2) we can obtain

$$s_r = B\cos(2\pi f_0(t - \frac{2(R_0 - v_{LOS}t)}{c}) + \varphi_0)$$

(2.5)

This can be simplified to

$$s_r = B\cos(2\pi(f_0 + f_d)t + \varphi_r) \tag{2.6}$$

where phase  $\varphi_r$  is

$$\varphi_{r} = \varphi_{0} - \frac{4\pi f_{0} R_{0}}{c} \tag{2.7}$$

and frequency shift  $f_d$  is

$$f_d = \frac{2v_{LOS}}{c} f_0 \tag{2.8}$$

This  $f_d$  is the Doppler frequency shift which is produced because the target has an LOS velocity component. Therefore, the speed of the target moving toward the antenna  $v_{los}$  can be calculated from measuring the Doppler frequency:

$$v_{LOS} = \frac{f_d c}{2 f_0} \tag{2.9}$$

Since the velocity calculation depends on the measured Doppler frequency shift, the accuracy of velocity is determined by the accuracy of frequency measurement. The velocity resolution can be computed as,

$$v_{res} = \frac{f_{d,res}c}{2f_0} \tag{2.10}$$

where  $v_{res}$  is velocity resolution,  $f_{d,res}$  is Doppler frequency resolution. At the same time,  $f_{d,res}$  is a reciprocal parameter of measurement period T, namely, we have

$$v_{res} = \frac{c}{2f_0T} \tag{2.11}$$

Once the frequency of the transmitted signal is given, the velocity measurement resolution is determined by measurement period T.

Due to the fact that velocity  $v_{los}$  has its direction, towards or away from the radar reference, the Doppler shift frequency gets its own positive or negative direction. By determining whether the Doppler shift frequency is positive or negative, the radar can detect the moving direction of the target.

#### 1.4. Frequency Modulated Continuous Wave

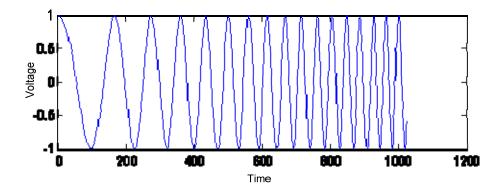

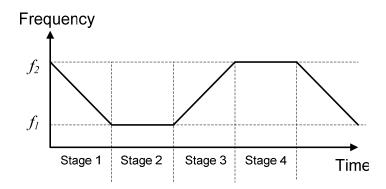

Besides the velocity measurement, range measurement is another issue in the development of radar technology. One way to measure the range is using pulsed-modulated radar. Pulsed-modulated radar measures the range by measuring the traveling time of a very short pulse between the radar and the target. Since it is not easy to realize a very narrow pulse width, it is difficult to yield a high resolution of range. As a substitute, the frequency modulated continuous wave can be employed in radar system in order to obtain a higher resolution in range measurement. Frequency modulated continuous wave also features a low power level, which allows using solid state microwave circuits. Figure 1.3 shows an example of linear FMCW waveform.

The linear FMCW waveform shown in Figure 1.3 can be expressed by

$$s_t = \cos[2\pi (f_0 + f_r t)t] \tag{2.12}$$

where  $f_0$  is the frequency of signal at time t=0,  $f_r$  is the frequency slew rate. In this case  $S_r$  is a positive constant value. If  $S_r$  is a negative constant value, the frequency will decrease over time.

Figure 1.3 Linear FMCW waveform

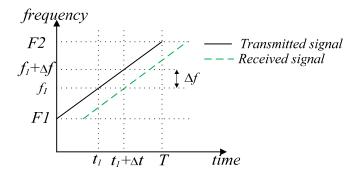

Figure 1.4 Principle of FMCW radar system

Figure 1.4 shows how the FMCW works in range measurement process. In Figure 1.4, the solid black leaning line represents the transmitted signal's frequency and the dash green (maybe black or gray due to the printer) leaning line represents the frequency of received signal which is reflected back by the target at position of range R to the radar. Obviously, the received signal's frequency is retarded by time delay  $\Delta t$  according to the time during the signal traveling from the radar to the target and returning from the target to the radar, a total range is 2R.

As we can detect the frequency shift between the transmitted signal's frequency and received signal's frequency, it is easy to obtain the traveling time of signal between the radar and the target.

Observing Figure 1.4, we have the following relation

$$\frac{\Delta t}{\Delta f} = \frac{T}{F_2 - F_1} \tag{2.13}$$

Then the equation for the traveling time is:

$$\Delta t = \frac{T}{F_2 - F_1} \Delta f \tag{2.14}$$

where  $\Delta t$  is the travelling time, T is the frequency scanning time from F1 to F2,  $\Delta f$  is the frequency difference between the received and transmitted signals.

Finally, we can get the target range by

$$R = \frac{\triangle t \times c}{2} \tag{2.15}$$

namely,

$$R = \frac{Tc}{2(F_2 - F_1)} \triangle f \tag{2.16}$$

where R is the range between the radar and the target, c is the speed of light. The resolution of measured range depends on the resolution of  $\Delta f$ . The resolution of  $\Delta f$  depends on the scanning time T:

$$\triangle f_{resolution} = \frac{1}{T}$$

Then the resolution of range can be formulated by the following equation

$$R_{resolution} = \frac{c}{2(F_2 - F_1)} \tag{2.17}$$

From Equation (2.17) we can see that the range resolution of FMCW system is decided by the sweep bandwidth of the transmitted signal.

Similar to Doppler radar, FMCW radar is also able to collect multi-range information of multi-target by distinguishing different frequency from one single signal.

All of the above discussions are made based on one assumption that the target is fixed on its location without LOS velocity. If LOS velocity is present, the Doppler frequency shift will be mixed in the receiving frequency, leading to the fact that  $\Delta f$  includes not only the range information but also the speed information. It is a challenge to separate them from each other, especially when there are multiple targets in the detection range of the radar. In our system, we combine the FMCW and CW platforms together in order to collect the range information from FMCW signal without ambiguity.

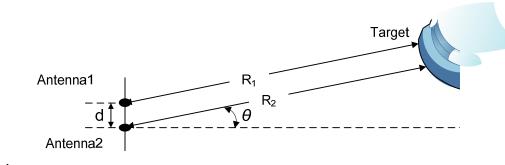

## 1.5. Principle of Angle Measurement

Angle measurement is another function that is always required to be implemented in radar system. Angle measurement could be two dimension (2D) angle measurement or three dimension (3D) angle measurement. In our project, the 2D angle measurement is used.

There are several methods of measuring arriving angle of targets. We make use of two receiving antennas and the arriving angle of target can be calculated by measuring the phase difference between the EMW signals received by the two antennas. The principle of angle measurement is shown in Figure 1.5.

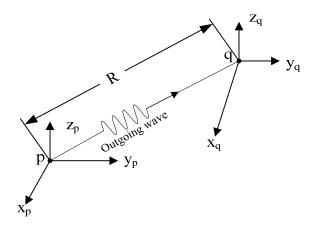

The distance between the two antennas is d. The ranges from the two antennas to the target are  $R_1$  and  $R_2$  respectively. The difference between  $R_1$  and  $R_2$  can be evaluated by:

$$R_d = R_2 - R_1 = d\sin(\theta) \tag{2.18}$$

Figure 1.5 Angle measurement with phase difference

The measured phase difference between two received signals is related to  $R_d$  by

$$\varphi_d = \frac{2\pi R_d}{\lambda} \tag{2.19}$$

where  $\lambda$  is the wavelength of the transmitting signal. From (2.18) and (2.19), we can get the arriving angle of the target by

$$\theta = \arcsin\left(\frac{R_d}{d}\right) = \arcsin\left(\frac{\lambda \varphi_d}{2\pi d}\right) = \arcsin\left(\frac{\varphi_d c}{2\pi d f_0}\right)$$

(2.20)

where c is the speed of light in m/s, and  $f_0$  is the frequency of transmitting signal.

## 1.6. **Radar Equation**

The radar equation is a way to assess the radar effective range, which is also called "radar range equation". For a monostatic radar system, in order to assess the maximum effective range, the first step is to obtain the power received by the radar antenna, which can be calculated by radar equation [6].

Basically, the target can be considered as an antenna that can receive and reflect signal through its own property. As shown in Figure 2.6, the radar antenna is located at point p and the target as an antenna is located point q. In Figure 2.6, the target at point q is regarded as a receiving antenna.

The first step is to calculate the power density at the position of the target. Assuming a total power  $P_T$  is radiated into the surrounding space by the radar antenna at point p, then the power density received by target at point q will be

$$\left(\frac{dP_t}{dA}\right)_q = \frac{P_T G_T}{4\pi R^2} \tag{2.21}$$

Figure 1.6 Radar equation for transmission

where  $\left(\frac{dP_t}{dA}\right)_a$  is the power density at the position q of target,  $G_T$  is the gain of radar

antenna, and R is the distance between the radar antenna and the target. The second step is to obtain the received power by radar antenna. The target intercepts a portion of the incident energy and reradiates it in various directions. It is only the power density reradiated in the direction of the radar that is of interest. Then the reradiated power density back at the radar can be expressed by

$$\left(\frac{dP_r}{dA}\right)_p = \frac{P_T G_T}{4\pi r^2} \cdot \frac{\sigma}{4\pi R^2}$$

(2.22)

where  $\sigma$  is the radar cross section and has units of area. It is more dependent on the target's shape than on its physical size. The target determines the power density returned to the radar for a particular power density incident on the target. Then the received signal power by the receiving antenna is

$$P_r = \left(\frac{dP_r}{dA}\right)_p \bullet A_e = \frac{P_T G_T}{4\pi R^2} \bullet \frac{\sigma}{4\pi R^2} \bullet A_e = \frac{P_T G_T A_e \sigma}{(4\pi)^2 R^4}, \tag{2.23}$$

where  $A_e$  is the effective area of the receiving antenna. According to antenna theory, the relationship between the gain of antenna and the effective area is given by

$$G = \frac{4\pi A_e}{\lambda^2} \tag{2.24}$$

where G is the gain of antenna,  $\lambda$  is the wavelength of the signal. Substituting (2.24) into(2.23), we get the final form of received power as

$$P_{r} = \frac{P_{T}G_{T}G_{R}\lambda^{2}\sigma}{(4\pi)^{3}R^{4}}.$$

(2.25)

$G_R$  is the gain of receiving antenna. From equation (2.25), the maximum range of a radar  $R_{\text{max}}$  can be calculated as

$$R_{\text{max}} = \sqrt[4]{\frac{P_T G_T G_R \lambda^2 \sigma}{(4\pi)^3 P_{\text{min}}}}.$$

(2.26)

where the  $P_{min}$  is the minimum power of detectable signal of the radar system.

## 1.7. Software-Defined Radar System

The main feature of this radar system is its reconfigurable capability by software. The reconfigurable parameters include the operating frequency within a certain range, frequency modulation type and its parameters. Operating at 35 GHz, the proposed radar system is mainly composed of six parts, as shown in Figure 1.7.

The six parts are as follows:

#### 1) Antennas.

In the system, the transmitting antenna and receiving antenna are separated. We do not use a circulator to realize the multiplexing of antenna. Therefore, the integration

of system is easy and the isolation between the receiving and transmitting channels is much higher. The receiving antenna set contains two channels in order to measure the arriving angle of targets.

#### 2) Millimeter-wave frond-end.

The transmitter includes low noise amplifiers (LNA) and power amplifier (PA). The receiver includes LNA and mixers.

Figure 1.7 Diagram of the proposed radar system

3) Reconfigurable frequency synthesizer.

The frequency synthesizer module consists of DDS, PLL, voltage controlled oscillator (VCO) and frequency tripler. The frequency synthesizer produces the required waveform for CW and FMCW functions.

4) Intermediate frequency (IF) modules.

The IF module includes several amplifiers and band pass filters through which the IF signal is filtered and amplified to a proper range of voltage and then drives the analog-to-digital converter (ADC) embedded in DSP module.

5) Digital signal processing module with embedded analog to digital convertor; This module converts the analog IF signal into digital signal and processes the signal according to a digital signal processing algorithm. Moreover, this module configures the reconfigurable frequency synthesizer and interacts with the user interface.

#### 6) Power module.

The power module includes several DC-DC converters, linear power regulators and ripple suppression filters, which generate +5V, -5V, +3.3V powers for each part of the radar system.

The main purpose of this project is to realize different radar functions within one single hardware platform. The switching and combination of different radar functions are realized by the software that controls the signal synthesizer and digital signal processing parts. In our study, CW radar and FMCW radar functions are integrated. The CW function can detect the speed information of targets and the FMCW function can detect the range information of targets.

In order to realize small sized radar, our system works at 35.1 GHz. Therefore, the antenna can be very compact. In addition, we implement the SIW into our antenna design, which features low loss and planar form that can be made compatible with standard printed circuit board (PCB) technology.

The linearity of the FMCW signal decides the accuracy of the range measurement. There are several techniques for realizing a linear FMCW signal, such as PLL, triangular wave modulated VCO, etc. We use DDS combined with PLL to realize an ideal linear FMCW microwave signal. The microwave signal is then multiplied to millimeter-wave signal for driving the transmitting stage and LO source.

The millimeter-wave front-end is integrated into several boards. The boards are packaged into a single enclosure. The whole system is in the form of a planar structure. The receiver is in a homodyne configuration, which is simple and presents phase noise coherent features. The receiver has two identical channels. The two channels are connected with two identical closely-spaced receiving antennas. Therefore, the arrival angle of the targets can be detected for both CW and FMCW modes.

The IF signals are filtered and amplified before the ADC. The digitalized IF signals are processed in the DSP system according to corresponding algorithms. In this study, fast fourier transform (FFT) is the main algorithm for digital processing to evaluate the spectrum information of the received IF signal. The speed, range, and arriving angle of the targets are calculated in DSP. In addition, some software codes are created for communication between DSP and computer as well as interface to the users.

The transmitted frequency of signal in CW mode is 35.1GHz. According to equation(2.8), the Doppler frequency for a speed range of 10km/h and 200 km/h is between 650Hz and 13 KHz.

With measurement period 50ms, the velocity resolution is

$$v_{res} = \frac{c}{2f_0T} = 0.085m / s = 0.3Km / h$$

(2.27)

The transmitted frequency of signal in FMCW mode is 35.1GHz~35.6GHz. The bandwidth is 500MHz so the range resolution is

$$R_{resolution} = \frac{c}{2(F_2 - F_1)} = 0.3 \text{m}$$

(2.28)

According to (2.16), the frequency measured for static target in a range between 1m and 100 m is from 66.6 Hz to 6.66KHz.

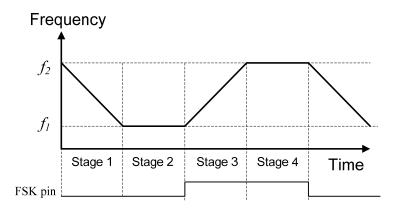

In real environment, the target cannot be static. Therefore, the Doppler frequency shift could also be added to the received FMCW signal. The range information can be calculated from the combination of the FMCW signal and CW signals. In our project, the combination of CW and FMCW waveforms is shown in Figure 1.8.

Figure 1.8. Combination of CW and FMCW

In Figure 1.8, stage 1 and stage 3 are FMCW stages in which frequency is scanned linearly from f1 up to f2 or from f2 down to f1. Stage 2, stage 4 are CW stages in which only one single frequency signal is generated. In the FMCW stage, the frequency shift measured may contain both velocity and range information. In the CW stage, the frequency shift measured only contains the Doppler shift. In different FMCW stages, the combinations of velocity and range are different, as shown in Table 1-2.

FMCW stage Receding target Approaching target

Frequency Increasing  $abs(f_r + f_d)$   $abs(f_r - f_d)$ Frequency Decreasing  $abs(f_r - f_d)$   $abs(f_r + f_d)$

Table 1-2 Frequency shift in FMCW stage

In Table 1-2,  $f_r$  is the frequency shift due to range,  $f_d$  is Doppler shift due to velocity and abs is the absolute value function.

# CHAPTER 2 FREQUENCY SYNTHESIZER DESIGN AND IMPLEMENTATION

# 2.1. Brief description of Frequency Synthesizer Module

Typically, there are a number of methods to create a linear frequency sweep, for example, digital or analog frequency control loop and fractional N phase locked loop [28]. In this work, we chose the DDS combined with PLL to realize a linear frequency sweep signal. Compared with the others, DDS has several advantages as the followings:

- 1) DDS is a matured product;

- 2) DDS has more competitive commercial performance-price ratio than others;

- 3) It is easy to connect to a standard PLL circuit product;

- 4) It is very easy and flexible to configure it to a number of functions and parameters.

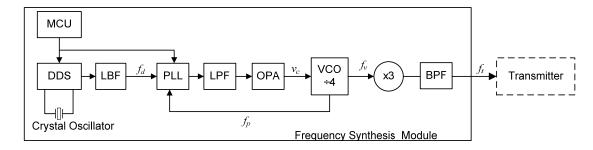

Operating at frequency 35.1GHz and with reconfigurable features, the radar involves a millimeter-wave frequency synthesizer that is mainly composed of DDS, PLL, VCO and frequency multiplier. The diagram of this frequency synthesizer is shown in Figure 2.1.

Figure 2.1 Diagram of Frequency Synthesizer.

According to the sampling theory, a DDS can produce almost any frequency signal within 100MHz with a crystal oscillator of 200MHz under the control of a MCU. In this project, DDS outputs both single frequency signal and FMCW signal with frequency denoted by  $f_d$ , 45.7~46.4MHz. The PLL locks VCO output  $f_p$  to 64\* $f_d$ . Then, the microwave signal is

multiplied by x3 frequency multiplier and we generate the transmitting signal with frequency  $f_t$ .

#### 2.2. **DDS**

#### 2.2.1 Introduction of DDS Device AD9854

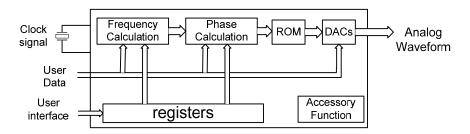

DDS is a kind of digital and analog mixed device which allows us to create the expected relative low frequency and frequency modulated signal. Generally speaking, DDS is a DSP technology on the basis of sampling theorem [29]. The key point of DDS technology is based on a sinusoid wave amplitude value table stored in a ROM which is addressed by phase value. The diagram of operating principle is shown in Figure 2.2.

Figure 2.2 Diagram of DDS operating principle

After being configured by user with the expected frequency list, initial phase and necessary time arguments are driven by a clock signal, DDS calculates a phase on every clock based on some condition for example external data pin. Then DDS addresses the memory with the phase value as index to get the sine wave amplitude values. At last, the amplitude values are sent to internal or external DACs to form expected waveform. Thanks to the adding of digital technique, DDS has any flexibility.

In our project, we employed an integrated DDS chip AD9854 from Analog Device Inc. to form single tone continuous waveform and linear frequency modulated continuous waveform signals.

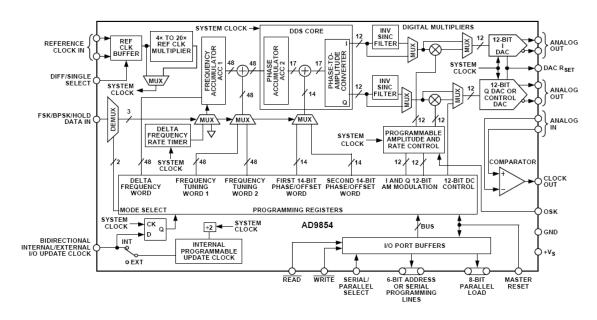

AD9854 is a highly integrated digital and analog mixed device. With the help of external oscillator and embedded two internal high speed, high performance quadrature DACs, this DDS is capable of forming a digitally programmable I and Q synthesizer function. When referenced to an accurate clock source, AD9854 generates highly stable, frequency-phase, amplitude-programmable sine and cosine outputs that can be used as an agile LO in communications, radar and many other applications. The innovative high speed DDS core of the AD9854 provides 48-bit frequency resolution. For our project, 200MHz external oscillator is used as the system clock of DDS. Diagram of this DDS is shown in Figure 2.3, which is from the datasheet of AD9854 [11].

The AD9854 quadrature output digital synthesizer is a highly flexible device that addresses a wide range of applications. The device consists of a numerically-controlled oscillator (NCO) with a 48-bit phase accumulator, a programmable reference clock multiplier, inverse sin filters, digital multipliers, two 12-bit high speed DACs, a high speed analog comparator, and interface logic. This highly integrated device can be configured to serve as a synthesized LO, an agile clock generator, or an FSK/BPSK modulator [11].

Figure 2.3 Function block diagram of AD9854 [11]

## 2.2.2 Operating Modes of AD9854

With twelve registers which allow user to operate the device with a great flexibility, AD9854 has five programmable operating modes which are shown in Table 2-1, where mode bit 2,1,0 are all bits from the control register.

| Mode bit 2 | Mode bit 1 | Mode bit 0 | Operating mode |

|------------|------------|------------|----------------|

| 0          | 0          | 0          | Single tone    |

| 0          | 0          | 1          | FSK            |

| 0          | 1          | 0          | Ramped FSK     |

| 0          | 1          | 1          | Chirp          |

| 1          | 0          | 0          | BPSK           |

Table 2-1 Operating modes of AD9854

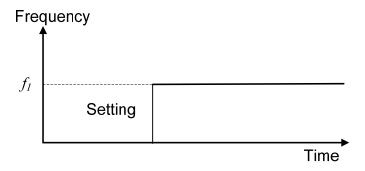

The first mode is single tone which is the default mode after power on or reset, in which only a single tone signal is produced as shown in Figure 2.4. This mode is well suitable for Doppler radar applications because frequency  $f_I$  can be changed easily.

Figure 2.4 Single tone mode

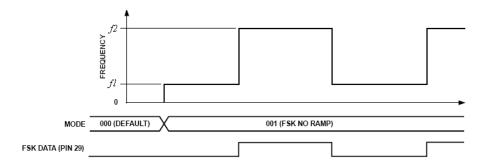

The second mode is unramped FSK mode, namely frequency-shift keying, shown in Figure 2.5. When this mode is selected, the output frequency of the device is selected by FSK Pin 29 between the two frequencies loaded into Frequency Tuning Word Registers 1 and 2. A logic low on FSK Pin chooses  $f_1$  (Frequency Tuning Word 1), and a logic high

chooses  $f_2$  (Frequency Tuning Word 2). Changes in frequency are phase continuous and are internally coincident with the FSK data pin. Note that there is a deterministic pipeline delay between the FSK data signal and the DAC output.

Figure 2.5 Unramped FSK function [11]

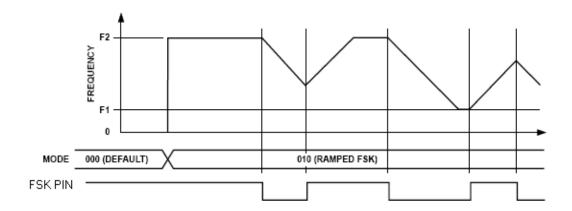

The third mode is ramped FSK mode which is used in our project to generate the FMCW signal. When this mode is selected, the change between  $f_1$  and  $f_2$  is ramped but not instantaneous.

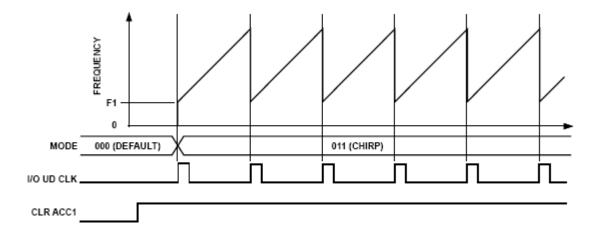

The fourth chirp mode is similar to the ramped FSK mode but without  $f_2$  setting. One example of chirp mode is shown in Figure 2.6. In this example, the ramped and linear frequency sweep is ideal for some types of radar application. For example, we can use this mode to produce repetitive FMCW signals which are applied for range measurements in radar system.

The last one is BPSK mode. Binary, biphase, or bipolar phase shift keying is a means of communication. In this mode, the FSK pin functions as the phase control pin. Since this is not related to radar technique, we will not discuss this mode in this work.

Figure 2.6 Example of chirp mode [11]

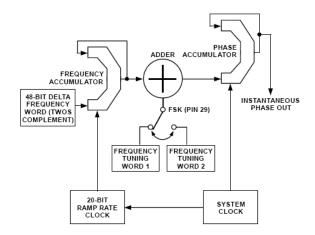

## 2.2.3 Ramped FSK Mode for FMCW signal

Unlike the unramped FSK mode, whereby the frequency change between the two frequencies is instantaneous, the change of frequency is ramped and linear. And unlike the chip mode, we can indicate the terminating sweep frequency. In other words, there is a frequency sweep procedure that we can control completely. Similar to the unramped FSK mode, the frequency output by device is also controlled by FSK pin 29.

Furthermore, this mode requires that f1 must be lower than f2. The frequency sweep speed and resolution should also be programmed in respective register before the function becoming available. Referring to Figure 2.7, the device employs a frequency accumulator and a phase accumulator to realize the frequency sweep. The 48-bit delta frequency word decides the minimum frequency change as well as the 20-bit ramp rate clock register decides the time spent on each frequency. The two frequency tuning word registers decide the starting and ending sweep frequency. An example of ramped FSK is shown in

Figure 2.8.

Figure 2.7 Block diagram of ramped FSK function [11]

Figure 2.8 An example of ramped FSK function [11]

This example shows how the output frequency is controlled by FSK pin. The key point of FSK pin is its level overturns. When the FSK pin gives an overturn from low to high, the frequency begins to sweep upwards to F2 until frequency arrives to F2 or the FSK pin gives an overturn from high to low. The case is similar when the FSK pin has an overturn from high to low level that the frequency begins to sweep downwards F1 until frequency arrives to F1 or the FSK pin gives an overturn from low to high level. From

Figure 2.8, we can see that both FMCW and CW waveforms can be controlled in the ramped FSK mode. Every time when the FMCW signal sweeps to its termination frequency F1 or F2, the signal frequency is preserved and continued at the termination

frequency F1 or F2 which becomes to a single tone signal. On the other hand, we can get FMCW and CW waveforms only in one mode as long as we control the FSK pin well.

Setting the sweep time to 50ms and the stable time of FSK pin to 100ms, we can get the following ideal waveform for our radar system in Figure 2.9 in which every stage is 50ms.

Figure 2.9 Ramped FSK mode for FMCW/CW waveform generation.

# 2.2.4 Implement of AD9854 in Software Defined Radar System

As shown in Figure 2.9, the ramped FSK mode of AD9854 can be used ideally in this radar system. Figure 2.10 shows the circuit schematic for the AD9854 part of the software defined radar.

The component Y1 located at the left-bottom corner of the Figure 2.10 is a stable crystal oscillator whose oscillating frequency is 200MHz. This oscillator provides the frequency reference for AD9854. The component MN3 LT1963AEQ-3.3 is a voltage converter from 5.0V to 3.3V. The two logic chips SN74LV595 is a converter from serial digital signal to parallel digital signal, through which the MCU in DSP module is able to access all the register in AD9854. The FSK (net label DDS\_FSK) pin is an individual signal wire directly connected to MCU through an individual signal wire. This individual FSK signal makes the accessing speed faster than the serial-parallel path.

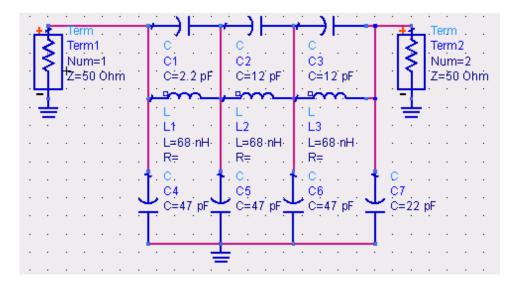

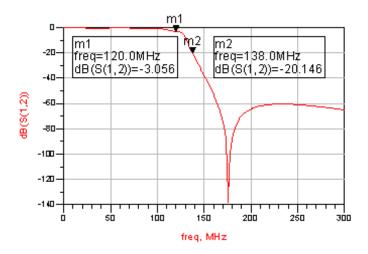

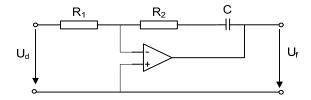

The last part of this schematic is the output low pass filter for the DDS output1. This low pass filter is simulated in ADS, as shown in Figure 2.10 and Fig. 3.11. The -3dB point of the low pass filter is around 120MHz and the -20dB point is at 138MHz. Since AD9854 is a chip mixing both digital circuits and analog circuits, the noise from digital part and the harmonic signal from the limited resolution DACs may be passed onto the analog signal labeled with 'TO PLL'. This low pass filter produces a "clear" signal for PLL.

Figure 2.10 AD9854 circuit.

Figure 2.11 Filter for DDS output in ADS

Figure 2.12 Simulation results of our DDS low pass filter

In Table 2-2, dds\_work\_for\_radar() is called by the main function running in the MCU to initialize AD9854 to a proper condition. ddsSetRef(200) sets the external reference oscillator frequency (200MHz here). The function ddsSetPll(200) sets the internal frequency multiplier to generate a 200MHz internal system clock. Then, two frequency tuning words are set for the sweep beginning and ending frequency, 45.7 and 46.4MHz, respectively. Then, the code set the operating mode of AD9854 to the ramped FSK mode. ddsSetScanArgument (14,1) sets the frequency scanning step to 14Hz per micro-second.

Lines 11 and 12 set the DAC output magnitude to maximum by writing 0xFFF to register No.8. At last, DDSGo() validates all of the above settings and starts AD9854 in the corresponding mode.

Table 2-2 Initialization code of AD9854

```

1. #define DDS LOW FREO MHZ

#define DDS HIGH FREQ MHZ 46.4

2.

3.

4. void dds work for radar(void)

5.

{

6.