|                         | Exploration of Nonlinear Devices and Nonlinear Transmission Line<br>Techniques for Microwaves Applications                                                                                                                                                                           |

|-------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Auteur: Author:         | Yangping Zhao                                                                                                                                                                                                                                                                        |

| Date:                   | 2018                                                                                                                                                                                                                                                                                 |

| Type:                   | Mémoire ou thèse / Dissertation or Thesis                                                                                                                                                                                                                                            |

| Référence:<br>Citation: | Zhao, Y. (2018). Exploration of Nonlinear Devices and Nonlinear Transmission Line Techniques for Microwaves Applications [Thèse de doctorat, École Polytechnique de Montréal]. PolyPublie. <a href="https://publications.polymtl.ca/3679/">https://publications.polymtl.ca/3679/</a> |

# Document en libre accès dans PolyPublie Open Access document in PolyPublie

| URL de PolyPublie:<br>PolyPublie URL:    | https://publications.polymtl.ca/3679/ |

|------------------------------------------|---------------------------------------|

| Directeurs de<br>recherche:<br>Advisors: | Ke Wu, & Simon Hemour                 |

| <b>Programme:</b><br>Program:            | génie électrique                      |

## UNIVERSITÉ DE MONTRÉAL

# EXPLORATION OF NONLINEAR DEVICES AND NONLINEAR TRANSMISSION LINE TECHNIQUES FOR MICROWAVES APPLICATIONS

# YANGPING ZHAO DÉPARTEMENT DE GÉNIE ÉLECTRIQUE ÉCOLE POLYTECHNIQUE DE MONTRÉAL

THÈSE PRÉSENTÉE EN VUE DE L'OBTENTION

DU DIPLÔME DE PHILOSOPHIAE DOCTOR

(GÉNIE ÉLECTRIQUE)

SEPTEMBRE 2018

## UNIVERSITÉ DE MONTRÉAL

# ÉCOLE POLYTECHNIQUE DE MONTRÉAL

#### Cette thèse intitulée:

# EXPLORATION OF NONLINEAR DEVICES AND NONLINEAR TRANSMISSION LINE TECHNIQUES FOR MICROWAVES APPLICATIONS

présentée par : ZHAO Yangping

en vue de l'obtention du diplôme de : <u>Philosophiae Doctor</u>

a été dûment acceptée par le jury d'examen constitué de :

- M. LAURIN Jean-Jacques, Ph. D., président

- M. WU Ke, Ph. D., membre et directeur de recherche

- M. <u>HEMOUR Simon</u>, Ph. D., membre et codirecteur de recherche

- M. AKYEL Cevdet, D. Sc. A., membre

- M. NABKI Frédéric, Ph. D., membre externe

# **DEDICATION**

To my parents and sisters

To my wife Xian Liu

#### **ACKNOWLEDGEMENTS**

I would like to express my sincere gratitude to many people who helped on my Ph.D. projects and the completion of my thesis. Foremost, I would like to express my deepest gratitude to my supervisor Prof. Ke Wu for providing me the opportunity to purse my Ph.D. in his group. What I learned from him is not only the strict research attitude, but also the way to communicate with people and to integrate with the local culture. His opinions on leadership, volunteer, innovation, and creativities etc. give me large impact on my career and life. Thanks for his inspiring guidance, encouragement on each of my project, and the tolerance on the time I spent on volunteer work for student association as well as non-for-profit organization.

I would like to thank my co-supervisor Prof. Simon Hemour for his guidance. I started to work with him on the first project when I just arrived Montreal. I was impressed by his open mind, strong theoretical foundation and strong problem-solving ability. I still can remember the moments he taught me to use the software Origin, Labview and probe station etc. step by step. Thanks for those countless deep discussions on the projects.

I would also like to thank the president Prof. Jean-Jacques Laurin, and other committee members Prof. Akyel Cevdet and Prof. Nabki Frederic for reviewing my thesis in the beautiful summer time and providing me with their valuable insights and comments.

I would like to thank my master's supervisor Prof. Taijun Liu, I may not have the chance to study abroad without his help. Thanks for his consistent guidance and support during my Ph.D. study. I also would like to thank Prof. Yan Ye for her help when I applied my master university, I still can remember that a few minutes when she saw my application email just before the deadline. Lucky thing usually happens at those inadvertent minutes.

I would like to thank all the technicians at Poly-Grames Research Center, Mr. Jules Gauthier, Mr. Traian Antonescu, Mr. Steve Dubé, Mr. Maxime Thibault, Mr. Jean-Sébastien Décarie, and Mr. David Dousset for their support in the realization of my research. "Nothing Is Impossible" could be the best words to describe their work. My sincere gratitude extends to Mrs. Nathalie Levesque and Mrs. Rachel Lortie for all their administrative works during my study.

I am very grateful to my colleagues in our research group for their friendship and help. I would like to thank Kuangda Wang, who sat behind my seat, for all those useful discussions although we

are not in the same project. We always have lunch and dinner together in the school cafeteria, and work together until midnight. Thanks for Dr. Jiapin Guo for those valuable discussion on my project when we walk together to home, which push me continuedly explore the innovativeness of the projects. I would also appreciate the discussions with other colleagues such as Xiaoqiang Gu, Jiudong Wu, Dr. Lei Guo, Dr. Fang Zhu, Wei Wang, Tao Jiang, Wentao Lin, Ruizhi Liu, Yifan Yin, Desong Wang, Muhib Ur Rahman, Tae Hak Lee, etc.

I would like to extend my gratitude to the colleagues from the Department of Physics Astronomy of University of Manitoba, Prof. Can-Ming Hu, Dr. Lihui Bai, Dr. Yongsheng Gui, Dr. Zhaohui Zhang, for the collaboration and discussion on my first project.

During my Ph.D. study, I co-founded a non-for-profit organization, called Research & Development Frontiers Institute, which aims to build the youth generation high-tech talent ecosystem. The platform is helping hundreds and thousands of researchers and entrepreneurs. Thanks for the effort of my partners and our team, we already gained considerable achievements, which makes my research career more colorful.

I will express my sincere gratitude to my parents, two sisters and parents-in-law for their endless love, encouragement and unconditional support. Special thanks to my wife Dr. Xian Liu, who accompany with me in my hardest time and best time in the past 11 years. Her support and encouragement gave me more confidence and possibility to do what I want and to realize my dream.

#### RÉSUMÉ

Les systèmes de communication modernes dépendent fortement des circuits non linéaires, tels que les amplificateurs de puissance (PA), les mélangeurs, les multiplicateurs, les oscillateurs, les commutateurs, etc., qui sont construits à partir de composants non linéaires passifs (comme des diodes) ou actifs (par exemple des transistors). Cette thèse étudie les dispositifs non linéaires passifs traditionnels et émergents, ainsi que les techniques de lignes de transmission non linéaires (NLTL). Plusieurs de leurs applications micro-ondes ont également été étudiées, y compris la récupération d'énergie sans fil, la synthèse d'impédance électronique et l'adaptation d'impédance bidimensionnelle (inductive et capacitive).

Dans le chapitre 1, sont d'abord étudiés les dispositifs non linéaires traditionnels résistifs, capacitifs et inductifs. Les dispositifs non linéaires émergents, y compris les dispositifs MEMS et la spindiode, sont ensuite explorés. La construction physique de base, les principes de fonctionnement, ainsi que les caractéristiques et applications pour divers types de dispositifs non linéaires sont expliqués et comparés. Les lignes de transmission non-linéaires (NLTL) traditionnelles utilisant des dispositifs non linéaires capacitifs (varactor, BST etc.) ou inductifs (ferrite saturée), et la technique hybride NLTL émergente utilisant à la fois des dispositifs non linéaires capacitifs et inductifs sont également étudiées.

Le chapitre 2 examine les techniques de conversion d'énergie micro-ondes à courant-continu de faible puissance à la fine pointe de la technologie. Une image complète de l'état de l'art sur cet aspect est donnée graphiquement. Elle compare différentes technologies telles que le transistor, la diode et les technologies CMOS. Depuis le tout début des techniques intégrées RF et micro-ondes et de la récupération d'énergie, les diodes Schottky ont été le plus souvent utilisées dans les circuits de mélange et de redressement. Cependant, dans des applications spécifiques de récupération d'énergie, la technique des diodes Schottky ne parvient pas à fournir une efficacité satisfaisante de conversion RF-dc. Suite aux limitations mises en évidence des dispositifs actuels, ce travail introduit, pour la première fois, un composant non linéaire pour une redressement de faible puissance, basé sur une découverte récente en spintronique, à savoir, la jonction tunnel magnétique, parfois appelée spindiode. Un modèle équivalent de spindiode est développé pour décrire le comportement en fréquence. Des études paramétriques complètes montrent que la capacité d'interface, plutôt que la capacité géométrique, joue un rôle clé dans son efficacité aux

hyperfréquences. L'ingénierie de la résistance d'interface est proposée comme une solution pour améliorer les pertes dues aux composants parasites, ainsi que la fréquence de fonctionnement de la spindiode. En plus d'une analyse du rôle de la non-linéarité et de la résistance en absence de polarisation dans le processus de redressement de la spindiode, le travail explique comment la spindiode pourrait améliorer le rendement de redressement même à très faible puissance et comment cette technique changerait les paradigmes de conception des dispositifs et circuits à diodes.

Au chapitre 3, un syntoniseur d'impédance électronique utilisant la résistance négative des diodes à effet tunnel est proposé. Outre le fait qu'il s'agisse d'une solution intéressante pour synthétiser l'impédance avec un coefficient de réflexion supérieur à un, ce schéma s'avère plus simple et consomme moins de puissance que les techniques de l'état de l'art. La topologie globale du circuit comprend deux parties, à savoir un bloc d'impédance comprenant une diode PIN combiné avec une diode à effet tunnel pour générer un ensemble de points d'impédance, et un déphaseur à 360° basé sur une géométrie de ligne de transmission non linéaire (NLTL) pour faire tourner l'ensemble des points d'impédance autour du diagramme de Smith de 1.5 à 5 GHz. La puissance de fonctionnement du syntoniseur électronique est inférieure à -25 dBm, limitée par la diode à effet tunnel. Dans le cas le plus défavorable, la consommation d'énergie maximale du syntoniseur électronique est inférieure à 3 mW, ce qui signifie qu'il pourrait fonctionner avec une pile. Un tel accordeur électronique serait utile pour le développement de systèmes de caractérisation du bruit sur gaufre.

Dans le chapitre 4, nous proposons et présentons tout d'abord une procédure de conception analytique pour le synthétiseur à impédance électronique distribuée (EIS). Bénéficiant de caractéristiques avantageuses tels qu'un réglage rapide, un faible encombrement et une intégration facile, l'EIS a été développé pour les systèmes de caractérisation load-pull sur gaufre, les réseaux accordables (TMN), les appareils et systèmes reconfigurables, etc. Les conceptions précédentes de l'EIS étaient principalement basées sur des données empiriques plutôt que sur des solutions analytiques. Dans ce travail, la méthode d'optimisation d'essaim de particules (PSO) est également introduite pour optimiser l'EIS non uniformément distribué que nous proposons et qui comprend un circuit de réglage et un circuit non uniformément distribué. Les résultats expérimentaux démontrent que la structure non uniformément distribuée proposée permet non seulement d'améliorer la couverture de l'abaque de Smith, mais aussi de réduire sa taille (par rapport à une structure uniforme). L'EIS non uniforme fabriqué fonctionne de 0.8 à 2.5 GHz et présente un bon

accord entre la théorie et la mesure. En outre, un ensemble complet de figures de mérite est présenté pour évaluer l'EIS fabriqué, parmi lesquelles une théorie de distribution de tension qui est développée pour l'EIS distribué et fournit un moyen de comprendre et prédire la tenue en puissance et la non-linéarité de EIS au bord de sa région linéaire.

Dans le chapitre 5, un circuit d'accord bidimensionnel basé sur une technique hybride de ligne de transmission non linéaire NLTL est analysé dans les domaines temporel et fréquentiel. Les paramètres de la permittivité et perméabilité effective sont extraits des S-paramètres de la structure périodique. L'impédance caractéristique ainsi que la vitesse de phase de la ligne de transmission non linéaire NLTL sont étudiées théoriquement en accordant à la fois la permittivité effective et la perméabilité. La théorie sera ensuite validée par des expériences et des simulations pour les matériaux non-magnétiques, NLTL avec varactors ainsi que la ligne microruban à base de ferrite. Enfin, les applications en mode petit et grand signaux des circuits d'accord bidimensionnel sont discutés.

#### **ABSTRACT**

Modern communication systems are heavily dependent on nonlinear circuits, such as PA, mixer, multiplier, oscillator, switch, etc., the core of which are either passive nonlinear elements and devices (e.g. diodes) or active nonlinear components and devices (e.g. transistors). This thesis aims at investigating a number of traditional and emerging passive nonlinear devices and nonlinear transmission line (NLTL) techniques, and developing four of their microwave applications such as wireless power harvesting, electronic impedance synthesizer, and two-dimensional tuning circuit.

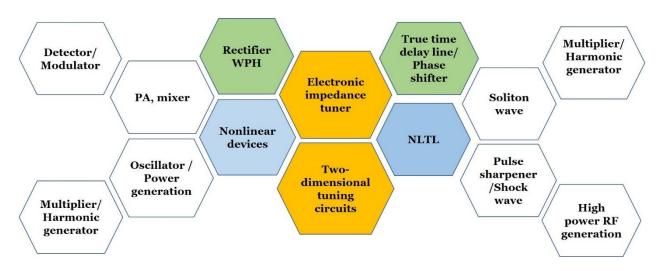

In Chapter 1, traditional nonlinear devices in terms of the categories of resistive, capacitive and inductive are firstly investigated. Emerging nonlinear devices including microelectromechanical system (MEMS) devices and spindiodes are then explored. The basic physical constructions, operation principles, and characteristics as well as applications of various types of nonlinear devices are explained and compared. Traditional NLTL techniques make use of either capacitive nonlinear devices (varactor, BST etc.) or inductive nonlinear devices (saturated ferrite), and emerging hybrid NLTL techniques are also studied through the deployment of both nonlinear capacitive and inductive devices.

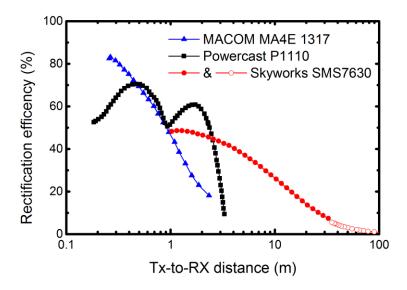

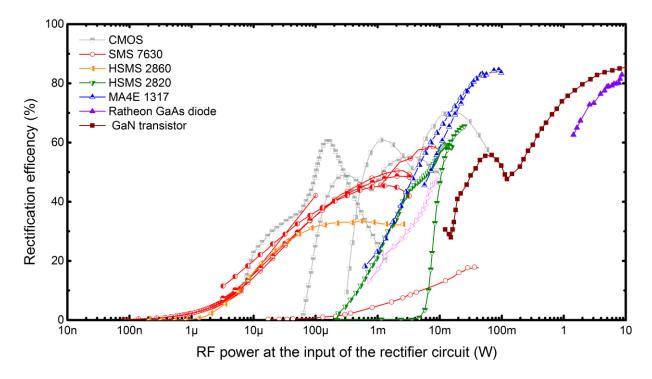

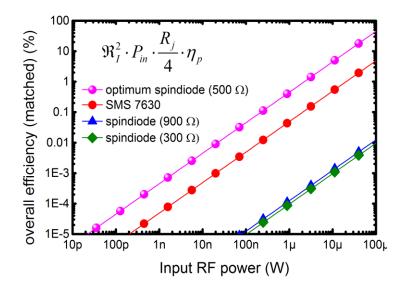

Chapter 2 examines the state-of-the-art low-power microwave-to-dc energy conversion techniques. A comprehensive picture of the state-of-the-art on this aspect is given graphically, which compares different technologies such as transistor, diode, and CMOS schemes. Since the very beginning of RF and microwave integrated techniques and energy harvesting, Schottky diodes as the undisputable dominant choice, have been widely used in mixing and rectifying circuits. However, in specific µW power-harvesting applications, the Schottky diode technique seemingly fails to provide a satisfactory RF–dc conversion. Subsequent to the highlighted limitations of current devices, this work introduces, for the first time, a nonlinear component for low-power rectification based on a recent discovery in spintronics, namely, the Magnetic Tunnel Junction, also called spindiode. An equivalent model of spindiode is developed to describe the frequency behavior. Full parametric studies show that the interfacial capacitance, rather than the geometric capacitance, as it is usually the case for diode, plays a crucial role in the drop of efficiency in microwave frequency applications. Interfacial resistance engineering is proposed as a solution to improve the parasitic factor, as well as the operation frequency of spindiode. Along with an analysis of the role of nonlinearity and zero bias resistance in the rectification process of the spindiode, it is shown how

the spindiode could enhance the rectification efficiency even at a very low-power level and how this technique would shift the design paradigms of diode-based devices and circuits.

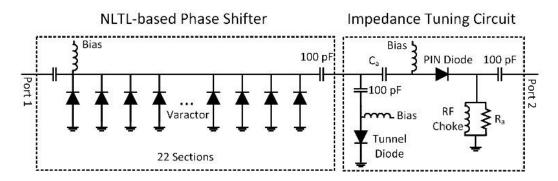

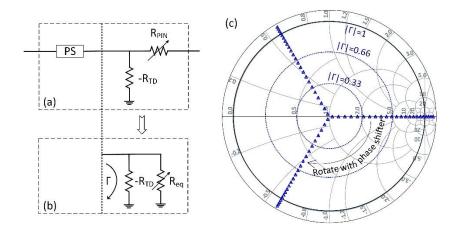

In Chapter 3, an electronic impedance tuner using the negative resistance of a tunneling diode is proposed. Aside from the fact that it is an interesting solution to synthesize impedance with reflection coefficient larger than one, this scheme is proven to be simpler and consume less power than the state-of-the-art techniques. The overall circuit topology consists of two parts, namely impedance tuning circuit including a hybrid block of PIN and tunneling diode for generating a set of impedance points, and wideband nonlinear transmission line (NLTL)-based 360° phase shifter for rotating the set of impedance points around the Smith chart from 1.5 to 5 GHz. The operating power of the electronic tuner is below -25 dBm, which is limited by the tunneling diode negative slope range. The worse-case maximum power consumption of the electronic tuner is as low as 3 mW, which would allow battery-powered operation. Such an electronic tuner should be useful for the development of on-wafer noise characterization systems.

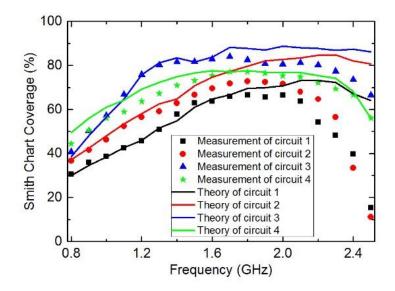

In Chapter 4, we propose and present, first of all, a semi-closed form design procedure for the distributed electronic impedance synthesizer (EIS). Benefiting from advantageous features of fast tuning, small size and easy integration, the EIS has been developed for on-wafer load-pull characterization systems, tunable matching networks (TMN), reconfigurable devices and systems etc. However, the previous designs of the EIS were mostly based on empirical data instead of closed-form design. Moreover, incomplete figures of merit are usually utilized to optimize and evaluate the EIS. In this work, a particle swarm optimization (PSO) method is introduced to optimize the proposed non-uniformly distributed EIS, which comprises an adjusting circuit and a non-uniformly distributed circuit. Experimental results demonstrate that the proposed non-uniformly distributed structure can not only improve the Smith chart coverage but also reduce the size, as compared to the uniform counterpart. The fabricated non-uniform EIS operating from 0.8 to 2.5 GHz, exhibits a good agreement between theory and measurement. Furthermore, the most comprehensive figures of merit are presented to evaluate the fabricated EIS, among which a voltage distribution theory is developed for the distributed EIS, it provides a way of understanding and predicting the power-handling capacity and nonlinearity of EIS from its linear region.

In Chapter 5, two-dimensional tuning circuit based on hybrid NLTL technique is analyzed in both time domain and frequency domain. The parameter extraction method of effective permittivity and

permeability is developed based on the S-parameters analysis. The characteristics of the impedance and phase velocity of ferrite-based NLTL are studied theoretically by tuning both the effective permittivity and permeability. The theory is then validated by experiments and simulations for non-magnetic material, namely NLTL with varactors as well as ferrite-based microstrip line. Finally, the small signal and large signal applications of two-dimensional tuning circuits are discussed.

# TABLE OF CONTENTS

| DE  | ICATION                                               | III      |

|-----|-------------------------------------------------------|----------|

| AC  | NOWLEDGEMENTS                                         | IV       |

| RÉ  | J <b>M</b> É                                          | VI       |

| ΑB  | TRACT                                                 | IX       |

| TA  | LE OF CONTENTS                                        | XII      |

| LIS | OF TABLES                                             | XV       |

| LIS | OF FIGURES                                            | XVI      |

| LIS | OF SYMBOLS AND ABBREVIATIONS                          | XXV      |

| СН  | PTER 1 INTRODUCTION                                   | 1        |

| 1.1 | Traditional RF and microwave nonlinear devices        | 2        |

|     | 1.1.1 Resistive nonlinear devices                     | 2        |

|     | 1.1.2 Capacitive nonlinear devices                    | 18       |

|     | 1.1.3 Inductive nonlinear devices                     | 19       |

| 1.2 | Emerging RF and microwave nonlinear devices           | 20       |

| 1.3 | Traditional NLTL techniques                           | 25       |

|     | 1.3.1 Classification of NLTL                          | 26       |

|     | 1.3.2 Application of NLTL                             |          |

| 1.4 | Emerging hybrid NLTL                                  | 28       |

| 1.5 | Thesis Outline                                        | 30       |

| СН  | PTER 2 LOW-POWER HIGH-EFFICIENCY RF AND MICROWAVI     | E ENERGY |

| HA  | VESTING                                               | 31       |

| 2.1 | Physical limitation of RF and microwave rectification | 35       |

|     | 2.1.1 Matching efficiency                             | 36       |

|     | 2.1.2 Parasitic component efficiency                  | 37       |

|     | 2.1.3 RF-to-dc conversion efficiency                  | 38       |

|     | 2.1.4 DC power transfer efficiency                    | 40       |

|     | 2.1.5          | Overall efficiency                                             | 40          |

|-----|----------------|----------------------------------------------------------------|-------------|

| 2.2 |                | Strength and limitation of Schottky diodes                     | 41          |

| 2.3 |                | Use of spindiode for rectification                             | 43          |

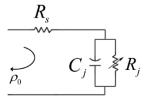

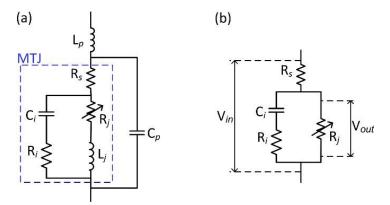

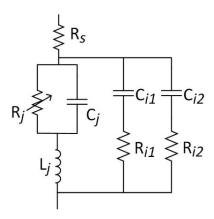

|     | 2.3.1          | Device modeling                                                | 44          |

| 2.4 |                | Comparison of Schottky diode and spindiode                     | 58          |

| 2.5 |                | Discussion of capability of spindiode rectification            | 60          |

| 2.6 |                | Conclusion                                                     | 61          |

| CH  | APTEF          | R 3 NEGATIVE RESISTANCE-BASED ELECTRONIC IMPEDANCE             | E TUNER. 63 |

| 3.1 |                | Principle of negative resistance-based tuner                   | 63          |

| 3.2 |                | Modeling of tunneling diode and PIN diode                      | 65          |

| 3.3 |                | Design of NLTL-based phase shifter                             | 66          |

| 3.4 |                | Validation of the proposed tuner                               | 72          |

| 3.5 |                | Conclusion                                                     | 76          |

|     | APTEF<br>NTHES | R 4 NON-UNIFORMLY DISTRIBUTED ELECTRONIC I                     |             |

| 4.1 |                | Semi-closed form design procedure                              | 80          |

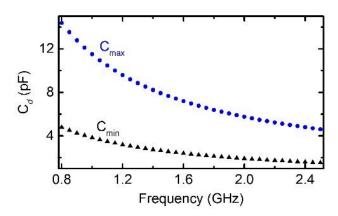

|     | 4.1.1          | Determination of the range of loading capacitance              | 81          |

|     | 4.1.2          | Determination of the range of distance d                       | 83          |

|     | 4.1.3          | Selection of PIN diode and determination of Z <sub>0</sub>     | 86          |

| 4.2 |                | Optimization                                                   | 88          |

|     | 4.2.1          | Definition of fitness function                                 | 88          |

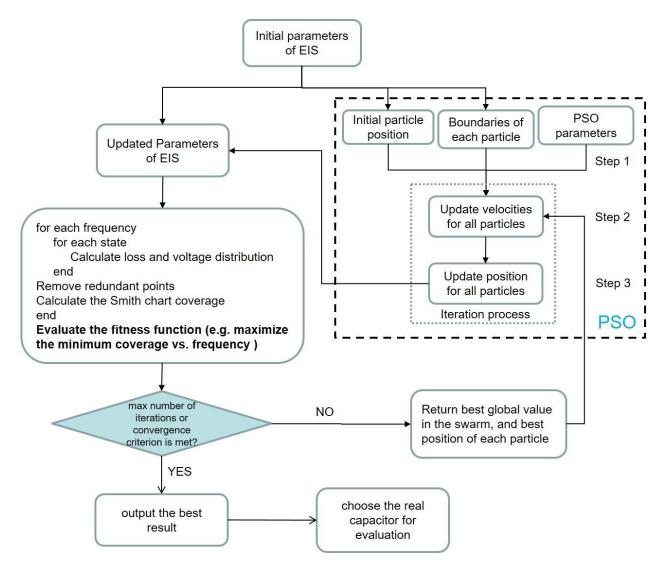

|     | 4.2.2          | Description of optimization process of PSO                     | 97          |

| 4.3 |                | Experiment                                                     | 99          |

| 4.4 |                | Evaluation                                                     | 104         |

| 4.5 |                | Conclusion                                                     | 114         |

| CH  | APTEF          | R 5 TWO-DIMENSIONAL TUNING CIRCUITS AND APPLICATION            | ONS 116     |

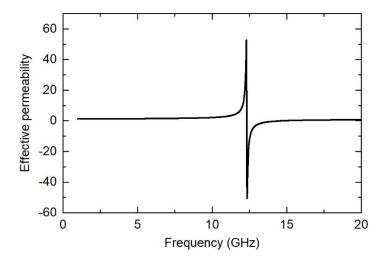

| 5.1 |                | Analysis of hybrid NLTL technique                              | 116         |

| 5.2 |                | Study of ferrite                                               | 119         |

| 5.3 |                | Parameters extraction of complex permittivity and permeability | 124         |

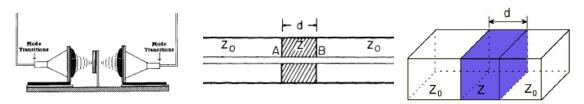

|     | 5.3.1          | Methodology                                                    | 126         |

|     | 5.3.2          | Validation                                                     | 132         |

| 5.4 |                | Small signal application of two-dimensional tuning circuits    | 136         |

| 5.5     | Large | e signal application of two-dimensional tuning circuits | 138 |

|---------|-------|---------------------------------------------------------|-----|

| 5.6     | Conc  | lusion                                                  | 139 |

| CHAPTE  | R 6   | CONCLUSION AND FUTURE WORK                              | 140 |

| BIBLIOG | RAPH  | Y                                                       | 143 |

| APPENDI | IX    |                                                         | 160 |

# LIST OF TABLES

| Table 1.1: Comparison of traditional and emerging passive nonlinear devices          | 2           |

|--------------------------------------------------------------------------------------|-------------|

| Table 1.2: Comparison of traditional and emerging nonlinear transmission line (NLTL) | techniques. |

|                                                                                      | 25          |

| Table 2.1: Description of circuits reported in Fig. 2.2                              | 34          |

| Table 2.2: Value of equivalent model elements shown in Fig. 2.12.                    | 59          |

| Table 3.1: Comparison with the state-of-the-art work of electronic impedance tuner   | 75          |

| Table 4.1: Studies of power-handling capacity and nonlinearity of EIS.               | 93          |

| Table 4.2: Final dimension of non-uniform distributed EIS. Unit: capacitor: pF; imp  | oedance: Ω; |

| distance: mm.                                                                        | 103         |

| Table 4.3: Summarization of criteria to evaluate TMN and EIS.                        | 106         |

# LIST OF FIGURES

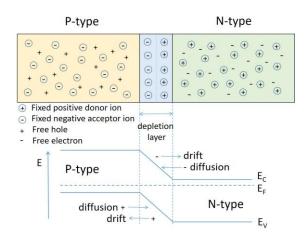

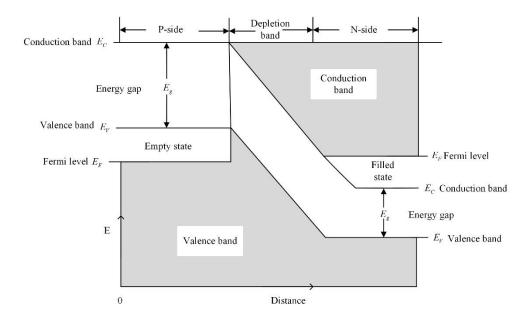

| Figure 1.1: Energy band diagram of PN junction diode.                                                                                  | 3  |

|----------------------------------------------------------------------------------------------------------------------------------------|----|

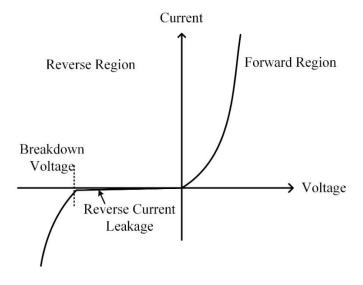

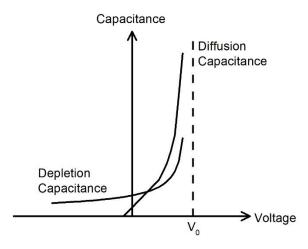

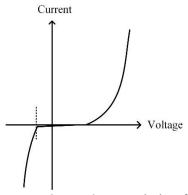

| Figure 1.2: IV characteristic of conventional PN junction diode                                                                        | 4  |

| Figure 1.3: Junction capacitance-voltage characteristic of PN junction diode                                                           | 5  |

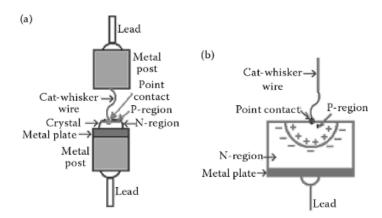

| Figure 1.4: Point-Contact diode. (a) Construction and constituents and (b) p-region contact [1]                                        | _  |

| Figure 1.5: Schottky diode. (a) Point-contact type, (b) deposited metal type [1]                                                       | 7  |

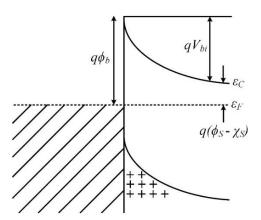

| Figure 1.6: Energy band diagram for ideal Schottky barrier junction [2]                                                                | 7  |

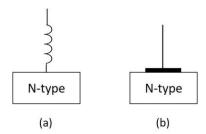

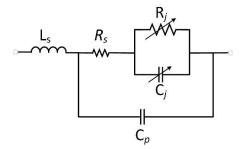

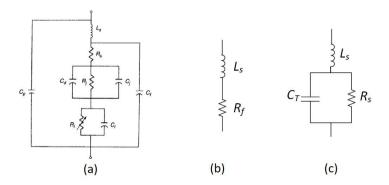

| Figure 1.7: Equivalent circuit of Schottky diode.                                                                                      | 8  |

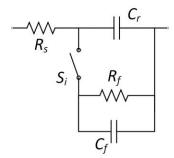

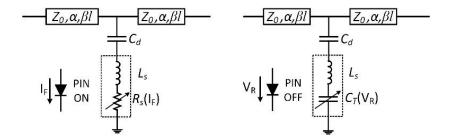

| Figure 1.8: (a) Equivalent circuits of PIN diode; Simplified equivalent circuit (b) us bias and (c) under reverse bias [1, 2].         |    |

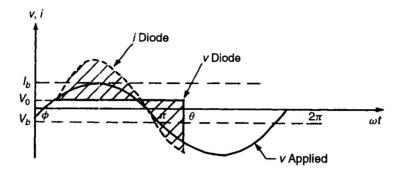

| Figure 1.9: Diagram of current and voltage waveforms of SRD [2]                                                                        | 11 |

| Figure 1.10: Equivalent circuit of SRD [2].                                                                                            | 12 |

| Figure 1.11: Energy bands of tunnel diode at zero-bias condition [1]                                                                   | 13 |

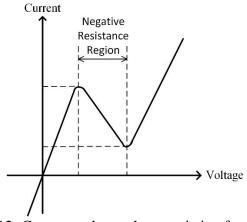

| Figure 1.12: Current-voltage characteristic of tunnel diode.                                                                           | 13 |

| Figure 1.13: Current-voltage characteristic of backward diode                                                                          | 14 |

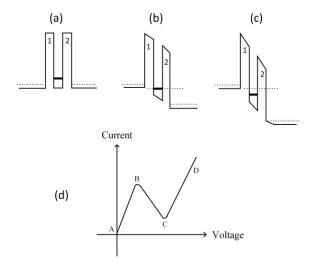

| Figure 1.14: Operation mechanism of double-barrier RTD. Energy bands for three (a)-(c); (d) IV curve of RTD.                           |    |

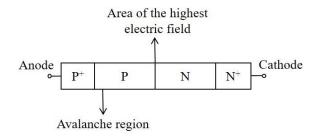

| Figure 1.15: Schematic diagram of IMPATT diode.                                                                                        | 18 |

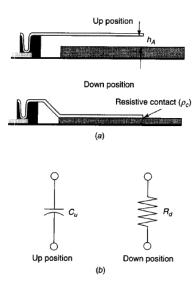

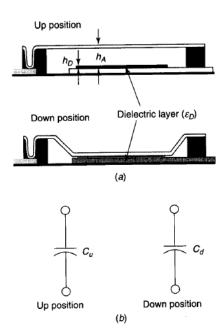

| Figure 1.16: (a) Cross-sectional view and (b) equivalent circuit of resistive contact M [2].                                           |    |

| Figure 1.17: (a) Cross-sectional view and (b) equivalent circuit of capacitive contact M  [2].                                         |    |

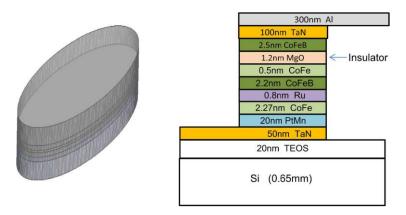

| Figure 1.18: Description of the device (sketch on the right not to scale). Elliptical particular typical section of 85nm x 220nm [27]. |    |

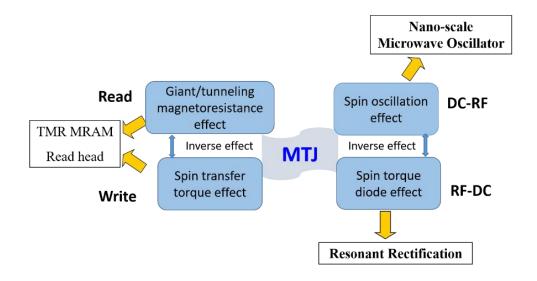

| Figure 1.19: Four properties and corresponding applications of MTJ                                                                     | 22 |

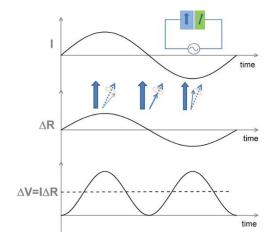

| Figure 1.20: Spin torque diode effect24                                                                                                                                                                                                                               |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

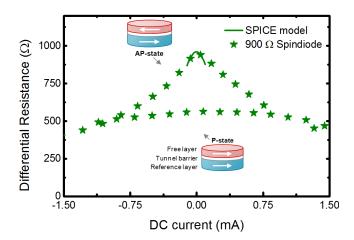

| Figure 1.21: Measurements and modeling results of differential resistance of devices obtained by taking the first derivative of voltage with respect to current                                                                                                       |

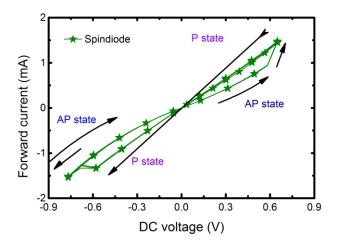

| Figure 1.22: IV characteristic of spindiode. Transitions between the two magnetic states of a spindiode are obtained for an applied voltage of 600 mV for AP-to-P and -600 mV for P-to-AP.                                                                            |

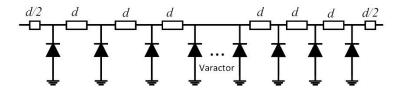

| Figure 1.23: Circuit diagram of varactor-loaded NLTL                                                                                                                                                                                                                  |

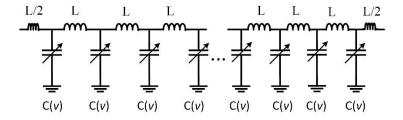

| Figure 1.24: Equivalent LC circuit of varactor-loaded NLTL                                                                                                                                                                                                            |

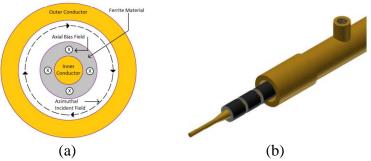

| Figure 1.25: (a) Cross sectional diagram and (b) 3D model of the ferrite-loaded NLTL [48]27                                                                                                                                                                           |

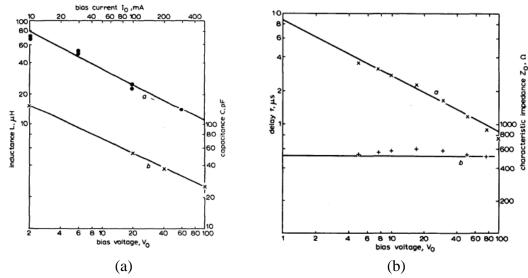

| Figure 1.26: (a) Characteristics of nonlinear inductance and capacitance; (b) variation of delay and characteristic impedance with bias [72].                                                                                                                         |

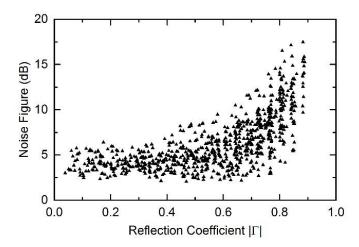

| Figure 2.1: Maximum rectification efficiency that can be expected from state-of-the-art commercial rectifying devices.                                                                                                                                                |

| Figure 2.2: State of the art microwave rectifier circuits (measurements). Color/shape of the scatters indicate on which nonlinear device a circuit of interest is based (see Table 2.1). Rectifiers that do not include matching circuit losses are not reported here |

| Figure 2.3: Efficiency link of a rectifying circuit, from RF power to dc power. $\eta_M$ stands for                                                                                                                                                                   |

| matching efficiency, $\eta_p$ is the efficiency associated with parasitic losses, $\eta_0$ is the efficiency                                                                                                                                                          |

| of conversion that takes place in the nonlinear device (core conversion), and $\eta_{DC\_transfer}$ is the                                                                                                                                                            |

| efficiency of dc power transfer from the nonlinear device to the dc load. (A full rectenna would also include the antenna radiation efficiency and dc/dc converter efficiency). The efficiency link is illustrated in Fig. 2.7 for SMS7630 diode.                     |

| Figure 2.4: Model of a nonlinear component used in the analysis of this section                                                                                                                                                                                       |

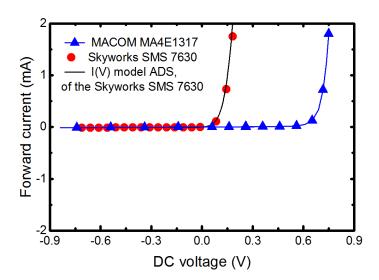

| Figure 2.5: I (V) curve of Skyworks SMS7630 low barrier Schottky diode (red dots) and M/A-COM MAE1317 high barrier Schottky diode                                                                                                                                     |

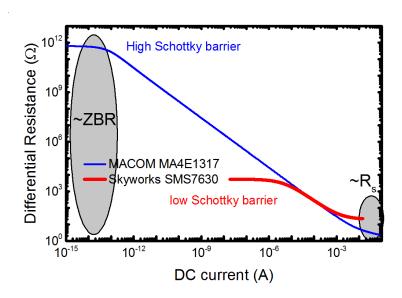

| Figure 2.6: Differential resistance of the devices obtained by taking the first derivative of the voltage with respect to the current (Data calculated from the spice model). Under high                                                                              |

| bias (> 100mA), the differential resistance is very close to the series resistance (Rs). Also,       |

|------------------------------------------------------------------------------------------------------|

| under low bias (< pA), the value tends to the Zero Bias Resistance (ZBR). Note that in reality,      |

| differential resistance does not reach value higher than few hundreds of kilo-Ohm due to             |

| leakage current in the device42                                                                      |

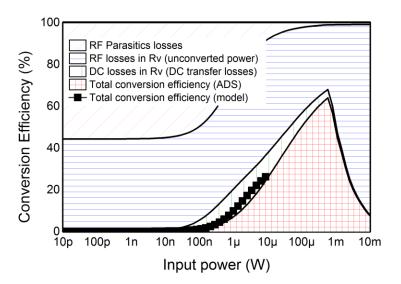

| Figure 2.7: Study of the losses in a rectifying circuit based on the SMS7630 diode. Result are given |

| considering a perfect matching and no circuit losses based on circuit simulation (ADS). The          |

| low power analytical model described in section 2.1 is plotted with boxes. Frequency is              |

| 2.45GHz and output load is 1 k $\Omega$                                                              |

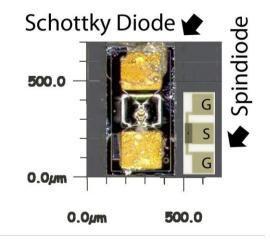

| Figure 2.8: Photograph describing the Schottky diode MACOM MA4E13 (left) and the on-wafer            |

| spindiode (right) from Everspin Technologies. Three pads are used for measurement purposes           |

| using a Ground-Signal-Ground (GSG) RF probe. The spindiode area is less than 0.015µm²                |

| and is therefore not visible on the microscope image. Its location is indicated by a black dot.      |

| 44                                                                                                   |

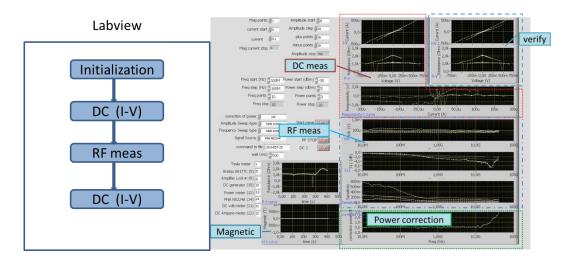

| Figure 2.9: The frame and front panel of the developed program for spin diode measurement45          |

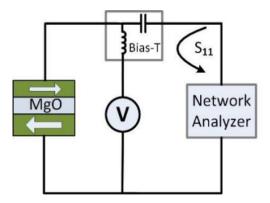

| Figure 2.10: Schematic diagram of the setup based on Vector Network Analyzer that is used to         |

| measure voltage coefficient, the voltmeter is assigned to measure the non-resonant                   |

| rectification through a bias-T45                                                                     |

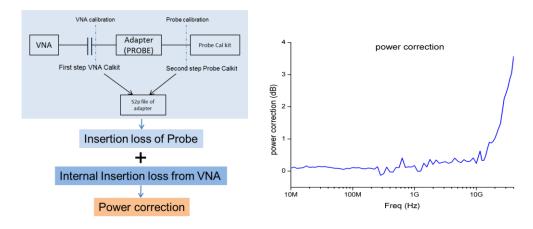

| Figure 2.11: Power calibration with de-embedding technique and power correction                      |

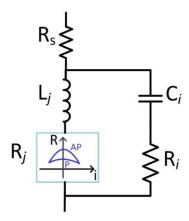

| Figure 2.12: Equivalent MTJ model with nonlinear description of junction resistance and high         |

| frequency parasitic components. Test pads effect is not shown in this model47                        |

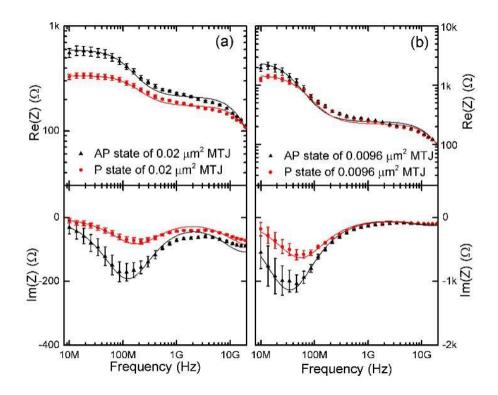

| Figure 2.13: Real and imaginary parts (Re(Z) and Im(Z), respectively) of the impedance for two       |

| MTJs with different junction areas (a) 0.02 and (b) 0.0096 µm² in both AP and P states. The          |

| points with error bar denote the experimental data while the solid lines represent the               |

| simulation data using the model                                                                      |

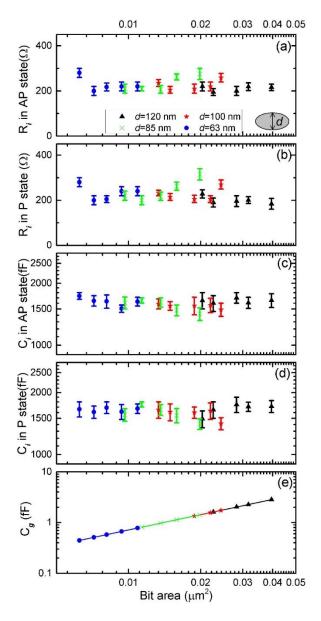

| Figure 2.14: (a) - (d) Parametric study of interfacial resistance and interfacial capacitance with   |

| error bar in both AP and P state. (e) Calculated geometrical capacitance for all of the samples      |

| with different bit area. Circle and cross denote the samples with short axis 63 nm and 85 nm,        |

| respectively, while star and triangle denote the samples with short axis 100 nm and 120 nm,          |

| respectively50                                                                                       |

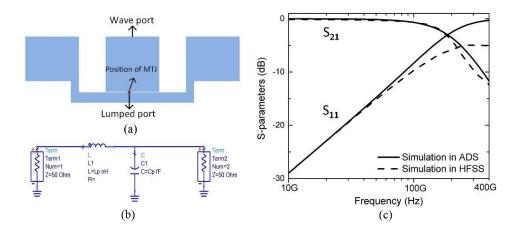

| Figure 2.15: (a) 3-D electromagnetic model of test pads, in which the wave port is defined as port             |

|----------------------------------------------------------------------------------------------------------------|

| 1, and the lumped port is defined as port 2. (b) Equivalent circuit model in ADS. (c)                          |

| Comparison of S-parameters from two simulations                                                                |

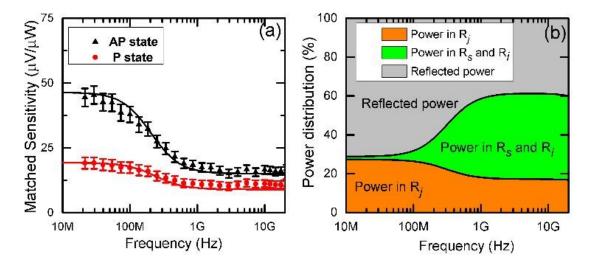

| Figure 2.16: (a) Matched sensitivity calculated from measurement of rectified voltage and injected             |

| power, considering the uncertainty from VNA and volt-meter. (b) Stacked area chart of power                    |

| distribution analysis for the $0.02~\mu\text{m}^2$ MTJ sample, the gray part stands for the power reflected    |

| towards the generator, the orange part represents the power passing through the nonlinear                      |

| junction resistance and the green part represents the power consumed in the series resistance                  |

| R <sub>s</sub> and interfacial resistance R <sub>i</sub> 53                                                    |

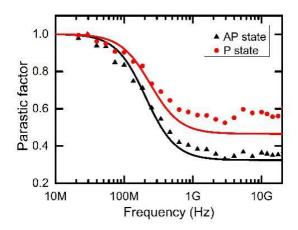

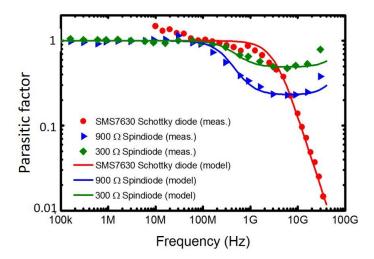

| Figure 2.17: Extracted parasitic factor is used to evaluate the performance of MTJs at microwave               |

| frequencies. The points denote the experimental data of the 0.02 µm² MTJ sample while solid                    |

| lines are from simulation using the equivalent model                                                           |

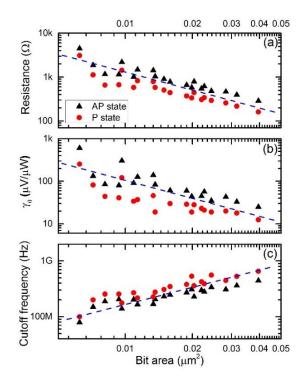

| Figure 2.18: Analysis of (a) junction resistance (b) voltage sensitivity when frequency tends to zero          |

| hertz, and (c) 3 dB cutoff frequency for all of samples in both AP and P state. The points are                 |

| from measurements, the blue dash line is just a guide for the eyes54                                           |

| Figure 2.19: (a) Complete model for MTJ including test pads effect. (b) Simplified model in order              |

| to analyze cutoff frequency55                                                                                  |

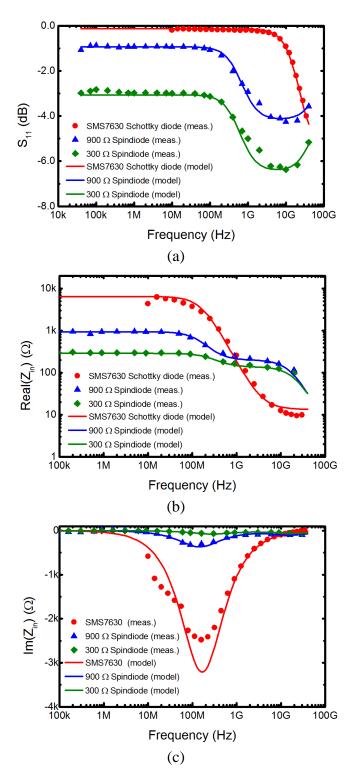

| Figure 2.20: Comparison of (a) S <sub>11</sub> , (b) real part and (c) imaginary part of impedance between two |

| spindiodes with different junction resistances and a commercial SMS7630 Schottky diode.                        |

| During measurement, power entering the nonlinear device was kept below – 40 dBm57                              |

| Figure 2.21: Efficiency related to the parasitic losses. Data shown are calculated as the square of            |

| measured responsivity, normalized to low frequency value, with a compensation of insertion                     |

| losses                                                                                                         |

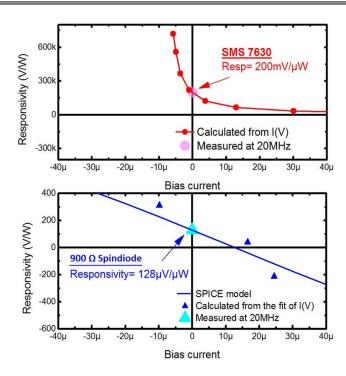

| Figure 2.22: Calculated dc responsivity from I(V) measurements results. The point located at zero-             |

| bias indicates a low frequency low power measurements to validate the responsivity                             |

| extraction59                                                                                                   |

| Figure 2.23: Complex model of MTJ [130].                                                                       |

| Figure 2.24: Low power diode efficiency under the matched conditions and the load condition                                                                     |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| $R_j = R_L$ . Data were calculated based on the measurement of responsivity, ZBR and parasition                                                                 |

| efficiency at 30 GHz61                                                                                                                                          |

| Figure 3.1: Diagram of electronic tuner: it consists of a wideband NLTL-based phase shifter and                                                                 |

| an impedance tuning circuit64                                                                                                                                   |

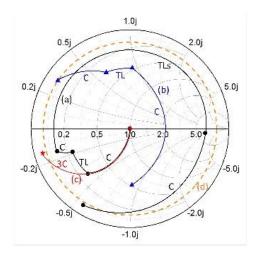

| Figure 3.2: (a) Ideal circuit of the proposed topology; (b) Simplified circuit to generate impedance values; (c) Operation principle illustrated on Smith chart |

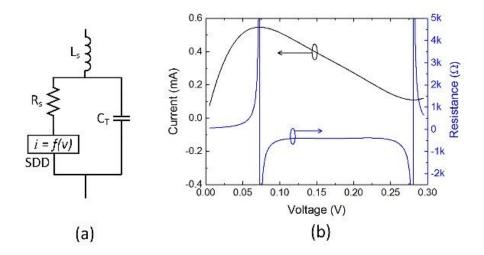

| Figure 3.3: (a) Tunneling diode model with Symbolically Defined Devices (SDD), (b) I(V) curve                                                                   |

| and extracted resistance of tunneling diode MBD5057-E28X from MACOM Technology                                                                                  |

| Solutions66                                                                                                                                                     |

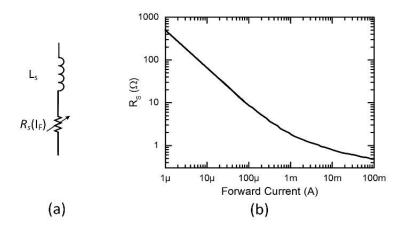

| Figure 3.4: (a) SPICE model for PIN diode under forward bias; (b) Equivalent series resistance Riode PIN diode SMP1320 from Skyworks Solutions Inc.             |

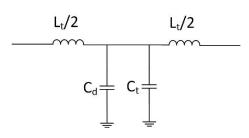

| Figure 3.5: LC model of unit cell of NLTL.                                                                                                                      |

| Figure 3.6: LC model of unit cell of NLTL with loss.                                                                                                            |

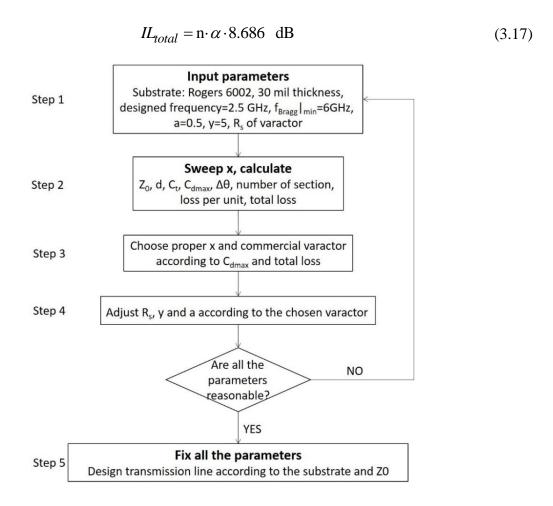

| Figure 3.7: Diagram of design procedure of NLTL-based phase shifter70                                                                                           |

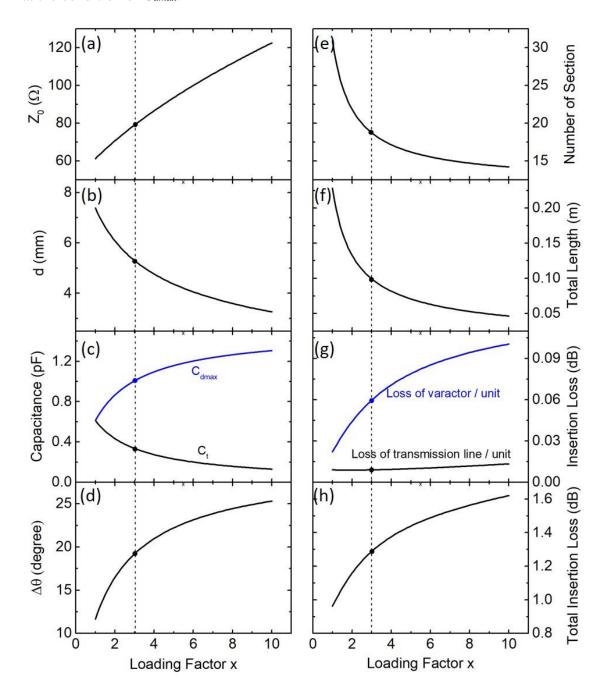

| Figure 3.8: Design results of NLTL-based phase shifter                                                                                                          |

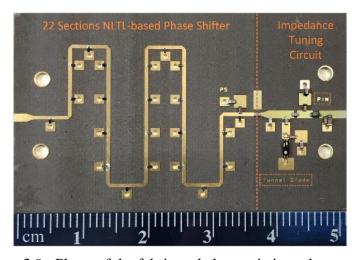

| Figure 3.9: Photo of the fabricated electronic impedance tuner                                                                                                  |

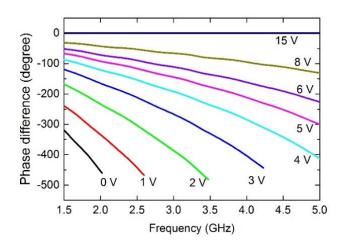

| Figure 3.10: Measured phase difference of the NLTL-based phase shifter73                                                                                        |

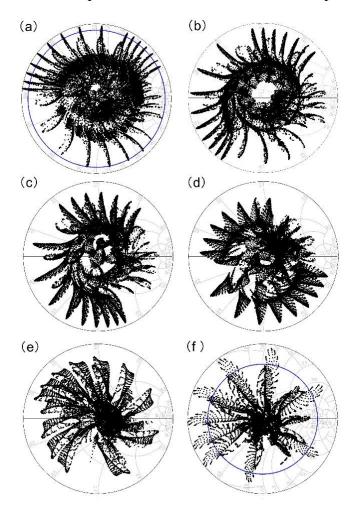

| Figure 3.11: Measured 25740 impedance states for the proposed electronic impedance tuner at (a                                                                  |

| 1.5 GHz, (b) 2 GHz, (c) 2.5 GHz, (d) 3 GHz, (e) 4 GHZ, and (f) 5 GHz. The blue circle in (a                                                                     |

| and (f) stands for the reflection coefficient equals to 1                                                                                                       |

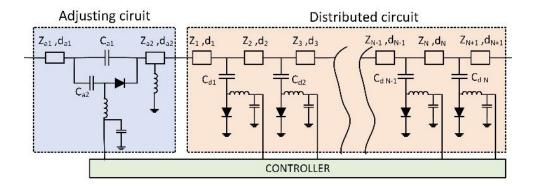

| Figure 4.1: Topology of non-uniform EIS consists of an adjusting circuit and a distributed circuit                                                              |

| Figure 4.2: Illustration of the effect of the adjusting circuit. Impedance distribution on Smith char                                                           |

| when PIN diode is (a) ON, and (b) OFF; (c) the total effect of the adjusting circuit on the                                                                     |

| improvement of Smith chart coverage.                                                                                                                            |

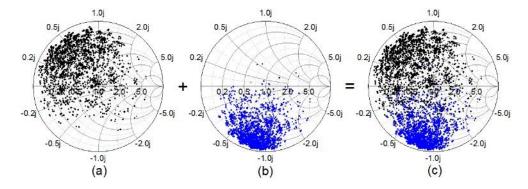

| Figure 4.3: (a) Predefined 1116 impedance points on Smith chart; (b) measured impedance points (c) selected measured points; and (d) selected predefined points                                                                                                                             |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 4.4: Impedance movement after (a) loading capacitance on the capacitive part of Smith chart, (b) loading with $C \cdot N/4$ (N = 12), (c) loading with capacitance on the inductive part of Smith chart; (d) Required constant reflection coefficient circle83                       |

| Figure 4.5: Lower and upper boundaries of loading capacitance.                                                                                                                                                                                                                              |

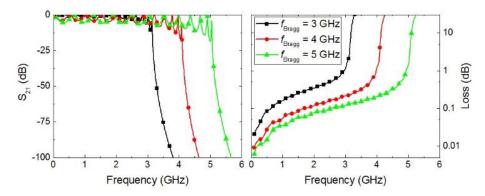

| Figure 4.6: (a) Transmission response and (b) loss feature of EIS with $f_{Bragg}$ of 3 GHz, 4 GHz and                                                                                                                                                                                      |

| 5 GHz. Only the conductive loss and dielectric loss are taken into consideration in the total loss. The ripples in transmission response are because of the mismatching at this impedance state. Note that it is only the response of the impedance state with all the PIN diode turned ON. |

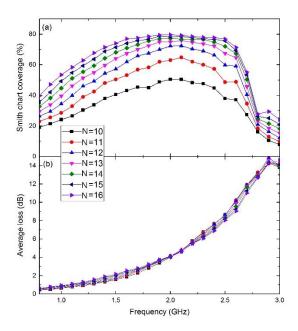

| Figure 4.7: The investigation of (a) Smith chart coverage as well as (b) mean loss of the EIS with different number of sections while keeping $f_{Bragg}$ as 4 GHz. Mean loss is the average loss for                                                                                       |

| the selected impedance points. Reactive parasitic parameters from commercial PIN diode and capacitor are not taken into consideration in the loss                                                                                                                                           |

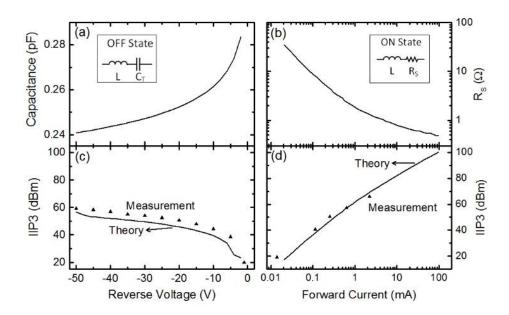

| Figure 4.8: Nonlinearity of (a) R <sub>s</sub> (I <sub>F</sub> ) and (b) C <sub>T</sub> (V <sub>r</sub> ) characteristics of PIN diode SMP1320. IME test for both (c) OFF and (d) ON states. Dots denote measurement while line denotes theoretical predictions.                            |

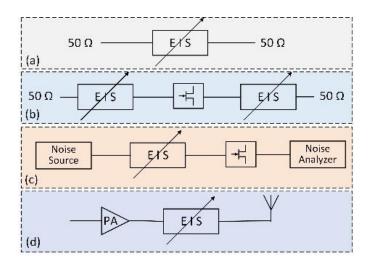

| Figure 4.9: Four different scenarios to use EIS: (a) Calibration with VNA; (b) Load-Pul characterization system; (c) Noise measurement; (d) TMN for reconfigurable PA or antenna                                                                                                            |

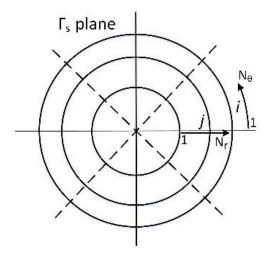

| Figure 4.10: The division of Smith chart to calculate the uniformity factor                                                                                                                                                                                                                 |

| Figure 4.11: Traditional topology of distributed electronic impedance synthesizer92                                                                                                                                                                                                         |

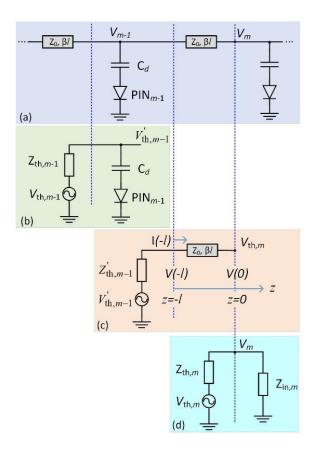

| Figure 4.12: Diagram for voltage distribution analysis. (a) Equivalent circuit of (m-1) <sup>th</sup> section Thevenin equivalent circuit (b) at node m-1 with open termination; (c) at node m with open termination; (d) at node m with load.                                              |

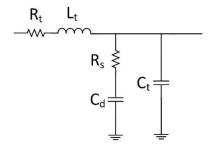

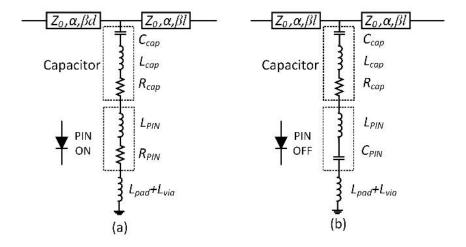

| Figure 4.13: Equivalent unit circuit model with PIN diode at (a) ON state, and (b) OFF state.                                                                                                                                                                                                                                                                                                                                       |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Loading capacitor is still considered as ideal capacitor in order to keep the calculation concise.                                                                                                                                                                                                                                                                                                                                  |

| The biasing circuit is not shown in the model95                                                                                                                                                                                                                                                                                                                                                                                     |

| Figure 4.14: Diagram of optimization process using PSO                                                                                                                                                                                                                                                                                                                                                                              |

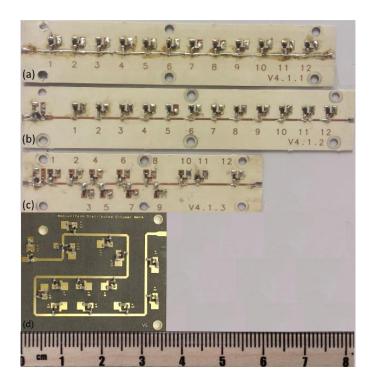

| Figure 4.15: Fabricated uniform and non-uniform circuits, biasing wires are not shown. (a) Circuit                                                                                                                                                                                                                                                                                                                                  |

| 1: 12 section uniform distributed topology without adjusting circuit. (b) Circuit 2: 12 section                                                                                                                                                                                                                                                                                                                                     |

| uniform distributed topology with one section of adjusting circuit. (c) Circuit 3: 12 section                                                                                                                                                                                                                                                                                                                                       |

| non-uniform distributed topology with one section of adjusting circuit. (d) Circuit 4: New 13                                                                                                                                                                                                                                                                                                                                       |

| section non-uniform distributed EIS with one section of adjusting circuit100                                                                                                                                                                                                                                                                                                                                                        |

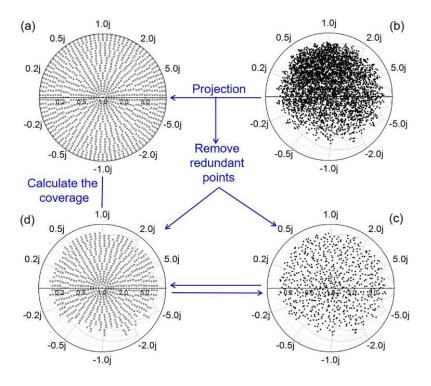

| Figure 4.16: (a) Comparison of measured and theoretically calculated Smith chart coverage for four fabricated circuits.                                                                                                                                                                                                                                                                                                             |

| Figure 4.17: Equivalent circuit model of a unit circuit when PIN diode is turned (a) ON and (b) OFF                                                                                                                                                                                                                                                                                                                                 |

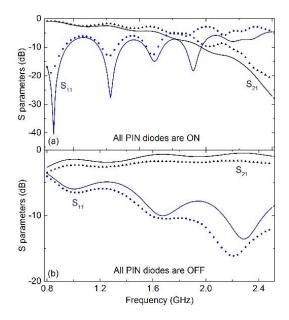

| Figure 4.18: Comparison of measured and theoretical S parameters for impedance states with all PIN diodes are turned (a) ON and (b) OFF. Dots denotes measurement, while solid line denotes theory.                                                                                                                                                                                                                                 |

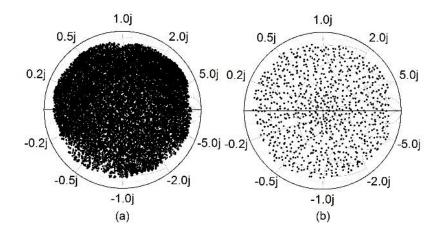

| Figure 4.19: (a) All 16384 measured impedance points; (b) Selected points for the calculation of Smith chart coverage                                                                                                                                                                                                                                                                                                               |

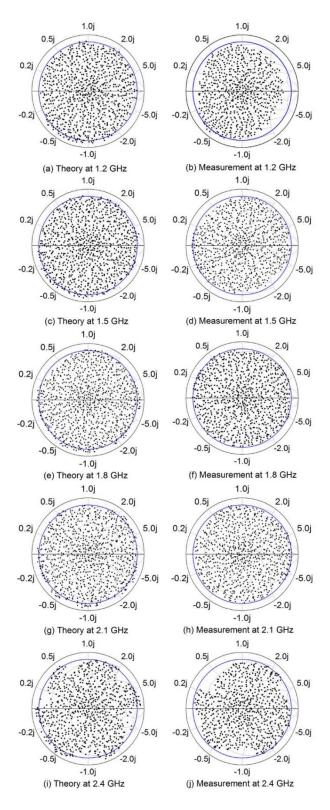

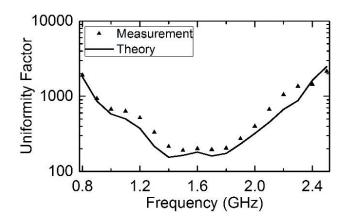

| Figure 4.20: (a) Measured and (b) theoretical impedance distribution at 1.2 GHz; (c) Measured and (d) theoretical impedance distribution at 1.5 GHz; (e) Measured and (f) theoretical impedance distribution at 1.8 GHz; (g) Measured and (h) theoretical impedance distribution at 2.1 GHz; (i) Measured and (j) theoretical impedance distribution at 2.4 GHz. The blue circle represents the constant VSWR=15 circle ( Γ =0.875) |

| Figure 4.21: The comparison of measured and theoretically calculated uniformity factor 109                                                                                                                                                                                                                                                                                                                                          |

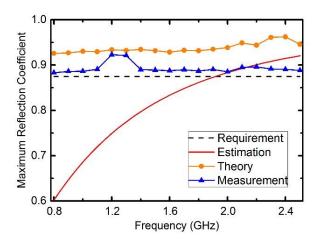

| Figure 4.22: Comparison of required $\Gamma$ (black dash line), estimated maximum $\Gamma$ (red solid line), theoretical maximum $\Gamma$ (orange solid line with circle marker), and measured maximum $\Gamma$ (blue)                                                                                                                                                                                                              |

| solid line with triangle marker)                                                                                                                                                                                                                                                                                                                                                                                                    |

| Figure 4.23: (a) Theoretical and (b) measured loss for the selected impedance points at 1.5 GHz;                         |

|--------------------------------------------------------------------------------------------------------------------------|

| (c) Comparison of theoretical and measured mean loss over frequency110                                                   |

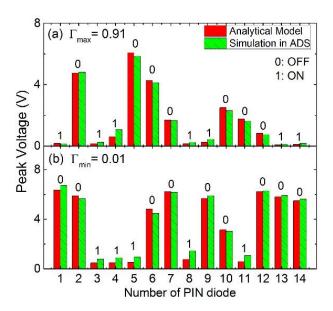

| Figure 4.24: Comparison of theoretical and simulated voltage distribution along the transmission                         |

| line under average power of 0.5 watt for the (a) highest $\Gamma$ state ( $ \Gamma $ =0.9) and (b) lowest $\Gamma$ state |

| $( \Gamma =0.01)$                                                                                                        |

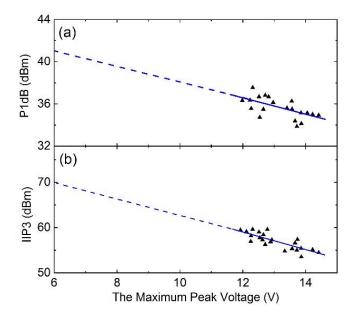

| Figure 4.25: Simulated relationship of (a) P1 dB and (b) IIP3 with the maximum peak voltage along                        |

| the transmission line for 20 impedance points under input power of 0.5 watt. Solid line is the                           |

| linear fitting curve of the selected 20 points, while the dash line is the extension of the fitting                      |

| curve112                                                                                                                 |

| Figure 4.26: Noise figure of the proposed non-uniform EIS at 1.5 GHz for 816 selected impedance                          |

| states                                                                                                                   |

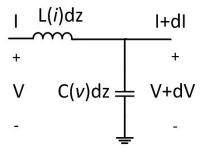

| Figure 5.1: Equivalent circuit model of fully distributed hybrid NLTL per unit length116                                 |

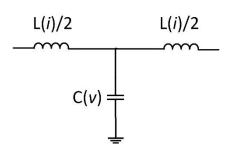

| Figure 5.2: Equivalent LC circuit model of unit cell of periodically loaded hybrid NLTL118                               |

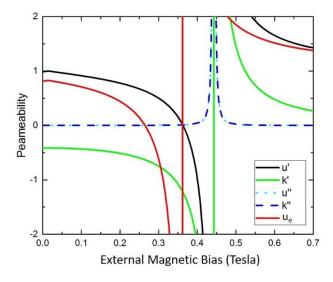

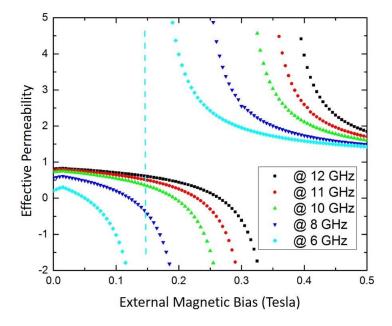

| Figure 5.3: Permeability tensor elements and effective permeability versus magnetic bias121                              |

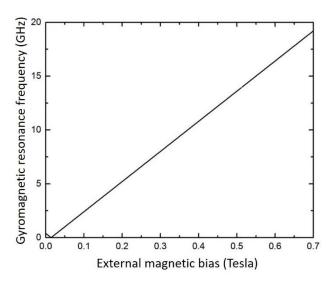

| Figure 5.4: Gyromagnetic resonance frequency versus external magnetic bias                                               |

| Figure 5.5: Effective permeability versus external magnetic bias at different operation frequency.                       |

|                                                                                                                          |

| Figure 5.6: Effective permeability versus operation frequency at 0.44 tesla magnetic bias condition.                     |

| Figure 5.7: (a) Free space measurement [196], (b) air-filled coaxial line configuration [192], (c)                       |

| waveguide configuration [185].                                                                                           |

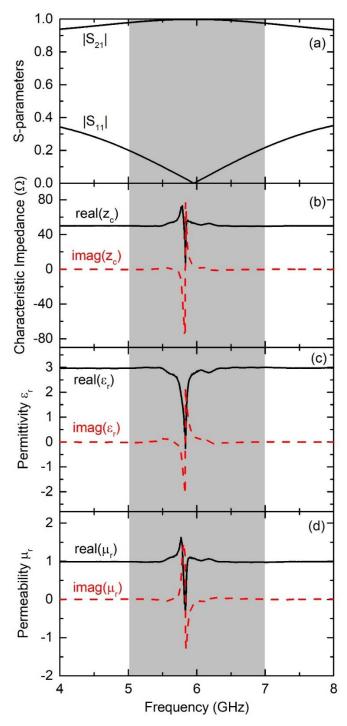

| Figure 5.8: (a) Measured S-parameters, (b) extracted impedance, (c) extracted permittivity and (d)                       |

| extracted permeability                                                                                                   |

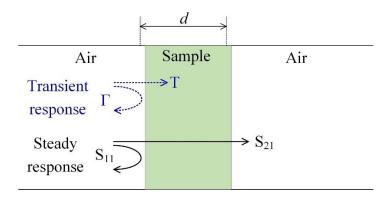

| Figure 5.9: Diagram of setup of air-filled coaxial line                                                                  |

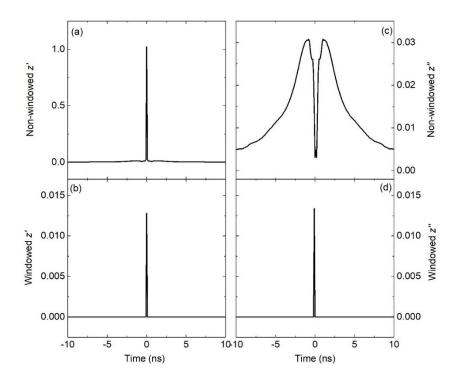

| Figure 5.10: (a) Non-windowed and (b) windowed real part of time domain impedance, (c) Non-                              |

| windowed and (d) windowed imaginary part of time domain impedance                                                        |

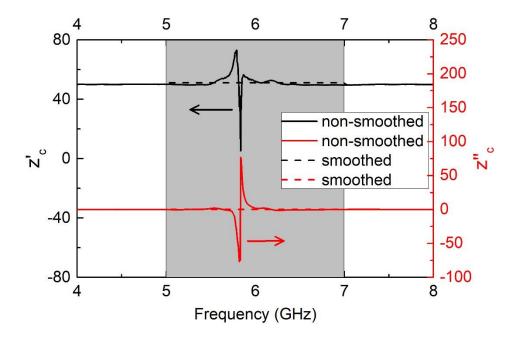

| Figure 5.11: Frequency domain response of impedance with and without time domain smoothing       |

|--------------------------------------------------------------------------------------------------|

| technique. The gray region indicates the truncated frequency range                               |

| Figure 5.12: Extracted permittivity with and without time domain smoothing technique. The gray   |

| region indicates the truncated frequency range                                                   |

| Figure 5.13: Extracted permeability with and without time domain smoothing technique. The gray   |

| region indicates the truncated frequency range                                                   |

| Figure 5.14: Extracted effective permittivity at three frequencies for NLTL with varactor135     |

| Figure 5.15: Extracted effective permittivity at three frequencies for YIG-based circuit136      |

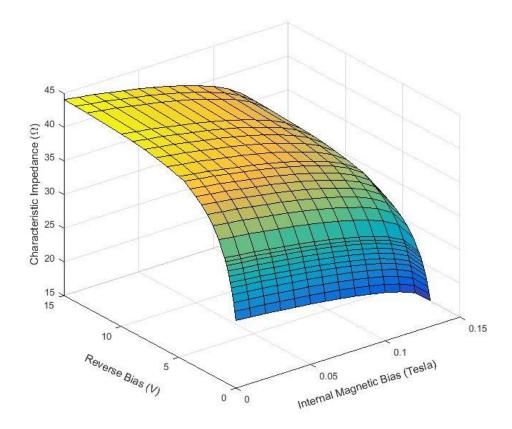

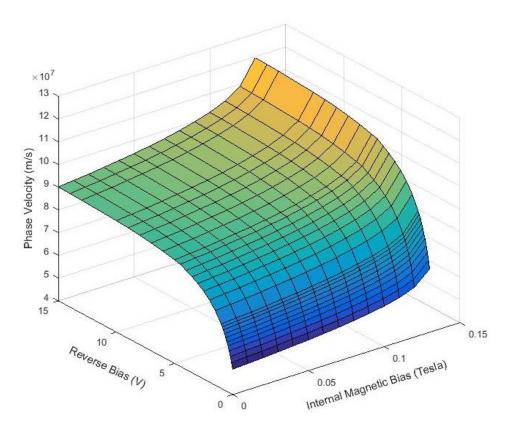

| Figure 5.16: Calculated characteristic impedance of hybrid NLTL when tuning the internal         |

| magnetic bias and reverse voltage bias                                                           |

| Figure 5.17: Calculated phase velocity of hybrid NLTL when tuning the internal magnetic bias and |

| reverse voltage bias                                                                             |

## LIST OF SYMBOLS AND ABBREVIATIONS

ADS Advanced Design System

AP Anti-parallel

BST Barium strontium titanate

C(V) Capacitance-voltage

CMOS Complementary Metal-Oxide-Semiconductor Transistor

CPW Coplanar waveguide

CW Continuous wave

dc Direct current

DUT Device under test

EIS Electronic impedance synthesizer

FCC Federal Communications Commission

FMR Ferromagnetic resonance

FOM Figures of merit

GaAs Gallium arsenide

GMR Giant magnetoresistance

GSG Ground-Signal-Ground

GPIB General Purpose Interface Bus

HB Harmonic Balance

HFSS High Frequency Structural Simulator

IIP3 Input third-order intercept point

IMD Intermodulation Distortion

IMPATT IMPact Avalanche Transit Time

IP3 Third-order intercept point

I(V) Current-voltage

LC Inductance-capacitance

MEMS Microelectromechanical Systems

MIM Metal-Insulator-Metal

MMIC Monolithic microwave integrated circuit

MPH Microwave power harvesting

MPT Microwave power transfer

MR Magnetoresistance

MRAM Magnetic random access memory

MTJ Magnetic tunnel junction

NLTL Nonlinear transmission line

NVNA Nonlinear Vector Network Analyser

P Parallel

PA Power amplifier

PCB Printed circuit board

PIN P-Intrinsic-N

PSO Particle Swarm Optimization

RF Radio frequency

RTD Resonant tunneling diode

SDD Symbolically Defined Devices

SRD Step recovery diode

ST-FMR Spin-torque-driven ferromagnetic resonance

TED Transferred electron device

TMN Tunable matching networks

TMR Tunnel magnetoresistance

VNA Vector Network Analyser

VSWR Voltage standing wave ratio

WPT Wireless power transfer

YIG Yttrium Iron Garnet

ZBR Zero-bias resistance

#### CHAPTER 1 INTRODUCTION

Modern wireless and communication systems are heavily dependent on nonlinear circuits such as power amplifier (PA), mixer, multiplier, oscillator, switch, etc., the core of which are passive nonlinear devices (e.g. diodes) or active nonlinear devices (e.g. transistors). The term "nonlinear" intuitively means that the output signals and input signals are not in a linear relationship, it essentially indicates that one parameter is nonlinear with voltage or current. It should be noted that it is different from the nonlinearity of frequency responses, for instance, dispersion.

In this work, we focus on passive nonlinear devices. One purpose of this thesis is to provide a way for the readers to understand and choose proper nonlinear devices in accordance with different applications. Traditional nonlinear devices in terms of the categories of resistive, capacitive and inductive are firstly investigated in the following.

As listed in Table 1.1, the resistive devices include conventional PN junction diode, Point-Contact diode, Schottky diode, PIN diode, Step-Recovery diode (SRD), Metal-Insulator-Metal (MIM) diode, Tunnel diode (Esaki diode), Backward diode, Resonant Tunneling diode (RTD), Gunn diode, IMPATT diode, etc. [1, 2], among which the last five diodes present a differential negative resistance region in their current-voltage (I(V)) characteristics. The basic physical construction, operation principles as well as characteristics and applications for various types of diode are explained and compared.

The capacitive nonlinear devices include semiconductor and ferroelectric ceramics, whereas the inductive nonlinear devices usually use ferrite and other magnetic materials. Emerging nonlinear devices includes microelectromechanical system (MEMS) devices and spindiodes.

Nonlinear transmission line (NLTL) is a transmission line periodically loaded with nonlinear devices. Traditional NLTL technique uses either capacitive nonlinear devices (varactor, BST, PZT etc.) or inductive nonlinear devices (saturated ferrite). Emerging hybrid NLTL technique uses both nonlinear capacitive and inductive devices.

Table 1.1: Comparison of traditional and emerging passive nonlinear devices.

| Categary                         | Nonlinear Type | Nonlinear Device          | Specialty              | Applications                                                                                                                      |

|----------------------------------|----------------|---------------------------|------------------------|-----------------------------------------------------------------------------------------------------------------------------------|

|                                  | resistive      | PN junction diode         |                        | detector, rectifier, modulator, switch, demoudulator circuit, etc.                                                                |

|                                  |                | point-contact diode       |                        | mixer, detector, etc                                                                                                              |

|                                  |                | Schottky diode            |                        | detector, mixer, rectifier, etc.                                                                                                  |

|                                  |                | PIN diode                 |                        | switch, attenuator, phase shifter, limiter, modulator, etc.                                                                       |

|                                  |                | step-recovery diode       |                        | short pulse generator, frequency multiplier, comb generator, etc.                                                                 |

|                                  | TOSISTIVE      | MIM diode                 |                        | Mixer, rectifier, etc.                                                                                                            |

|                                  |                | tunnel diode              | negative<br>resistance | oscillator, amplifier, mixer, detector, etc.                                                                                      |

| traditional                      |                | backward diode            |                        | detector, rectfier, switch, etc.                                                                                                  |

| nonlinear<br>devices             |                | RTD                       |                        | Oscillator, switch, etc.                                                                                                          |

|                                  |                | Gunn diode                |                        | Oscillator, amplifier, radar speed gun, etc.                                                                                      |

|                                  |                | IMPATT diode              |                        | power generation, etc.                                                                                                            |

|                                  | capacitive     | semiconductor<br>varactor |                        | VCO, parametric amplifier, harmonic generator, frequency multipliers, mixer, microwave signal synthesizers, tunable circuit, etc. |

|                                  |                | BST                       |                        | phase shifter, capacitor, DRAM, etc.                                                                                              |

|                                  |                | PZT                       |                        |                                                                                                                                   |

|                                  | inductive      | ferrite                   |                        | tunable filter, oscillator, amplifier,<br>circuilator, isolators, phase shifter,<br>bandstop filter, magnet recording, etc.       |

| emerging<br>nonlinear<br>devices |                | MEMS devices              |                        | phase shifters, tunable filters, impedance tuners, oscillators, mixer, switch, etc.                                               |

|                                  |                | MTJ                       |                        | MRAM, oscillator, rectifier, etc.                                                                                                 |

# 1.1 Traditional RF and microwave nonlinear devices

## 1.1.1 Resistive nonlinear devices

#### 1.1.1.1 Conventional PN junction diode

#### Construction

The conventional PN junction diode is the most basic and simplest solid state electronic device. It is constructed by the combination of P-type and N-type of semiconductors [1, 2]. By doping an

intrinsic semiconductor with acceptor impurities, a P-type semiconductor is formed, in which holes are the majority carriers while electrons are the minority carriers. The term P-type denotes the positive charge of the hole. As opposed to P-type semiconductors, N-type semiconductors are formed by doping an intrinsic semiconductor with donor impurities, in which free electrons have a more massive concentration than holes. The term N-type refers to the negative charge of the electron.

Figure 1.1: Energy band diagram of PN junction diode.

#### **Operation principle and characteristics**

As depicted in Fig. 1.1, a PN junction will be formed when a P-type semiconductor is placed in contact with a N-type semiconductor. The density gradient at both sides of the PN junction results in the free holes in P-type side that diffuse across the interface and recombine when they reach N-type side, and leave behind the fixed negatively charged acceptor ions. Similarly, it also results in the free electrons that diffuse from N-type side to P-type side, and leave behind the fixed positively charged donor ions. The negatively and positively charged ions will create an electrostatic potential barrier, which will prevent the diffusion of free charge carriers. A depletion layer will be formed when an equilibrium state will be reached, and no free charge carriers will exist in this layer. The extra energy that is required to overcome the barrier is called the barrier potential, which depends on the semiconductor material, doping level as well as temperature, and is about 0.7 V for silicon and 0.3 V for germanium.

Opposite to the diffusion current that is caused by the majority carriers, the drift current is due to the minority carriers that are moving across the junction and accelerated by the barrier potential. In the unbiased condition, the net current is zero since the drift current and diffusion current are equal to each other.

#### **Ohmic effects**

In the forward bias condition, the P-type and N-type semiconductors are connected with the positive and negative electrode of the voltage source, respectively. The external voltage can push the majority carriers (holes) in the P-type side and the majority carriers (electrons) in the N-type side toward and then neutralize the depletion layer so that the width of the depletion layer is reduced. There is almost no current when the external voltage is less than the barrier potential since the free electrons and holes cannot overcome the barrier. As shown in the I(V) characteristic of PN junction diode in Fig. 1.2, with the increases of the forward bias, the depletion zone decreases, eventually results in an electrical resistance reduction. The relationship of IV characteristic of PN junction diode can be expressed as [2]

$$I = I_{s} \left( e^{\frac{q(V - IR_{s})}{nKT}} - 1 \right)$$

(1.1)

where  $I_s$  is the reverse saturation current, q is the electron charge, V is the external bias,  $R_s$  is the series resistance of PN junction, n is ideality factor, K is Boltzmann constant, and T is absolute temperature.

Figure 1.2: IV characteristic of conventional PN junction diode.

In the reverse bias condition, the P-type and N-type semiconductors are connected with the negative and positive electrode of the voltage source, respectively. The reverse bias pulls the holes in the P-type side and electrons in the N-type side away from the junction, which increases the width of the depletion layer, so that results in a high resistance allowing a small current across the junction. As shown in Fig. 1.2, when the reverse bias increases beyond a critical level, the depletion region breaks down and current begins to flow, and it is called the avalanche effect.

#### Junction capacitance

Two types of capacitance mechanisms are involved in PN junction, namely depletion capacitance and diffusion capacitance, respectively, as shown in the capacitance-voltage (C(V)) characteristic of a PN junction diode in Fig. 1.3. The depletion capacitance is caused by the impurity atoms, and it dominates under the reverse bias condition. It can be calculated as [2]

$$C_{j} = \frac{C_{0}}{(1 - \frac{V}{V_{0}})^{\gamma}} \tag{1.2}$$

where  $C_0$  is the zero-bias capacitance, V is the reverse bias voltage, V<sub>0</sub> is built-in potential,  $\gamma$  is a constant, it is 1/2 for an abrupt junction, 1/3 for a graded junction, and 1 to 2 for a hyperabrupt junction. The diffusion capacitance is caused by the injected minority charge, and it dominates under the forward bias condition. It is proportional to the minority carrier lifetime, therefore related to the switching characteristic of the PN junction diode.

Figure 1.3: Junction capacitance-voltage characteristic of PN junction diode.

#### **Application**

The PN junction diodes can be found in the applications of detector, rectifier, modulator, switch, demodulation circuit, clamping circuit, clipping circuit, clamping circuit, etc. [2]

#### 1.1.1.2 Point-Contact diode

#### Construction

Similar to conventional PN junction, Point-Contact diode is also one of the most basic forms of diodes. It has been developed during the Second World War, and is often used as mixer or detector. As depicted in Fig. 1.4, it is made by a cat whisker metal wire placed on a piece of N-type semiconductor [1, 2]. During the formation of a Point-Contact diode, a relatively high current will pass through the cat whisker wire to the semiconductor, part of the metal will migrate into the semiconductor, a small P-type region will be formed in the vicinity of the point contact, thus a PN junction is formed which behaves the same as a conventional PN junction.

Figure 1.4: Point-Contact diode. (a) Construction and constituents and (b) p-region around point contact [1].

#### **Operation principle**

The operation mechanism of Point-Contact diode is quite similar to a conventional PN junction diode. However, the characteristics are different under forward and reverse bias conditions, mainly because of the small contact between the cat whisker and the semiconductor. The resistance of Point-Contact diode in the forward bias condition is larger than the conventional PN junction diode, while the capacitance in the reverse bias condition is smaller. The very low junction capacitance

leads to a better switching ability than a conventional PN diode, thus ideal for many RF applications. However, the small junction also limits the power handling of a high current [1].

#### **Applications**

With the advantages of fast switching and the small junction capacitance due to small junction area, Point-Contact diode is suitable for high-frequency applications, such as mixer, detector, etc. [1].

#### 1.1.1.3 Schottky diode

#### Construction

The Schottky diode can be considered as a variation of point-contact diode, it can be manufactured in different forms, in which the simplest form is a point-contact diode (Fig. 1.5(a)). As shown in Fig. 1.5(b), the metal-semiconductor junction in the deposited metal Schottky diode is a surface rather than a point contact [1]. A large contact area between the metal and the semiconductor enables a low forward resistance and low capacitance.

Figure 1.5: Schottky diode. (a) Point-contact type, (b) deposited metal type [1].

#### Operation principle and chracteristics

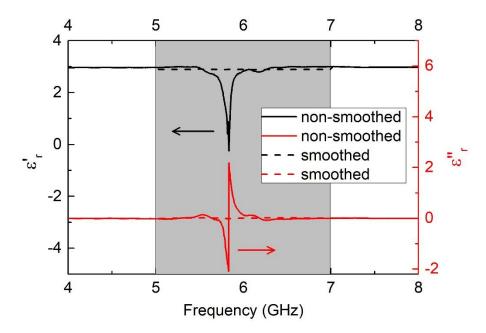

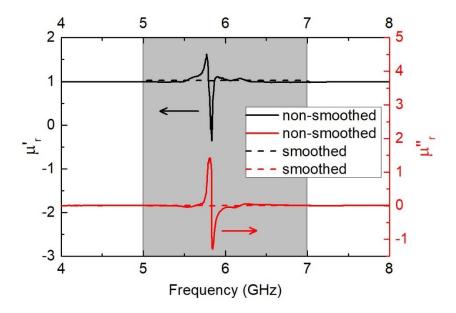

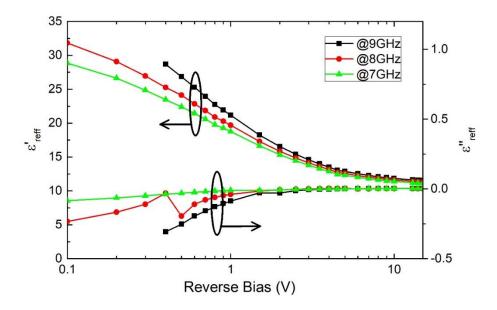

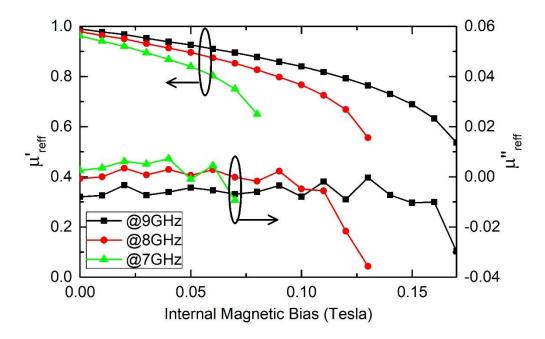

Figure 1.6: Energy band diagram for ideal Schottky barrier junction [2].