**Titre:** Génération de stimuli efficaces en énergie pour la microstimulation électrique intracorticale

Title: **électrique intracorticale**

**Auteur:** Sébastien Ethier

Author:

**Date:** 2010

**Type:** Mémoire ou thèse / Dissertation or Thesis

**Référence:** Ethier, S. (2010). Génération de stimuli efficaces en énergie pour la microstimulation électrique intracorticale [Mémoire de maîtrise, École Polytechnique de Montréal]. PolyPublie. <https://publications.polymtl.ca/352/>

Citation:

## Document en libre accès dans PolyPublie

Open Access document in PolyPublie

**URL de PolyPublie:** <https://publications.polymtl.ca/352/>

PolyPublie URL:

**Directeurs de recherche:** Mohamad Sawan

Advisors:

**Programme:** génie électrique

Program:

UNIVERSITÉ DE MONTRÉAL

GÉNÉRATION DE STIMULI EFFICACES EN ÉNERGIE POUR LA MICROSTIMULATION

ÉLECTRIQUE INTRACORTICALE

SÉBASTIEN ETHIER

DÉPARTEMENT DE GÉNIE ÉLECTRIQUE

ÉCOLE POLYTECHNIQUE DE MONTRÉAL

MÉMOIRE PRÉSENTÉ EN VUE DE L'OBTENTION

DU DIPLÔME DE MAÎTRISE ÈS SCIENCES APPLIQUÉES

(GÉNIE ÉLECTRIQUE)

JUILLET 2010

UNIVERSITÉ DE MONTRÉAL

ÉCOLE POLYTECHNIQUE DE MONTRÉAL

Ce mémoire intitulé:

GÉNÉRATION DE STIMULI EFFICACES EN ÉNERGIE POUR LA MICROSTIMULATION

ÉLECTRIQUE INTRACORTICALE

présenté par: ETHIER Sébastien

en vue de l'obtention du diplôme de: Maîtrise ès sciences appliquées

a été dûment accepté par le jury d'examen constitué de:

M. AUDET Yves, Ph.D., président

M. SAWAN Mohamad, Ph.D., membre et directeur de recherche

M. ZHU Guchuan, Doct., membre

“Inside every small problem is a large problem struggling to get out.”

- Second Law of Blissful Ignorance

“There are two kinds of dissertations, perfect and done”

- Anonyme

## REMERCIEMENTS

D'abord, je tiens à remercier sincèrement mon directeur de recherche M. Mohamad Sawan, professeur à l'École Polytechnique Montréal, pour m'avoir donné la chance de travailler sur un projet aussi stimulant au sein de son équipe. Mes remerciements s'adressent ensuite à M. Yves Audet et M. Guchuan Zhu, également professeurs à l'École Polytechnique, pour avoir accepté de faire partie du jury d'examen de mon mémoire.

Plusieurs personnes m'ont été d'une aide inestimable à un moment ou un autre de ma maîtrise grâce à leurs précieux conseils. Je pense particulièrement à Louis-François, Benoît, Fayçal, Mona, Jonathan et Rahul. Merci à vous. De plus, je remercie les techniciens ainsi que les secrétaires du département de génie électrique pour leur efficacité.

Ensuite, je remercie tous mes amis de Polystim et du GR2M, plus particulièrement ceux qui sont passés par le local M-5306 au fil du temps. Je pense à Félix, Pierre-Yves, Charles, Roula et Amer à mon arrivée, ainsi qu'à Nicolas, Guillaume S., Anthony, Sébastien, Tariq, Étienne et Marc-André à mon départ, sans oublier Omar, Guillaume D. et particulièrement Gilbert. Merci à vous mes amis d'avoir enduré mes sauts d'humeur et d'avoir fait en sorte que ma maîtrise soit si agréable.

Je tiens à remercier ma famille en débutant par mes parents, Nicole et Serge, ainsi que mon frère Martin pour leur support inconditionnel et les encouragements qu'ils m'ont témoignés tout au long de mes études. De manière plus particulière, je remercie du fond du cœur ma copine Julia pour son écoute, son amour et surtout sa patience sans limite lorsque le moral était au plus bas.

Je remercie CMC Microsystems pour les outils de conception et la fabrication des circuits intégrés, ainsi que la Chaire de recherche du Canada en dispositifs médicaux intelligents et le ReSMiQ pour le support financier essentiel à la réalisation de ce projet.

Enfin, merci à Jorge Cham de PhD Comics pour les moments de détente et le support moral !

## RÉSUMÉ

Ce mémoire a comme objectif principal la mise en oeuvre de circuits dédiés à l'amélioration de l'efficacité de la stimulation électrique de tissus situés au niveau du cortex visuel primaire. Le stimulateur proposé permet la génération de nouveaux stimuli flexibles de forme exponentielle et demi-sinusoidale dans l'optique de réduire la consommation de puissance globale de l'implant. En plus d'être potentiellement plus efficaces que les stimulations rectangulaires standard pour exciter les tissus, ces formes d'impulsions permettraient également de réduire la concentration d'ions toxiques relâchés par les électrodes. Le second objectif de ce projet est de permettre la stimulation à pleine échelle, soit au moins  $150 \mu\text{A}$ , à travers l'interface microélectrode-tissus qui est caractérisée par une impédance élevée. Un étage de sortie à haute-tension a donc également été réalisé afin de générer des tensions d'alimentation d'environ  $\pm 9 \text{ V}$  et d'augmenter ainsi l'excursion de tension des stimuli tout en étant entièrement intégré.

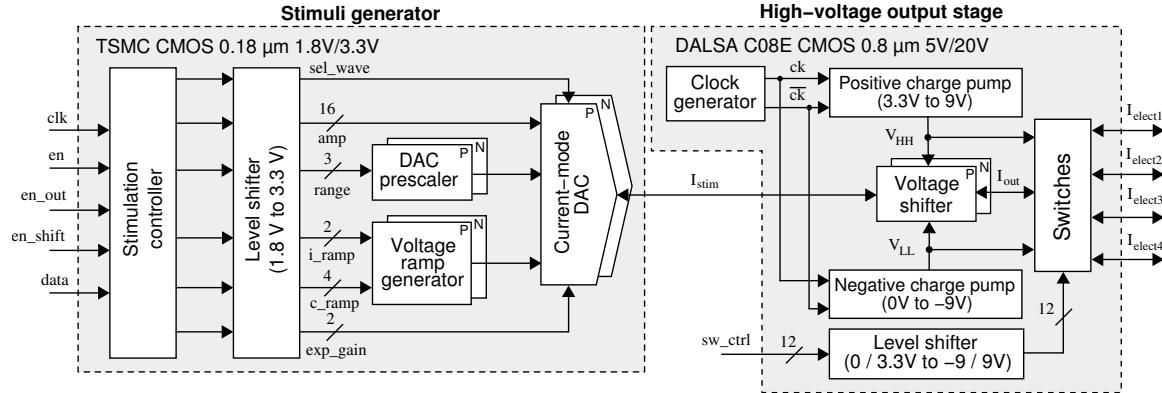

Une architecture comportant deux circuits intégrés indépendants est proposée dans ce mémoire. Le générateur de stimuli est implémenté dans la technologie CMOS  $0,18\text{-}\mu\text{m } 1,8\text{V}/3,3\text{V}$  de TSMC afin de limiter sa consommation de puissance. Pour ce qui est de l'étage de sortie, il est intégré à l'aide du procédé C08E CMOS/DMOS  $0,8\text{-}\mu\text{m } 5\text{V}/20\text{V}$  de DALSA Semiconductors, technologie supportant les niveaux de tension requis.

Les deux puces ainsi fabriquées ont été testées. L'intensité des stimuli rectangulaires couvre une plage de  $1,6$  à  $167,2 \mu\text{A}$  des erreurs de non-linéarité différentielle et intégrale de  $0,10$  et  $0,16$  LSB respectivement. Les impulsions exponentielles ont une plage dynamique de  $34,36 \text{ dB}$  pour une erreur de  $\pm 0,5 \text{ dB}$  par rapport à la fonction théorique. La consommation de puissance du générateur de stimuli atteint en moyenne  $29,1 \mu\text{W}$  en mode rectangulaire et de  $28,5$  à  $88,3 \mu\text{W}$  en mode exponentiel. Les résultats obtenus pour la demi-sinusoidale proviennent de simulations. En moyenne,  $80,2 \%$  de la durée des impulsions demi-sinusoidales a une erreur inférieure à  $\pm 1 \%$  par rapport à la fonction idéale. Le générateur de stimuli complet consomme de  $46,7$  à  $199,1 \mu\text{W}$  en mode demi-sinusoidal. En ce qui a trait à l'étage de sortie, des tensions de  $8,95$  et  $-8,46 \text{ V}$  sont générées avec succès, permettant à l'excursion de tension d'atteindre  $13,6 \text{ V}$  à travers une charge de  $100 \text{ k}\Omega$ . Toutefois, cette puce dissipe  $51,37 \text{ mW}$  lors de son fonctionnement normal.

## ABSTRACT

This master thesis' main objective is the implementation of circuits dedicated to electrical stimulation efficiency enhancement for tissues in the primary visual cortex. The proposed stimulator allows novel stimuli waveform generation such as flexible exponential and half-sine pulses in order to reduce the implant's global power consumption. In addition of being potentially more efficient to excite neural tissues than standard rectangular pulse-based stimulations, these waveforms should also reduce toxic ions concentration released by the electrodes. Moreover, this project's second objective is to allow full-scale stimulation, i.e., at least  $150 \mu\text{A}$ , through high-impedance microelectrode-tissue interfaces. A high-voltage output stage has also been realized to generate  $\pm 9 \text{ V}$  voltage supplies to increase the voltage swing while being fully-integrated.

An architecture composed of two independent integrated circuits has been proposed. The stimuli generator is implemented in TSMC CMOS  $0.18\text{-}\mu\text{m}$   $1.8\text{V}/3.3\text{V}$  technology to limit its power consumption. On the other hand, the output stage is integrated in C08E CMOS/DMOS  $0.8\text{-}\mu\text{m}$   $5\text{V}/20\text{V}$  process from DALSA Semiconductors as this technology supports the required voltage levels.

These two fabricated chips were tested. Rectangular stimuli intensity varies from  $1.6$  to  $167.2 \mu\text{A}$  with differential and integral nonlinearities of  $0.10$  and  $0.16 \text{ LSB}$ , respectively. Exponential pulses show a dynamic range of  $34.36 \text{ dB}$  for an error of  $\pm 0.5 \text{ dB}$  with the theoretical waveform. The stimuli generator's power consumption reaches an average of  $29.1 \mu\text{W}$  in rectangular mode and from  $28.5$  to  $88.3 \mu\text{W}$  in exponential mode. Half-sine results are obtained from simulations. An average of  $80.2 \%$  of half-sine pulse duration has an error lower than  $\pm 1 \%$  with the ideal sine function. The whole stimuli generator consumes from  $46.7$  to  $199.1 \mu\text{W}$  in half-sine mode. For the output stage, voltages of  $8.95$  and  $-8.46 \text{ V}$  are successfully generated, allowing the output voltage compliance to reach  $13.6 \text{ V}$  through a  $100 \text{ k}\Omega$  load. However, this chip dissipates  $51.37 \text{ mW}$  when operating normally.

## TABLE DES MATIÈRES

|                                                                   |       |

|-------------------------------------------------------------------|-------|

| REMERCIEMENTS . . . . .                                           | iv    |

| RÉSUMÉ . . . . .                                                  | v     |

| ABSTRACT . . . . .                                                | vi    |

| TABLE DES MATIÈRES . . . . .                                      | vii   |

| LISTE DES FIGURES . . . . .                                       | x     |

| LISTE DES TABLEAUX . . . . .                                      | xvii  |

| LISTE DES ANNEXES . . . . .                                       | xviii |

| LISTE DES NOTATIONS ET DES SYMBOLES . . . . .                     | xix   |

| INTRODUCTION . . . . .                                            | 1     |

| CHAPITRE 1      NOTIONS ÉLECTROPHYSIOLOGIQUES FONDAMENTALES . . . | 4     |

| 1.1 Le neurone . . . . .                                          | 4     |

| 1.1.1 La membrane cytoplasmique . . . . .                         | 5     |

| 1.1.2 Le potentiel d'action . . . . .                             | 6     |

| 1.1.3 Propagation d'un potentiel d'action . . . . .               | 8     |

| 1.2 Système visuel . . . . .                                      | 9     |

| 1.2.1 Cortex visuel primaire . . . . .                            | 10    |

| 1.3 Électrodes de stimulation . . . . .                           | 12    |

| 1.3.1 Réactions à l'interface électrode-électrolyte . . . . .     | 12    |

| 1.3.2 Modèle de l'interface . . . . .                             | 13    |

| 1.3.3 Types d'électrodes . . . . .                                | 14    |

| 1.4 Principe de stimulation électrique fonctionnelle . . . . .    | 14    |

| 1.4.1 Notions de sécurité . . . . .                               | 15    |

| 1.4.2 Paramètres . . . . .                                        | 16    |

|                                                                                                               |           |

|---------------------------------------------------------------------------------------------------------------|-----------|

| 1.5 Conclusion . . . . .                                                                                      | 18        |

| <b>CHAPITRE 2 TRAVAUX DE POINTE DANS LE DOMAINE . . . . .</b>                                                 | <b>19</b> |

| 2.1 Stimulation électrique du système visuel . . . . .                                                        | 19        |

| 2.1.1 Stimulation de la rétine . . . . .                                                                      | 19        |

| 2.1.2 Stimulation du nerf optique . . . . .                                                                   | 20        |

| 2.1.3 Stimulation du cortex visuel primaire . . . . .                                                         | 21        |

| 2.2 Efficacité de la stimulation . . . . .                                                                    | 29        |

| 2.2.1 Étude des formes d'impulsions . . . . .                                                                 | 30        |

| 2.2.2 Génération d'impulsions exponentielles croissantes de courant . . . . .                                 | 31        |

| 2.2.3 Génération d'impulsions demi-sinusoidales de courant . . . . .                                          | 36        |

| 2.3 Interface haute-tension . . . . .                                                                         | 40        |

| 2.3.1 Architectures de pompe de charge . . . . .                                                              | 40        |

| 2.3.2 Comparaison des pompes de charge . . . . .                                                              | 46        |

| 2.4 Conclusion . . . . .                                                                                      | 46        |

| <b>CHAPITRE 3 GÉNÉRATEUR DE STIMULI EXPONENTIELS ET ÉTAGE DE SOR-<br/>TIE À HAUTE-TENSION . . . . .</b>       | <b>47</b> |

| 3.1 Présentation de l'article . . . . .                                                                       | 47        |

| 3.2 EXPONENTIAL CURRENT PULSE GENERATION FOR EFFICIENT VERY<br>HIGH-IMPEDANCE MULTISITE STIMULATION . . . . . | 48        |

| 3.2.1 Introduction . . . . .                                                                                  | 48        |

| 3.2.2 Stimuli generator . . . . .                                                                             | 51        |

| 3.2.3 High-voltage output stage . . . . .                                                                     | 56        |

| 3.2.4 Experimental results . . . . .                                                                          | 58        |

| 3.2.5 Discussion . . . . .                                                                                    | 60        |

| 3.2.6 Conclusion . . . . .                                                                                    | 62        |

| 3.2.7 Acknowledgement . . . . .                                                                               | 62        |

| 3.2.8 References . . . . .                                                                                    | 62        |

| 3.2.9 Figures . . . . .                                                                                       | 68        |

| 3.2.10 Tables . . . . .                                                                                       | 76        |

|                                                                  |     |

|------------------------------------------------------------------|-----|

| CHAPITRE 4      GÉNÉRATEUR DE STIMULI DEMI-SINUSOIDAUX . . . . . | 77  |

| 4.1 Conception et fonctionnement du circuit . . . . .            | 77  |

| 4.2 Intégration et résultats . . . . .                           | 80  |

| 4.3 Discussion . . . . .                                         | 84  |

| 4.4 Conclusion . . . . .                                         | 85  |

| CHAPITRE 5      DISCUSSION GÉNÉRALE . . . . .                    | 86  |

| 5.1 Discussion sur l'ensemble de l'ouvrage . . . . .             | 86  |

| 5.2 Imperfections des puces fabriquées . . . . .                 | 87  |

| CONCLUSION . . . . .                                             | 91  |

| RÉFÉRENCES . . . . .                                             | 95  |

| ANNEXES . . . . .                                                | 105 |

## LISTE DES FIGURES

|             |                                                                                                                                                                                                                                                                                                                      |    |

|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| FIGURE 1.1  | Physiologie du neurone. <i>Modifié à partir de (StateMaster, 2009)</i> . . . . .                                                                                                                                                                                                                                     | 4  |

| FIGURE 1.2  | Mécanisme de déclenchement d'un potentiel d'action. (a) Variation temporelle du potentiel de membrane. (b) Illustration du mécanisme au niveau des canaux ioniques de la membrane. . . . .                                                                                                                           | 7  |

| FIGURE 1.3  | Propagation d'un potentiel d'action le long d'un axone myélinisé de neurone. . . . .                                                                                                                                                                                                                                 | 8  |

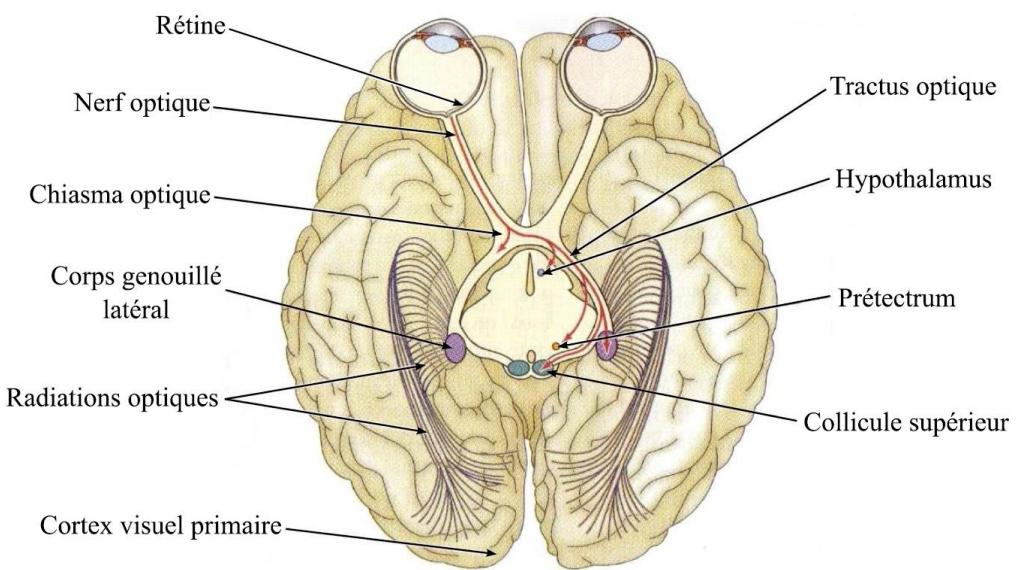

| FIGURE 1.4  | Anatomie du système visuel humain. <i>Modifié à partir de (Coulombe, 2007)</i> . . . . .                                                                                                                                                                                                                             | 9  |

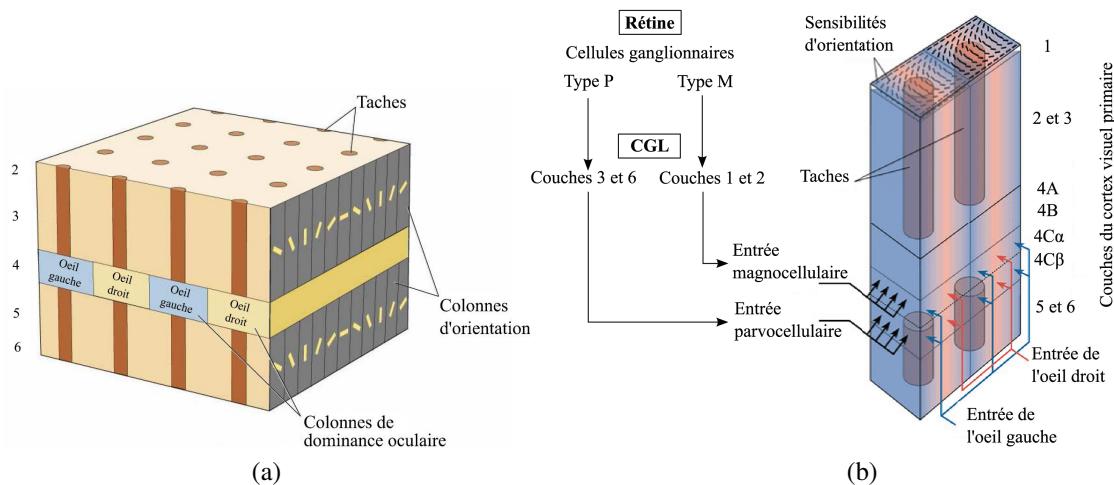

| FIGURE 1.5  | Organisation du cortex visuel primaire. (a) Module cortical, (b) Détail d'une colonne du cortex V1 montrant les couches. <i>Modifiés à partir de (McGill University, 2009)</i> . . . . .                                                                                                                             | 11 |

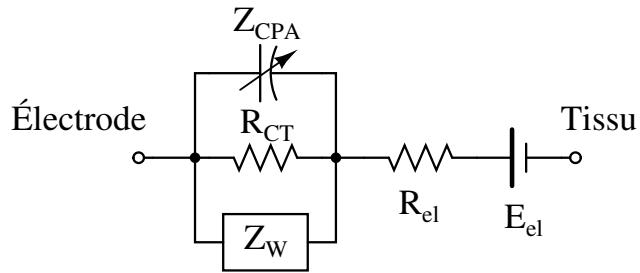

| FIGURE 1.6  | Modèle de l'interface électrode-tissus. . . . .                                                                                                                                                                                                                                                                      | 13 |

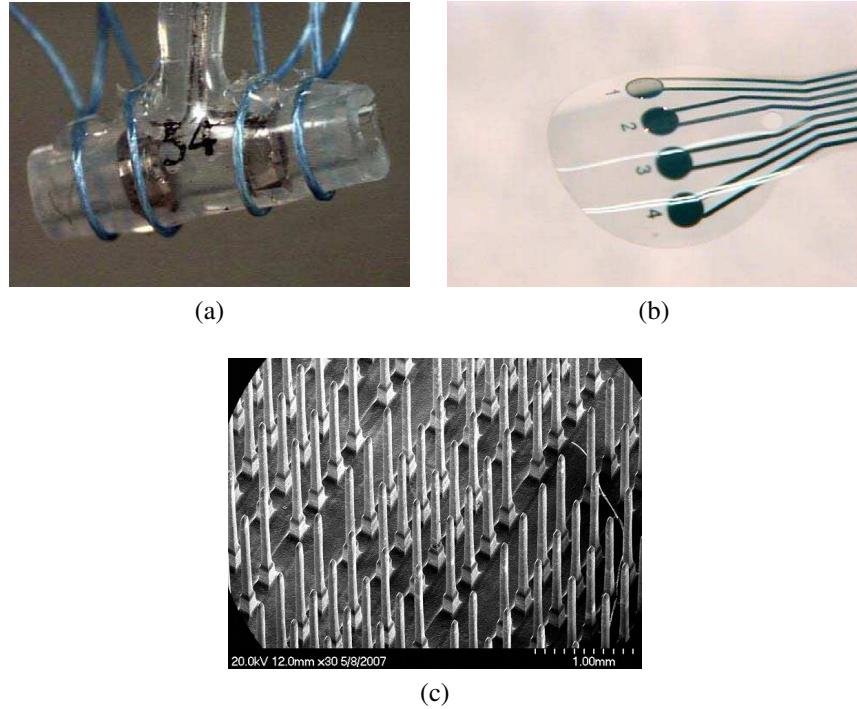

| FIGURE 1.7  | Différents exemples d'électrodes implantables. (a) Électrode à gaine. <i>Tiré de (Crampon, 1999)</i> . (b) Électrodes de surface. <i>Tiré de (Rodger et al., 2006) avec l'autorisation de l'IEEE</i> . © 2006 IEEE. (c) Matrice de microélectrodes. <i>Tiré de (Ayoub, 2007)</i> . . . . .                           | 15 |

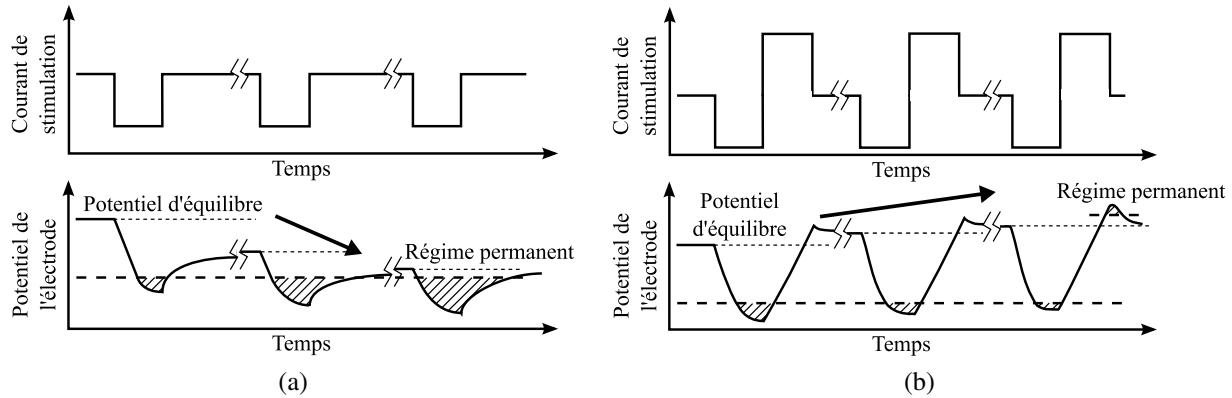

| FIGURE 1.8  | Évolution du potentiel de l'électrode lors de stimulation (a) de type monophasique, et (b) de type biphasique. Les régions hachurées correspondent aux réactions irréversibles. . . . .                                                                                                                              | 16 |

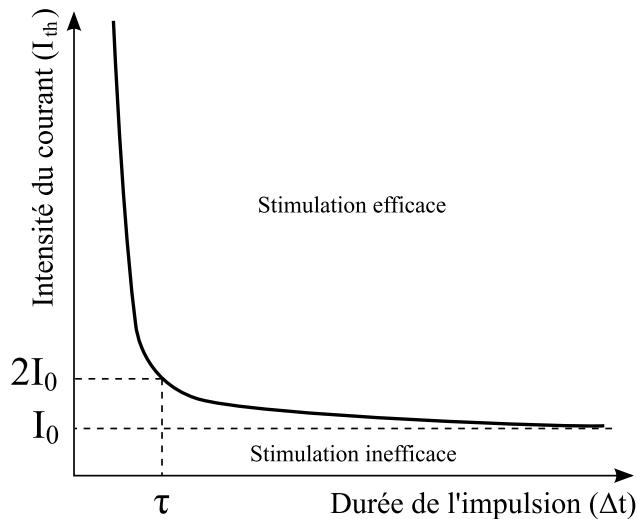

| FIGURE 1.9  | Courbe intensité-durée délimitant le seuil d'excitation du neurone. . . . .                                                                                                                                                                                                                                          | 17 |

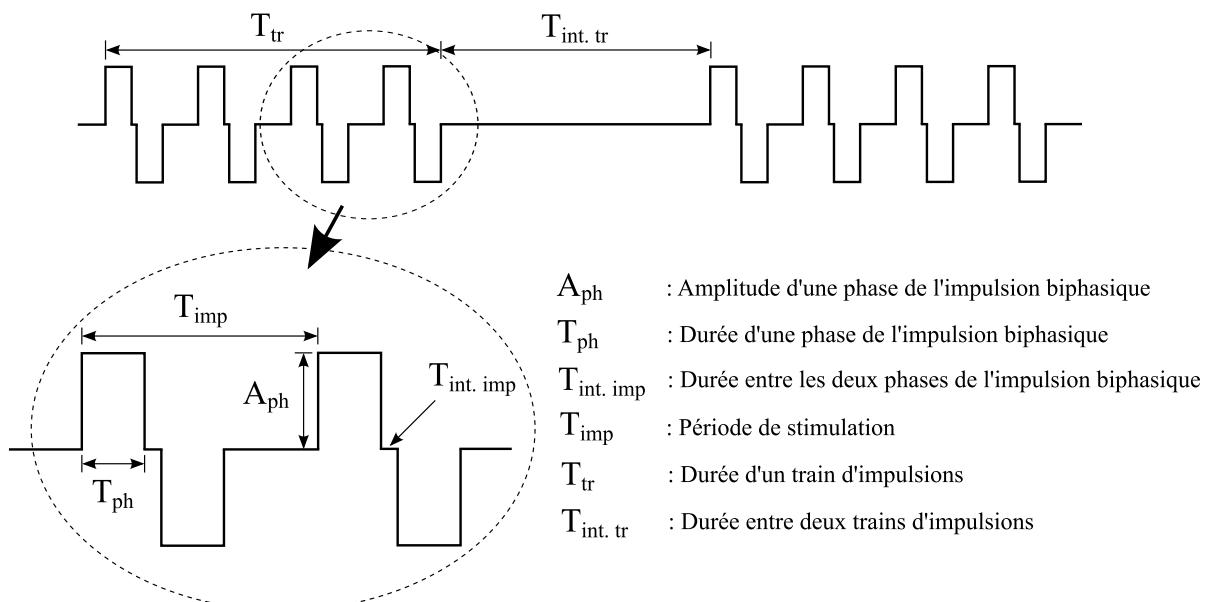

| FIGURE 1.10 | Train d'impulsions biphasiques de courant avec l'ensemble des paramètres de stimulation. . . . .                                                                                                                                                                                                                     | 17 |

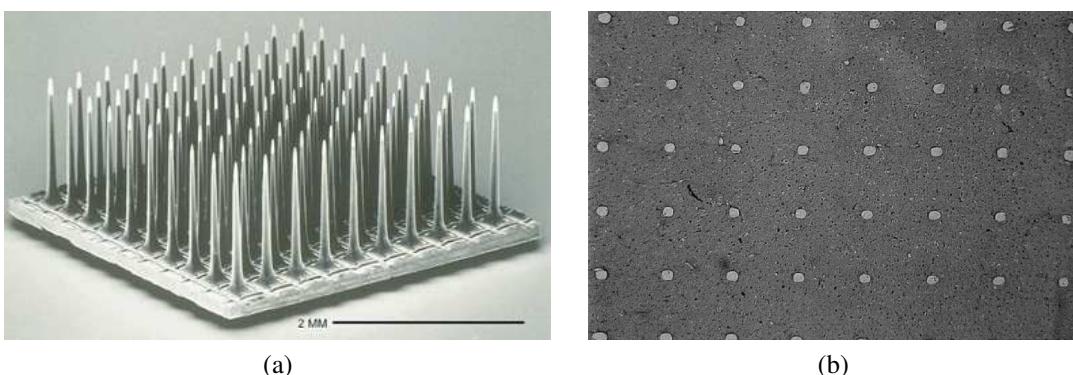

| FIGURE 2.1  | (a) Matrice de microélectrodes Utah. <i>Tiré de (House et al., 2006) avec l'autorisation du JNS</i> (b) Photographie de la surface du cortex visuel après six mois d'implantation. Des taches sont visibles aux sites d'implantation. <i>Tiré de (Normann et al., 1999) avec l'autorisation d'Elsevier</i> . . . . . | 22 |

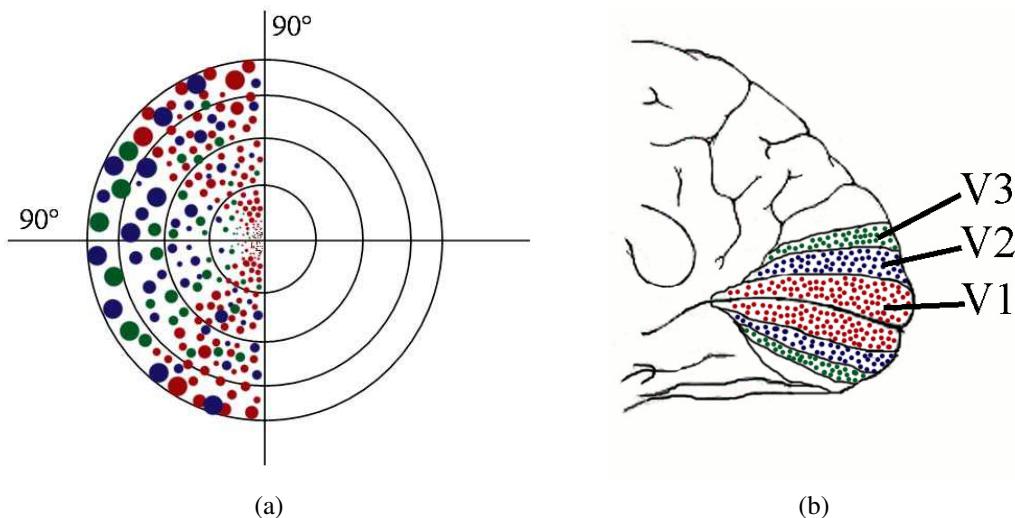

| FIGURE 2.2  | Correspondance visuotopique des cortex V1 (rouge), V2 (bleu) et V3 (vert). (a) Phosphènes dans le champ visuel selon (b) les sites de stimulation sur le cortex occipital. <i>Modifiés à partir de (Srivastava et al., 2007) avec l'autorisation de l'IEEE</i> . © 2007 IEEE. . . . .                                | 23 |

|             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |    |

|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

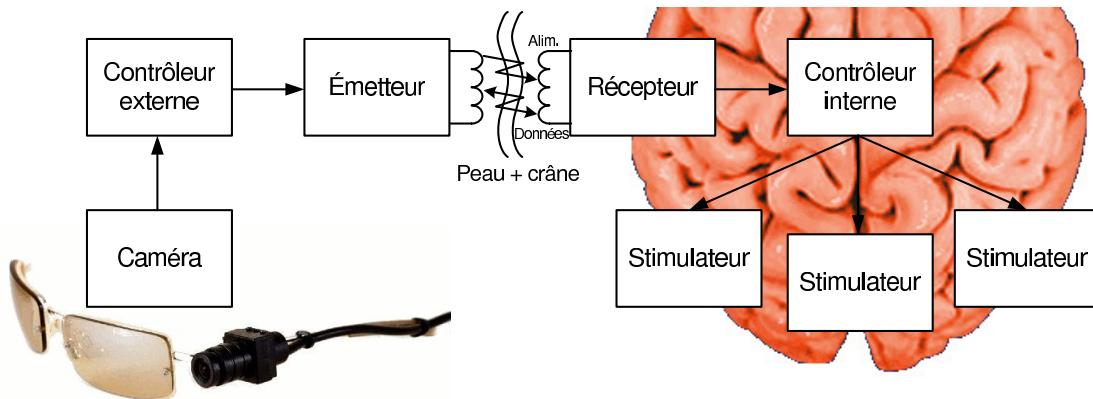

| FIGURE 2.3  | Architecture typique d'une prothèse visuelle corticale. . . . .                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 24 |

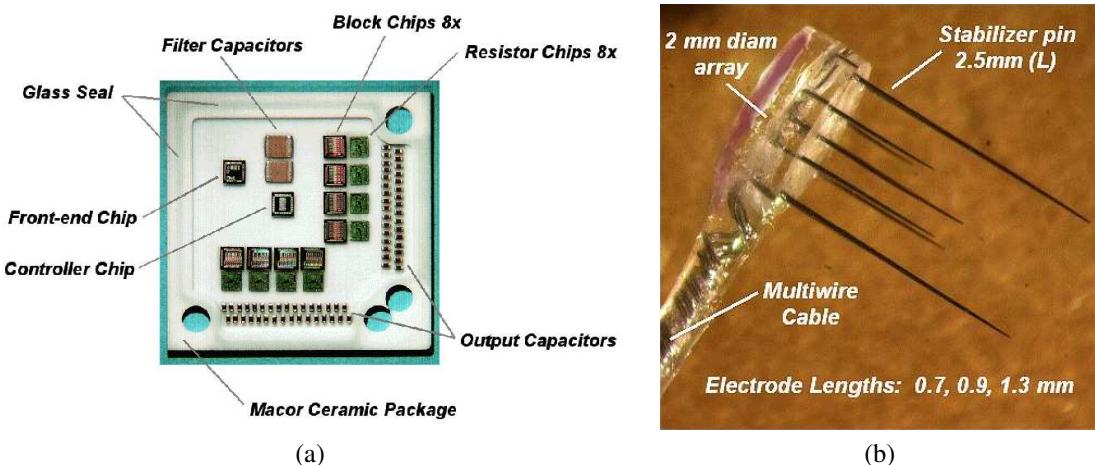

| FIGURE 2.4  | Implant de l'Illinois Institute of Technology. (a) Modules de l'implant à 64 canaux dans son encapsulation. (b) Électrodes intracorticales utilisées lors de tests <i>in vivo</i> . <i>Tirés de</i> (Troyk, 2009). . . . .                                                                                                                                                                                                                                                                                                        | 25 |

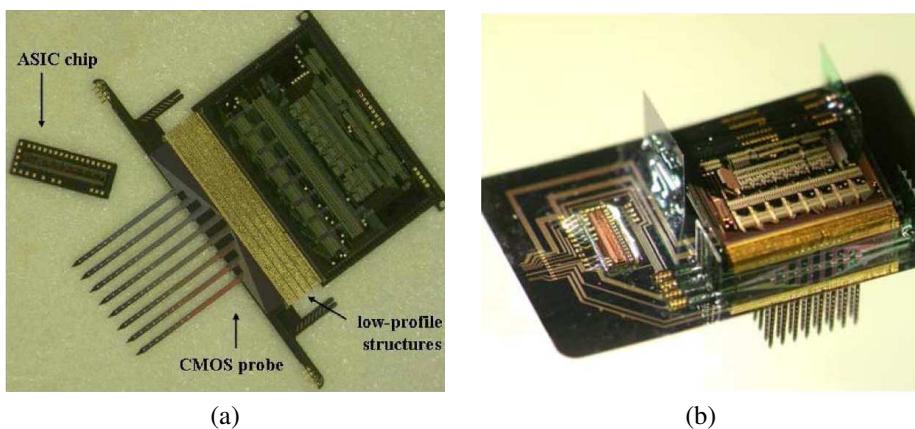

| FIGURE 2.5  | Implant de l'University of Michigan. (a) Sonde à huit canaux. (b) Micro-système assemblé. <i>Tirés de</i> (Yao <i>et al.</i> , 2007) avec l'autorisation de l'IEEE. © 2007 IEEE. . . . .                                                                                                                                                                                                                                                                                                                                          | 26 |

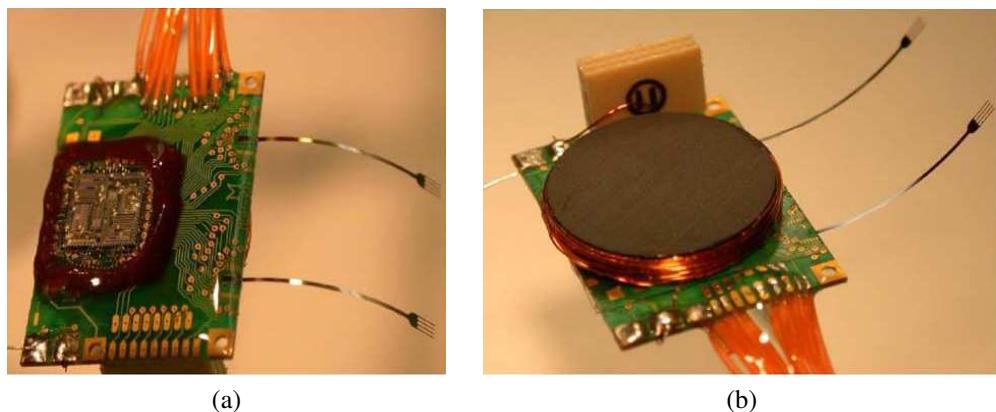

| FIGURE 2.6  | Implant Interestim-2B à 32 canaux du North Carolina State University. (a) Vue du dessus montrant l'implant fixé à l'aide d'époxy. (b) Vue du dessous montrant l'inductance du système télémétrique. <i>Tirés de</i> (Ghovanloo & Najafi, 2007) avec l'autorisation de l'IEEE. © 2007 IEEE. . . . .                                                                                                                                                                                                                                | 27 |

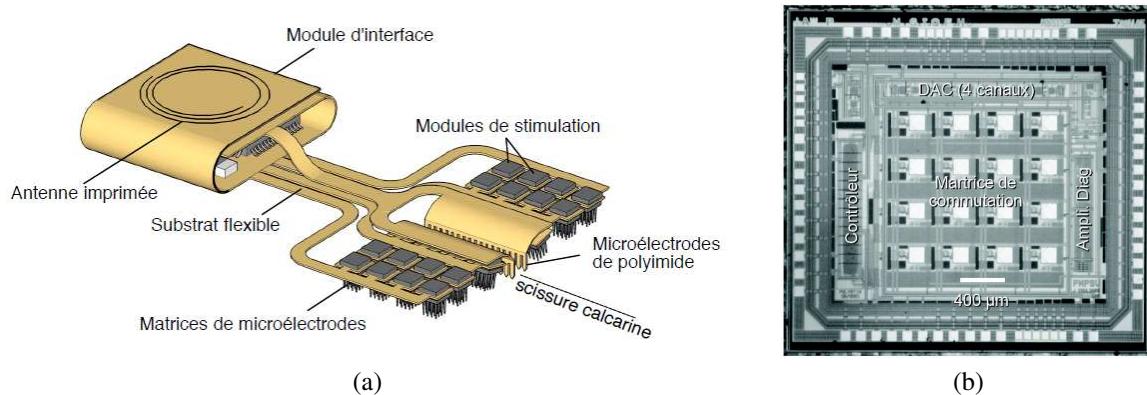

| FIGURE 2.7  | Implant visuel intracortical Cortivsion. (a) Illustration de l'implant complet. (b) Microphotographie du module de stimulation. <i>Tirés de</i> (Coulombe, 2007). . . . .                                                                                                                                                                                                                                                                                                                                                         | 28 |

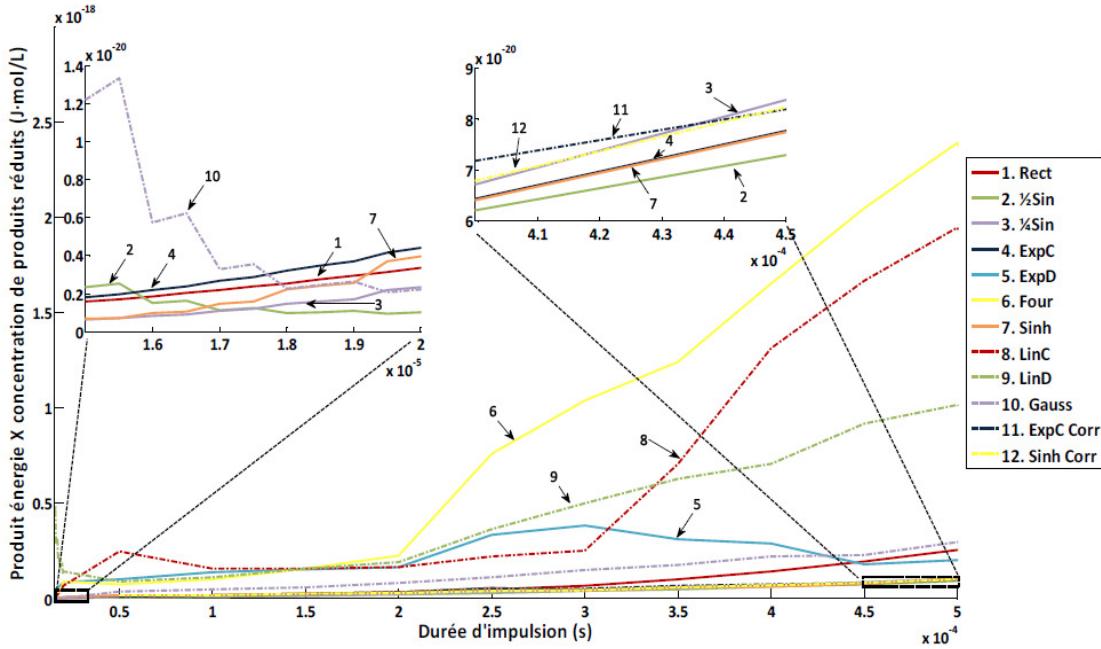

| FIGURE 2.8  | Figure de mérite (Énergie dissipée × CPR) selon la durée de la stimulation pour chaque forme d'impulsion étudiée. <i>Tiré de</i> (Robillard, 2008). . . . .                                                                                                                                                                                                                                                                                                                                                                       | 31 |

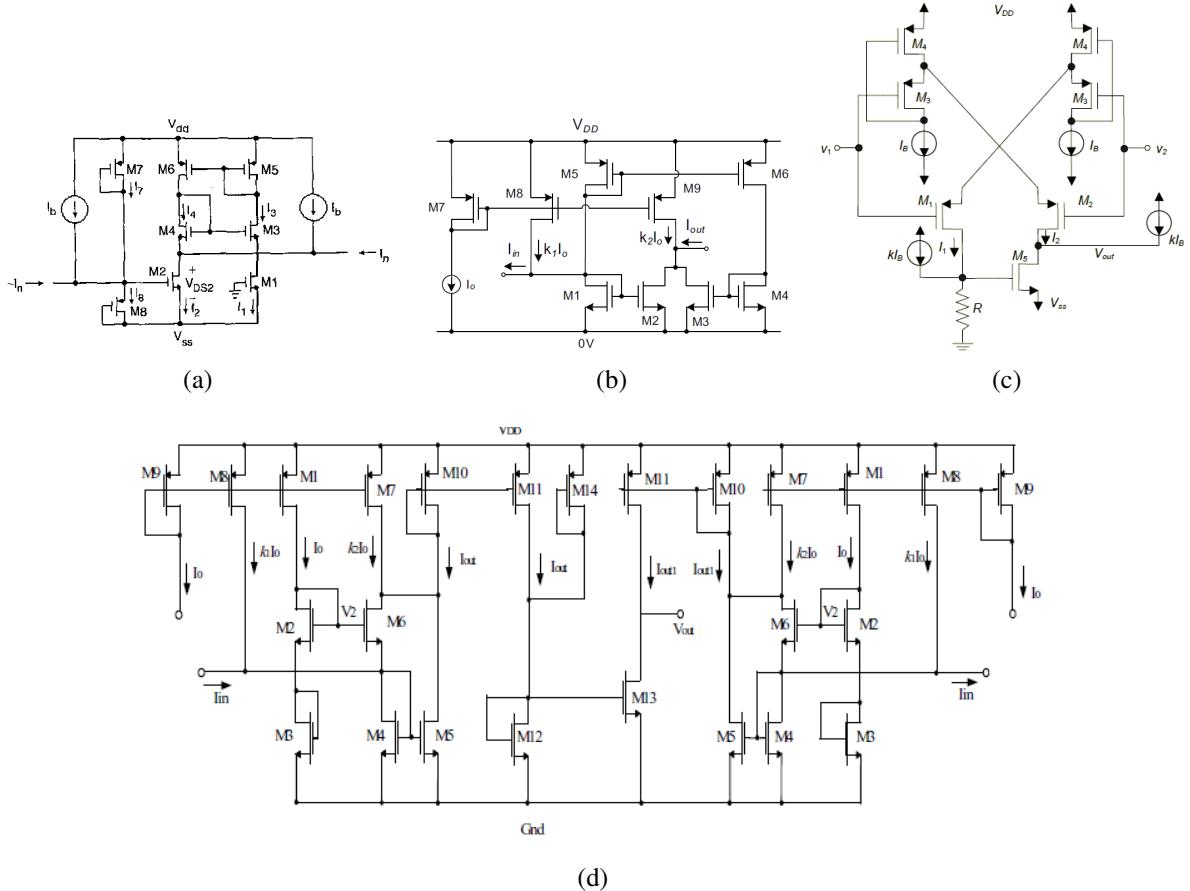

| FIGURE 2.9  | Exemples de circuits générant une approximation de la fonction exponentielle. (a) Pseudo-exponentielle. <i>Tiré de</i> (Liu & Liu, 2003) avec l'autorisation de l'IET. (b) Taylor de 2 <sup>e</sup> ordre. <i>Tiré de</i> (Kumngern <i>et al.</i> , 2008) avec l'autorisation de l'IEEE. © 2008 IEEE. (c) Pseudo-Taylor. <i>Tiré de</i> (De La Cruz-Blas & Lopez-Martin, 2006) avec l'autorisation de l'ETRI. (d) Pseudo-Taylor. <i>Tiré de</i> (Duong <i>et al.</i> , 2004b) avec l'autorisation de l'IEEE. © 2004 IEEE. . . . . | 35 |

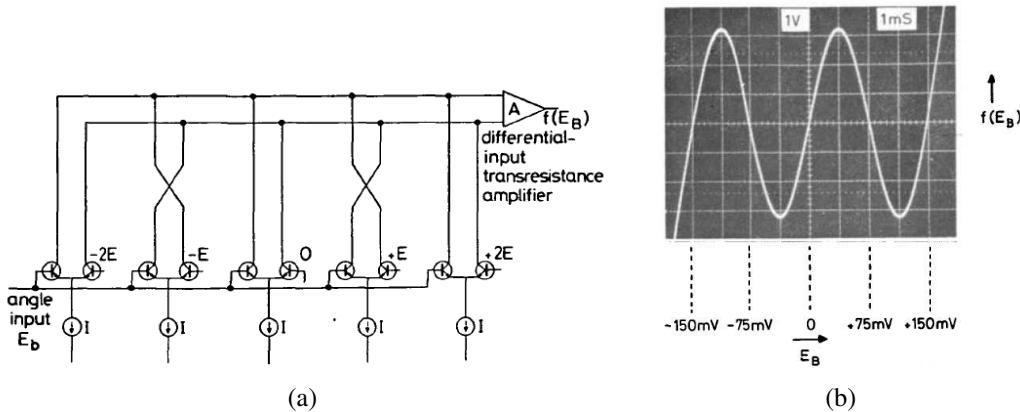

| FIGURE 2.10 | Génération d'une sinusoïde à l'aide de paires différentielles de transistors bipolaires. À noter que $E = 75$ mV. (a) Implémentation avec $N = 5$ . (b) Sinusoïde résultante de deux périodes. <i>Tirés de</i> (Gilbert, 1977) avec l'autorisation de l'IET. . . . .                                                                                                                                                                                                                                                              | 37 |

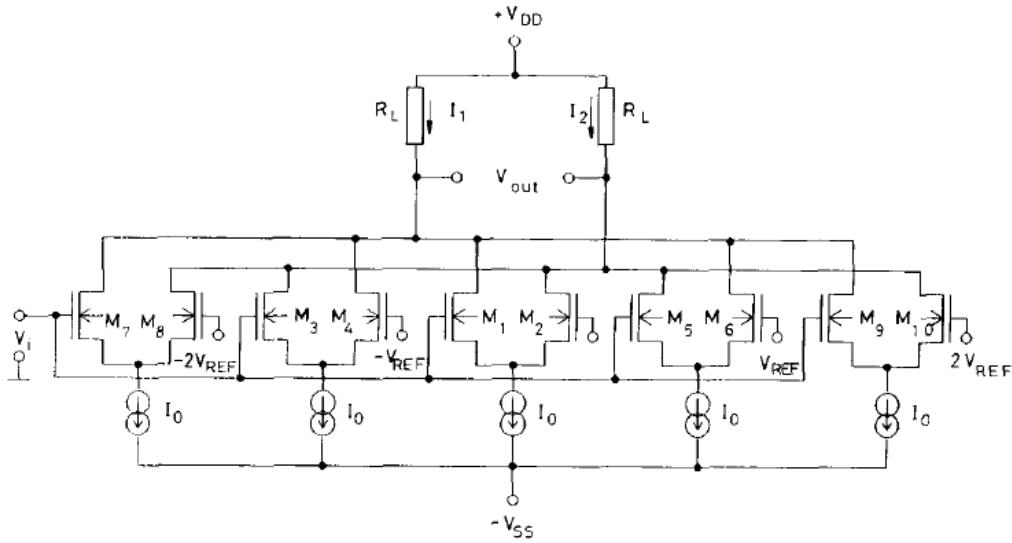

| FIGURE 2.11 | Générateur de sinusoïde implémenté à l'aide de transistors MOS en inversion faible ( $N = 5$ ). <i>Tiré de</i> (Ishizuka <i>et al.</i> , 1991) avec l'autorisation de l'IET. . . . .                                                                                                                                                                                                                                                                                                                                              | 39 |

|             |                                                                                                                                                                                                                                                                                                                                                                                                                                                      |    |

|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

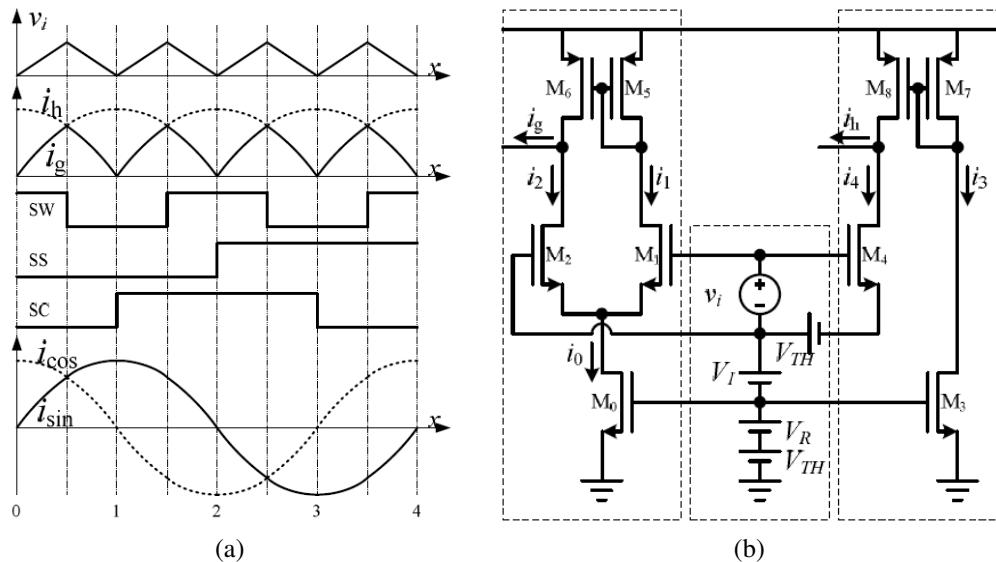

| FIGURE 2.12 | Construction d'une sinusoïde en quadrature à l'aide de portions de sinus et cosinus d'angle de 0 à $\pi/4$ rad. (a) Principe de construction. (b) Circuit générant les courants $i_g$ et $i_h$ . <i>Tirés de (Pengwon &amp; Leelarasamee, 2008) avec l'autorisation de l'IEEE. © 2008 IEEE.</i>                                                                                                                                                      | 39 |

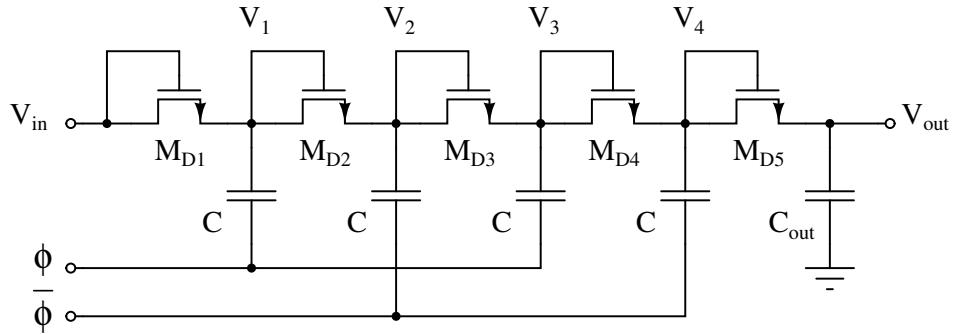

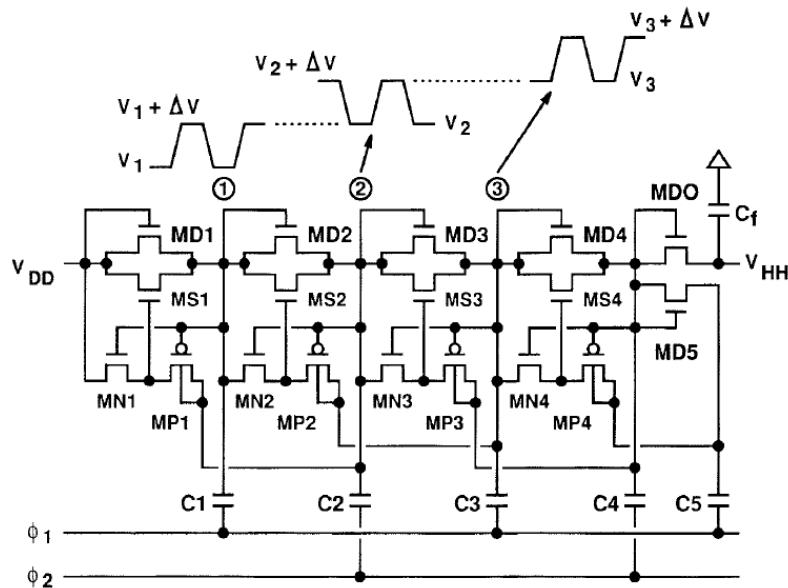

| FIGURE 2.13 | Pompe de charge de Dickson à quatre étages.                                                                                                                                                                                                                                                                                                                                                                                                          | 41 |

| FIGURE 2.14 | Pompe de charge NCP-2 à quatre étages. <i>Tiré de (Wu &amp; Chang, 1998) avec l'autorisation de l'IEEE. © 1998 IEEE.</i>                                                                                                                                                                                                                                                                                                                             | 42 |

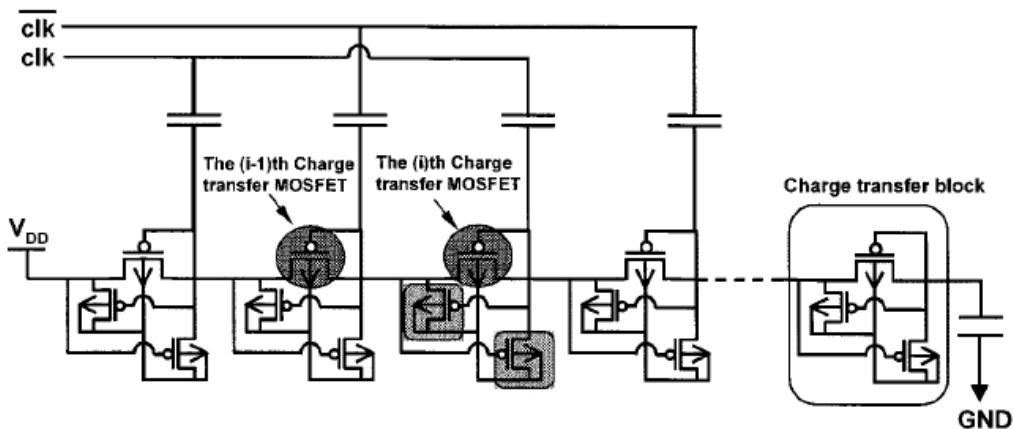

| FIGURE 2.15 | Pompe de charge avec polarisation dynamique du substrat. <i>Tiré de (Shin et al., 2000) avec l'autorisation de l'IEEE. © 2000 IEEE.</i>                                                                                                                                                                                                                                                                                                              | 43 |

| FIGURE 2.16 | Un étage de la pompe de charge de Pelliconi. <i>Tiré de (Pelliconi et al., 2001) avec l'autorisation de l'IEEE. © 2001 IEEE.</i>                                                                                                                                                                                                                                                                                                                     | 44 |

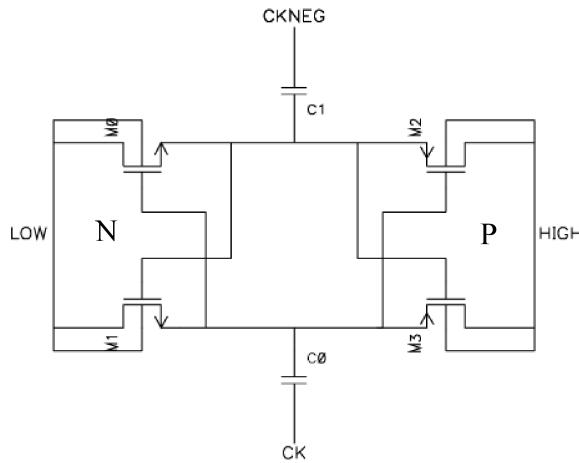

| FIGURE 2.17 | Circuit doubleur d'horloge. <i>Tiré de (Huang et al., 2008) avec l'autorisation de l'IEEE. © 2008 IEEE.</i>                                                                                                                                                                                                                                                                                                                                          | 45 |

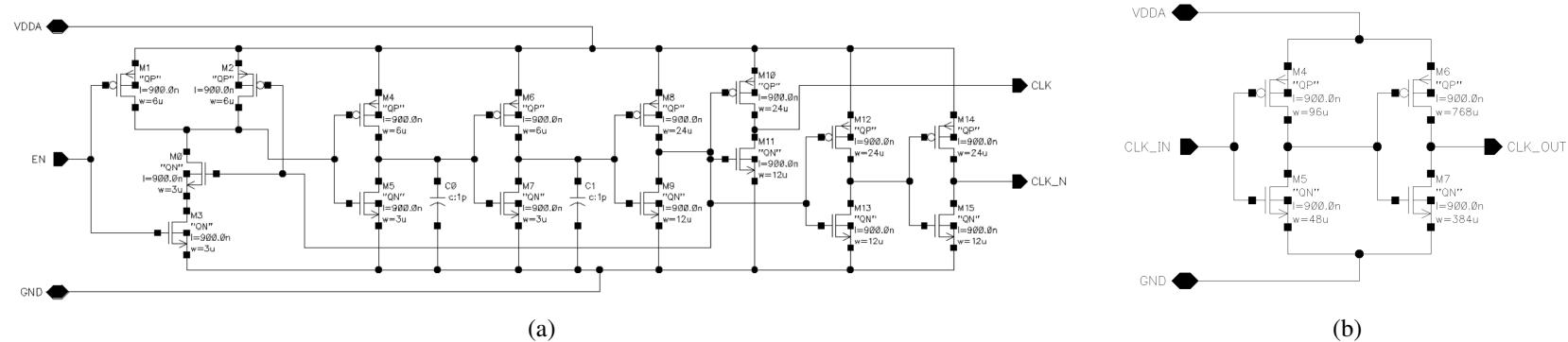

| FIGURE 3.1  | Block diagram of the proposed microstimulator. It is composed of a multiwaveform stimuli generator implemented in CMOS 0.18- $\mu$ m technology and a high-voltage output stage in CMOS 0.8- $\mu$ m technology. The DAC prescaler, the voltage ramp generator, the current-mode DAC, and the voltage shifter are composed of two complementary circuits that source (P) and sink (N) current to support biphasic stimulation.                       | 68 |

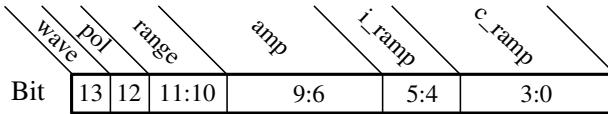

| FIGURE 3.2  | The 14-bit programming word containing the required stimulation parameters, where <i>wave</i> sets the waveform (0 = rectangular, 1 = exponential), <i>pol</i> sets the pulse polarity (0 = positive, 1 = negative), <i>range</i> sets the prescaling voltage and the exponential current gain, <i>amp</i> sets the current pulse amplitude, <i>i_ramp</i> sets the voltage ramp input current, and <i>c_ramp</i> sets the voltage ramp capacitance. | 68 |

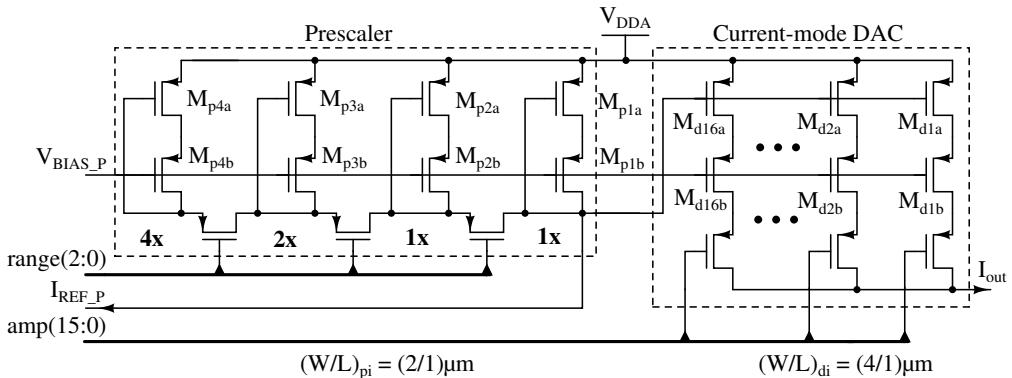

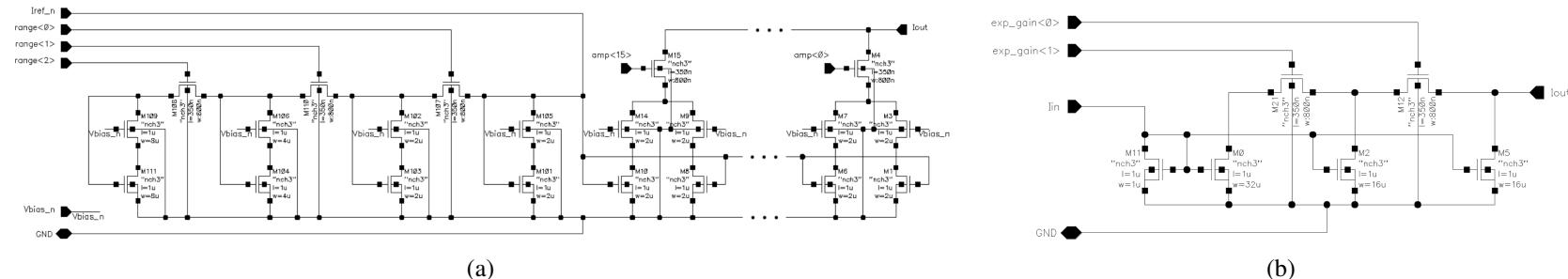

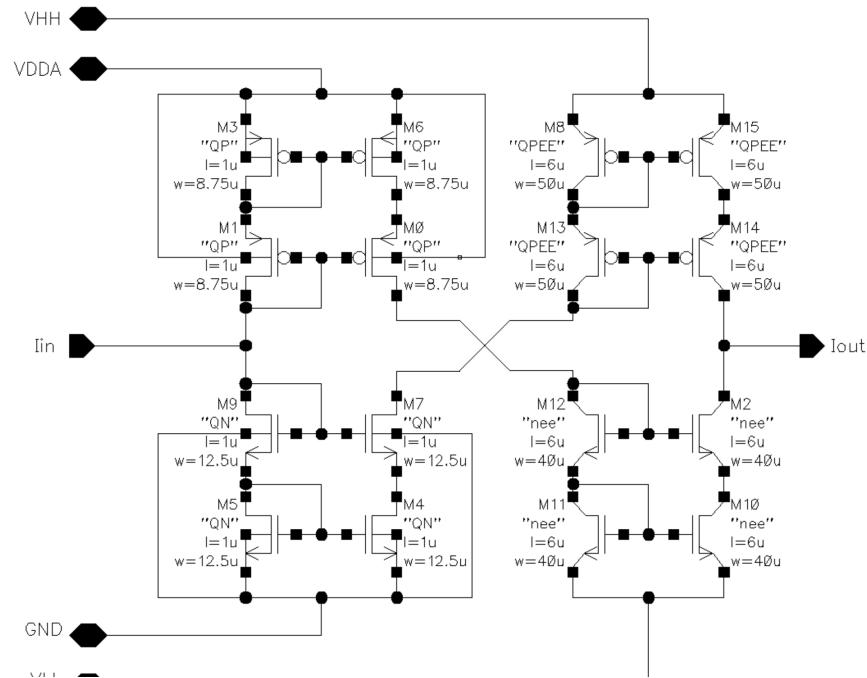

| FIGURE 3.3  | Current-mode DAC schematic in rectangular pulse generation mode. Only the positive current generator (P) is shown. The biasing conditions are $ I_{ref\_p/n}  = 5 \mu\text{A}$ , $V_{bias\_p} = 2.02 \text{ V}$ , and $V_{bias\_n} = 2.64 \text{ V}$ .                                                                                                                                                                                               | 68 |

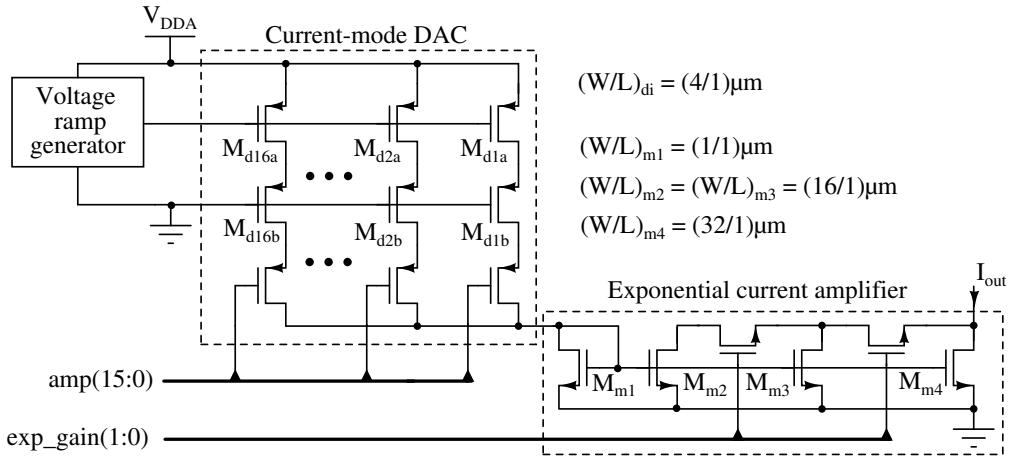

| FIGURE 3.4  | Current-mode DAC schematic in exponential pulse generation mode. Only the negative current generator (N) is shown.                                                                                                                                                                                                                                                                                                                                   | 69 |

|             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |    |

|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

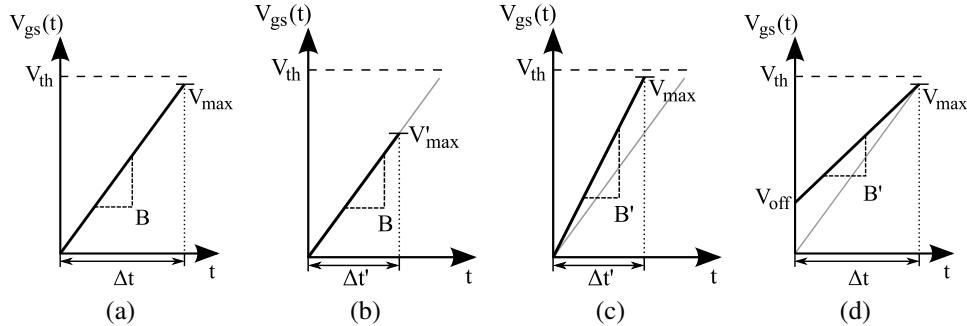

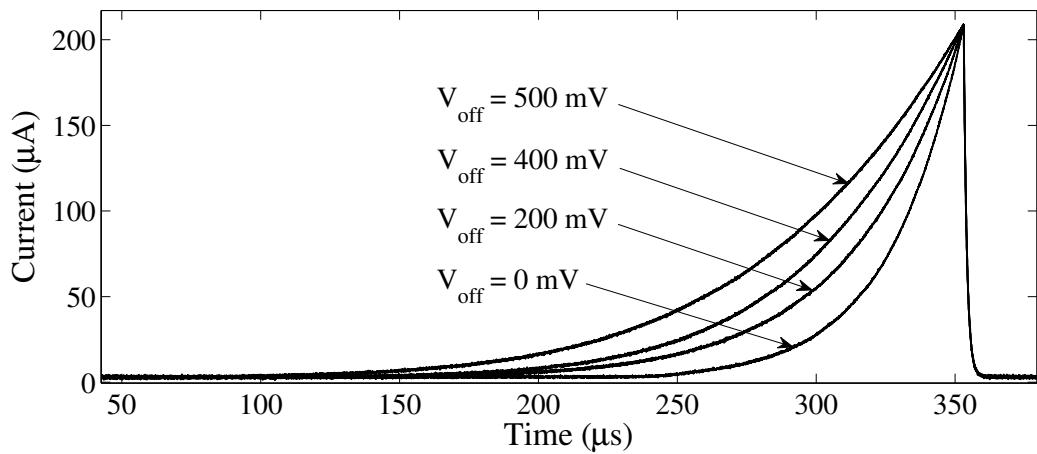

| FIGURE 3.5  | Effects of the parameters variation of the voltage ramp. (a) Basic voltage ramp. (b) Pulse duration $\Delta t$ variation directly affects the maximal voltage $V_{max}$ , which is to be avoided as $\Delta t$ and the amplitude are modified together. (c) To vary $\Delta t$ solely, the slope $B$ has to be adjusted to keep $V_{max}$ constant. (d) Variation of the time constant is achieved by adding a voltage offset $V_{off}$ and by adjusting $B$ to keep both $\Delta t$ and $V_{max}$ constant. . . . . | 69 |

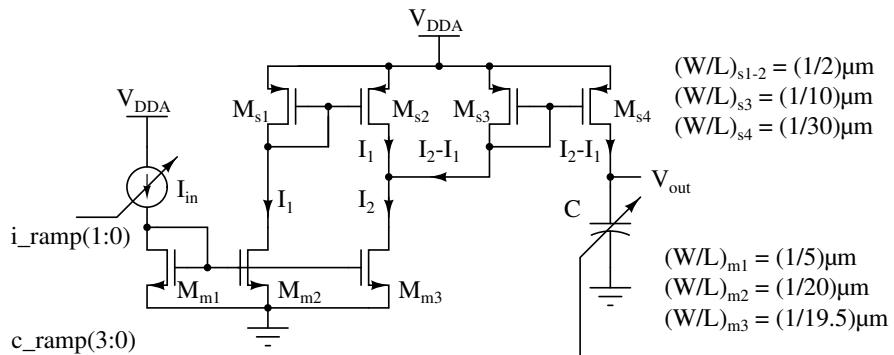

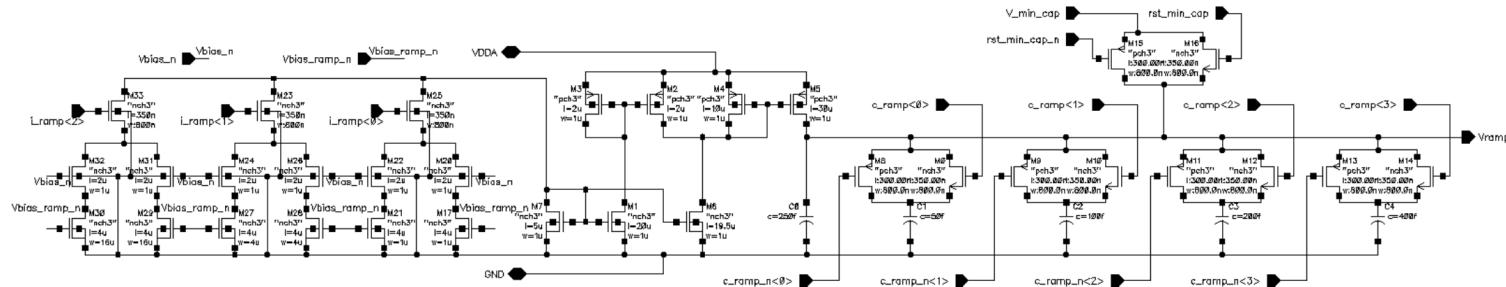

| FIGURE 3.6  | Voltage ramp generator schematic. Only the rising voltage ramp generator (P) is shown. . . . .                                                                                                                                                                                                                                                                                                                                                                                                                       | 69 |

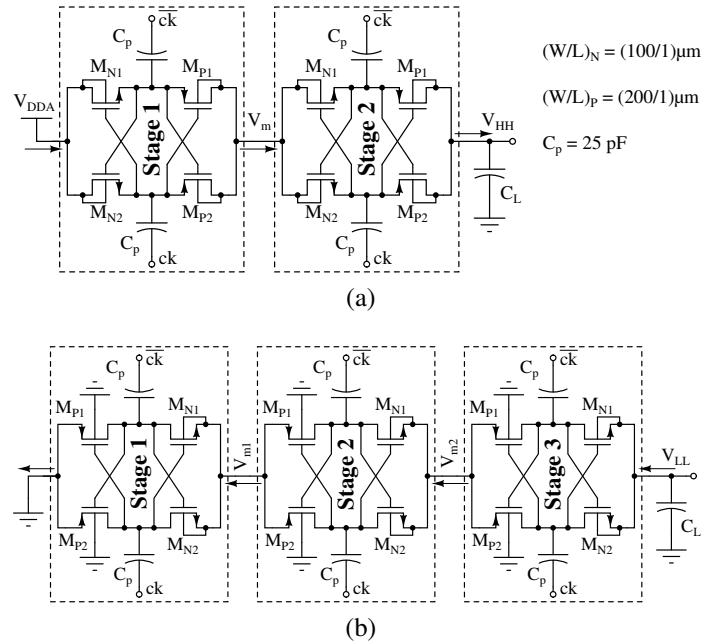

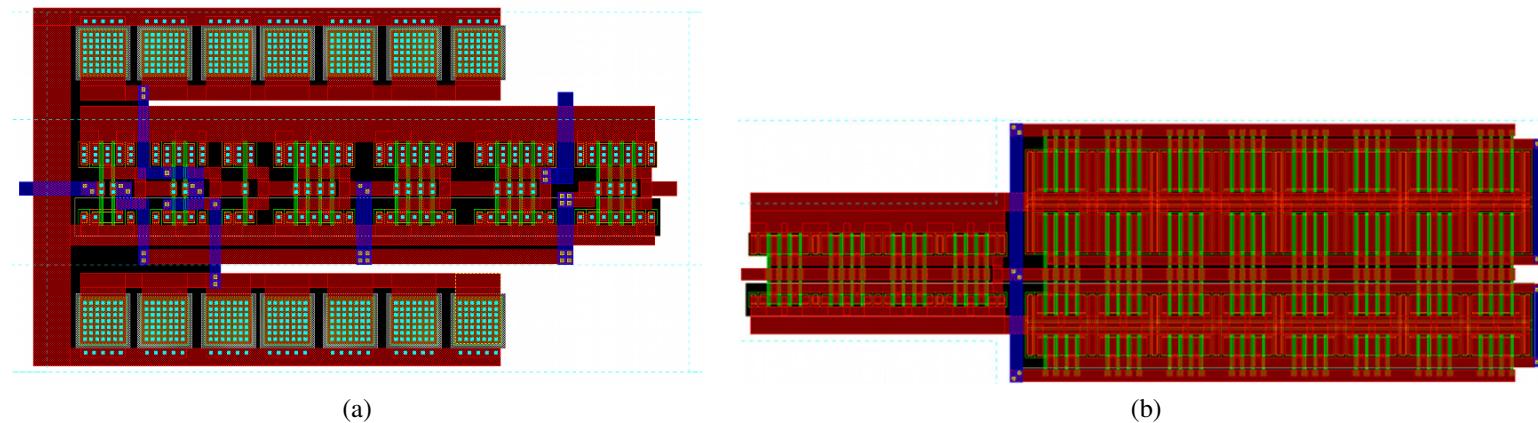

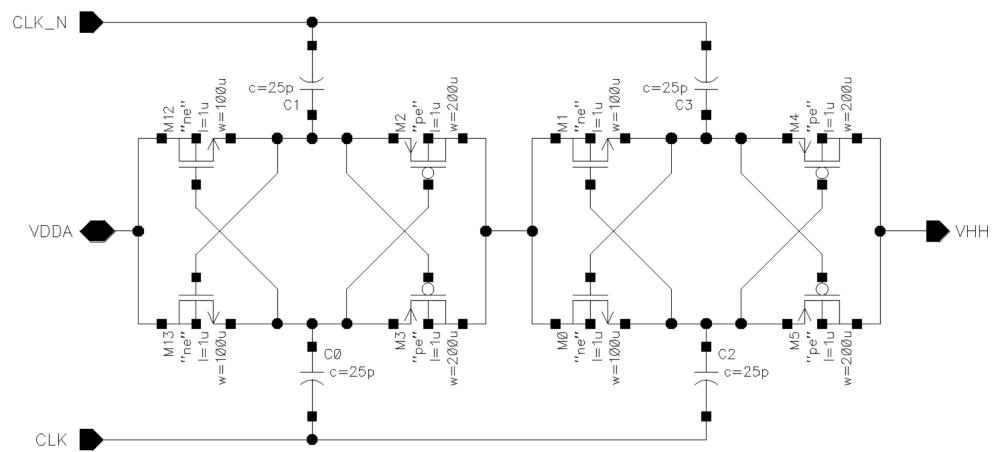

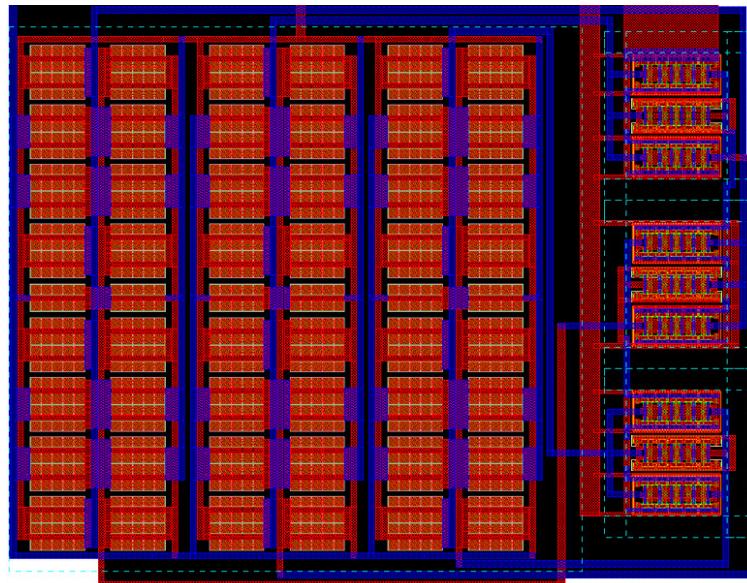

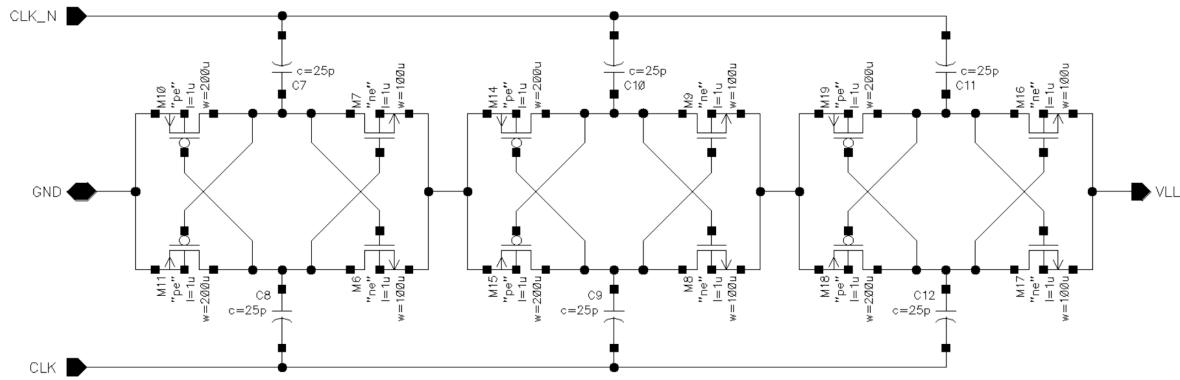

| FIGURE 3.7  | Charge pumps schematics where the arrows indicate the charge flow direction. (a) Positive charge pump with $C_L = 56$ pF (plus pads capacitance). (b) Negative charge pump with $C_L = 36$ pF (plus pads and substrate capacitances). The bulk of the PMOS devices (deep N-wells) are tied to the ground to prevent latch-up triggering [35]. . . . .                                                                                                                                                                | 70 |

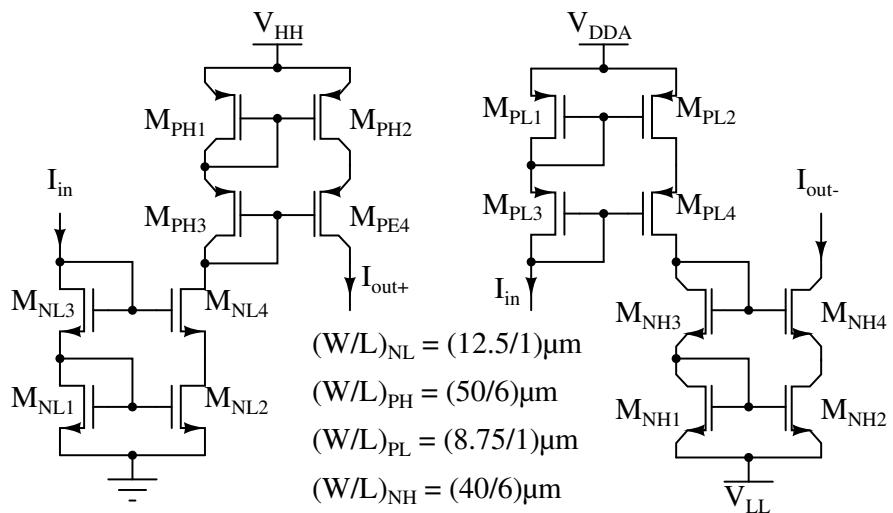

| FIGURE 3.8  | Voltage shifter cascode current mirrors. $M_{xL}$ devices are 5-V CMOS transistors and $M_{xH}$ devices are 20-V CMOS transistors. . . . .                                                                                                                                                                                                                                                                                                                                                                           | 70 |

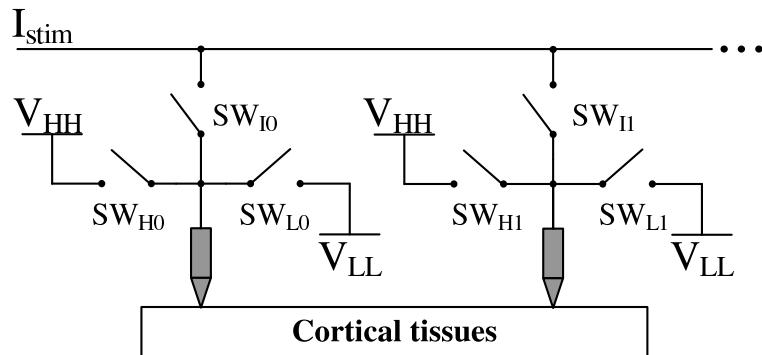

| FIGURE 3.9  | Microelectrodes connections through high-voltage switches to support monopolar and bipolar biphasic stimulation. . . . .                                                                                                                                                                                                                                                                                                                                                                                             | 71 |

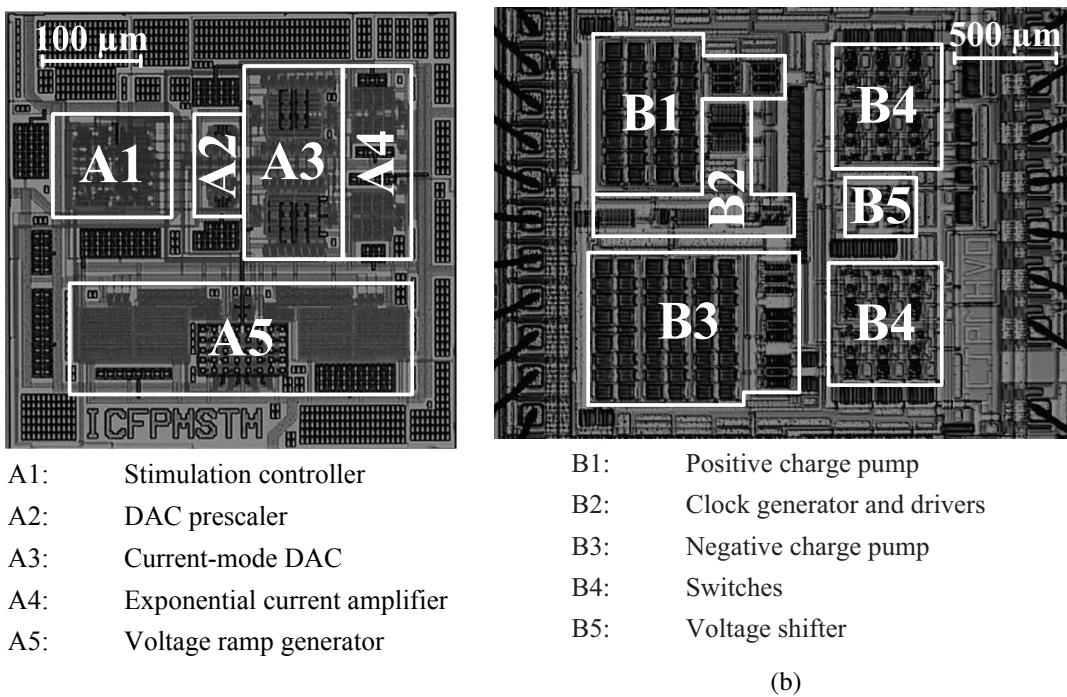

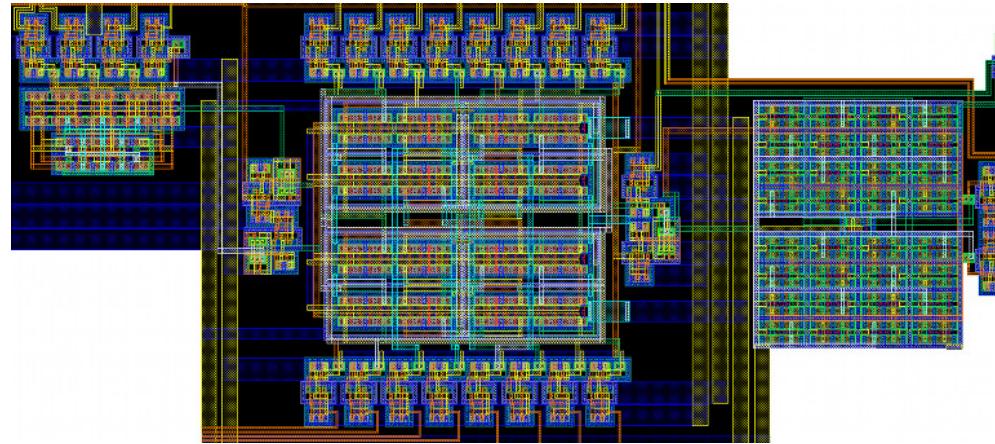

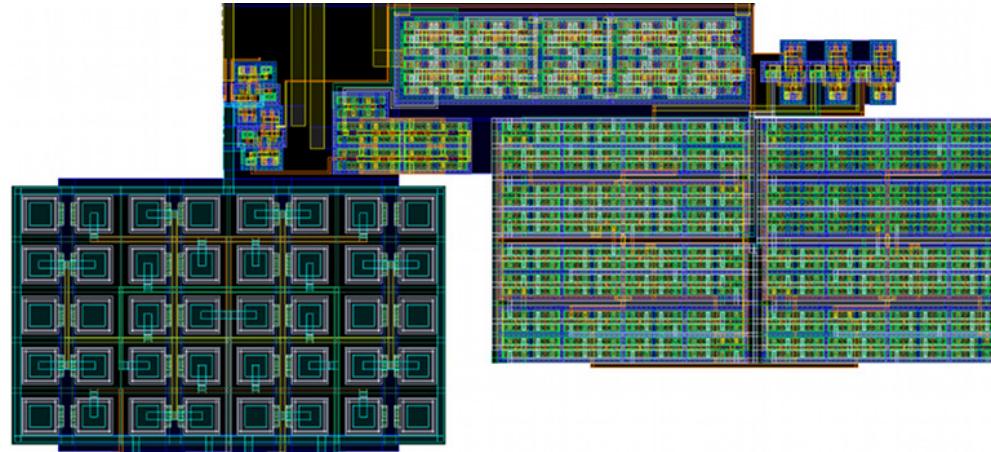

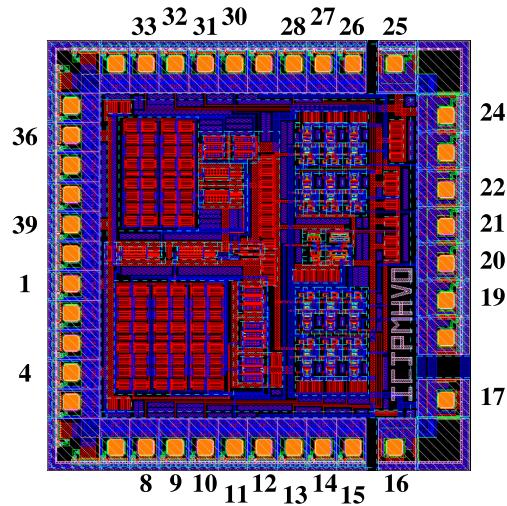

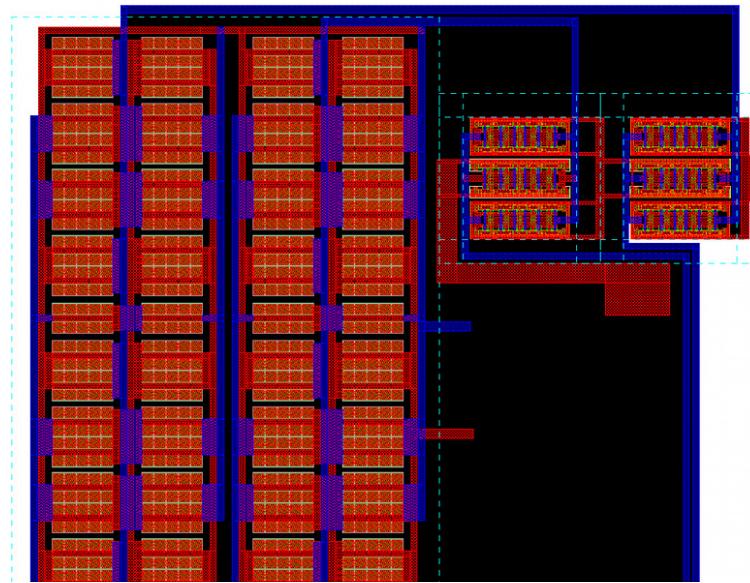

| FIGURE 3.10 | Microphotographs of the two IC composing the proposed system. (a) The stimuli generator produces rectangular and exponential biphasic current pulses according to the stimulation configuration. It is implemented in 0.18- $\mu$ m CMOS process and has a total area of 1.02 mm <sup>2</sup> . (b) The output stage generates high-voltage supplies and increases the stimulation voltage swing. It presents an area of 8.38 mm <sup>2</sup> in 0.8- $\mu$ m CMOS/DMOS technology. . .                              | 71 |

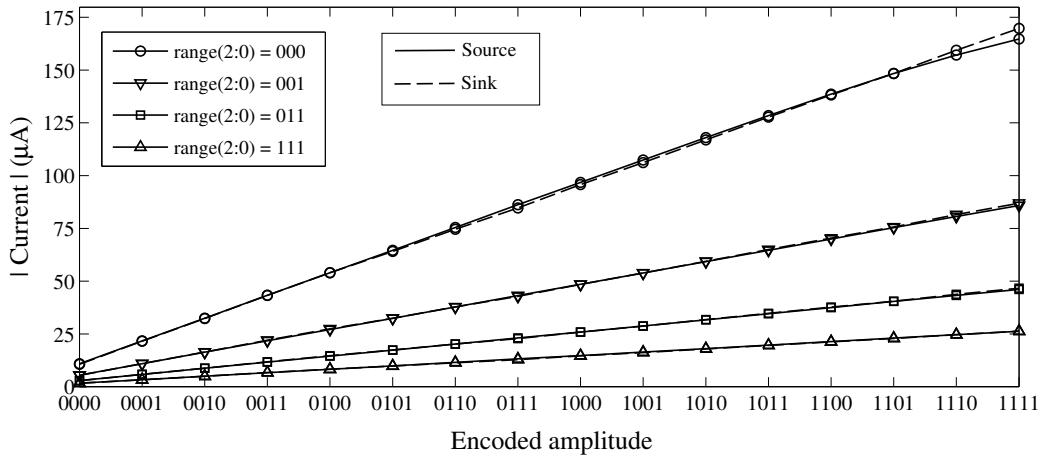

| FIGURE 3.11 | Experimental source and sink currents of the current-mode DAC in rectangular mode for all 4 ranges of 16 binary input codes. . . . .                                                                                                                                                                                                                                                                                                                                                                                 | 72 |

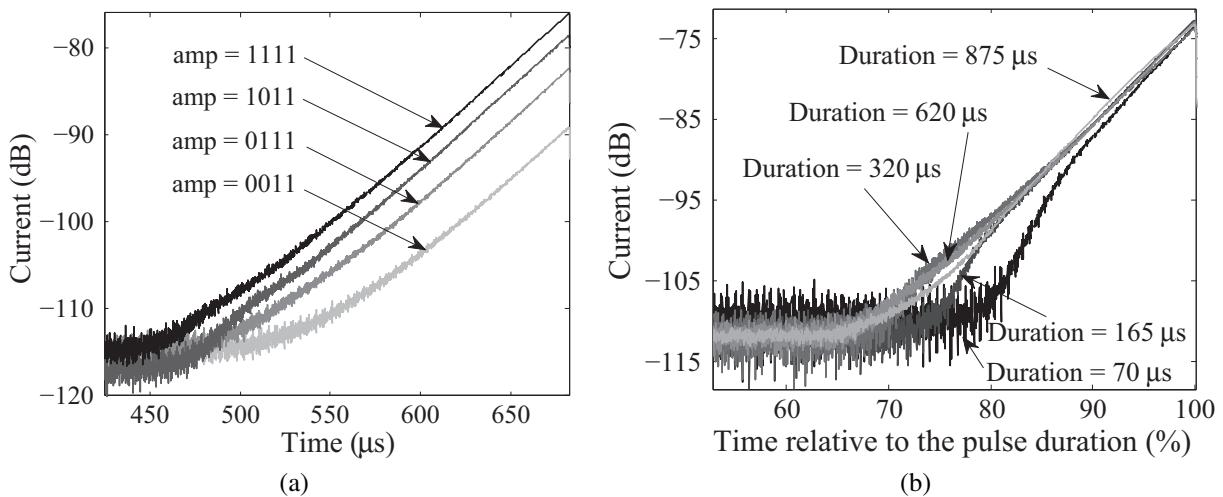

| FIGURE 3.12 | Experimental exponential source current pulses expressed in dB. (a) Current versus time for various stimuli amplitudes. The pulse duration is fixed to 690 $\mu$ s and $exp\_gain = 11$ . (b) Current versus time relative to pulse duration for stimuli of 70, 165, 320, 620, and 875 $\mu$ s. The amplitude is fixed to $exp\_gain = 11$ and $amp = 1111$ . . . . .                                                                                                                                                | 72 |

|             |                                                                                                                                                                                                                                                                                                                                                                               |     |

|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| FIGURE 3.13 | Experimental time constant variation of the exponential current pulse with $V_{off} = 0, 200, 400$ , and $500$ mV. . . . .                                                                                                                                                                                                                                                    | 73  |

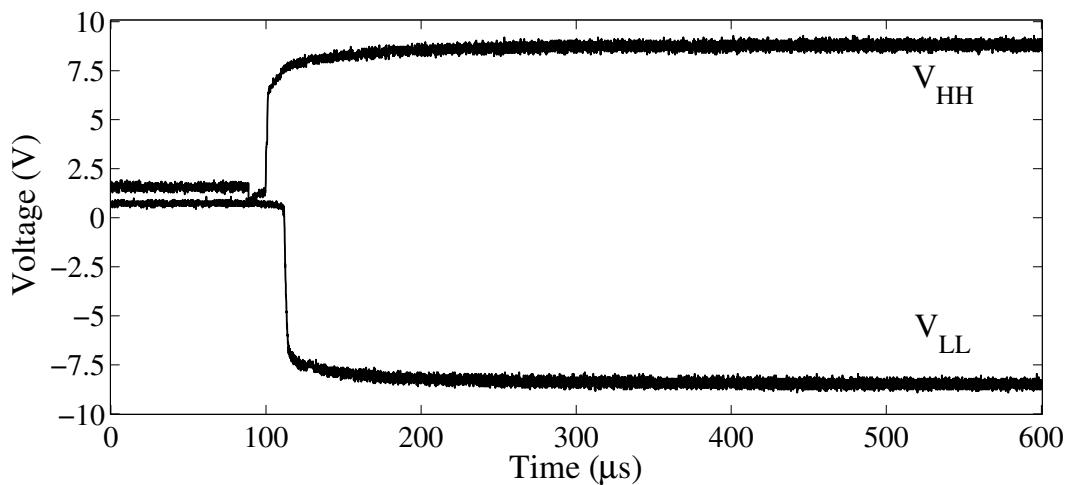

| FIGURE 3.14 | Start-up of the high-voltage $V_{HH}$ and $V_{LL}$ generation used to supply the output stage. . . . .                                                                                                                                                                                                                                                                        | 73  |

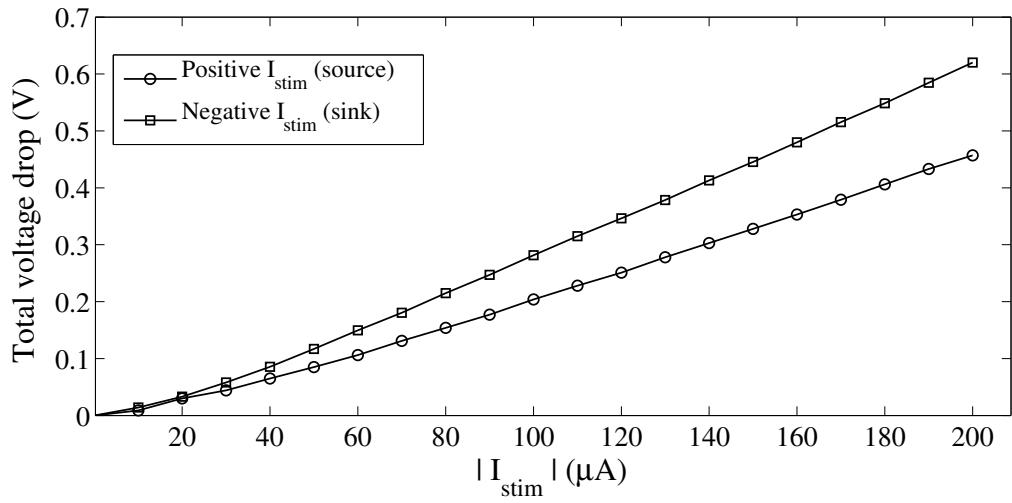

| FIGURE 3.15 | High-voltage supplies drop versus the stimulation current $I_{stim}$ for positive and negative current pulses. . . . .                                                                                                                                                                                                                                                        | 74  |

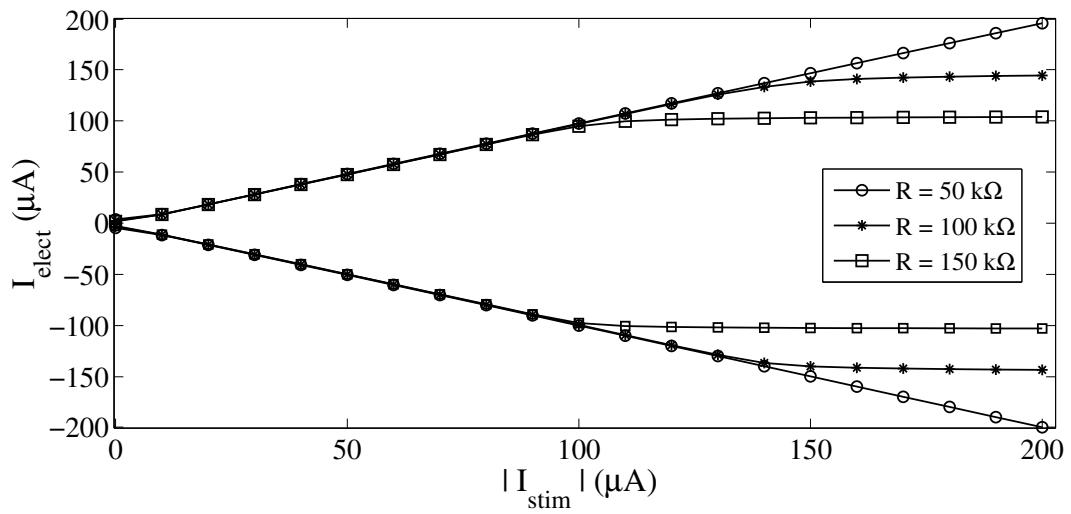

| FIGURE 3.16 | Experimental linearity of the electrode driver expressed by the output current versus the input current for loads $R$ of $50, 100$ , and $150$ k $\Omega$ . . . . .                                                                                                                                                                                                           | 74  |

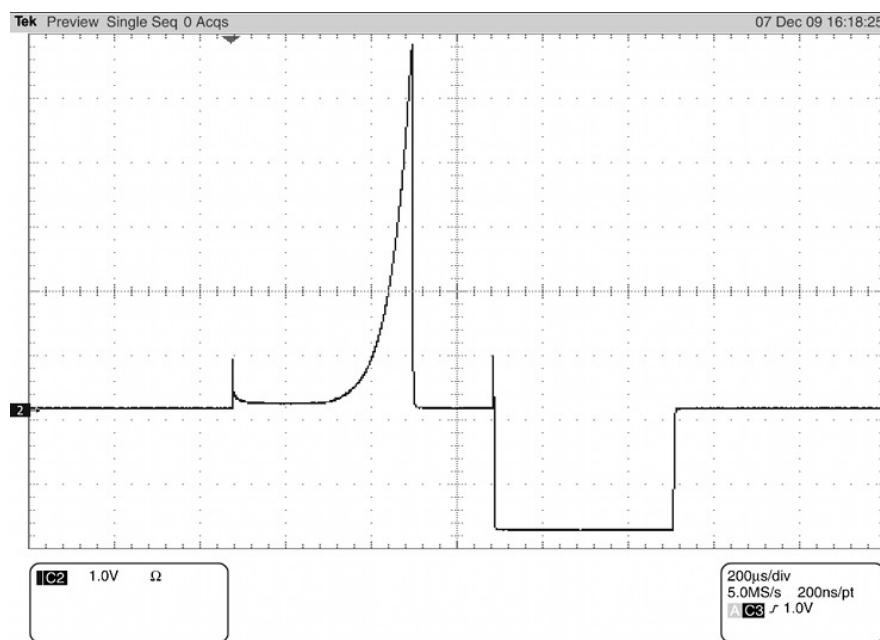

| FIGURE 3.17 | Oscilloscope trace showing a biphasic (exponential/rectangular) stimulation pulse injected into a $100$ k $\Omega$ resistive load. . . . .                                                                                                                                                                                                                                    | 75  |

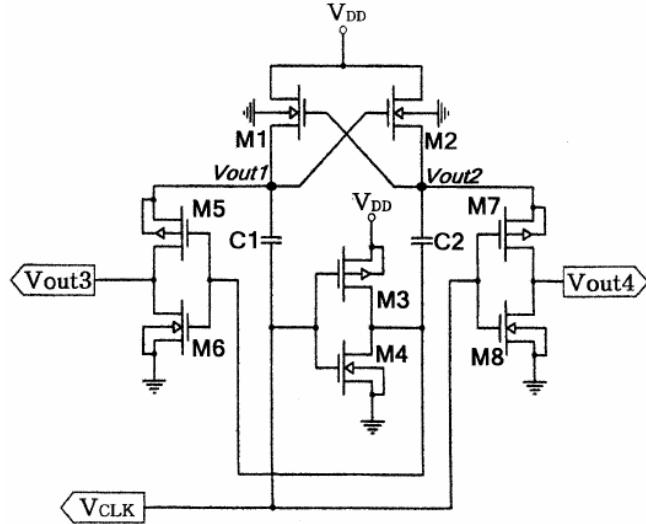

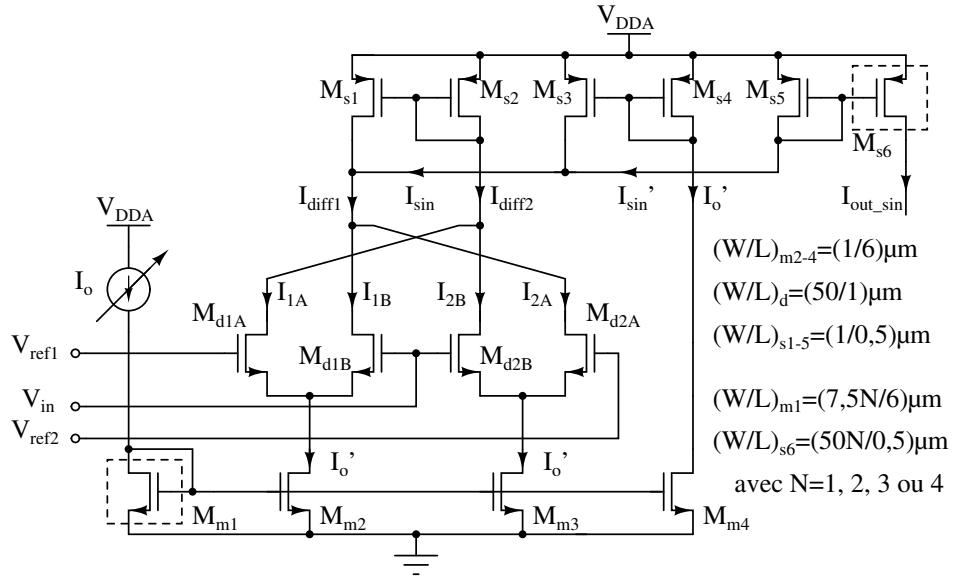

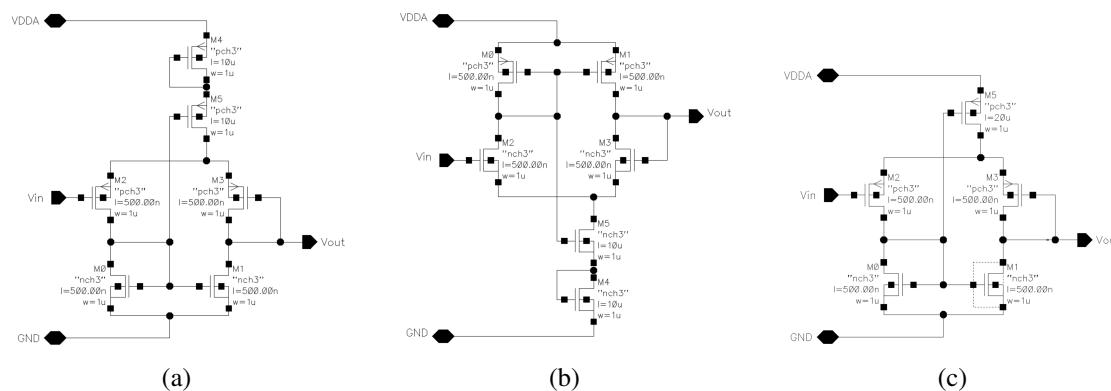

| FIGURE 4.1  | Schéma du générateur d'impulsions demi-sinusoidales positives de courant. . . . .                                                                                                                                                                                                                                                                                             | 78  |

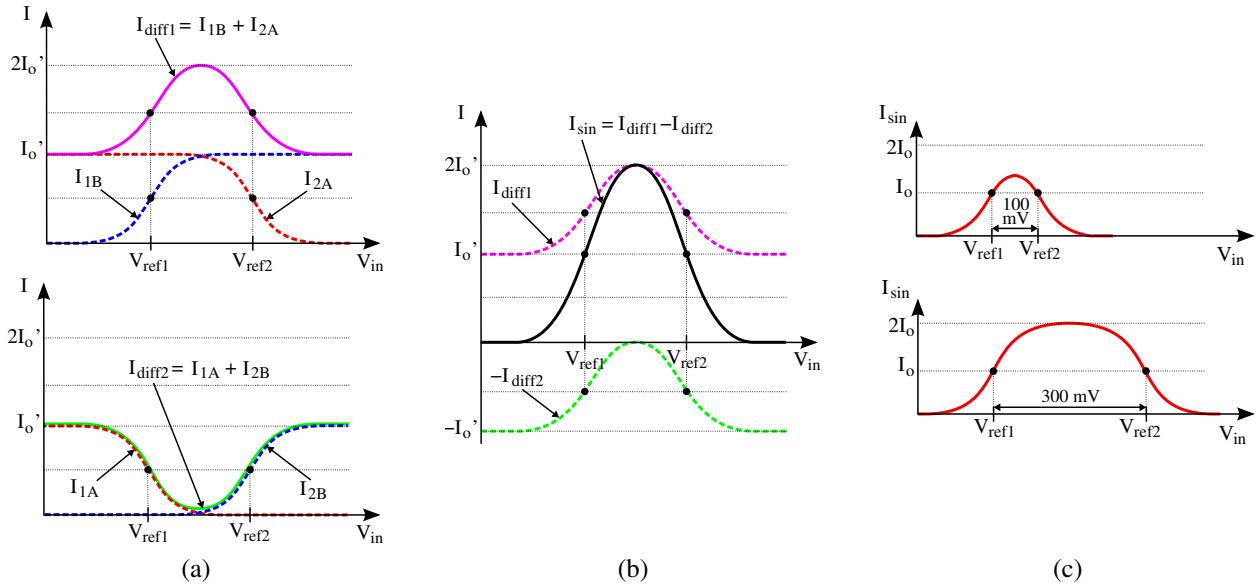

| FIGURE 4.2  | Illustration de la génération de l'impulsion demi-sinusoidale de courant en fonction de $V_{in}$ . (a) Génération des courants $I_{diff1}$ et $I_{diff2}$ à partir des courants des branches des paires différentielles. (b) Génération de $I_{sin}$ à partir de $I_{diff1}$ et $I_{diff2}$ . (c) Effet de la variation de $V_{ref2} - V_{ref1}$ sur la forme d'onde. . . . . | 79  |

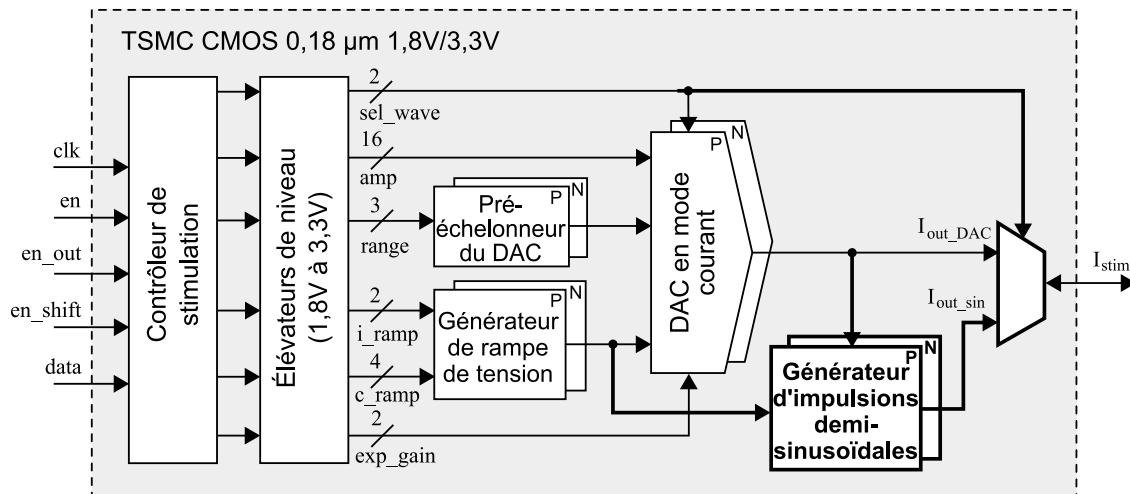

| FIGURE 4.3  | Schéma-bloc du générateur de stimuli avec demi-sinusoïde. La partie en gras montre l'ajout du générateur d'impulsions demi-sinusoidales de courant. . . . .                                                                                                                                                                                                                   | 80  |

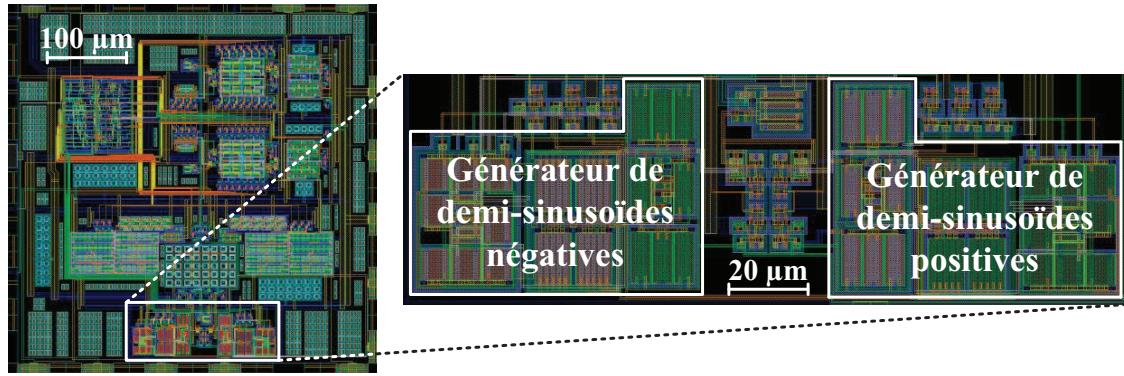

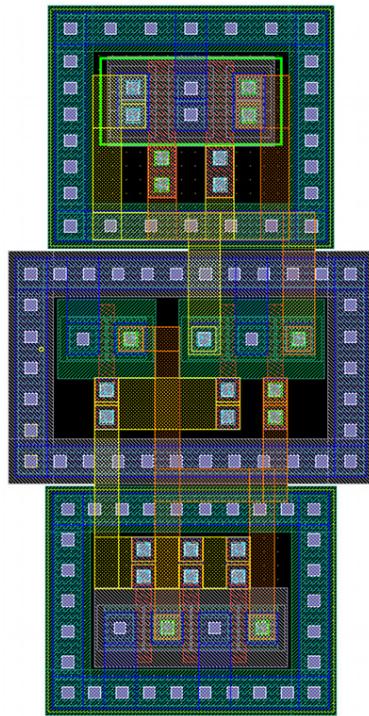

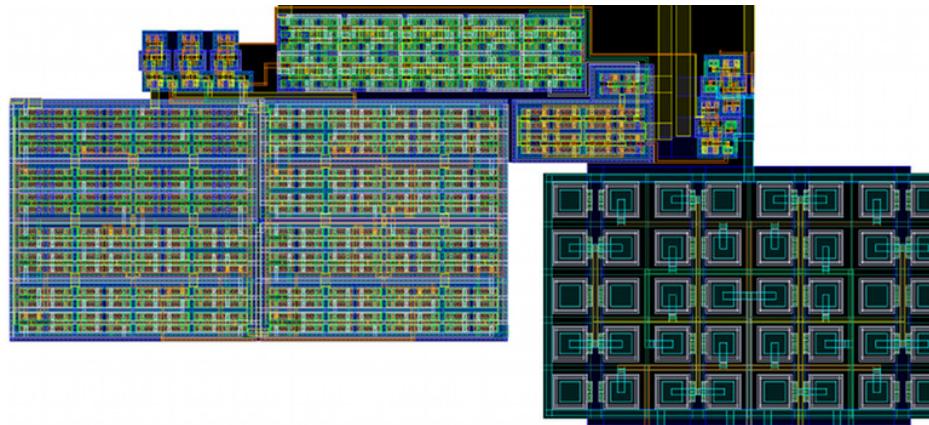

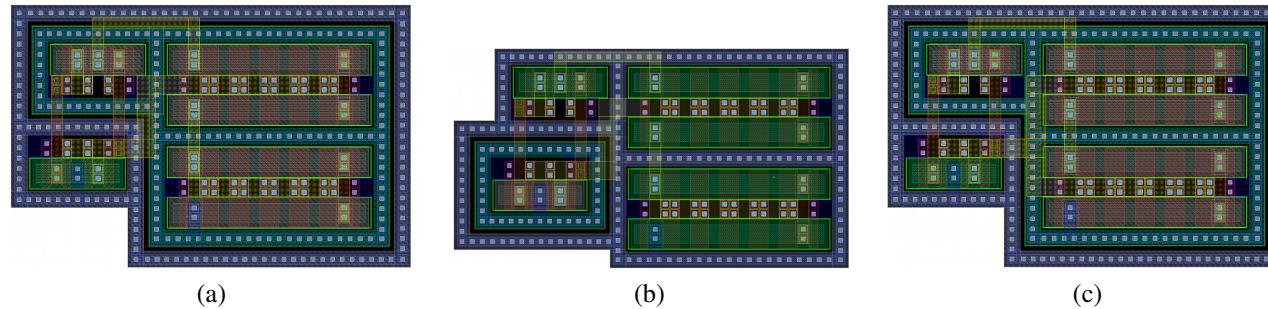

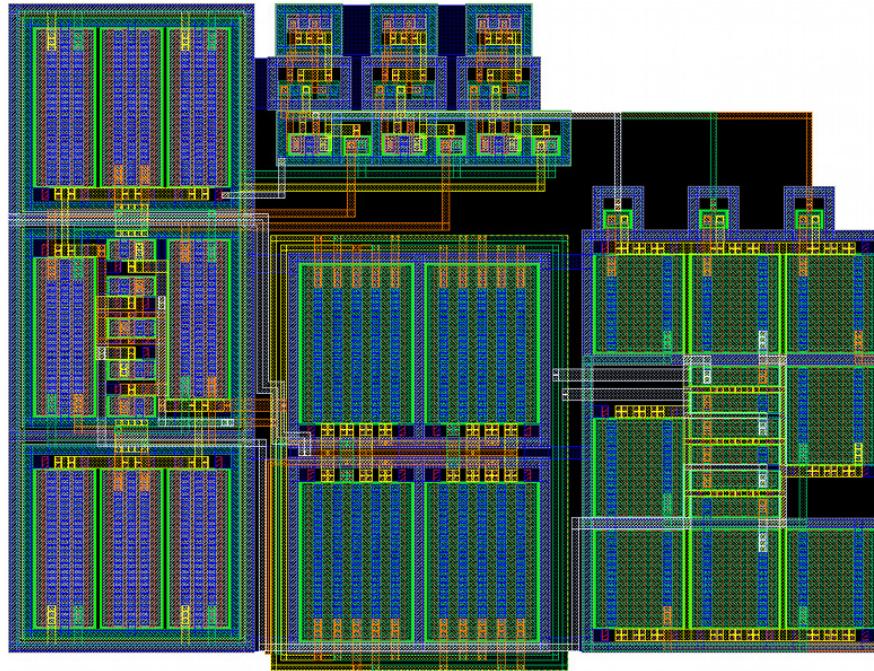

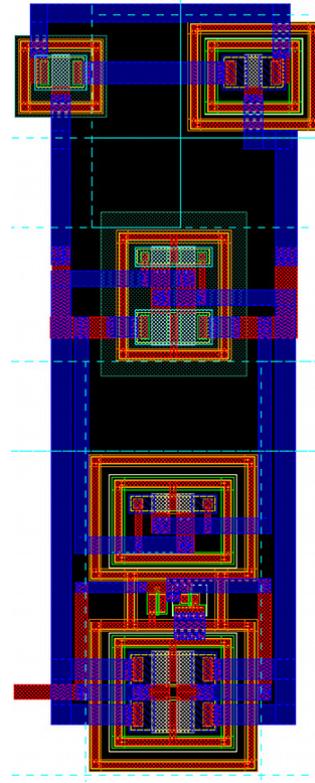

| FIGURE 4.4  | Dessin des masques du générateur de stimuli avec demi-sinusoïde avec un agrandissement du générateur de stimuli demi-sinusoidaux. . . . .                                                                                                                                                                                                                                     | 81  |

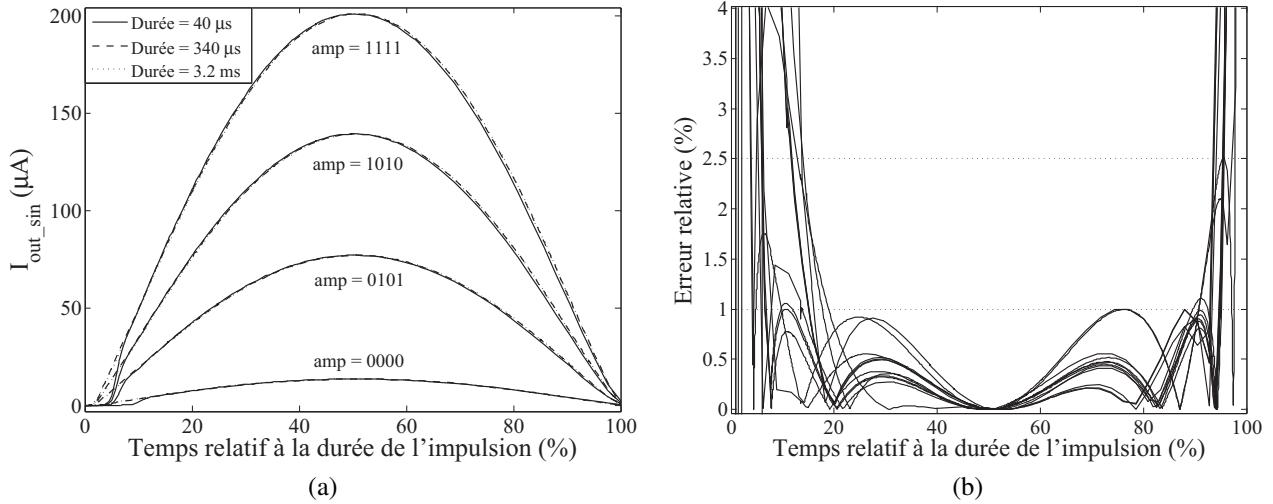

| FIGURE 4.5  | Résultats de simulation suite à l'extraction du dessin des masques du générateur de stimuli avec demi-sinusoïde. (a) Impulsions demi-sinusoidales pour diverses amplitudes et durées en fonction du temps relatif à la durée des impulsions. (b) Répartition de l'erreur relative par rapport à des demi-sinusoides idéales en fonction du temps relatif à la durée. . . . .  | 82  |

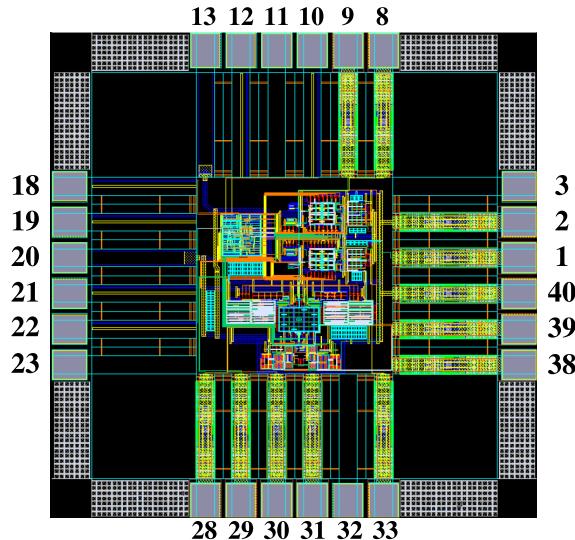

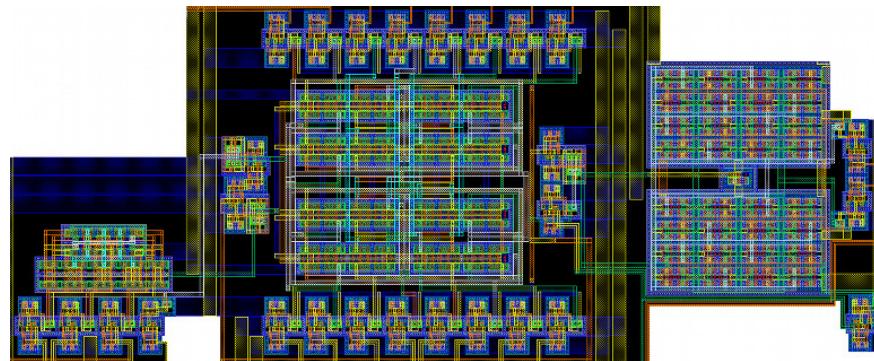

| FIGURE I.1  | Dessin des masques du générateur de stimuli ICFPMSTM. . . . .                                                                                                                                                                                                                                                                                                                 | 105 |

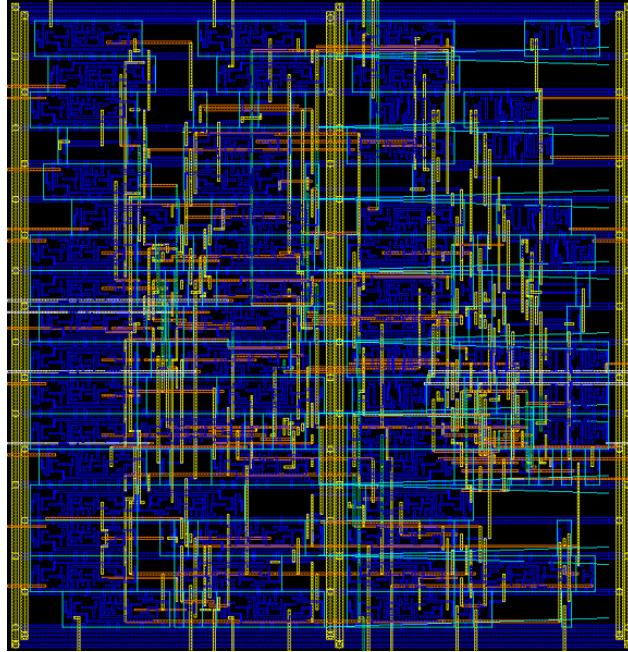

| FIGURE I.2  | Dessin des masques généré automatiquement du contrôleur de stimulation. . . . .                                                                                                                                                                                                                                                                                               | 111 |

| FIGURE I.3  | Dessin des masques de l'éleveur de niveau de $1,8$ V à $3,3$ V. . . . .                                                                                                                                                                                                                                                                                                       | 112 |

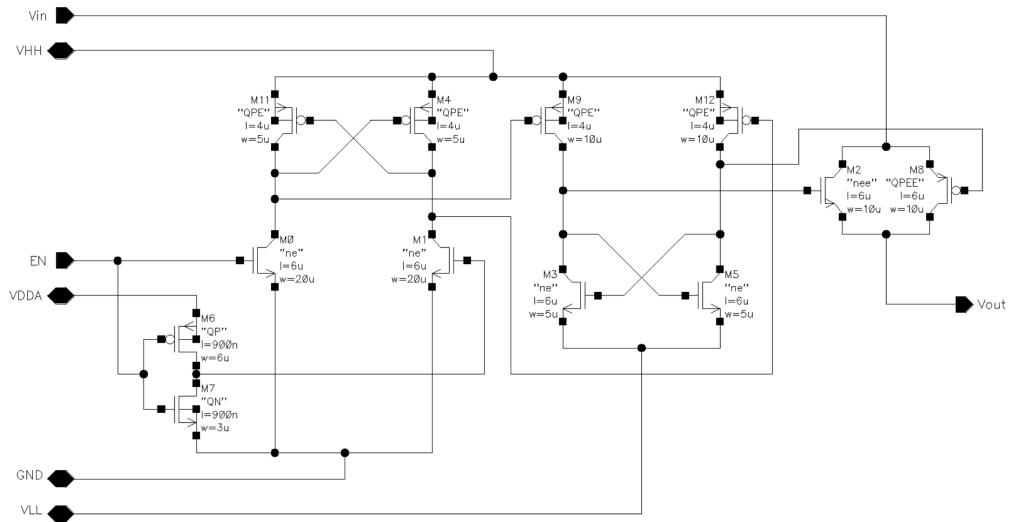

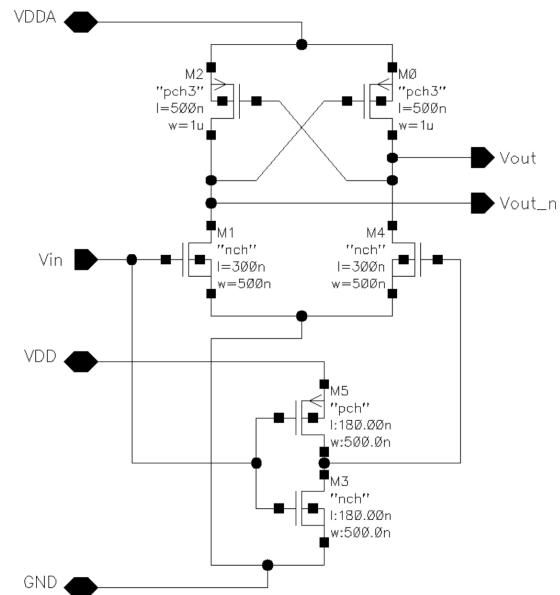

| FIGURE I.4  | Schéma de l'éleveur de niveau de $1,8$ V à $3,3$ V. . . . .                                                                                                                                                                                                                                                                                                                   | 112 |

|             |                                                                                                                                                                                                     |     |

|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| FIGURE I.5  | Dessin des masques de la partie positive du DAC en mode courant incluant le pré-échelonneur et l'amplificateur de courant exponentiel. . . . .                                                      | 113 |

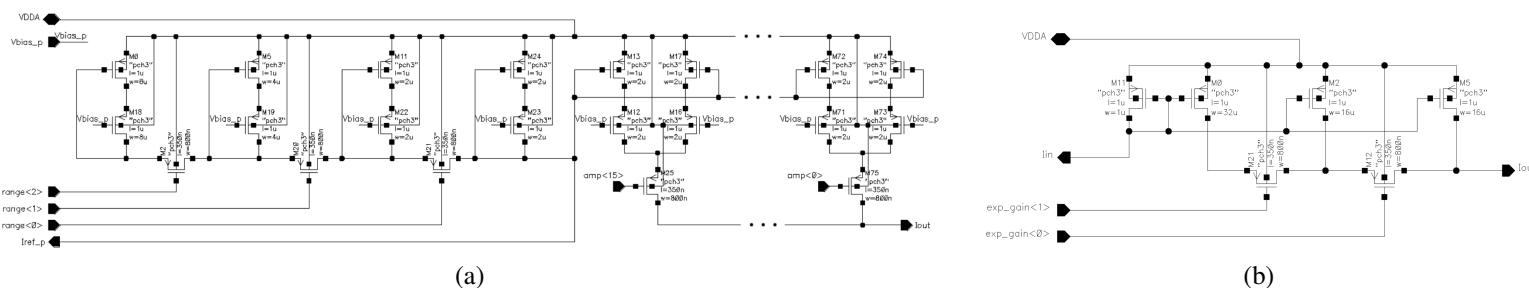

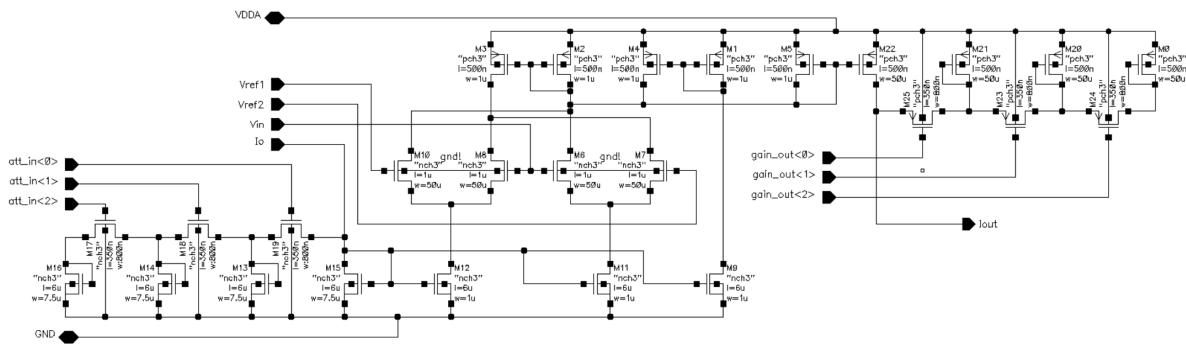

| FIGURE I.6  | (a) Schéma de la partie positive du DAC en mode courant incluant le pré-échelonneur. (b) Schéma de la partie négative de l'amplificateur de courant exponentiel. . . . .                            | 113 |

| FIGURE I.7  | Dessin des masques de la partie négative du DAC en mode courant incluant le pré-échelonneur et l'amplificateur de courant exponentiel. . . . .                                                      | 114 |

| FIGURE I.8  | (a) Schéma de la partie négative du DAC en mode courant incluant le pré-échelonneur. (b) Schéma de la partie positive de l'amplificateur de courant exponentiel. . . . .                            | 114 |

| FIGURE I.9  | Dessin des masques de la partie positive du générateur de rampe de tension. . . . .                                                                                                                 | 115 |

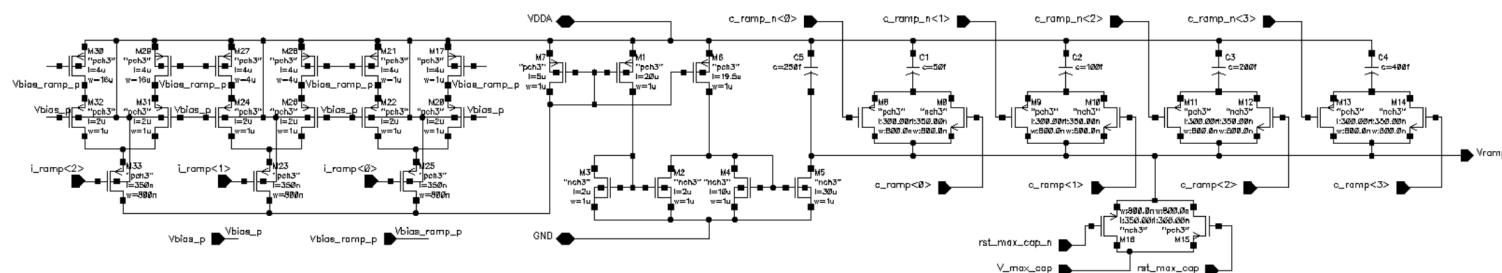

| FIGURE I.10 | Schéma de la partie positive du générateur de rampe de tension. . . . .                                                                                                                             | 115 |

| FIGURE I.11 | Dessin des masques de la partie négative du générateur de rampe de tension. . . . .                                                                                                                 | 116 |

| FIGURE I.12 | Schéma de la partie négative du générateur de rampe de tension. . . . .                                                                                                                             | 116 |

| FIGURE I.13 | (a) Dessin des masques du suiveur pour l'exponentielle positive. (b) Dessin des masques du suiveur pour l'exponentielle négative. (c) Dessin des masques du suiveur pour la demi-sinusoïde. . . . . | 117 |

| FIGURE I.14 | (a) Schéma du suiveur pour l'exponentielle positive. (b) Schéma du suiveur pour l'exponentielle négative. (c) Schéma du suiveur pour la demi-sinusoïde. . . . .                                     | 117 |

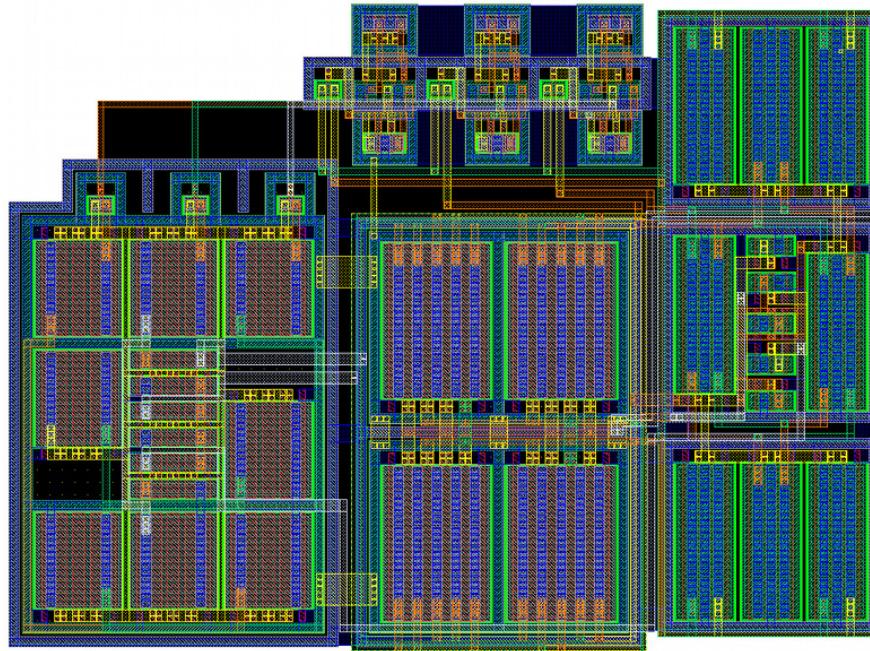

| FIGURE I.15 | Dessin des masques de la partie positive du générateur d'impulsions demi-sinusoidales. . . . .                                                                                                      | 118 |

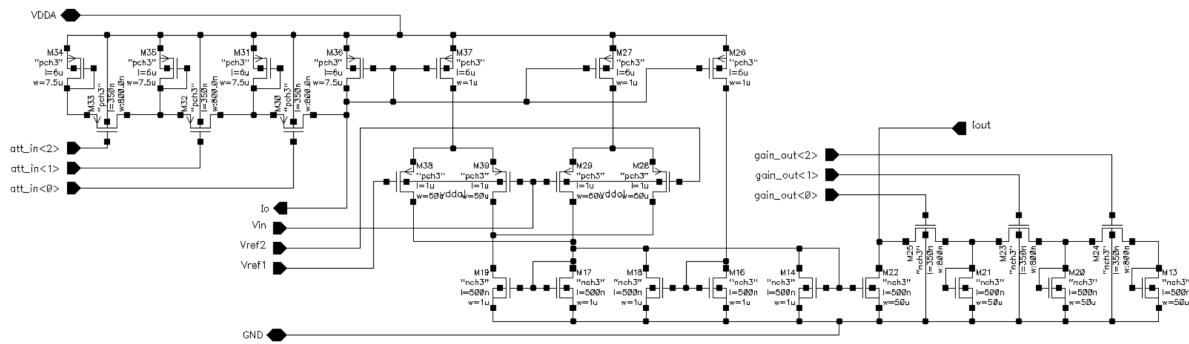

| FIGURE I.16 | Schéma de la partie positive du générateur d'impulsions demi-sinusoidales. . . . .                                                                                                                  | 118 |

| FIGURE I.17 | Dessin des masques de la partie négative du générateur d'impulsions demi-sinusoidales. . . . .                                                                                                      | 119 |

| FIGURE I.18 | Schéma de la partie négative du générateur d'impulsions demi-sinusoidales. . . . .                                                                                                                  | 119 |

| FIGURE II.1 | Dessin des masques de l'étage de sortie haute-tension ICJPMHVO. . . . .                                                                                                                             | 120 |

| FIGURE II.2 | Dessins des masques (a) du générateur d'horloges (oscillateur en anneau) et (b) d'un amplificateur d'horloge. . . . .                                                                               | 121 |

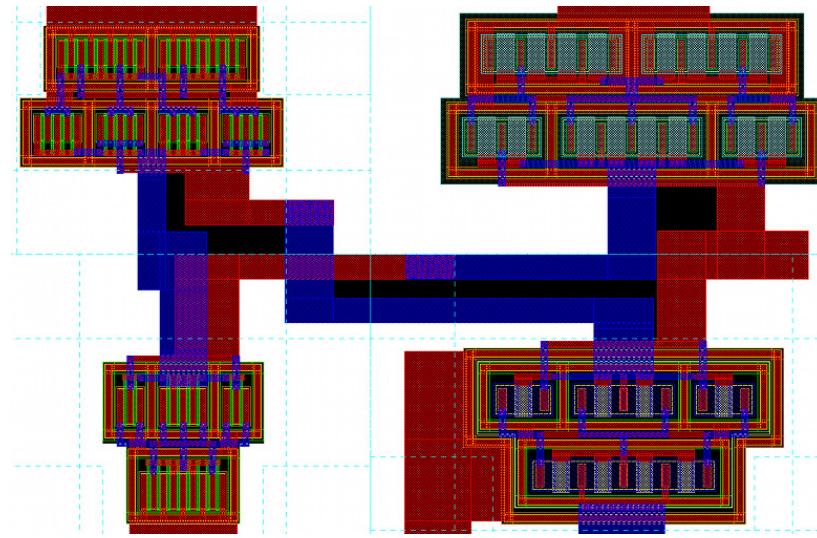

| FIGURE II.3 | Schémas (a) du générateur d'horloges (oscillateur en anneau) et (b) d'un amplificateur d'horloge. . . . .                                                                                           | 121 |

|              |                                                              |     |

|--------------|--------------------------------------------------------------|-----|

| FIGURE II.4  | Dessin des masques de la pompe de charge positive. . . . .   | 122 |

| FIGURE II.5  | Schéma de la pompe de charge positive. . . . .               | 122 |

| FIGURE II.6  | Dessin des masques de la pompe de charge négative. . . . .   | 123 |

| FIGURE II.7  | Schéma de la pompe de charge négative. . . . .               | 123 |

| FIGURE II.8  | Dessin des masques de l'élévateur de tension. . . . .        | 124 |

| FIGURE II.9  | Schéma de l'élévateur de tension. . . . .                    | 124 |

| FIGURE II.10 | Dessin des masques d'un commutateur à haute-tension. . . . . | 125 |

| FIGURE II.11 | Schéma d'un commutateur à haute-tension. . . . .             | 125 |

## LISTE DES TABLEAUX

|              |                                                                                                                                                                            |     |

|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| TABLEAU 2.1  | Comparaison sommaires des principaux implants visuels intracorticaux. . . . .                                                                                              | 29  |

| TABLEAU 2.2  | Synthèse des gains (%) en efficacité énergétique et en CPR de diverse formes d'onde par rapport à l'impulsion rectangulaire. <i>Modifié de (Robillard, 2008)</i> . . . . . | 32  |

| TABLEAU 2.3  | Synthèse de circuits générant la fonction exponentielle par approximation mathématique. . . . .                                                                            | 36  |

| TABLEAU 3.1  | Performances and specifications summary . . . . .                                                                                                                          | 76  |

| TABLEAU 4.1  | Pourcentages moyens des durées des impulsions demi-sinusoidales ayant une erreur relative inférieure ou égale à 1 et 2.5 %. . . . .                                        | 83  |

| TABLEAU 4.2  | Consommation de puissance du générateur de stimuli complet en mode demi-sinusoidal. . . . .                                                                                | 84  |

| TABLEAU I.1  | Assignation des broches d'entrée et sortie de la puce ICFPMSTM. . . . .                                                                                                    | 105 |

| TABLEAU I.2  | Sommaire des cellules standard (librairie Artisan) composant le contrôleur de stimulation. . . . .                                                                         | 111 |

| TABLEAU II.1 | Assignation des broches d'entrée et sortie de la puce ICJPMHVO. . . . .                                                                                                    | 120 |

## LISTE DES ANNEXES

|                  |                                                                                                  |            |

|------------------|--------------------------------------------------------------------------------------------------|------------|

| <b>ANNEXE I</b>  | <b>SCHÉMAS ET DESSINS DES MASQUES DES CIRCUITS DU GÉNÉRATEUR DE STIMULI (ICFPMSTM)</b>           | <b>105</b> |

| I.1              | Vue d'ensemble de la puce                                                                        | 105        |

| I.2              | Contrôleur de stimulation                                                                        | 106        |

| I.2.1            | Code VHDL                                                                                        | 106        |

| I.2.2            | Dessin des masques généré automatiquement                                                        | 111        |

| I.3              | Éleveur de niveau                                                                                | 112        |

| I.4              | DAC en mode courant (avec pré-échelonneur et amplificateur de courant exponentiel)               | 113        |

| I.4.1            | Partie P                                                                                         | 113        |

| I.4.2            | Partie N                                                                                         | 114        |

| I.5              | Générateur de rampe de tension                                                                   | 115        |

| I.5.1            | Partie P                                                                                         | 115        |

| I.5.2            | Partie N                                                                                         | 116        |

| I.6              | Suiveurs pour la rampe de tension                                                                | 117        |

| I.7              | Générateur d'impulsions demi-sinusoidales                                                        | 118        |

| I.7.1            | Partie P                                                                                         | 118        |

| I.7.2            | Partie N                                                                                         | 119        |

| <b>ANNEXE II</b> | <b>SCHÉMAS ET DESSINS DES MASQUES DES CIRCUITS DE L'ÉTAGE DE SORTIE HAUTE-TENSION (ICJPMHVO)</b> | <b>120</b> |

| II.1             | Vue d'ensemble de la puce                                                                        | 120        |

| II.2             | Générateur et amplificateurs d'horloge                                                           | 121        |

| II.3             | Pompes de charge                                                                                 | 122        |

| II.3.1           | Partie P                                                                                         | 122        |

| II.3.2           | Partie N                                                                                         | 123        |

| II.4             | Élevateur de tension                                                                             | 124        |

| II.5             | Commutateurs haute-tension                                                                       | 125        |

## LISTE DES NOTATIONS ET DES SYMBOLES

|        |                                                                                          |

|--------|------------------------------------------------------------------------------------------|

| ATP    | Adénosine TriPhosphate                                                                   |

| BJT    | Transistor bipolaire ( <i>Bipolar Junction Transistor</i> )                              |

| CGL    | Corps Genouillé Latéral                                                                  |

| CMOS   | <i>Complementary Metal Oxyde Semiconductor</i>                                           |

| CPR    | Concentration de Produits Réduits                                                        |

| DAC    | Convertisseur numérique à analogique ( <i>Digital-to-Analog Converter</i> )              |

| DC     | Courant continu ( <i>Direct Current</i> )                                                |

| DNL    | Non-linéarité différentielle ( <i>Differential NonLinearity</i> )                        |

| FPGA   | <i>Field-Programmable Gate Array</i>                                                     |

| IC     | Circuit intégré ( <i>Integrated Circuit</i> )                                            |

| INL    | Non-linéarité intégrale ( <i>Integral NonLinearity</i> )                                 |

| MOSFET | Transistor à effet de champ ( <i>Metal Oxyde Semiconductor Field Effect Transistor</i> ) |

| MSB    | Bit le moins significatifs ( <i>Most Significant Bit</i> )                               |

| OMS    | Organisation Mondiale de la Santé                                                        |

| RF     | Radio-Fréquence                                                                          |

| THD    | Taux de distorsion harmonique ( <i>Total Harmonic Distortion</i> )                       |

| VCO    | Oscillateur commandé en tension ( <i>Voltage-Controlled Oscillator</i> )                 |

| VGA    | Amplificateur à gain variable ( <i>Variable Gain Amplifier</i> )                         |

|          |                                      |

|----------|--------------------------------------|

| n        | Facteur de pente                     |

| $V_T$    | Tension thermale                     |

| $V_A$    | Tension d'Early                      |

| $V_{th}$ | Tension de seuil d'un transistor MOS |

## INTRODUCTION

La recherche dans le domaine du génie biomédical a connu une croissance remarquable au cours des dernières décennies. Cette effervescence est particulièrement notable dans le cas des dispositifs médicaux implantables. Comme suite aux succès techniques et commerciaux du stimulateur cardiaque et de l'implant cochléaire, les stimulateurs implantables deviennent une avenue couramment envisagée pour rétablir des fonctions physiologiques perdues. Cette tendance est soutenue par la miniaturisation presqu'exponentielle de la microélectronique permettant d'intégrer des systèmes de complexité grandissante sur des surfaces de l'ordre du mm<sup>2</sup>.

La cécité est un exemple typique de trouble physiologique qui suscite beaucoup d'intérêt dans la communauté scientifique depuis longtemps. En mai 2009, approximativement 45 millions de personnes aveugles à travers le monde ont été répertoriées (Organisation Mondiale de la Santé [OMS], 2009). Selon l'organisme, 75 % de ces cas de cécité pourraient être évités ou soignés. Afin d'être en mesure de traiter les autres cas jugés irréversibles, de nombreux chercheurs se penchent sur le développement de prothèses électroniques permettant aux personnes atteintes de retrouver une vision fonctionnelle. C'est dans ce contexte que le laboratoire de neurotechnologies Polystim de l'École Polytechnique Montréal a mis en branle le projet Cortivision, soit un implant visuel stimulant directement le cortex visuel. Les dernières avancées dans ce projet font état d'un prototype fonctionnel utilisé avec succès lors d'expérimentations *in vivo* chez les rats (Coulombe, 2007).

Une contrainte importante pour tout dispositif implantable est la consommation de puissance. Dans le cas de Cortivision, l'implant est alimenté en énergie par une pile externe dont la puissance lui est transmise par un lien inductif sans-fil. Le système étant utilisé sur une base quotidienne à raison de plusieurs heures par jour, il est crucial de limiter la consommation d'énergie afin de prolonger l'autonomie énergétique de l'implant. Une seconde contrainte de conception d'un stimulateur intracortical est l'impédance élevée de l'interface entre les électrodes et les tissus biologiques. Celle-ci nécessite l'utilisation de tensions élevées souvent incompatibles avec les procédés de fabrication basse-tension.

L'objectif principal de ce projet de recherche est la réalisation d'un microstimulateur intracorti-

cal ayant une consommation de puissance réduite par rapport au prototype précédent (Coulombe, 2007). Pour y arriver, de nouvelles formes de stimuli potentiellement plus efficaces seront générées et pourront être comparées à la stimulation de base. L'idée est de générer des stimulations dont la forme d'onde est plus efficace énergétiquement pour déclencher une excitation équivalente des tissus corticaux. Il s'ensuivrait alors une diminution considérable de la puissance consommée par la circuiterie puisqu'un total de plus de 1000 canaux est envisagé. Le prototype résultant permettra de valider expérimentalement les résultats obtenus à l'aide du modèle cortical développé par Polystim (Robillard, 2008). Un autre objectif de ce travail est la réalisation d'un étage de sortie intégré à haute-tension permettant d'interfacer l'impédance élevée du contact microélectrode-tissus. Ce circuit est essentiel pour le prototypage d'un système entièrement implantable ne comprenant aucun composant discret.

Ce mémoire est constitué de cinq chapitres. Le premier chapitre résume plusieurs notions de base de physiologie qui s'avèrent nécessaires à l'identification des spécifications du système. Il y est question en premier lieu du neurone, cellule de base du système nerveux, ainsi que de son processus d'excitation. En second lieu, le système visuel humain est brièvement décrit avec une emphase particulière sur le cortex visuel. En troisième lieu, il est question de l'interface formée entre les électrodes et les tissus, de même que son modèle. Enfin, les principes de base de la stimulation électrique fonctionnelle sont décrits.

Le second chapitre est consacré à la revue de la littérature. D'abord, un tour d'horizon présentant les divers implants visuels existants et leurs particularités est effectué. Par la suite, une revue des divers circuits utiles pour ce projet est présentée. Ces circuits concernent la génération de diverses formes d'impulsions employées pour la stimulation, ainsi que la génération des tensions élevées.

En guise de troisième chapitre, l'article “ *Exponential Current Pulse Generation for Efficient Very High-Impedance Multisite Stimulation* ” soumis à la revue scientifique “ IEEE Transactions on Biomedical Circuits and Systems ” est présenté en version intégrale. Celui-ci regroupe les détails techniques concernant le générateur de stimuli et l'étage de sortie haute-tension, de même que les résultats expérimentaux obtenus avec ces deux circuits intégrés.

Ensuite, un complément regroupant tous les circuits qui n'ont pas pu être traités dans cet article

forme le quatrième chapitre. Brièvement, un générateur d'impulsions sinusoïdales y est détaillé, de même que les résultats de simulation obtenus après l'extraction des dessins des masques.

Une discussion générale faisant des liens entre les différentes parties du mémoire est effectuée au cinquième chapitre. Un complément de discussion présentant des défauts des circuits fabriqués et ne se retrouvant pas dans l'article s'y retrouve également.

Finalement, la conclusion résume l'ensemble du travail réalisé dans ce mémoire et rappelle les résultats importants. Des recommandations inspirées des résultats et qui concernent les prochaines étapes du projet Cortivision sont aussi mentionnées.

## CHAPITRE 1

### NOTIONS ÉLECTROPHYSIOLOGIQUES FONDAMENTALES

Il est tout d'abord primordial de rappeler certains concepts de physiologie et de bioélectricité de base nécessaires à la compréhension des phénomènes et des systèmes composant le cœur de ce mémoire. Ce premier chapitre regroupe ces notions essentielles en débutant avec le neurone et son principe d'excitation. Par la suite, l'ensemble du système visuel est décrit, particulièrement le cortex visuel primaire. Puis, les types d'électrodes de stimulation et l'interface qu'elles forment avec les tissus vivants sont détaillés. Enfin, il est question de la stimulation électrique fonctionnelle, de ses paramètres, ainsi que de notions de sécurité.

#### 1.1 Le neurone

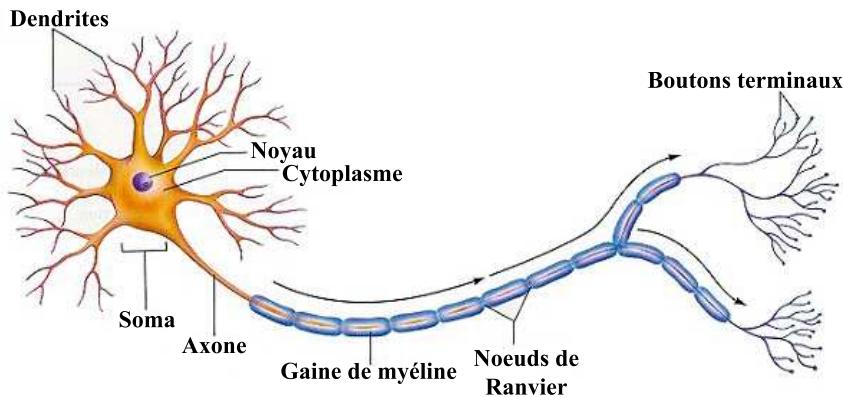

Le neurone est l'élément de base du système nerveux. Cette cellule permet la génération et la propagation de l'influx nerveux dans le corps. La Figure 1.1 illustre l'anatomie du neurone typique.

FIGURE 1.1: Physiologie du neurone. *Modifié à partir de (StateMaster, 2009).*

Les dendrites sont considérées comme les entrées du neurone. Celles-ci captent les stimuli provenant des cellules avoisinantes. À l'autre extrémité, les boutons terminaux consistent les sorties permettant de transmettre l'influx nerveux à d'autres neurones. La connexion entre deux neurones,

appelée synapse, n'est pas directe. Il s'agit plutôt d'un espace étroit dans lequel voyagent des substances biochimiques nommées neurotransmetteurs. Ceux-ci sont libérés par les boutons terminaux du neurone transmetteur à l'arrivée de l'influx nerveux et sont captés par les dendrites du neurone récepteur. Cette captation de neurotransmetteurs régénère l'influx nerveux qui converge vers le cœur du neurone récepteur, c'est-à-dire le soma. Un traitement de l'ensemble des signaux captés par les dendrites est alors effectué selon le type de neurone. La réponse du soma est par la suite propagée le long de l'axone. Des gaines de myéline, constituées de cellules de Schwann enroulées, enveloppent l'axone du neurone. Certaines sections de l'axone n'en sont pas recouvertes, elles se nomment noeuds de Ranvier. Cette structure a pour but d'accélérer la propagation de l'influx le long de l'axone qui peut faire plus d'un mètre de long selon le type de neurone.

### 1.1.1 La membrane cytoplasmique

La membrane cellulaire du neurone joue un rôle fondamental dans la génération et la propagation de l'influx nerveux. Comme pour l'ensemble des cellules de l'organisme, elle est constituée d'une double couche de phosphoglycérolipides, couche peu perméable aux molécules et ions. Elle est toutefois traversée par des protéines agissant comme canaux et comme pompes ioniques. Ces protéines facilitent la diffusion et permettent le transport sélectif d'ions entre les milieux intracellulaire et extracellulaire, assurant ainsi l'auto-régulation de la cellule. Les principaux ions participant aux phénomènes bioélectriques sont le  $\text{Na}^+$ , le  $\text{Cl}^-$ , le  $\text{K}^-$  et le  $\text{Ca}^{2+}$ . À l'équilibre, le milieu extracellulaire a typiquement une concentration plus importante d'ions sodium et chlore, alors que le milieu intracellulaire a une concentration plus élevée en ions potassium.

Les concentrations des différents ions dans les milieux intracellulaire et extracellulaire font en sorte qu'il existe une différence de potentiel électrique de part et d'autre de la membrane cytoplasmique. Cette tension transmembranaire, définie par convention comme le potentiel de l'intérieur du neurone par rapport au potentiel externe, est d'environ -70 mV. Il s'agit du potentiel de Nerst, aussi connu comme le potentiel d'équilibre ou de repos de la cellule. La tension membranaire est au cœur des phénomènes bioélectriques de la cellule. Par exemple, les canaux ioniques possèdent un certain nombre de portes dont l'état, c'est-à-dire ouvert ou fermé, est dépendant de ce potentiel.

Cela leur permet de diffuser les ions à travers la membrane ou de les bloquer. Ce sont ces mécanismes d'ouverture et de fermeture des différentes portes qui permettent la génération de potentiels d'action.

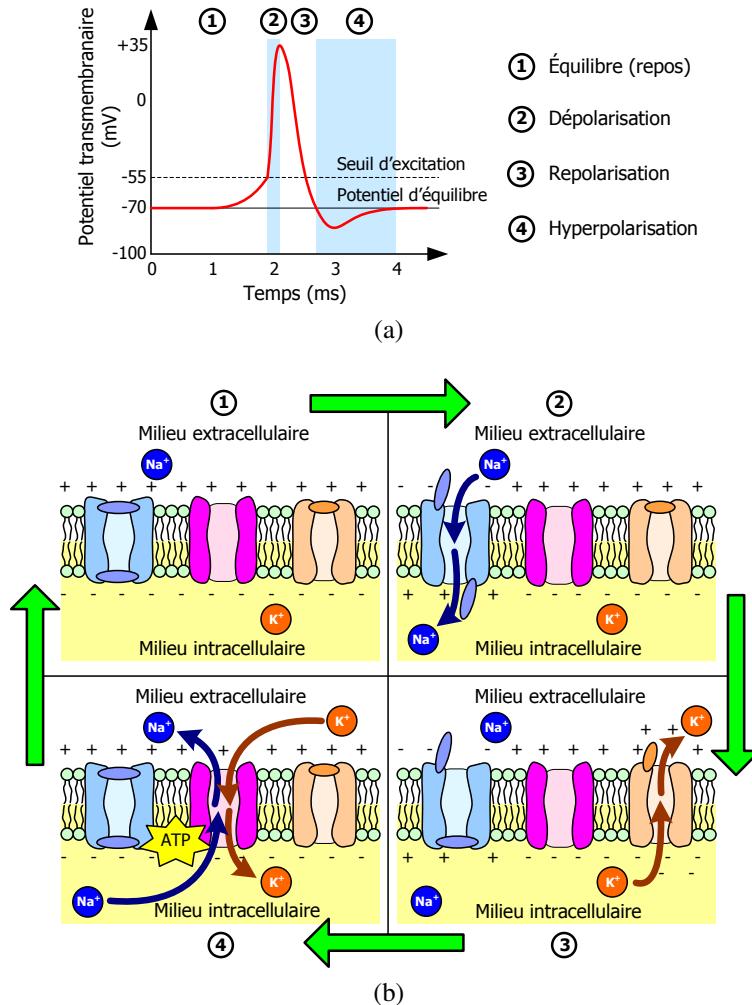

### 1.1.2 Le potentiel d'action

Plusieurs phénomènes peuvent perturber l'équilibre électrique du neurone. Dans le cas des neurones sensoriels, des changements physiques de l'environnement, comme la température, la pression ou la lumière, ont un effet direct sur leur potentiel interne. Une autre perturbation possible est la réception d'un influx nerveux provenant d'un neurone voisin. Un dernier cas est une variation locale du potentiel extracellulaire engendrée par une stimulation électrique externe par exemple.

Ces perturbations de l'équilibre électrochimique de la cellule modifient sa tension transmembranaire. Si cette dernière est maintenue sous le seuil d'excitation du neurone (environ -55 mV), les mécanismes de diffusion et de transport ionique rétablissent l'équilibre et aucune excitation n'est générée. Par contre, lorsque le potentiel de membrane dépasse ce seuil, une impulsion électrique est déclenchée. Il s'agit du potentiel d'action. Ce dernier est généré par un mécanisme de type "tout ou rien", c'est-à-dire que l'amplitude et la durée du potentiel d'action sont indépendants de l'intensité du stimulus à son origine.

Le phénomène de déclenchement est illustré sommairement à la Figure 1.2. D'abord, à l'étape 1, le neurone est à l'équilibre et son potentiel de membrane est de -70 mV. Un stimulus vient par la suite augmenter son potentiel interne jusqu'au seuil d'excitation de la cellule. À partir de ce moment, il y a dépolarisation locale de la membrane du neurone, ce qui correspond à l'étape 2 de la Figure 1.2. Il s'agit d'une augmentation brusque de la tension transmembranaire causée par l'entrée massive d'ions  $\text{Na}^+$  à l'intérieur de la cellule à la suite de l'ouverture des portes des canaux sodiques. Lorsque le potentiel d'action atteint sa valeur maximale, soit environ 35 mV, le phénomène de repolarisation est mis en marche. Alors qu'une des portes des canaux sodiques se ferme, la porte des canaux potassiques s'ouvre, permettant ainsi une sortie importante d'ions  $\text{K}^+$  vers le milieu extracellulaire. Il s'ensuit une diminution du potentiel de membrane, comme il

FIGURE 1.2: Mécanisme de déclenchement d'un potentiel d'action. (a) Variation temporelle du potentiel de membrane. (b) Illustration du mécanisme au niveau des canaux ioniques de la membrane.

est montré à l'étape 3, entraînant l'hyperpolarisation de la membrane cellulaire. Cela signifie que le potentiel membranaire devient inférieur à sa valeur d'équilibre. À ce moment, soit à l'étape 4, les pompes Na<sup>+</sup> - K<sup>+</sup> échangent des ions Na<sup>+</sup> (vers l'extérieur) et K<sup>+</sup> (vers l'intérieur) de manière à rééquilibrer le potentiel interne du neurone. Ces transferts d'ions se produisant contre le gradient de diffusion électrochimique, les pompes dépensent de l'énergie fournie par de l'adénosine triphosphate (ATP) pour les réaliser.

Le potentiel d'action ayant une amplitude fixe, l'intensité du stimulus à son origine est plutôt modulée par la fréquence de déclenchement des potentiels d'action du neurone. Cette fréquence, aussi appelée fréquence de tir, a par contre une limite. Immédiatement après le déclenchement d'un po-

tentiel d'action, il existe un certain délai durant lequel la membrane est insensible au potentiel extracellulaire, empêchant ainsi la génération d'un second potentiel d'action. Cette période, due à l'hyperpolarisation de la membrane, se nomme période réfractaire.

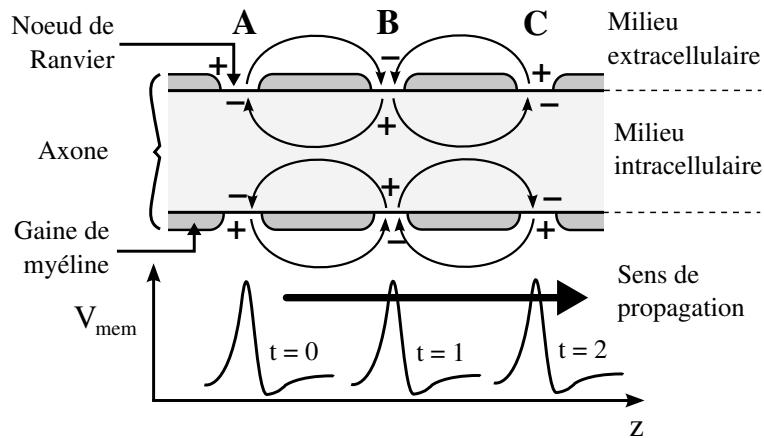

### 1.1.3 Propagation d'un potentiel d'action

Une fois déclenché, l'influx doit être transmis à travers le système nerveux pour être interprété. Cette propagation du potentiel d'action le long de l'axone est expliquée par la théorie du câble (Gulrajani, 1998), dont le phénomène est schématisé à la Figure 1.3. Brièvement, les milieux intracellulaire et extracellulaire sont considérés comme conducteurs de courant ionique. Lorsqu'un potentiel d'action est déclenché en un point A de la membrane, le potentiel de membrane est modifié à cet endroit. Les différences de potentiel entre ce point A et un point B plus éloigné génèrent alors des courants ioniques intracellulaire et extracellulaire de A à B lors de la dépolarisation. Ces courants dépolarisent la membrane en B et, s'ils atteignent le seuil d'excitabilité, déclenchent un autre potentiel d'action à ce point. Ce phénomène se répète de B à C et ainsi de suite tout au long de l'axone ; il s'agit d'une réaction en chaîne conservative.

FIGURE 1.3: Propagation d'un potentiel d'action le long d'un axone myélinisé de neurone.

Lorsque l'axone est myélinisé, les gaines de myéline empêchent tout passage d'ions à travers certaines sections de la membrane cellulaire. Les régions de la membrane où des potentiels d'action peuvent être générés sont alors discrépantes par noeuds de Ranvier comme illustré à la Figure 1.3. La distance entre deux noeuds fait en sorte que le déclenchement d'un potentiel d'action en un

point permet l'excitation directe du noeud suivant sans être ralenti par sa propre période réfractaire. Ce type de propagation, appelé conduction saltatoire, s'effectue alors de manière plus rapide qu'en absence de myéline.

Les notions concernant le potentiel d'action étant introduites, la prochaine section traite du système visuel humain, plus particulièrement du cortex visuel primaire qui représente une aire d'intérêt dans cet ouvrage.

## 1.2 Système visuel

Le système visuel chez l'humain est fondamental et complexe. Il s'étend principalement de la rétine jusqu'au cortex visuel situé à l'arrière du cerveau. Plusieurs autres aires corticales sont sollicitées pour des traitements plus cognitifs, mais elles ne seront pas considérées ici. La Figure 1.4 illustre l'anatomie de ce système ainsi que le chemin qu'emprunte l'information captée par les yeux.

FIGURE 1.4: Anatomie du système visuel humain. *Modifié à partir de (Coulombe, 2007)*.

La lumière est d'abord transformée en influx nerveux par les rétines situées au fond de chaque œil. Elles sont composées de trois couches superposées de neurones aux fonctions spécifiques, soient les photorécepteurs, les neurones bipolaires et les cellules ganglionnaires. Déjà au niveau

de la rétine, un traitement de l'information visuelle est effectué. Les axones des cellules ganglionnaires se rencontrent en un point de la rétine, appelé disque optique, pour former le nerf optique. Celui-ci entre dans la boîte crânienne et parcourt le chiasma optique, où il y a croisement partiel des axones, et le tractus optique. Chacun de ces points a son rôle dans le traitement de l'influx nerveux. Les axones atteignent ensuite le corps genouillé latéral (CGL), seul relais avant le cortex visuel primaire. Le CGL est composé de six couches distinctes de cellules, chacune recevant une projection particulière provenant de la rétine. Jusqu'à ce point, la propagation et le traitement des signaux générés par les rétines s'effectuent en parallèle. De plus, il est à noter qu'environ 80 % des connexions excitatrices du CGL proviennent du cortex visuel primaire, celui-ci effectue donc une rétroaction importante sur le traitement au niveau du CGL. Enfin, l'information est transmise au cortex visuel primaire par l'entremise de projections appelées radiations optiques.

### **1.2.1 Cortex visuel primaire**

Le cortex visuel est constitué de quelques dizaines d'aires effectuant des traitements simples, comme l'analyse d'orientation et de couleurs, ou des traitements cognitifs et associatifs tels que la reconnaissance d'objets ou le positionnement spatial. Seul le cortex visuel primaire, aussi appelé cortex strié ou aire V1, est considéré dans ce mémoire puisqu'il s'agit du point d'entrée du traitement plus complexe de l'information visuelle.

D'une épaisseur totale de 2 mm, le cortex visuel primaire se situe au niveau postérieur du lobe occipital. On y retrouve de nombreux types de neurones, principalement des cellules pyramidales et stellaires. Cette aire du cortex est divisée en six couches distinctes ayant chacune une composition et des fonctions particulières. En étudiant les liaisons neuronales entre ces couches et entre les différentes aires, il a été montré que les signaux provenant du CGL entrent dans le cortex visuel par la couche 4 de l'aire V1. Cette couche, plus particulièrement la sous-couche 4C, joue donc un rôle déterminant dans le cheminement et le traitement de l'information de la vision. Par la suite, l'information est projetée aux couches 2, 3 et 5, en plus de la rétroaction vers le CGL. Ces couches retransmettent les signaux reçus de la couche 4 aux régions avoisinantes pour un traitement plus avancé.

À cet agencement en couches s'ajoute une organisation du cortex visuel primaire en colonnes, comme l'illustre la Figure 1.5. Dans un premier temps, la couche 4C est divisée de manière régulière en colonnes de dominance oculaire par alternance de bandes d'environ 0,5 mm de largeur. Dans un second temps, des colonnes d'orientation s'étalent dans la direction orthogonale à celle de la dominance oculaire. Pour chacune de ces colonnes du cortex, l'activité électrique est dépendante d'une orientation fixe de la stimulation lumineuse. Il a été montré expérimentalement que 180° sont couverts sur 1 mm en moyenne. Finalement, les derniers éléments de colonnes sont les taches. Ces piliers cylindriques recueillent et traitent l'information sur la couleur. À la Figure 1.5a, un module cortical est schématisé, c'est-à-dire un bloc de 2 mm × 2 mm comprenant deux groupes complets de dominance oculaire, deux fois l'orientation sur 180° et 16 taches. En guise de synthèse, la Figure 1.5b représente une colonne détaillée du cortex V1 sur laquelle les différentes couches et les entrées des signaux sont identifiées. Les entrées magnocellulaire et parvocellulaire proviennent respectivement des couches 1 et 2, et 3 à 6 du CGL. Elles ont pour différence le type de cellules ganglionnaires de la rétine duquel elles sont projetées.

FIGURE 1.5: Organisation du cortex visuel primaire. (a) Module cortical, (b) Détail d'une colonne du cortex V1 montrant les couches. *Modifiés à partir de (McGill University, 2009).*

### 1.3 Électrodes de stimulation

Dans le domaine biomédical, les électrodes sont essentielles à la fois pour l’acquisition de signaux biologiques et pour la stimulation des tissus. Elles ont une fonction de transducteur permettant de convertir le courant électrique en courant ionique et vice versa. Cette conversion s’effectue grâce aux réactions électrochimiques complexes ayant lieu à l’interface électrode-tissus. L’impédance de cette interface est non-linéaire et dépend de plusieurs facteurs comme le stimulus à mesurer/injecter (intensité, fréquence), l’électrode (matériau, géométrie, surface) et le milieu (température, concentrations ioniques).

#### 1.3.1 Réactions à l’interface électrode-électrolyte

Le contact entre une électrode et un tissu biologique se résume par un phénomène électrochimique entre un métal et un électrolyte (Merrill et al., 2005). Le milieu cellulaire est considéré comme l’électrolyte contenant des ions  $\text{Na}^+$ ,  $\text{Cl}^-$  et  $\text{K}^-$ . Dès que l’électrode y est plongée, une interface composée d’une double couche de charges se forme à sa surface. Celle-ci est le résultat de la redistribution des charges dans les deux milieux, de l’adsorption de certains anions et de l’attraction de molécules polarisées telles que les molécules d’eau. L’équilibre est alors atteint.