**Titre:** Profilage, caractérisation et partitionnement fonctionnel dans une plate-forme de conception de systèmes embarqués

Title: Profilage, caractérisation et partitionnement fonctionnel dans une plate-forme de conception de systèmes embarqués

**Auteur:** Laurent Moss

Author:

**Date:** 2010

**Type:** Mémoire ou thèse / Dissertation or Thesis

**Référence:** Moss, L. (2010). Profilage, caractérisation et partitionnement fonctionnel dans une plate-forme de conception de systèmes embarqués [Thèse de doctorat, École Polytechnique de Montréal]. PolyPublie. <https://publications.polymtl.ca/338/>

Citation:

## Document en libre accès dans PolyPublie

Open Access document in PolyPublie

**URL de PolyPublie:** <https://publications.polymtl.ca/338/>

PolyPublie URL:

**Directeurs de recherche:** Guy Bois, & Mostapha Aboulhamid

Advisors:

**Programme:** Génie informatique

Program:

UNIVERSITÉ DE MONTRÉAL

PROFILAGE, CARACTÉRISATION ET PARTITIONNEMENT FONCTIONNEL DANS

UNE PLATE-FORME DE CONCEPTION DE SYSTÈMES EMBARQUÉS

LAURENT MOSS

DÉPARTEMENT DE GÉNIE INFORMATIQUE ET GÉNIE LOGICIEL

ÉCOLE POLYTECHNIQUE DE MONTRÉAL

THÈSE PRÉSENTÉE EN VUE DE L'OBTENTION DU DIPLÔME DE

PHILOSOPHIÆ DOCTOR

(GÉNIE INFORMATIQUE)

JUIN 2010

UNIVERSITÉ DE MONTRÉAL

ÉCOLE POLYTECHNIQUE DE MONTRÉAL

Cette thèse intitulée :

PROFILAGE, CARACTÉRISATION ET PARTITIONNEMENT FONCTIONNEL DANS

UNE PLATE-FORME DE CONCEPTION DE SYSTÈMES EMBARQUÉS

présentée par : MOSS, Laurent

en vue de l'obtention du diplôme de : Philosophiæ Doctor

a été dûment acceptée par le jury d'examen constitué de :

Mme. NICOLESCU, Gabriela, Doct., présidente.

M. BOIS, Guy, Ph.D., membre et directeur de recherche.

M. ABOULHAMID, El Mostapha, Ph.D., membre et codirecteur de recherche.

M. BOLAND, Jean-François, Ph.D., membre.

M. PÉTROT, Frédéric, Ph.D., membre.

## REMERCIEMENTS

Je tiens à remercier chaleureusement mon directeur de recherche, le professeur Guy Bois, dont les judicieux conseils, le constant appui et la grande disponibilité ont été indispensables à la réalisation de ce projet de recherche. Je remercie également mon co-directeur de recherche, le professeur El Mostapha Aboulhamid, dont les sages conseils ont alimenté ma réflexion tout au long de ce projet de recherche. Je remercie aussi les professeurs Gabriela Nicolescu et Yvon Savaria pour leurs pertinents conseils lors de mon examen général de synthèse. Je remercie les professeurs Jean-François Boland et Frédéric Pétrot, de même que les autres membres du jury, d'avoir pris le temps de réviser ma thèse.

Je remercie mes collègues Luc Filion, Maxime de Nanclas, Marc-André Cantin et Sébastien Fontaine pour leur précieuse collaboration dans la rédaction d'articles pour les conférences DVCN, DATE et RSP. Pour leur collaboration et leur soutien, je remercie aussi mes autres collègues du laboratoire de recherche en codesign CIRCUS et de Space Codesign, notamment Jérôme Chevalier, Benoit Pilote, Sylvain Goyette, Ahmed Faiz, Cédric Migliorini, Fatoumata-Lamaranah Bah, Sébastien Le Beux, Hubert Guérard, Mathieu McKinnon et Michel Rogers-Vallée.

Je remercie Réjean Lepage pour la qualité du support technique qu'il m'a offert dans l'utilisation des équipements du Groupe de Recherche en Microélectronique et Microsystèmes de l'École Polytechnique de Montréal. Je remercie Jeanne Daunais pour son soutien administratif, notamment en lien avec mes participations à diverses conférences.

Je remercie le Conseil de recherches en sciences naturelles et en génie, le Regroupement Stratégique en Microsystèmes du Québec et l'École Polytechnique de Montréal pour leur appui financier qui m'a permis de me consacrer entièrement à la réalisation de ce projet de recherche.

Finalement, je remercie mes parents, Philippe et Louise, pour leur appui indéfectible dans tous mes projets et plus particulièrement dans mes études universitaires et ce projet de recherche.

## RÉSUMÉ

La complexité architecturale des systèmes embarqués augmente constamment et ceux-ci comprennent maintenant plusieurs processeurs, bus, périphériques et accélérateurs matériels. Les méthodologies présentement utilisées par l'industrie pour la conception des systèmes embarqués n'arrivent pas à suivre cette évolution. Des méthodologies de niveau système ont été proposées pour hauser le niveau d'abstraction de la conception des systèmes embarqués. Une telle méthodologie comporte une plate-forme virtuelle qui permet d'allouer des composants, d'y assigner la fonctionnalité de l'application et de simuler l'architecture résultante à un niveau transactionnel. Une méthodologie de niveau système peut accélérer la conception des systèmes embarqués en partant d'une spécification exécutable, en explorant automatiquement l'espace de conception et en synthétisant une architecture optimisée pour l'application.

Cependant, les méthodologies de niveau système existantes ont plusieurs lacunes. Elles supposent typiquement que l'application est modélisée avec un modèle de calcul restrictif et n'automatisent pas la synthèse des modules de l'application vers des blocs matériels. Elles n'intègrent pas un profilage non-intrusif de l'application ou d'une architecture qui l'implémente. Leurs méthodes d'estimation n'automatisent pas la caractérisation de l'application ou de la plate-forme. Ces méthodologies considèrent séparément les problèmes de l'allocation des processeurs, de l'assignation des tâches aux processeurs et du choix d'une topologie de communication.

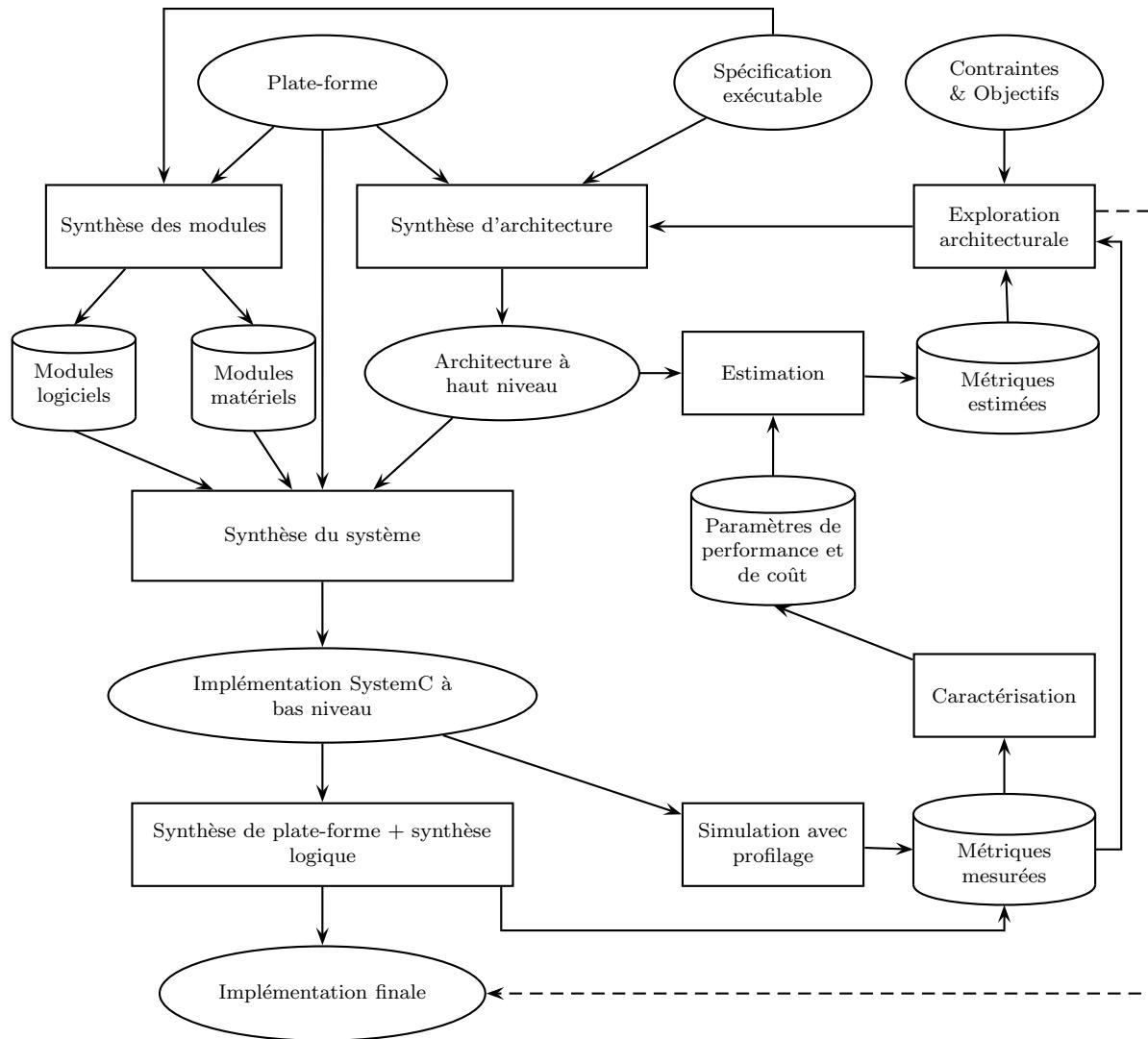

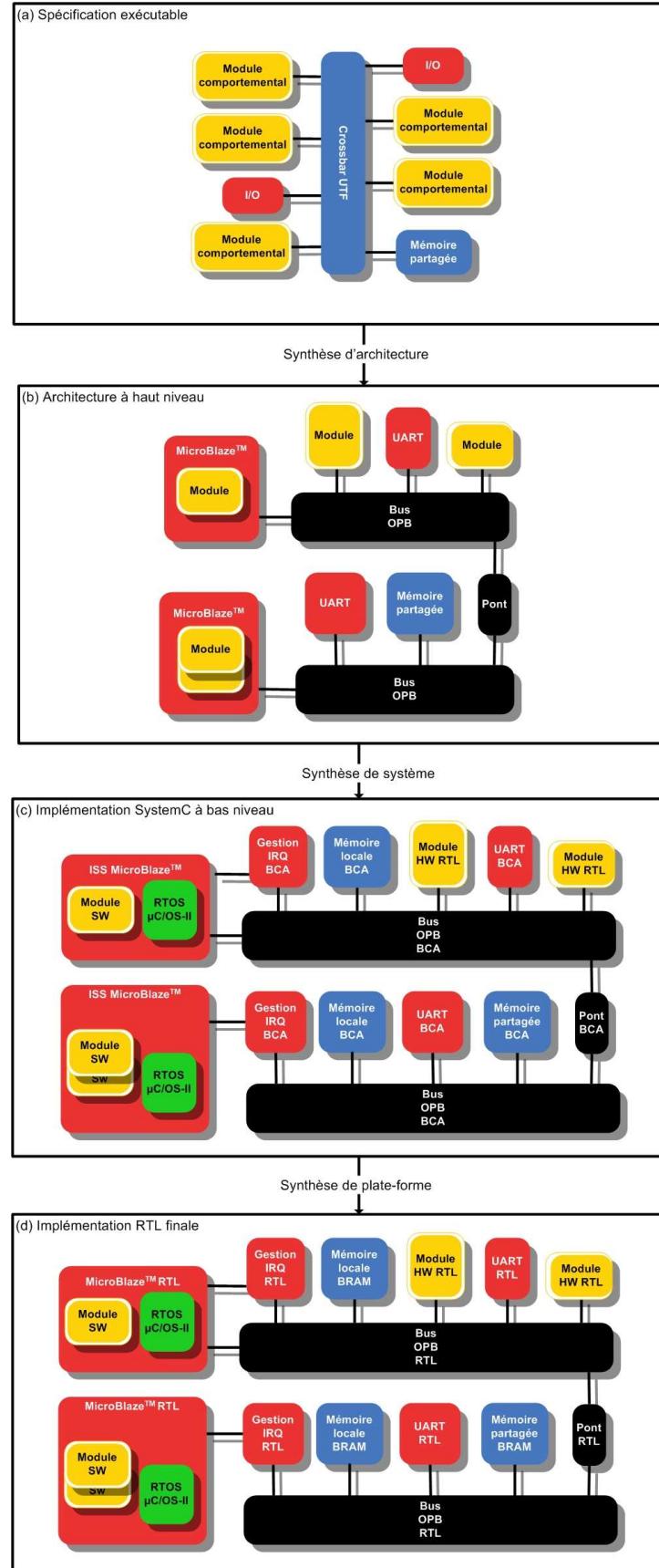

Nous présentons une méthodologie de niveau système pour la conception, l'exploration architecturale et la synthèse des systèmes embarqués basée sur la technologie Space Code-sign™ et sa plate-forme virtuelle SPACE. Cette méthodologie répond aux problématiques soulevées car elle combine un modèle de calcul plus expressif, une méthode de synthèse matérielle automatisée des modules d'une spécification SystemC, un profilage non-intrusif au niveau système, une méthode de caractérisation automatisée de l'application et du système d'exploitation temps-réel (RTOS), ainsi que des heuristiques pour une formulation unifiée du problème d'exploration architecturale.

Ainsi, nous avons défini pour notre méthodologie un nouveau modèle de calcul, les réseaux de processus temps-réel (RTPN) qui sont une extension des réseaux de processus Kahn. Cette extension permet de modéliser des aspects importants du traitement temps-réel tels que la scrutation, les senseurs échantillonnés, les périphériques d'entrée/sortie et les contraintes temps-réel. La sémantique dénotationnelle des RTPN est définie afin de vérifier si le raffinement d'une spécification exécutable SystemC vers une implémentation concrète est fonctionnellement correct.

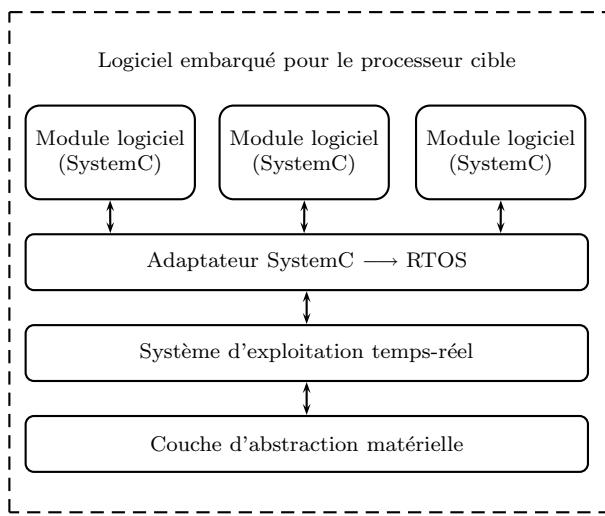

Notre méthodologie inclut une méthode automatisée de raffinement des communications transactionnelles vers des protocoles précis au cycle et à la broche près ainsi que la génération automatique de blocs matériels pour les modules de l'application. Cette méthode permet, conjointement avec une méthode de génération de code embarqué incluant un RTOS, de générer une implémentation de l'application qui peut être simulée avec la plate-forme virtuelle ou synthétisée et exécutée sur la cible finale. Une nouvelle méthode de profilage au niveau système est appliquée à une telle simulation, ce qui permet d'extraire non-intrusivement des données sur la performance des modules, des processeurs, du RTOS, des bus et des mémoires.

Une nouvelle méthode automatisée permet de caractériser, par des simulations profilées, à la fois la fonctionnalité de l'application et les implémentations logicielles et matérielles de ses modules. Les périphériques et les bus de la plate-forme virtuelle ont également été caractérisés et une nouvelle méthode automatise la caractérisation du RTOS. Ces caractérisations configurent un simulateur de performance à haut niveau qui estime précisément et très rapidement la performance d'un ensemble d'architectures pour l'application en tenant compte de la contention sur les bus et de l'ordonnancement des tâches sur les processeurs. Cette caractérisation mène également à une estimation précise et rapide des besoins en ressources matérielles.

Nous présentons une formulation du problème d'exploration architecturale qui combine le partitionnement logiciel/matériel, l'allocation des processeurs, l'assignation des tâches aux processeurs et le choix d'une topologie de communication. L'exploration architecturale évalue les architectures selon des critères de performance et de coût matériel à l'aide de notre méthode d'estimation. Nous présentons pour la première fois une analyse combinatoire de ce problème et sa formulation comme un problème de recherche locale, pour la résolution duquel nous définissons des heuristiques basées sur un recuit simulé adaptatif et sur une recherche tabou réactive. L'architecture retenue par l'exploration architecturale peut ensuite être synthétisée vers une implémentation finale dans un flot de conception RTL bien établi. La méthodologie dans son ensemble est appliquée à trois études de cas : un système de guidage d'un astromobile, un décodeur JPEG avec détection de peau et un encodeur/décodeur WiMAX.

## ABSTRACT

Embedded systems have increasingly complex architectures and are now composed of several processors, buses, peripherals and hardware accelerators. Embedded system design methodologies currently used in industry are not keeping up with this evolution. System-level methodologies have been proposed in order to raise the level of abstraction of embedded system design. Such a methodology includes a virtual platform in which components can be allocated while application tasks can be bound to allocated components for a transaction-level simulation of the resulting architecture. A system-level methodology can accelerate embedded system design by using an executable specification, automating design space exploration and synthesizing an optimized architecture for the application.

However, current system-level methodologies have several shortcomings. They typically assume that the application is modeled with a restrictive model of computation and do not automate the synthesis of hardware blocks from application modules. They do not support a non-intrusive profiling of the application or of an architecture implementing the application. Their estimation methods do not automate the characterization of the application or of the platform. These methodologies consider processor allocation, task binding to processors and the choice of a communication topology to be separate problems instead of being different aspects of a single problem.

We present a system-level methodology for the design, architectural exploration and synthesis of embedded systems based on the Space Codesign™ technology and its SPACE virtual platform. This methodology tackles these problems by combining a more expressive model of computation, a method for the automated synthesis of hardware blocks from a SystemC specification's modules, a non-intrusive system-level profiling, a method for the automated characterization of the application and of the real-time operating system (RTOS), as well as heuristics for a unified formulation of the architectural exploration problem.

We have thus defined for our methodology a novel model of computation, called real-time process networks (RTPN), which is an extension of Kahn process networks. This extension enables the modeling of important aspects of real-time processing, such as polling, sensor sampling, input/output peripherals and real-time constraints. We define the denotational semantics of RTPNs, which is used to verify the functional correctness of a refinement from a SystemC executable specification to a concrete implementation.

Our methodology includes an automated refinement from transaction-level communications to cycle- and pin-accurate protocols as well as an automated generation of hardware blocks from application modules. This method enables, when combined with an embedded

software generation method which includes a RTOS, the generation of an implementation of the application, which can be simulated with the virtual platform or synthesized and executed on the final target. A novel profiling method is applied to such simulations in order to non-intrusively extract data on the performance of modules, processors, RTOS, buses and memories.

A novel automated method characterizes, through profiled simulations, both the application functionality and the software and hardware implementations of its modules. The devices and buses of the virtual platform have also been characterized and a novel method automates the characterization of the RTOS. These characterizations configure a high-level performance simulator for an accurate and very fast estimation of the performance of several candidate architectures for the application, taking into account bus contention and task scheduling on processors. This characterization also powers a fast and accurate estimation of required hardware resources.

A formulation of the architectural exploration problem is given such that it combines hardware/software partitioning, processor allocation, task binding on processors and the selection of a communication topology. This architectural exploration evaluates architectures for criteria of performance and hardware cost with our estimation method. We present for the first time a combinatorial analysis of this problem and its formulation as a local search problem, for which heuristics based on adaptative simulated annealing and reactive tabu search are defined. The architecture selected by the architectural exploration can then be synthesized towards a final implementation in a well-established RTL design flow. The methodology as a whole has been applied to three case studies: a rover guiding system, a JPEG decoder with skin detection and a WiMAX encoder/decoder.

## TABLE DES MATIÈRES

|                                                             |      |

|-------------------------------------------------------------|------|

| REMERCIEMENTS . . . . .                                     | iii  |

| RÉSUMÉ . . . . .                                            | iv   |

| ABSTRACT . . . . .                                          | vi   |

| TABLE DES MATIÈRES . . . . .                                | viii |

| LISTE DES TABLEAUX . . . . .                                | xiv  |

| LISTE DES FIGURES . . . . .                                 | xvi  |

| LISTE DES ANNEXES . . . . .                                 | xix  |

| LISTE DES SIGLES ET ABRÉVIATIONS . . . . .                  | xx   |

| <br>                                                        |      |

| CHAPITRE 1 INTRODUCTION . . . . .                           | 1    |

| 1.1 Mise en contexte et problématique . . . . .             | 1    |

| 1.2 Objectif . . . . .                                      | 2    |

| 1.3 Contributions . . . . .                                 | 3    |

| <br>                                                        |      |

| CHAPITRE 2 REVUE DE LITTÉRATURE . . . . .                   | 6    |

| 2.1 Modèles de calcul parallèles . . . . .                  | 6    |

| 2.1.1 Flots de données synchrones (SDF) . . . . .           | 7    |

| 2.1.2 Flots de données cyclo-statiques (CSDF) . . . . .     | 7    |

| 2.1.3 Flots de données booléens (BDF) . . . . .             | 8    |

| 2.1.4 Réseaux de processus Kahn (KPN) . . . . .             | 8    |

| 2.1.4.1 Sémantique dénotationalle . . . . .                 | 9    |

| 2.1.4.2 Limites et extensions . . . . .                     | 10   |

| 2.1.5 Modèles temporisés de flots de données . . . . .      | 11   |

| 2.1.6 Réseaux de processus temps-réel . . . . .             | 12   |

| 2.2 Synthèse matérielle au niveau système . . . . .         | 13   |

| 2.2.1 Intégration d'un bloc matériel existant . . . . .     | 13   |

| 2.2.2 Synthèse comportementale d'un bloc matériel . . . . . | 13   |

| 2.2.3 Raffinement des communications . . . . .              | 14   |

|            |                                                           |    |

|------------|-----------------------------------------------------------|----|

| 2.2.4      | Raffinement des communications et synthèse matérielle     | 15 |

| 2.3        | Profilage de performance                                  | 16 |

| 2.3.1      | Profilage d'un code logiciel                              | 16 |

| 2.3.1.1    | Profilage par exécution sur FPGA                          | 16 |

| 2.3.1.2    | Profilage par simulation sur ISS                          | 17 |

| 2.3.2      | Profilage d'une plate-forme logicielle/matérielle         | 18 |

| 2.3.3      | Profilage des changements de contexte                     | 19 |

| 2.3.4      | Profilage des arguments et des valeurs de retour          | 19 |

| 2.3.5      | Portabilité du profilage                                  | 20 |

| 2.4        | Estimation du temps d'exécution                           | 20 |

| 2.4.1      | Analyse statique                                          | 20 |

| 2.4.1.1    | Estimation par ordonnancement statique                    | 20 |

| 2.4.1.2    | Estimation statique du WCET                               | 22 |

| 2.4.2      | Annotation temporelle d'une simulation TLM                | 24 |

| 2.4.2.1    | Annotation temporelle par analyse statique                | 25 |

| 2.4.2.2    | Annotation temporelle par analyse dynamique               | 27 |

| 2.4.3      | Évaluation d'une trace dynamique                          | 29 |

| 2.4.3.1    | Évaluation par analyse statique                           | 29 |

| 2.4.3.2    | Évaluation par analyse dynamique                          | 30 |

| 2.5        | Algorithmes d'exploration architecturale                  | 33 |

| 2.5.1      | Partitionnement logiciel/matériel avec un processeur      | 34 |

| 2.5.2      | Exploration architecturale avec plusieurs processeurs     | 35 |

| 2.5.2.1    | Nombre fixe de processeurs                                | 36 |

| 2.5.2.2    | Exploration de l'allocation des processeurs               | 37 |

| 2.5.2.3    | Allocation des processeurs et topologie de communications | 39 |

| 2.5.3      | Algorithmes de recherche locale                           | 40 |

| 2.6        | Méthodologies intégrées                                   | 42 |

| 2.6.1      | SoCDAL                                                    | 42 |

| 2.6.2      | PeaCE                                                     | 43 |

| 2.6.3      | Koski                                                     | 45 |

| 2.6.4      | Daedalus                                                  | 46 |

| 2.6.5      | SystemCoDesigner                                          | 48 |

| CHAPITRE 3 | PRÉSENTATION DE LA MÉTHODOLOGIE                           | 50 |

| 3.1        | Aperçu général                                            | 50 |

| 3.2        | Présentation des éléments de la méthodologie              | 52 |

|                                                                                    |                                                            |    |

|------------------------------------------------------------------------------------|------------------------------------------------------------|----|

| 3.2.1                                                                              | Modèle de calcul RTPN . . . . .                            | 52 |

| 3.2.2                                                                              | Spécification exécutable parallèle . . . . .               | 55 |

| 3.2.3                                                                              | Plate-forme virtuelle SPACE . . . . .                      | 57 |

| 3.2.4                                                                              | Synthèse d'architecture . . . . .                          | 58 |

| 3.2.5                                                                              | Synthèse des modules . . . . .                             | 59 |

| 3.2.5.1                                                                            | Synthèse logicielle . . . . .                              | 60 |

| 3.2.5.2                                                                            | Synthèse des modules matériels . . . . .                   | 61 |

| 3.2.6                                                                              | Synthèse du système . . . . .                              | 61 |

| 3.2.7                                                                              | Synthèse de plate-forme et synthèse logique . . . . .      | 63 |

| 3.2.8                                                                              | Profilage au niveau système . . . . .                      | 63 |

| 3.2.9                                                                              | Caractérisation et estimation . . . . .                    | 63 |

| 3.2.10                                                                             | Exploration architecturale . . . . .                       | 64 |

| <b>CHAPITRE 4 RÉSEAUX DE PROCESSUS TEMPS-RÉEL . . . . .</b>                        |                                                            | 65 |

| 4.1                                                                                | Définition des réseaux de processus temps-réel . . . . .   | 65 |

| 4.1.1                                                                              | Évènements et relation de précédence . . . . .             | 66 |

| 4.1.2                                                                              | Types de canaux et de réseaux de processus . . . . .       | 67 |

| 4.2                                                                                | Sémantique dénotationnelle des RTPN . . . . .              | 69 |

| 4.2.1                                                                              | Ordonnancements équivalents à un KPN classique . . . . .   | 70 |

| 4.2.2                                                                              | Classes d'ordonnancements équivalents . . . . .            | 72 |

| 4.2.3                                                                              | Représentation d'un RTPN comme un KPN paramétré . . . . .  | 73 |

| 4.3                                                                                | Applications aux systèmes embarqués . . . . .              | 75 |

| 4.3.1                                                                              | Mémoire partagée . . . . .                                 | 75 |

| 4.3.2                                                                              | Senseur échantillonné . . . . .                            | 75 |

| 4.3.3                                                                              | Périphériques d'entrée et de sortie . . . . .              | 76 |

| 4.3.4                                                                              | Contraintes temps-réel . . . . .                           | 76 |

| 4.3.5                                                                              | Modélisation d'une application SPACE par un RTPN . . . . . | 77 |

| <b>CHAPITRE 5 RAFFINEMENT DES COMMUNICATIONS ET SYNTHÈSE DU MATERIEL . . . . .</b> |                                                            | 79 |

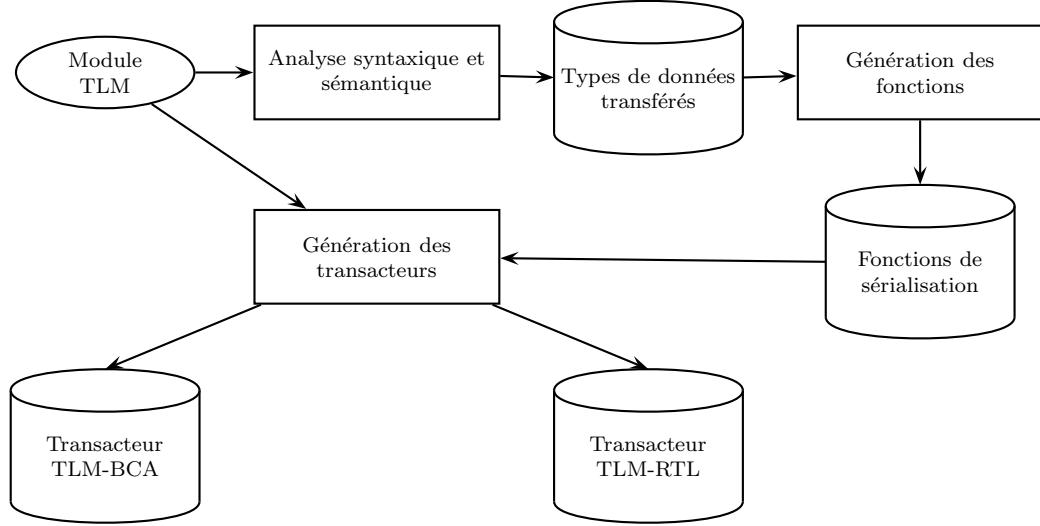

| 5.1                                                                                | Sérialisation des types de données . . . . .               | 80 |

| 5.1.1                                                                              | Sérialisation triviale . . . . .                           | 80 |

| 5.1.2                                                                              | Sérialisation standardisée . . . . .                       | 80 |

| 5.2                                                                                | Raffinement des communications . . . . .                   | 82 |

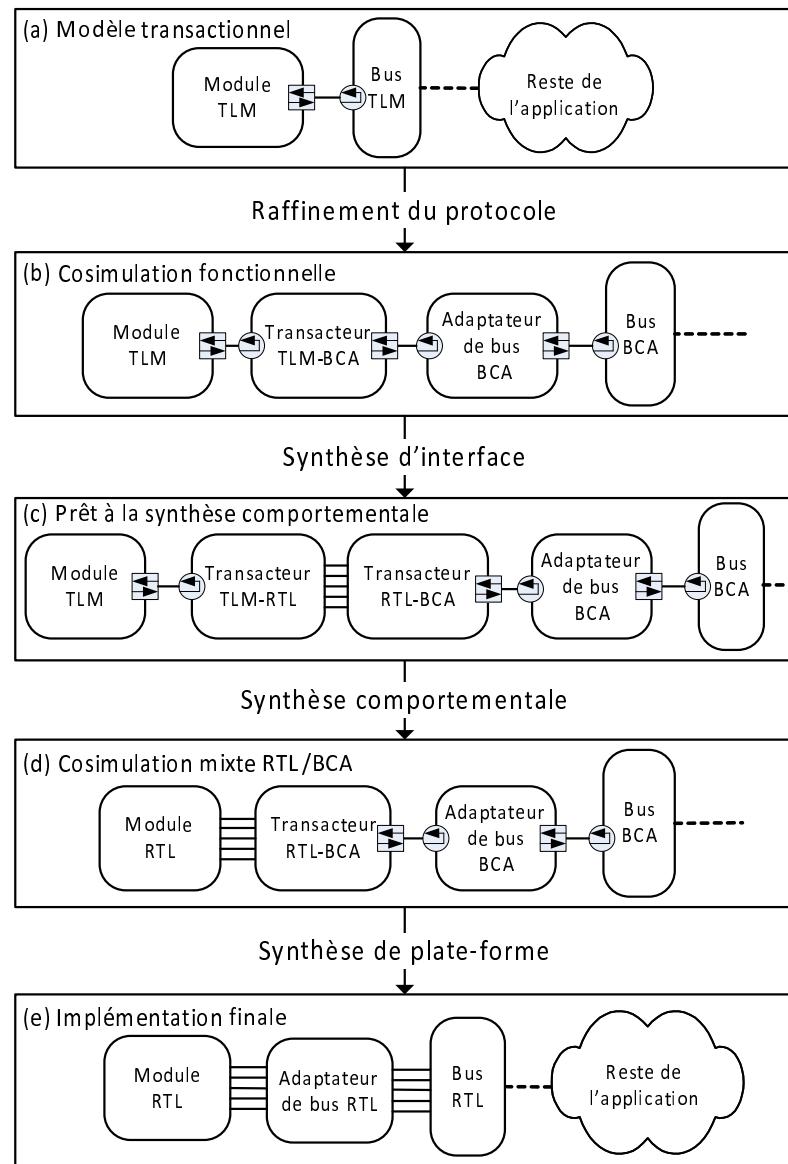

| 5.2.1                                                                              | Spécification exécutable au niveau TLM . . . . .           | 82 |

| 5.2.2                                                                              | Raffinement du protocole de communications . . . . .       | 84 |

| 5.2.3                                                                              | Synthèse d'interface . . . . .                             | 85 |

|                                                    |                                                                   |     |

|----------------------------------------------------|-------------------------------------------------------------------|-----|

| 5.3                                                | Synthèse du matériel . . . . .                                    | 85  |

| 5.3.1                                              | Synthèse comportementale . . . . .                                | 85  |

| 5.3.2                                              | Synthèse de la plate-forme . . . . .                              | 89  |

| CHAPITRE 6 PROFILAGE AU NIVEAU SYSTÈME . . . . .   |                                                                   | 90  |

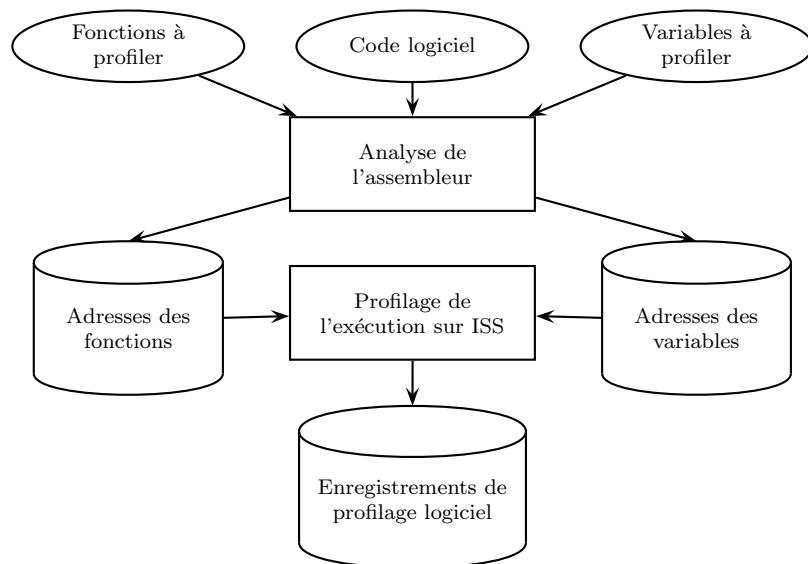

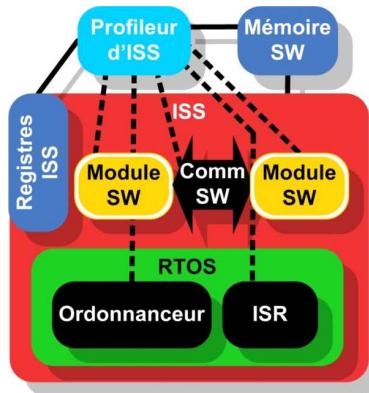

| 6.1                                                | Profilage non-intrusif de code logiciel . . . . .                 | 91  |

| 6.1.1                                              | Fonctionnement général du profileur d'ISS . . . . .               | 92  |

| 6.1.2                                              | Implémentation du profileur d'ISS . . . . .                       | 93  |

| 6.1.2.1                                            | Implémentation du profileur d'ISS pour le MicroBlaze . . . . .    | 94  |

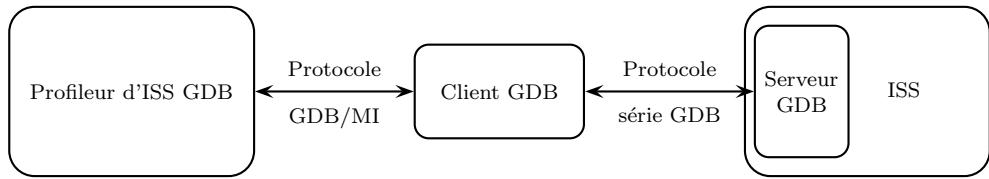

| 6.1.2.2                                            | Implémentation générique avec GDB . . . . .                       | 95  |

| 6.1.3                                              | Profilage du RTOS et de l'API logicielle de SPACE . . . . .       | 97  |

| 6.1.3.1                                            | Algorithmes du profileur d'ISS SPACE . . . . .                    | 97  |

| 6.1.3.2                                            | Implémentation pour $\mu$ COS/II . . . . .                        | 99  |

| 6.1.4                                              | Profilage exhaustif du code logiciel . . . . .                    | 100 |

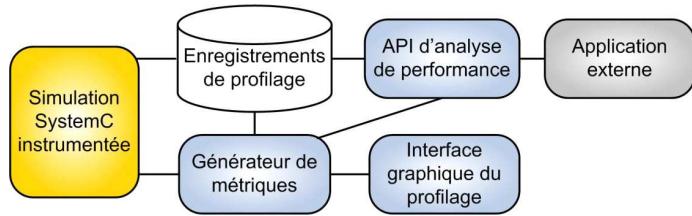

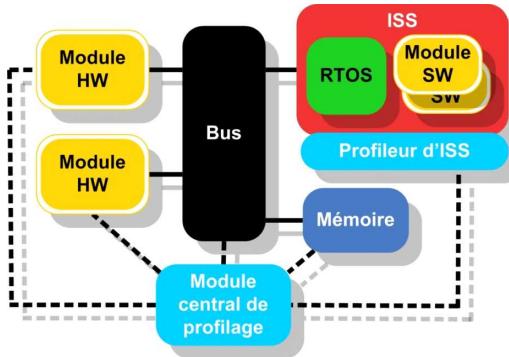

| 6.2                                                | Profilage au niveau système dans SPACE . . . . .                  | 100 |

| 6.2.1                                              | Instrumentation de la plate-forme SPACE . . . . .                 | 101 |

| 6.2.2                                              | Informations et métriques extraites du profilage . . . . .        | 103 |

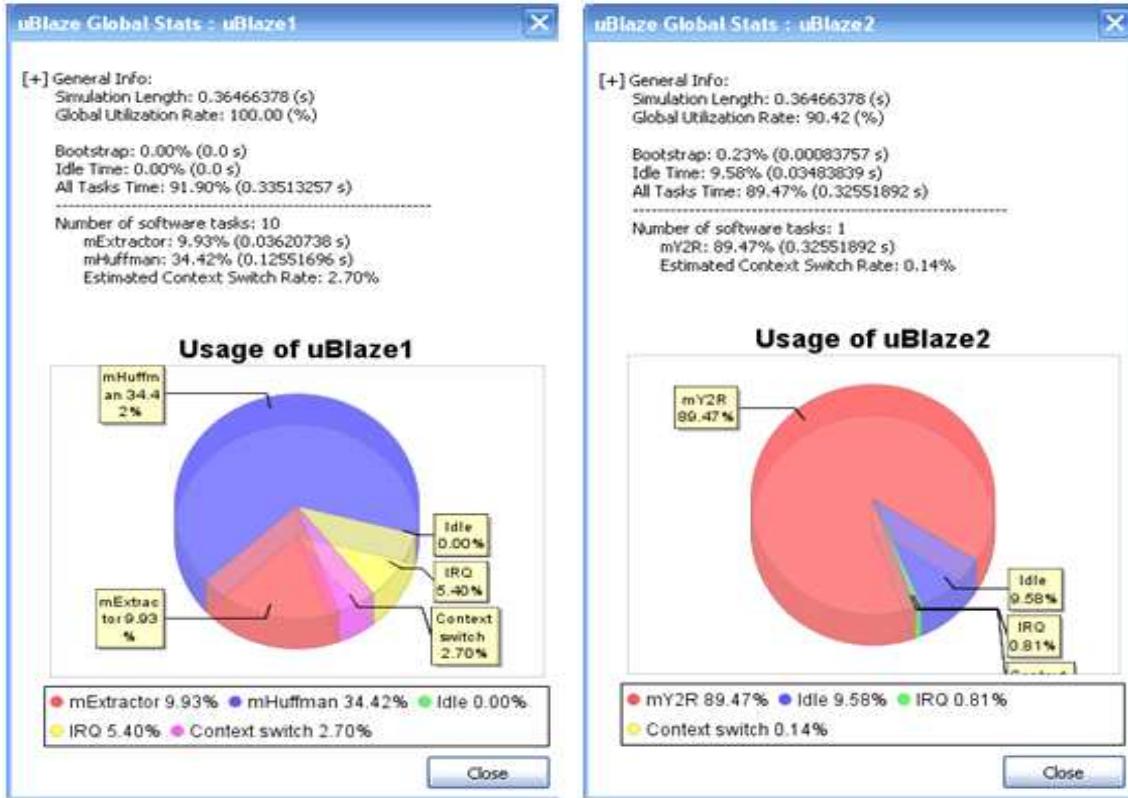

| 6.2.2.1                                            | Exécution des modules et du RTOS . . . . .                        | 103 |

| 6.2.2.2                                            | Communication des modules de bout en bout . . . . .               | 104 |

| 6.2.2.3                                            | Transferts sur le bus . . . . .                                   | 105 |

| 6.2.2.4                                            | Accès à la mémoire . . . . .                                      | 106 |

| CHAPITRE 7 CARACTÉRISATION ET ESTIMATION . . . . . |                                                                   | 108 |

| 7.1                                                | Définition des métriques . . . . .                                | 108 |

| 7.2                                                | Performance et validité fonctionnelle . . . . .                   | 109 |

| 7.2.1                                              | Caractérisation de la fonctionnalité de l'application . . . . .   | 110 |

| 7.2.1.1                                            | Définition de la trace fonctionnelle . . . . .                    | 110 |

| 7.2.1.2                                            | Extraction d'un CPG par profilage . . . . .                       | 112 |

| 7.2.2                                              | Caractérisation du temps d'exécution des modules . . . . .        | 115 |

| 7.2.2.1                                            | Définition des fonctions de caractérisation des modules . . . . . | 116 |

| 7.2.2.2                                            | Profilage d'une implémentation d'un module . . . . .              | 117 |

| 7.2.2.3                                            | Analyse des enregistrements de profilage . . . . .                | 117 |

| 7.2.3                                              | Caractérisation de la plate-forme . . . . .                       | 119 |

| 7.2.3.1                                            | Caractérisation des périphériques . . . . .                       | 119 |

| 7.2.3.2                                            | Caractérisation des adaptateurs de bus . . . . .                  | 120 |

| 7.2.3.3                                            | Caractérisation des bus et des ponts . . . . .                    | 120 |

| 7.2.3.4                                            | Caractérisation du RTOS et de l'API logicielle . . . . .          | 121 |

|                                                        |                                                               |            |

|--------------------------------------------------------|---------------------------------------------------------------|------------|

| 7.2.4                                                  | Estimation par une simulation de performance . . . . .        | 124        |

| 7.2.4.1                                                | Fonctionnement général du simulateur de performance . . . . . | 125        |

| 7.2.4.2                                                | Implémentation du simulateur de performance . . . . .         | 126        |

| 7.2.4.3                                                | Validité de l'estimation . . . . .                            | 127        |

| 7.3                                                    | Quantité de ressources matérielles . . . . .                  | 128        |

| 7.3.1                                                  | Caractérisation des modules matériels . . . . .               | 129        |

| 7.3.2                                                  | Caractérisation des modules logiciels . . . . .               | 130        |

| 7.3.3                                                  | Caractérisation de la plate-forme . . . . .                   | 131        |

| 7.3.4                                                  | Estimation des quantités des ressources matérielles . . . . . | 133        |

| <b>CHAPITRE 8 EXPLORATION ARCHITECTURALE . . . . .</b> |                                                               | <b>134</b> |

| 8.1                                                    | Définition de l'espace de recherche . . . . .                 | 134        |

| 8.2                                                    | Problèmes d'exploration architecturale . . . . .              | 136        |

| 8.3                                                    | Fonctions objectives . . . . .                                | 139        |

| 8.4                                                    | Algorithmes d'exploration architecturale . . . . .            | 141        |

| 8.4.1                                                  | Complexité de l'exploration architecturale . . . . .          | 142        |

| 8.4.2                                                  | Algorithme de parcours en profondeur . . . . .                | 142        |

| 8.4.3                                                  | Algorithme glouton . . . . .                                  | 144        |

| 8.4.4                                                  | Recherche locale . . . . .                                    | 146        |

| 8.4.4.1                                                | Définition du voisinage . . . . .                             | 147        |

| 8.4.4.2                                                | Marche aléatoire . . . . .                                    | 148        |

| 8.4.4.3                                                | Descente . . . . .                                            | 148        |

| 8.4.4.4                                                | Recuit simulé adaptatif . . . . .                             | 150        |

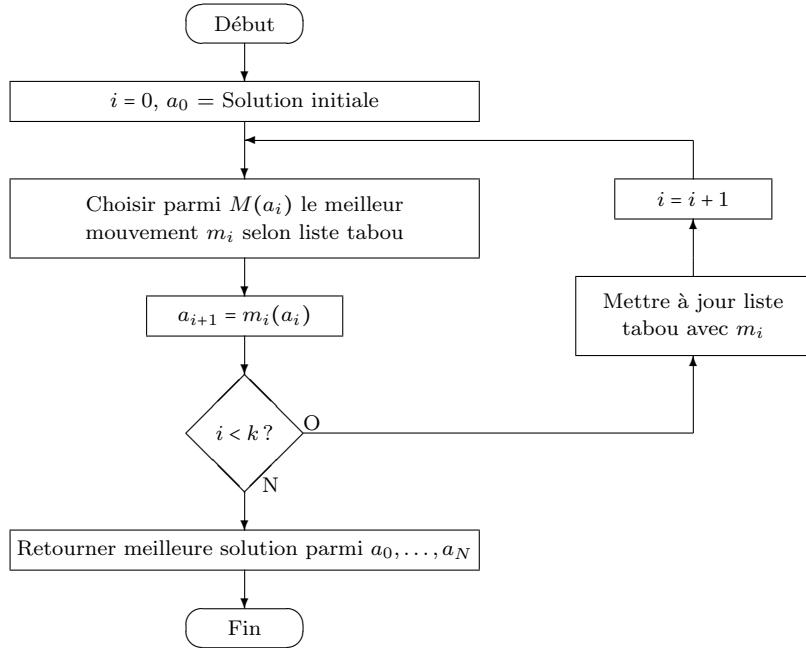

| 8.4.4.5                                                | Recherche tabou . . . . .                                     | 153        |

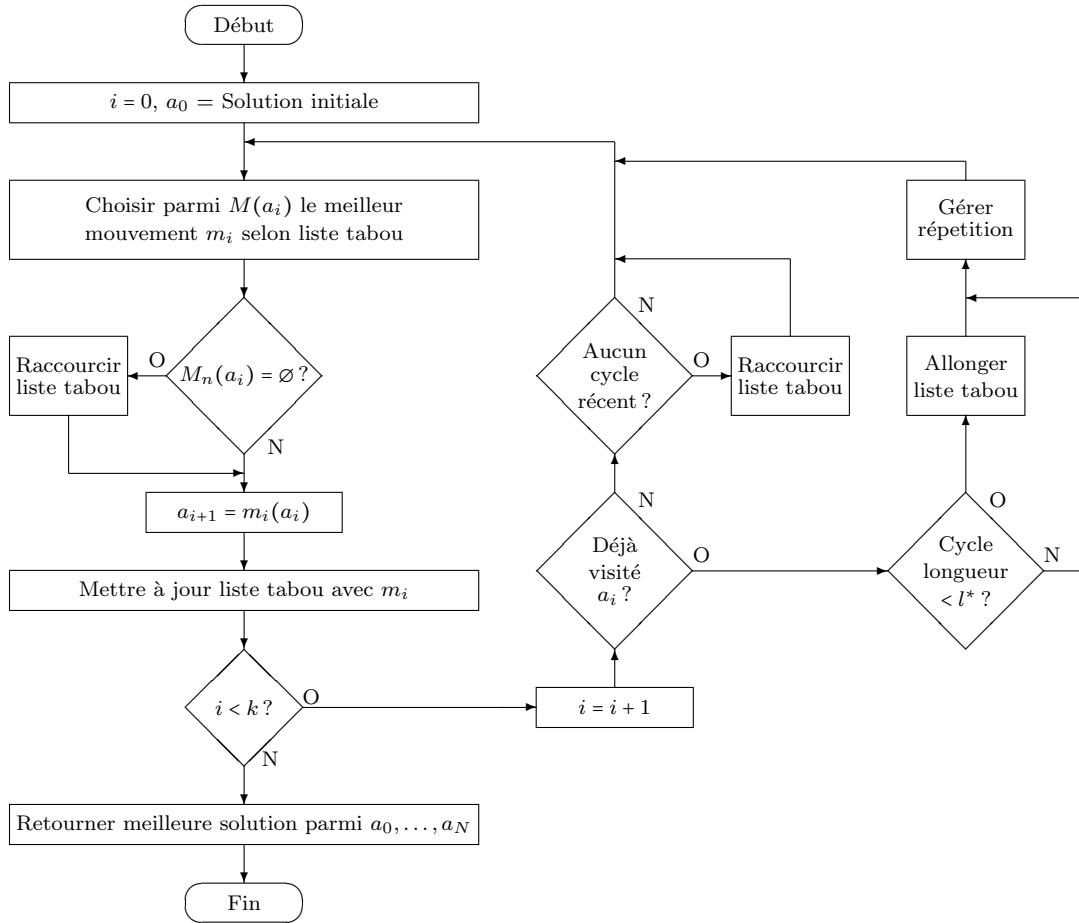

| 8.4.4.6                                                | Recherche tabou réactive . . . . .                            | 155        |

| <b>CHAPITRE 9 RÉSULTATS ET DISCUSSION . . . . .</b>    |                                                               | <b>159</b> |

| 9.1                                                    | Présentation des études de cas . . . . .                      | 159        |

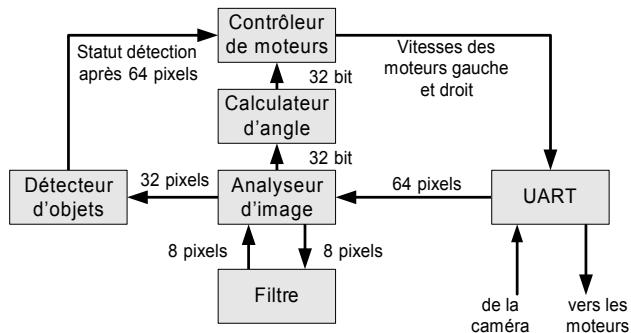

| 9.1.1                                                  | Système de guidage d'un rover . . . . .                       | 159        |

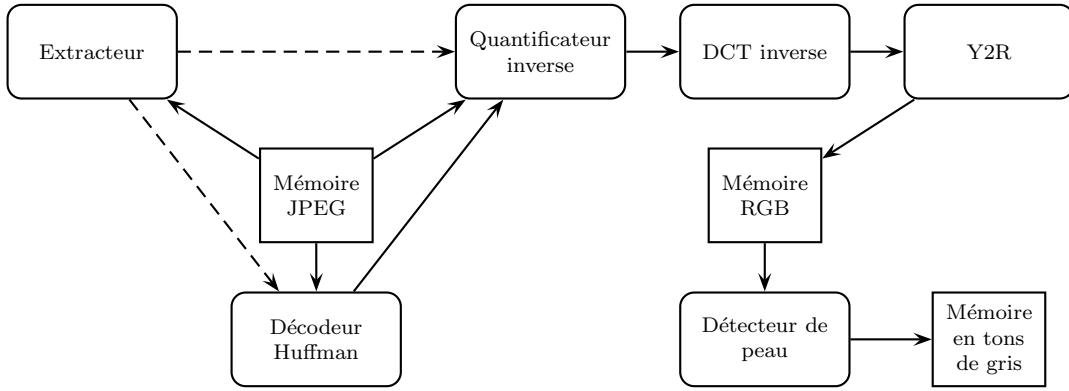

| 9.1.2                                                  | Décodeur JPEG avec détection de la peau . . . . .             | 160        |

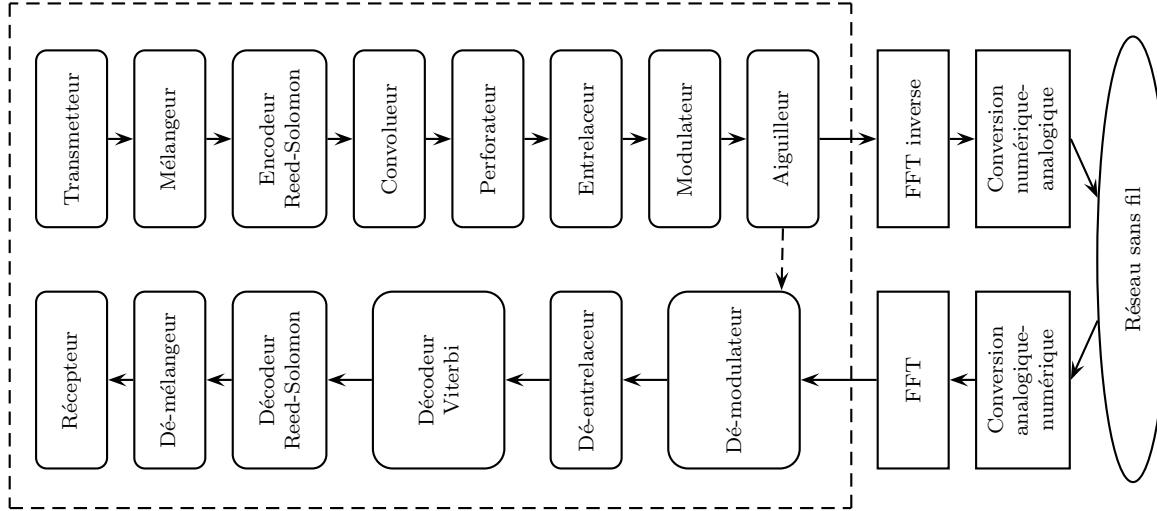

| 9.1.3                                                  | Encodeur/décodeur WIMAX . . . . .                             | 161        |

| 9.2                                                    | Modèles RTPN . . . . .                                        | 162        |

| 9.3                                                    | Synthèse matérielle et des communications . . . . .           | 163        |

| 9.3.1                                                  | Synthèse des modules matériels . . . . .                      | 163        |

| 9.3.2                                                  | Simulation à différents niveaux . . . . .                     | 167        |

| 9.3.3                                                  | Synthèse sur FPGA . . . . .                                   | 168        |

| 9.4                                                    | Profilage au niveau système . . . . .                         | 170        |

|                        |                                                     |     |

|------------------------|-----------------------------------------------------|-----|

| 9.4.1                  | Architectures testées                               | 170 |

| 9.4.2                  | Impact du profilage                                 | 171 |

| 9.5                    | Caractérisation et estimation                       | 174 |

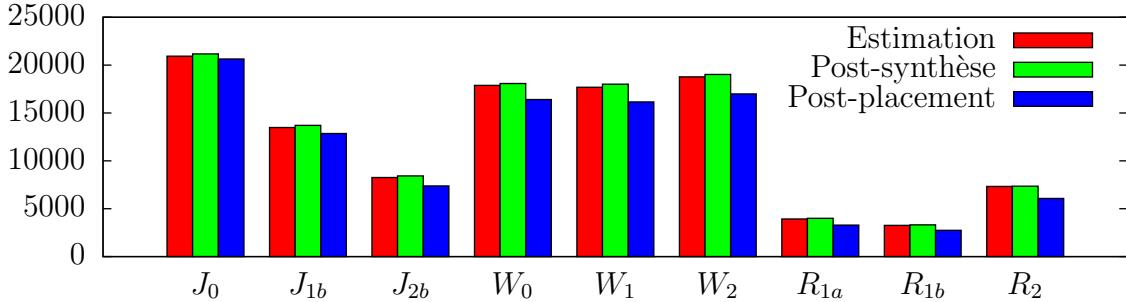

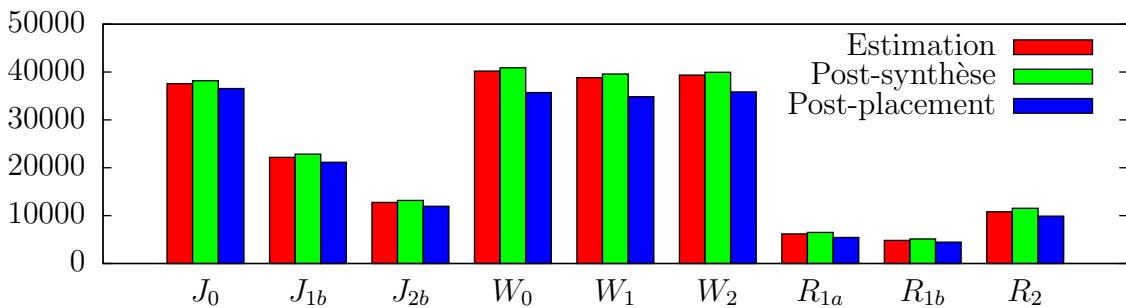

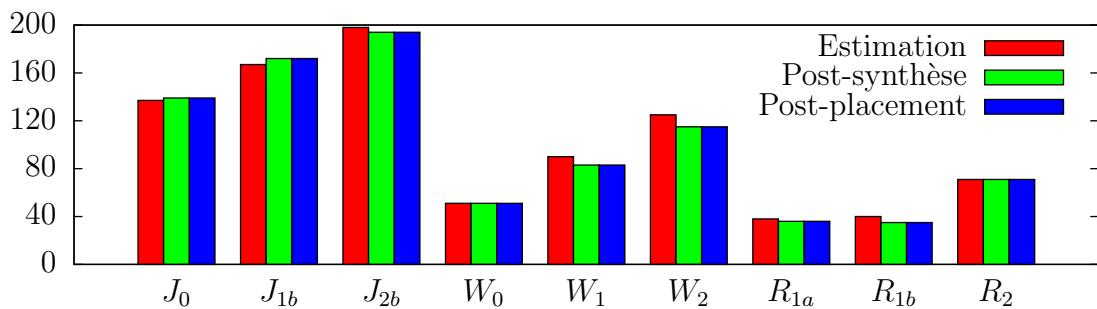

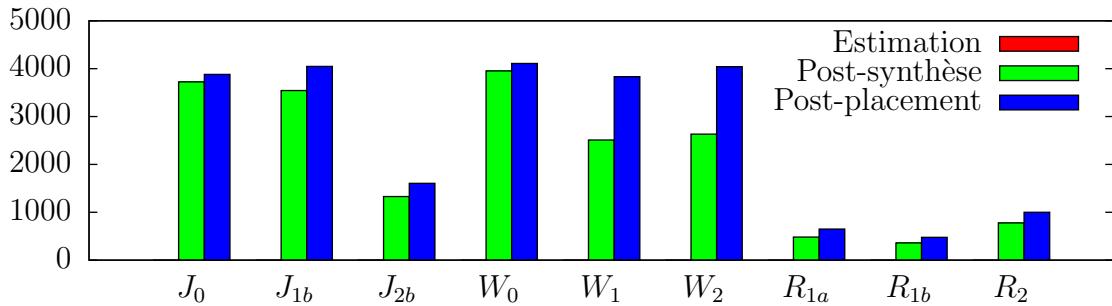

| 9.5.1                  | Estimation de la quantité de ressources matérielles | 174 |

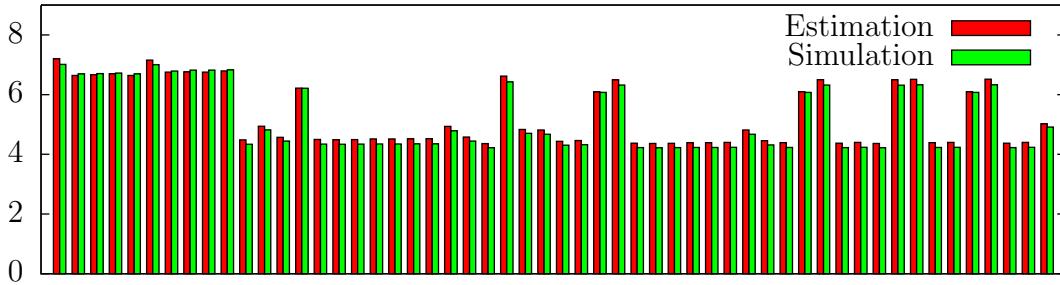

| 9.5.2                  | Estimation du temps d'exécution                     | 177 |

| 9.6                    | Exploration architecturale                          | 179 |

| 9.6.1                  | Espace de recherche et analyse combinatoire         | 183 |

| 9.6.2                  | Comparaisons des algorithmes de recherche locale    | 184 |

| 9.6.3                  | Caractéristiques des solutions obtenues             | 189 |

| CHAPITRE 10 CONCLUSION |                                                     | 191 |

| 10.1                   | Synthèse des travaux                                | 191 |

| 10.2                   | Limites et améliorations futures                    | 192 |

| 10.2.1                 | Équivalence des ordonnancements                     | 192 |

| 10.2.2                 | Consommation de puissance et d'énergie              | 193 |

| 10.2.3                 | Temps de caractérisation des modules logiciels      | 195 |

| 10.2.4                 | Généralisation de l'exploration architecturale      | 196 |

| 10.2.5                 | Performance du logiciel embarqué                    | 197 |

| 10.2.6                 | Évaluation industrielle de la méthodologie          | 198 |

| RÉFÉRENCES             |                                                     | 200 |

| ANNEXES                |                                                     | 219 |

## LISTE DES TABLEAUX

|              |                                                                                                                                                                                |     |

|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Tableau 3.1  | Paramètres des fonctions de communication de SPACE . . . . .                                                                                                                   | 56  |

| Tableau 3.2  | Conversion des types de données SystemC pour un logiciel embarqué .                                                                                                            | 61  |

| Tableau 4.1  | Définition des canaux Kahn, POLL, $N$ -BREG et $N$ -REG . . . . .                                                                                                              | 68  |

| Tableau 4.2  | Conditions à respecter pour qu'un canal se comporte comme un canal Kahn . . . . .                                                                                              | 71  |

| Tableau 5.1  | Conversion, pour différents types de données, de la valeur de 32 bits 0x0A0B0C0D d'une représentation <i>big endian</i> vers une représentation <i>little endian</i> . . . . . | 81  |

| Tableau 7.1  | Définition des attributs des opérations de communication . . . . .                                                                                                             | 113 |

| Tableau 7.2  | Attributs des enregistrements de communication de bout en bout utilisés pour l'extraction du CPG . . . . .                                                                     | 113 |

| Tableau 7.3  | Fonctions de caractérisation du temps d'exécution des segments de programme d'un module $m$ . . . . .                                                                          | 116 |

| Tableau 7.4  | Paramètres de performance pour différents périphériques avec interface OPB . . . . .                                                                                           | 120 |

| Tableau 7.5  | Paramètres de performance du bus OPB et du pont OPB-OPB . . . .                                                                                                                | 122 |

| Tableau 7.6  | Paramètres de performance du RTOS $\mu$ COS II et de l'API logicielle .                                                                                                        | 123 |

| Tableau 7.7  | Paramètres des composants RTL d'un FPGA Virtex ciblé par SPACE                                                                                                                 | 132 |

| Tableau 8.1  | Définitions des métriques appliquées aux modules . . . . .                                                                                                                     | 145 |

| Tableau 8.2  | Définitions des attributs pour la recherche tabou . . . . .                                                                                                                    | 155 |

| Tableau 9.1  | Ressources matérielles utilisées par les modules du décodeur JPEG .                                                                                                            | 164 |

| Tableau 9.2  | Ressources matérielles utilisées par les modules du rover . . . . .                                                                                                            | 165 |

| Tableau 9.3  | Ressources matérielles utilisées par les modules du codec WiMAX .                                                                                                              | 166 |

| Tableau 9.4  | Simulation à différents niveaux du système de guidage du rover . .                                                                                                             | 167 |

| Tableau 9.5  | Simulation à différents niveaux du décodeur JPEG . . . . .                                                                                                                     | 167 |

| Tableau 9.6  | Simulation à différents niveaux de l'encodeur/décodeur WiMAX . .                                                                                                               | 168 |

| Tableau 9.7  | Ressources matérielles et latence pour l'architecture de la figure 9.5 .                                                                                                       | 170 |

| Tableau 9.8  | Simulation avec et sans profilage des architectures du rover . . . .                                                                                                           | 172 |

| Tableau 9.9  | Simulation avec et sans profilage des architectures du décodeur JPEG                                                                                                           | 172 |

| Tableau 9.10 | Simulation avec et sans profilage des architectures du codec WiMAX .                                                                                                           | 172 |

| Tableau 9.11 | WCT nécessaire à l'estimation et à la mesure par simulation du temps d'exécution des architectures du système de guidage du rover . . . .                                      | 180 |

|              |                                                                                                                                           |     |

|--------------|-------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Tableau 9.12 | WCT nécessaire à l'estimation et à la mesure par simulation du temps d'exécution des architectures du décodeur JPEG . . . . .             | 180 |

| Tableau 9.13 | WCT nécessaire à l'estimation et à la mesure par simulation du temps d'exécution des architectures de l'encodeur/décodeur WiMAX . . . . . | 180 |

| Tableau 9.14 | FPGA Virtex ciblés par les tests d'exploration architecturale . . . . .                                                                   | 182 |

| Tableau 9.15 | Plate-forme cibles et contraintes $T_{MAX}$ pour le décodeur JPEG avec détection de peau . . . . .                                        | 182 |

| Tableau 9.16 | Plate-forme cibles et contraintes $T_{MAX}$ pour l'encodeur/décodeur WiMAX . . . . .                                                      | 182 |

| Tableau 9.17 | Disponibilité des bascules et LUTs et contraintes $T_{MAX}$ pour le système de guidage du rover . . . . .                                 | 183 |

| Tableau C.1  | Bornes inférieures de $E_2(n, d)$ pour $0 \leq n \leq 10$ et $0 \leq d \leq 4$ . . . . .                                                  | 244 |

## LISTE DES FIGURES

|            |                                                                                                                                |     |

|------------|--------------------------------------------------------------------------------------------------------------------------------|-----|

| Figure 2.1 | Exemple de graphe orienté $G = (V, A)$ représentant un réseau de processus                                                     | 7   |

| Figure 3.1 | Aperçu général de la méthodologie proposée                                                                                     | 53  |

| Figure 3.2 | Évolution d'une application à différentes étapes de la méthodologie                                                            | 54  |

| Figure 3.3 | Structure d'un logiciel embarqué synthétisé pour un processeur dans SPACE                                                      | 60  |

| Figure 4.1 | Exemple de réseau de processus                                                                                                 | 66  |

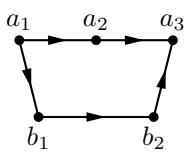

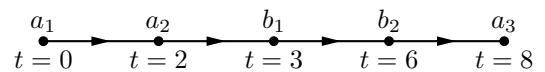

| Figure 4.2 | Évènements des processus $a$ et $b$ selon une relation de précédence                                                           | 69  |

| Figure 4.3 | Évènements des processus $a$ et $b$ selon un ordonnancement $t$                                                                | 69  |

| Figure 4.4 | Représentation d'un canal RTPN comme un processus KPN paramétré par des séquences de bits de lecture et d'écriture             | 74  |

| Figure 4.5 | KPN paramétré équivalent au RTPN de la figure 4.1                                                                              | 74  |

| Figure 4.6 | Producteur et consommateur communiquant via une mémoire partagée                                                               | 76  |

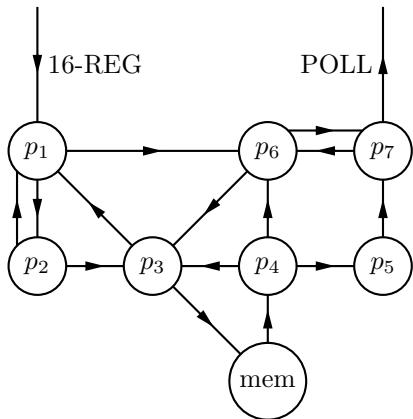

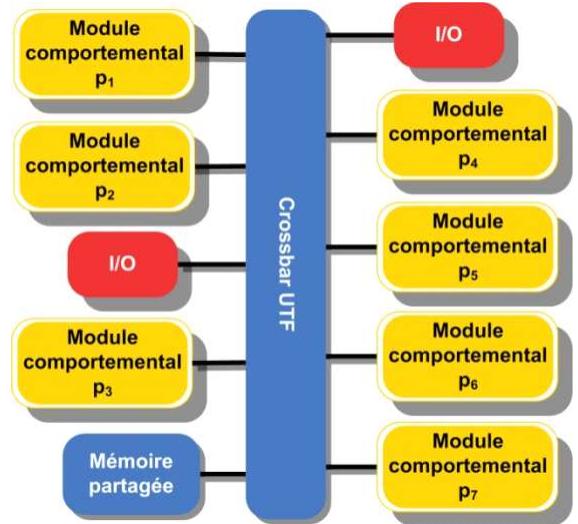

| Figure 4.7 | Modélisation d'un système embarqué par un RTPN                                                                                 | 78  |

| Figure 4.8 | Spécification exécutable parallèle d'un système embarqué avec SPACE                                                            | 78  |

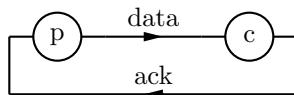

| Figure 4.9 | Modélisation d'une écriture rendez-vous avec un canal d'acquittement                                                           | 78  |

| Figure 5.1 | Flot de sérialisation standardisée                                                                                             | 82  |

| Figure 5.2 | Flot automatisé pour le raffinement des communications et la synthèse du matériel                                              | 83  |

| Figure 5.3 | Exemple d'un fil d'exécution d'un module comportemental                                                                        | 84  |

| Figure 5.4 | Un exemple de structure de données à transférer                                                                                | 86  |

| Figure 5.5 | Un exemple d'une sérialisation standardisée au niveau RTL                                                                      | 86  |

| Figure 5.6 | Un exemple d'une désérialisation standardisée au niveau RTL                                                                    | 87  |

| Figure 6.1 | Fonctionnement général du profileur d'ISS                                                                                      | 92  |

| Figure 6.2 | Implémentation générique du profileur d'ISS avec client/serveur GDB                                                            | 95  |

| Figure 6.3 | Le profileur d'ISS SPACE surveille la mémoire et les registres pour détecter les communications et les changements de contexte | 97  |

| Figure 6.4 | Architecture générale du co-profilage                                                                                          | 101 |

| Figure 6.5 | Instrumentation de la plate-forme SPACE. Les lignes pointillées représentent les accès faits par le profilage                  | 101 |

| Figure 6.6 | Fichier de métriques de performance produit par le profilage au niveau système pour le module Y2R de l'exemple du JPEG         | 104 |

| Figure 6.7 | Charge des processeurs pour l'exemple du JPEG                                                                                  | 105 |

|             |                                                                                                                  |     |

|-------------|------------------------------------------------------------------------------------------------------------------|-----|

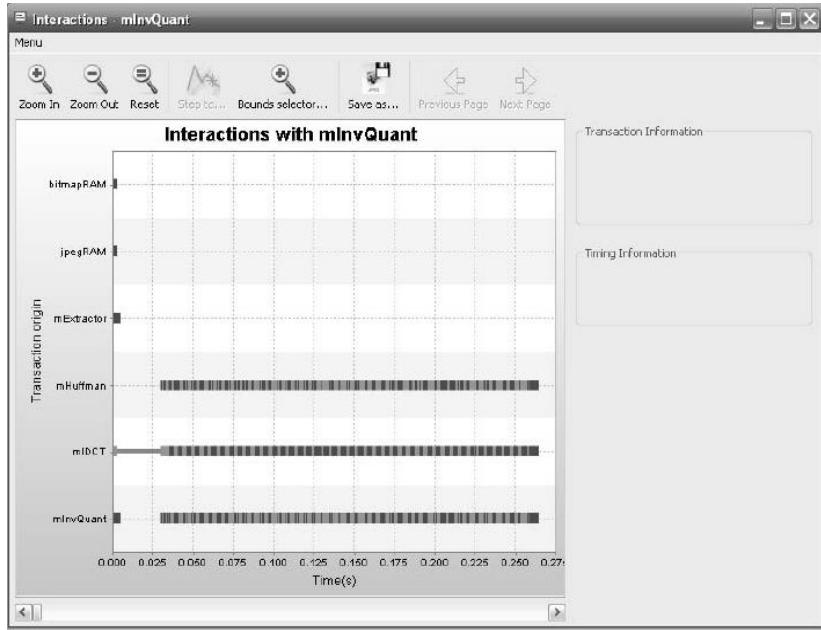

| Figure 6.8  | Diagramme de Gantt des opérations de calcul et de communication du quantificateur inverse dans l'exemple du JPEG | 106 |

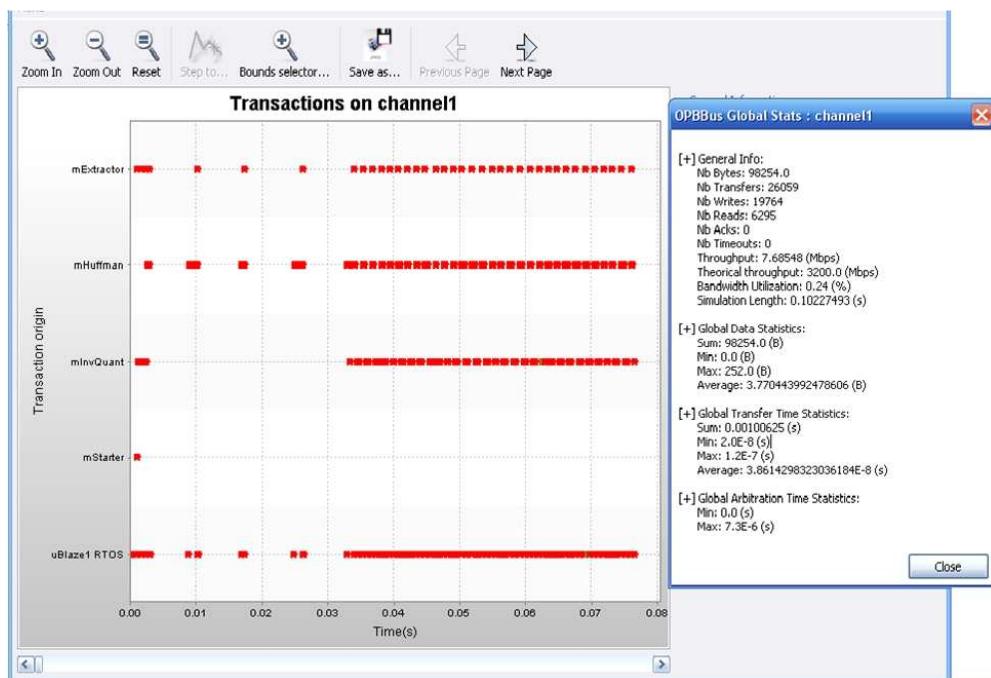

| Figure 6.9  | Diagramme de Gantt des transferts sur le bus et métriques sur la charge du bus pour l'exemple du JPEG            | 107 |

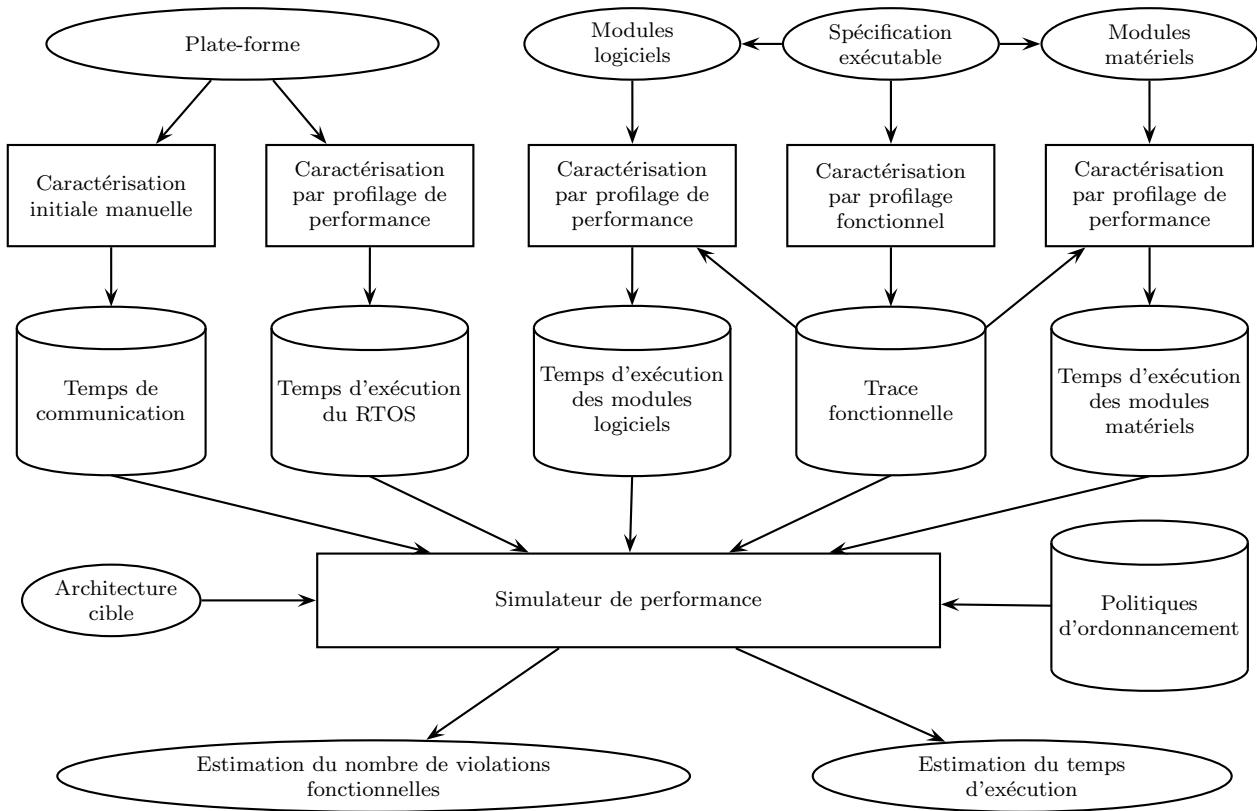

| Figure 7.1  | Méthode de caractérisation et d'estimation de la performance et du nombre de violations fonctionnelles           | 111 |

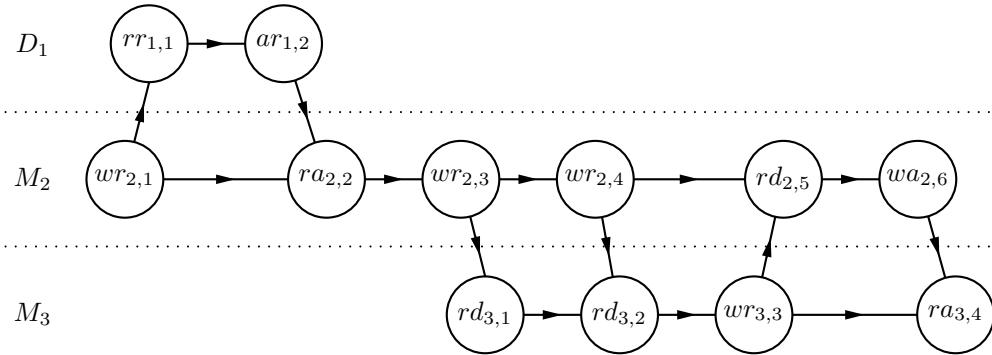

| Figure 7.2  | Opérations du module $M_2$                                                                                       | 114 |

| Figure 7.3  | Opérations du module $M_3$                                                                                       | 114 |

| Figure 7.4  | CPG des communications du périphérique $P_1$ et des modules $M_2$ et $M_3$                                       | 114 |

| Figure 7.5  | Méthode de caractérisation et d'estimation de la quantité de ressources matérielles                              | 129 |

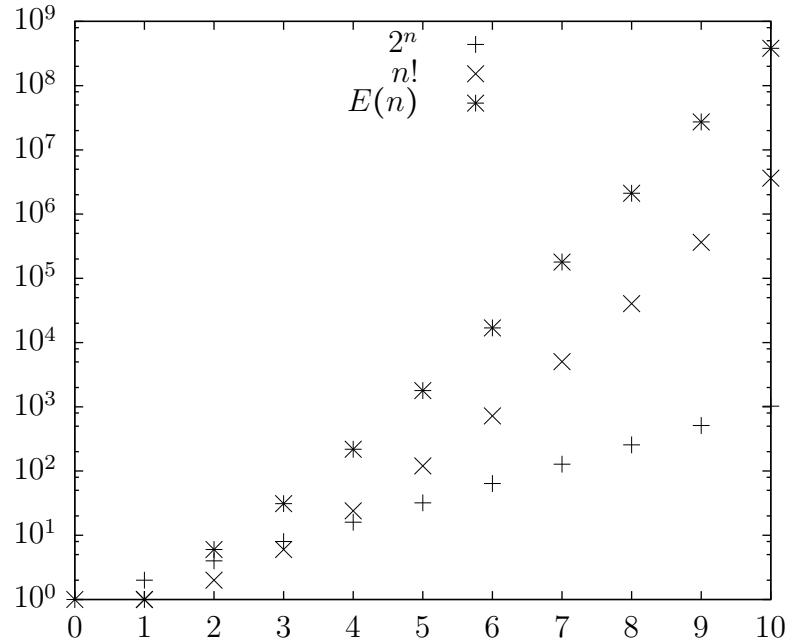

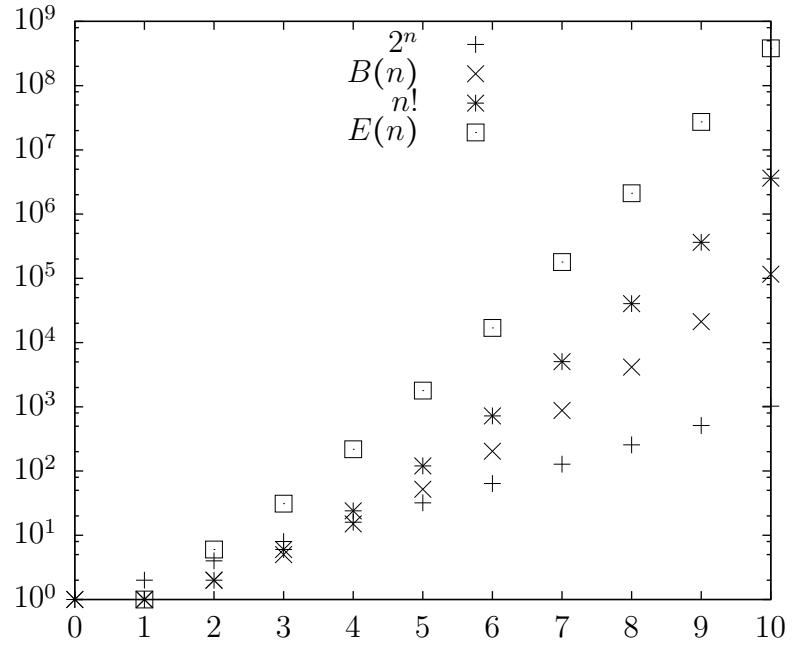

| Figure 8.1  | Comparaison de la croissance du nombre $E(n)$ d'architectures pour $n$ modules avec celle de $2^n$ et $n!$       | 143 |

| Figure 8.2  | Fonctionnement général de l'algorithme de parcours en profondeur                                                 | 143 |

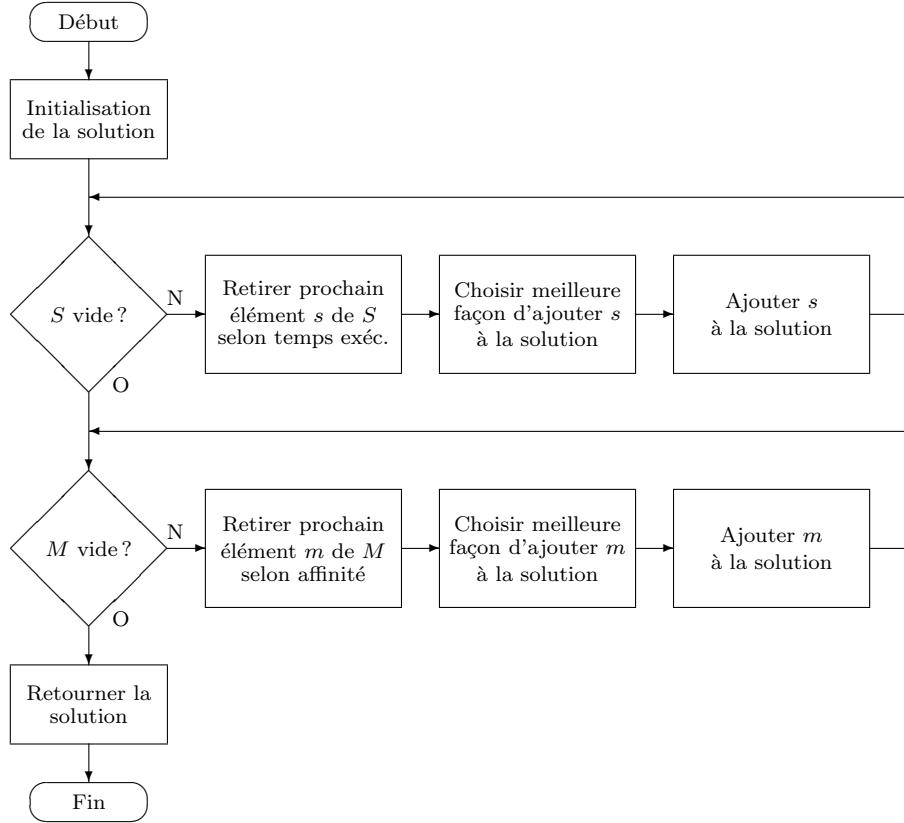

| Figure 8.3  | Fonctionnement général de l'algorithme glouton                                                                   | 146 |

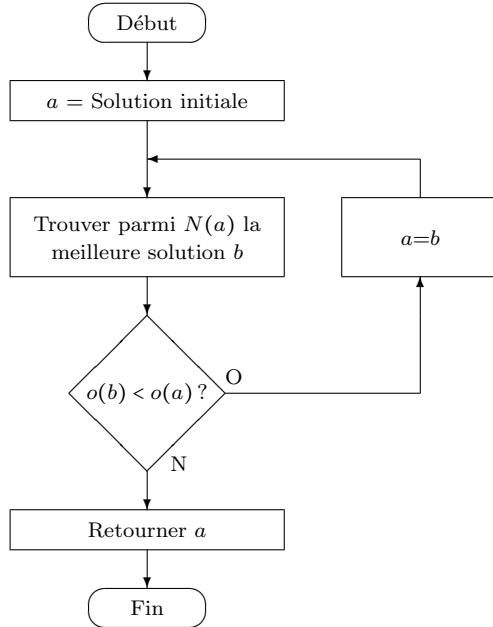

| Figure 8.4  | Fonctionnement général de l'algorithme de descente                                                               | 149 |

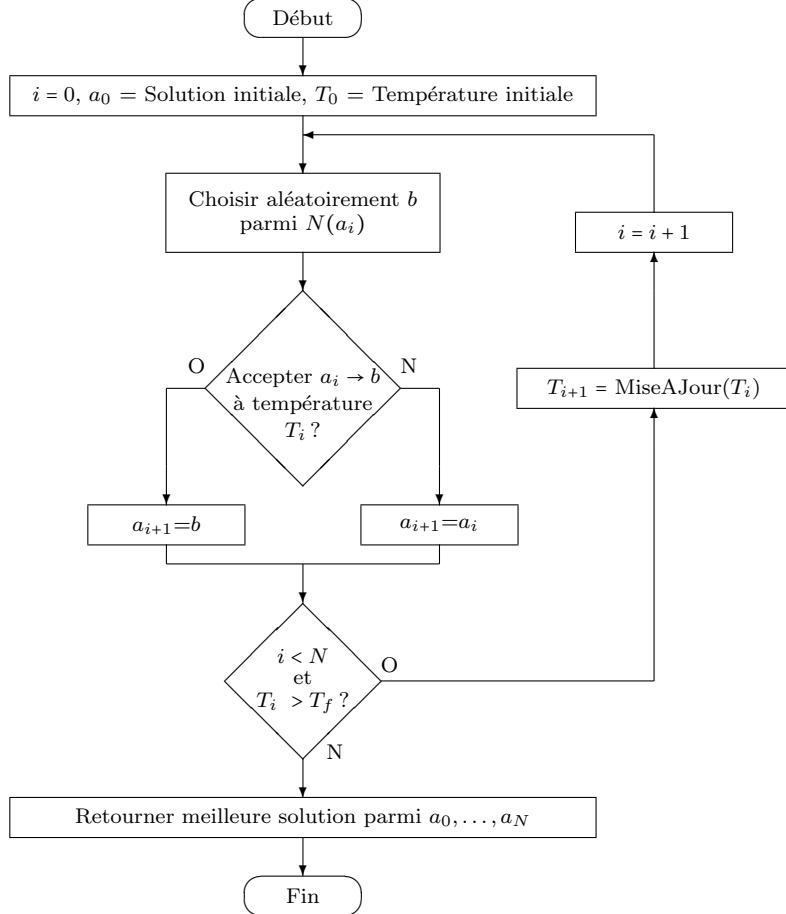

| Figure 8.5  | Fonctionnement général de l'algorithme de recuit simulé                                                          | 151 |

| Figure 8.6  | Fonctionnement général de l'algorithme de recherche tabou                                                        | 153 |

| Figure 8.7  | Fonctionnement général de l'algorithme de recherche tabou réactive                                               | 156 |

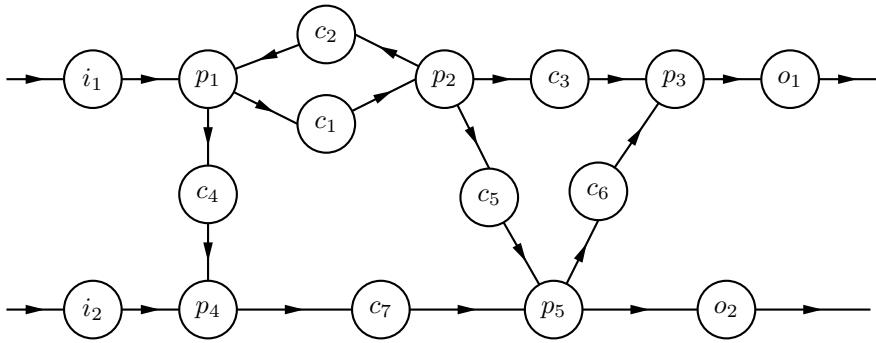

| Figure 9.1  | Schéma de la spécification exécutable du système de guidage du rover                                             | 159 |

| Figure 9.2  | Schéma des modules et périphériques du décodeur JPEG                                                             | 161 |

| Figure 9.3  | Schéma des modules de l'encodeur/décodeur WiMAX                                                                  | 162 |

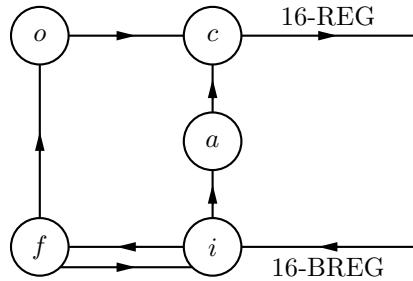

| Figure 9.4  | Modèle RTPN du rover                                                                                             | 163 |

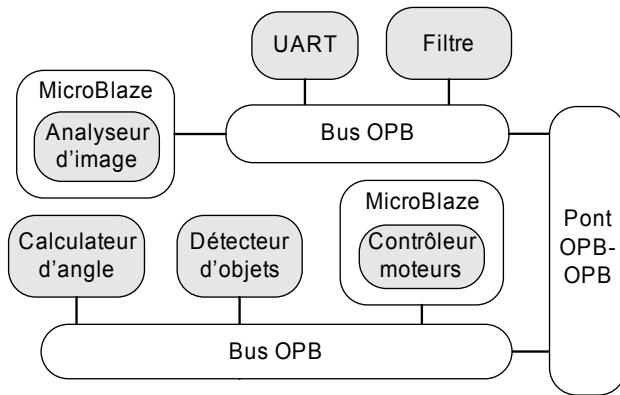

| Figure 9.5  | L'architecture cible pour le système de guidage                                                                  | 169 |

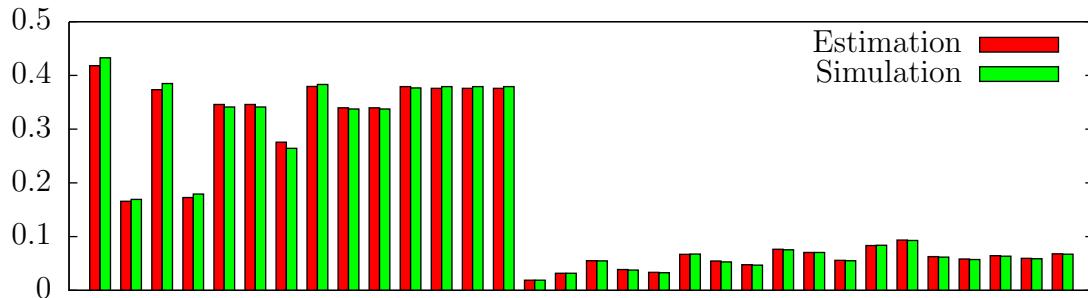

| Figure 9.6  | Comparaison du nombre estimé et mesuré de bascules                                                               | 176 |

| Figure 9.7  | Comparaison du nombre estimé et mesuré de LUTs                                                                   | 176 |

| Figure 9.8  | Comparaison du nombre estimé et mesuré de mémoires BRAMs                                                         | 176 |

| Figure 9.9  | Comparaison du nombre estimé et mesuré de multiplicateurs                                                        | 177 |

| Figure 9.10 | Comparaison du temps pris par l'estimation, la synthèse logique et le placement                                  | 177 |

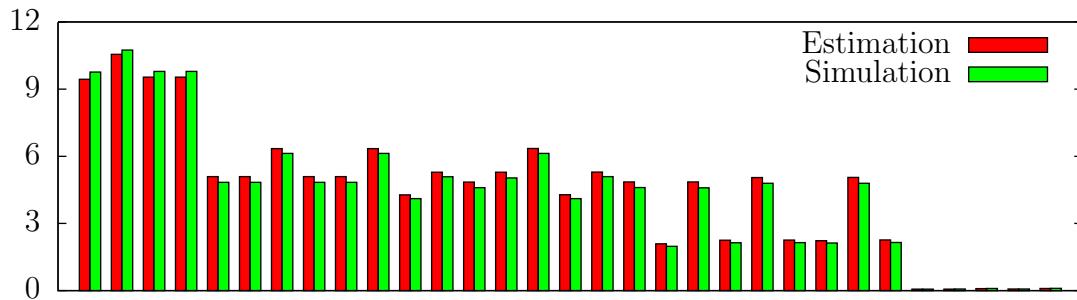

| Figure 9.11 | Comparaison du temps d'exécution estimé et simulé pour 54 architectures du système de guidage du rover           | 179 |

| Figure 9.12 | Comparaison du temps d'exécution estimé et simulé pour 31 architectures du décodeur JPEG avec détection de peau  | 179 |

| Figure 9.13 | Comparaison du temps d'exécution estimé et simulé pour 32 architectures de l'encodeur/décodeur WiMAX             | 180 |

|             |                                                                                                                                                                                                                                        |     |

|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

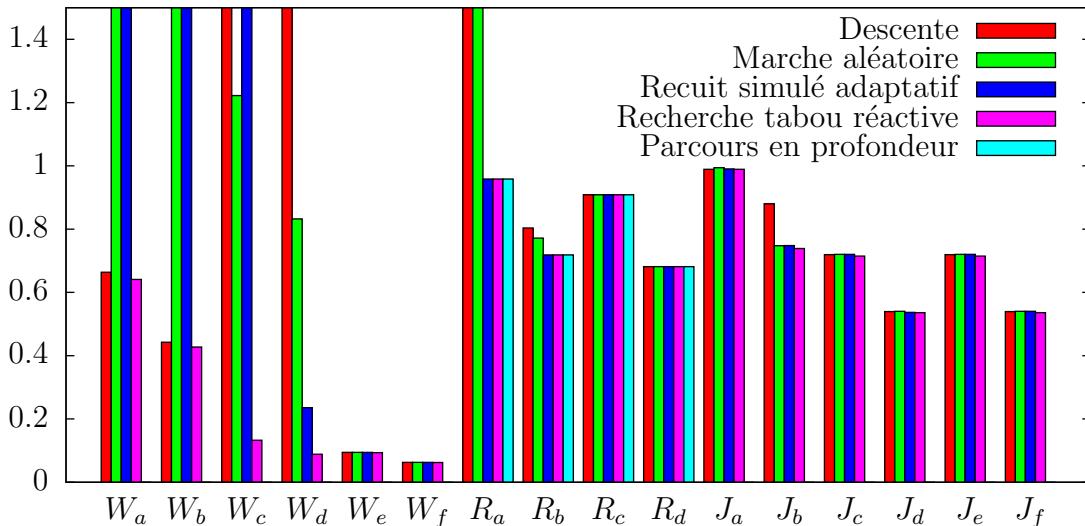

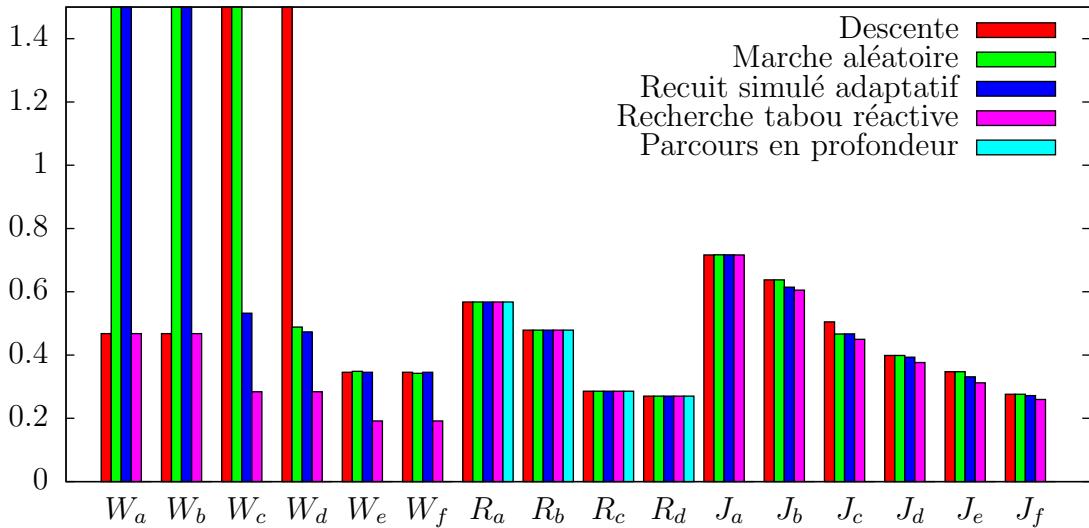

| Figure 9.14 | Comparaison des valeurs objectives obtenues par les algorithmes de recherche locale pour la maximisation de la performance pour différentes configurations . . . . .                                                                   | 185 |

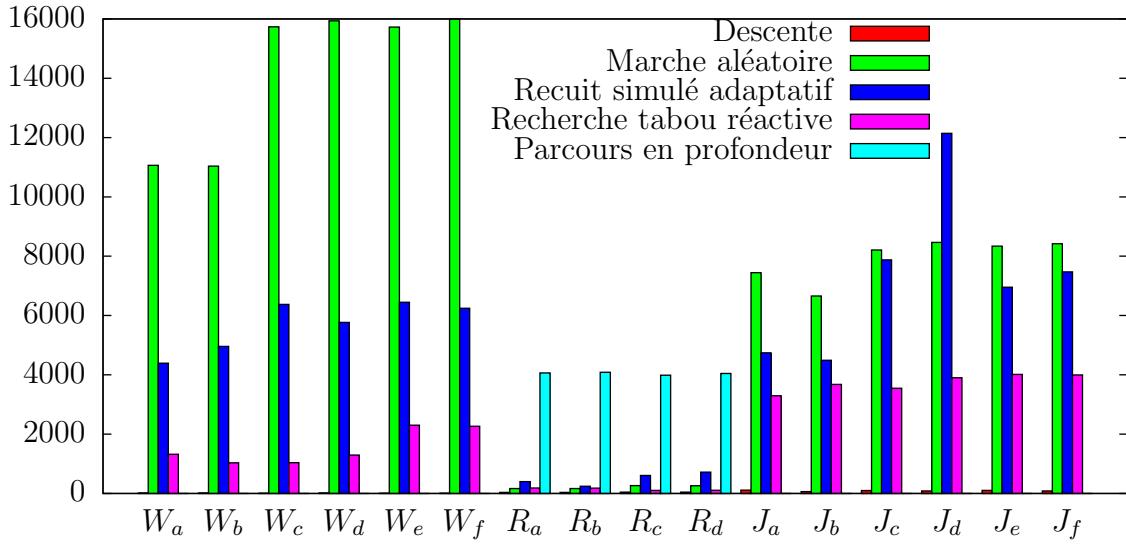

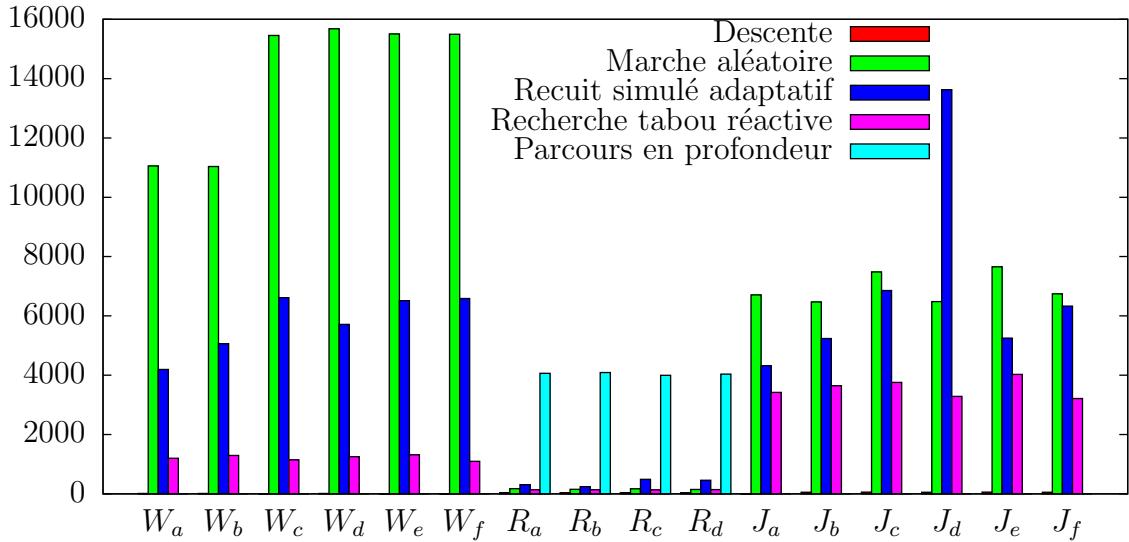

| Figure 9.15 | Comparaison du WCT (en secondes) pour les algorithmes de recherche locale pour la maximisation de la performance pour différentes configurations . . . . .                                                                             | 186 |

| Figure 9.16 | Comparaison des valeurs objectives obtenues par les algorithmes de recherche locale pour la minimisation de la quantité de ressources matérielles pour différentes configurations . . . . .                                            | 186 |

| Figure 9.17 | Comparaison du WCT (en secondes) pour les algorithmes de recherche locale pour la minimisation de la quantité de ressources matérielles pour différentes configurations . . . . .                                                      | 187 |

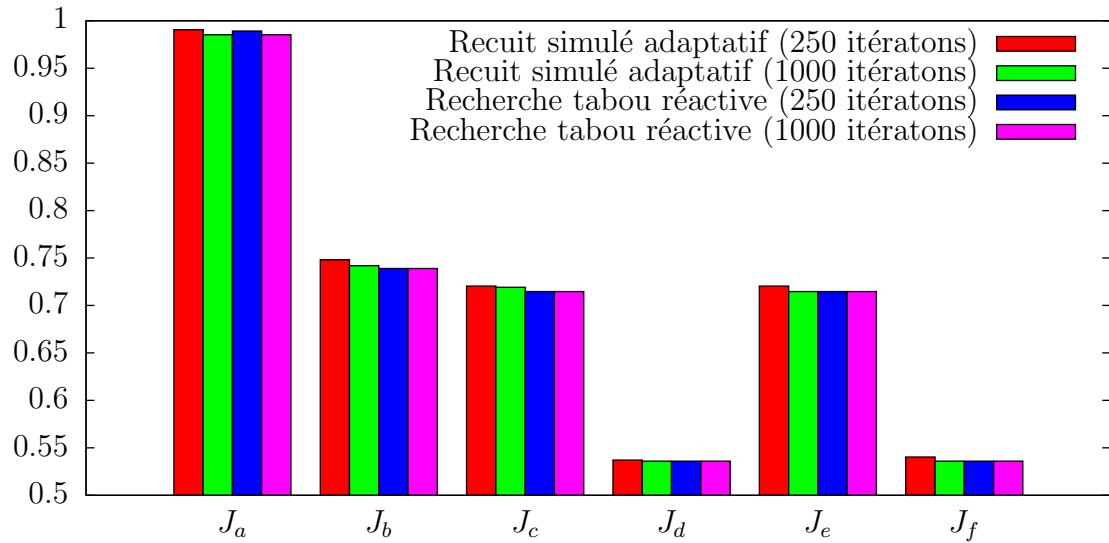

| Figure 9.18 | Comparaison des valeurs objectives selon le nombre d'itérations pour les algorithmes de recherche locale pour la maximisation de la performance du décodeur JPEG sur différentes plates-formes cibles . . . . .                        | 188 |

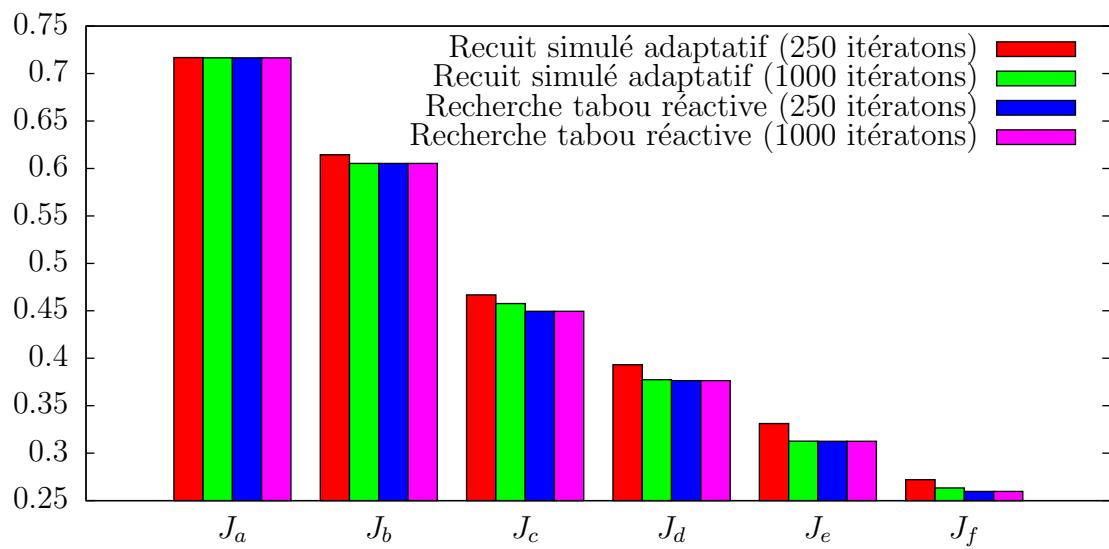

| Figure 9.19 | Comparaison des valeurs objectives selon le nombre d'itérations pour les algorithmes de recherche locale pour la minimisation de la quantité de ressources matérielles du décodeur JPEG sur différentes plates-formes cibles . . . . . | 188 |

| Figure 10.1 | Un processus RTPN qui utilise une lecture non-bloquante comme une lecture bloquante . . . . .                                                                                                                                          | 194 |

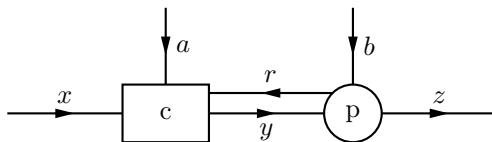

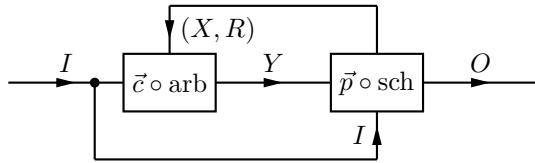

| Figure A.1  | Un processus $p$ avec un canal $c$ d'entrée, un signal $a$ d'arbitrage, un signal $b$ d'ordonnancement, un signal $r$ de requête et des signaux $x, y$ et $z$ de données . . . . .                                                     | 221 |

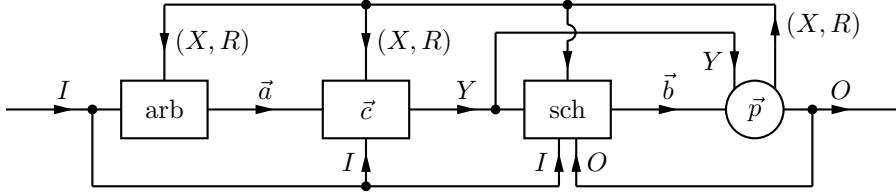

| Figure A.2  | Modèle général d'un RTPN en tant que DEPN . . . . .                                                                                                                                                                                    | 222 |

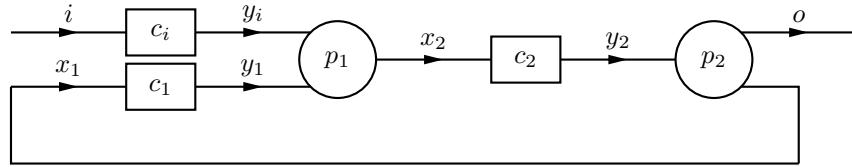

| Figure A.3  | Modèle d'un DEPN non déterministe avec $x_1 = y_1 = x_2 = y_2 = o$ . . . . .                                                                                                                                                           | 223 |

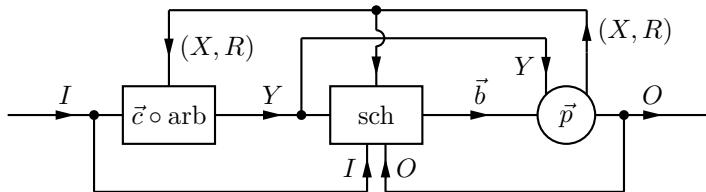

| Figure A.4  | Modèle du RTPN après composition de l'arbitre avec les canaux . . . . .                                                                                                                                                                | 223 |

| Figure A.5  | Modèle du RTPN après composition de l'ordonnanceur avec les processus . . . . .                                                                                                                                                        | 224 |

| Figure C.1  | Comparaison de la croissance de $E(n)$ avec $2^n$ , $B(n)$ et $n!$ . . . . .                                                                                                                                                           | 236 |

| Figure C.2  | Définition combinatoire de $f_1$ dans Maple . . . . .                                                                                                                                                                                  | 237 |

**LISTE DES ANNEXES**

|          |                                                                          |     |

|----------|--------------------------------------------------------------------------|-----|

| Annexe A | TRANSFORMATION D'UN RTPN EN DEPN . . . . .                               | 219 |

| Annexe B | PROCÉDURE DE CARACTÉRISATION DU RTOS ET DE L'API<br>LOGICIELLE . . . . . | 226 |

| Annexe C | COMPLEXITÉ COMBINATOIRE DE L'EXPLORATION ARCHI-<br>TECTURALE . . . . .   | 231 |

| Annexe D | COMPLEXITÉ ALGORITHMIQUE DE L'EXPLORATION ARCHI-<br>TECTURALE . . . . .  | 245 |

| Annexe E | GÉNÉRATION ALÉATOIRE D'UNE ARCHITECTURE . . . . .                        | 247 |

| Annexe F | DÉTAILS DES ÉTUDES DE CAS . . . . .                                      | 249 |

## LISTE DES SIGLES ET ABRÉVIATIONS

|       |                                                    |

|-------|----------------------------------------------------|

| ABI   | Application Binary Interface                       |

| ALU   | Arithmetic and Logic Unit                          |

| API   | Application Programming Interface                  |

| ASCII | American Standard Code for Information Interchange |

| ASIC  | Application-Specific Integrated Circuit            |

| AST   | Abstract Syntax Tree                               |

| BCA   | Bus Cycle-Accurate                                 |

| BDF   | Boolean Data Flow                                  |

| BRAM  | Block Random Access Memory                         |

| CFG   | Control Flow Graph                                 |

| CPG   | Communication Precedence Graph                     |

| CSDF  | Cyclo-Static Data Flow                             |

| DAG   | Directed Acyclic Graph                             |

| DCT   | Discrete Cosine Transform                          |

| DEPN  | Discrete Event Process Networks                    |

| DSP   | Digital Signal Processing                          |

| EDK   | Embedded Development Kit                           |

| FIFO  | First In, First Out                                |

| FPGA  | Field Programmable Gate Array                      |

| FSL   | Fast Simplex Link                                  |

| GDB   | GNU Debugger                                       |

| GUI   | Graphical User Interface                           |

| HAL   | Hardware Abstraction Layer                         |

| HDL   | Hardware Description Language                      |

| ID    | Identifier                                         |

| IDCT  | Inverse Discrete Cosine Transform                  |

| IEEE  | Institute of Electrical and Electronics Engineers  |

| ILP   | Integer Linear Programming                         |

| IP    | Intellectual Property                              |

| IR    | Intermediate Representation                        |

| ISR   | Interrupt Service Routine                          |

| ISS   | Instruction Set Simulator                          |

| JPEG  | Joint Photographic Experts Group                   |

|       |                                                 |

|-------|-------------------------------------------------|

| KPN   | Kahn Process Network                            |

| LFSR  | Linear Feedback Shift Register                  |

| LUT   | Look-up Table                                   |

| NP    | Nondeterministic Polynomial                     |

| OPB   | On-chip Peripheral Bus                          |

| PC    | Program Counter                                 |

| PLB   | Processor Local Bus                             |

| PN    | Process Network                                 |

| PTAS  | Polynomial-Time Approximation Scheme            |

| RAM   | Random Access Memory                            |

| RGB   | Red Green Blue                                  |

| RLE   | Run-Length Encoding                             |

| RPN   | Reactive Process Networks                       |

| RTL   | Register Transfer Level                         |

| RTOS  | Real-Time Operating System                      |

| RTPN  | Real-Time Process Network                       |

| SDF   | Synchronous Data Flow                           |

| SDRAM | Synchronous Dynamic Random Access Memory        |

| SoC   | System-on-Chip                                  |

| SRAM  | Static Random Access Memory                     |

| SW    | Software                                        |

| TIG   | Task Interaction Graph                          |

| TLM   | Transaction-Level Modeling                      |

| TPG   | Task Precedence Graph                           |

| UART  | Universal Asynchronous Receiver-Transmitter     |

| UML   | Unified Modeling Language                       |

| VHDL  | VHSIC Hardware Description Language             |

| VHSIC | Very High Speed Integrated Circuits             |

| WCET  | Worst-Case Execution Time                       |

| WCT   | Wall Clock Time                                 |

| WiMAX | Worldwide Interoperability for Microwave Access |

## CHAPITRE 1

### INTRODUCTION

#### 1.1 Mise en contexte et problématique

La complexité et les requis de performance des systèmes embarqués augmentent constamment. Pour répondre à ces requis, les systèmes embarqués sont maintenant des systèmes sur puce (SoC), qui peuvent intégrer plusieurs processeurs, bus, périphériques et accélérateurs matériels sur une seule et même puce, le tout étant relié par une topologie de communications. Cette évolution a notamment pour conséquence d'augmenter grandement l'importance du développement logiciel dans la conception des systèmes embarqués. Ainsi, il est estimé que le développement des logiciels embarqués compte pour près de 60% du coût de développement des systèmes embarqués utilisant une technologie 90nm (International Business Strategies Inc., 2004). De plus, la grande majorité des concepteurs de systèmes embarqués rapportent que leur équipe de travail consacre autant sinon plus d'argent, de temps et de ressources humaines aux aspects logiciels de leurs projets qu'à leurs aspects matériels (CMP Media LLC, 2006).

Les méthodologies au niveau transfert de registres (RTL) présentement utilisées par l'industrie pour la conception des systèmes embarqués n'arrivent pas à suivre cette évolution vers des architectures plus complexes et ayant un plus grand contenu logiciel. Ainsi, la grande majorité des projets de conception de systèmes embarqués respectent moins de 90% de leurs requis de fonctionnalité et de performance alors qu'environ 30% des projets respectent moins de 50% de ces requis (Krasner, 2003). De plus, la majorité des projets de conception de systèmes embarqués sont soit annulés, soit livrés avec un retard moyen de quatre mois (Krasner, 2003; CMP Media LLC, 2006). Étant donné que les systèmes embarqués sont fréquemment des produits avec une courte durée de vie économique, de tels retards sont lourds de conséquences et impliquent une réduction importante des ventes du produit à la fois par une réduction de la période de vente et par une part de marché réduite (Rowe, 2010). L'annonce d'un retard dans l'introduction d'un nouveau produit a donc un impact négatif significatif sur la valeur marchande de la compagnie qui développe ce produit (Hendricks et Singhal, 1997).

L'activité technique qui cause le plus souvent des retards dans les projets de systèmes embarqués est la conception et la spécification de l'architecture du système. Ainsi, dans près de la moitié des cas, cette activité est la cause des retards dans le développement du

logiciel embarqué (Volckmann *et al.*, 2008). La conception et la spécification de l'architecture comptent pour 25% du coût associé au développement du matériel d'un système utilisant une technologie 90nm et cette proportion suit une tendance à la hausse (International Business Strategies Inc., 2004). La réduction du temps de mise en marché des systèmes embarqués nécessite donc des méthodes qui permettent de faciliter la conception et la spécification de l'architecture du système et d'accélérer le développement du logiciel embarqué pour cette architecture.

## 1.2 Objectif

Afin de s'attaquer à ces problèmes, il a été proposé de hausser le niveau d'abstraction de la conception des systèmes embarqués à l'aide de méthodologies de niveau système (Bailey *et al.*, 2007). Ainsi, ces méthodologies visent une conception de haut niveau qui sépare la spécification de la fonctionnalité et de l'architecture, et qui sépare également la réalisation des calculs et des communications (Keutzer *et al.*, 2000). Grâce à une plate-forme virtuelle qui permet d'assigner la fonctionnalité de l'application à un modèle fonctionnel d'une architecture logicielle/matérielle, il est possible de simuler cette implémentation à haut niveau et d'avoir un aperçu de son comportement et de sa performance. Cela comporte deux avantages. Premièrement, il devient alors possible de débuter le développement du logiciel avant que l'architecture matérielle ait été fixée, ce qui réduit les risques de dépassement d'échéancier. Deuxièmement, il est possible de faire une exploration architecturale de l'application tôt dans le processus de développement, c'est-à-dire de tester plusieurs architectures possibles pour l'application et de sélectionner la meilleure à la lumière des résultats obtenus. Cela évite de développer une implémentation complète sur une architecture qui se révèle finalement inadéquate (Bailey *et al.*, 2007).

Il est possible de réaliser le plein potentiel des méthodologies de niveau système en définissant une méthodologie intégrée de conception, d'exploration architecturale et de synthèse des systèmes embarqués. Une telle méthodologie vise autant que possible à hausser le niveau d'abstraction de la conception tout en automatisant le raffinement vers une implémentation finale. Elle doit donc inclure les éléments suivants :

1. Un modèle de calcul formel qui permet de définir la fonctionnalité de l'application et de s'assurer que sa fonctionnalité est préservée lors de son raffinement vers une implémentation.

2. Une synthèse automatisée, pour une architecture donnée, des modules de l'application vers un logiciel embarqué et des accélérateurs matériels de même qu'un raffinement automatisé des communications entre modules vers des protocoles et des liens de communications concrets. Cela permet d'éviter la duplication des efforts de programmation entre le niveau

système et le niveau de l'implémentation, qui serait autrement une barrière significative à l'adoption des méthodologies de niveau système.

3. Un profilage au niveau système qui inclut les modules de l'application, le système d'exploitation temps-réel (RTOS), les processeurs et les bus. En effet, le manque de visibilité au niveau de l'ensemble du système a été identifié comme une cause majeure des retards dans les projets de systèmes embarqués (Krasner, 2003).

4. Une méthode d'estimation rapide du temps d'exécution et des ressources matérielles, qui permet d'évaluer rapidement différentes architectures sans avoir à réaliser à chaque fois une simulation précise au cycle près ou une synthèse logique. Une telle méthode demande généralement une caractérisation de l'application et celle-ci doit être automatisée afin d'accélérer le développement et de pouvoir rapidement re-caractériser l'application si elle évolue au cours du projet.

5. Une méthode d'exploration architecturale capable d'évaluer automatiquement un grand nombre d'architectures possibles et de sélectionner celle qui est la meilleure selon des critères de performance et de coût matériel.

L'objectif de cette thèse est de présenter, à l'aide de la technologie Space Codesign™ et de sa plate-forme virtuelle SPACE (Filion *et al.*, 2007; Bois *et al.*, 2010), la mise en oeuvre de ces différents éléments de même que leur intégration en une méthodologie de conception, d'exploration architecturale et de synthèse des systèmes embarqués.

### 1.3 Contributions

Cette thèse effectue les contributions suivantes à l'état de l'art :

1. Une nouvelle méthodologie intégrée de conception, d'exploration architecturale et de synthèse des systèmes embarqués qui est basée sur les éléments ci-dessous.

2. Un nouveau modèle de calcul, les réseaux de processus temps-réel (RTPN), qui est une extension des réseaux de processus Kahn. Cette extension permet de modéliser des aspects importants du traitement temps-réel tels que la scrutation, les senseurs échantillonnés, les périphériques d'entrée/sortie et les contraintes temps-réel. La sémantique dénotationnelle des RTPN est définie afin de vérifier si le raffinement d'une spécification exécutable SystemC vers une implémentation concrète est fonctionnellement correct. Ainsi, on montre sous quelles conditions deux ordonnancements d'un RTPN sont fonctionnellement équivalents et comment un tel ordonnancement peut être caractérisé par un ensemble de séquences de bits.

3. Une méthode qui automatise le raffinement des communications transactionnelles vers des protocoles précis au cycle et à la broche près ainsi que la génération des blocs matériels pour les modules de l'application. Ce raffinement inclut une sérialisation standardisée des

types de données abstraits vers une représentation précise au bit près qui est compatible avec les implémentations logicielles et matérielles des modules. Cette méthode permet, conjointement avec une méthode de génération de code logiciel embarqué incluant un RTOS, de générer, pour une architecture donnée, une implémentation de l'application qui peut être simulée avec la plate-forme virtuelle ou synthétisée et exécutée sur la cible finale.

4. Une nouvelle méthode de profilage non-intrusif d'un logiciel embarqué qui permet de profiler le temps à l'entrée et à la sortie de chaque appel de fonction de même que la valeur des arguments passés en paramètre et de la valeur de retour. Ce profilage du logiciel est appliqué à une nouvelle méthode de profilage au niveau système qui permet d'extraire non-intrusivement des données sur la performance des modules logiciels et matériels, des processeurs, du RTOS, des bus et des mémoires à partir d'une simulation du système.

5. Une nouvelle méthode automatisée qui permet de caractériser, par des simulations profilées, à la fois la fonctionnalité de l'application et les implémentations logicielles et matérielles de ses modules. Les périphériques et les bus de la plate-forme virtuelle ont également été caractérisés et une nouvelle méthode automatisée la caractérisation du RTOS. Ces caractérisations configurent un simulateur de performance à haut niveau qui estime précisément et très rapidement la performance d'un ensemble d'architectures pour l'application en tenant compte de la contention sur les bus et de l'ordonnancement des tâches sur les processeurs. Cette caractérisation mène également à une estimation précise et rapide des besoins en ressources matérielles.

6. Une nouvelle formulation du problème d'exploration architecturale qui combine le partitionnement logiciel/matériel, l'allocation des processeurs, l'assignation des tâches aux processeurs et le choix d'une topologie de communication. L'exploration architecturale évalue les architectures selon des critères de performance et de coût matériel à l'aide de notre méthode d'estimation. Nous présentons pour la première fois une analyse combinatoire de ce problème et sa formulation comme un problème de recherche locale. Nous définissons également les heuristiques suivantes pour la résolution de ce problème : un parcours en profondeur, une marche aléatoire, un recuit simulé adaptatif et une recherche tabou réactive. L'architecture retenue par l'exploration architecturale peut ensuite être synthétisée vers une implémentation finale dans un flot de conception RTL bien établi.

La méthodologie dans son ensemble est appliquée à trois études de cas : un système de guidage d'un astromobile, un décodeur JPEG avec détection de peau et un encodeur/décodeur WiMAX. Les résultats montrent que notre méthode de synthèse matérielle s'applique à des modules aussi complexes qu'un décodeur Reed-Solomon ou Huffman. De plus, il est montré qu'il est possible d'implémenter un profilage non-intrusif au niveau système avec un impact minime sur la vitesse de simulation. La méthode d'estimation permet d'évaluer le

temps d'exécution d'un ensemble d'architectures avec une précision de 8% et une vitesse de 400 à 48000 fois plus rapide qu'une simulation complète. La méthode d'estimation permet également d'estimer la quantité de ressources matérielles avec une précision de 20% et avec une vitesse 200000 fois plus rapide que la synthèse logique avec placement. Finalement, la recherche tabou réactive obtient systématiquement de meilleurs résultats que la marche aléatoire et le recuit simulé adaptatif. Dans les cas où il a été possible de trouver une solution optimale avec un parcours en profondeur, la recherche tabou réactive a également pu trouver cette solution optimale.

Cette thèse est structurée comme suit. Le chapitre 2 présente une revue de littérature afin de situer nos contributions par rapport à l'état de l'art. Le chapitre 3 présente dans son ensemble notre méthodologie intégrée de conception, d'exploration architecturale et de synthèse des systèmes embarqués. Le chapitre 4 décrit les réseaux de processus temps-réel. Le chapitre 5 présente notre méthode automatisée de synthèse matérielle. Le chapitre 6 décrit notre méthode de profilage au niveau système. Le chapitre 7 présente la méthode de caractérisation et d'estimation du temps d'exécution et de la quantité de ressources matérielles. Le chapitre 8 présente la formulation du problème d'exploration architecturale et différents algorithmes pour le résoudre. Le chapitre 9 applique cette méthodologie aux études de cas et en présente les résultats. Finalement, le chapitre 10 effectue une synthèse des travaux et propose des améliorations futures à la méthodologie.

## CHAPITRE 2

### REVUE DE LITTÉRATURE

Ce chapitre passe en revue les travaux pertinents à notre méthodologie et à ses différentes étapes et décrit notre contribution par rapport à ces travaux. On passe d'abord en revue les travaux portant sur les modèles de calcul parallèles, puis sur la synthèse matérielle au niveau système. Le chapitre se poursuit par une revue du profilage de performance et des méthodes d'estimation du temps d'exécution. On passe ensuite en revue les algorithmes d'exploration architecturale. Finalement, notre méthodologie est comparée avec d'autres travaux présentant des méthodologies intégrées de conception, d'exploration architecturale et de synthèse des systèmes embarqués

#### 2.1 Modèles de calcul parallèles

Les systèmes embarqués sont fréquemment spécifiés sous la forme d'un ensemble de tâches parallèles ou implémentés par une architecture comprenant plusieurs processeurs et accélérateurs matériels s'exécutant en parallèle. Il est cependant difficile de raisonner sur le parallélisme au niveau des langages de programmation impératifs couramment utilisés pour les spécifications exécutables et les logiciels embarqués (Lee, 2006). Les modèles de calcul parallèles sont des formalismes mathématiques qui permettent d'analyser les systèmes embarqués à un plus haut niveau d'abstraction et aident notamment au raffinement d'une spécification vers une implémentation conforme à celle-ci. Plus le pouvoir expressif d'un modèle de calcul est élevé, plus grand est l'ensemble des programmes parallèles qui peuvent être exprimés à l'aide de ce modèle de calcul, mais plus la capacité d'analyse statique de ces programmes parallèles devient réduite. Différents modèles de calcul représentent différents compromis entre le pouvoir expressif et la capacité d'analyse statique.

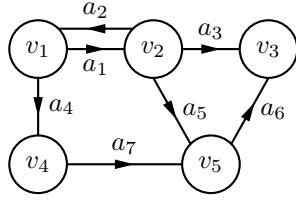

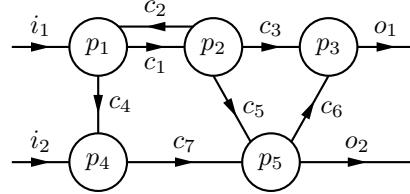

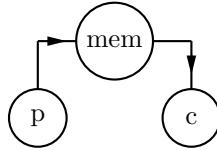

Les modèles de calculs les plus souvent utilisés pour l'exploration architecturale et la synthèse des systèmes embarqués sont les modèles de réseaux de processus. Tel qu'illustré à la figure 2.1, un réseau de processus est un graphe orienté  $G = (V, A)$  tel que les noeuds  $V$  sont un ensemble de processus et les arcs  $A$  sont un ensemble de canaux FIFO. Dans la sémantique opérationnelle de ces modèles de calcul, les processus communiquent entre eux uniquement au moyen de ces canaux et non au moyen de variables partagées. Les principaux modèles de calcul de réseaux de processus sont présentés ici par ordre croissant de pouvoir expressif.

Figure 2.1 Exemple de graphe orienté  $G = (V, A)$  représentant un réseau de processus

### 2.1.1 Flots de données synchrones (SDF)